Patents

Literature

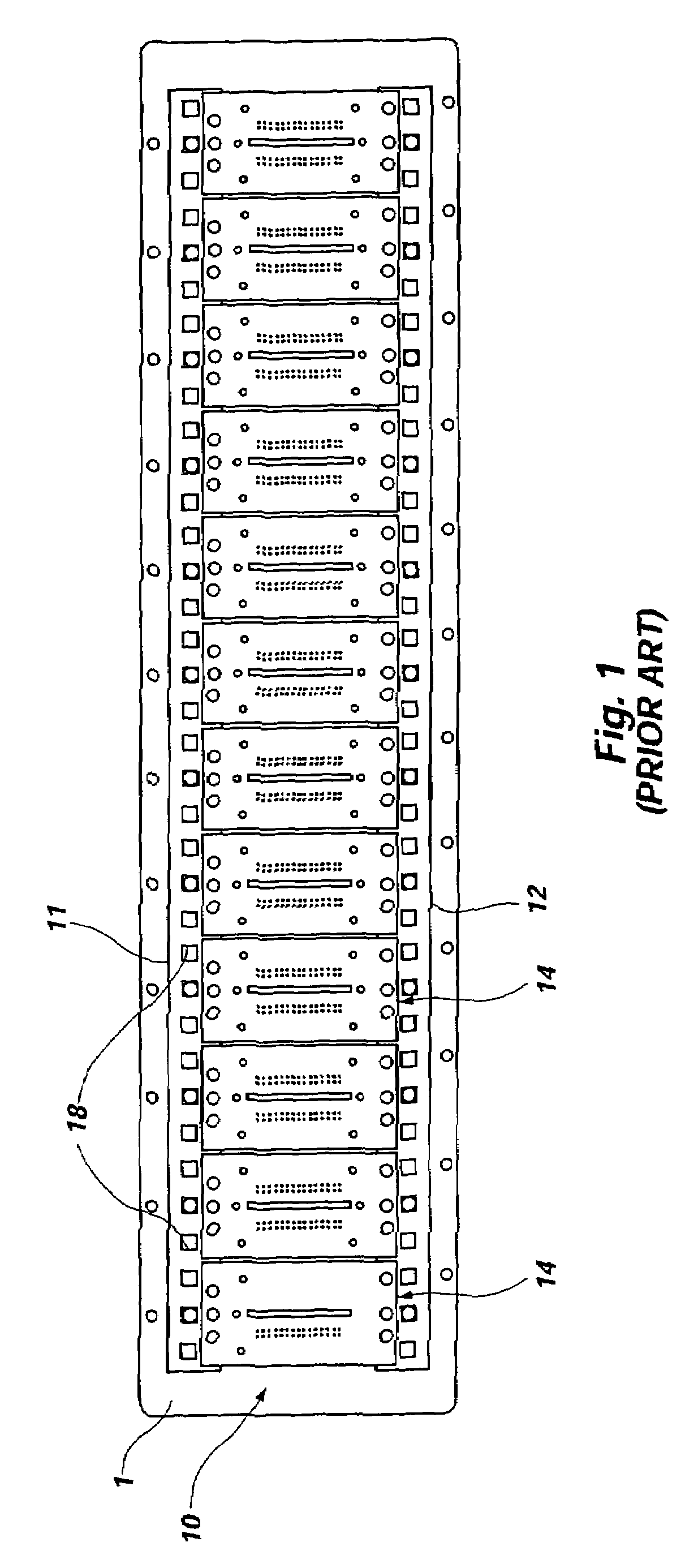

58 results about "Tape-automated bonding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

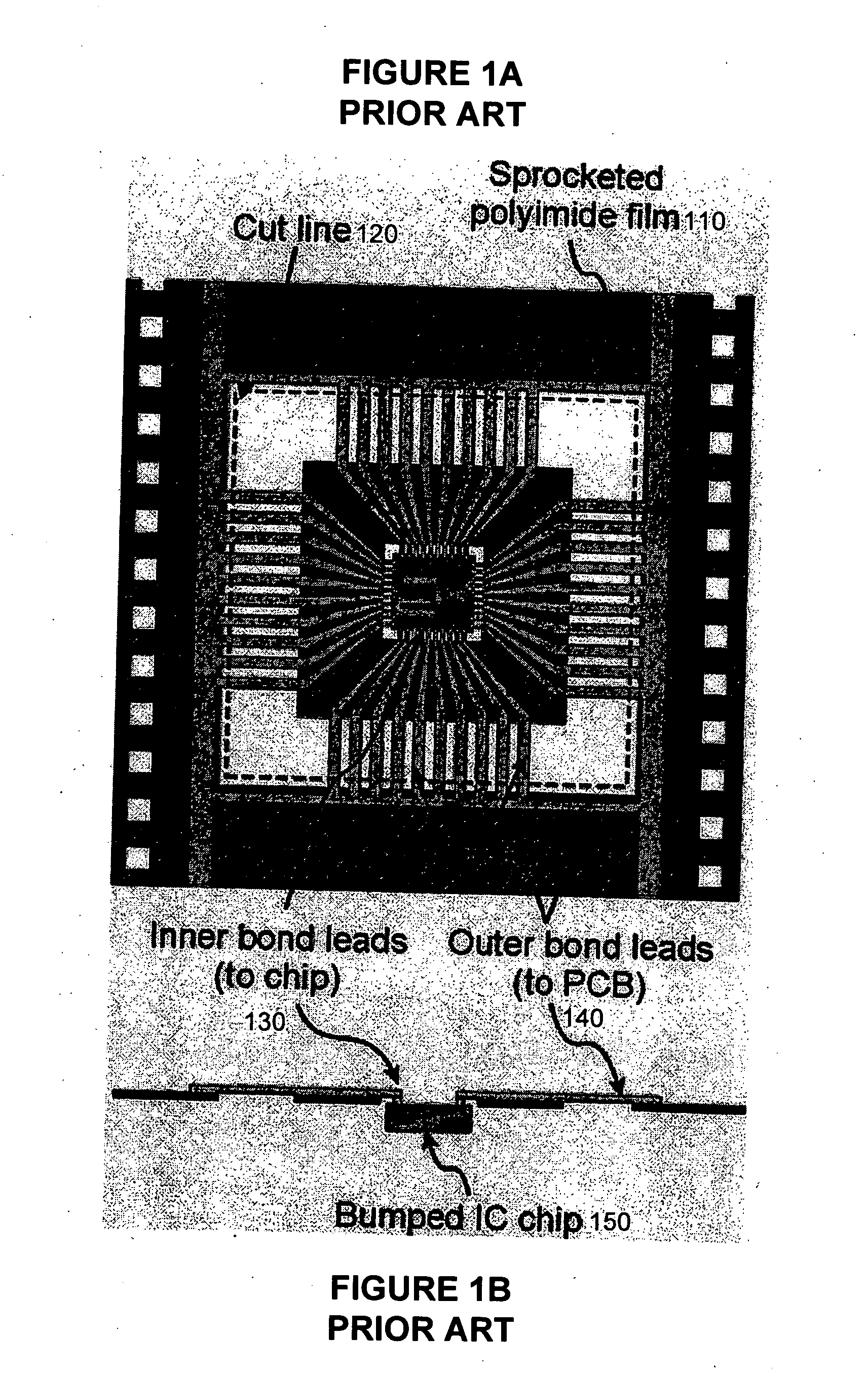

Tape-automated bonding (TAB) is a process that places bare integrated circuits onto a flexible printed circuit board (FPC) by attaching them to fine conductors in a polyamide or polyimide film, thus providing a means to directly connect to external circuits.

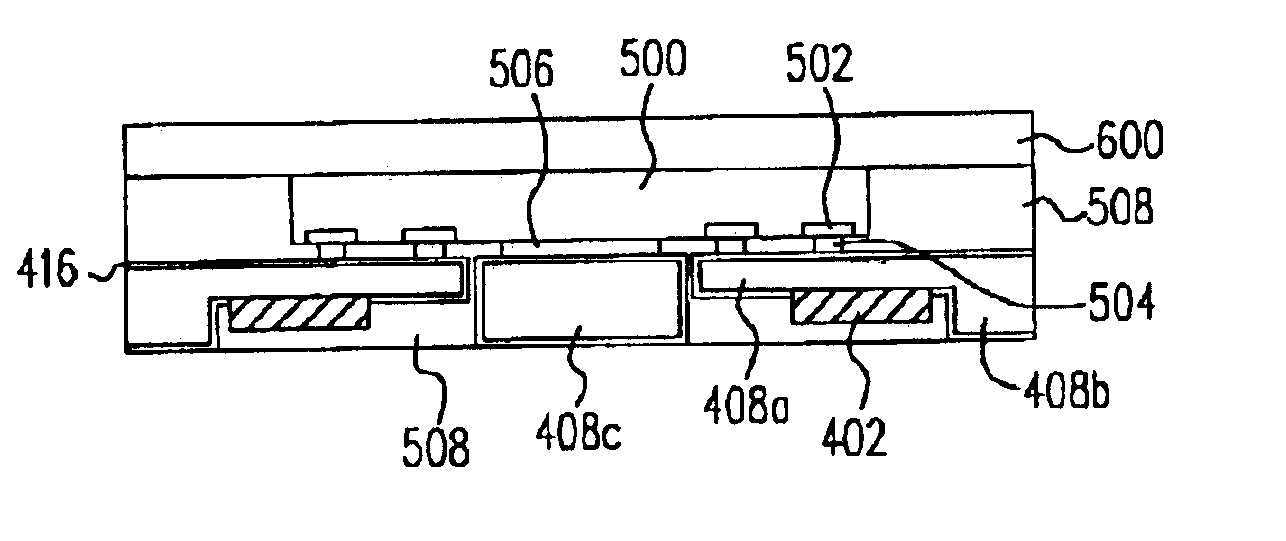

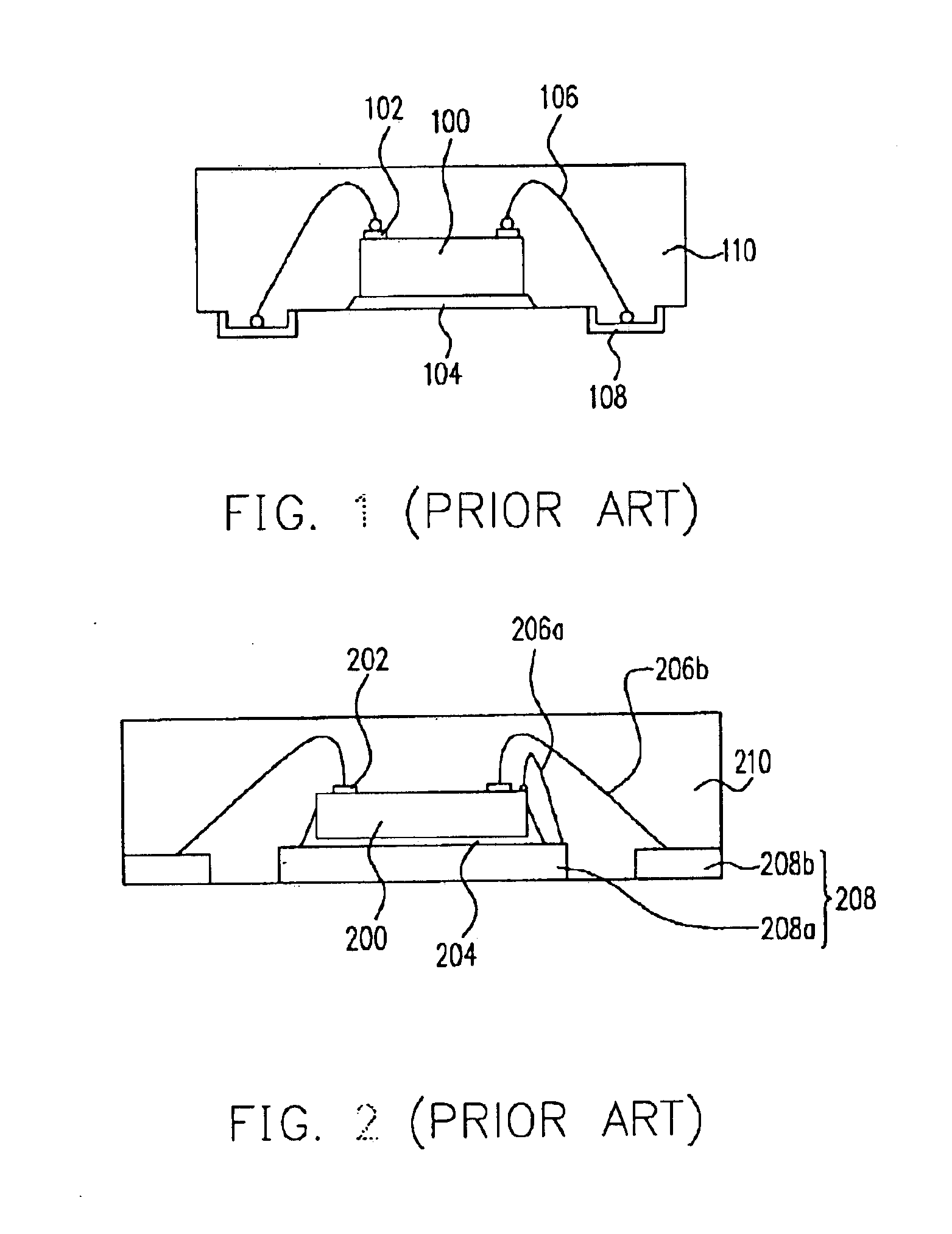

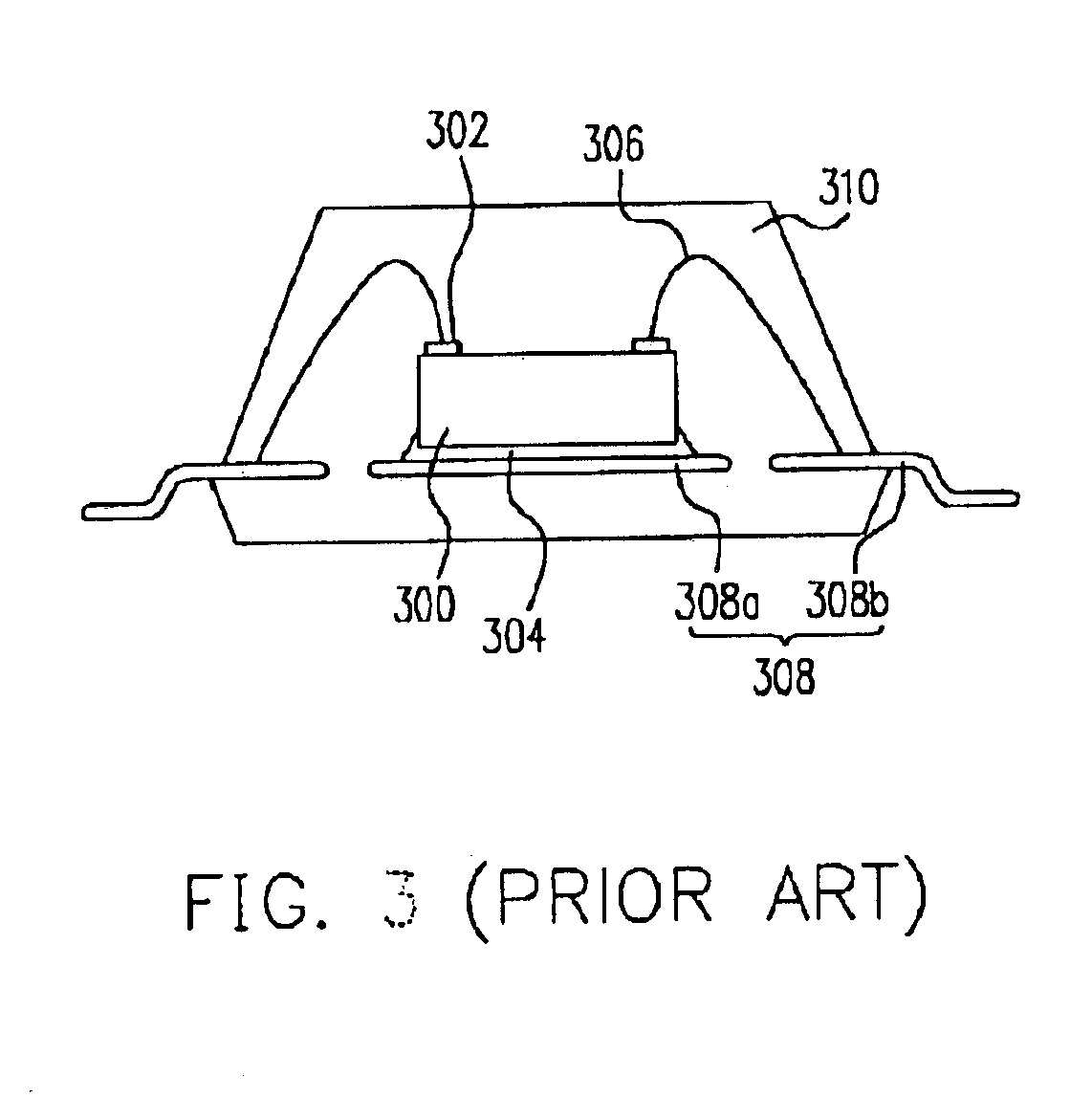

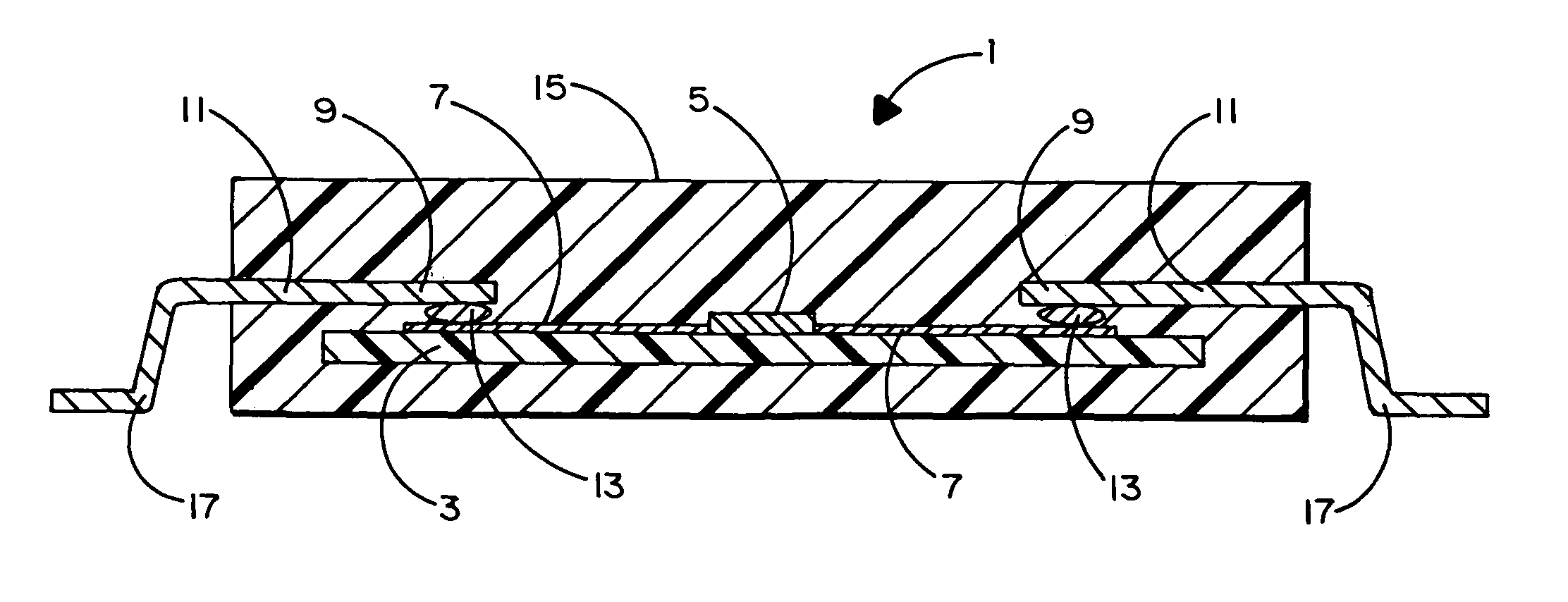

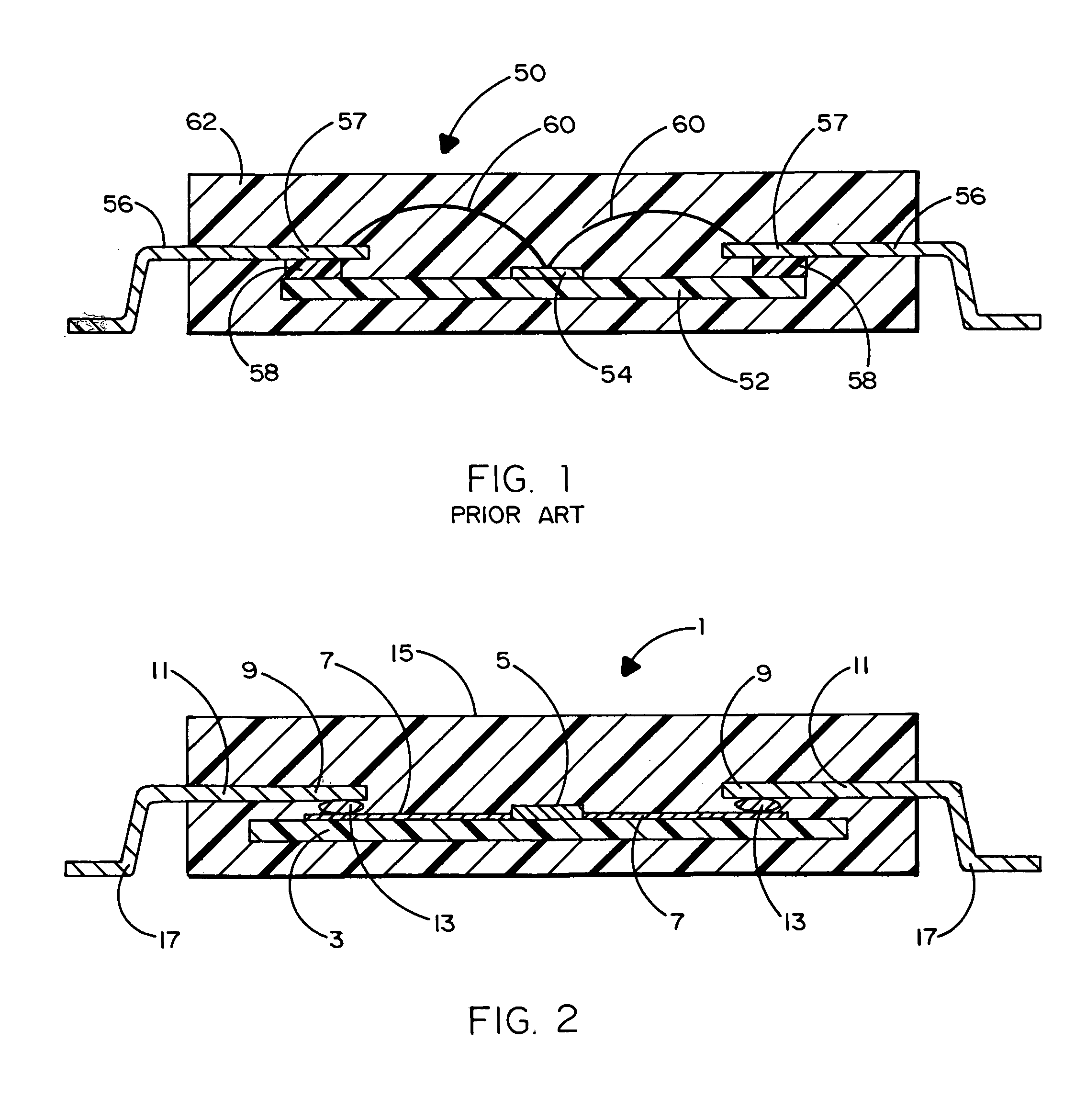

Structure employing electrically conductive adhesives

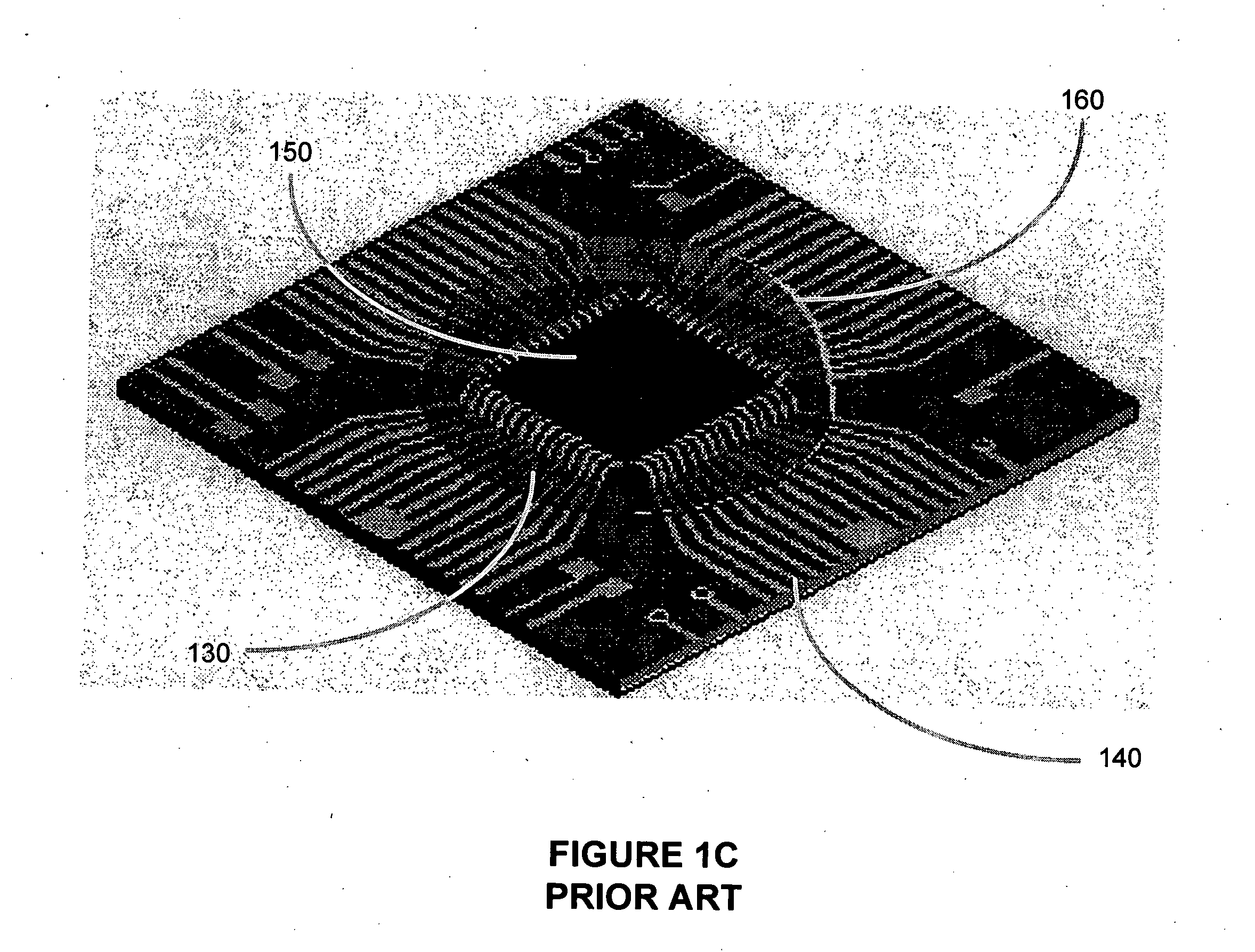

InactiveUS6337522B1Stable TAB joint structureImprove fatigue lifePrinted circuit assemblingLayered productsInterfacial reactionActive-matrix liquid-crystal display

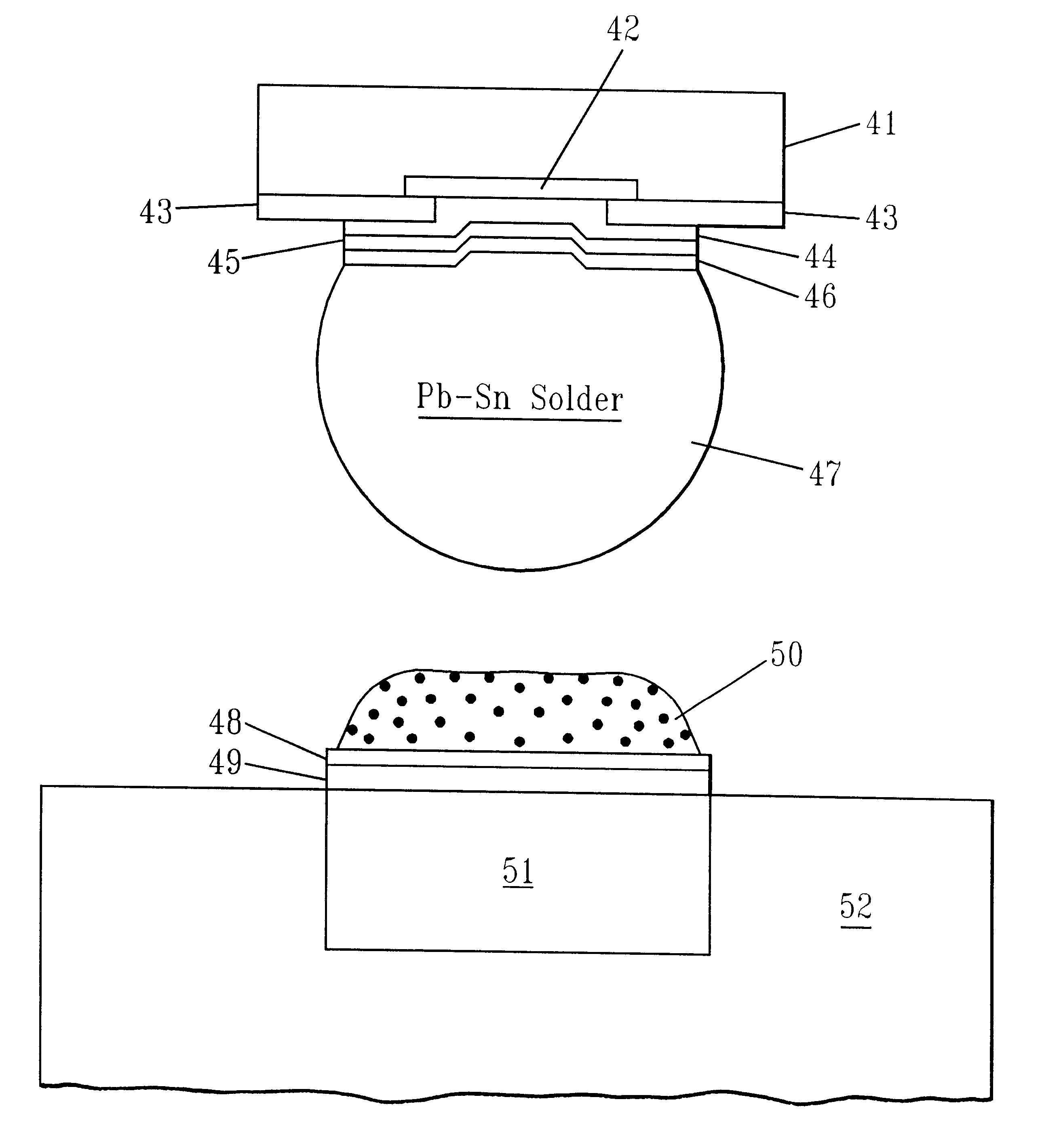

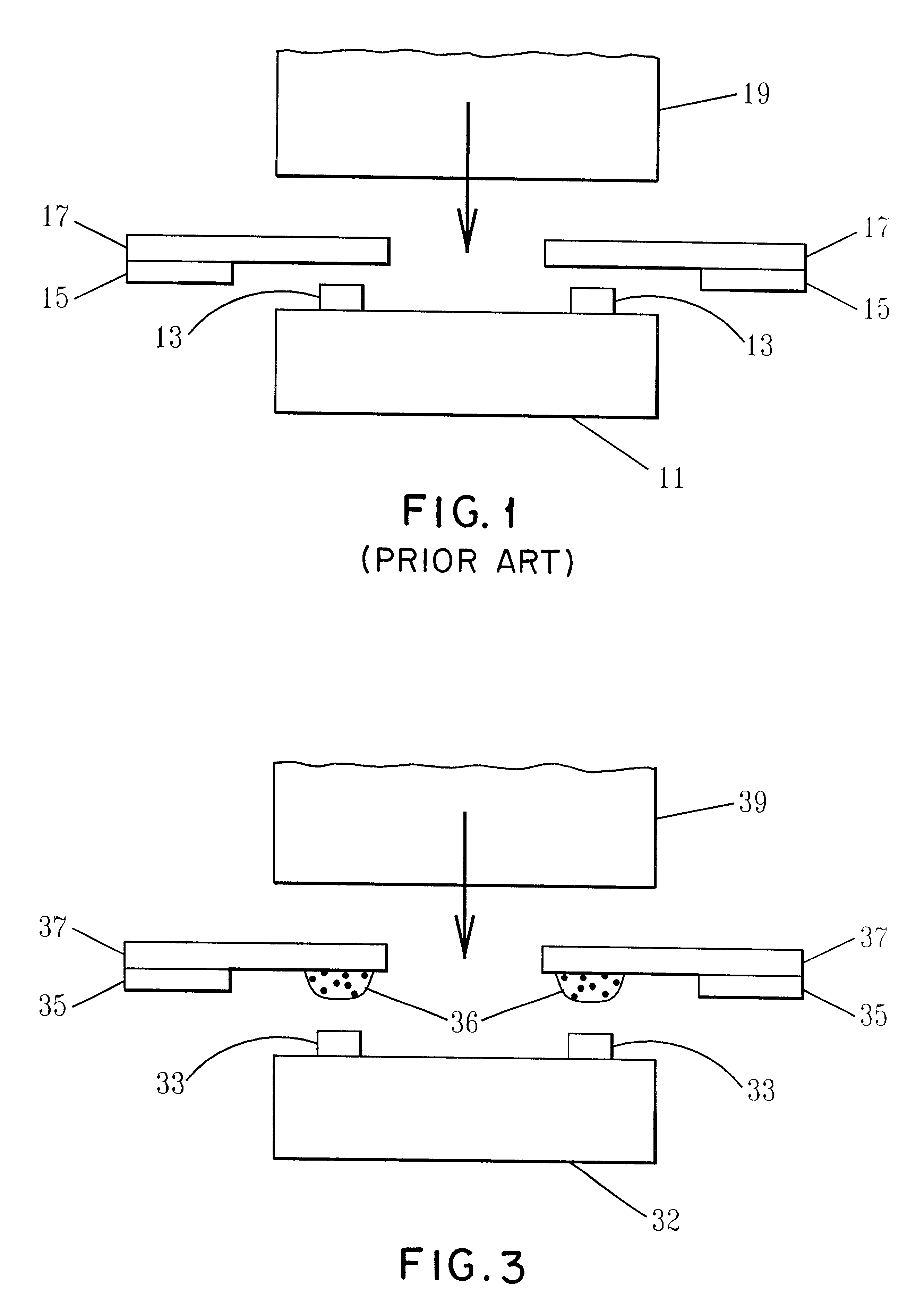

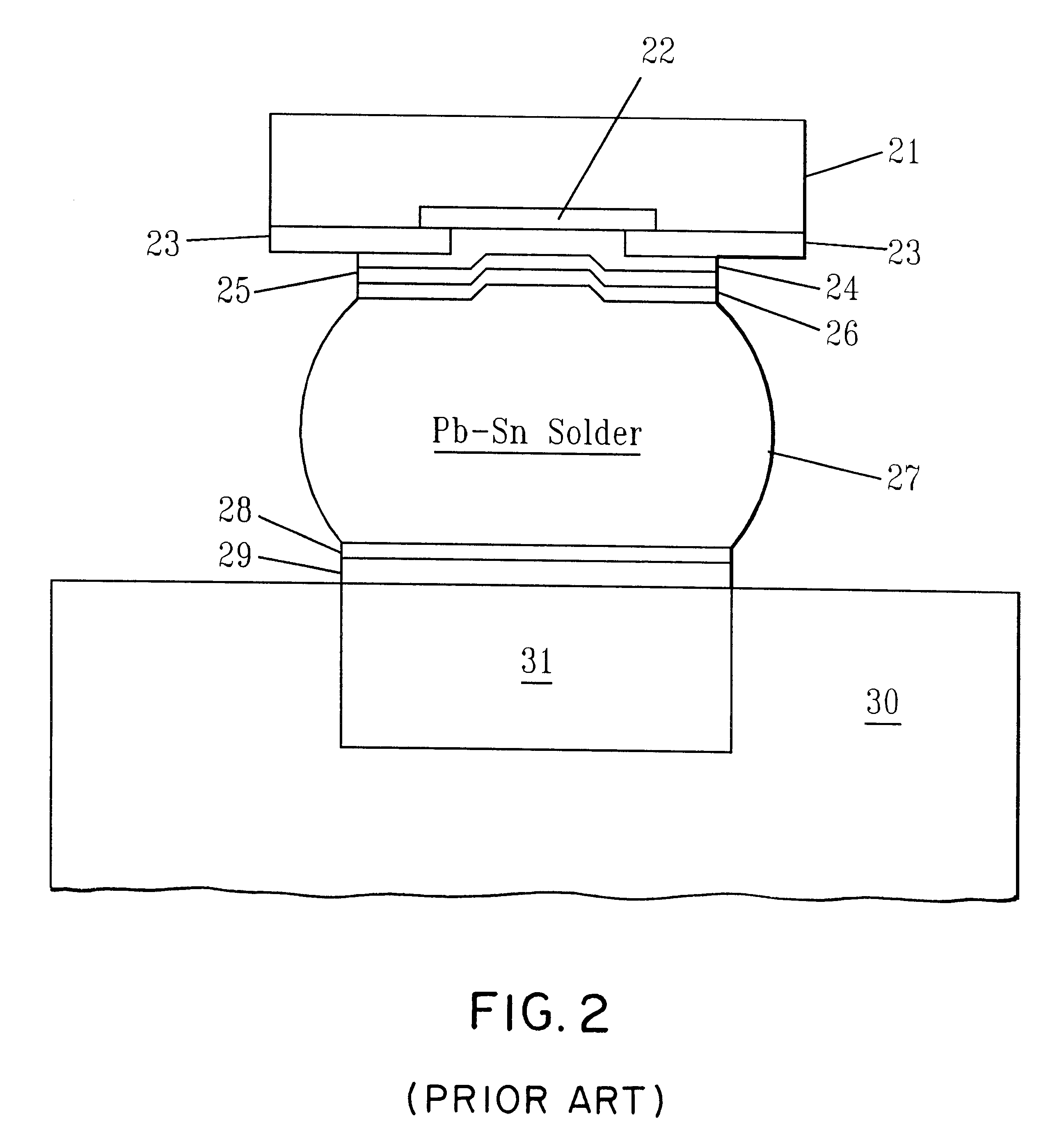

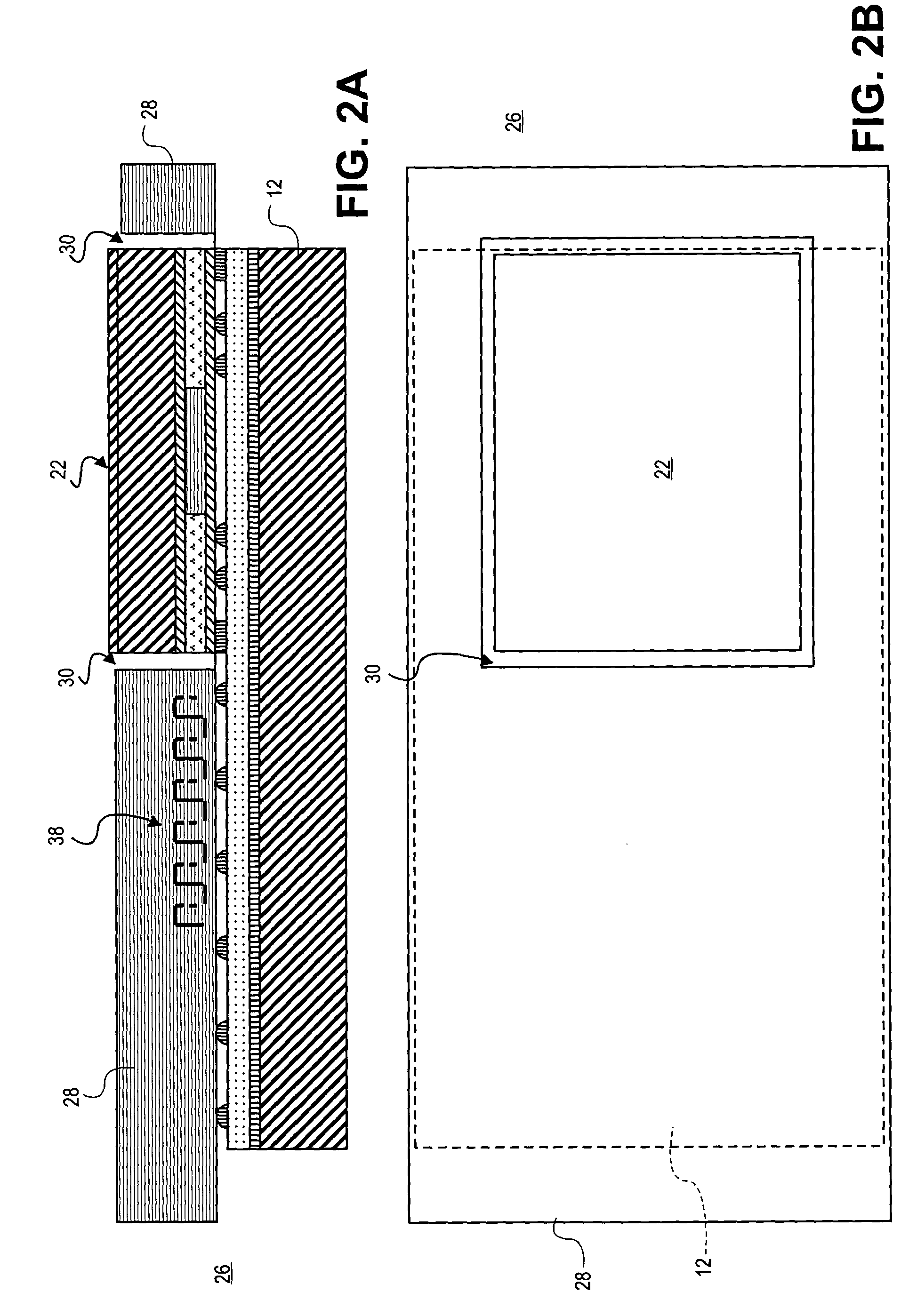

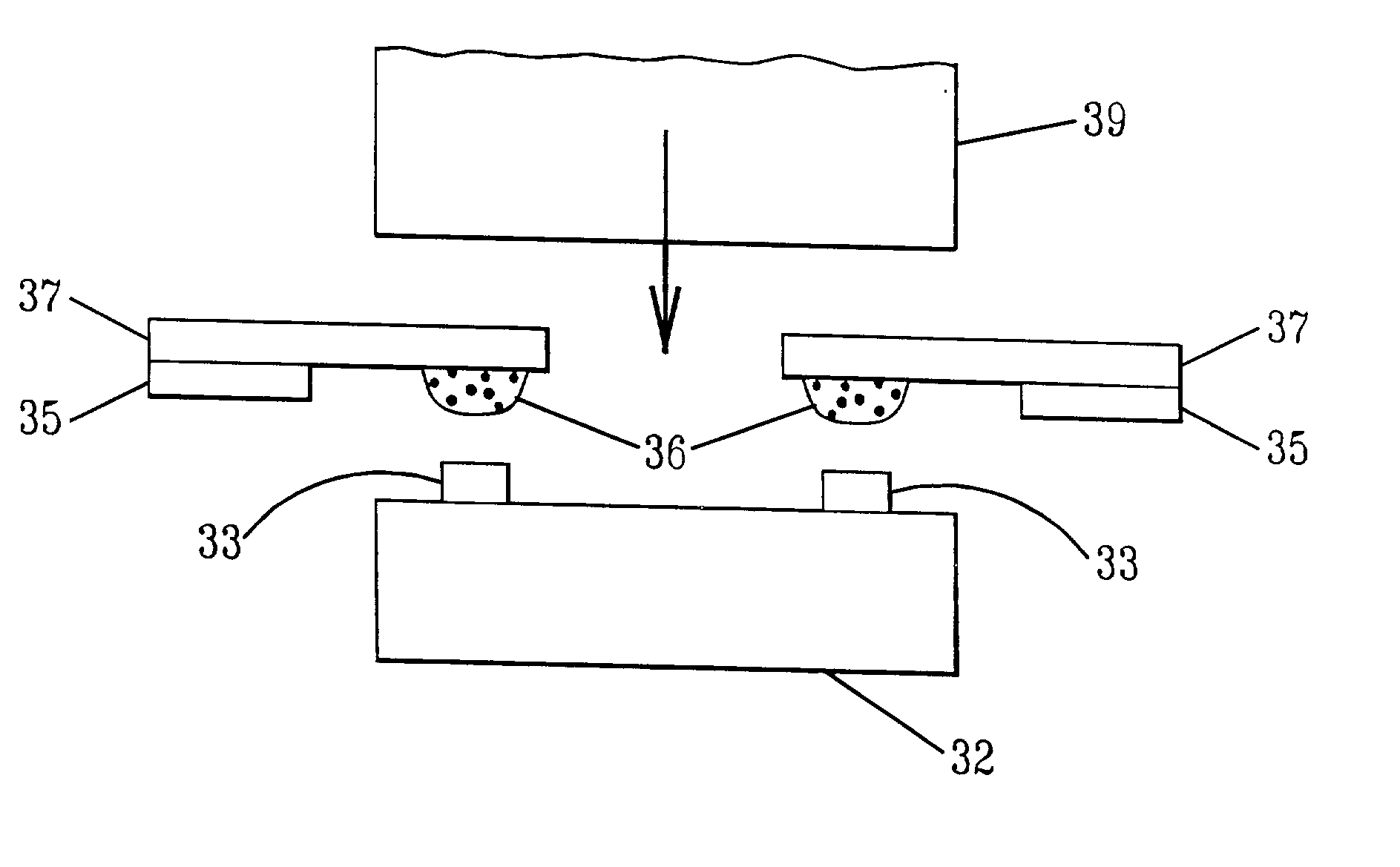

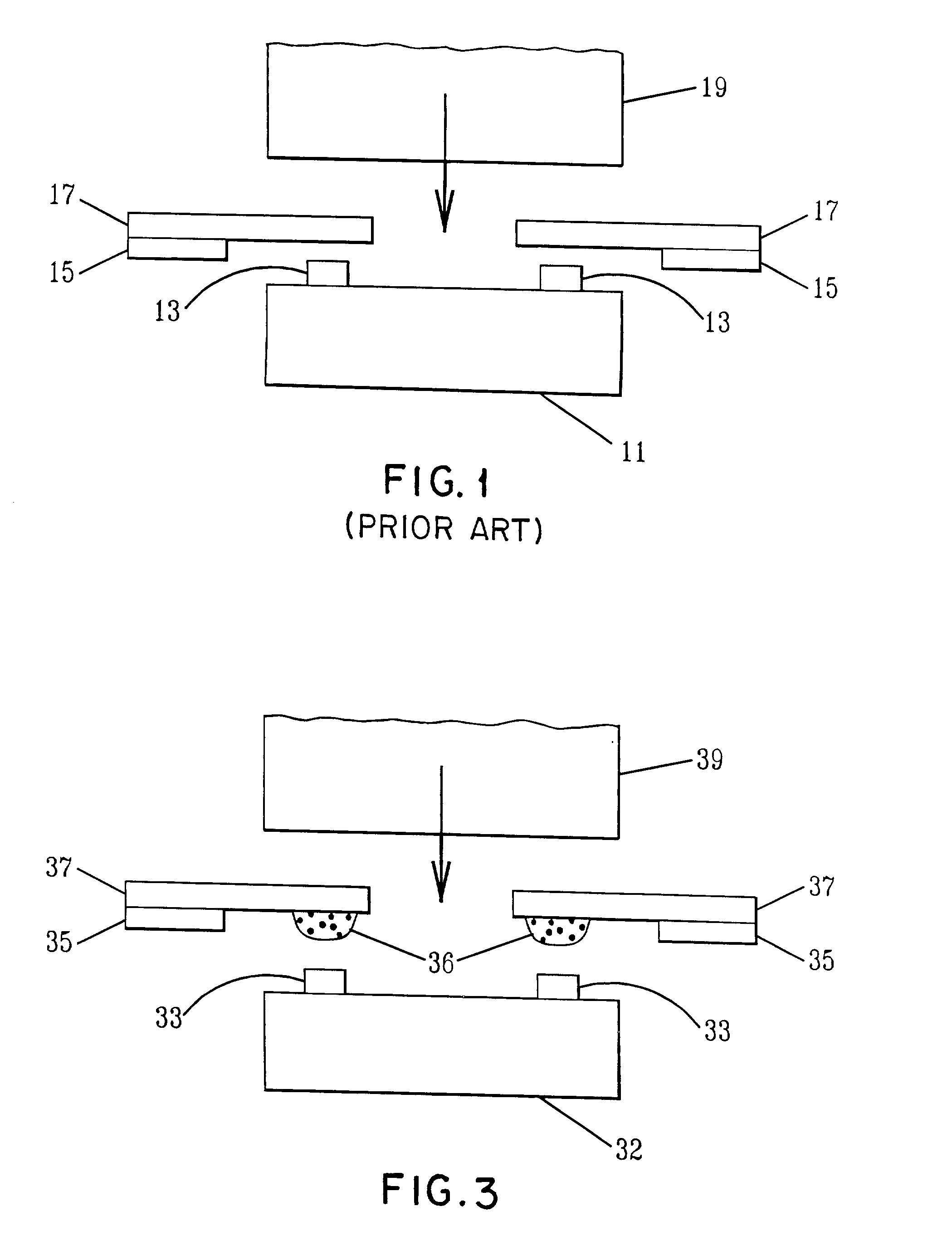

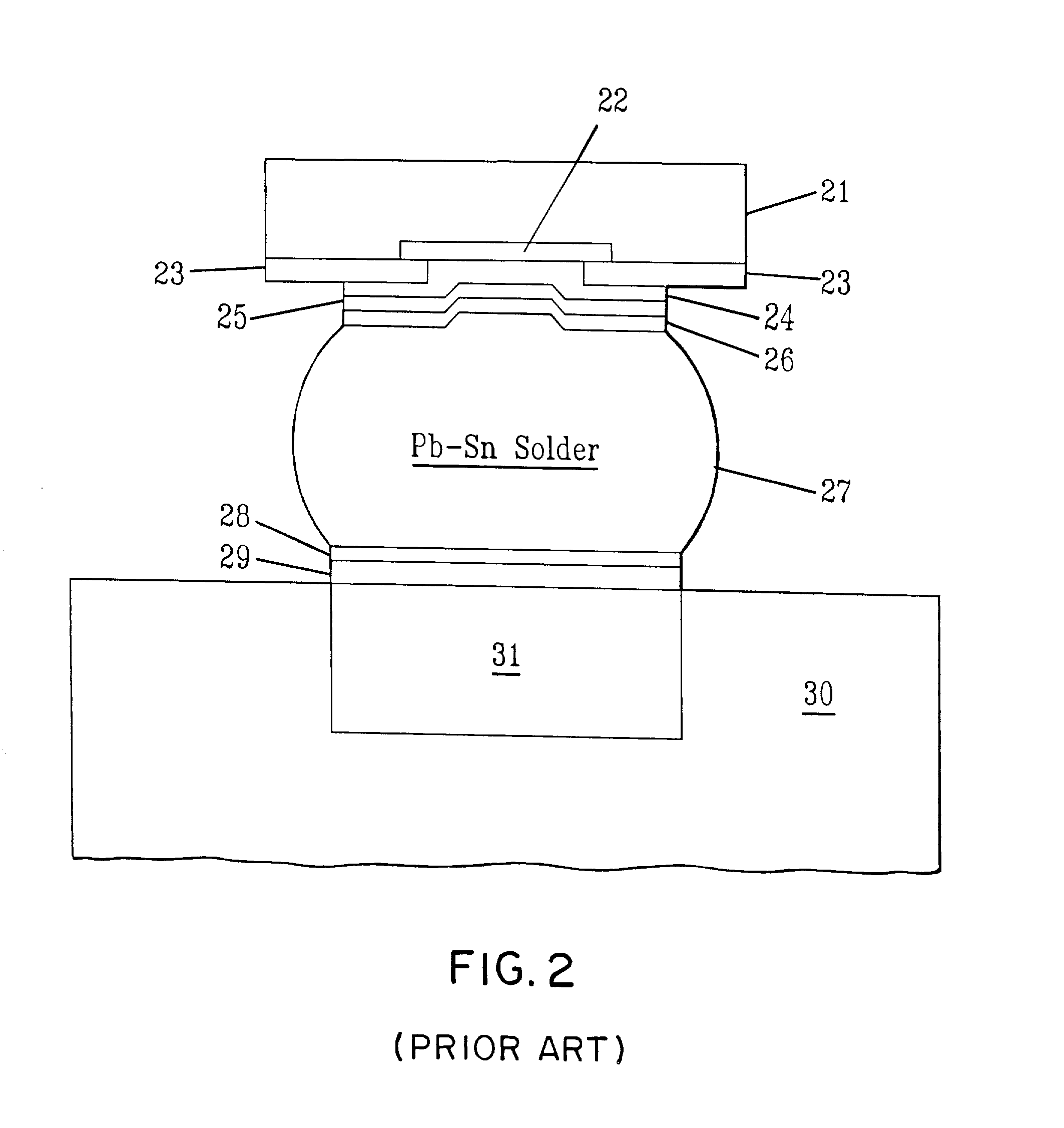

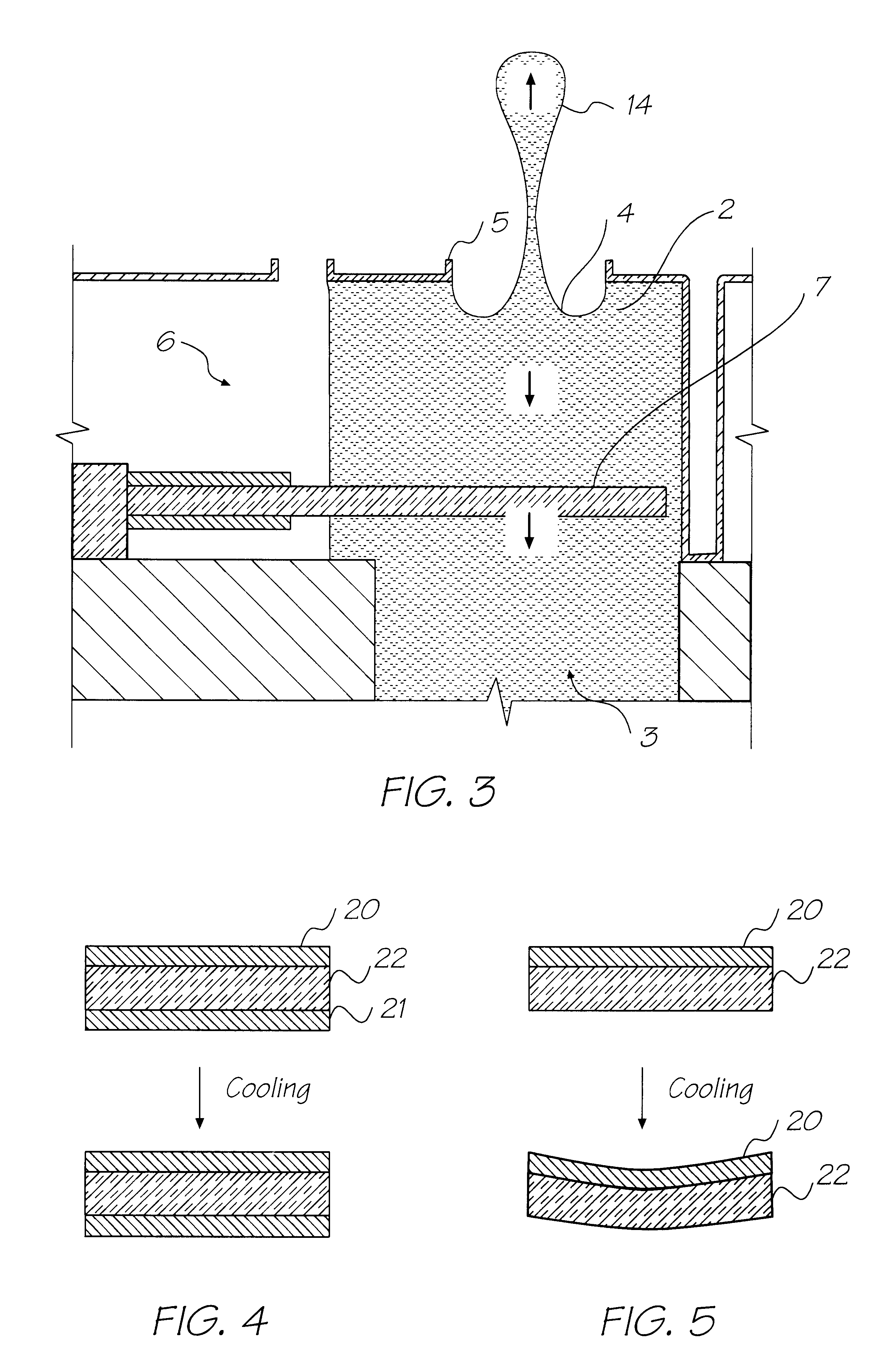

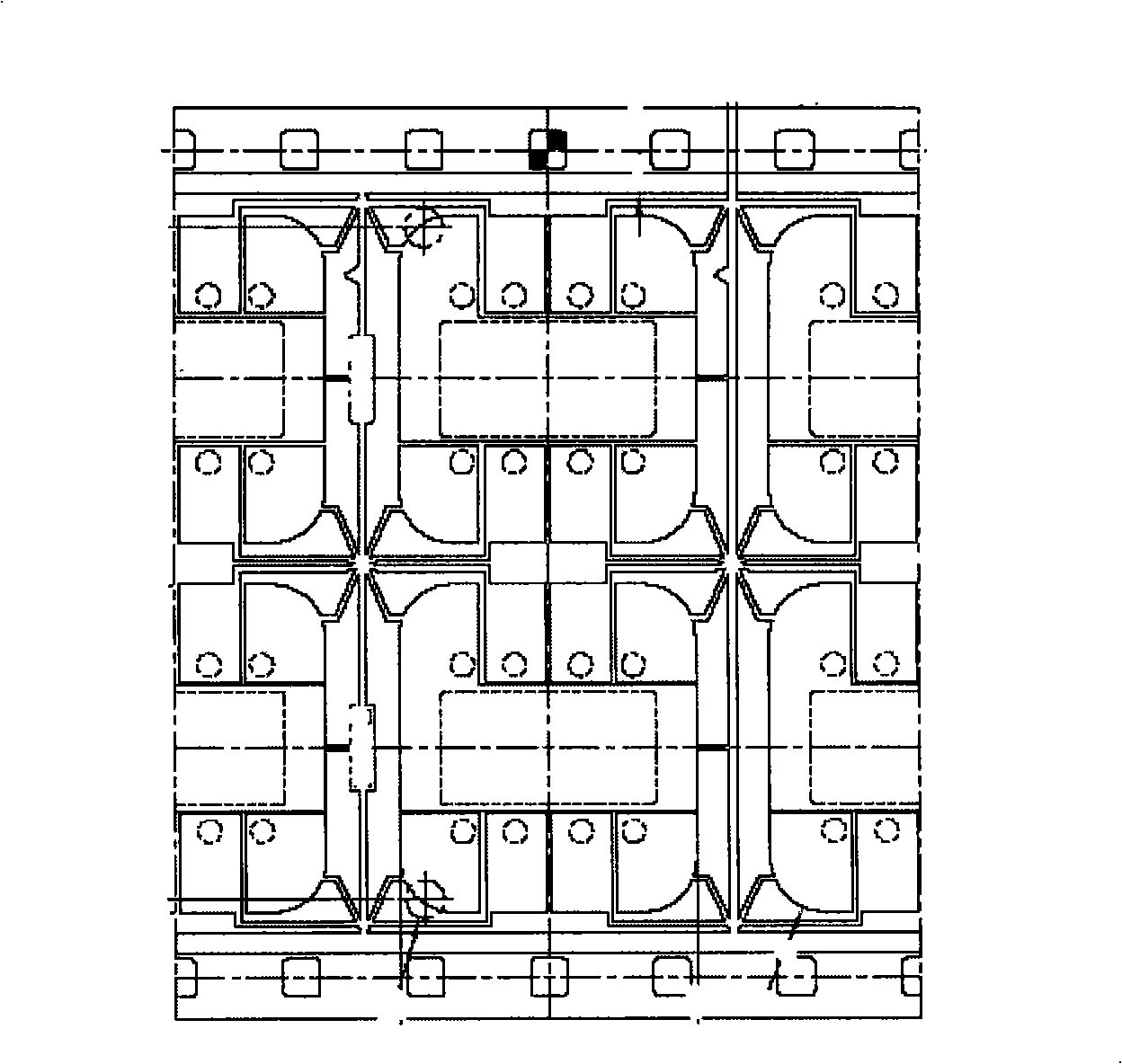

A new interconnection scheme is disclosed for a tape automated bonding (TAB) package, a flip chip package and an active matrix liquid crystal display (AMLCD) panel, where an electrically conducting adhesive is used to form an electrical interconnection between an active electronic device and its components. The electrically conducting adhesive can be a mixture comprising a polymer resin, a no-clean solder flux, a plurality of electrically conducting particles with an electrically conducting fusible coating which provides a metallurgical bond between the conducting particles as well as to the substrates. The advantages of using the electrically conducting adhesives include reduction in bonding pressure and / or bonding temperature, control of interfacial reactions, promotion of stable metallurgical bonds, enhanced reliability of the joints, and others.

Owner:AU OPTRONICS CORP

Two-dimensional laser diode array light-emitting device

InactiveUS6934309B2Reduce manufacturing costSimplify the electrical connection structureOptical wave guidanceSemiconductor laser arrangementsManufacturing cost reductionElectrical connection

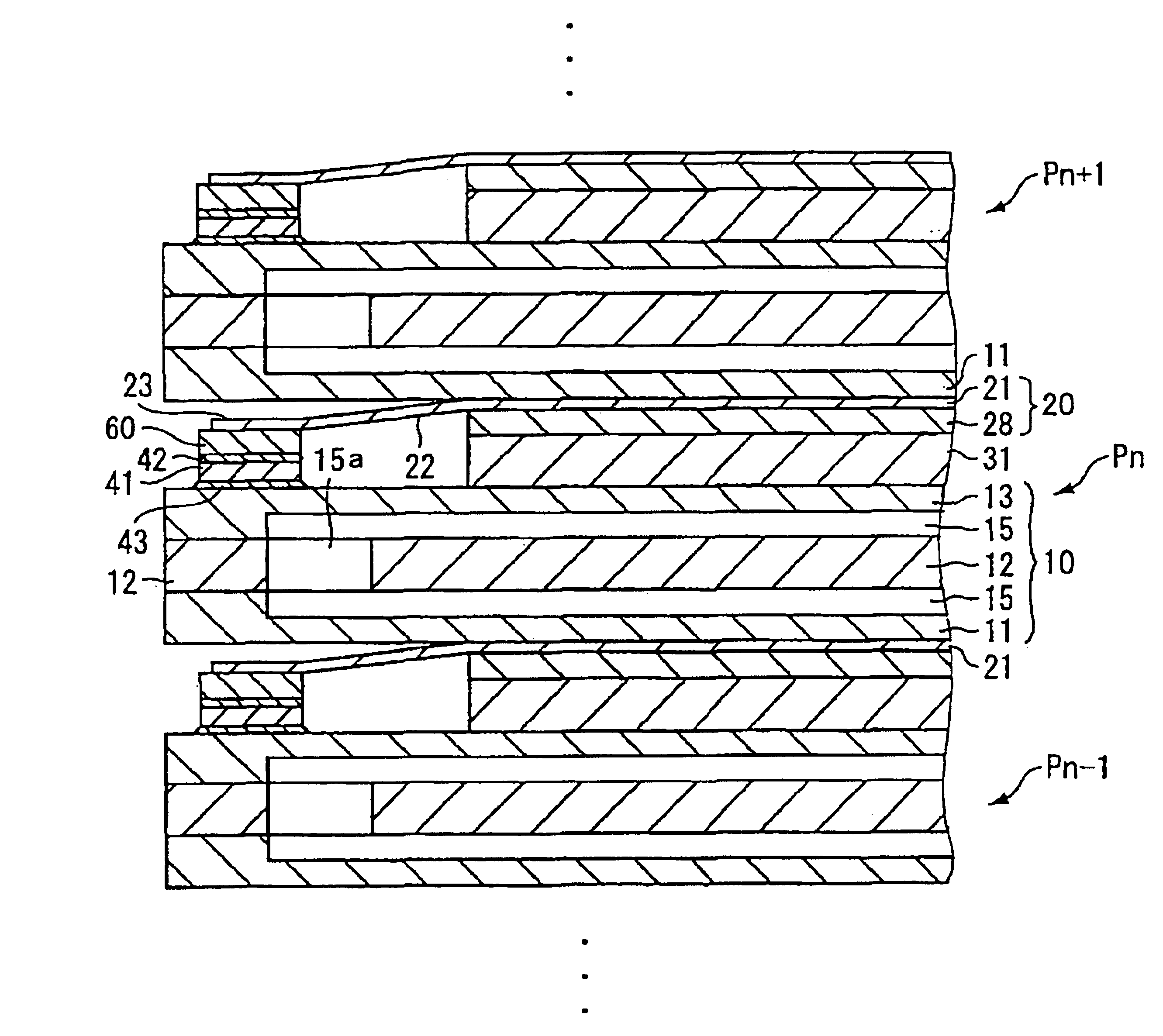

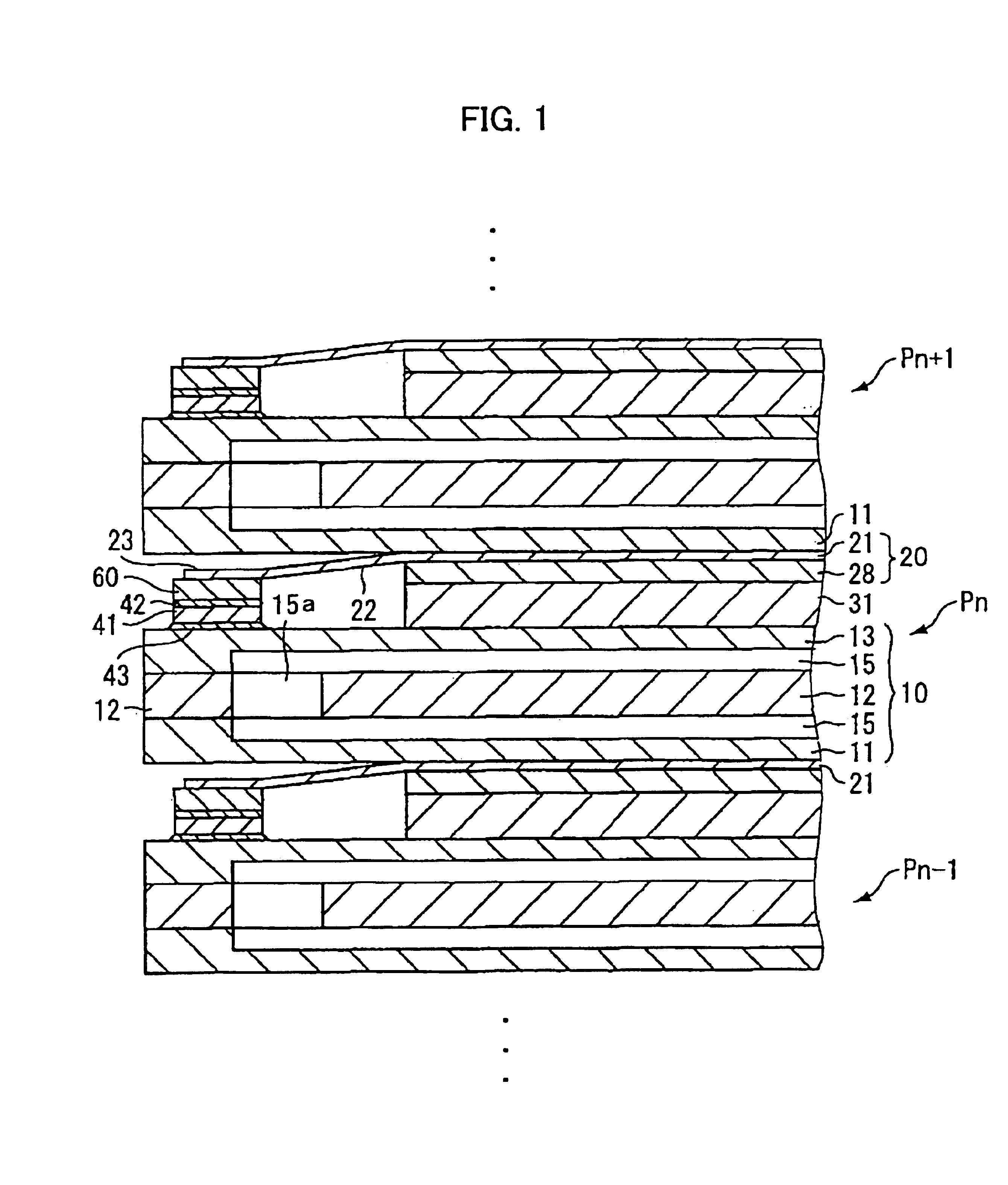

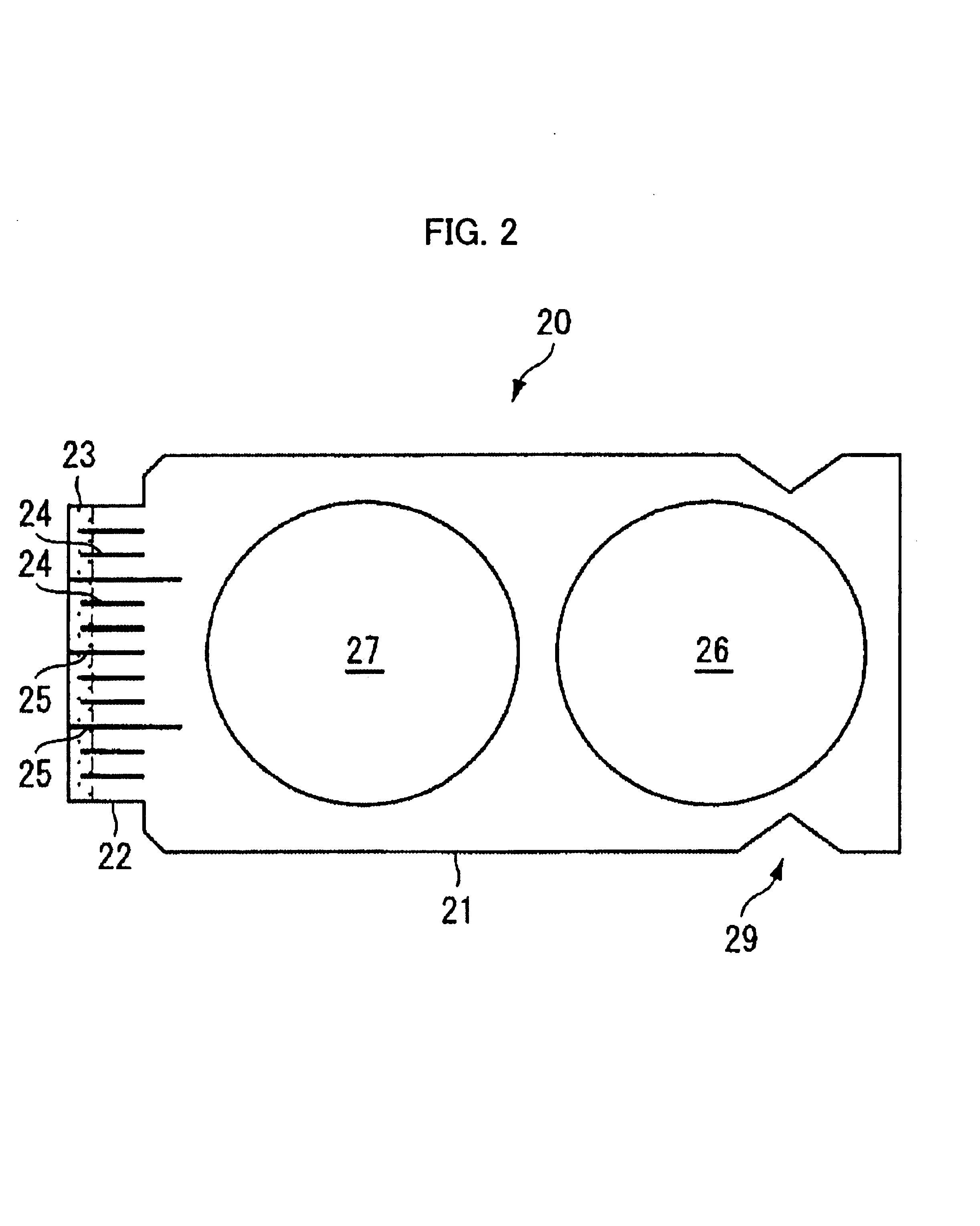

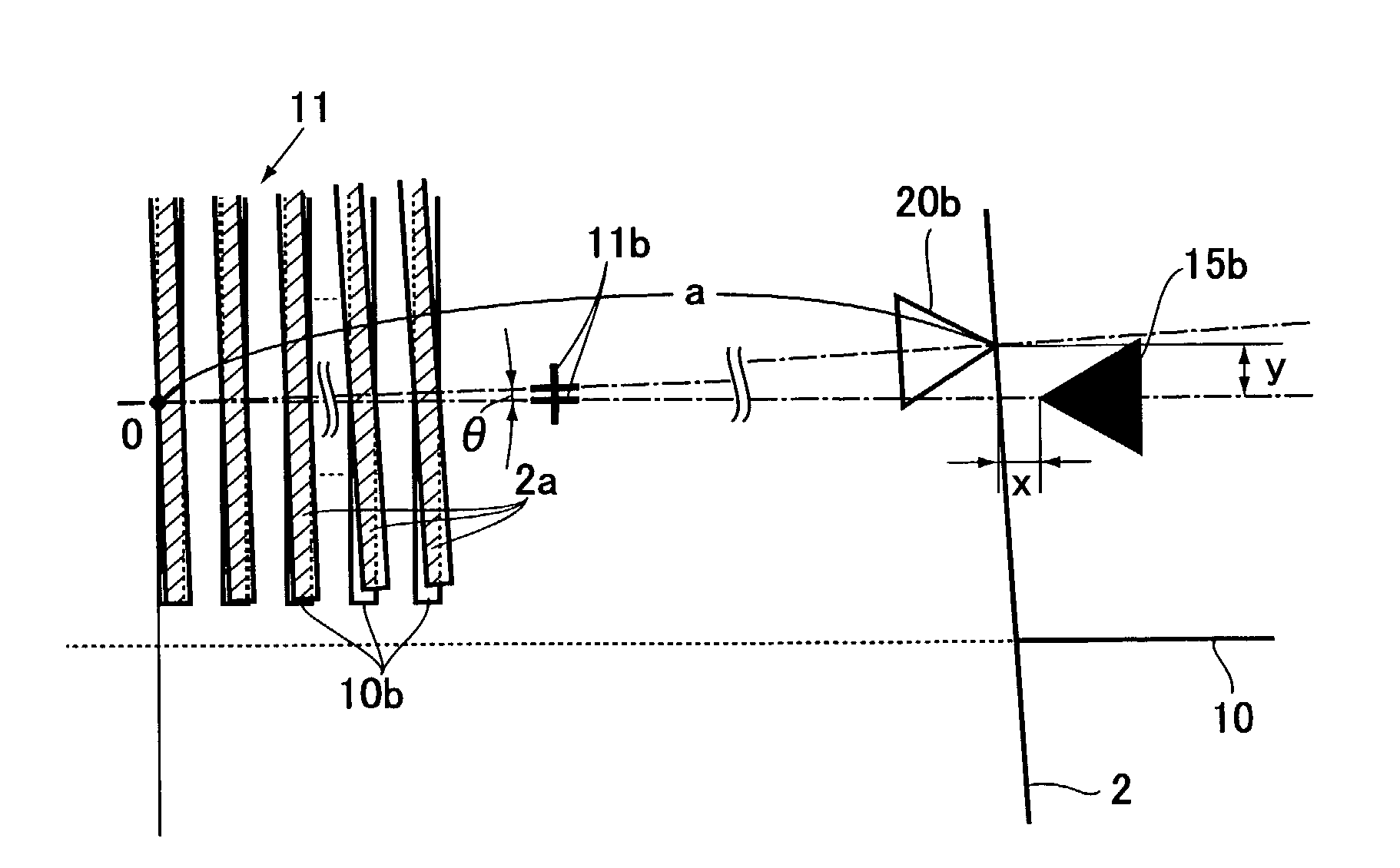

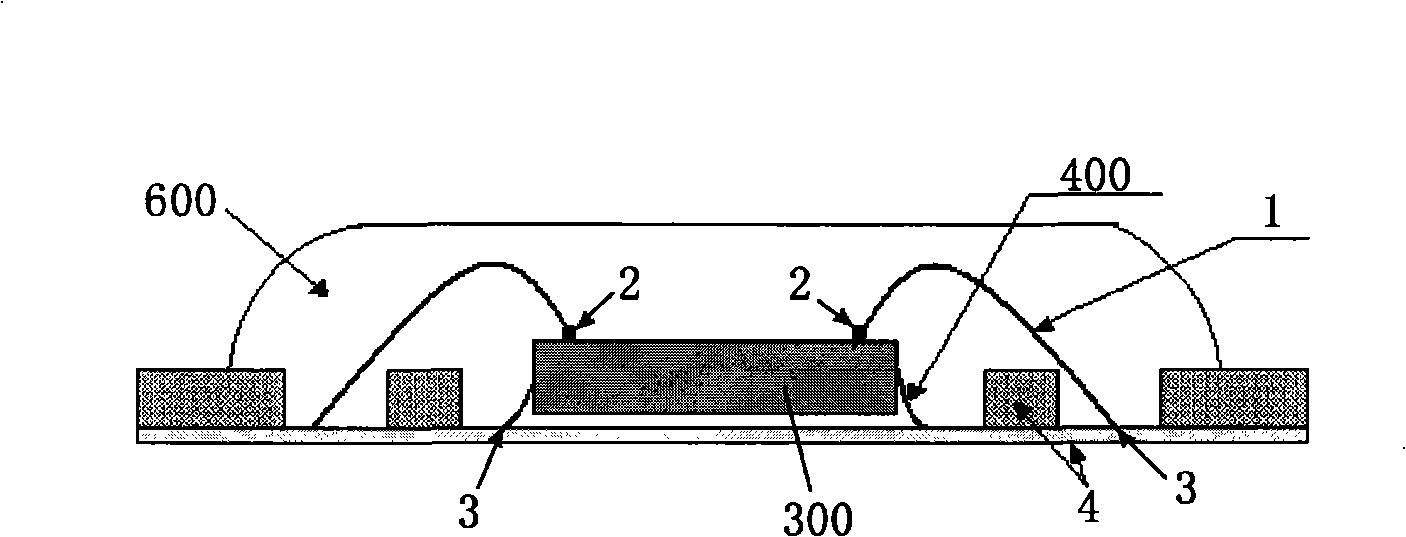

A two-dimensional LD (laser diode) array light-emitting device constituted by stacking light-emitting units each having a LD bar and a cooling assembly for cooling the LD bar with a simplified electrical connection structure to reduce manufacturing cost. The cooling assembly is electrically connected with one electrode of the LD bar through the die spacer so that a part of the cooling assembly serves as one electrode of the light-emitting unit. The other electrode of the LD bar is electrically connected with a webbed extending section of a conductive layer of a TAB (tape-automated bonding) sheet so that the conductive layer serves as the other electrode of the light-emitting unit. A space between the adjacent cooling assemblies for arranging the LD bar is adjusted by the spacer sheet intervened between the TAB sheet and the cooling assembly.

Owner:FANUC LTD

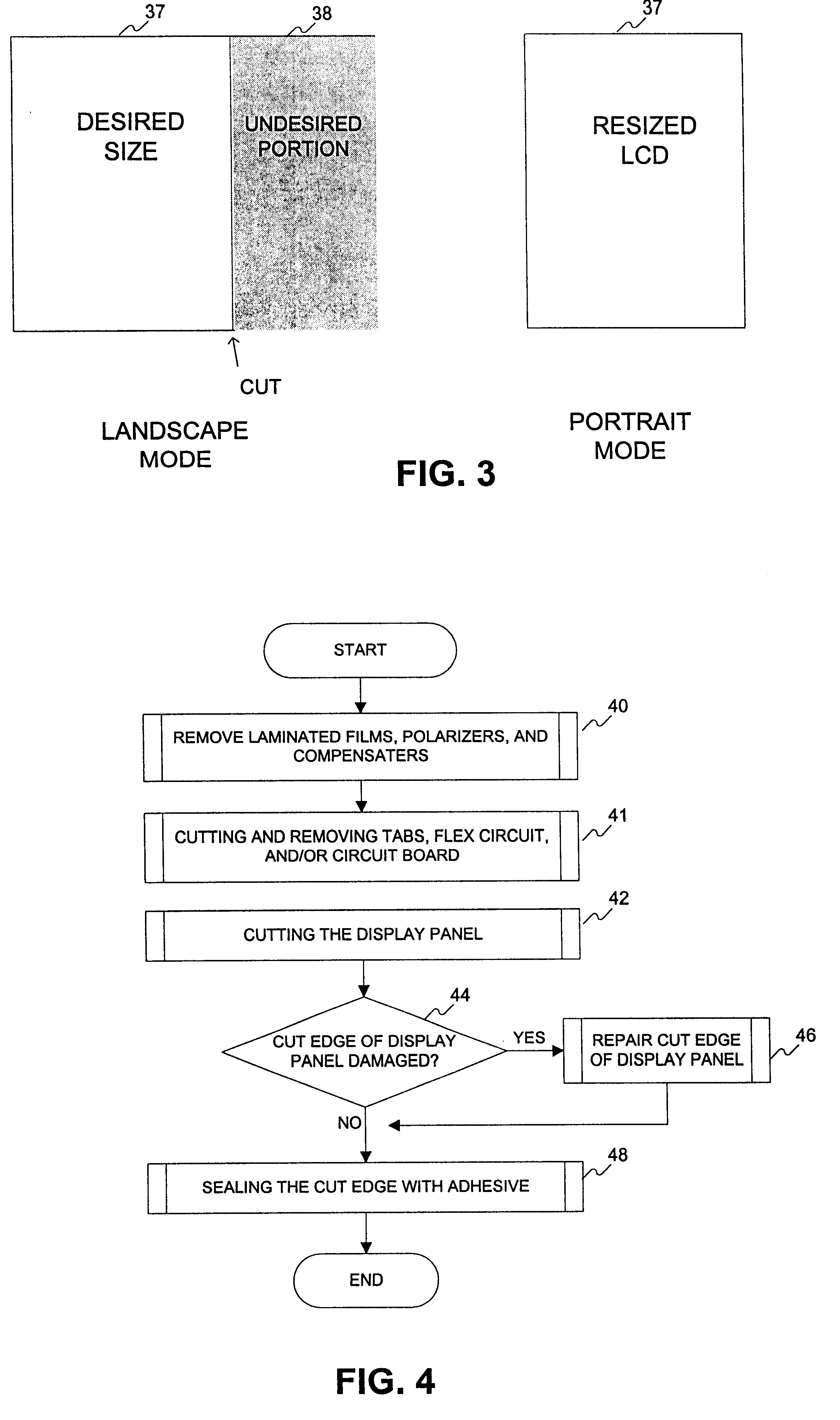

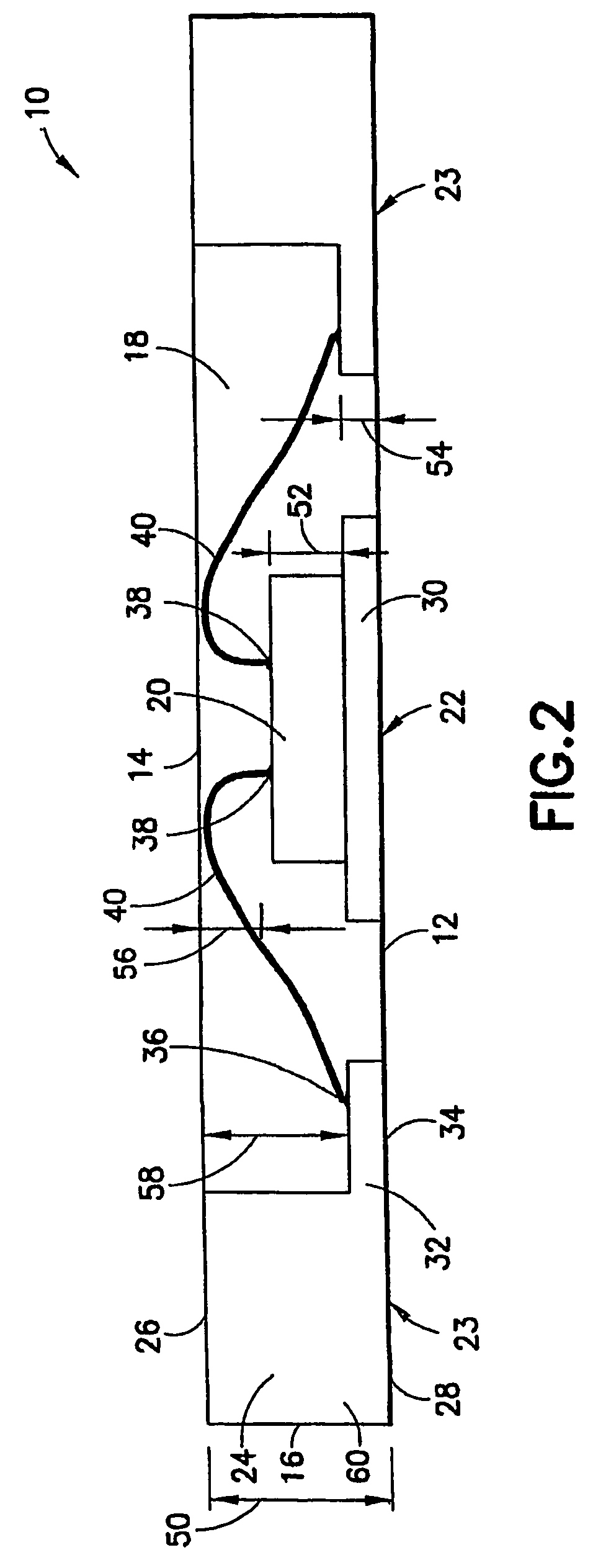

Method of resizing a liquid crystal display

InactiveUS6509949B1Static indicating devicesNon-linear opticsLiquid-crystal displayFlexible circuits

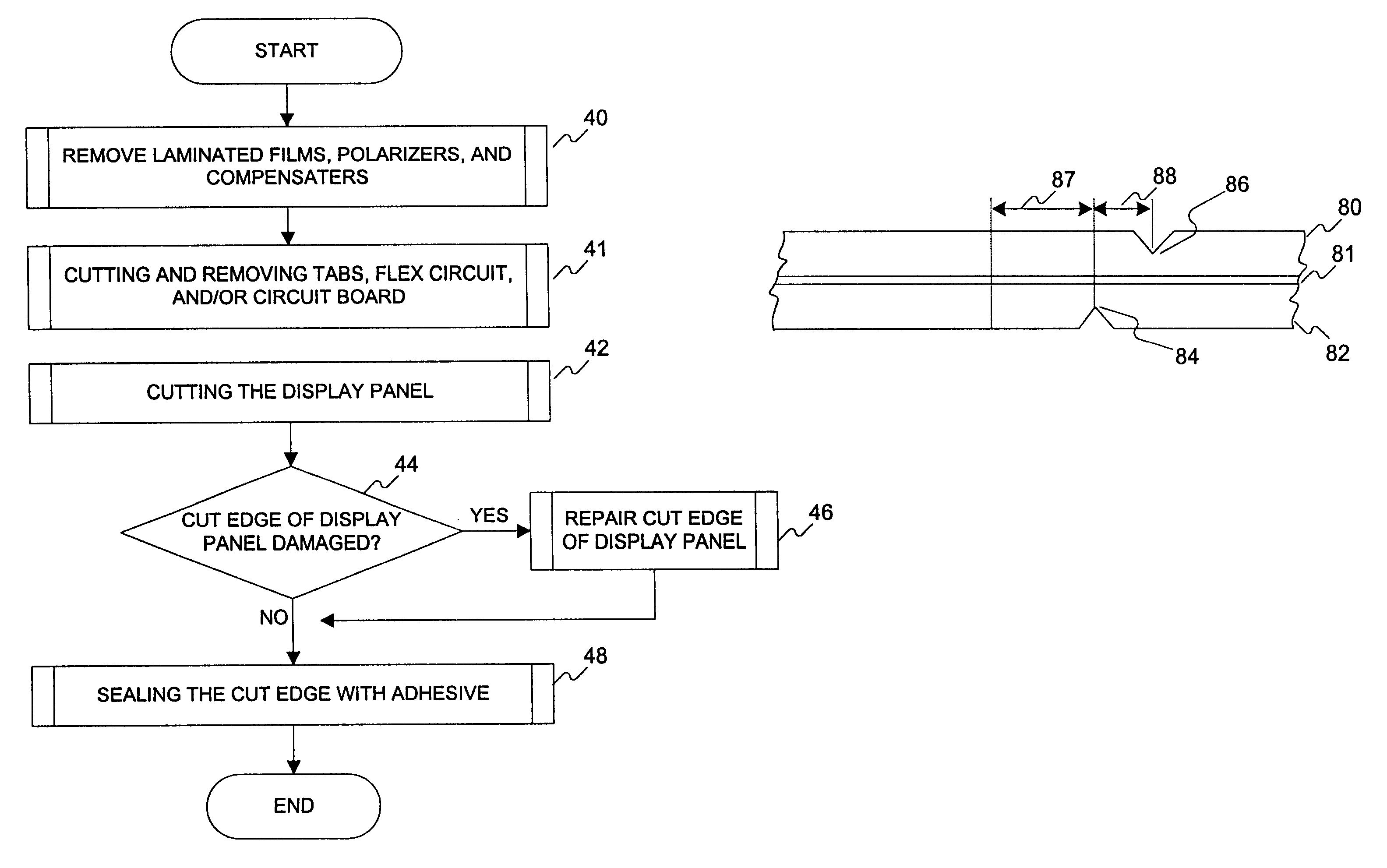

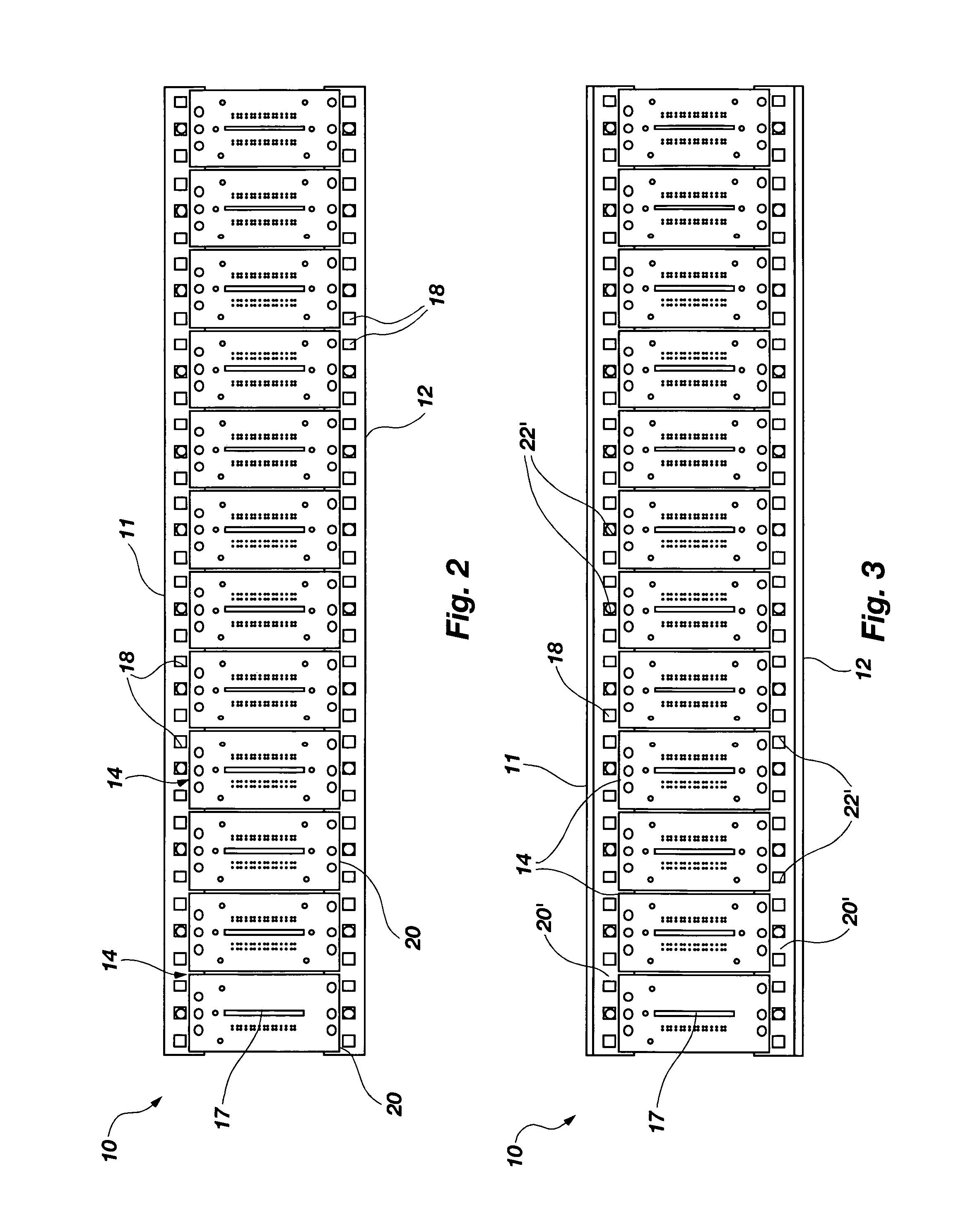

A method of resizing a liquid crystal display (LCD) includes the steps of first determining a desired size for the LCD, thereby identifying an undesired portion of the LCD. Any tape automated bonding strips (TABs) corresponding to the undesired portions of the LCD are then removed. Any flex circuits, or portion thereof, corresponding to the undesired portion of the LCD are cut and removed. Any circuit boards, or portions thereof, corresponding to the undesired portion of the LCD are cut and removed. The display panel is cut to remove a portion of the display panel corresponding to the undesired portion of the LCD. Finally, the cut edge of the display panel is sealed.

Owner:HONEYWELL INT INC

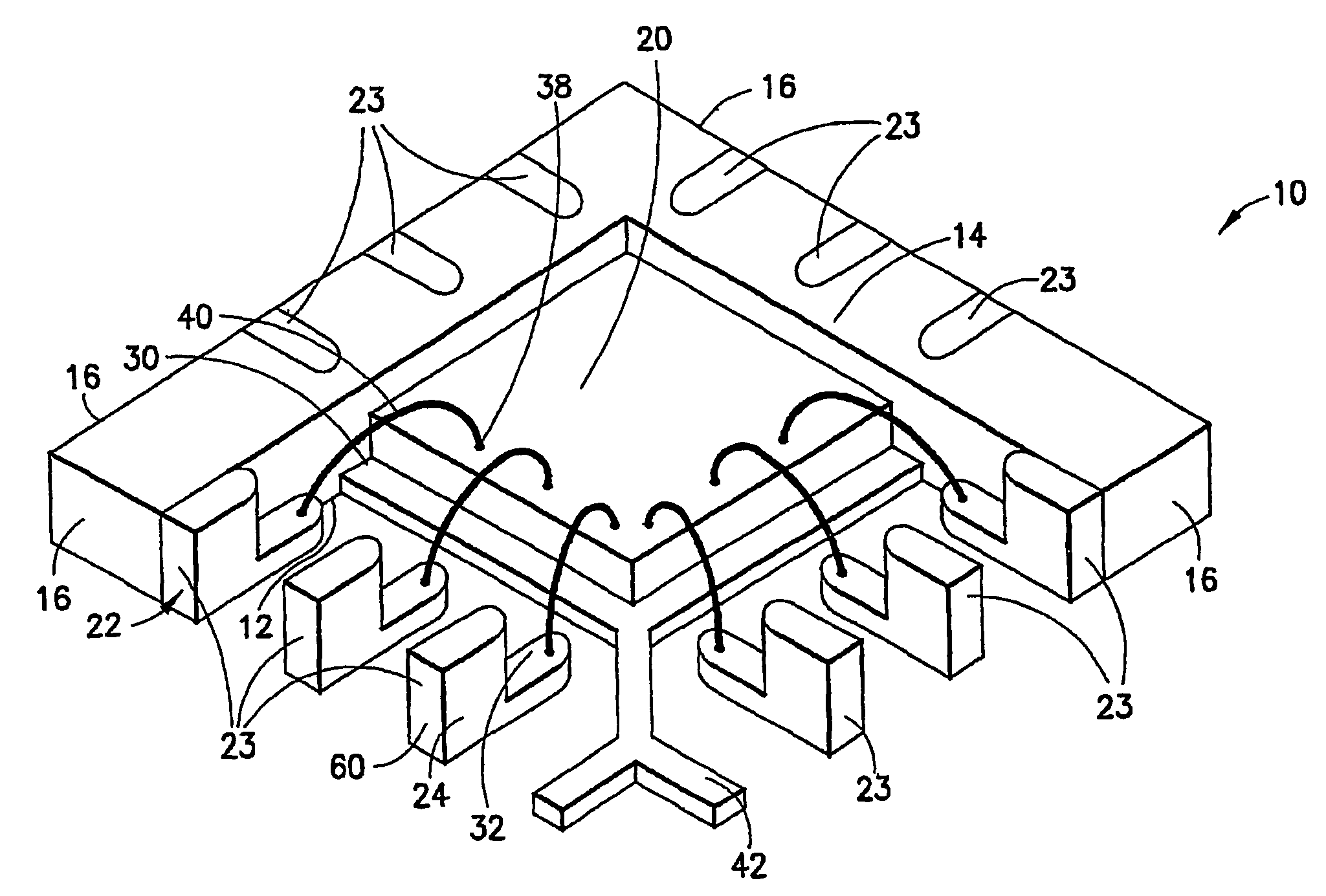

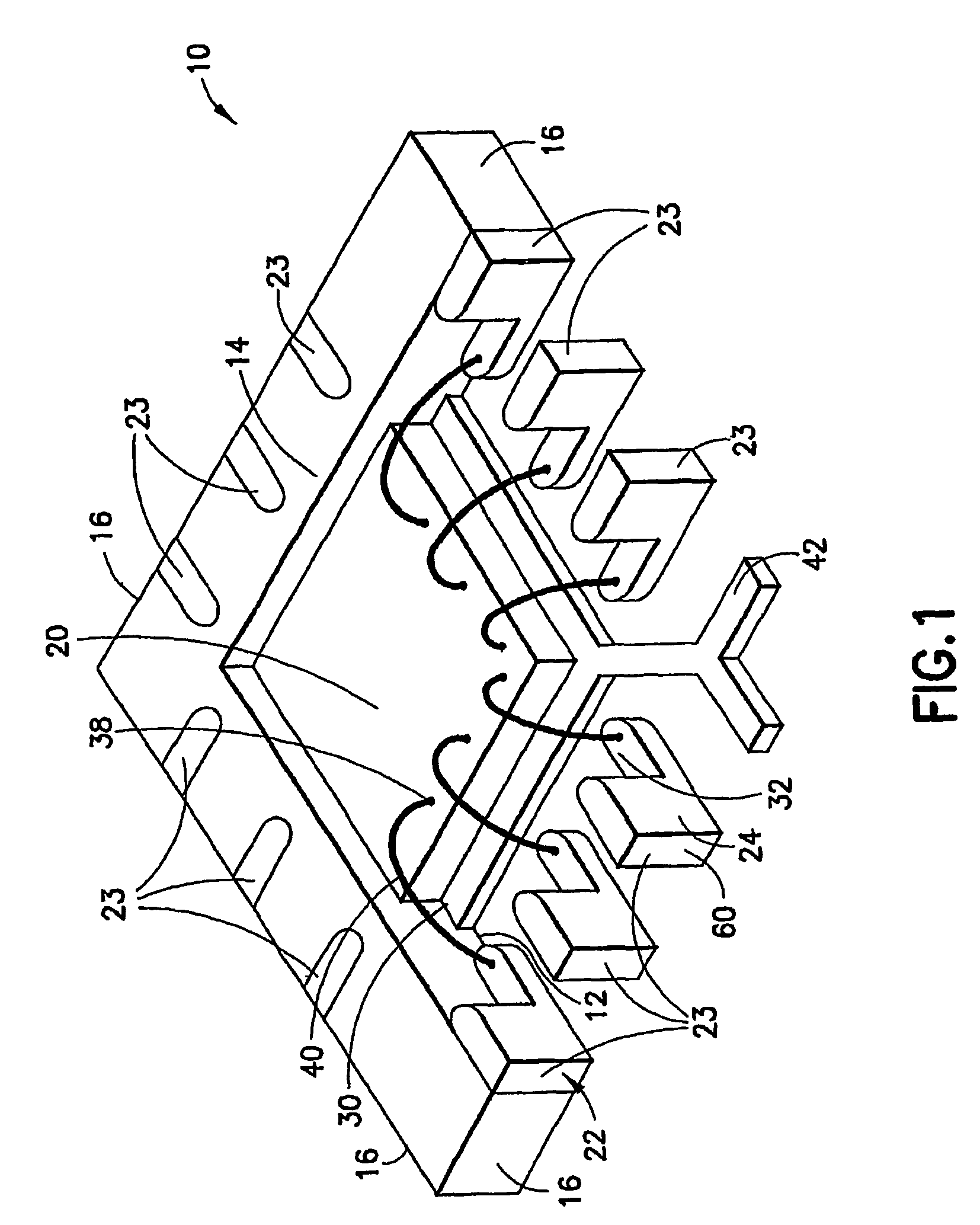

Reversible leadless package and methods of making and using same

A semiconductor device package includes an electrically conductive lead frame having a plurality of posts disposed at a perimeter of the package. Each of the posts has a first contact surface disposed at the first package face and a second contact surface disposed at the second package face. The lead frame also includes a plurality of post extensions disposed at the second package face. Each of the post extensions includes a bond site formed on a surface of the post extension opposite the second package face. At least one I / O pad on the semiconductor device is electrically connected to the post extension at the bond site using wirebonding, tape automated bonding, or flip-chip methods. The package can be assembled using a lead frame having pre-formed leads, with or without taping, or using partially etched lead frames. A stack of the semiconductor device packages may be formed.

Owner:UNISEM M BERHAD

Reversible leadless package and methods of making and using same

ActiveUS20070111374A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialLead bonding

A semiconductor device package includes an electrically conductive lead frame having a plurality of posts disposed at a perimeter of the package. Each of the posts has a first contact surface disposed at the first package face and a second contact surface disposed at the second package face. The lead frame also includes a plurality of post extensions disposed at the second package face. Each of the post extensions includes a bond site formed on a surface of the post extension opposite the second package face. At least one I / O pads on the semiconductor device is electrically connected to the post extension at the bond site using wirebonding, tape automated bonding, or flip-chip methods. The package can be assembled use a lead frame having pre-formed leads, with or without taping, or it can employ the use of partially etched lead frames. A stack of the semiconductor device packages may be formed.

Owner:UNISEM M BERHAD

MEMS device integrated chip package, and method of making same

The present invention relates to a chip package that includes a semiconductor device and at least one micro electromechanical structure (MEMS) such that the semiconductor device and the MEMS form an integrated package. One embodiment of the present invention includes a semiconductor device, a first MEMS device disposed in a conveyance such as a film, and a second MEMS device disposed upon the semiconductor device through a via in the conveyance.The present invention also relates to a process of forming a chip package that includes providing a conveyance such as a tape automated bonding (TAB) structure, that may hold at least one MEMS device. The method is further carried out by disposing the conveyance over the active surface of the device in a manner that causes the at least one MEMS to communicate electrically to the active surface. Where appropriate, a sealing structure such as a solder ring may be used to protect the MEMS.

Owner:INTEL CORP

Interconnections with electrically conductive adhesives: structures, materials, method and their applications

InactiveUS20020056925A1Stable structureImprove fatigue lifePrinted circuit assemblingSemiconductor/solid-state device detailsInterfacial reactionElectrically conductive adhesive

A new interconnection scheme is disclosed for a tape automated bonding (TAB) package, a flip chip package and an active matrix liquid crystal display (AMLCD) panel, where an electrically conducting adhesive is used to form an electrical interconnection between an active electronic device and its components. The electrically conducting adhesive can be a mixture comprising a polymer resin, a no-clean solder flux, a plurality of electrically conducting particles with an electrically conducting fusible coating which provides a metallurgical bond between the conducting particles as well as to the substrates. The advantages of using the electrically conducting adhesives include reduction in bonding pressure and / or bonding temperature, control of interfacial reactions, promotion of stable metallurgical bonds, enhanced reliability of the joints, and others.

Owner:AU OPTRONICS CORP

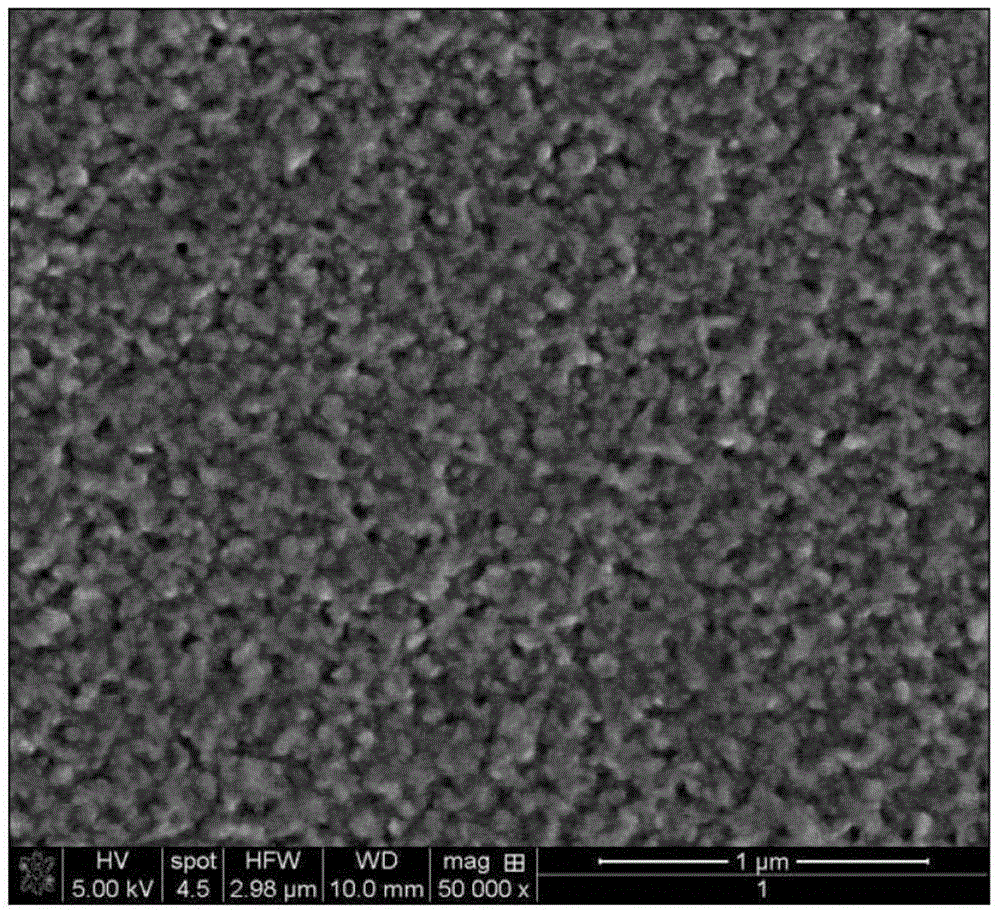

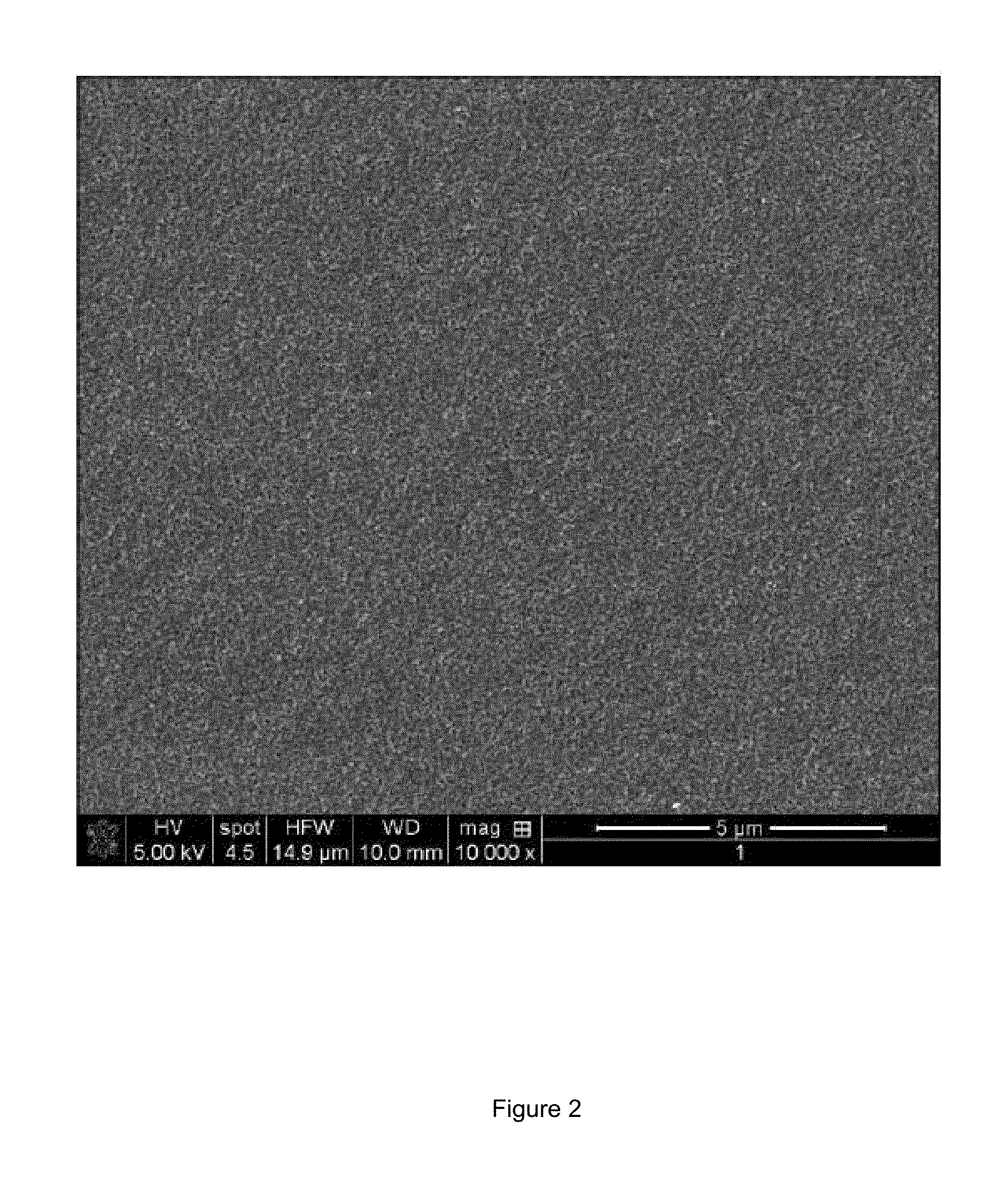

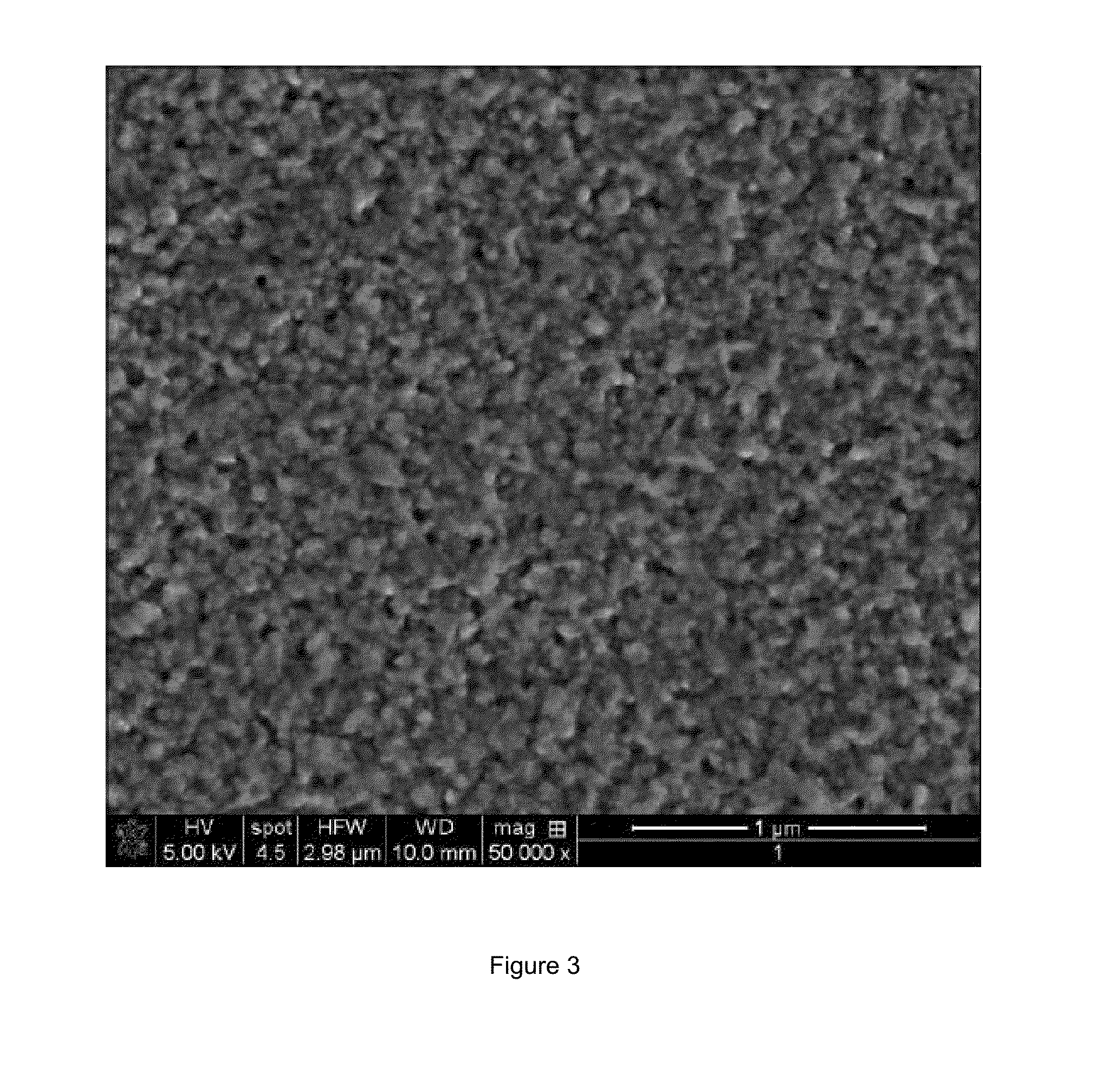

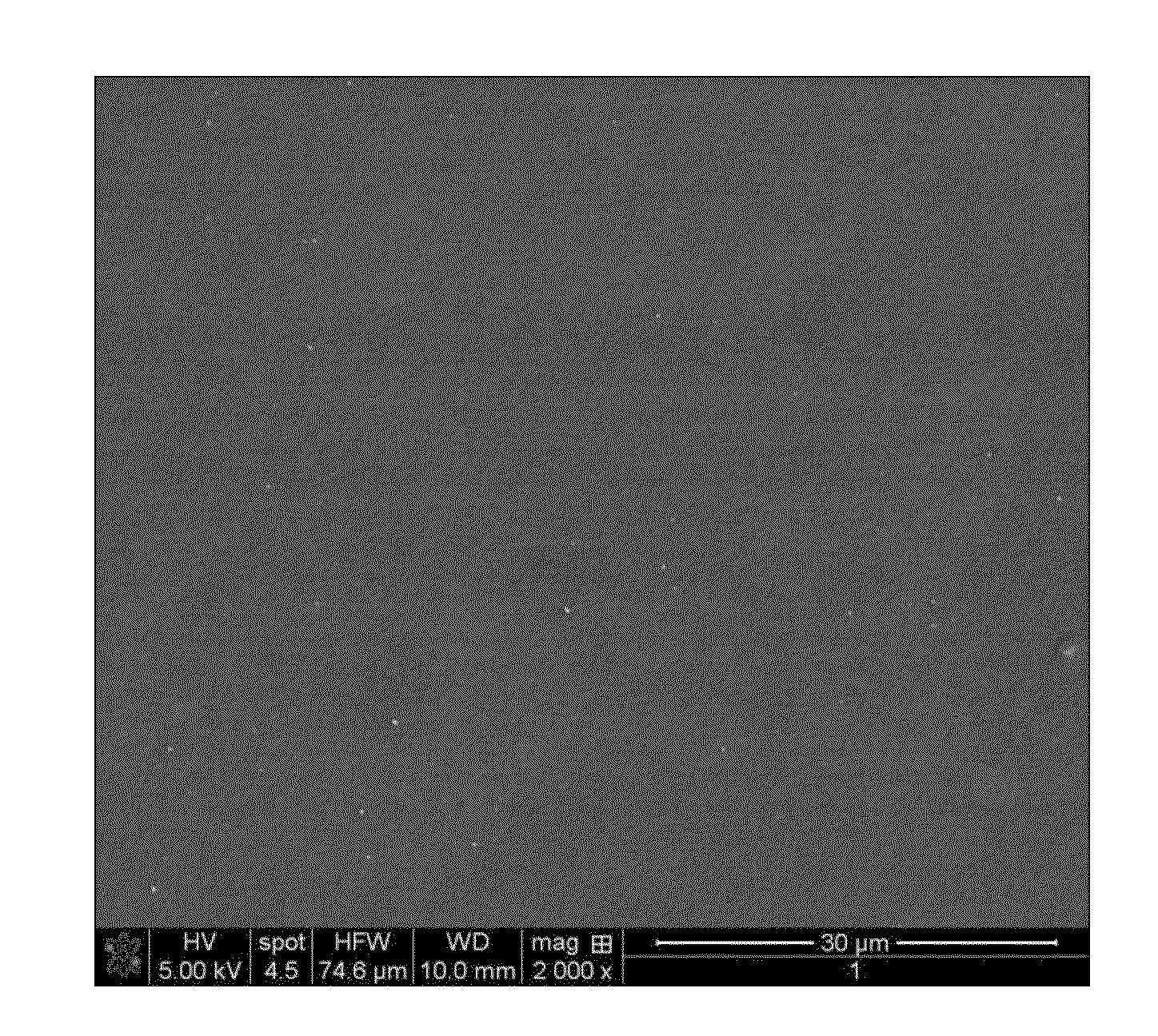

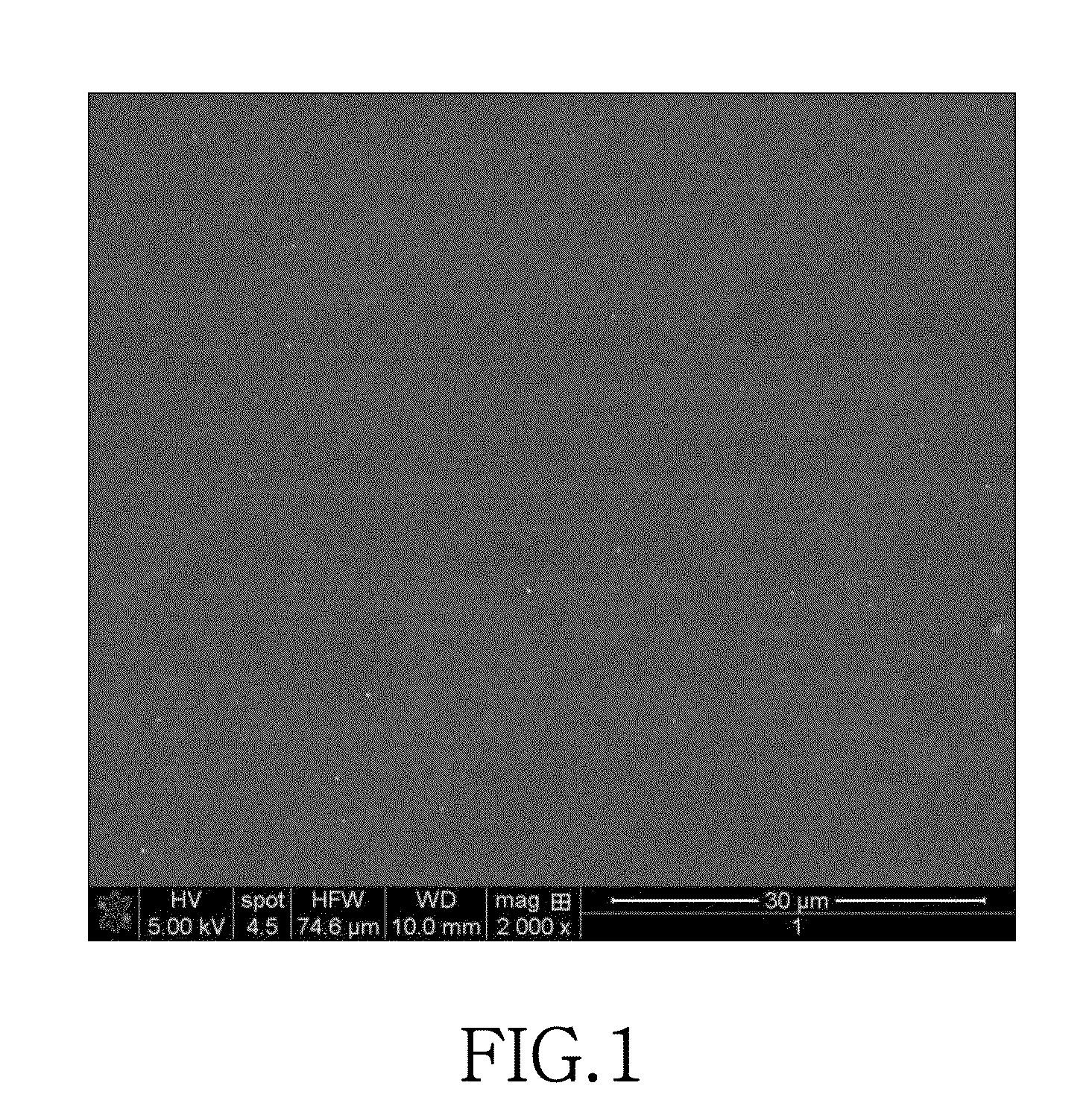

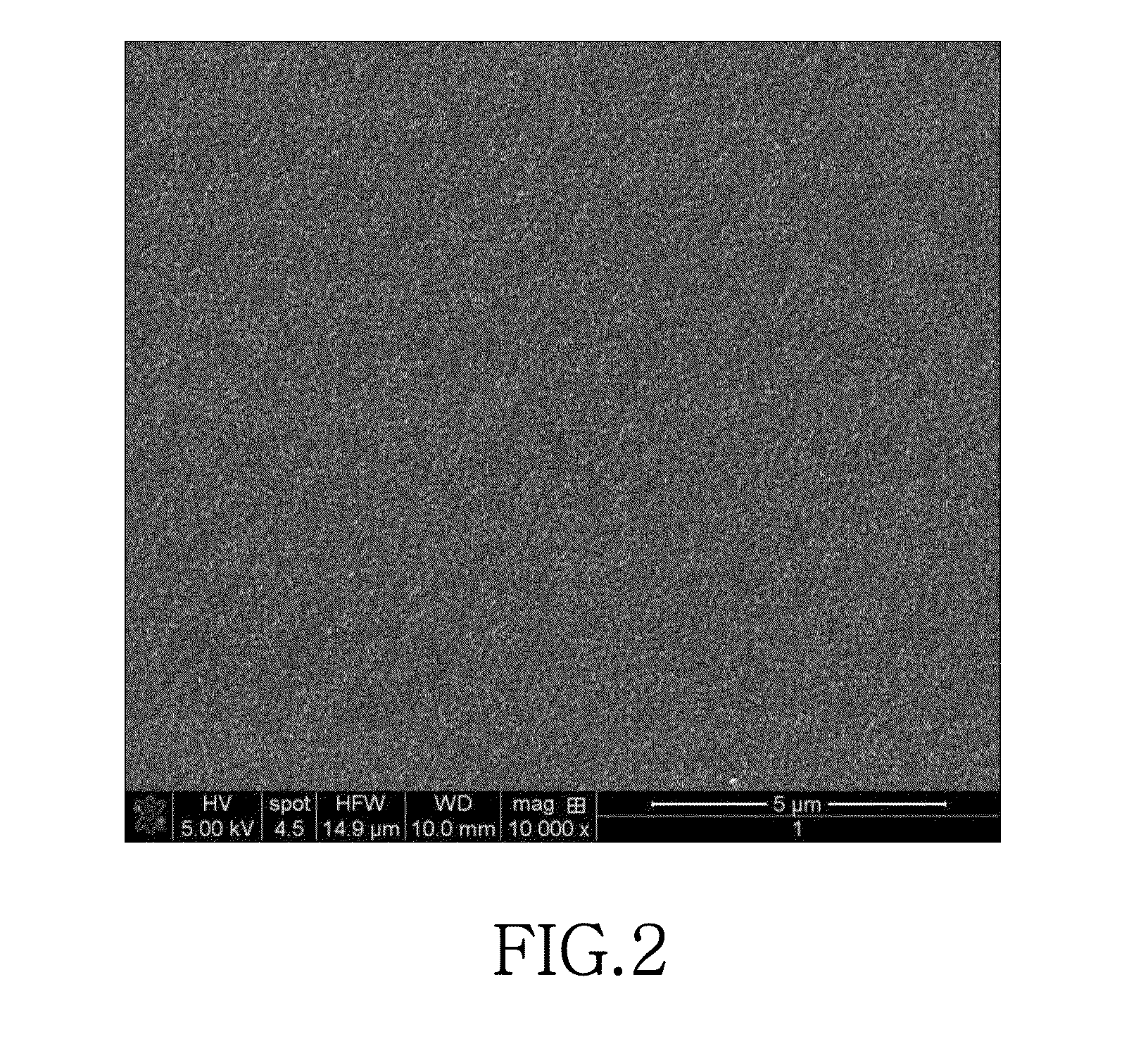

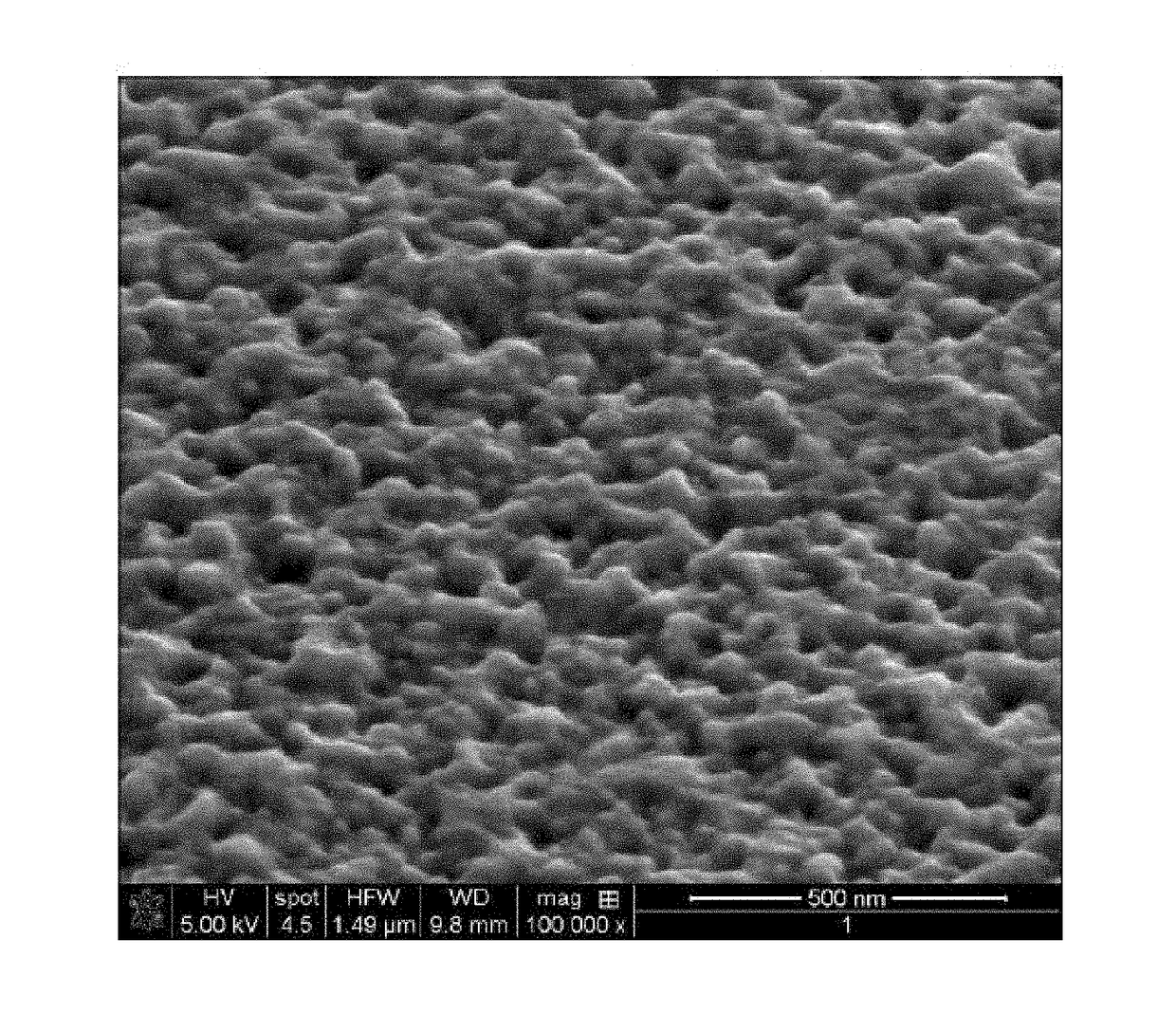

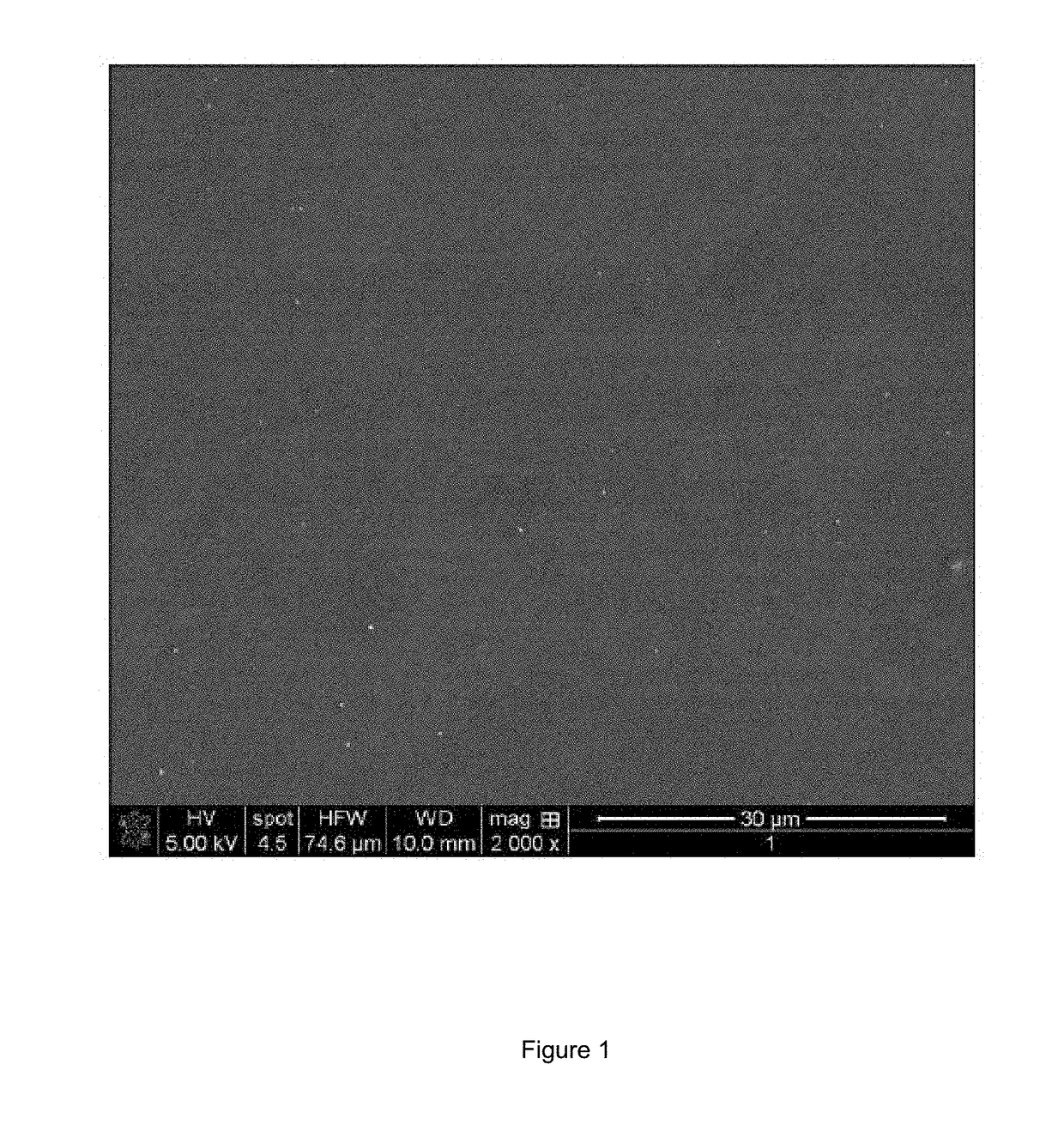

Electrolytic foil, electrical component containing electrolyte foil and battery

The invention relates to an electrolytic foil, an electrical component containing the electrolytic foil and a battery. The invention provides the electrolytic foil, wherein the average diameter of pores of an area among prominent surface elements of a separating-out surface is 1 nanometer to 100 nanometers. The electrolytic foil shows high elongation rate while maintaining low roughness and high strength, thus being applicable to semiconductor packaging substrates for tape automated bonding used in current collector and tape carrier package of large and medium lithium ion secondary batteries.

Owner:ILJIN MATERIALS CO LTD

Electrolytic Copper Foil, Electric Component and Battery Including the Same

Disclosed herein is an electrolytic copper foil in which an average diameter of a pore which is a region between surface elements protruding from a matte side is 1 mm to 100 nm. The electrolytic copper foil has high elongation while maintaining low roughness and high strength and thus may be used in a current collector of a medium-large size lithium ion secondary battery and a semiconductor packaging substrate, and the like, for tape automated bonding (TAB) which is used in a tape carrier package (TCP).

Owner:ILJIN MATERIALS CO LTD

Polyimide film, method of manufacture, and metal interconnect board with polyimide film substrate

InactiveUS6908685B2Synthetic resin layered productsWood working apparatusMetal interconnectFlexible circuits

The invention provides a polyimide film manufactured from a polyamic acid prepared from pyromellitic dianhydride in combination with 10 to 60 mol % of phenylenediamine and 40 to 90 mol % of 3,4′-oxydianiline, based on the overall diamine. The polyimide film, when used as a metal interconnect board substrate in flexible circuits, chip scale packages (CSP), ball grid arrays (BGA) or tape-automated bonding (TAB) tape by providing metal interconnects on the surface thereof, achieves a good balance between a high elastic modulus, a low thermal expansion coefficient, alkali etchability and film formability.

Owner:DUPONT TORAY CO LTD +1

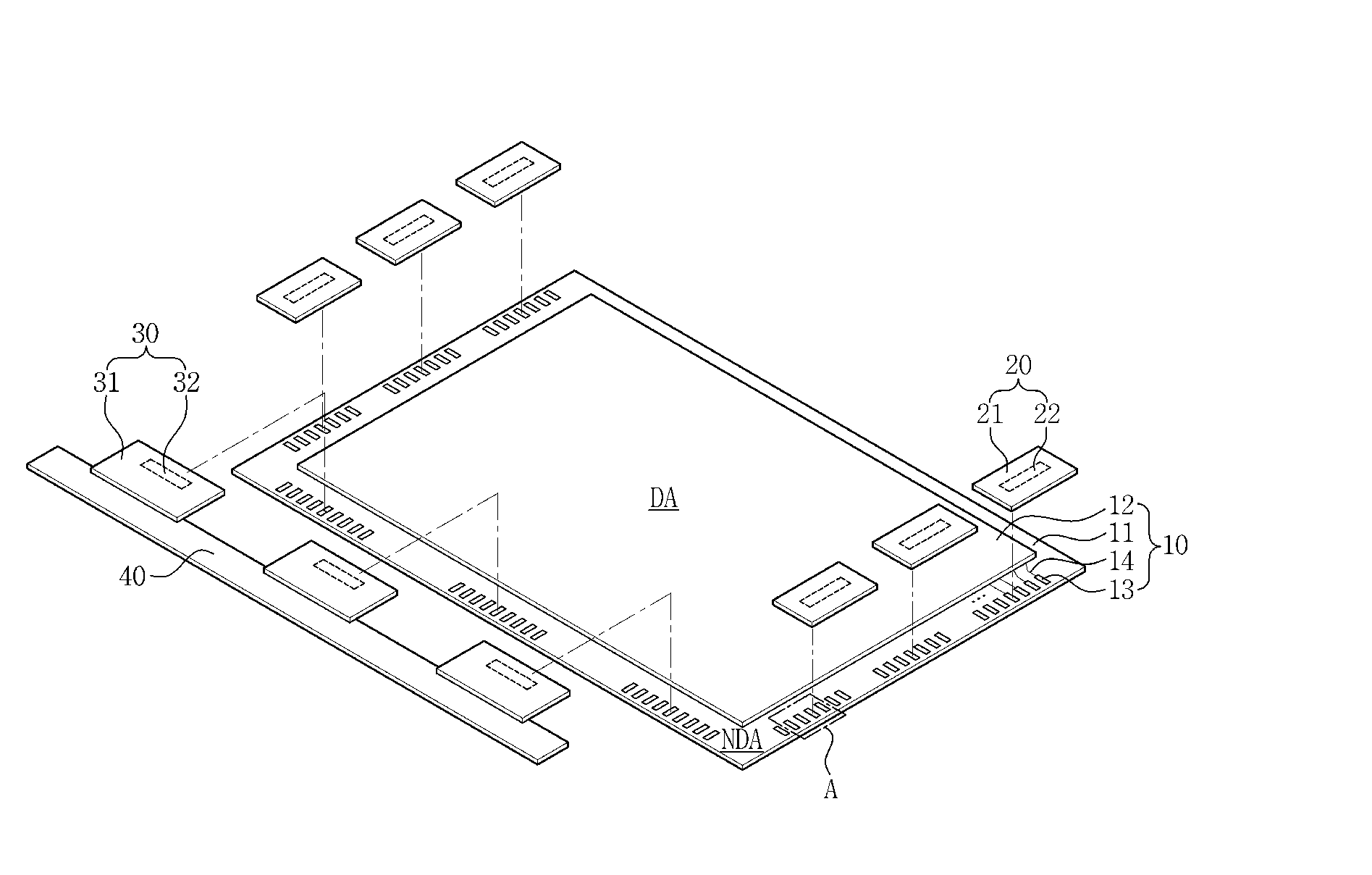

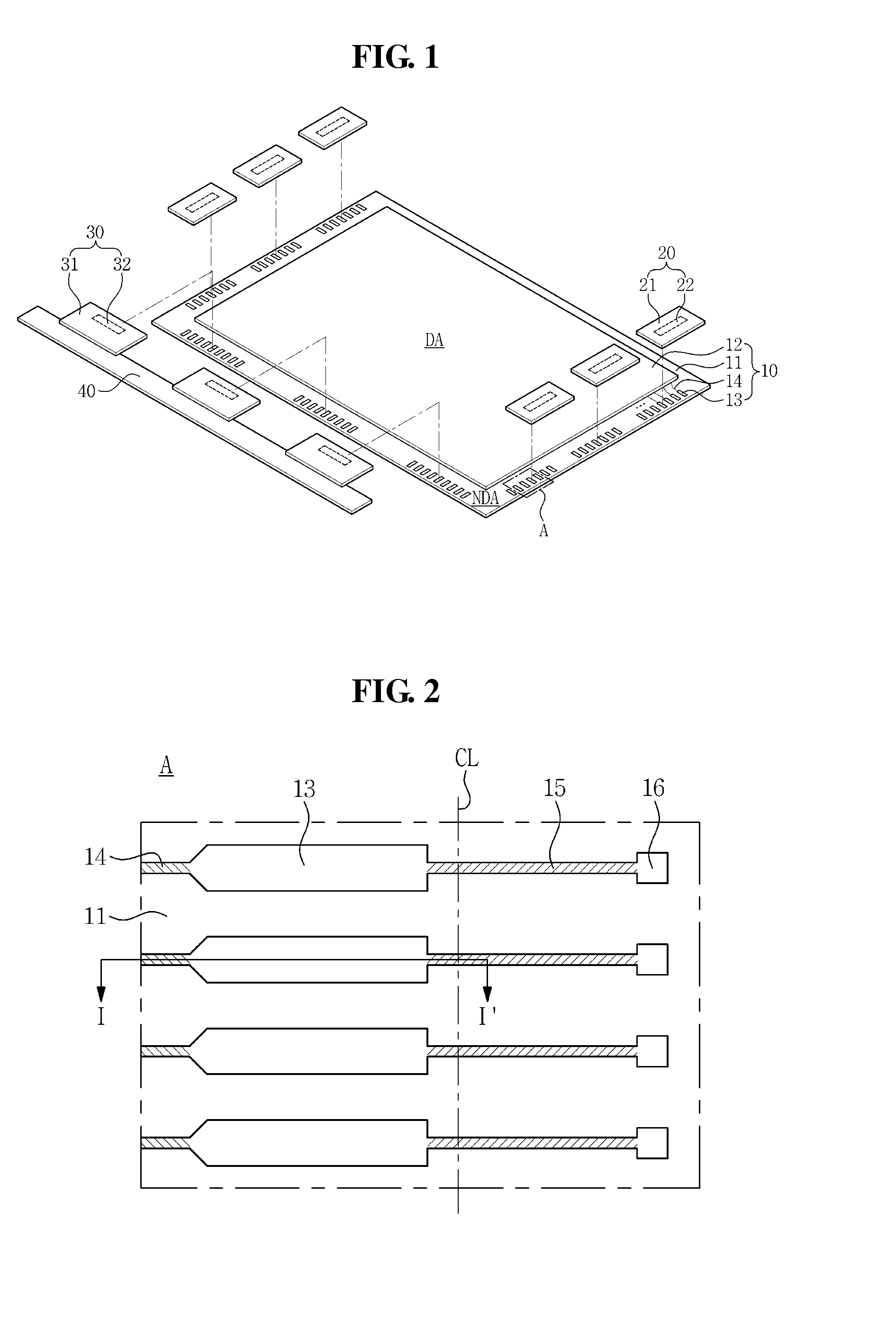

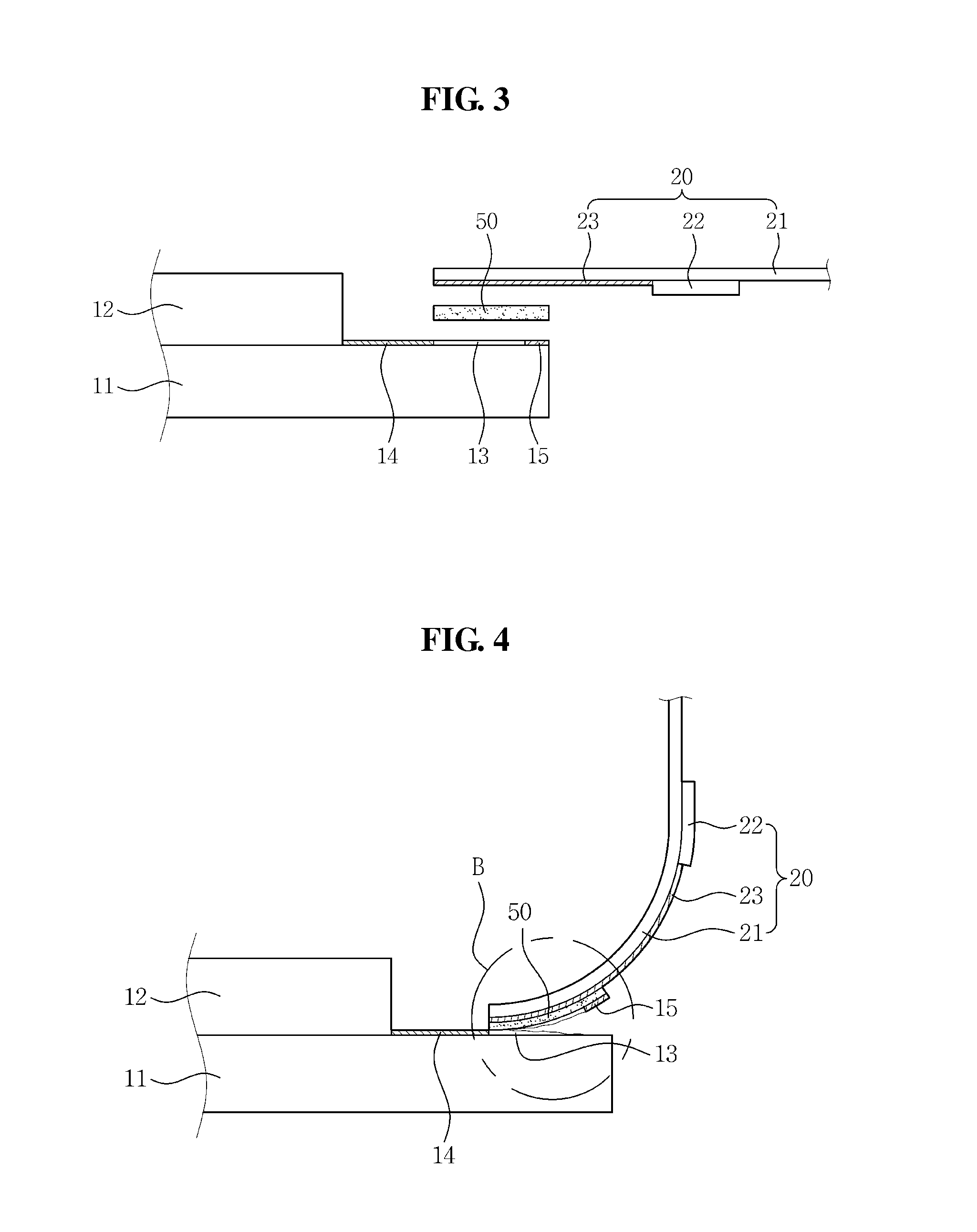

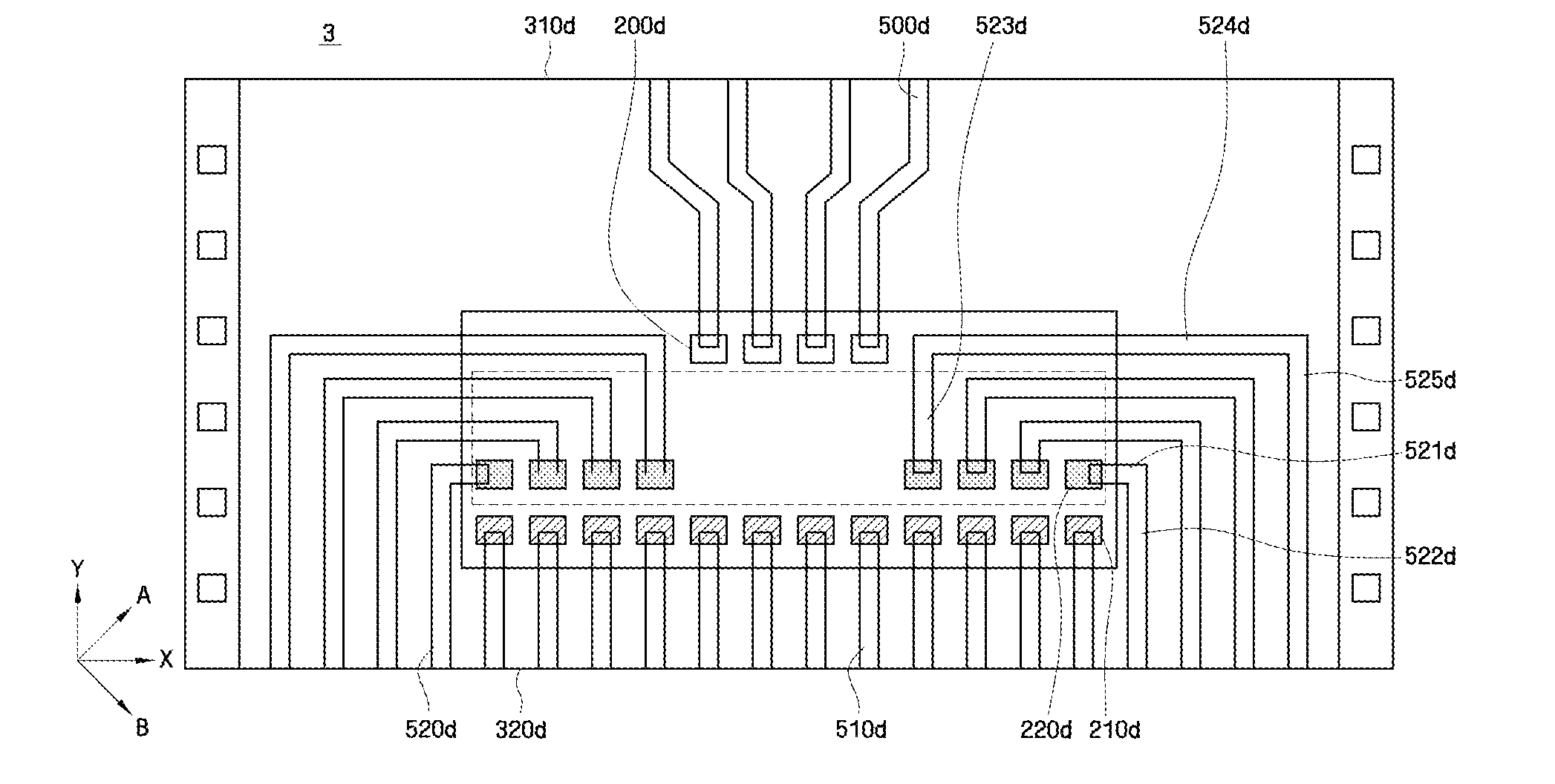

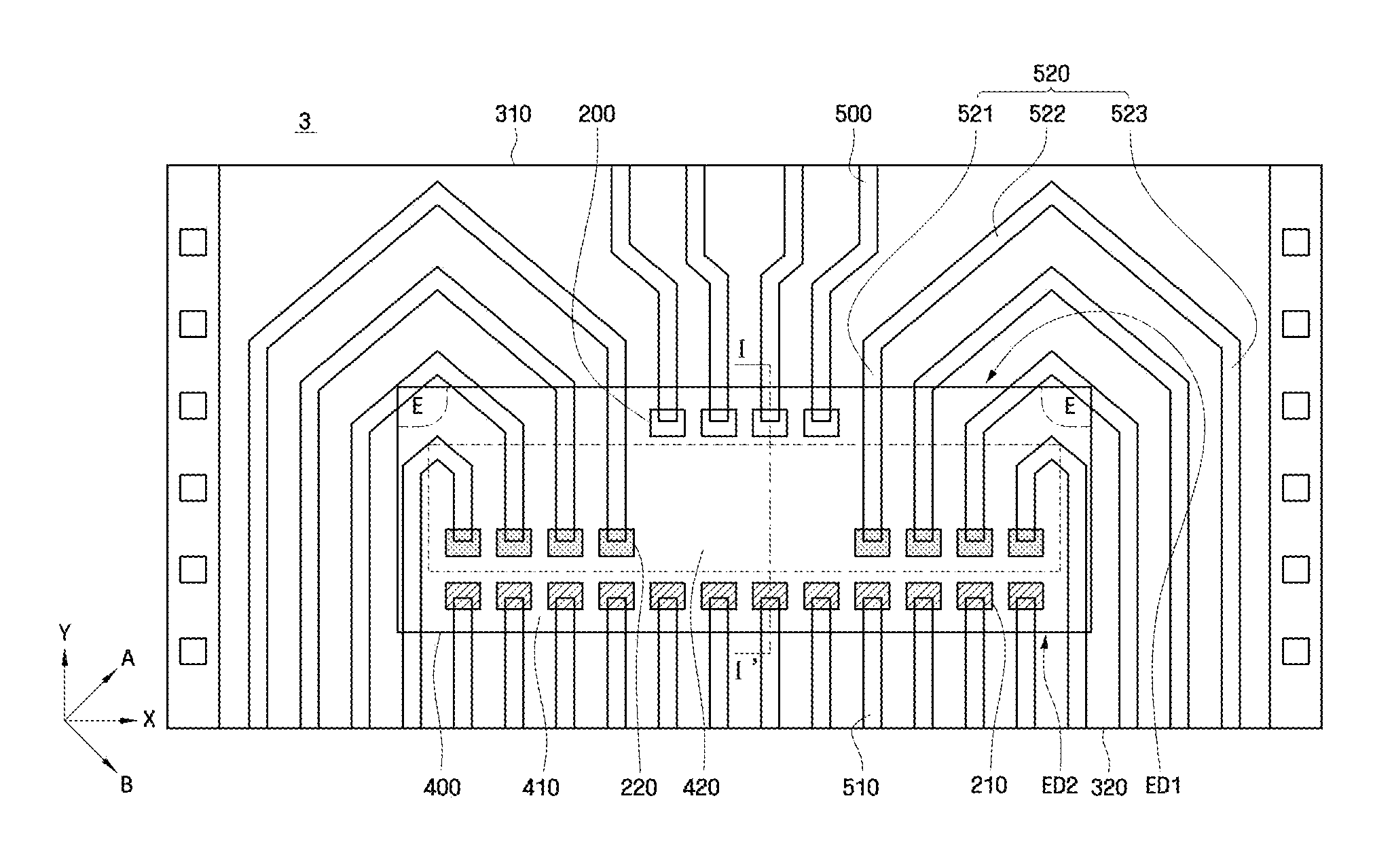

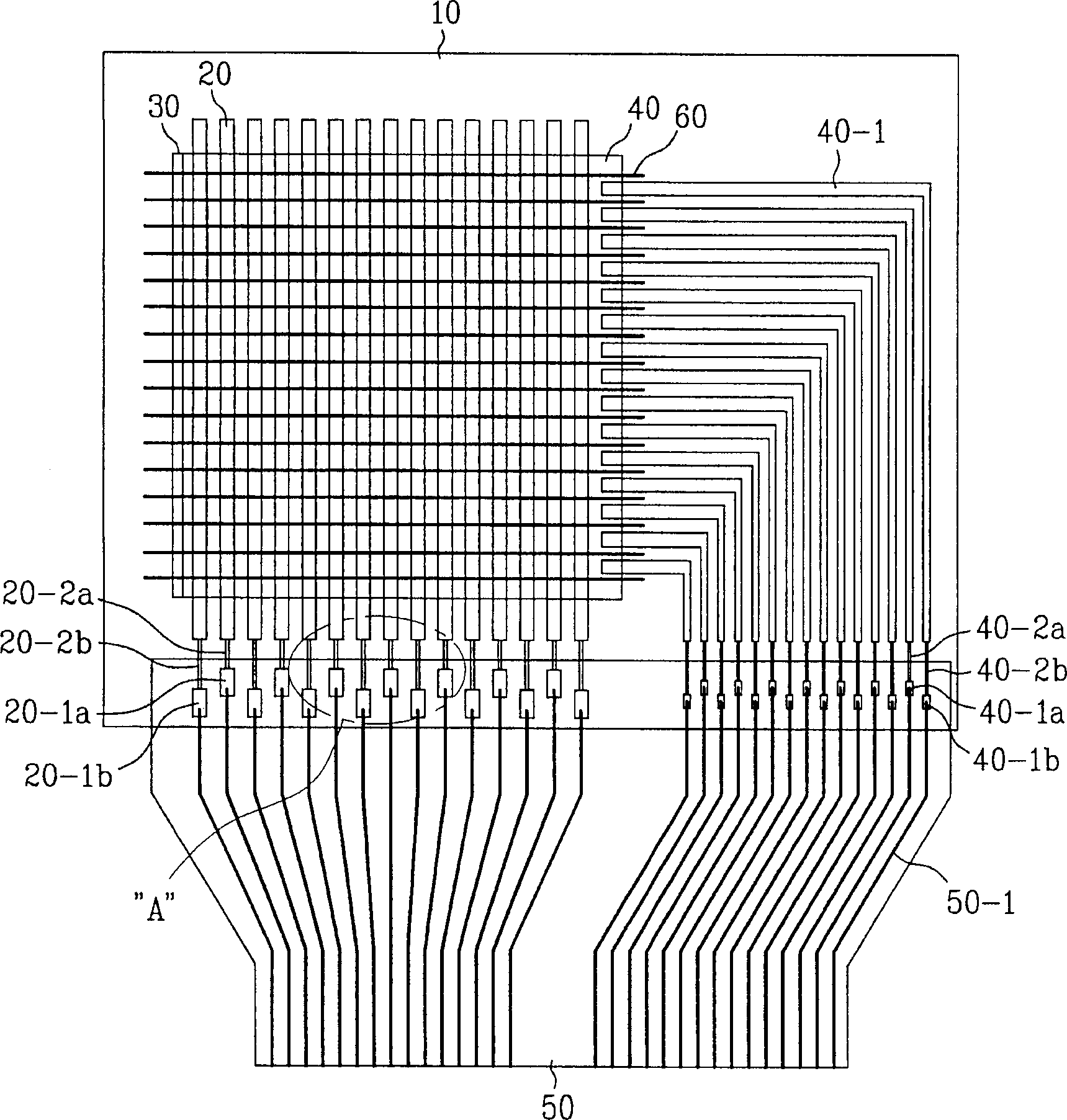

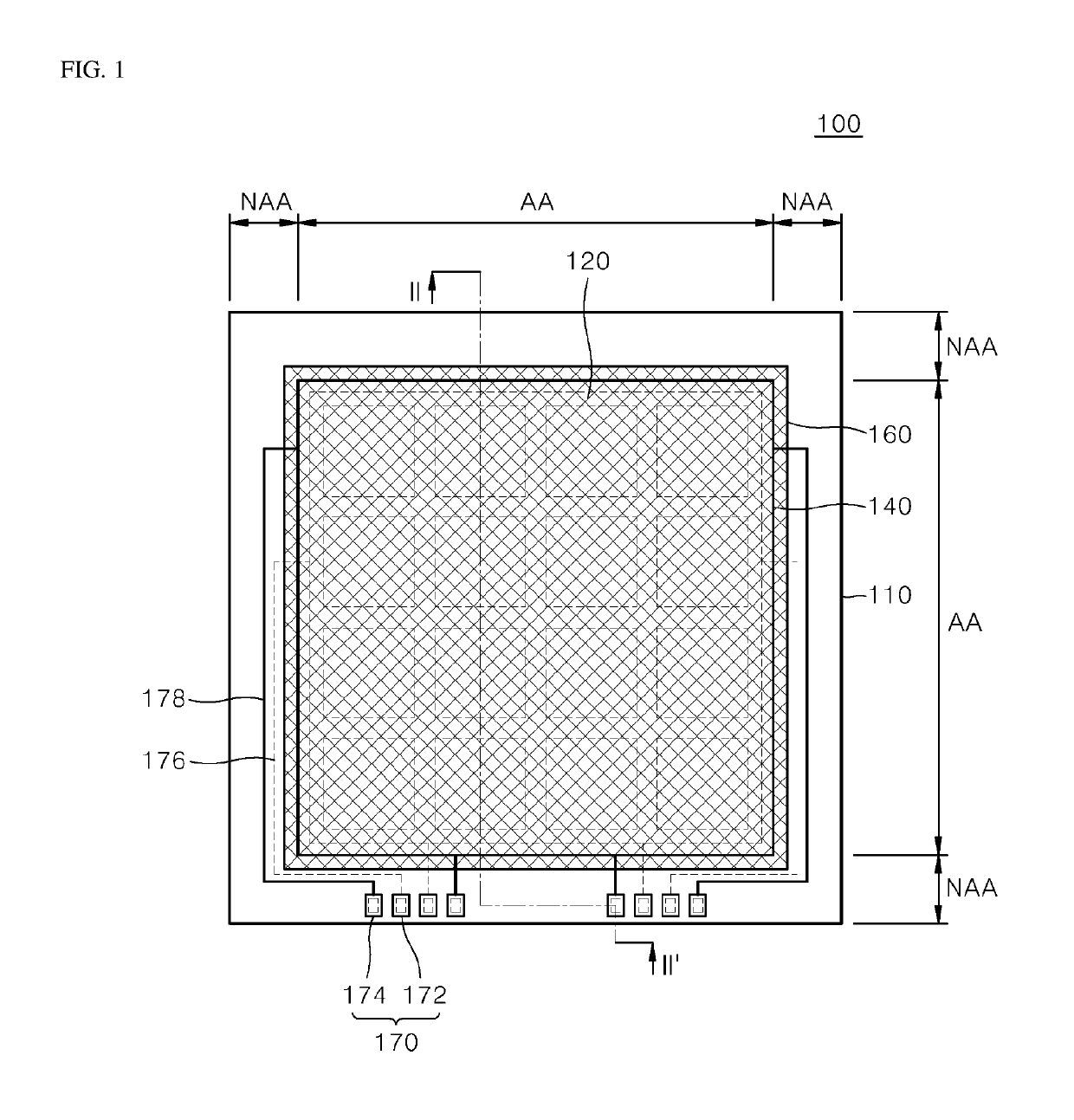

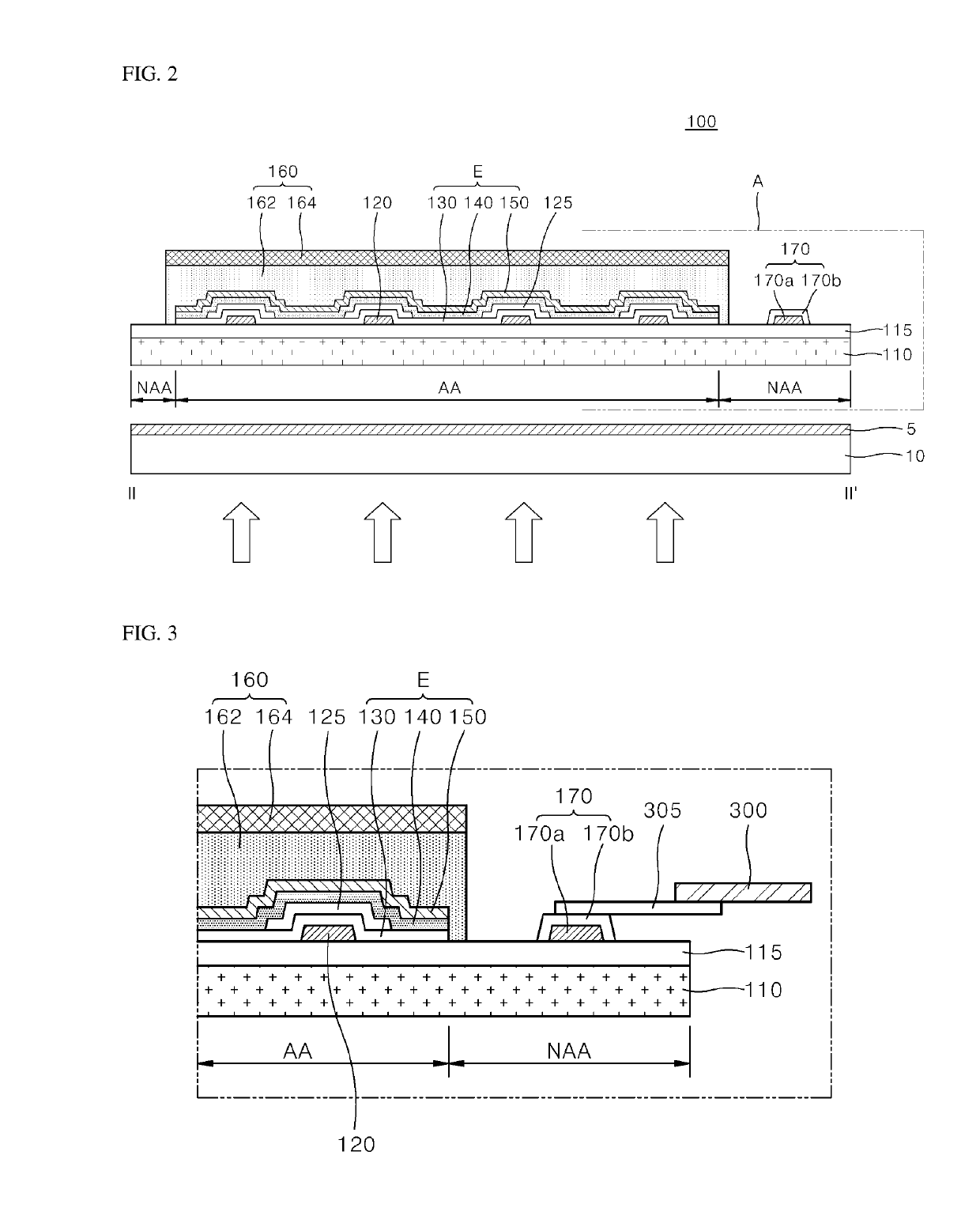

Display device

ActiveUS20160165718A1Avoid damageSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsDisplay deviceIntegrated circuit

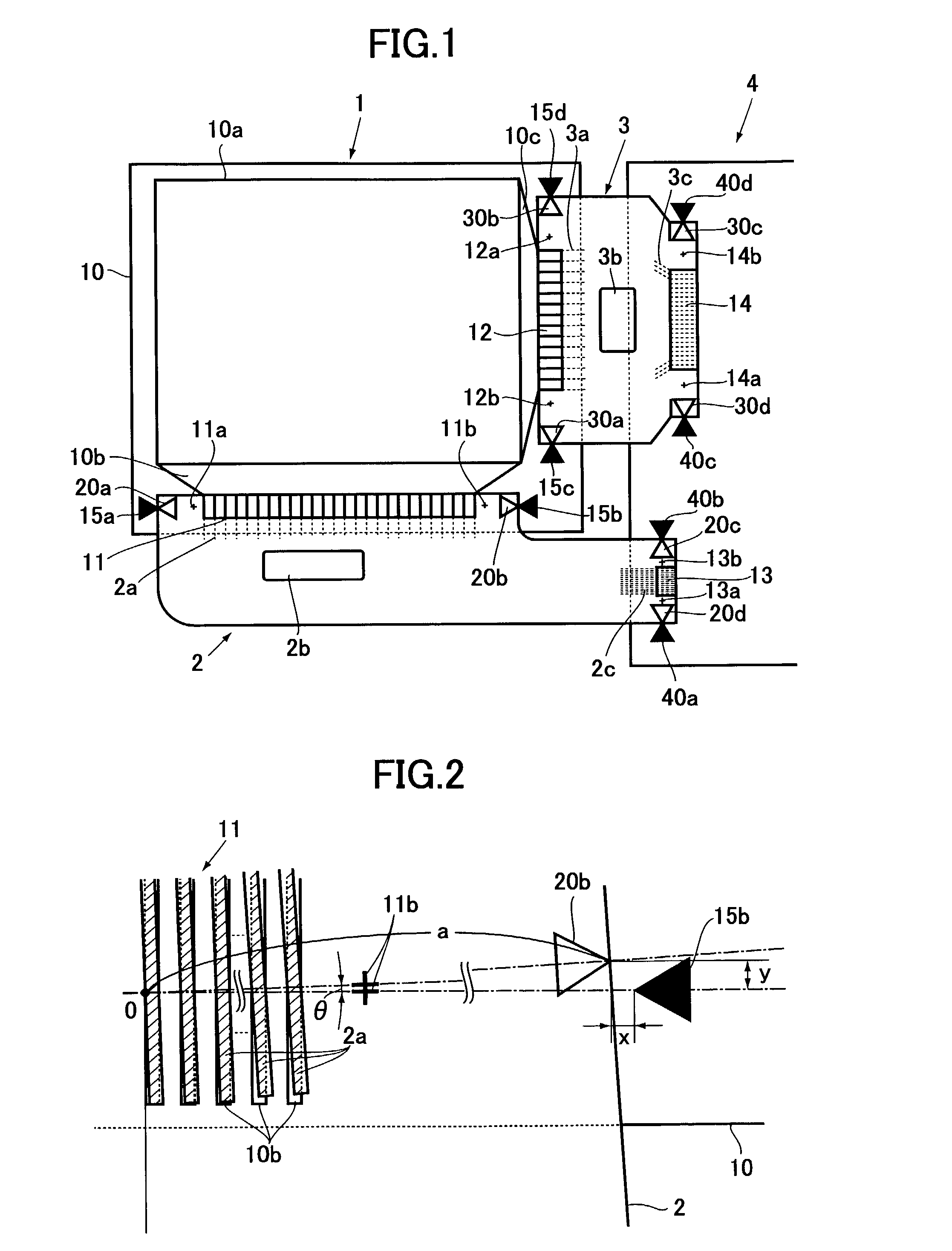

A display device includes: a substrate including a display area in which a plurality of pixels are disposed and a non-display area adjacent to the display area; a plurality of pads disposed in the non-display area; an inspection line disposed in the non-display area of the substrate and being spaced apart from the pad; a conductive member connecting the pad and the inspection line; and a tape-automated bonding integrated circuit (TAB-IC) disposed on the conductive member.

Owner:SAMSUNG DISPLAY CO LTD

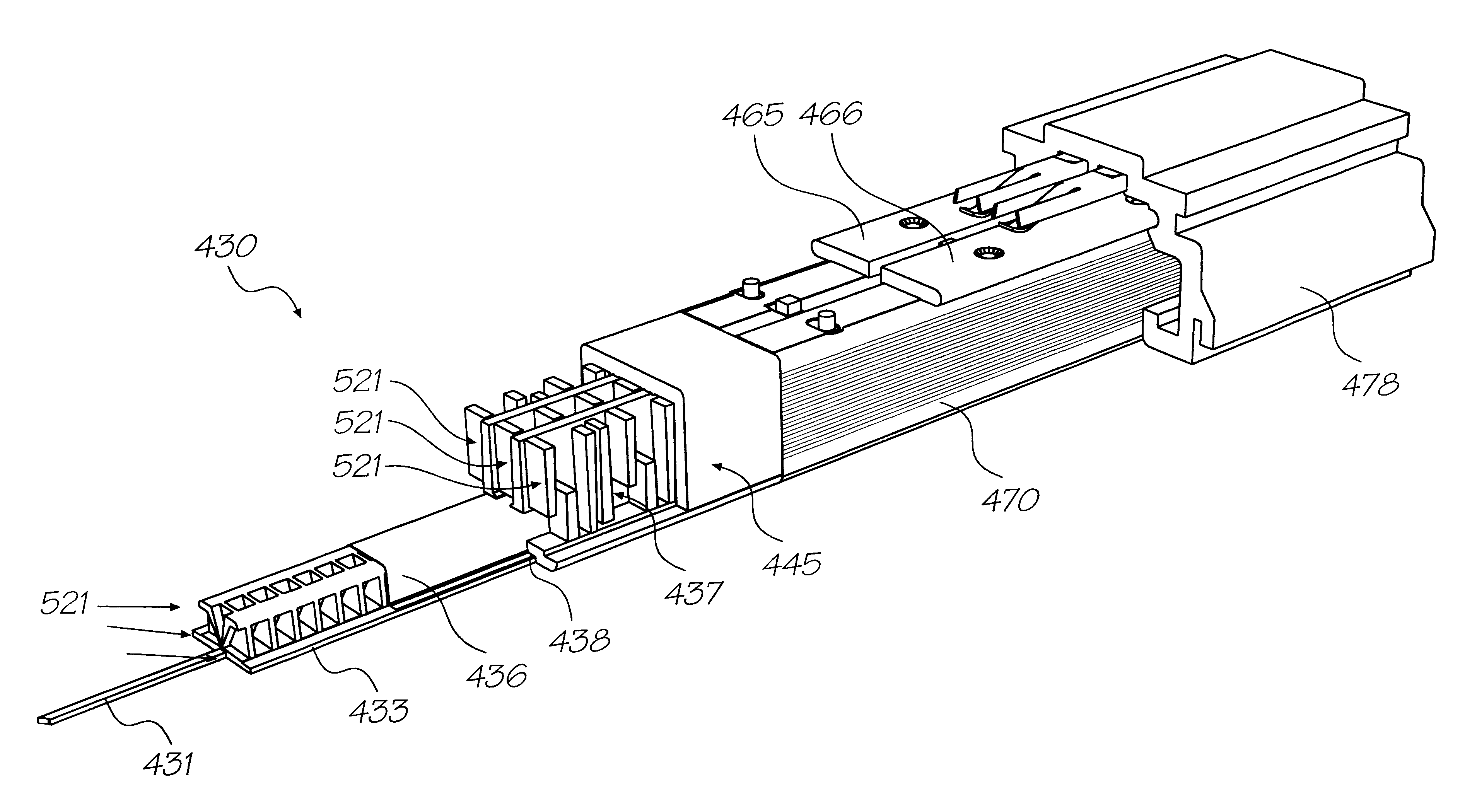

Bonding Tool

InactiveUS20080197172A1Accelerate TAB bonding processEnhanced bondingWelding/cutting auxillary devicesSolid-state devicesEngineeringManufacturing line

Means to increase the UPH of TAB bonding on an HSA manufacturing line to allow a higher UPH to keep cost down and also allow the use of one or more grounds to be add to an HSA to help control ESD without lowering the UPH or redesigning the lines through the use of a multi-head contact TAB bonding tool as described herein A bonding tool for use in tape automated bonding (TAB) is provided that is for multi-contact. The multi-contact TAB bonding tool is ESD safe so as not to damage a device being bonded.

Owner:REIBER STEVEN F

Tab package

InactiveUS6894904B2Reduce thicknessShorter circuit pathElectrically conductive connectionsSemiconductor/solid-state device detailsThermal compressionEngineering

A tape automated bonding (TAB) package and a method for fabricating the same is provided. A chip (a wire-bond chip or a flip chip) is bonded to a tape carrier through thermal compression. The chip and the tape carrier are encapsulated inside a molding compound. To enhance the TAB package thermally, a heat sink is attached to the backside of the chip.

Owner:VIA TECH INC

Electrodeposited copper foil, and electrical component and battery comprising same

ActiveUS20160260981A1High glossImprove product qualityPrinted circuit aspectsElectrode carriers/collectorsElectricityMetallurgy

Disclosed is an electrodeposited copper foil, in which a center line roughness average Ra (μm), a maximum height Rmax (μm), and a ten-point height average Rz (μm) of a matte side satisfy an Equation below, 1.5≦(Rmax−Rz) / Ra≦6.5. The electrodeposited copper foil according to the present invention maintains low roughness and high strength, and exhibits a high elongation rate, and particularly, has excellent glossiness, so that the electrodeposited copper foil may be used in a current collector of a medium and large lithigum ion secondary battery and a semiconductor packaging substrate for Tape Automated Bonding (TAB) used in a Tape Carrier Package (TCP).

Owner:ILJIN MATERIALS CO LTD

Electrolytic copper foil, electric component and battery including the same

Owner:ILJIN MATERIALS CO LTD

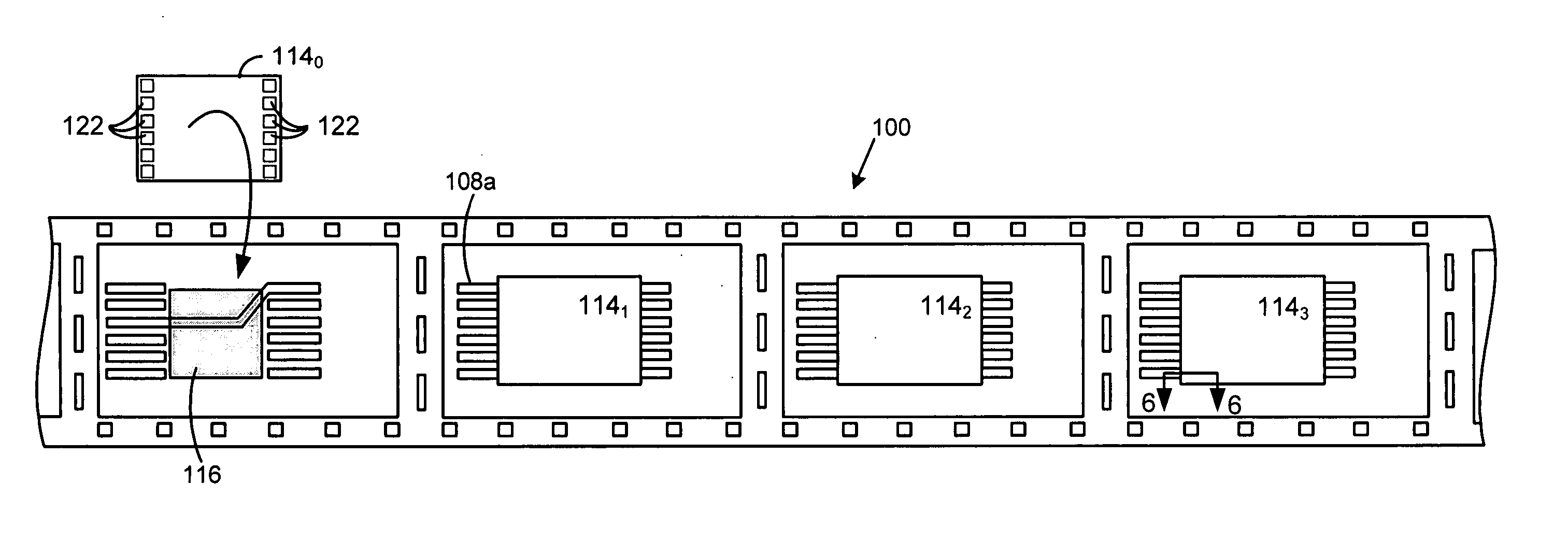

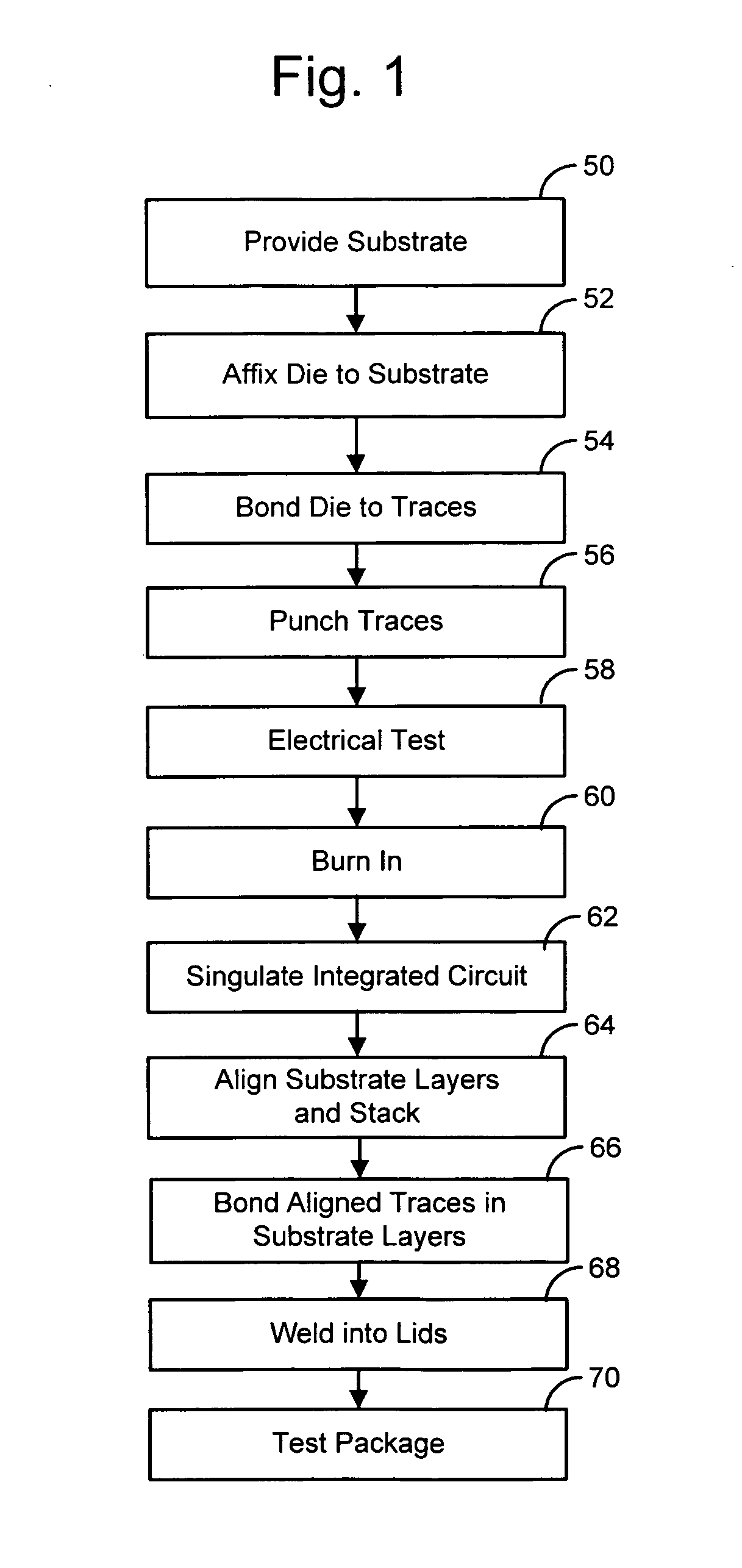

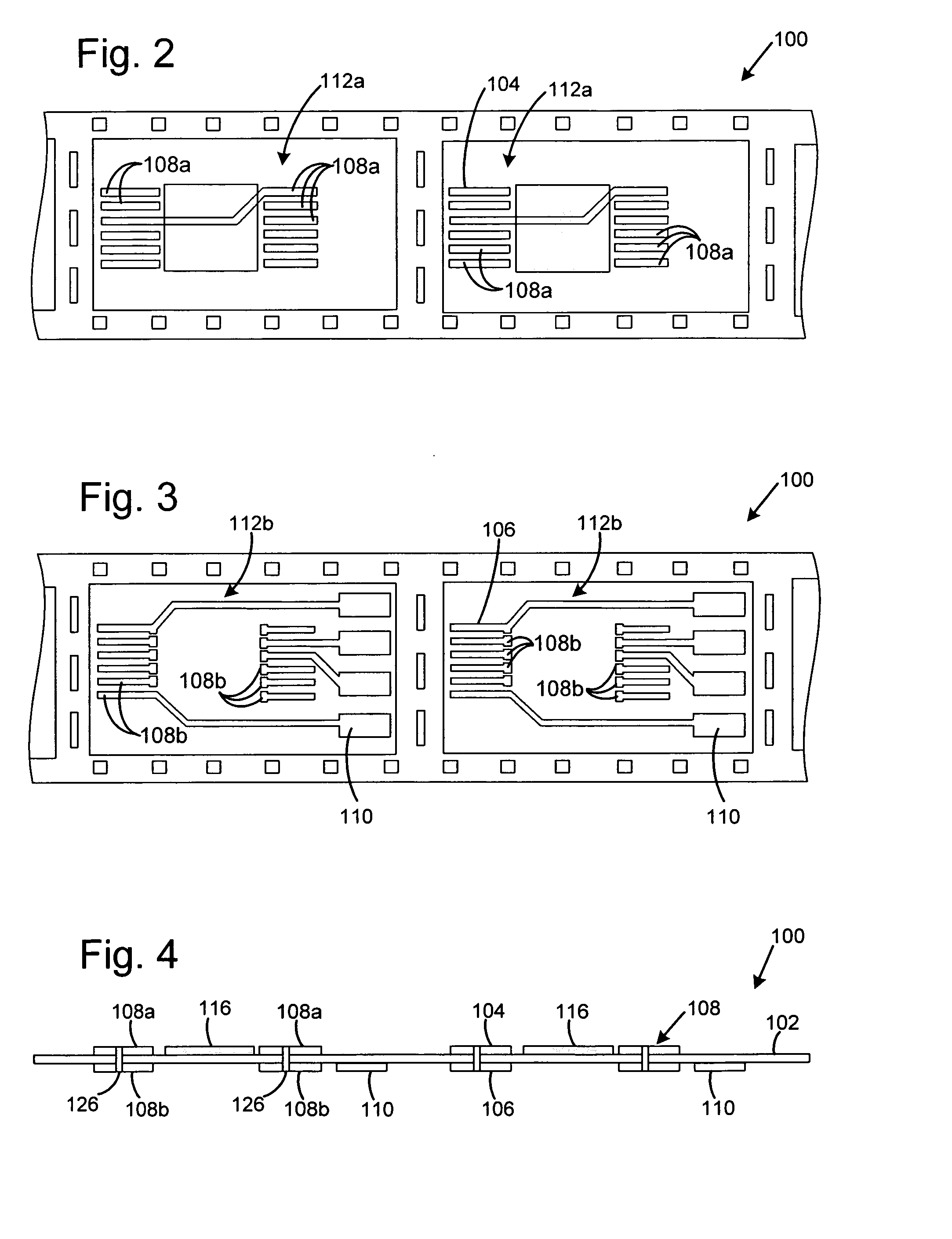

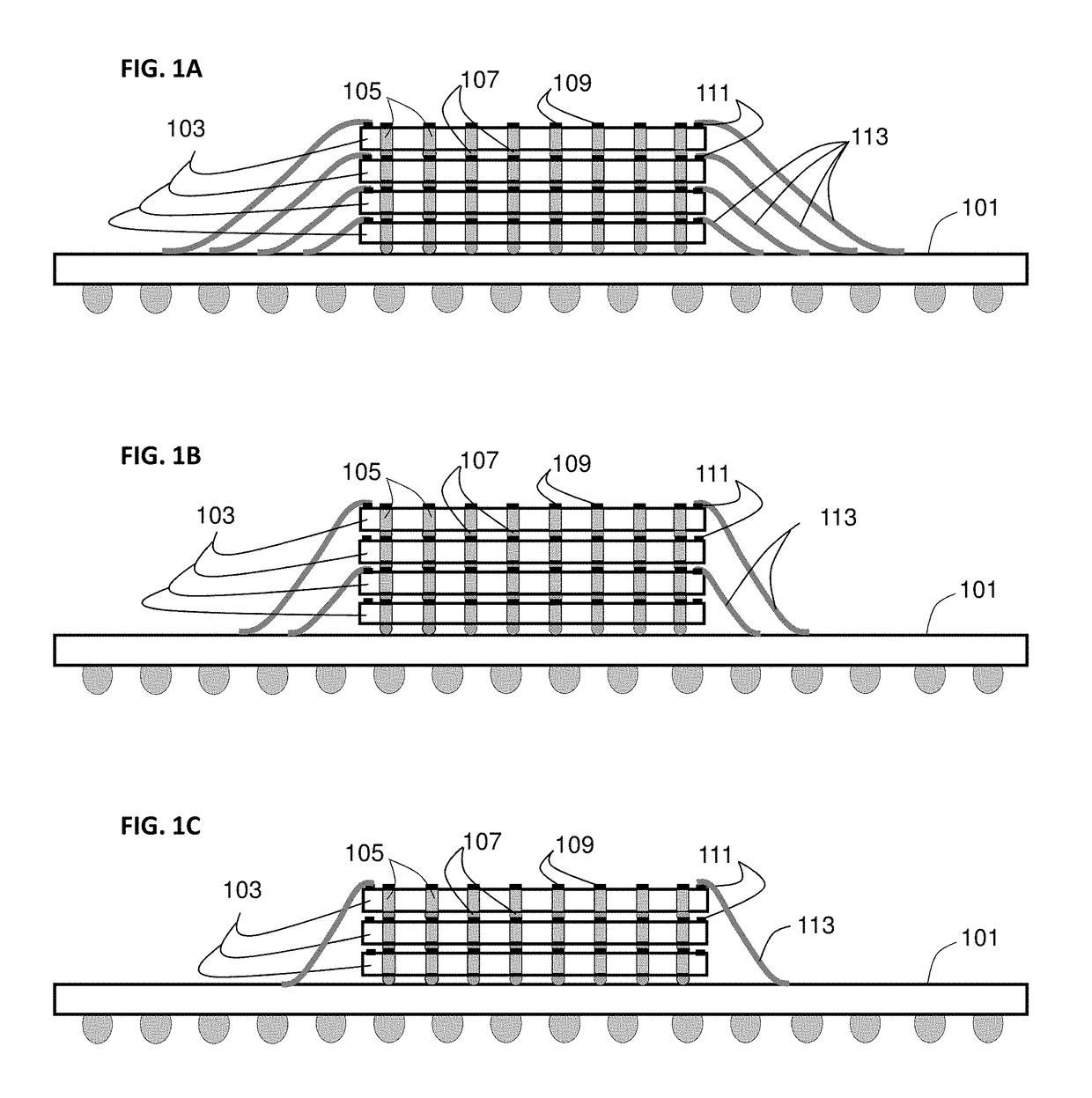

High density three dimensional semiconductor die package

ActiveUS20070096266A1Semiconductor/solid-state device detailsSolid-state devicesContact padHigh density

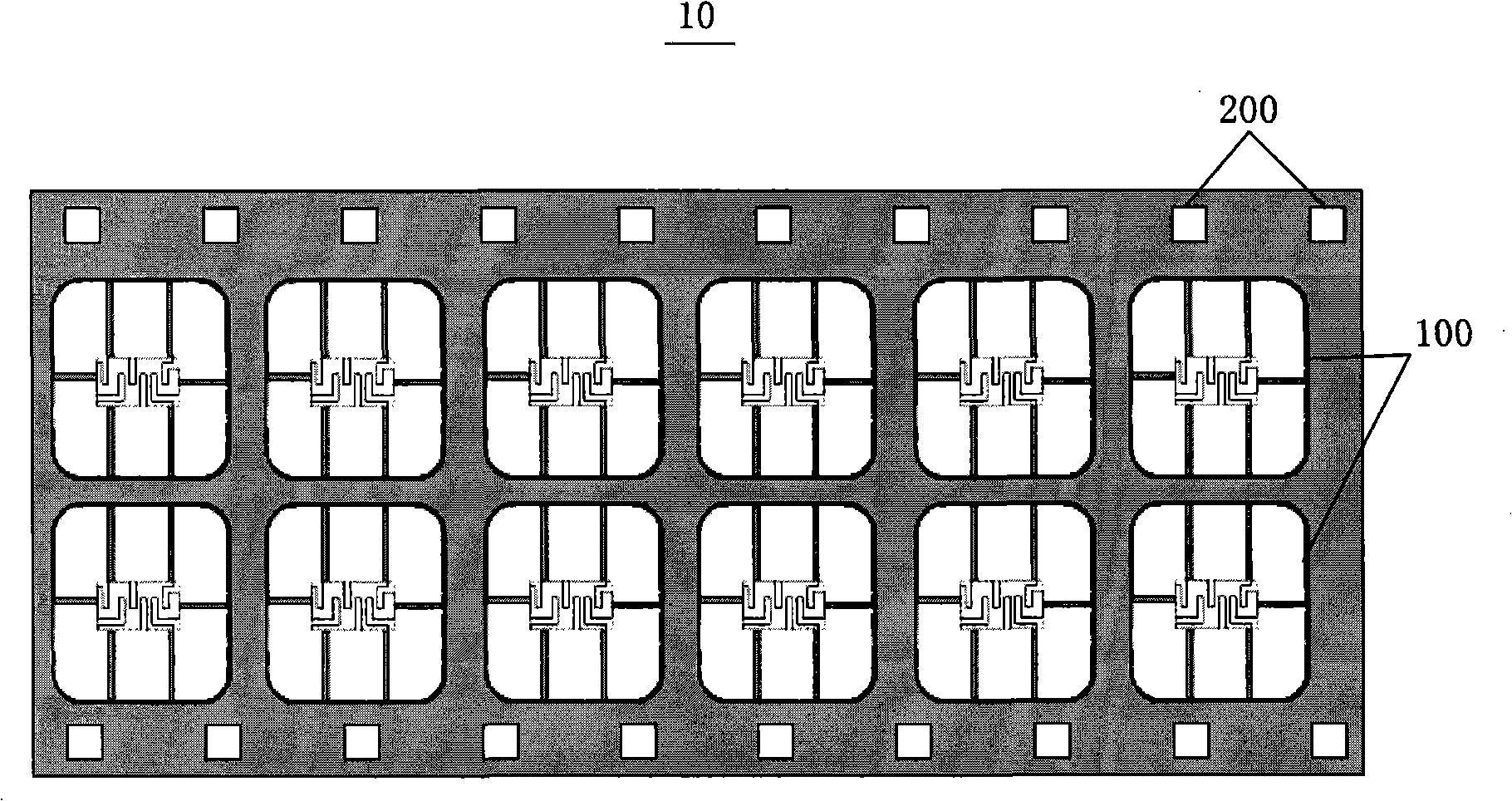

A semiconductor package is disclosed including a plurality semiconductor die mounted on stacked and bonded layers of substrate, for example polyimide tape used in tape automated bonding processes. The tape may have a plurality of repeating patterns of traces and contact pads formed thereon. The traces each include aligned interconnect pads on the respective top and bottom surfaces of the substrate for bonding the traces of one pattern to the traces of another pattern after the patterns have been singulated from the substrate, aligned and stacked. Semiconductor die such as flash memory and a controller die are mounted on the traces of the respective patterns on the substrate. In order for the controller die to uniquely address a specific flash memory die in the stack, a group of traces on each substrate supporting the memory die are used as address pins and punched in a unique layout relative to the layout of the traces other substrates. By providing each flash memory semiconductor die on a substrate with a unique layout of address traces, each memory die may be selectively addressed by the controller die.

Owner:SANDISK TECH LLC

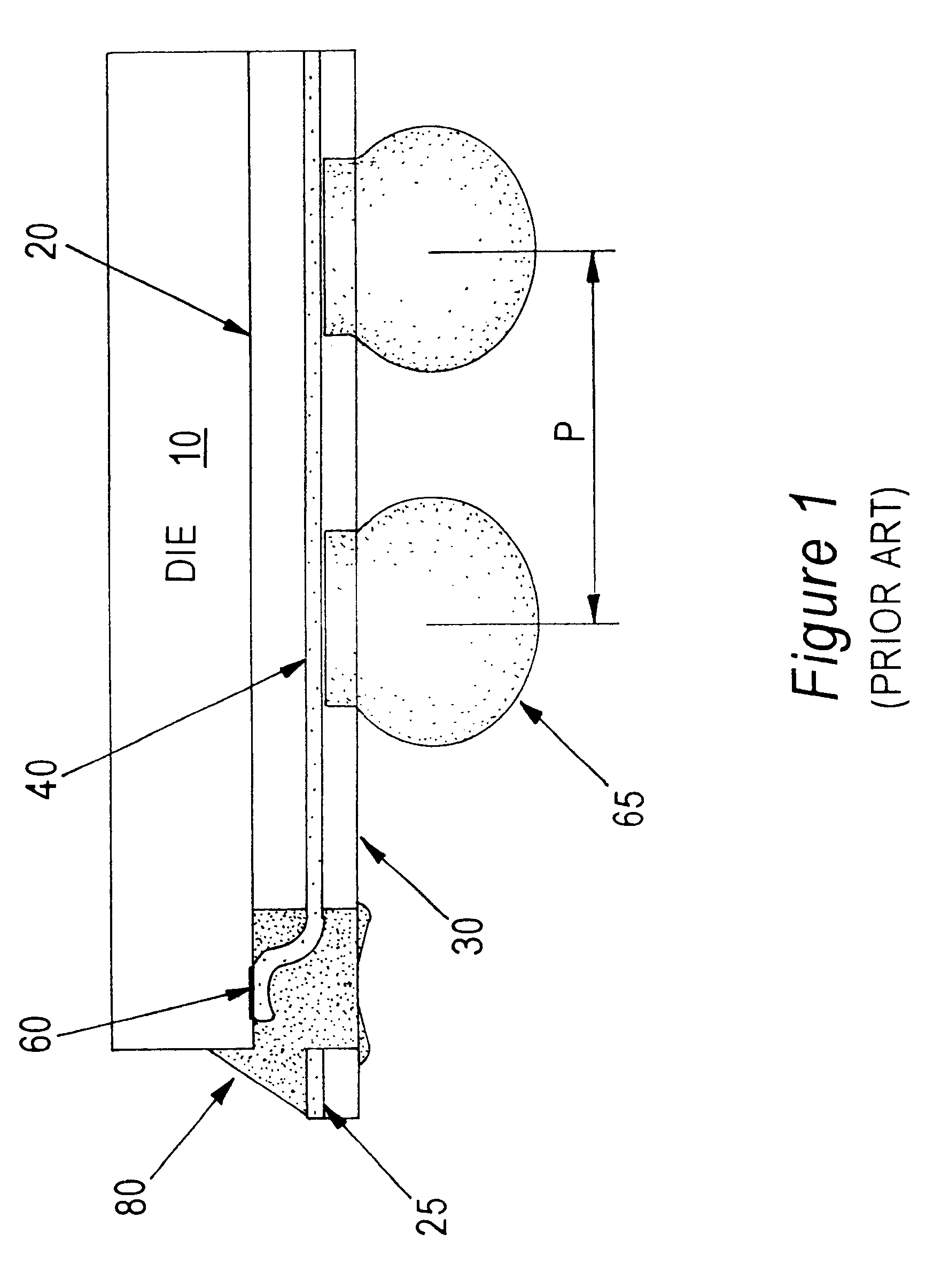

Encapsulated leadframe semiconductor package for random access memory integrated circuits

ActiveUS7781873B2Semiconductor/solid-state device detailsSolid-state devicesStatic random-access memoryEngineering

A thin, small outline IC leadframe plastic package to be used to assemble high performance, high speed semiconductor memory IC devices such as dynamic random access memories (DRAM) having a high data transfer rate in the range of 1 GigaHertz. The package leadframe is electrically interconnected to the IC device input-output pads by either electrically conductive (e.g. solder) bumps that are flip-chip bonded to the IC device or by of an interposer. The interposer contains integral curled micro-spring contacts at opposite ends of conductive fan out traces. The interposer is attached to the leadframe bonding pads by way of tape automated bonding, soldering, or adhesive bonding. The leadframe that is interconnected to the IC device by the aforementioned flip-chip bumps or the interposer is encapsulated and trimmed to form either gull-wing style perimeter leads as a standard thin small outline package (TSOP) or wrap around leads as a micro-leadframe (MLF) package.

Owner:KINGSTON DIGITAL CO LTD

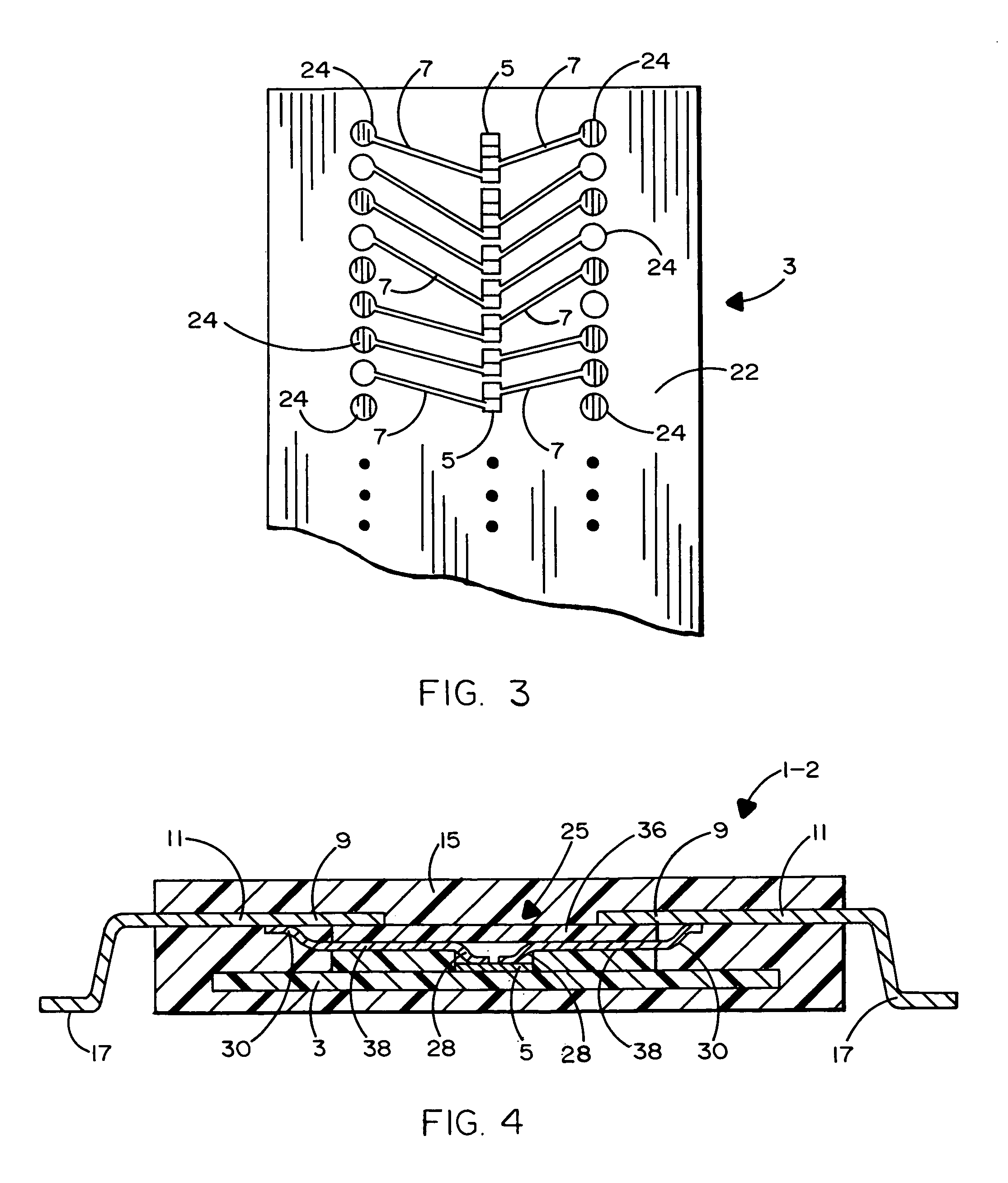

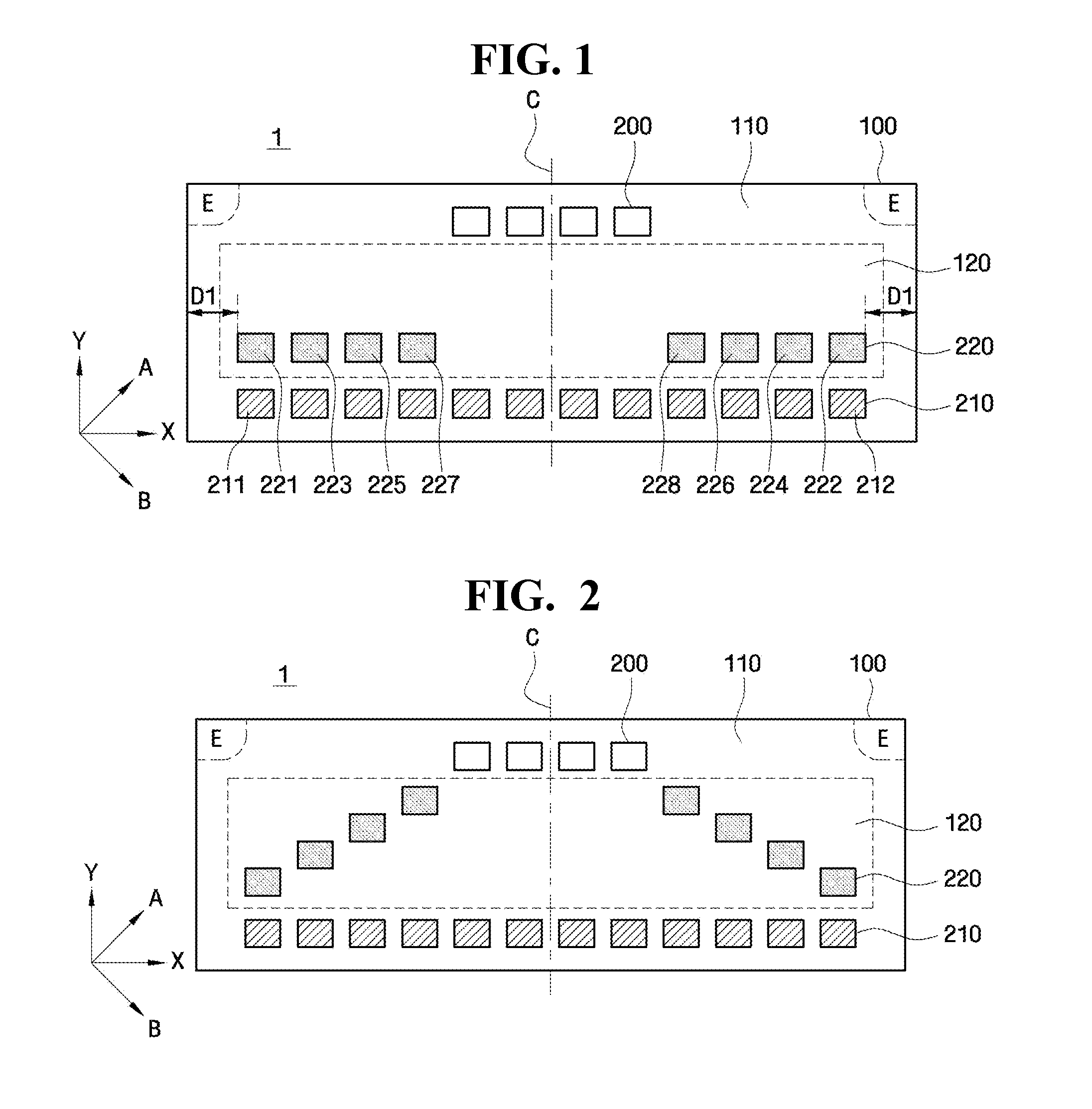

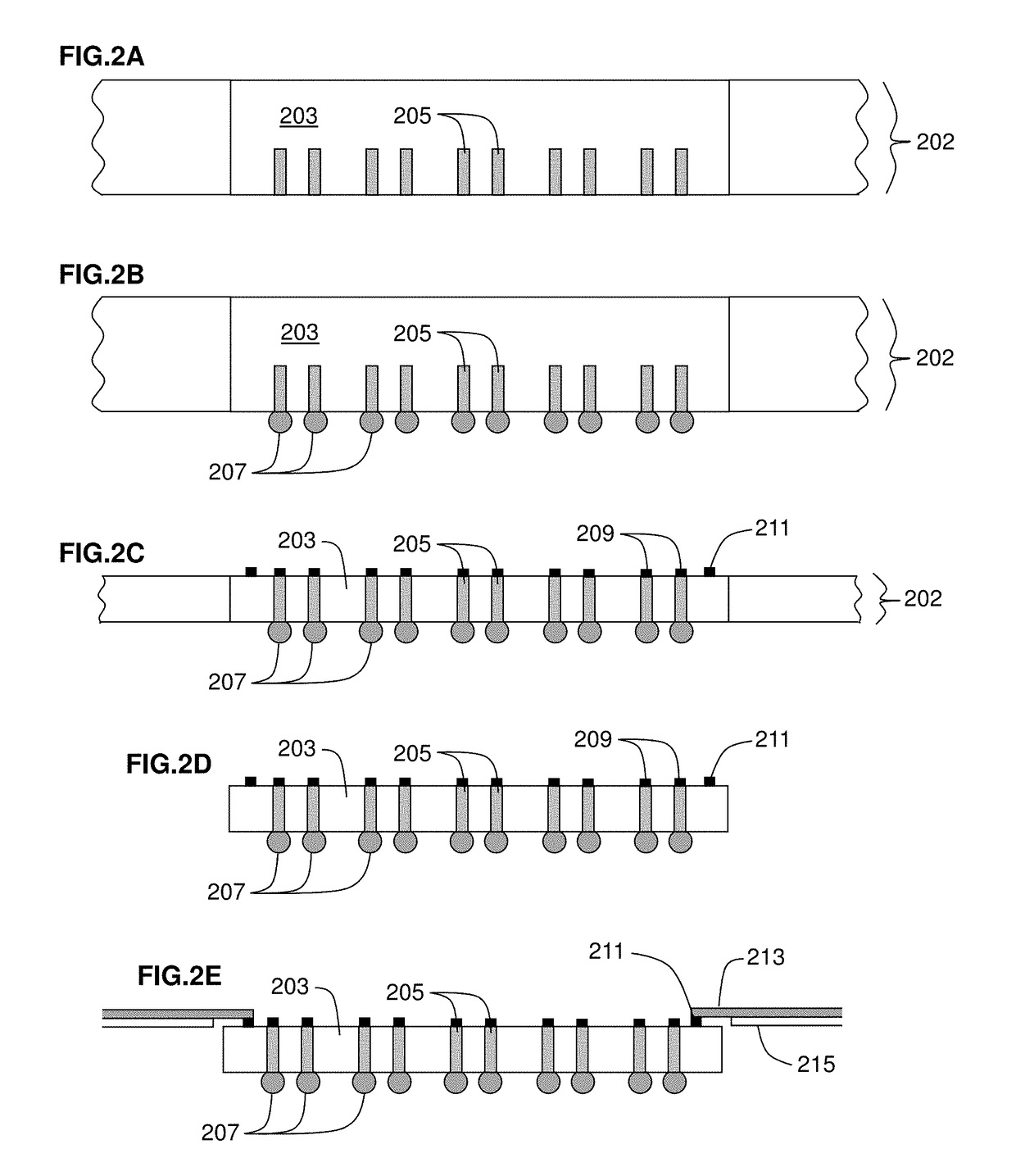

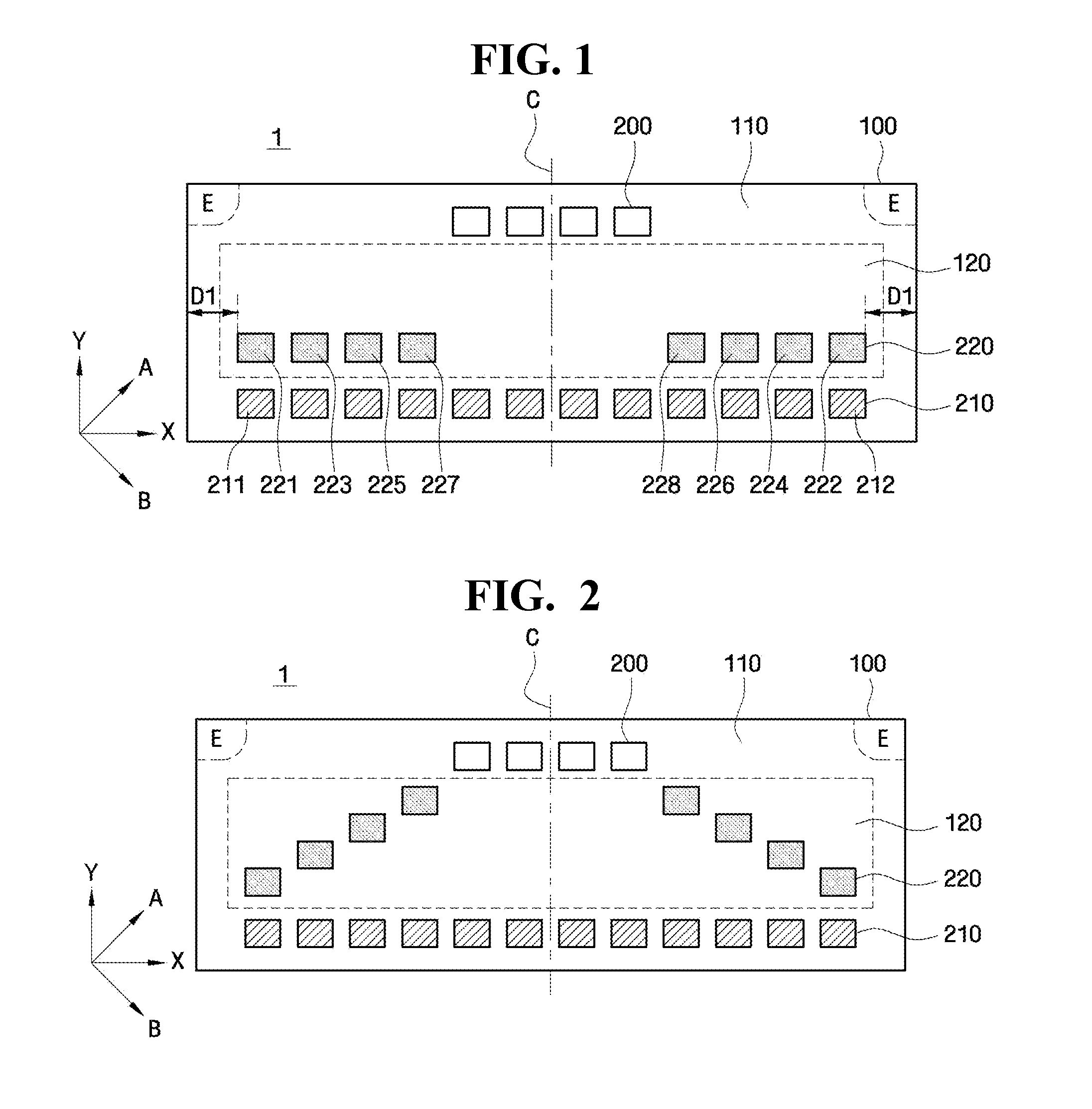

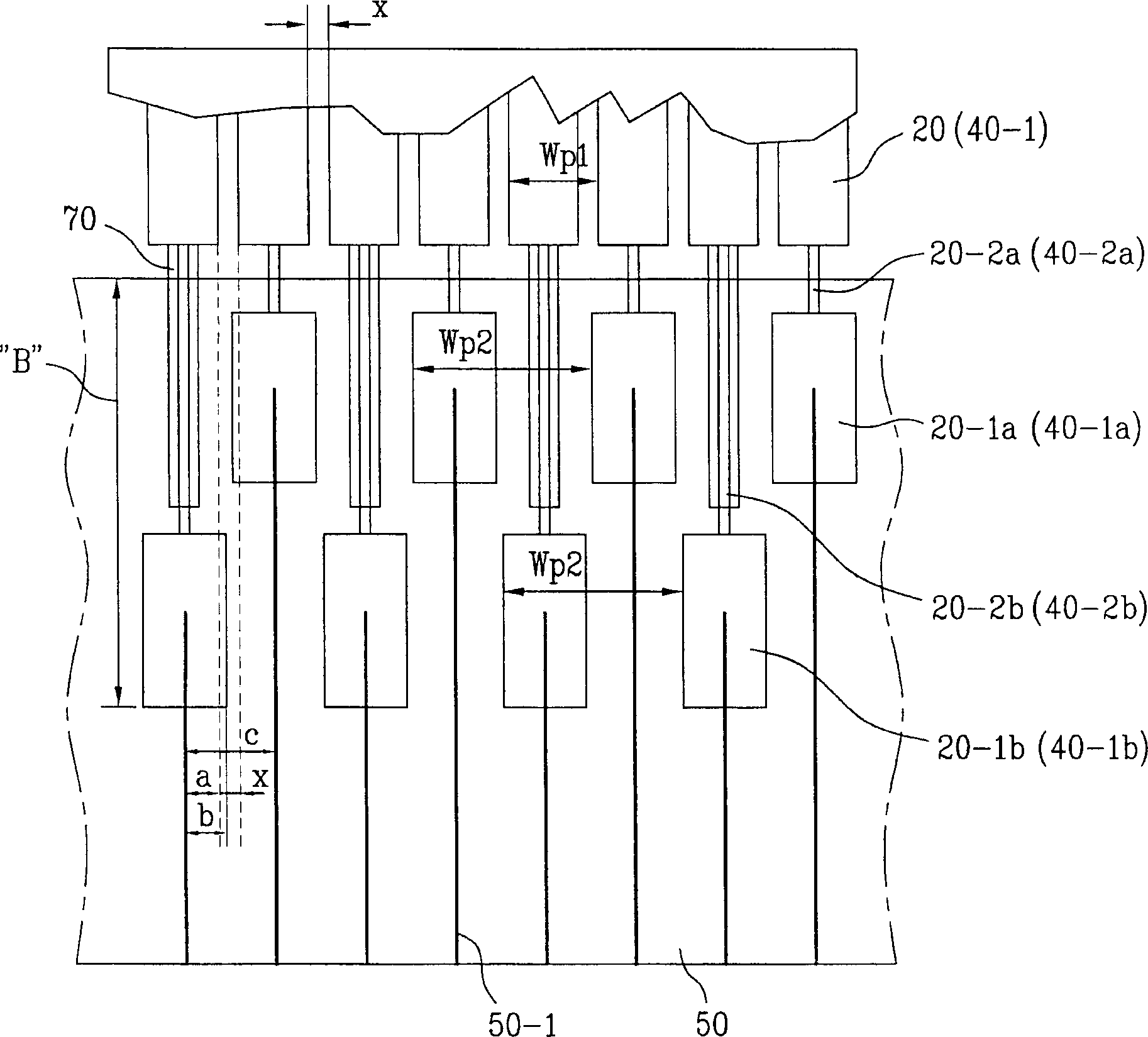

Semiconductor chip and film and tab package comprising the chip and film

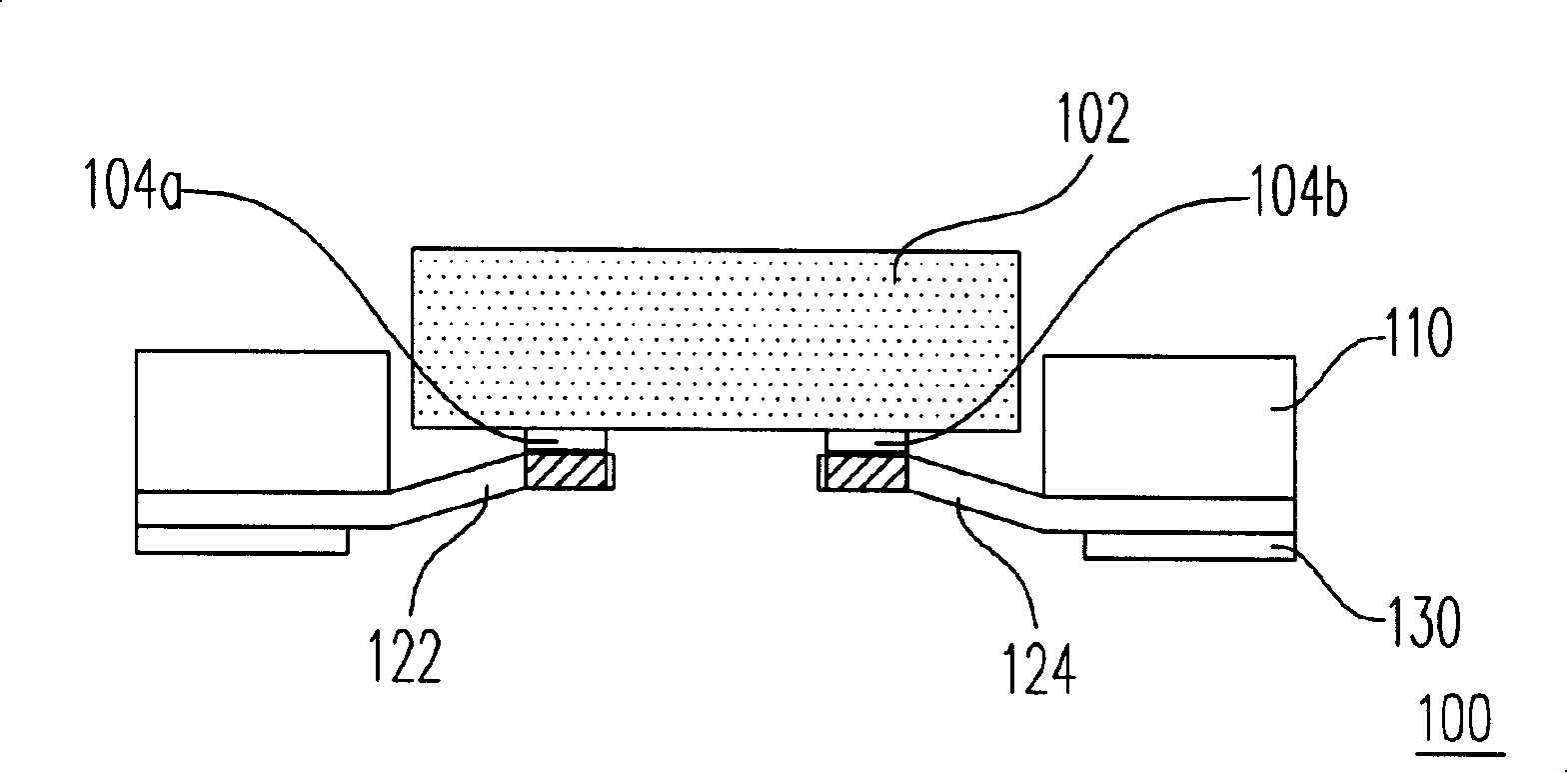

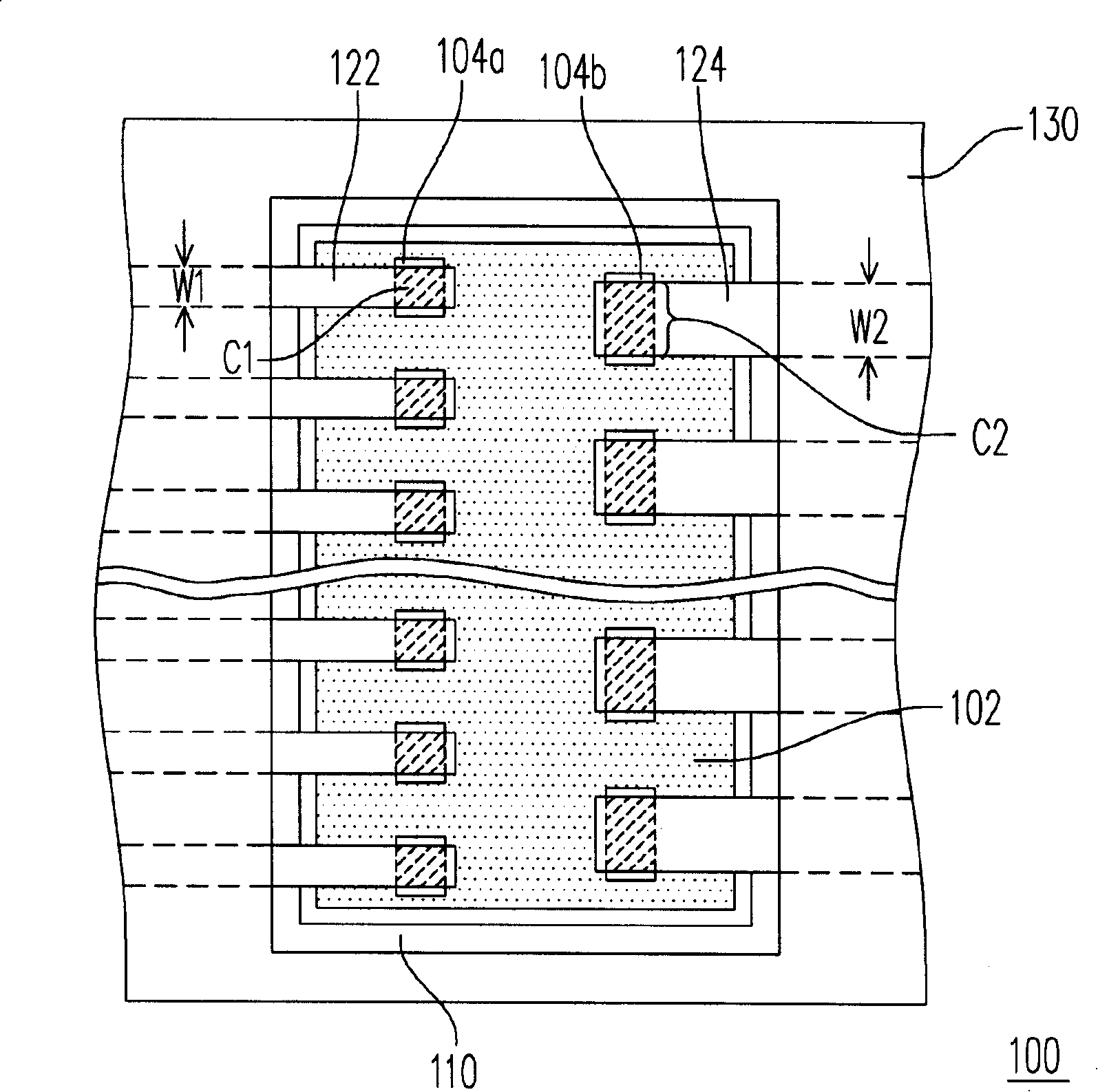

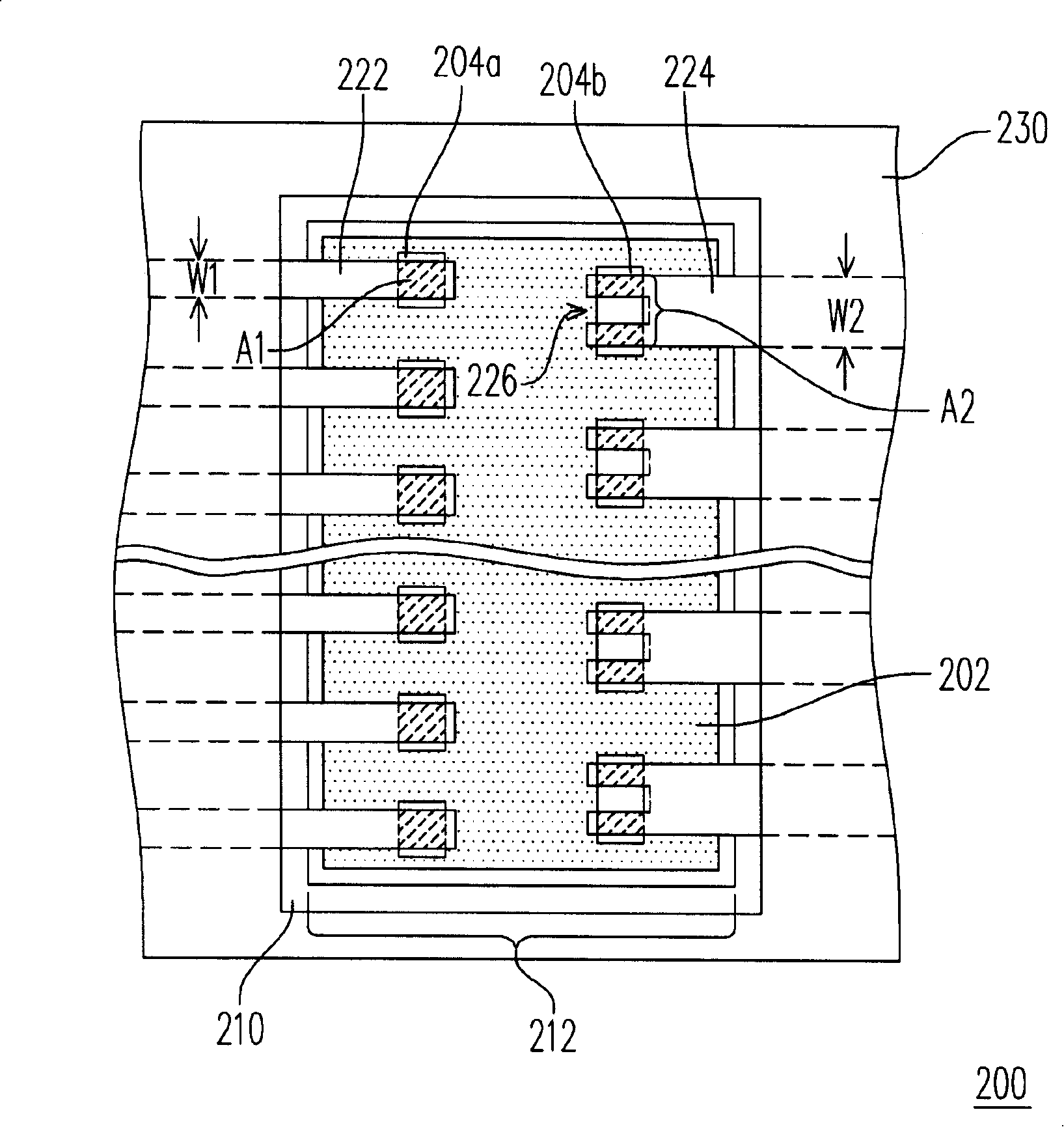

ActiveUS20110210433A1Improve reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipTape-automated bonding

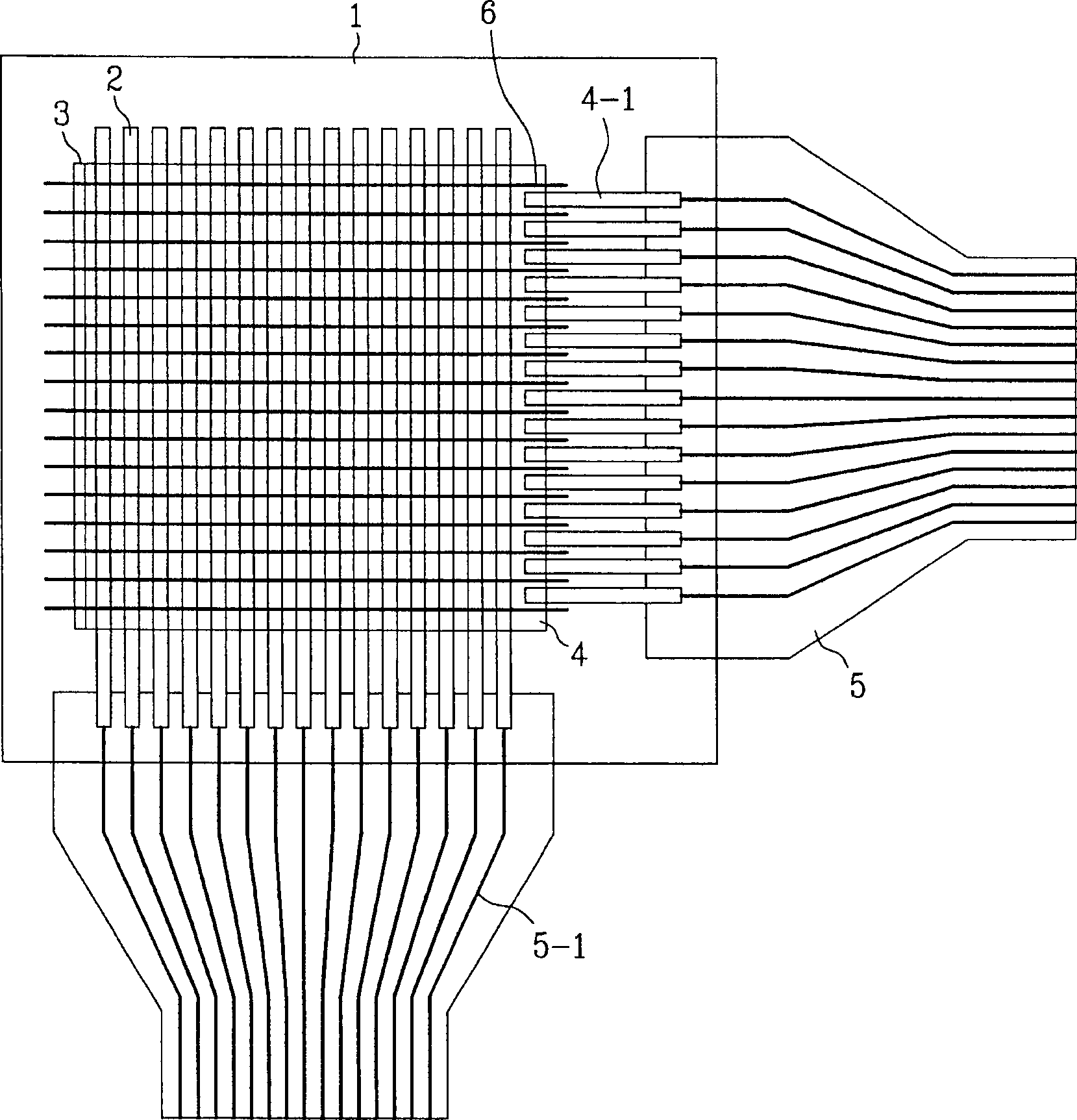

A semiconductor chip for a tape automated bonding (TAB) package is disclosed. The semiconductor chip comprises a connection surface including a set of input pads connected to internal circuitry of the chip and for conveying external signals to the internal circuitry, the set of input pads comprising all of the input pads on the chip. The connection surface includes a set of output pads connected to internal circuitry of the chip and for conveying internal chip signals to outside the chip, the set of output pads comprising all of the output pads on the chip. The connection surface includes a first edge and a second edge that are substantially parallel to each other and are opposite each other on a respective first side and second side of the chip, and a third edge and fourth edge that are substantially perpendicular to the first and second edges, and are opposite each other on a respective third side and fourth side of the chip. A plurality of input pads of the set of input pads are adjacent the first edge, and are arranged in a first row substantially parallel to the first edge and extending in a first direction; a plurality of first output pads of the set of output pads are adjacent the second edge, and are arranged in a second row substantially parallel to the second edge and extending in the first direction; and a plurality of second output pads of the set of output pads are located between the first row and the second row. The plurality of second output pads include at least first and second outermost pads located a certain distance from the respective third edge and fourth edge, and at least first and second inner pads located a greater distance from the respective third edge and fourth edge than the first and second outermost pads.

Owner:SAMSUNG ELECTRONICS CO LTD

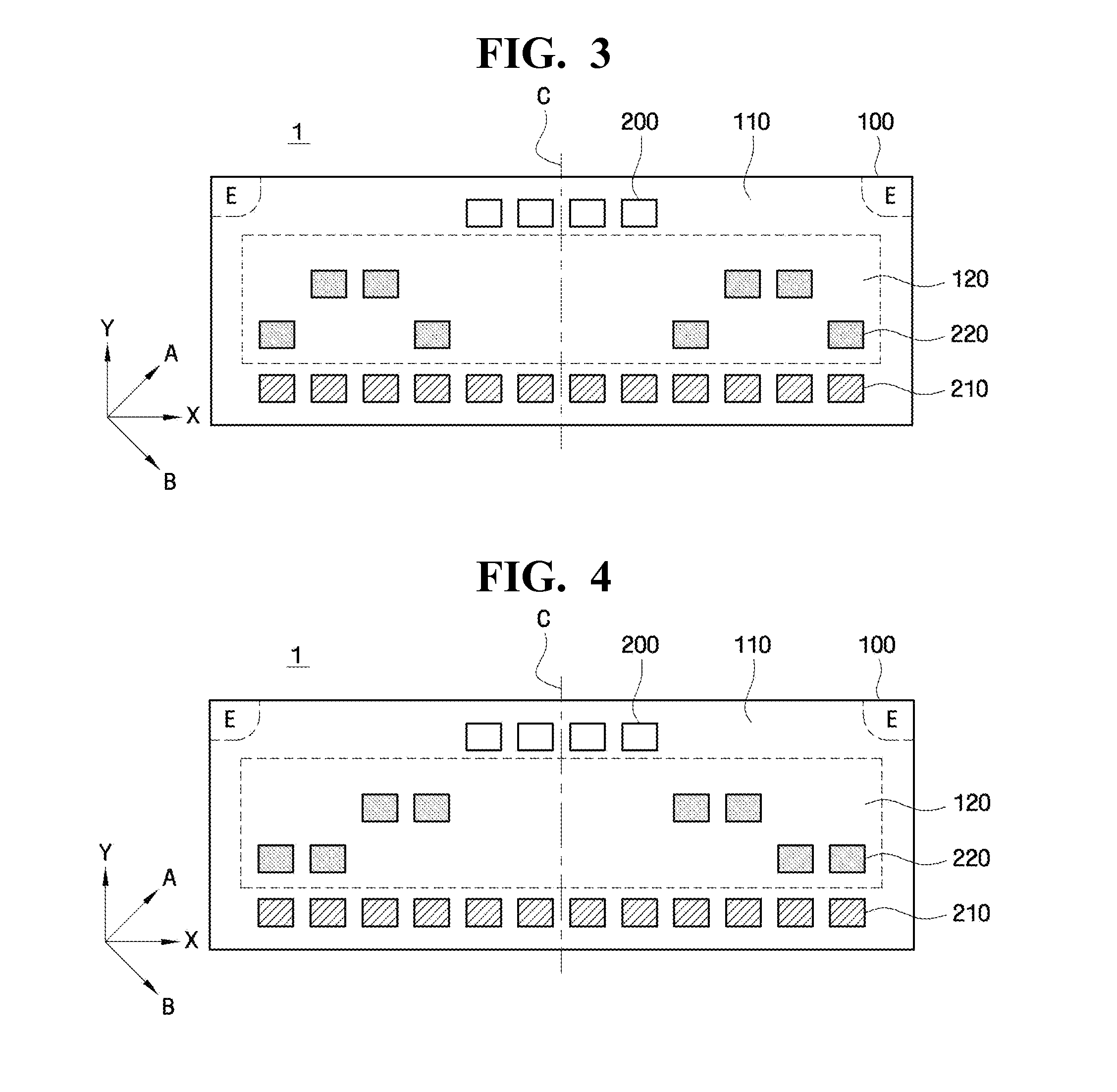

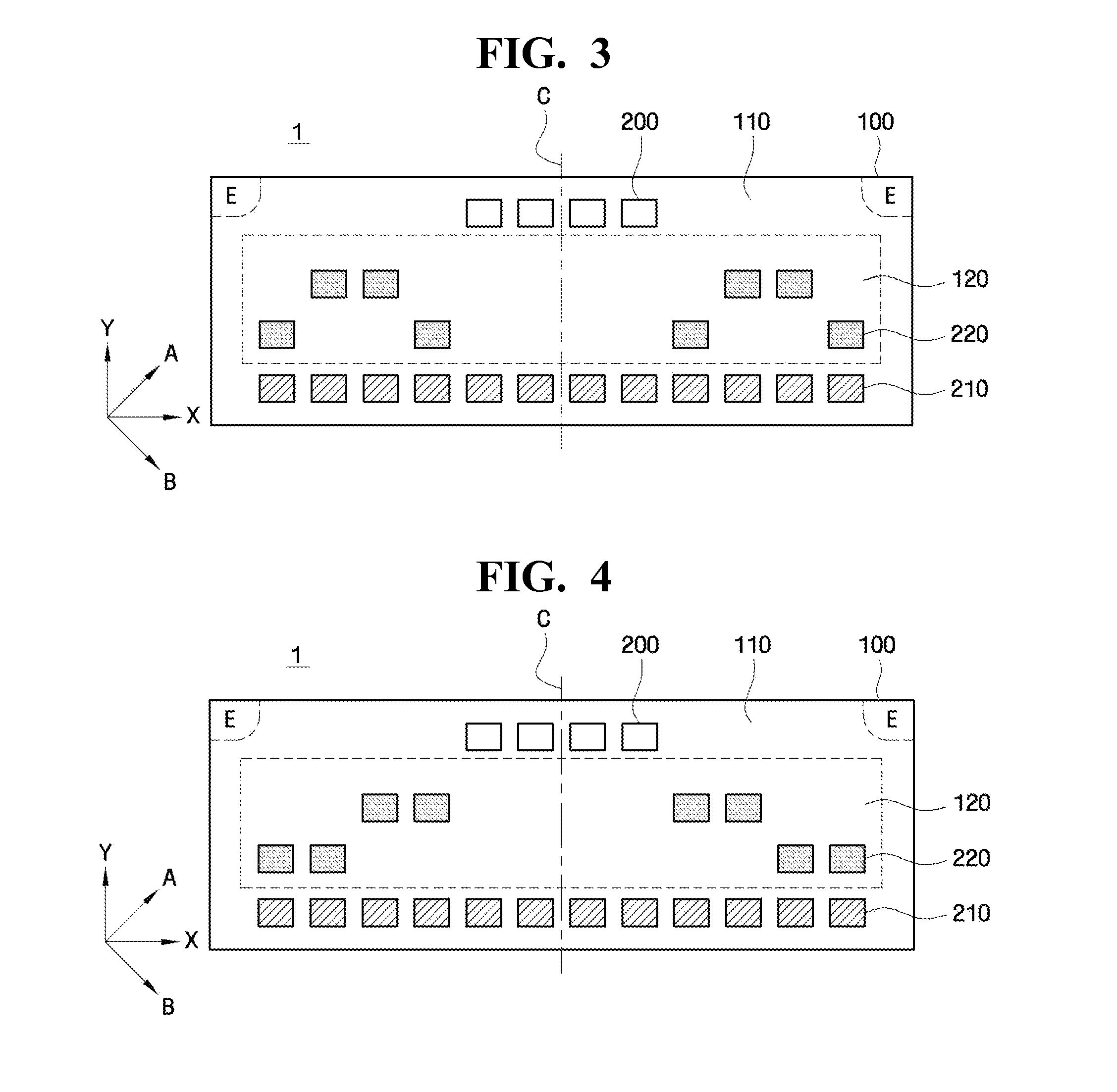

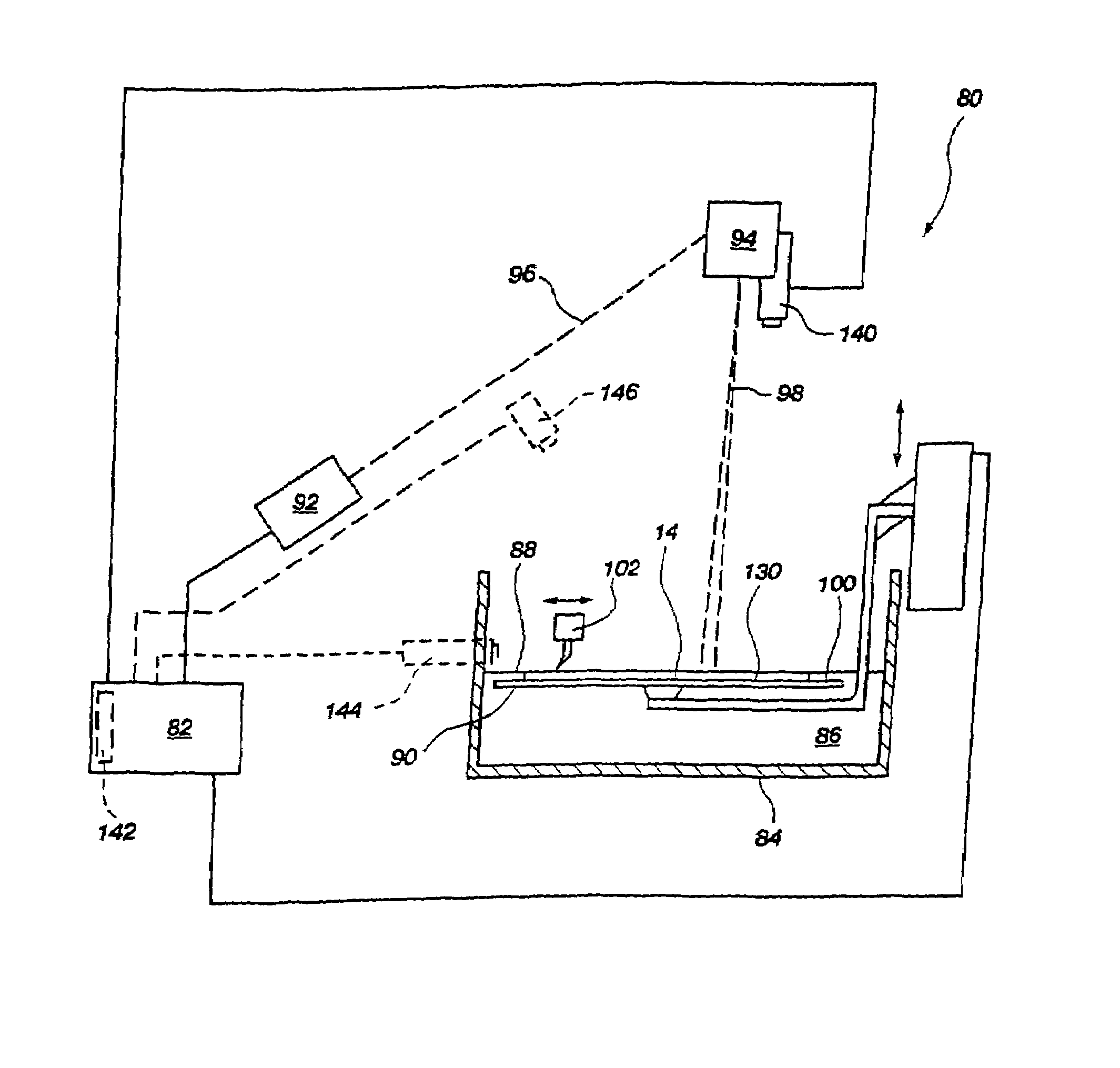

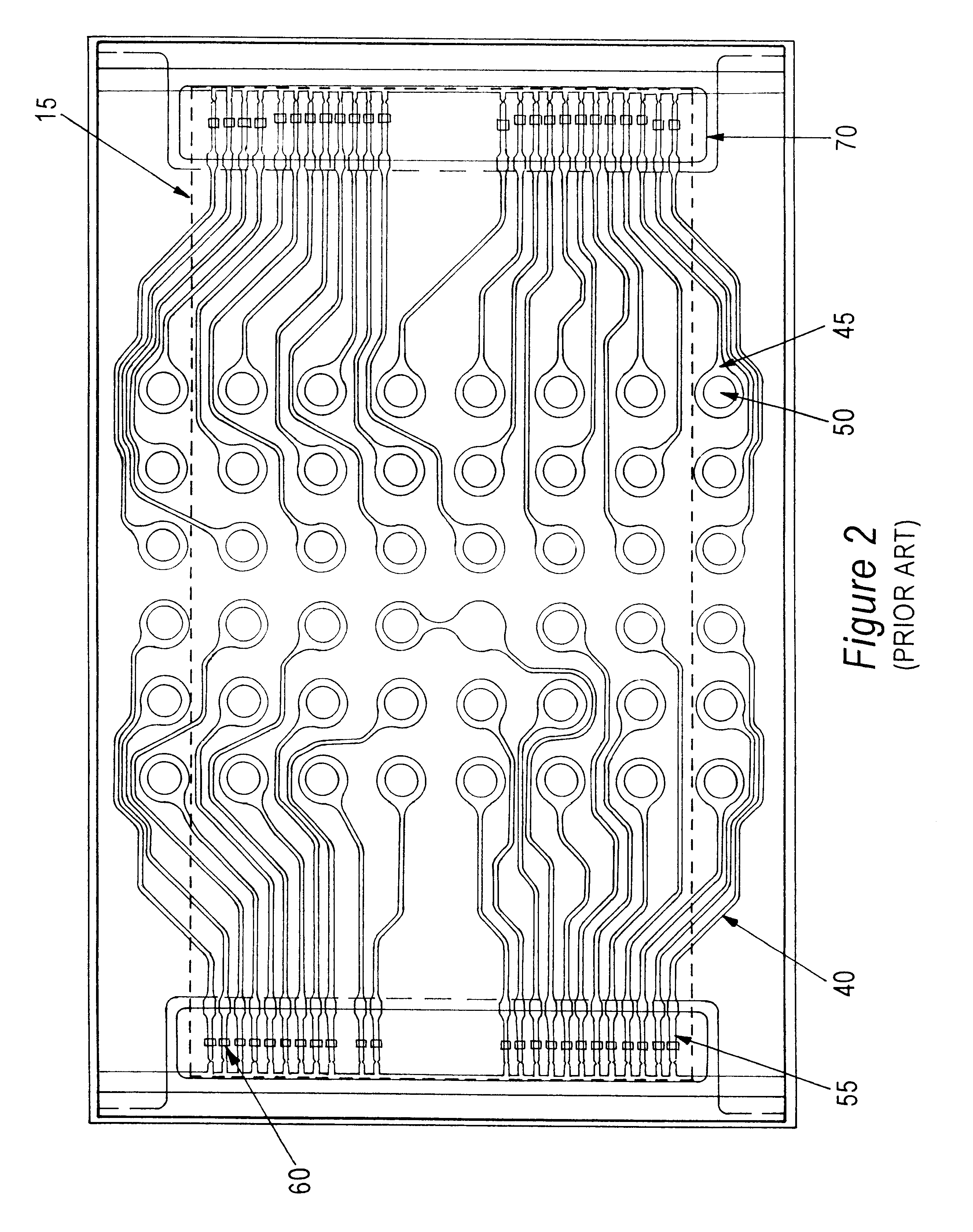

Power distribution arrangement for an injet printhead

An ink supply unit for supplying separate color inks to a portable ink jet print head, the ink supply unit including: a slot for insertion of the printhead; a series of elongated chambers for the storage of the separate color inks, the chambers being interconnected with the slot for the supply of ink to the printhead; a series of conductive rails along the outside of the ink supply unit, each conductive rail interconnected to a power supply at a series of points along the conductive rail; a tape automated bonding strip along the outside of the ink supply unit having a series of control lines along one surface thereof for mating with a corresponding external series of control lines, the tape automated bonding strip further having a repeating series of interconnects to the printhead, the interconnects interconnecting the control lines and the conductive rails to the printhead. The unit can be detachable from the power supply and the external series of control lines.

Owner:SILVERBROOK RES PTY LTD +1

Mark for visual inspection upon assembling a display

InactiveUS7236624B2Guaranteed to workReduce inspectionSolid-state devicesElectric connection testingHigh rateVisual inspection

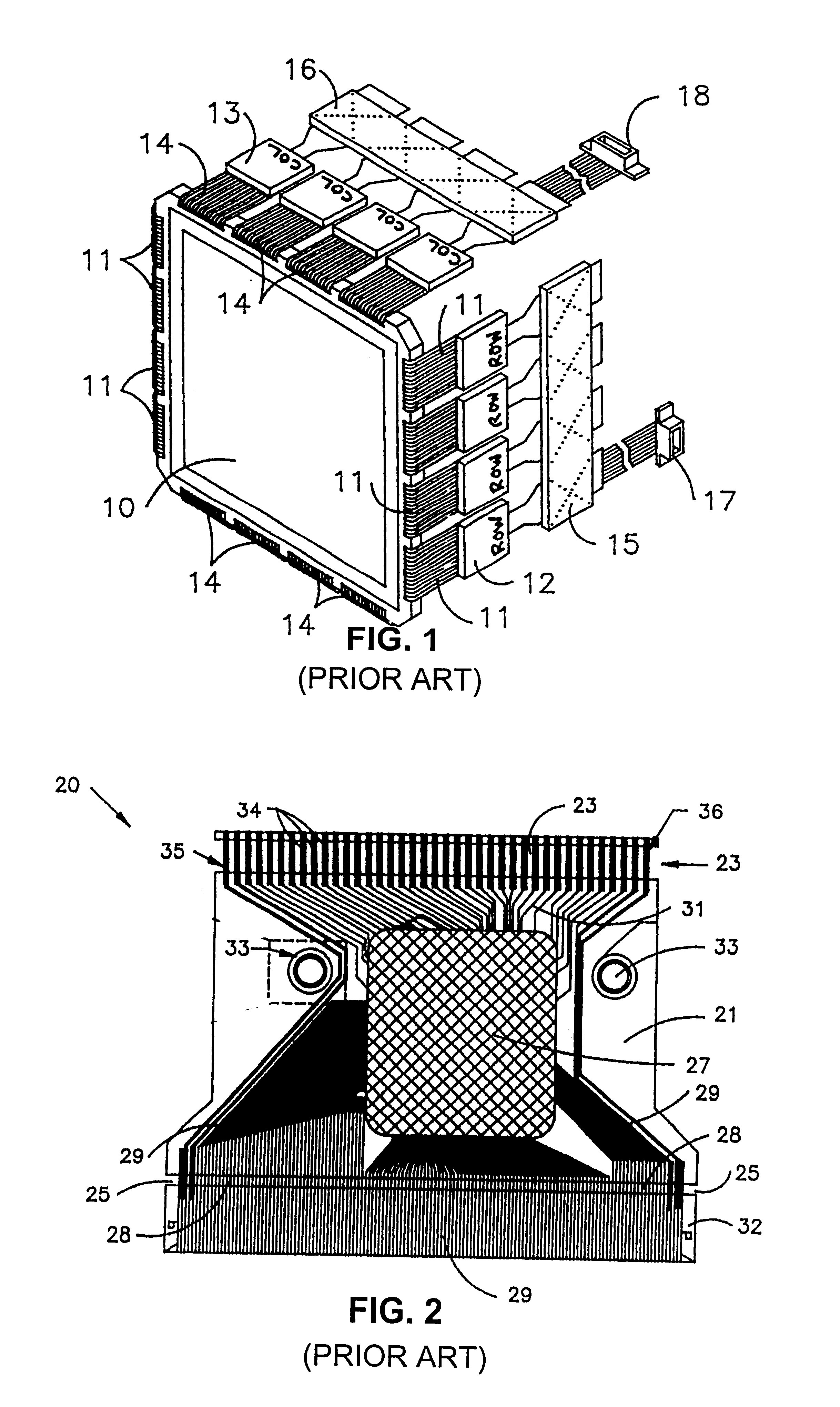

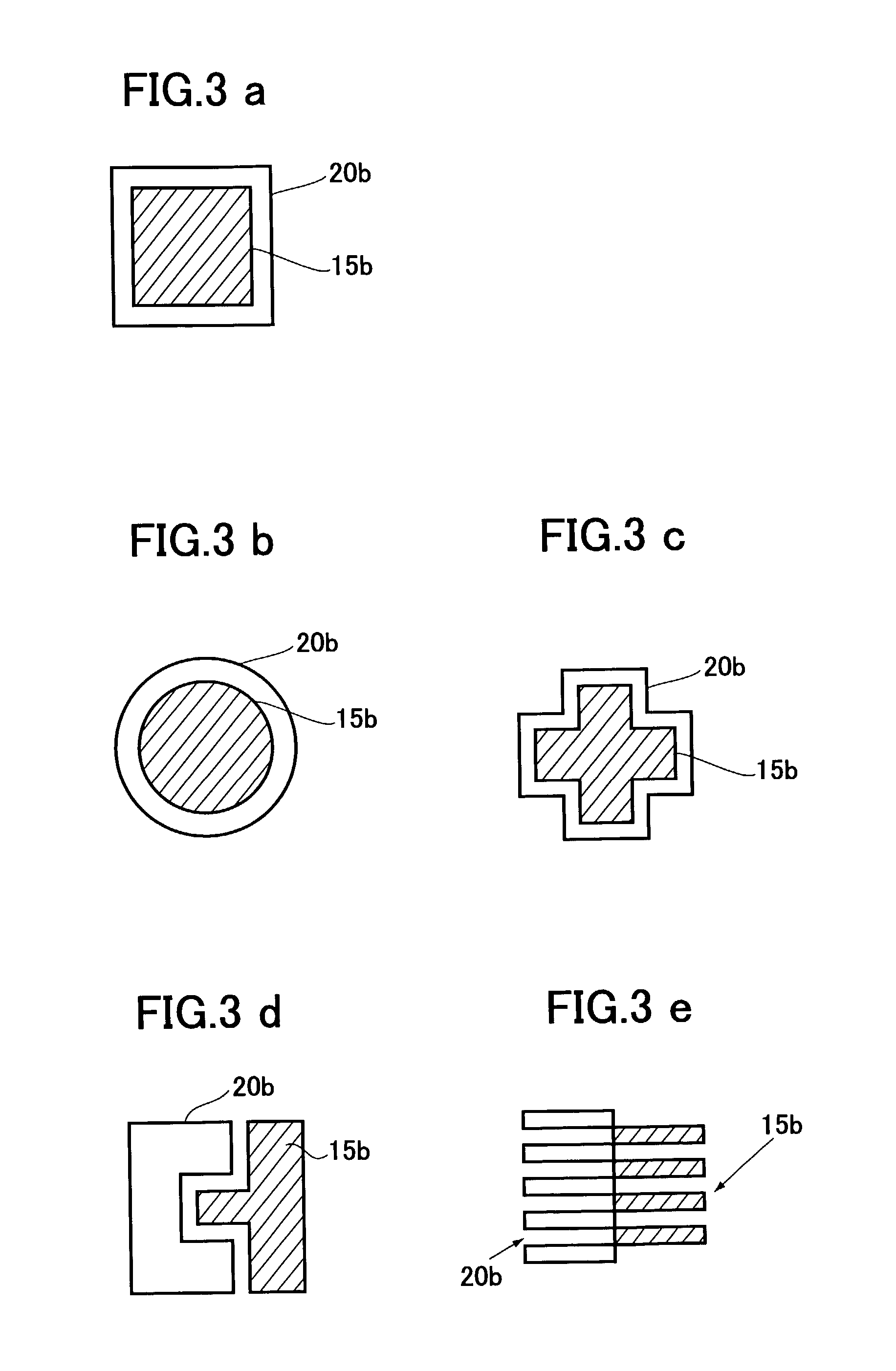

In the neighborhood of each connecting region of a panel substrate, tape automated bonding (TAB) substrates, and a flexible substrate, marks for a visual inspection are provided at a preset distance apart from the connecting region. According to the present marks, inferior products are eliminated with a high rate of accuracy upon visual inspection after completing a connection of display panel.

Owner:TOHOKU PIONEER CORP

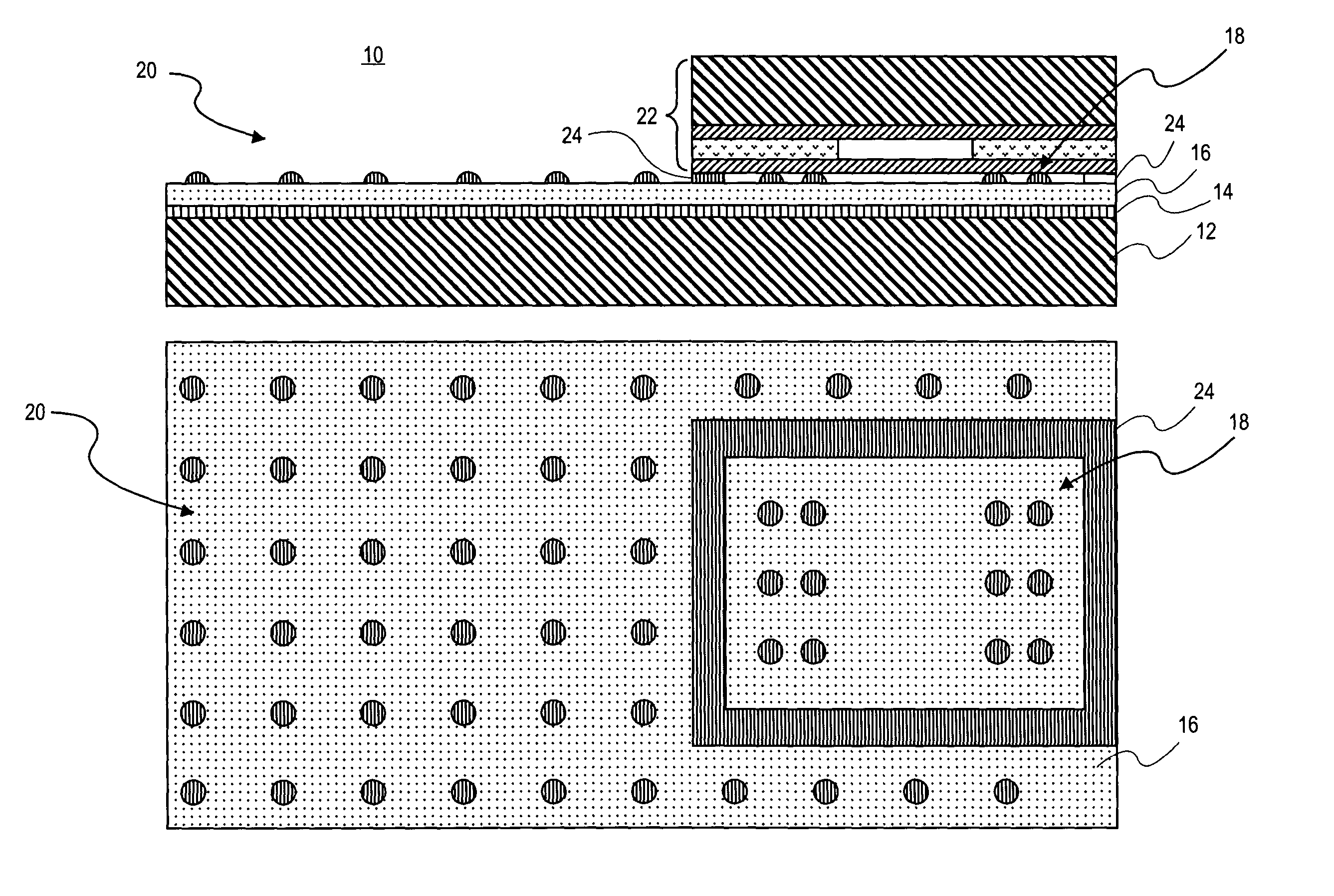

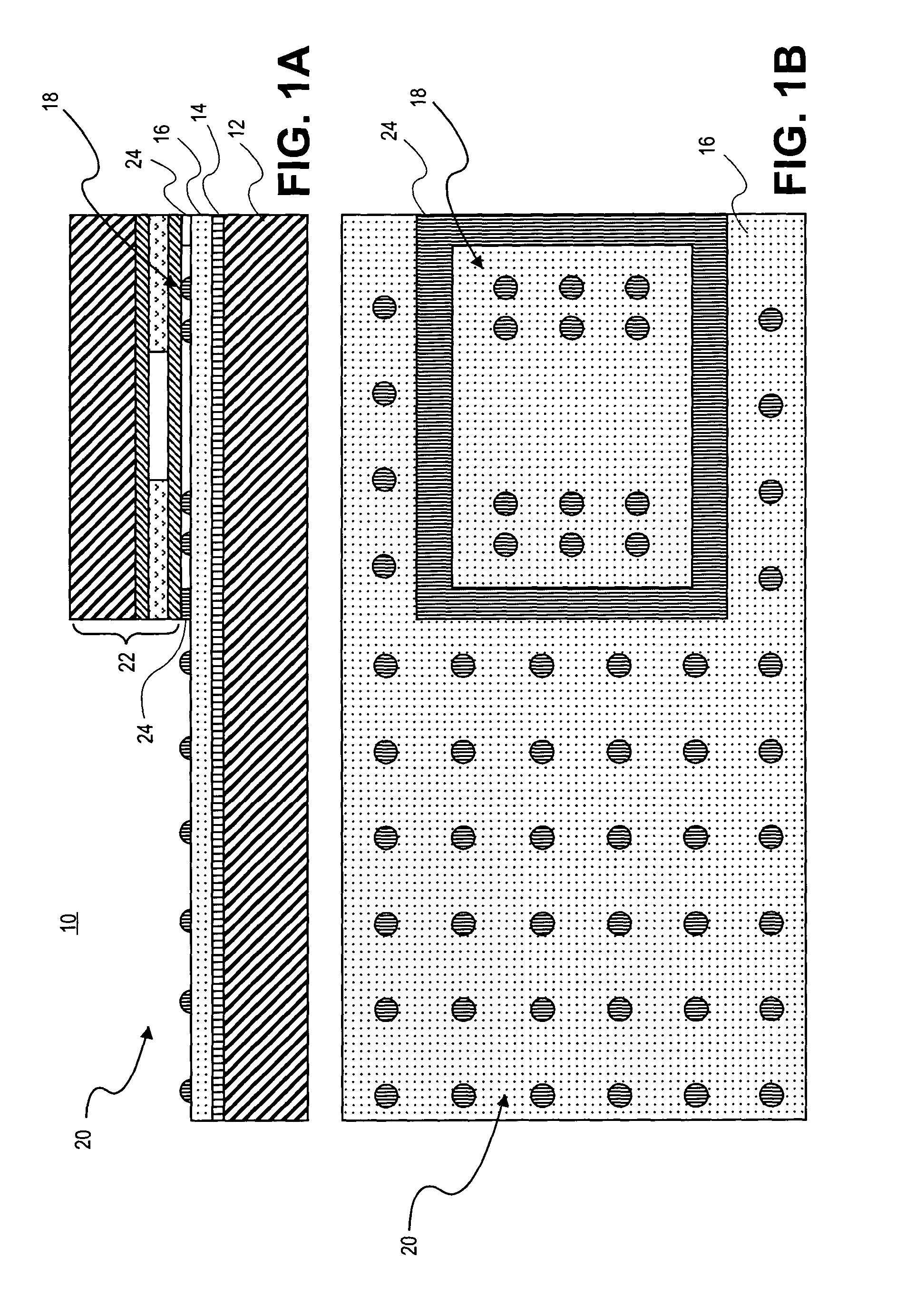

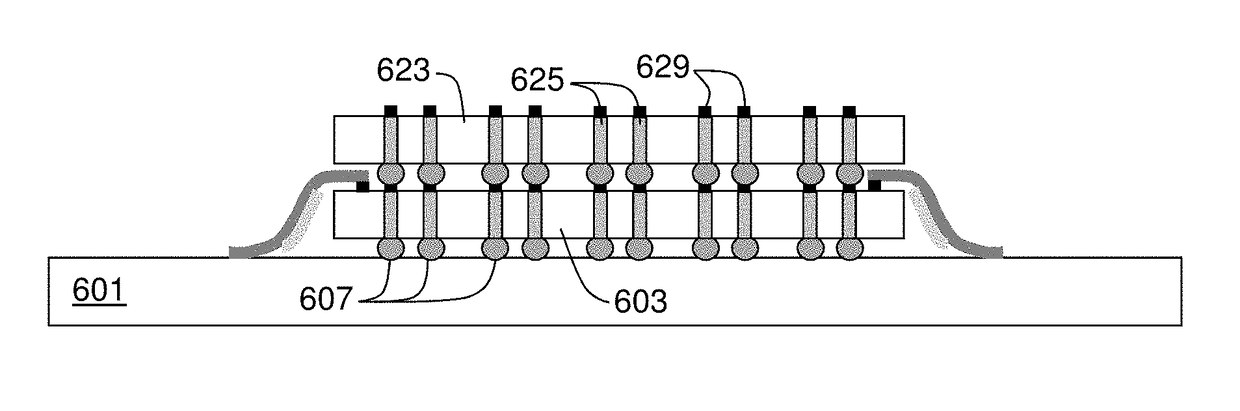

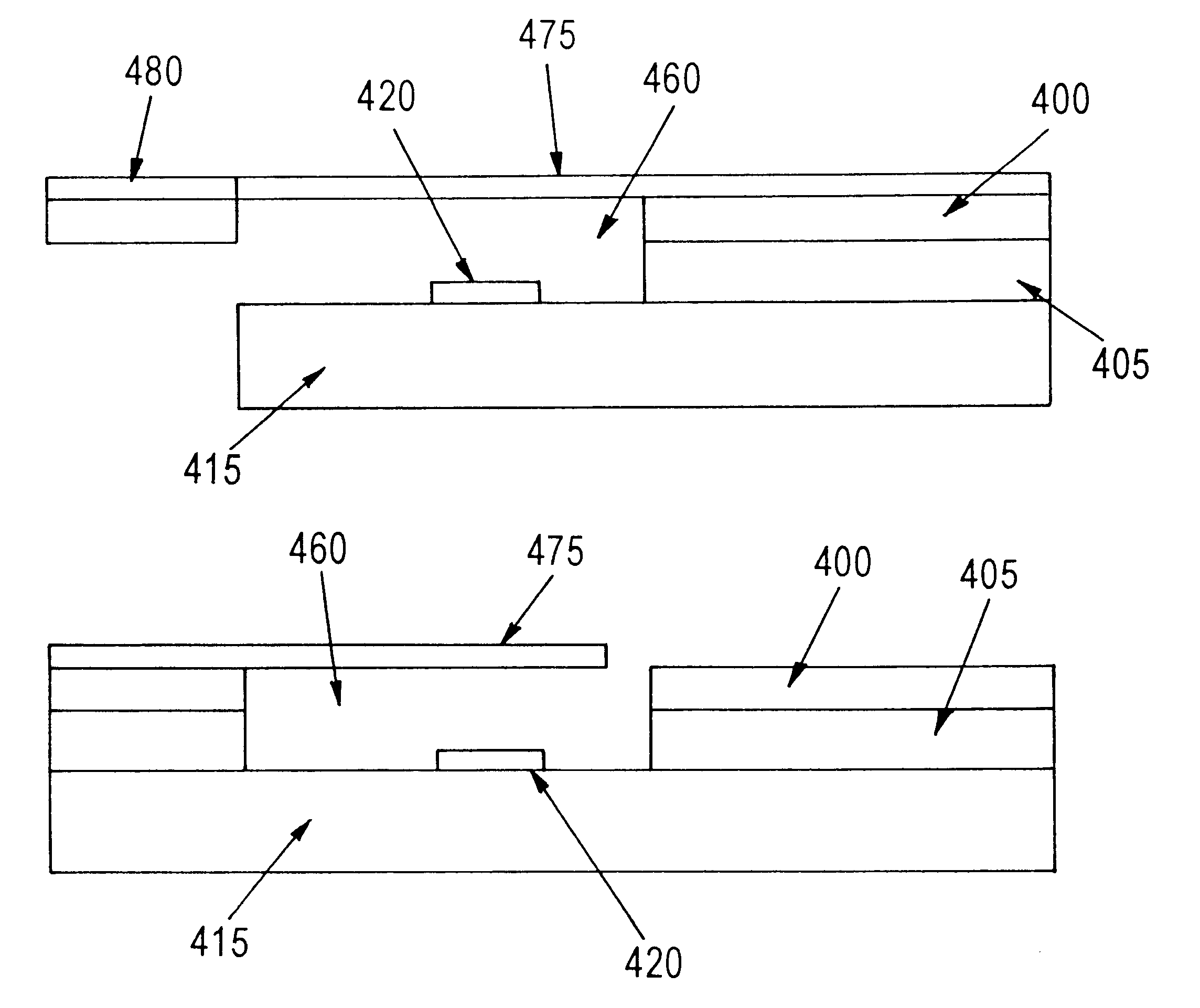

Three-dimensional hybrid packaging with through-silicon-vias and tape-automated-bonding

ActiveUS20170200698A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringChip stacking

A 3-dimensional hybrid package including an integrated circuit chip stack formed on a laminate, the integrated chip stack further including a first chip and a second chip. The first chip is connected to the laminate through first solder bumps, each associated with a first through-silicon via (TSV), and first metal leads embedded in a first polymer tape that extends from first peripheral metal pads formed on a back side of the first chip to the laminate. The second chip is connected to the first peripheral metal pads on the back side of the first chip through second solder bumps formed on a front side of the second chip. The second chip is connected to the laminate by second metal leads, embedded in a second polymer tape that extend from second peripheral metal pads formed on a back side of the second chip to the laminate.

Owner:GLOBALFOUNDRIES US INC

Semiconductor chip and film and TAB package comprising the chip and film

ActiveUS8575735B2Improve reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip for a tape automated bonding (TAB) package is disclosed. The semiconductor chip comprises a connection surface including a set of input pads connected to internal circuitry of the chip and for conveying external signals to the internal circuitry, the set of input pads comprising all of the input pads on the chip. The connection surface includes a set of output pads connected to internal circuitry of the chip and for conveying internal chip signals to outside the chip, the set of output pads comprising all of the output pads on the chip.

Owner:SAMSUNG ELECTRONICS CO LTD

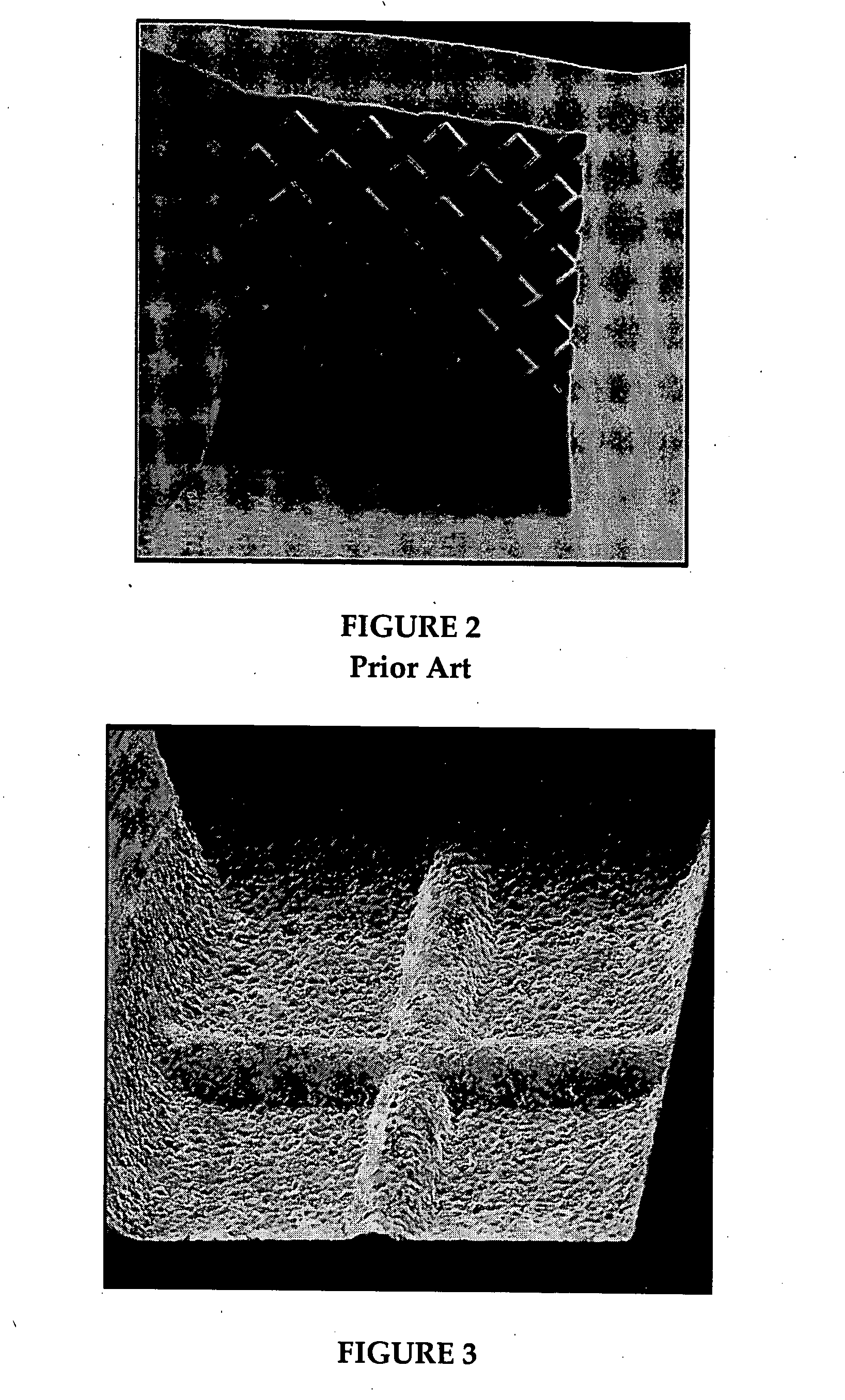

Tape stiffener, semiconductor device component assemblies including same, and stereolithographic methods for fabricating same

InactiveUS7029954B2Additive manufacturing apparatusSemiconductor/solid-state device detailsBand shapeDevice material

Stiffeners for tapes, films, or other connective structures, which are configured to be secured to a semiconductor device component, such as a semiconductor die or substrate, by tape-automated bonding processes, are fabricated by stereolithographic processes and may include one or two or more layers. The stiffeners are configured to prevent torsional flexion or bending of the connective structure to which they are to be secured. The stiffeners may reinforce sprocket or indexing holes in connective structures. The stiffeners may include apertures through which intermediate conductive elements or other structures secured to the connective structure may be exposed or protrude. The stereolithographic method for fabricating stiffeners may include use of a machine vision system that recognizes the position and orientation of one or more connective structures on which at least an element of each of the stiffeners is to be fabricated so that the application of material thereto may be controlled.

Owner:MICRON TECH INC

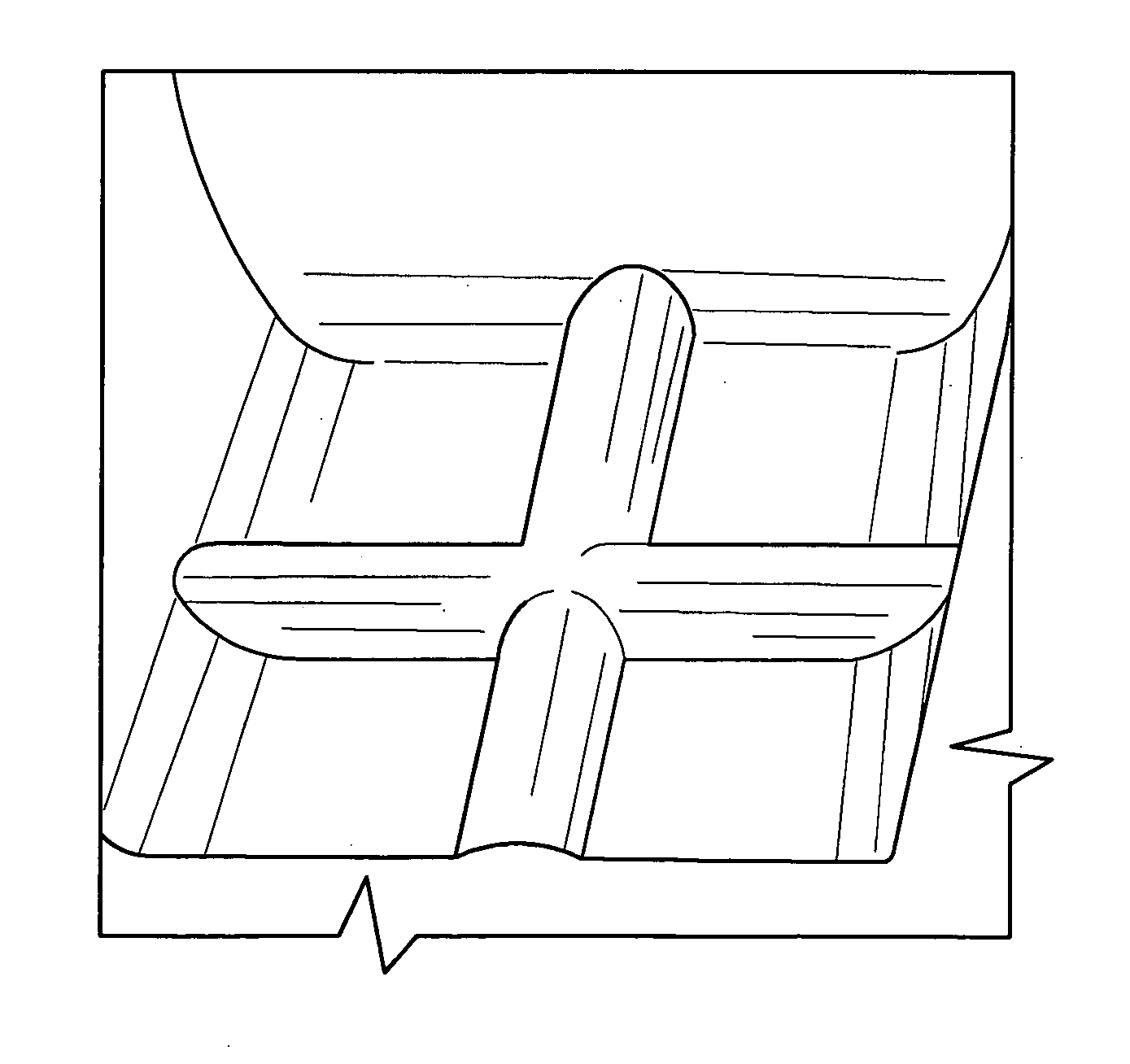

Inner pin joint packaging

InactiveCN101231979AReduced area of eutectic bondingNot produce strengthSemiconductor/solid-state device detailsSolid-state devicesEngineeringUltimate tensile strength

The invention discloses an inner pin bonding package, which is suitable for bonding a chip on a soft panel by using tape automated bonding technology. The inner lead bonding package comprises a chip, the soft panel and a plurality of pins arranged on the soft panel and extended to a chip bonding section. The chip includes a bump eutectically bonded with the pins, and the pins include a first pin and a second pin, wherein the first pin includes a first eutectic-bonding region with the same width as that of the first pin at one end corresponding to the bump, and the second pin includes at least one groove at one end corresponding to the bump to form a second eutectic bonding region with a smaller width than that of the second pin. Accordingly, the eutectic bonding area between the first / second pin and the bump is uniformized. Accordingly, the inner pin bonding package process can be achieved in one step without causing the problems of poor bonding strength or solder wicking.

Owner:CHIPMOS TECH INC

Loading belt for smart card, encapsulation module for smart card using the same and manufacturing method thereof

InactiveCN101355075ASemiconductor/solid-state device detailsSolid-state devicesAdhesiveComputer module

The invention provides a carrier tape for an intelligent card, a packaging module for the intelligent card adopting the carrier tape and a method for making the same. The carrier tape for the intelligent card has an open window, a beam lead is led out from each contact pin to the middle part of the open window; and at least one part of the front end of the beam lead is positioned in the same horizontal line. The packaging module for the intelligent card comprises the carrier tape, a semiconductor chip and a colloid, wherein the semiconductor chip is adhered to the lower surface of the carrier tape faceup from a bonding pad under the carrier tape through adhesive; and after adhered to the carrier tape, the bonding pad of the semiconductor chip is positioned in the middle of the open window. A tape automated bonding (TAB) process is adopted to realize bonding between all bonding pads and corresponding beam leads at one time, thereby improving packaging efficiency and reducing manufacturing cost.

Owner:SAMSUNG SEMICON CHINA RES & DEV +1

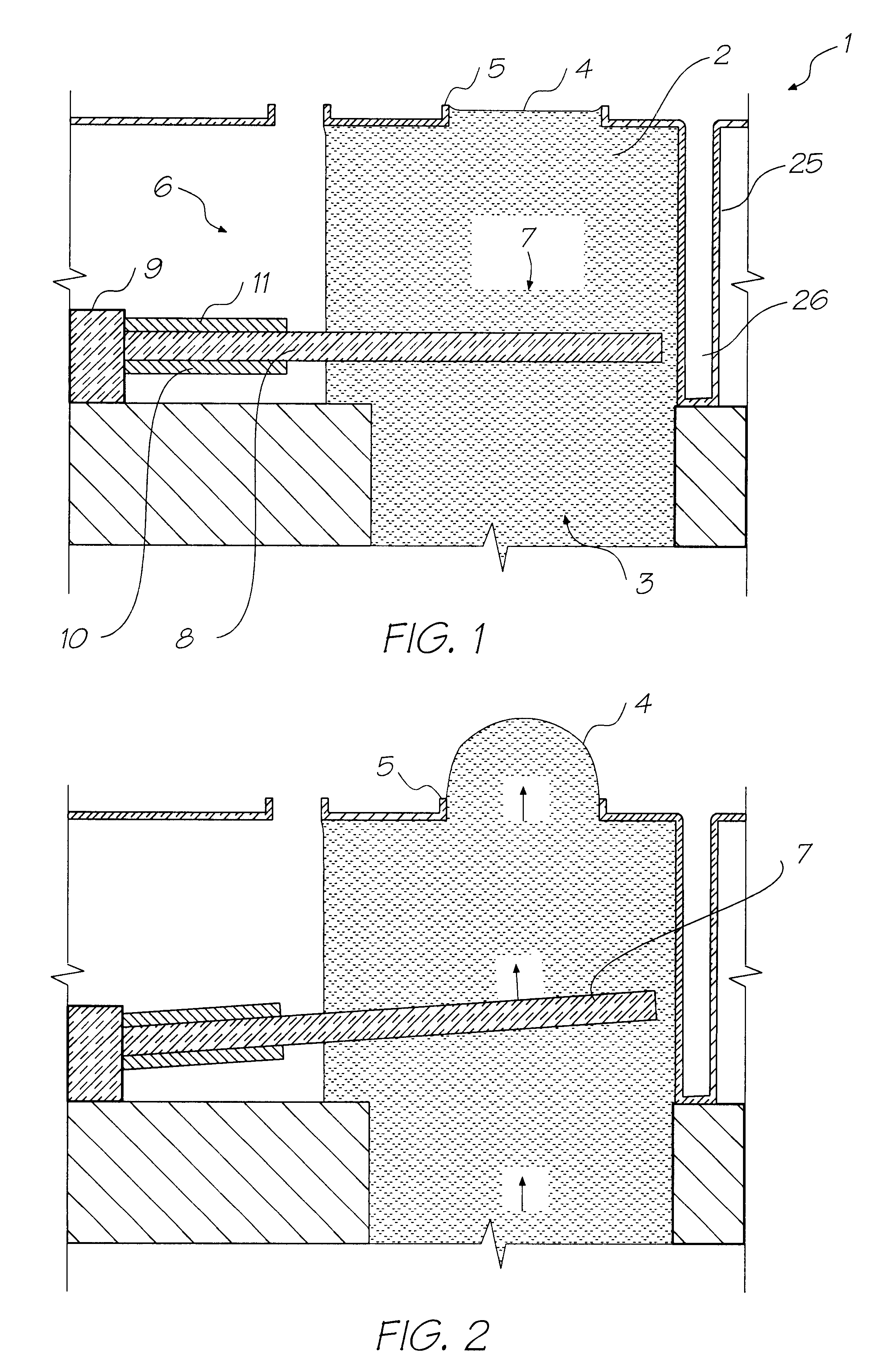

Organic electroluminance display

An organic EL display device is disclosed, which is fabricated in a tape automated bonding (TAB) method. The organic EL display device includes a driving part; a display panel including a substrate, a plurality of first and second electrodes formed on the substrate in a matrix type; and first and second lines having different lengths for being alternately arranged, and respectively applying signals from the driving part to the first and second electrodes; and a connecting part including a third line for electrically connecting the first and second lines to the driving part.

Owner:LG ELECTRONICS INC

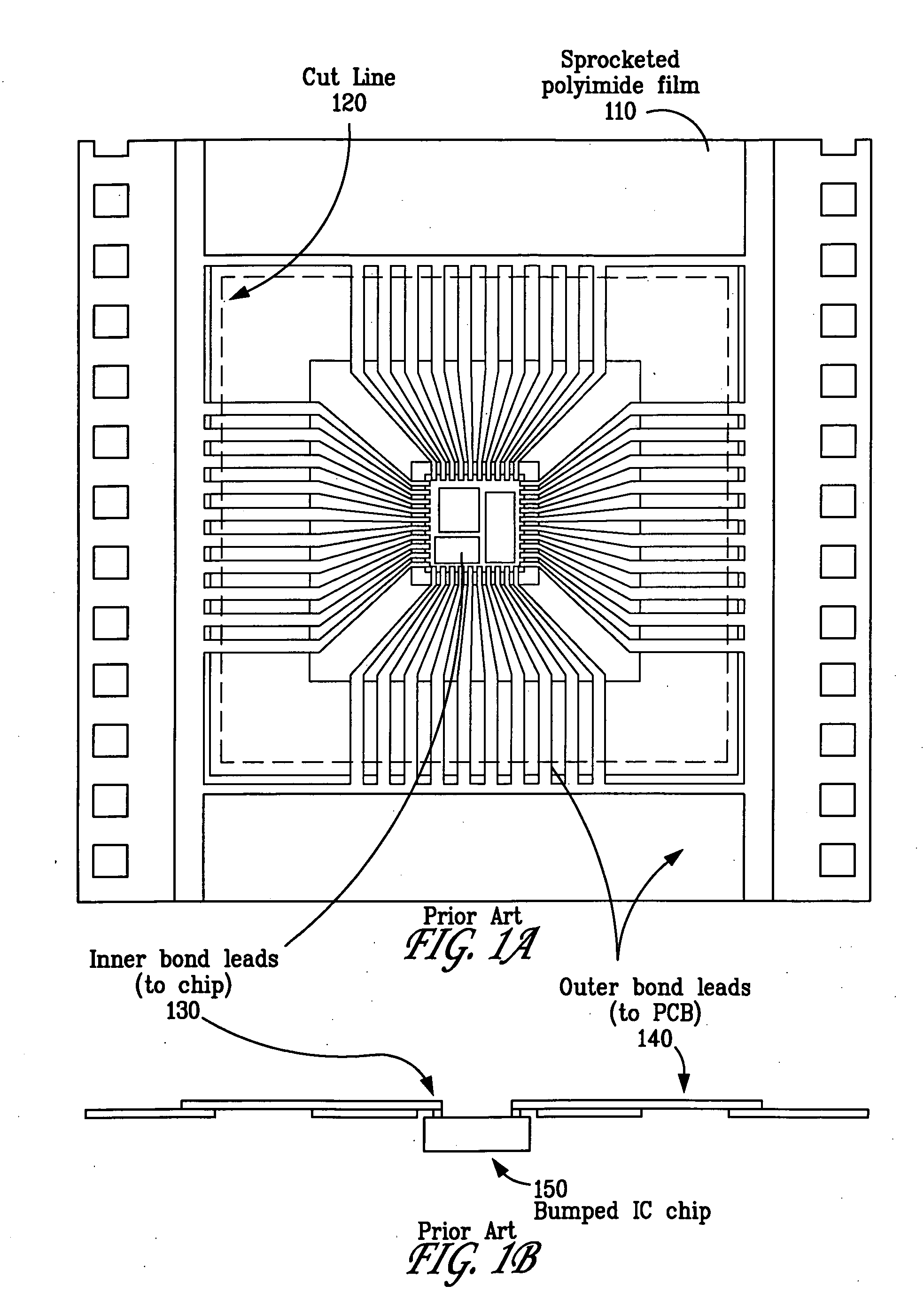

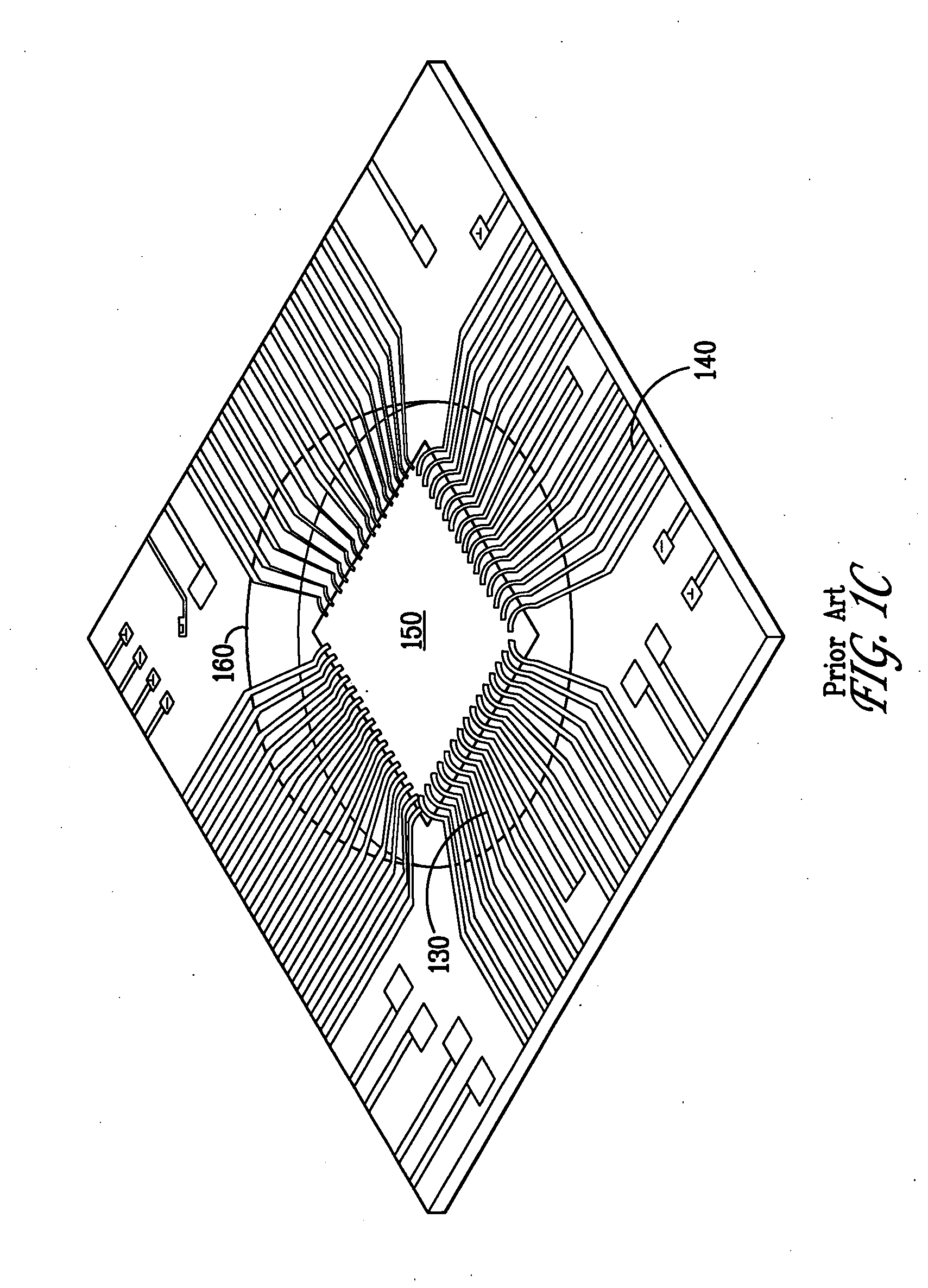

Micro-BGA beam lead connection with cantilevered beam leads

InactiveUS6515354B1Potent inhibitionIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesCantilevered beamMagnetic tape

A tape automated bonding (TAB) tape is provided with an insulating tape having a die receiving section. The TAB tape also has a conductive wiring pattern forming a plurality of traces including a land at one end and a beam lead at another end. A tape window is formed in a portion of the tape die receiving section. At least one trace beam lead extends over the tape window from a first direction and is connected to a tie bar adjacent an opposing side of the tape window and at least one trace beam lead extends over the tape window from a second direction different than the first direction and is cantilevered over the tape window.

Owner:ADVANCED MICRO DEVICES INC

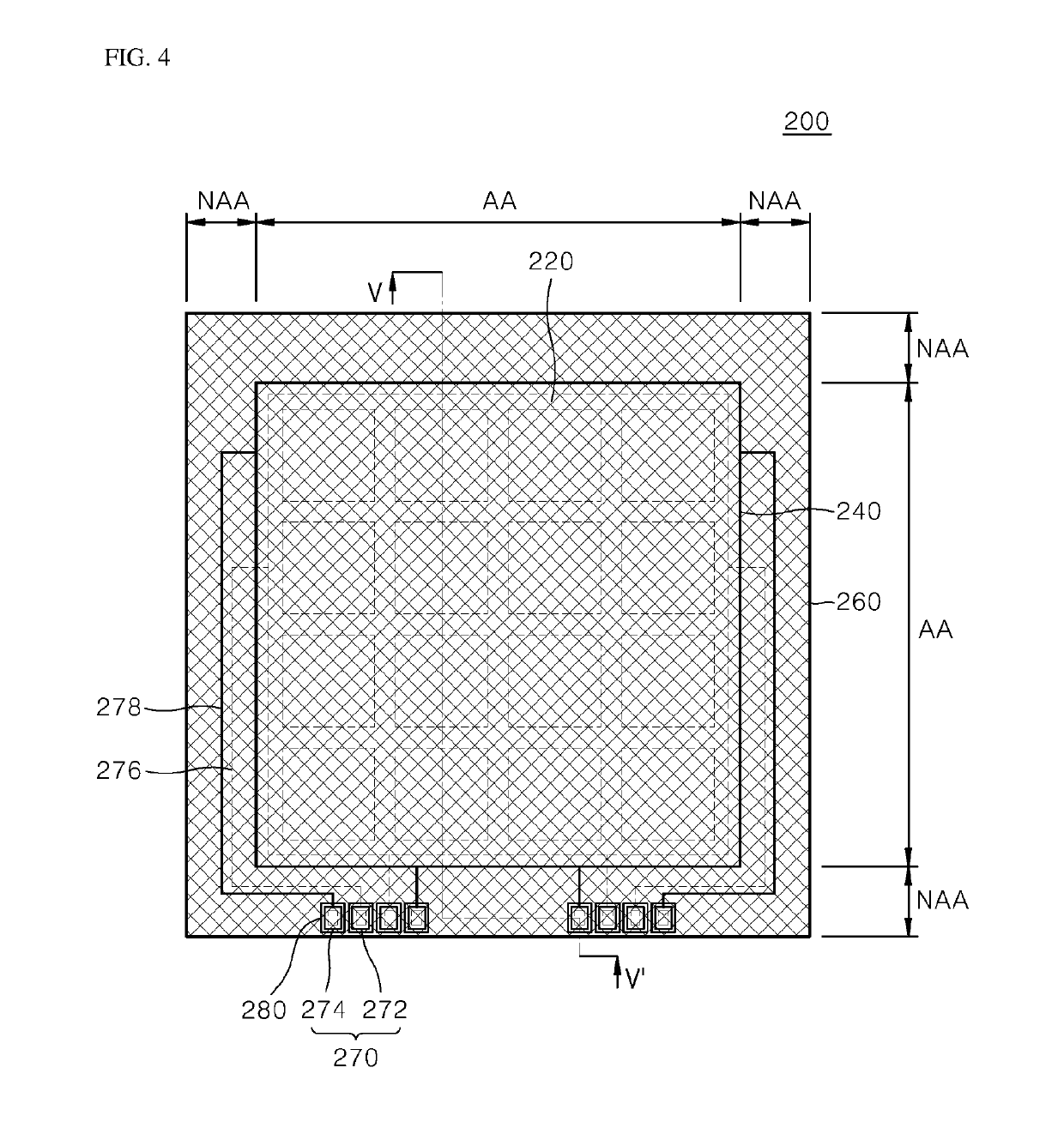

OLED lighting apparatus

ActiveUS20190165297A1Improve reliabilityReduce manufacturing costStatic indicating devicesFinal product manufactureEffect lightElectrical connection

Disclosed herein is an OLED lighting apparatus which can achieve both improvement in reliability and reduction in manufacturing cost. In the OLED lighting apparatus, an encapsulation layer is disposed over the active area and the non-active area on a buffer layer, such that a pad disposed in the non-active area of the buffer layer can be stably secured by the encapsulation layer bonded thereto. Accordingly, upon tape automated bonding between an FPCB substrate with a COF tape attached thereto and a via electrode, the COF tape does not directly contact the pad but contacts the via electrode connected to the pad, particularly a connection terminal of the via electrode disposed on an upper surface of the encapsulation layer, thereby establishing electrical connection between the FPCB substrate and the via electrode. In this way, the connection terminal of the via electrode is electrically connected to the FPCB substrate via the COF tape, whereby a signal from the outside can be applied to the pad connected to the via electrode.

Owner:LG DISPLAY CO LTD

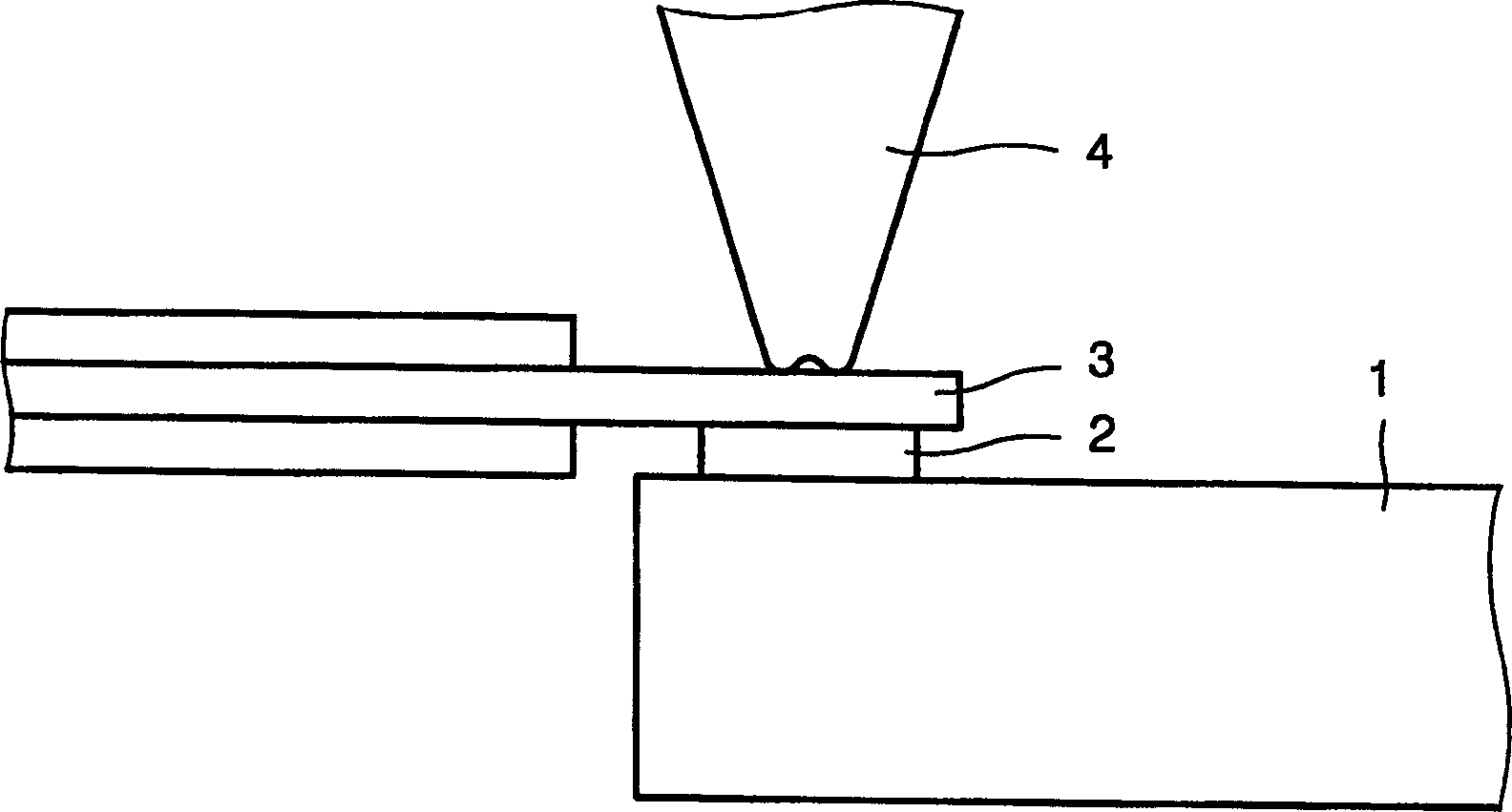

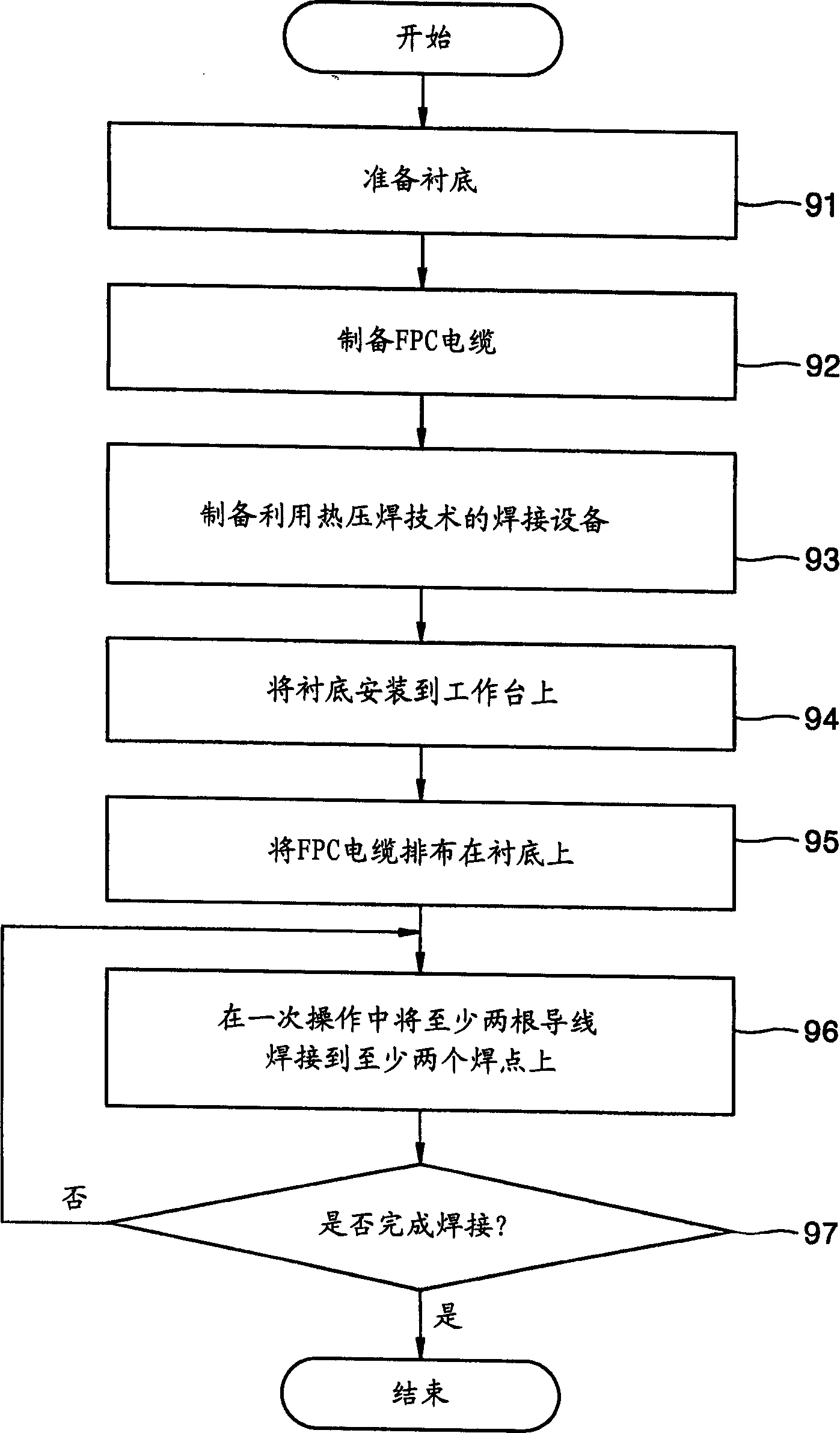

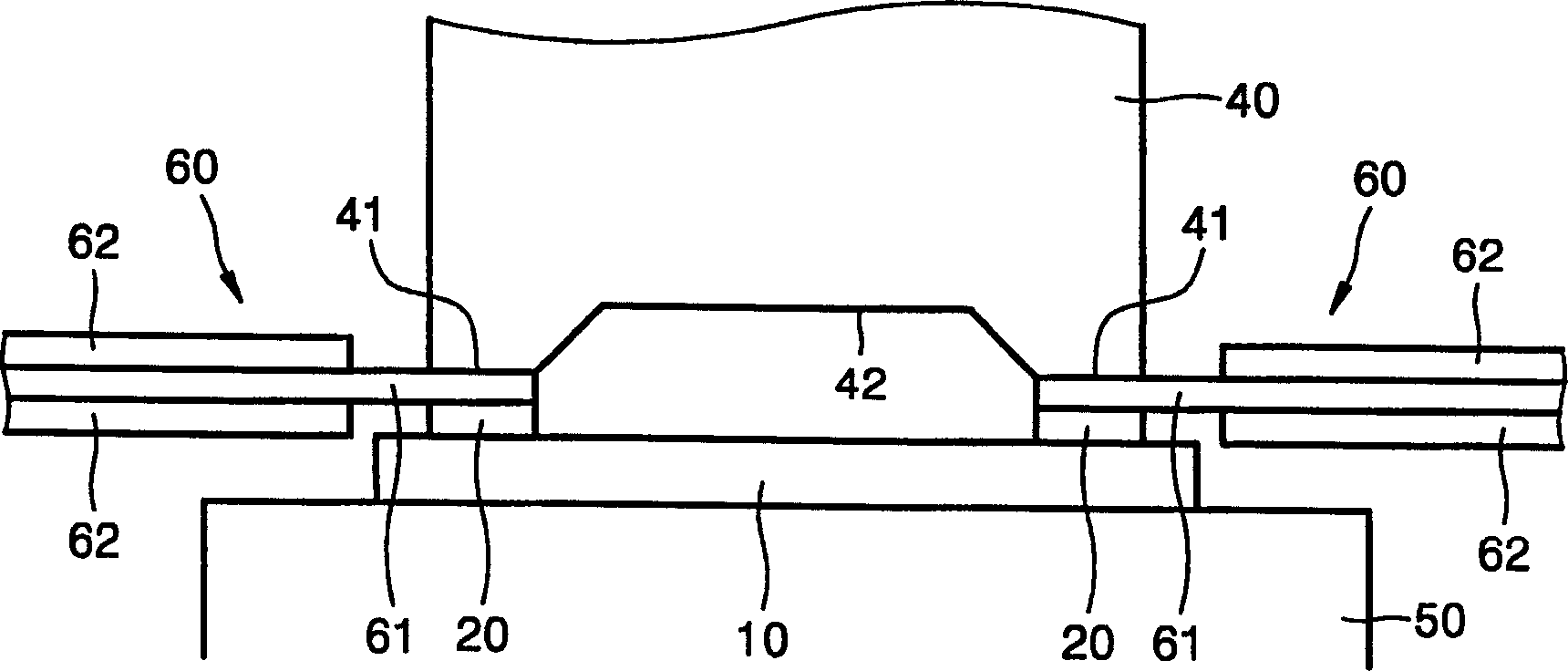

Ink jet printer head and method and device for welding flexible printed circuit wire of printer head

InactiveCN1459352AShorten the timeImprove structural strengthPrinted circuit assemblingPrinted circuit aspectsEngineeringOff phenomenon

Owner:SAMSUNG ELECTRONICS CO LTD

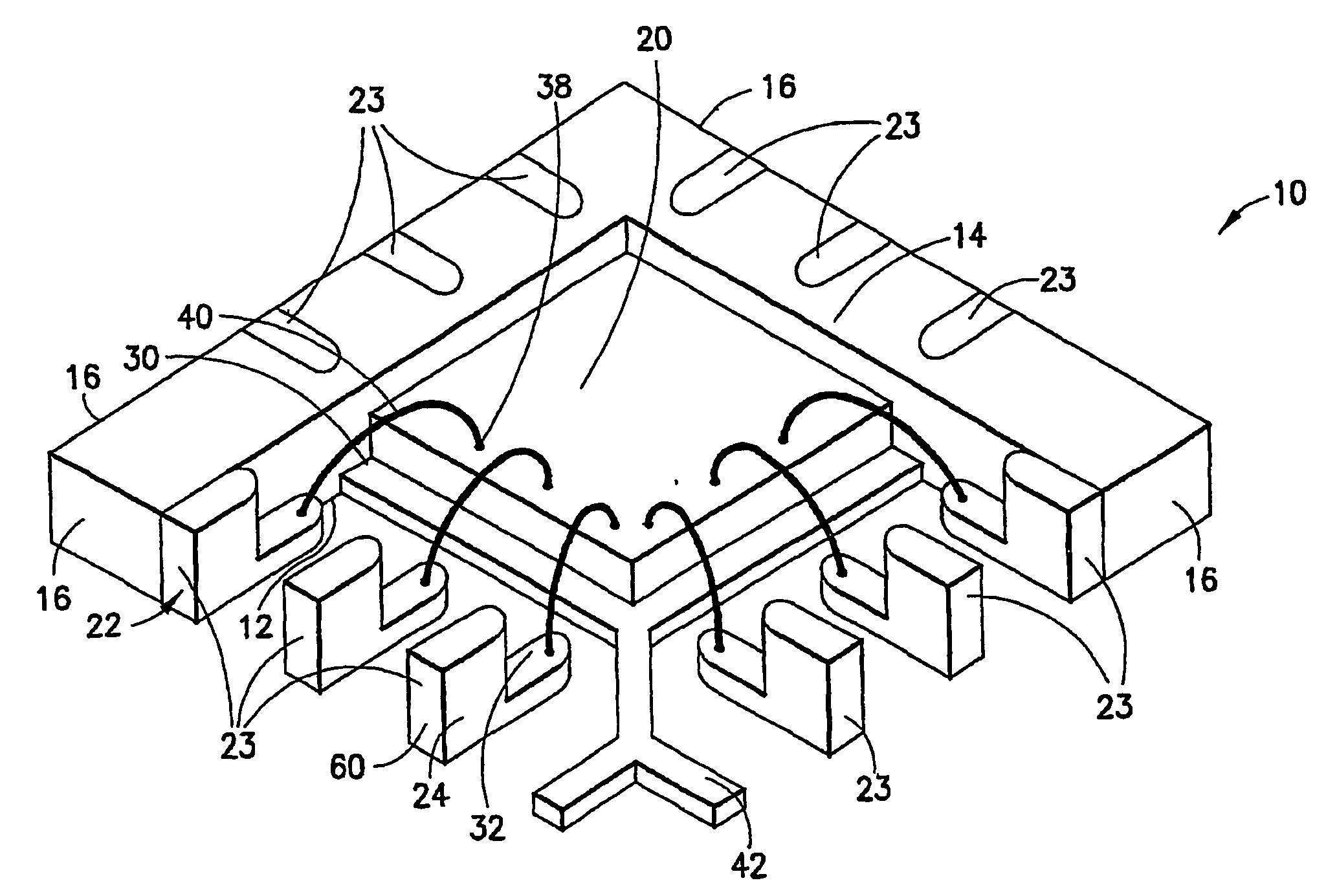

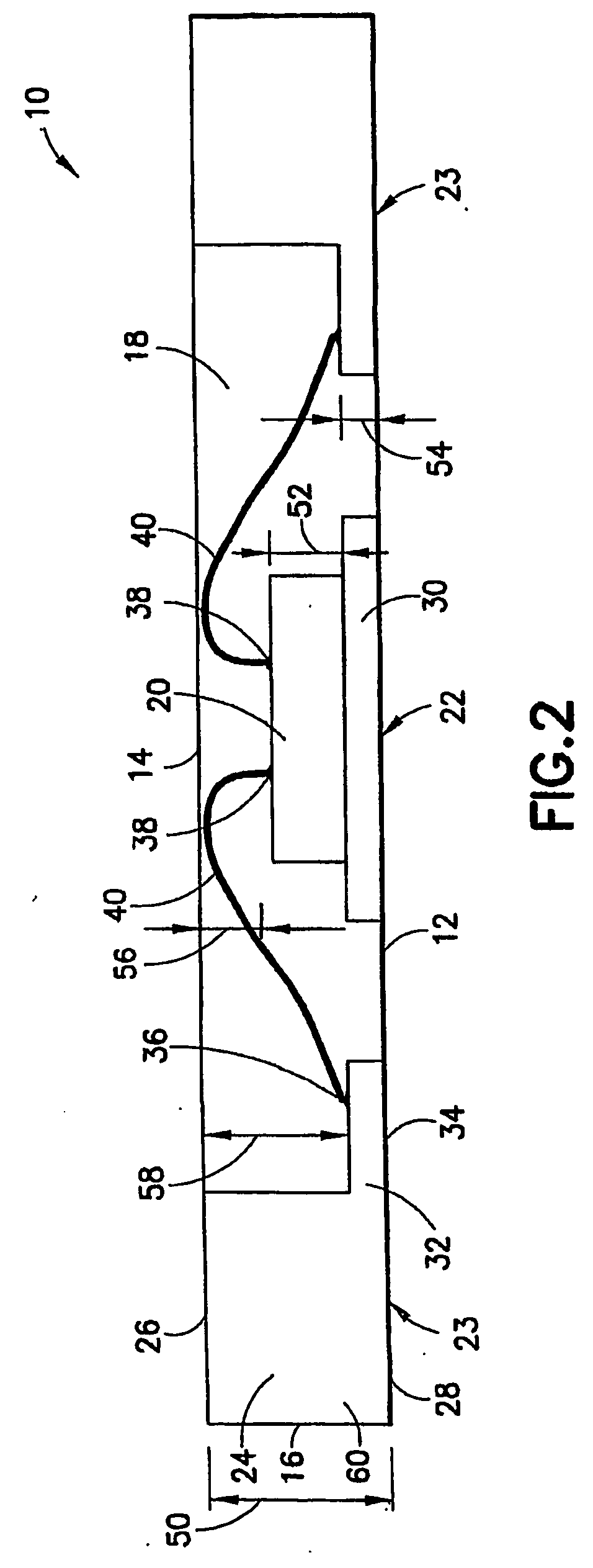

Multi-head tab bonding tool

InactiveUS20060071050A1Accelerate TAB bonding processEnhanced bondingWelding/cutting auxillary devicesAuxillary welding devicesTape-automated bondingPower flow

A bonding tool for use in multi-head tape automated bonding (TAB) is provided. The bonding tool comprises a plurality of TAB bonding heads, the TAB bonding heads providing for electrical dissipation wherein current flow is low enough so as not to damage a device being bonded and high enough to avoid the build up of a charge that may discharge to the device being bonded.

Owner:REIBER STEVEN F