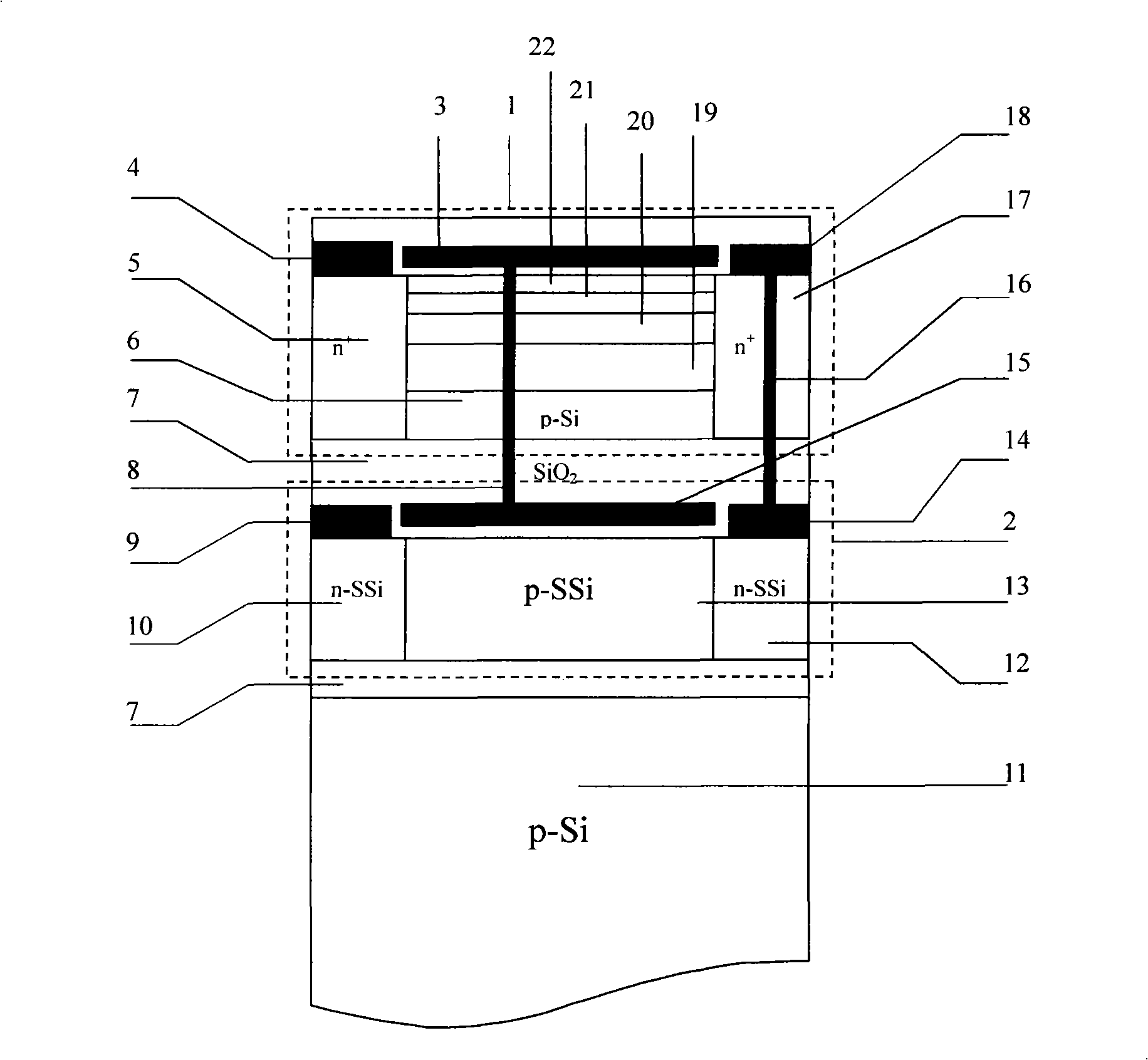

Three-dimensional quantum well NMOS integrated component and preparation method thereof

A technology of integrated devices and quantum wells, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problem of low speed, reduce carrier scattering, enhance carrier transport capacity, The effect of increasing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

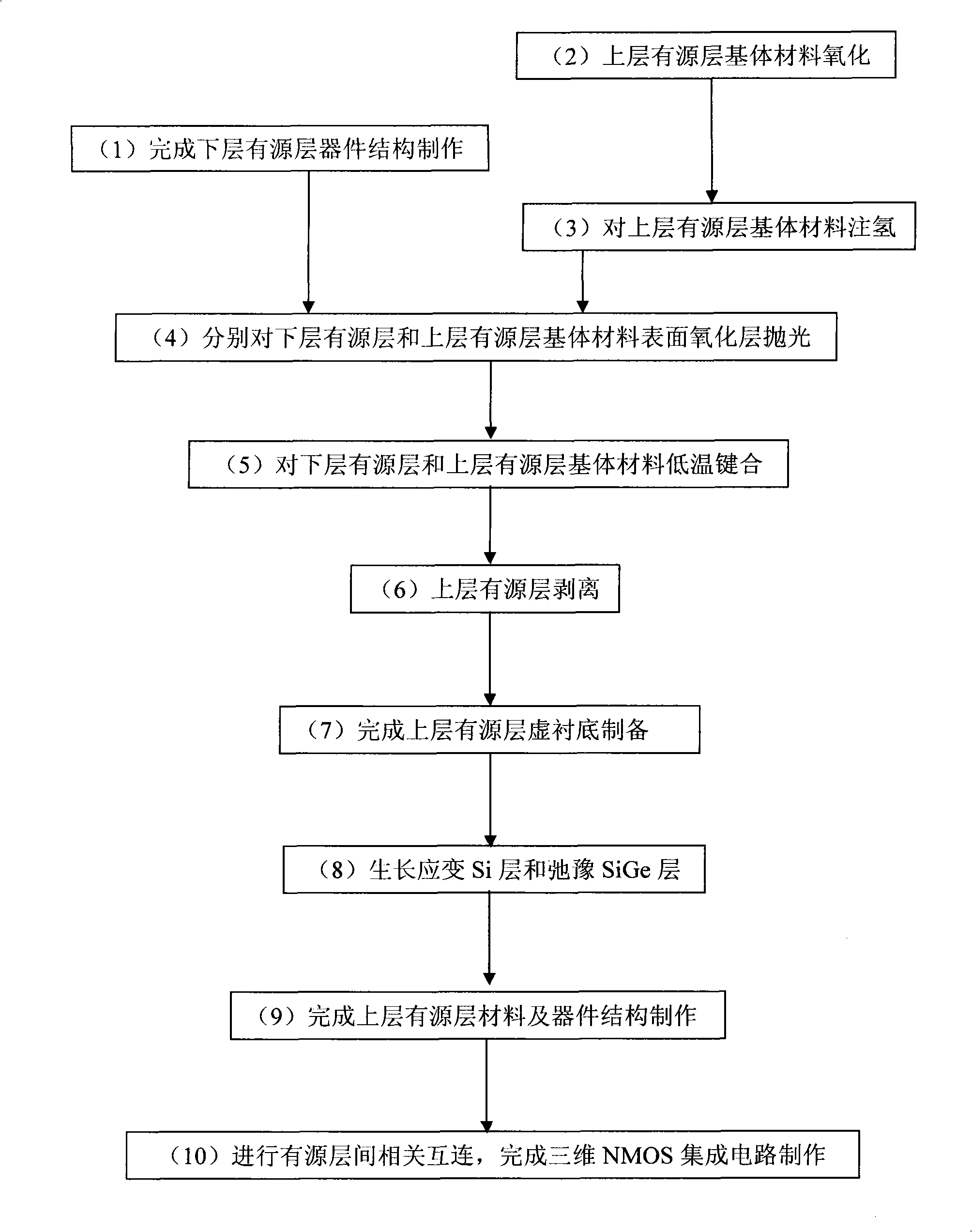

[0039] Embodiment 1: the steps of making a three-dimensional quantum well NMOS integrated device with a conductive channel of 90nm are as follows:

[0040] (1) Select SSOI substrates with stress > 1Gpa;

[0041] (2) On the SSOI substrate, use oxidation-photolithography source, drain, gate region-gate oxidation-deposit polysilicon-photolithography polysilicon and diffusion layer contact hole-deposition polysilicon-photolithography polysilicon-phosphorus implantation-low temperature deposition Product SiO 2 - Lithographic wiring holes - polysilicon wiring - low temperature deposition of SiO 2 For the dielectric layer, make a strained Si nMOSFET device structure and interconnection with a conductive channel of 90nm, and complete the lower active layer structure;

[0042] (3) Deposit SiO on the surface of the above active layer 2 medium layer;

[0043] (4) Carry out surface oxidation to the cleaned p-type Si sheet, as the upper substrate material;

[0044] (5) Using an ion im...

Embodiment 2

[0052] Embodiment 2: the steps of making a three-dimensional quantum well NMOS integrated device with a conductive channel of 130nm are as follows:

[0053] (1) Select SSOI substrates with stress > 1Gpa;

[0054] (2) On the SSOI substrate, use oxidation-photolithography source, drain, gate region-gate oxidation-deposit polysilicon-photolithography polysilicon and diffusion layer contact hole-deposition polysilicon-photolithography polysilicon-phosphorus implantation-low temperature deposition Product SiO 2 - Lithographic wiring holes - polysilicon wiring - low temperature deposition of SiO 2 For the dielectric layer, make a strained Si nMOSFET device structure and interconnections with a conductive channel of 130nm, and complete the lower active layer structure;

[0055] (3) Deposit SiO on the surface of the above active layer 2 medium layer;

[0056] (4) Carry out surface oxidation to the cleaned p-type Si sheet, as the upper substrate material;

[0057] (5) Using an ion...

Embodiment 3

[0065] Embodiment 3: the steps of making a three-dimensional quantum well NMOS integrated device with a conductive channel of 65nm are as follows:

[0066] (1) Select SSOI substrates with stress > 1Gpa;

[0067] (2) On the SSOI substrate, use oxidation-photolithography source, drain, gate region-gate oxidation-deposit polysilicon-photolithography polysilicon and diffusion layer contact hole-deposition polysilicon-photolithography polysilicon-phosphorus implantation-low temperature deposition Product SiO 2 - Lithographic wiring holes - polysilicon wiring - low temperature deposition of SiO 2 For the dielectric layer, make a strained Si nMOSFET device structure and interconnections with a conductive channel of 65nm, and complete the lower active layer structure;

[0068] (3) Deposit SiO on the surface of the above active layer 2 medium layer;

[0069] (4) Carry out surface oxidation to the cleaned p-type Si sheet, as the upper substrate material;

[0070] (5) Using an ion i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com