Patents

Literature

398results about How to "Simplify the packaging process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

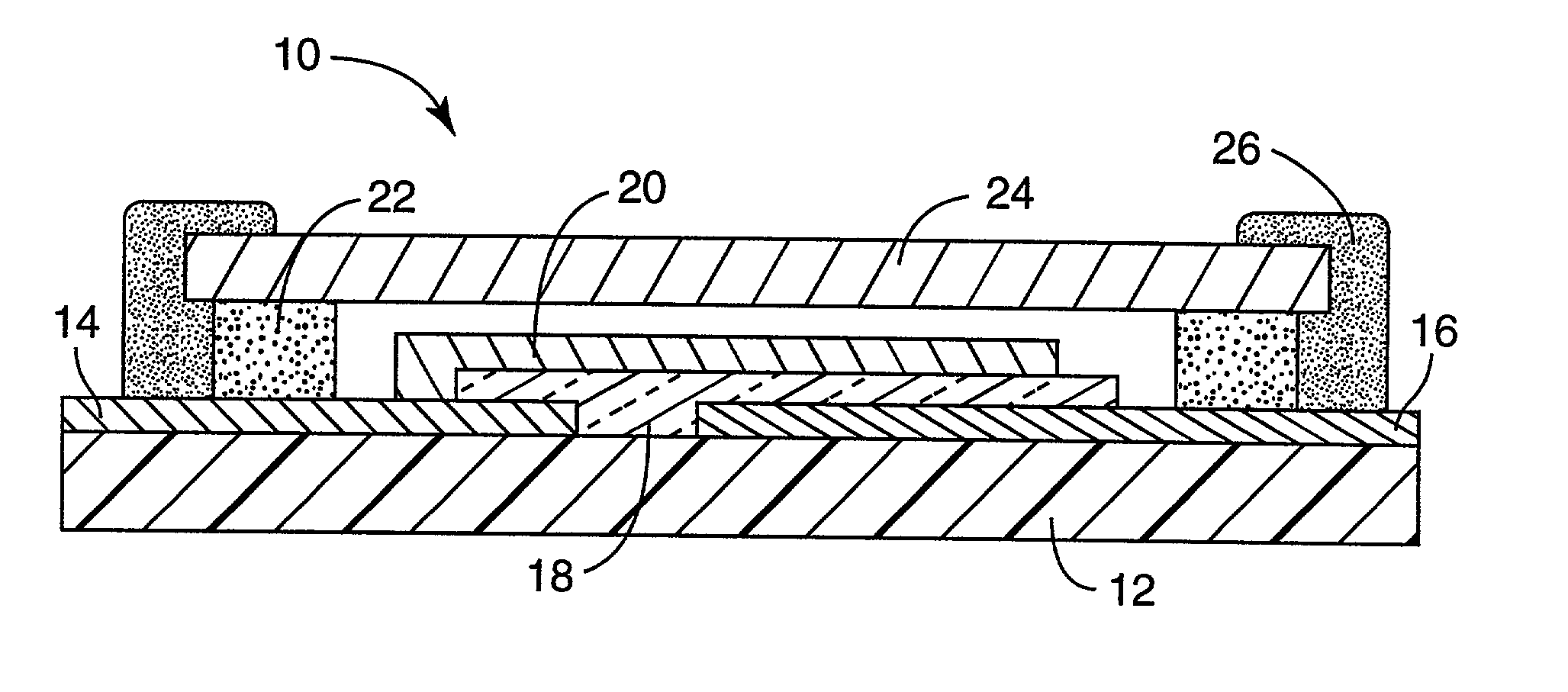

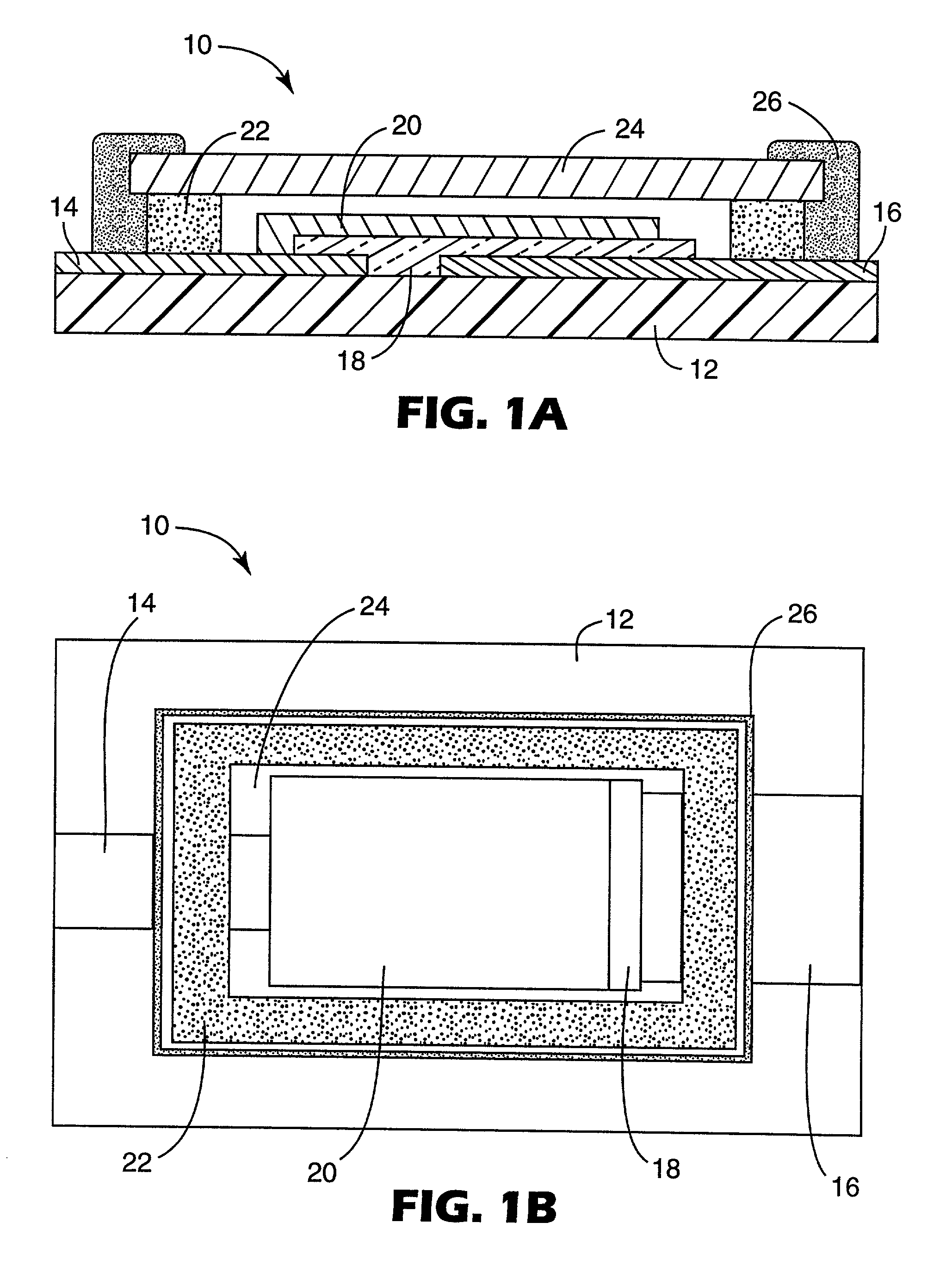

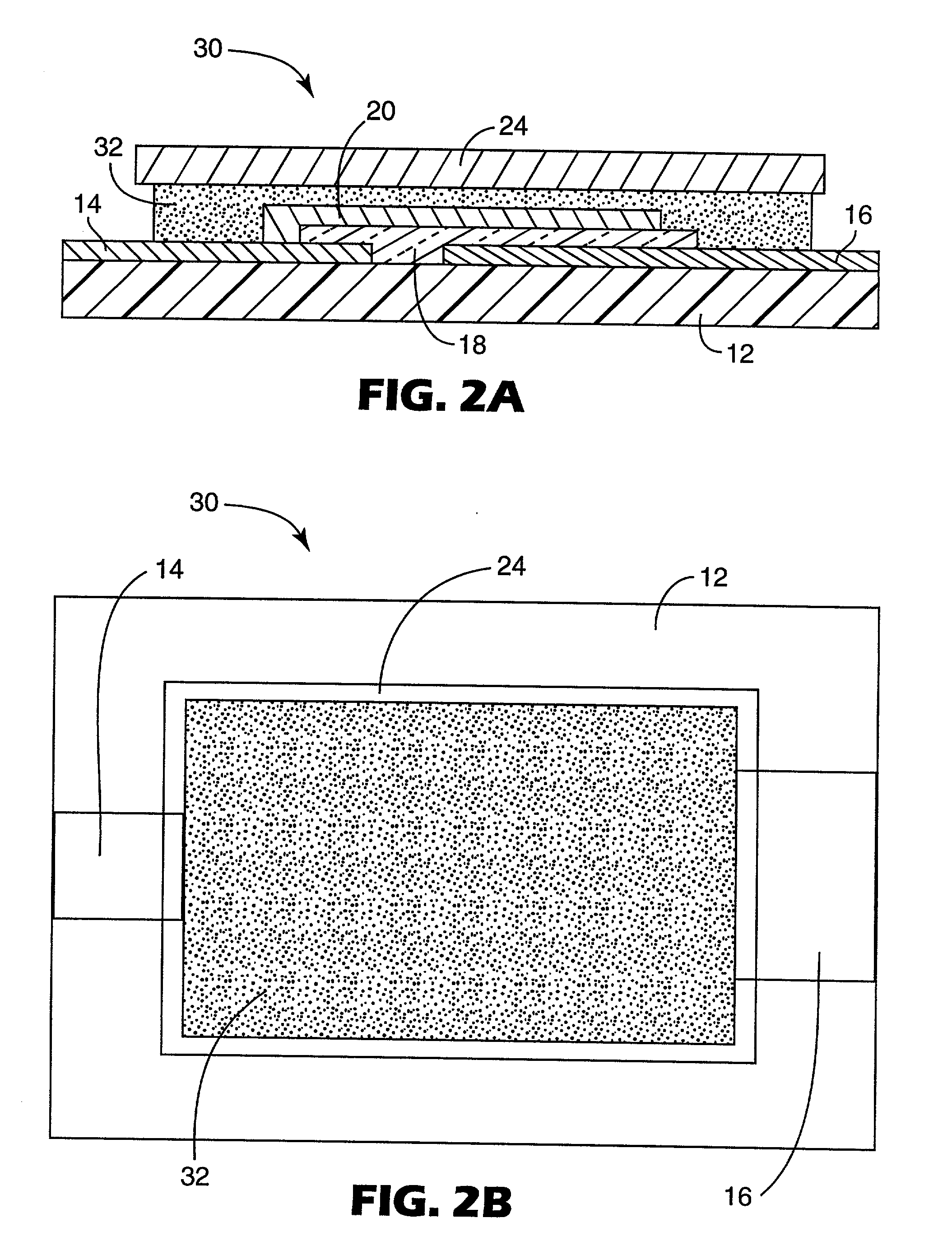

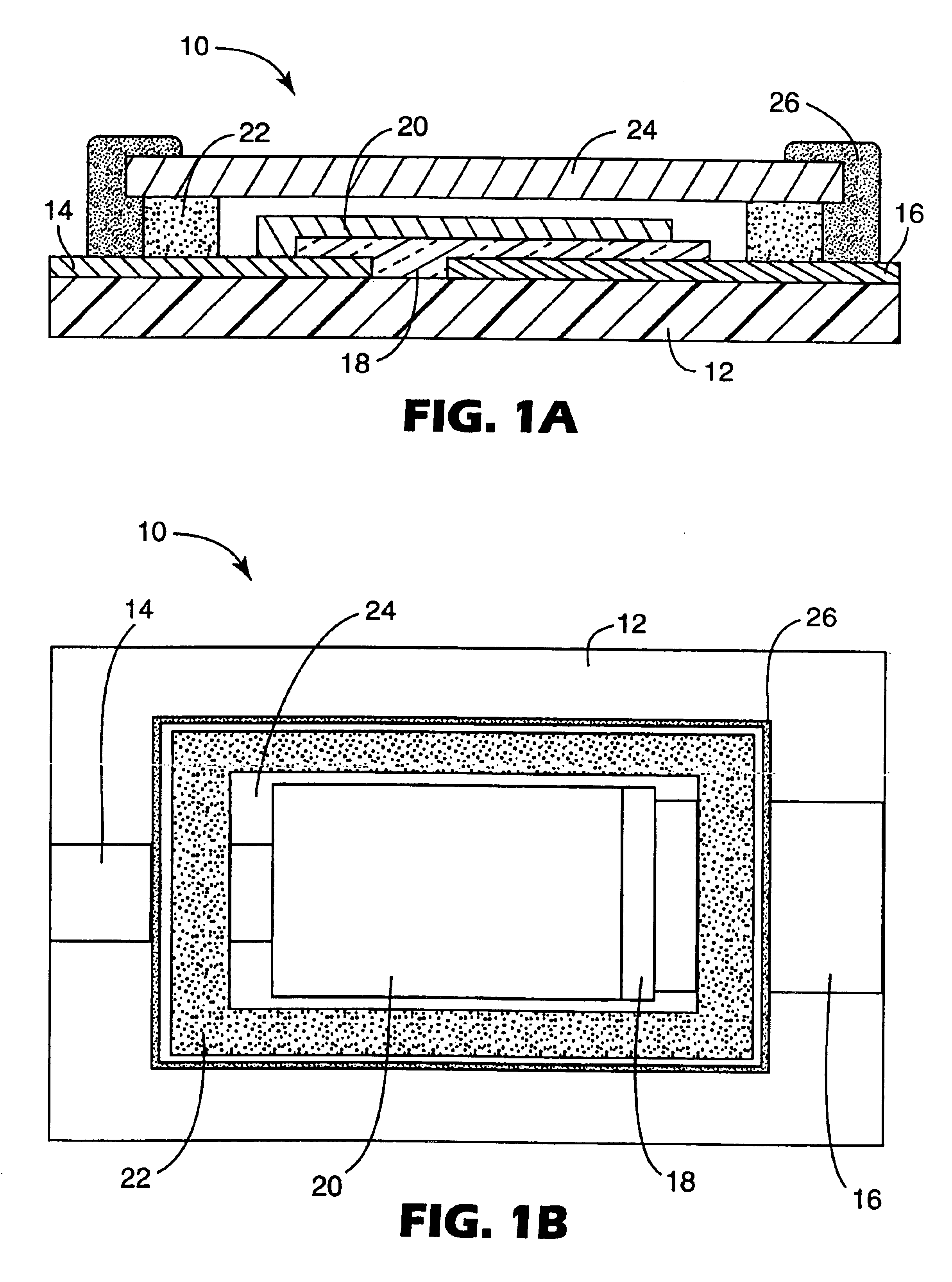

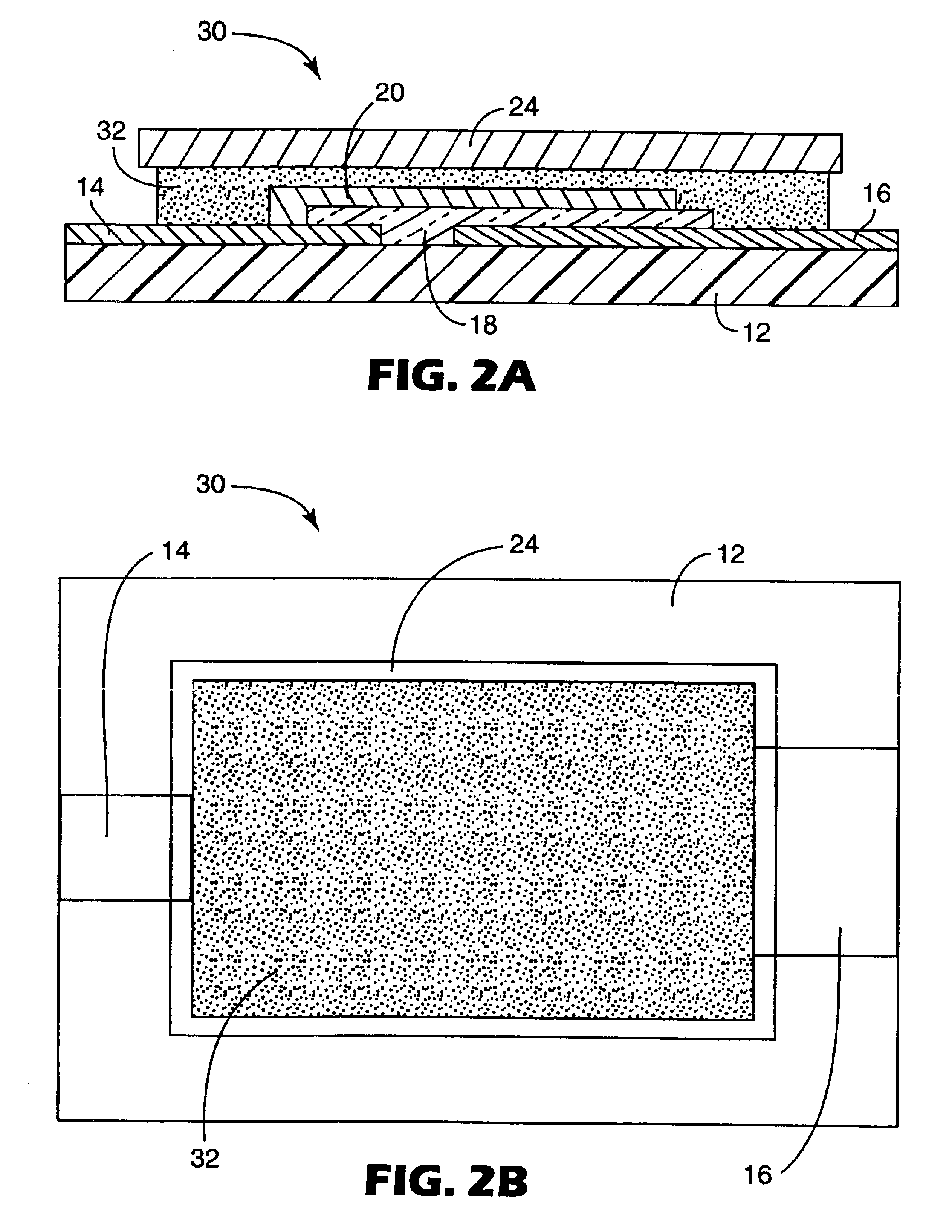

Encapsulation of organic electronic devices using adsorbent loaded adhesives

InactiveUS20030143423A1Effective and easy-to-applyImprove abilitiesDischarge tube luminescnet screensElectroluminescent light sourcesDesiccantSorbent

Disclosed herein are organic electronic devices that are encapsulated at least in part by adsorbent-loaded transfer adhesives. The adsorbent material may be a dessicant and / or a getterer. The adsorbent-loaded transfer adhesive may form a gasket around the periphery of the device, or may cover the entire device and its periphery. An encapsulating lid covers the device.

Owner:3M INNOVATIVE PROPERTIES CO

Encapsulation of organic electronic devices using adsorbent loaded adhesives

InactiveUS6936131B2Improve abilitiesSimplify the packaging processSolid-state devicesSemiconductor/solid-state device manufacturingDesiccantSorbent

Owner:3M INNOVATIVE PROPERTIES CO

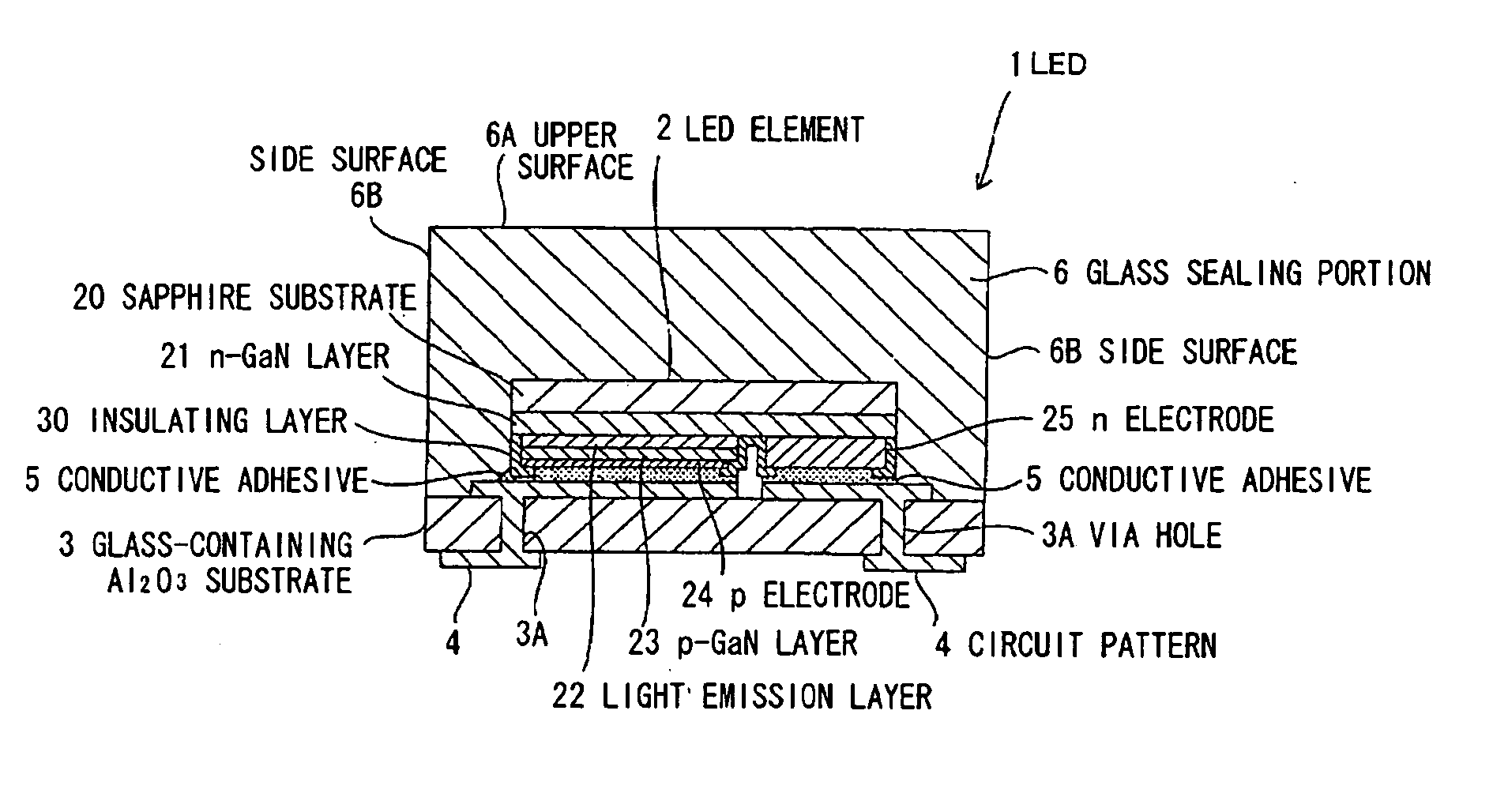

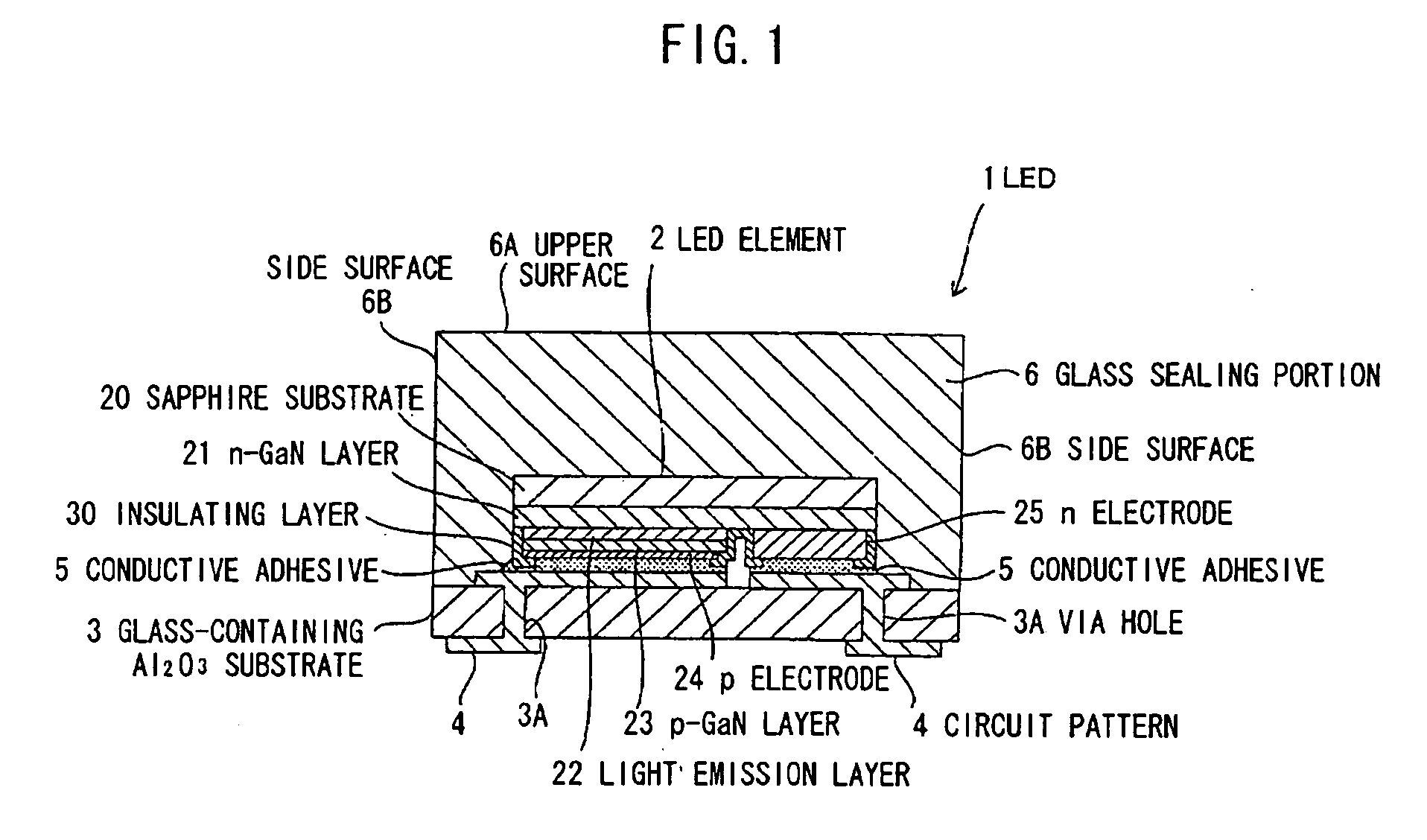

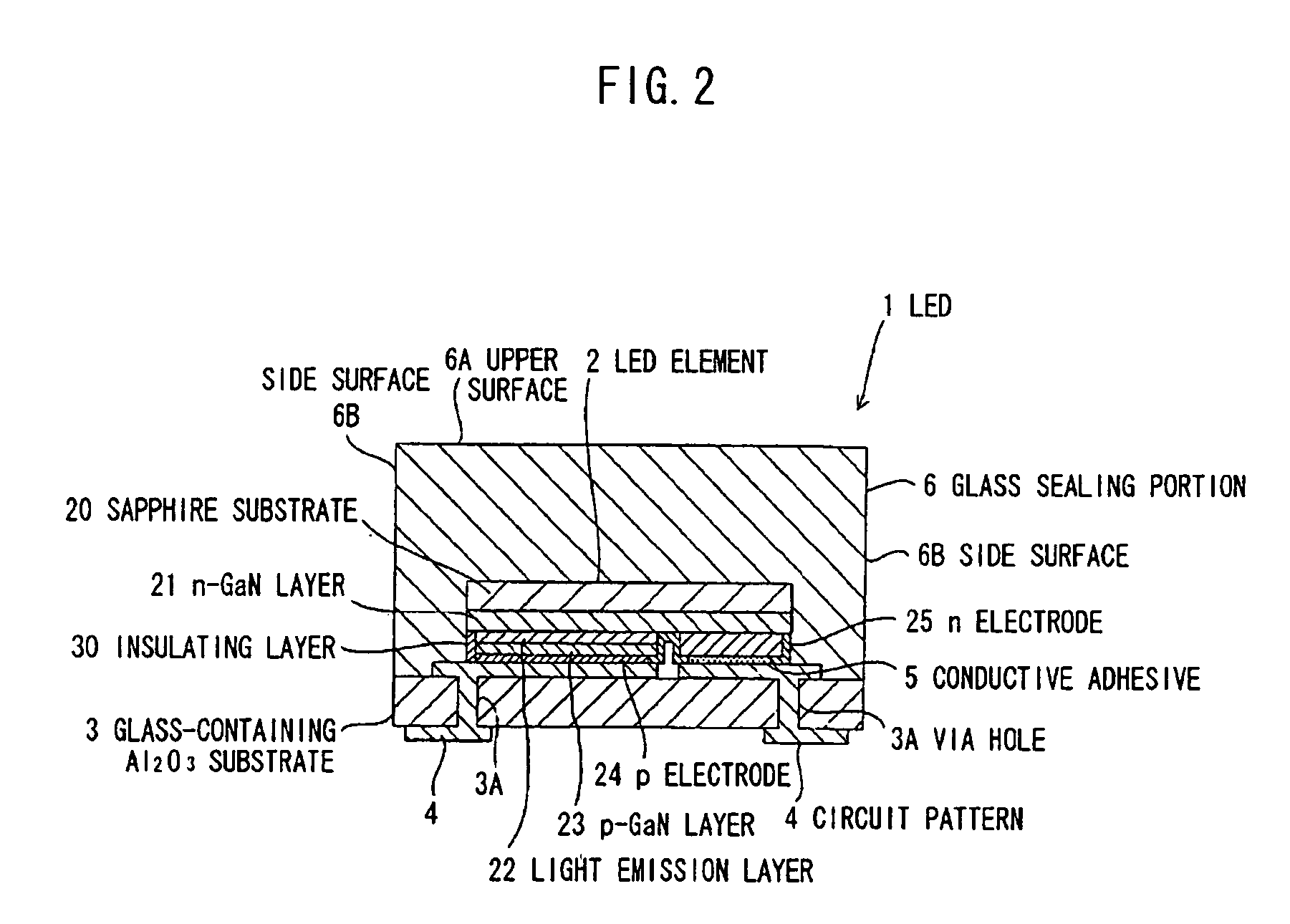

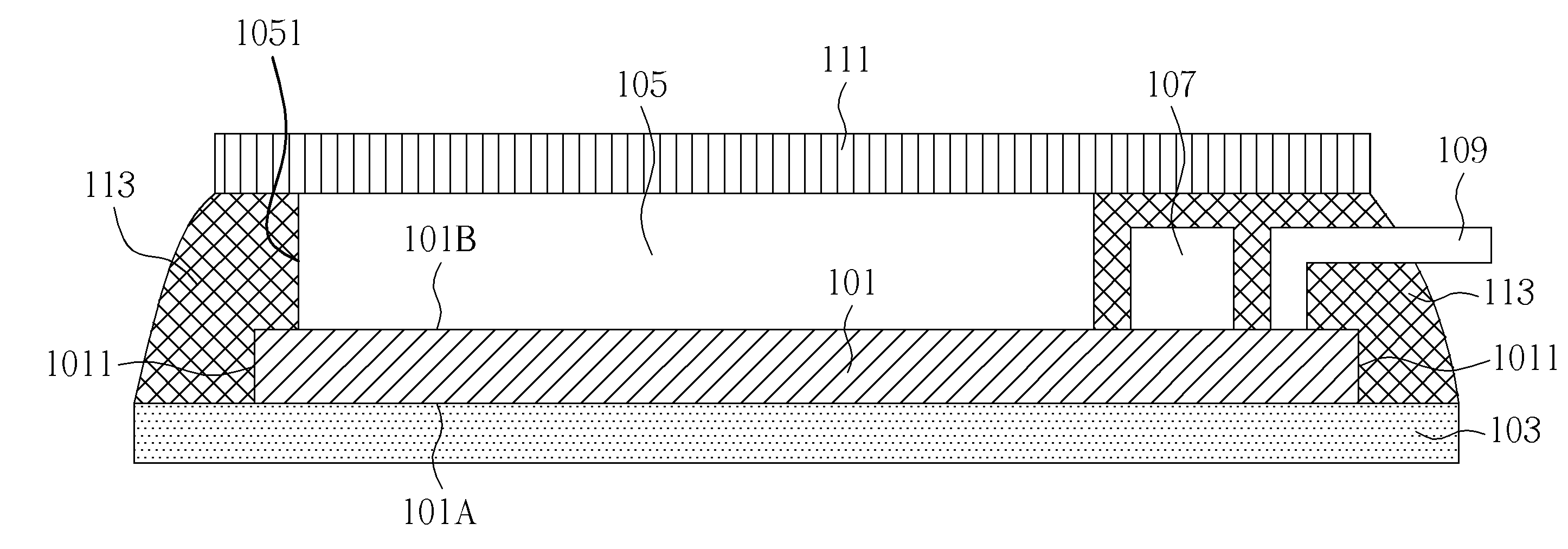

Solid state device and light-emitting element

ActiveUS20060049335A1Excellent in componentFirmly connectedLighting support devicesSemiconductor/solid-state device detailsSolid massThermal expansion

A solid-state device having: a flip-chip mounted solid-state element; a power receiving / feeding portion having a mounting substrate to allow that a mounting surface of the solid-state element forms substantially the same plane as a surface of the mounting substrate; and an inorganic sealing portion made of an inorganic sealing material having a thermal expansion coefficient equal to that of the power receiving / feeding portion for sealing the solid-state element.

Owner:TOYODA GOSEI CO LTD

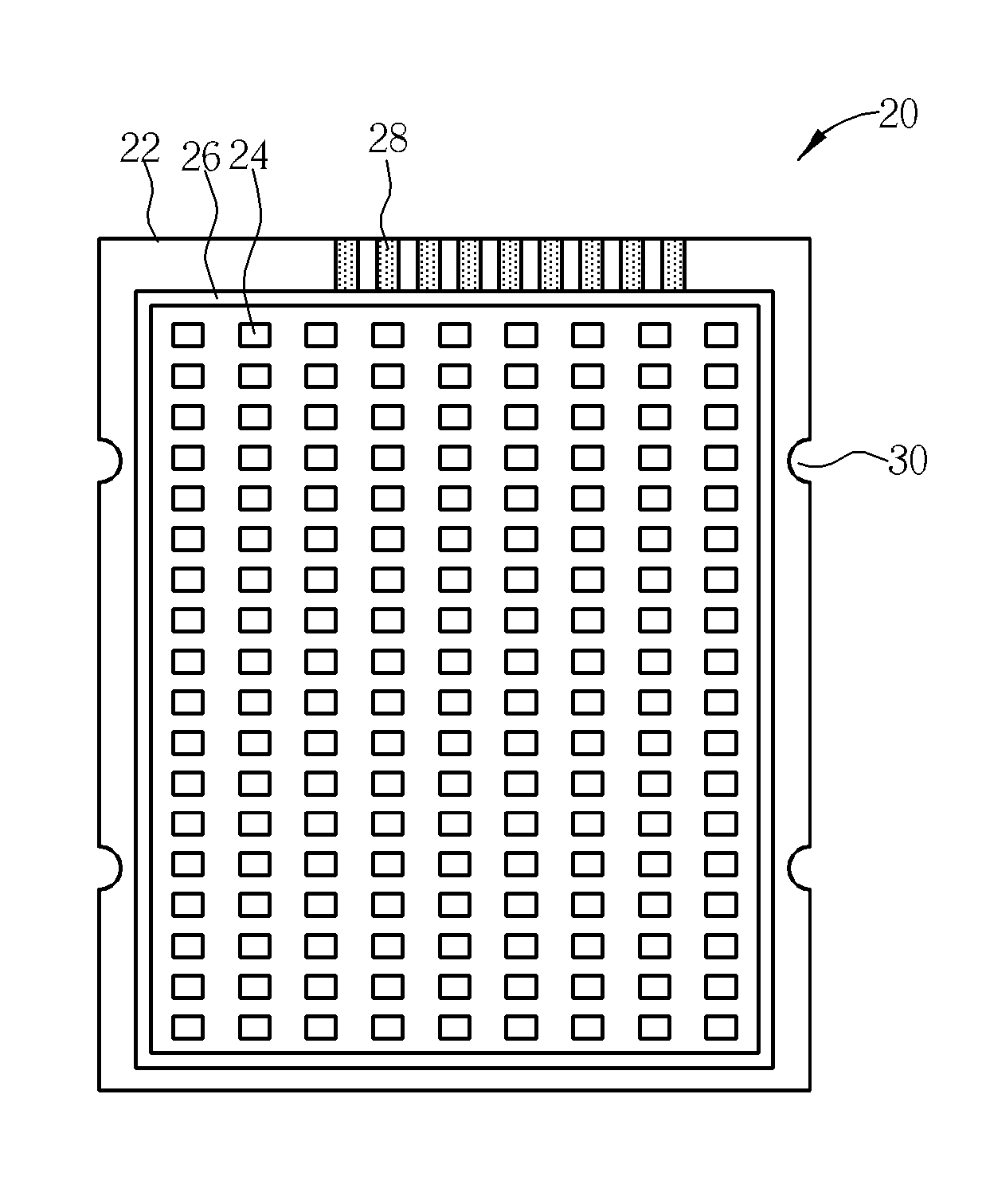

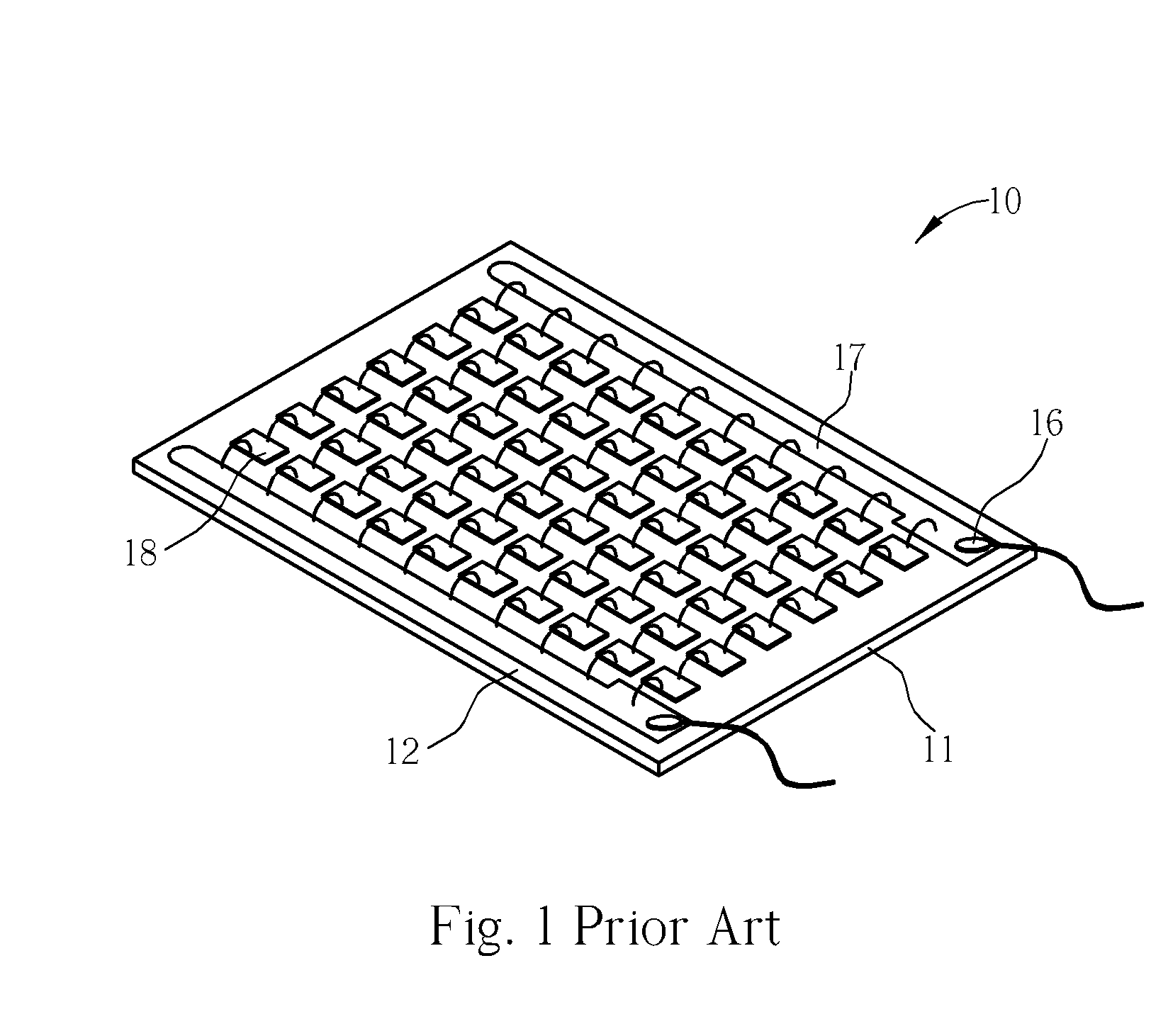

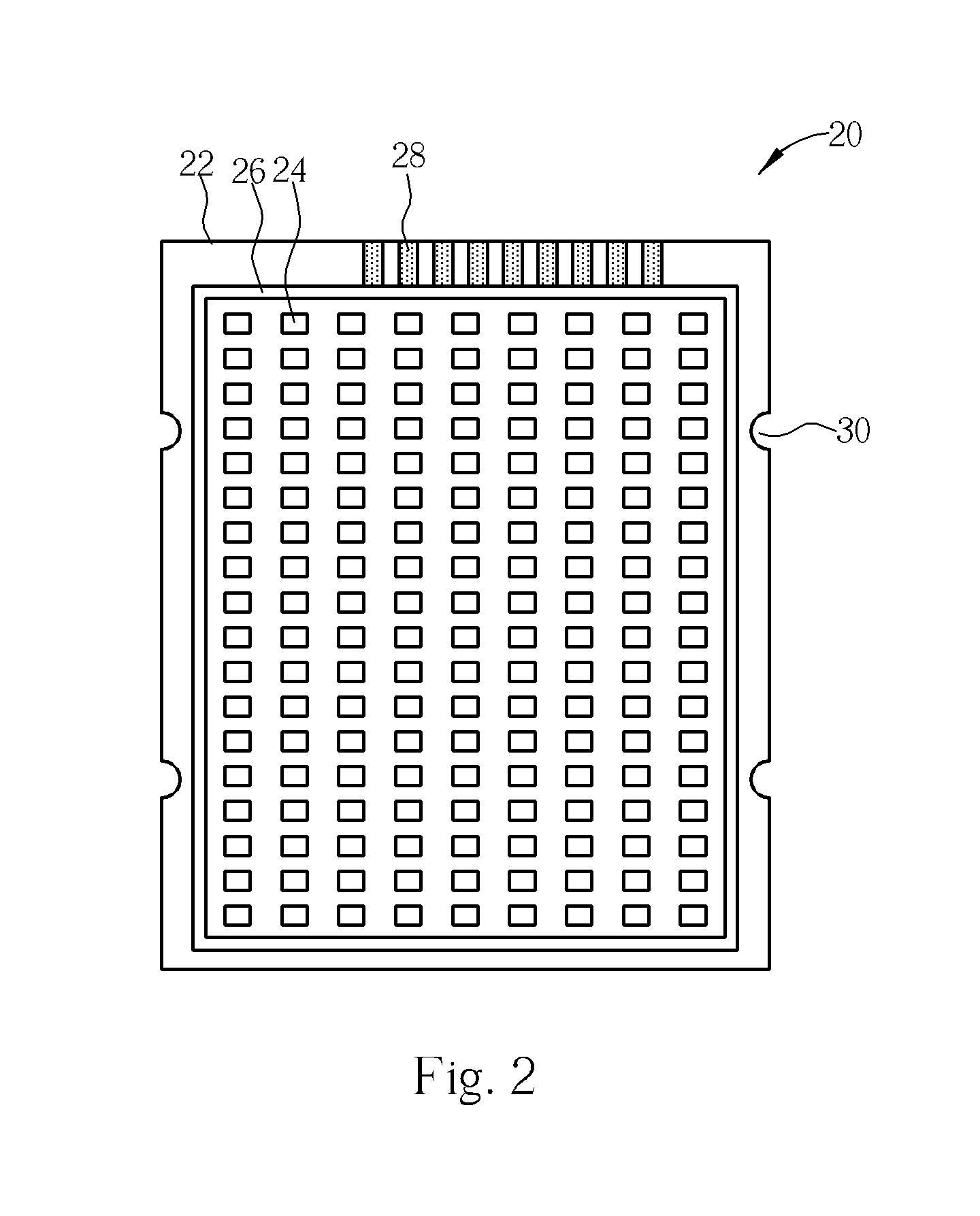

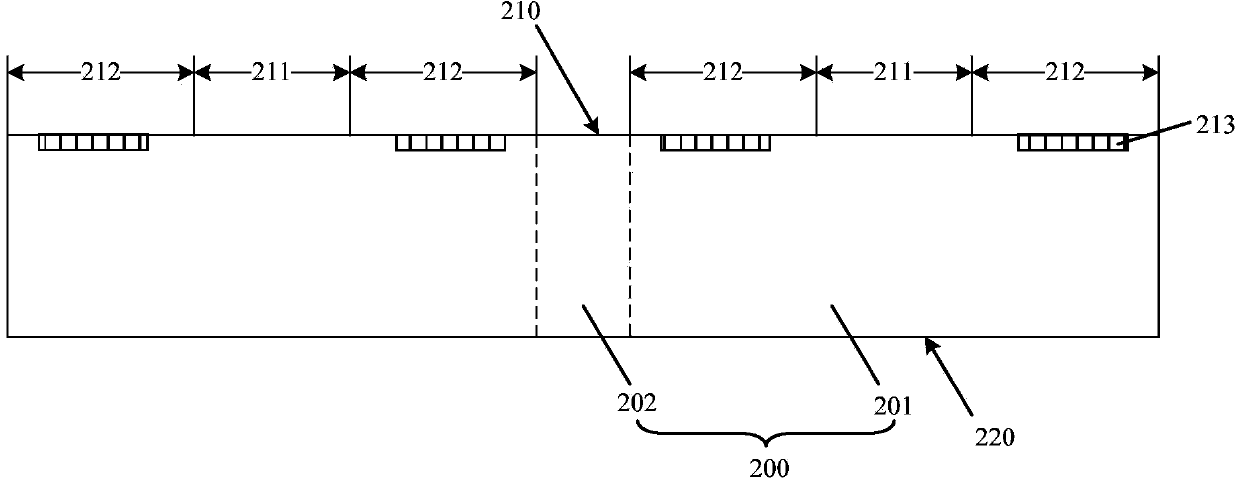

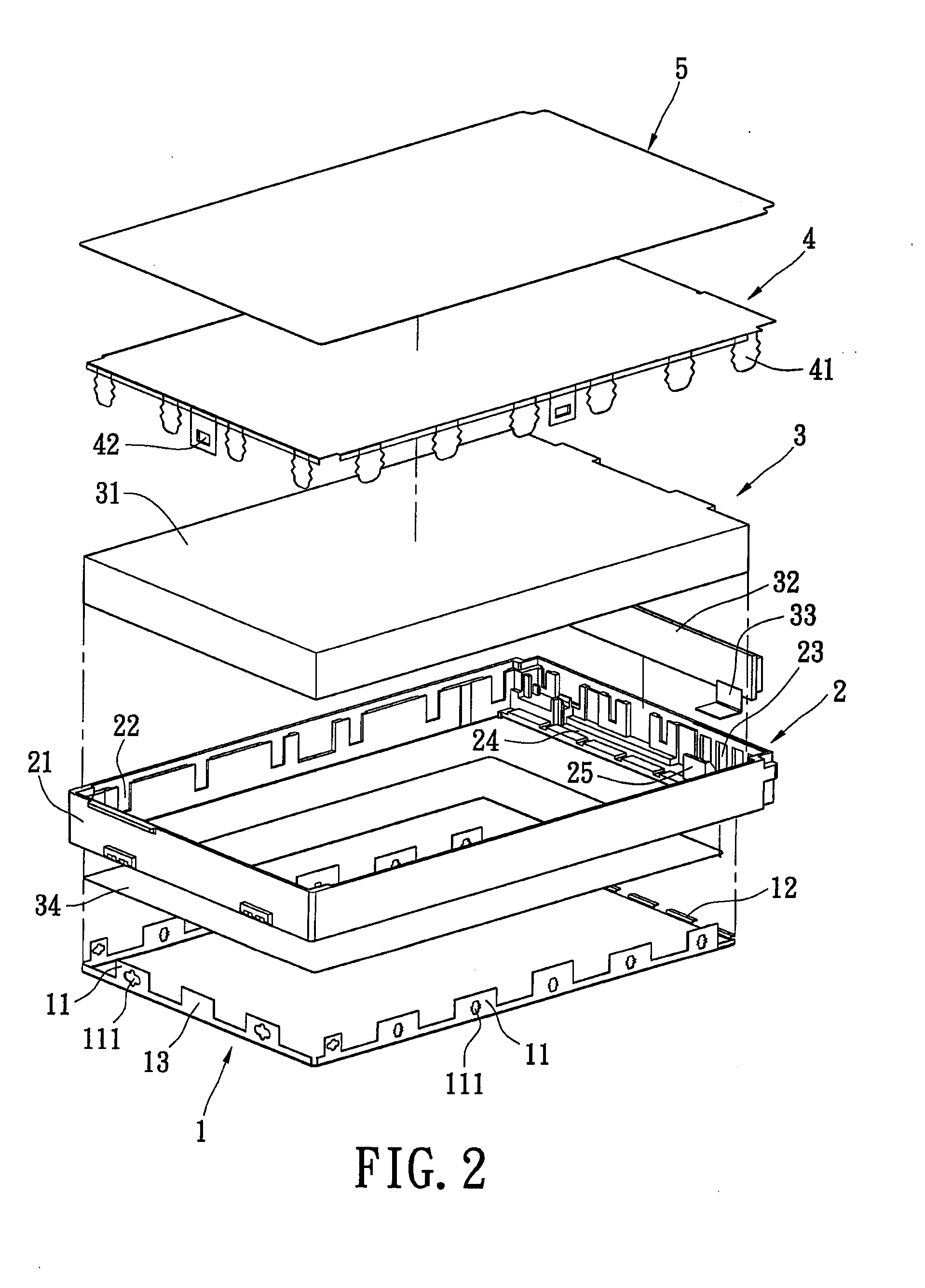

Sectional light emitting diode backlight unit

InactiveUS20070103939A1Small sizeSimplify the packaging processOptical light guidesNon-linear opticsEngineeringLight-emitting diode

A sectional light emitting diode backlight unit comprising a circuit board, a frame disposed on the circuit board, a plurality of light emitting diode dies disposed on the circuit board inside the frame, each light emitting diode die being electrically connected to a circuit on the circuit board, a plurality of connecting pads disposed on a first side of the circuit board outside the frame, the connecting pads being electrically connected to a circuit on the circuit board, and an encapsulating material positioned on the circuit board inside the frame to cover the light emitting diode dies; wherein at least one second side of the circuit board has a connection means for connecting to another sectional light emitting diode backlight unit.

Owner:LIGHTHOUSE TECH

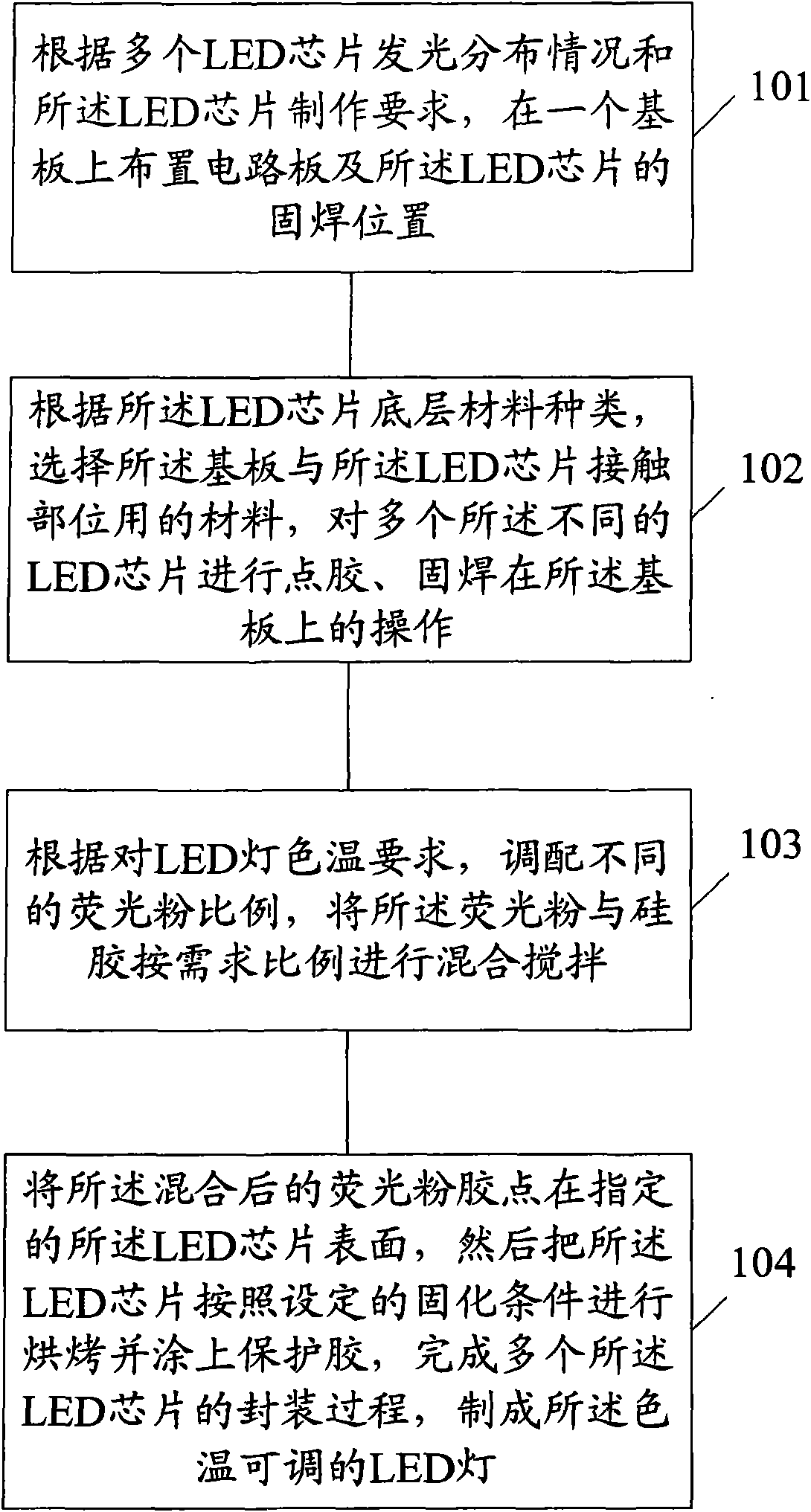

Method for manufacturing color temperature tunable LED lamp and LED lamp

InactiveCN101592291AHigh color rendering indexImprove luminous efficiencyLine/current collector detailsPoint-like light sourceMaterial typeColor rendering index

The invention discloses a method for manufacturing a color temperature tunable LED lamp and the LED lamp. The method comprises the following steps: distributing a circuit board and fixed welding positions of LED chips on a substrate according to the luminance distribution conditions and manufacturing requirements of a plurality of LED chips; selecting a material for contact positions of the substrate and the LED chips according to material types of base layers of the LED chips, and carrying out adhesive dispensing and fixed welding on the substrate; blending different proportions of fluorescent powder according to the color temperature requirement of the LED lamp, and mixing and stirring the fluorescent powder and silica gel according to the required proportion; dispensing the mixed fluorescent powder gel on the surfaces of the LED chips; and baking the LED chips, coating with protective adhesive, and completing the encapsulation process of the plurality of LED chips. The manufacturing method has advanced process and easily controlled flow. The color temperature tunable LED lamp has good color rendering index and high luminous efficiency, and the color rendering index and the luminous efficiency cannot be reduced because of the change of the color temperature.

Owner:GUANGDONG SEEDCOM ELECTRICAL & LIGHTING +1

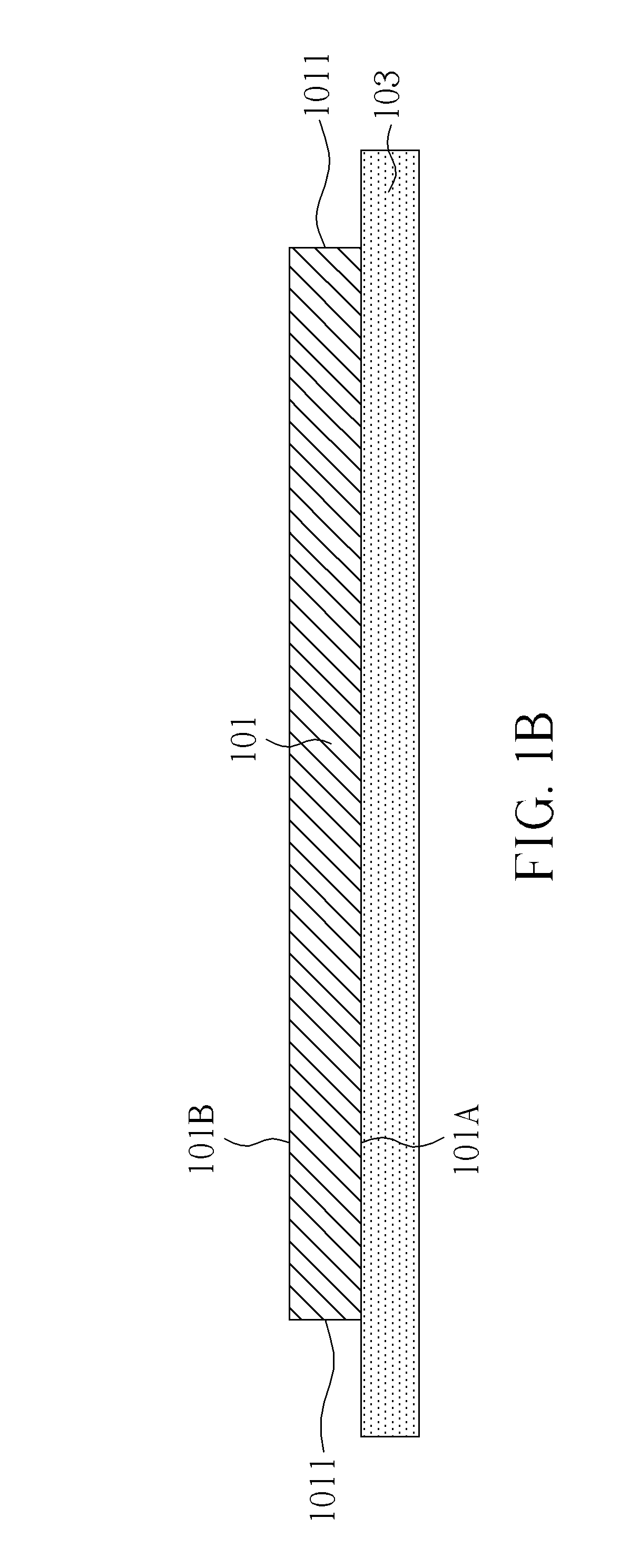

Display device and method of fabricating the same

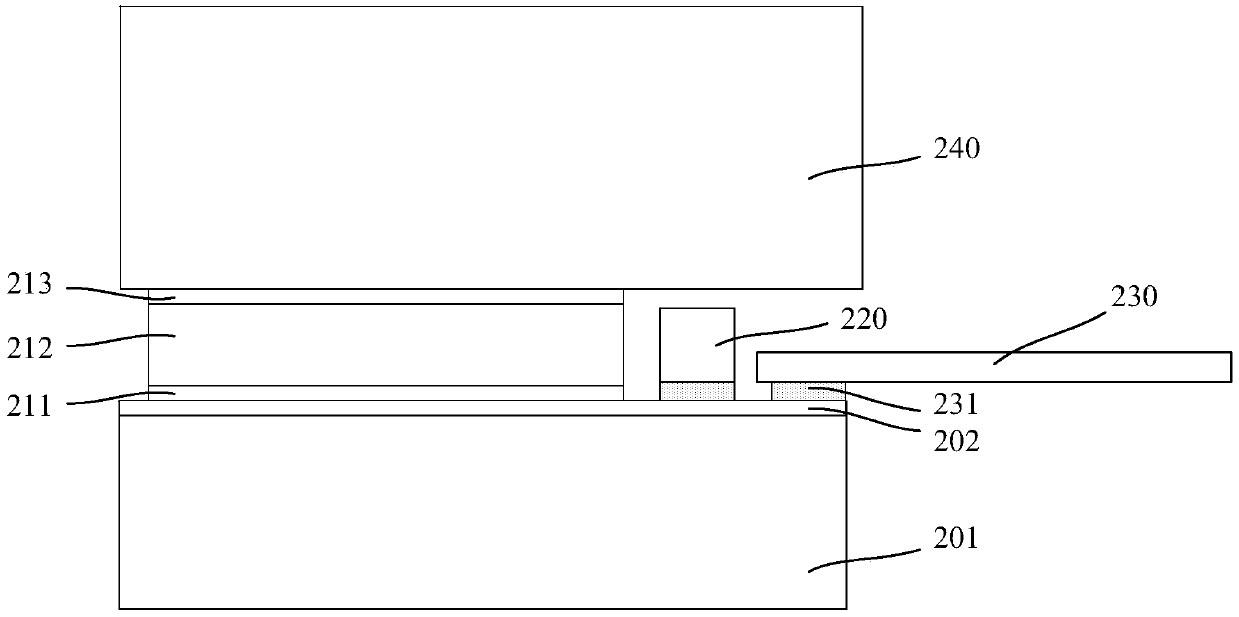

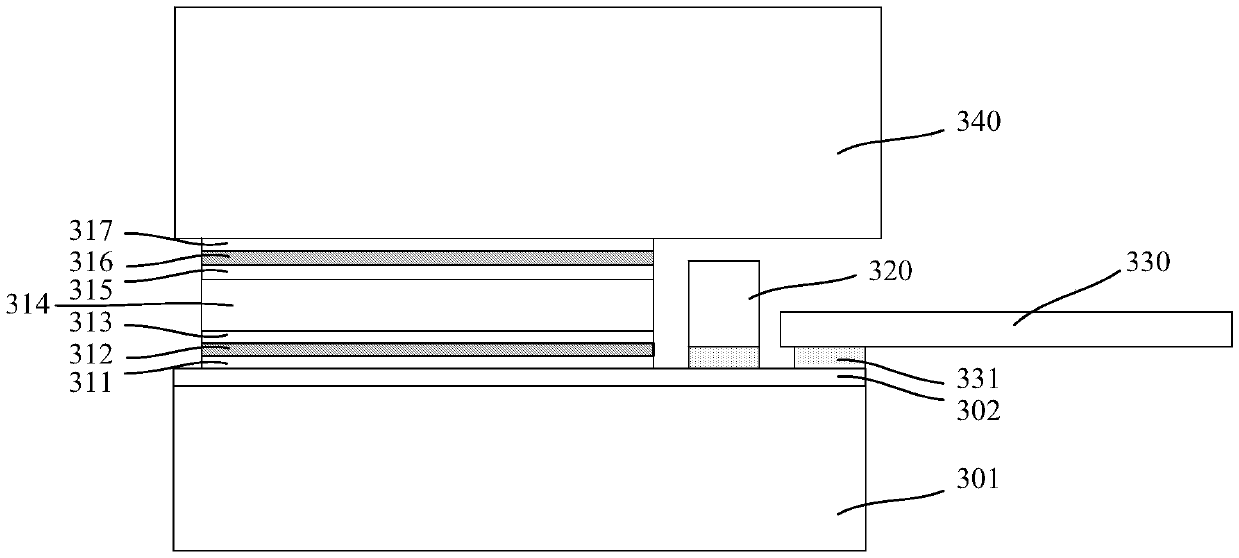

ActiveUS20120120364A1Simplify the packaging processNon-linear opticsCold cathode manufactureDisplay deviceEngineering

A display device includes a substrate, a backplane, a display medium layer, a protective layer, a driving component, a flexible printed circuit (FPC) and a sealant. The backplane and the display medium layer are disposed on the lower side and the upper side of the substrate, respectively. The protective layer covers the display medium layer and prevents moisture and oxygen from permeating into the display medium layer to deteriorate its performance. The sealant surrounds the first side surface of the substrate and the second side surface of the display medium layer, and wraps at least a portion of the driving component and a portion of the FPC. Additionally, a manufacturing method of a display device is also provided.

Owner:AU OPTRONICS CORP

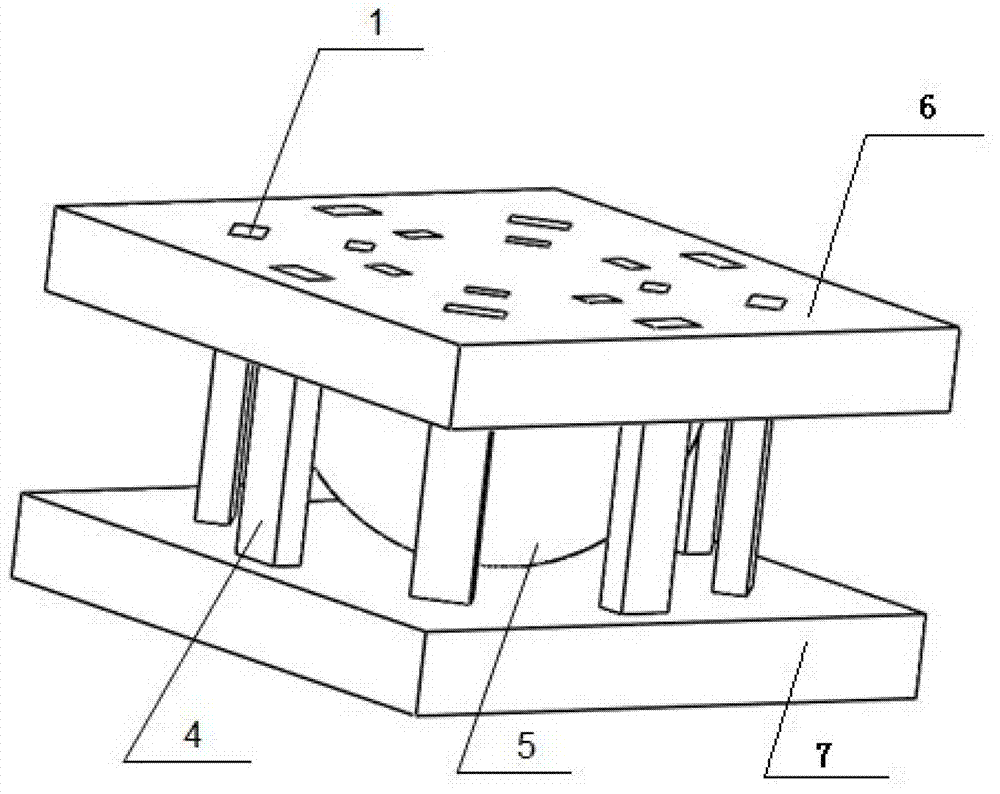

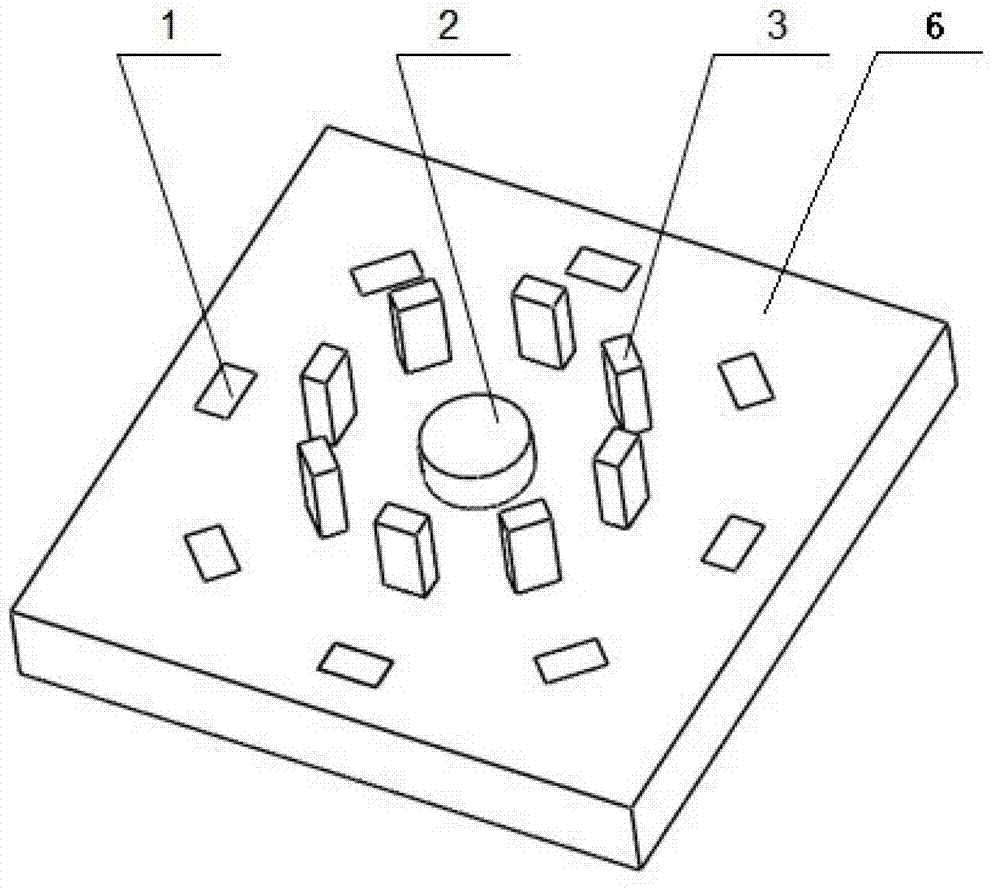

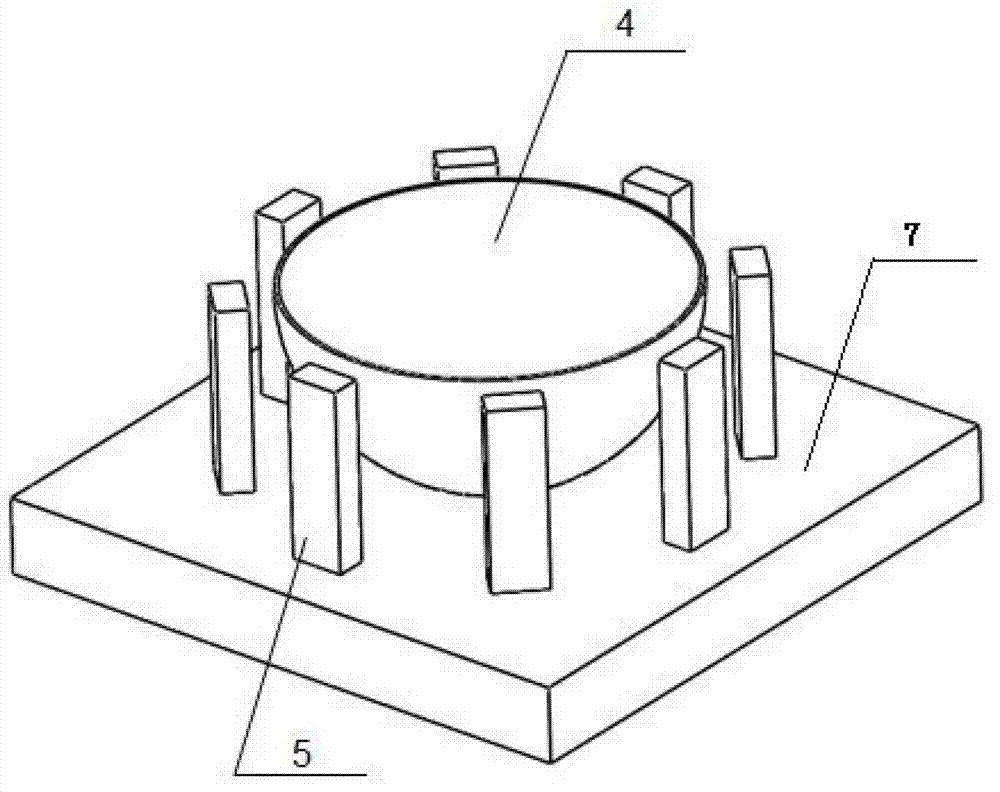

Double-wafer integrated silicon-based super-thin micro-hemispherical resonator gyroscope and preparation method thereof

InactiveCN103322994AAchieve electrical performanceAchieve mechanical propertiesDecorative surface effectsSolid-state devicesHemispherical resonator gyroscopeElectron

The invention discloses a double-wafer integrated-form silicon-based ultrathin micro-hemispherical resonator gyroscope. The double-wafer integrated-form silicon-based ultrathin micro-hemispherical resonator gyroscope comprises a first silicon wafer, a second silicon wafer, a micro-hemisphere casing, driving electrodes and detecting electrodes. The micro-hemispherical casing is arranged between the first silicon wafer and the second silicon wafer. The casing bottom of the micro-hemispherical casing is fixedly connected with the second silicon wafer, and the upper edge of the micro-hemispherical casing is in contacted with the lower surface of the first silicon wafer. The driving electrodes are arranged on the periphery of the micro-hemispherical casing and between the first silicon wafer and the second silicon wafer. One ends of the driving electrodes are fixedly connected with the second silicon wafer, and the other ends of the driving electrodes are movably connected with the first silicon wafer. One ends of the detecting electrodes are fixedly connected with the first silicon wafer, and the other ends of the detecting electrodes are movably connected with the inner wall of the micro-hemispherical casing. The double-wafer integrated-form silicon-based ultrathin micro-hemispherical resonator gyroscope has the advantages of small volume, light weight, low cost, high reliability, low power consumption, mass production and the like, is expected to be widely used in the fields of aerospace, automobile, medical treatment, photography, electronics consumption and the like, and has very broad application prospects.

Owner:SOUTHEAST UNIV

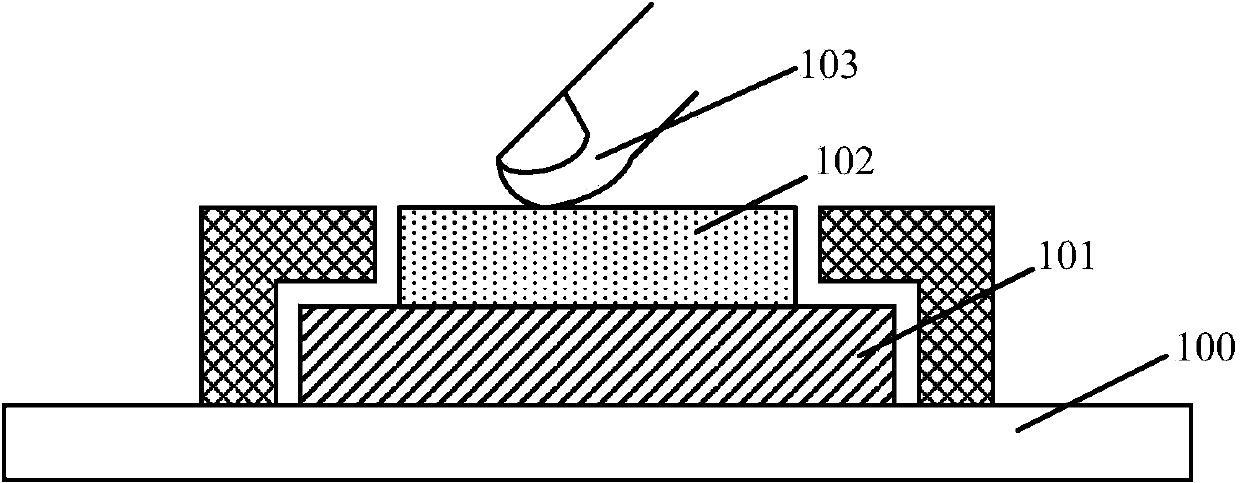

Wafer-level fingerprint recognition chip packaging structure and method

InactiveCN104201115ASimplify the packaging processReduce damageMeasurement apparatus componentsSemiconductor/solid-state device detailsFingerprintComputer science

Disclosed is a wafer-level fingerprint recognition chip packaging structure and method. The method includes: providing a substrate which comprises a plurality of induction chip areas and is provided with a first surface and a second surface opposite to the first surface, wherein a first surface of each induction chip area comprises an induction area; forming a covering layer on the first surface of the substrate; forming a plug structure in each induction chip area of the substrate, wherein one end of each plug structure is electrically connected with the corresponding induction area, and the other end of each plug structure is exposed out of the second surface of the substrate. By the forming method, the packaging process of a fingerprint recognition chip can be simplified, the requirement on sensitivity of the induction chip is lowered, and the packaging method is wider in application.

Owner:CHINA WAFER LEVEL CSP

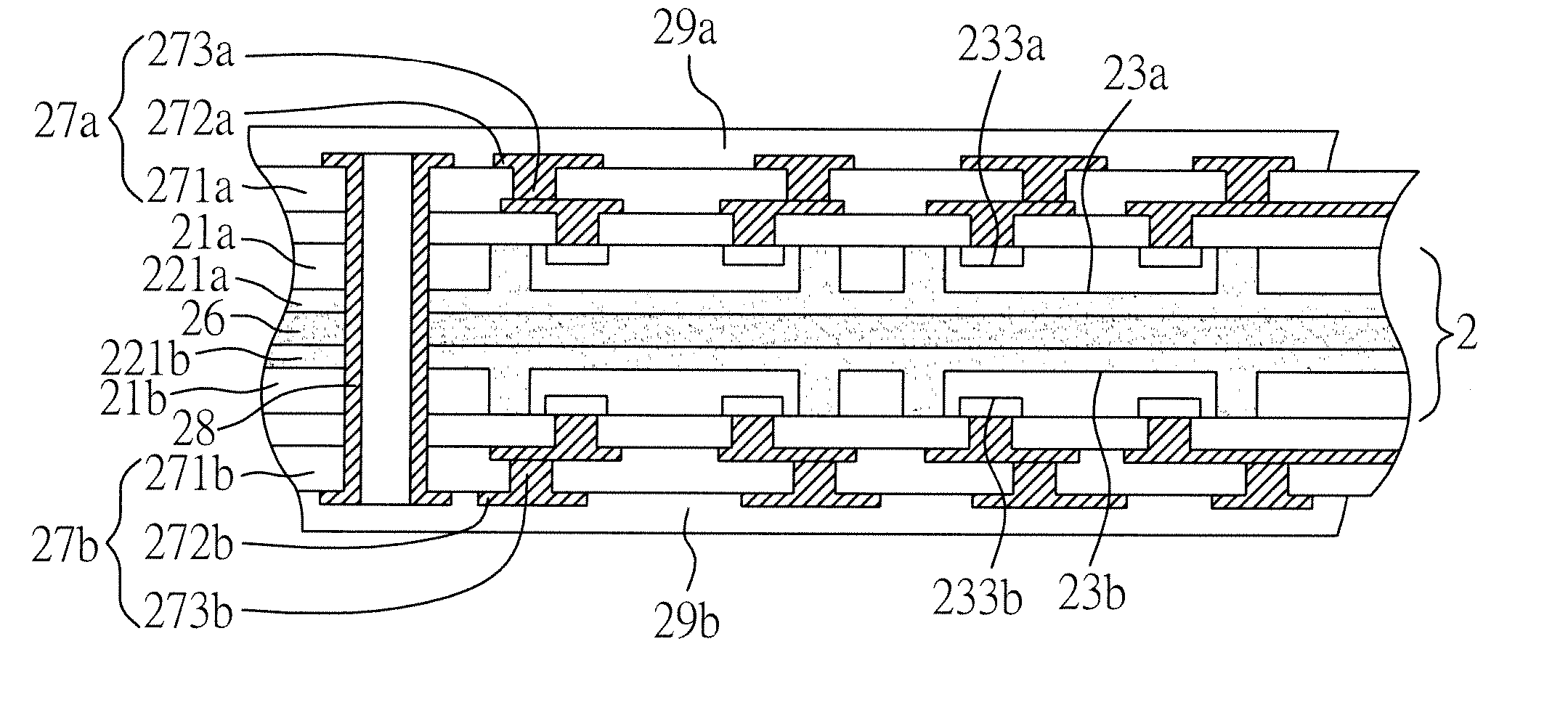

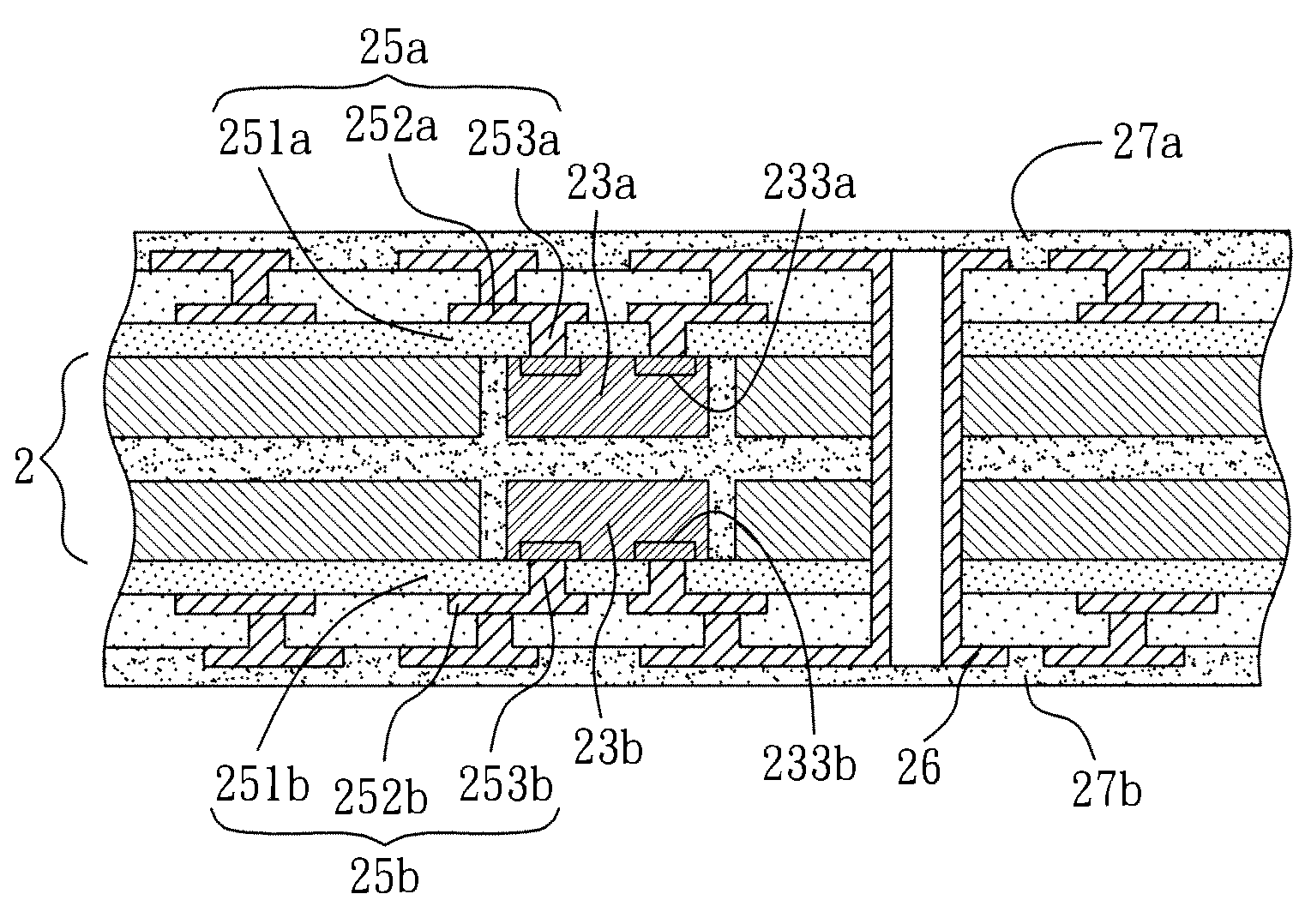

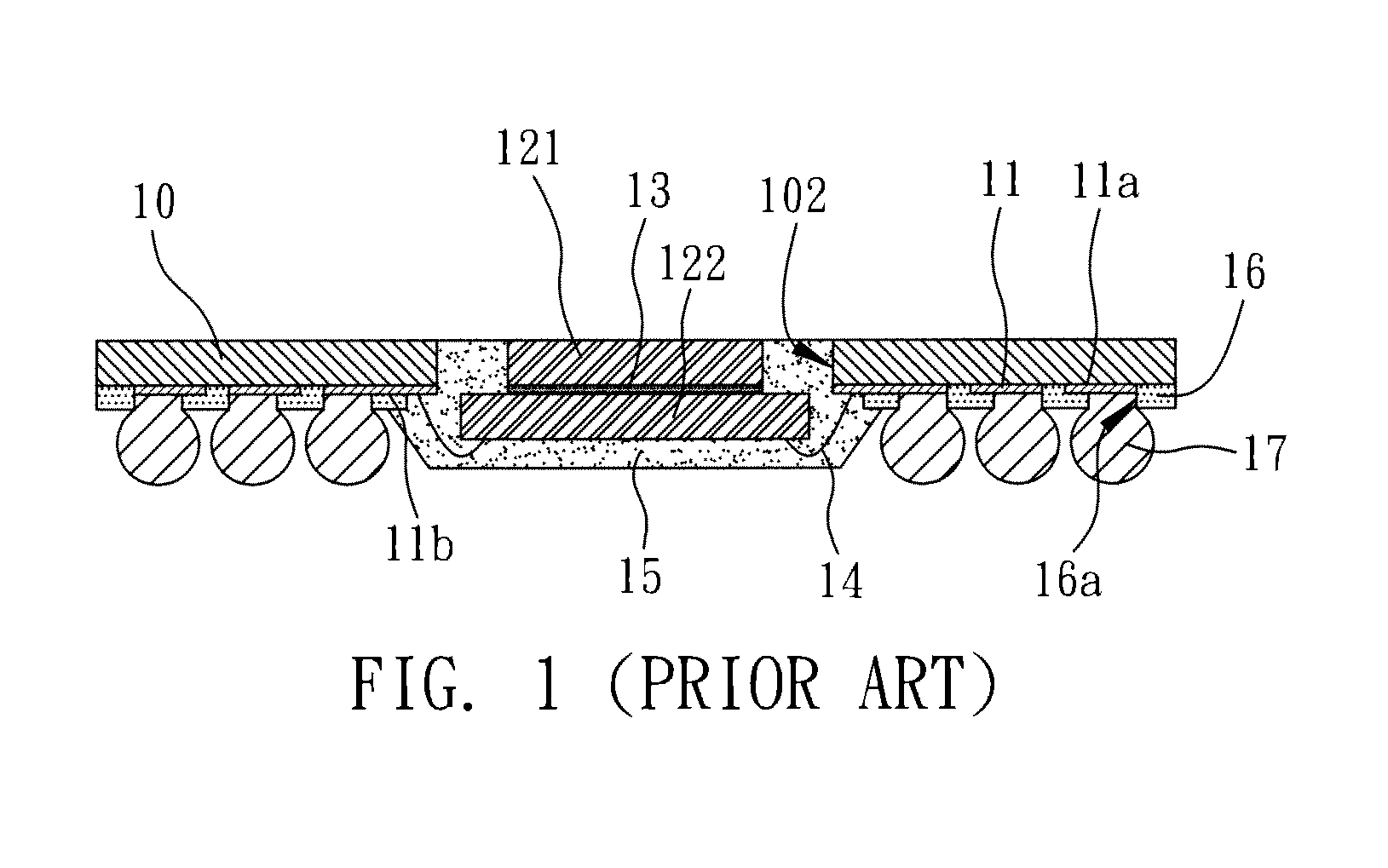

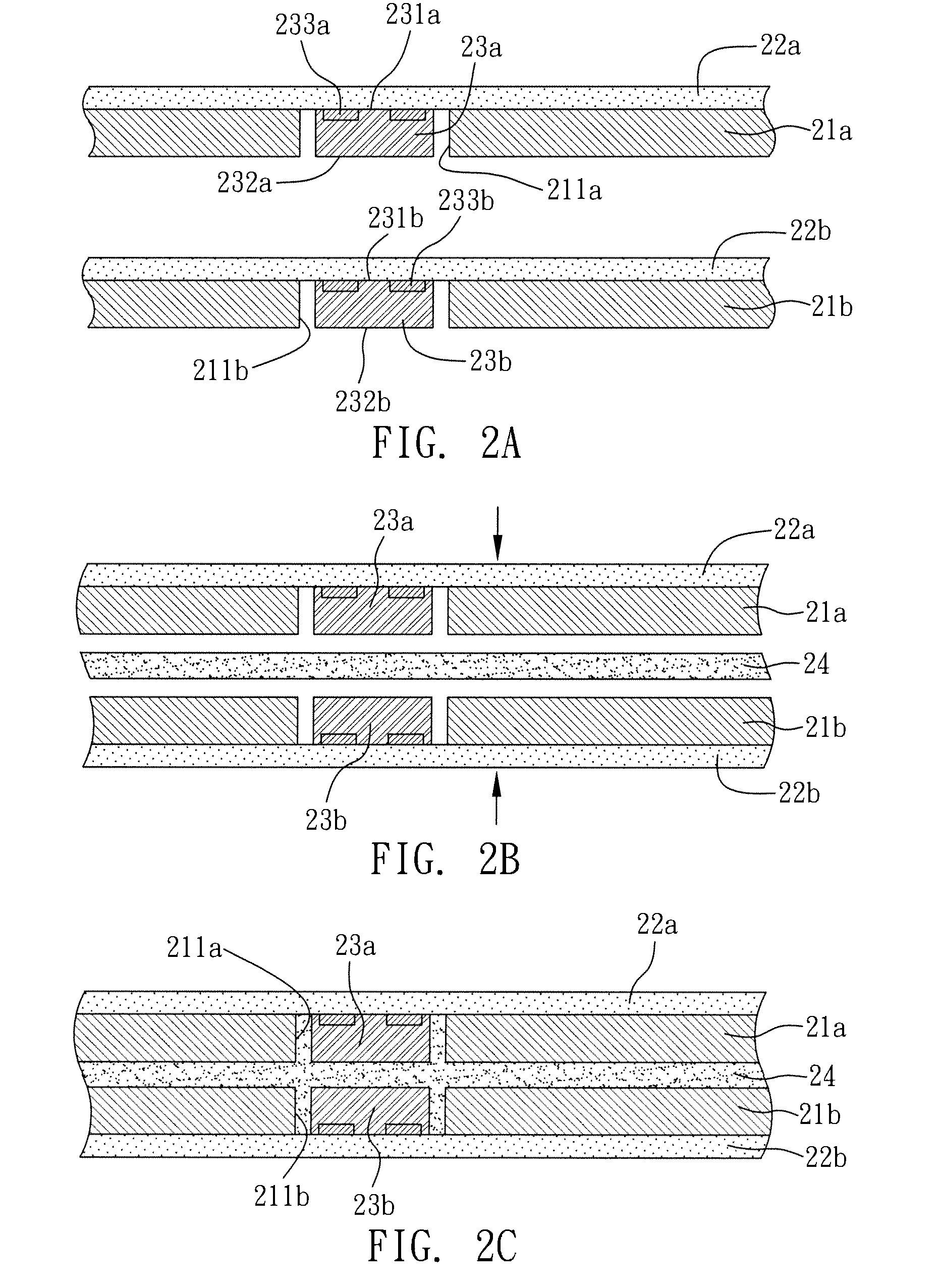

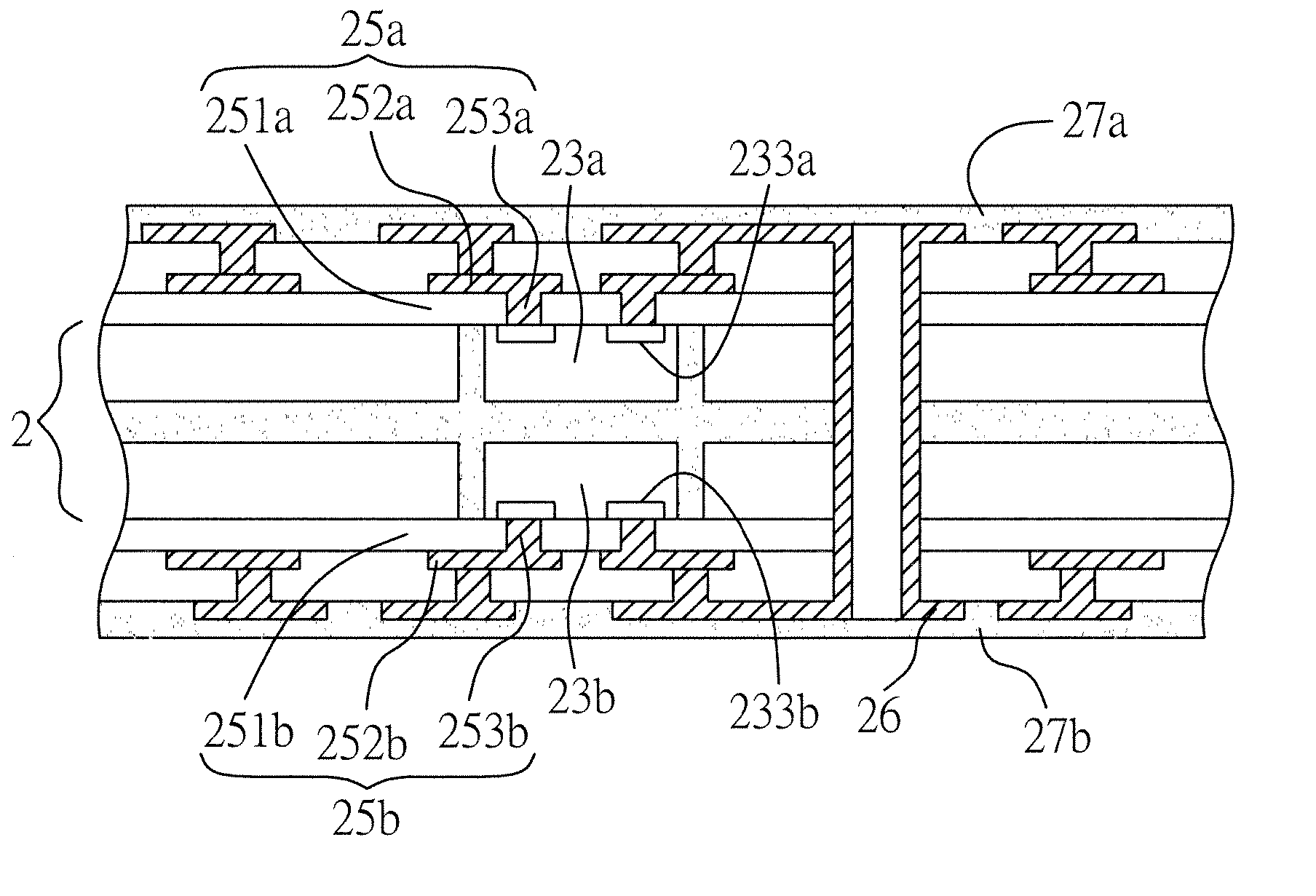

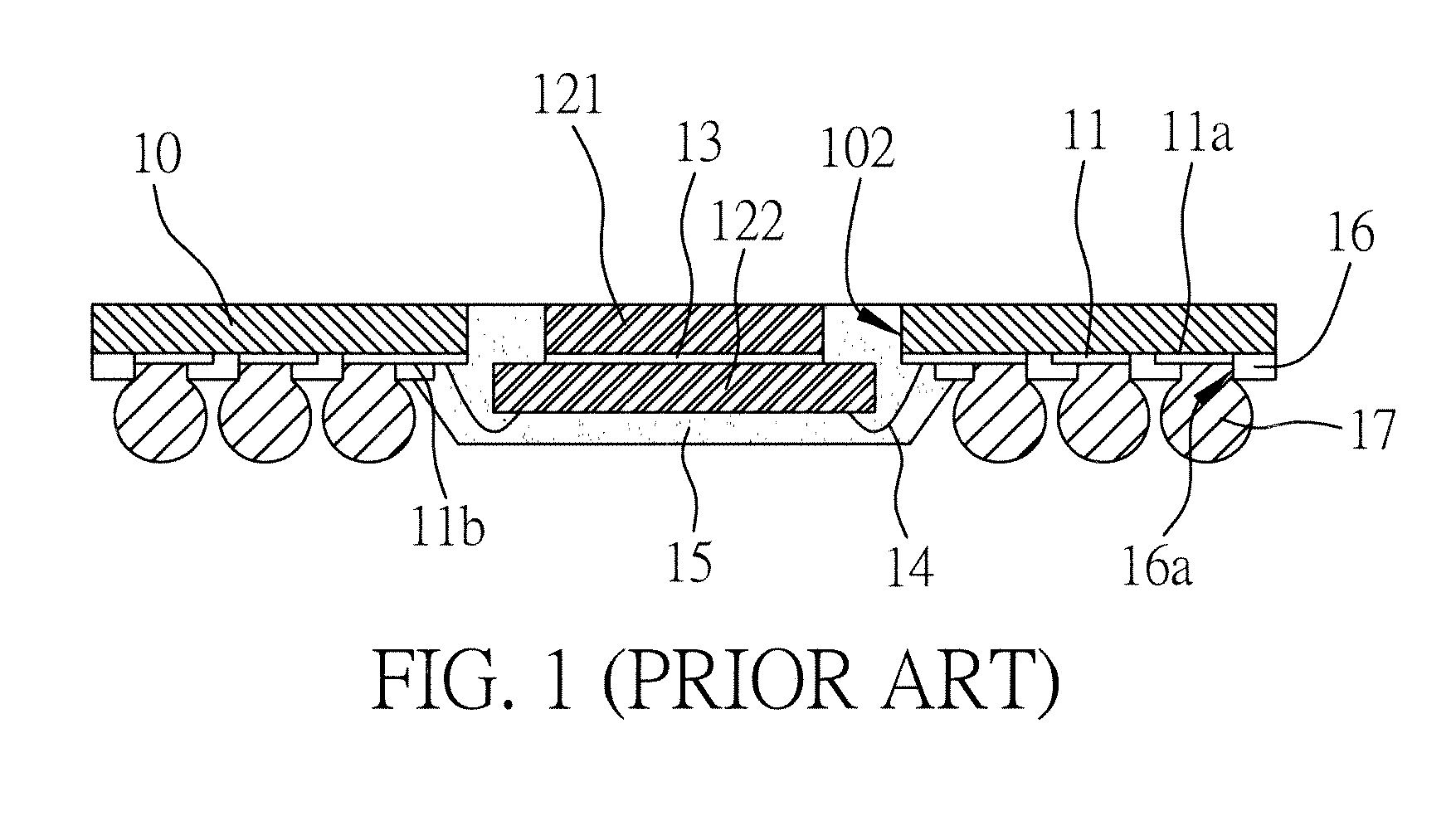

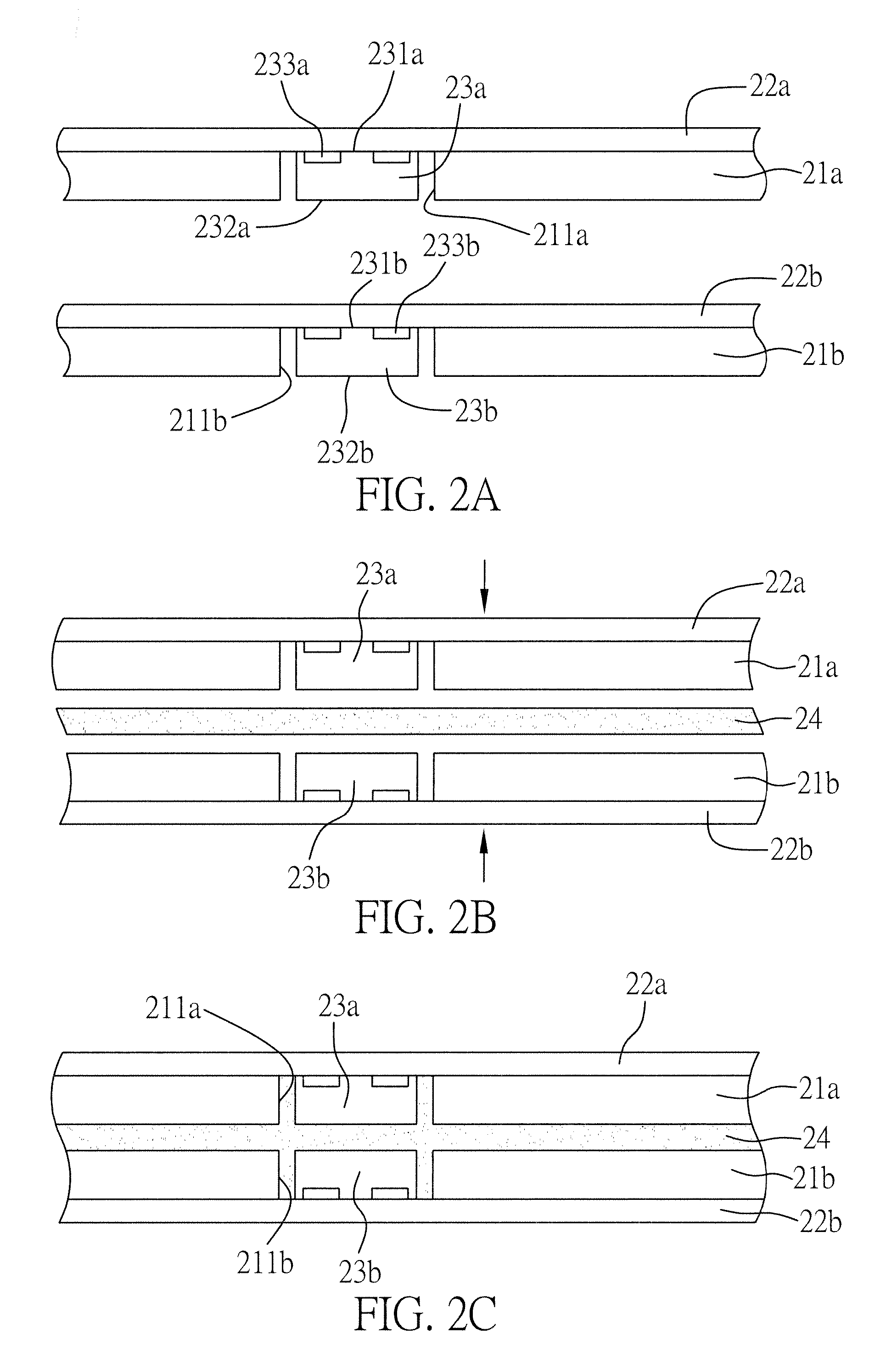

Stack Structure of Carrier Board Embedded with Semiconductor Components and Method for Fabricating the same

ActiveUS20070085188A1Reduced dimensionSimplify semiconductor packaging processPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringDielectric layer

A stack structure of a carrier board embedded with semiconductor components and a method for fabricating the same are proposed. The stack structure includes first and second carrier boards having a through hole respectively, first and second semiconductors component disposed in through holes of the first and second semiconductor components respectively, and a dielectric layer structure clamped between the first carrier board and the second carrier board and having a first dielectric layer formed on the first carrier board and an inactive surface of the first semiconductor component and filled in gaps between the first carrier board and the first semiconductor component, a second dielectric layer formed on the second carrier board and an inactive of the second semiconductor component and filled in gaps between the second carrier board and the second semiconductor component, and a bonding layer clamped between the first dielectric layer and the second dielectric layer.

Owner:PHOENIX PRECISION TECH CORP

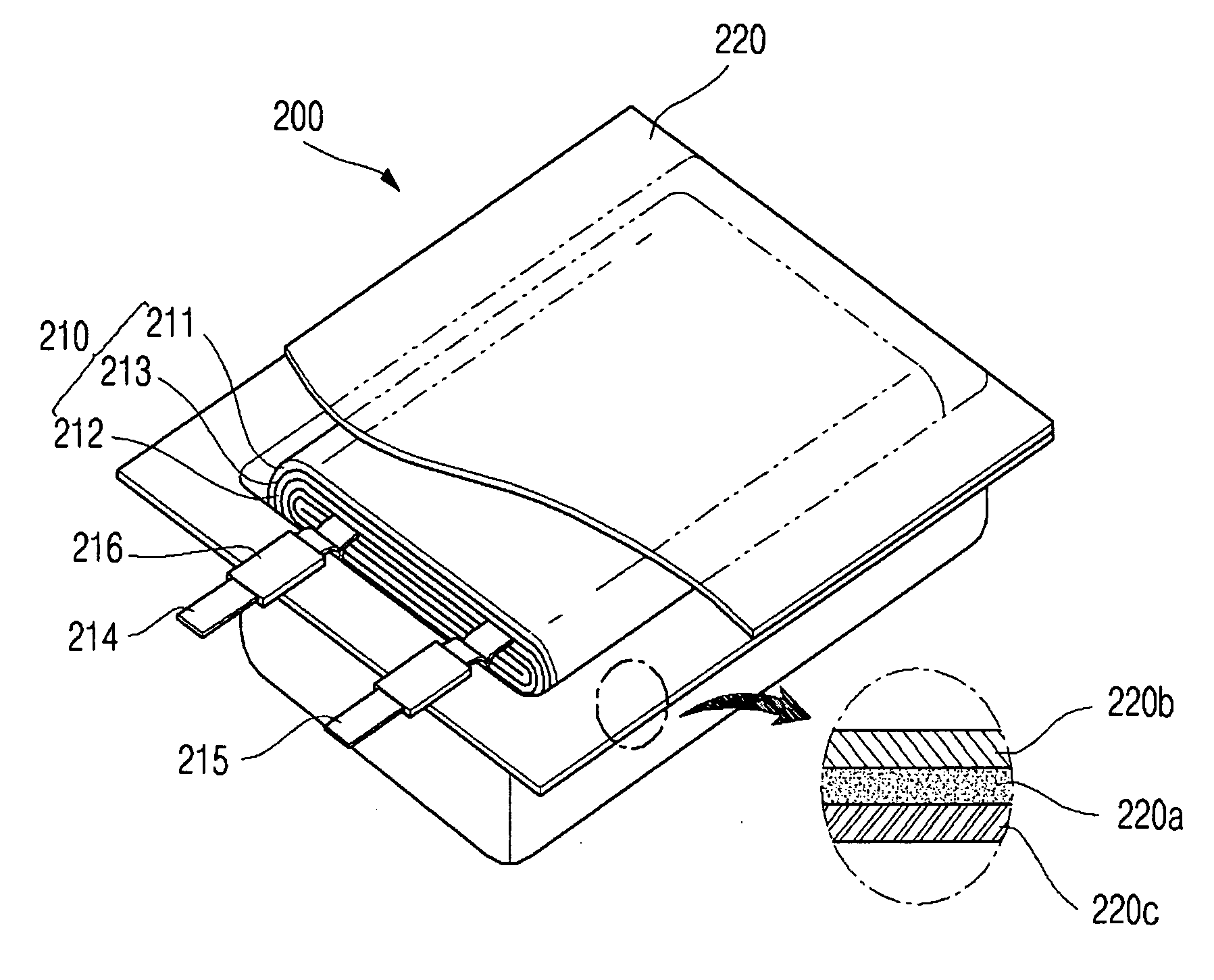

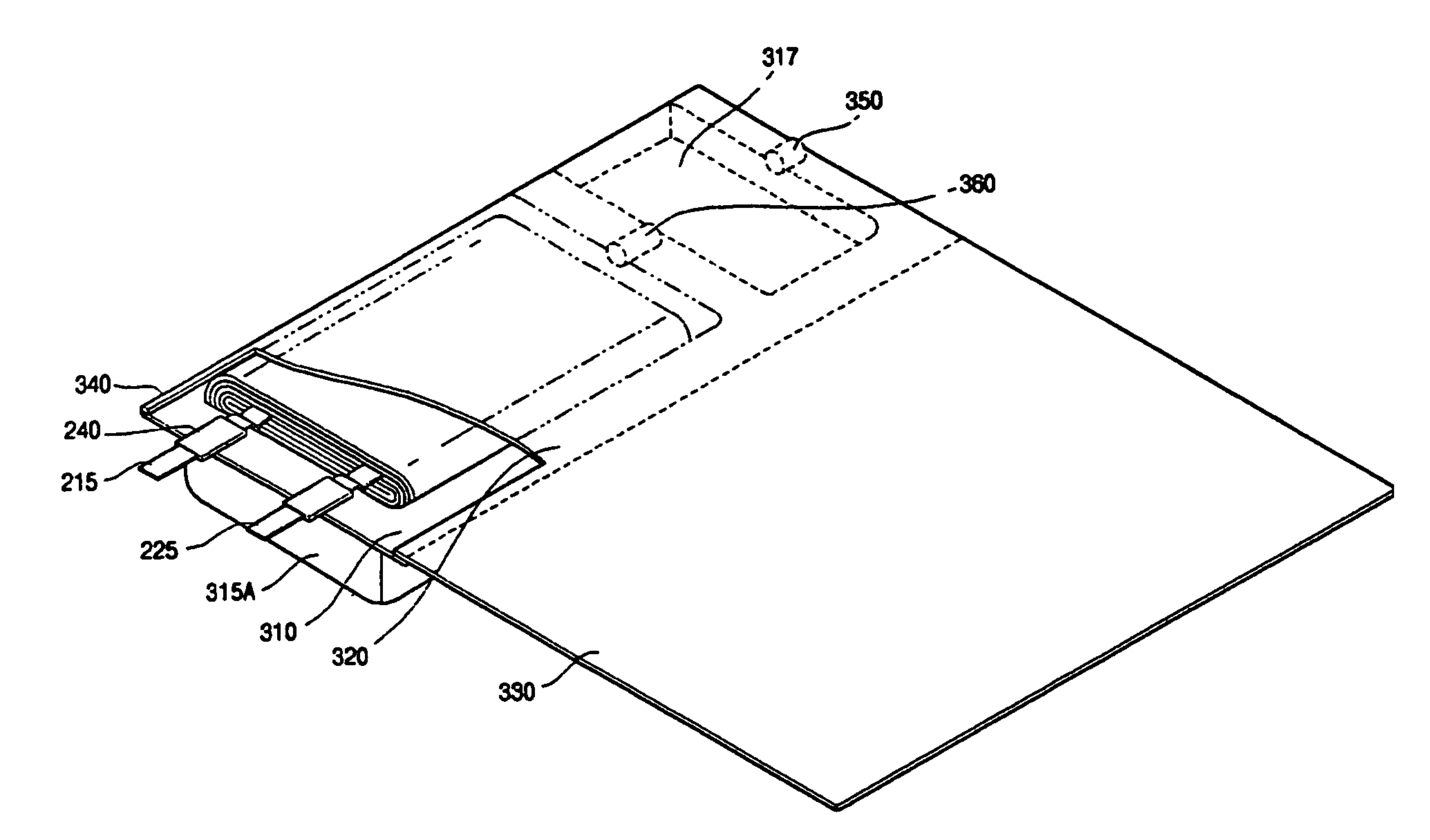

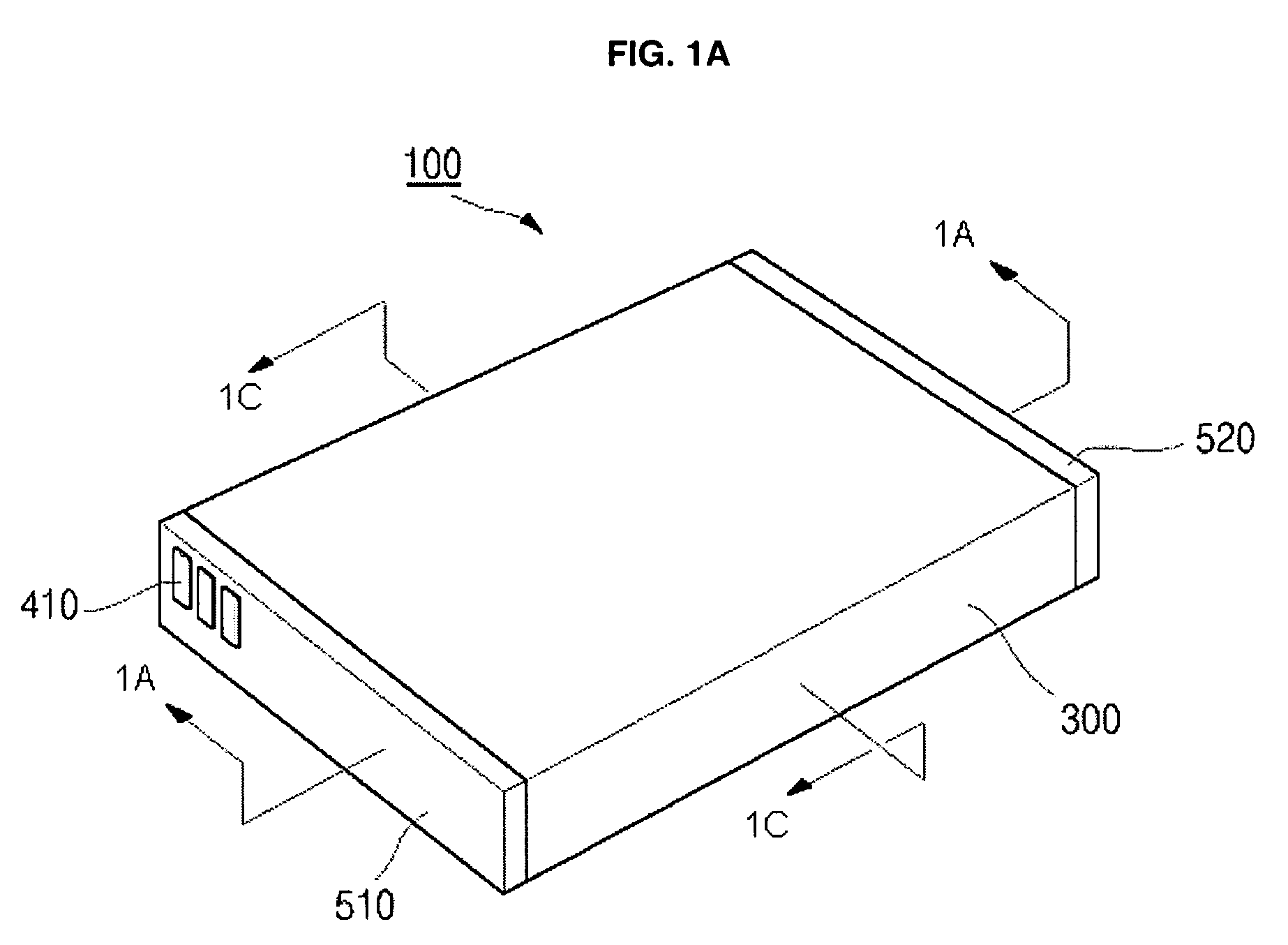

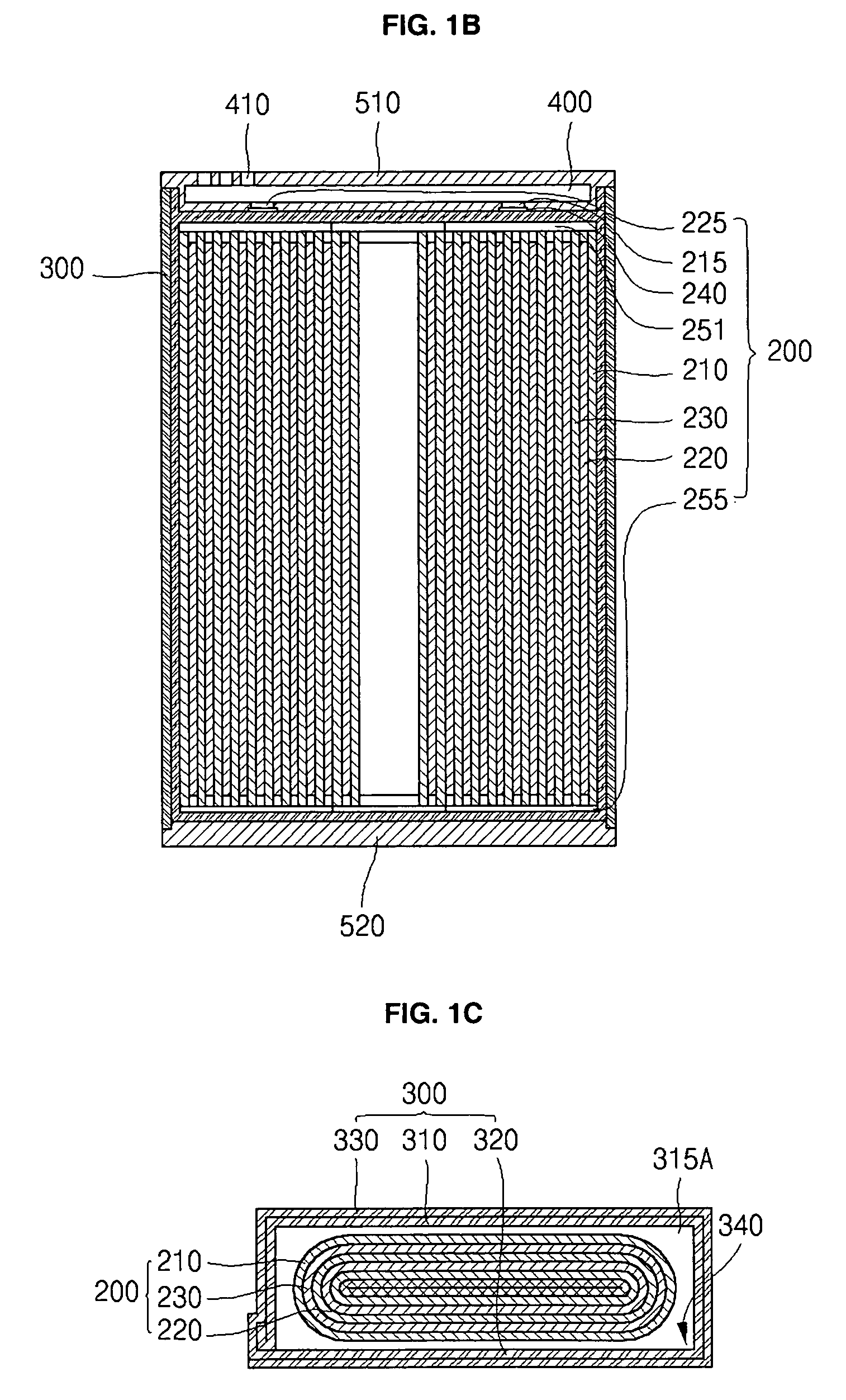

Pouch-type lithium secondary battery and fabricating method thereof

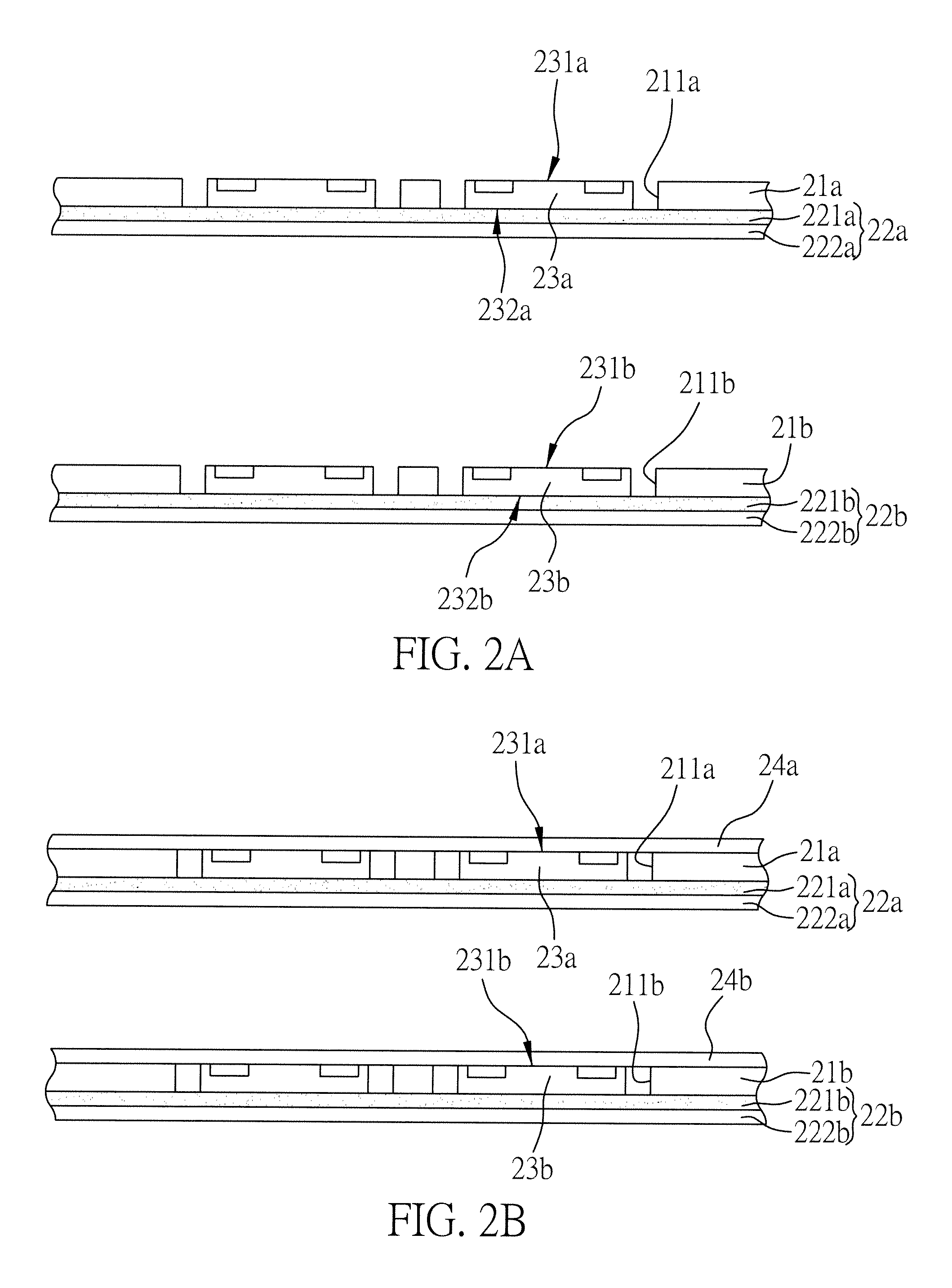

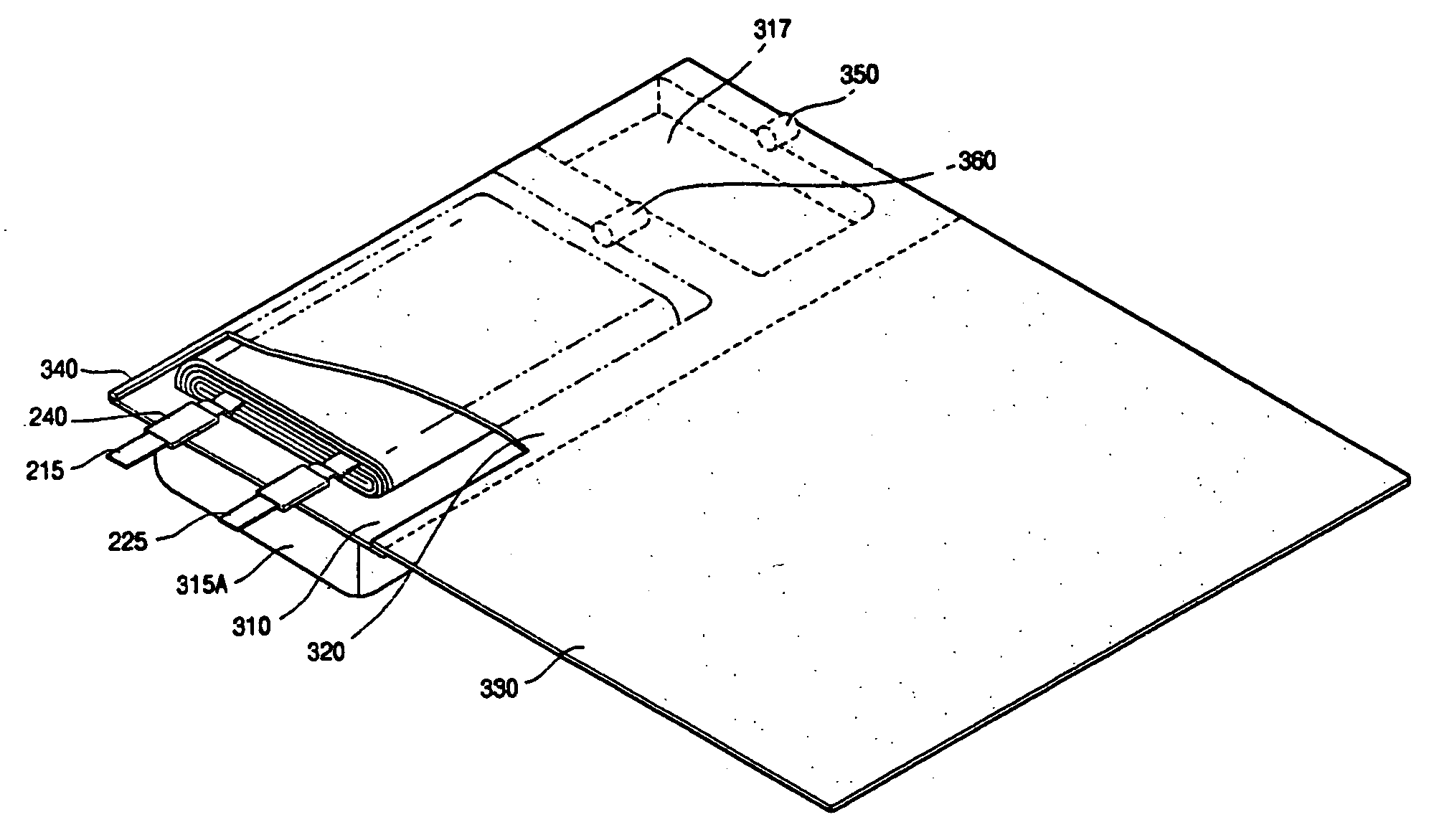

InactiveUS20070072071A1Simplify packing processSimplify the packaging processFinal product manufactureSmall-sized cells cases/jacketsWrap aroundElectrical and Electronics engineering

A pouch-type lithium secondary battery in which an additional packing case is not used is provided. The pouch material is used to perform packing processes, thereby simplifying packing processes and methods of manufacturing. The pouch-type lithium secondary battery includes an electrode assembly and a pouch material. The electrode assembly includes a first electrode plate to which a first electrode tab is attached, a second electrode plate to which a second electrode tab is attached, and a separator between the first and second electrode plates. The pouch material has first, second, and third surfaces. The first and second surfaces are folded along a first fold to form an electrode assembly accommodating unit for accommodating the electrode assembly. The third surface wraps around the electrode assembly accommodating unit at least once. The first fold is parallel to a line along which the first electrode tab and the second electrode tab extend.

Owner:SAMSUNG SDI CO LTD

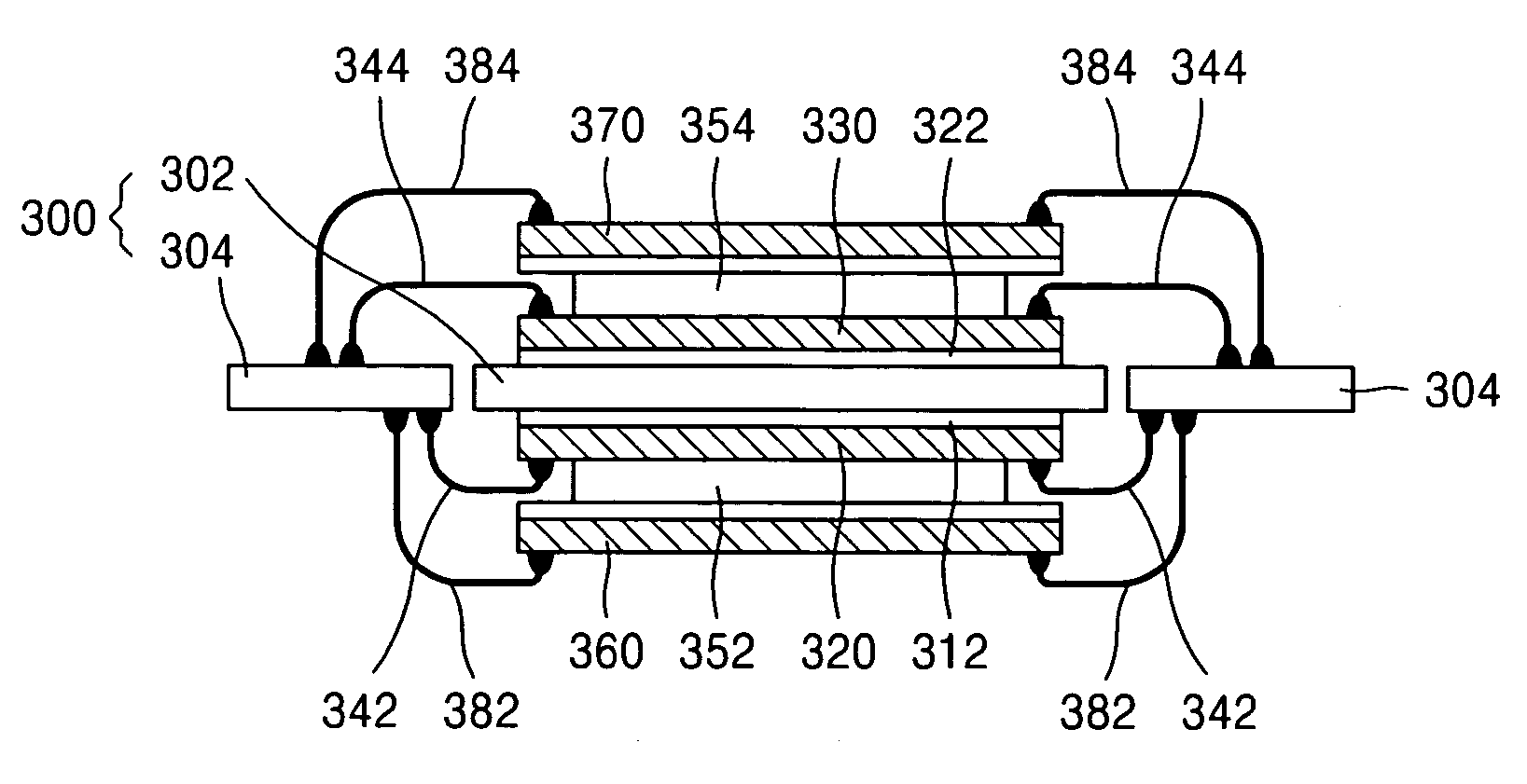

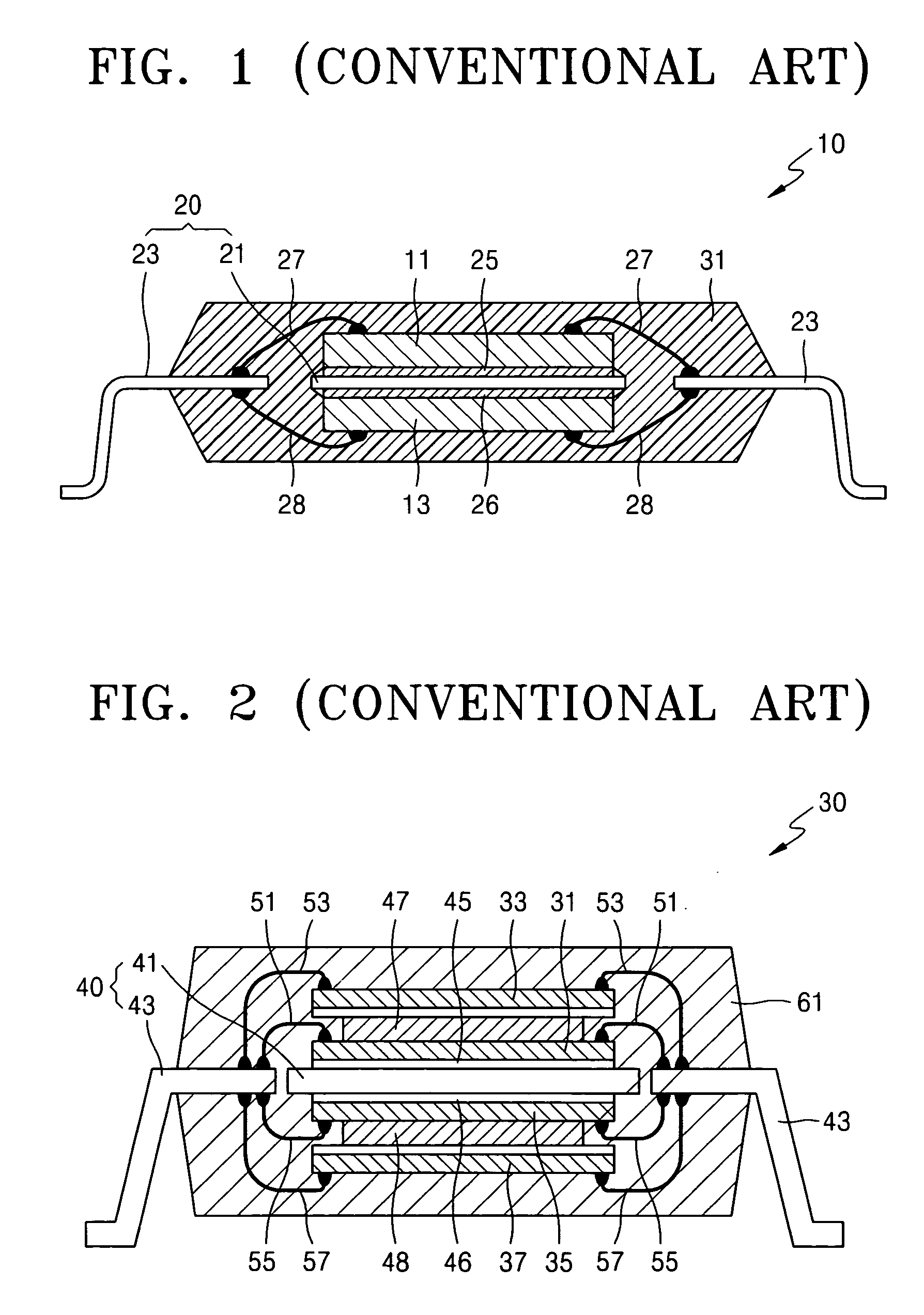

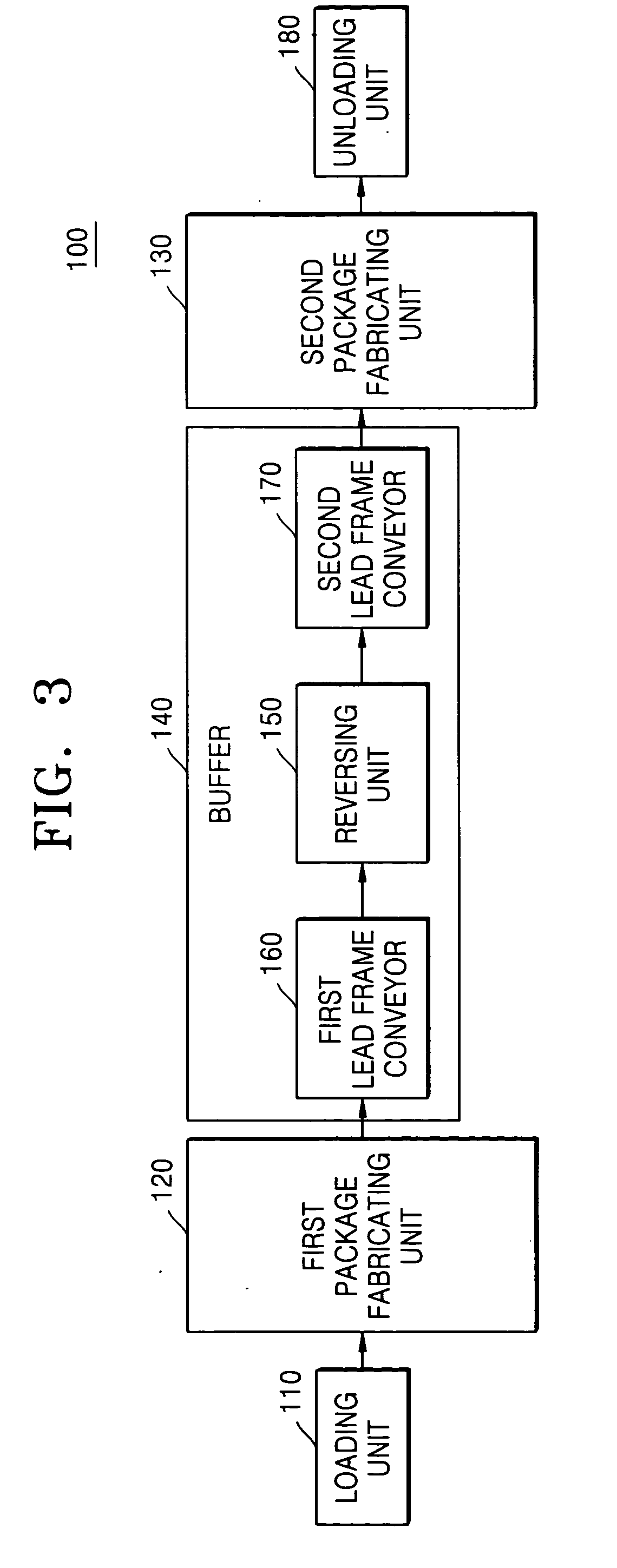

In-line apparatus and method for manufacturing double-sided stacked multi-chip packages

ActiveUS20050006743A1Reduce needSimplify the packaging processSemiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor chip

Provided are in-line semiconductor chip packaging apparatuses that include a buffer assembly in which a reversing unit rotates a lead frame 180° between die attaching and / or wire bonding operations and methods of manufacturing an integrated circuit chip package using such an in-line integrated circuit chip packaging apparatus. Between packaging process operations, the lead frame, which includes first and second surfaces may be rotated, thereby reversing the orientation of the first and second surfaces. The apparatuses will include one or more processing units for attaching semiconductor chips to the leadframe, or a previously mounted semiconductor chip, or for forming wire bonds between the attached semiconductor chip(s) and the corresponding lead fingers of the lead frame, attached to and / or separated by an in-line buffer assembly that includes a reversing unit.

Owner:SAMSUNG ELECTRONICS CO LTD

Stack structure of carrier boards embedded with semiconductor components and method for fabricating the same

ActiveUS7507915B2Minimize capacitySimple processPrinted electric component incorporationSemiconductor/solid-state device detailsEngineeringDielectric layer

A stack structure of carrier boards embedded with semiconductor components and a method for fabricating the same are proposed. A first carrier board and a second carrier board, each of which having at least one through hole, are provided. A first protecting layer and a second protecting layer are formed on a surface of the first and second carrier boards respectively. At least one first semiconductor component and at least one second semiconductor component are disposed on the first and second protecting layers and accommodated in the first and second through holes respectively. A dielectric layer is laminated between the surfaces of the first and second carrier boards without the protecting layers formed thereon. Thus, a modularized package structure with reduced space waste is formed.

Owner:PHOENIX PRECISION TECH CORP

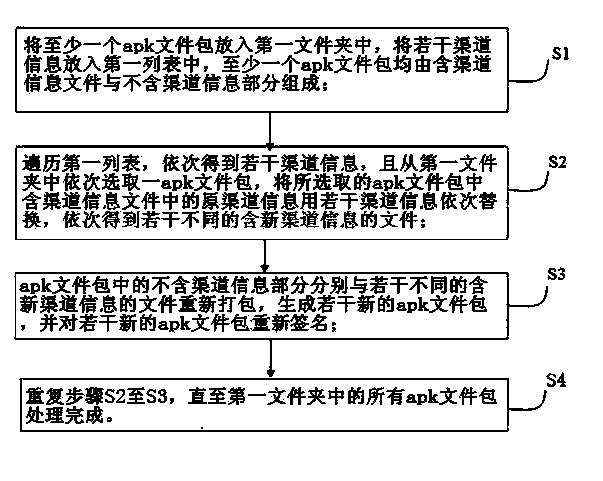

Method for generating multi-channel apk file packages in batches

InactiveCN103729186ASimplify the packaging processEasy to changeSpecific program execution arrangementsDatabaseMulti channel

The invention relates to a method for generating multi-channel apk file packages in batches. Multi-channel apk files can be generated efficiently in batches, and the error rate is reduced. The method includes the following steps that first, at least one apk file package is placed in the first file, and a plurality of pieces of channel information is placed into a first list; second, traversal of the first list is performed, a plurality of pieces of channel information is sequentially obtained, the apk file packages are sequentially selected from the first file, original channel information in the files, containing the channel information, in the apk file packages are sequentially replaced with the plurality of pieces of channel information, and a plurality of different files containing new channel information are sequentially obtained; third, the part without containing the channel information of the apk file packages and the different files containing the new channel information are respectively repackaged, and a plurality of new apk file packages are generated and signed; fourth, the second step and the third step are repeated till all the apk file packages in the first file are processed.

Owner:上海网达软件股份有限公司

Pouch type lithium secondary battery and method of of fabricating the same

ActiveUS20060216585A1Simplify the packaging processFinal product manufactureSmall-sized cells cases/jacketsLithiumEngineering

A pouch type lithium secondary battery includes a pouch bare cell having an electrode assembly and a pouch exterior for storing the electrode assembly and a sleeve member winding around the pouch bare cell. A method of fabricating a pouch type lithium secondary battery includes forming a pouch bare cell by storing an electrode assembly in a pouch exterior and wrapping the pouch bare cell with a sleeve member.

Owner:SAMSUNG SDI CO LTD

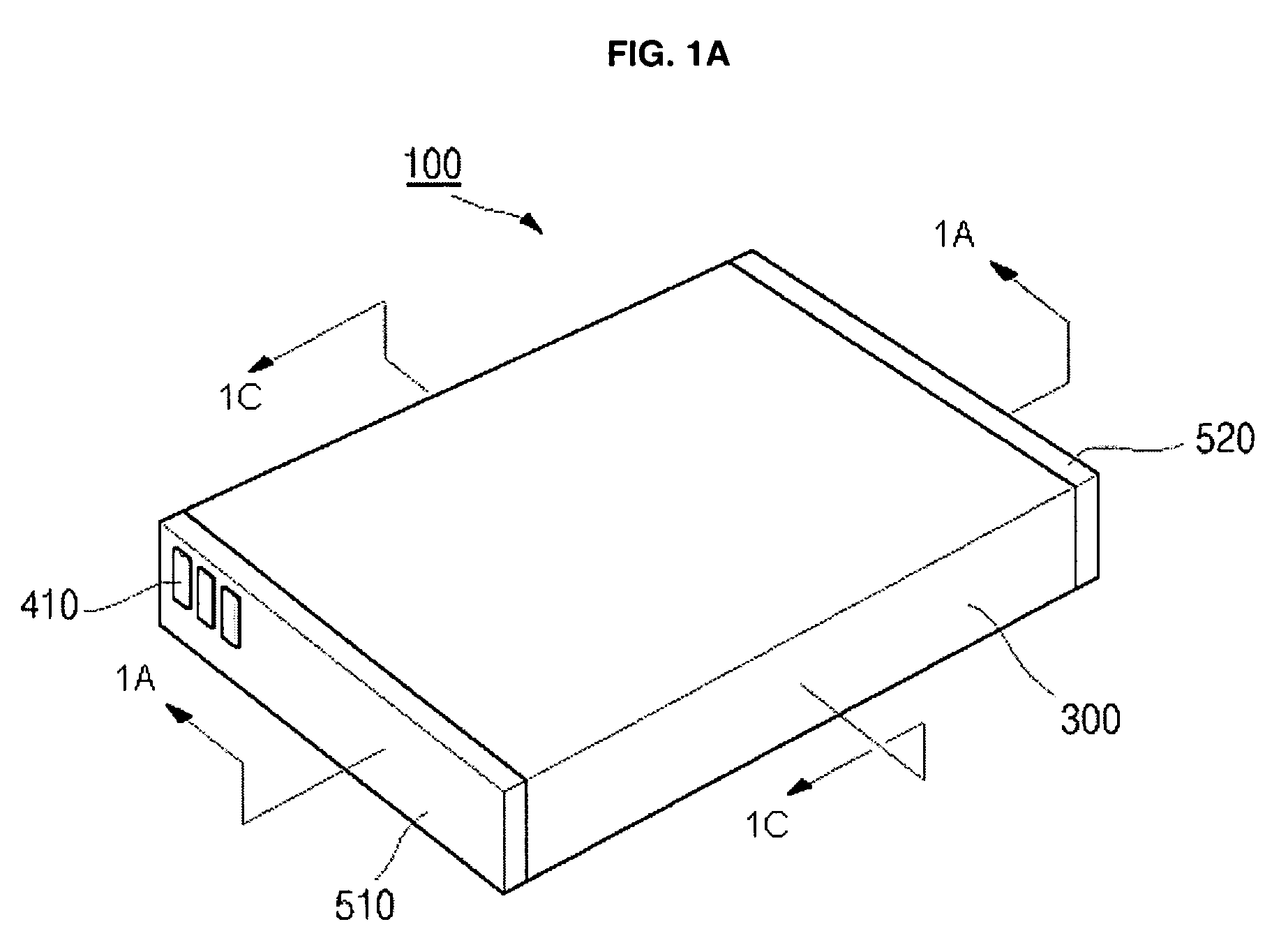

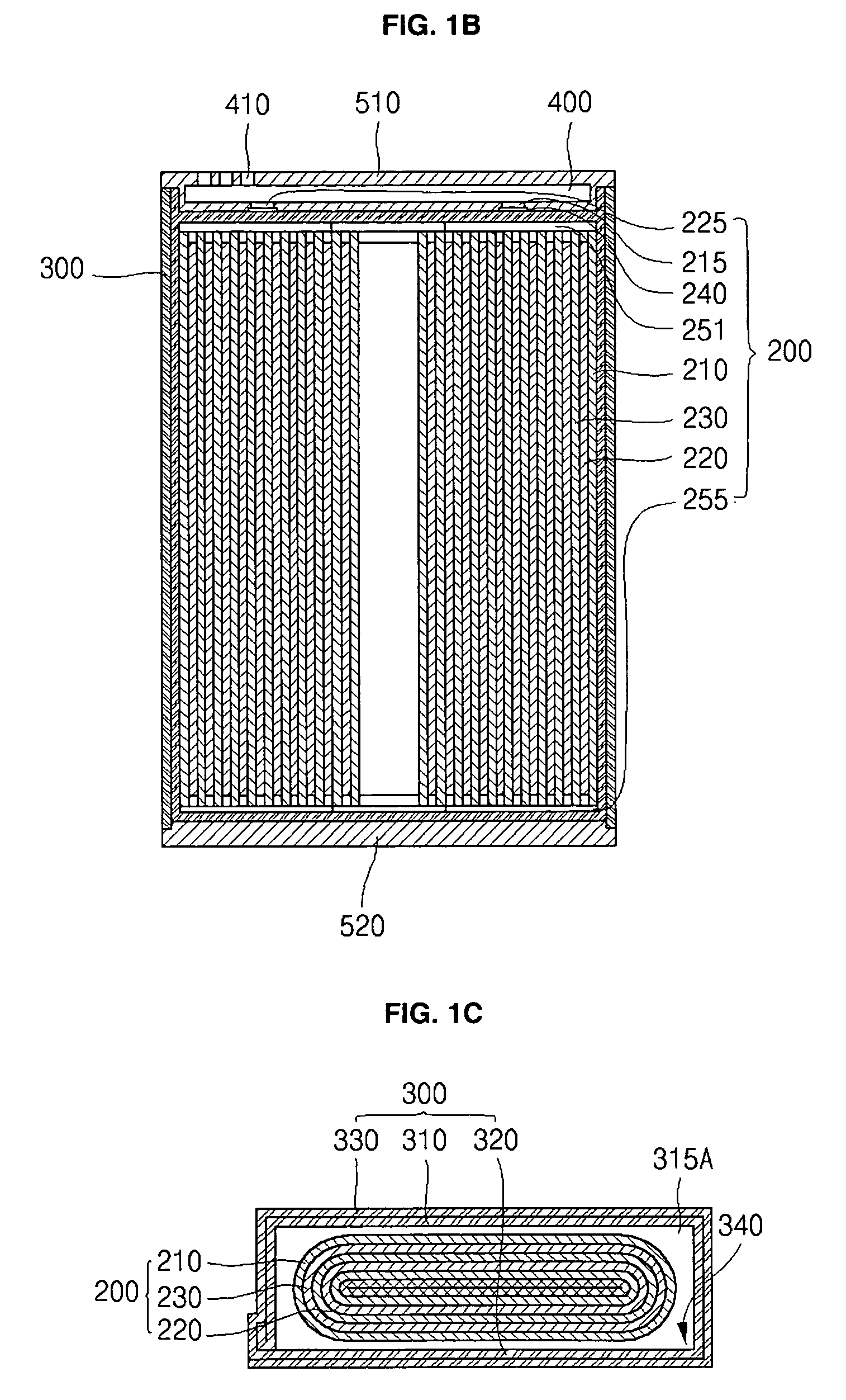

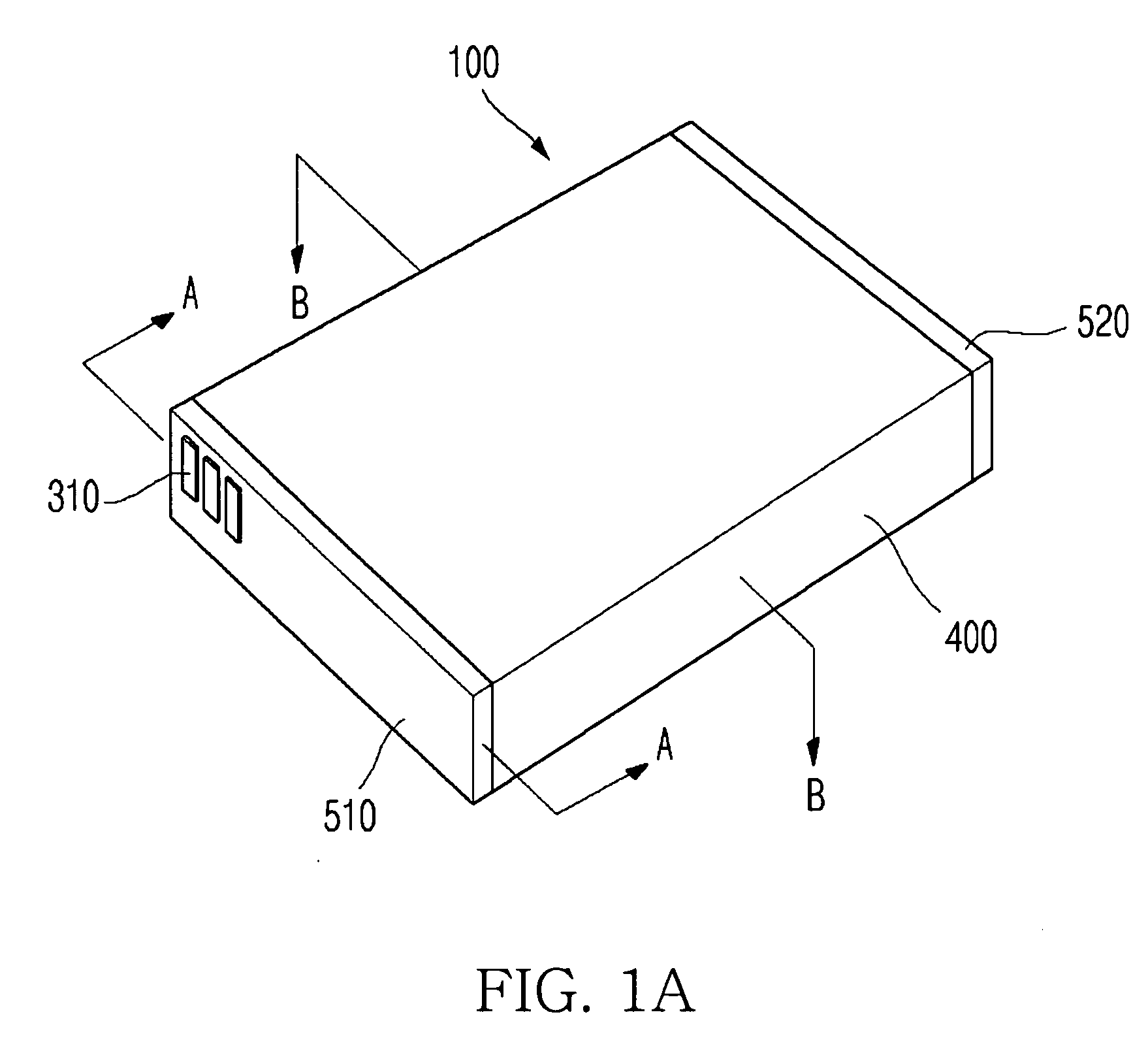

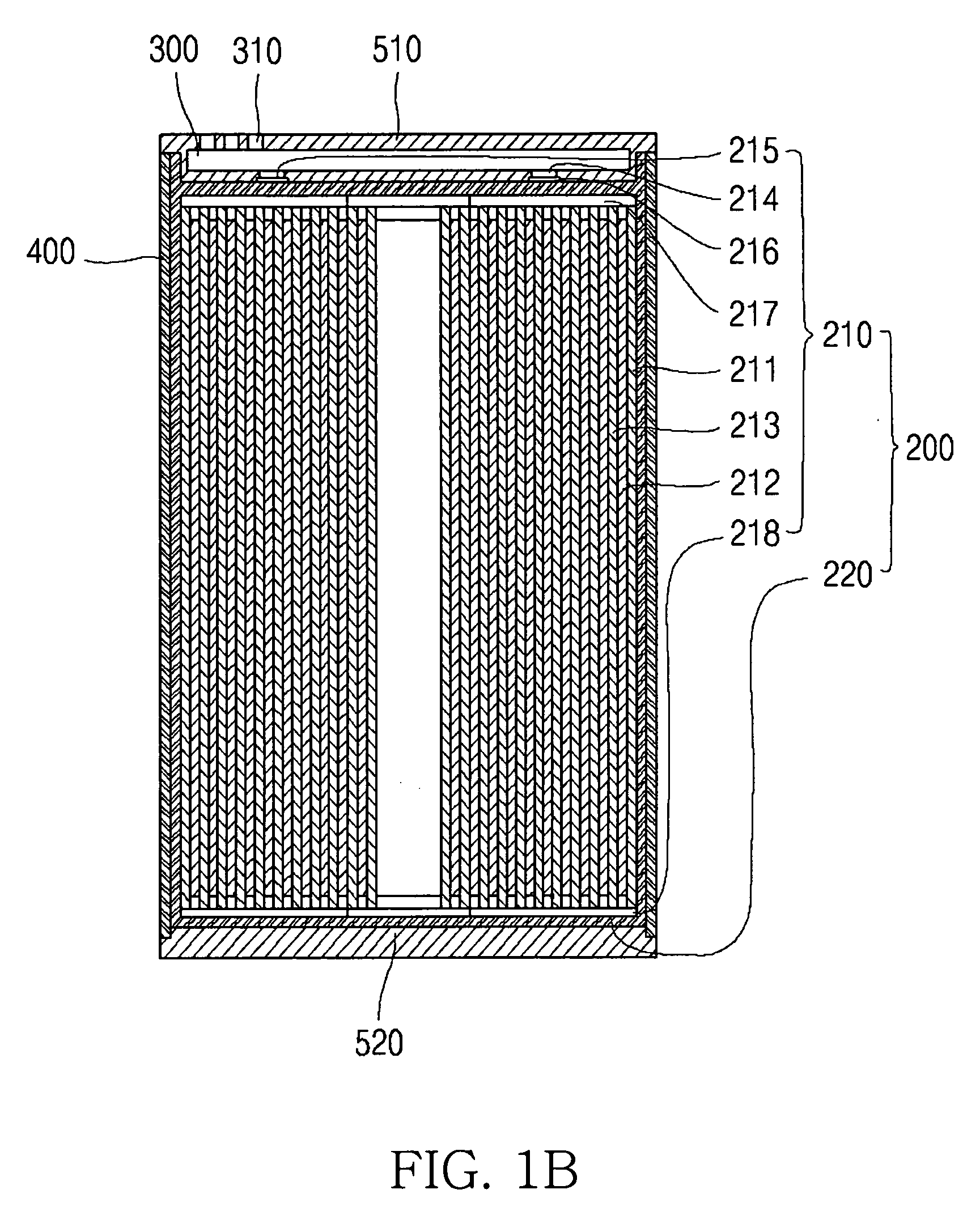

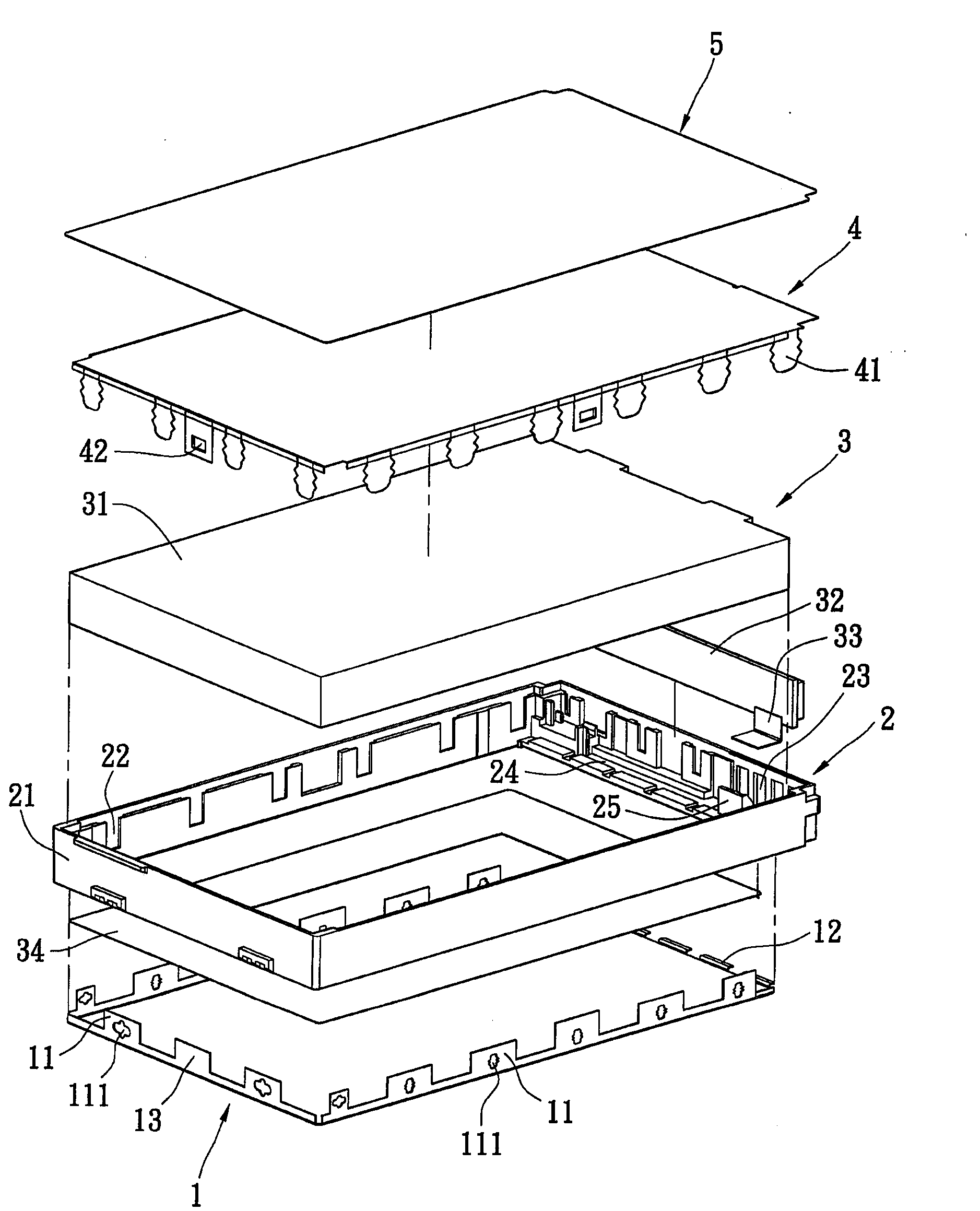

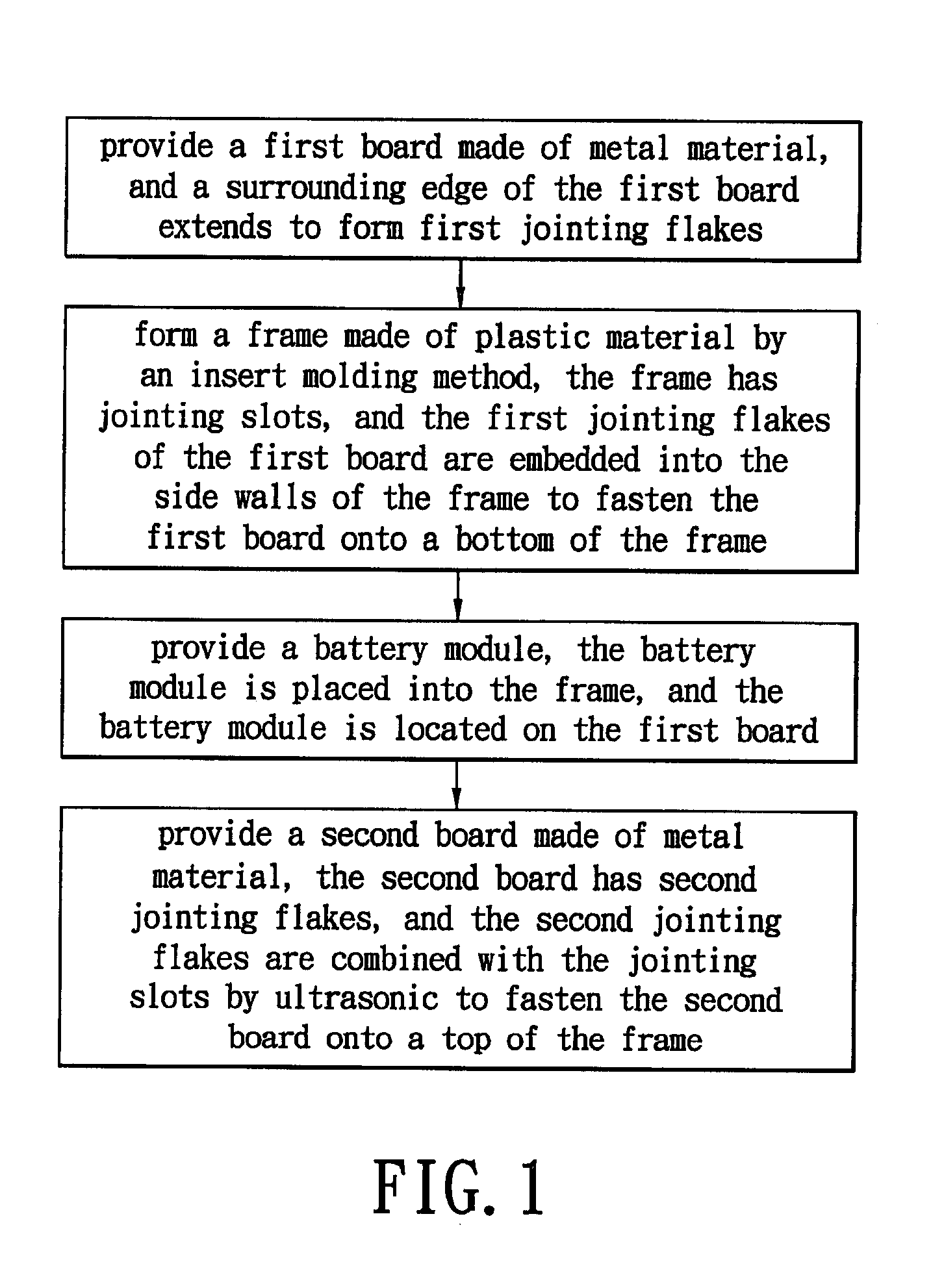

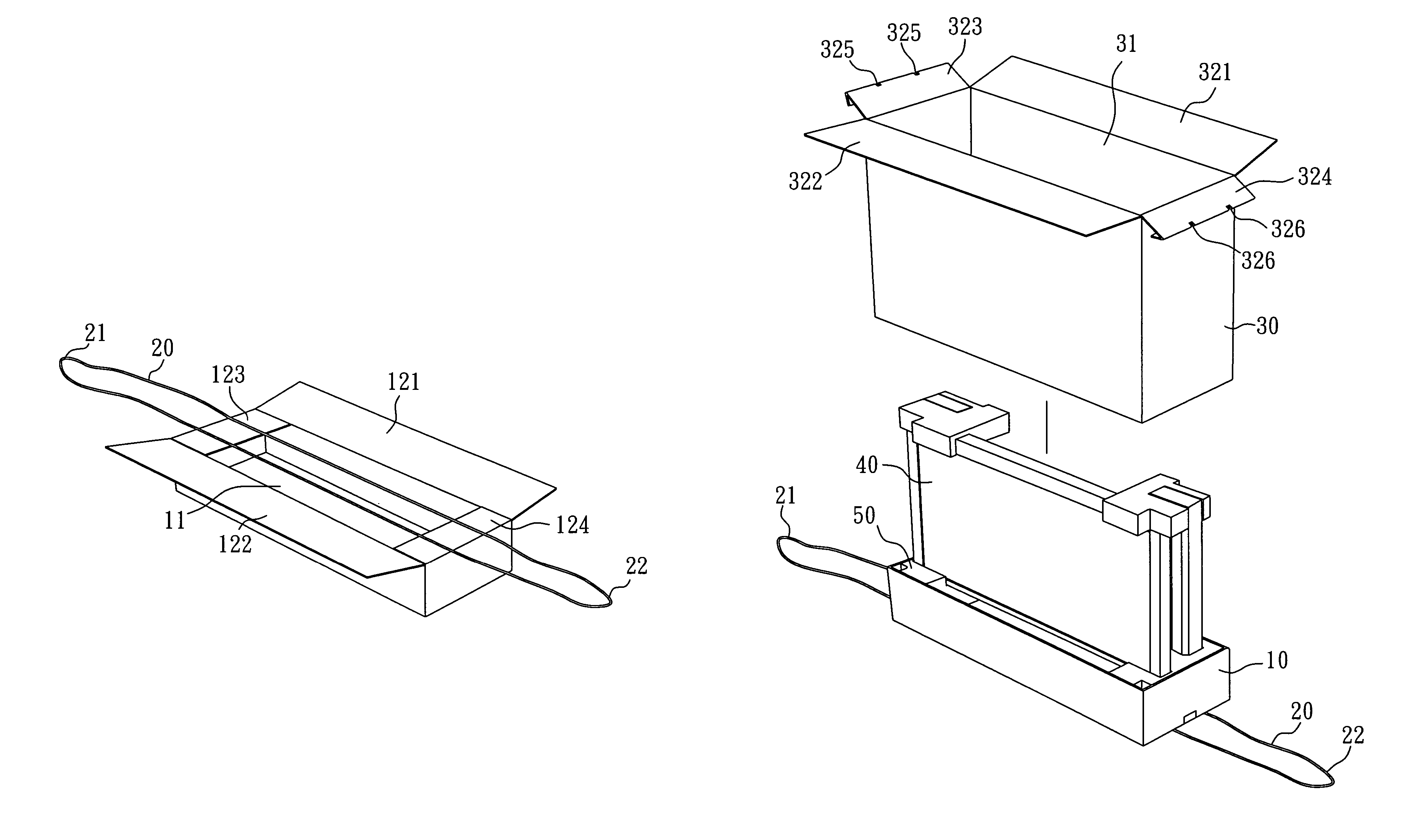

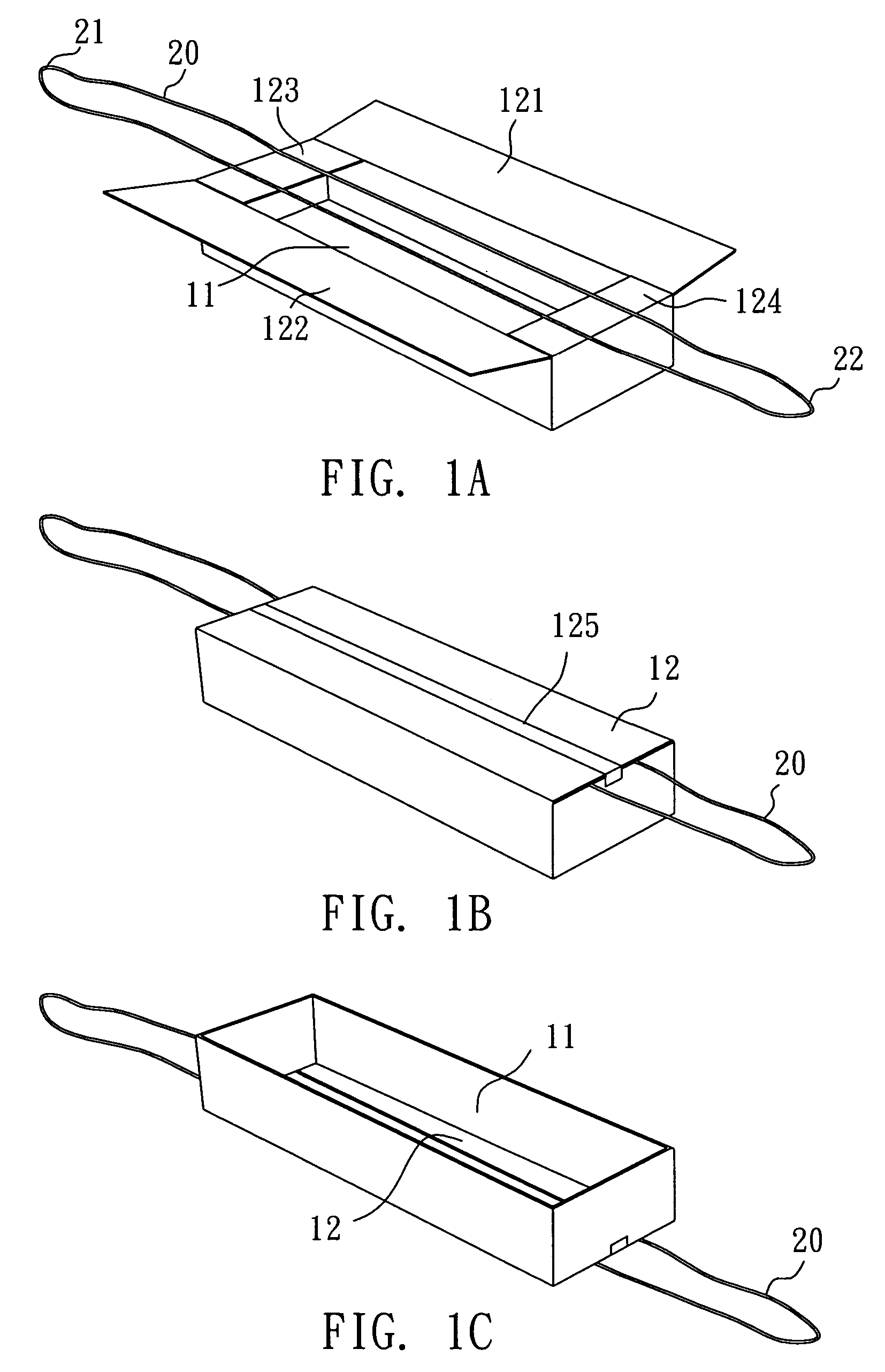

Packaging process for slim batteries and products thereof

InactiveUS20080261109A1Easy to packReduce the amount requiredSmall-sized cells cases/jacketsLarge-sized cells cases/jacketsElectrical and Electronics engineeringEngineering

Owner:SIMPLO TECH COMPANY

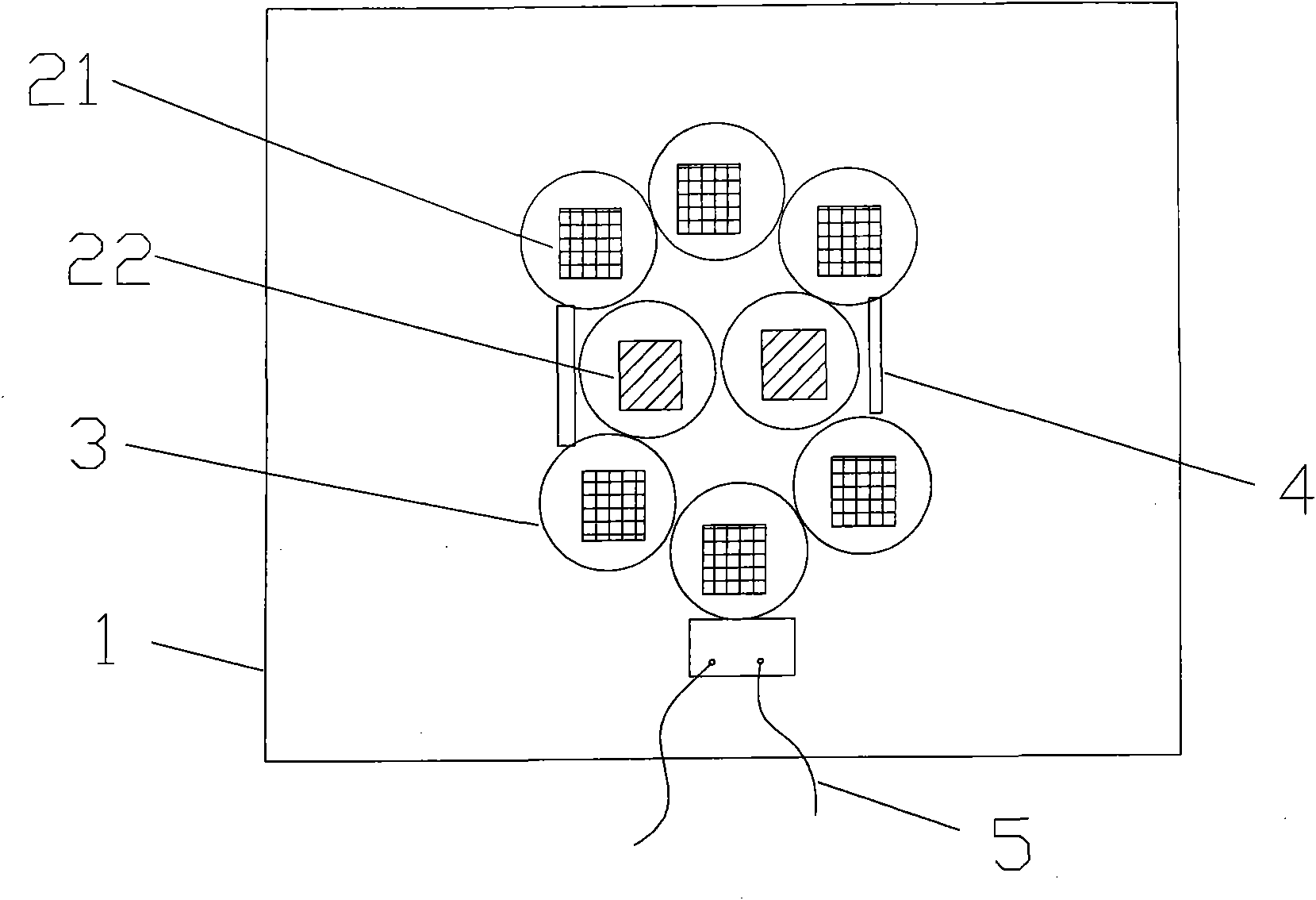

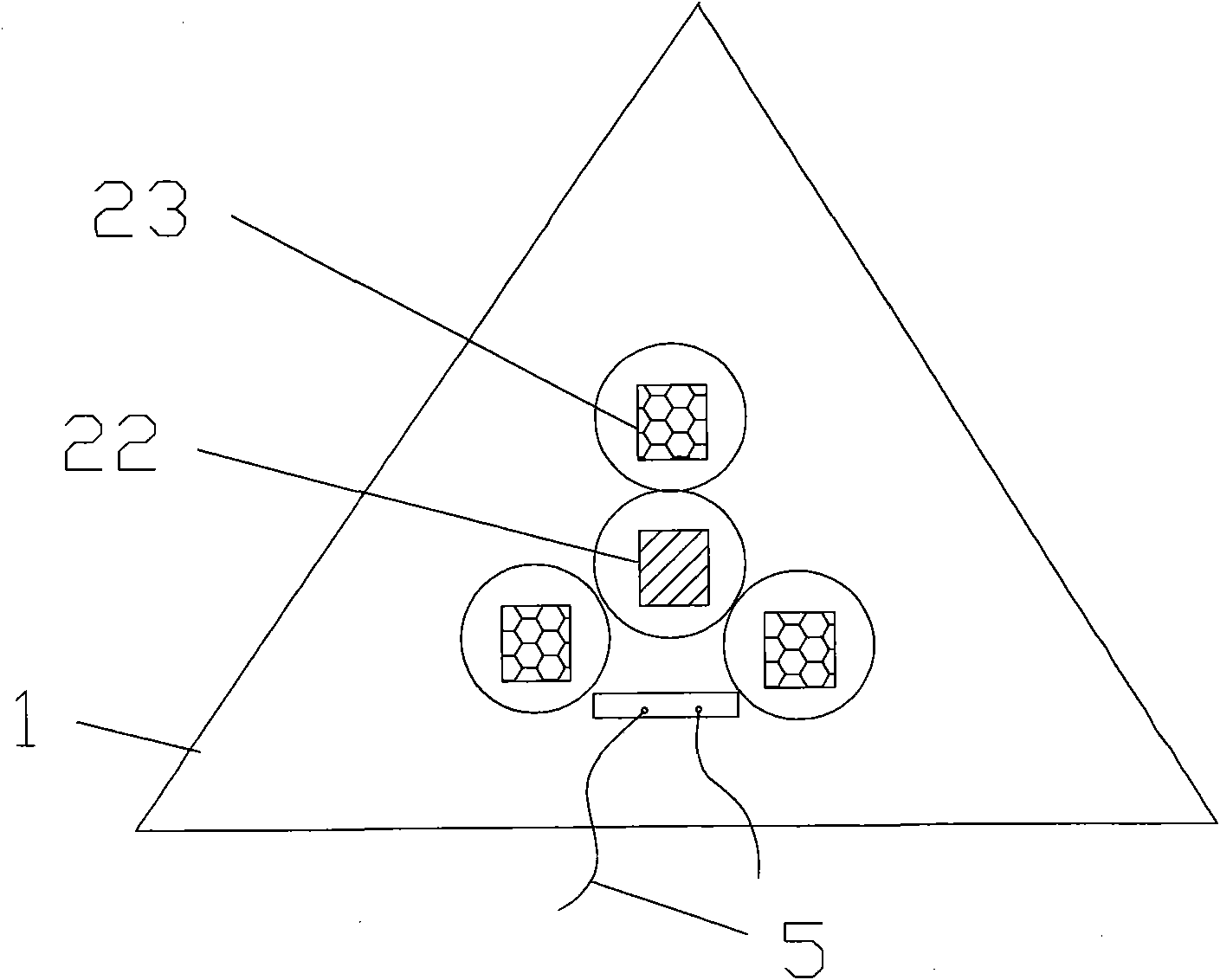

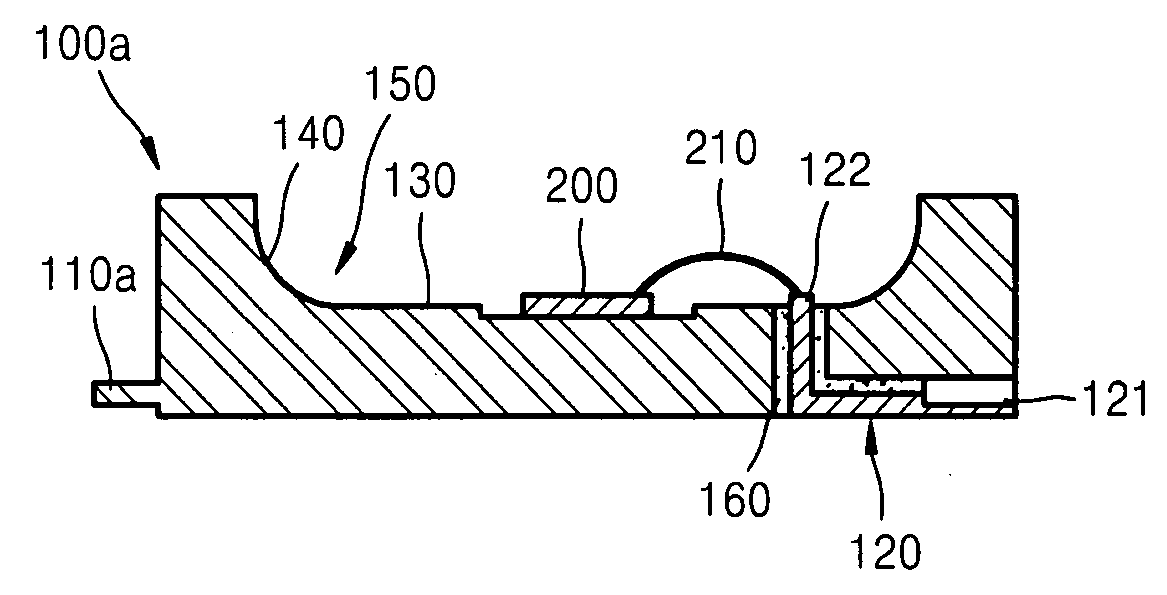

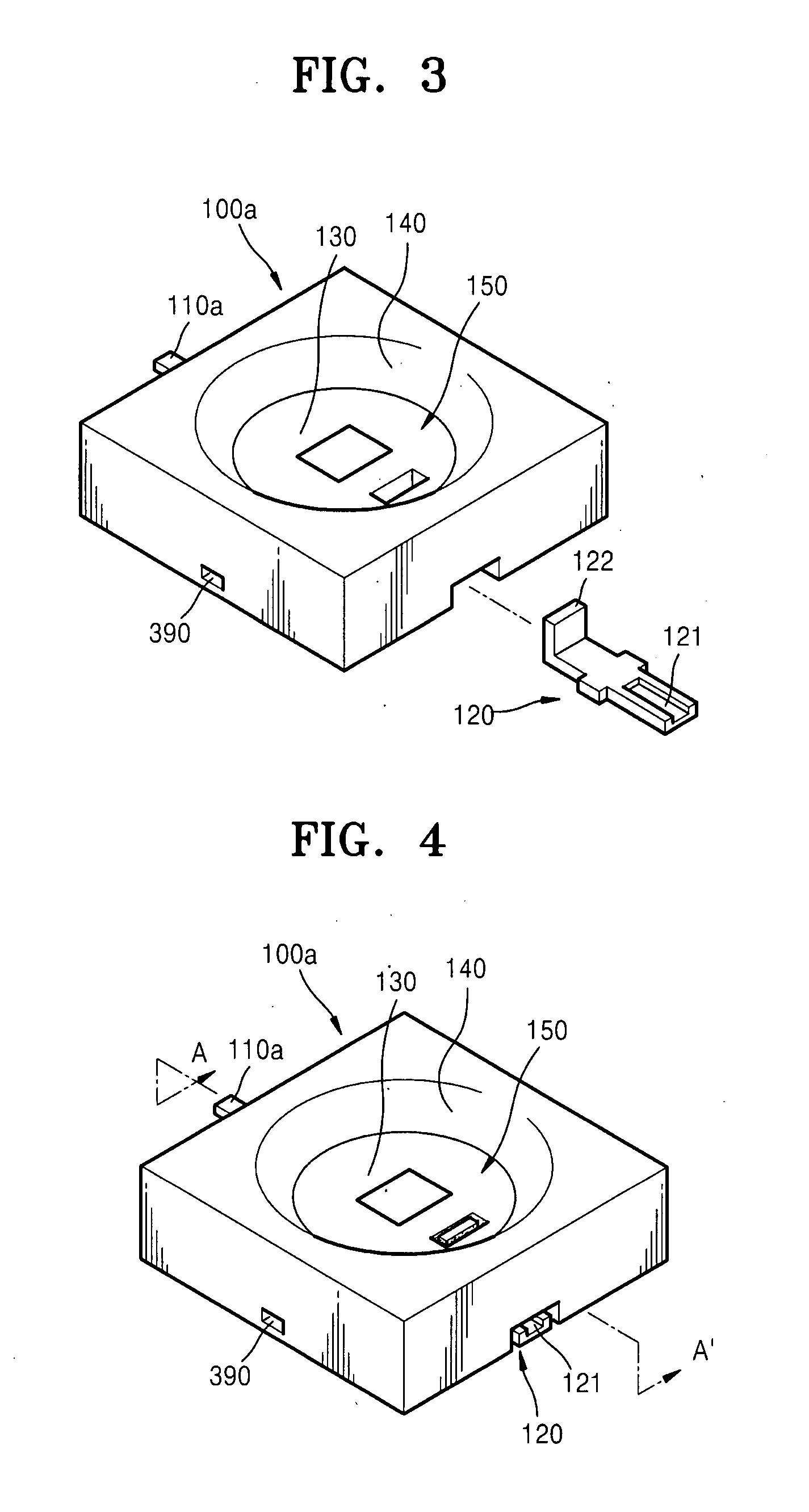

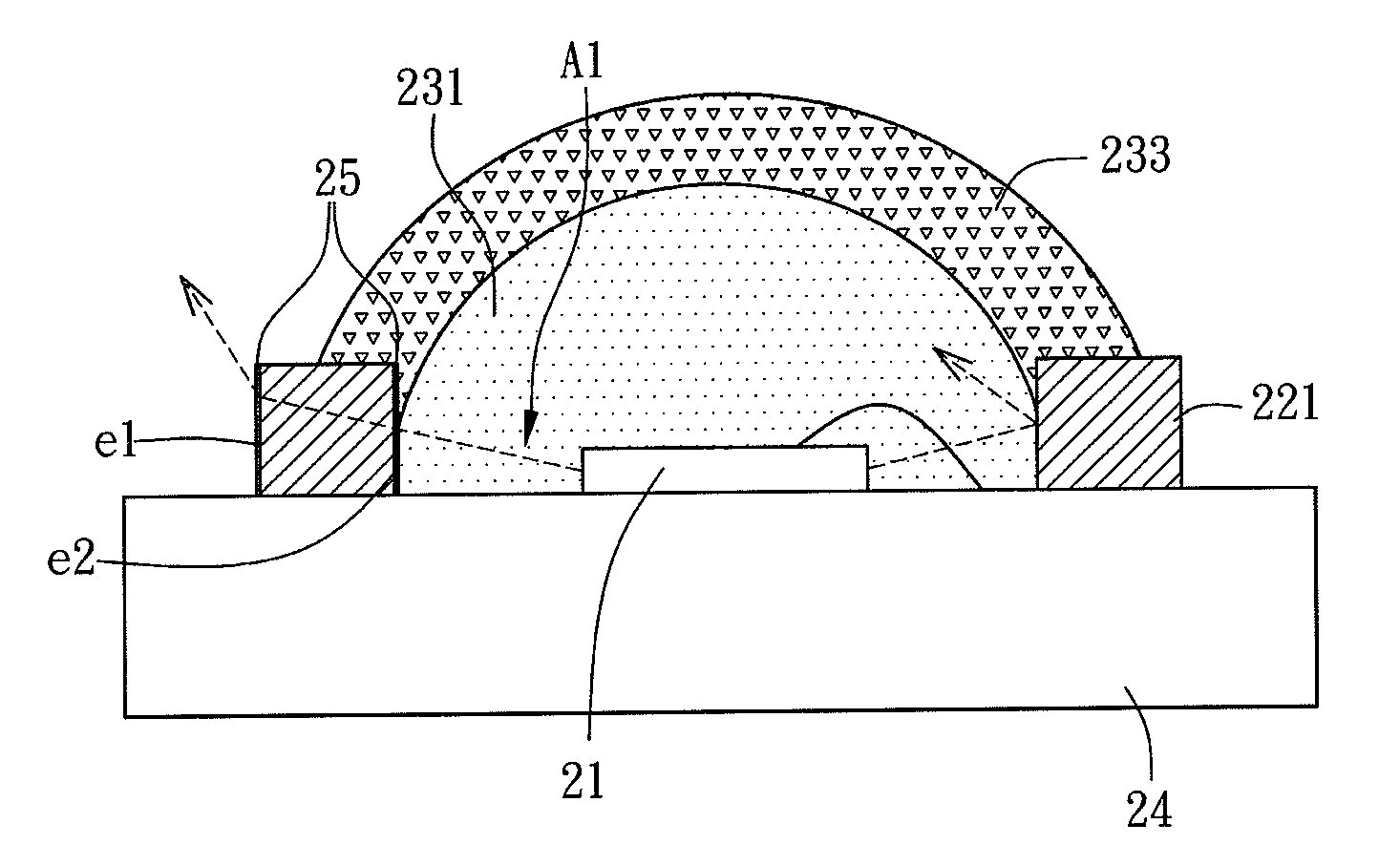

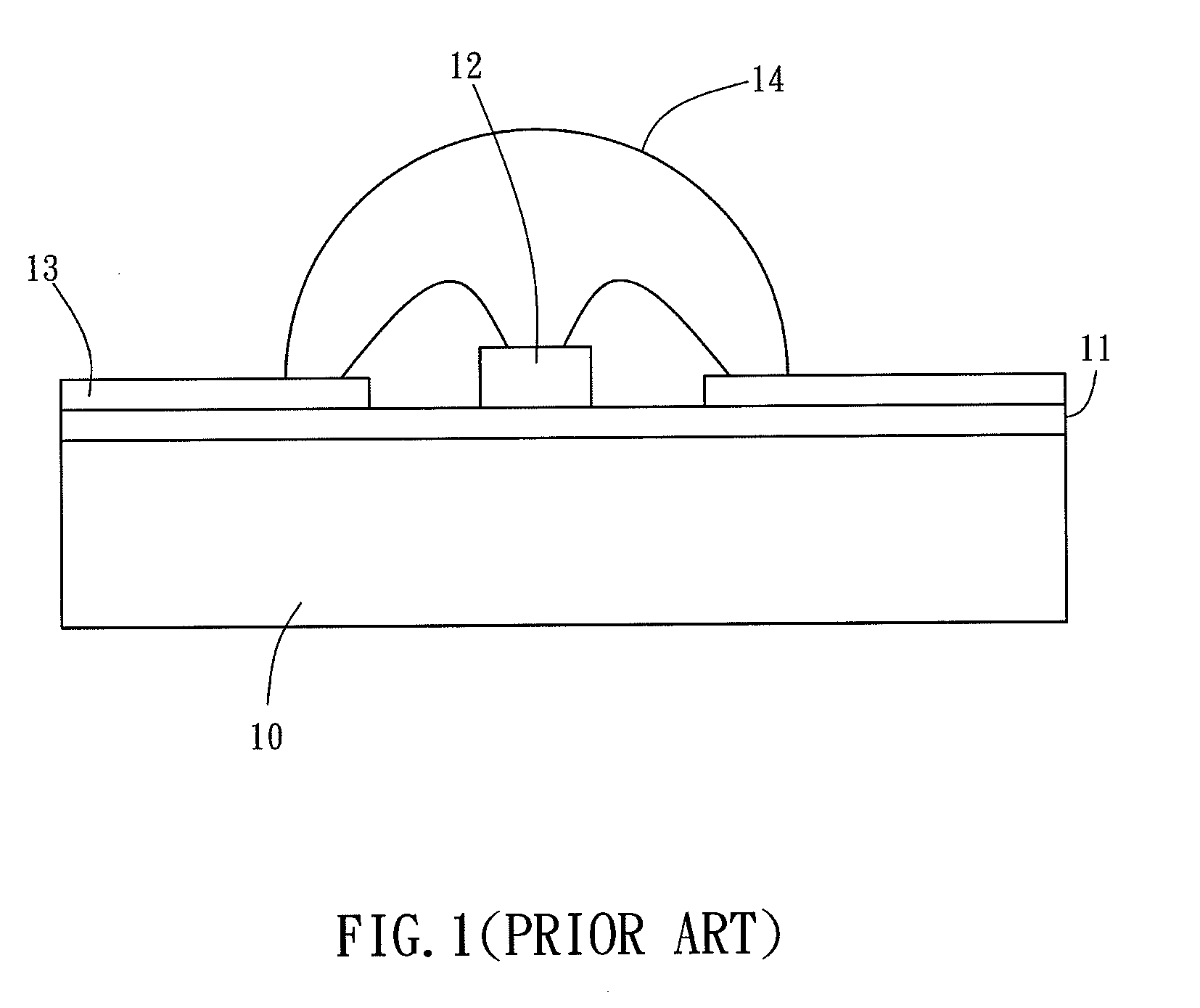

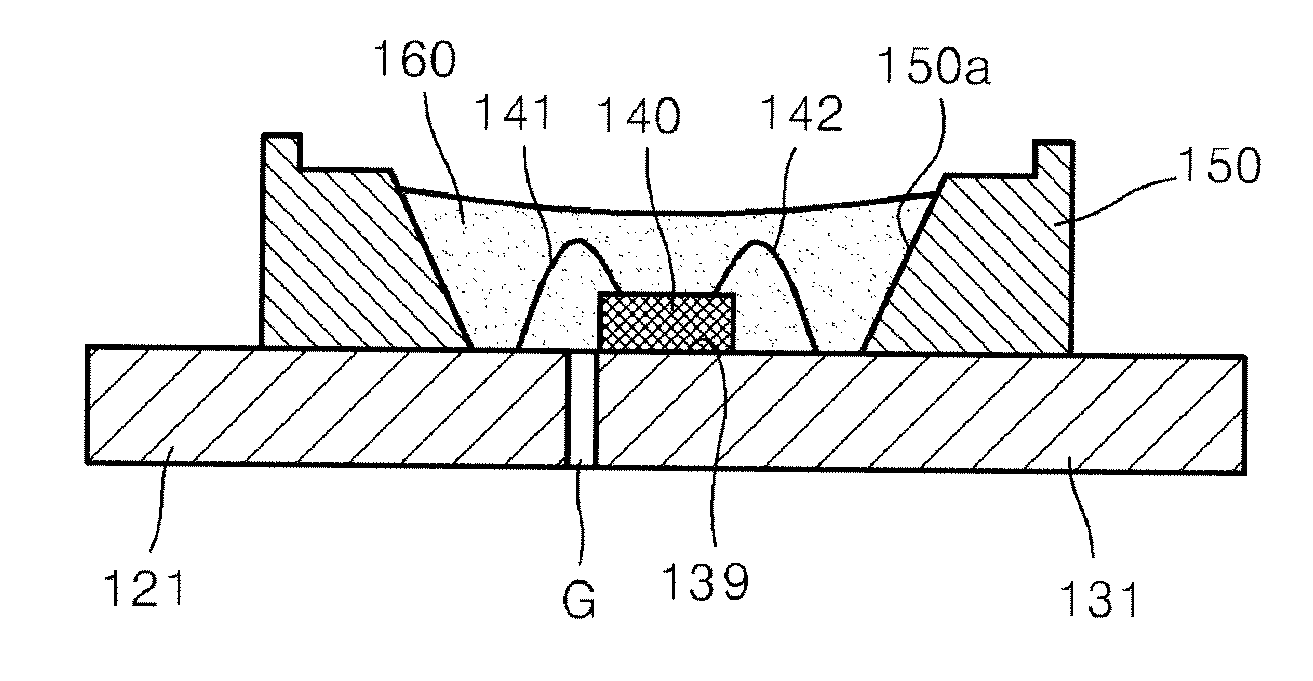

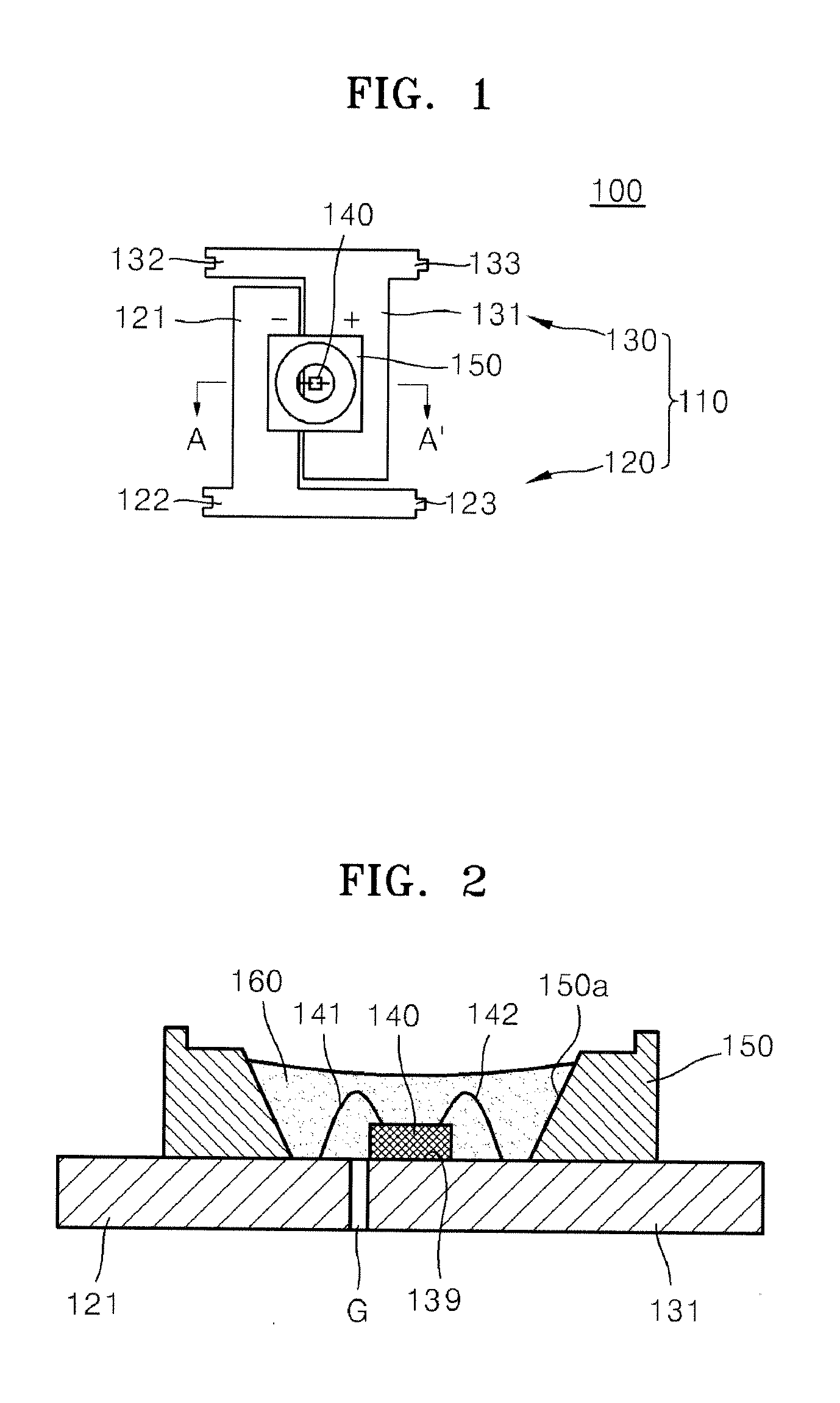

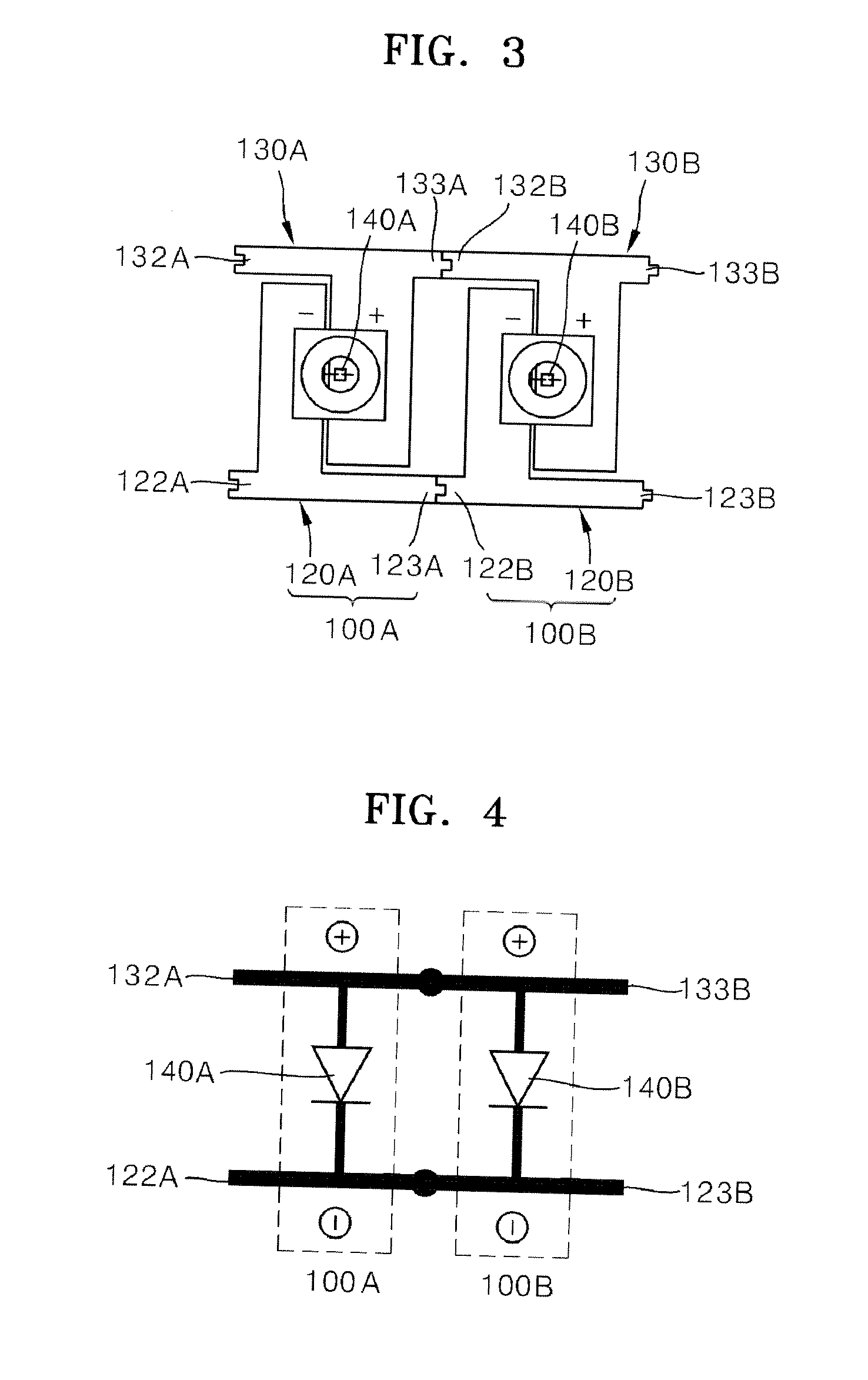

Light emitting package and light emitting package array

InactiveUS20070267637A1Simplify second package processReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesLight emitting devicePhysics

Example embodiments may include a light emitting device package. The light emitting device package may include a light emitting device, a package body including a cavity having a bottom surface on which the light emitting device is mounted and a side surface for reflecting light emitted from the light emitting device, a first electrode protruding from the package body, and a second electrode coupled with the package body. The first and second electrodes may be designed to couple respectively with the second and first electrodes of another light emitting device package, thereby forming an array of light emitting device packages.

Owner:SAMSUNG ELECTRONICS CO LTD

Stack structure of carrier boards embedded with semiconductor components and method for fabricating the same

ActiveUS20070084628A1Solve large capacitySimplify semiconductor package processPrinted electric component incorporationSemiconductor/solid-state device detailsDielectric layerSemiconductor components

A stack structure of carrier boards embedded with semiconductor components and a method for fabricating the same are proposed. A first carrier board and a second carrier board, each of which having at least one through hole, are provided. A first protecting layer and a second protecting layer are formed on a surface of the first and second carrier boards respectively. At least one first semiconductor component and at least one second semiconductor component are disposed on the first and second protecting layers and accommodated in the first and second through holes respectively. A dielectric layer is laminated between the surfaces of the first and second carrier boards without the protecting layers formed thereon. Thus, a modularized package structure with reduced space waste is formed.

Owner:PHOENIX PRECISION TECH CORP

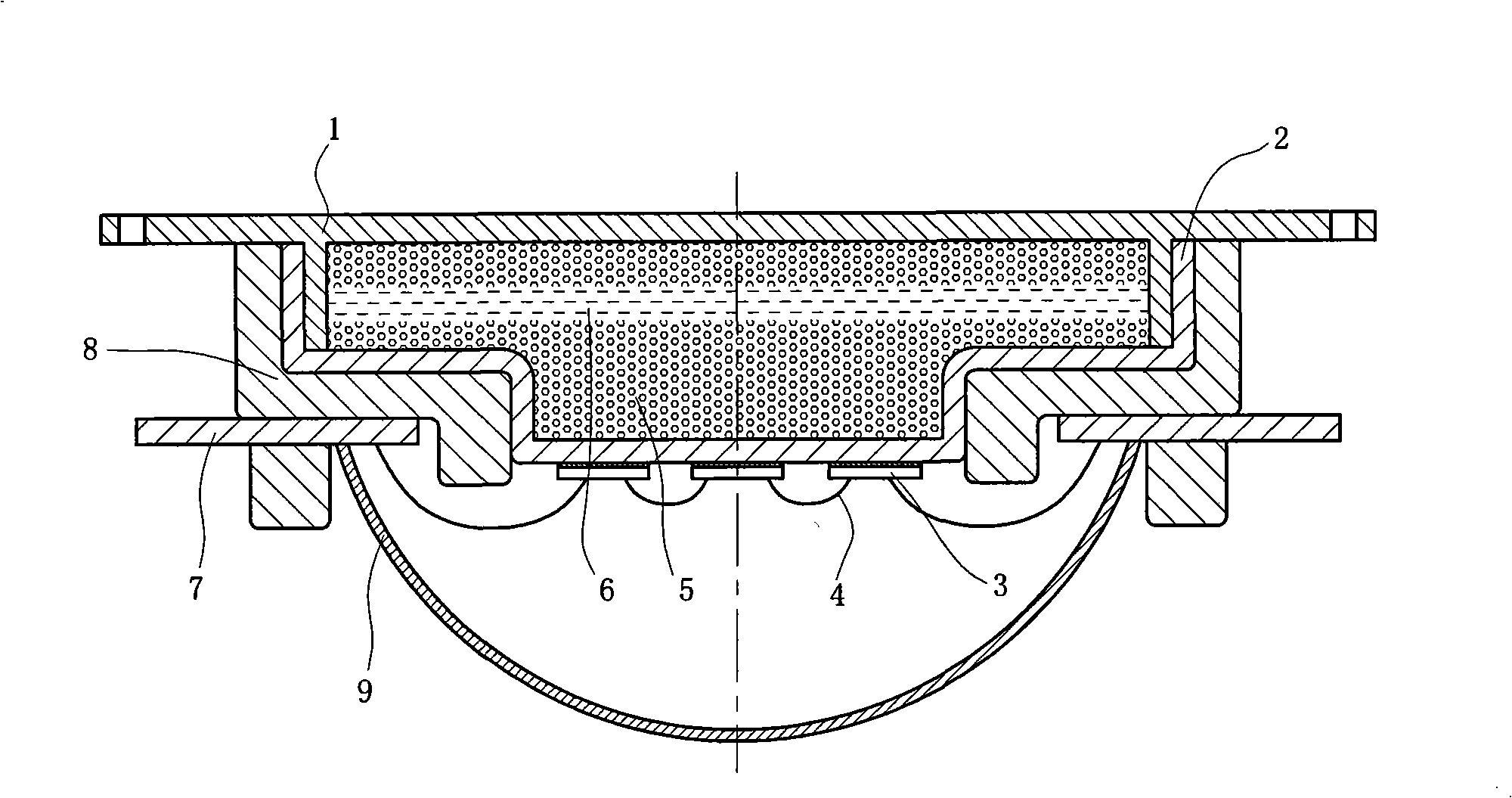

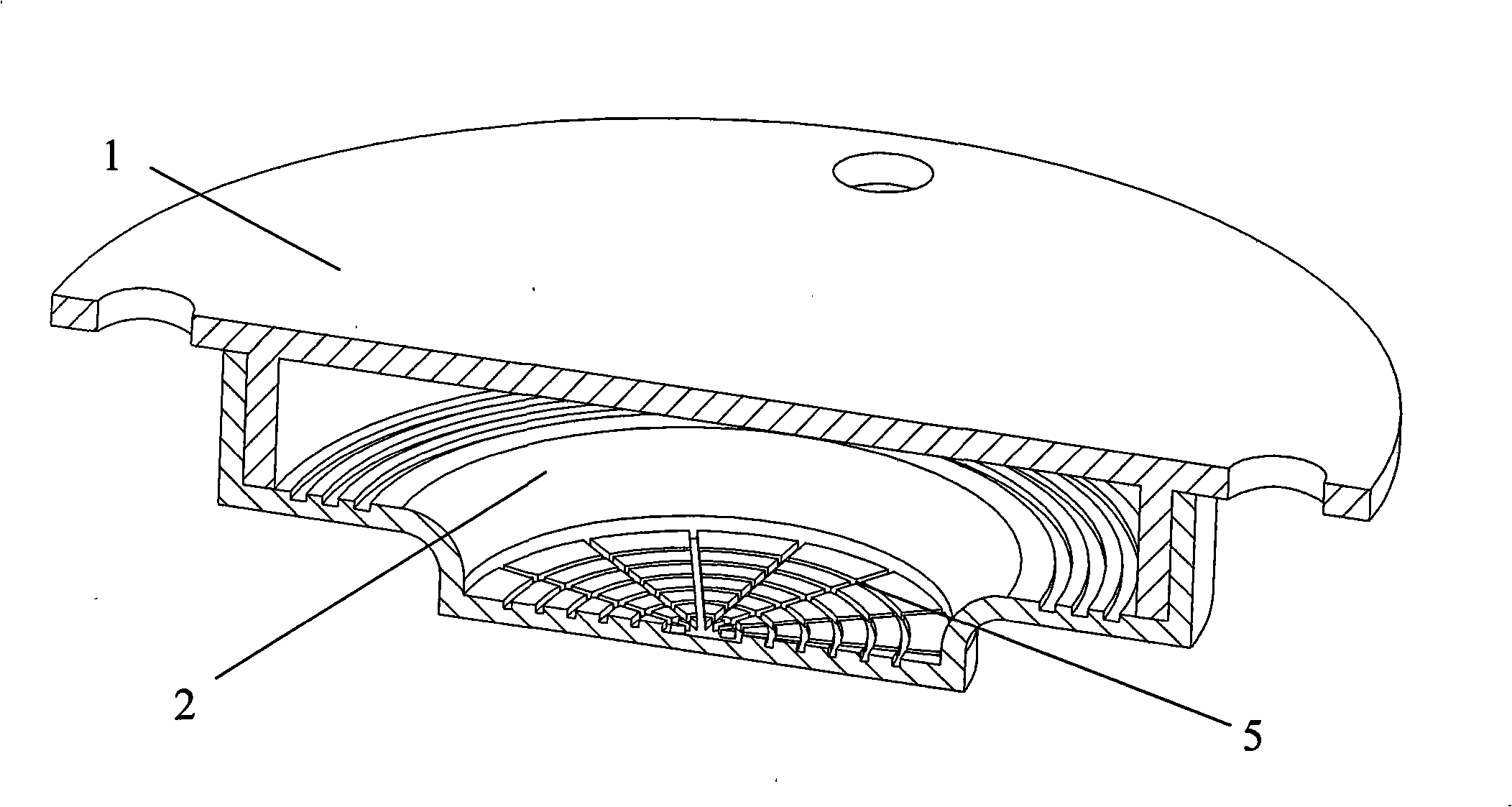

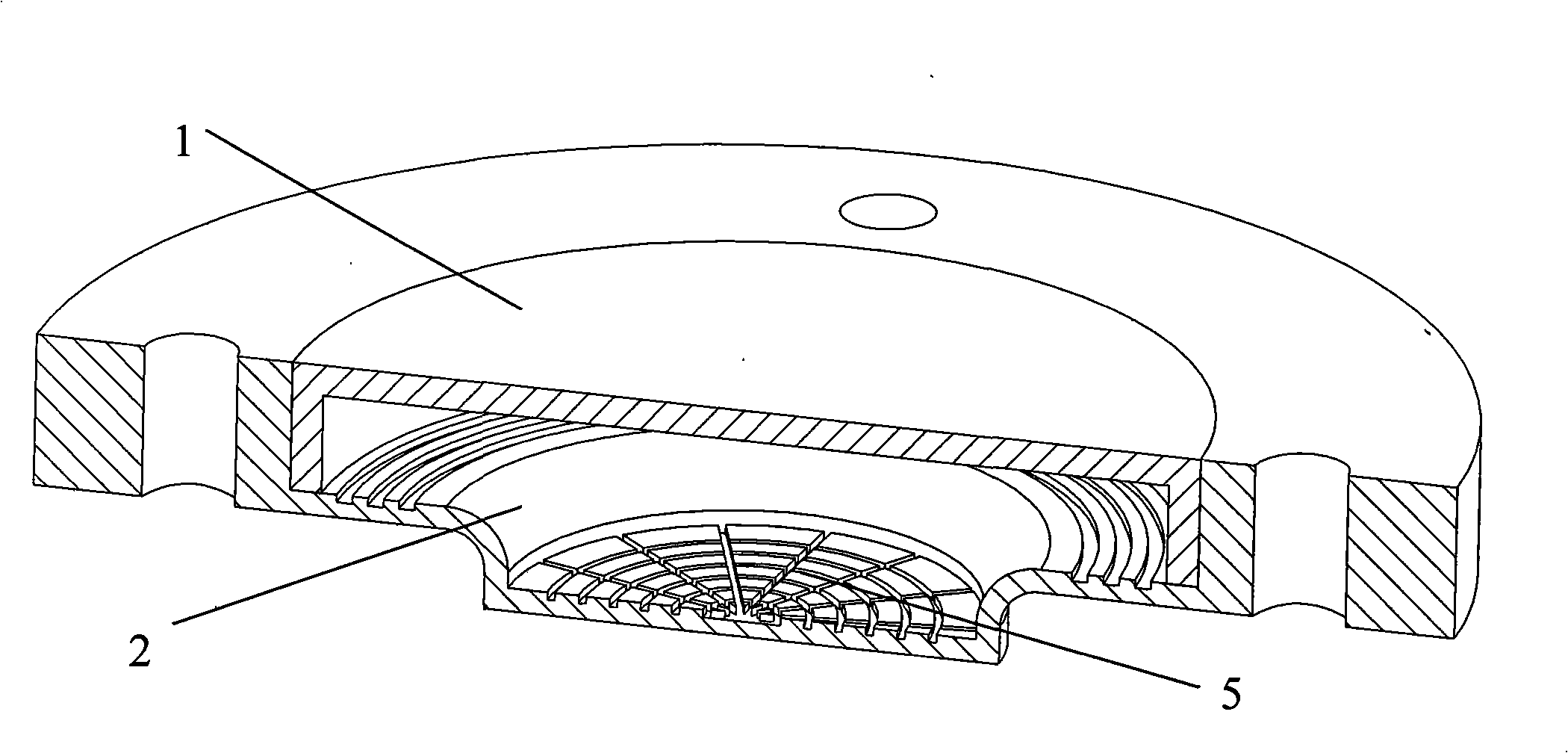

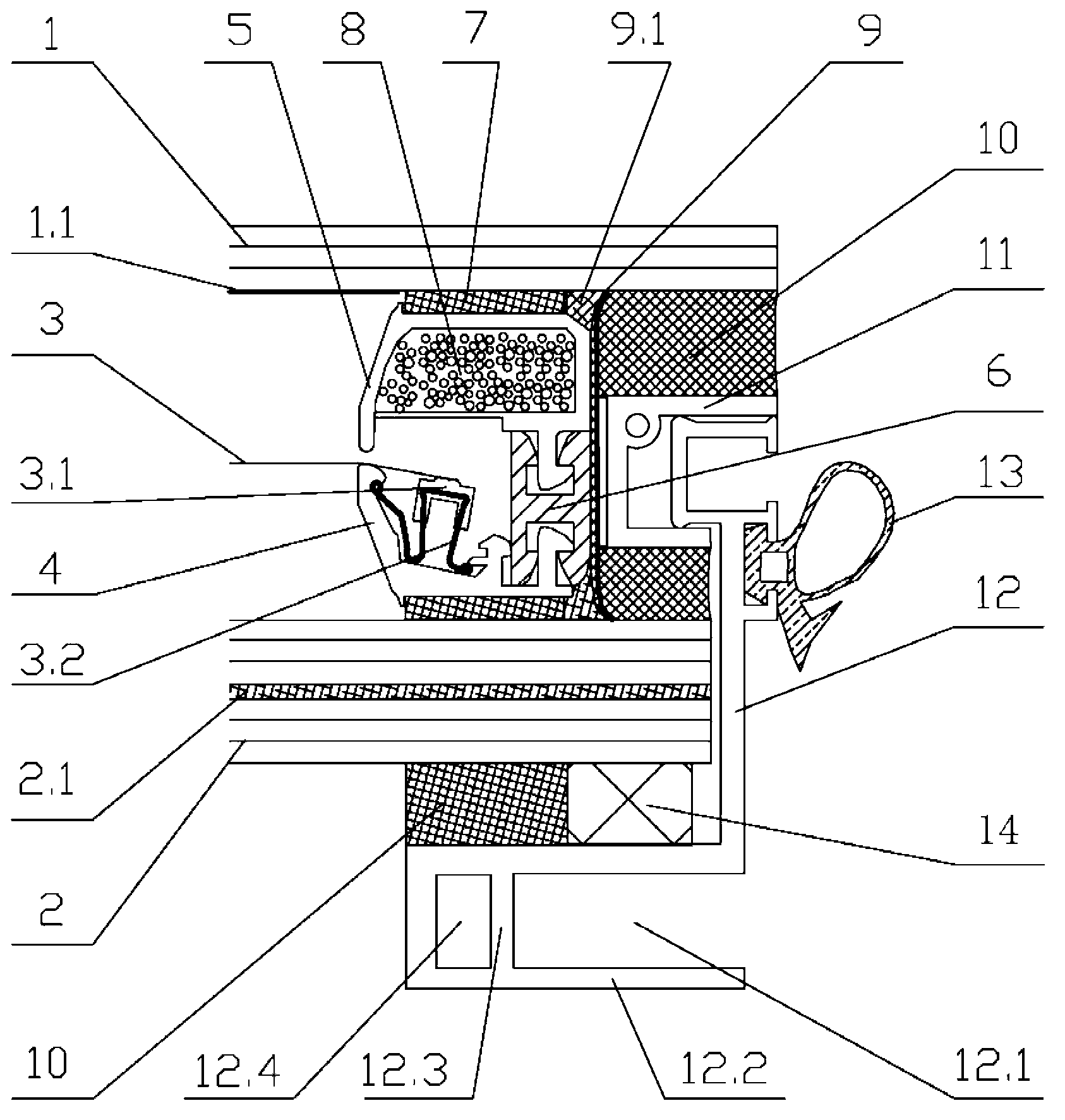

High power LED phase transition heat sink structure

InactiveCN101315927AEfficient transferImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesEngineeringTemperature difference

The invention discloses a high-power LED phase-change heat sink structure, the heat sink body of the structure is a circular or square structure with an cavity, a boiling structure and a low temperature boiling heat transfer working medium are arranged in the cavity, a sealing end cover is arranged at the upper end of the heat sink body and tightly connected with the heat sink body, thus forming the closed cavity, the inner surface of the sealing end cover is a condensation structure, and the cavity is sealed into the vacuum state; at least one high-power LED chip is fixed at the lower end of the outside of the heat sink body, an electrode is arranged outside of the phase-change heat sink, the phase-change heat sink, the electrode and a lens are connected by packaging resin, and the high-power LED chip is directly connected with the electrode by a gold wire. The high-power LED phase-change heat sink structure utilizes the liquid-gas phase change of the working medium to realize the isothermal effect of the heat sink body to reduce the temperature difference at upper and lower ends of the heat sink, thus effectively conducting the generated heat of the high-power LED chip out, realizing the integration of the high-power LED and a high-efficiency heat radiating device and having the advantages of light weight, high power, simple structure, high heat radiation efficiency, long service life and no consumption of additional energy, etc.

Owner:SOUTH CHINA UNIV OF TECH

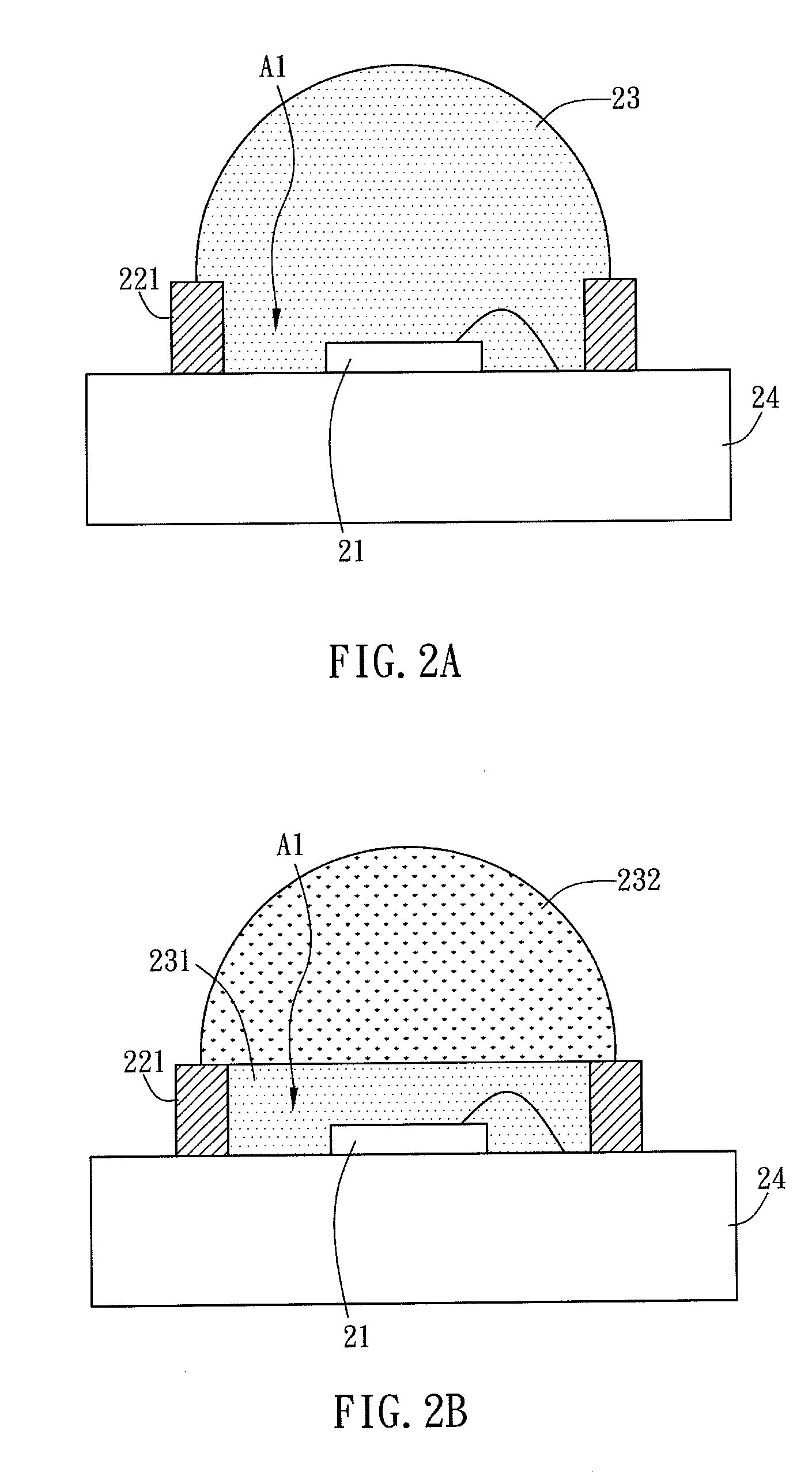

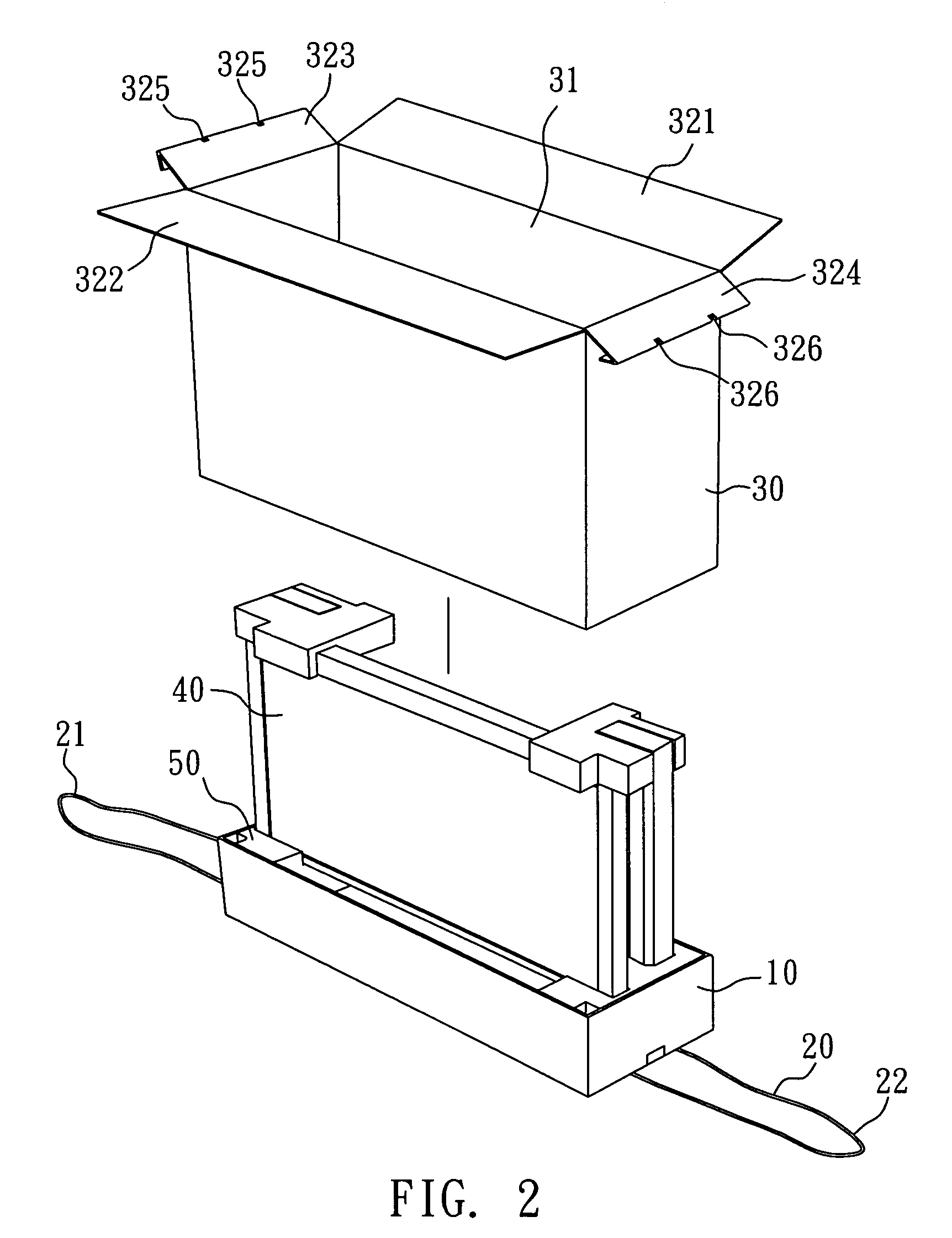

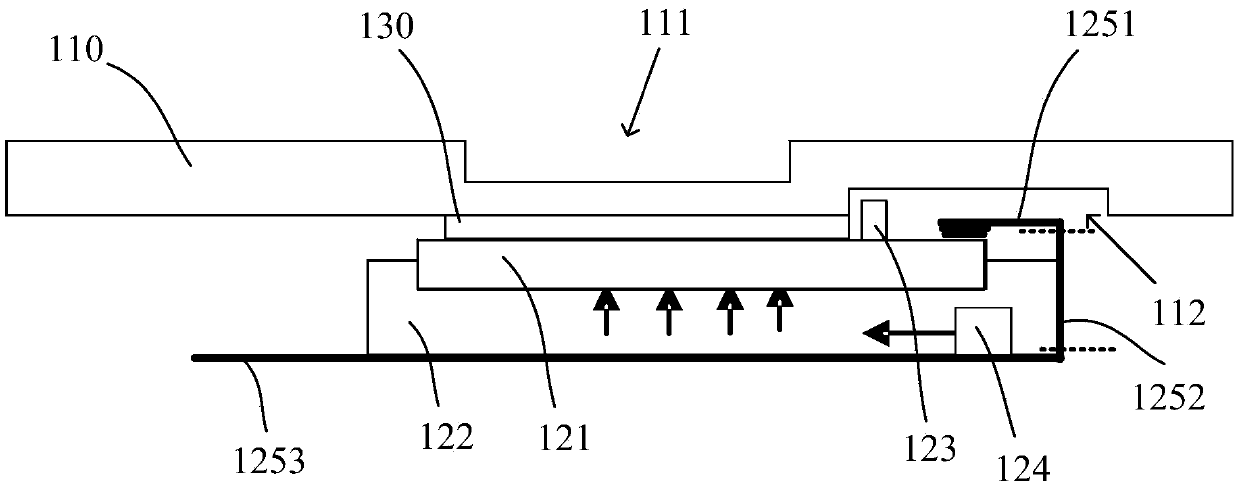

Illuminating device and packaging method thereof

ActiveUS20100321920A1Precise alignmentSimplify the packaging processLighting support devicesSolid-state devicesEngineeringPacking method

Owner:DELTA ELECTRONICS INC

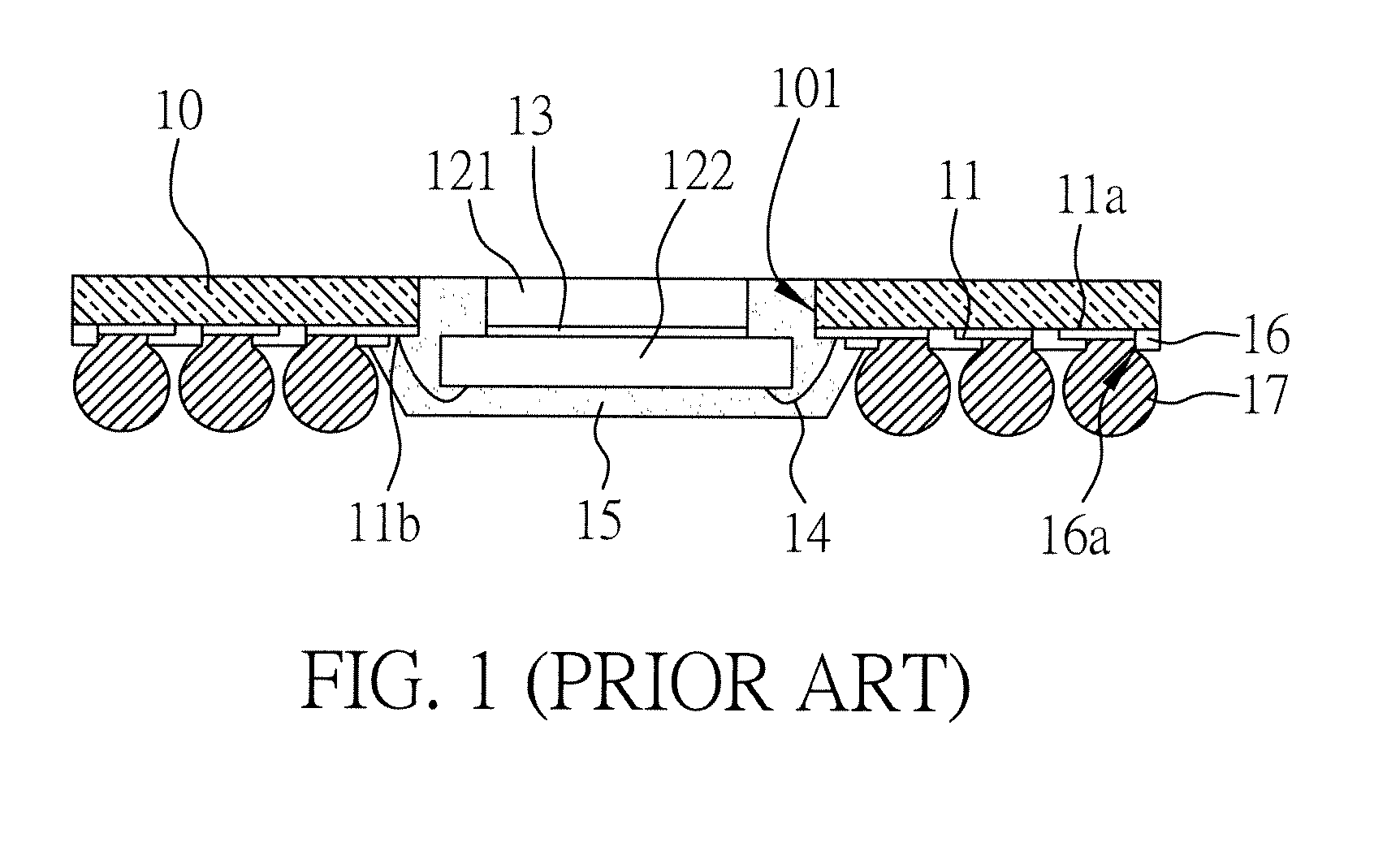

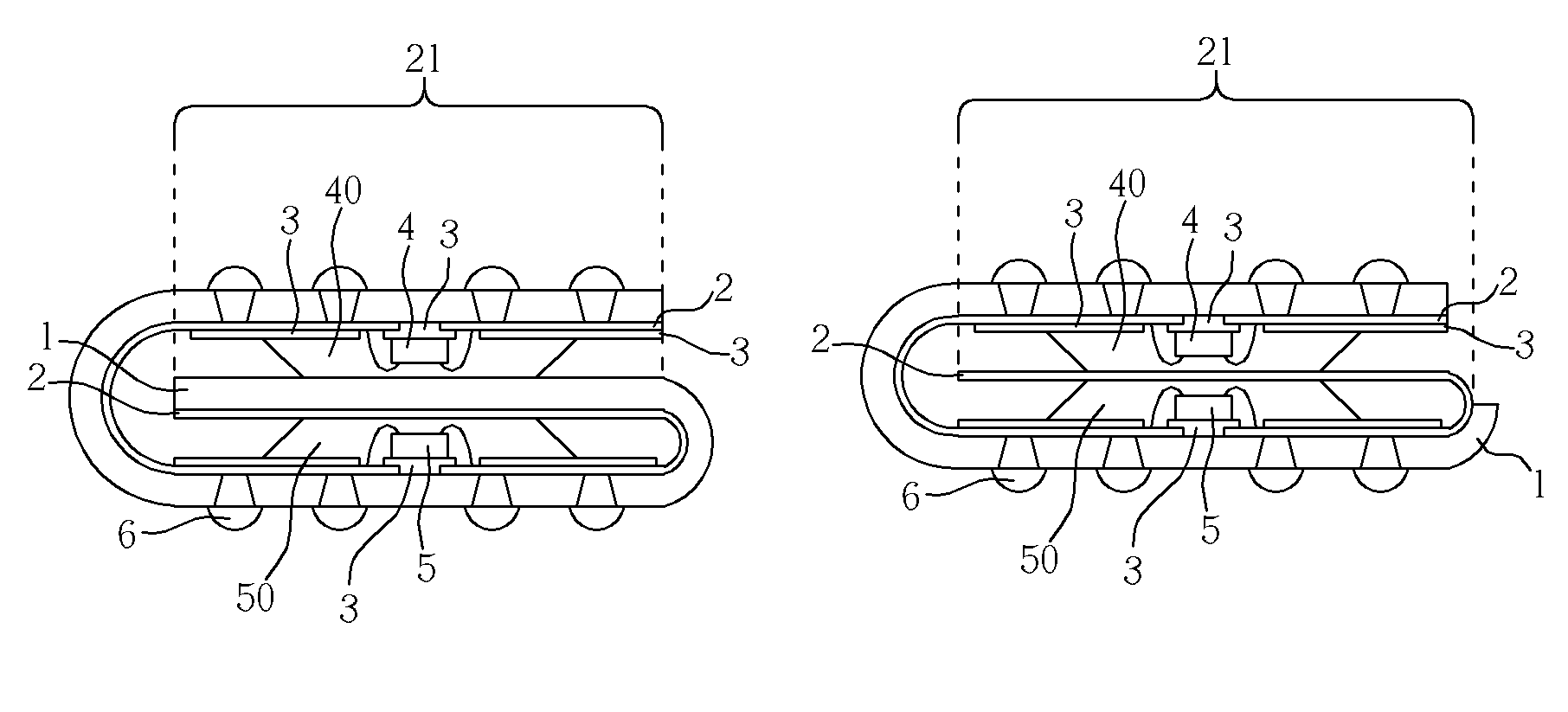

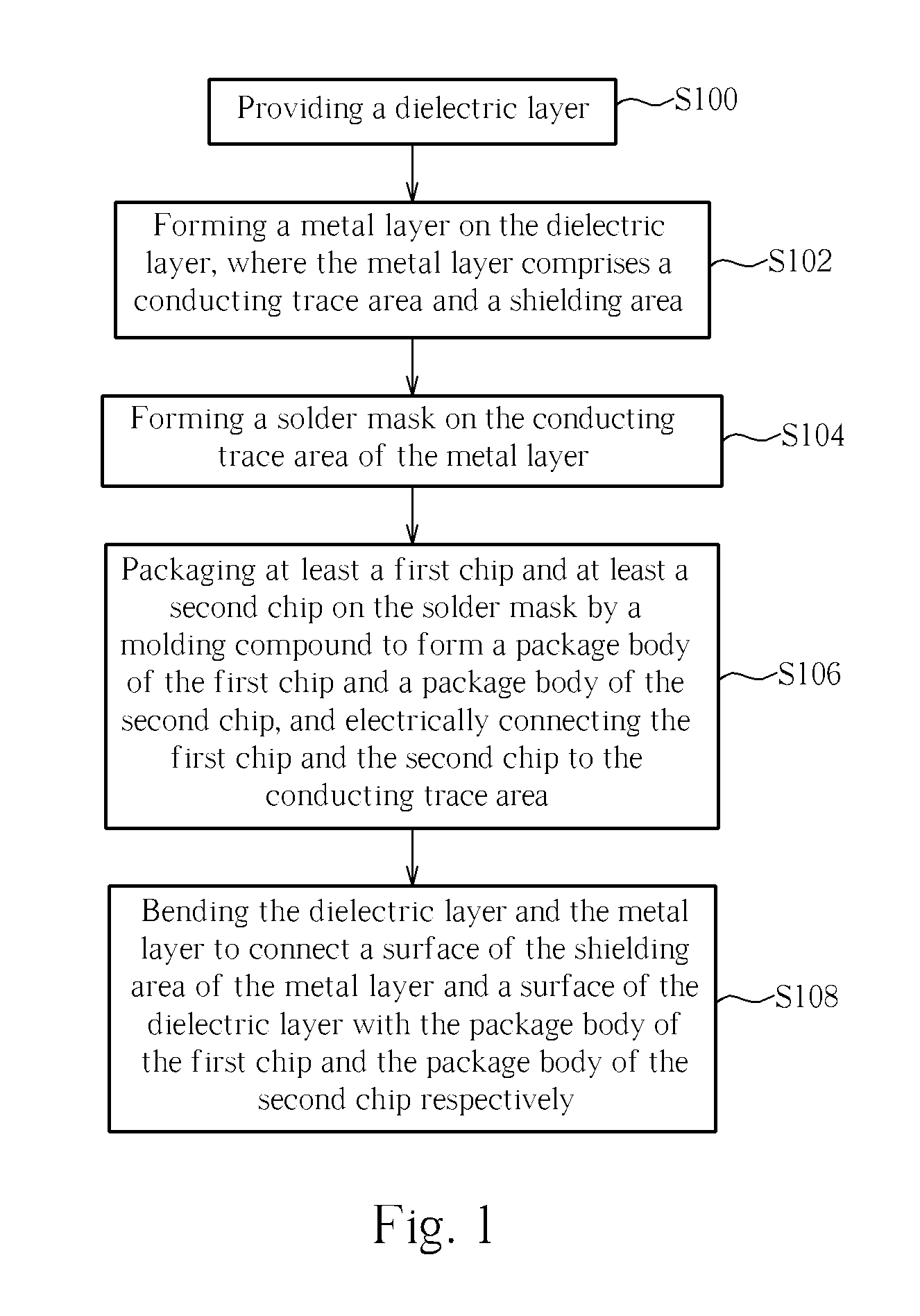

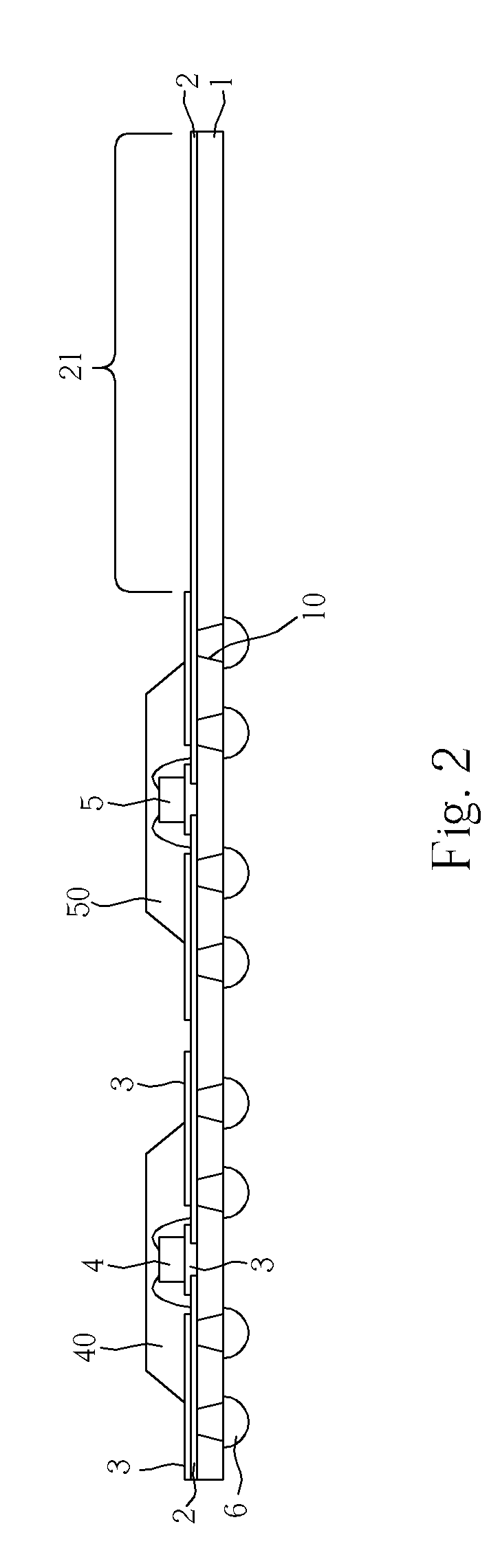

Packaging method of a plurality of chips stacked on each other and package structure thereof

ActiveUS7436055B2Efficient processSimplify the packaging processSemiconductor/solid-state device detailsSolid-state devicesSolder maskEngineering

A package structure with a plurality of chips stacked on each other includes a substrate, a first chip and second chip. The substrate has a dielectric layer, a metal layer having a conducting trace area and a shielding area formed on the dielectric layer, and a solder mask formed on the conducting trace area. The first chip and the second chip are electrically connected to the conducting trace area and arranged on the solder mask respectively. The first chip has a package body connected with one surface of the metal layer for arranging the first chip between the solder mask and the shielding area of the metal layer. The second chip has a package body connected with the other surface of the metal layer for arranging the second chip between the solder mask and the shielding area of the metal layer.

Owner:ADVANCED SEMICON ENG INC

Packing box

InactiveUS6986456B2Simplify the packaging processReduce in quantityRemovable lids/coversLidsEngineeringPackaging Case

Owner:TATUNG COMPANY

Optical fingerprint sensor module

InactiveCN105512645AImprove clarityImprove accuracyPrint image acquisitionFingerprintProtection layer

The invention discloses an optical fingerprint sensor module, comprising an optical fingerprint sensor, a protection layer located above the optical fingerprint sensor, and a heightening layer located between the protection layer and the optical fingerprint sensor, wherein the optical fingerprint sensor is provided with a light transmitting base plate and a device layer located on the surface of the light transmitting base plate, the device layer is provided with a pixel zone, the pixel zone is provided with multiple pixels, each pixel is provided with a light transmitting area and a lightproof area, each lightproof area is provided with a photosensitive element, each light transmitting area enables light rays to penetrate through the pixel zone, and the optical fingerprint sensor is provided with a binding zone; the heightening layer at least covers the pixel zone. The optical fingerprint sensor module is simplified in structure and improved in reliability.

Owner:SHANGHAI OXI TECH

Lead frame for chip package, chip package, package module, and illumination apparatus including chip package module

ActiveUS20110272716A1Simplify the packaging processConvenient ArrangementSemiconductor/solid-state device detailsSolid-state devicesCouplingComputer module

A lead frame for a chip package, a chip package, a package module, and an illumination apparatus including the chip package module. The chip package includes a first coupling portion and a second coupling portion that are coupled to each other on edges of a lead frame for mounting a chip thereon, and thus a package module is easily embodied by coupling the first coupling portion and the second coupling portion to each other.

Owner:SAMSUNG ELECTRONICS CO LTD

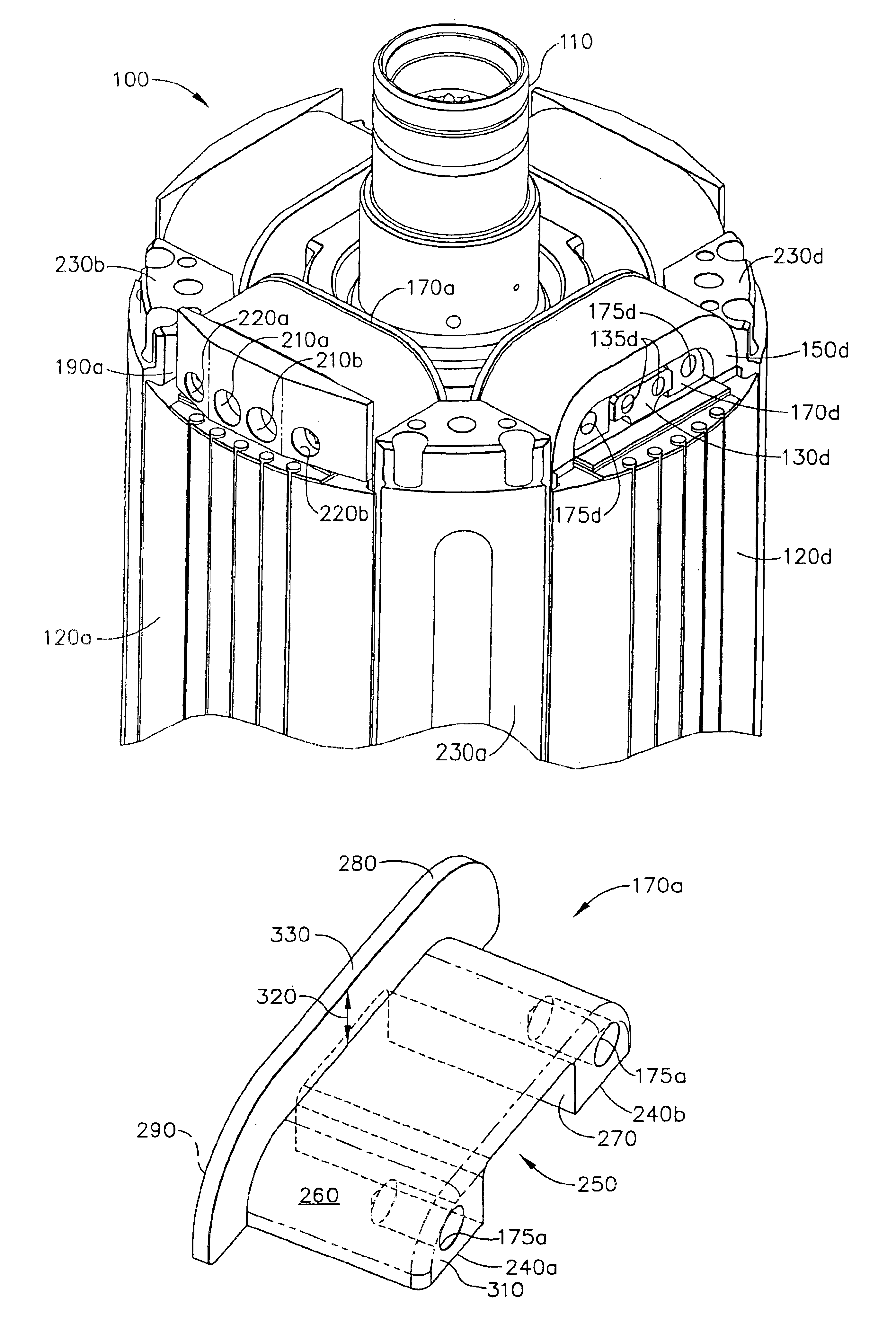

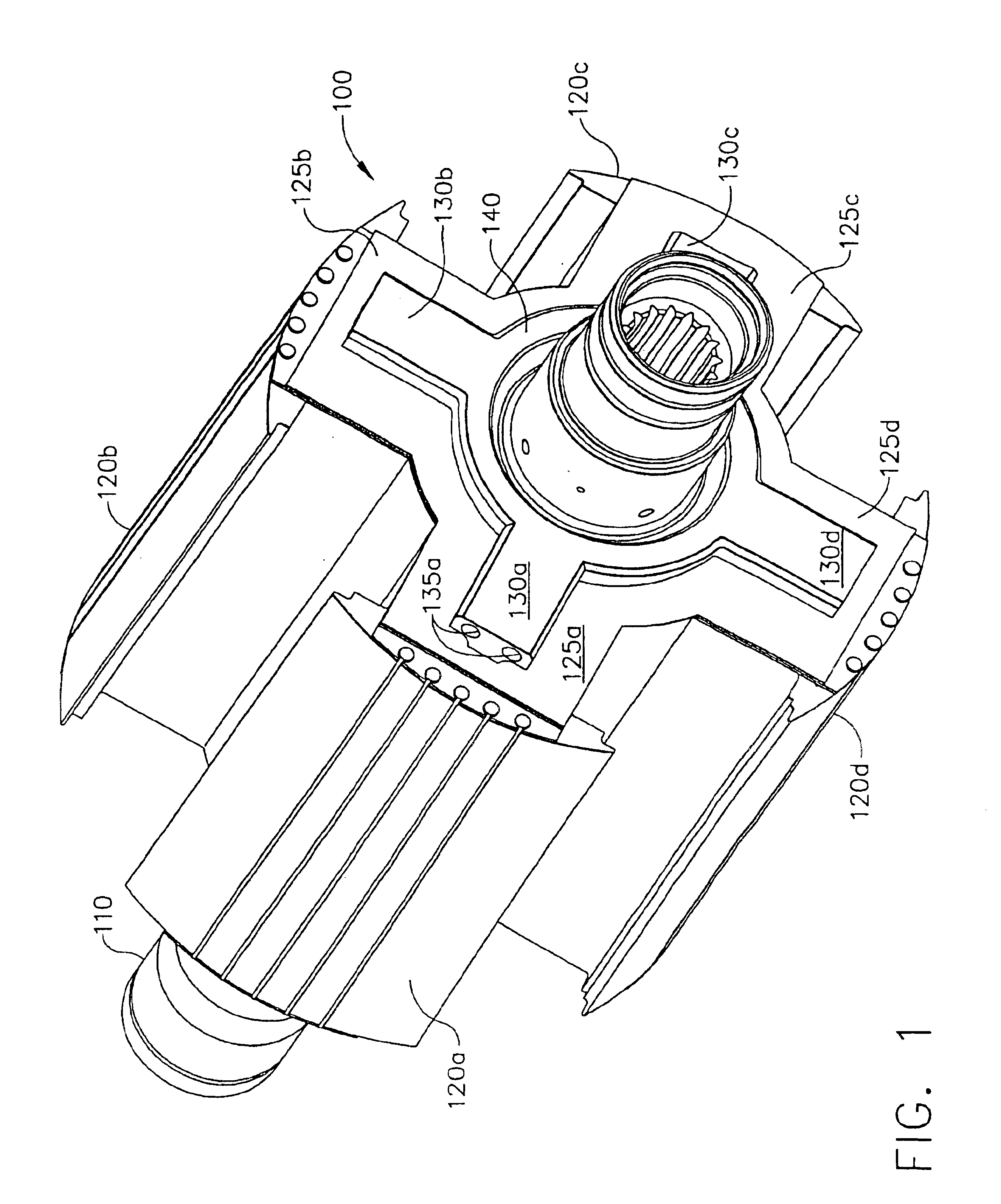

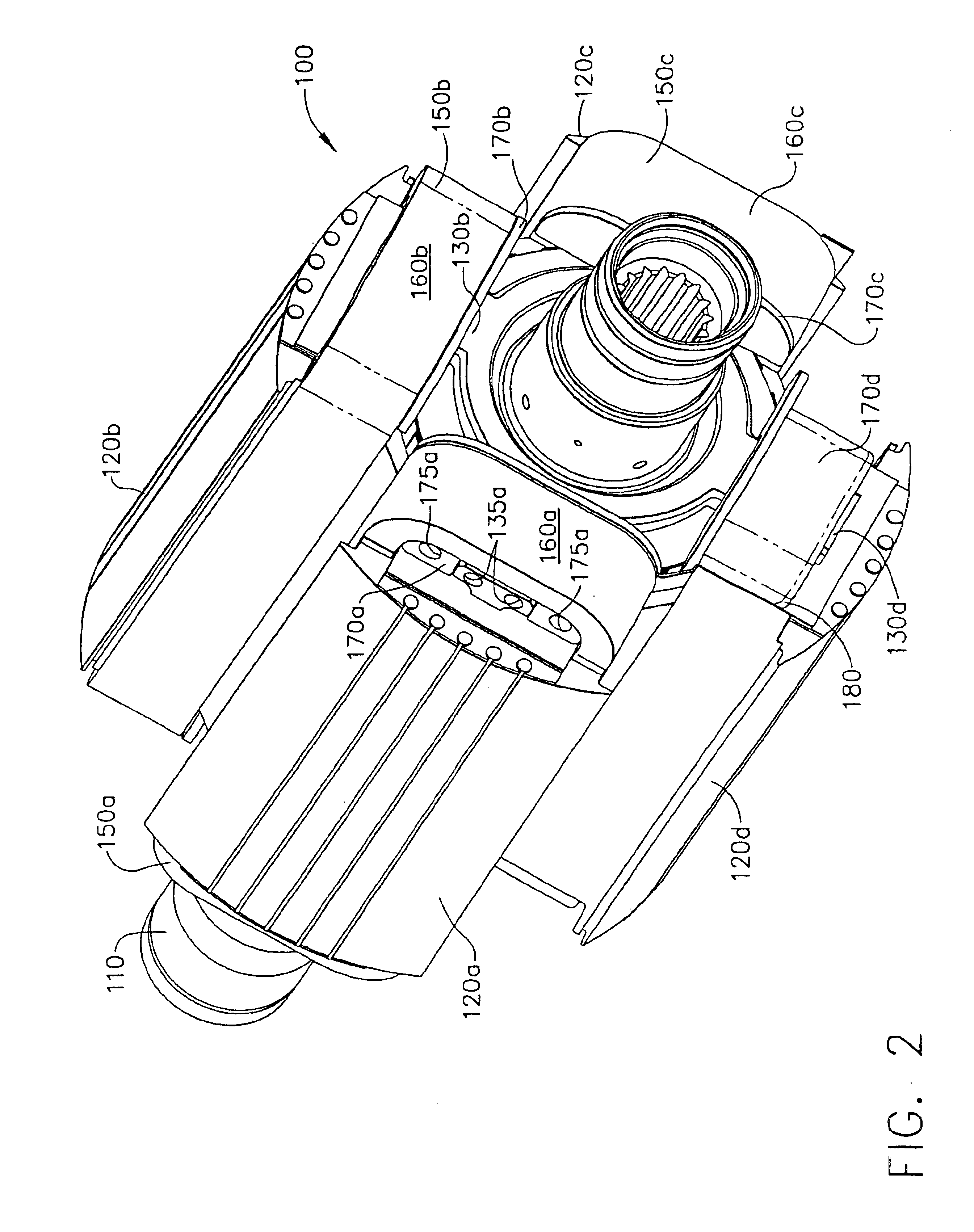

System and method for end turn retention on a high speed generator rotor

InactiveUS6849987B2Improving rotor balanceImprove robustnessWindingsMagnetic circuit rotating partsEngineeringConductor Coil

A new improved system and method for end turn retention for wires on a generator rotor for use in high speed applications such as in aircraft applications. The rotor includes a shaft, spokes, supports, and wire winding coils, and at least one cap device. The spokes extend radially outwardly from the shaft, and each support is positioned on an associated spoke. Each coil wraps around an associated support and spoke. Each cap device is coupled to an end of its associated spoke to prevent the windings from moving radially outwardly while the rotor spins. Each support is coupled to an associated cap device, and includes at its radially inward edge a flange protruding away from the respective spoke. Because of the flange and the cap device, slack of the wire coil between the flange and the associated cap is taken up.

Owner:HONEYWELL INT INC

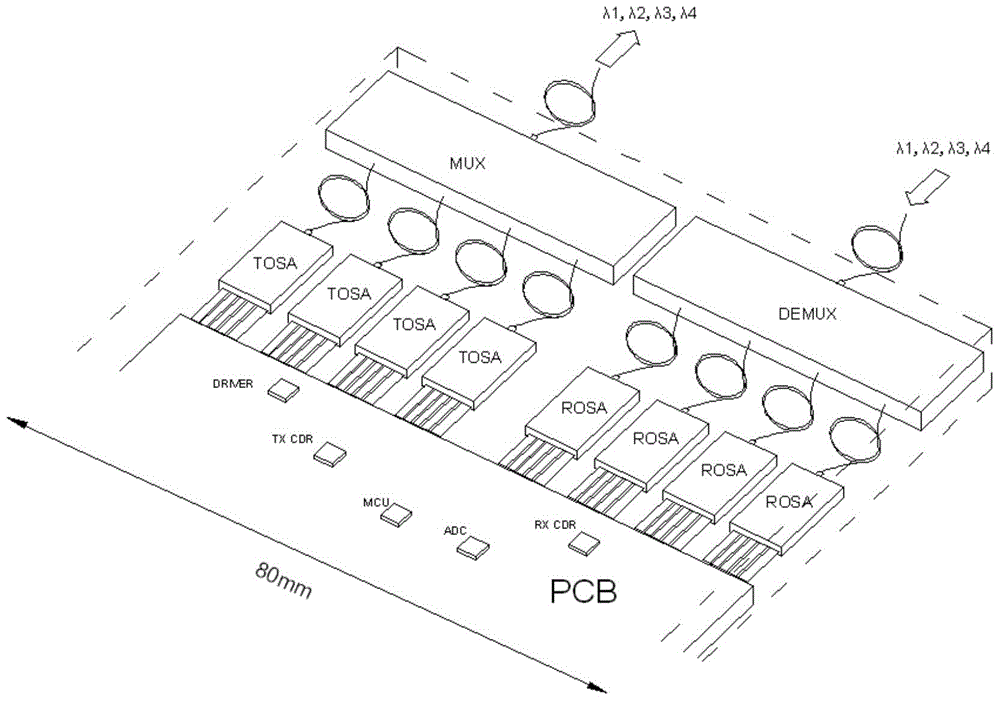

400 Gbps hot-plug high-speed optical transceiver module

ActiveCN104601244ARealize transmissionReduced assembly stepsElectromagnetic transceiversShortest distanceEngineering

The invention provides a 400 Gbps hot-plug high-speed optical transceiver module which is suitable for the optical communication technical field. The 400 Gbps hot-plug high-speed optical transceiver module comprises an optical interface unit, a photoelectric transceiver unit and an electrical interface unit; the photoelectric transceiver unit is used for achieving the functions of photoelectric conversion and high-speed electrical signal processing through a photoelectric transceiver chip; the internal working process of the photoelectric transceiver chip comprises receiving an electrical signal input through the electrical interface unit by a transmitting terminal data clock recovery circuit, loading the electrical signal to a laser after the pretreatment through a driving circuit, converting the high-speed electrical signal into a high-speed optical signal through the laser, reusing the high-speed optical signal through a wavelength division multiplexer to be output, reusing the received optical signal into a 16-channel optical signal through a wavelength division demultiplexer to be transmitted to an optical detector and transmitting the 16-channel optical signal to a trans-impedance amplifier and a receiving terminal data clock recovery circuit after photoelectric conversion to be processed. According to the 400 Gbps hot-plug high-speed optical transceiver module, the factors such as the cost, the transmission loss, the chromatic dispersion and the size are considered to select different optical transceiver modules and accordingly the long-distance single-mode optical fiber transmission or the short-distance multimode transmission is implemented.

Owner:WUHAN TELECOMM DEVICES

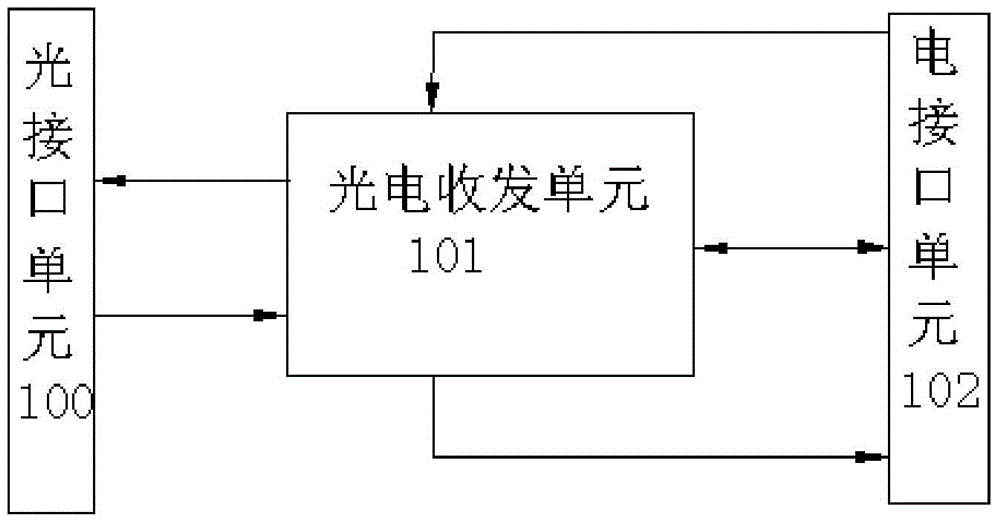

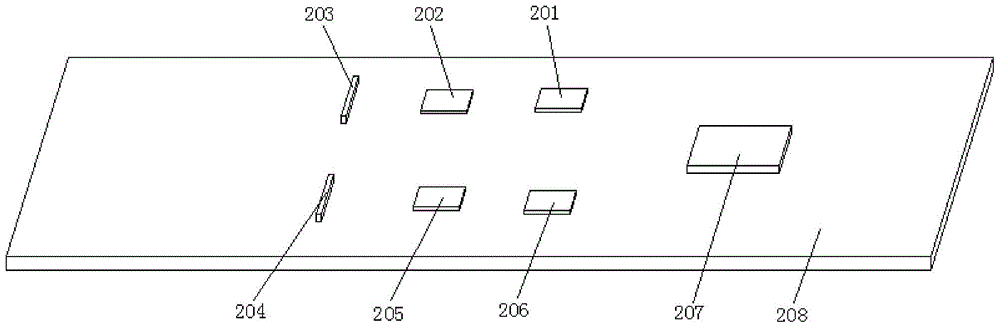

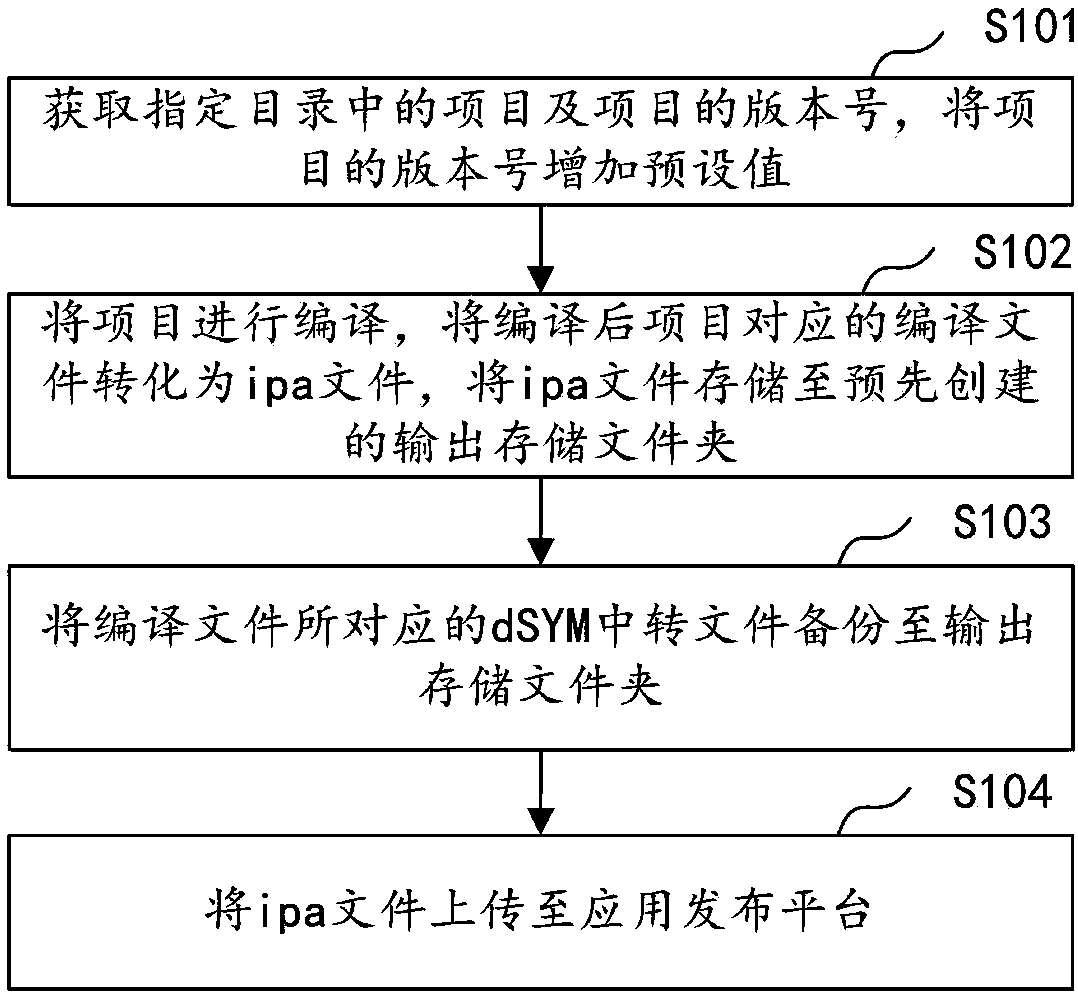

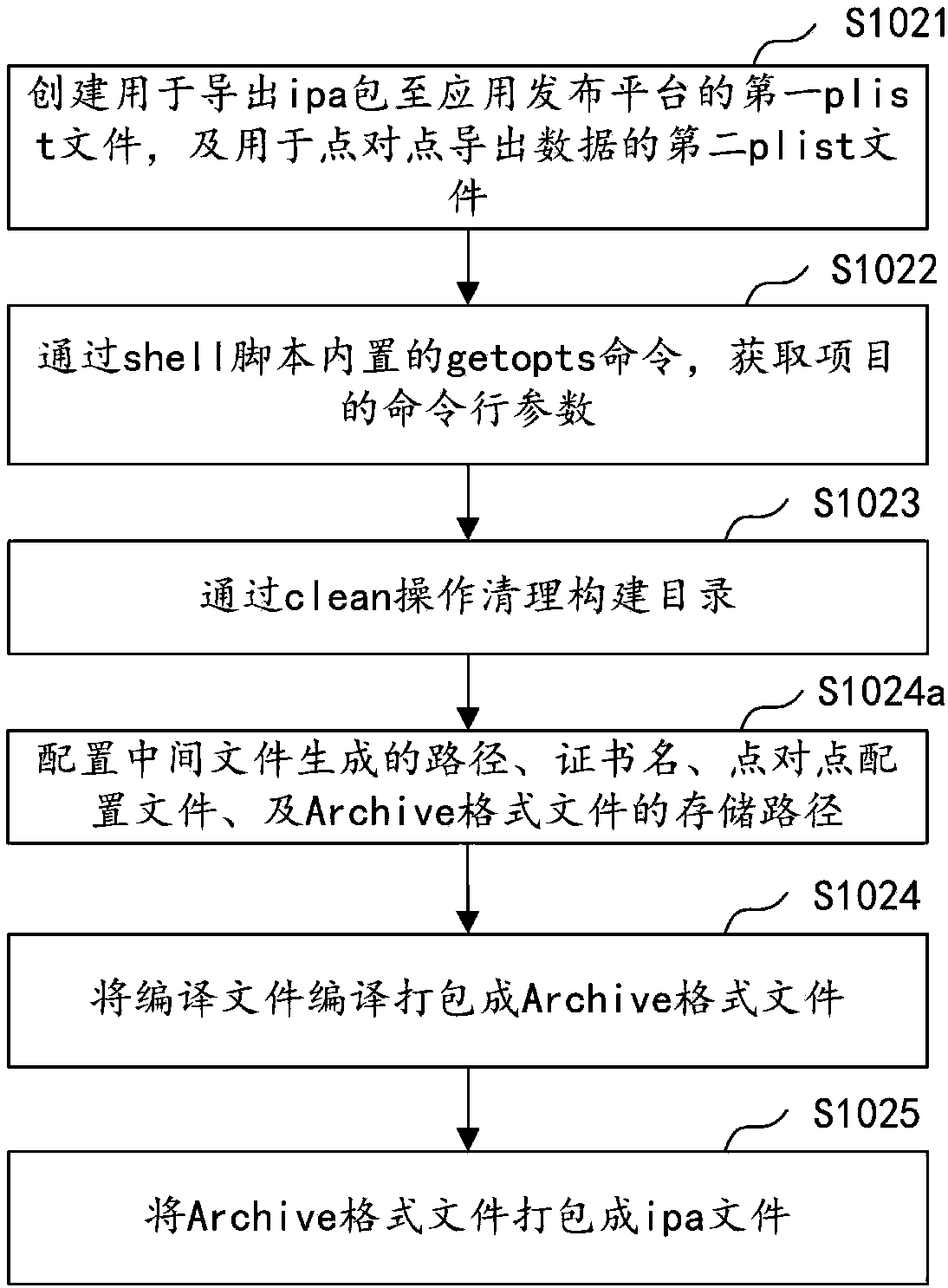

Application packaging and uploading method and device, computer equipment and storage medium

InactiveCN108469957AAutomate packagingSimplify the packaging processVersion controlSoftware deploymentComputer engineeringAutomation

The invention discloses an application packaging and uploading method and device, computer equipment and a storage medium. The method comprises the following steps of: obtaining a project in an appointed catalog and a version number of the project; adding a preset value to the version number of the project; compiling the project, converting a compilation file corresponding to the compiled projectinto an ipa file, and storing the ipa file to a pre-created output storage folder; backing up a dSYM transfer file corresponding to the compilation file to the output storage folder; and uploading theipa file to an application publishing platform. The method is capable of realizing packaging automation and simplified packaging operation flows without independently configuring monitoring environment, so that the packaging efficiency is improved.

Owner:PING AN TECH (SHENZHEN) CO LTD

Pouch-type lithium secondary battery and fabricating method thereof

InactiveUS7976981B2Simplify the packaging processFinal product manufactureSmall-sized cells cases/jacketsLithiumEngineering

A pouch-type lithium secondary battery in which an additional packing case is not used is provided. The pouch material is used to perform packing processes, thereby simplifying packing processes and methods of manufacturing. The pouch-type lithium secondary battery includes an electrode assembly and a pouch material. The electrode assembly includes a first electrode plate to which a first electrode tab is attached, a second electrode plate to which a second electrode tab is attached, and a separator between the first and second electrode plates. The pouch material has first, second, and third surfaces. The first and second surfaces are folded along a first fold to form an electrode assembly accommodating unit for accommodating the electrode assembly. The third surface wraps around the electrode assembly accommodating unit at least once. The first fold is parallel to a line along which the first electrode tab and the second electrode tab extend.

Owner:SAMSUNG SDI CO LTD

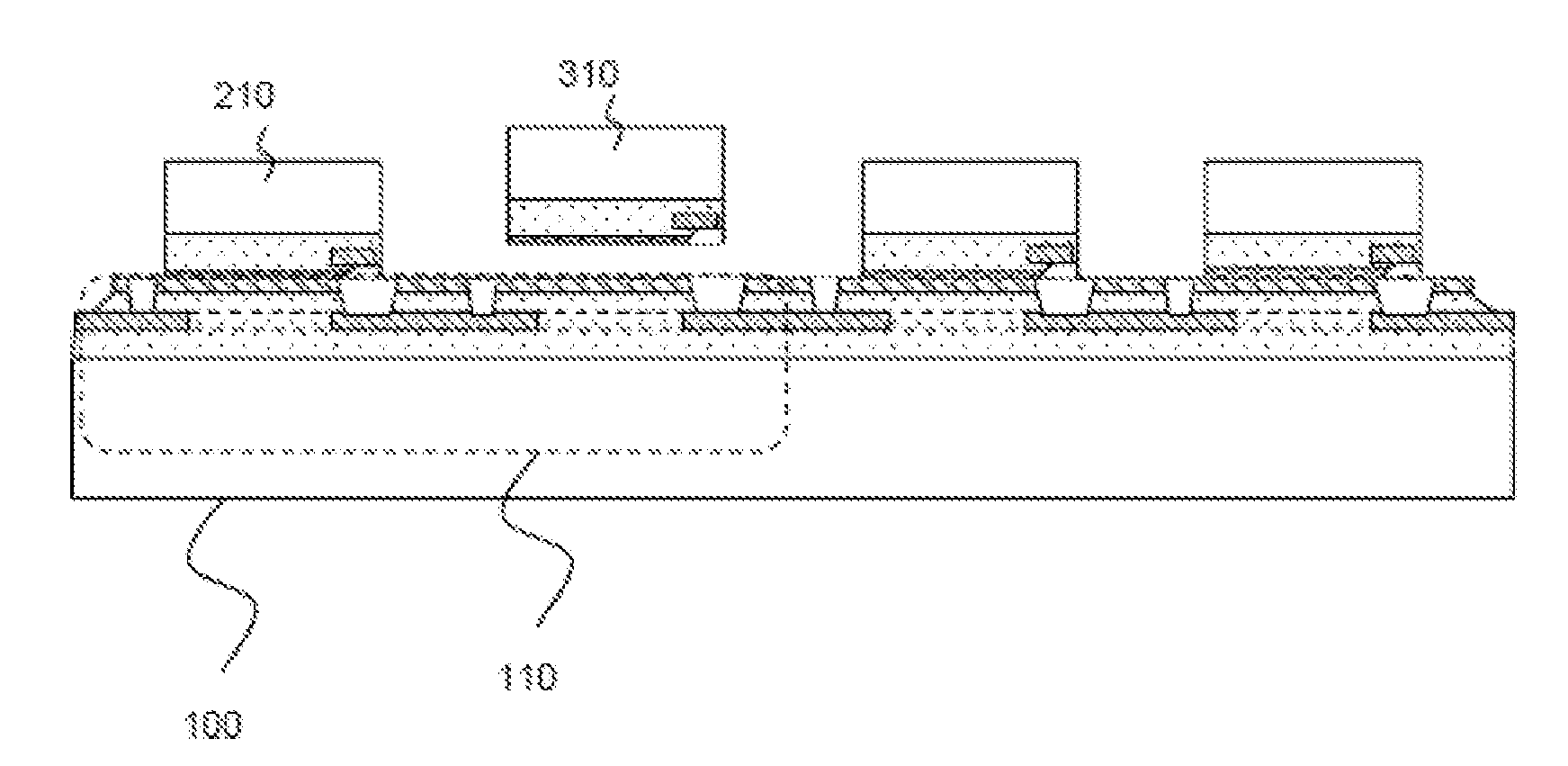

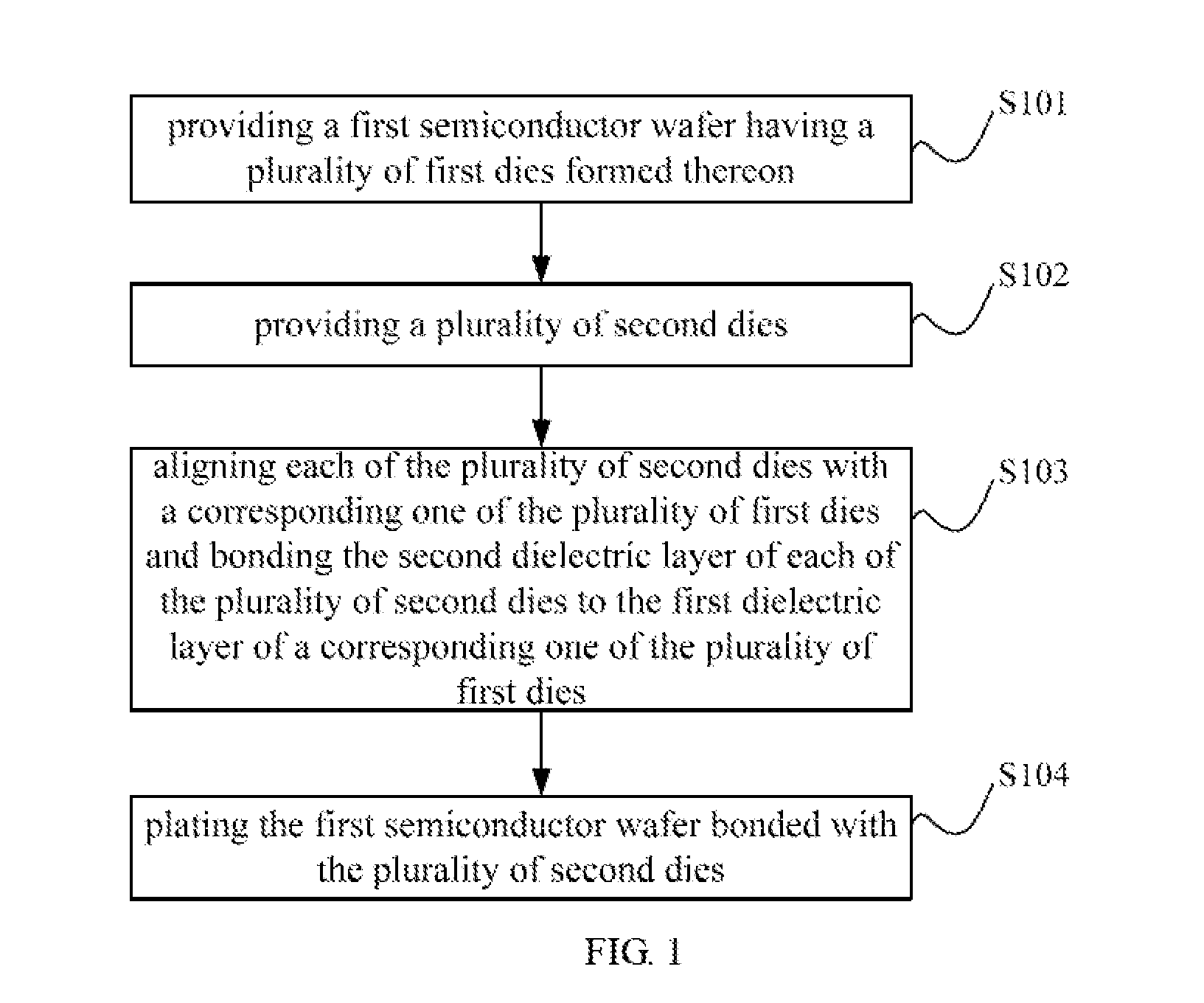

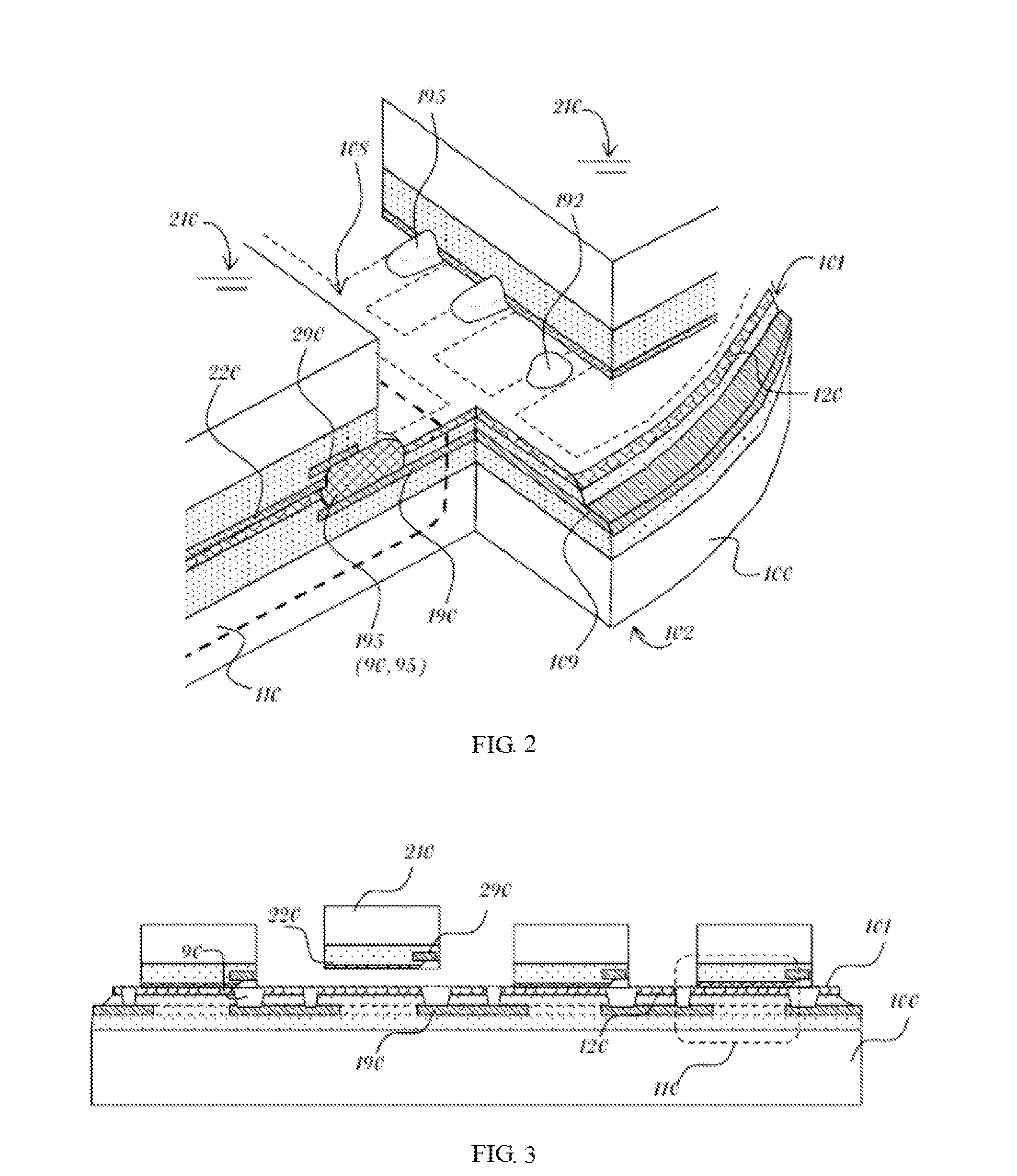

Methods of Fabrication and Testing of Three-Dimensional Stacked Integrated Circuit System-In-Package

ActiveUS20150311188A1Easy to integrateLow costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsLead bondingEngineering

The present invention provides a method of fabricating a 3D stacked IC SiP which includes: providing a first semiconductor wafer having a plurality of first dies formed thereon, each having a first wire bond pad and a first dielectric layer, at least a portion of the first wire bond pad is not covered by the first dielectric layer and constitutes an exposed area of the first die; providing a plurality of second dies, each having a second wire bond pad and a second dielectric layer, at least a portion of the second wire bond pad is not covered by the second dielectric layer and constitutes an exposed area of the second die different in size from that of the first die; aligning the second dies with the first dies and bonding the second dielectric layer to the first dielectric layer; plating the first semiconductor wafer bonded with the second dies.

Owner:NINGBO SEMICON INT CORP

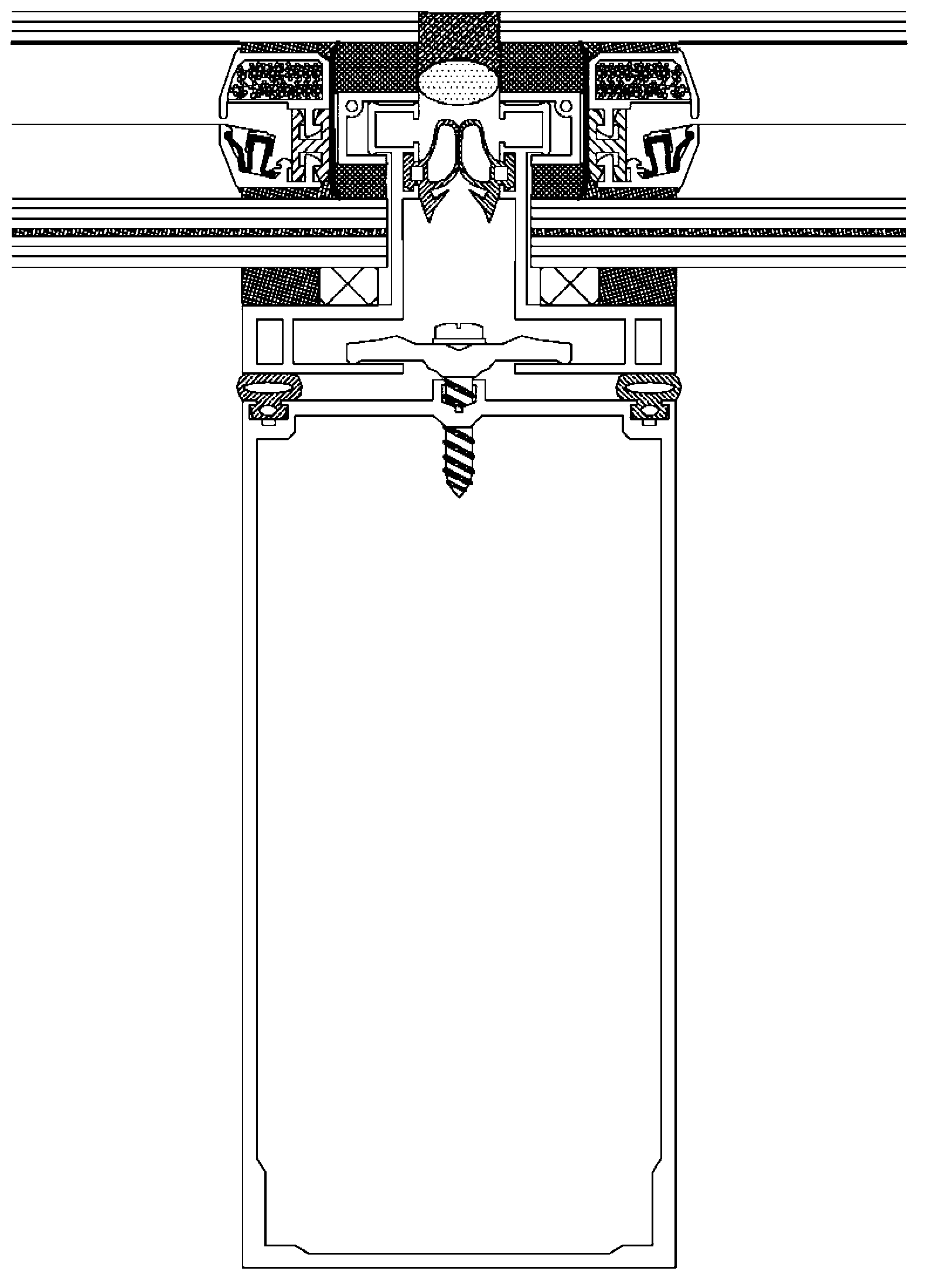

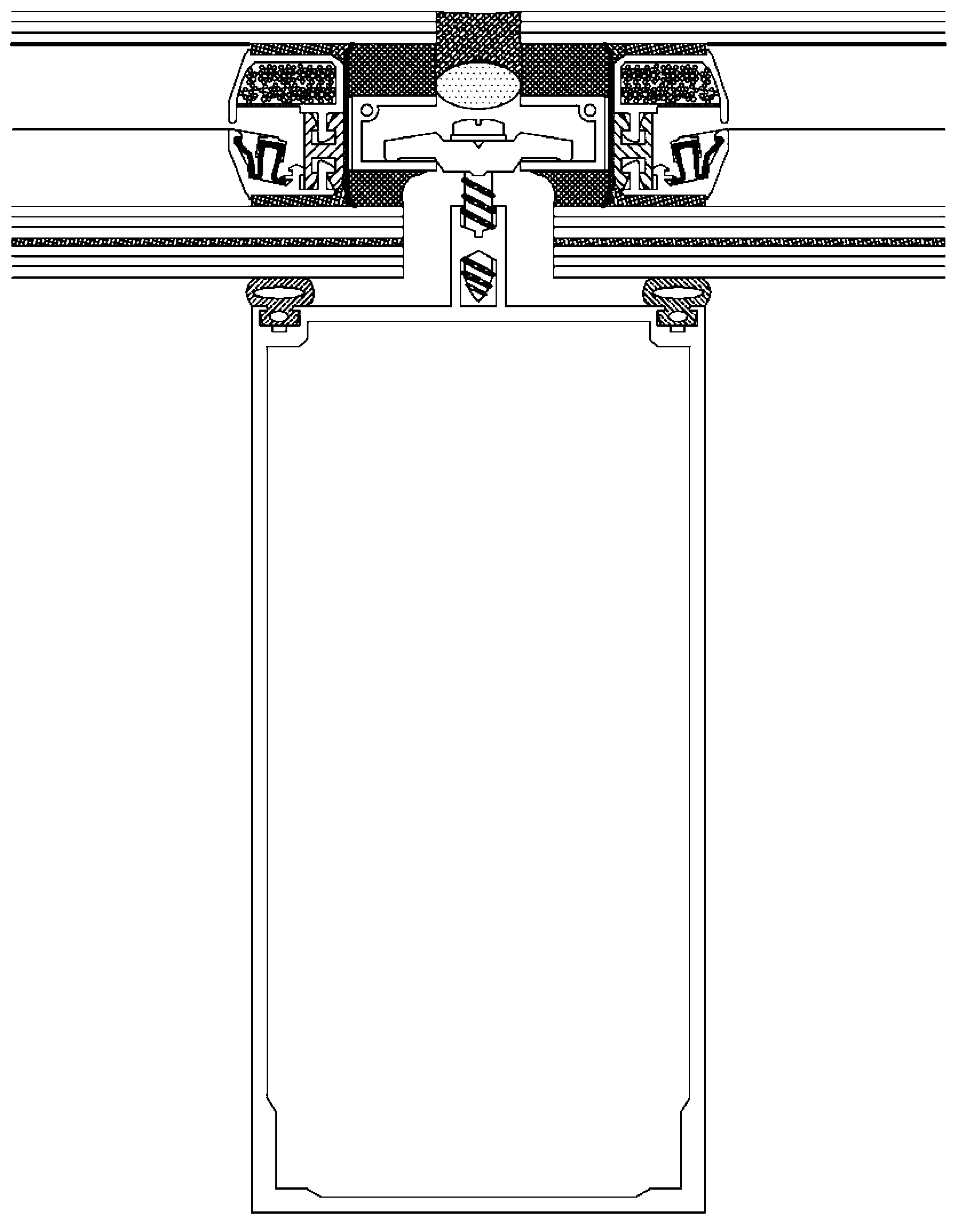

Double-hollow glass ceiling module with film suspended therein

ActiveCN103074966AConvenient lightingImprove heat insulationRoof covering using slabs/sheetsWallsMoisture condensationThermal deformation

The invention discloses a double-hollow glass ceiling module with a film suspended therein. An optical control film serves as a middle layer, and an internally suspended film structure frame, a mounting structure frame, a reinforcing separating strip and glass are sealed into an integral double-hollow glass plate. An inner structure frame and an outer structure frame are made from a novel heat-isolating material with a coefficient of thermal expansion similar to that of the glass. The internally suspended film structure frame is structurally connected through a heat-isolating bridge. A butyl rubber tape on the outer surface of the internally suspended film structure frame serves as a first sealing layer. A second sealing layer consists of the external reinforcing separating strip and a silicone structural sealant, the whole structure is always consistent to the thermal deformation of the glass, so that the sealing capability of the whole system is more reliable, and the heat-isolating property, the moisture condensation-preventing property, the sound-isolating property and the like are greatly improved. Dirt is not easily accumulated on the outer surface of a mounted ceiling, so that the ceiling is convenient to clean and maintain. The double-hollow glass ceiling module has a flexible assembling and mounting way, and can be applied to different vertical surfaces of an outer building rail.

Owner:伟视幕墙(淮安)有限公司

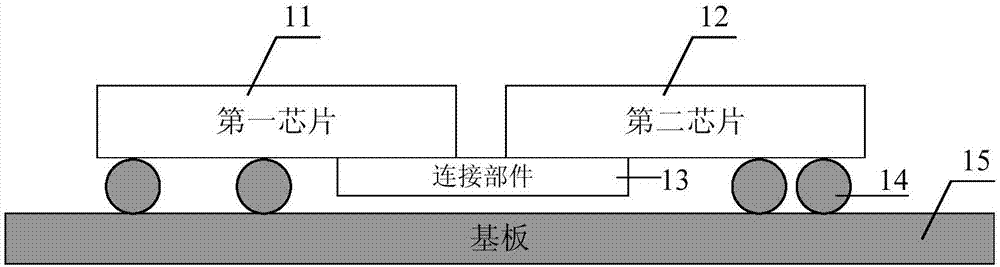

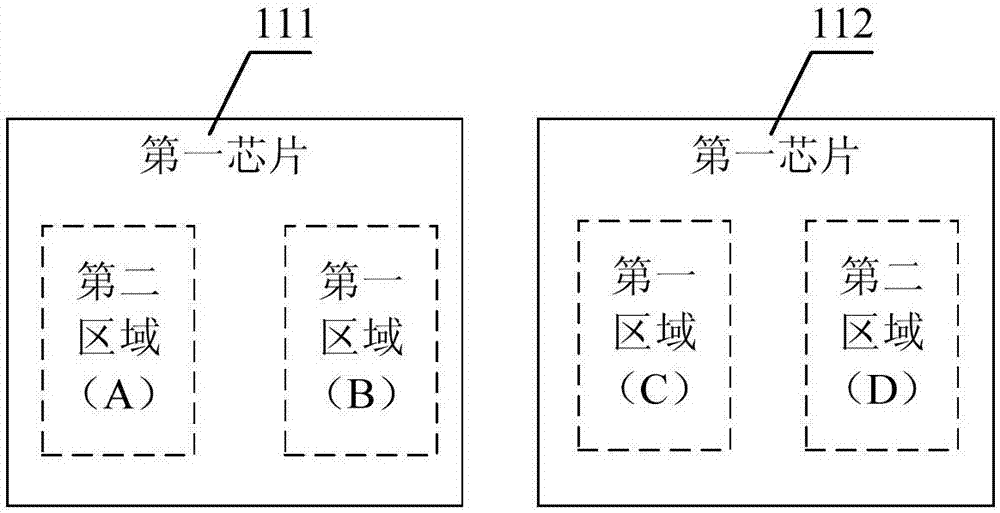

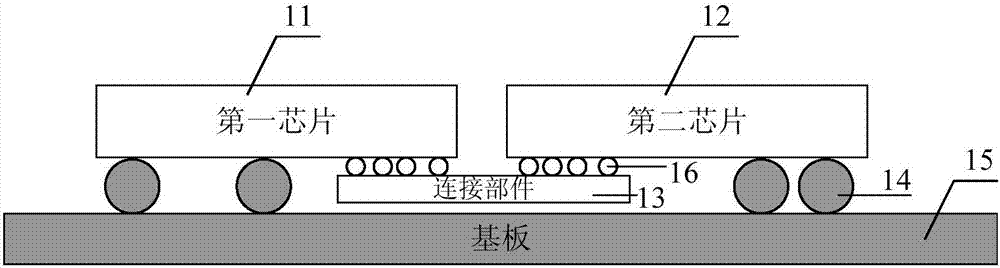

Chip encapsulation structure and circuit structure

InactiveCN107104096ASimplify the packaging processImprove packaging efficiencySemiconductor/solid-state device detailsSolid-state devicesSurface phaseMetal

The invention provides a chip encapsulation structure and a circuit structure. The chip encapsulation structure comprises at least two chips, a connection part, multiple second welding balls and a substrate; the active surface of each chip in the at least two chips is positioned in the same plane; the active surface of each chip comprises a first area and a second area; multiple first bonding pads are arranged in the first area; at least one second bonding pad is arranged in the second area; the at least two chips comprise a first chip and a second chip, which are adjacent; multiple first metal wires are distributed in the connection part; both two ends of each first metal wire are exposed on the first surface of the connection part; one end of each first metal wire is connected with one first bonding pad of the first chip; the other end of each first metal wire is connected with one first bonding pad of the second chip; each second bonding pad of the first chip and the second chip is connected with the upper surface of the substrate through a second welding ball; and the upper surface of the substrate is towards the active surface of the chip. By means of the chip encapsulation structure and the circuit structure provided by the invention, the chip encapsulation efficiency is increased.

Owner:HUAWEI TECH CO LTD