Chip encapsulation structure and circuit structure

A chip packaging structure and chip technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of low chip packaging efficiency, complex process, complex chip packaging process, etc. Simple packaging process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

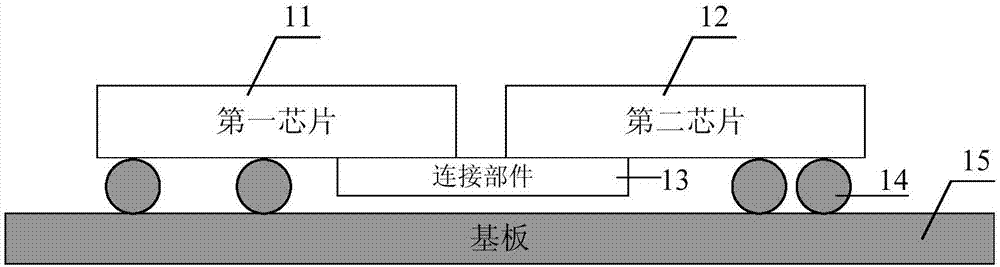

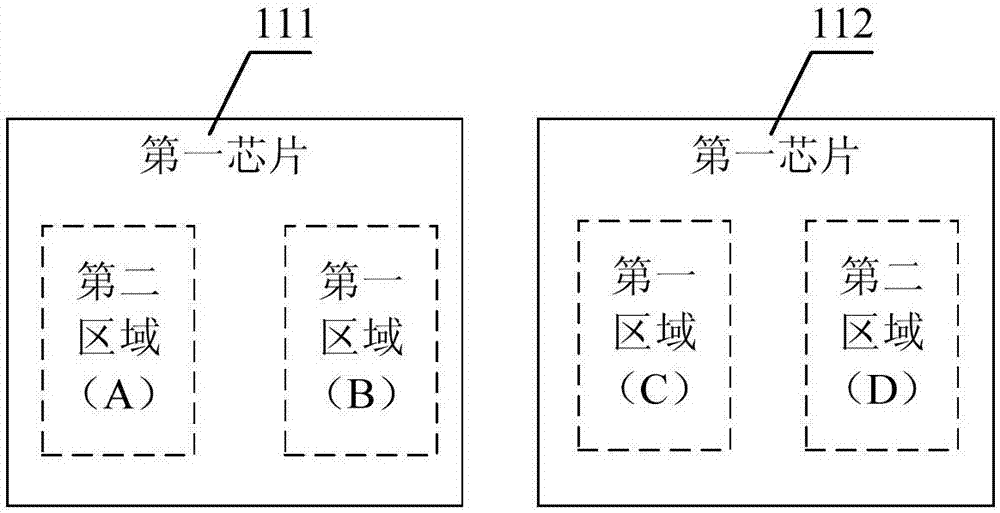

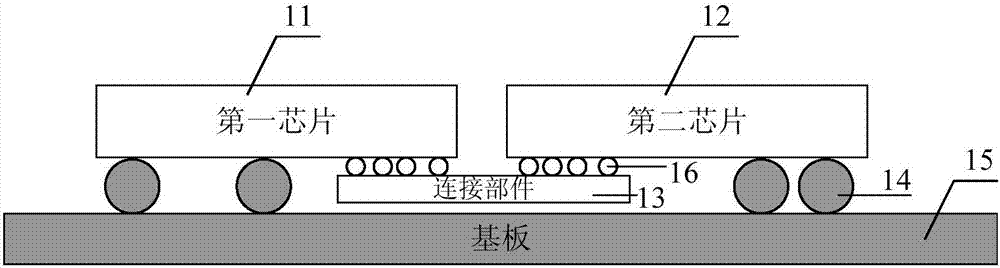

[0097] The chip packaging structure involved in the present application includes at least two chips, and the at least two chips are connected to each other so as to realize mutual communication between the chips. Optionally, the chips shown in this application may be logic chips or memory chips. The chip packaging structure shown in this application aims to simplify the chip packaging process and improve the chip packaging efficiency.

[0098] In the following, the chip packaging structure described in this application will be described in detail through specific embodiments. It should be noted that the following specific embodiments may be combined with each other, and the same or similar content will not be repeated in different embodiments. It should also be noted that the lengths, widths, and heights (or thicknesses) of various components shown in the drawings of this application are only illustrative, and not limiting to the chip packaging structure described in this app...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More