Patents

Literature

374 results about "Match line" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

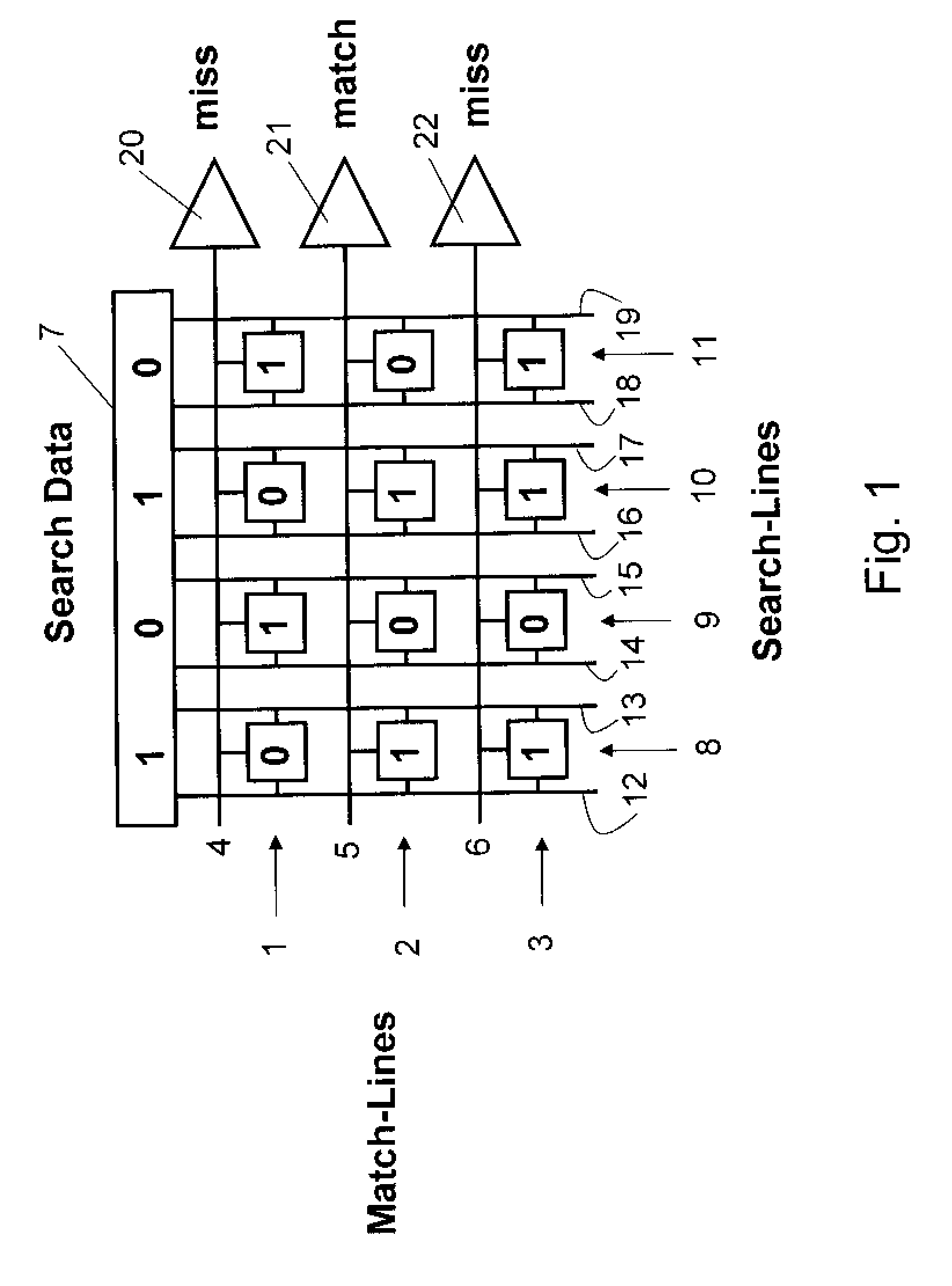

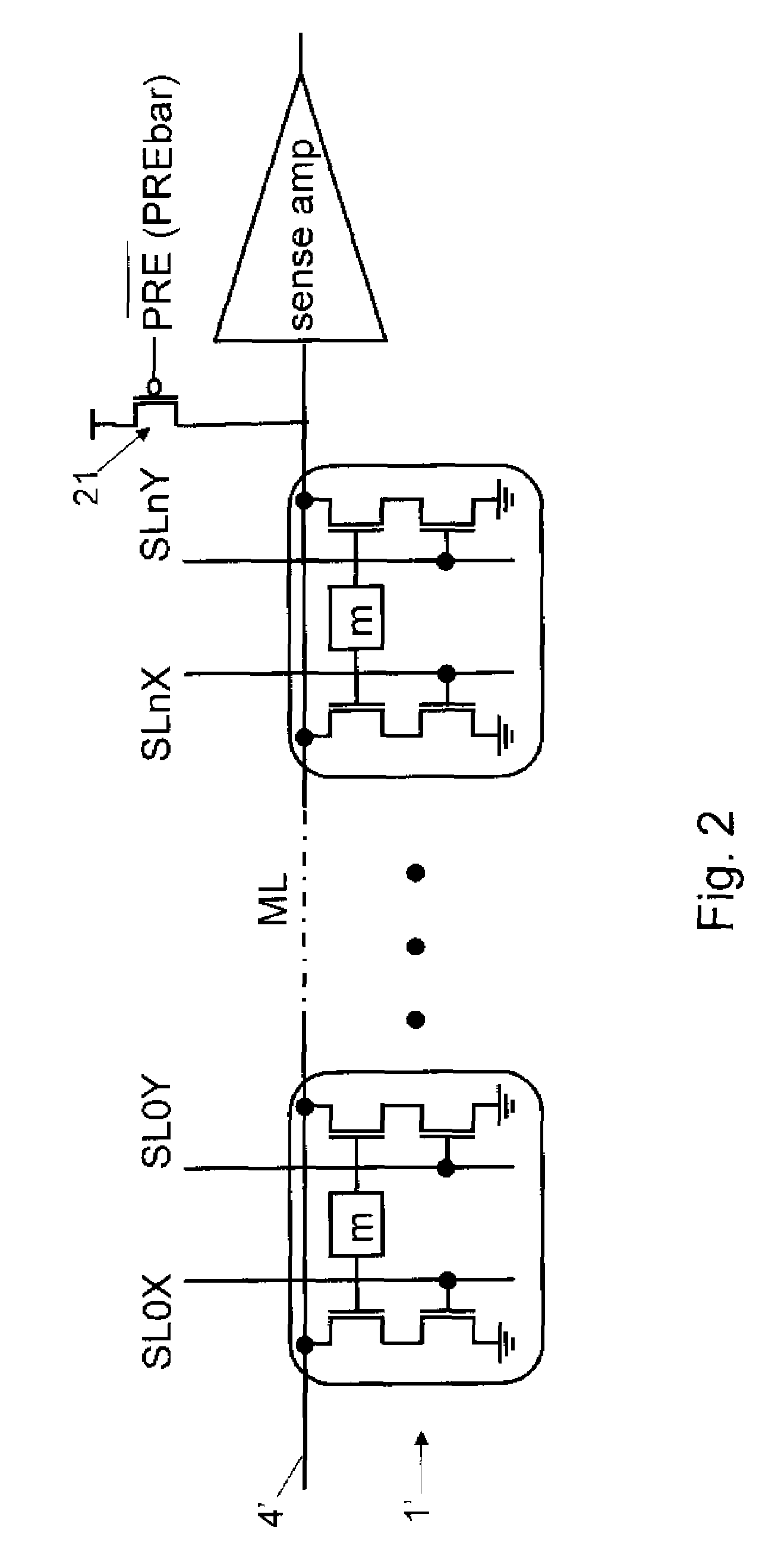

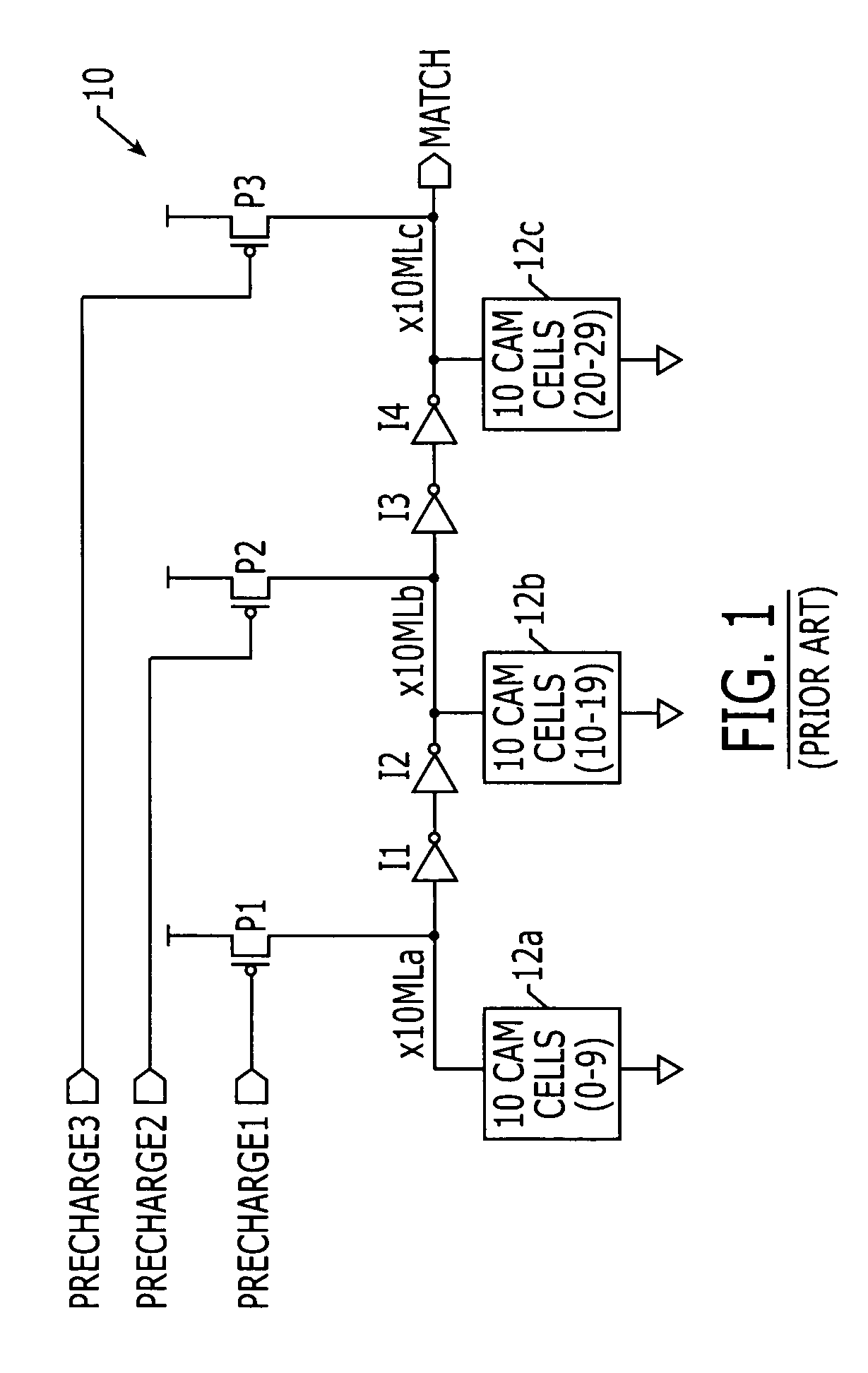

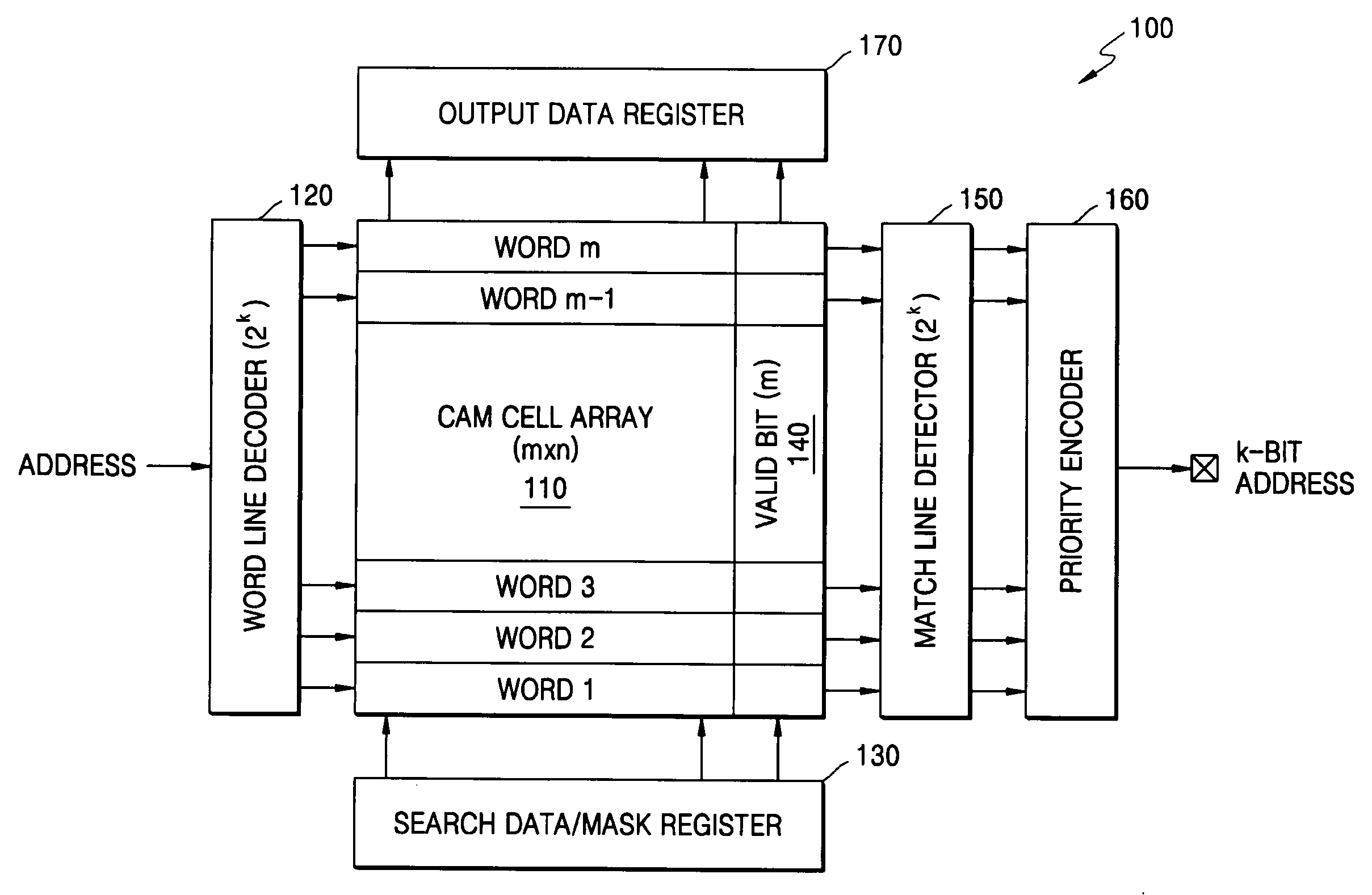

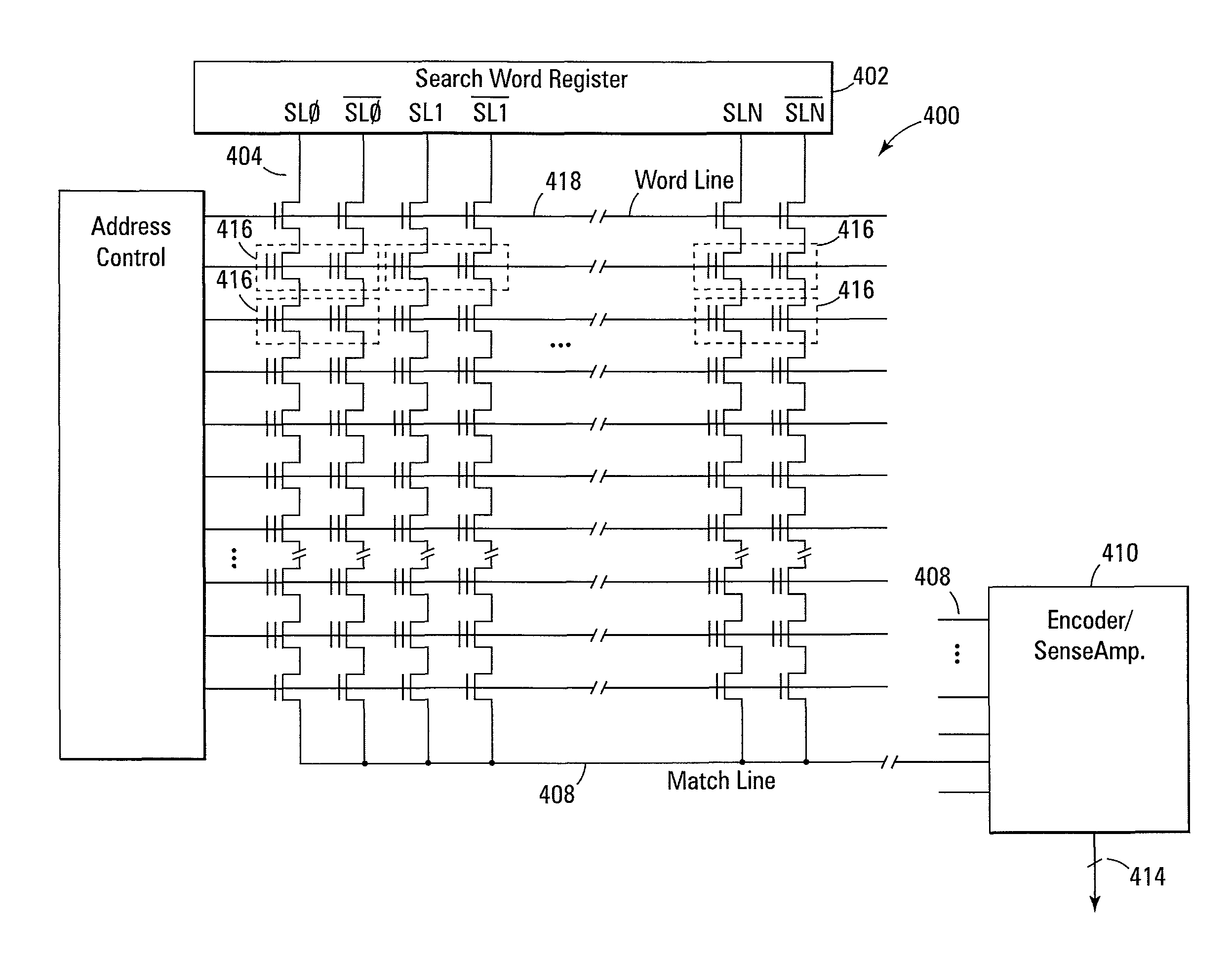

Self-Referenced Match-Line Sense Amplifier For Content Addressable Memories

ActiveUS20080025073A1Reduce the impactReduce impactCurrent/voltage measurementDigital storageAudio power amplifierComputer science

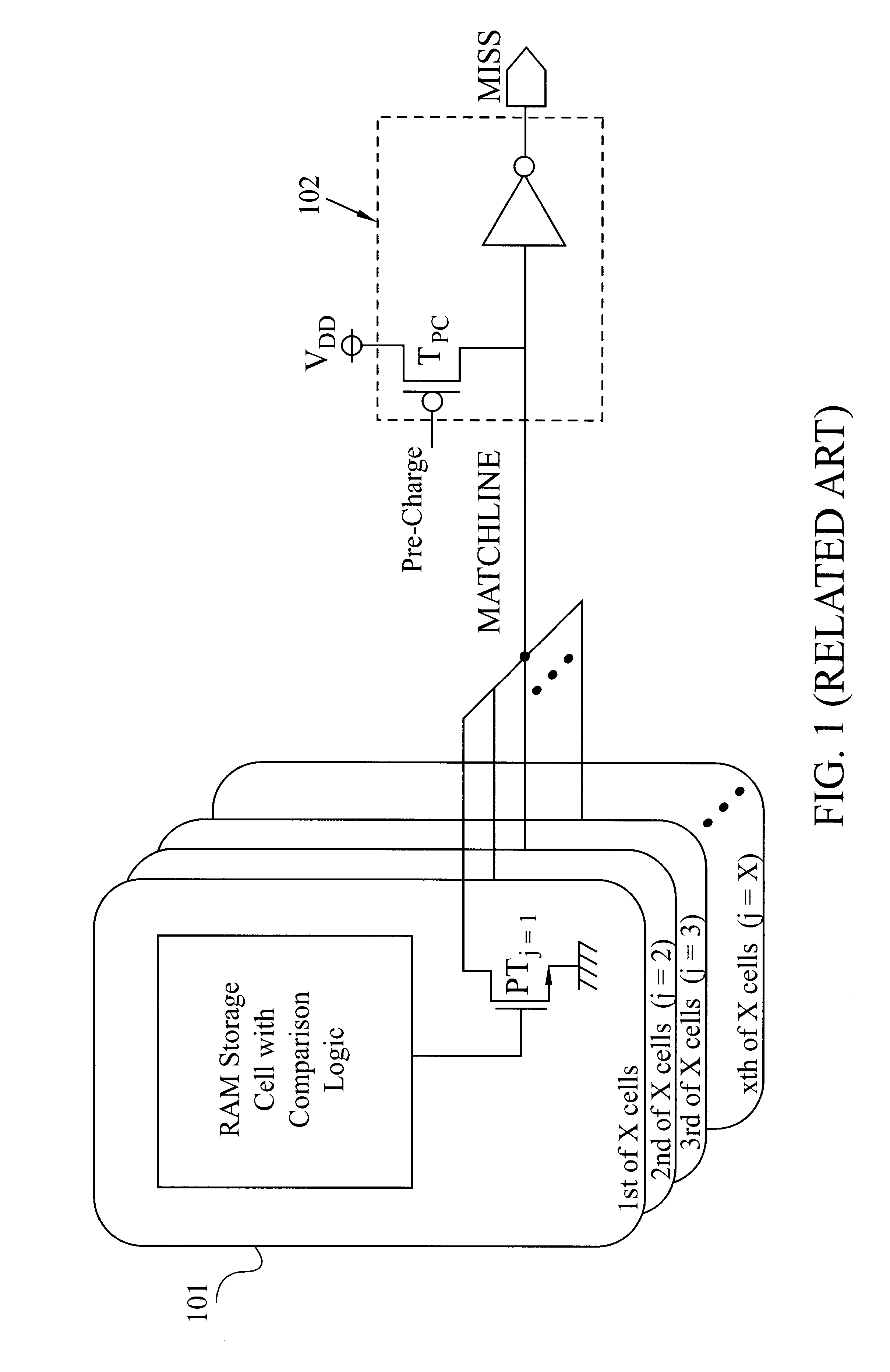

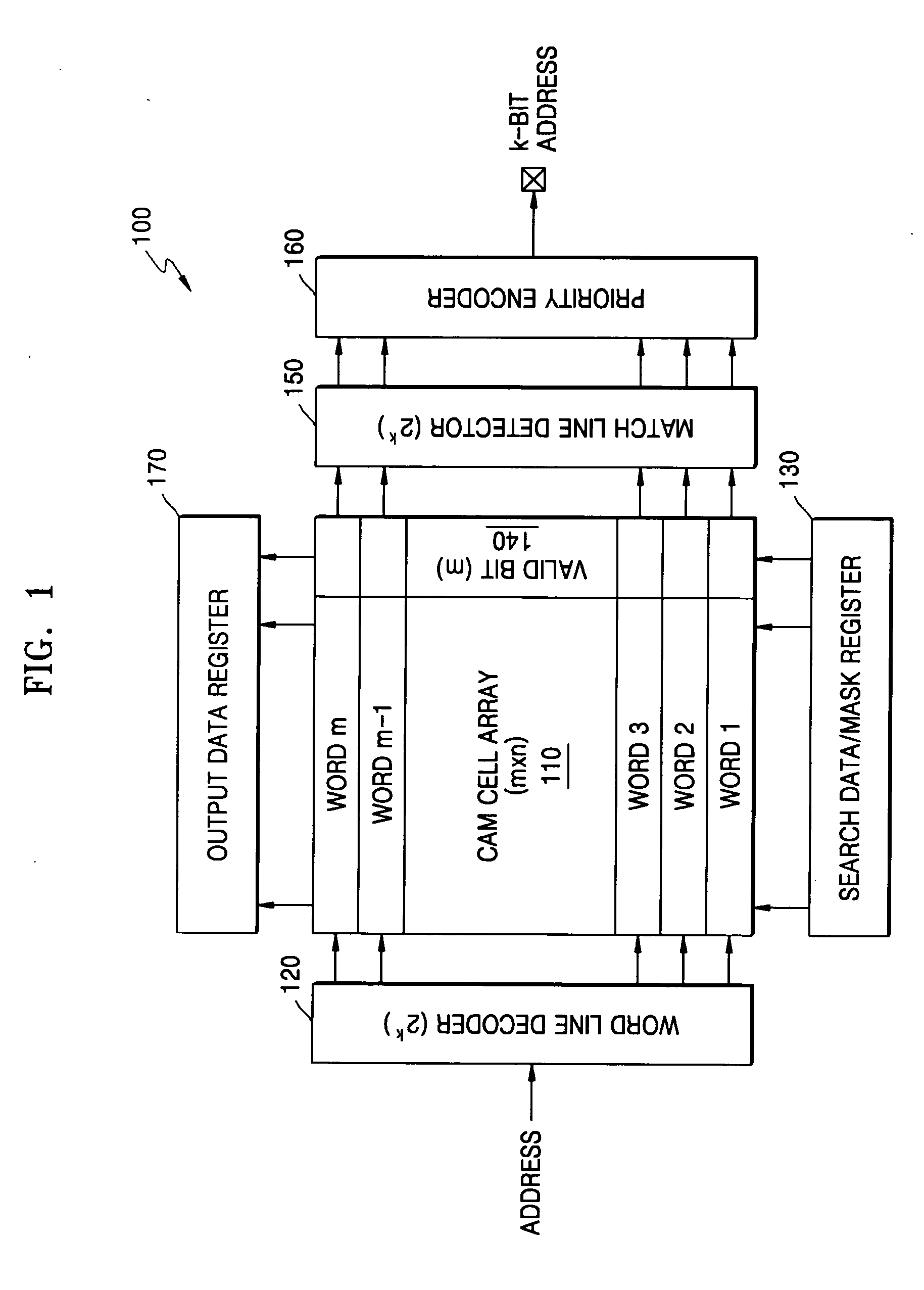

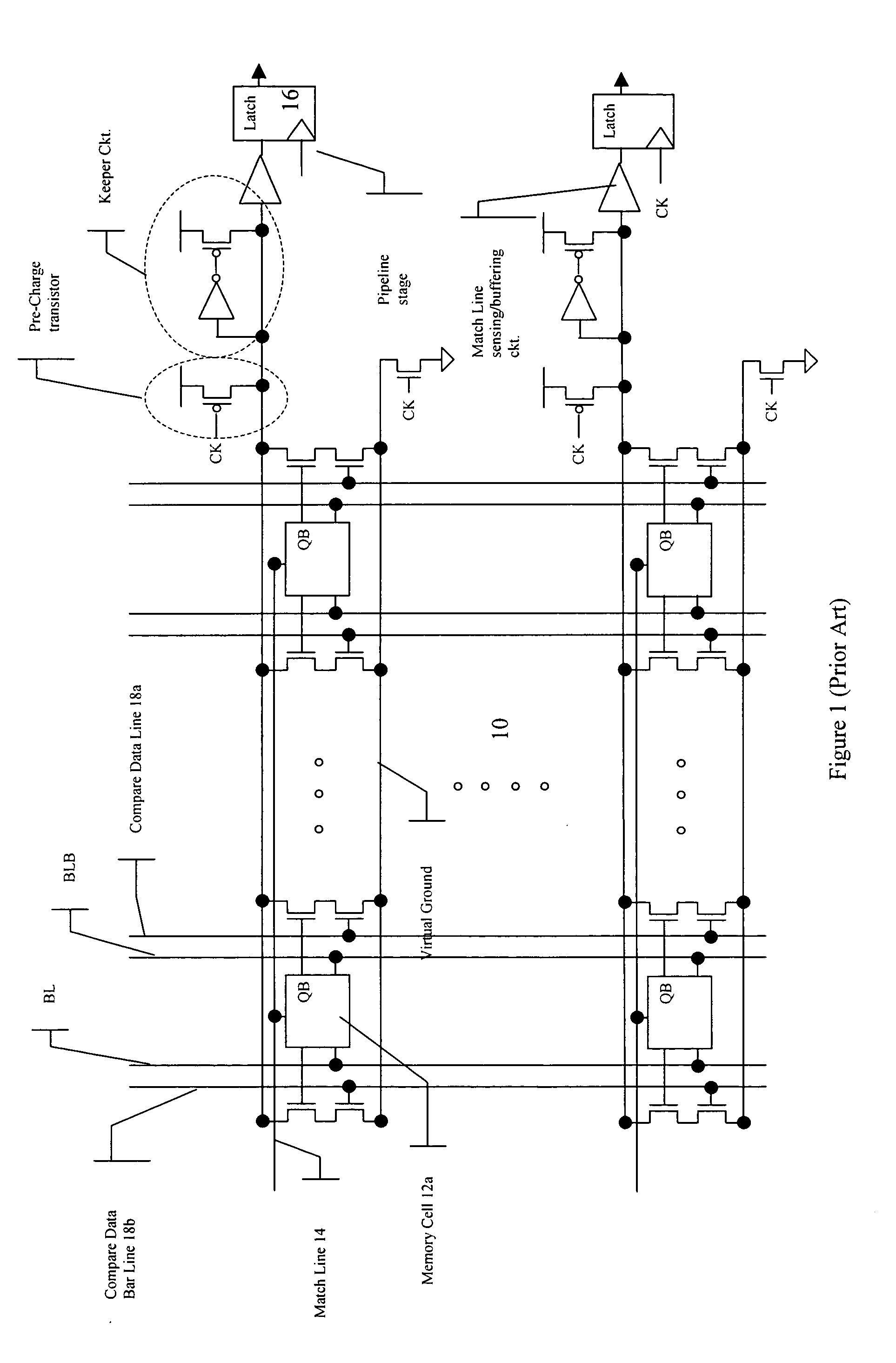

A content addressable memory (CAM) device and process for searching a CAM. The CAM device includes a plurality of CAM cells, match-lines (MLs), search lines, and ML sense amplifiers. The ML sense amplifiers are capable of self-calibration to their respective thresholds to reduce effects of random device variation between adjacent sense amplifiers.

Owner:MARVELL ASIA PTE LTD

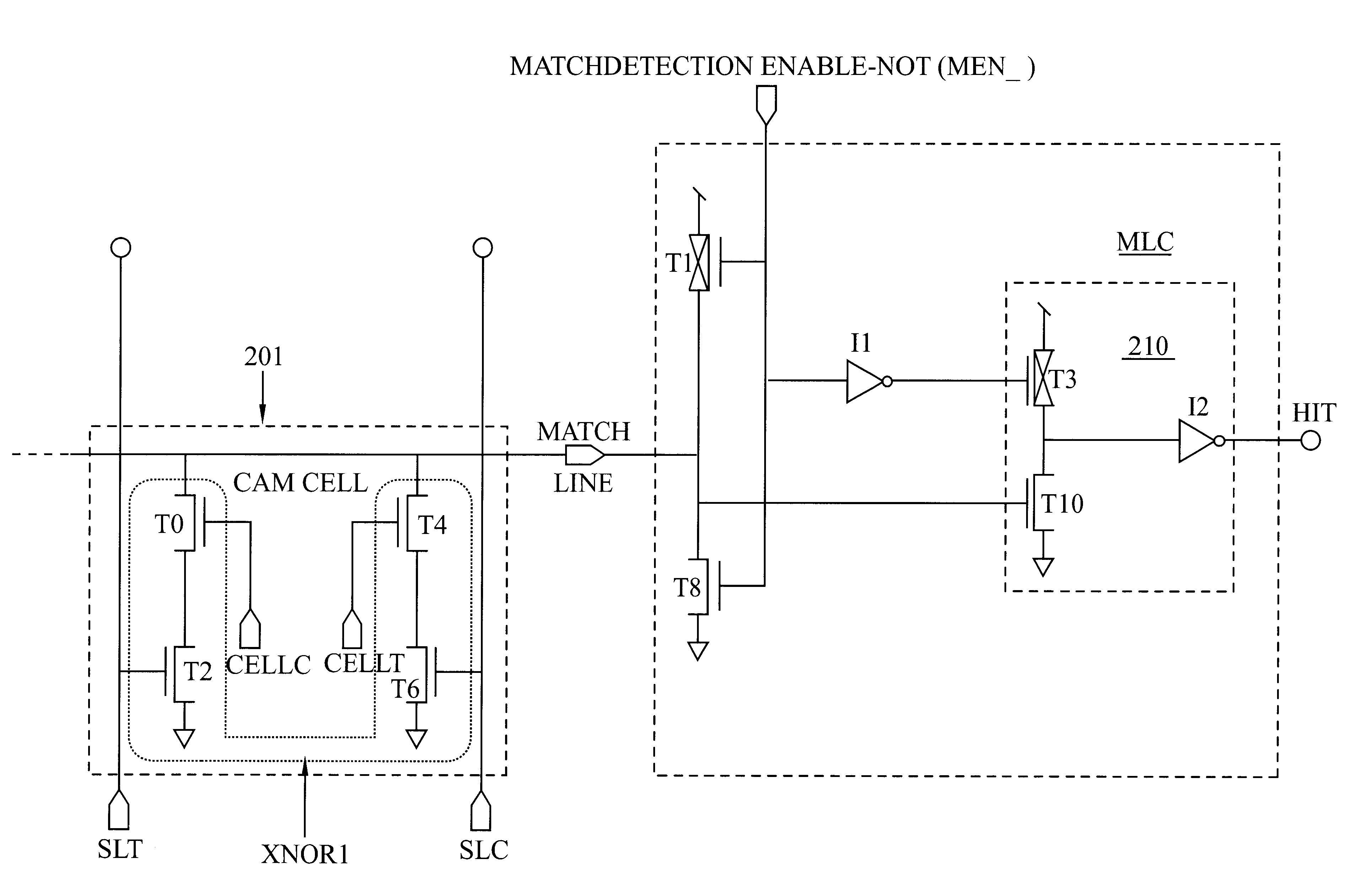

Low power CAM match line circuit

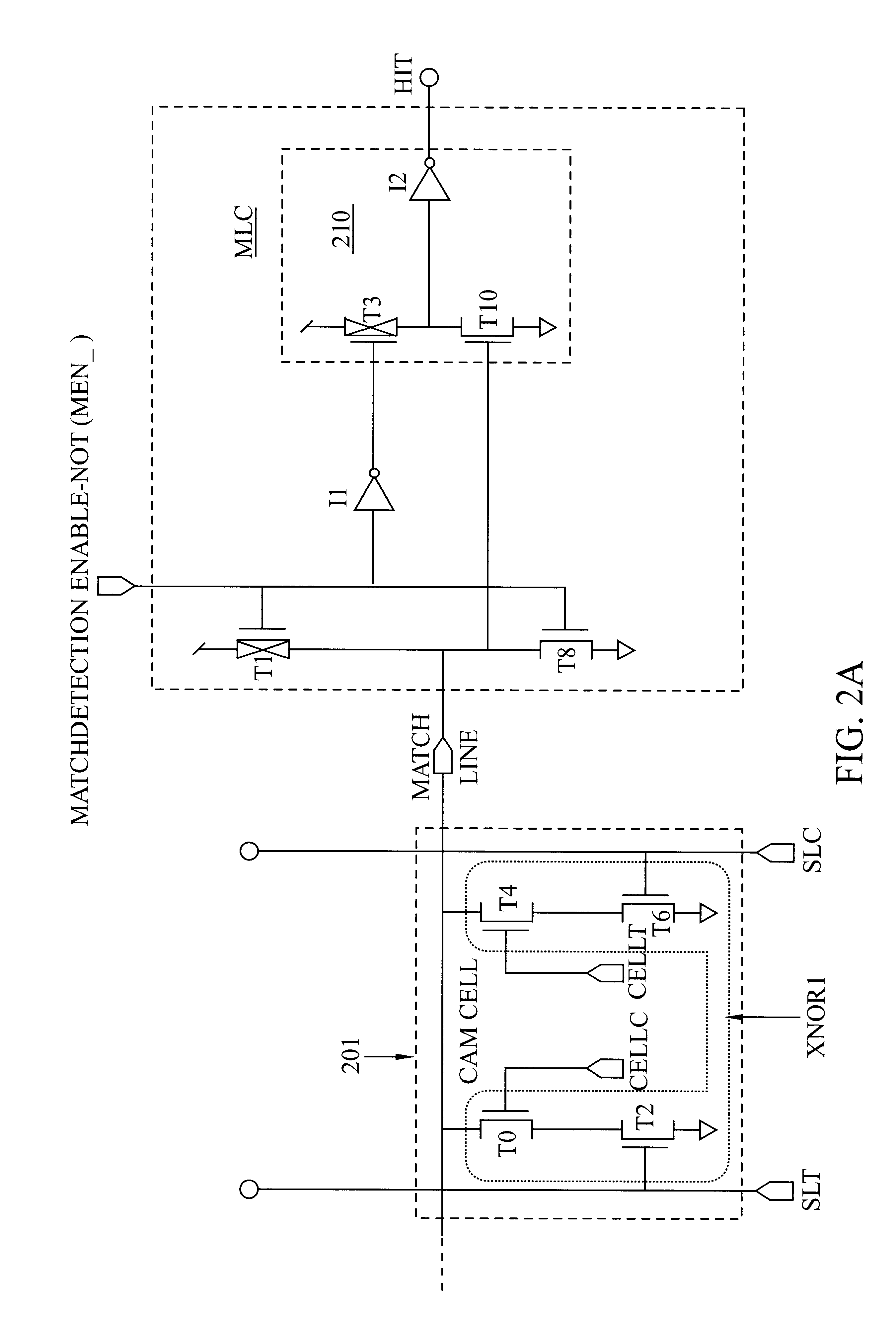

A Match-Detection Circuit and Match-Detection method, for low-power-consuming searches in a Content Addressable Memory. A HIT is output when the Match Line rises from a Low voltage level to a higher Match Detection Voltage. The Match Detection Voltage is approximately the conducting threshold voltage of an N-channel Field Effect Transistor (FET), and is normally less than One Half of the Power Supply Voltage. Circuits and methods to turn of the through-current in each MISS-ing entry by a carefully timed control signal at the end of a brief Match Detection Period, are disclosed.

Owner:IBM CORP

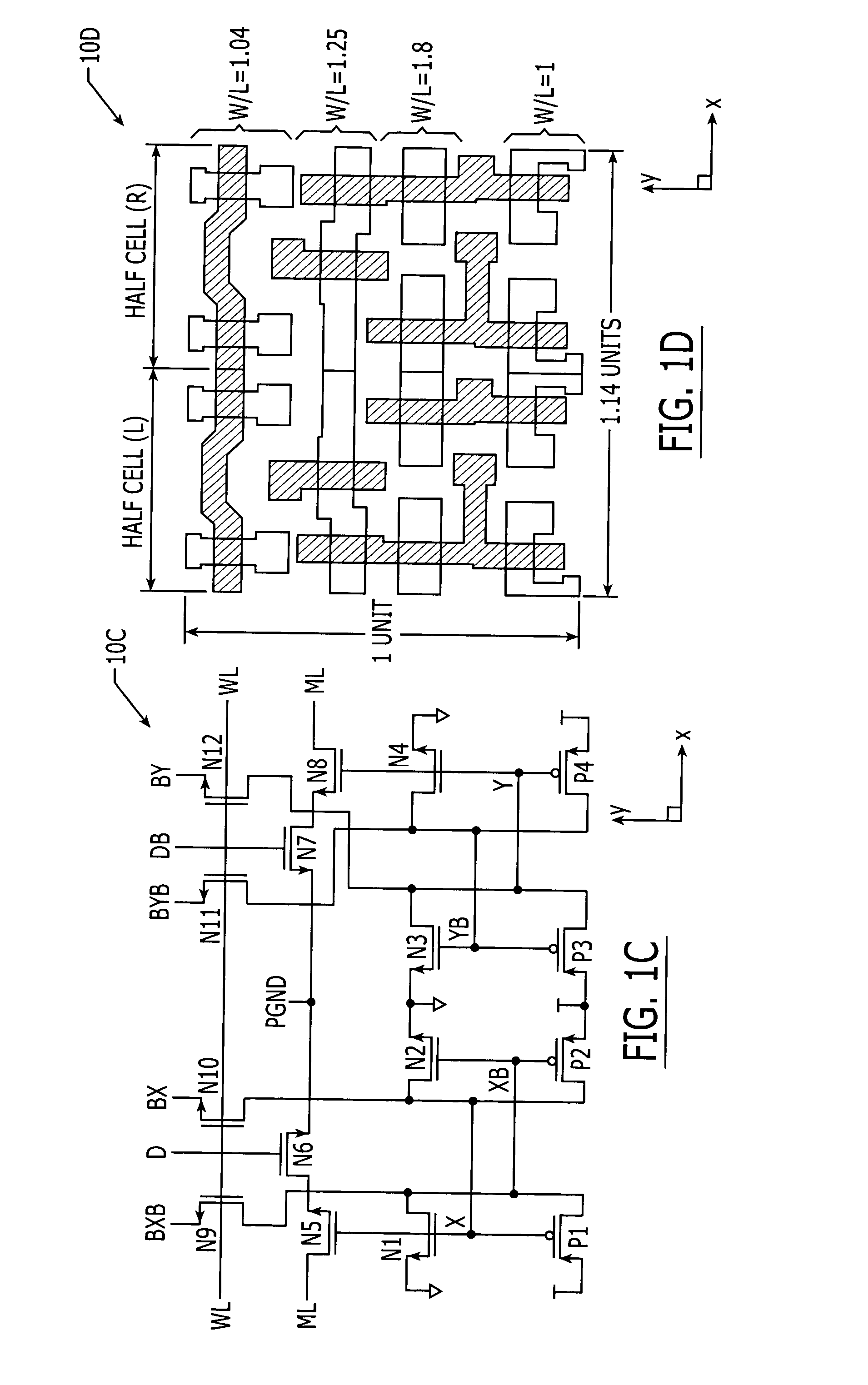

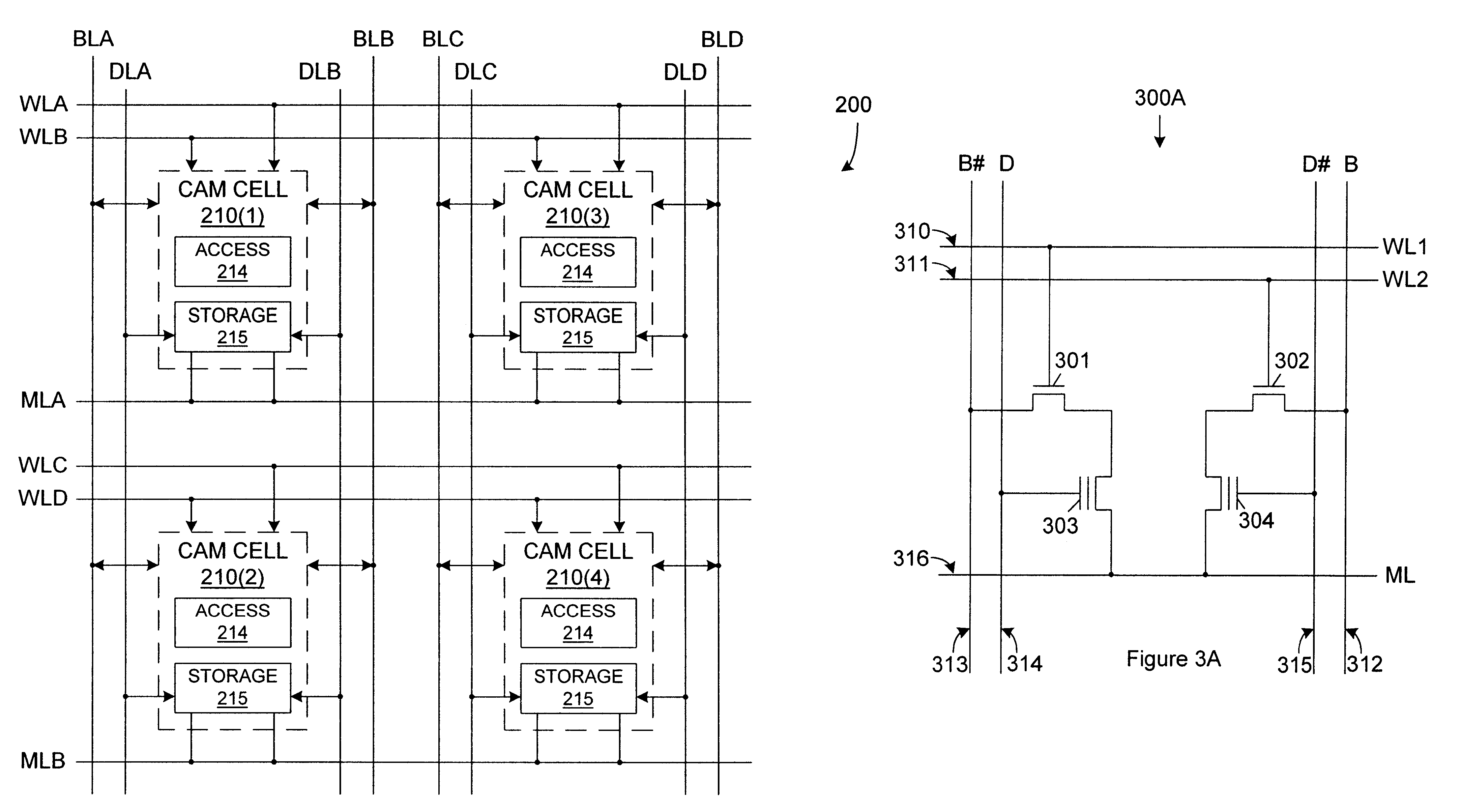

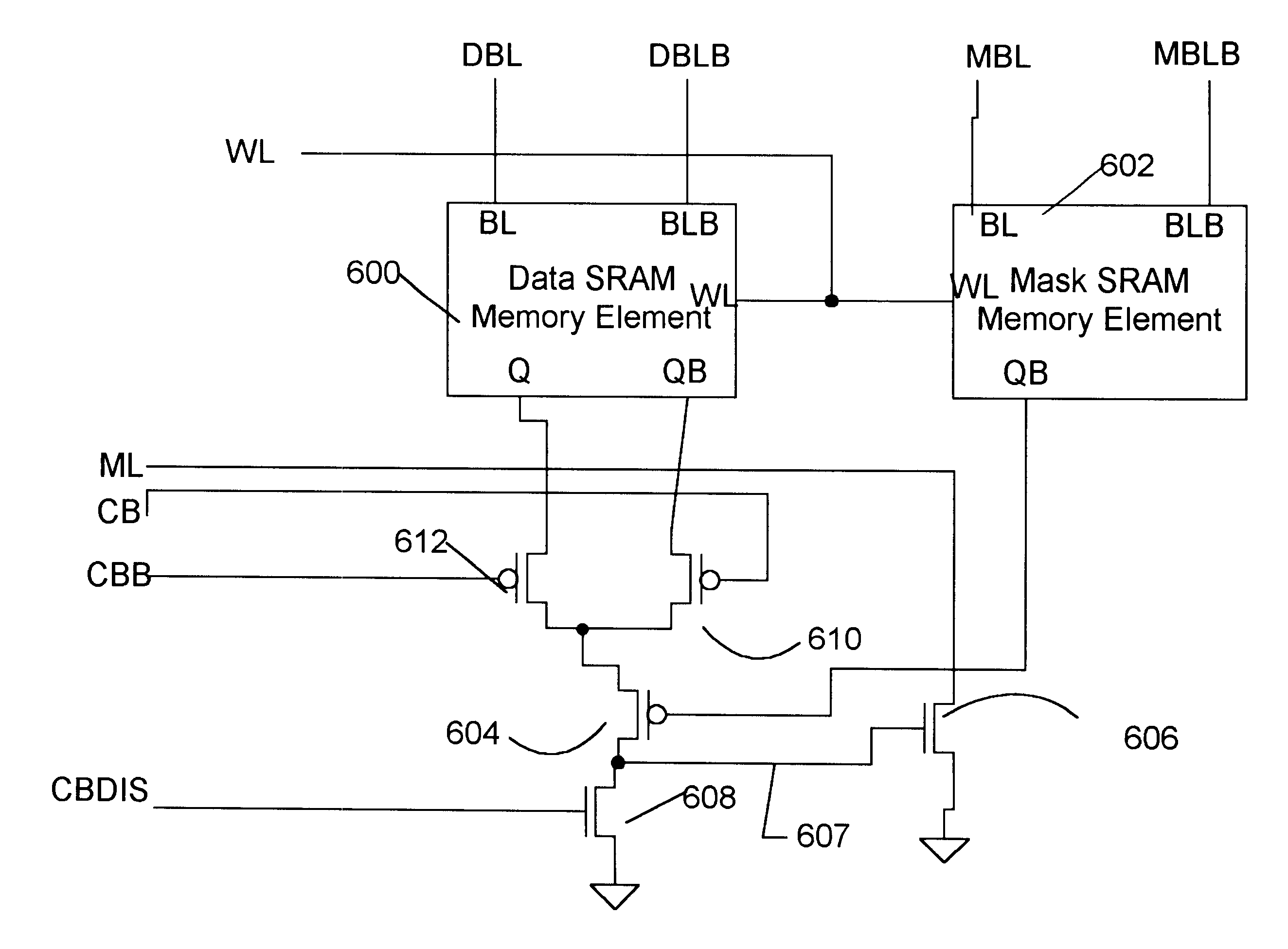

Ternary content addressable memory (TCAM) cells with small footprint size and efficient layout aspect ratio

InactiveUS20050135134A1Small layout footprint sizeEnhance scalability and uniformityDigital storageExtensibilityEngineering

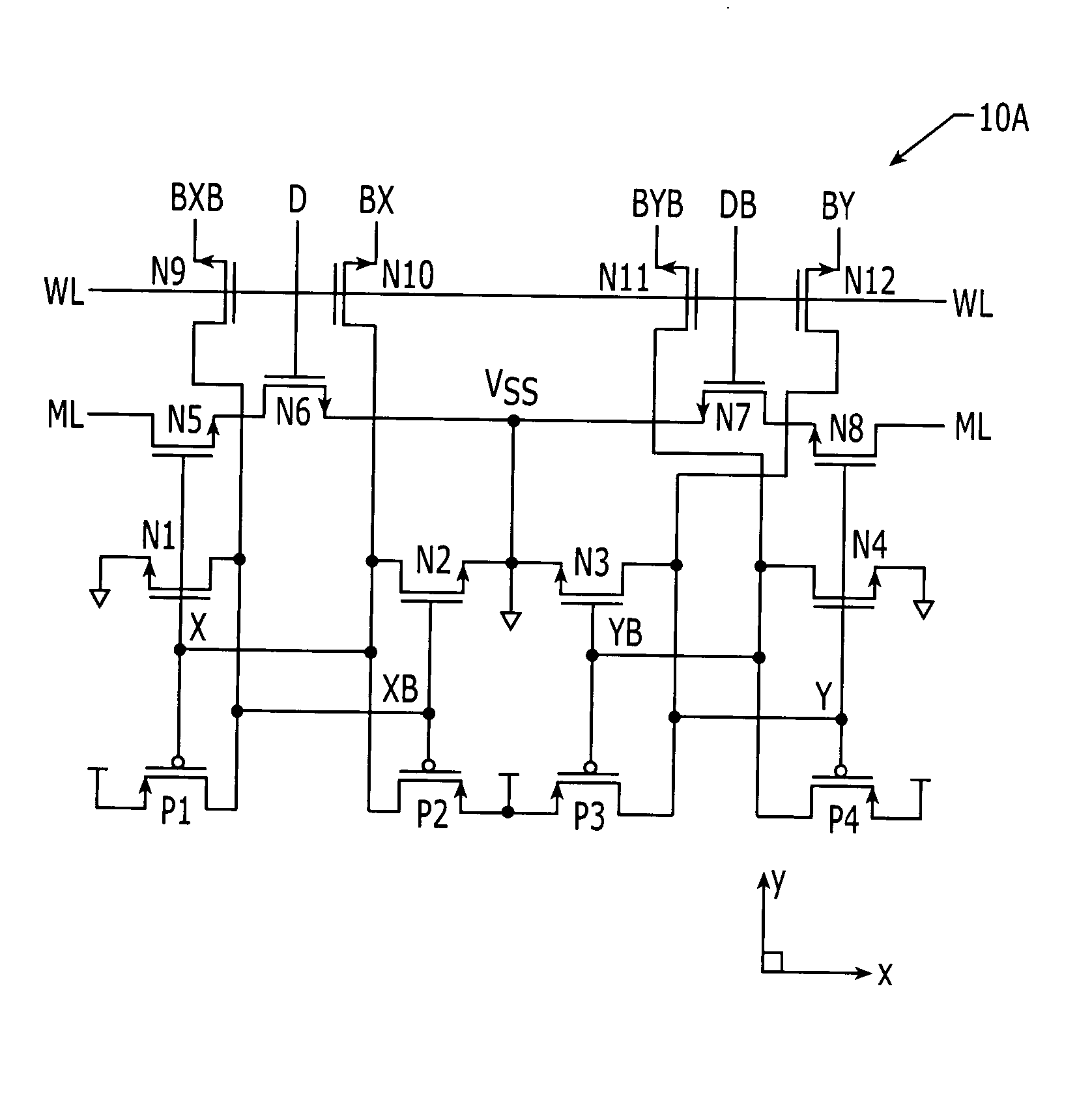

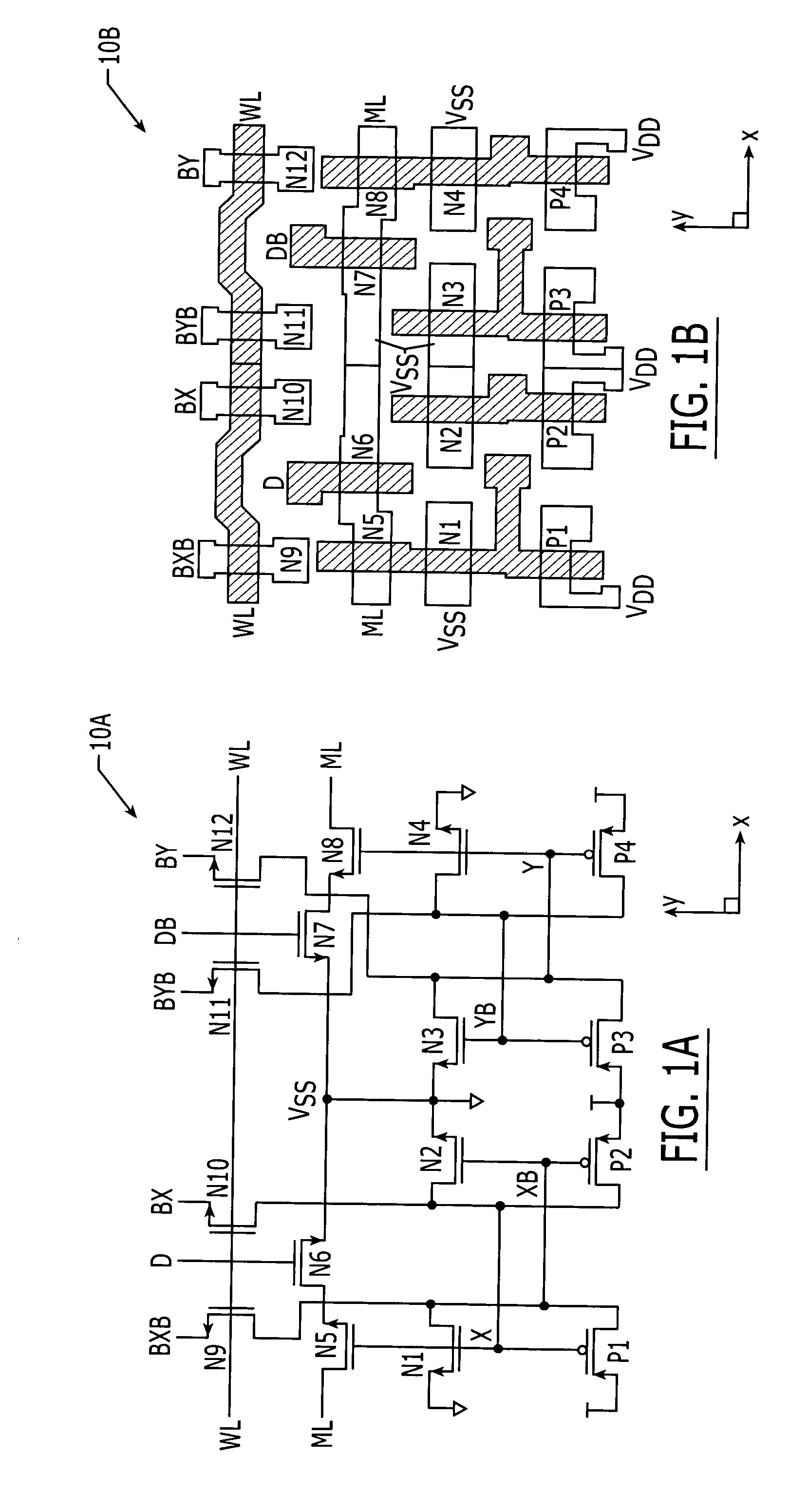

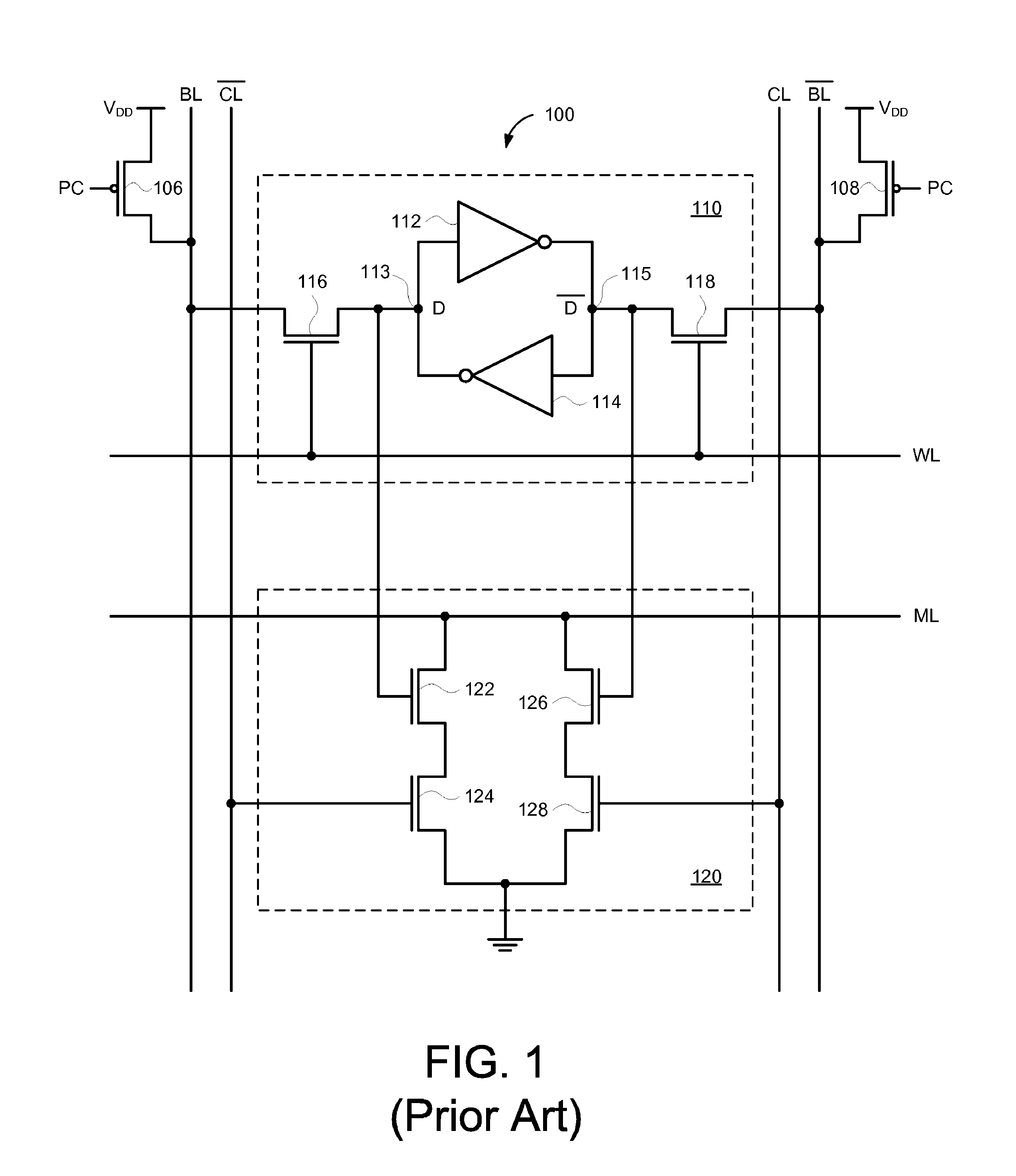

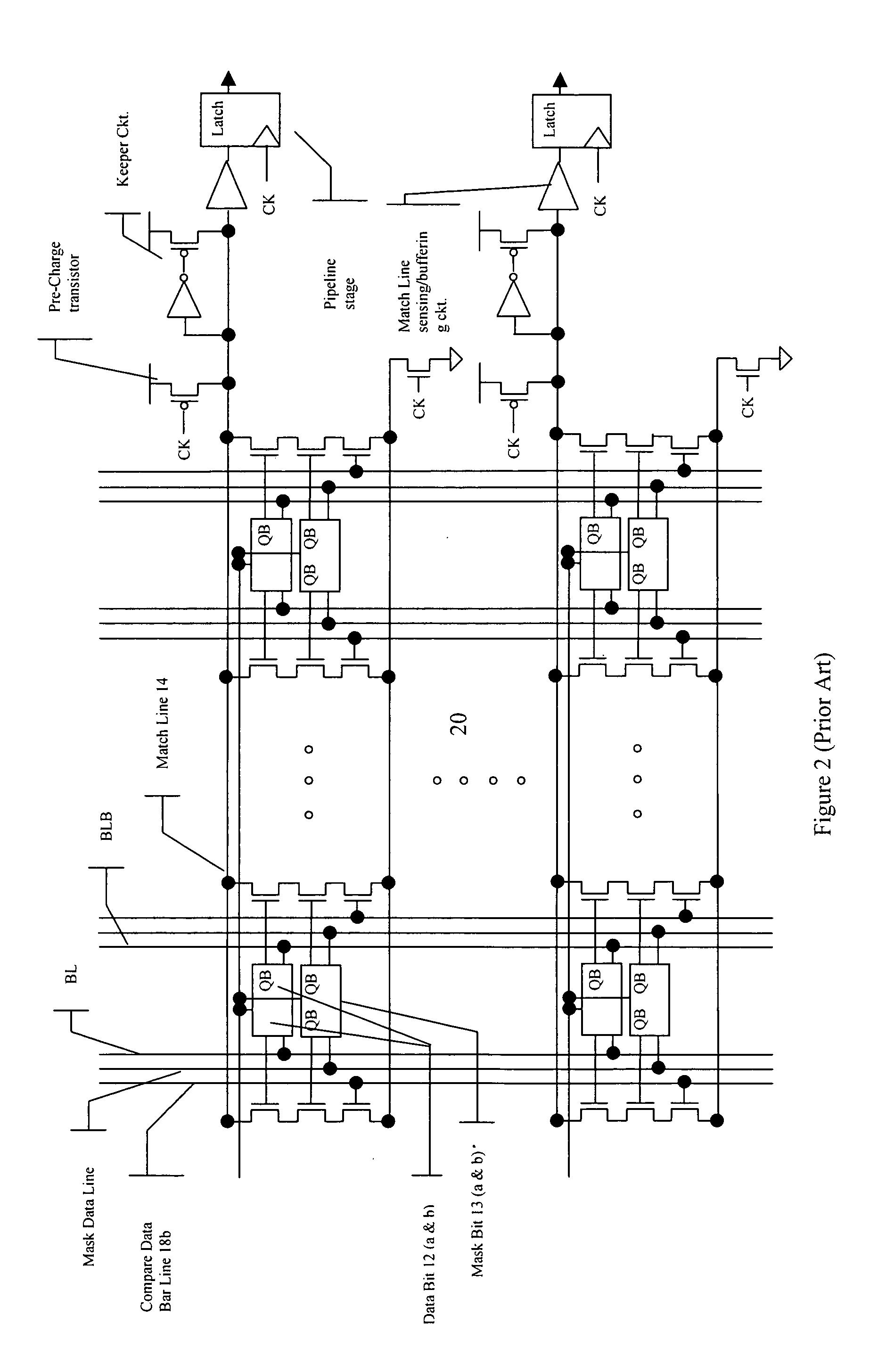

Ternary CAM cells are provided that have extremely small layout footprint size and efficient layout aspect ratios that enhance scalability. The cells also have high degrees of symmetry that facilitate high yield interconnections to bit, data and match lines. A 16T ternary CAM cell includes first and second pairs of access transistors that extend adjacent a first side of the cell, and first and second pairs of cross-coupled inverters that extend adjacent a second side of the cell. First and second halves of a 4T compare circuit are also provided. The first half of the 4T compare circuit is positioned so that is extends between the first pair of access transistors and the first pair of cross-coupled inverters. Similarly, the second half of the 4T compare circuit is positioned so that it extends between the second pair of access transistors and the second pair of cross-coupled inverters.

Owner:AVAGO TECH INT SALES PTE LTD

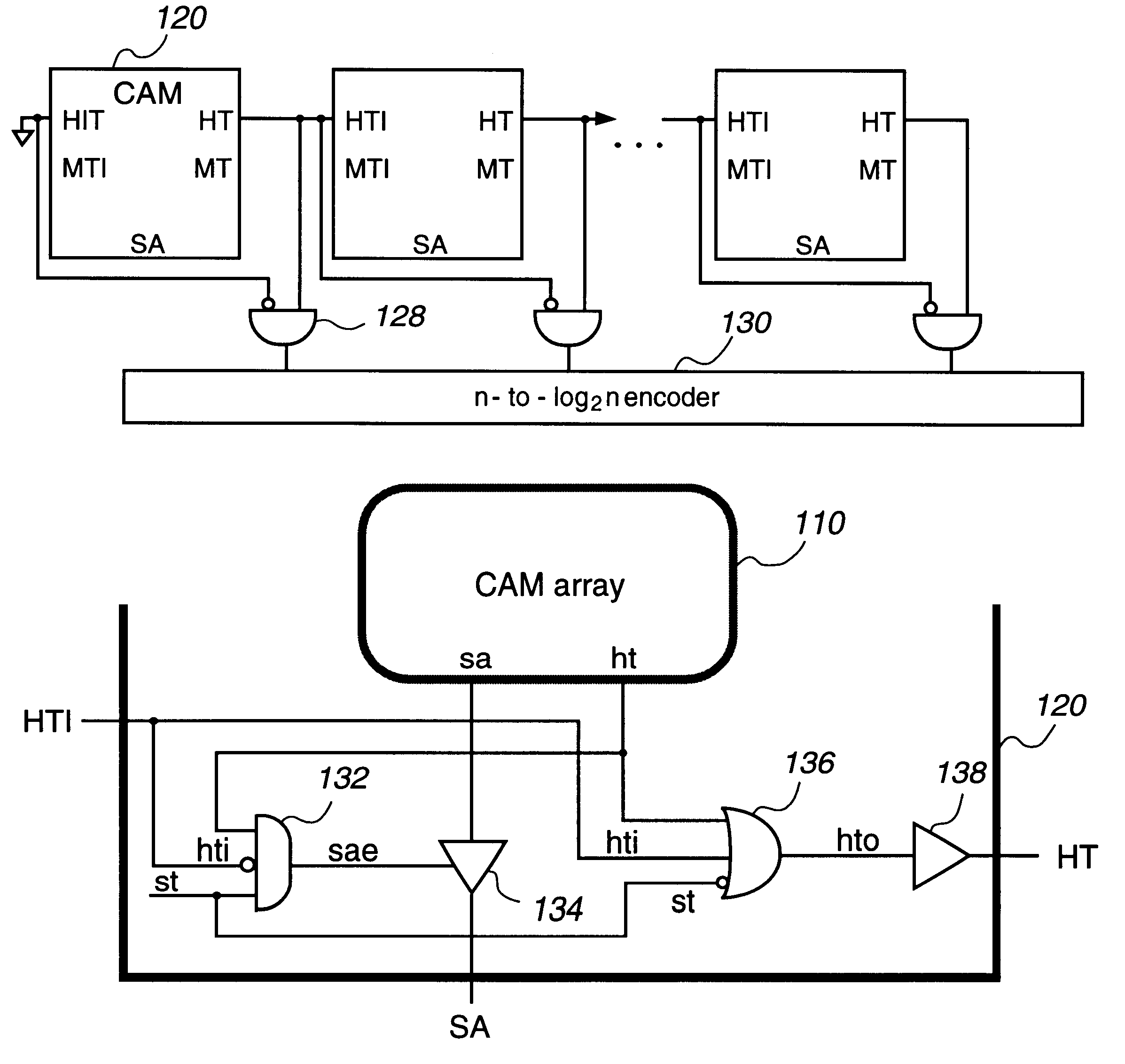

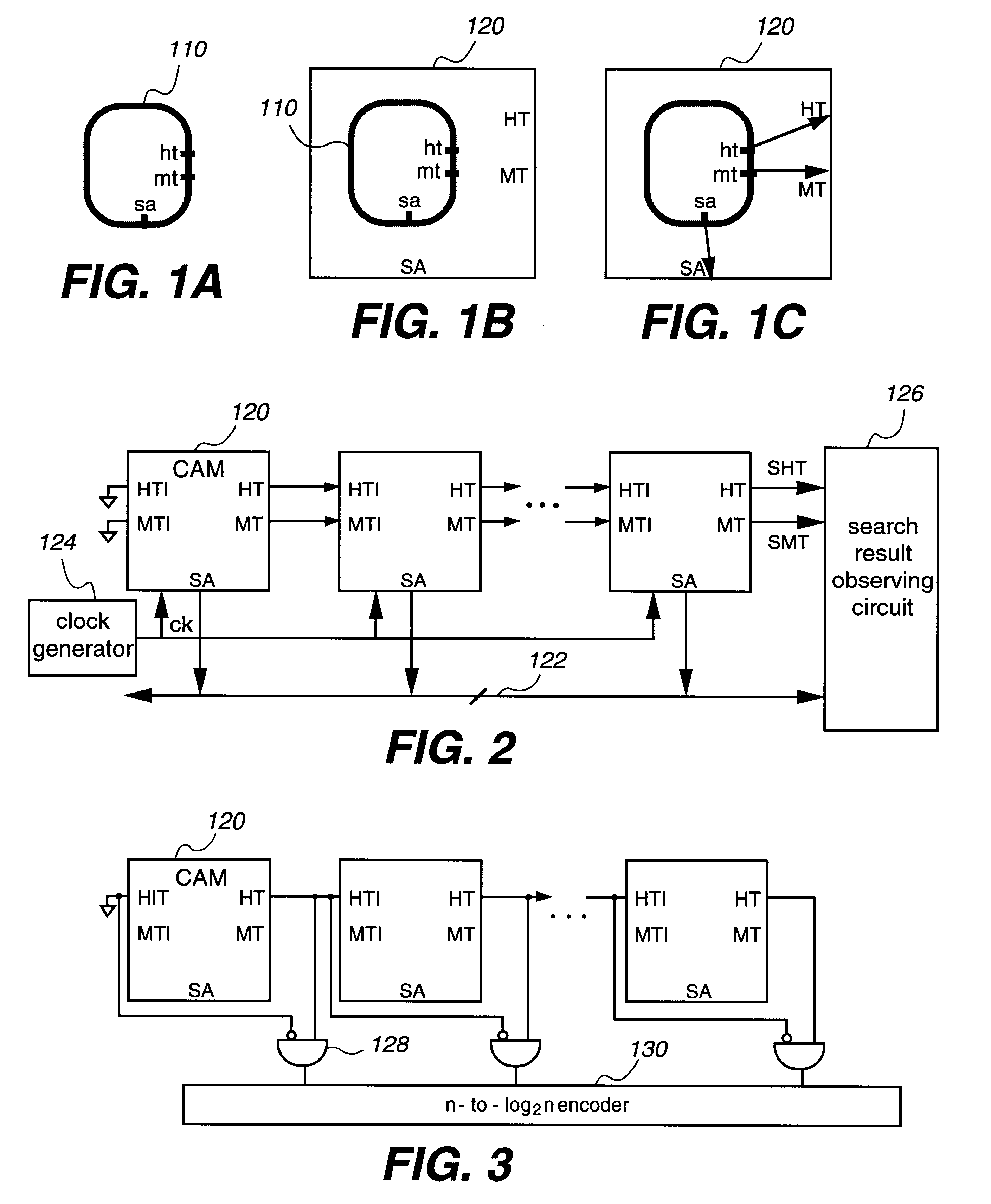

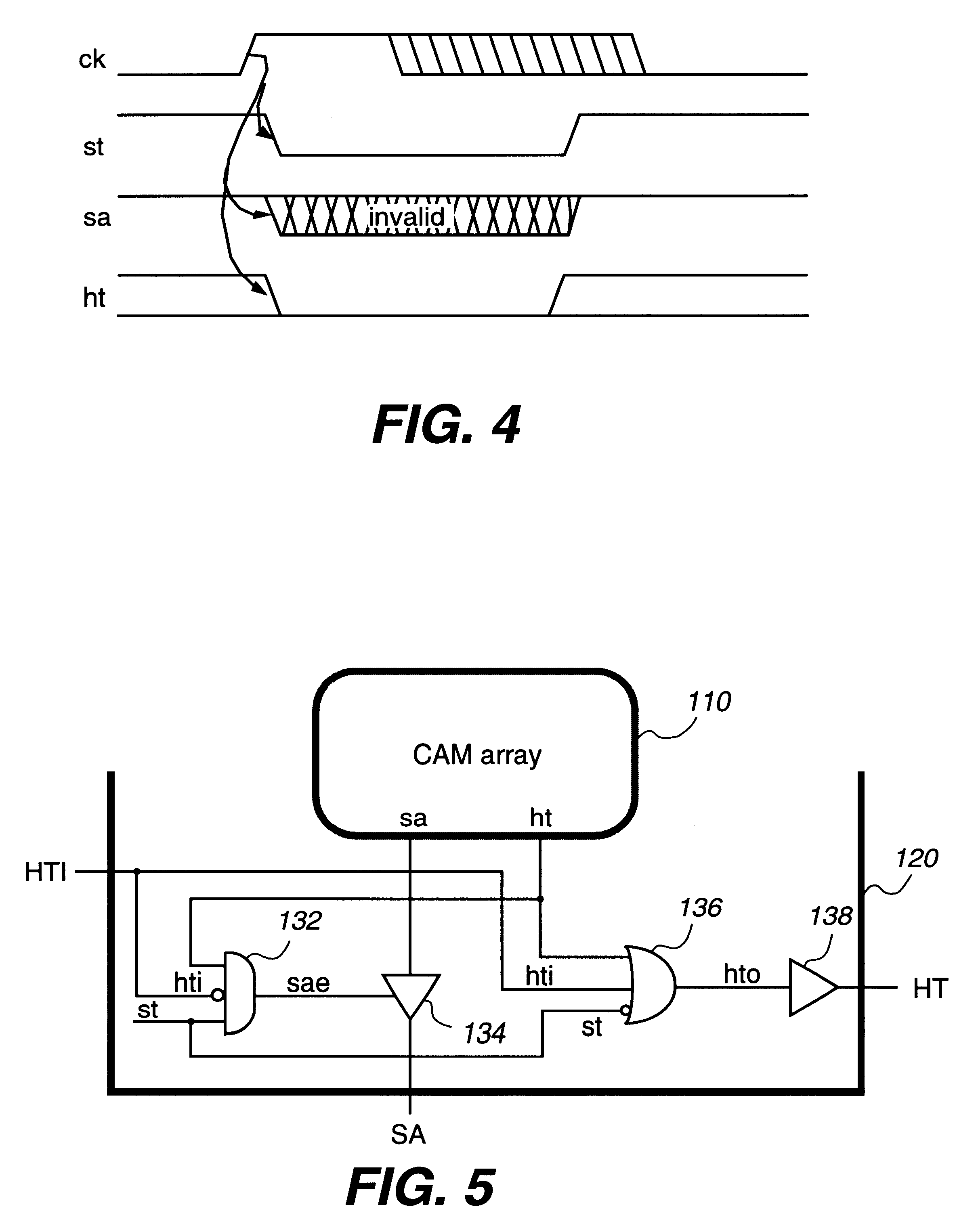

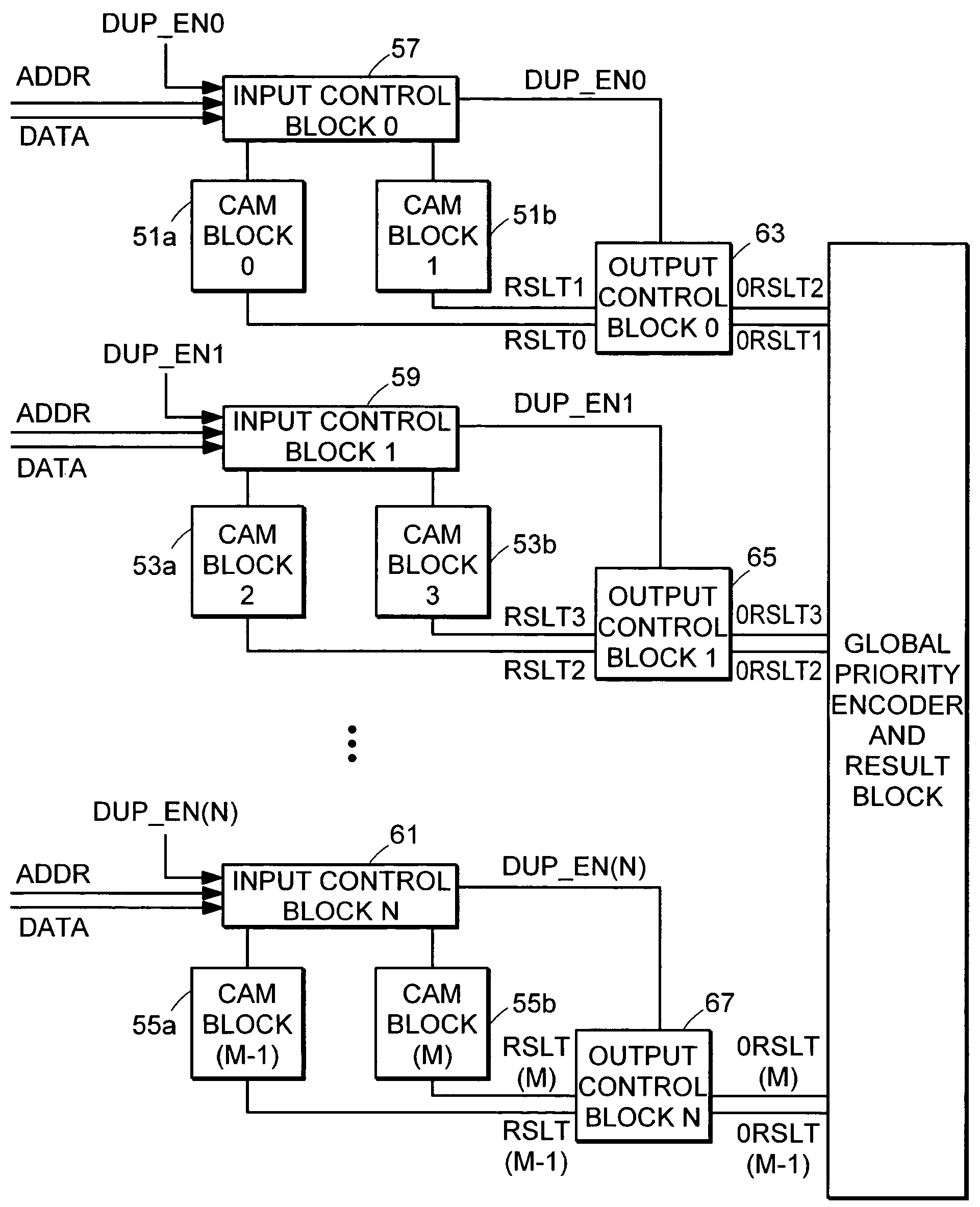

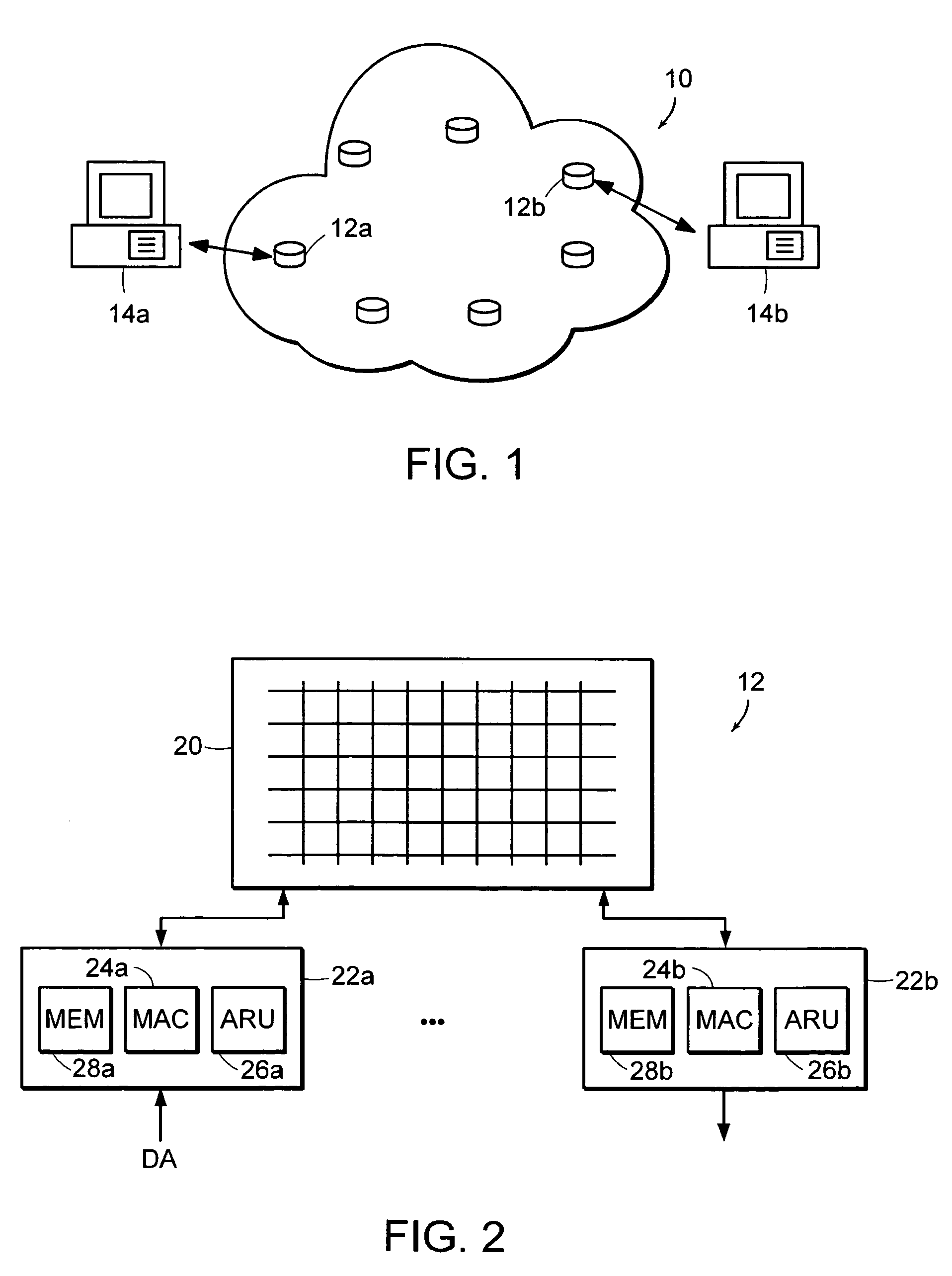

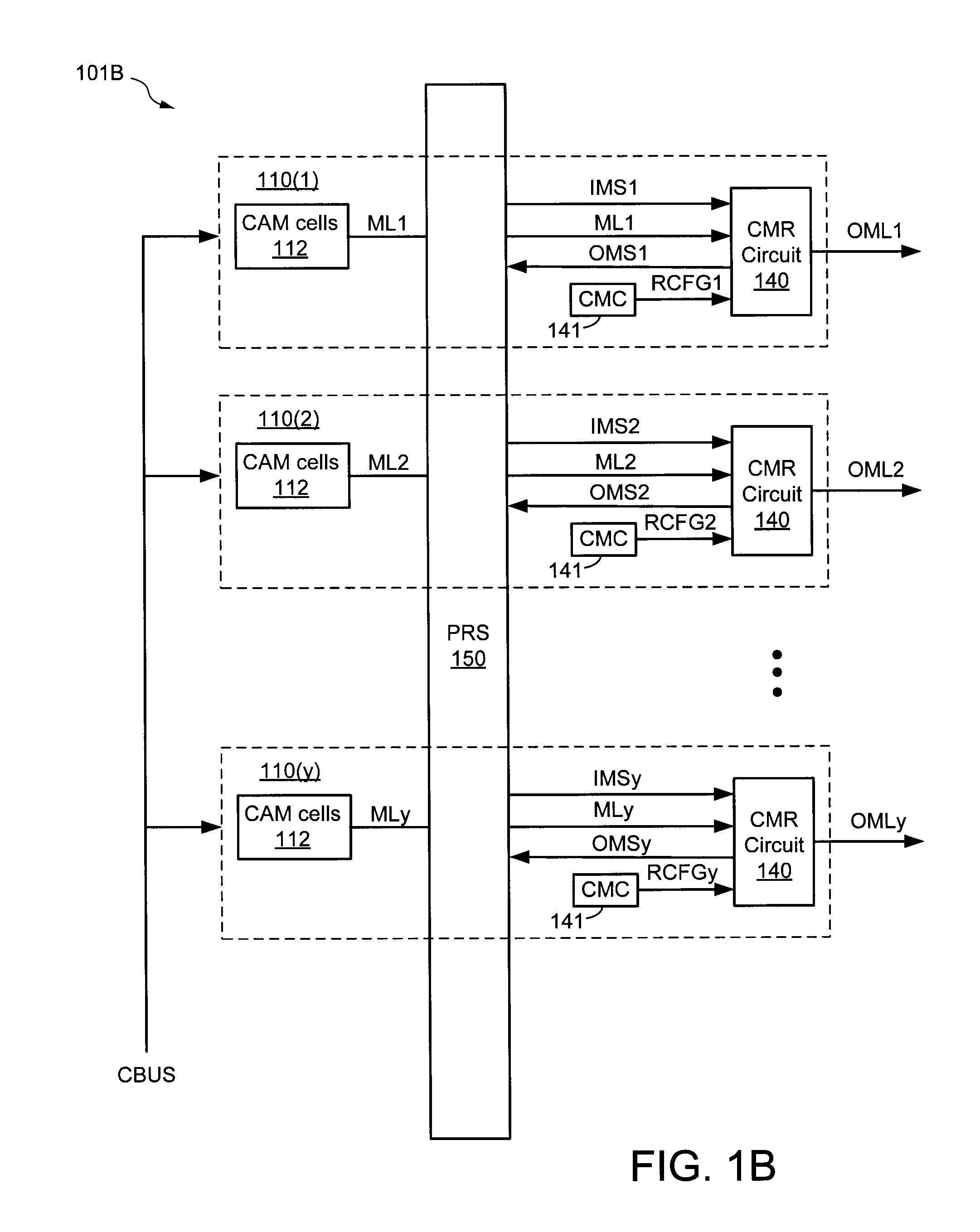

Content addressable memory system with cascaded memories and self timed signals

InactiveUS6301636B1Memory adressing/allocation/relocationDigital storageHemt circuitsSignal generator

A system includes cascaded content addressable memory (CAM) chips connected to a common bus. Each CAM chip includes a CAM array, a self-timed signal generator and hit propagation and match address transfer circuits. Each CAM array including an array of core cells provides, through its encoder, hit and match address signals resulting from a search operation in response to a clock signal. Each match address transfer circuit transfers the match address signal to the common bus, in response to a self-timed signal, the hit signal and a propagation-in hit signal provided from an upstream CAM chip, so that more than one CAM chip is prevented from providing the match address signal to the common bus simultaneously. Each hit propagation circuit provides a propagation-out hit signal to a downstream CAM chip, in response to the self-timed signal, the hit signal and the propagation-in hit signal from the upstream CAM chip, so that a hit signal is propagated from an upstream CAM chip to a downstream CAM chip. Each CAM chip may include an extra row for providing a modelmiss signal or a modelhit signal which is used for a generating self-timed signal. Each word may be divided into two halves and two match lines of the two halves are coupled by a logic circuit. The system may also observe a multiple match status and the highest priority chip indicating a match.

Owner:FOOTHILLS IP LLC +1

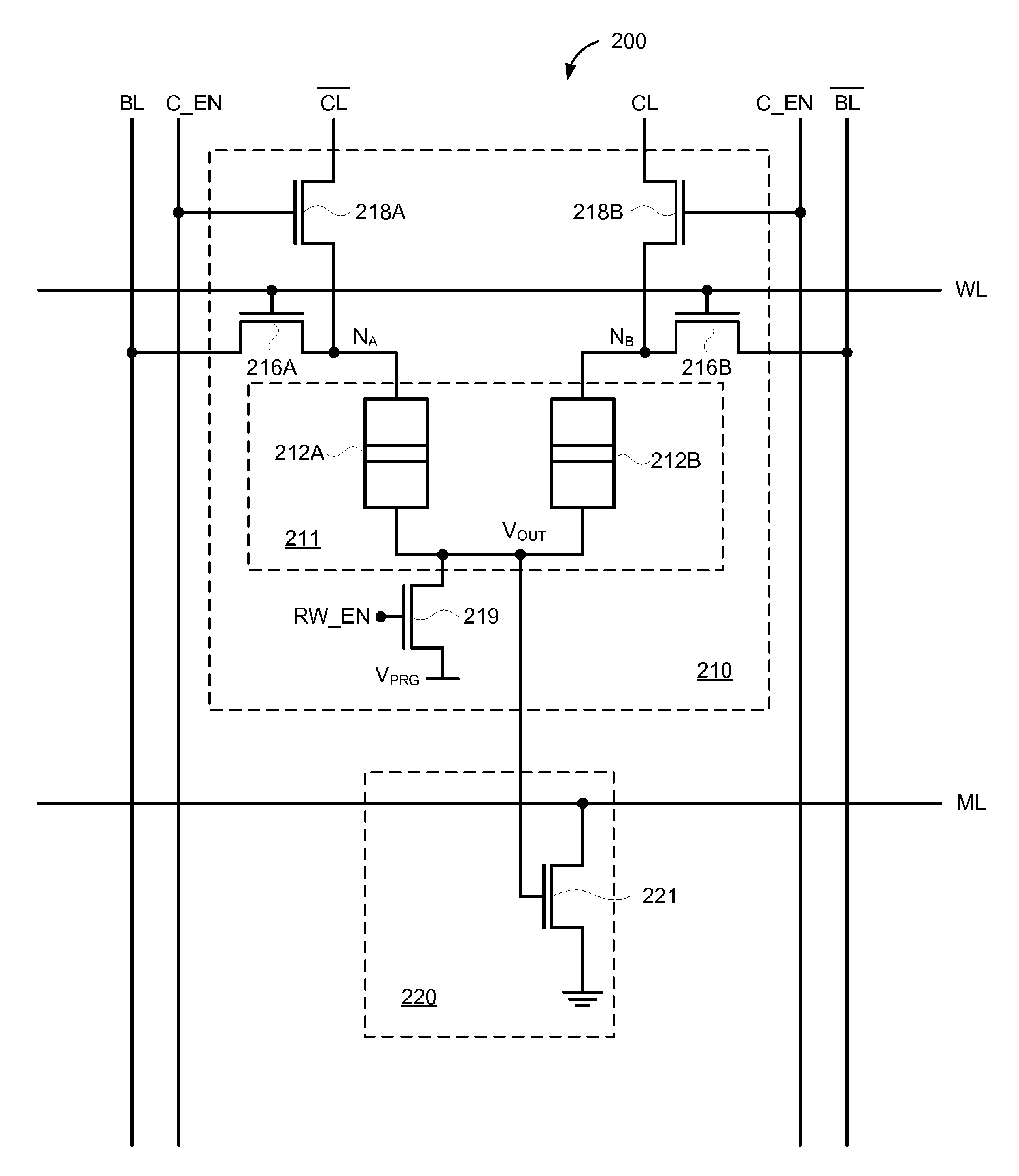

Content addressable memory device having spin torque transfer memory cells

A CAM device includes an array of CAM cells each having a spin torque transfer (STT) storage cell to store a data bit. Each STT storage cell includes a first magnetic tunnel junction (MTJ) element coupled between a first input node and an output node of the CAM cell, a second MTJ element coupled between a second input node and the output node of the CAM cell, and a first match transistor coupled between the match line and ground potential and having a gate coupled to the output node. The logic state of the data bit is represented by the relative resistances of the first and second MTJ elements.

Owner:AVAGO TECH INT SALES PTE LTD

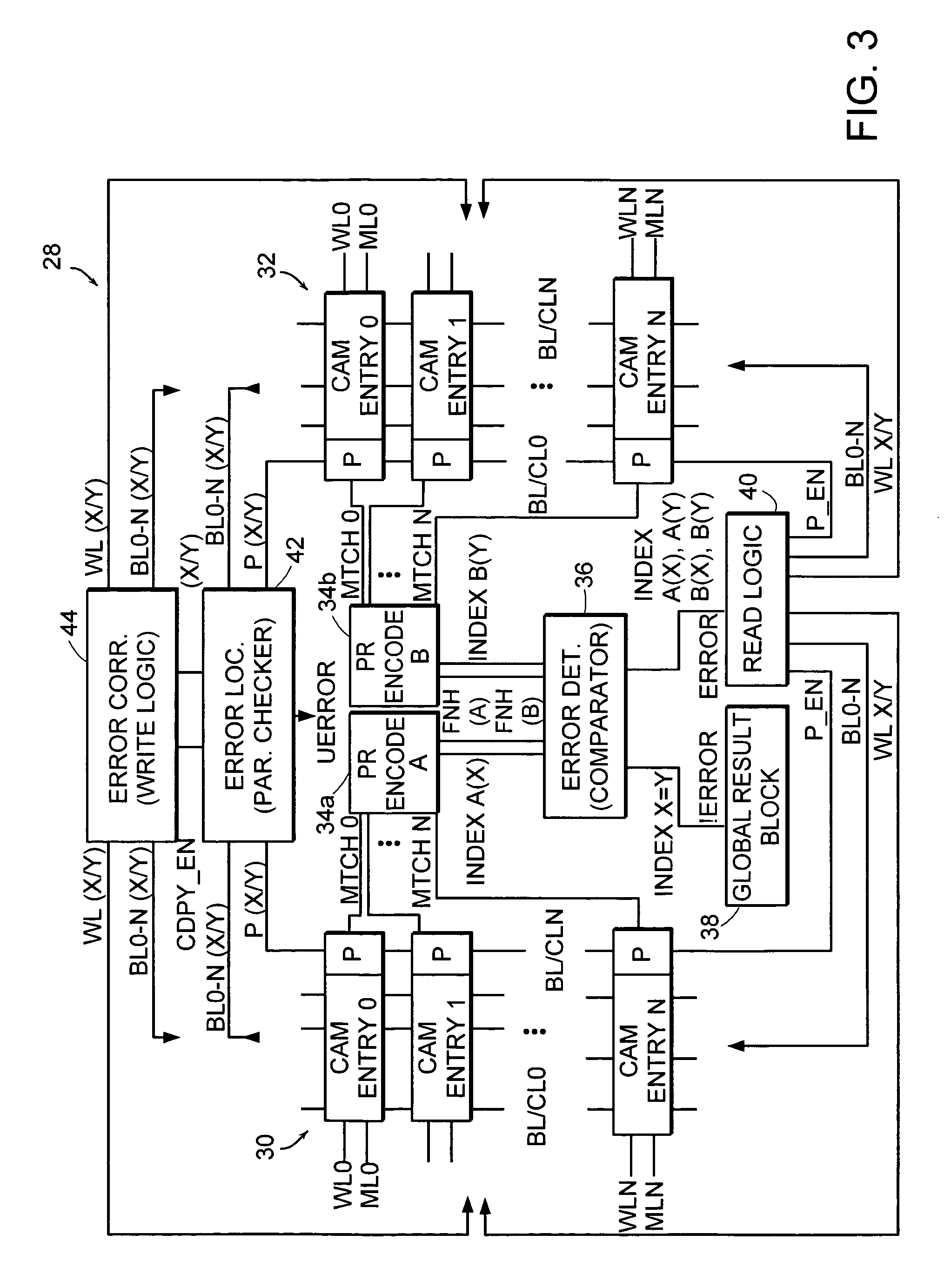

Error correcting content addressable memory

InactiveUS7254748B1Maximize usable CAM spaceRedundant data error correctionMemory systemsSoft errorMatch line

A CAM and method for operating a CAM are presented. Copies of a CAM database are duplicated and placed in a first set of CAM locations and a second set of CAM locations. An error detector is used to determine false matches in the case of soft errors within the entries producing those false matches. While the entries producing a match should have the same index location, errors might cause those match lines to have an offset. If so, the present CAM, through use of duplicative sets of CAM locations, will detect the offset and thereafter the values in each index location that produces a match, along with the corresponding parity or error detection encoding bit(s). If the parity or error detection encoding bit(s) indicate an error in a particular entry, then that error is located and the corresponding entry at the same index within the other, duplicative set of CAM locations is copied into the that erroneous entry. Since duplicative copies are by design placed into the first and second sets of CAM locations, whatever value exists in the opposing entry can be written into the erroneous entry to correct errors in that search location. The first and second sets of CAM locations are configurable to be duplicative or distinct in content, allowing error detection and correction to be performed at multiple user-specified granularities. The error detection and correction during search is backward compatible to interim parity scrubbing and ECC scan, as well as use of FNH bits set by a user or provider.

Owner:AVAGO TECH INT SALES PTE LTD

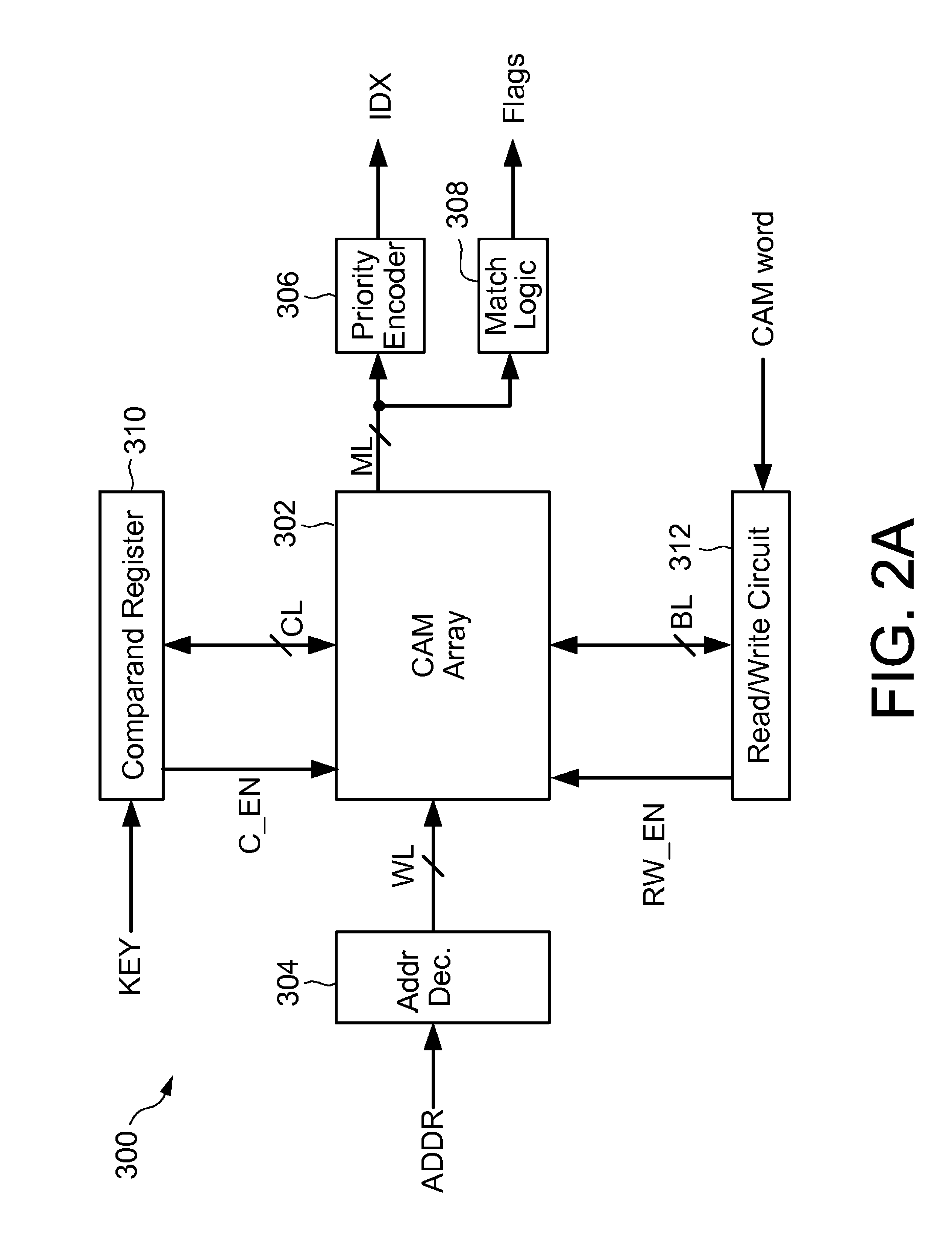

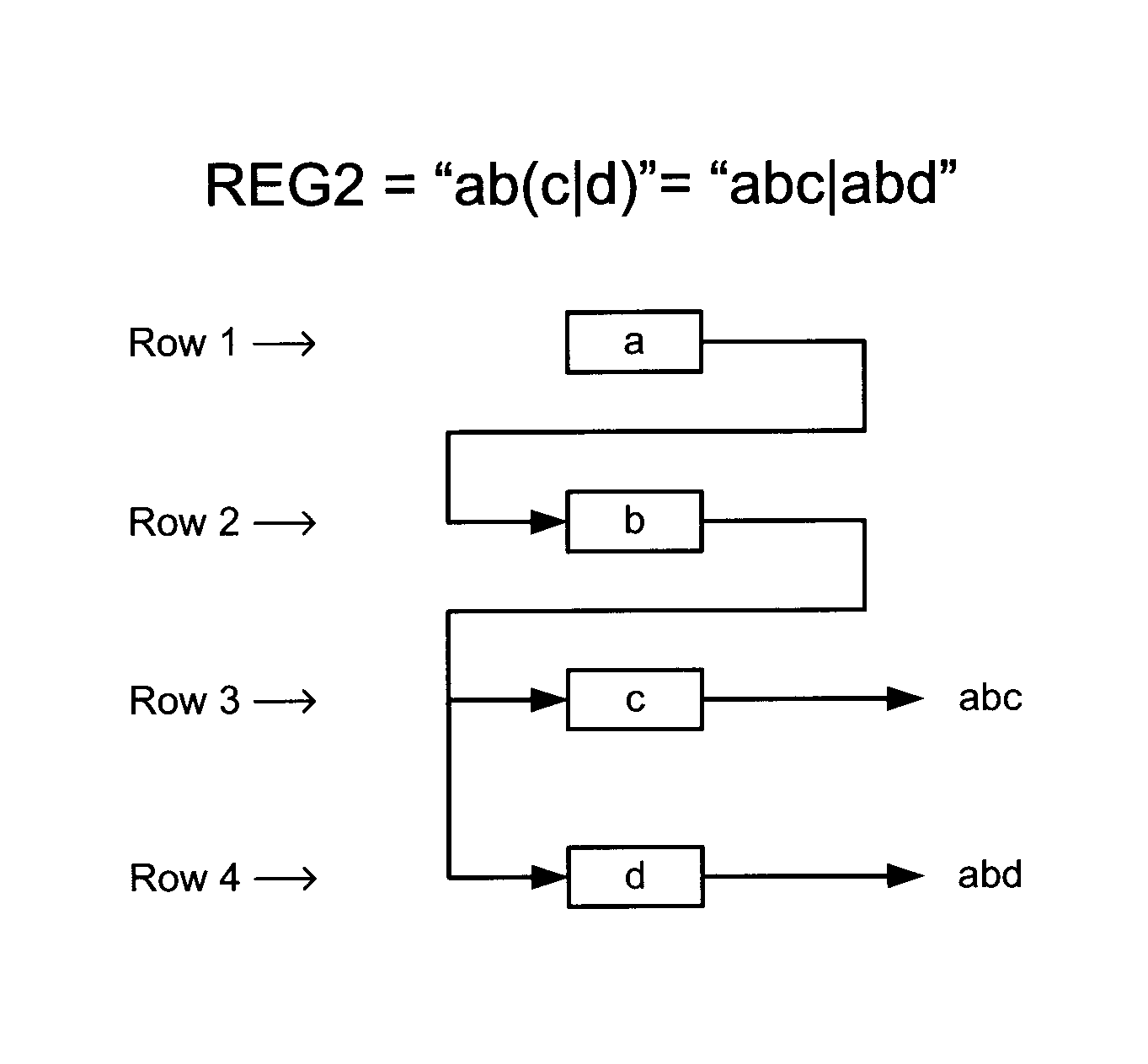

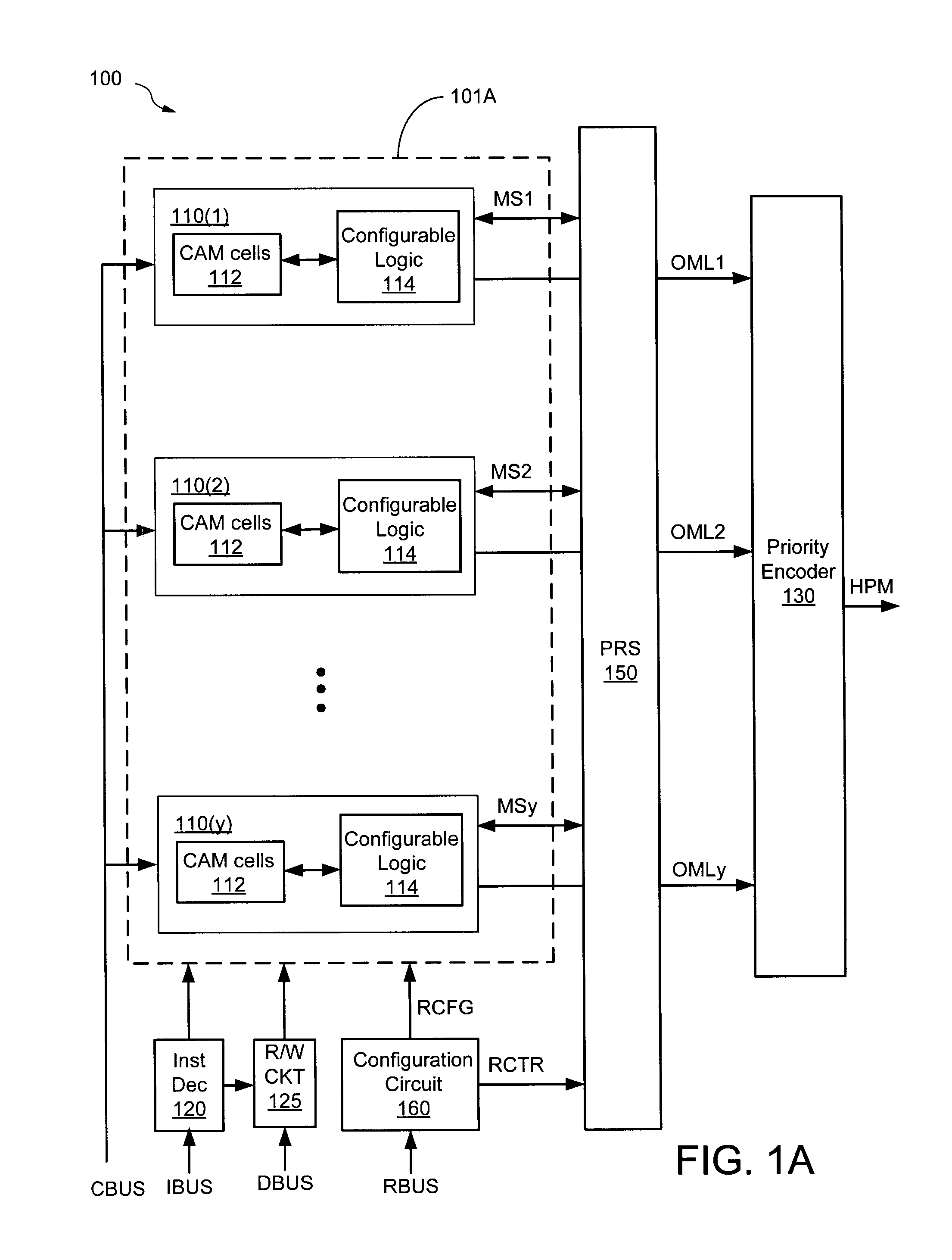

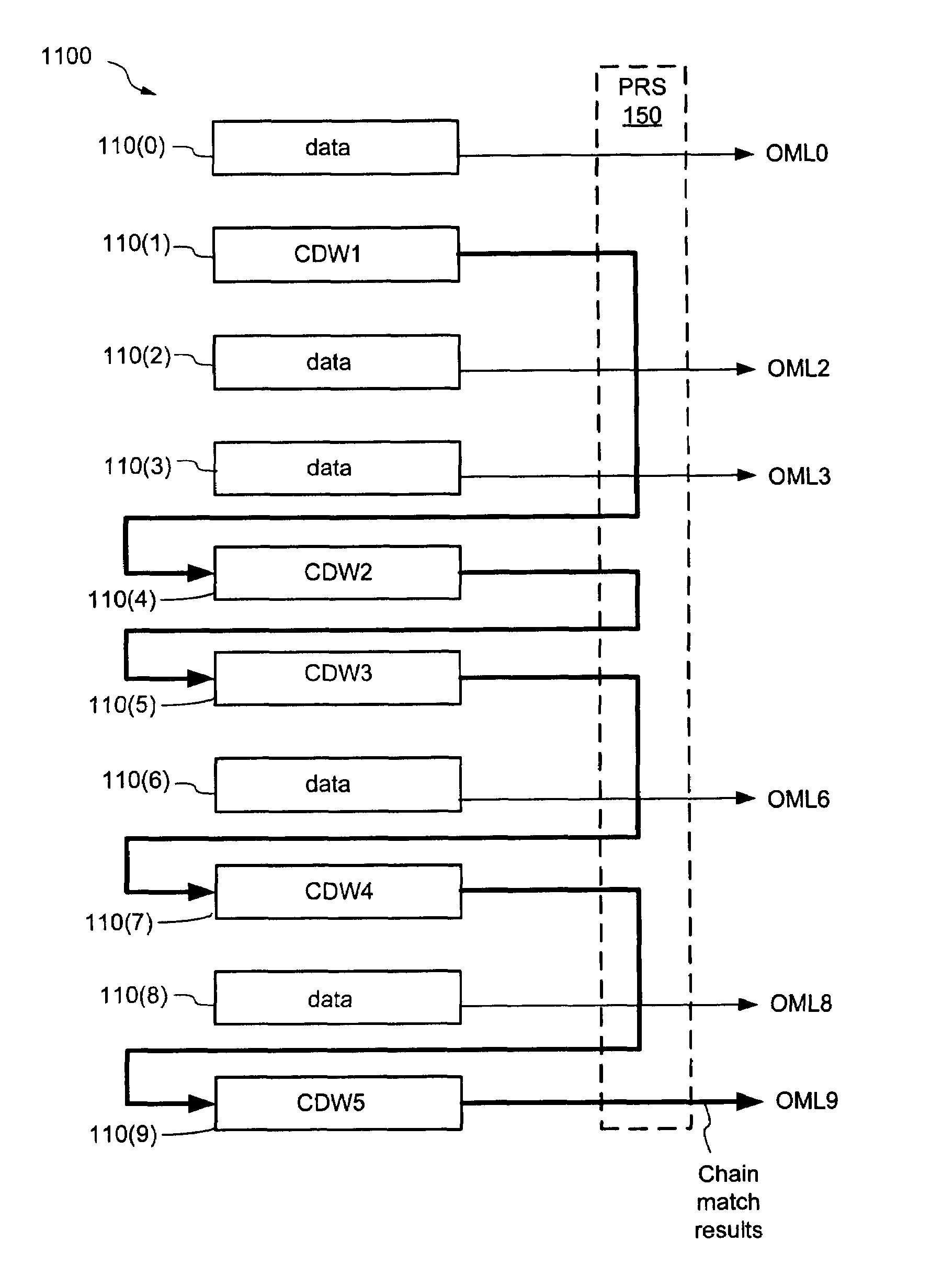

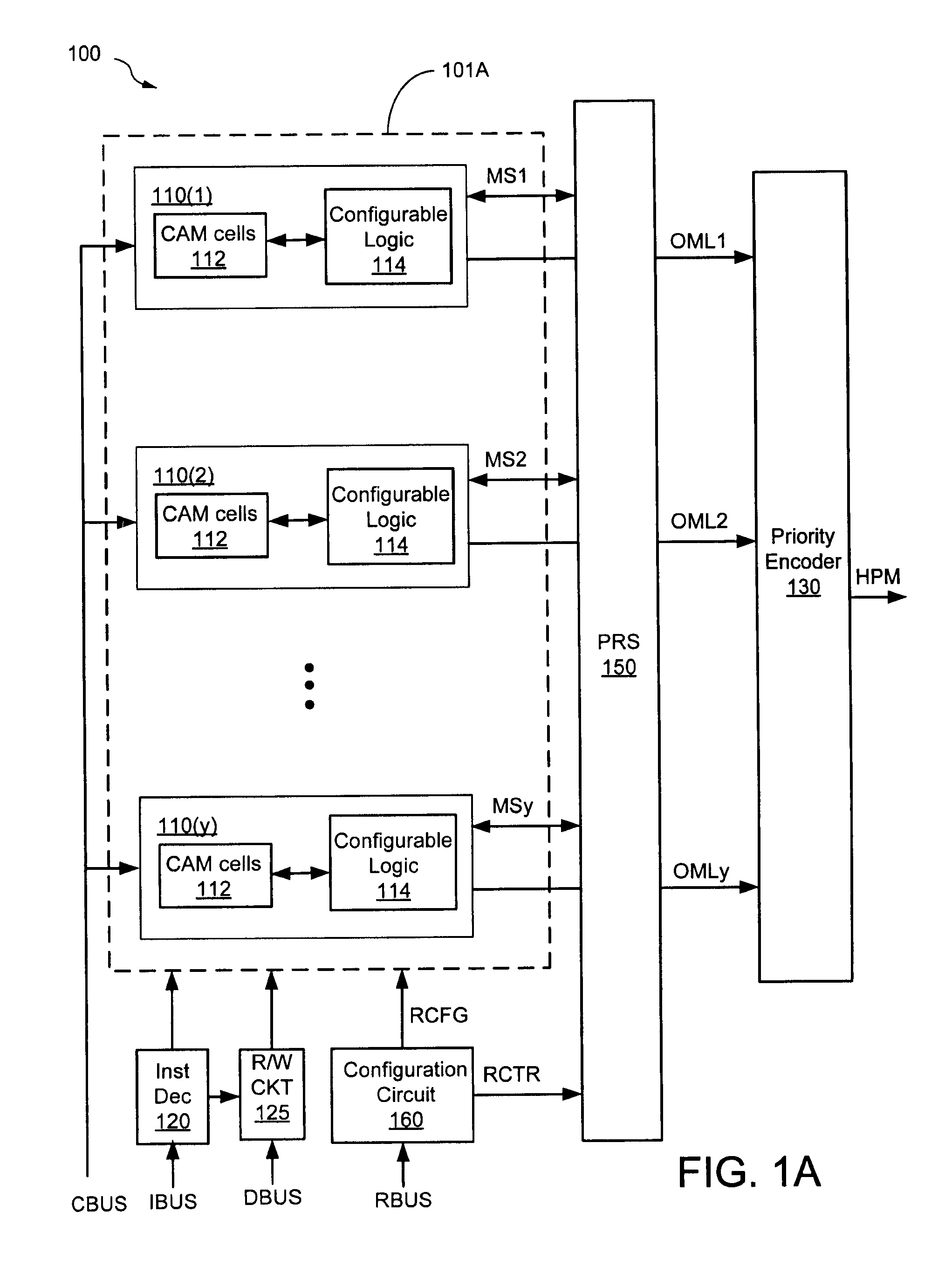

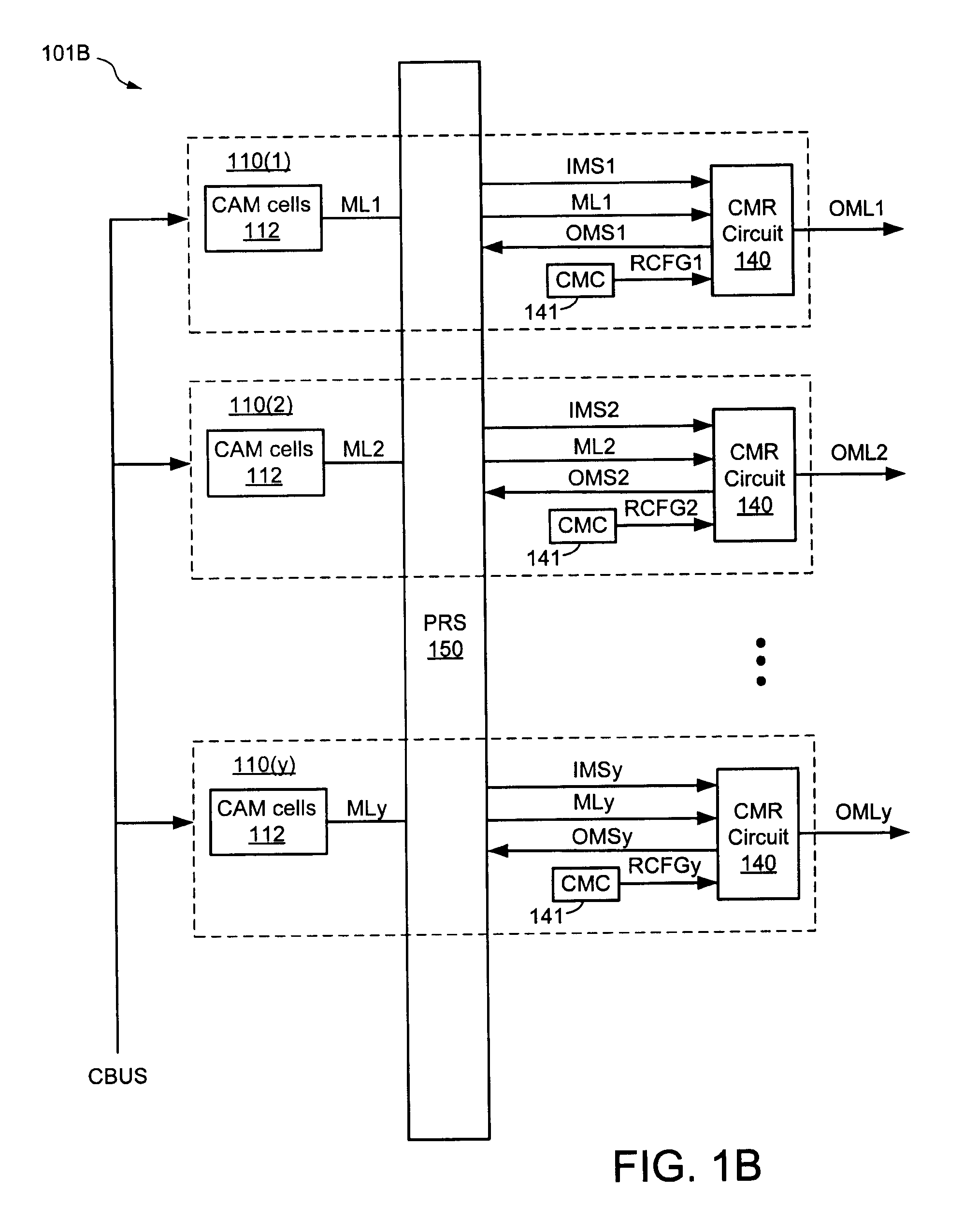

Content addressable memory having programmable interconnect structure

A content addressable memory (CAM) device includes a CAM array, a programmable interconnect structure, and a priority encoder. The CAM array includes a plurality of CAM rows, each row including a number of CAM cells for storing a data word and coupled to a match line that indicates a match result for the CAM row. The programmable interconnect structure is coupled to each CAM row and is configured to selectively route the match results from a first CAM row as an input match signal to any number of arbitrarily selected CAM rows at the same time.

Owner:AVAGO TECH INT SALES PTE LTD

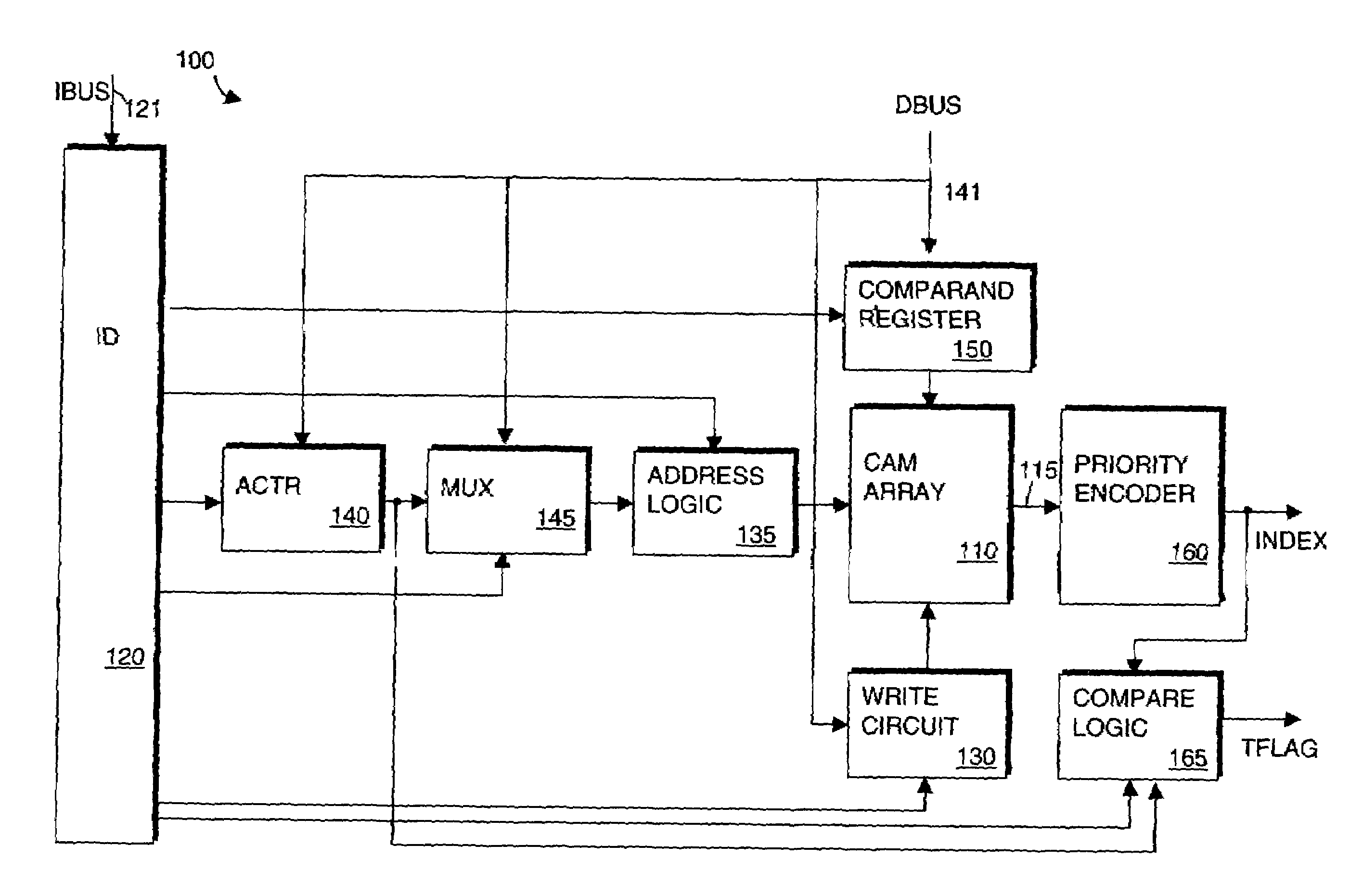

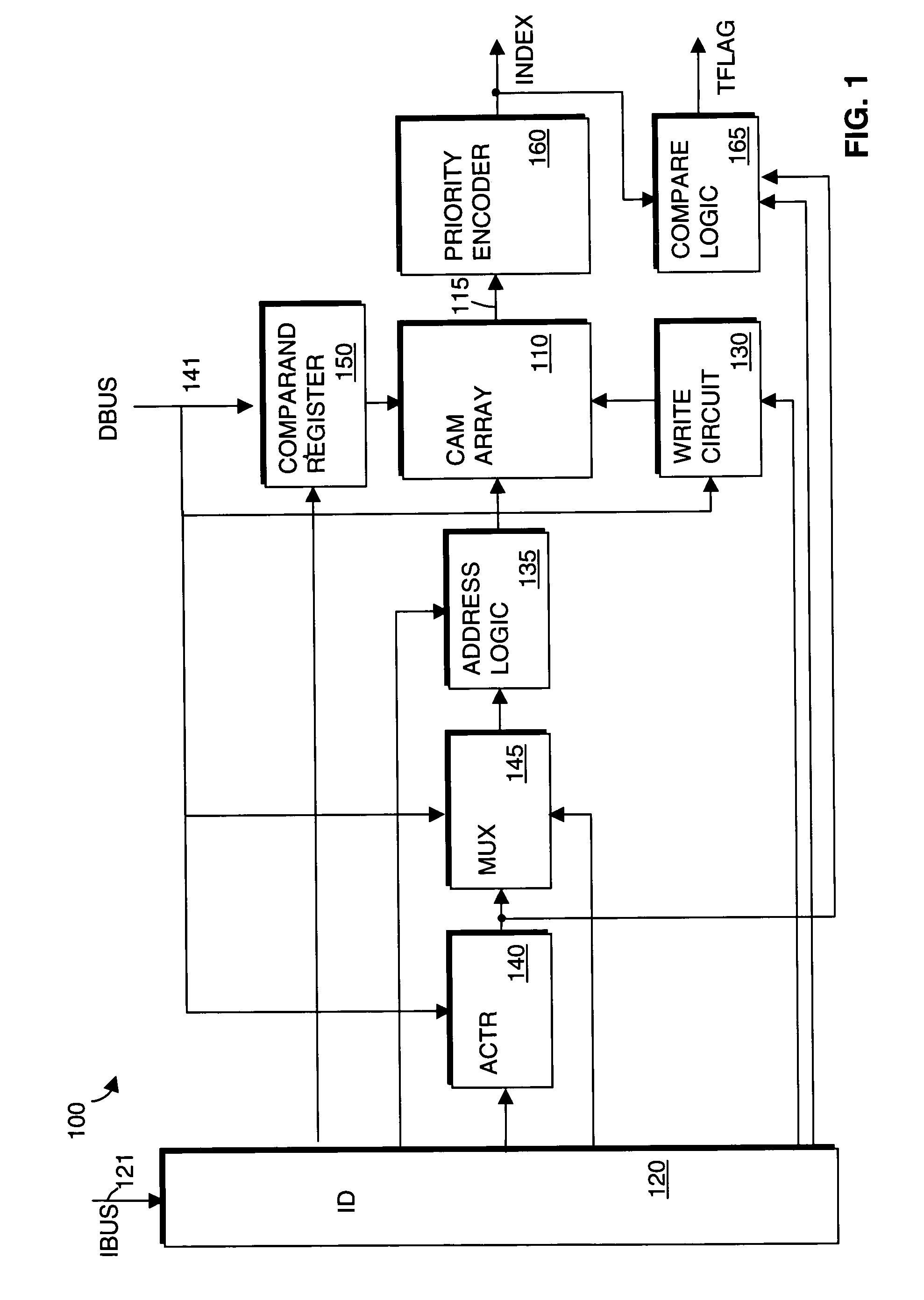

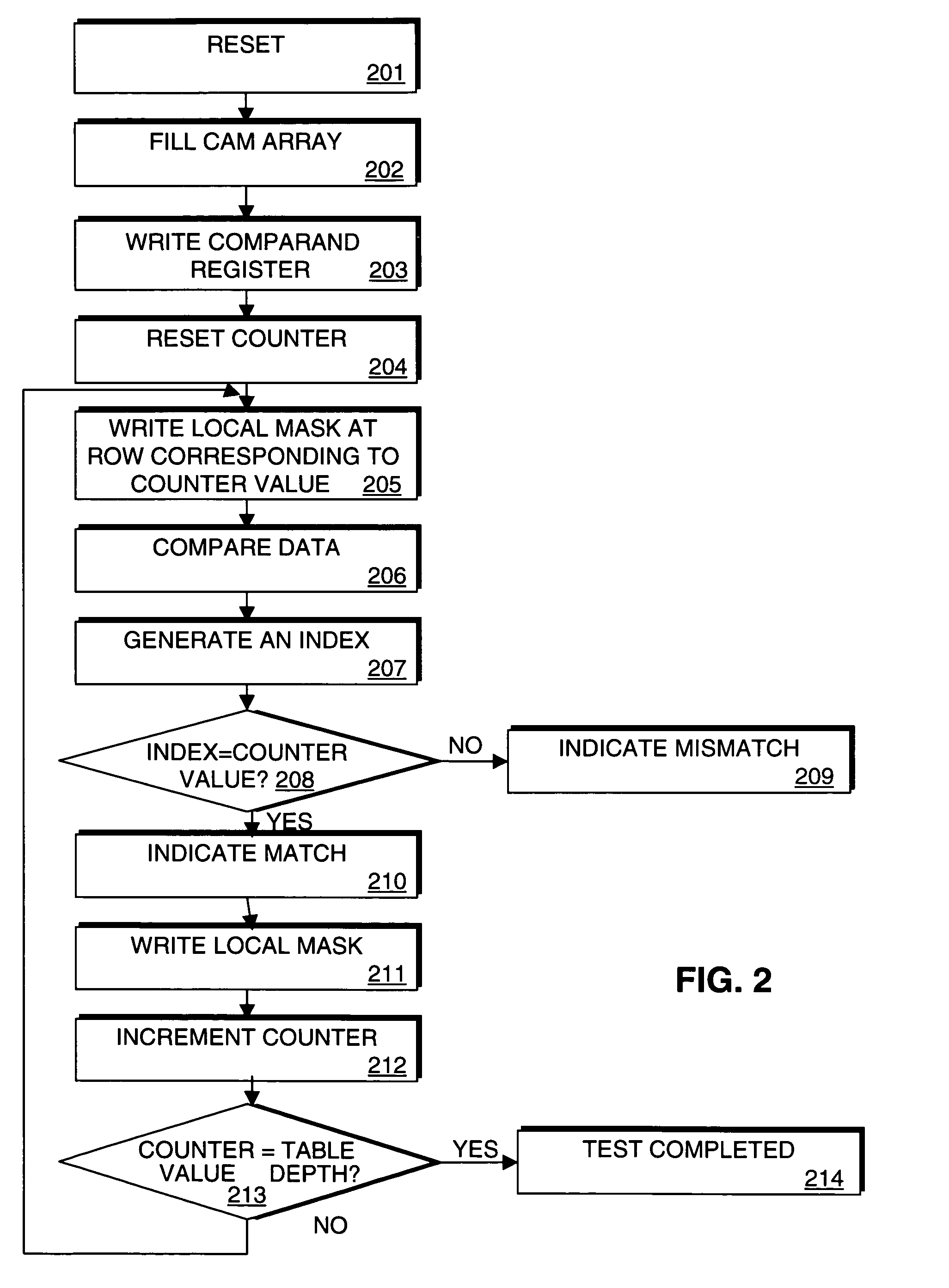

Method and apparatus for testing a content addressable memory device

According to one embodiment of the present invention, the CAM device includes a CAM array that includes a plurality of rows of CAM cells each coupled to a match line, a priority encoder coupled to the match lines to generate an index, a counter and compare logic coupled to the counter and the priority encoder to compare the index and a counter value from the counter.

Owner:AVAGO TECH INT SALES PTE LTD

Content addresable memory having selectively interconnected counter circuits

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Cam array with minimum cell size

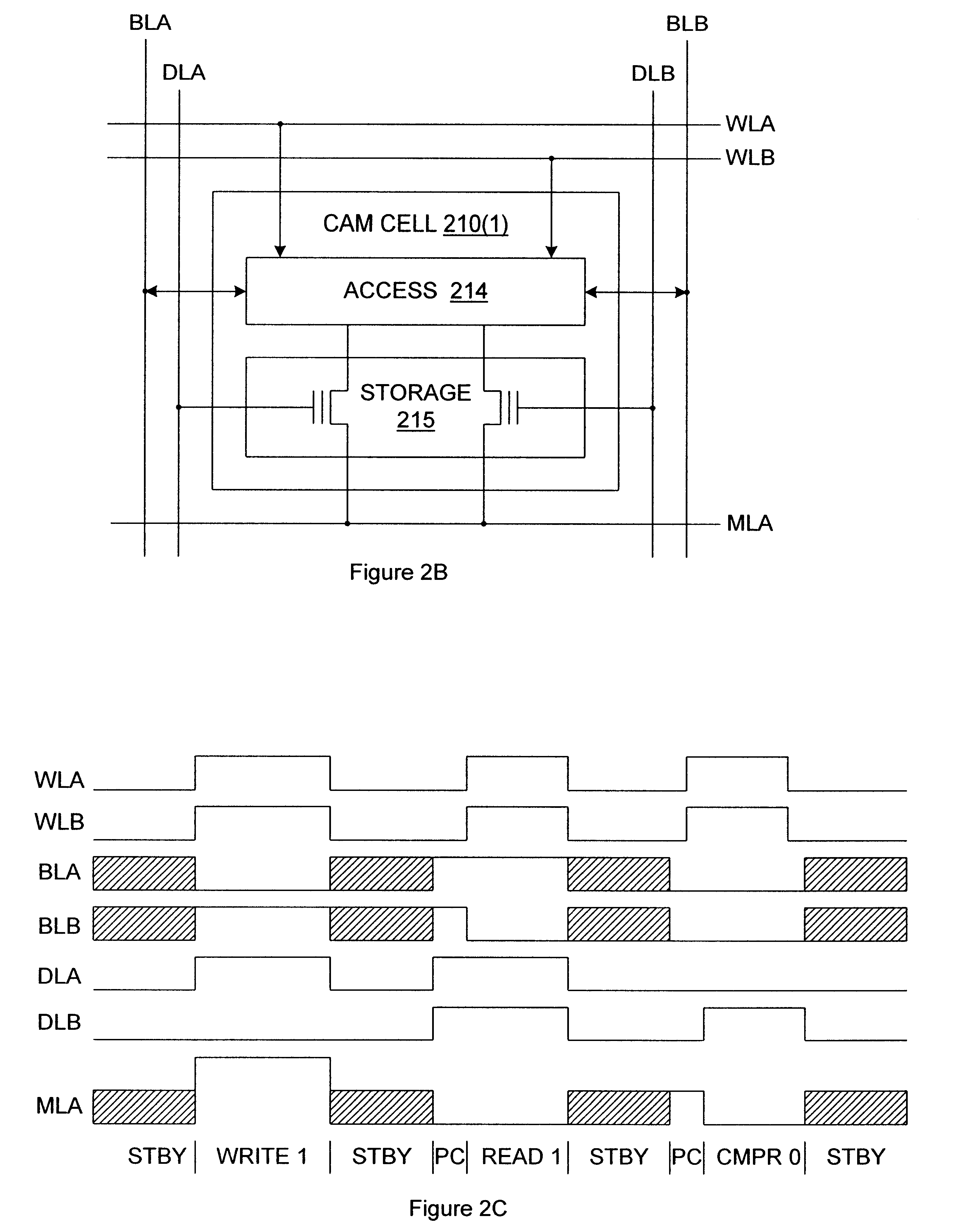

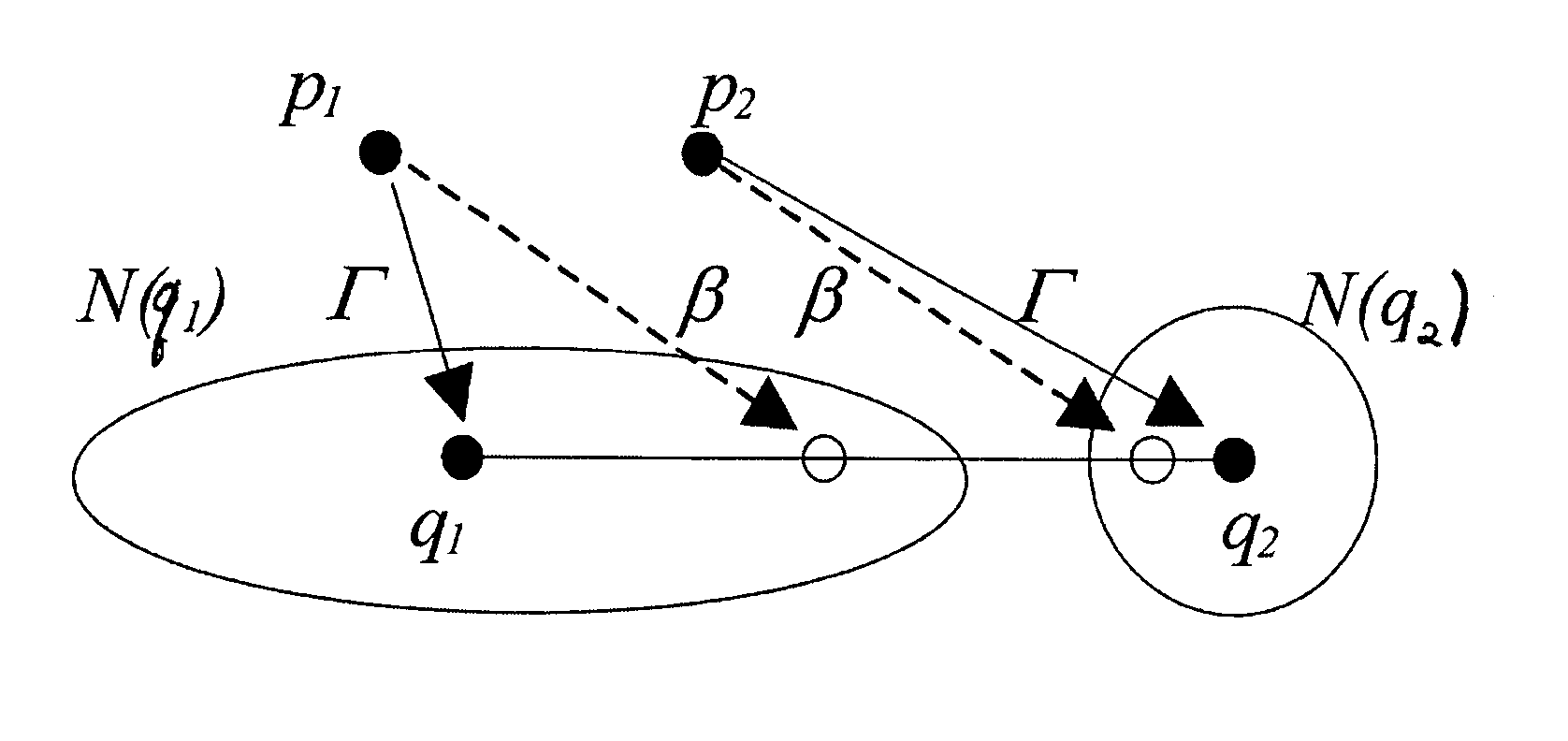

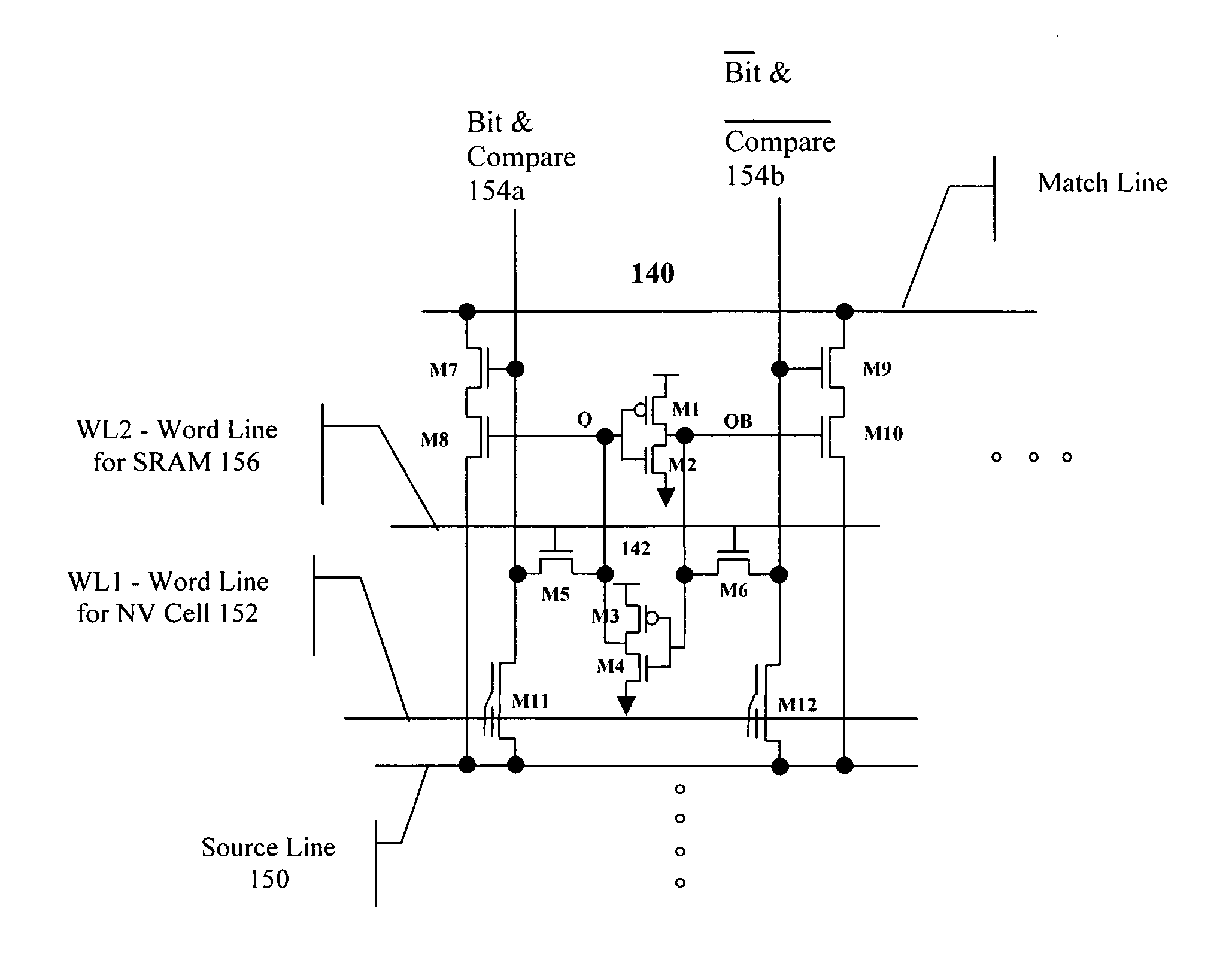

A CAM array includes non-volatile ternary CAM cells that use access transistors to easily read from and write to the non-volatile transistors. Each ternary CAM cell includes a pair of storage elements that are used to store a data bit value, and an access element that is used during CAM array operation. During a comparison operation, when the applied data value matches the stored value, the storage elements de-couple the match line from a discharging bit line (i.e., a high voltage on the match line remains high). Conversely, when the applied data value does not match the stored value, the storage elements couple the match line to a discharging bit line, thereby discharging the match line.

Owner:AVAGO TECH INT SALES PTE LTD

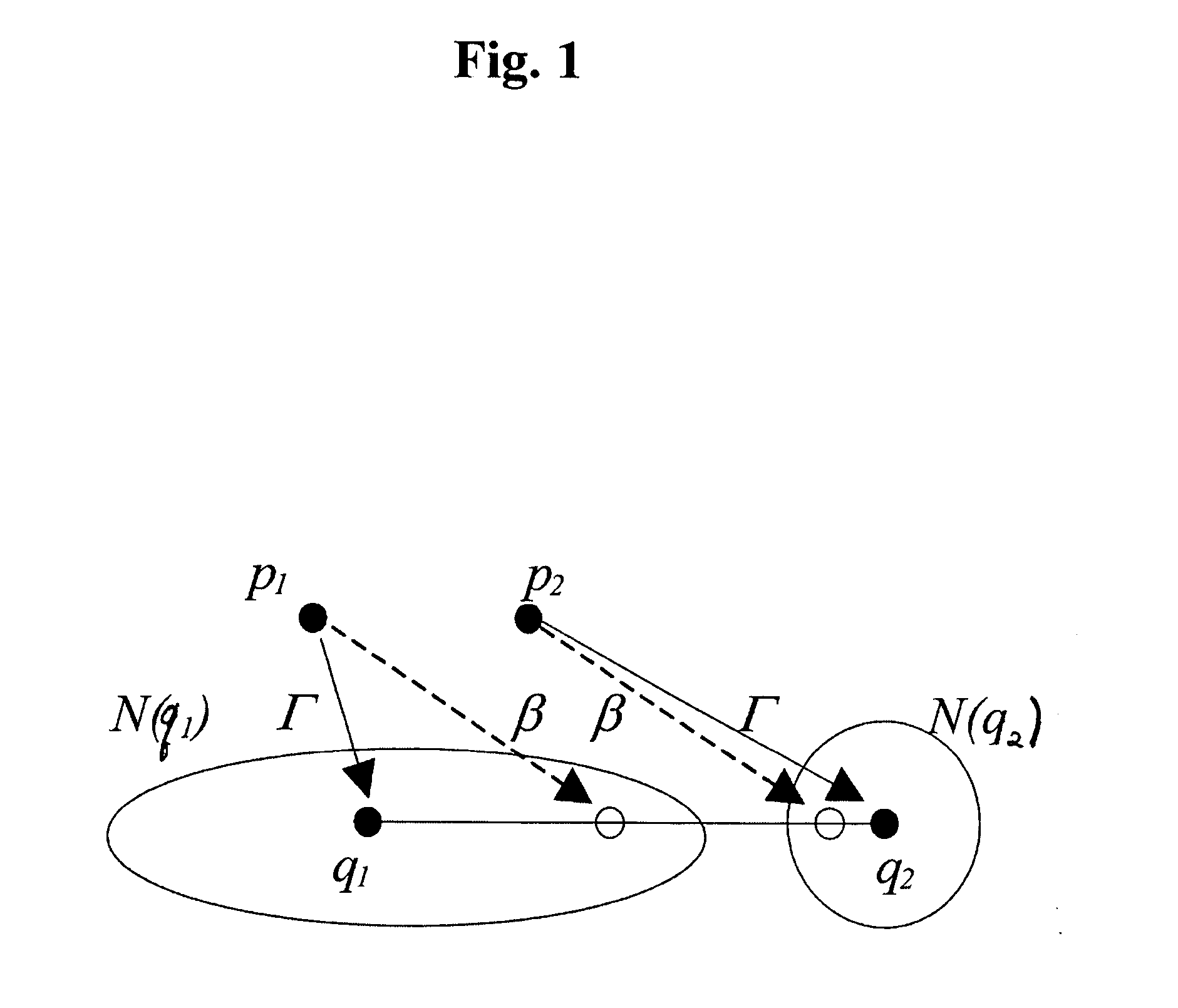

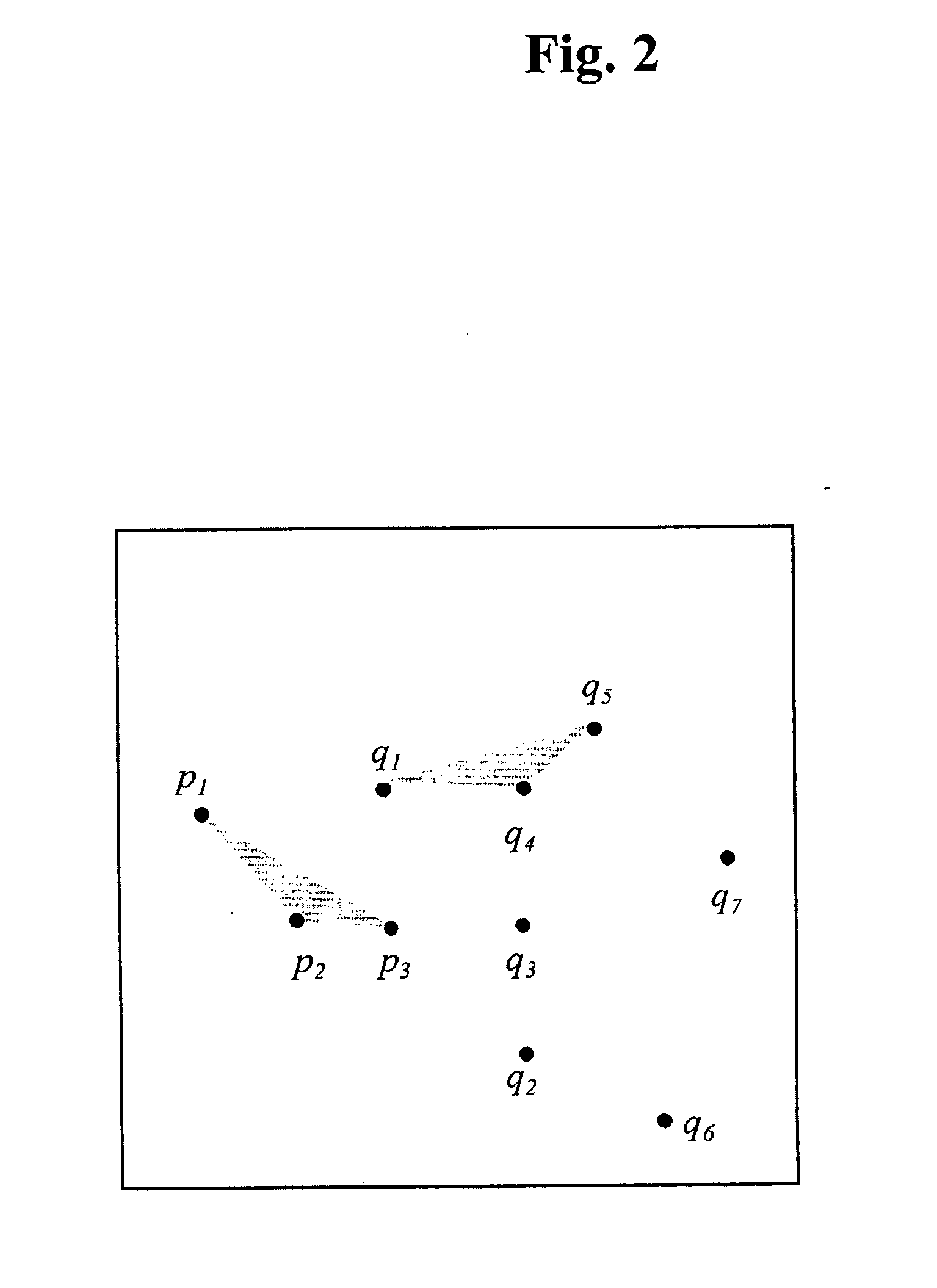

Distance sorting algorithm for matching patterns

The invention provides methods and systems for performing a matching function between a first pattern and a second pattern. This technique involves creating a set of all distance measurements between pairs of points in the first pattern and all distance measurements between pairs of points in the second pattern. This set is then partitioned into subsets of nearly equal distance elements. Those subsets containing at least one element derived from each pattern determine possible line segment matches which are then analyzed mathematically to determine the partial transform that maps the associated points of the first pattern into the points of the second pattern. The resulting set of partial transforms is then reviewed to determine matched line segments between the two patterns.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

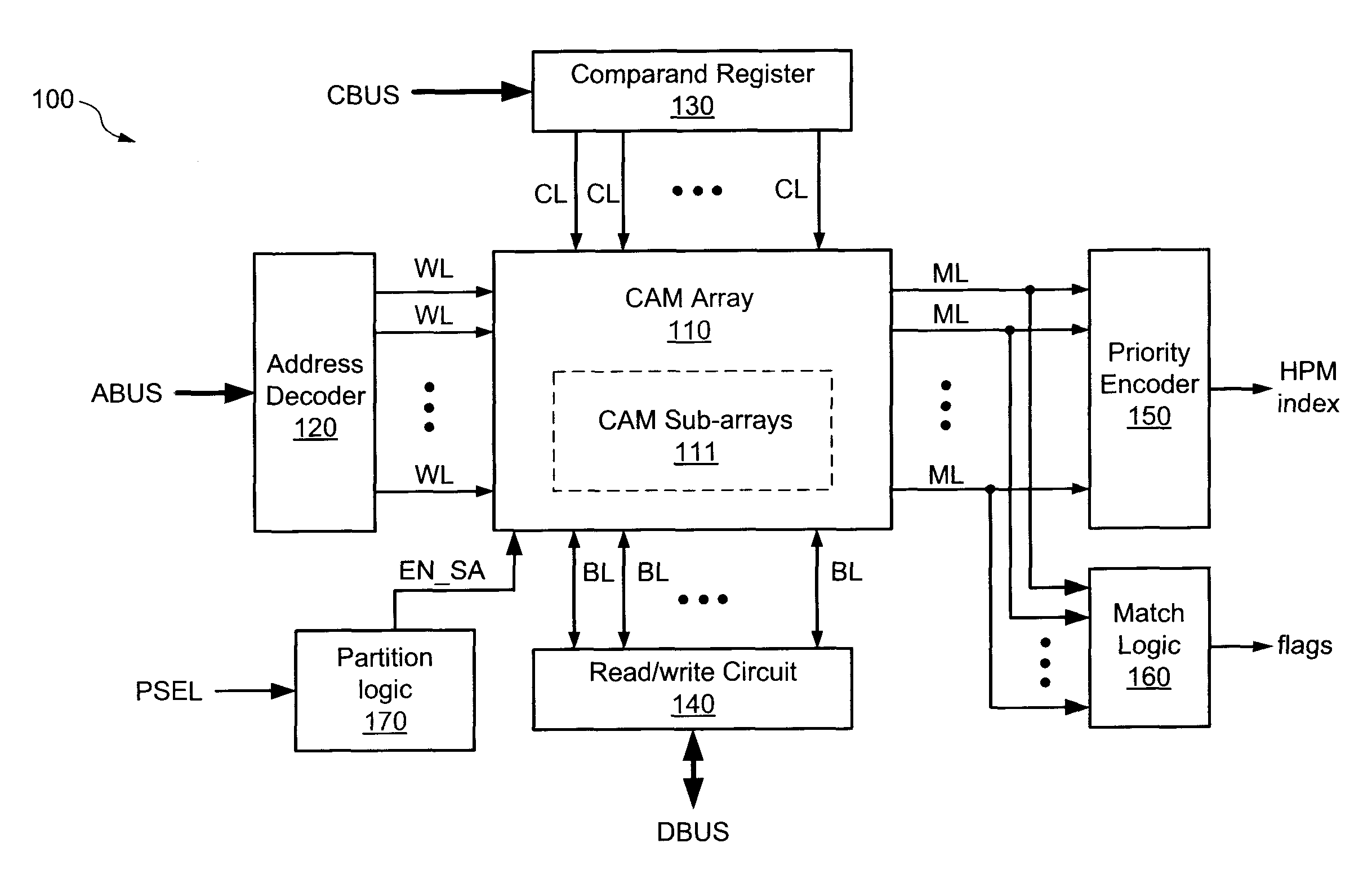

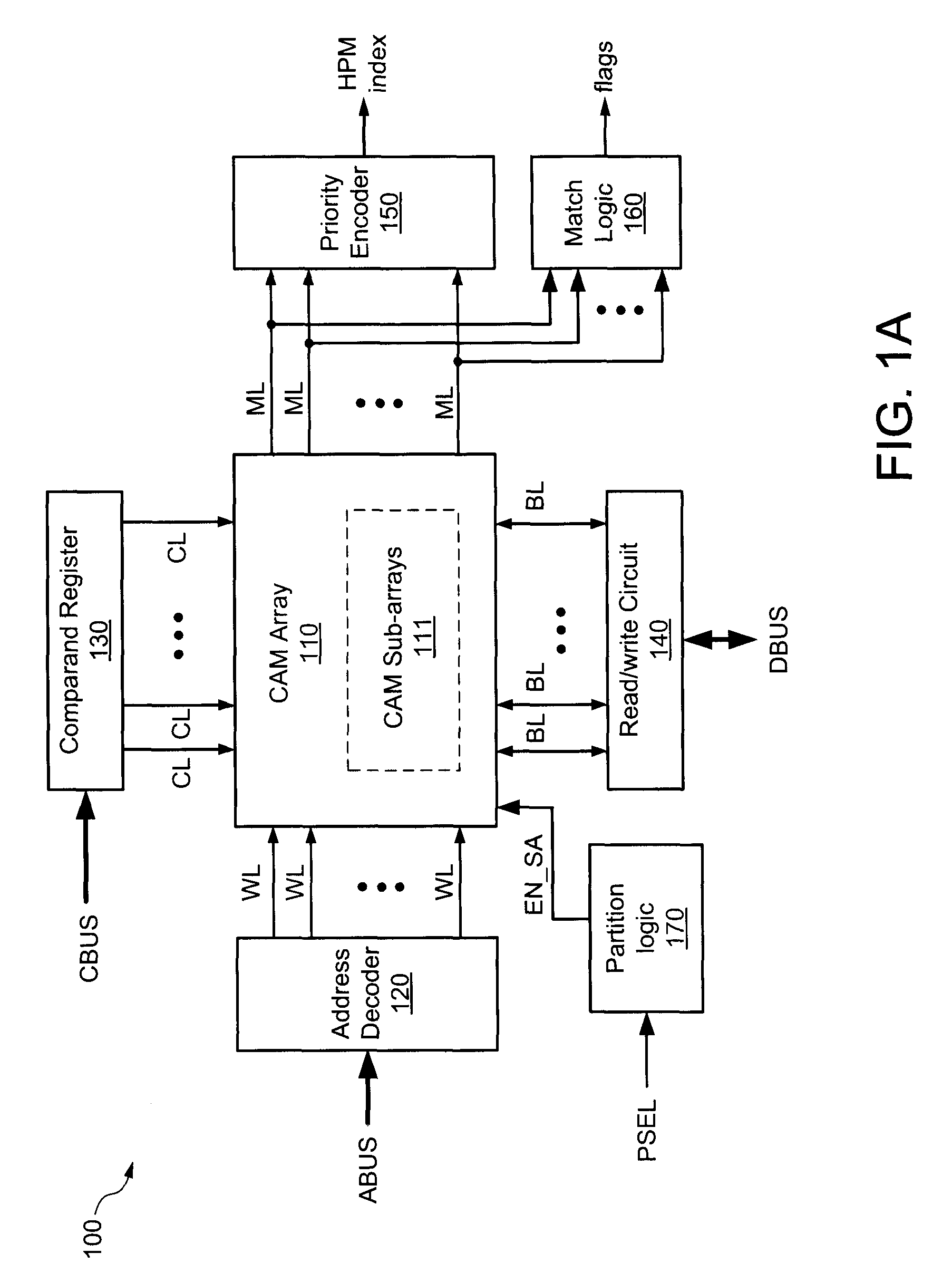

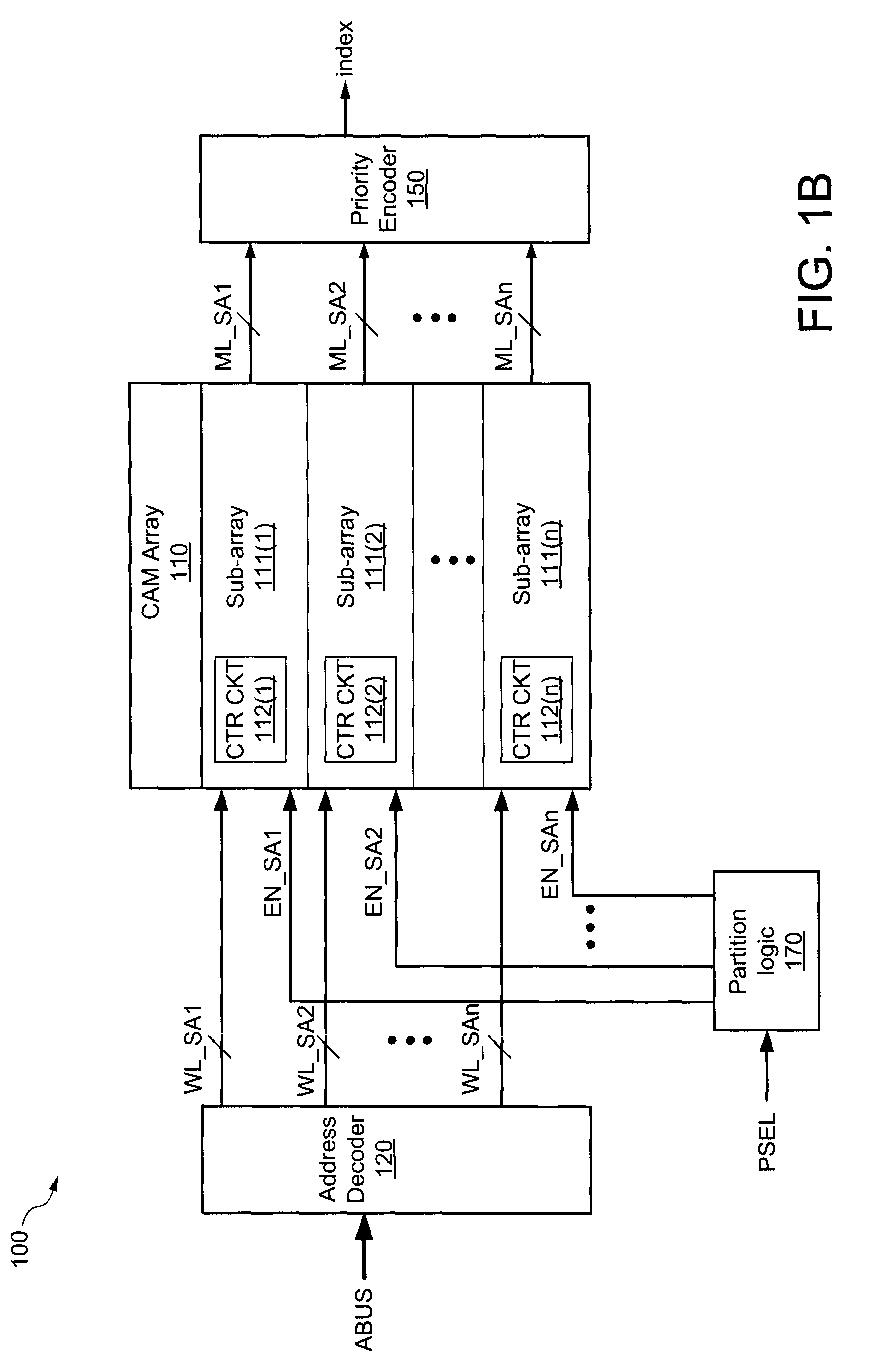

Dynamically partitioned CAM array

A content addressable memory (CAM) device includes a comparand register, a CAM array, and partition logic. The comparand register has inputs to receive a search key, and outputs coupled to the CAM array, which includes a plurality of individually selectable sub-arrays. Each sub-array includes a number of rows of CAM cells and a control circuit, wherein each row of CAM cells is coupled to a match line, and wherein the control circuit has an input to receive a corresponding sub-array enable signal. The partition logic has an input to receive a partition select signal, and is configured to generate the sub-array enable signals in response to the partition select signal. The control circuits selectively propagate the search key through the sub-arrays in response to the sub-array enable signals.

Owner:AVAGO TECH INT SALES PTE LTD

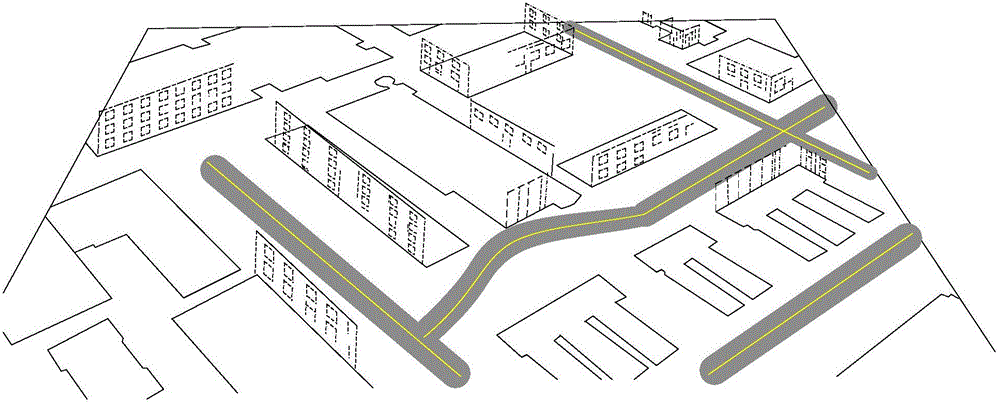

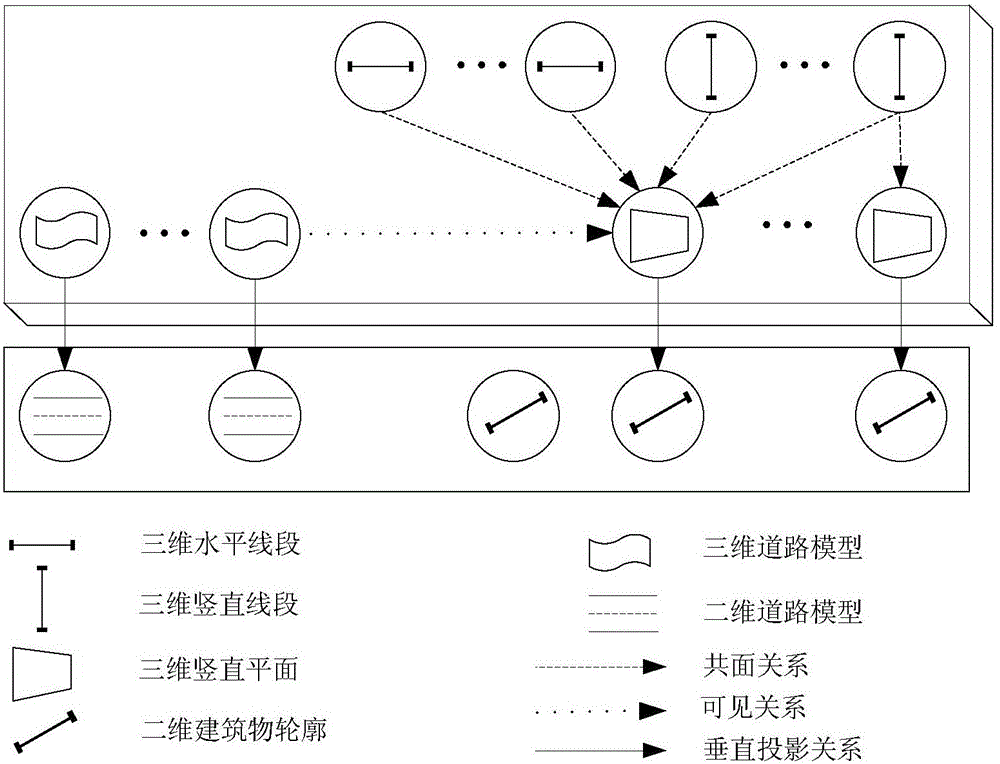

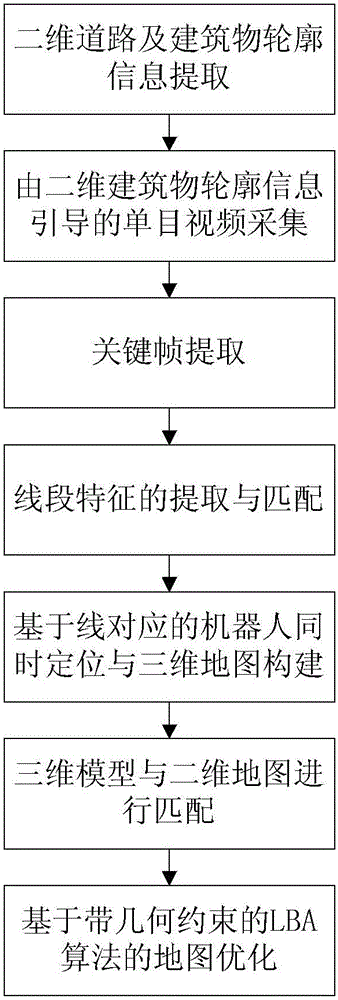

Method for automatically generating geographic maps for large-range complex urban environment

ActiveCN105096386AExpand the scope of applicable scenariosImprove robustness3D modellingBundle adjustmentVideo image

A method for generating geographic maps for large-range complex urban environment includes extracting two-dimensional roads and two-dimensional building contour information, generating a two-dimensional geographic map; a monocular PTZ camera, under the guidance of the two-dimensional geographic map, conducting video acquisition and obtaining video images; extracting key frames from the video images, extracting line segment characteristics of matching adjacent key frames to obtain line segment correspondence, positioning and establishing an environment three-dimensional geographic model based on a mobile robot of matching line characteristics; matching a three dimensional geographic model and the two-dimensional geographic map, determining the corresponding relation between the two, and generating an enhanced city geographic map; and optimizing the enhanced city geographic map based on bundle adjustment algorithm with geometrical constraints. Compared with the prior art, the method is wide in application scope, high in robustness and precision, small in storage space needed, and low in cost.

Owner:成都圭目机器人有限公司

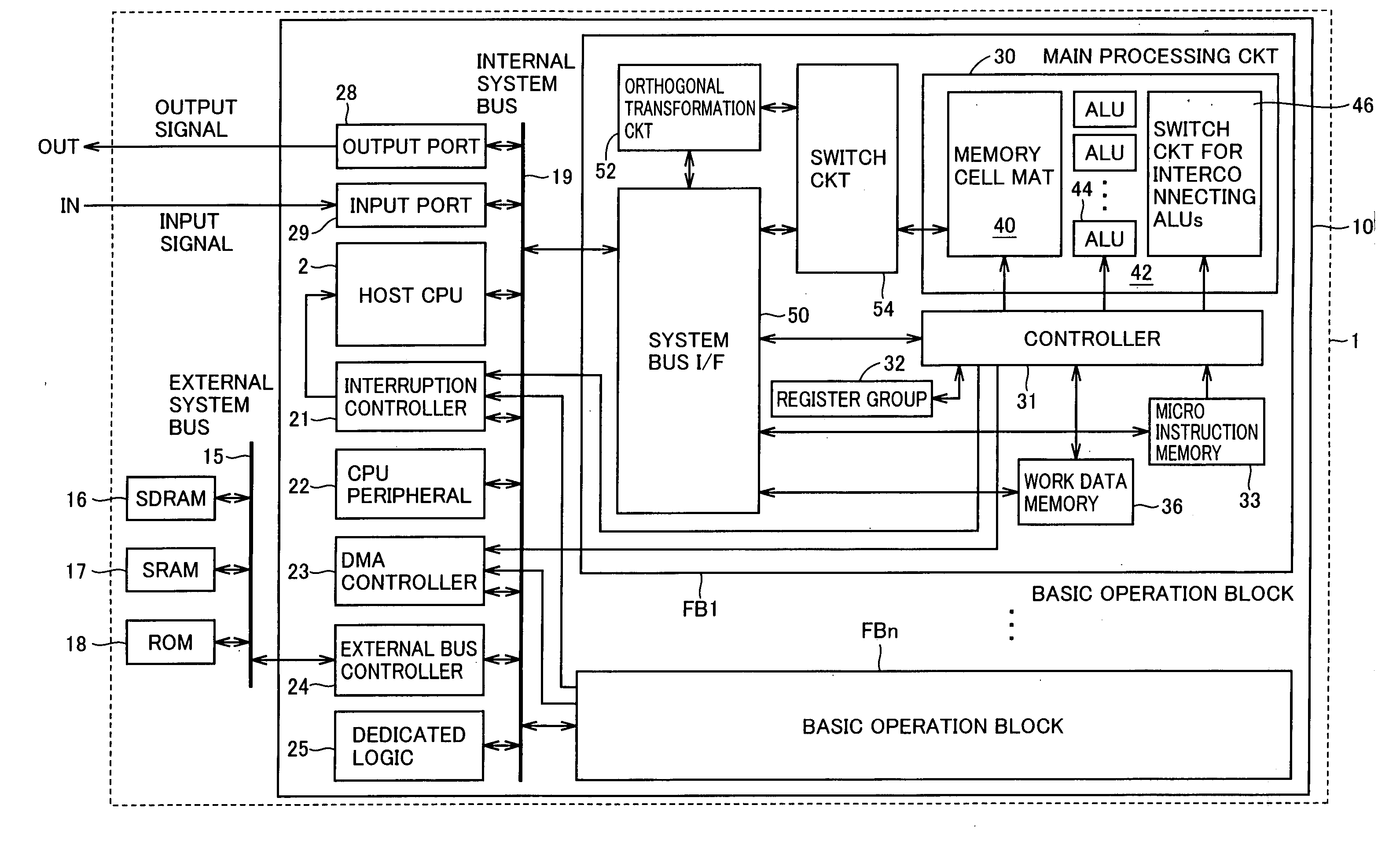

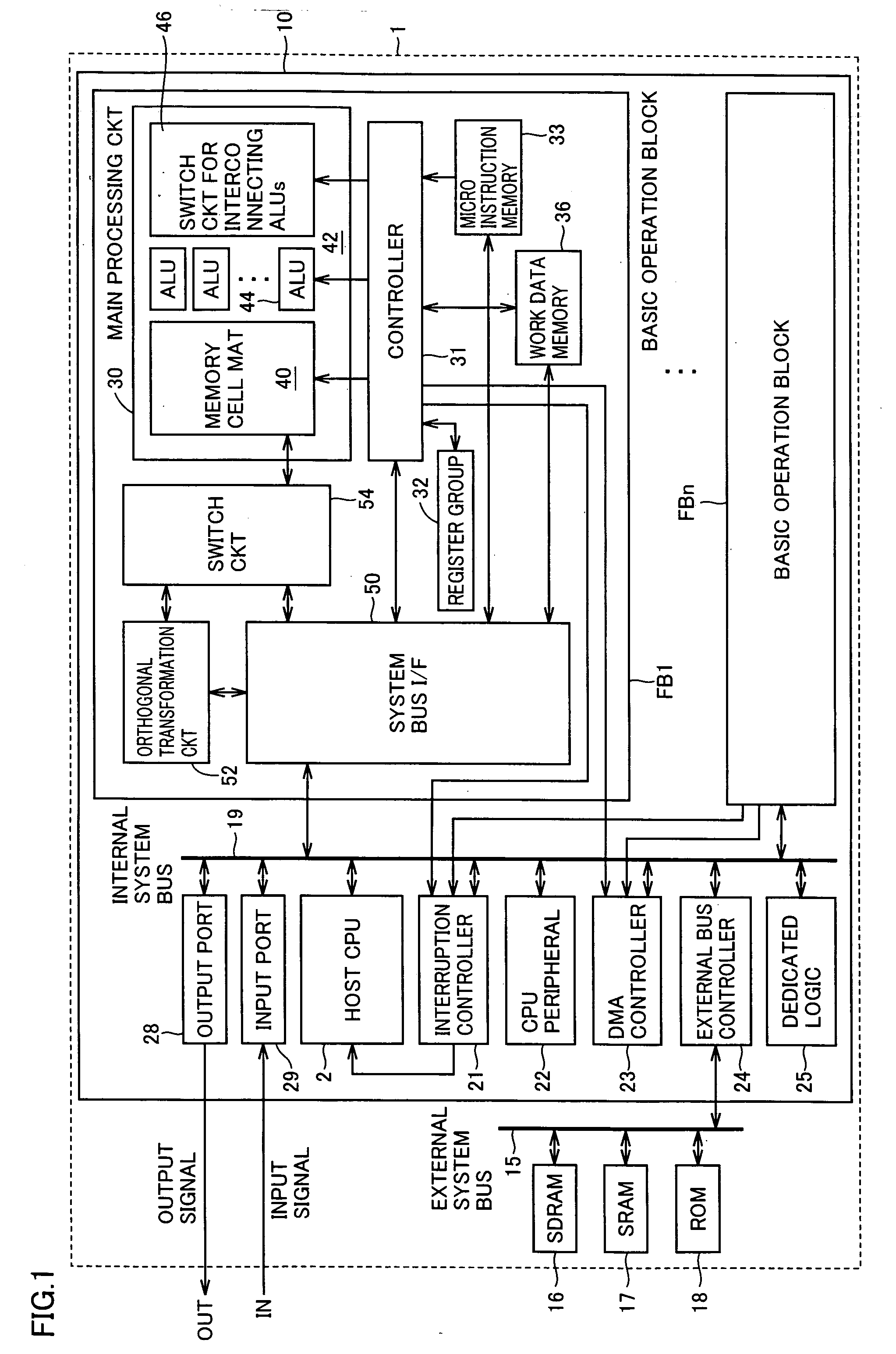

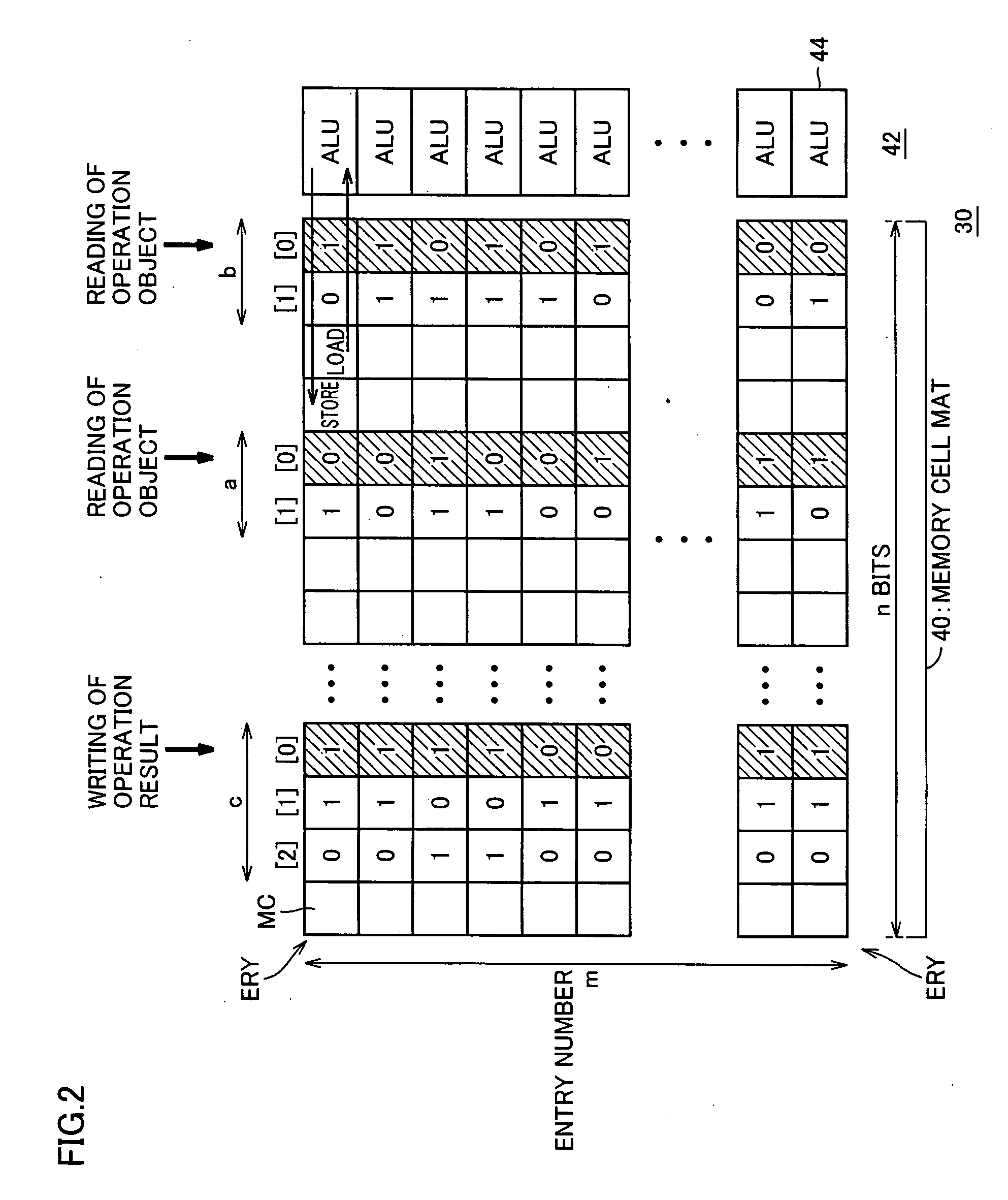

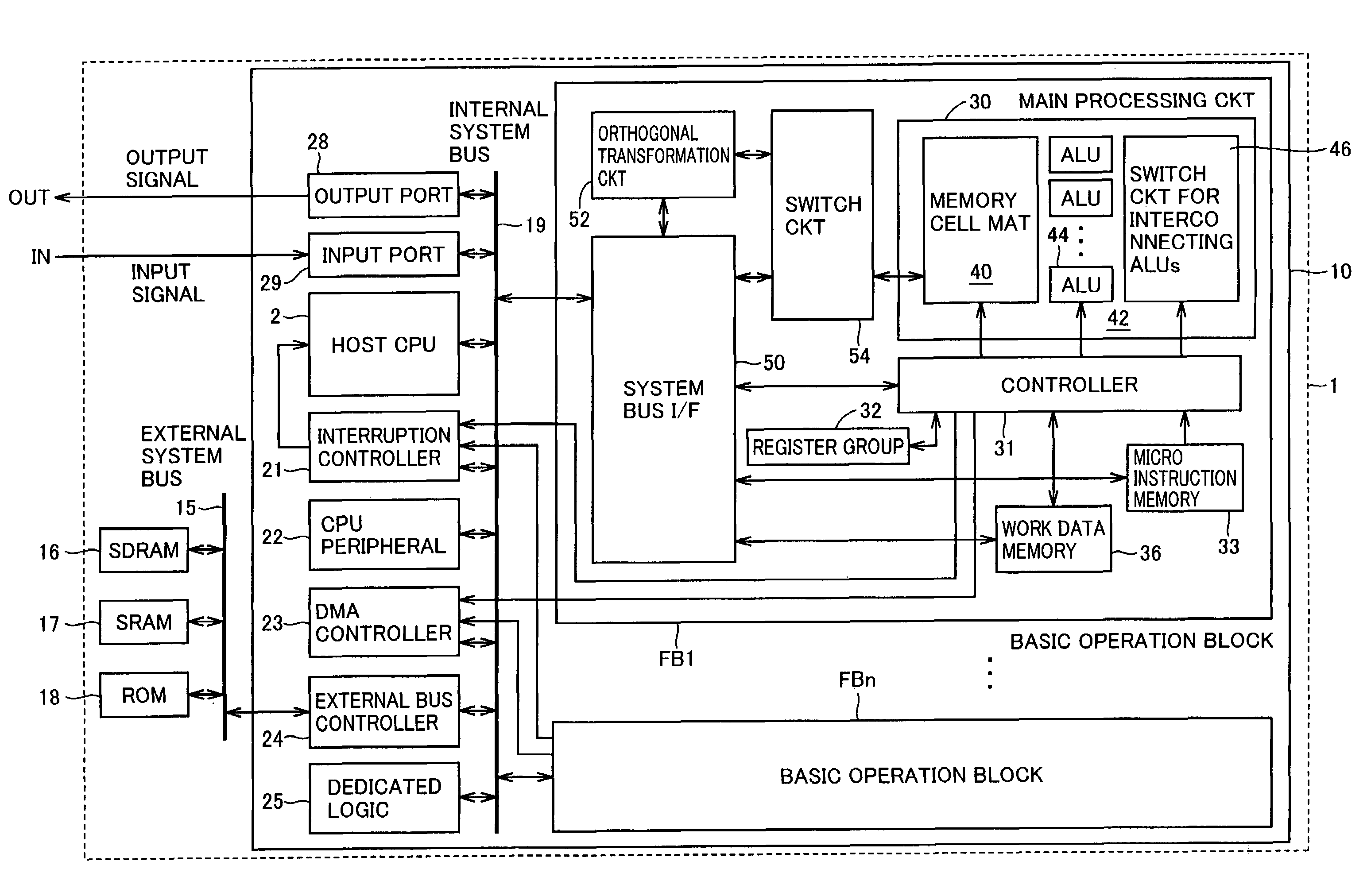

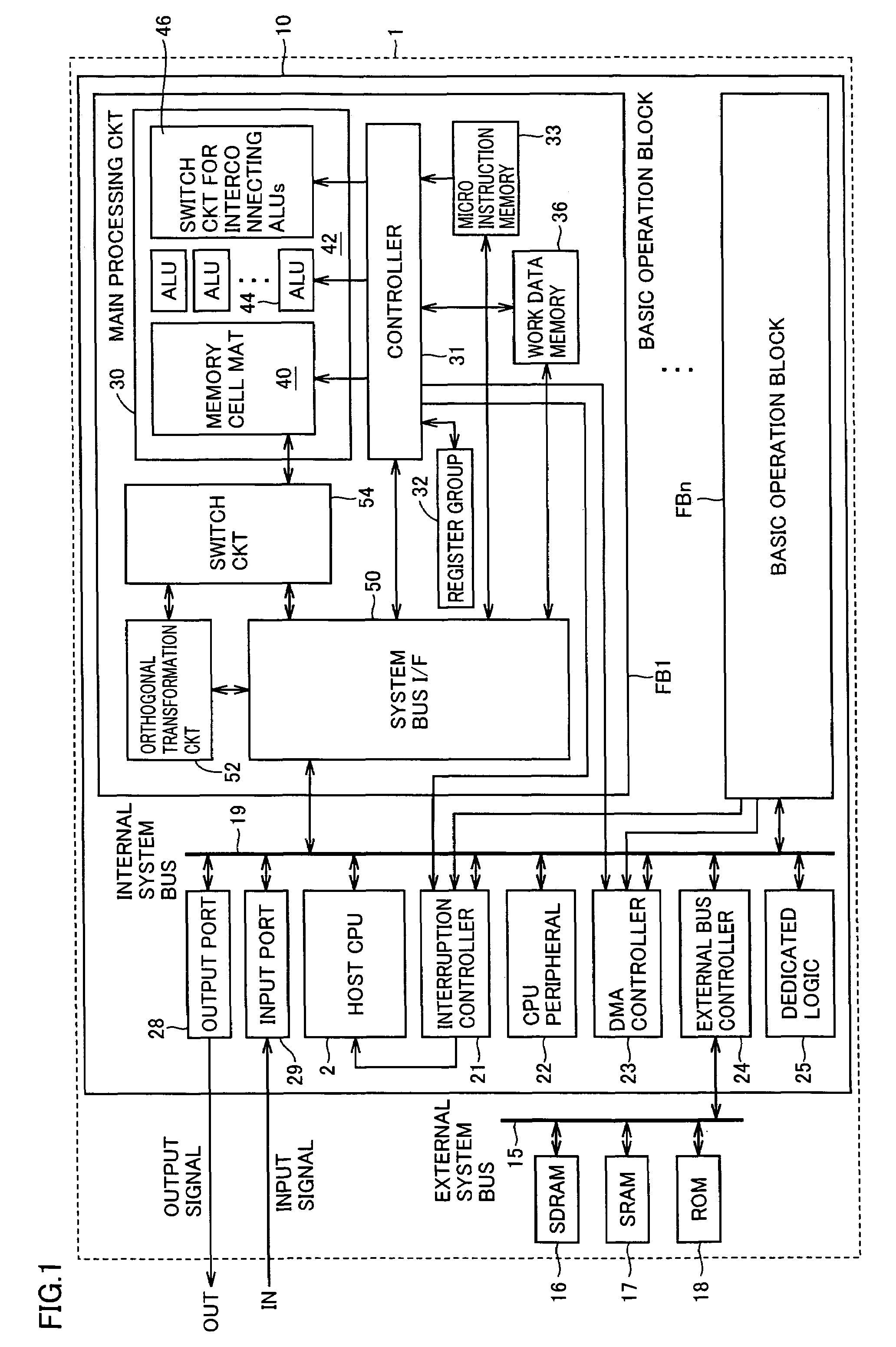

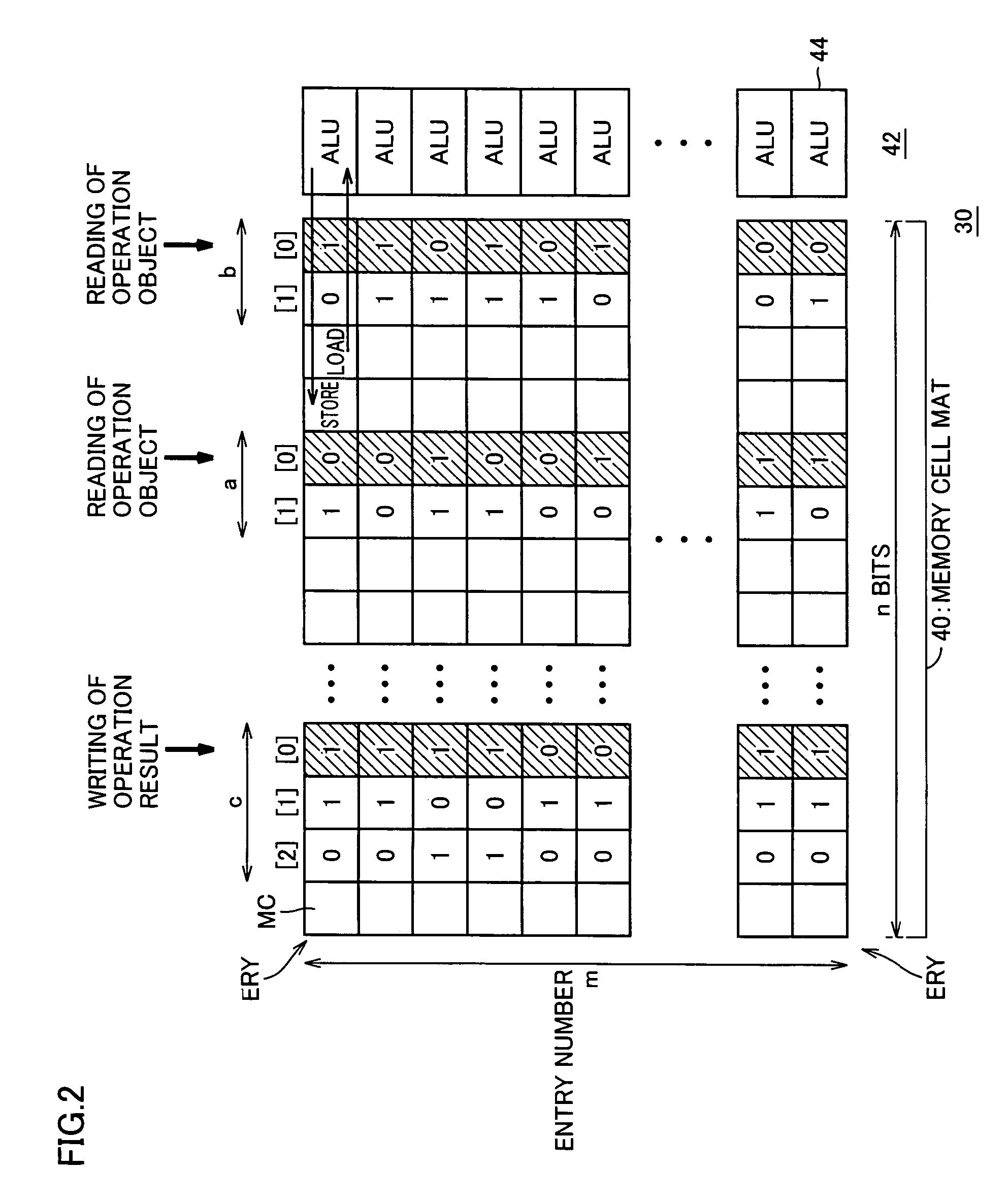

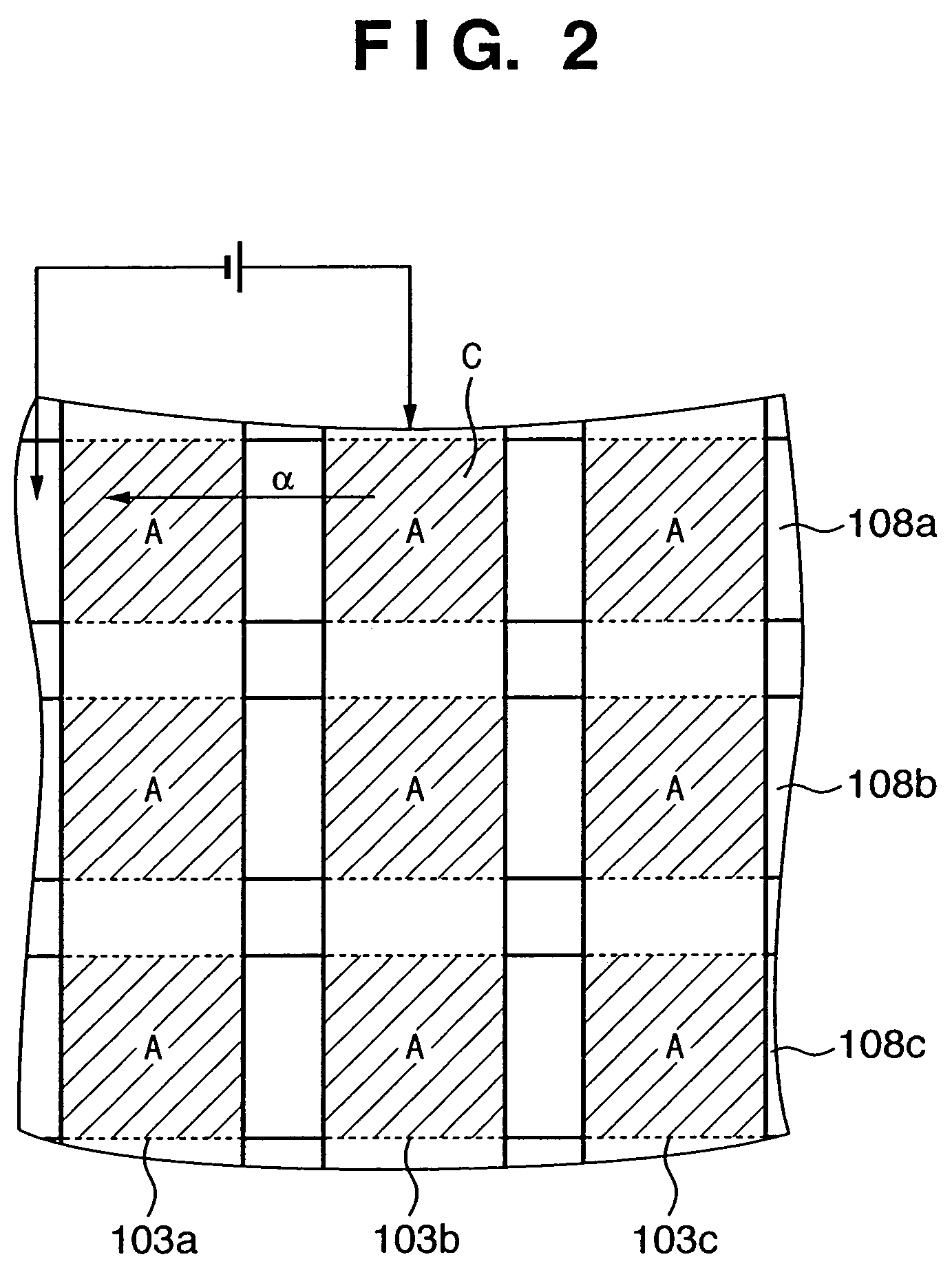

Semiconductor memory device

A CAM (Content Addressable Memory) cell includes first and second data storage portions storing data, horizontal port write gates for storing data applied through a match line pair in the data storage portions in a data write through a horizontal port, and search / read gates for driving the match lines of the match line pair in accordance with the data stored in the data storage portions in a search operation and in a data read through the horizontal port. The match lines are used as horizontal bit line pair, or signal lines for accessing the horizontal port. As the first and second data storage portions are used, it becomes possible to store ternary data, and accordingly, a write mask function of inhibiting a data write at a destination of data transfer is realized. Further, as the CAM cell is used, an arithmetic / logic operation following a search process can be executed selectively, and high speed data writing / reading becomes possible.

Owner:RENESAS ELECTRONICS CORP

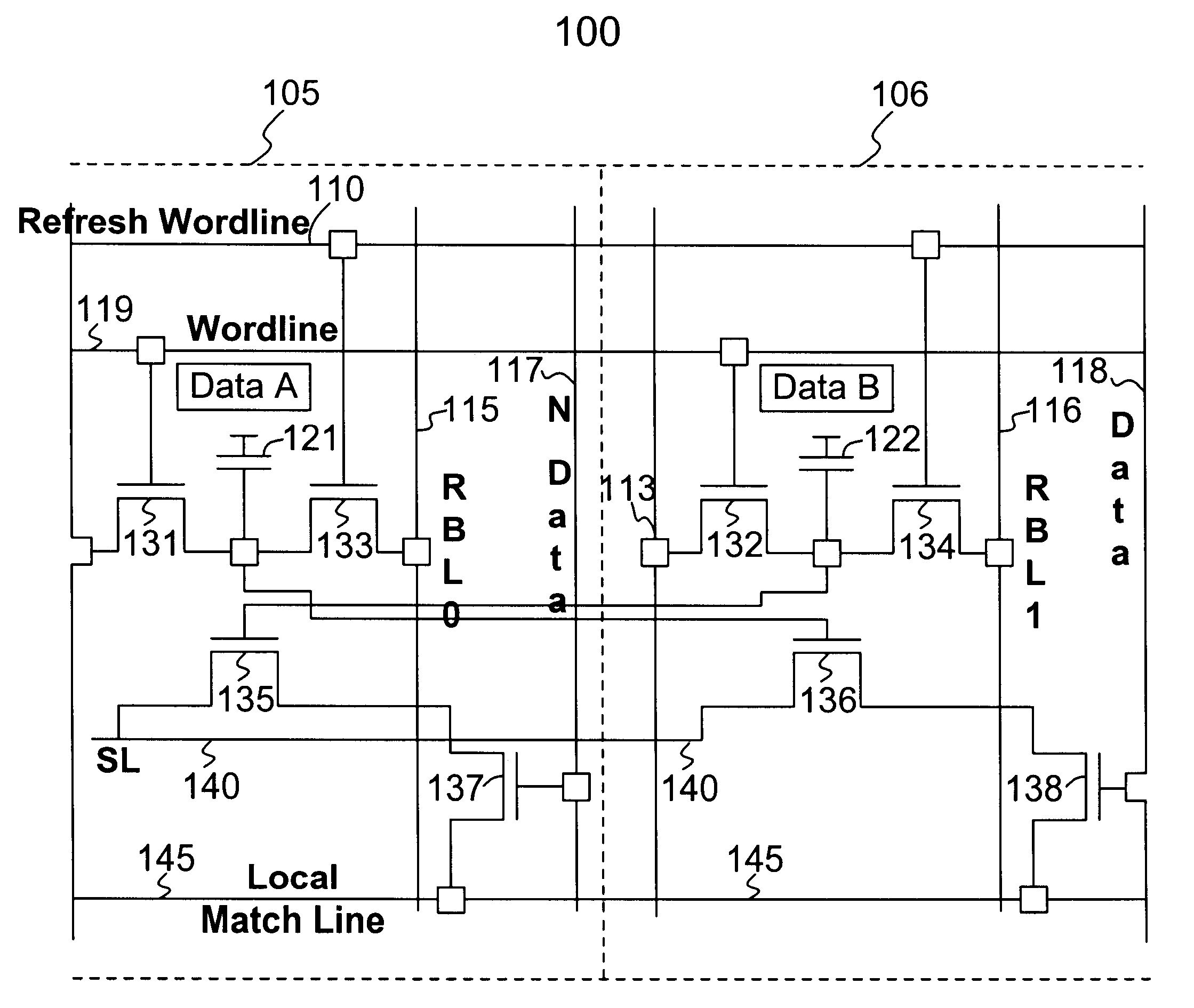

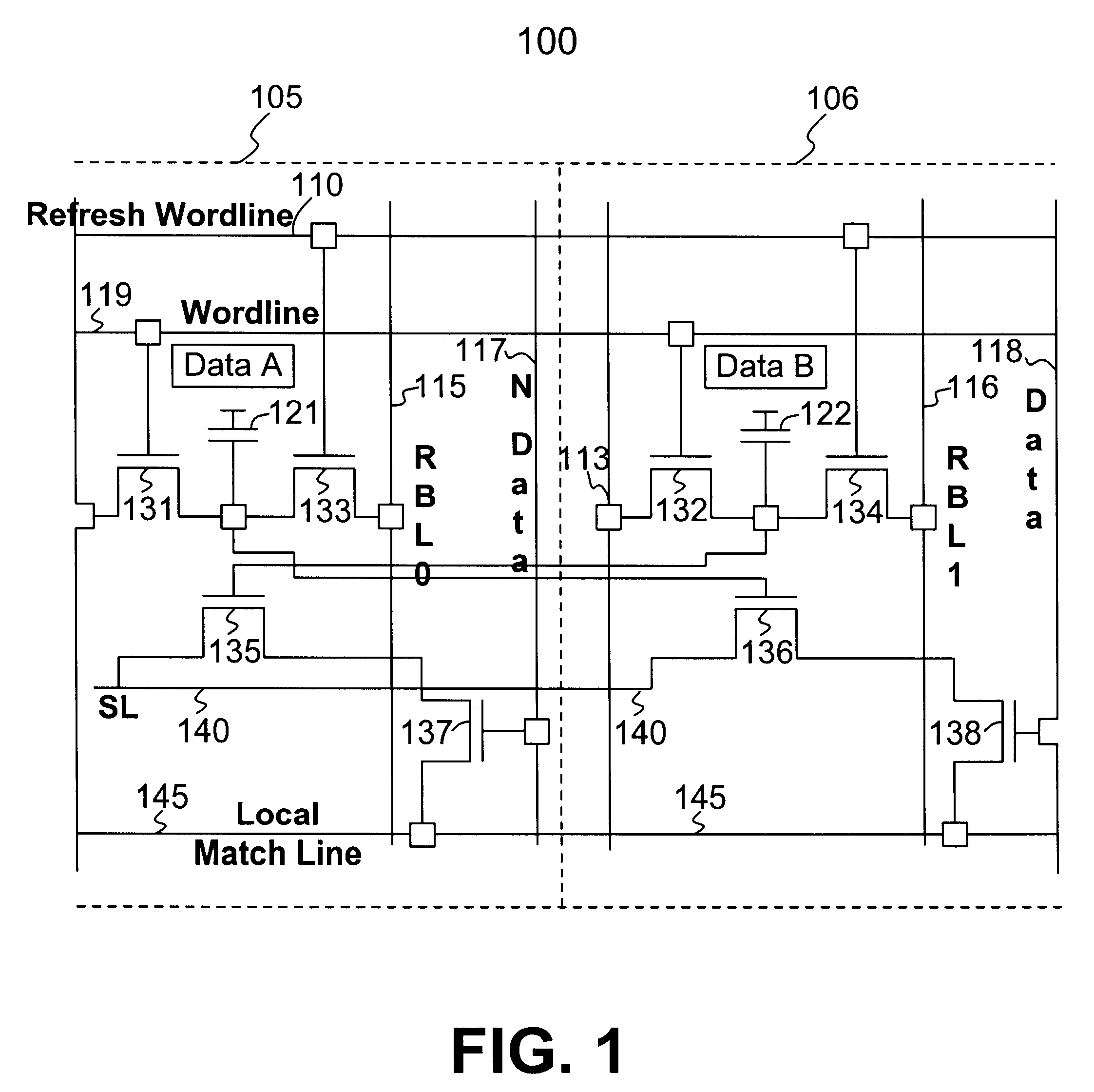

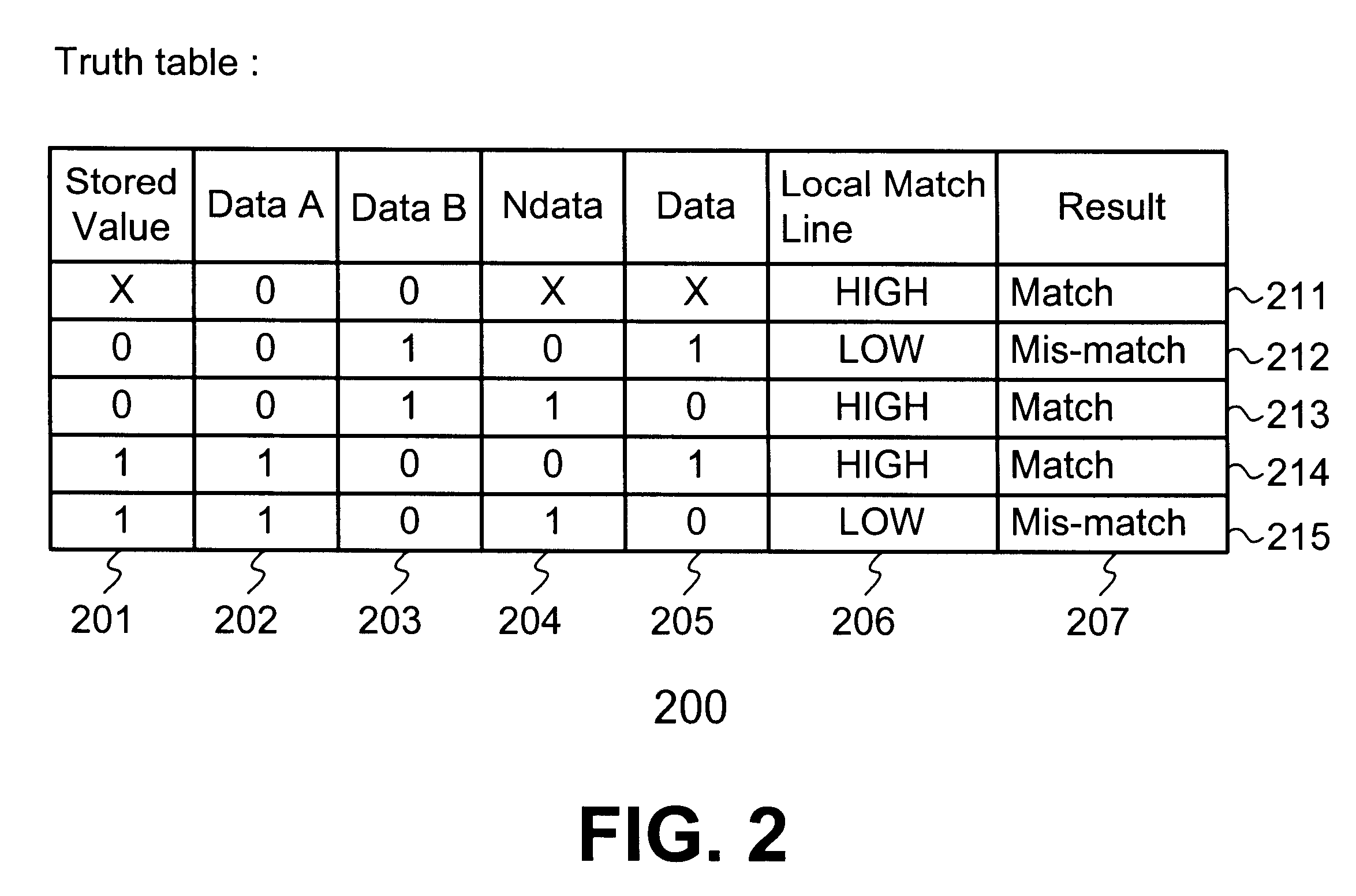

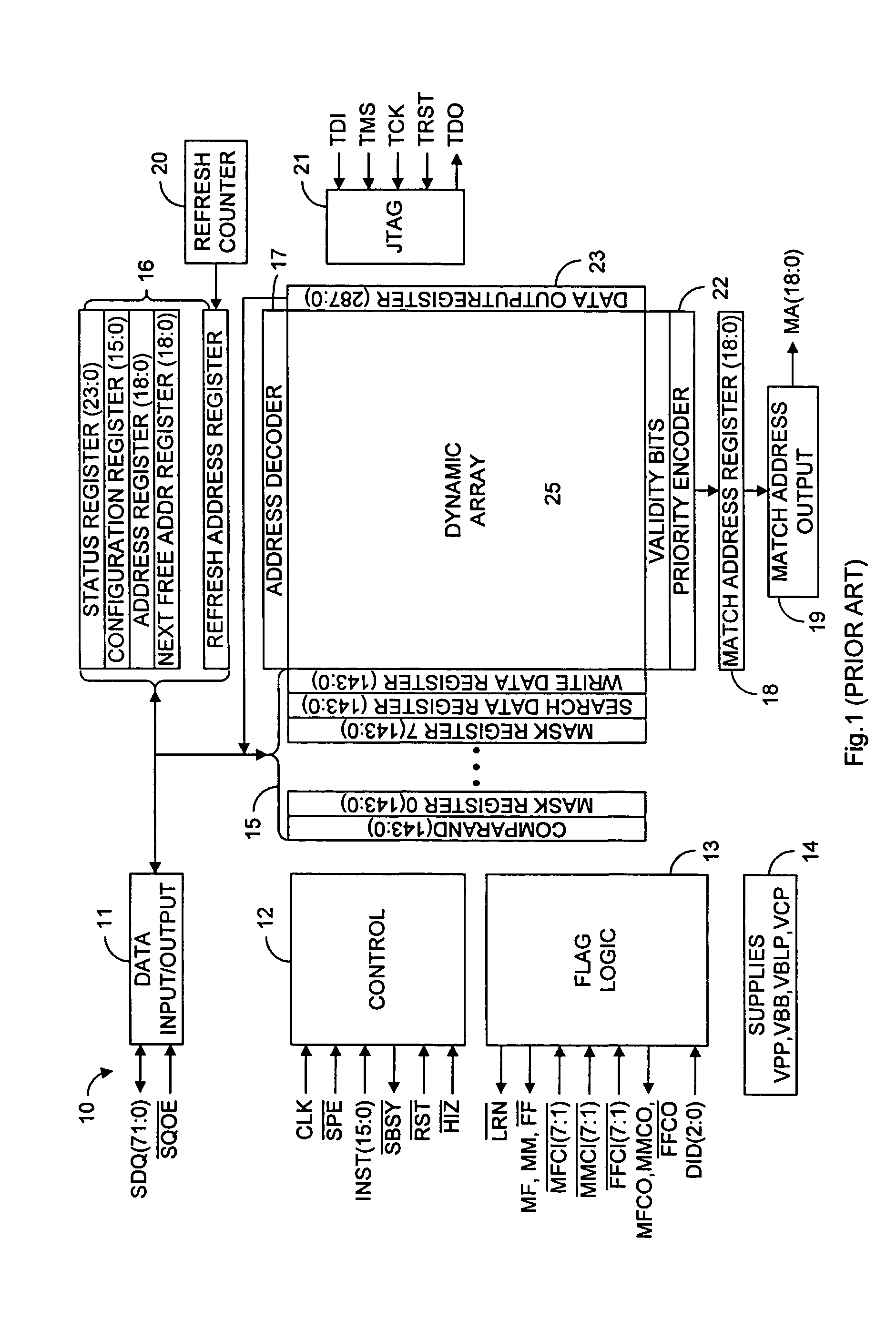

DRAM based refresh-free ternary CAM

A ternary state content addressable memory (CAM) cell that includes two DRAM cells. In addition to a port for controlling and transmitting data to the CAM, another port is exclusively used for refreshing the DRAM cells. A refresh word line is coupled to the two DRAM cells for performing DRAW cell refresh. A refresh bit line is coupled to the first of the two DRAM cells for refreshing this first DRAM cell. A refresh bit line is coupled to the second of the two DRAM cells for refreshing this second DRAM cell. Problematic power consumption and voltage swing found in a conventional CAM are overcome in the CAM. A swing line (SL) is coupled to said first and second DRAM cells and a local match line (LML) of said CAM cell, said SL having an adjustable voltage level for changing voltage swing in said LML to regulate trade-off between power consumption and speed of said CAM cell.

Owner:ATEL VENTURE FUND LLC

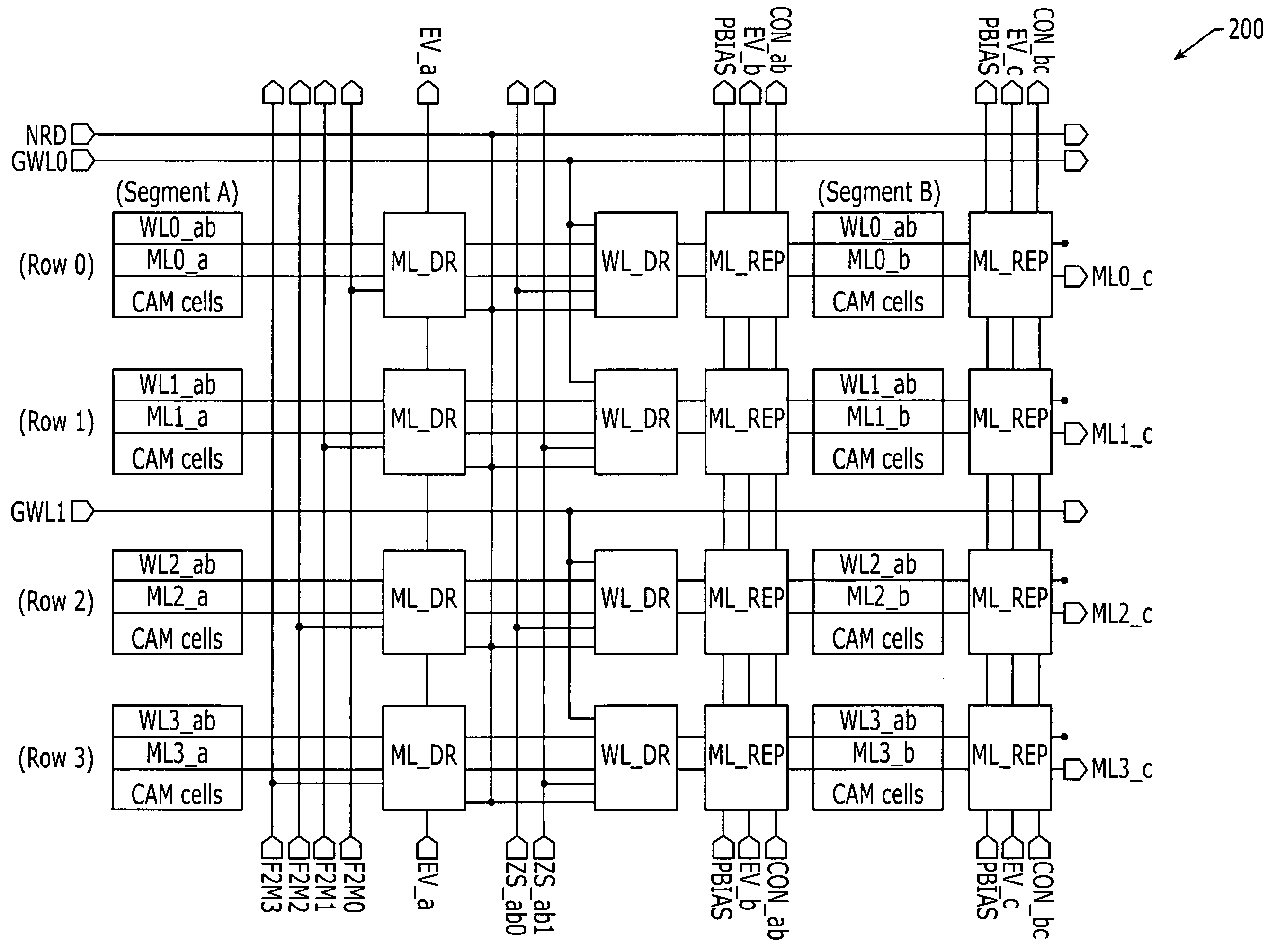

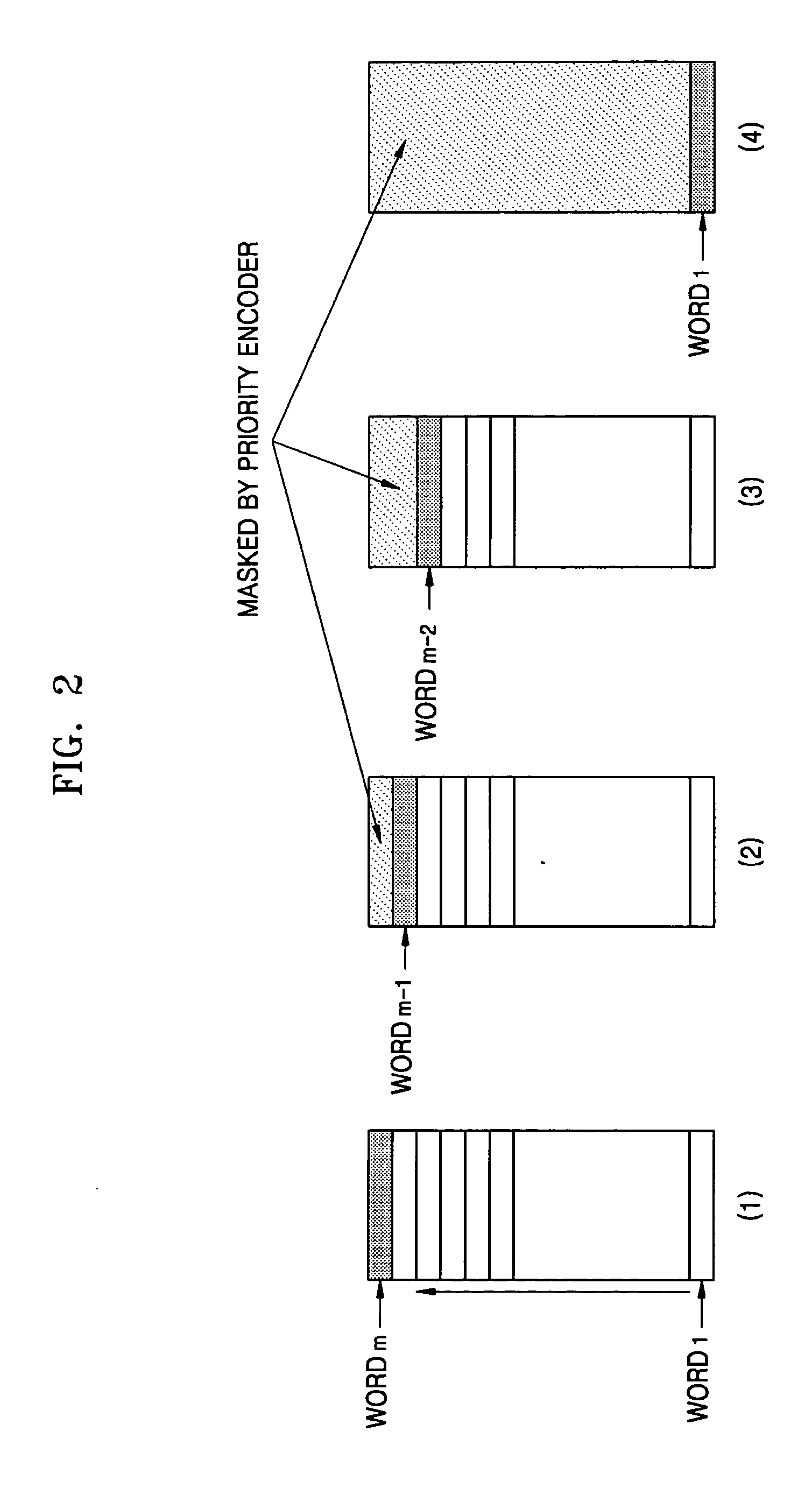

Content addressable memory (CAM) devices that utilize segmented match lines and word lines to support pipelined search and write operations and methods of operating same

InactiveUS6967856B1Correction errorIncrease speedDigital storageMemory systemsControl signalWord search

CAM devices include a segmented CAM array that is configured to support a long word search operation (e.g., x8N search) as a plurality of overlapping segment-to-segment search operations that are each performed across different rows within a group of rows in the CAM array and staggered in time relative to one another. To provide enhanced soft error immunity, these CAM devices may also include a CAM array having a row of lateral XY TCAM cells therein that are arranged in a repeating low-even, low-odd, high-even, high-odd sequence, where “low” and “high” represent the first and second halves of a CAM entry. Methods of operating a CAM device may include staggering the timing of overlapping segment-to-segment search operations across different rows within a CAM array using force-to-miss control signals to establish miss conditions on match lines of rows that are not to participate in a respective ones of the segment-to-segment search operations.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

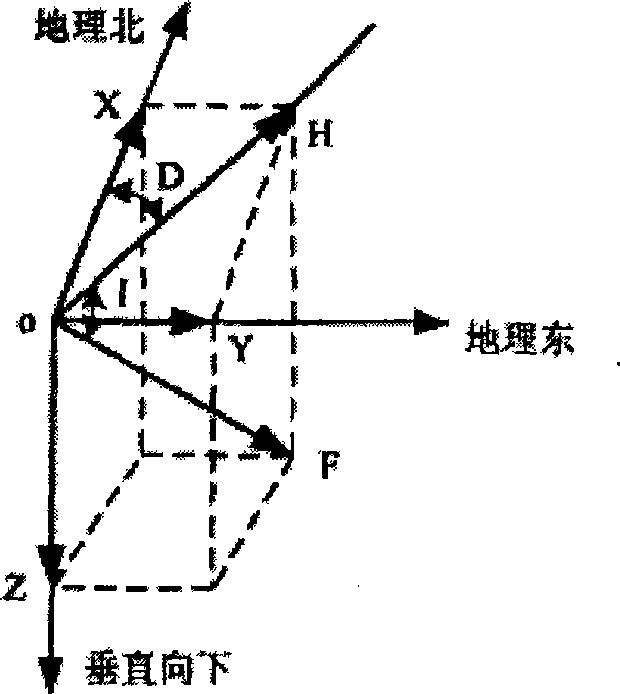

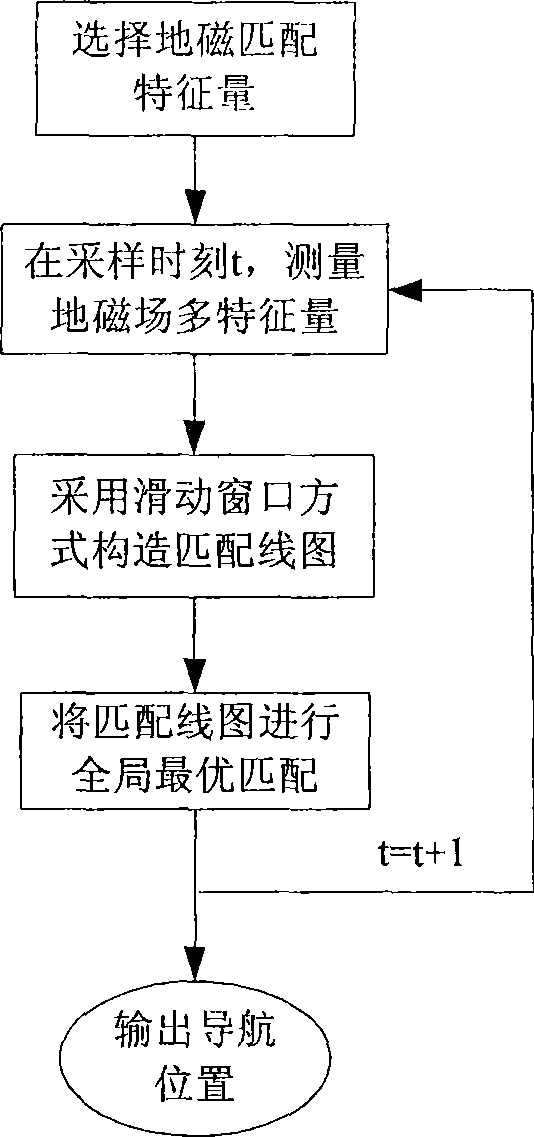

Method for autonomous navigation using geomagnetic field line map

InactiveCN101520328ATake advantage ofUsing multiple characteristic quantities of the geomagnetic field to jointly match fullyInstruments for comonautical navigationNavigation by terrestrial meansTerrainCruise missile

The invention discloses a method for autonomous navigation using a geomagnetic field line map. Firstly, a plurality of characteristic quantities of the geomagnetic filed on a path of an aerial vehicle are measured continuously according to a preset frequency, and measurement data are used to build a matched line map of the corresponding characteristic quantities in a sliding window mode with fixed-point number; and a matched line map of the plurality of characteristic quantities is matched and compared with a reference map by using an algorithm for fining global optimum according to a matching similarity rule and a matching result fusion rule to acquire the position information of the aerial vehicle. The technology makes full use of the characteristics of the plurality of characteristic quantities of the geomagnetic field to calculate the accurate position of the aerial vehicle, avoids navigation accumulated error under a condition of long flight period, is particularly suitable for navigation in environments without typical geomorphic features such as ocean and plain, can meet requirements of future cruise missiles, unmanned aerial vehicles, submarines and the like for passive, all-sky time, all-weather and all-terrain navigation, and also can be used in civil area.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Content addressable memory (CAM) capable of finding errors in a CAM cell array and a method thereof

A method of finding errors in a content addressable memory (CAM) and a CAM cell array, the CAM being capable of finding errors in the CAM cell array, is disclosed. The CAM includes the CAM cell array having a plurality of CAM cells and a match line state storing unit. The match line state storing unit is connected to a word line and a match line of the plurality of CAM cells and has a plurality of state cells in which a logic level of stored data is changed according to a logic level of the match line. Errors in the CAM cell array are found by reading data stored in the plurality of state cells. The data stored in the plurality of state cells are matched when there are no errors in the CAM cell array.

Owner:SAMSUNG ELECTRONICS CO LTD

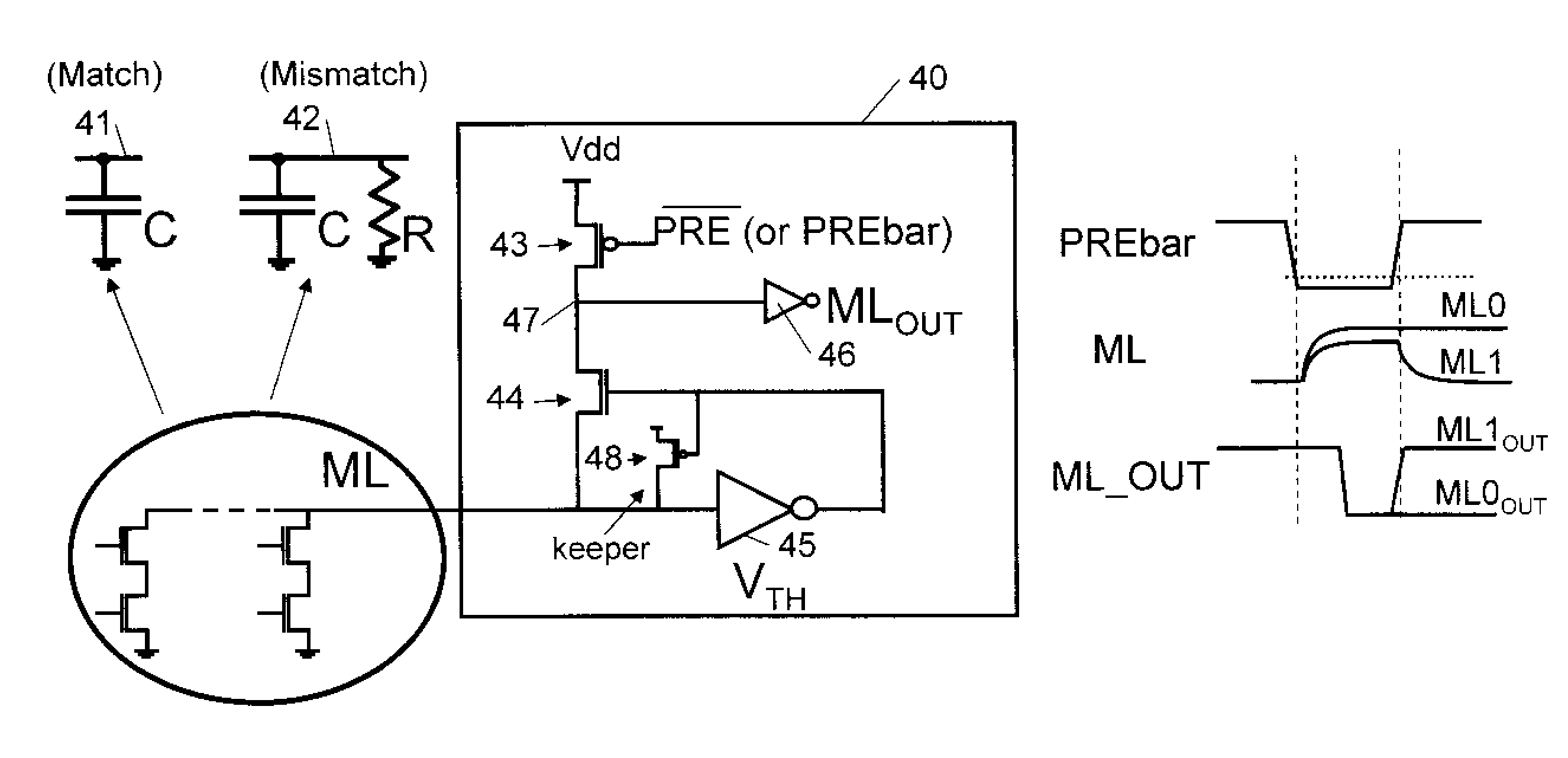

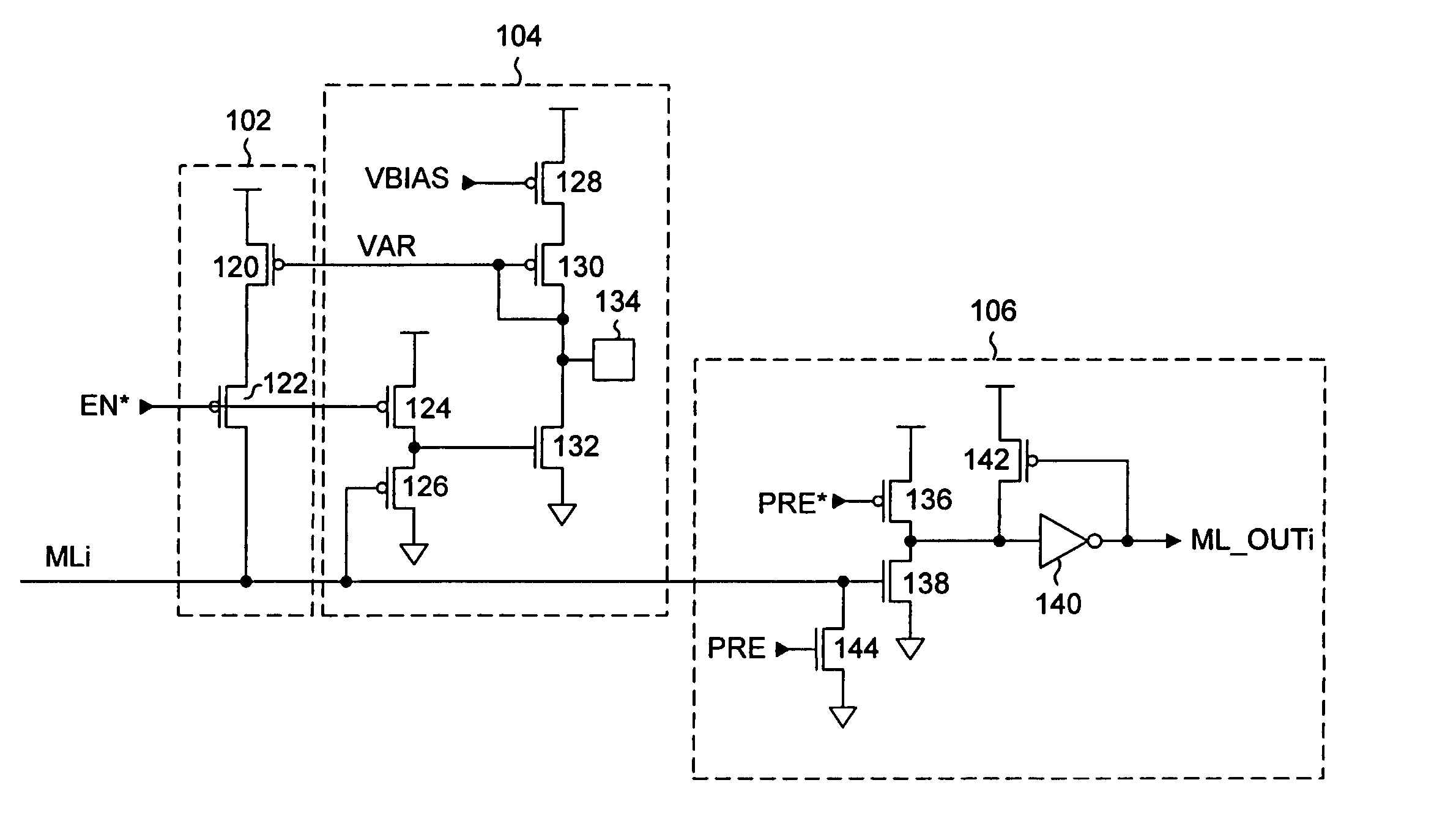

Mismatch-dependent power allocation technique for match-line sensing in content-addressable memories

A low power matchline sensing scheme where power is distributed according to the number of mismatching bits occurring on a matchline is disclosed. In particular, match decisions involving a larger number of mismatched bits consume less power compared to match decisions having a lesser number of mismatched bits. The low power matchline sensing scheme is based upon a precharge-to-miss sensing architecture, and includes a current control circuit coupled to each matchline of the content addressable memory array for monitoring the voltage level of the matchline during a search operation. The current control circuit provides a voltage control signal to the current source of the matchline to adjust the amount of current applied to the matchline in response to the voltage of the matchline. In otherwords, matchlines that are slow to reach the match threshold voltage due to the presence of one or more mismatching bits will receive less current than matchlines having no mismatching bits. Significant power reduction without compromising search speed is realized since matchlines carrying a match result are provided with the maximum amount of current.

Owner:CONVERSANT INTPROP MANAGEMENT INC

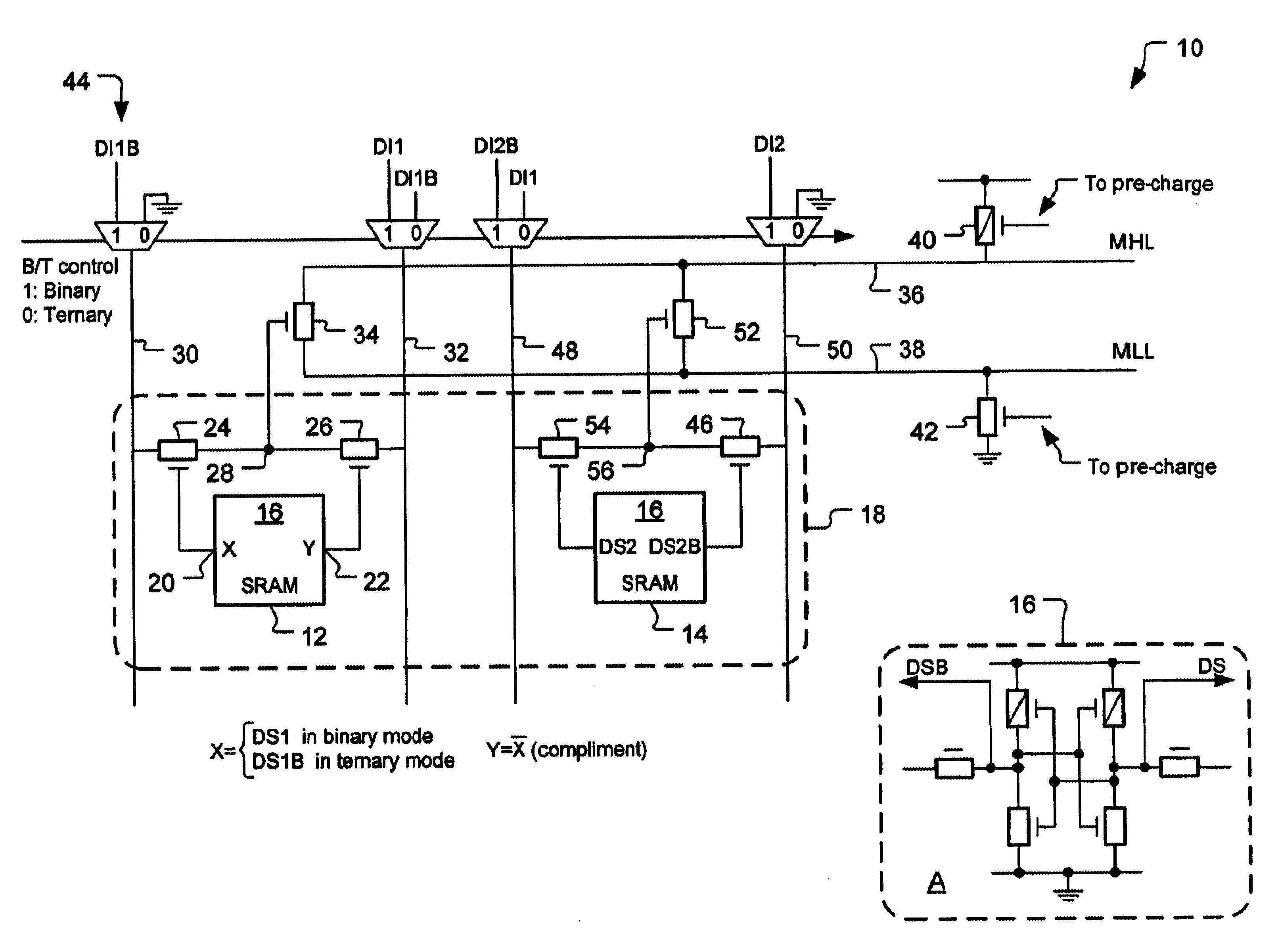

Dual match-line, twin-cell, binary-ternary CAM

Owner:CONVERSANT INTPROP MANAGEMENT INC

High-speed and low-power differential non-volatile content addressable memory cell and array

A differential non-volatile content addressable memory array has a differential non-volatile content addressable memory cell which uses a pair of non-volatile storage elements. Each of the non-volatile storage elements can be a split-gate floating gate transistor or a stack gate floating gate transistor having a first terminal, a second terminal, a channel therebetween and a floating gate over at least a portion of the channel to control the conduction of electrons in the channel, and a control gate. The floating gate storage transistor can be in one of two states: a first state, such as erase, in which current can flow between the first terminal and the second terminal, and a second state, such as programmed, in which substantially no current flows between the first terminal and the second terminal. A pair of differential compare data lines connects to the control gate of each of the pair of non-volatile floating gate transistors. A match line connects to the first terminal of each of the pair of non-volatile floating gate transistors to a first voltage. Finally, the second terminals of each storage element is connected to a second voltage, different from the first voltage. A current passing through the memory cell is indicative of a mis-match between the contents of the compare data lines and the contents of the storage elements.

Owner:SILICON STORAGE TECHNOLOGY

Thyristor-based content addressable memory (CAM) cells

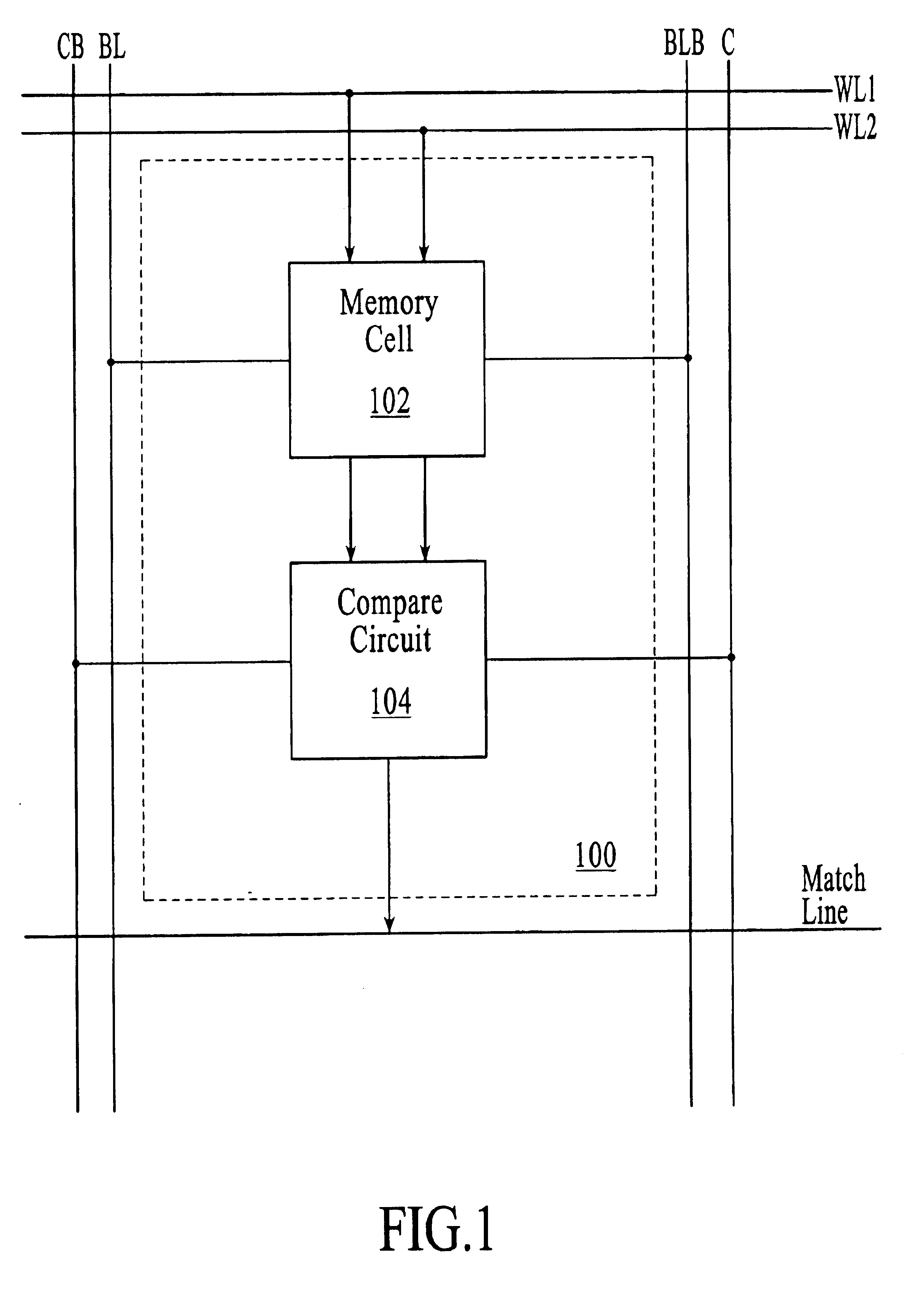

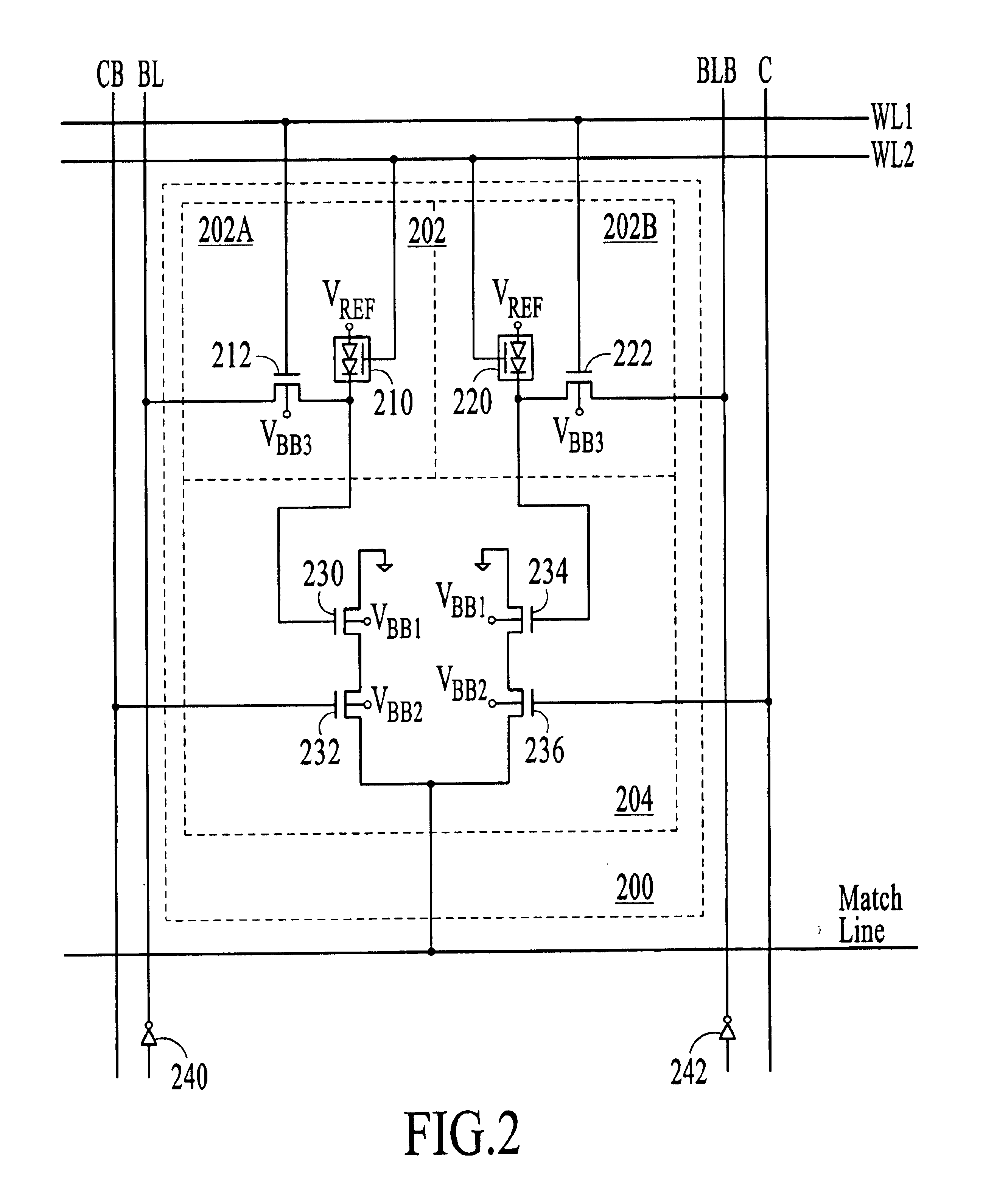

A content addressable memory (CAM) cell includes a memory cell storing data values. The memory cell includes a surrounding-gate thyristor and an access transistor. The CAM cell also includes a compare circuit coupled among the memory cell and a match line. The compare circuit receives data and comparand data and affects a logical state of a match line in response to a predetermined relationship between the data and comparand data. The compare circuit includes a first transistor set coupled for conduction state control by signals representative of the data, and a second transistor set coupled for conduction state control by signals representative of the comparand data.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

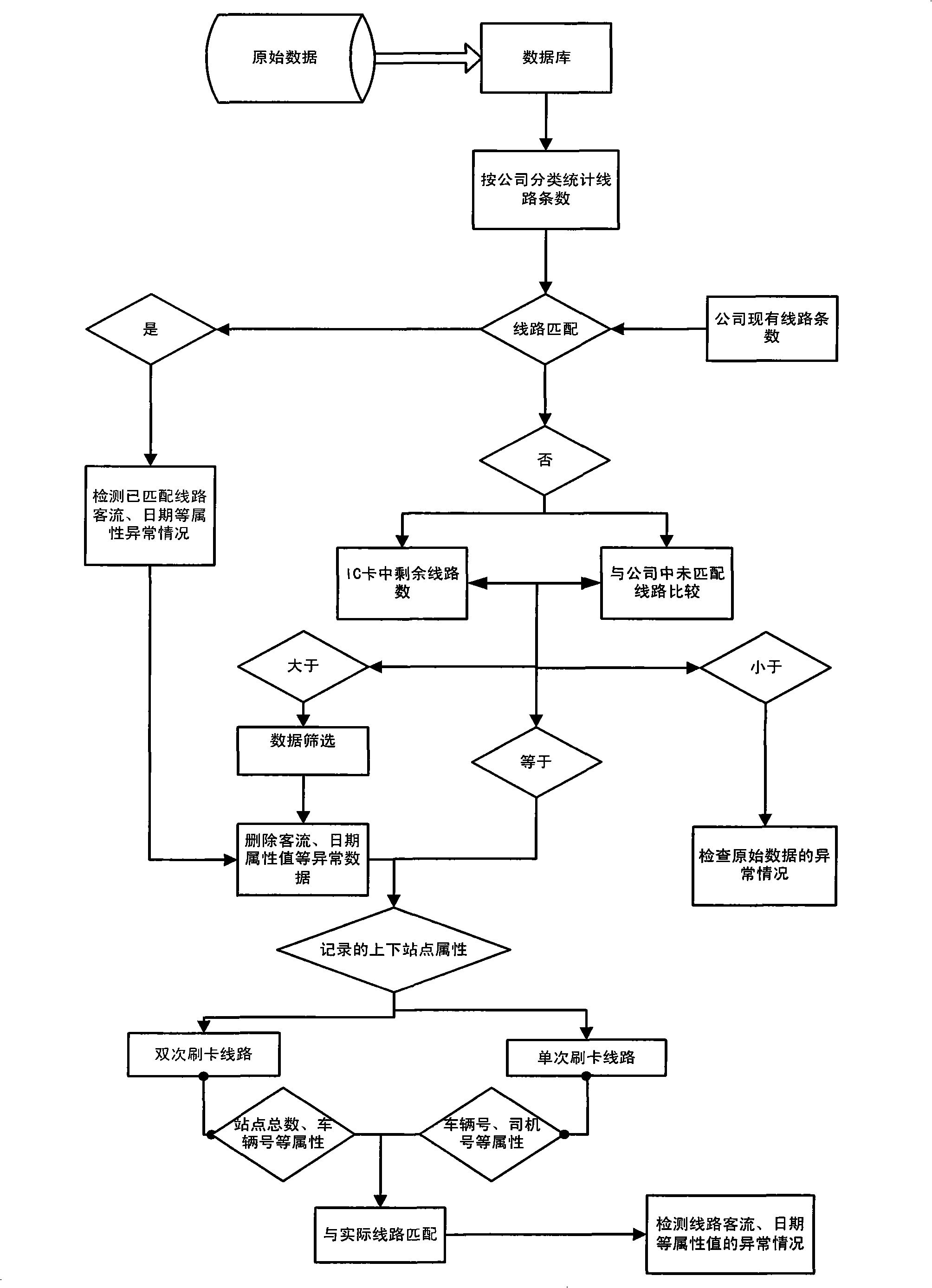

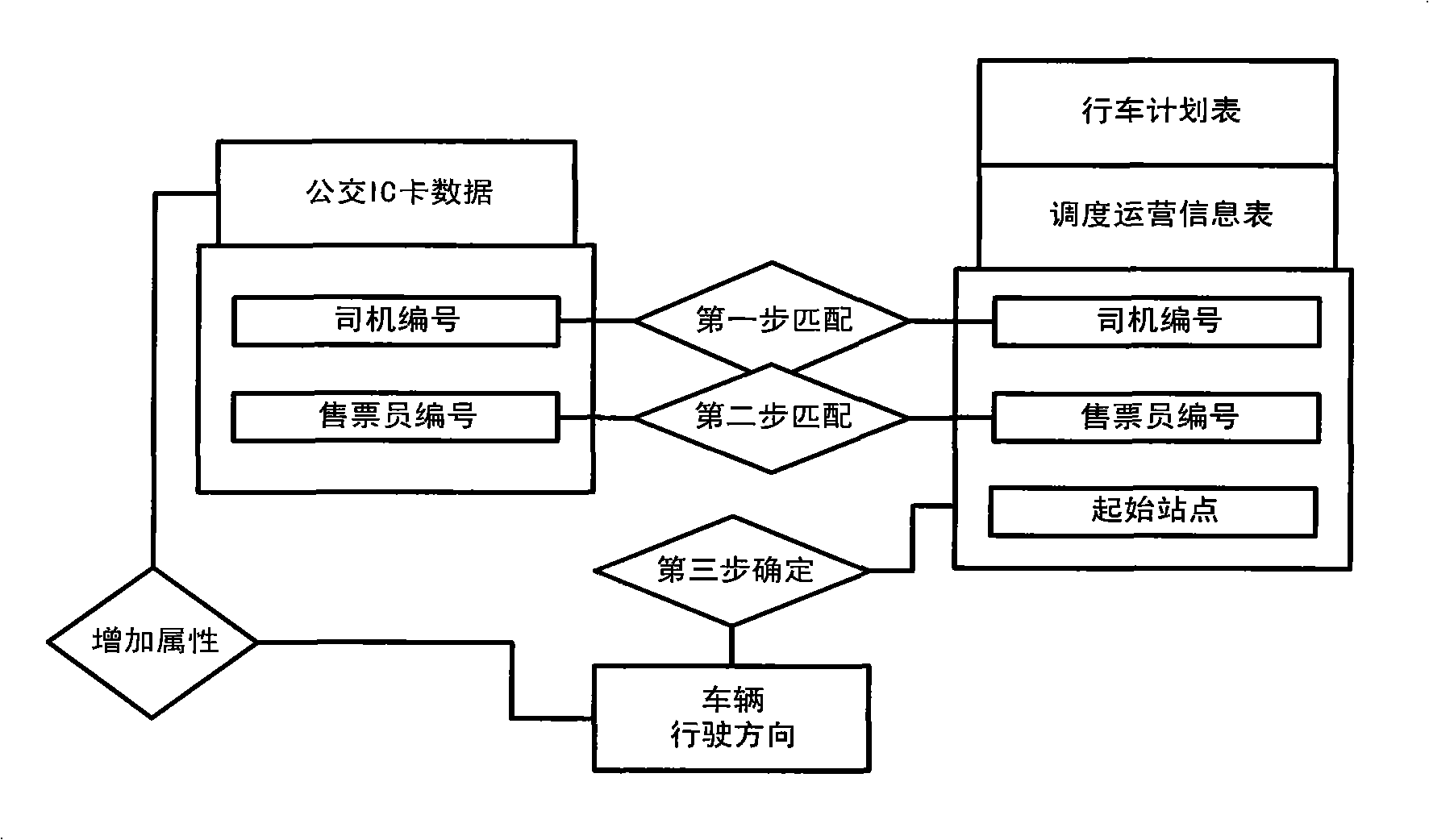

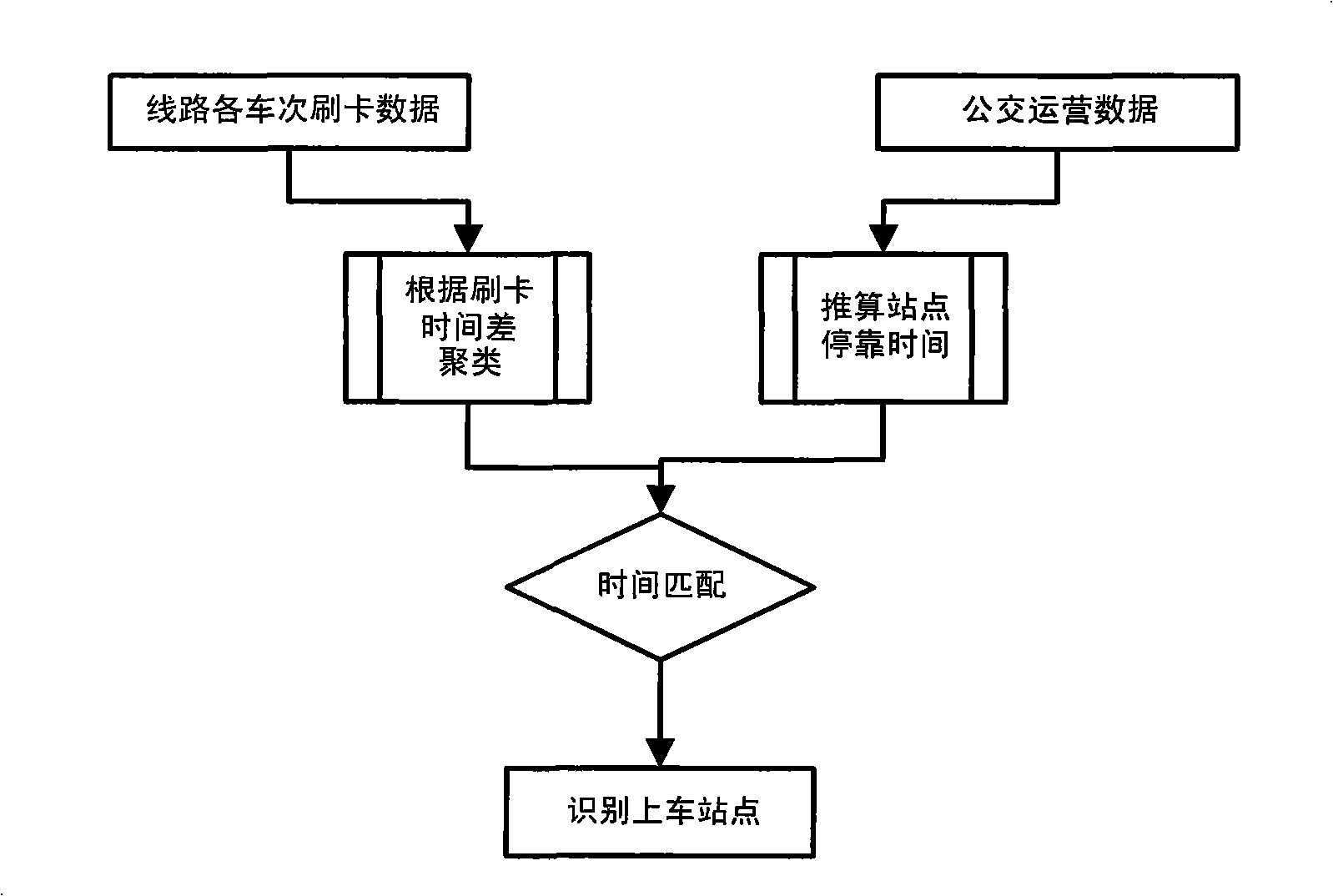

Matching method based on public transport IC card lines

The invention discloses a matching method based on public transport IC card lines, and belongs to the field of public transport information treatment and integration. The method comprises the steps of matching public transport IC card line numbers, matching vehicle running directions, and judging bus getting-on station platforms based on cluster analysis; matching the non-matched lines for many times according to the public transport IC card station platform attribute, vehicle number and attribute of driver number; associating the line serial number with the vehicle serial number and the public transport scheduling information list in a many-to-one manner according to the card swiping time records of the data of a universal public transport card; performing cluster analysis for the card swiping data according to the card swiping time difference of different station platforms, and selecting a proper time difference threshold value; and identifying the bus getting-on station platforms according to the selection of time difference threshold value. The invention performs pre-treatment including filtration, integration and convention for IC card data, deeply excavates the data, and finally obtains the station platform passenger number of the line. The invention provides planning evidence for public transport designers and provides evidence of public transport operation policy for public transport managers.

Owner:BEIJING UNIV OF TECH

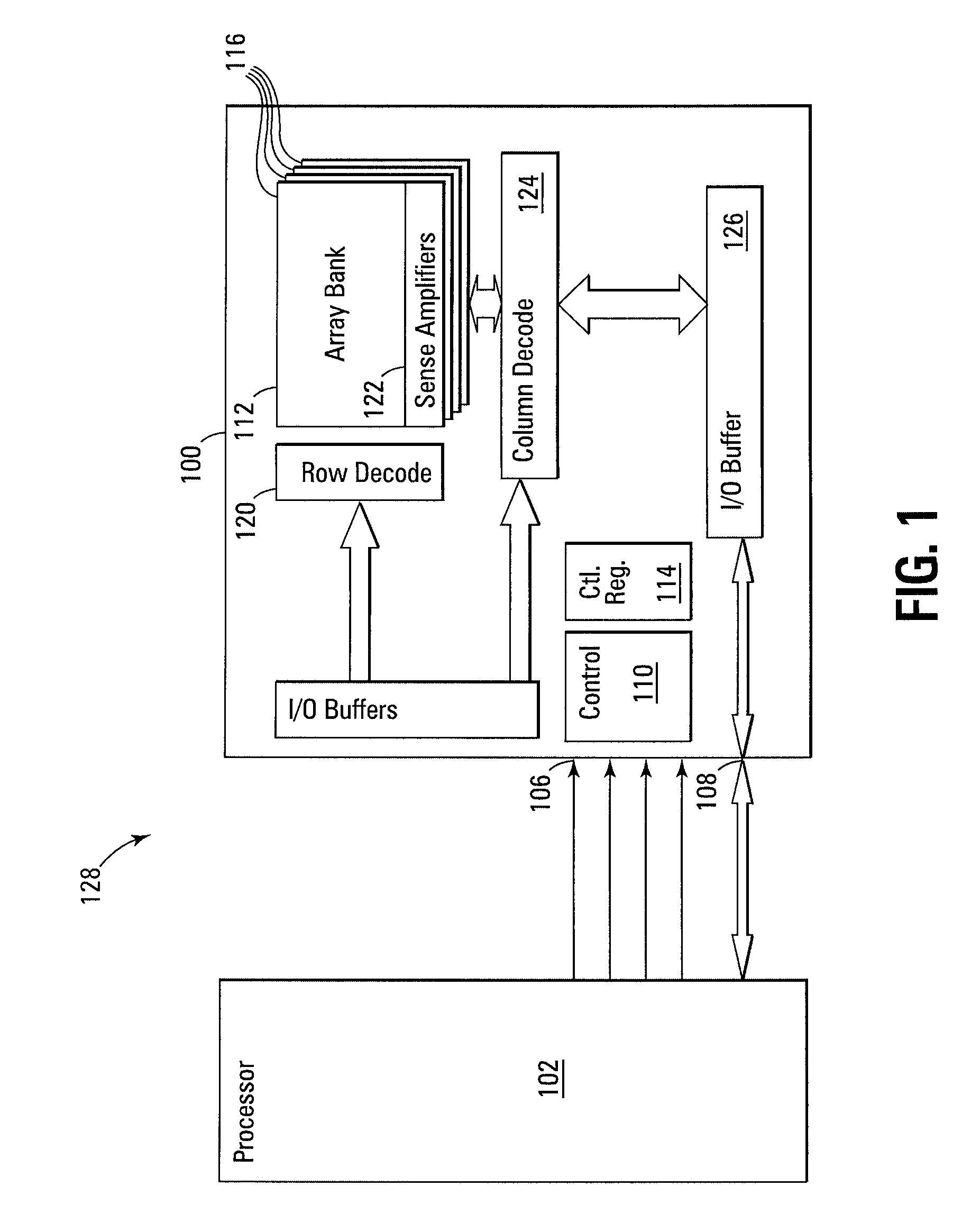

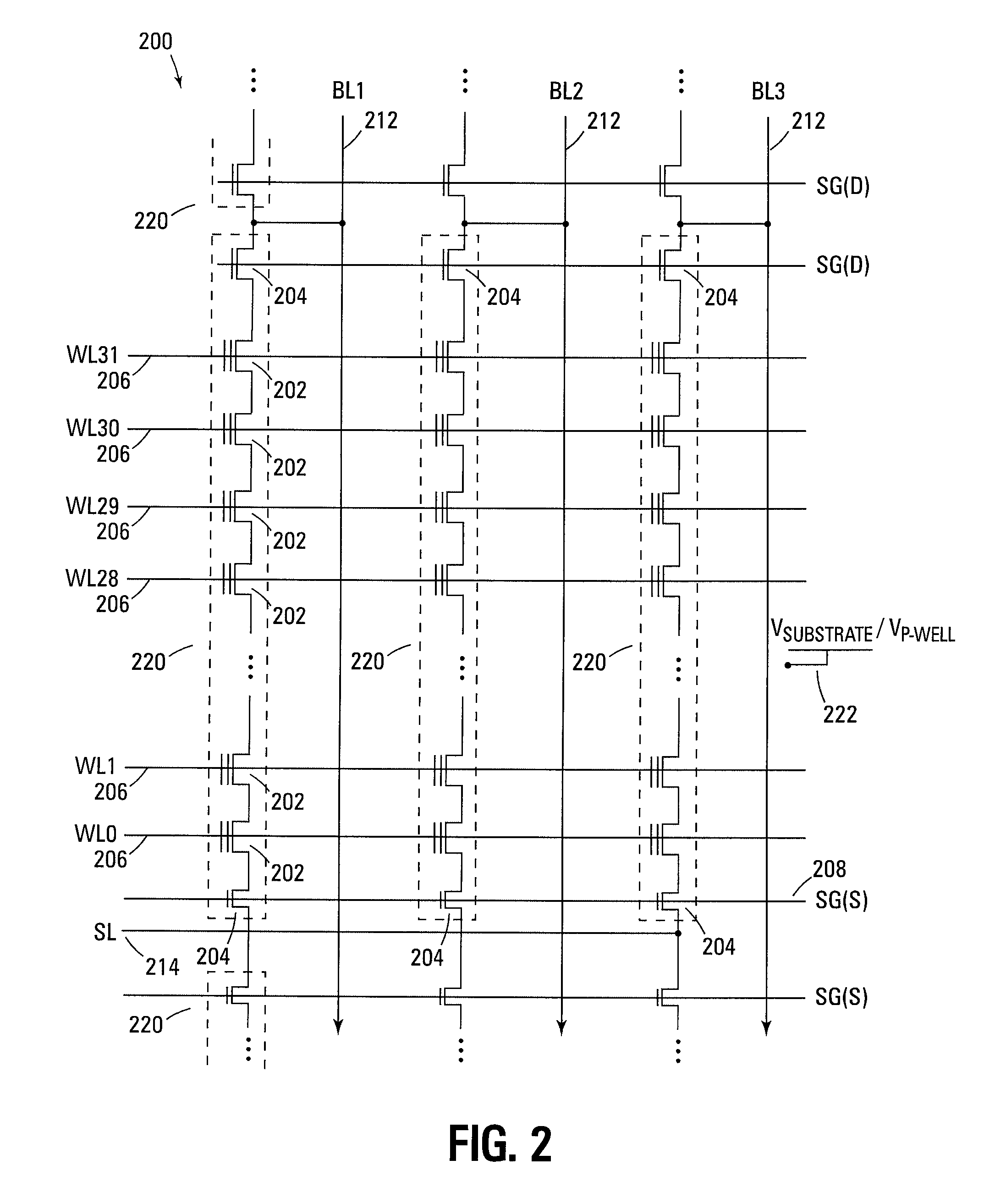

NAND flash content addressable memory

NAND architecture non-volatile content addressable (CAM) memory devices and methods are described that allows for high density, low cost CAM devices. In addition, the NAND architecture non-volatile CAM memory operates with reduced power consumption characteristics for low power and portable applications. In one NAND architecture non-volatile CAM memory embodiment a wired NOR match line array is utilized. In another embodiment a NAND match line array is shown. In yet other embodiments, hierarchal addressing, hash addressing, tree search and algorithmic / hardware engine based search is detailed utilizing both conventional NAND architecture non-volatile Flash memory arrays and dedicated NAND architecture CAM arrays utilizing wired NOR and wired NAND match lines.

Owner:MICRON TECH INC

Semiconductor memory device

A CAM (Content Addressable Memory) cell includes first and second data storage portions storing data, horizontal port write gates for storing data applied through a match line pair in the data storage portions in a data write through a horizontal port, and search / read gates for driving the match lines of the match line pair in accordance with the data stored in the data storage portions in a search operation and in a data read through the horizontal port. The match lines are used as horizontal bit line pair, or signal lines for accessing the horizontal port. As the first and second data storage portions are used, it becomes possible to store ternary data, and accordingly, a write mask function of inhibiting a data write at a destination of data transfer is realized. Further, as the CAM cell is used, an arithmetic / logic operation following a search process can be executed selectively, and high speed data writing / reading becomes possible.

Owner:RENESAS ELECTRONICS CORP

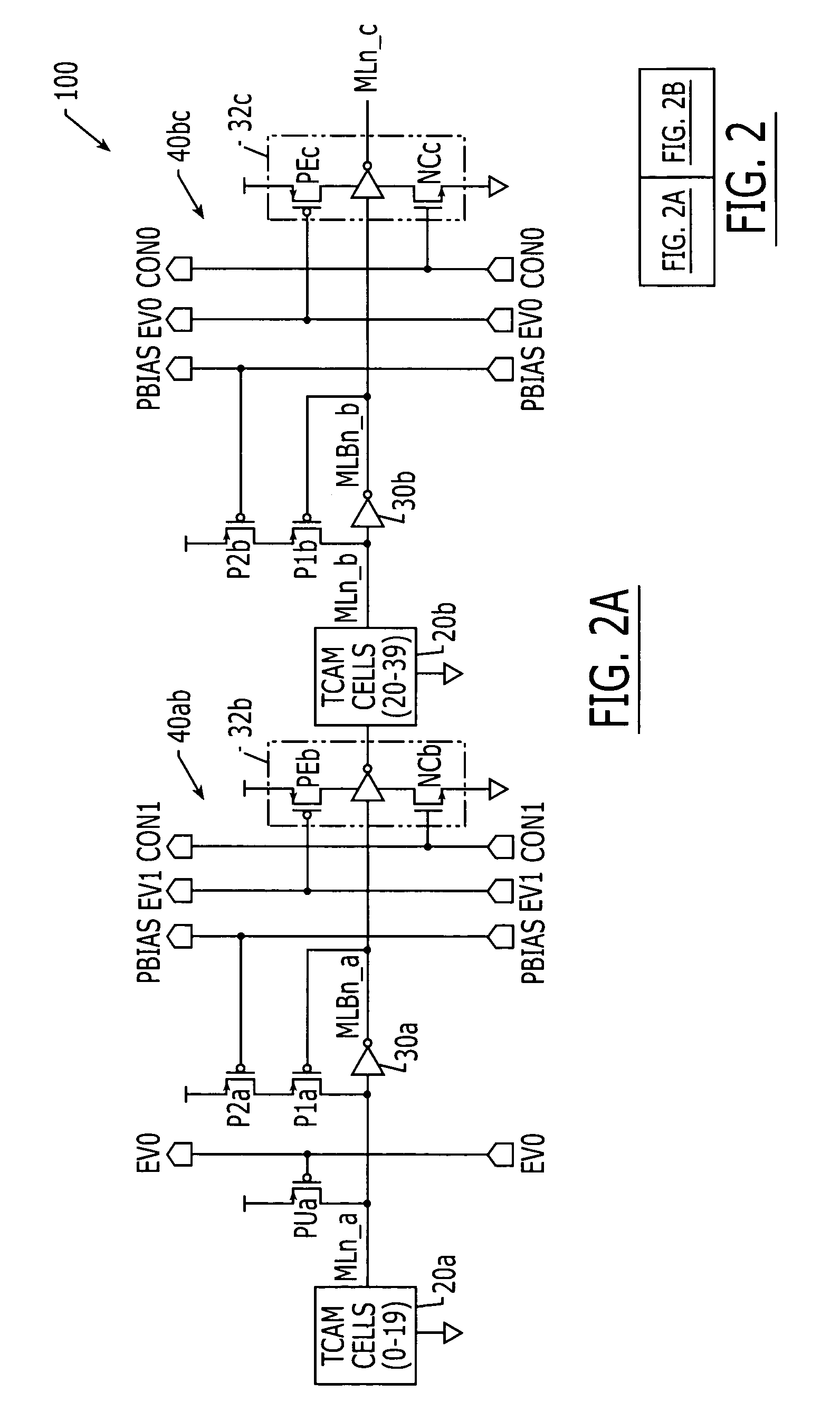

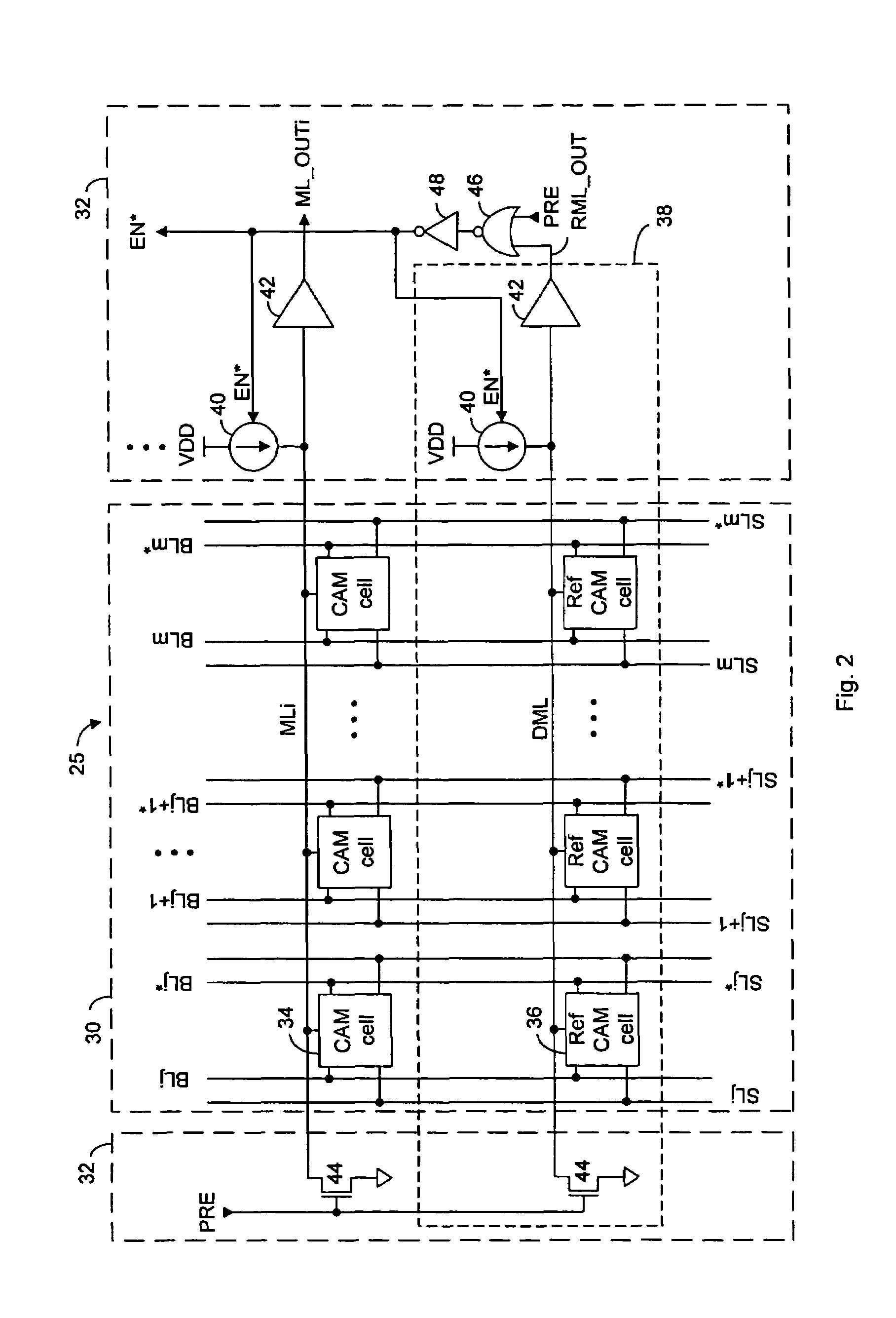

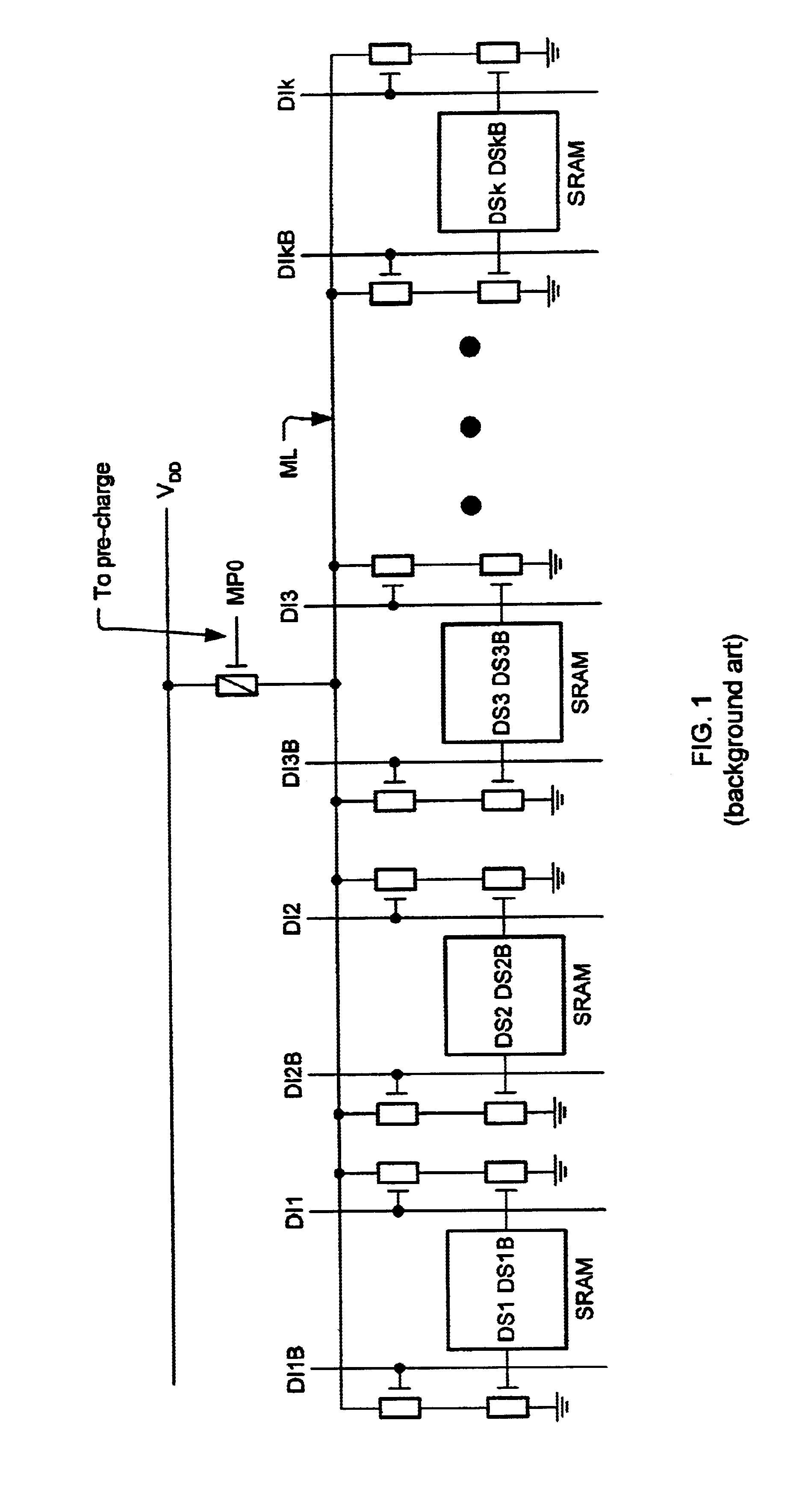

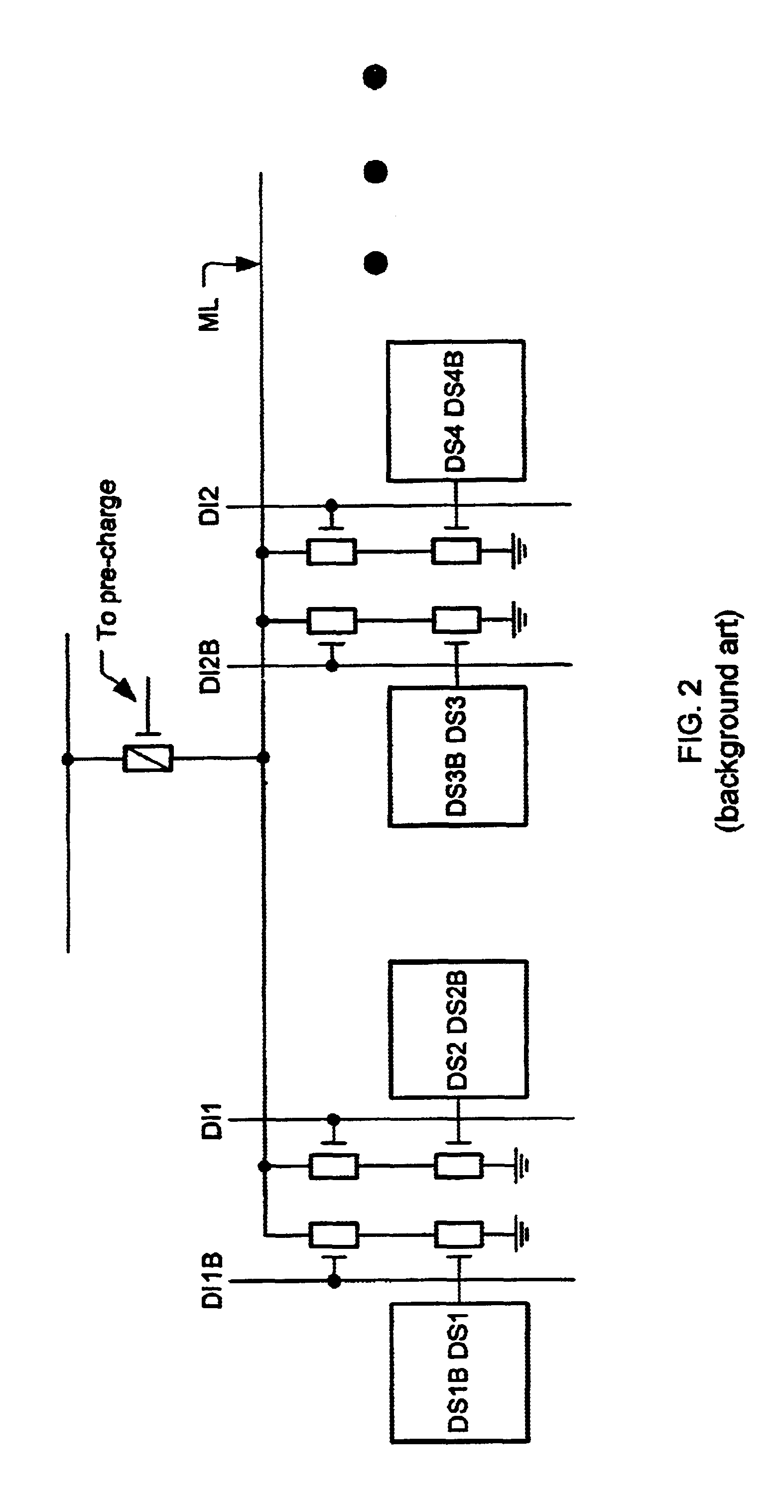

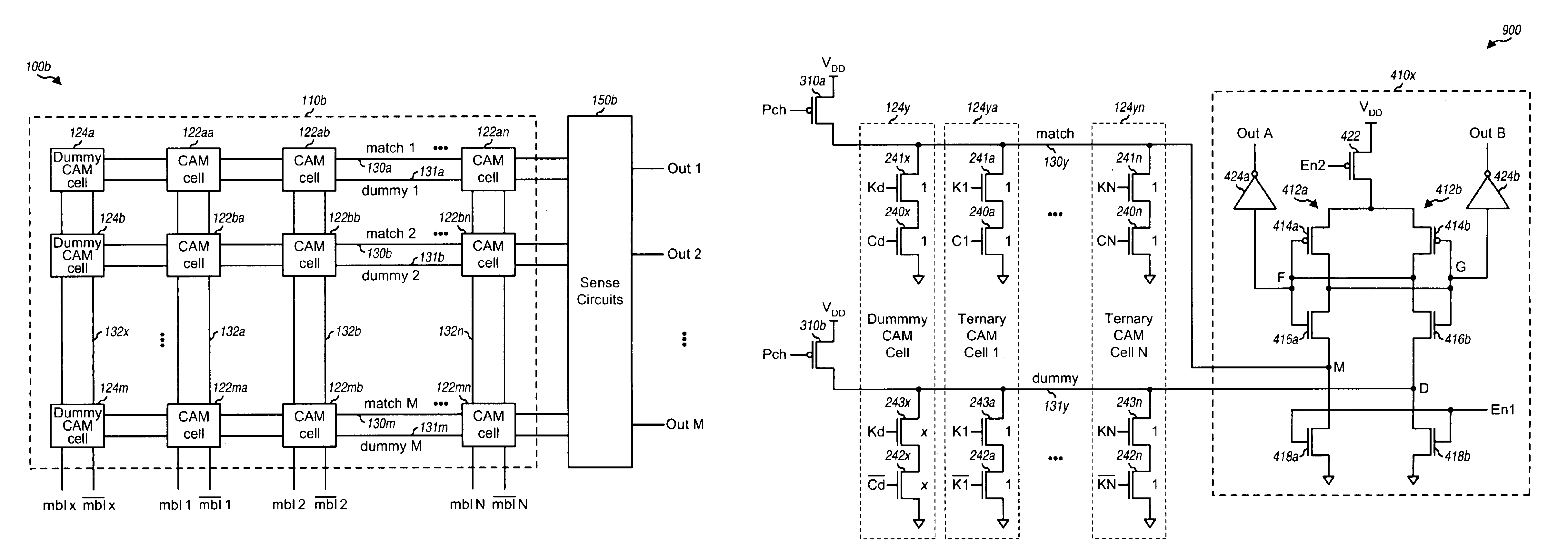

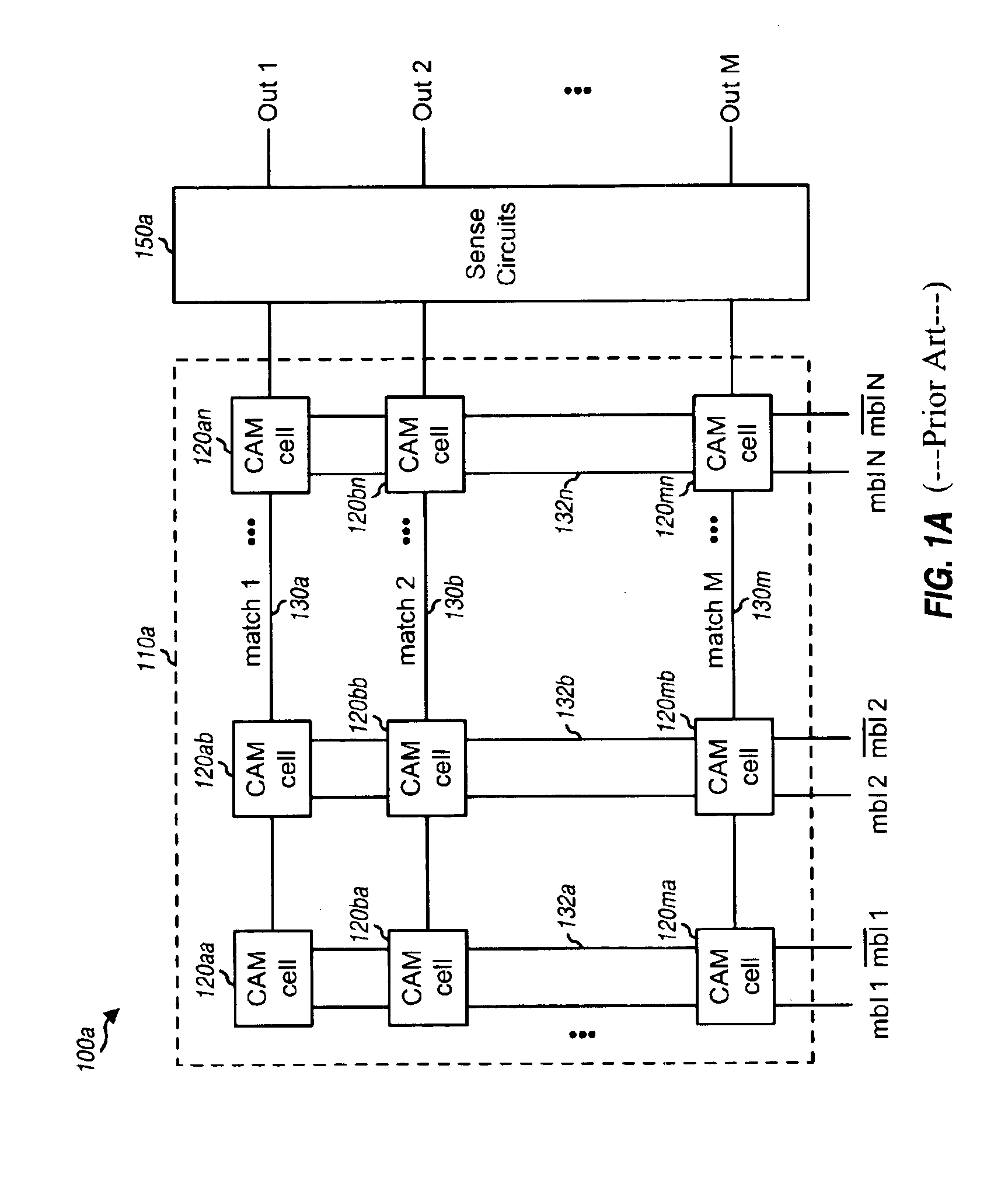

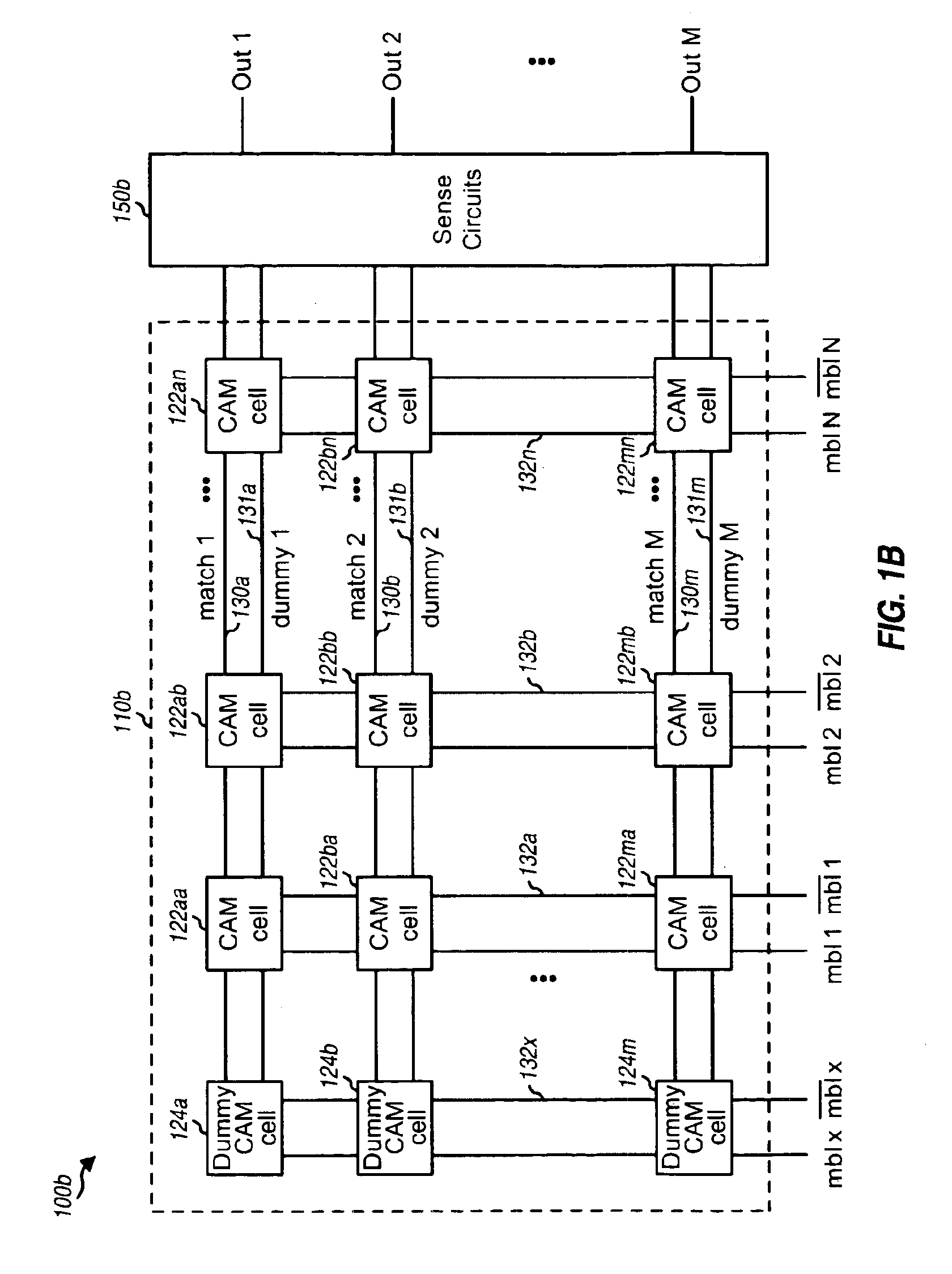

CAM cells and differential sense circuits for content addressable memory (CAM)

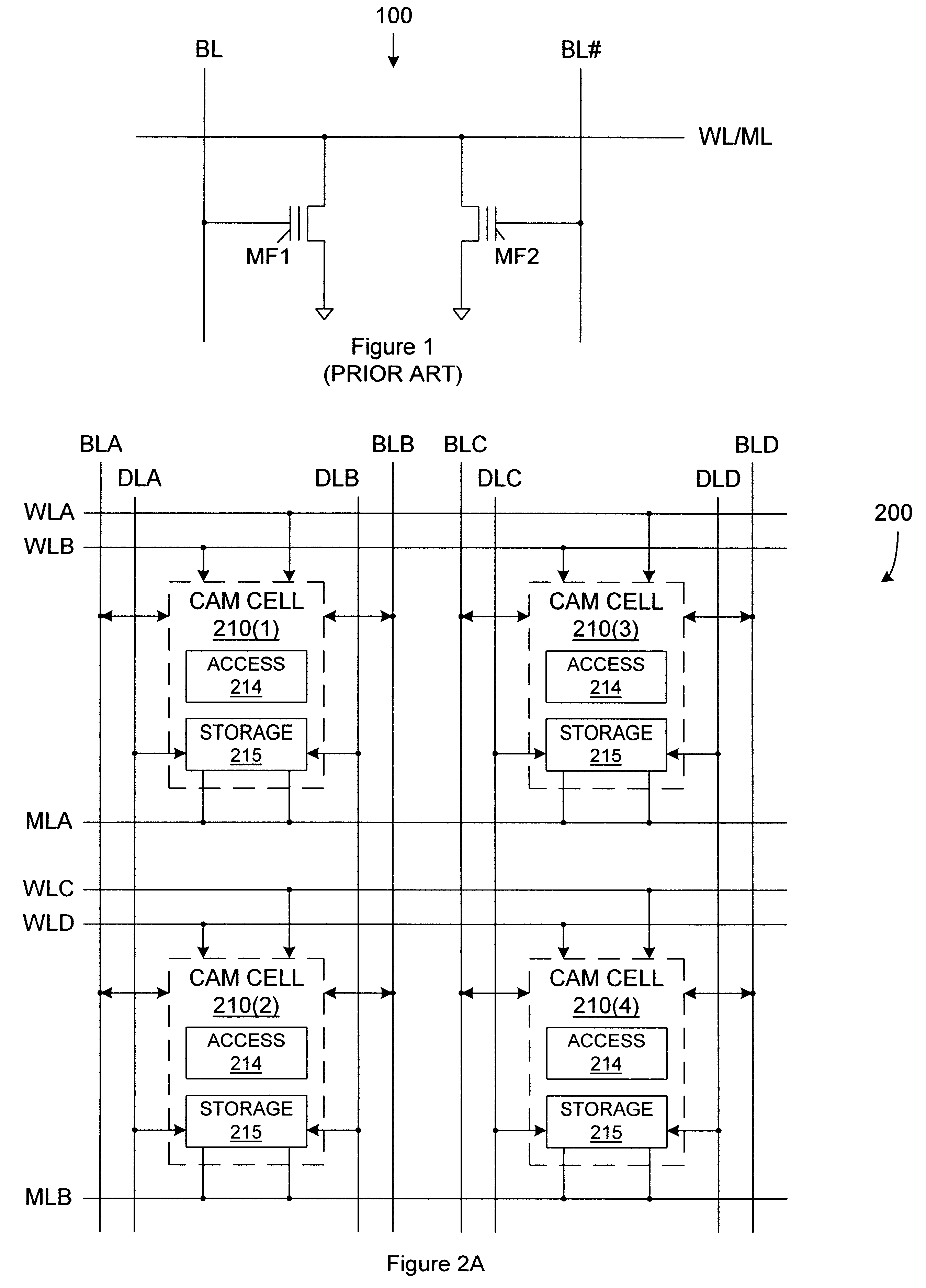

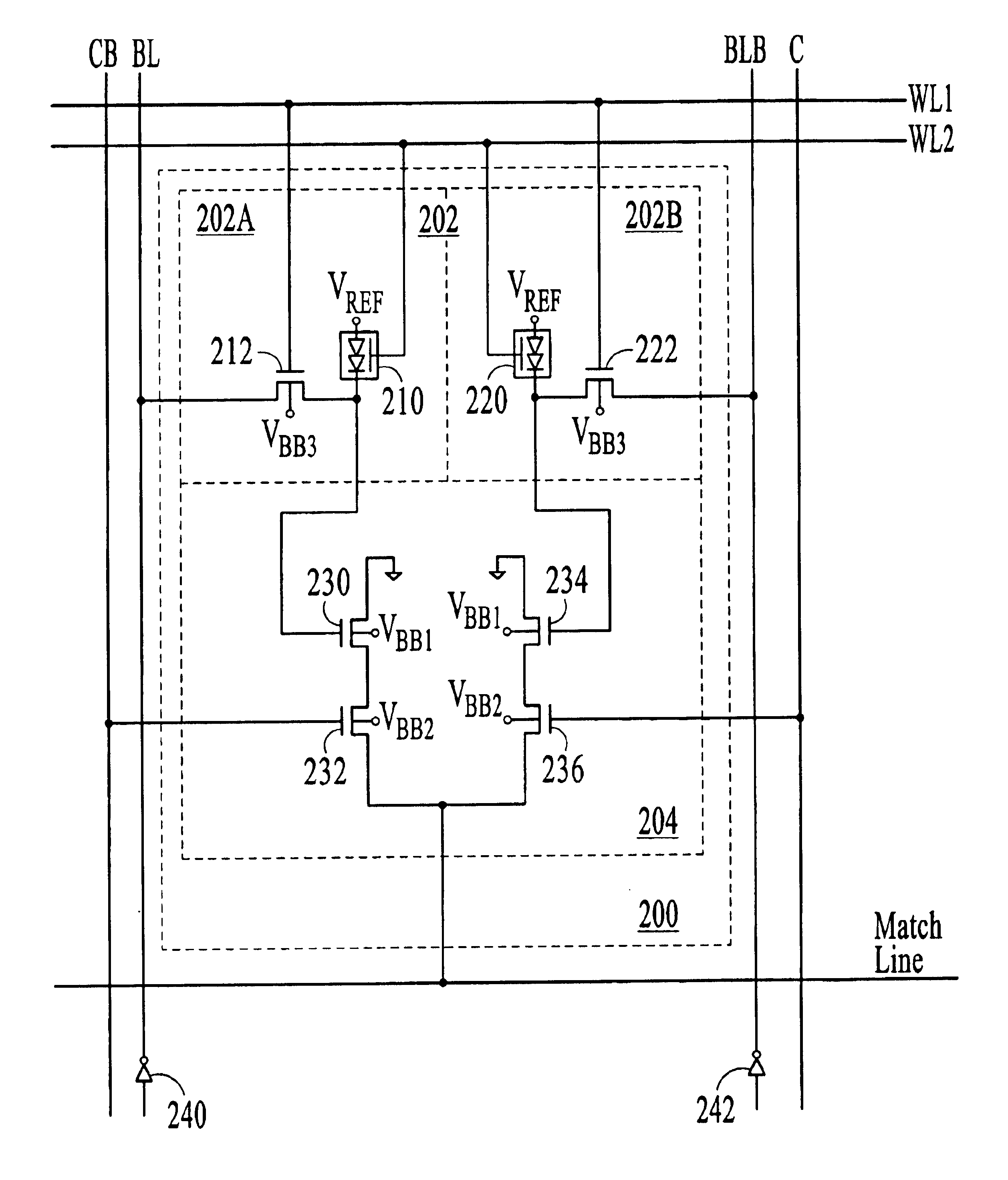

InactiveUS6999331B2Improve performanceFast operationDigital storageMemory systemsPower applicationHemt circuits

A dummy Content-addressable memory (CAM) cell and a dummy Ternary Content-addressable memory (TCAM) cell are connected to each row in a CAM and a ternary CAM array, respectively, to enable a differential match line sensing based on the content stored. The ternary content-addressable memory (TCAM) cell is for a differential match line sensing in low power applications. A method includes generating a voltage difference between match line signal and a reference line signal, and then detecting and amplifying the voltage difference to determine a match or a mismatch.

Owner:HUANG XIAOHUA

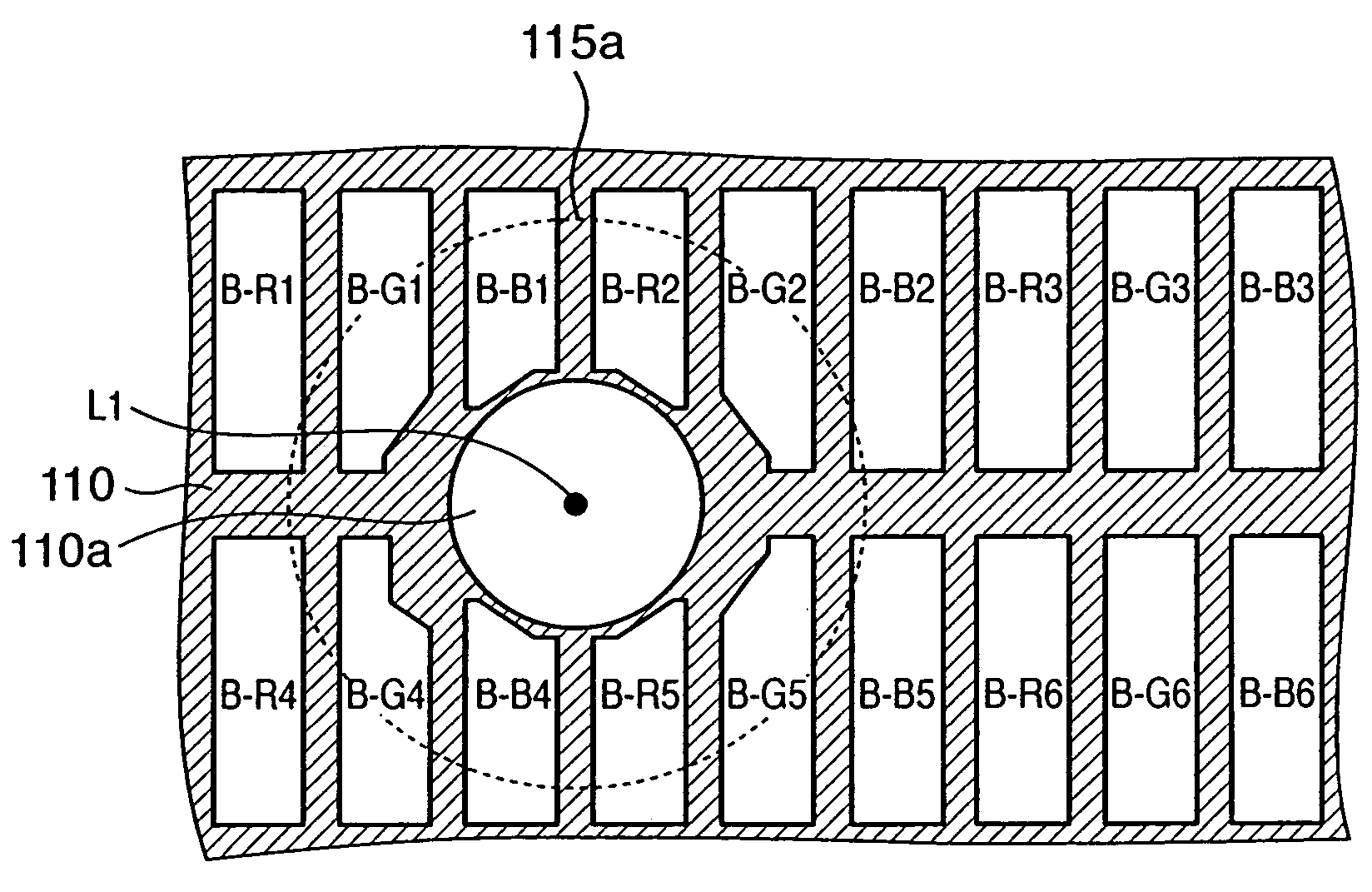

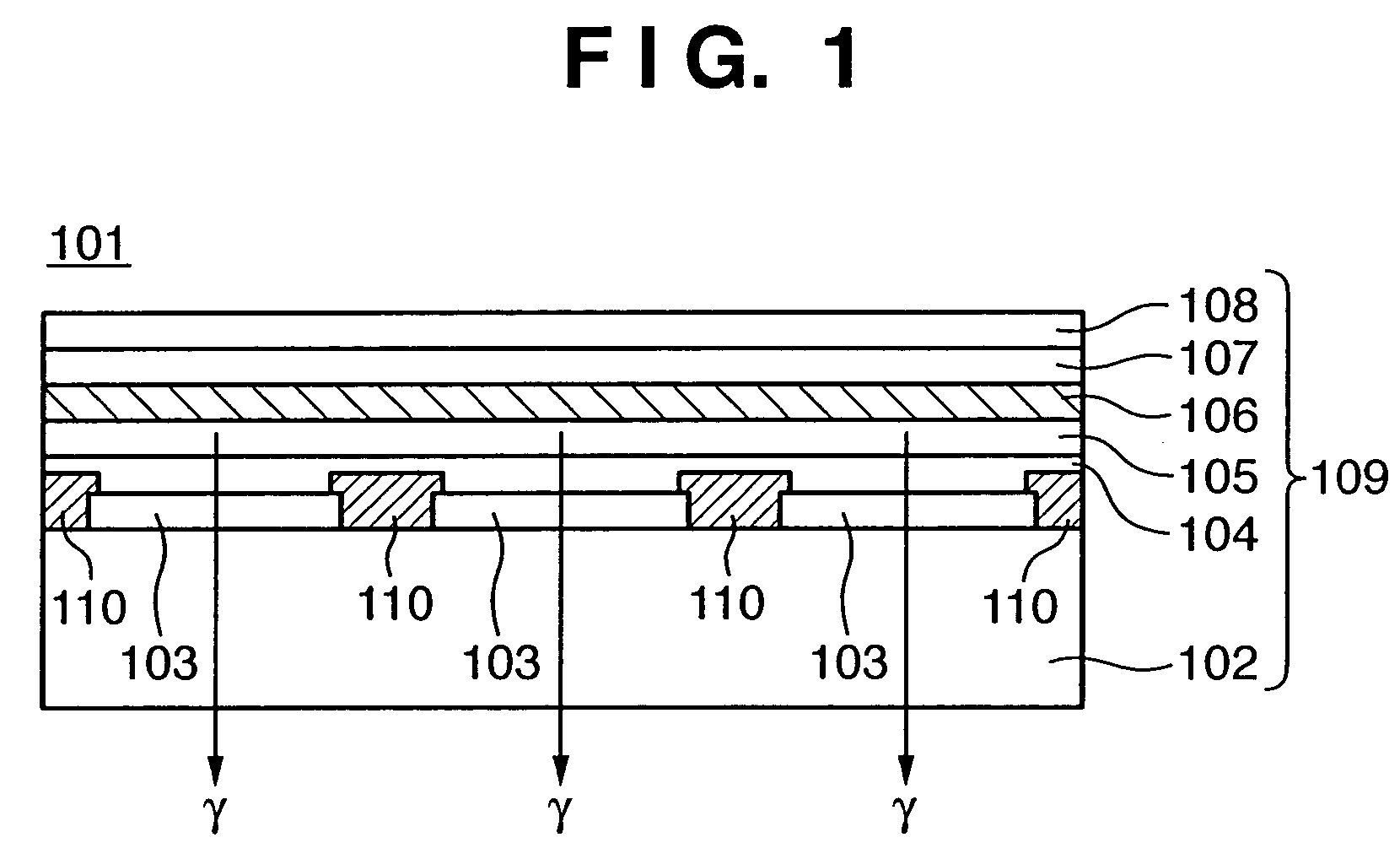

Display device with image sensing device

InactiveUS7420608B2Increase pixel densityLow costTelevision system detailsPrintersPixel densityDisplay device

The object of this invention is to provide a display device with an image sensing device, which can match lines of sight by a simple arrangement and realize a high pixel density, low cost and low profile. To this end, the display device with an image sensing device has a display unit that includes a plurality of display pixels, a light-shielding member arranged between neighboring display pixels, and an image sensing unit arranged on a back portion of the display unit; the light-shielding member has an opening for guiding light toward the image sensing unit and the image sensing unit has an imaging lens at a position corresponding to the opening.

Owner:CANON KK

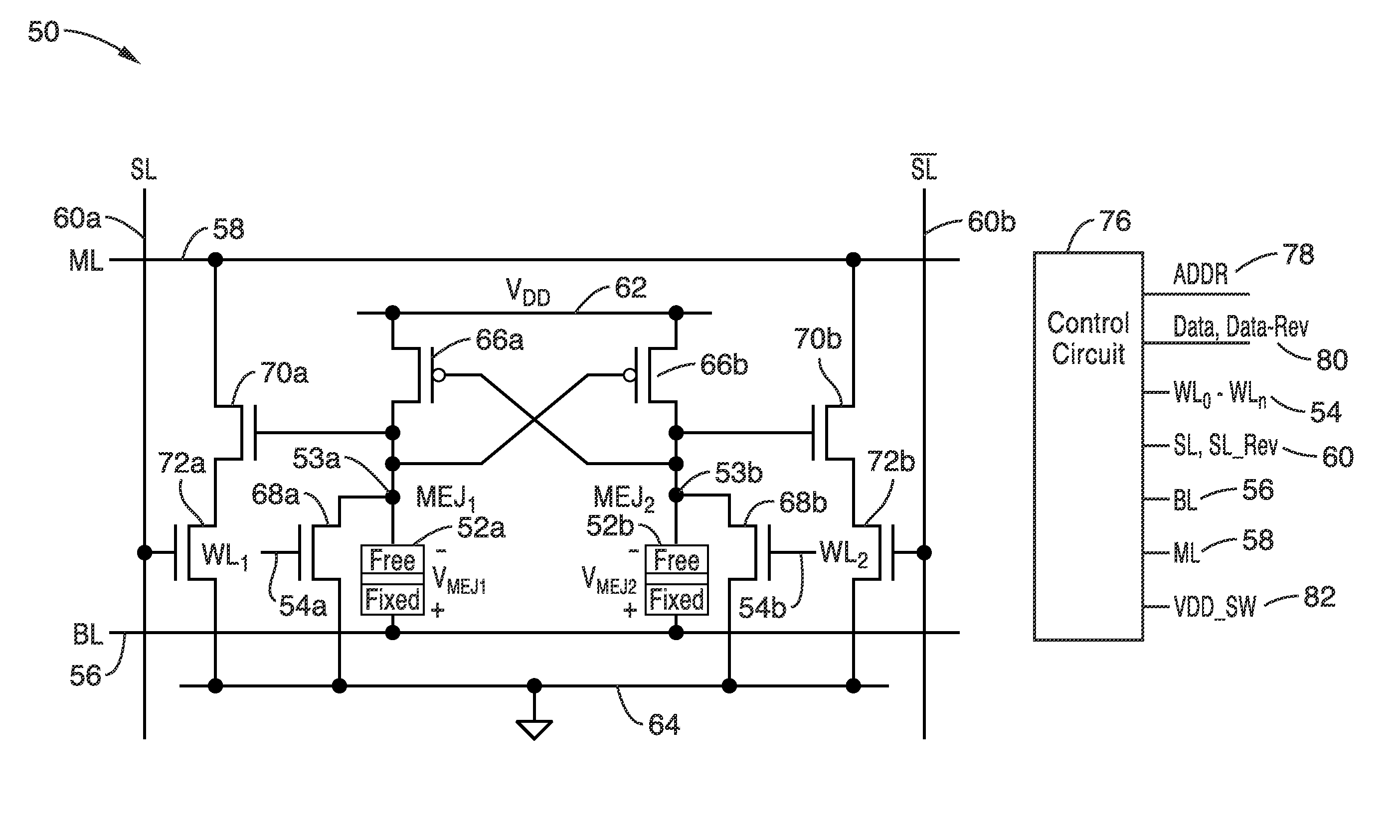

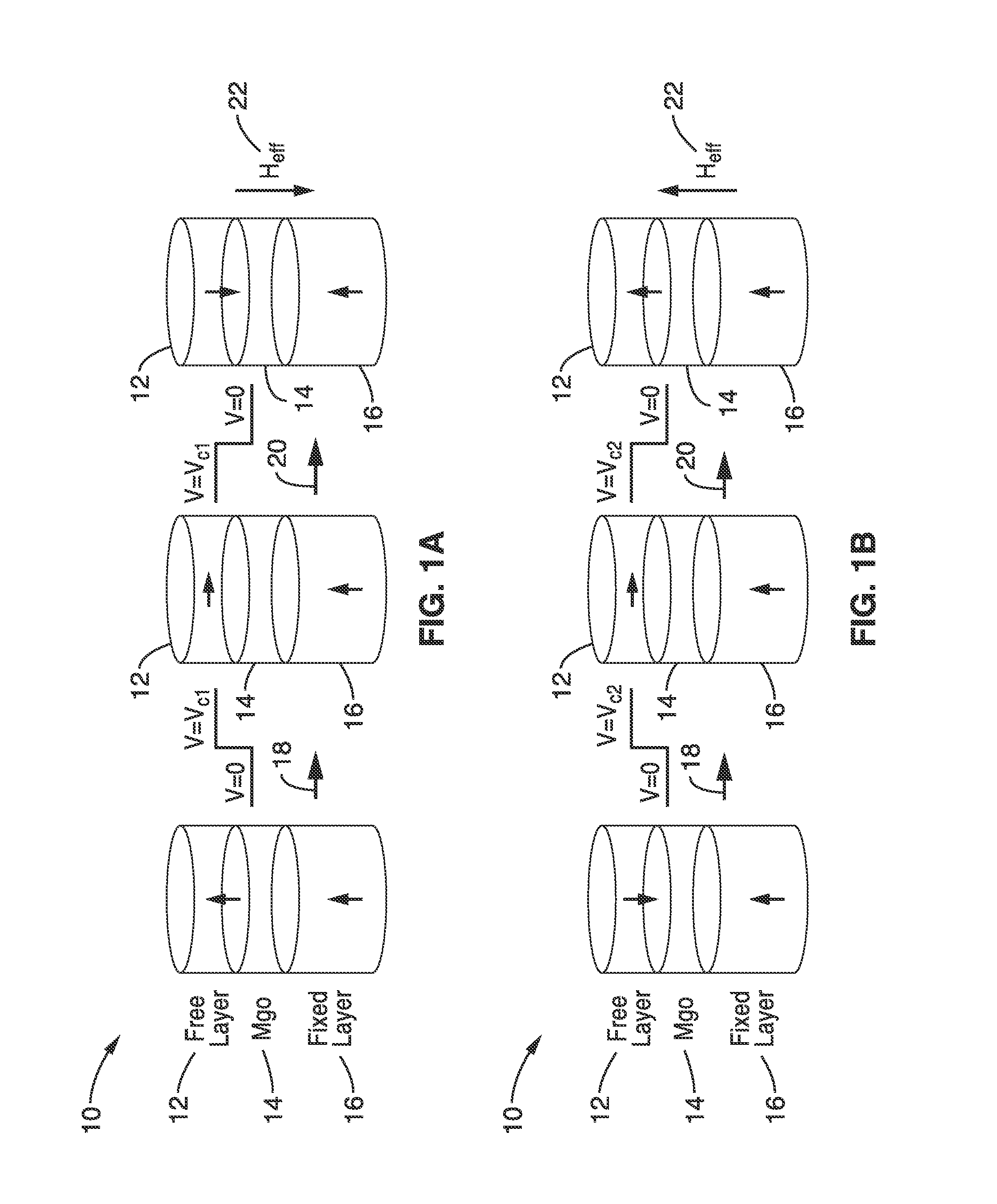

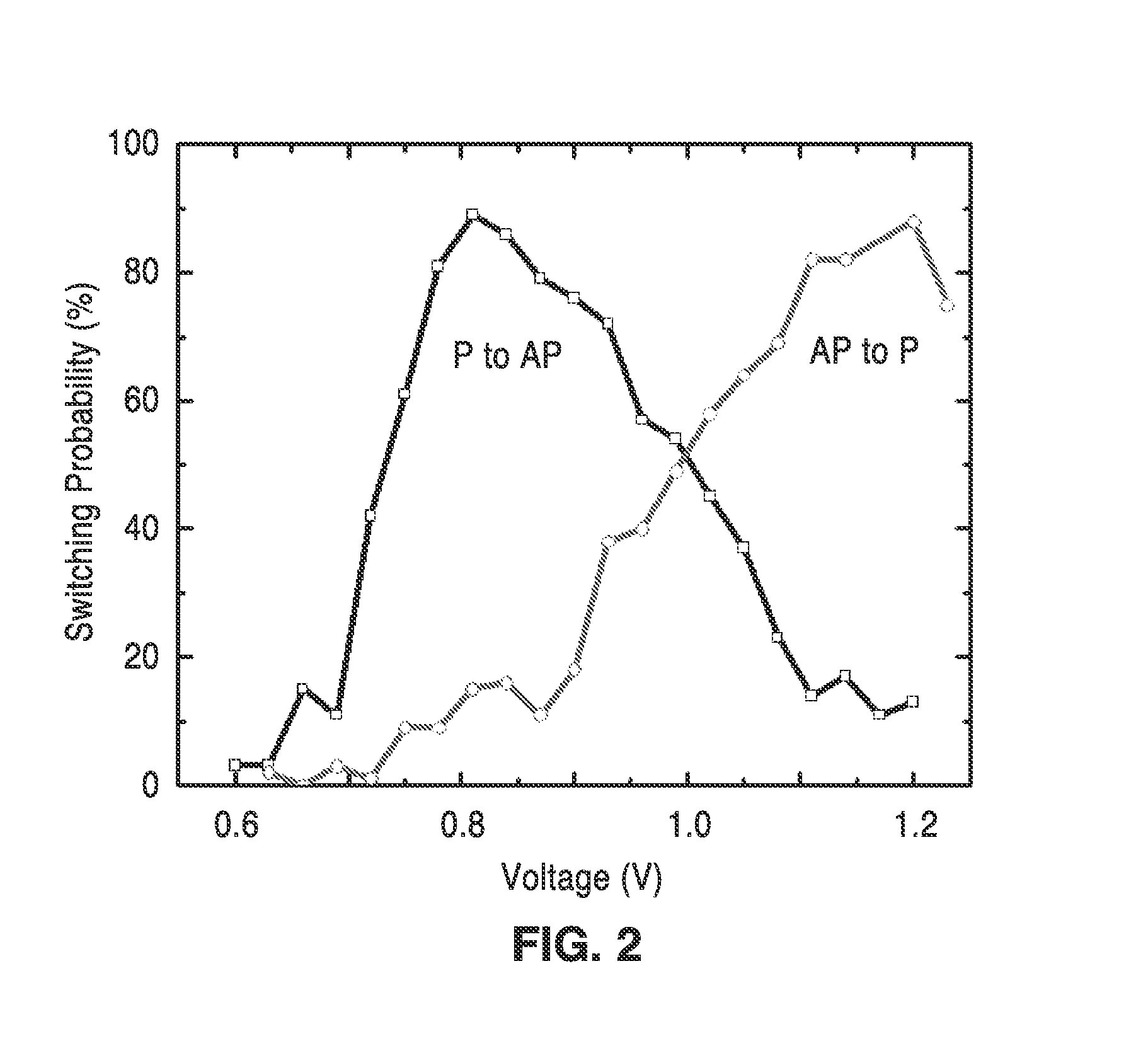

Read-disturbance-free nonvolatile content addressable memory (CAM)

ActiveUS20140071728A1High operating requirementsSuperior scaling behaviorDigital storageThin magnetic filmsComputer hardwareElectrical polarity

Voltage controlled magnetoelectric tunnel junction (MEJ) based content addressable memory is described which provides efficient high speed switching of MEJs toward eliminating any read disturbance of written data. Each cell of said CAM having two MEJs and transistor circuitry for performing a write at voltages of a first polarity, and reads at voltages of a second polarity. If the data searched does not equal the data written in the CAM, then the match line state is changed.

Owner:RGT UNIV OF CALIFORNIA

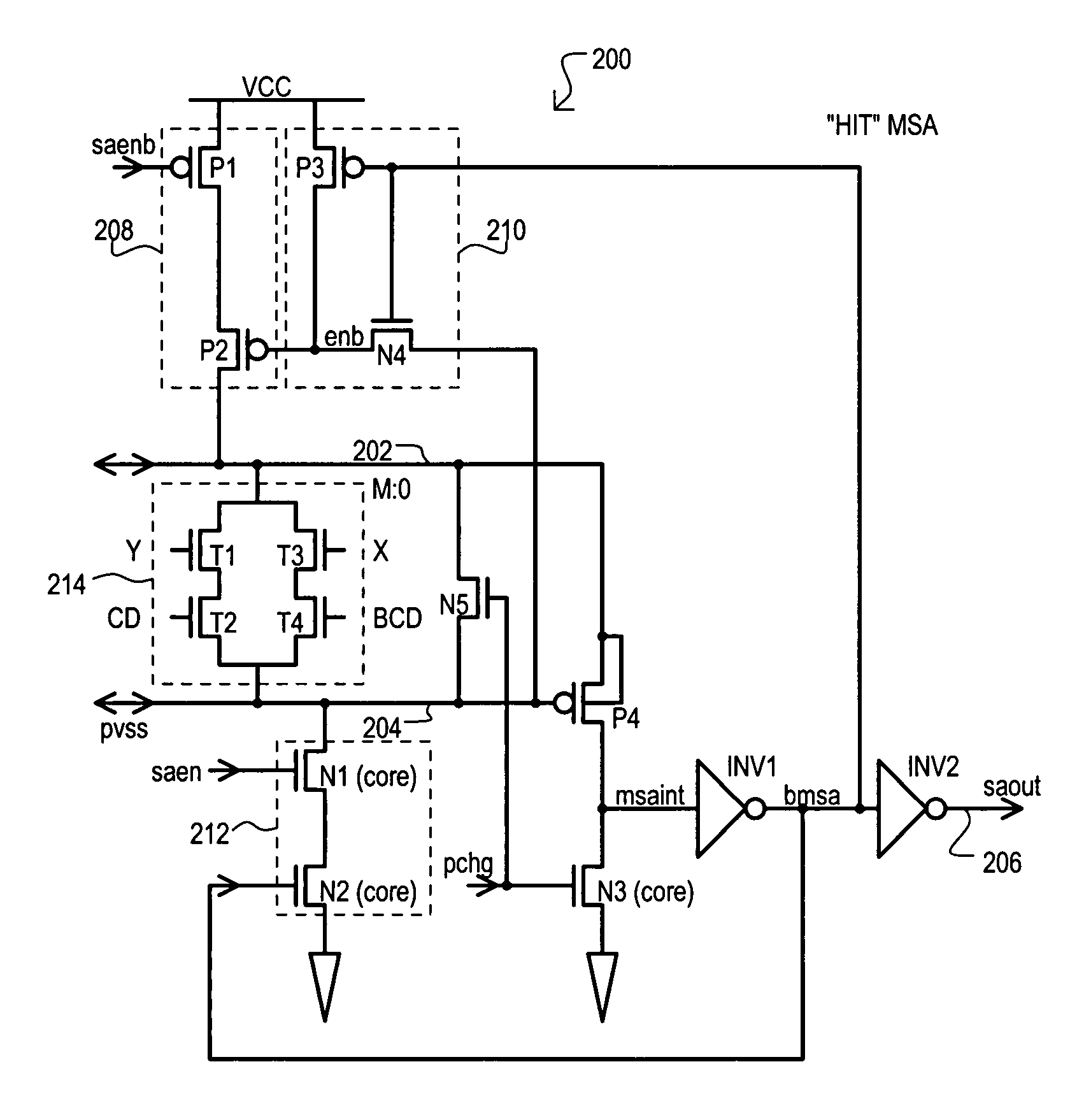

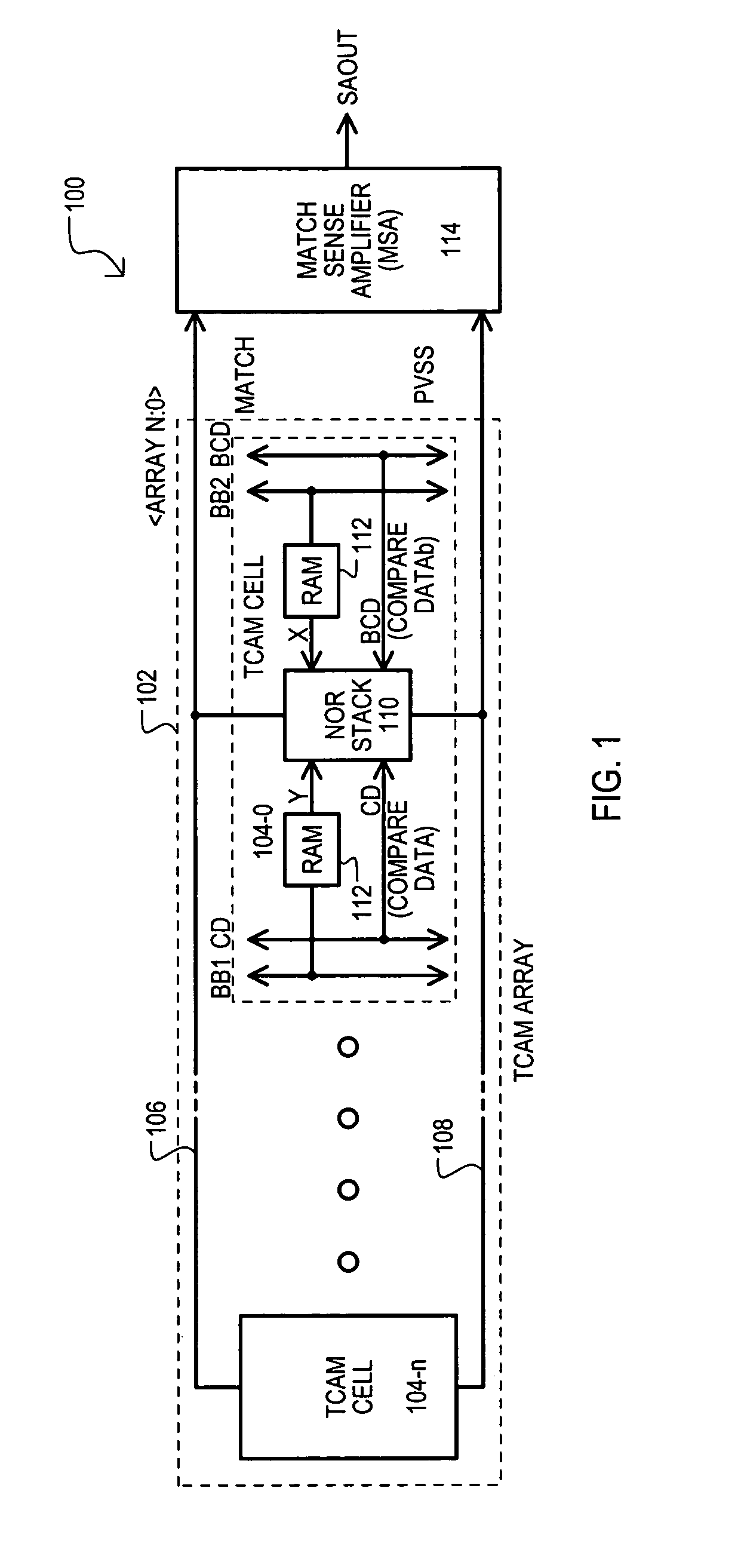

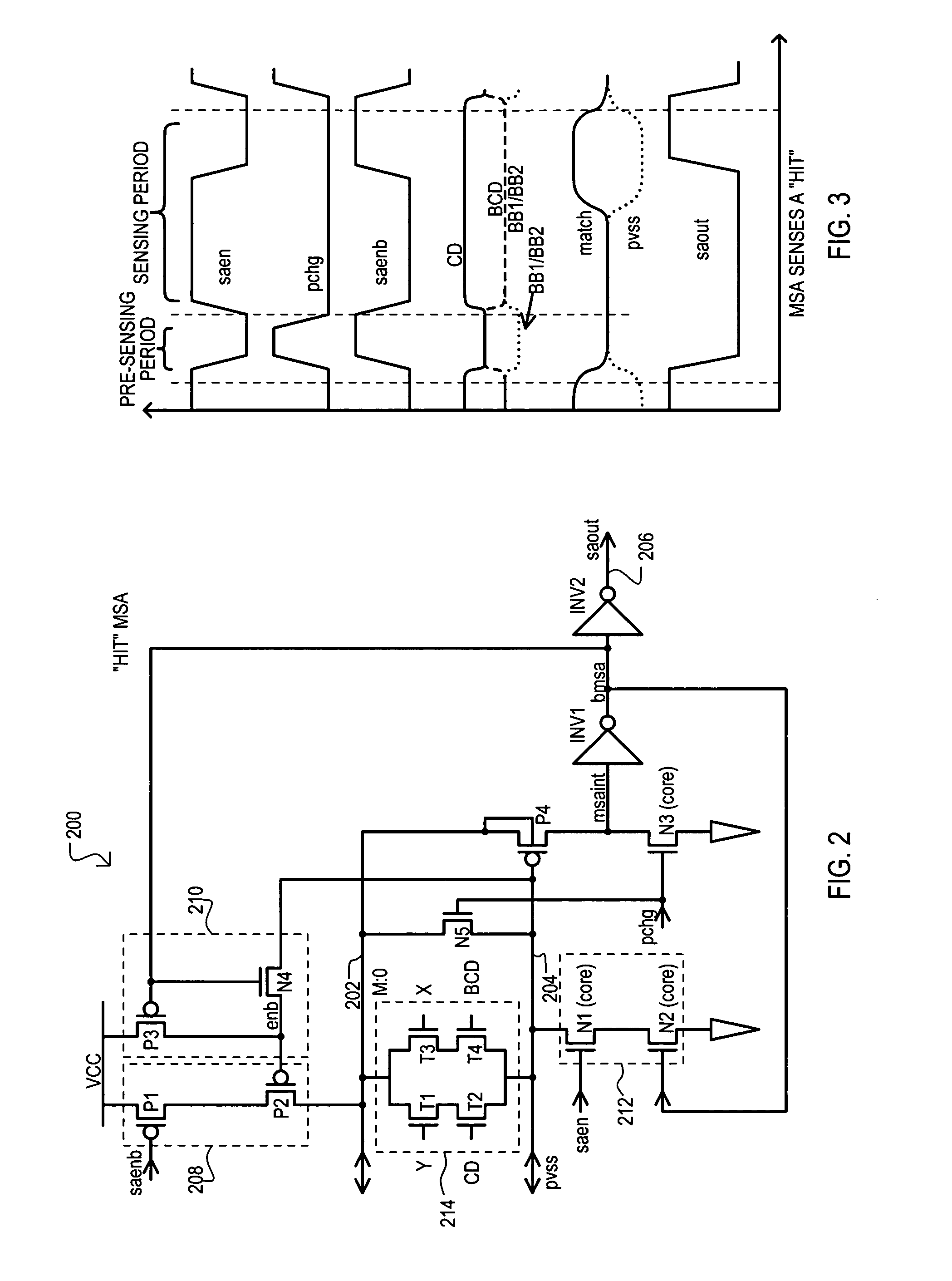

Sense amplifier architecture for content addressable memory device

ActiveUS7126834B1Increase power consumptionReduce power consumptionDigital storageBit lineAudio power amplifier

A content addressable memory (CAM) device (200) can equalize a potential between a match line (202) and corresponding pseudo-supply (PVSS) line (204) in a pre-sense operation. In a sense operation, a sensing device (P4) can determine a match condition exists when the match line (202) potential varies from the PVSS line (204) potential. Complementary compare data lines (CD and BCD) can be equalized with one another in a pre-sense operation, while one compare data line (CD or BCD) can be equalized with bit lines (BB1 and / or BB2) in the sensing operation.

Owner:AVAGO TECH INT SALES PTE LTD

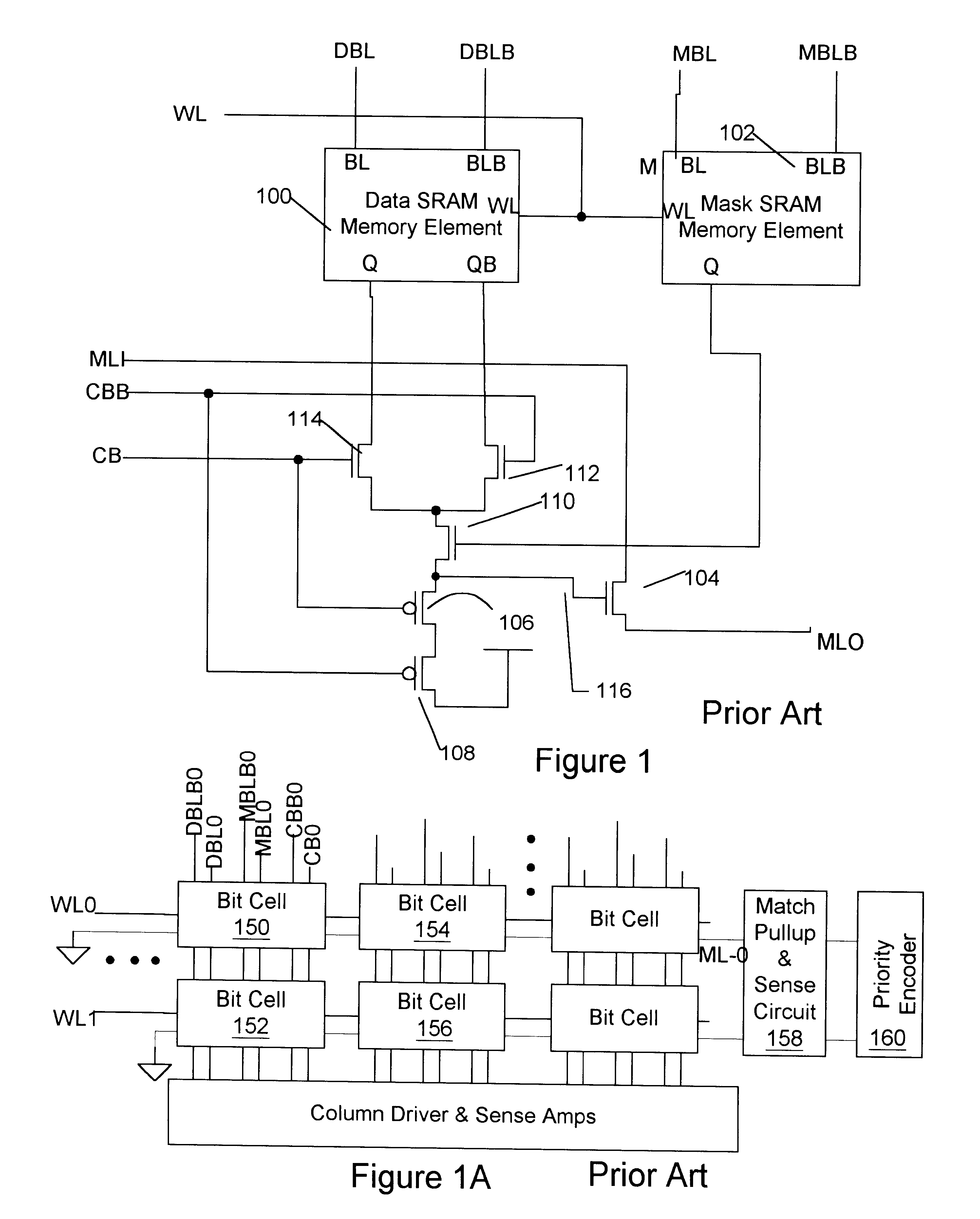

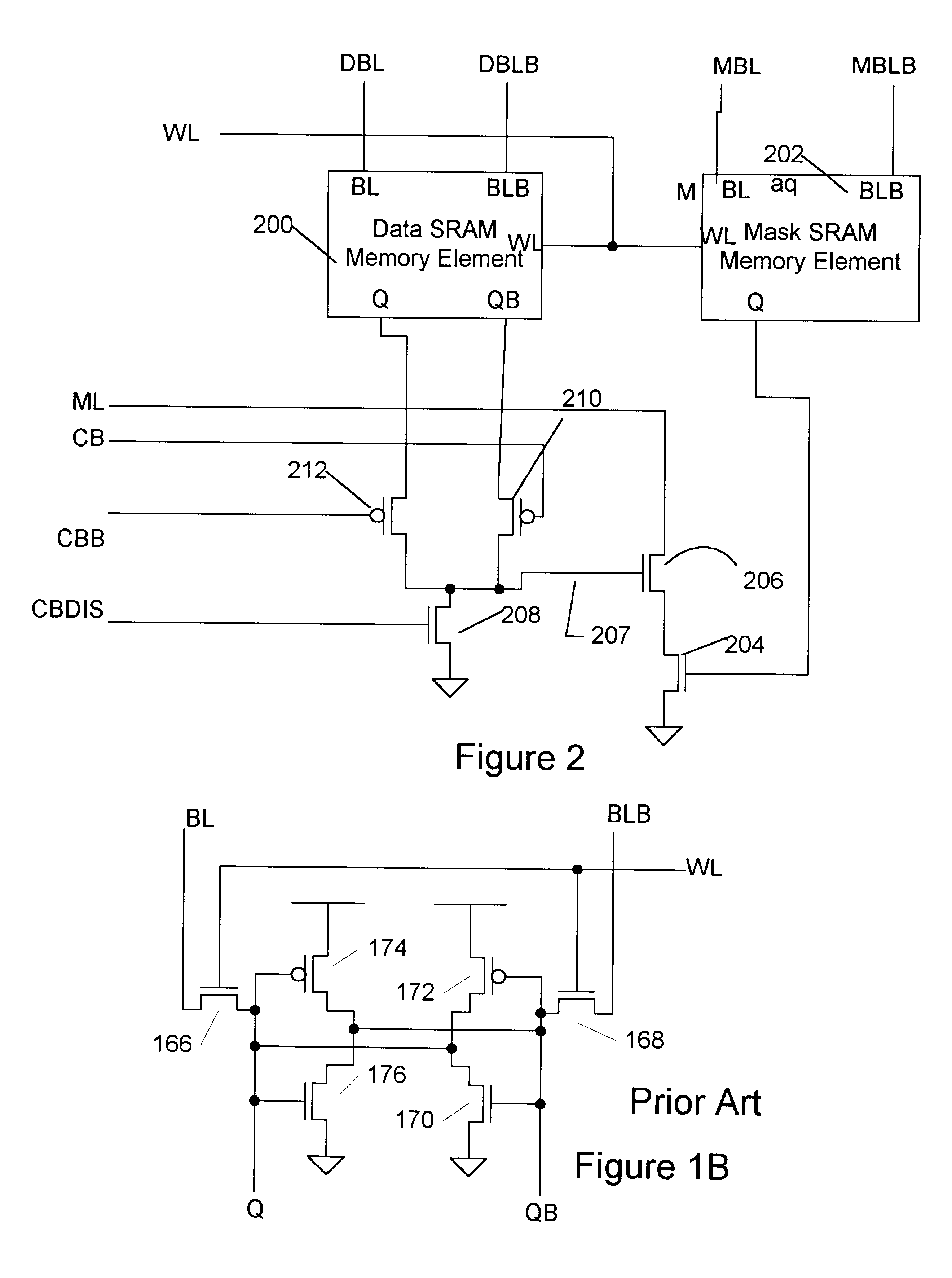

Content Addressable Memory array, cell, and method using 5-transistor compare circuit and avoiding crowbar current

A content addressable memory system has rows and columns of CAM cells. Each CAM cell has a data memory, and comparison circuitry for comparing the data bit of the memory element with a compare data, and for driving a signal onto a match line when the data bit is not equal to the compare data. The comparison circuitry has a mismatch node with a pre-discharge device, and drives a match line drive device coupled to the match line. The mismatch node also couples to a first comparison device having source an output of the data memory and gate coupled to the compare data, and a second comparison device having source a second output of the data memory and gate coupled to compare data. Disclosed is a ternary implementation of the CAM cell also having a mask bit. Also disclosed is CAM timing such that the CAM cells operate without crowbar current.

Owner:TALITY