Emulator of Multi-core Memory System Based on On-Chip Network Interconnection

A storage system and network-on-chip technology, which is applied in the field of multi-core storage system emulators, can solve storage system interconnection problems, achieve the effects of accelerating development speed, improving communication efficiency and data transmission bandwidth, and facilitating expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

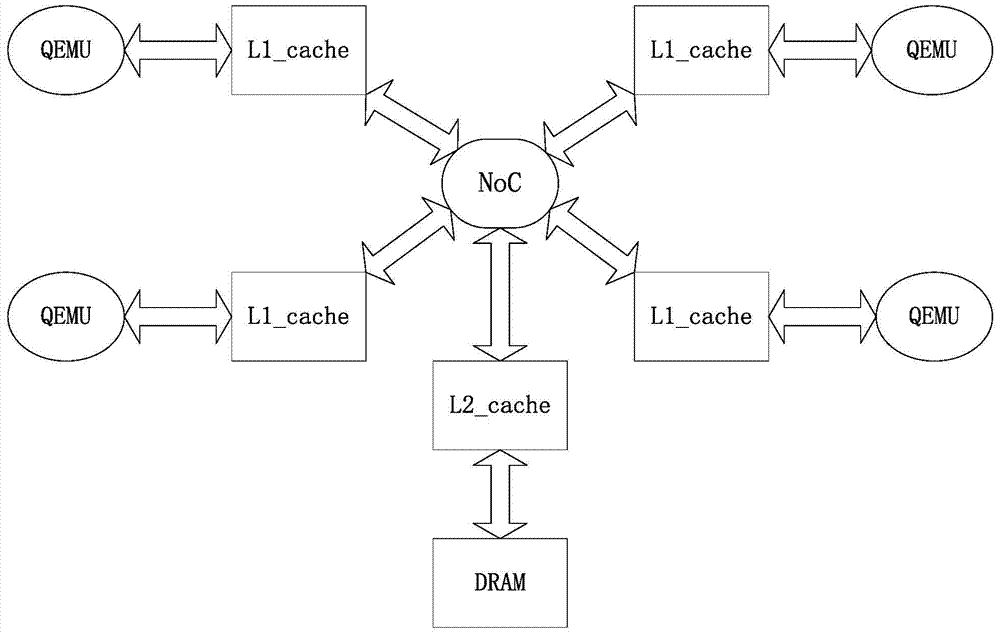

[0027] This embodiment adopts a new interconnection mode: a network-on-chip interconnection mode. The cache under multi-core adopts a hierarchical structure, using a two-level cache structure. The first-level cache is private to each core, and the second-level cache is shared by each core; since the first-level cache is private to multiple cores, each core caches the same cache block The data in performs different operations, so it is easy to cause data inconsistency.

[0028] 1. Cache module

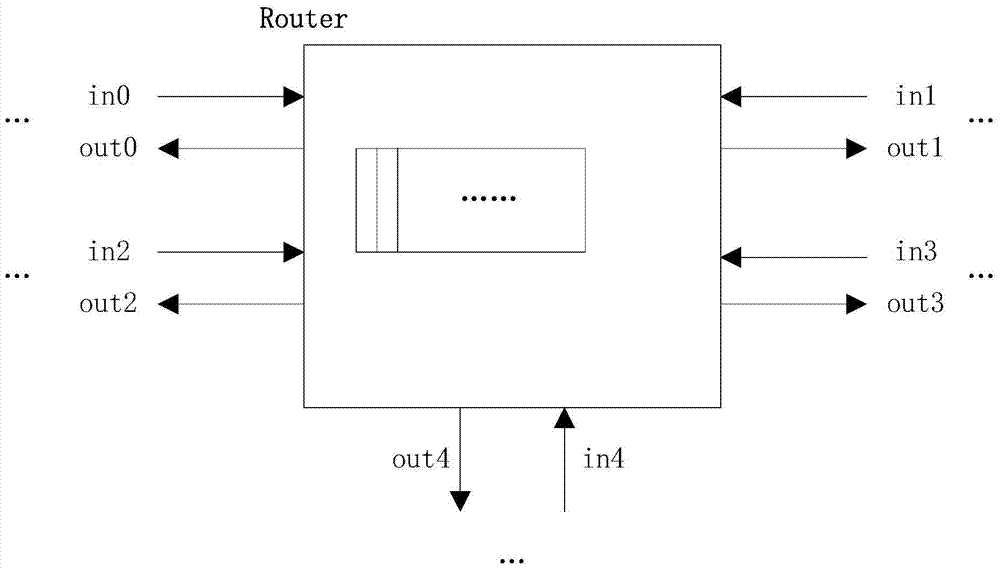

[0029] The cache module is implemented according to its definition, using group associative mapping strategy, write-back method, and randomly selecting a cache line when replacing. First, a pointer is used to point to the Cache Block. There are many pointers in these cache blocks. These pointers point to the unit that actually stores information. This unit is called a cache line (cache line). Both private caches and shared caches use cache lines, but only the first-level cache needs t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More