Communication interface method of processor reference model under multiple simulation and verification platforms

A technology of communication interface and reference model, applied in the direction of inter-program communication, multi-program device, etc., to achieve the effect of improving efficiency and quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

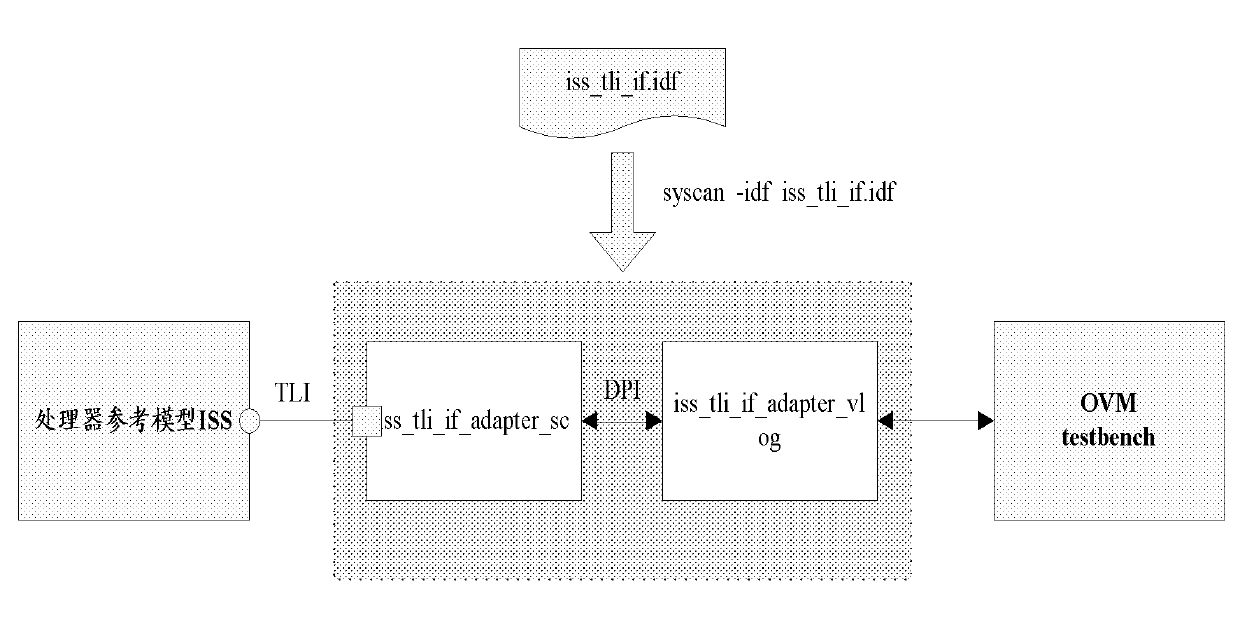

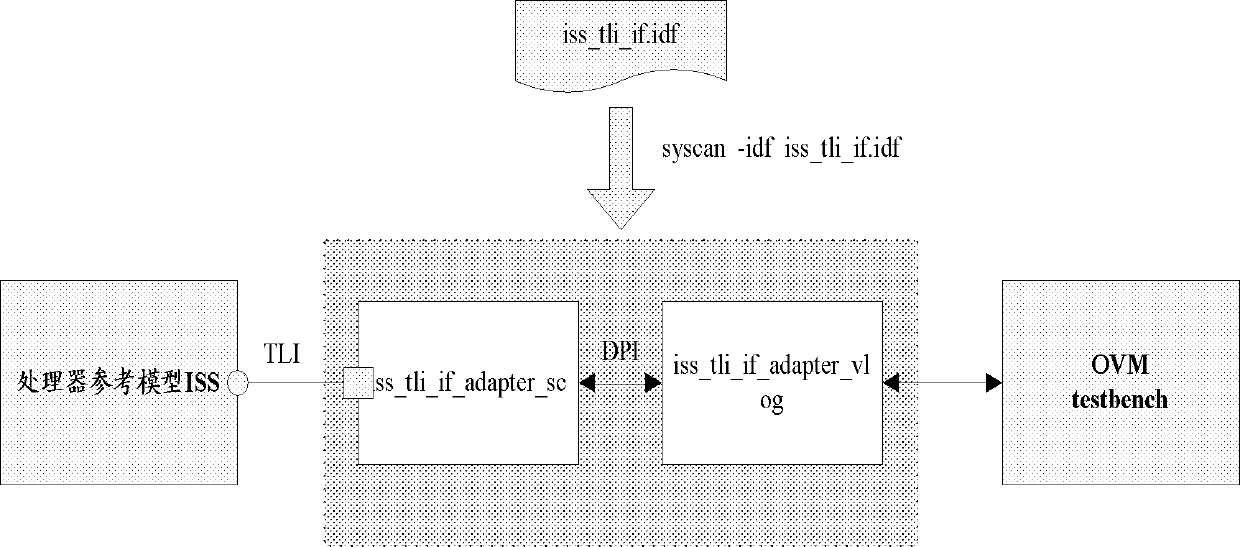

[0033] figure 1 It is a schematic diagram of the transaction-level communication interface method of the processor reference model applicable to the VCS simulation verification platform.

[0034] For example, when verifying a processor, implement a blockable transaction-level communication interface between the processor reference model and the verification platform according to the following method steps:

[0035](1) Define the transaction-level communication interface (.h file), including the write command interface, read back write data interface, and read command execution status interface, such as defining the following three TLI interface function declarations, namely write, read back write, and The function declaration of the read instruction interface, in figure 1 The middle refers to the TLI interface on the left.

[0036] In order t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More