Patents

Literature

452 results about "Parallel simulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A parallel simulation is a simulation which is contained a program that is off site of the client's computer systems, whereas a embedded audit module is actually within the system. I like to imagine the example of two cars, in parallel simulation you have two exact cars driving beside each other...

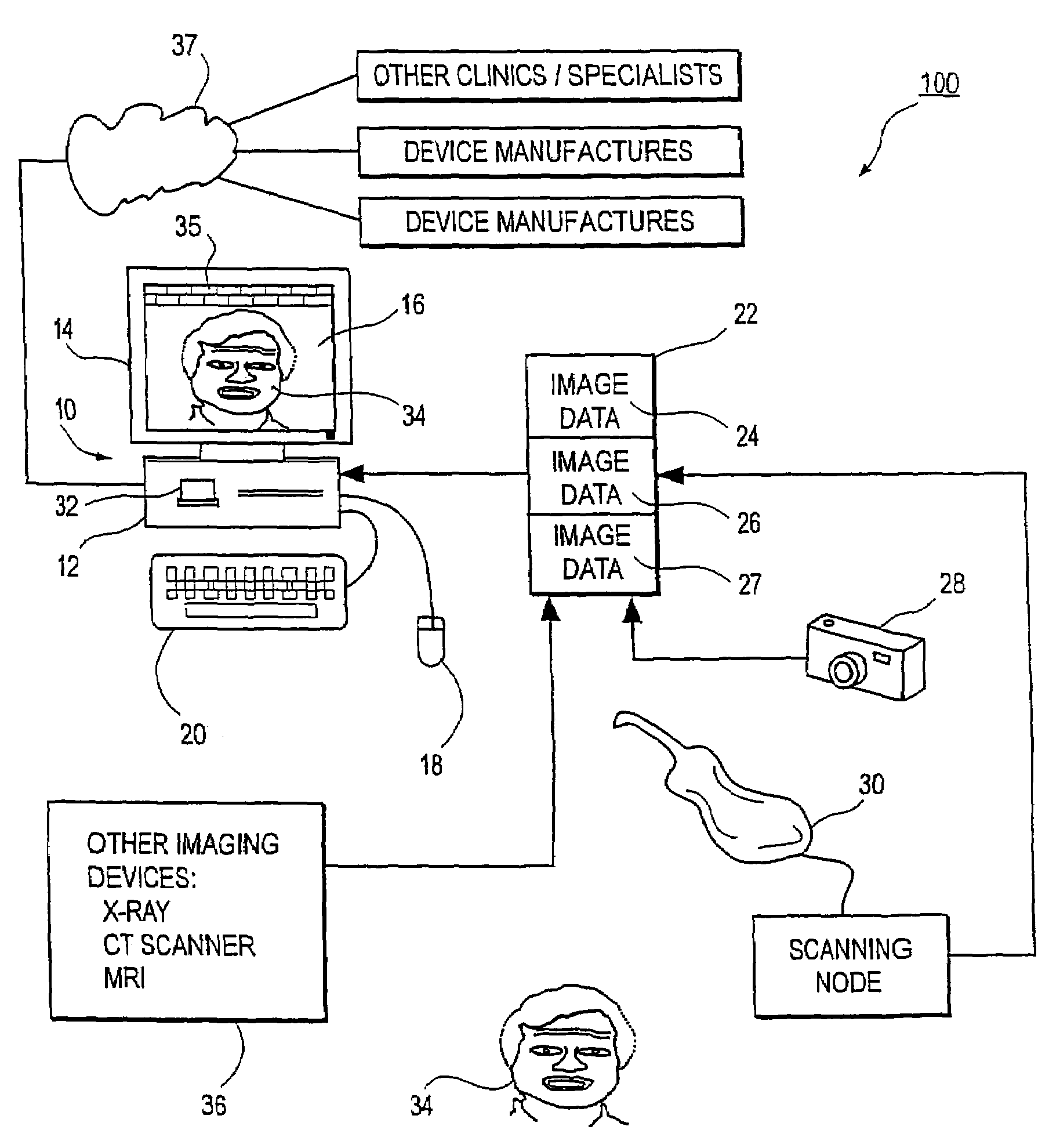

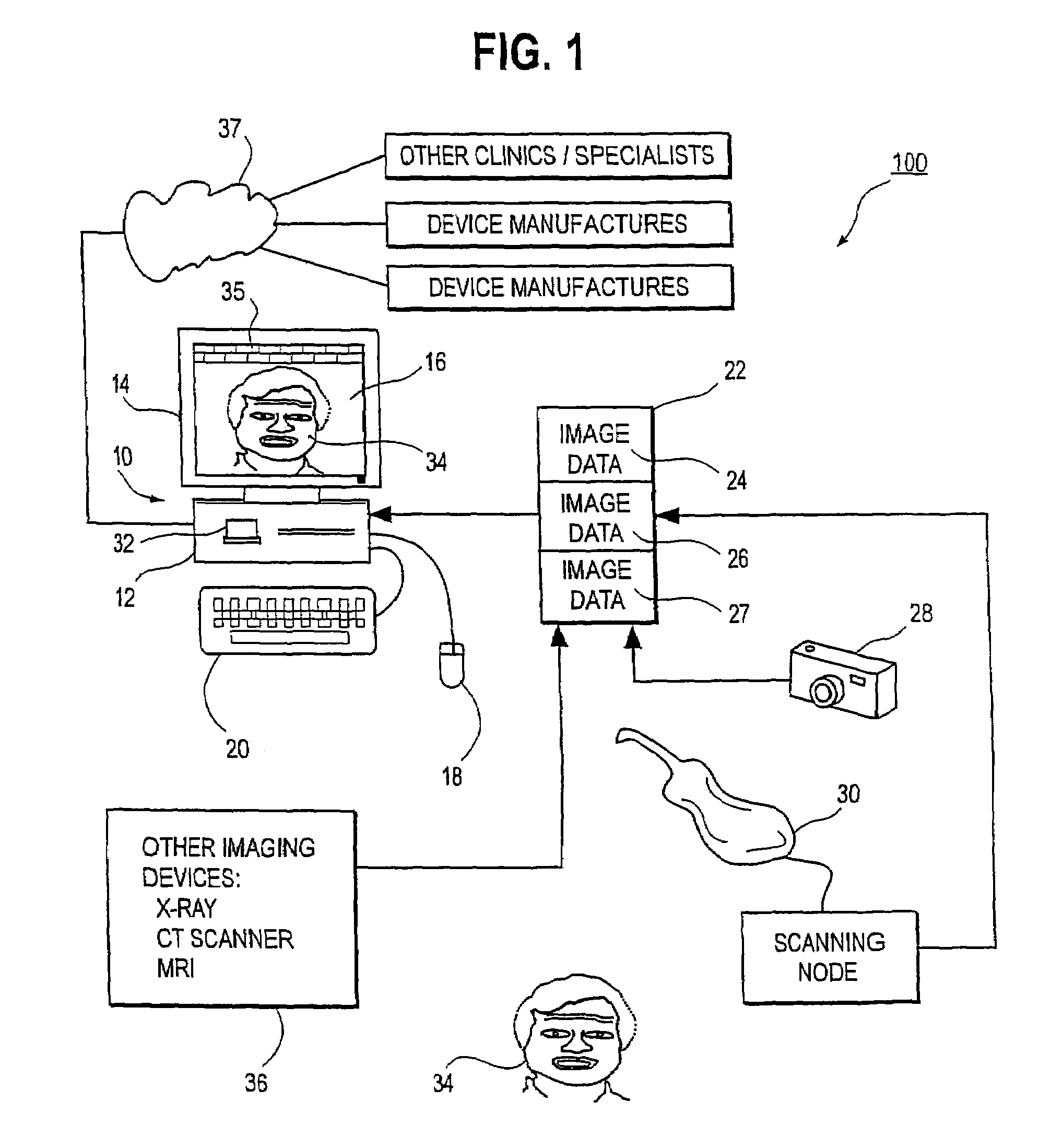

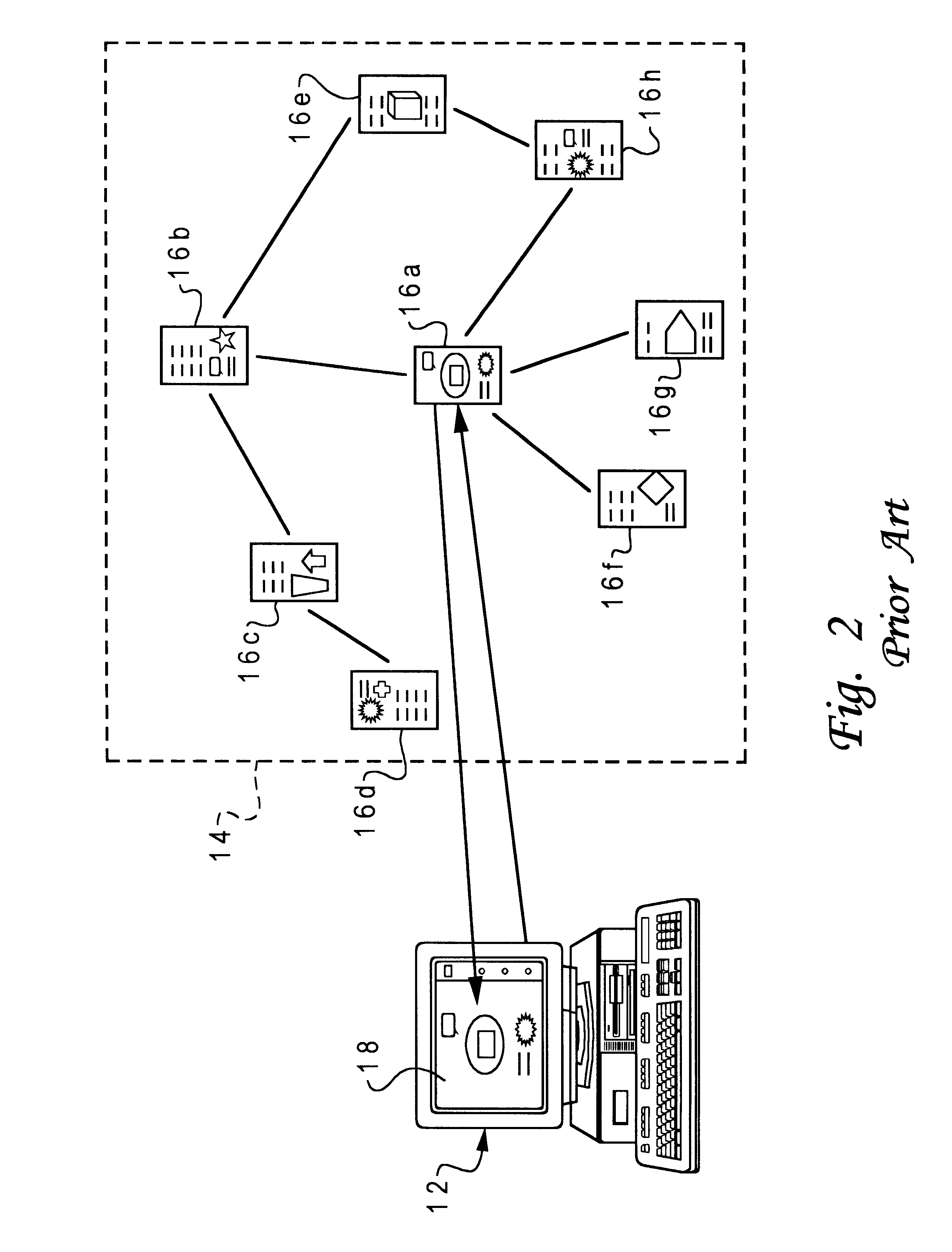

Unified workstation for virtual craniofacial diagnosis, treatment planning and therapeutics

InactiveUS7234937B2Quick analysisPowerful toolDental implantsImpression capsPlan treatmentPatient model

An integrated system is described in which digital image data of a patient, obtained from a variety of image sources, including CT scanner, X-Ray, 2D or 3D scanners and color photographs, are combined into a common coordinate system to create a virtual three-dimensional patient model. Software tools are provided for manipulating the virtual patient model to simulation changes in position or orientation of craniofacial structures (e.g., jaw or teeth) and simulate their affect on the appearance of the patient. The simulation (which may be pure simulations or may be so-called “morphing” type simulations) enables a comprehensive approach to planning treatment for the patient. In one embodiment, the treatment may encompass orthodontic treatment. Similarly, surgical treatment plans can be created. Data is extracted from the virtual patient model or simulations thereof for purposes of manufacture of customized therapeutic devices for any component of the craniofacial structures, e.g., orthodontic appliances.

Owner:ORAMETRIX

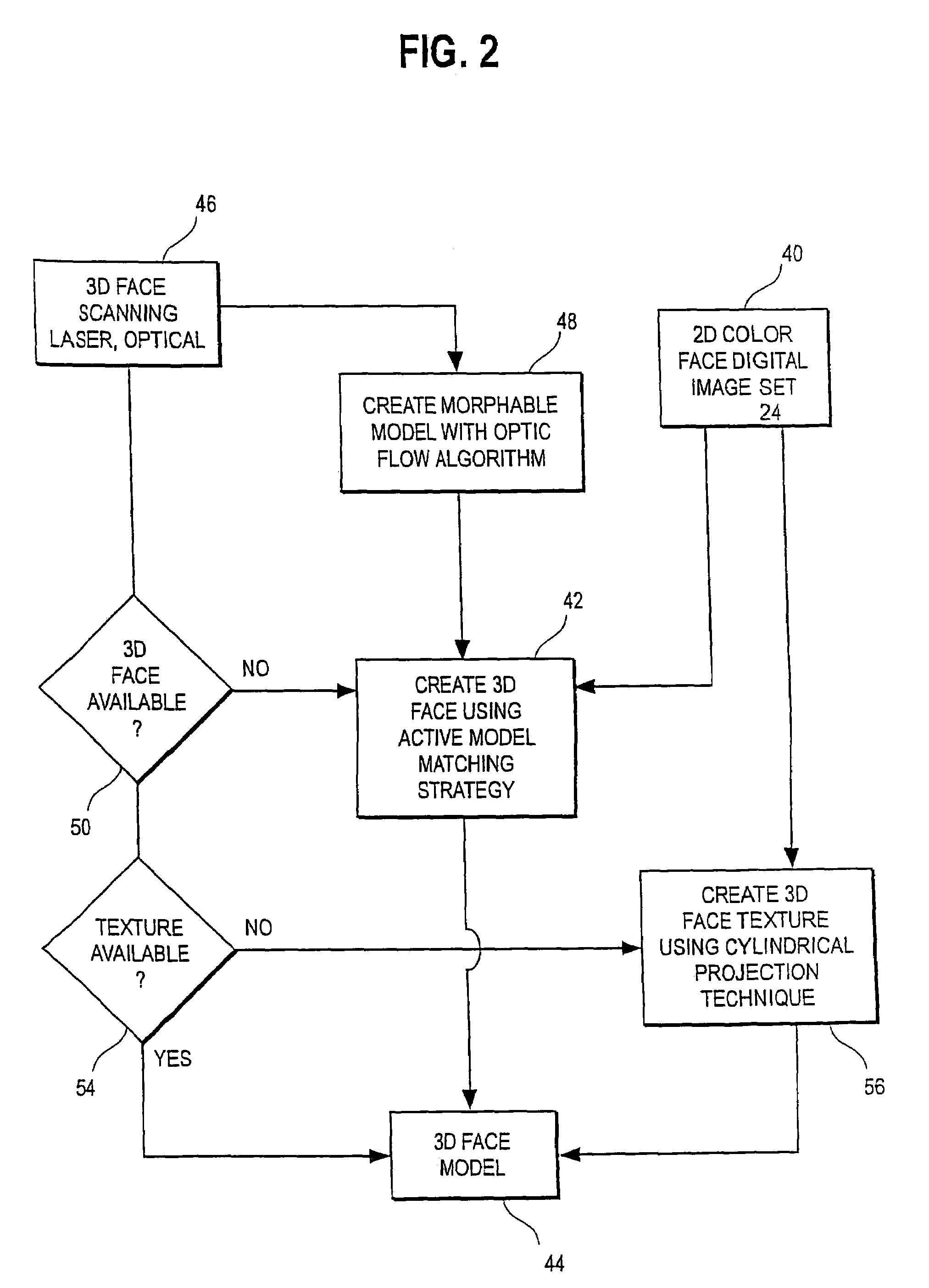

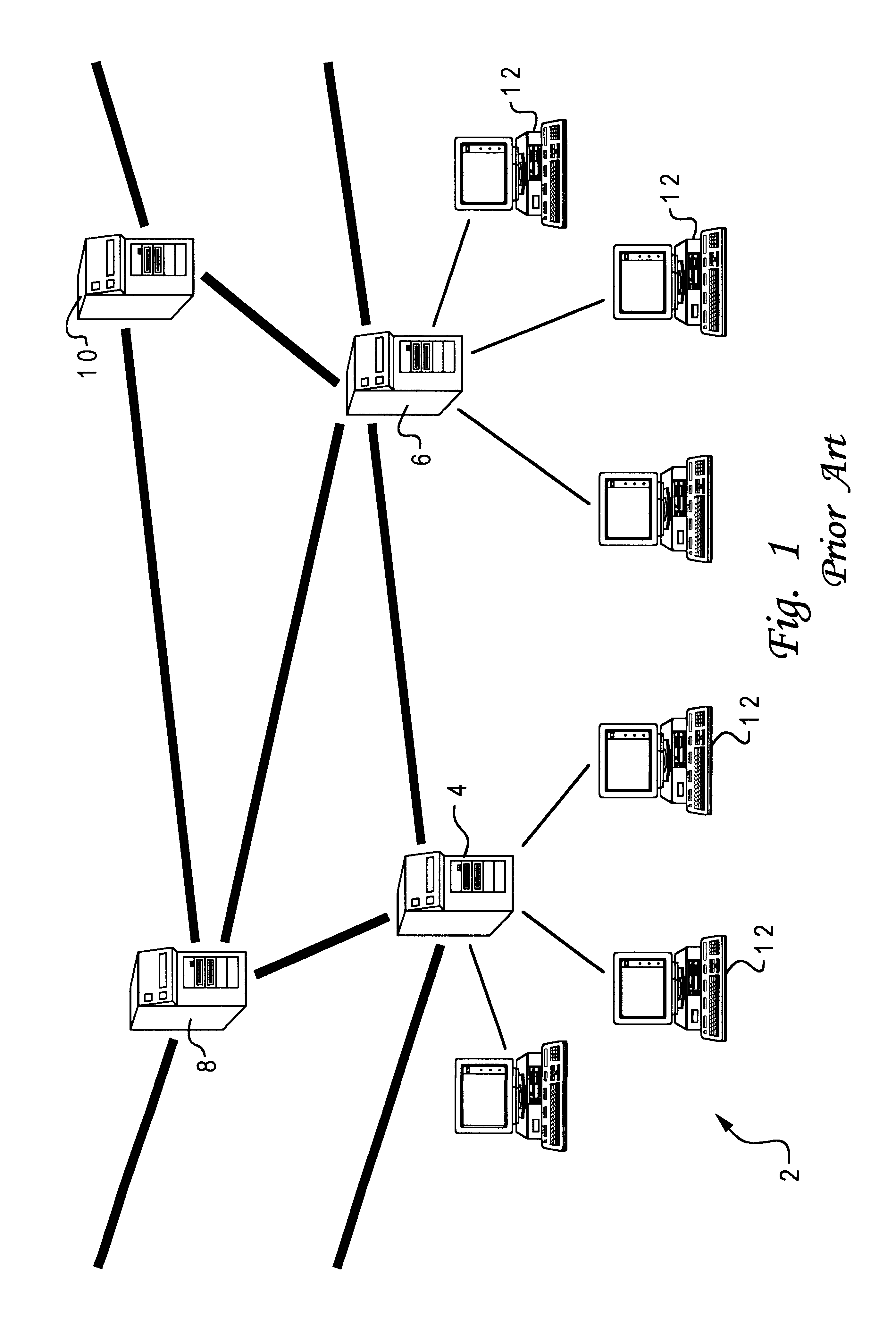

Method for parallel selection of URL's

InactiveUS6211874B1Digital data information retrievalMultiple digital computer combinationsDisplay deviceMulti link

A method of accessing files located in a computer system, by selecting a plurality of embedded links (such as hypertext links) from one or more pages displayed in a browser window, and processing the plurality of embedded links concurrently. The embedded links may include at least two embedded links from a single page displayed in the browser window, or may include at least one embedded link from a first page and at least one other embedded link from a second page. In one implementation, a pop-up menu is displayed once the links have all been selected, wherein the pop-up menu has a plurality of menu items associated with different types of link processing. The types of link processing include: concurrently displaying pages associated with the plurality of embedded links in a plurality of respective browser windows on the display; concurrently printing pages associated with the plurality of embedded links using a printing device of the computer system; or concurrently downloading pages associated with the plurality of embedded links, to a storage device of the computer system. Selection of the links may be facilitated by allowing the user to switch to a multi-link selection mode.

Owner:IBM CORP

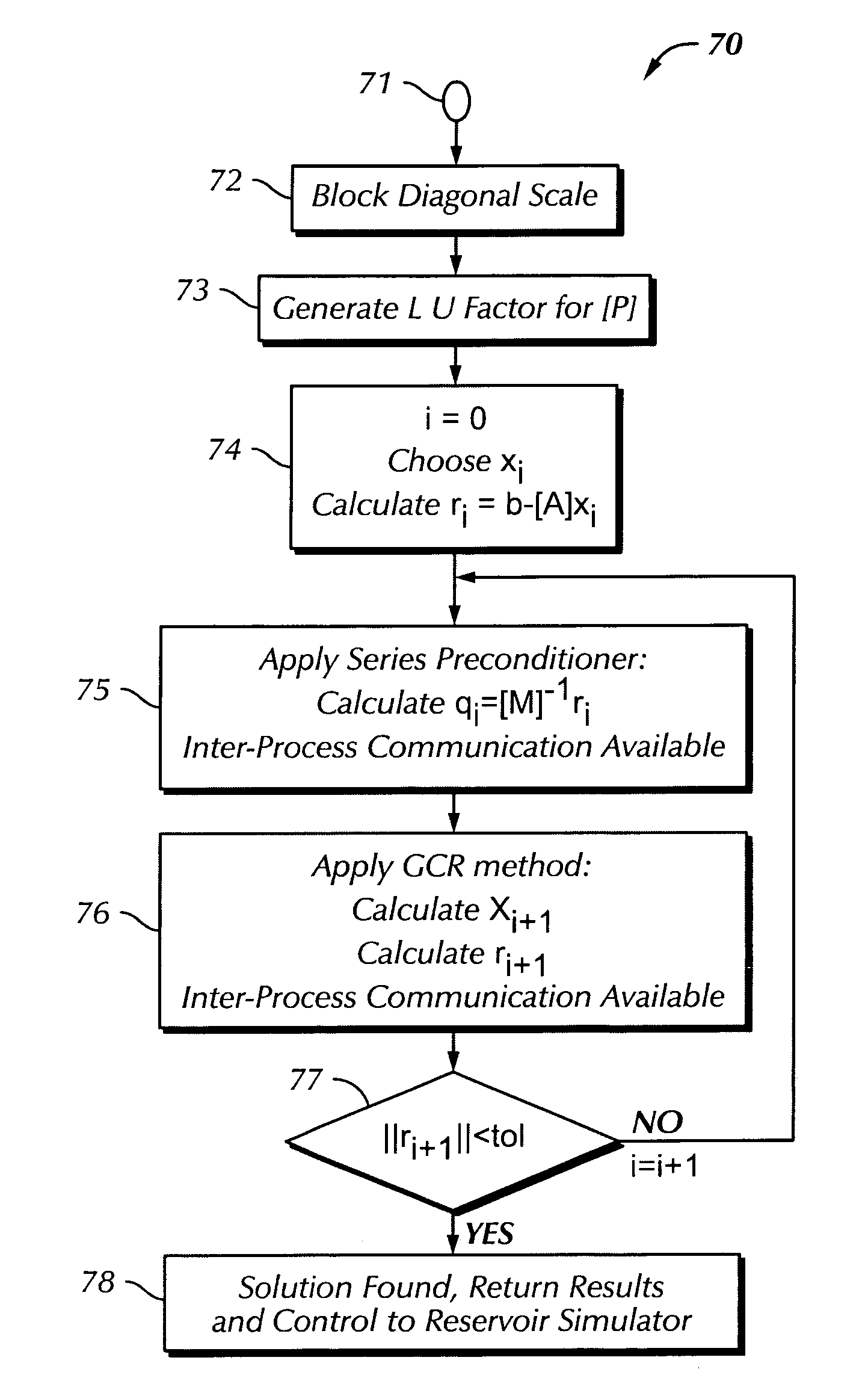

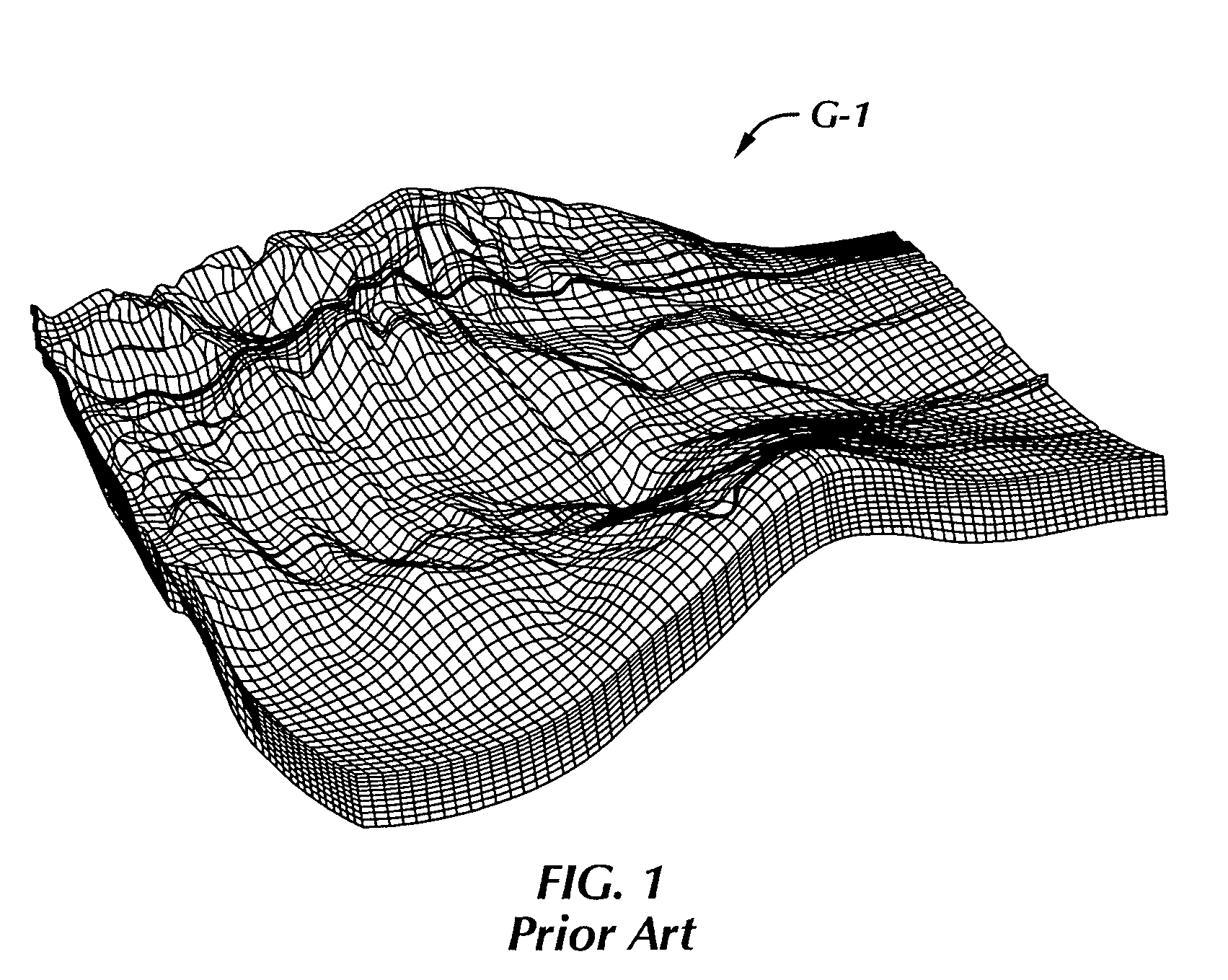

Solution method and apparatus for large-scale simulation of layered formations

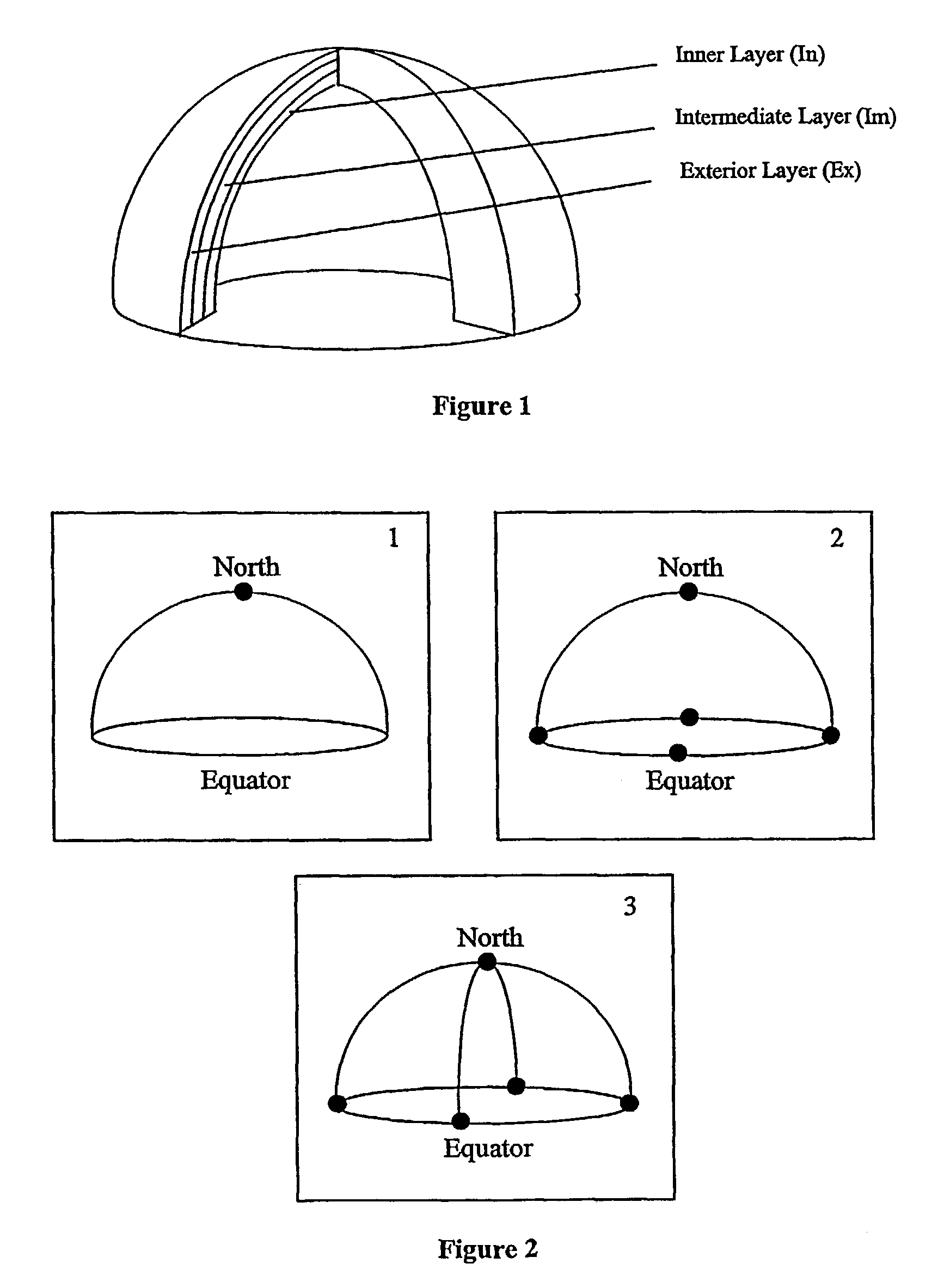

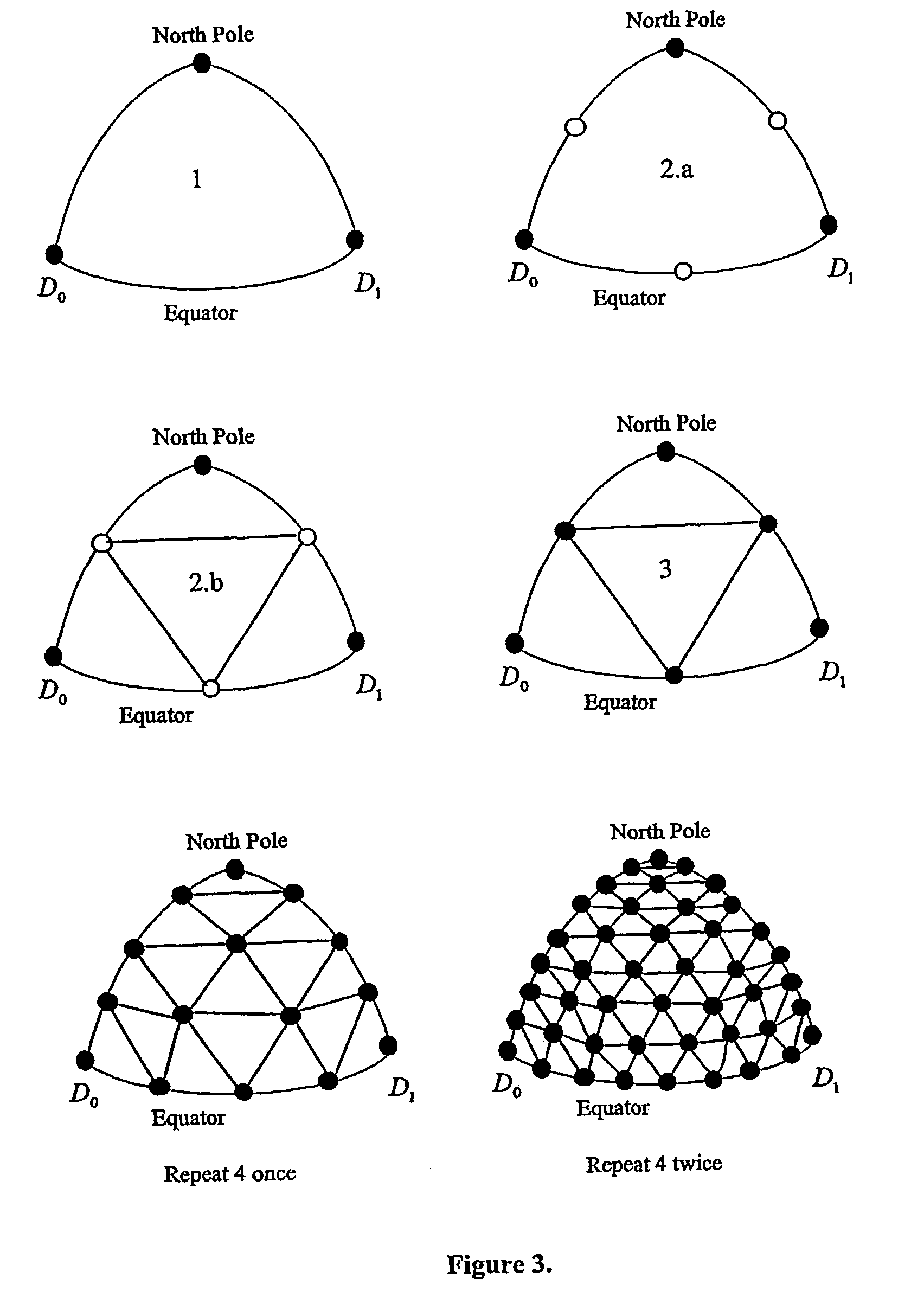

ActiveUS7596480B2Design optimisation/simulationSpecial data processing applicationsSupercomputerTypes of mesh

A targeted heterogeneous medium in the form of an underground layered formation is gridded into a layered structured grid or a layered semi-unstructured grid. The structured grid can be of the irregular corner-point-geometry grid type or the simple Cartesian grid type. The semi-unstructured grid is really unstructured, formed by arbitrarily connected control-volumes derived from the dual grid of a suitable triangulation; but the connectivity pattern does not change from layer to layer. Problems with determining fluid movement and other state changes in the formation are solved by exploiting the layered structure of the medium. The techniques are particularly suited for large-scale simulation by parallel processing on a supercomputer with multiple central processing units (CPU's).

Owner:SAUDI ARABIAN OIL CO

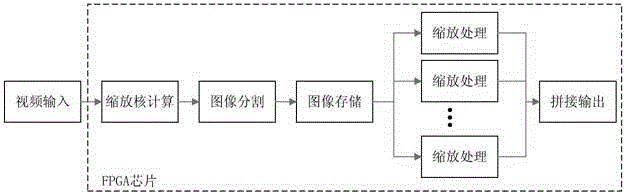

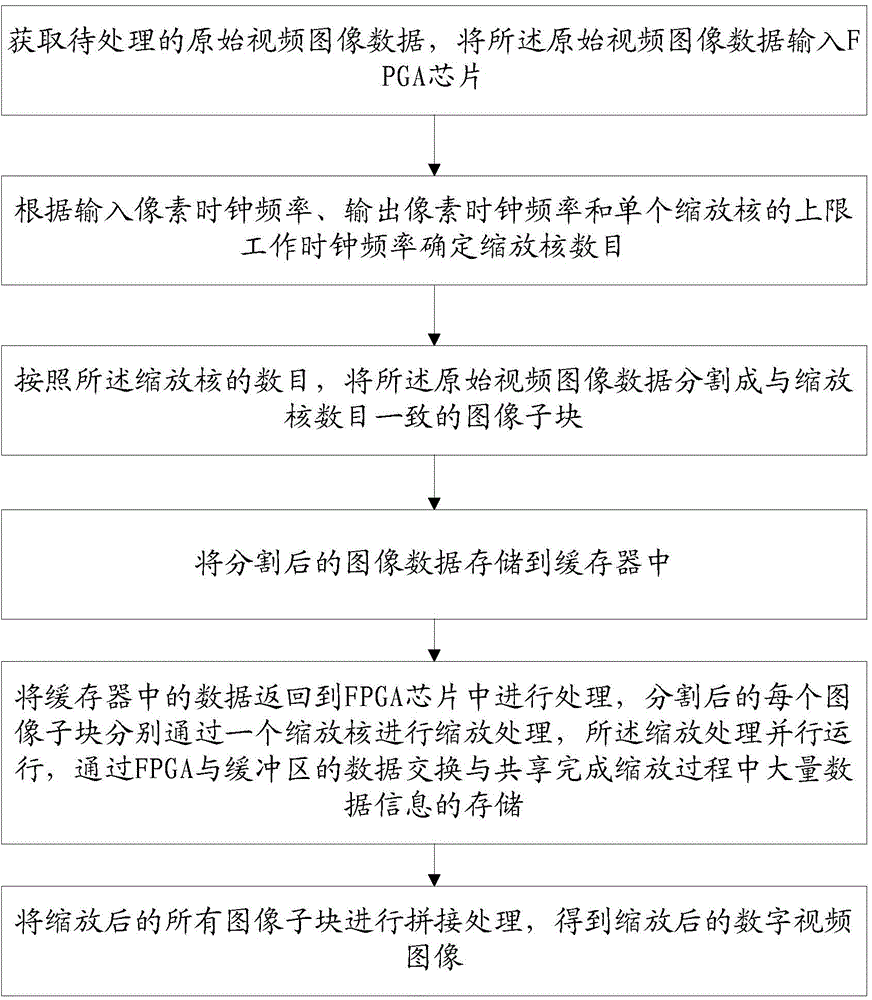

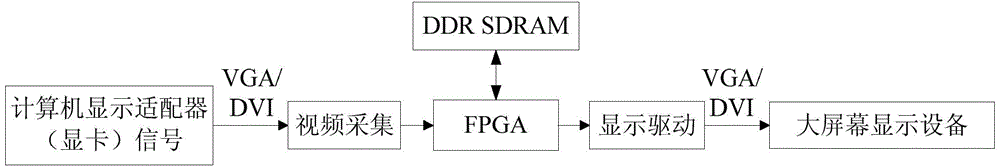

Parallel multi-core FPGA digital image real-time zooming processing method and device

InactiveCN104104888AReduce complexityGuaranteed uptimeTelevision system detailsColor television detailsDigital videoComputer graphics (images)

Provided is a parallel multi-core FPGA digital image real-time zooming processing method and device. The method comprises the steps that original video image data to be processed are acquired firstly. The original video image data are inputted to an FPGA chip and the number of zooming cores is confirmed, and the original video image data are divided into image sub-blocks having the same number with that of the zooming cores. Then the divided data are stored in a buffer, the data in the buffer are returned to the FPGA and parallel zooming processing is performed on each image sub-block via one zooming core respectively so that zooming is completed. All the image sub-blocks after zooming are displayed after splicing processing. The method has certain guiding effect on high throughput and high real-time application of digital video images.

Owner:DALIAN NATIONALITIES UNIVERSITY

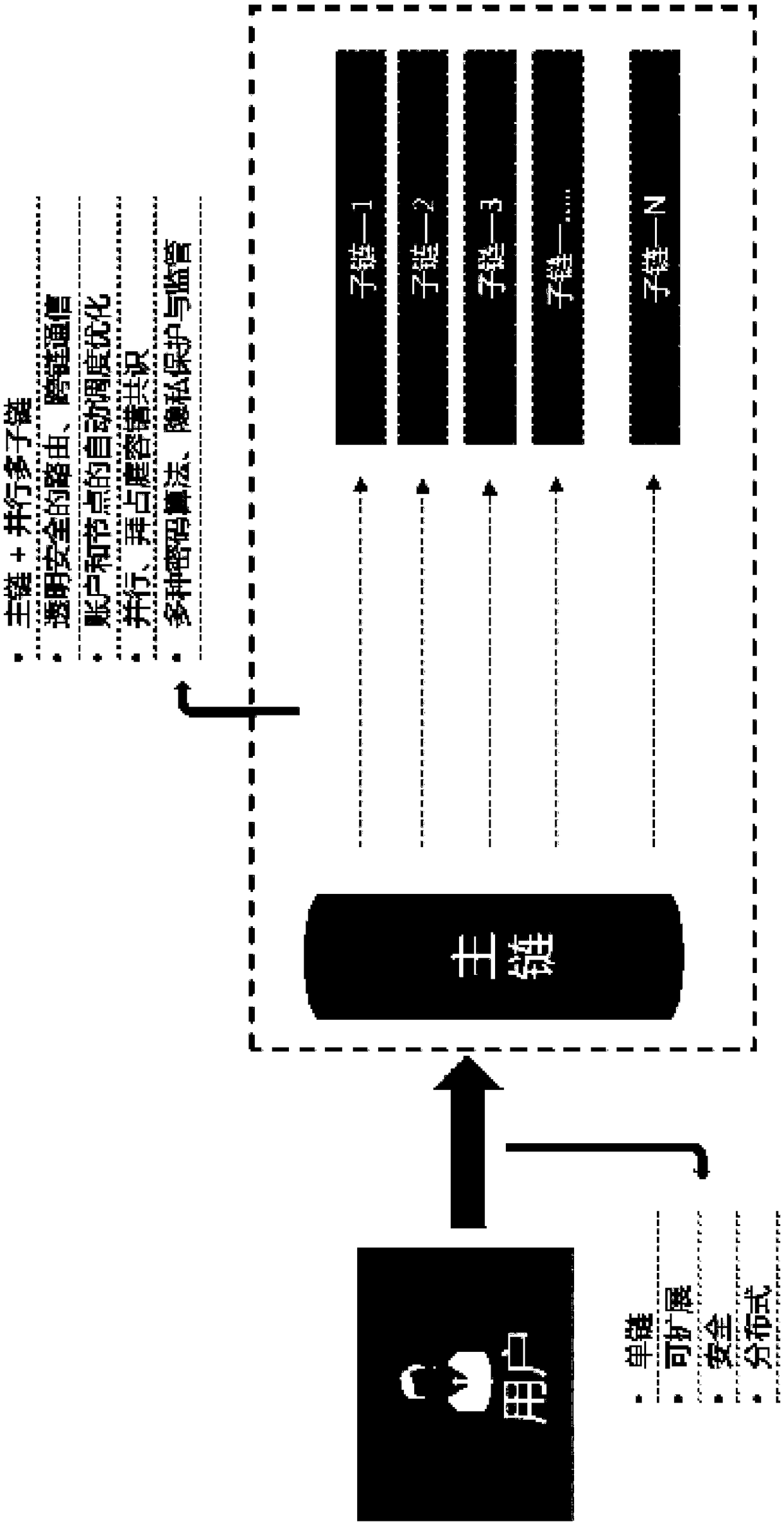

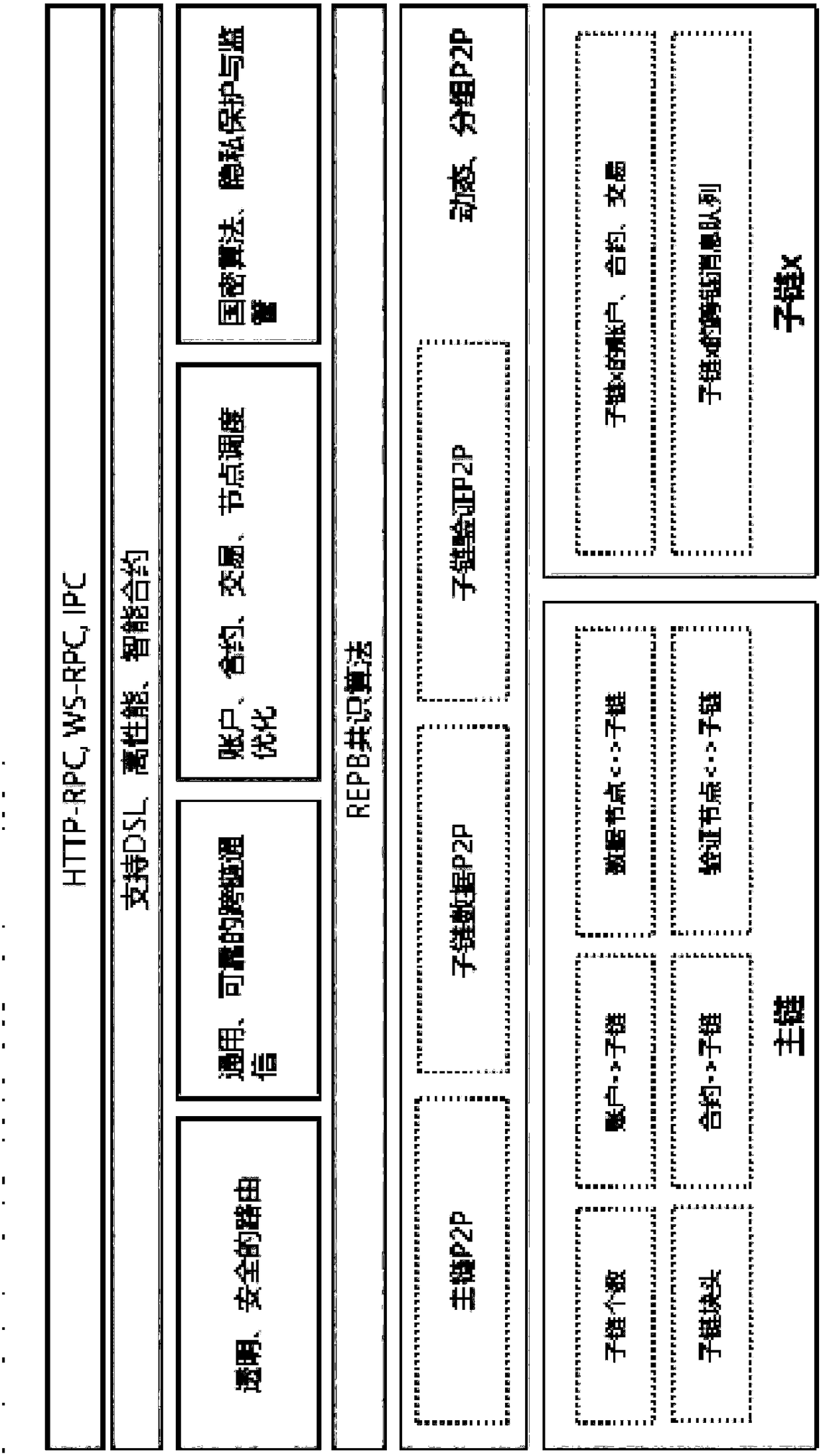

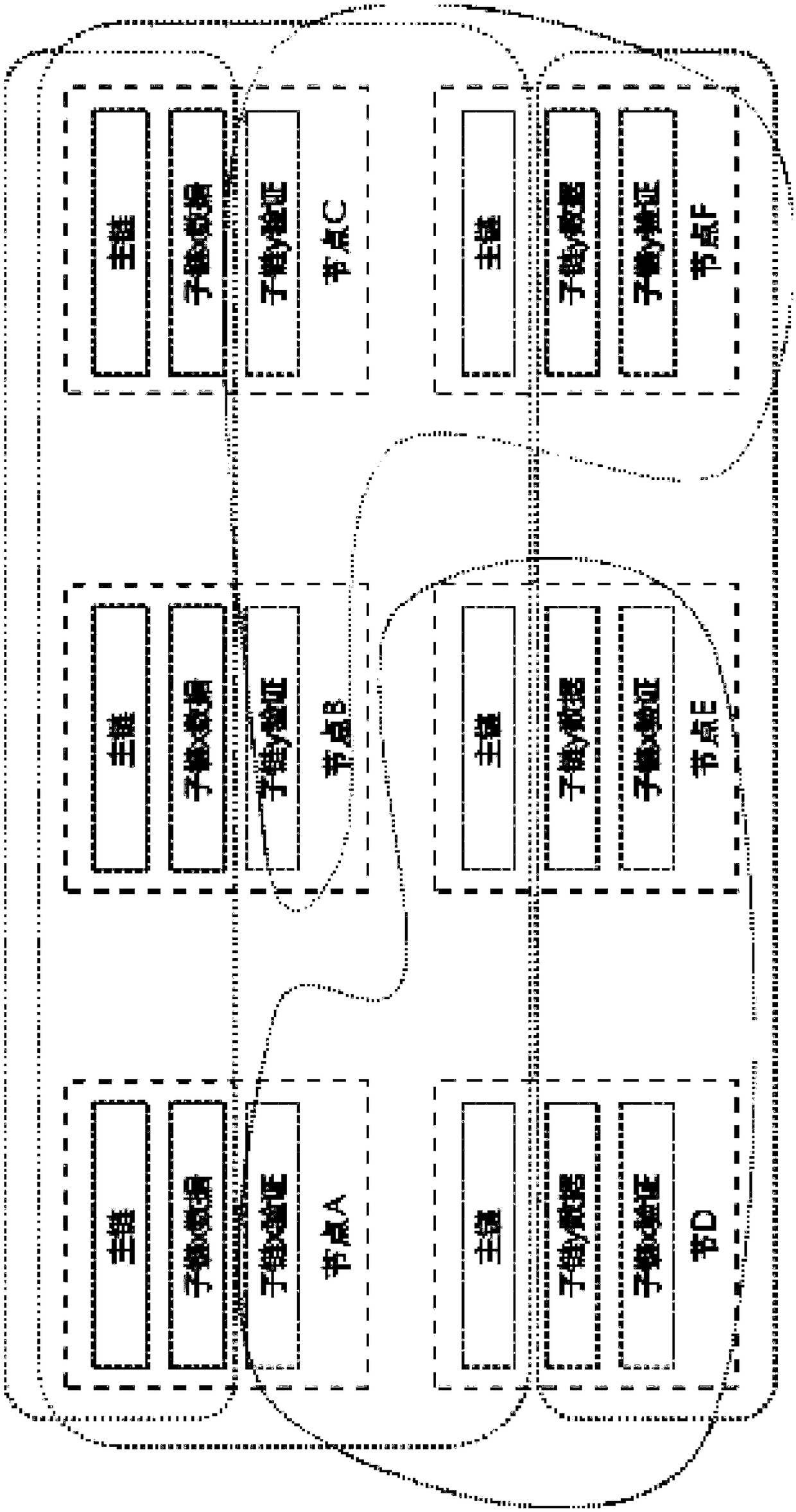

REPB consensus based on block chain backbone plus parallel multi-subchains

ActiveCN109508982AFix security issuesImprove scalabilityEncryption apparatus with shift registers/memoriesPayment protocolsByzantine fault toleranceMulti link

The invention is based on the REPB consensus of the block chain main chain and the parallel multi-sub-chain, and solves the problems of safety and decentralization by randomly selecting the consensusnode, and has high scalability. Encryption is performed to ensure the security of random values. Parallel processing of multi-linked data is carried out to solve performance problems. Byzantine fault-tolerant mechanism to quickly reach consensus, prevent bifurcation, and solve performance problems. Through an effective fusion of the above four technologies, the problems of decentralization, security and performance in the consensus algorithm are solved.

Owner:北京蓝石环球区块链科技有限公司

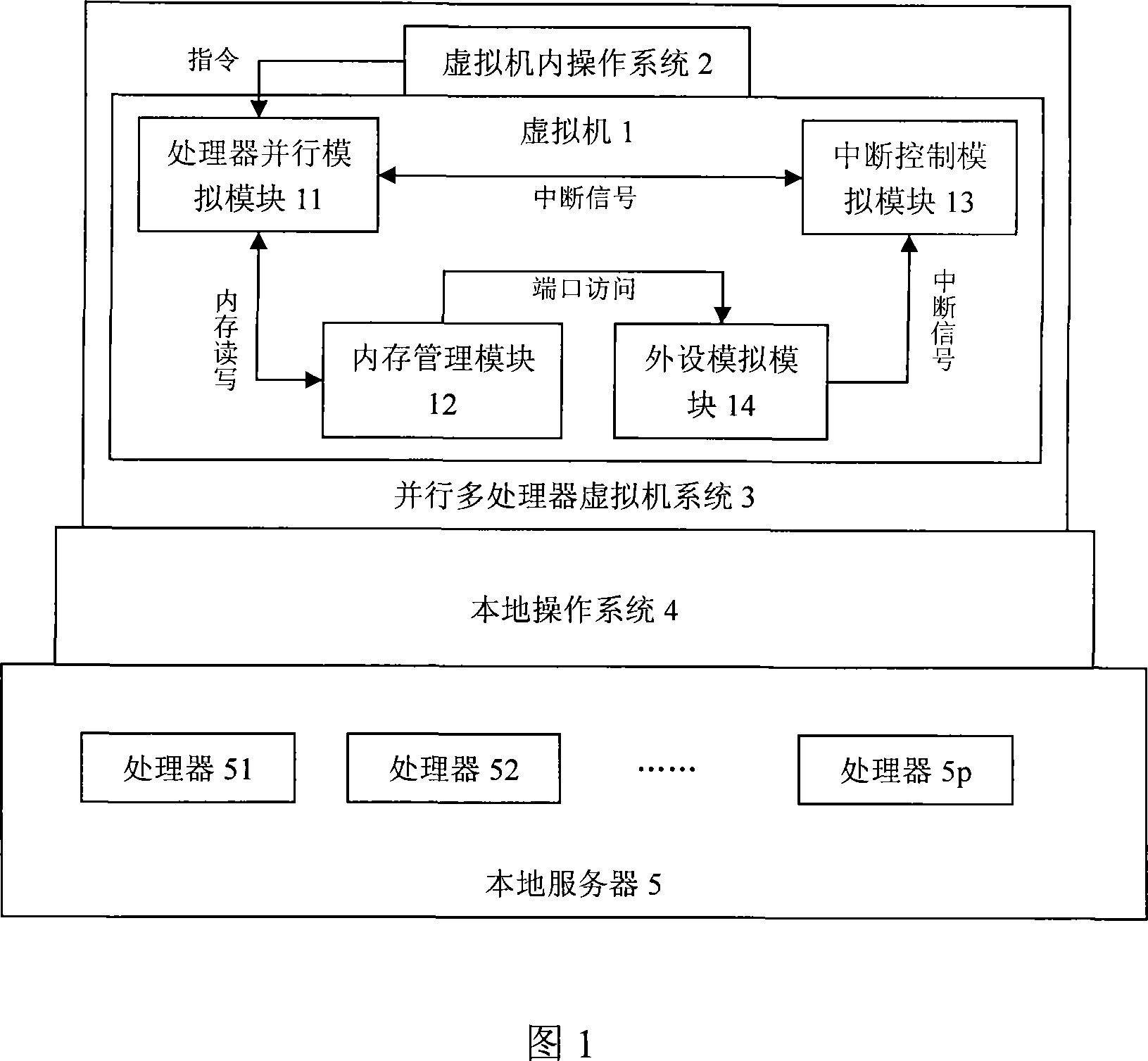

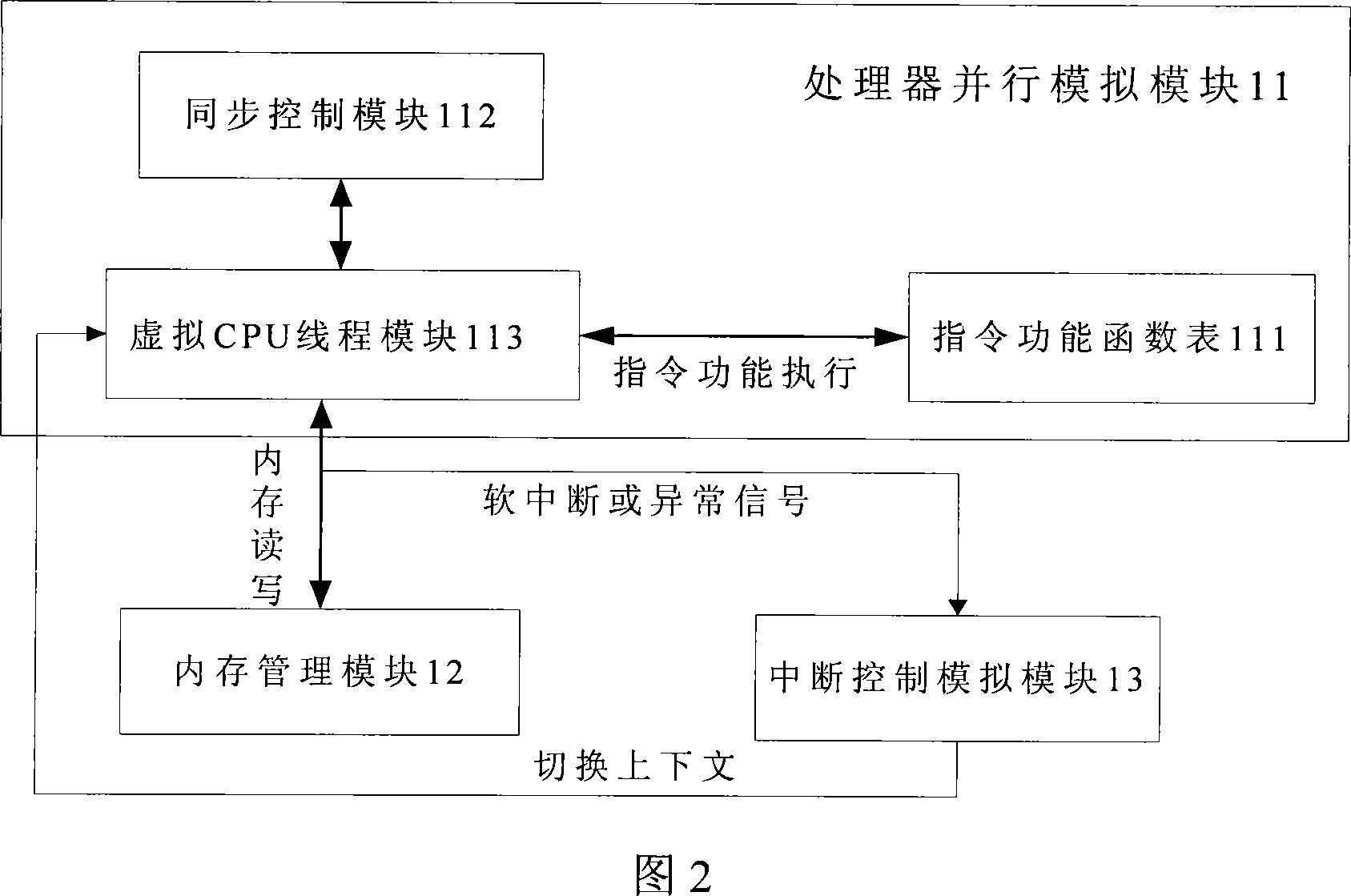

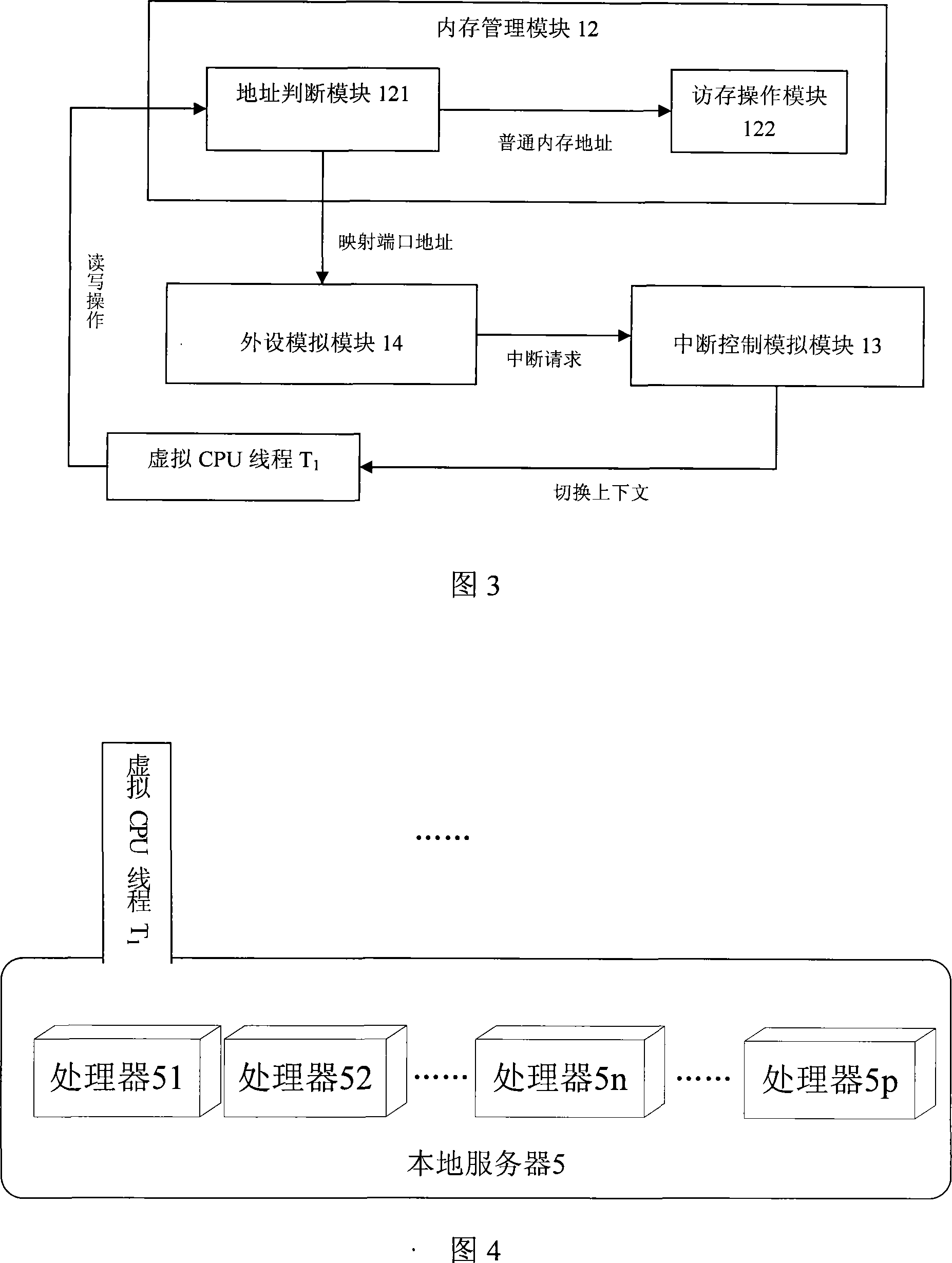

Paralleling multi-processor virtual machine system

InactiveCN101183315AMake the most of processing resourcesIncrease workloadMultiprogramming arrangementsSoftware simulation/interpretation/emulationOperational systemMulti processor

The invention discloses a concurrent multiprocessor virtual machine system supporting CPU simultaneous execution, which comprises a virtual machine and an operating system running on the virtual machine. The virtual machine system can simulate not less than one virtual processor, which comprises a processor concurrent simulation module, a memory management module, an interrupt controlling simulation module and a peripheral simulation module; the machine instruction of the operating system is transferred to the processor simulation module through the memory management module of the virtual machine; the processor simulation module can simulate multiple virtual processors used for executing the operating system instruction translated by an instruction translation module and make the processors concurrently execute; the invention also provides a synchronous and access control algorithm in the concurrent execution process; and the peripheral simulation module and the processor simulation module are coordinated by the interrupt controlling simulation module. The invention has the advantages of suitability for simulating a concurrent execution environment of complete simulating hardware on an SMP server or a multi-core server.

Owner:HUAZHONG UNIV OF SCI & TECH

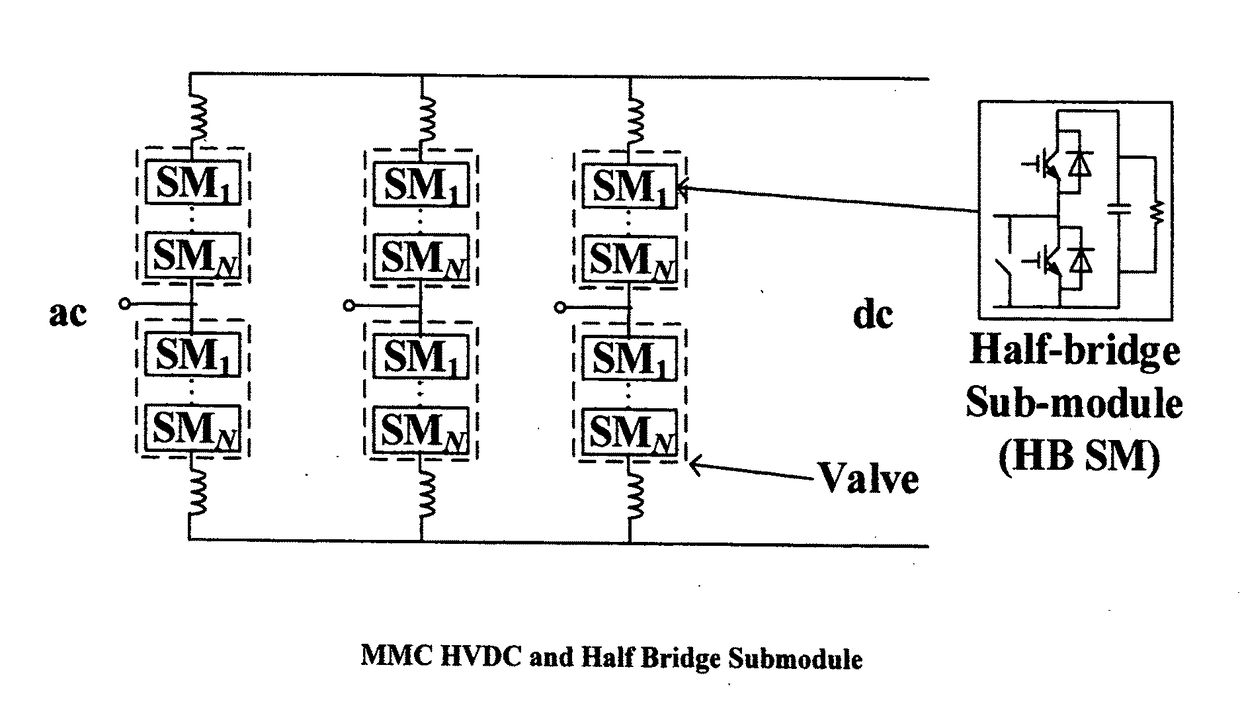

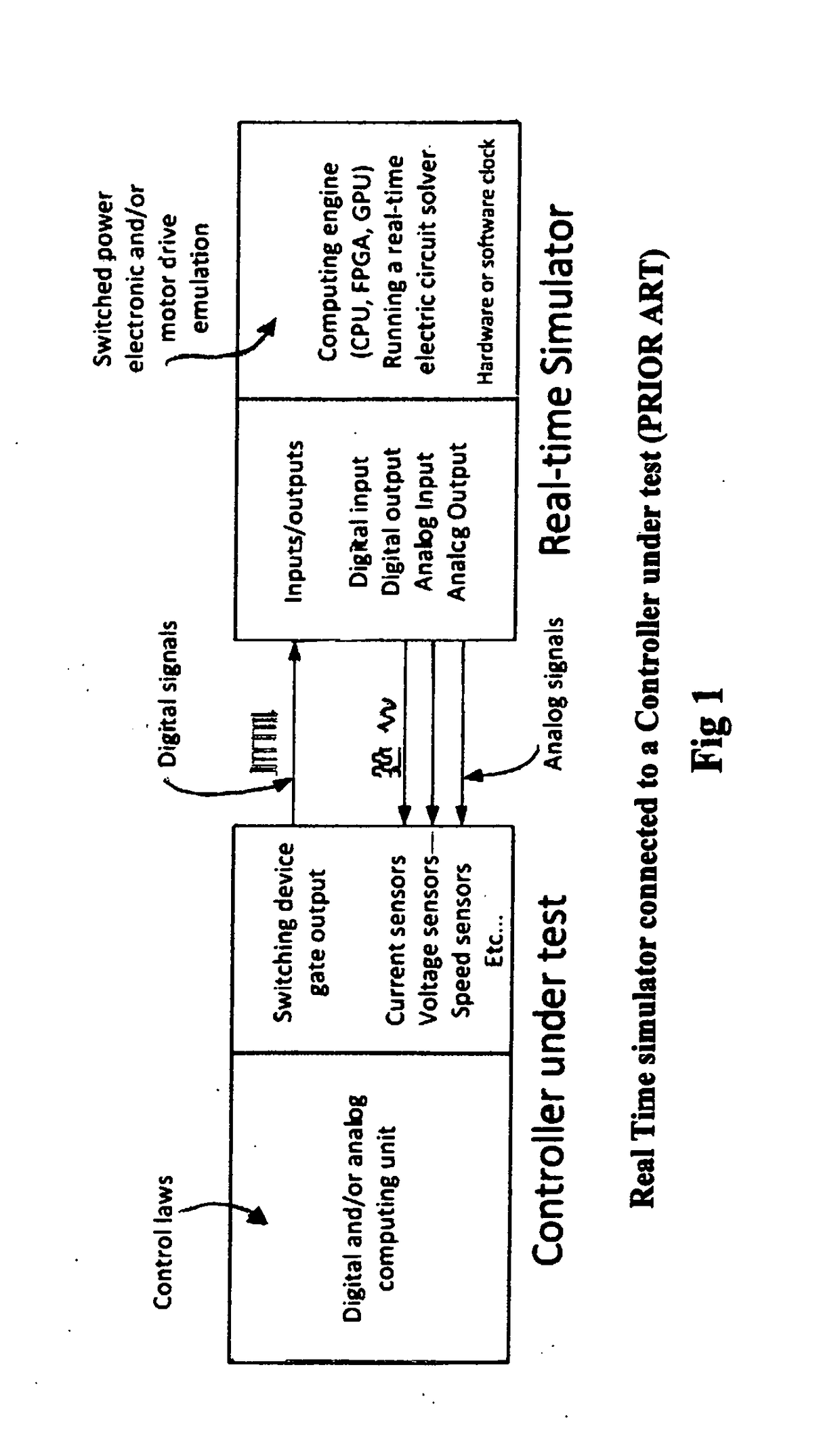

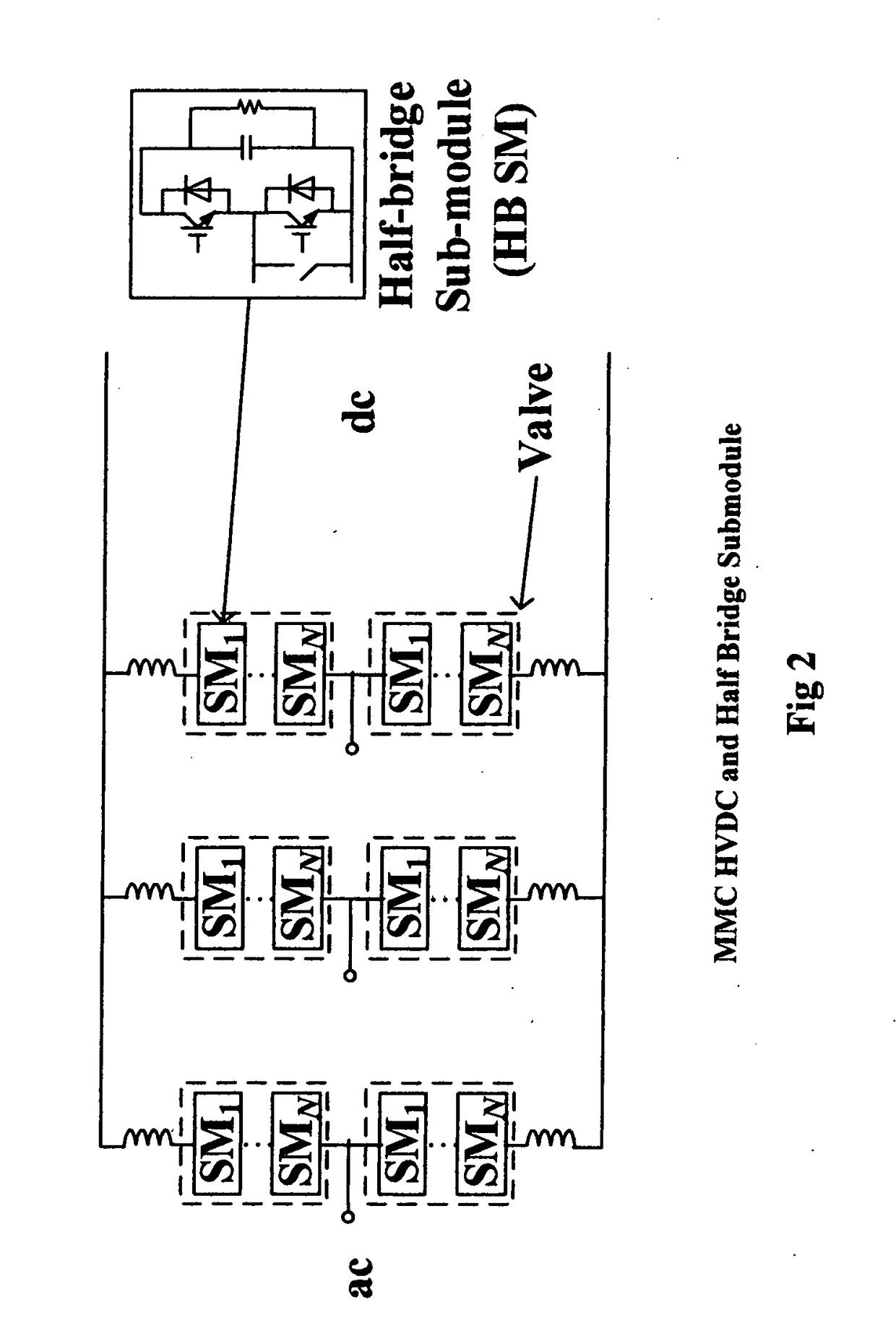

Apparatus and method for modelling a modular multilevel converter in an electronic simulator

ActiveUS20170132337A1Easy and faster functionallyImprove efficiencyAc-dc conversionDesign optimisation/simulationReal-time simulationModularity

Method and apparatus for simulating a MMC system in an electronic simulator uses a computing unit and a connected input / output interface. The electronic simulator comprises a simulation model of a modular multilevel converter (MMC) system including at least one MMC valve, each MMC valve including a plurality of connected converter-submodules (SMs), each SM preferably comprising at least two controlled switches, a capacitor and auxiliary switches. The inventive approach replaces each MMC valve by an equivalent circuit whereby each SM in the valves may be solved separately. Multiple computing units are used to simulate those SMs in parallel, thus achieving fast or real-time simulation speed. The computing unit may comprise multiple computing means using CPU cores, FPGA or GPU cores and combinations thereof. The present inventive method keeps the model-detail including its precision, and enables a real time simulator to achieve fast or real-time speed for very large MMC system-simulations.

Owner:OPAL RT TECH INC

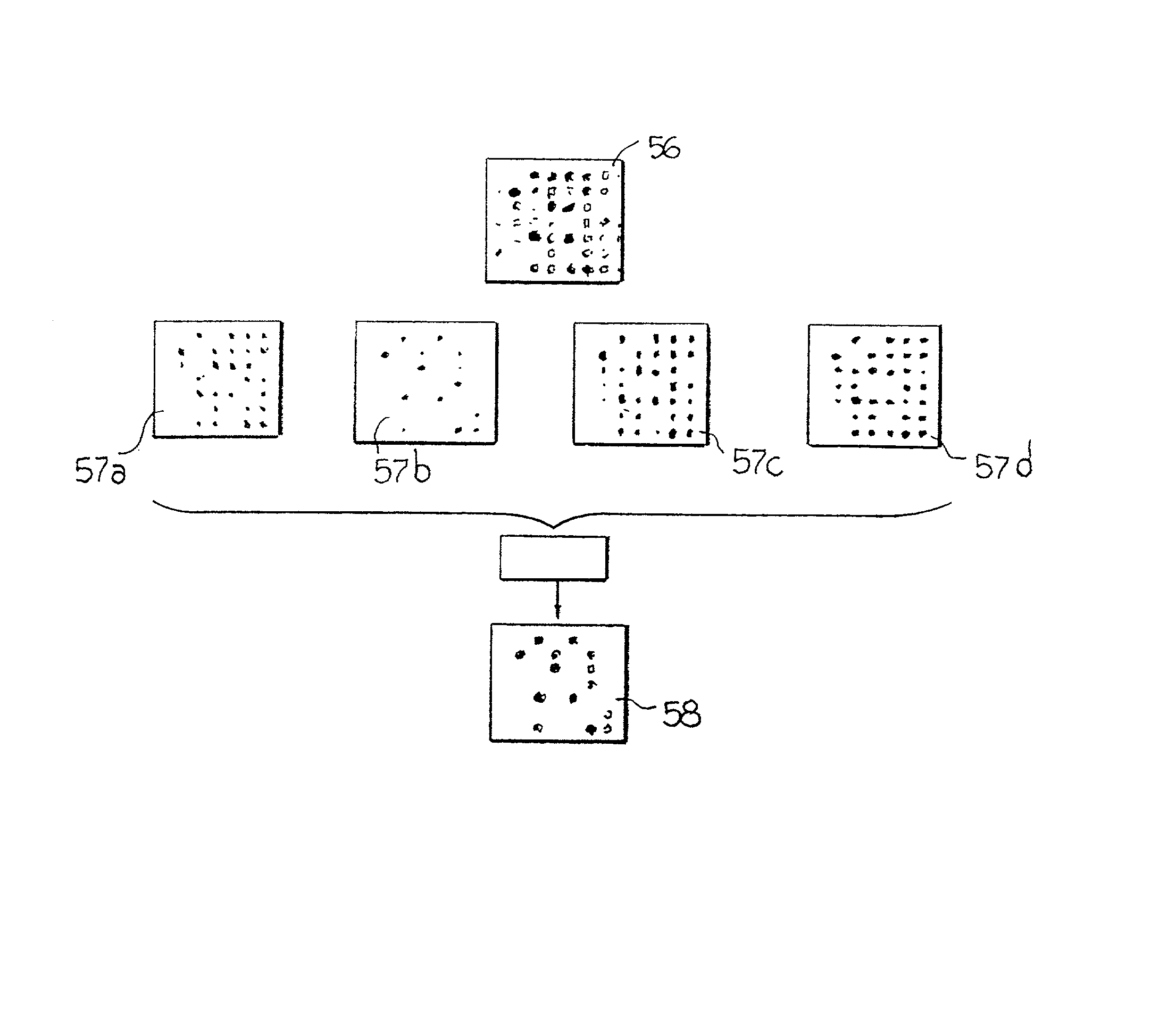

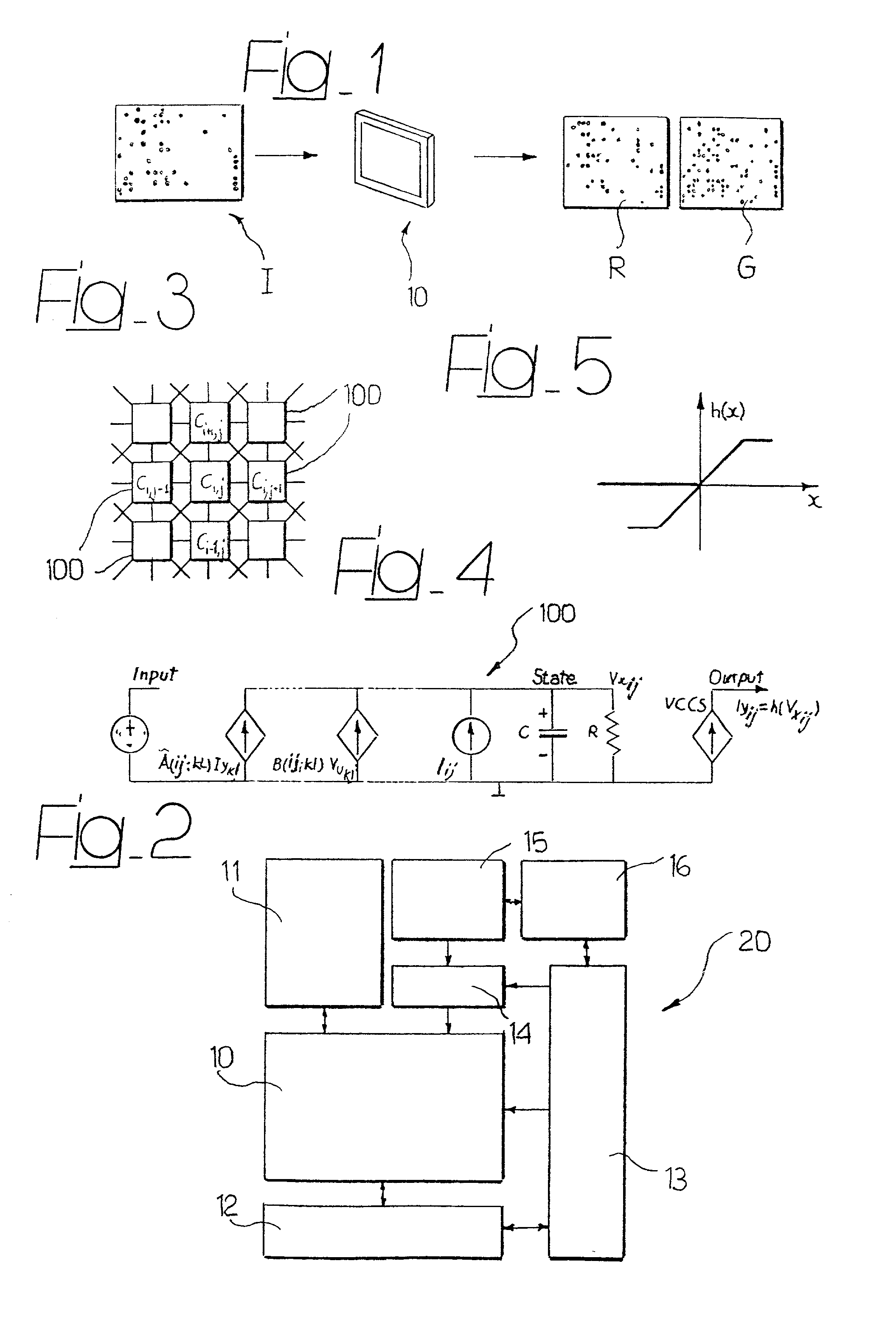

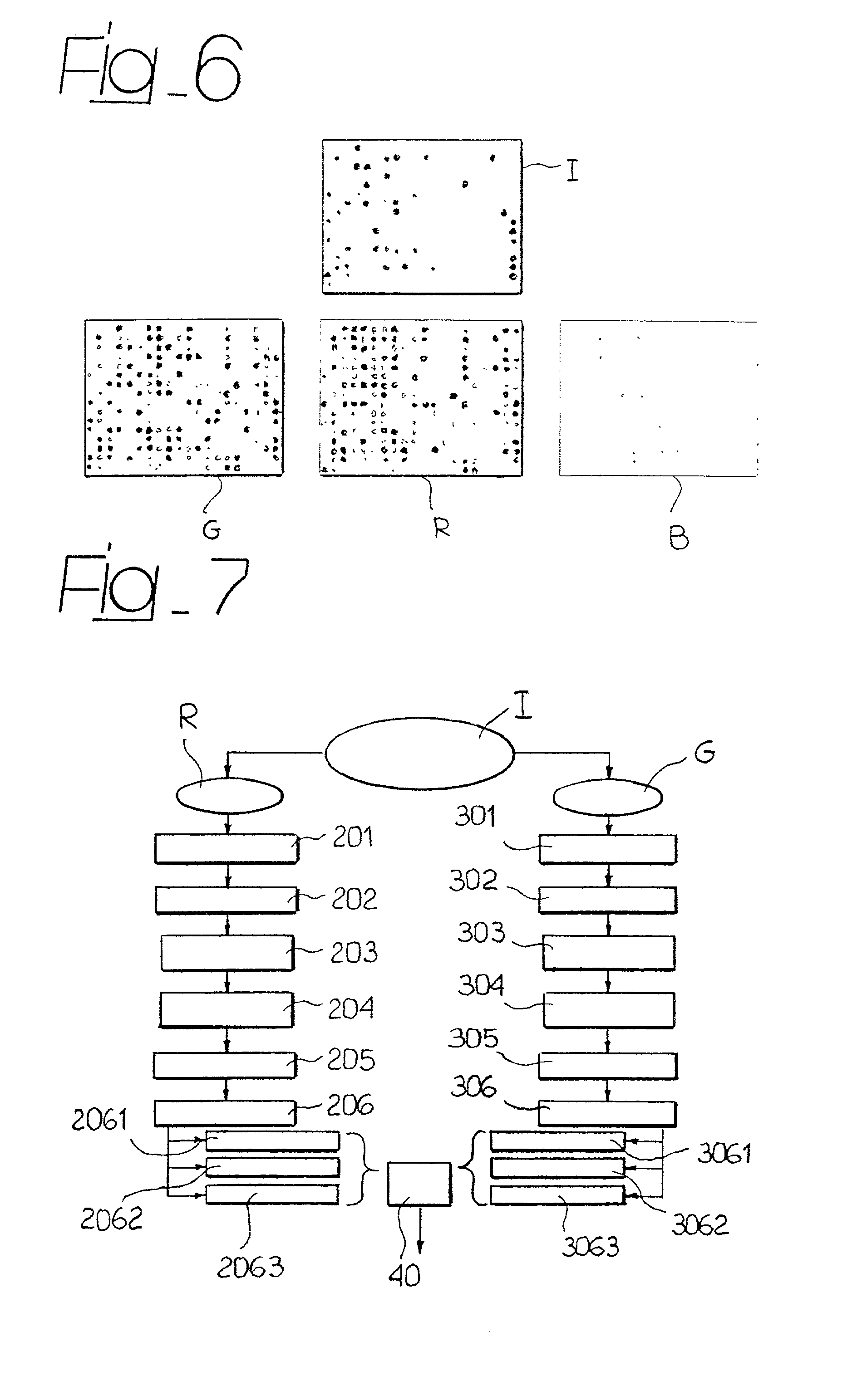

System for the automatic analysis of images such as DNA microarray images

InactiveUS20020097900A1Efficient and rapid automatic analysis of imageImage enhancementBioreactor/fermenter combinationsCMOSDNA microarray

The system can be used for the automatic analysis of images (I), comprising a matrix of spots, such as images of DNA microarrays after hybridisation. The system can be associated-and preferably integrated in a single monolithic component implementing VLSI CMOS technology-to a sensor (10) for acquiring said images (I). The system comprises a circuit (20) for processing the signals corresponding to the images (I), configured according to a cellular neural network (CNN) architecture for the parallel analogue processing of signals.

Owner:STMICROELECTRONICS SRL

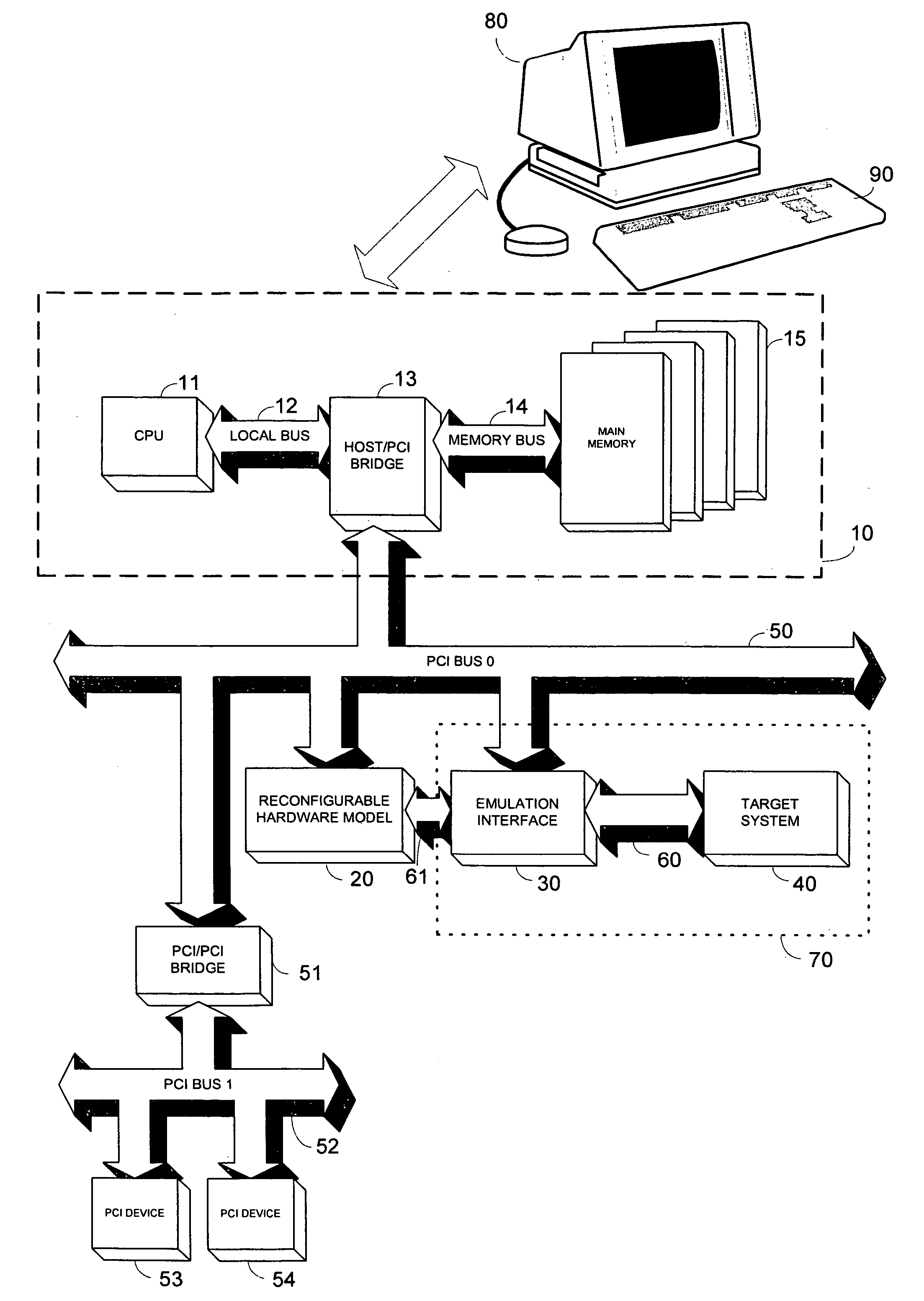

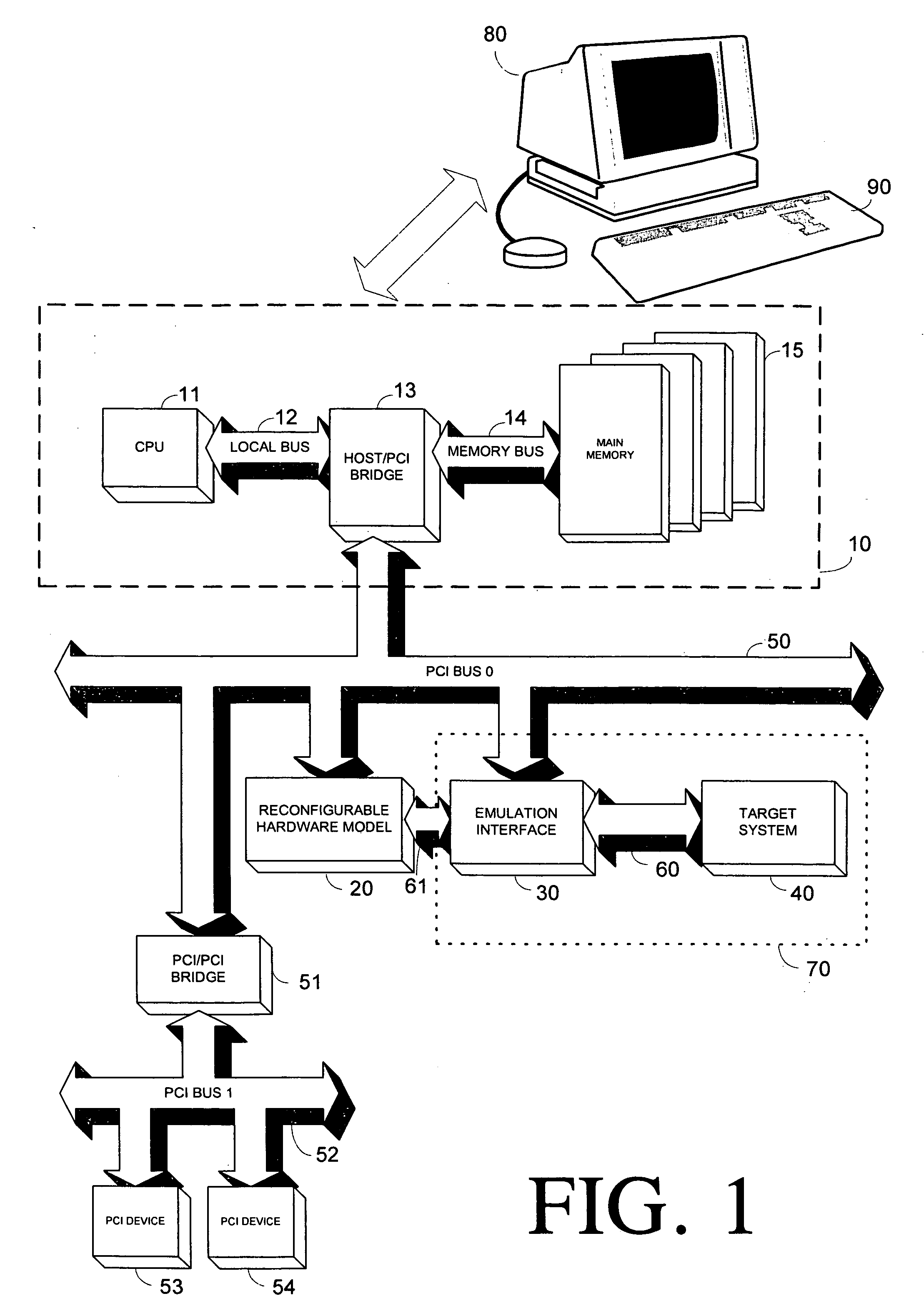

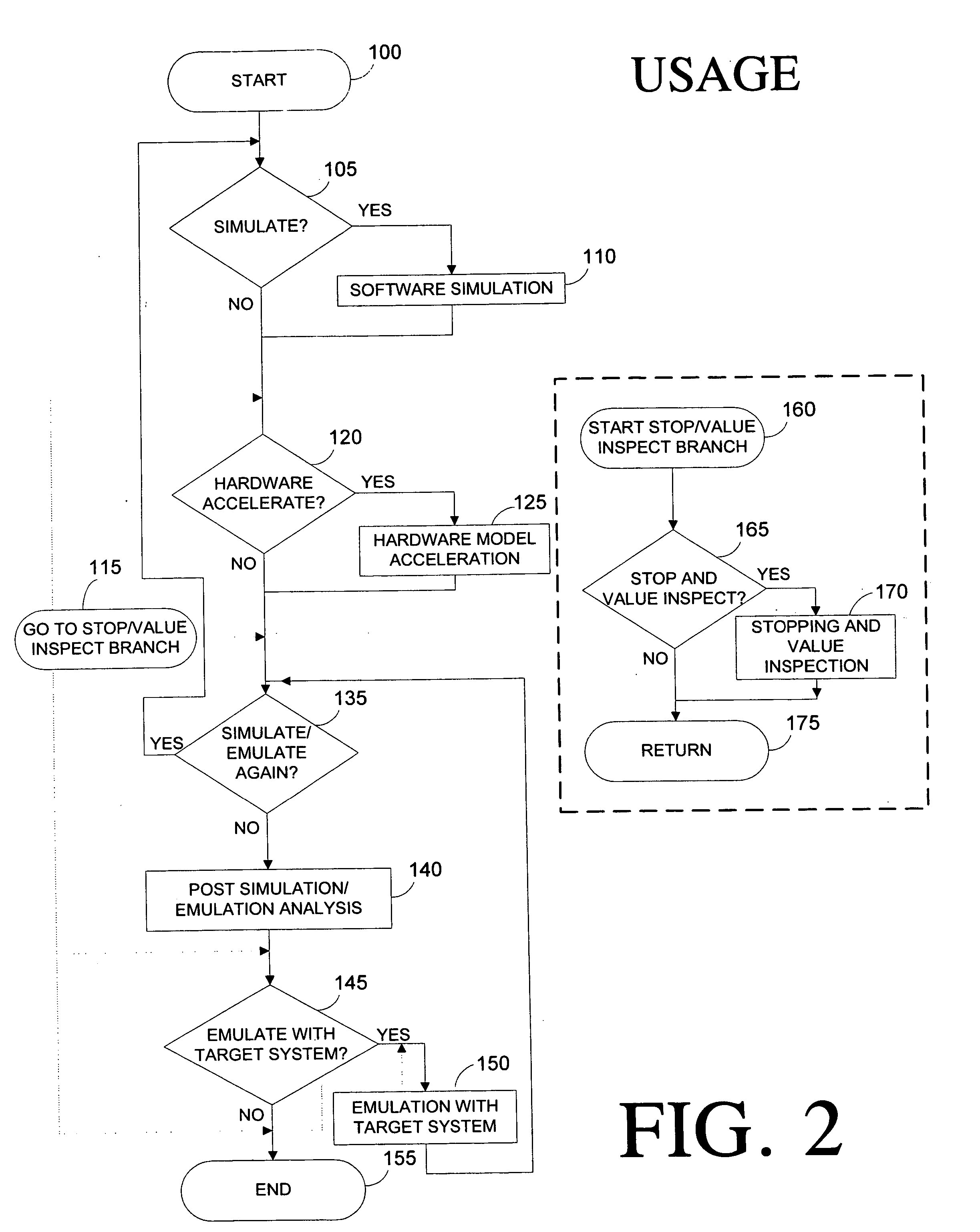

VCD-on-demand system and method

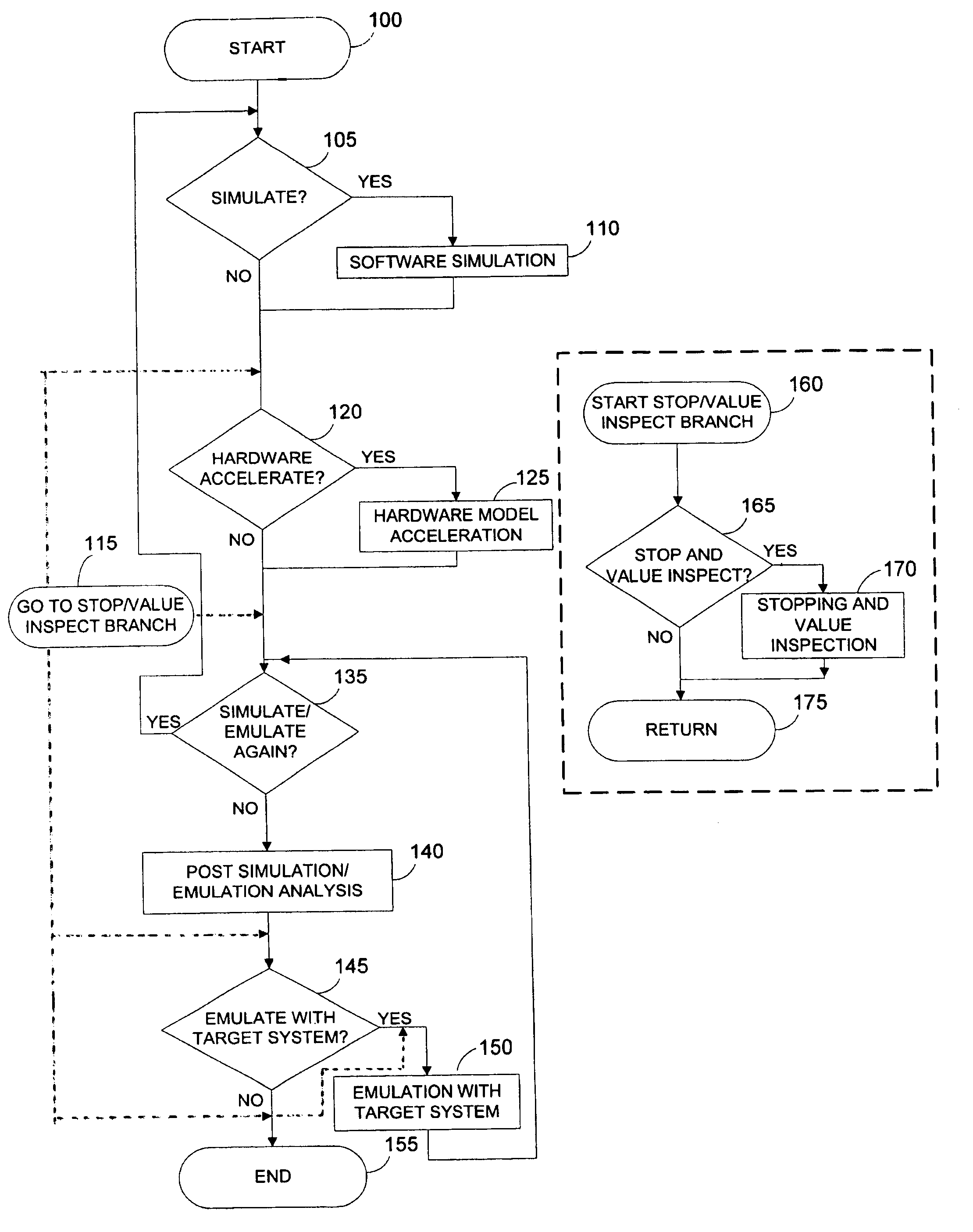

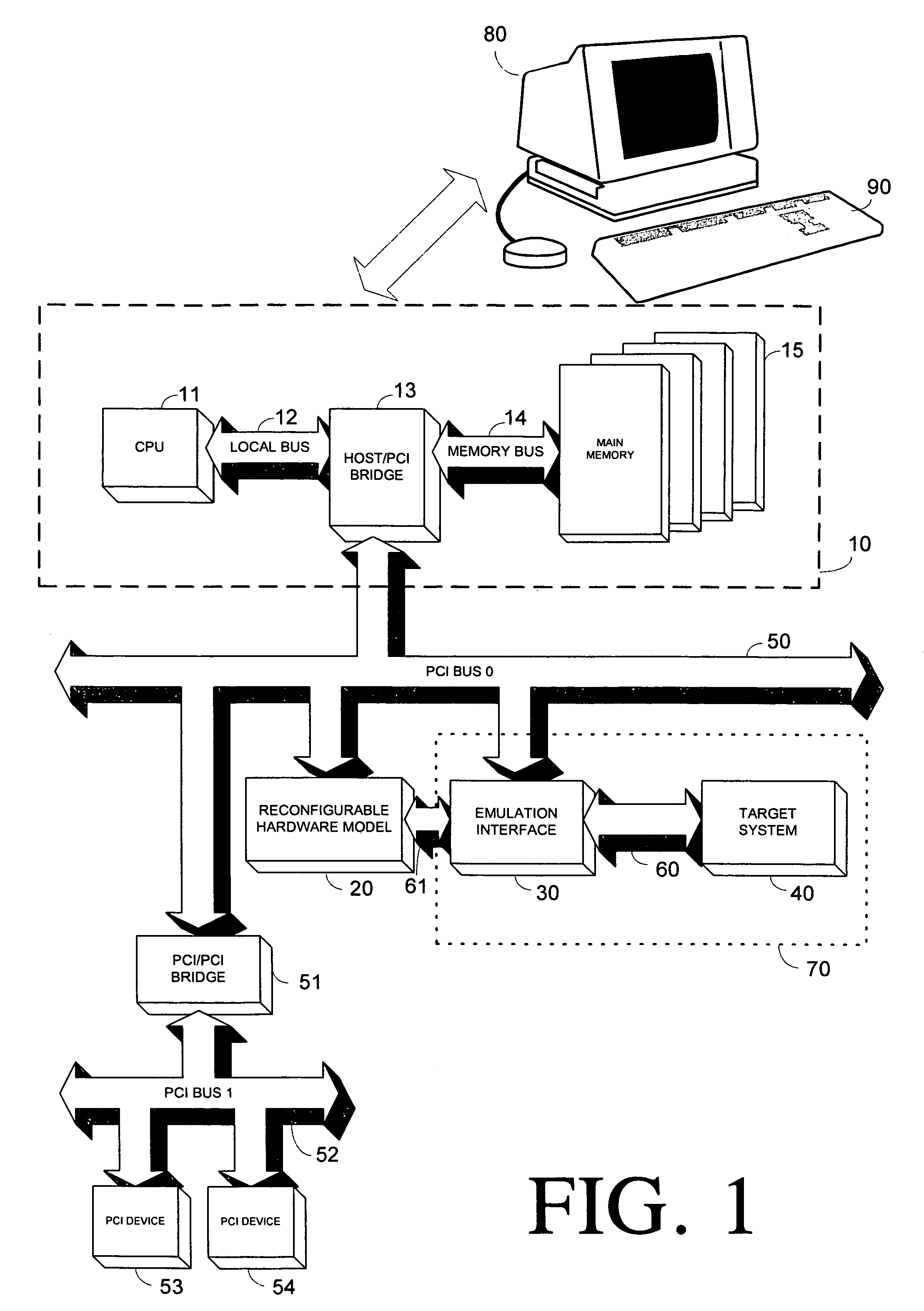

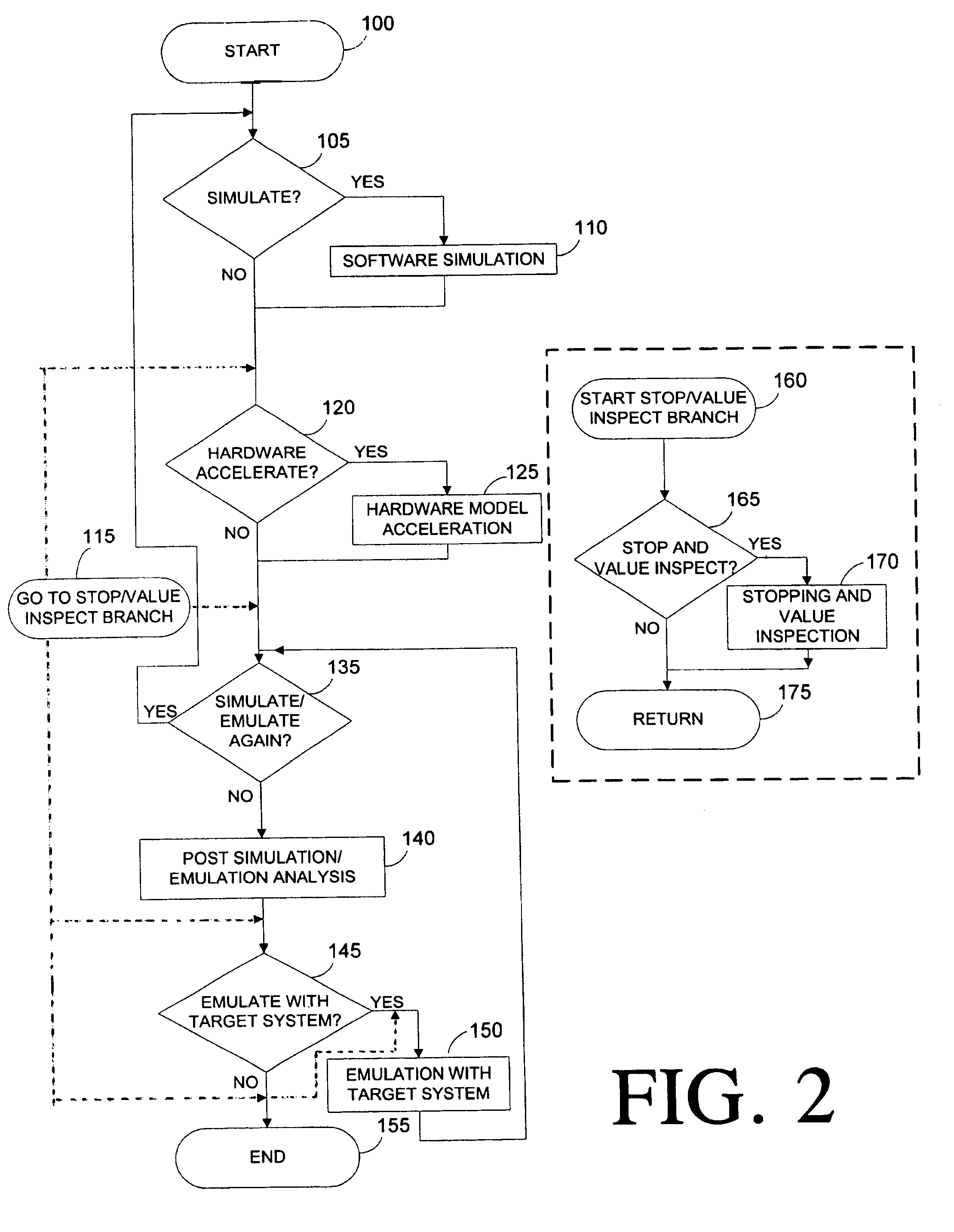

InactiveUS7480606B2Speed up the debugging processReturn quicklyAnalogue computers for electric apparatusAnalogue computers for nuclear physicsTest benchParallel simulation

In the VCD-On-Demand system, the EDA tool has the following attributes: (1) RCC-based parallel simulation history compression and recording, (2) RCC-based parallel simulation history decompression and VCD file generation, and (3) On-demand software regeneration for a selected simulation target range without simulation rerun. When the user selects a simulation session range, the RCC System records a highly compressed version of the primary inputs from the test bench process. The user then selects a narrower region, the simulation target range, within the simulation session range for a more focused analysis. The RCC System dumps the hardware state information of the hardware model into a VCD file. The RCC System then allows the user to proceed directly to view the VCD file from the beginning of the simulation target range without having to rerun the entire simulation from the beginning of the simulation session range.

Owner:CADENCE DESIGN SYST INC

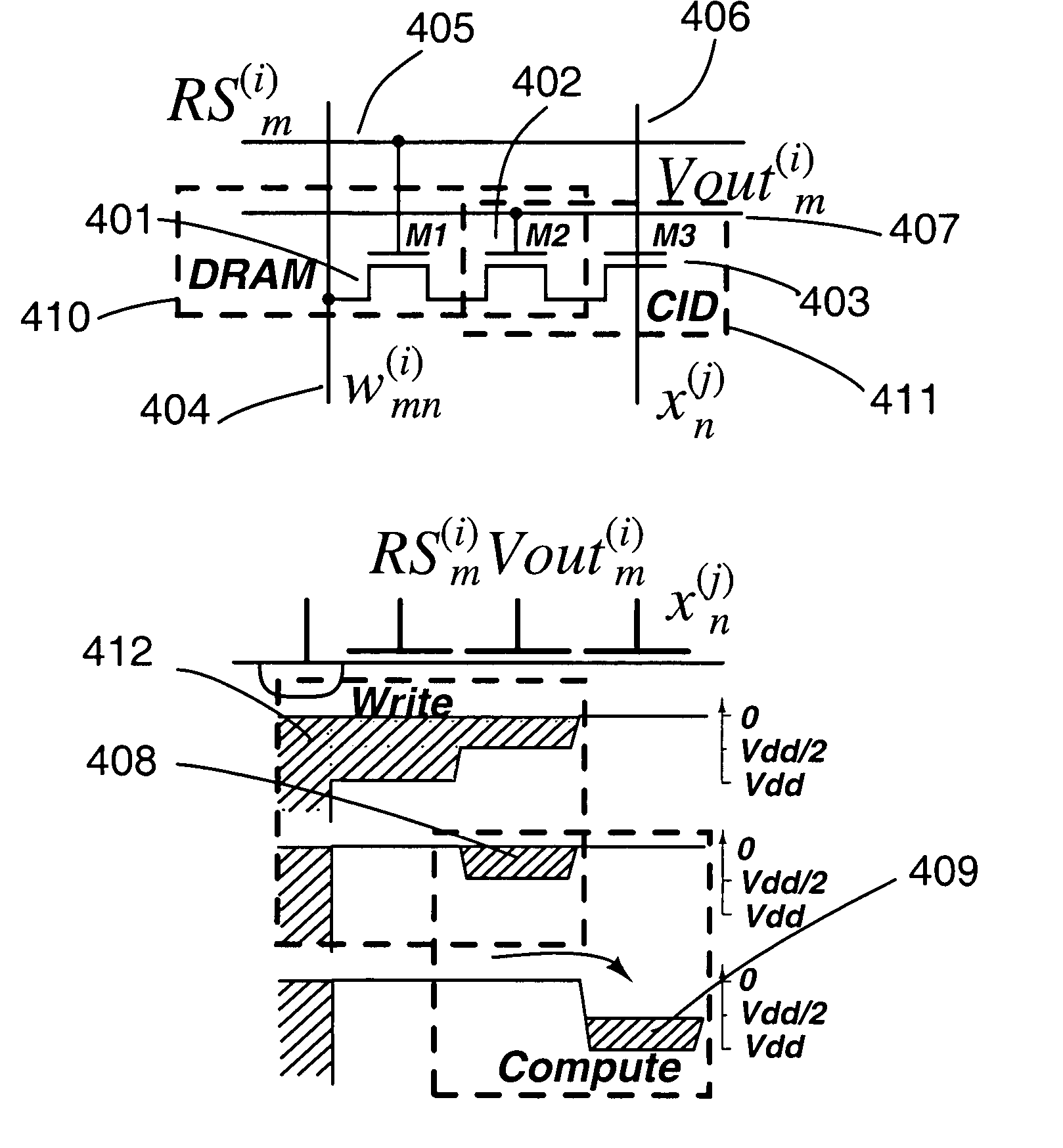

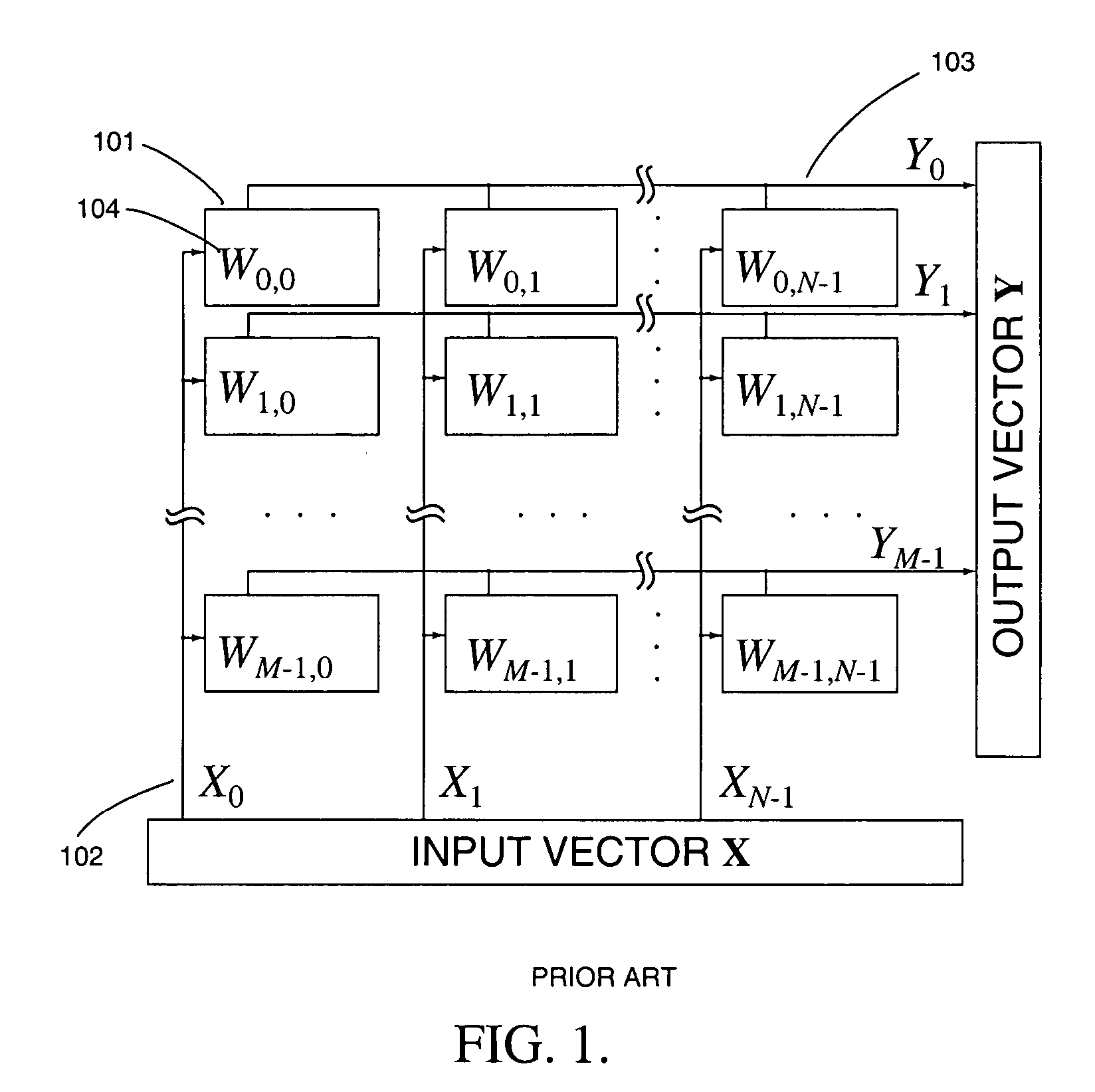

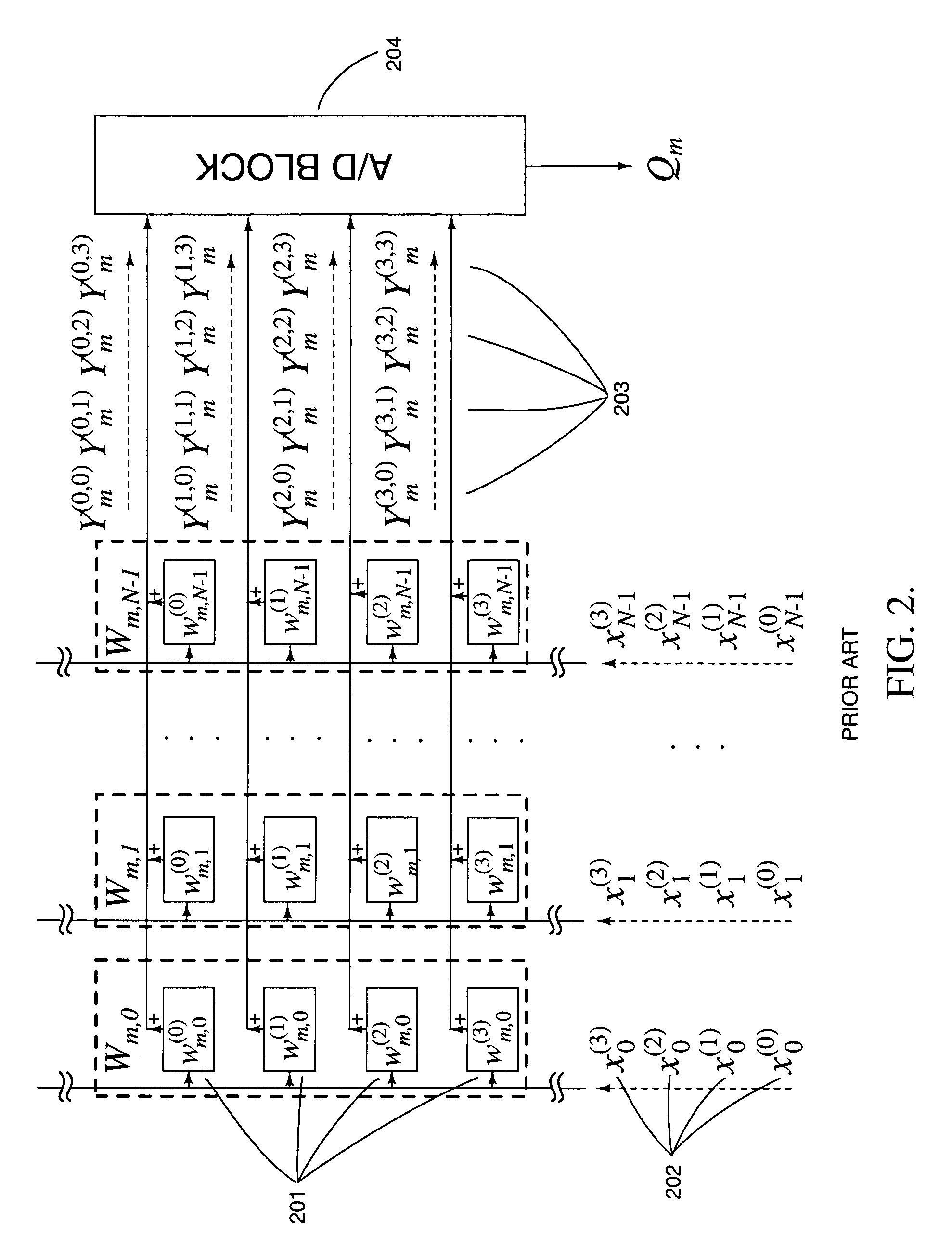

High-precision matrix-vector multiplication on a charge-mode array with embedded dynamic memory and stochastic method thereof

InactiveUS20050125477A1Efficient multiplicationIncrease cell densityComputation using non-contact making devicesPhysical realisationRandom methodReal time signal processing

Analog computational arrays for matrix-vector multiplication offer very large integration density and throughput as, for instance, needed for real-time signal processing in video. Despite the success of adaptive algorithms and architectures in reducing the effect of analog component mismatch and noise on system performance, the precision and repeatability of analog VLSI computation under process and environmental variations is inadequate for some applications. Digital implementation offers absolute precision limited only by wordlength, but at the cost of significantly larger silicon area and power dissipation compared with dedicated, fine-grain parallel analog implementation. The present invention comprises a hybrid analog and digital technology for fast and accurate computing of a product of a long vector (thousands of dimensions) with a large matrix (thousands of rows and columns). At the core of the externally digital architecture is a high-density, low-power analog array performing binary-binary partial matrix-vector multiplication. Digital multiplication of variable resolution is obtained with bit-serial inputs and bit-parallel storage of matrix elements, by combining quantized outputs from one or more rows of cells over time. Full digital resolution is maintained even with low-resolution analog-to-digital conversion, owing to random statistics in the analog summation of binary products. A random modulation scheme produces near-Bernoulli statistics even for highly correlated inputs. The approach has been validated by electronic prototypes achieving computational efficiency (number of computations per unit time using unit power) and integration density (number of computations per unit time on a unit chip area) each a factor of 100 to 10,000 higher than that of existing signal processors making the invention highly suitable for inexpensive micropower implementations of high-data-rate real-time signal processors.

Owner:GENOV ROMAN A +1

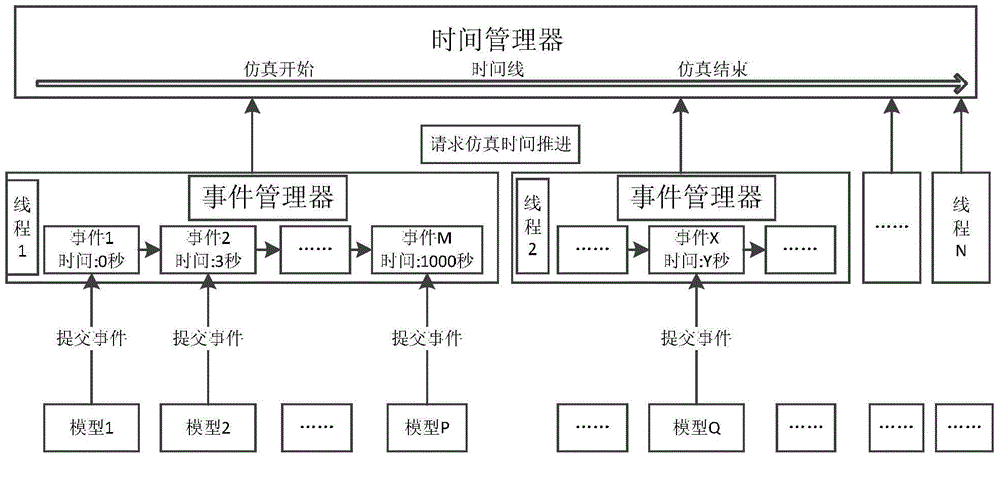

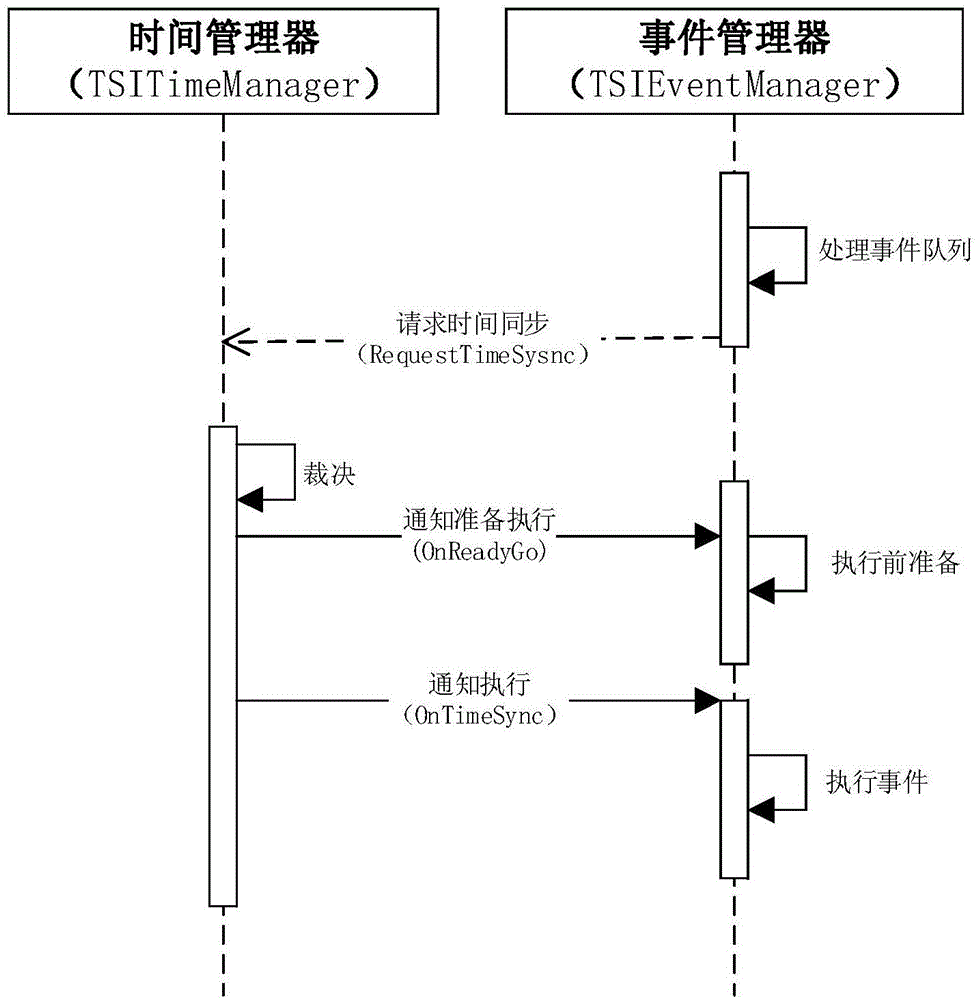

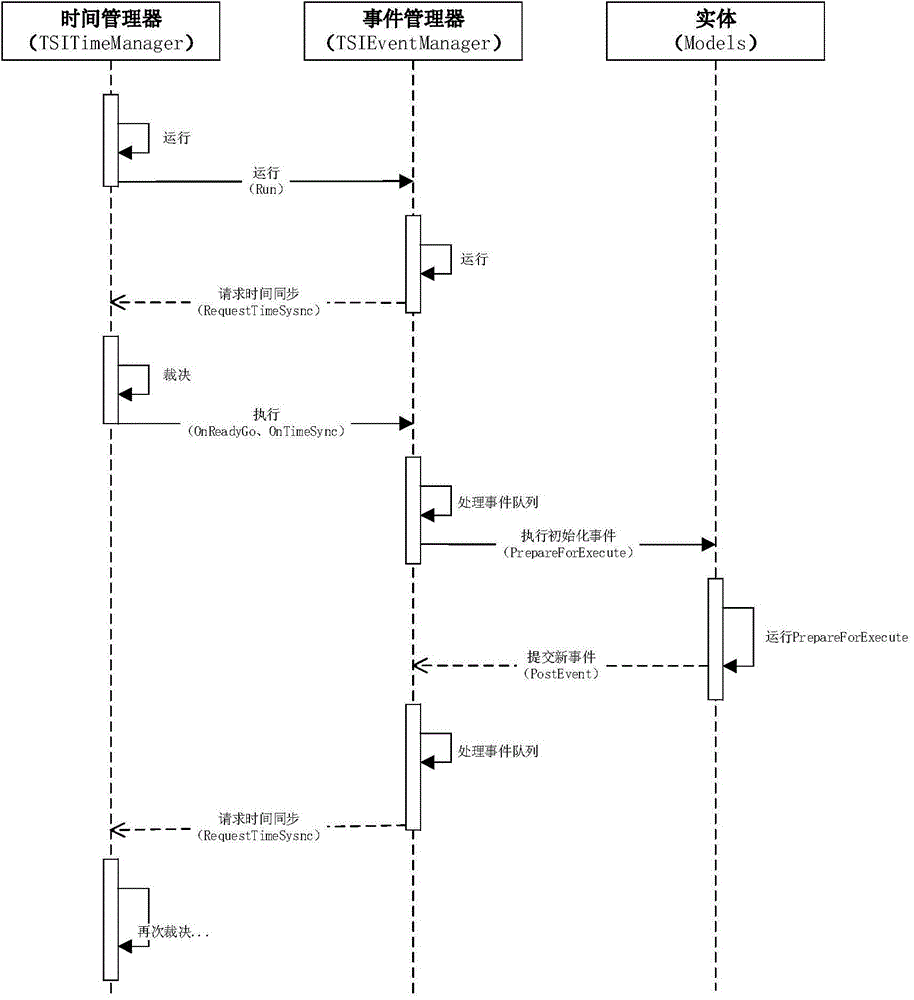

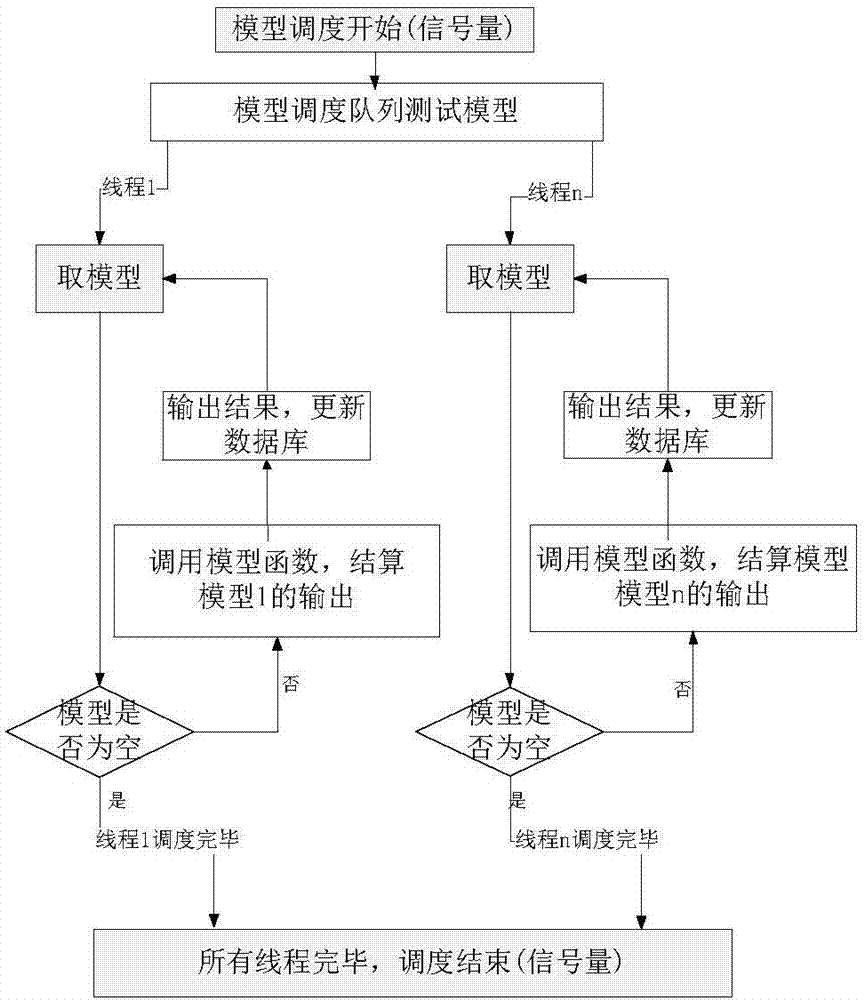

Multi-task-based discrete event parallel simulation and time synchronization method

ActiveCN104866374AAvoid the disadvantage of not being able to fully utilize hardware resourcesAvoid overheadProgram initiation/switchingSoftware simulation/interpretation/emulationEvent synchronizationTime management

Owner:BEIJING HUARU TECH

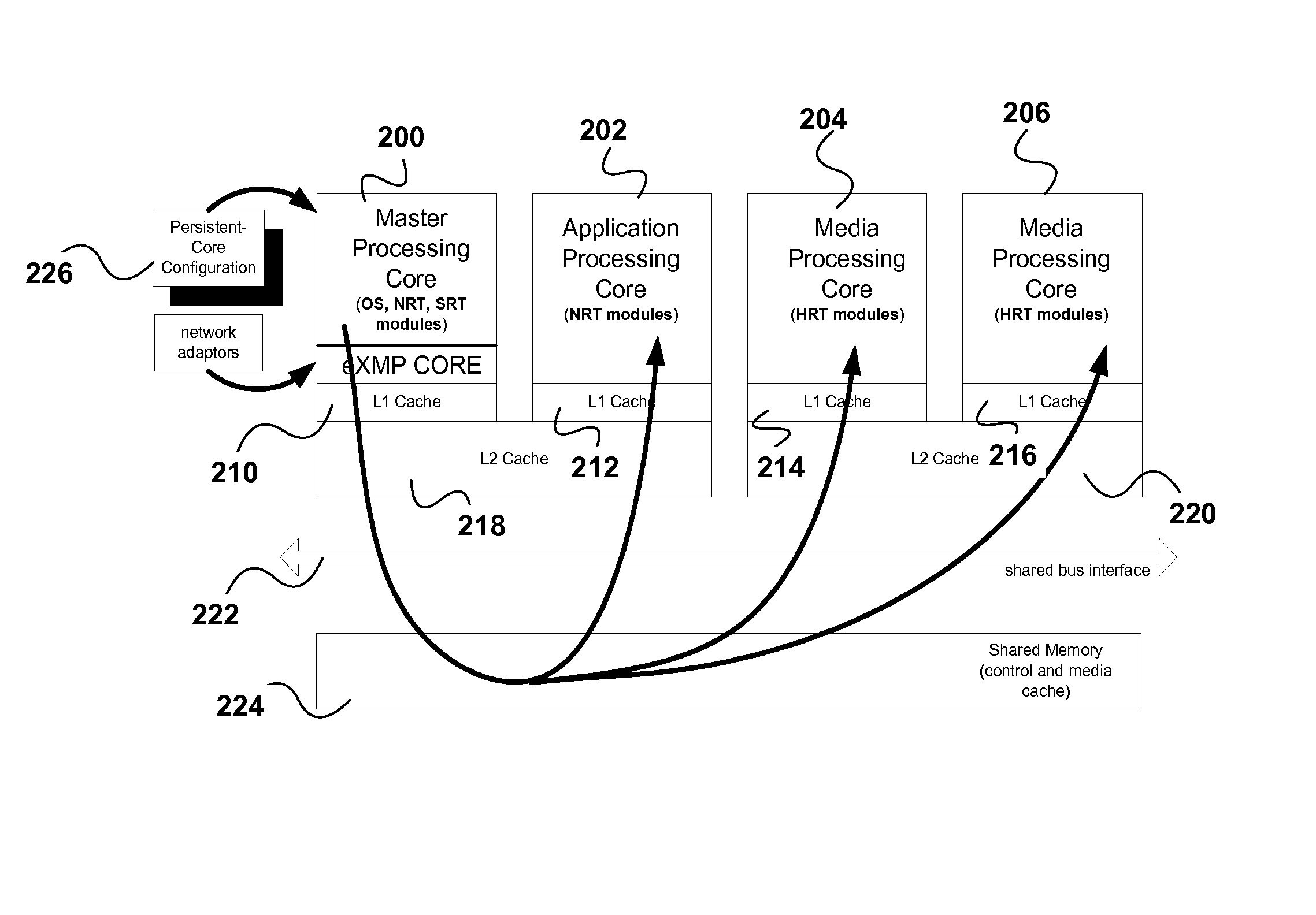

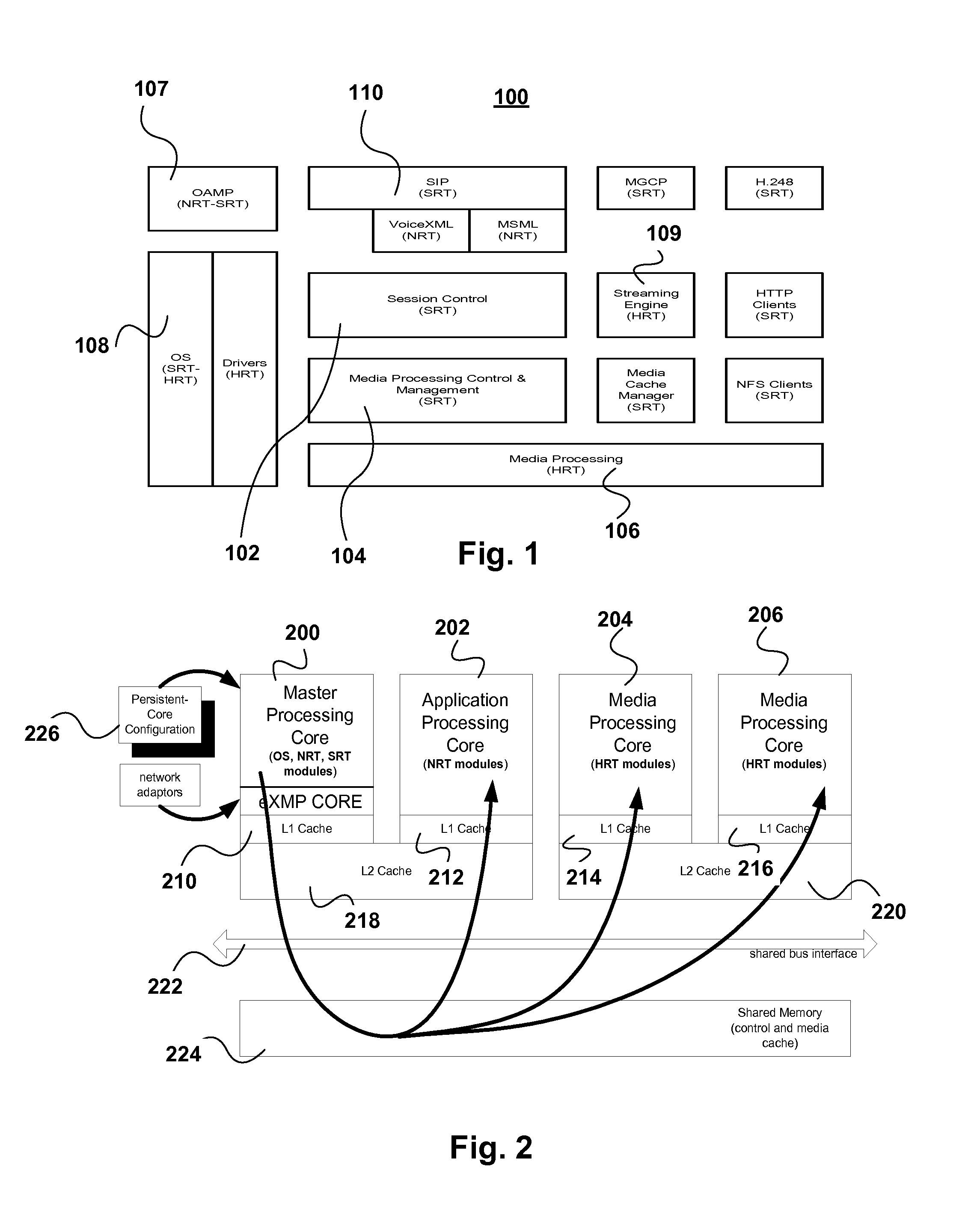

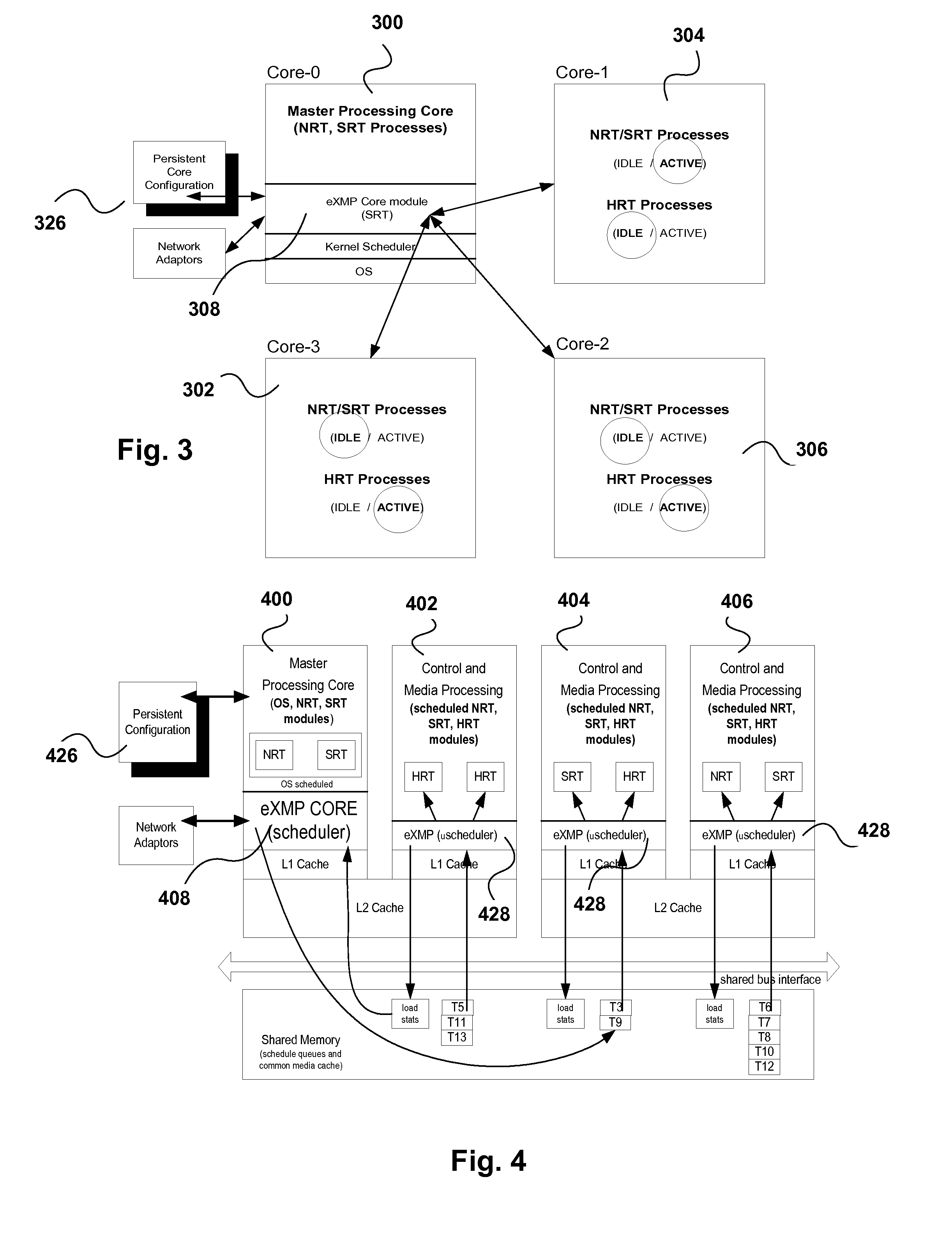

Multimedia processing in parallel multi-core computation architectures

ActiveUS20090083516A1Program control using wired connectionsMultiple digital computer combinationsTime responseMedia server

In a media server for processing data packets, media server functions are implemented by a plurality of modules categorized by real-time response requirements.

Owner:RADISYS CORP

Method and apparatus for parallel multi-view point video capturing and compression

InactiveUS7035453B2Remove uncertaintyTelevision system detailsPicture reproducers using cathode ray tubesDigital videoInstructions per second

A method and apparatus for digital video capturing and compression supports multi-viewpoint interactive video applications. Multiple (typically hundreds of) video cameras centripetally placed in a three dimensional space acquire real-time visual pictures of the same 3D scene from multiple viewpoints at the rate of 20˜30 frames per second (fps). Parallel Multi-Viewpoint Video Capturing and Compression (PMVCC) supports the operation of the apparatus. In an exemplary realization, a Multi-DSP Array (MDA) architecture uses hundreds of high-performance digital signal processors (DSPs) working in parallel to obtain a sustained computation power of hundreds of GIPS (Giga Instructions Per Second).

Owner:REALITY COMMERCE CORP

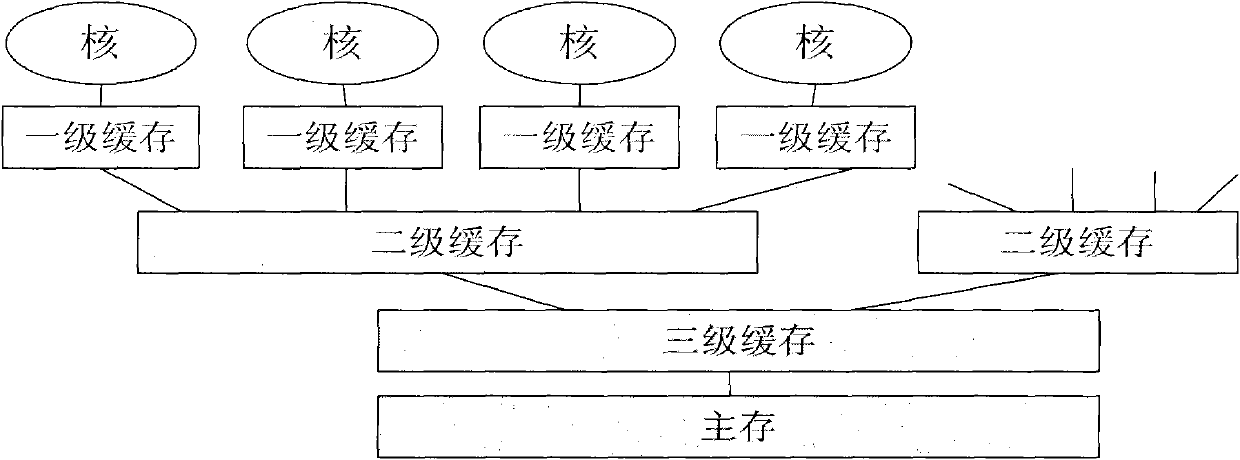

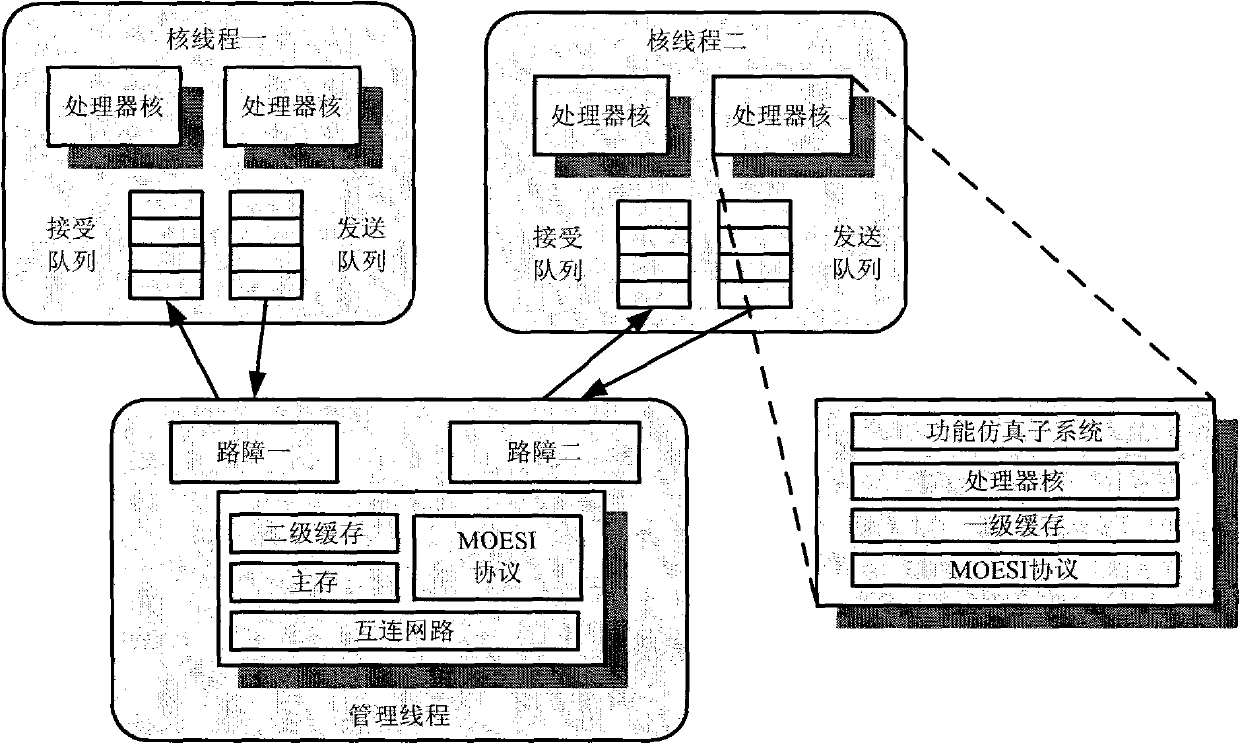

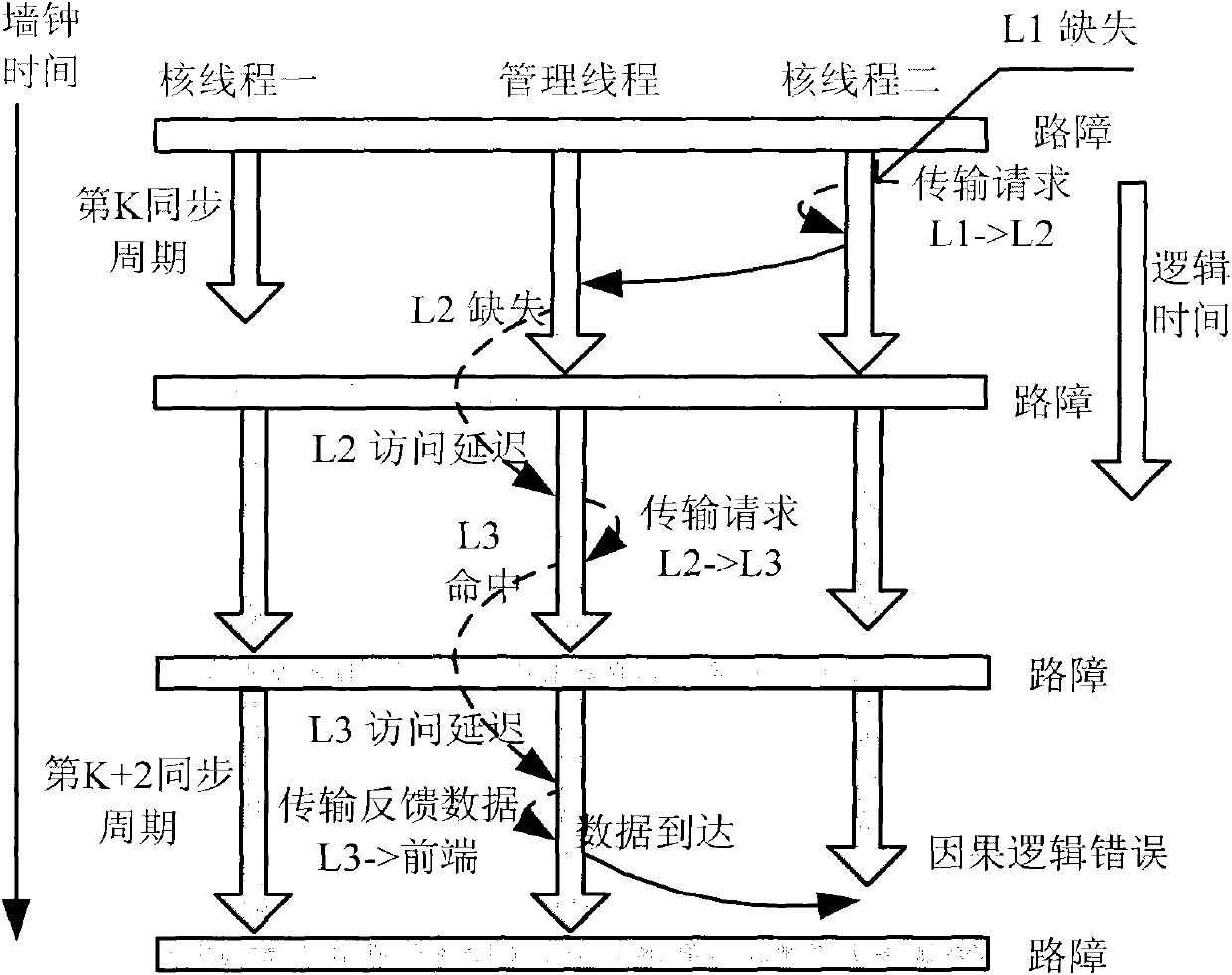

Chip multi-core processor clock precision parallel simulation system and simulation method thereof

InactiveCN101788919AHigh precisionImprove the simulation effectSoftware simulation/interpretation/emulationMulti-core processorObject system

The invention discloses a chip multi-core processor clock precision parallel simulation system and a method thereof. The system comprises a management thread of an initialization simulation system; the management thread establishes a core thread according to a core number of a simulation object system or parameters given by a user; and the system is characterized in that: the management thread receives access data events sent by the core thread and a suspended barrier acting on the core thread is set; and when the core thread of the maximum local lock does not receive data when reaching a preset clock period, the core thread moves the suspended barrier to synchronously advance to form a sliding simulation time window. Simulation experiments prove that the system greatly improves the accuracy and simulation performance of the multi-core processor parallel simulation.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

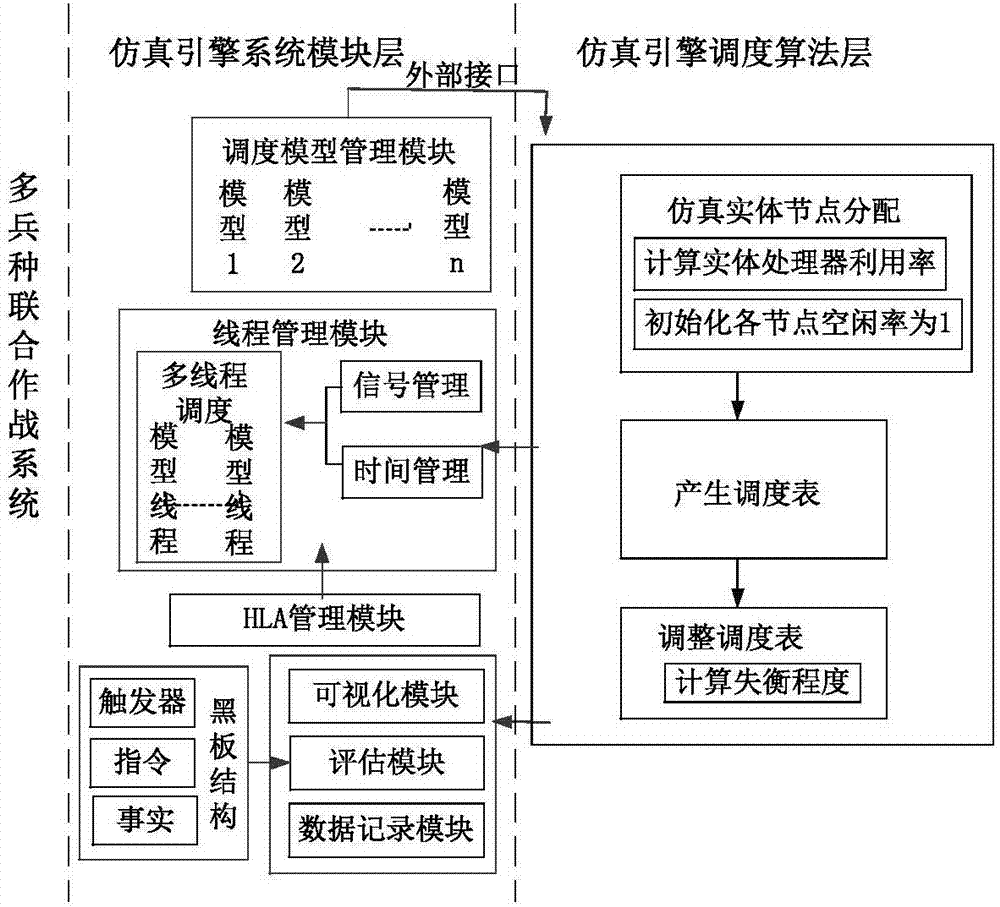

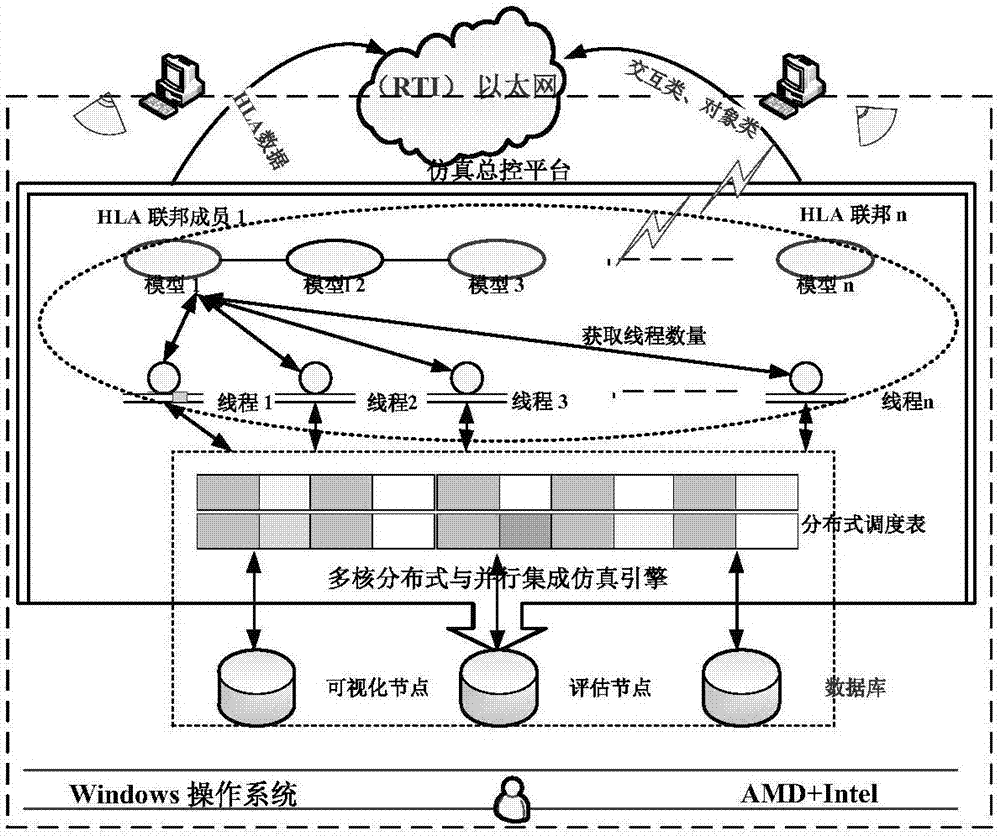

Multi-core parallel simulation engine system supporting joint operations

ActiveCN107193639ASolve the problem that real-time is vulnerableStrong independenceData processing applicationsSoftware simulation/interpretation/emulationNODALPhysical model

The invention discloses a multi-core parallel simulation engine system supporting joint operations. The system solves the problem that the real-time performance of a traditional joint operation system is easily influenced when step length is used to forward logic time. The system includes a model scheduling management module, a thread management module, an external interface management module and a high-level architecture (HLA) management module. According to the system, target nodes are assigned for simulation entities to enable total computation amounts of models on each node to be equivalent; then through the model scheduling management module, a scheduling schedule of each node is generated based on a principle of load balancing, the simulation step length is assigned for the models, and during a simulation process, the scheduling schedule is adjusted and the simulation step length of the destroyed entities and generated new entities is adjusted. The system can autonomously divide the scheduling schedule according to operating cycles of the models and the system step length, allow the entities to use the different physical models or the behavior models according to needs for simulation, and support real-time scheduling of large-scale simulation and the high-fidelity operation models.

Owner:BEIHANG UNIV

VCD-on-demand system and method

InactiveUS20050228630A1Speed up the debugging processReturn quicklyAnalogue computers for electric apparatusAnalogue computers for nuclear physicsDesign reviewParallel simulation

The disclosed technology is called VCD on demand. In a typical system, the EDA tool incorporating the VCD on-demand technology has the following high level attributes: (1) RCC-based parallel simulation history compression and recording, (2) RCC-based parallel simulation history decompression and VCD file generation, and (3) On-demand software regeneration for a selected simulation target range and design review without simulation rerun. Each of these attributes will be discussed in greater detail below. When the user selects a simulation session range, the RCC System records a highly compressed version of the primary inputs from the test bench process. The user then selects a narrower region, called the simulation target range, within the simulation session range for a more focused analysis. The RCC System dumps the hardware state information (i.e., primary outputs) of the hardware model into a VCD file. The RCC System then allows the user to proceed directly to view the VCD file from the beginning of the simulation target range without having to rerun the entire simulations from the very beginning of the simulation session range.

Owner:CADENCE DESIGN SYST INC

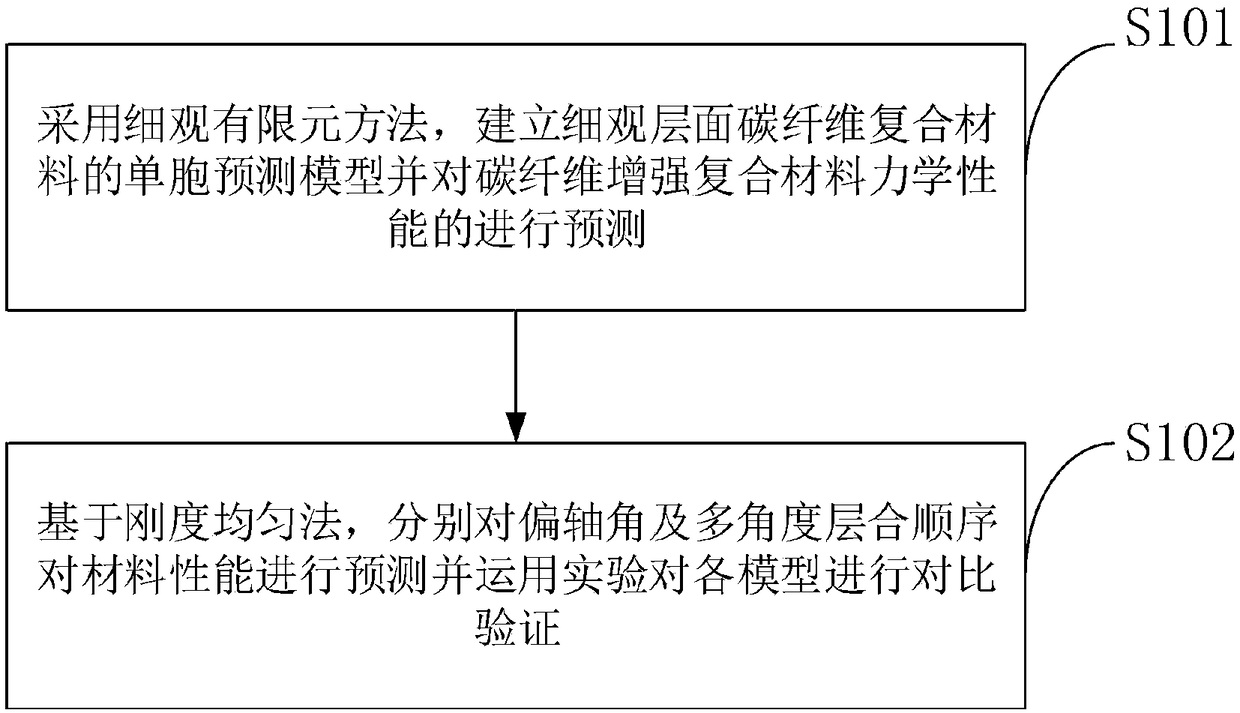

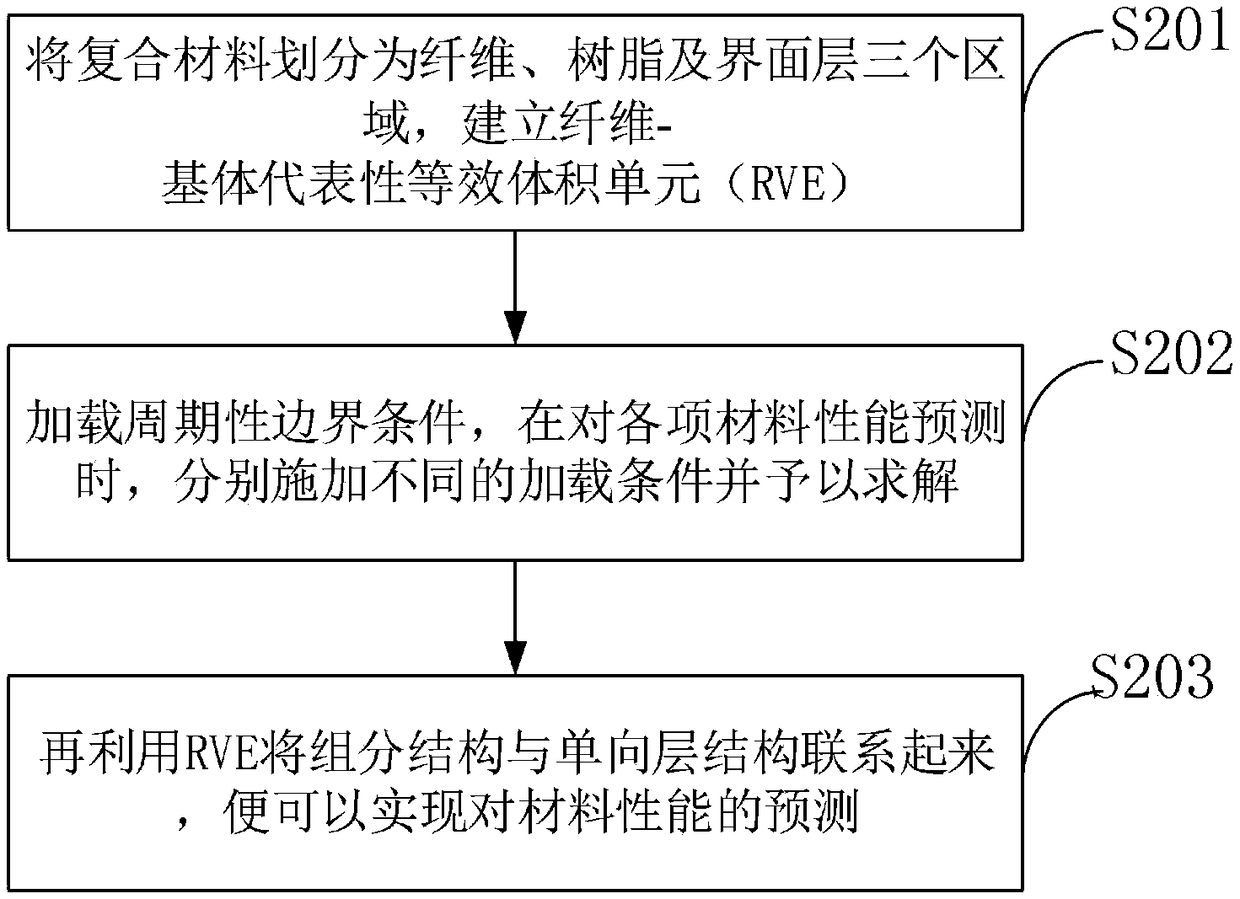

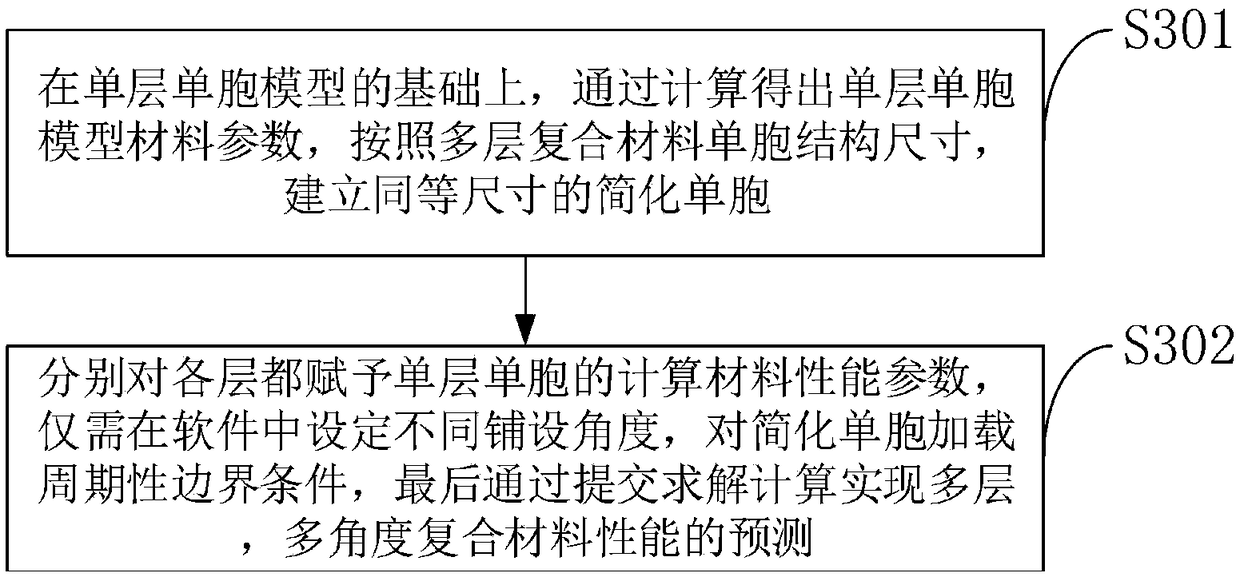

Carbon fiber reinforced composite material mechanical performance prediction method based on cross-scale simulation

ActiveCN109241650AImprove mechanical propertiesSustainable transportationDesign optimisation/simulationPredictive methodsFinite element method

The invention belongs to the technical field of composite material prediction, and discloses a carbon fiber reinforced composite material mechanical performance prediction method based on cross-scalesimulation. The prediction method comprises the following steps: adopting a meso-finite element method, establishing a single cell prediction model of a meso-level carbon fiber composite material andpredicting the mechanical performance of the carbon fiber reinforced composite material; Based on the stiffness homogeneity method, predicting the off-axis angle and multi-angle lamination sequence and verifying the models by experiments. The invention provides a method for predicting the mechanical properties of the composite material, and the experimental results are consistent with the theoretical model.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

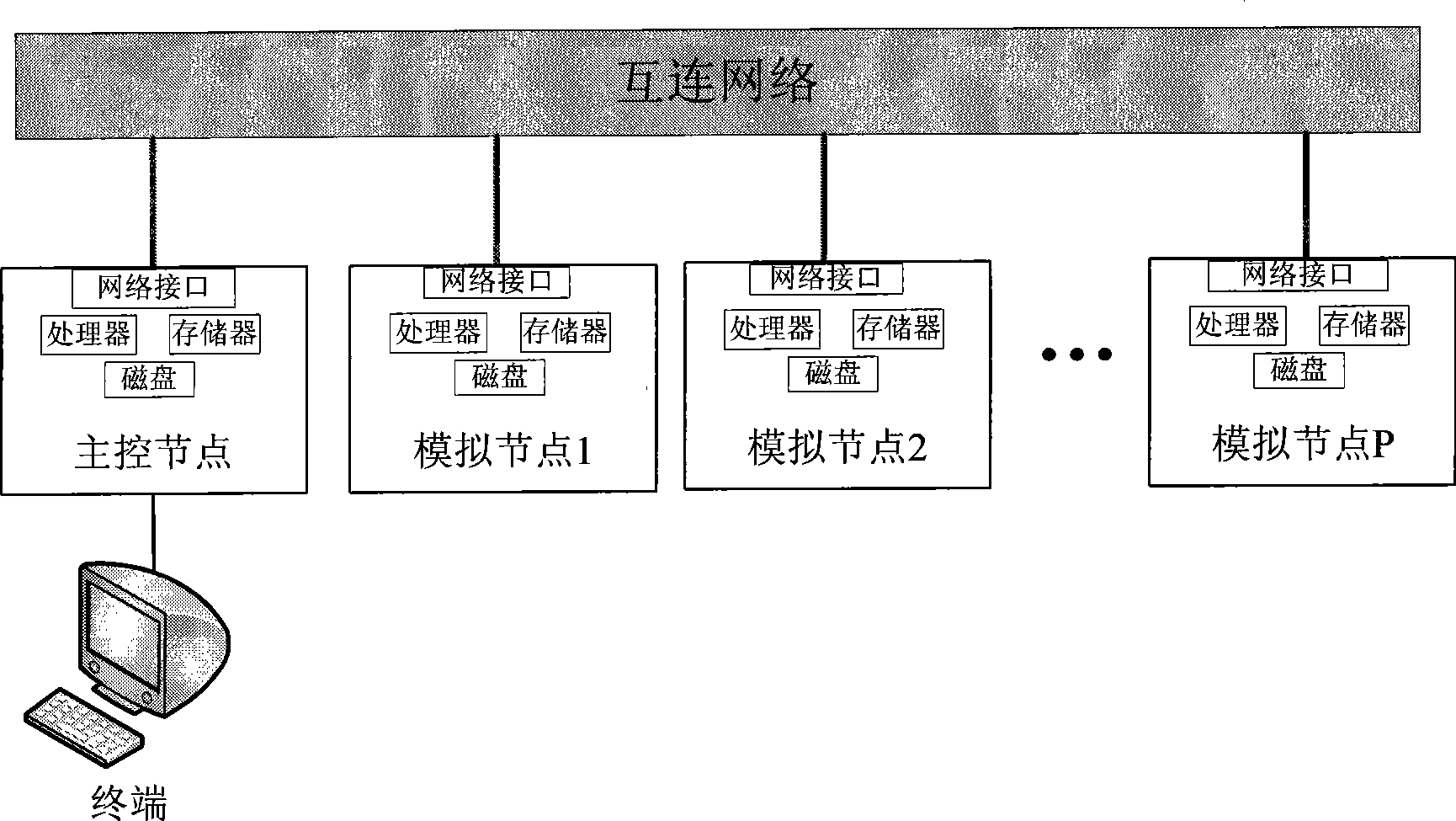

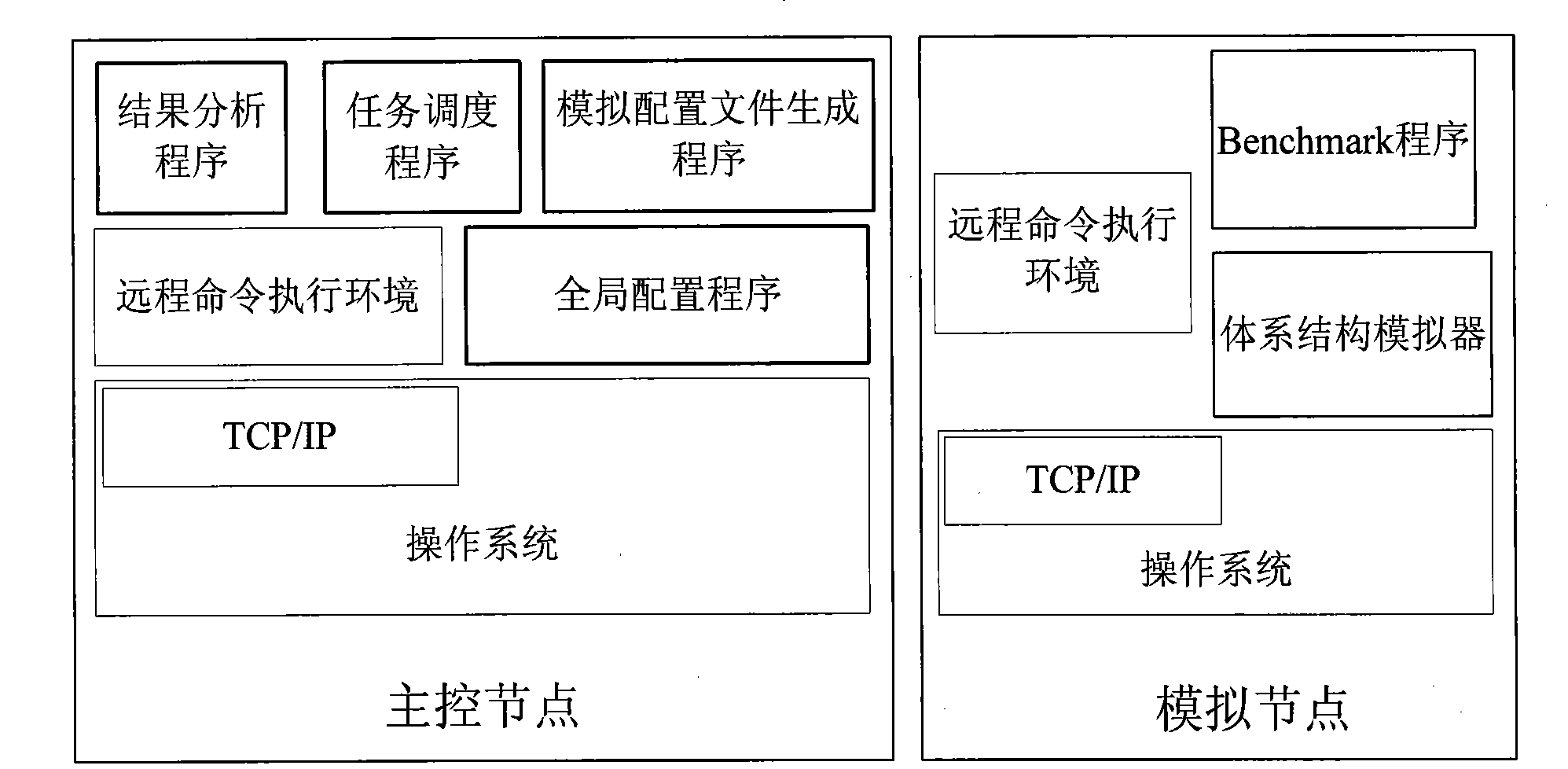

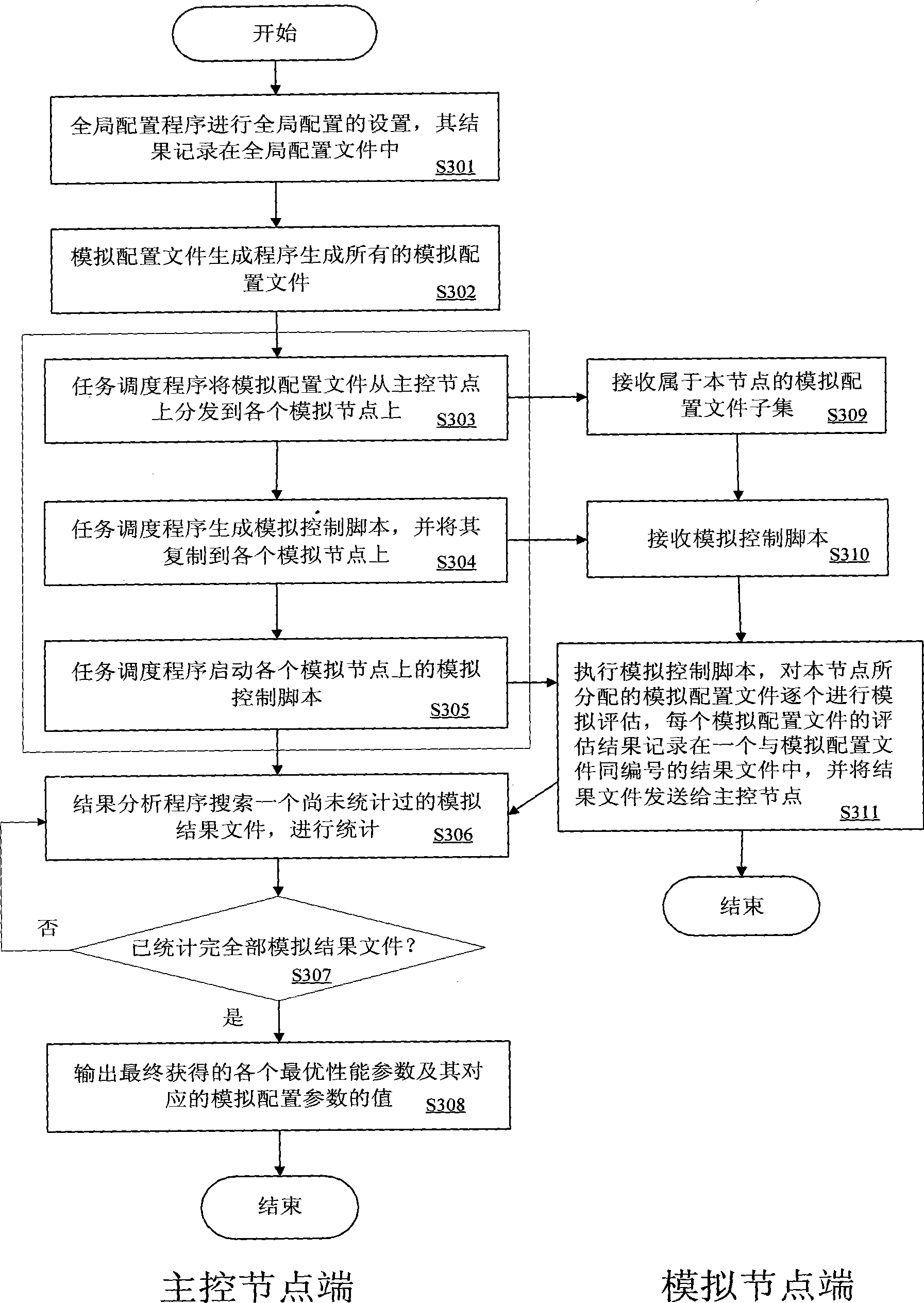

Computer architecture scheme parallel simulation optimization method based on cluster system

InactiveCN101464922ARealize automatic generationRealize automatic schedulingDigital computer detailsSoftware simulation/interpretation/emulationCluster systemsComputerized system

The invention discloses a parallel method for simulating and optimizing the computer architecture scheme based on a cluster system, and aims to provide a parallel method for simulating and optimizing the design scheme of the computer architecture. The technical scheme is that a parallel computer system which consists of a main control node and simulation nodes and is provided with a remote command execution environment is firstly built, and a global configuration program, a simulated configuration file generating program, a task dispatching program and a result analyzing program are arranged on the main control node, wherein, the global configuration program is used for arranging global configuration; the simulated configuration file generating program is used for generating all simulated configuration files; the task dispatching program distributes simulation evaluation tasks to each node, controls each simulation node and performs simulation evaluation; and the result analyzing program searches simulation result files sent from the simulation nodes for statistics, screens out optimal configuration parameter values, and outputs a report. By adopting the invention, the time for evaluation and optimization can be reduced, and the selection accuracy is improved.

Owner:NAT UNIV OF DEFENSE TECH

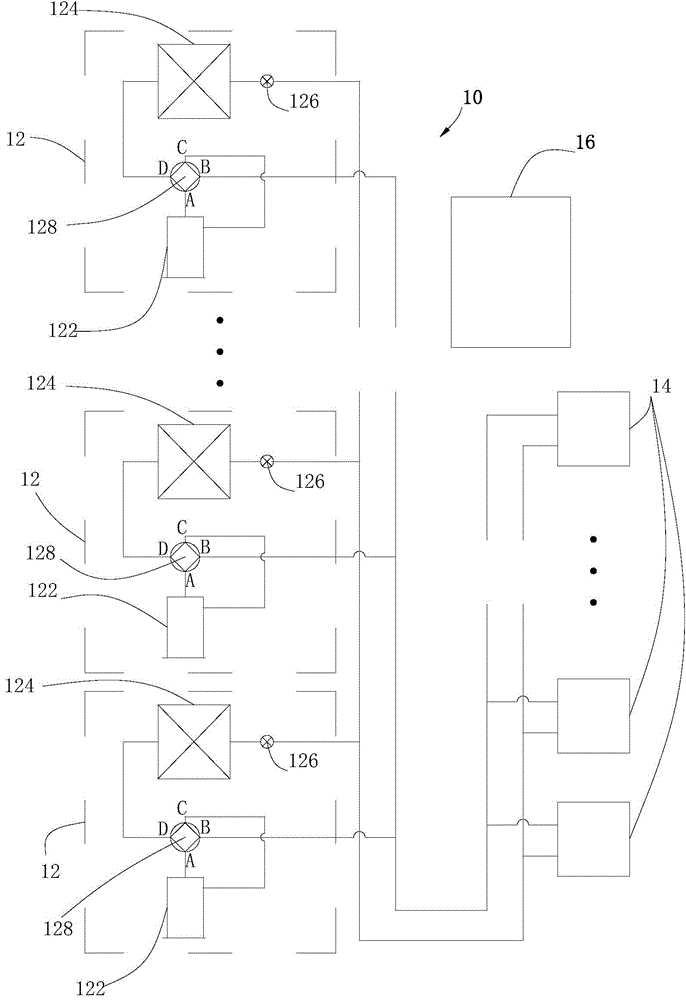

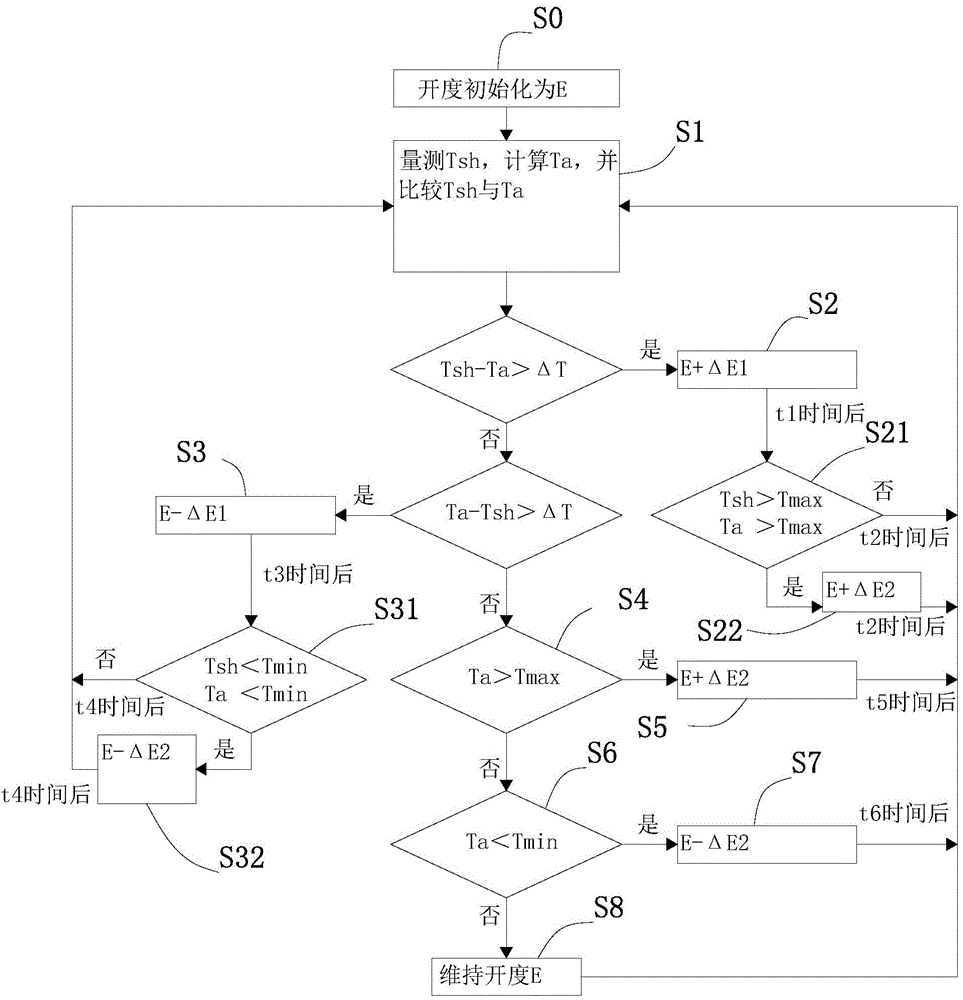

Refrigerant control method of parallel multi-split air-conditioner

ActiveCN104566823AExtended operating rangeImprove reliabilityMechanical apparatusSpace heating and ventilation safety systemsEngineeringParallel simulation

The invention discloses a refrigerant control method of a parallel multi-split air-conditioner. The method comprises the steps of S1, in a heating mode, comparing the degree of superheat of each outdoor unit with the average degree of superheat of a plurality of outdoor units, S2, when the degree of superheat of the current outdoor unit is overhigh in contrast with the average degree of superheat, increasing the amount of the refrigerant going into the current outdoor unit, and S3, when the degree of superheat of the current outdoor unit is overlow in contrast with the average degree of superheat, reducing the amount of the refrigerant going into the current outdoor unit. In this way, the amount of the refrigerant going into each outdoor unit is decided by comparing the degree of superheat of the current outdoor unit and the average degree of superheat (system); the amount of the refrigerant going into each outdoor unit is adjusted from the overall aspect of the system so that the compressor can be enabled to be within an excellent running range, and therefore, the problems caused by overhigh or insufficient superheat of the compressor can be avoided and the reliability of the multi-split air-conditioner during operation is improved.

Owner:GD MIDEA HEATING & VENTILATING EQUIP CO LTD +1

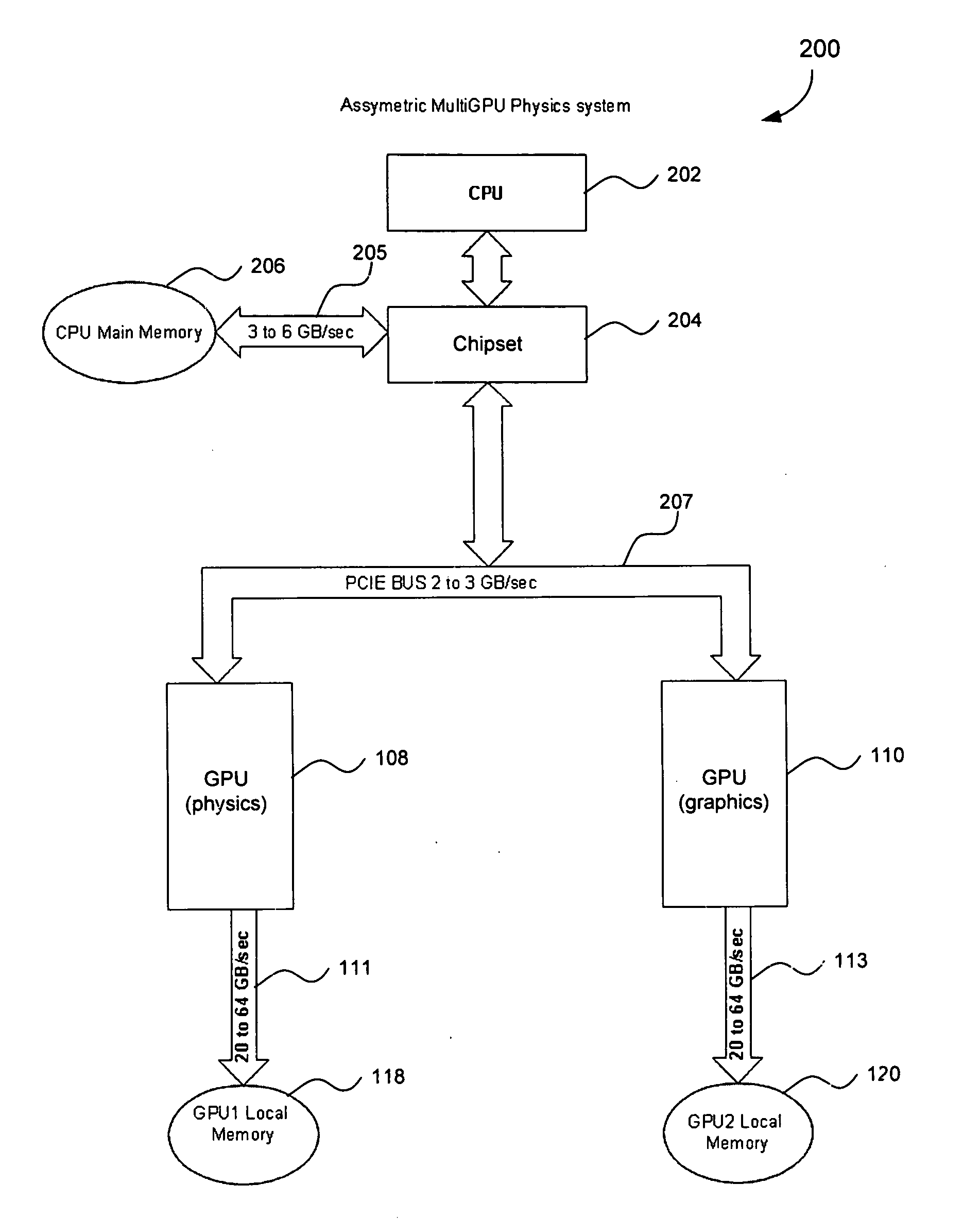

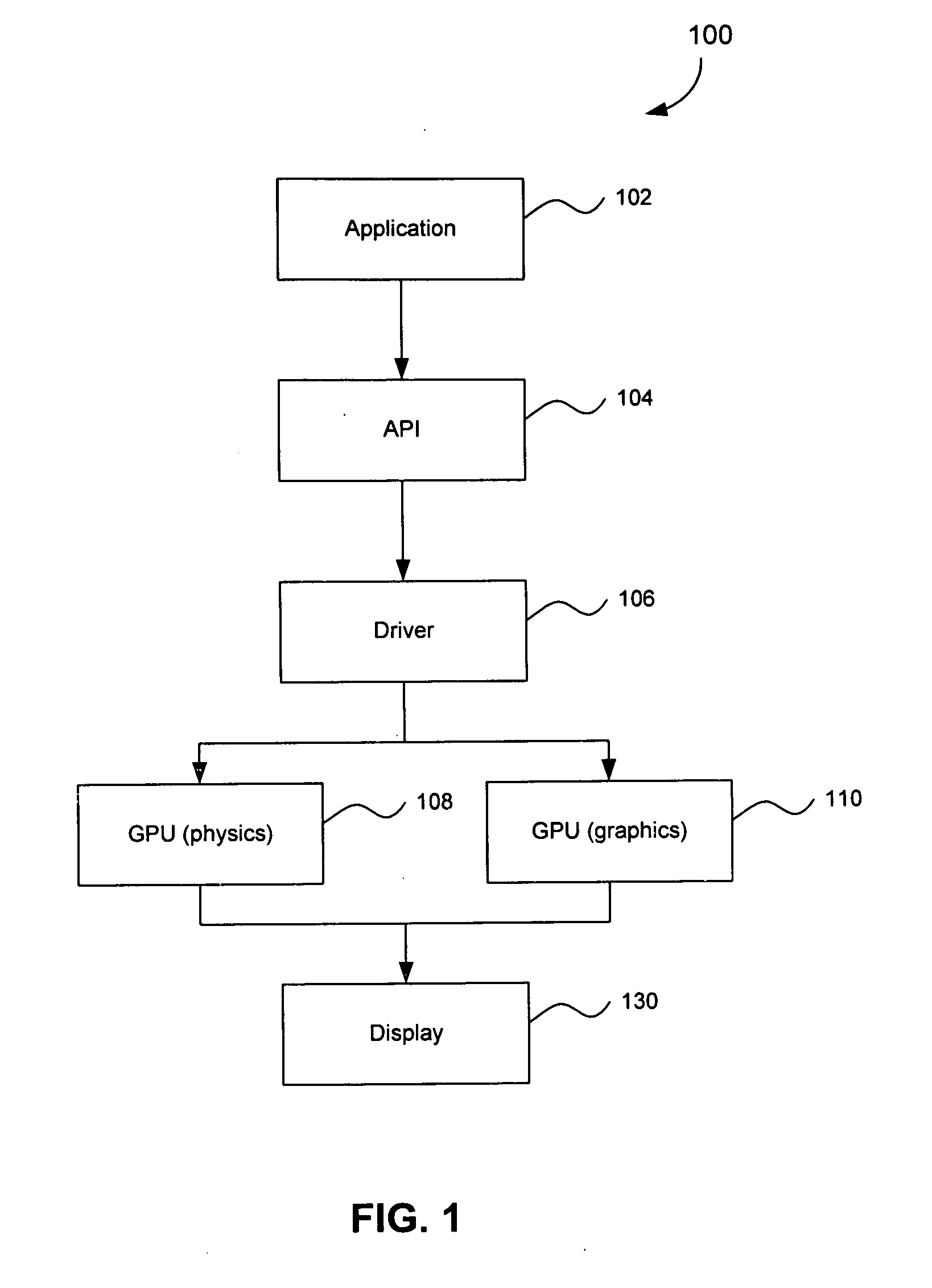

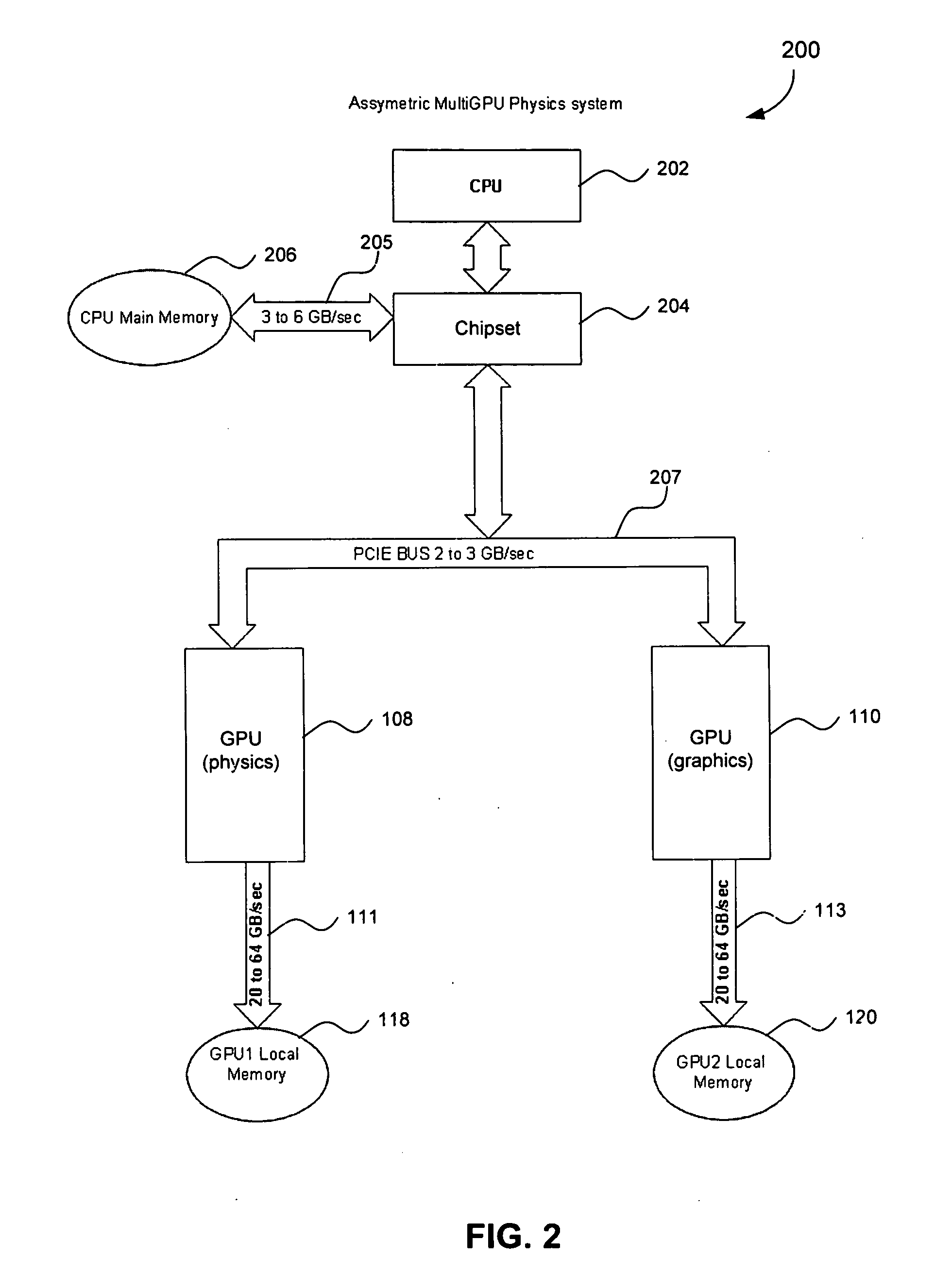

Parallel physics simulation and graphics processing

Embodiments of the present invention are directed to a method and computer program product for performing physics simulations and graphics processing on at least one graphics processor unit (GPU). Such a method for performing physics simulations and graphics processing on at least one GPU includes the following steps. First, physics simulations are executed on a first device embodied in the at least one GPU. Then, graphics are processed on a second device embodied in the at least one GPU responsive to the physics simulations executed on the first device. In an embodiment, the first device and second device are embodied on a single GPU. In another embodiment, the first device is embodied on a first GPU and the second device is embodied on a second GPU.

Owner:ATI TECH INC

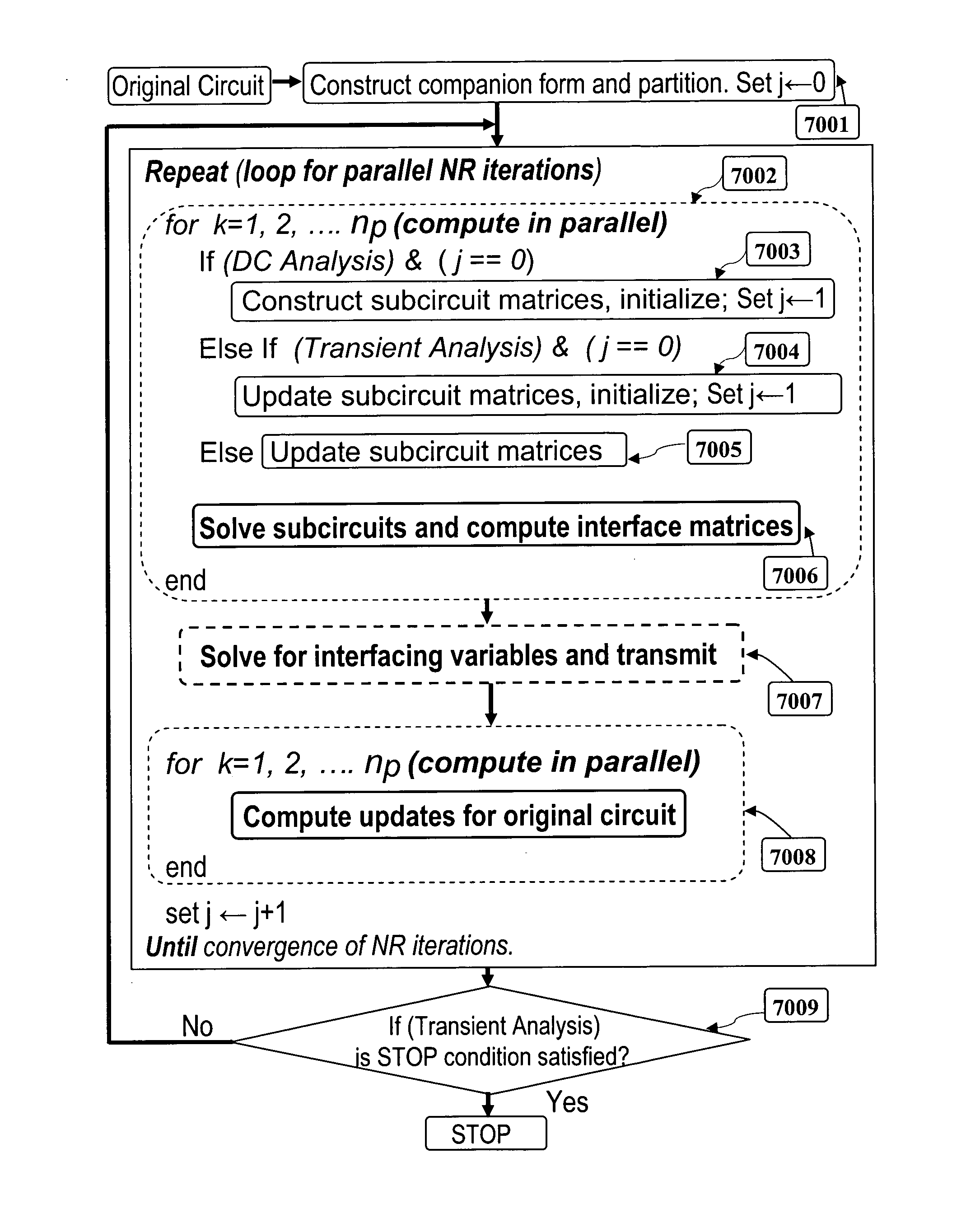

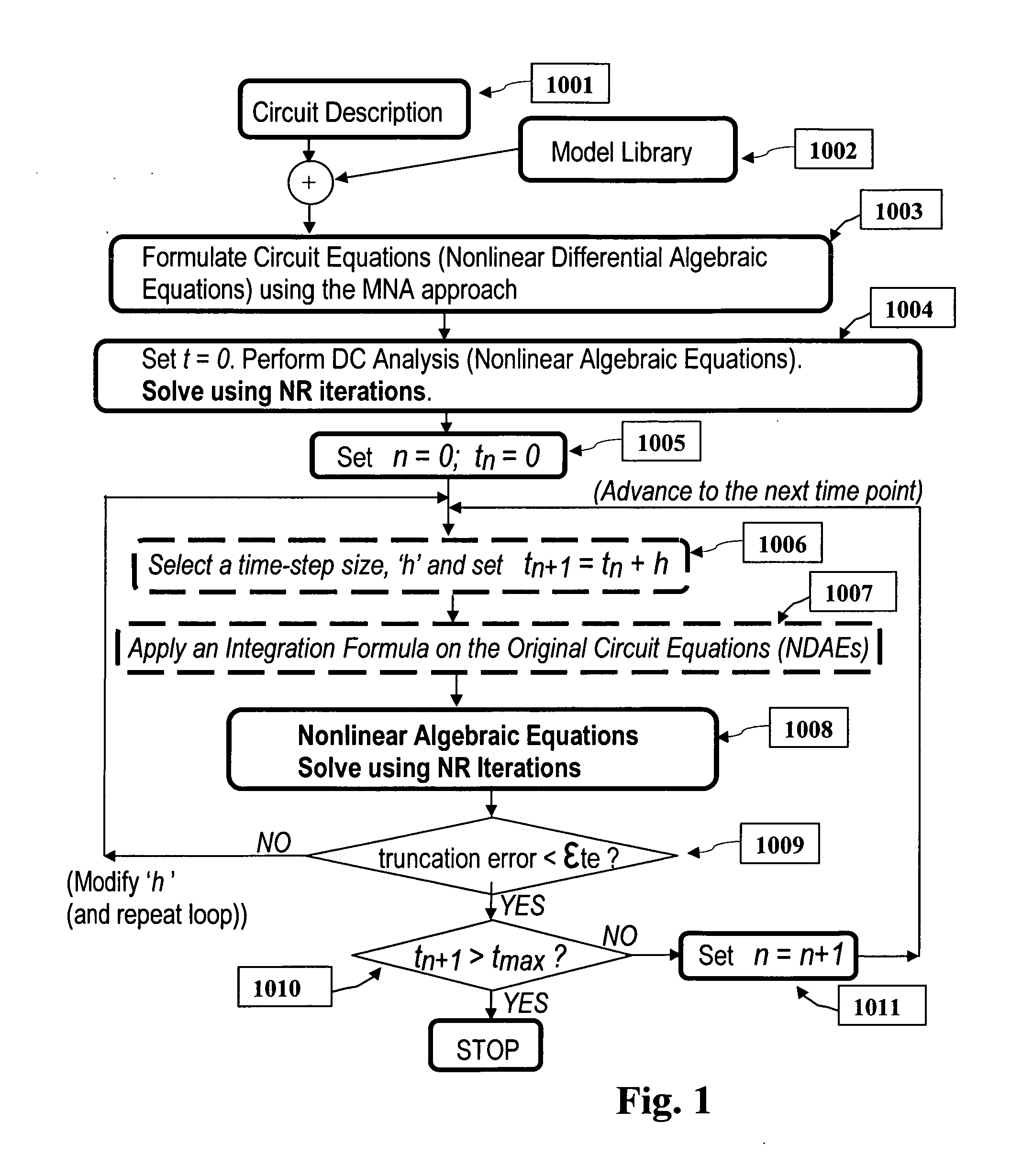

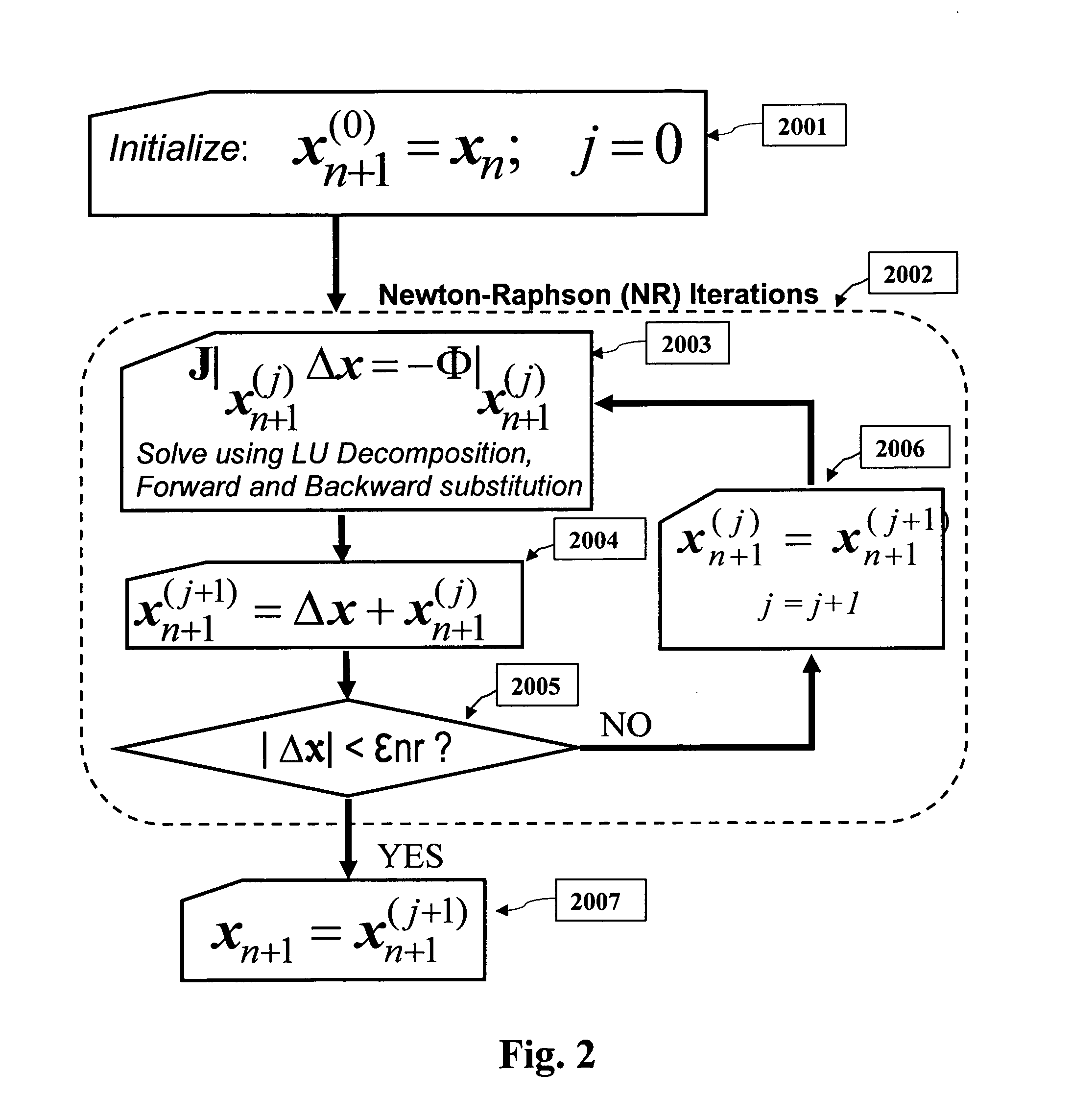

Parallel simulation of general electrical and mixed-domain circuits

InactiveUS20100332202A1Computation can be minimizedMinimize overheadComputation using non-denominational number representationComputer aided designExtensibilityTime domain

A new method for simulation of general electrical circuits on parallel computing platforms is disclosed. Parallel simulation of general time-domain circuits that are represented by nonlinear / linear differential algebraic equations is accomplished by partitioning them into smaller subcircuits via a novel combination of the companion form representation of the given circuit and an efficient form of node splitting, during Newton Raphson iterations, at any time point. The new invention formulates the interface vectors between partitions, through purely binary vectors, leading to a high degree of parallelism, scalability and reduced computational and communication costs for synchronizing the solutions between various partitions. Parallel platforms considered can be diverse such as (including but not restricted to) multicore CPUs, distributed systems of computers. The new invention also provides for scalable parallel simulation of mixed-domain formulations, such as (including but not restricted to), integrated circuits, electronic packages, PCBs, electromagnetic modules, MEMS and optical components etc.

Owner:OMNIZ DESIGN AUTOMATION CORP

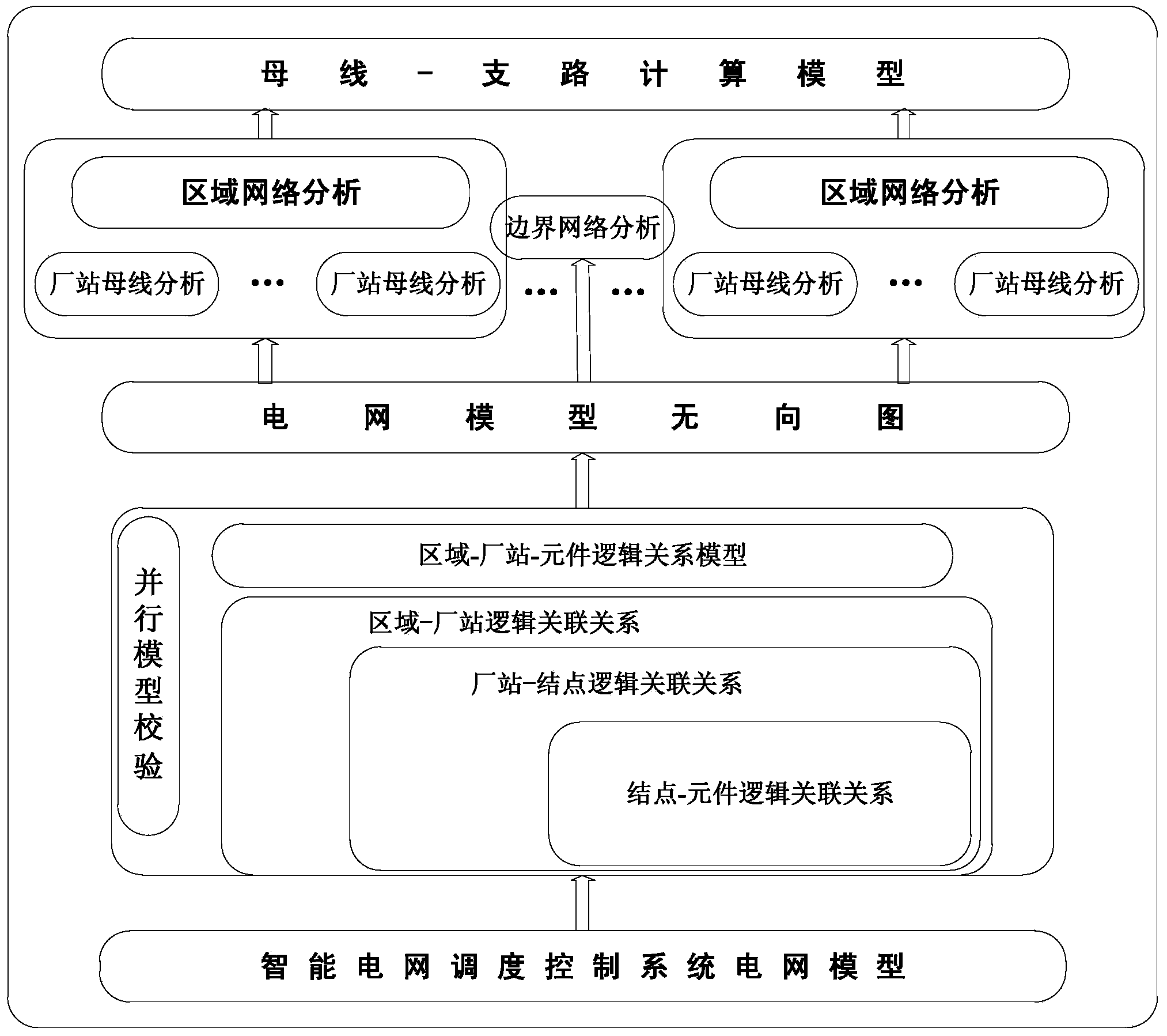

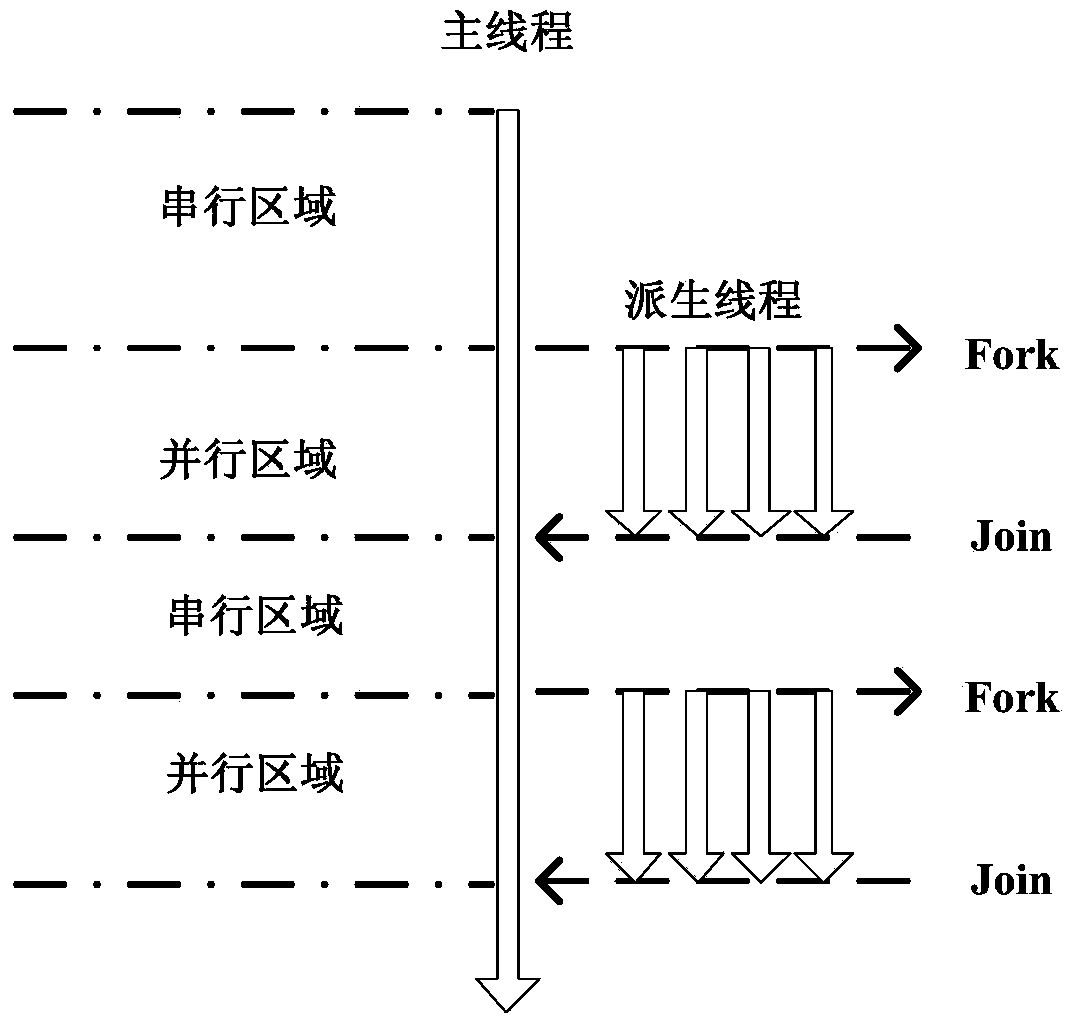

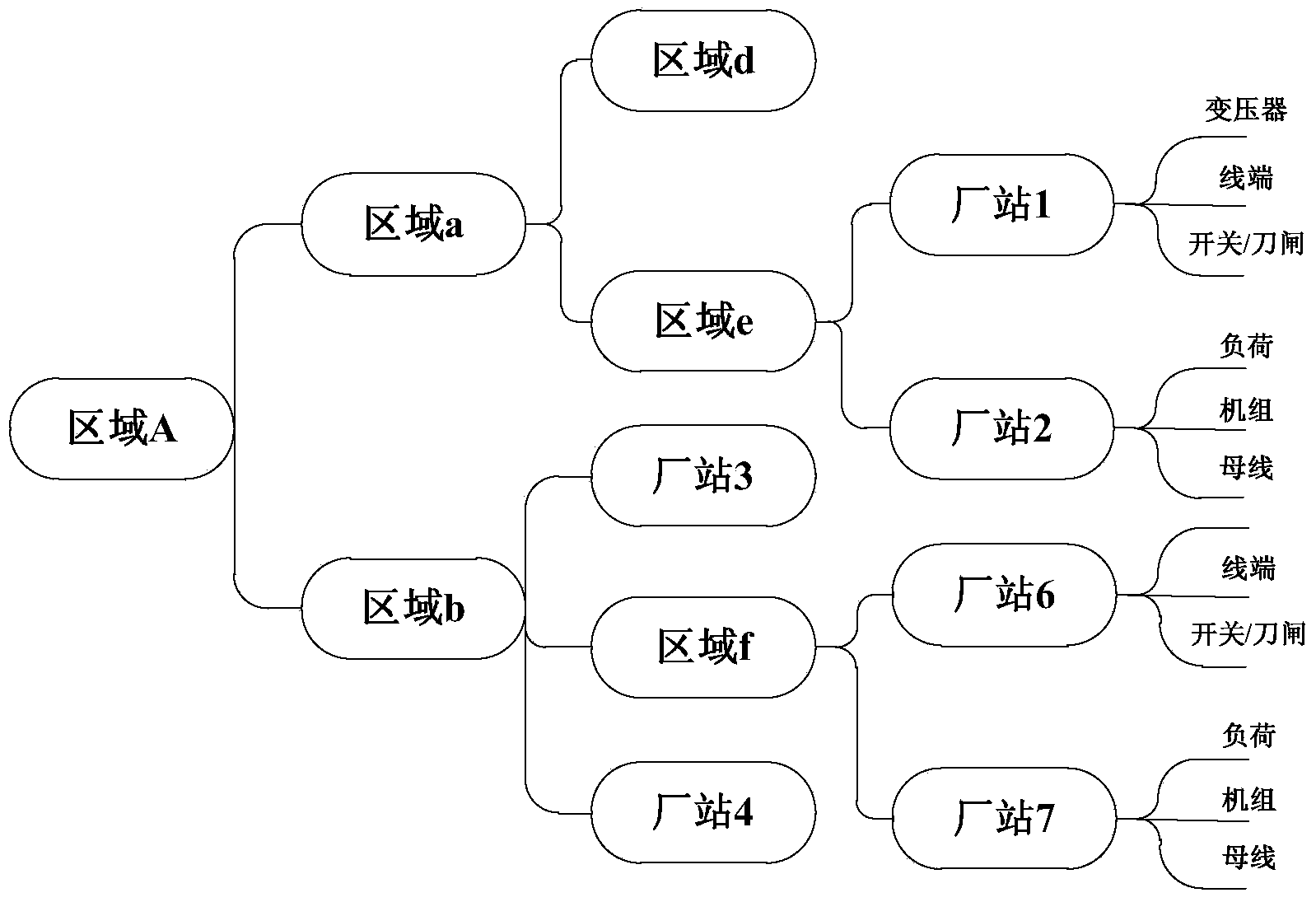

Large power grid parallel network topology analyzing method

ActiveCN104167736AAvoid gettingImprove execution efficiencyAc network circuit arrangementsControl systemSmart grid

The invention provides a large power grid parallel network topology analyzing method. The method comprises the following steps that a smart power grid dispatcher control system power grid model is read, parallel verifying is carried out on the smart power grid dispatcher control system power grid model, and the large power grid parallel network topology is analyzed. According to the large power grid parallel network topology analyzing method, data of the power grid model are divided according to areas and stations, the topology searching function is packaged, parallel processing is carried out on the model data according to the different areas and the different stations, and accordingly parallel computation on the power grid topology analyzing is achieved. The result of the measurement on the actual power grid shows that the method has good stability and real-time performance, and the requirements for the topology analysis of the online system simulation, analysis and control application are met.

Owner:STATE GRID CORP OF CHINA +2

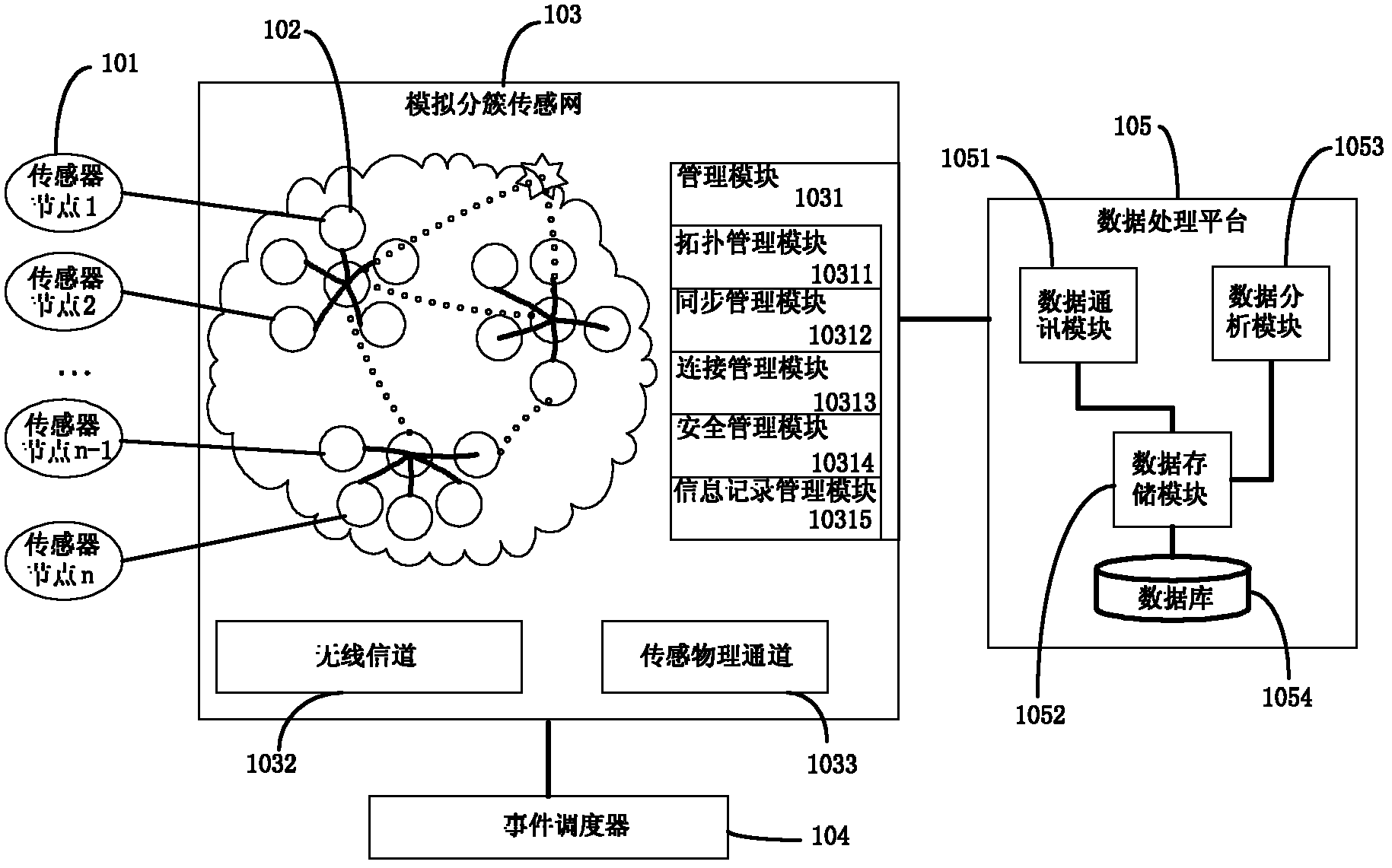

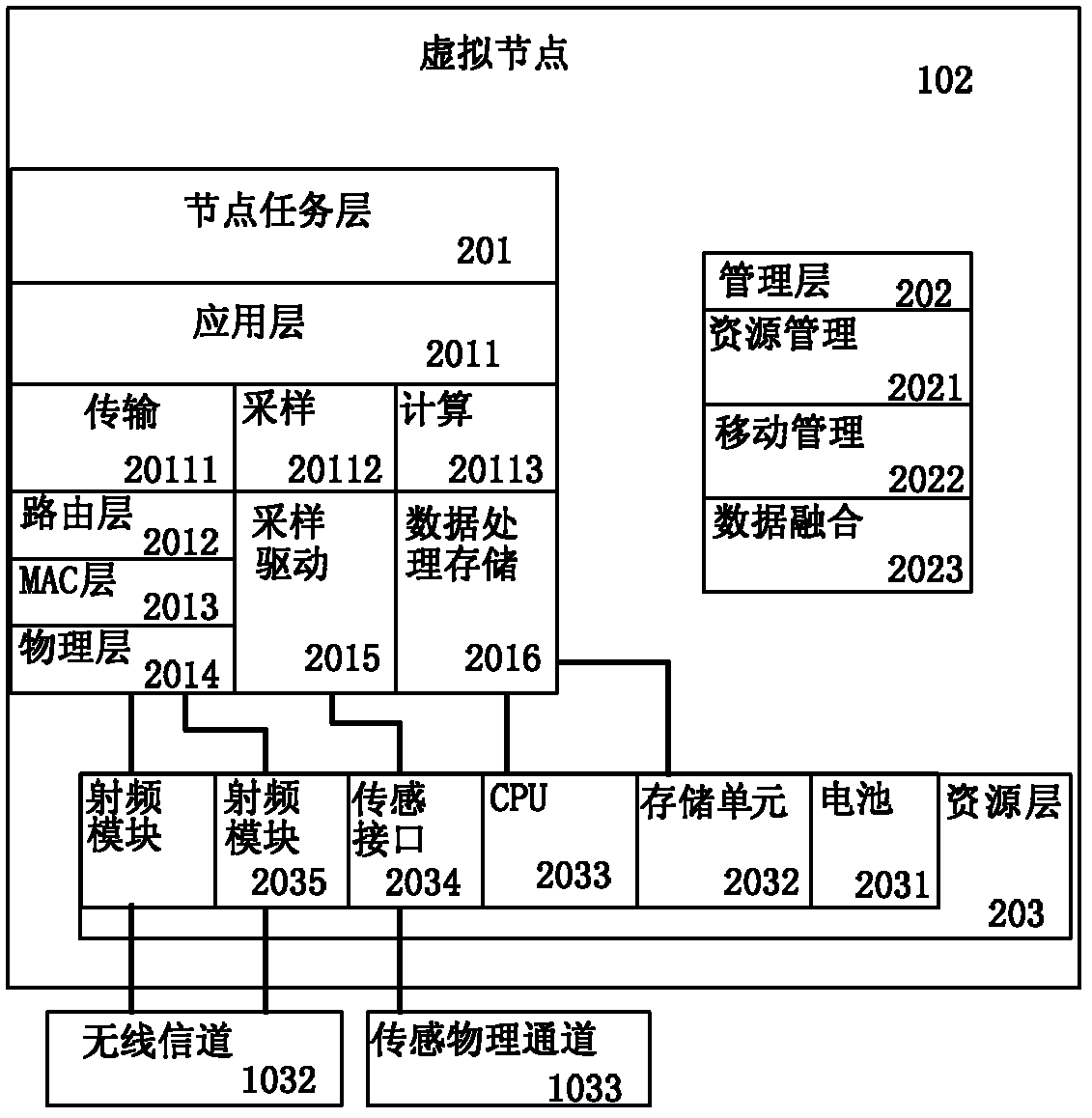

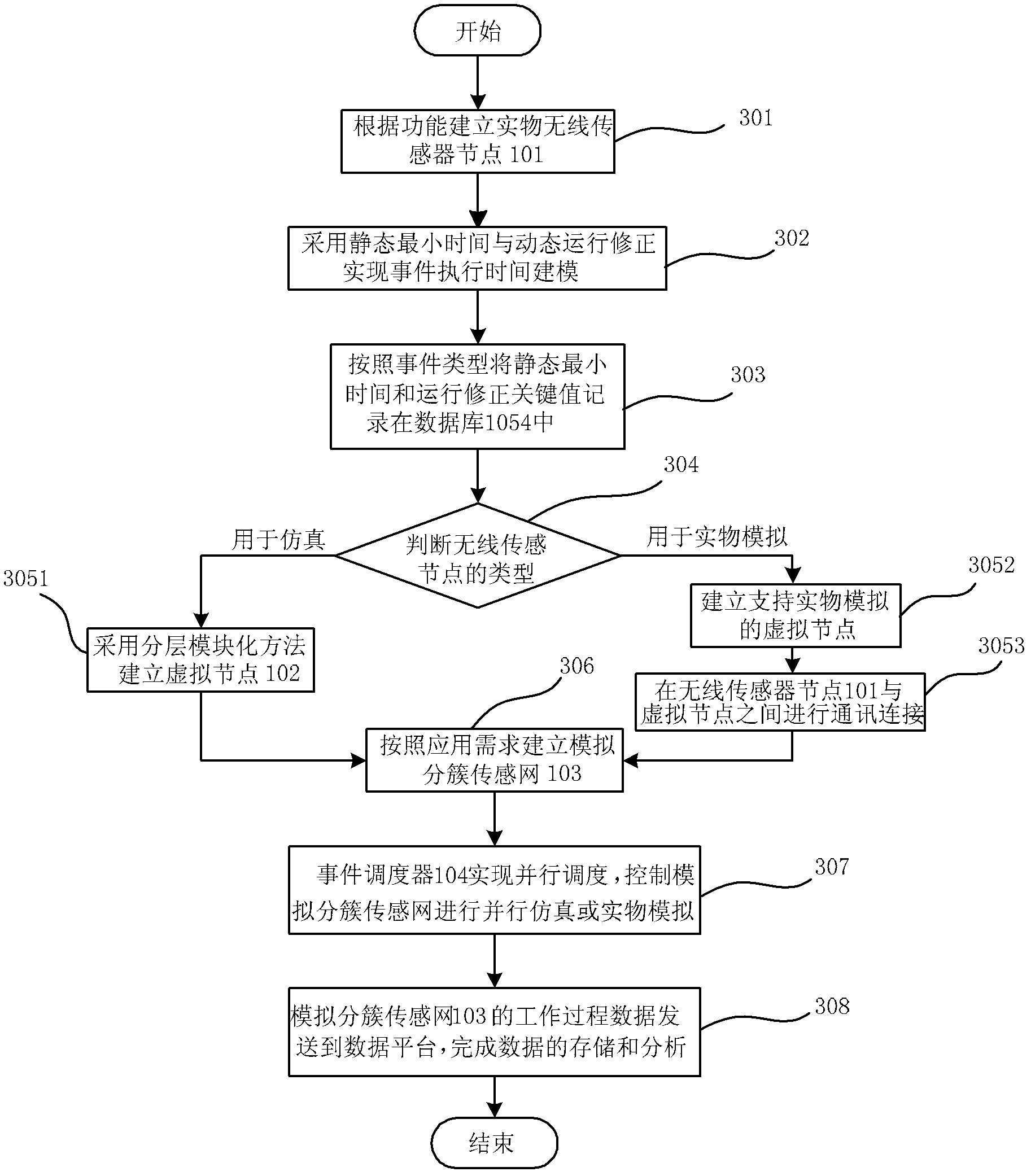

Device and method for supporting parallel simulation and physical simulation of wireless sensor network

ActiveCN102307369AImprove energy efficiencyImprove reliabilityNetwork topologiesPropogation channels monitoringNetwork managementParallel simulation

The invention discloses a device and method for supporting the parallel simulation and the physical simulation of a wireless sensor network. The device comprises a plurality of sensor nodes, a simulation decluster sensor network, a parallel event scheduler and a data processing platform, wherein the multiple sensor nodes are used to transmit working parameters, map the working parameters into virtual nodes, realize online debugging and integrate to the simulation decluster sensor network; the simulation decluster sensor network is used to establish a model, support the network management, integrate a wireless sensor network which can simulate specific applications in simulation, support online software debugging of the sensor nodes and support actual performance analysis of a simulation actual sensor network; the parallel event scheduler is connected with the communication of the simulation decluster sensor network and is used to complete multithreaded programming, execute the simulation events in parallel and maintain a global event queue; and the data processing platform is in communicating junction with the simulation decluster sensor network and is used to receive, store, analyze and display data. By the device, the wireless sensor network performance and node debugging information in different modeling complexities can be accurately described.

Owner:UNIV OF SCI & TECH BEIJING

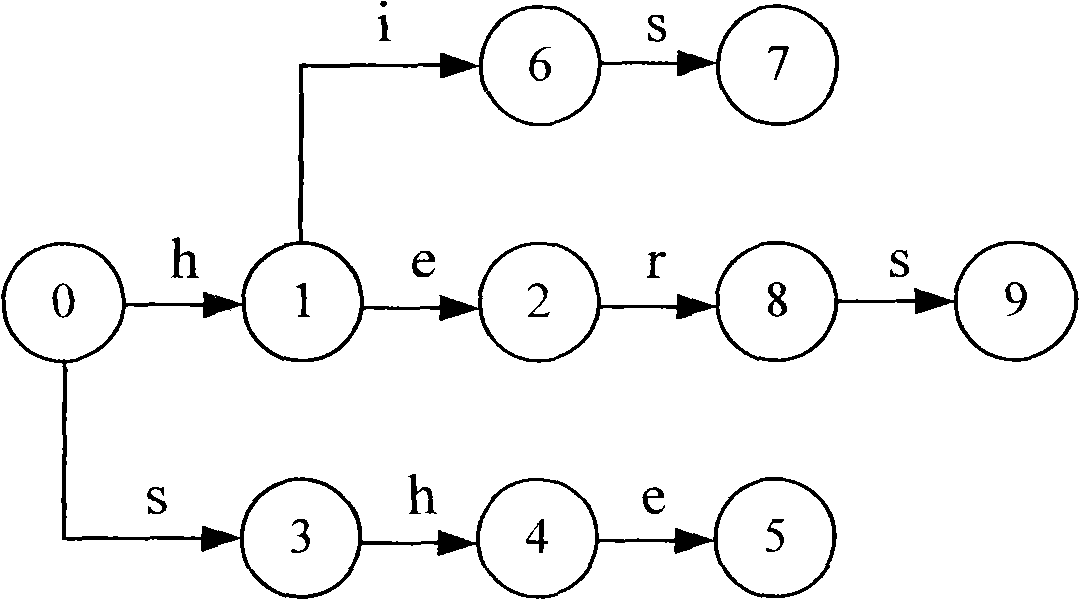

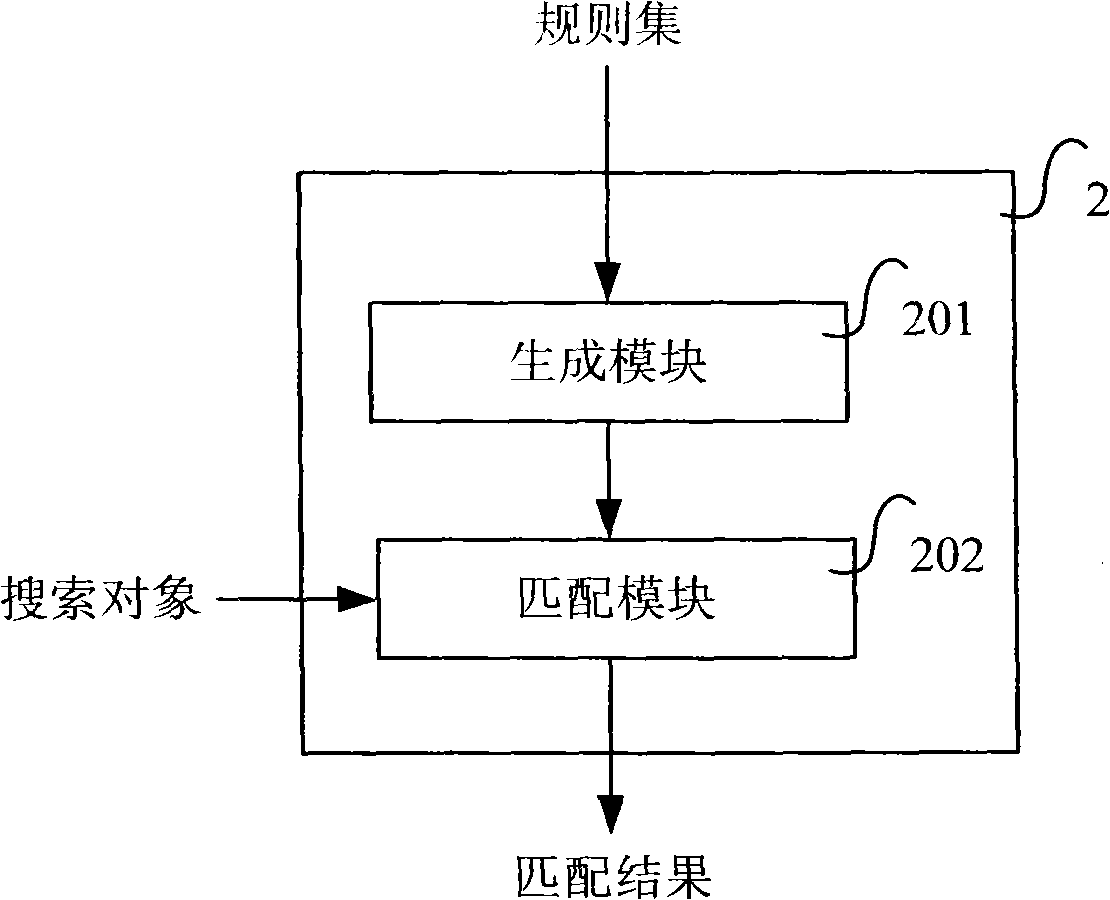

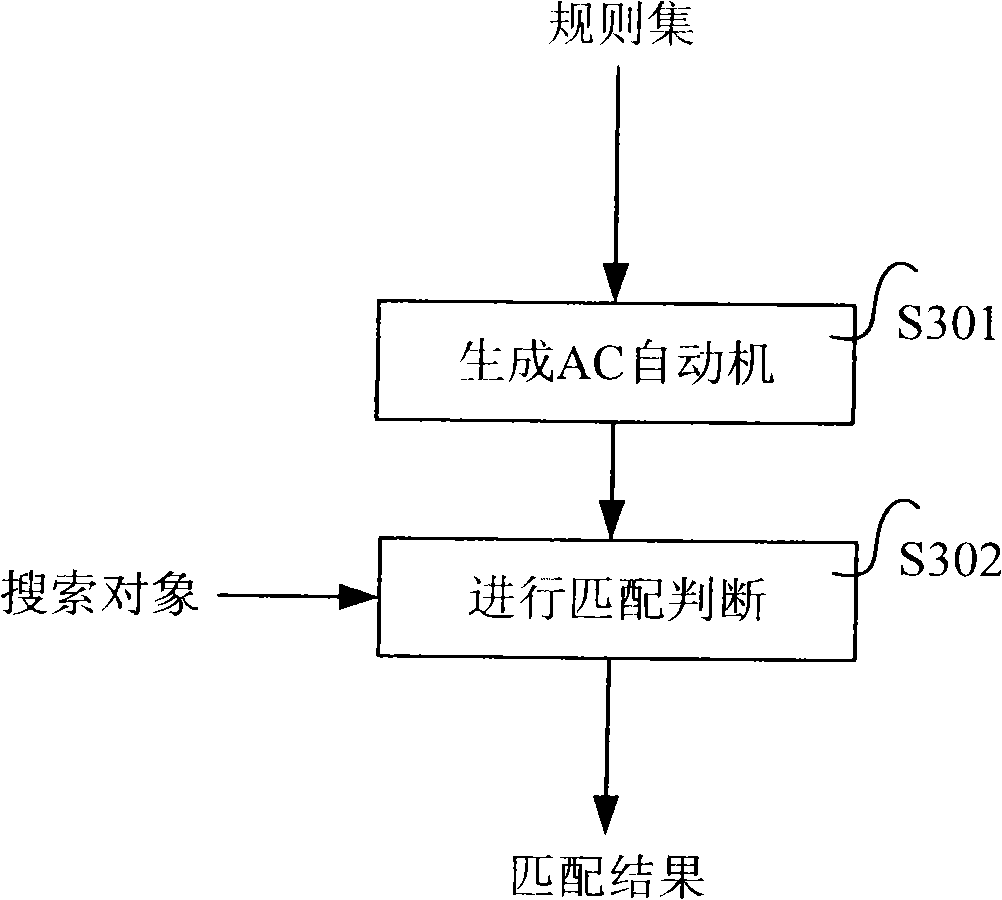

Parallel multi-mode matching method and system therefor

InactiveCN101286988AOvercome the inability to handle matching of non-deterministic rules containing wildcardsImprove efficiencySpecial data processing applicationsSecuring communicationAlgorithmMatch rule

The invention relates to a parallel multi-mode matching method and a system. The system comprises a generation module and a matching module, wherein, the generation module is used for reading a rule set including matching rules; matching rules comprising asterisk wildcards in the rule set are divided into sub rules of the matching rules from the asterisk wildcards; the sub rules exclude the asterisk wildcards; matching rules excluding asterisk wildcards in the rule set are the sub rules of the matching rules; all sub rules are generated into an AC automaton according to AC algorithms and output from the AC automaton; the matching module is used for reading a search object and the AC automaton which is applied to searching according to the AC algorithms; whether the search object matches all sub rules of the matching rules according to the sequence of the sub rules in the matching rules is judged; if so, the search object matches the matching rules, and matching results are output, thereby not only retaining the high efficiency of the AC algorithms, but also matching indefinite rules comprising the asterisk wildcards.

Owner:BEIJING VENUS INFORMATION TECH

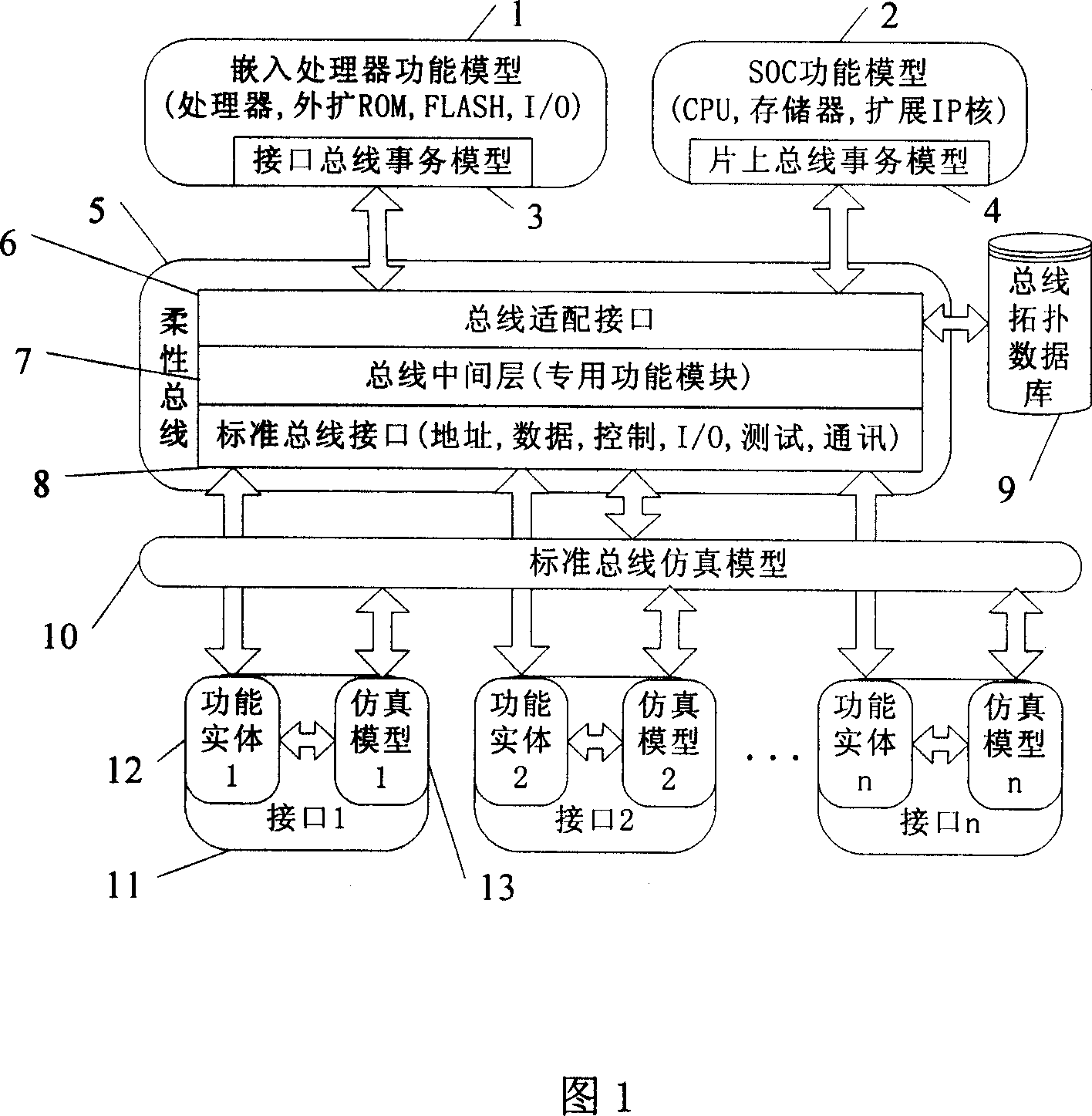

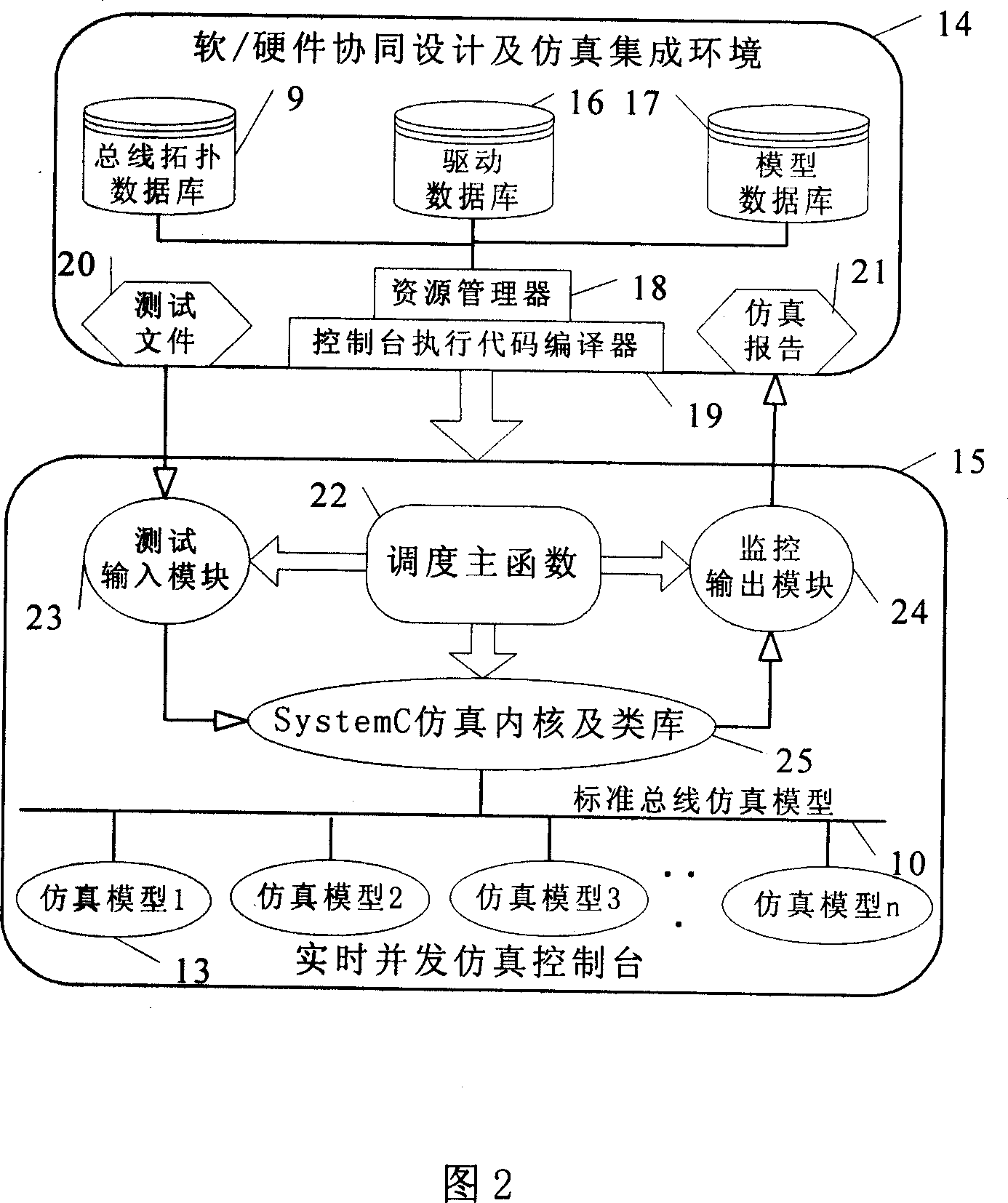

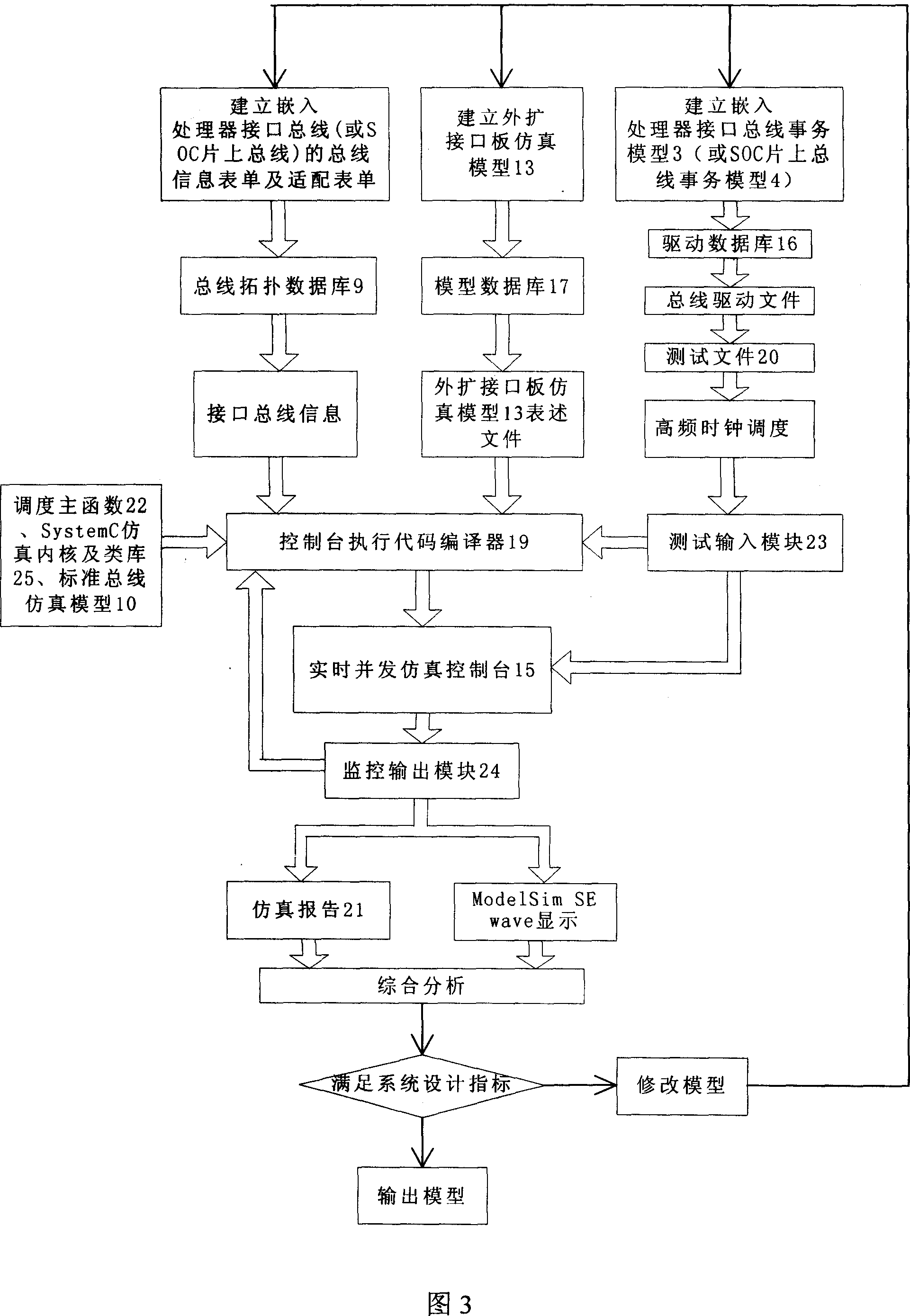

Bus model-based embedded system emulated platform

InactiveCN101059773ALarge simulation coverageHas hardware concurrencySoftware testing/debuggingSystemCSystems Modeling Language

The invention relates to an embedded system simulate platform based on bus model, which leads in the embedded system flexible bus design theory, to realize the uniformity of various embedded system bottom structure, and use a system model language SystemC to build a processor host simulate model and an expansion interface board simulate model. The processor host simulate model comprises an embedded processor function model, an interface bus mission model or a SOC (on-chip system) function model, and an on-chip mission model. The invention uses software / hardware cooperate design and simulation integrated environment to realize the development of embedded system simulation model, and uses a real-time parallel simulation console to realize the parallel execution and detection of embedded system simulation model.

Owner:BEIHANG UNIV

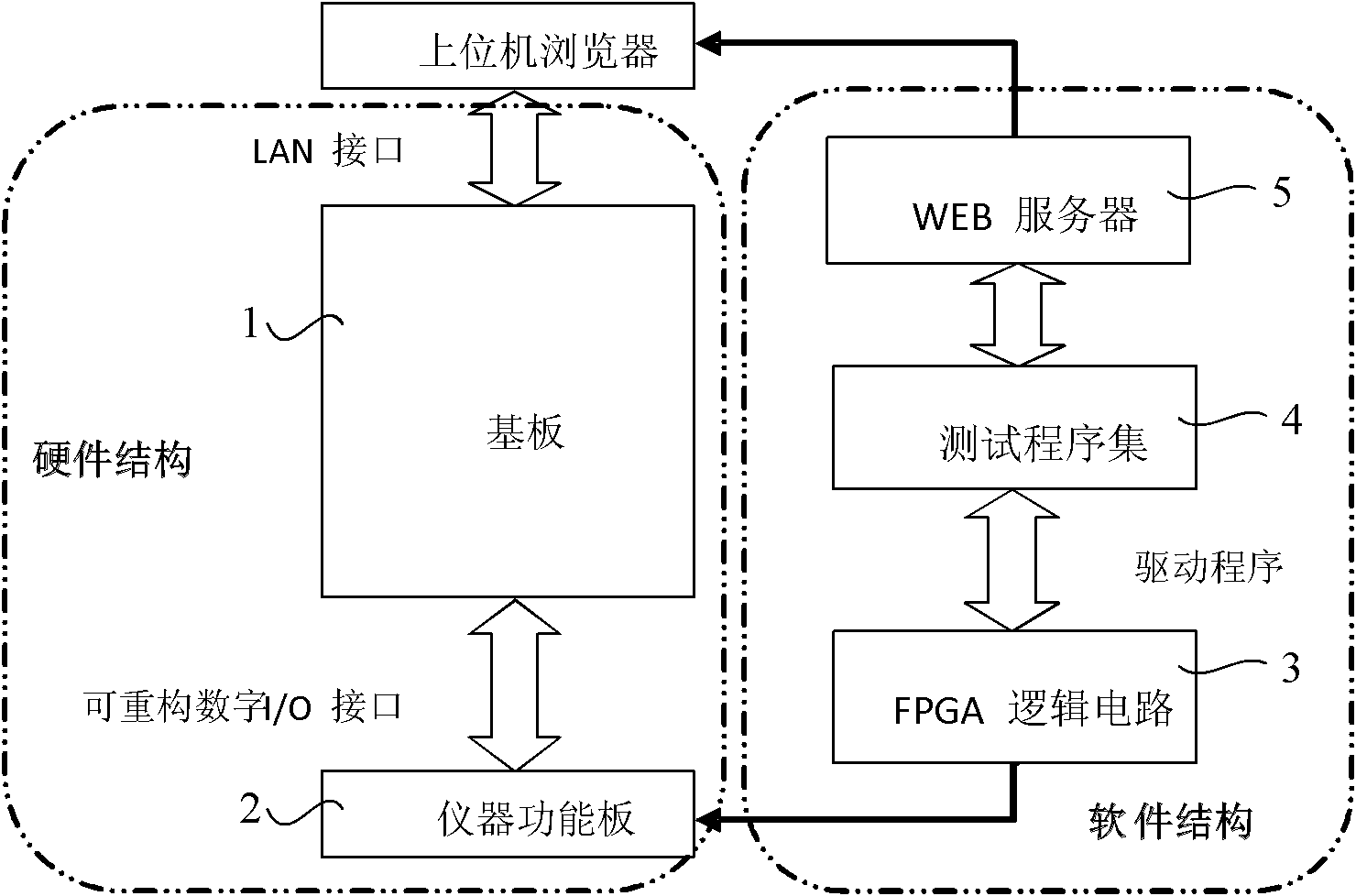

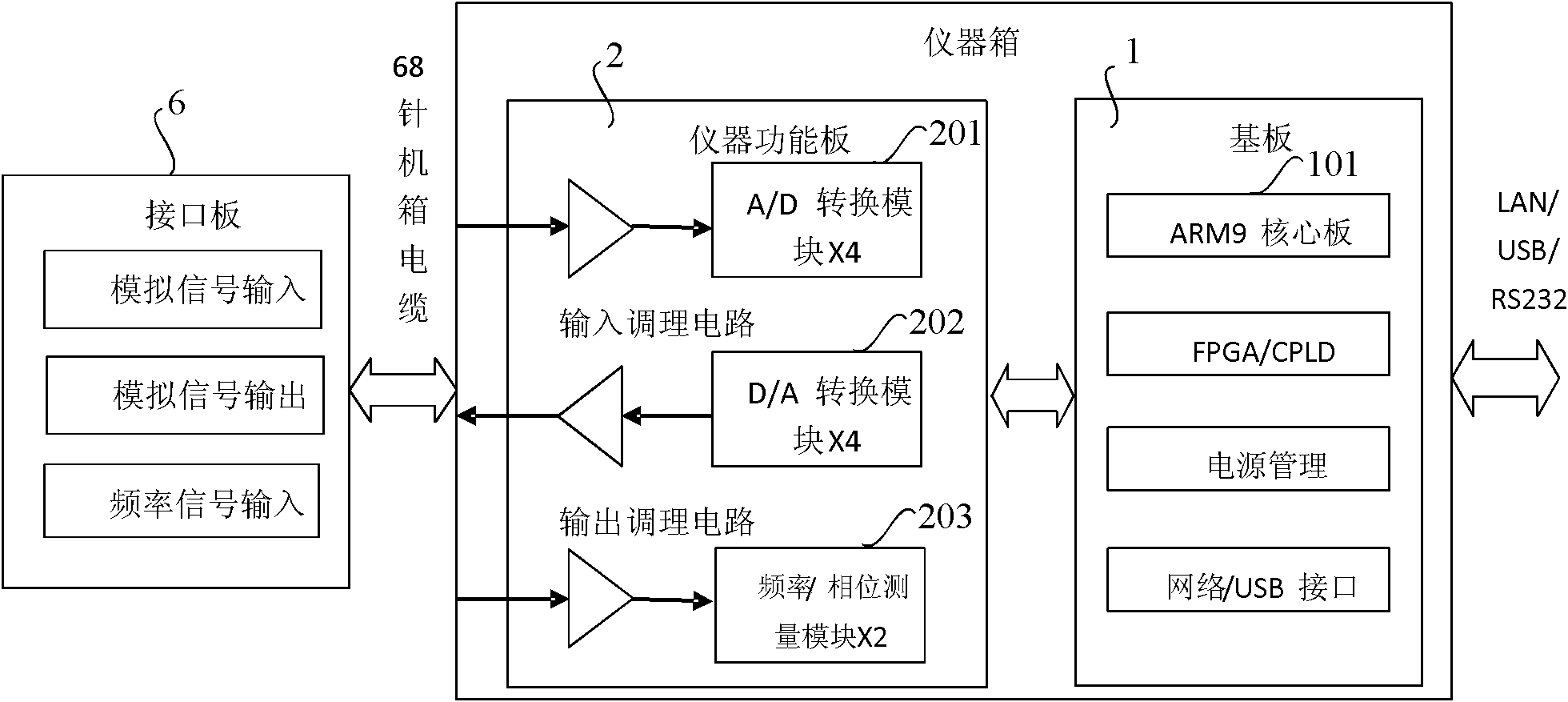

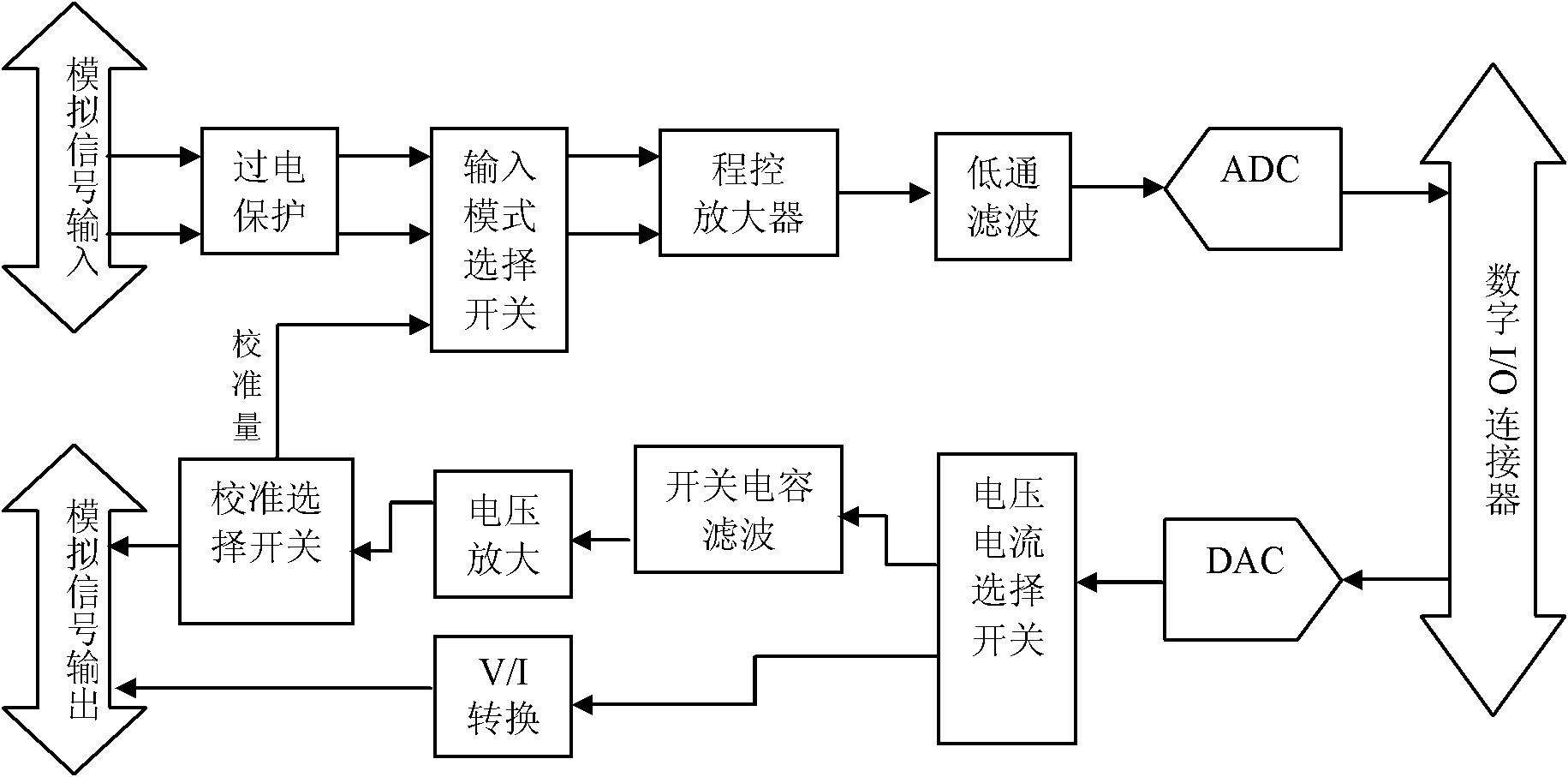

LXI-based parallel multi-channel reconfigurable instrument

InactiveCN102136970AEasy for secondary developmentFlexibility to change functionsData switching networksInstrument functionWeb service

The invention discloses an LXI-based parallel multi-channel reconfigurable instrument, comprising a substrate, an instrument function board, a field programmable gate array (FPGA) logical circuit, a test program set and a Web server, wherein the substrate and the instrument function board are the main components of the reconfigurable instrument and arranged in an instrument case together; the substrate is mainly used for realizing a software function and a hardware logical circuit of the system; and the instrument function board is mainly used for realizing the conversion between analog signals and digital signals. Based on the LXI standard design, the instrument is convenient for secondary development; the instrument has a multi-channel parallel test capacity, and each channel can flexibly change the function of the instrument; and the instrument can be used without installing software and can be operated and configured on line only by a browser.

Owner:BEIHANG UNIV

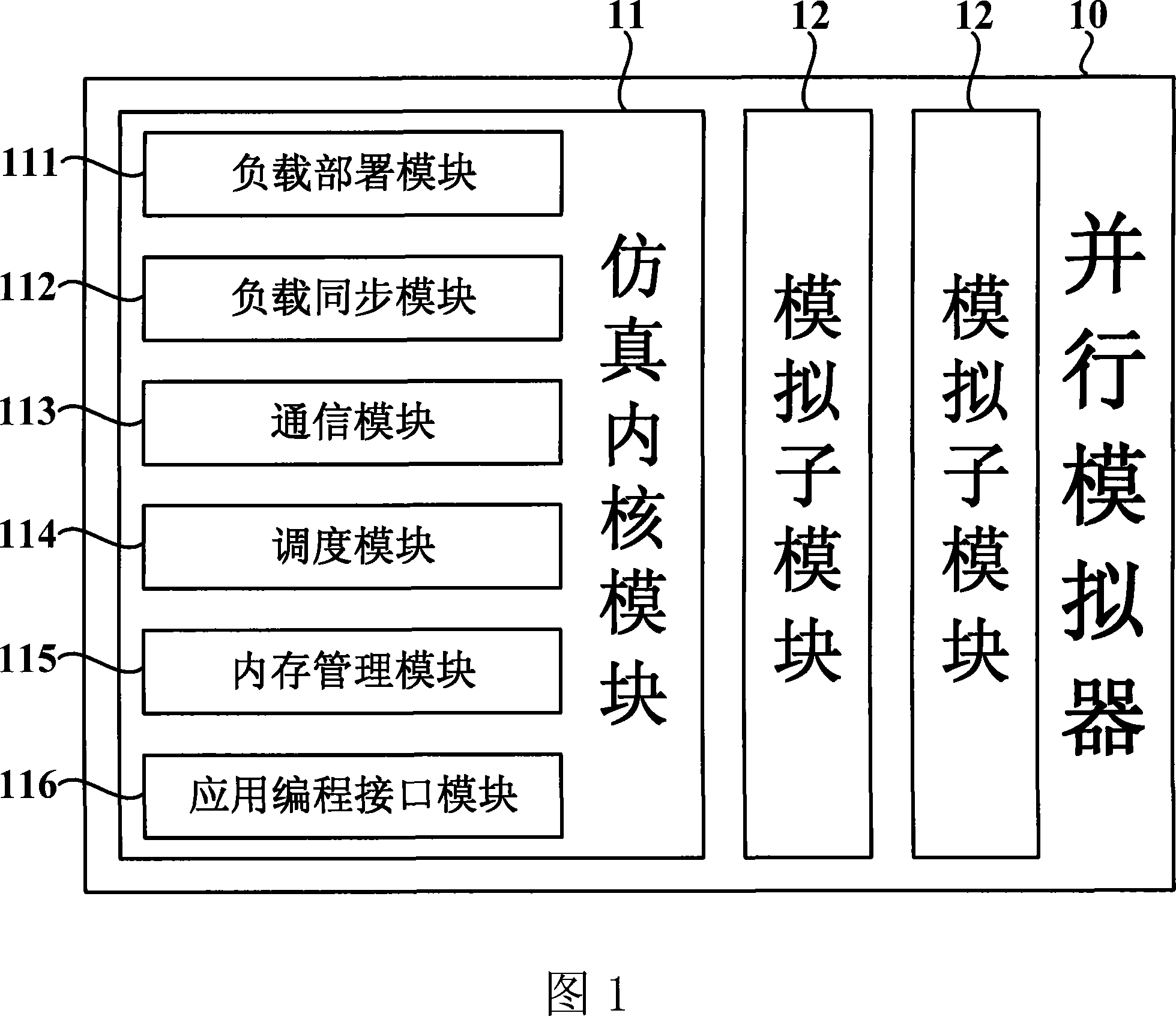

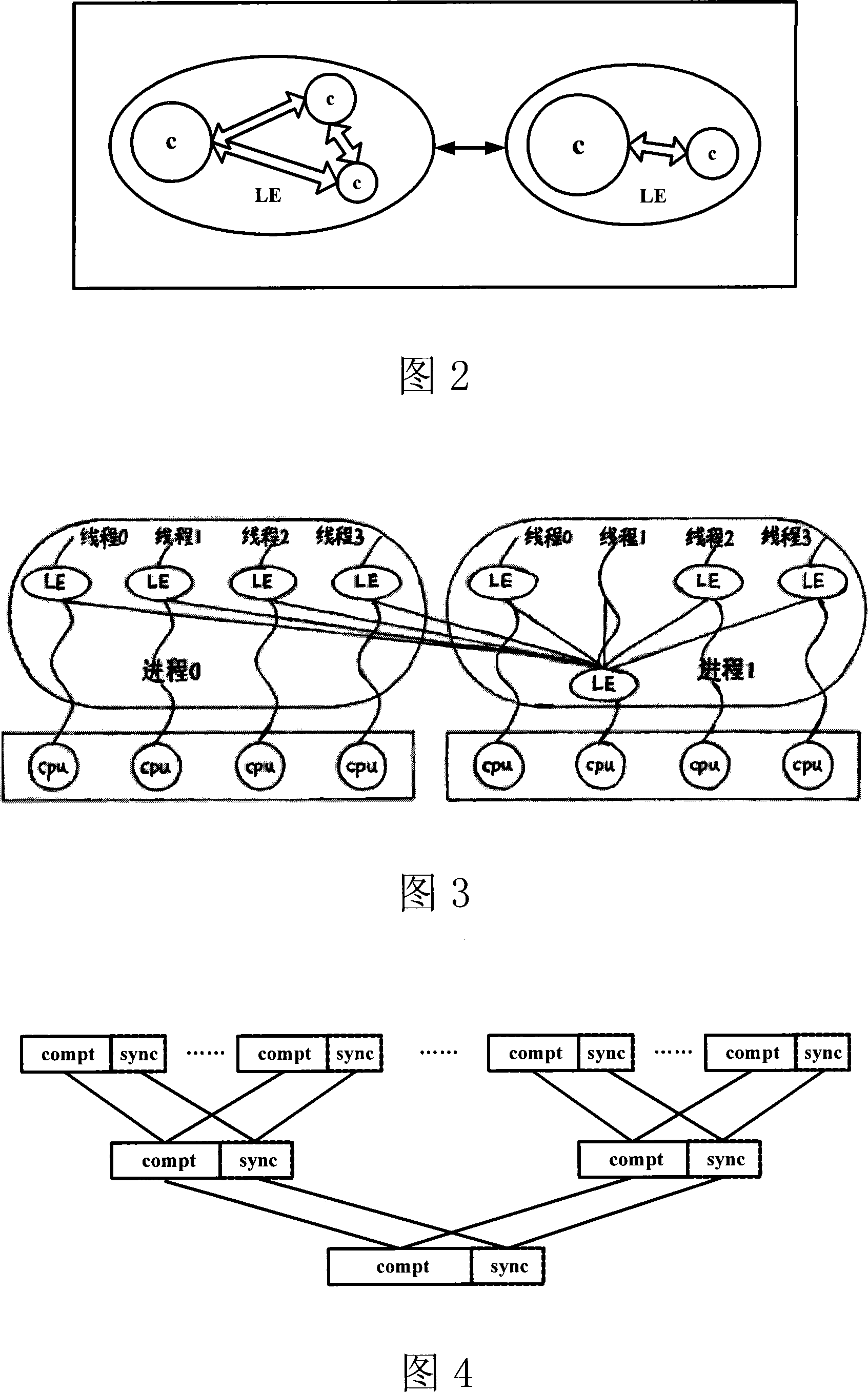

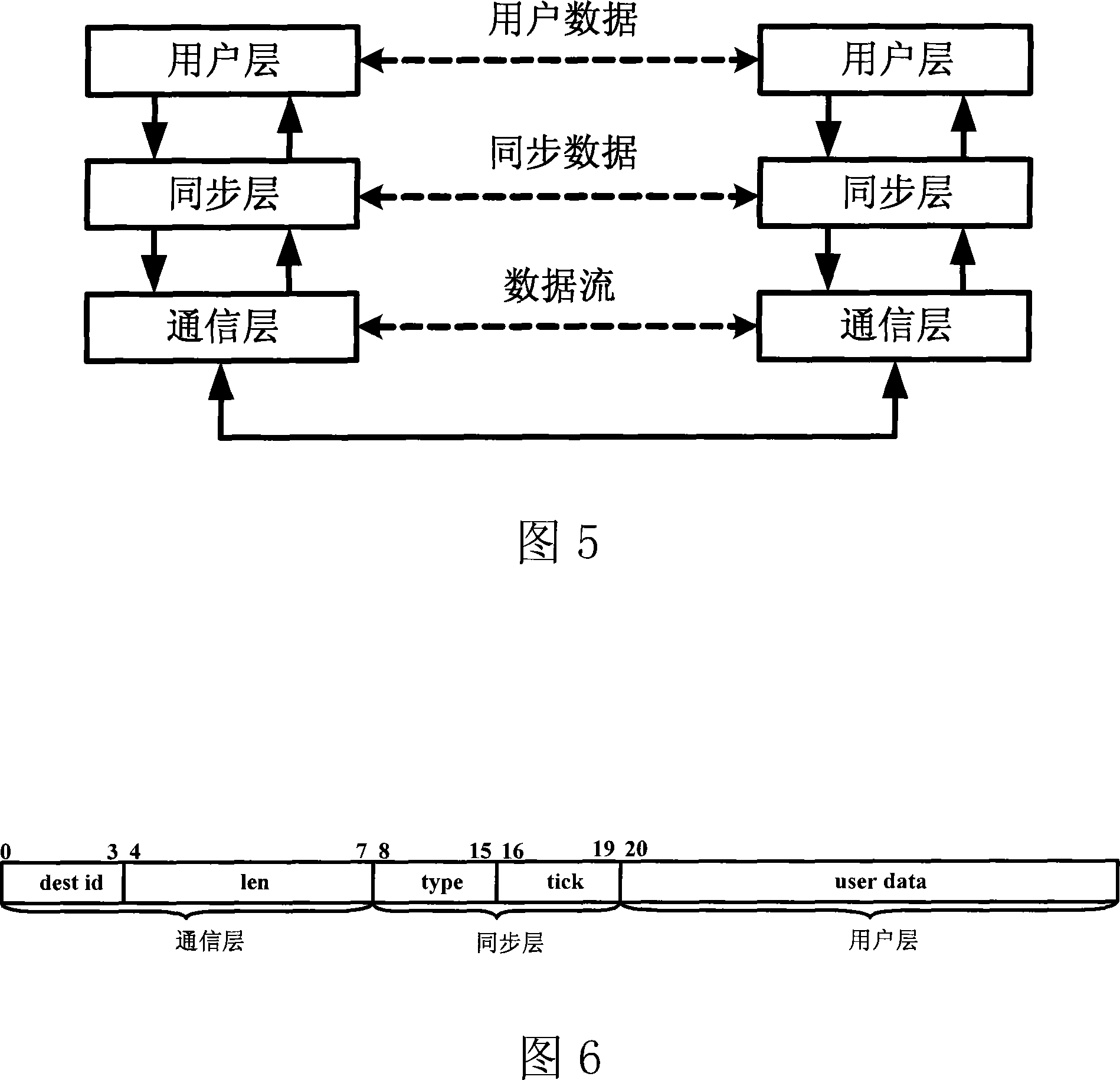

Parallel simulator and method

InactiveCN101196827AImprove productivityEasy to joinInterprogram communicationSoftware simulation/interpretation/emulationApplication programming interfaceComputer science

The invention relates to the computer field, which discloses a parallel simulator and the related method. The parallel simulator and method integrate functions of synchronization, communication and scheduling, etc. in the parallel simulator, so as to form a framework; simultaneously, the invention provides a basic application programming interface API for user, the function of the parallel simulator can be realized when user calls the basic application programming interface API under the precondition that only the framework constraint is satisfied.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

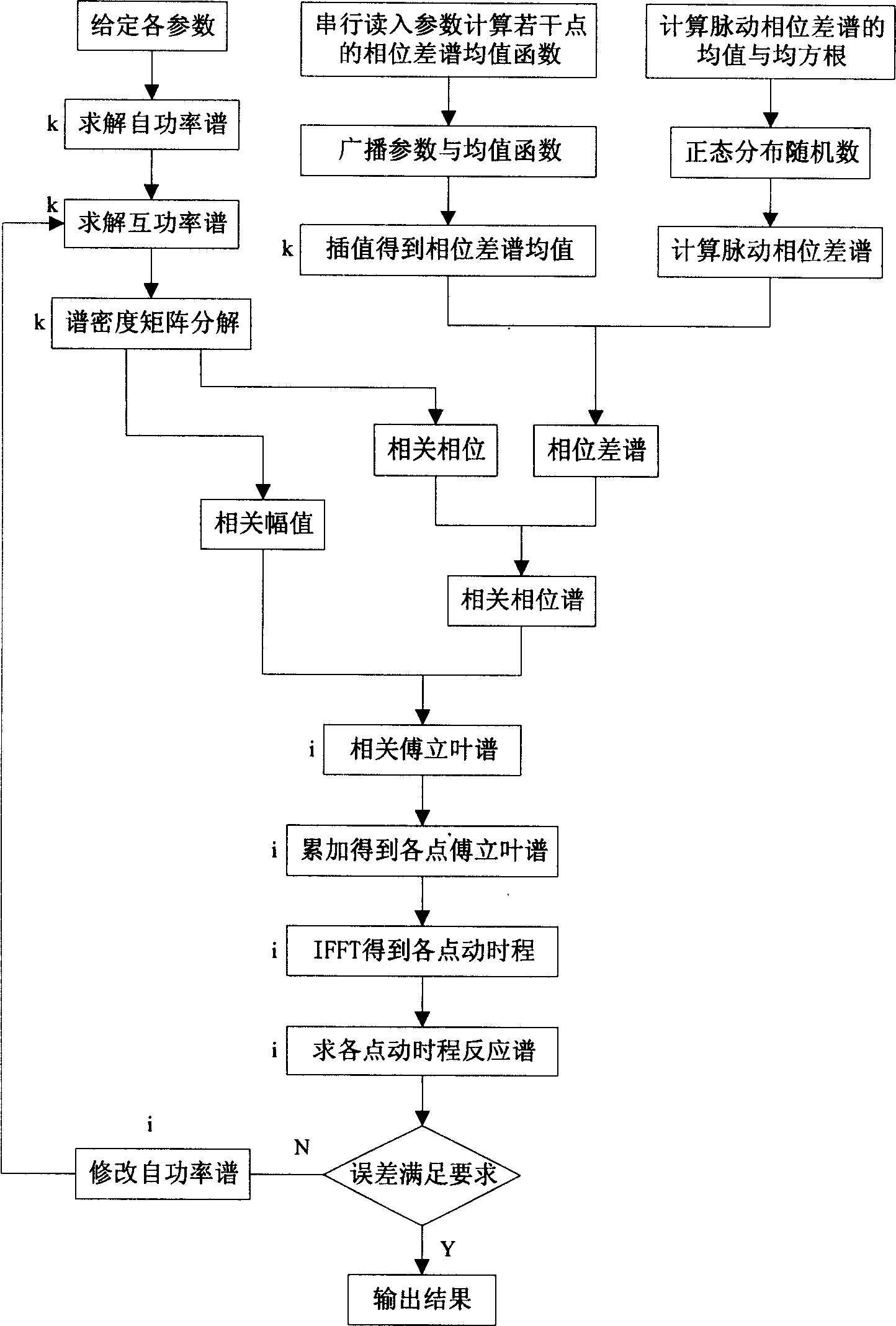

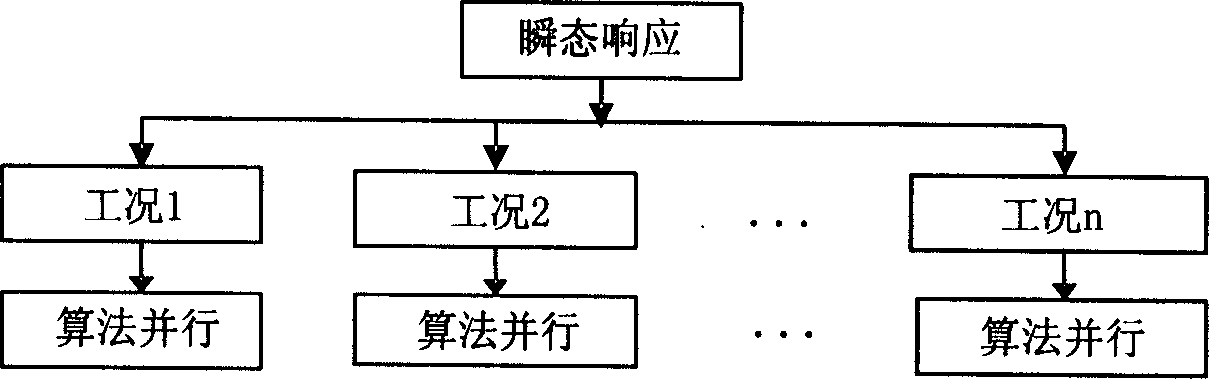

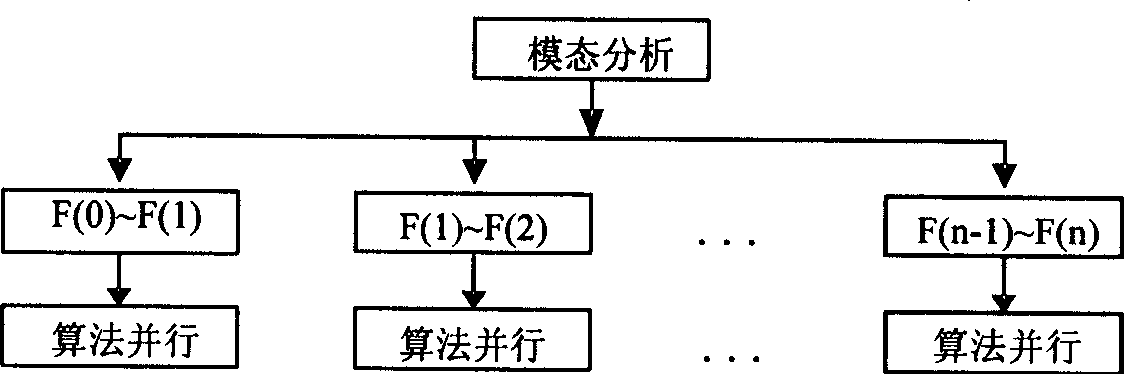

Earthquake safety prediction of super-huge engineering actuated by computer

A method for predicting seismic safety for extremely large engineering project includes using finite element (FE) preprocessing software to set up FE module, inputting parameters required by active time histories of seism for obtaining mathematical module, transmitting the model and time step length to supercomputer to carry out transient response analysis and model analysis for parallel calculation, sending data back to FE analysis software for following calculation and carry out visual processing by using FE post processing software to read in calculation result .

Owner:SHANGHAI JIAO TONG UNIV

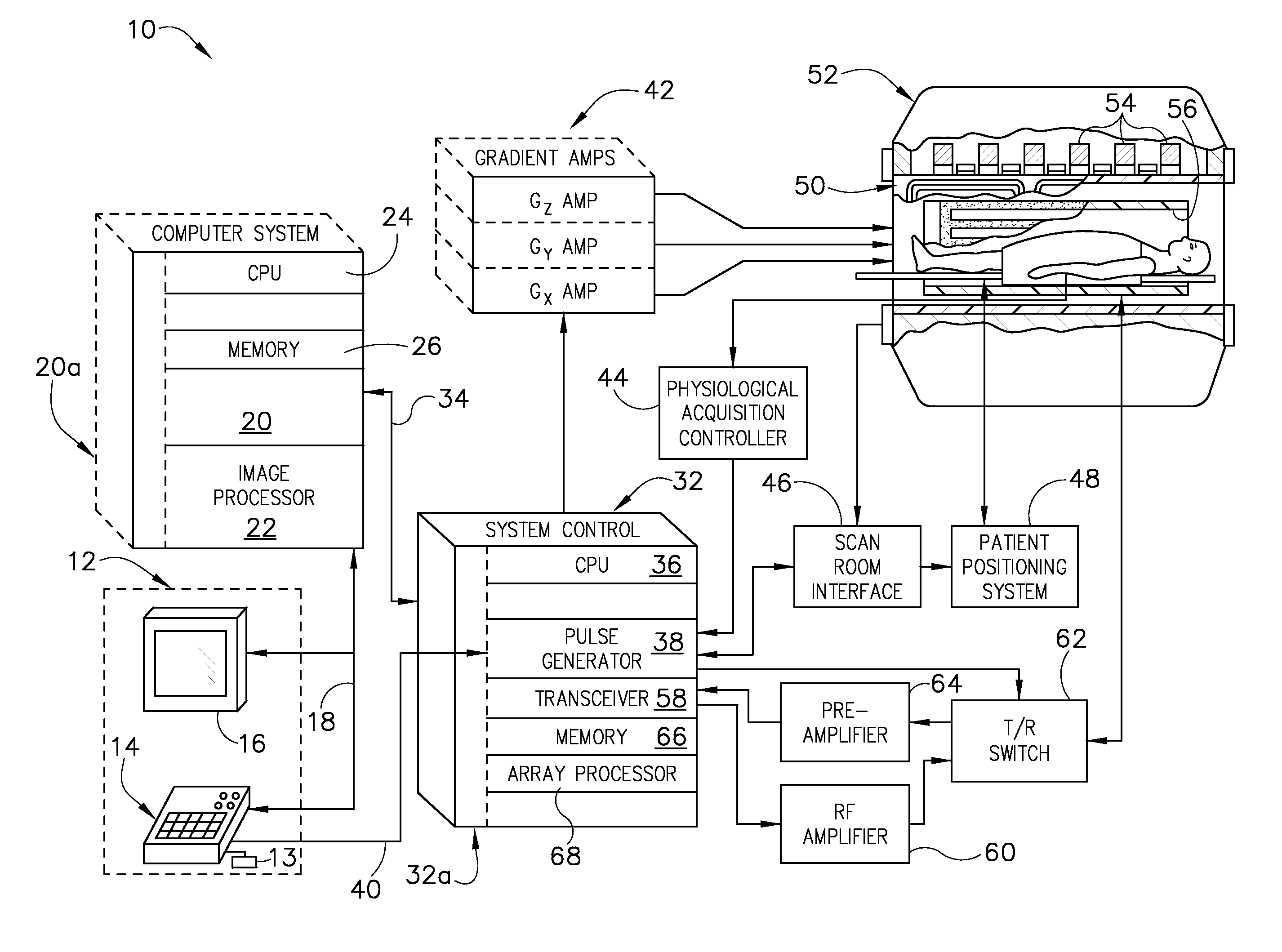

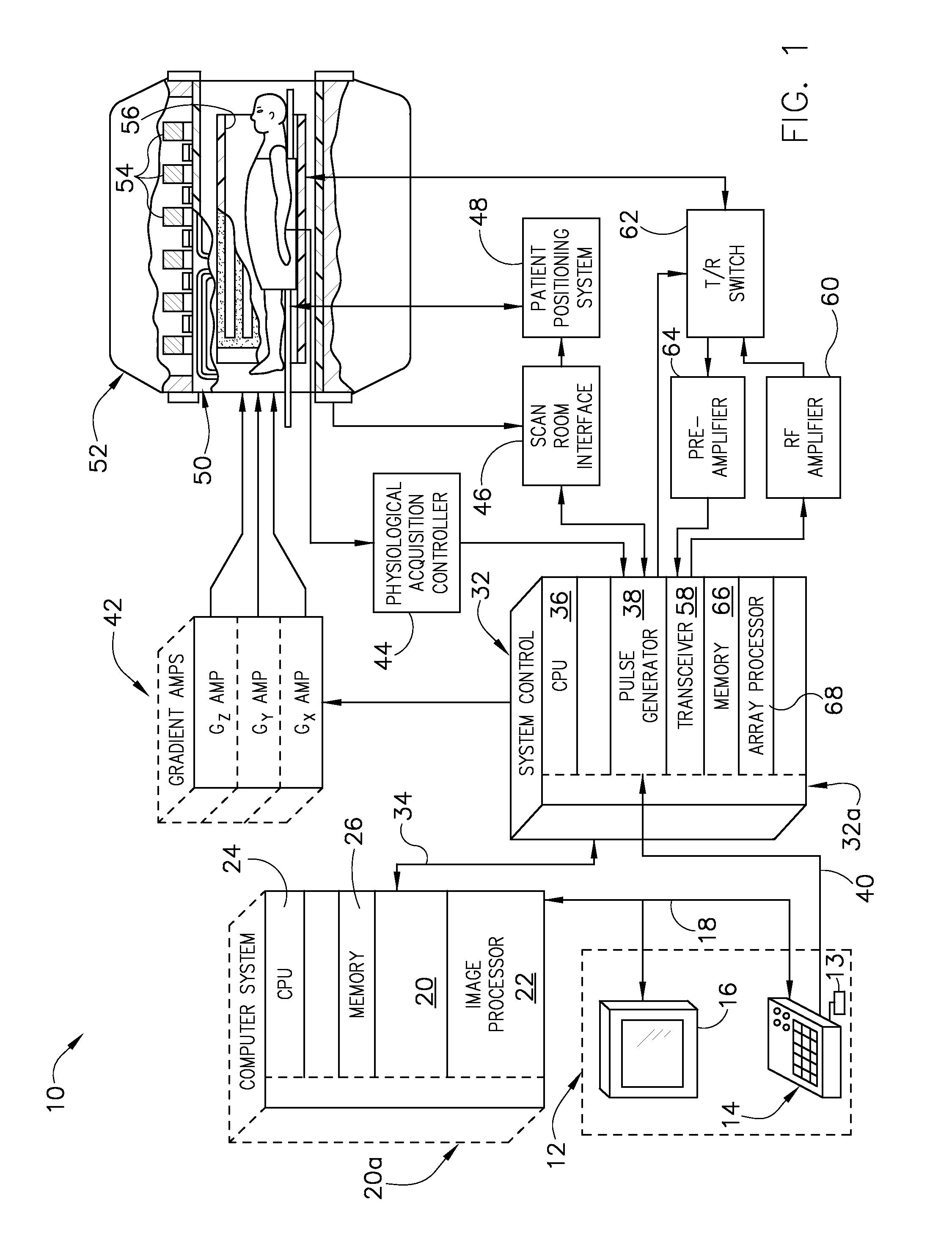

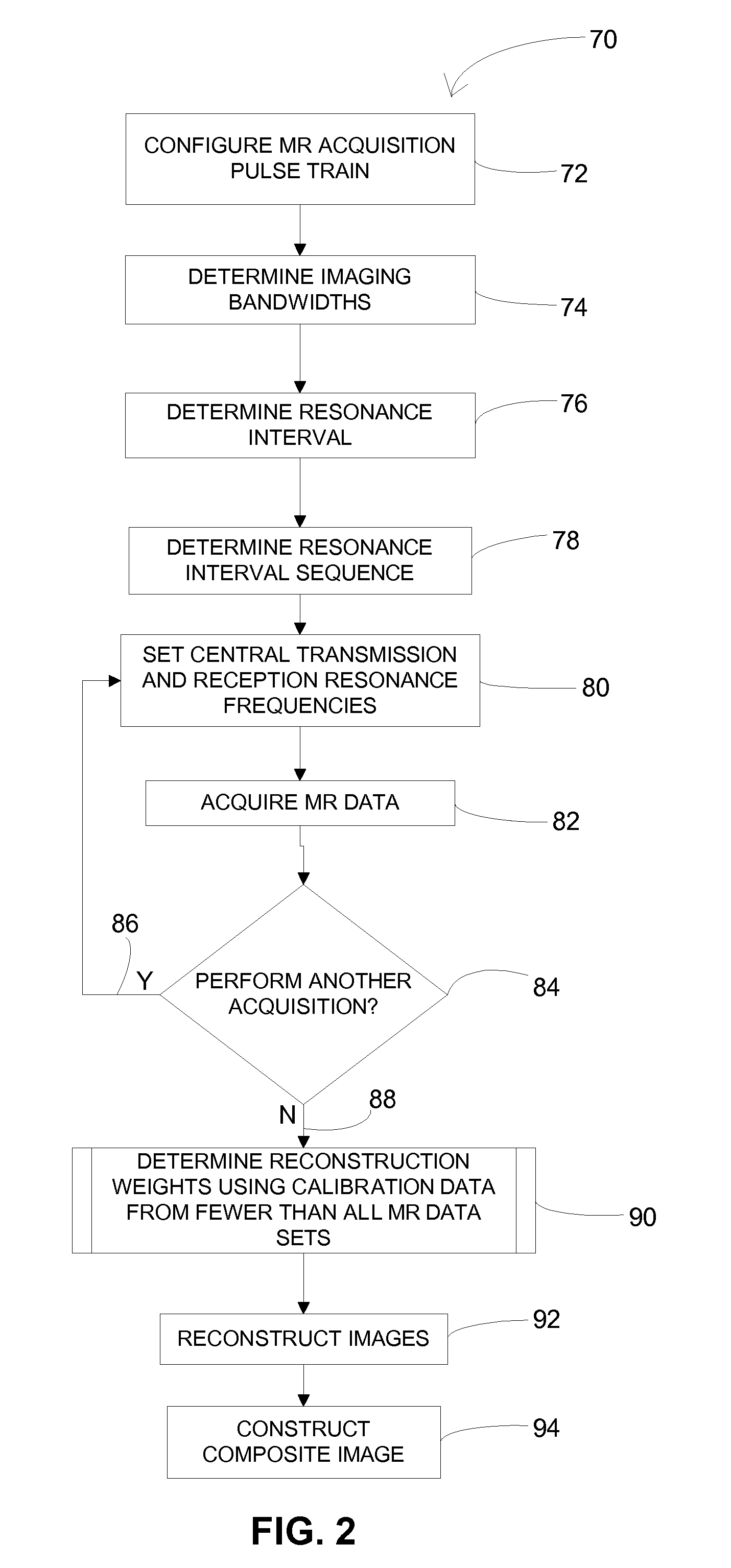

System and method of parallel imaging for magnetic resonance imaging near metallic implants

ActiveUS20110241669A1Reduced calibration computation timeMeasurements using NMR imaging systemsElectric/magnetic detectionData setResonance

A system and method for magnetic resonance imaging is disclosed, the MRI apparatus comprising a computer programmed to acquire a plurality of 3D MR data sets, each 3D MR data set acquired using a central transmit frequency and a central receive frequency set to an offset frequency value that is distinct for each 3D MR data set, wherein at least a portion of each 3D MR data set is accelerated k-space data, and wherein at least one of the plurality of 3D MR data sets comprises fully-sampled calibration k-space data lines. The computer is also programmed to determine reconstruction weights from the fully-sampled calibration k-space data lines, reconstruct an image for each 3D MR data set using the reconstruction weights from the fully-sampled calibration k-space data lines to synthesize unacquired data, and generate a composite image from the reconstructed images based on the plurality of 3D MR data sets.

Owner:GENERAL ELECTRIC CO

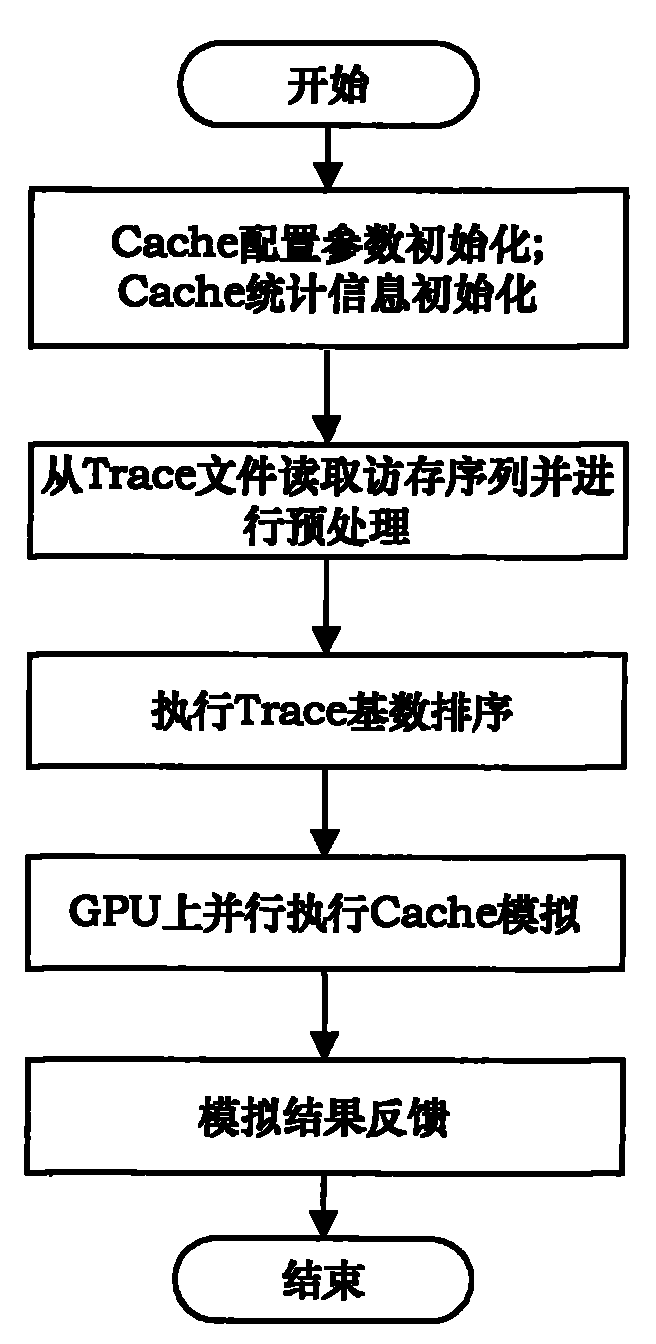

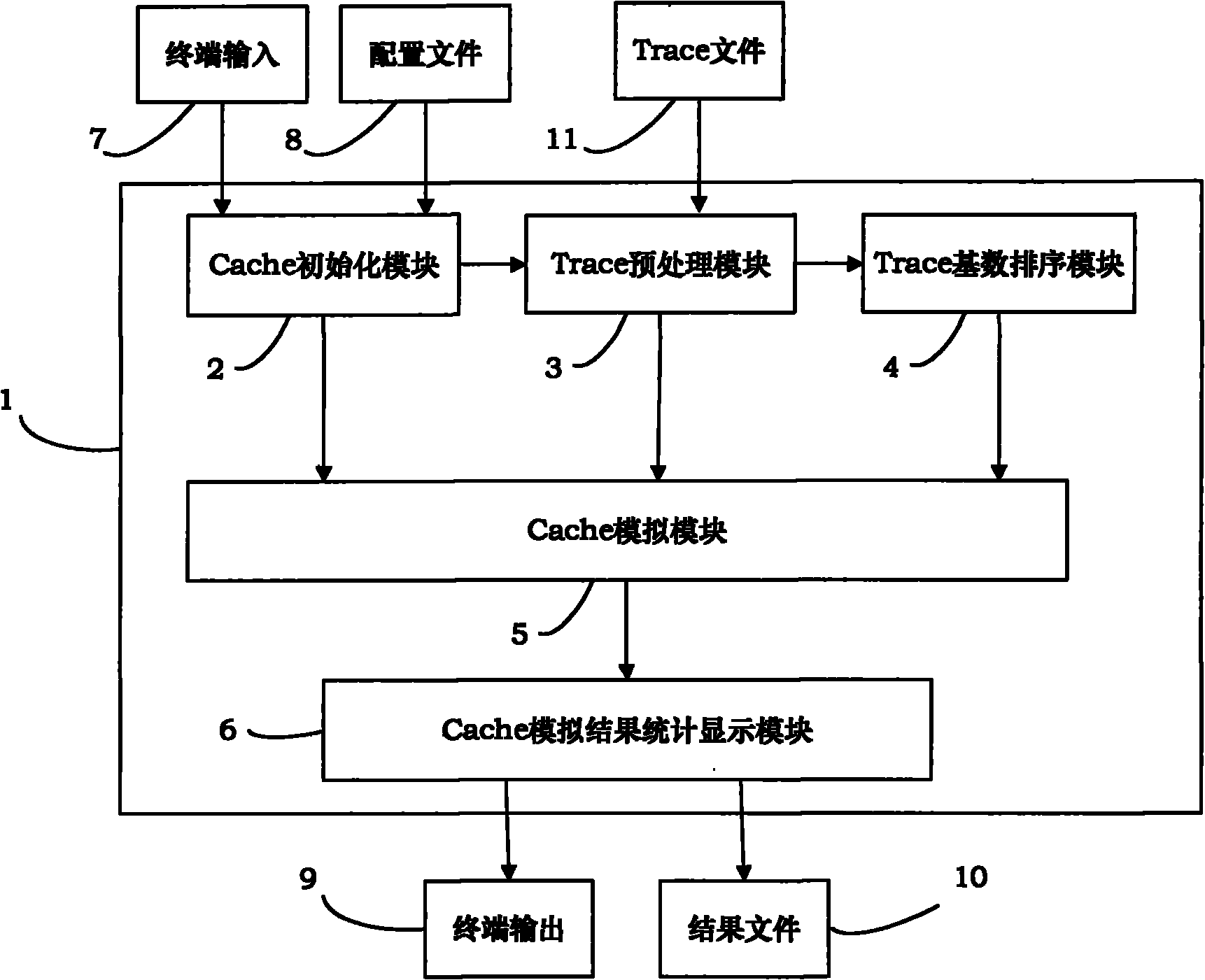

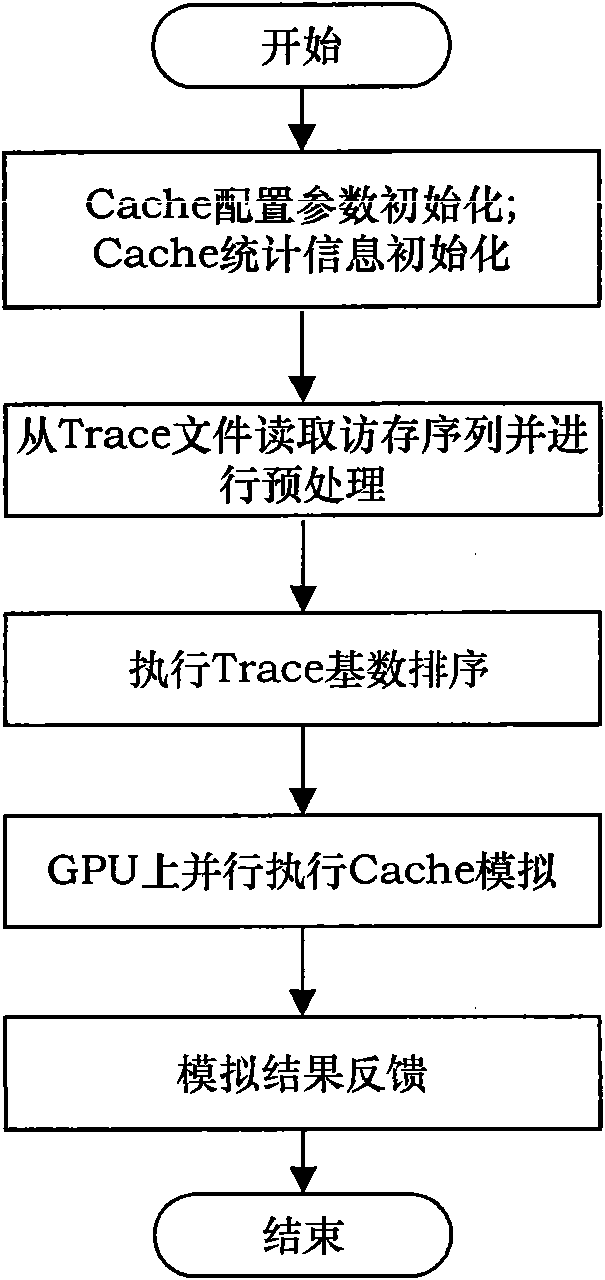

GPU-based Cache simulator and spatial parallel acceleration simulation method thereof

InactiveCN101814039AImprove Simulation EfficiencyReduced simulation timeMemory adressing/allocation/relocationImage memory managementRadix sortParallel sorting

The invention provides a GPU-based Cache simulator and a spatial parallel acceleration method thereof. The Cache simulator comprises a Cache initialization module, a Trace preprocessing module, a Trace radix sorting module, a Cache simulation module and a Cache simulation result summarization and display module. The invention adopts powerful parallel processing resources of the GPU to preprocess memory access sequences, and utilizes the relevance of Cache configuration files to parallel sort the memory access sequences through a radix sorting algorithm operating on the GPU, thereby obtaining continuous memory access sequences mapped in each group and achieving inter-group parallel Cache simulation. Moreover, due to the parallel simulation algorithm with different levels and different grain sizes, the invention effectively reduces the Cache simulation time, improves the Cache simulation efficiency and realizes the accurate simulation of behaviors of the Cache. Moreover, the invention has the advantages of simple development environment and easy implementation.

Owner:BEIHANG UNIV