Chip multi-core processor clock precision parallel simulation system and simulation method thereof

A multi-core processor, simulation system technology, applied in software simulation/interpretation/simulation, program control devices, etc., can solve the problems of false sharing of dynamic variables, logic deadlock, causal logic errors, etc., to improve accuracy and simulation performance Effect

Inactive Publication Date: 2010-07-28

SUZHOU INST FOR ADVANCED STUDY USTC

View PDF3 Cites 32 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

[0008] The object of the present invention is to provide an on-chip multi-core processor clock accurate parallel simulation system, which solves the causal logic errors caused by parallel simulators in the prior art, the logical deadlock caused by competitive access to shared variables, and the cross-allocation of different threads Dynamic variables cause problems such as false sharing

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment approach

[0082] for(i=0; i

[0083] private_space[i]=create_mspace(0,0);

[0084] …

[0085] for(i=0; i

[0086] {

[0087] event_procs[i] = mspace_calloc(private_space[i], 1, sizeof(struct list_t));

[0088] list_create(private_space[i], event_procs[i], 10);

[0089] heap_create(private_space[i], 20, event_heap[i]);

[0090] repos_create(private_space[i], sizeof(struct event_t), "event_repos",

[0091] event_repos[i]);

[0092] host_thd[i].self.event_out_q.pool=

[0093] mspace_calloc(private_space[i], eq_len, sizeof(eq_entry));

[0094] host_thd[i].mnger.event_in_q.pool=

[0095] mspace_calloc(private_space[i], eq_len, sizeogf(eq_entry));

[0096]}

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

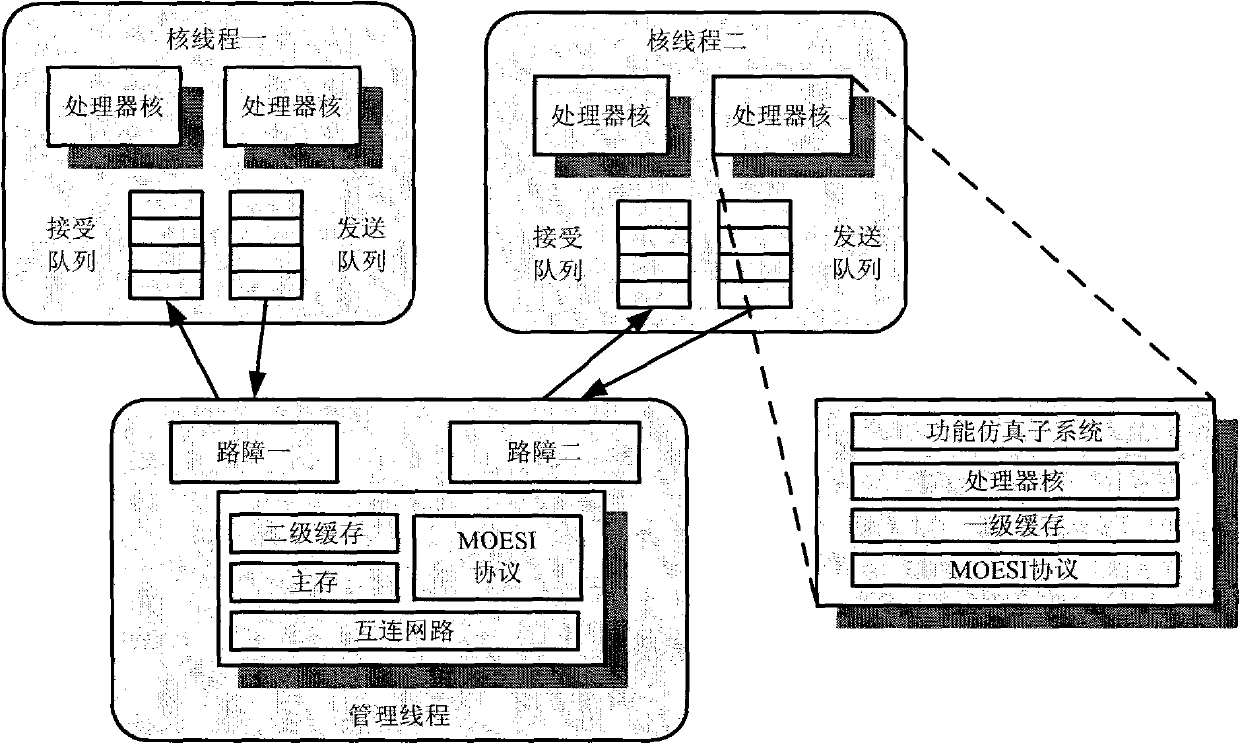

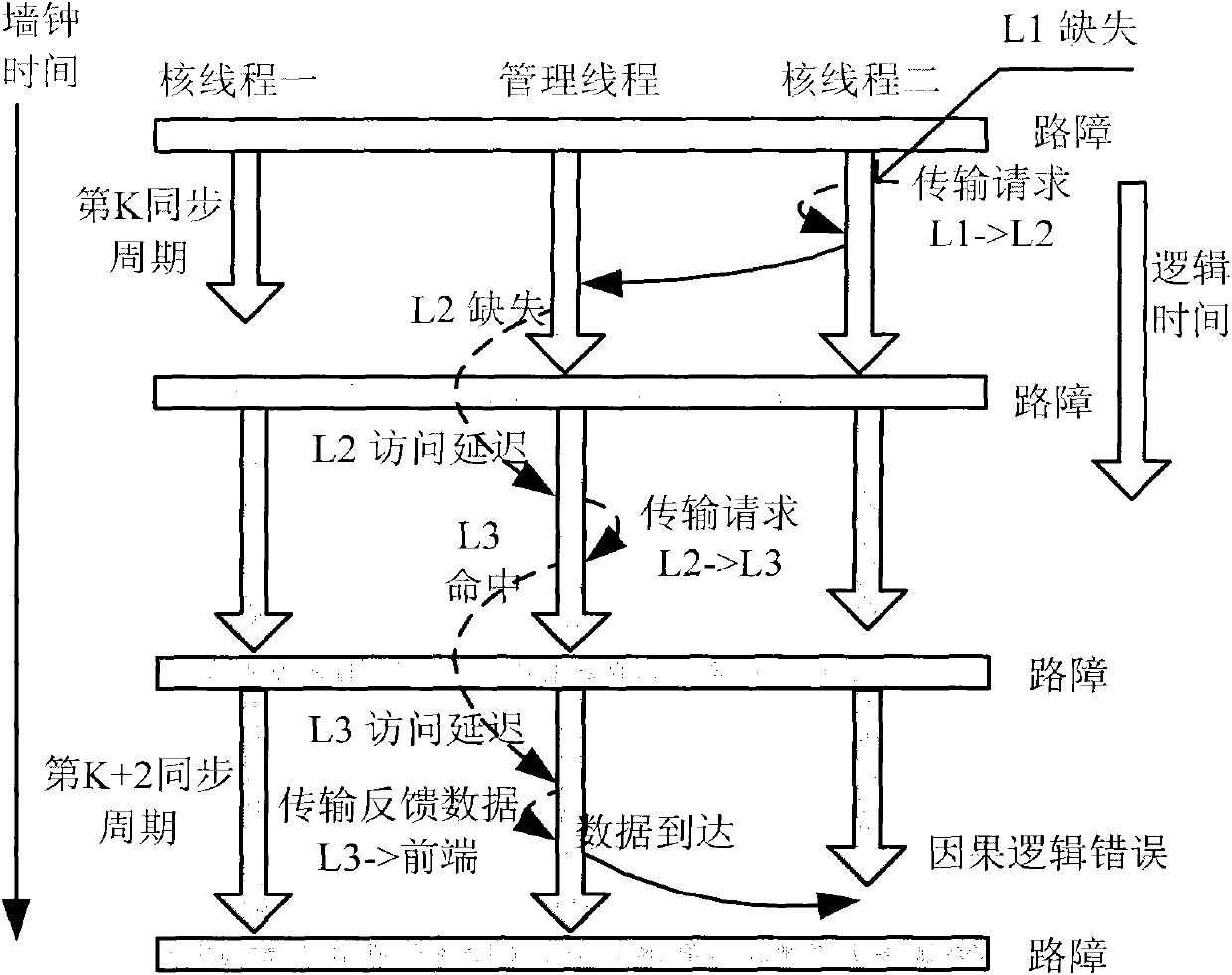

The invention discloses a chip multi-core processor clock precision parallel simulation system and a method thereof. The system comprises a management thread of an initialization simulation system; the management thread establishes a core thread according to a core number of a simulation object system or parameters given by a user; and the system is characterized in that: the management thread receives access data events sent by the core thread and a suspended barrier acting on the core thread is set; and when the core thread of the maximum local lock does not receive data when reaching a preset clock period, the core thread moves the suspended barrier to synchronously advance to form a sliding simulation time window. Simulation experiments prove that the system greatly improves the accuracy and simulation performance of the multi-core processor parallel simulation.

Description

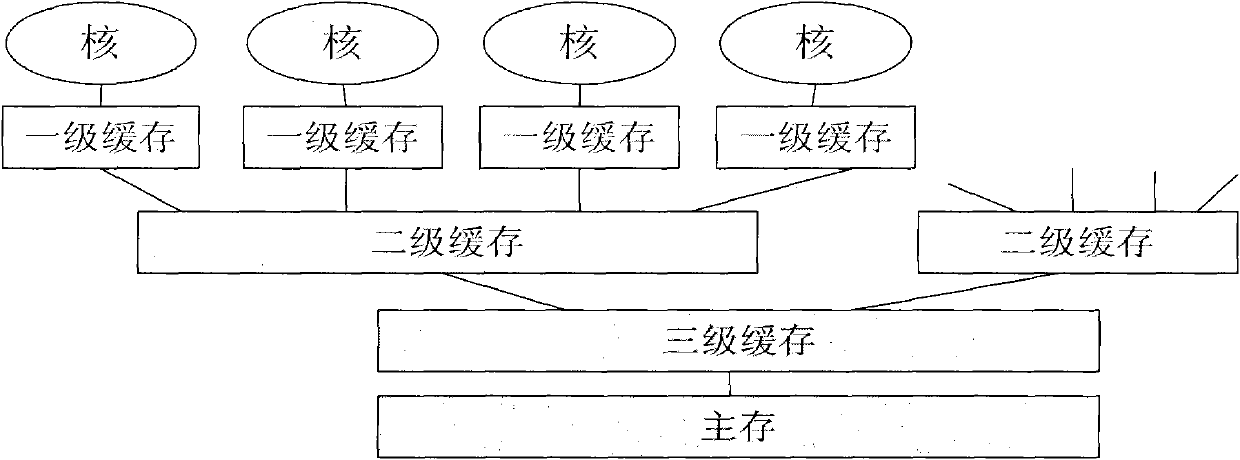

technical field [0001] The invention belongs to the simulation field of information processing system processors, and specifically relates to a technology for parallel simulation of on-chip multi-core processors with accurate clocks on a shared-storage multi-processor machine platform. Background technique [0002] Computer architecture simulator technology uses software methods to simulate the behavior of computer systems at the architecture level from time to time. It is an important tool that researchers of computer architecture and software theory rely on, and has a wide range of applications in academia and industry. The main simulation object of this type of simulator in the early stage is a single-processor system, and performance, flexibility, and degree of detail are the main indicators to measure this type of simulator. [0003] With the advent of the multi-core era, this type of simulator extends the simulation objects to multi-core processor systems. However, the...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More IPC IPC(8): G06F9/455

Inventor 吴俊敏朱小东隋秀峰尹巍赵小雨唐轶轩

Owner SUZHOU INST FOR ADVANCED STUDY USTC