Patents

Literature

276 results about "Design analysis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

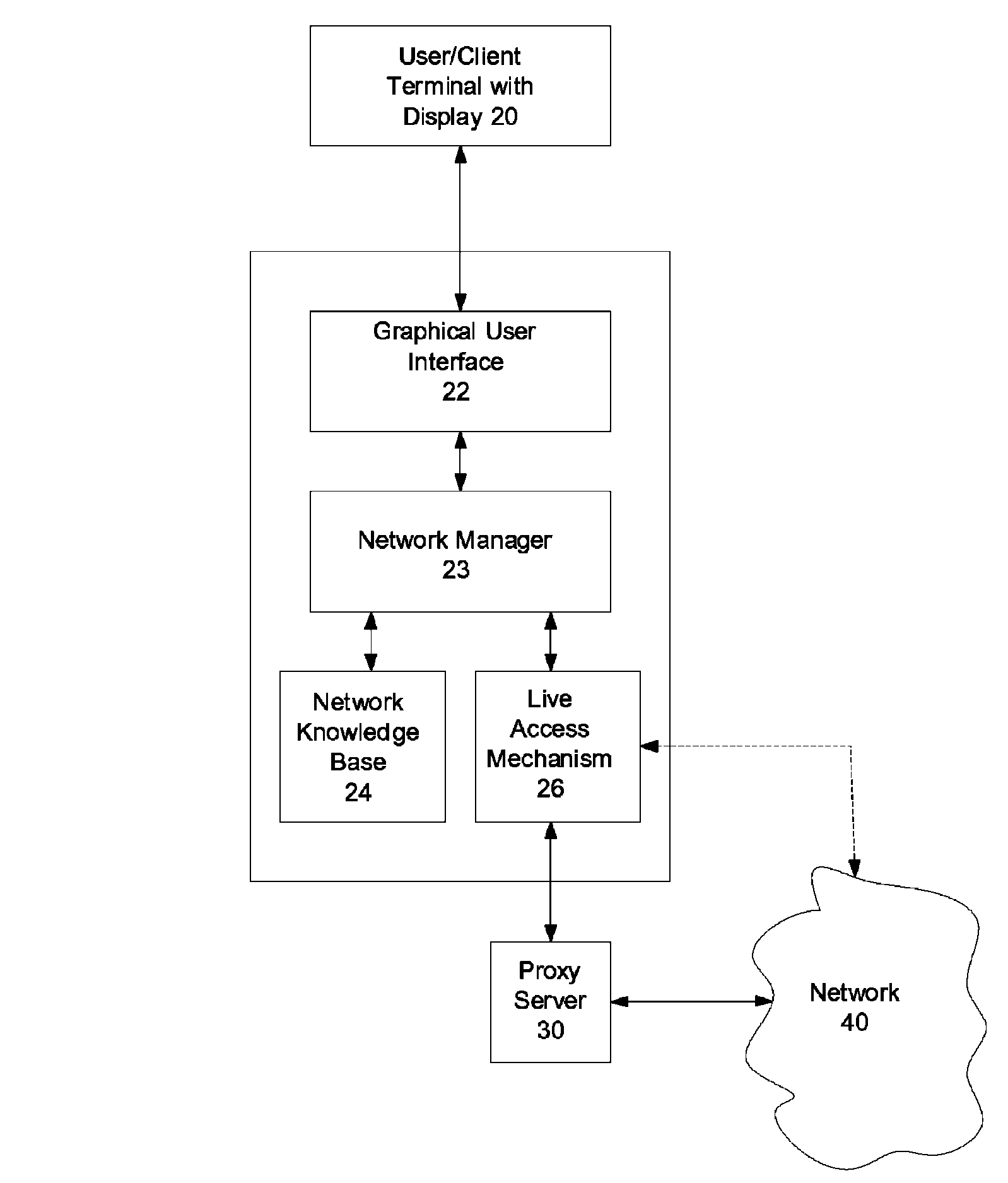

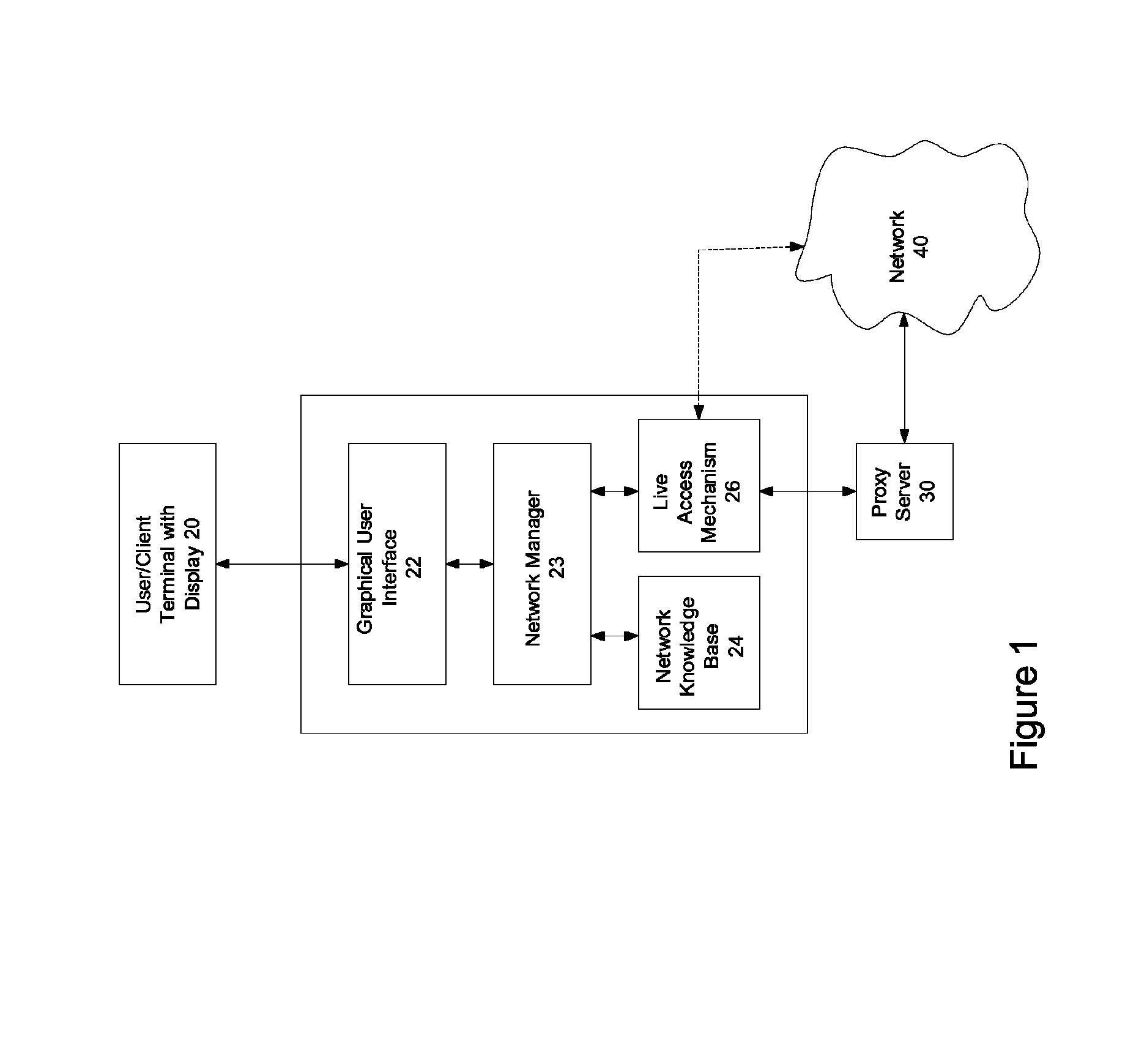

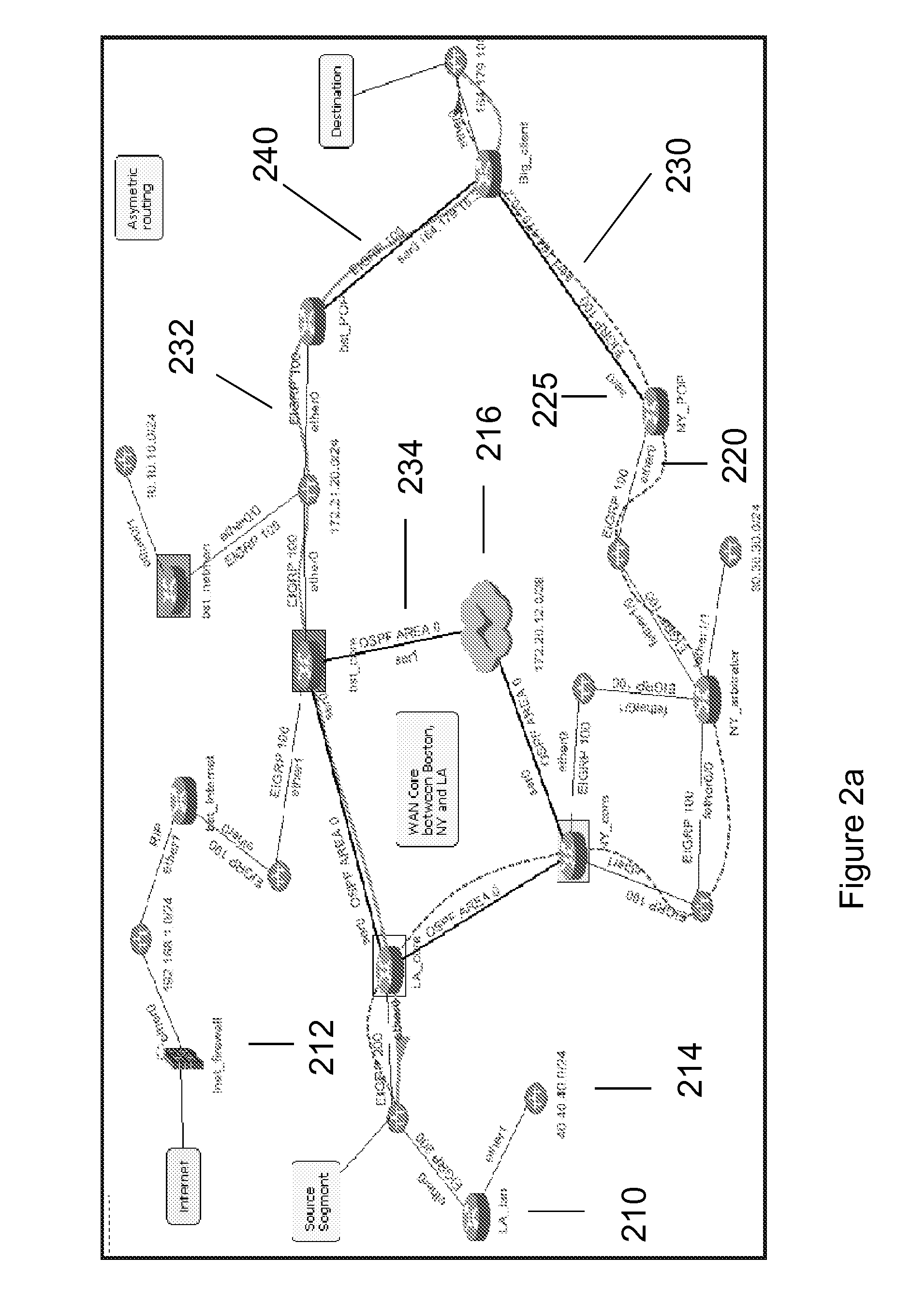

Computer aided network engineering system, apparatus, and method

A computer aided network engineering (CANE) system provides an integrated network management platform that not only decodes a user's network but also provides an interactive environment, based on data-driven maps, to allow users to define and automate network tasks. Among other things, the CANE system allows users to drive automation via self-contained interactive model-driven maps (referred to as Q-maps). Some of the tasks that can be automated include, without limitation: a) network diagramming and documentation; b) performance troubleshooting; and c) design analysis.

Owner:NETBRAIN TECH

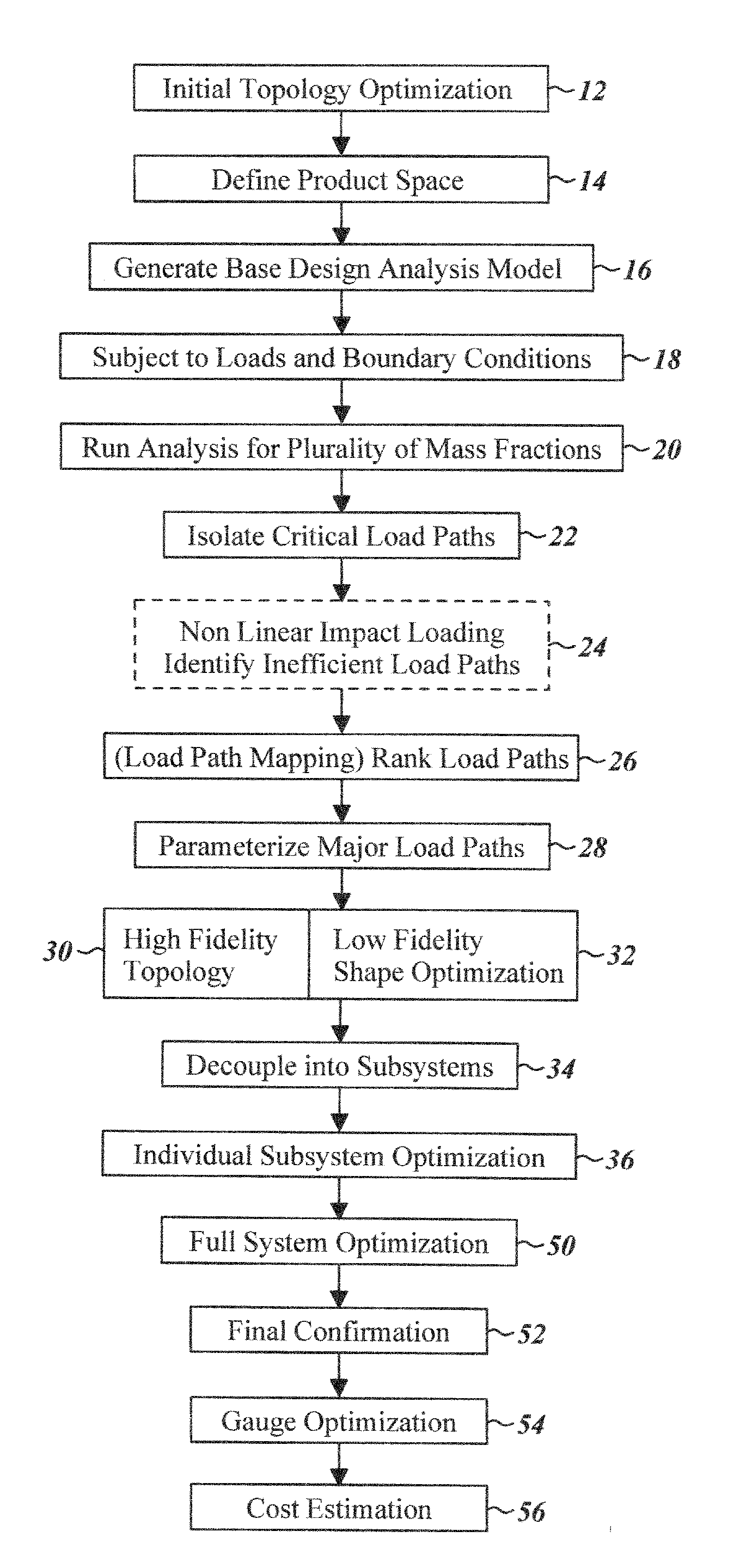

Design Optimization System

ActiveUS20110137443A1Geometric CADDesign optimisation/simulationCritical structureTopology optimization

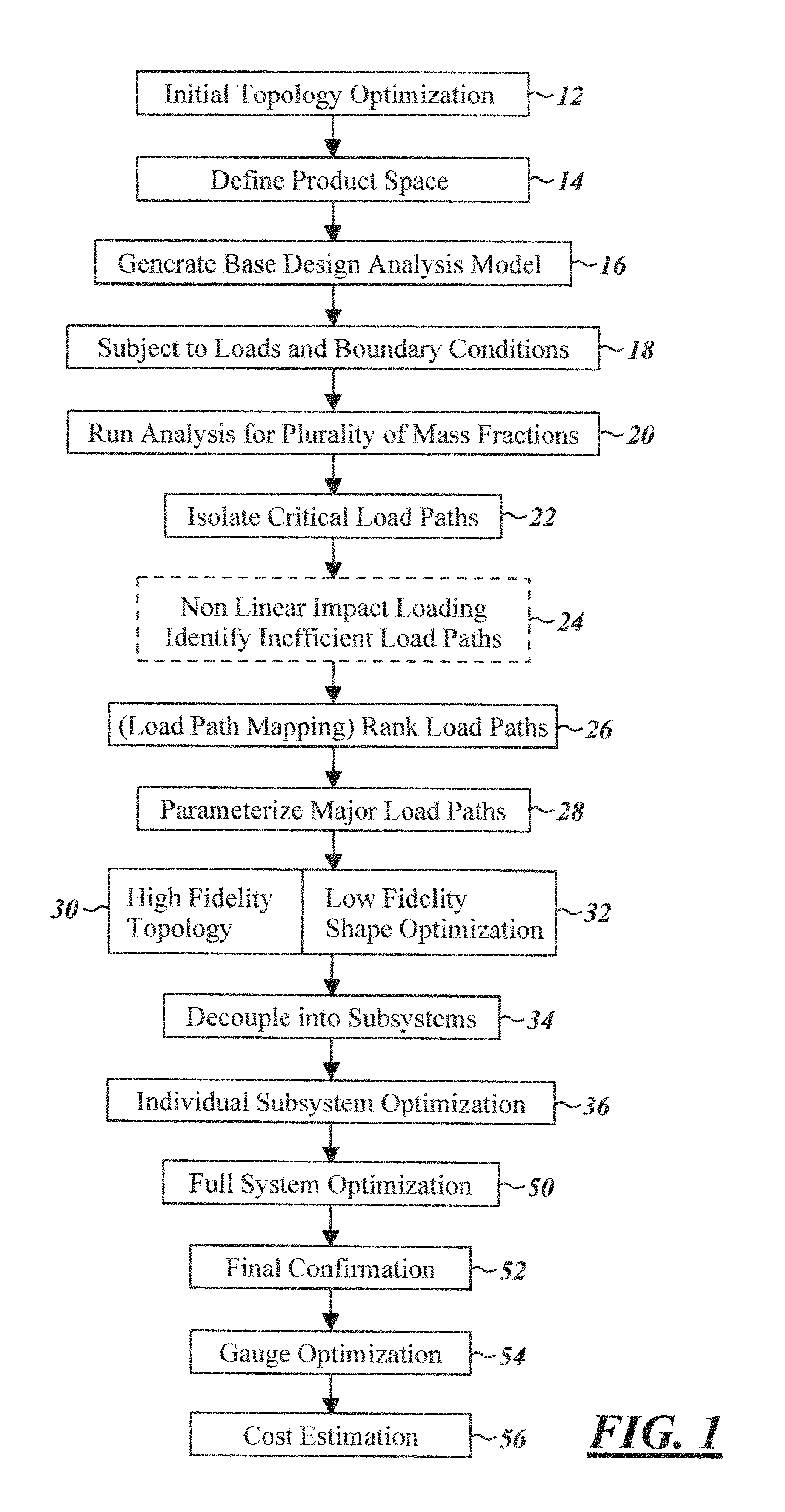

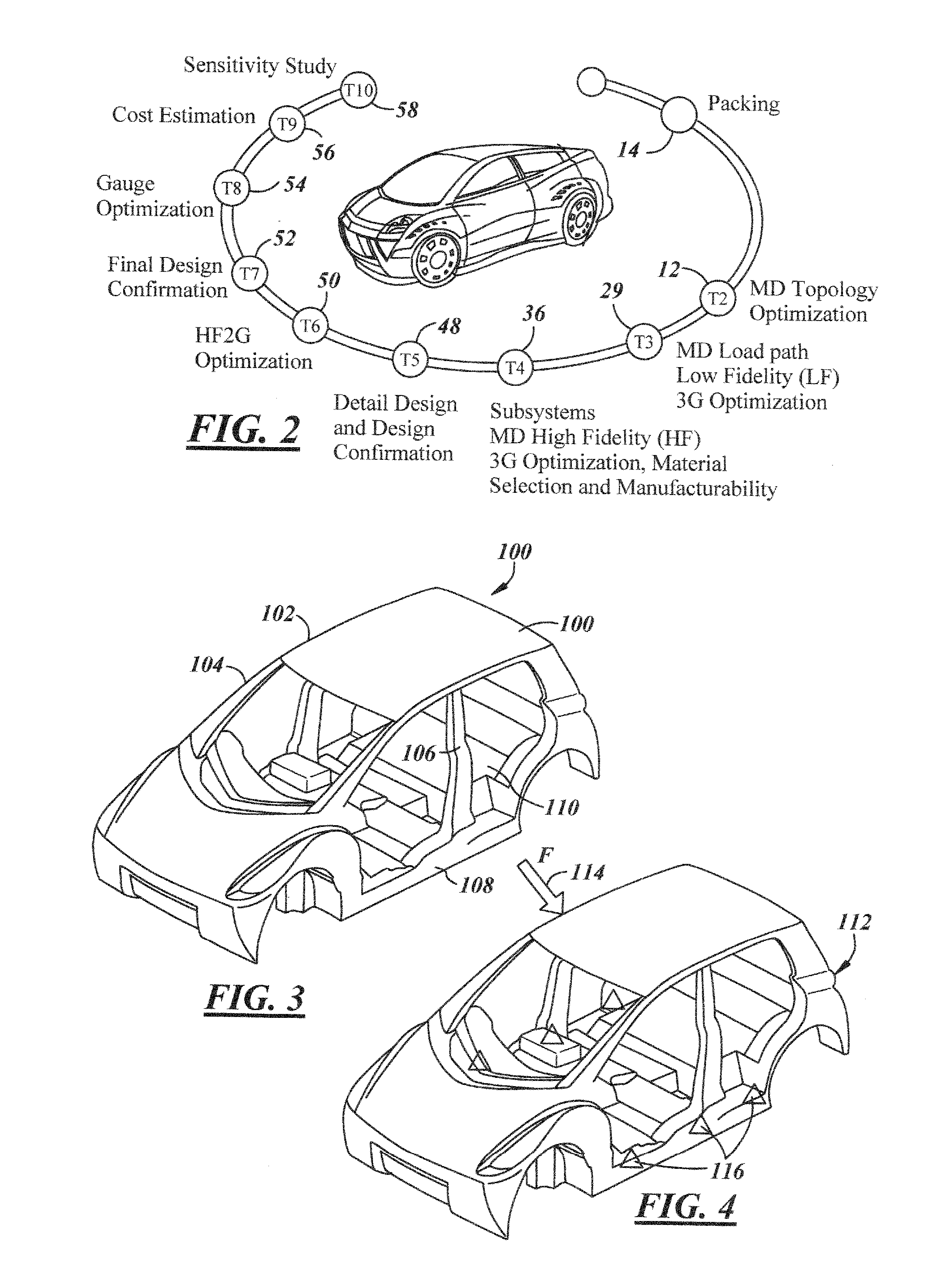

In accordance with the objects of the present invention, a method of complex product design is provided. The method defines a product design space a base design analysis model is then automatically generated within the product design space. A topology optimization of the base design analysis model is performed including solving the topology optimization for multiple mass fractions to identify critical structure areas. The results of the topology optimizations are utilized to identify a plurality of load paths. An optimization of said plurality of load paths is performed to find the optimized load paths. Critical structure areas along the plurality of optimized load paths are then parameterized. An optimization is performed utilizing a multi-disciplinary optimization to optimize geometry, material and thickness along the optimized load paths. A manufacturing analysis of the shape optimized structure is performed and the shape optimized structure is modified to comply with manufacture requirements. An optimization is then performed using multi-disciplinary optimization comprising a gauge and grade optimization.

Owner:NITED STATES STEEL CORP +1

Computer process for prescribing second-order tetrahedral elements during deformation simulation in the design analysis of structures

InactiveUS6044210AComputation using non-denominational number representationDesign optimisation/simulationElement modelEngineering

A computer implemented process prescribes second-order tetrahedral elements during simulation in the design analysis of structure. The computer implemented process includes the steps of defining a finite element model for an element including at least one tetrahedral element, and defining the at least one tetrahedral element as a combination of hexahedral sub-elements. The computer implemented process also includes the steps of executing the simulation, and evaluating the structure for structural integrity responsive thereto.

Owner:DASSAULT SYSTEMES SIMULIA CORP

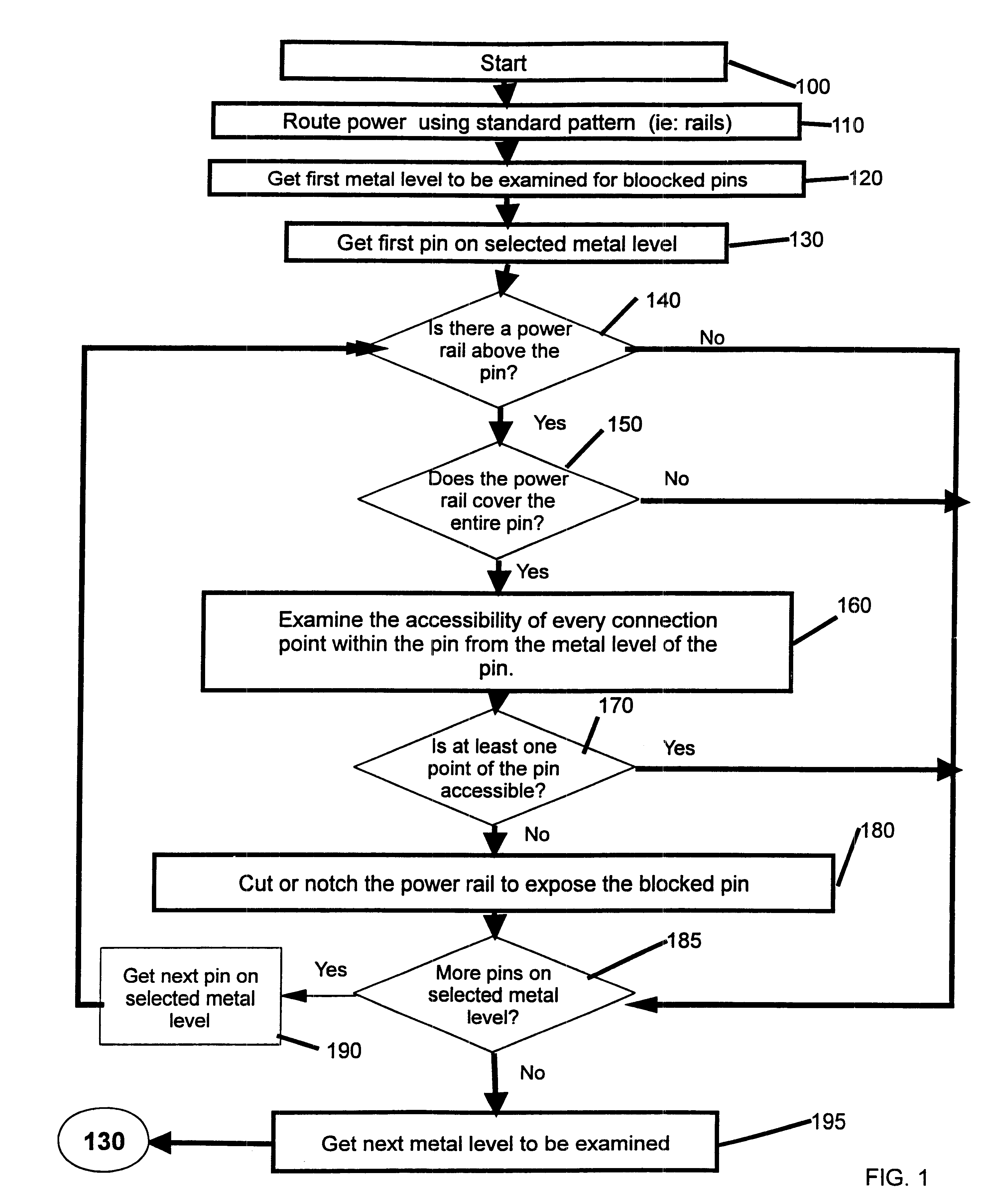

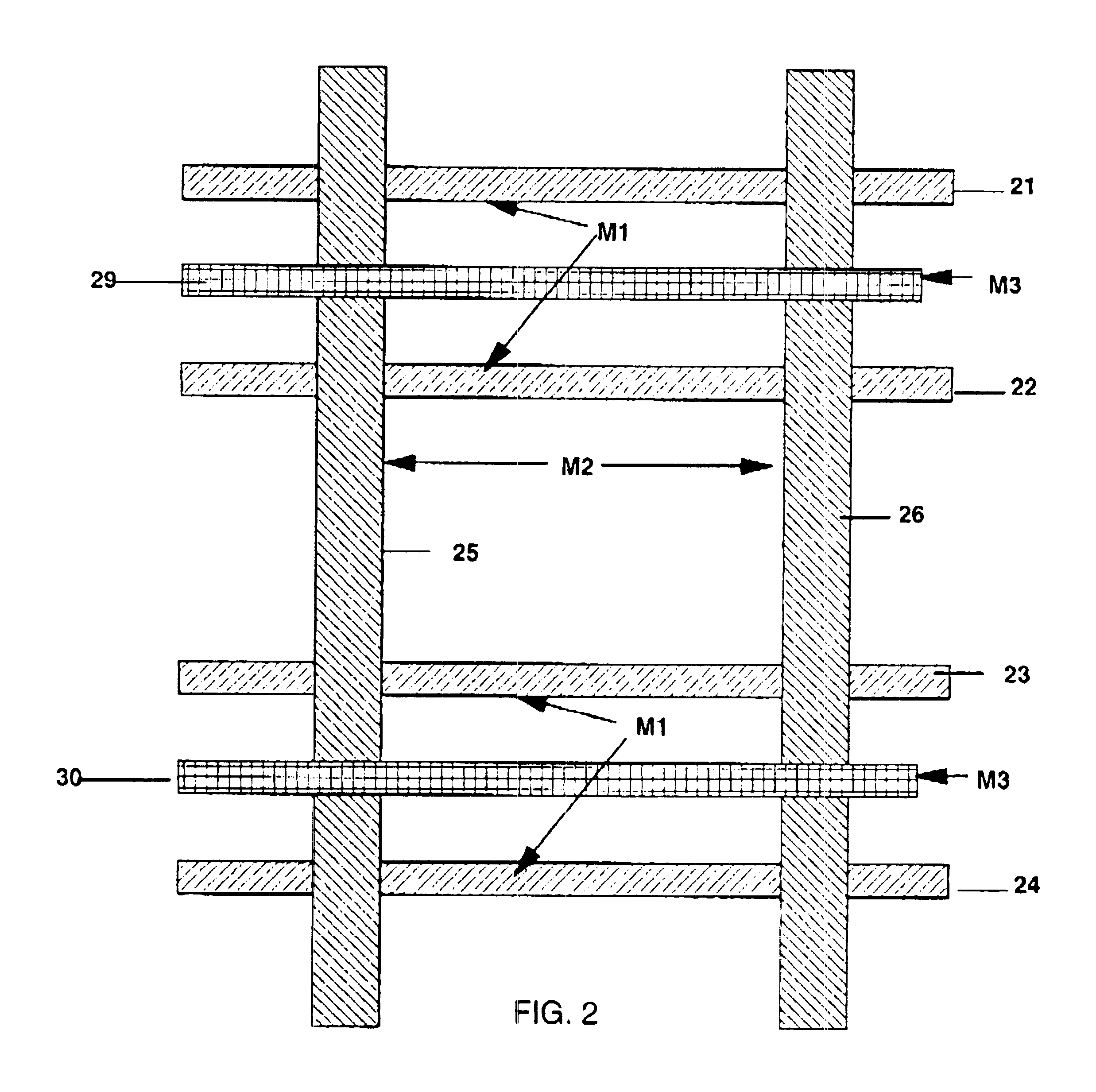

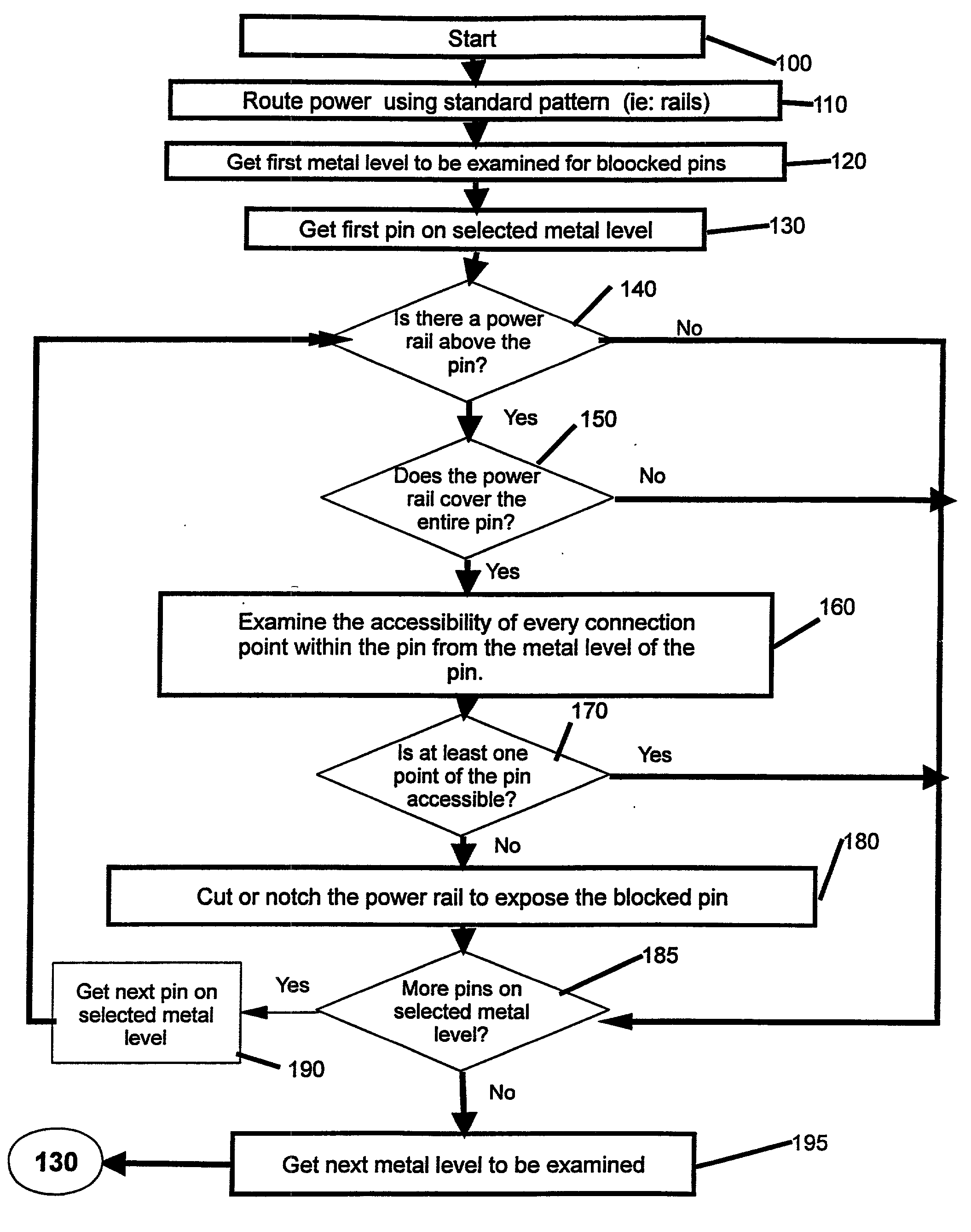

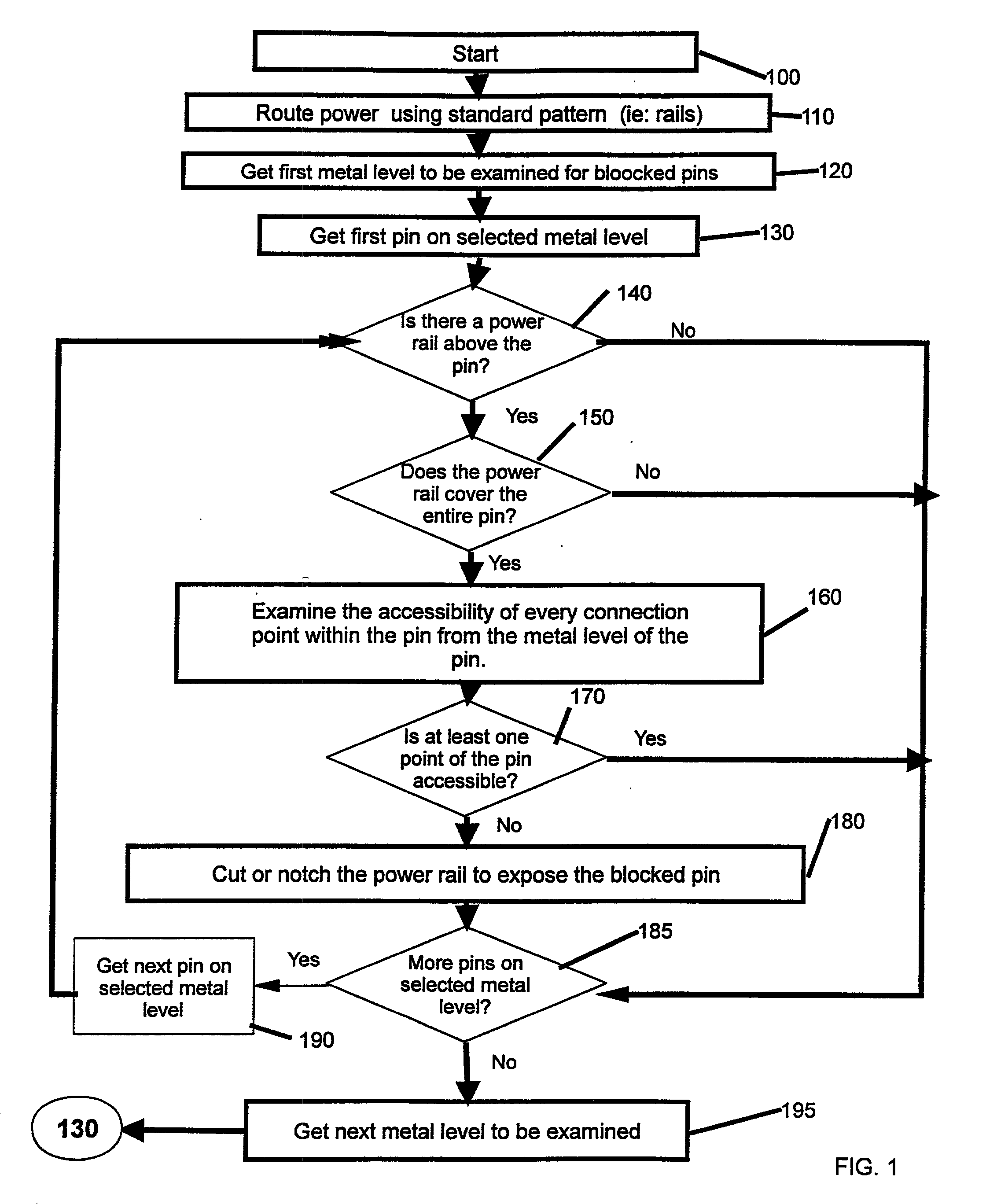

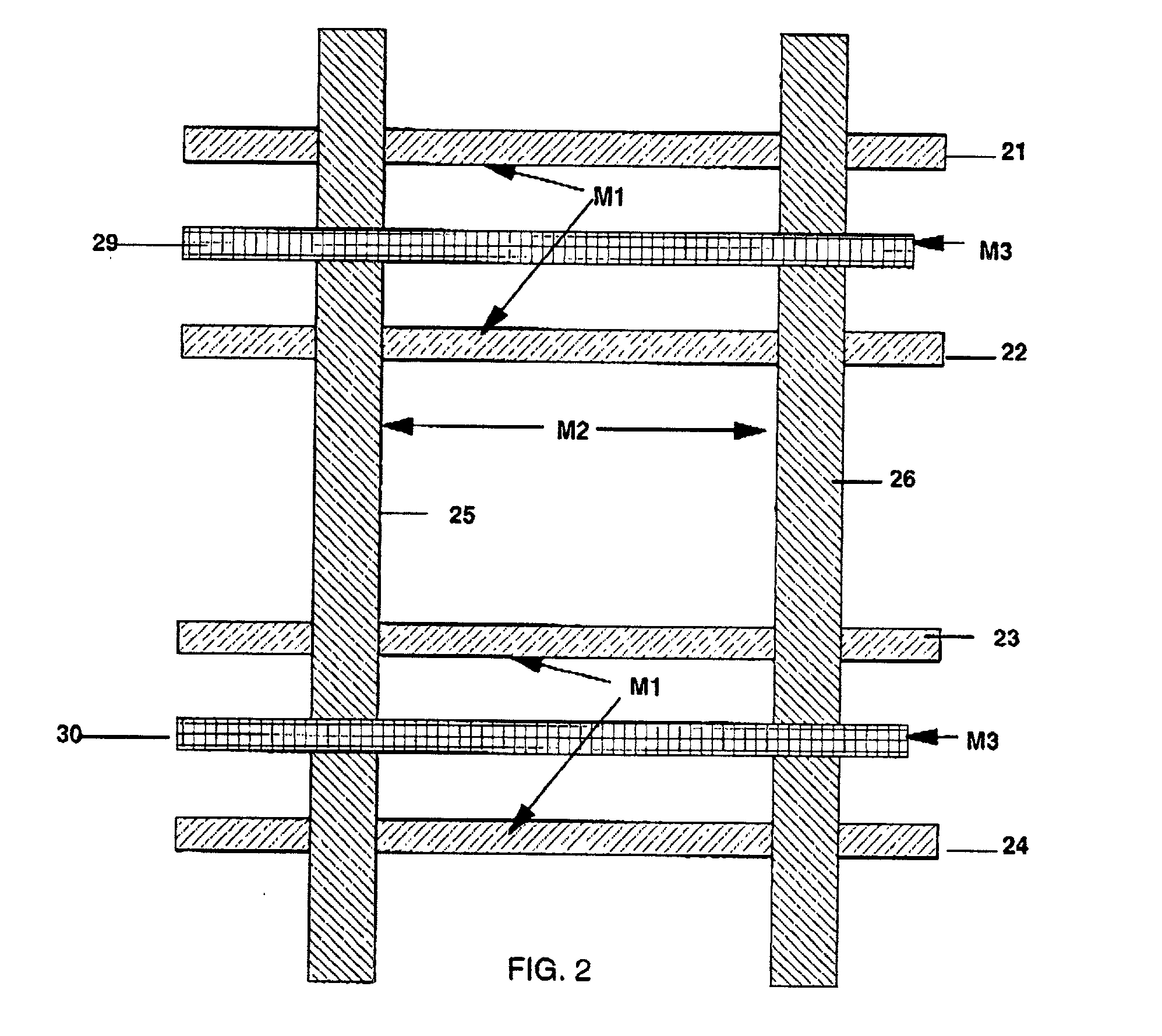

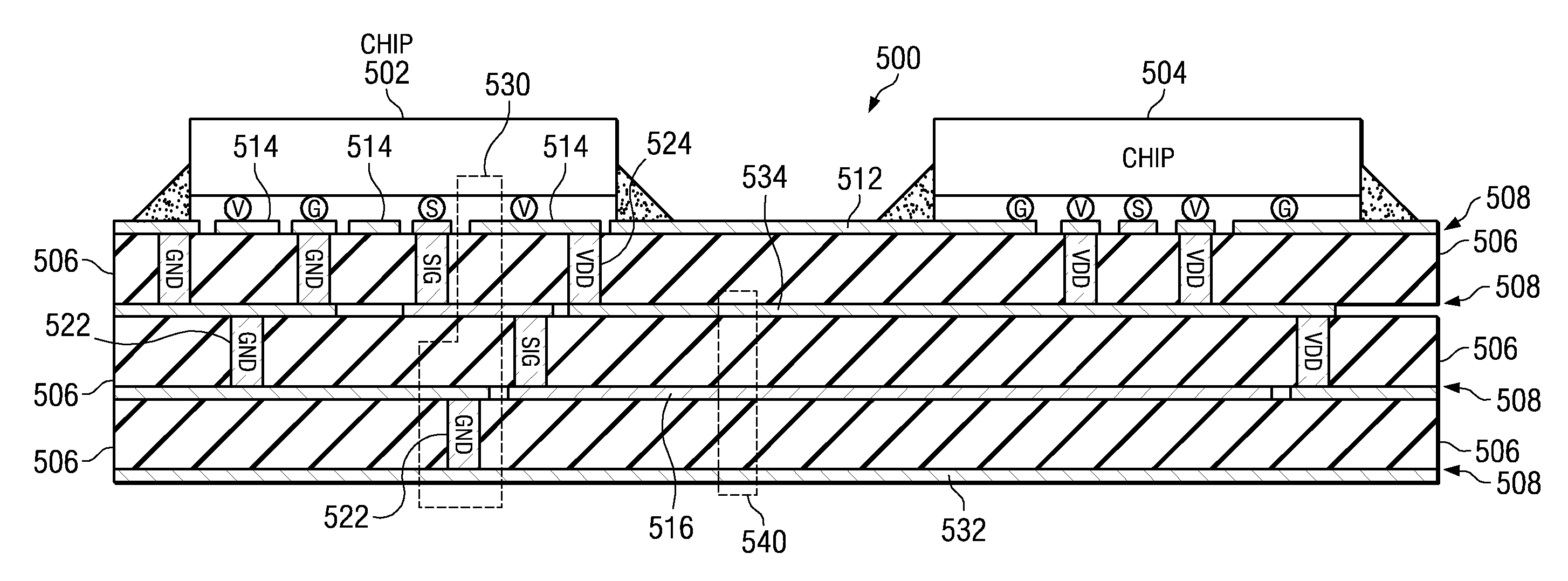

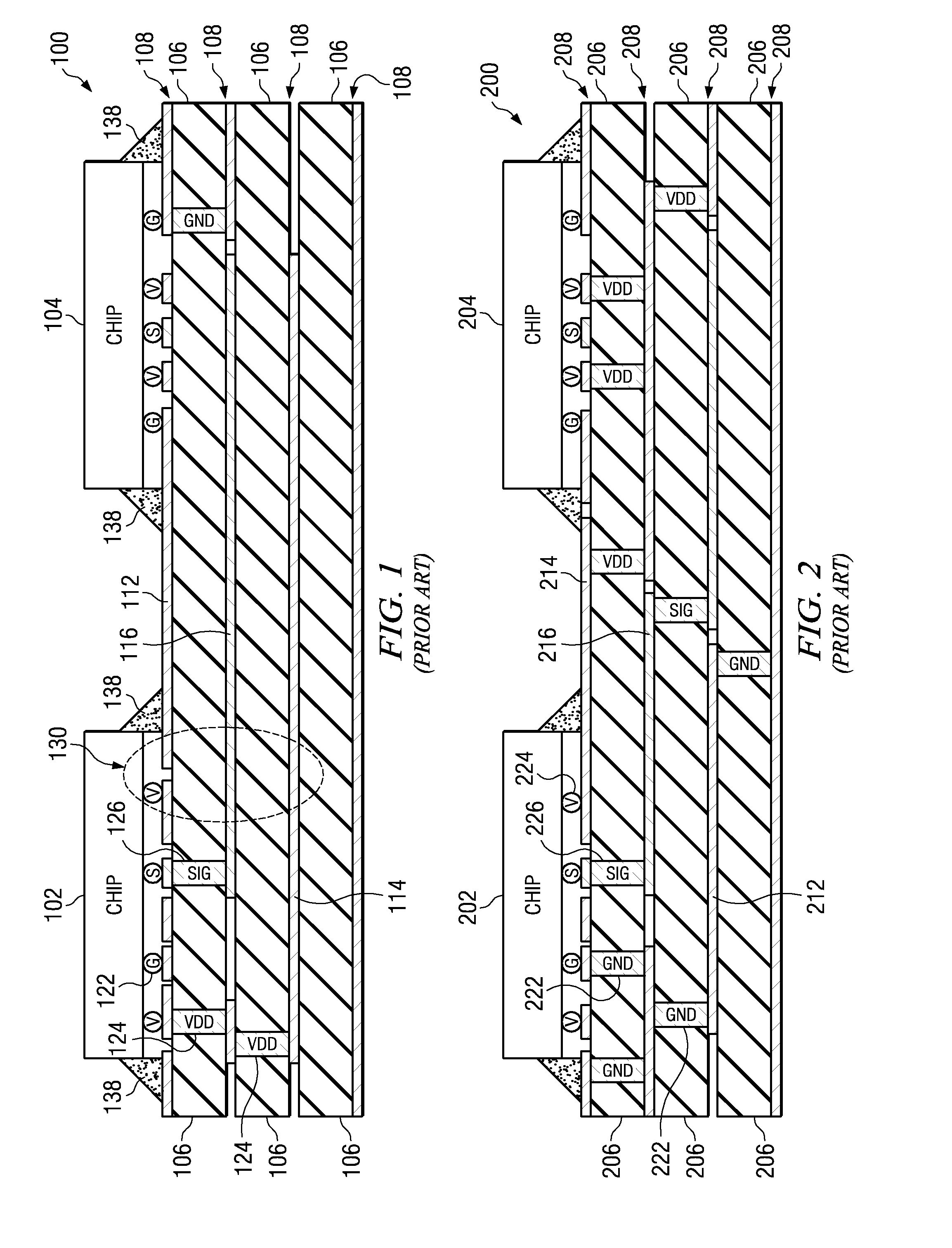

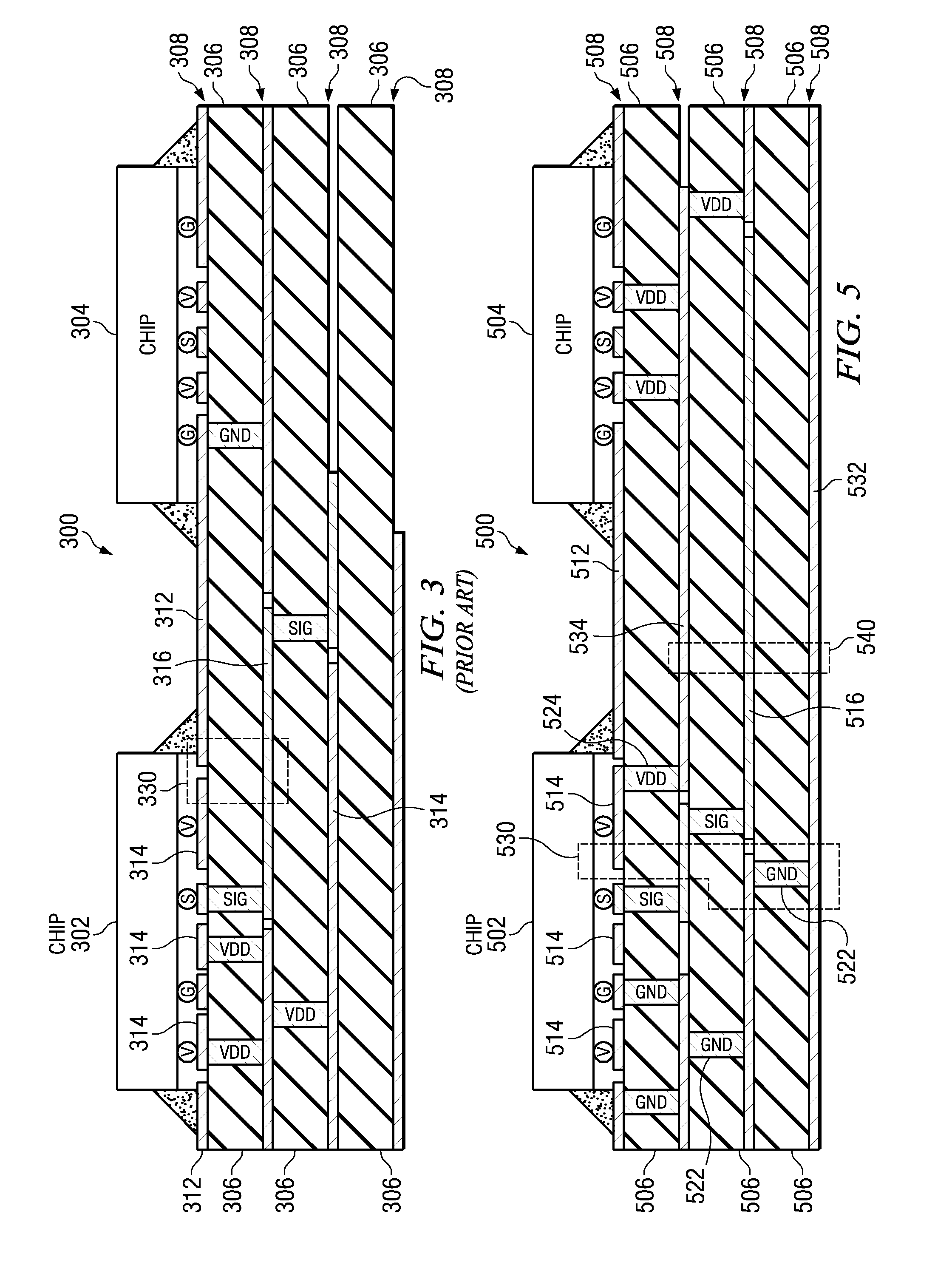

Method and system of modifying integrated circuit power rails

InactiveUS6598206B2Reduce congestionImprove wireabilitySemiconductor/solid-state device detailsSolid-state devicesElectric powerIntegrated circuit

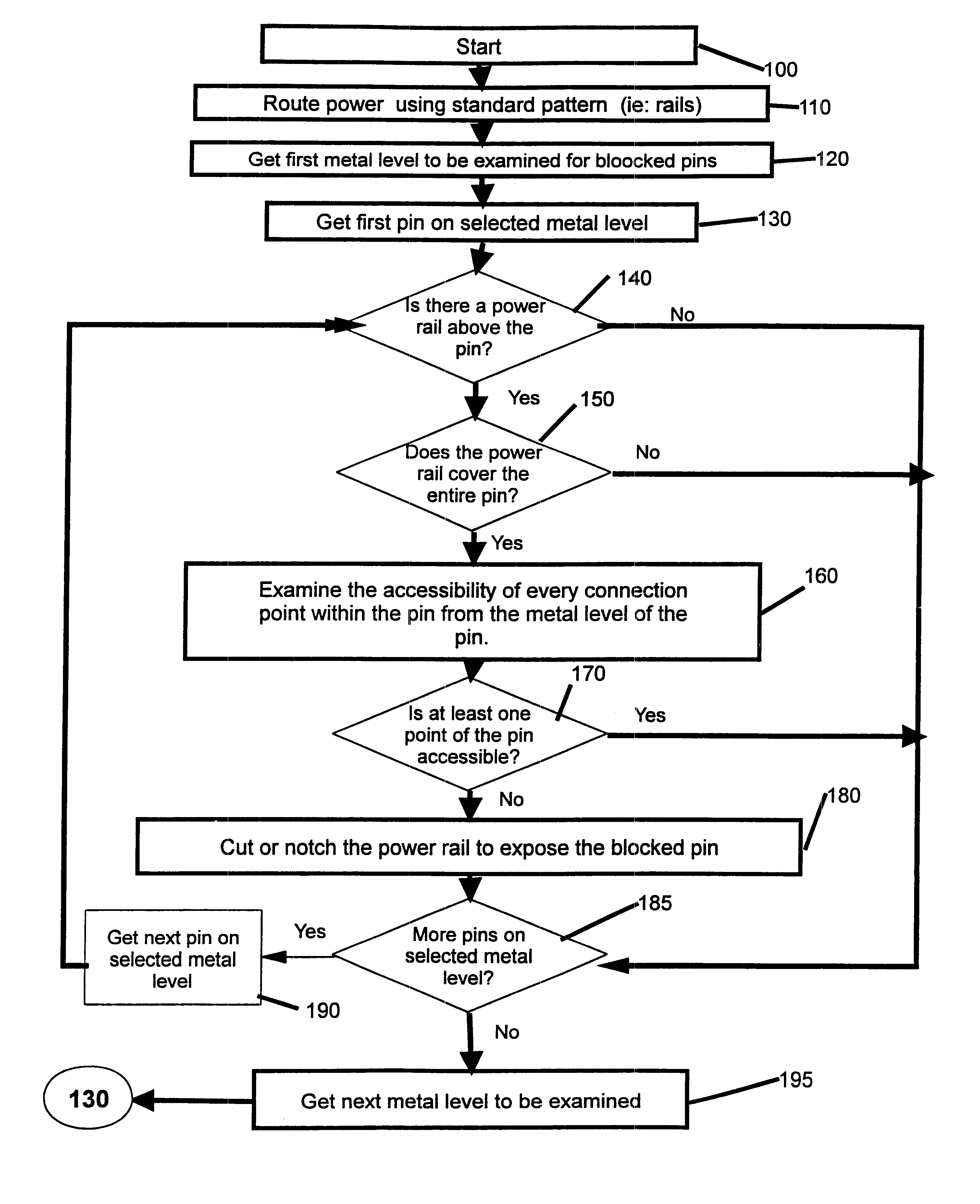

A method and system for modifying power rails of an integrated circuit having improved wireability. This is accomplished by initially generating a power railing design of the integrated circuit into a three-dimensional rail based model. Next, analysis of the design is performed as to placement of the power rails in relation to neighboring elements that affects a predefined wireability. Finally, modification of a segment of each power rail that affects wireability is performed so that required power supply to the neighboring elements (e.g., pins, rails etc.) remains unaffected.

Owner:PERLEGEN SCIENCES INC +1

Method and system of modifying integrated circuit power rails

InactiveUS20020170020A1Reduce congestionImprove wireabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringElectric power

A method and system for modifying power rails of an integrated circuit having improved wireability. This is accomplished by initially generating a power railing design of the integrated circuit into a three-dimensional rail based model. Next, analysis of the design is performed as to placement of the power rails in relation to neighboring elements that affects a predefined wireability. Finally, modification of a segment of each power rail that affects wireability is performed so that required power supply to the neighboring elements (e.g., pins, rails etc.) remains unaffected.

Owner:PERLEGEN SCIENCES INC +1

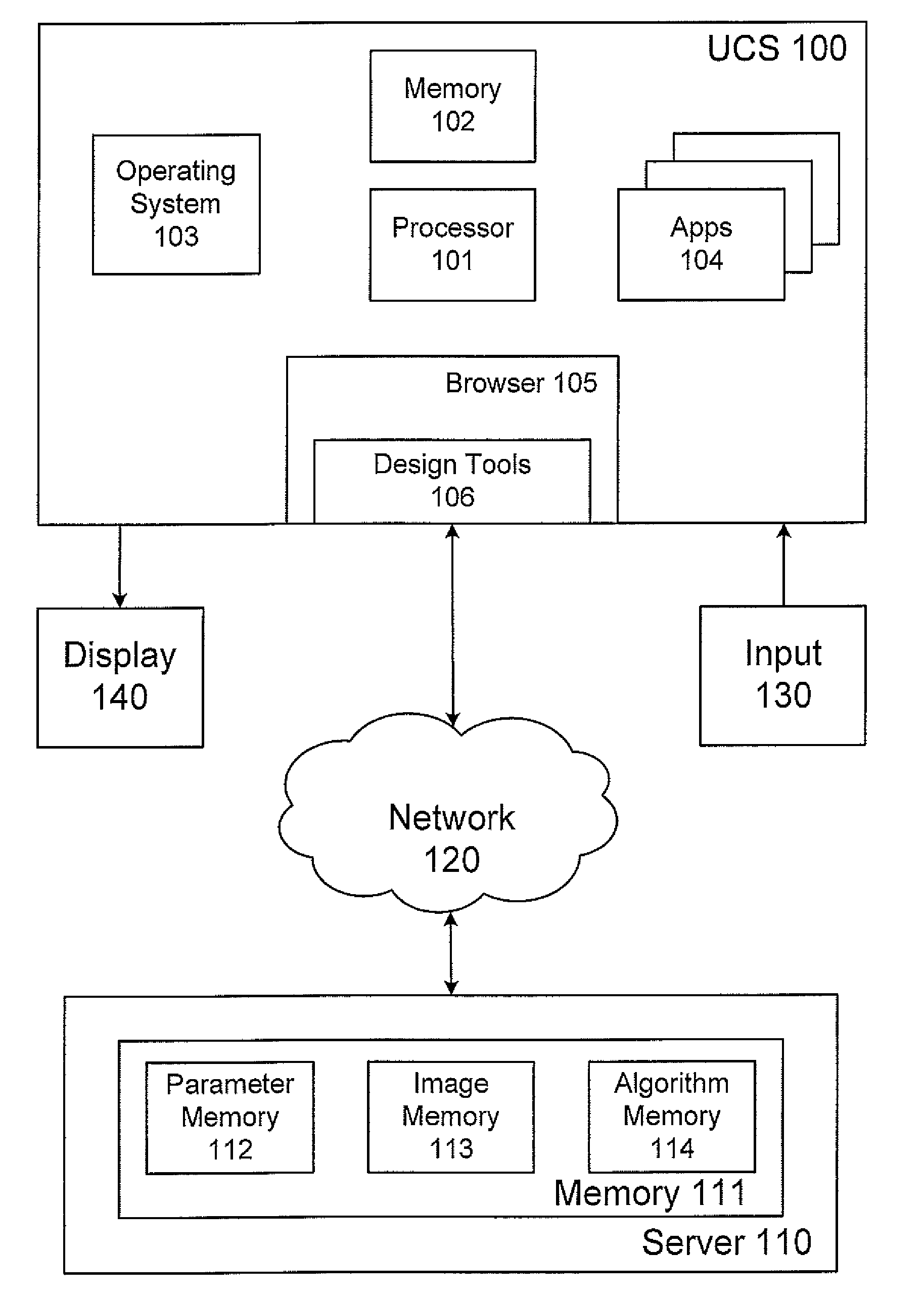

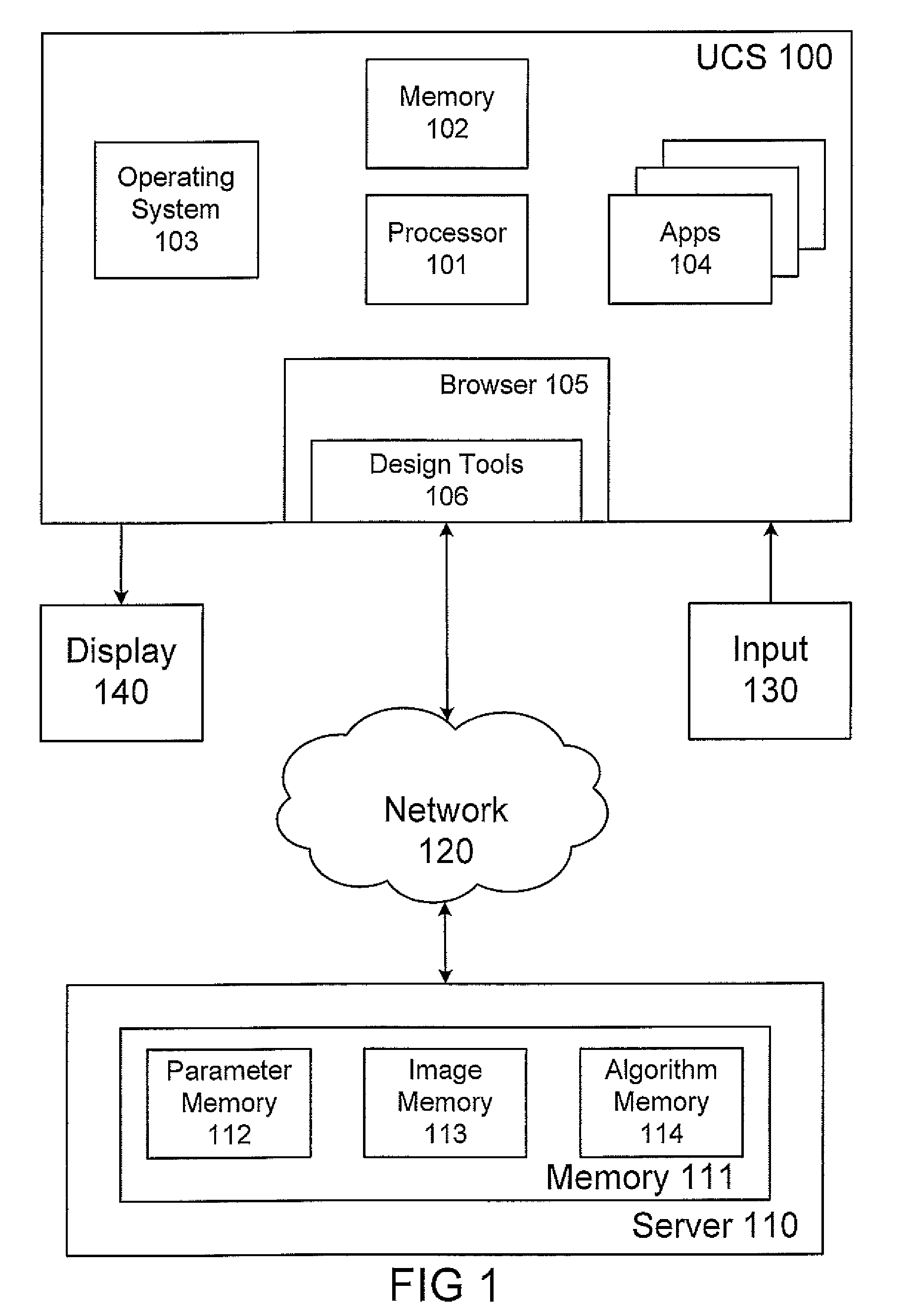

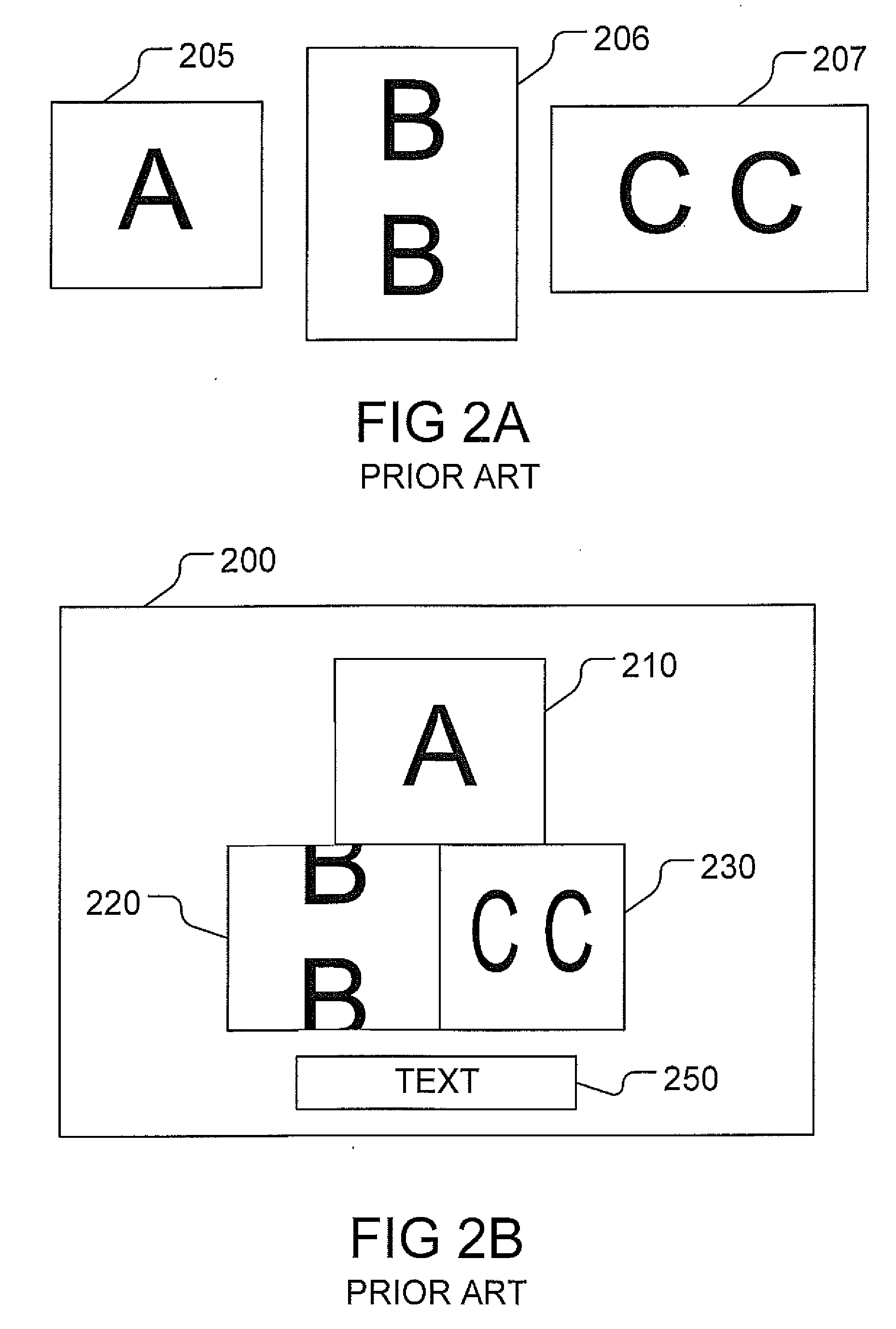

Dynamic sizing and positioning of multiple images

ActiveUS20090067753A1Increase the areaMaintaining aspect ratioGeometric image transformationCharacter and pattern recognitionData displayComputer graphics (images)

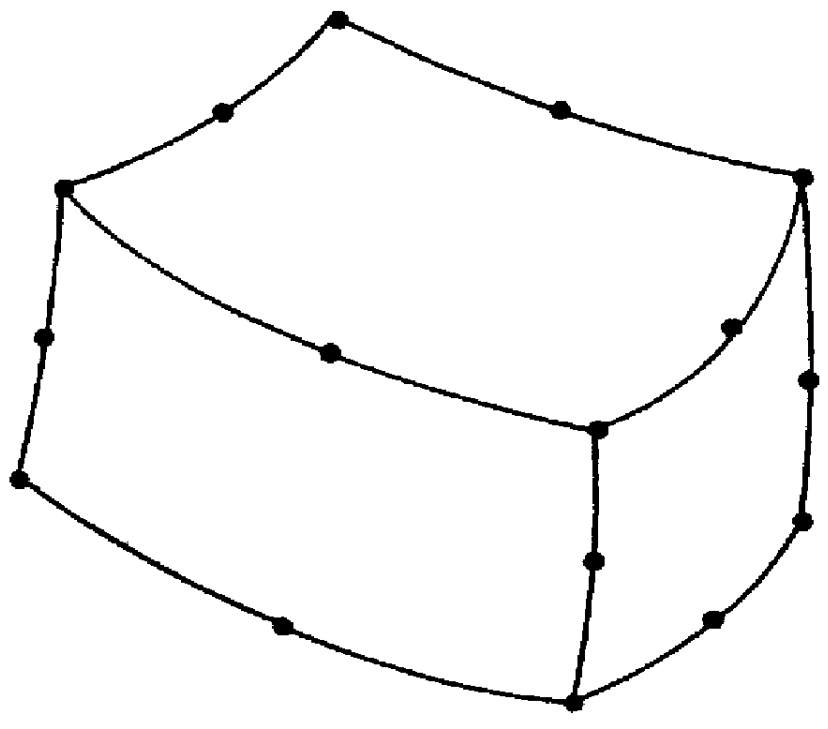

A method of arranging images provides for automated scaling, positioning and organizing of a plurality of images on an image display, which may be transferred to a printed or electronic product design. A plurality of images are analyzed to produce image data. Display parameters determine permissible arrangement of the images. Based on the image data and the display parameters, an arrangement on the image display for each of the plurality of images is defined. The arrangement may be further defined to maximize at least one dimension of the images.

Owner:CIMPRESS SCHWEIZ

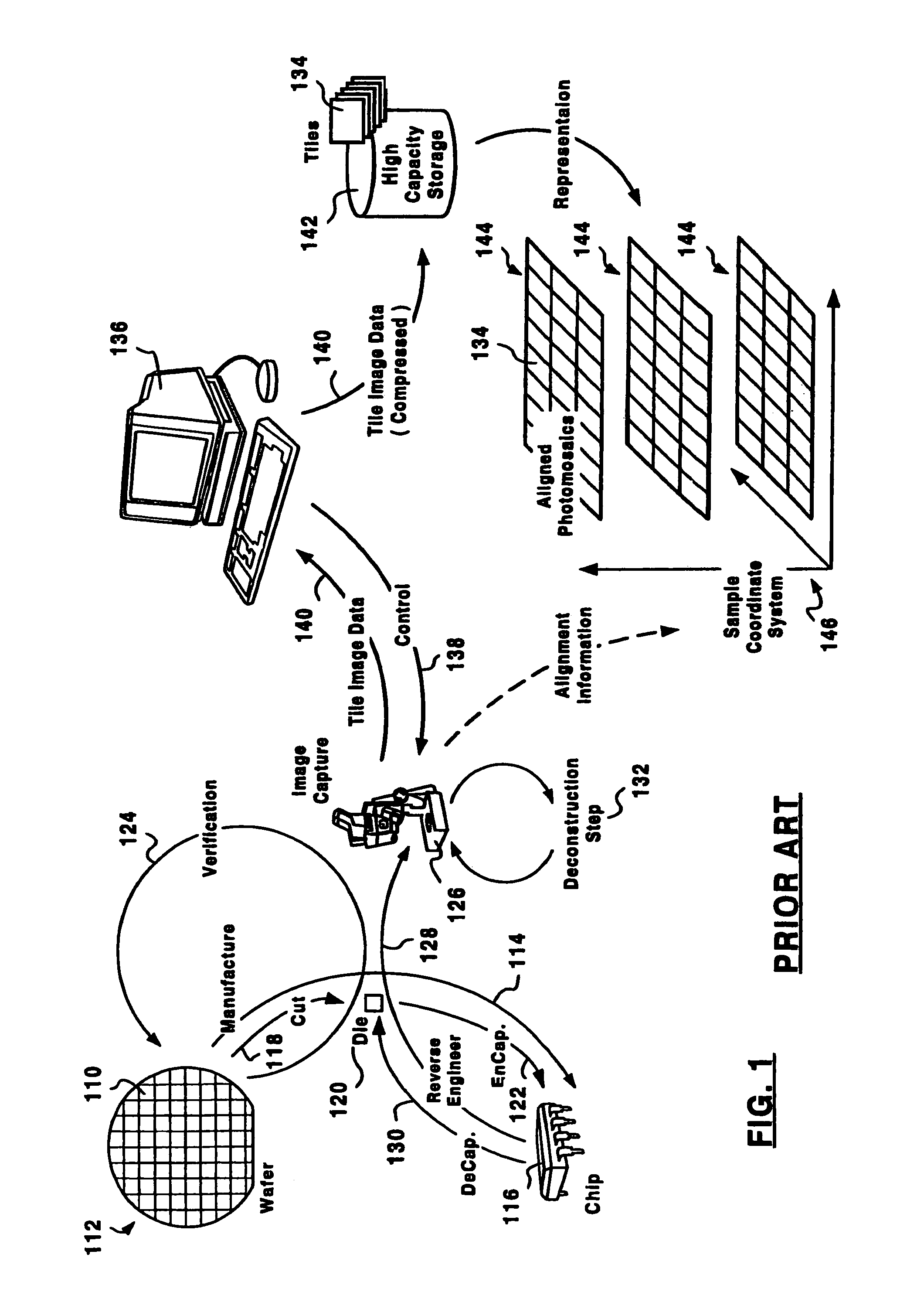

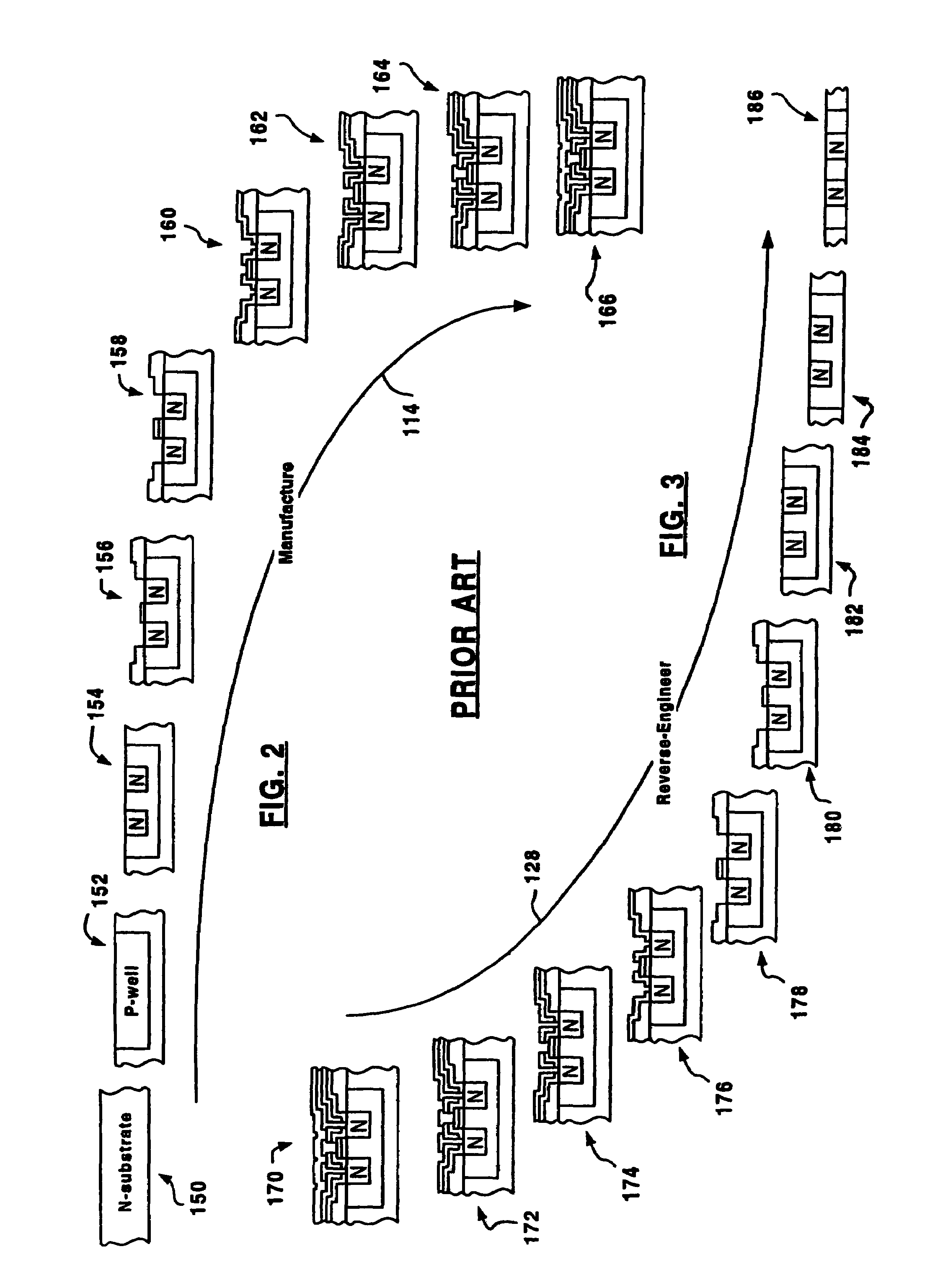

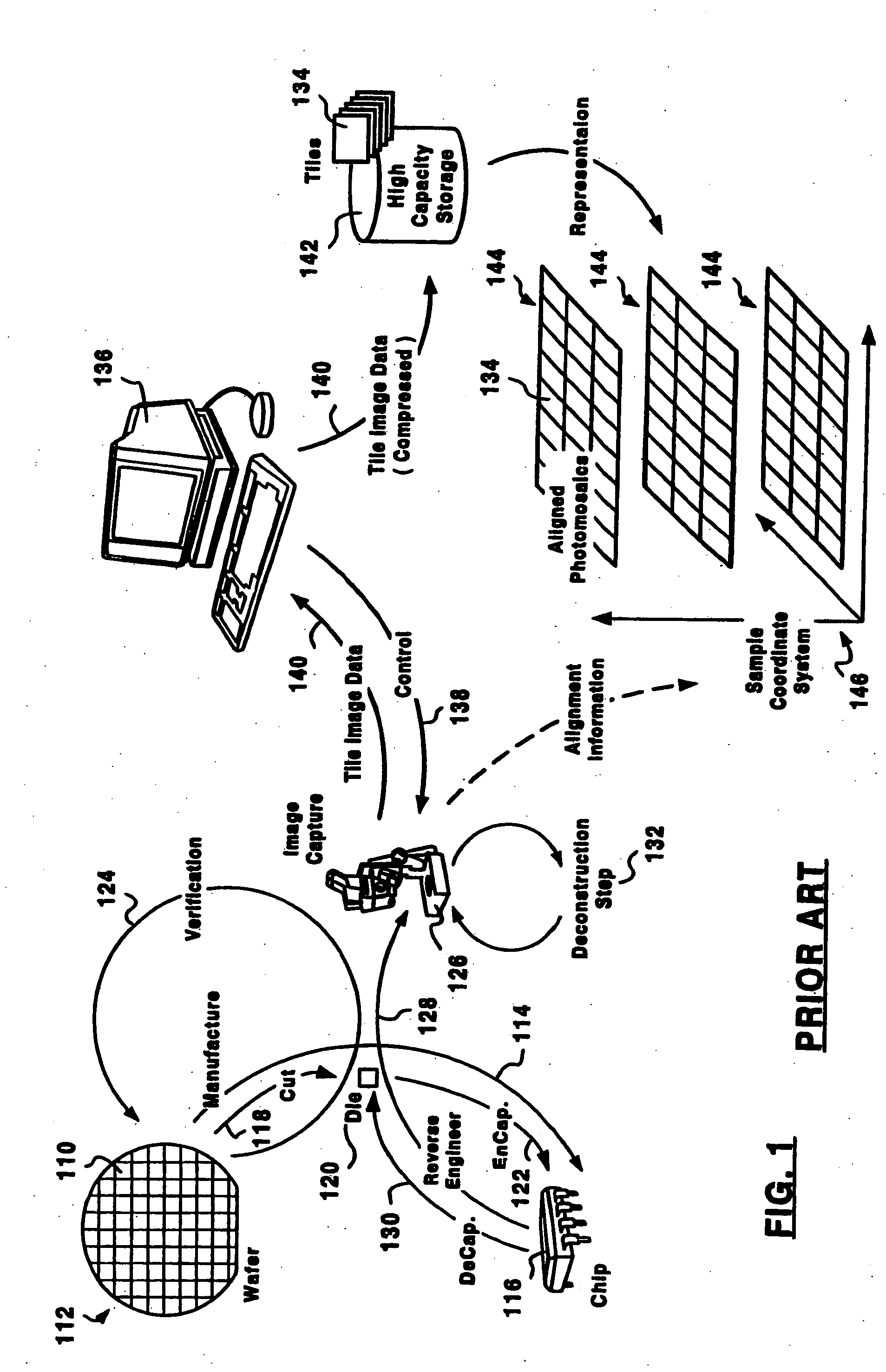

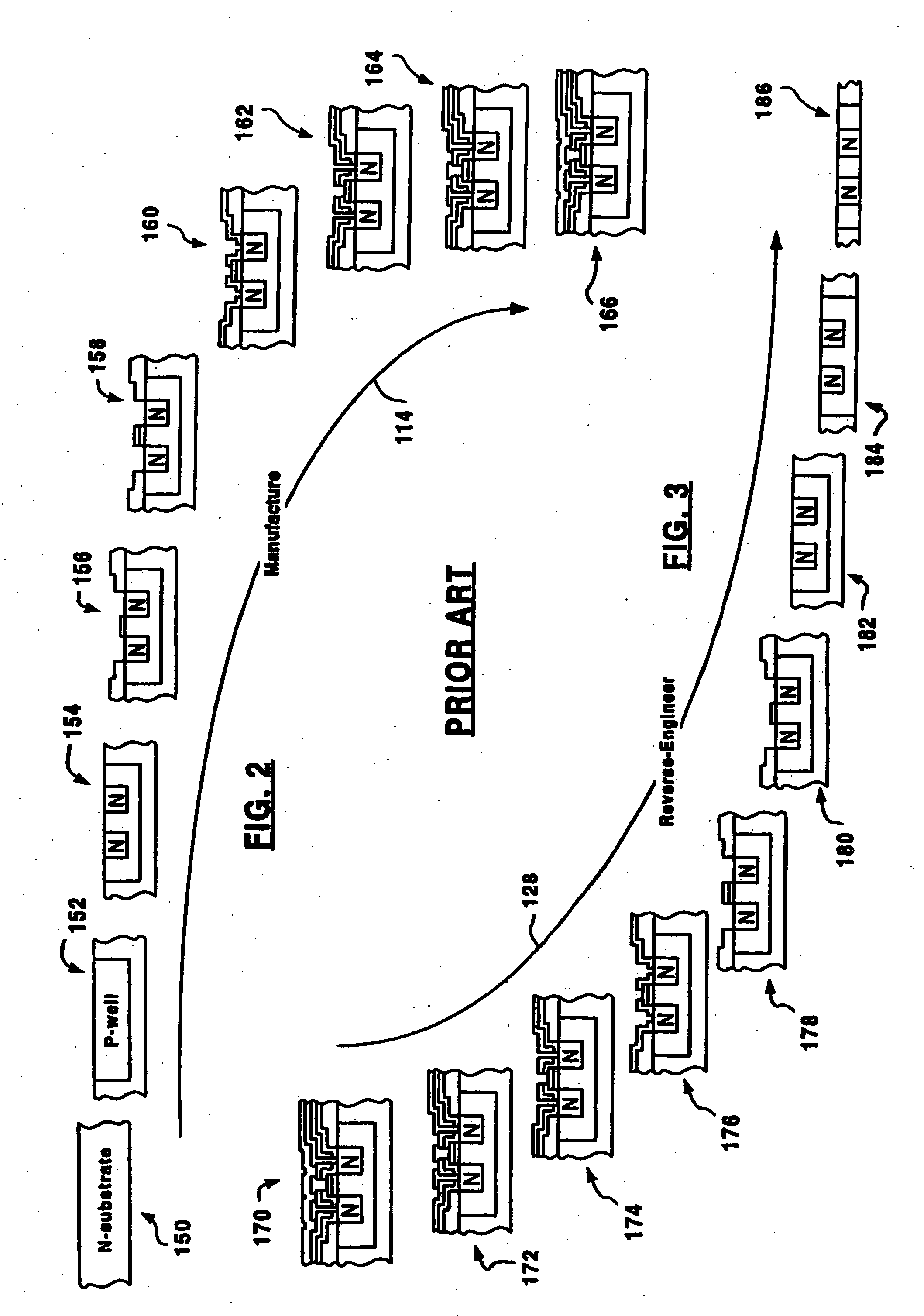

Method of design analysis of existing integrated circuits

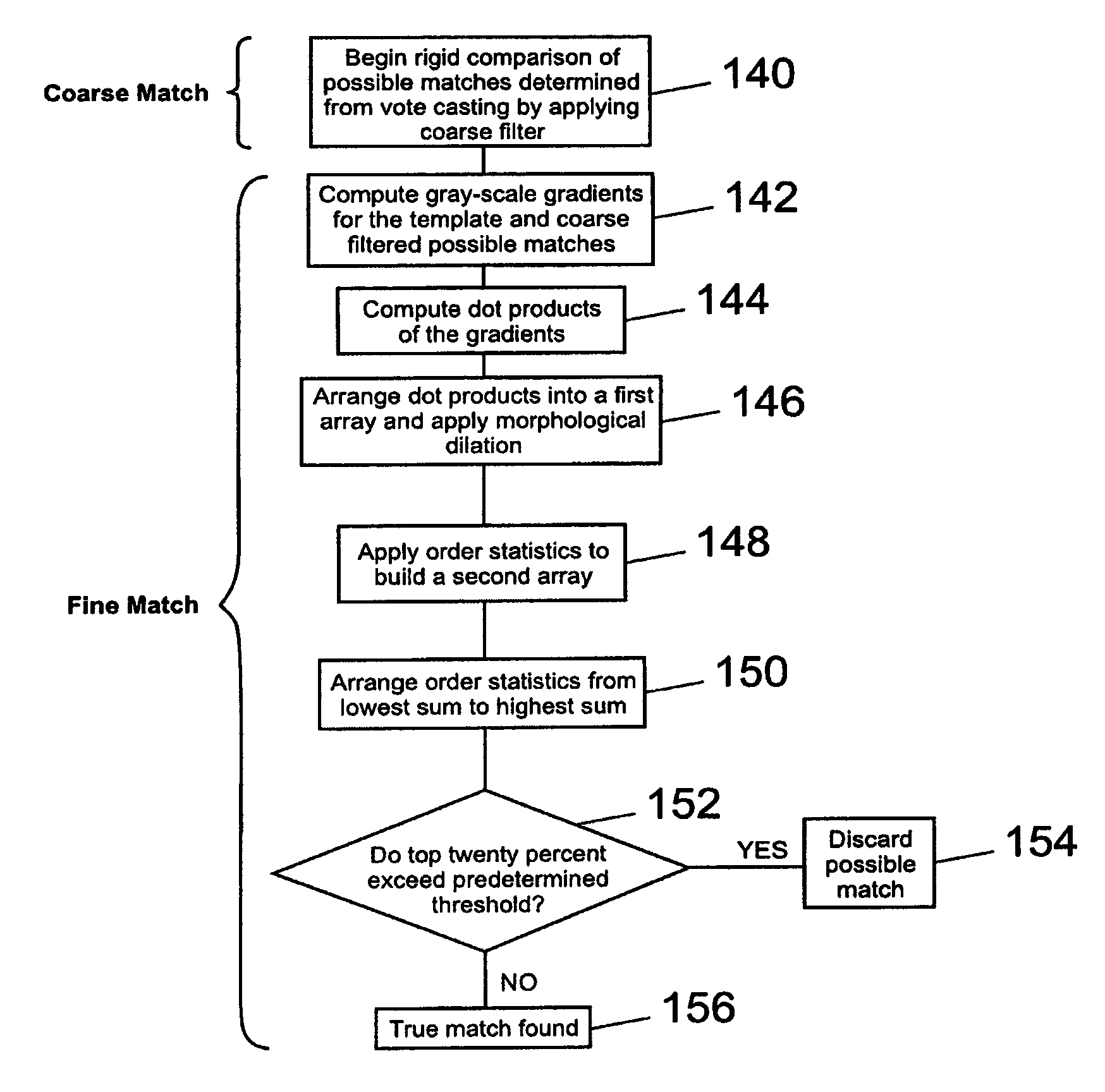

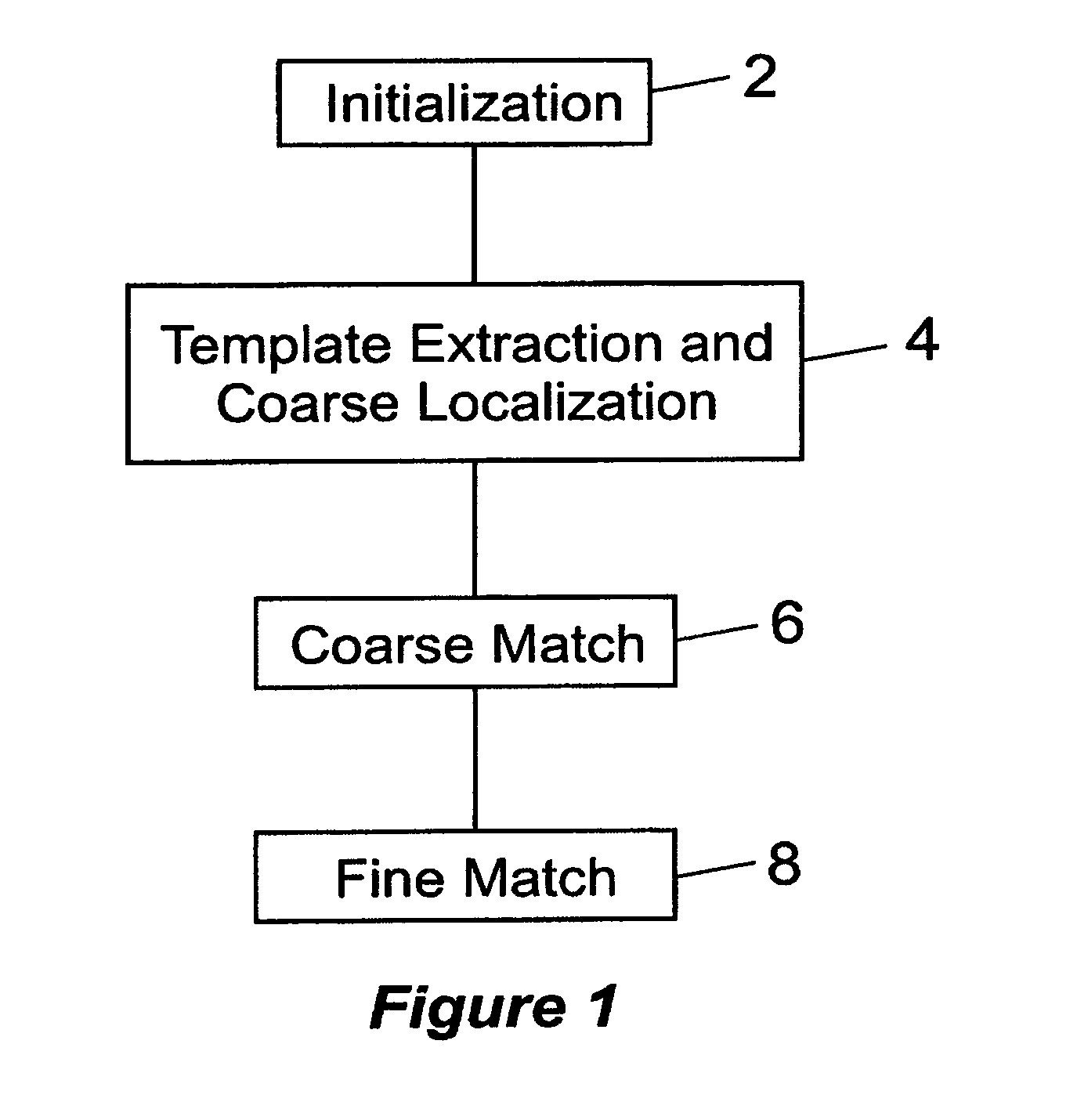

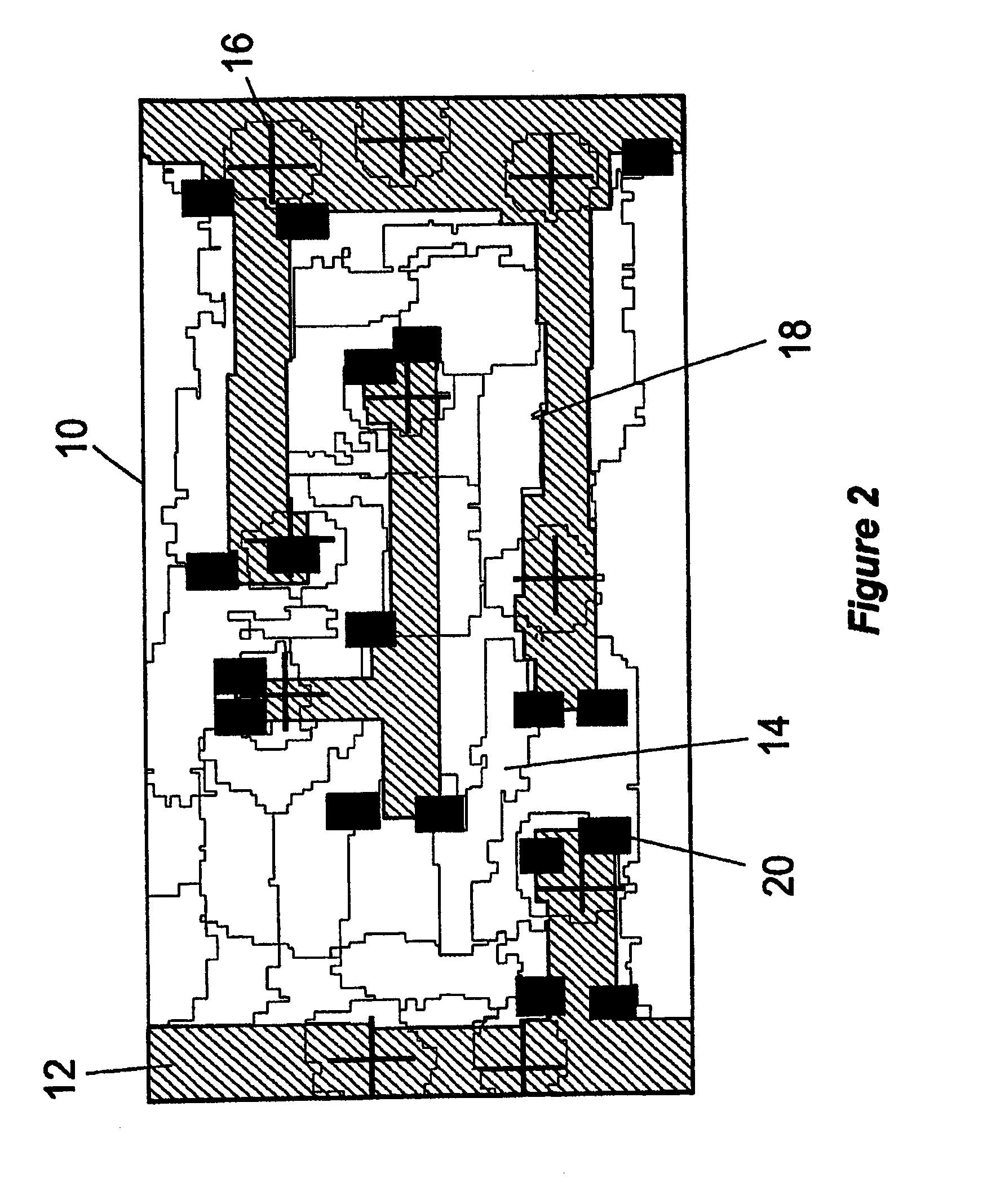

The present invention involves a computationally efficient method of determining the locations of standard cells in an image of an IC layout. The initial step extracts and characterizes points of interest of the image. A coarse localization of possible standard cell locations is performed and is based on a comparison of the points of interest of an instance of an extracted standard cell and the remaining points of interest in the image. A more rigid comparison is made on the list of possible locations comprising a coarse match and a fine match. The coarse match results in a shortlist of possible locations. The fine match performs comparisons between the template and the shortlist. Further filtering is done to remove the effects of noise and texture variations and statistics on the results are generated to achieve the locations of the standard cells on the IC layout.

Owner:TECHINSIGHTS

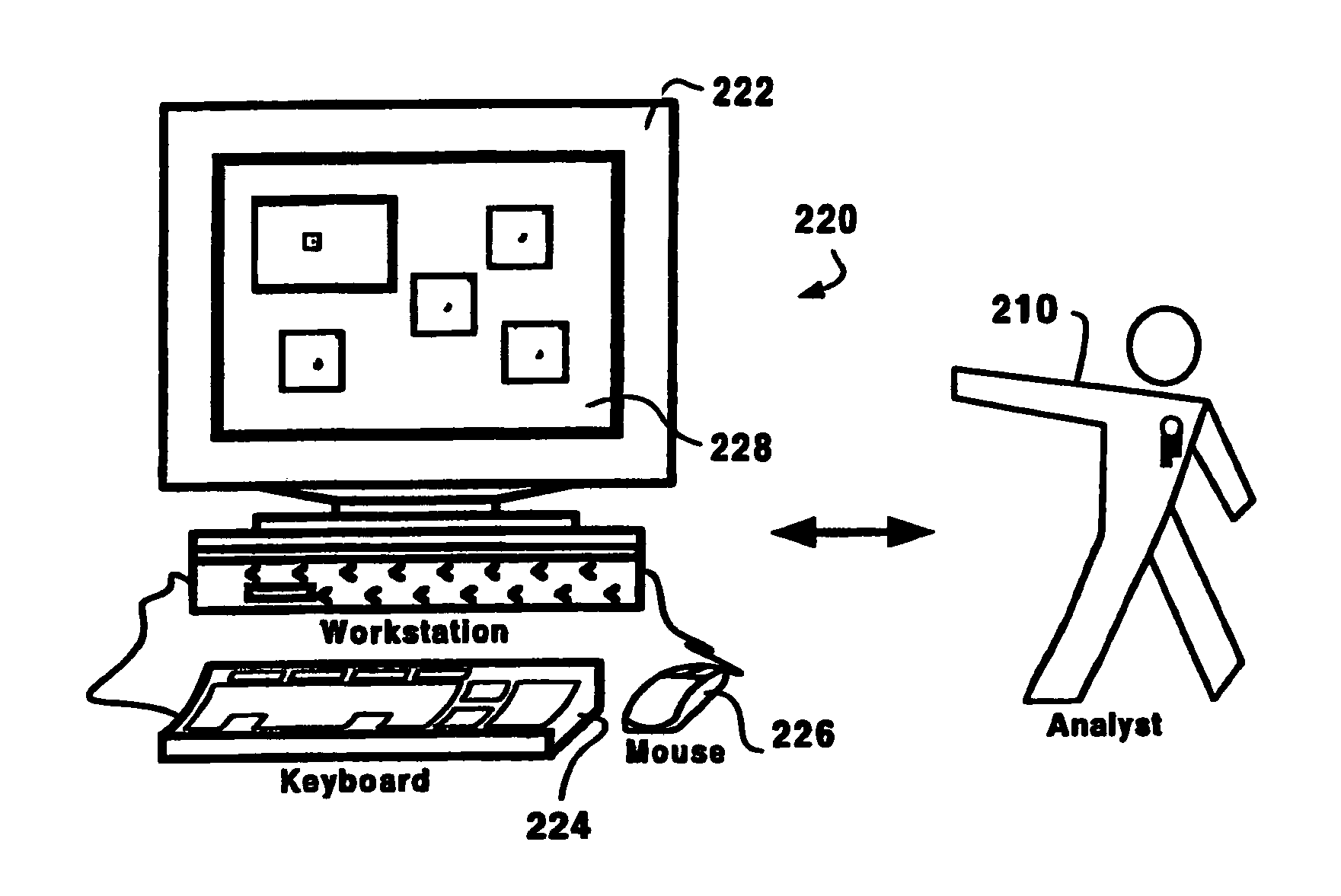

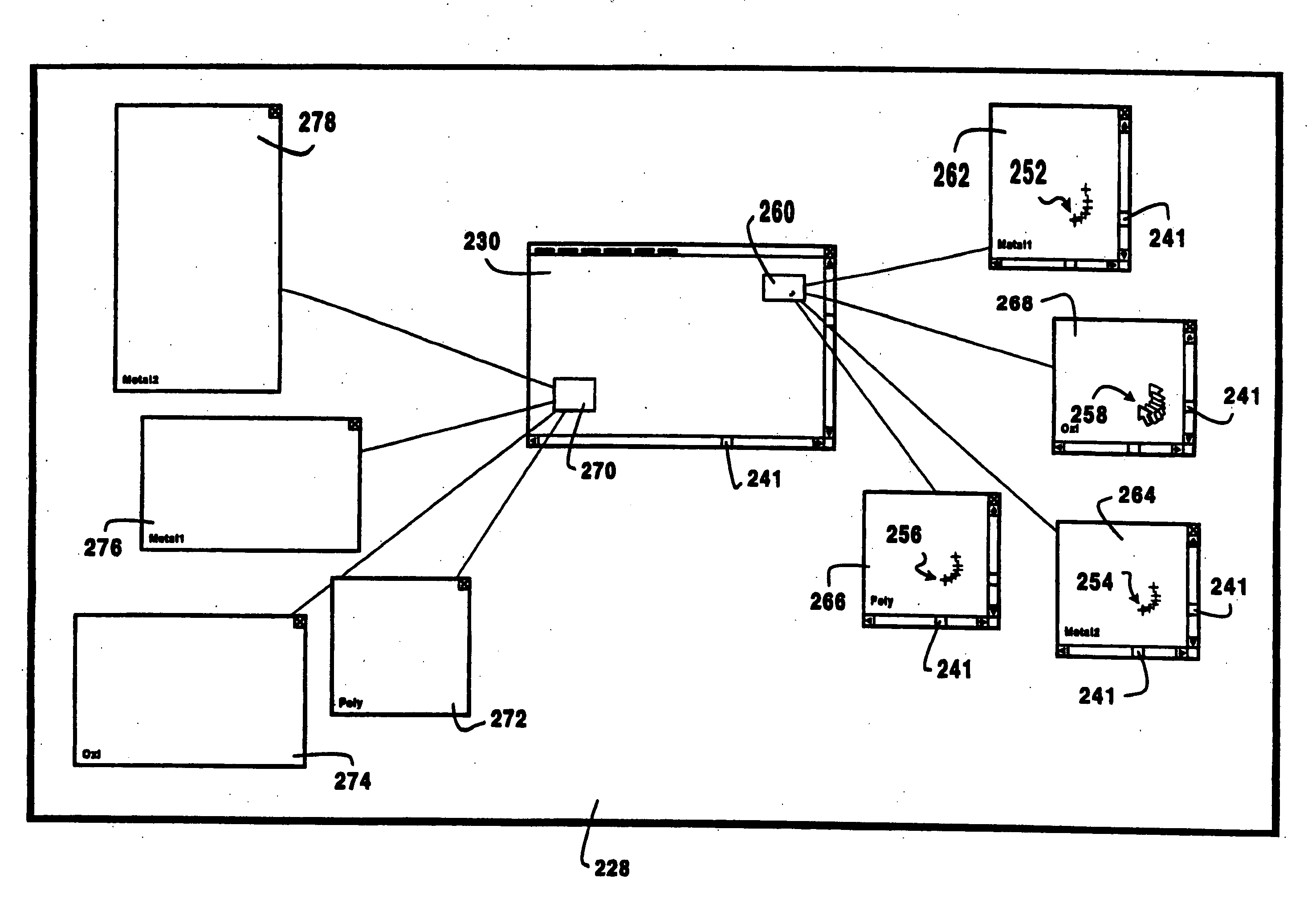

Design analysis workstation for analyzing integrated circuits

A design analysis workstation for performing design analysis of integrated circuits provides facilities for extracting design and layout information from digital image-mosaics captured during deconstruction of an integrated circuit. Each image-mosaic is displayed in at least one mosaic-view as a background image that is overlaid with at least one annotation overlay. An engineer analyst creates annotation objects on the annotation overlay based on information inferred concurrently from one or more image-mosaics. Concurrent display of a plurality of image-mosaics facilitates the understanding of interrelations between components on different layers. The design analysis workstation displays a plurality of cursors in respective views of mosaic-images, the cursors having lock-step motion to facilitate comprehension of the alignment of features on different concurrently displayed image-mosaics. The design analysis workstation provides facilities for performing operations on created annotation objects including grouping, cell definition, signal carrier creation, contact creation, signal propagation, net-list generation, etc. The advantages include annotation of image-mosaics using information derived from a plurality of concurrently displayed mosaic-views to facilitate tracing of interconnected busses and an understanding of interrelations between components.

Owner:TECHINSIGHTS

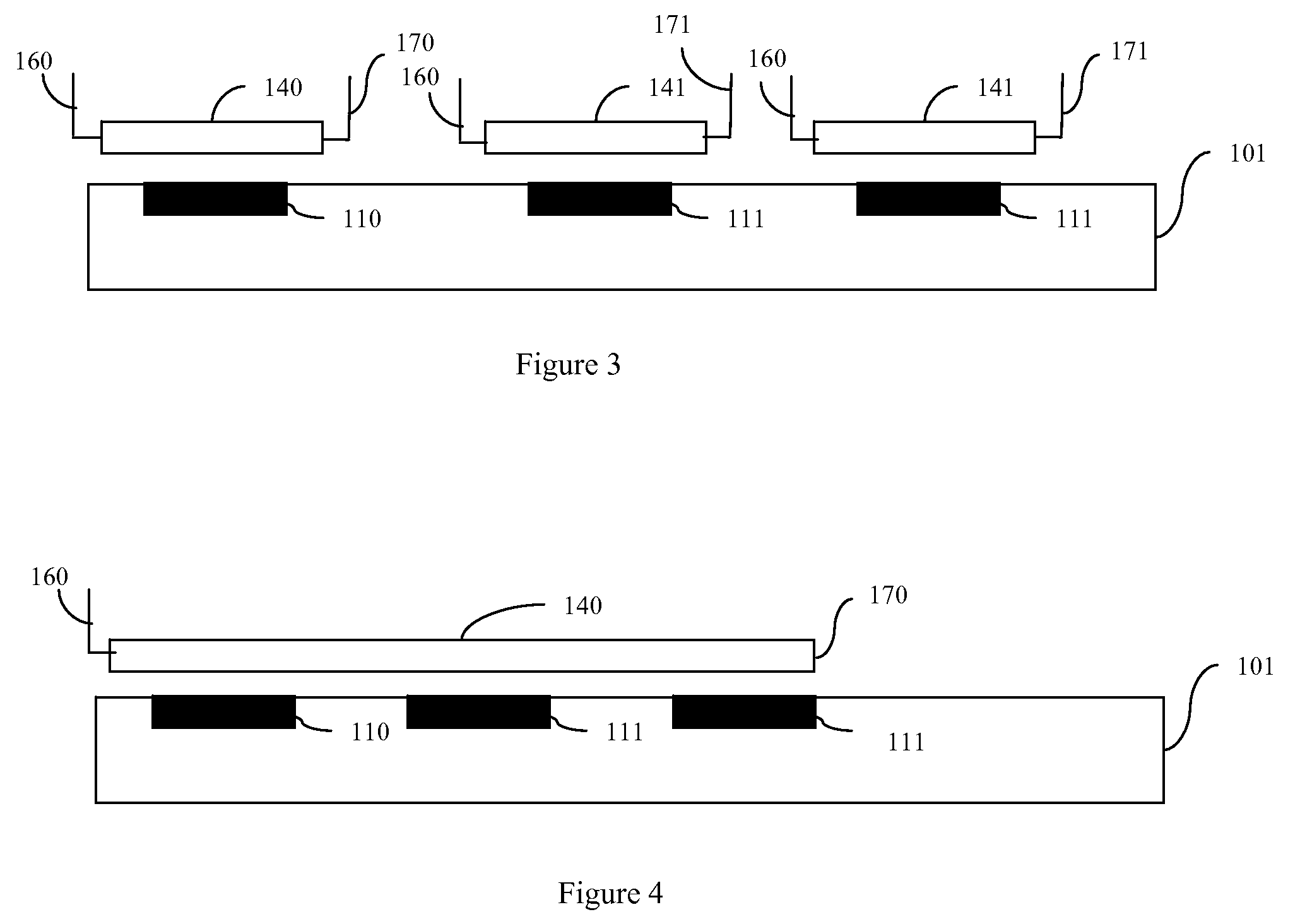

Continuously Referencing Signals over Multiple Layers in Laminate Packages

InactiveUS20080093726A1Final product manufactureSemiconductor/solid-state device detailsPackage designGround plane

A mechanism for continuously referencing signals over multiple layers in laminate packages provides a continuous path for signals from one layer to another while using the ideal voltage reference for all areas of the package and still avoiding discontinuities in the voltage reference. A reference plane adjustment engine analyzes a package design and identifies an ideal top plane for all areas of the package, including areas under particular chip die(s) and areas that are not under a chip die. The reference plane adjustment engine then modifies the package design to reposition ground planes, source voltage planes, signal planes, and vias between layers to maintain a continuous voltage reference regardless of the top layer. The reference plane adjustment engine provides the resulting mixed voltage plane package design to a design analysis engine. A package fabrication system fabricates the package.

Owner:GLOBALFOUNDRIES INC

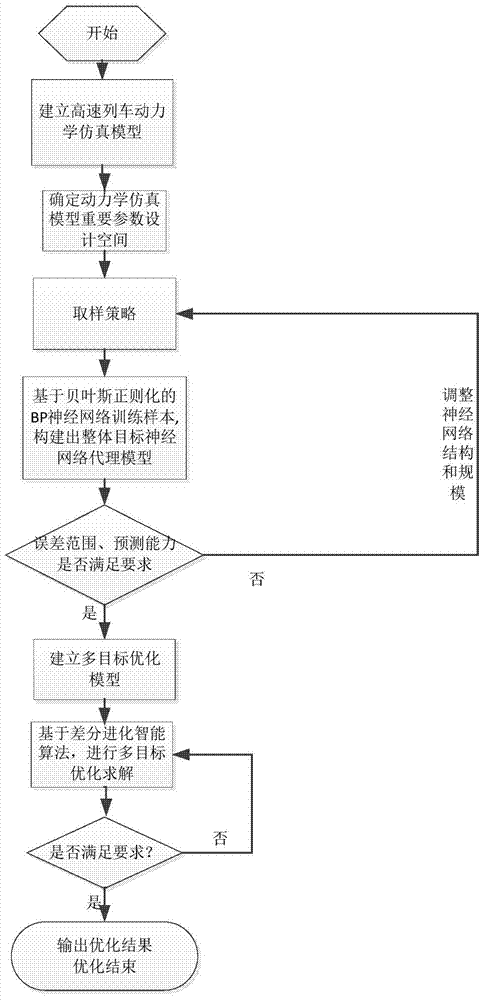

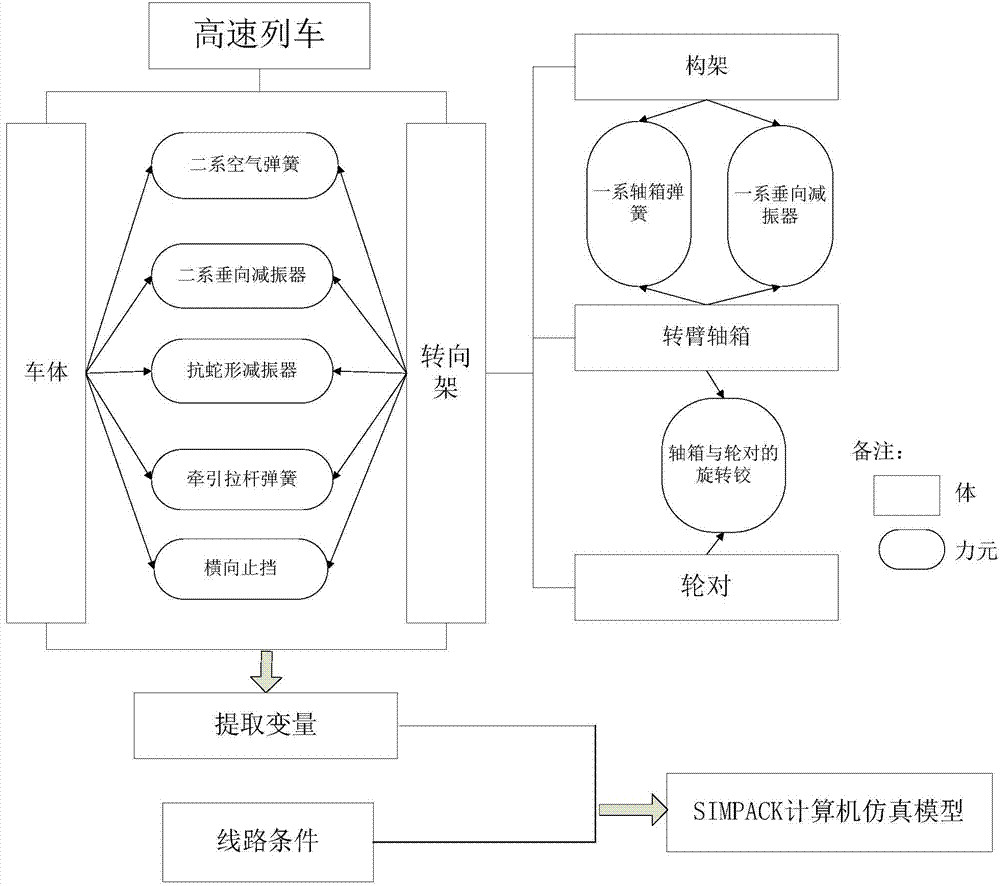

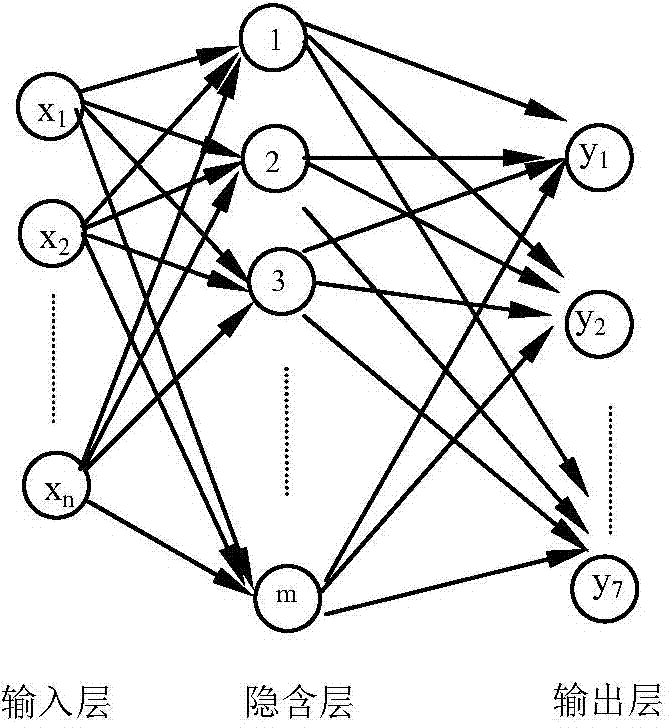

Dynamics performance parameter optimizing method of high-speed train

ActiveCN104765916AImprove operational safetyImproved smoothness and comfortSpecial data processing applicationsNetwork modelDesign space

The invention provides a dynamics performance parameter optimizing method of a high-speed train, relates to the field of parameter design optimizing based on the dynamics simulation analysis of the high-speed train, and aims at effectively replacing a dynamics simulation model of the high-speed train by a comprehensive target neural network agent model and combining the design analysis and the multi-target optimization algorithm of the high-speed train in the multi-disciplinary field to analyze and optimize the dynamics simulation approximation model of the high-speed train. The method specifically comprises the steps of building a multi-rigidity dynamics simulation model for the high-speed train; determining related important input / output design spaces; selecting sampling strategy to obtain a design space sample set suitable for the dynamics performance analysis of the high-speed train; improving the generalization accuracy of the comprehensive target neural network by the bayesian regularization method; adjusting the number of nodes in a hidden layer to build the comprehensive target neural network agent network model of which the error is controlled to be within a certain of range; performing multi-target optimization through the intelligent differential evolution algorithm by using the improved comprehensive target neural network agent network model to obtain the optimized high-speed train design parameters. The method is mainly applied to the dynamics analysis and design optimization of the high-speed train.

Owner:成都天佑创软科技有限公司

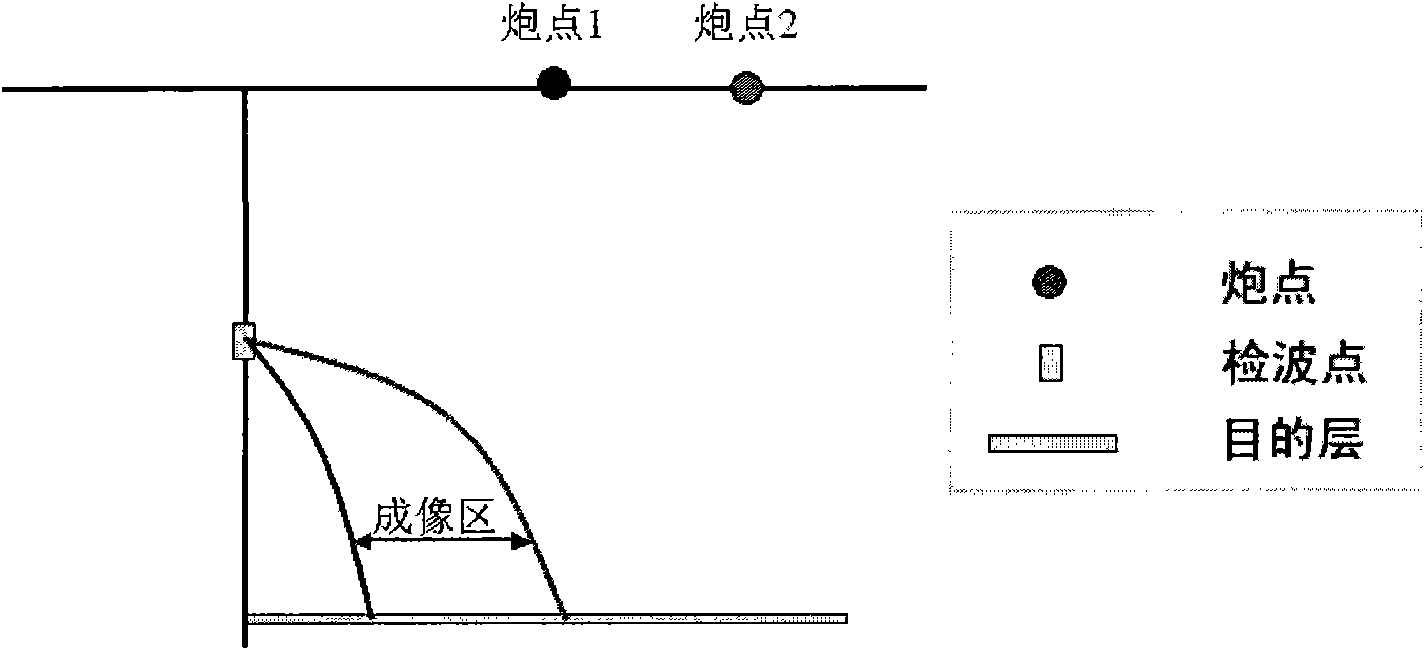

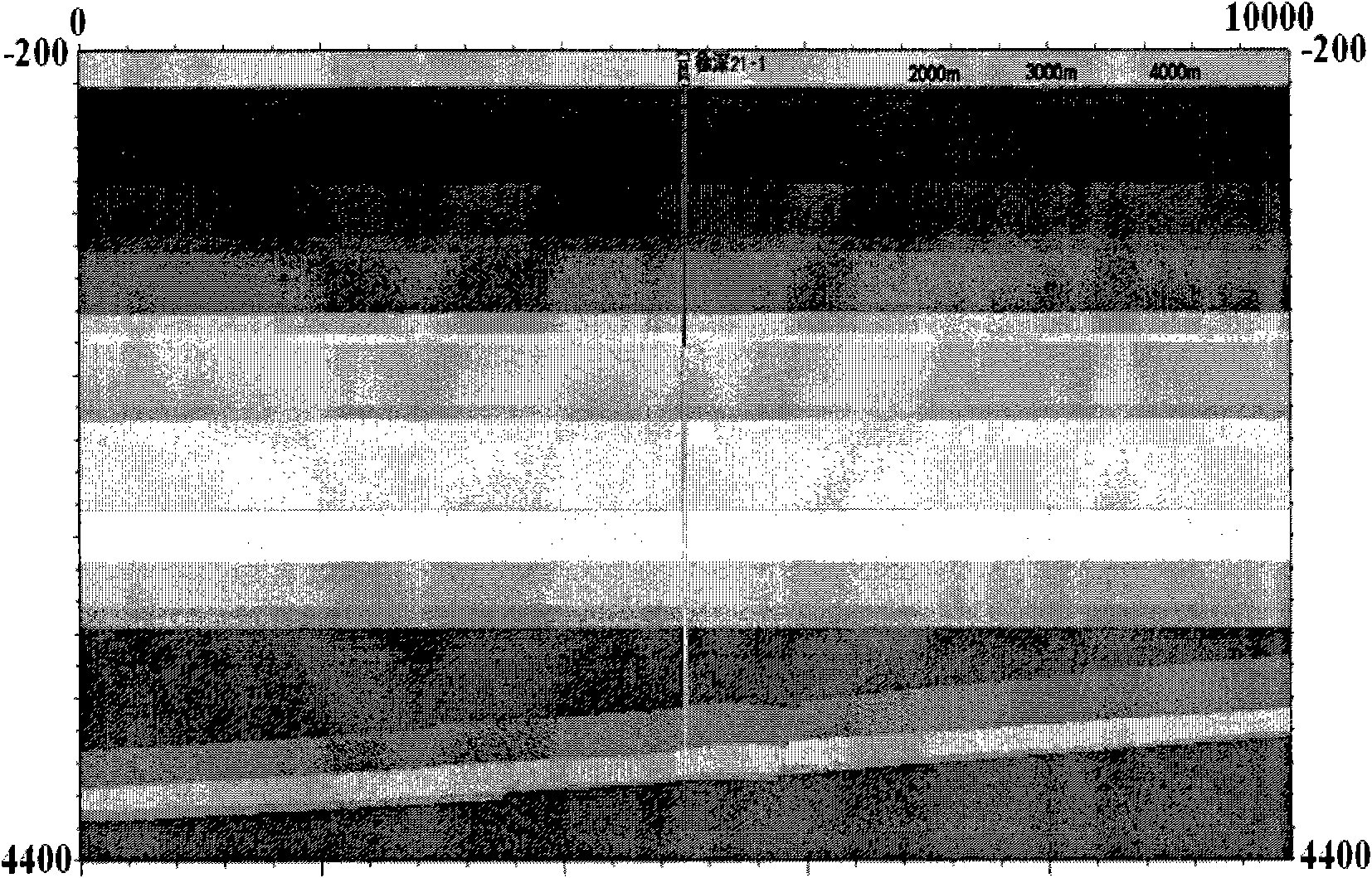

Method for optimizing design of vertical seismic profile observation system

ActiveCN101625417AEasy to separateReasonableSeismic signal processingSeismology for water-loggingSystems designData acquisition

Owner:BGP OF CHINA NAT GASOLINEEUM CORP

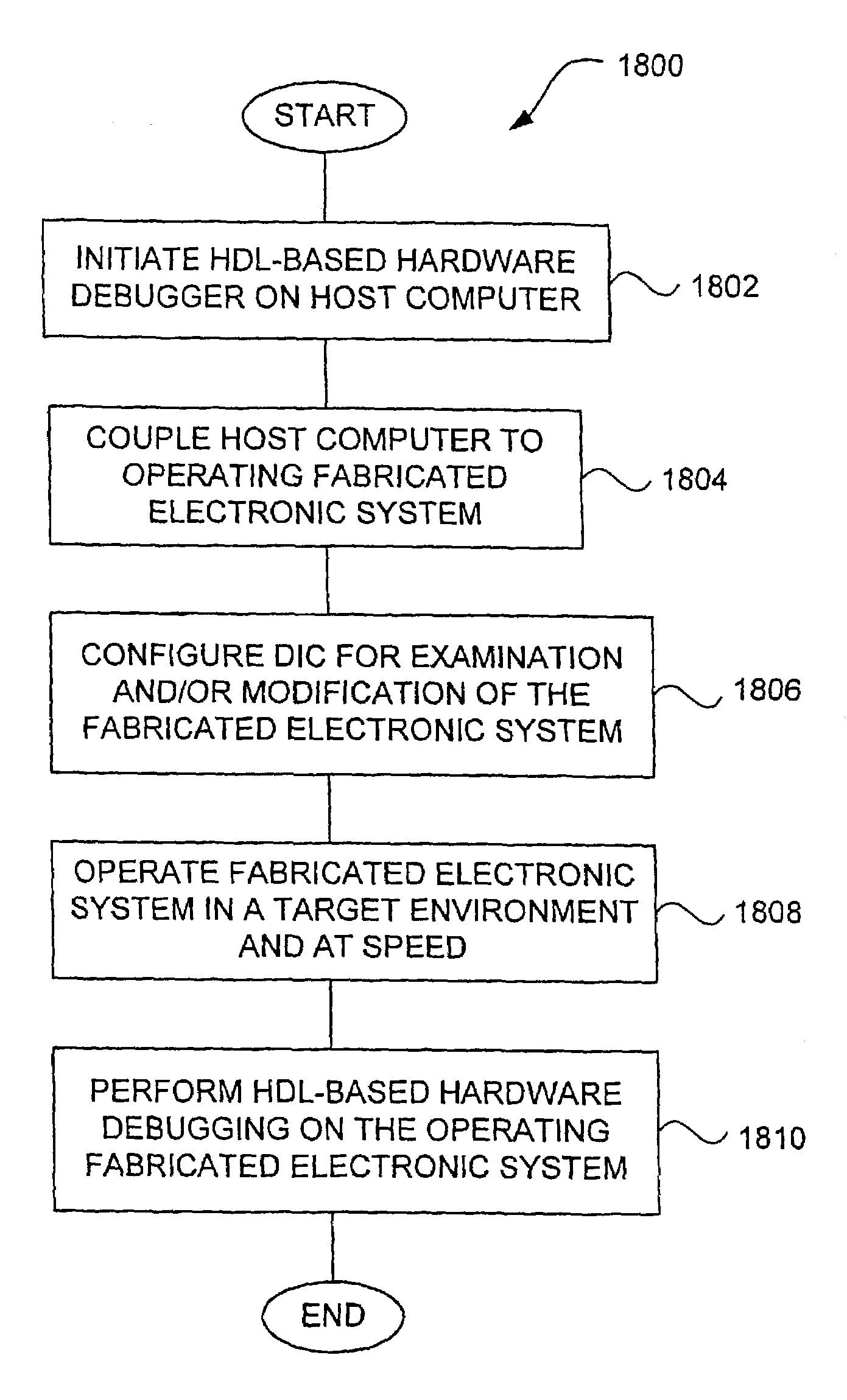

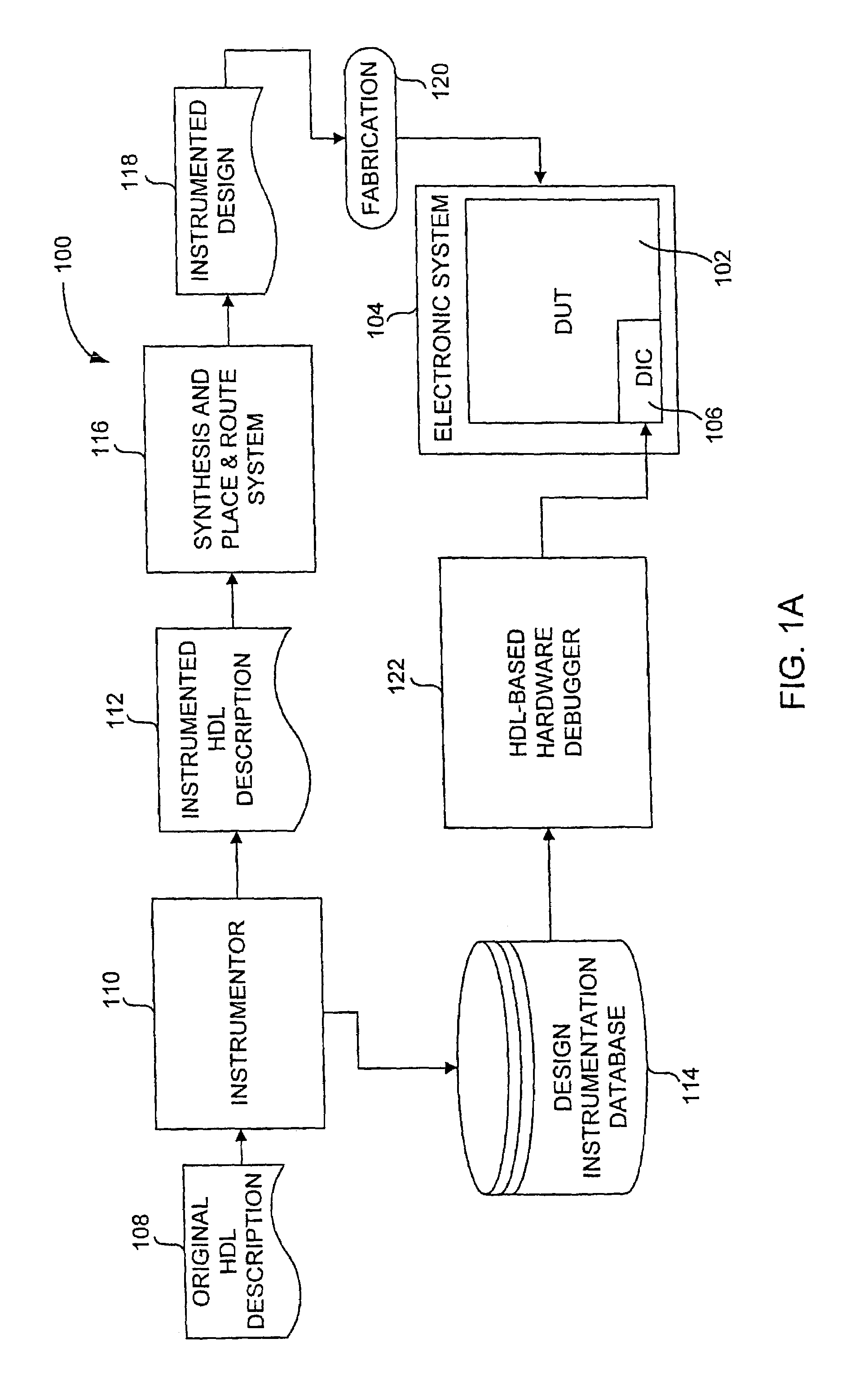

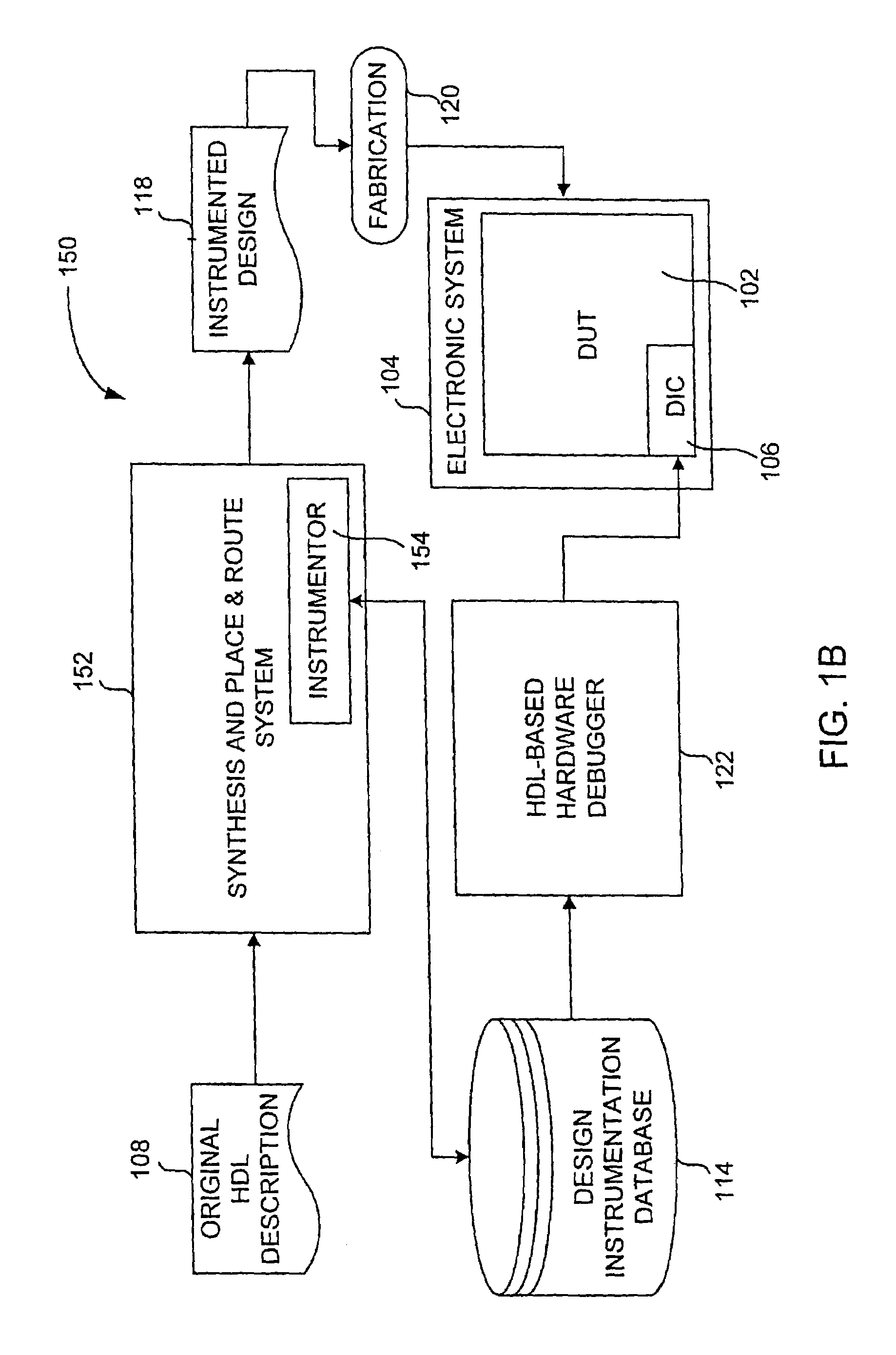

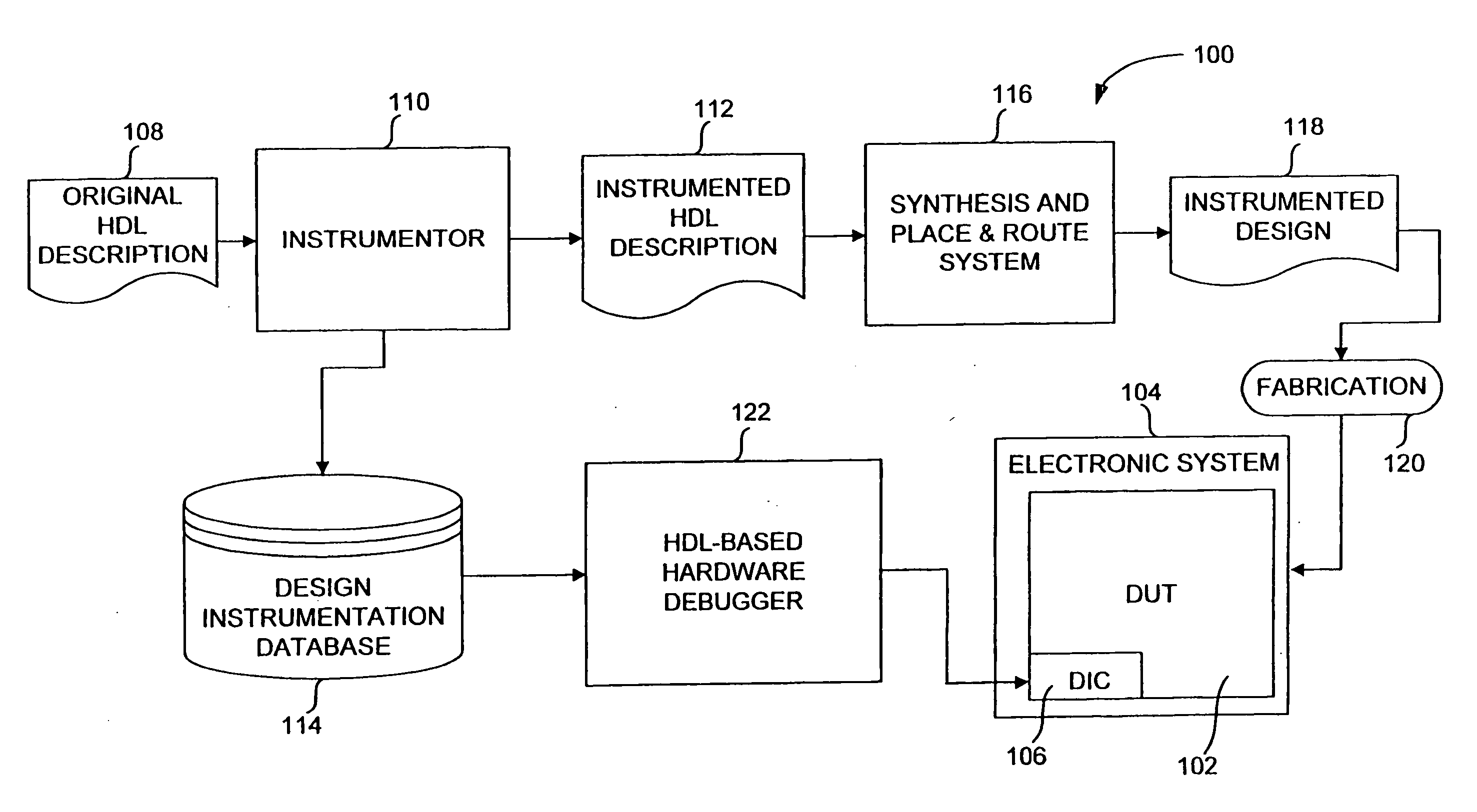

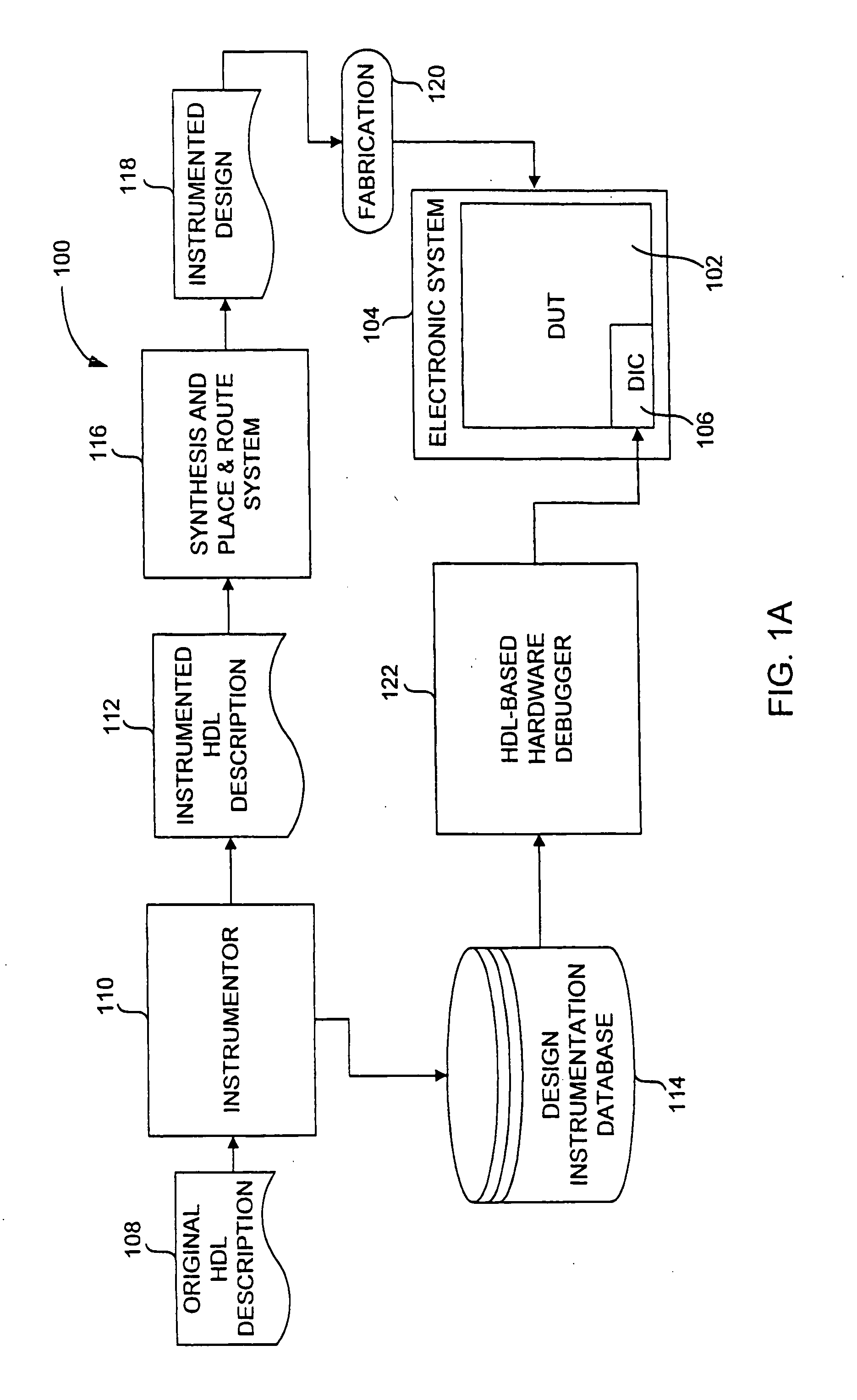

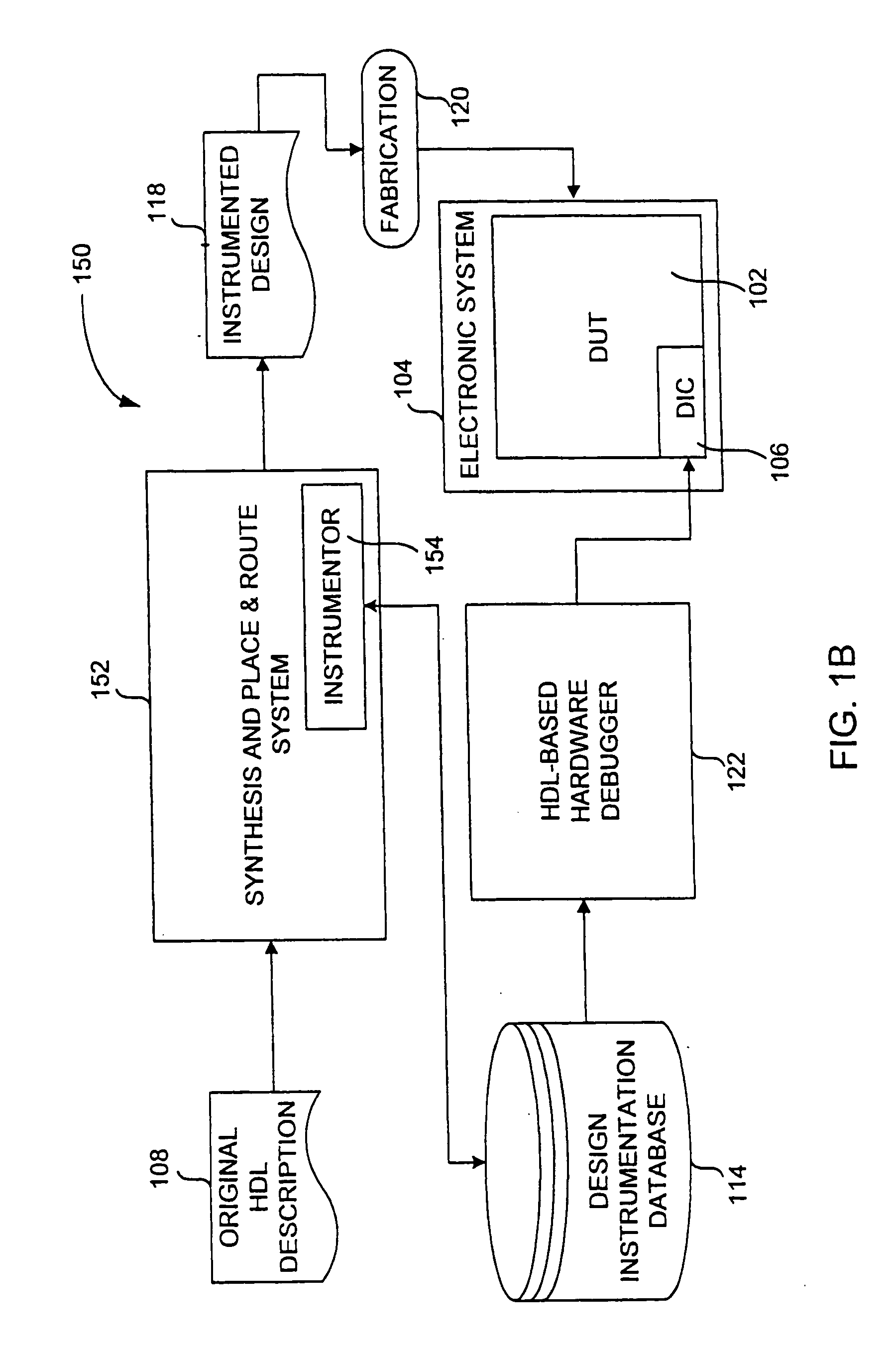

Hardware-based HDL code coverage and design analysis

InactiveUS7222315B2Easy to correctEasy to adjustCAD circuit designSoftware simulation/interpretation/emulationComputer architectureCode coverage

Techniques and systems for analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level are described. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input / output pins, the techniques and systems enable the hardware designs within the integrated circuit products to be analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the hardware designs. Moreover, various embodiments related to HDL code coverage are described.

Owner:SYNOPSYS INC

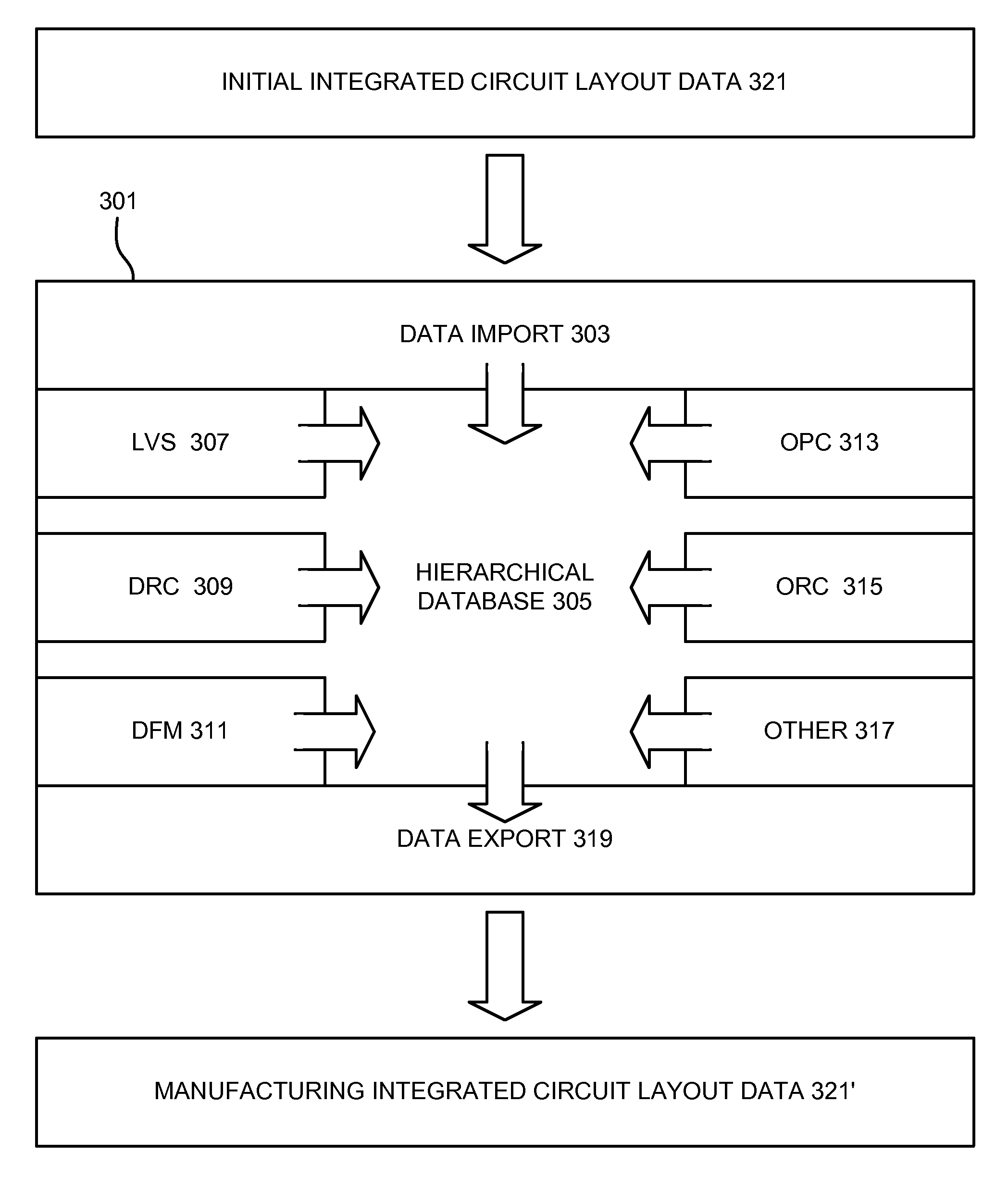

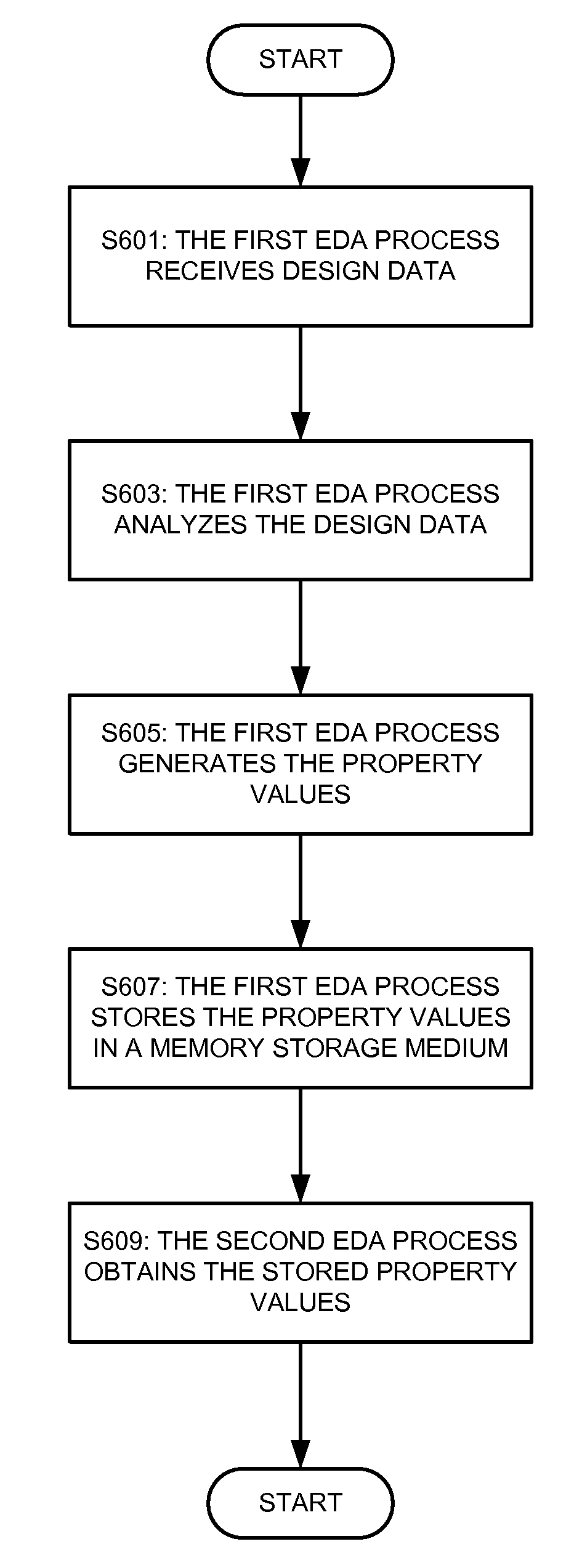

Properties In Electronic Design Automation

InactiveUS20080115096A1Easily calculateComputer aided designTotal factory controlComputer architectureLogic circuit design

One or more properties can be associated with a design object in a microdevice design. The design object may be an object in a physical layout design for a microdevice, such as a geometric element in a layout design. The design object also may be a collection of geometric elements in a layout design, such as a net, a cell in a hierarchical design, or even a collection of all of the geometric elements in a layer of a design. Still further, the design object may even be an item in a logical circuit design, such as a net in a logical circuit design for an integrated circuit. The values of one or more properties may be statically assigned for or dynamically generated during a design process performed by an electronic design automation tool. A property may be assigned a constant value or a value defined by an equation or other type of script that includes one or more variables. A property may be simple, where the definition of the property's value is not dependent upon the value of any other properties. Alternately, a property may be a compound property, where the definition of the property's value incorporates another, previously-determined property value. Still further, a property may be an alternative property, where the property is assigned one value definition under a first set of conditions and assigned another value definition under a second set of conditions. A first electronic design automation process may generate one or more property values. The generated property values then can be passed to another electronic design automation process in the design analysis flow for its use.

Owner:MENTOR GRAPHICS CORP

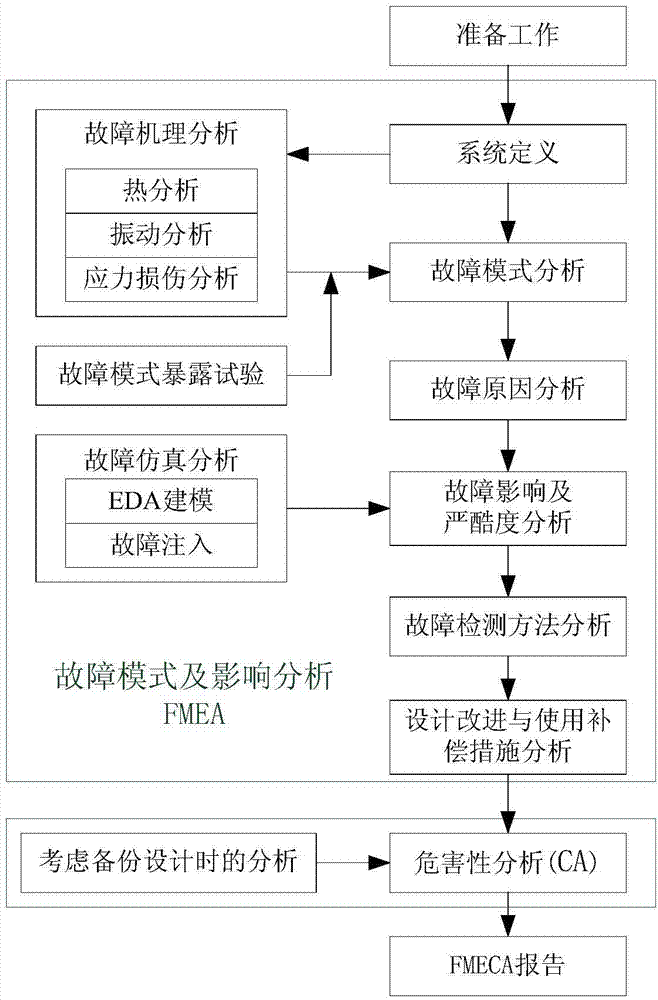

Newly-developed aviation electronic product hardware comprehensive FMECA method

ActiveCN103760886AQuick extractionAccurate descriptionElectric testing/monitoringAviationDesign improvement

A newly-developed aviation electronic product hardware comprehensive FMECA method comprises the first step of defining a system to be analyzed, the second step of determining fault modes and reasons of appointed layers of a product based on a fault information database, fault mechanism analyzing and a fault module exposure test method, the third step of acquiring fault effects based on a fault simulation analytical method, the fourth step of carrying out the quantification hazard analysis, taking the multiple fault effects caused by the redundancy design into consideration and providing a quantification hazard analyzing method based on the multiple fault effects, and the fifth step of filling in an FMECA table and filling the fault modes, the reasons, the effect and the hazard degree all of which are acquired through analyzing into the FMECA table. The newly-developed aviation electronic product hardware comprehensive FMECA method is a hardware FMECA method based on the fault information database, fault mechanism analyzing, fault mode exposure testing, fault simulating and analyzing and the multiple fault effects, and is capable of providing more objective quantification for design and analyze workers and providing a basis for the design improvement on electronic products.

Owner:BEIHANG UNIV

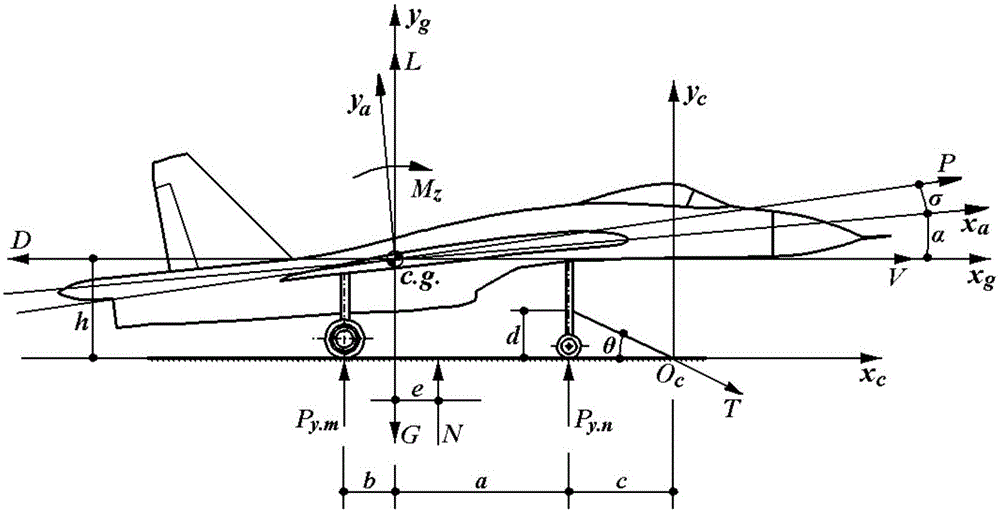

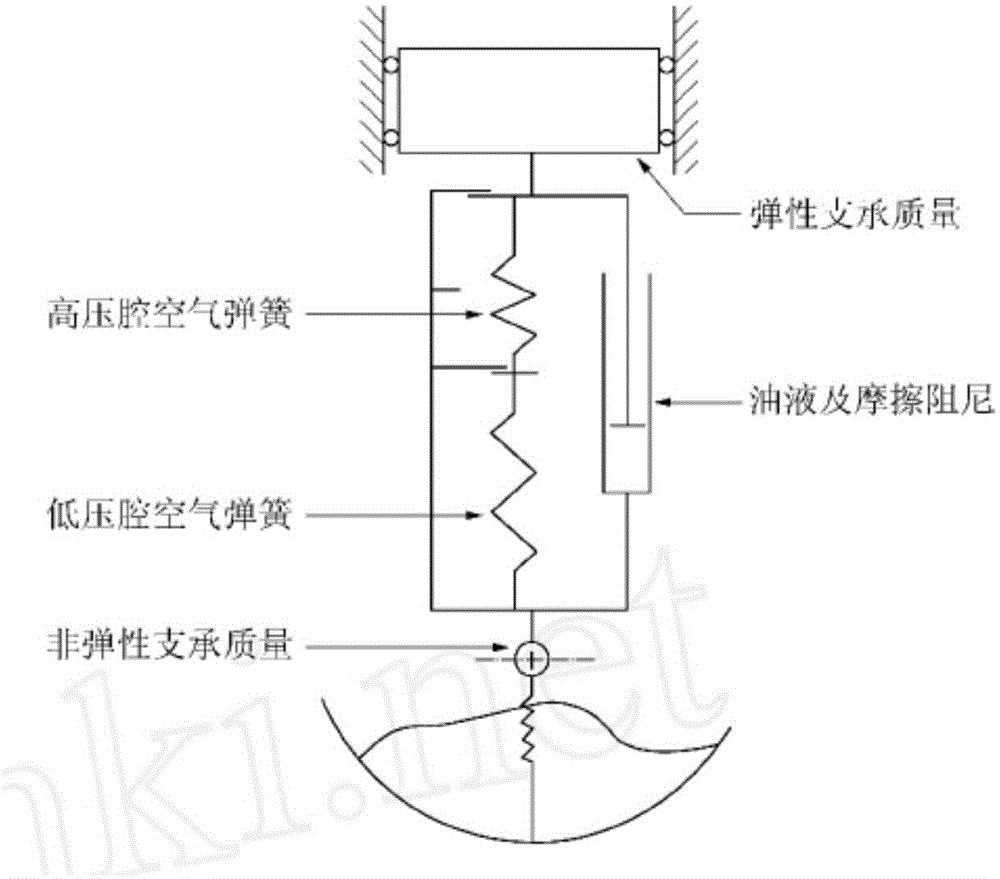

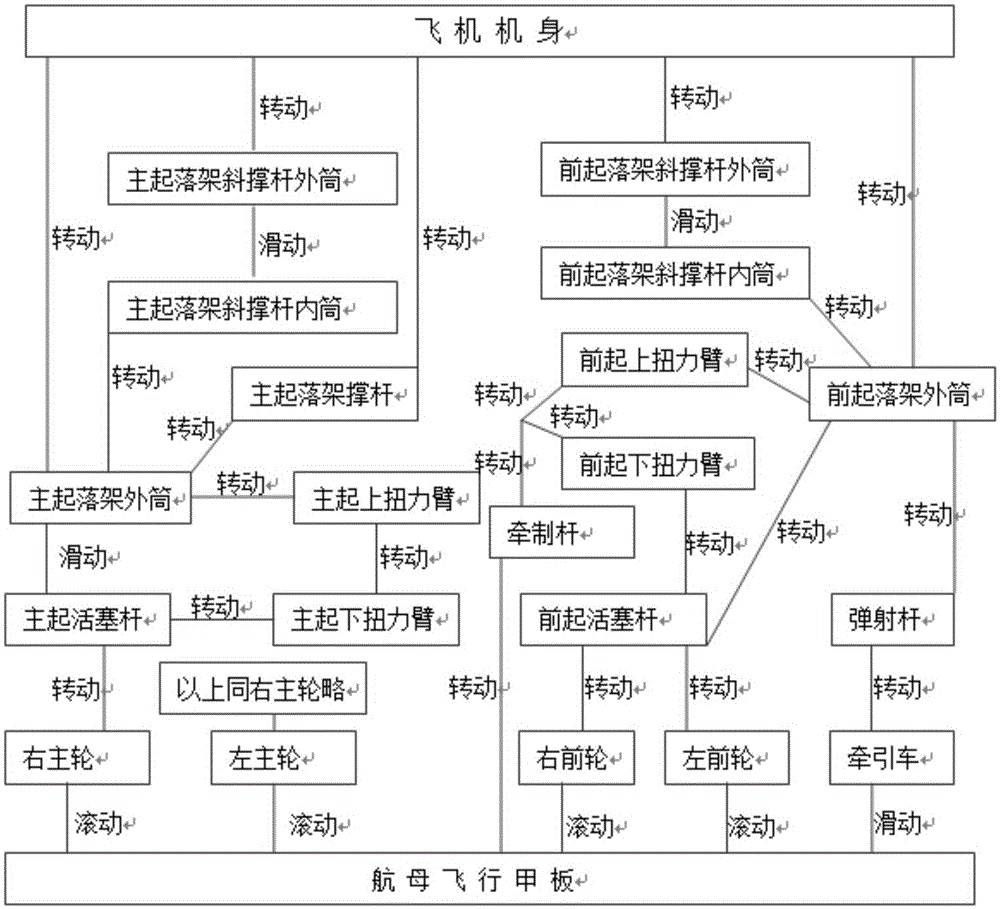

Load simulation method for cataplane landing gear

InactiveCN105138805ASolving design and analysis problems of landing gear loadsGuaranteed flight test verificationSpecial data processing applicationsMechanical equilibriumGravity center

The invention discloses a load simulation method for a cataplane landing gear, and belongs to the field of strength design of the cataplane landing gear. The load simulation method mainly comprises the following steps: analyzing stress on the whole cataplane, a nose gear and a main landing gear of a cataplane, so as to establish a corresponding mechanic equilibrium equation; establishing a nose gear simulation analysis model, a main landing gear simulation analysis model and a whole cataplane dynamic simulation analysis model according to the nose gear mechanic equilibrium equation; finally, correcting the whole cataplane dynamic simulation analysis model according to testing gravity center data and a front main landing gear load curve during practical catapult launching of the cataplane. The corrected model is the model capable of being used for catapult launching load simulation of the cataplane, problems in load design and analysis of the landing gear during catapult launching of the cataplane are solved, and the flight test verification of a carrier-based aircraft in an aircraft carrier platform and a land-based training ground is guaranteed.

Owner:SHENYANG AIRCRAFT DESIGN INST AVIATION IND CORP OF CHINA

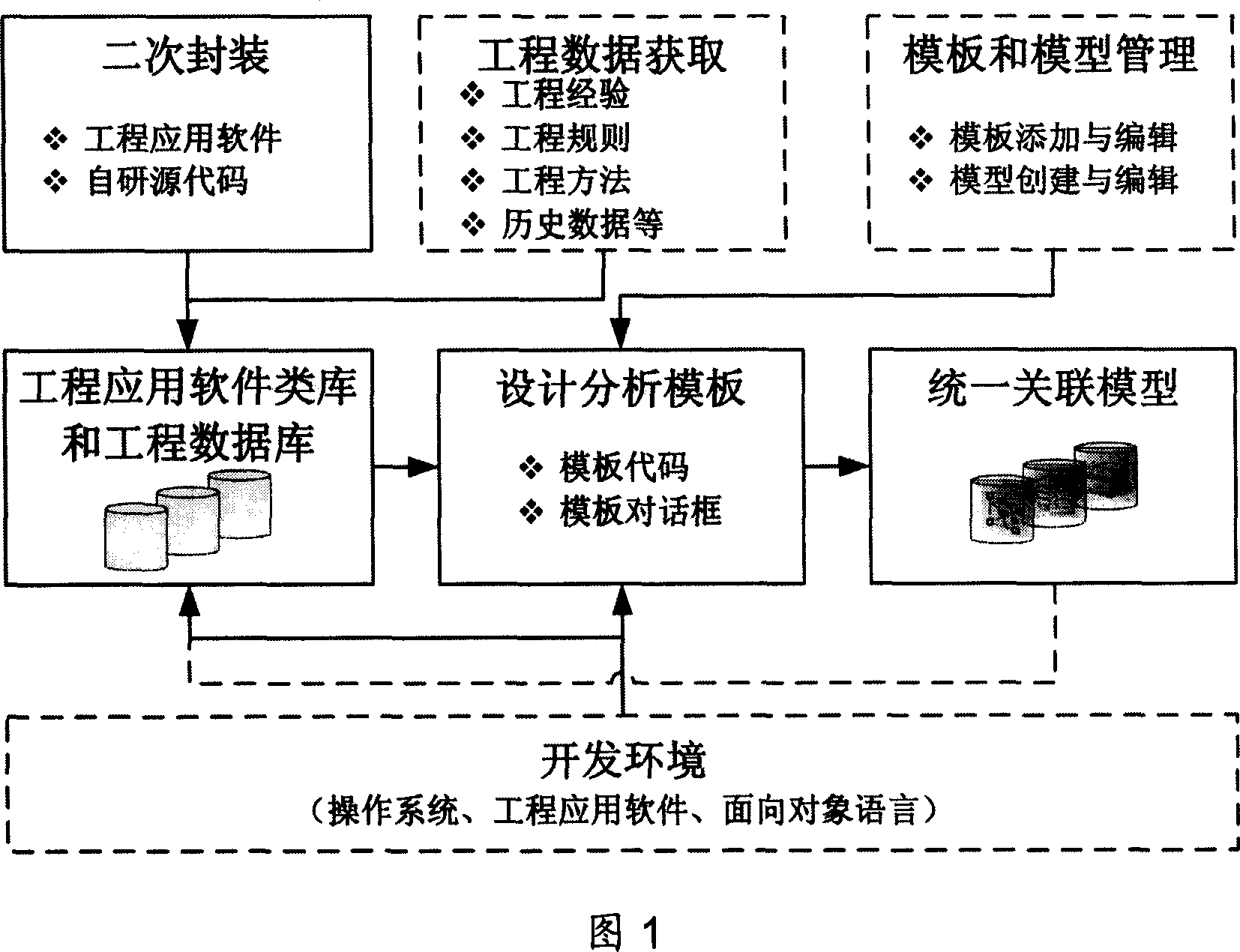

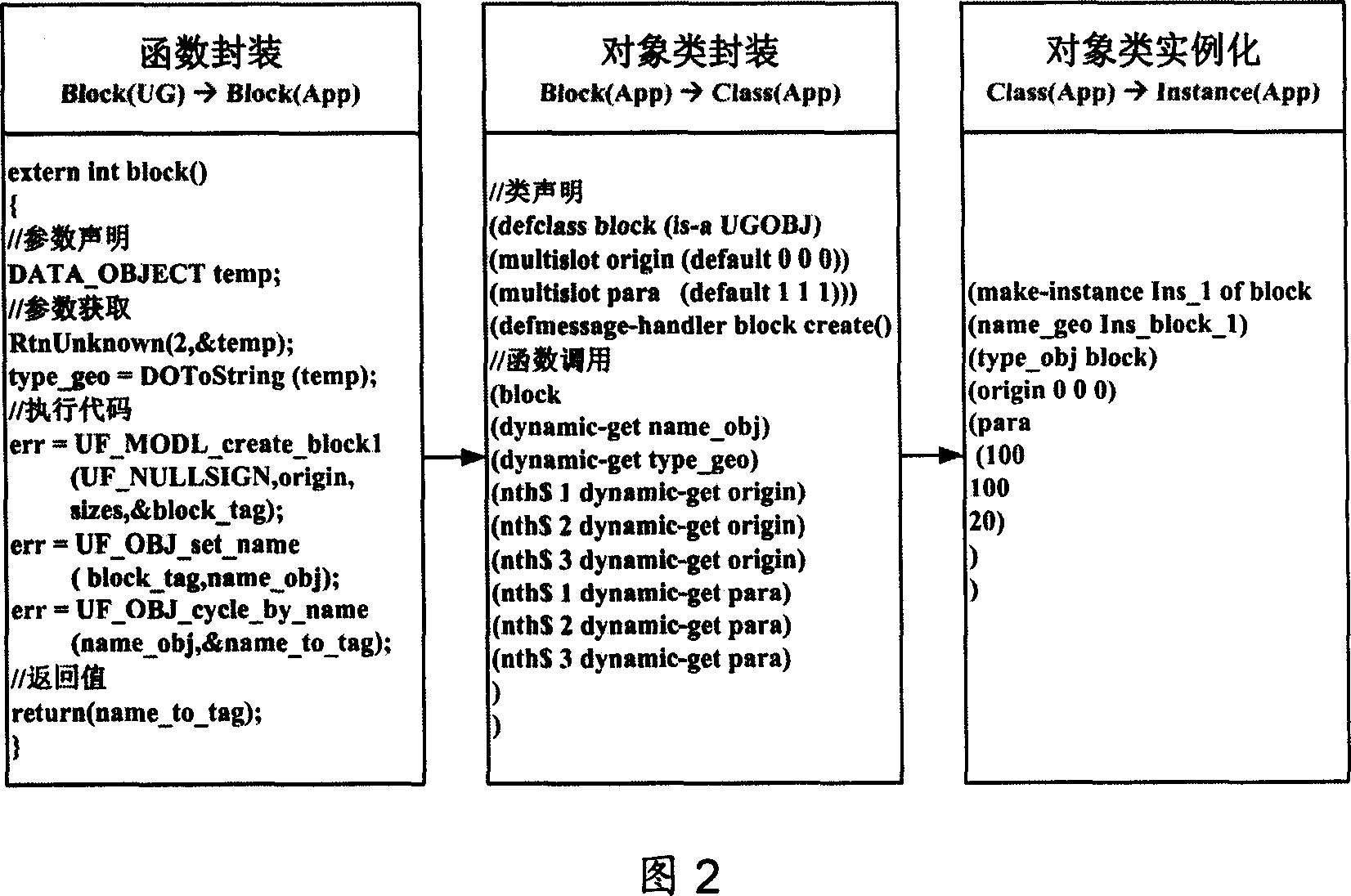

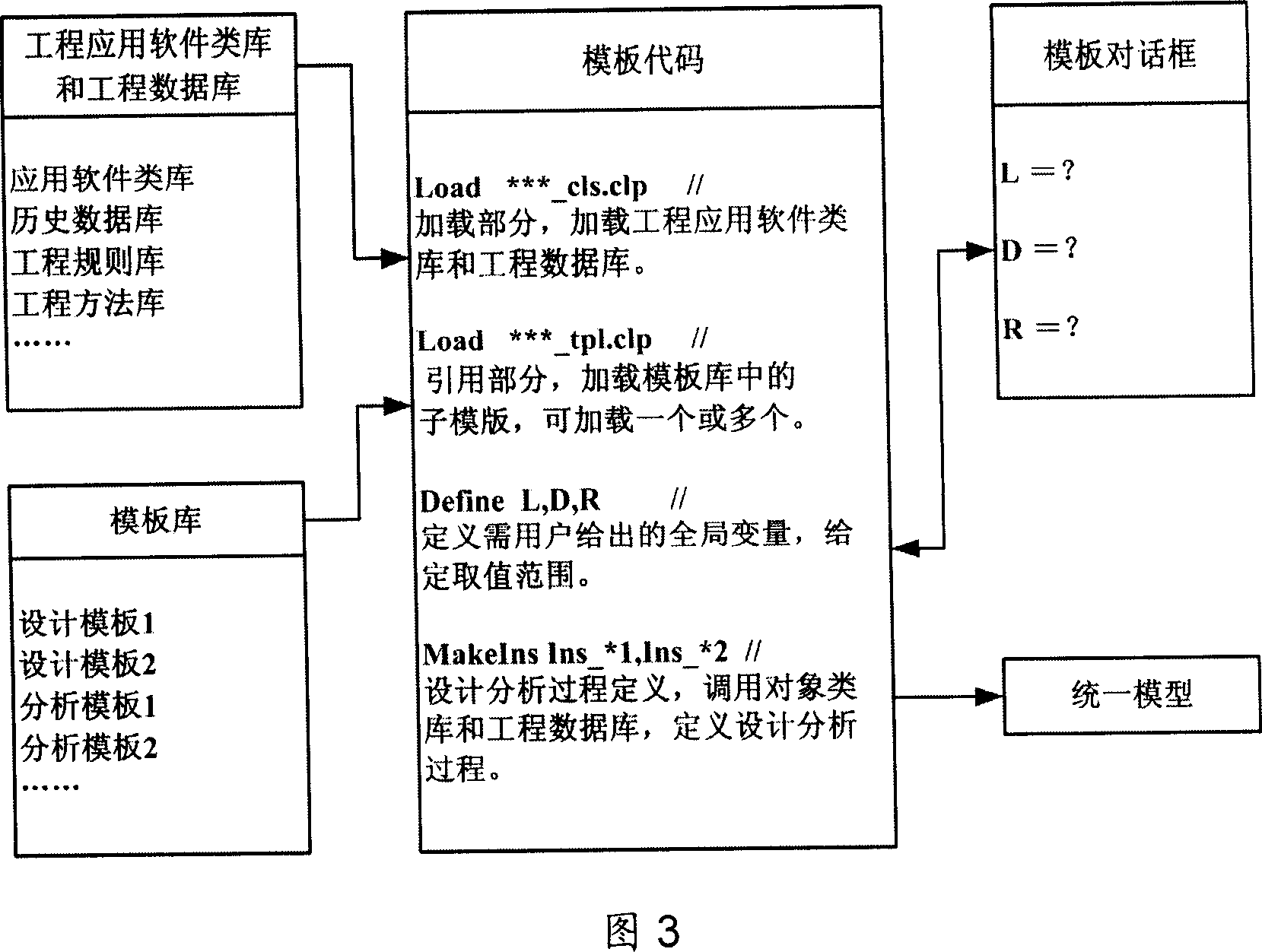

Module based fast engineering design method

InactiveCN1928815ARealize drive controlAchieve acquisitionSpecial data processing applicationsSpecific program execution arrangementsSoftware engineeringTemplate based

The template-based fast engineering design method comprises: secondary packing integration of different engineering application or self-developed software to build software database for control and calling; acquiring engineering data (such as rule, history data, method and case) to build engineering database; building design and analysis template included code to call database and dialog box for interactivity, and implementing the design analysis automation. This invention improves design efficiency and quality with less cost.

Owner:中国航天科技集团公司第一研究院

Hardware-based HDL code coverage and design analysis

InactiveUS20070198959A1Facilitates correction and adjustmentAnalogue computers for electric apparatusCAD circuit designComputer architectureCode coverage

Owner:SYNOPSYS INC

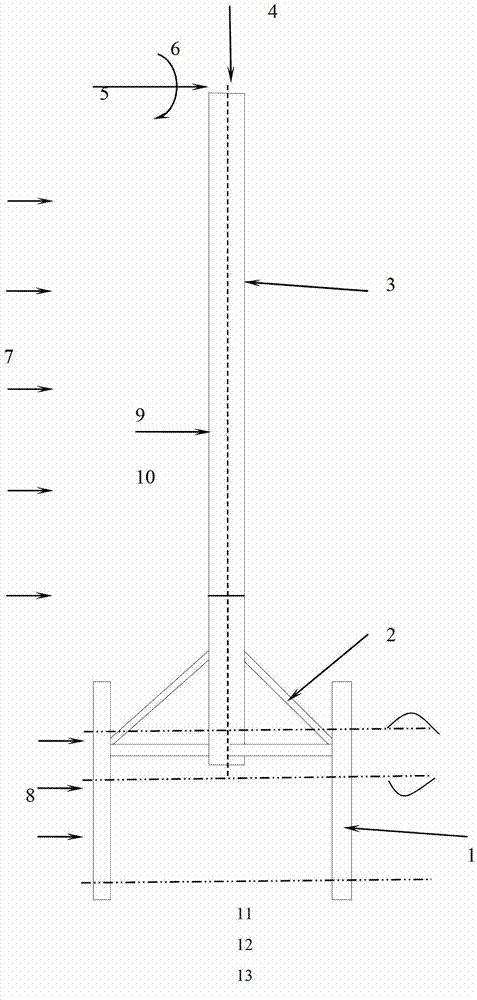

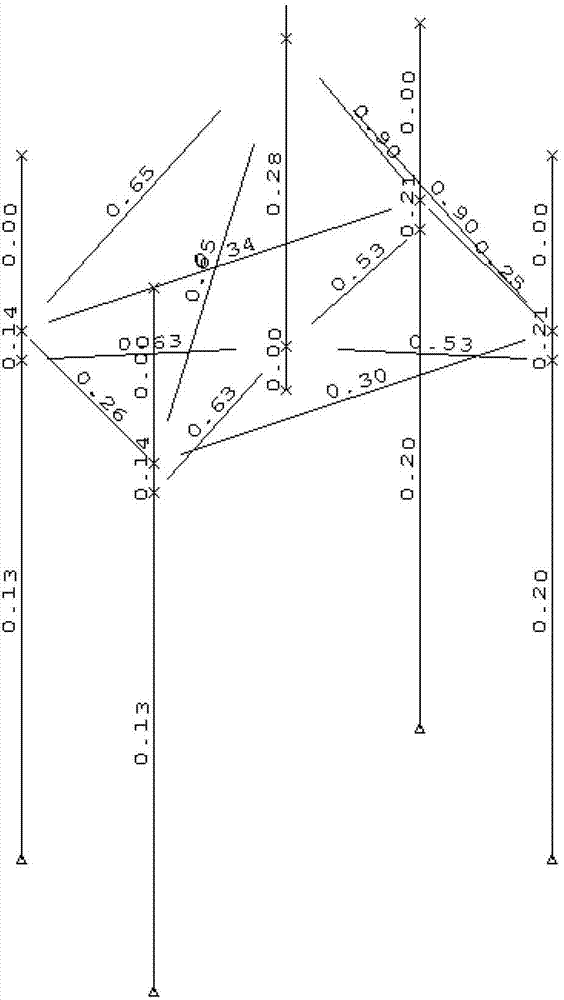

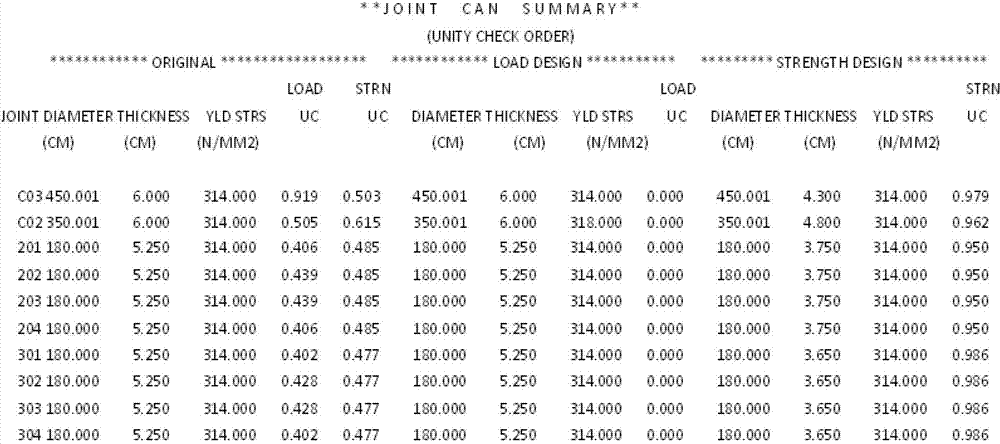

Offshore fan pile foundation design method and application thereof

ActiveCN102926399AReasonable designReasonable design methodFoundation engineeringStructural analysisEngineering

The invention discloses an offshore fan pile foundation design method and application thereof. According to the offshore fan foundation design specifications and the offshore fixed platform design specifications, design calculation analysis is carried out based on ocean engineering design analysis software structural analysis computer system (SACS). The design calculation analysis comprises a fundamental analysis, a modal analysis, a seismic analysis, an ice load analysis, a hoisting analysis, a transportation analysis and an installation analysis. Through the method, actual environmental conditions of offshore fans are totally considered in the method, the analyses are accurate, results are reliable and design efficiency is high. Meanwhile, all aspects of foundation design, hoisting, transportation and installation of the offshore fans are considered in the design method. Therefore, the offshore fan pile foundation design method has the advantages of systematicness and comprehensiveness, and can be applied to intertidal belt fan pile foundation design.

Owner:GUODIAN UNITED POWER TECH

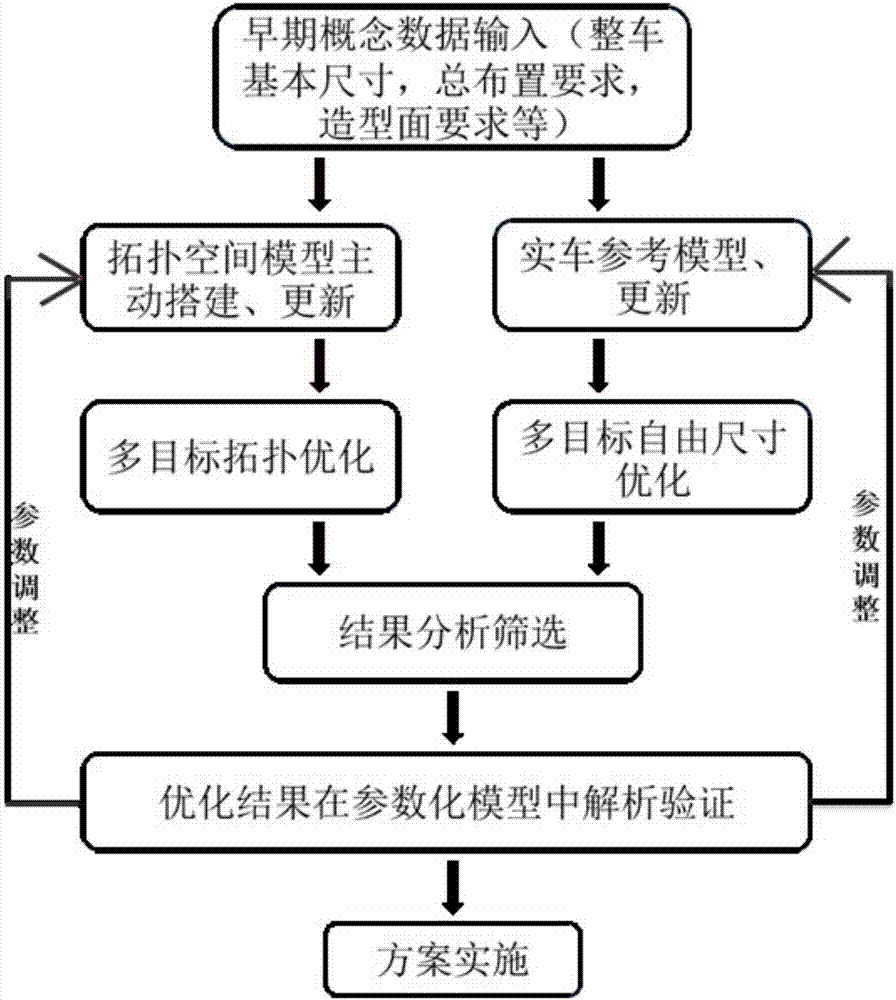

Early-stage concept development and topological optimization method for white body of car

InactiveCN107169211AMeet engineering design requirementsShorten the development and design cycleGeometric CADInternal combustion piston enginesTopology optimizationConcept development

The invention relates to an early-stage concept development and topological optimization method for a white body of a car. The invention brings forward a method for optimization design analysis and parsing of topological space in the early concept of the white body of the car by actively building a model and carrying out topological optimization based on a parameterized model. By actively building a space model and a referential car model, the model is subjected to topological optimization. Then, a topological optimization result is analyzed to the referential car model for verification. After the feasibility of the model is verified, the analysis result is updated to the space model for further optimization in repeated steps till the major force transferring path of the white body of the car is parsed. Through the final force transferring path parsed by the invention, the structural design of the white body of the car is guided so as to meet the requirement for basic performance of the white body of the car.

Owner:上海典凡信息科技有限公司

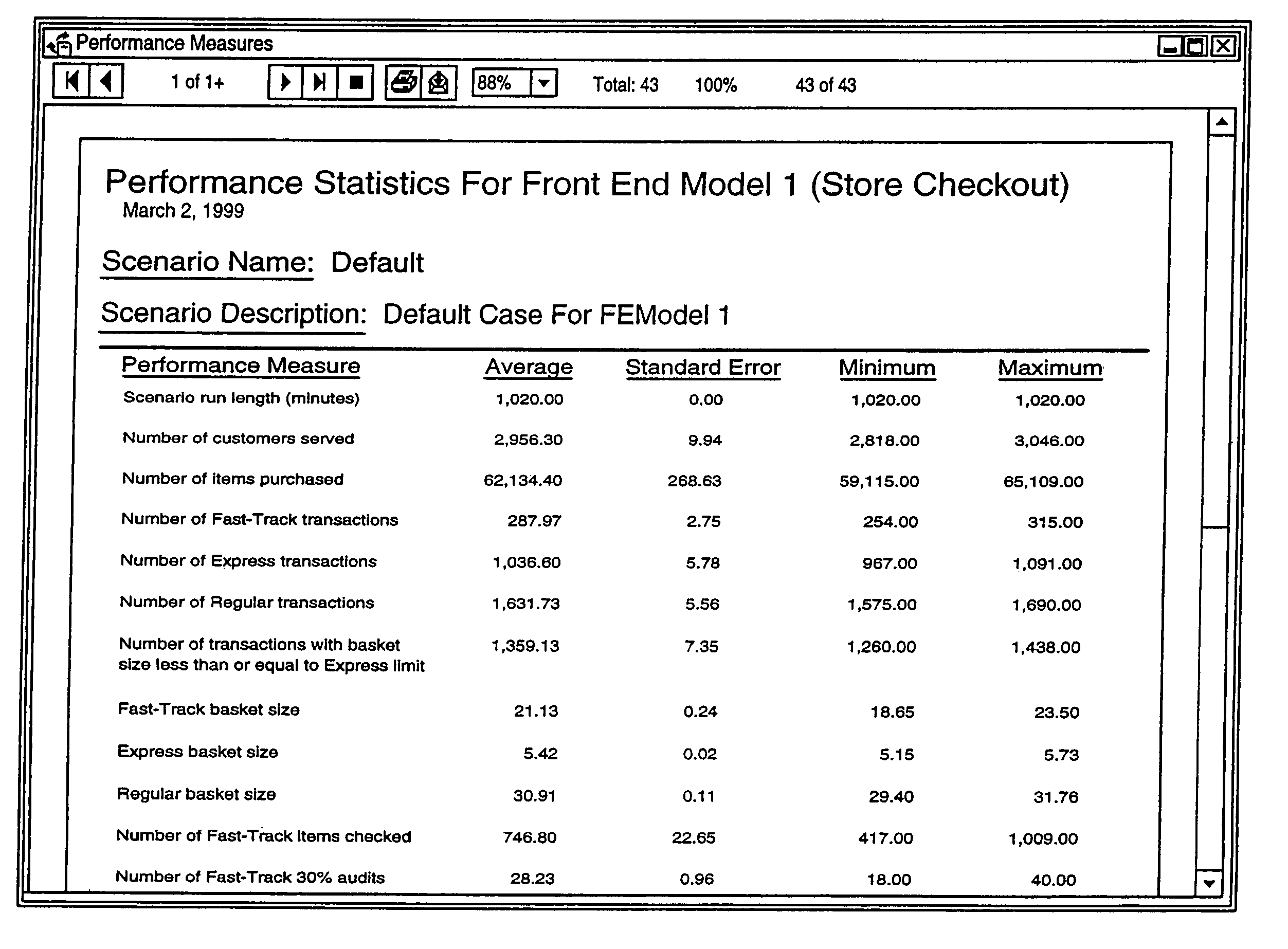

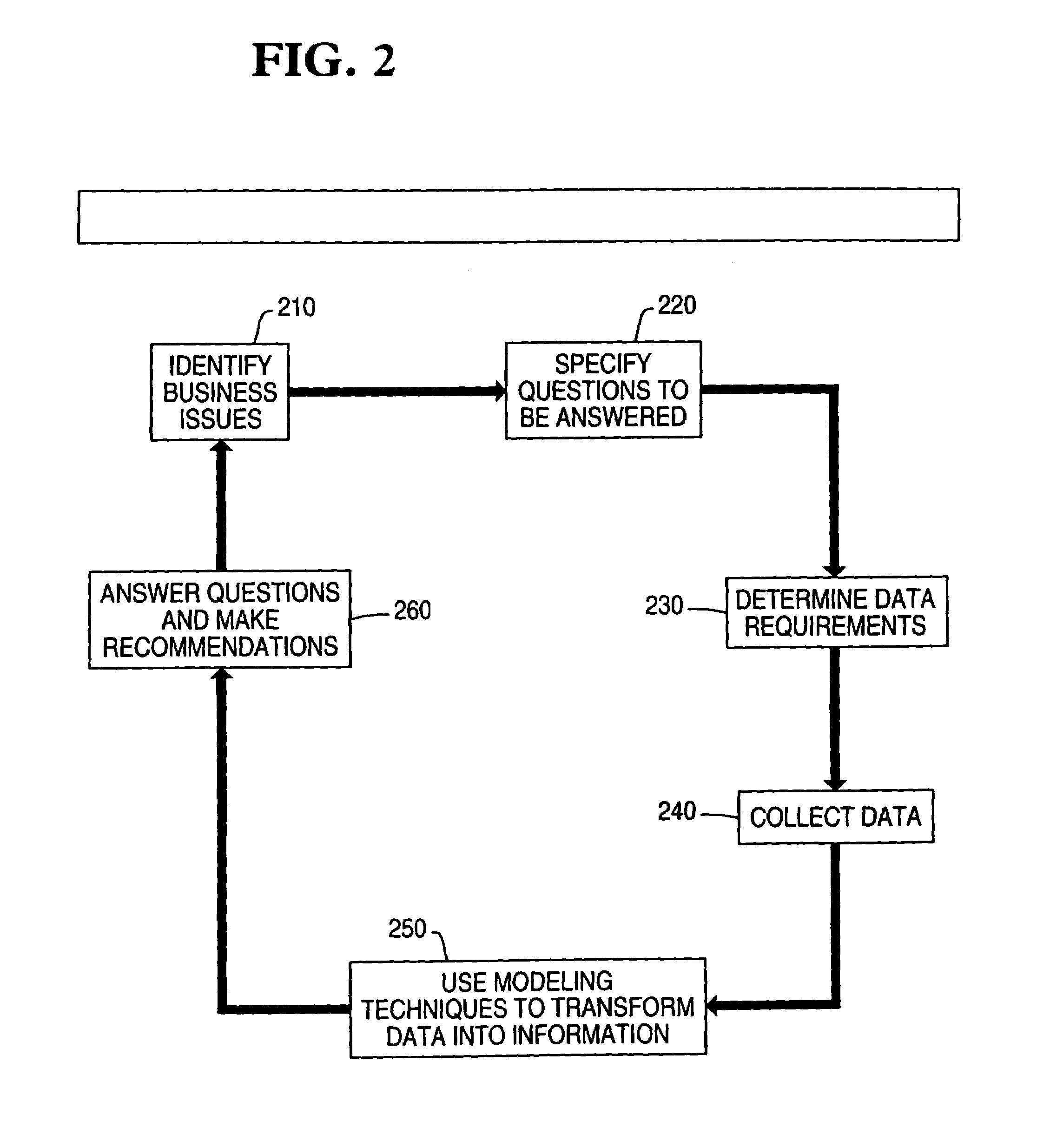

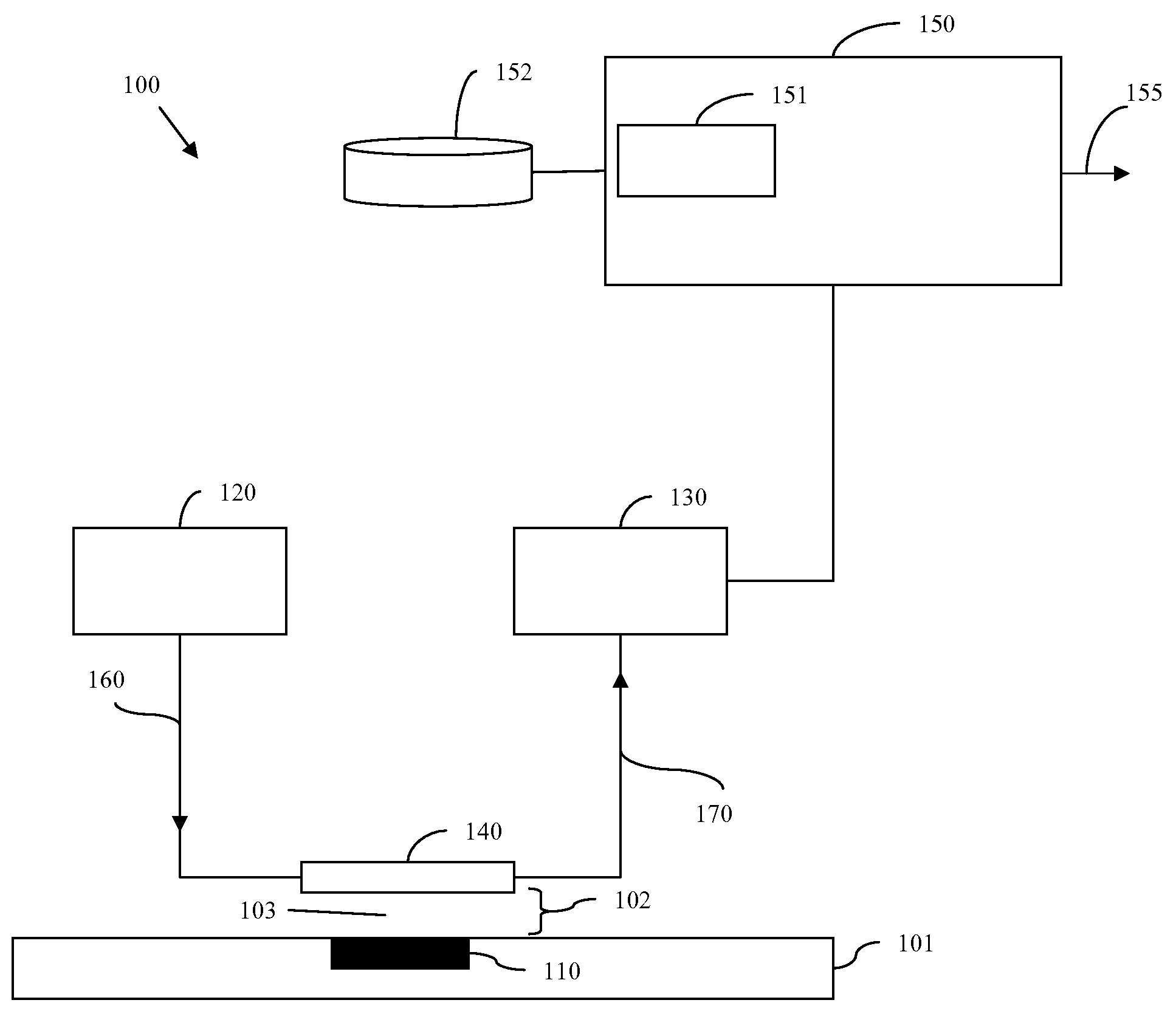

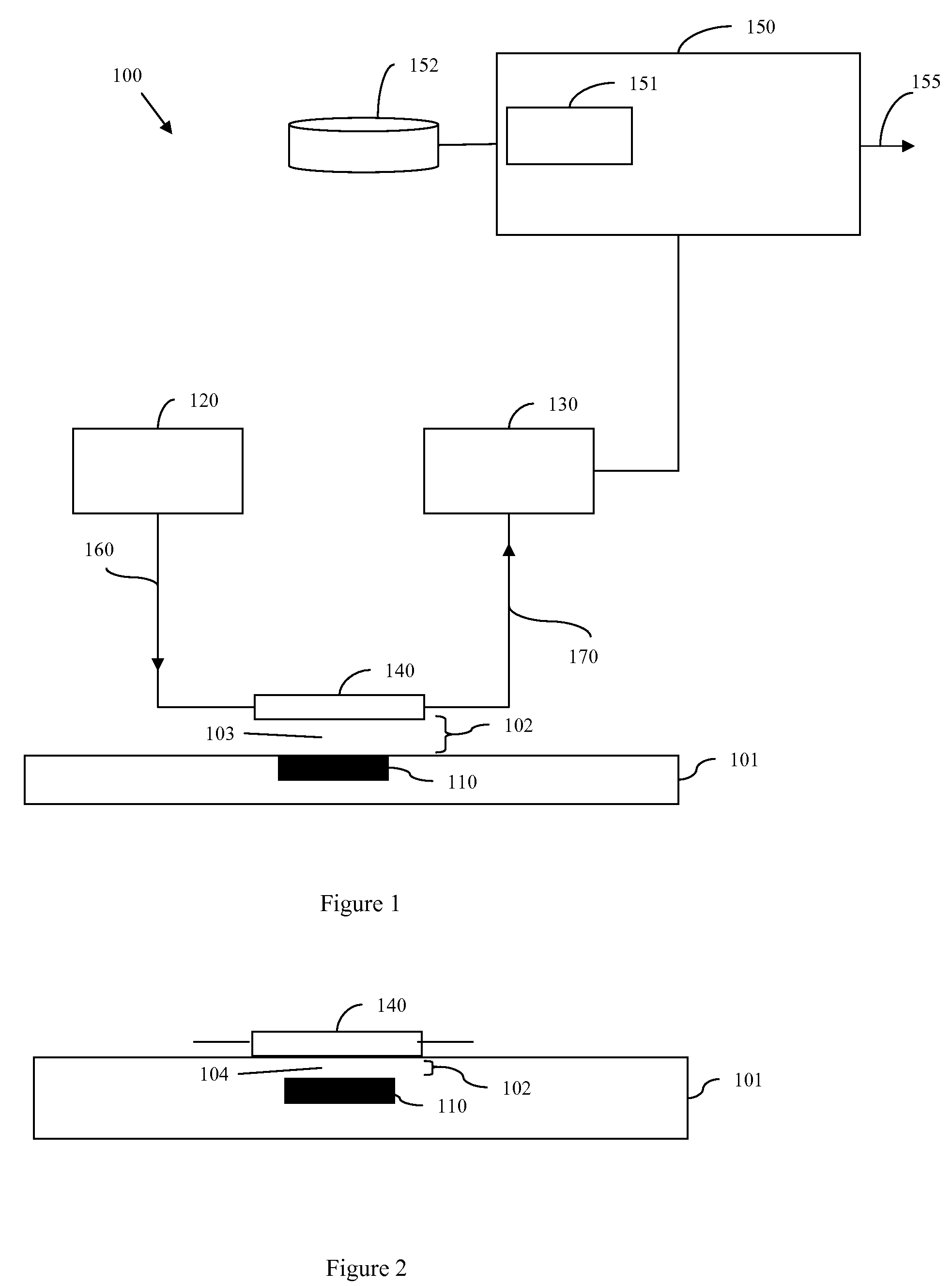

Method and apparatus for lane and front-end planning and design analysis

ActiveUS7146304B1Easy to useReduce riskHardware monitoringMultiprogramming arrangementsApplication softwareComputer science

The Lane and Front-end Effectiveness Model (LFEM) is a self-contained PC desktop application that allows an analyst to quantitatively predict the impact of changes to their checkout operations. This application, according to the present invention, includes four simulation models representing the complex interactions between customers, staff, and checkstand resources. Three of these models are detailed lane models and the fourth is a store front-end checkout model. An analyst can use the LFEM to evaluate, in detail, different checkstand configurations and transaction processes and the effect these changes have on overall front-end performance. The purpose of this application is to provide retailers with timely information to reduce the risk and uncertainties of investing in new technologies or design changes by predicting their impact and return before committing resources to their acquisition or implementation.

Owner:NCR CORP

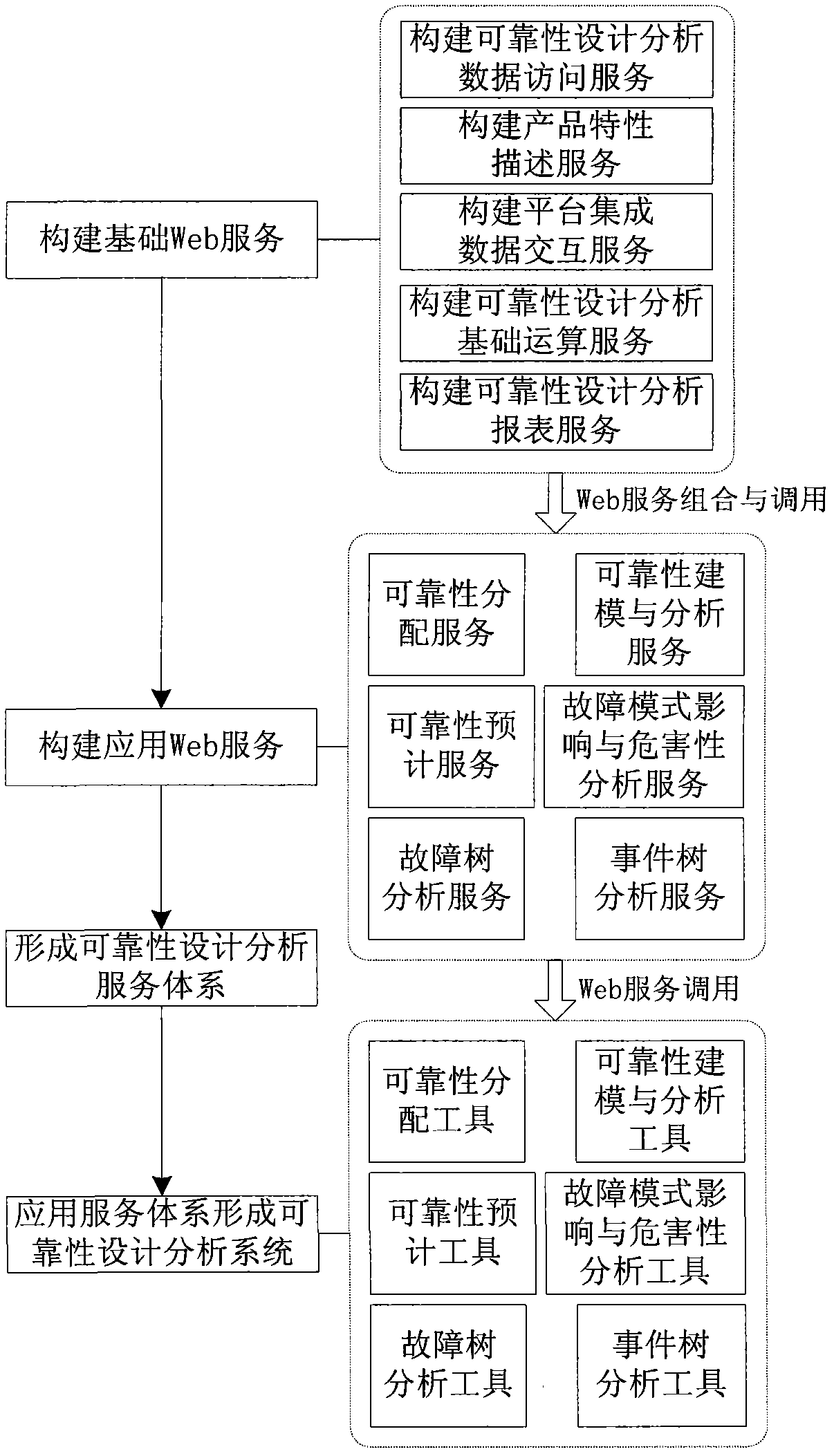

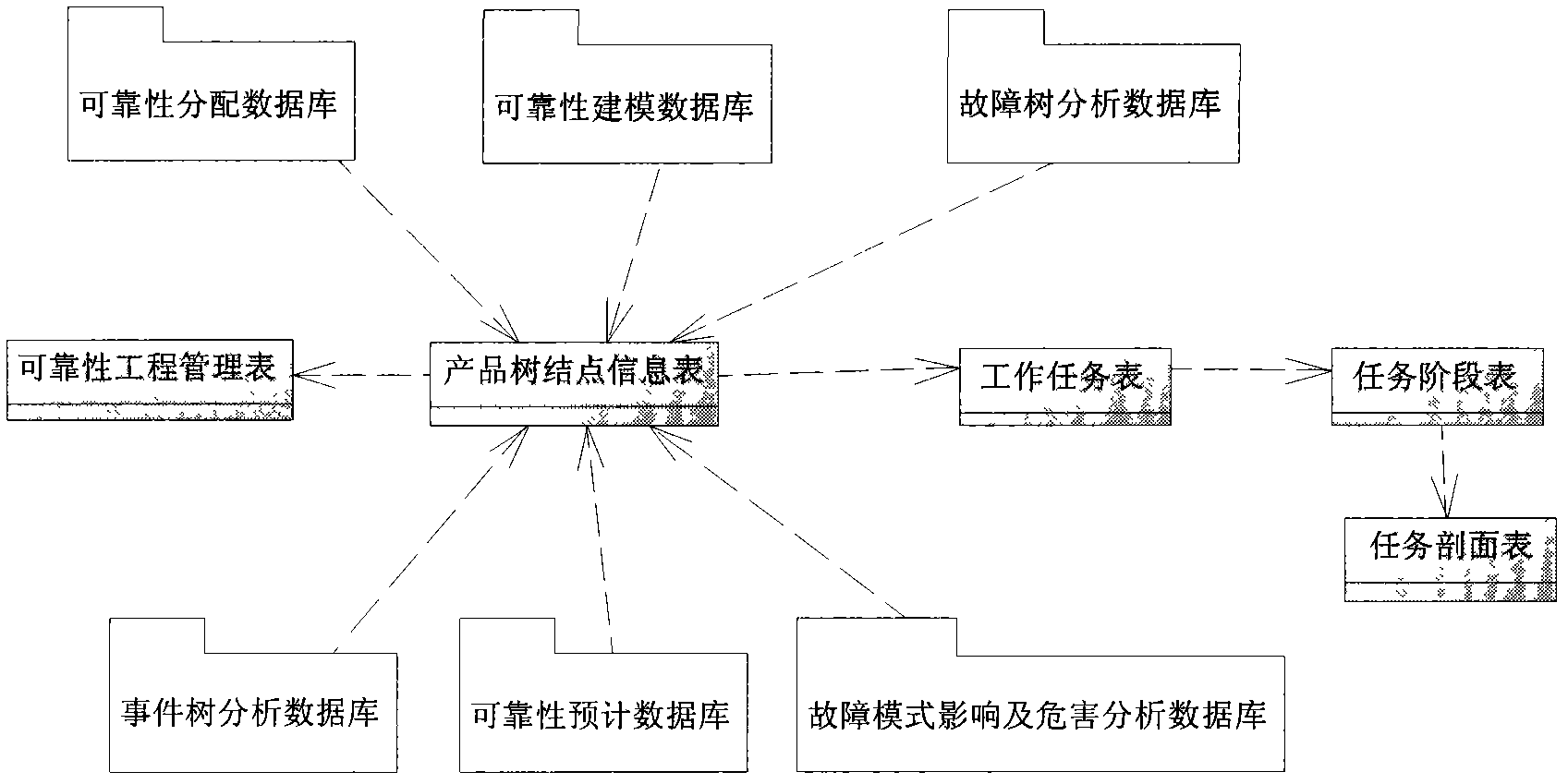

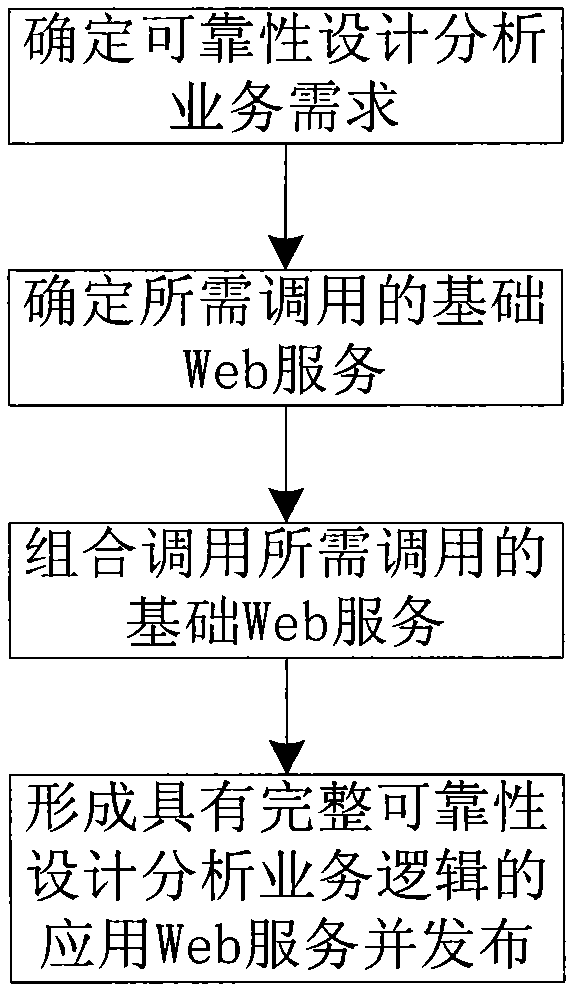

Constructing method of reliability design analysis service system of service oriented architecture

ActiveCN102024204AImprove efficiencyGood effectData processing applicationsSpecial data processing applicationsData accessComputer access

The invention relates to a constructing method of a reliability design analysis service system of a service oriented architecture, which comprises the following steps: 1) constructing basic Web services comprising basic business logic services of product characteristic description, data access, basic algorithm, report generation and platform integrated data interaction; 2) constructing an application Web service which is formed by combining the basic Web services and has complete reliability design analysis business logic; and 3) forming a reliability design analysis service system, and realizing a complete reliability design analysis software tool by combining a client showing technology. The Web services provided by the invention can be developed by any program language supporting Web service development. The Web services can be deployed on any server in an enterprise wide area network and can be accessed by any computer in the network, so as to realize cross-regional synergistic reliability design analysis, wherein the algorithm service having higher requirements for operation can be deployed on an operation server, so as to realize distributed computation; and the Web services can be integrated with other design platforms by the platform integrated data interaction service, thus realizing integration of performance and reliability design.

Owner:北京可维创业科技有限公司

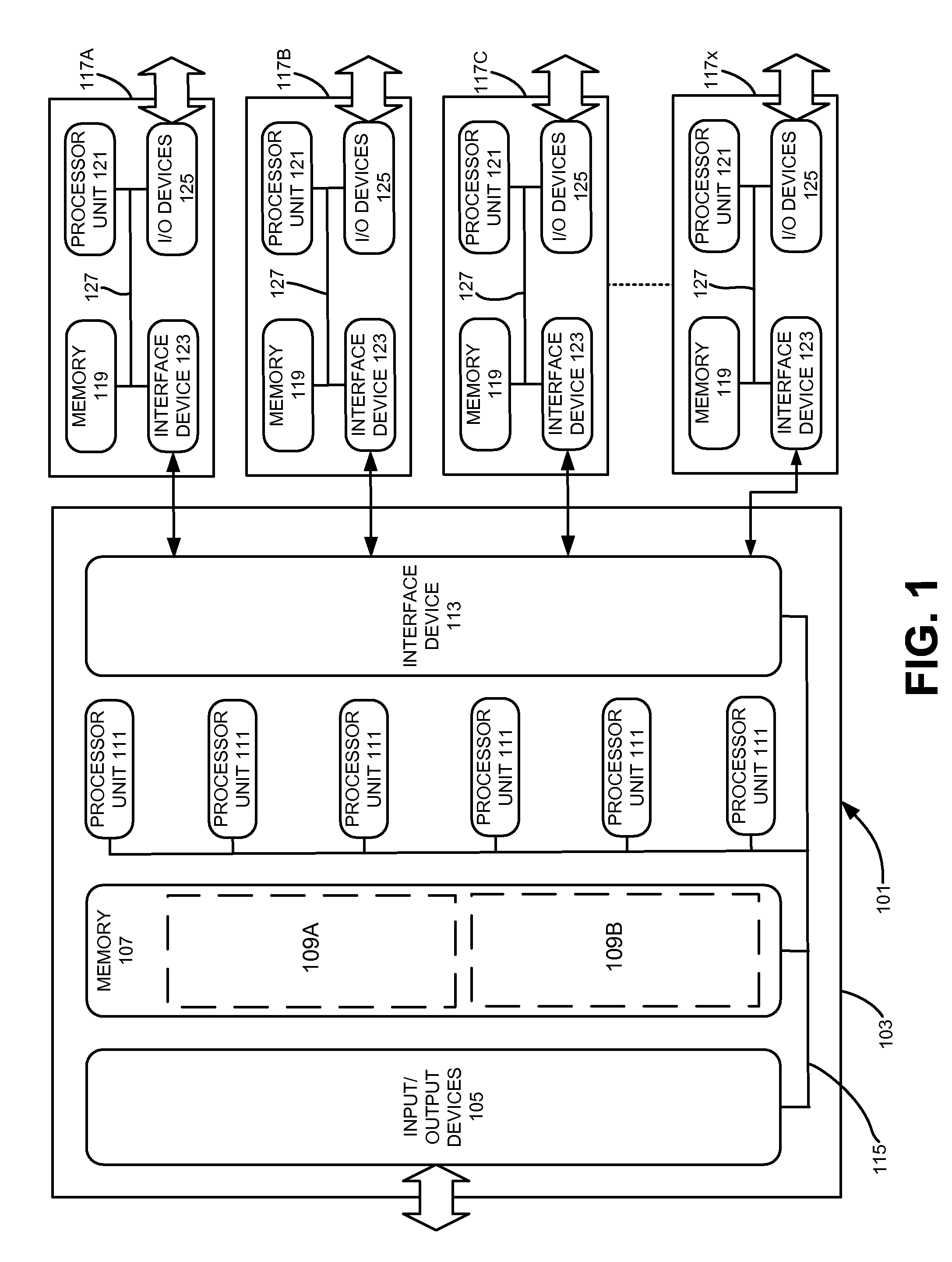

Integrated Circuit Chip Design Flow Methodology Including Insertion of On-Chip or Scribe Line Wireless Process Monitoring and Feedback Circuitry

ActiveUS20090239313A1Semiconductor/solid-state device testing/measurementDetecting faulty computer hardwareEngineeringFeedback circuits

Disclosed are embodiments of a design and manufacturing system and an associated method that allow for design analysis and for insertion, during wafer manufacture, of intra-process monitoring circuitry. These embodiments use a library of pre-qualified intra-process monitoring circuits and a cross-correlation table that links different monitoring circuits with different IC chip components. Specifically, these embodiments analyze integrated circuit chip design data to identify the components designed into the chip. Then, one or more intra-process monitoring circuits are selected from the library and the design data is modified to include the selected monitoring circuit(s).

Owner:MARVELL ASIA PTE LTD

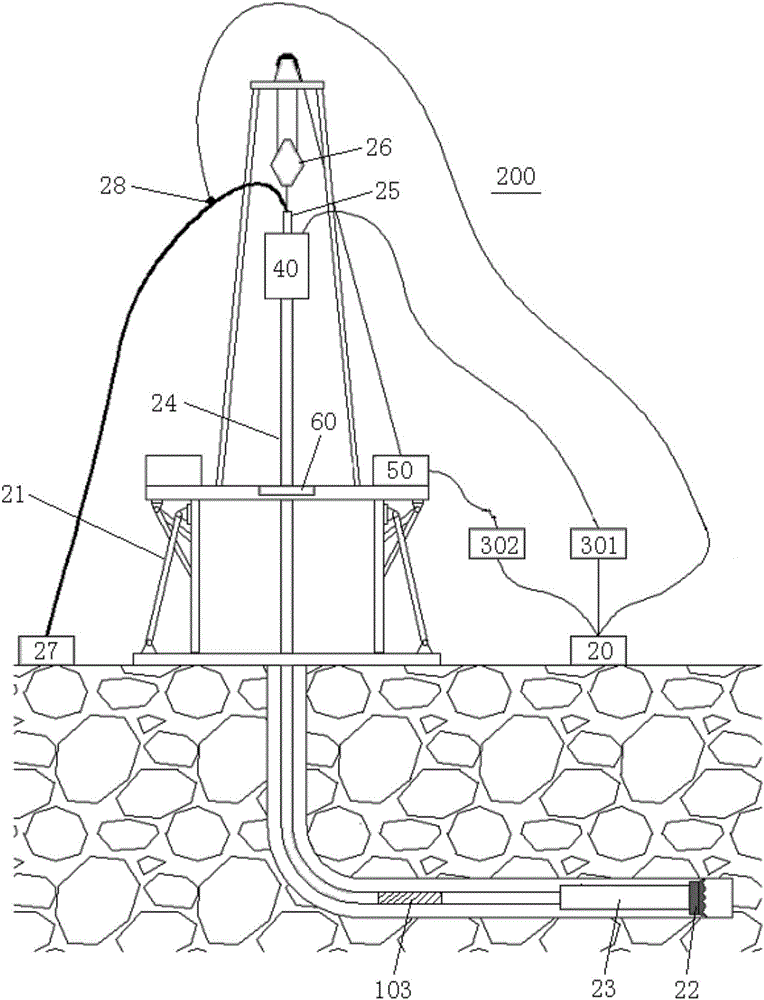

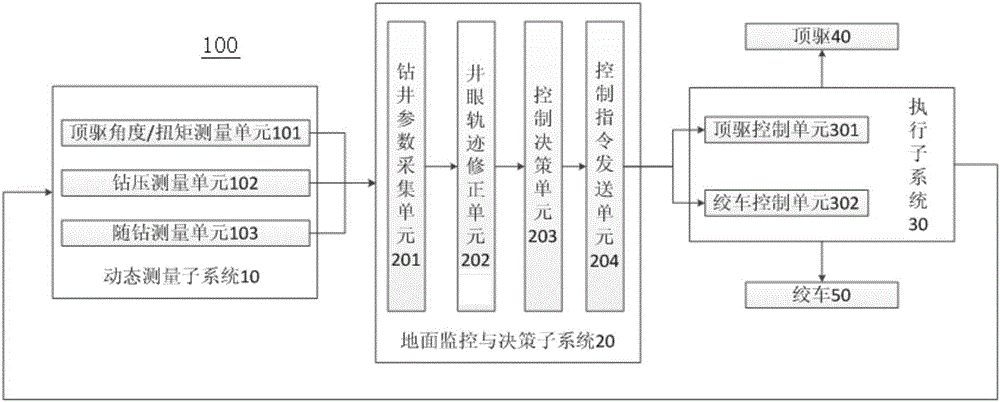

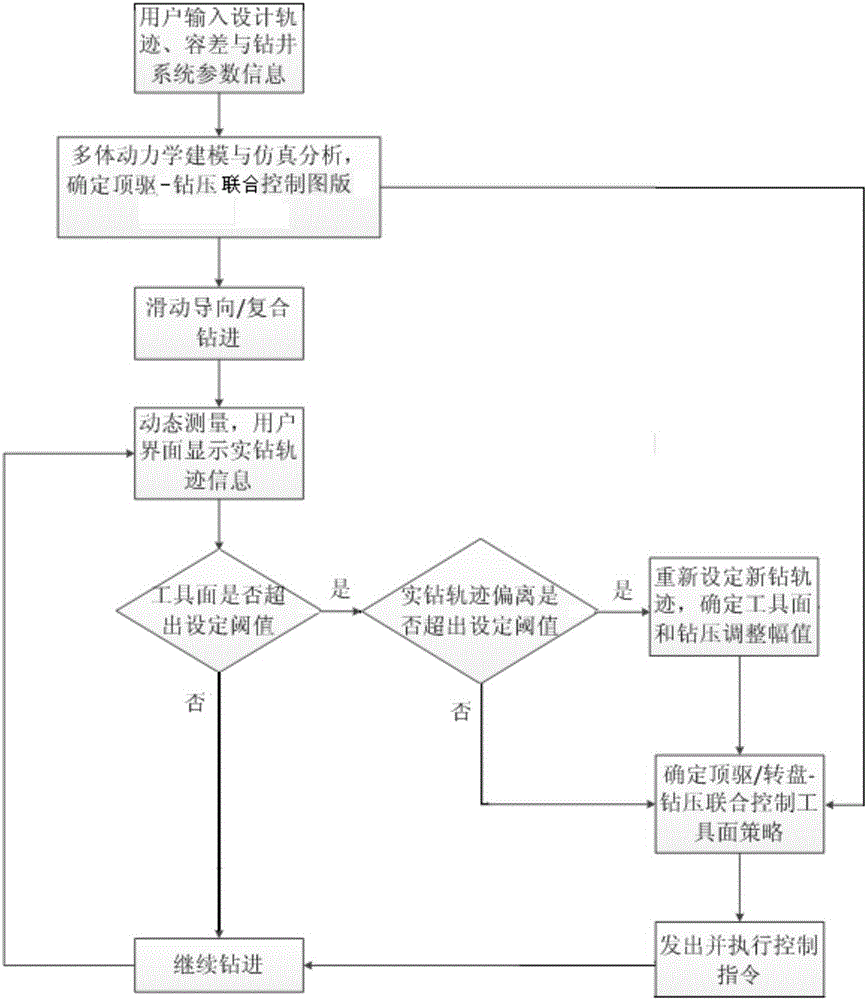

Drilling machine system based on sliding guide drilling closed loop control and drilling method

ActiveCN105041210AQuality improvementImprove work efficiencyDirectional drillingAutomatic control for drillingLoop controlAutomatic control

The invention relates to a drilling machine system based on sliding guide drilling closed loop control and a drilling method. The system comprises a dynamic measuring unit sub system, a ground monitoring sub system, an execution sub system and a guide drilling system, wherein the dynamic measuring unit sub system measures the parameters such as the well deviation, the orientation and the tool surface of an underground power drill tool in real time, and sends the parameters to the ground monitoring sub system; the ground monitoring sub system achieves the goal of re-determining the trace of a borehole to be drilled according to the designed borehole track and the target point when the condition that the borehole track deviates the designed borehole track is found through comparison; the ground monitoring sub system determines the top drive / turntable rotating angle and the drilling pressure regulation strategy through being combined with a top drive / turntable-drilling pressure combined control chart obtained according to the many-body dynamics simulation design analysis, and then dynamically regulates the drilling pressure and the drift of the tool surface of the underground power drilling tool through regulating the rotating angle of a top drive / turntable and the speed of a traveling block by the execution sub system, so that the stability of the underground tool surface and the drilling pressure is maintained; the closed loop automatic control of the sliding guide drilling borehole track is realized; the operation efficiency and the control precision of the directional well borehole track are effectively improved; and the borehole quality is improved.

Owner:CHINA NAT OFFSHORE OIL CORP +1

Design analysis workstation for analyzing integrated circuits

A design analysis workstation for performing design analysis of integrated circuits provides facilities for extracting design and layout information from digital image-mosaics captured during deconstruction of an integrated circuit. The design analysis workstation enables propagation of signal information from an annotation object having a signal property to at least one connected annotation object in order to point to errors in the design analysis.

Owner:TECHINSIGHTS

Properties In Electronic Design Automation

InactiveUS20080141193A1Easily calculateComputer aided designTotal factory controlComputer architectureLogic circuit design

One or more properties can be associated with a design object in a microdevice design. The design object may be an object in a physical layout design for a microdevice, such as a geometric element in a layout design. The design object also may be a collection of geometric elements in a layout design, such as a net, a cell in a hierarchical design, or even a collection of all of the geometric elements in a layer of a design. Still further, the design object may even be an item in a logical circuit design, such as a net in a logical circuit design for an integrated circuit. The values of one or more properties may be statically assigned for or dynamically generated during a design process performed by an electronic design automation tool. A property may be assigned a constant value or a value defined by an equation or other type of script that includes one or more variables. A property may be simple, where the definition of the property's value is not dependent upon the value of any other properties. Alternately, a property may be a compound property, where the definition of the property's value incorporates another, previously-determined property value. Still further, a property may be an alternative property, where the property is assigned one value definition under a first set of conditions and assigned another value definition under a second set of conditions. A first electronic design automation process may generate one or more property values. The generated property values then can be passed to another electronic design automation process in the design analysis flow for its use.

Owner:MENTOR GRAPHICS CORP

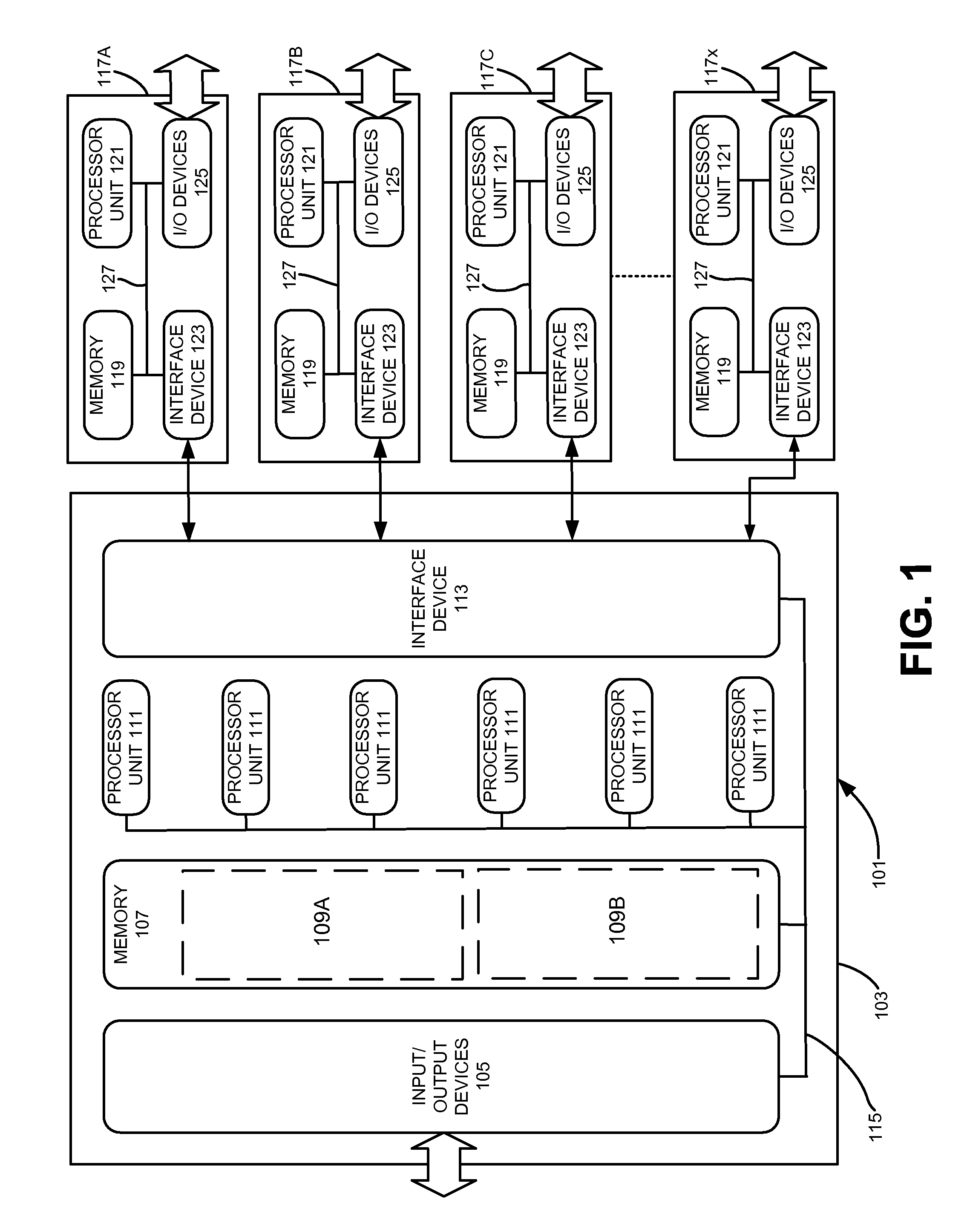

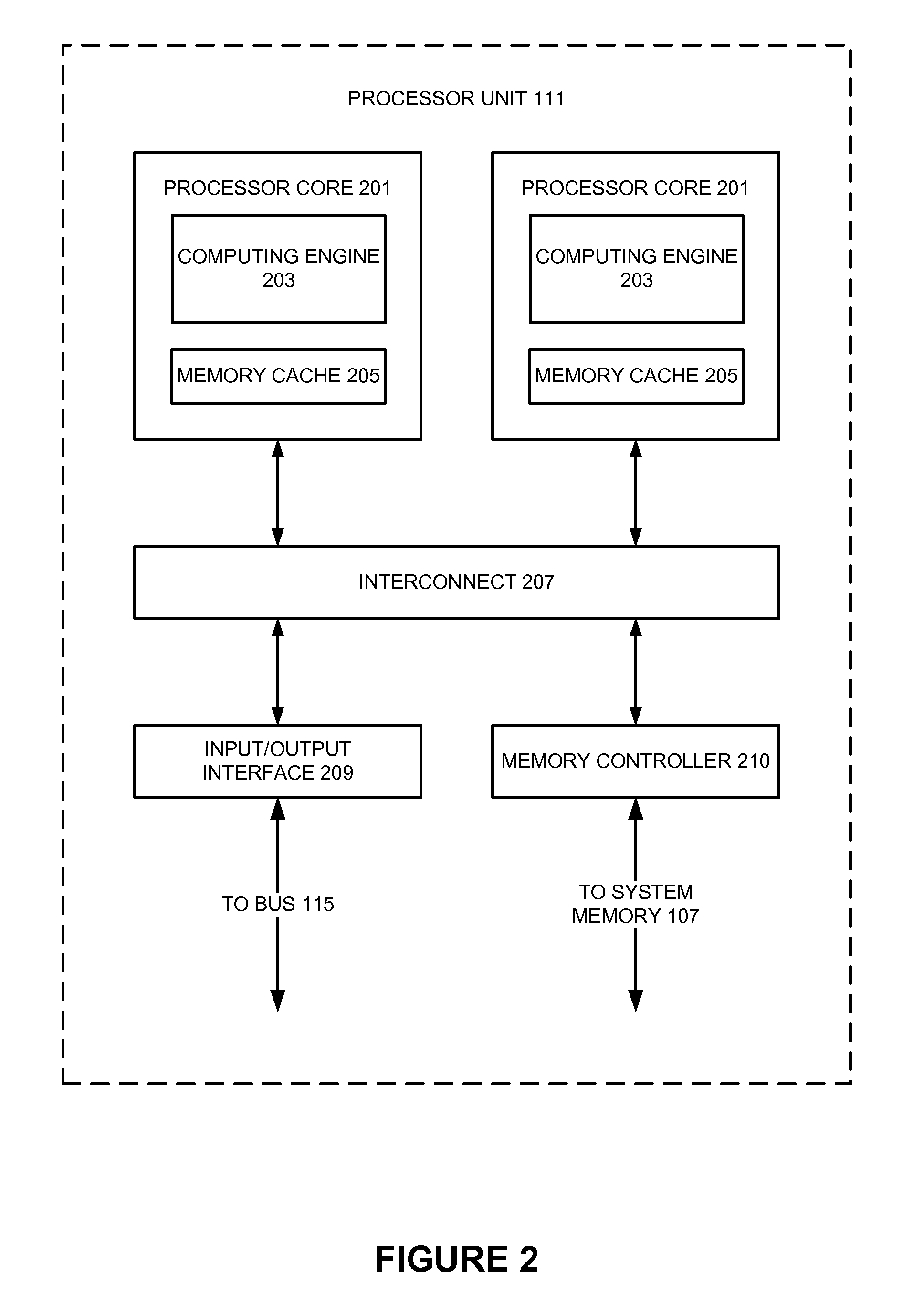

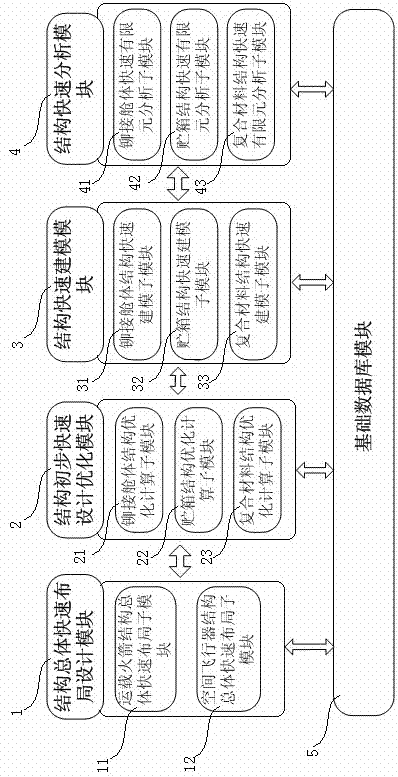

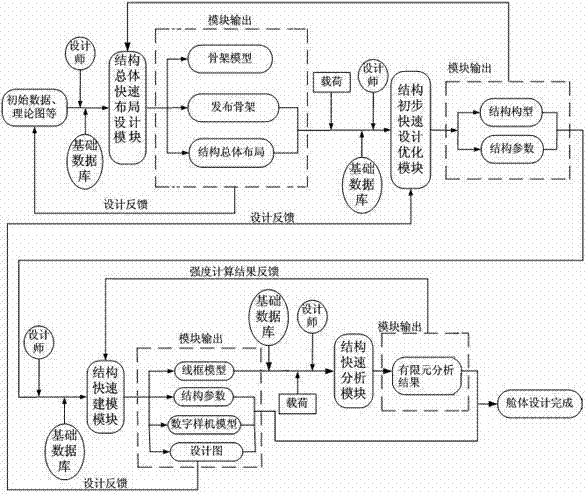

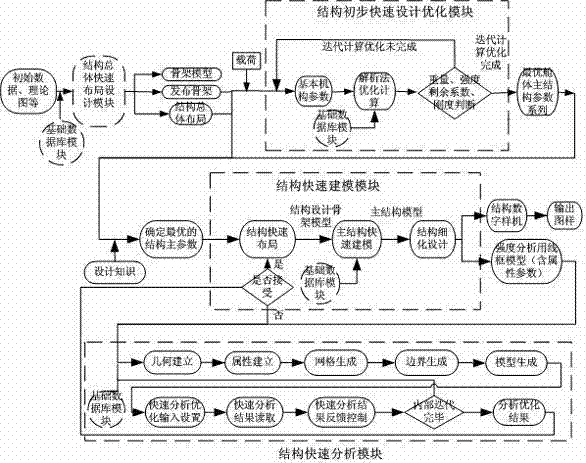

Rapid design, analysis and optimization system of large-scale structure based on modularization

InactiveCN103870635AAuto-optimize fastDesign speedSpecial data processing applicationsElement modelElement analysis

The invention discloses a rapid design, analysis and optimization system of a large-scale structure based on modularization. The rapid designing, analyzing and optimizing system comprises a structural overall rapid layout design module, a structural preliminary rapid design and optimization module, a structural rapid modeling module, a structural rapid analysis module and a base database module. According to the whole design process of demand parameter input, structural design and strength analysis of products, rapid automatic optimization, rapid automatic modeling, automatic finite element model establishment, an automatic rapid finite element solution, automatic drawing of typical parts and process data management of the design process are realized by using a parameterized design idea, a modular system constructing technology, a database technology, a digitalized modeling technology, a finite element analysis technology, full-digitalization design and an analysis module customizing technology and fusing an automatic optimizing design method, a knowledge-driven design method and a top-down design method; the whole-process design acceleration is realized, the design efficiency is increased and the development cycle of products is shortened.

Owner:SHANGHAI AEROSPACE SYST ENG INST

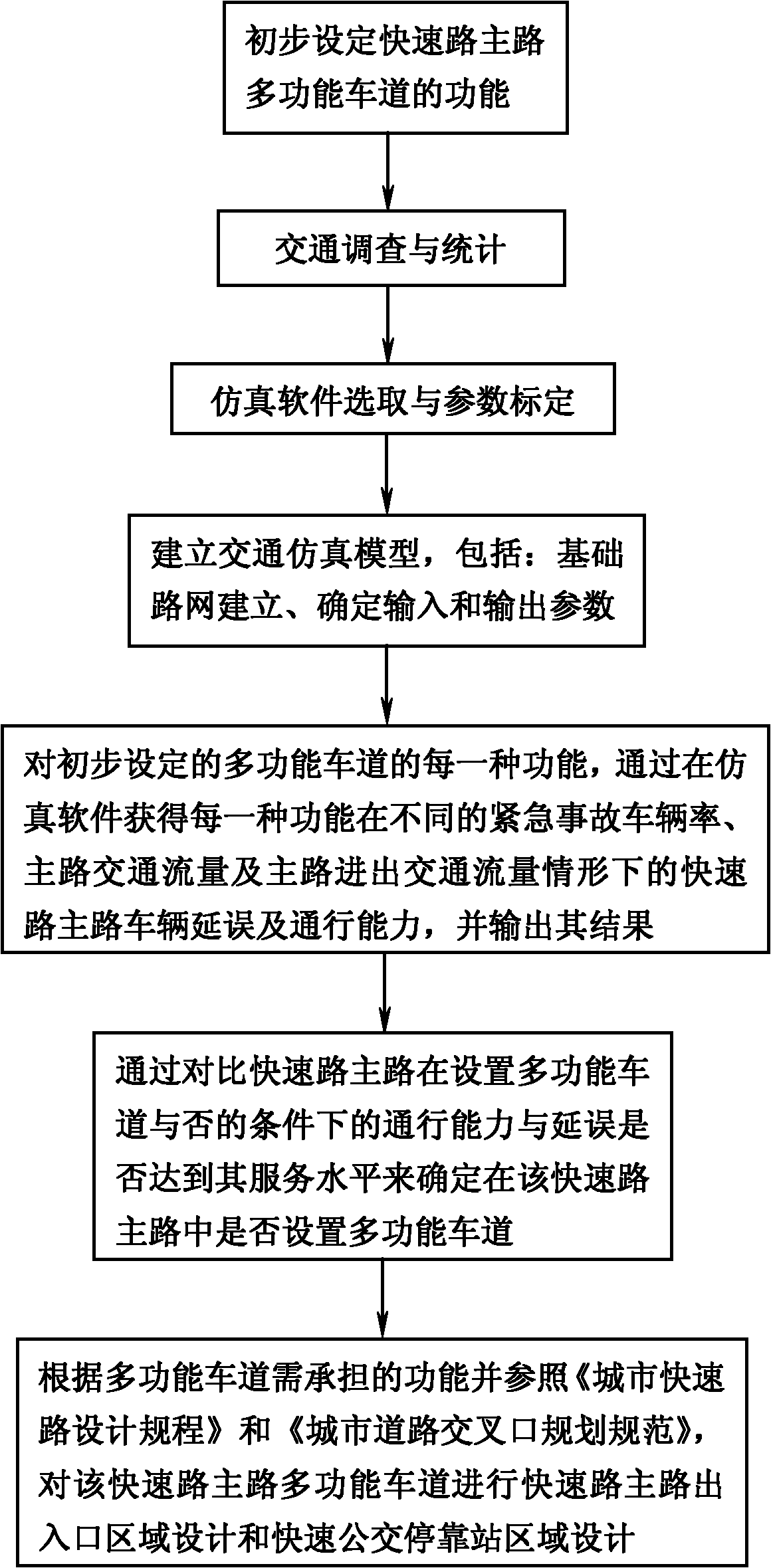

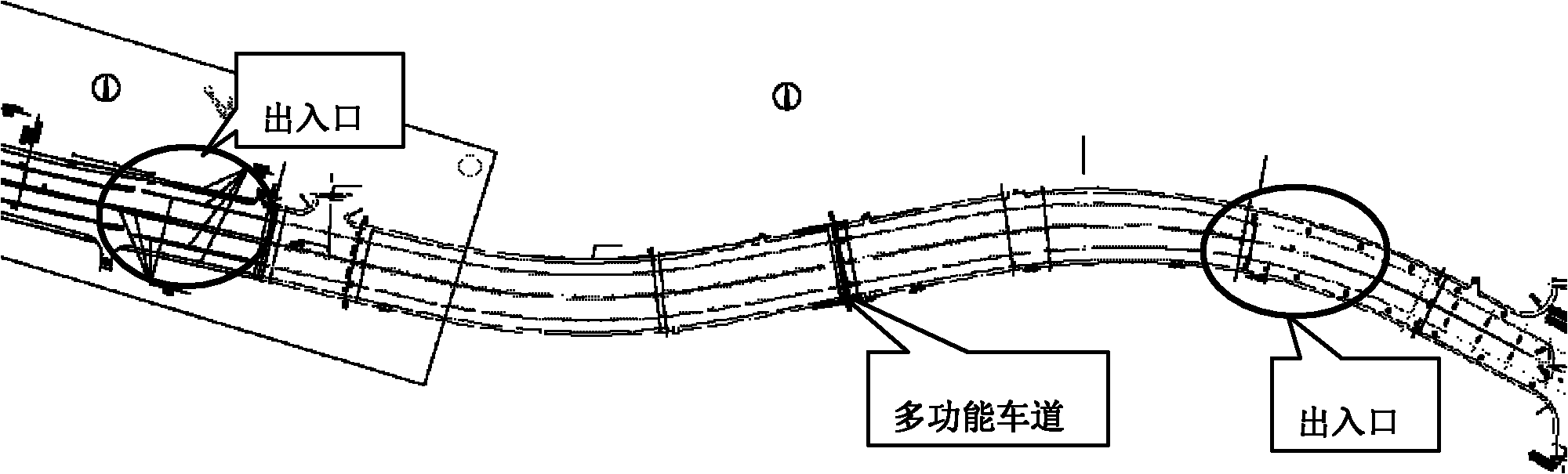

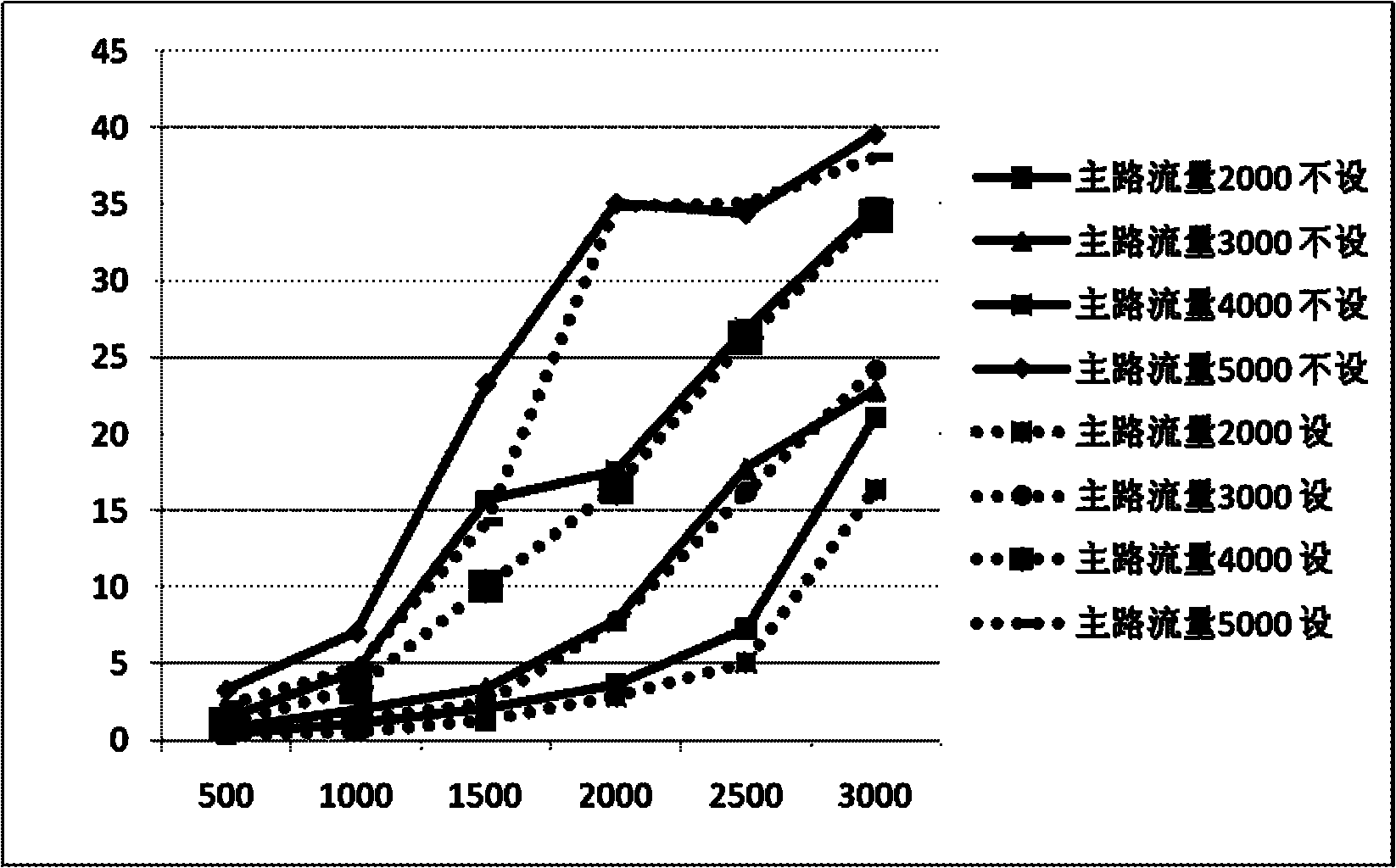

Method for designing main road multifunctional lane of express way based on delay and traffic capacity

ActiveCN102156790AQuality improvementImprove efficiencyRoad vehicles traffic controlSpecial data processing applicationsTraffic capacityDriver/operator

The invention discloses a method for designing a main road multifunctional lane of an express way based on delay and traffic capacity, comprising the following steps of: determining functions of the main road multifunctional lane of the express way; investigating and counting the traffic to obtain road traffic condition and driver behavior parameters of the express way; selecting a simulation software and calibrating a model; creating a traffic simulation model; for each function of the multifunctional lane, adjusting conditions, such as main road traffic flow, composition and the like of theexpress way, obtaining main road vehicle delay and traffic capacity of the express way under different situations, and analyzing the obtained information to get the conclusion of setting analysis on the multifunctional lane based on different functions; synthesizing the conclusion of the setting analysis under each function to get the conclusion of design analysis on the multifunctional lane, andperforming traffic design of the multifunctional lane based on the final conclusion. The method provided by the invention fills a gap in design analysis and method of the multifunctional lane, and can provide basis for scientific and rational design of the main road multifunctional lane of the express way.

Owner:TIANJIN MUNICIPAL ENG DESIGN & RES INST

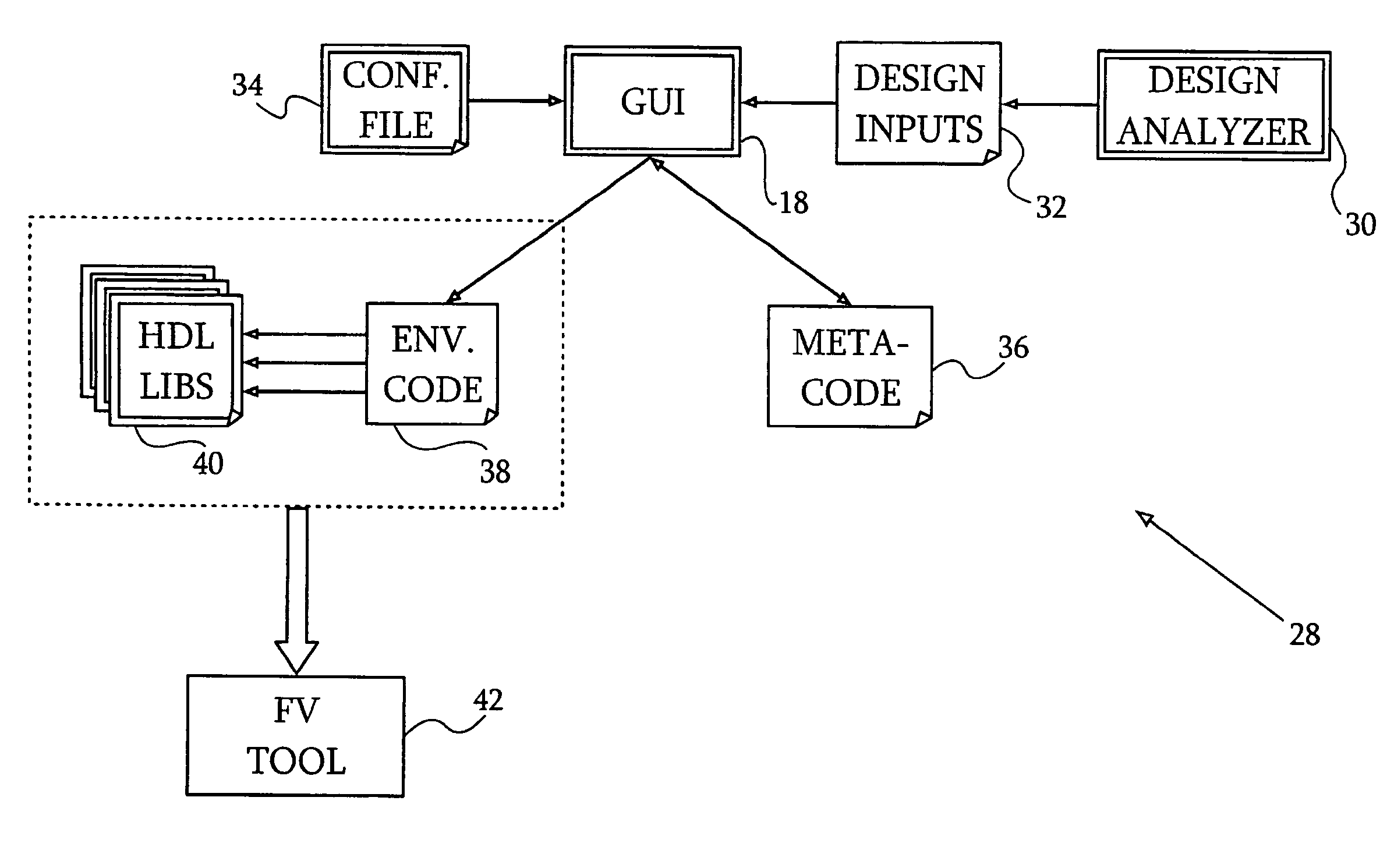

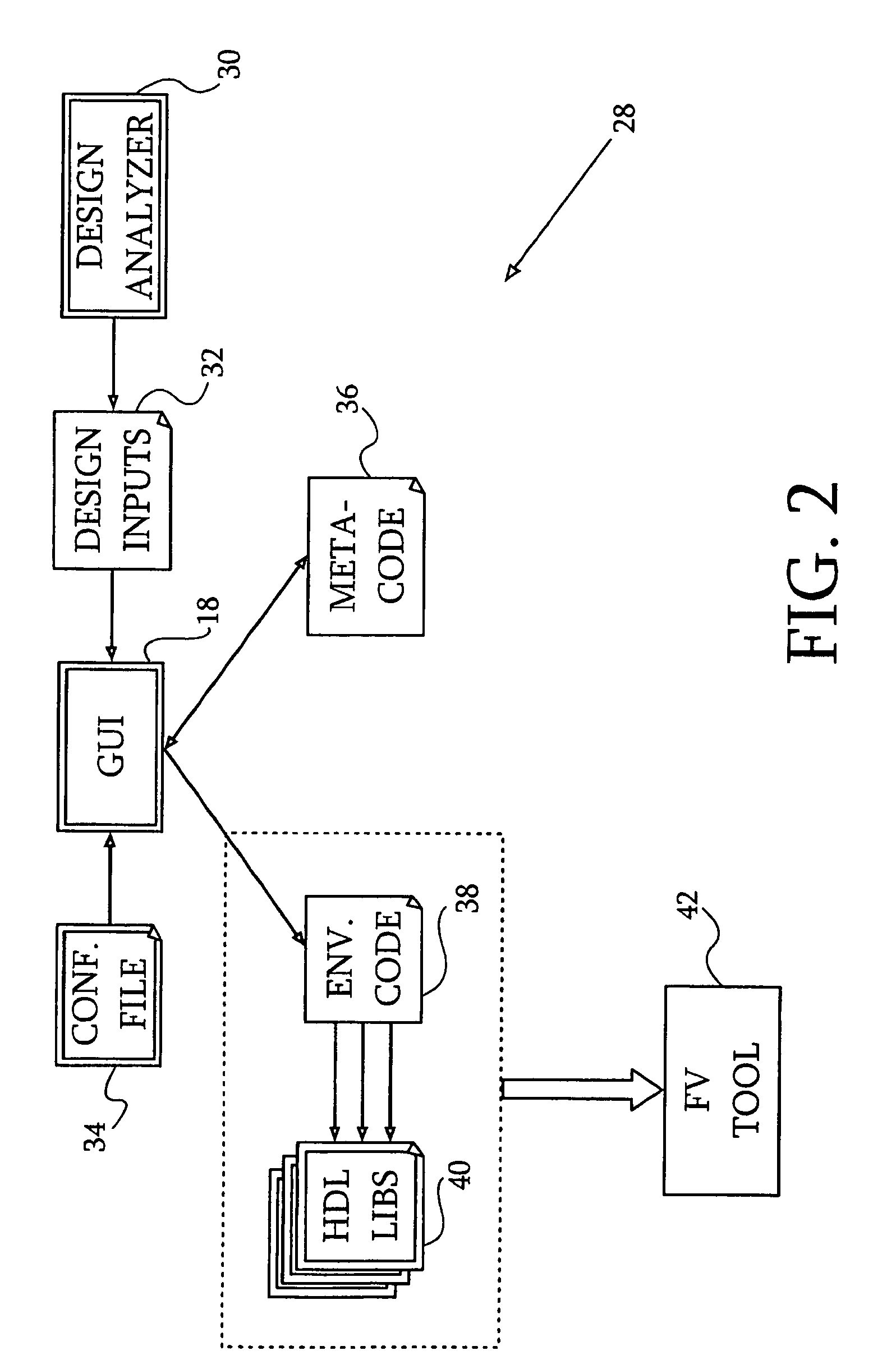

System for quickly specifying formal verification environments

ActiveUS8127261B2Detecting faulty computer hardwareComputer programmed simultaneously with data introductionGraphicsGraphical user interface

Computer-implemented techniques are disclosed for defining an environment for formal verification of a design-under-test. Initially there is extraction of design inputs by a design analysis module, and presentation of the inputs on a graphical user interface. Behavior options for the design inputs are offered on the graphical user interface for selection by an operator. Environment code that is descriptive of the design inputs and selected behavior options is emitted, typically in a hardware description language, for submission to a formal verification tool. A meta-code file containing the assigned behavior options is generated to aid subsequent sessions.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

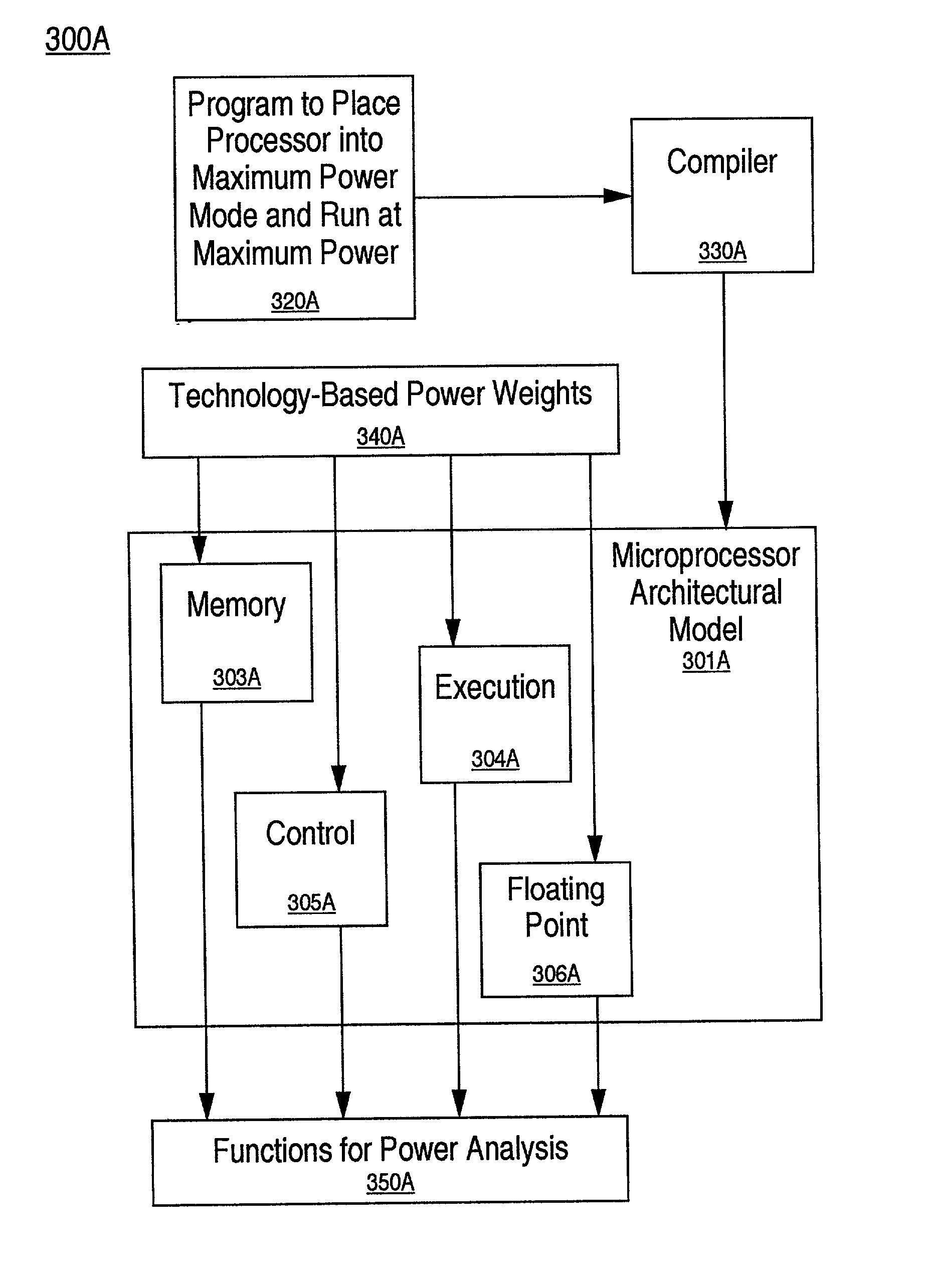

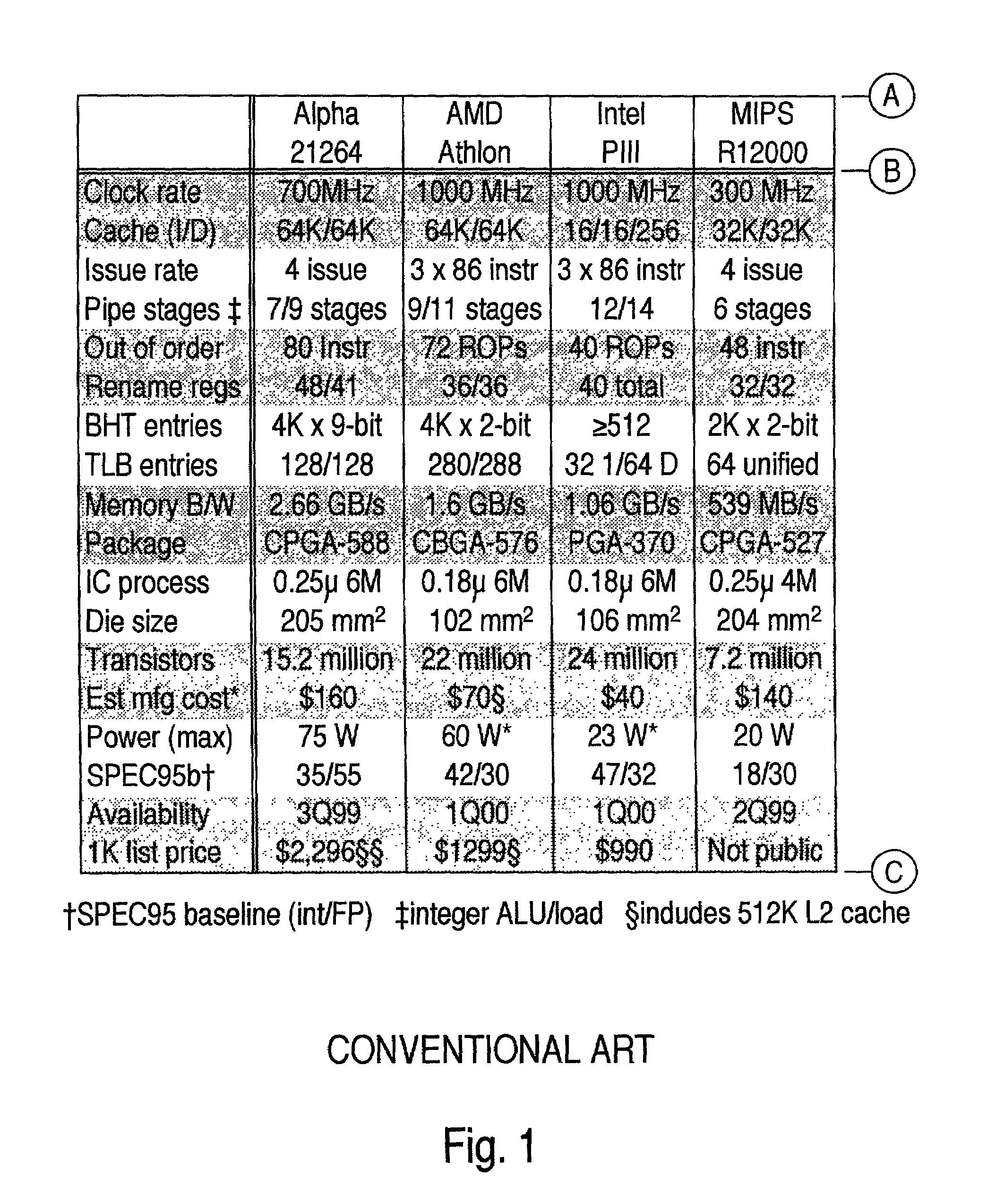

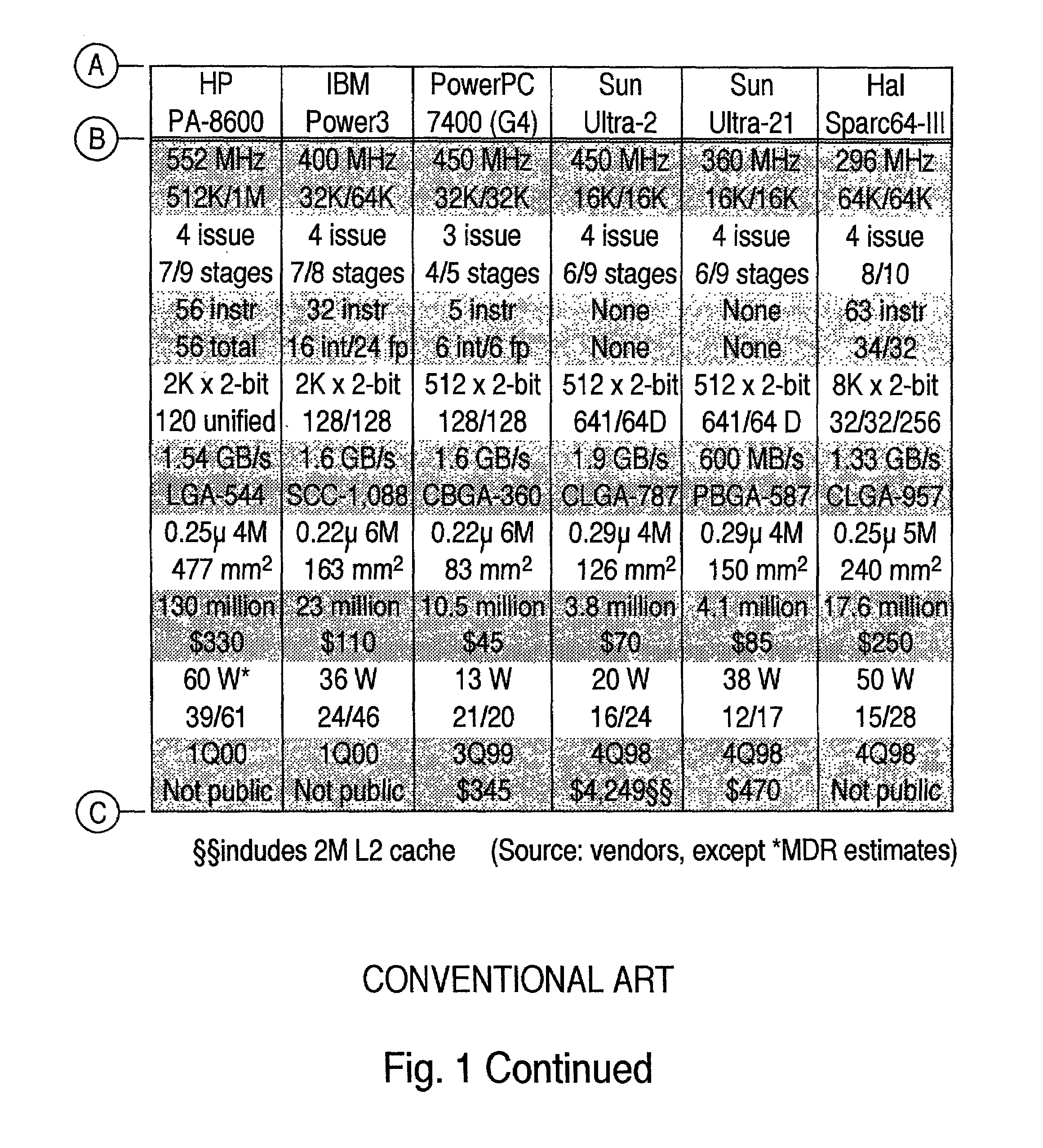

Method for deriving the benchmark program for estimating the maximum power consumed in a microprocessor

InactiveUS7003441B2Extensive analysisVolume/mass flow measurementAnalogue computers for electric apparatusSystemCInstruction stream

In one embodiment, for an electronic architecture with a functional constitution performing a number of functions characterized by separate stages performing subfunctions, a method of deriving a benchmark program for estimating the maximum power consumption by modeling a functional model of the architecture, compiling the benchmark program into a corresponding instruction stream, valuating power weights for each stage of each function of each constituent, inserting the power weights, running the model in a maximum power consumption mode, and summarizing power consumption. In one embodiment, the benchmark program is applied by specifying a design analysis to be performed, selecting a function, designating a stages performing that function, removing a set of instruction set architecture instructions corresponding the designated stage, emulating the constituent subfunction corresponding to the stages designated stage, and summarizing. In one embodiment, the model is written in SystemC. In one embodiment, a compiler used is a PERL script.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

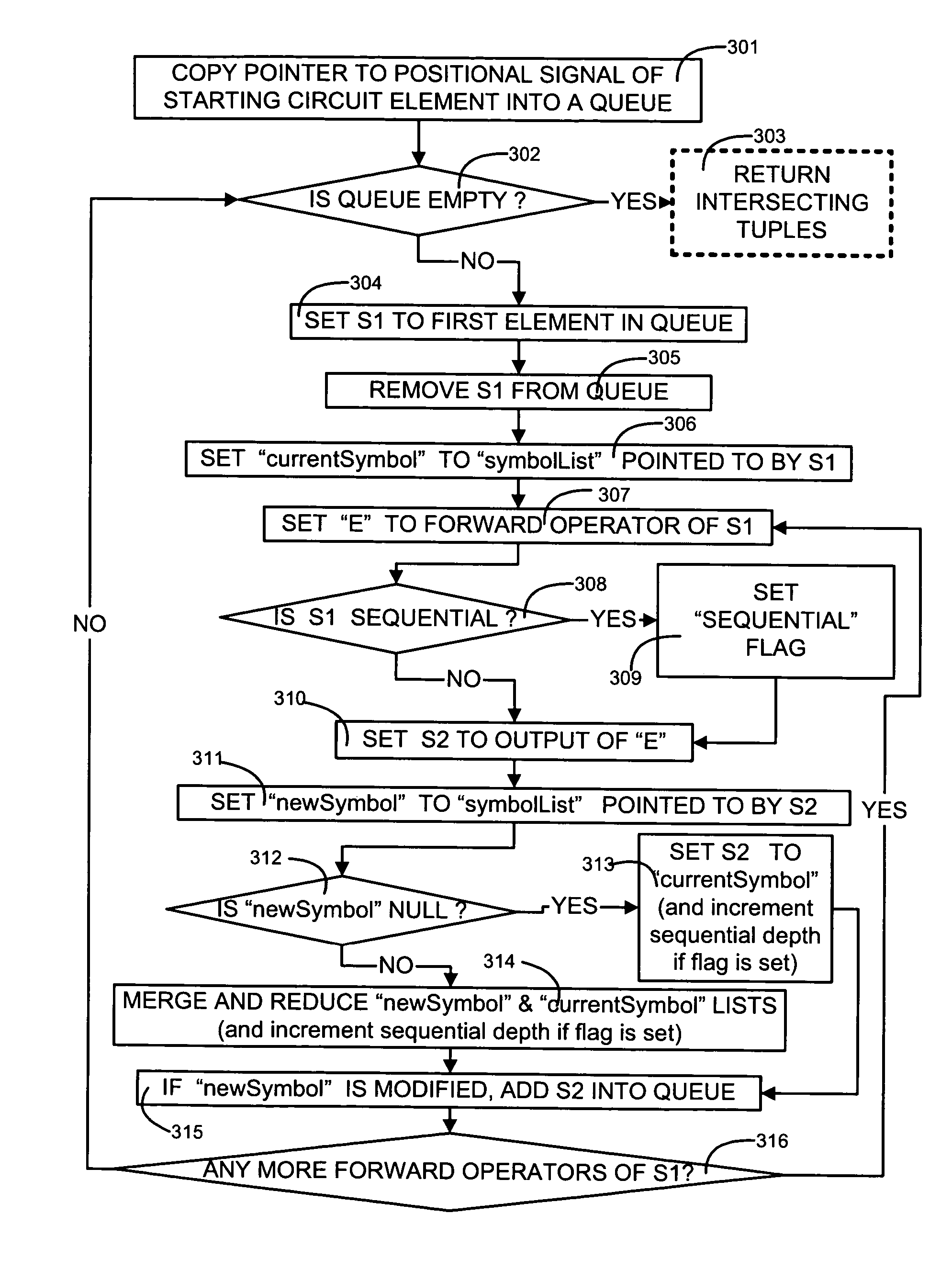

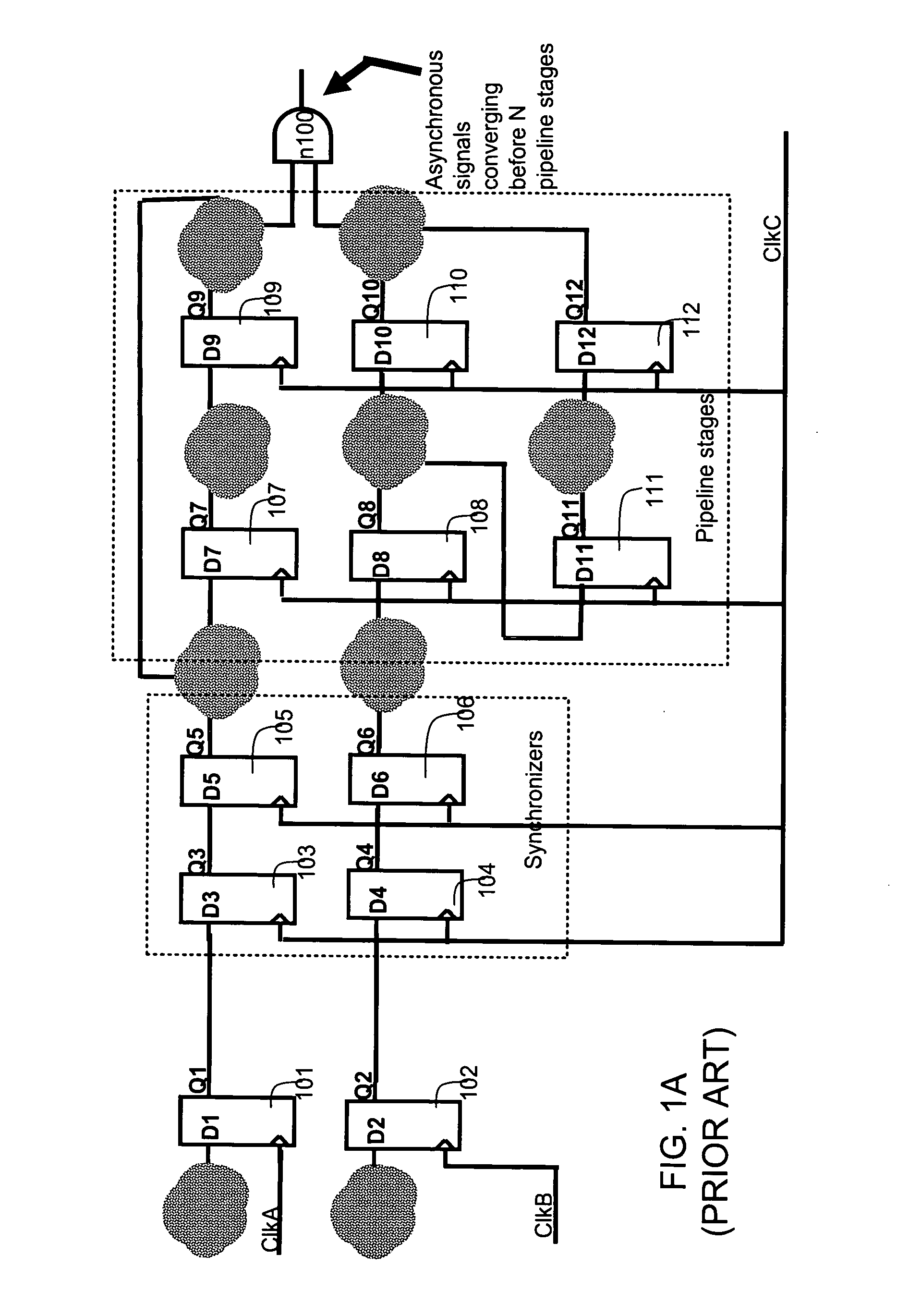

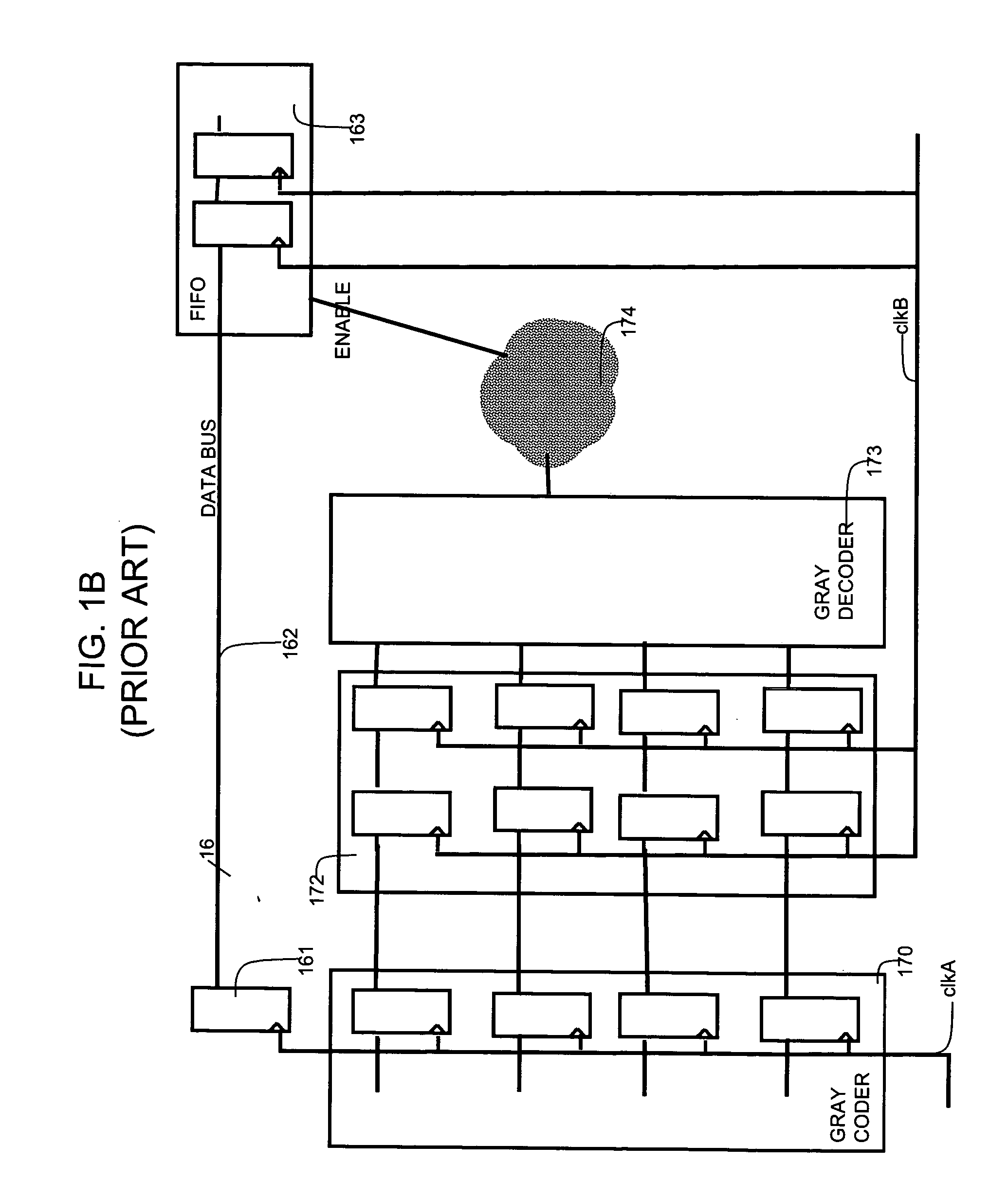

Tuple propagator and its use in analysis of mixed clock domain designs

ActiveUS20050273735A1Electronic circuit testingDetecting faulty computer hardwareAlgorithmPropagator

Names of signals are propagated through a circuit design inside tuples, with each tuple including at least a signal name and a sequential depth. A tuple being propagated is added to a list of zero or more tuples currently identified with a circuit element, unless a tuple of the same signal name is already present in the list. If already present in the list, then propagation of that tuple is stopped. Propagation of tuples may also be stopped depending on user-defined limits, e.g. on sequential depth. Tuple propagation may be used, depending on the embodiment, to identify features of interest in the circuit design, e.g. (a) a point of convergence of differently clocked signals, (b) location of gray coders, and (c) location of synchronizers, by appropriate identification of circuit elements from which tuple propagation is to start, and by appropriate checks on lists of tuples that result from tuple propagation.

Owner:SYNOPSYS INC