Continuously Referencing Signals over Multiple Layers in Laminate Packages

a signal and laminate technology, applied in the direction of high frequency circuit adaptation, sustainable manufacturing/processing, final product manufacturing, etc., can solve the problems of degrading the signal being transmitted, unable to provide more and more input/output (i/o) interconnections to chips that are shrinking in size and growing in complexity, and unable to meet the needs of increasing the number of chips, so as to avoid discontinuities in voltage reference.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

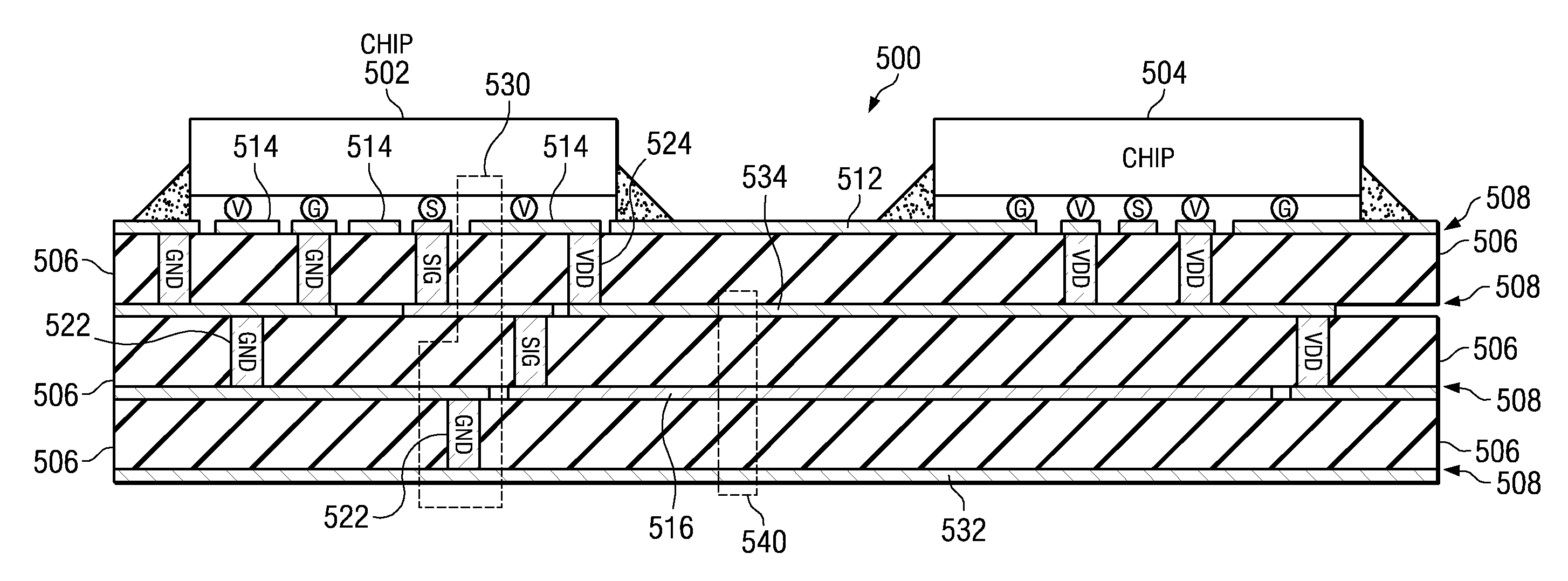

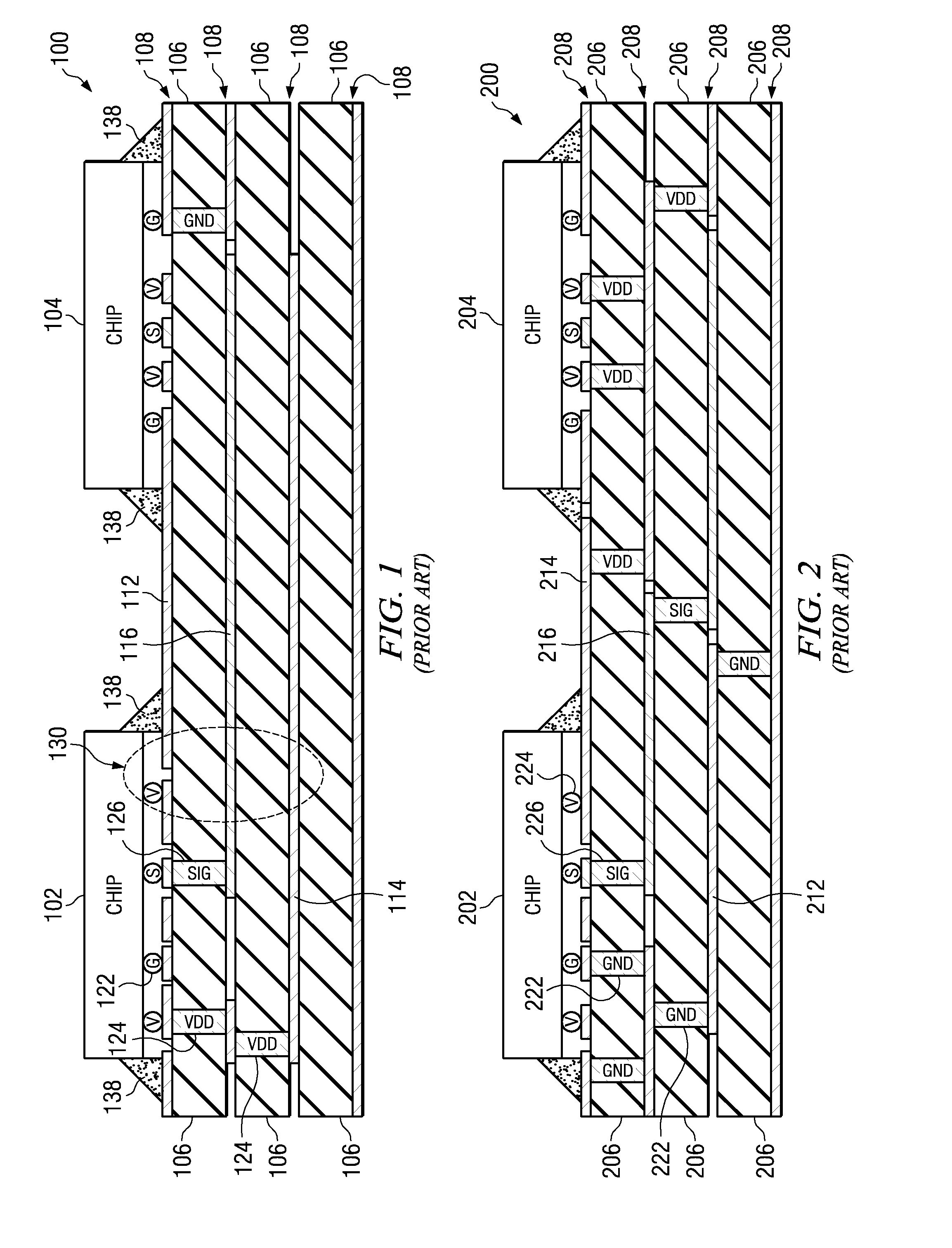

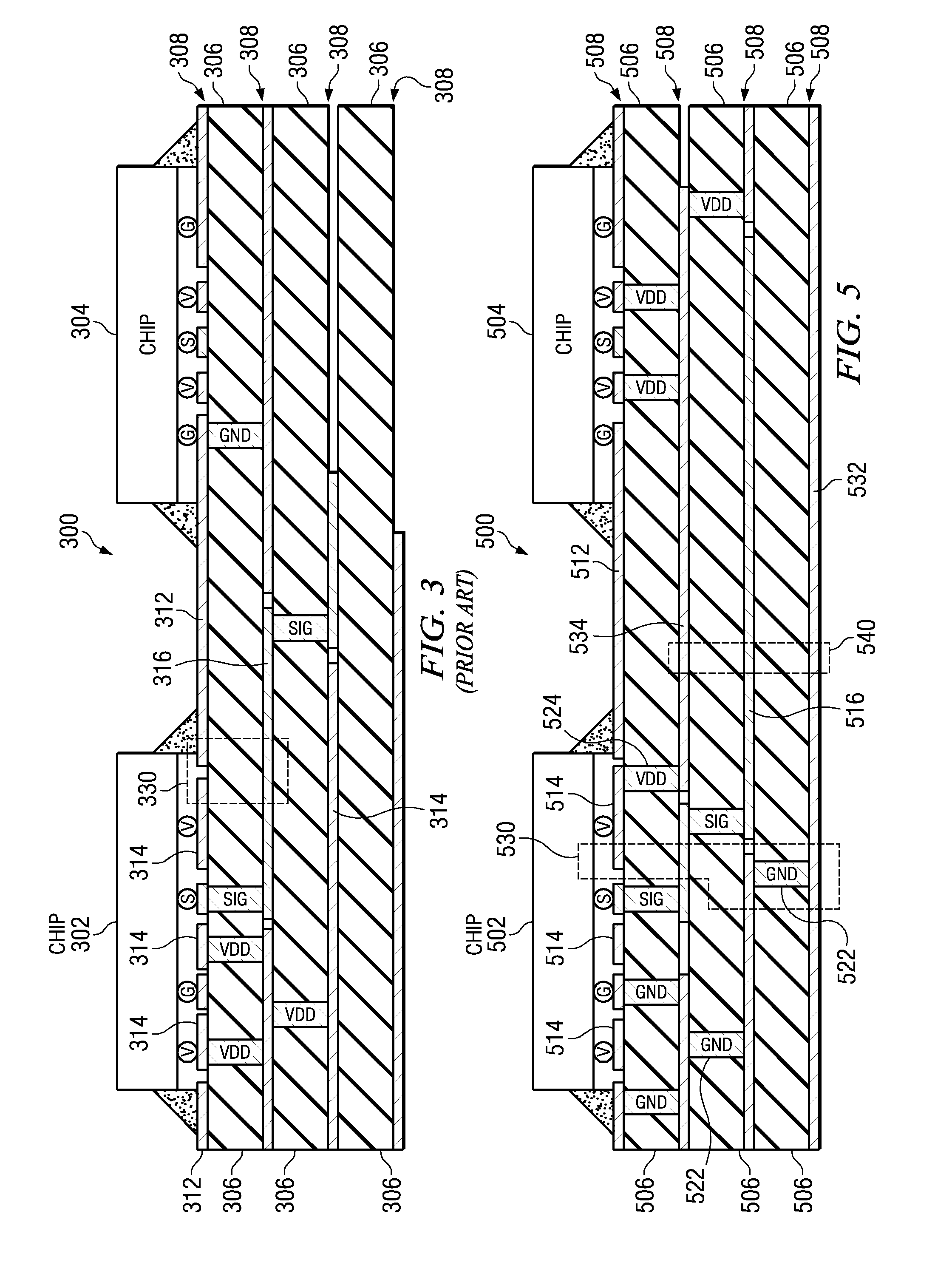

[0040]The illustrative embodiments provide an improved mechanism for continuously referencing signals over multiple layers in laminate packages. In order to illustrate the primary configuration differences between the improved package design configuration and known laminate packages, reference will first be made to FIGS. 1-4, which illustrate various views of known package designs.

[0041]FIG. 1 illustrates an example cross-section of a chip package with a ground voltage, or potential, plane on top. The package includes chip 102 and chip 104, which are placed on package 100. Package 100 comprises a plurality of insulator layers 106 and a plurality of patterned conductor layers 108. Package 100 may also be referred to as a “chip carrier” or “substrate.” Chips 102, 104 may be sealed to the package substrate using hermetic seal 138, for example.

[0042]In the example depicted in FIG. 1, ground voltage plane 112 is the top voltage plane. Chip 102 may be connected to ground (GND) plane 112 u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More