Patents

Literature

429 results about "Package design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Simply defined, package design is the discipline of creating the container, graphics and visible outer presence of a product a consumer buys at retail or might receive in the mail. This container may range from a simple bottle and label to an elaborate box or system of boxes and inner packaging.

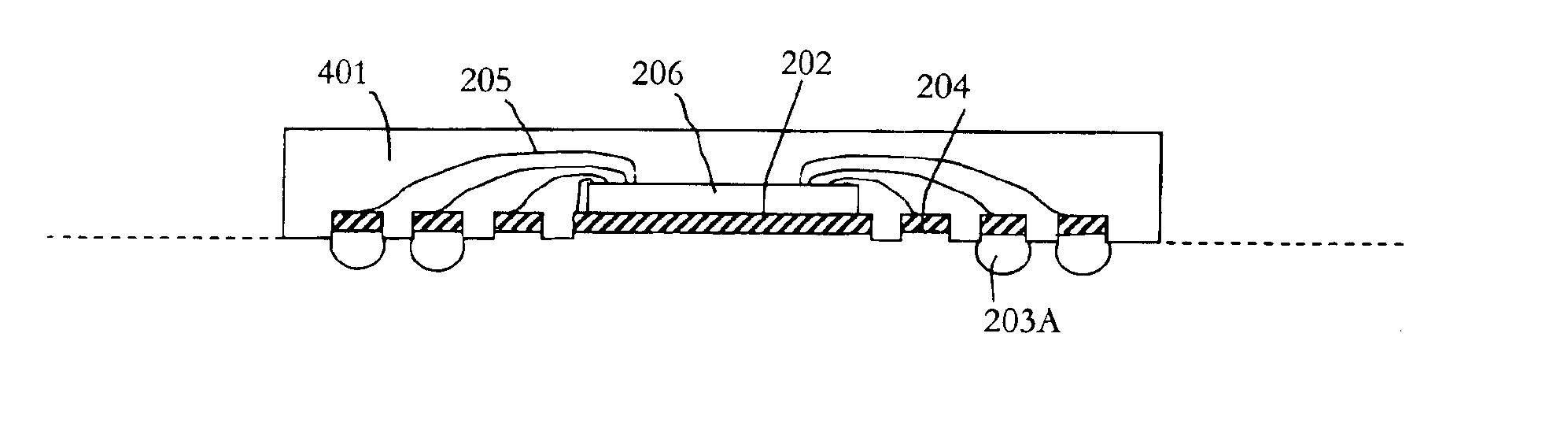

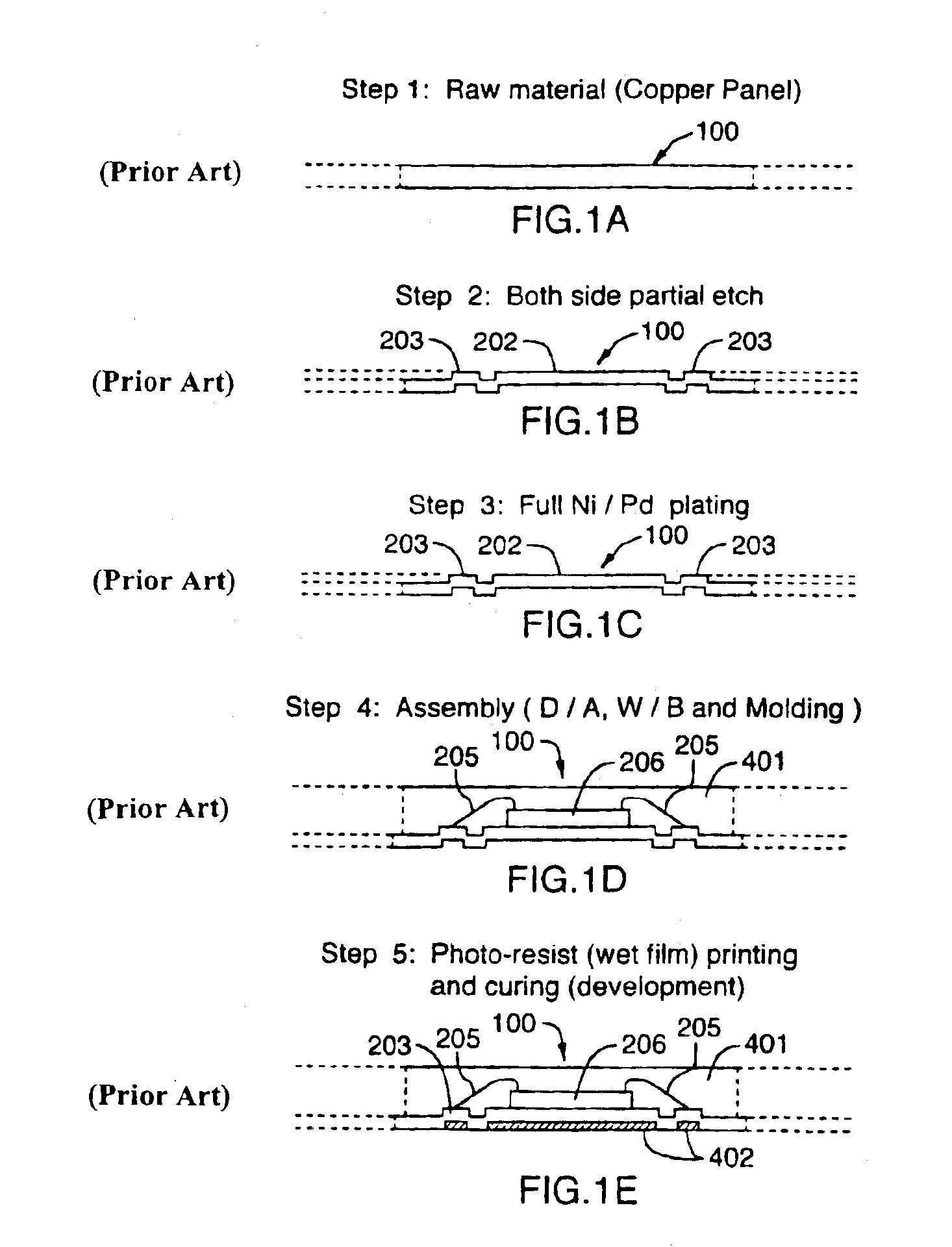

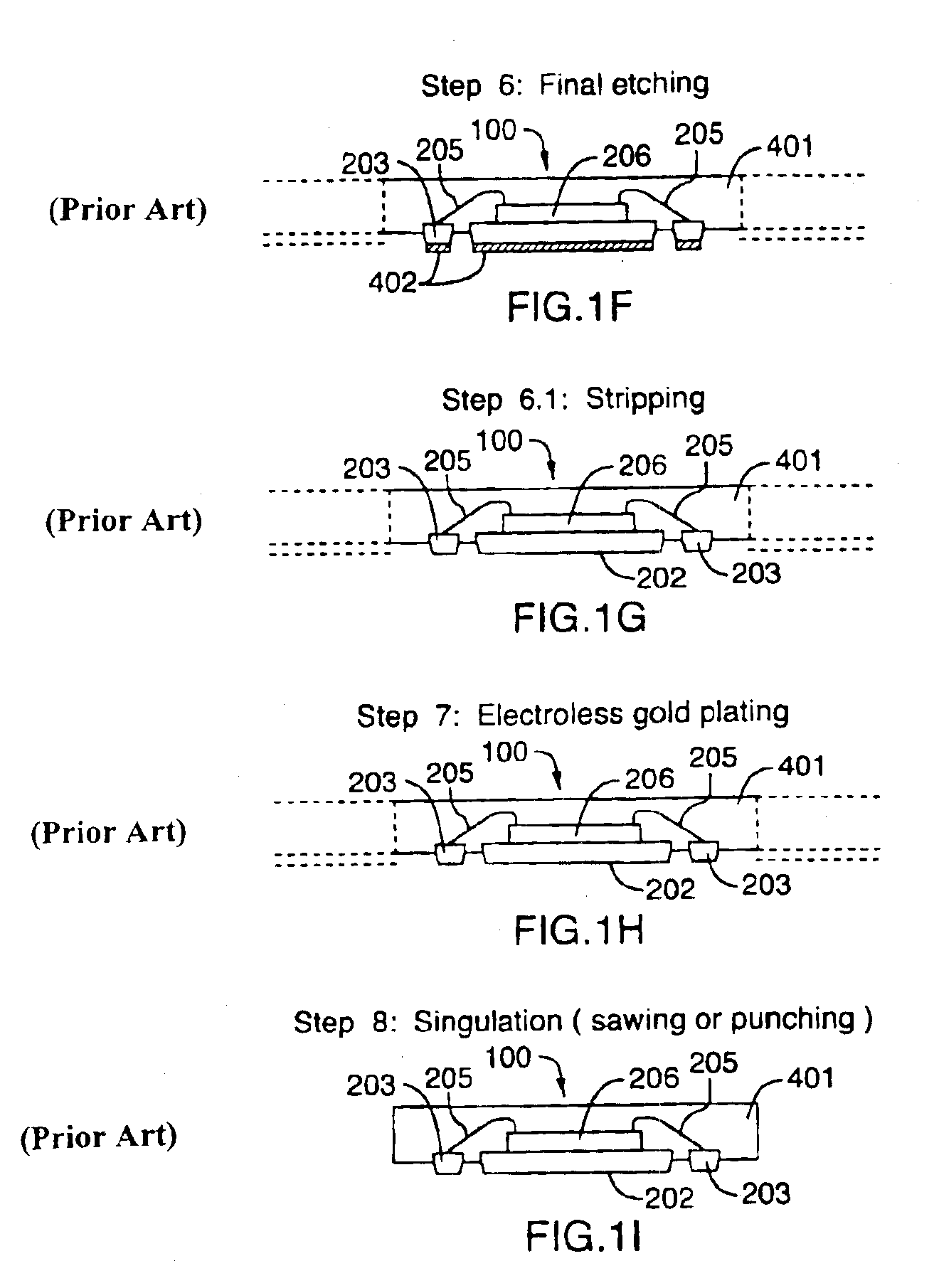

Leadless plastic chip carrier with etch back pad singulation

InactiveUS6933594B2Improve interlockEasy alignmentSemiconductor/solid-state device detailsSolid-state devicesEtchingPunching

A leadless plastic chip carrier is constructed by half etching one or both sides of the package design onto a leadframe strip so as to create unique design features such as power and / or ground ring surrounding the die attach pad, interlocking rivet head construction for the contact pads, and an interlocking pattern for the die attach pad. After wire bonding and molding, a further etching is performed to isolate and expose contact pads. Singulation of individual chip packages from the leadframe strip is then performed by saw singulation or die punching.

Owner:UTAC HEADQUARTERS PTE LTD

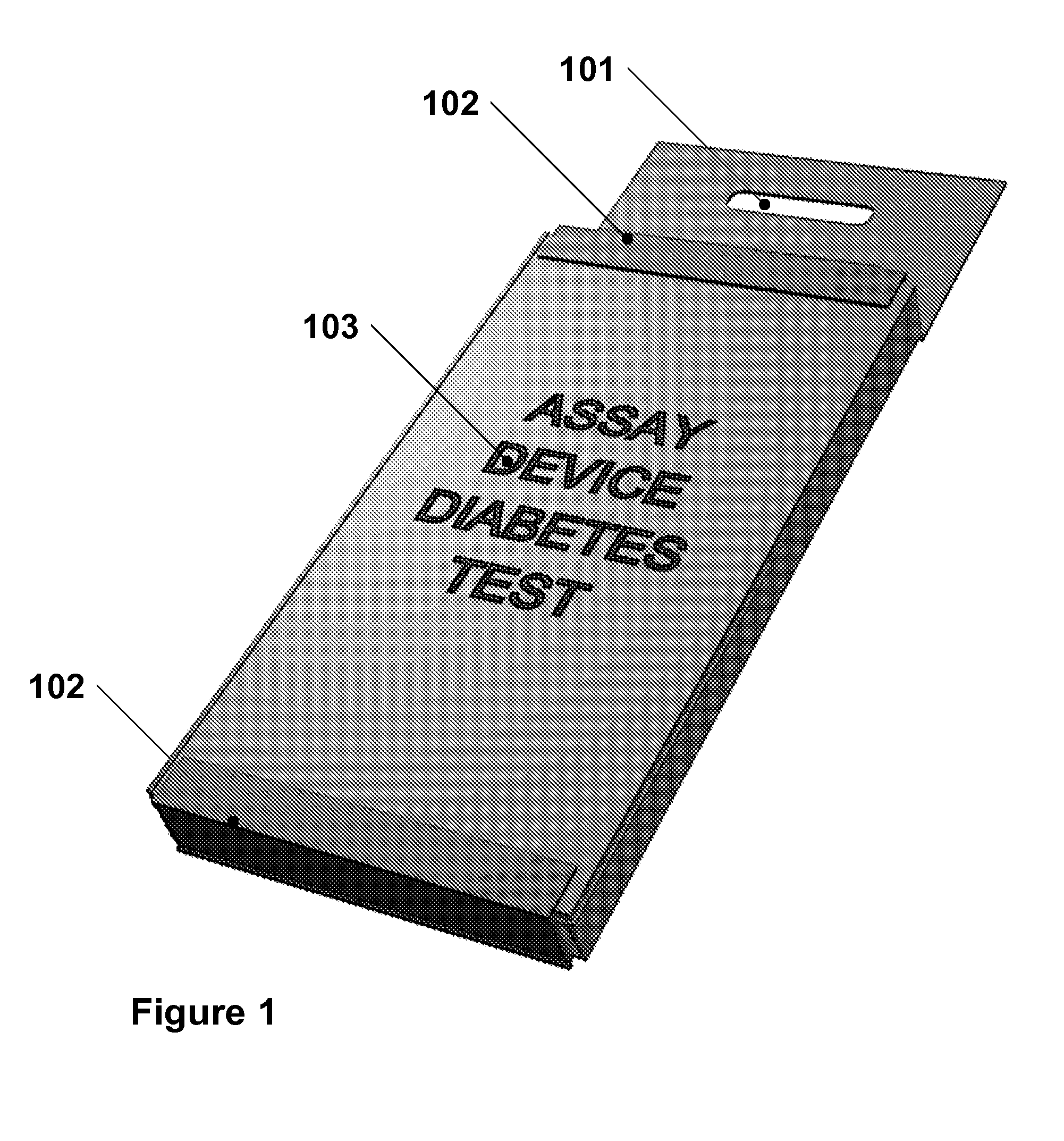

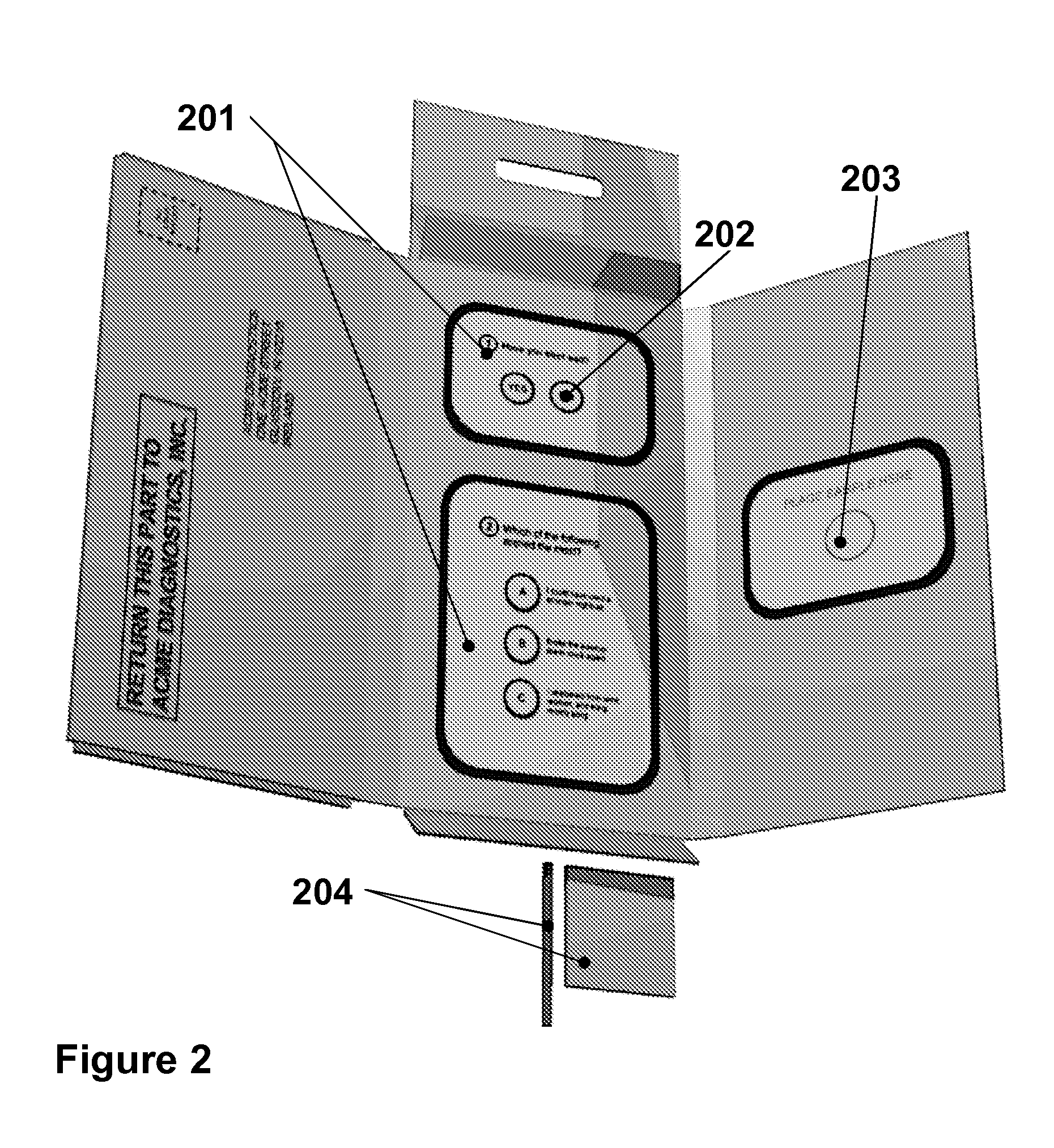

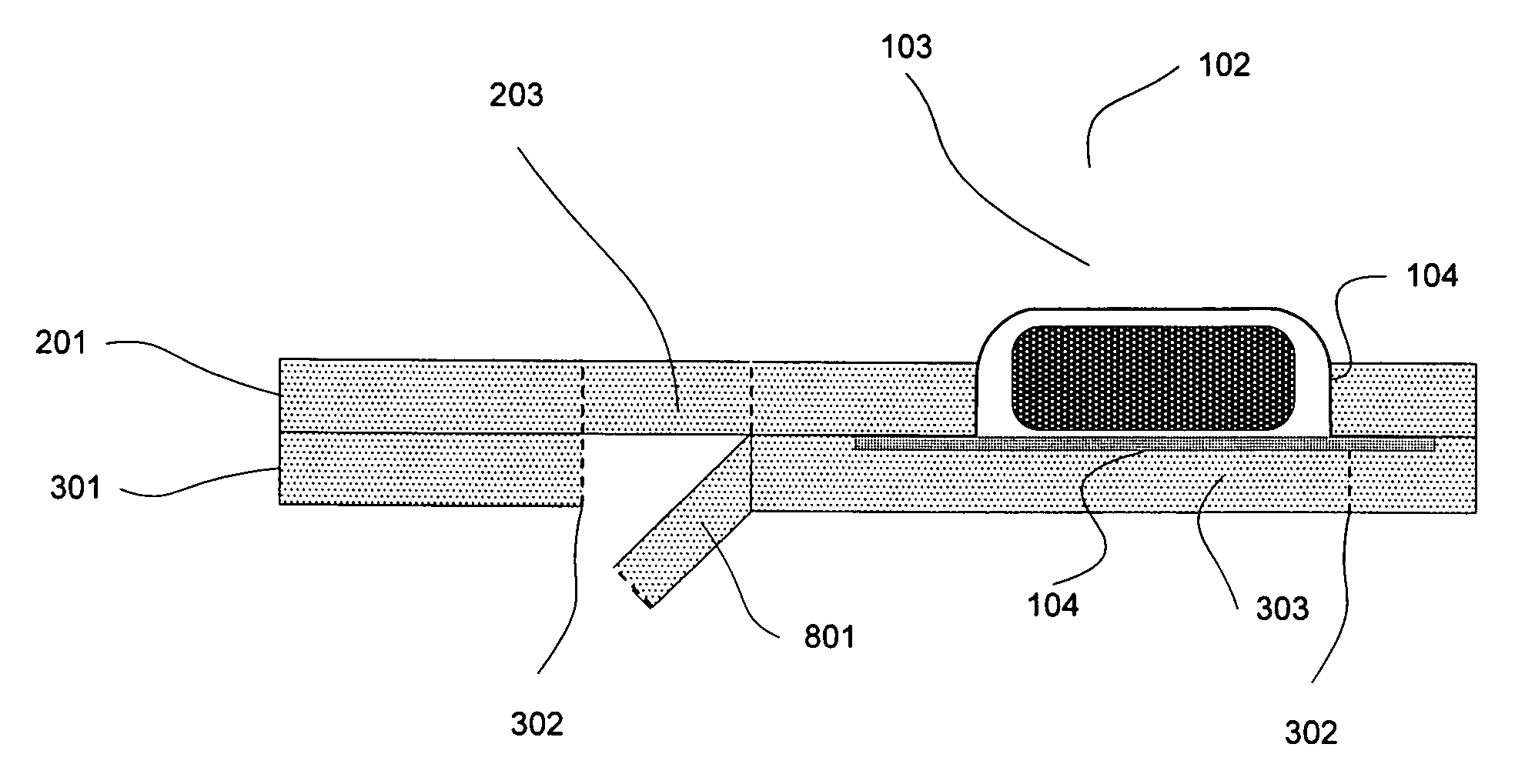

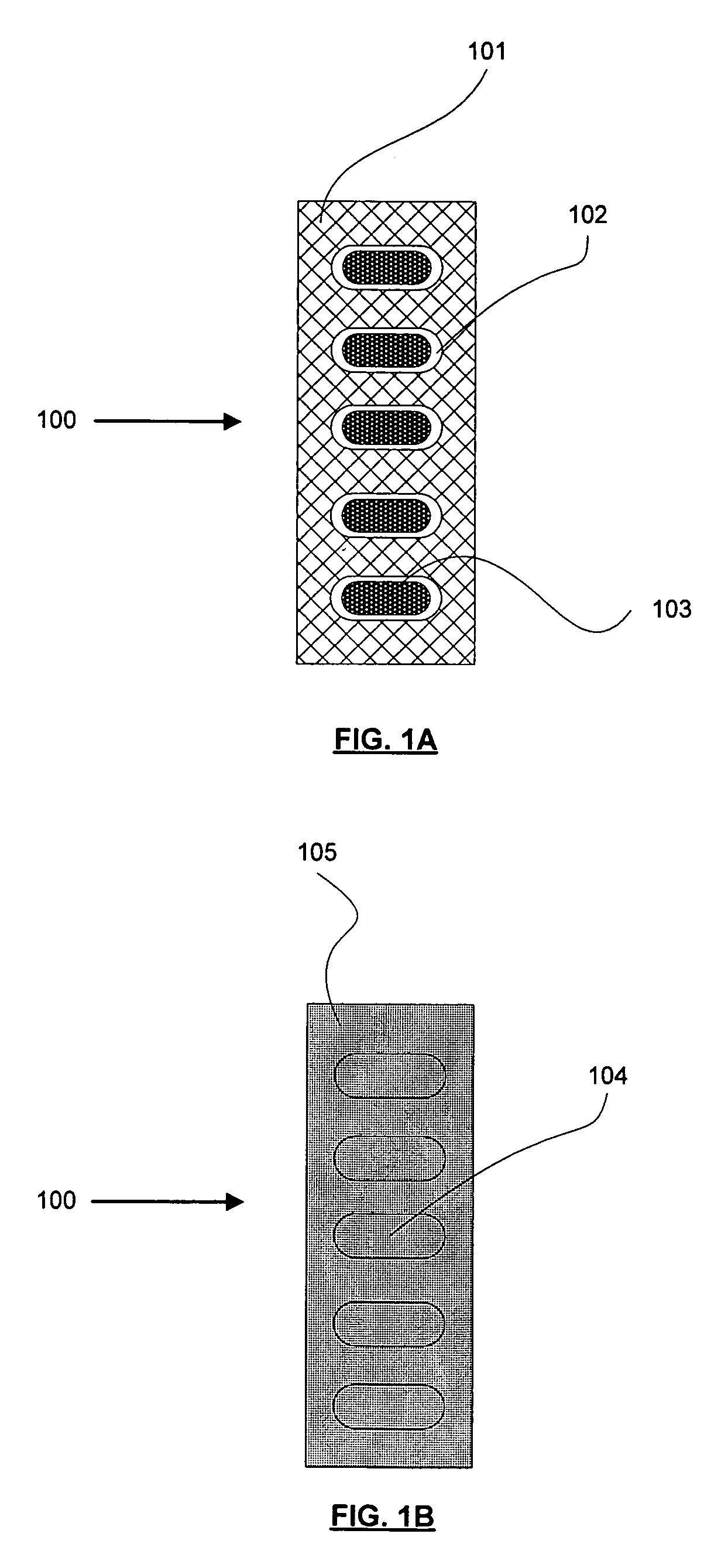

Single use, self-contained assay device for quantitative and qualitative measurements

InactiveUS20080053222A1ConfidenceReliable resultsFluid pressure measurementSpeed/acceleration/shock instrument detailsMeasurement deviceData acquisition

The invention comprises a single-use, self-contained measuring device, comprising a data entry- and sampling part including a sensor for measuring of physical or chemical property of a foreign substance and a data acquisition part including electronic processing- and storage means, where the parts are integral parts of a packaging, formed of a sheet-like, printable and foldable material, the packaging being designed to enclose and protect the parts contained therein. The packaging may also include various instruments needed to perform a test.

Owner:CYPAK +1

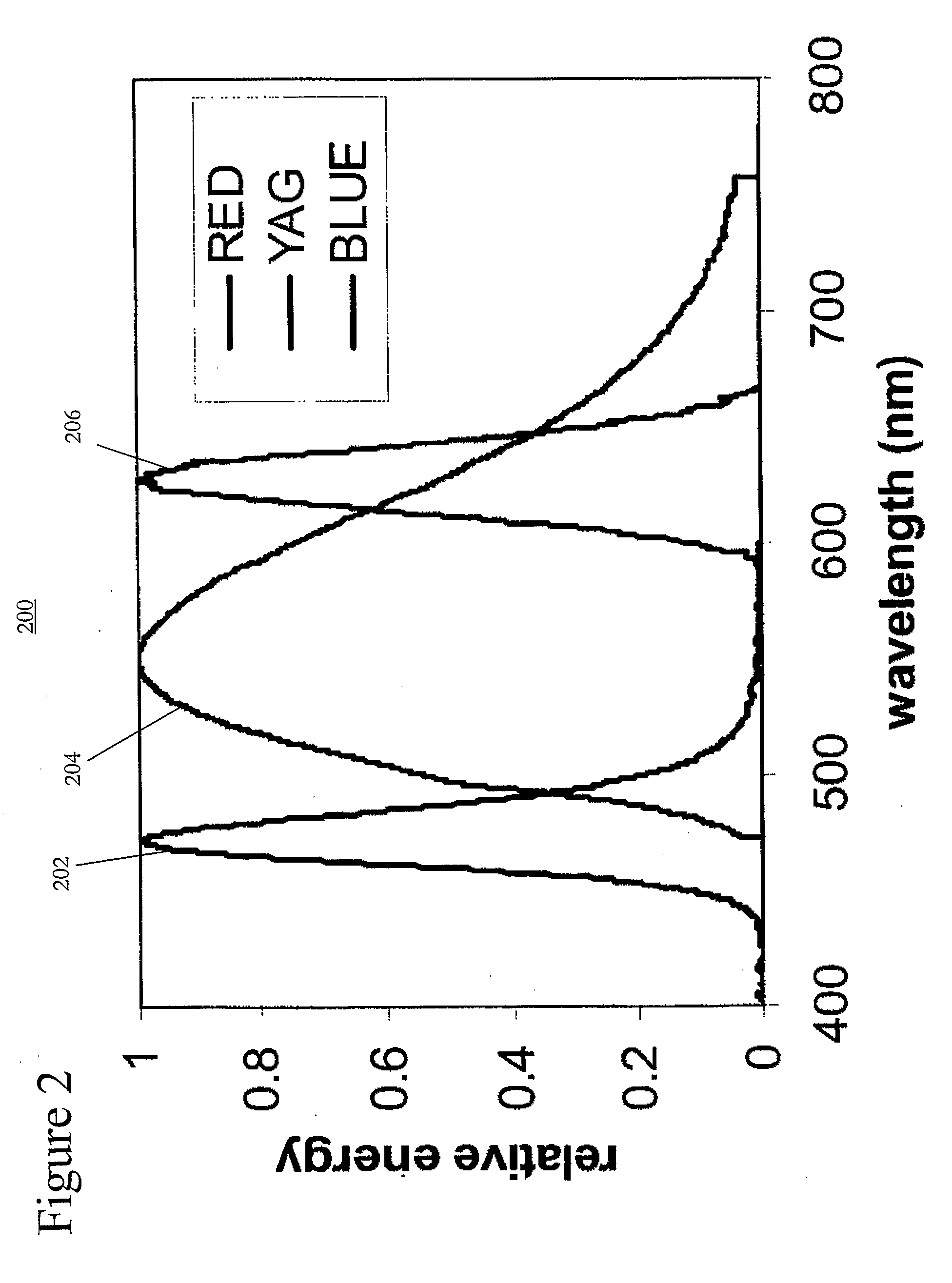

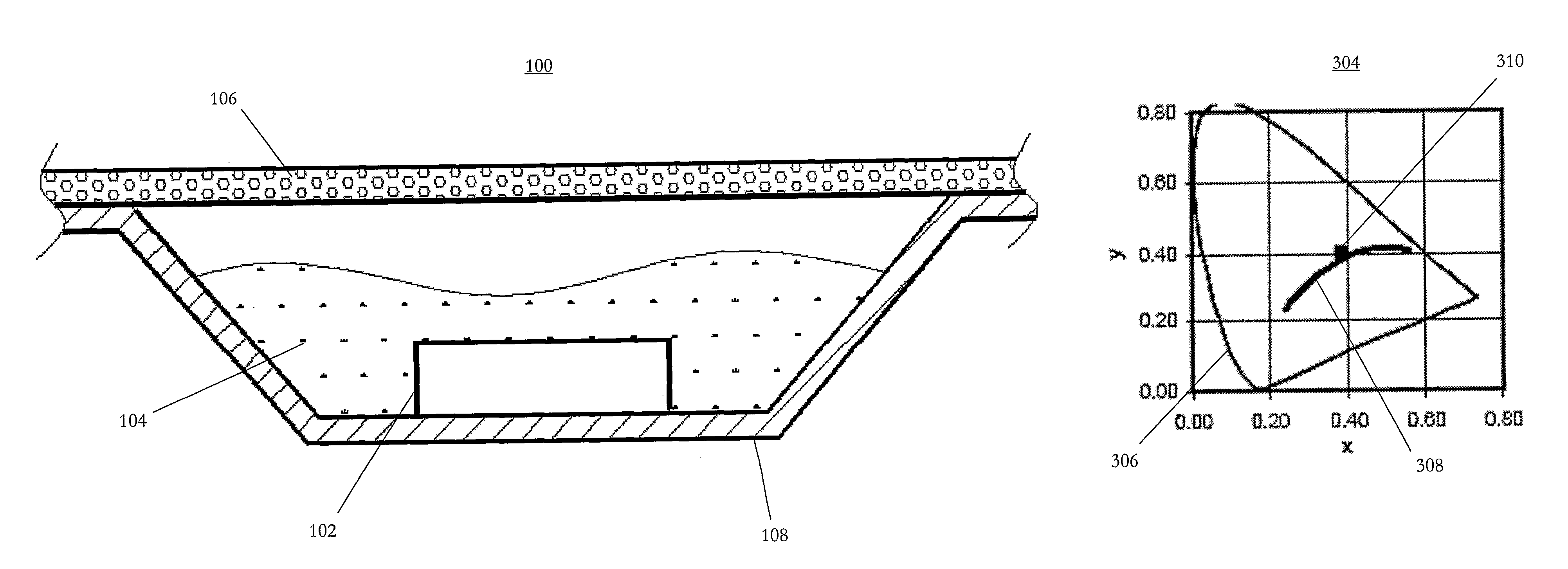

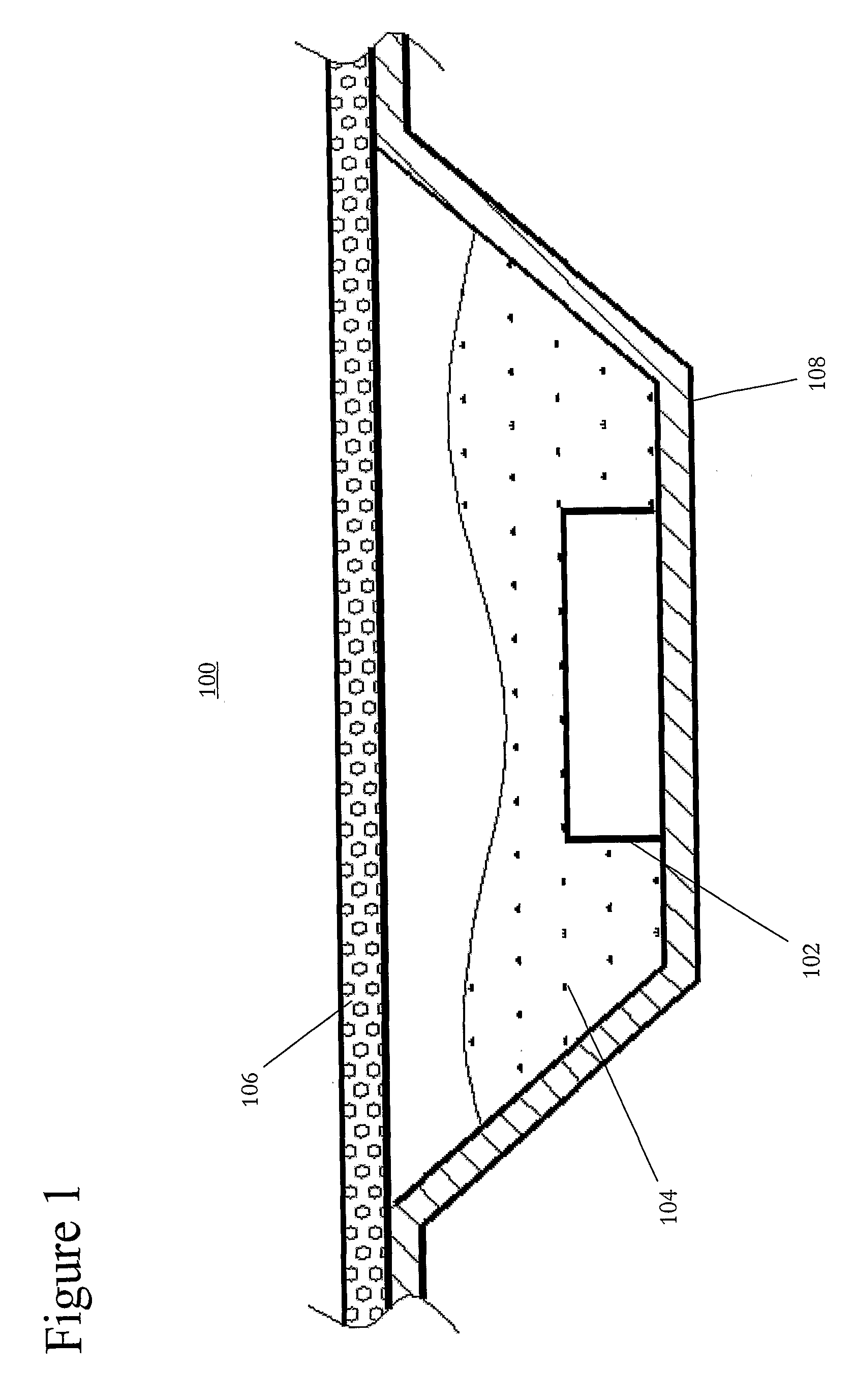

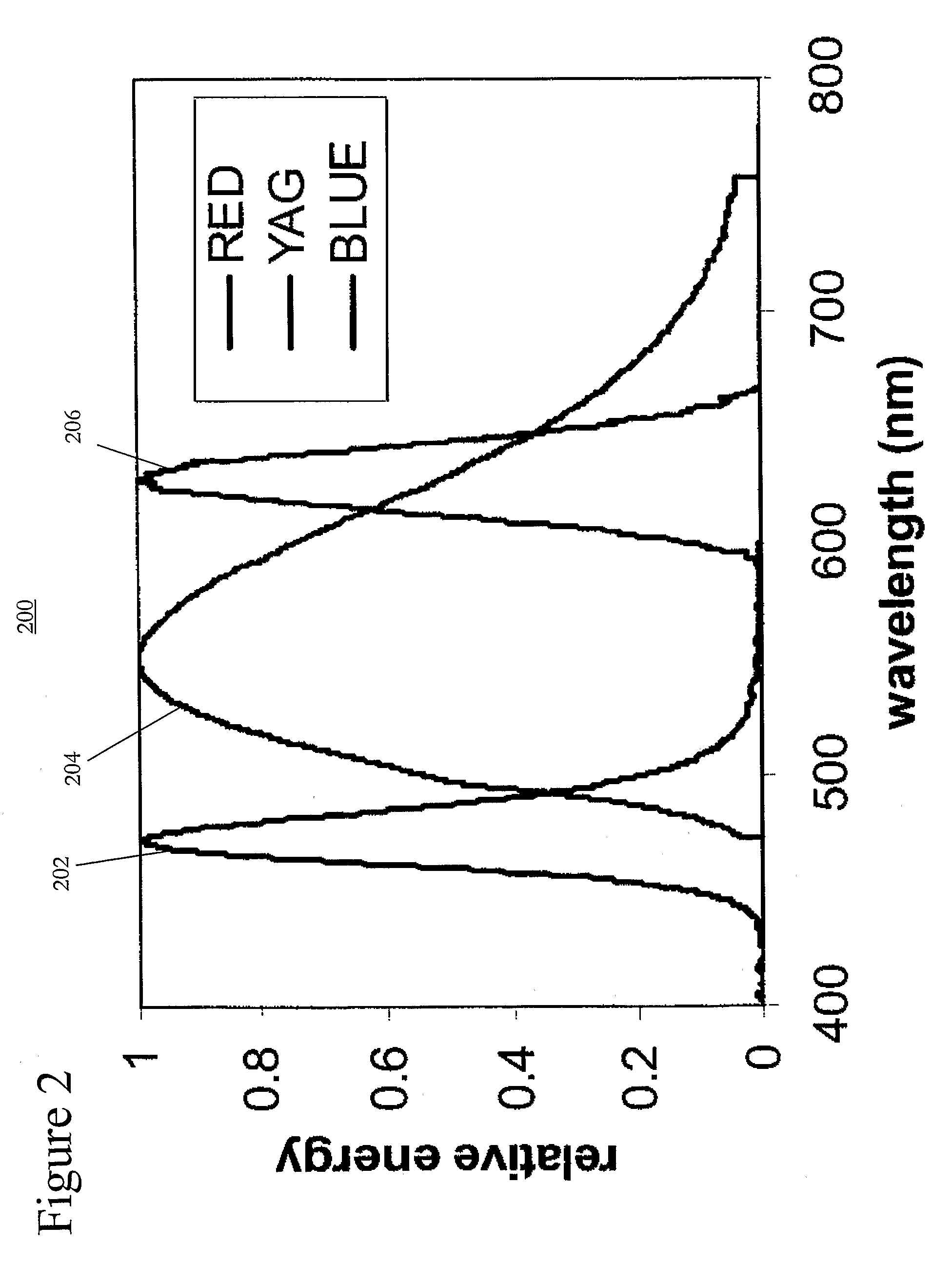

Package Design for Producing White Light With Short-Wavelength Leds and Down-Conversion Materials

A broad bandwidth light source including: a solid state light emitting device that generates short wavelength light; and quantum dot material and phosphor material that are each irradiated by some of the short wavelength light. The short wavelength light has a spectrum with a first peak wavelength shorter than about 500 nm. The quantum dot material absorbs some of the short wavelength light and reemits it as long wavelength light having a spectrum with a second peak wavelength longer than about 600 nm. The phosphor material absorbs some of the short wavelength light and reemits it as mid wavelength light having a spectrum with a peak wavelength between the first and second peak wavelength. The light source is configured such that some of each light (short, mid, and long wavelength) is emitted coincidently as a light having a chromaticity value near the blackbody locus and a color rendering index greater than 80.

Owner:RENESSELAER POLYTECHNIC INST

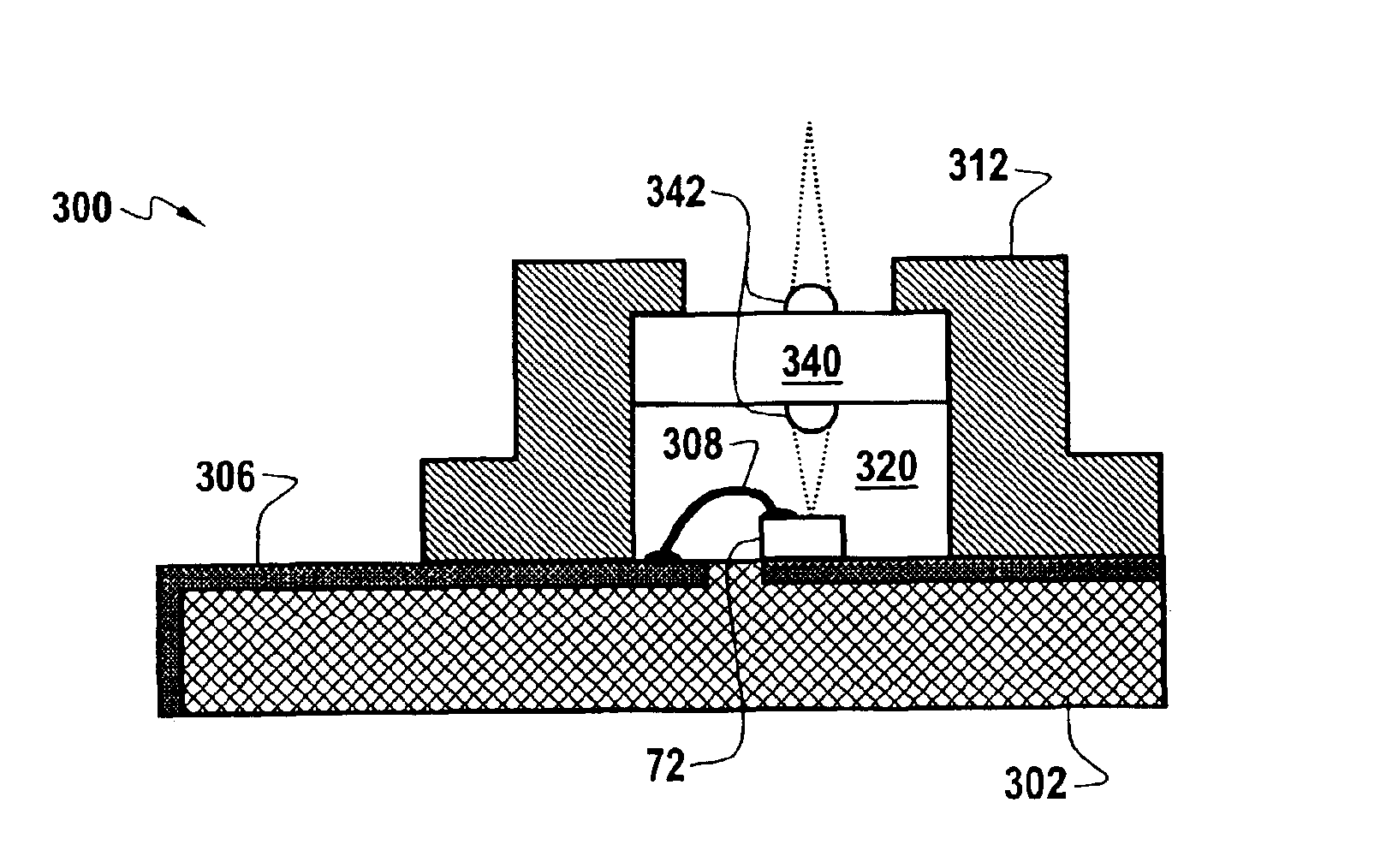

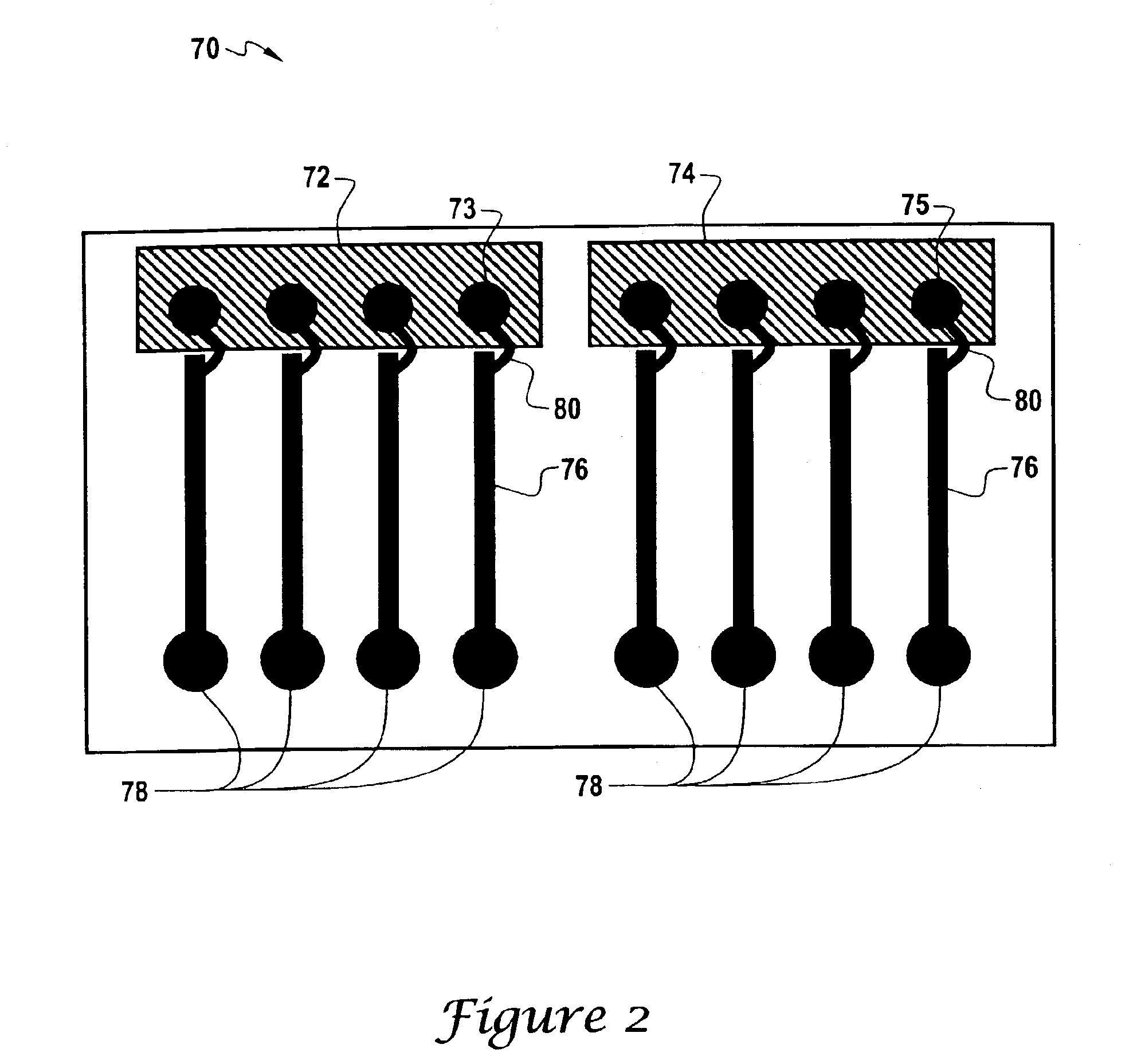

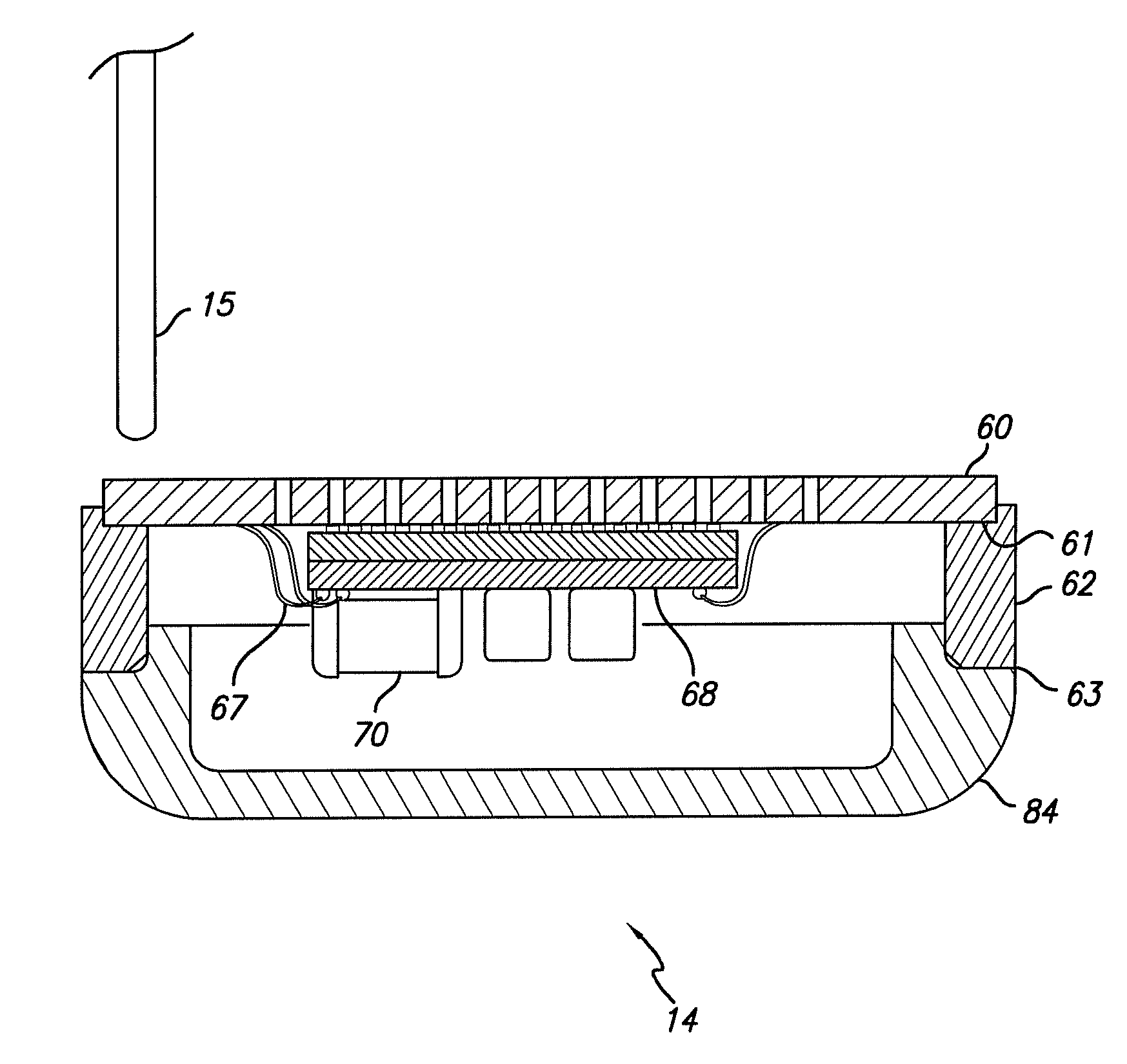

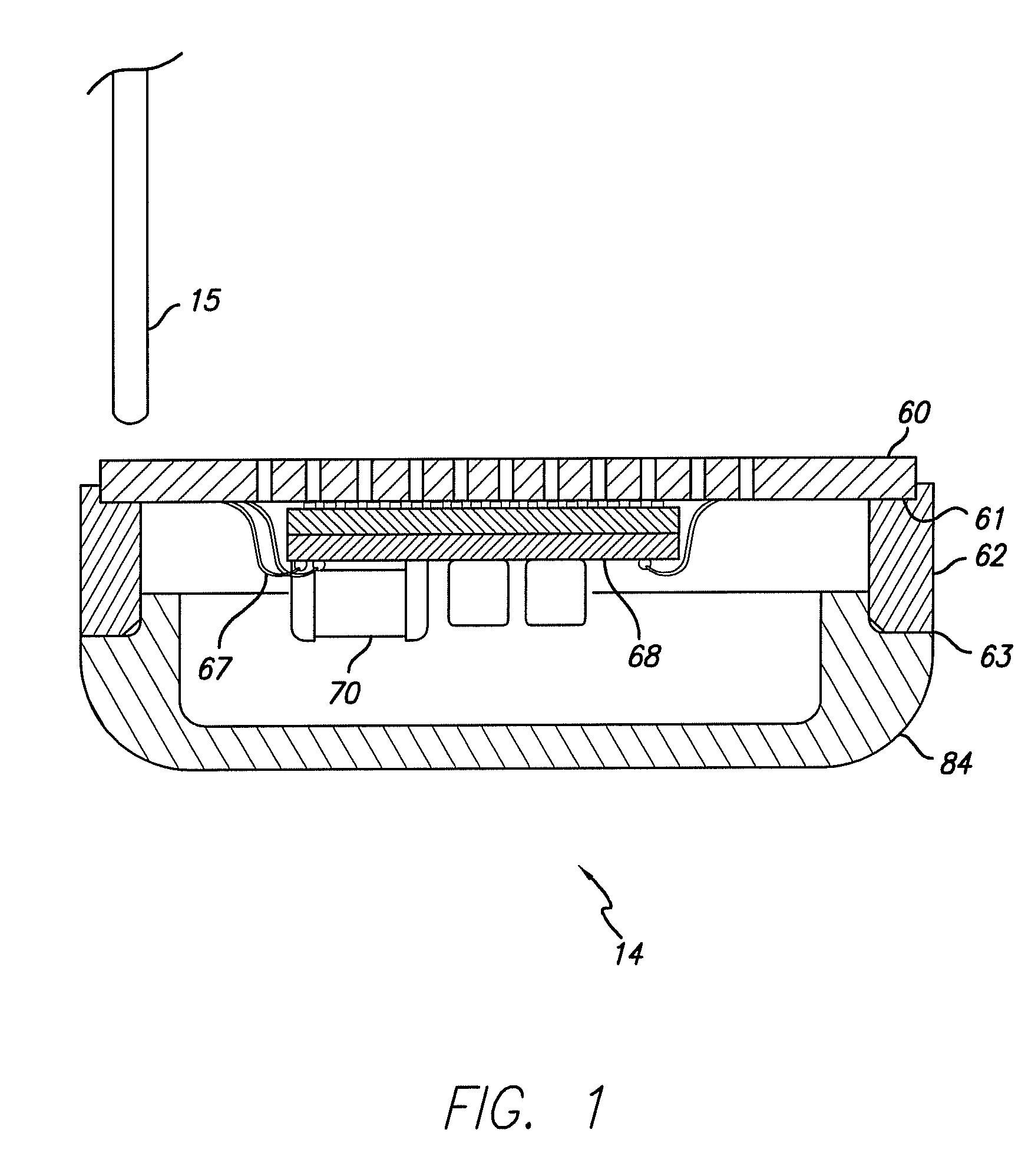

Compact package design for vertical cavity surface emitting laser array to optical fiber cable connection

InactiveUS6953291B2Printed circuit assemblingCircuit optical detailsVertical-cavity surface-emitting laserEngineering

A hermetically sealed, opto-electronic array housing assembly having a ceramic base, electrical connectors, a metal can, and a glass window. The glass window can support a micro-lens array. The metal can receives the glass window. The electrical impedance of the electrical connectors is beneficially carefully controlled to enable high-speed data communications. A multi-element optical fiber connector can provide for optical communications to and / or from an opto-electronic array contained within the housing.

Owner:II VI DELAWARE INC

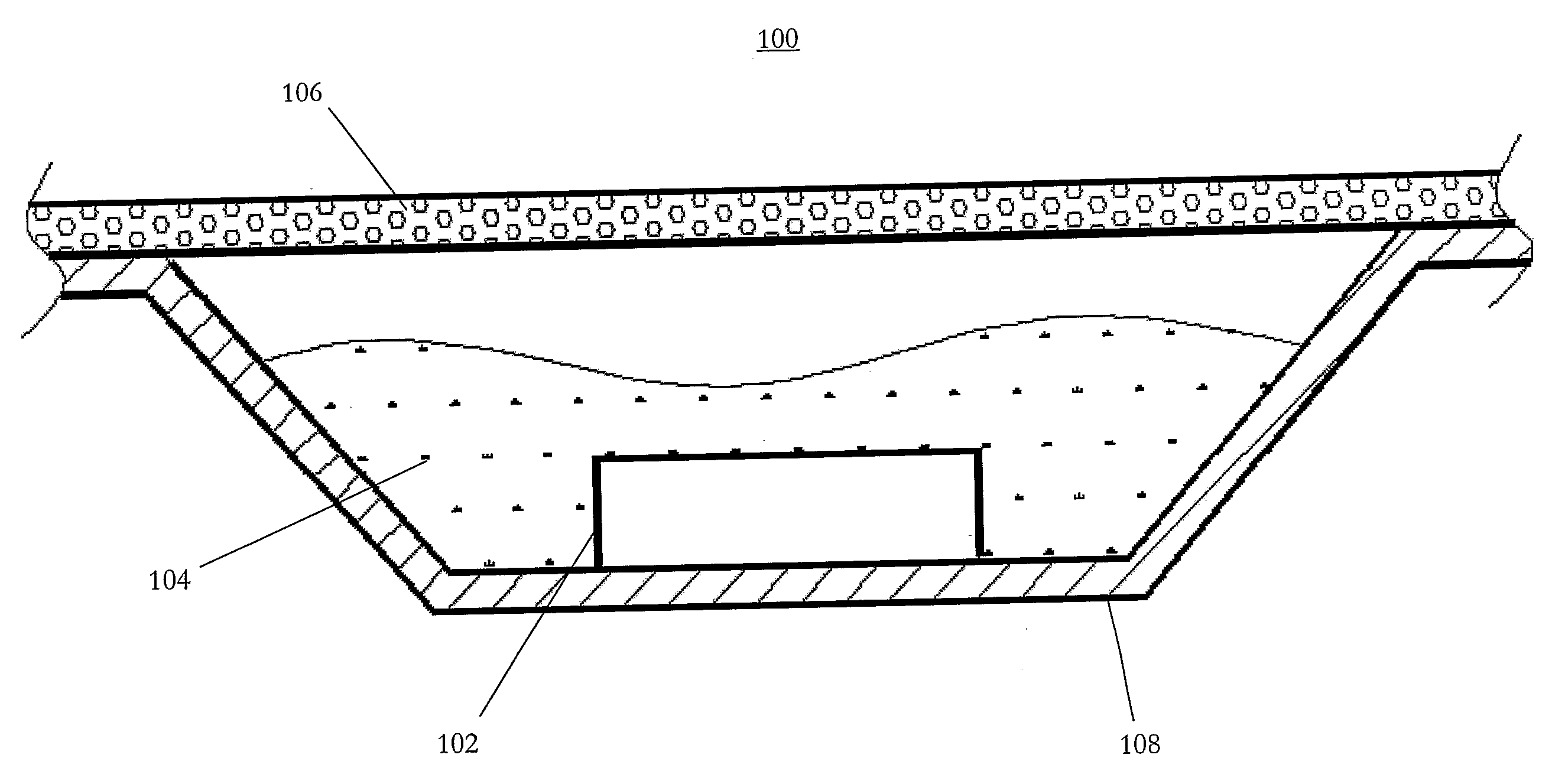

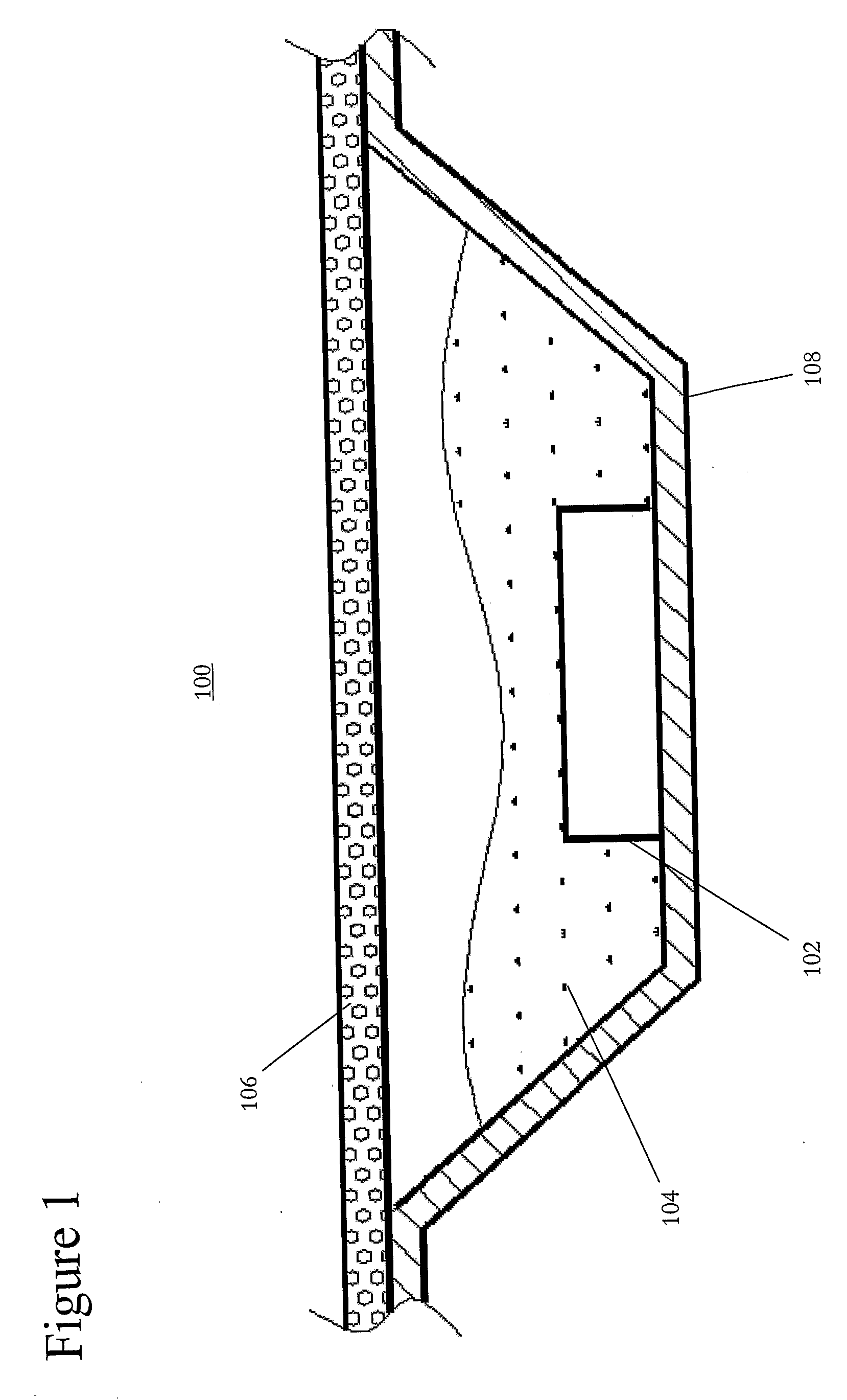

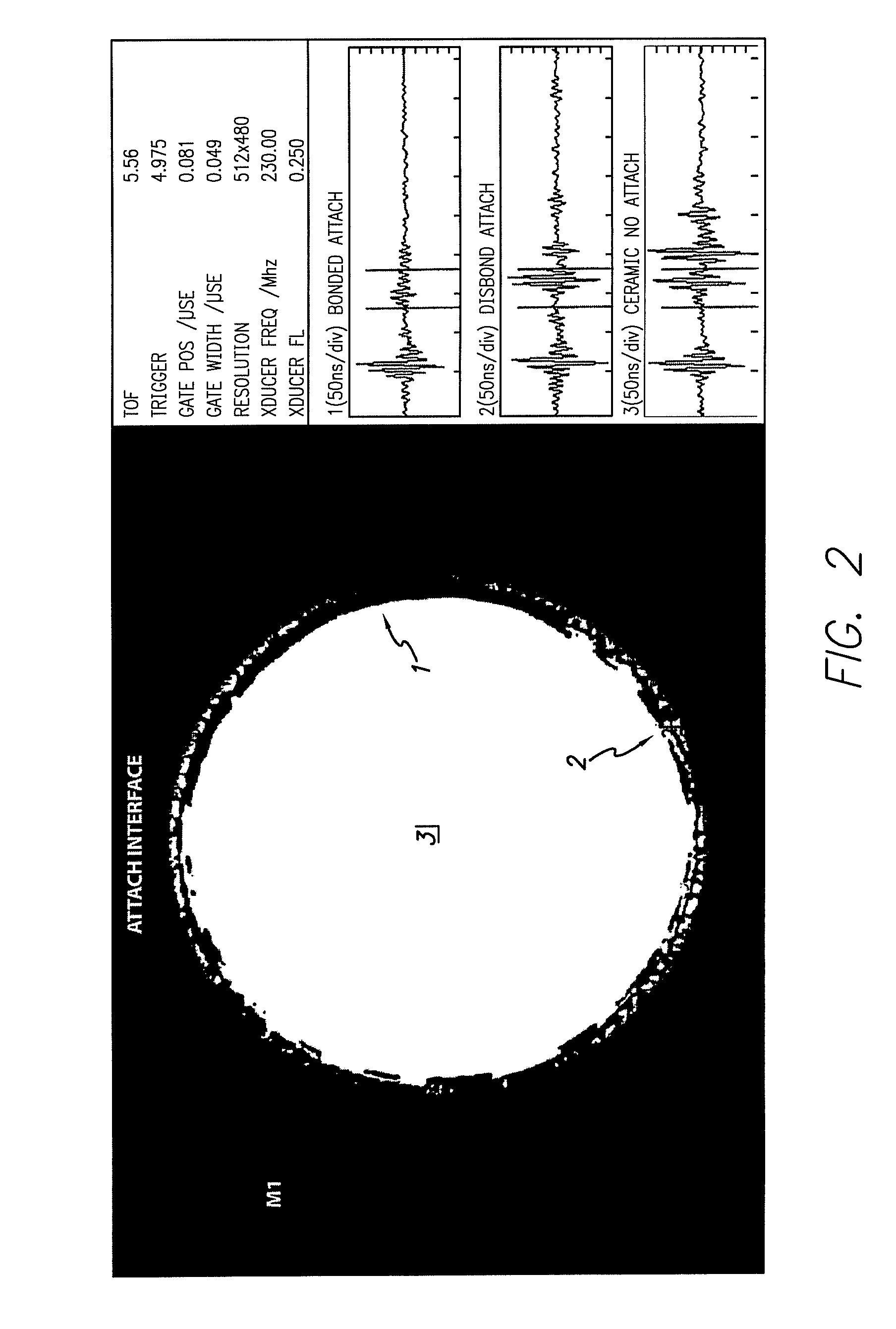

Method of inspection of materials for defects

ActiveUS8131376B1Material analysis using sonic/ultrasonic/infrasonic wavesHead electrodesNon destructiveVisual prosthesis

The present invention is a non-destructive method of inspecting a bond, particularly a braze bond, in a hermetic package. The invention involves a unique hermetic package design adapted for ultrasonic inspection and a method of inspecting the package. This package and non-destructive inspection process are particularly useful in implantable neural stimulators such as visual prostheses.

Owner:CORTIGENT INC

Package design for producing white light with short-wavelength LEDS and down-conversion materials

A broad bandwidth light source including: a solid state light emitting device that generates short wavelength light; and quantum dot material and phosphor material that are each irradiated by some of the short wavelength light. The short wavelength light has a spectrum with a first peak wavelength shorter than about 500 nm. The quantum dot material absorbs some of the short wavelength light and reemits it as long wavelength light having a spectrum with a second peak wavelength longer than about 600 nm. The phosphor material absorbs some of the short wavelength light and reemits it as mid wavelength light having a spectrum with a peak wavelength between the first and second peak wavelength. The light source is configured such that some of each light (short, mid, and long wavelength) is emitted coincidentally as a light having a chromaticity value near the blackbody locus and a color rendering index greater than 80.

Owner:RENESSELAER POLYTECHNIC INST

Multigrade engine oil prepared from Fischer-Tropsch distillate base oil

InactiveUS20060027486A1Refining to change hydrocarbon structural skeletonLiquid carbonaceous fuelsCycloparaffinsPackage design

A multigrade engine oil meeting the specifications for SAE J300 revised June 2001 requirements and a process for preparing it, said engine oil comprising (a) between about 15 to about 94.5 wt % of a hydroisomerized distillate Fischer-Tropsch base oil characterized by (i) a kinematic viscosity between about 2.5 and about 8 cSt at 100° C., (ii) at least about 3 wt % of the molecules having cycloparaffin functionality, and (iii) a ratio of weight percent molecules with monocycloparaffin functionality to weight percent of molecules with multicycloparaffin functionality greater than about 15; (b) between about 0.5 to about 20 wt % of a pour point depressing base oil blending component prepared from an hydroisomerized bottoms material having an average degree of branching in the molecules between about 5 and 9 alkyl-branches per 100 carbon atoms and wherein not more than 10 wt % boils below about 900° F.; and (c) between about 5 to about 30 wt % of an additive package designed to meet the specifications for ILSAC GF-3.

Owner:CHEVROU USA INC

Child-resistant and senior-friendly blister card package

InactiveUS7063211B2Easy to useImprove the level ofSmall article dispensingOther accessoriesPackage designEngineering

The present invention is a novel child-resistant senior-friendly blister card packaging that is cheap and easy to manufacture. The packaging requires a push-peel-push method for opening, which is cognitively and physically challenging for children and mentally impaired adults. Yet, competent adults can easily open the package, especially after reading instructions. More specifically, opening the package requires the user to: 1) Push through an aperture to create a pull tab; 2) Pull on the pull tab to remove a panel; and 3) Push the blister to force the contents through the blister's seal. Furthermore, the packaging is designed to be tear resistant and to halt any propagation of a tear. Advantageously, the present invention is designed such that information such as instructions and product information can be easily printed directly on the packaging. Moreover, users may also record information directly on the packaging. Thus, the present invention not only provides child-resistant and senior-friendly features, but also provides convenience for viewing and recording information.

Owner:KEY PAK TECH

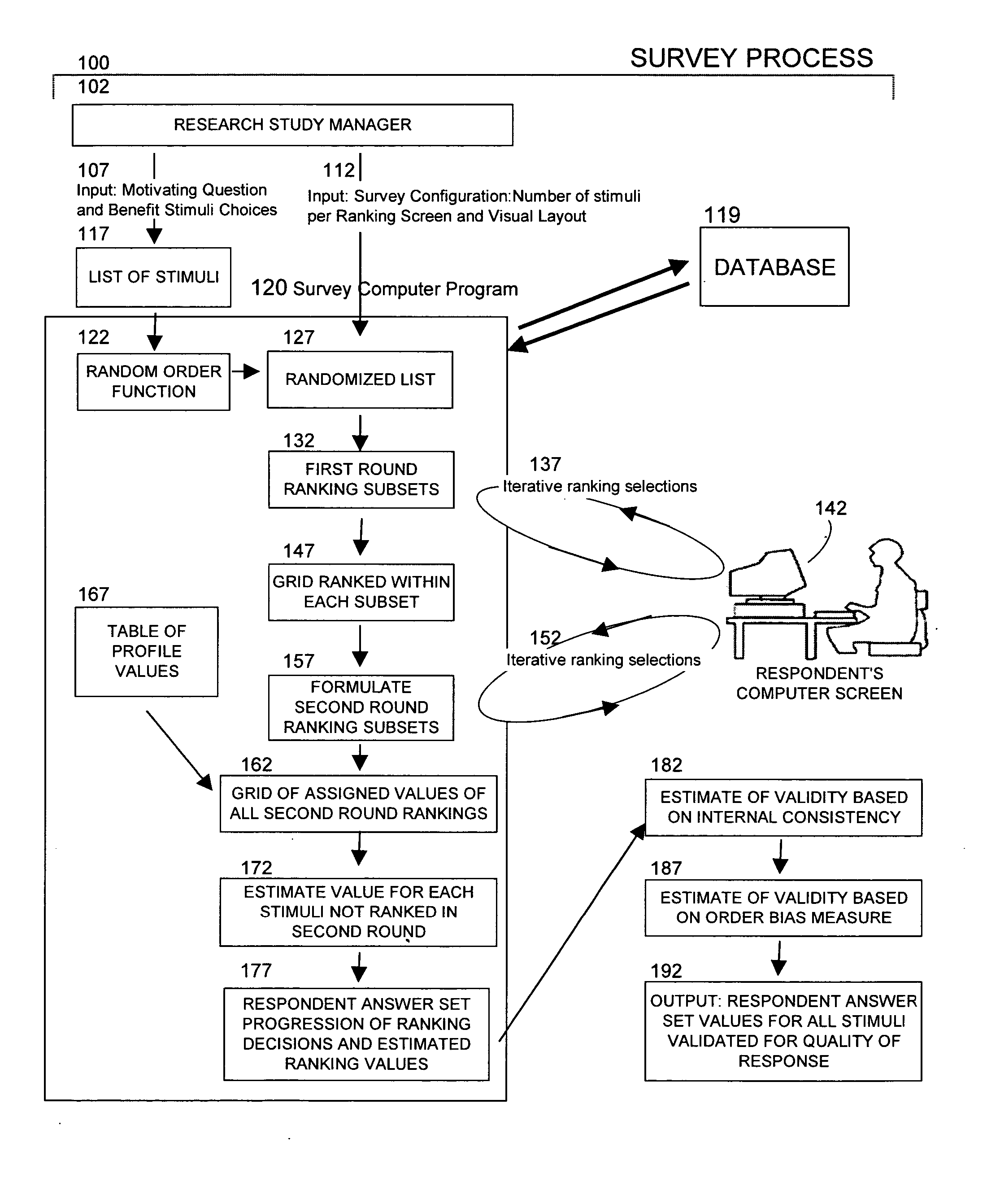

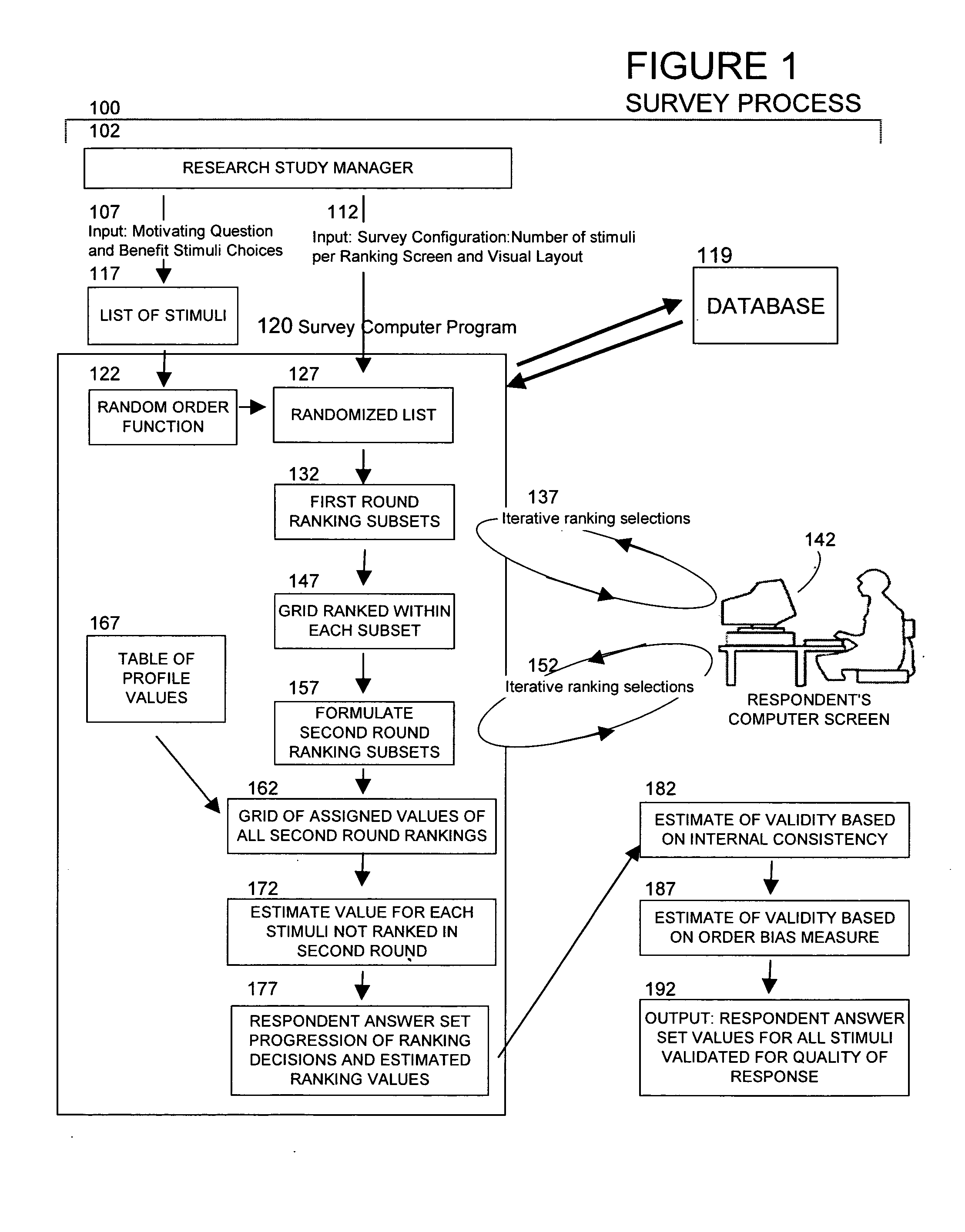

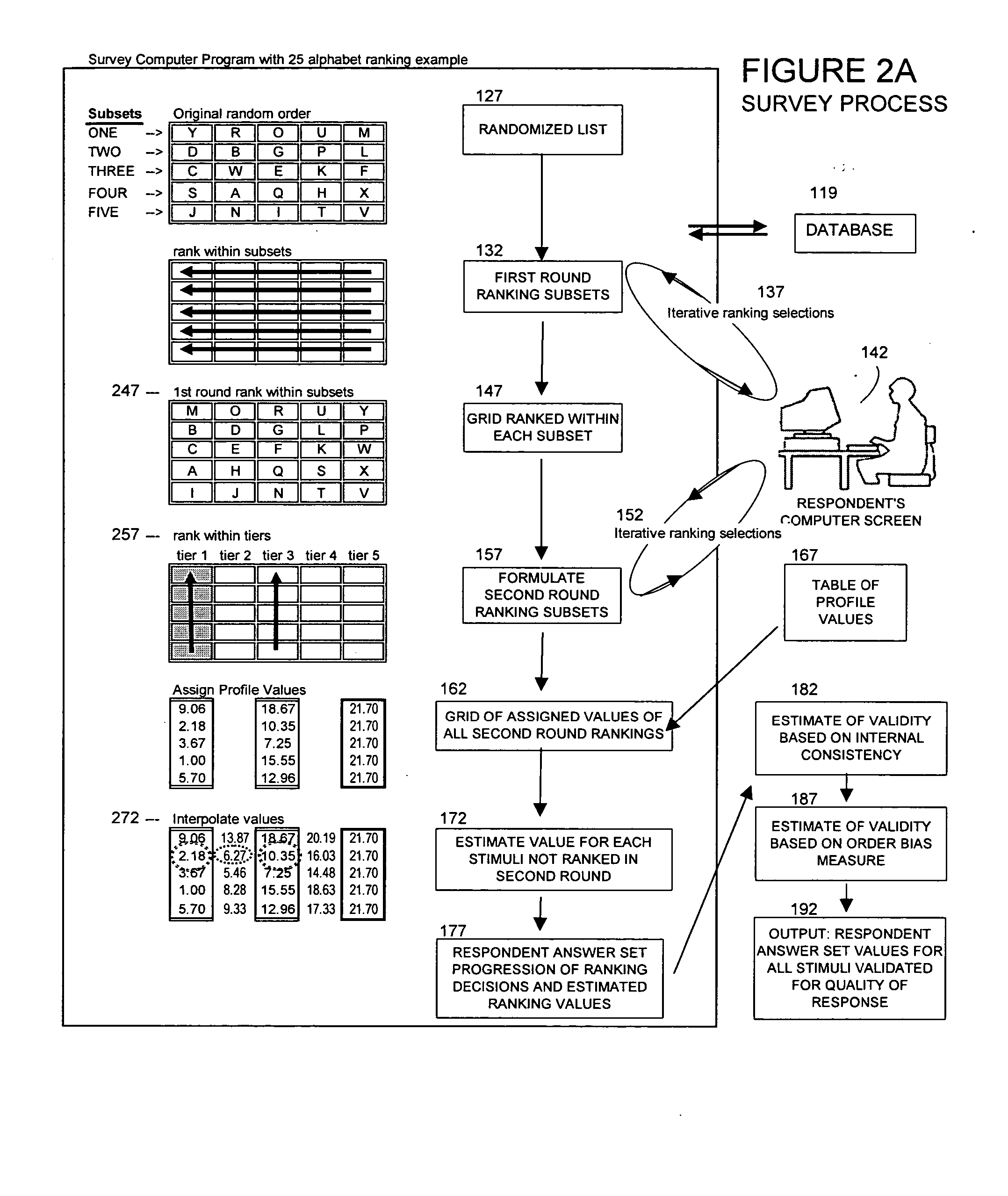

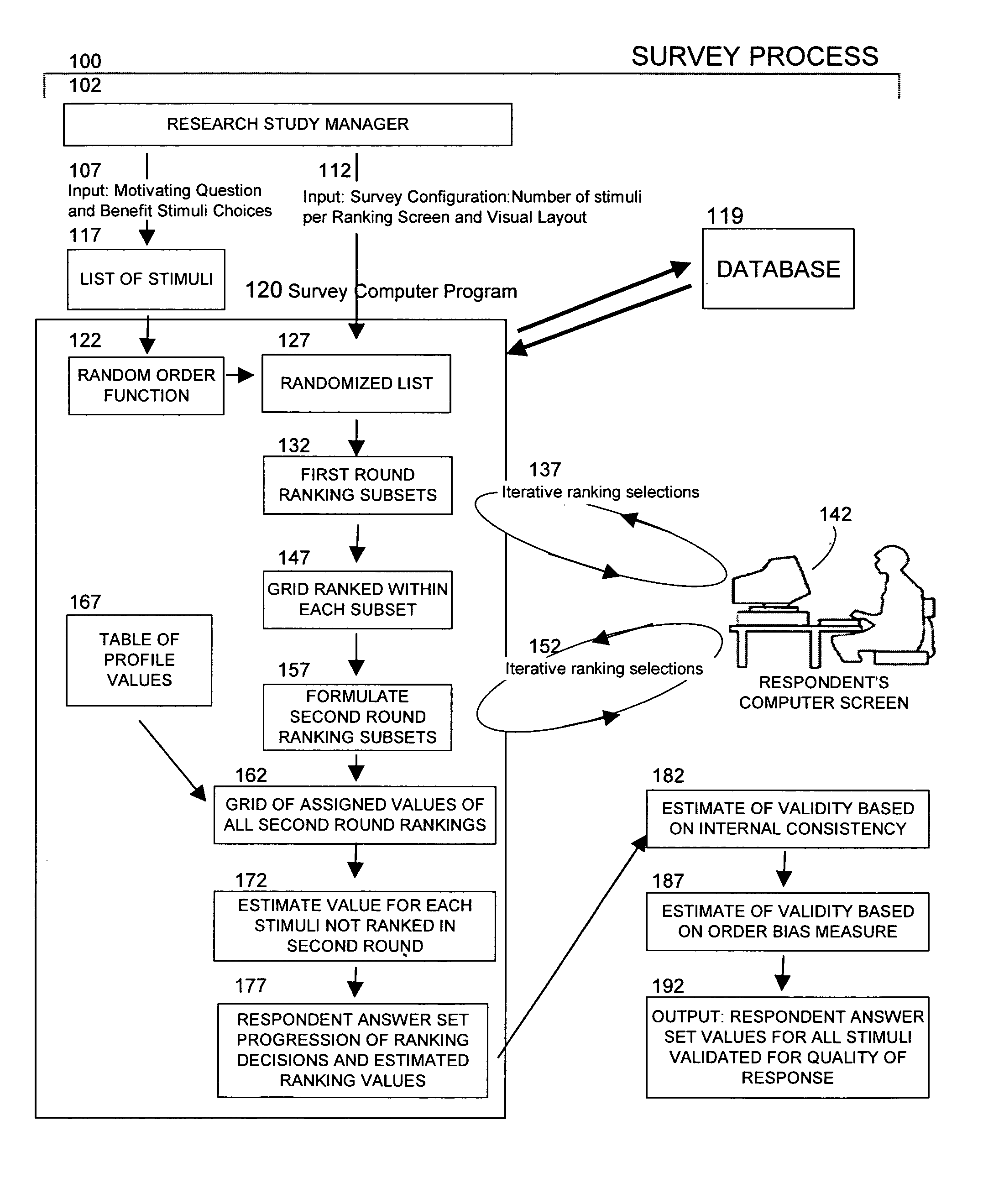

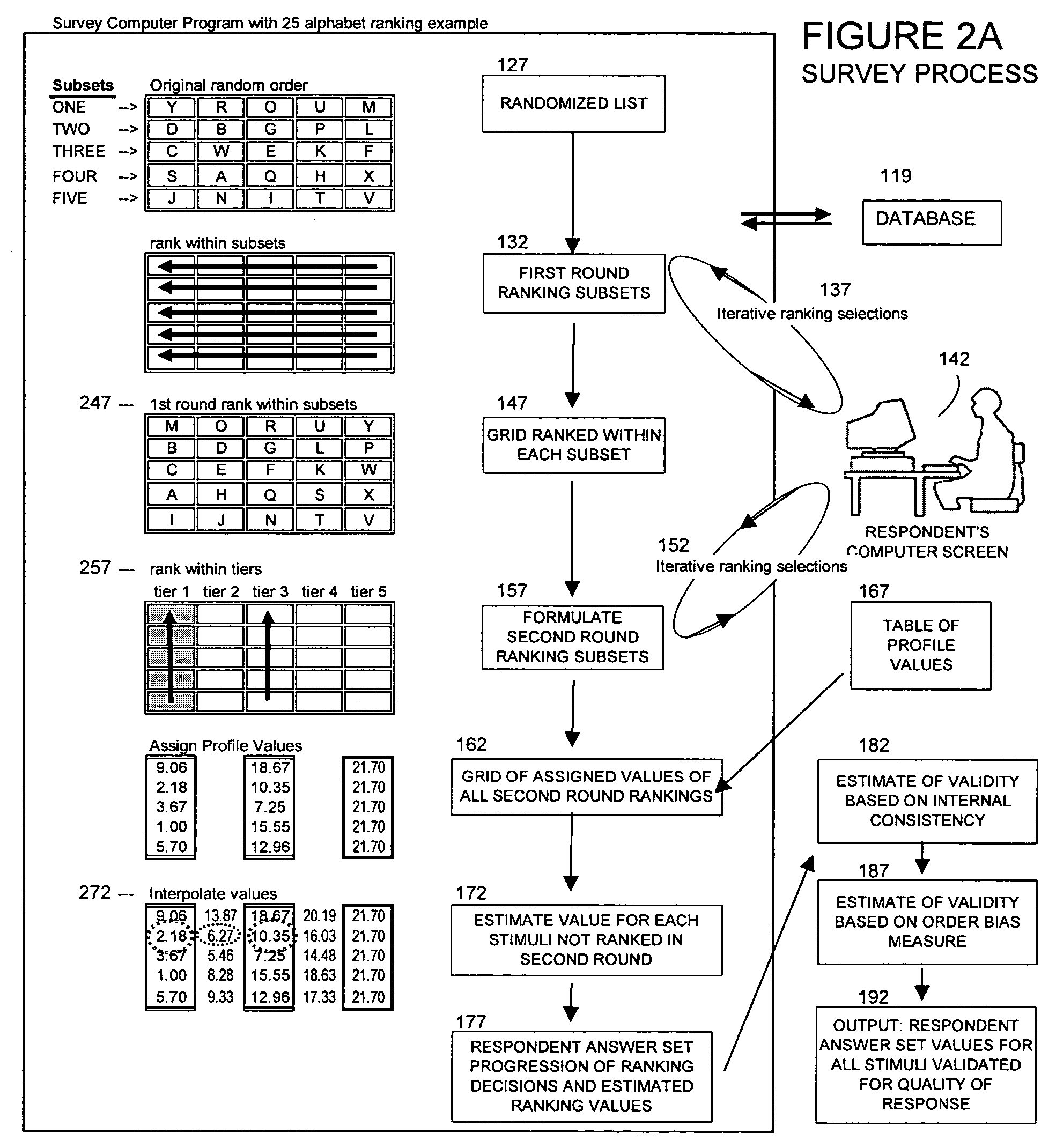

Method for estimating respondent rank order of a set of stimuli

ActiveUS20050060222A1Increase in capacity is limitedControl rateMarket predictionsResourcesGraphicsAlgorithm

A computer implemented method to estimate a respondent's or a set of respondents' rank order with respect to a number of attribute options (i.e. alternative prices, features, benefits, ways of expressing benefits, brand names, slogans, logos, graphic treatments such as package design elements and any other stimuli that the researcher believes may influence the individual's opinion such as a statement, graphic or brief audio). The method can be used when the number of stimuli to be presented exceeds the number that can be presented at one time to a respondent, most typically, exceeding the number that can be legibly displayed on one computer screen for rank ordering by a respondent. The estimated rank order is highly accurate, especially for the highest ranked stimuli, but requires only a small fraction of the respondent input that would be needed to capture a complete rank order from that respondent. This abstract is provided as an aid for finding relevant disclosures and not as a limitation on the scope of the claims.

Owner:WHITE WILLIAM DONALD

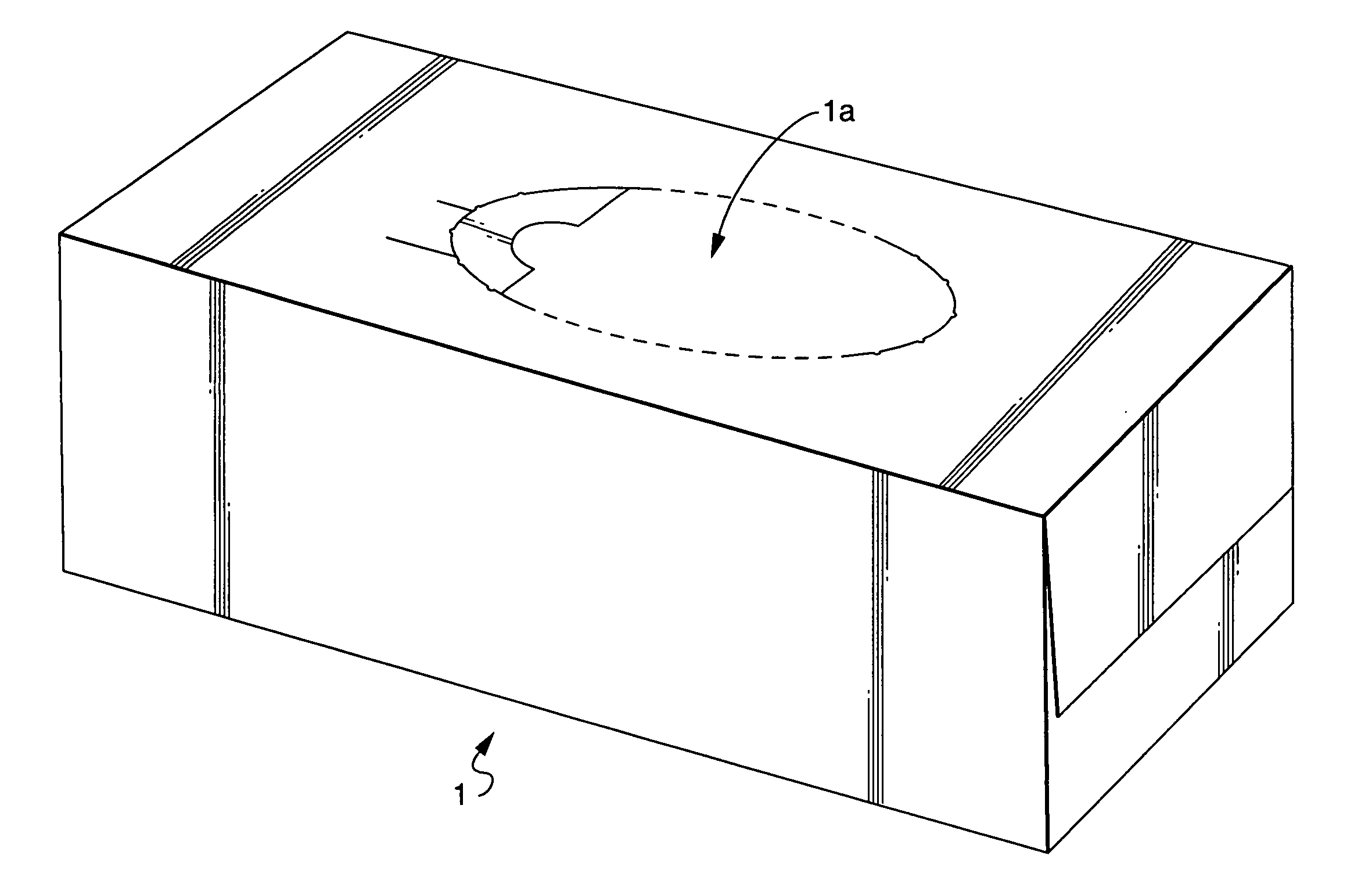

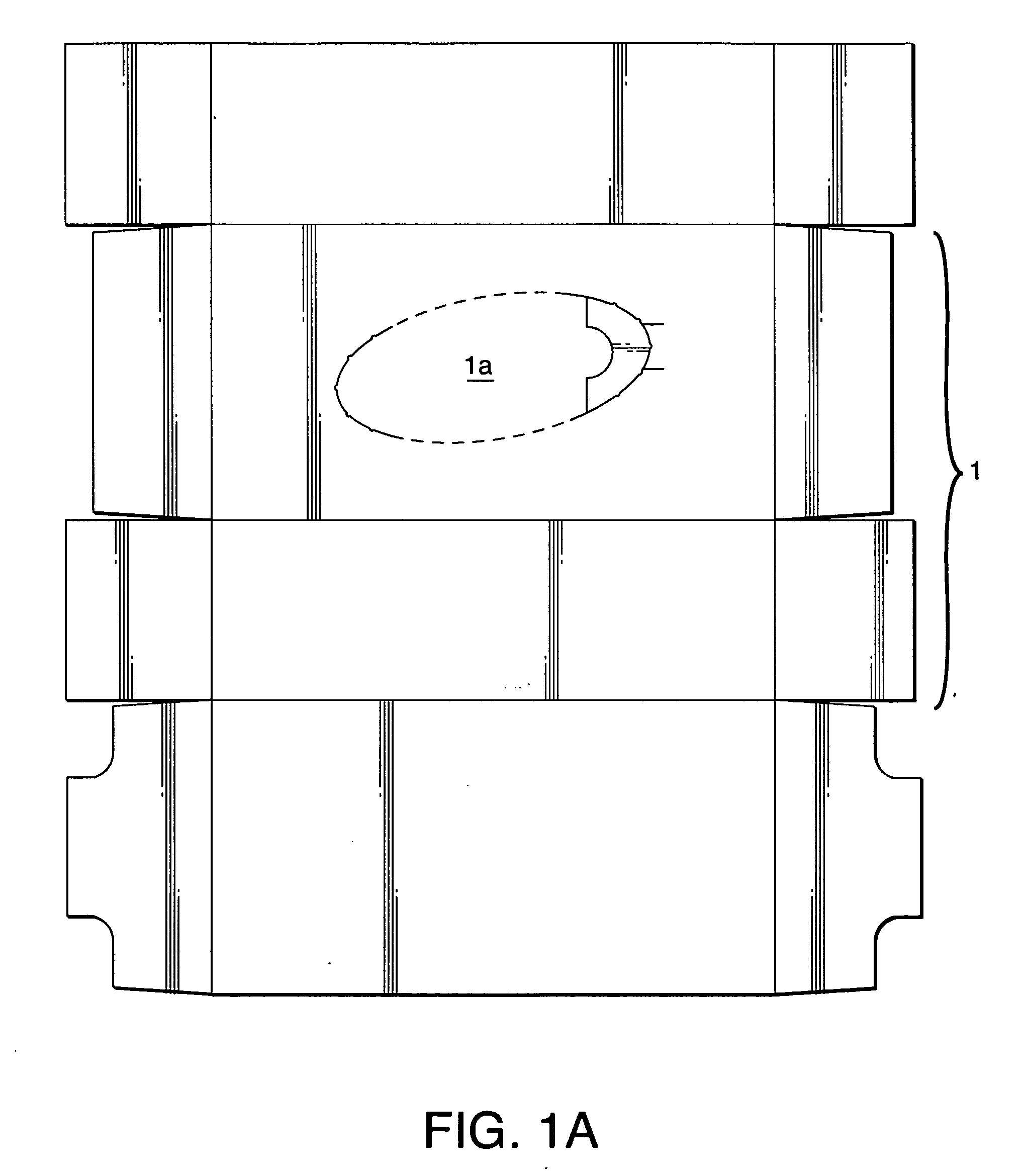

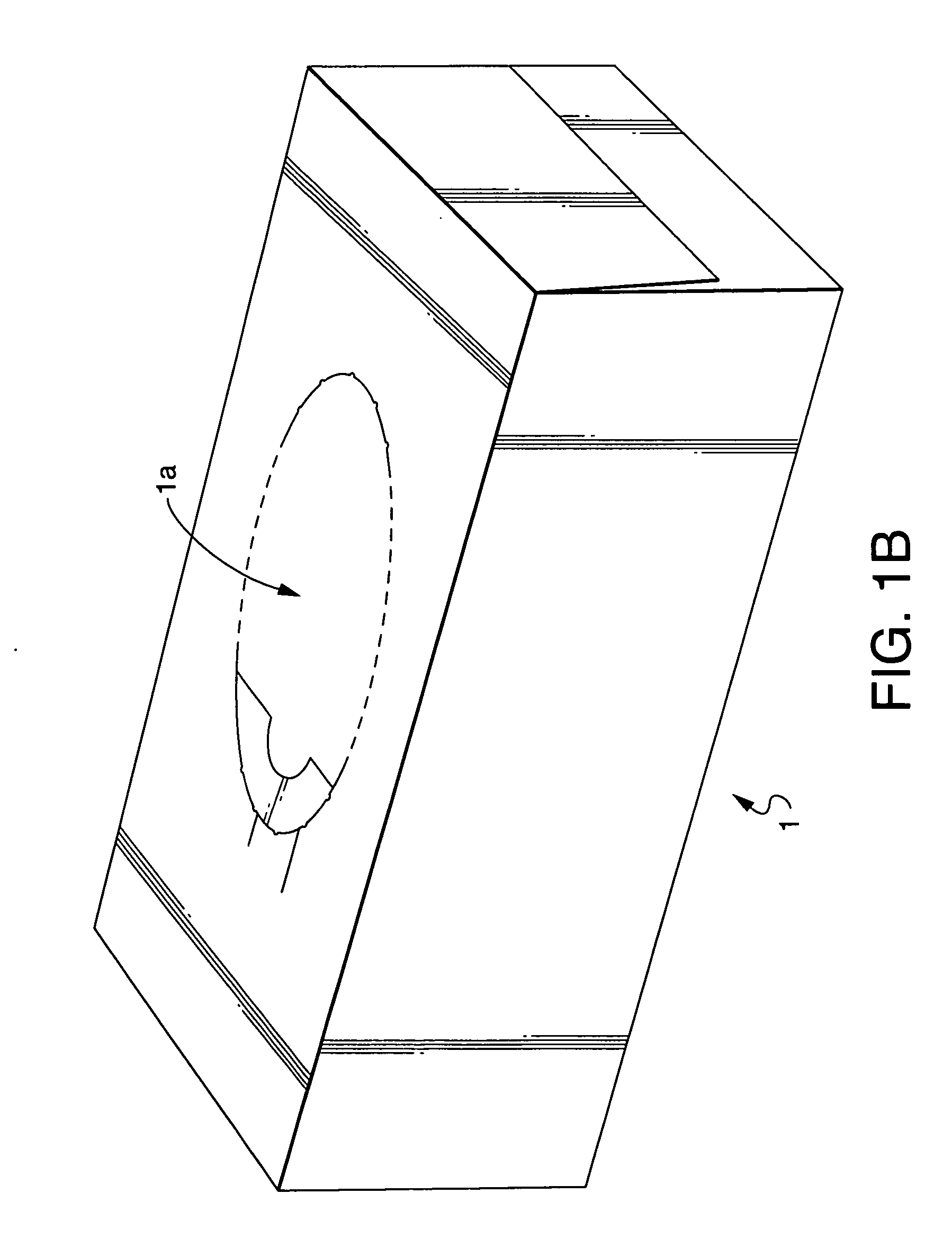

High-volume package dispenser

InactiveUS20070210096A1Easy accessAvoid pollutionDispensing apparatusRigid containersPackage designLarge capacity

A dispenser package system for protective articles, having a new substantially vertical product storage orientation and package design, is described. The package includes a double or multi-chambered dispenser unit that can provide within substantially the same footprint as a conventional dispenser container a greater volume of product. The package can store and dispense at least 50%, up to about 200% or greater capacity than conventional dispenser for protective article products such as gloves or face masks.

Owner:KIMBERLY-CLARK WORLDWIDE INC

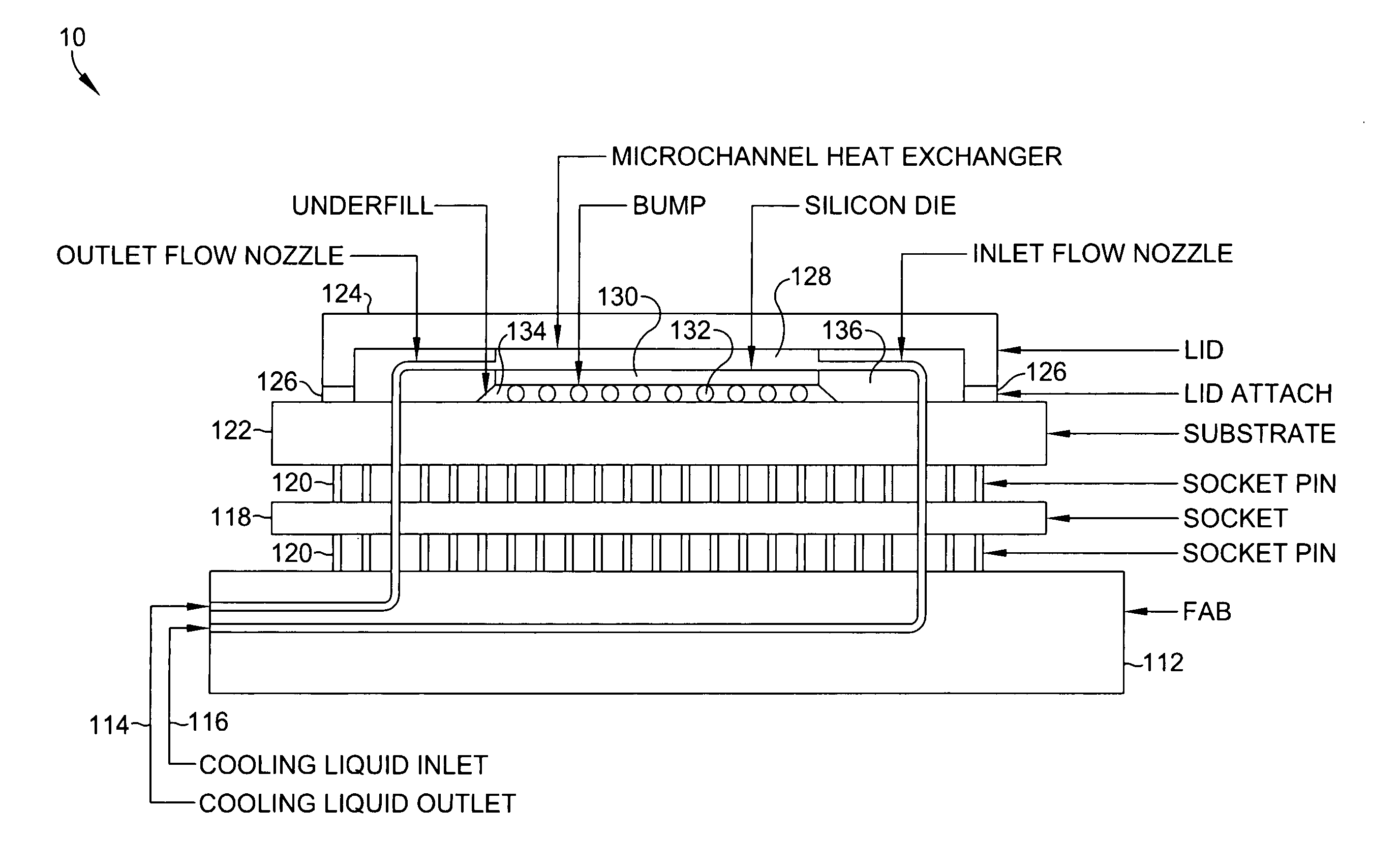

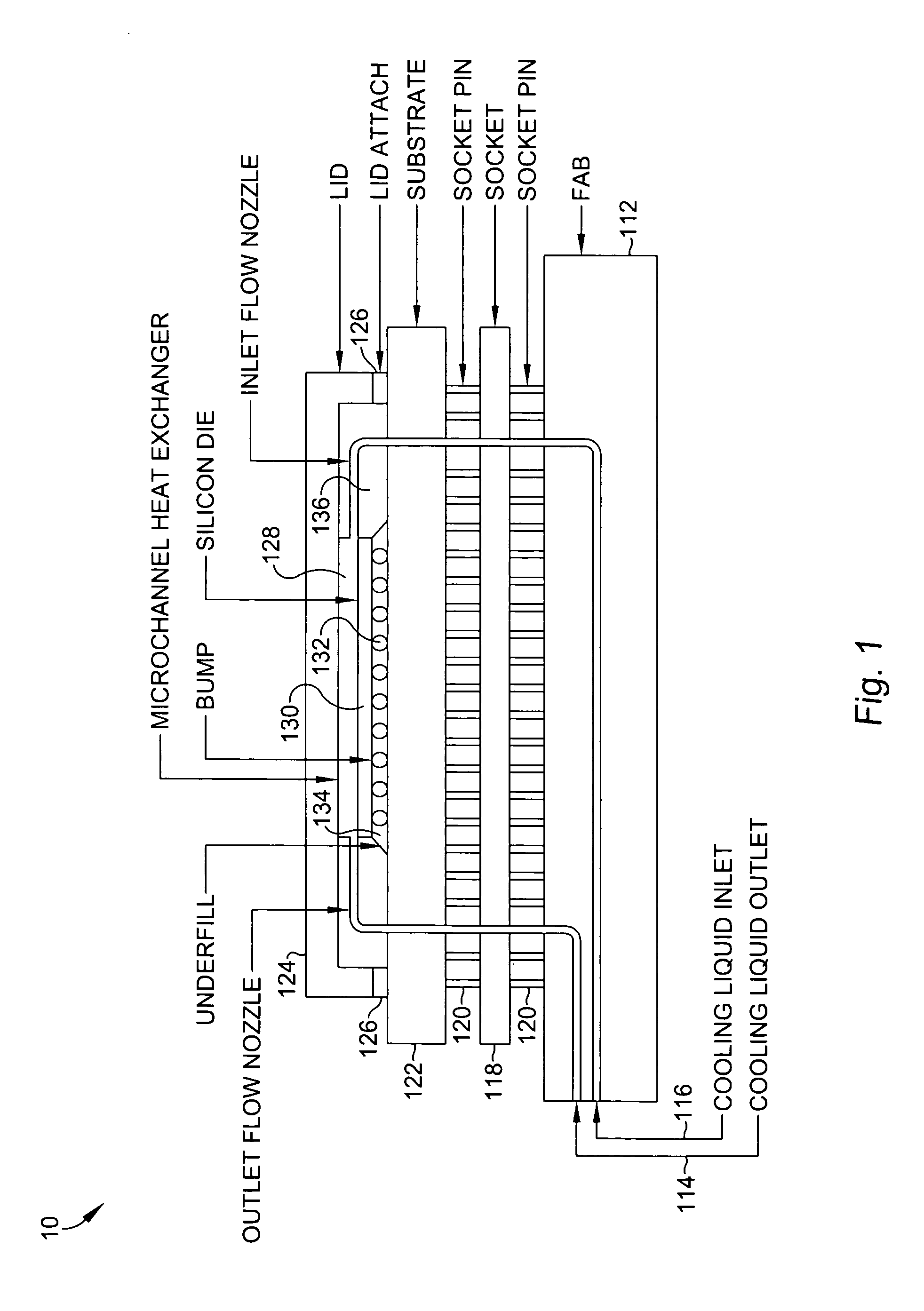

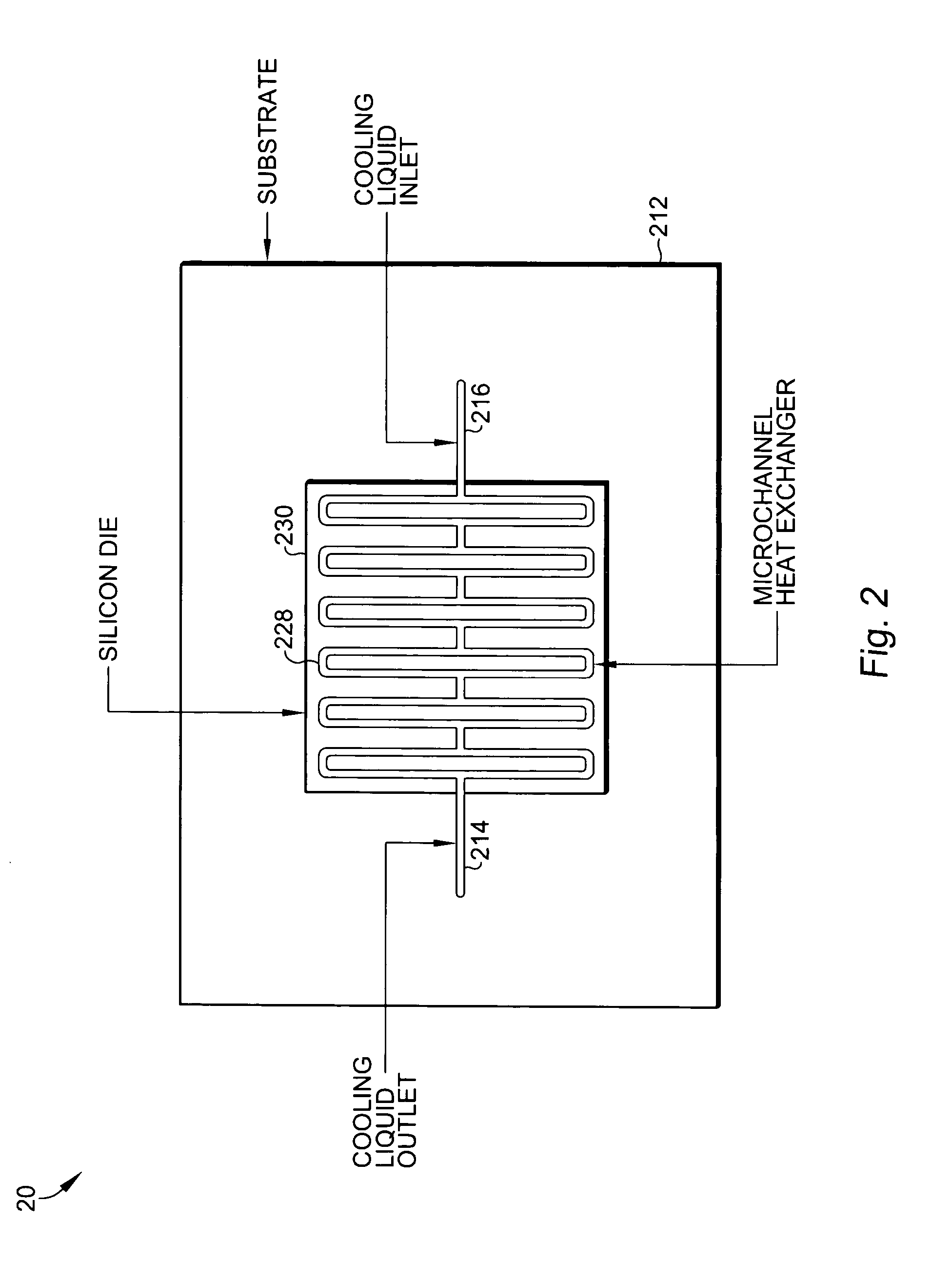

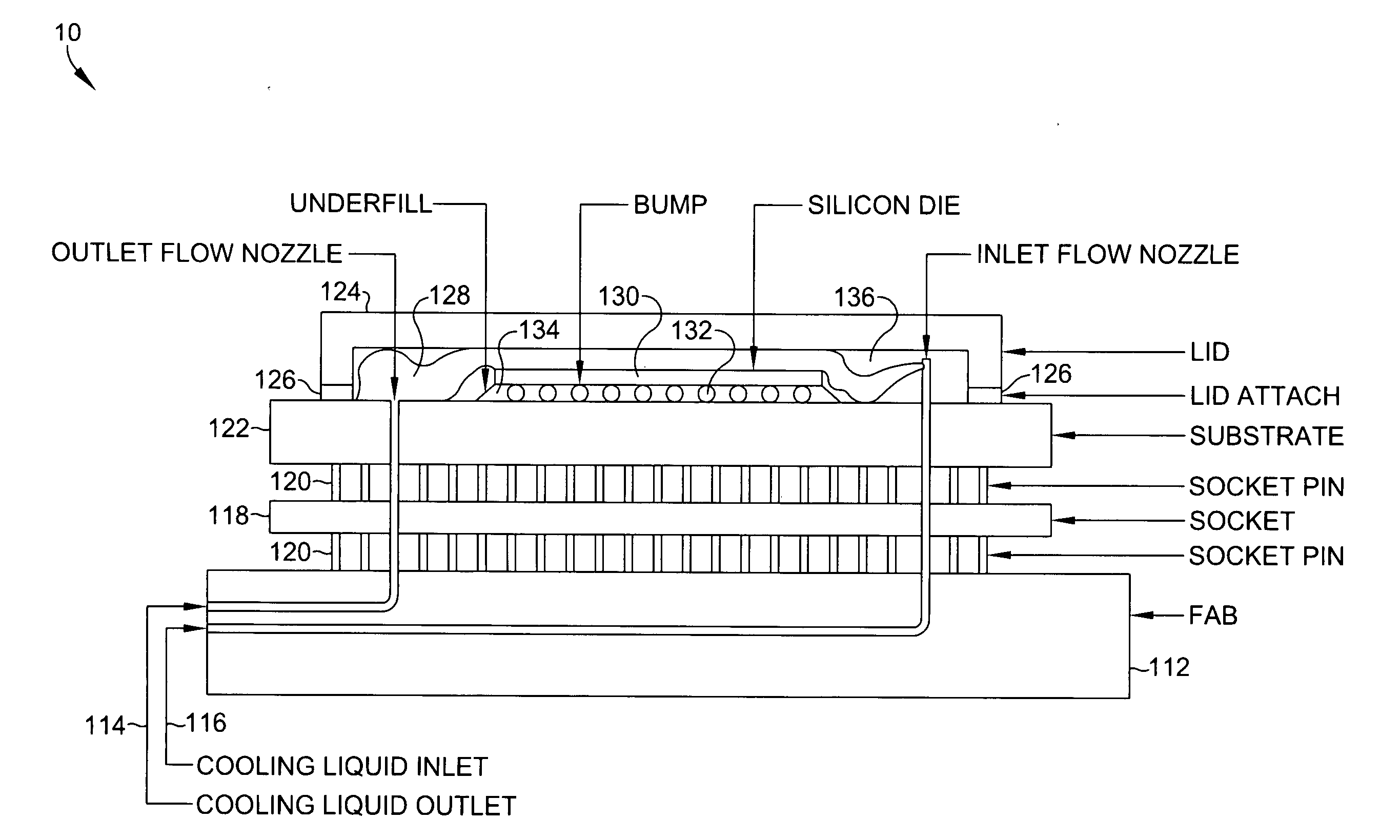

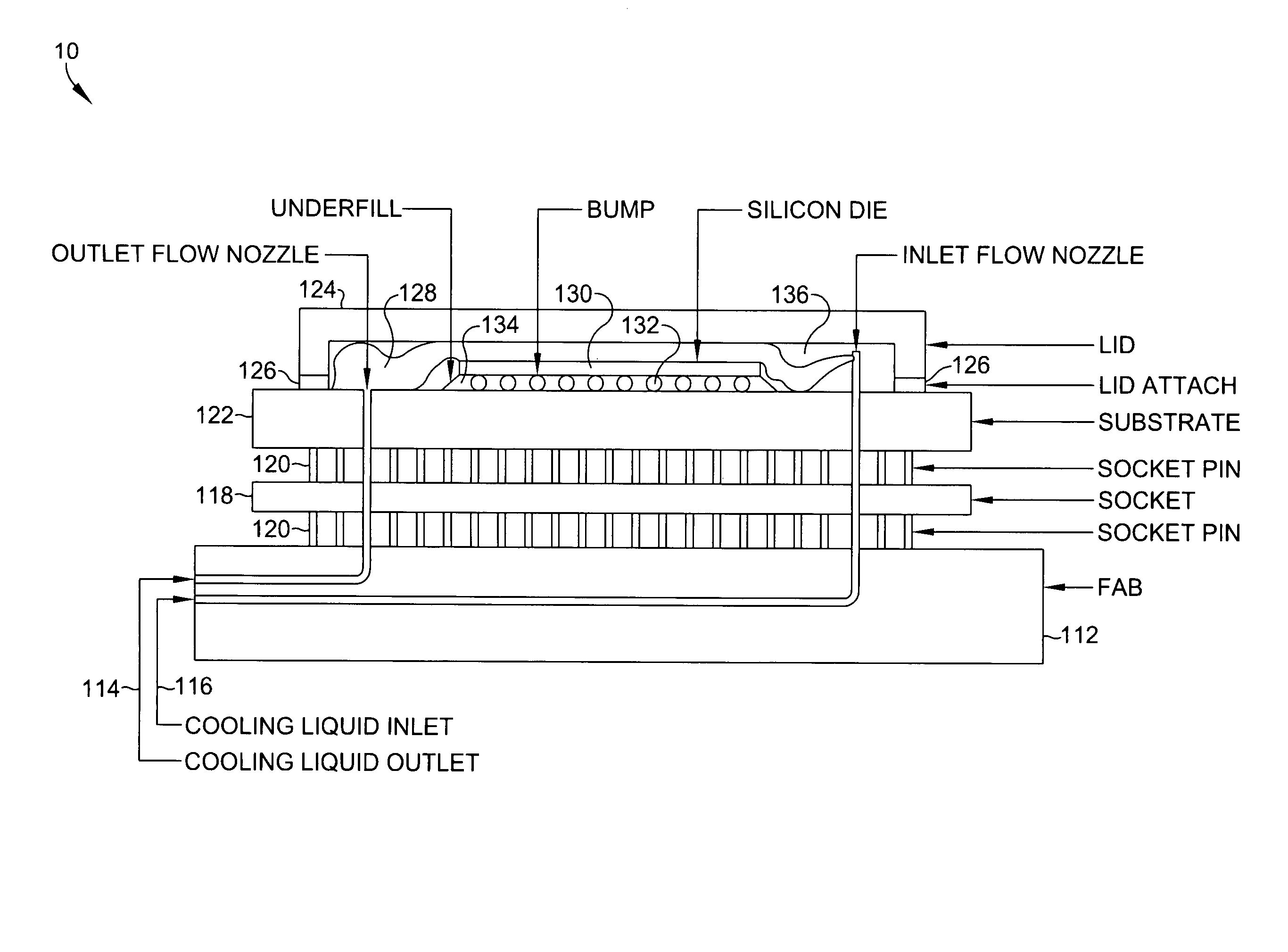

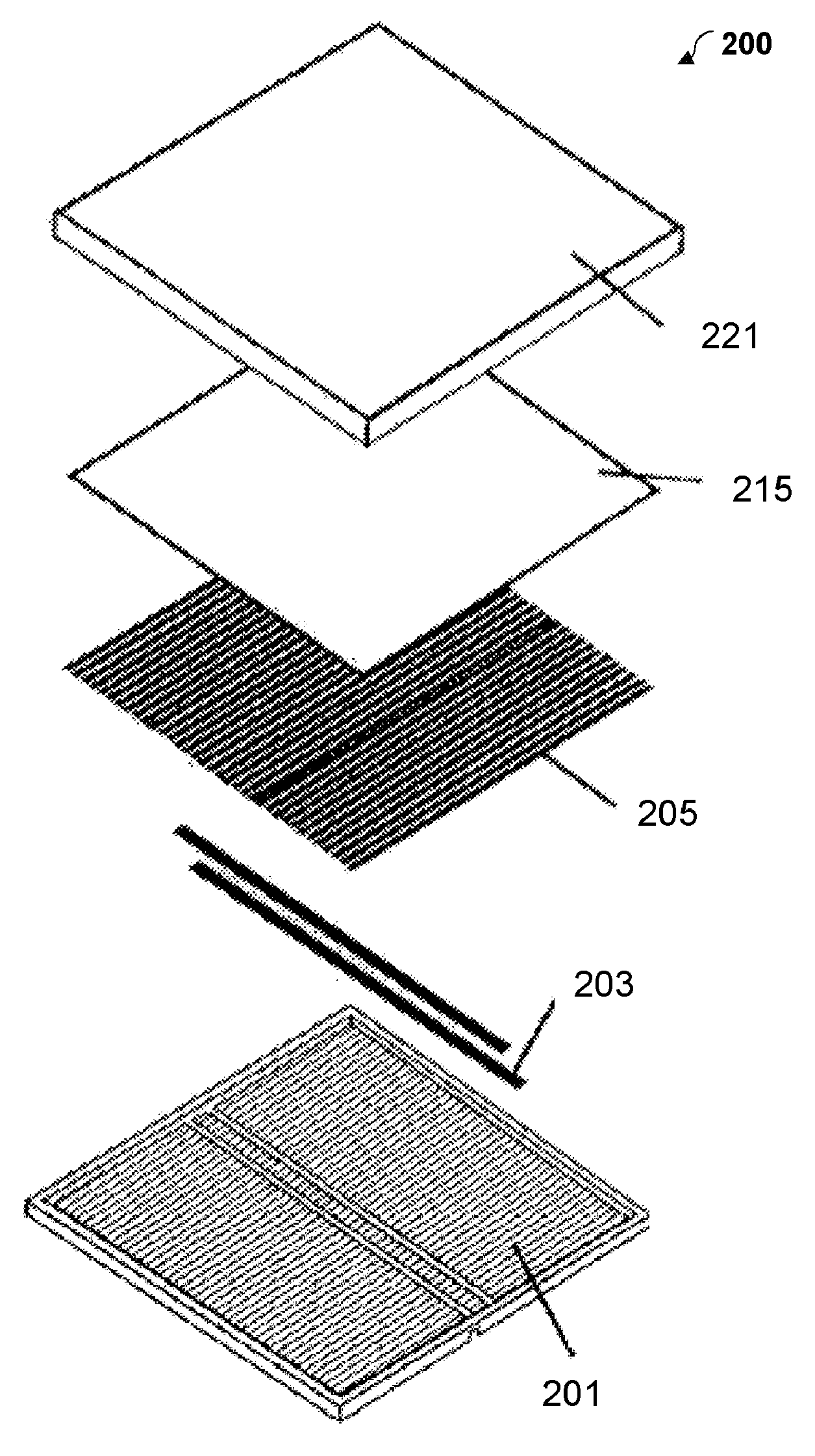

Embedded microchannel cooling package for a central processor unit

ActiveUS7515415B2Efficient thermal managementImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEmbedded system

An indirect cooling liquid embedded package design for use with a computer central processor unit is suitable for thermal management of high heat dissipation electronic components such as server processors. The indirect contact cooling liquid embedded packaged CPU has mechanical coupling and embedded plumbing that attaches to the board pumped liquid supply and indirect cooling of the heat-generating portion of the CPU with an embedded microchannel heat exchanger. The coolant package system for the CPU removes higher levels of heat indirectly from the core of the processors by convective cooling. Cooling liquid is introduced into the package of the server CPU by mechanically attaching the CPU to the board through a socket interconnect. Pins of the socket serves to provide electrical connection between the board and the CPU, while a few pins are designed for the purpose of inletting and outletting cooling liquid into and out of the CPU package.

Owner:ORACLE INT CORP

Method for estimating respondent rank order of a set stimuli

A computer implemented method to estimate a respondent's or a set of respondents' rank order with respect to a number of attribute options (i.e. alternative prices, features, benefits, ways of expressing benefits, brand names, slogans, logos, graphic treatments such as package design elements and any other stimuli that the researcher believes may influence the individual's opinion such as a statement, graphic or brief audio). The method can be used when the number of stimuli to be presented exceeds the number that can be presented at one time to a respondent, most typically, exceeding the number that can be legibly displayed on one computer screen for rank ordering by a respondent. The estimated rank order is highly accurate, especially for the highest ranked stimuli, but requires only a small fraction of the respondent input that would be needed to capture a complete rank order from that respondent. This abstract is provided as an aid for finding relevant disclosures and not as a limitation on the scope of the claims.

Owner:WHITE WILLIAM DONALD

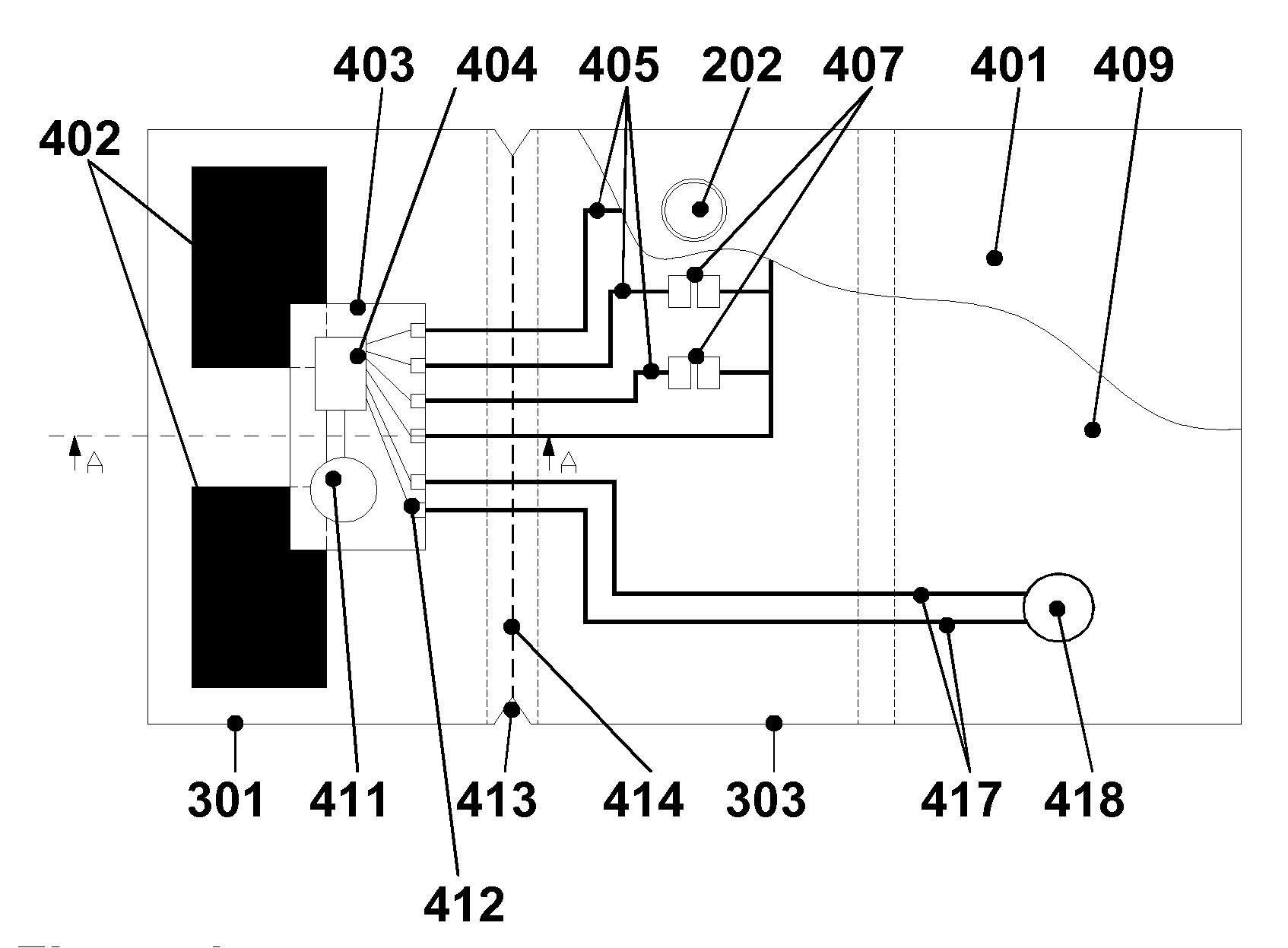

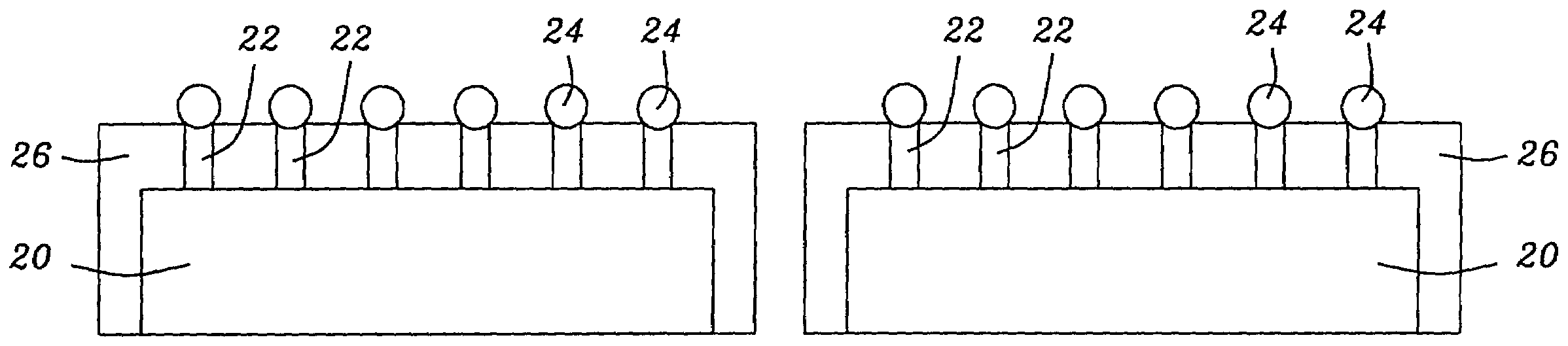

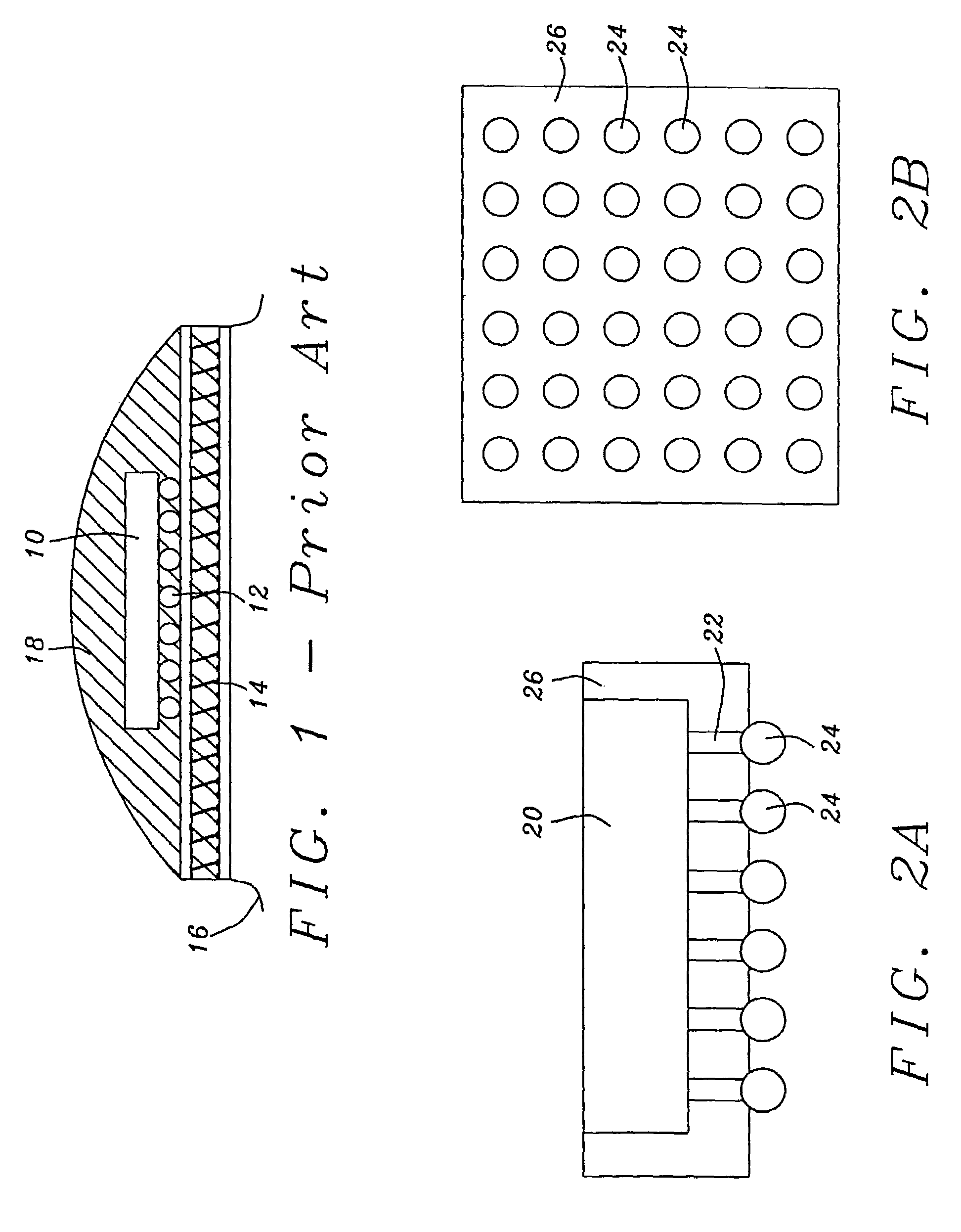

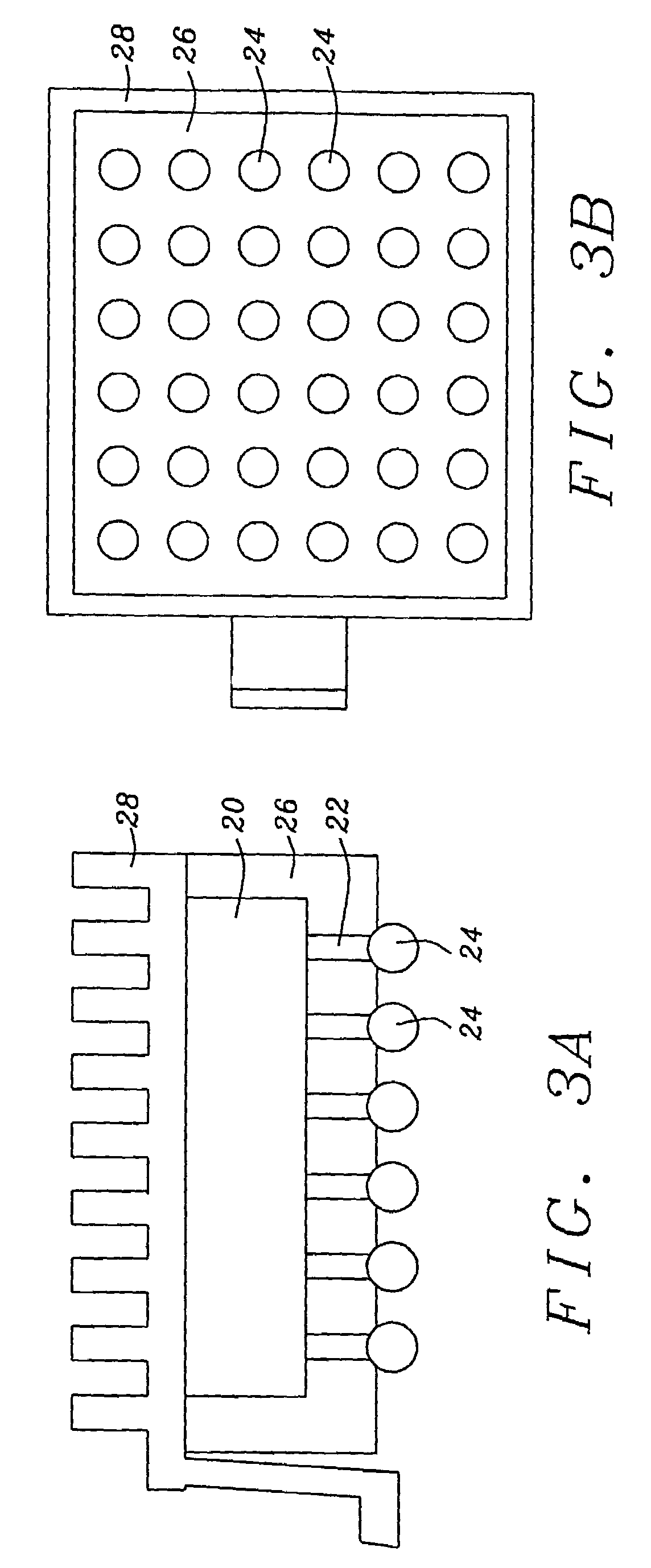

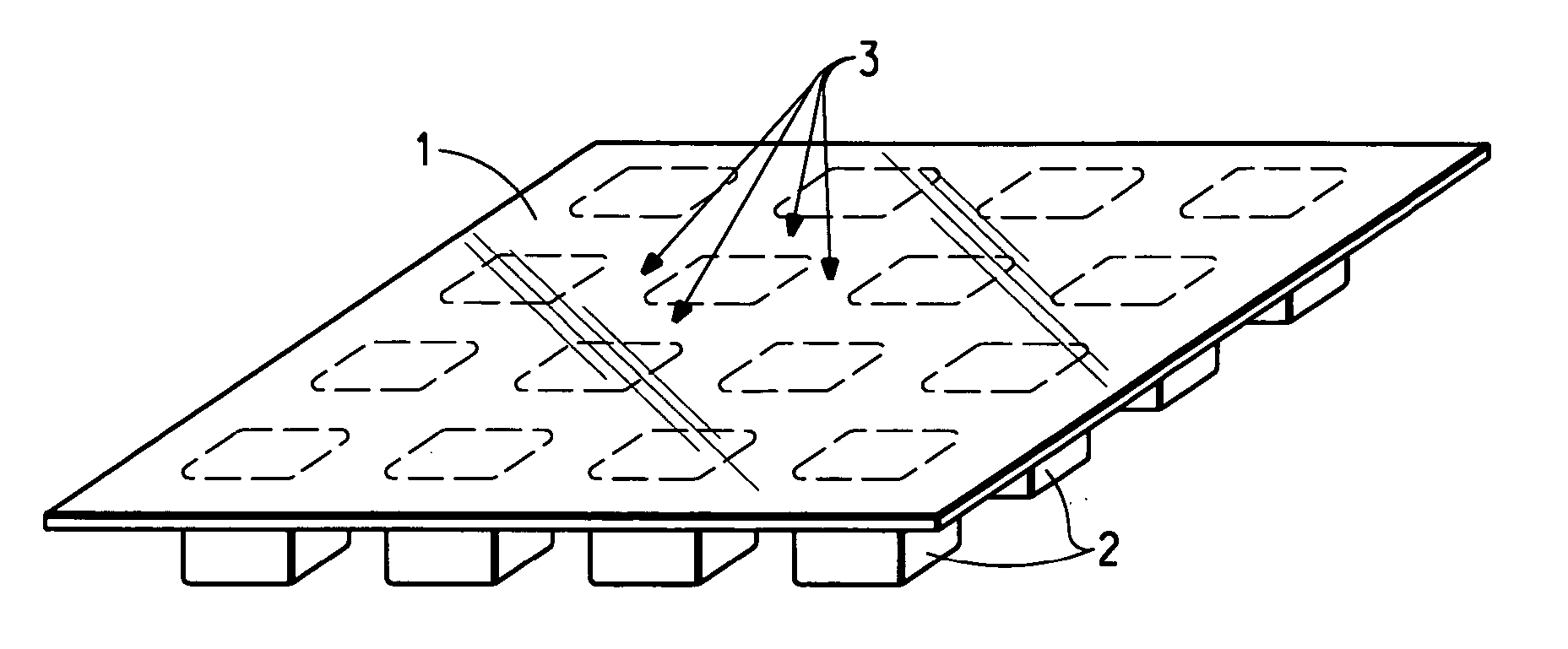

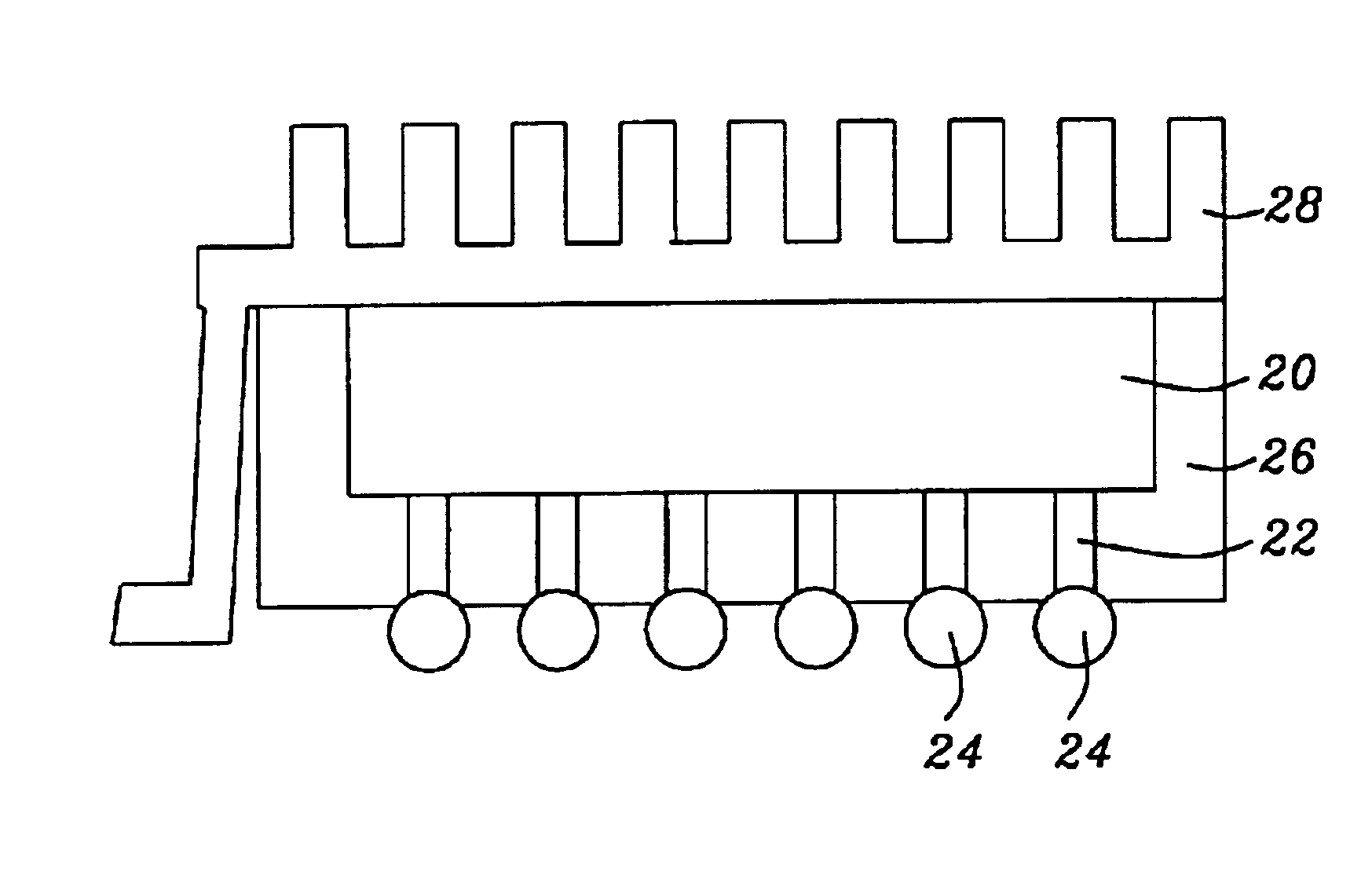

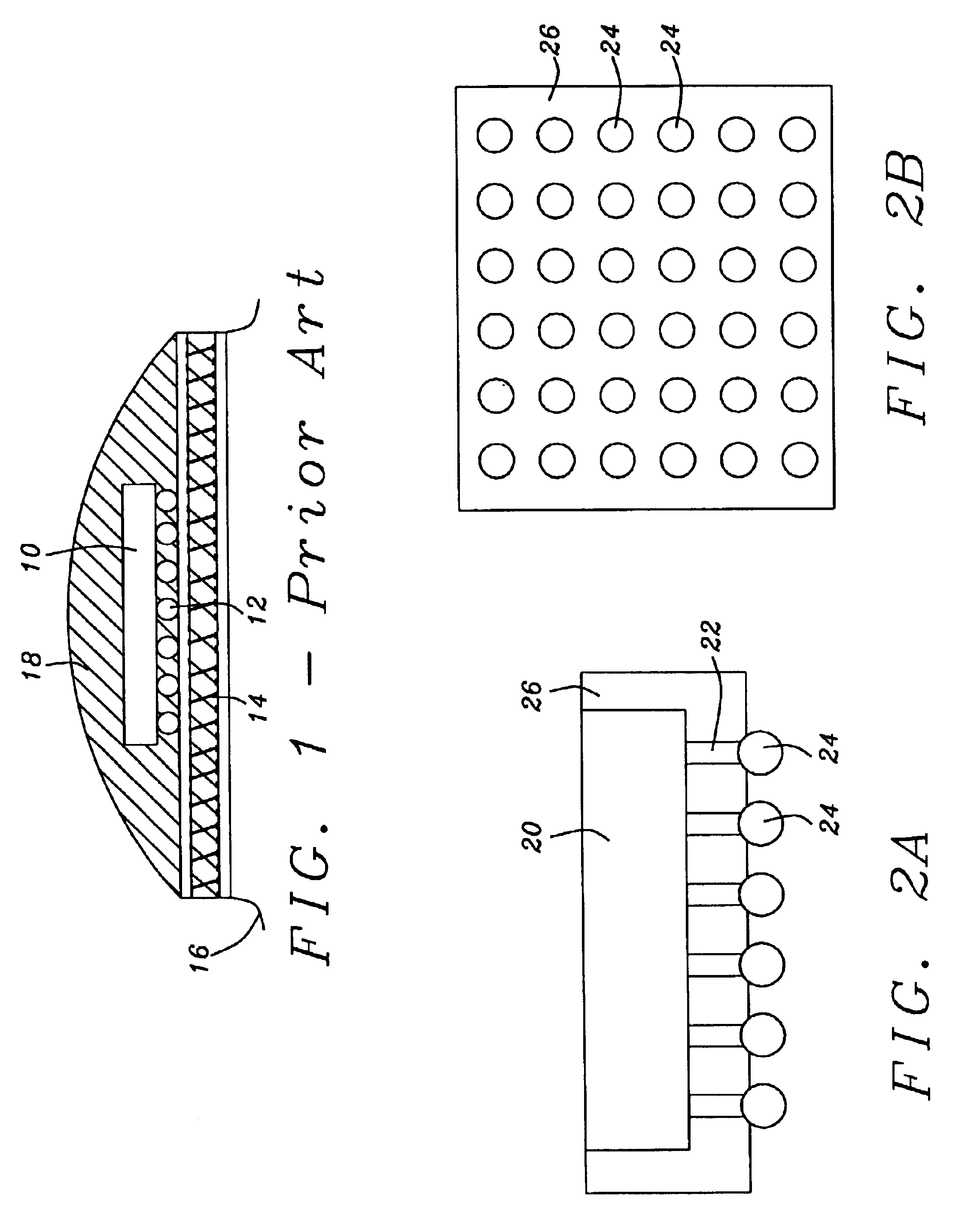

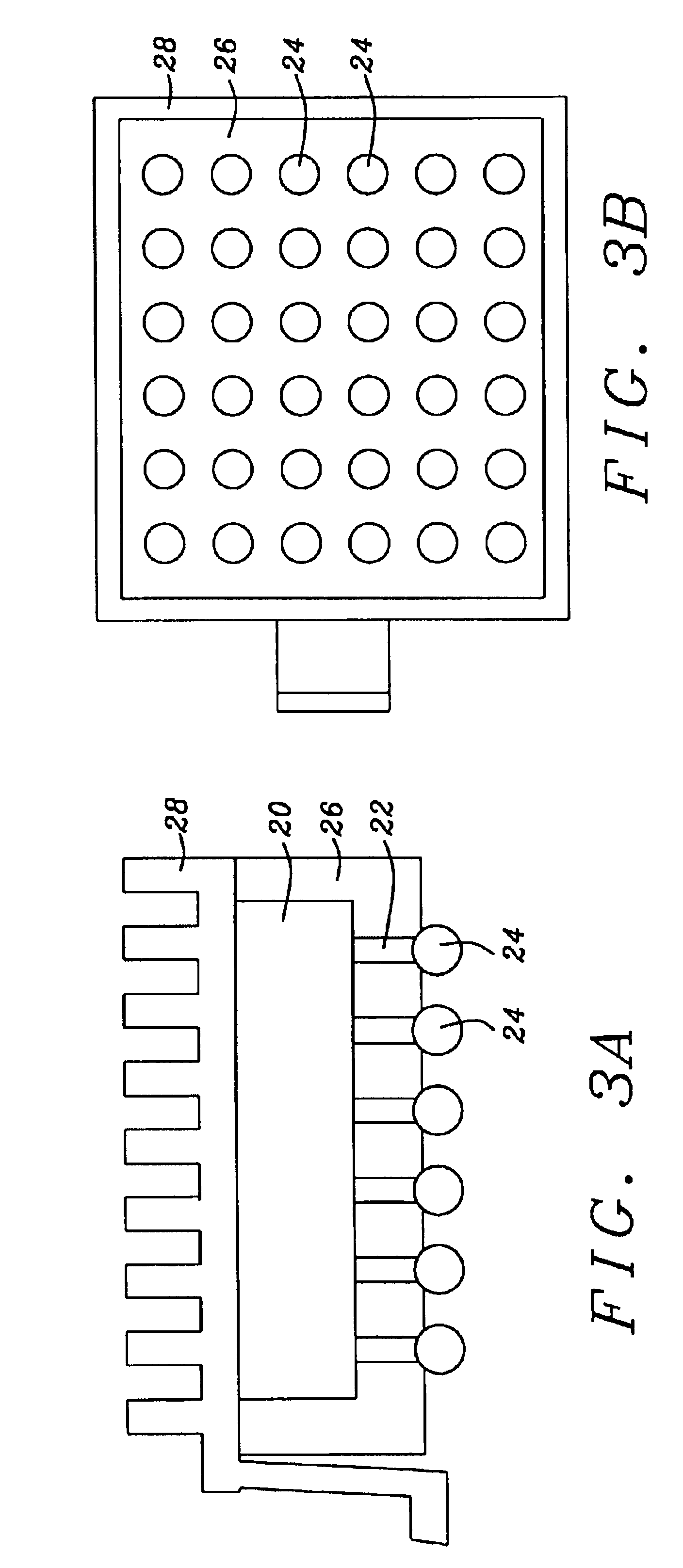

Package design and method of manufacture for chip grid array

InactiveUS7456496B2Eliminate needProtect environmentSemiconductor/solid-state device detailsSolid-state devicesPackage designSemiconductor chip

A chip level package utilizing a CGA is described. A semiconductor chip with pillars is molded in an encapsulant. Solder balls are added and connected to the chip pillars. The final package does not require a first level substrate or interposer and is able to be assembled to the next level as is. An additional embodiment describes the addition of a thermal heat sink to the packaged chip.

Owner:ADVANPAK SOLUTIONS PTE

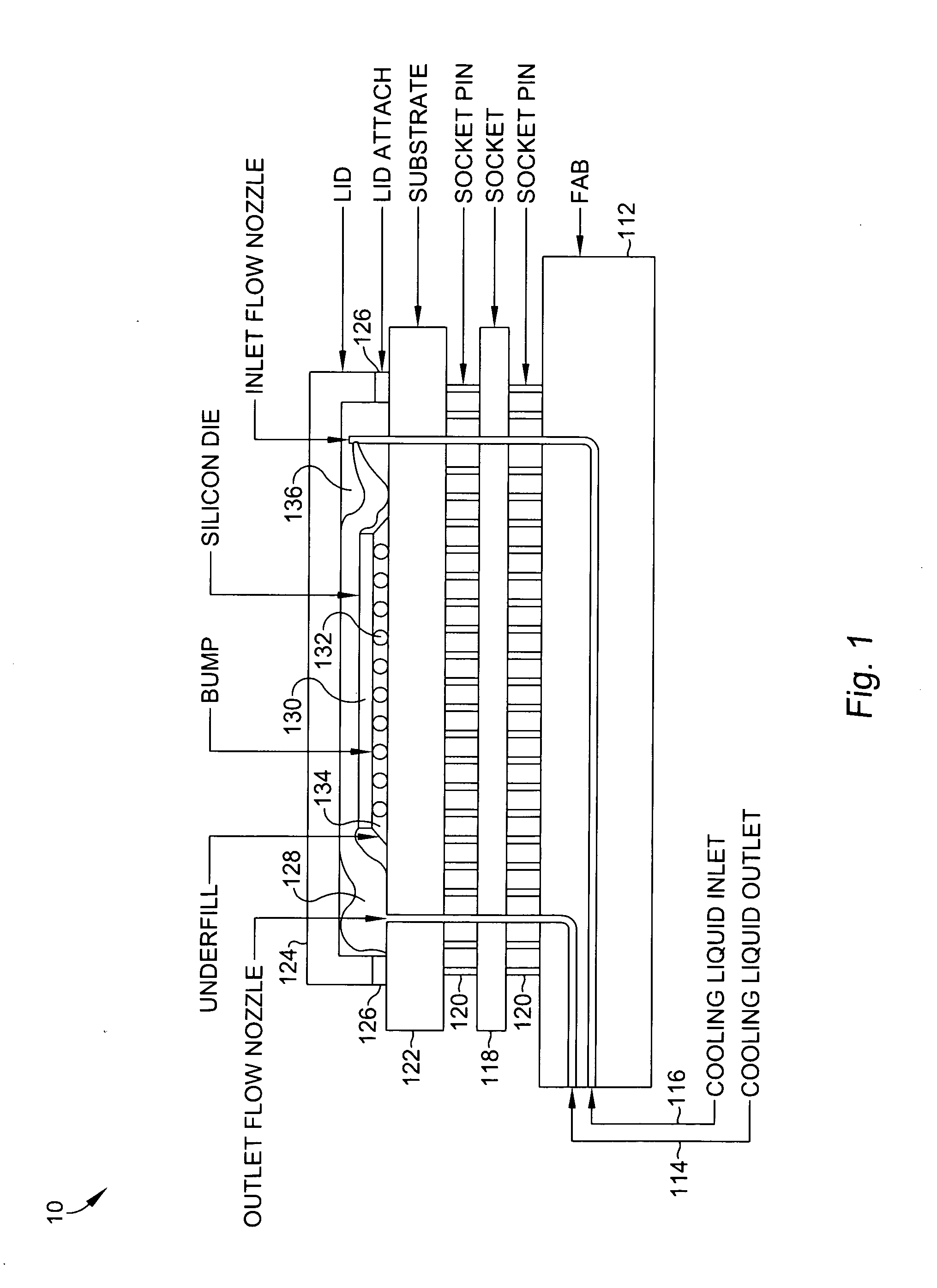

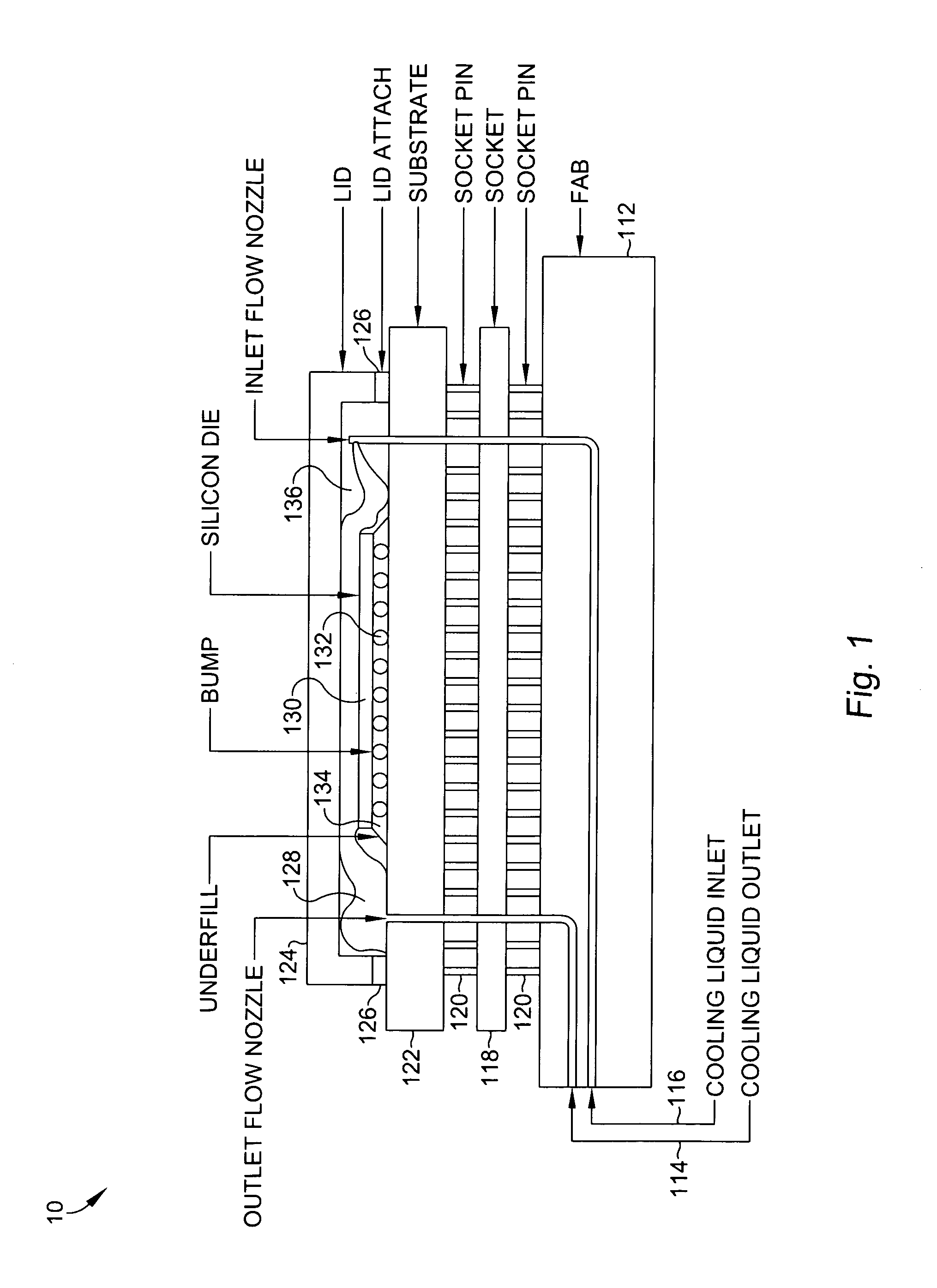

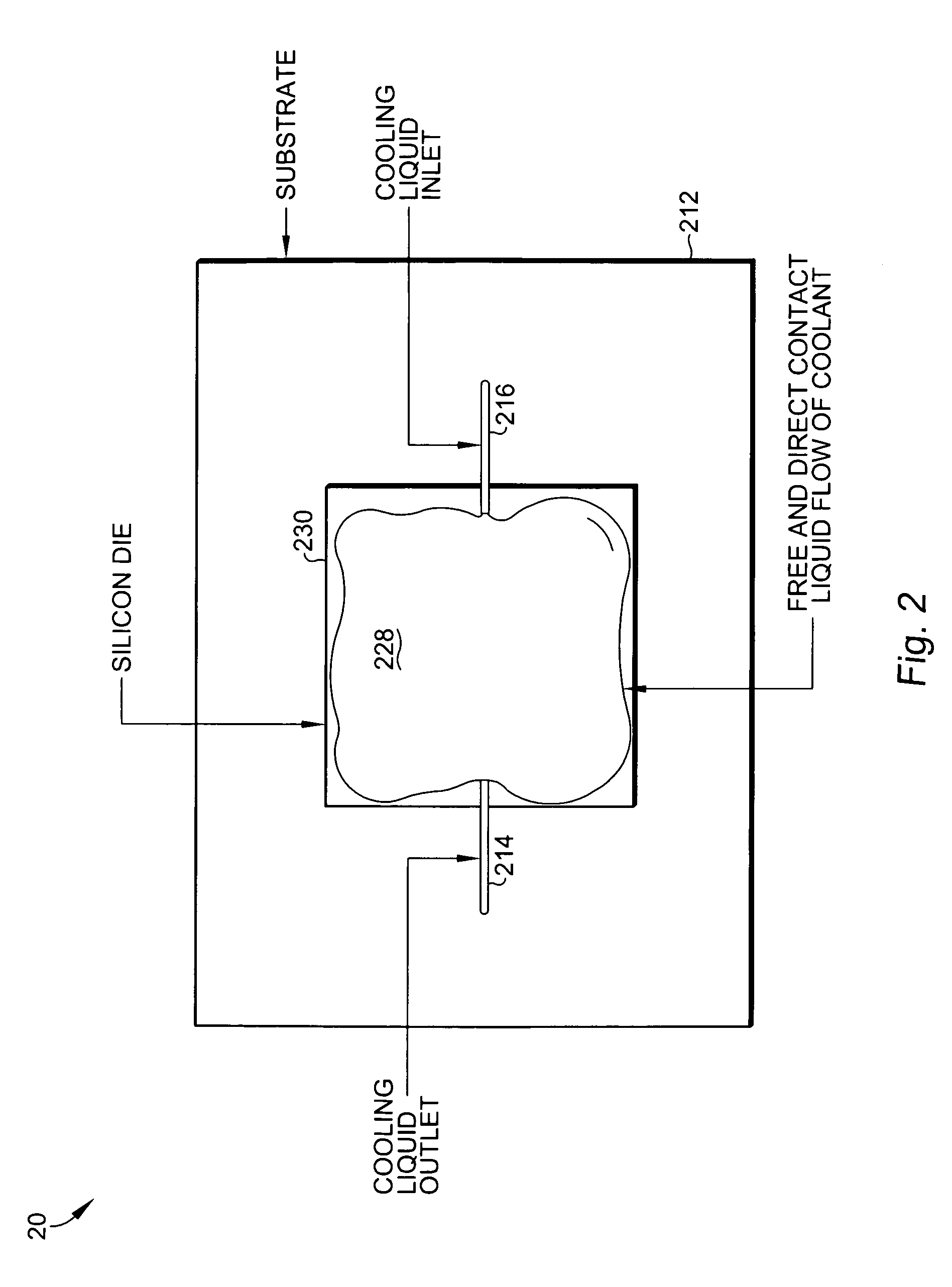

Direct contact cooling liquid embedded package for a central processor unit

ActiveUS20070177352A1Avoid a lotAvoid introducingSemiconductor/solid-state device detailsSolid-state devicesCouplingPackage design

A direct contact cooling liquid embedded package design for use with a computer central processor unit is suitable for thermal management of high heat dissipation electronic components such as server processors. The direct contact cooling liquid embedded packaged CPU has mechanical coupling and embedded plumbing that attaches to the board pumped liquid supply and direct contact cooling liquid of the heat-generating portion of the CPU. A direct contact cooling liquid embedded packaged CPU removes higher levels of heat directly from the core of the processors by convective cooling. Cooling liquid is introduced into the package of the server CPU by mechanically attaching the CPU to the board through a socket interconnect. Pins of the socket serve to provide electrical connection between the board and the CPU, while a few pins are designed for the purpose of inlet and outletting cooling liquid into and out of the CPU package.

Owner:ORACLE INT CORP

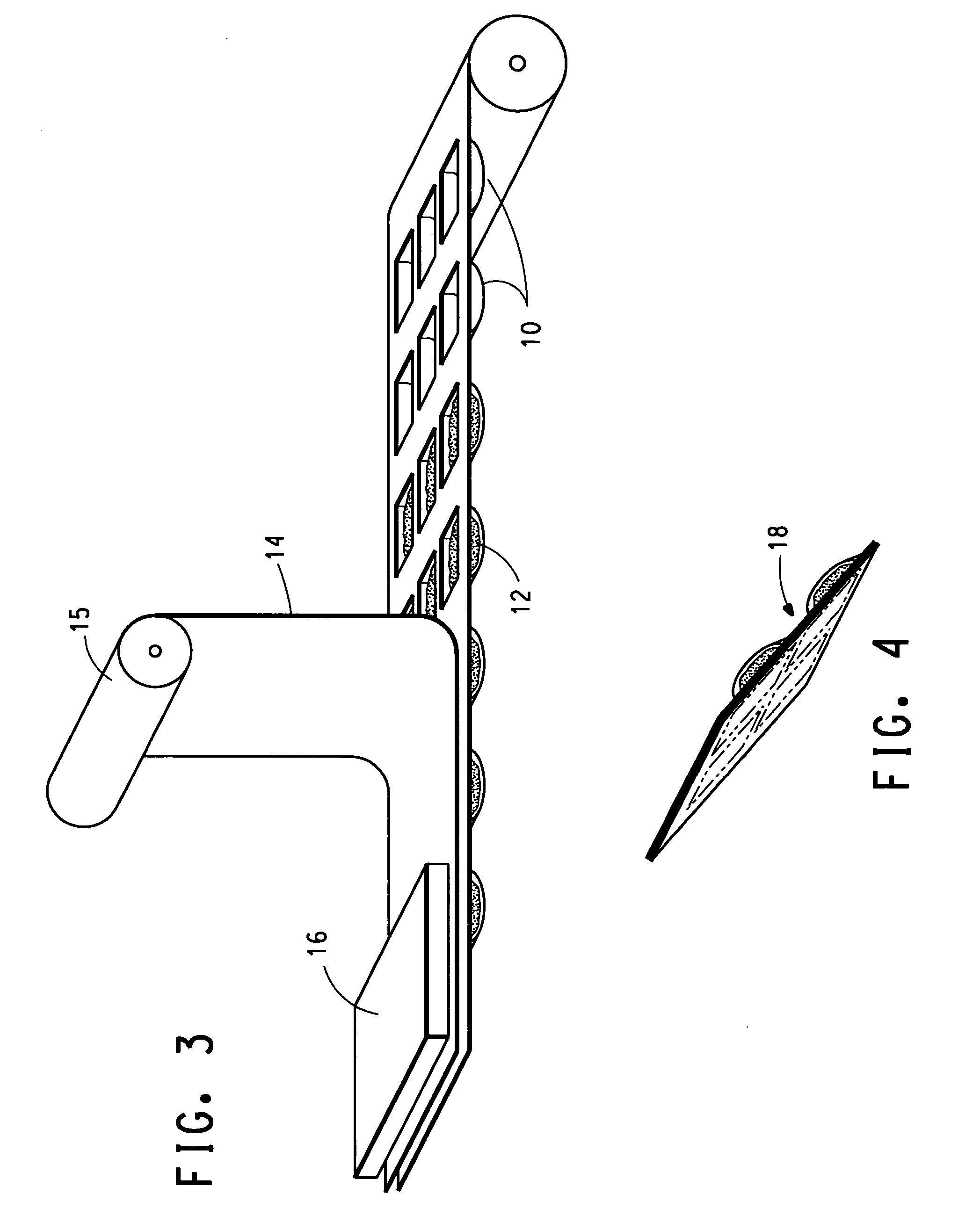

Child-resistant blister package

InactiveUS20050139505A1Small article dispensingSynthetic resin layered productsPackage designPuncture resistance

An improved child-resistant blister package is provided in which the lidding component includes a tear-resistant nonwoven layer and a barrier layer. The nonwoven layer can be a melt-spun continuous filament nonwoven web or a flash spun plexifilamentary sheet. The lidding component used in peel off-push through blister packages of the invention contains fewer layers and has improved puncture resistance compared to lidding components used in child-resistant packages known in the art. In addition, in peel off-push through and peel-open package designs of the present invention, the lidding peels more cleanly from the blister component compared to packages known in the art which have a tendency to tear during peeling.

Owner:EI DU PONT DE NEMOURS & CO

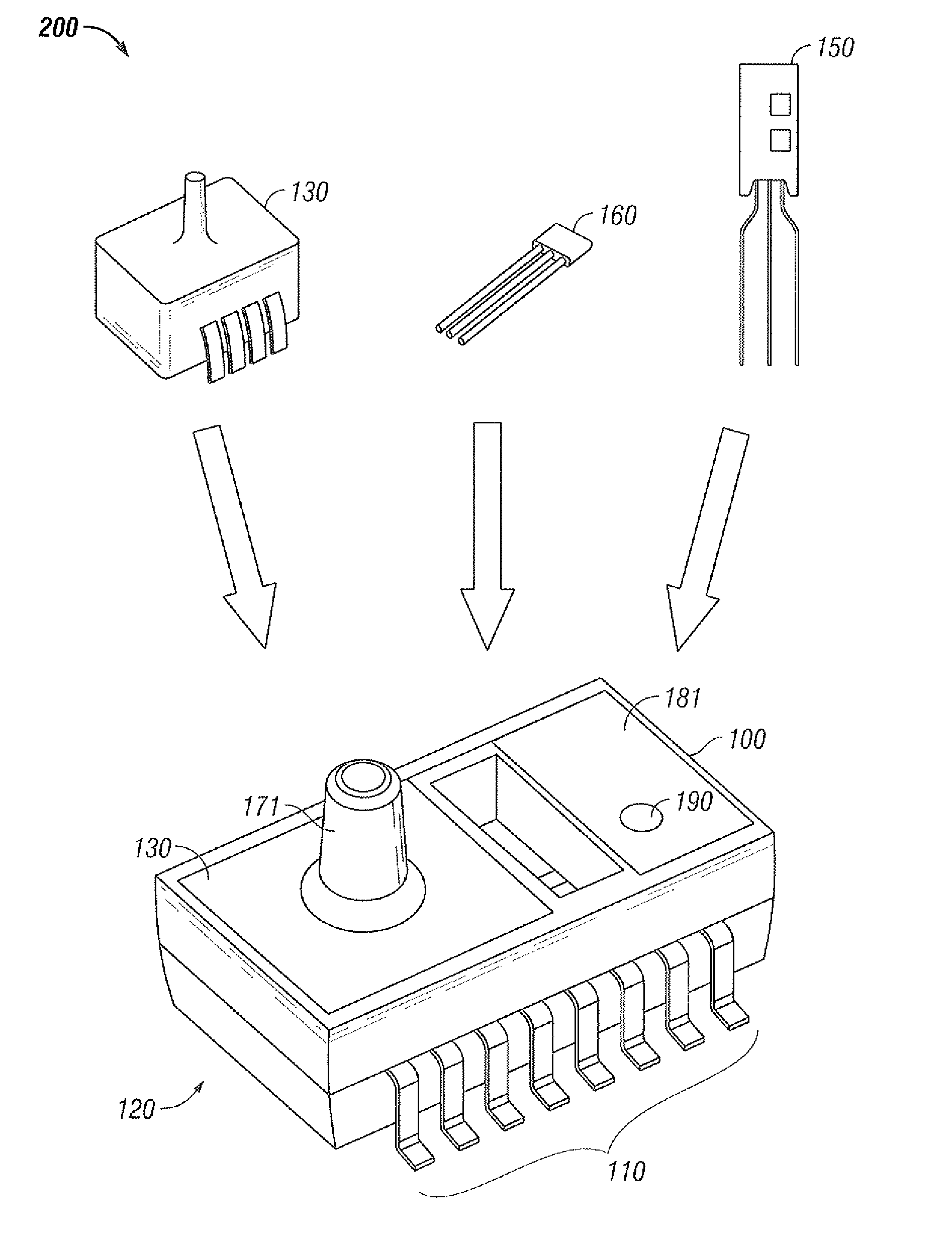

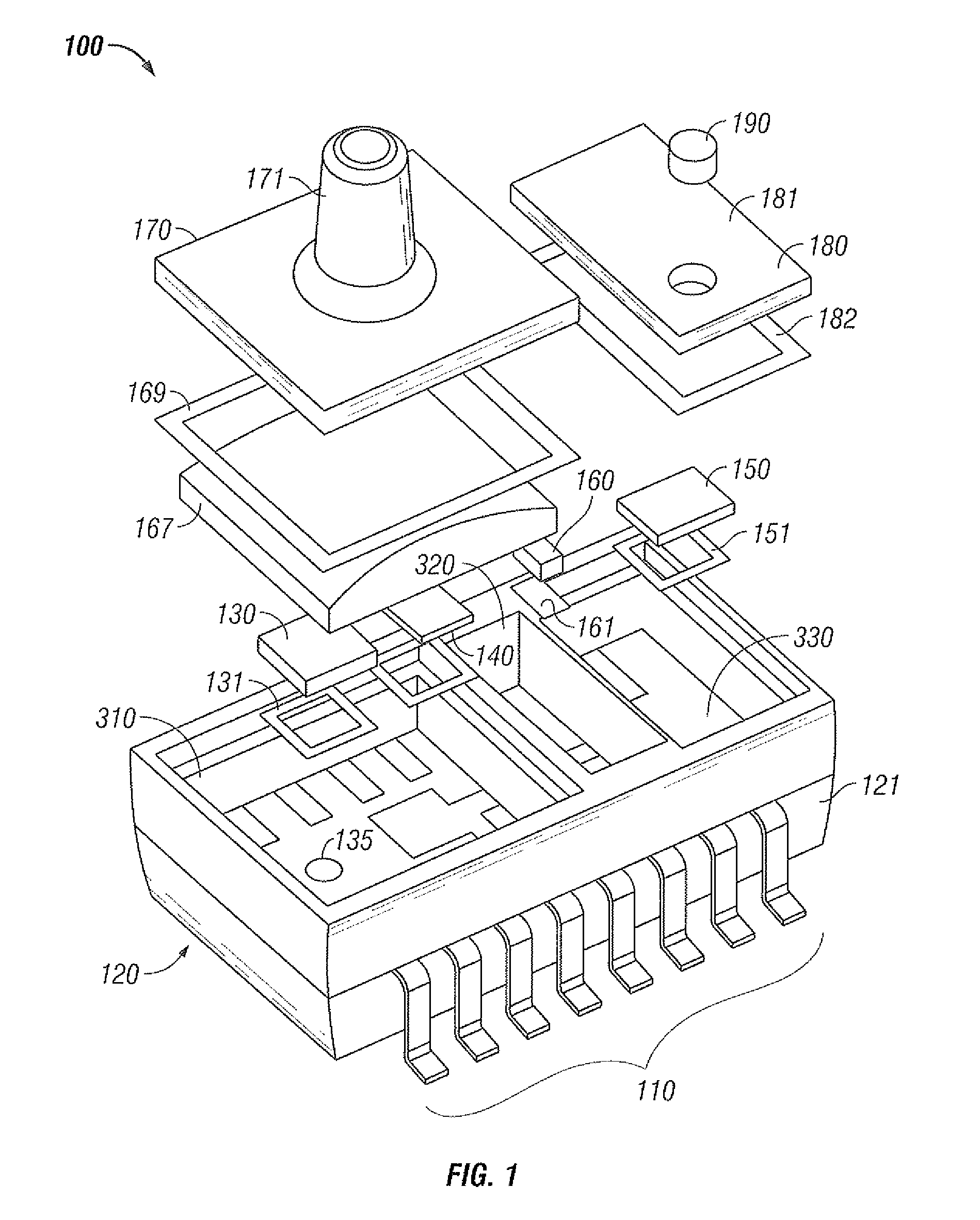

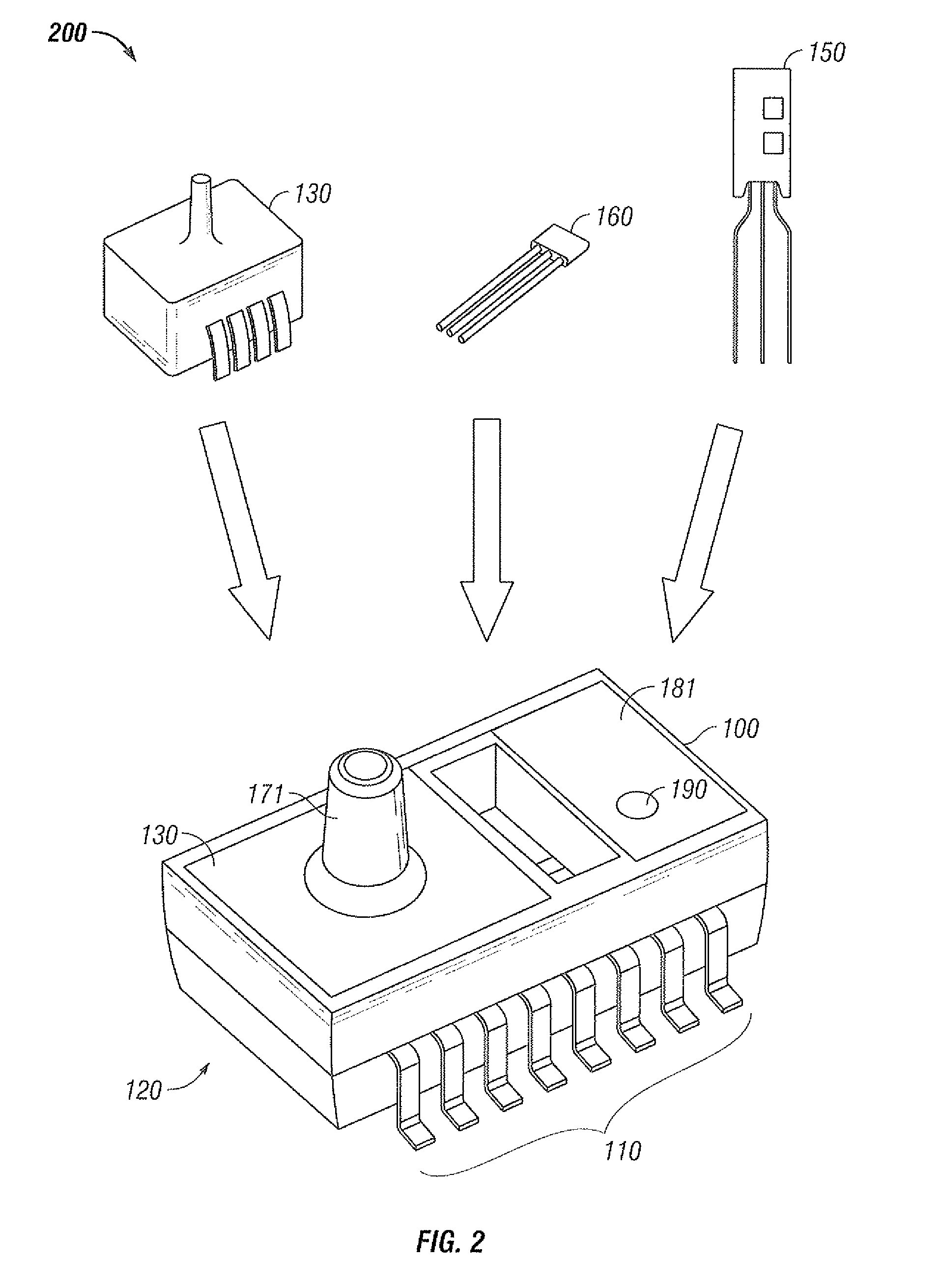

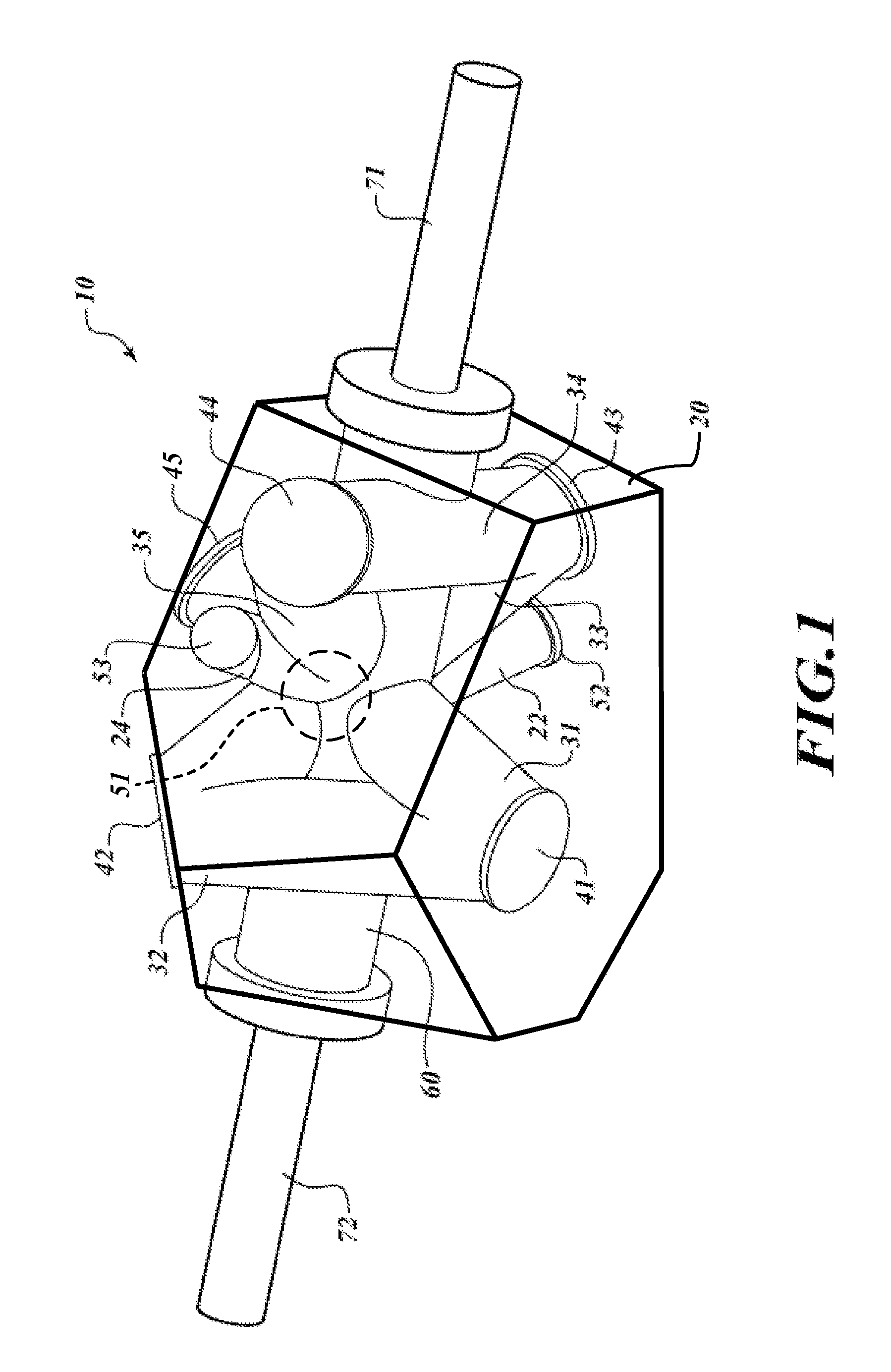

Integrated mechanical package design for combi sensor apparatus

InactiveUS20090288484A1Low costSmall sizeThermometer detailsMeasurement apparatus componentsPackage designElectrical connection

An integrated mechanical combi sensor apparatus and method for measuring humidity, pressure and temperature. A pressure sensor and an ASIC can be mounted in a first compartment, and a temperature sensor mounted in a second compartment of a housing. Similarly, a humidity sensor can be mounted in a third compartment such that the pressure sensor, temperature sensor, and humidity sensor are isolated from each other. The sensor element associated with the sensors and the ASIC can be connected to a lead frame terminal by wire bonding for electrical connection. A pressure cover and a humidity cover can be utilized for covering the pressure sensor and the humidity sensor. The humidity sensor can include a hydrophobic filter for preventing moisture-saturated air from reaching the sensing element in order to provide accurate sensor measurements thereof.

Owner:HONEYWELL INT INC

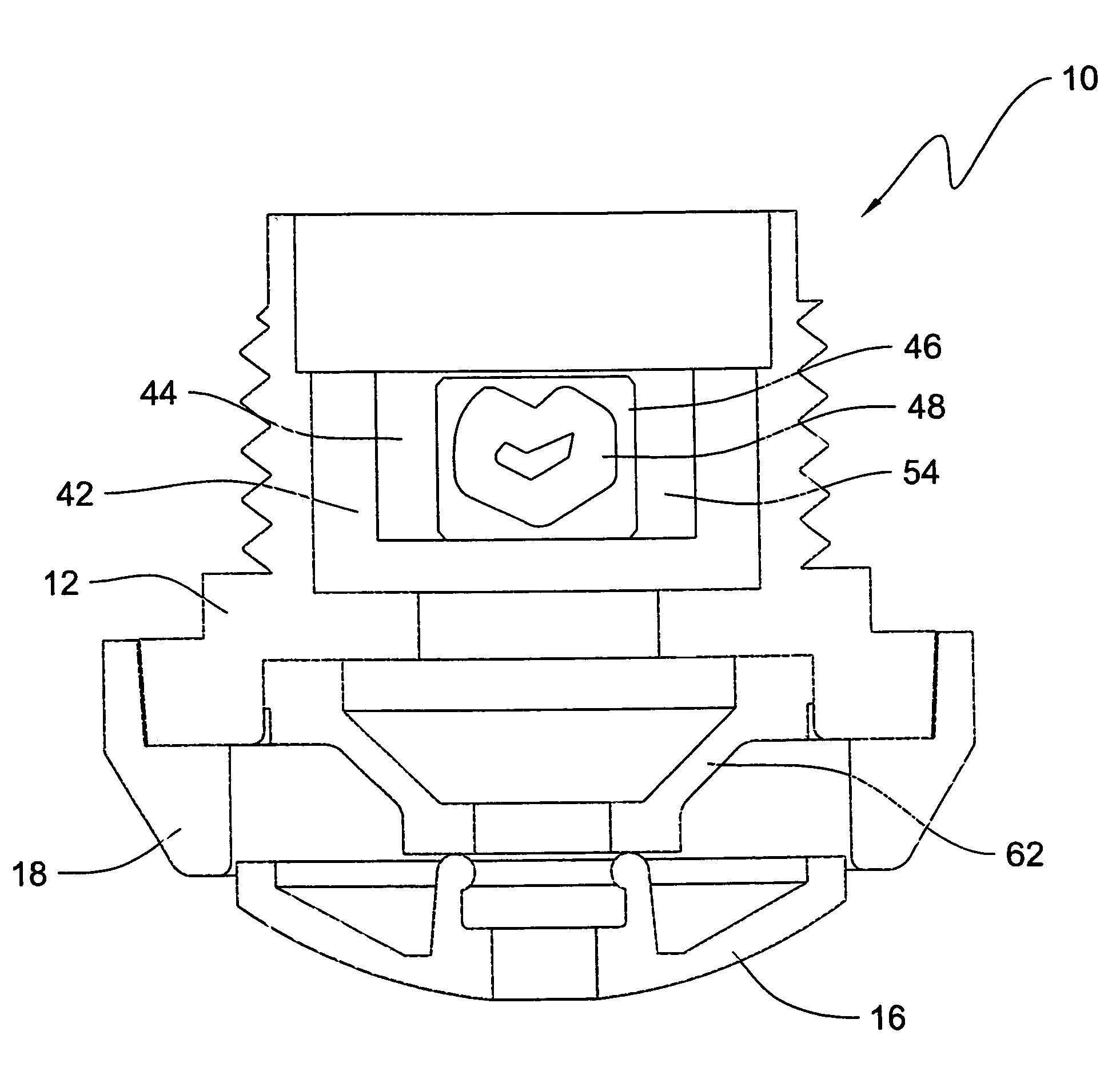

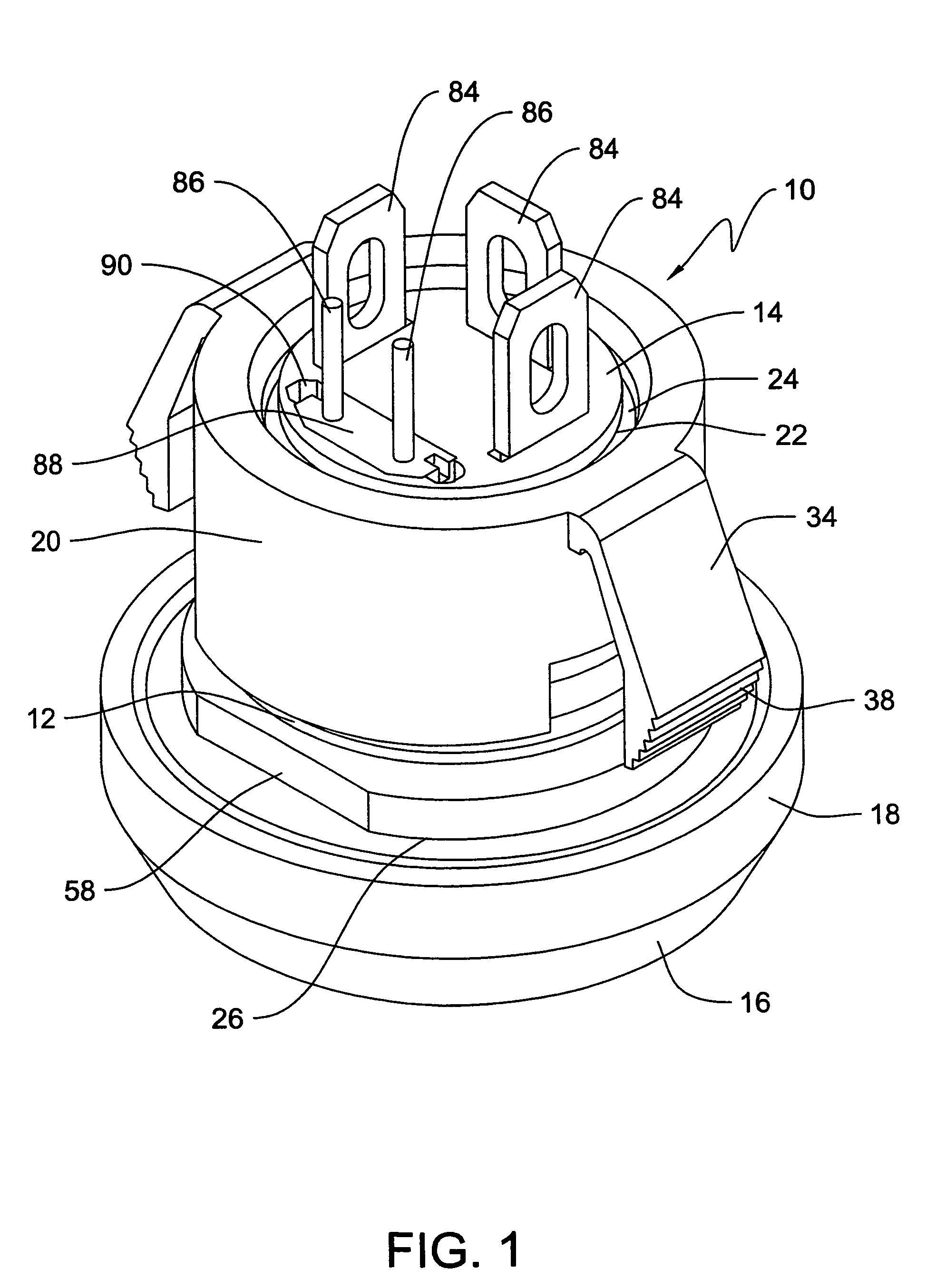

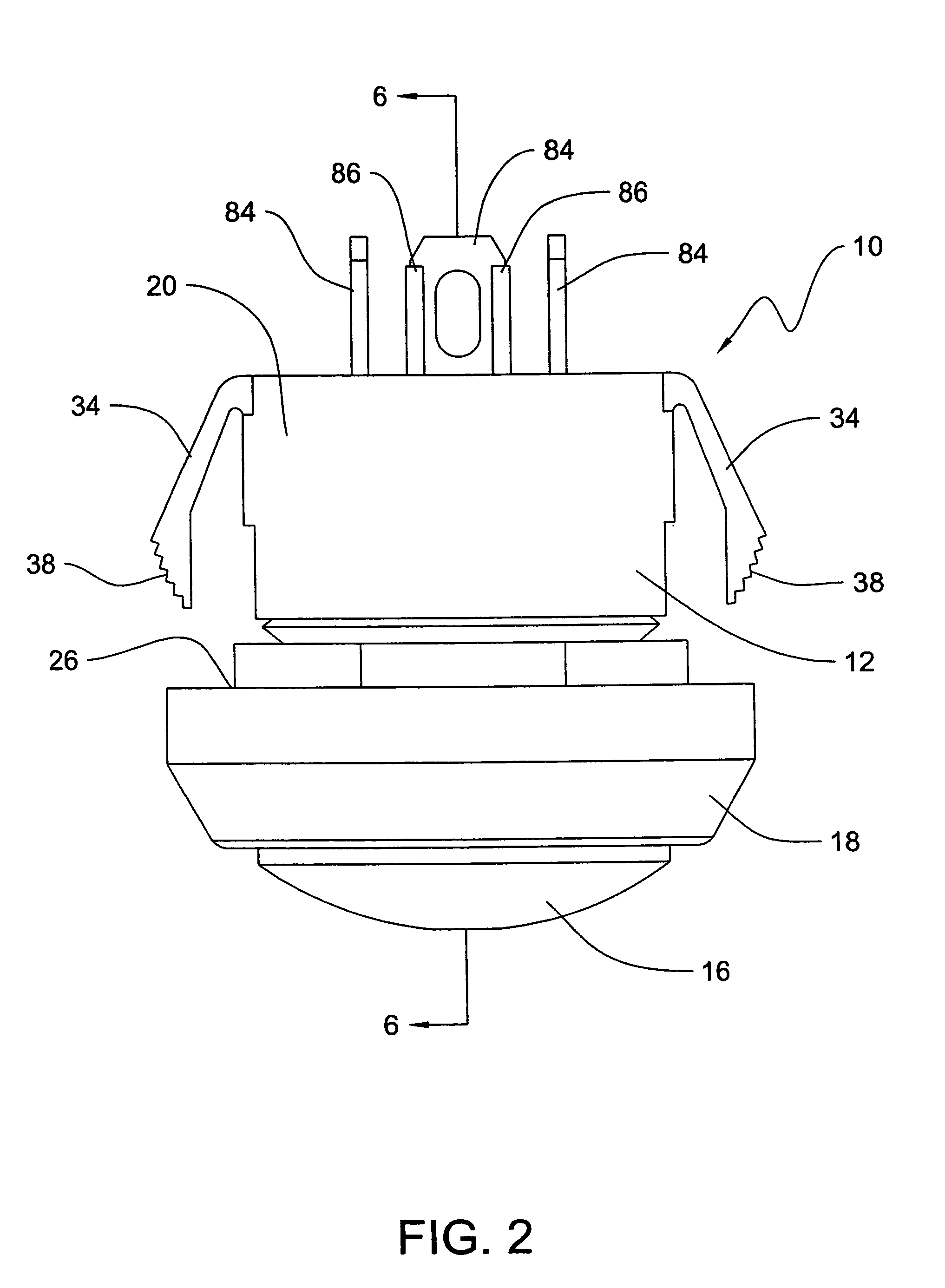

Push-button switch

A push-button switch includes a universal assembly comprising a single body design, a single plunger design, and a single base design to provide various switch options in an overall single package design. The push-button switch of the invention may be operated by either a mechanical switch assembly or a hall-effect system. The push-button switch may also provide a momentary switch connection, such as a single push system, or a maintained switch connection, such as a push-push system. Further, the push-button switch may include feedback mechanisms, such as LED components and the like that provide a visible feedback of the switch connection, and tactile feedback components that also indicate the switch connection.

Owner:ILLINOIS TOOL WORKS INC

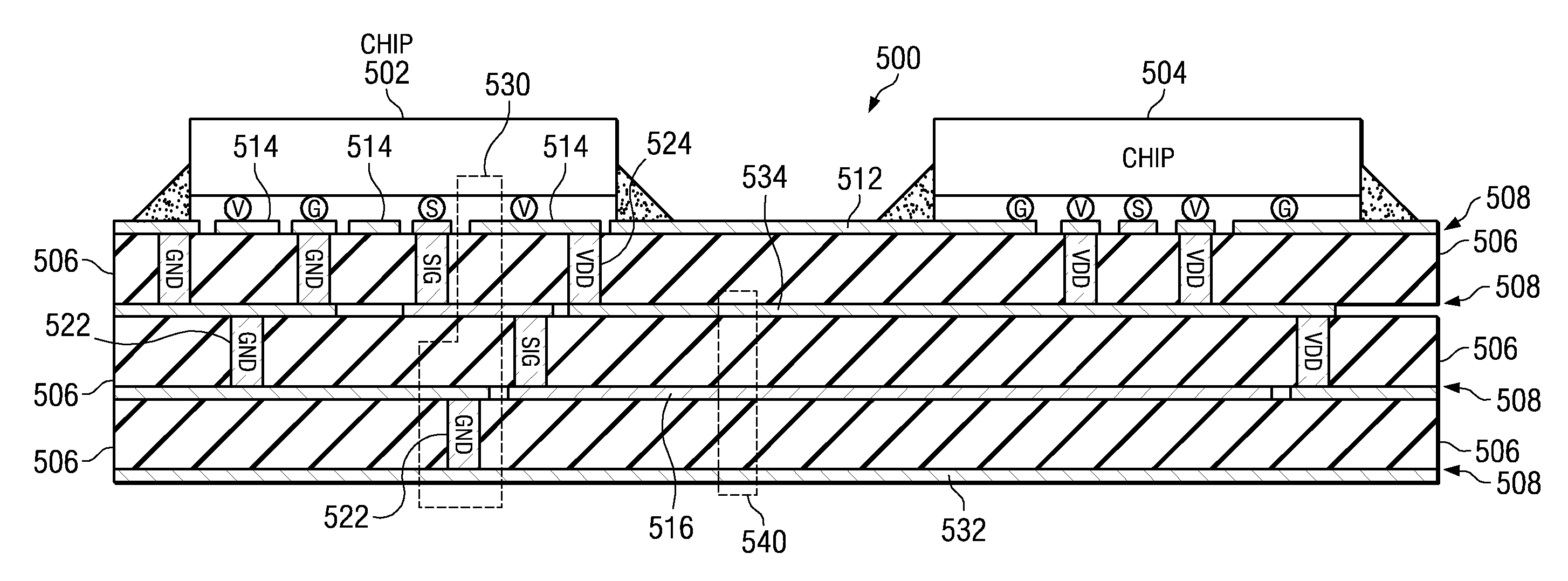

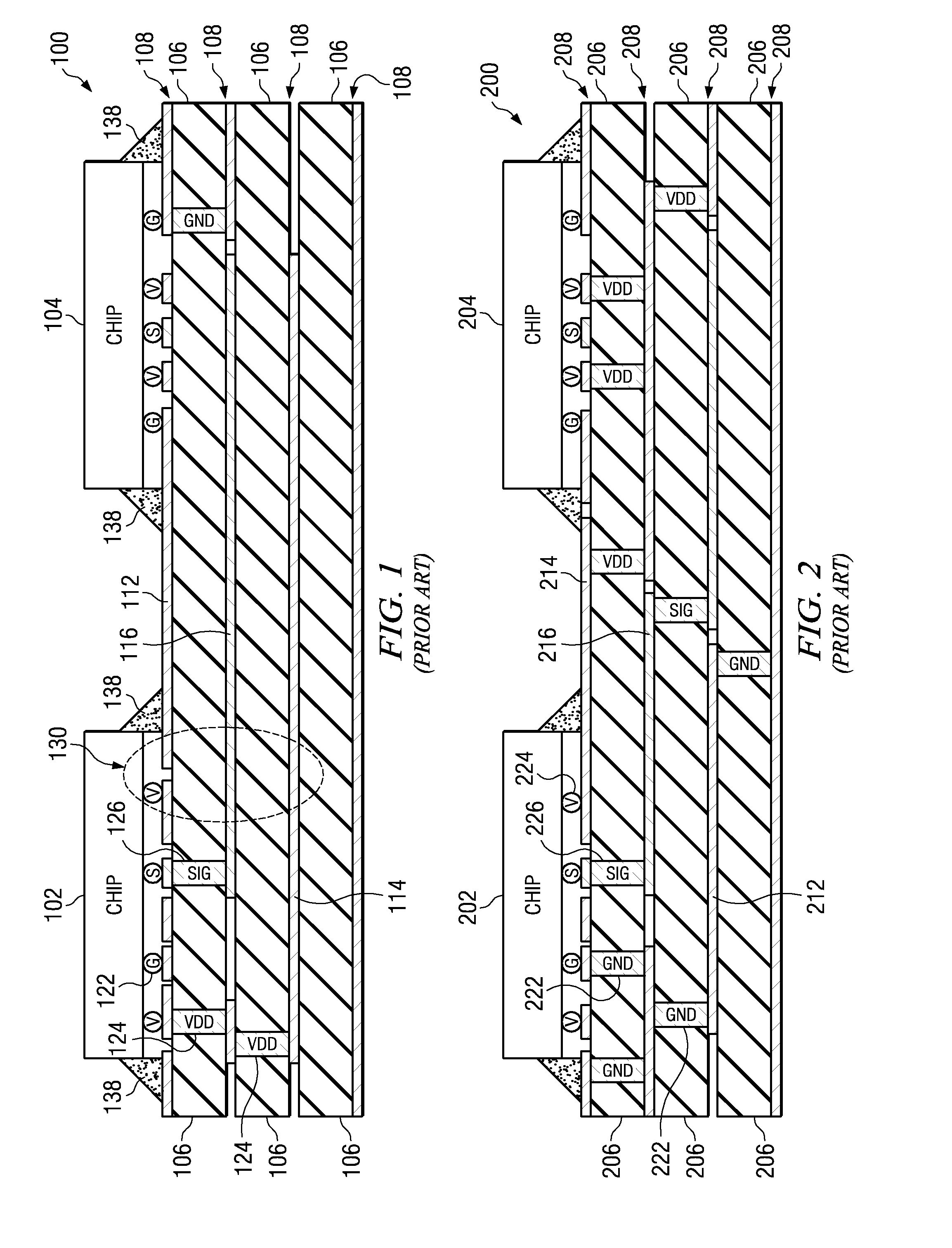

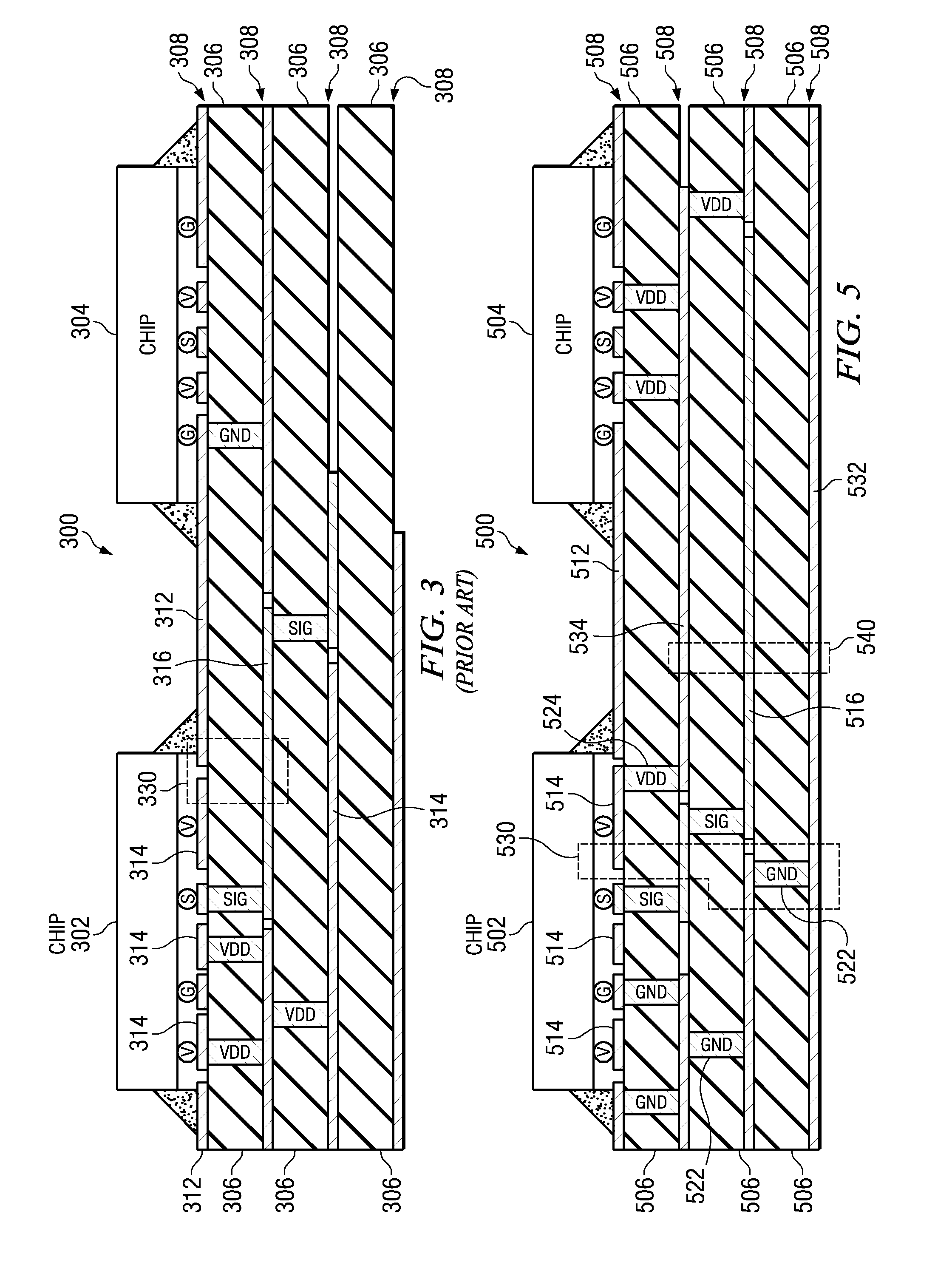

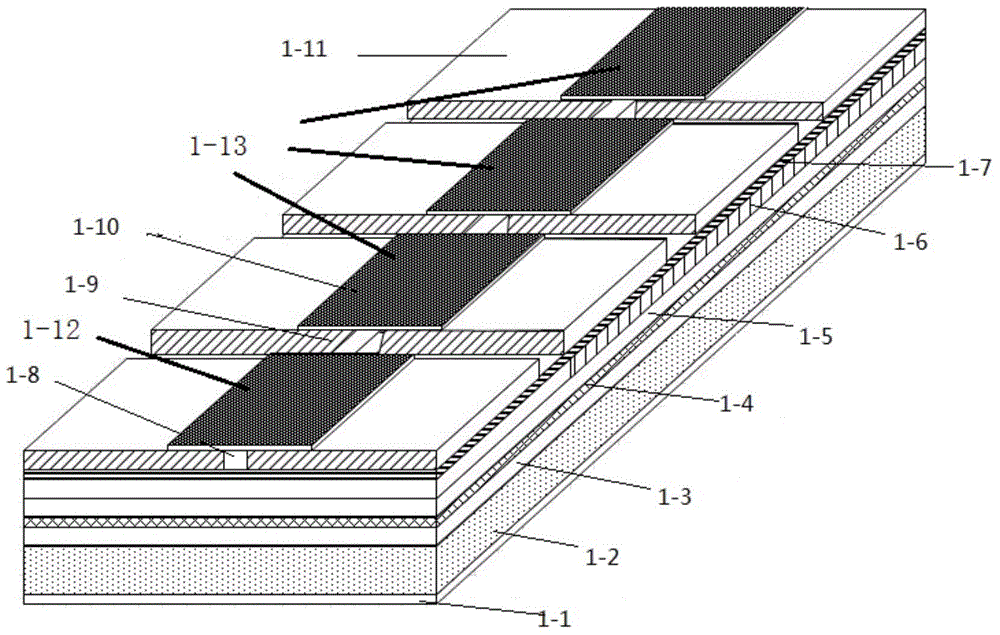

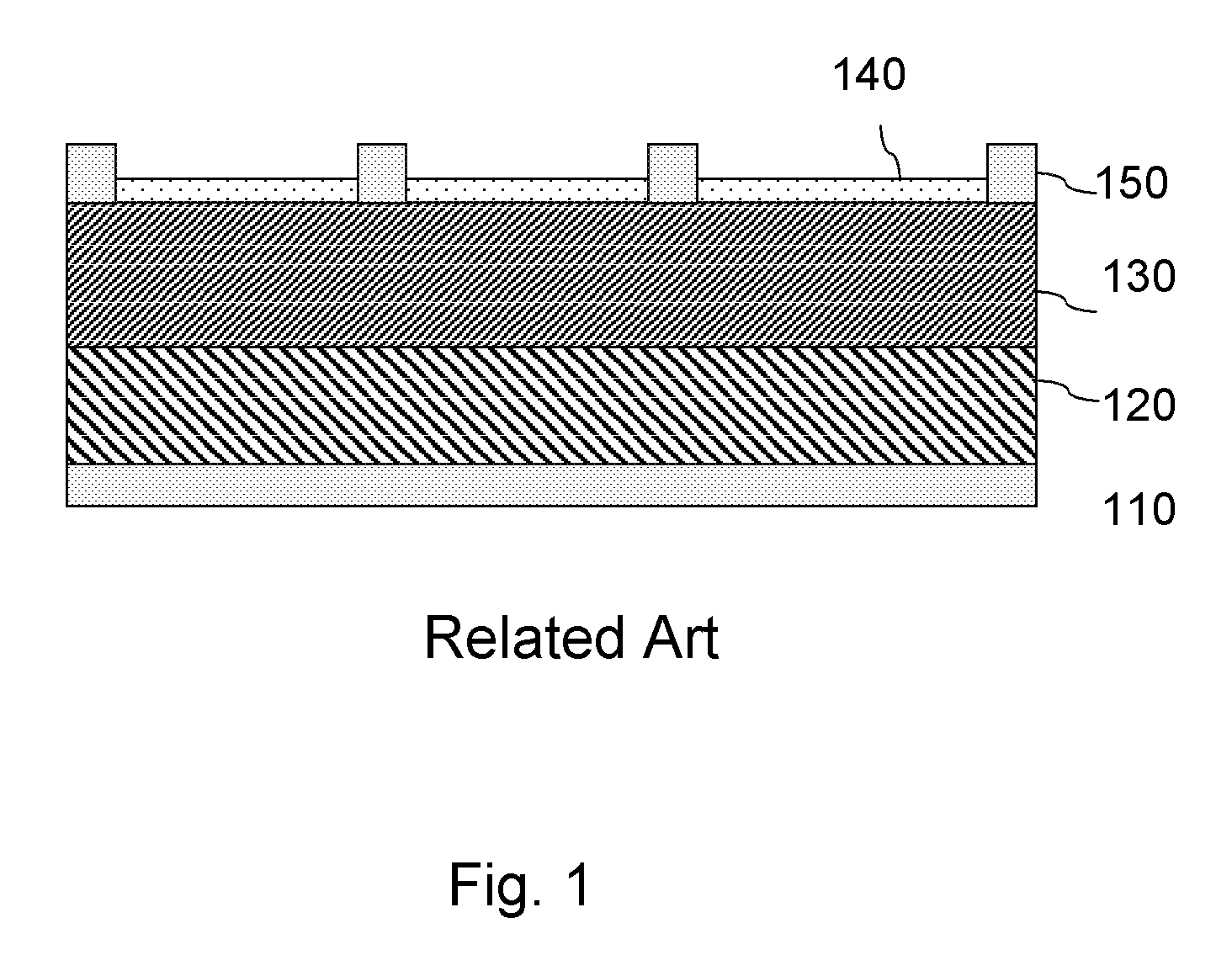

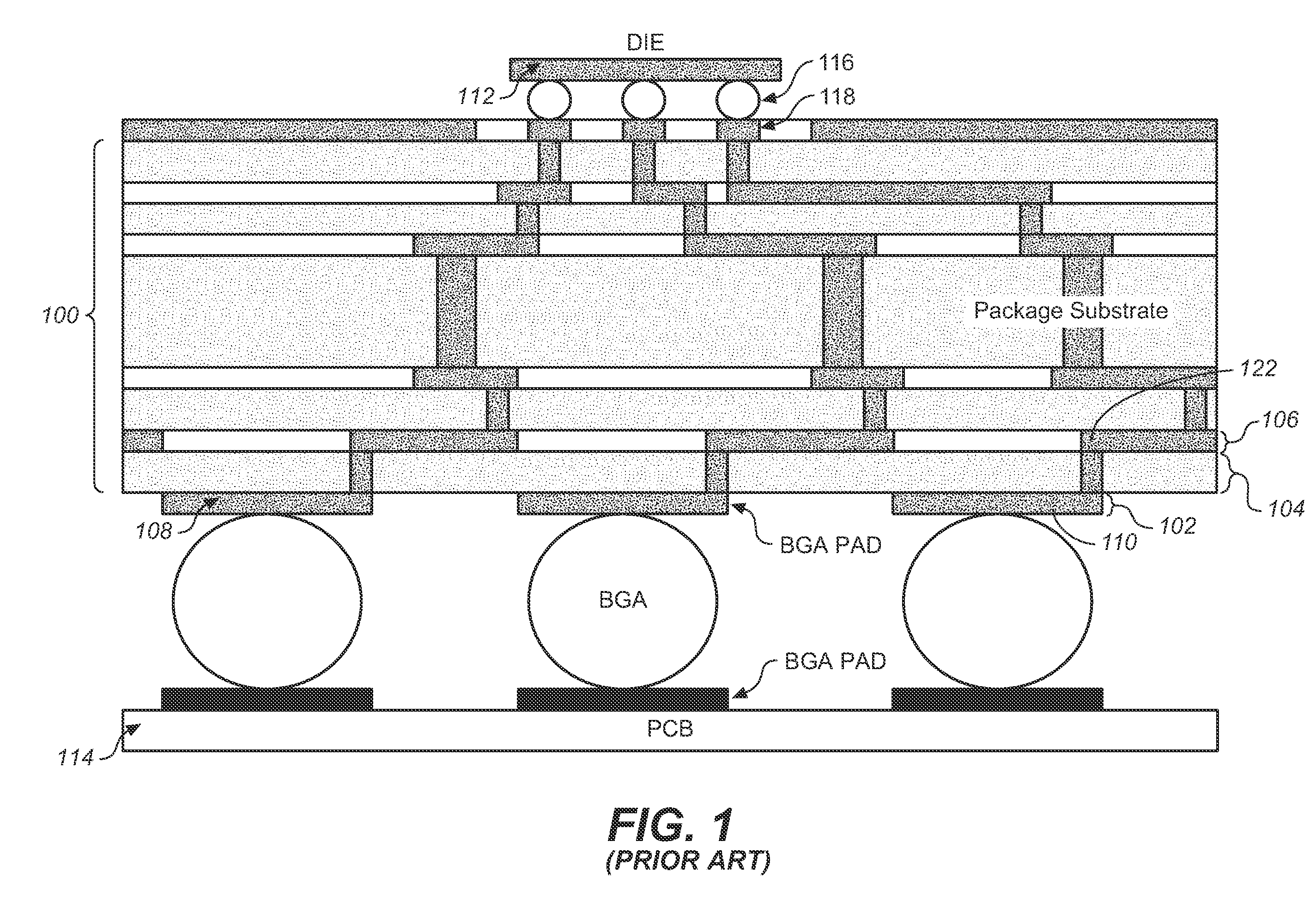

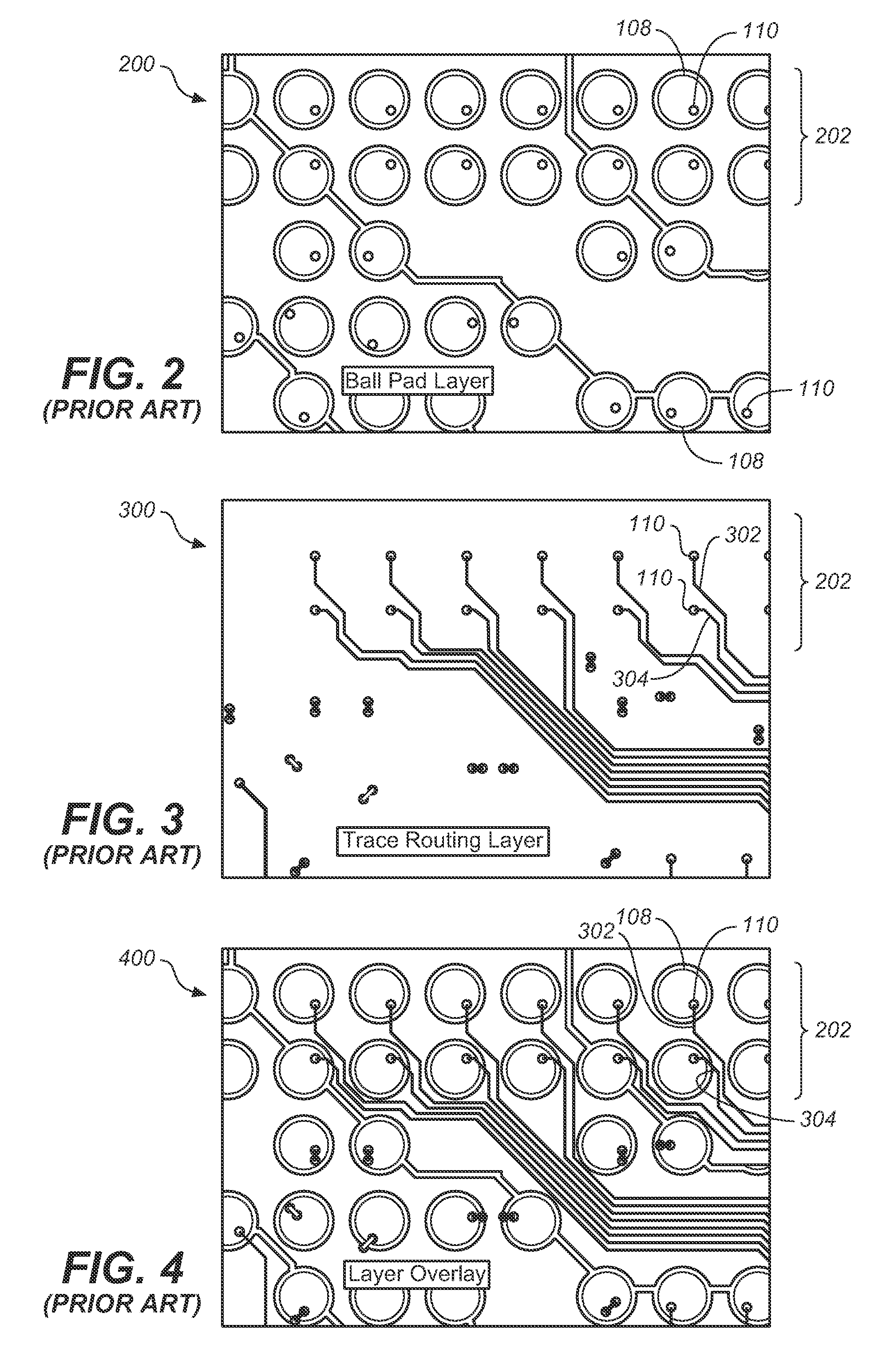

Continuously Referencing Signals over Multiple Layers in Laminate Packages

InactiveUS20080093726A1Final product manufactureSemiconductor/solid-state device detailsPackage designGround plane

A mechanism for continuously referencing signals over multiple layers in laminate packages provides a continuous path for signals from one layer to another while using the ideal voltage reference for all areas of the package and still avoiding discontinuities in the voltage reference. A reference plane adjustment engine analyzes a package design and identifies an ideal top plane for all areas of the package, including areas under particular chip die(s) and areas that are not under a chip die. The reference plane adjustment engine then modifies the package design to reposition ground planes, source voltage planes, signal planes, and vias between layers to maintain a continuous voltage reference regardless of the top layer. The reference plane adjustment engine provides the resulting mixed voltage plane package design to a design analysis engine. A package fabrication system fabricates the package.

Owner:GLOBALFOUNDRIES INC

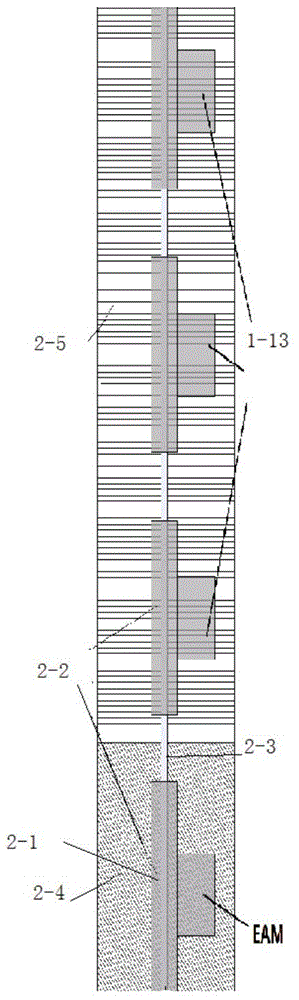

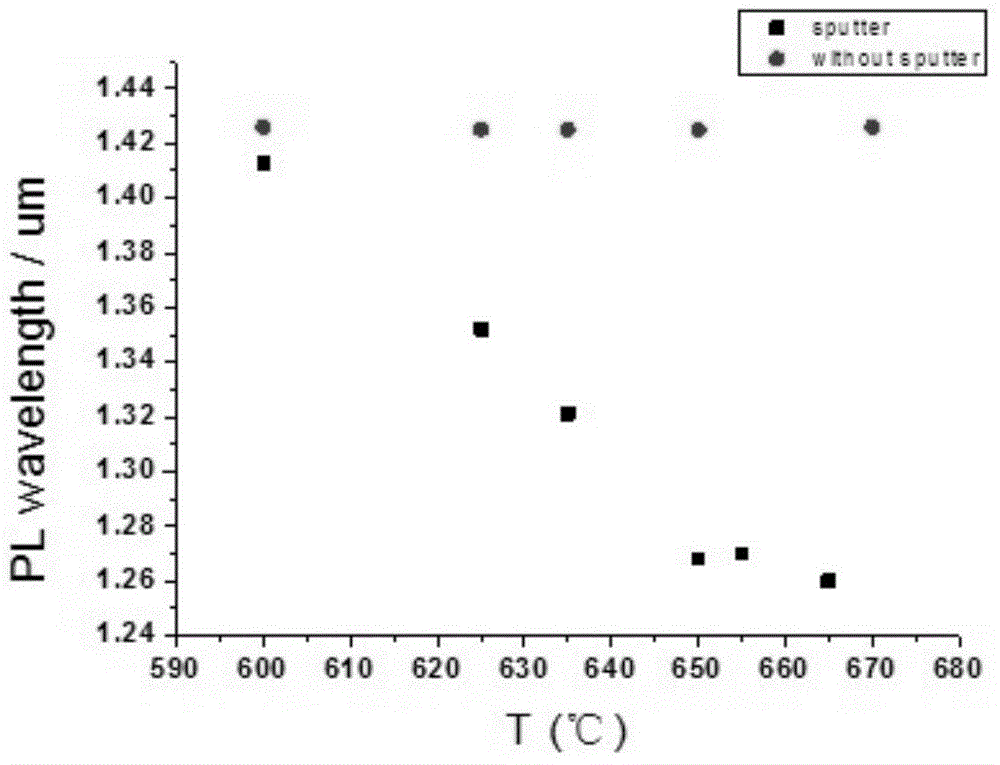

Low-cost tunable DFB semiconductor laser device of integrated modulator and manufacturing method

ActiveCN103956652APackage structure design is simpleReduce complexityLaser optical resonator constructionSemiconductor laser arrangementsElectricityElectro-absorption modulator

The invention discloses a low-cost tunable DFB semiconductor laser device of an integrated modulator. The tunable DFB semiconductor laser device is manufactured with the reconstruction-equivalent chirped technology, multiple DFB semiconductor laser devices share one modulator, and the tunable wavelength range can be expanded by increasing the number of laser devices or adopting the active and passive integration method. The integrated modulator is an semiconductor optical amplifier modulator (SOA), or an electric absorption modulator (EAM), or a Mach-Zehnder modulator (MZM) and can be realized by means of the quantum well intermixing technology (QWI), the Butt-joint growth technology or the selective area growth technology (SAG), and quantum well materials are based on the InP / InGaAsP or InP / AlGaInAs material system. Due to the fact that only one radio frequency port is needed for modulation at least, cost can be reduced by simplifying package design, and practicality and usability are improved greatly.

Owner:南京华飞光电科技有限公司

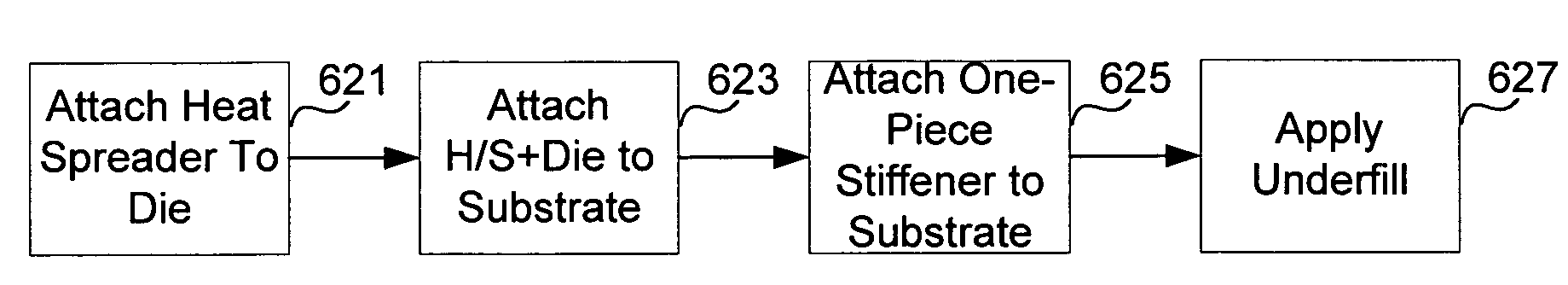

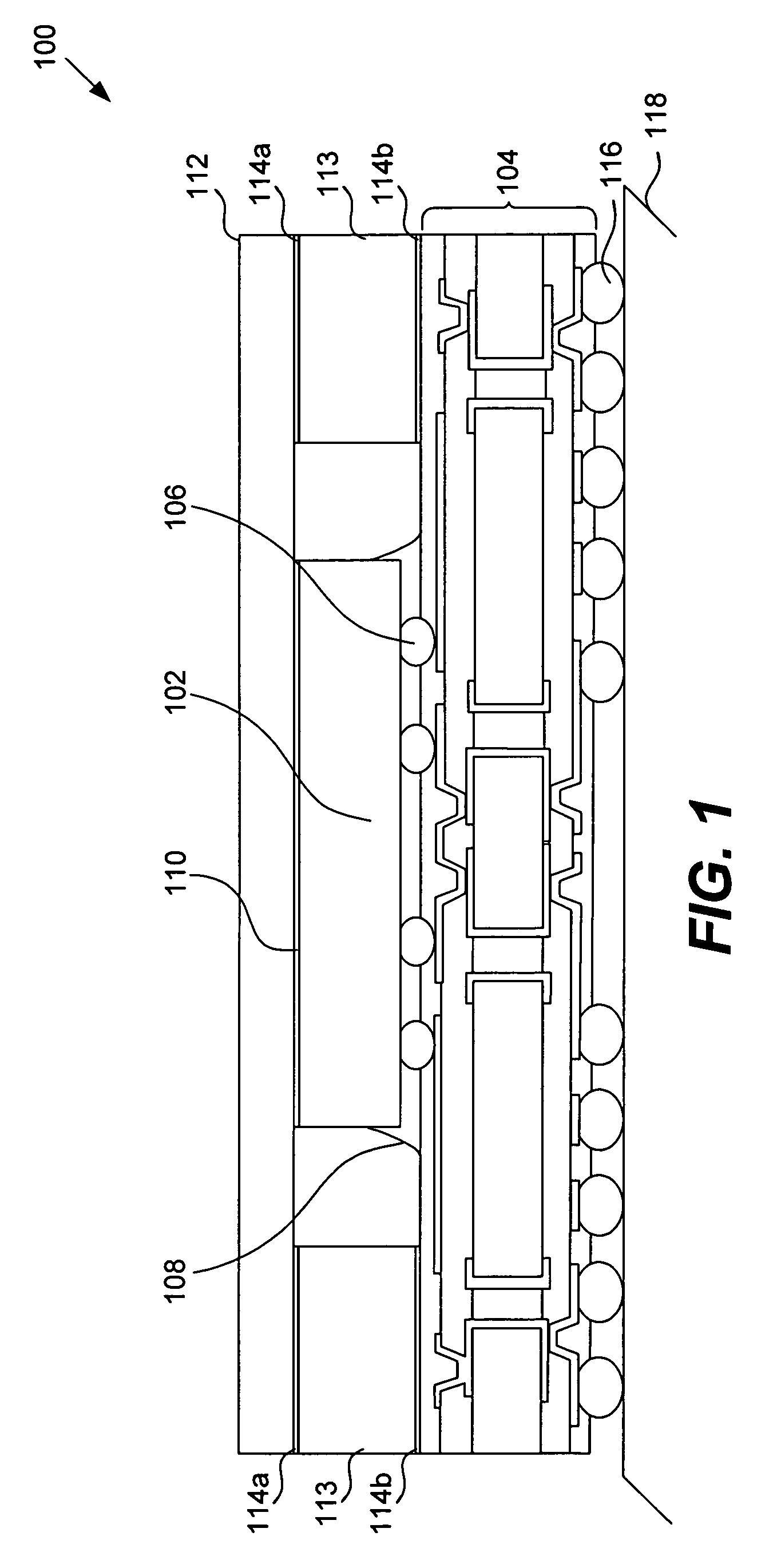

Structure and assembly procedure for low stress thin die flip chip packages designed for low-K Si and thin core substrate

InactiveUS7585702B1Easy to manageStress minimizationSemiconductor/solid-state device detailsSolid-state devicesPackage designEngineering

Provided are semiconductor die flip chip packages and semiconductor die flip chip package components where certain properties of the packages / components are controlled to facilitate management of the package stresses. Also provided are fabrication methods for such packages and package components. For instance, the thickness of a die can be controlled such that the stress generated / experienced by the die is minimized. As such, the package stress is managed to suitable levels for incorporation of a low-K Si die and / or a thin package substrate. Further, a thin die can be attached to a heat spreader to increase the rigidity for easier handling during fabrication of the semiconductor die flip chip package.

Owner:ALTERA CORP

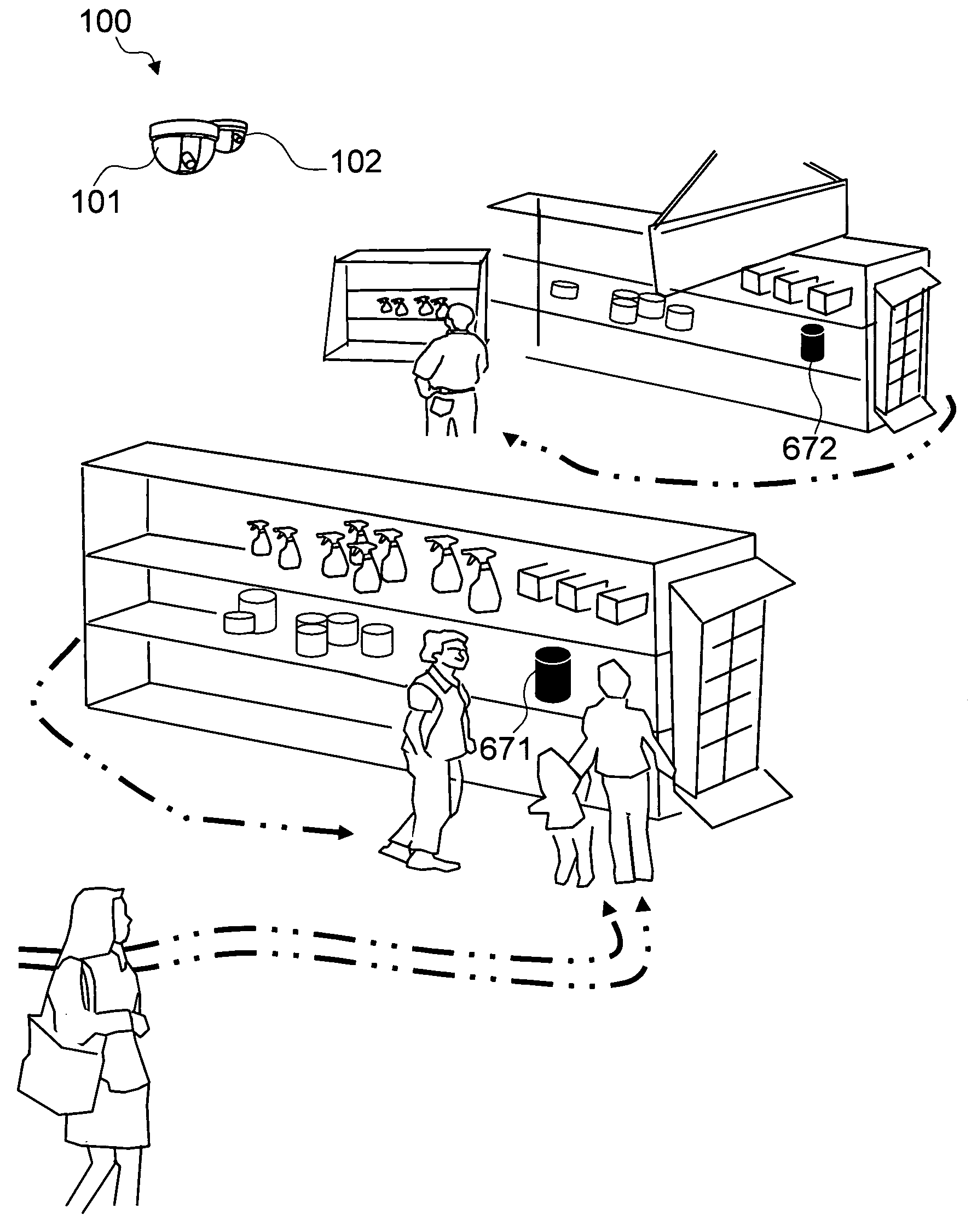

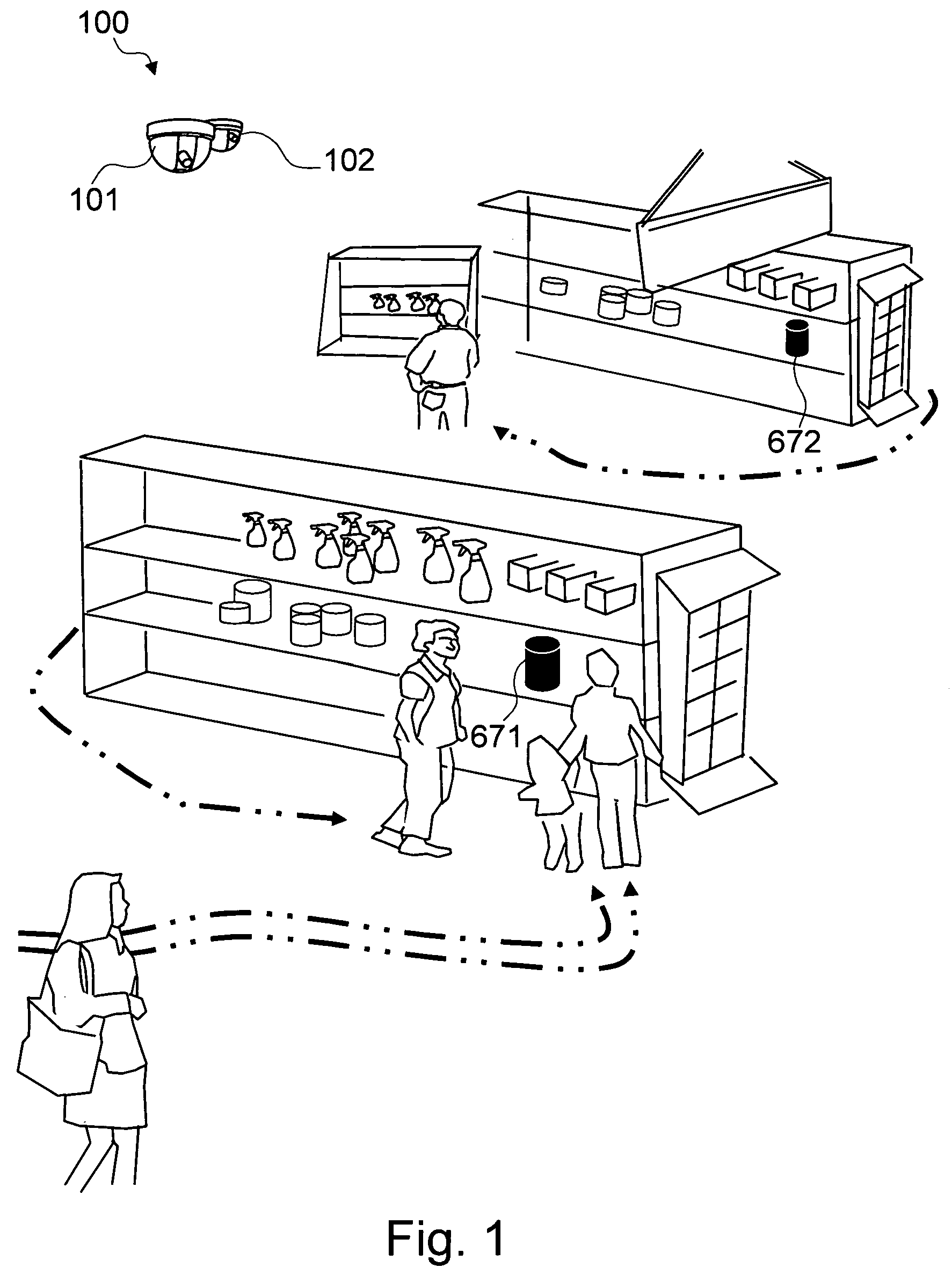

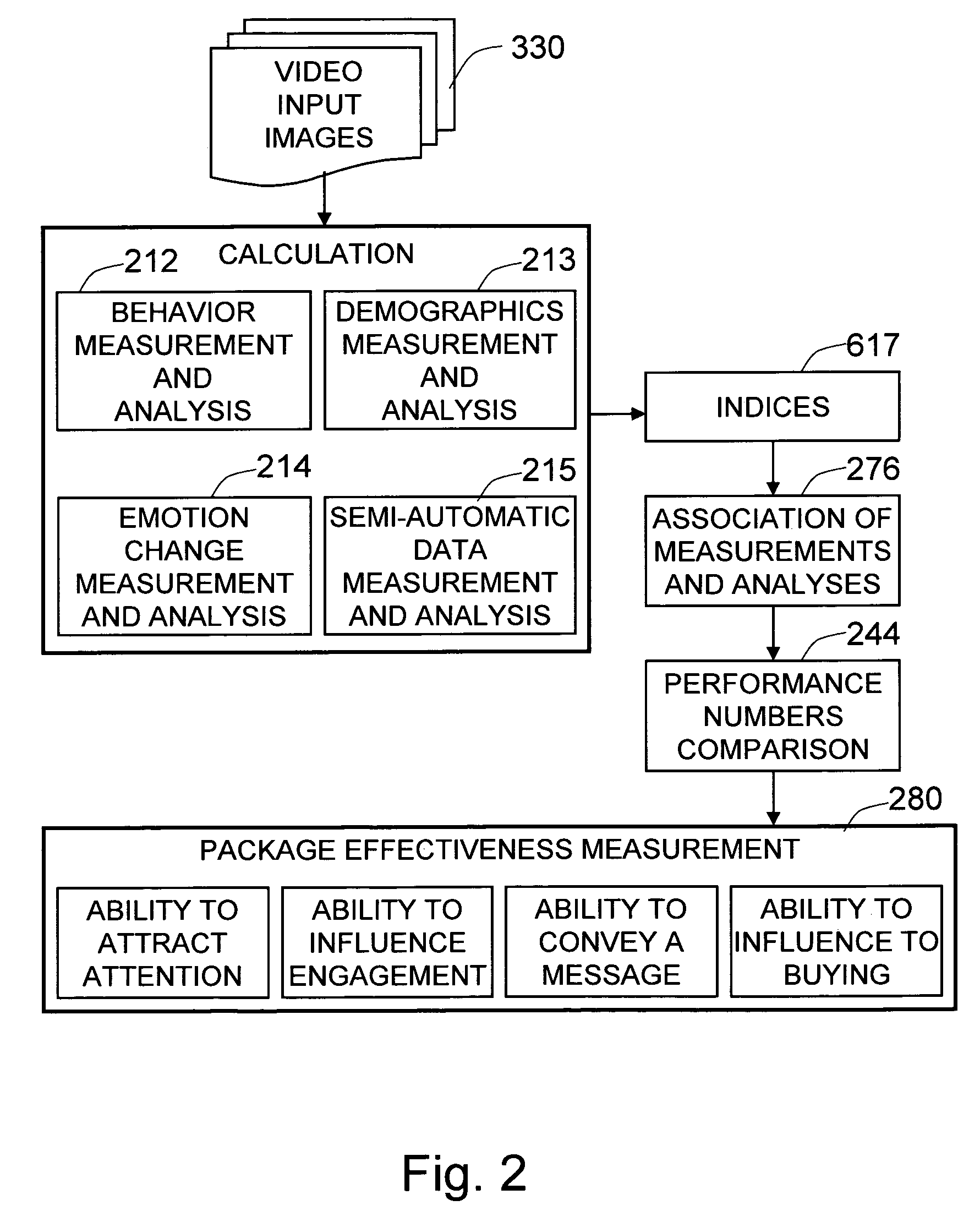

Method and system for measuring packaging effectiveness using video-based analysis of in-store shopper response

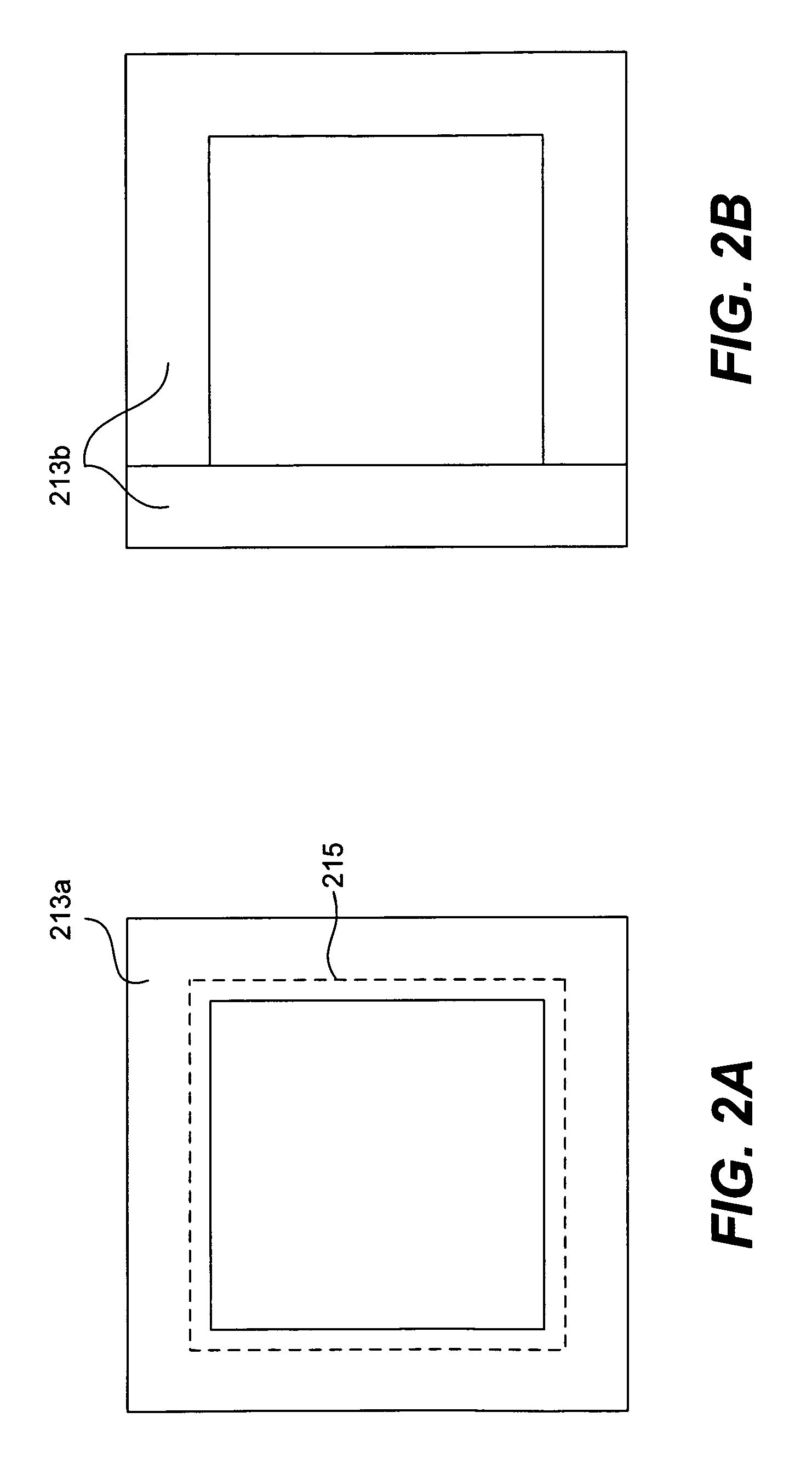

ActiveUS8433612B1Measure their effectivenessEffectiveness of the newly changed package concepts can be measuredBuying/selling/leasing transactionsBehavioral analyticsPackage design

The present invention is a method and system for measuring packaging effectiveness based on video-based analysis of people in the vicinity of a plurality of package concepts. The present invention measures the response of people to the different packaging concepts, wherein the quantified response measurement shows the ability of the packaging concepts to attract, engage, and motivate people to purchase. The video-based analysis comprises behavior analysis, demographic analysis, and emotion change detection in response to the package effectiveness. The present invention captures a plurality of input images of the people in the vicinity of a plurality of package concepts by a plurality of means for capturing images. The plurality of input images is processed in order to understand the effectiveness of packaging design and changes. The processes are based on a novel usage of a plurality of computer vision technologies to analyze the visual characterization of the people from the plurality of input images in relation to the packaging design and changes.

Owner:VIDEOMINING CORP

Direct contact cooling liquid embedded package for a central processor unit

ActiveUS7289326B2Increase the number ofEliminate needSemiconductor/solid-state device detailsSolid-state devicesElectricityCoupling

A direct contact cooling liquid embedded package design for use with a computer central processor unit is suitable for thermal management of high heat dissipation electronic components such as server processors. The direct contact cooling liquid embedded packaged CPU has mechanical coupling and embedded plumbing that attaches to the board pumped liquid supply and direct contact cooling liquid of the heat-generating portion of the CPU. A direct contact cooling liquid embedded packaged CPU removes higher levels of heat directly from the core of the processors by convective cooling. Cooling liquid is introduced into the package of the server CPU by mechanically attaching the CPU to the board through a socket interconnect. Pins of the socket serve to provide electrical connection between the board and the CPU, while a few pins are designed for the purpose of inlet and outletting cooling liquid into and out of the CPU package.

Owner:ORACLE INT CORP

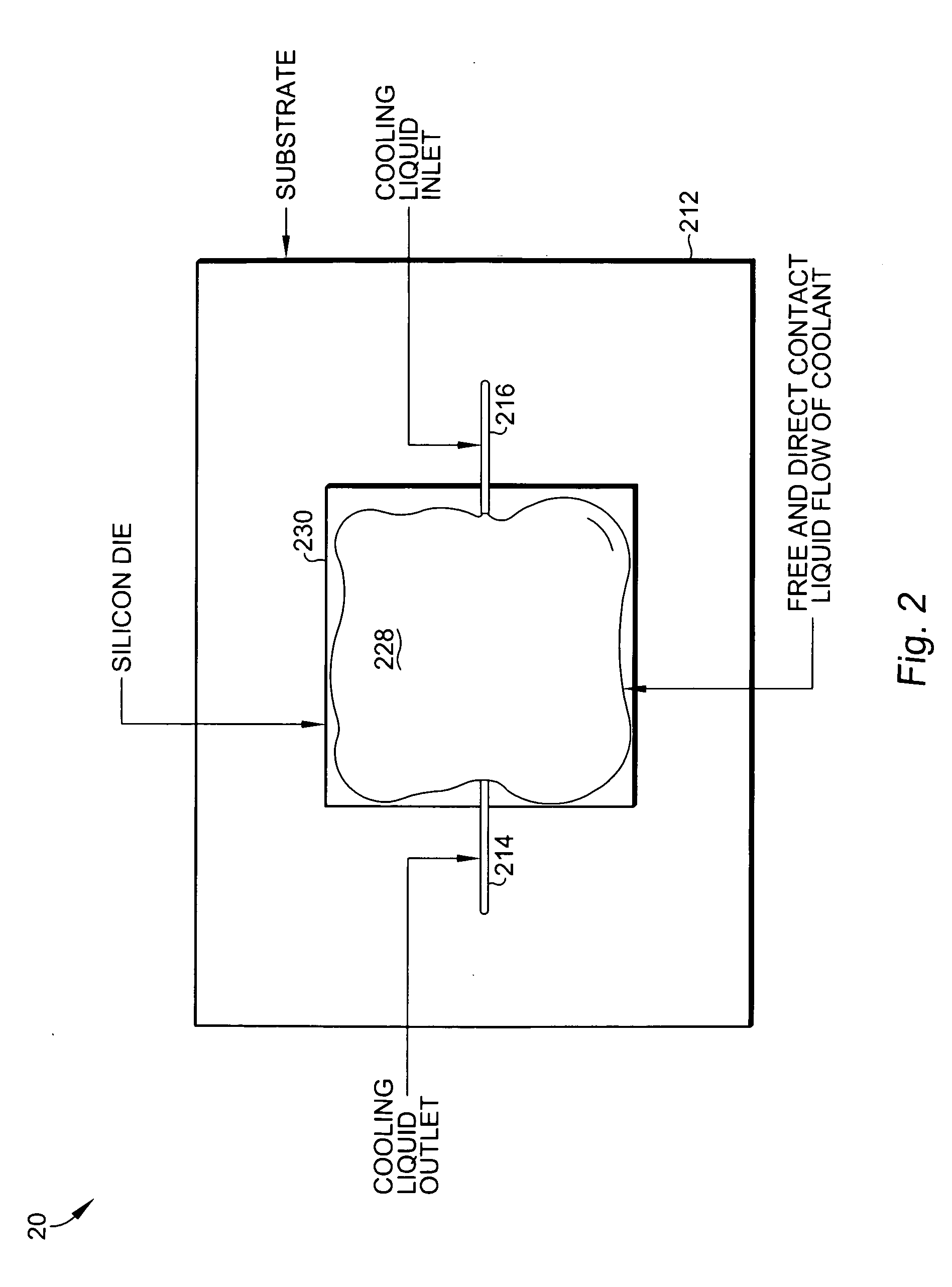

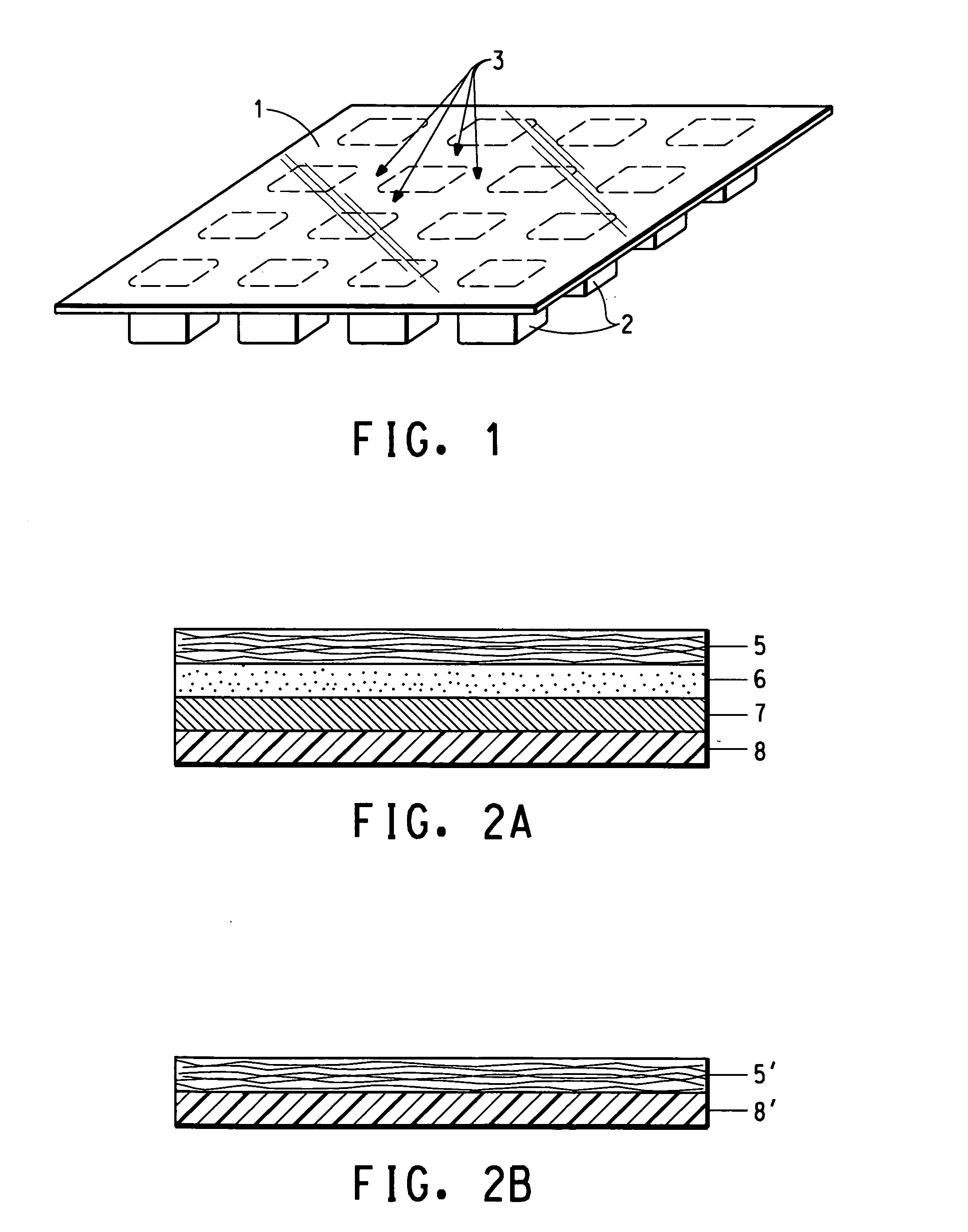

Method and device for fabricating a solar cell using an interface pattern for a packaged design

InactiveUS20110017263A1Easily use processLess blocking effectPV power plantsSemiconductor/solid-state device manufacturingGrid patternPackage design

A method and device of fabricating a photovoltaic strip. The method includes providing a photovoltaic cell having a front surface and a back surface and forming a first grid pattern on the front surface and second grid pattern on the back surface. The first grid pattern includes a first plurality of strip columns in parallel in a first direction and a plurality of grid lines in parallel in a second direction perpendicularly crossing the first plurality of strip columns. The second grid pattern includes a plurality of blocks separated by a plurality of streets parallel in the second direction and a second plurality of strip columns parallel in the first direction. The method further includes dicing the photovoltaic cell along the plurality of streets into a plurality of photovoltaic strips. Each of the plurality of photovoltaic strips includes at least one of the plurality of grid lines.

Owner:SOLARIA CORP

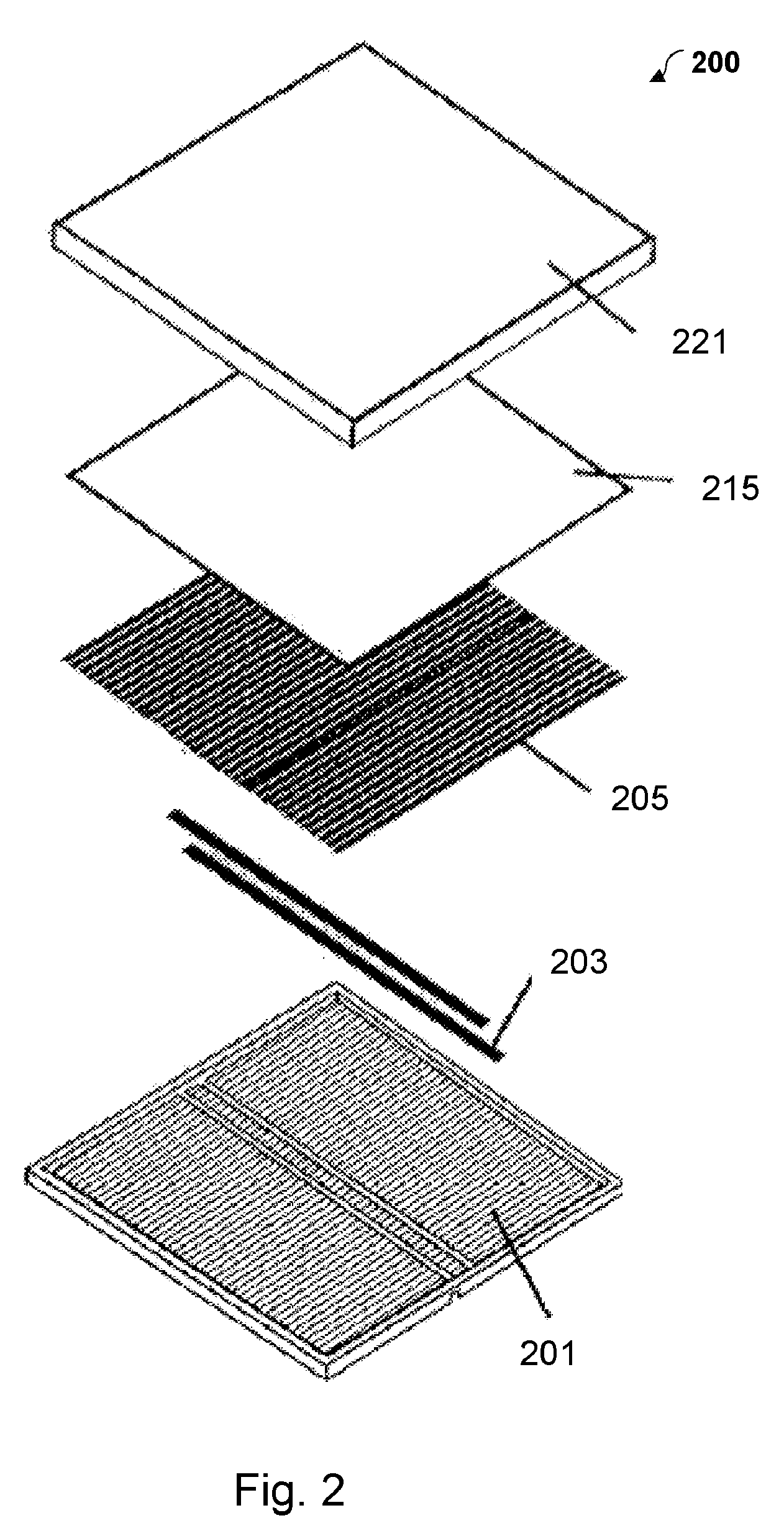

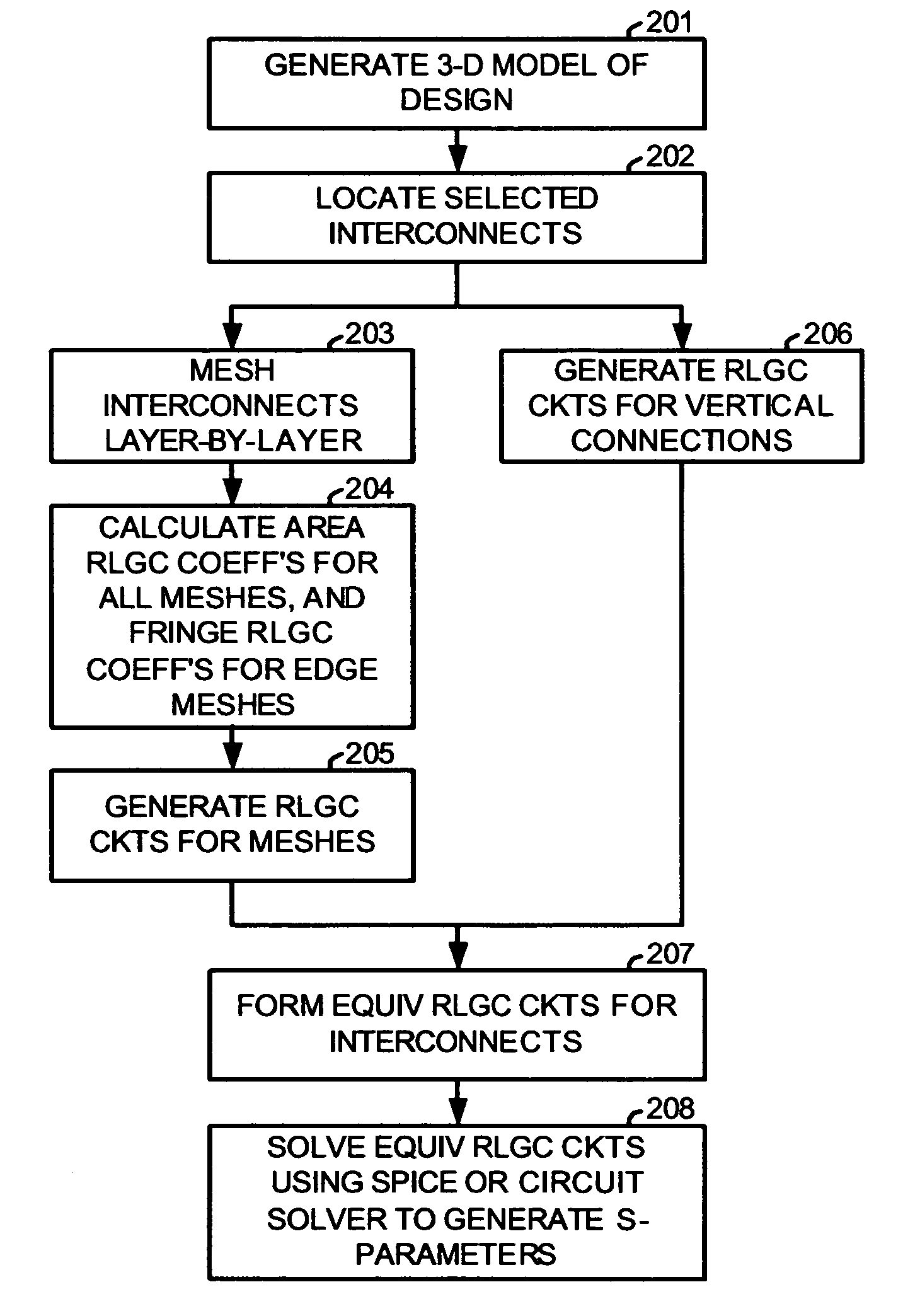

Fringe RLGC model for interconnect parasitic extraction

ActiveUS7231618B2Simulation is accurateAnalogue computers for electric apparatusComputer aided designPackage designEngineering

Owner:OPTIMAL CORP

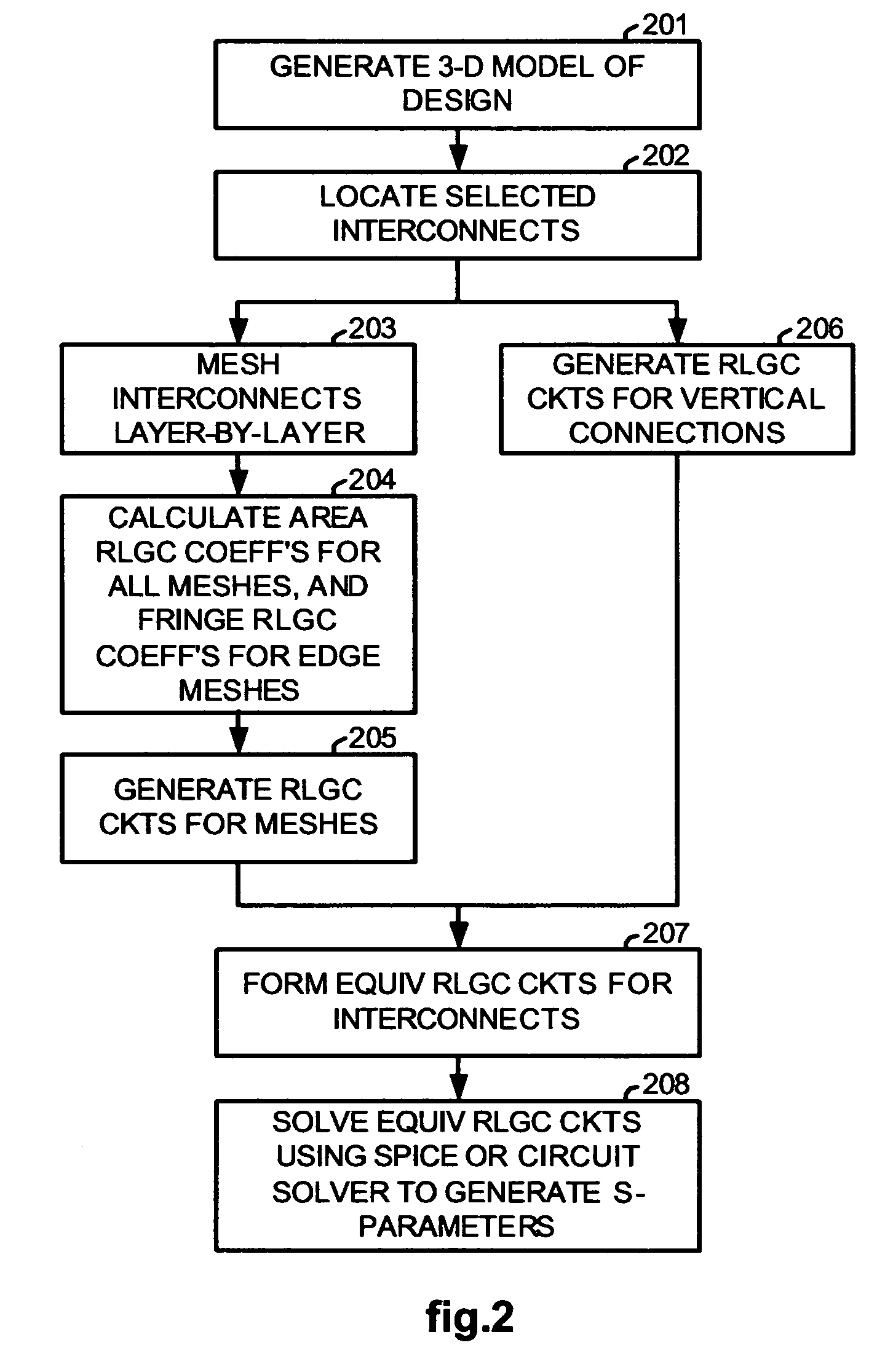

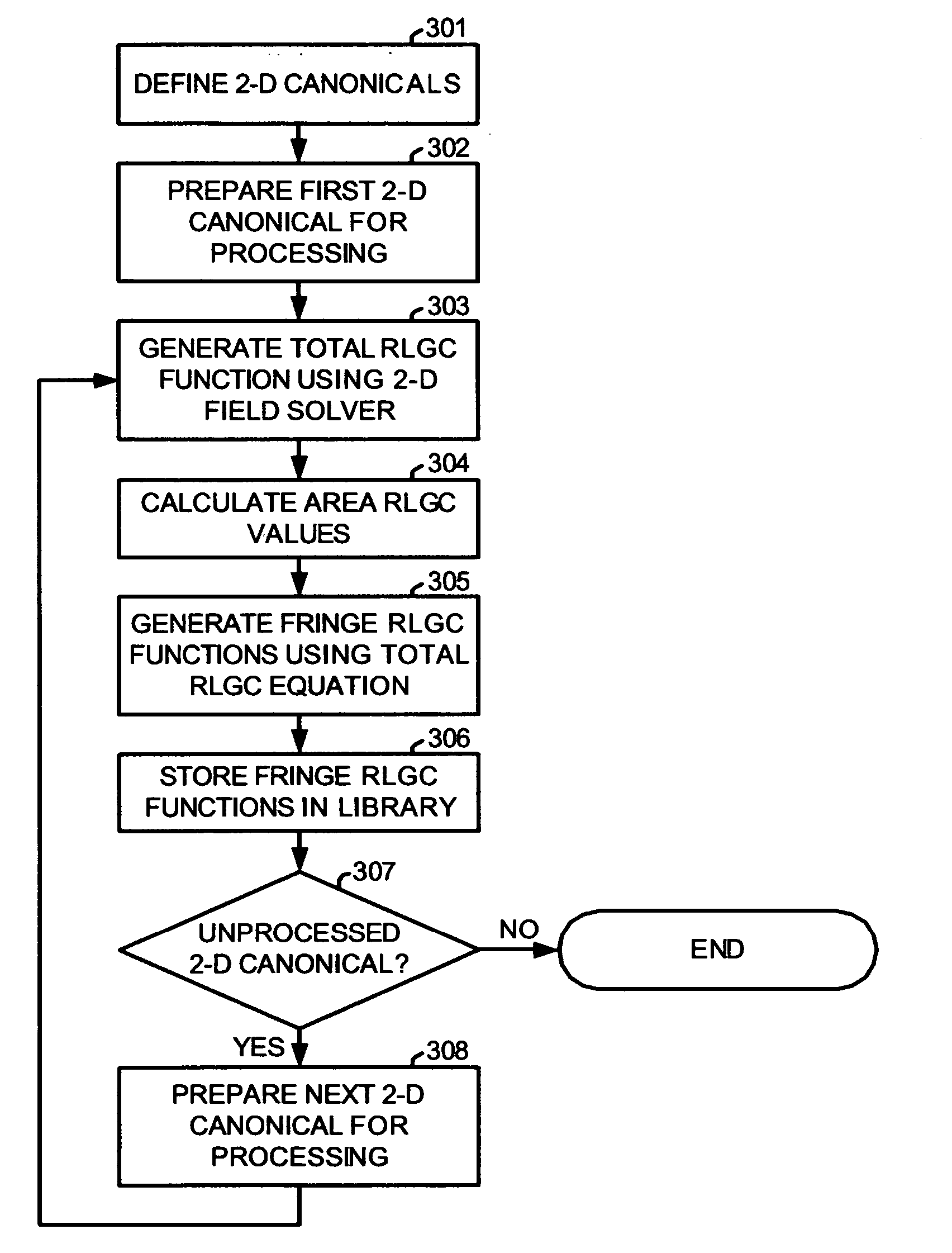

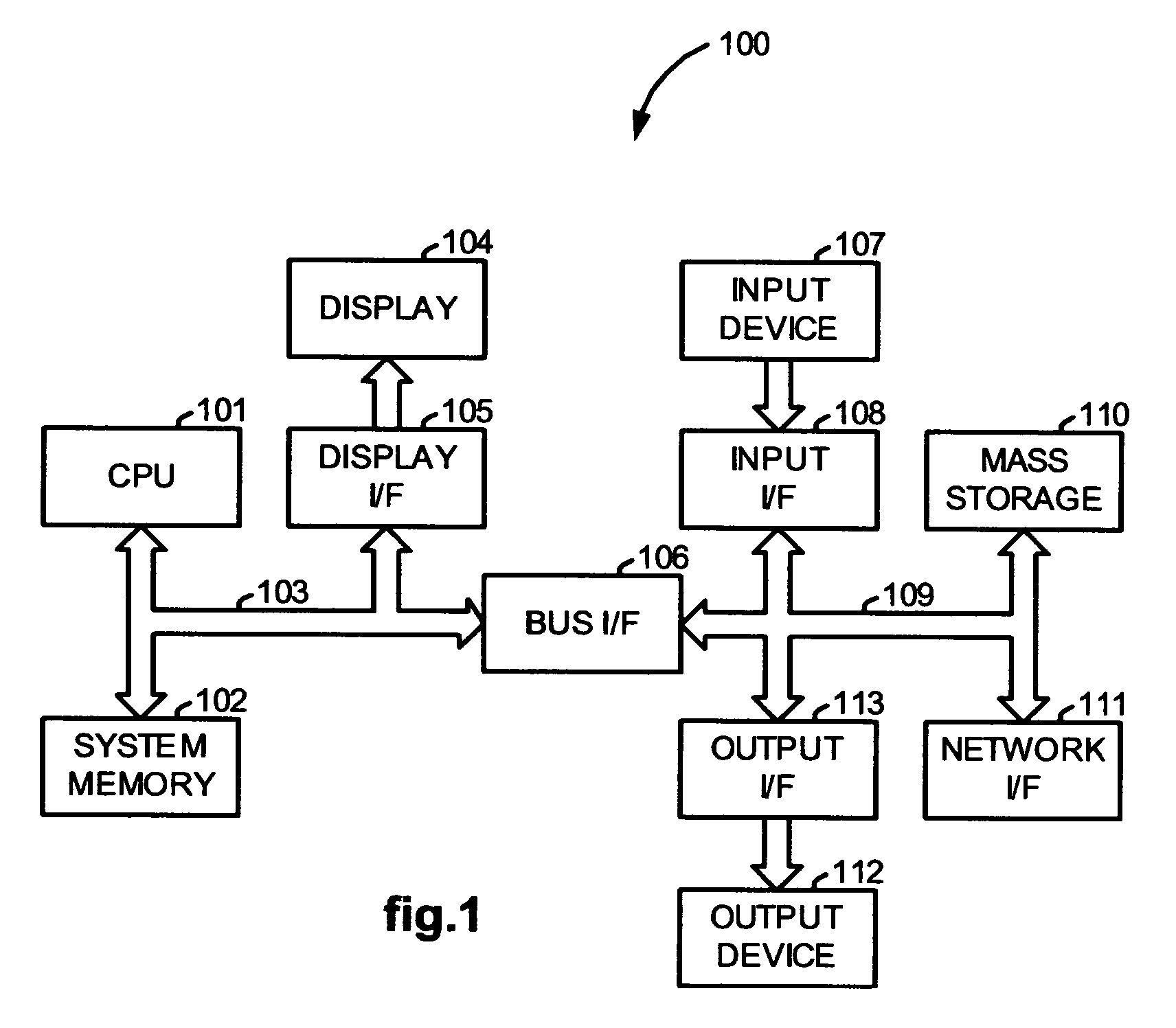

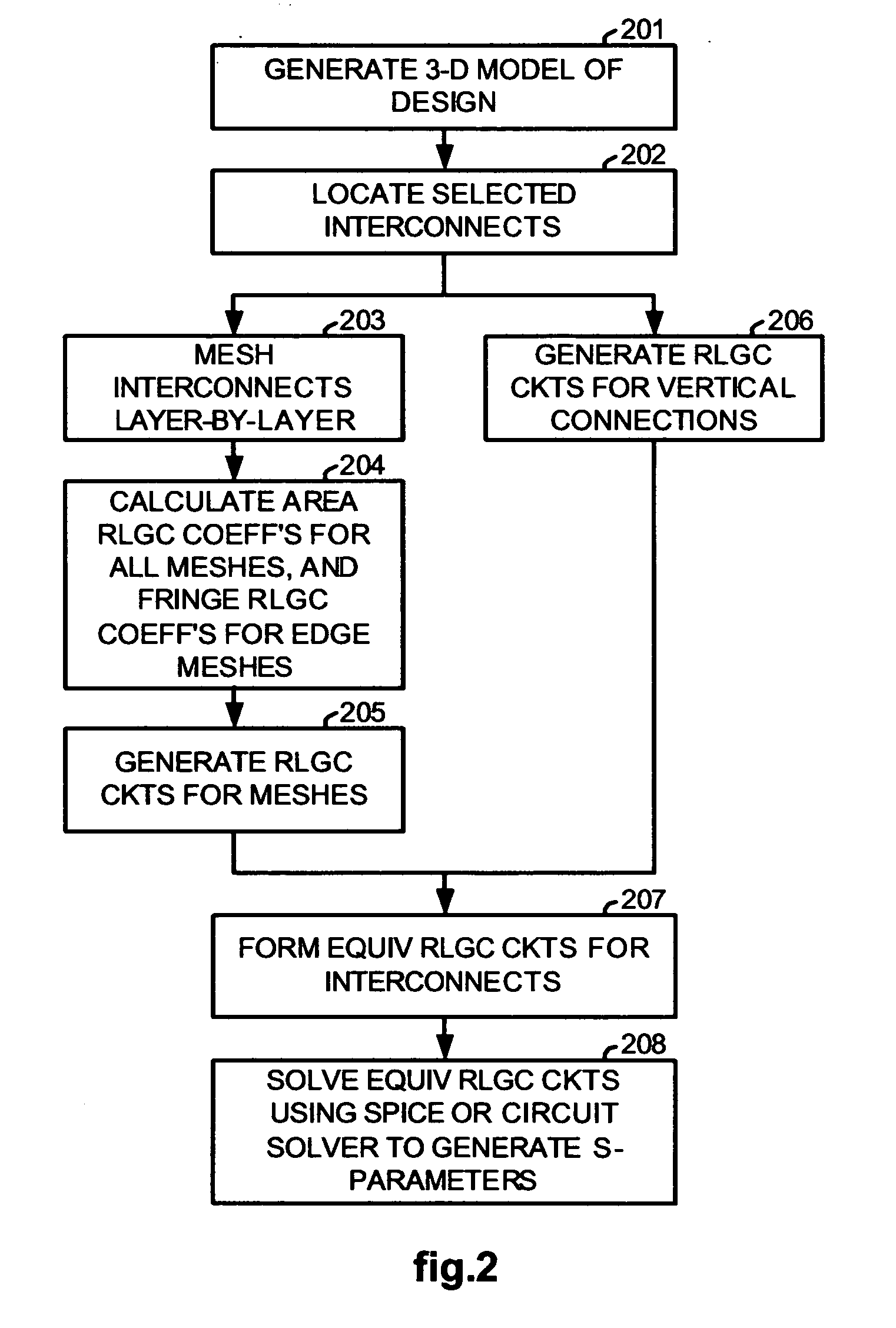

Fringe RLGC model for interconnect parasitic extraction

ActiveUS20050240883A1Simulation is accurateAnalogue computers for electric apparatusComputer aided designPackage designPrinted circuit board

An RLGC library is generated so as to include fringe RLCG functions for 2-D canonical interconnect structures. During parameter extraction for selected interconnect structures of an integrated circuit, printed circuit board, or integrated circuit package design, the RLGC library is used to generate fringe RLGC coefficients which in addition to area RLGC coefficients calculated on-the-fly, are used to generate equivalent RLGC circuits or S-parameters for simulating the interconnect structures.

Owner:OPTIMAL CORP

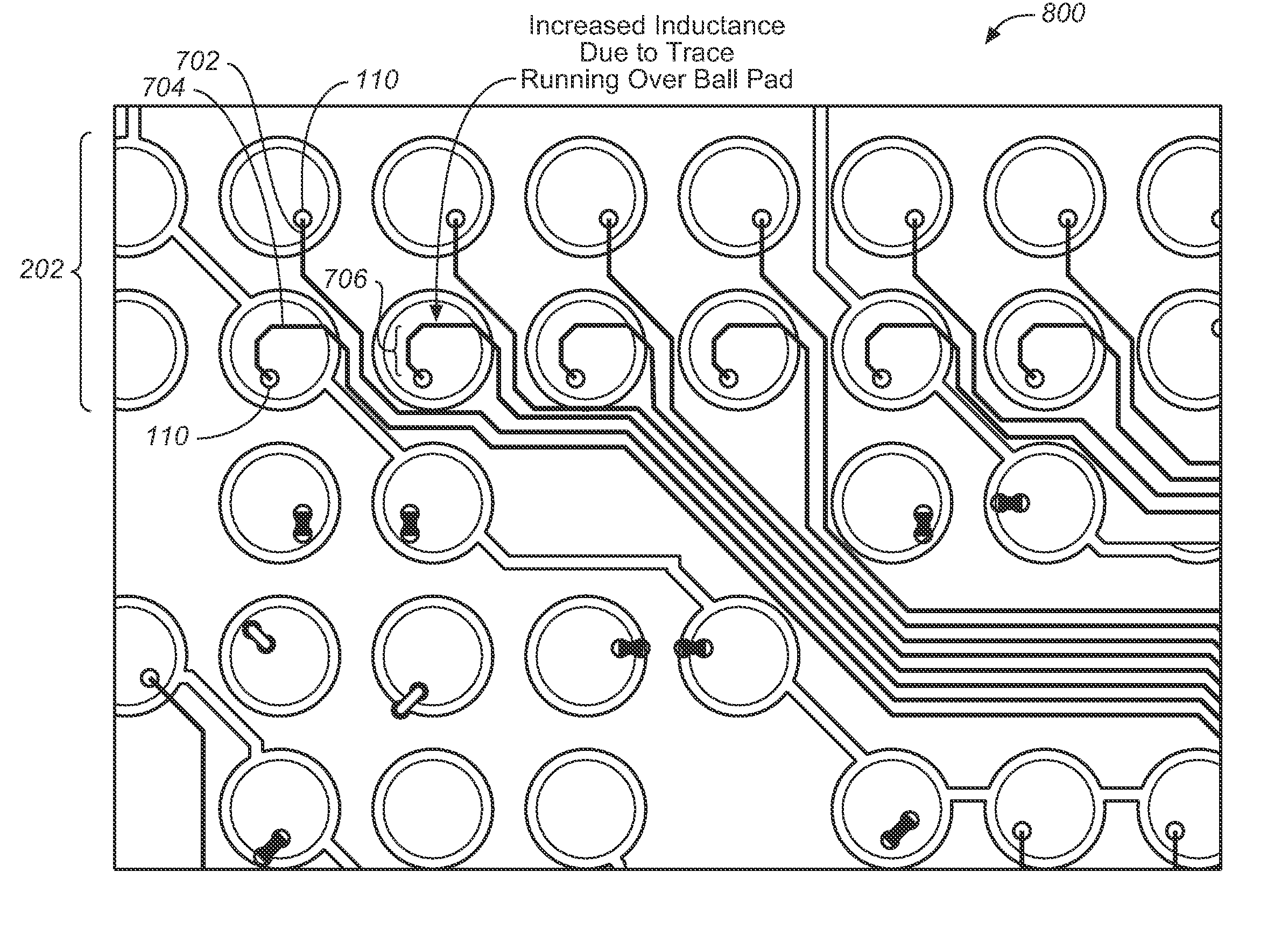

Device for minimizing differential pair length mismatch and impedance discontinuities in an integrated circuit package design

ActiveUS7180011B1Minimizing differential pair length mismatch and impedance discontinuitySemiconductor/solid-state device detailsPrinted circuit aspectsElectricityContact pad

A method of routing an integrated circuit package design includes steps of receiving as input at least a portion of an integrated circuit design including a differential pair of two electrical conductors, calculating a value of length mismatch between the two electrical conductors, calculating an added trace length to compensate for an impedance discontinuity of a shorter one of the two electrical conductors, and extending the shorter one of the two electrical conductors by routing the added trace length entirely inside an area surrounded by a contact pad that electrically terminates the shorter one of the two electrical conductors. The routing for the differential pair with the added trace length is generated as output in the integrated circuit design.

Owner:BELL SEMICON LLC

Package design and method of manufacture for chip grid array

InactiveUS6929981B2Eliminate needProtect environmentSemiconductor/solid-state device detailsSolid-state devicesPackage designSolder ball

A chip level package utilizing a CGA is described. A semiconductor chip with pillars is molded in an encapsulant. Solder balls are added and connected to the chip pillars. The final package does not require a first level substrate or interposer and is able to be assembled to the next level as is. An additional embodiment describes the addition of a thermal heat sink to the packaged chip.

Owner:ADVANPAK SOLUTIONS PTE

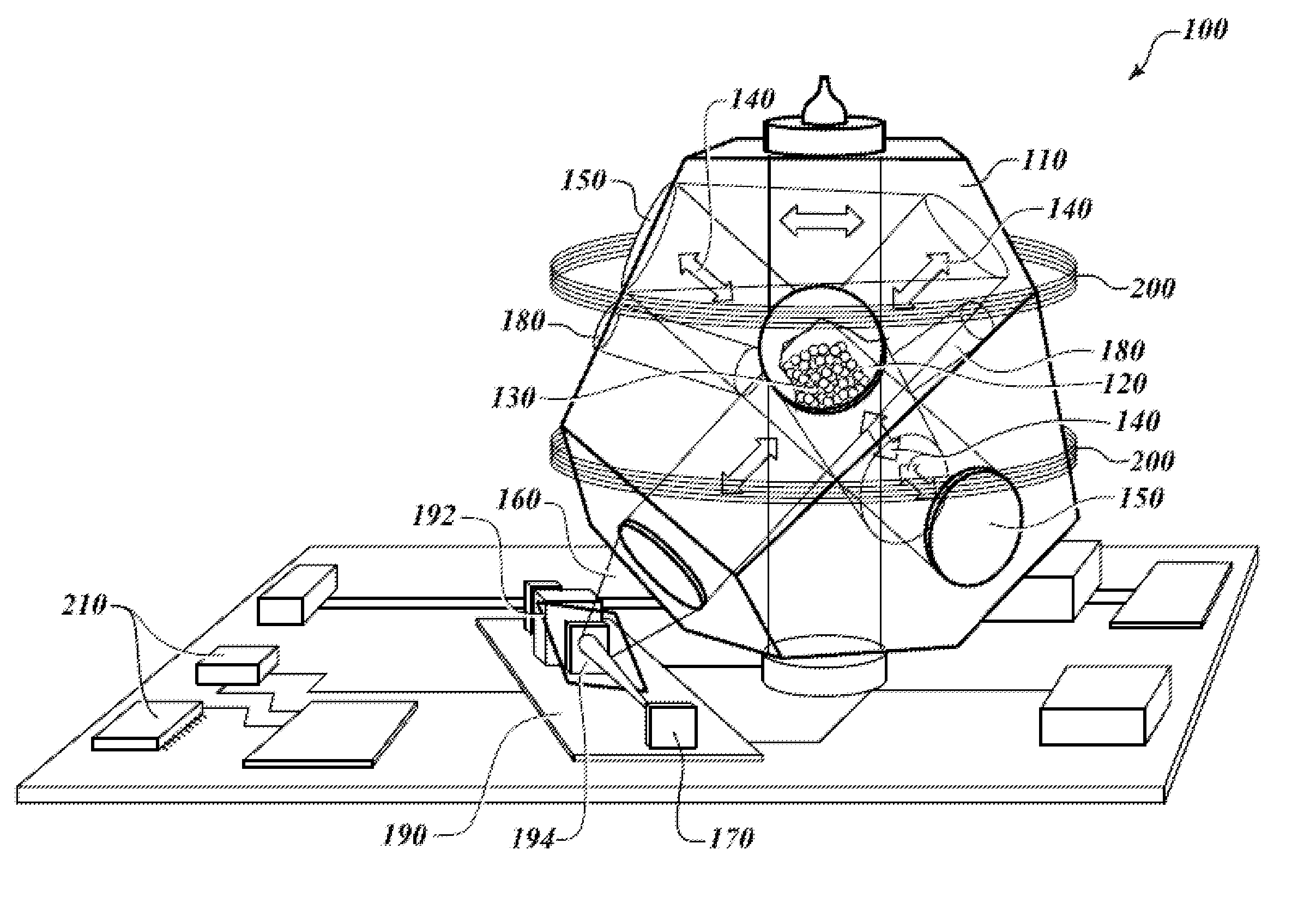

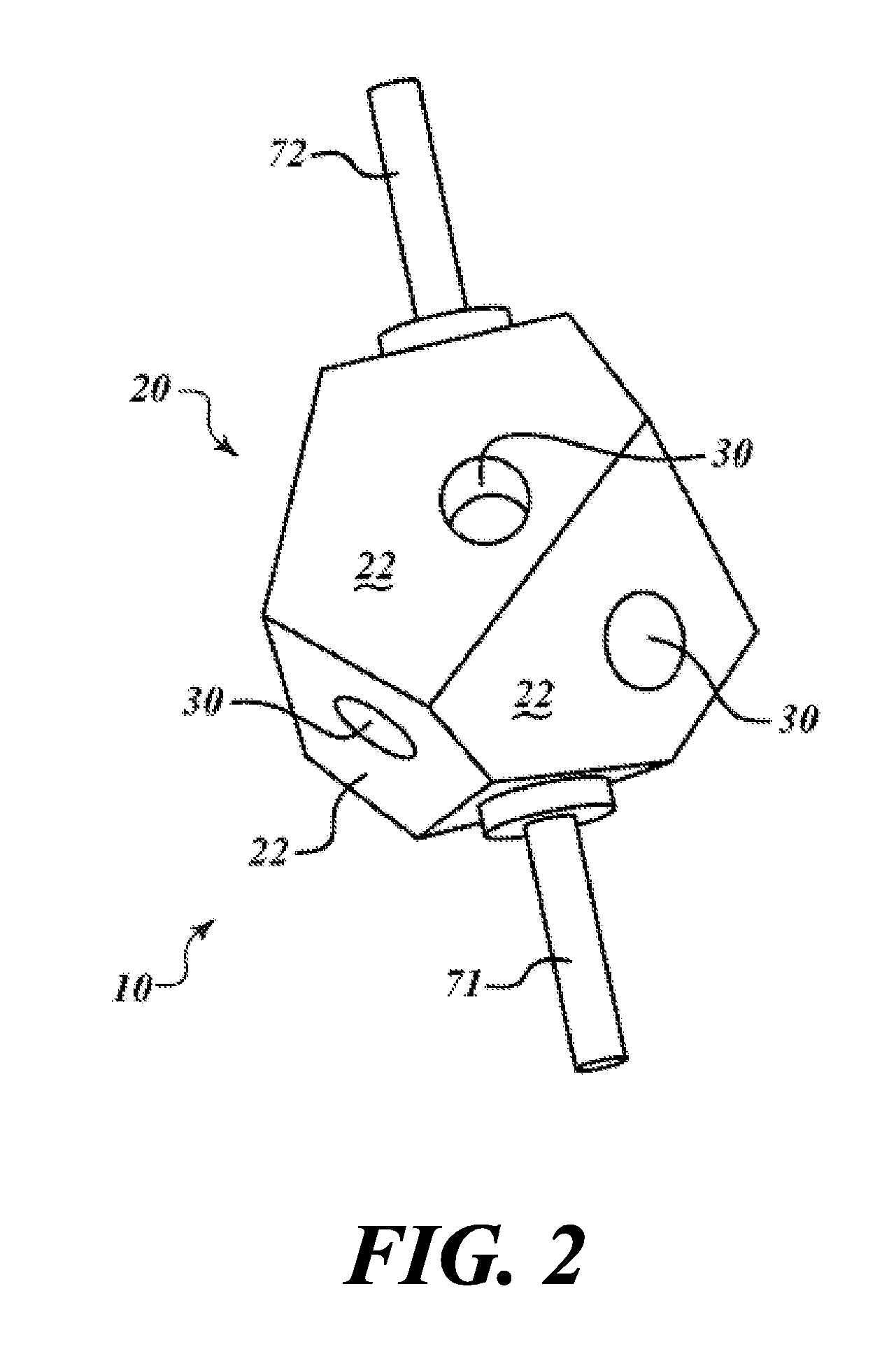

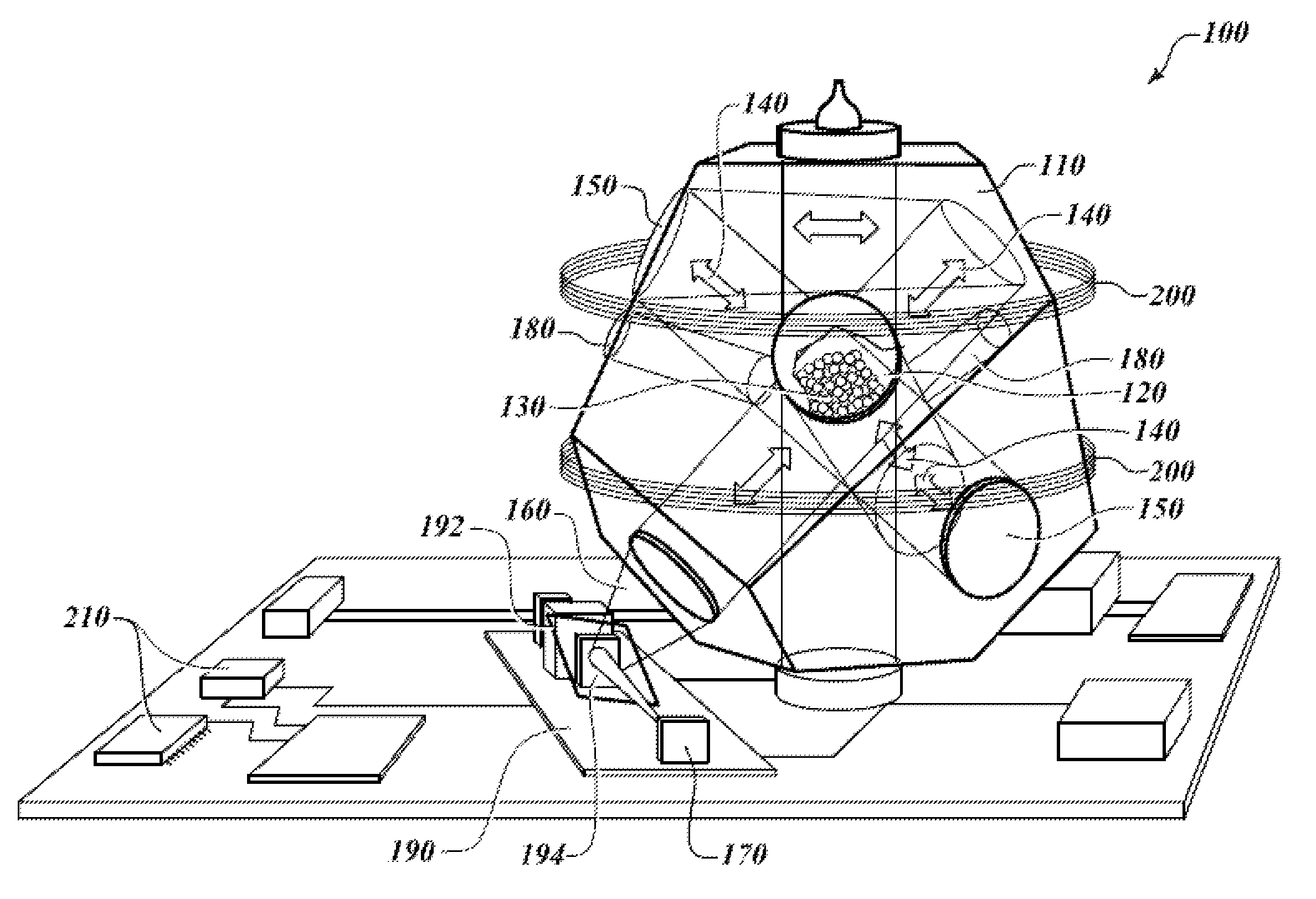

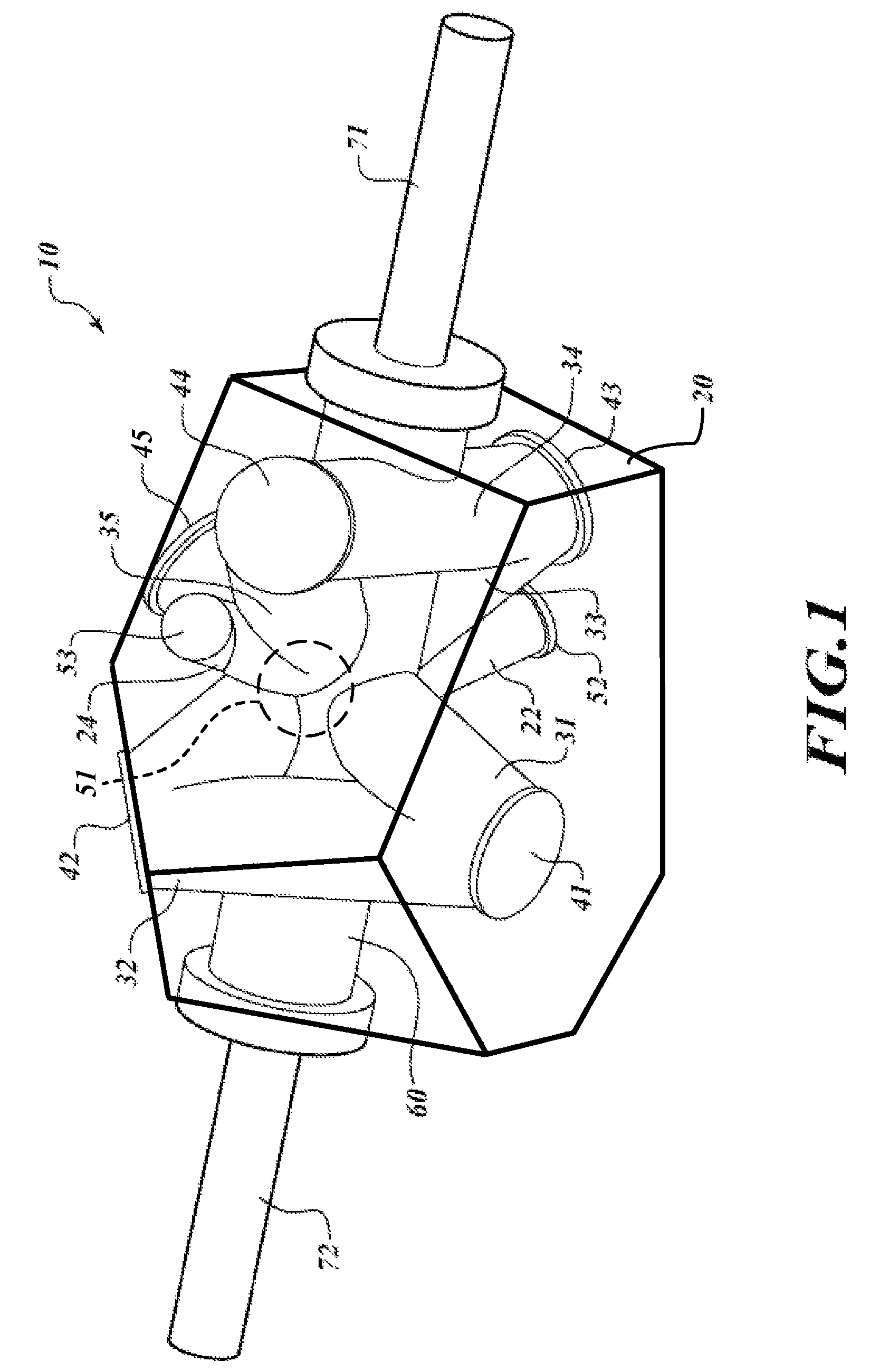

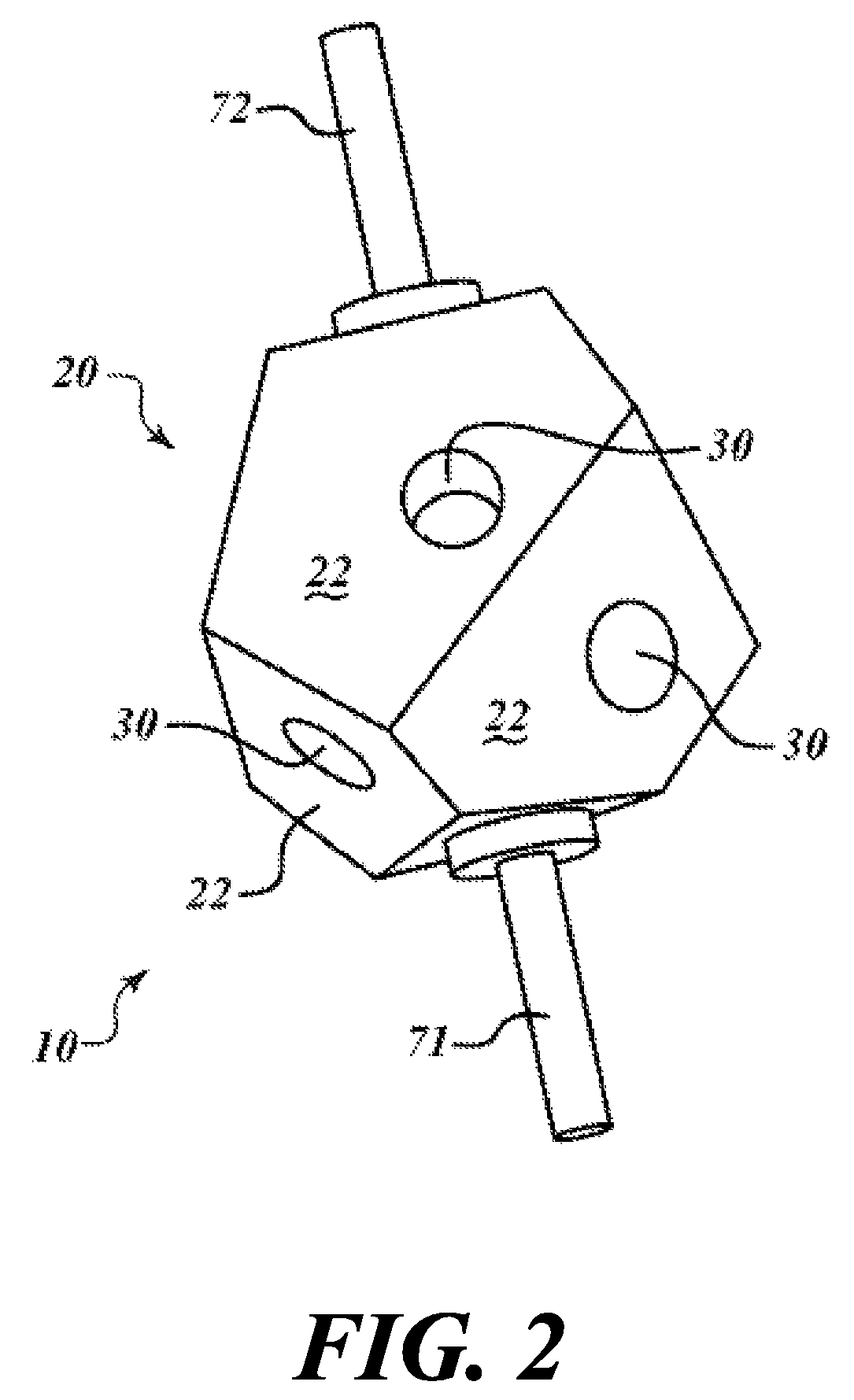

Physics package design for a cold atom primary frequency standard

InactiveUS20100033255A1Keep vacuumingLaser detailsPulse automatic controlPackage designUltra-high vacuum

A physic package for an atomic clock comprising: a block made of optical glass, a glass ceramic material or another suitable material that includes a plurality of faces on its exterior and a plurality of angled borings that serve as a vacuum chamber cavity, light paths and measurement bores; mirrors fixedly attached using a vacuum tight seal to the exterior of the block at certain locations where two light paths intersect; optically clear windows fixedly attached using a vacuum tight seal to the block's exterior over openings of the measurement bores and at one location where two light paths intersect; and fill tubes fixedly attached using a vacuum tight seal to the exterior of the block over the ends of the vacuum chamber cavity. This physics package design makes possible atomic clocks having reduced size and power consumption and capable of maintaining an ultra-high vacuum without active pumping.

Owner:HONEYWELL INT INC

Physics package design for a cold atom primary frequency standard

Owner:HONEYWELL INT INC

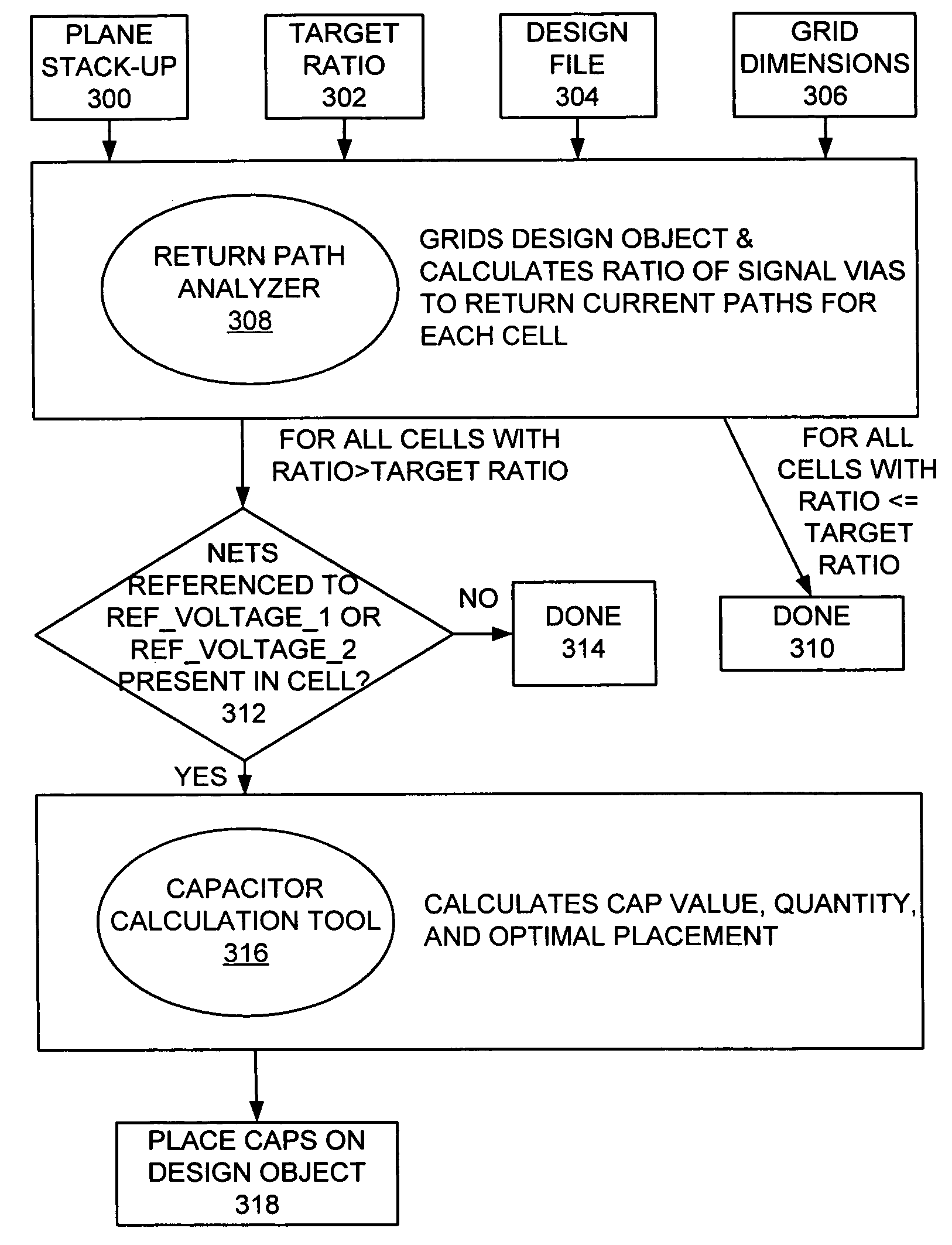

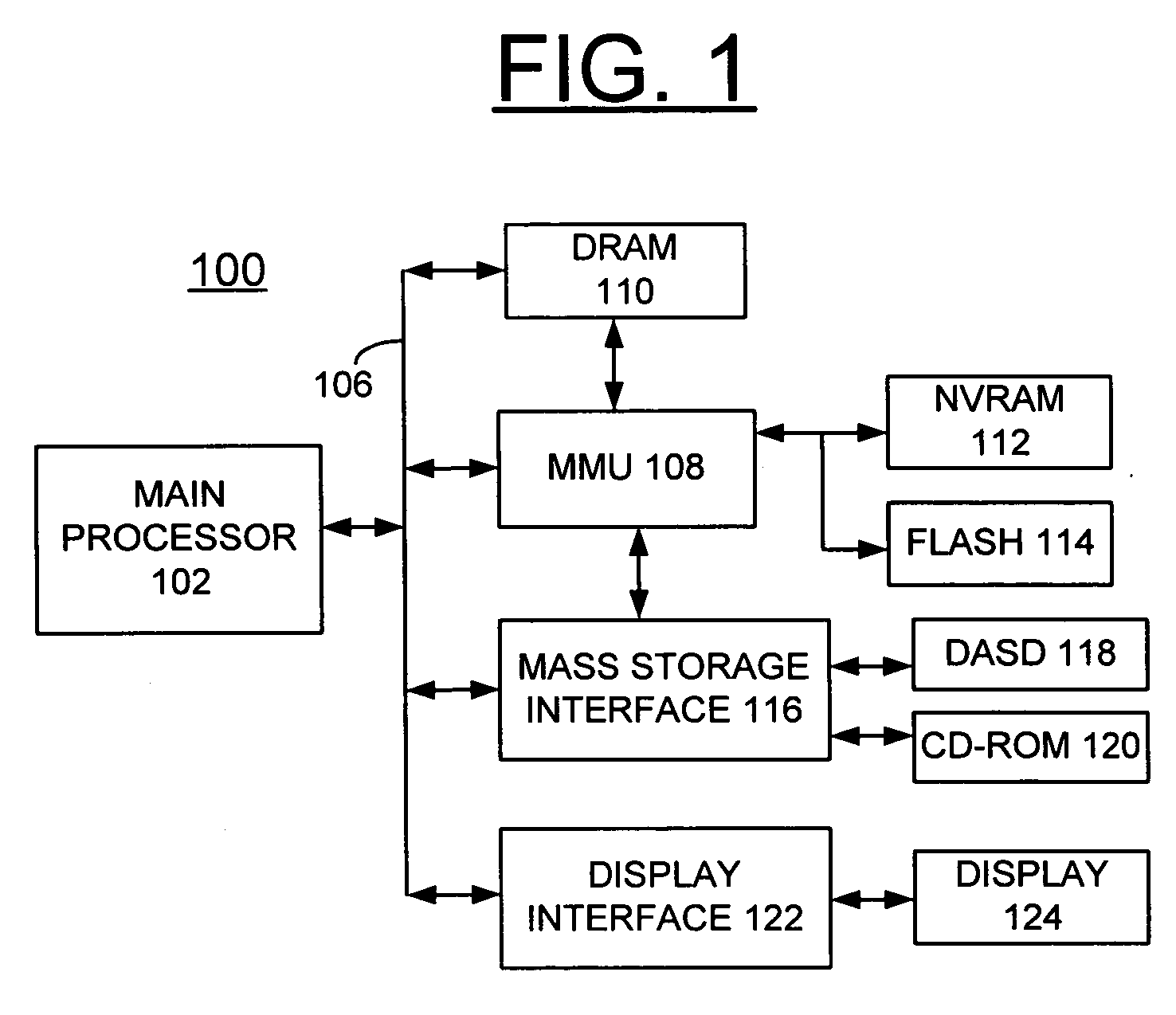

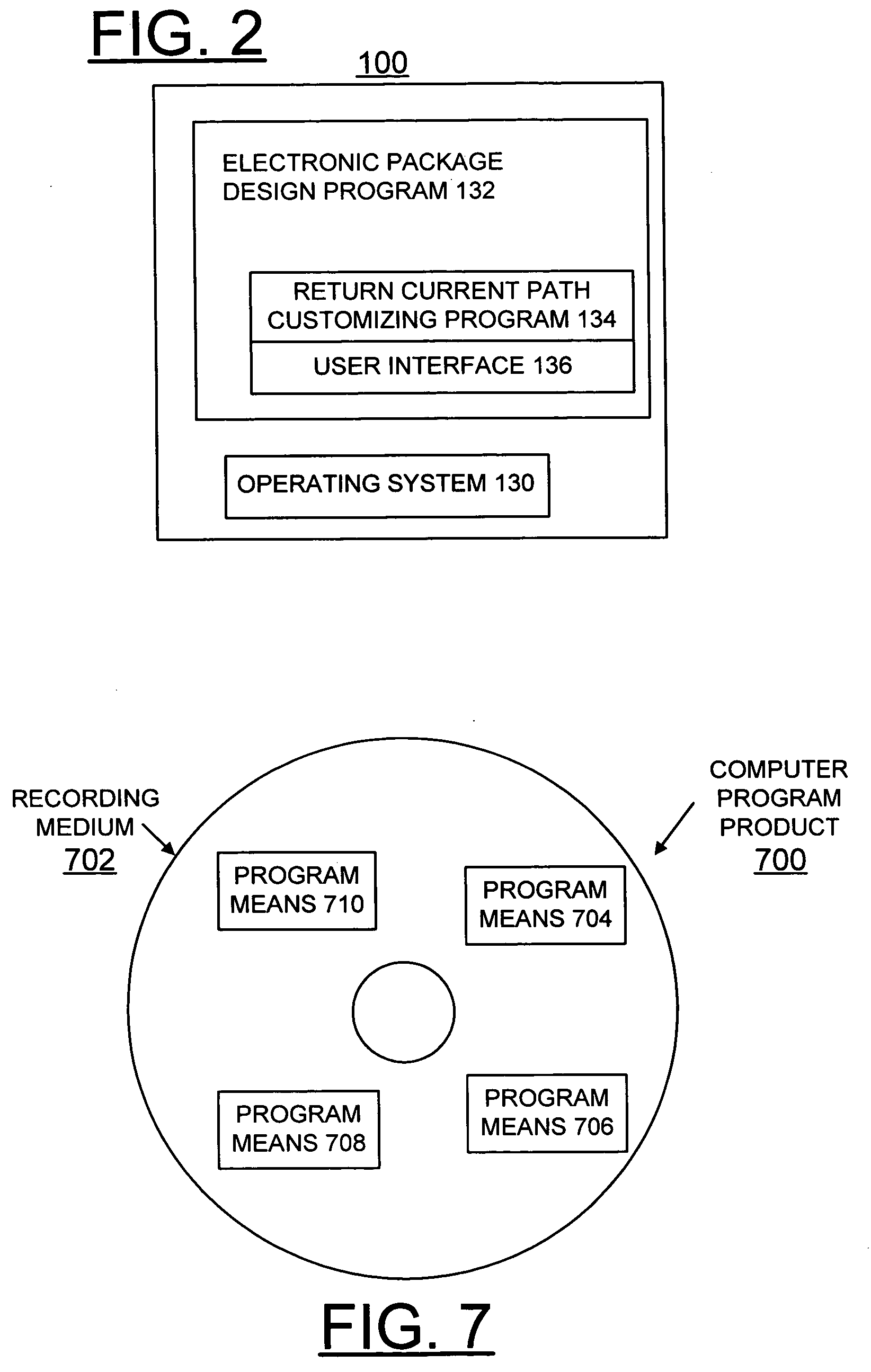

Method, apparatus and computer program product for implementing enhanced high frequency return current paths utilizing decoupling capacitors in a package design

InactiveUS20050108671A1Cross-talk/noise/interference reductionHigh voltage circuit adaptationsReturn currentPackage design

A method, apparatus and computer program product are provided for implementing high frequency return current paths utilizing decoupling capacitors within electronic packages. Electronic package physical design data are received for identifying a board layout. For each of a plurality of cells in a grid of a set cell size within the identified board layout, a respective number of signal vias are identified. A ratio of signal vias to return current paths is calculated for each of the plurality of cells. Each cell having a calculated ratio greater than a target ratio is identified. One or more decoupling capacitors are selectively added within each of the identified cells to provide high frequency return current paths.

Owner:GOOGLE LLC