Patents

Literature

56 results about "Texel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

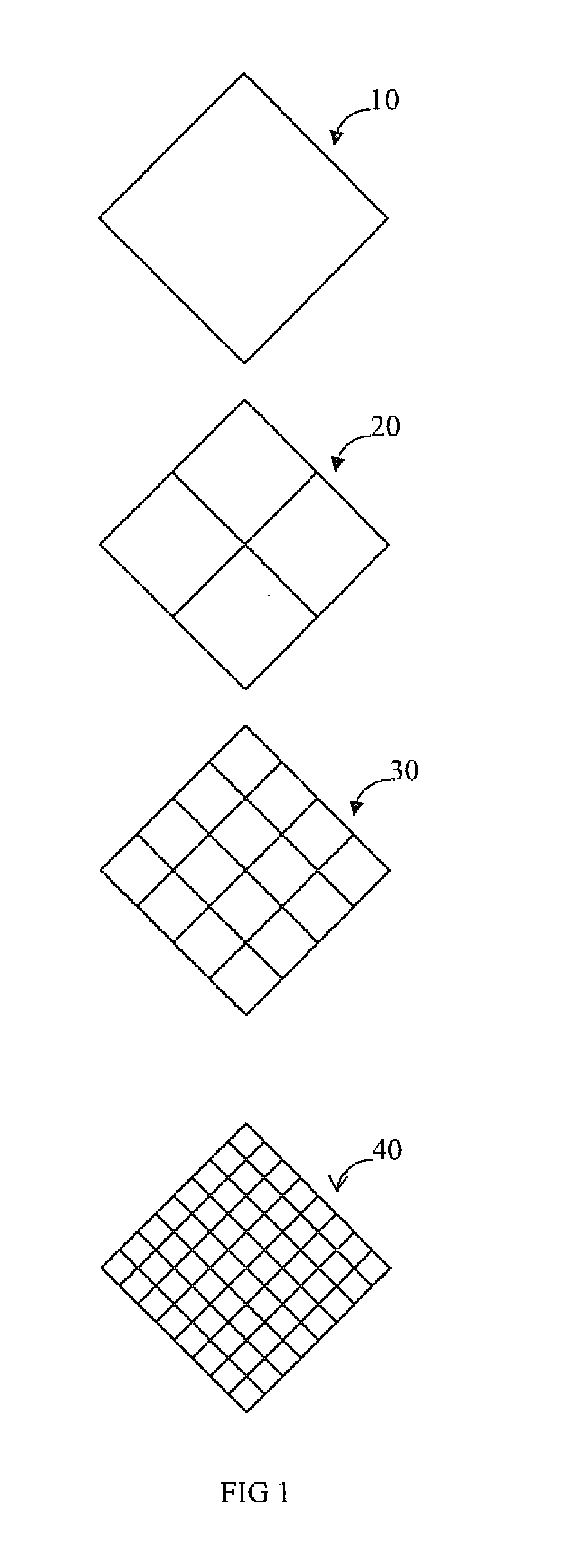

A texel, texture element, or texture pixel is the fundamental unit of a texture map, used in computer graphics. Textures are represented by arrays of texels representing the texture space, just as other images are represented by arrays of pixels.

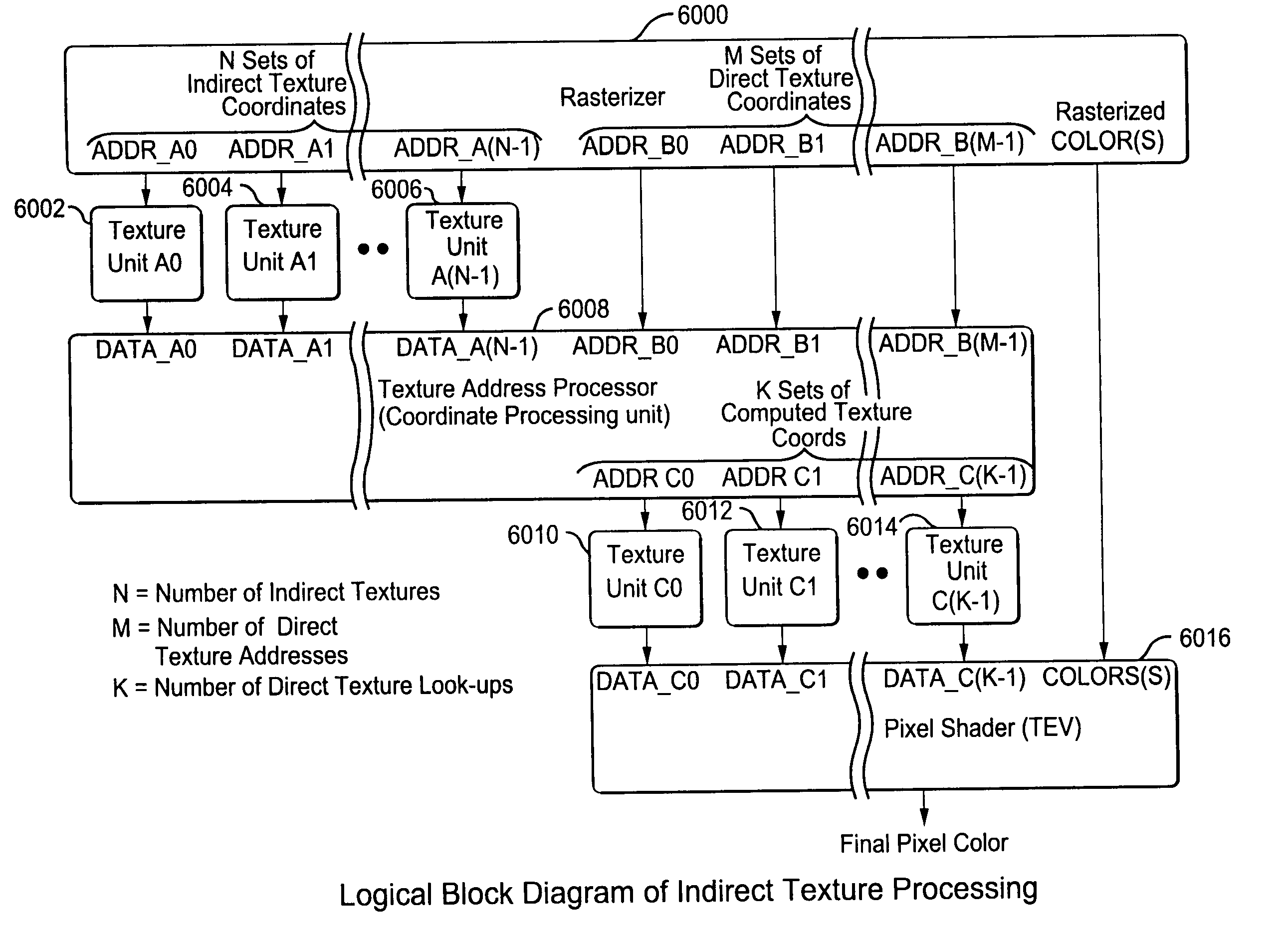

Method and apparatus for interleaved processing of direct and indirect texture coordinates in a graphics system

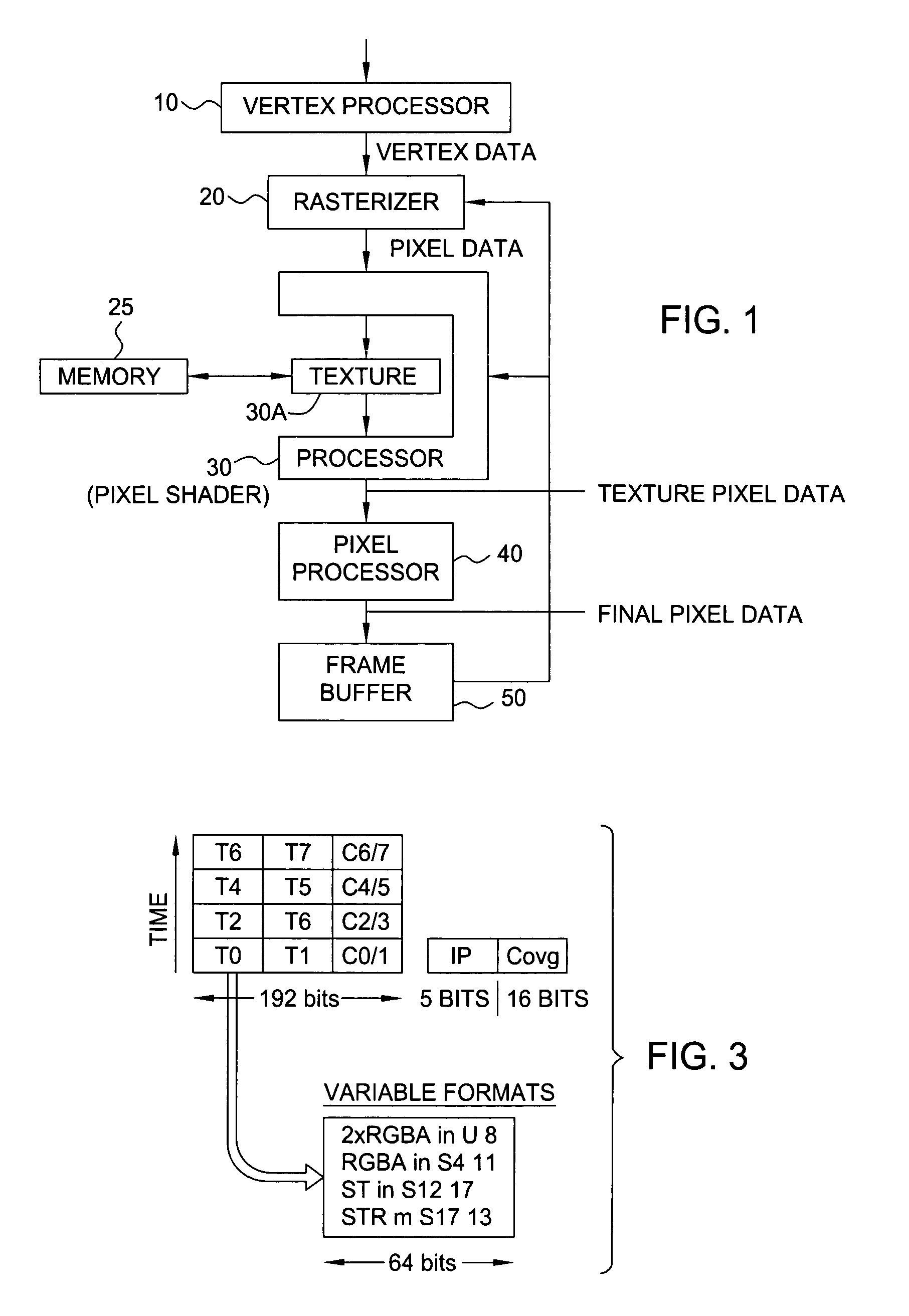

InactiveUS7002591B1Efficient implementationIncrease in texture mapping hardware complexityCathode-ray tube indicators3D-image renderingPattern recognitionProcessing

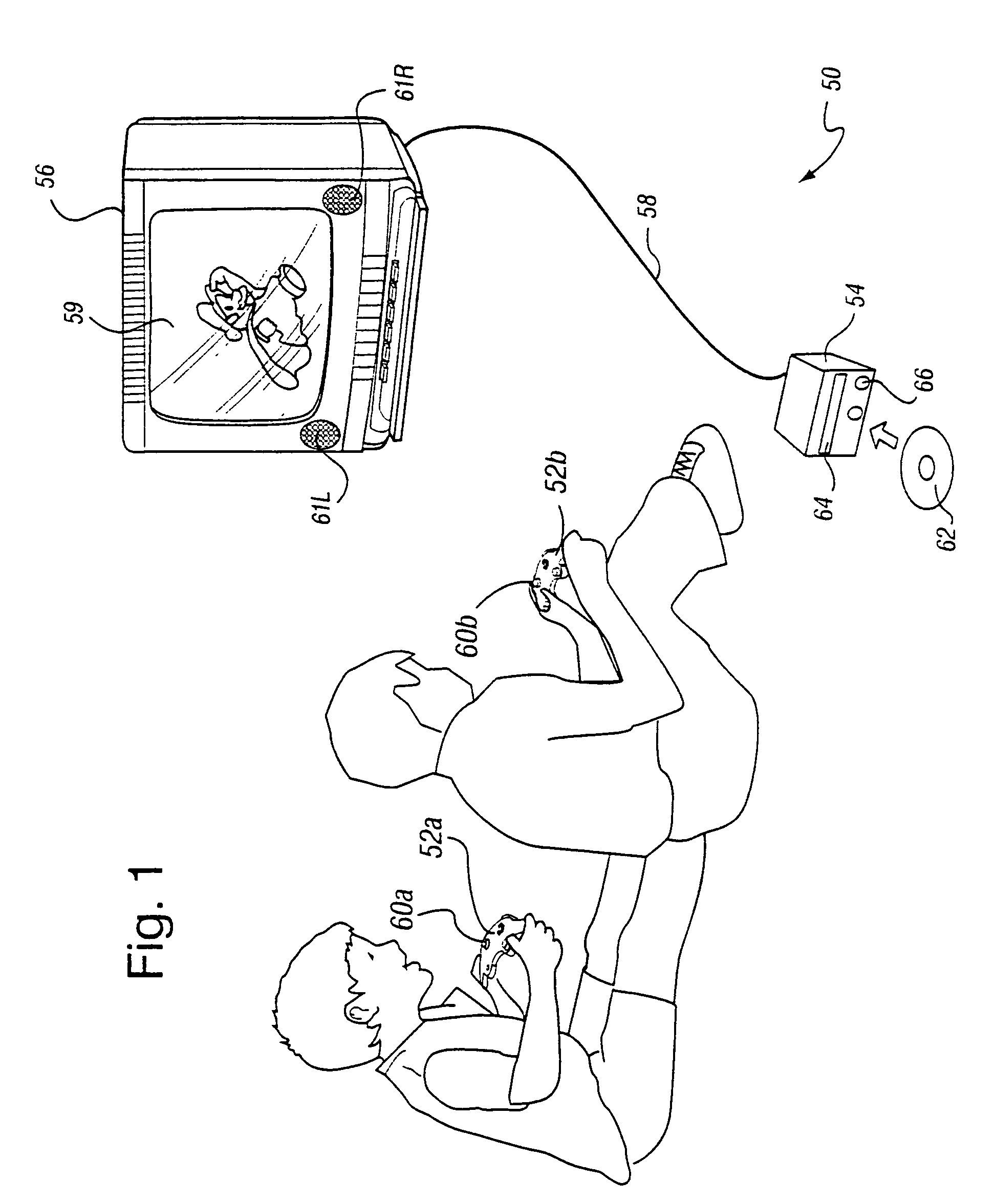

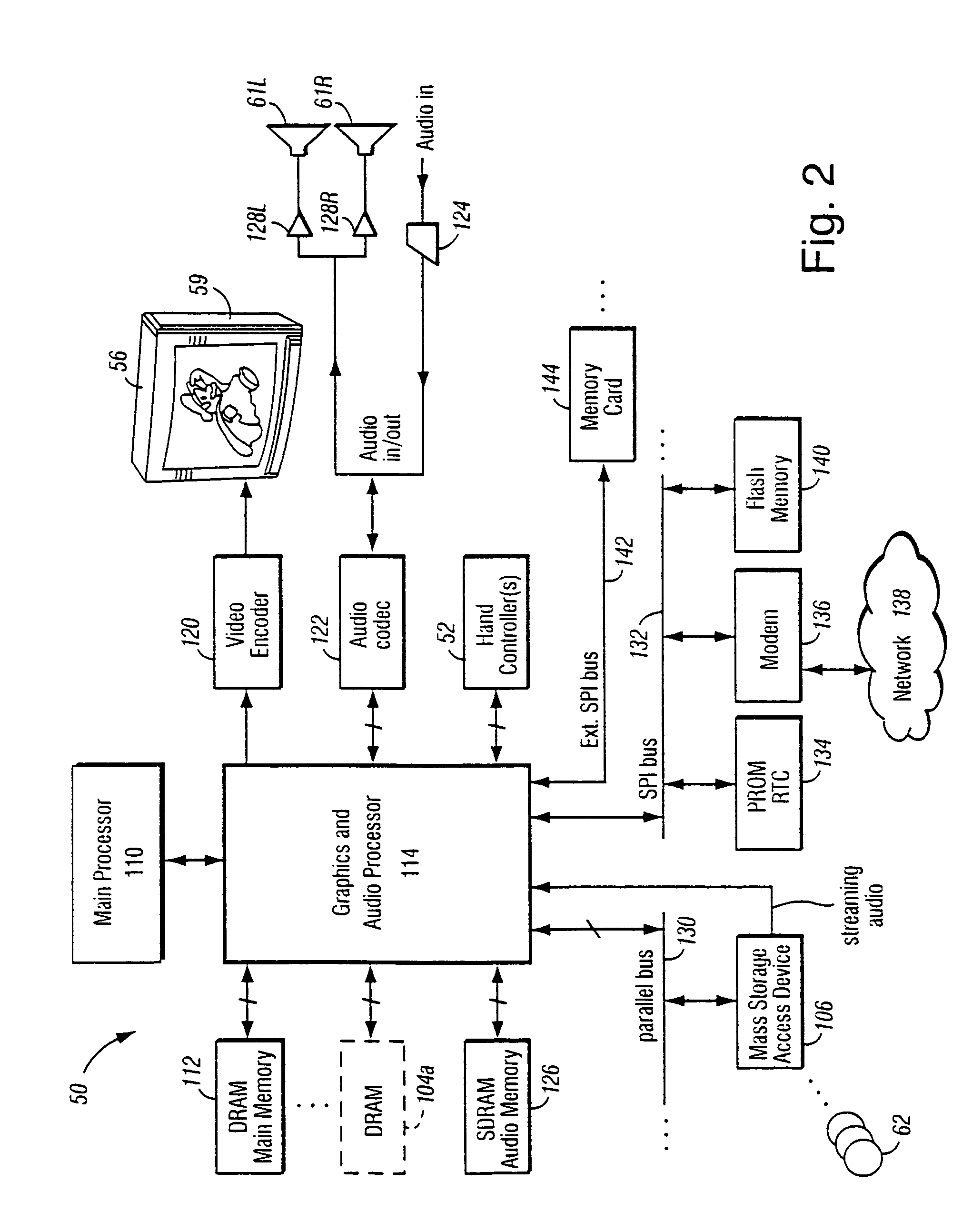

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The graphics pipeline renders and prepares images for display at least in part in response to polygon vertex attribute data and texel color data stored as a texture images in an associated memory. An efficient texturing pipeline arrangement achieves a relatively low chip-footprint by utilizing a single texture coordinate / data processing unit that interleaves the processing of logical direct and indirect texture coordinate data and a texture lookup data feedback path for “recirculating” indirect texture lookup data retrieved from a single texture retrieval unit back to the texture coordinate / data processing unit. Versatile indirect texture referencing is achieved by using the same texture coordinate / data processing unit to transform the recirculated texture lookup data into offsets that may be added to the texture coordinates of a direct texture lookup. A generalized indirect texture API function is provided that supports defining at least four indirect texture referencing operations and allows for selectively associating one of at least eight different texture images with each indirect texture defined. Retrieved indirect texture lookup data is processed as multi-bit binary data triplets of three, four, five, or eight bits. The data triplets are multiplied by a 3×2 texture coordinate offset matrix before being optionally combined with regular non-indirect coordinate data or coordinate data from a previous cycle / stage of processing. Values of the offset matrix elements are variable and may be dynamically defined for each cycle / stage using selected constants. Two additional variable matrix configurations are also defined containing element values obtained from current direct texture coordinates. Circuitry for optionally biasing and scaling retrieved texture data is also provided.

Owner:NINTENDO CO LTD

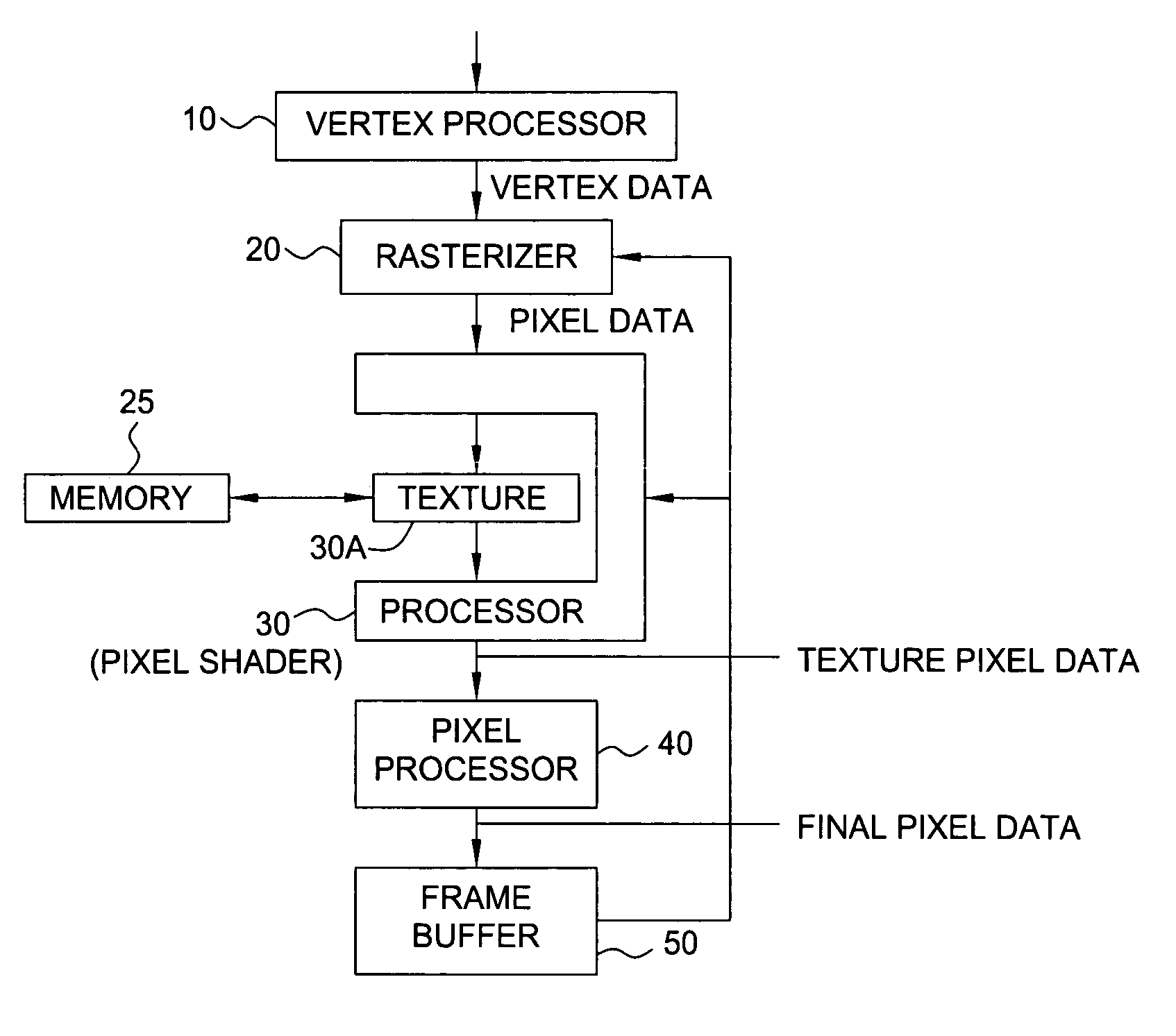

Method and system for scalable, dataflow-based, programmable processing of graphics data

ActiveUS6980209B1Improve system performanceLess system performanceCathode-ray tube indicatorsProcessor architectures/configurationArray data structureNetwork packet

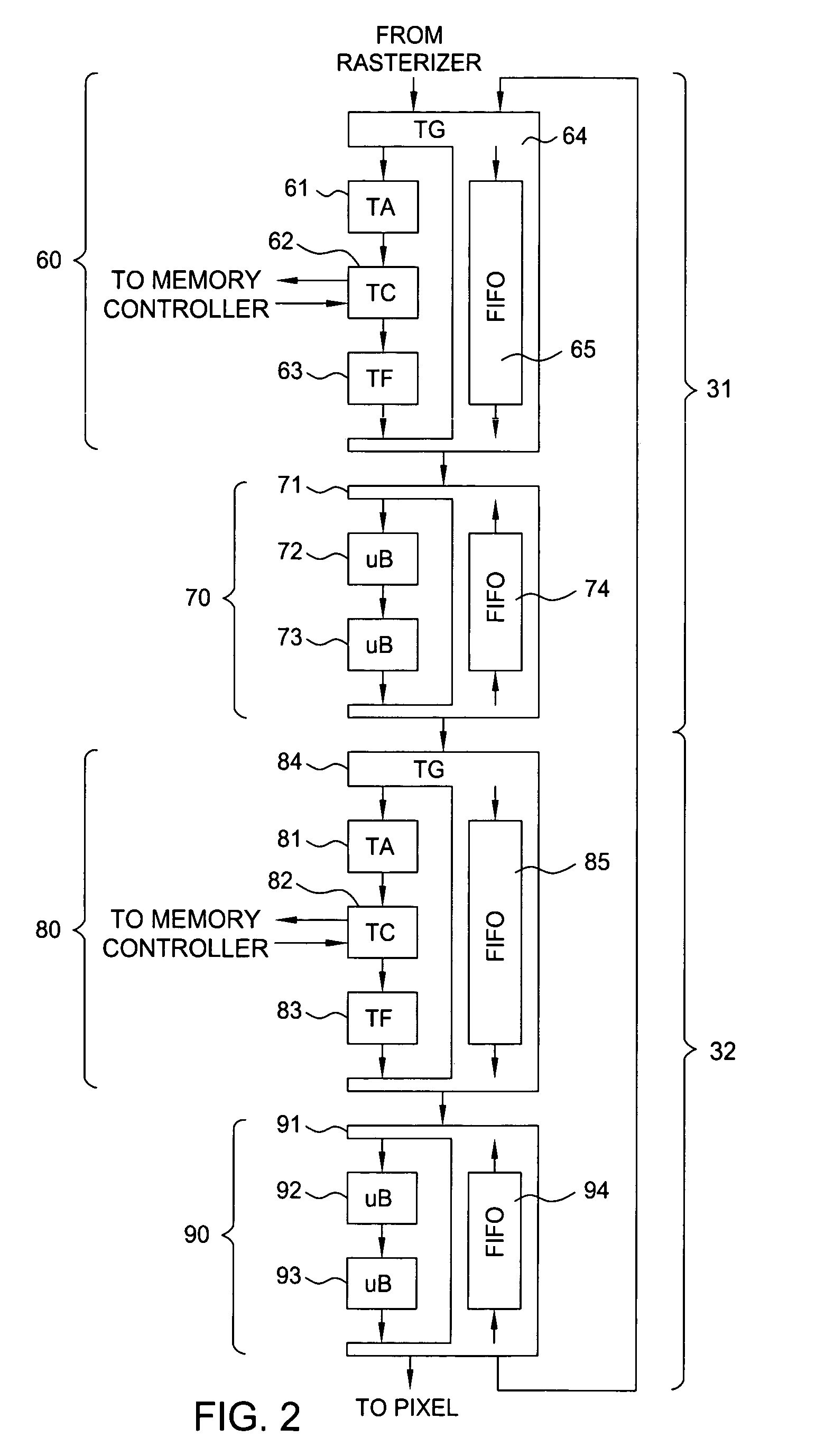

A scalable pipelined pixel shader that processes packets of data and preserves the format of each packet at each processing stage. Each packet is an ordered array of data values, at least one of which is an instruction pointer. Each member of the ordered array can be indicative of any type of data. As a packet progresses through the pixel shader during processing, each member of the ordered array can be replaced by a sequence of data values indicative of different types of data (e.g., an address of a texel, a texel, or a partially or fully processed color value). Information required for the pixel shader to process each packet is contained in the packet, and thus the pixel shader is scalable in the sense that it can be implemented in modular fashion to include any number of identical pipelined processing stages and can execute the same program regardless of the number of stages. Preferably, each processing stage is itself scalable, can be implemented to include an arbitrary number of identical pipelined instruction execution stages known as microblenders, and can execute the same program regardless of the number of microblenders. The current value of the instruction pointer (IP) in a packet determines the next instruction to be executed on the data contained in the packet. Any processing unit can change the instruction that will be executed by a subsequent processing unit by modifying the IP (and / or condition codes) of a packet that it asserts to the subsequent processing unit. Other aspects of the invention include graphics processors (each including a pixel shader configured in accordance with the invention), methods and systems for generating packets of data for processing in accordance with the invention, and methods for pipelined processing of packets of data.

Owner:PVC CONTAINER CORP +1

Method, system, and computer program product for updating texture with overscan

A system, method, and computer program product are provided for updating texture on a graphical display object with overscan. A preprocessor stage defines an overscan region representing an extension of an object surface rasterized in texture space. A texture update stage creates a dilated texture map that includes updated mapped texels for a mapped region and updated overscan texels corresponding to the overscan region, such that texture is updated in the mapped region and the overscan region. Texel-based and polygon-based preprocessor stages and texture update stages are provided.

Owner:AUTODESK INC

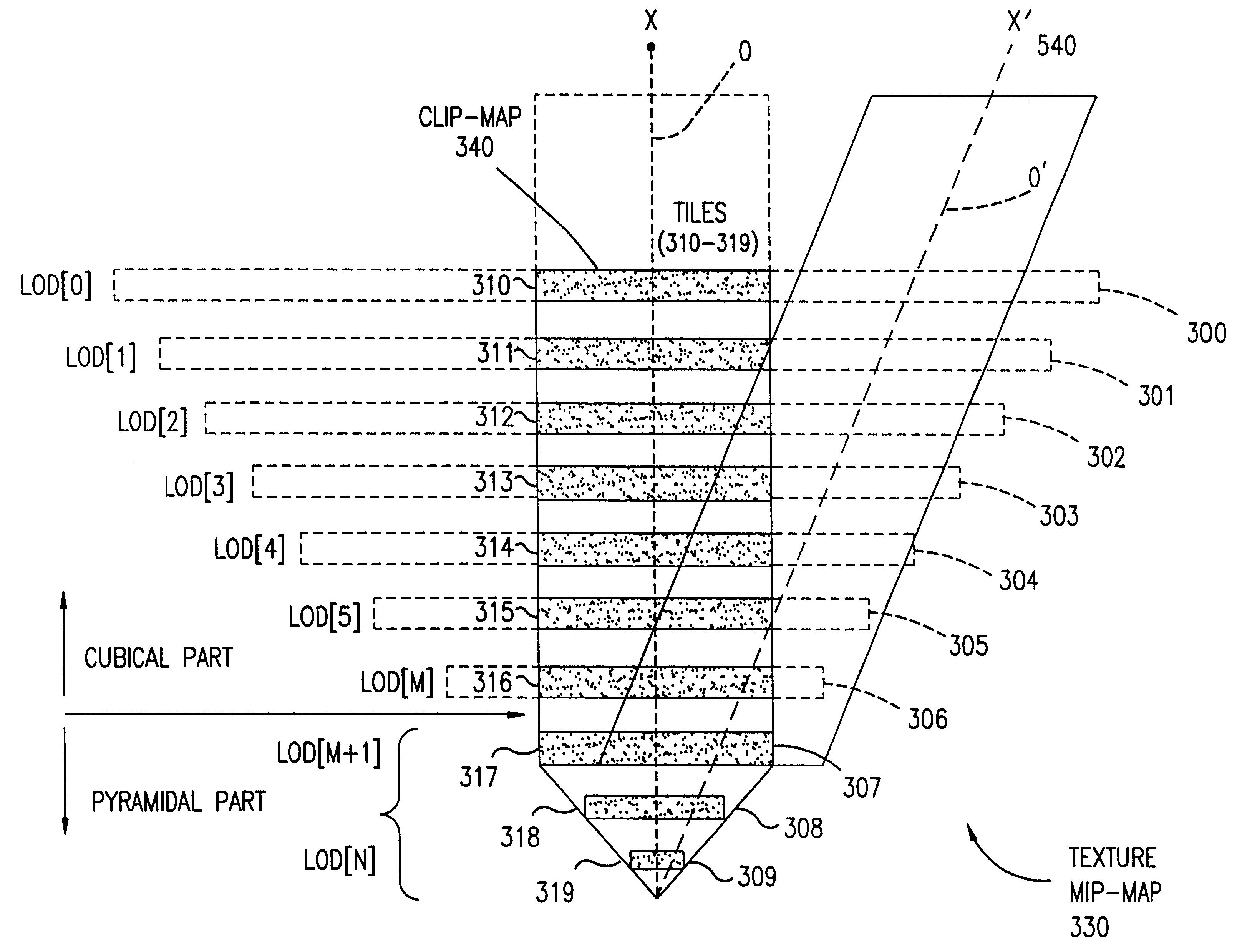

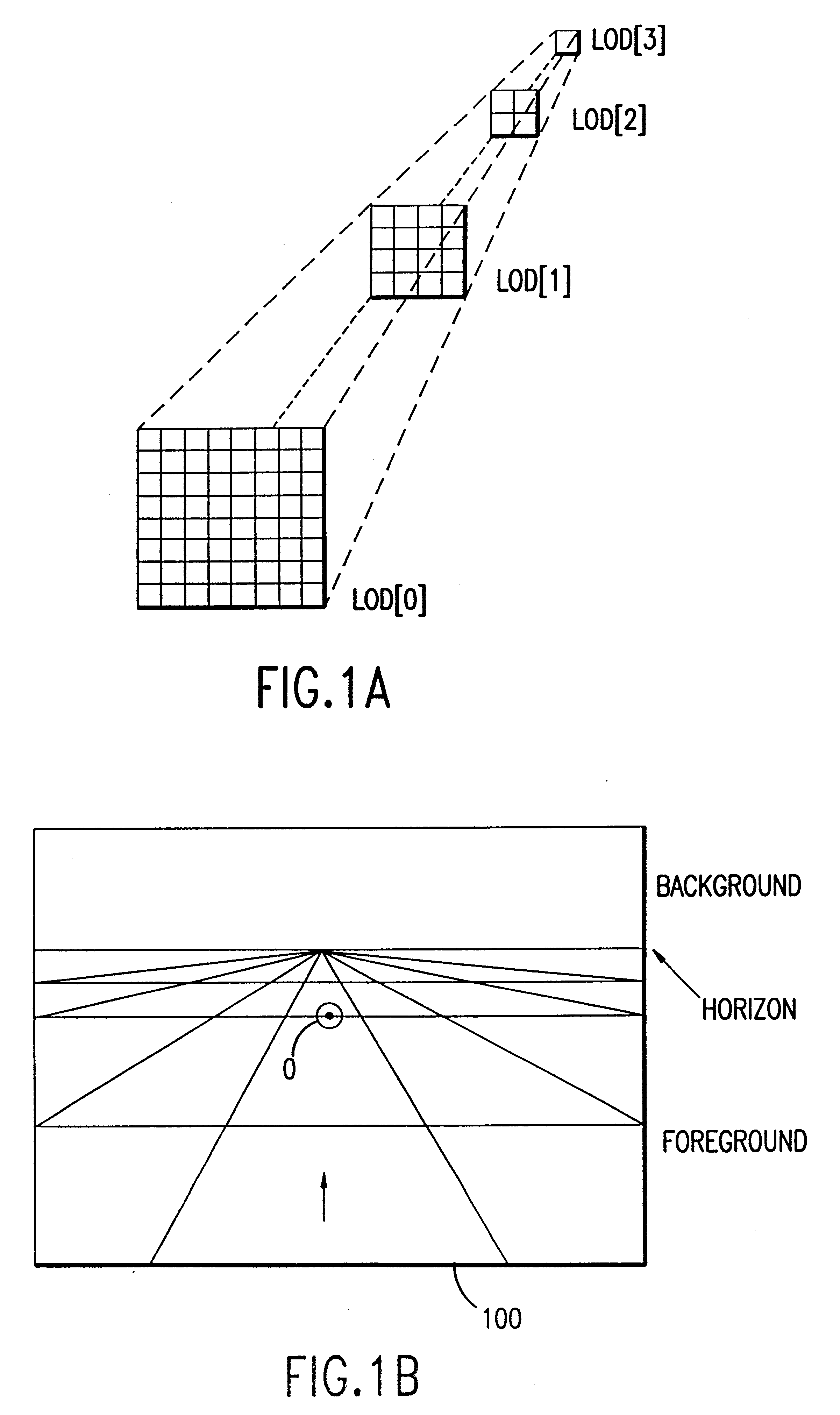

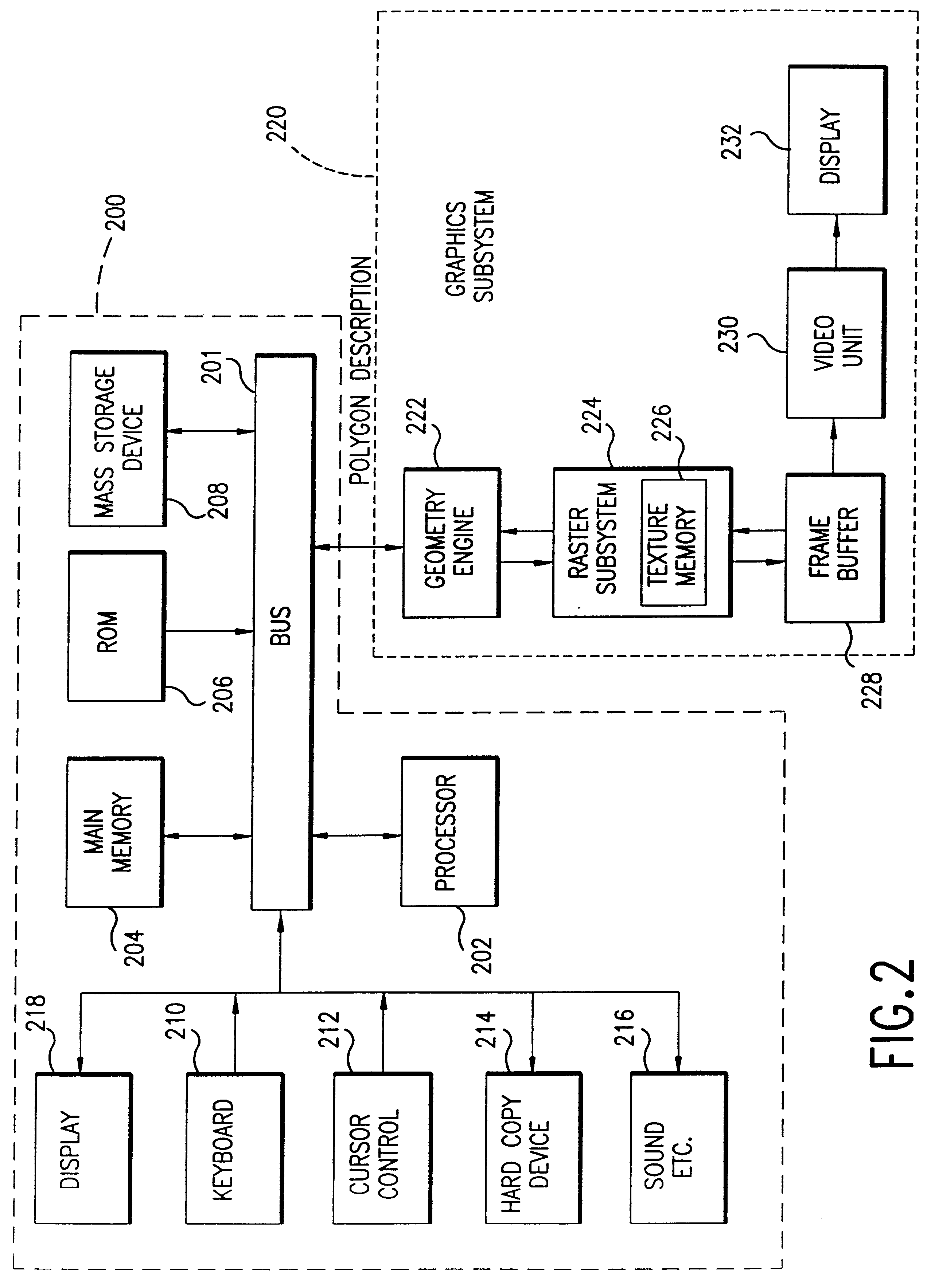

Method and system for providing texture using a selected portion of a texture map

InactiveUS6417860B1Cathode-ray tube indicatorsFilling planer surface with attributesTerrainMass storage

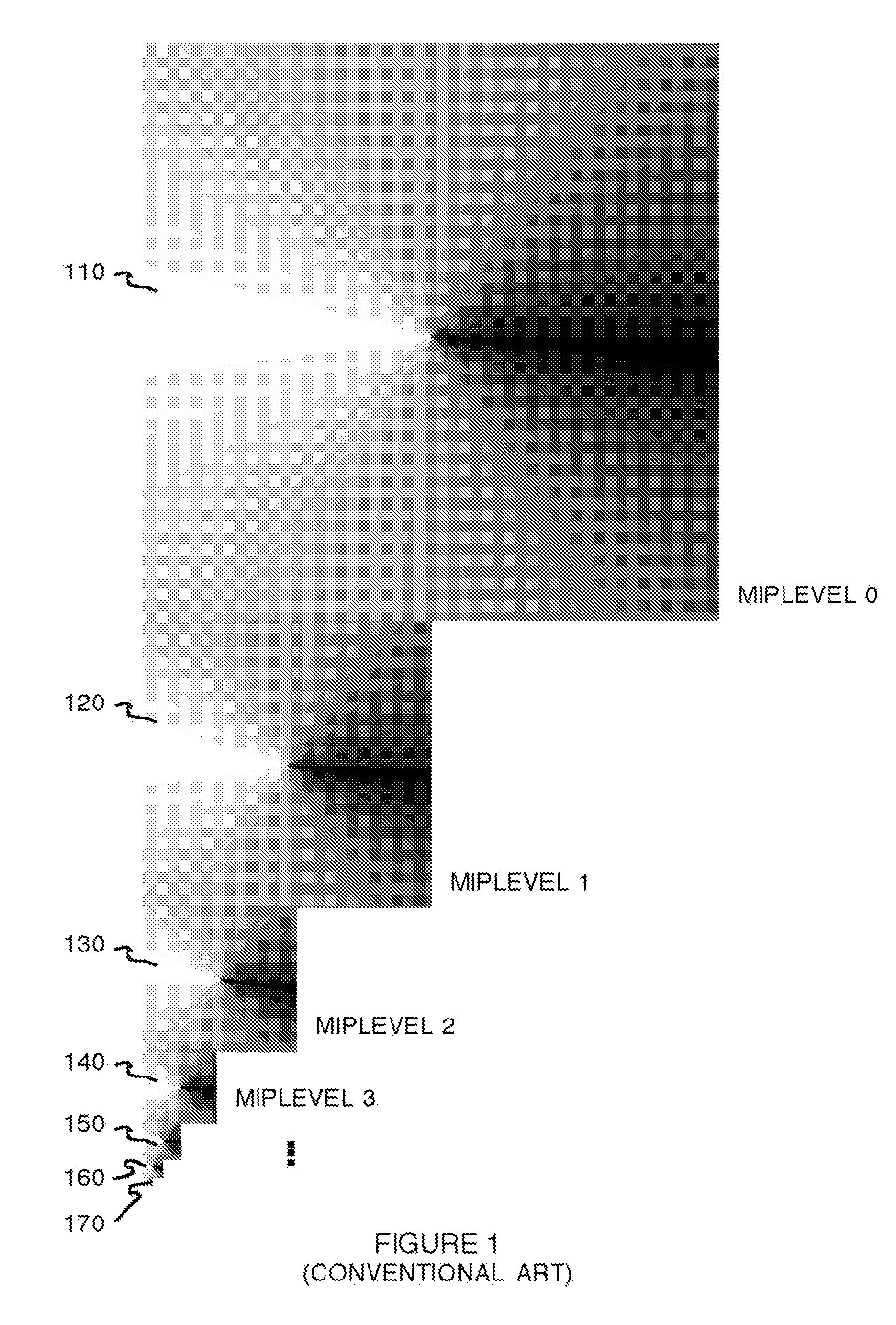

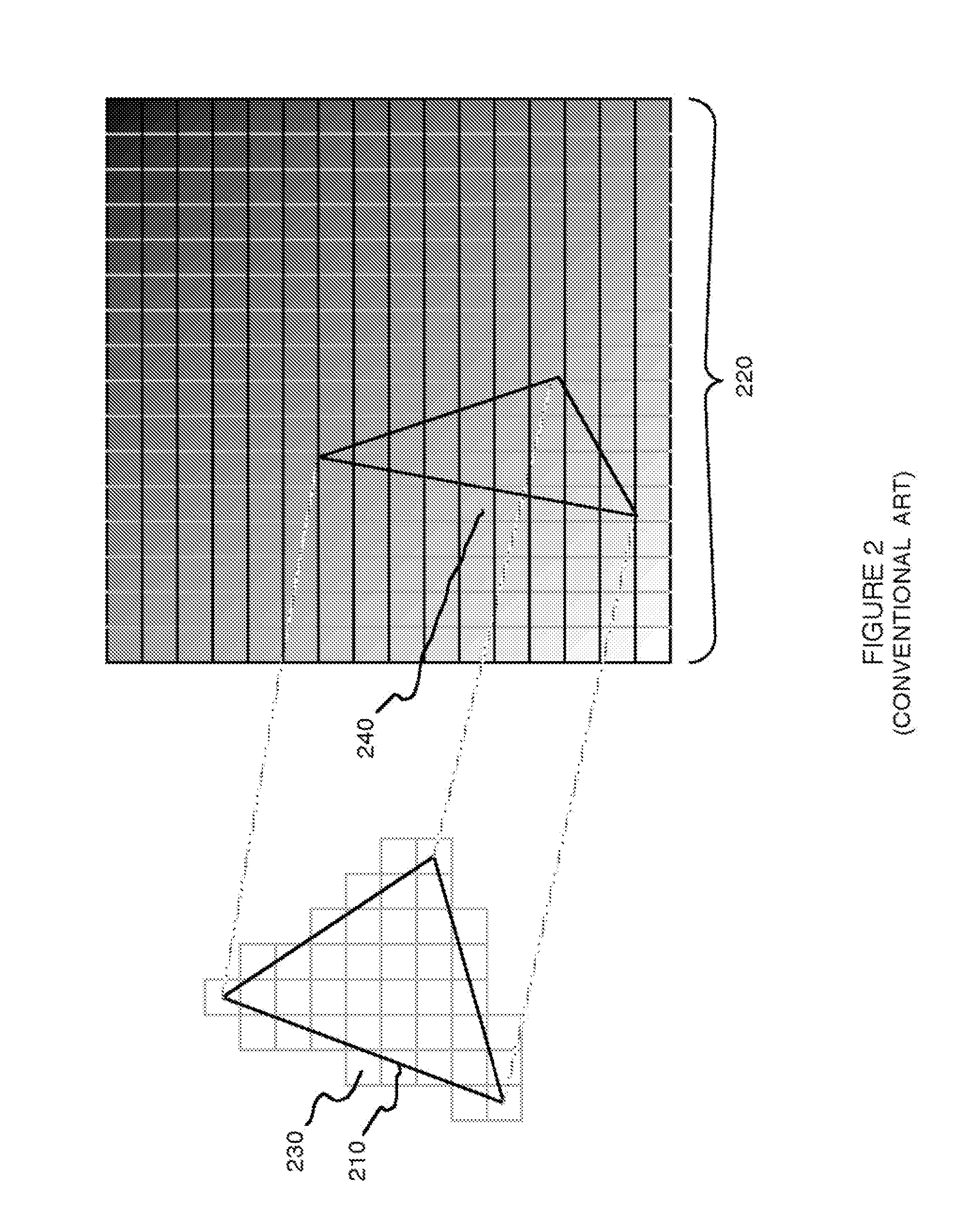

An apparatus and method for quickly and efficiently providing texel data relevant for displaying a textured-image. A large amount of texture source data, such as photographic terrain texture, is stored as a two-dimensional or three-dimensional texture MIP-map on one or more mass storage devices. Only a relatively small clip-map representing selected portions of the complete texture MIP-map is loaded into faster, more expensive memory. These selected texture MIP-map portions forming the clip-map consist of tiles which contain those texel values at each respective level of detail that are most likely to be mapped to pixels being rendered for display based upon the viewer's eyepoint and field of view. To efficiently update the clip-map in real-time, texel data is loaded and discarded from the edges of tiles. Attempts to access a texel lying outside of a particular clip-map tile are accommodated by utilizing a substitute texel value obtained from the next coarser resolution clip-map tile which encompasses the sought texel.

Owner:MICROSOFT TECH LICENSING LLC

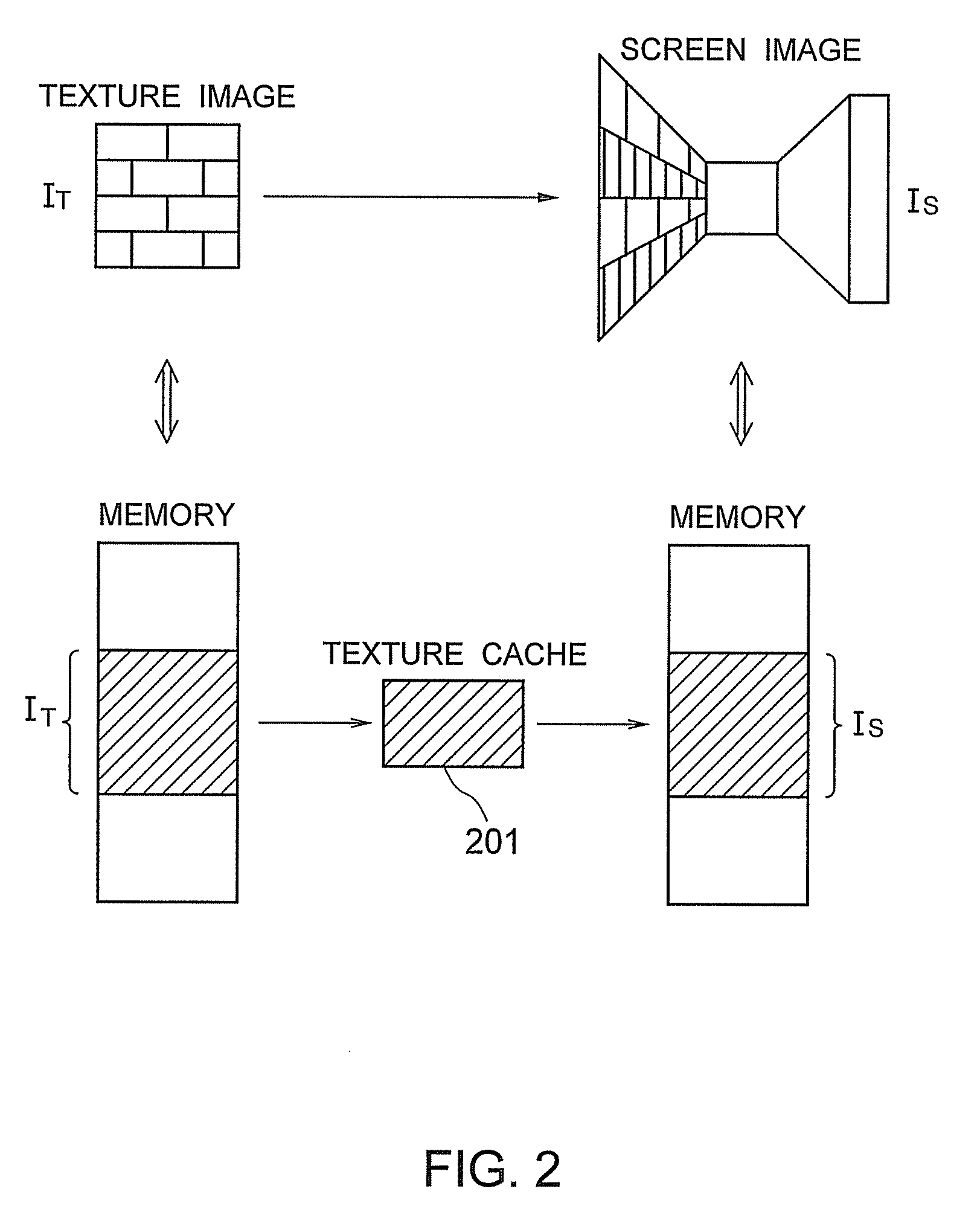

3-D rendering texture caching scheme

InactiveUS7050063B1Improve efficiencyEliminate significant numberMemory adressing/allocation/relocationImage memory managementComputational scienceParallel computing

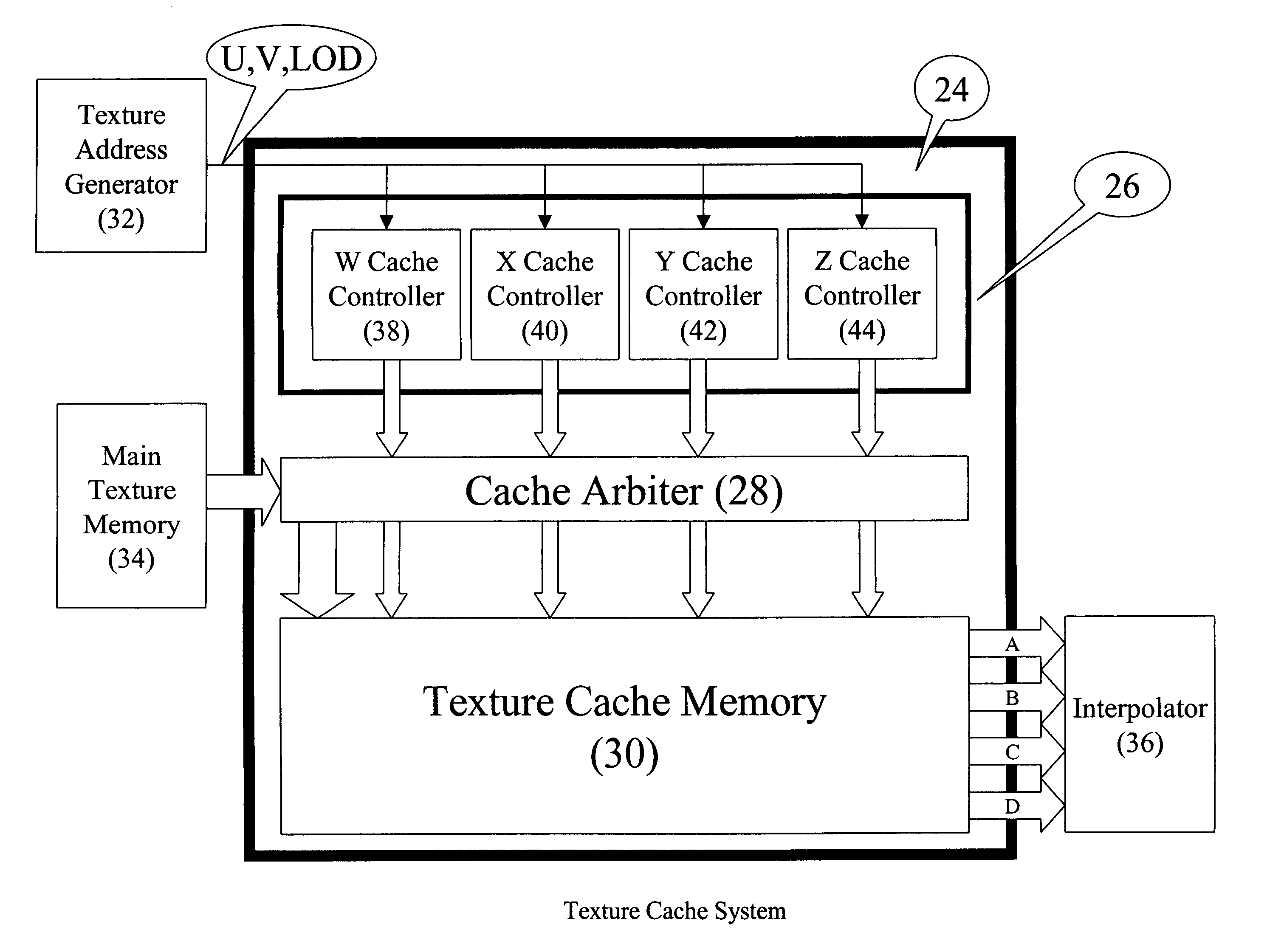

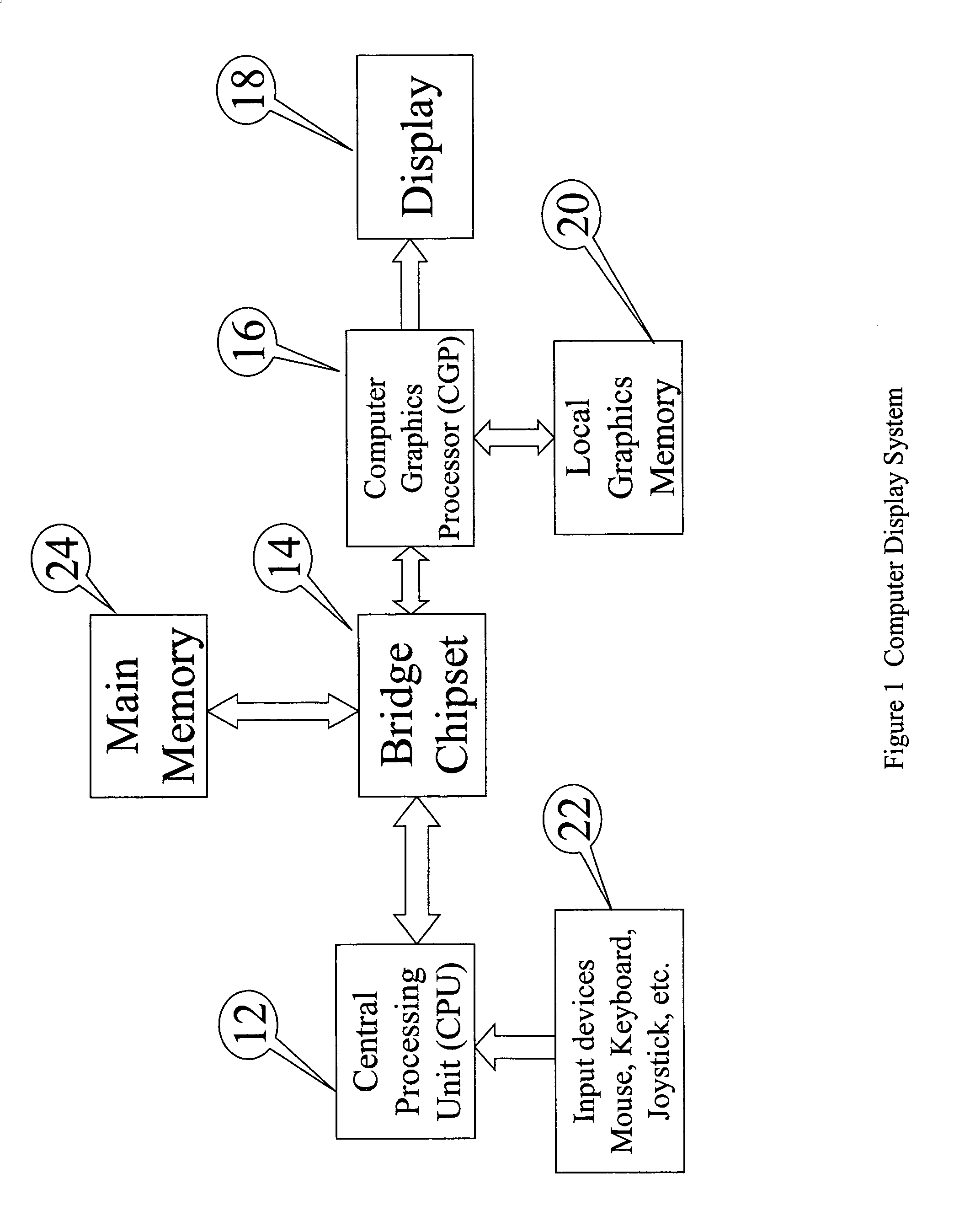

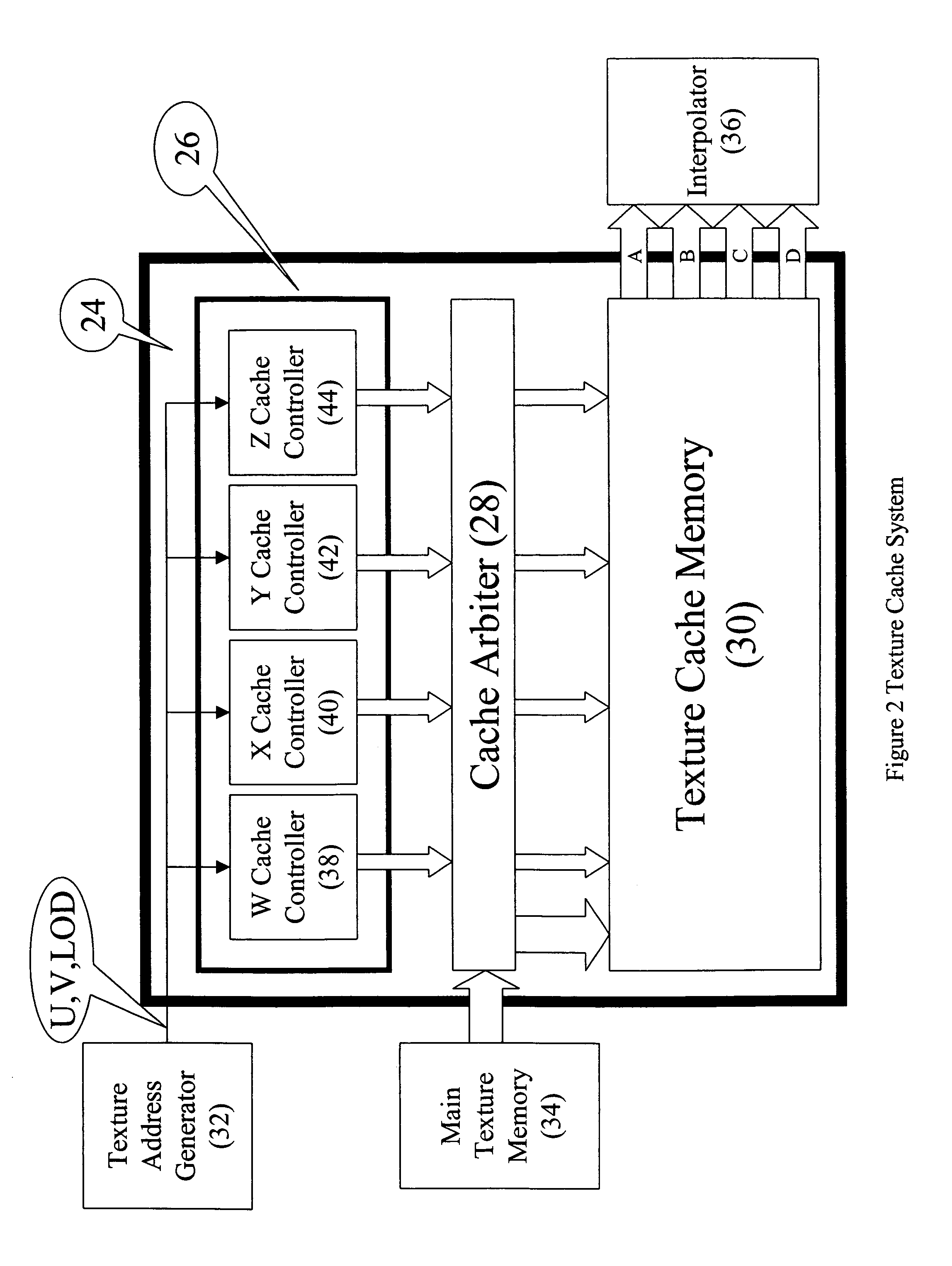

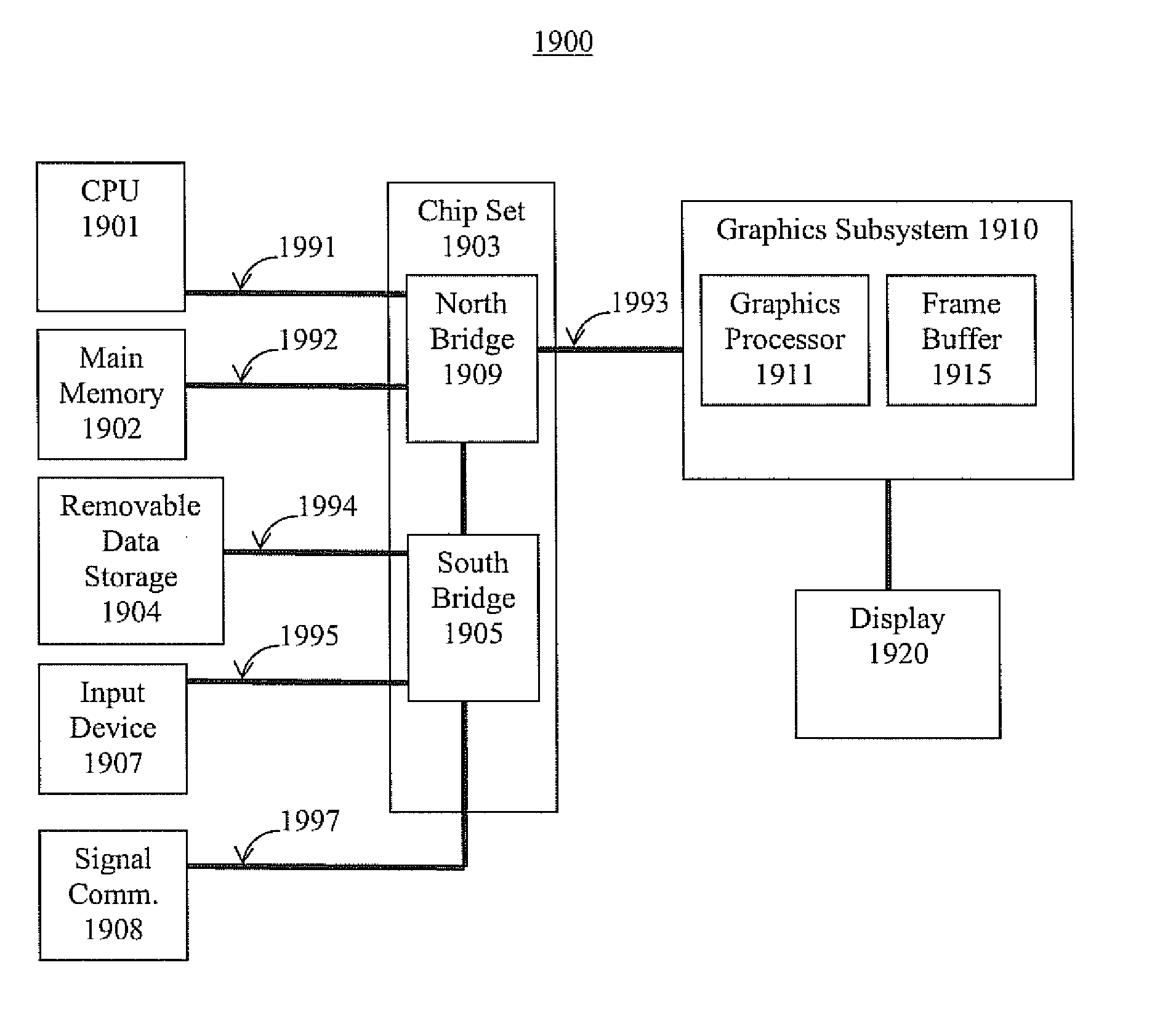

A 3D rendering texture caching scheme that minimizes external bandwidth requirements for texture and increases the rate at which textured pixels are available. The texture caching scheme efficiently pre-fetches data at the main memory access granularity and stores it in cache memory. The data in the main memory and texture cache memory is organized in a manner to achieve large reuse of texels with a minimum of cache memory to minimize cache misses. The texture main memory stores a two dimensional array of texels, each texel having an address and one of N identifiers. The texture cache memory has addresses partitioned into N banks, each bank containing texels transferred from the main memory that have the corresponding identifier. A cache controller determines which texels need to be transferred from the texture main memory to the texture cache memory and which texels are currently in the cache using a least most recently used algorithm. By labeling the texture map blocks (double quad words), a partitioning scheme is developed which allow the cache controller structure to be very modular and easily realized. The texture cache arbiter is used for scheduling and controlling the actual transfer of texels from the texture main memory into the texture cache memory and controlling the outputting of texels for each pixel to an interpolating filter from the cache memory.

Owner:INTEL CORP

Sparse texture systems and methods

ActiveUS20110157207A1Cathode-ray tube indicators3D-image renderingPattern recognitionTexture processing

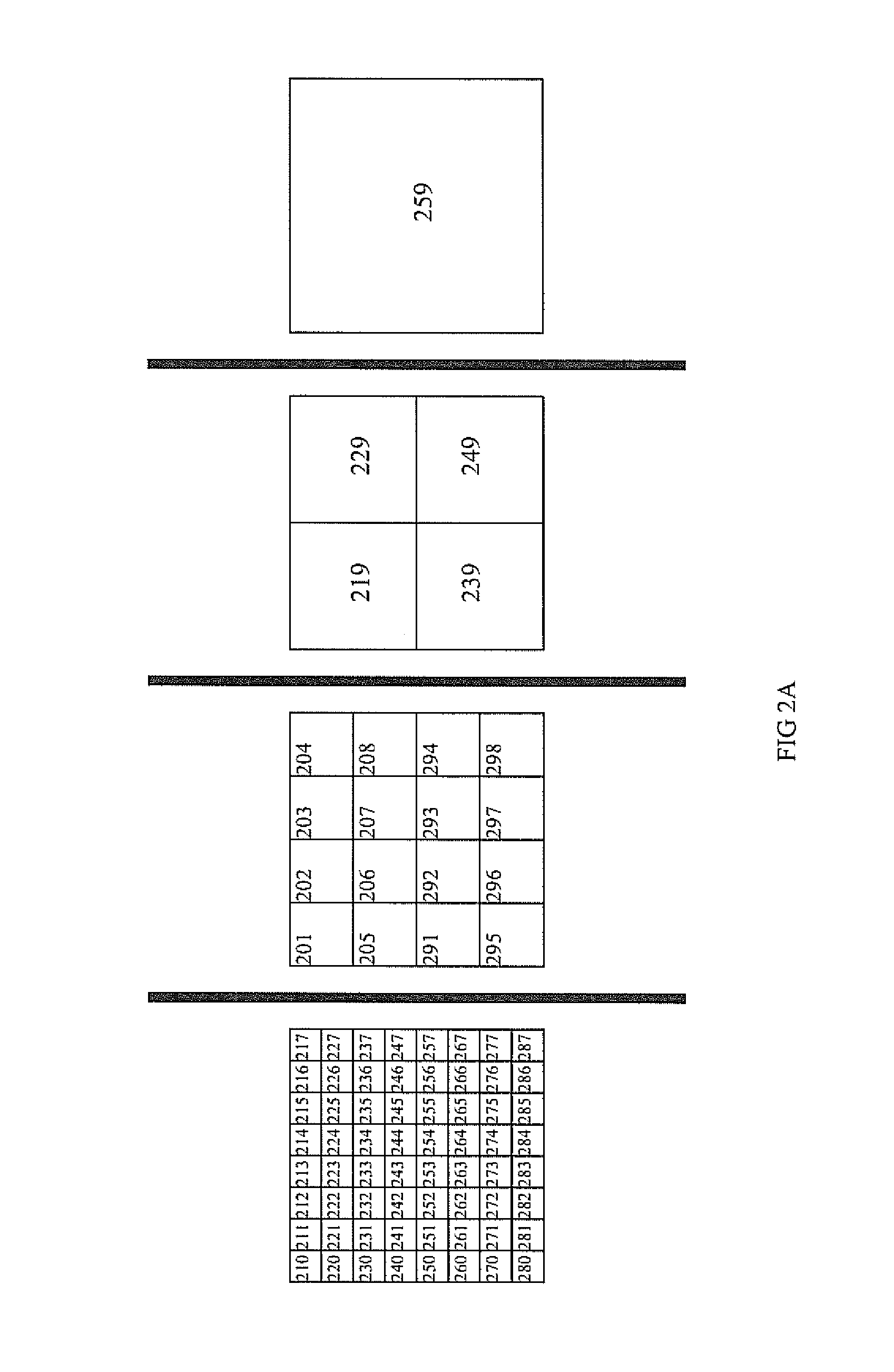

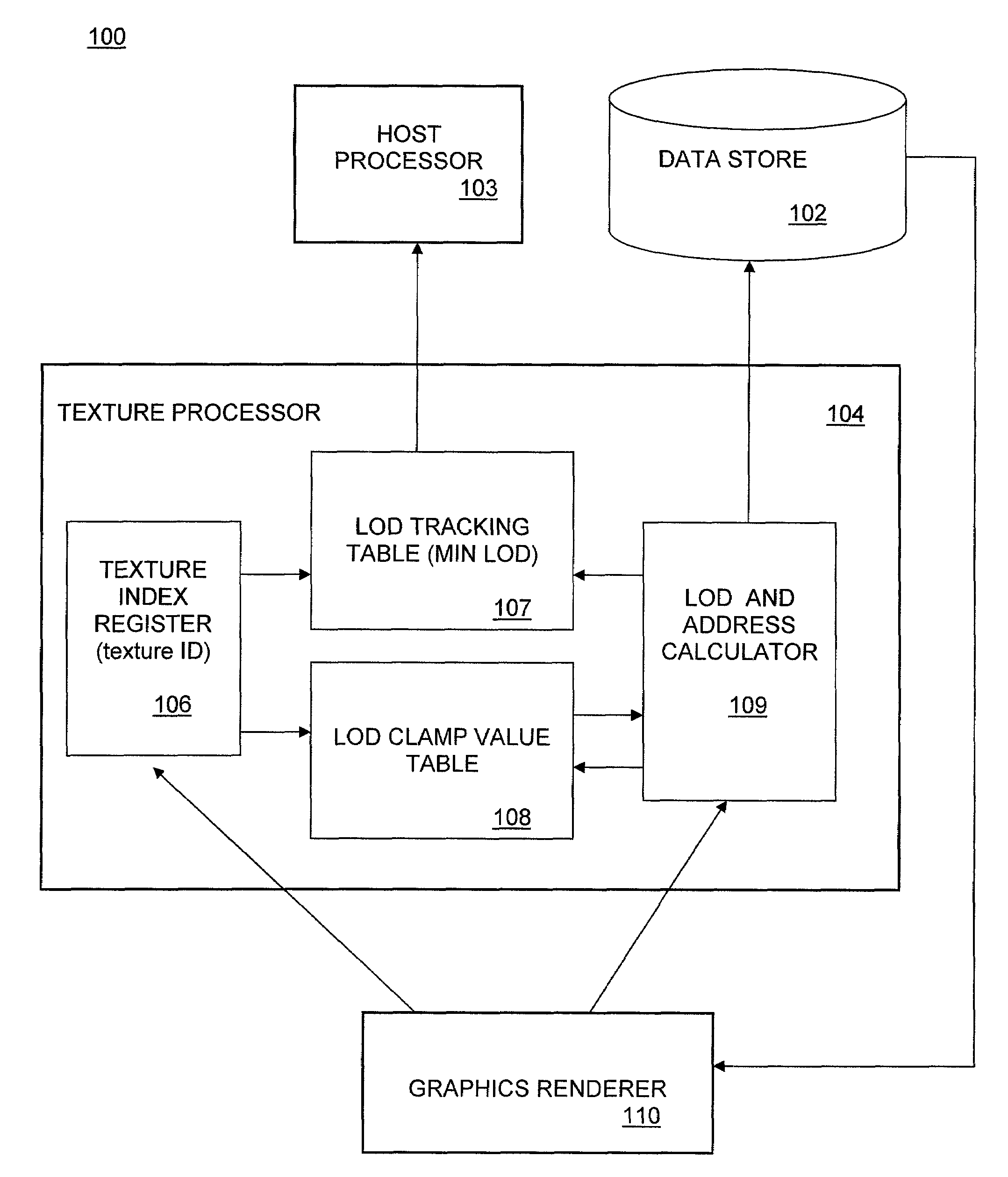

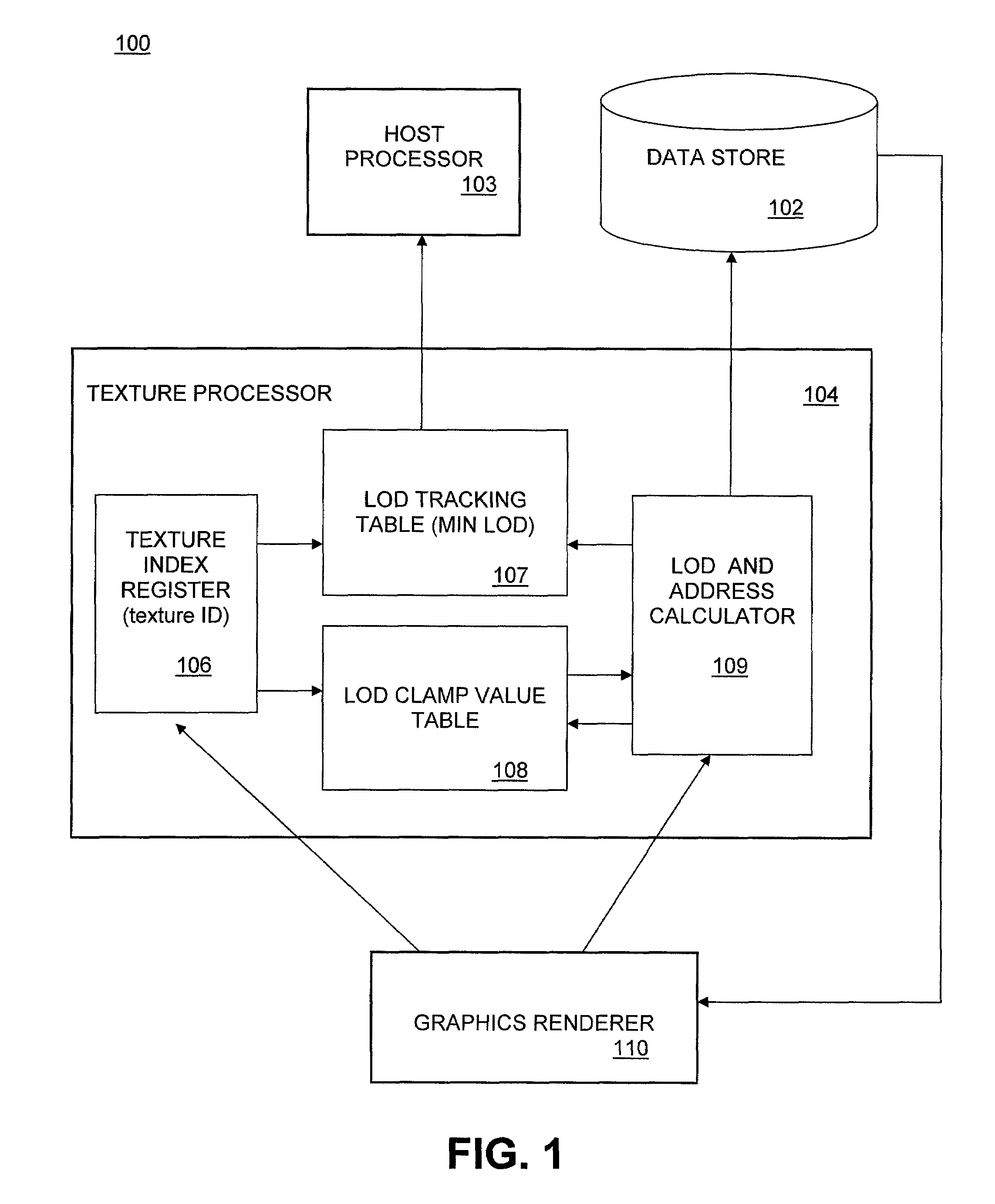

Systems and methods for texture processing are presented. In one embodiment a texture method includes creating a sparse texture residency translation map; performing a probe process utilizing the sparse texture residency translation map information to return a finest LOD that contains the texels for a texture lookup operation; and performing the texture lookup operation utilizing the finest LOD. In one exemplary implementation, the finest LOD is utilized as a minimum LOD clamp during the texture lookup operation. A finest LOD number indicates a minimum resident LOD and a sparse texture residency translation map includes one finest LOD number per tile of a sparse texture. The sparse texture residency translation can indicate a minimum resident LOD.

Owner:NVIDIA CORP

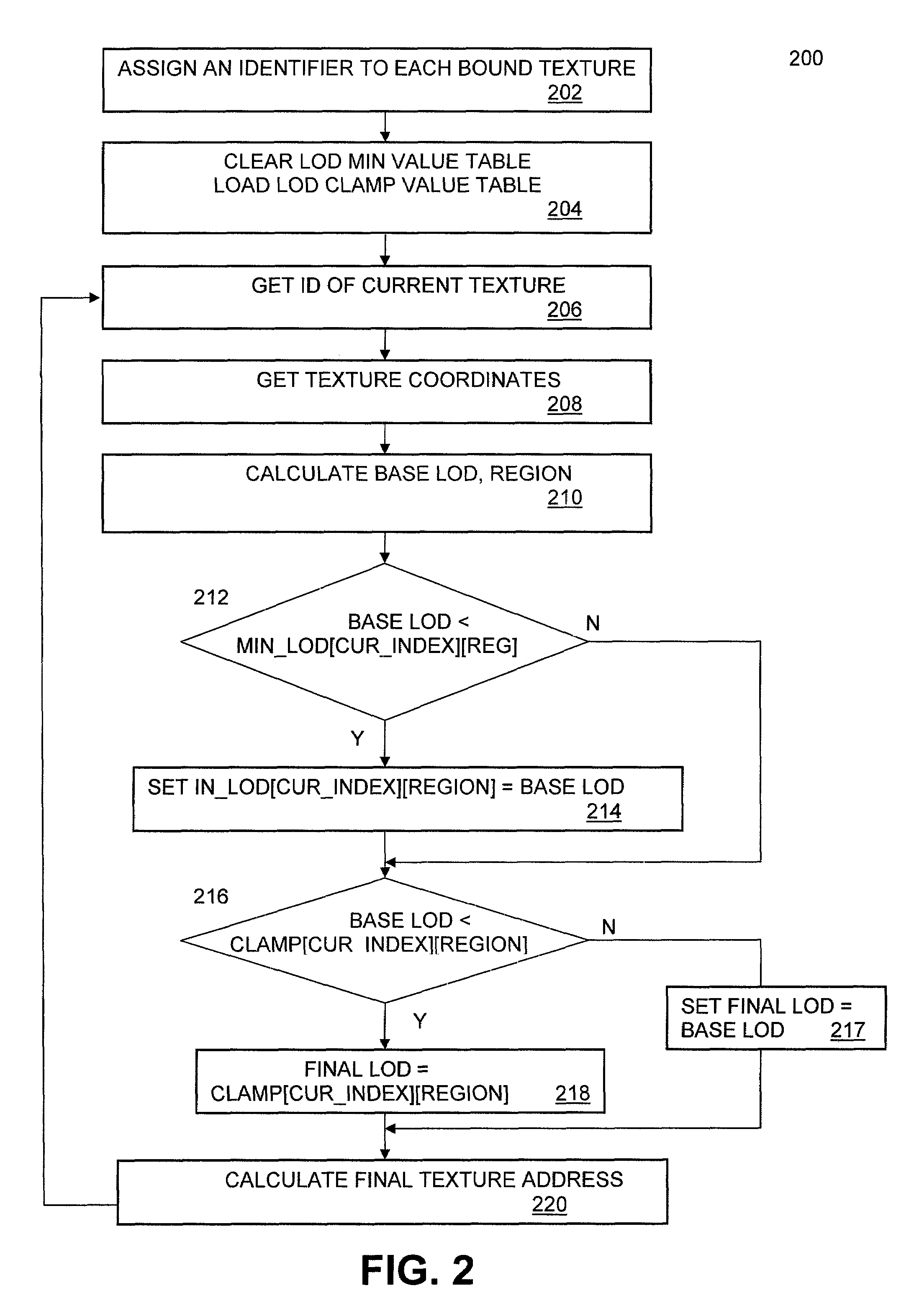

Texture Level Tracking, Feedback, and Clamping System for Graphics Processors

Embodiments include a texture mapping processor incorporating a dynamic level of detail map for use in a graphics processing system. Level of detail values are defined, with 0 being the finest and corresponding to the largest mipmap level. Each bound texture in a graphics object is assigned an identifier. This identifier is used as an index into a minimum-LOD value tracking table that is updated whenever a texel is fetched. A texture processing module controls when the tracking table is initialized and read back, and which identifiers are tracked. The minimum-LOD values in the tracking table are accompanied by a coarse region access mask to associate a minimum LOD value with a specific region of the image or object. A clamping table contains LOD clamp values for each region and a region code that specifies the coarseness of the LOD associated with each region of the texture.

Owner:ADVANCED MICRO DEVICES INC

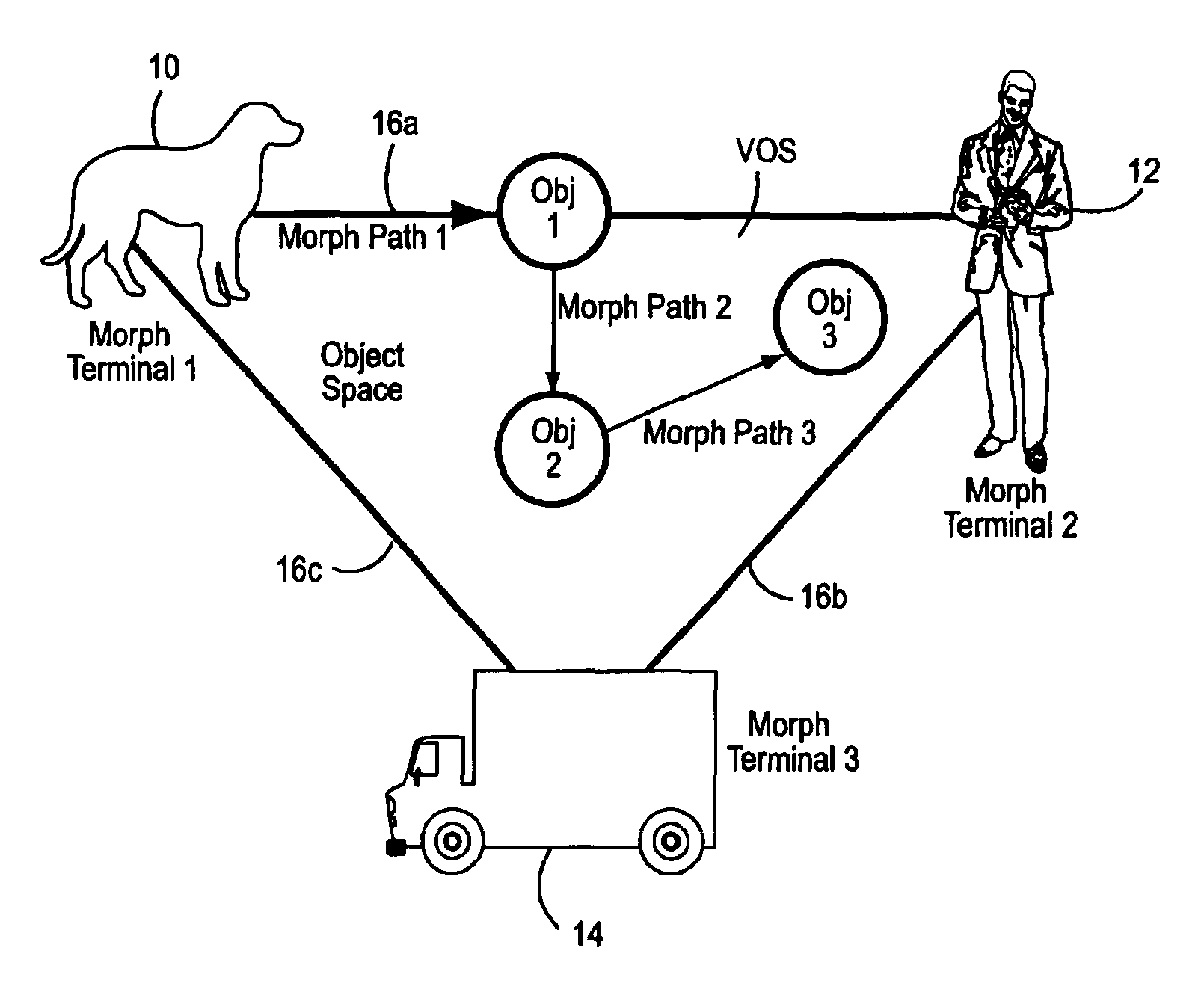

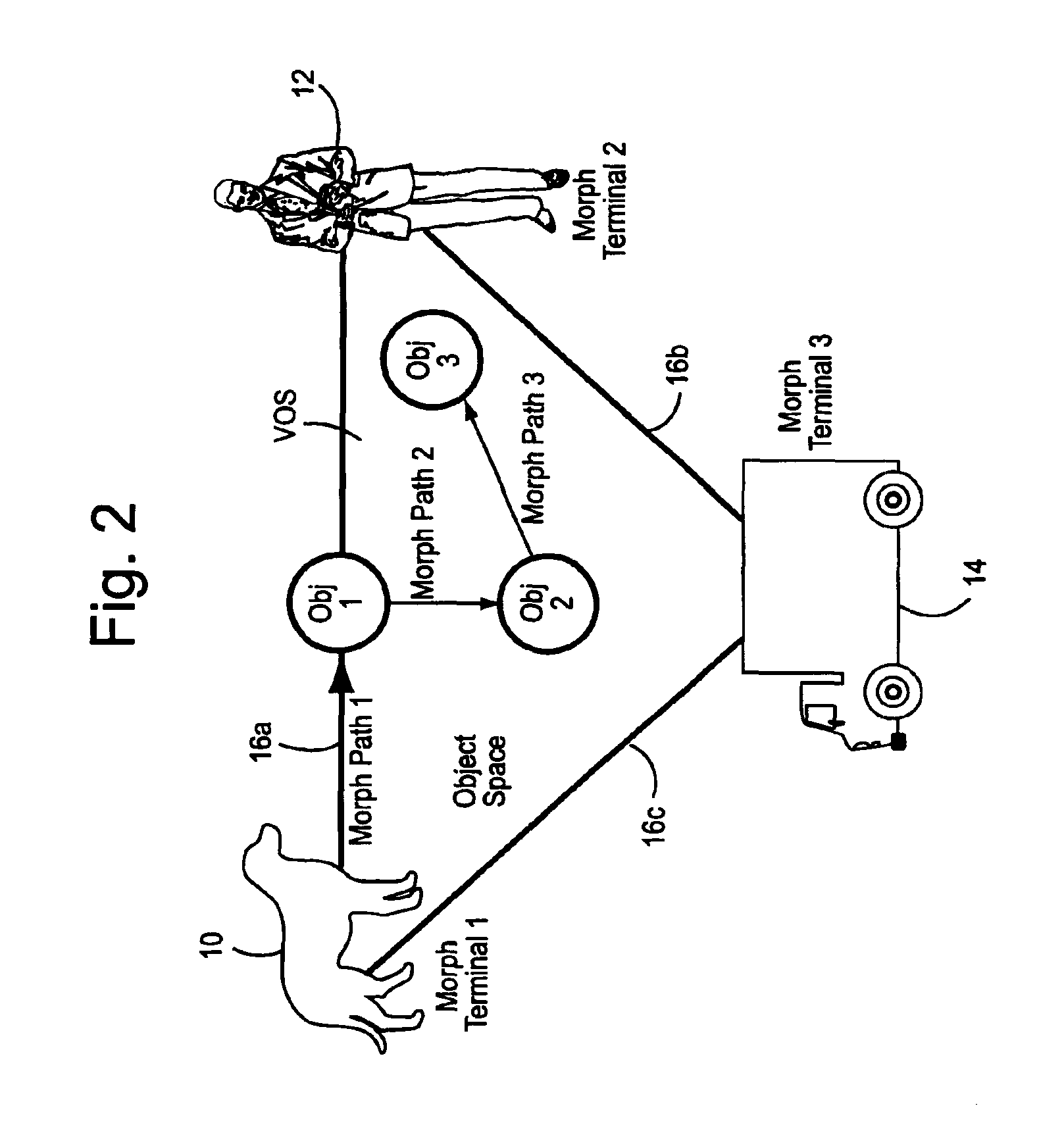

Texture morphing process provided by the preferred embodiment of the present invention

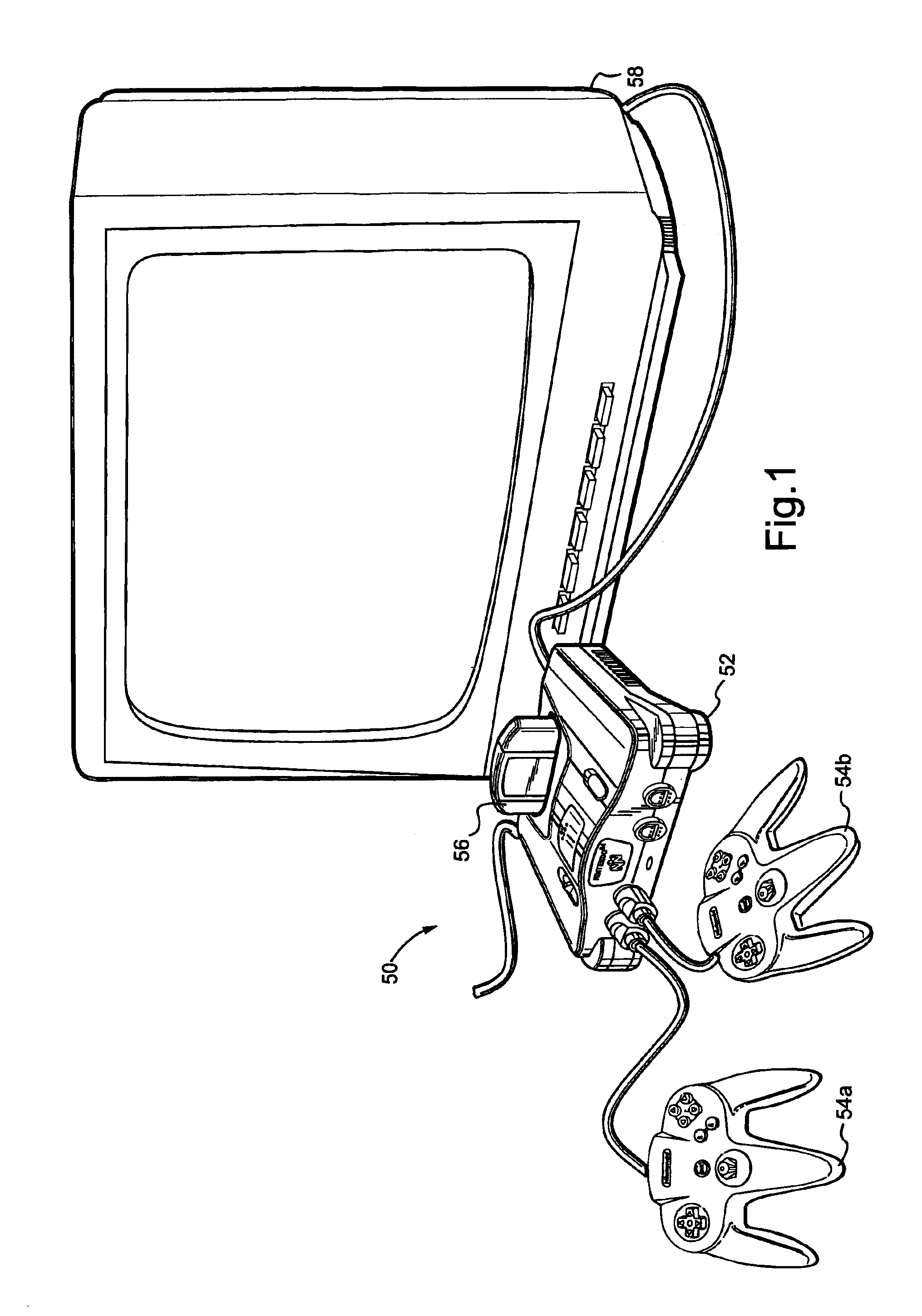

InactiveUS6906732B1Simplify and reduce computationFast and efficientCathode-ray tube indicatorsAnimationMorphingComputational science

A fast, texture morphing algorithm for real-time computer simulation and video games dynamically generates objects “on the fly” by simplifying and reducing the computational load required for a texture morphing / blending process. Incremental interpolation techniques compute a morph parameter based on previous value and morph change rate. Precomputed initial and incremental morph parameter values for each texel component are applied during real-time morphing procedures using integer arithmetic. Approximation errors are reduced by incrementing / decrementing by an extra integer value when the number of morph iterations is a multiple of a frame counter. The frame counter avoids over-runs, and the morphing procedure is “snapped” the texel value to the precise texture target value to prevent under-runs and corresponding artifacts. Interlacing (applying interpolation to a subset of the texels each frame) significantly reduces computational load without introducing significant image artifacts. The morph texture buffer data structure is initially decomposed off-line to reduce the number of real-time calculations required to manipulate texel component data.

Owner:NINTENDO CO LTD

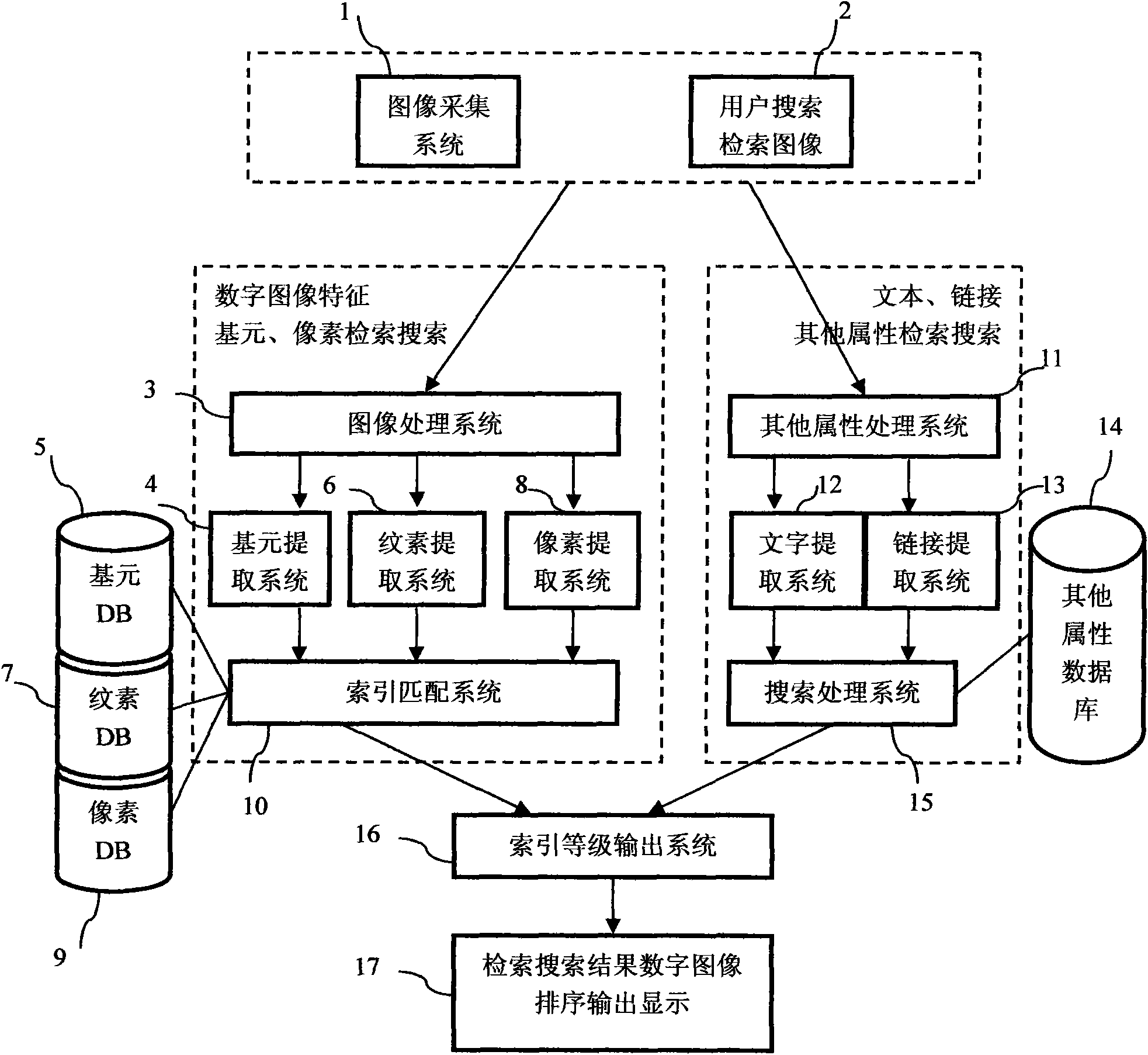

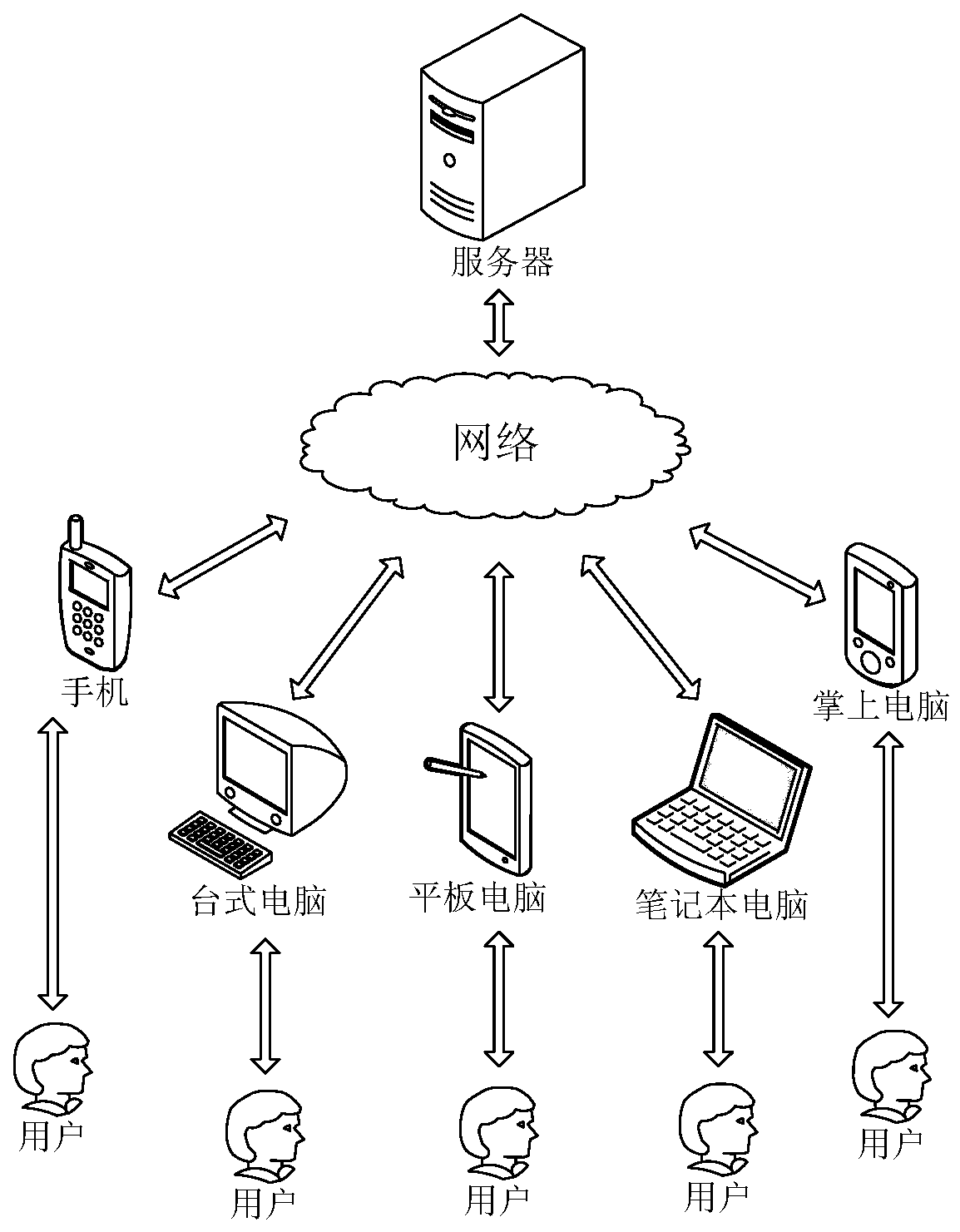

Digital image visualized management and retrieval for communication network

InactiveCN101930461AReduce space storage data capacityIndexing is simple and clearSpecial data processing applicationsGraphicsPattern recognition

The invention discloses a visualized management and retrieval method for a digital image. The method comprises the following steps: establishing a binary bitmap sequence for the digital image by a digital image processing technological system and extracting a plurality of feature primitives from the sequence (the primitives refer to factors in the image which are different from pixels, such as a line segment, a curve, a closed figure, texture and the like); correspondingly extracting RGB, a gray value and other data of pixels in the peripheral range of relevant positions from the original digital image according to the position range of the primitives, extracting a set of texture elements according to the texture range related to the primitives, and indexing the digital image according to a plurality of the primitives, the set of the texture elements and corresponding pixel values; and storing the digital image and the image indexing, relevant text comment, network link analysis and the like for retrieving the digital image. In the invention, indexing of the digital image is established based on the binary bitmap sequence, the primitives, the texture elements, the pixels and the like, thus achieving small data quantity and fast and convenient retrieval and being applicable to digital image management, retrieval and search for a mobile communication network and the Internet.

Owner:郑茂

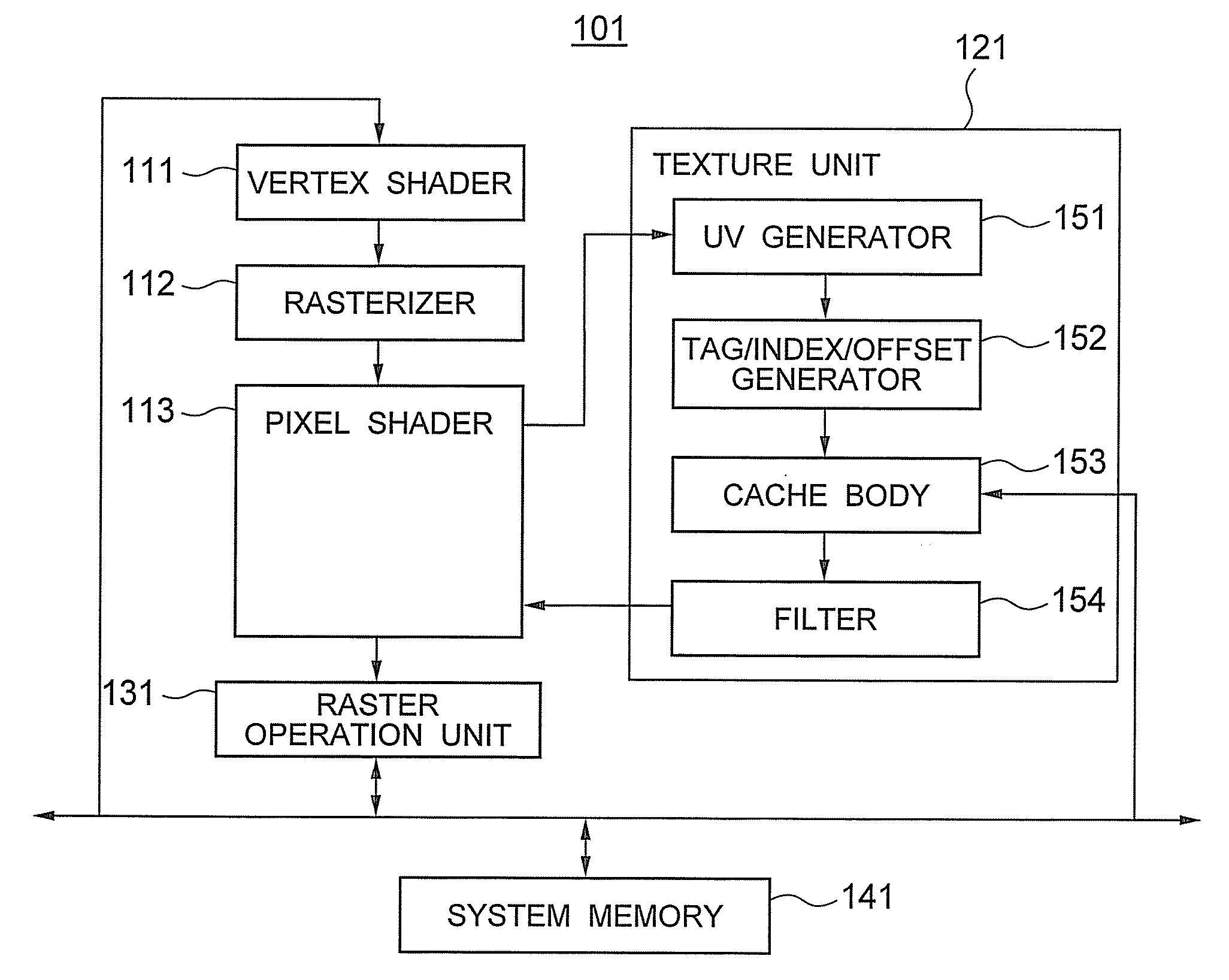

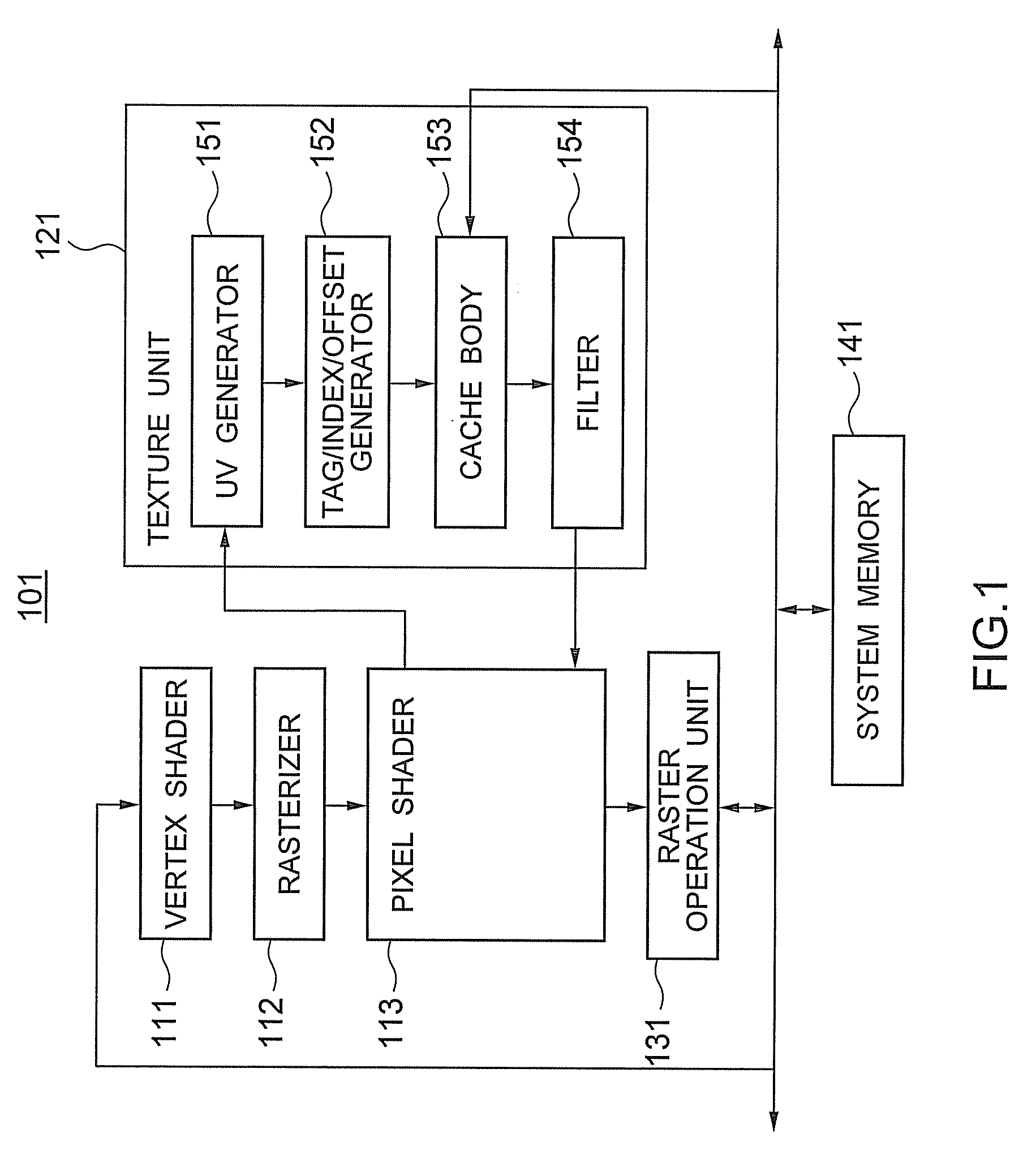

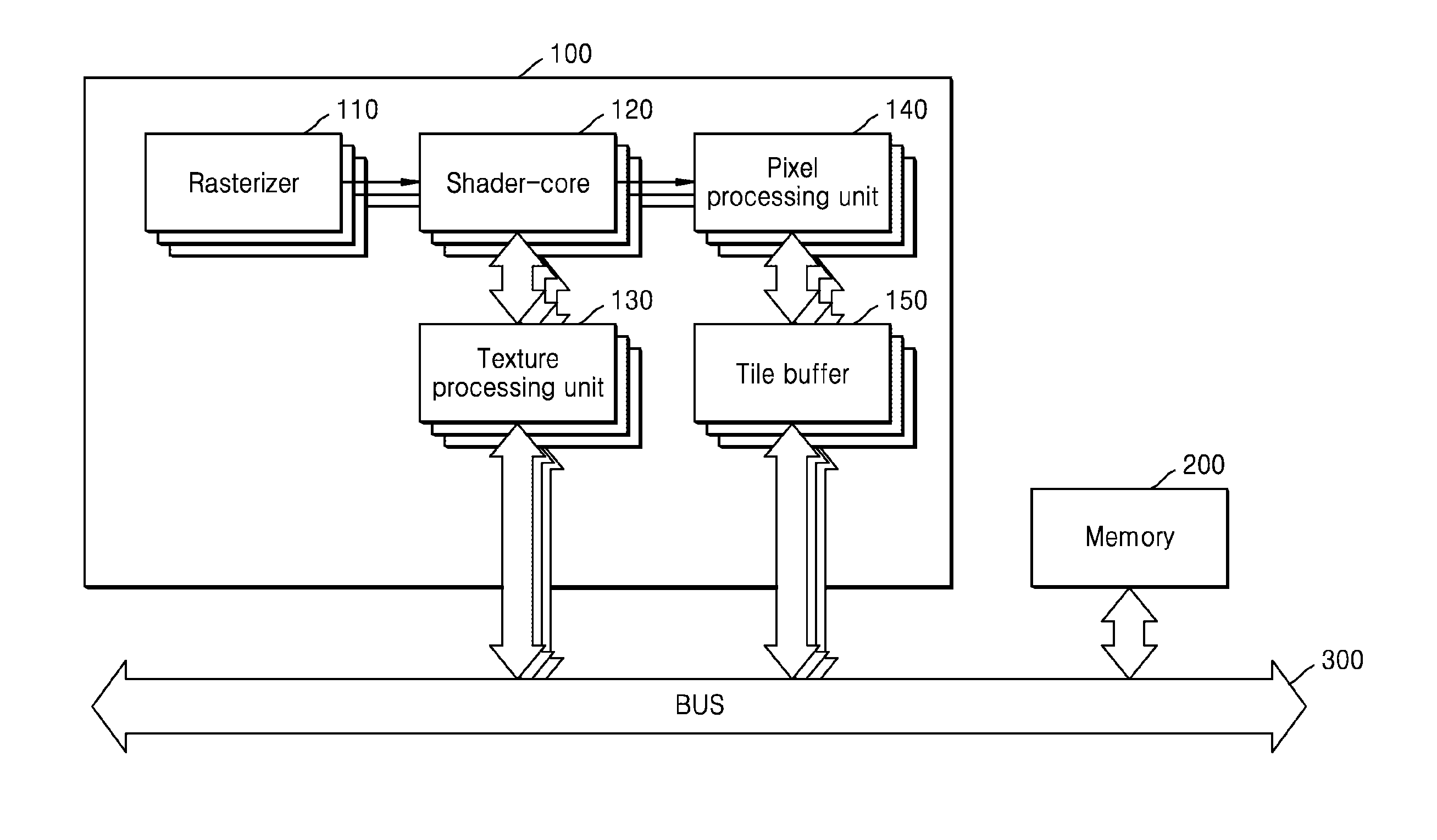

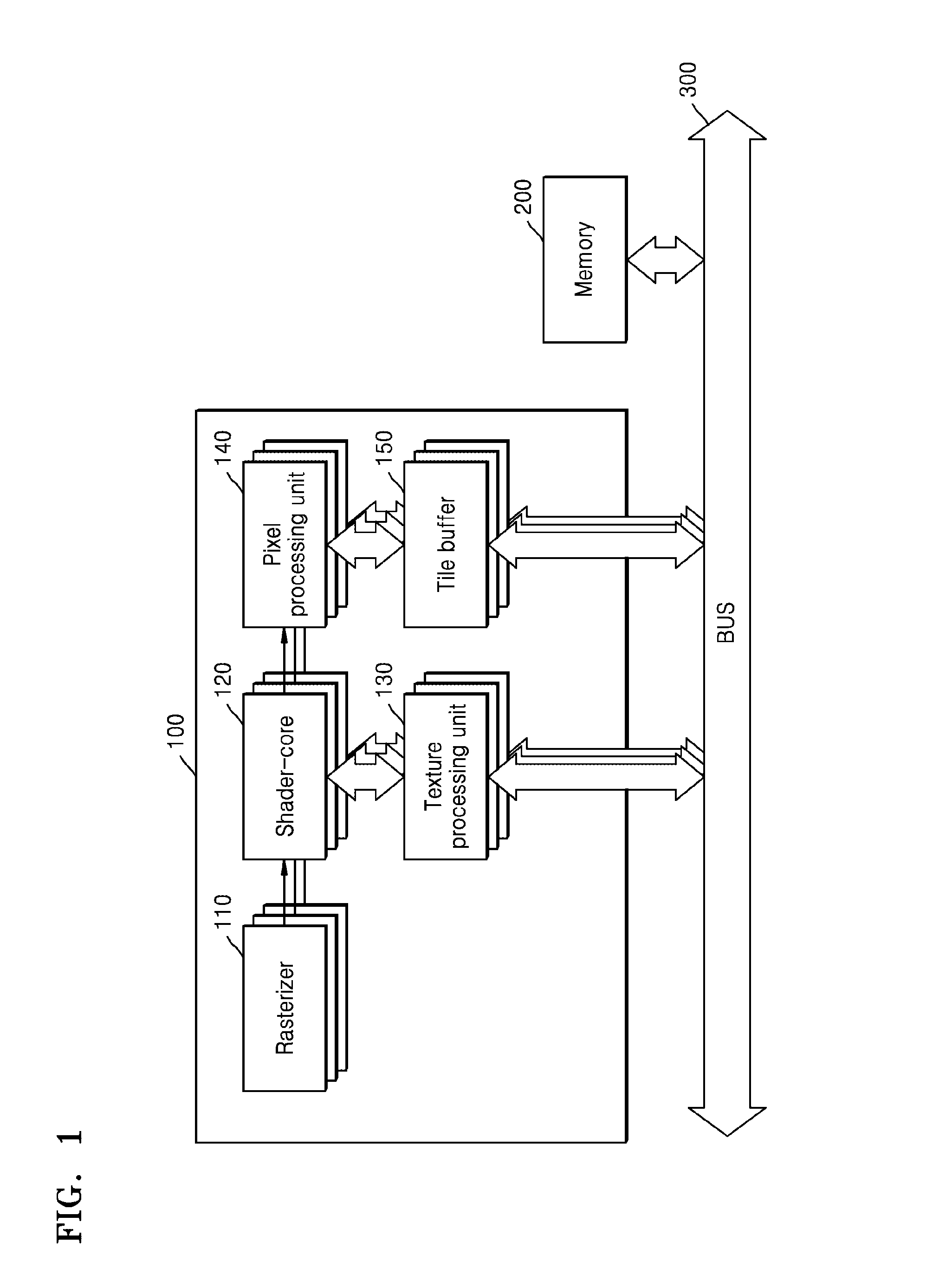

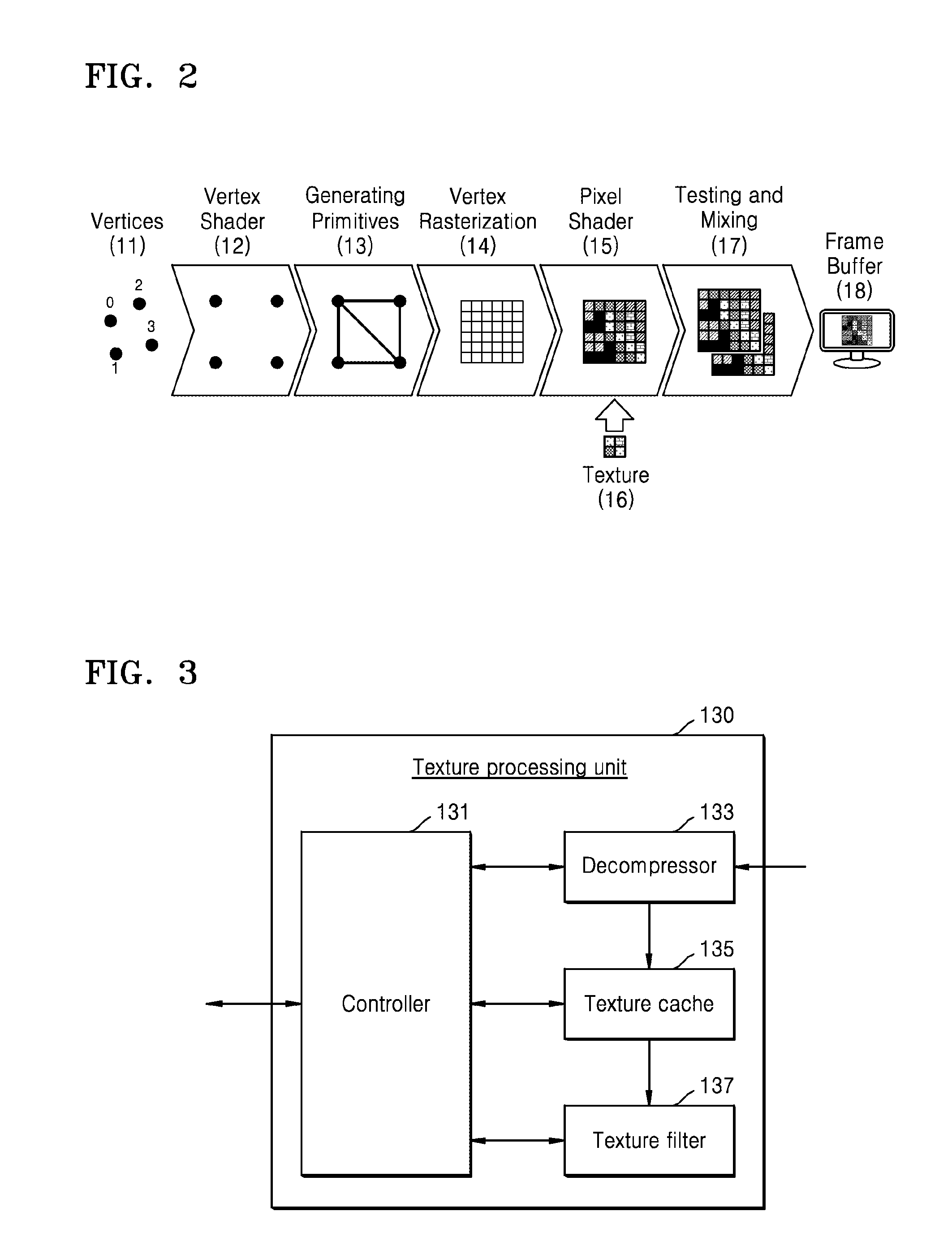

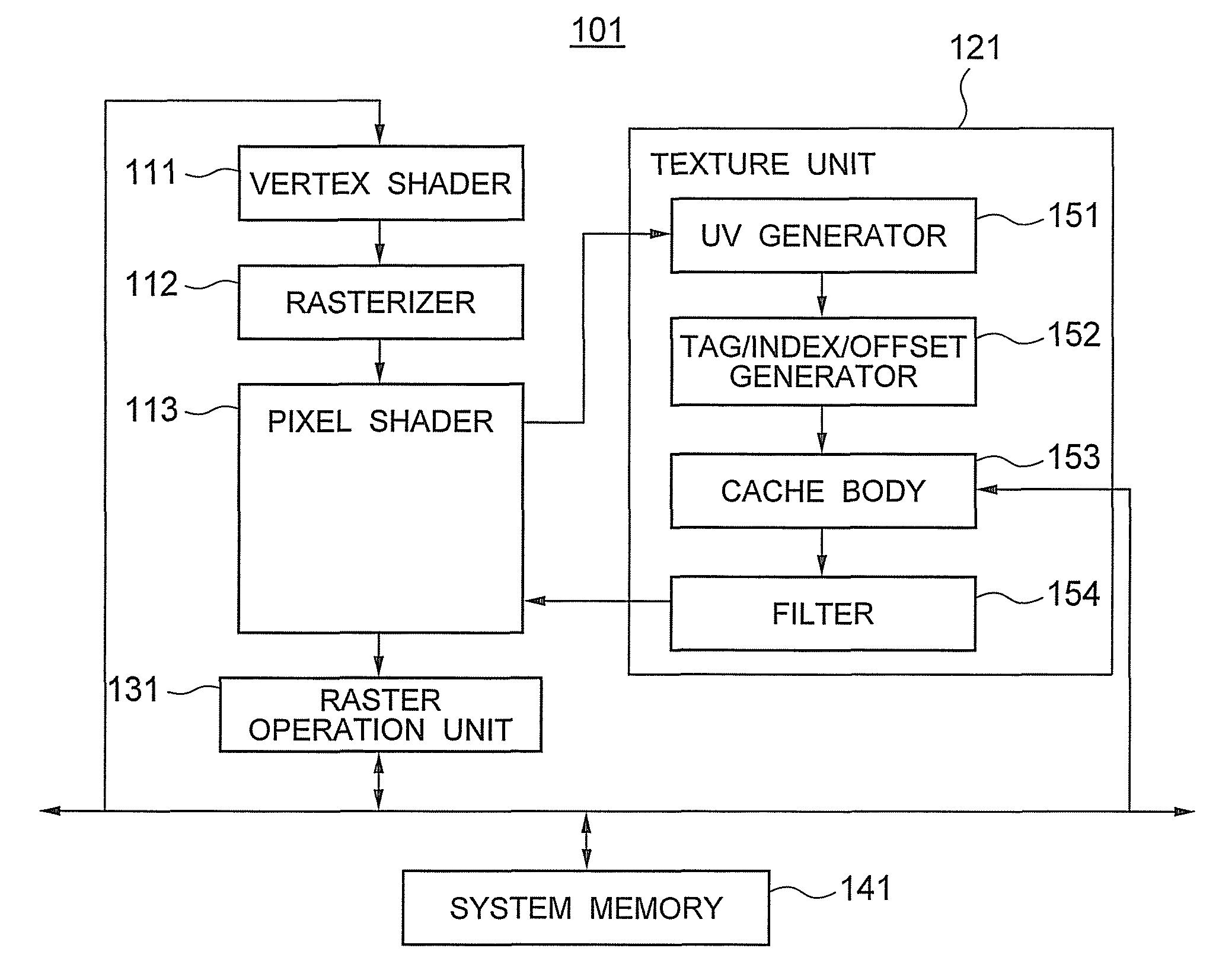

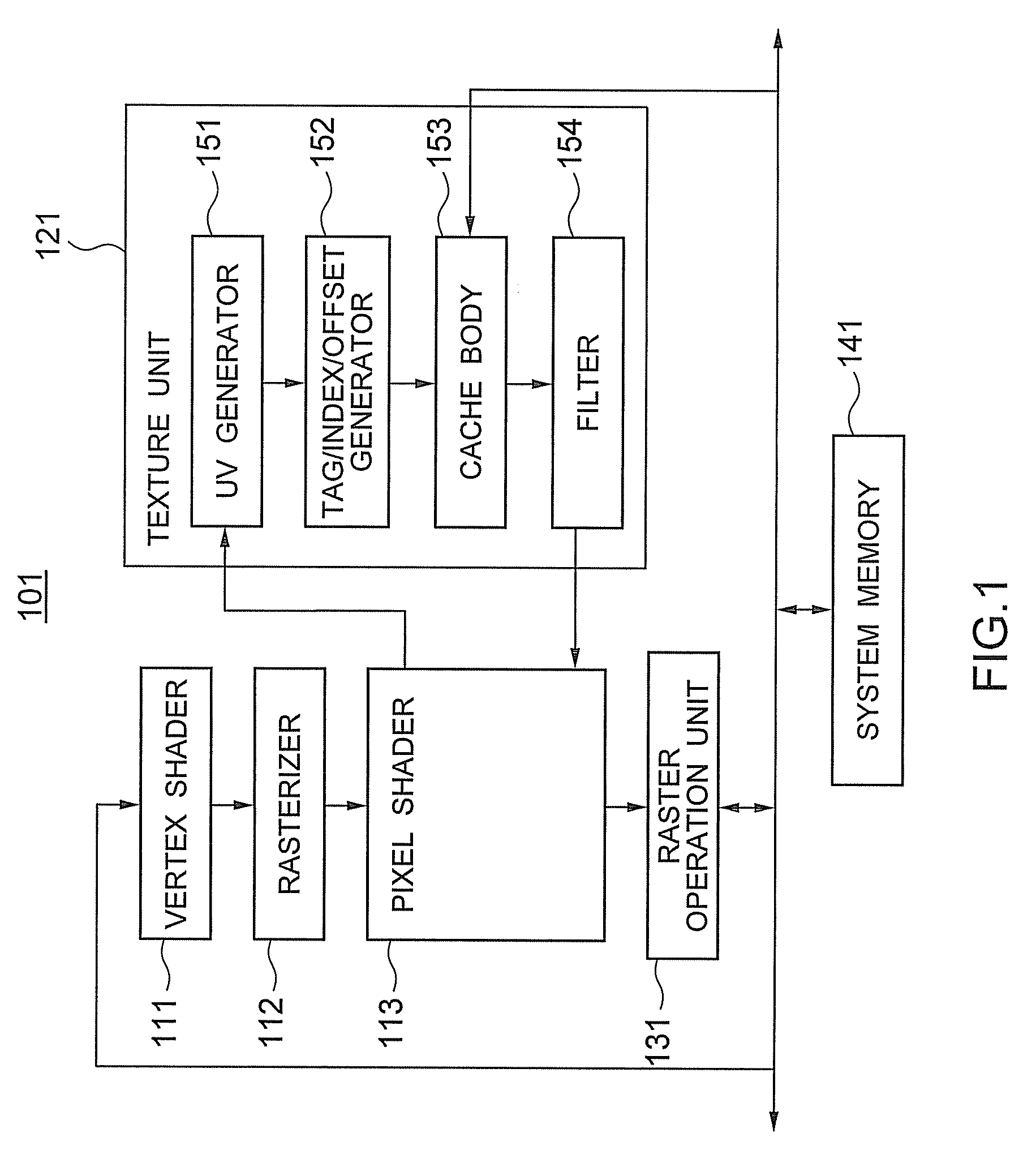

Computer graphics rendering apparatus and method

InactiveUS20090102851A1Character and pattern recognitionCathode-ray tube indicatorsGraphicsComputer science

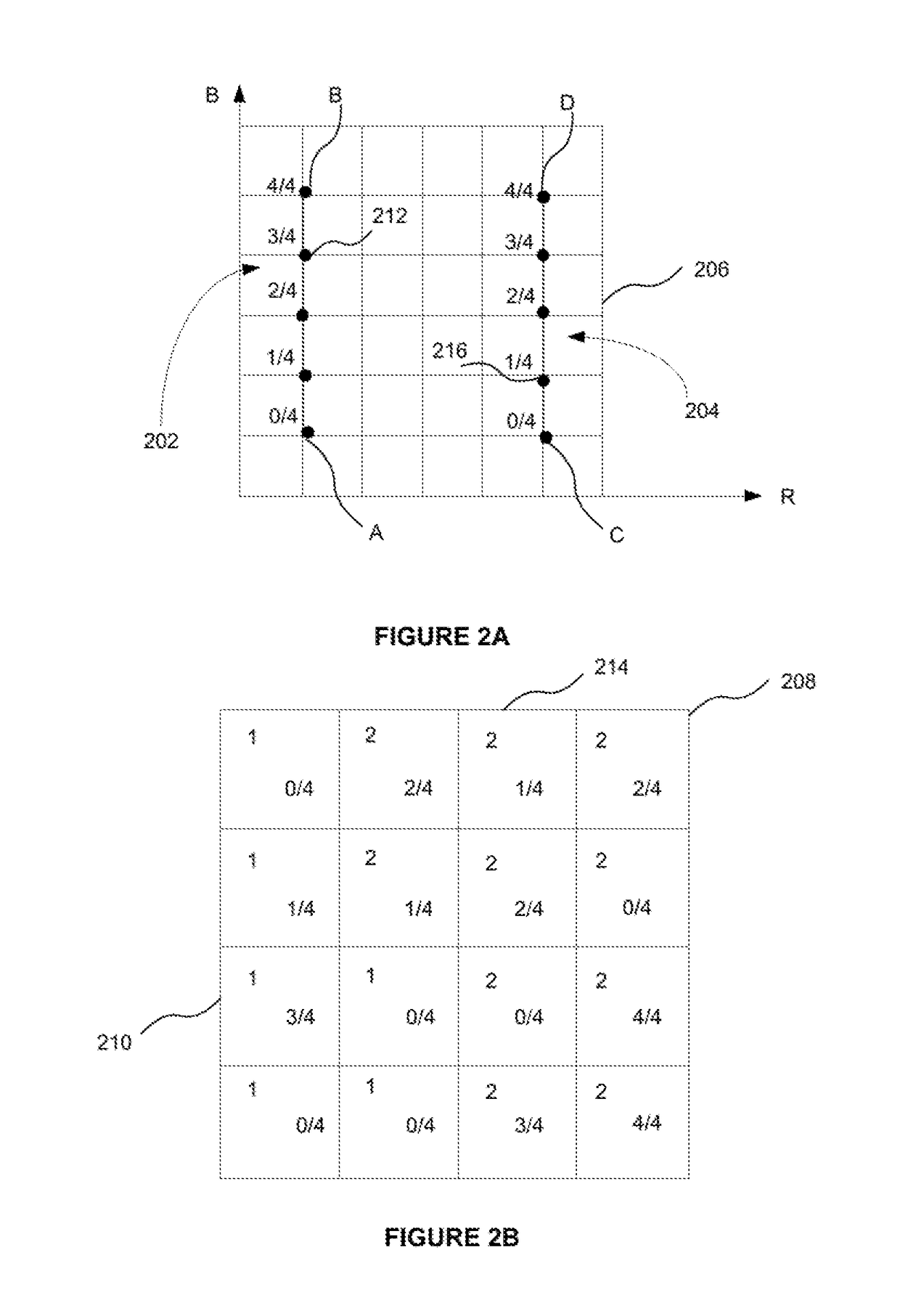

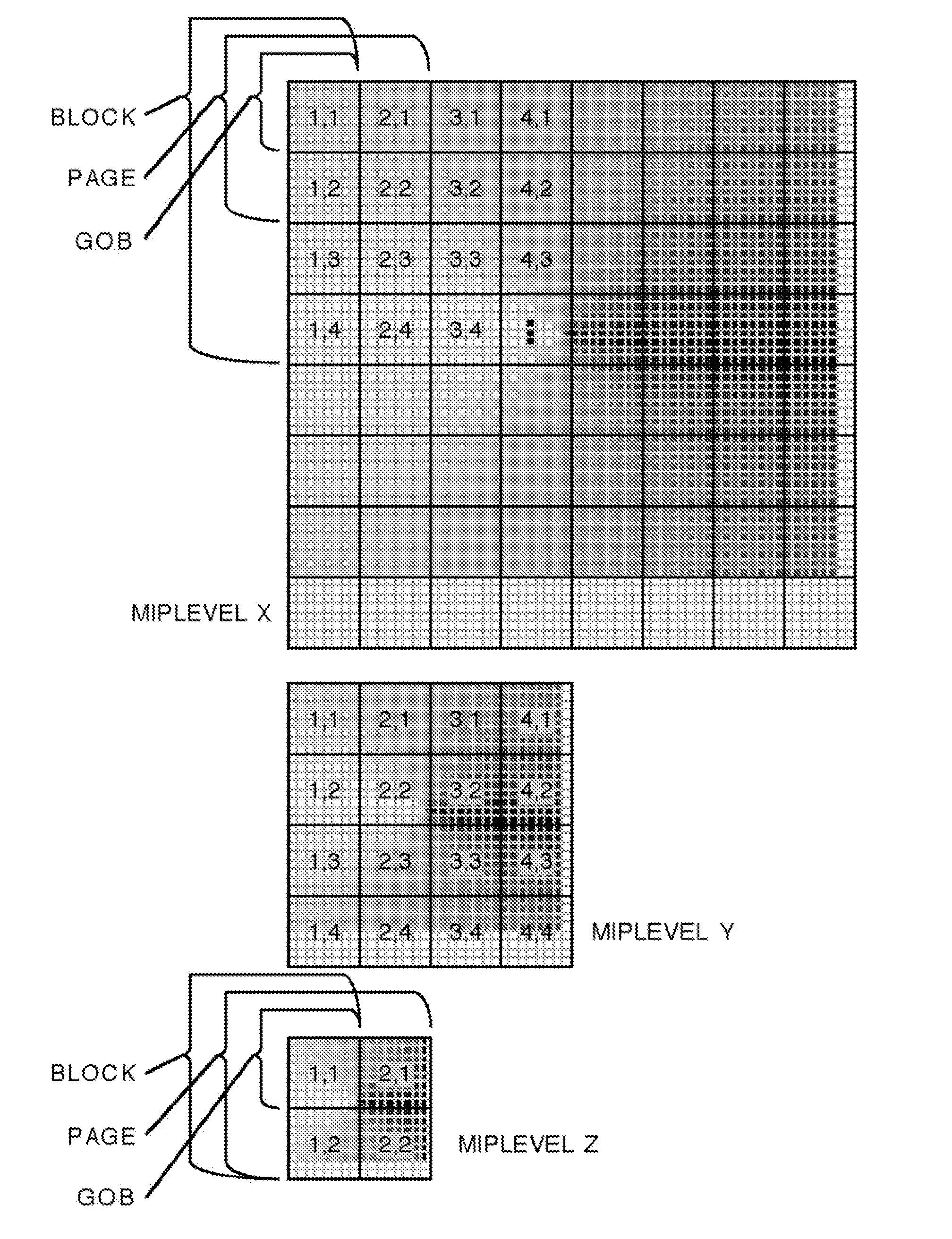

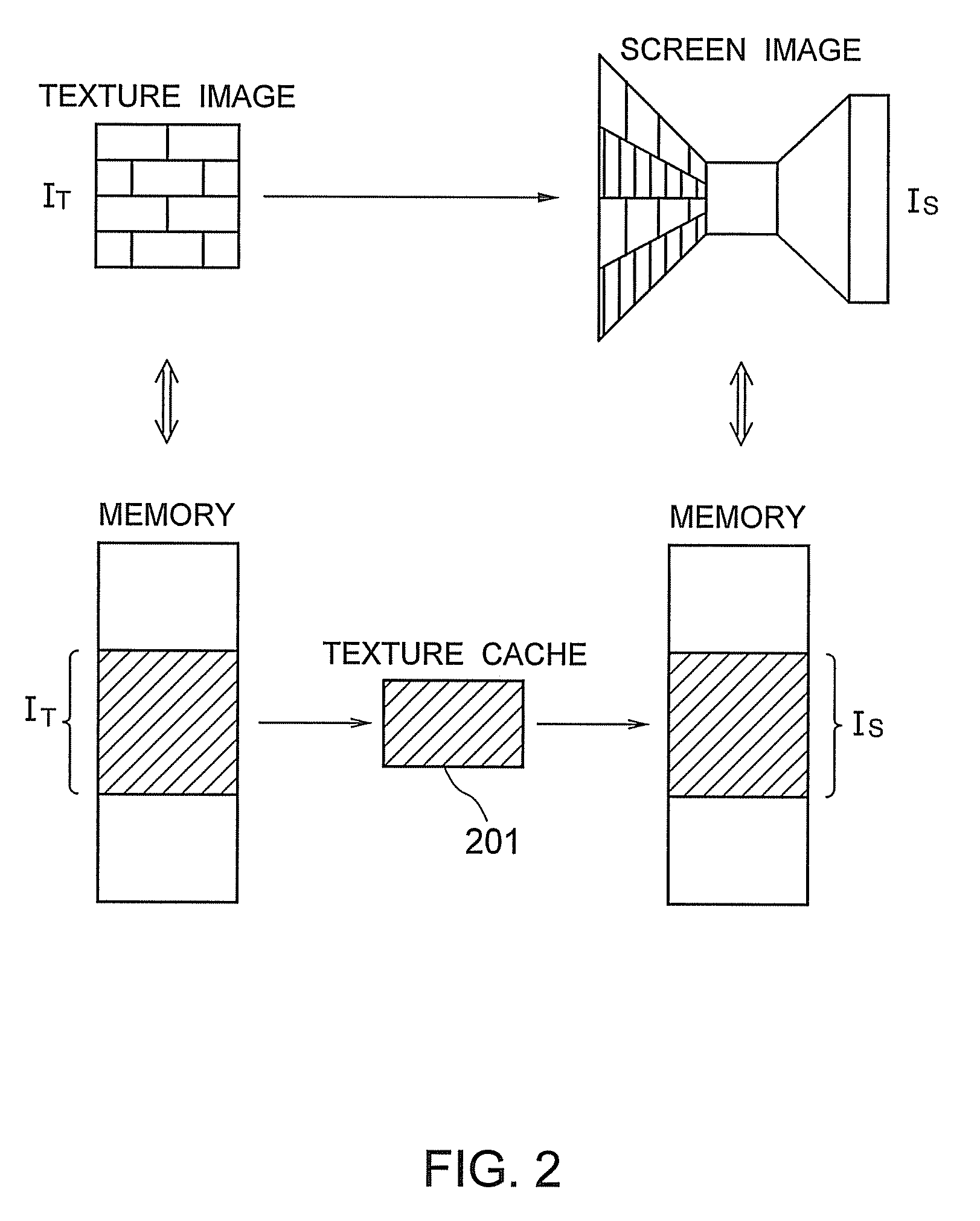

A computer graphics rendering apparatus according to an embodiment of the present invention generates a screen image, using plural texture images having different mipmap levels. The apparatus generates a normalized texture coordinate of a texture image, generates, from the normalized texture coordinate of the texture image, a texel coordinate of a texel in the texture image, according to a mipmap level of the texture image, and generates, regarding an image block in the texture image, an index value indicating a cache line corresponding to the image block, using a texel coordinate of a texel in the image block. The apparatus generates the index value such that index values of image blocks in the same position are different, between two texture images having mipmap levels adjacent to each other.

Owner:KK TOSHIBA

Method and apparatus for processing texture

InactiveUS20160078666A1Details involving 3D image dataImage memory managementPattern recognitionTexture processing

A method and apparatus for processing a texture are provided. The method of processing the texture includes acquiring a texture address corresponding to a pixel address and frequency information of the texture, determining a number of texels to be used for texture filtering according to the frequency information of the texture, reading texel values corresponding to the determined number of texels based on the texture address, and performing the texture filtering by using the read texel values.

Owner:SAMSUNG ELECTRONICS CO LTD

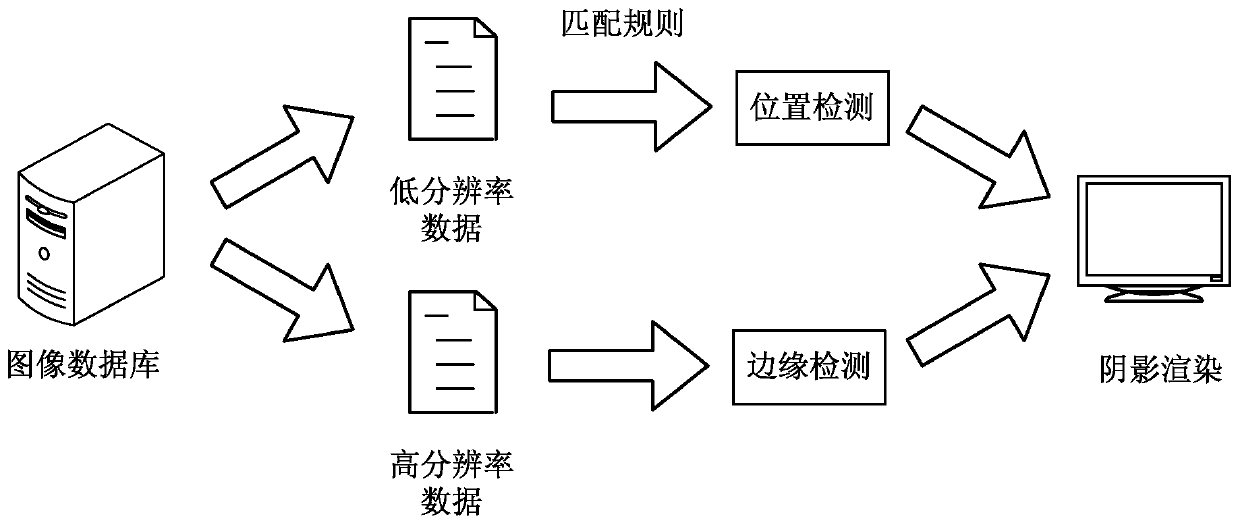

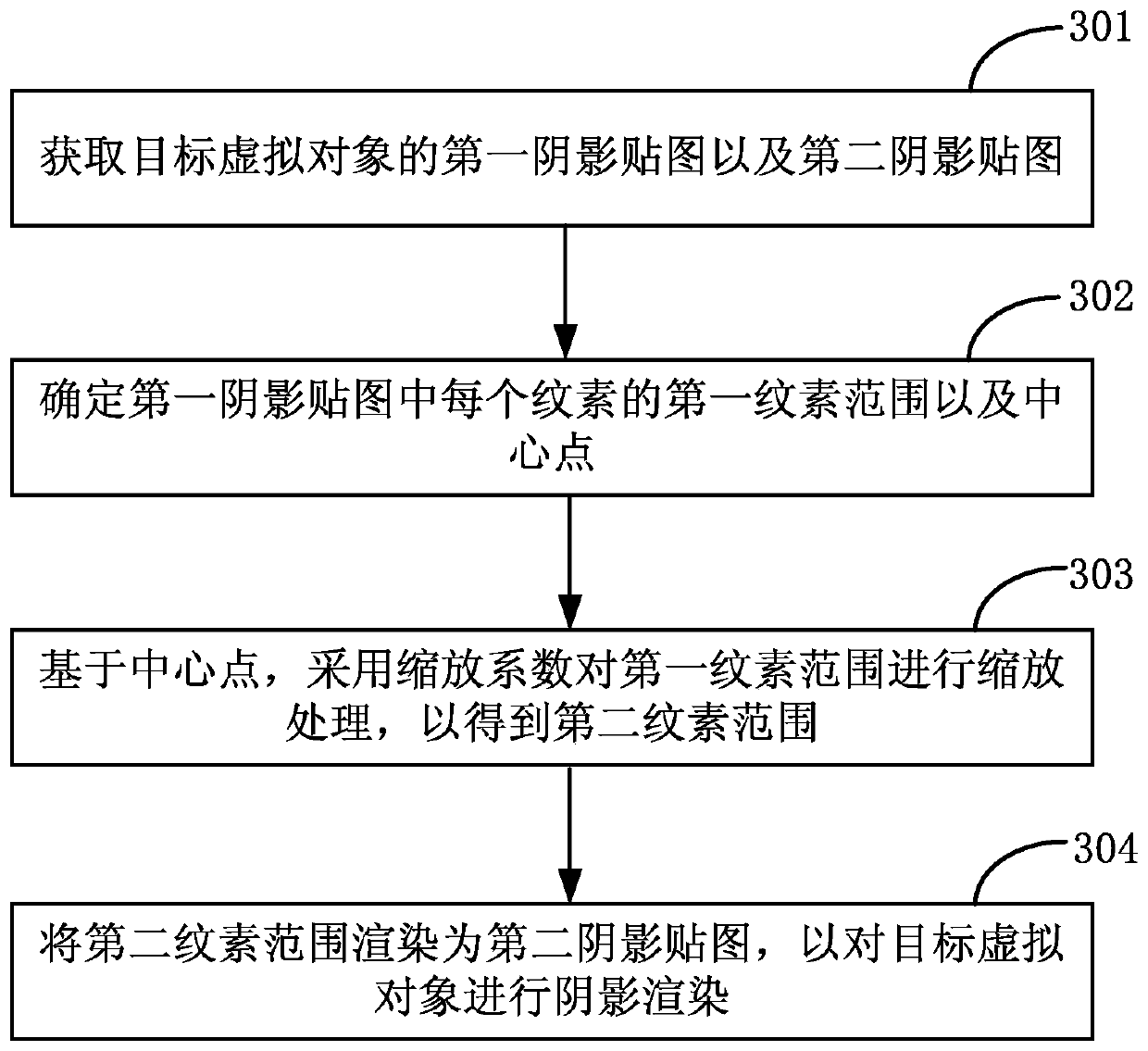

Image rendering method and related device

ActiveCN111292405AGuaranteed claritySmall amount of calculationVideo gamesImage renderingShadow mappingComputer graphics (images)

The invention discloses an image rendering method and a related device. The method comprises the steps of obtaining a low-resolution first shadow map and a high-resolution second shadow map of a target virtual object; determining a first texel range and a central point of each texel in the first shadow map; and performing scaling processing on the first texel range by using a scaling coefficient based on the central point to obtain a second texel range, and rendering the second texel range into a second shadow map to perform shadow rendering on the target virtual object. Therefore, the image rendering process based on the shadow map is realized, and the calculation amount of determining the map position through the low-resolution map is relatively small, so that the image rendering efficiency is improved; and then, the high-resolution shadow map is rendered, so that edge sawteeth are avoided, and the image rendering effect is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

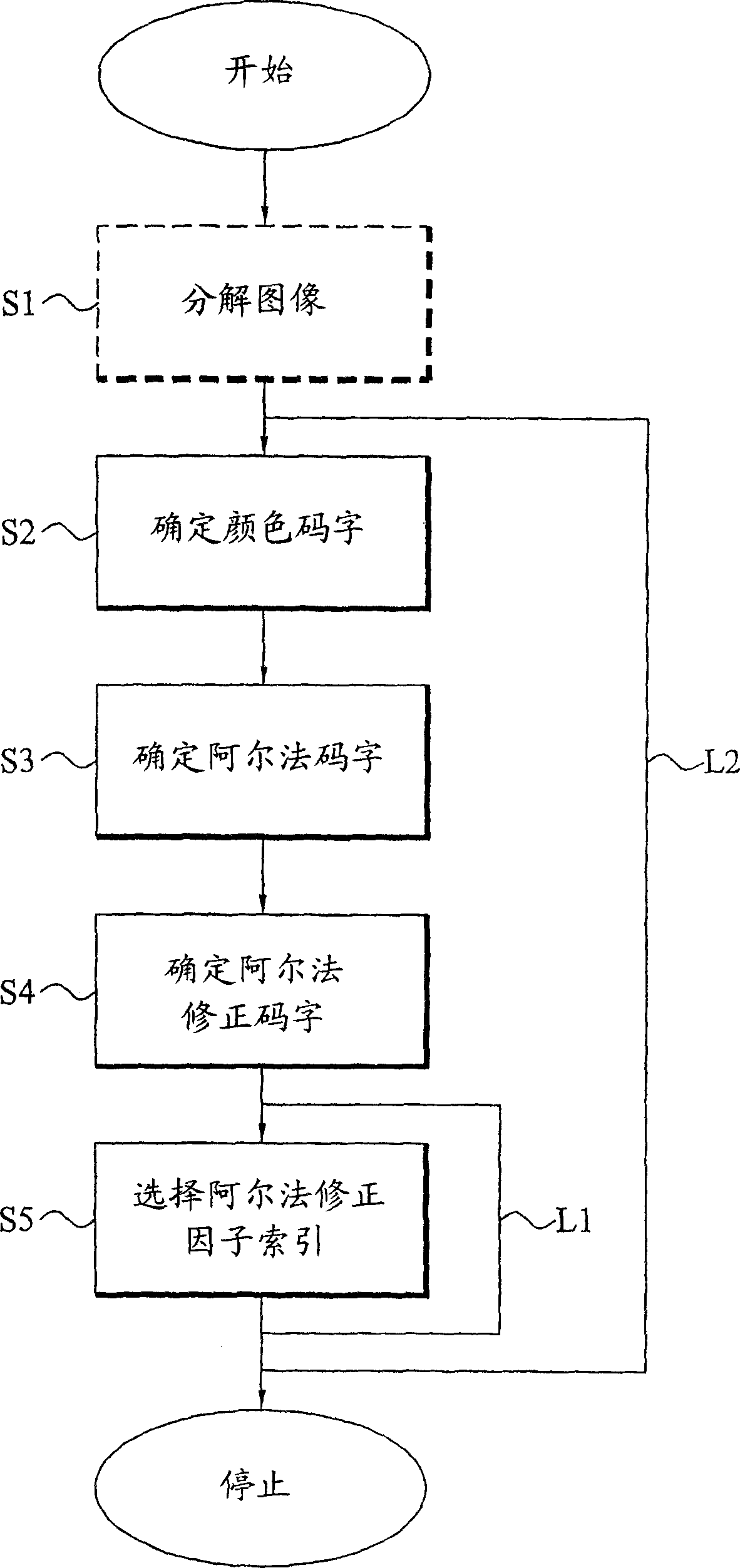

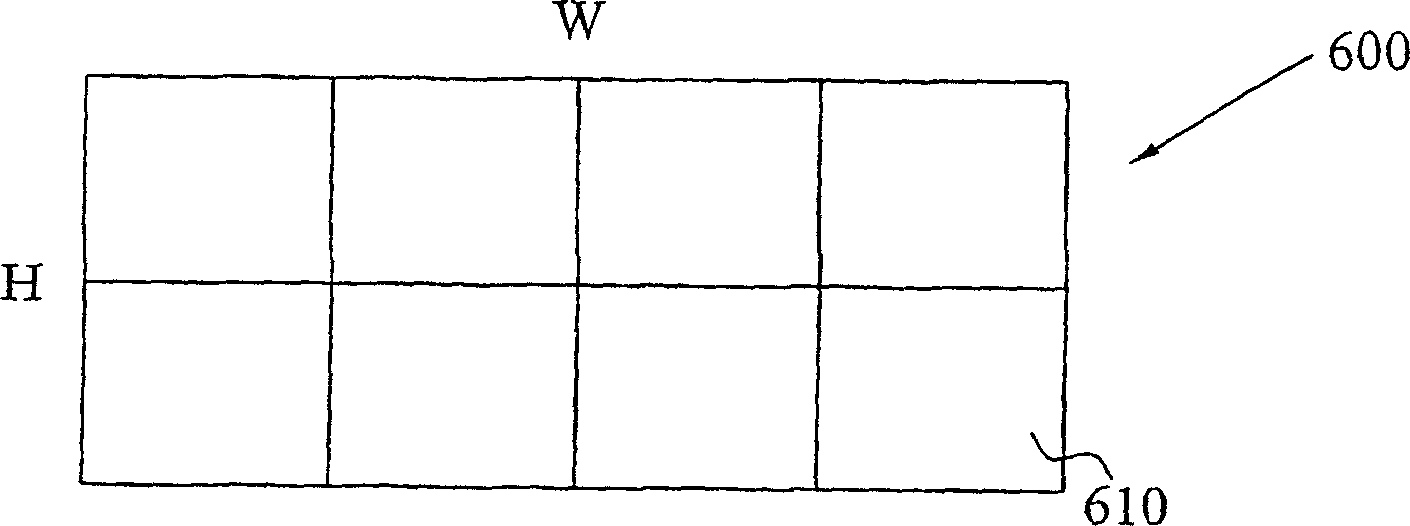

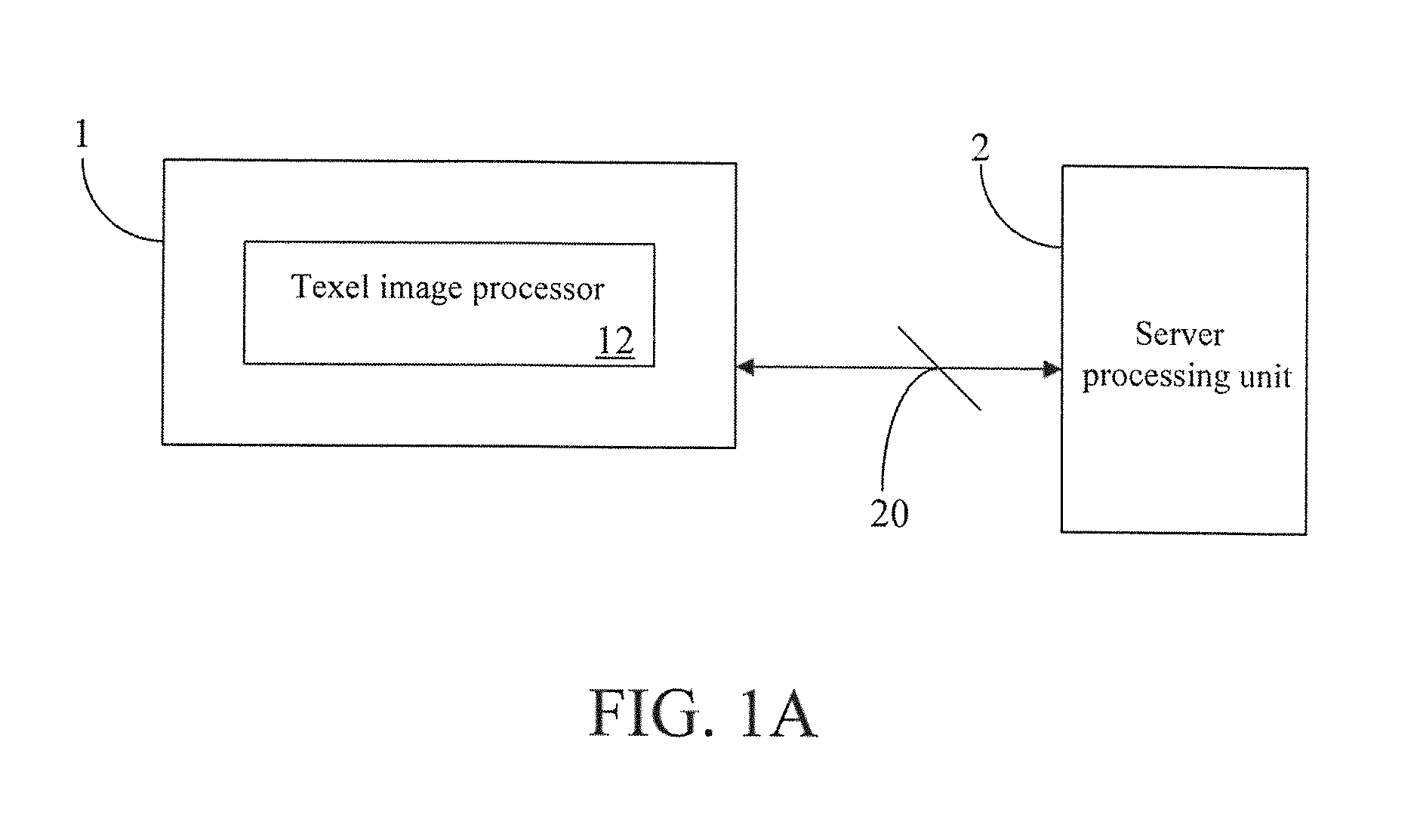

Multi-mode image processing

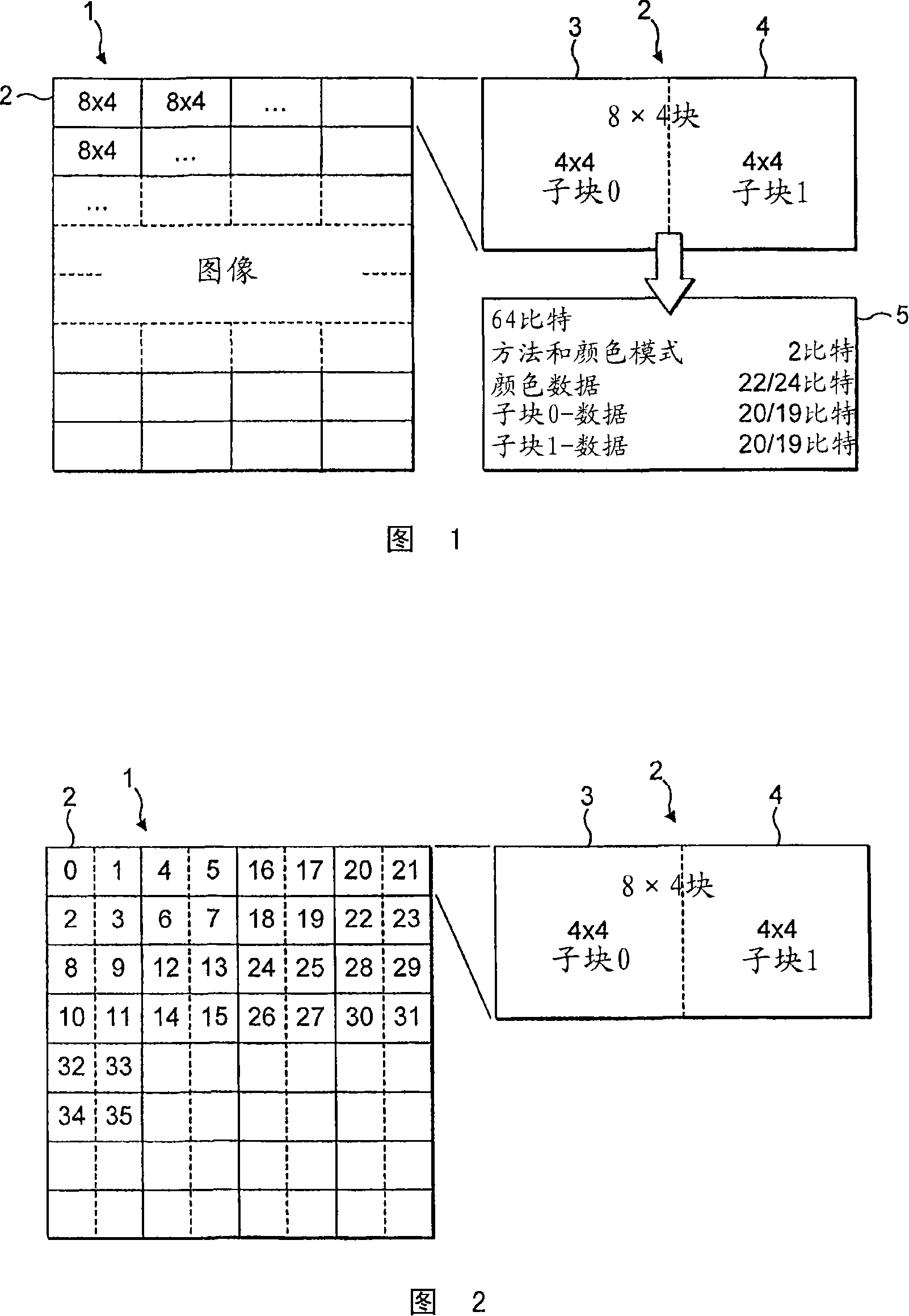

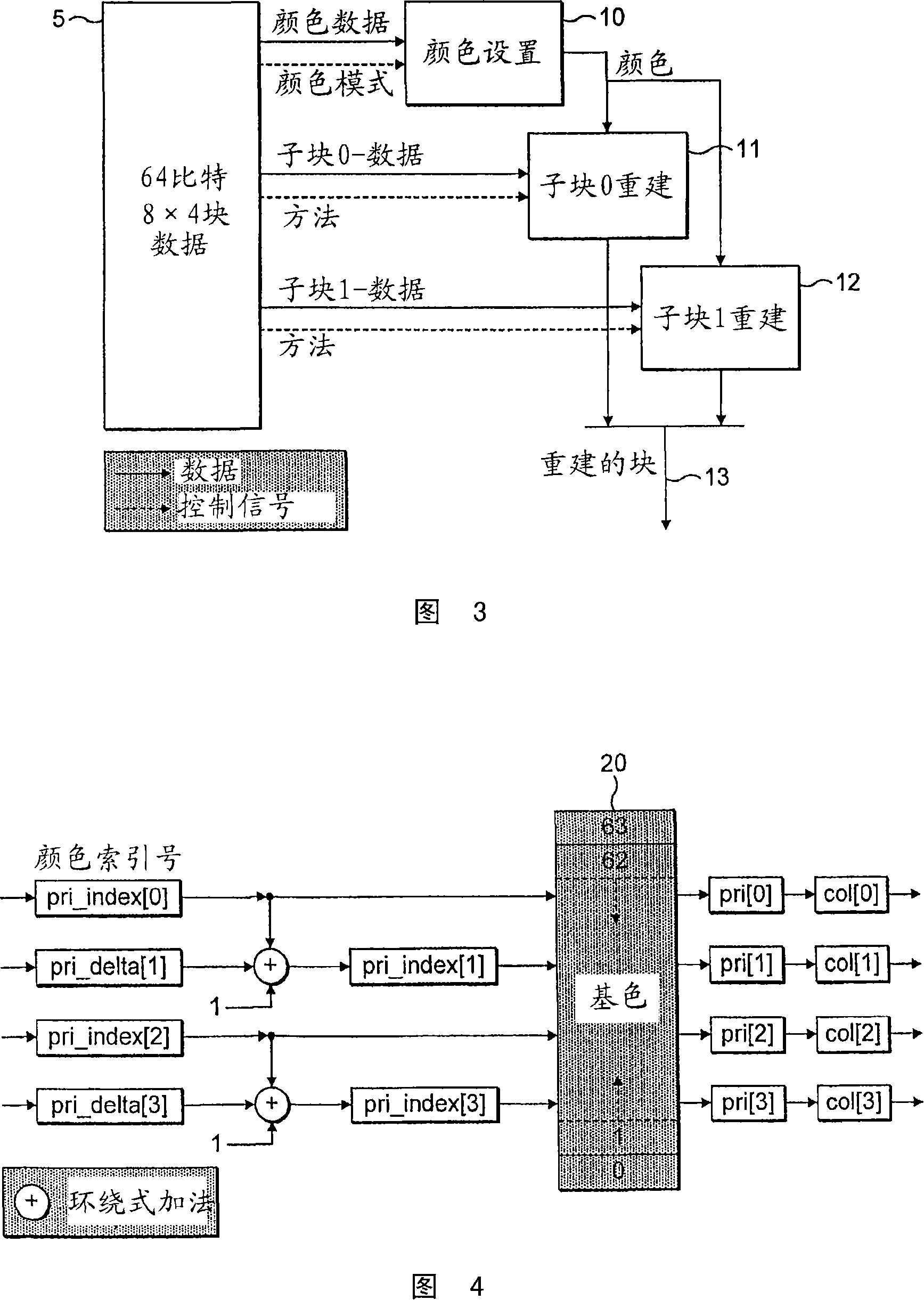

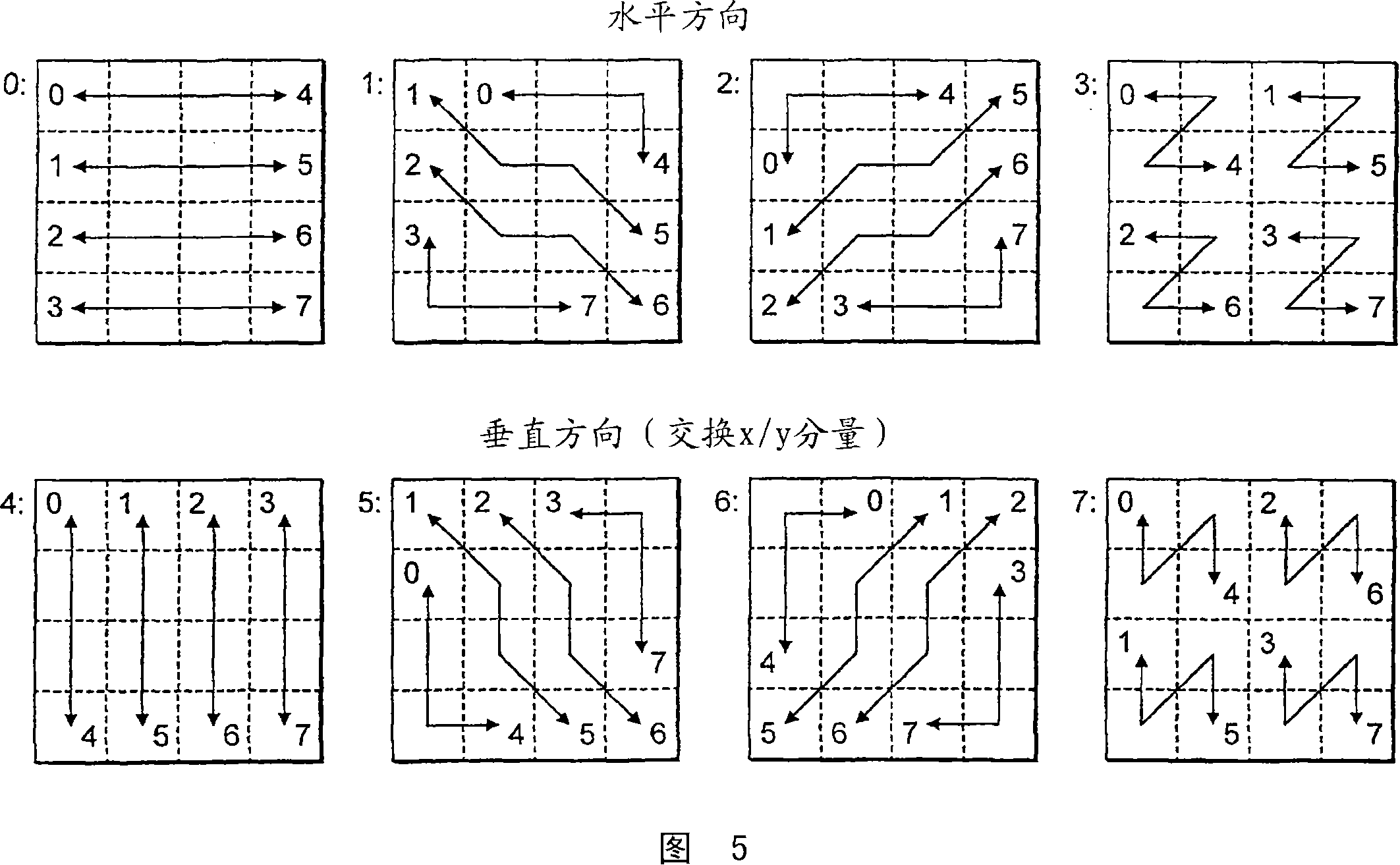

ActiveCN1898699AQuality improvementEasy to implementImage codingTelevision systemsPattern recognitionImaging processing

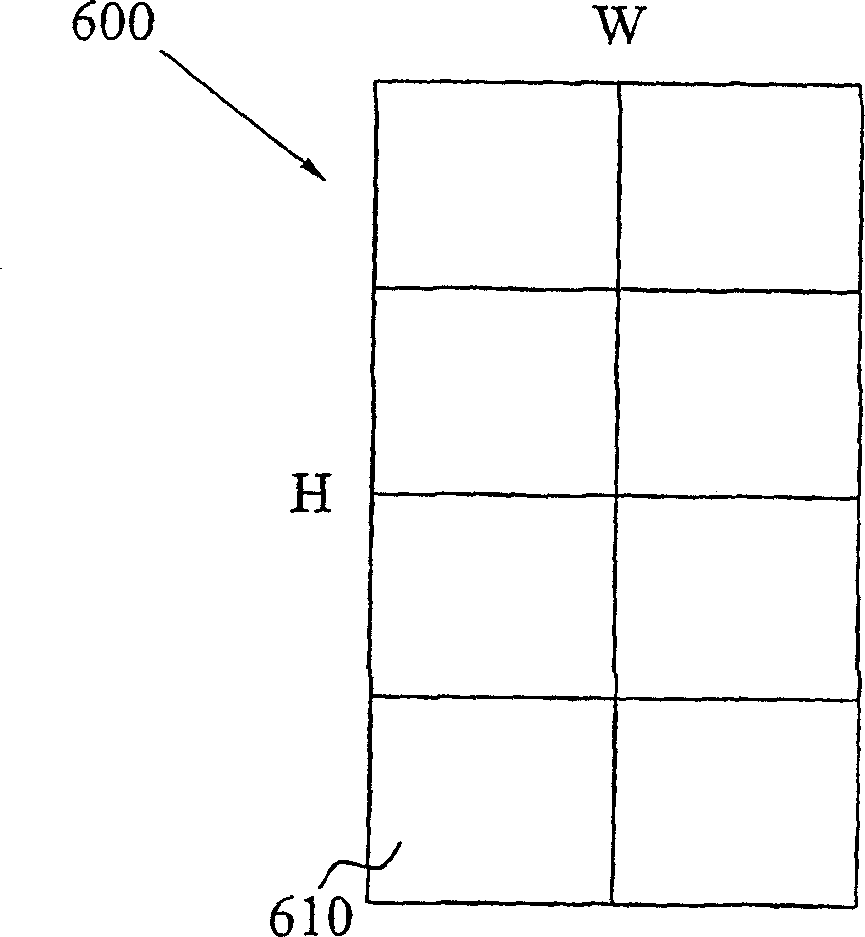

In an image-encoding scheme, an input image is decomposed into several image blocks (600) comprising multiple image elements (610), e.g. pixels or texels. The image blocks (600) are then encoded into encoded block representations (700). Such a block representation (700) comprises a color codeword (710), an intensity codeword (720) and a sequence (730) of intensity representations. The color codeword (710) is a representation of the colors of the image elements (610) of the block (600). The intensity codeword (720) is a representation of a set of multiple intensity modifiers for modifying the intensity of the image elements (610) in the block (600). The representation sequence (730) includes an intensity representation for each image element (610) in the block (600), where a representation identifies one of intensity modifiers in the intensity modifier set. During decoding, the color and intensity codewords (710, 720) and intensity representations (730) are used to generate a decoded representation of the image elements (610) in the block (600).

Owner:TELEFON AB LM ERICSSON (PUBL)

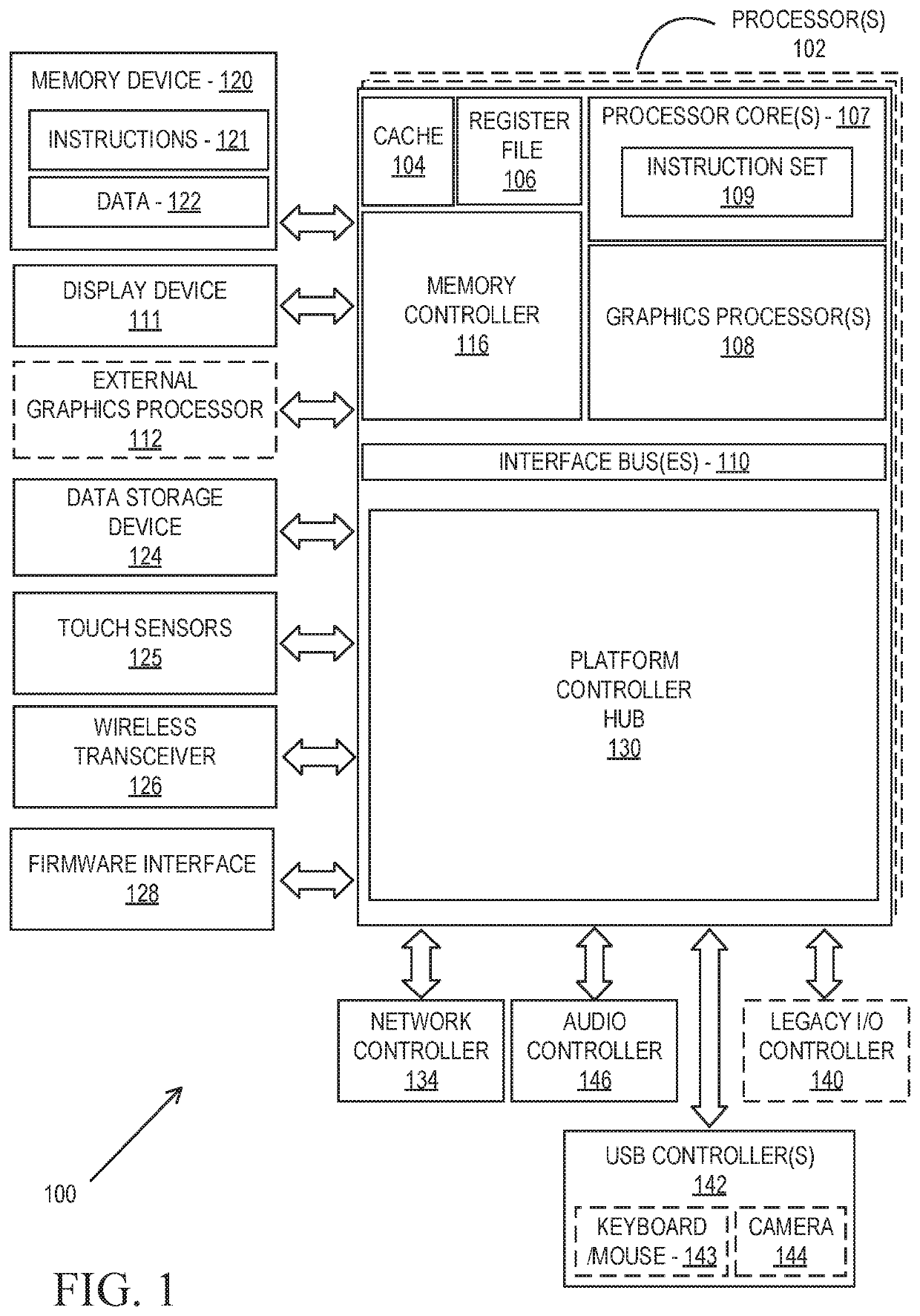

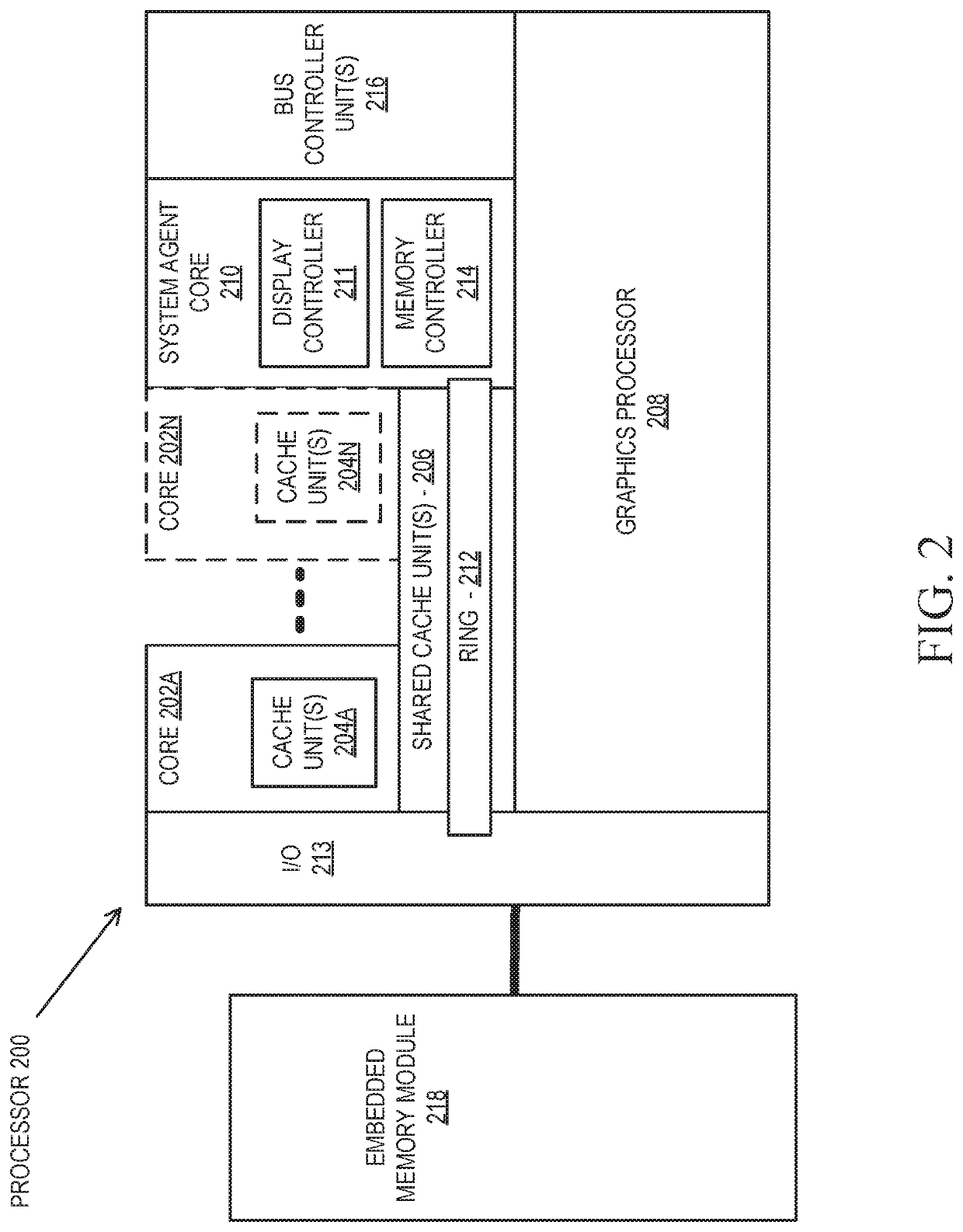

Multi-pass apparatus and method for early termination of graphics shading

Multi-pass apparatus and method for ray tracing shading. For example, one embodiment of an apparatus comprises: graphics processing circuitry to execute a sequence of visibility testing operations related to texels within a texture domain to generate visibility results; a register or memory to store a texel mask; texel mask update circuitry / logic to update the texel mask based on the visibility results, the texel mask comprising a plurality of bits to indicate visibility of the texels within the texture domain, the texel mask update circuitry / logic to set a first bit to indicate whether any bits in the texel mask indicate a visible texel; a shader dispatcher to initiate conditional dispatch operations only if the first bit is set to indicate that at least one bit in the texel mask indicates a visible texel, wherein to perform the conditional dispatch operations, the shader dispatcher is to dispatch texel shaders for only those texels that the texel mask indicates may be visible; and a plurality of execution units (EUs) to execute the shaders dispatched by the shader dispatcher.

Owner:INTEL CORP

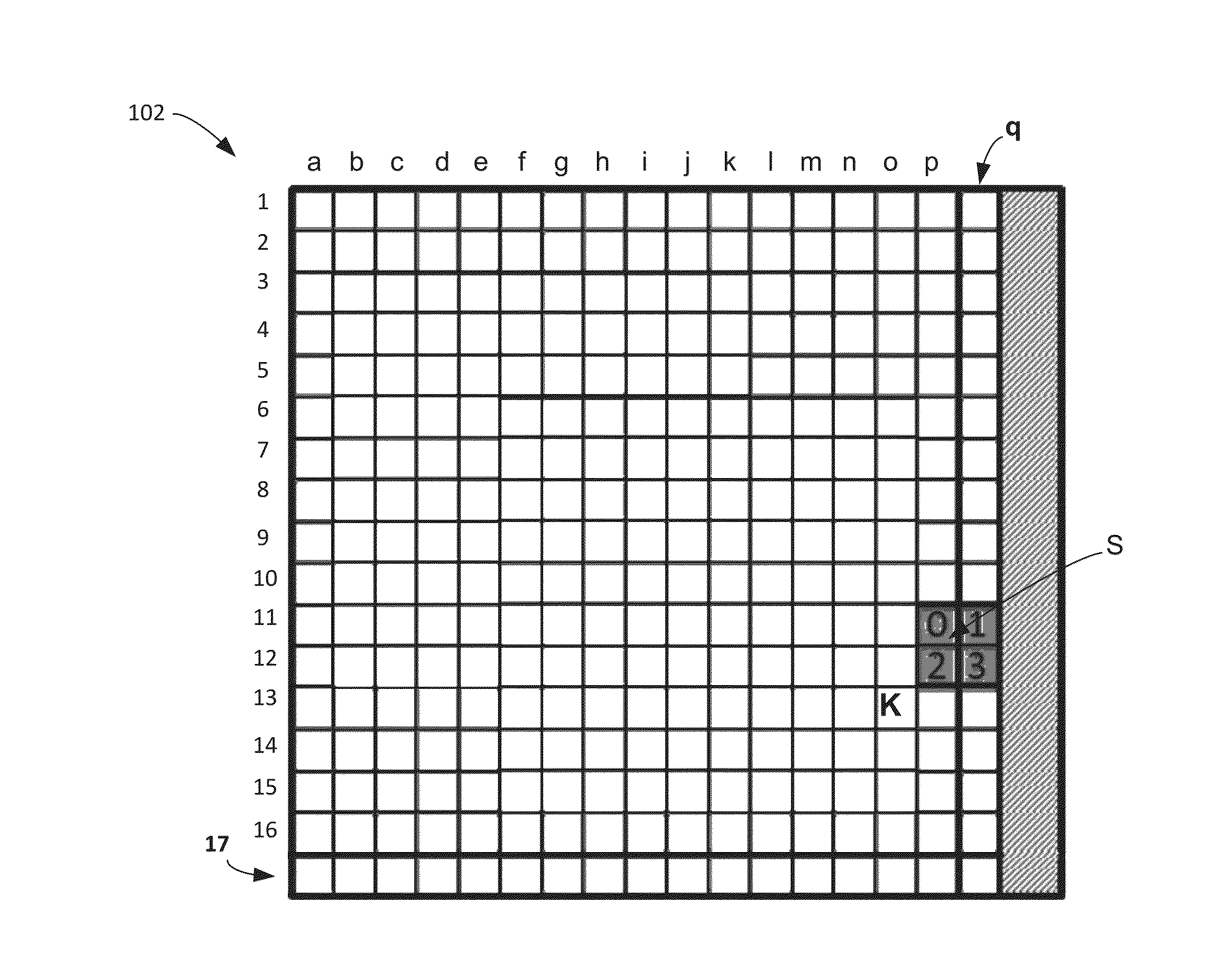

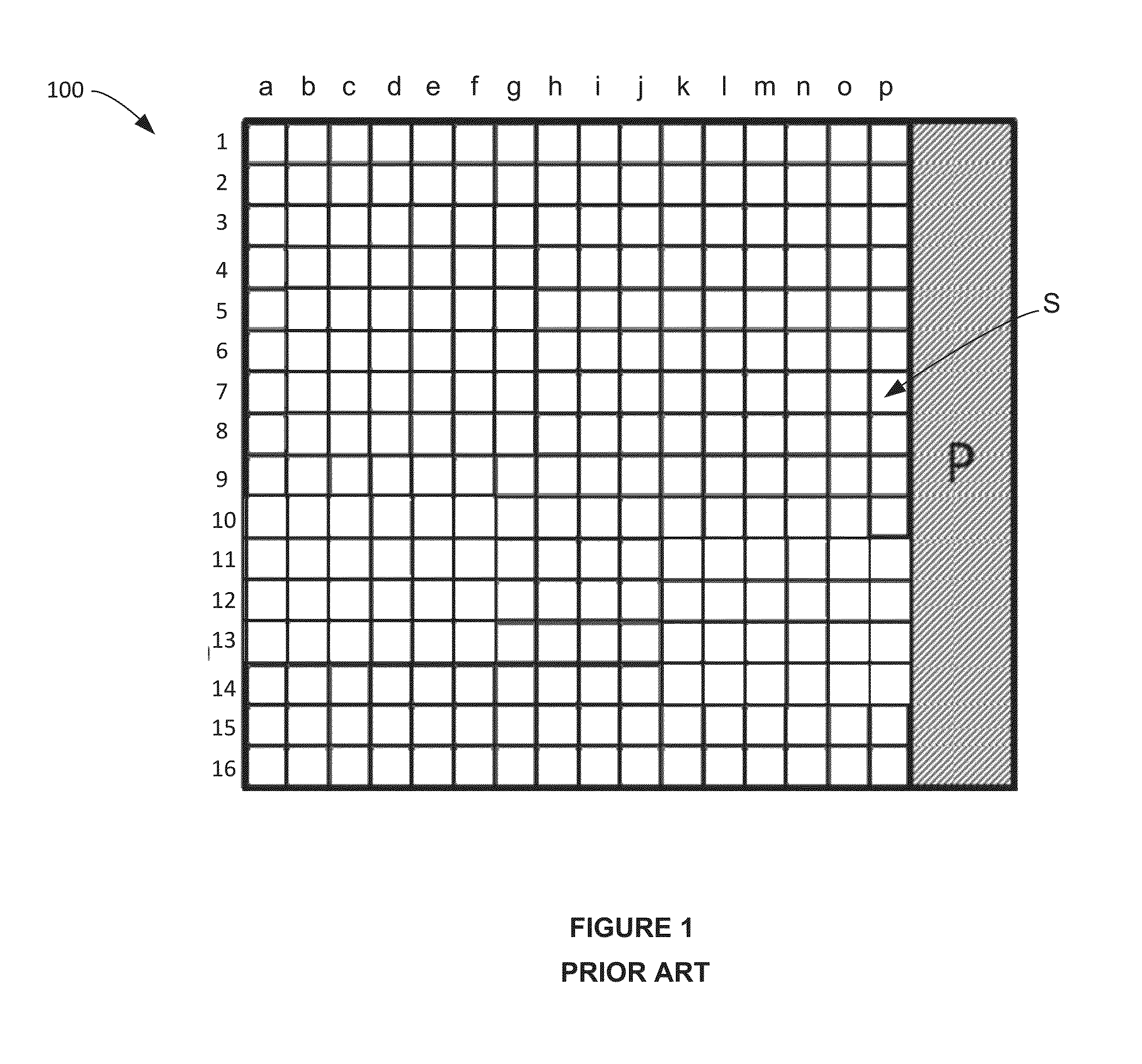

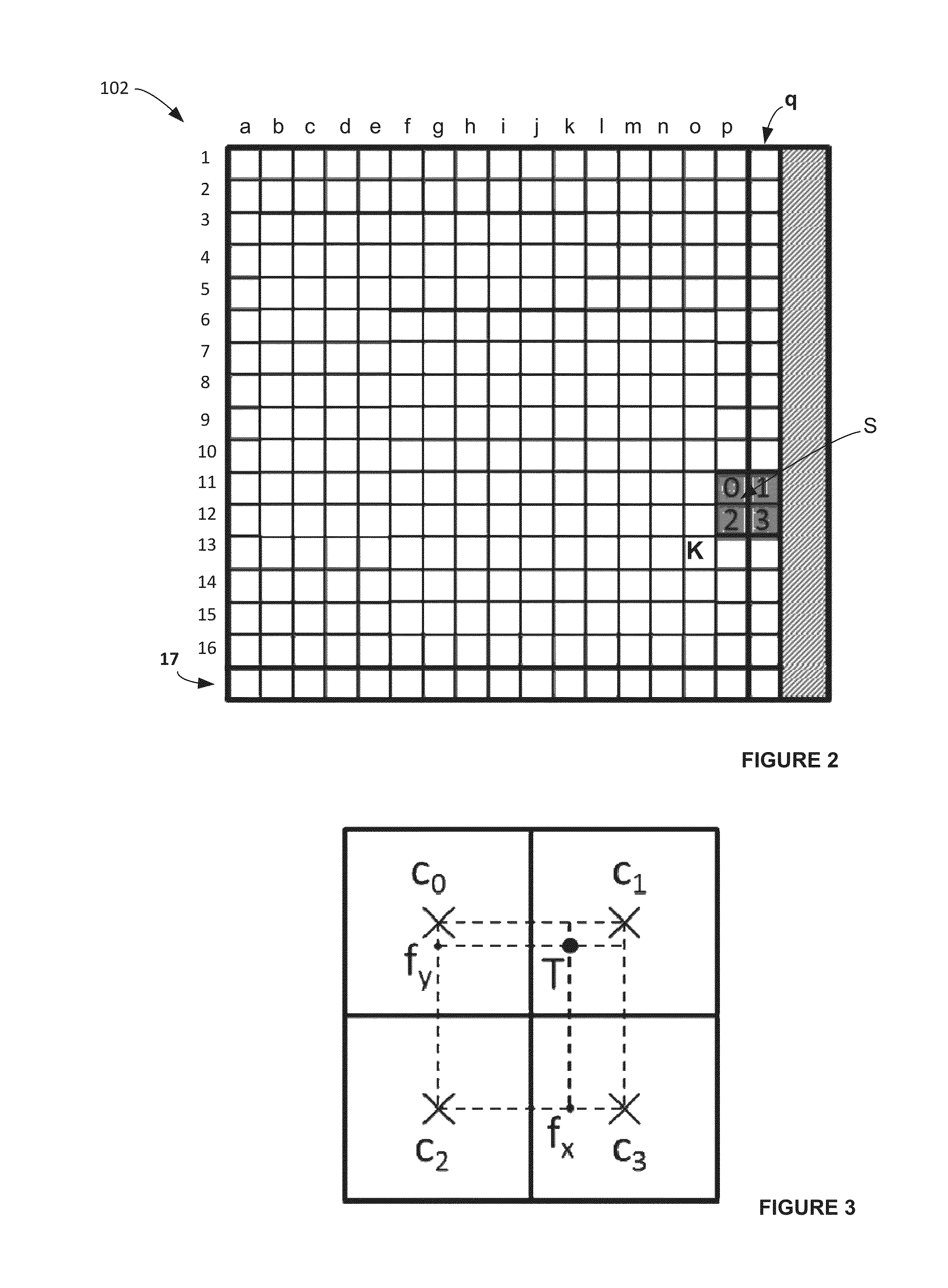

Method and system for expediting bilinear filtering

InactiveUS20150199825A1Fast readReduce impactImage enhancementImage analysisComputational scienceOriginal data

The present document describes a method and system for expediting bilinear filtering of textures, by reducing the number of data load operations. The method expands the original data layout with additional borders containing replicated texels. The replicated texels correspond either to wrapped-around texels for two-dimensional textures or neighboring faces in cube textures. Therefore, a 2×2 filter kernel for bilinear filtering is built which requires only one texel address to be computed, with all texel data readable with two load operations which are a predetermined stride apart. Different addressing modes are implemented by adjusting the sampling locus.

Owner:GOOGLE LLC

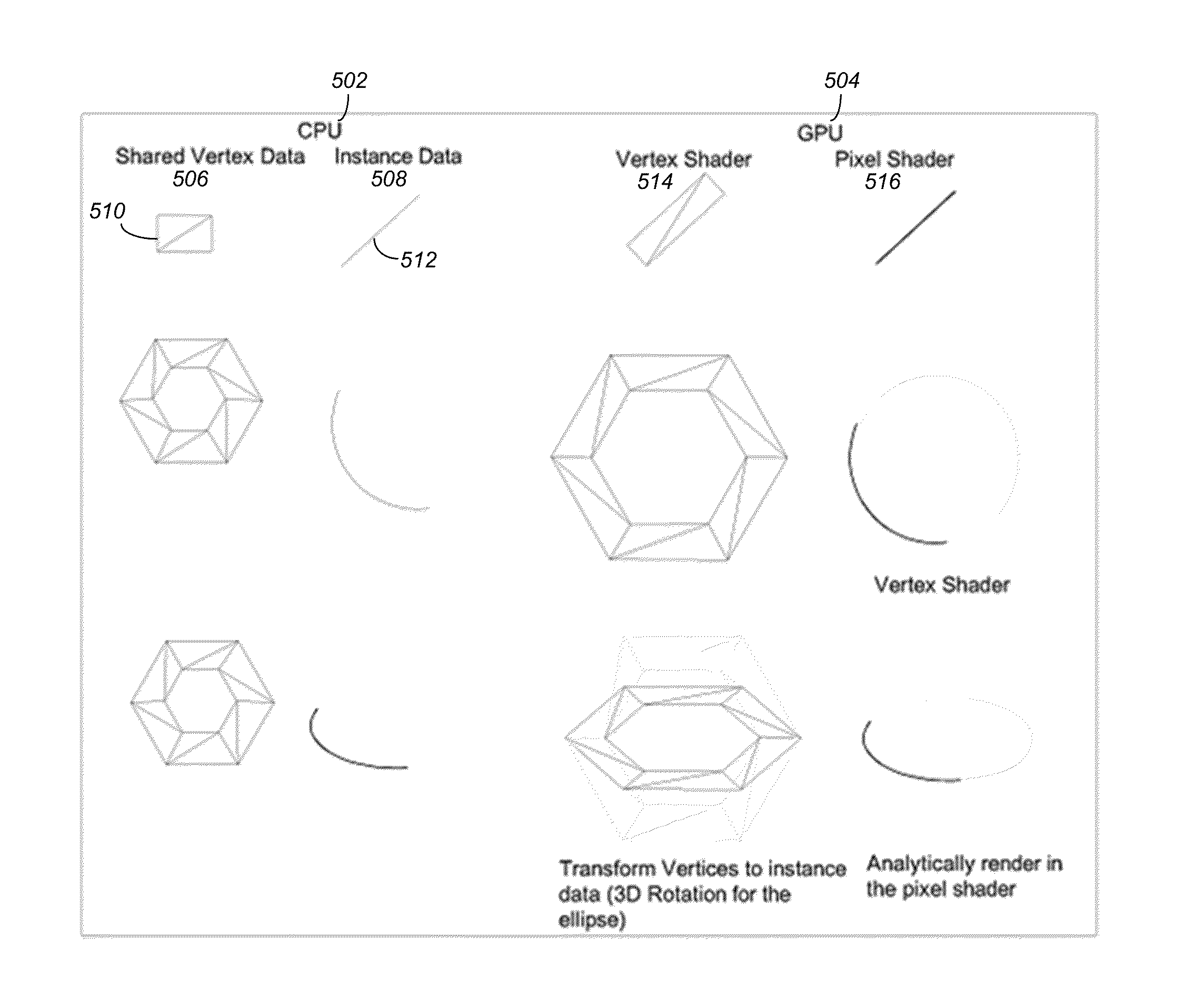

Line stylization through graphics processor unit (GPU) textures

ActiveUS20160012618A1Improve performanceDrawing from basic elementsProcessor architectures/configurationComputational scienceGraphics

A method, apparatus, system, and computer program product provide the ability to render a line having line stylization / linetype pattern via texture mapping of a graphics processing unit (GPU). Linetype information for a pattern of a linetype for the line is acquired. The pattern is stored in a texture by encoding a type of element of the pattern and a texel center location. The GPU renders the line by computing a distance between a pixel of the line and the texel center location, determining if the distance exceeds a threshold, and rendering the pixel if the distance is within the threshold.

Owner:AUTODESK INC

Multi-Output Decoder for Texture Decompression

ActiveUS20180315218A1Texturing/coloringImage codingParallel computingAdaptive Scalable Texture Compression

A decoder is configured to decode a plurality of texels from a received block of texture data encoded according to the Adaptive Scalable Texture Compression (ASTC) format, and includes a parameter decode unit configured to decode configuration data for the received block of texture data, a colour decode unit configured to decode colour endpoint data for the plurality of texels of the received block in dependence on the configuration data, a weight decode unit configured to decode interpolation weight data for each of the plurality of texels of the received block in dependence on the configuration data, and at least one interpolator unit configured to calculate a colour value for each of the plurality of texels of the received block using the interpolation weight data for that texel and a pair of colour endpoints from the colour endpoint data. At least one of the parameter decode unit, colour decode unit and weight decode unit are configured to decode intermediate data from the received block that is common to the decoding of at least a subset of texels of that block and to use that decoded intermediate data as part of the decoding of at least two of the plurality of texels from the received block of texture data.

Owner:IMAGINATION TECH LTD

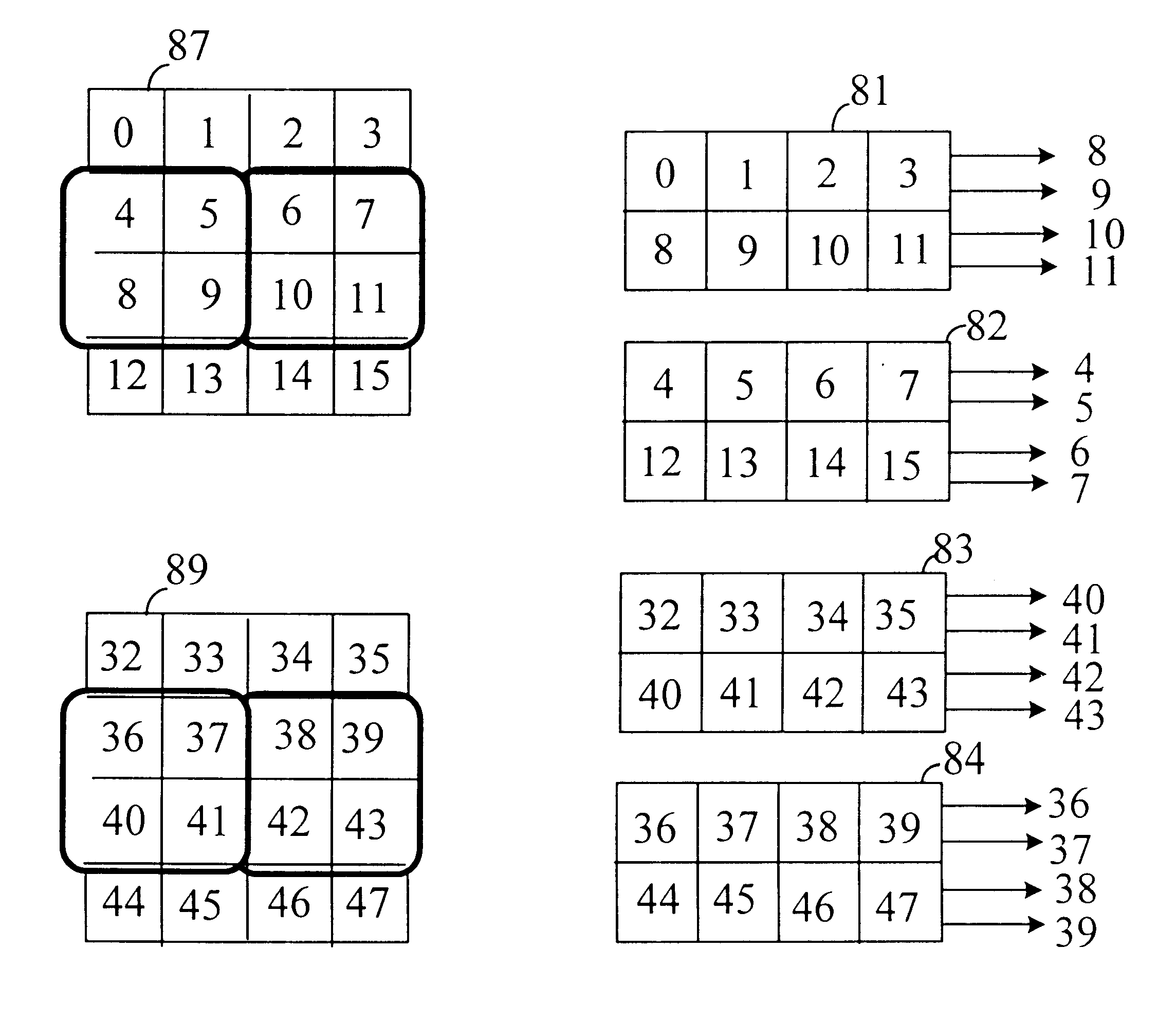

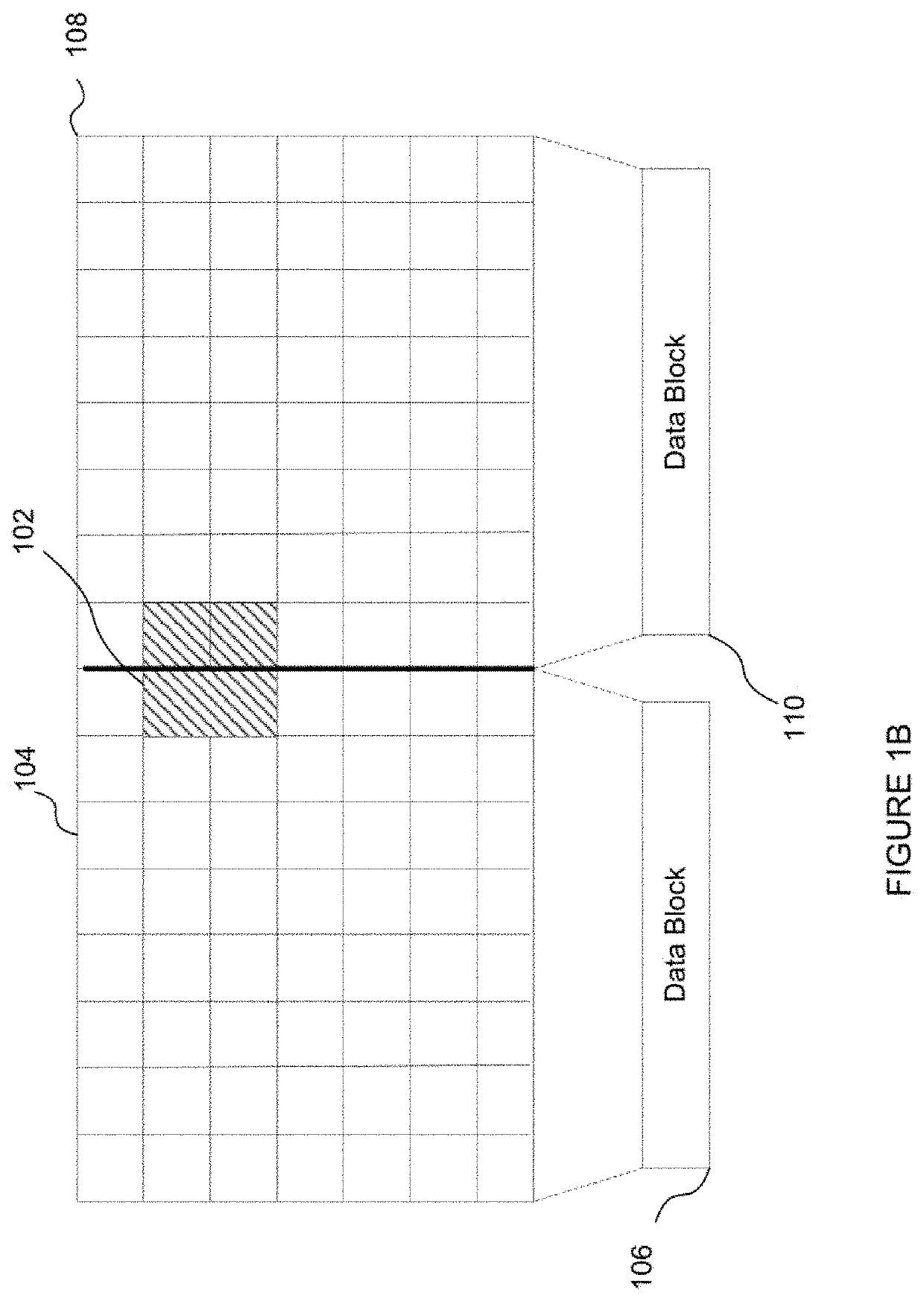

Block linear memory ordering of texture data

ActiveUS20110169850A1Memory adressing/allocation/relocationImage memory managementMemory orderingParallel computing

Owner:NVIDIA CORP

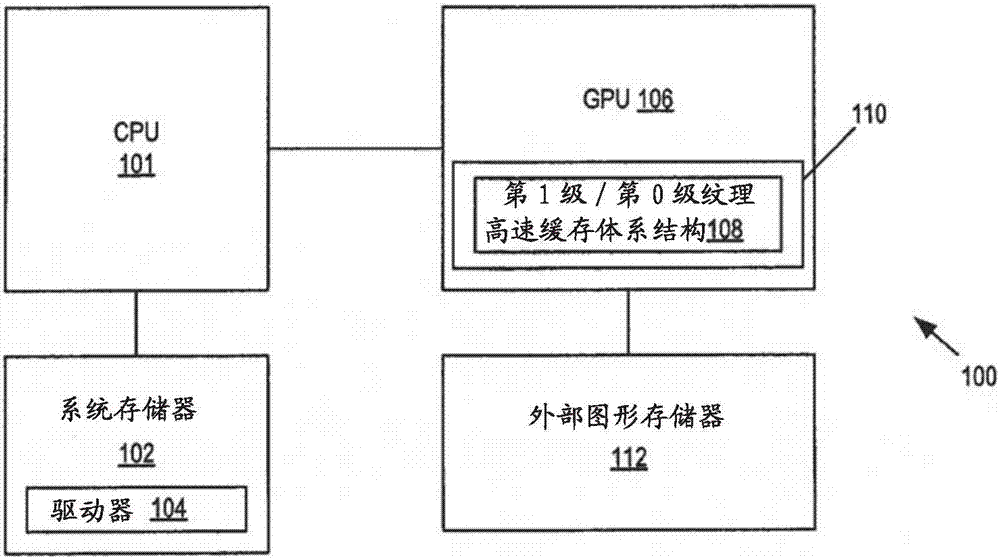

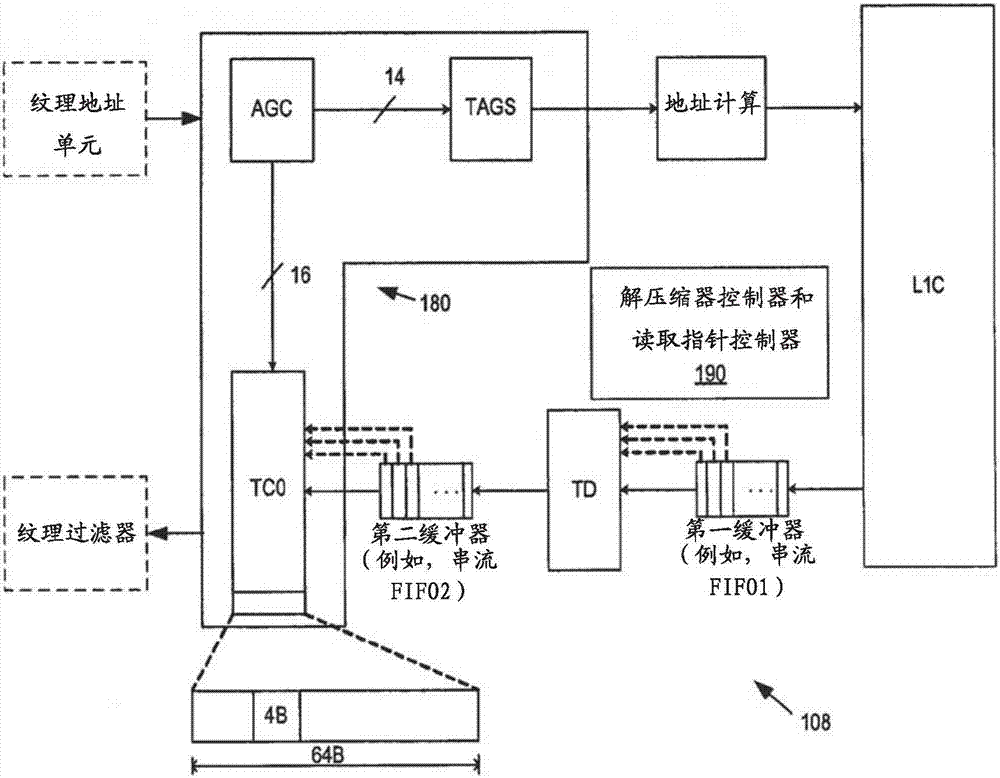

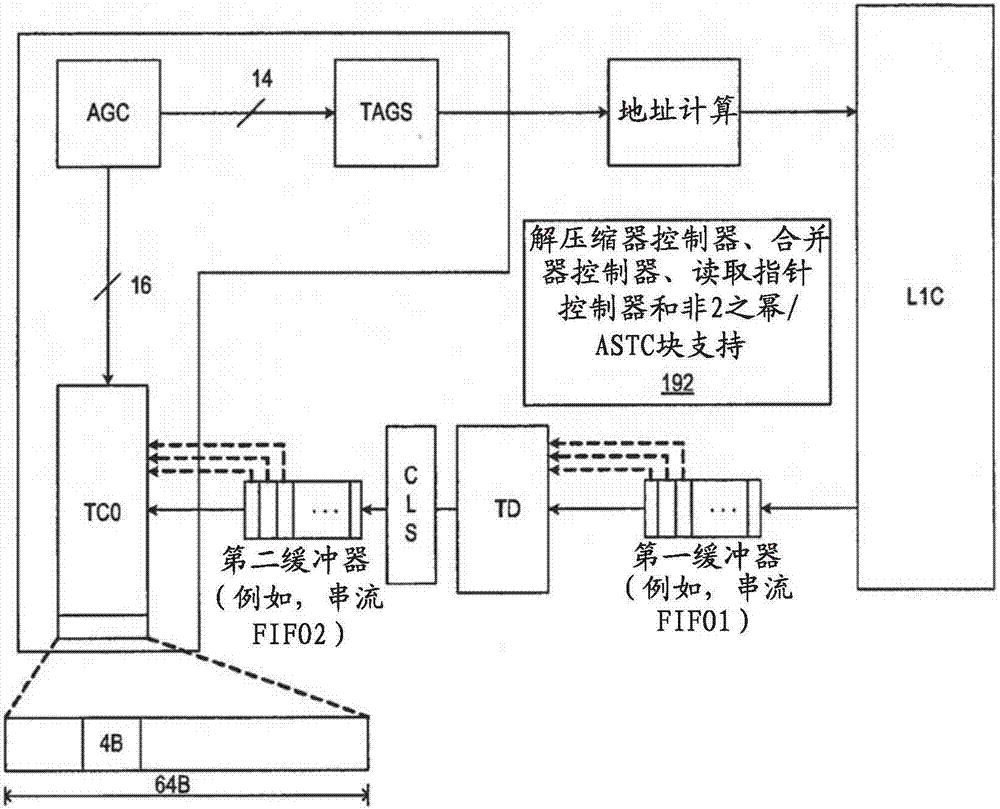

Cache architecture for efficiently accessing texture data using buffers

ActiveCN107153617AImage memory managementMemory systemsData storeAdaptive Scalable Texture Compression

A texture cache architecture facilitates access of compressed texture data in non-power of two formats, such as the Adaptive Scalable Texture Compression (ASTC) codec. In one implementation, the texture cache architecture includes a controller, a first buffer, a second buffer, and a texture decompressor. A first buffer stores one or more blocks of compressed texel data fetched, in response to a first request, from a first texture cache, where the one or more blocks of compressed texel data including at least requested texel data. The second buffer stores decompressed one or more blocks of compressed texel data and provides the decompressed requested texel data as output to a second texture cache. The one or more blocks of compressed texel data stored by the first buffer includes second texel data in addition to the requested texel data.

Owner:SAMSUNG ELECTRONICS CO LTD

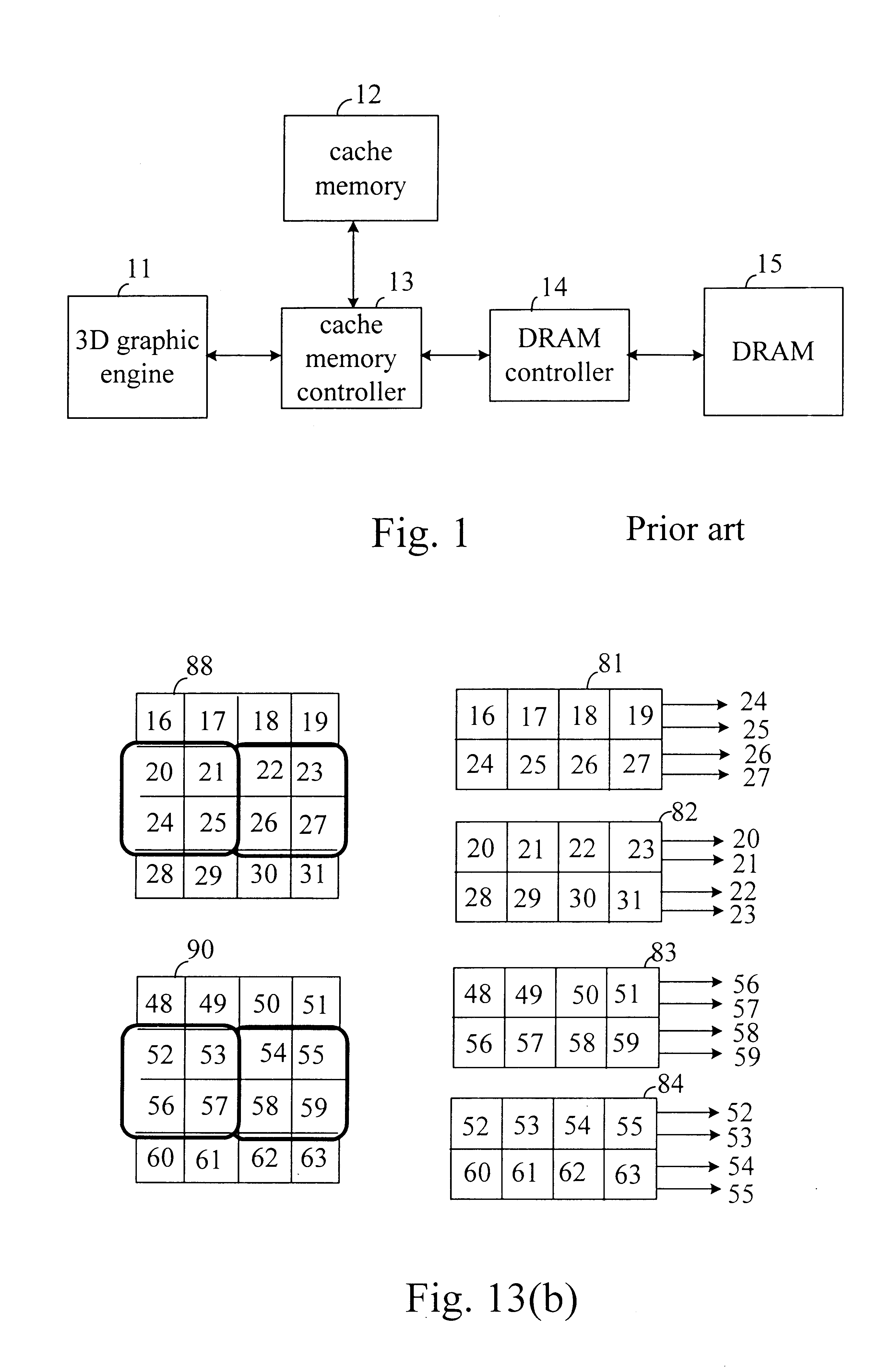

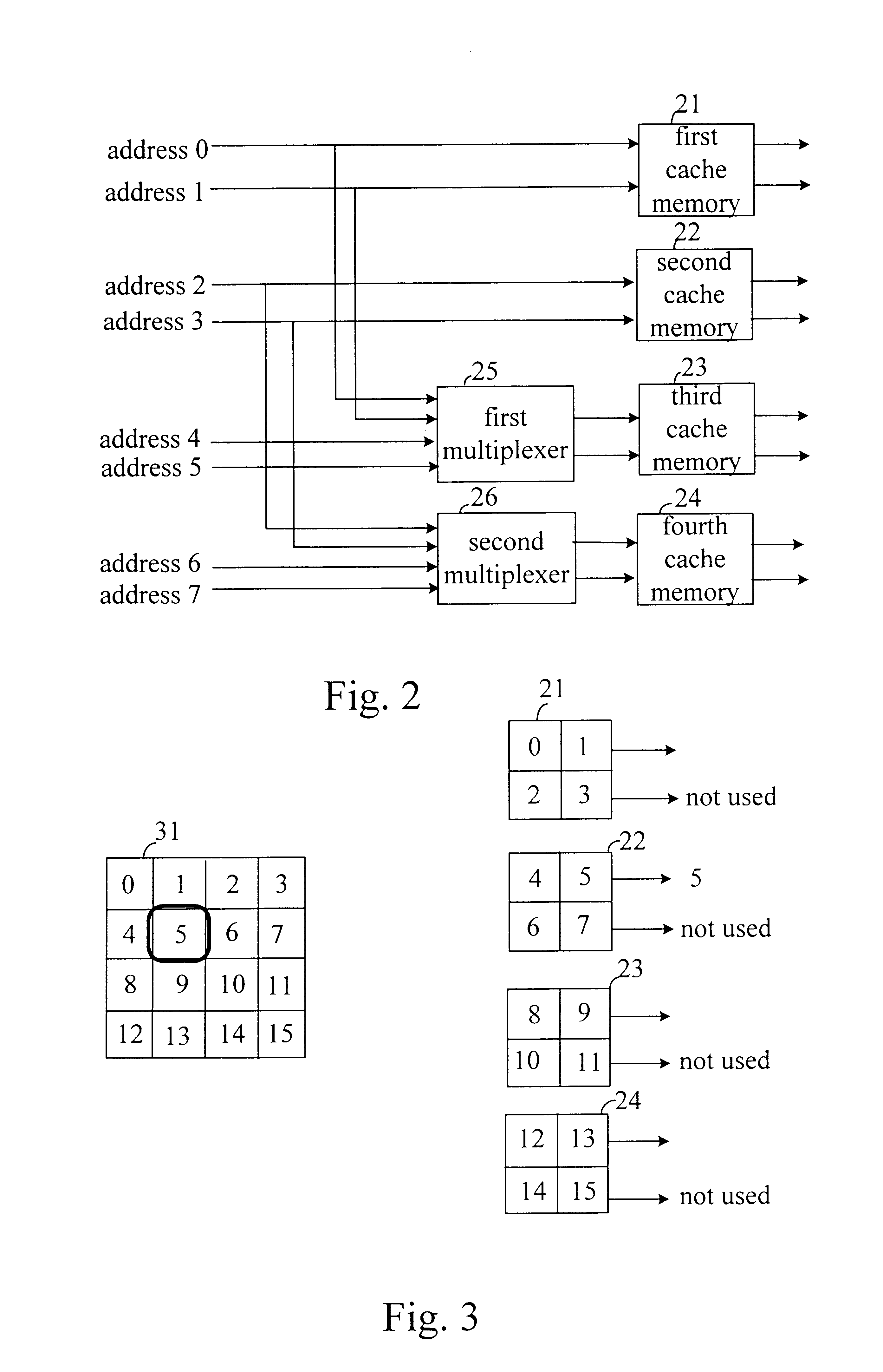

Apparatus and method for cache memory connection of texture mapping

InactiveUS6573902B1Cathode-ray tube indicatorsFilling planer surface with attributesGraphicsBilinear filtering

The present invention discloses an apparatus and method for cache memory connection of texture mapping, applied in a computer graphic processing system by storing image texels in cache memories. The apparatus comprises a plurality of cache memories. An array of image texels are stored in a plurality of cache memories to reduce the area occupied by cache memories of the computer graphic processing system. Besides, the apparatus and method of the present invention can be applied in the well-known mapping methods: selecting the nearest point, bilinear filtering and trilinear filtering. A plurality of multiplexers are used to reorganize the plurality of cache memories so as to increase the utilization efficiency of the apparatus of the present invention.

Owner:XGI TECHNOLOGY

Multi-pass apparatus and method for early termination of graphics shading

Multi-pass apparatus and method for ray tracing shading. For example, one embodiment of an apparatus comprises: graphics processing circuitry to execute a sequence of visibility testing operations related to texels within a texture domain to generate visibility results; a register or memory to store a texel mask; texel mask update circuitry / logic to update the texel mask based on the visibility results, the texel mask comprising a plurality of bits to indicate visibility of the texels within the texture domain, the texel mask update circuitry / logic to set a first bit to indicate whether any bits in the texel mask indicate a visible texel; a shader dispatcher to initiate conditional dispatch operations only if the first bit is set to indicate that at least one bit in the texel mask indicates a visible texel, wherein to perform the conditional dispatch operations, the shader dispatcher is to dispatch texel shaders for only those texels that the texel mask indicates may be visible; and a plurality of execution units (EUs) to execute the shaders dispatched by the shader dispatcher.

Owner:INTEL CORP

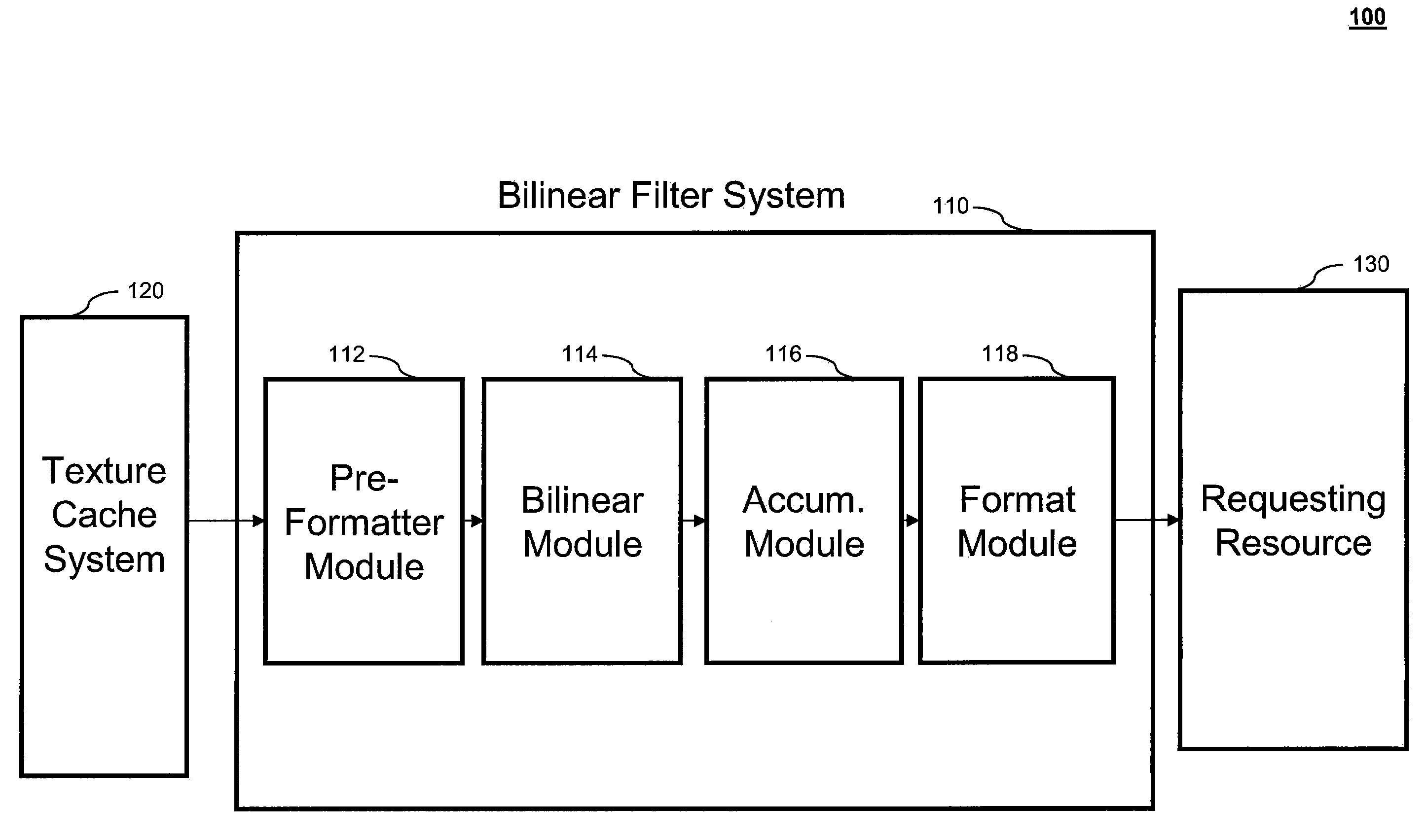

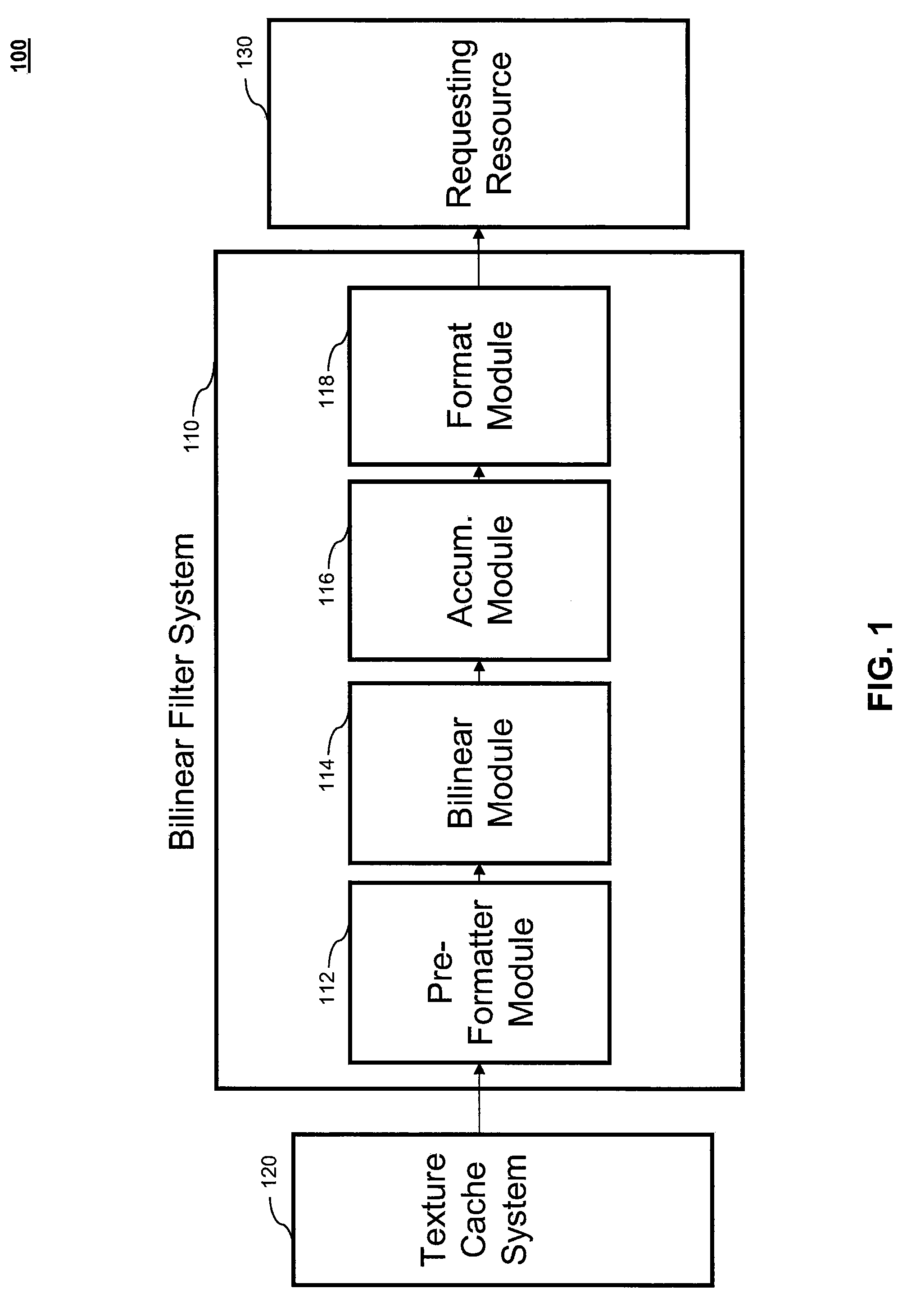

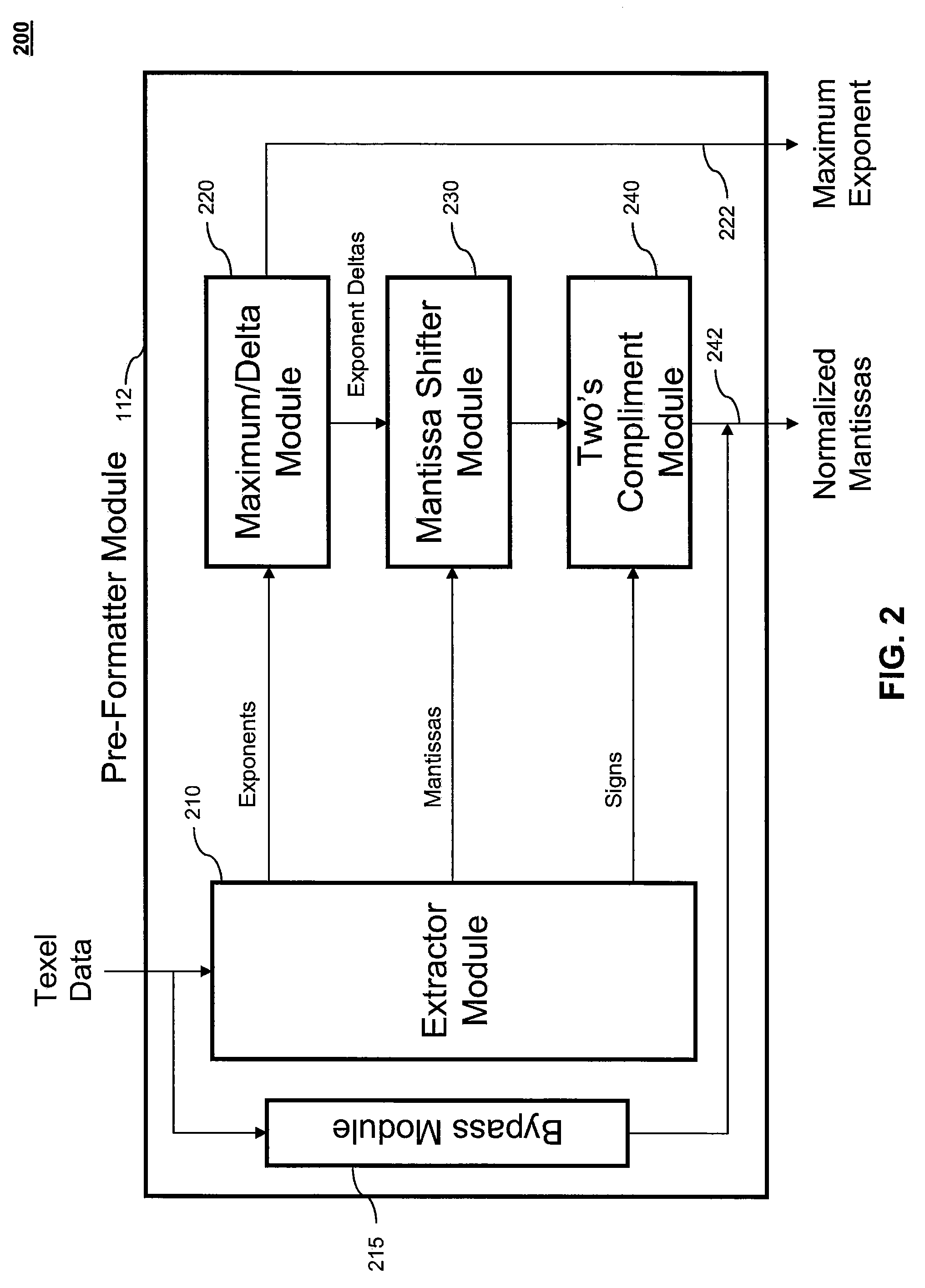

Dynamically Configurable Bilinear Filtering System

ActiveUS20090289949A1Texturing/coloringCathode-ray tube indicatorsExtended precisionBilinear filtering

Apparatus and methods for a bilinear filter system comprising a pre-formatter module, a bilinear module, an accumulator module, and a format module. The pre-formatter module is configured to receive texel data and convert it to a normalized fixed point format. The bilinear module is dynamically reconfigurable to perform an interpolation or an extended precision interpolation on the normalized fixed point texel data from the pre-formatter module and generate re-normalized floating point texel data. The interpolator analyzes the exponent range of fixed point texel data from the pre-formatter module to determine if an extended precision calculation is appropriate. The accumulator module is configured to accumulate floating point texel data from the bilinear module to achieve the desired level of bilinear, trilinear, and anisotropic filtering. The format module is configured to convert texel data from the accumulator module into a standard floating point representation.

Owner:ADVANCED MICRO DEVICES INC

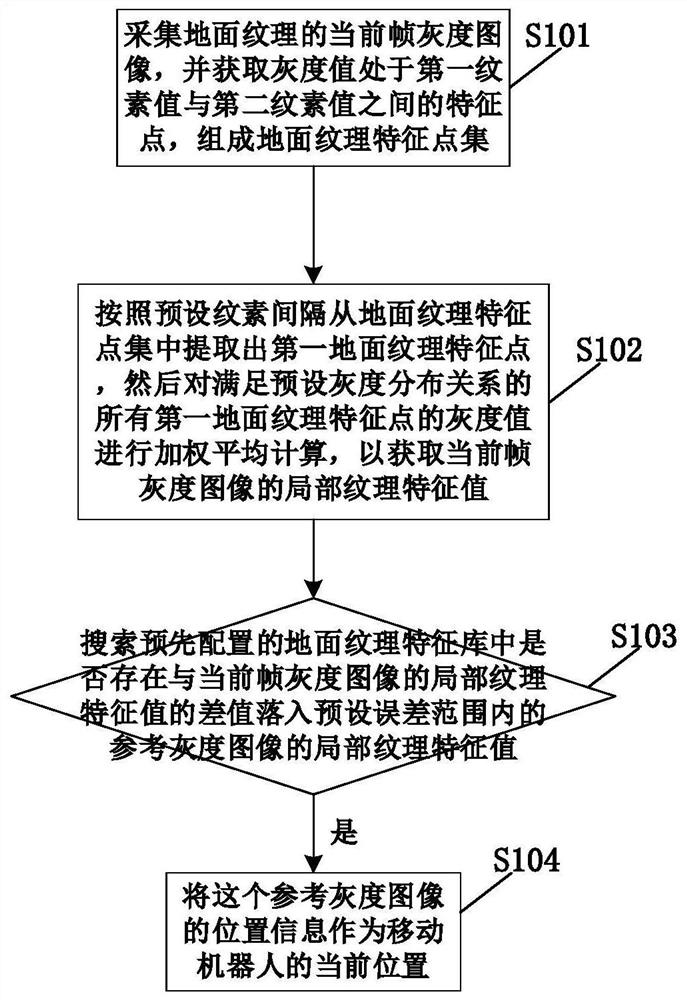

Visual positioning method based on ground texture, chip and mobile robot

PendingCN112150549AUndisturbedEffective highlightImage enhancementInstruments for road network navigationEngineeringMachine

The invention discloses a visual positioning method based on ground texture, a chip and a mobile robot, and belongs to the technical field of monocular visual navigation. Compared with the prior art,a camera disclosed by the invention is mounted at the bottom of a machine body, so that the camera is not interfered by an external light source and can be applied to indoor and outdoor working areas.Extra image acquisition processing does not need to be carried out on the periphery of the vehicle body or above the ground in the navigation positioning process; according to the visual positioningmethod, in the navigation positioning process of the mobile robot, mean weighting operation is carried out on gray values of first ground texture feature points by utilizing pre-configured texel intervals and a gray level distribution relationship, and feature value difference matching search is carried out in cooperation with a pre-configured ground texture feature library, so that a natural background is effectively inhibited; ground texture is highlighted, and effective local texture information is extracted through matching to complete high-precision visual positioning.

Owner:AMICRO SEMICON CORP

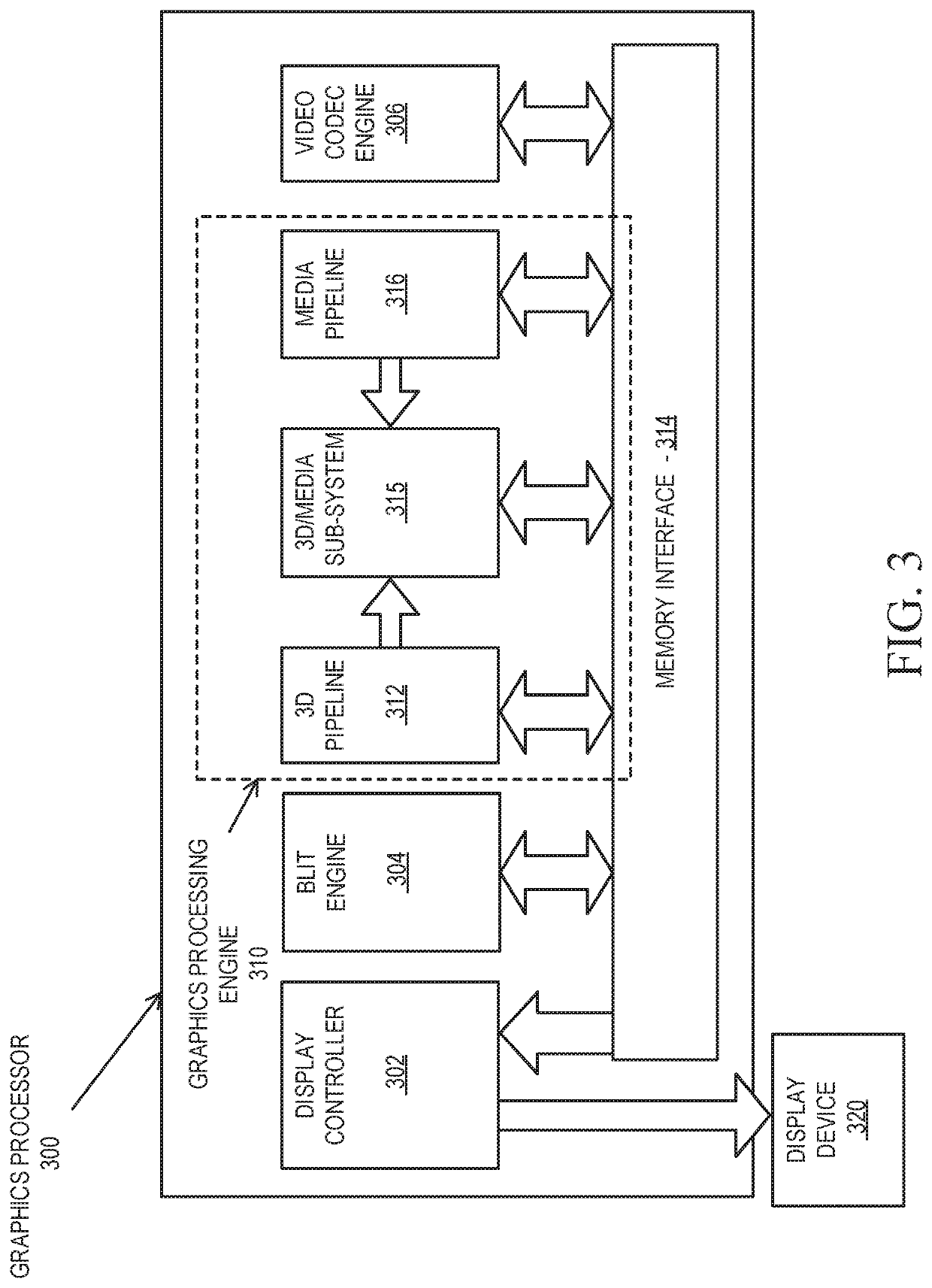

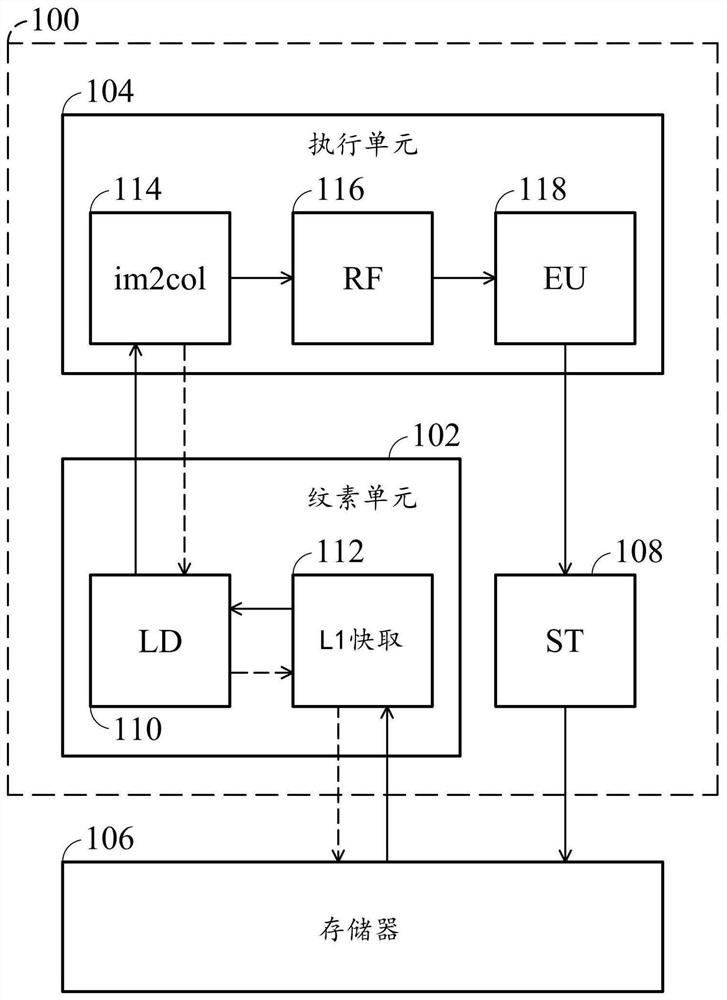

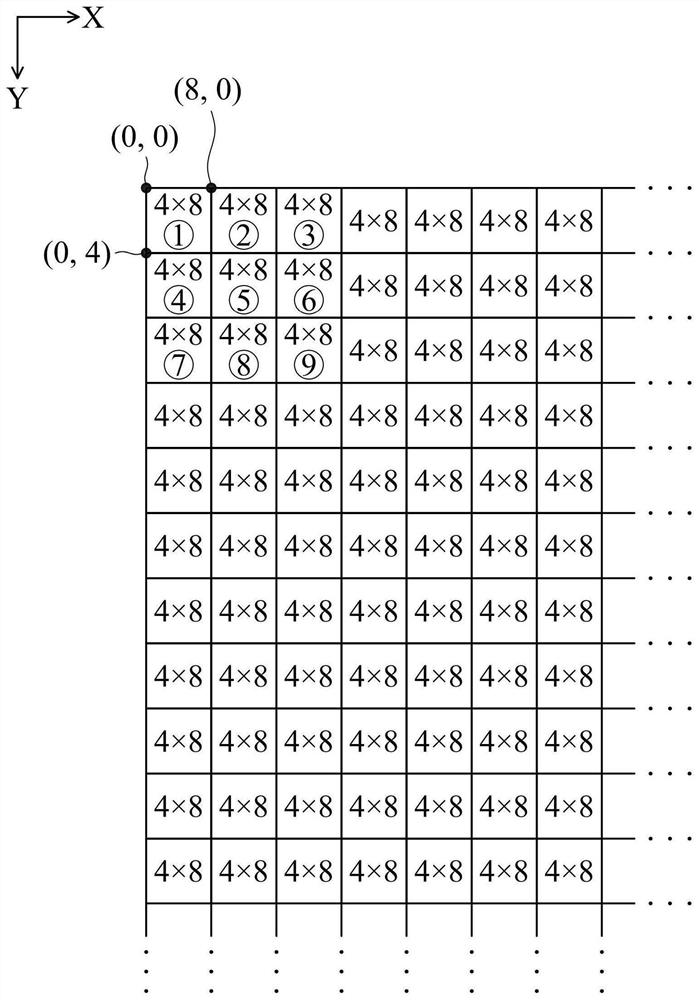

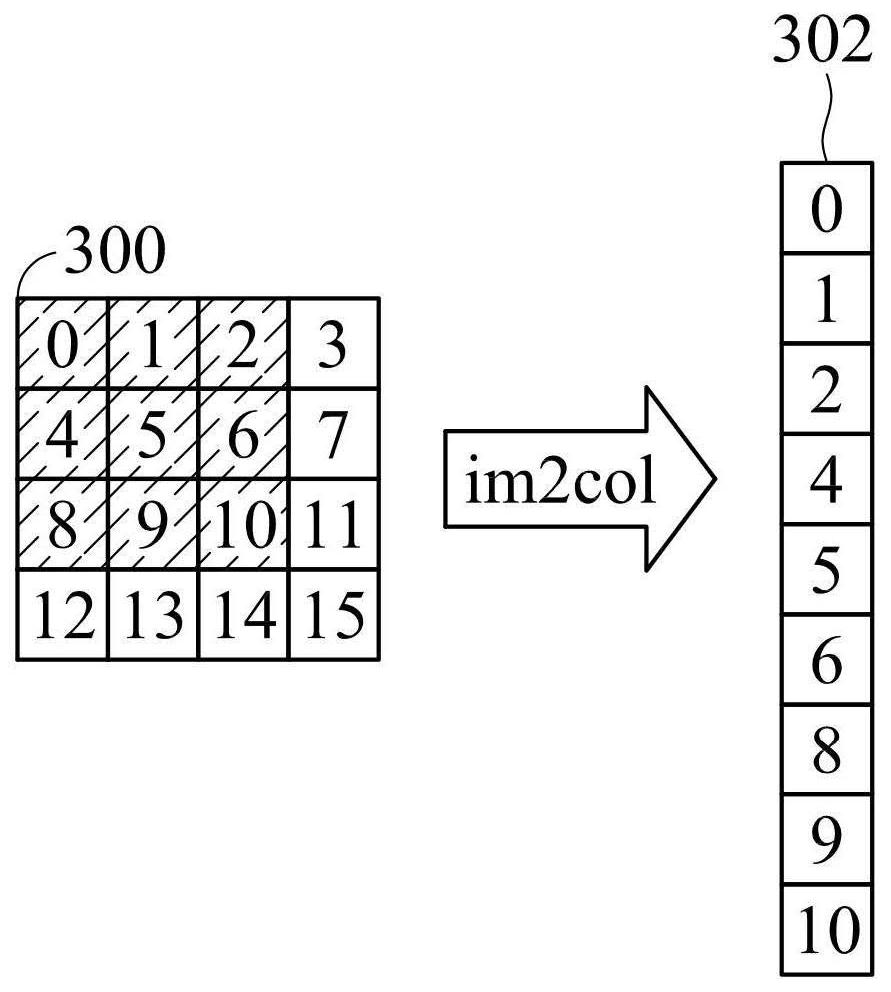

Graphics processor and acceleration method thereof

PendingCN112241509AMemory architecture accessing/allocationImage memory managementComputer hardwareComputational science

The invention provides a graphics processor and an acceleration method thereof. The graphics processor comprises a texel unit and an execution unit. The texel unit comprises a reading module. The execution unit comprises: an im2col module which is used for executing an im2col algorithm and expanding an original matrix according to the size of a convolution kernel to obtain an expanded matrix; an execution unit which multiplies the extended matrix by the convolution kernel to obtain a feature matrix; a reading module which calculates a characteristic coordinate of each element of the characteristic matrix according to the coordinate of the extended matrix, and obtains an original coordinate of each element of the original matrix according to the characteristic coordinate, the convolution kernel, the pace value and the filling value, wherein the reading module reads at least one of the storage blocks covered by the original coordinates of each element of the original matrix, and transmits data corresponding to the original coordinates in the at least one of the storage blocks to the im2col module.

Owner:GLENFLY TECH CO LTD

Decoder unit for texture decompression

A decoder unit is configured to decode a plurality of texels in accordance with a texel request, the plurality of texels being encoded across one or more blocks of encoded texture data each encoding a block of texels, and includes a first set of one or more decoders, each of the first set of decoders being configured to decode n texels from a single received block of encoded texture data; a second set of or more decoders, each of the second set of decoders being configured to decode p texels from a single received block of encoded texture data, where p<n; and control logic configured to allocate blocks of encoded texture data to the decoders in accordance with the texel request.

Owner:IMAGINATION TECH LTD

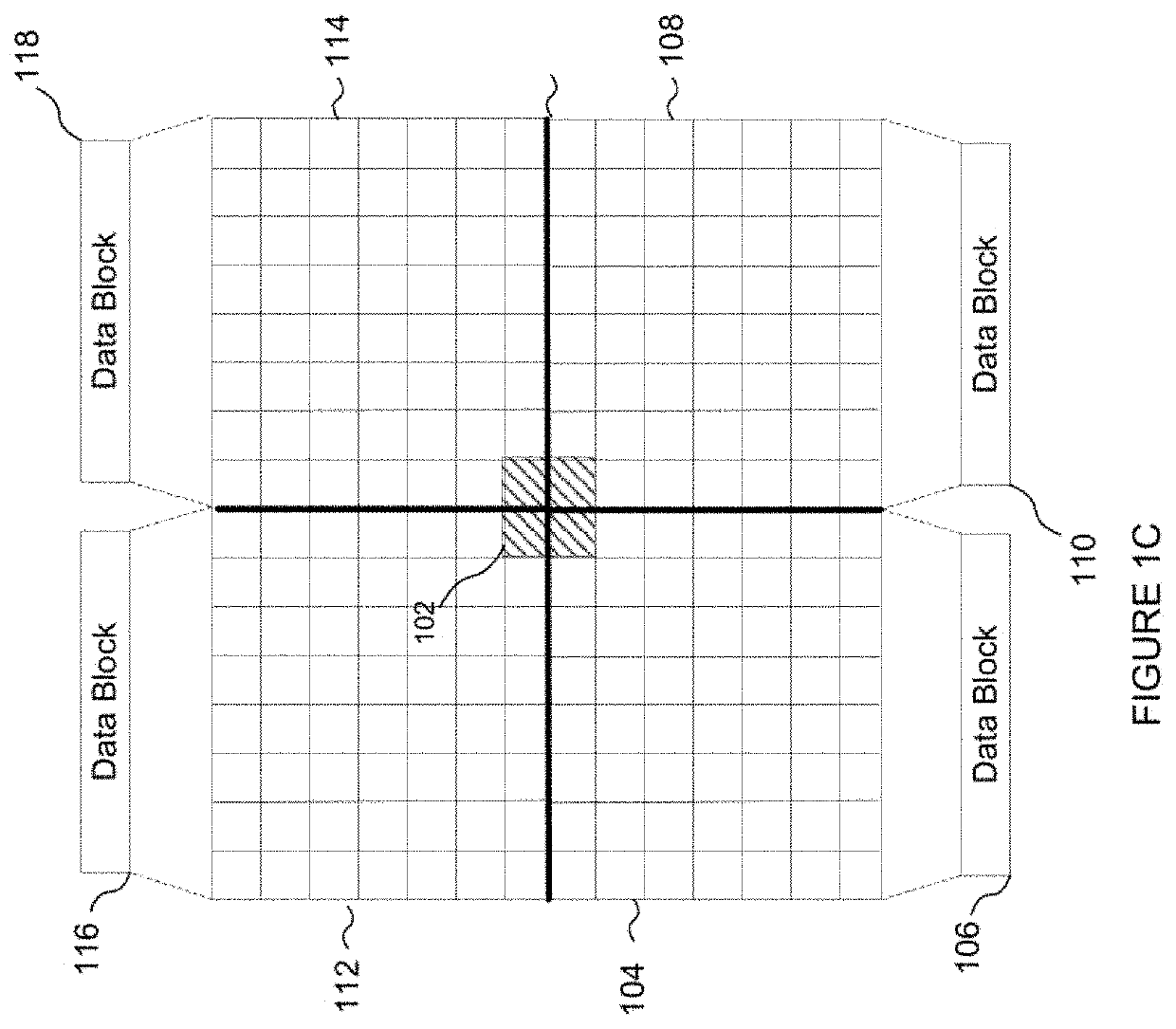

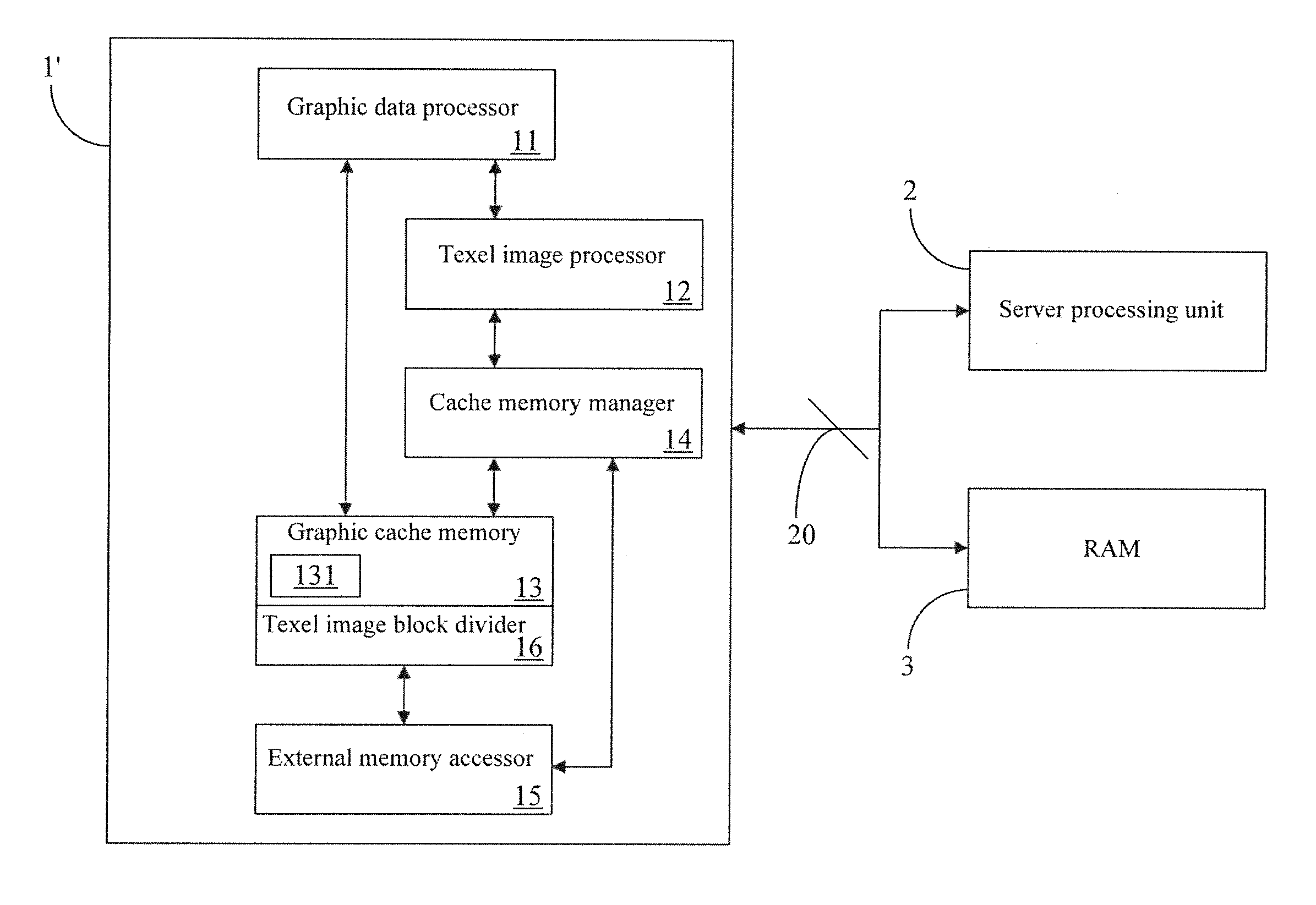

Graphic processing unit and graphic data accessing method thereof

InactiveUS20130222398A1Improve utilization efficiencyIncrease flexibilityMemory architecture accessing/allocationImage memory managementGraphicsAccess method

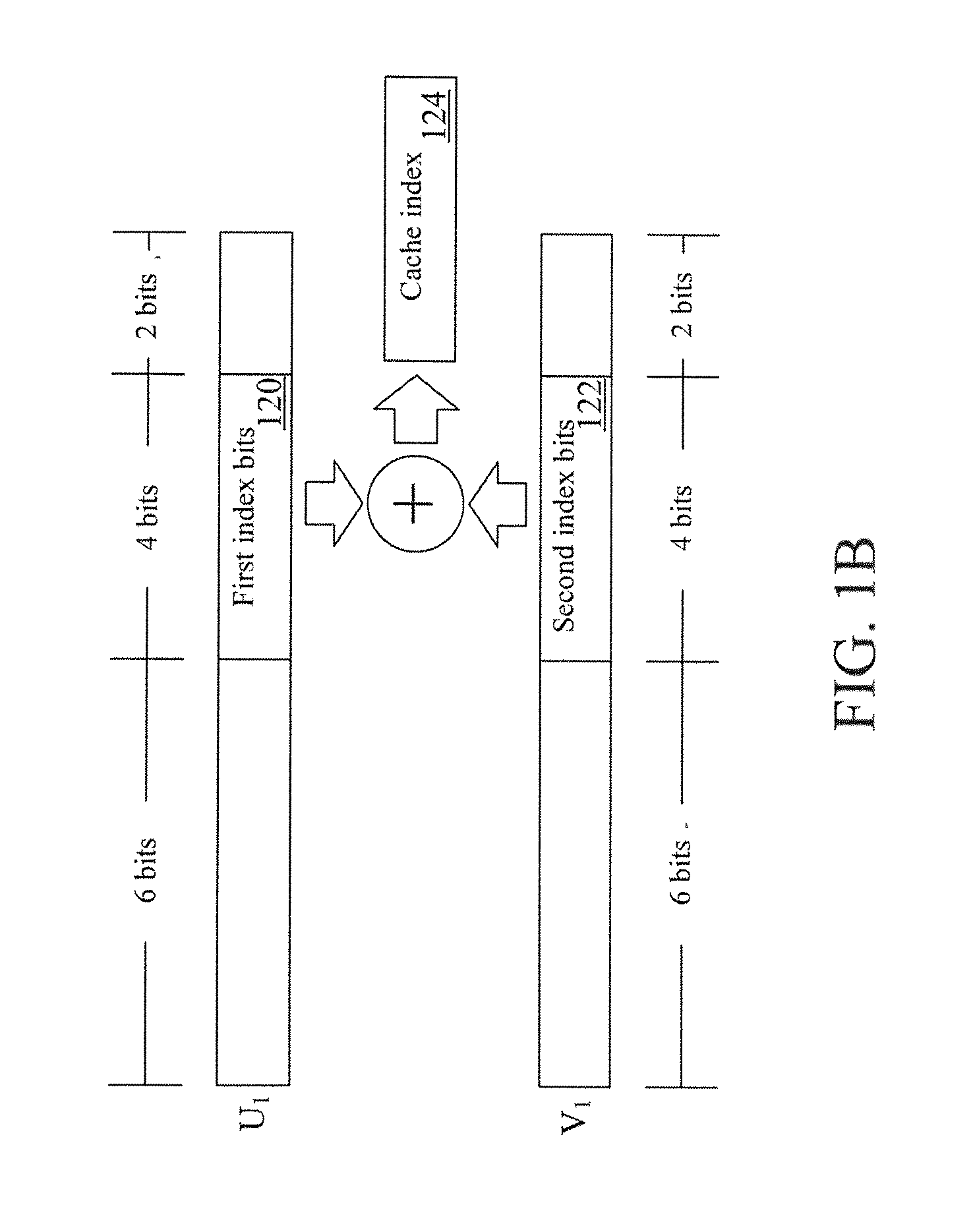

A graphic processing unit and a graphic data accessing method are provided. The graphic processing unit receives a graphic processing request instruction which comprises a first coordinate bits and a second coordinate bits of a under processing texel image, from the server processing unit. The graphic processing unit retrieves at least one first bit of the first coordination bits, retrieves at least one second bit of the second coordination bits, and derives a cache index from the at least one first bits and the at least one second bits via an arithmetic logic operation.

Owner:INSTITUTE FOR INFORMATION INDUSTRY

Method and equipment for encoding data

ActiveCN101203886AEasy to useGood image reconstructionImage coding3D-image renderingPattern recognitionData chunk

Owner:ARM NORWAY

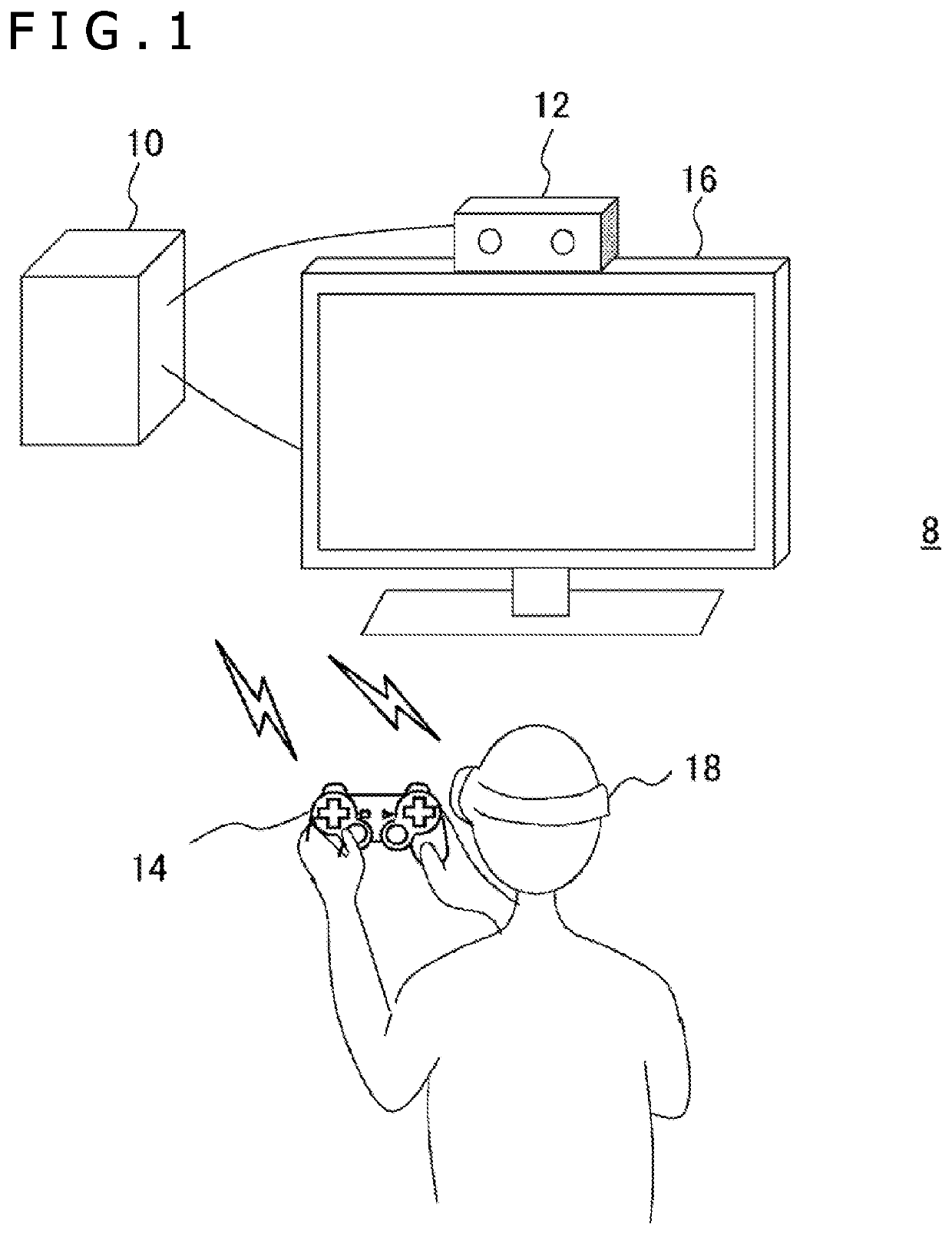

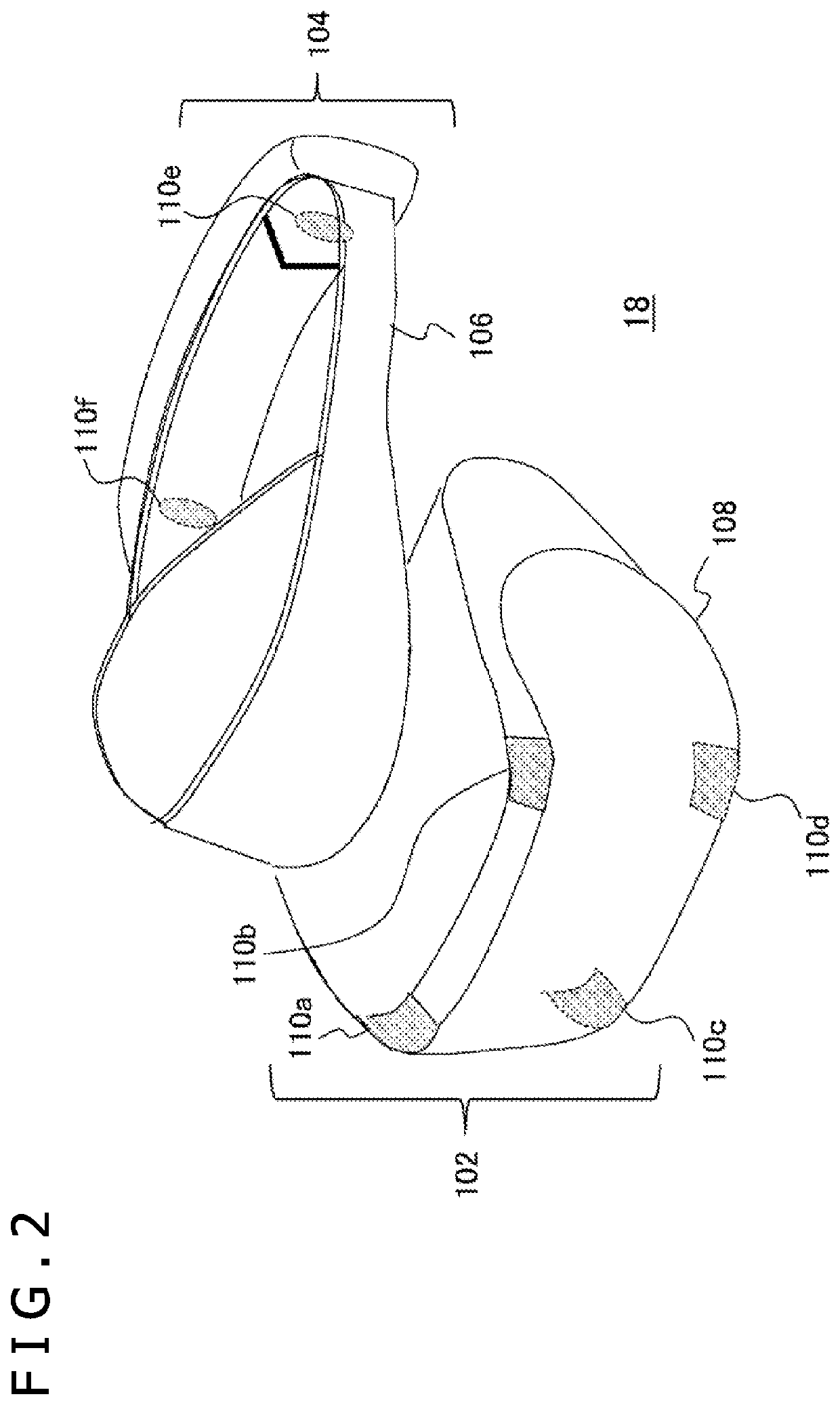

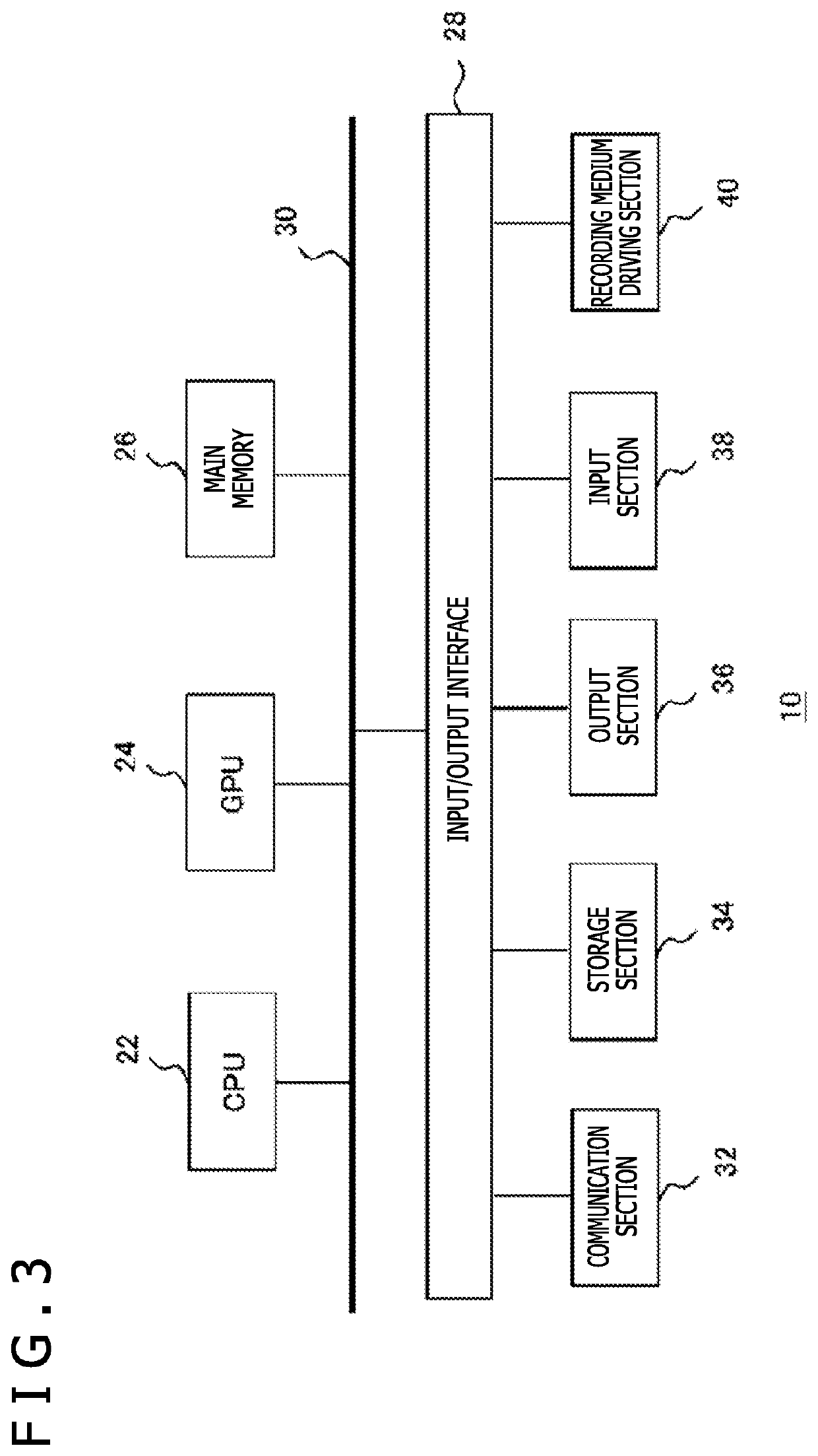

Image processing apparatus, information processing apparatus, and image processing method

ActiveUS10580192B2Input/output for user-computer interactionStatic indicating devicesPattern recognitionTarget surface

Regions 150 and 152 on a texture image plane 140 that correspond individually to pixels 146 and 148 representing an image on a texture image mapping target surface 144 in a screen plane 142 on which to define a display image are determined using predetermined transformation equations. The number of sampling points and their distribution are determined for the determined region in accordance with its shape and its size. Texel values in the determined region are then sampled. An average of the sampled values is acquired as the value of each of the original pixels 146 and 148.

Owner:SONY COMPUTER ENTERTAINMENT INC

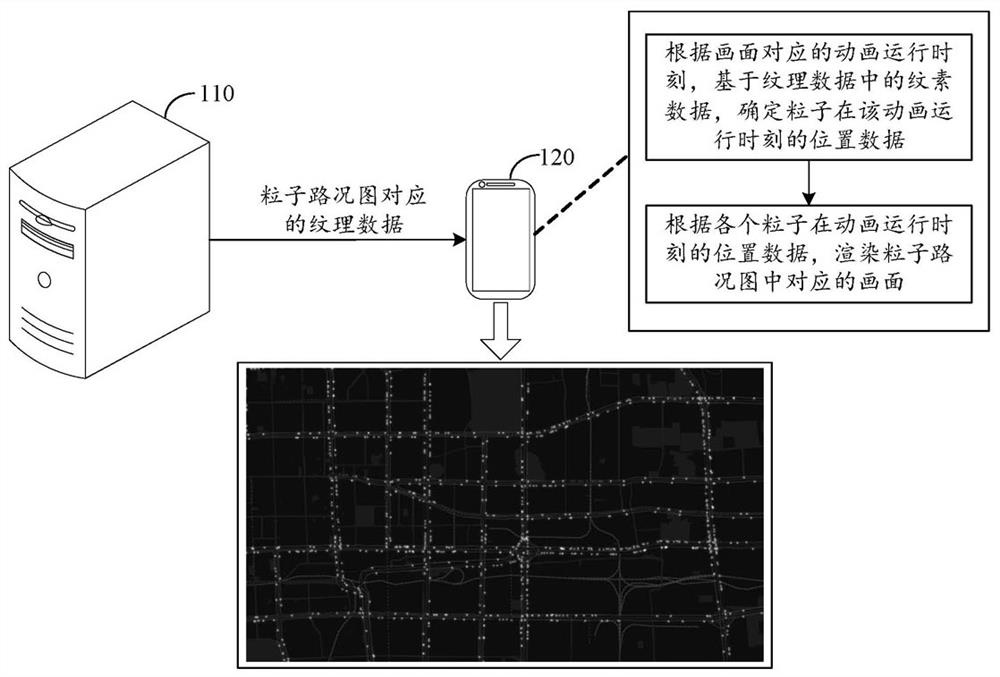

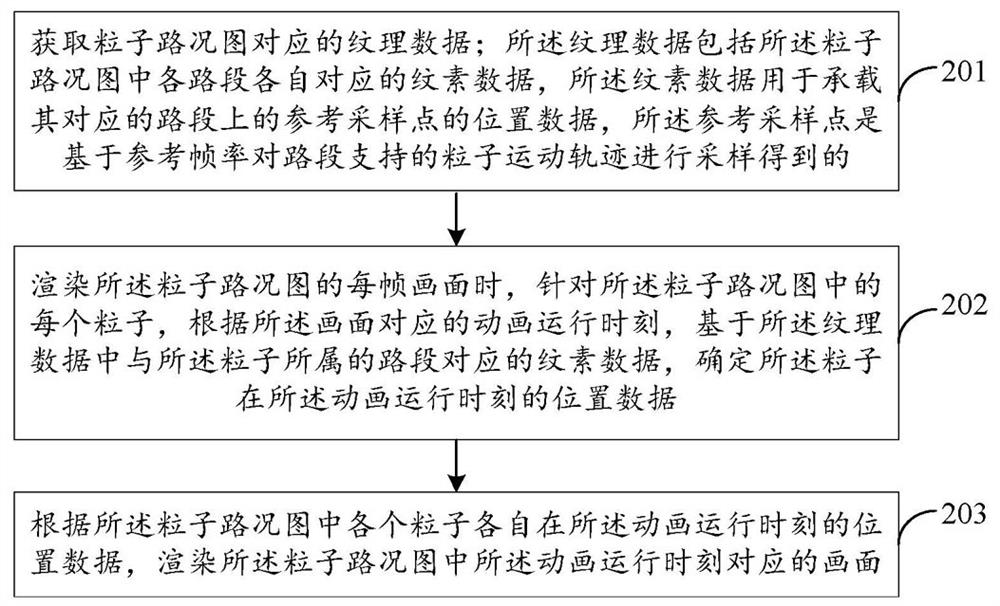

Image rendering method and related device

ActiveCN113658296AReduce expensive computational overheadReduce computational overheadImage analysisDrawing from basic elementsAnimationEngineering

The embodiment of the invention discloses an image rendering method and a related device, and the method comprises the steps: obtaining texture data corresponding to a particle road condition map, wherein the texture data comprises texel data corresponding to each road segment in the particle road condition map, the texel data is used for bearing the position data of a reference sampling point on the corresponding road segment, and the reference sampling point is obtained by sampling a particle motion track supported by a road section based on a reference frame rate; when each frame of picture of the particle road condition graph is rendered, aiming at each particle in the particle road condition graph, determining position data of the particle at an animation operation moment according to the animation operation moment corresponding to the picture and based on texel data corresponding to a road section to which the particle belongs in the texture data; and rendering the frame of picture in the particle road condition graph according to the position data of each particle in the particle road condition graph at the animation operation moment. The embodiment of the invention can be applied to the map field and the traffic field, the CPU calculation overhead can be reduced, and the rendering efficiency of the particle road condition graph is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Computer graphics rendering apparatus and method

A computer graphics rendering apparatus according to an embodiment of the present invention generates a screen image, using plural texture images having different mipmap levels. The apparatus generates a normalized texture coordinate of a texture image, generates, from the normalized texture coordinate of the texture image, a texel coordinate of a texel in the texture image, according to a mipmap level of the texture image, and generates, regarding an image block in the texture image, an index value indicating a cache line corresponding to the image block, using a texel coordinate of a texel in the image block. The apparatus generates the index value such that index values of image blocks in the same position are different, between two texture images having mipmap levels adjacent to each other.

Owner:KK TOSHIBA