Cache architecture for efficiently accessing texture data using buffers

A technology for caching and texture data, applied in memory systems, electrical digital data processing, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

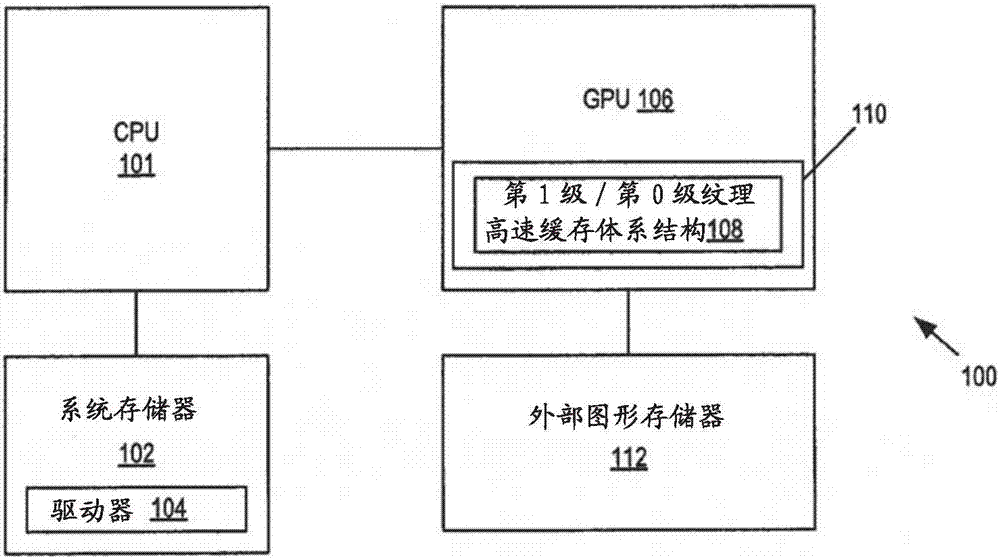

[0020] Figure 1A is a block diagram illustrating a graphics system 100 according to an embodiment. In one embodiment, texture cache unit 110 is part of graphics processing unit (GPU) 106 . In one embodiment, the texture cache unit 110 includes a texture cache architecture, described below with respect to Figure 1B Describe it in more detail.

[0021] In one embodiment, GPU 106 may include graphics hardware and implement a graphics pipeline including, for example, one or more shader cores. External graphics memory 112 may be provided to store additional texture data. In one embodiment, central processing unit (CPU) 101 and associated system memory 102 may include computer program instructions for driver software 104 . The bus may be used to communicatively couple CPU 101 to GPU 106 , system memory 102 to CPU 100 , and GPU 106 to external graphics memory 112 .

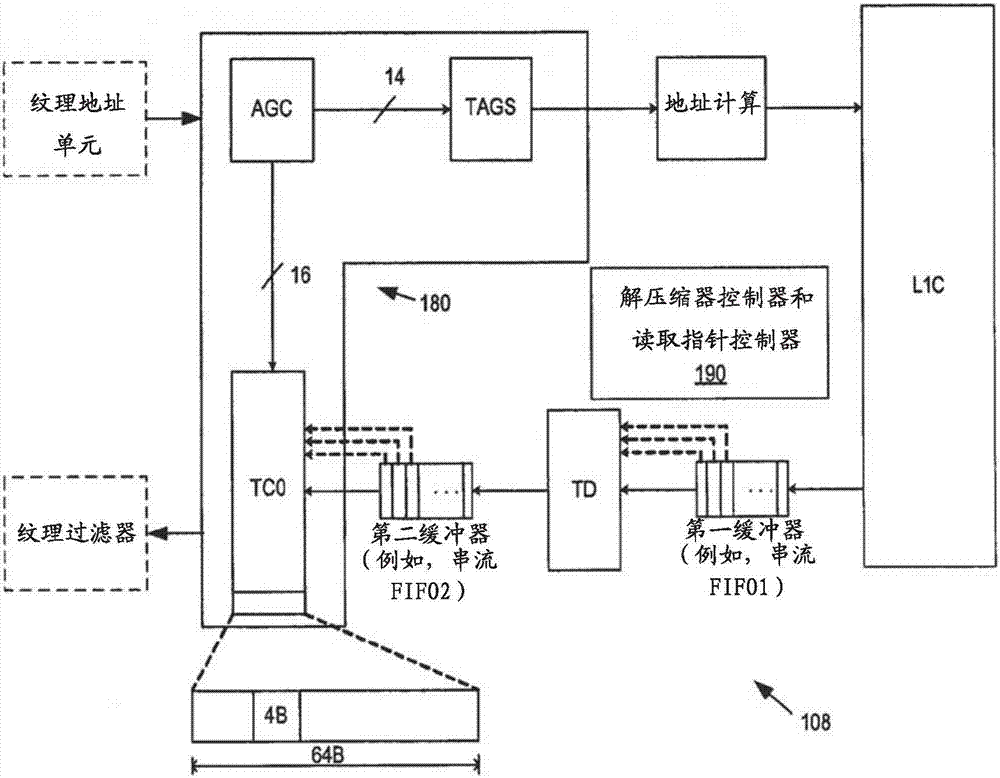

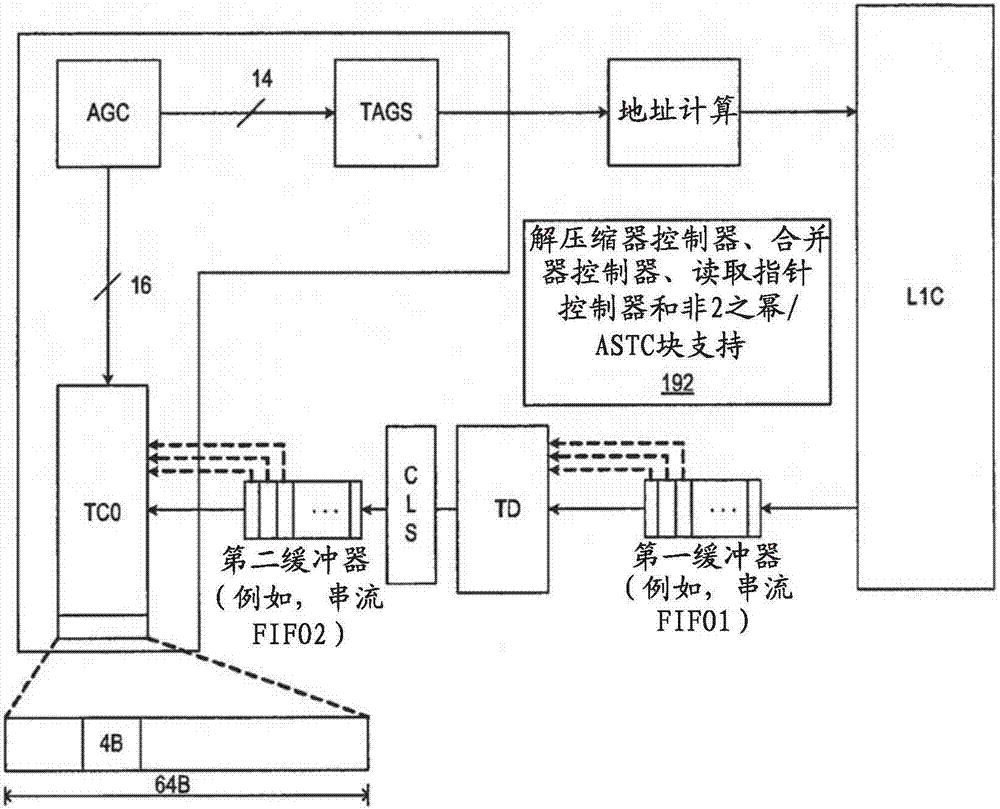

[0022] Figure 1B An embodiment of the texture cache architecture 108 is illustrated in more detail. A level 0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More