Apparatus and method for cache memory connection of texture mapping

a cache memory and texture mapping technology, applied in the field of cache memory connection apparatus and method, can solve the problems of large area occupied by prior single cache memory, slow texture mapping speed, and large area occupied by cache memory 12

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

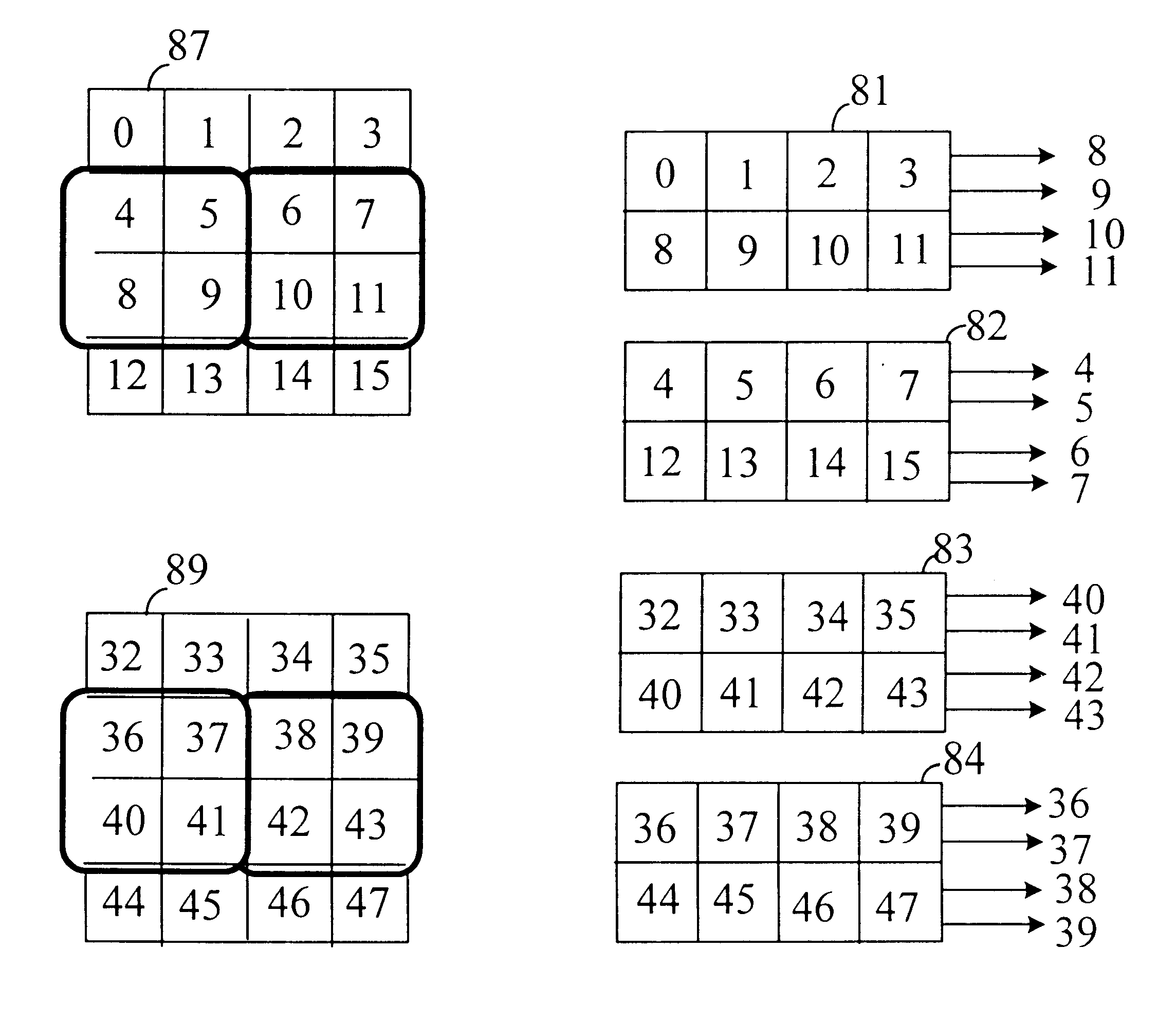

FIG. 2 is a schematic diagram of cache memories which implement a mapping method through a single pixel and single texture according to the first preferred embodiment of the present invention. The schematic diagram divides the prior single cache memory into four smaller cache memories with one fourth memory size of prior single cache memory and one fourth number of data ports of prior single cache memory, and the four smaller cache memories are named as a first cache memory 21, a second cache memory 22, a third cache memory 23 and a fourth memory 24. The input end is addresses 0 to 7, wherein address 0 is the address line of the first texel, by the same rule, address 7 is the address line of the eighth texel because one pixel is corresponding to eight texels at most in the major mapping methods of selecting the nearest point, bilinear filtering and trilinear filtering. There is a first multiplexer 25 between the third cache memory 23 and the input address end a second multiplexer 26...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More