Multi-core processor meeting SystemC grammar request and method for acquiring performing code

A multi-core processor and code execution technology, applied in the field of multi-core processors, can solve problems such as immature parallel languages and achieve the effect of reducing the difficulty of development

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

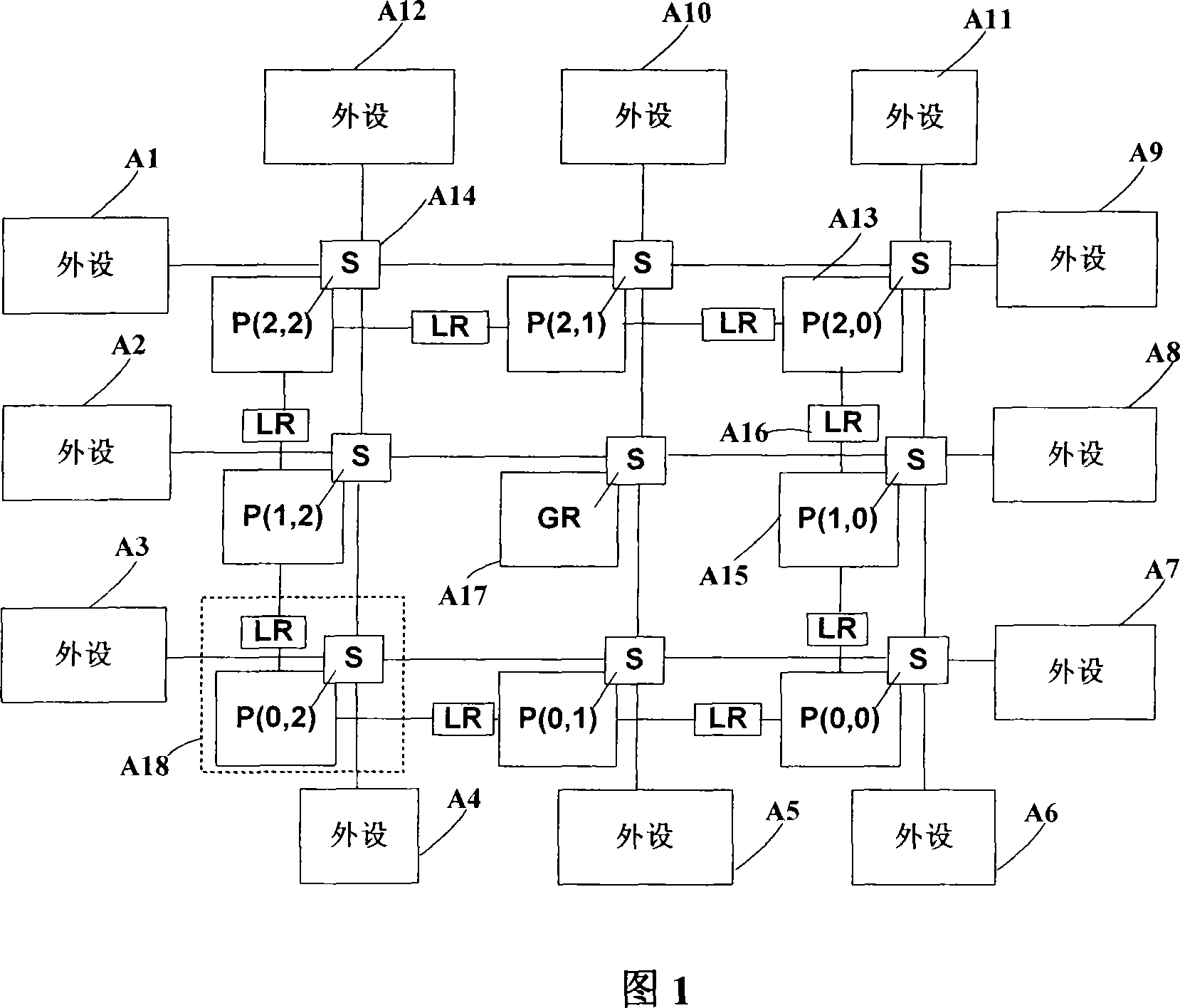

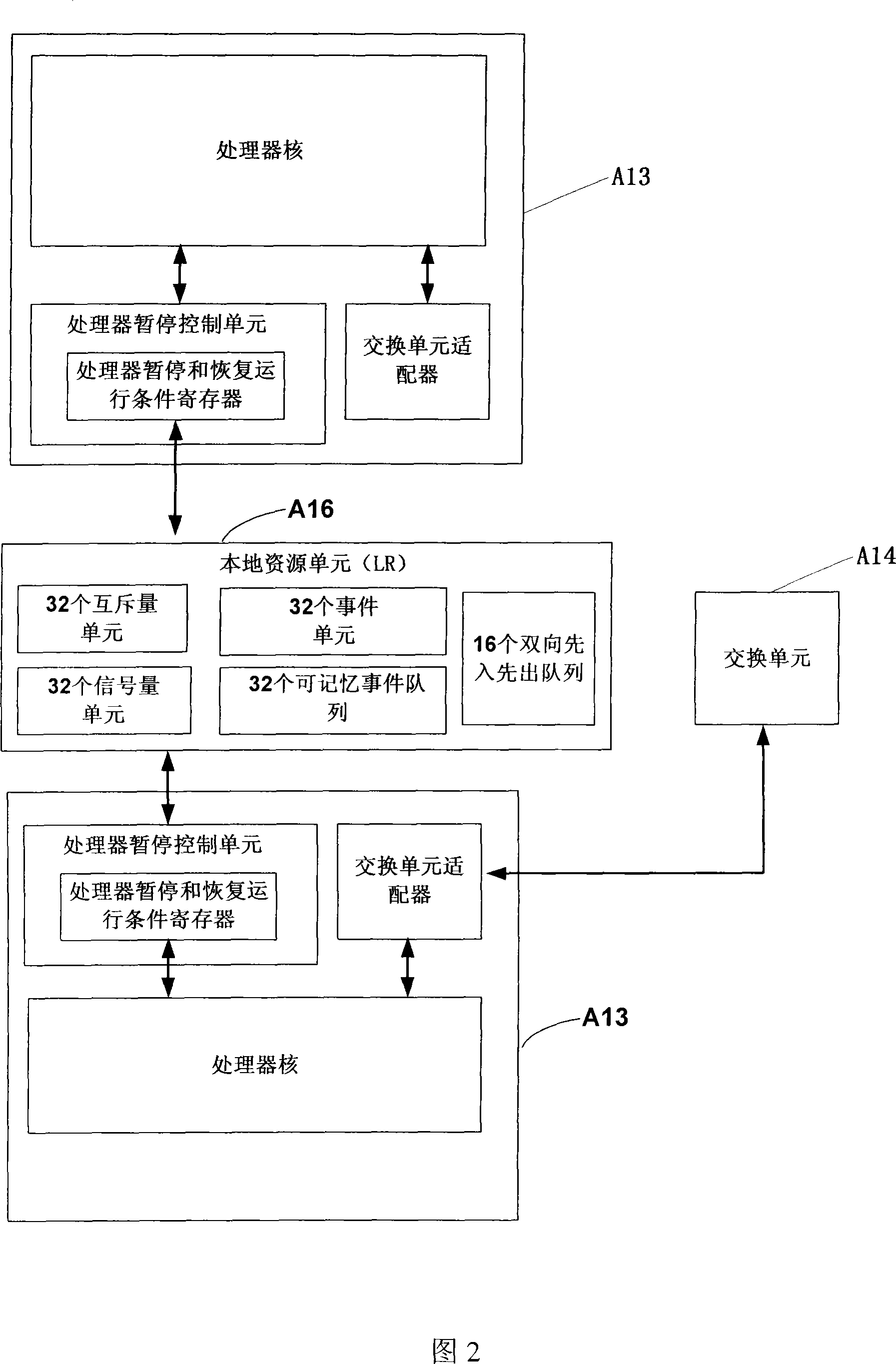

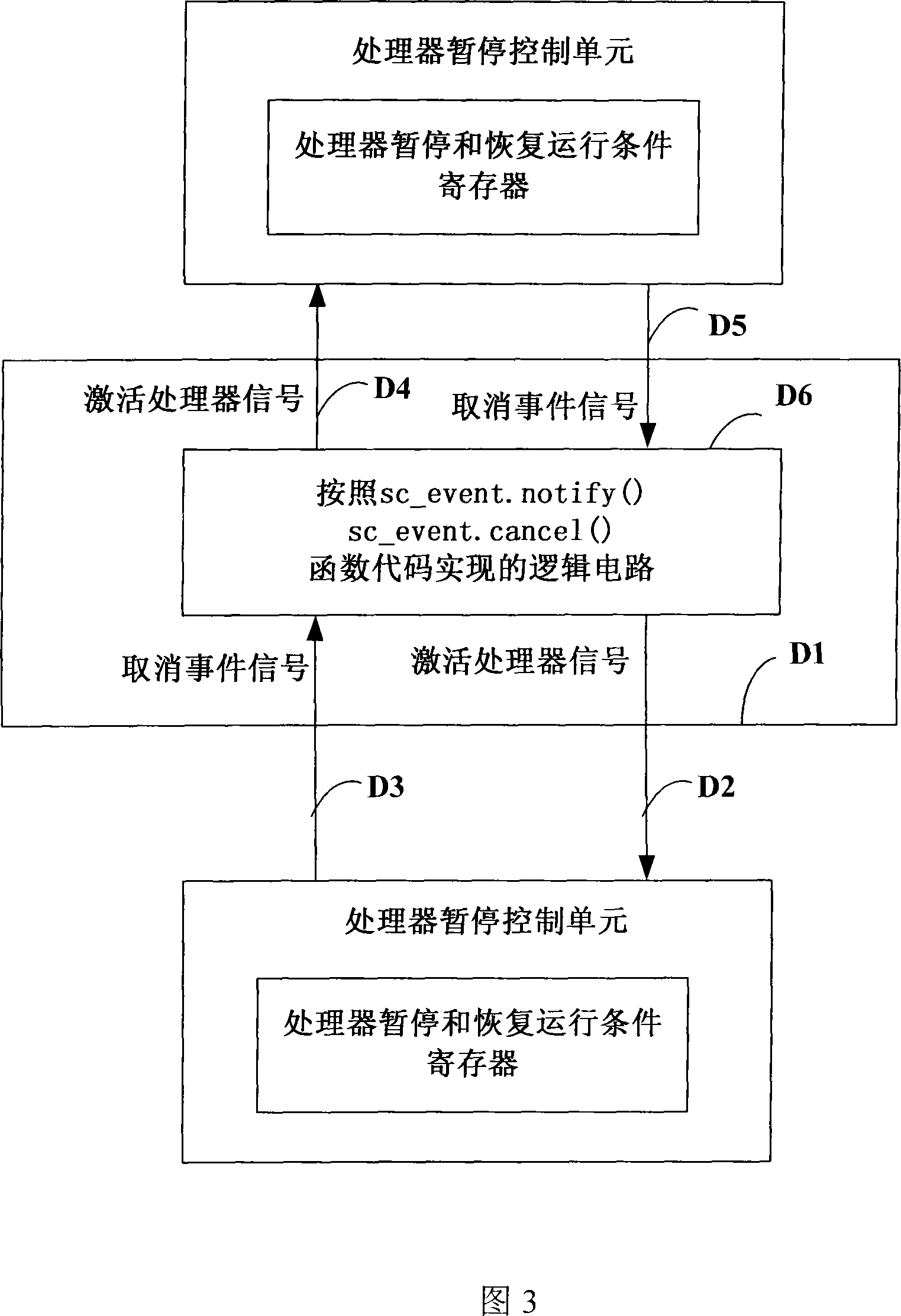

[0050] As shown in Figure 1, the multi-core processor that meets the SystemC syntax requirement of the present invention includes: a plurality of exchange units A14 connected to form an array for exchanging data, a plurality of processing units A13 for data processing and the exchange unit A14 Connection; also includes: a local resource unit A16 connected between adjacent processing units A13 for synchronization and data sharing between adjacent processing units, and at least one connected to the switching unit A14 for all processing units Global resource unit A17 for synchronization and data sharing.

[0051] As an implementable manner, in the multi-core processor shown in FIG. 1, the eight processing units P(0,0), P(0,1), P(0,2), P(1,0) , P(1,2), P(2,0), P(2,1) and P(2,2) communicate through the two-dimensional network formed by the switching unit A14, not all The components are all processors, of which A17 is a global resource unit. A16 is a local resource unit connected ...

Embodiment 2

[0085] The difference between this implementation and Example 1 is that: the local resource unit A16 includes a plurality of components that meet the syntax requirements of SystemC, and as an implementable manner, specifically includes: 1 instantaneous event (sc_event) unit, 1 memorable event queue (sc_event_queue), 1 mutex (sc_mutex) unit, 1 semaphore (sc_semaphore) unit, and 1 bidirectional input and output queue (sc_fifo); the global resource unit A17 includes a plurality of parts that meet the syntax requirements of SystemC, as An implementable manner specifically includes: 1 transient event (sc_event) unit, 1 memorable event queue (sc_event_queue), 1 mutex (sc_mutex) unit, 1 semaphore (sc_semaphore) unit, and 1 A bidirectional input and output queue (sc_fifo).

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More