Simulation apparatus and simulation method

A technology of simulation equipment and simulation methods, applied in software simulation/interpretation/simulation, binary to binary, program code conversion, etc., can solve problems such as slow processing speed, and achieve the effect of high-speed simulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

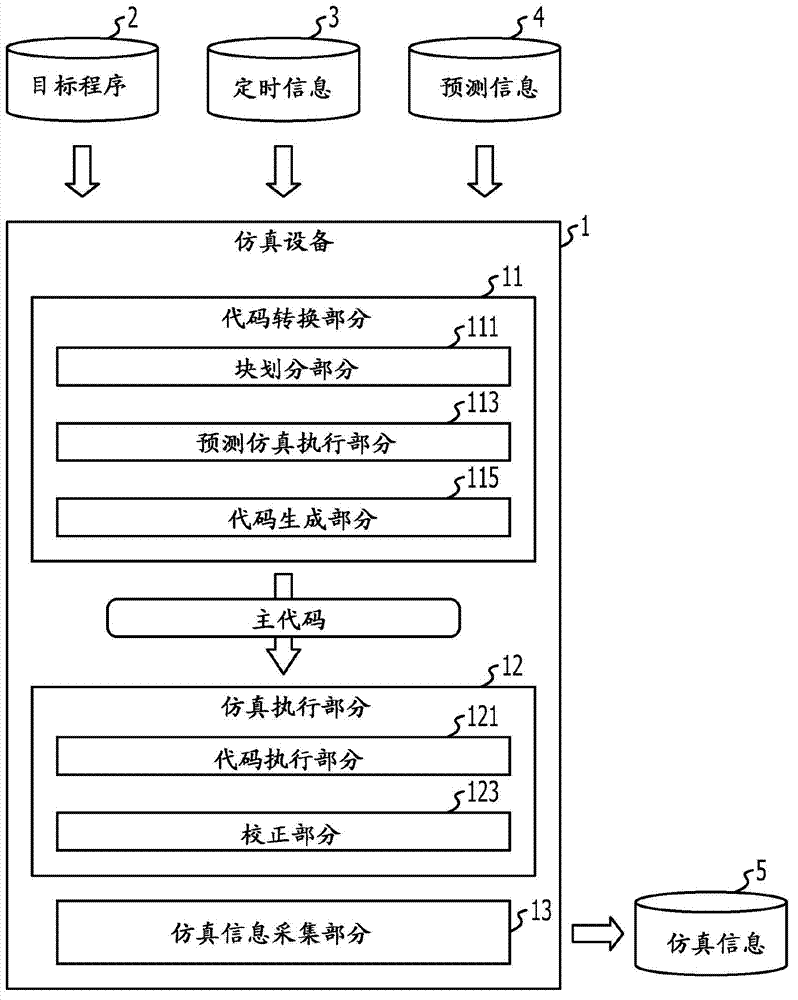

[0033] figure 1 The diagram illustrates an exemplary simulated device.

[0034] The emulation device 1 can perform performance emulation of instruction execution of a target CPU that controls pipeline processing.

[0035] The target CPU may be the control model of the CPU to be simulated. The simulation device 1 outputs cycle simulation information of each instruction as a result of performance simulation of instruction execution of the target CPU.

[0036] For example, the target CPU may be an ARM architecture CPU. For example, the simulation device 1 corresponding to the main CPU may be a computer installed with an X86 architecture CPU.

[0037] The simulation device 1 includes a code conversion part 11 , a simulation execution part 12 and a simulation information collection part 13 .

[0038] When the program of the target CPU is executed, the code conversion section 11 generates code (eg, host code) of the host CPU that executes the simulation from the program code (eg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More