Method, System, Computer Program Product, and Data Processing Program for Verification of Logic Circuit Designs Using Dynamic Clock Gating

a logic circuit and clock gating technology, applied in cad circuit design, program control, instruments, etc., can solve the problems of serious performance degradation, art functional verification methods cannot verify the design goal, and dynamic clock gating adds additional complexity to logic circuit design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

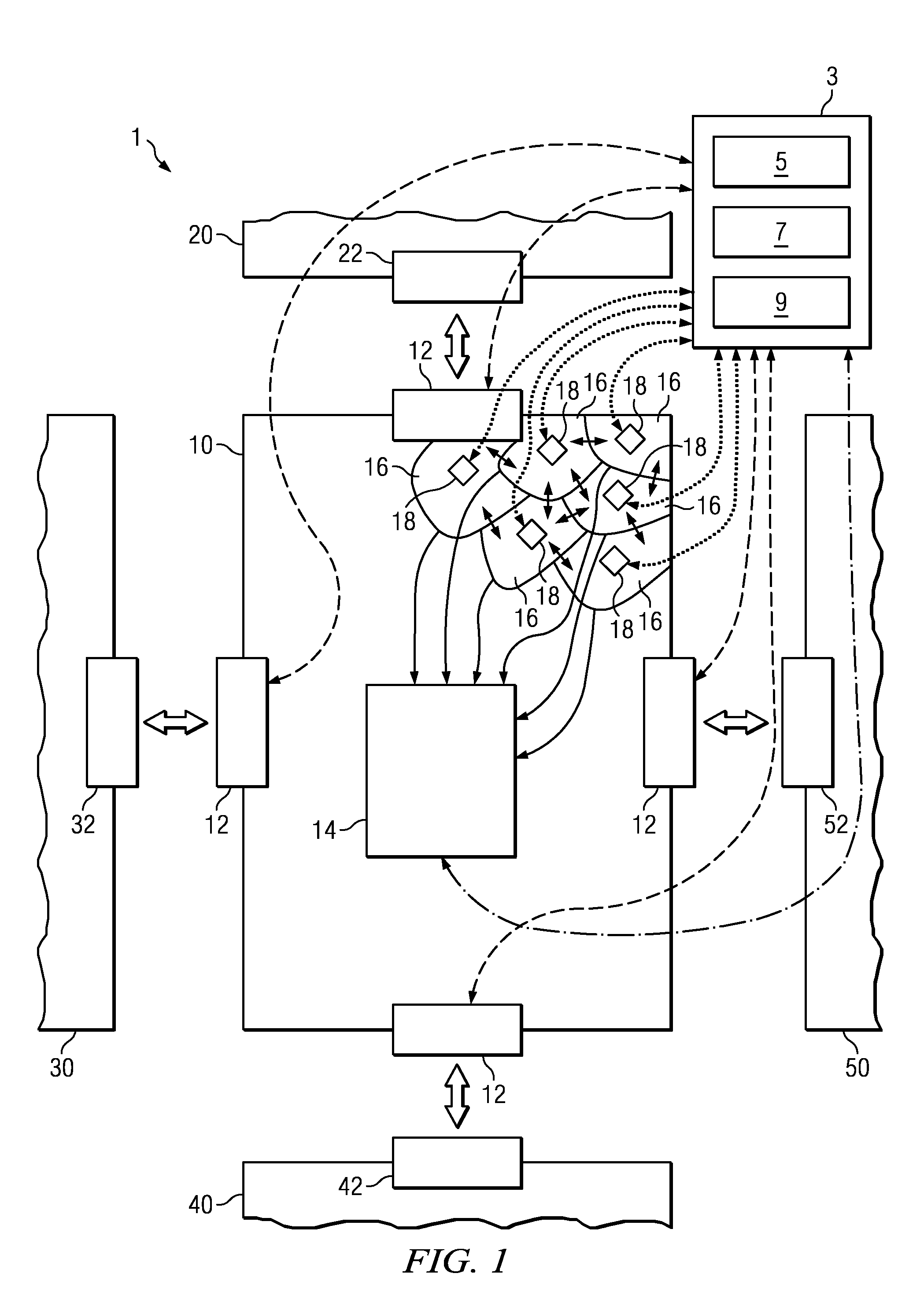

[0037]Referring to FIG. 1, the shown embodiment of the invention employs a system 1 for verifying a logic circuit design using dynamic clock gating, wherein the logic circuit design comprise processors, cores, units, macros and / or sub macros for example.

[0038]Referring to FIG. 1, the shown embodiment of the invention employs a system 1 for verifying a logic circuit design comprising a multiple of logic circuits 10, 20, 30, 40, 50 and a verification environment 3, whereas just the logic circuit 10 is shown in more detail for the purpose of clearness and a better understanding of the present invention. In the following detailed description, the invention is especially explained with regard to the logic circuit 10. According to the invention, the verification environment 3 chooses at least one master seed to determine initial values as initialization for the logic circuits 10, 20, 30, 40, 50 and / or stimuli data for at least one interface 12, 22, 32, 43, 52 of the logic circuits 10, 20,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More