Statistics static state sequential analysis method applied to near/sub threshold digital circuit

A technology of static timing analysis and digital circuits, applied in electrical digital data processing, special data processing applications, calculations, etc., can solve problems such as inconsistency, deterioration of near/subthreshold circuit stability, and infeasibility of large-scale digital circuits , to achieve significant advantages and improve timing reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the purpose, technical solutions and advantages of the present invention clearer, the following is based on SMIC130nm CMOS process to analyze the 8bit, 4th order FIR timing reliability of the near / subthreshold test circuit. This is a specific example and reference The accompanying drawings illustrate the present invention in further detail.

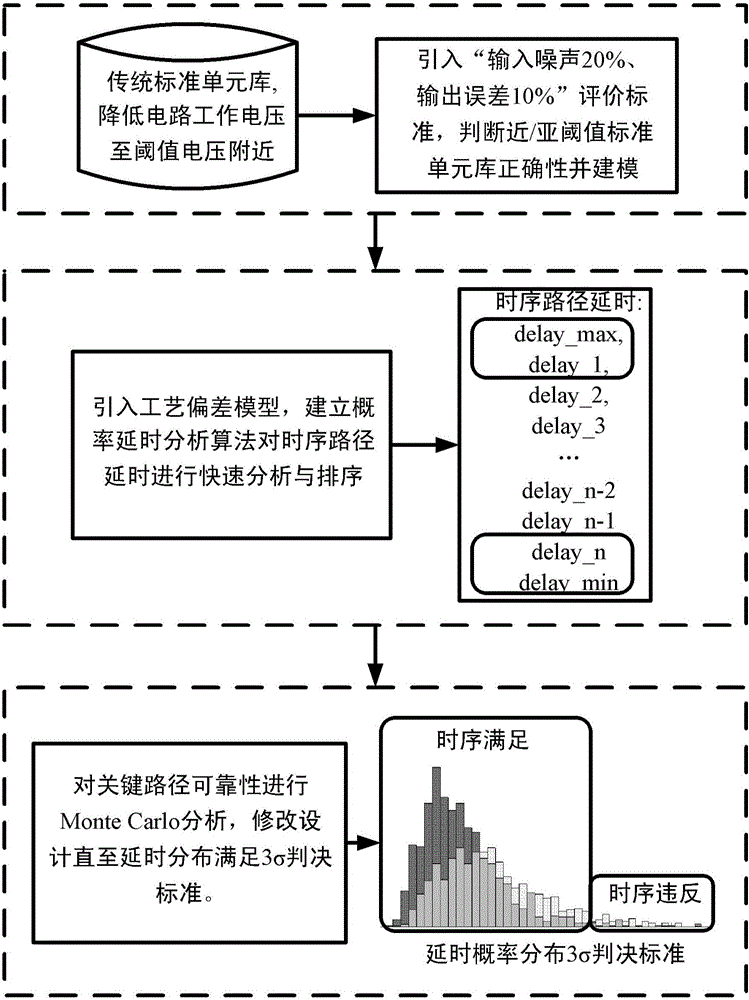

[0040] figure 1 It is a statistical static timing analysis method and flow of a near / sub-threshold digital circuit according to an embodiment of the present invention, which mainly includes the following steps:

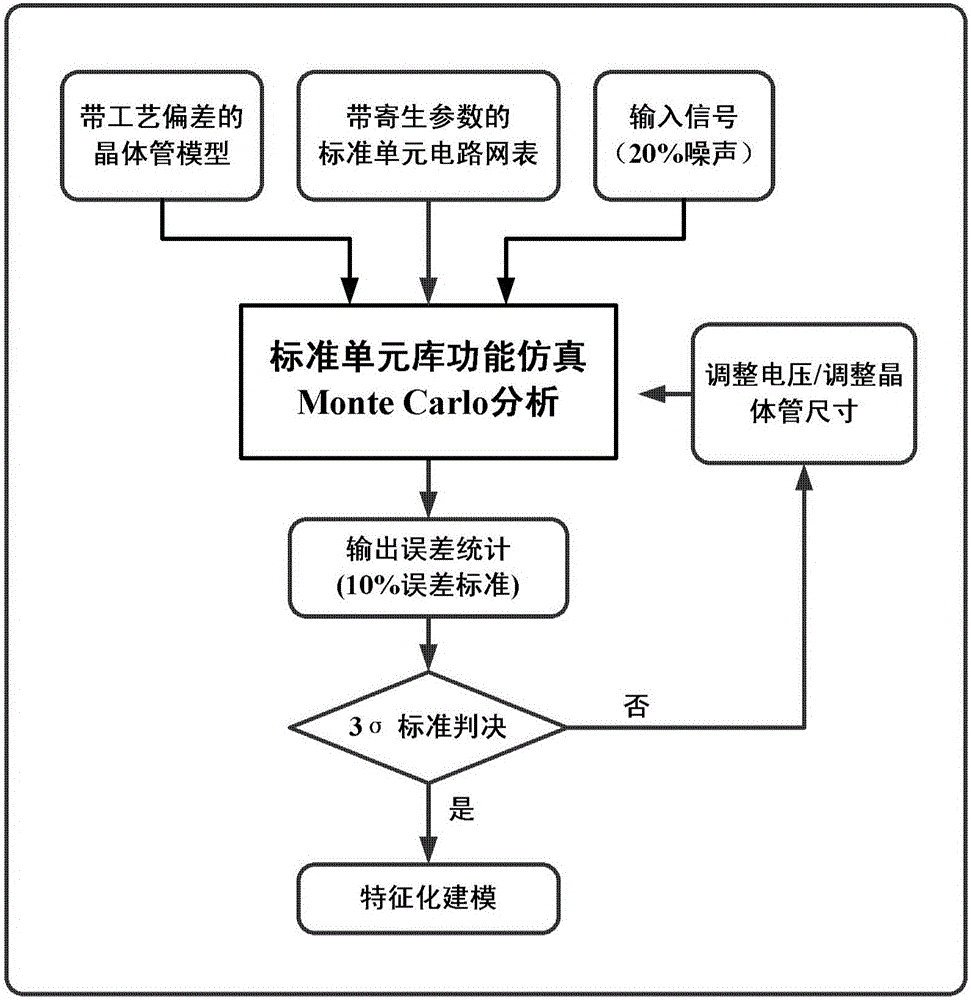

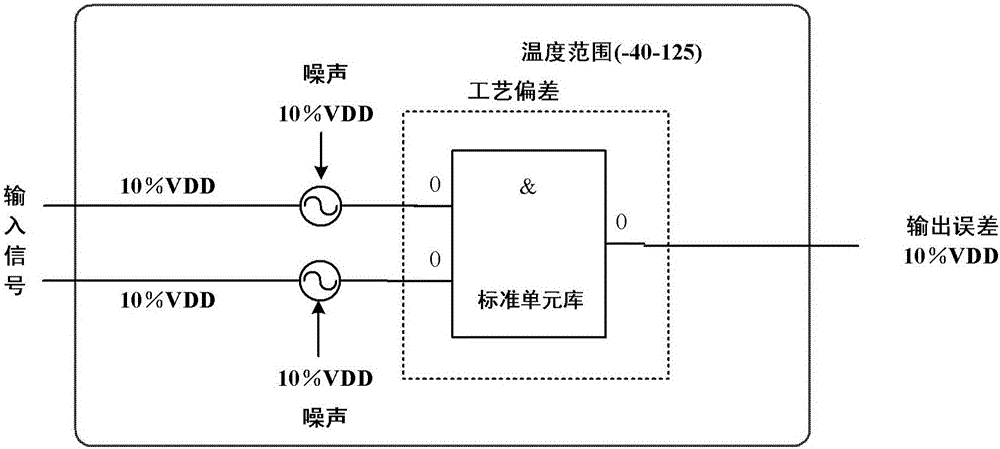

[0041] Step 1: Reduce the operating voltage of the standard cell library to near the threshold voltage, perform functional simulation and characterization modeling of the near / sub-threshold standard cell library, and provide an accurate delay model for subsequent sequence reliability analysis at the standard cell library level ;

[0042] Step 2: Use probabilistic delay analysis algorithm to quickly analyze and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More