Patents

Literature

286 results about "Peripheral bus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

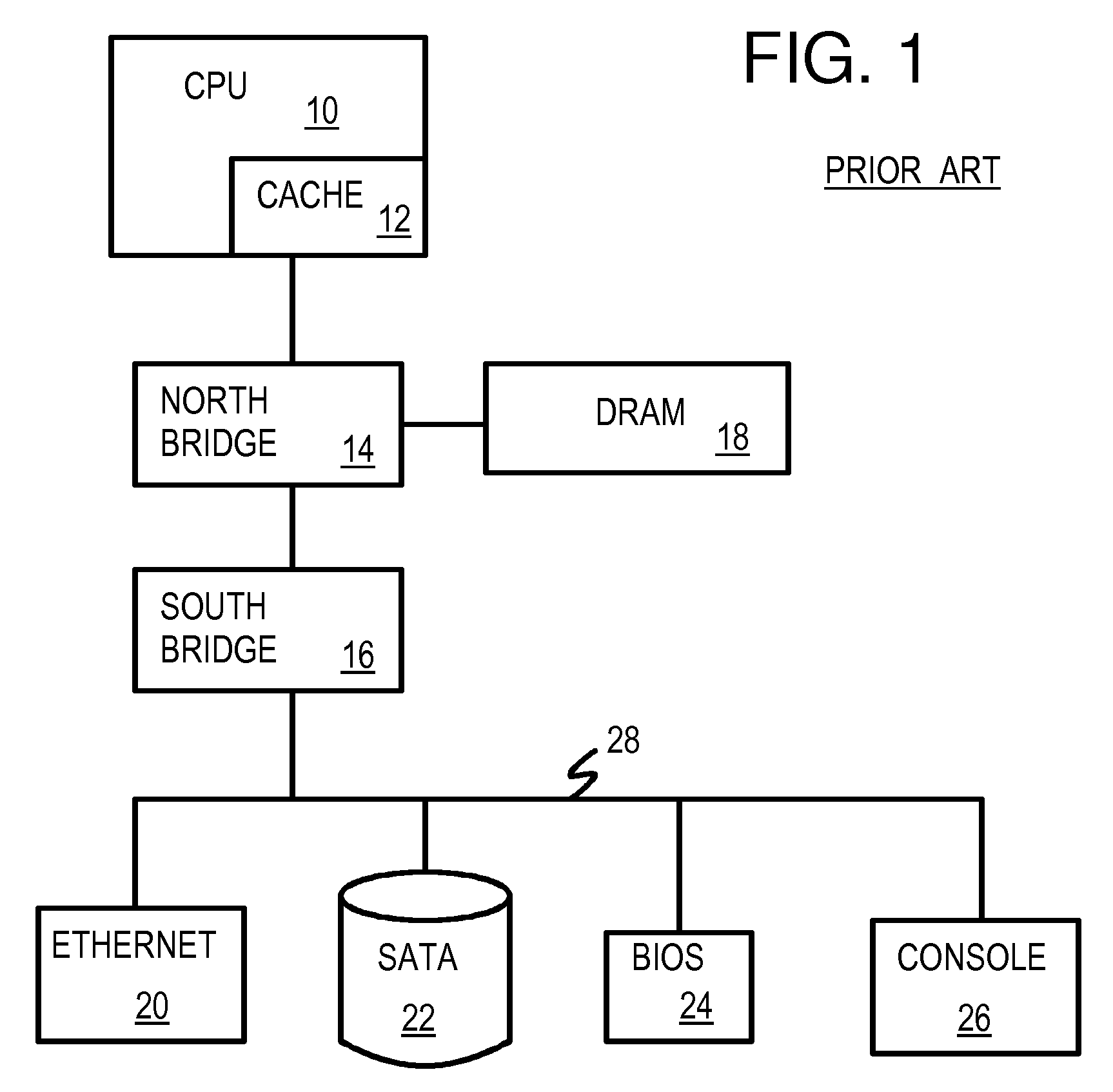

In computing, a peripheral bus is a computer bus designed to support computer peripherals like printers and hard drives. The term is generally used to refer to systems that offer support for a wide variety of devices, like Universal Serial Bus, as opposed to those that are dedicated to specific types of hardware. Serial AT Attachment, or SATA is designed and optimized for communication with mass storage devices.

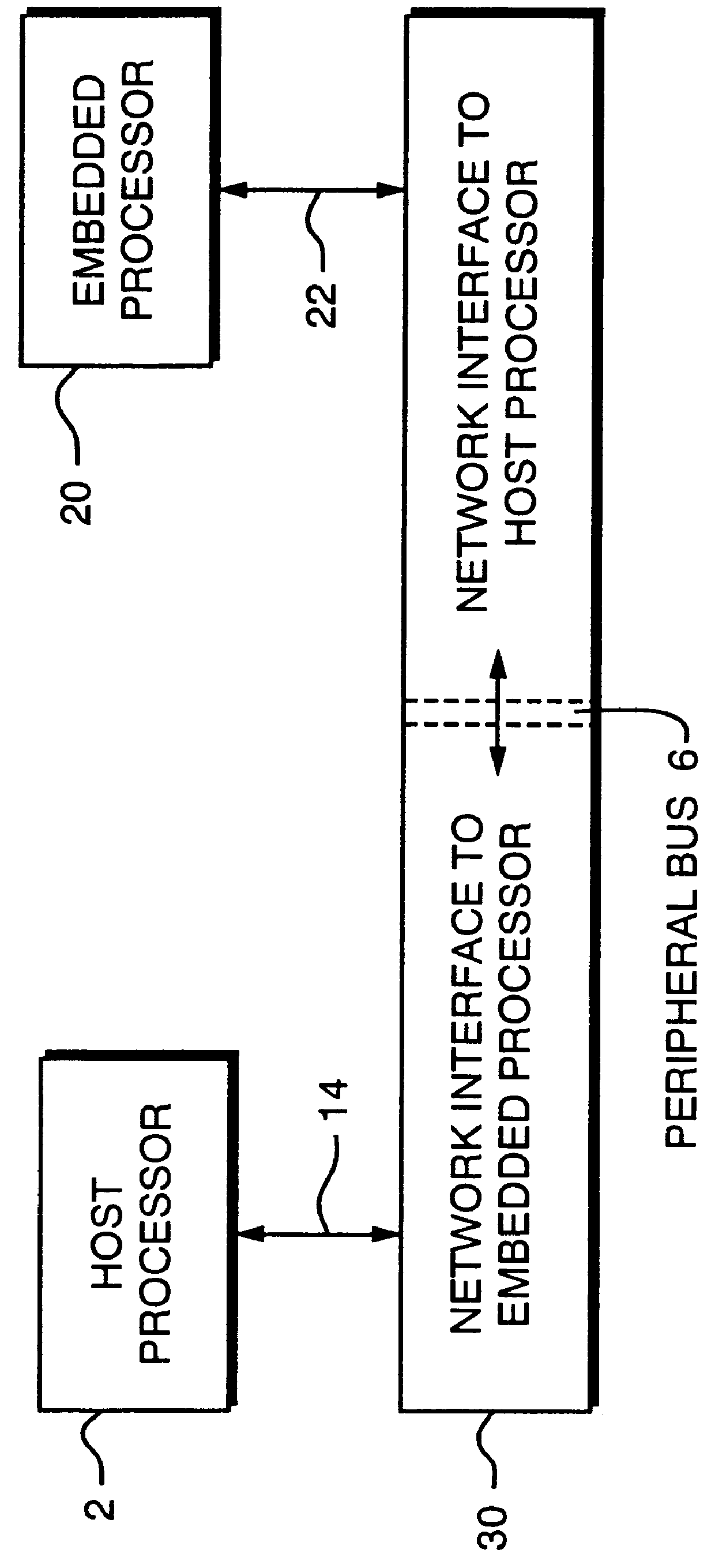

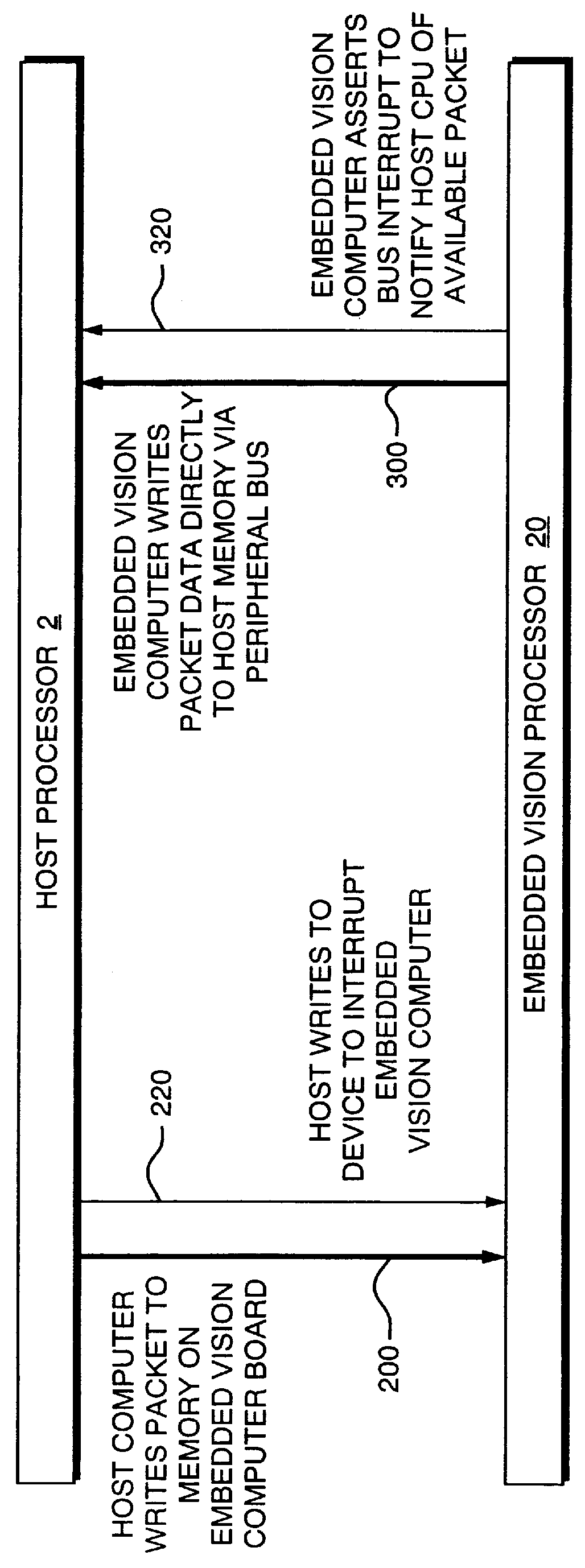

Apparent network interface for and between embedded and host processors

InactiveUS6058434ASignificant comprehensive benefitsMultiple digital computer combinationsElectric digital data processingPerformance enhancementWeb service

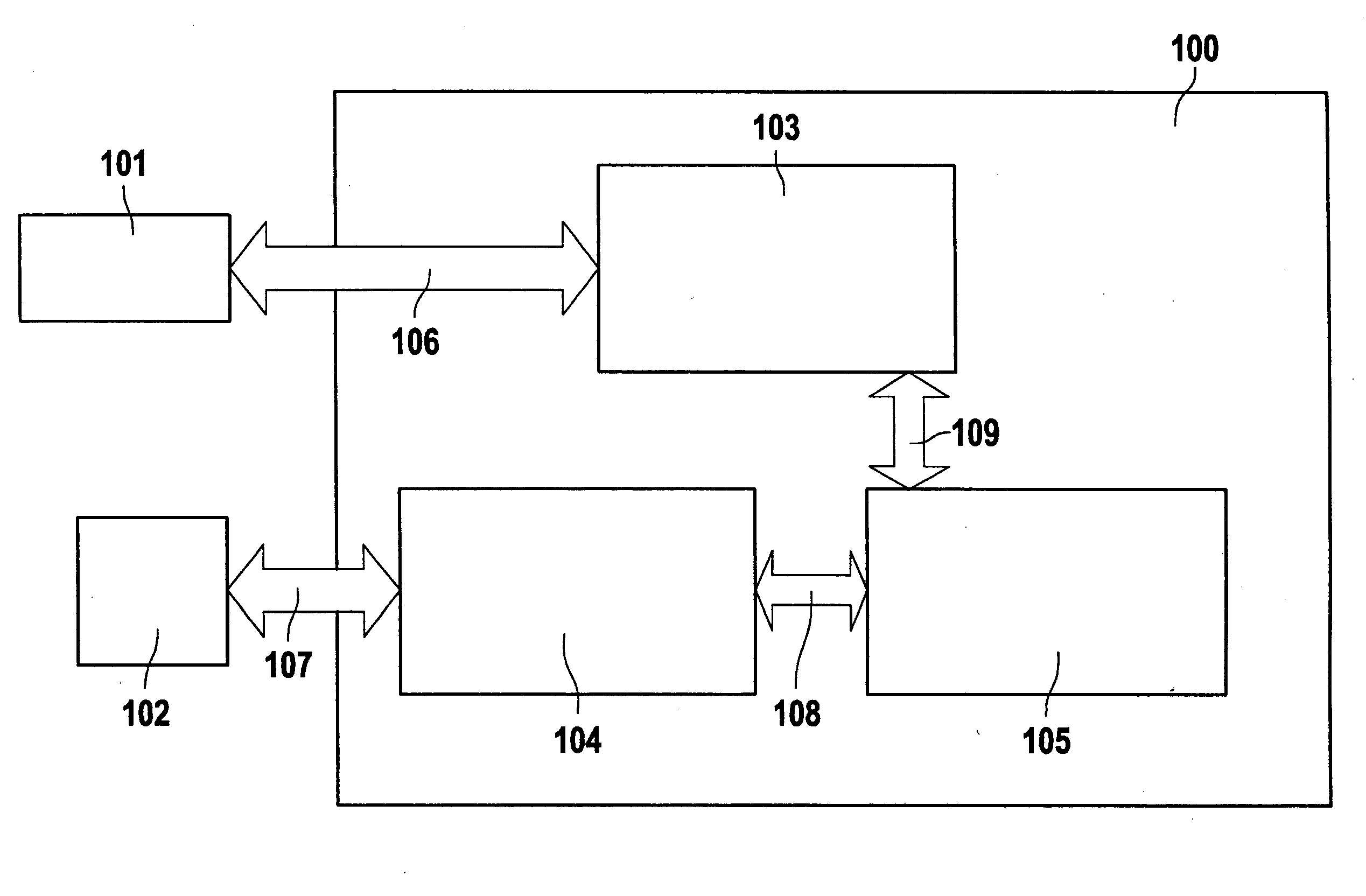

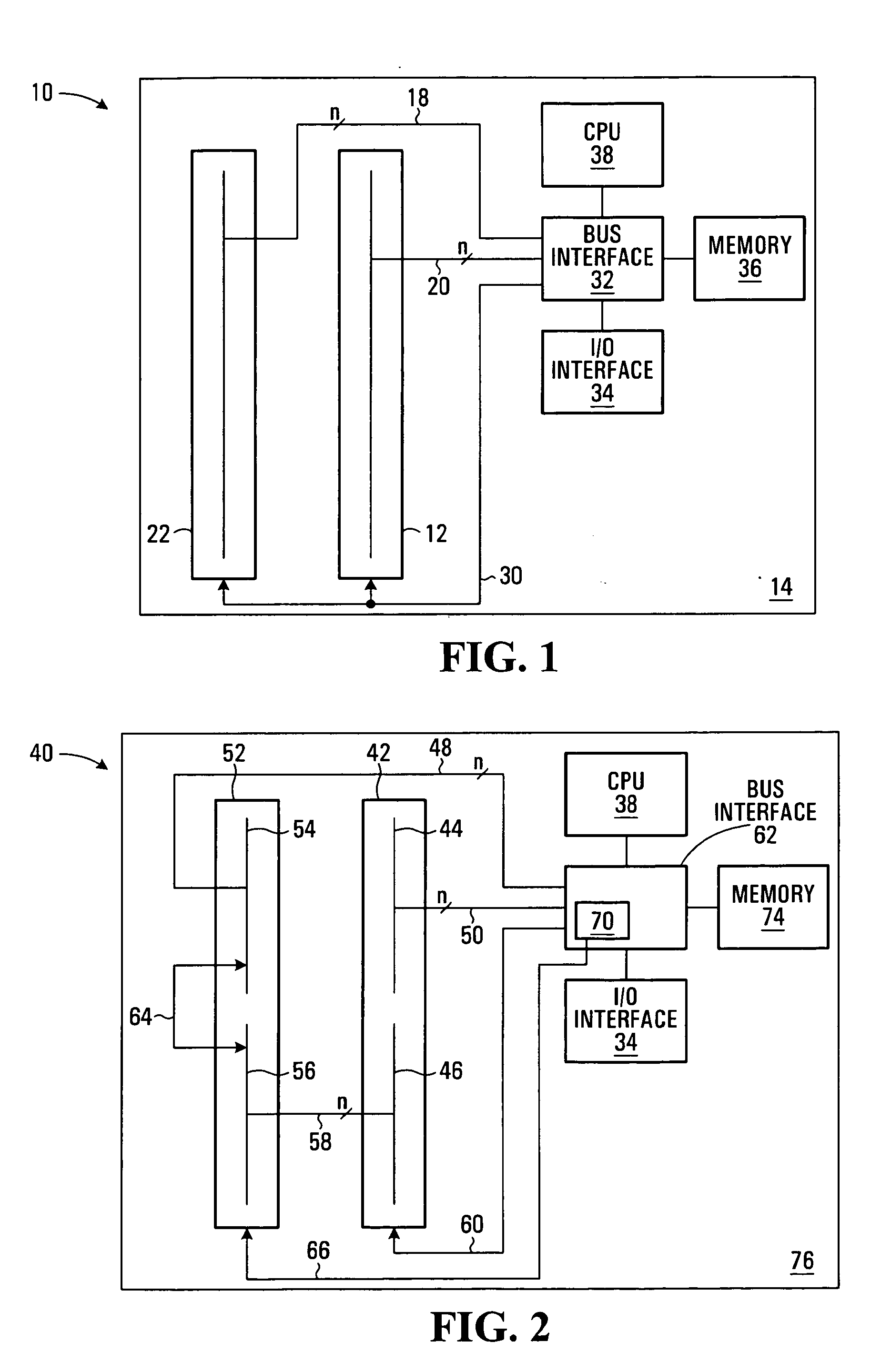

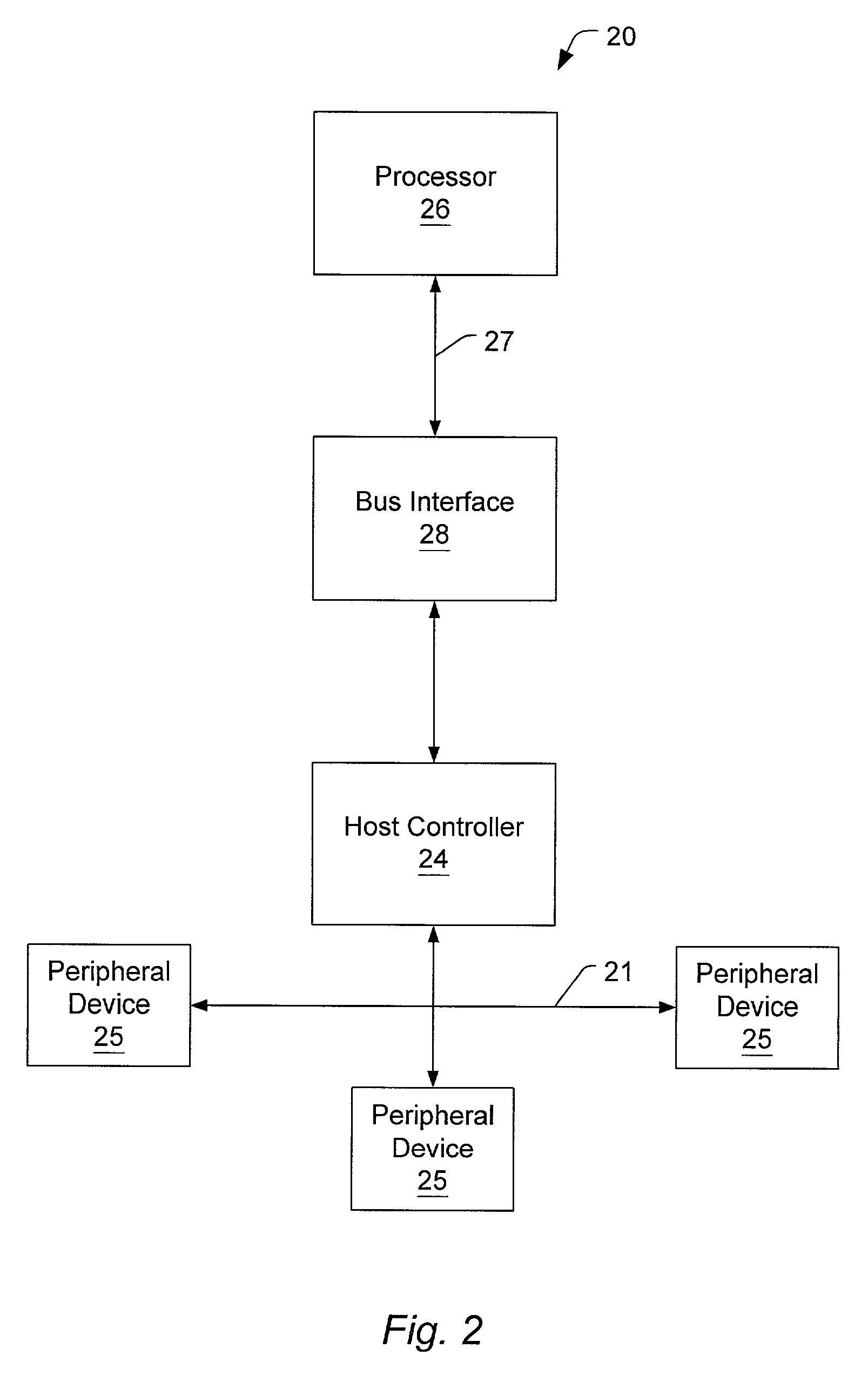

An apparent network interface permits one processor such as a processor embedded within a larger processing system (an embedded processor) to communicate to a host processor or other processors and devices on the network to which the embedded processor is attached, using standard network communication mechanisms / protocols such as TCP / IP, NFS, FTP, HTTP, etc. The web server protocol HTTP is particularly useful because it permits the embedded computer to publish a user interface for remote monitoring and remote control using a standard web browser application. The invention provides the host computer with an apparent network interface that appears to be a standard network device, such as an Ethernet interface card. This apparent interface communicates directly with the embedded processor, which appears to be a device on this apparent network. Significant cost savings and performance enhancements are realized by implementing the communication directly over the host computer's peripheral bus rather than using standard network hardware such as Ethernet hardware.

Owner:MICROSCAN SYSTEMS

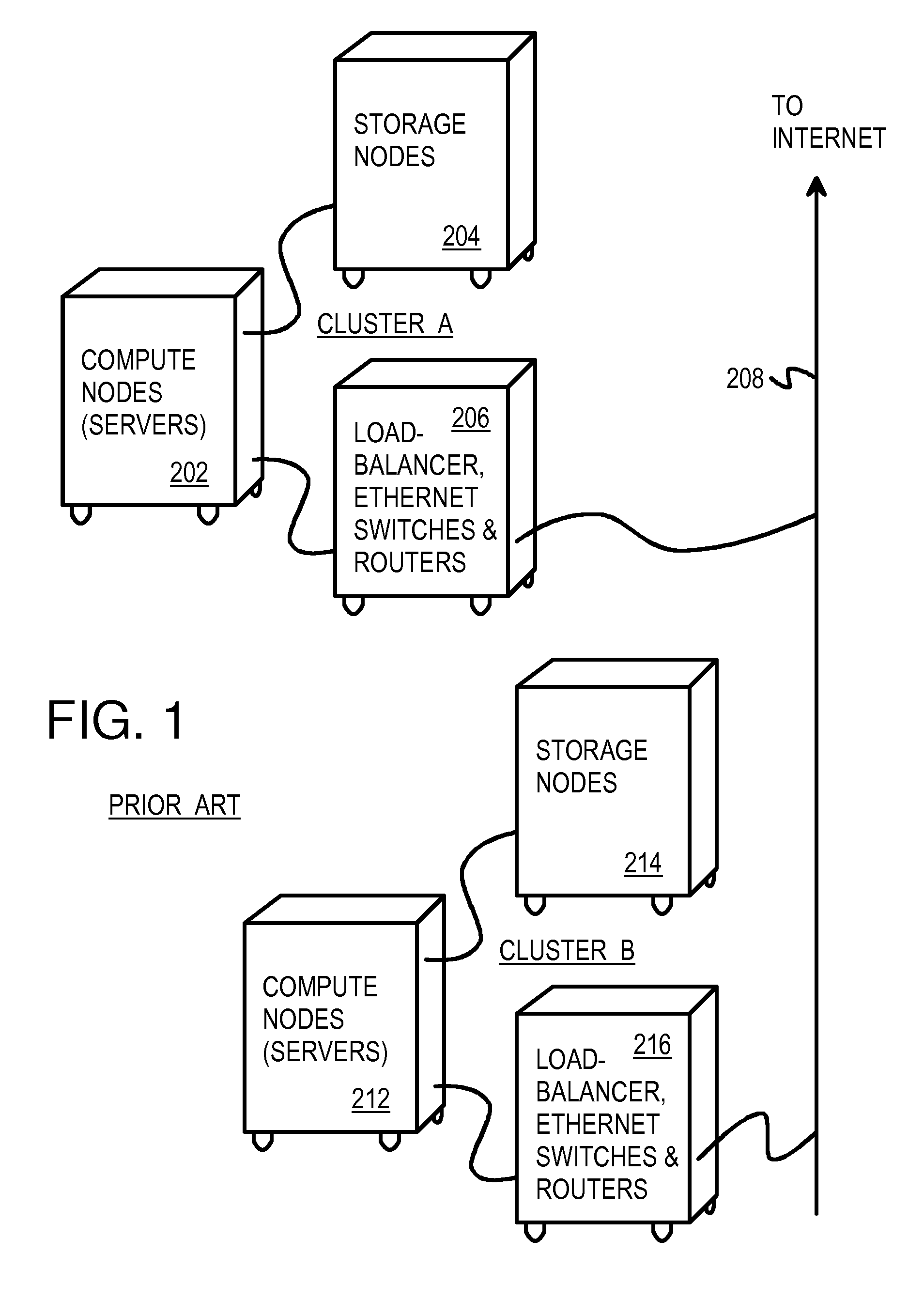

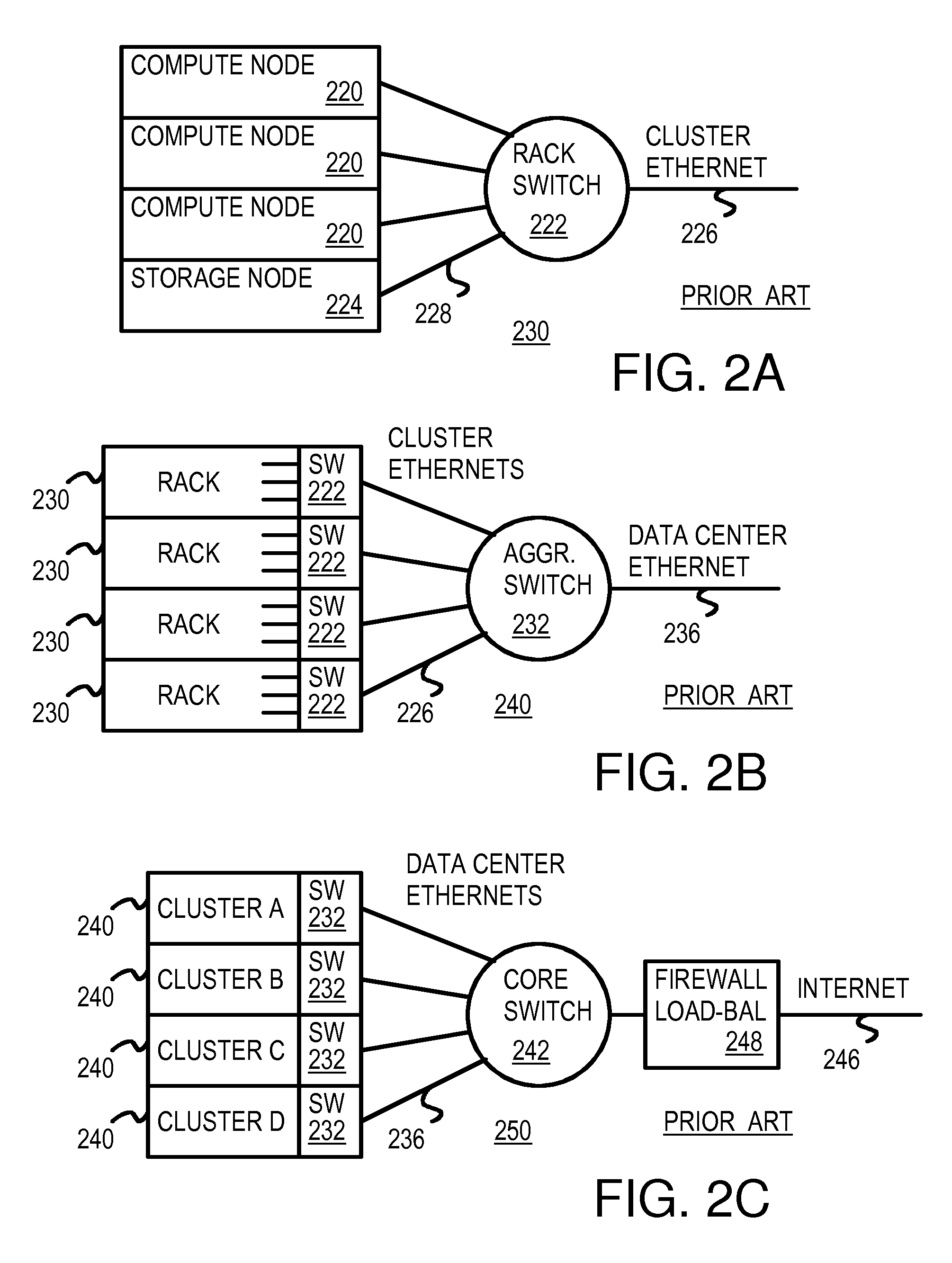

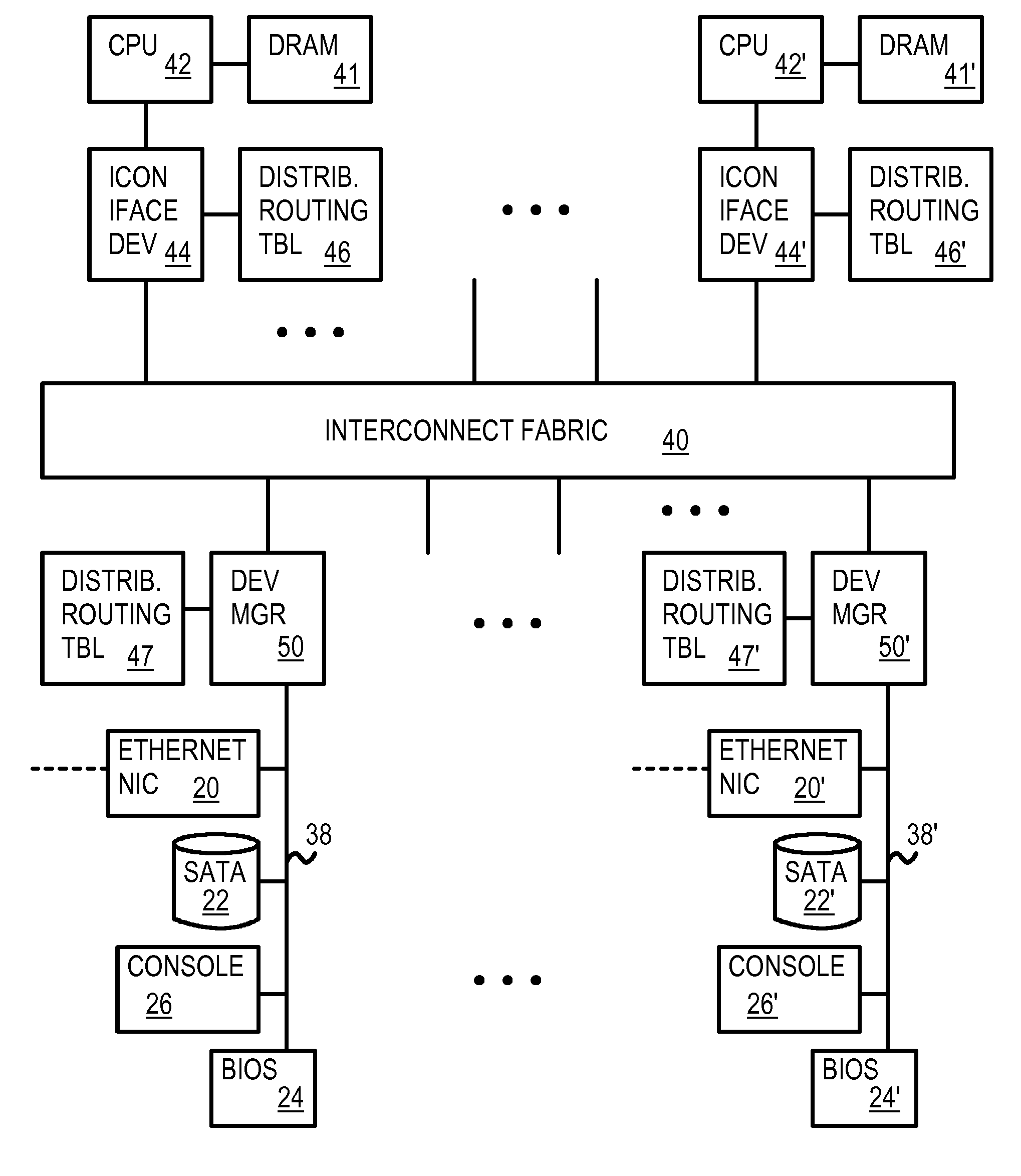

Dis-Aggregated and Distributed Data-Center Architecture Using a Direct Interconnect Fabric

ActiveUS20090216920A1Computer security arrangementsMultiple digital computer combinationsOperational systemData center

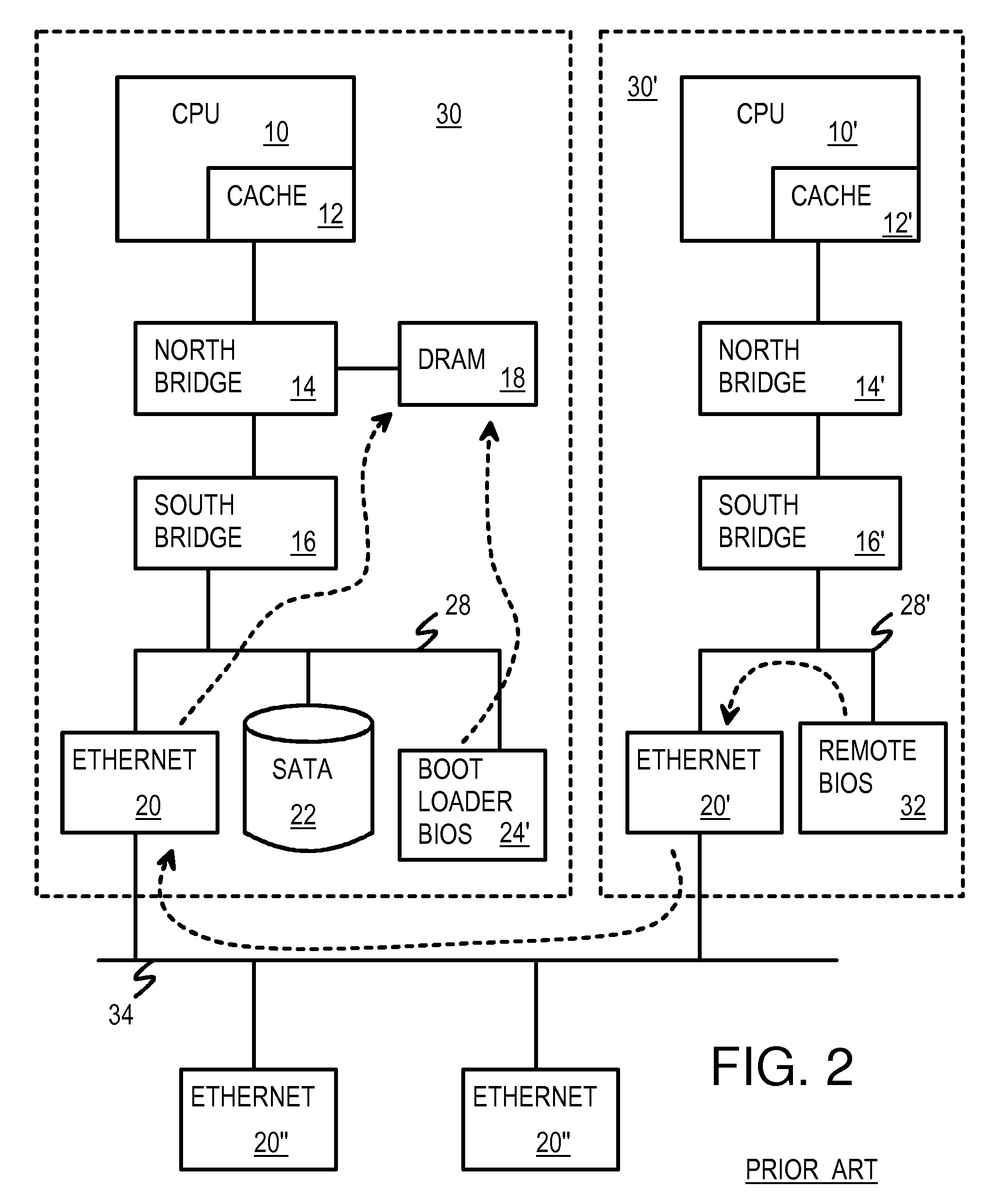

A data center has several dis-aggregated data clusters that connect to the Internet through a firewall and load-balancer. Each dis-aggregated data cluster has several dis-aggregated compute / switch / disk chassis that are connected together by a mesh of Ethernet links. Each dis-aggregated compute / switch / disk chassis has many processing nodes, disk nodes, and I / O nodes on node cards that are inserted into the chassis. These node cards are connected together by a direct interconnect fabric. Using the direct interconnect fabric, remote I / O and disk nodes appear to the operating system to be located on the local processor's own peripheral bus. A virtual Ethernet controller and a virtual generic peripheral act as virtual endpoints for the local processor's peripheral bus. I / O and disk node peripherals are virtualized by hardware without software drivers. Rack and aggregation Ethernet switches are eliminated using the direct interconnect fabric, which provides a flatter, dis-aggregated hierarchy.

Owner:SEAMICRO

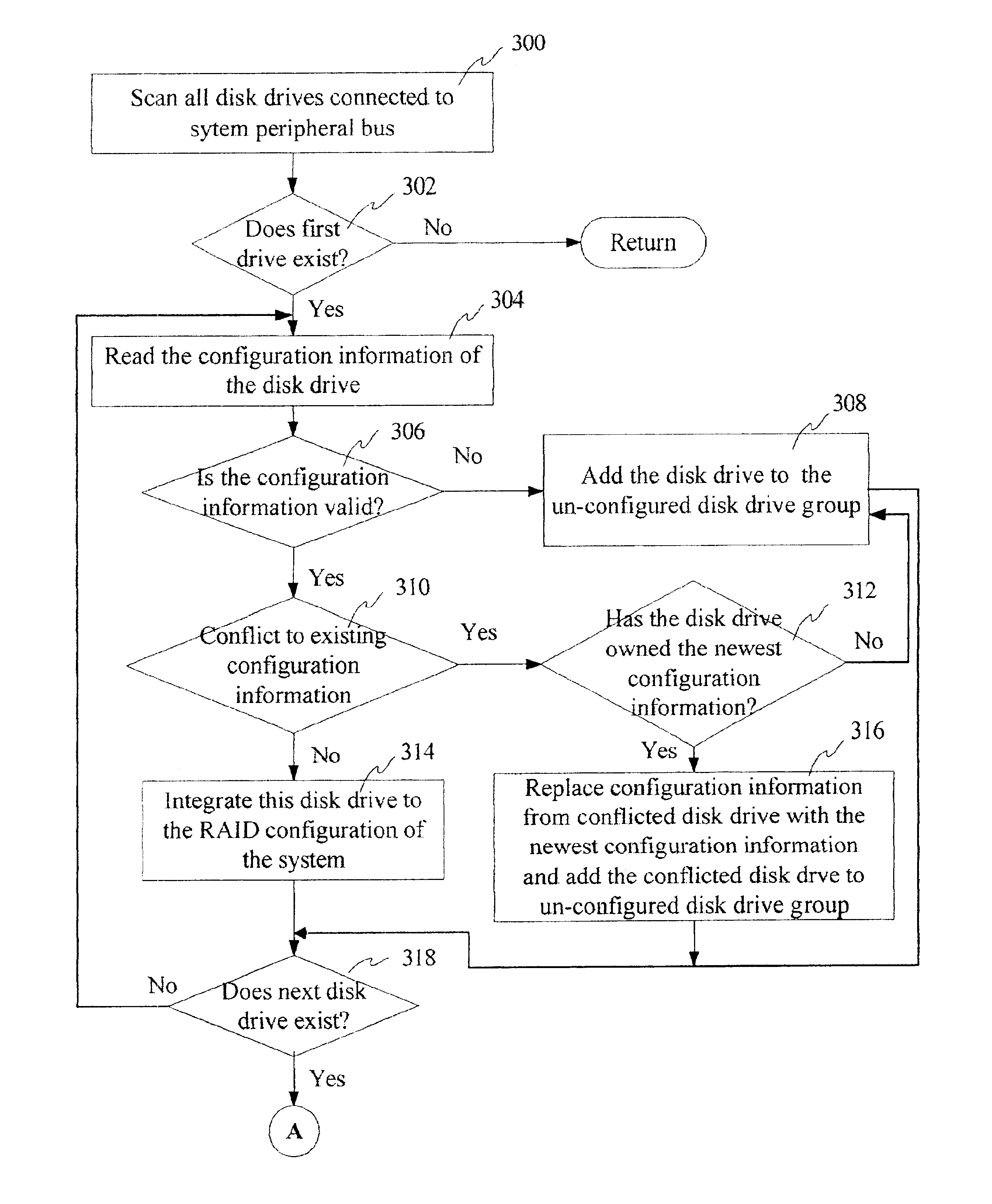

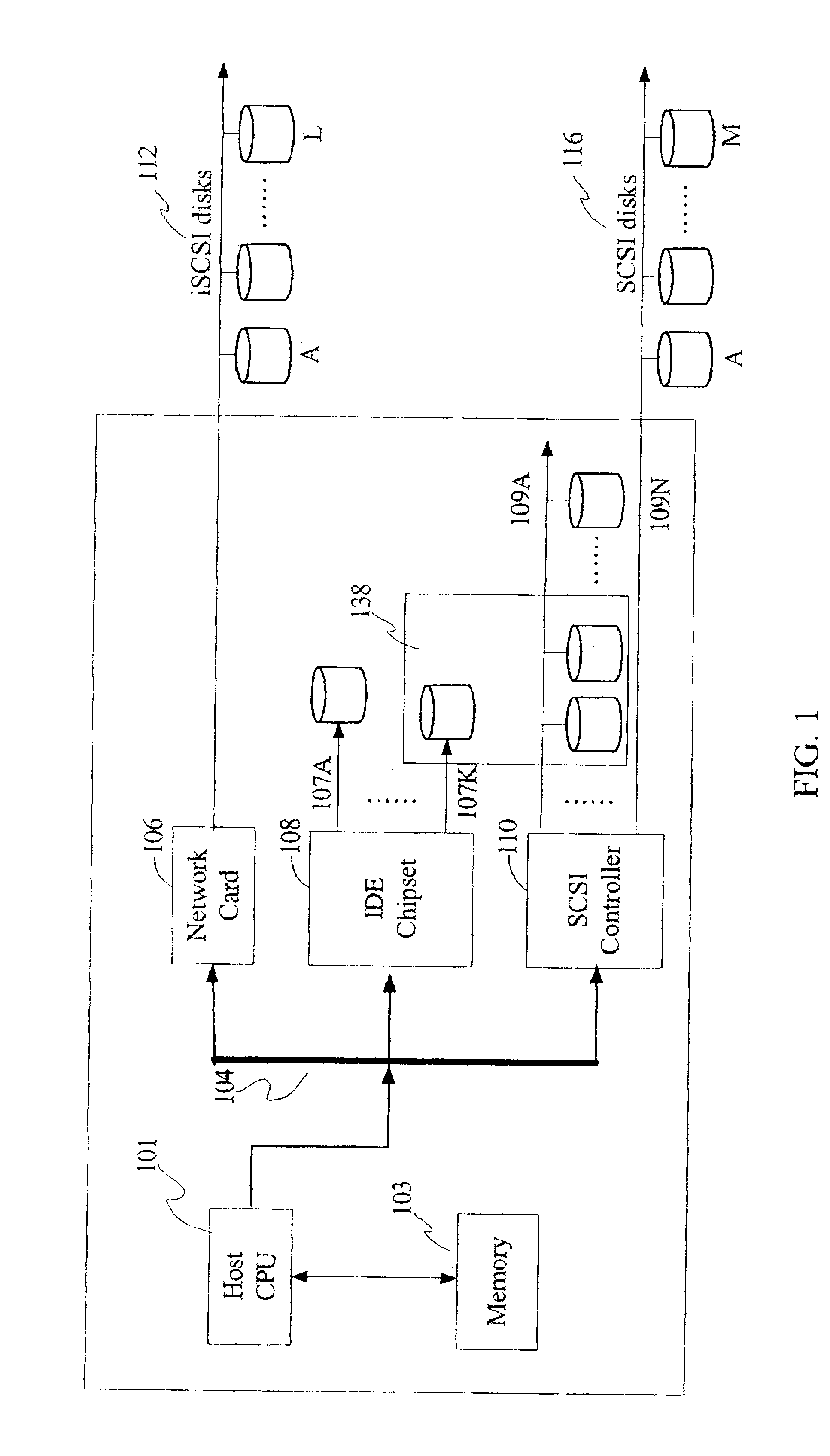

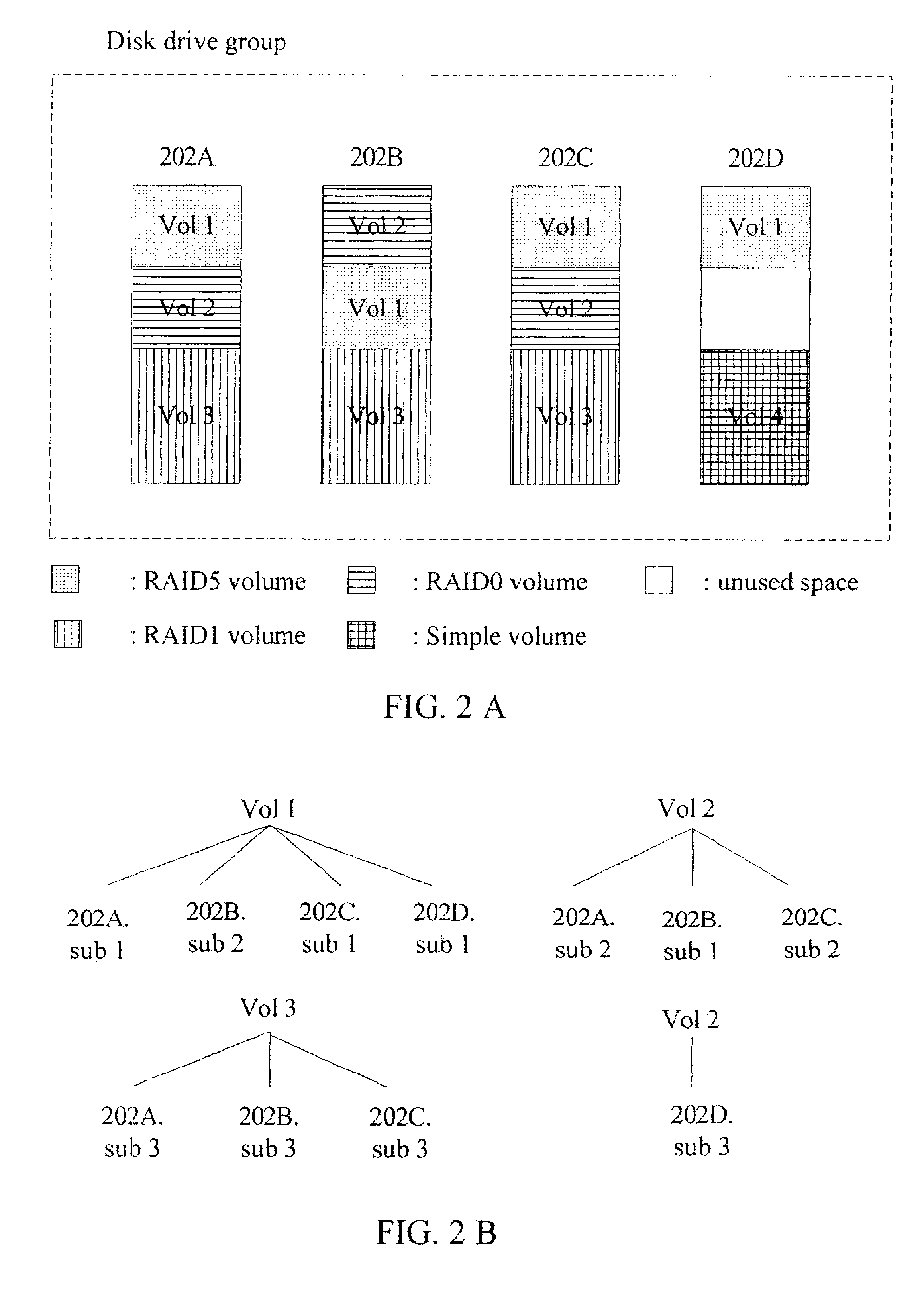

Method, system and apparatus for scanning newly added disk drives and automatically updating RAID configuration and rebuilding RAID data

InactiveUS6952794B2Raise countMaximum countInput/output to record carriersRedundant data error correctionRAIDOperational system

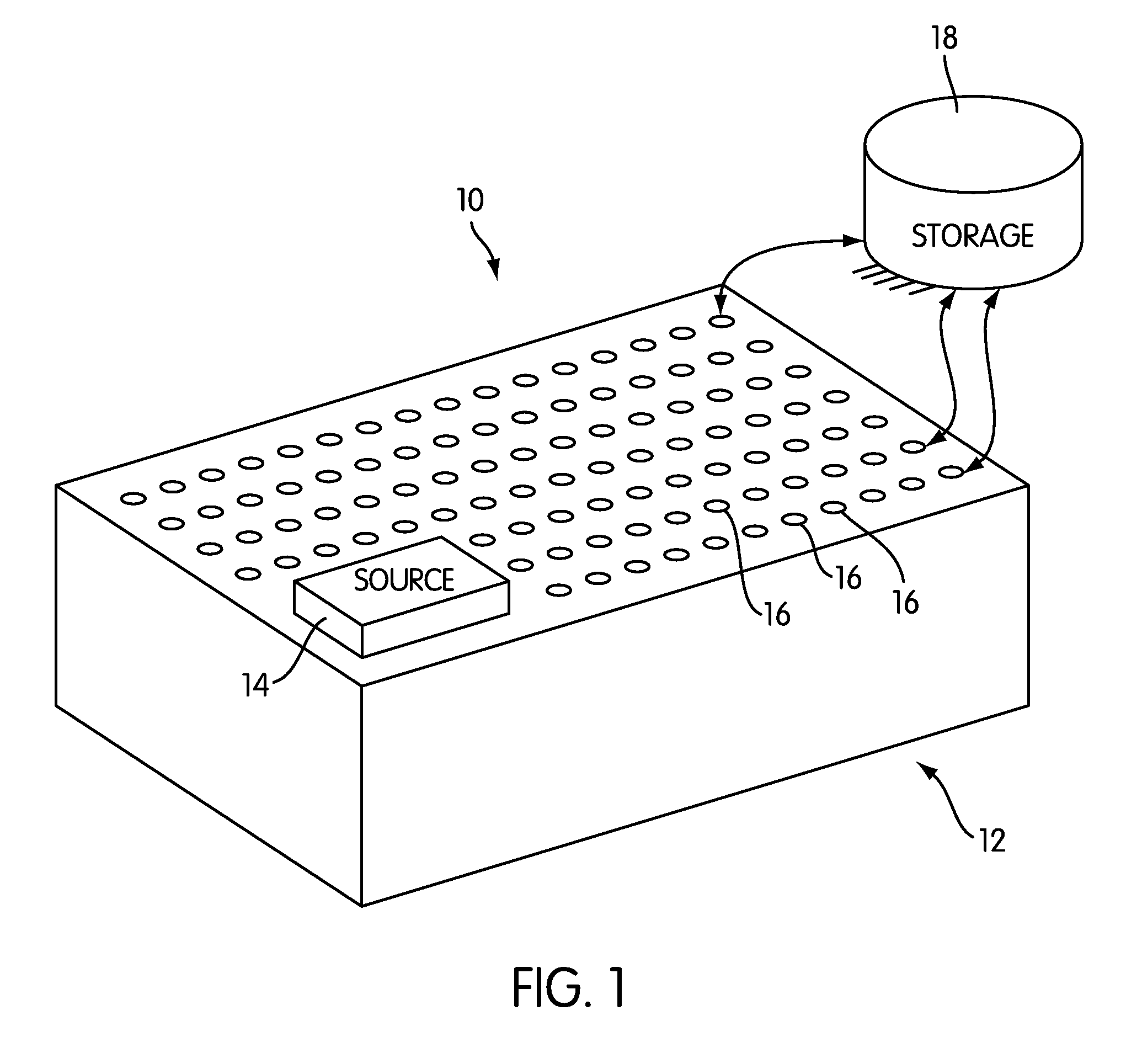

The present invention pertains to a computer software implemented method, system, and apparatus for automatic updating disk drive configuration and rebuilding RAID data to assure proper data storage in a RAID configured system. The computer software implemented configuration mechanism utilizing CPU and memory of a computer system automatically generates a full configuration of the disk drives connected to system peripheral bus both at system initialization time and runtime. The configuration mechanism uses a computer-implemented procedure for scanning a newly added disk drive, detecting conflict to the existing configuration, resolving conflicts, finding a proper target referenced or ruined disk drive, replacing this target disk drive with the newly added disk drive, rebuilding the RAID data into the added disk drive, updating RAID configuration with the added disk drive, and presenting to the host operating system the current configuration information.

Owner:SYNOLOGY INC

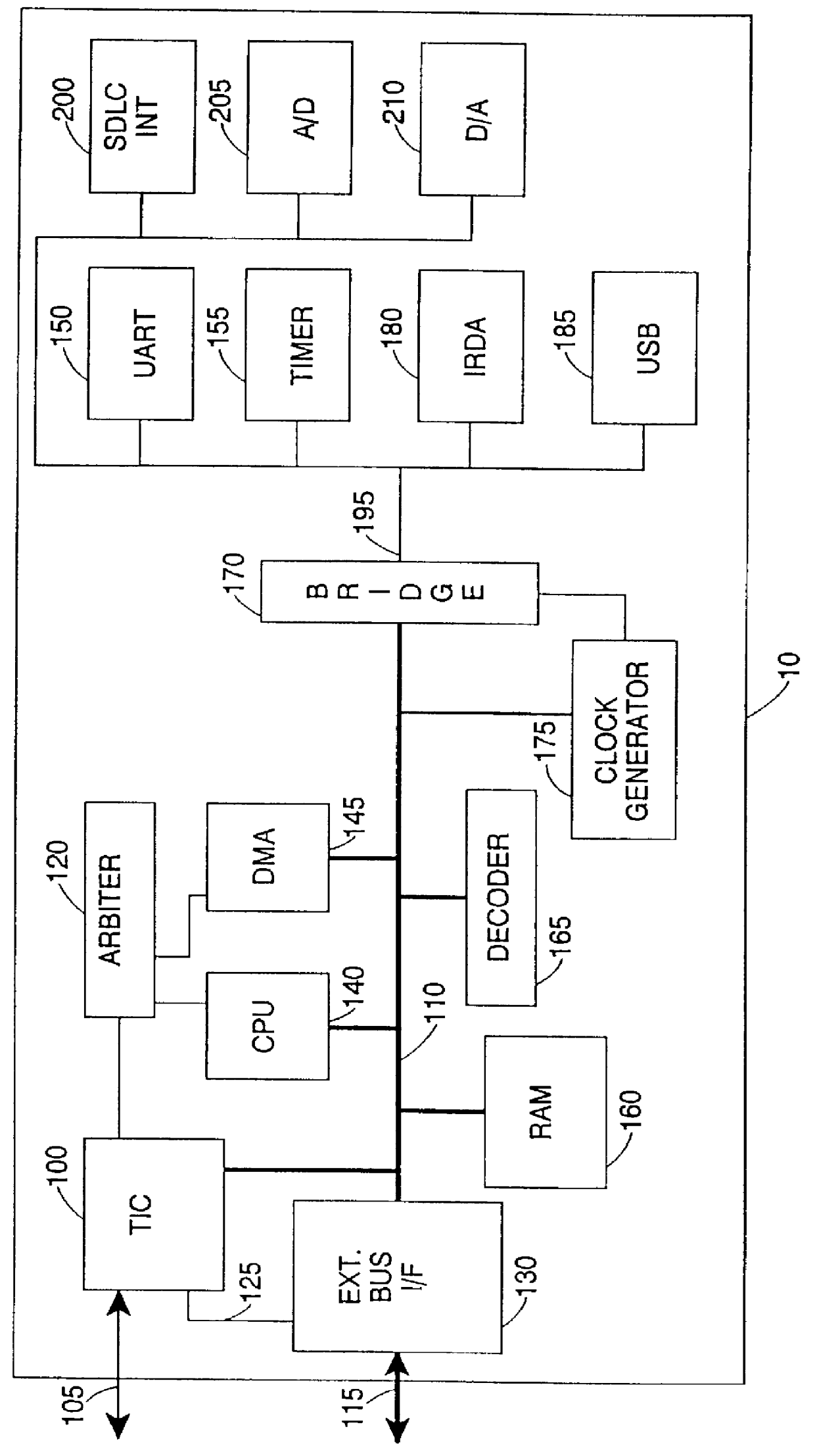

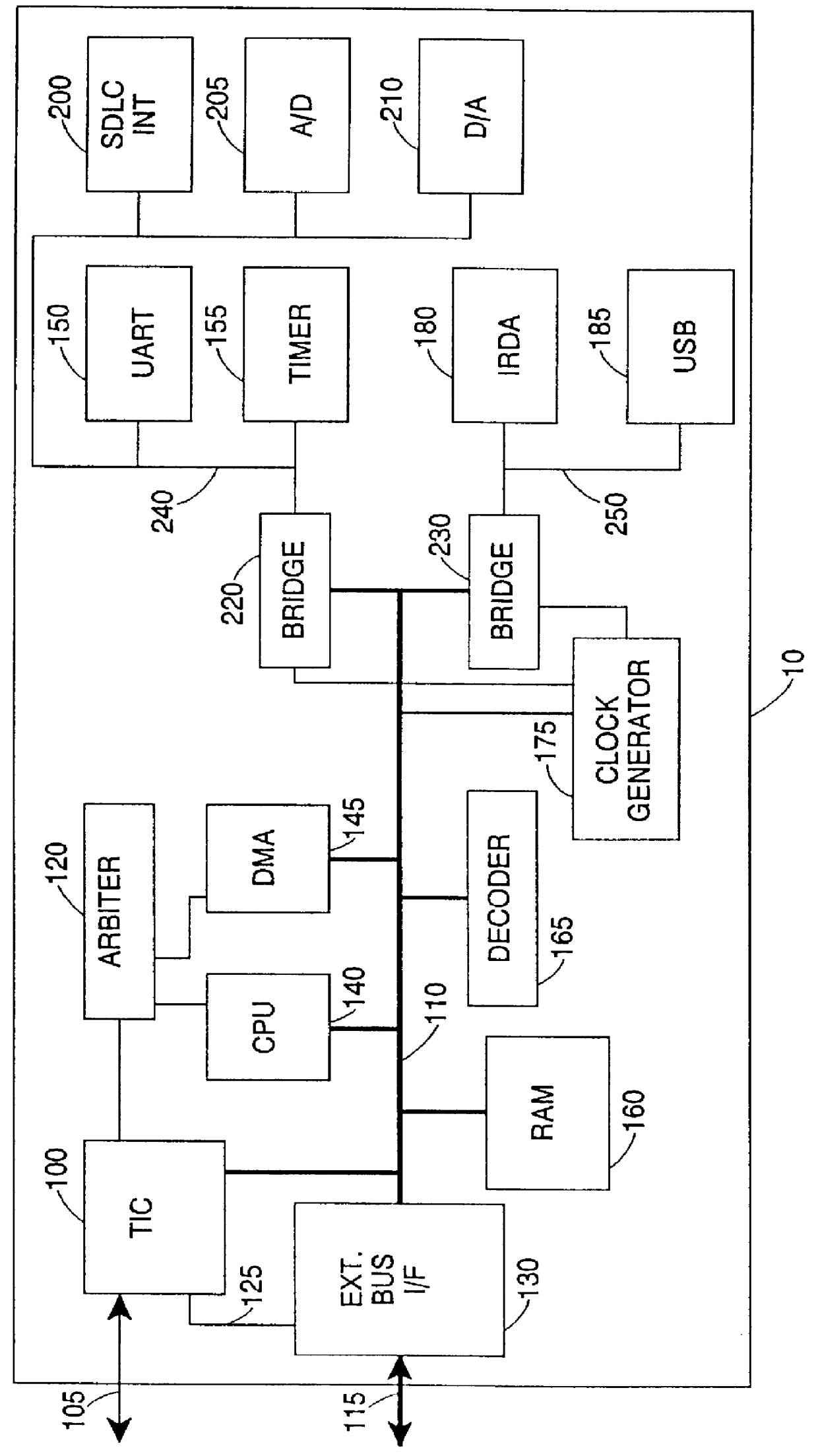

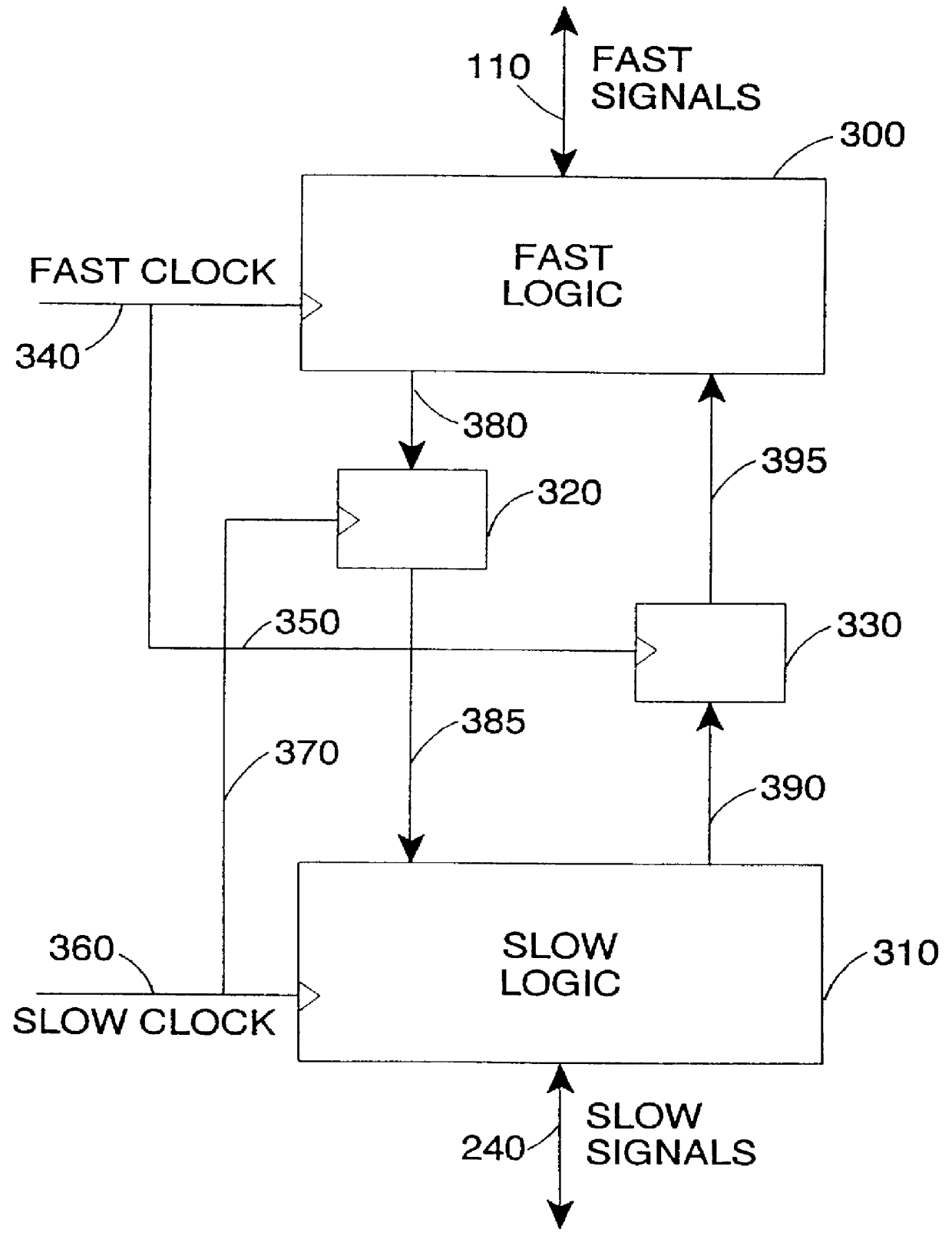

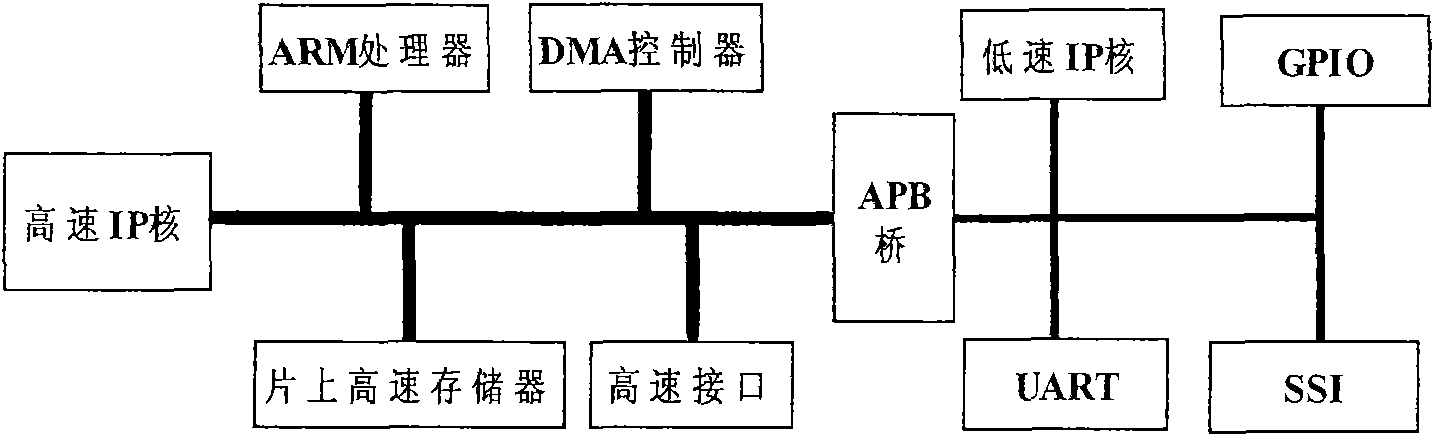

Peripheral buses for integrated circuit

InactiveUS6064626AReduce power consumptionAverage power consumptionEnergy efficient ICTDigital storageCapacitanceClock rate

The present invention provides an integrated circuit comprising a system bus to which a processor is connectable, and first and second peripheral buses to which peripheral units used by said processor are connected, the first peripheral bus operating at a higher clock speed than the second peripheral bus. Further, the integrated circuit comprises bridge logic for providing an interface between the system bus and the peripheral buses to enable signals to be passed between the system bus and the peripheral buses, the bridge logic comprising clock resynchronisation logic for synchronising the system bus and the peripheral buses. Through the provision of first and second peripheral buses operating at different clock speeds, the integrated circuit of the present invention provides a great deal of flexibility for reducing the power consumption of the integrated circuit as compared with a similar integrated circuit having only one peripheral bus. Since the power consumption of each peripheral bus is proportional to the clock frequency and capacitance, significant power consumption savings can be realised by ensuring that each peripheral unit is connected to the slowest peripheral bus appropriate for that peripheral unit.

Owner:ARM LTD

Subscriber and Communication Controller of a communication System and Method for Implementing a Gateway Functionality in a Subscriber of a Communication System

InactiveUS20090323708A1Reduce the burden onHeavy loadData switching by path configurationElectric digital data processingCommunications systemTelecommunications link

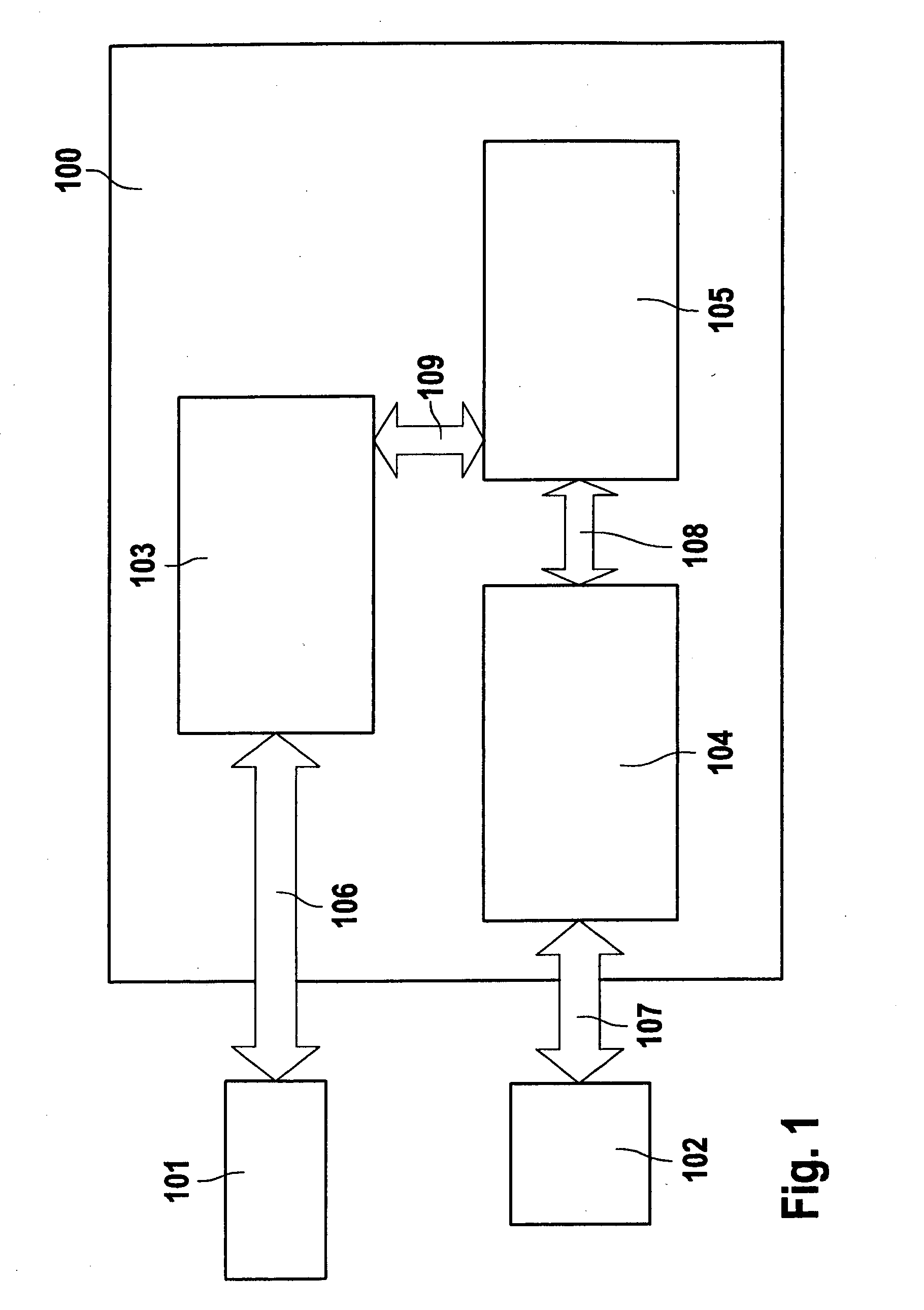

A subscriber of a communication system includes a microprocessor, at least two communication controllers and a peripheral bus. The microprocessor is connected to the communication controllers via the peripheral bus and is also connected via the communication controllers respectively to a communication link of the communication system, via which messages are transmitted. In order to optimize the gateway functionality within the subscriber, a provision is made that at least one of the communication controllers has an active interface via which the communication controller is connected to the peripheral bus and has a logic circuit for independently implementing a gateway functionality.

Owner:ROBERT BOSCH GMBH

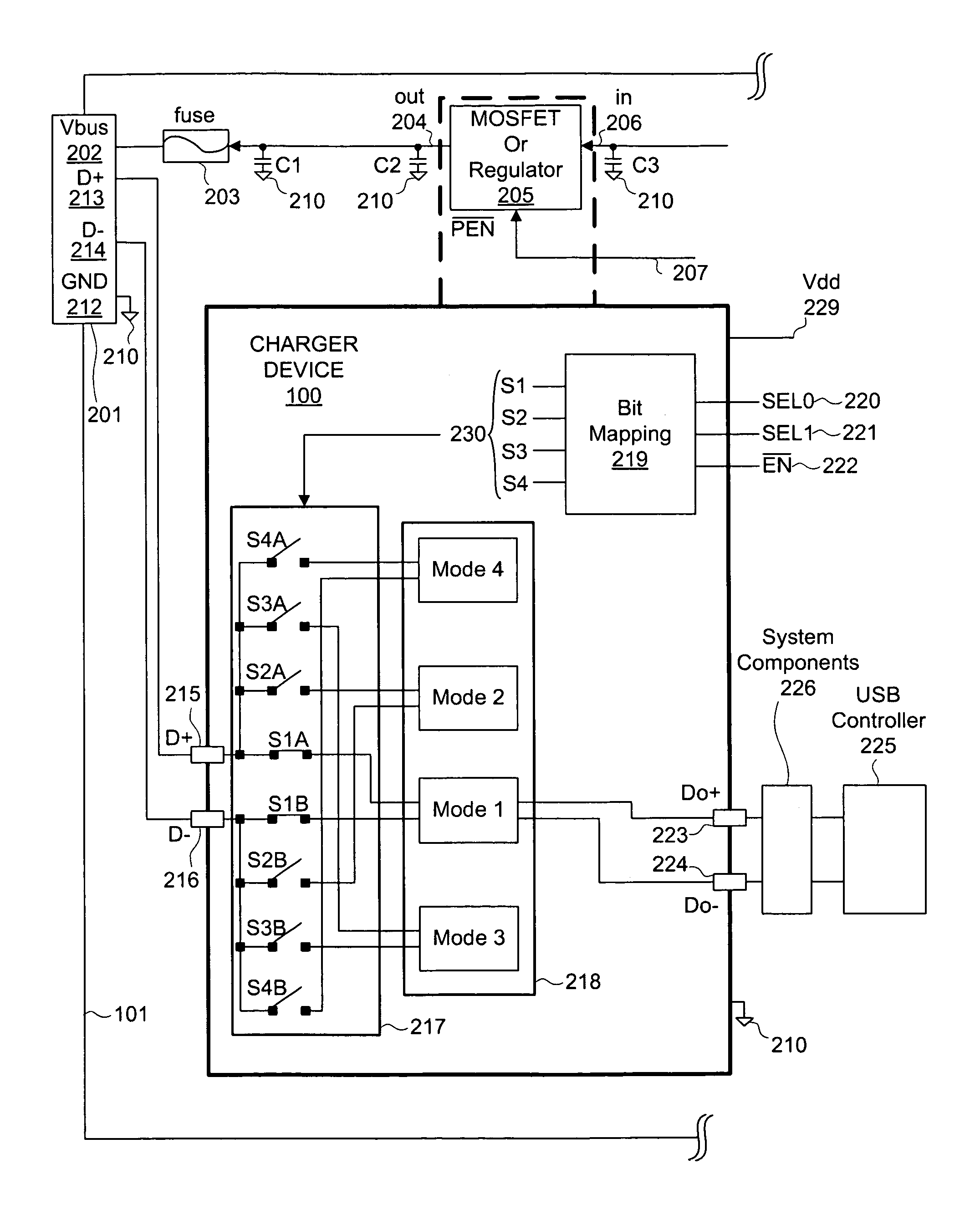

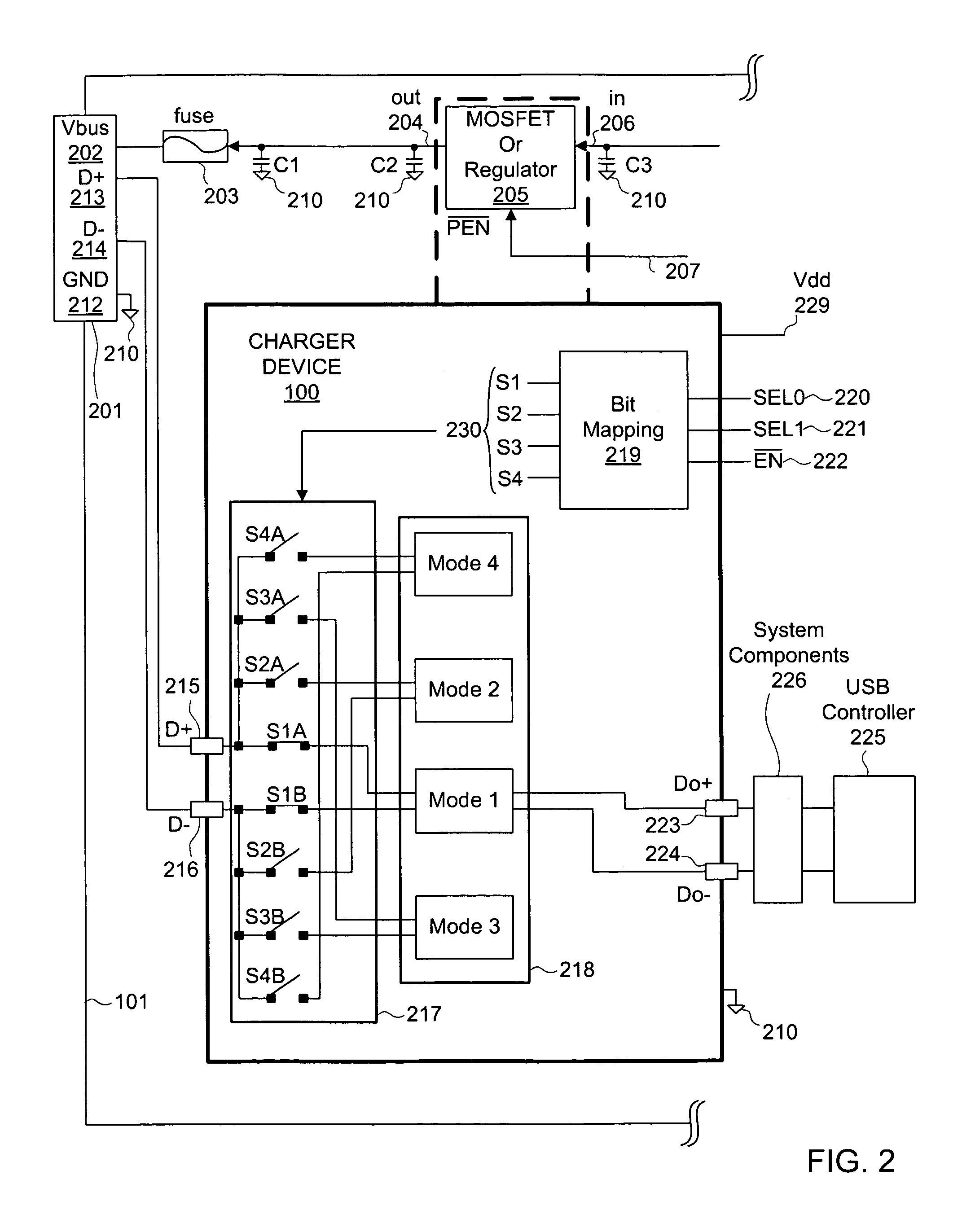

Multi-mode charger device

Multi-mode charger device for charging portable devices and methods of charging portable devices are described. In an embodiment, a multi-mode charger device has mode blocks respectively associated with modes of operation which are coupled to a switch module. The switch module is for coupling a selected one of the mode blocks to a peripheral bus and to decouple the mode blocks remaining from the peripheral bus. A first mode of the modes of operation is a pass through mode. A second mode of the modes of operation is a first charging mode. A third mode of the modes of operation is a second charging mode. The first charging mode and the second charging mode are different from one another.

Owner:DIODES INC

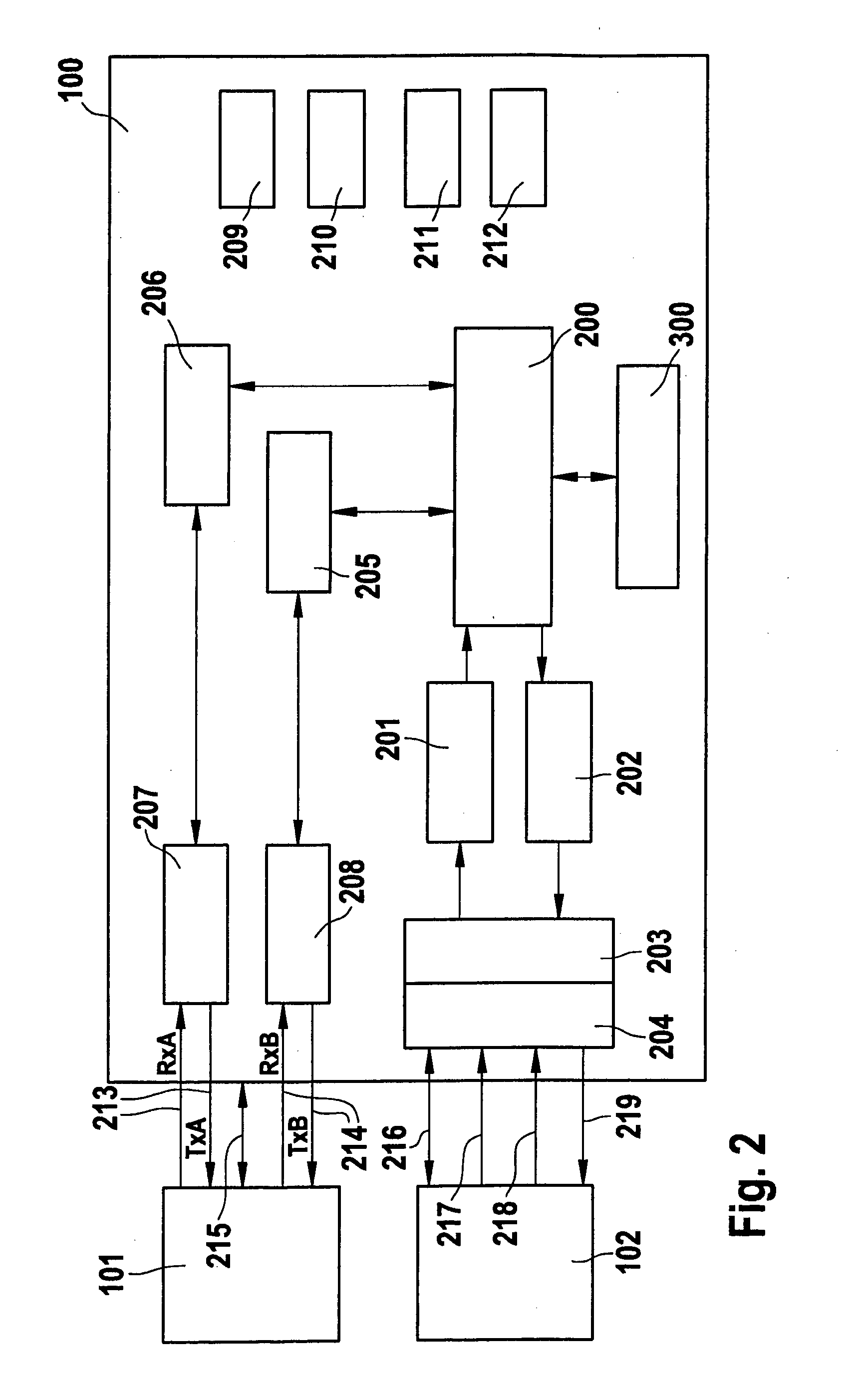

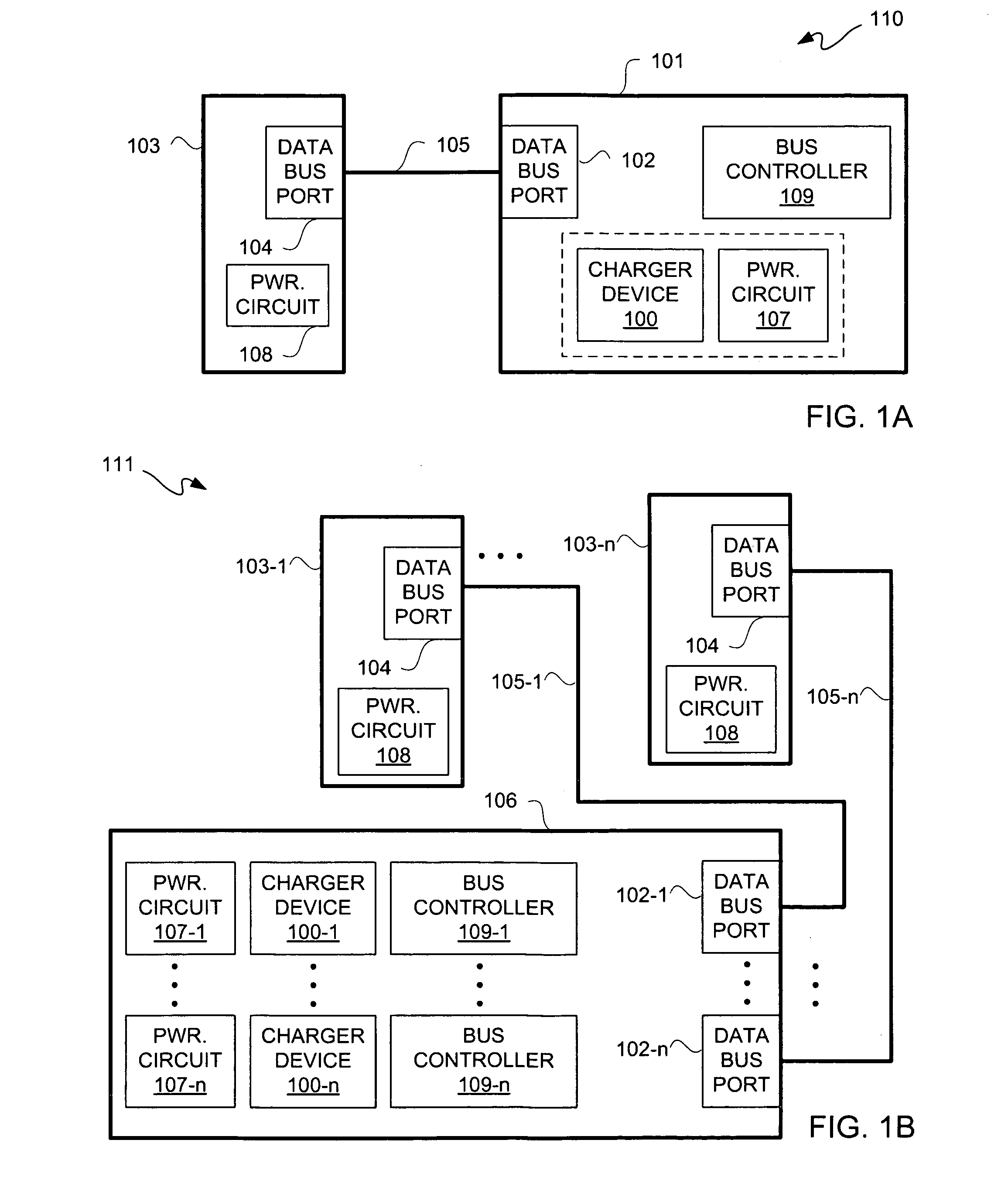

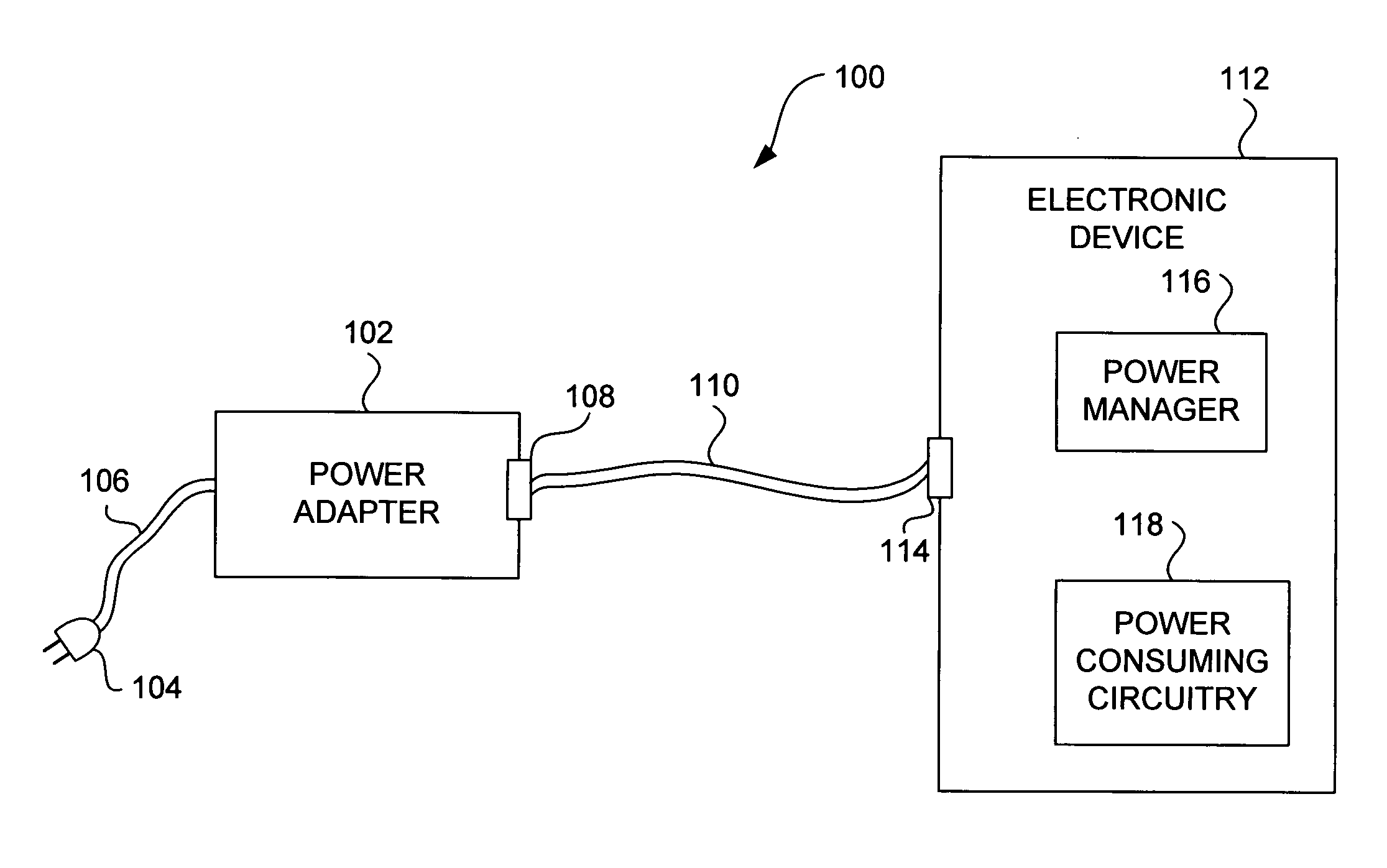

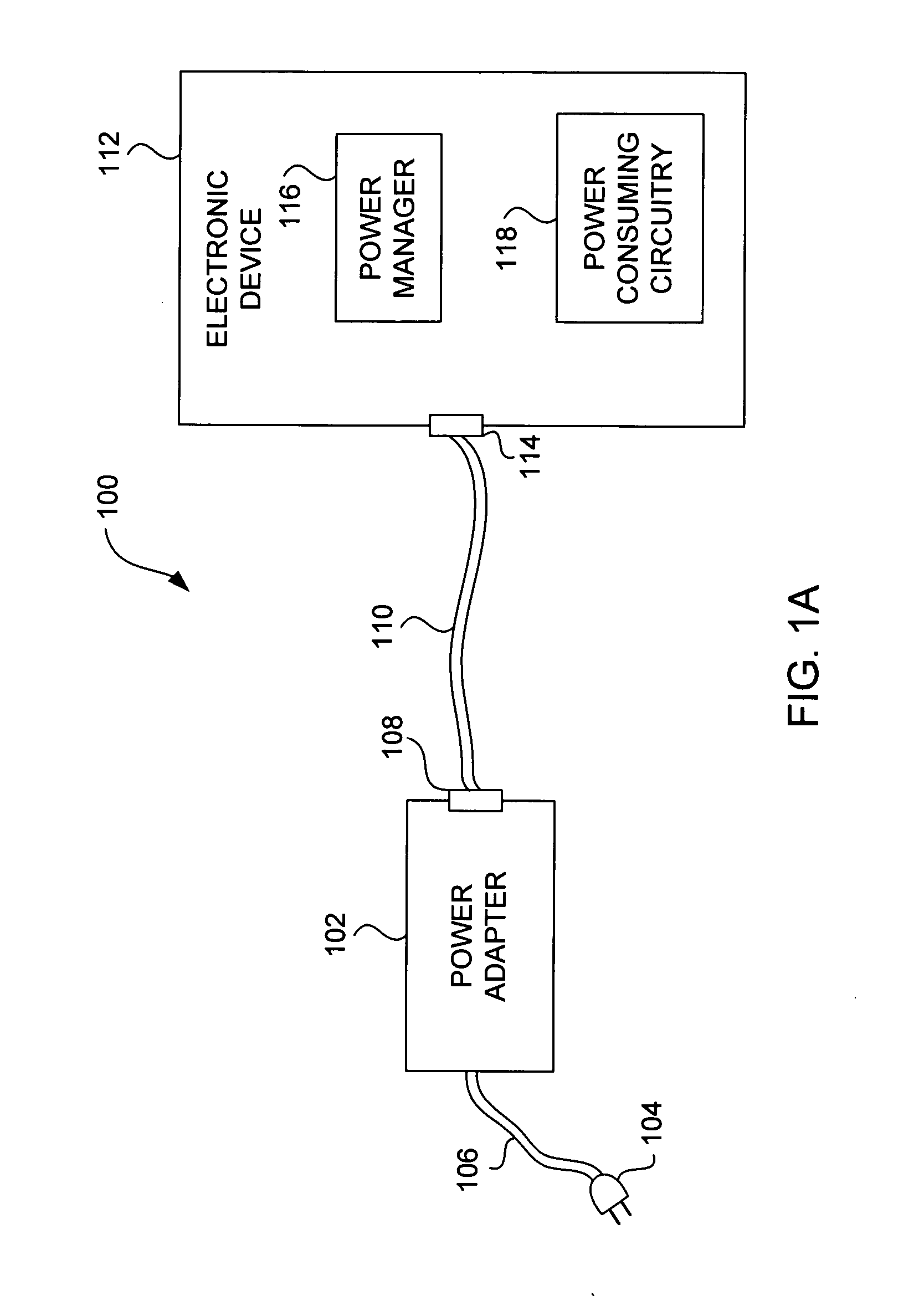

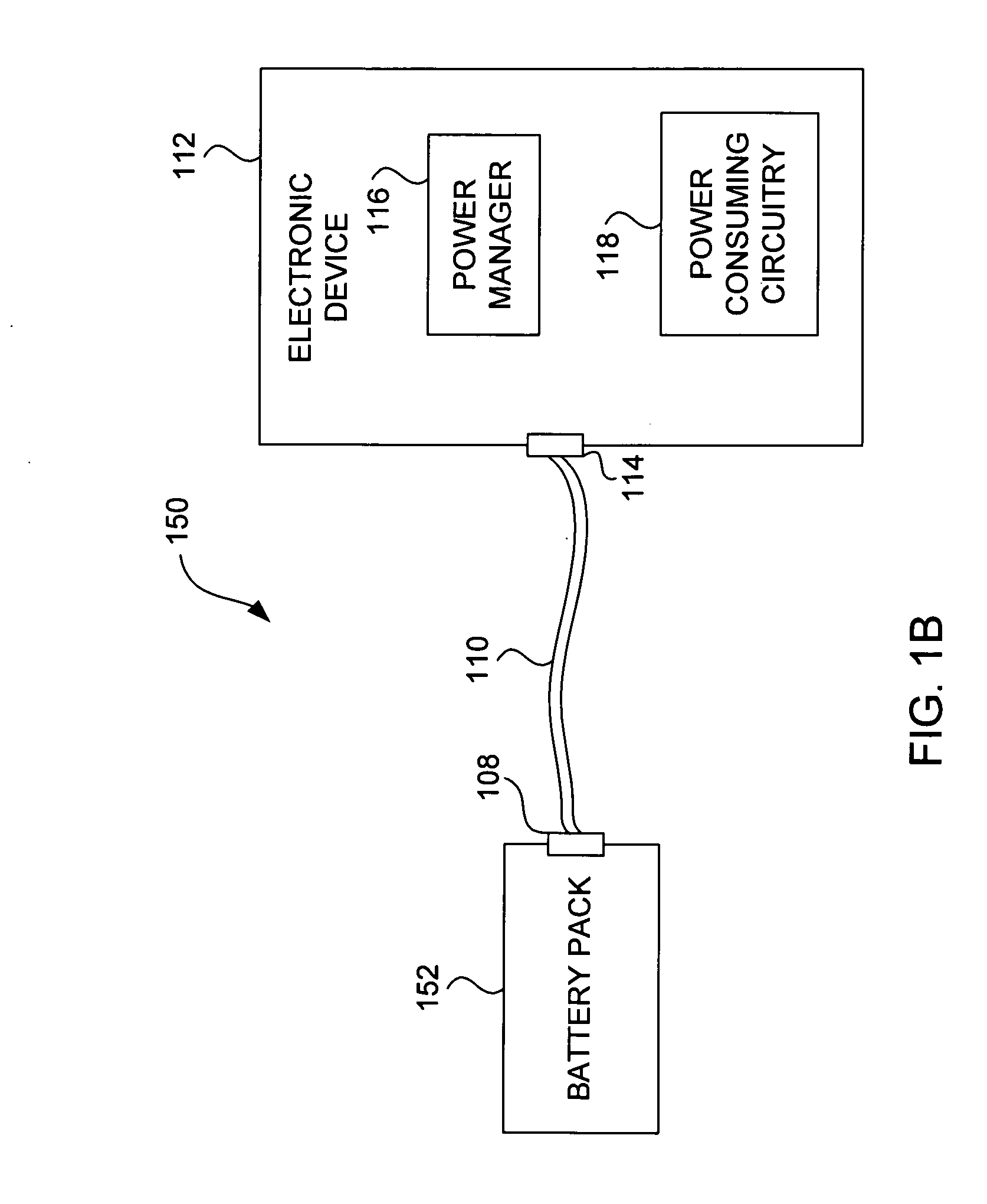

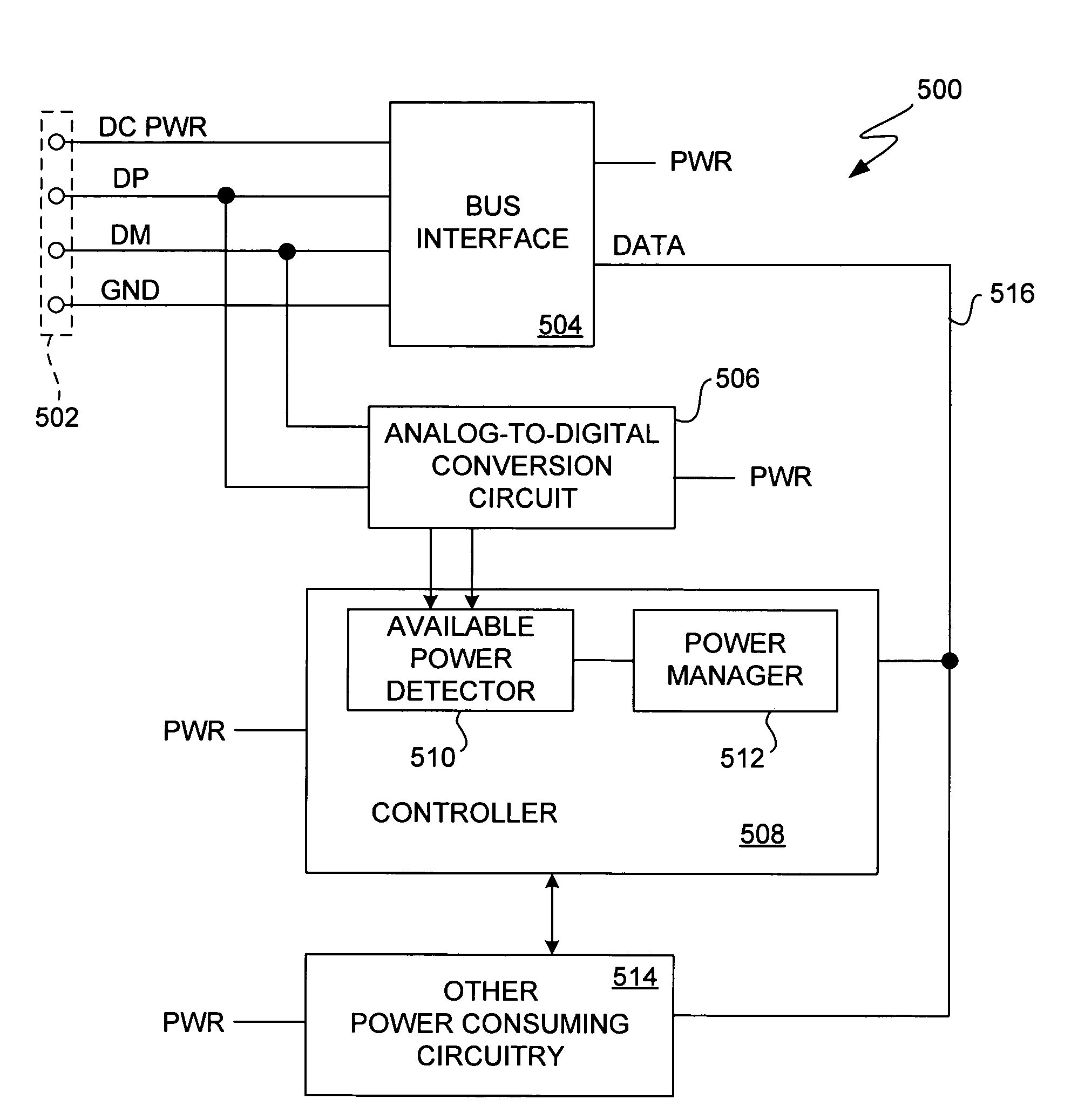

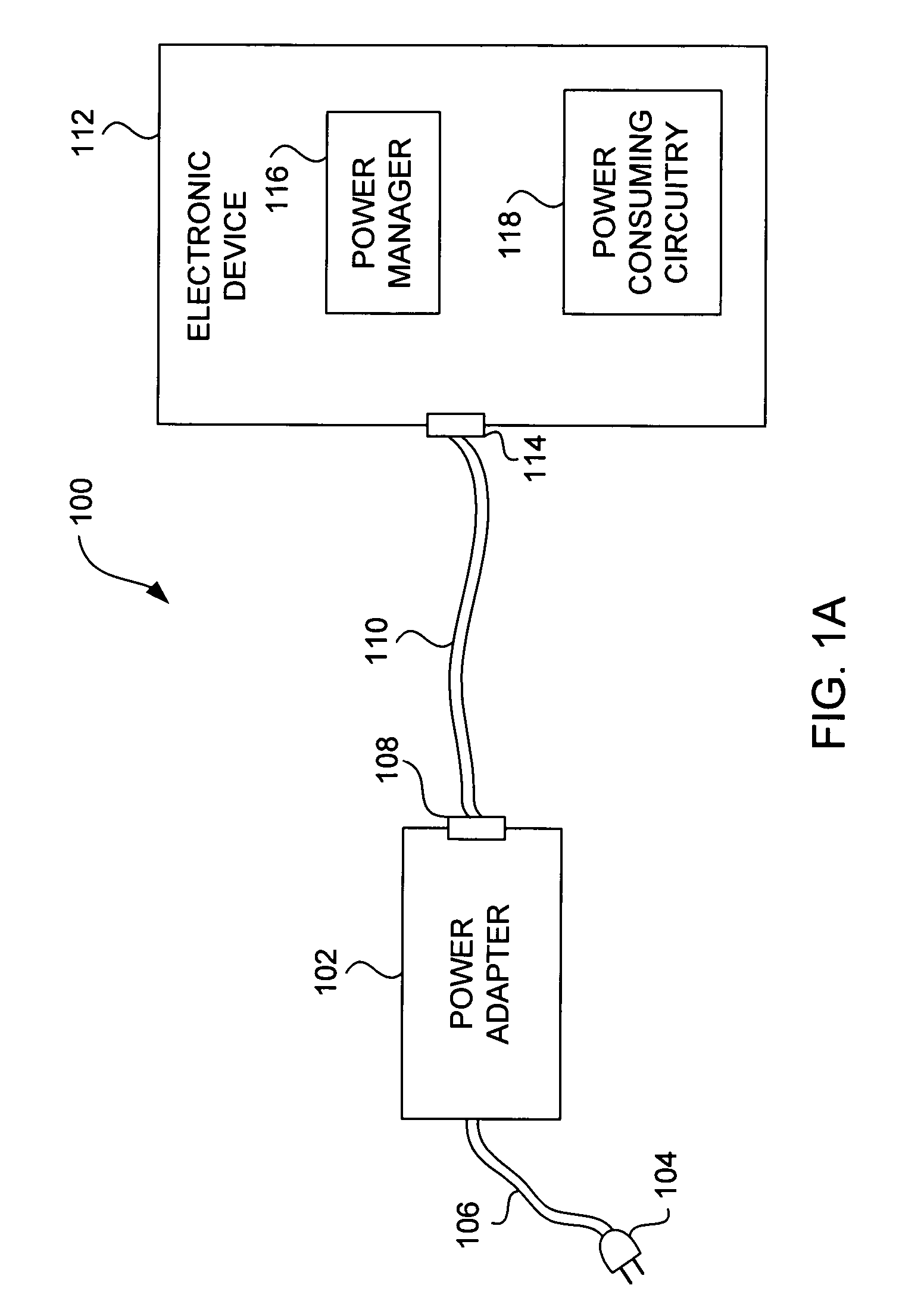

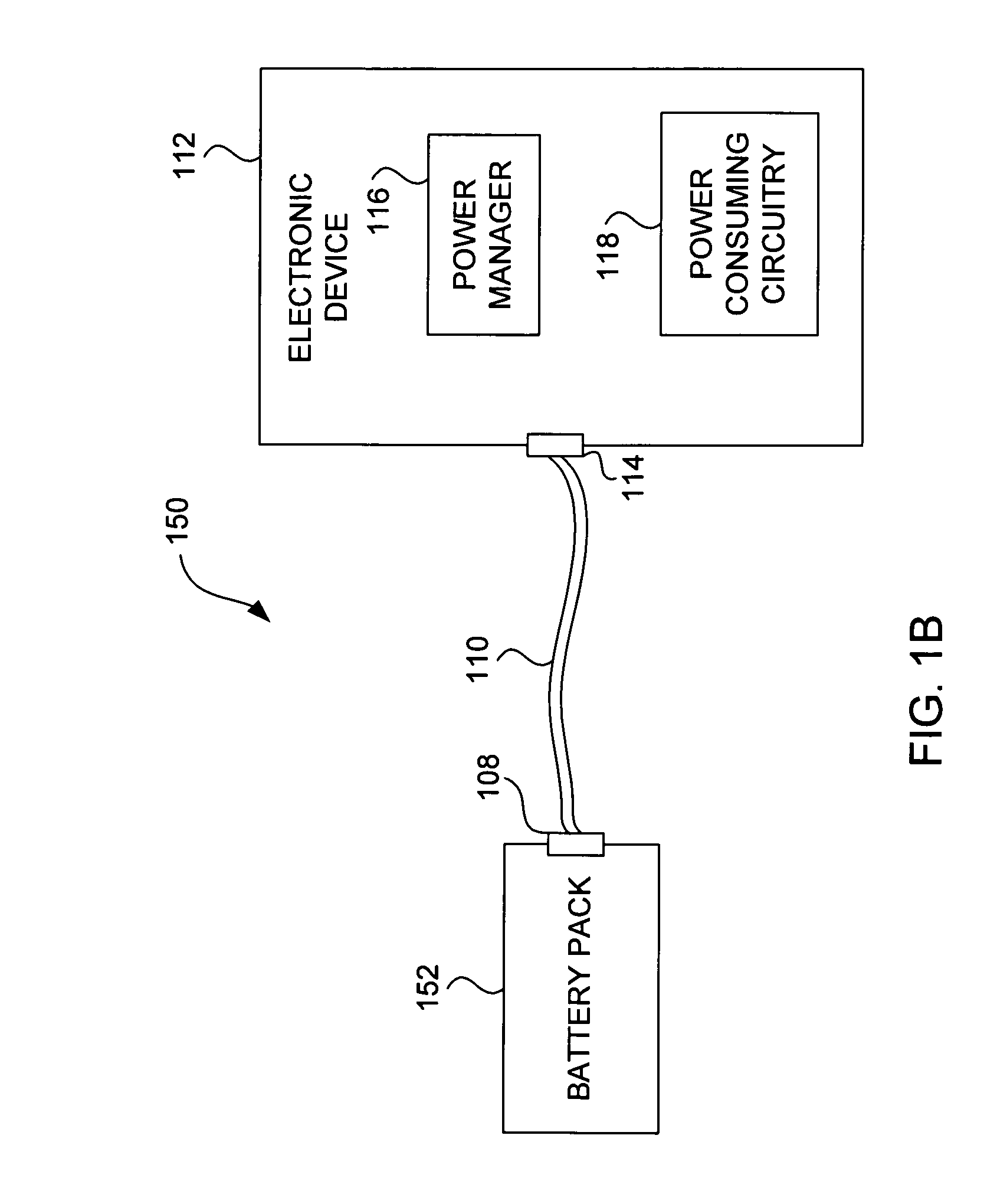

Method and system for discovering a power source on a peripheral bus

ActiveUS20060015757A1Stable and reliable mannerHardware monitoringPower supply for data processingEngineeringElectric power

Improved techniques to recognize a power source on a peripheral bus and / or determine power available from the power source via the peripheral bus are disclosed. Typically, the peripheral bus is supported by a cable connected between a host device and an electronic device. In this case, the host device is a power source (e.g., power adapter or battery pack) and the cable is used to provide power from the power source to the electronic device. Hence, by understanding the power available from the power source, the electronic device can manage its power utilization so as to operate in a stable and reliable manner. The electronic device is, for example, a portable computing device. Examples of portable computing devices include a Portable Digital Assistant (PDA) and a portable media player.

Owner:APPLE INC

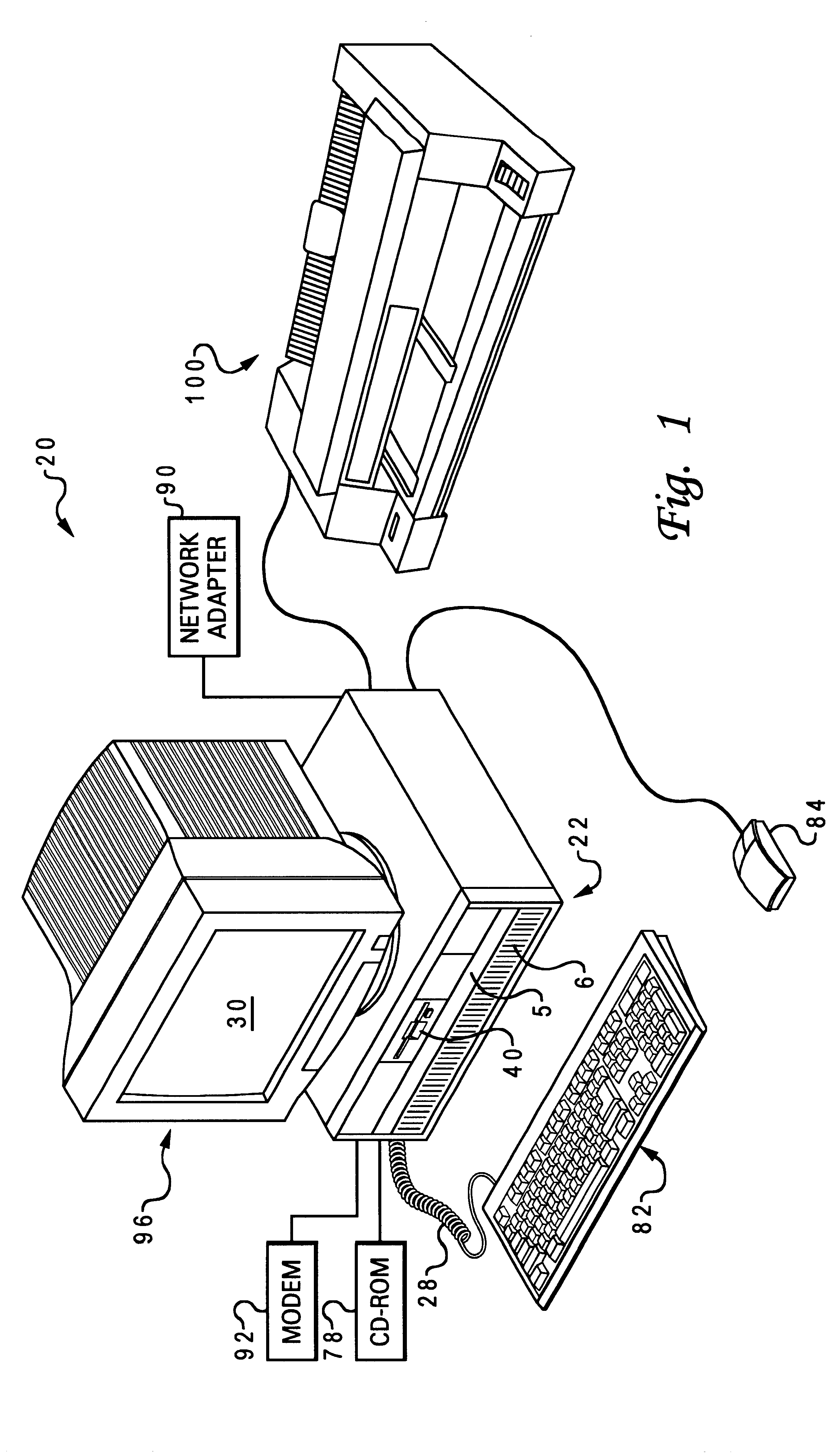

Computing device with flexibly configurable expansion slots, and method of operation

ActiveUS20060271713A1Component plug-in assemblagesElectric digital data processingExpansion cardGraphics

A computing device that allows for a flexible allocation of bandwidth among peripheral devices using a peripheral bus is disclosed. The computing device includes a peripheral bus and at least two slots. The computing device may be used with a single peripheral card or multiple peripheral cards. In a multi-card configuration the invention allows the bandwidth on the peripheral bus to be shared by all the cards. In a single-card configuration, the computing device allows available bandwidth on the peripheral bus to be used by a single card. The device is particularly useful with PCI express compliant expansion cards, such as graphics adapters.

Owner:ATI TECH INC

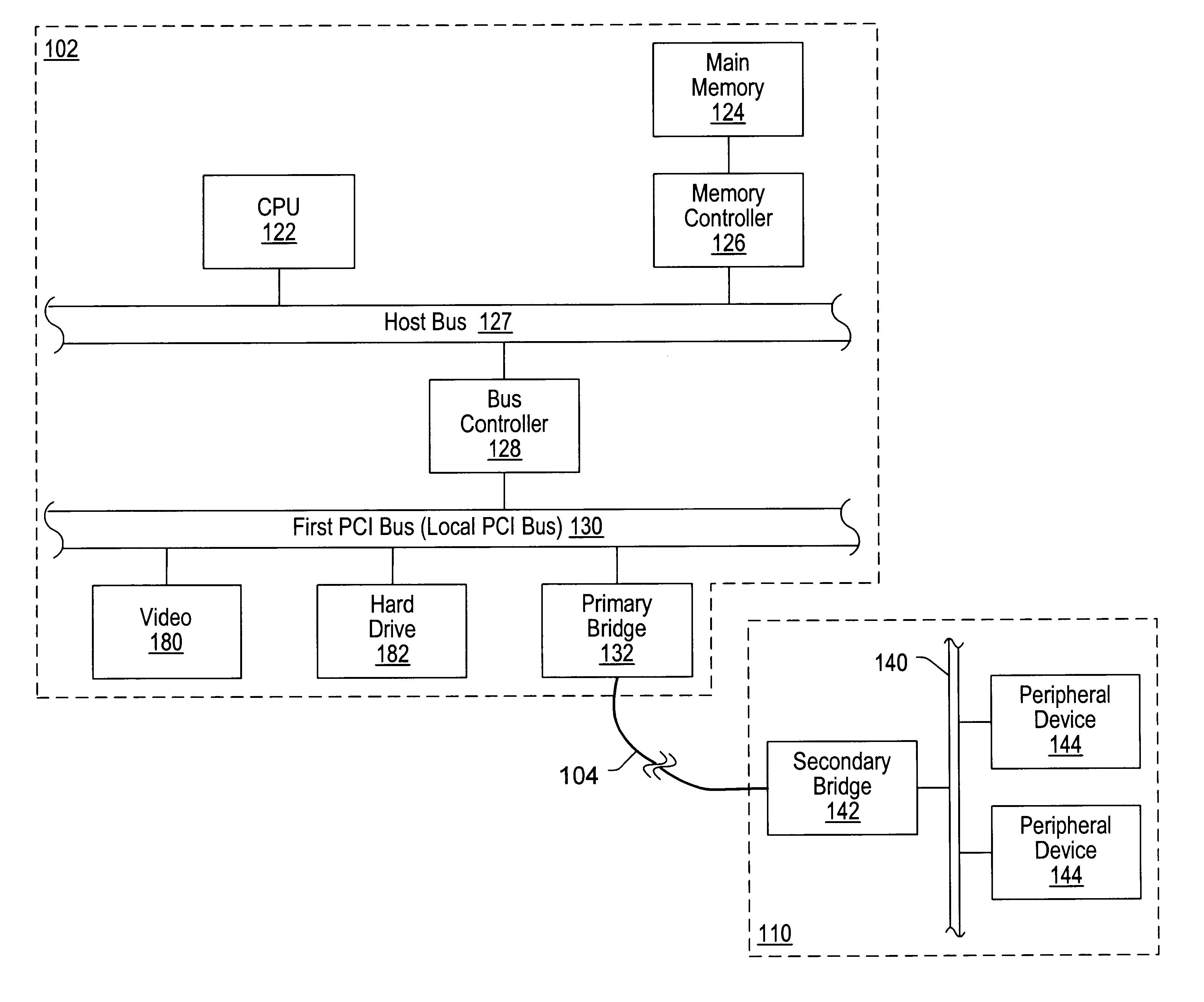

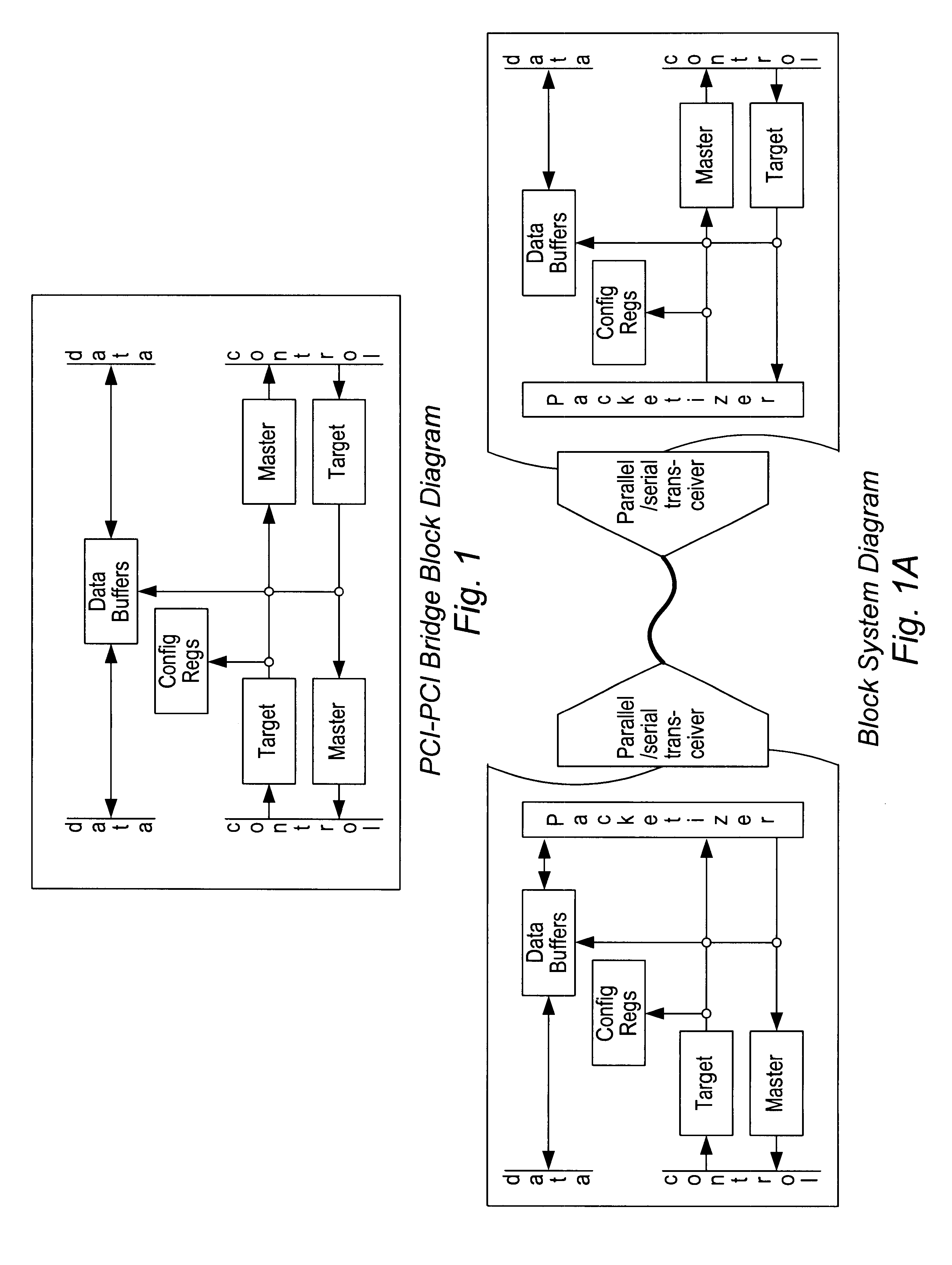

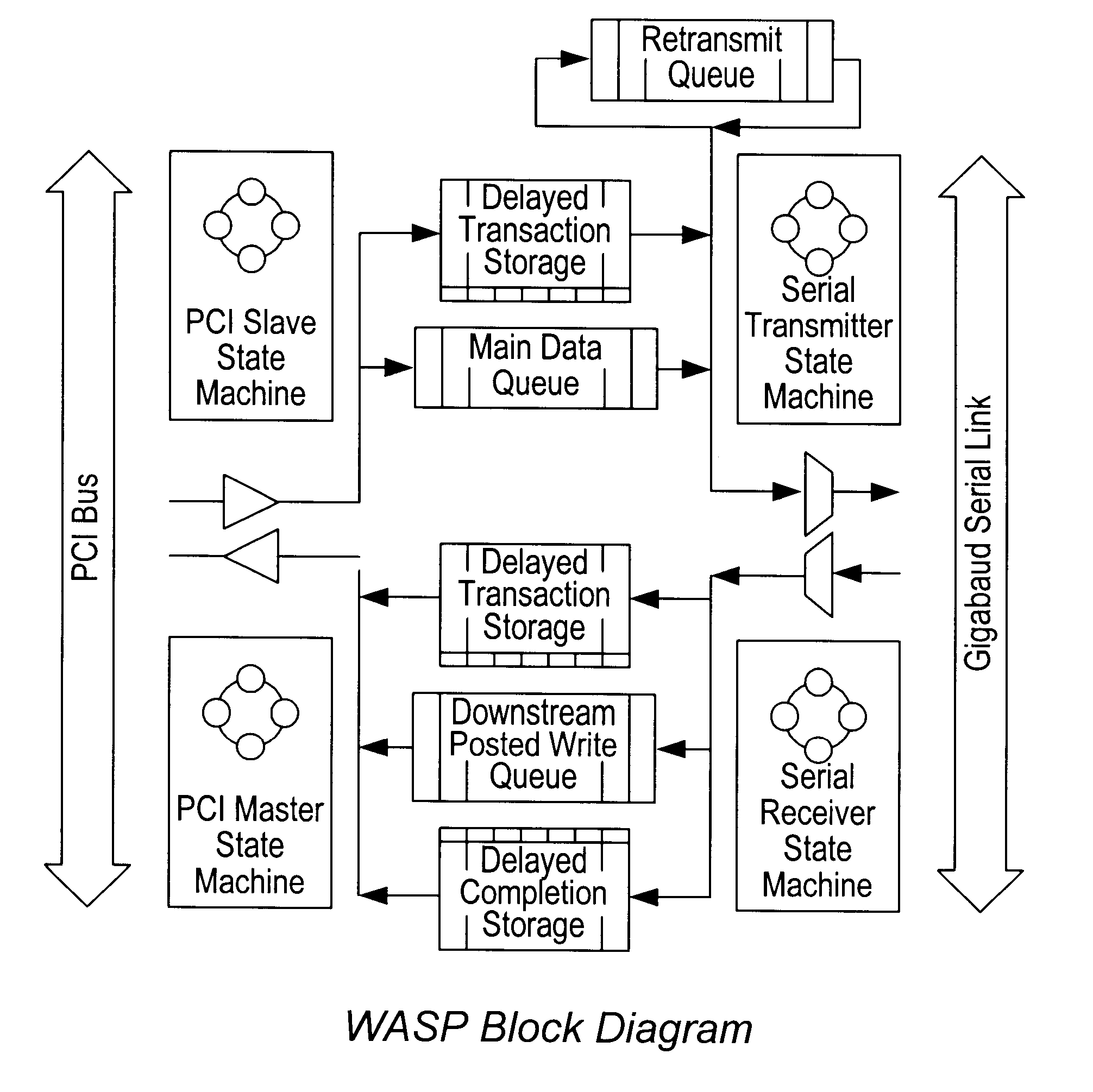

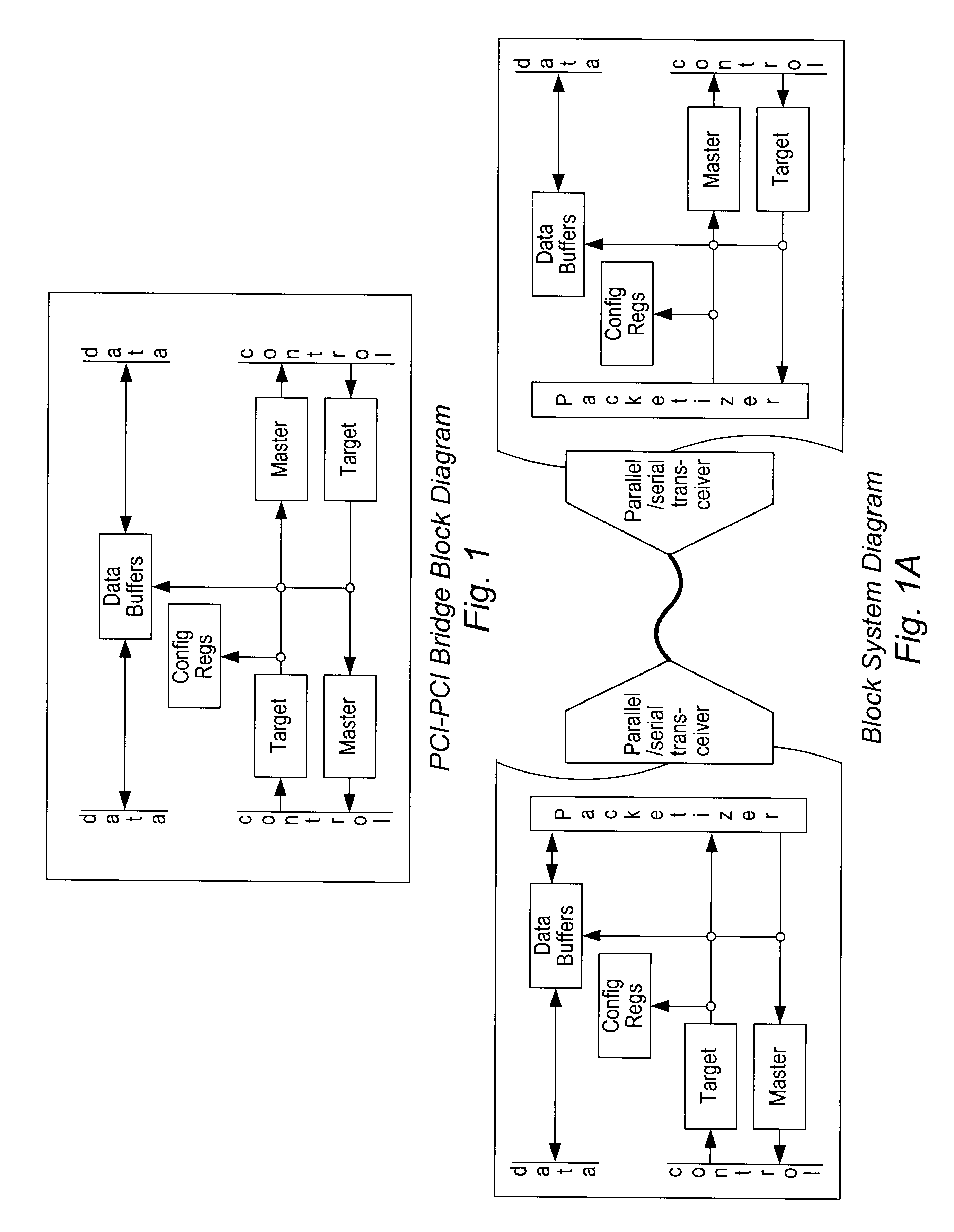

System and method for connecting peripheral buses through a serial bus

A Wide Area Serial PCI system for connecting peripheral devices to a computer. The WASP system includes a host computer system connected through a serial bus to a remote device. The serial bus can range from several meters to several kilometers or more. The host computer system includes a CPU and memory, and also includes a first Peripheral Component Interconnect (PCI) bus, also referred to as the local PCI bus. A primary bridge according to the present invention is coupled to the first PCI bus. The primary bridge includes PCI interface circuitry for interfacing to the first PCI bus. The remote device is located remotely from the computer system and comprises a second or remote PCI bus and one or more peripheral devices coupled to the second PCI bus. The remote device also includes a secondary bridge coupled to the second PCI bus. The secondary bridge includes PCI interface circuitry for interfacing to the second PCI bus. The serial bus is coupled between the primary bridge and the secondary bridge. Each of the primary bridge and secondary bridge include parallel / serial transceivers for converting parallel data generated on the first PCI bus and second PCI bus, respectively, to serial data for transmission on the serial bus and for converting serial data received from the serial bus to parallel data for generation on the first PCI bus and second PCI bus, respectively. The primary bridge and the secondary bridge collectively implement a PCI-PCI bridge register set.

Owner:NATIONAL INSTRUMENTS

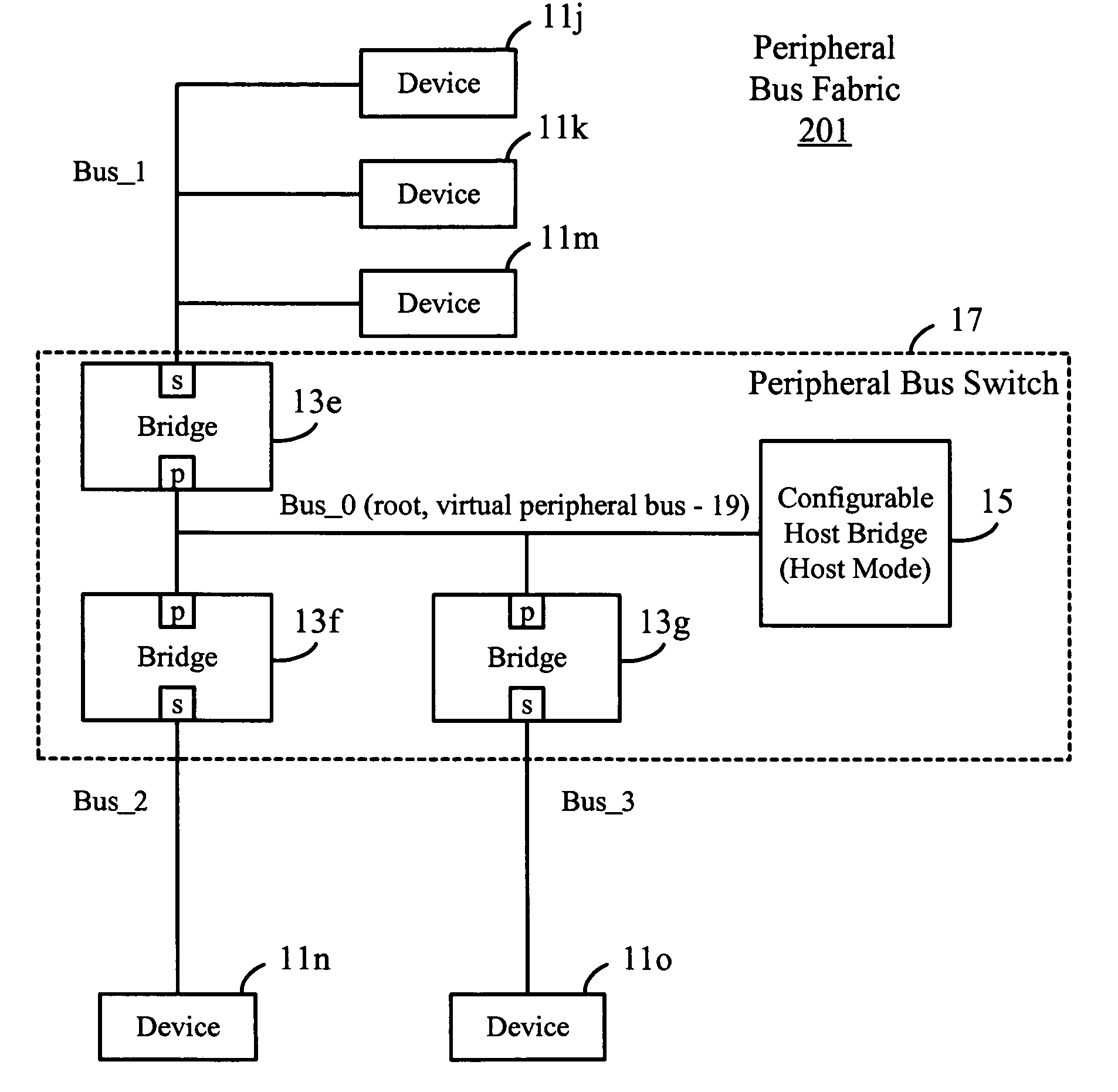

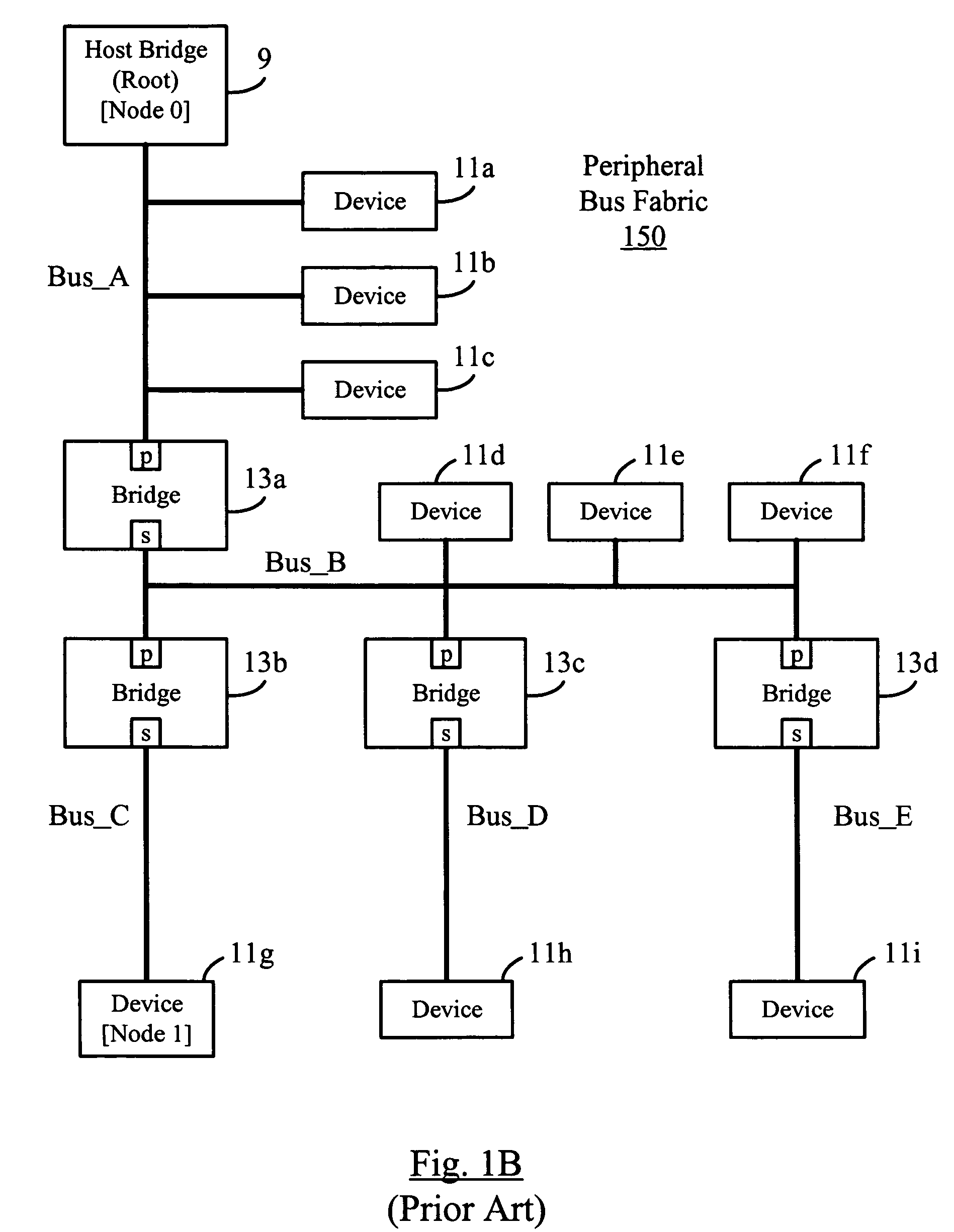

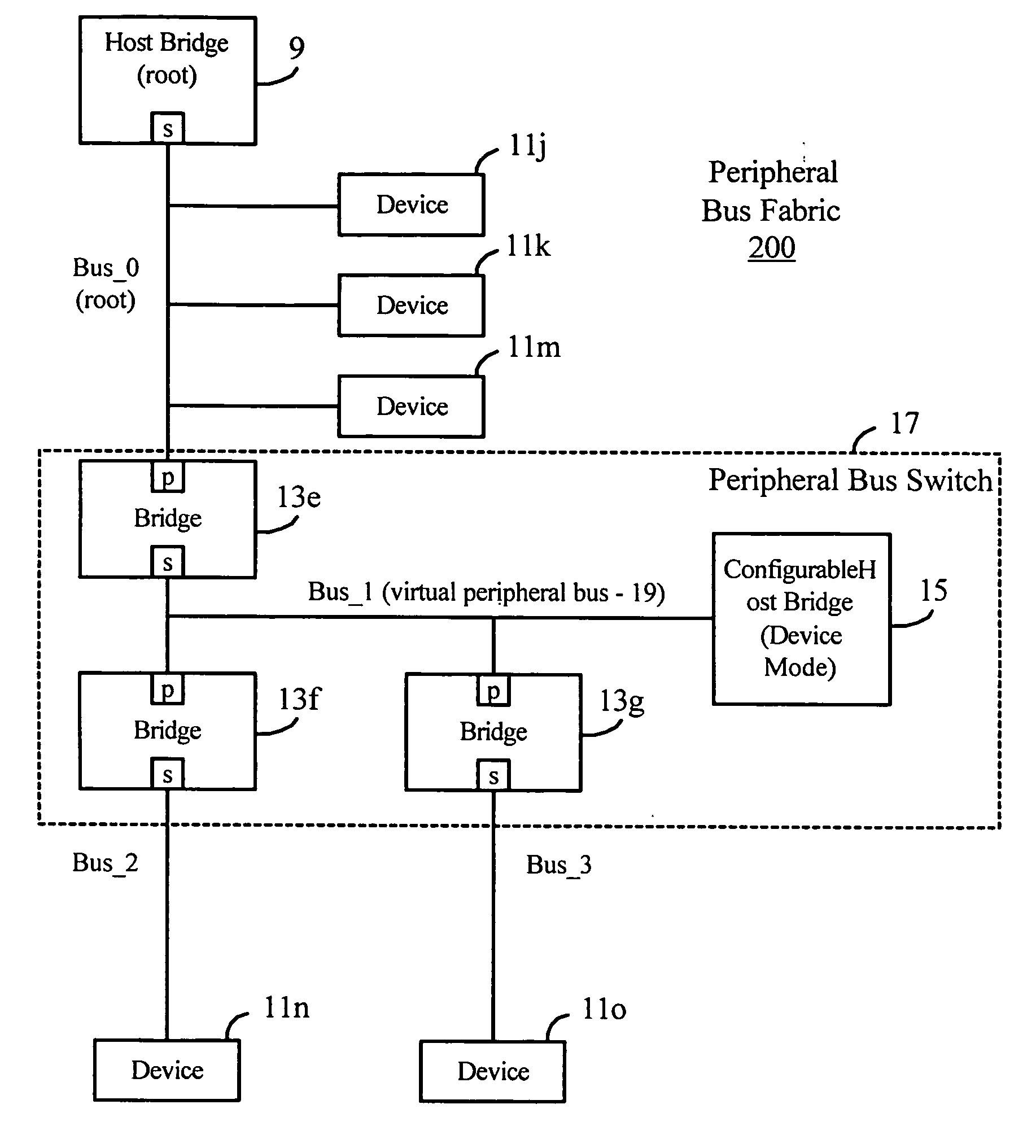

Peripheral bus switch having virtual peripheral bus and configurable host bridge

A peripheral bus switch includes a virtual peripheral bus, a plurality of bridges, and a configurable host bridge. A first bridge operably couples on a first side to the virtual peripheral bus and supports connection on a second side to a peripheral bus fabric. A second bridge operably couples on a first side to the virtual peripheral bus and supports connection on a second side to the peripheral bus fabric. The configurable host bridge operably couples to the virtual peripheral bus, supports a host mode of operation in which it serves as a host bridge, and supports a device mode of operation in which it operates as a device.

Owner:AVAGO TECH INT SALES PTE LTD

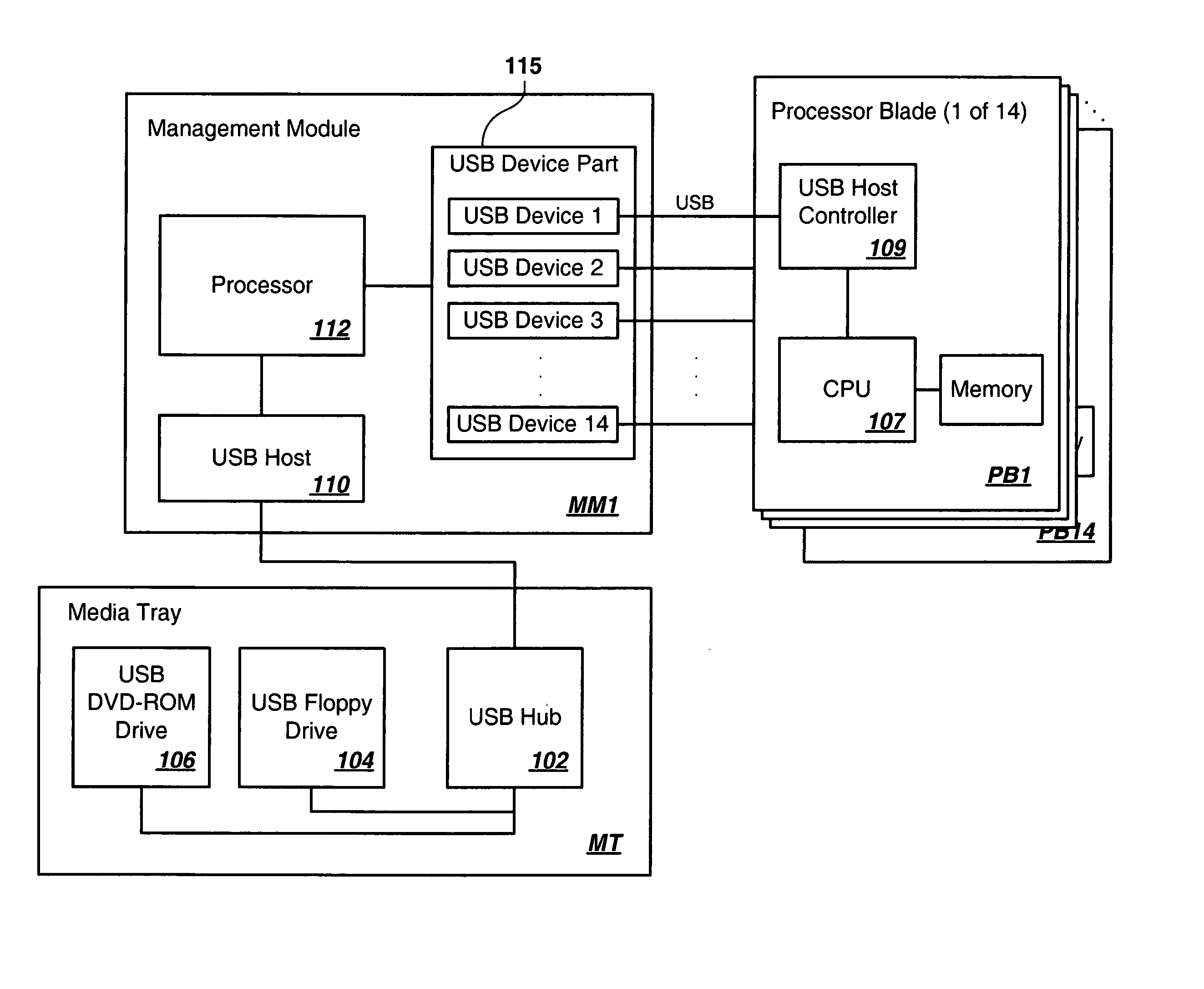

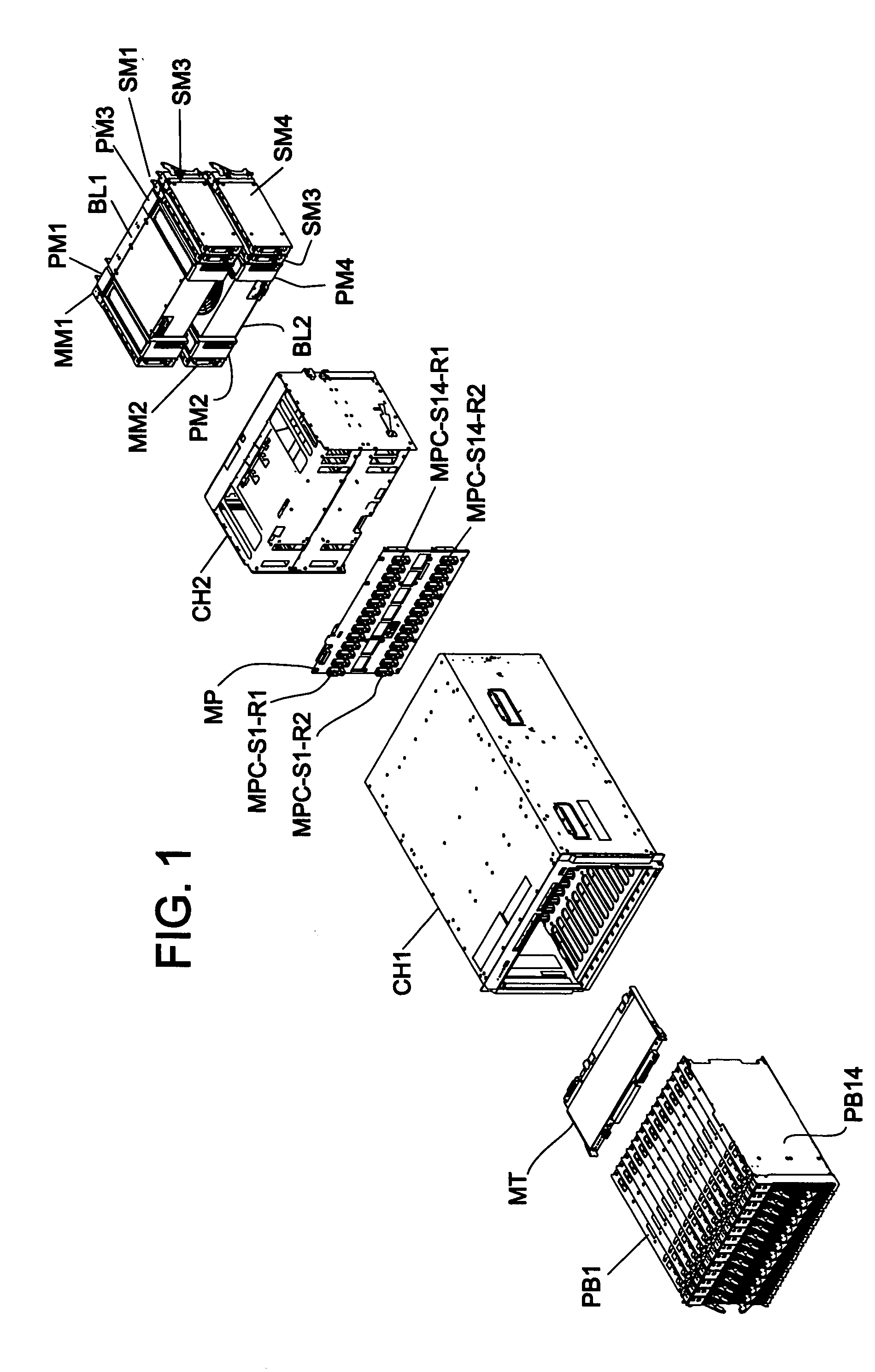

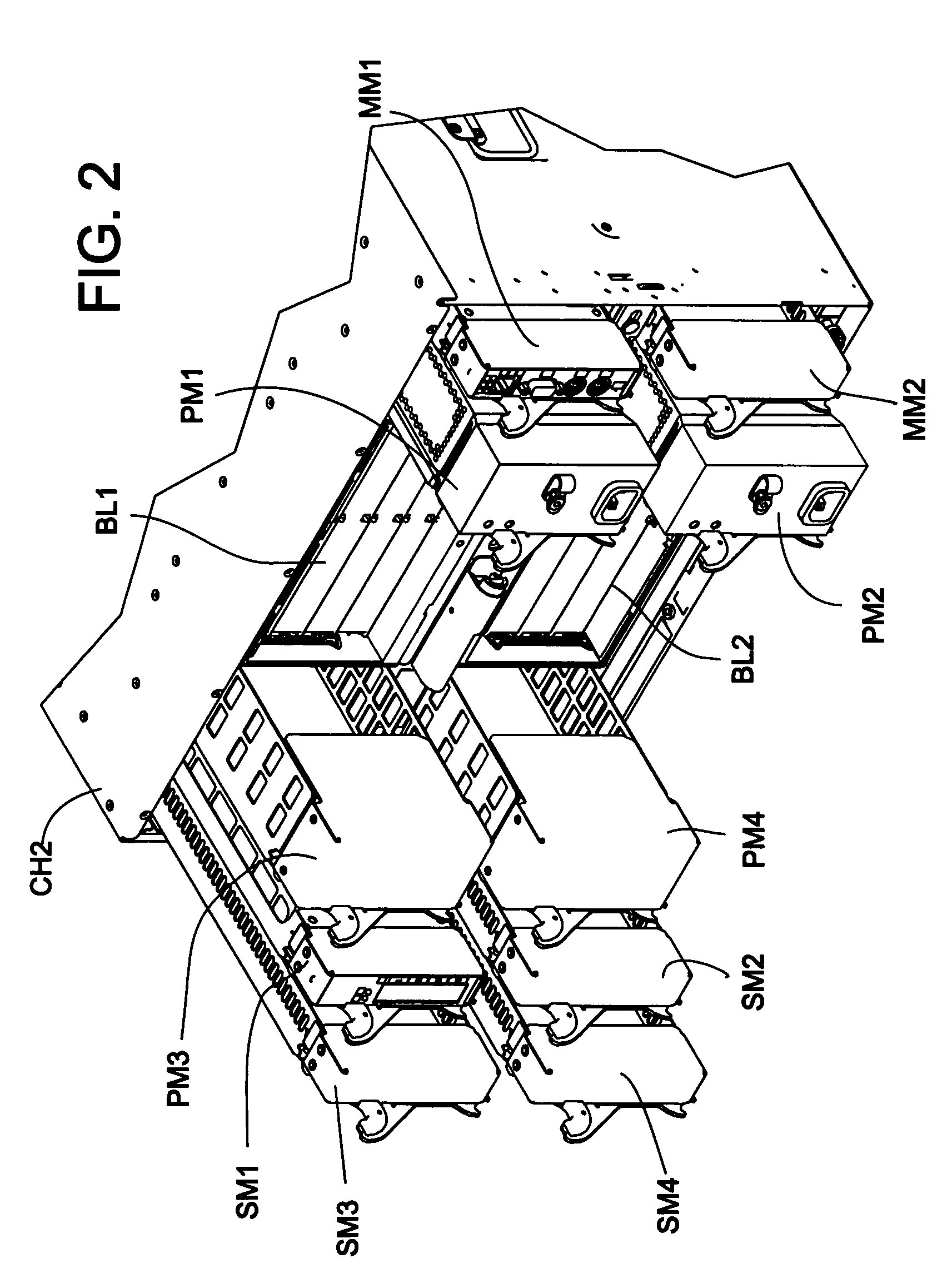

Shared simultaneously-connected drives

ActiveUS20060095595A1Eliminate needDigital data processing detailsError detection/correctionComputer hardwareControl engineering

Local drive presence is provided for local and remote drives by maintaining a plurality of uninterrupted protocol connections between a plurality of I / O controllers and a plurality of device interfaces through which peripheral bus commands are transmitted. Preferably, the I / O controllers are each housed in a separate server blade and provide each blade with access to the local and remote drives. At each of the device interfaces, rather than attaching an actual storage device, peripheral bus commands received at the device interfaces are serialized and conditionally passed or suppressed to and from the shared drive which is shared amongst the plurality of uninterrupted protocol connections. Preferably, the plurality of uninterrupted protocol connections is maintained such that the shared drives can be simultaneously shared. In one embodiment, the local drives are provided in a media tray which is shared amongst a plurality blades.

Owner:LENOVO GLOBAL TECH INT LTD

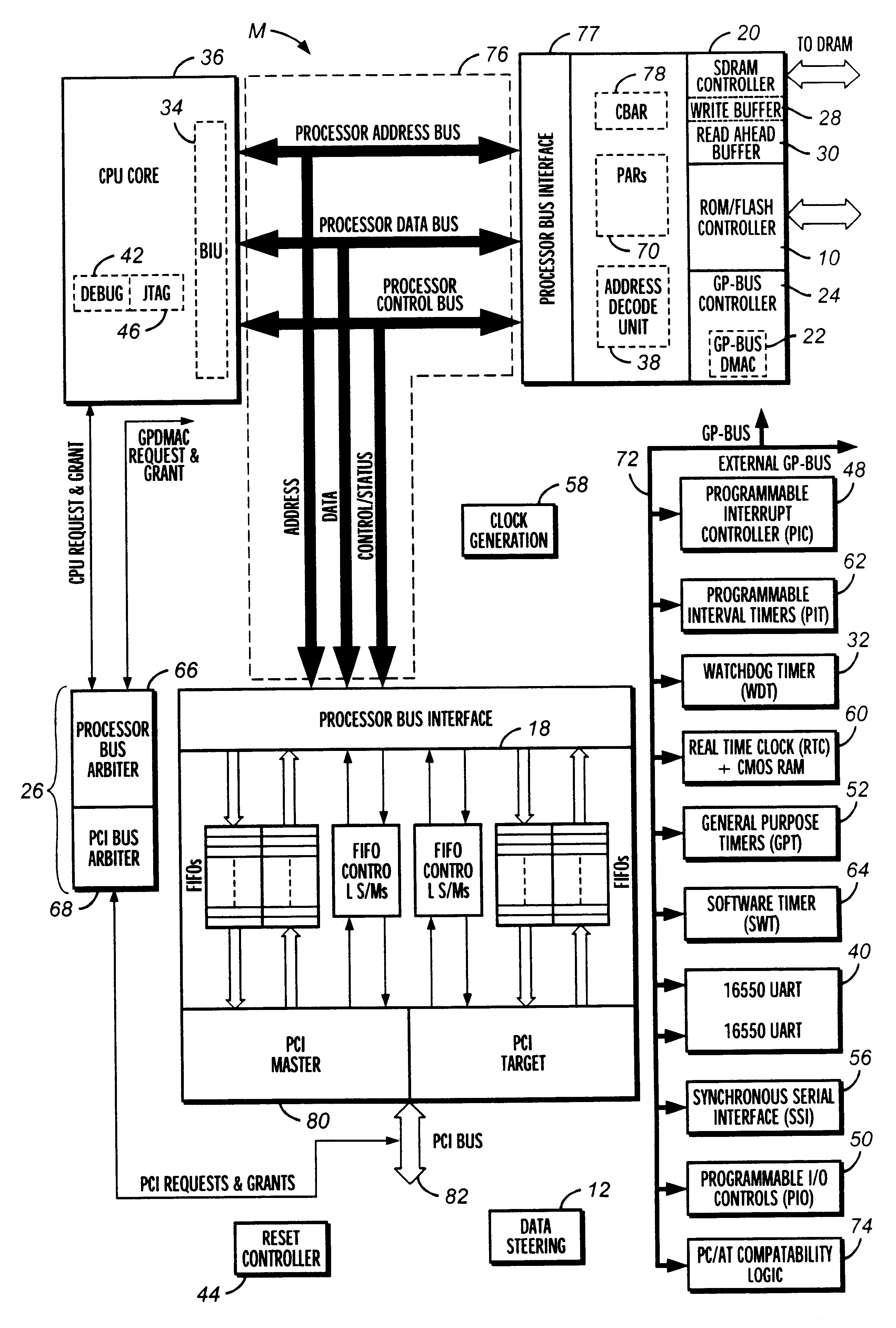

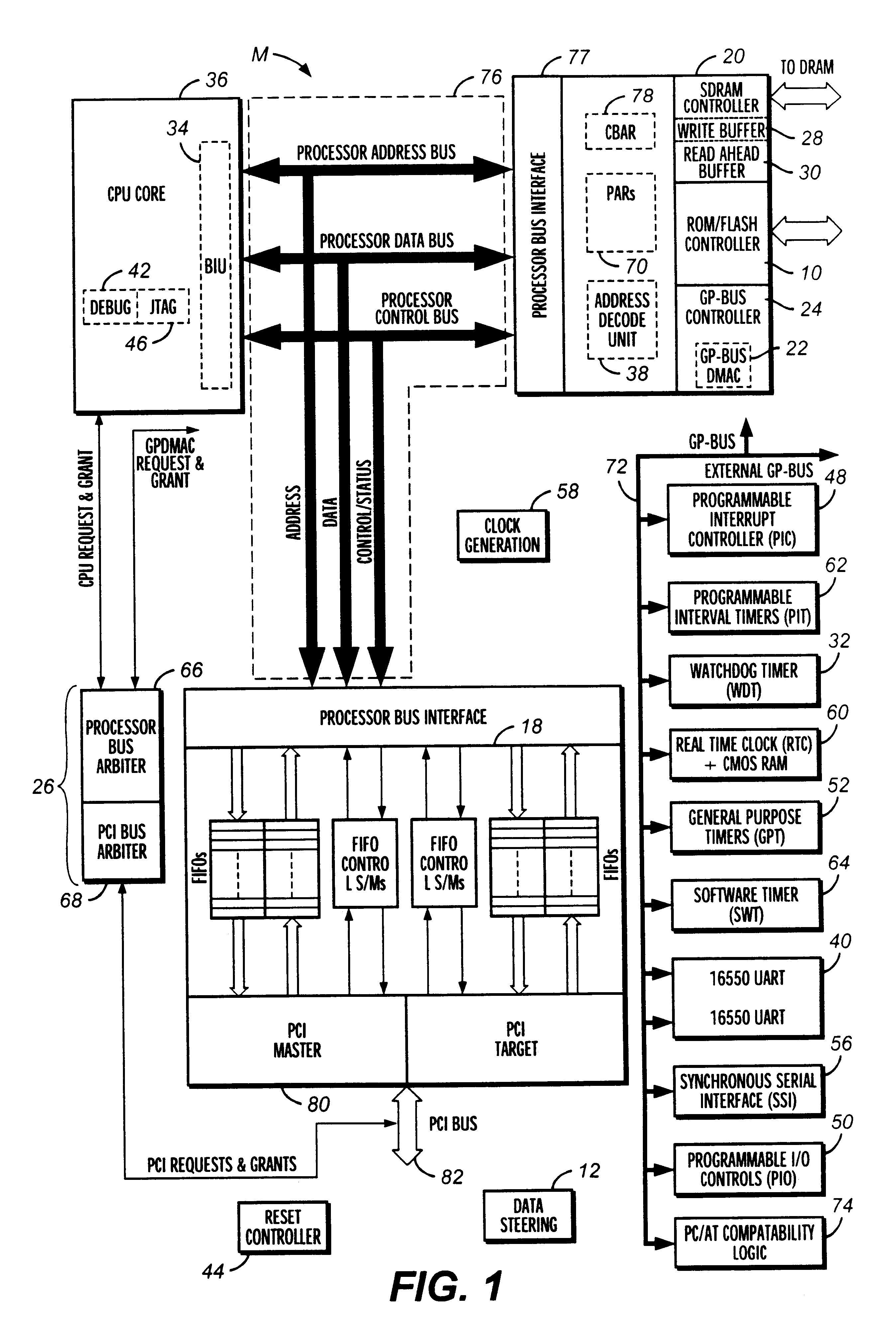

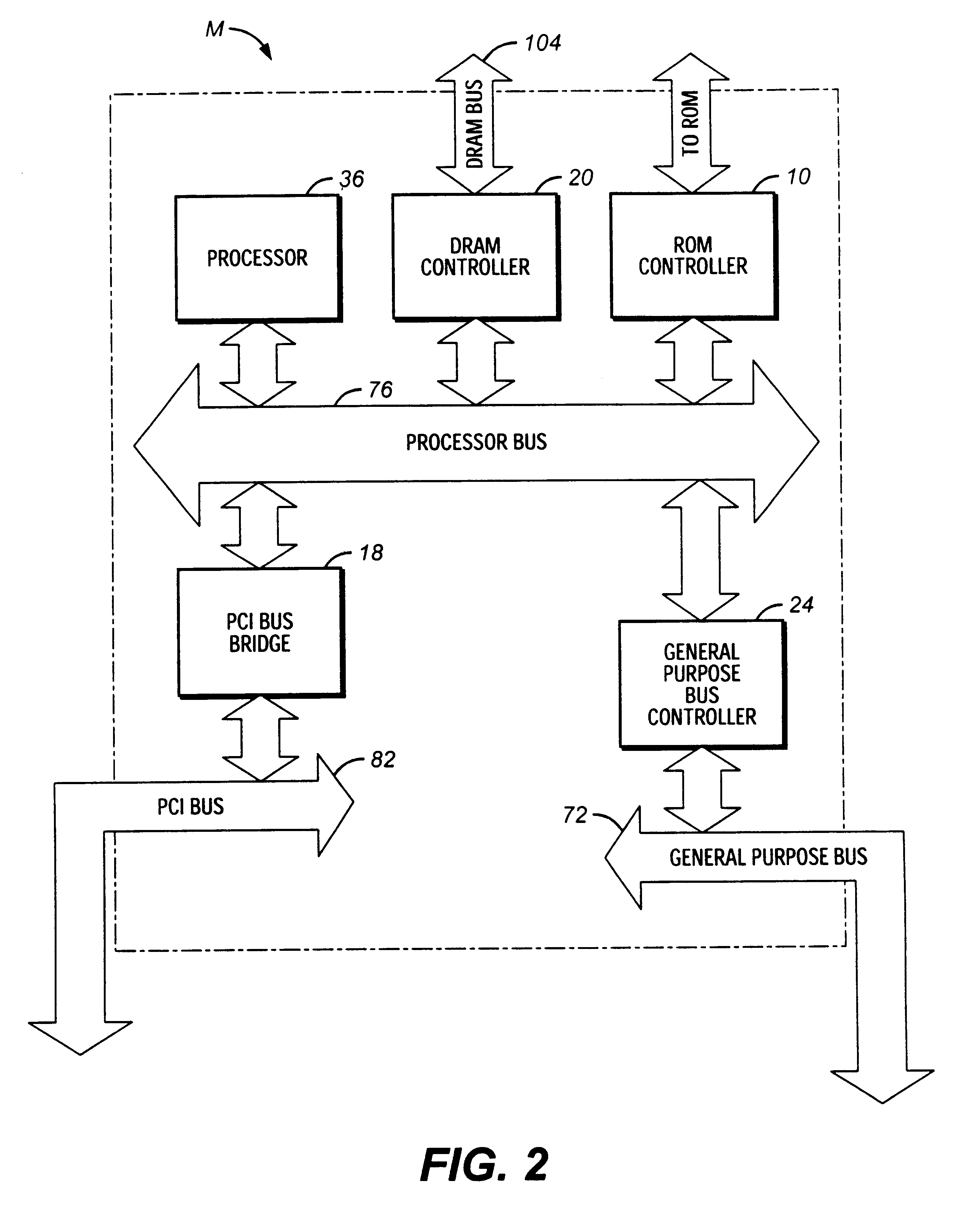

Flexible microcontroller architecture

A microcontroller provides a flexible architecture to readily support both general embedded applications and communications applications. The microcontroller includes an embedded processor, a relatively low-speed general purpose peripheral bus controller, a relatively high-speed peripheral bus host bridge, a primary memory controller, and a secondary memory controller, each coupled to a processor bus. The general purpose peripheral bus controller is coupled to a relatively low-speed general purpose peripheral bus which is coupled to a plurality of integrated general purpose peripherals. The relatively high-speed peripheral bus host bridge is coupled to a relatively high-speed peripheral bus capable of supporting a plurality of communication-oriented peripherals. The secondary memory controller shares an address bus with the general purpose peripheral bus controller and shares a data bus with either the primary memory controller or the general purpose peripheral bus controller. The control timing of the secondary memory controller is independent of the control timing of the general purpose peripheral bus controller. Also, a processor arbiter is coupled to the embedded processor, and a relatively high-speed peripheral bus arbiter is coupled to the peripheral bus host bridge. Aside from the microcontroller, an embedded system can include a relatively low-speed general purpose peripheral bus and a relatively high-speed peripheral bus, both external to the microcontroller. The external relatively lowspeed general purpose bus can be coupled to the relatively low-speed general purpose peripheral bus controller, and the external relatively high-speed peripheral bus can be coupled to the relatively high-speed peripheral bus host bridge.

Owner:ADVANCED MICRO DEVICES INC

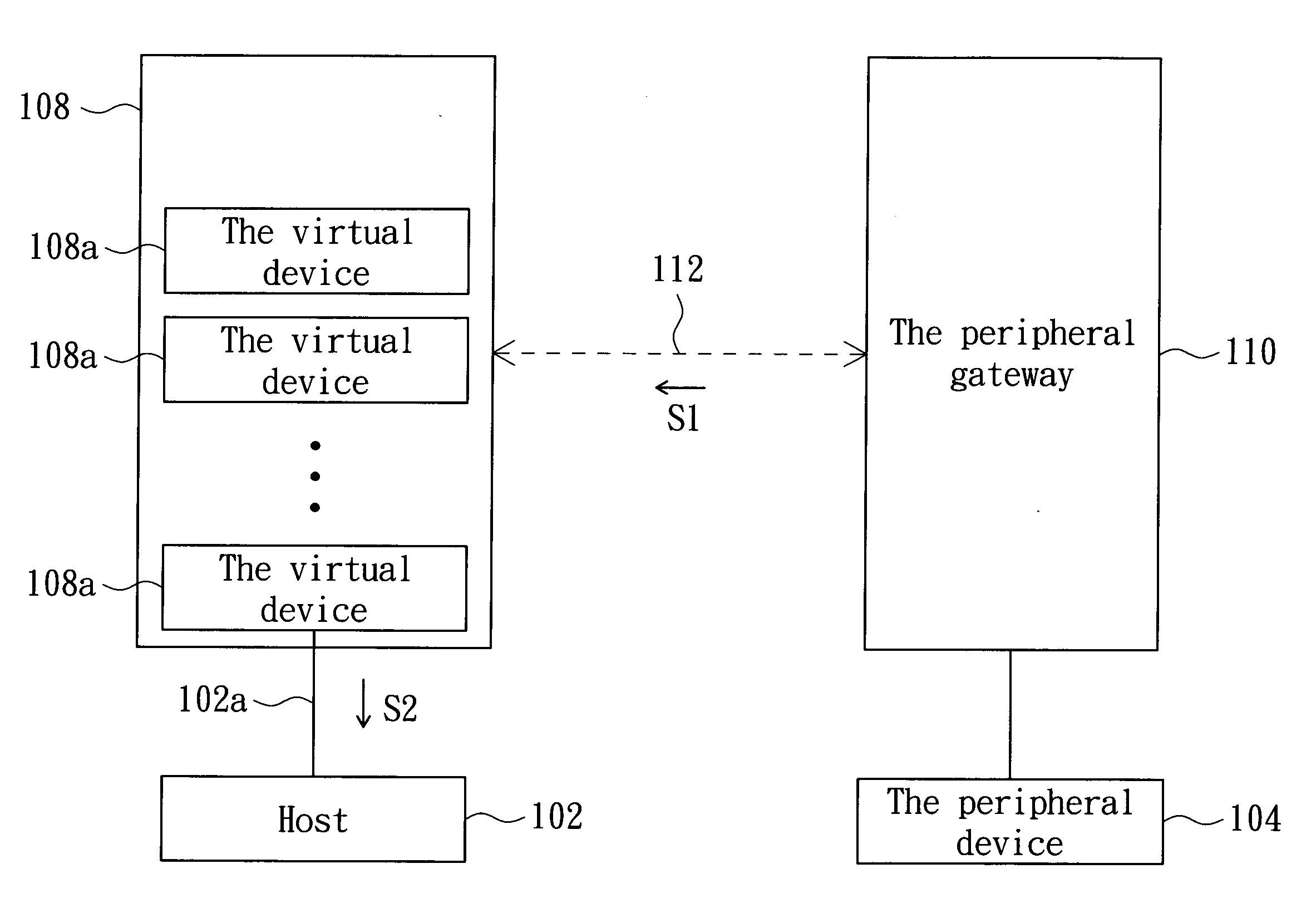

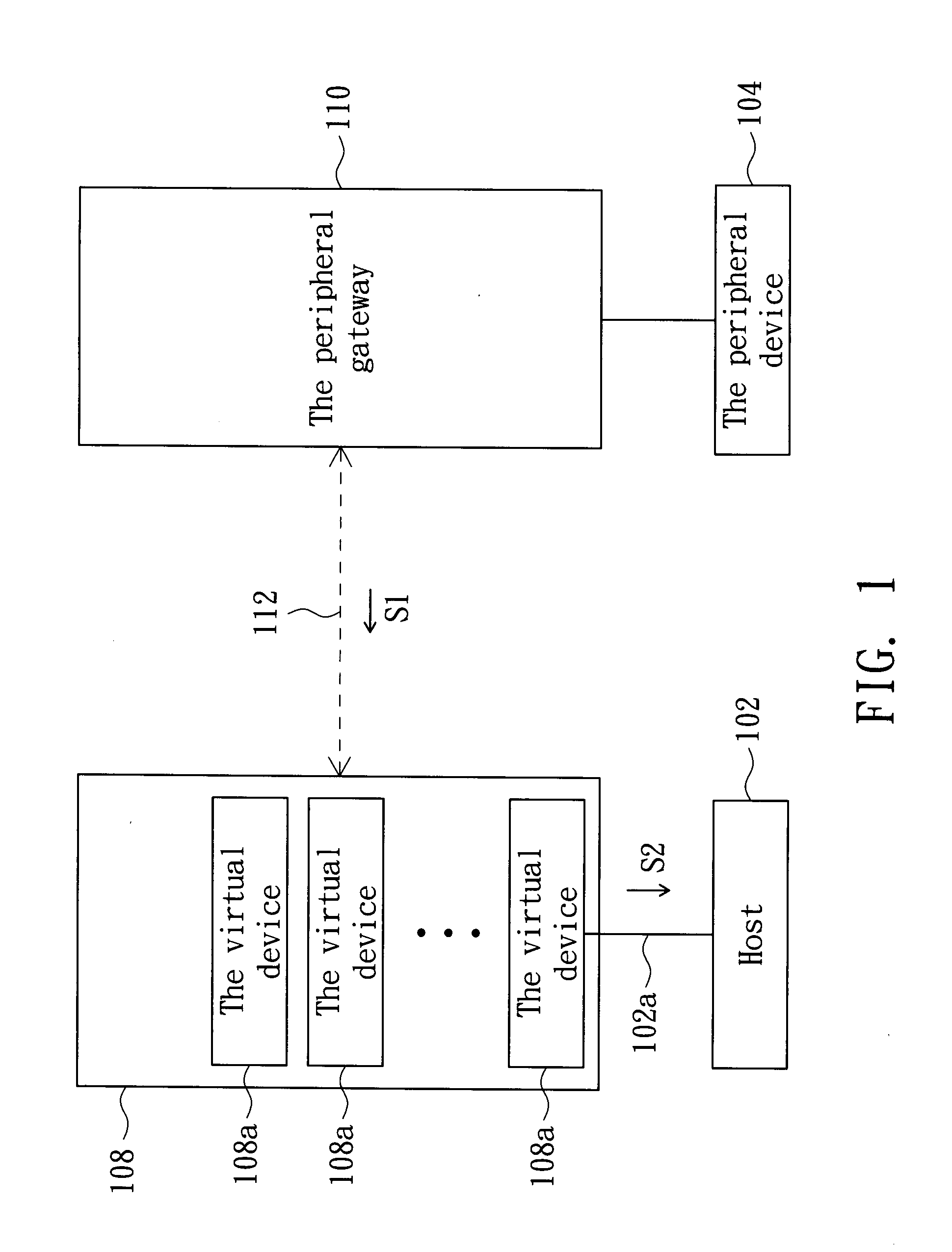

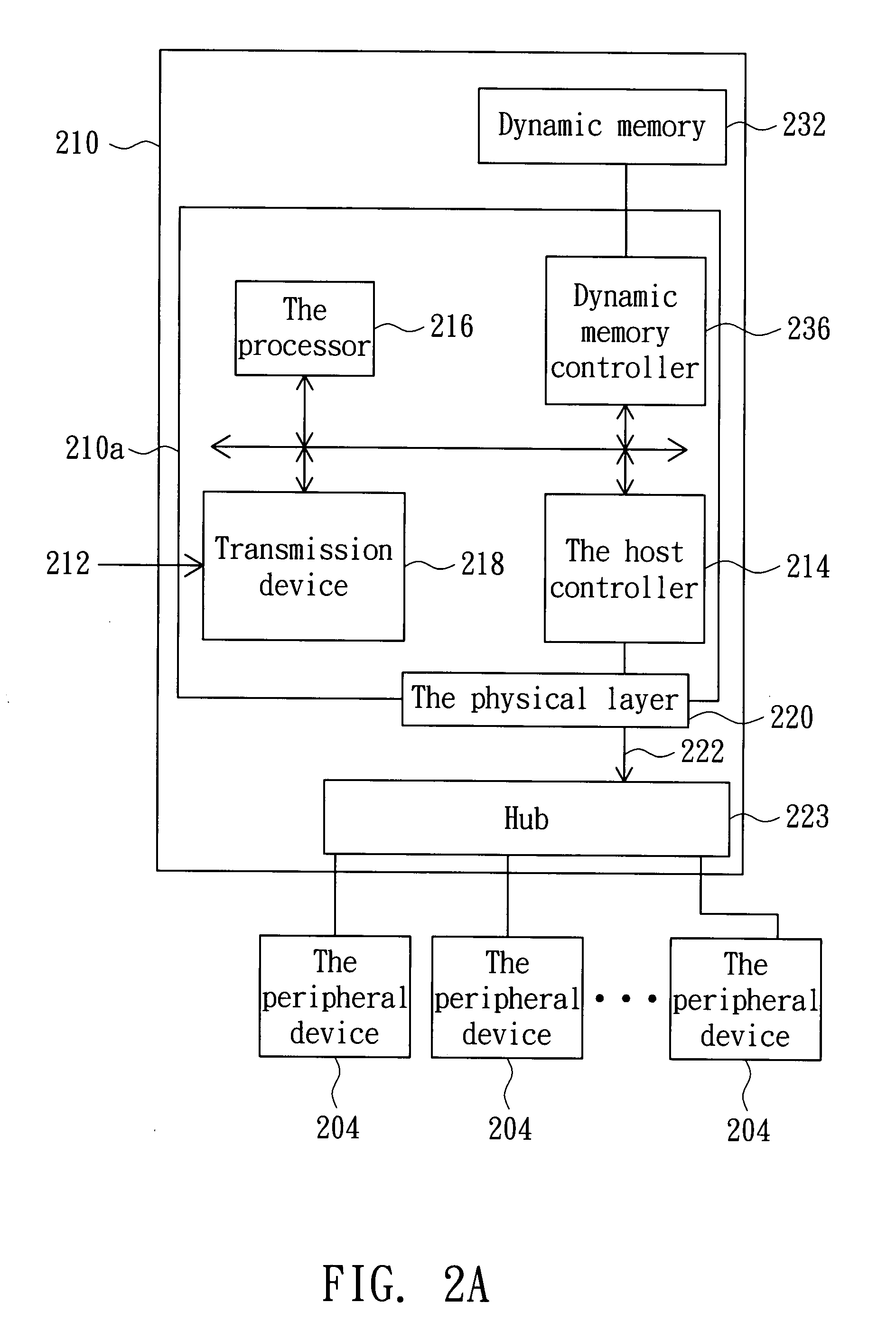

Device connection system and device connection method

InactiveUS20080071962A1TransmissionSoftware simulation/interpretation/emulationTelecommunications linkCommunication link

A device connection method for connecting a host having a peripheral bus to a peripheral device by the peripheral bus is provided. Firstly, as the peripheral device is connected to a peripheral gateway, a first information signal is outputted through a communication link. Next, a virtual device is mapped to the peripheral device in response to the first information signal, wherein the virtual device is compactable with the peripheral bus. Afterwards, as the peripheral bus of the host is connected to the virtual device, a second information signal is outputted through the peripheral bus in response to the first information signal to inform the host of a connection event taking place at the virtual device, so that the host enables the peripheral bus to install the peripheral device through the virtual device, wherein the host is connected to the peripheral device through the peripheral bus and the communication link.

Owner:QUANTA COMPUTER INC

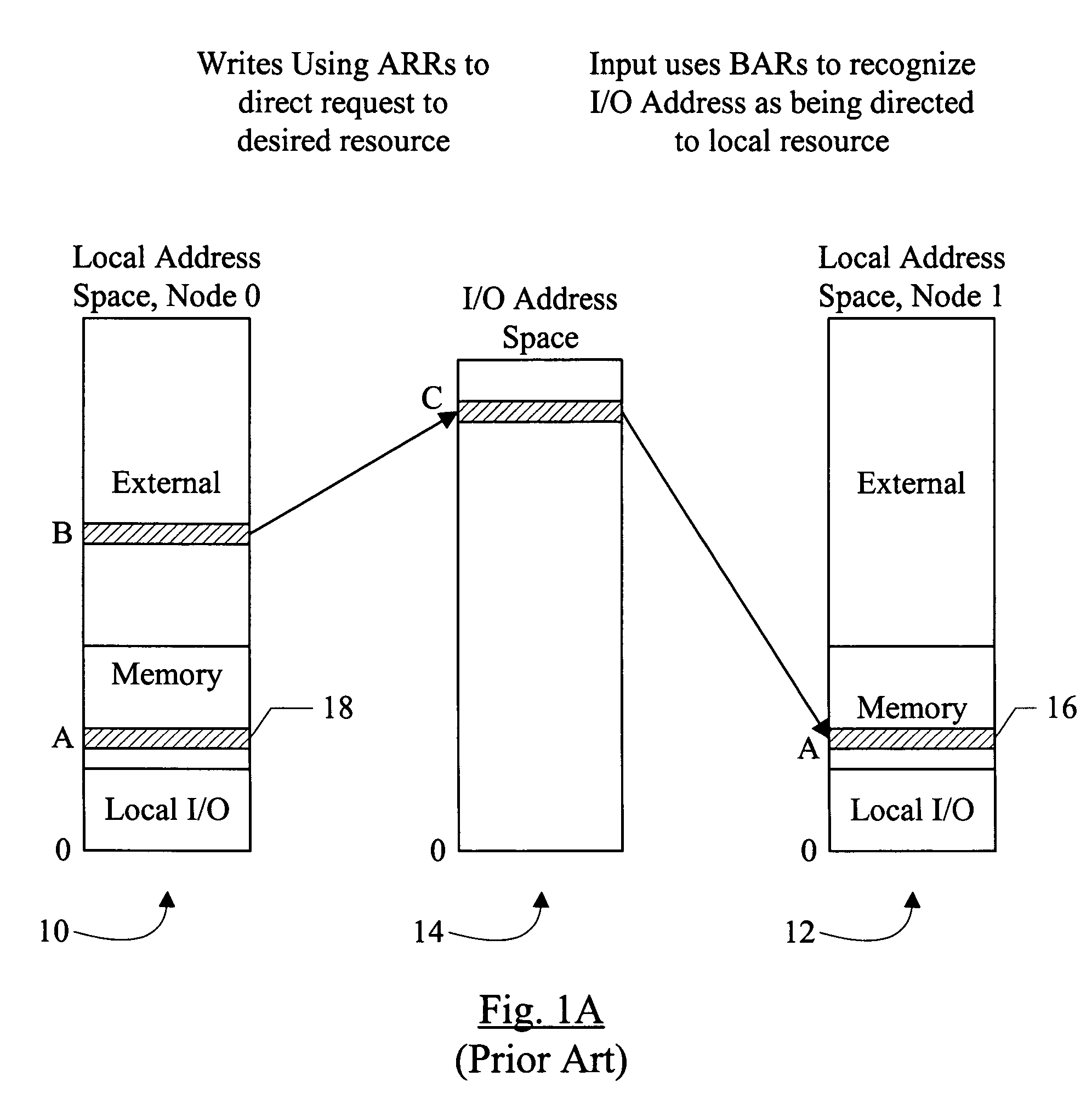

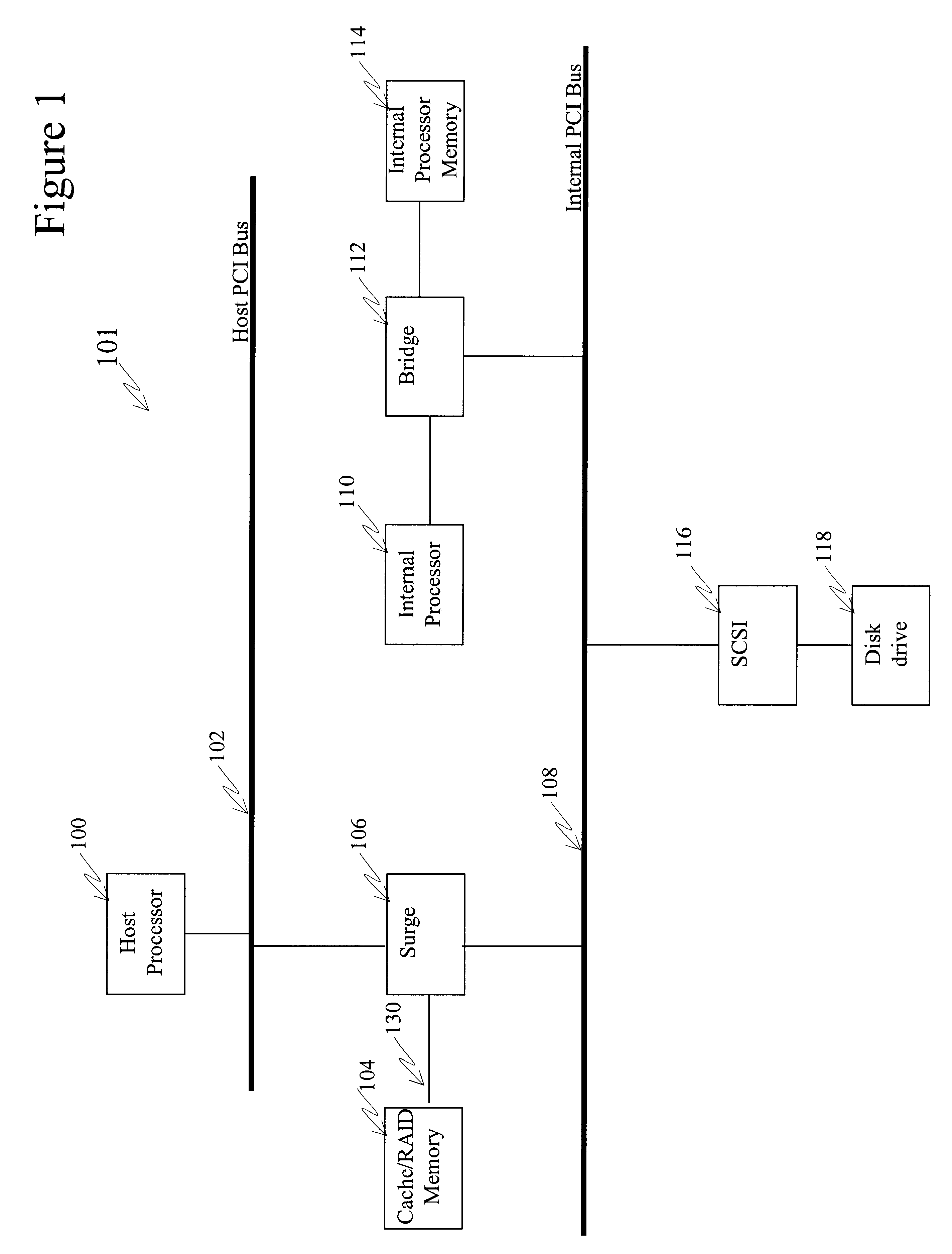

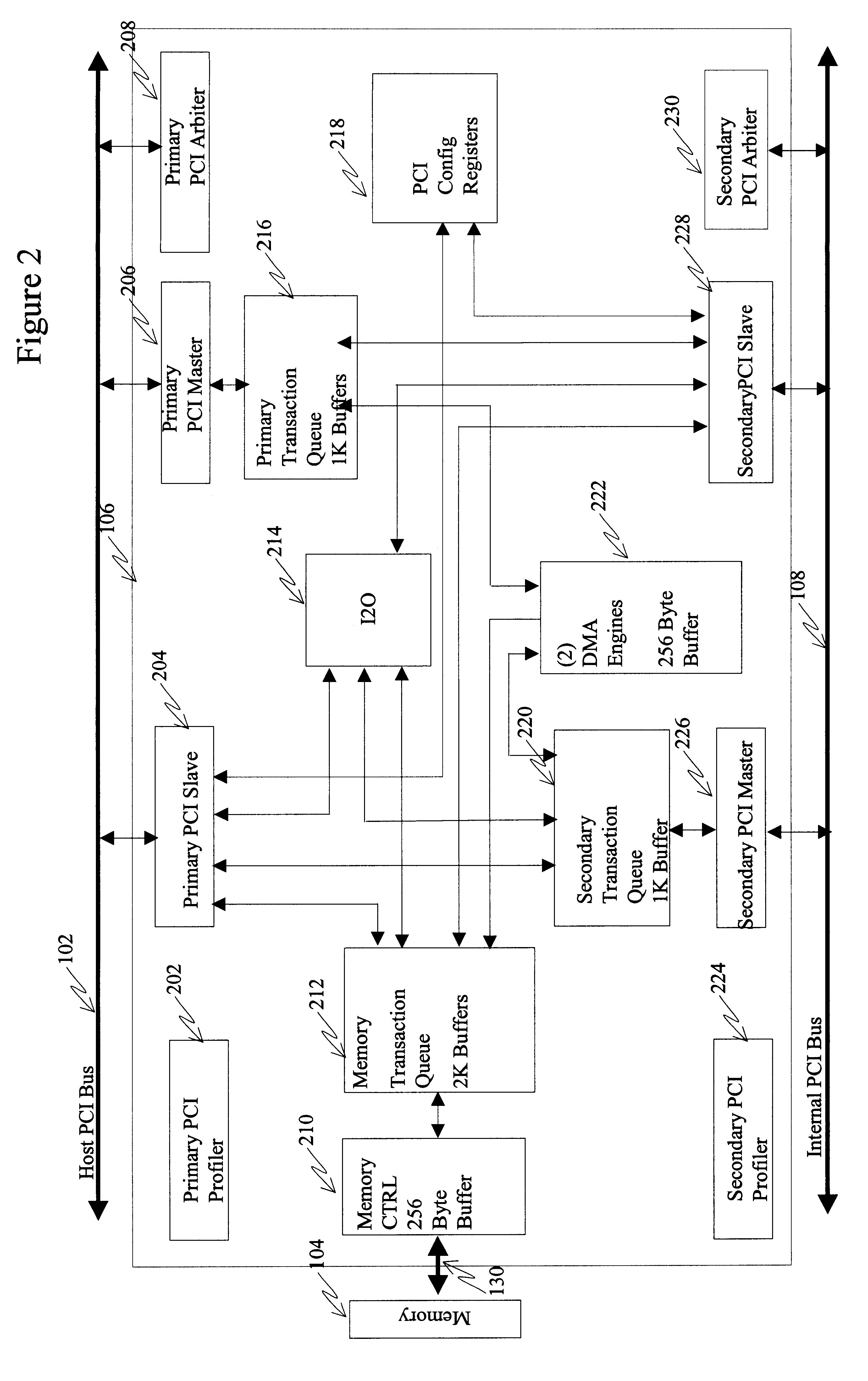

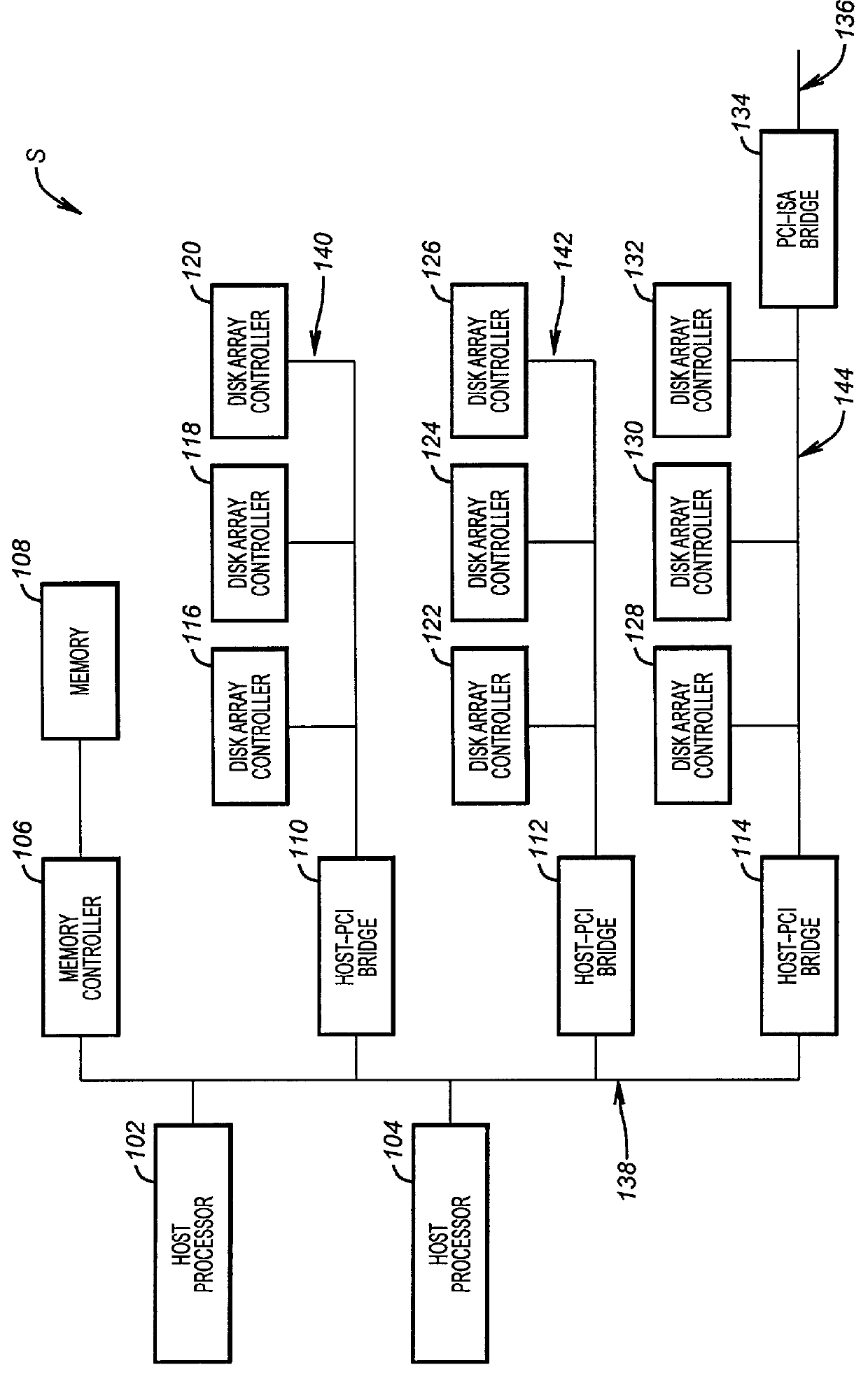

Dynamic routing of data across multiple data paths from a source controller to a destination controller

InactiveUS6675253B1Input/output to record carriersMemory adressing/allocation/relocationMemory interfaceDatapath

A drive array controller or other data handling system supports dynamic data routing across multiple data paths between a source controller and a destination controller. Each data path between the source controller and the data controller can include a cache memory. Based on detection of a cache address, the data path with the cache memory corresponding to the cache address is selected. Data transfer to a single destination controller can be alternated between different data paths based on detection of different cache addresses. Each data path can include a plurality of bus / memory interface devices and a peripheral bus such as a peripheral component interconnect (PCI) bus. As an alternative to dynamic data routing based on addressing, data routing can be based on command type.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Method and system for discovering a power source on a peripheral bus

ActiveUS7581119B2Stable and reliable mannerVolume/mass flow measurementHardware monitoringEngineeringElectric power

Improved techniques to recognize a power source on a peripheral bus and / or determine power available from the power source via the peripheral bus are disclosed. Typically, the peripheral bus is supported by a cable connected between a host device and an electronic device. In this case, the host device is a power source (e.g., power adapter or battery pack) and the cable is used to provide power from the power source to the electronic device. Hence, by understanding the power available from the power source, the electronic device can manage its power utilization so as to operate in a stable and reliable manner. The electronic device is, for example, a portable computing device. Examples of portable computing devices include a Portable Digital Assistant (PDA) and a portable media player.

Owner:APPLE INC

Peripheral bus switch having virtual peripheral bus and configurable host bridge

InactiveUS20060230217A1Software simulation/interpretation/emulationMemory systemsEmbedded systemPeripheral

Owner:AVAGO TECH INT SALES PTE LTD

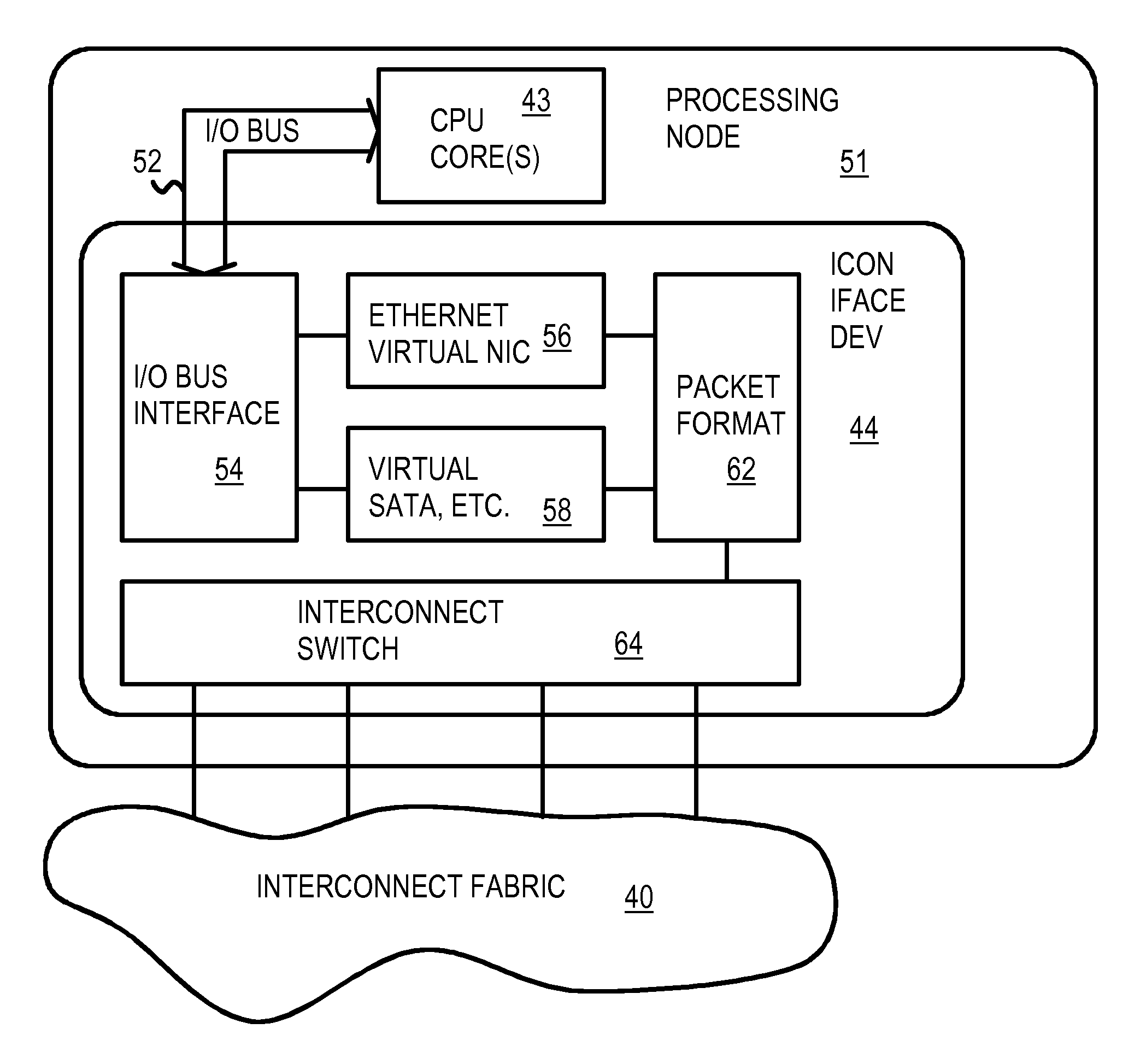

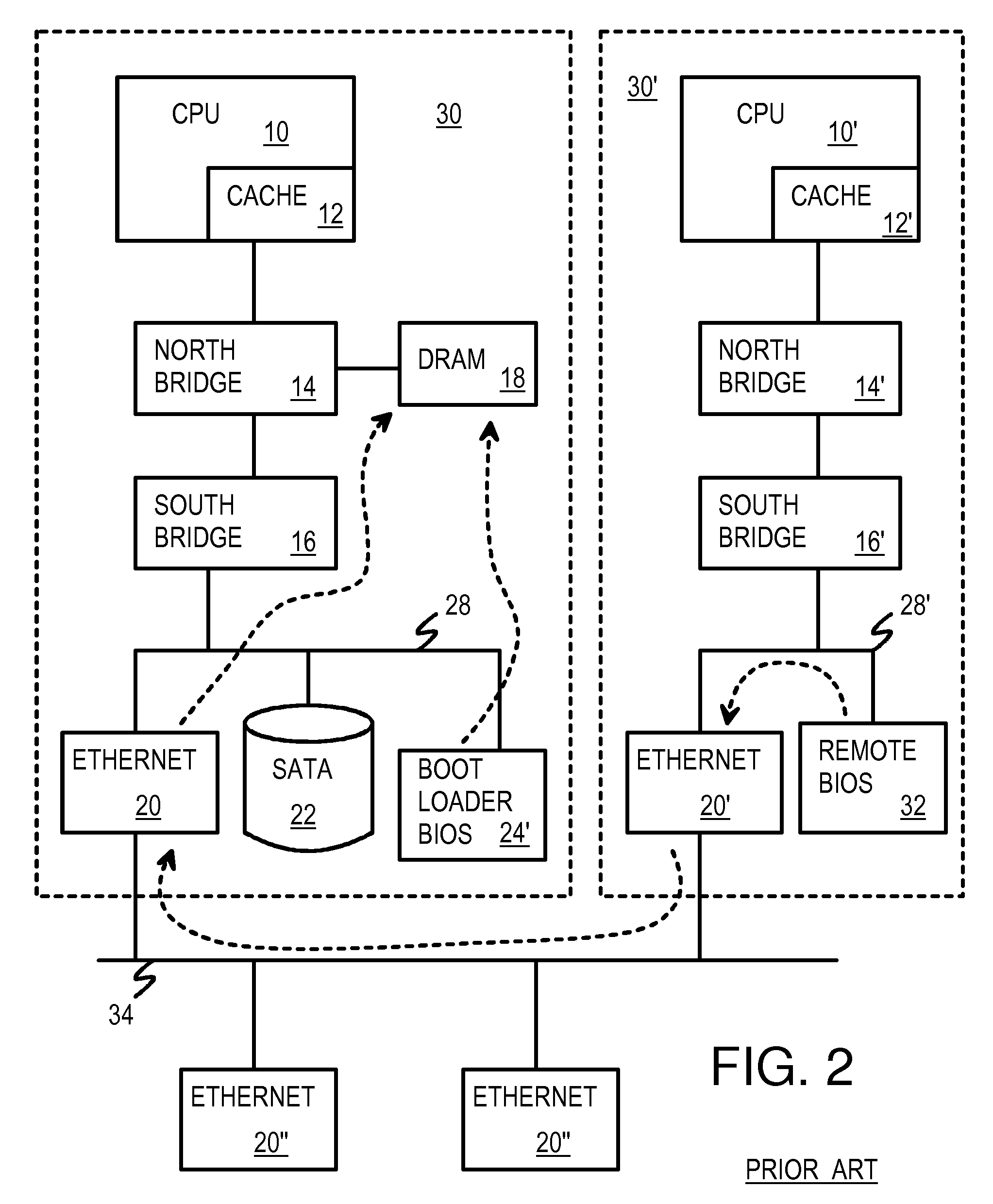

Hardware-Based Virtualization of BIOS, Disks, Network-Interfaces, & Consoles Using a Direct Interconnect Fabric

ActiveUS20080320181A1Program controlInput/output processes for data processingVirtualizationOperational system

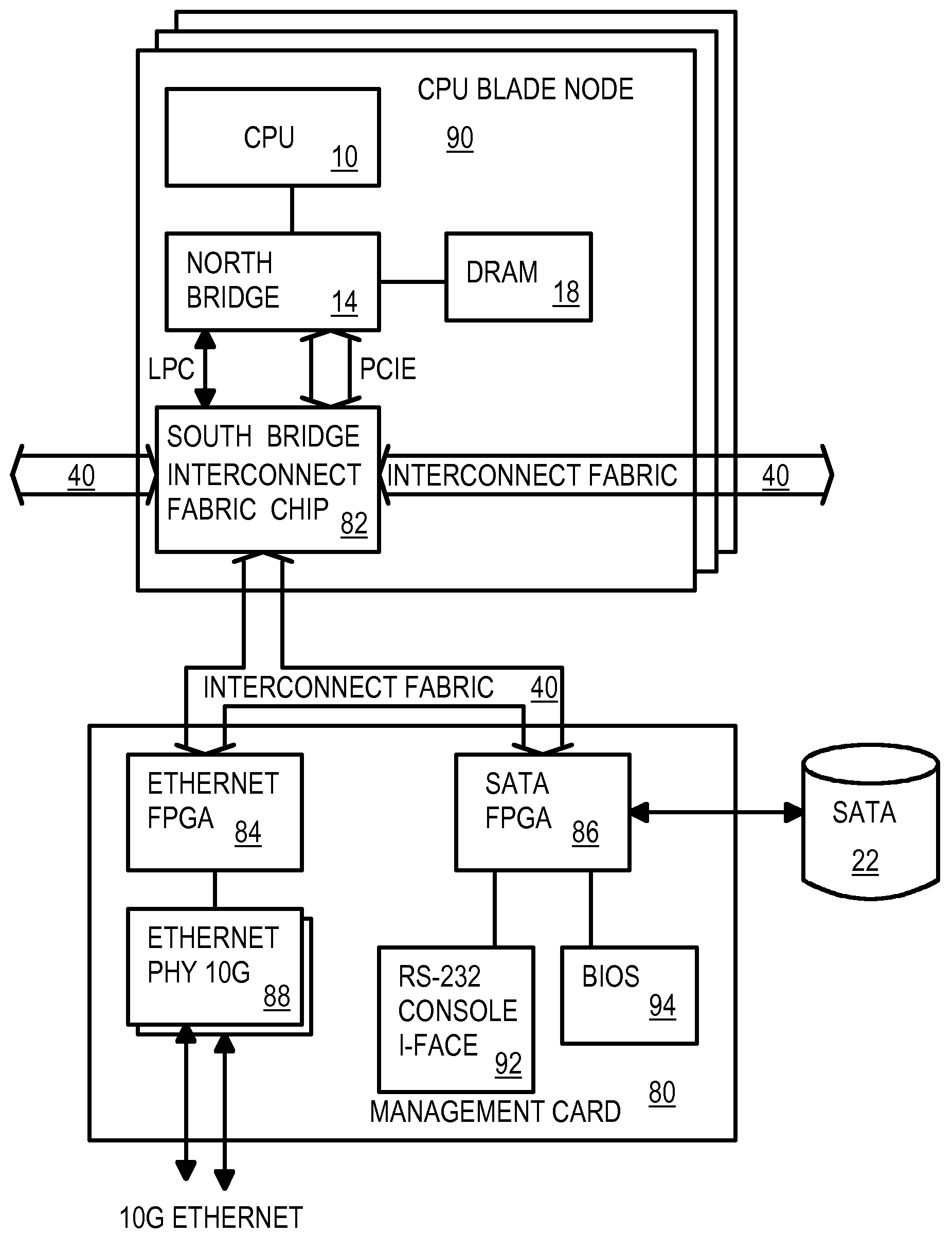

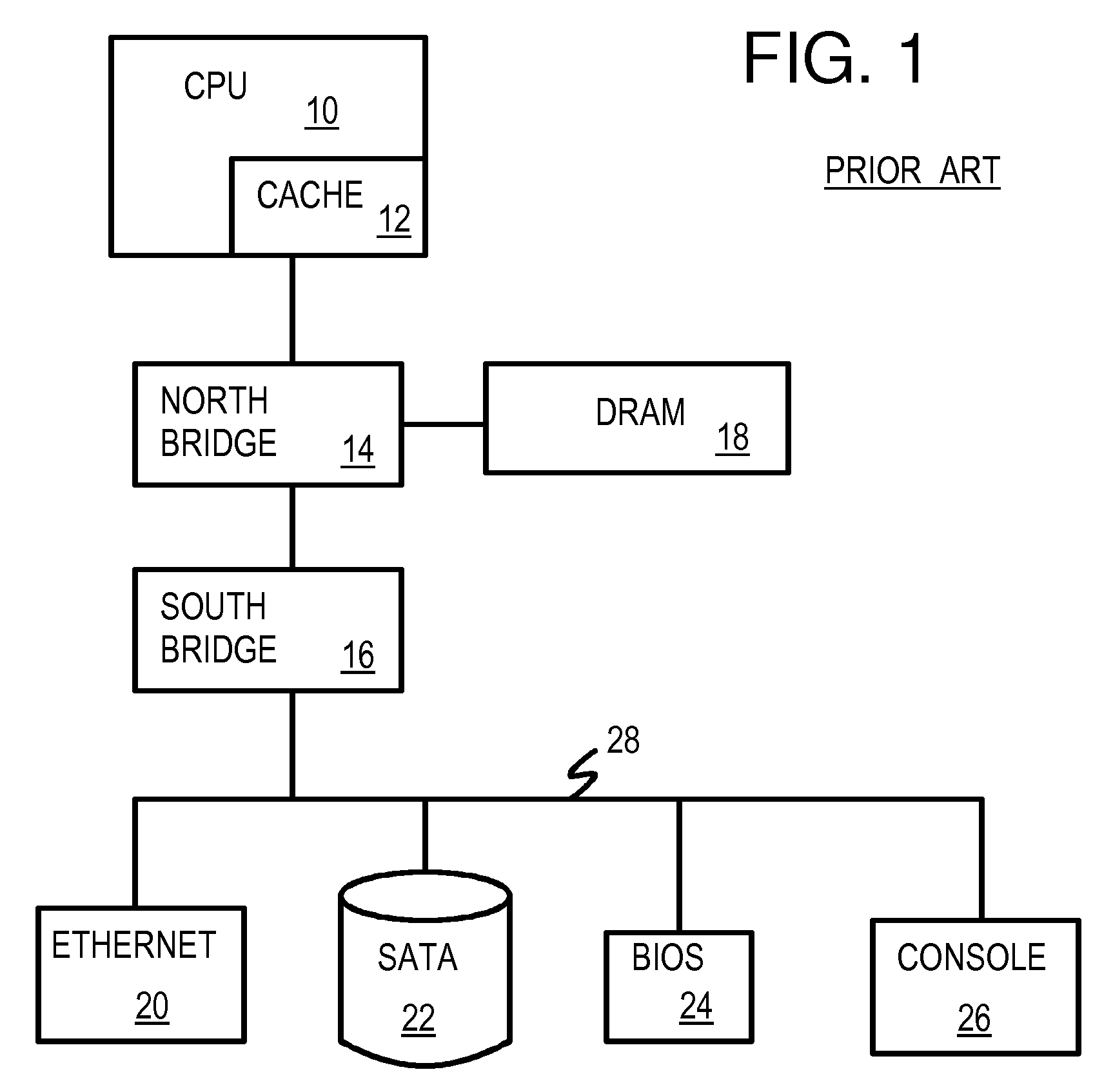

A multi-computer system has many processors that share peripherals. The peripherals are virtualized by hardware without software drivers. Remote peripherals appear to the operating system to be located on the local processor's own peripheral bus. A processor, DRAM, and north bridge connect to a south bridge interconnect fabric chip that has a virtual Ethernet controller and a virtual generic peripheral that act as virtual endpoints for the local processor's peripheral bus. Requests received by the virtual endpoints are encapsulated in interconnect packets and sent over an interconnect fabric to a device manager that accesses remote peripherals on a shared remote peripheral bus so that data can be returned. Ethernet Network Interface Cards (NIC), hard disks, consoles, and BIOS are remote peripherals that can be virtualized. Processors can boot entirely from the remote BIOS without additional drivers or a local BIOS. Peripheral costs are reduced by sharing remote peripherals.

Owner:SEAMICRO

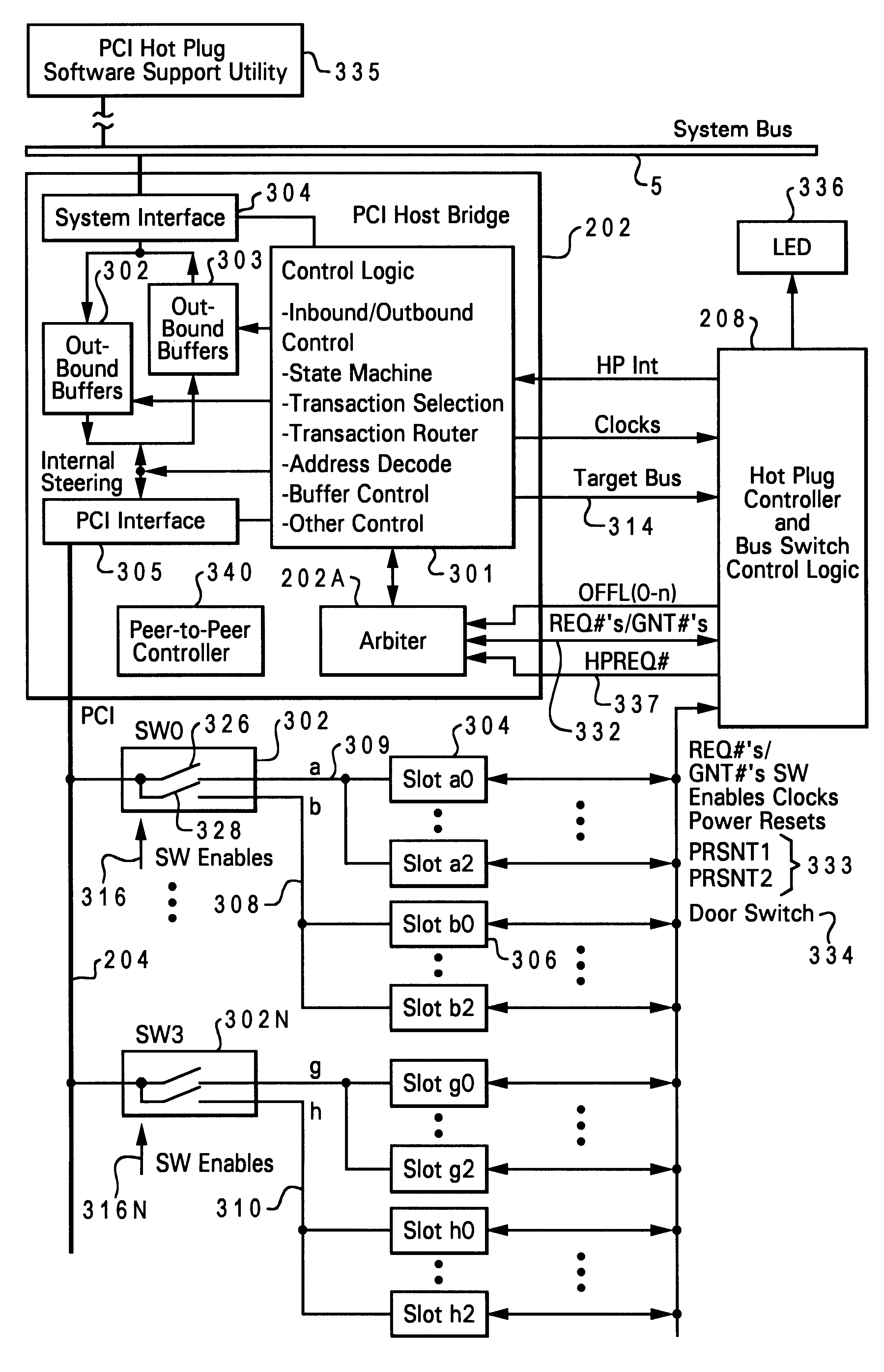

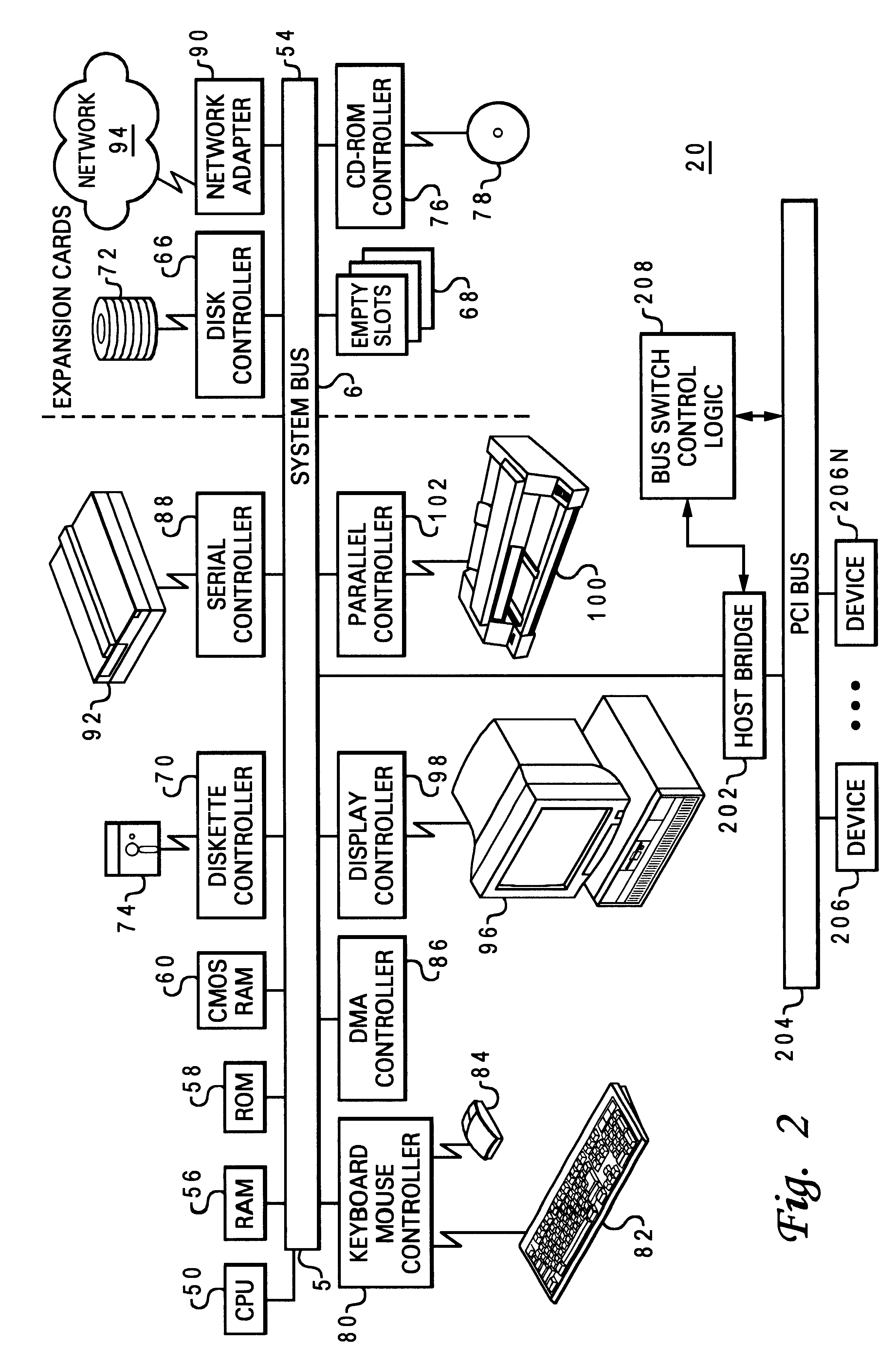

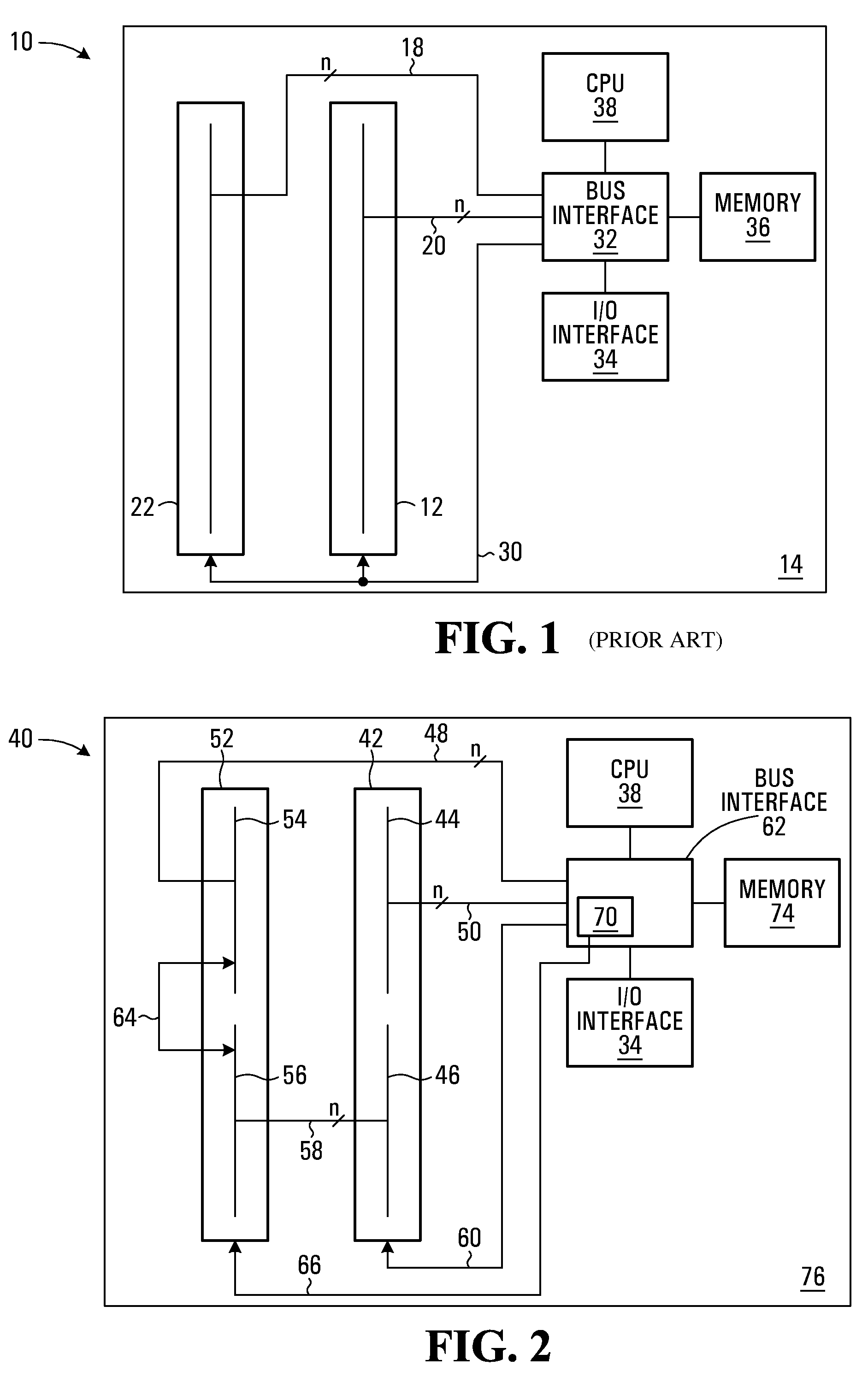

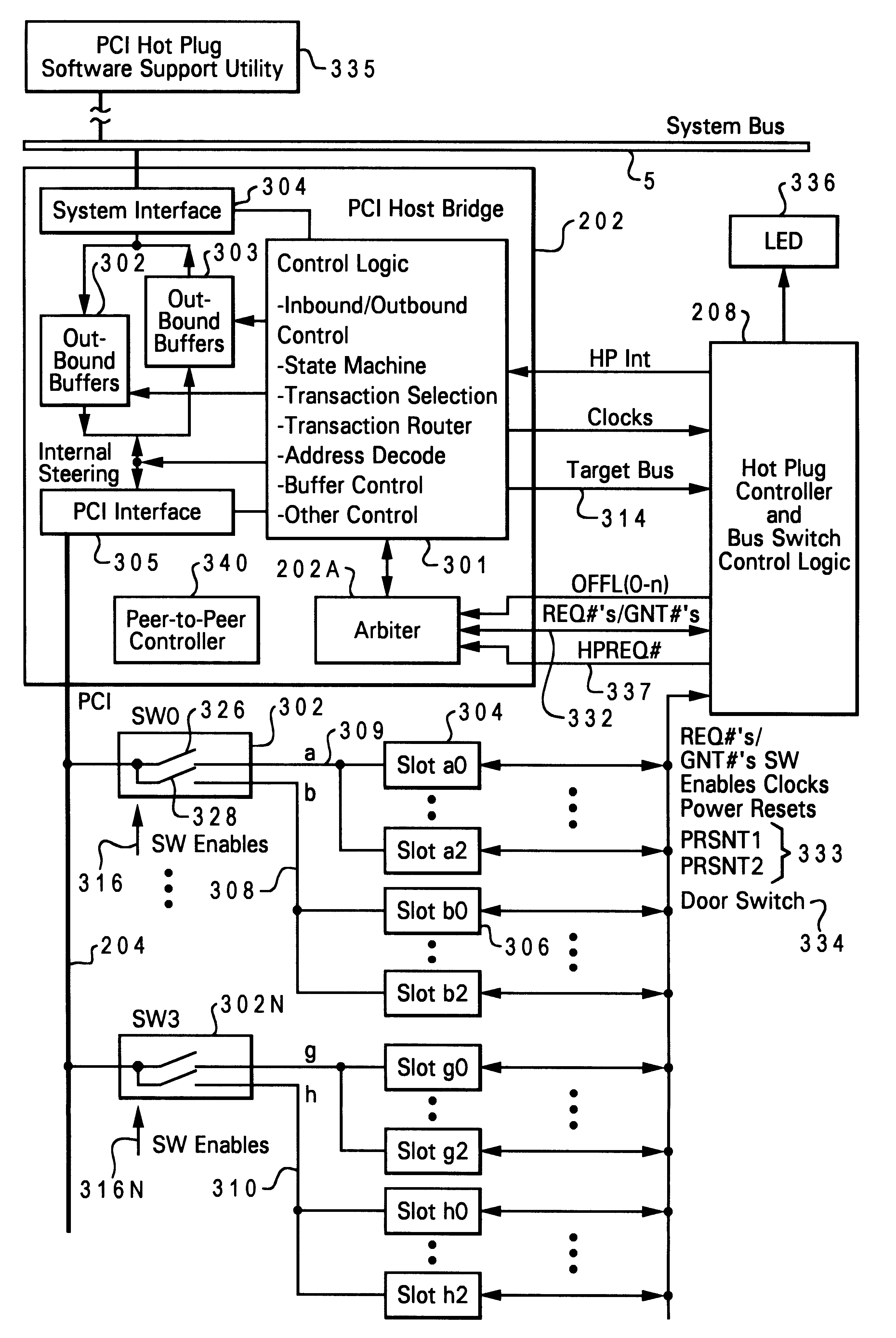

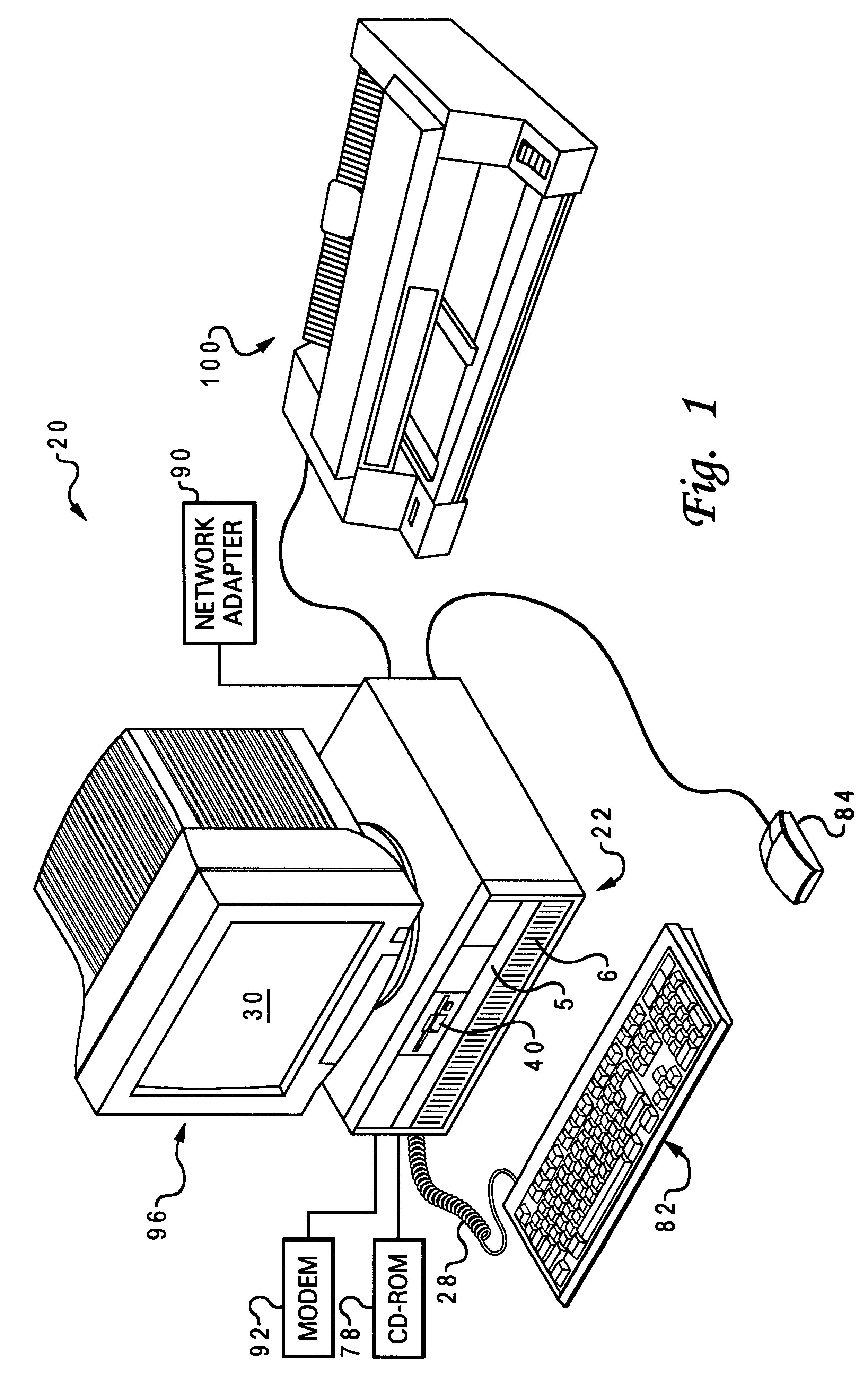

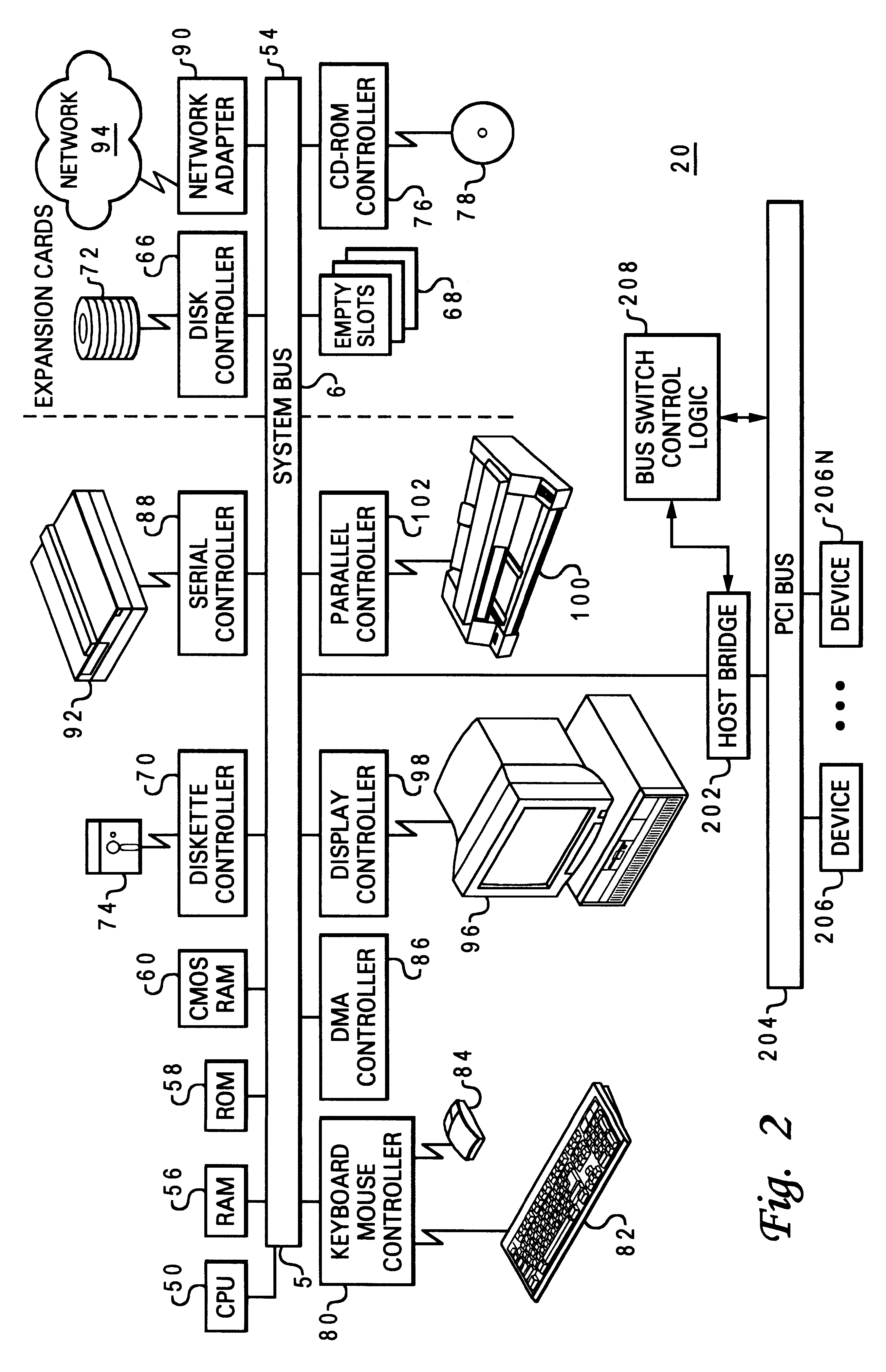

Method and system for providing hot plug of adapter cards in an expanded slot environment

InactiveUS6338107B1Component plug-in assemblagesElectric digital data processingAddress decoderMethod selection

A method of providing an interconnection between one or more peripheral devices and a system bus of a computer system selectively establishes and removes a connection from a primary peripheral bus to a secondary peripheral buses, and determines a target from among the one or more peripheral devices when a bus bridge is a master of the primary peripheral bus, using an address decoder. Access to and from the primary peripheral bus is controlled using an arbiter to select a master for the primary peripheral bus from among the one or more peripheral devices, to allow both (i) selective establishing and removing of a connection from the primary peripheral bus to one of the secondary peripheral buses in response to the selection of the master, and (ii) isolating of the master prior to establishing the connection to the secondary peripheral bus. Hot Plug Control Logic and Switch Control Logic in conjunction with the arbiter allows Hot Plug support along with the expanded slot environment.

Owner:IBM CORP

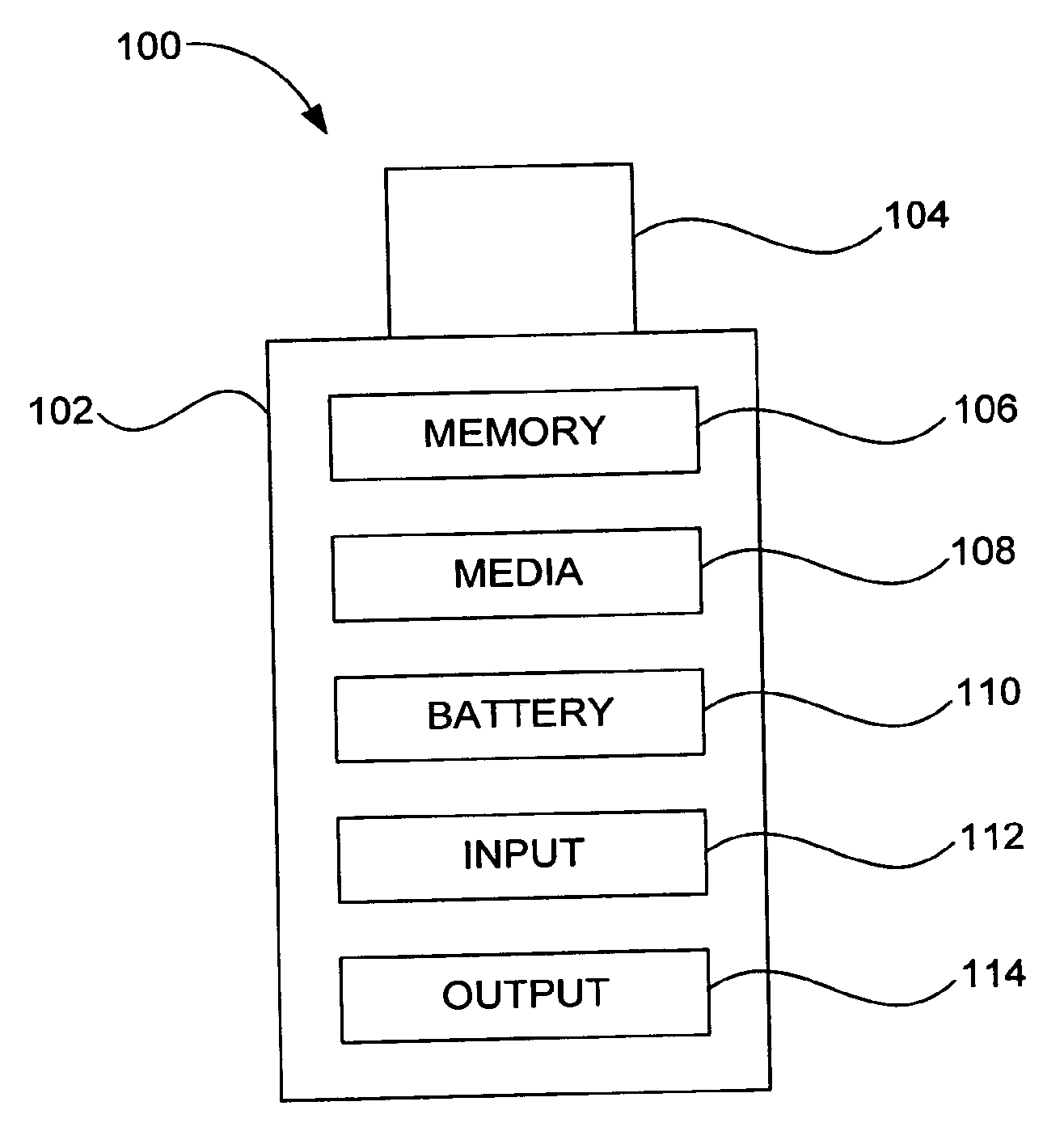

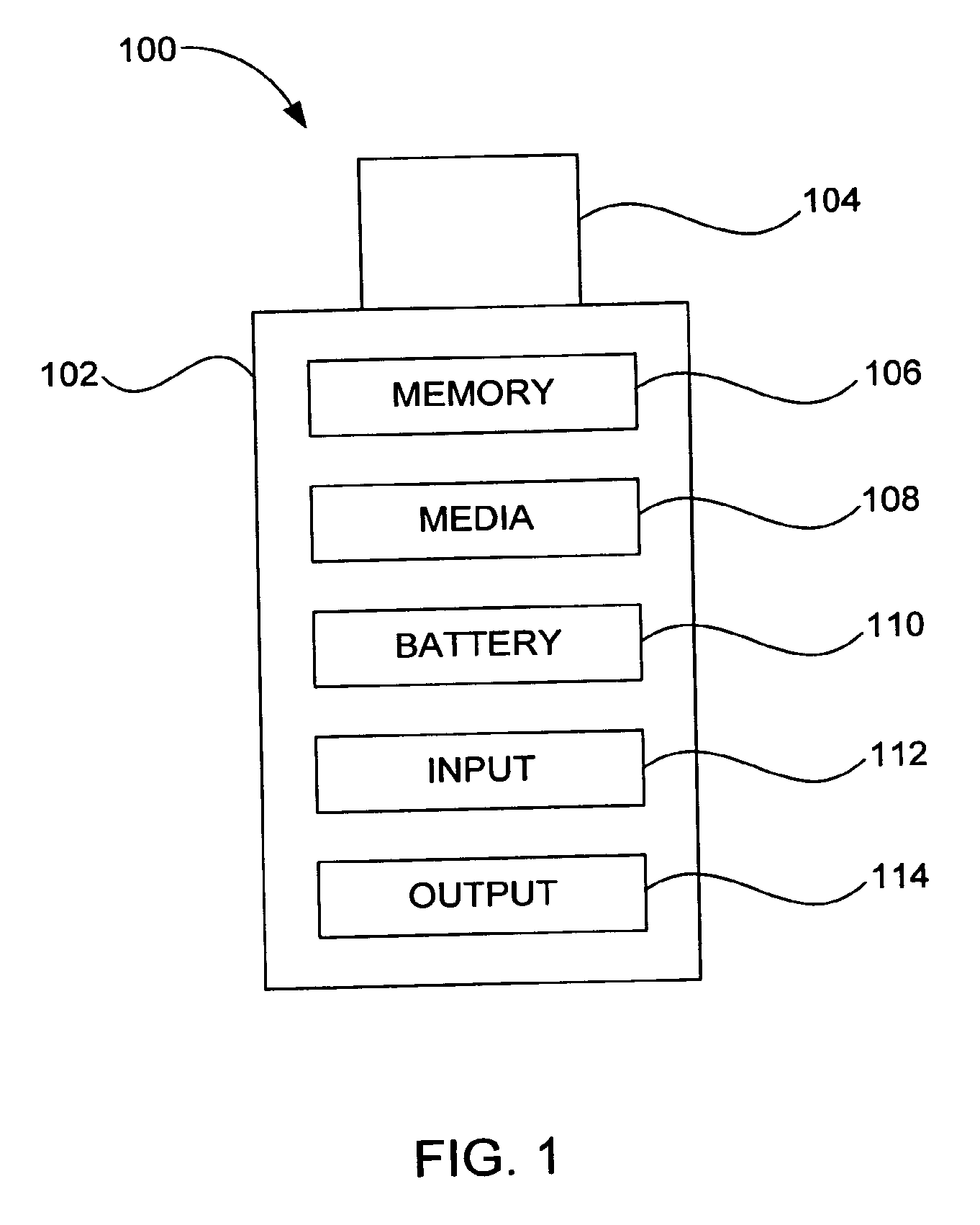

Highly portable media device

ActiveUS20080013274A1Firmly connectedElectronic editing digitised analogue information signalsRecord information storageHand heldDevice status

An improved portable media device and methods for operating a media device are disclosed. According to one aspect, the portable media device can also function as a solid-state drive for data storage. The form factor of the portable media device can be hand-held or smaller, such that it is highly portable. The portable media device can use one or more status indicators. The portable media device can also include a peripheral bus connector, a rechargeable battery, and one or more input devices. According to another aspect, the portable media device has the capability to store media device status information in persistent memory before powering down. Thereafter, when the portable media device is again powered up, the stored media player status information can be retrieved and utilized. According to still another aspect, the portable media device can form and / or traverse a media asset playlist in an efficient manner.

Owner:APPLE INC

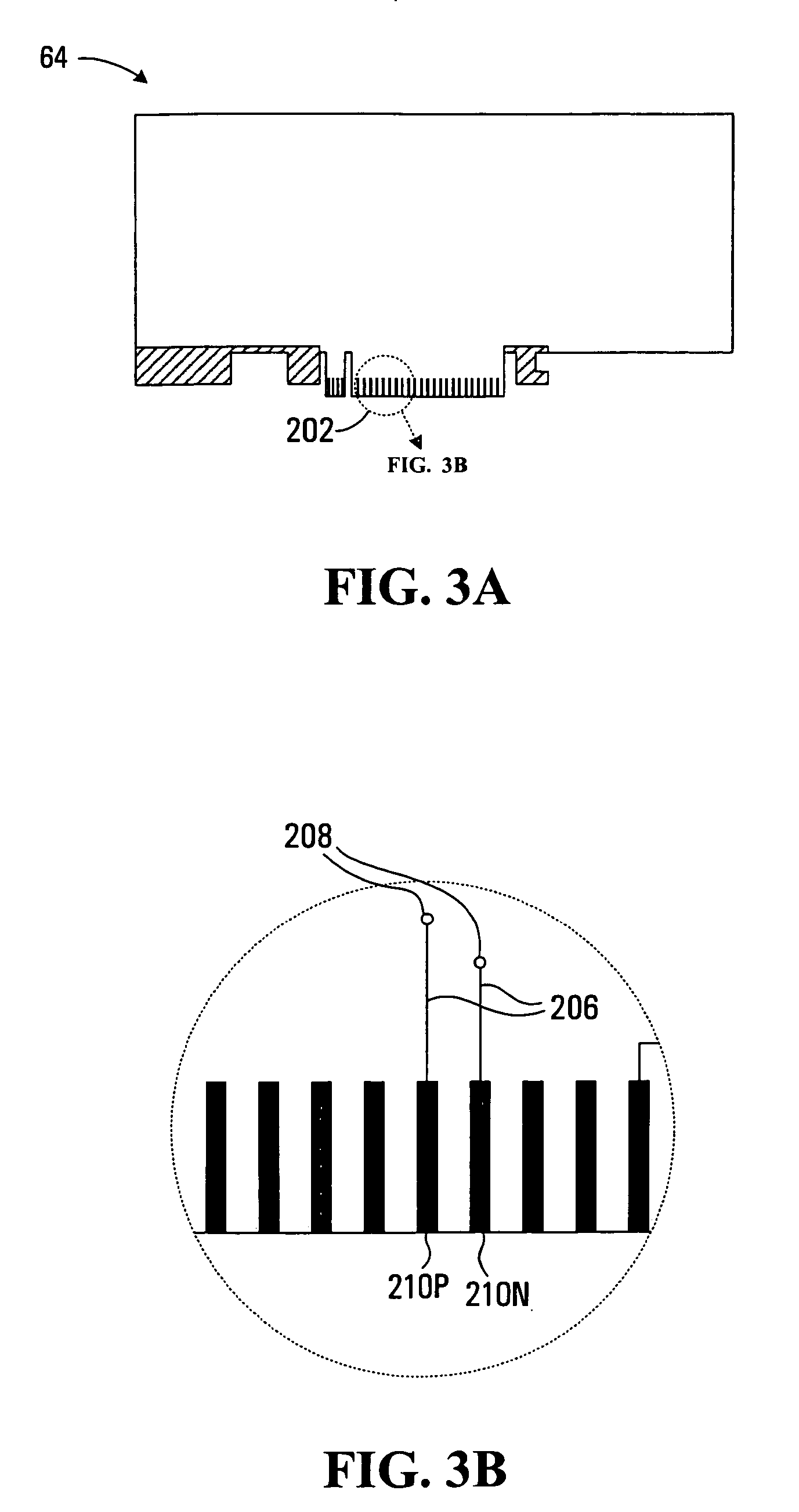

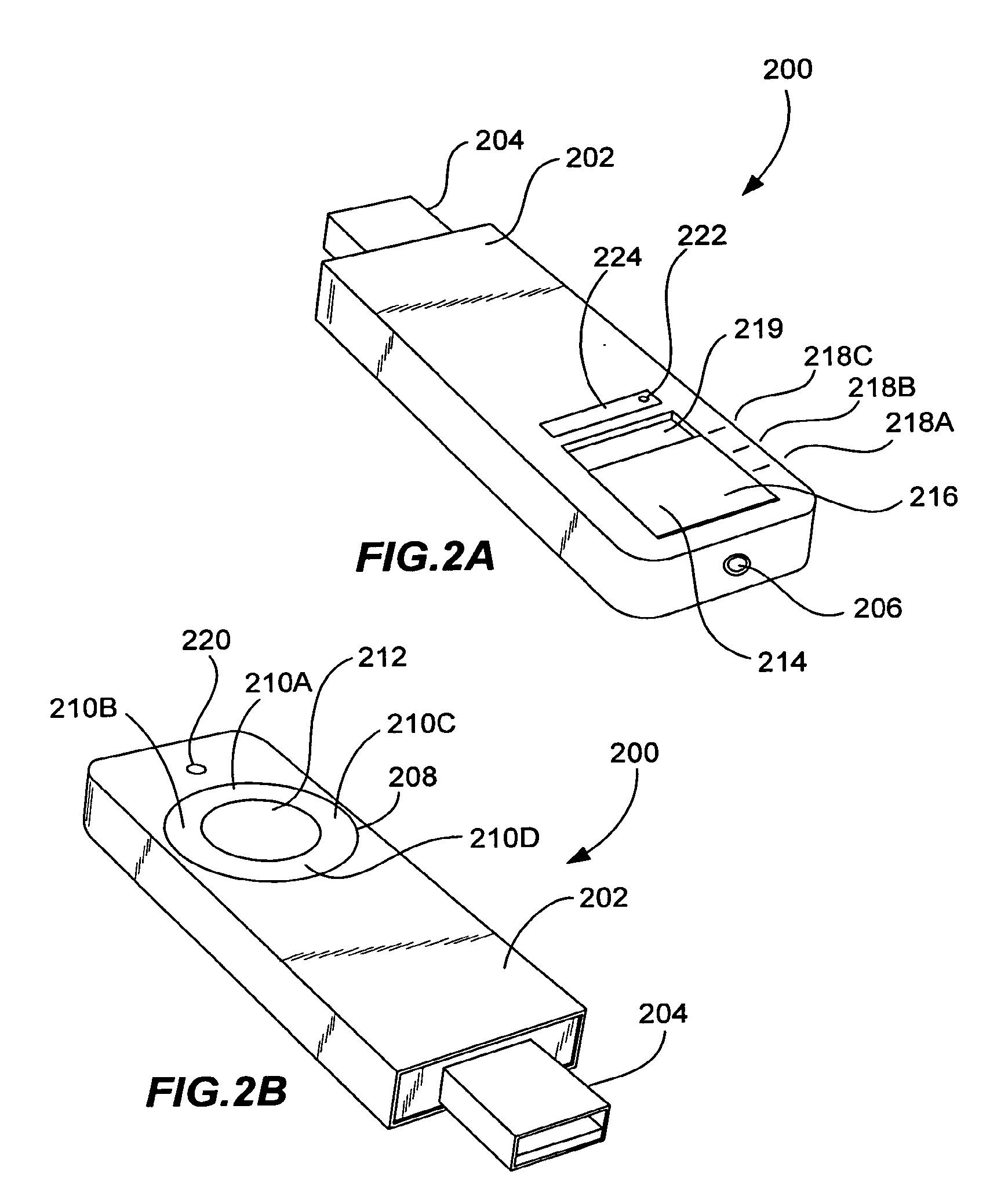

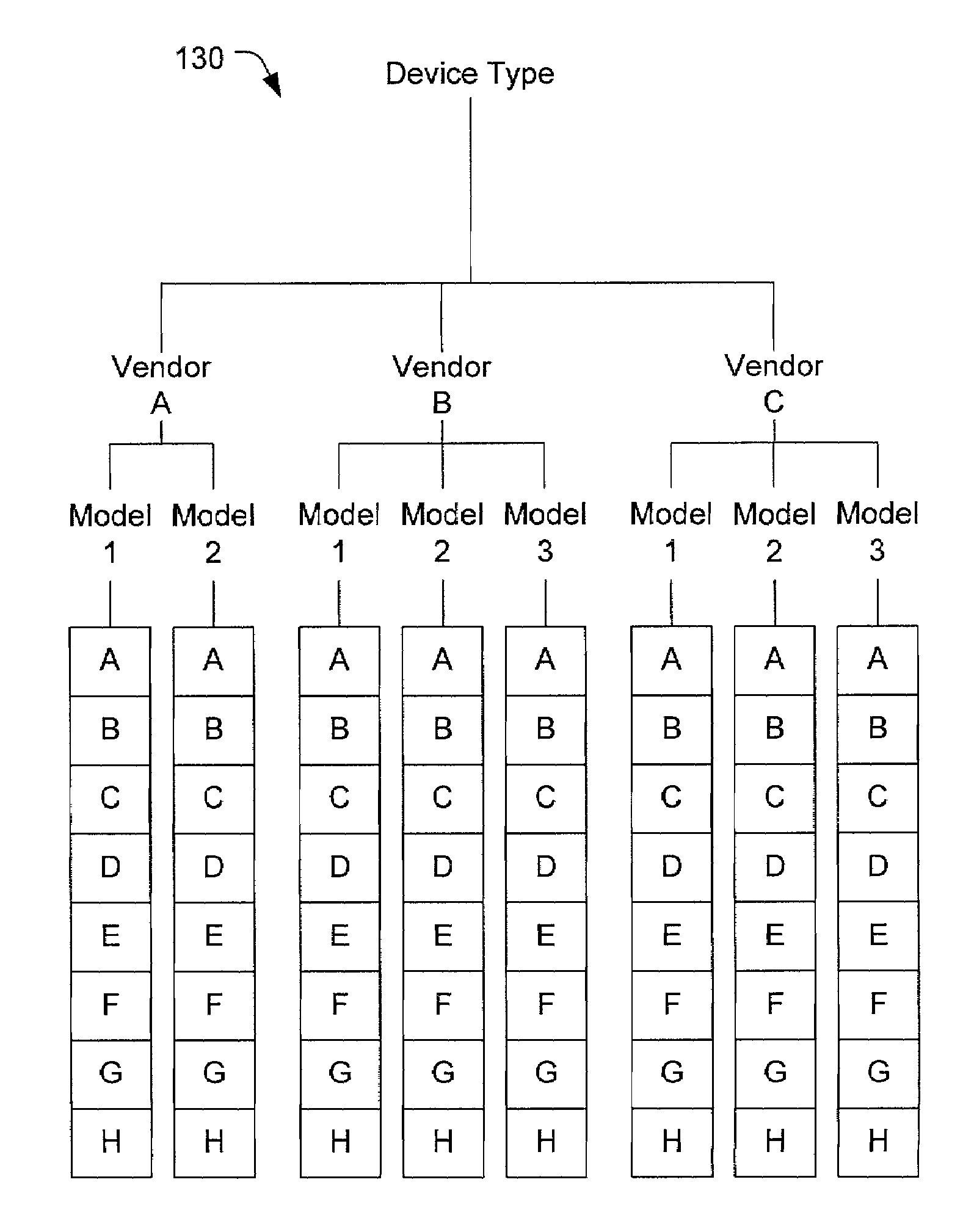

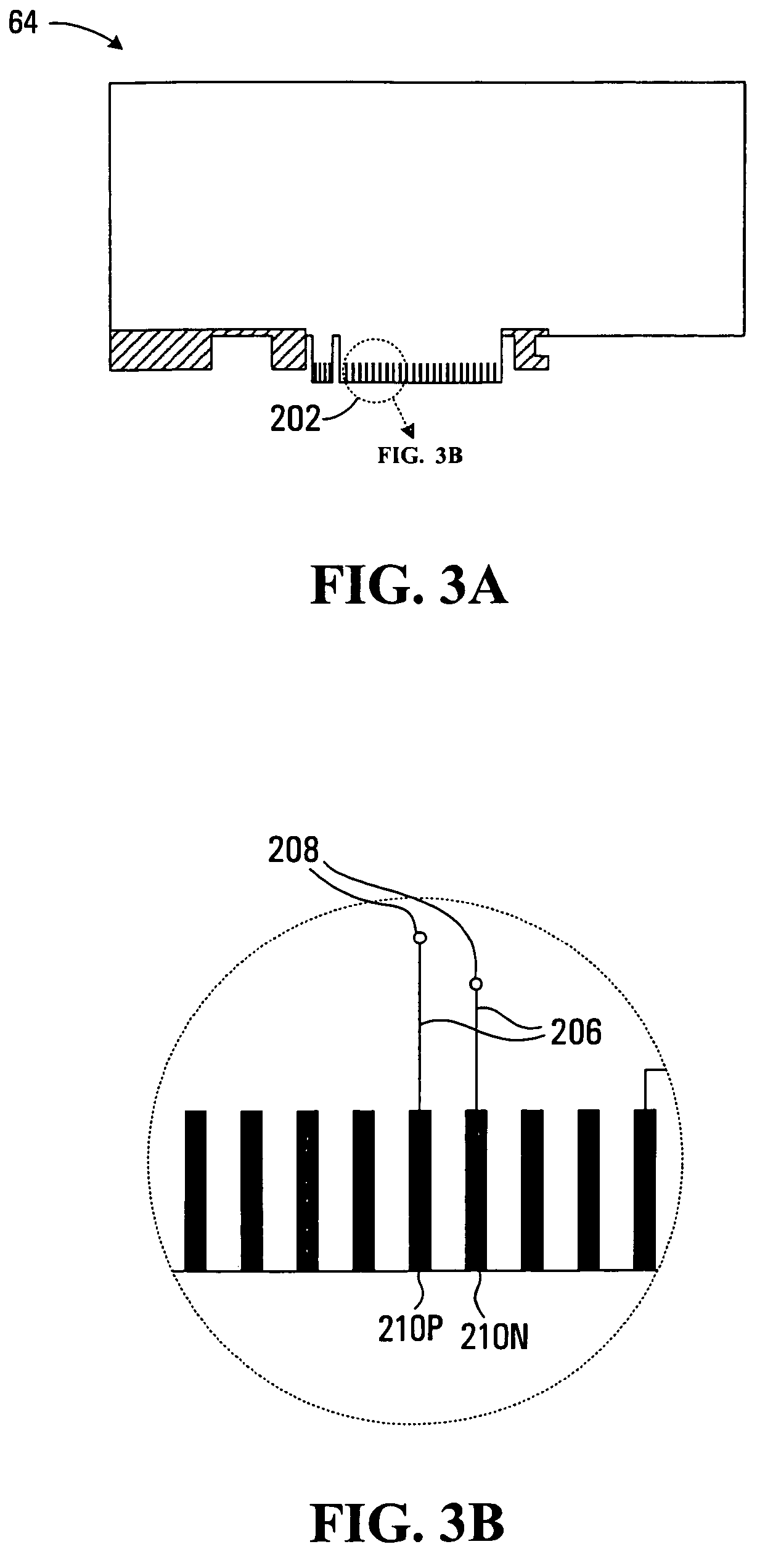

Method and apparatus for configuring a peripheral bus

A method an apparatus for providing capability information to a shared controller. In one embodiment, a peripheral bus host controller may be shared by a plurality of peripheral devices coupled to a peripheral bus. The peripheral devices may include coder / decoder (codec) circuitry, and may be implemented using a riser card. The host controller may be configured to query the bus for peripheral devices by reading each address on the bus. During the querying process, the host controller may detect one or more peripheral devices coupled to the bus. Following the completion of the querying of the bus, the host controller may then begin reading configuration information from each of the detected devices. The host controller may employ one or more of several different techniques in order to read configuration information from the peripheral device. The configuration information at a minimum includes a device identifier, which may identify the vendor and the function of the device. Additional information needed to configure the device to communicate over the peripheral bus may also be obtained with a read of the device, or various lookup mechanisms, such as a lookup table or a tree-like data structure. After configuration information has been obtained for each device coupled to the bus, the host controller may dynamically configure each of the devices for communication over the bus, thereby allowing the flexibility to enumerate riser cards and add new functions through peripheral devices to the computer system in which the bus is implemented.

Owner:ADVANCED MICRO DEVICES INC

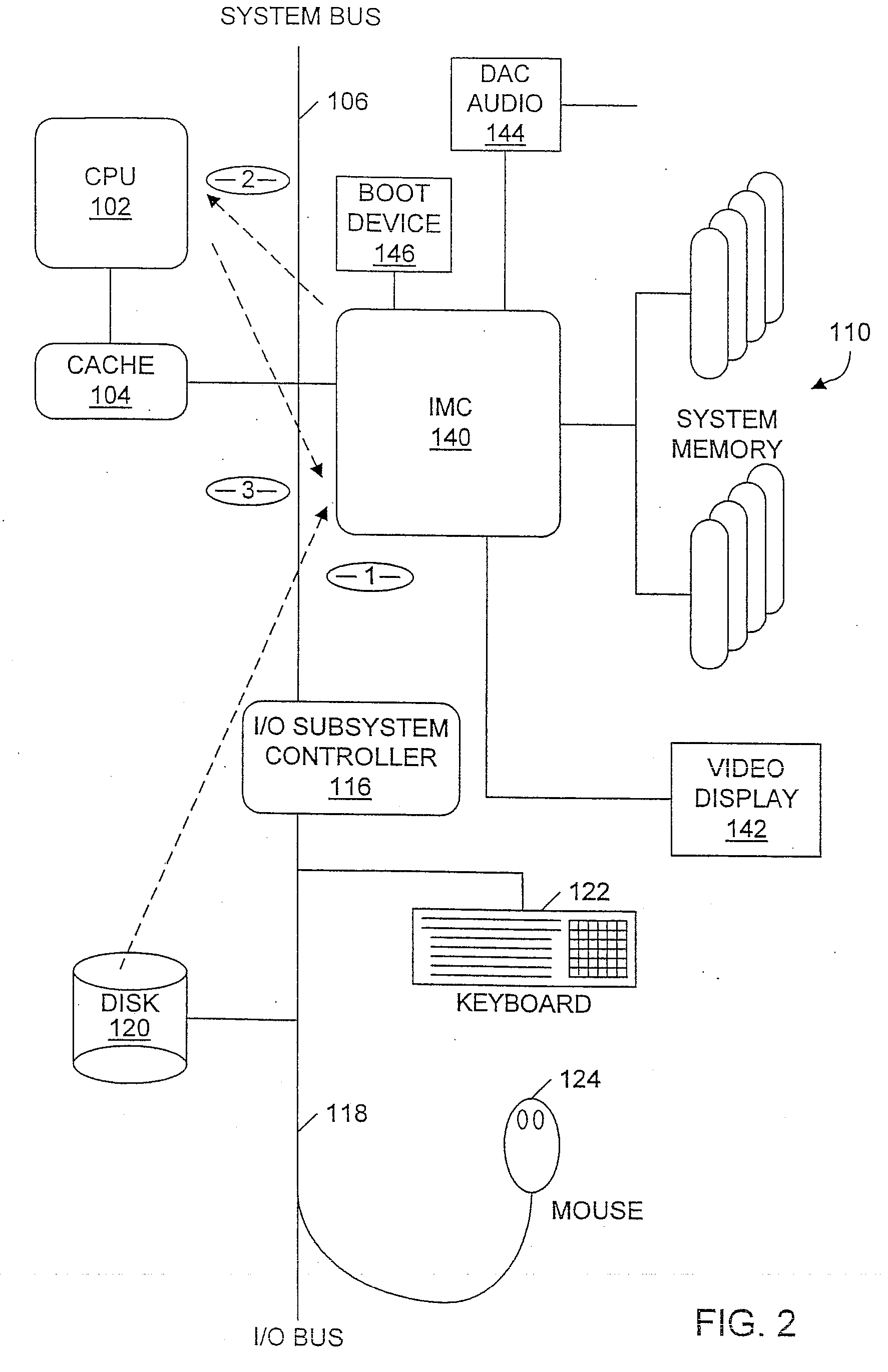

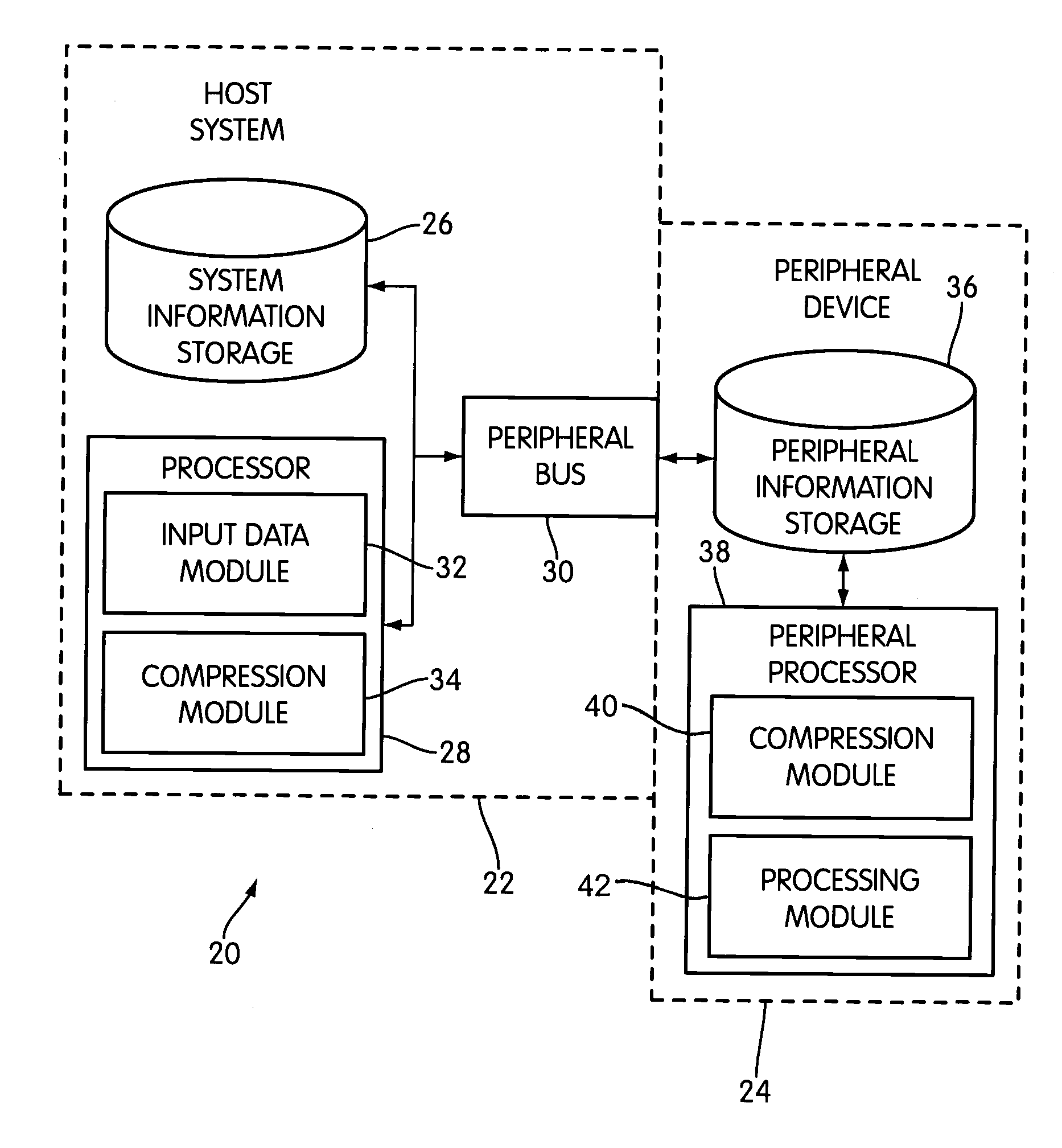

Memory controller including a hardware compression and decompression engine for managing system memory and graphical operations

InactiveUS20090125698A1Improve system performanceEliminate bottlenecksMemory architecture accessing/allocationDigital data processing detailsHard disc driveDigital video

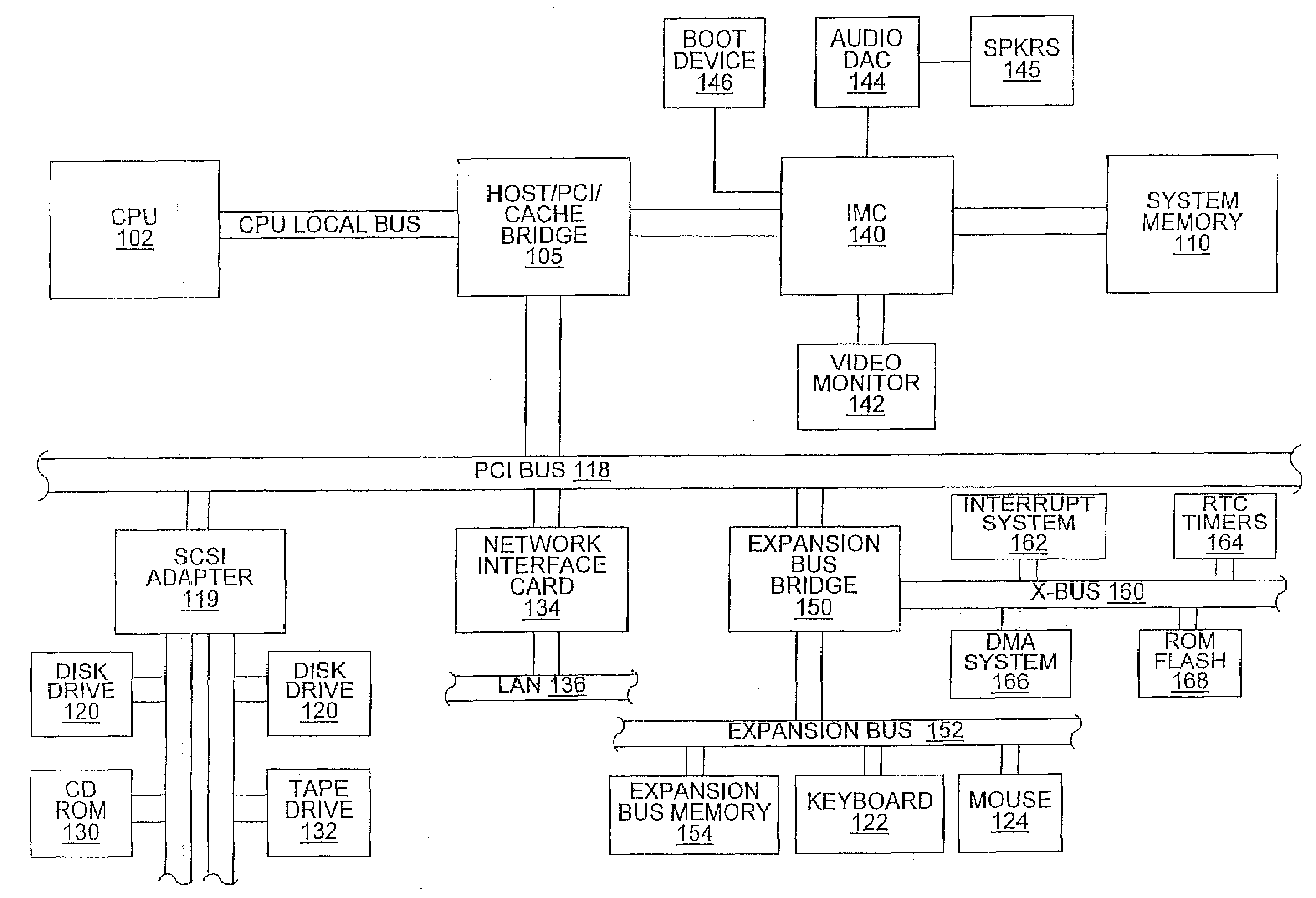

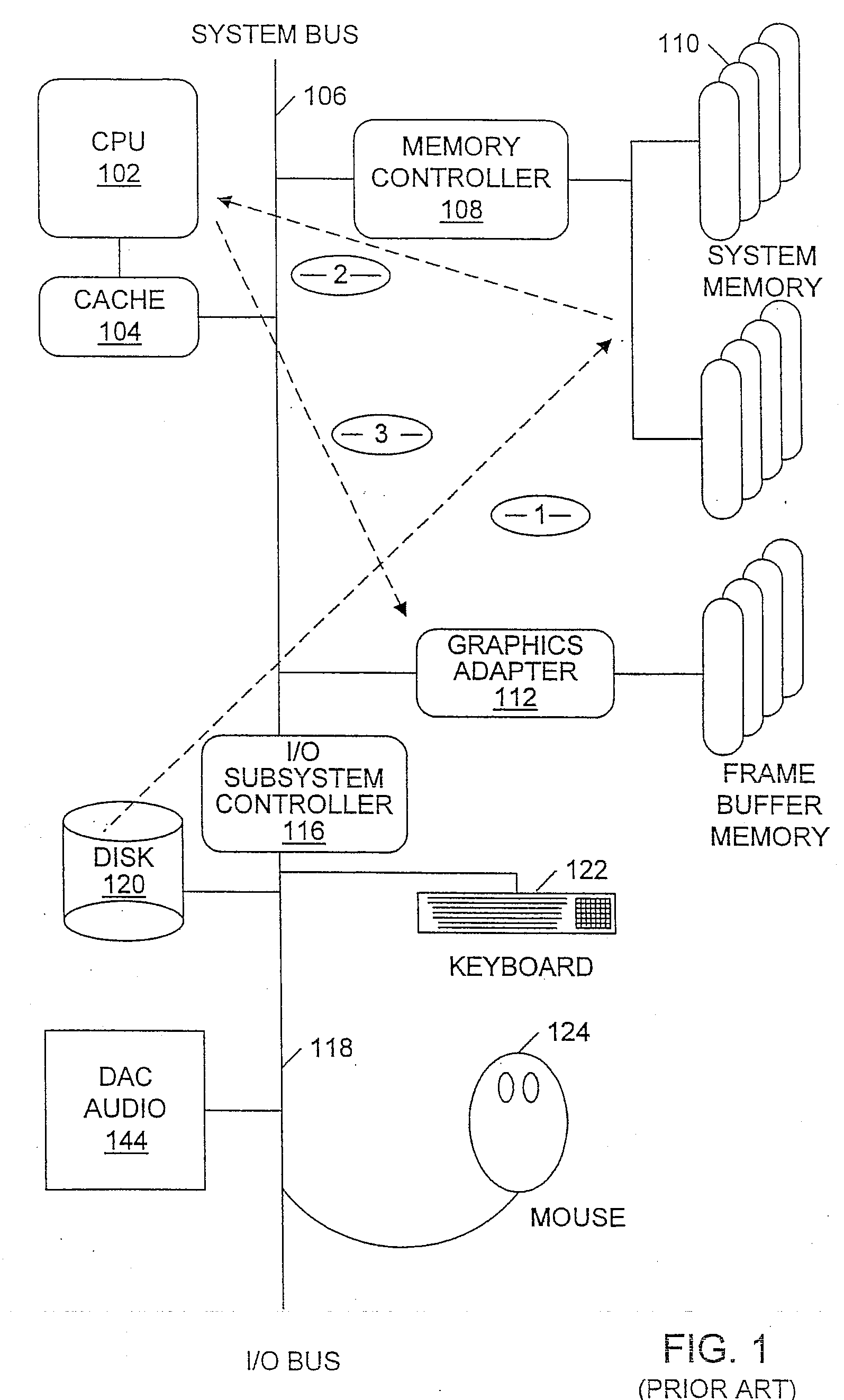

An integrated memory controller (IMC) which includes data compression and decompression engines for improved performance. The memory controller (IMC) of the present invention preferably sits on the main CPU bus or a high speed system peripheral bus such as the PCI bus and couples to system memory. The IMC preferably uses a lossless data compression and decompression scheme. Data transfers to and from the integrated memory controller of the present invention can thus be in either two formats, these being compressed or normal (non-compressed). The IMC also preferably includes microcode for specific decompression of particular data formats such as digital video and digital audio. Compressed data from system I / O peripherals such as the hard drive, floppy drive, or local area network (LAN) are decompressed in the IMC and stored into system memory or saved in the system memory in compressed format. Thus, data can be saved in either a normal or compressed format, retrieved from the system memory for CPU usage in a normal or compressed format, or transmitted and stored on a medium in a normal or compressed format. Internal memory mapping allows for format definition spaces which define the format of the data and the data type to be read or written. Software overrides may be placed in applications software in systems that desire to control data decompression at the software application level. The integrated data compression and decompression capabilities of the IMC remove system bottle-necks and increase performance. This allows lower cost systems due to smaller data storage requirements and reduced bandwidth requirements. This also increases system bandwidth and hence increases system performance. Thus the IMC of the present invention is a significant advance over the operation of current memory controllers.

Owner:INTELLECTUAL VENTURES I LLC

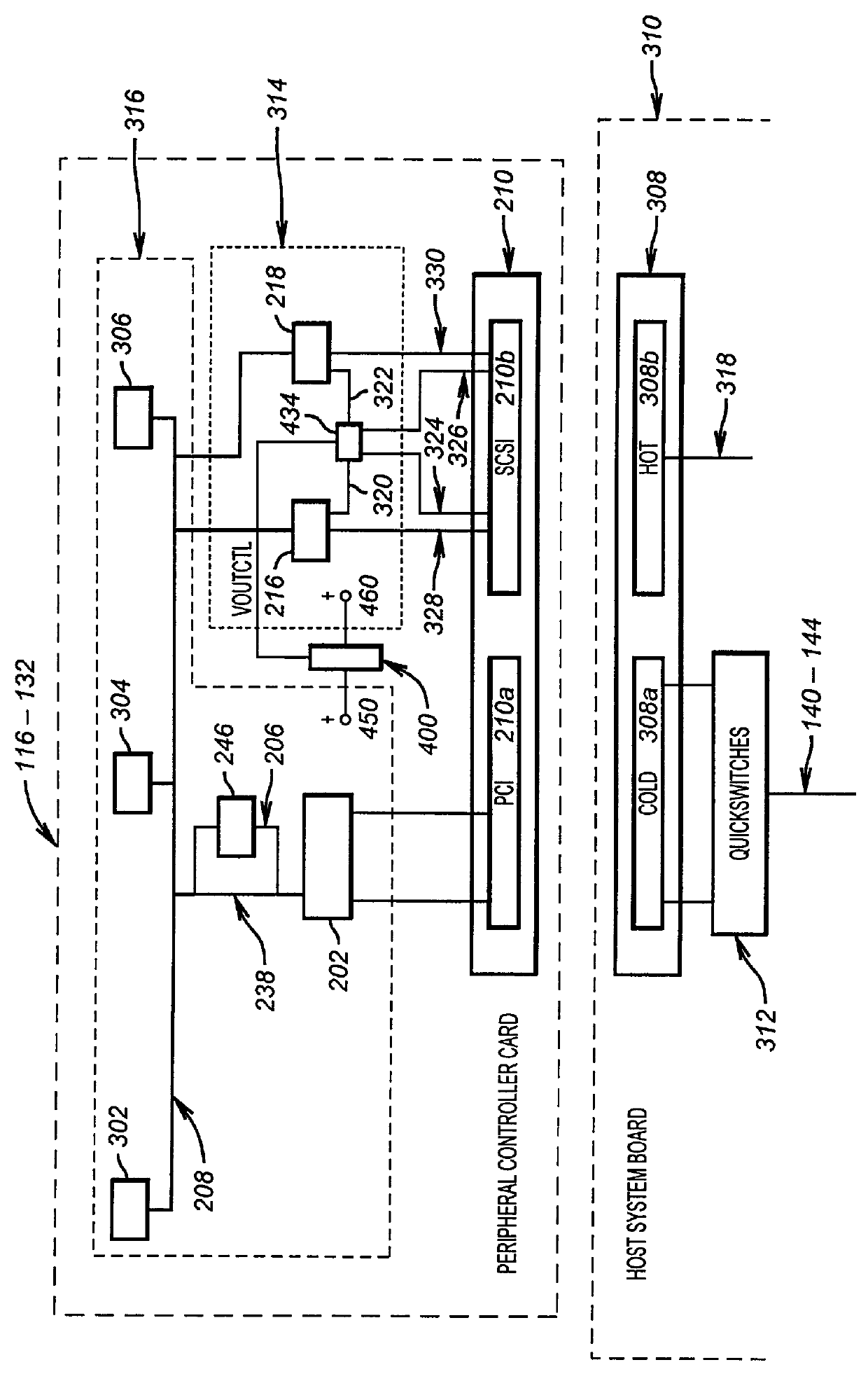

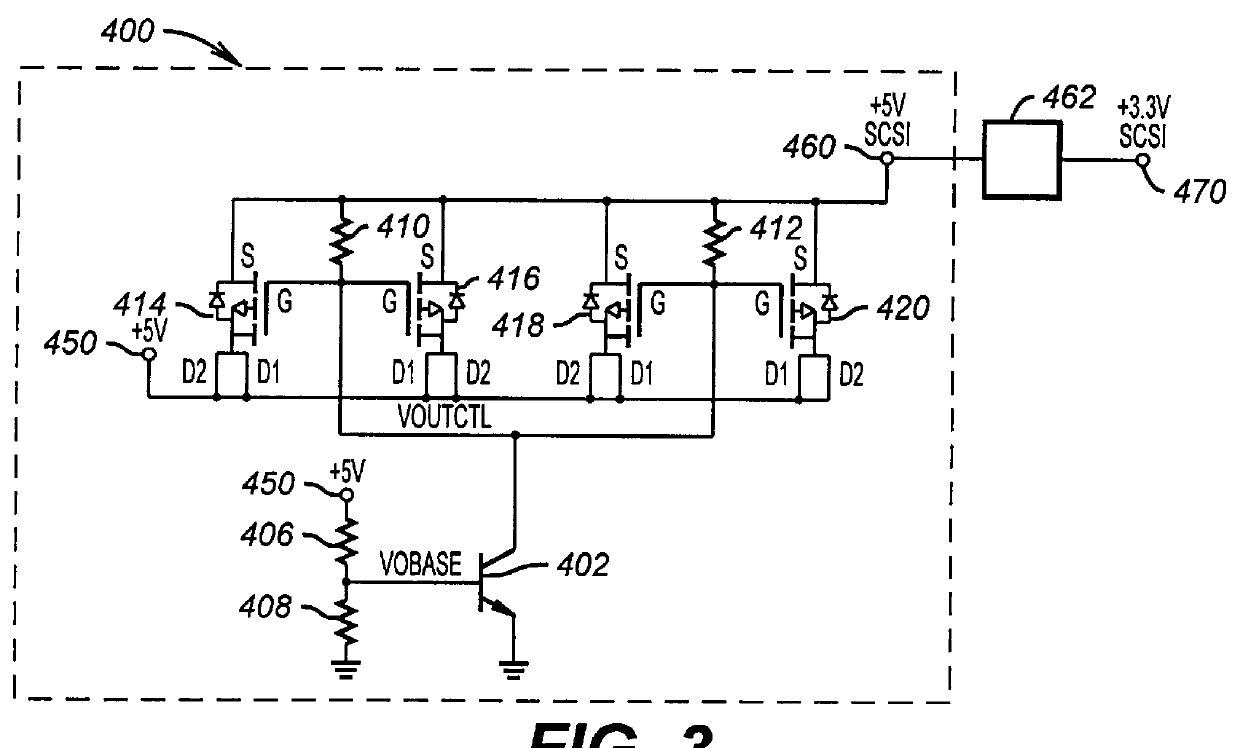

Technique for hot plugging a peripheral controller card containing PCI and SCSI buses on a single connector into a host system board

InactiveUS6061752AComponent plug-in assemblagesDigital processing power distributionMass storageOperational system

An embodiment of the present invention discloses a technique that allows hot plugging a peripheral controller card, containing both a local bus and a peripheral bus on a single connector, into a host system board containing a host system bus and a host I / O bus. When mating the peripheral controller card to the host system board a local device power supply (LDPS) is inactive, a peripheral device power bus (PDPB) is powered, and signal lines of a peripheral device are maintained in a high impedance state. Following a delay after the mating, the LDPS is activated by the host operating system (OS). Following the activation of the LDPS, the host system bus is coupled to the single connector through switches that are under OS control. In response to the activation of the LDPS, the signal lines of the peripheral device are enabled. In a disclosed embodiment the peripheral controller card is a disk array controller card, the local bus is a PCI bus, and the peripheral bus is a SCSI bus. In one embodiment the disk array controller card is coupled to a mass storage peripheral and in another embodiment is programmed for RAID. An advantage of an embodiment of the present invention is that a PCI bus and a SCSI bus are carried on a single peripheral connector which provides cable management and readily allows hot plugging a redundant peripheral controller card into the host system board.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

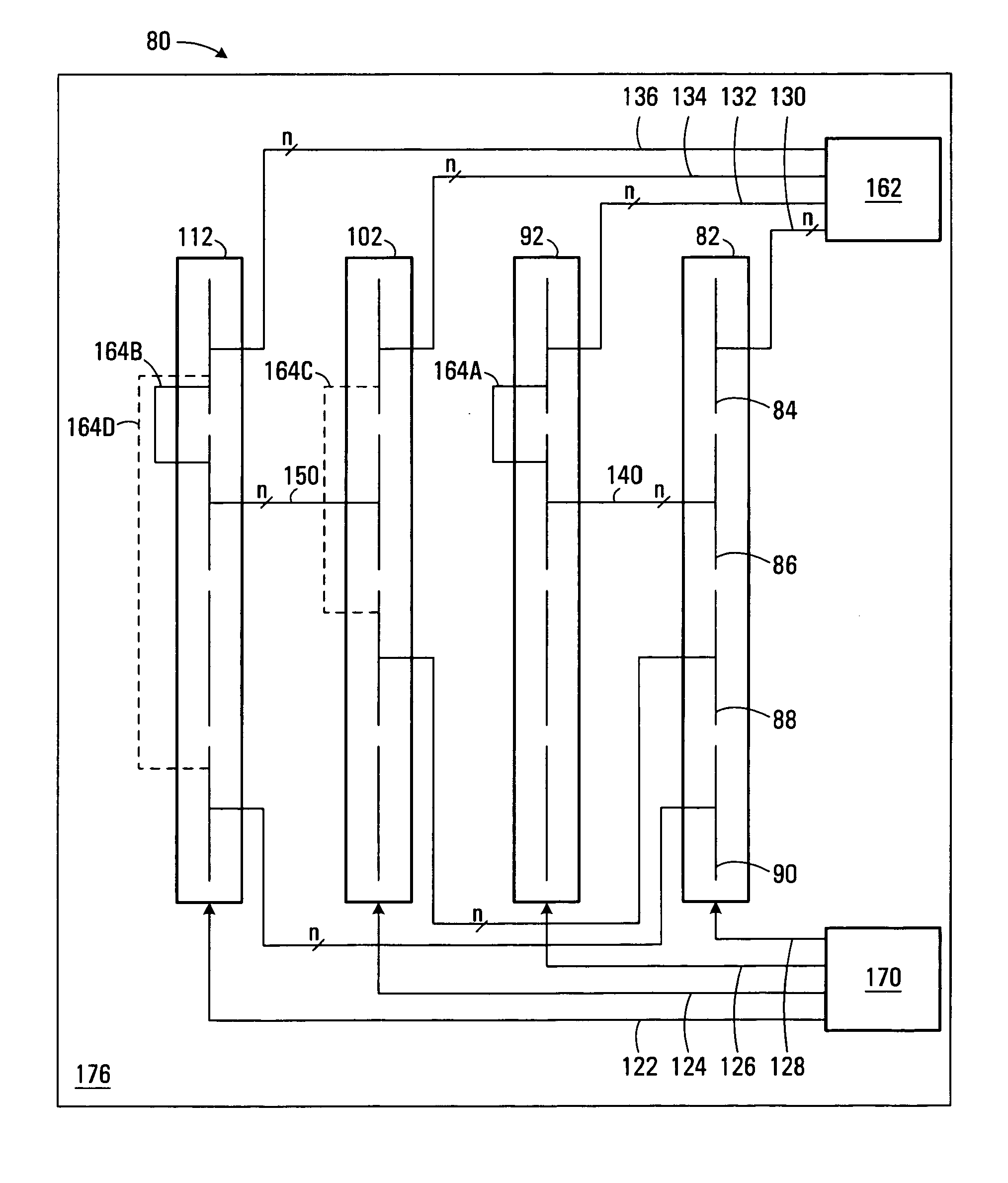

System and method for coupling peripheral buses through a serial bus using a split bridge implementation

A Wide Area Serial PCI system for connecting peripheral devices to a computer. The WASP system includes a host computer system connected through a serial bus to a remote device. The serial bus can range from several meters to several kilometers or more. The host computer system includes a CPU and memory, and also includes a first Peripheral Component Interconnect (PCI) bus, also referred to as the local PCI bus. A primary bridge according to the present invention is coupled to the first PCI bus. The primary bridge includes PCI interface circuitry for interfacing to the first PCI bus. The remote device is located remotely from the computer system and comprises a second or remote PCI bus and one or more peripheral devices coupled to the second PCI bus. The remote device also includes a secondary bridge coupled to the second PCI bus. The secondary bridge includes PCI interface circuitry for interfacing to the second PCI bus. The serial bus is coupled between the primary bridge and the secondary bridge. Each of the primary bridge and secondary bridge include parallel / serial transceivers for converting parallel data generated on the first PCI bus and second PCI bus, respectively, to serial data for transmission on the serial bus and for converting serial data received from the serial bus to parallel data for generation on the first PCI bus and second PCI bus, respectively. The primary bridge and the secondary bridge collectively implement a PCI-PCI bridge register set.

Owner:NATIONAL INSTRUMENTS

Hardware-based virtualization of BIOS, disks, network-interfaces, and consoles using a direct interconnect fabric

ActiveUS7925802B2Program controlInput/output processes for data processingVirtualizationNetwork packet

A multi-computer system has many processors that share peripherals. The peripherals are virtualized by hardware without software drivers. Remote peripherals appear to the operating system to be located on the local processor's own peripheral bus. A processor, DRAM, and north bridge connect to a south bridge interconnect fabric chip that has a virtual Ethernet controller and a virtual generic peripheral that act as virtual endpoints for the local processor's peripheral bus. Requests received by the virtual endpoints are encapsulated in interconnect packets and sent over an interconnect fabric to a device manager that accesses remote peripherals on a shared remote peripheral bus so that data can be returned. Ethernet Network Interface Cards (NIC), hard disks, consoles, and BIOS are remote peripherals that can be virtualized. Processors can boot entirely from the remote BIOS without additional drivers or a local BIOS. Peripheral costs are reduced by sharing remote peripherals.

Owner:SEAMICRO

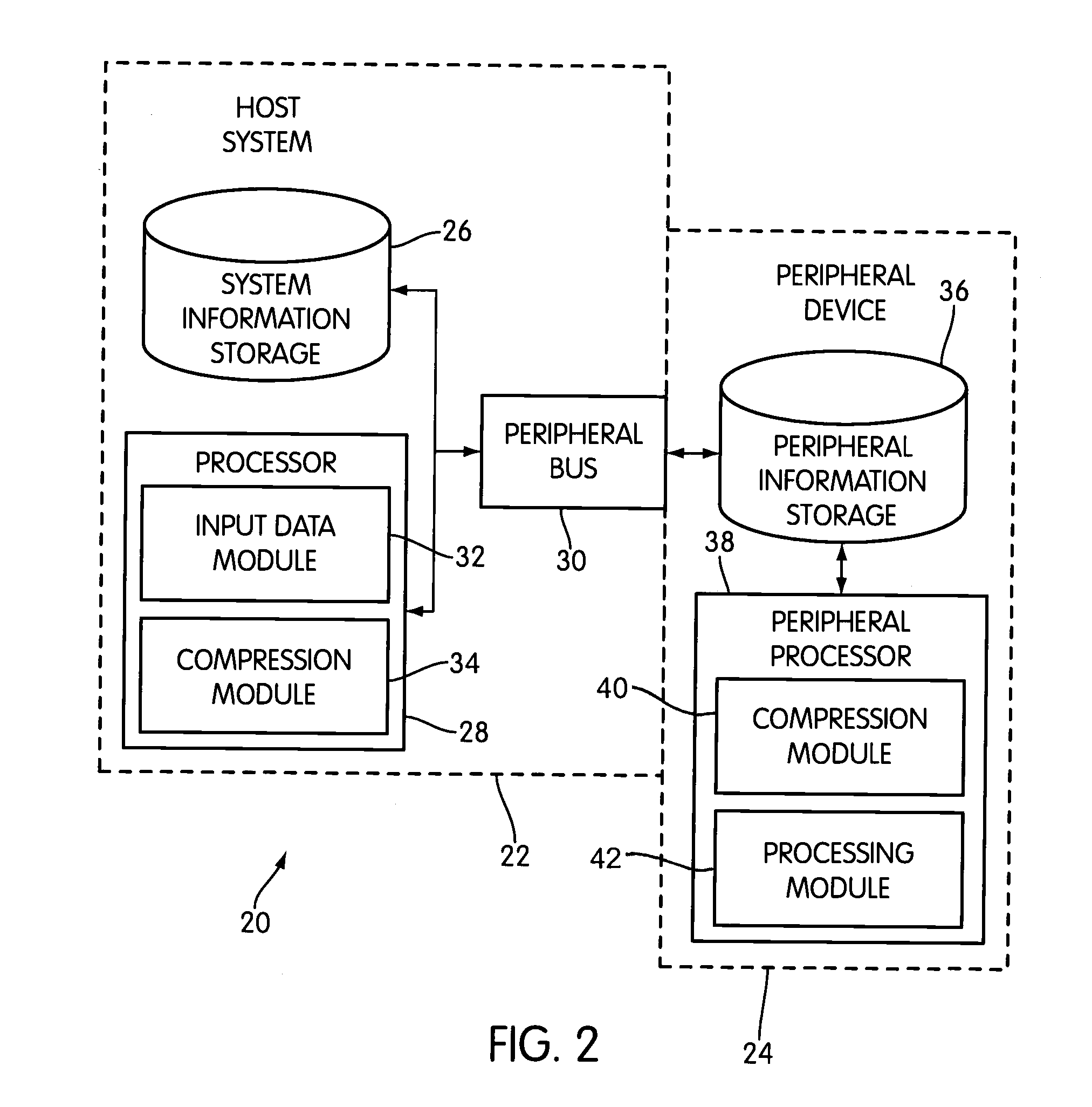

System and method of processing data on a peripheral device

ActiveUS20100030932A1Seismic signal transmissionSeismic signal processingData transmissionComputing systems

Owner:CHEVROU USA INC

Computing device with flexibly configurable expansion slots, and method of operation

ActiveUS7539801B2Component plug-in assemblagesElectric digital data processingGraphicsExpansion card

A computing device that allows for a flexible allocation of bandwidth among peripheral devices using a peripheral bus is disclosed. The computing device includes a peripheral bus and at least two slots. The computing device may be used with a single peripheral card or multiple peripheral cards. In a multi-card configuration the invention allows the bandwidth on the peripheral bus to be shared by all the cards. In a single-card configuration, the computing device allows available bandwidth on the peripheral bus to be used by a single card. The device is particularly useful with PCI express compliant expansion cards, such as graphics adapters.

Owner:ATI TECH INC

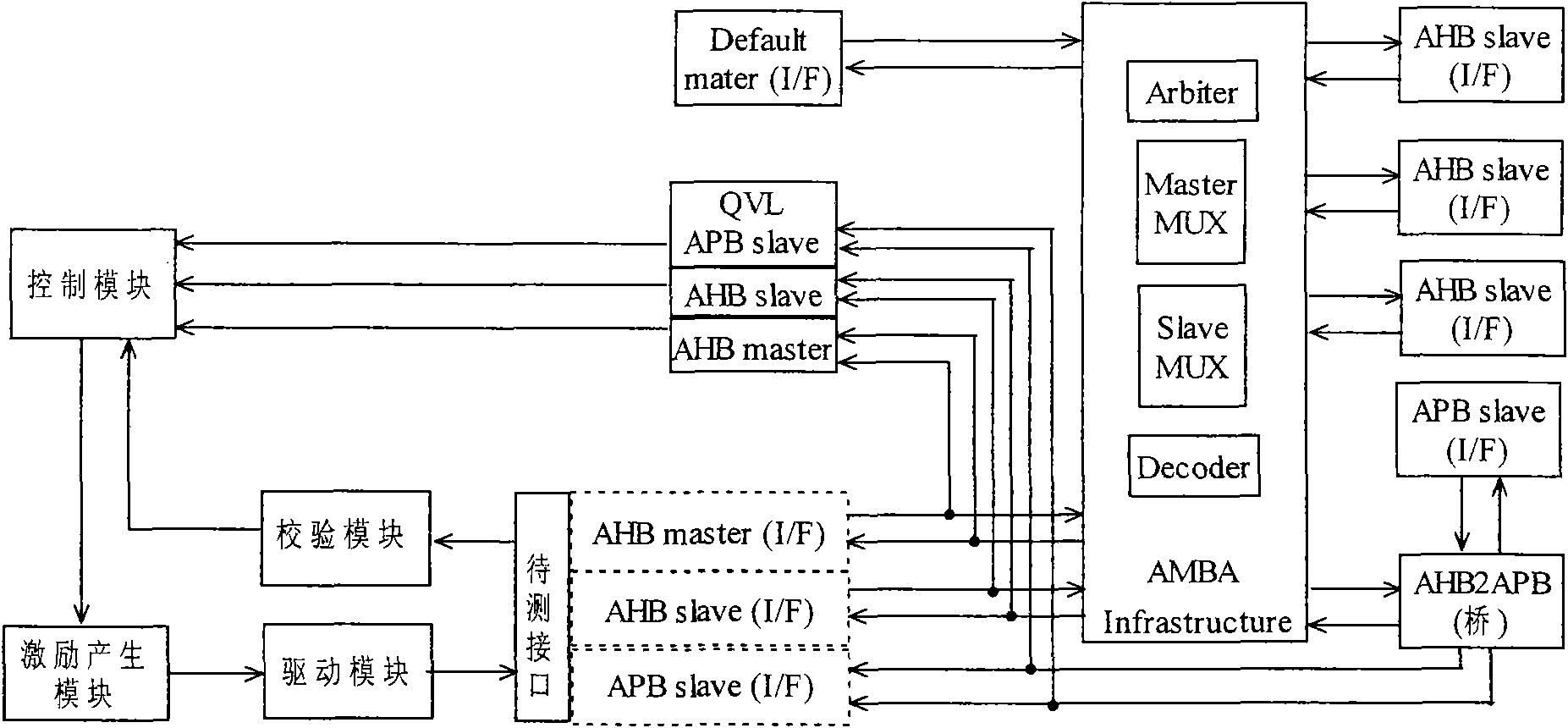

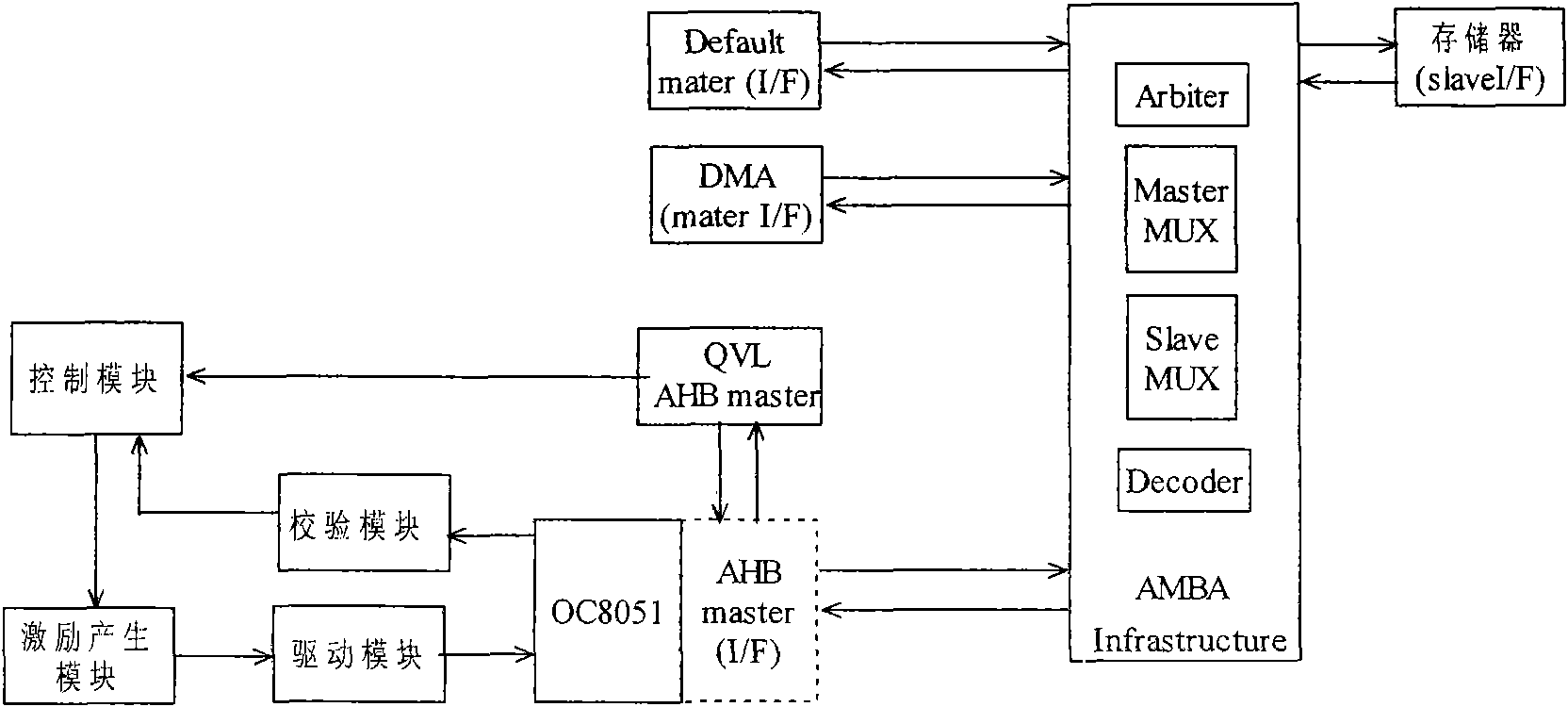

Universal method and platform for verifying compatibility between intellectual property (IP) core and advanced microcontroller bus architecture (AMBA) bus interface

InactiveCN102117238AImprove verification efficiencyImprove accuracyFunctional testingValidation methodsIntellectual property

The invention provides a universal platform of verifying compatibility between an intellectual property (IP) core and an advanced microcontroller bus architecture (AMBA) bus interface, which comprises a functional simulation tool, an AMBA bus infrastructure, a third-party verification IP core, a controller, a driver, a stimulus, a checker, an advanced peripheral bus (APB) bridge, an advanced high-performance bus (AHB) master interface, an AHB slave interface and an APB slave interface, wherein all the modules are connected to form an integrated coordinating verification environment by adopting a verification component and hierarchical packaging and interconnections ways provided by a SystemVerilog language and advanced verification methodology (AVM). The platform can verify the compatibility of different types of IP core interfaces, and the development time and cost of the verification platform and a verification method are reduced. The invention also provides the universal method for verifying the compatibility between the IP core and the AMBA bus interface. In the method, excitation is produced more normatively, scientifically and accurately, unnecessary iteration is reduced and the verification time is shortened.

Owner:SHANGHAI SILICON INTPROP EXCHANGE

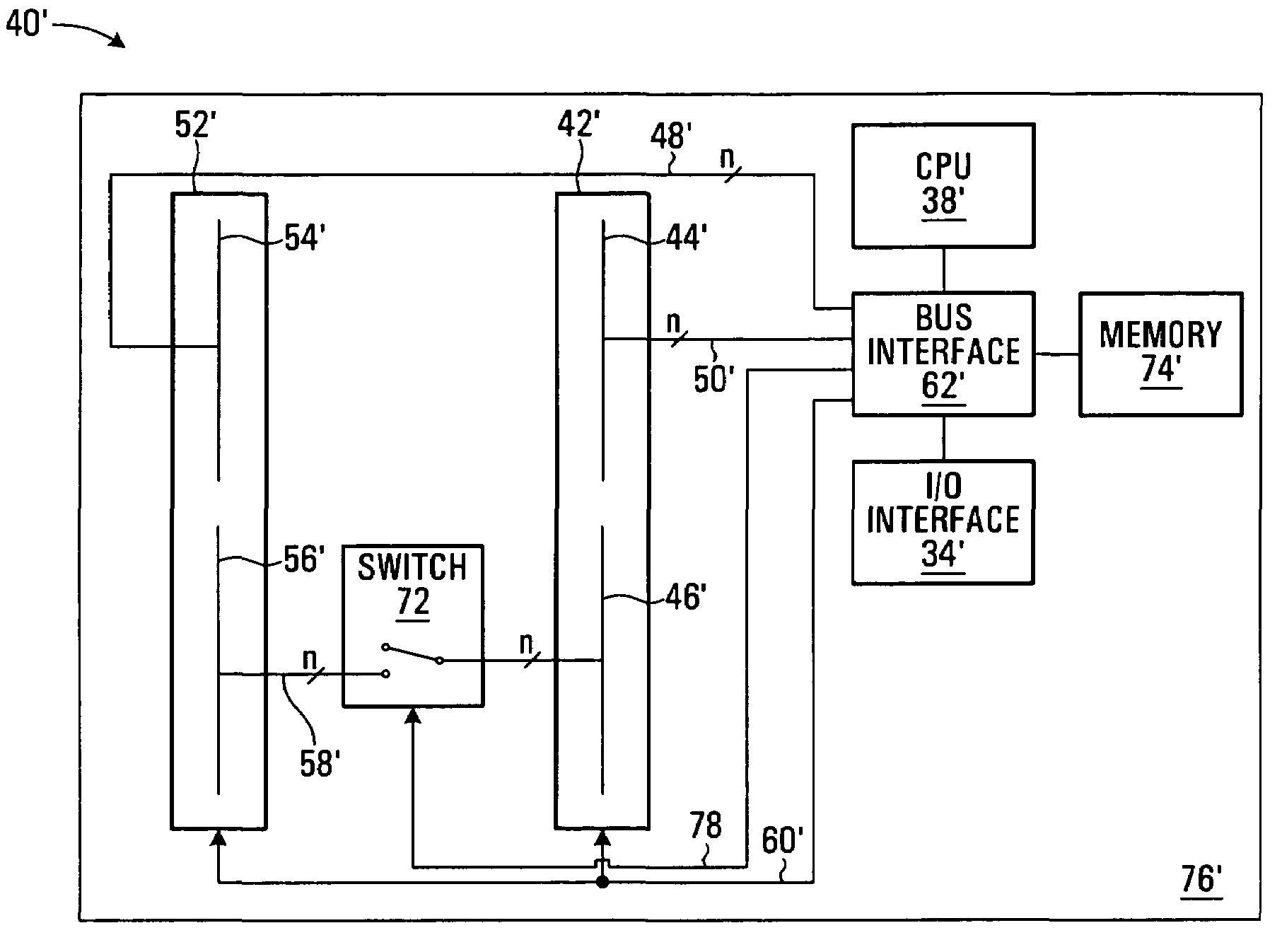

Method and system for PCI slot expansion via electrical isolation

A method of providing an interconnection between one or more peripheral devices and a system bus of a computer system selectively establishes and removes a connection from a primary peripheral bus to a secondary peripheral buses, and determines a target from among the one or more peripheral devices when a bus bridge is a master of the primary peripheral bus, using an address decoder. Access to and from the primary peripheral bus is controlled using an arbiter to select a master for the primary peripheral bus from among the one or more peripheral devices, to allow both (i) selective establishing and removing of a connection from the primary peripheral bus to one of the secondary peripheral buses in response to the selection of the master, and (ii) isolating of the master prior to establishing the connection to the secondary peripheral bus.

Owner:IBM CORP

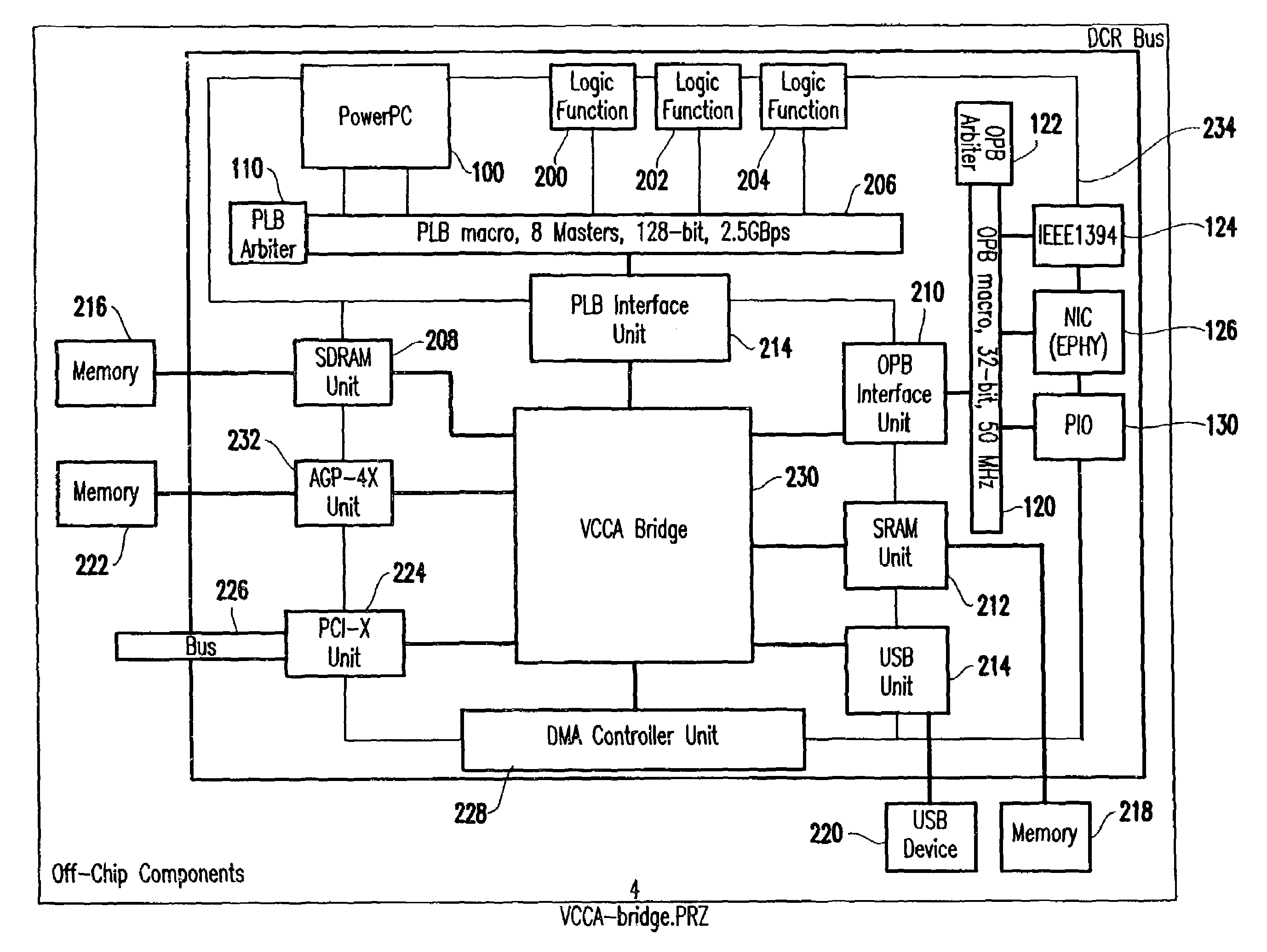

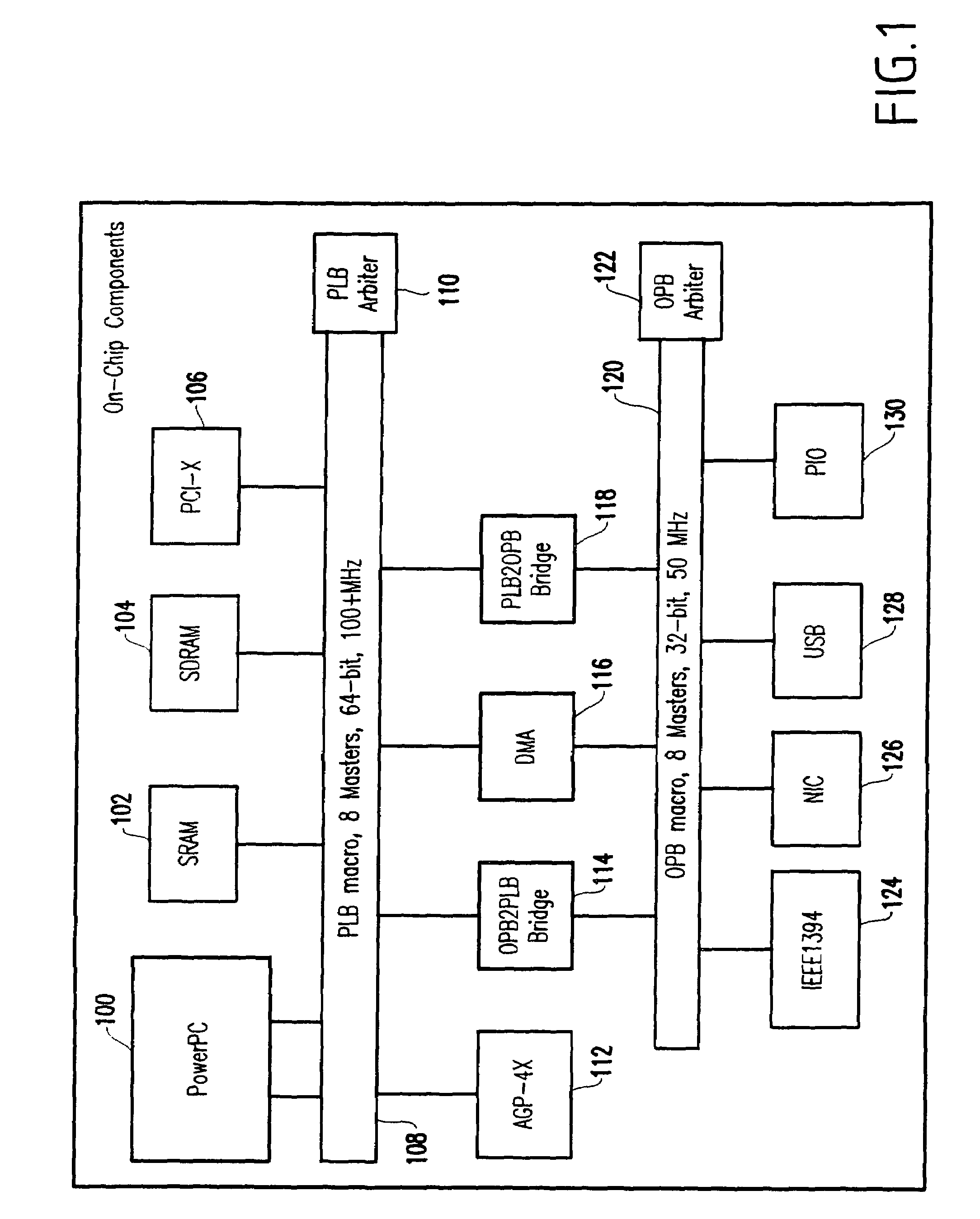

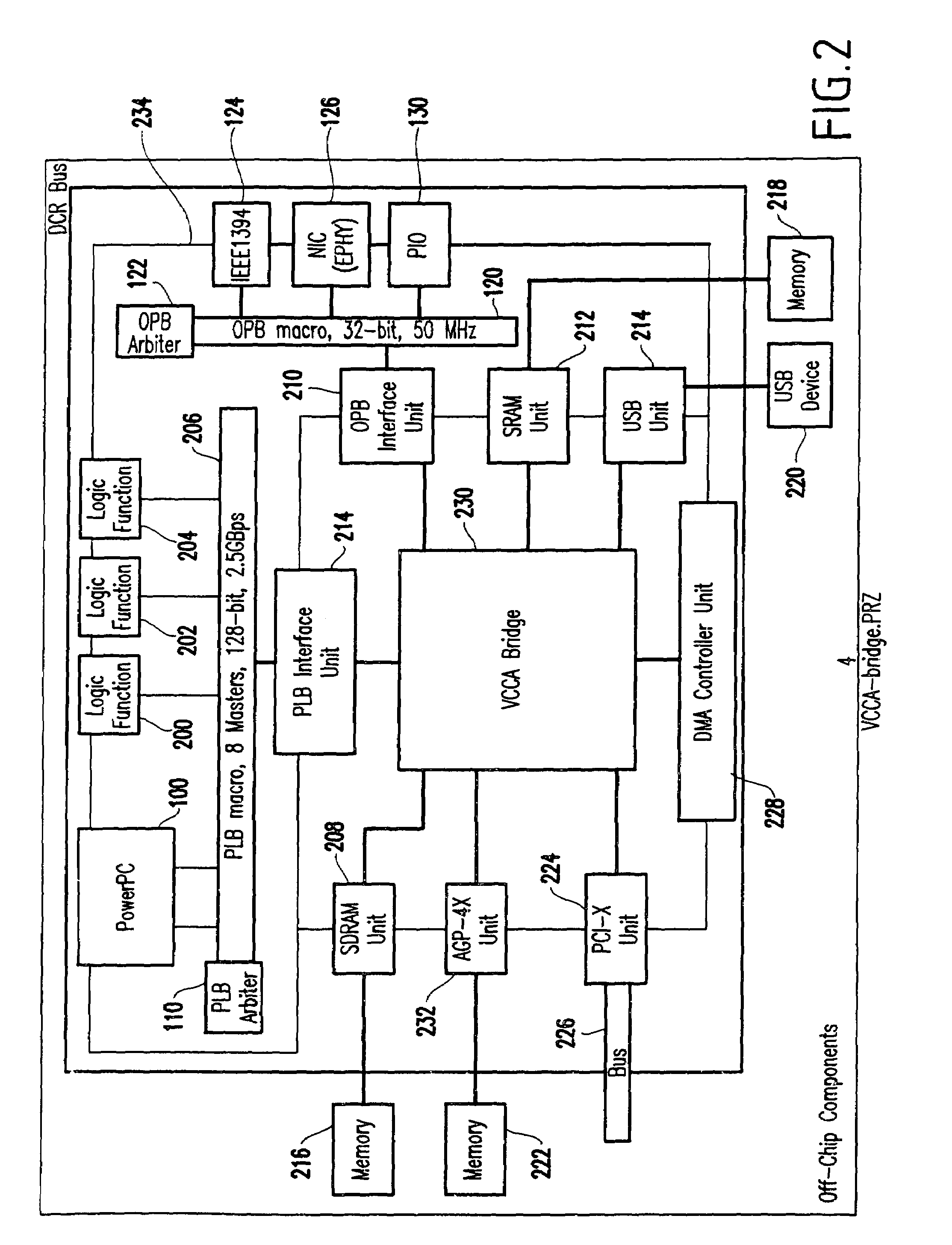

System-on-a-Chip structure having a multiple channel bus bridge

A system-on-a-chip integrated circuit structure includes a bridge having a plurality of channels, a processor local bus connected to the bridge (wherein the bridge includes a first channel dedicated to the processor local bus), at least one logic device connected to the processor local bus, a peripheral device bus connected to the bridge (wherein the bridge includes a second channel dedicated to the peripheral device bus), at least one peripheral device connected to the peripheral device bus, at least one memory unit connected to the bridge (wherein the bridge includes a third channel dedicated to the memory unit), and at least one input / output unit connected to the bridge (wherein the bridge includes a fourth channel dedicated to the input / output unit).

Owner:GLOBALFOUNDRIES US INC

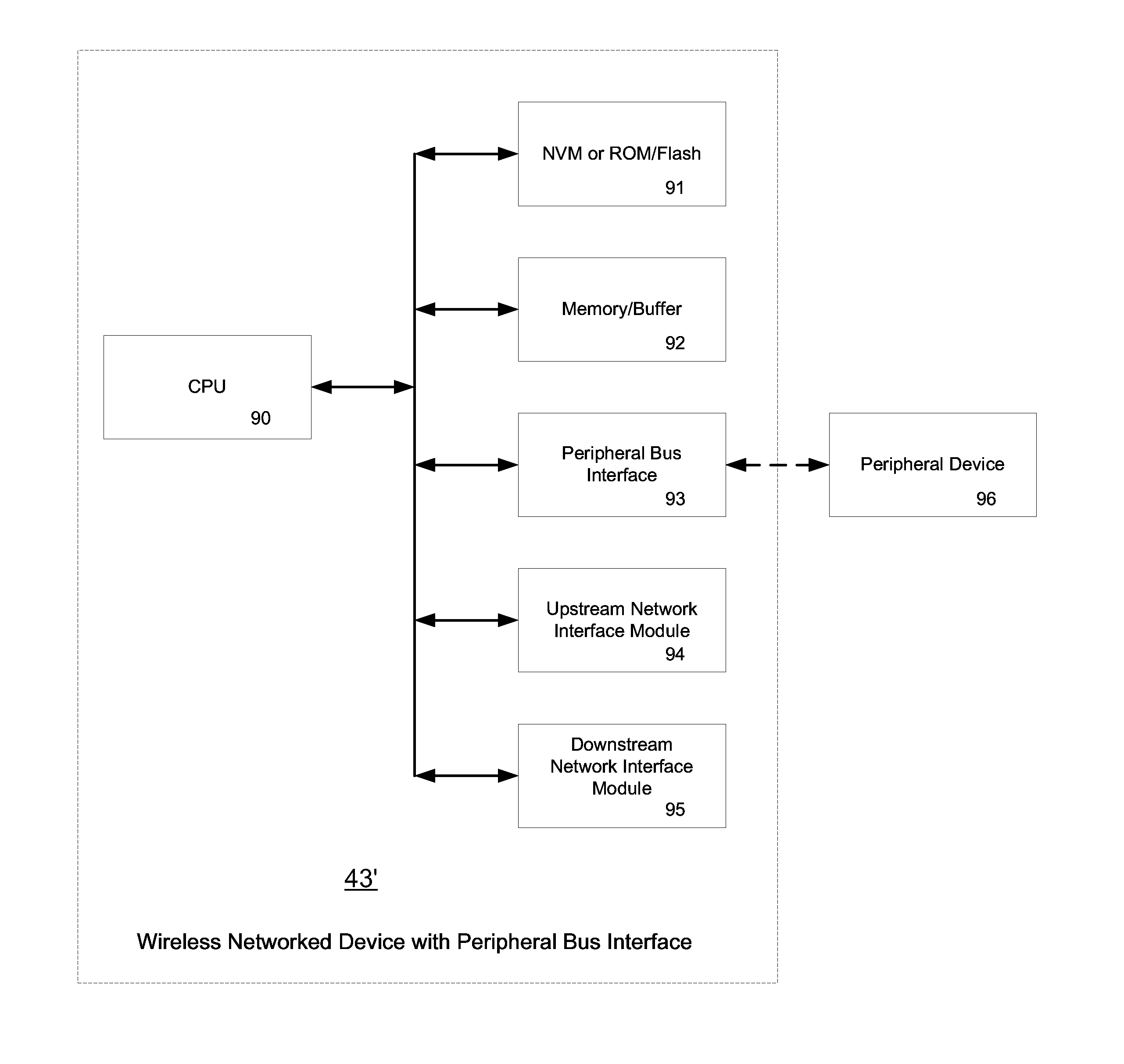

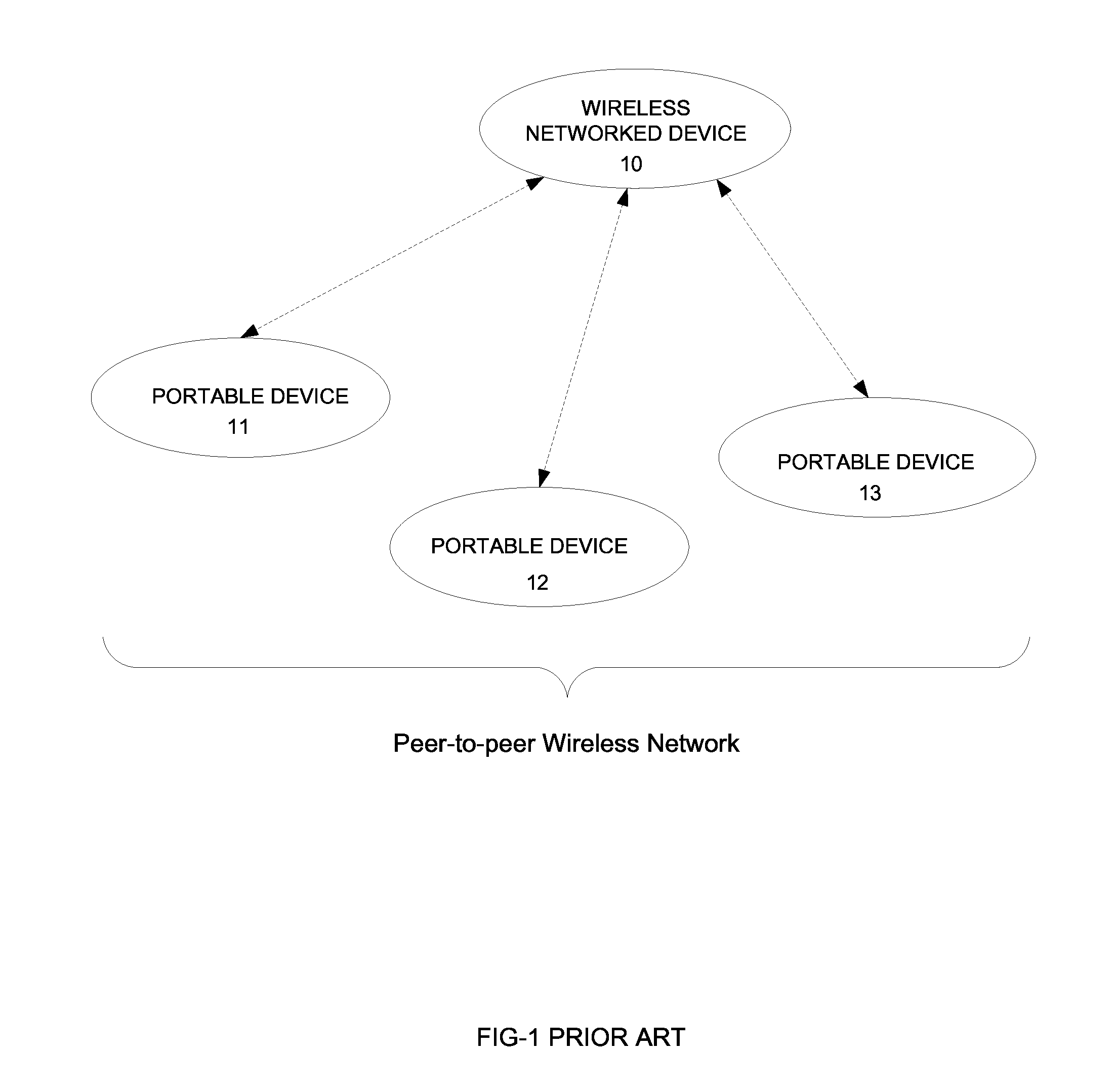

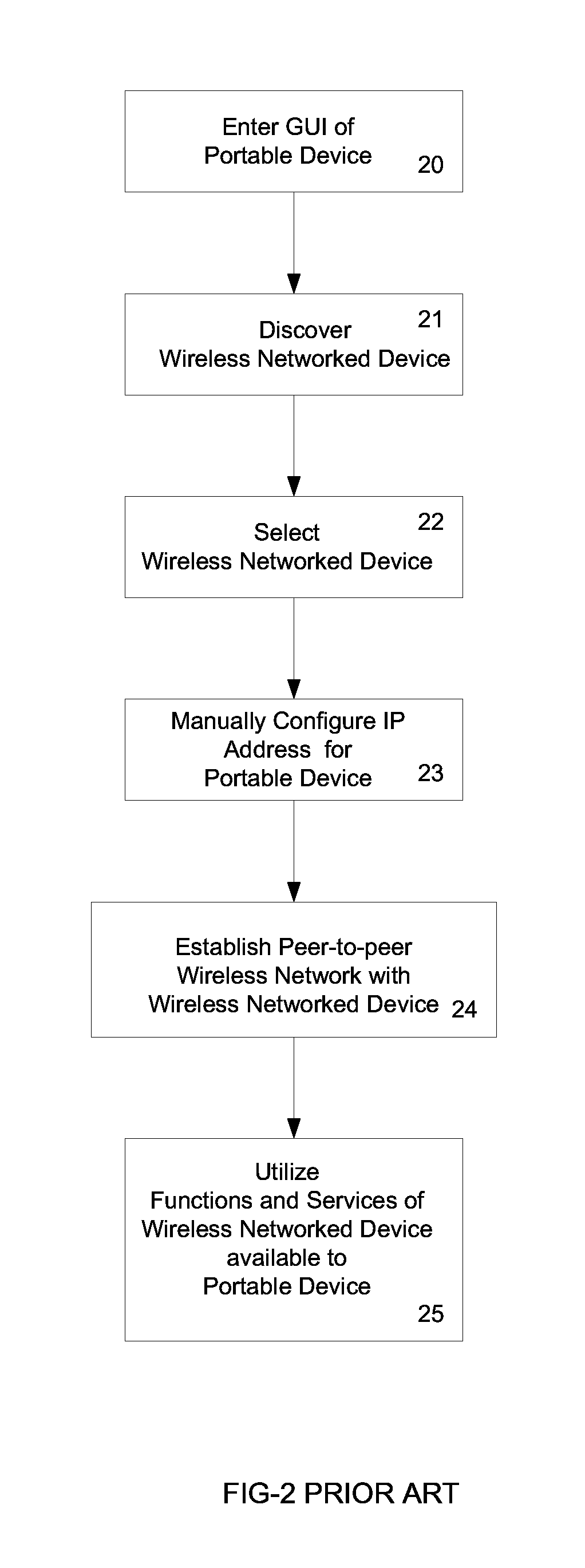

Dual-mode wireless networked device interface and automatic configuration thereof

A wireless networked device interface is disclosed. The wireless networked device interface comprises a central processing unit (CPU), a bus coupled to the CPU, a memory / buffer coupled to the bus, a peripheral bus interface coupled to the bus, an upstream network module coupled to the bus, a downstream network module coupled to the bus and a peripheral device. The device interface includes a nonvolatile memory (NVM) coupled to the bus. The NVM includes a configuration function which through a portable device can associate with one or more portable devices on the downstream wireless network and associate with one or more access points on the upstream wireless network. The wireless networked device as well as the access point can be discovered, selected and auto-configured through the graphic user interface of one of the portable devices on the downstream wireless network.

Owner:KINGSTON DIGITAL CO LTD