System-on-a-Chip structure having a multiple channel bus bridge

a technology of system-on-chip and bus bridge, which is applied in the direction of instruments, electric digital data processing, etc., can solve the problems of requiring several system clock cycles of latency, affecting the performance of bus system hierarchies, and achieving poor performance of conventional component-based system-on-a-chip communication architectures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

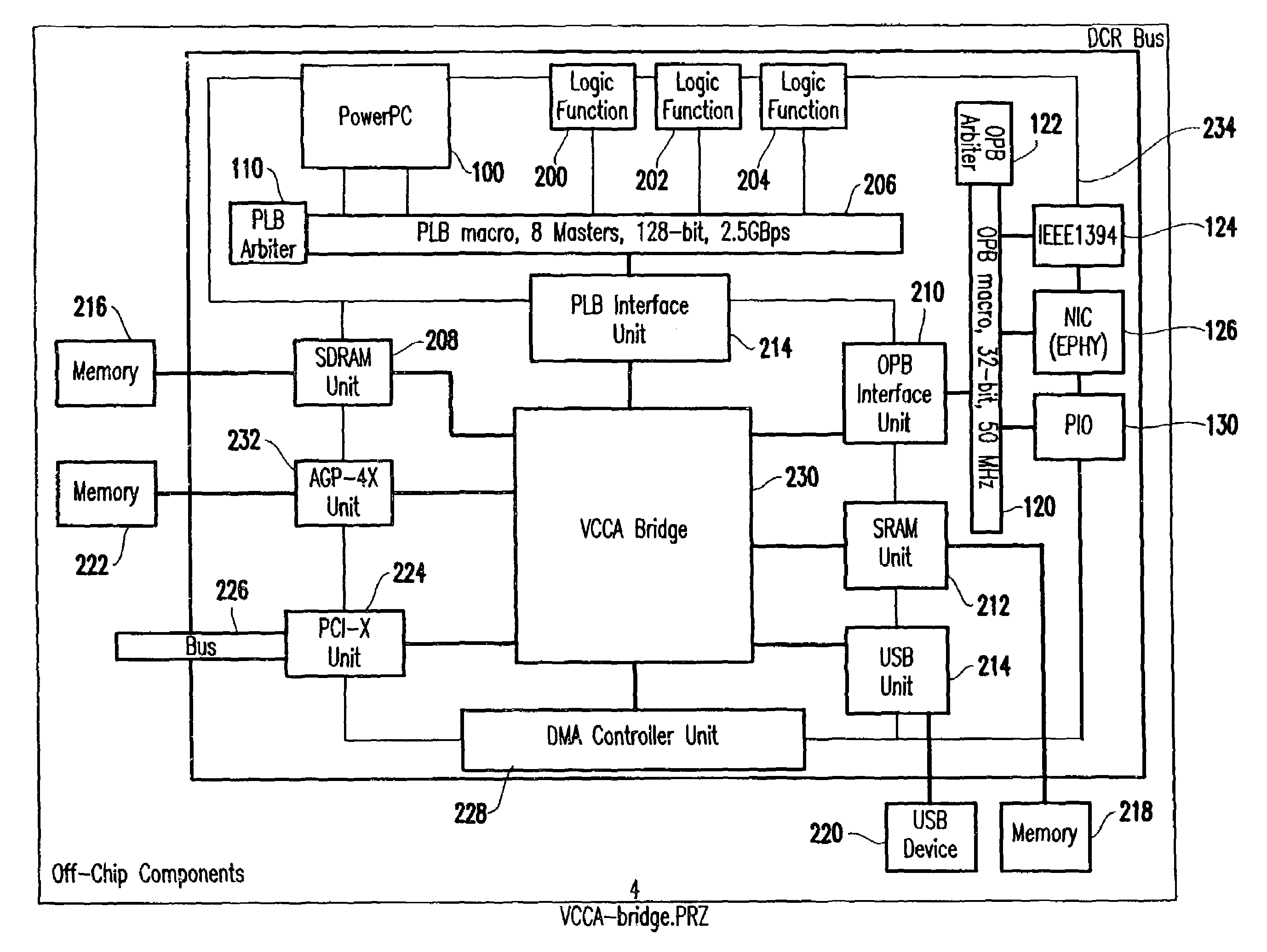

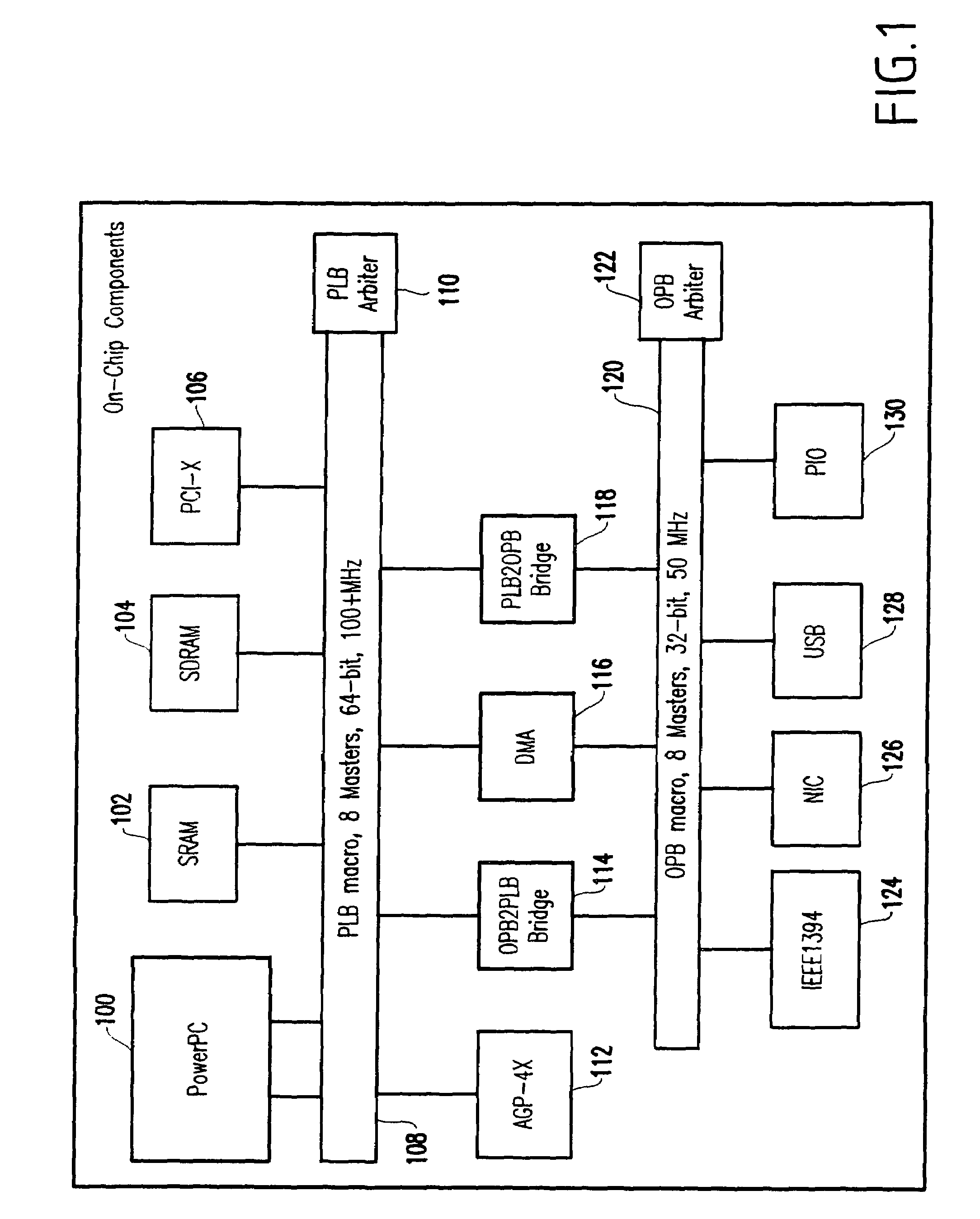

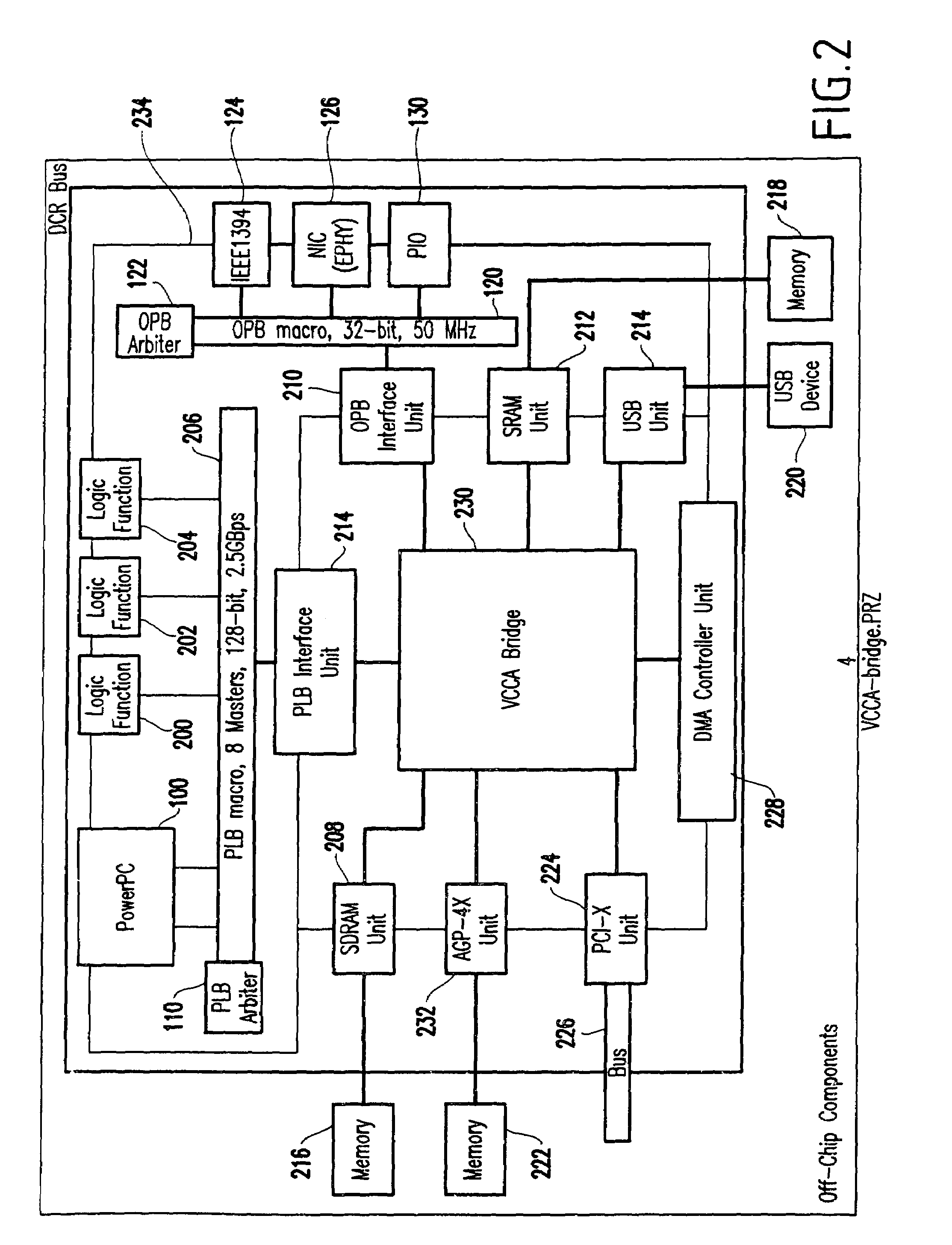

[0014]Referring now to the drawings, and more particularly to FIG. 1, a first System-on-a-Chip (SoC) system is illustrated that includes two buses, a processor local bus (PLB) 108 and an on-chip peripheral bus (OPB) 120. One or more logic devices 100 (such as the PowerPC available from IBM Corporation, Armonk N.Y., USA), are connected to the processor local bus 108. Additionally, memory devices, such as a static random access memory (SRAM) 102 and synchronous dynamic random access memory 104 (SDRAM) are connected to the processor local bus 108. Further, other peripheral interfaces, such as the peripheral component interface (PCI) and an advanced graphic pod (AGP) 112 are connected to the processor local bus 108. Various peripheral devices such as the IEEE1394 serial interface 124, network interface card (NIC) 126, universal serial bus (USB) 120, and a programmable input / output (PIO) are connected to the on-chip peripheral bus 120.

[0015]In operation, the PLB arbiter 110 and the OPB a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More