Patents

Literature

278 results about "Reference test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A laboratory that performs reference or calibration measurement procedures or assigns reference values to test objects, later potentially providing those associated reference values for references or sources of traceability of test results; alternate names include: reference measurement, reference testing, and calibration laboratory.

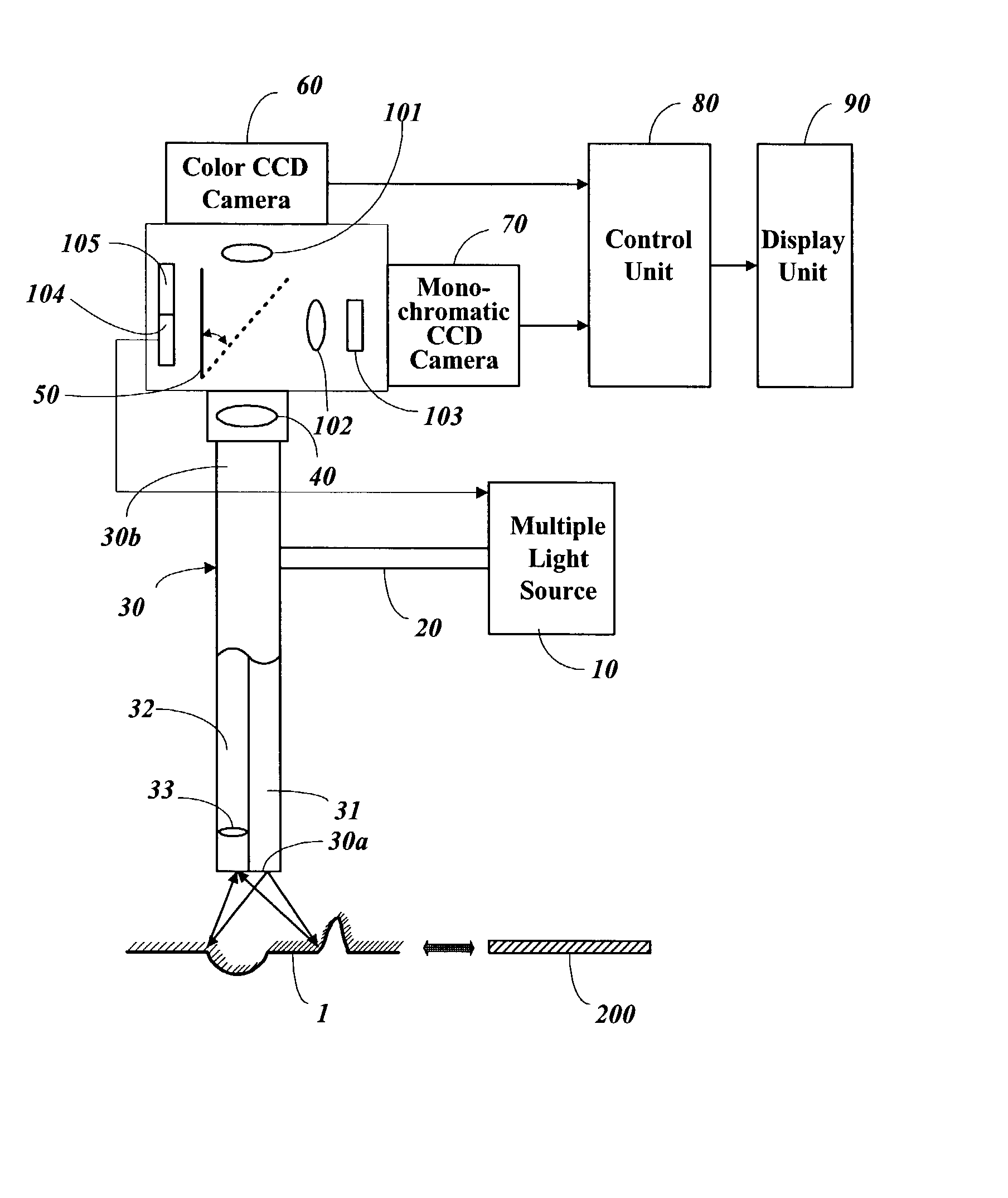

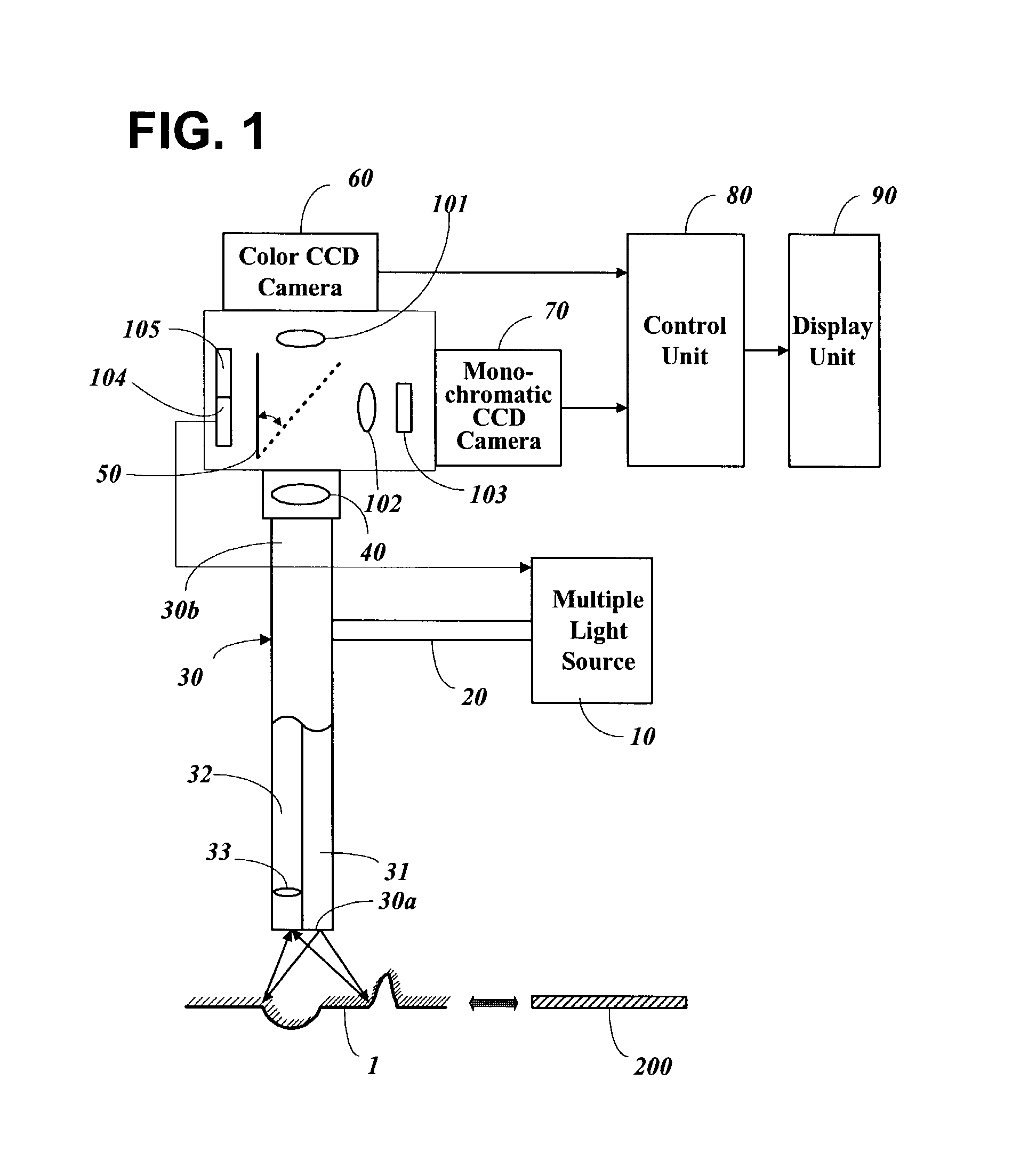

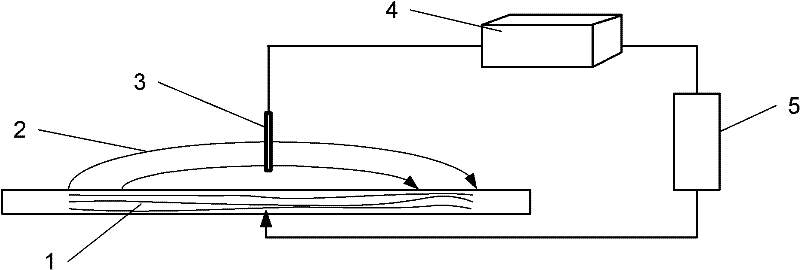

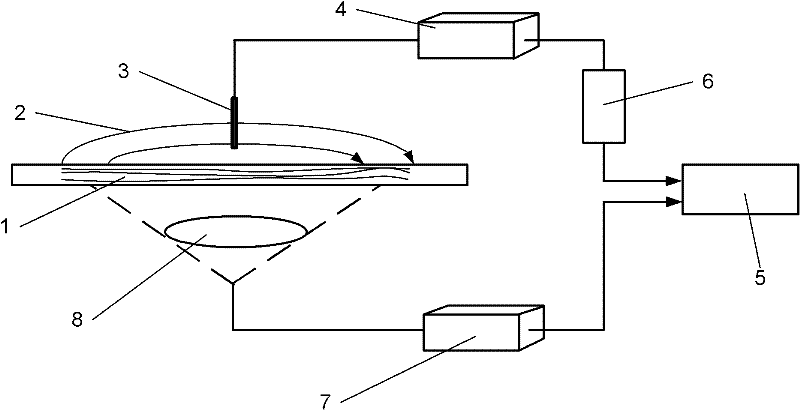

Fluorescence endoscope apparatus and method for imaging tissue within a body using the same

This present invention relates to a fluorescence endoscope apparatus, developed for diagnosing various illnesses within a body, especially for diagnosing a tumor inflamed region; and an application method of the same. The purpose of this invention is to enhance the accuracy of the examination. The fluorescence light endoscope apparatus in accordance with the present invention is comprised of an endoscope probe; a multiple light source that provides illumination light or excitation light of short wavelength onto a diagnostic region; a color CCD camera and a high sensitive monochromatic CCD camera placed on the back of an endoscope ocular lens; a reference test sample; a computer; and a monitor. The method of the present invention embodies a preliminary correction of the fluorescence endoscope apparatus of the present invention in accordance with the reference test sample; a general endoscopy using the illumination light, and an image observation and examination of the same diagnostic region using the fluorescence light and the reflected excitation light simultaneously; an auto-correction of brightness and unevenness of the fluorescence light images of the diagnostic region according to the reference test sample data; an evaluation of the brightness of the fluorescence light in the diagnosis region; storing numerical data that characterizing images and brightness of the fluorescence light in the diagnosis region; and storing image collected via two cameras as digital video clips.

Owner:MEDIMIR

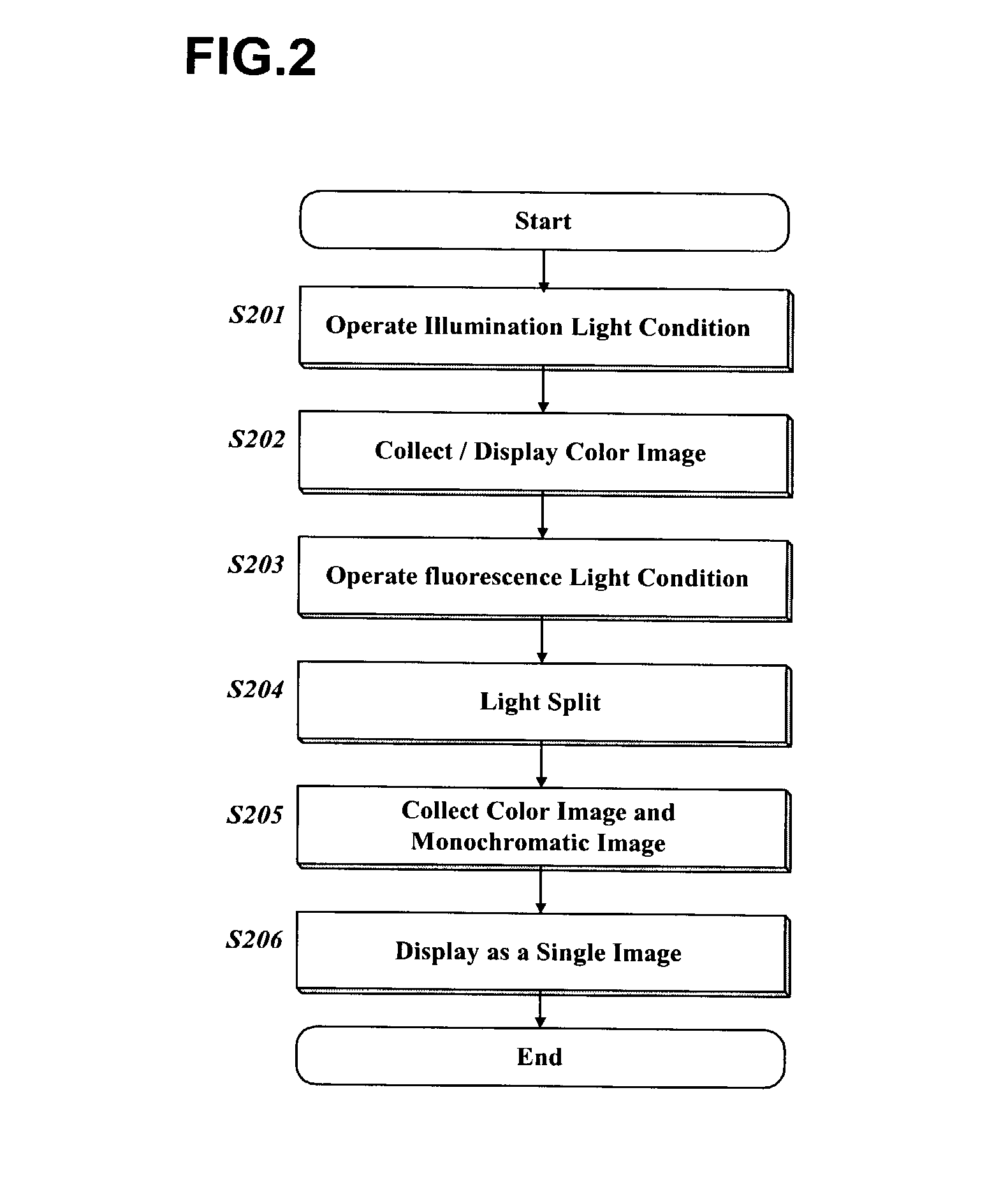

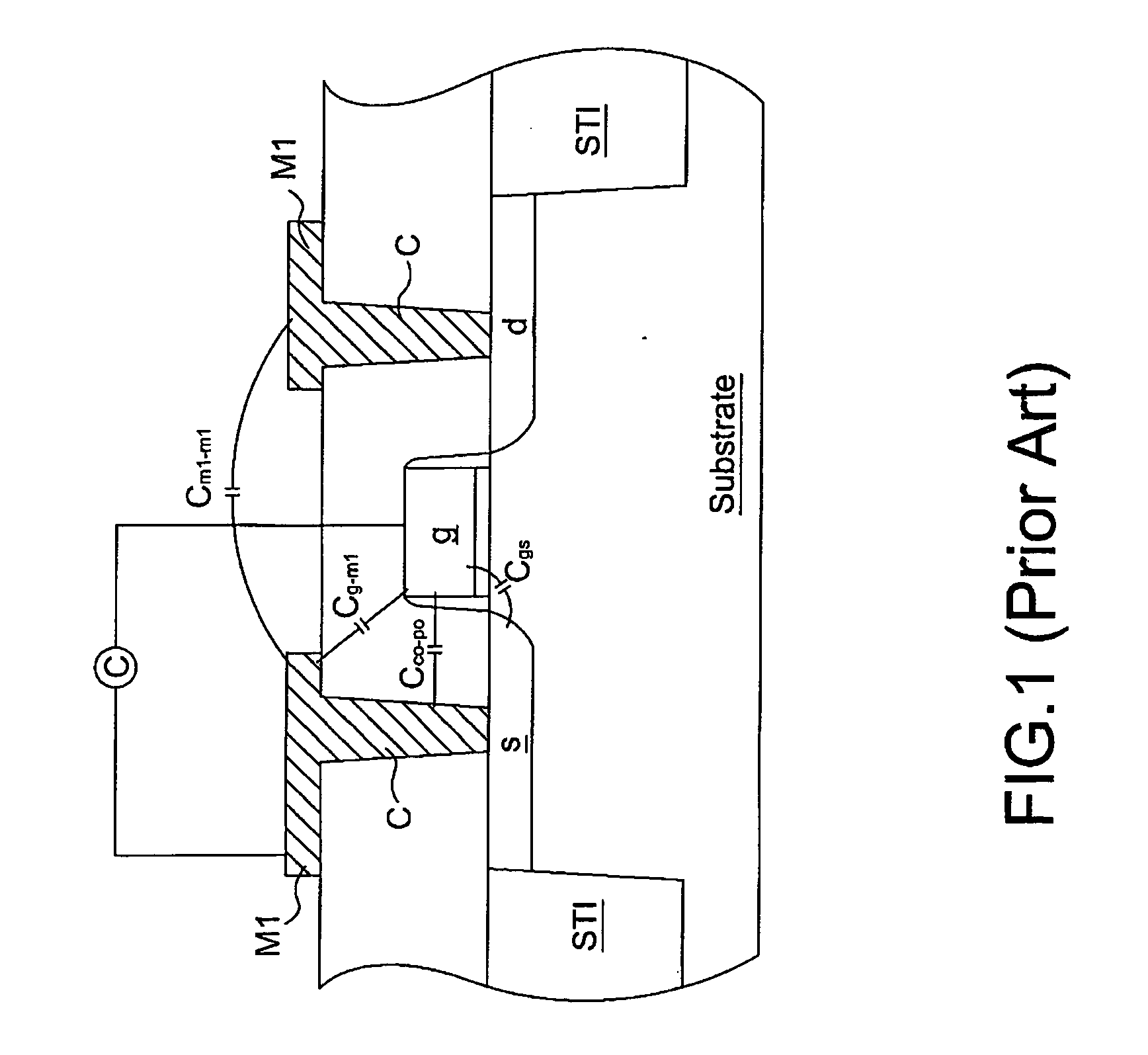

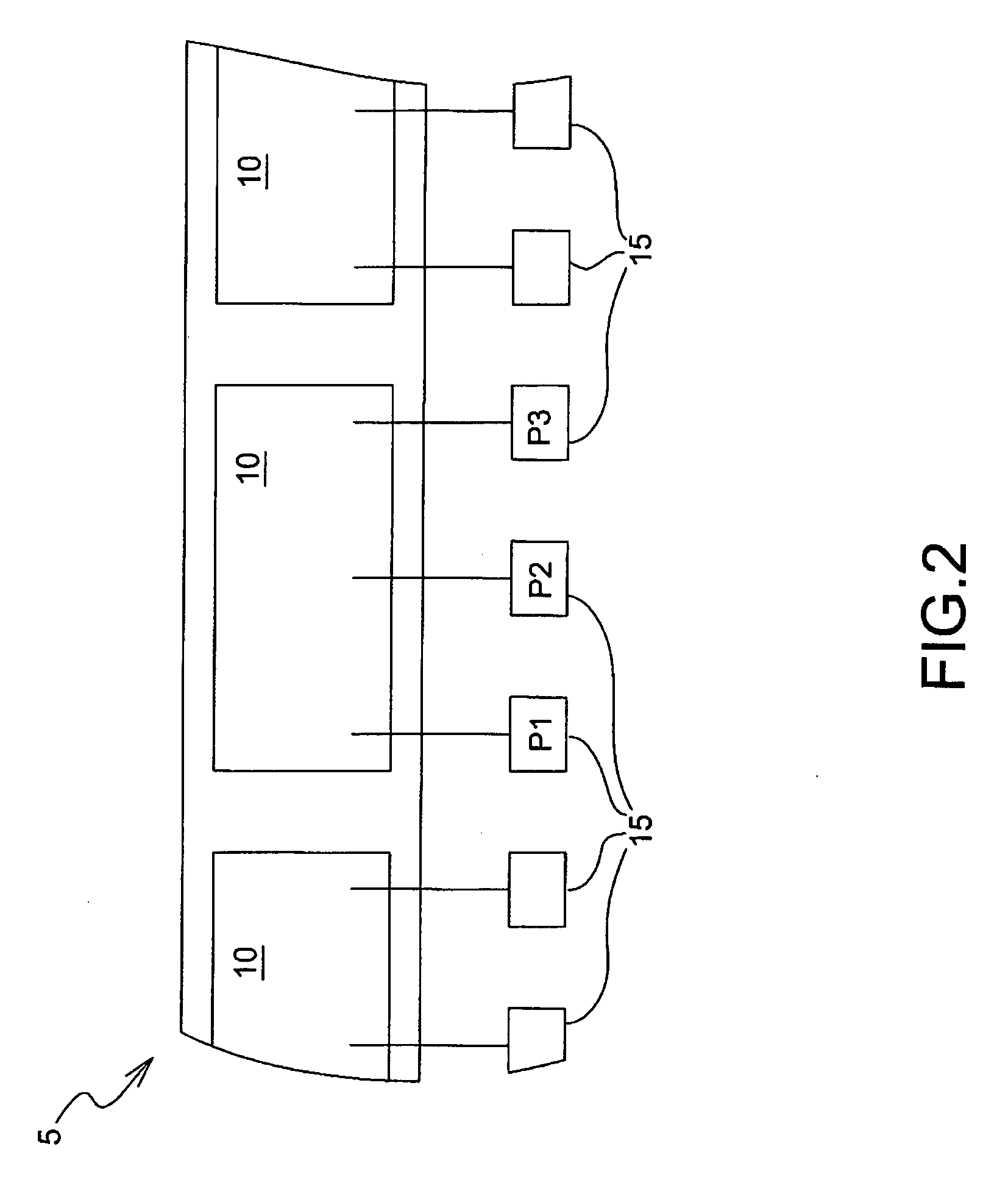

Accurate Capacitance Measurement for Ultra Large Scale Integrated Circuits

ActiveUS20090002012A1Improve accuracyEliminate the effects ofSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsVery large scale integrated circuitsReference test

Test structures and methods for measuring contact and via parasitic capacitance in an integrated circuit are provided. The accuracy of contact and via capacitance measurements are improved by eliminating not-to-be-measured capacitance from the measurement results. The capacitance is measured on a target test structure that has to-be-measured contact or via capacitance. Measurements are then repeated on a substantially similar reference test structure that is free of to-be-measured contact or via capacitances. By using the capacitance measurements of the two test structures, the to-be-measured contact and via capacitance can be calculated.

Owner:TAIWAN SEMICON MFG CO LTD

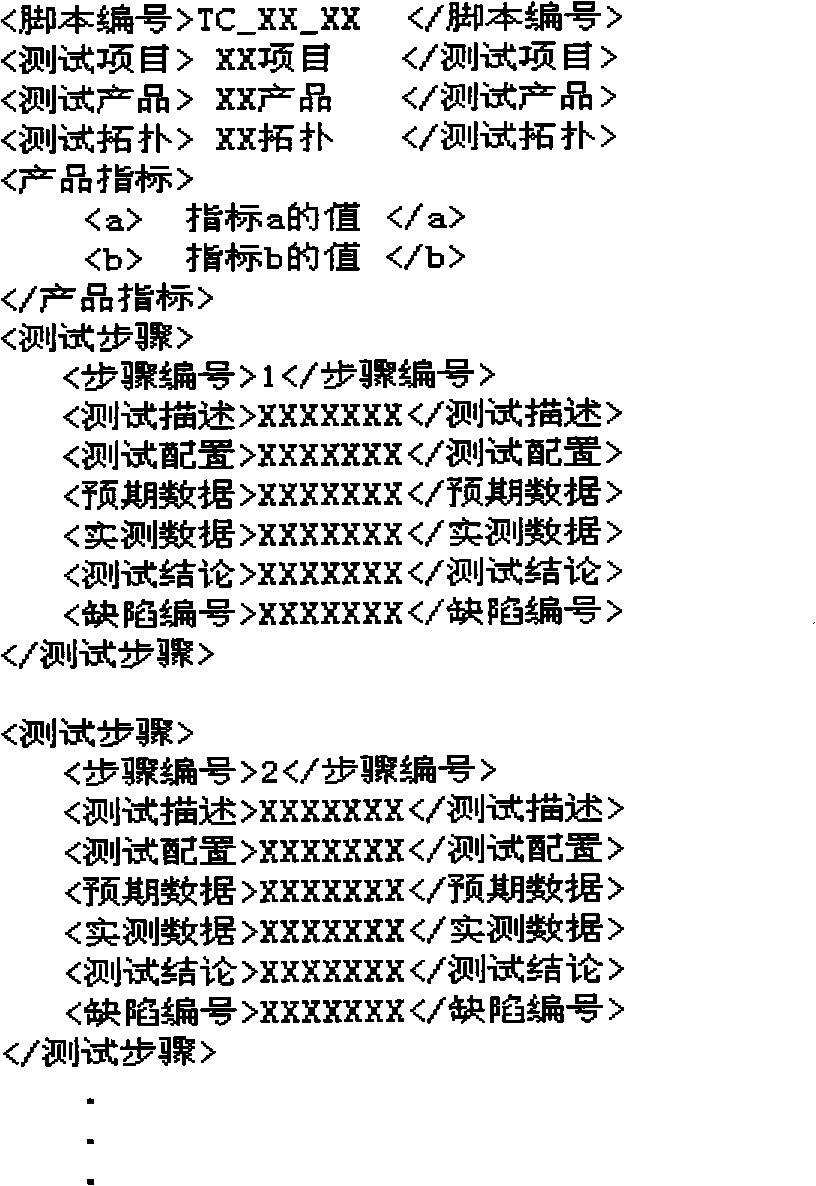

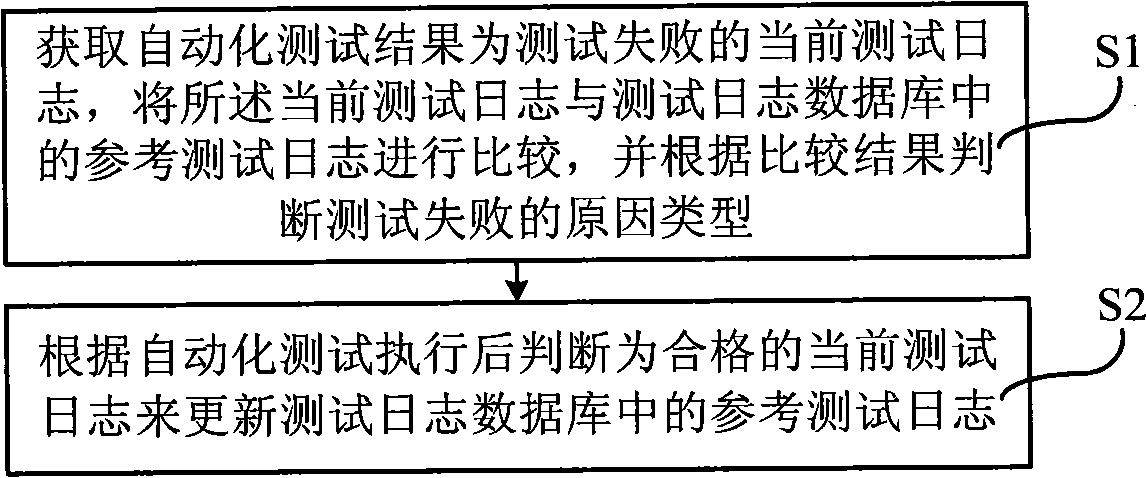

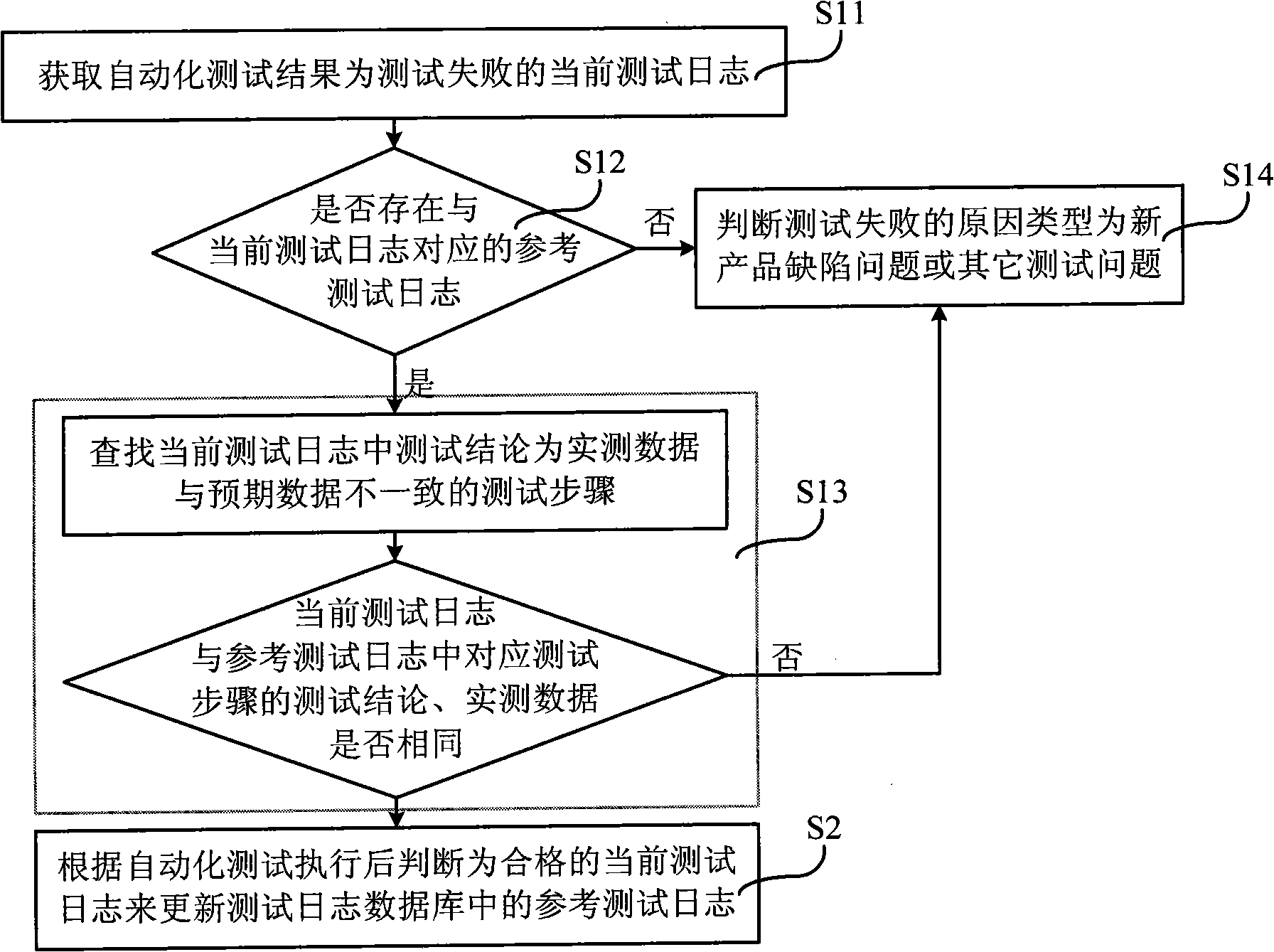

Analysis method for automatic test log and device

InactiveCN101556550ASolve the problem of inaccurate judgment of the type of test failure reasonSolve the problem of inaccurate judgmentHardware monitoringSoftware testing/debuggingReference testAnalysis method

The invention provides an analysis method for automatic test log and a device. The method comprises the following steps of: step S1, acquiring automatic test result as the current test log with test failure, comparing the current test log with a reference test log in a test log database and judging the reason types of test failure according to compared results; and step S2, updating the reference test log in the test log database according to the current test log which is judged to be qualified after the automatic test is executed. The method and the device can automatically recognize the test log with various reason types of test failures, solve the problem that the manual analysis for test log has inaccuracy judgment for the reason types of test failure, and lead the tester to be capable of analyzing test log pointedly.

Owner:BEIJING XINWANG RUIJIE NETWORK TECH CO LTD

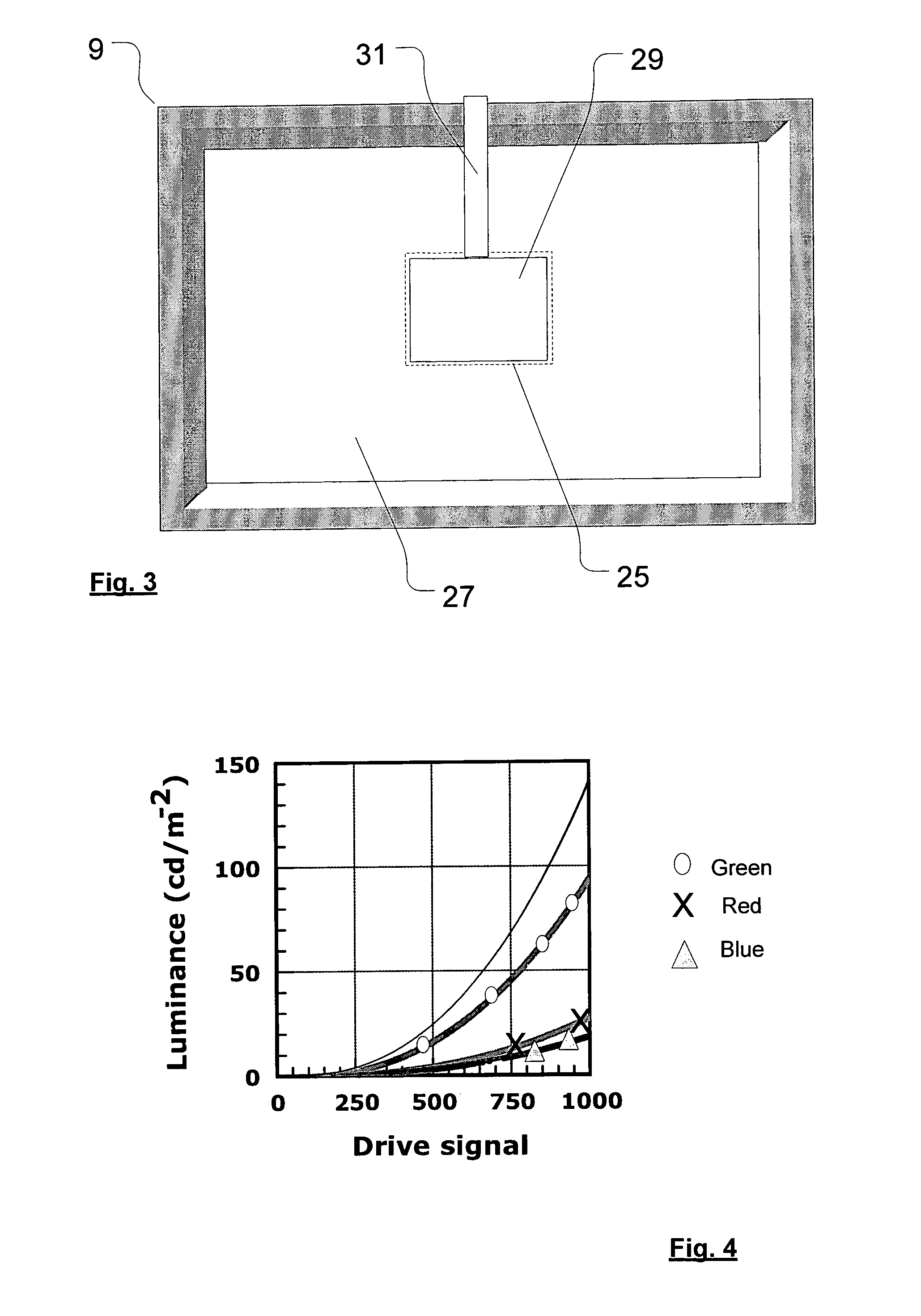

Vision testing apparatus and method

An embodiment of the invention relates to vision testing apparatus comprising: a local display (9); means (13) for obtaining data characterising the performance characteristics of said local display; means (9) for displaying to a user at said local display, a vision test that comprises an adaptation of a reference vision test; means (11) for registering user input in response to said displayed vision test; and means (9) for providing the user with the results of said displayed test; wherein said reference vision test comprises a test that is optimised for display on a high quality display, and the vision test for display at said local display is obtained by adapting said reference test in accordance with said characterising data so that the vision test displayed on said local display is a faithful reproduction of said reference test.

Owner:CITY UNIV

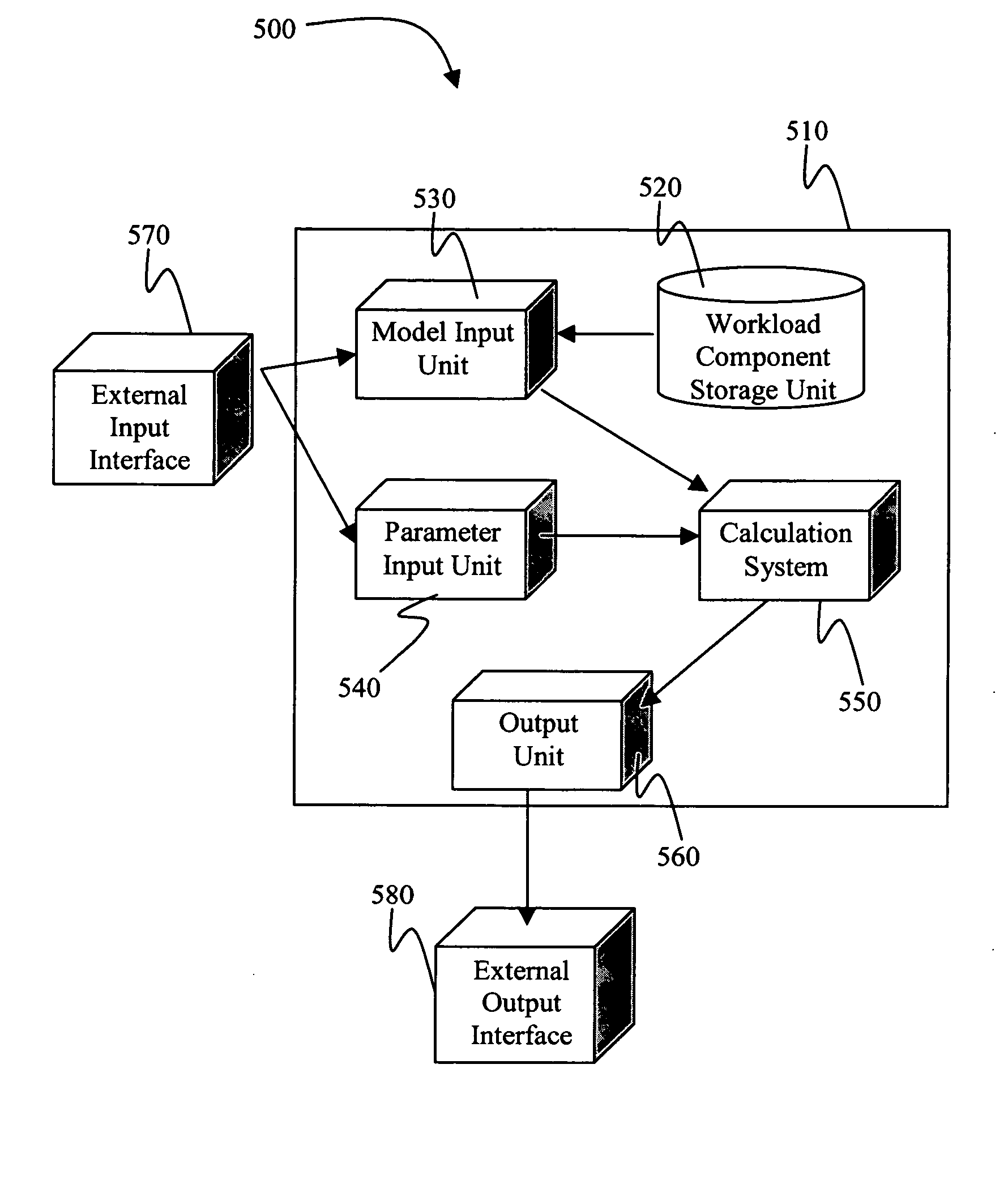

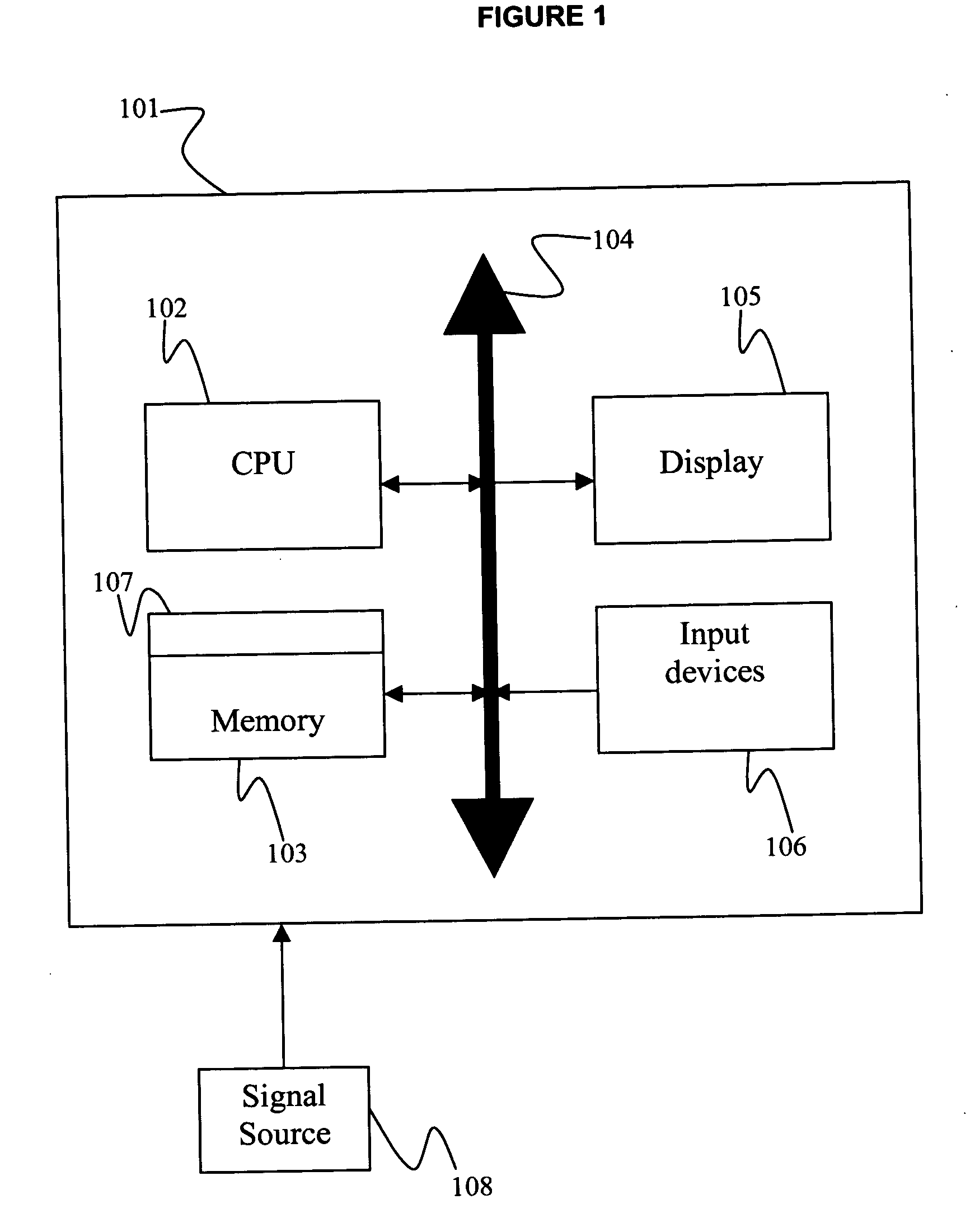

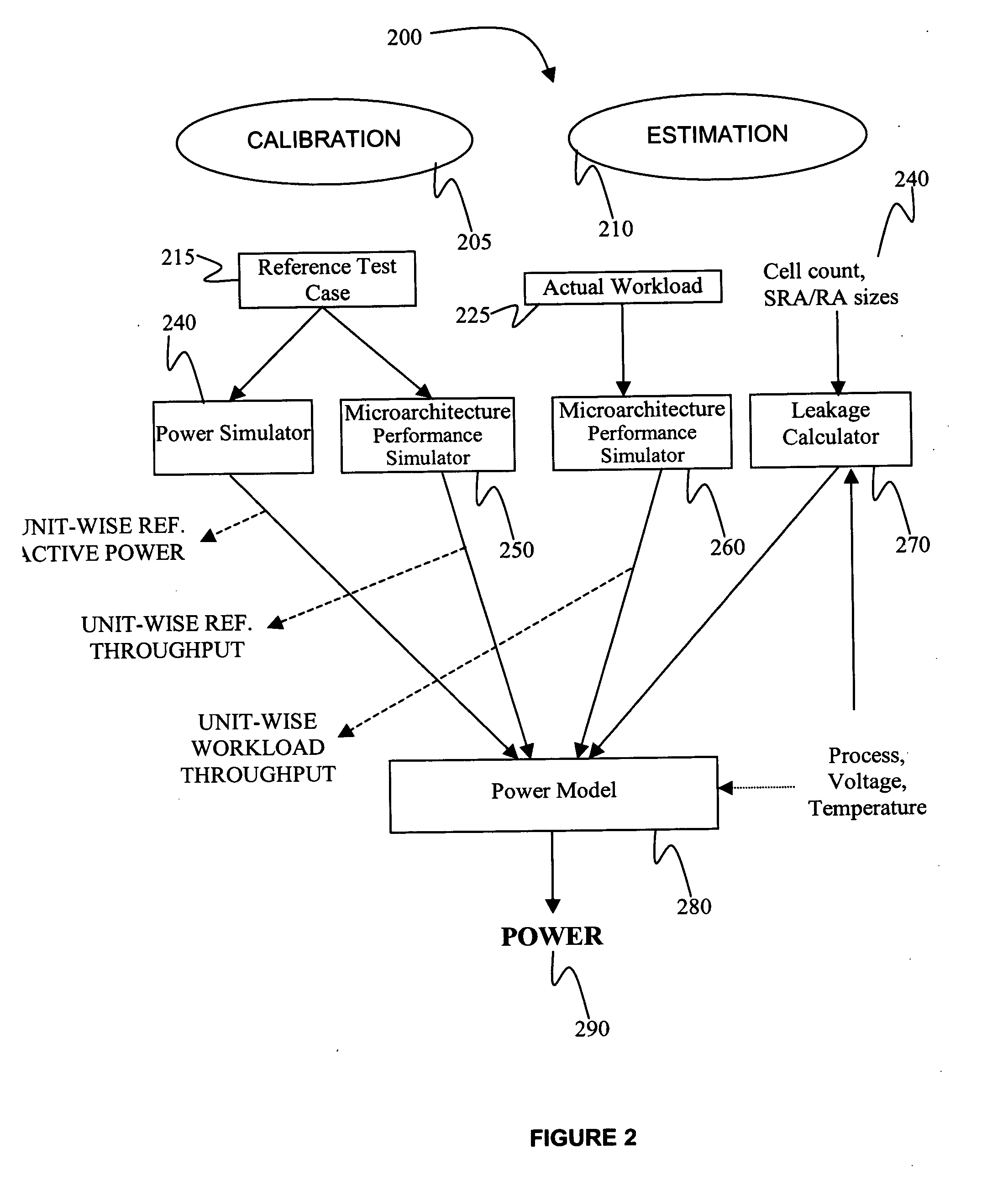

Architectural level throughput based power modeling methodology and apparatus for pervasively clock-gated processor cores

InactiveUS20060080625A1Improve performanceAnalogue computers for nuclear physicsCAD circuit designPower analysisReference test

A method, system, and apparatus for estimating the power dissipated by a processor core processing a workload, where the method includes analyzing a reference test case to generate a reference workload characteristic. Analyzing an actual workload to generate an actual workload characteristic. Performing a power analysis for the reference test case to establish a reference power dissipation value. Estimating an actual workload power dissipation value responsive to the actual and reference workload characteristics and the reference power dissipation value

Owner:GLOBALFOUNDRIES INC

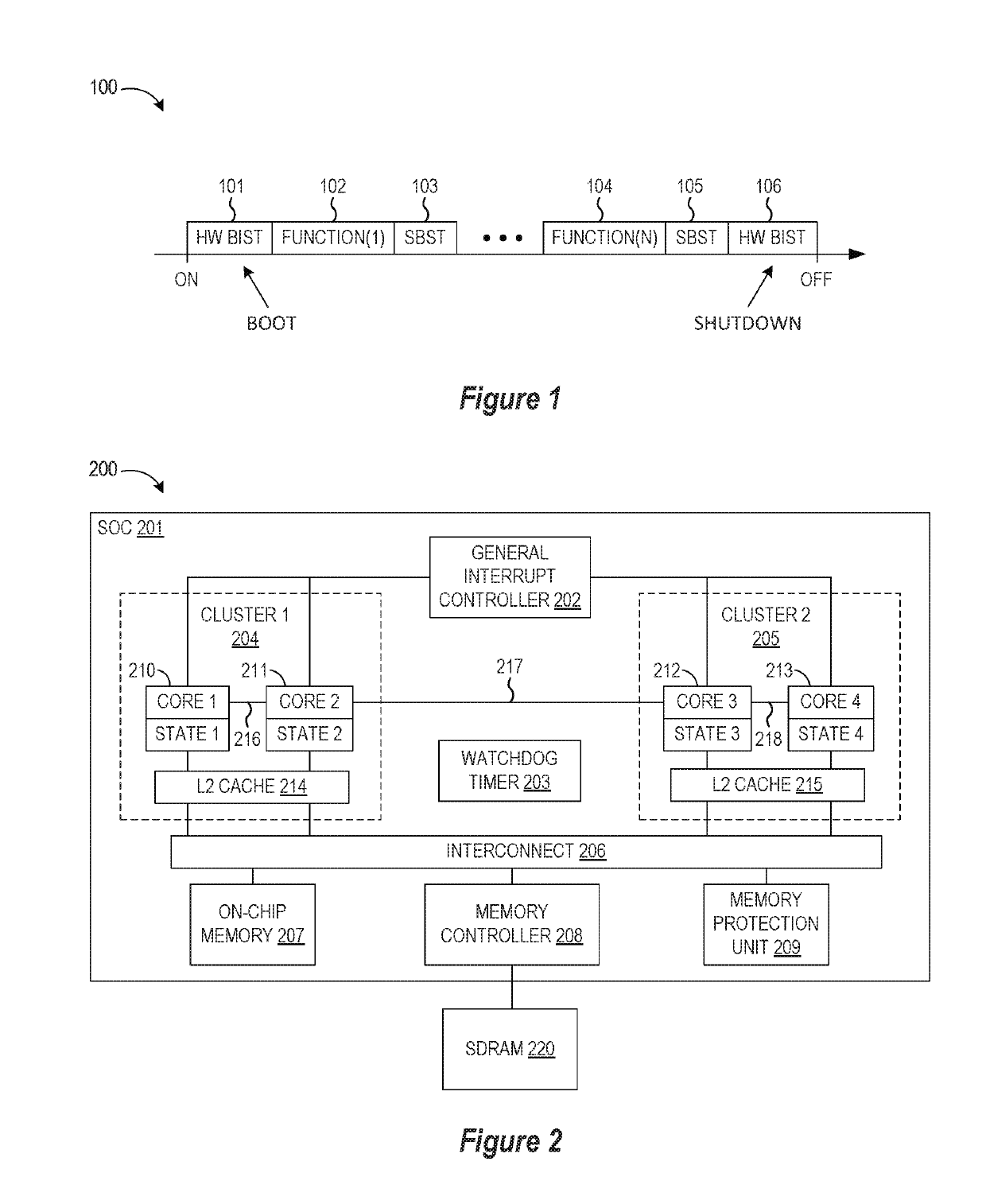

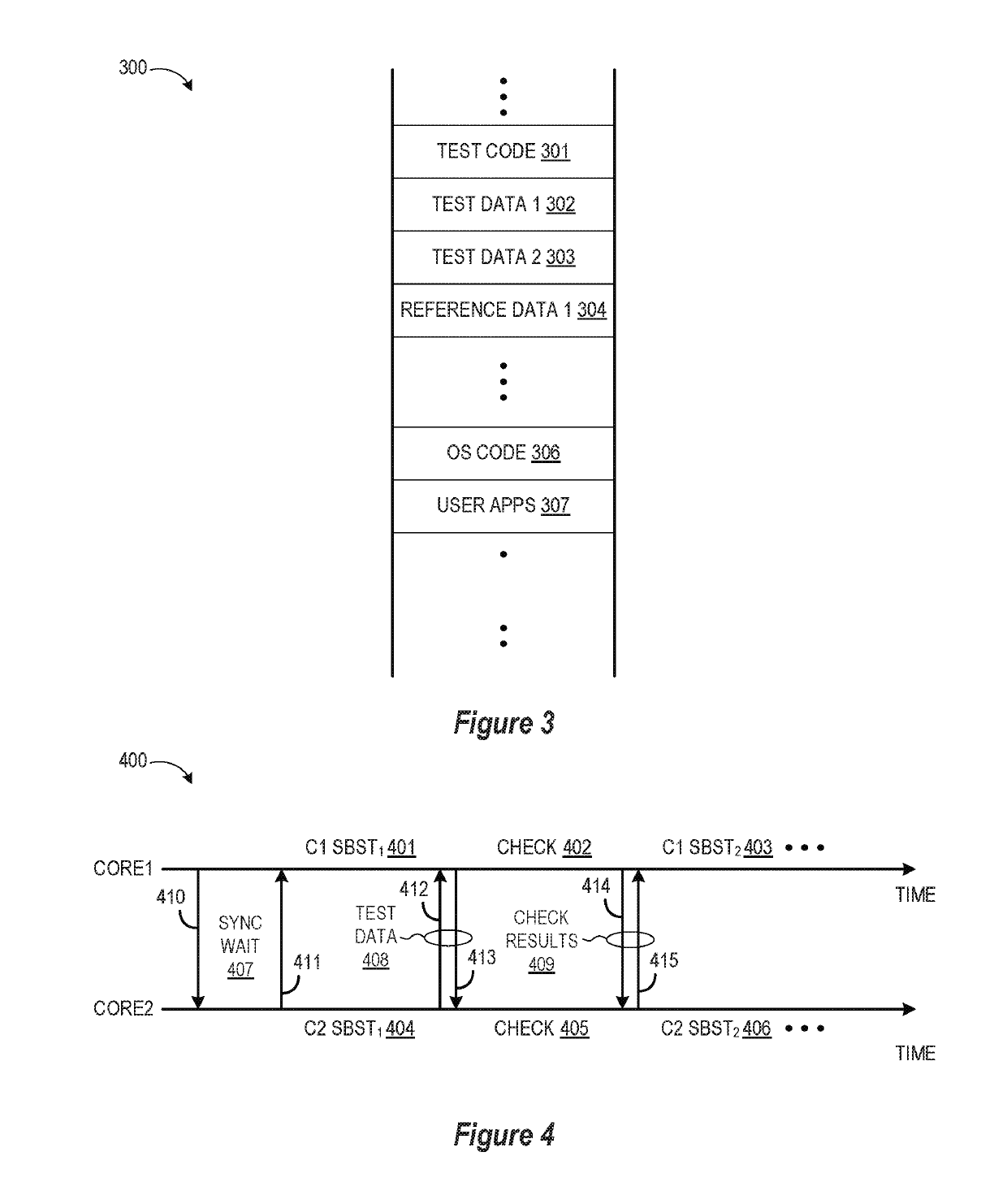

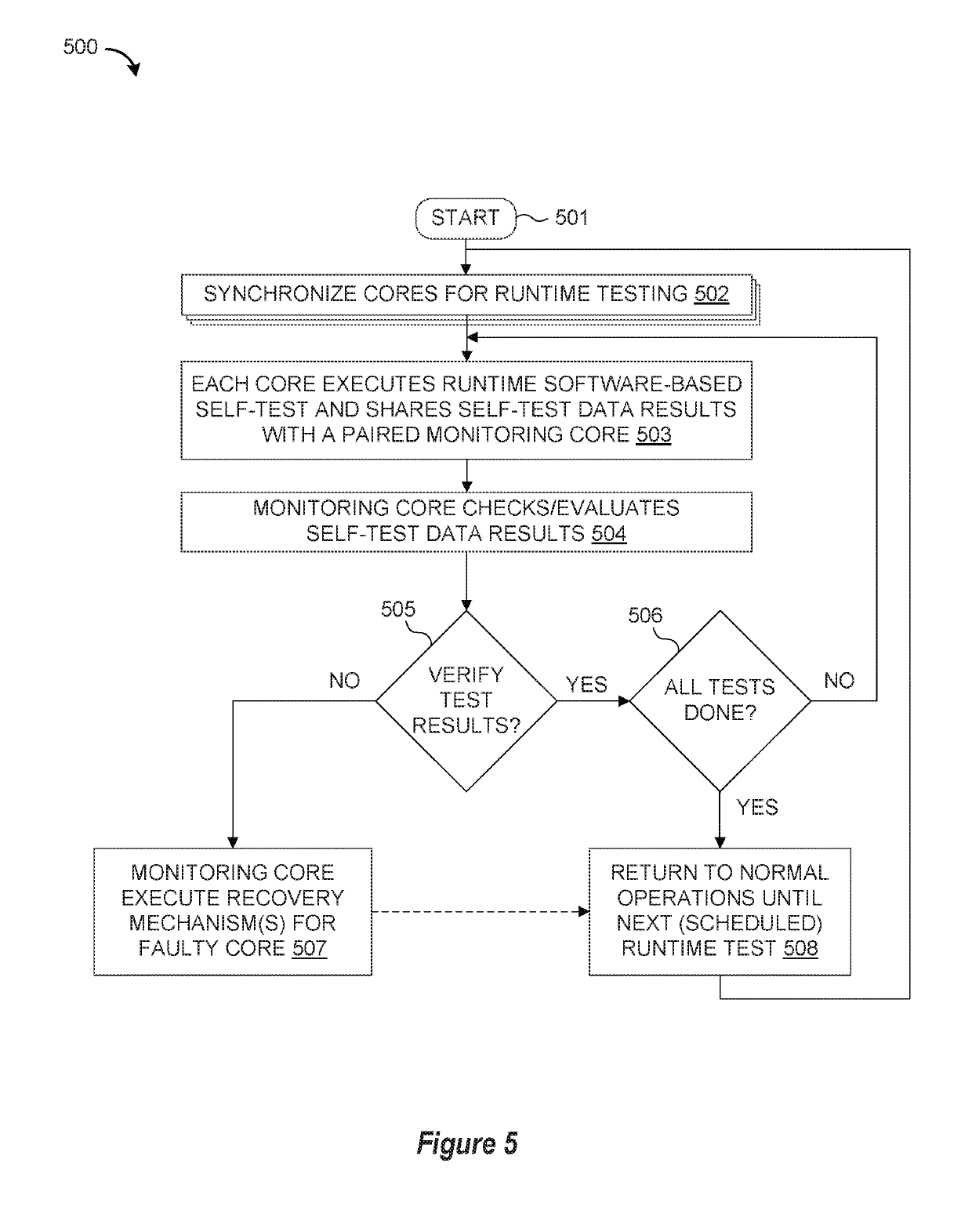

Runtime Software-Based Self-Test with Mutual Inter-Core Checking

A method, apparatus, article of manufacture, and system are provided for detecting hardware faults on a multi-core integrated circuit device by executing runtime software-based self-test code concurrently on multiple processor cores to generate a first set of self-test results from a first processor core and a second set of self-test results from a second processor core; performing mutual inter-core checking of the self-test results by using the first processor core to check the second set of self-test results from the second processor core while simultaneously using the second processor core to check the first set of self-test results from the first processor core; and then using the second processor core to immediately execute a recovery mechanism for the first processor core if comparison of the first set of self-test results against reference test results indicates there is a hardware failure at the first processor core.

Owner:NXP BV

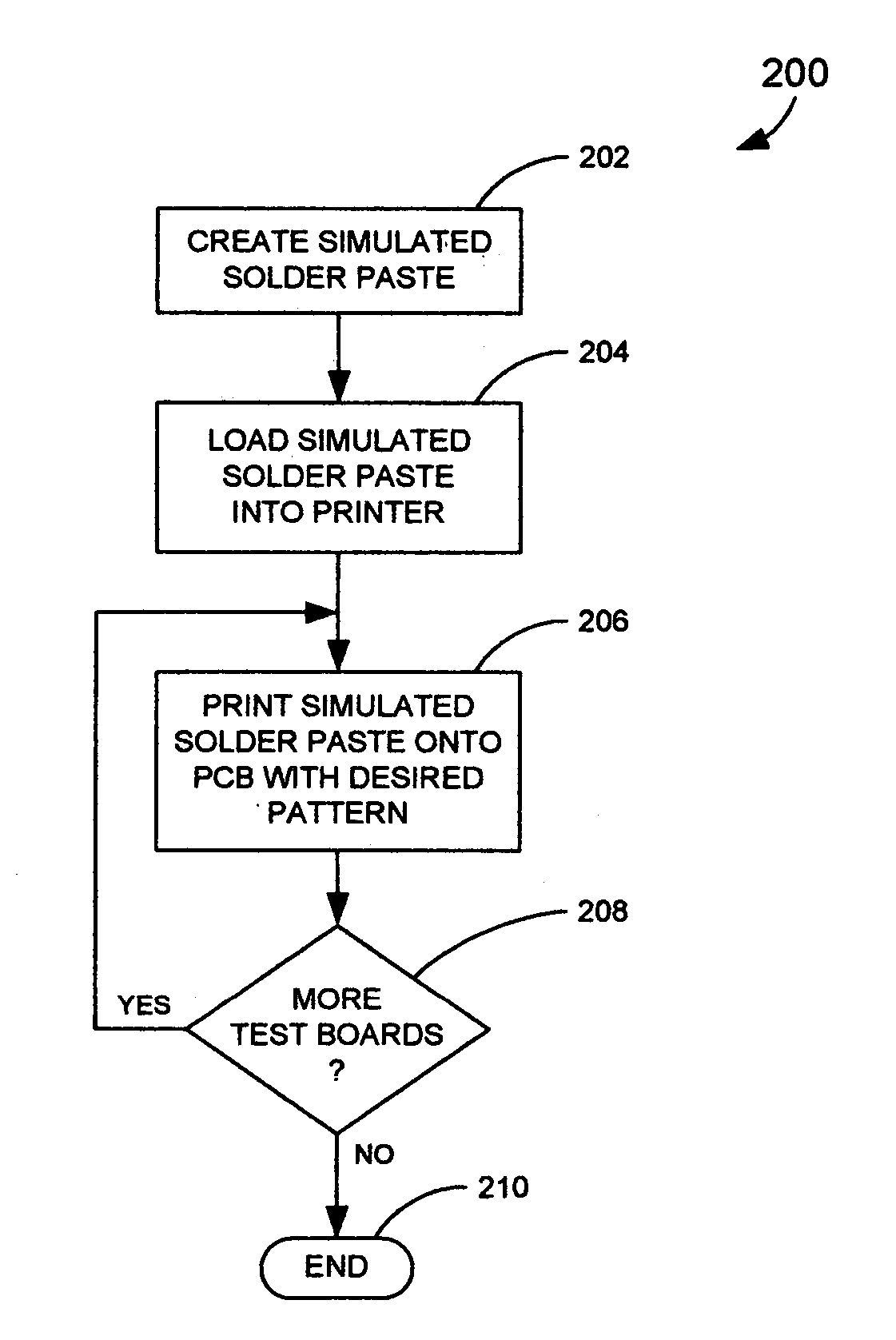

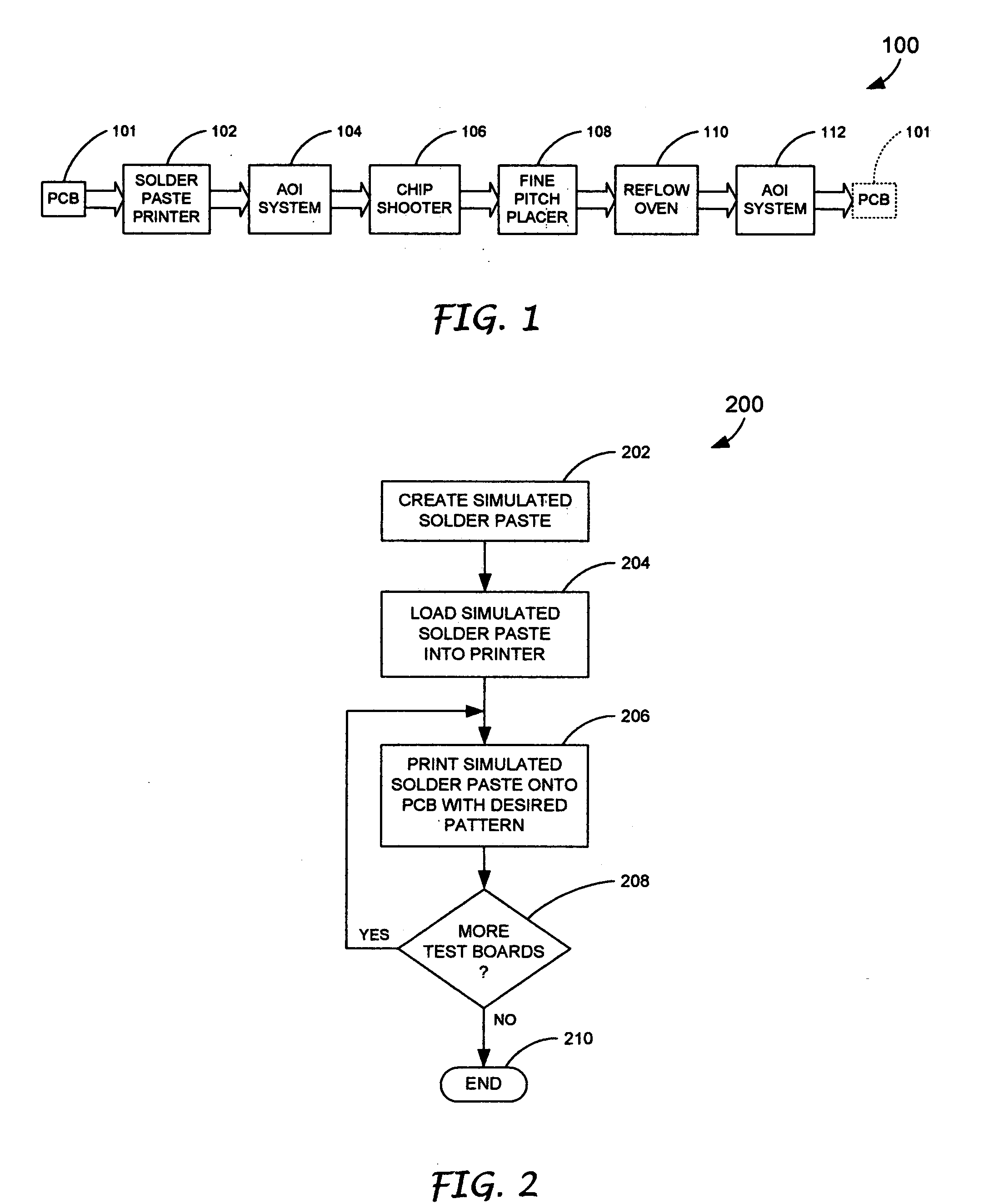

Technique for optical inspection system verification

A technique for optical inspection verification implements a number of steps. Initially, a simulated solder paste material, including a solder powder and an organic resin, is provided. Next, the simulated solder paste material is printed in a desired pattern on a base material to provide a reference test board. Then, the test board is cured to stabilize the simulated solder paste material. Next, the test board is utilized to train the optical inspection system to reject defective product.

Owner:DELPHI TECH INC

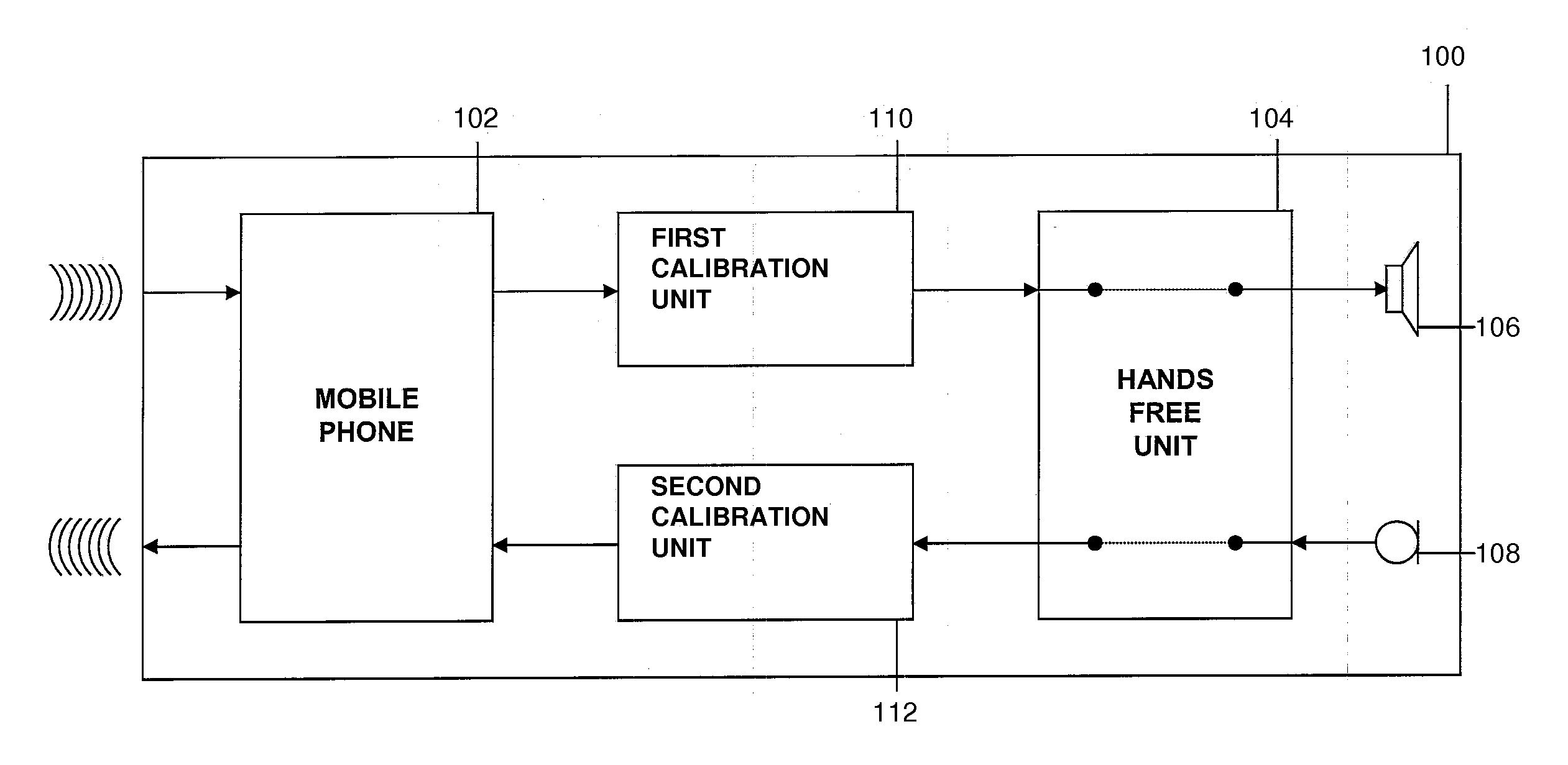

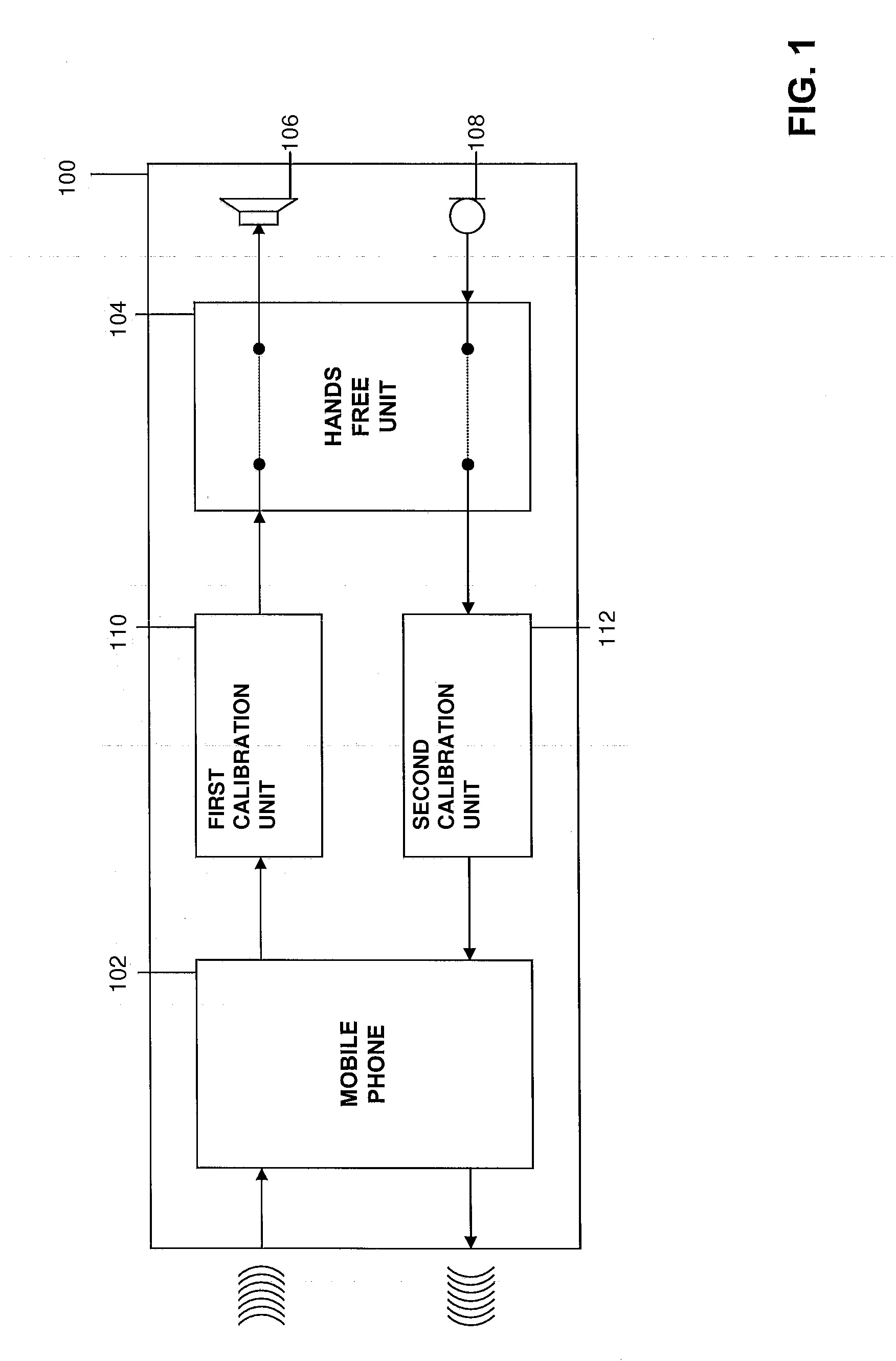

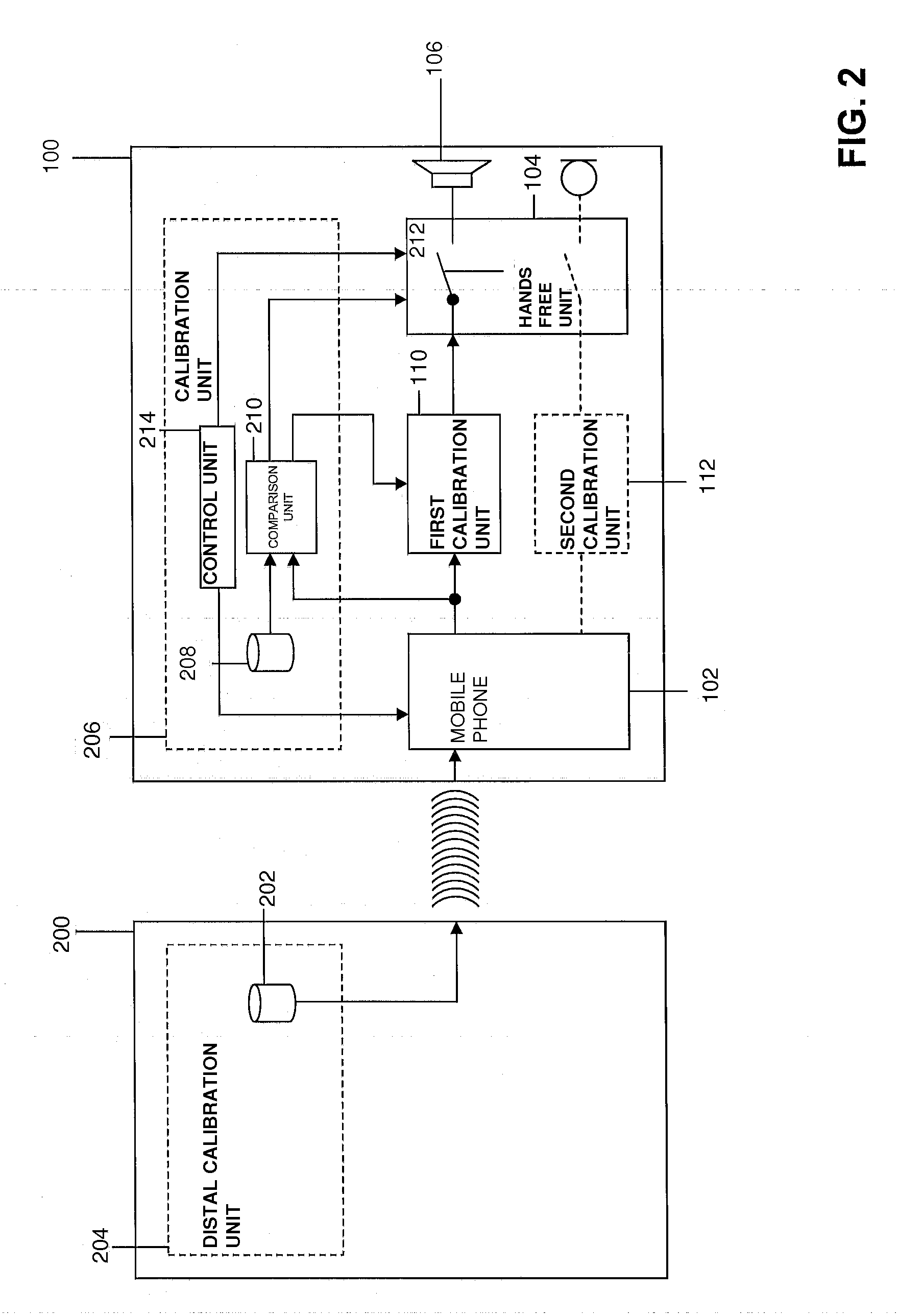

System for calibrating a hands-free system

ActiveUS20080020807A1Resistance/reactance/impedenceElectrical measurement instrument detailsReference testEngineering

A method for calibrating a hands-free system is provided. The hands-free system comprising a hands-free unit and a mobile phone, the method comprising the following steps of setting up a connection between the hands-free system and a distant terminal via a mobile telephony network of the mobile phone, transmitting a predetermined test signal from one of the hands-free system and the distant terminal to the other of the hands-free system and the distant terminal, the predetermined test signal being provided in both the hands-free system and the distant terminal as reference test signal, comparing the received test signal to the reference test signal stored in the other of the hands-free system and the distant terminal, and determining the calibration parameters of the hands-free system in accordance with the comparison.

Owner:HARMAN BECKER AUTOMOTIVE SYST

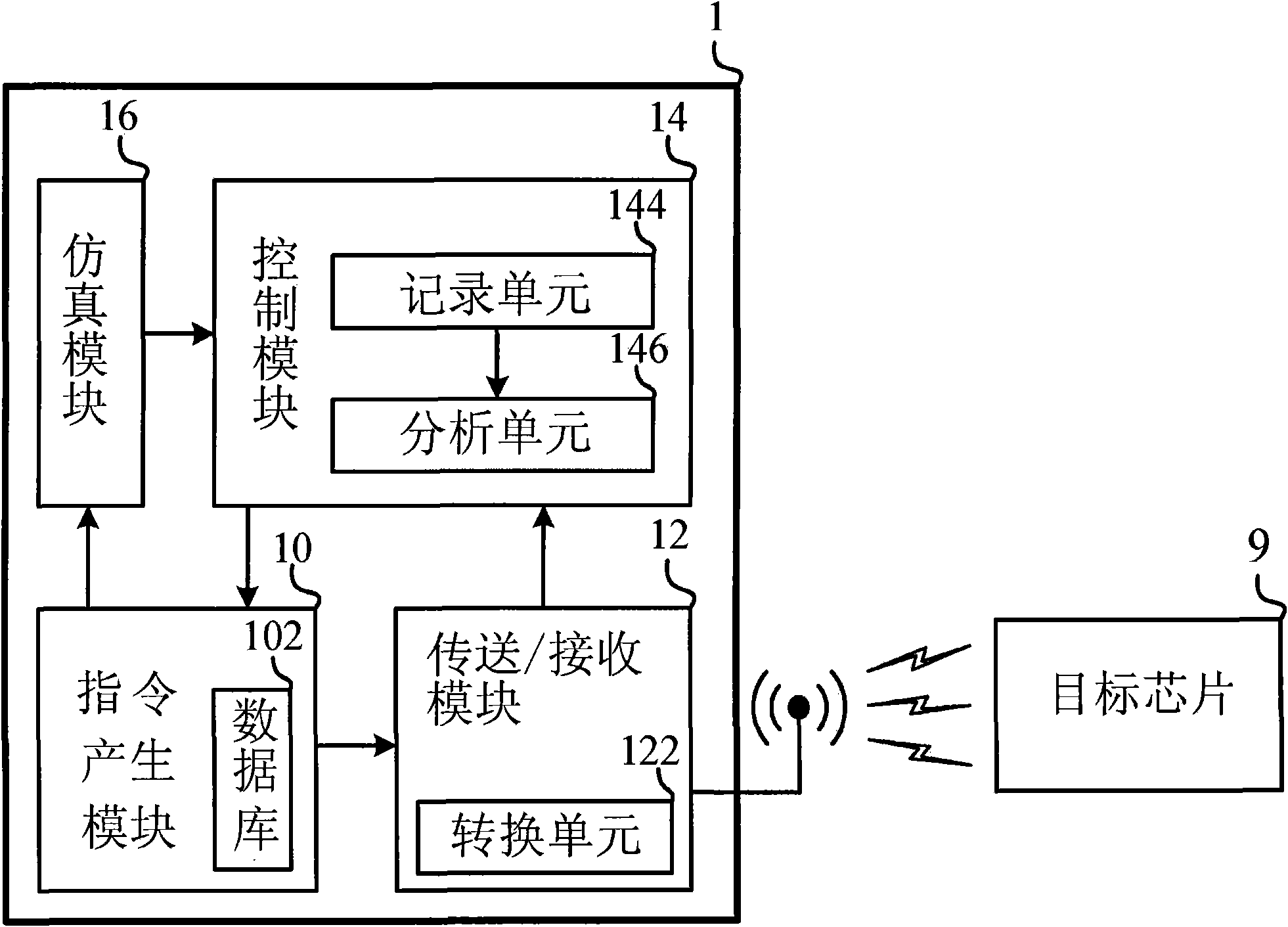

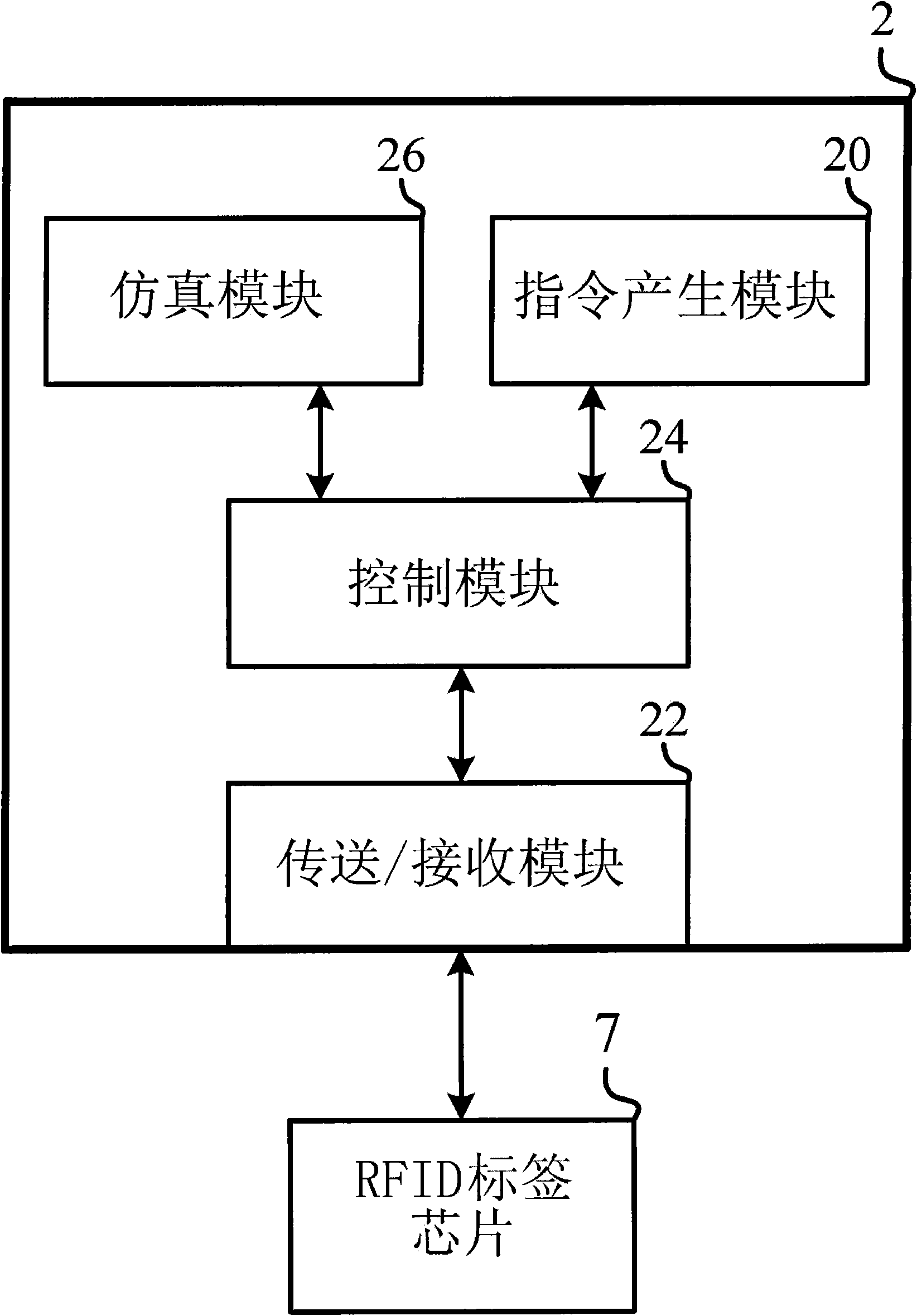

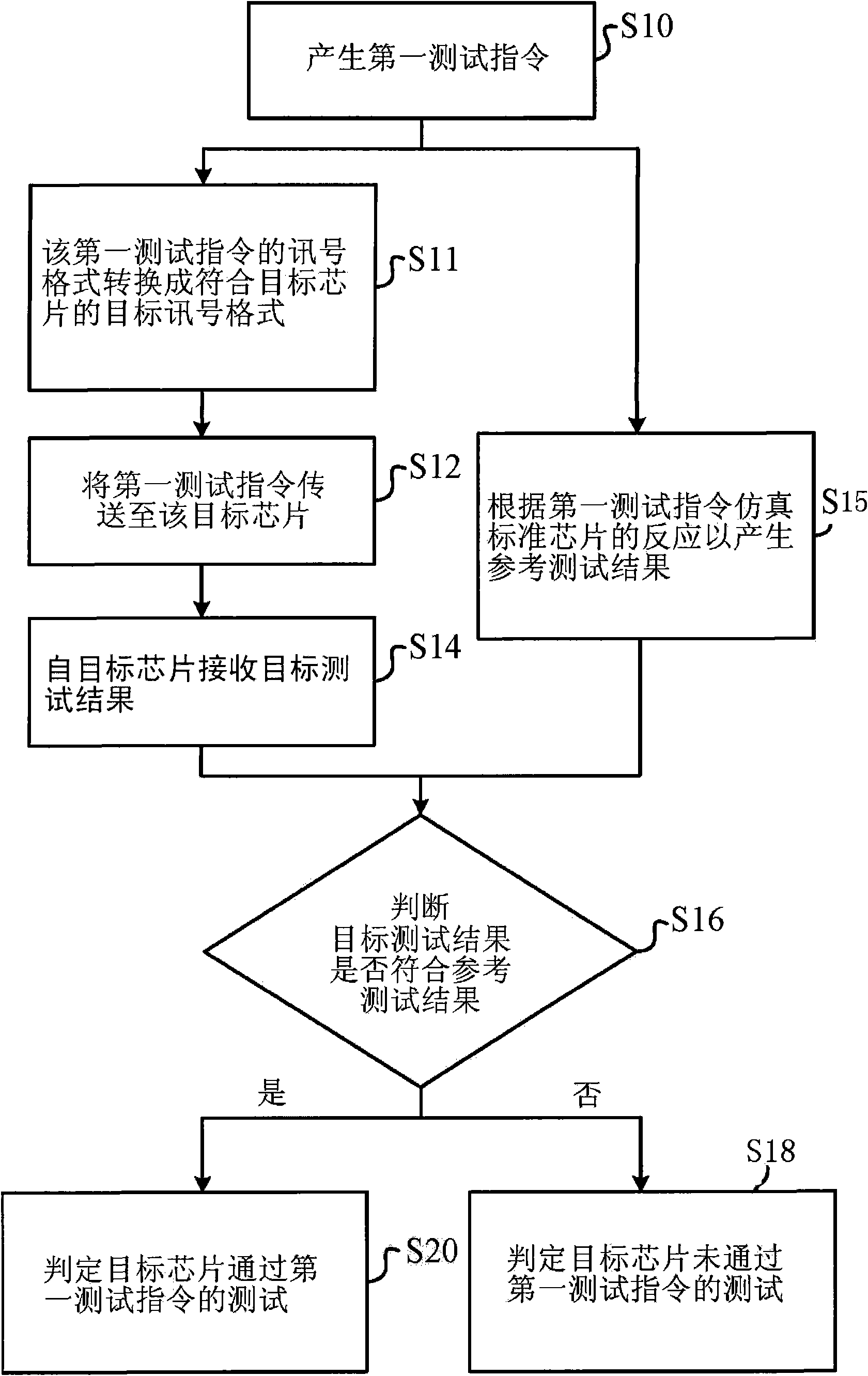

Chip testing device and chip testing method

ActiveCN101672878AIncrease coverageElectrical testingSensing record carriersComputer hardwareReference test

The invention discloses a chip testing device and a chip testing method. The chip testing device comprises an instruction generating module, a transmitting / receiving module and a control module. After the instruction generating module generates a first testing instruction, the transmitting / receiving module transmits the first testing instruction to a radio frequency identification label chip, andreceives a target testing result from the radio frequency identification label chip. The control module is used for judging whether the target testing result accords with a reference testing result or not. If the target testing result does not accord with the reference testing result according to the judgment result of the control module, the control module controls the instruction generating module to generate a second testing instruction for retesting the radio frequency identification label chip. The chip testing device and the chip testing method can achieve the effect of automatic randomand repeated testing on RFID label chips, and can improve the coverage rate of a testing instruction range of the RFID label chips besides saving time and labor of a user spending on editing the testing instruction.

Owner:MEDIATEK INC

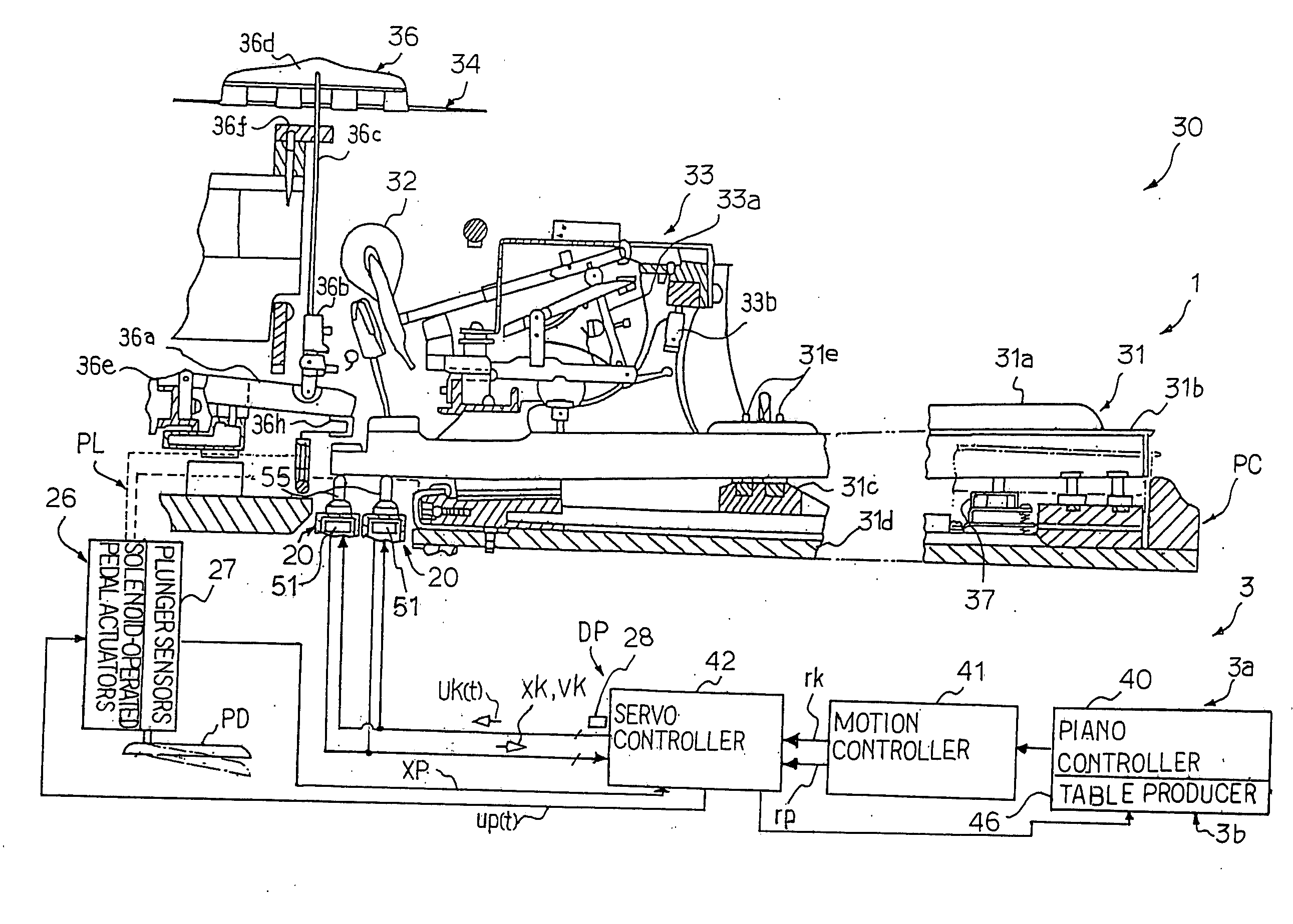

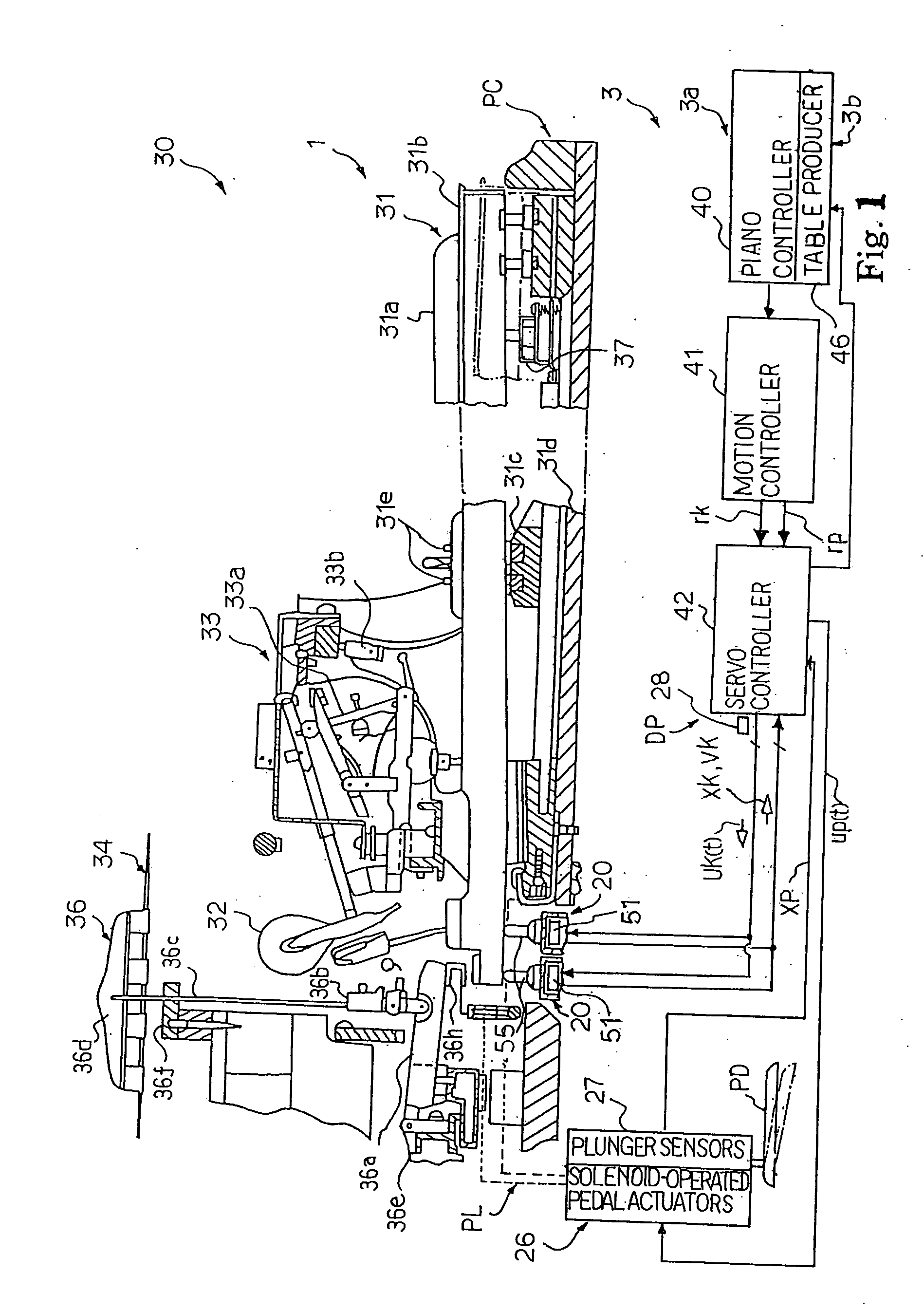

Data acquisition system preparing inner force sense data for inner sense controller

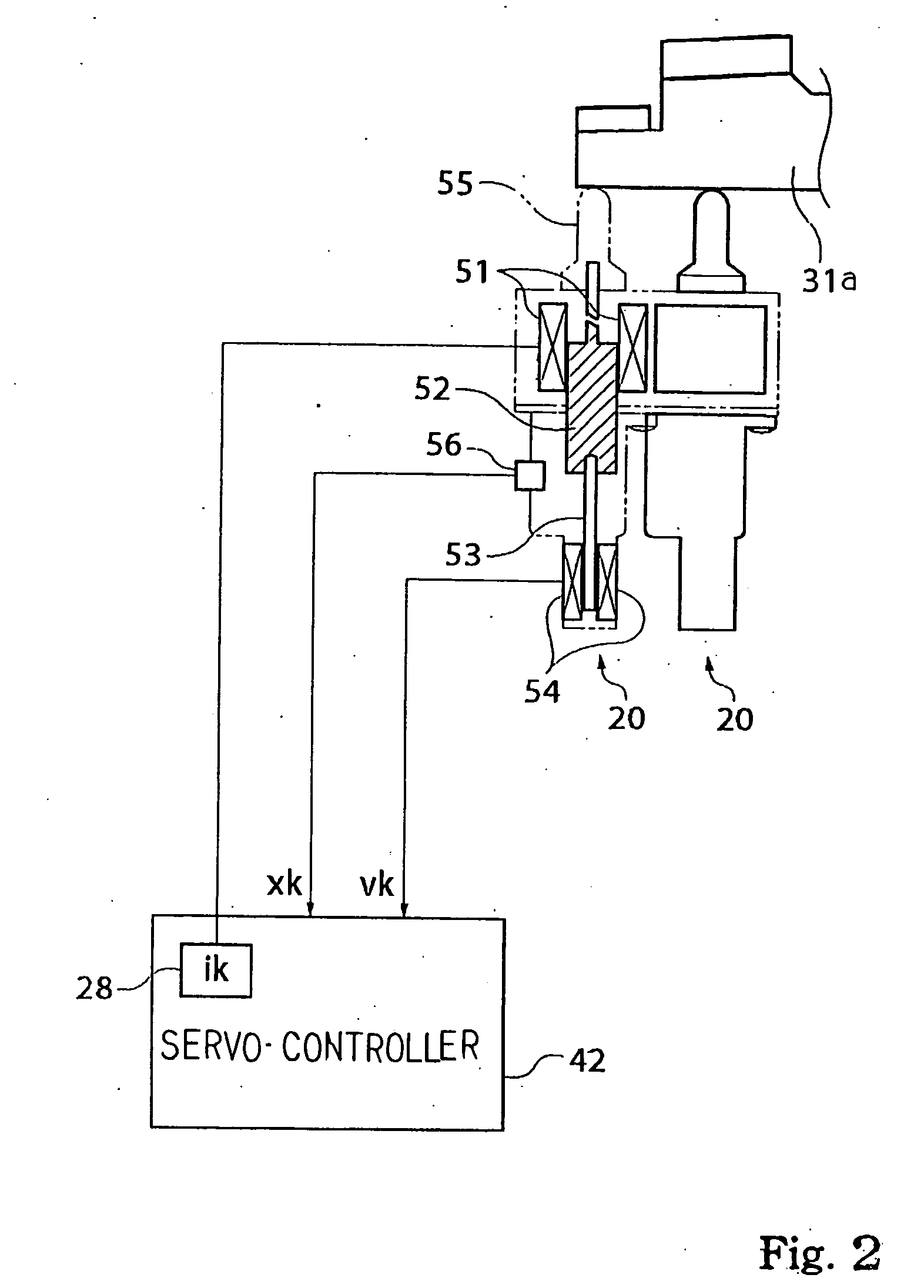

A data acquisition system is used in the transplantation of the piano key touch from an acoustic piano to an electronic piano, and the function thereof is broken down into a table producer, a motion controller and a servo-controller; a table, which expresses relation between current key positions and the amount of current supplied to key actuators, is stored in the table producer; the table producer supplies pieces of test data to the motion controller, which determines reference test trajectories, and the servo-controller forces the keys to travel thereon through the key actuators; sensors reports the current key positions and current key velocity to the table producer, and the table producer produces tables expressing pieces of inner force data through the analysis on these data; the tables are supplied to an inner force sense controlling system, which reproduce the key touch in the electronic piano.

Owner:YAMAHA CORP

Space radio-frequency performance test method and system in multi-antenna system

InactiveCN102148648AEasy to testEasy to implementSpatial transmit diversityTransmission monitoringReference testEngineering

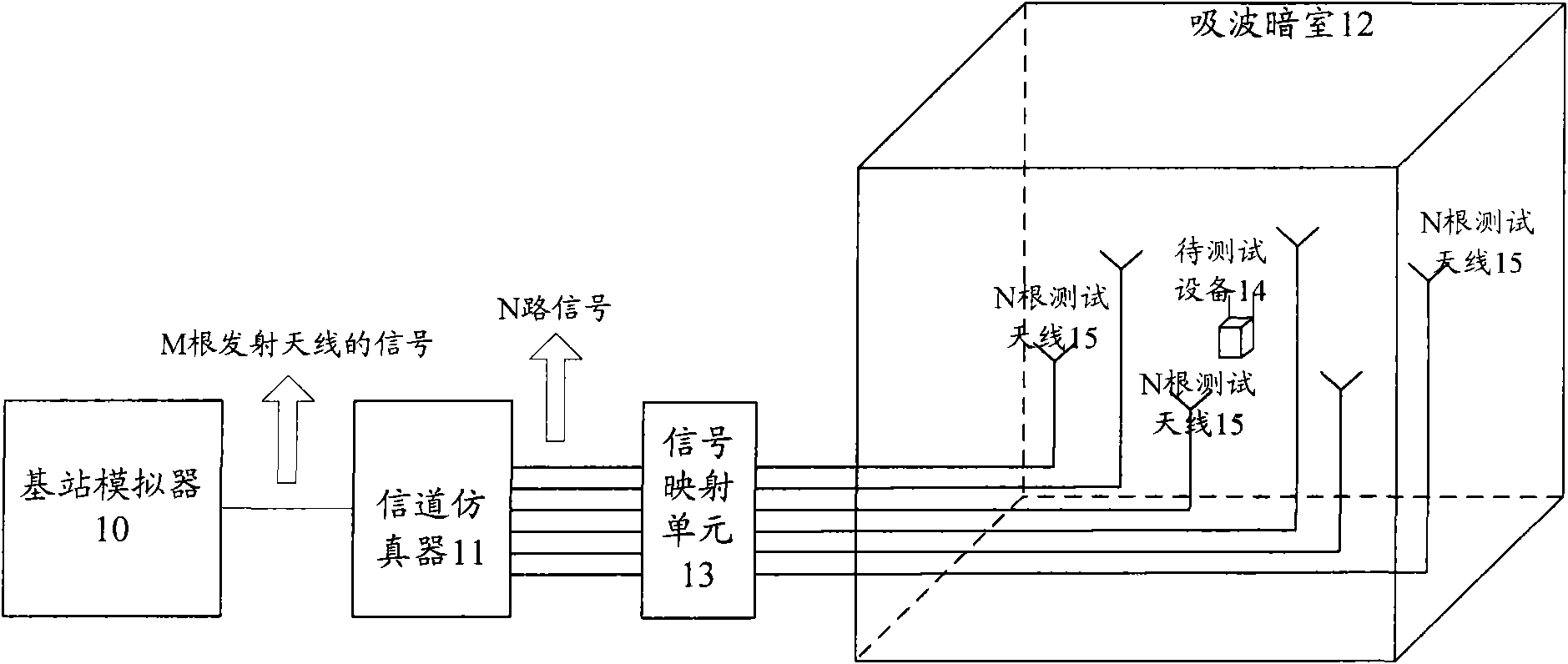

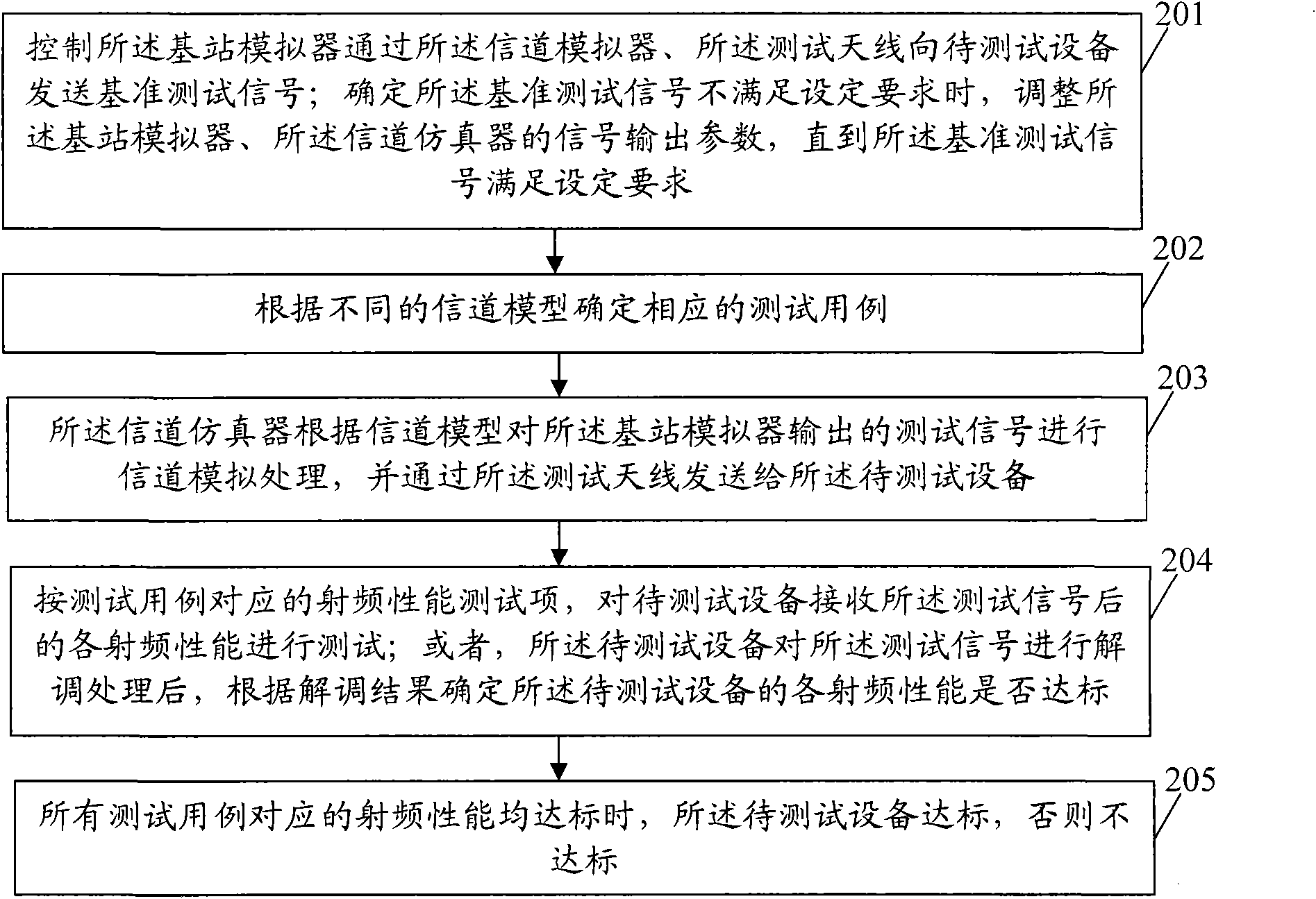

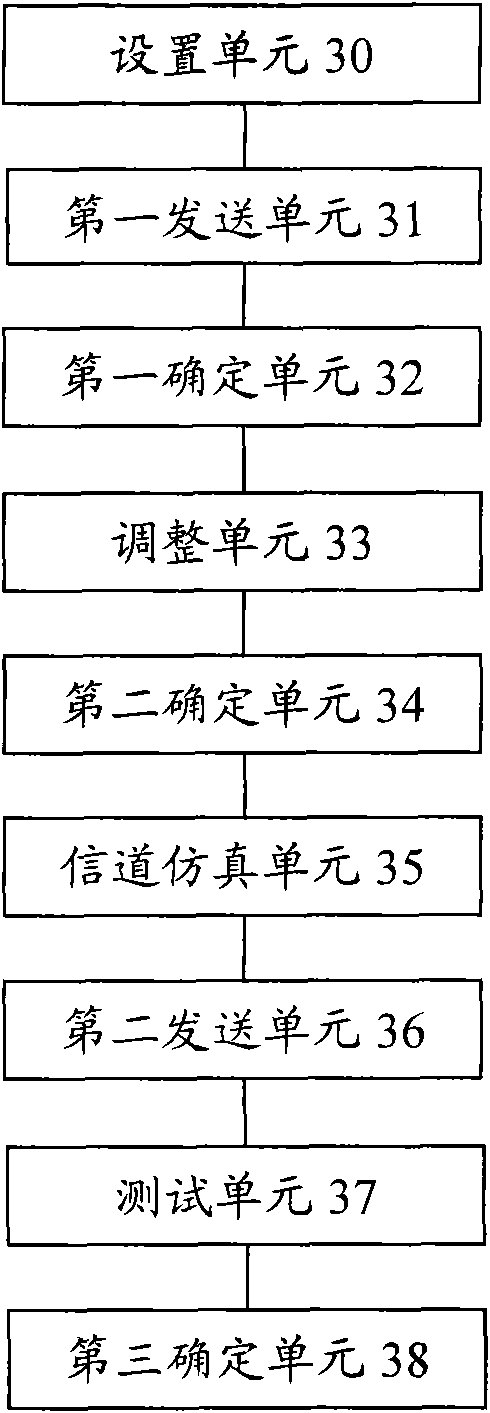

The invention discloses a space radio-frequency performance test method and a system in a multi-antenna system. More than two antennas are arranged on a dark absorbing chamber; a base station simulator is controlled to send a reference test signal to a device to be tested through a channel simulator and an antenna; when the reference test signal is determined to not satisfy set requirements, the reference test signal is adjusted until the set requirements are satisfied; corresponding test cases are determined according to different channel models; signal simulation is implemented by a channel emulator on the test signal outputted by the base station simulator, and then the test signal is sent to the device to be tested through the antenna; each radio-frequency performance of the device to be tested after the receiving of the test signal is tested according to the radio-frequency performance test items corresponding to the test cases; and when all the radio-frequency performances reach the standard, the space radio-frequency performance reaches the standard. The invention also discloses a space radio-frequency performance test system in the multi-antenna system. The invention is simple to realize and has lower cost.

Owner:李翠梅

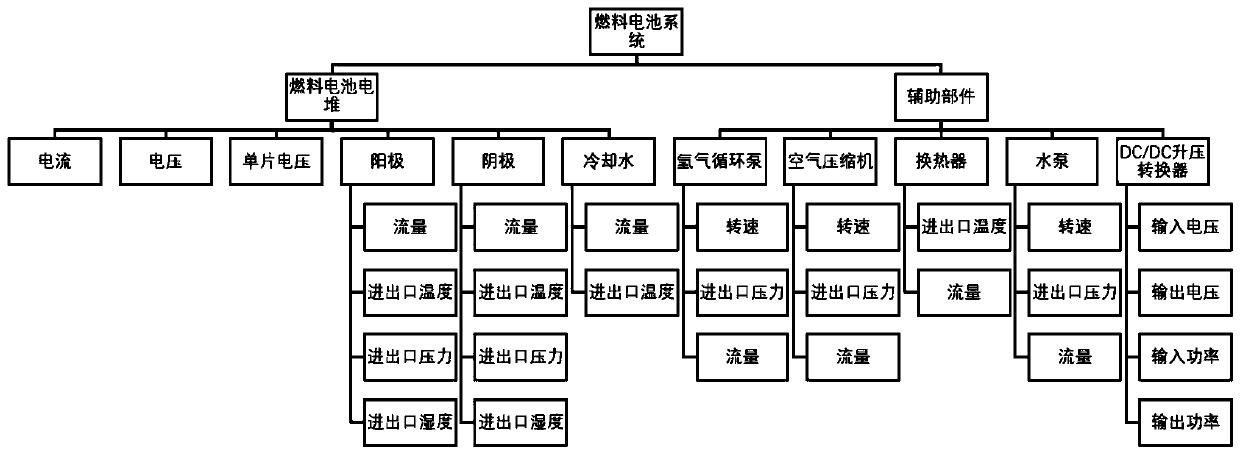

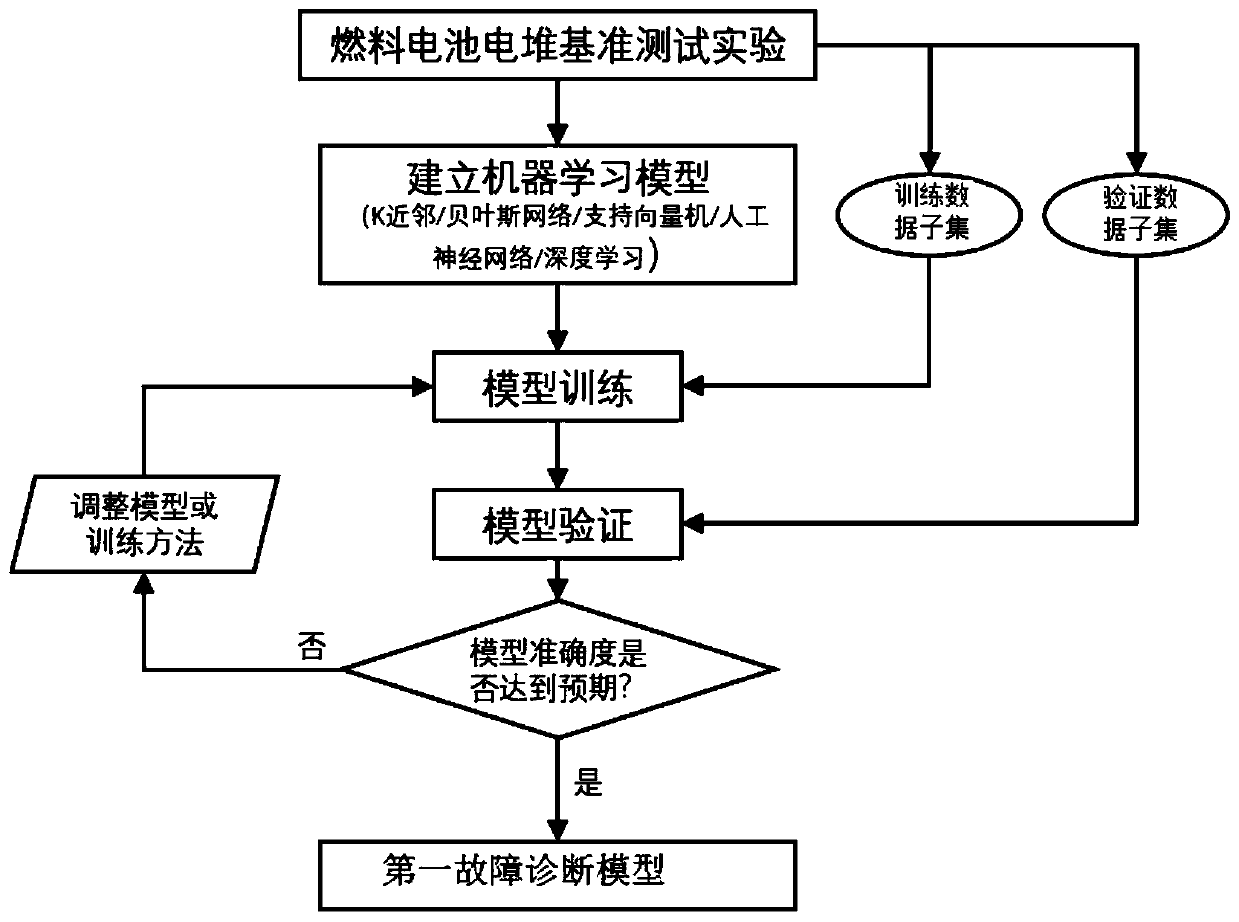

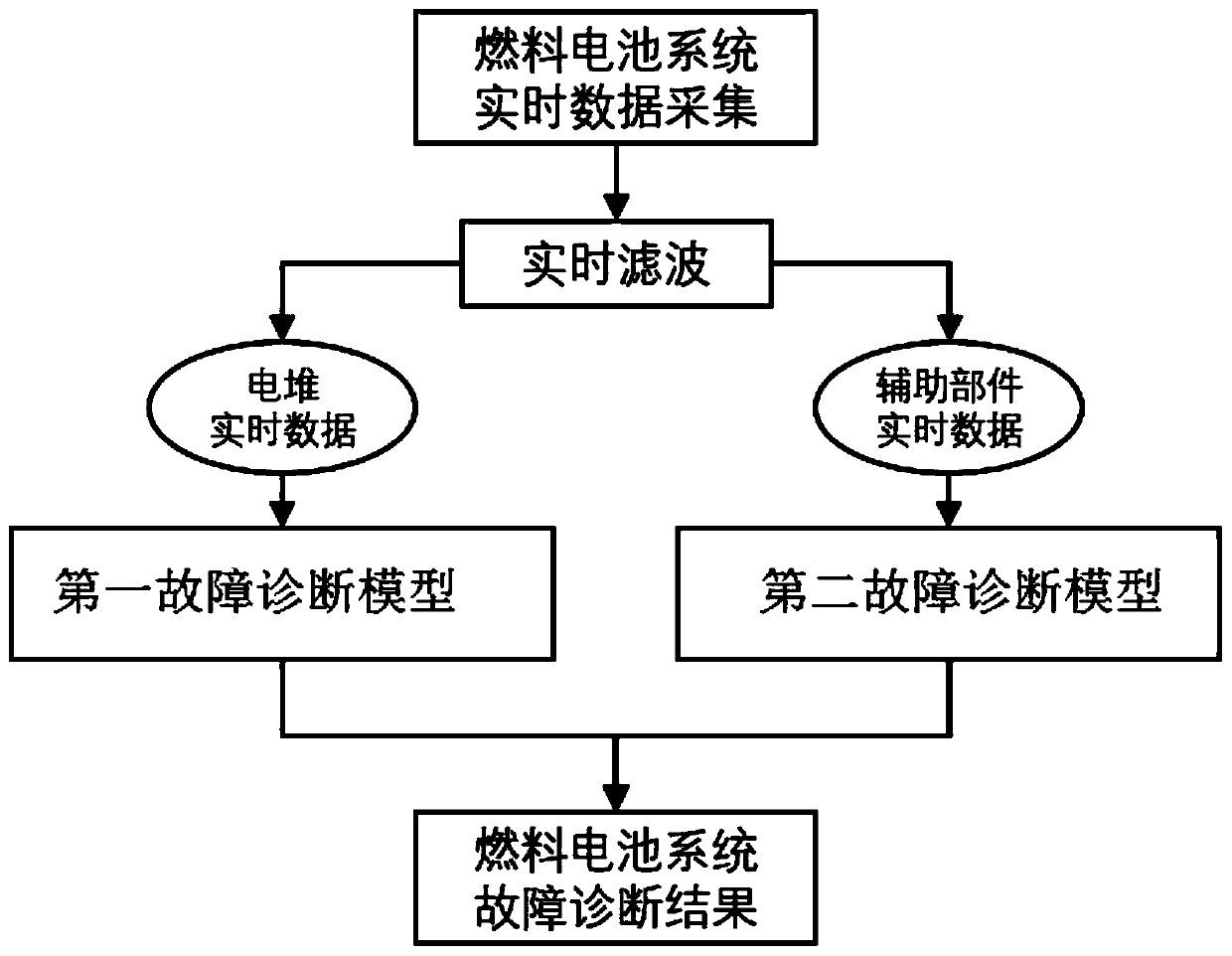

Online fault diagnosis method for fuel cell system

The present invention discloses an online fault diagnosis method for a fuel cell system. The method comprises the steps of: obtaining a first fault diagnosis model which is obtained based on the real-time data of a galvanic pile and through adoption of a machine learning method, the real-time data of the galvanic pile is obtained through a galvanic pile reference test experiment; in the operationprocess of the fuel cell system, the operation data of the galvanic pile is measured in real time and is taken as the input parameter of the first fault diagnosis model to obtain the fault diagnosis result of the galvanic pile; and a second fault diagnosis model is obtained, the second fault diagnosis model comprises standard data corresponding to secondary parts in the fuel cell system, the real-time operation data of the secondary parts in the fuel cell system are obtained and taken as the input parameters of the second fault diagnosis model to obtain the fault diagnosis results of the secondary parts. The current fuel cell system is taken as a basis with no need for extra addition of a sensor and a test device, the operation of the fuel cell system cannot be interfered, and therefore, the implementation cost is low, and promotion is easy.

Owner:昆山知氢信息科技有限公司

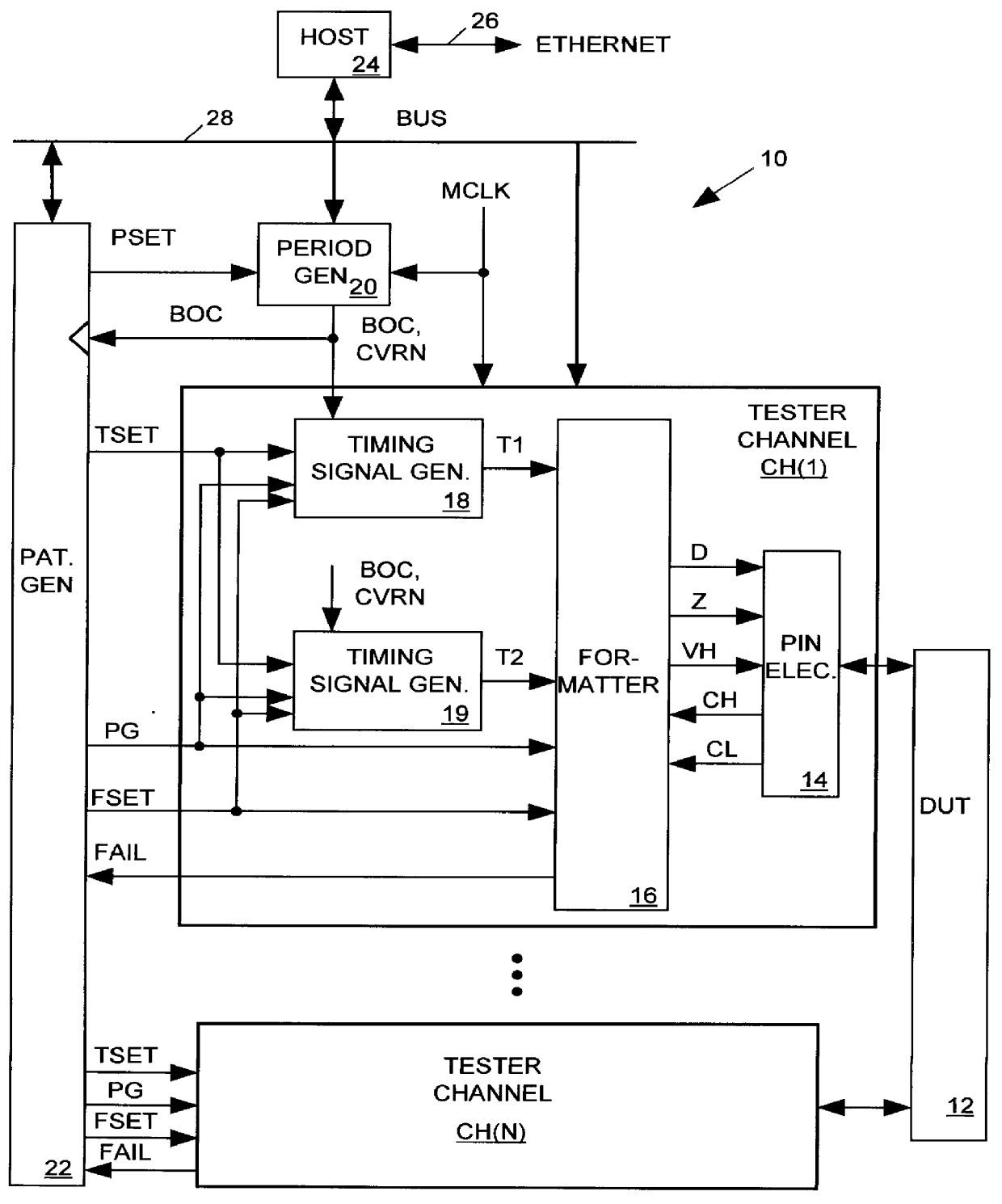

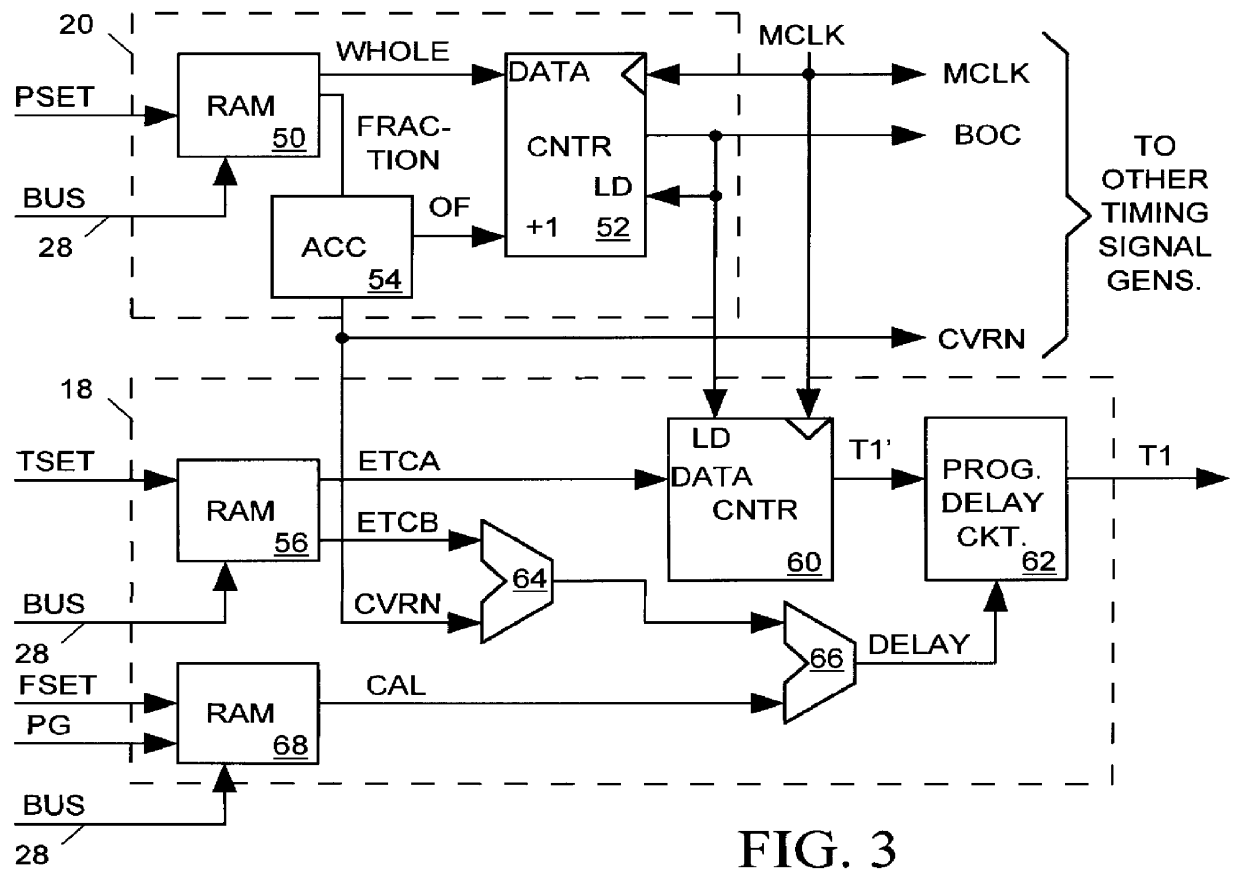

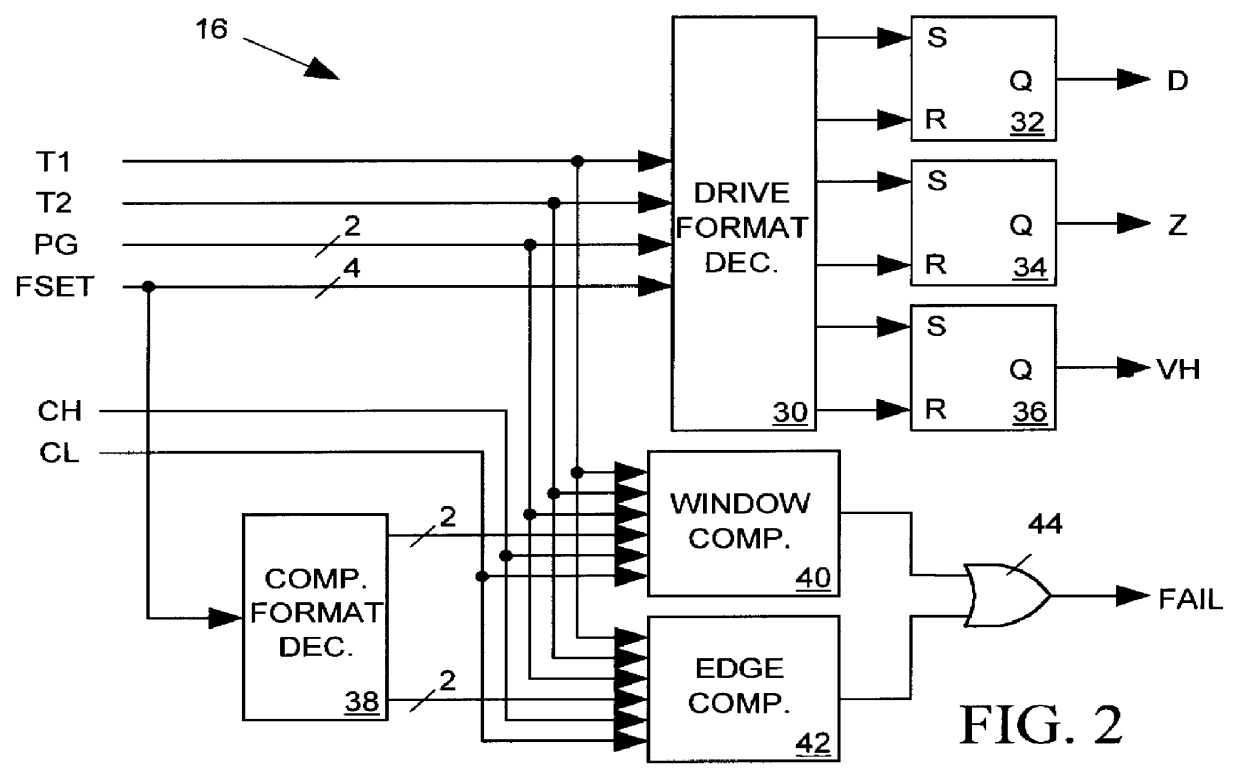

Format sensitive timing calibration for an integrated circuit tester

Each channel of an integrated circuit tester includes at least one timing signal generator for producing an output timing signal for triggering various types of test events carried out by the tester channel. At the start of each cycle of a test, each timing signal generator receivies input timing data referencing a time at which a test event is to occur and also receives input format data indicating the format of that test event. Each timing signal generator then generates its output timing signal before the event time referenced by the timing data with a lead time selected by the input format data. Each timing signal generator may be independently calibrated such that the format data always selects the appropriate lead time for the event to be triggered so that each type of event occurs at the time indicated by the input timing data regardless of the nature of the event being triggered.

Owner:CREDENCE SYSTEMS

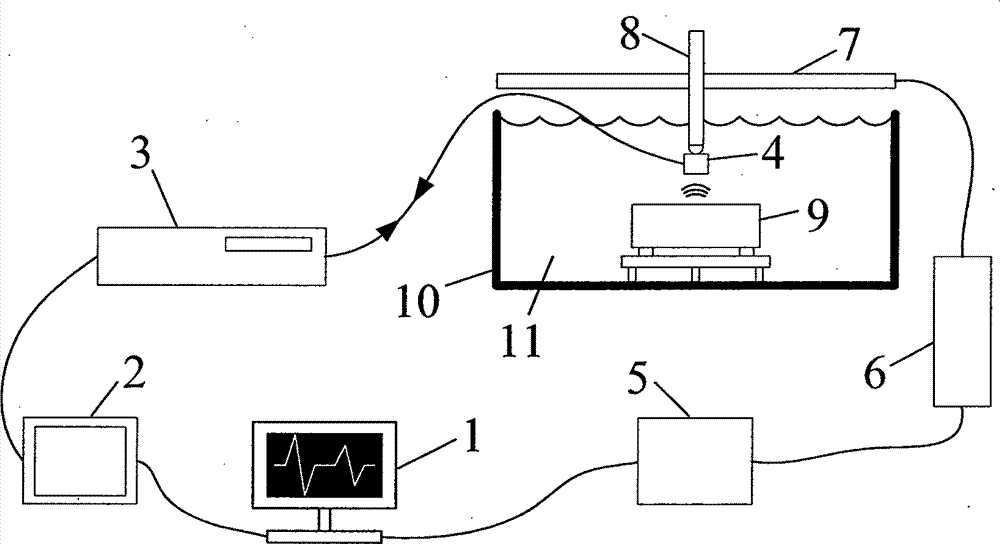

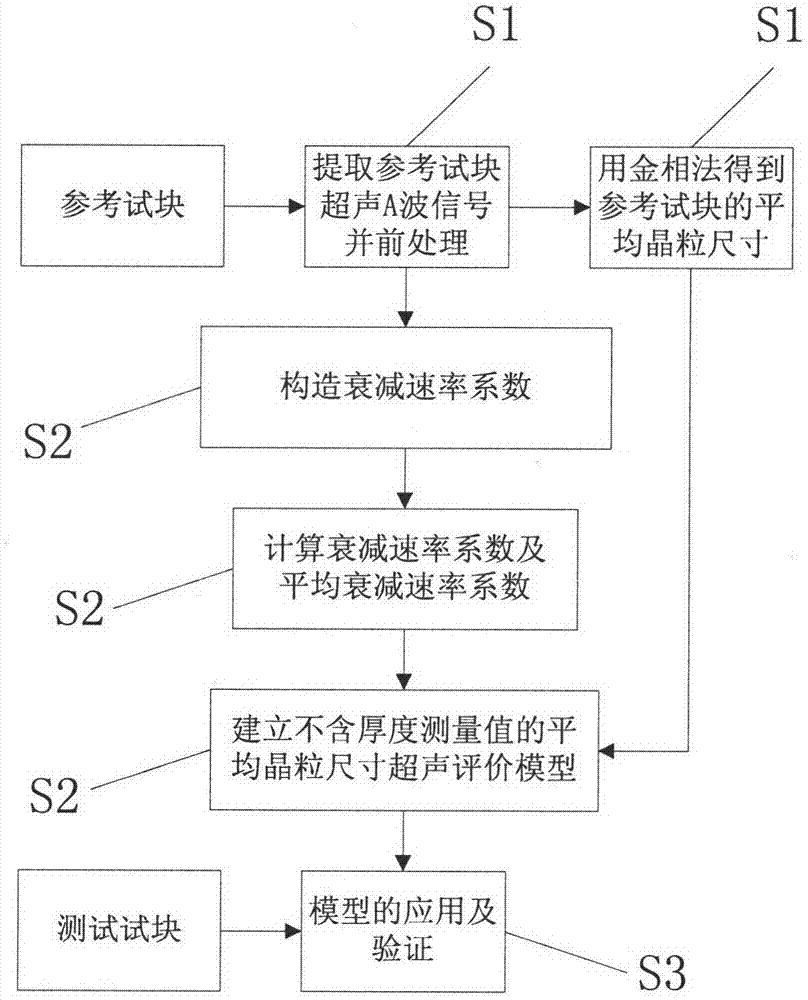

Crystal grain size ultrasonic non-destructive evaluation method without thickness measurement

ActiveCN104297110ASimplicity guaranteedGuaranteed repeatabilityParticle size analysisNon destructiveReference test

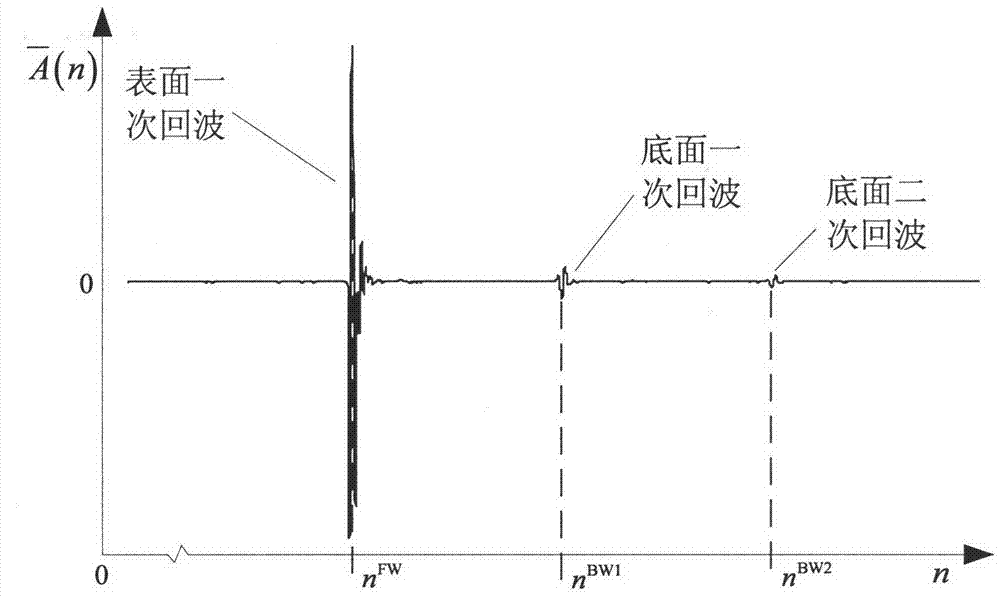

The invention discloses a crystal grain size ultrasonic non-destructive evaluation method without thickness measurement. The method comprises the following steps: carrying out data acquisition on a reference test block and carrying out pretreatment by adopting a signal averaging technology; constructing and calculating a decaying speed coefficient and an average decaying speed coefficient; establishing crystal grain size ultrasonic evaluation models with different thickness measured values; and carrying out crystal grain size evaluation on the test block with unknown crystal grain size. According to the method, the thickness does not need to be measured so that inconvenience on the thickness measurement of a tested object and the influence on the subsequent average crystal grain size, caused by inaccurate measurement, are avoided; the anti-interference capability of the method is effectively improved by a pretreatment means; the evaluation results of two tested test blocks with the average crystal grain sizes being 87.7 microns and 103.5 microns respectively, measured by a metallographic method, are 84.9 microns and 98.9 microns respectively; and errors can be controlled to be + / -5%. Visibly, the method disclosed by the invention provides a means that is not influenced by the thickness and can be used for effectively evaluating the crystal grain size of metal materials.

Owner:CENT SOUTH UNIV

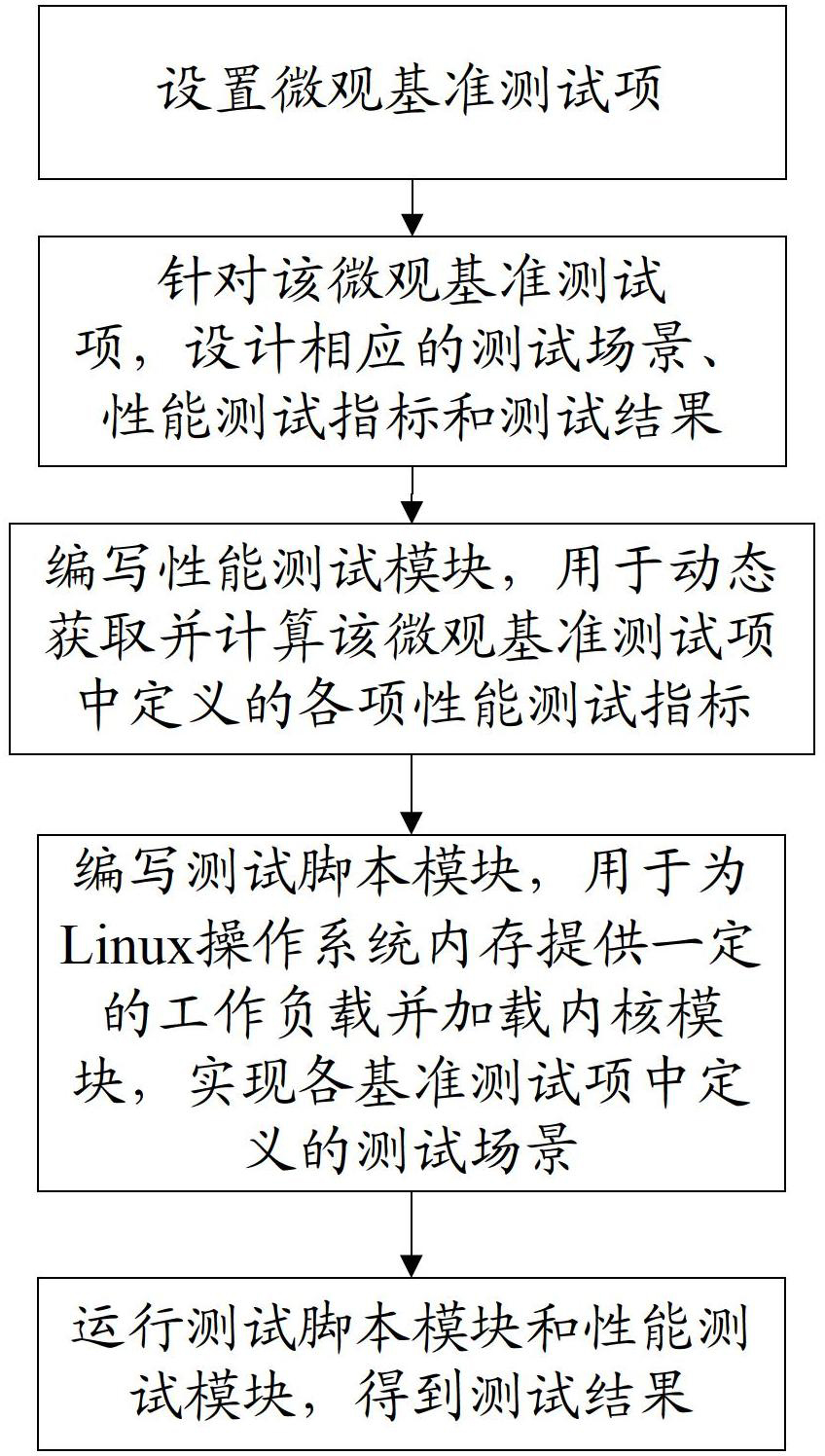

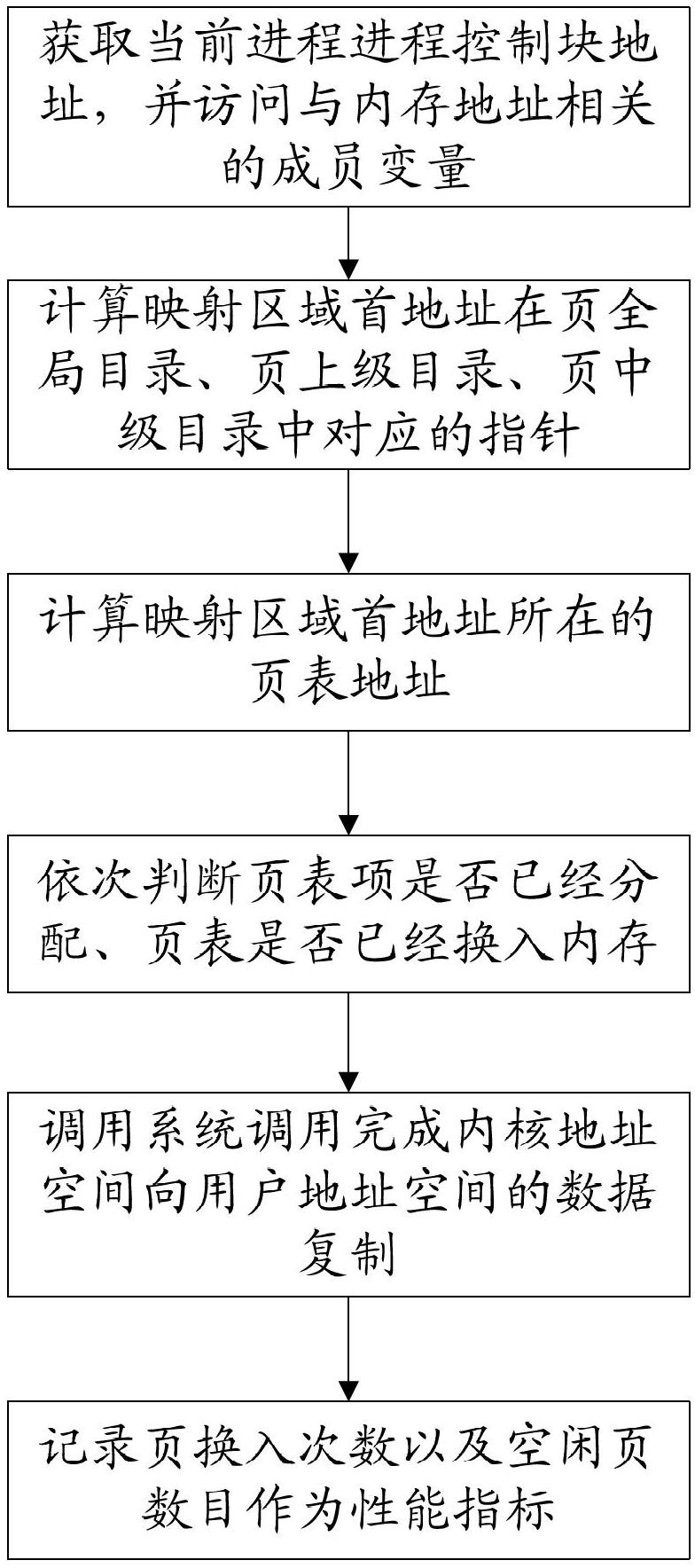

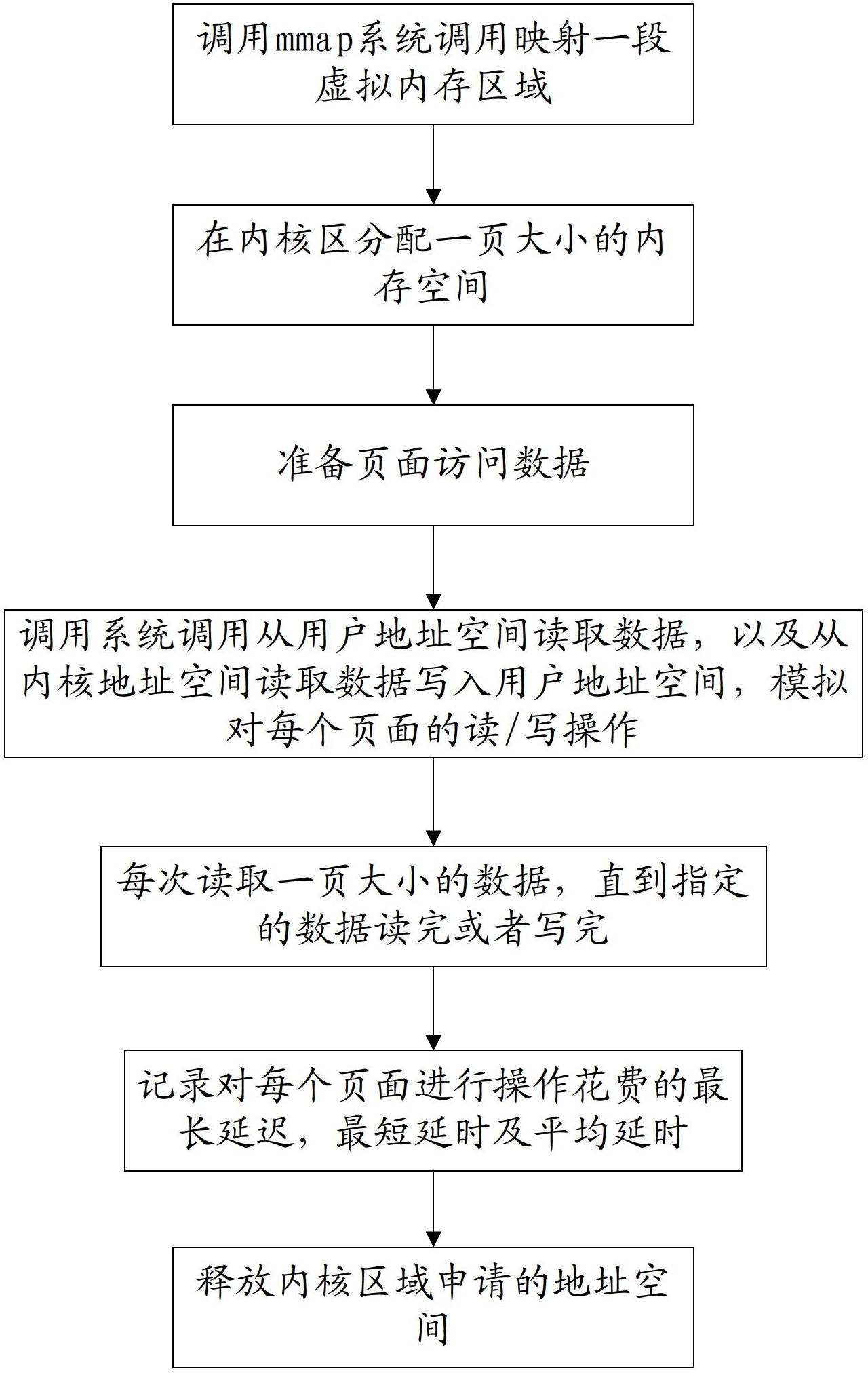

Method for carrying out performance test on memory management subsystem of Linux operation system

ActiveCN102681940AIncrease richnessImprove the problem of lack of targetingMemory adressing/allocation/relocationSoftware testing/debuggingOperational systemTest script

The invention provides a method for carrying out performance test for a memory management subsystem of a Linux operation system, which comprises the following steps: 1) setting microcosmic reference testing items; 2) for the microcosmic reference testing items, designing corresponding test scenes, performance test indexes and test results; 3) compiling a performance test module used for dynamically obtaining and calculating a performance test index defined for each item in the microcosmic reference testing items; 4) compiling a test script module used for providing a certain workload for a Linux operation system memory and uploading a core module to realize the test scenes defined in the reference testing items; and 5) operating the test script module and a performance test module to obtain test results. With the method, the problems of the current reference test tool for a Linux memory management subsystem, such as single test scene, poor pertinence in test indexes and small information amount in test results, are effectively solved.

Owner:慧之安信息技术股份有限公司

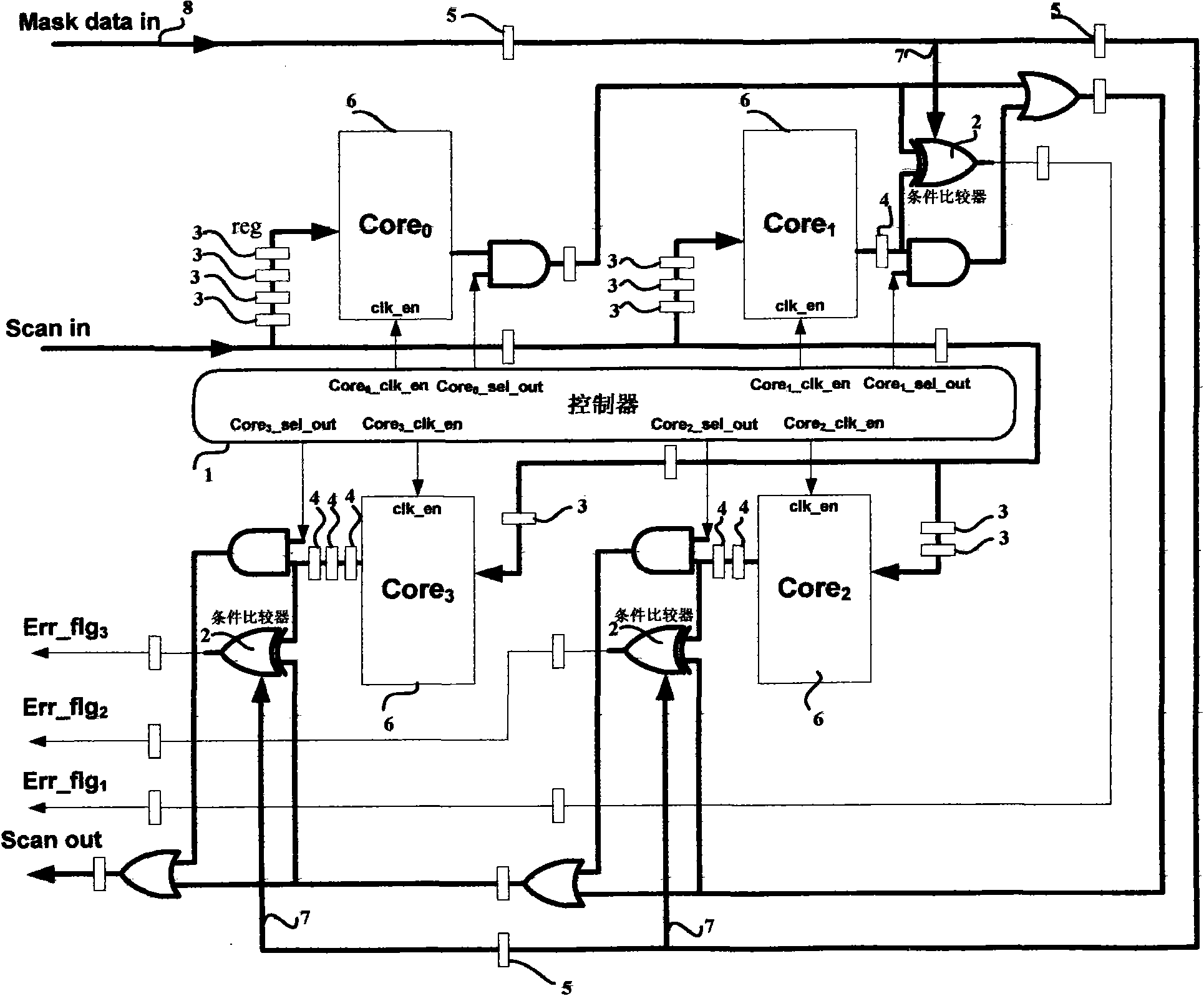

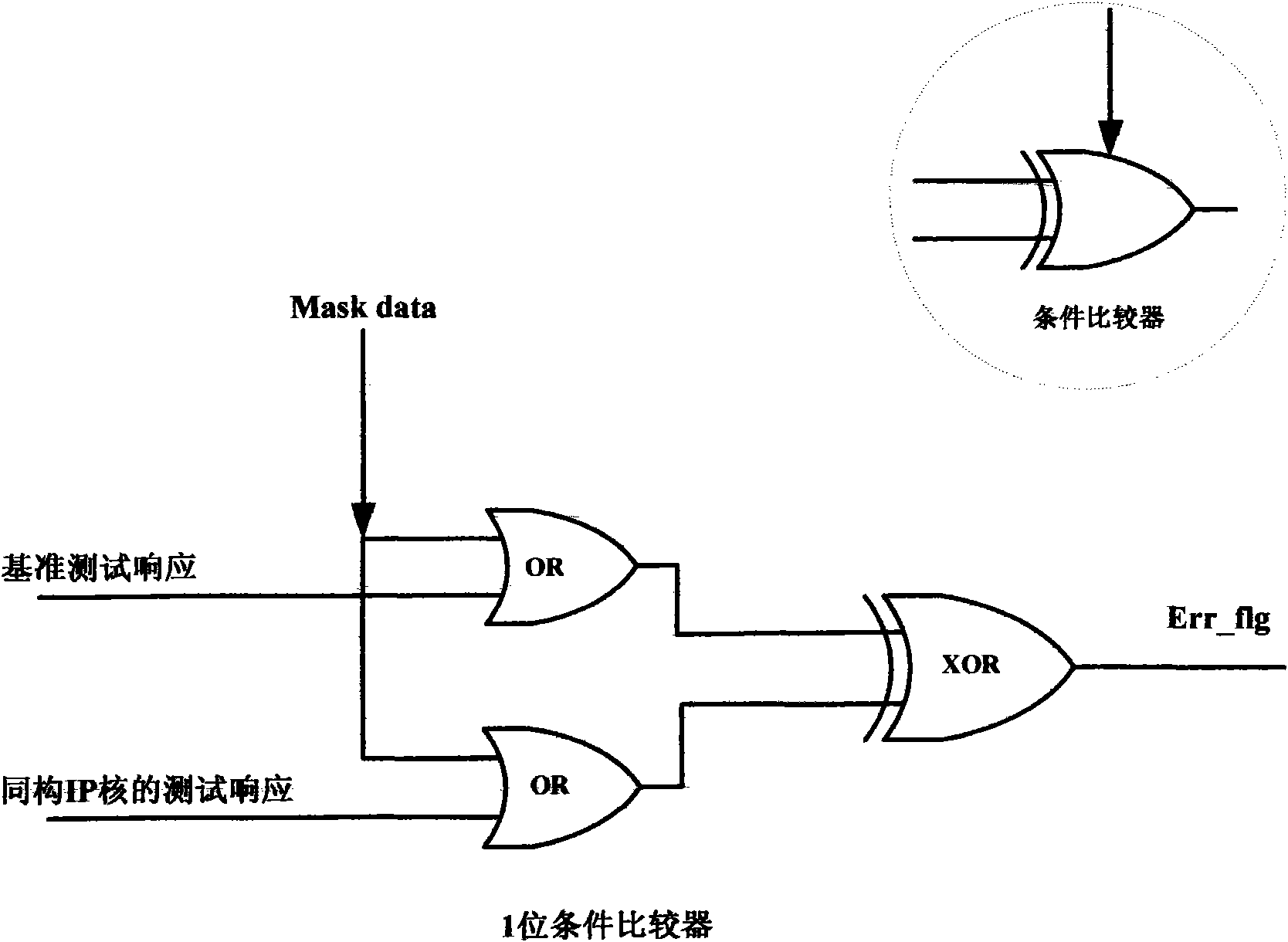

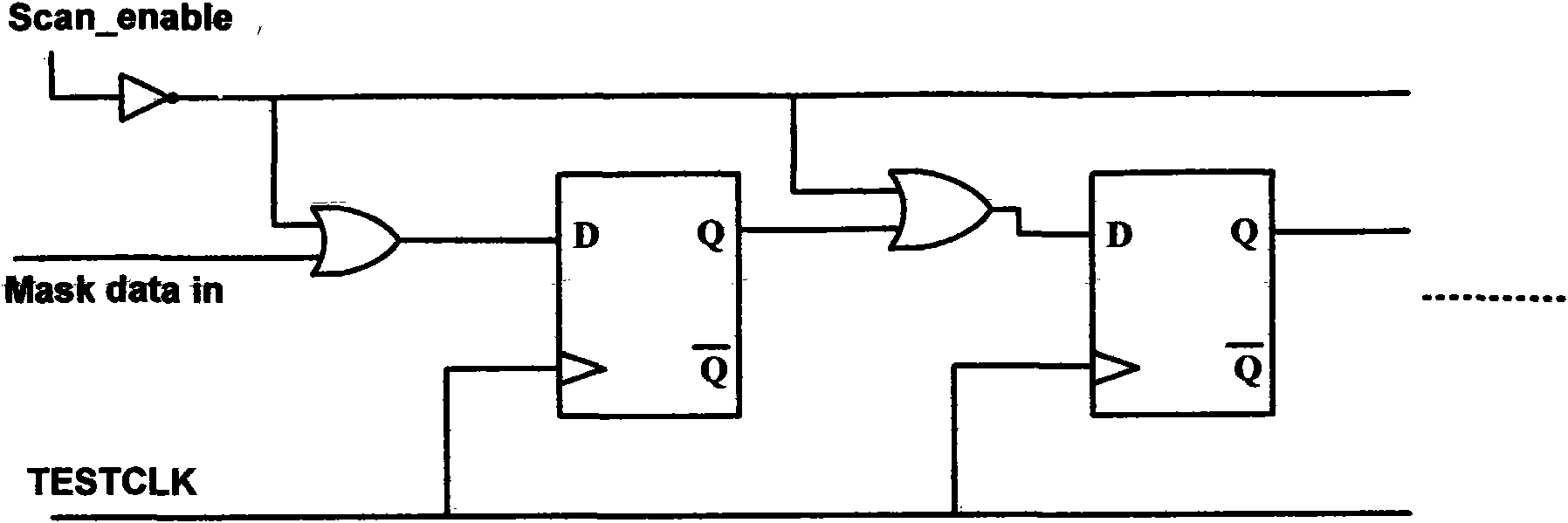

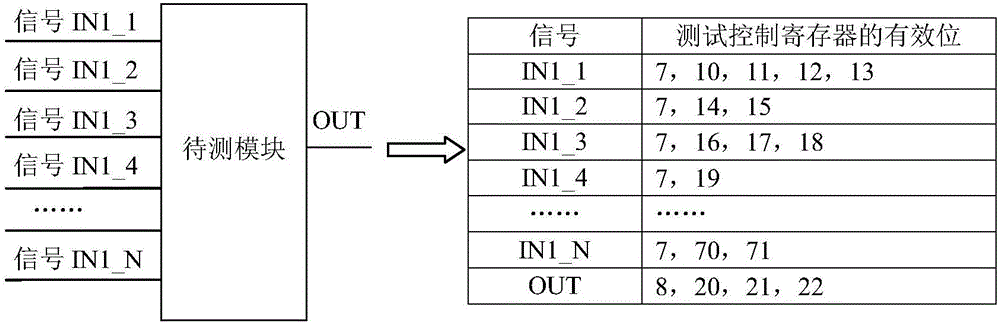

Device and method for testing system-on-chip chip with multiple isomorphic IP cores

ActiveCN101788644AReduced amount of test dataAvoid time costDigital circuit testingComputer hardwareReference test

The invention discloses a device and a method for testing a system-on-chip chip with a plurality of isomorphic IP cores. The device comprises a controller and a condition comparator, wherein the controller is provided with a plurality of control signal interfaces connected to each corresponding isomorphic IP core and is used for inputting a test control signal to each isomorphic IP core, controlling the test on one or more isomorphic IP cores, broadcasting the same test excitation data to the IP cores and simultaneously controlling the output of a test response of a certain IP core; the test response serves as a reference test response and is compared with the test responses of other IP cores; and the condition comparator is used for comparing the test response of a corresponding IP core with the reference test response and processing the comparison result to produce a one-bit error identification signal for identifying whether the comparison is accordant.

Owner:LOONGSON TECH CORP

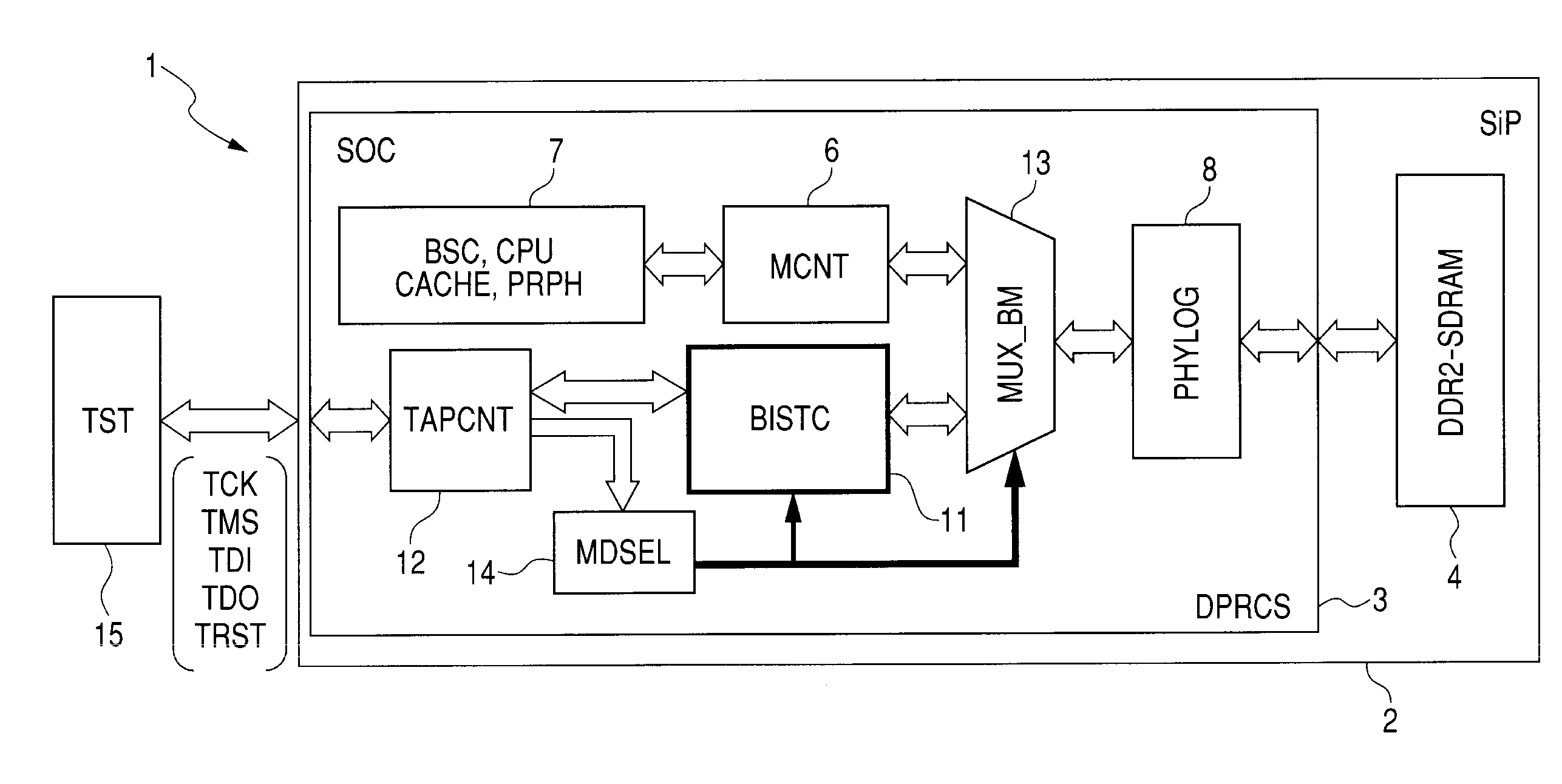

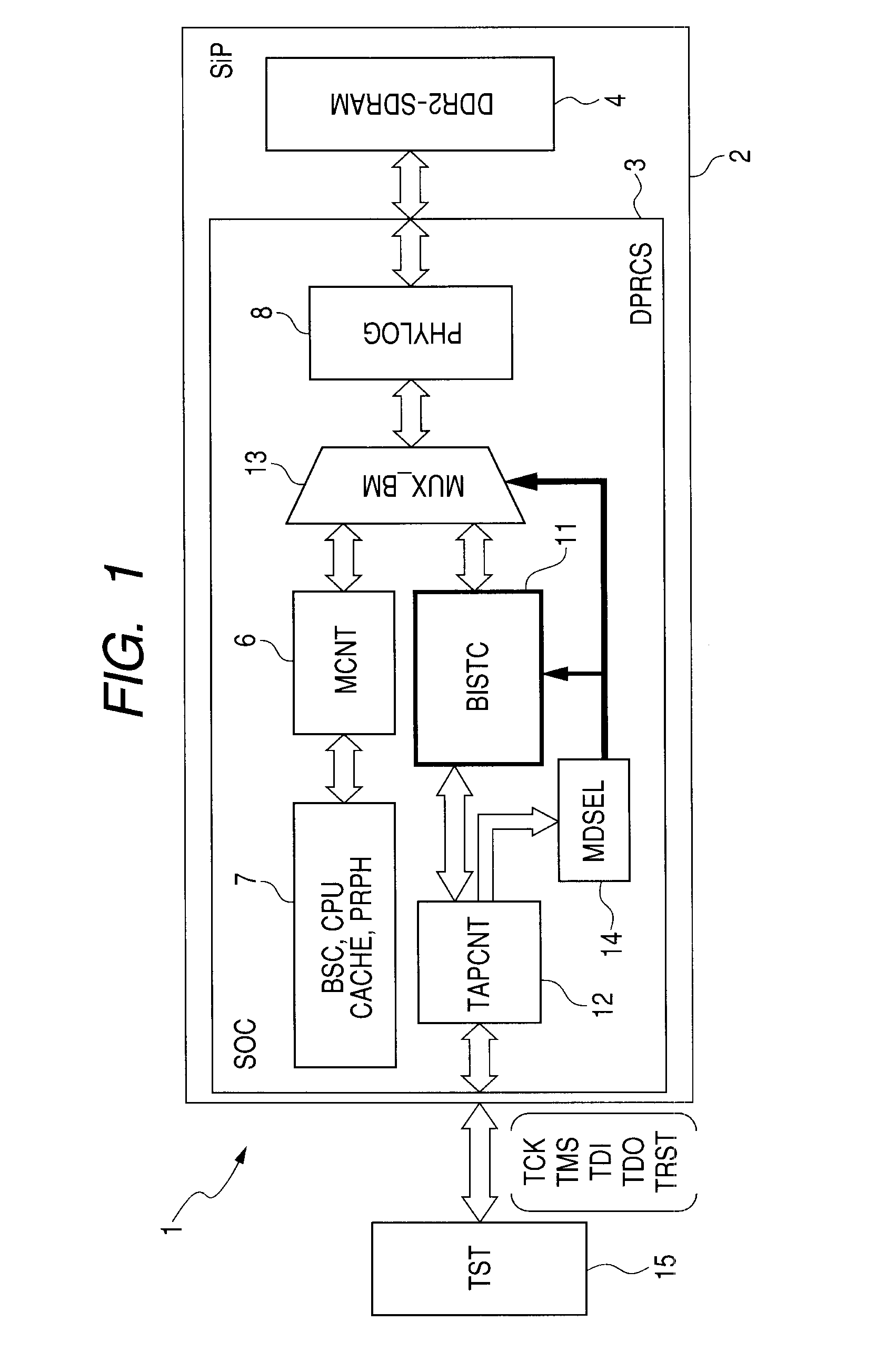

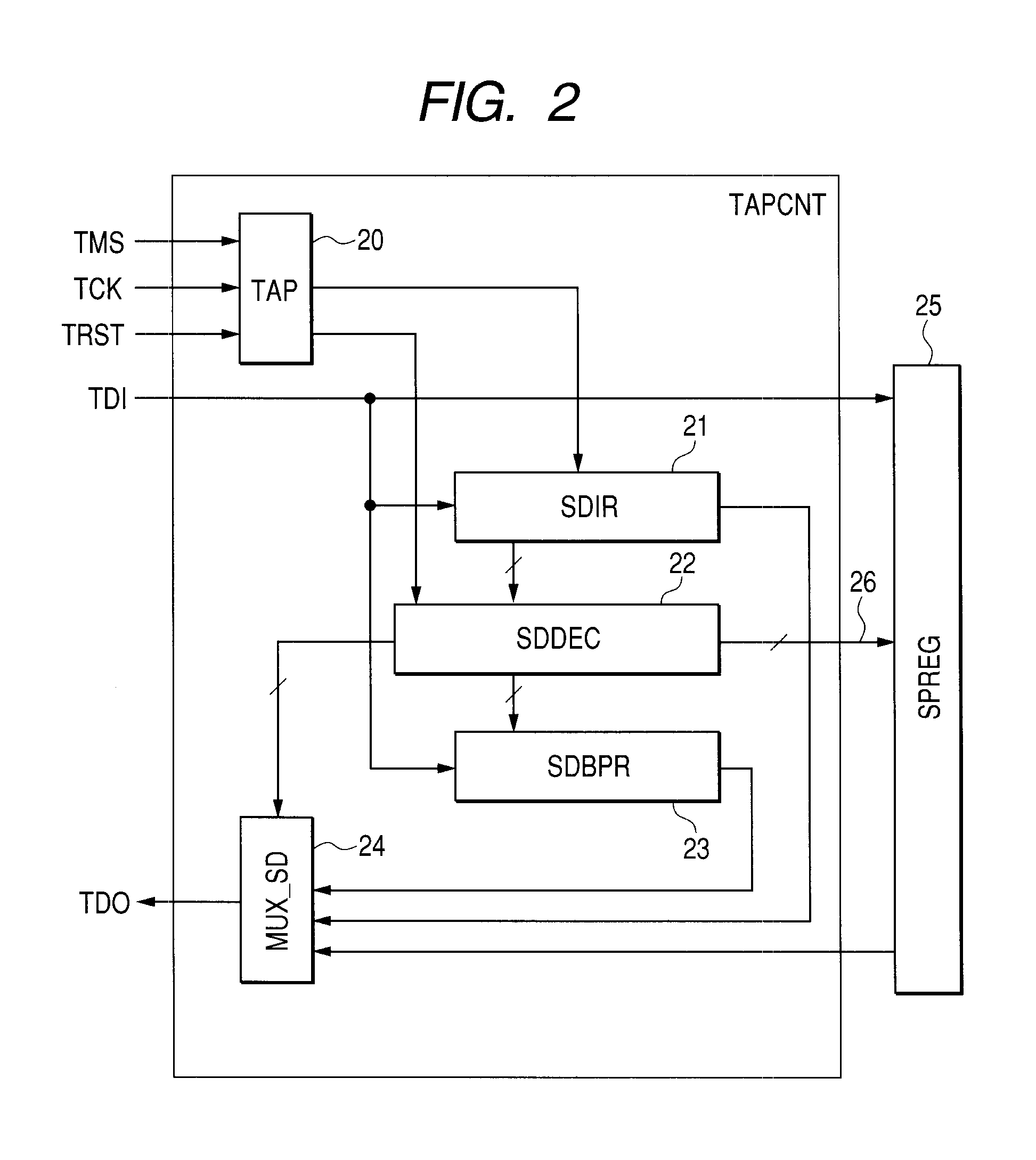

Semiconductor device and data processing system

InactiveUS20080263414A1Reduce test design costAdd supportElectronic circuit testingFunctional testingTest designMemory interface

The test design cost of a circuit capable of accessing an external memory is reduced. There is included a built-in self-test circuit for use in testing an external memory separately from a memory controller for performing memory control in response to an access request to the external memory capable of being coupled to a memory interface, and a TAP controller is used to control the built-in self-test circuit and referring to a test result. There is adopted a multiplexer for switchably selecting the memory controller or the built-in self-test circuit as a circuit for coupling to the memory interface in accordance with control information externally inputted through the TAP controller. The built-in self-test circuit programmably generates and outputs a pattern for a memory test in accordance with an instruction inputted through the TAP controller, and compares data read from the external memory with an expected value.

Owner:RENESAS ELECTRONICS CORP

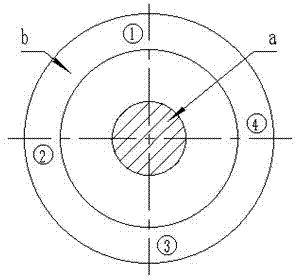

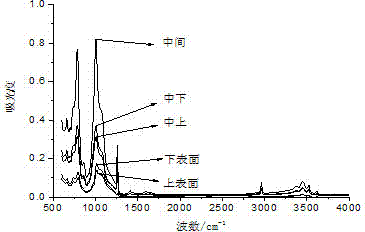

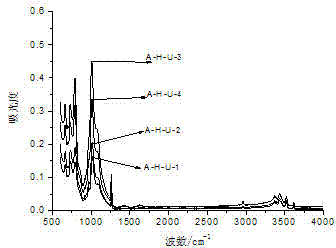

Evaluation method for ageing state of composite insulator

InactiveCN104764708AAccurate assessment of aging statusImprove accuracyMaterial analysis by optical meansComposite insulatorsReference test

The invention provides an evaluation method for the ageing state of a composite insulator. The method comprises the following steps: selecting the umbrella skirt of an insulator at a high-voltage or medium-voltage side of a string of insulators, taking samples at different positions and slicing the samples into test pieces; taking a middle test piece of the umbrella skirt of an insulator at a low-voltage side as a reference test piece; detecting the ageing degree of each test piece by using Fourier spectrometry and calculating the change rate of the mean values of absorption peaks of test pieces at different directions relative to the reference test piece; and evaluating the ageing degree of the composite insulator according to the change rate. According to the method, the ageing state of the composite insulator is quantitatively analyzed through standardized sampling and evaluating programs; and the method has the characteristics of simple and convenient testing and high accuracy.

Owner:广西电网有限责任公司河池供电局

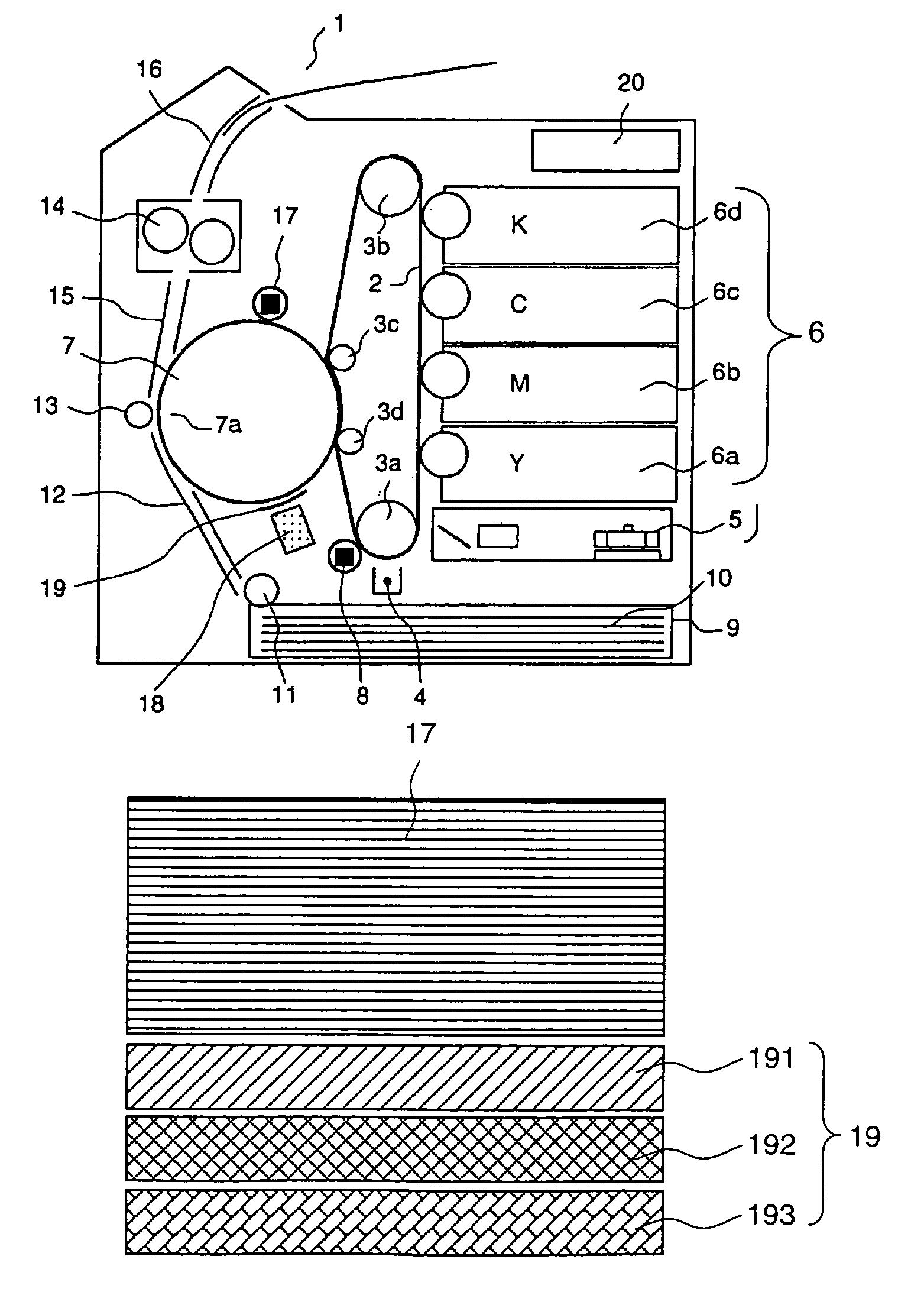

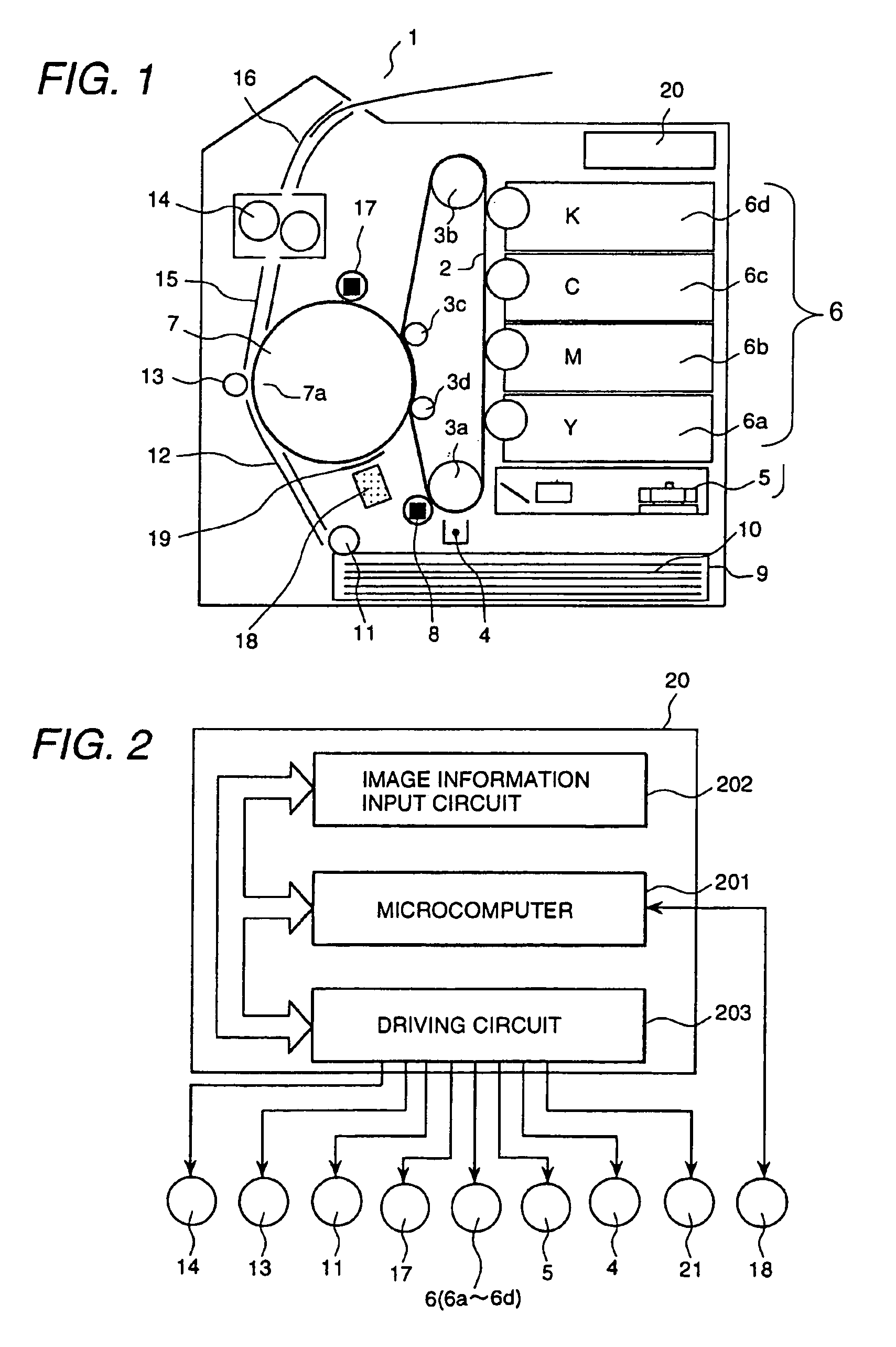

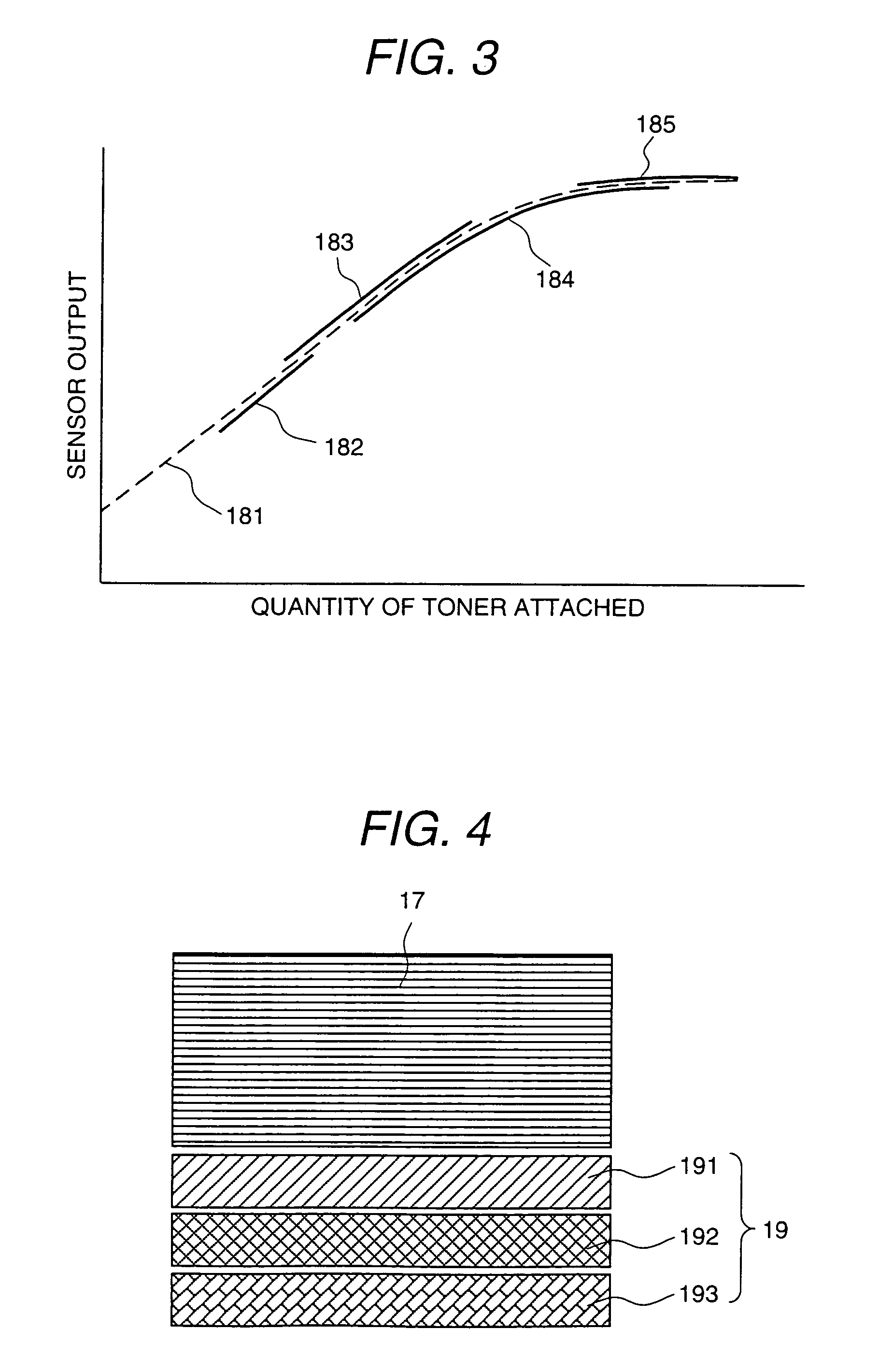

Image forming apparatus and method of detecting the detection characteristics of a reflection density sensor

An image forming apparatus is able to form steady test-pattern toner images for calibration of reflection density detection characteristics with ample toner. The operation consists of forming a test-pattern toner image for calibration of the reflection density detection characteristics, which is formed of a plurality of toner images of different colors aside from a reference test-pattern toner image for controlling image forming conditions, detecting the detection characteristics of a reflection density sensor from the result of detection of the quantity of toner attached to the test-pattern toner image for calibration of the reflection density detection characteristics, and calibrating the output characteristics of the reflection density sensor.

Owner:RICOH PRINTING SYST

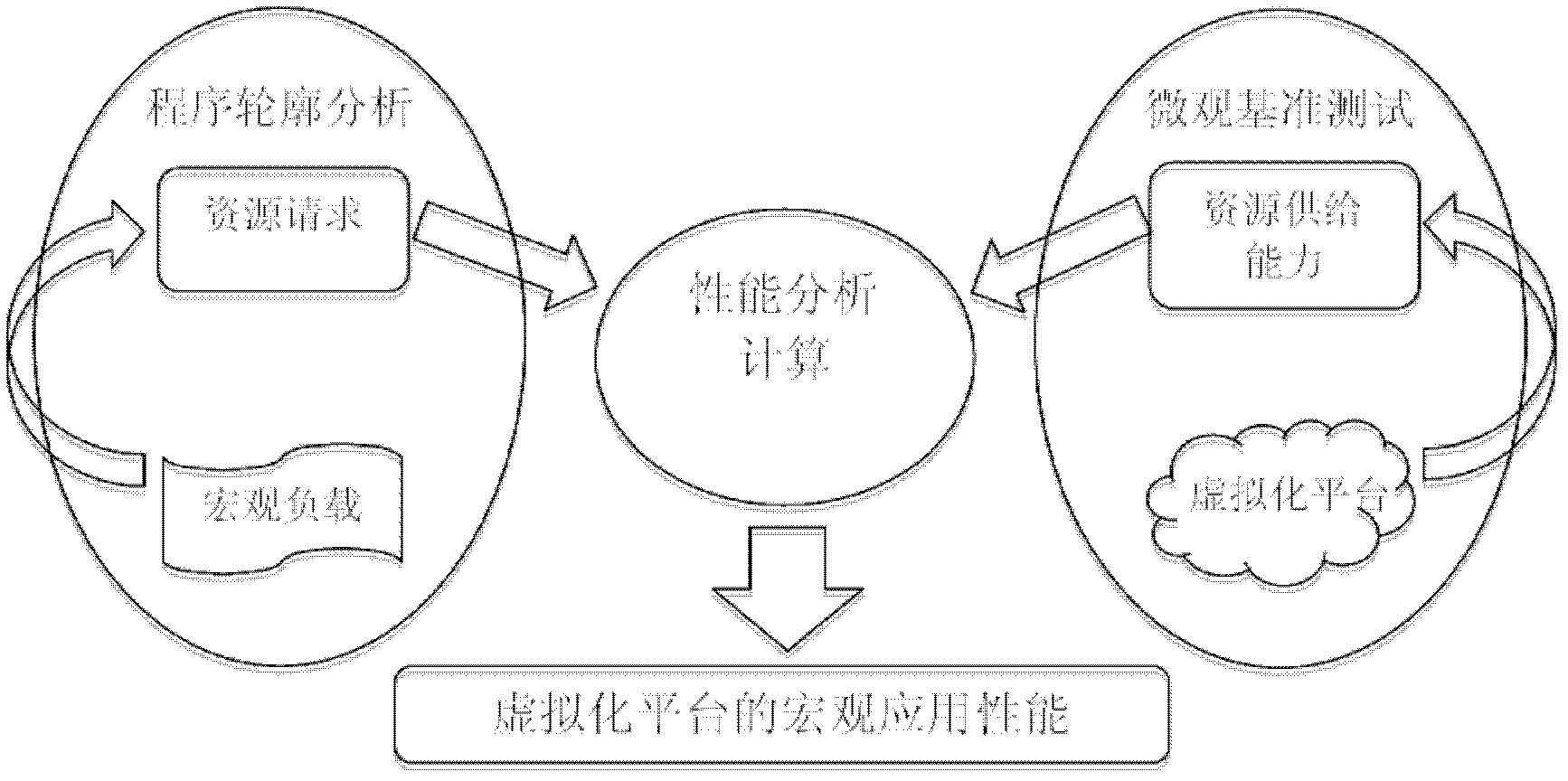

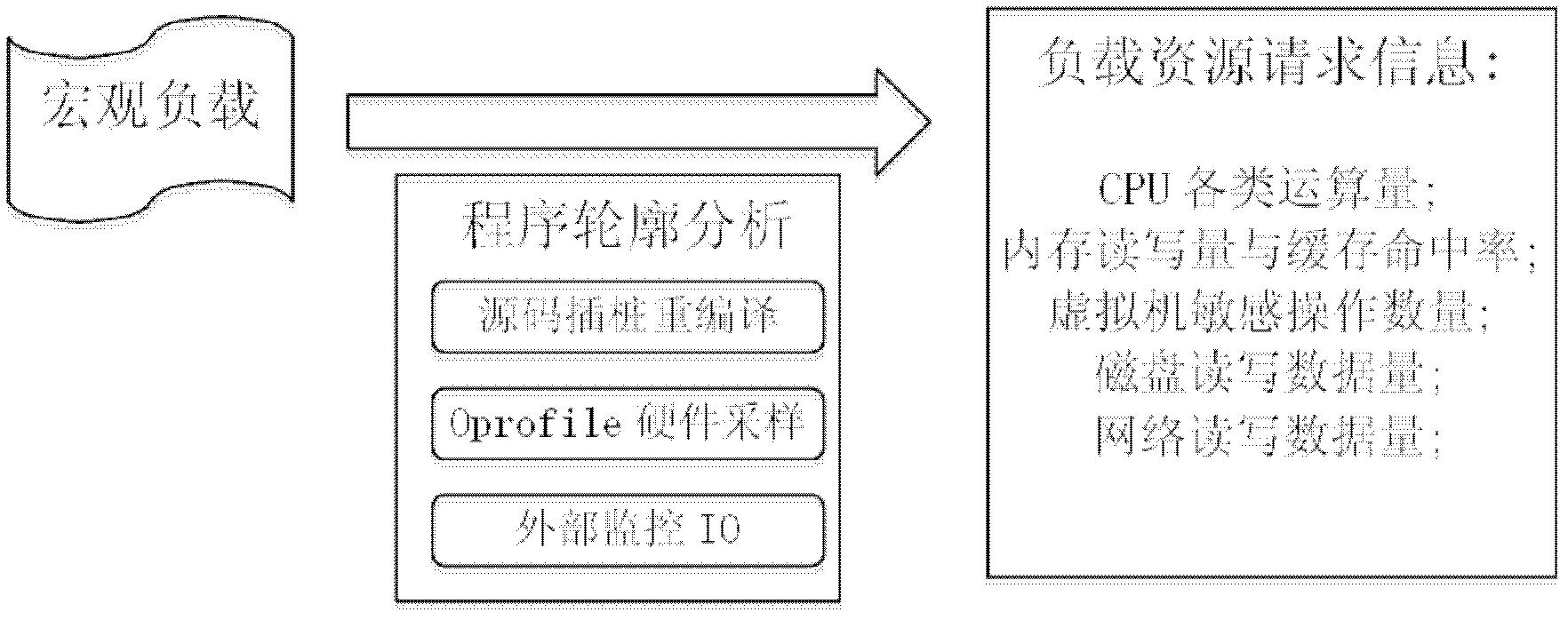

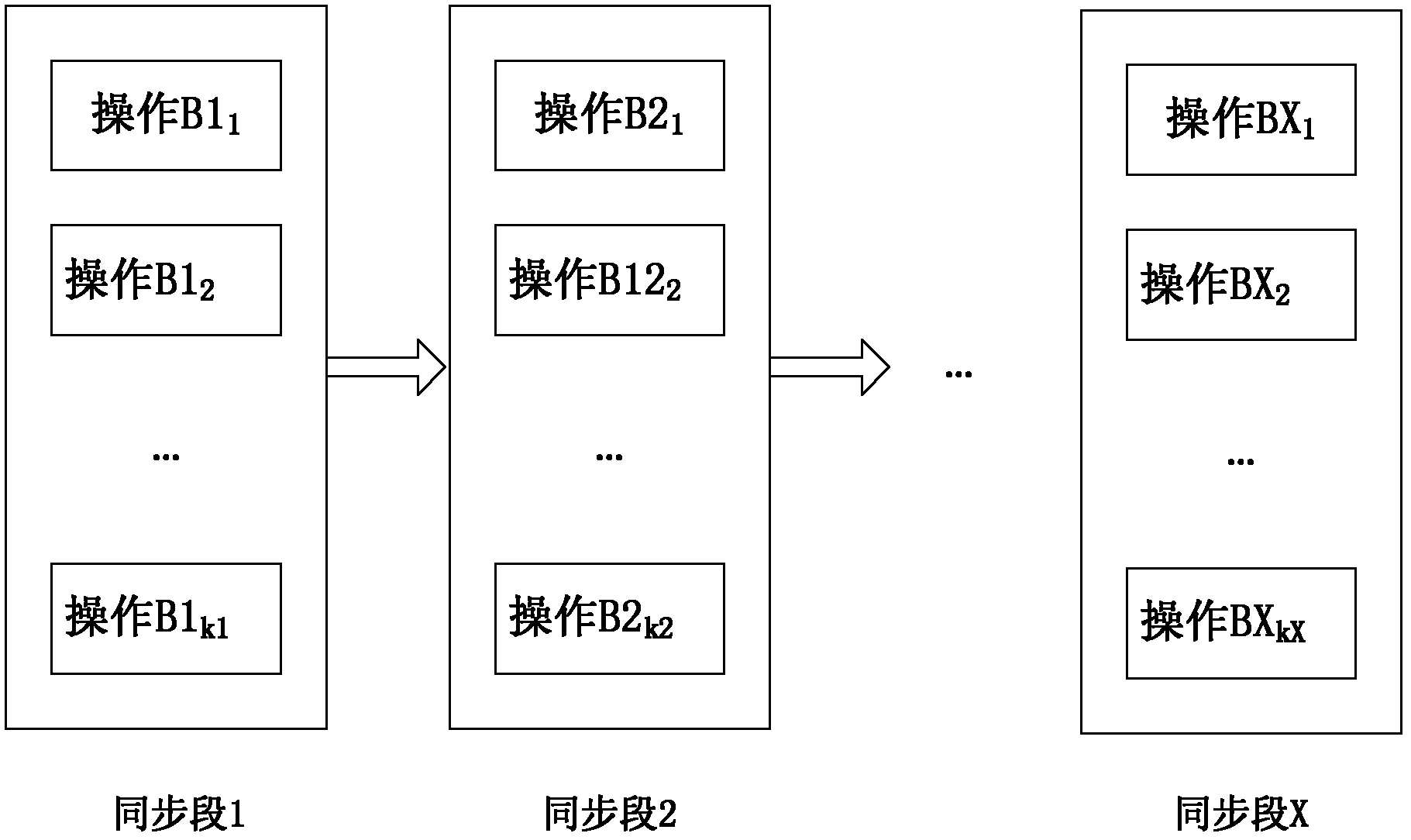

Virtualized platform performance evaluating method based on program contour analysis

The invention discloses a virtualized platform performance evaluating method based on program contour analysis, comprising the following steps of: acquiring the resource requests of a macro load by using a contour analysis technology, wherein the resource requests of the macro load includes various operation numbers of CPU (Central Processing Unit), virtual machine sensitive operation number causing context switching of a virtual machine, memory read-write number and cache hit ratio, disk read-write data volume and network read-write data volume; using micro-reference test to acquire the resource supply capability of a virtualized platform to be tested, wherein the resource supply capability includies various operation speed of a CPU, virtual machine sensitive operation delay, memory read-write speed and cache read-write speed, disk read-write speed and network read-write speed; and calculating the response time, CPU utilization ratio, disk utilization ratio and network utilization ratio of the macro load. The method uses the program contour analysis technology to acquire the resource requests of the macro load and uses the micro-reference test to acquire the resource supply of the virtualized platform to be tested; moreover, the macro-performance is analyzed and calculated so that the complexity and the cost of the test are decreased.

Owner:ZHEJIANG UNIV

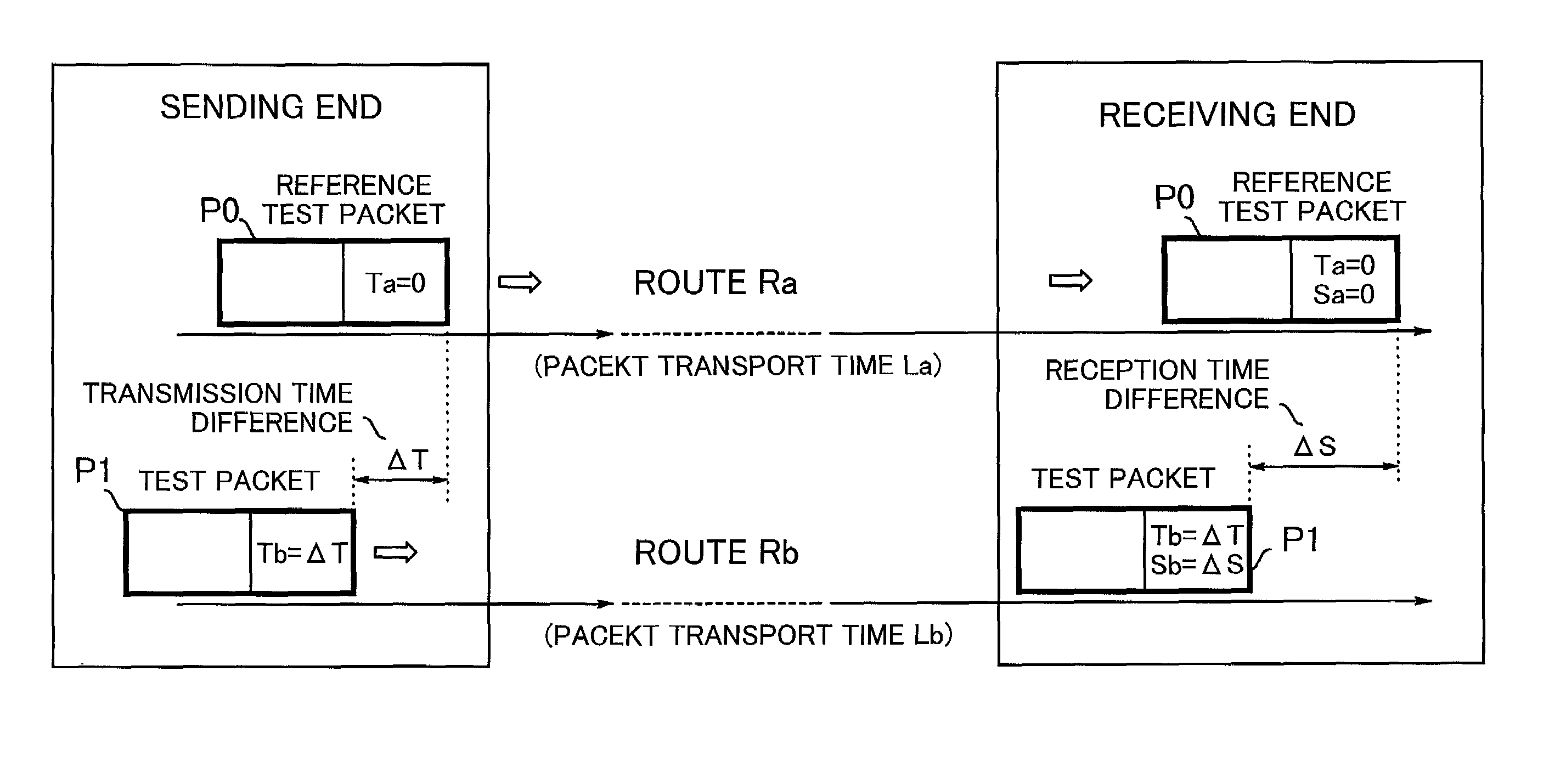

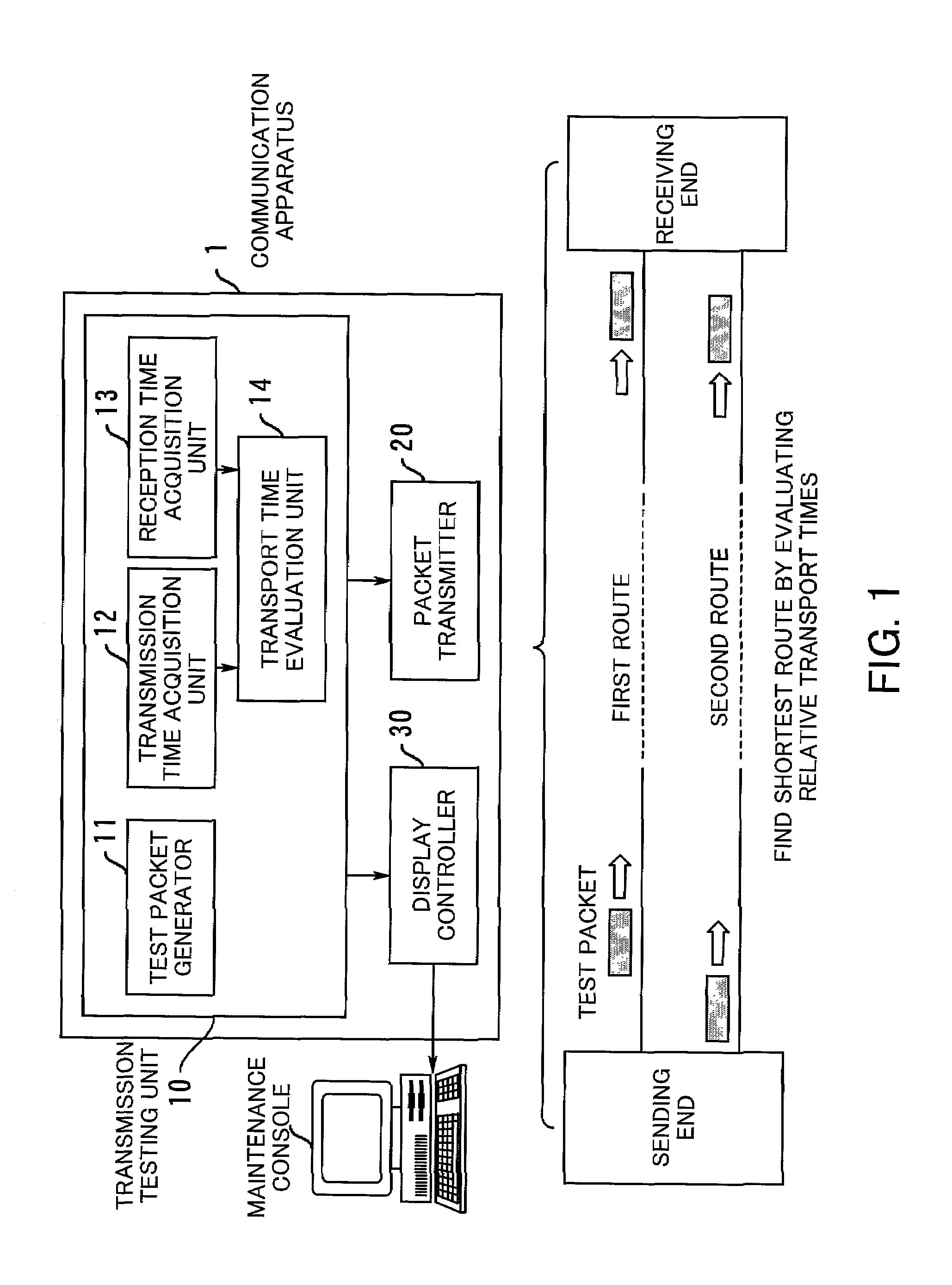

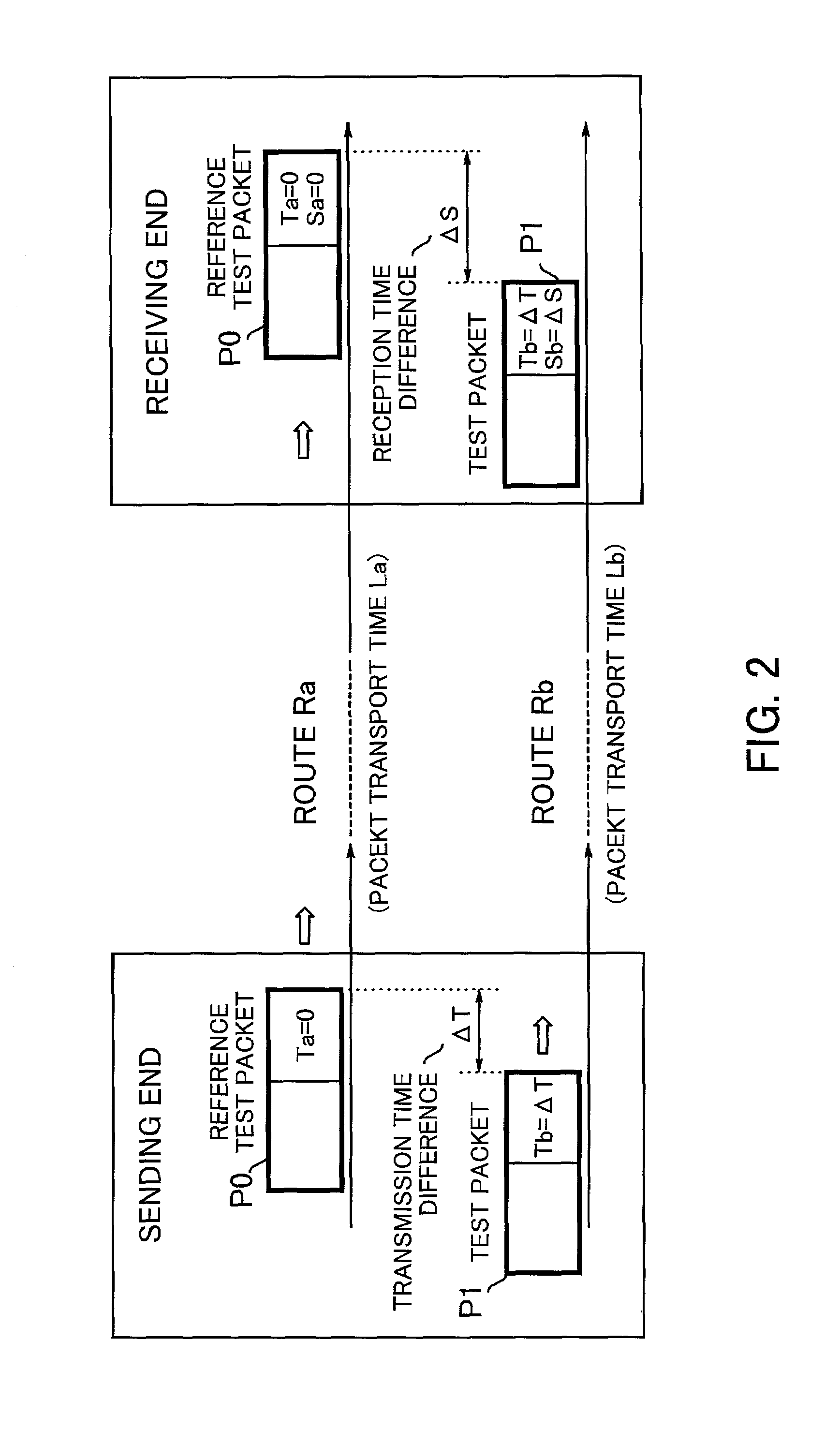

Communication device

InactiveUS6999422B2Efficient transportEasy to routeError preventionTransmission systemsTransport timeReference test

A communication device which efficiently transports packets through optimal routes. When there are two or more routes to reach a certain destination, a test packet generator generates a test packet for each route, one of them being designated as the reference test packet. A transmission time acquisition unit records the transmission time of each test packet, relative to that of the reference test packet. When a test packet is received, a reception time acquisition unit measures its reception time relative to the reception time of the reference test packet. Calculating the difference between the transmission and reception times and evaluating such difference values for all routes, a transport time evaluation unit ranks the routes in terms of their packet transport times. A packet transmitter selects an appropriate route from the ranked list of possible routes, and sends out packets to the selected route.

Owner:FUJITSU LTD

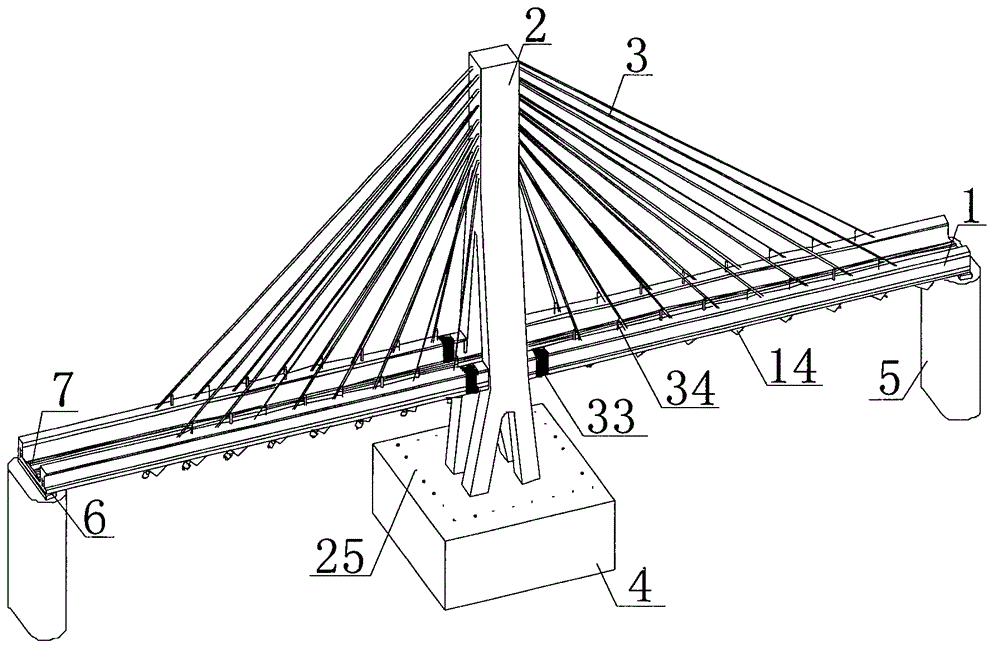

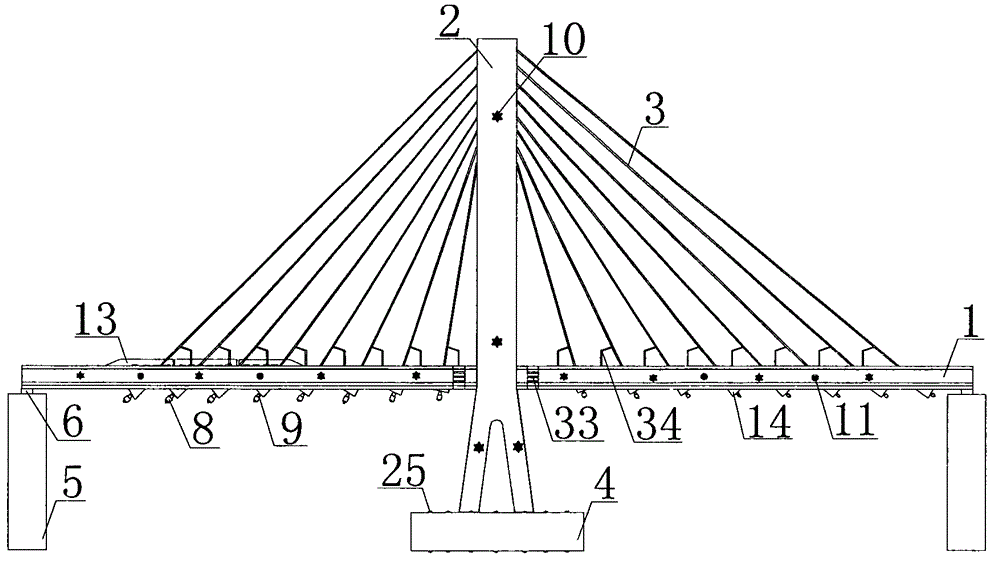

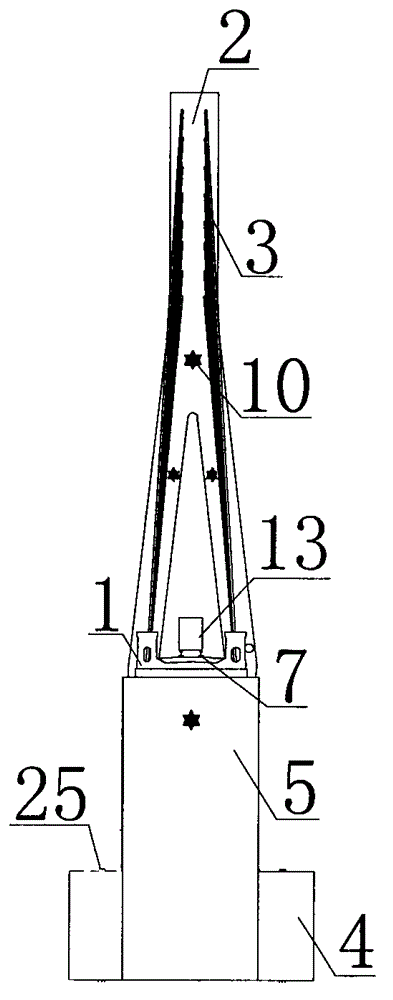

Railway cable-stayed bridge test model

InactiveCN104374597ALong term operationEasy to operateStructural/machines measurementReference testCable stayed

The invention relates to a railway cable-stayed bridge test model. The railway cable-stayed bridge test model comprises a railway cable-stayed bridge body, rigid bridge connectors and a steel rail, wherein the steel rail is paved on the railway cable-stayed bridge body and used for a test car to run thereon. The railway cable-stayed bridge body is manufactured sectionally and are combined and assembled by the rigid bridge connectors. A test loading device used for simulating static and dynamic load of a cable-stayed bridge and a data acquiring device used for acquiring test data are mounted on the railway cable-stayed bridge body. The railway cable-stayed bridge test model simulates static and dynamic load on the cable-stayed bridge using the test loading device and acquires bridge test data under the action of the static and dynamic load by the data acquiring device in time. The railway cable-stayed bridge test model can simulate structural responses of the cable-stayed bridge under working conditions of different loads and provides reference test data for bridge structure design and long-term and effective operation of the cable-stayed bridge is ensured.

Owner:CENT SOUTH UNIV

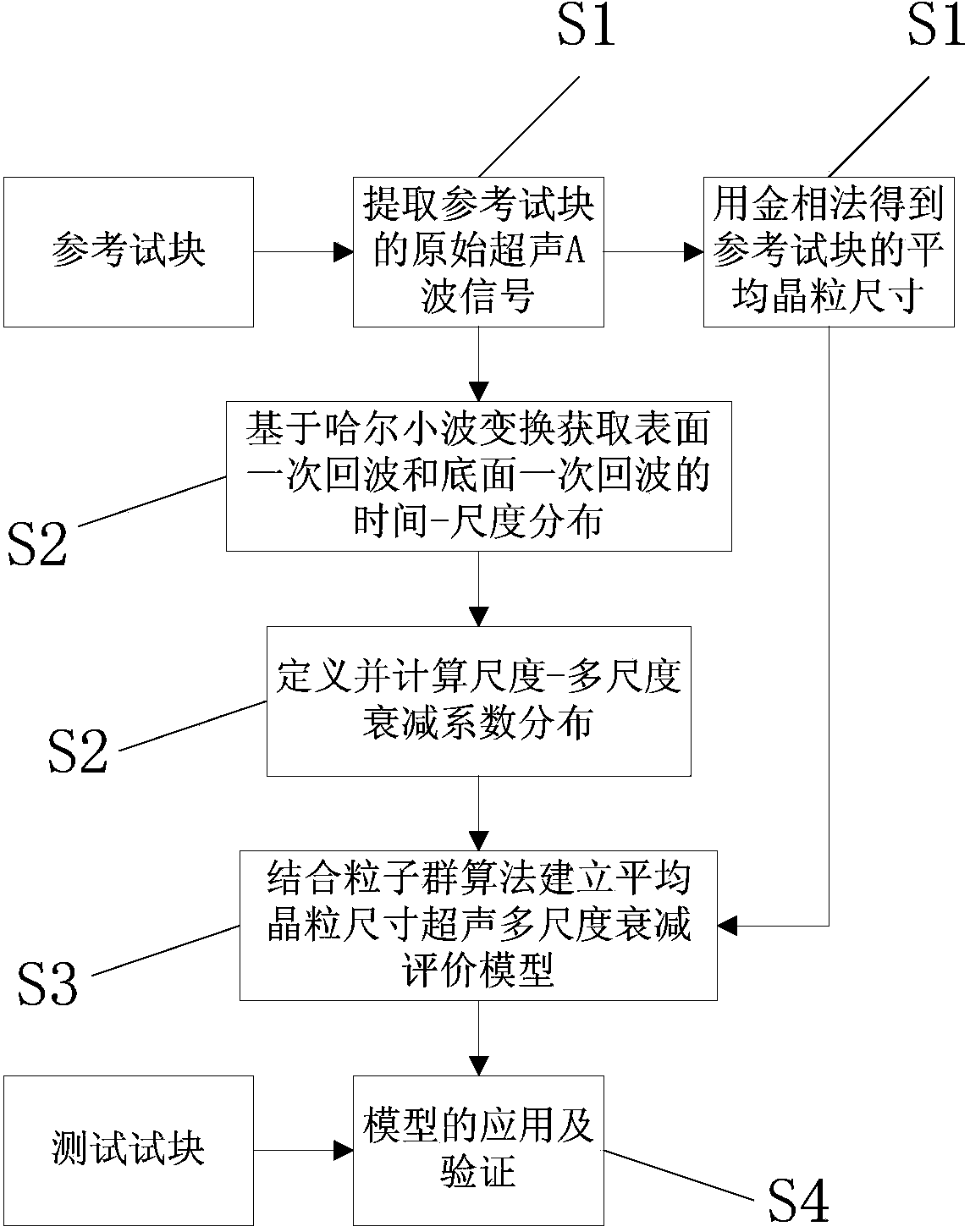

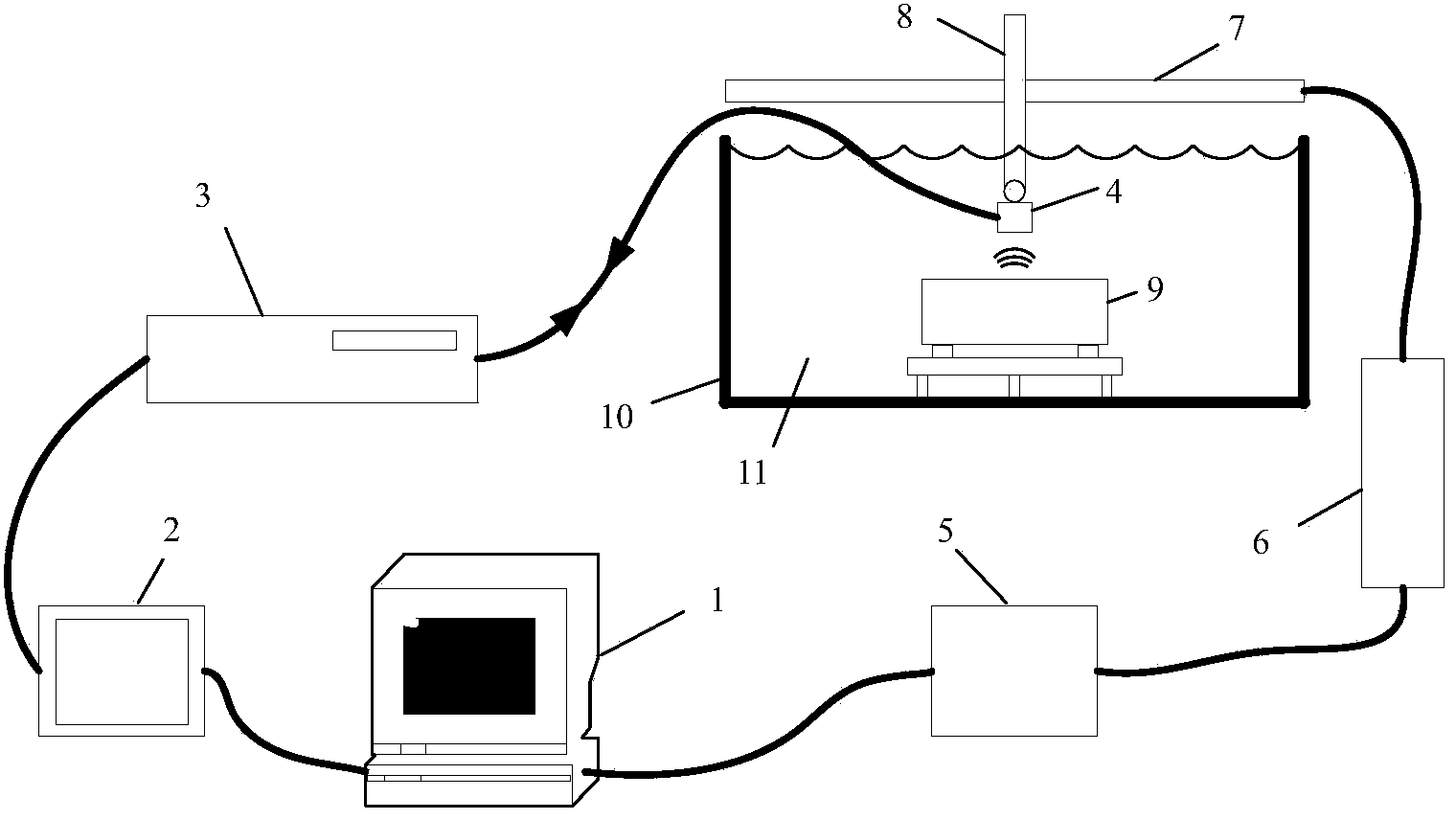

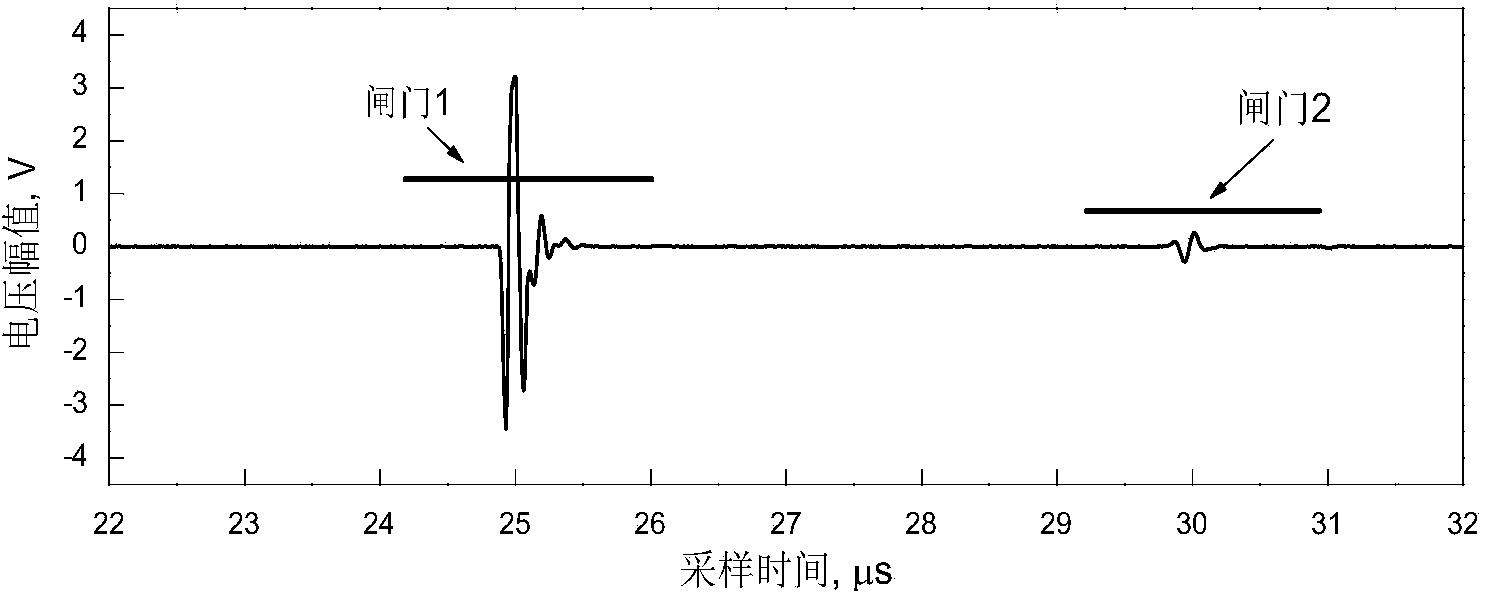

Grain size nondestructive evaluation method based on haar wavelet

ActiveCN104101651ASuppress random errorsReduce mistakesAnalysing solids using sonic/ultrasonic/infrasonic wavesSonificationData acquisition

The invention discloses a grain size nondestructive evaluation method based on haar wavelet. The method comprises the following steps: data acquisition is conducted on a reference test block, time-size distribution is obtained by utilizing haar wavelet transform, furthermore, the average multi-scale attenuation coefficient of all reference blocks is calculated, an ultrasonic multi-scale attenuation evaluation model for the average grain size is built according to the preset size assembly and the preset normalized weight, and finally grain size evaluation of the test block of which the grain size is unknown is realized through the built ultrasonic multi-scale attenuation evaluation model of the average grain size. The method reduces system errors in grain size measurement; for test blocks of which the average grain size is 103.5 [mu]m measured by adopting metallography, the evaluation result is 101.7 [mu]m, and the error is controlled to be + / -2%. Therefore, through multi-scale analysis of original ultrasonic A signals, the method provided by the invention can discover more rich grain size information in the original ultrasonic A signals, and further improves the nondestructive evaluation precision of the grain size.

Owner:CENT SOUTH UNIV

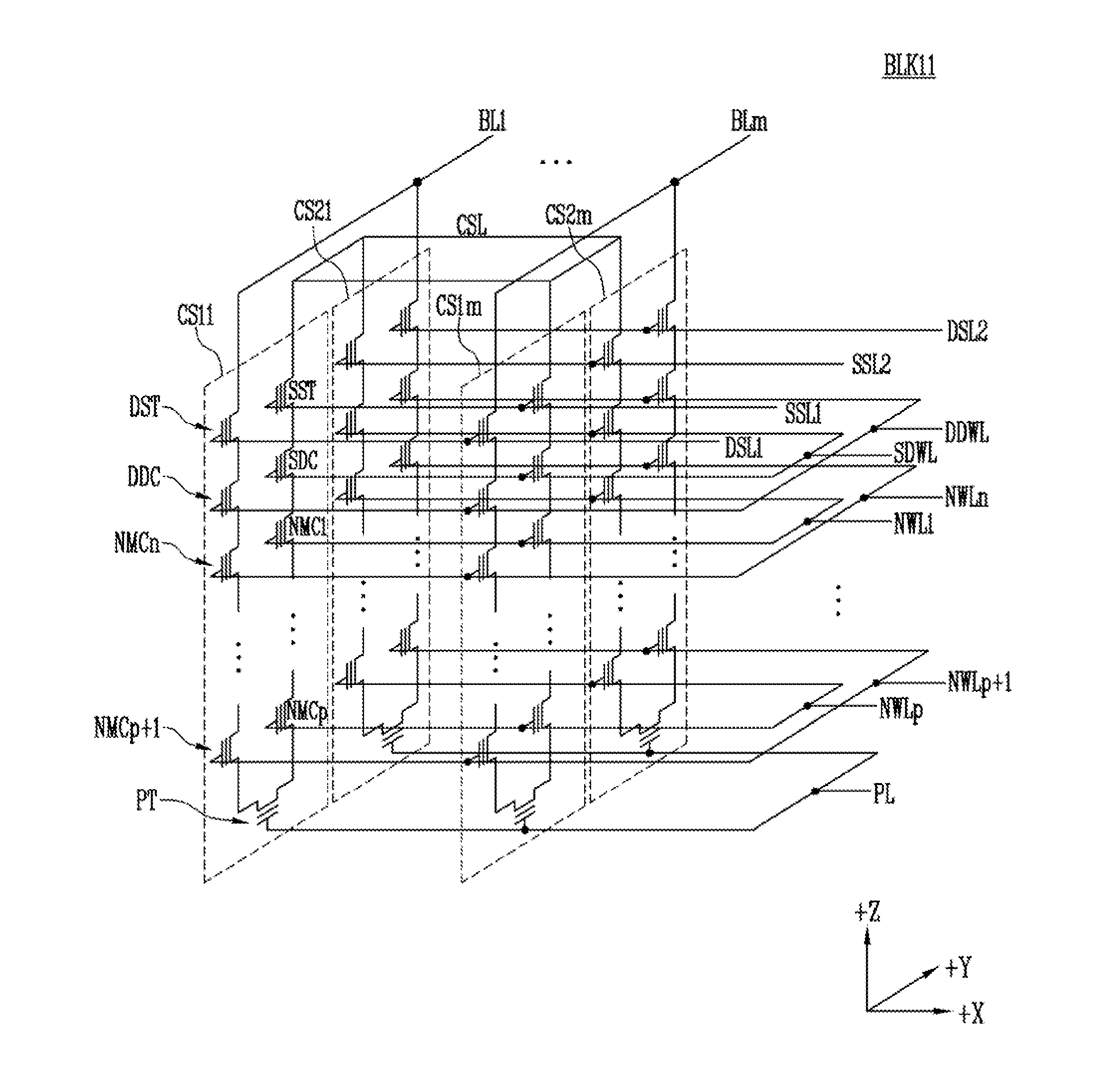

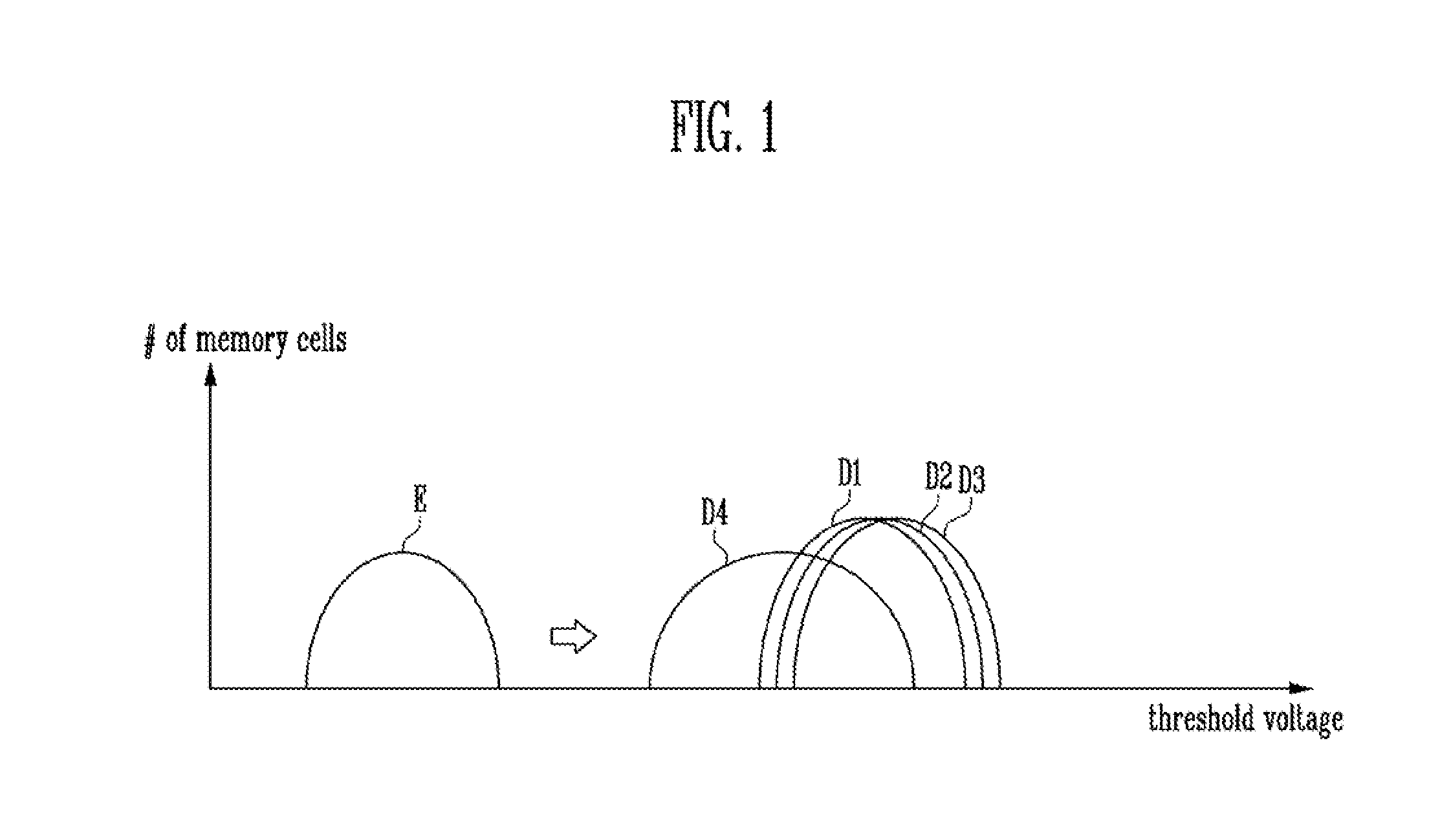

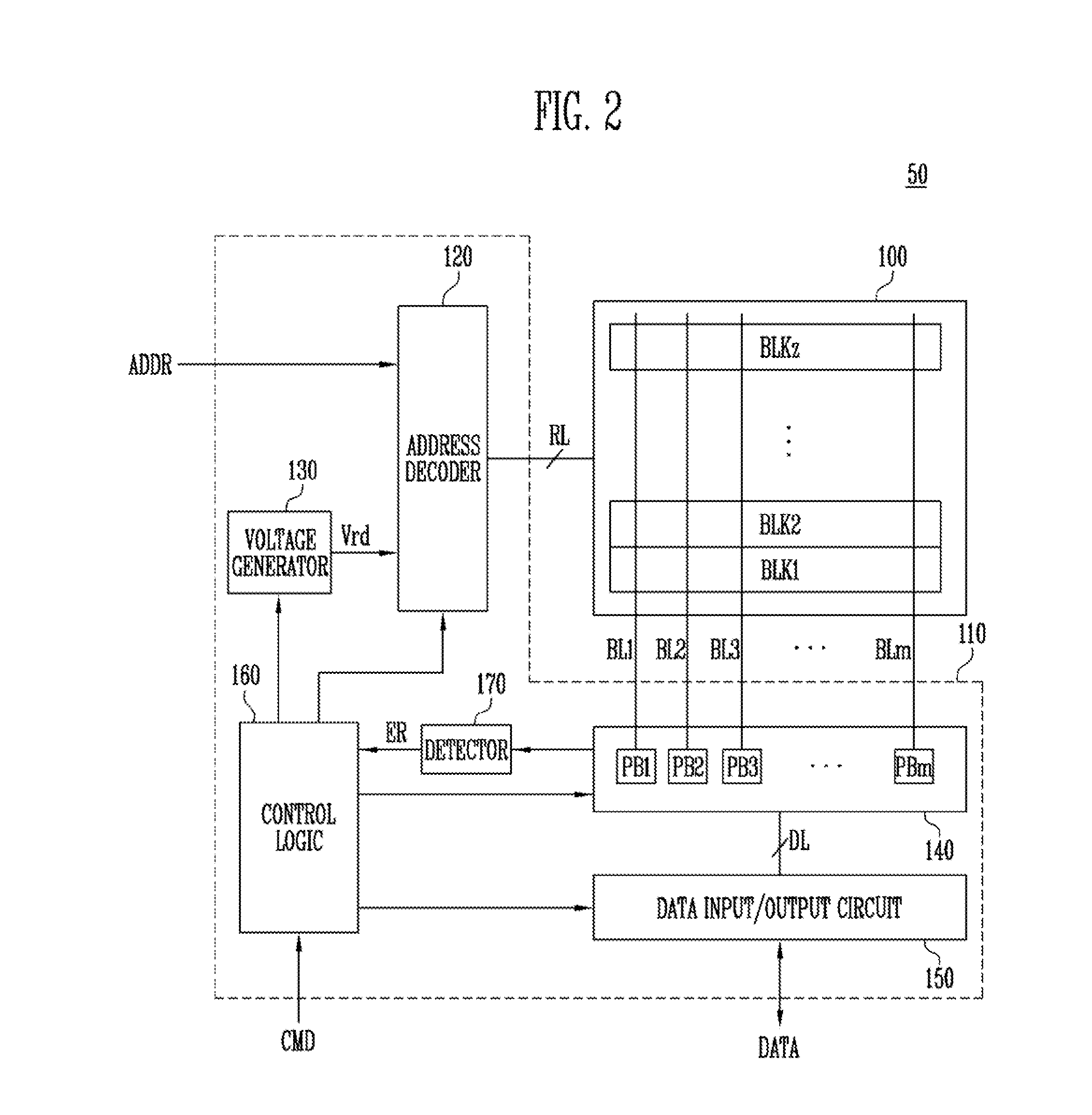

Semiconductor device and operating method thereof

A method of operating a semiconductor memory device includes applying a program pulse at least once to each of a plurality of pages; performing a pre-read operation on a reference page among the plurality of pages through an initial test voltage; repeating the pre-read operation by controlling the initial test voltage until a result of the pre-read operation is a pass; setting the initial test voltage of when the result of the pre-read operation is the pass as a reference test voltage; and detecting a defective page among the plurality of pages by performing read operations on the plurality of pages through the reference test voltage.

Owner:SK HYNIX INC

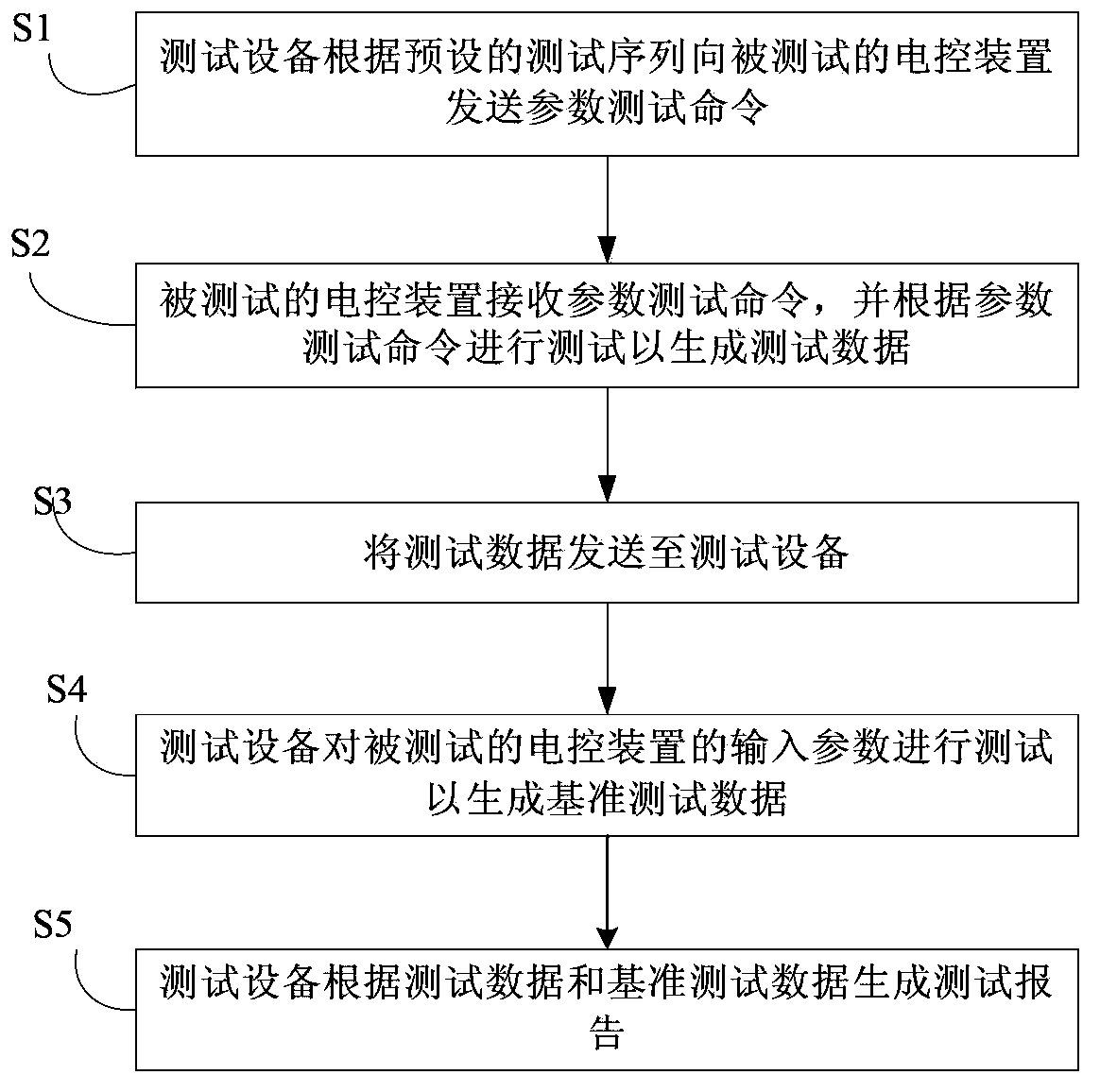

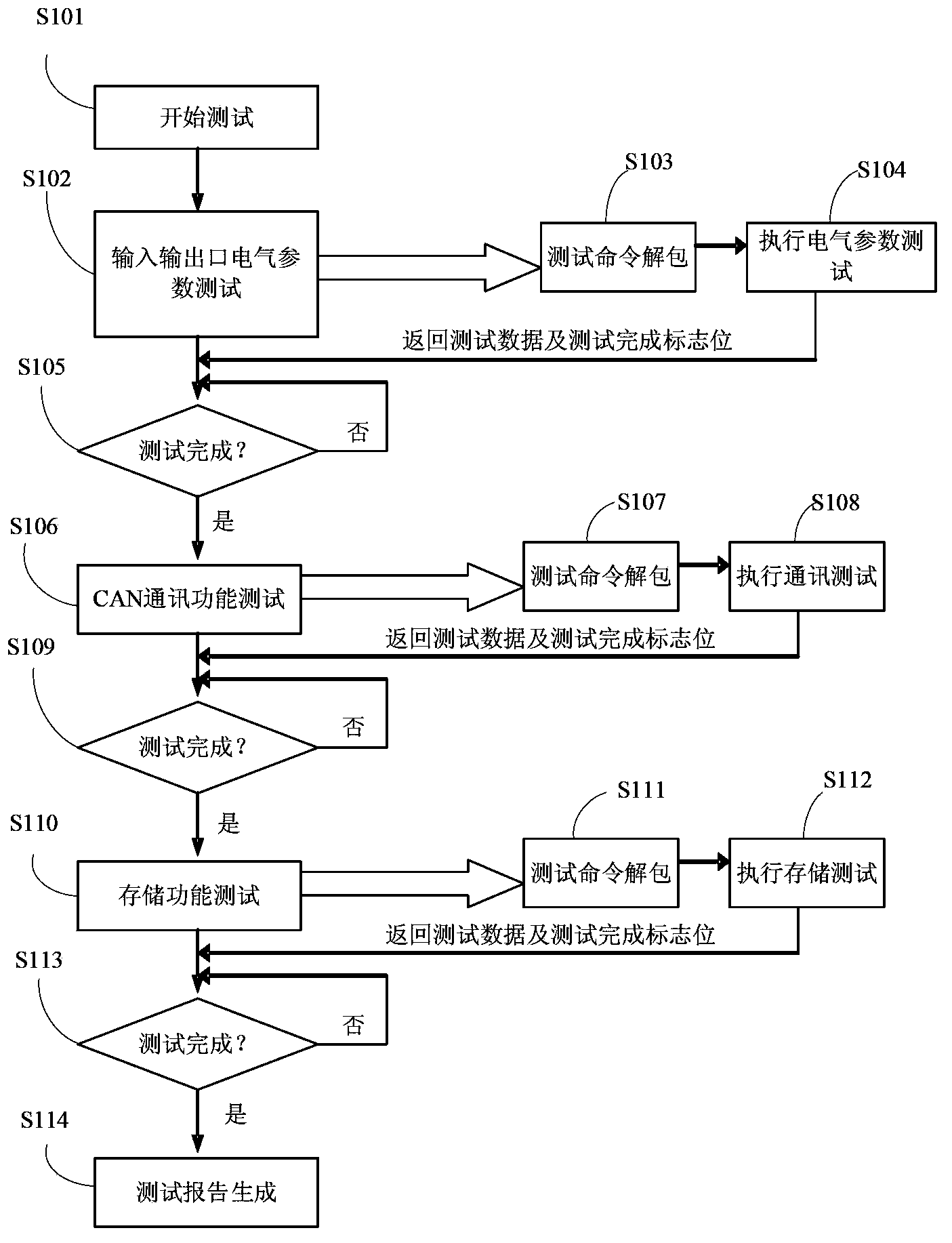

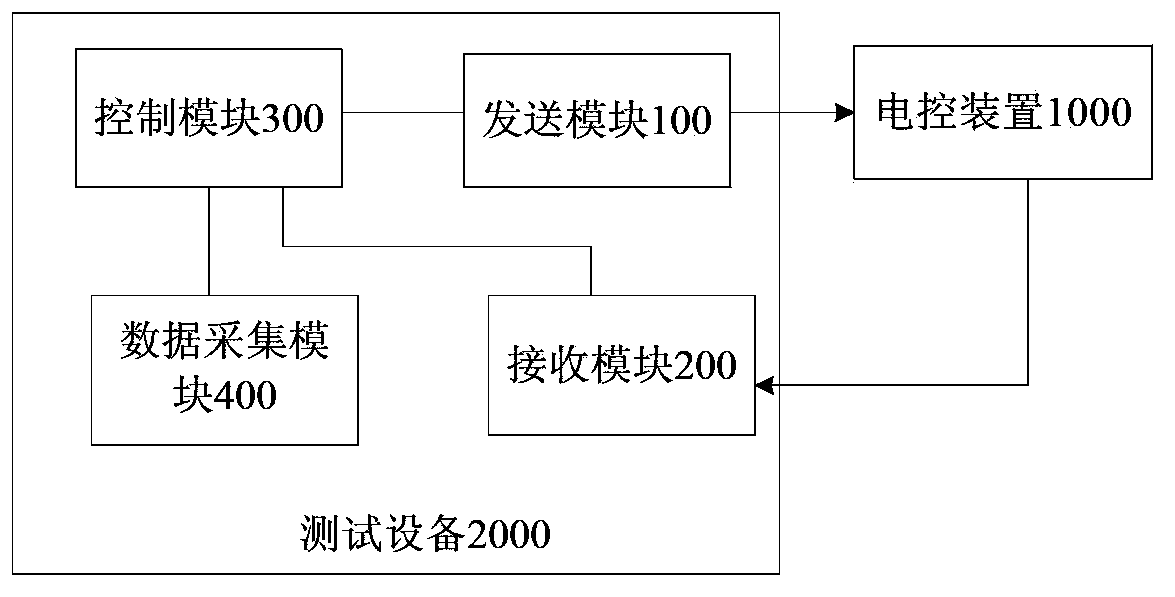

Method of carrying out automatic test on automobile electric control device and equipment

InactiveCN104076806AComprehensive and efficient testingAchieving Versatile TestingElectric testing/monitoringFunctional testingReference test

The invention provides a method of carrying out an automatic test on an automobile electric control device. the method comprises the following steps: S1, test equipment sends a parameter test command to a tested electric control device according to the preset test sequence; S2, the tested electric control device receives the parameter test command and a test is carried out according to the parameter test command to generate test data; S3, the test data are sent to the test equipment; S4, the test equipment carries out a test on input parameters of the tested electric control device to generate reference test data; and S5, the test equipment generates a test report according to the test data and the reference test data. The method of carrying out the automatic test on the automobile electric control device adopts a request-response mode to realize comprehensive and high-efficiency test on the electric control device, both the electrical parameters and other functions can be tested, and the test state is controllable. The invention also provides equipment for carrying out the automatic test on the automobile electric control device.

Owner:BEIJING BORGWARD AUTOMOBILE CO LTD

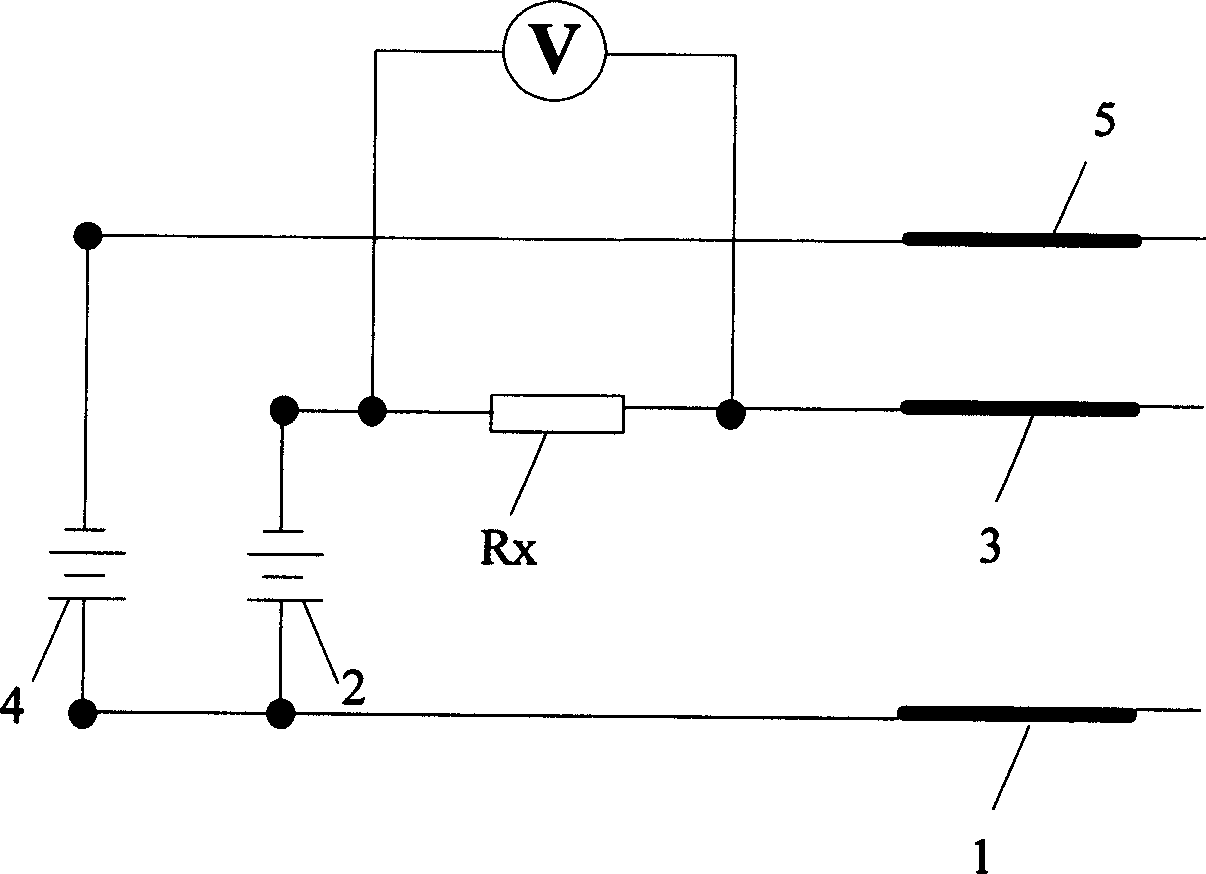

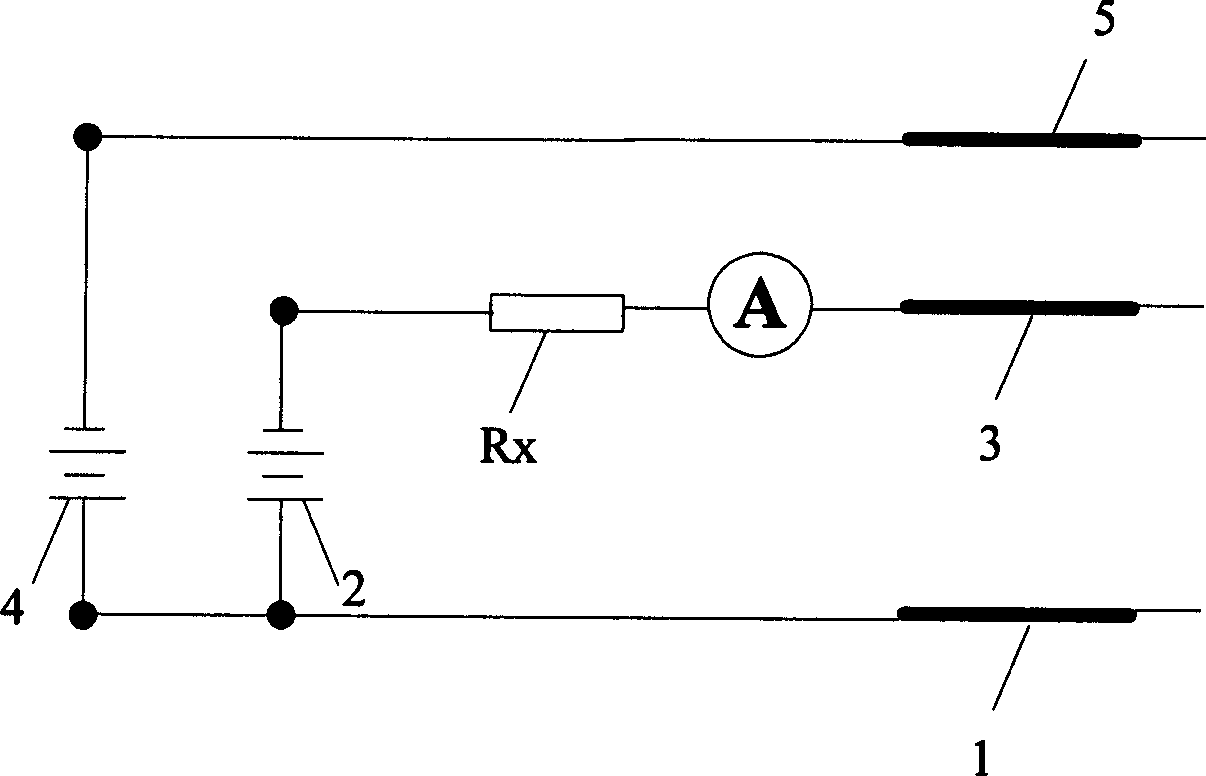

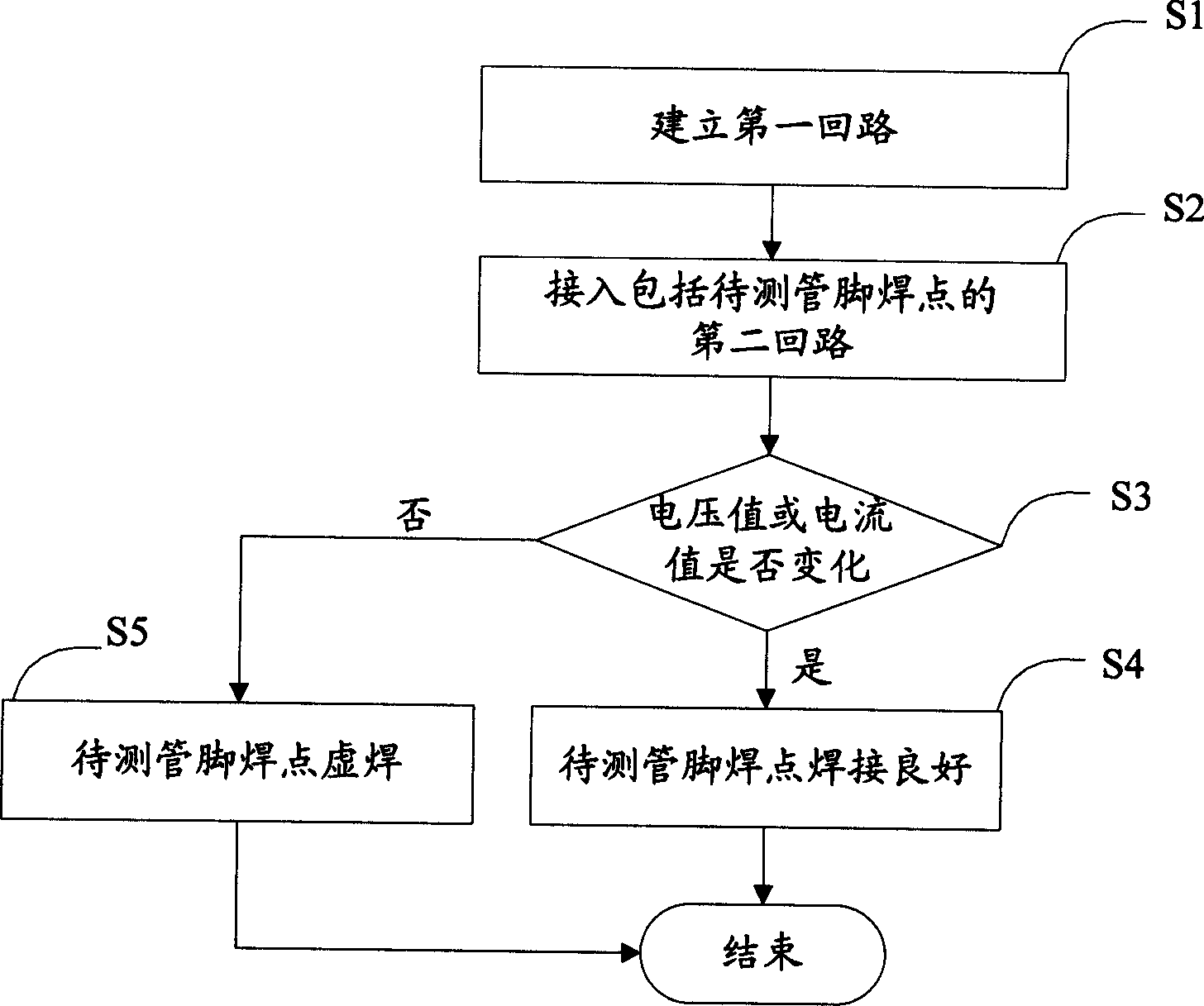

False pin soldering test device and method

InactiveCN1847866ASolving costly problemsQuick support meansElectrical testingElectrical resistance and conductanceReference test

The present invention discloses false pin soldering test device with low cost. One device includes one first opened circuit comprising an earth test lead, one first power source, a reference resistor and a reference test lead connected serially; one second opened circuit comprising the earth test lead, the first power source, one second power source with different voltage and a test lead connected serially; and one voltmeter connected in parallel to the reference resistor. One other test device is also disclosed. The simple method of testing false pin soldering with the devices is also disclosed.

Owner:HUAWEI TECH CO LTD

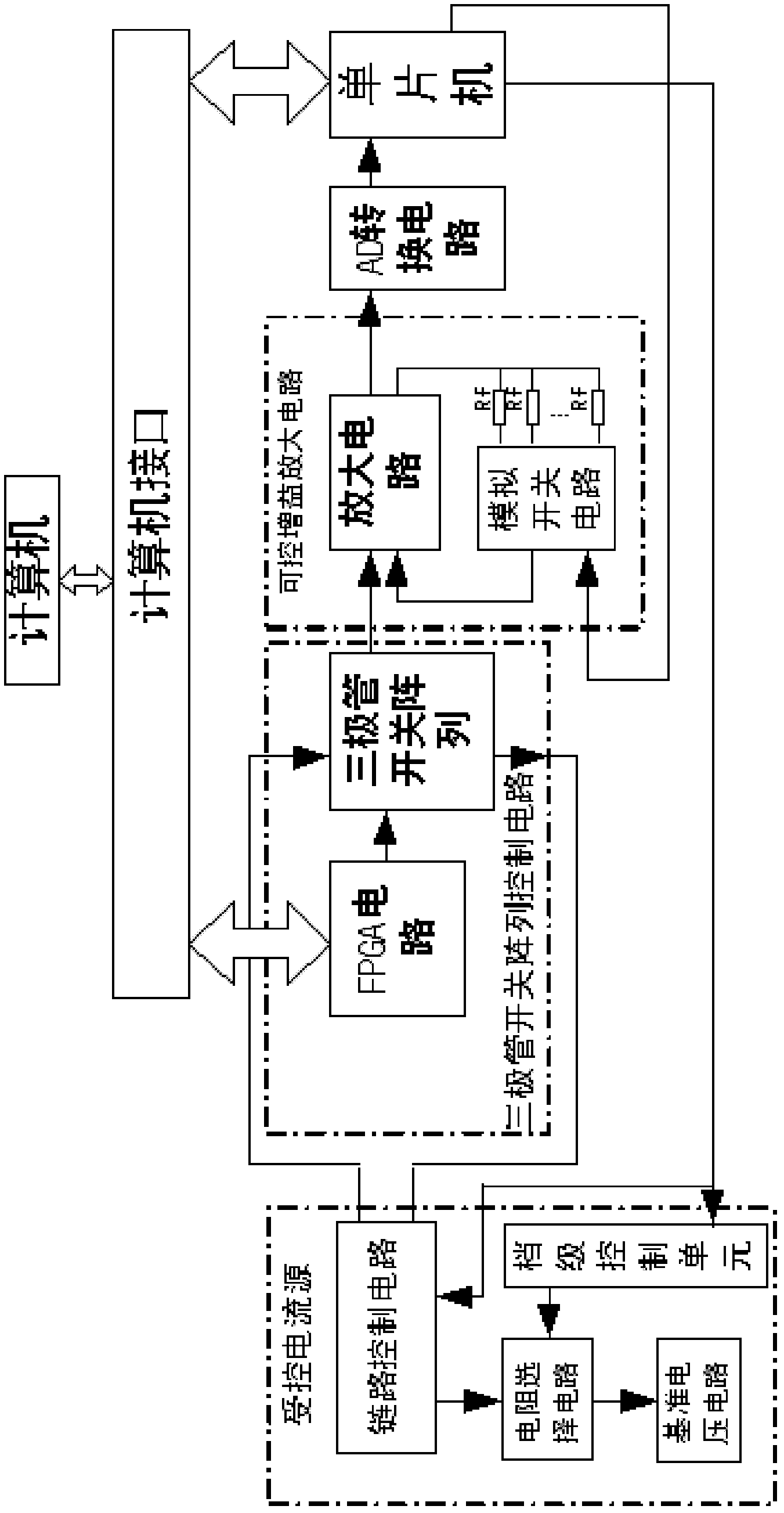

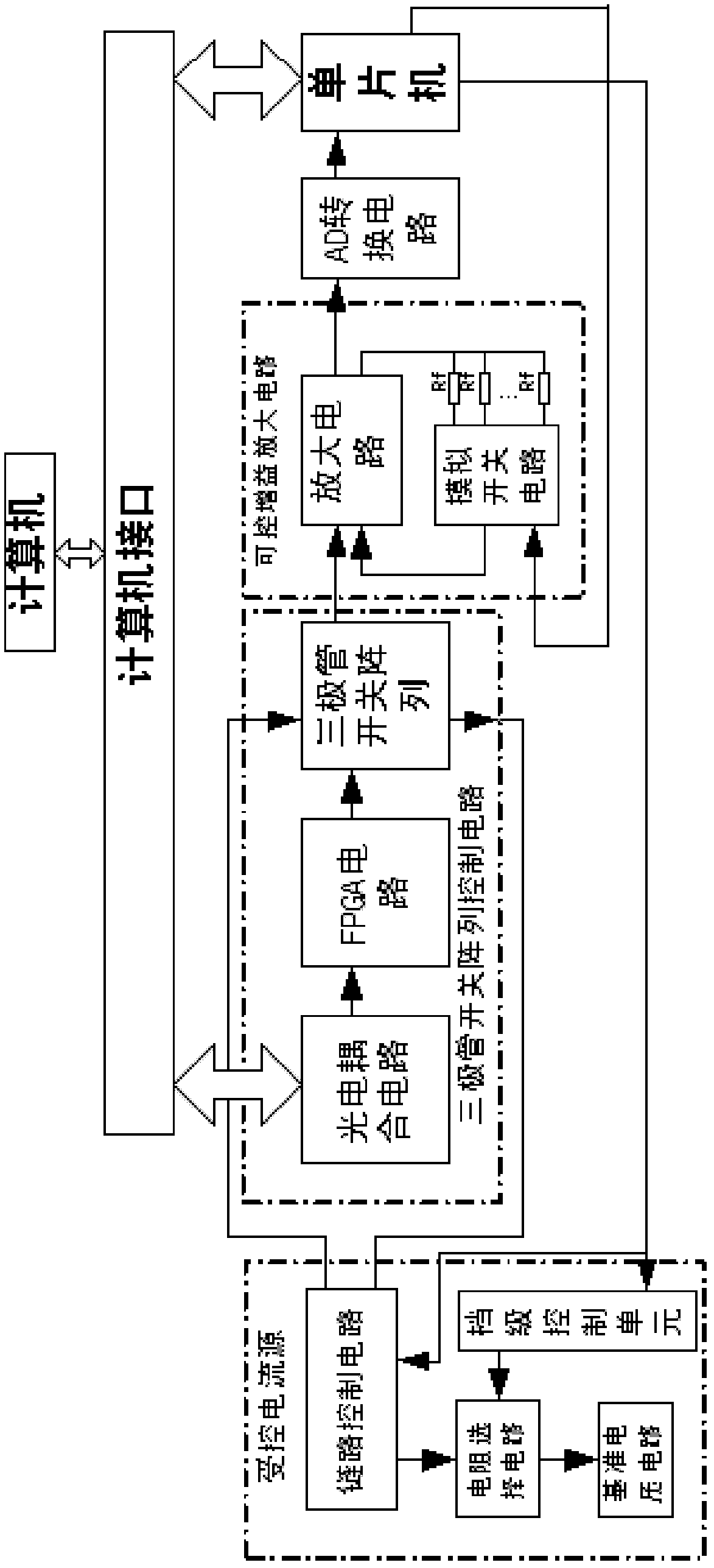

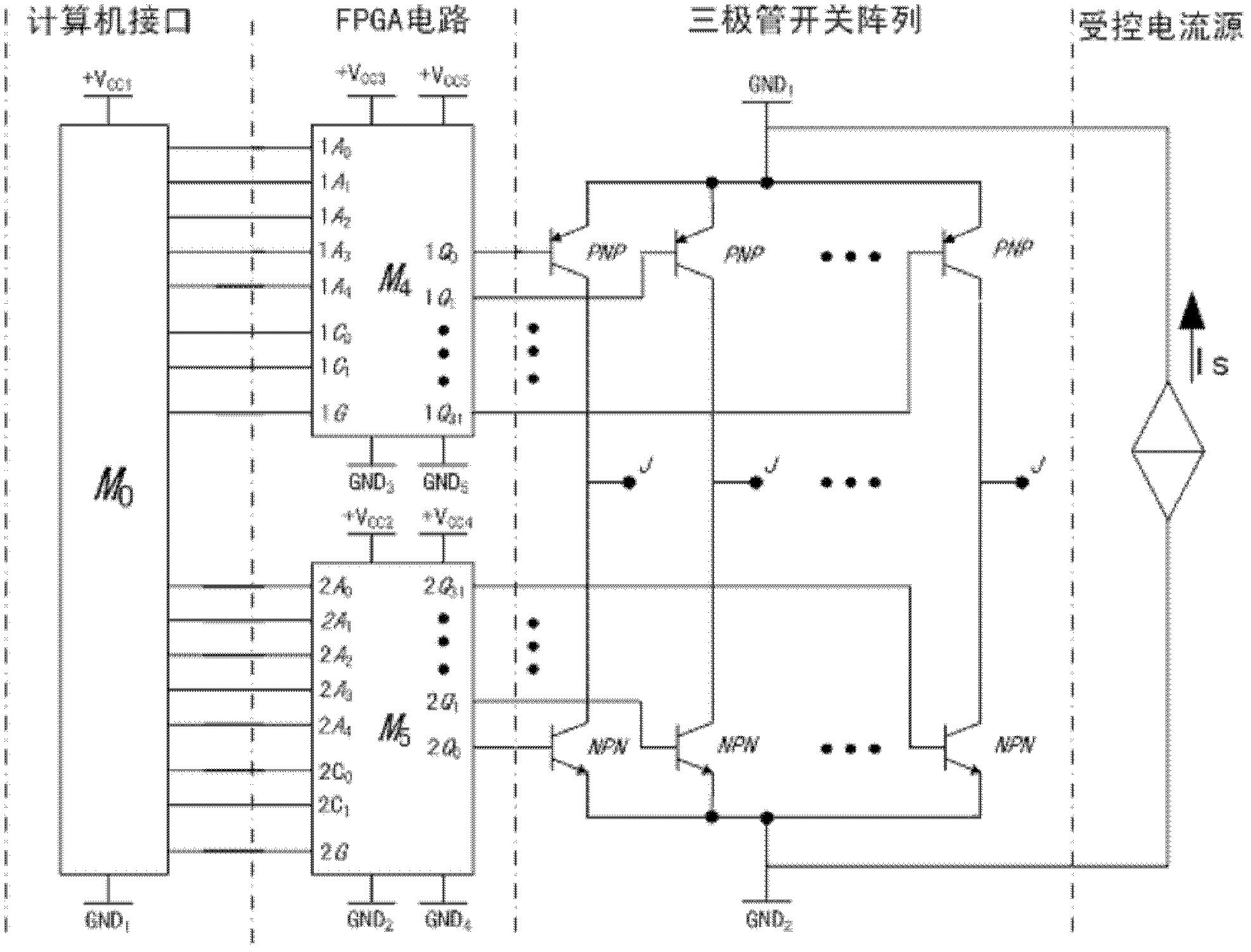

Testing method for circuit board testing system

InactiveCN102495354AImprove scalabilityAffect the volt-ampere relationshipElectronic circuit testingExtensibilityReference test

The invention relates to a testing method for a contact circuit board testing system. The testing system comprises a computer interface, a first field programmable gate array (FPGA) circuit, a second FPGA circuit and a triode switch array circuit, wherein the first and second FPGA circuits are connected with the computer interface; the triode switch array circuit is connected with the control signal output ends of the first and second FPGA circuits, and at least comprises two groups of geminate transistor circuits; each geminate transistor circuit comprises a PNP type triode and an NPN type triode; and the collectors of the PNP type triode and the NPN type triode are connected. A great number of test nodes are produced, and the FPGA circuits have high extensibility. An effective reference test node can be quickly found, and a node network based on the effective reference test node can be obtained. Anti-jamming capability is high, and the influence of leakage current or leakage voltage on the volt-ampere relationship of the node network can be avoided.

Owner:东莞市至高机械科技有限公司

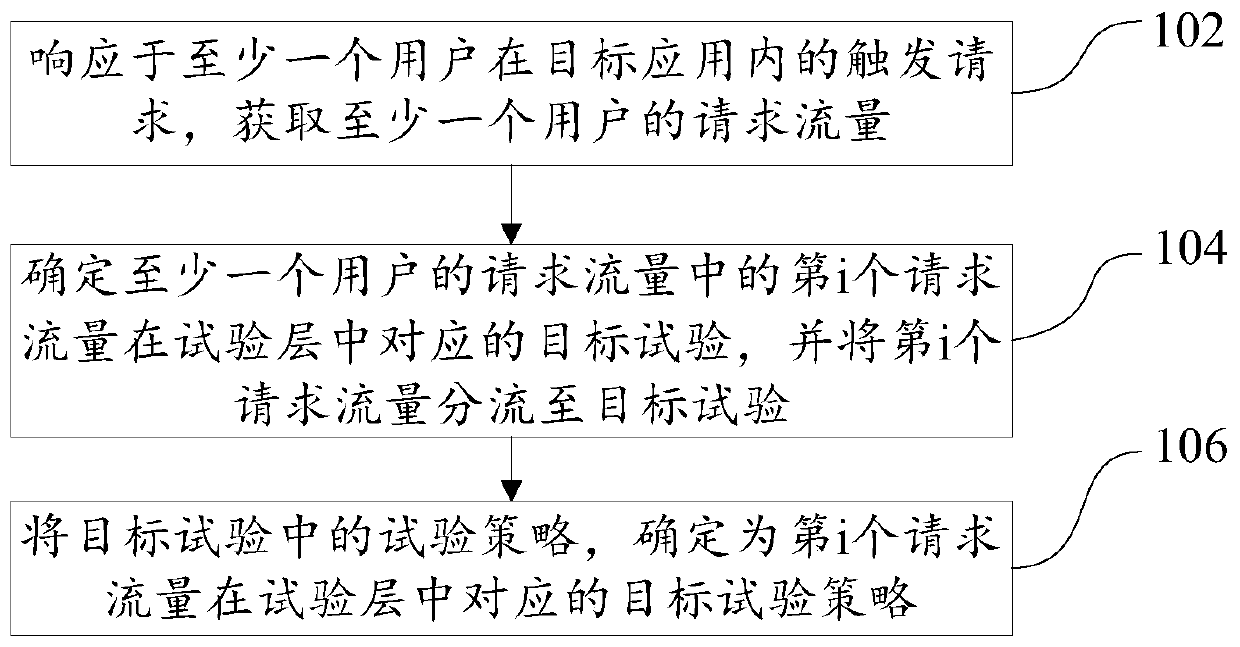

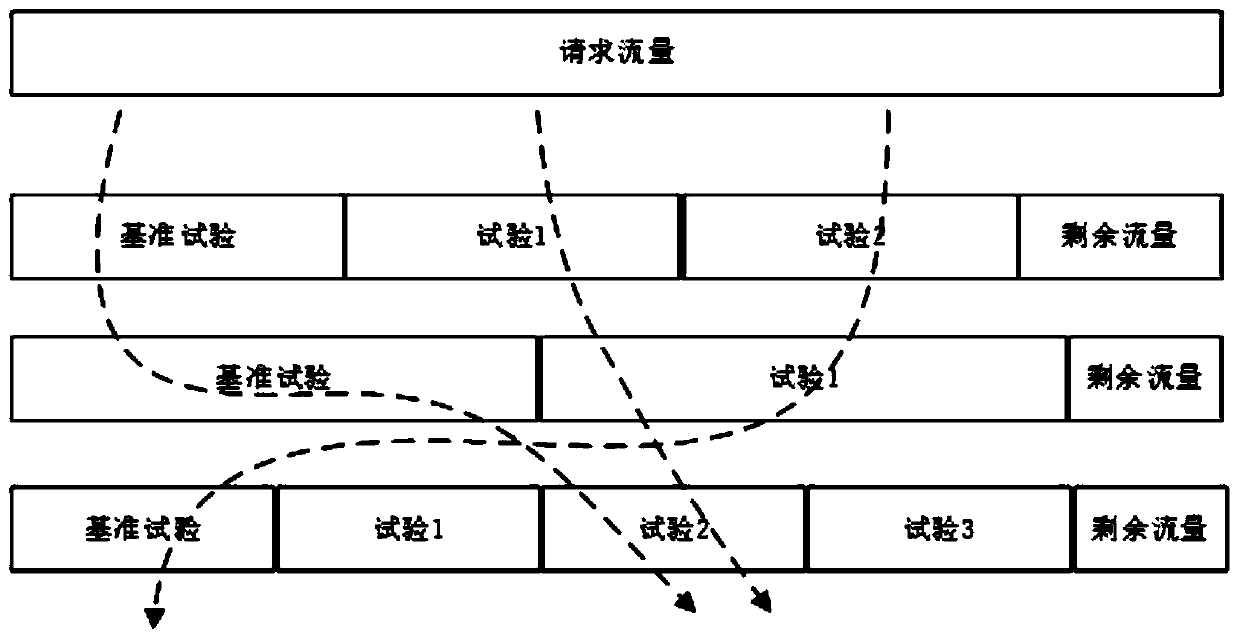

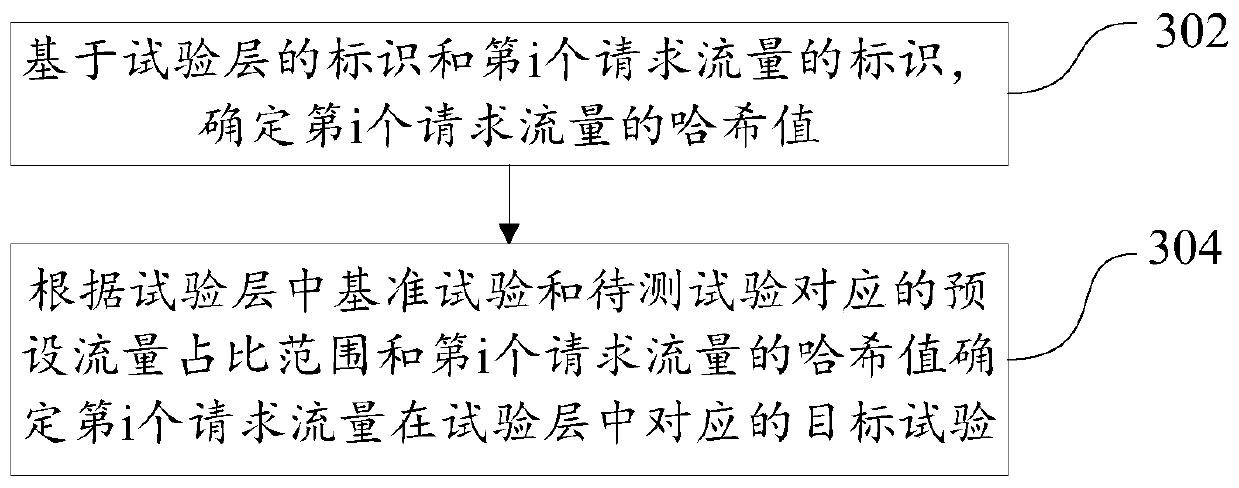

An AB test method and device

InactiveCN109739757AHigh speedSpeed up iterationSoftware testing/debuggingReference testLab test method

The embodiment of the invention discloses an AB test method and device. The method comprises a step of determining a test strategy for each test layer in a plurality of test layers, wherein the plurality of test layers are used for determining a target test strategy of each request flow in each test layer, each test layer in the plurality of test layers comprises a reference test and a test to betested, and the test strategy determination step comprises the following steps: obtaining the request flow of at least one user in response to a trigger request of at least one user in a target application; determining a target test corresponding to the i request flow in the request flow of at least one user in the test layer, and distributing the i request flow to the target test; and determining the test strategy in the target test as the corresponding target test strategy of the ith request flow in the test layer, i = 1,... N, and N being the number of the request flows of atleast one user. According to the embodiment of the invention, the problem of long optimization iteration period of a product caused by the fact that multiple tests cannot be carried out by a test method in the prior art is solved.

Owner:MICRO DREAM TECHTRONIC NETWORK TECH CHINACO

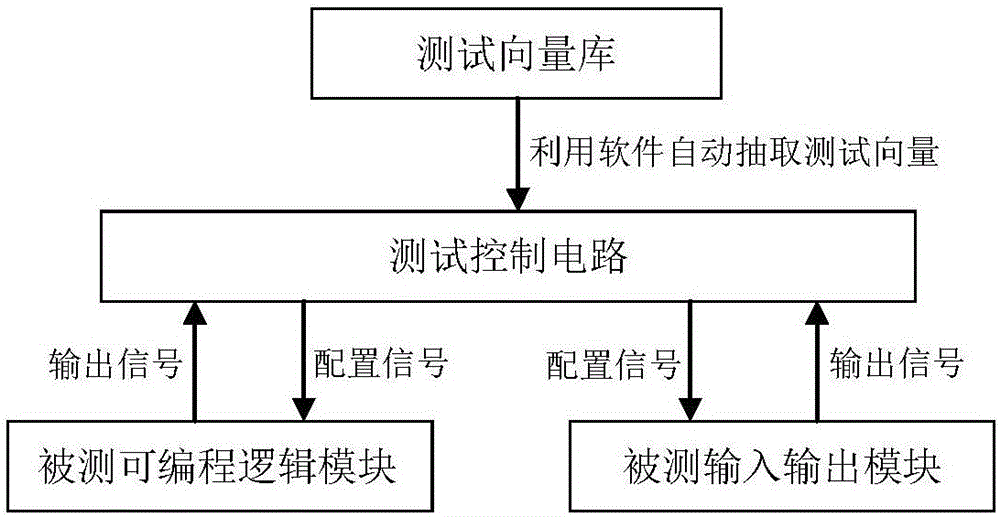

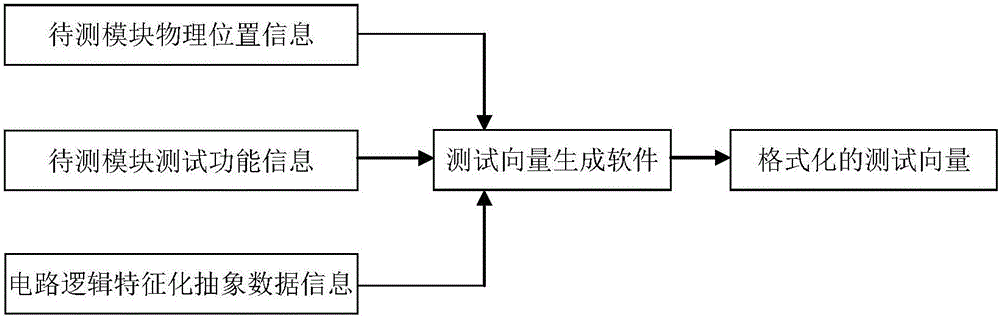

Automatic testing technique applied before anti-fuse FPGA (field programmable gate array) programming

The invention relates to an automatic testing technique applied before anti-fuse FPGA (field programmable gate array) programming. The technique can automatically test any anti-fuse FPGA before programming. The technique includes: building a testing vector library, utilizing a software way to automatically extract testing vectors from the testing vector library by a testing vector sending module, and respectively inputting the testing vectors into a circuit logic simulation excitation applying module and a circuit response verifying module at the same time for anti-fuse FPGA circuit simulation; after circuit simulation analysis and verification, inputting a tested anti-fuse FPGA chip; collecting a result output by the FPGA chip by a testing response verifying module, and comparing the result with reference testing information input in advance to automatically generate a testing report so as to realize automatic testing of the anti-fuse FPGA before programming. The whole testing process can effectively avoid a lot of manual intervention; after testing is finished, a testing result of the chip can be known by checking the testing report. By the technique, automatic testing of the anti-fuse FPGA before programming can be completely quickly, and testing efficiency of the anti-fuse FPGA chip can be improved remarkably.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

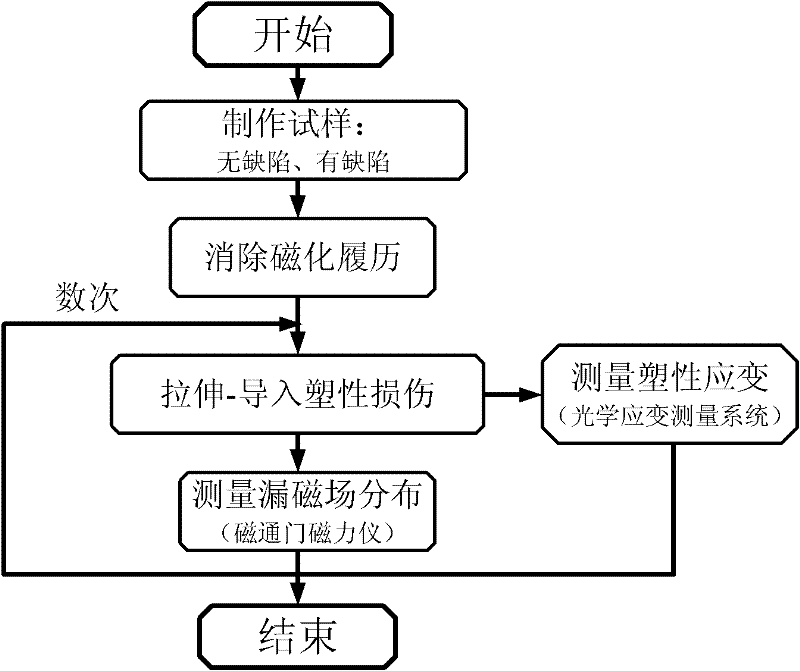

Natural magnetizing phenomenon-based austenitic stainless steel plastic damage quantitative detection method

InactiveCN102128879AEasy to operateNo surface treatment requiredUsing optical meansMaterial magnetic variablesReference testMagnetization

The invention discloses a natural magnetizing phenomenon-based austenitic stainless steel plastic damage quantitative detection method which belongs to the technical field of nondestructive detection. The method comprises the steps of establishment of a damage-magnetization calibrating curve and quantitative measurement of practical plastic damage on the basis of an austenitic stainless steel damage magnetization inducing phenomenon. The method comprises the following concrete steps of: establishing a mechanical damage-magnetization calibrating curve by a reference test; measuring natural magnetic field distribution nearby an object member by applying a fluxgate micromagnetic sensor; solving the natural magnetizing distribution inside a material by a reverse-question method and comparing the natural magnetizing distribution with the established damage-magnetization calibrating curve; and quantifying the plastic damage of the detected object. The nondestructive detection method can carry out quantitative detection on the weak magnetic austenitic stainless steel plastic damage degree and fills the blank of the austenitic stainless steel plastic damage degree detection method.

Owner:XI AN JIAOTONG UNIV