Patents

Literature

504 results about "Test failure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and System for Capturing Movie Shots at the Time of an Automated Graphical User Interface Test Failure

InactiveUS20090150868A1Error detection/correctionSpecific program execution arrangementsGraphicsComputer hardware

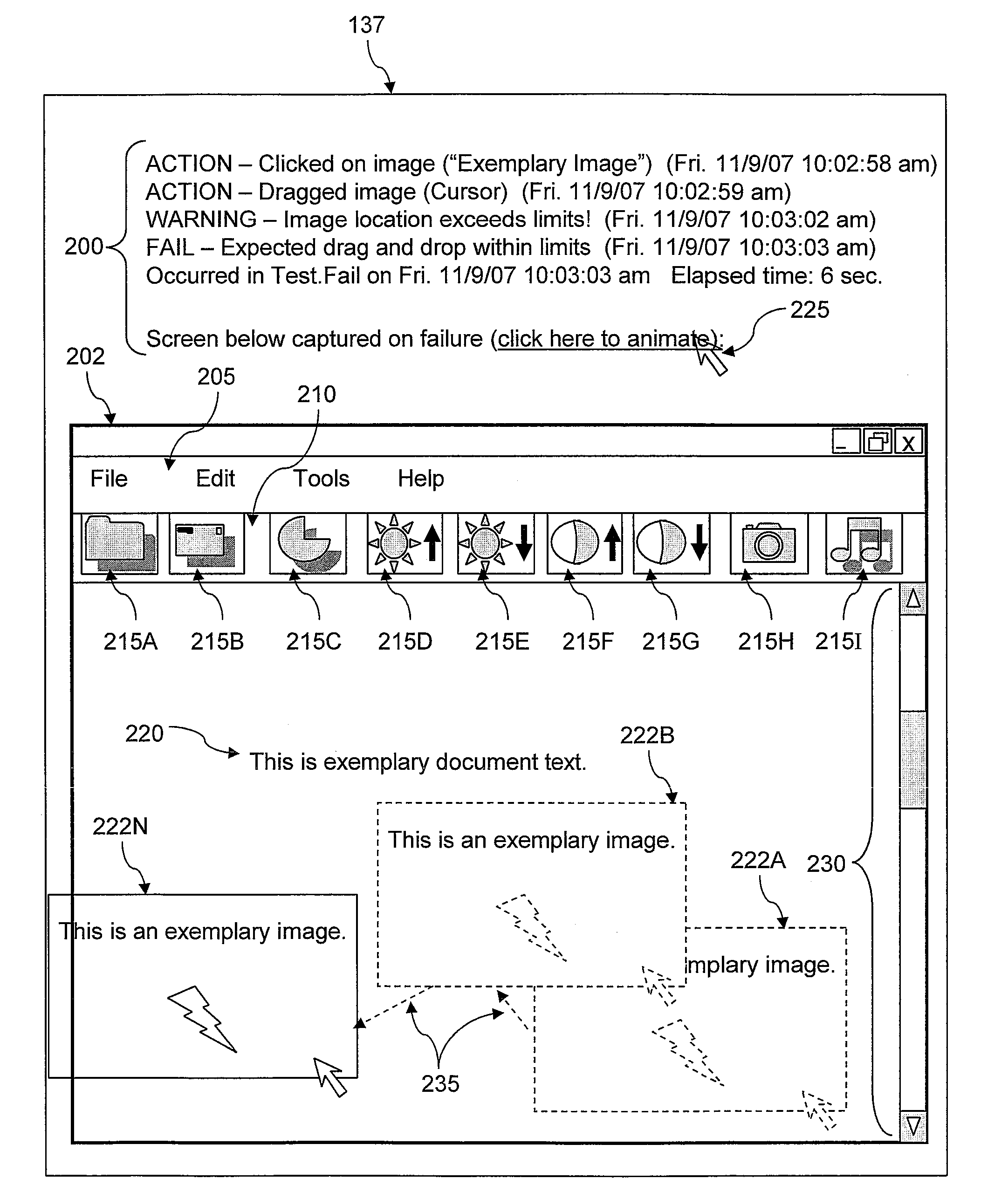

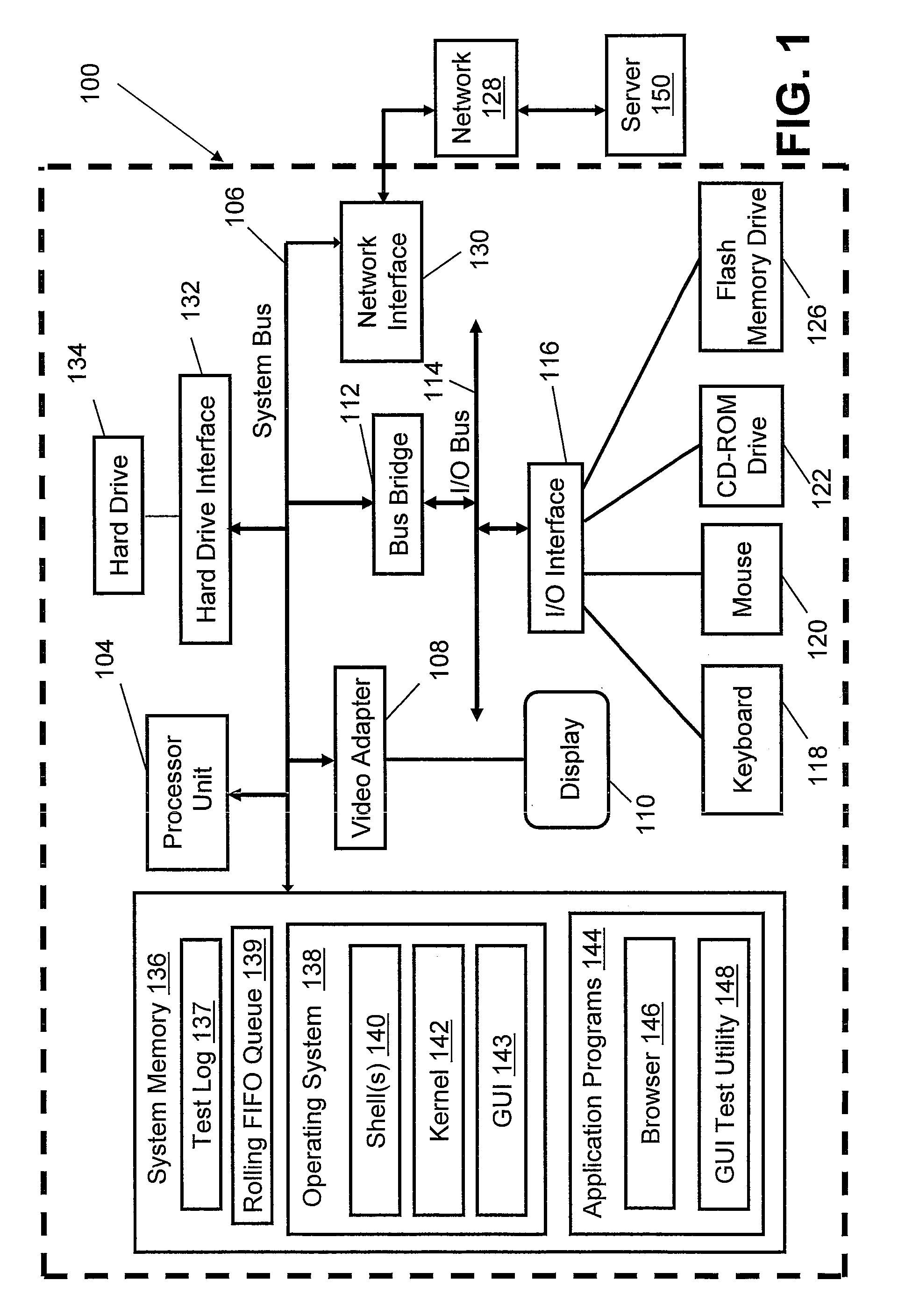

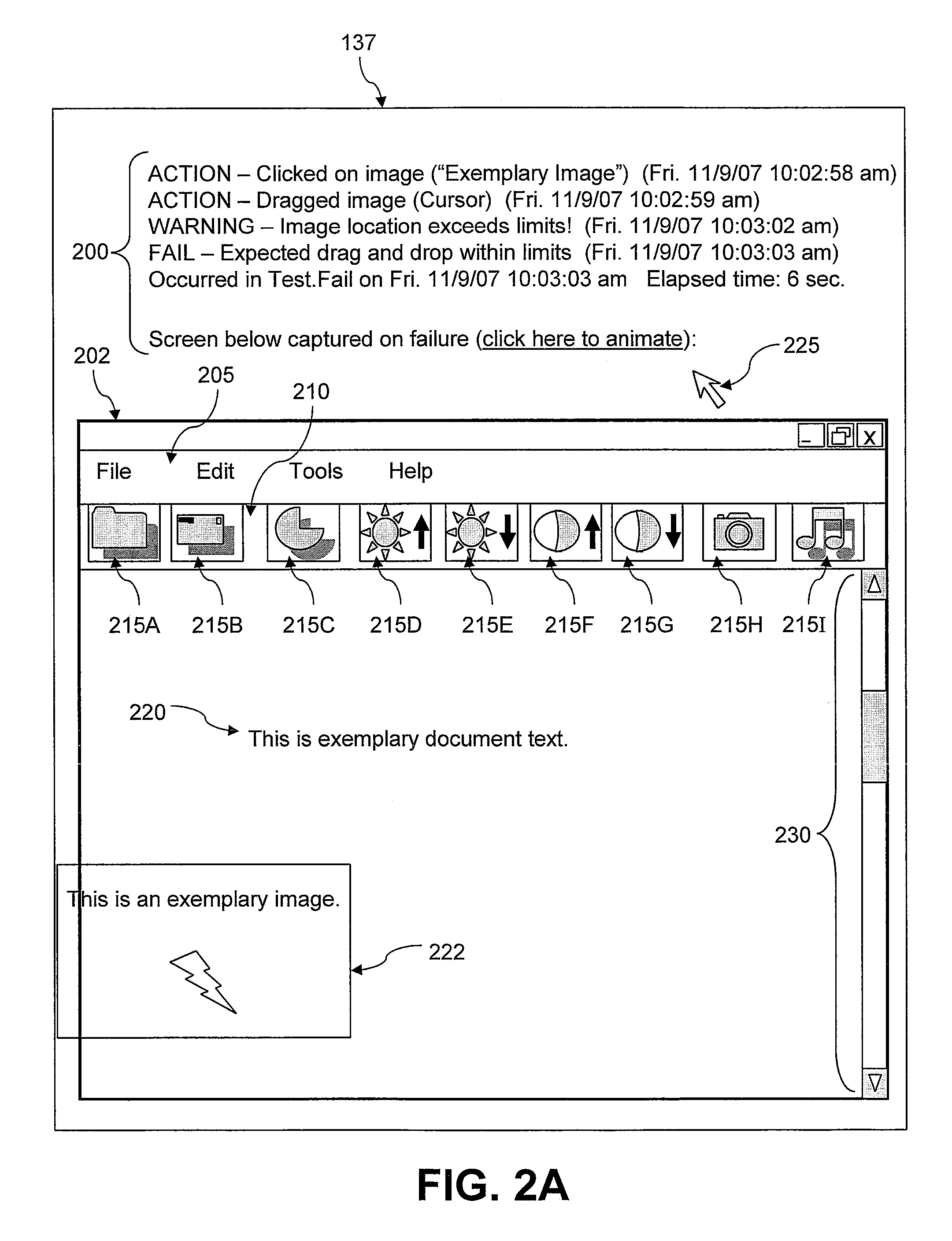

A method of capturing movie shots at the time of an automated Graphical User Interface (GUI) test failure. When an automated GUI test application performs an action during a test of a GUI, the GUI test application adds a text description of the action to a test log and captures a screenshot image of the GUI. The GUI test application adds the screenshot image to a rolling First-In-First-Out (FIFO) queue that includes up to a most recent N screenshot images, where N is a pre-defined configurable number. If an error occurs, the GUI test application captures a final failure point screenshot image. The GUI test application adds the final screenshot image to the rolling FIFO queue and the test log. The GUI test application assembles the screenshot images from the rolling FIFO queue into a chronologically animated movie file and attaches the movie file to the test log.

Owner:IBM CORP

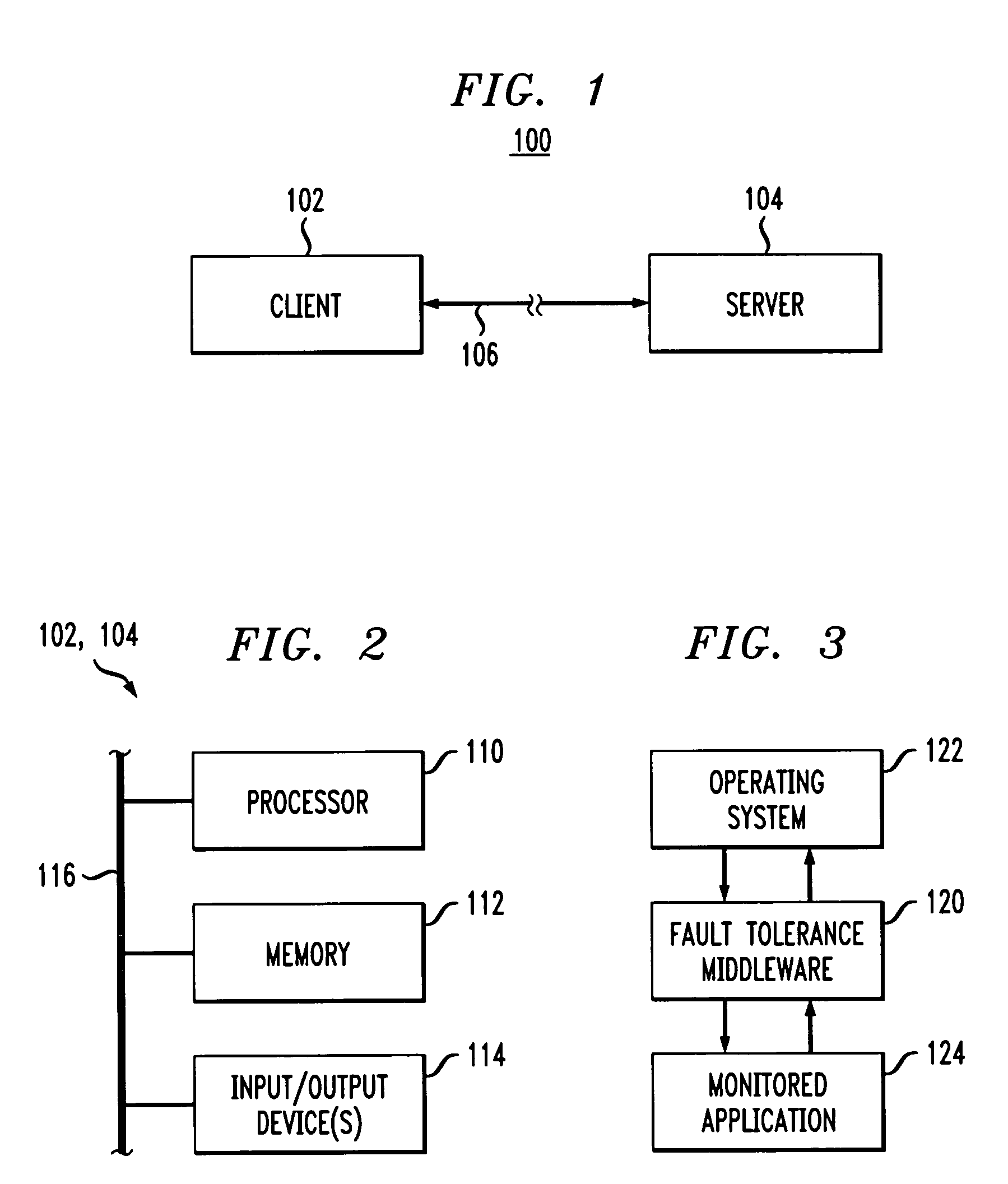

Fault tolerance software system with periodic external self-test failure detection

ActiveUS7096388B2Simple and rapid developmentImproved failure detectionSoftware testing/debuggingClient-sideMonitoring program

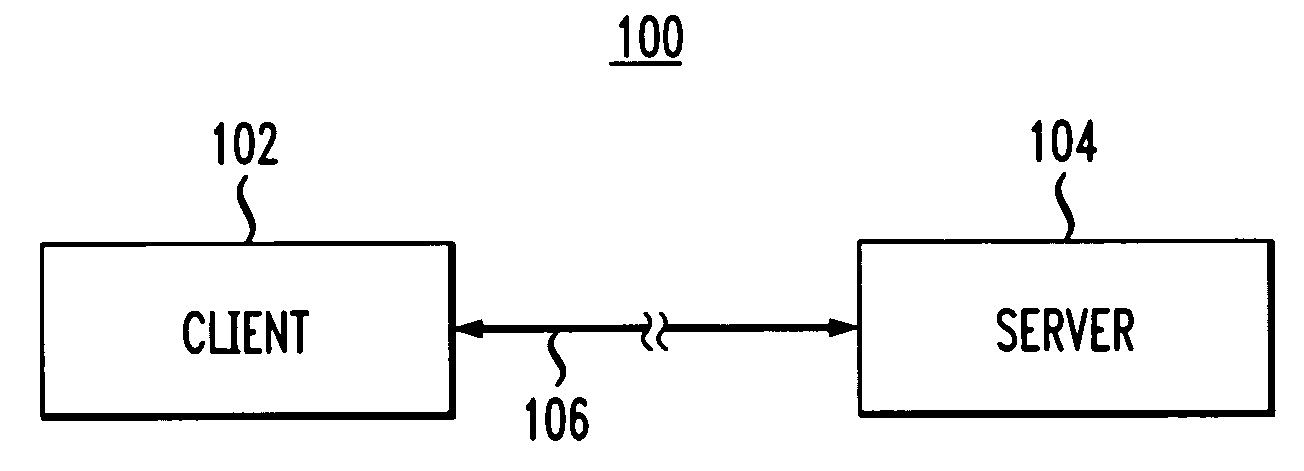

Fault tolerance is improved in a computing system which includes one or more computing machines by (i) executing a control thread or other control program in conjunction with a fault tolerance software system running on at least one of the machines, and (ii) initiating via the control program a test script program which sends one or more requests to a monitored program. The test script program also processes corresponding responses to the one or more requests, and generates a return value utilizable by the control program to indicate a failure condition in the monitored program. The computing system may be configured in accordance with a client-server architecture, with the fault tolerance software system and the monitored program both running on a server of the system. The test script program is preferably implemented in an object-oriented programming language such as Java, such that one or more components of the test script program comprise a base class from which one or more other components of the test script program are generatable for use with the monitored program.

Owner:AVAYA INC

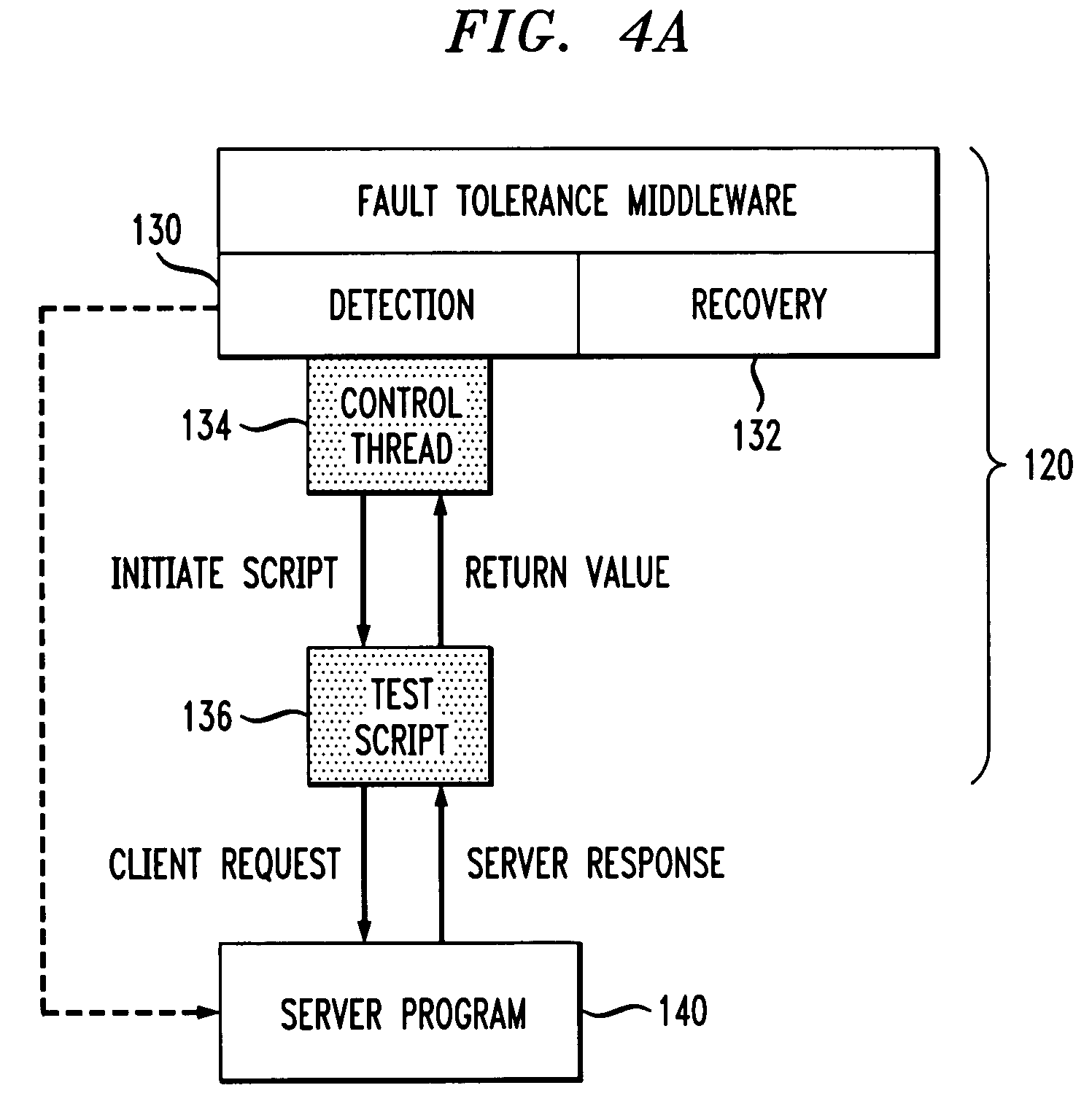

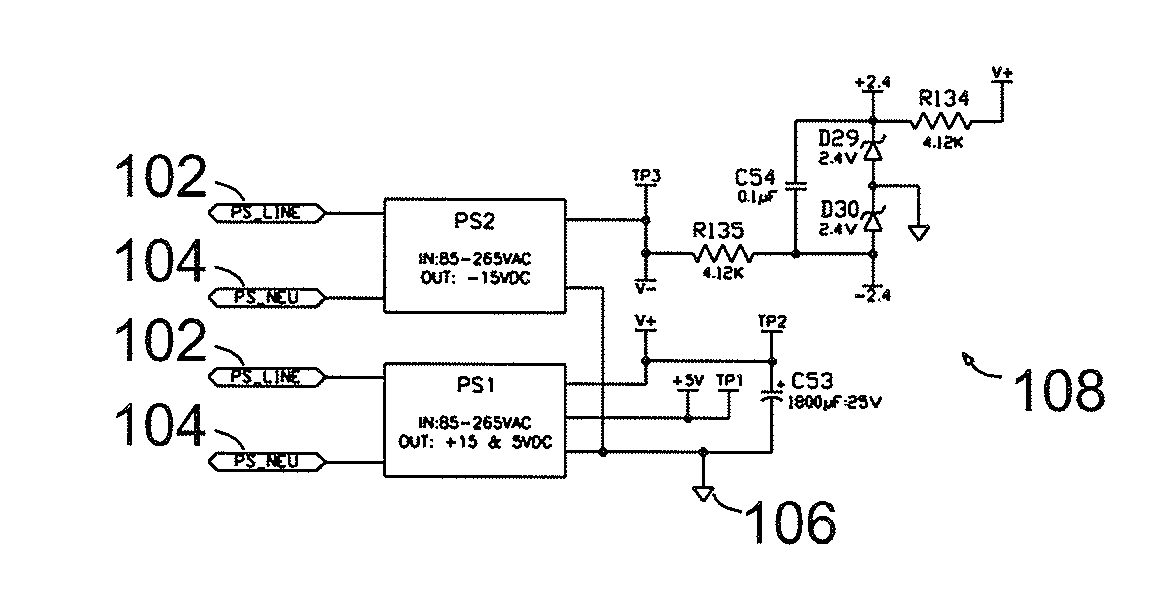

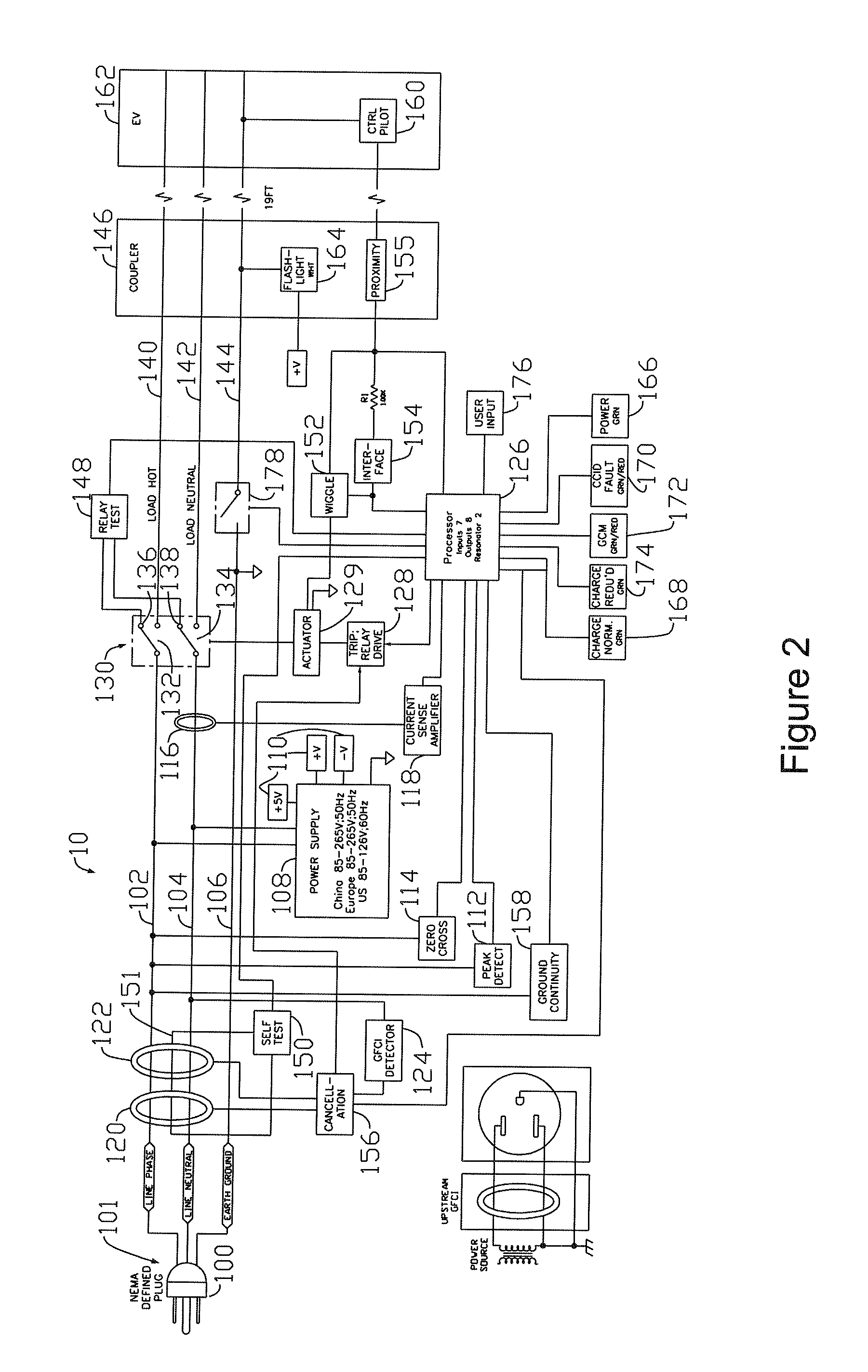

Protective device for an electrical supply facility

The present invention is directed to a protective device configured to be coupled between an AC power source and an electrical load. A ground continuity monitor is coupled to the ground conductor, the ground continuity monitor being configured to detect a ground discontinuity condition in the ground conductor. A circuit interrupter mechanism is configured to interrupt electrical continuity in a tripped state and establish electrical continuity in a reset state. A self-test circuit is coupled to the ground continuity monitor and configured to perform a simulated ground continuity test that simulates the ground discontinuity condition. The self-test circuit provides a test failure signal when the ground continuity monitor fails to provide an output signal in response to the simulated ground continuity test. The test failure signal is configured to trip the circuit interrupter mechanism.

Owner:PASS SEYMOUR

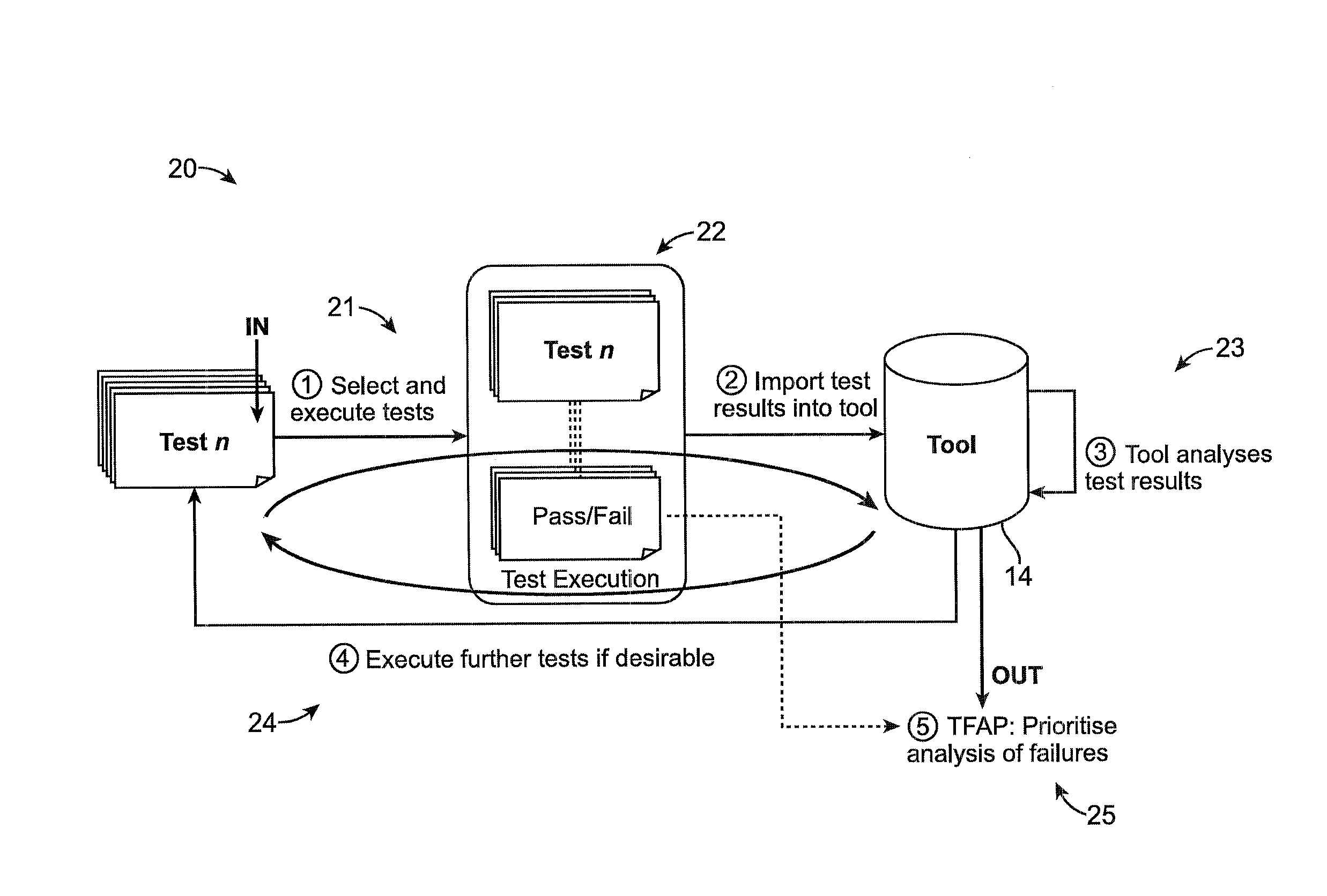

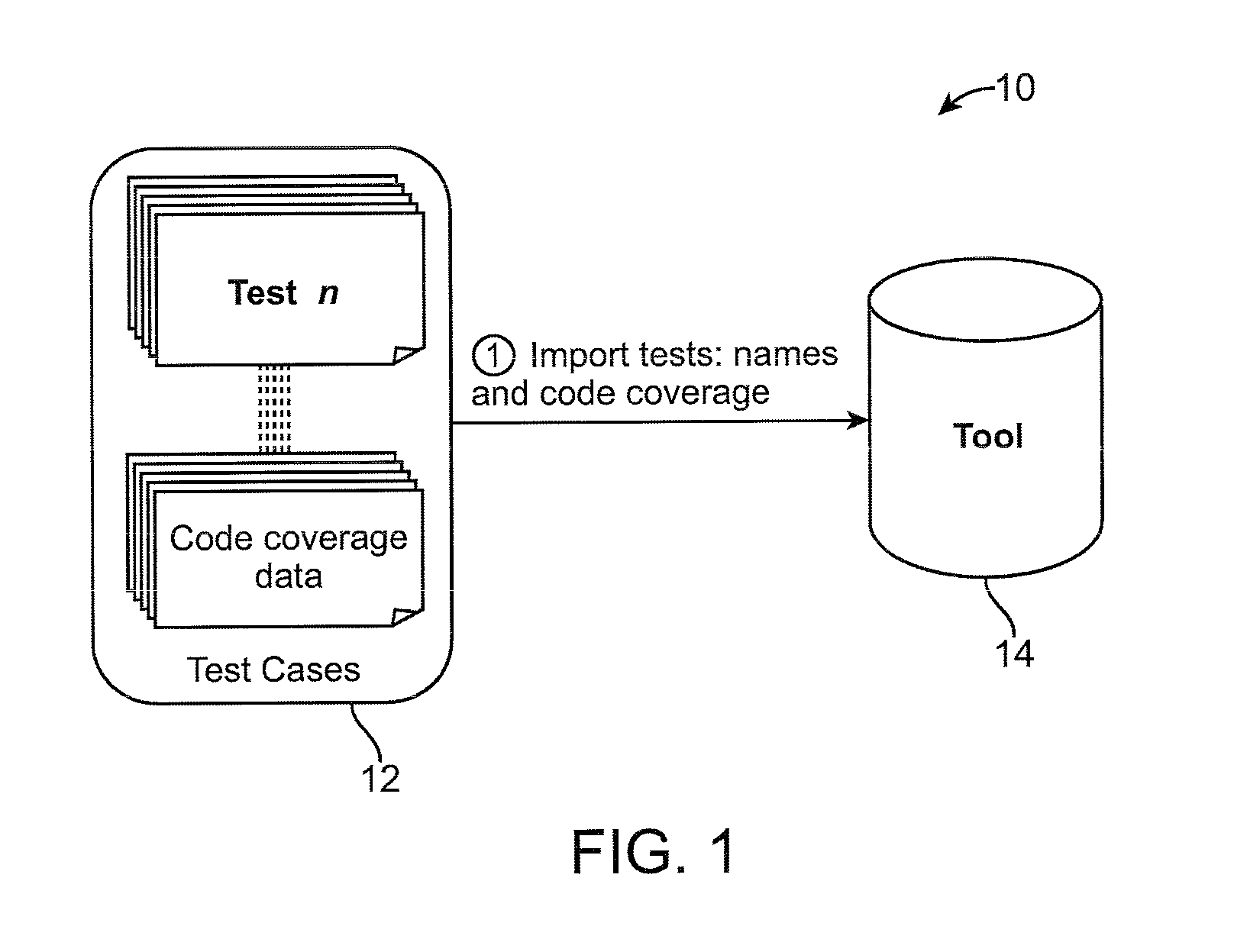

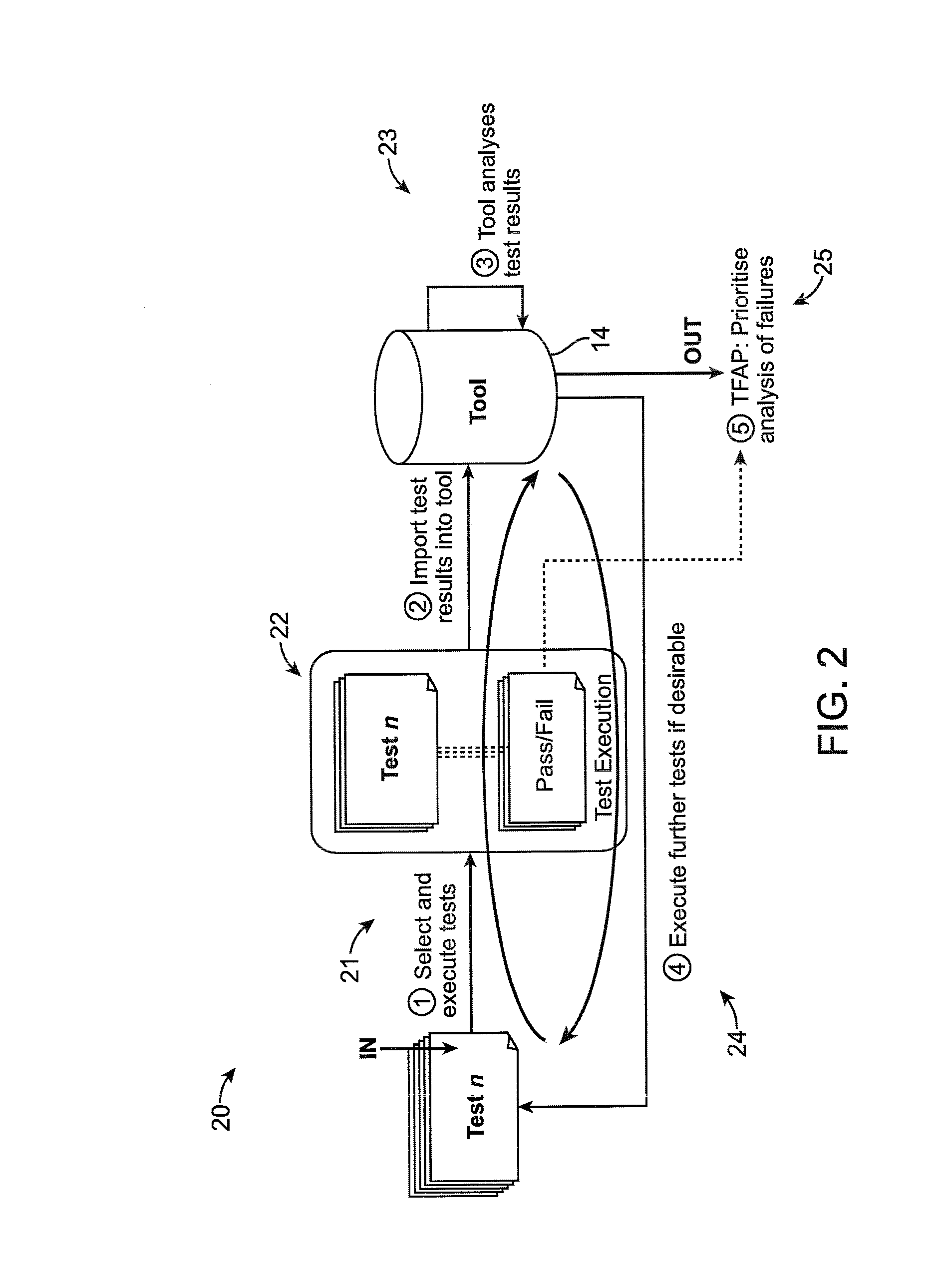

Method and system for test failure analysis prioritization for software code testing in automated test execution

InactiveUS20090265694A1Error detection/correctionSpecific program execution arrangementsQuality assuranceCode coverage

A method and system for software code testing for an automated test execution environment is provided. Testing involves importing test case information into a tooling environment based on code coverage and targeted testing, the test information including test name and code coverage data including classes and methods exercised by the code; generating a test hierarchy by analyzing the individual test case information; selecting tests including one or more of: all tests for a full regression run, a subset of tests for basic quality assurance or testing a particular area of functionality, and tests that exercise a recently changed class; executing selected tests to generate a pass / fail result for each test and correlating the test results; performing test failure analysis prioritization to prioritize any failures.

Owner:IBM CORP

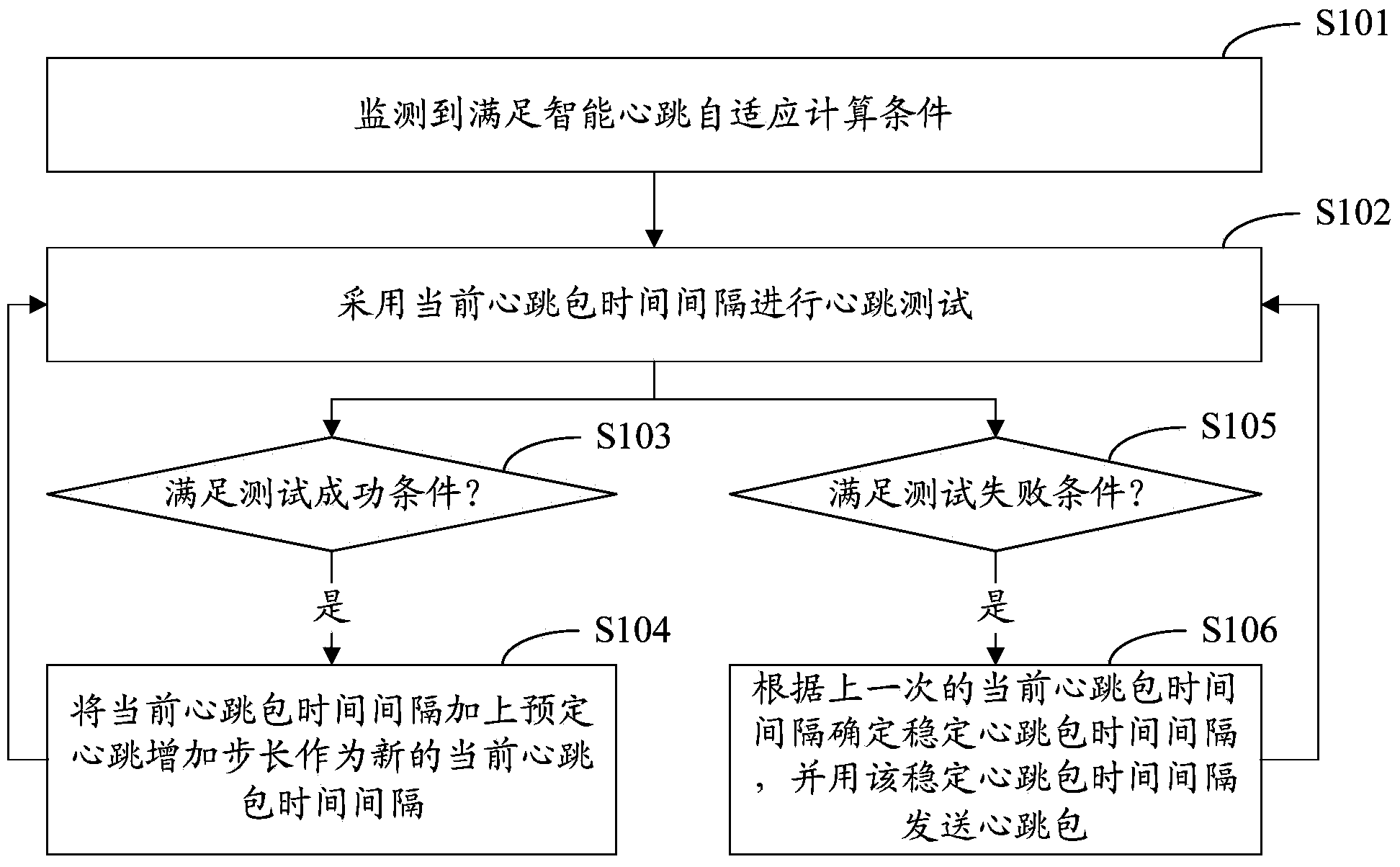

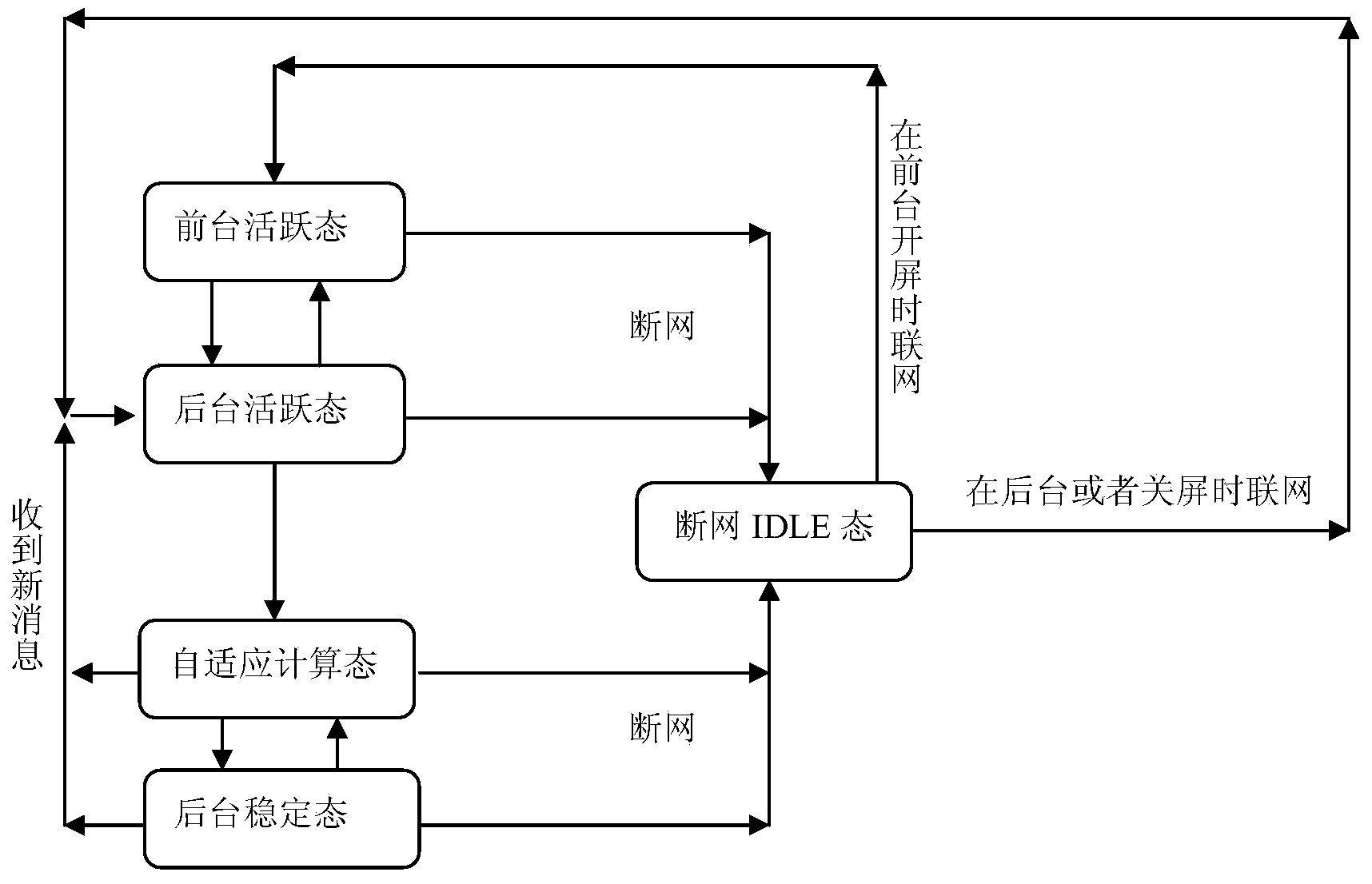

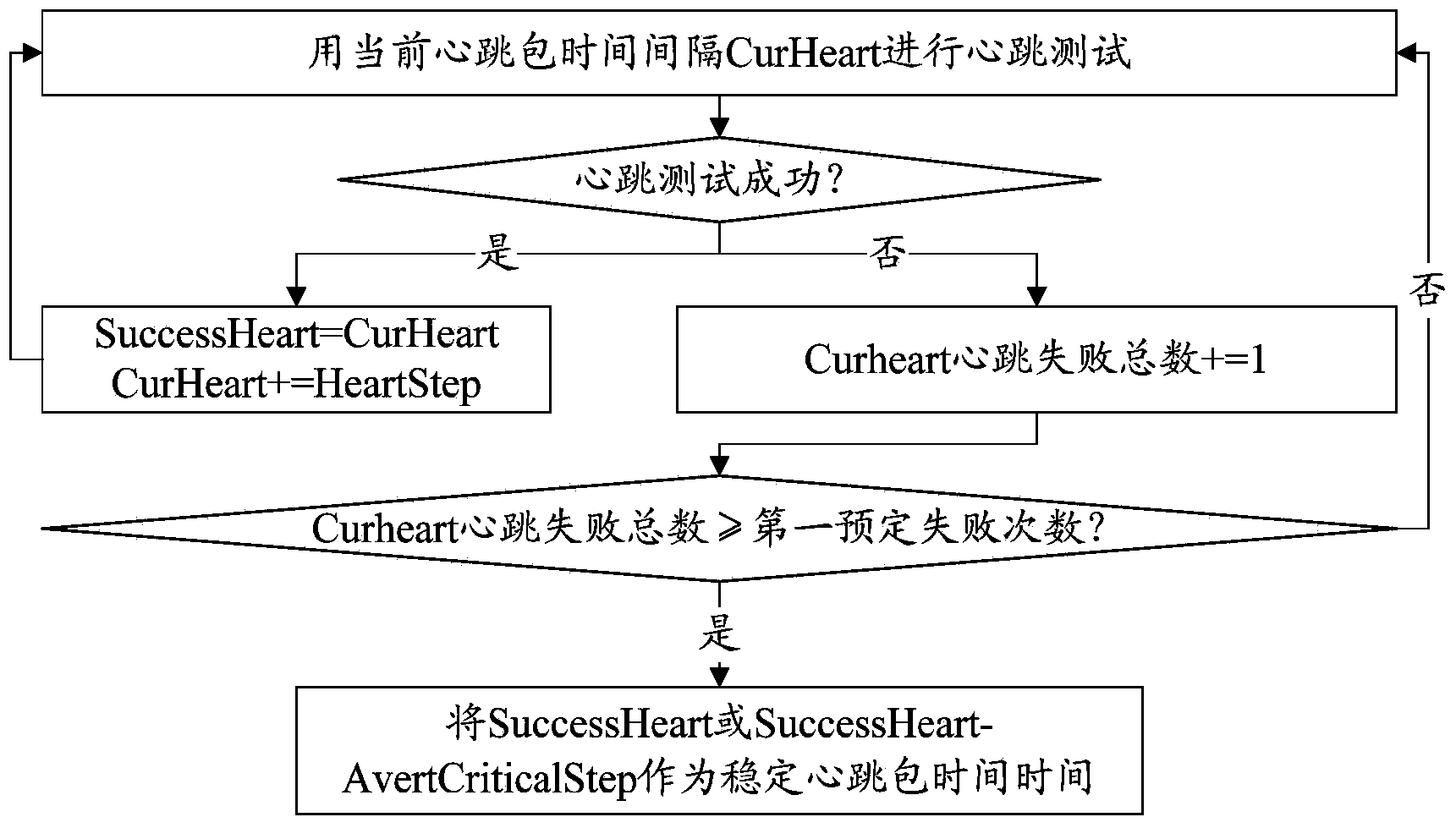

Intelligent heartbeat keeping method and system

ActiveCN104144159AHeartbeat packet time interval is largeSave powerConnection managementTransmissionNetwork connectionTest failure

The invention provides an intelligent heartbeat keeping method and system. The method comprises the steps that a heartbeat test is conducted according to a current heartbeat packet time interval when it is monitored that intelligent heartbeat self-adaptive computing conditions are met; when test success conditions are met, a predetermined heartbeat increased step length is added to the current heartbeat packet time interval to serve as a new current heartbeat packet time interval, and the step that the current heartbeat packet time interval is adopted to conduct the heartbeat test is executed again; when test failure conditions are met, a stable heartbeat packet time interval is determined according to the current heartbeat packet time interval. According to the scheme, a heartbeat packet time interval which adapts to a current network environment, can maintain network connection and is as large as possible can be obtained; due to the fact that the heartbeat packet time interval is as large as possible, the electric quantity, flow and network resources can also be saved to some extent.

Owner:TENCENT TECH (SHENZHEN) CO LTD +1

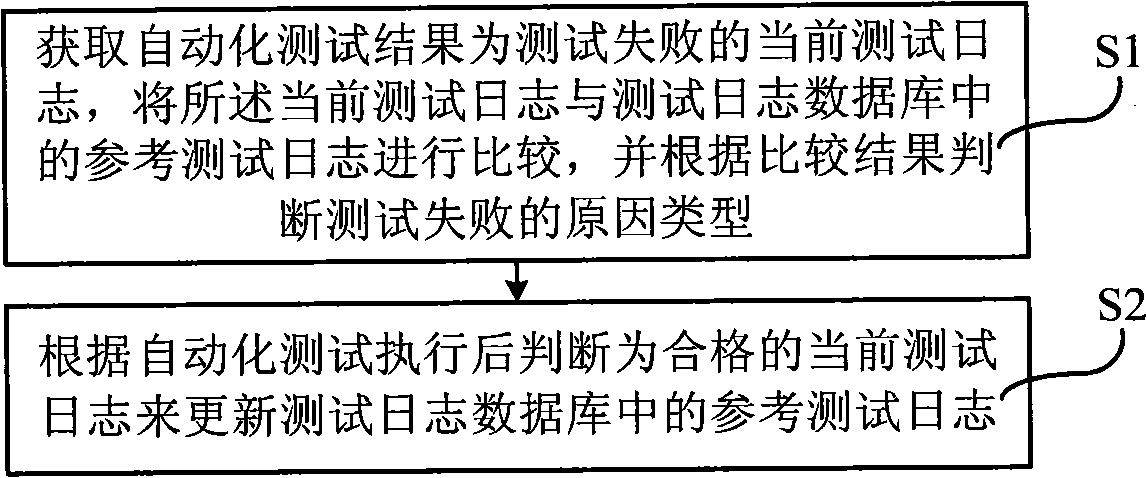

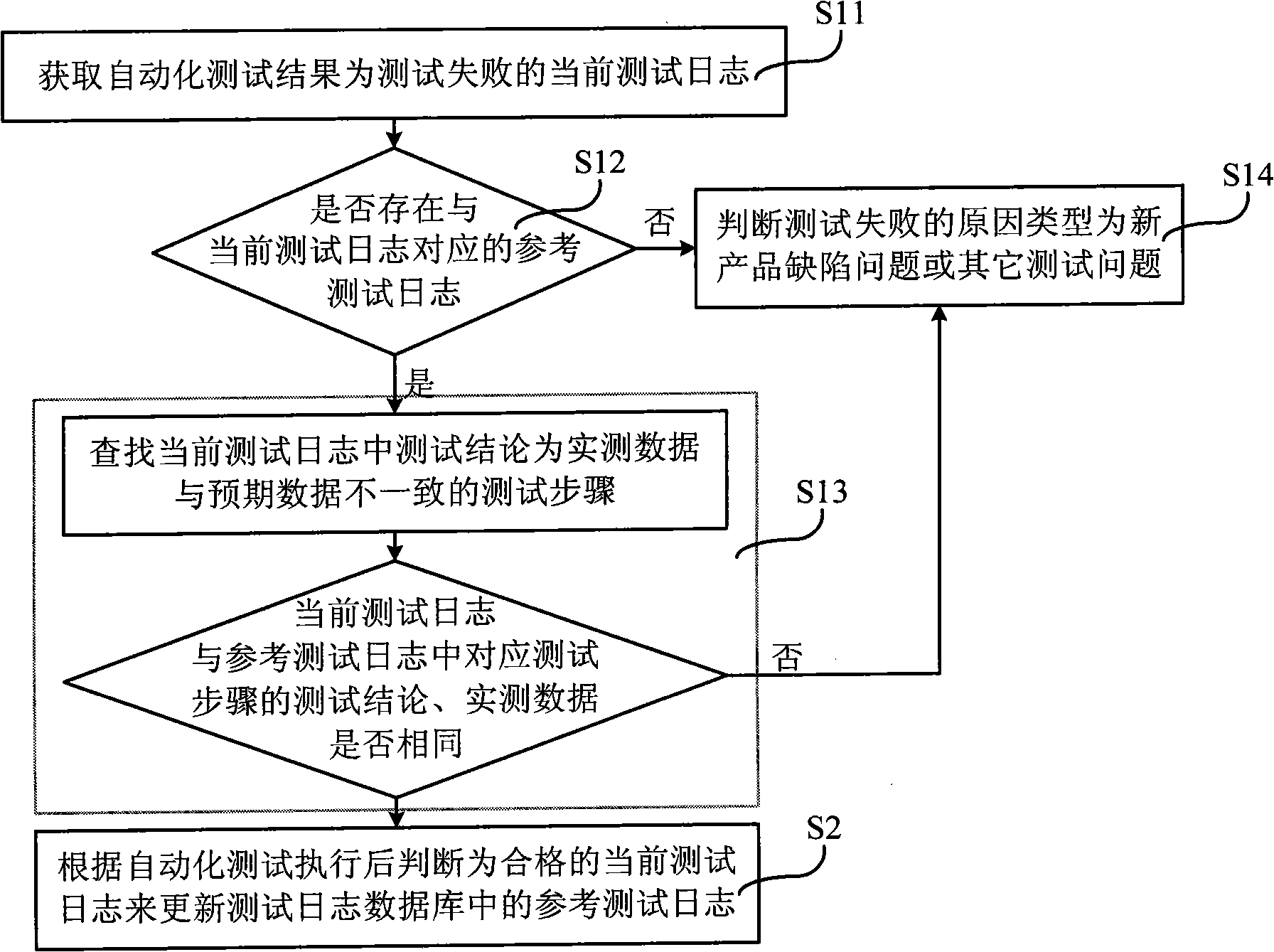

Analysis method for automatic test log and device

InactiveCN101556550ASolve the problem of inaccurate judgment of the type of test failure reasonSolve the problem of inaccurate judgmentHardware monitoringSoftware testing/debuggingReference testAnalysis method

The invention provides an analysis method for automatic test log and a device. The method comprises the following steps of: step S1, acquiring automatic test result as the current test log with test failure, comparing the current test log with a reference test log in a test log database and judging the reason types of test failure according to compared results; and step S2, updating the reference test log in the test log database according to the current test log which is judged to be qualified after the automatic test is executed. The method and the device can automatically recognize the test log with various reason types of test failures, solve the problem that the manual analysis for test log has inaccuracy judgment for the reason types of test failure, and lead the tester to be capable of analyzing test log pointedly.

Owner:BEIJING XINWANG RUIJIE NETWORK TECH CO LTD

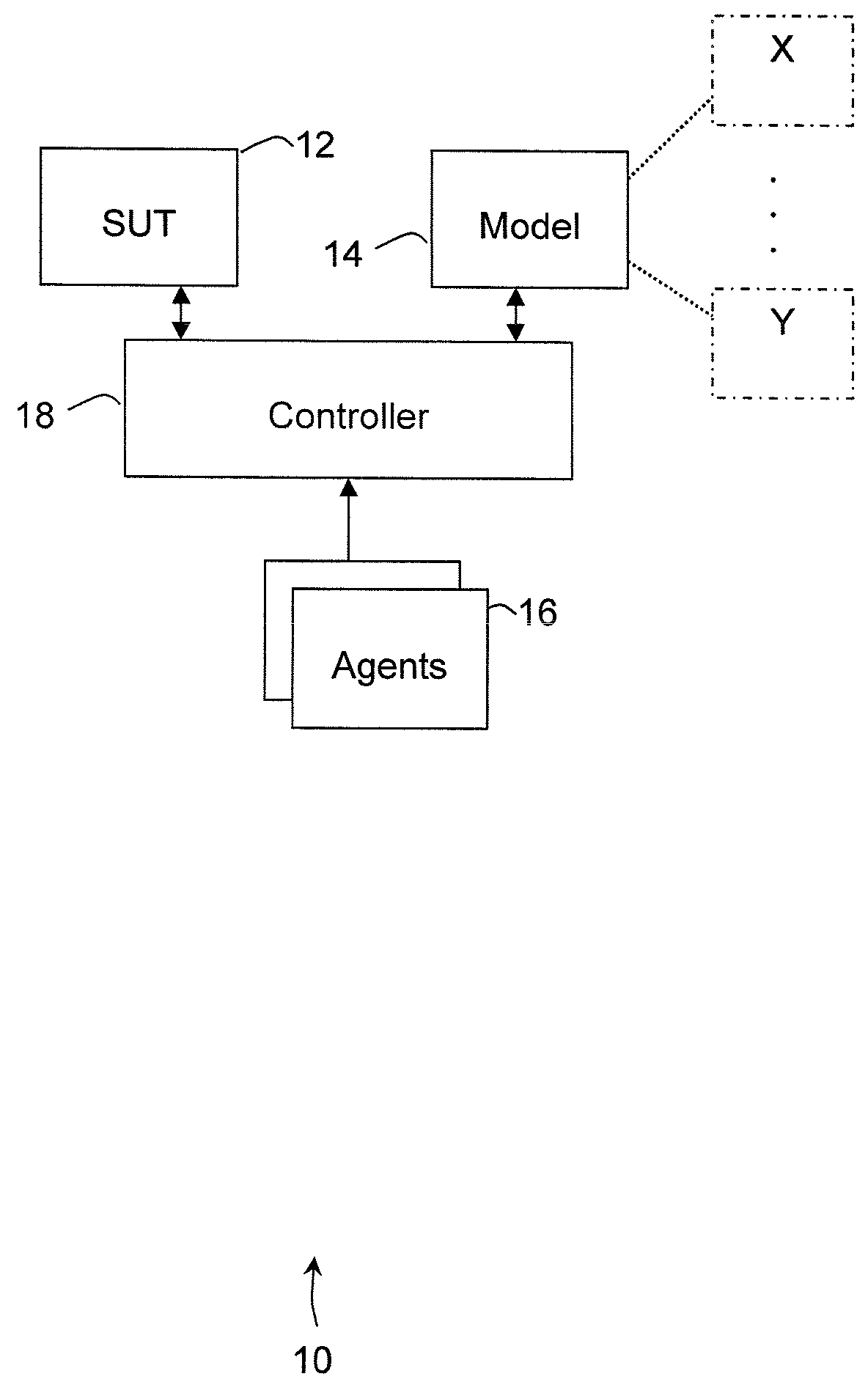

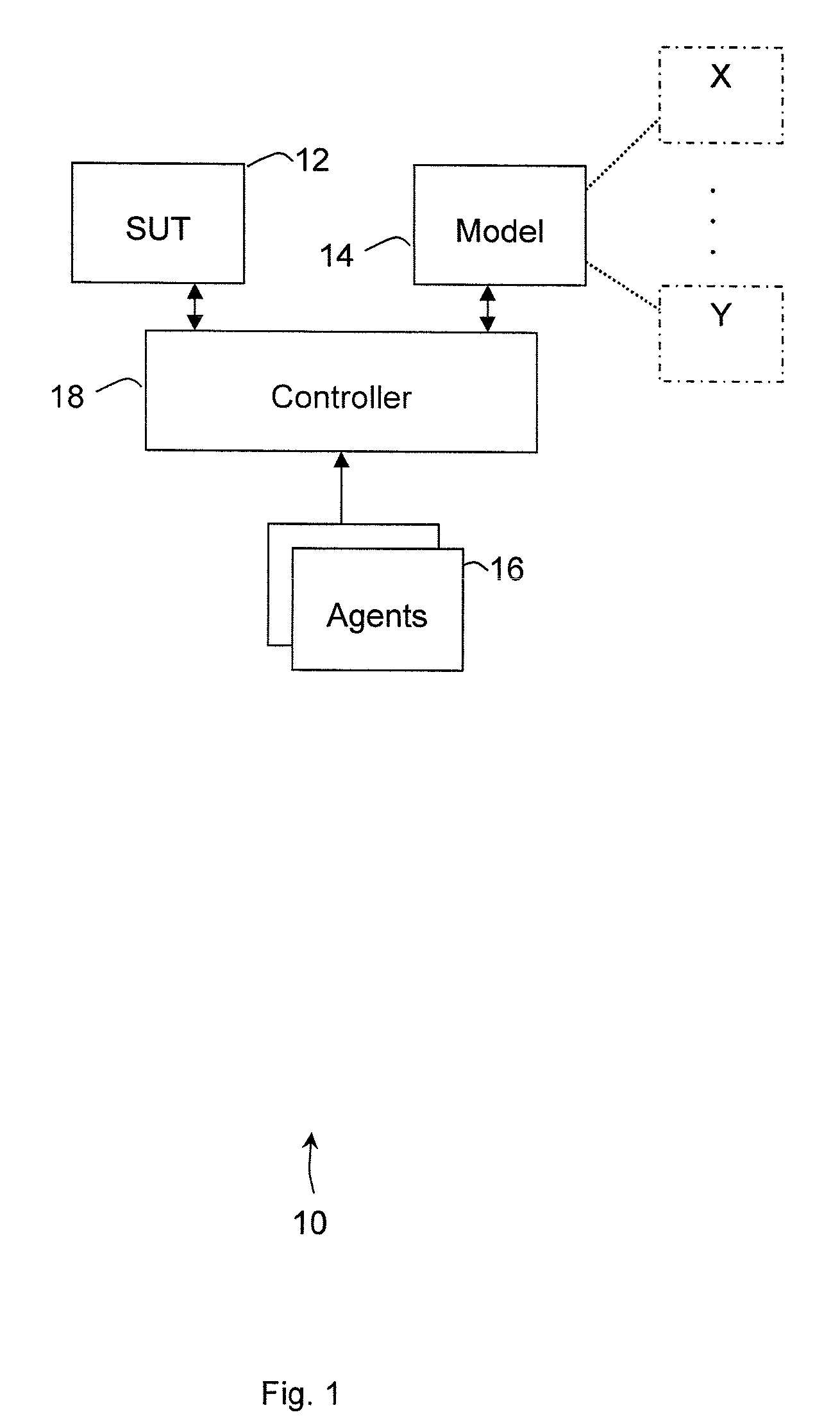

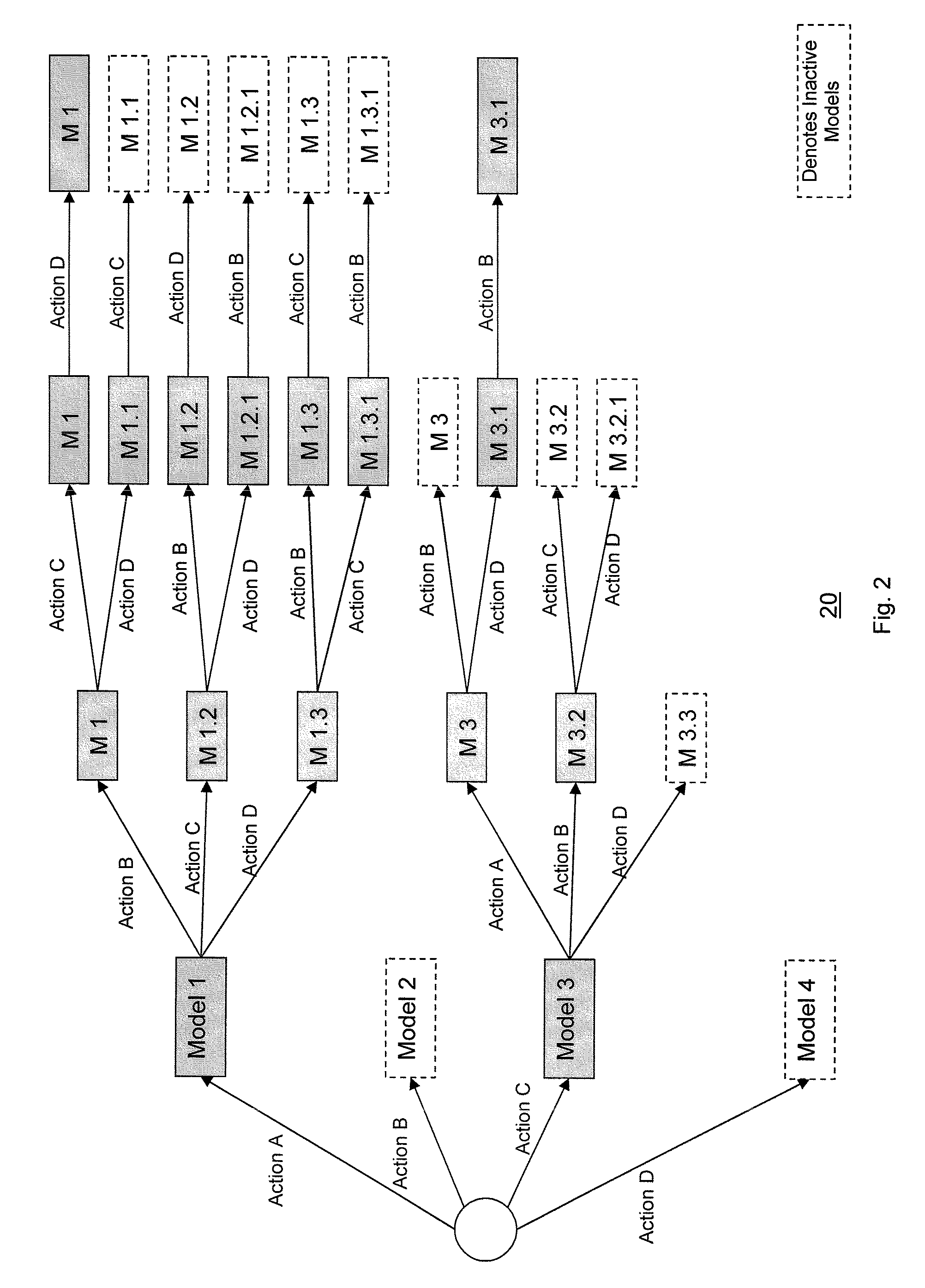

Method and apparatus for concurrency testing within a model-based testing environment

InactiveUS7539980B1Error detection/correctionSpecific program execution arrangementsSoftware systemTest failure

A method and apparatus for concurrency testing within a model-based testing environment is provided. One implementation involves concurrency testing within a model-based software system testing environment, by receiving concurrent test service requests; duplicating a model representing software under test, based on the number of requests; sending the concurrent requests to each of the duplicated models sequentially but in different orders; storing the outcomes of each of the models; comparing the outcomes from the models to the outcome from the software system under test; and if all comparisons fail, then indicating test failure.

Owner:IBM CORP

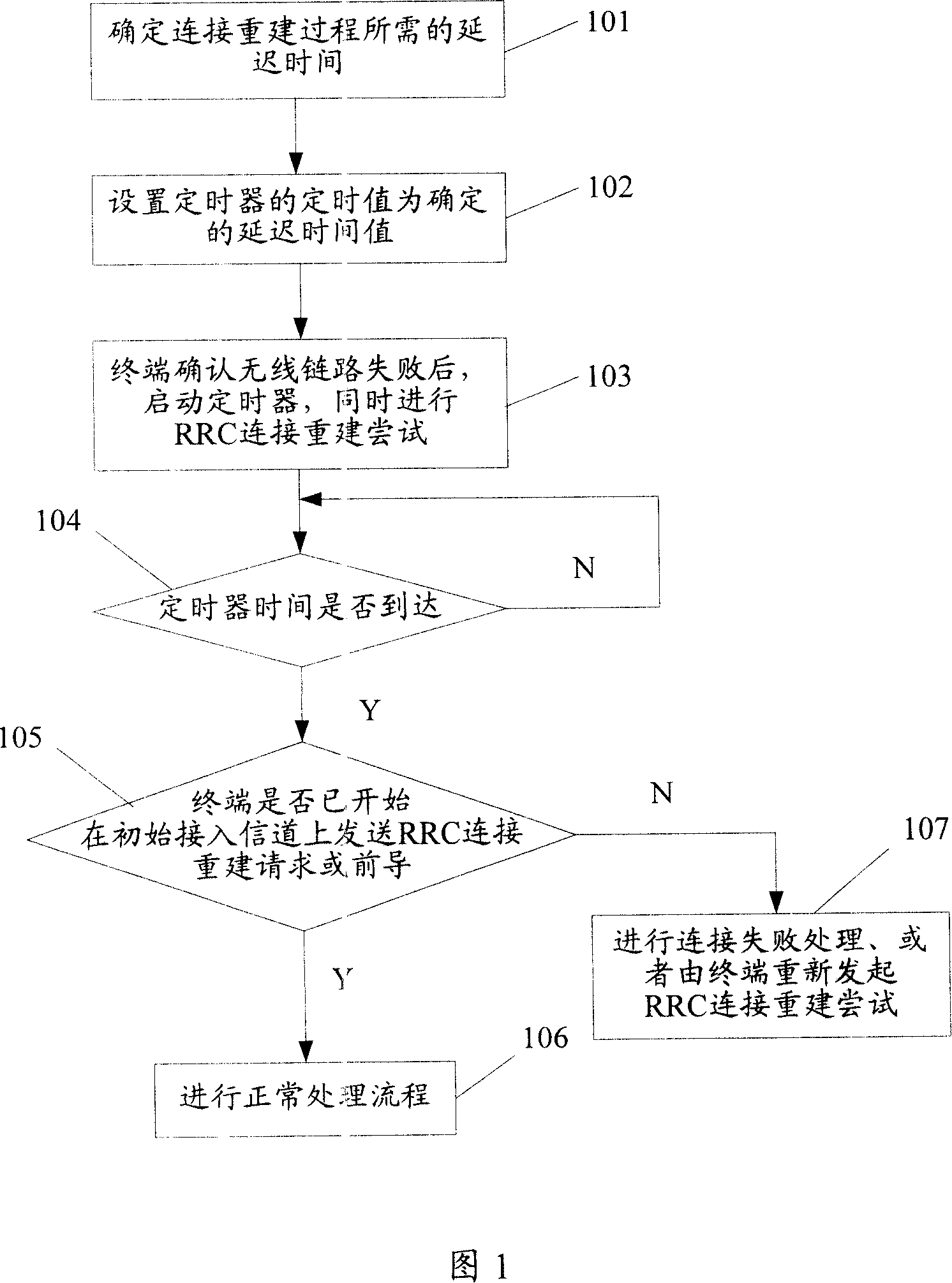

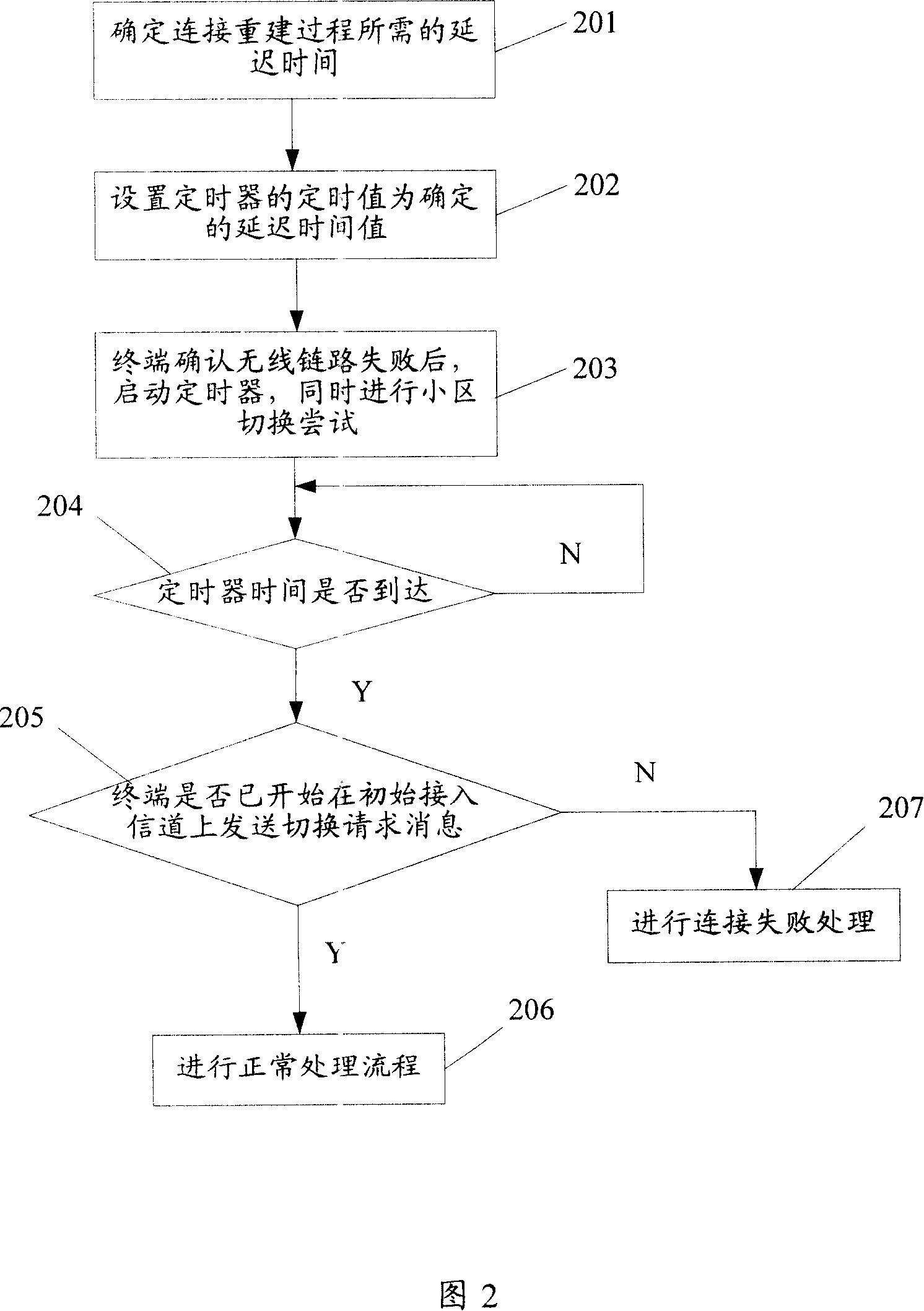

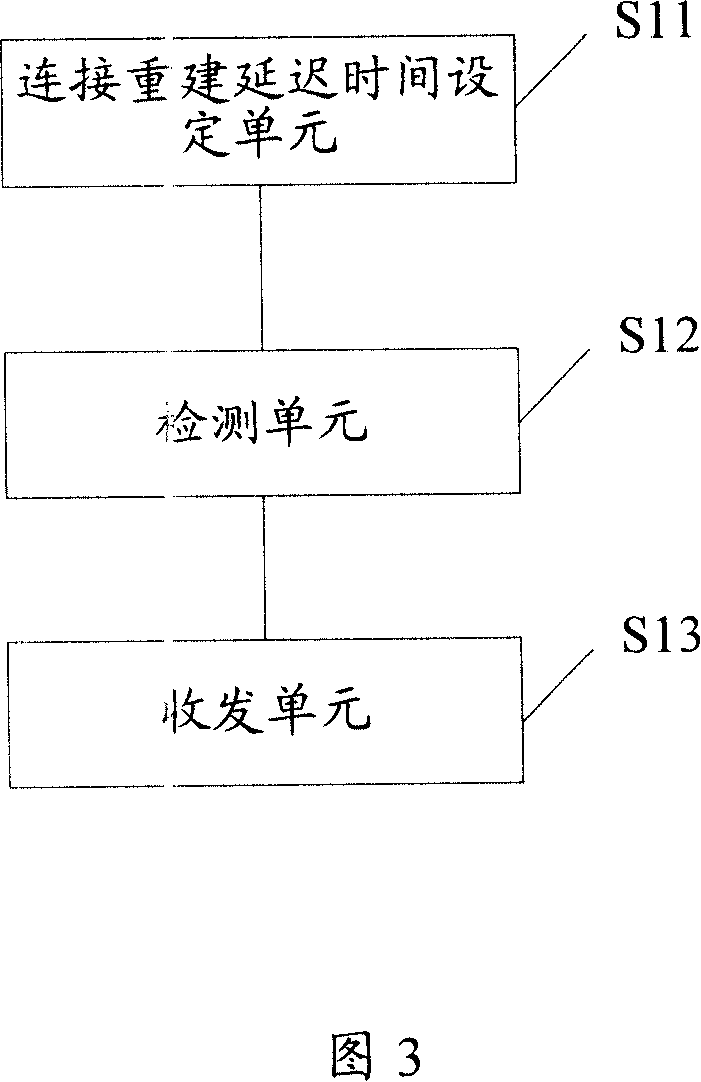

Method and terminal for controlling connection reconstruction in long-term evolution system

ActiveCN101132611AGuaranteed throughputReduce wasteConnection managementRadio/inductive link selection arrangementsDelayed timeTest failure

This invention discloses a method for controlling re-setting up connections in a long-term evolution system including: a terminal tests failure of a radio link and begins initial access operation on an initial access channel in the delay time of re-set up. This invention also discloses a terminal including a unit for setting delay time of re-setting up connection used in determining delay time according to the kind of target local area searched, a test unit connected with the set unit and used in testing if the executing time of the re-set up of the terminal exceeds the confirmed time.

Owner:HUAWEI TECH CO LTD

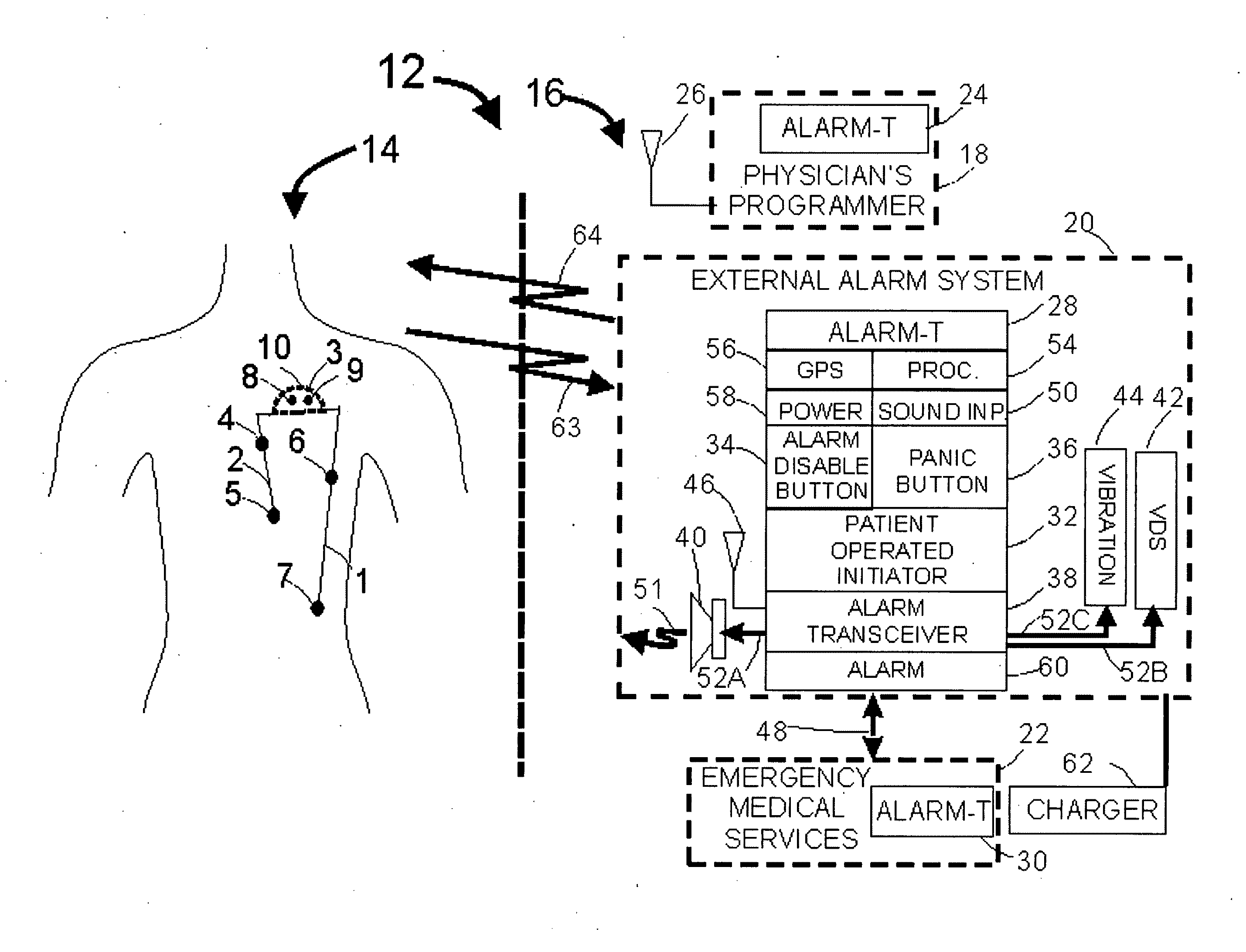

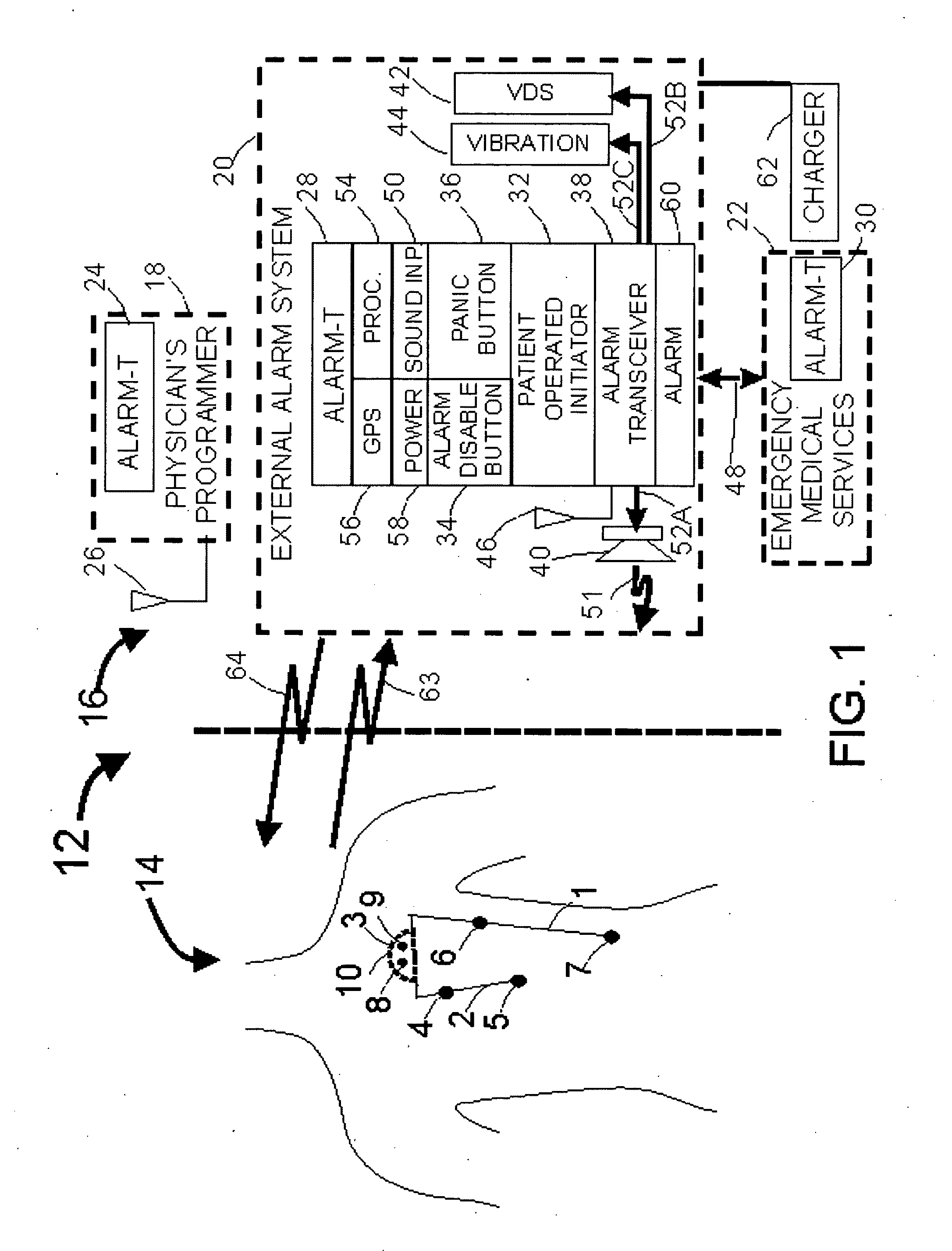

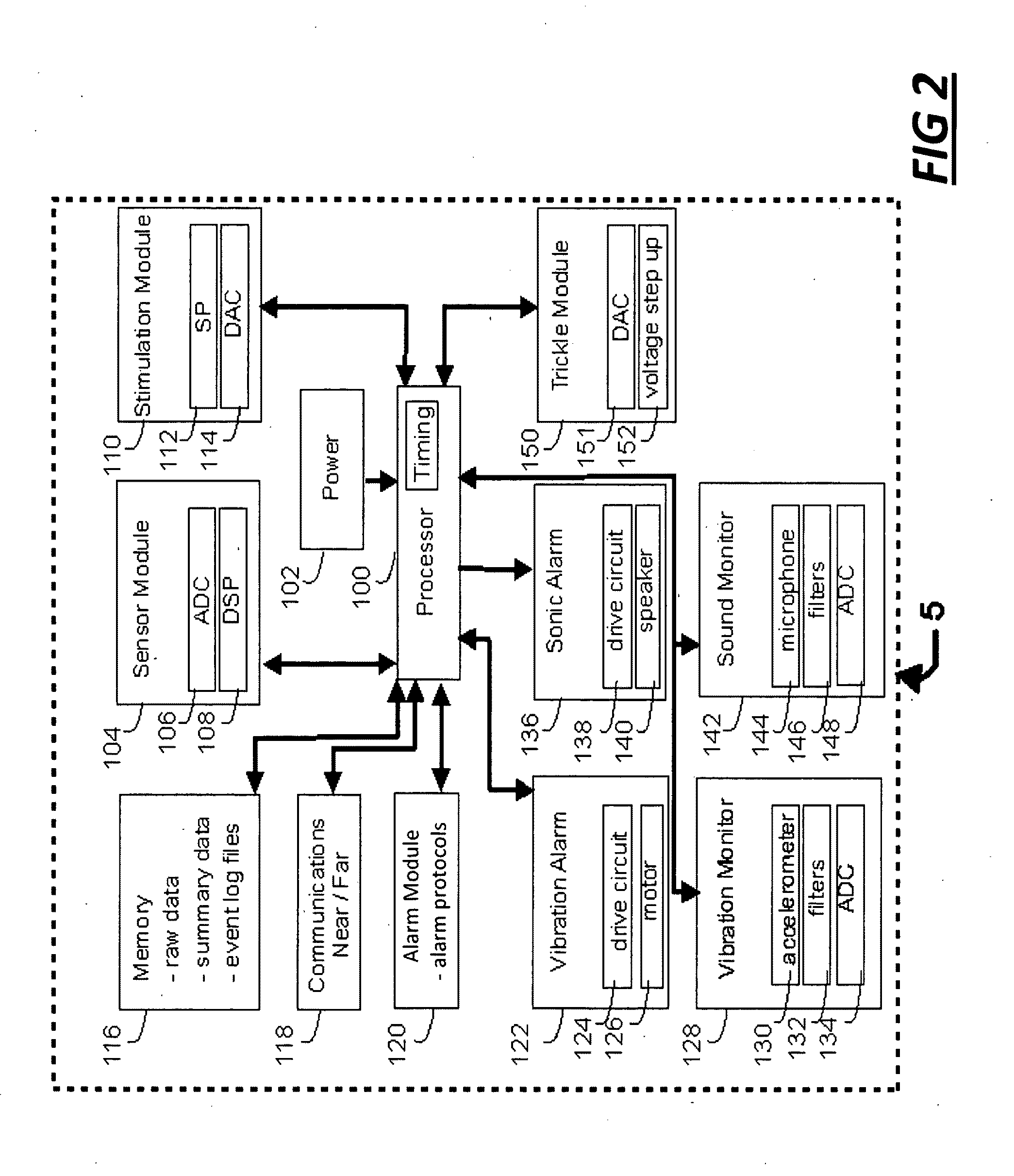

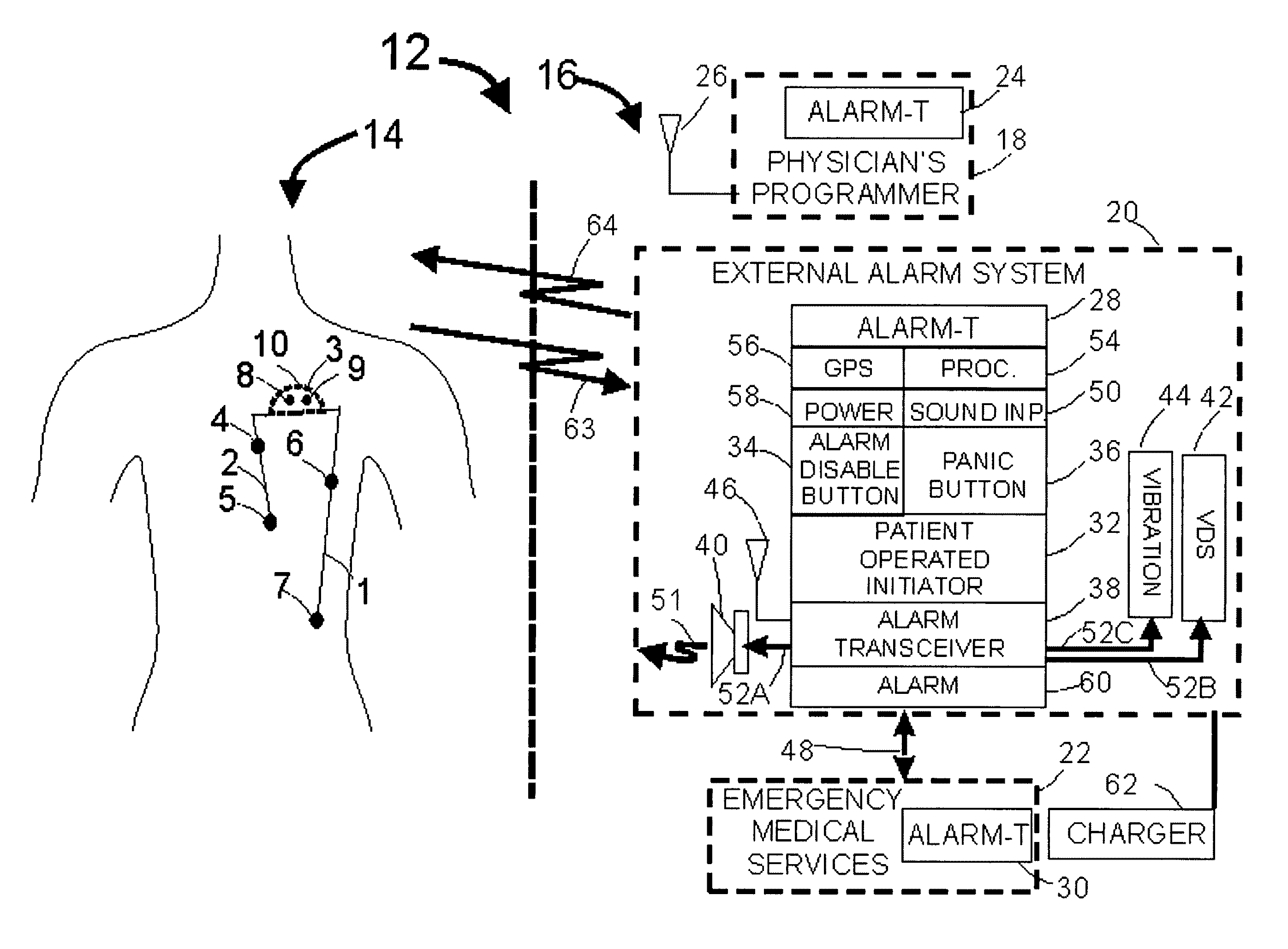

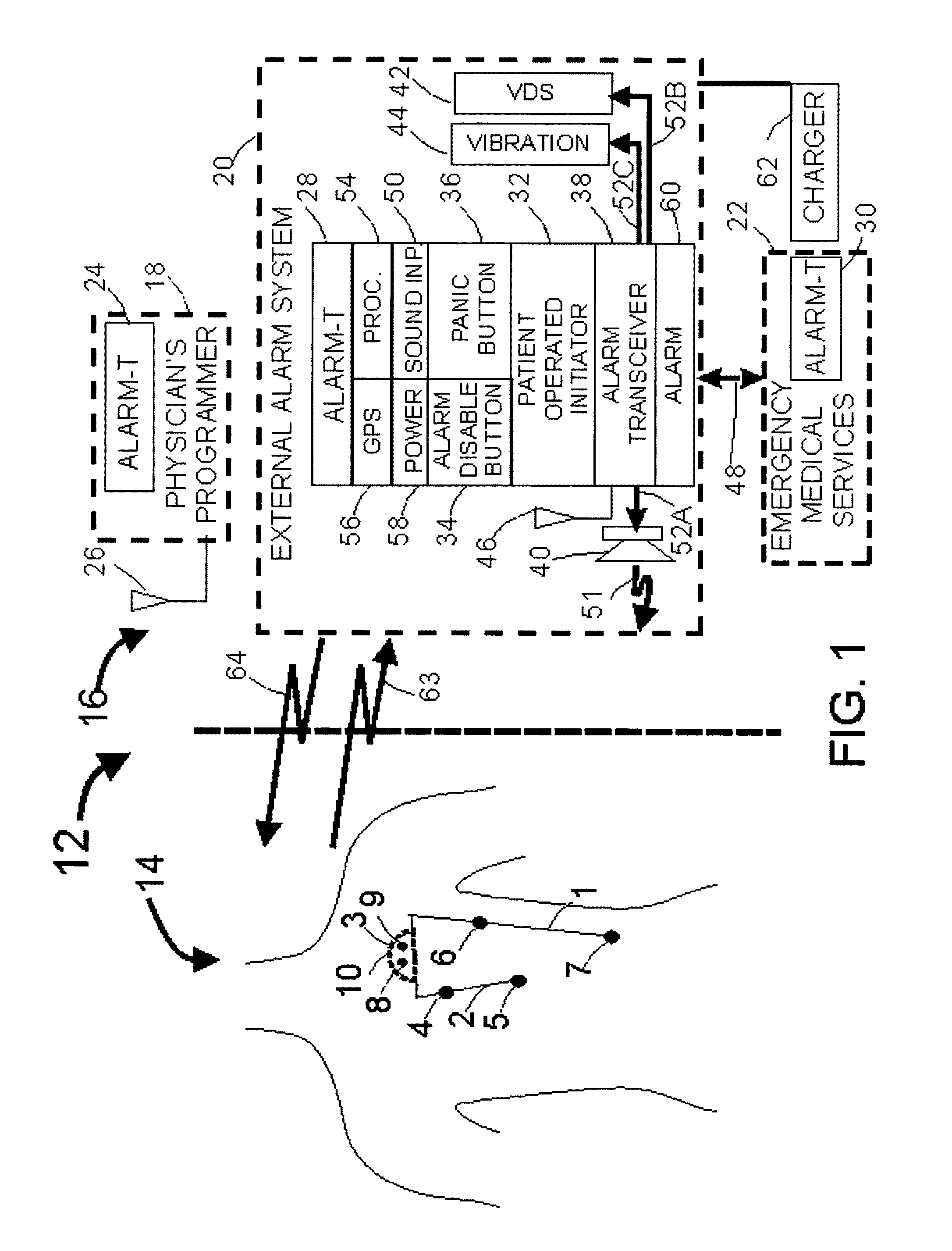

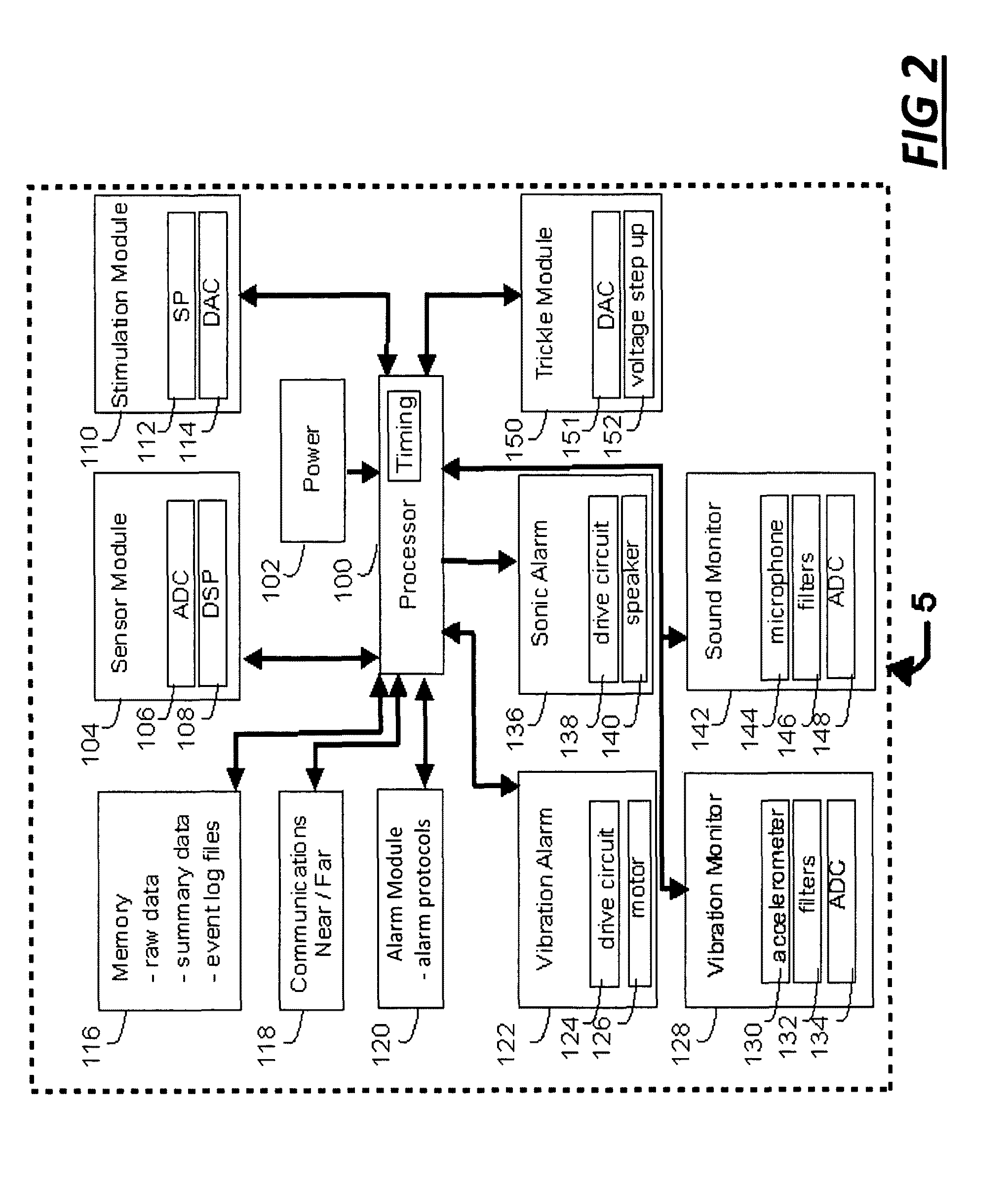

Systems and methods of alarm validation and backup in implanted medical devices

ActiveUS20110054264A1Reduce riskElectrotherapyDiagnostic recording/measuringDiagnostic Radiology ModalityTouch Perception

Alarm tests are disclosed which use alarm test signals to assess alarms provided by medical devices. Especially relevant are implanted devices that monitor cardiac activity and provide notification in response to medically relevant events. Alarm tests can occur periodically, or in response to a patient, doctor, or remote party initiating the alarm test. Alarm tests can also occur during the actual alarms issued to detected medical events. Alarm tests lead to pass or fail results, which in turn may cause operations to contingently occur. Alarm test failure in the auditory, visual, or tactile modality, may cause an alternatively defined alarm signal to be used as back-up. Alarm test logs can store alarm test results, including quantification of the measured alarm signal. Rapid alarm tests are described, as are various methods of accurately measuring characteristics of the test signal in ambulatory patients, which are especially relevant to a vibration alarm.

Owner:ANGEL MEDICAL SYST

Systems and methods of alarm validation and backup in implanted medical devices

ActiveUS8269634B2Reduce riskElectrotherapyDiagnostic recording/measuringDiagnostic Radiology ModalityTouch Perception

Alarm tests are disclosed which use alarm test signals to assess alarms provided by medical devices. Especially relevant are implanted devices that monitor cardiac activity and provide notification in response to medically relevant events. Alarm tests can occur periodically, or in response to a patient, doctor, or remote party initiating the alarm test. Alarm tests can also occur during the actual alarms issued to detected medical events. Alarm tests lead to pass or fail results, which in turn may cause operations to contingently occur. Alarm test failure in the auditory, visual, or tactile modality, may cause an alternatively defined alarm signal to be used as back-up. Alarm test logs can store alarm test results, including quantification of the measured alarm signal. Rapid alarm tests are described, as are various methods of accurately measuring characteristics of the test signal in ambulatory patients, which are especially relevant to a vibration alarm.

Owner:ANGEL MEDICAL SYST

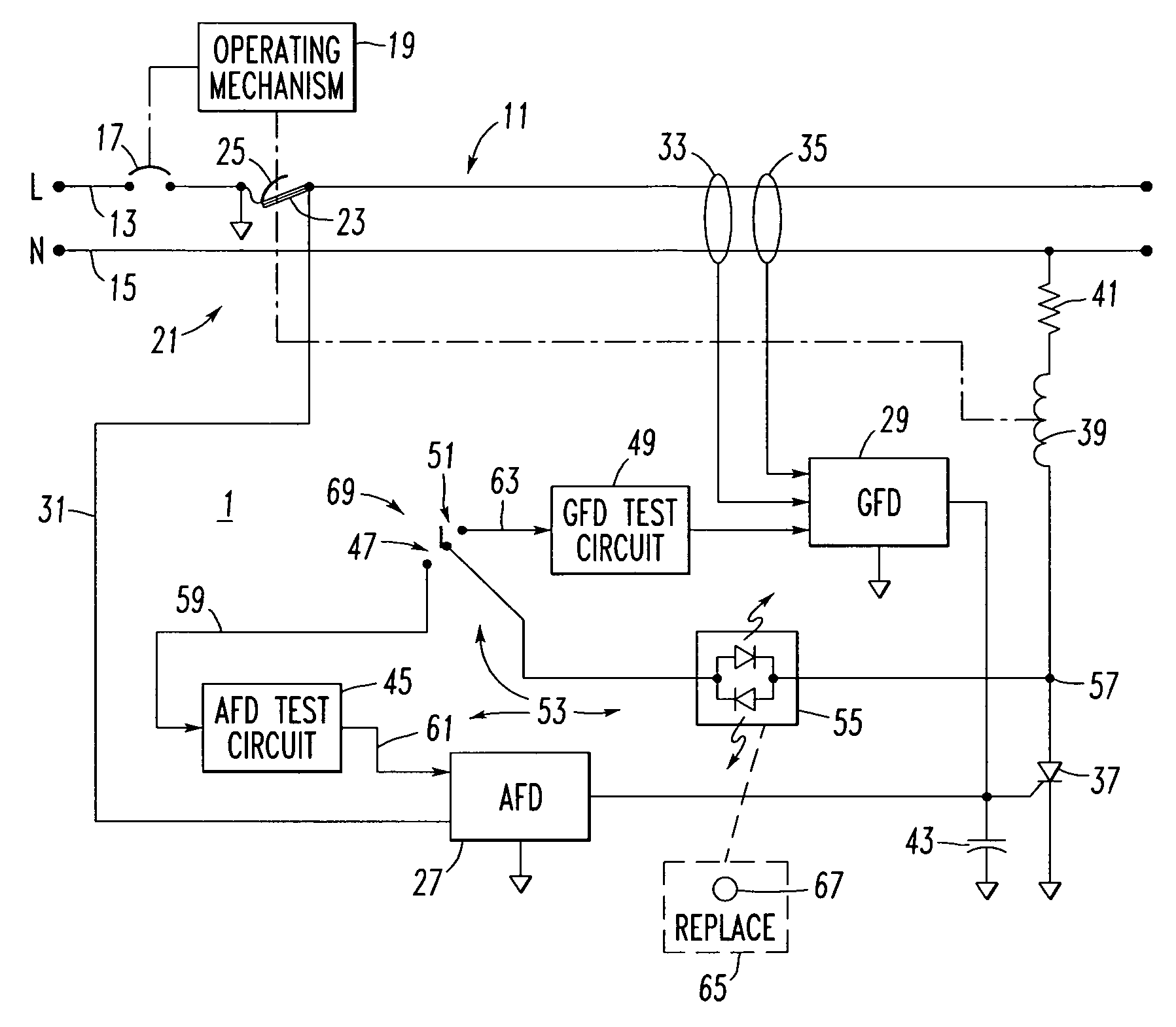

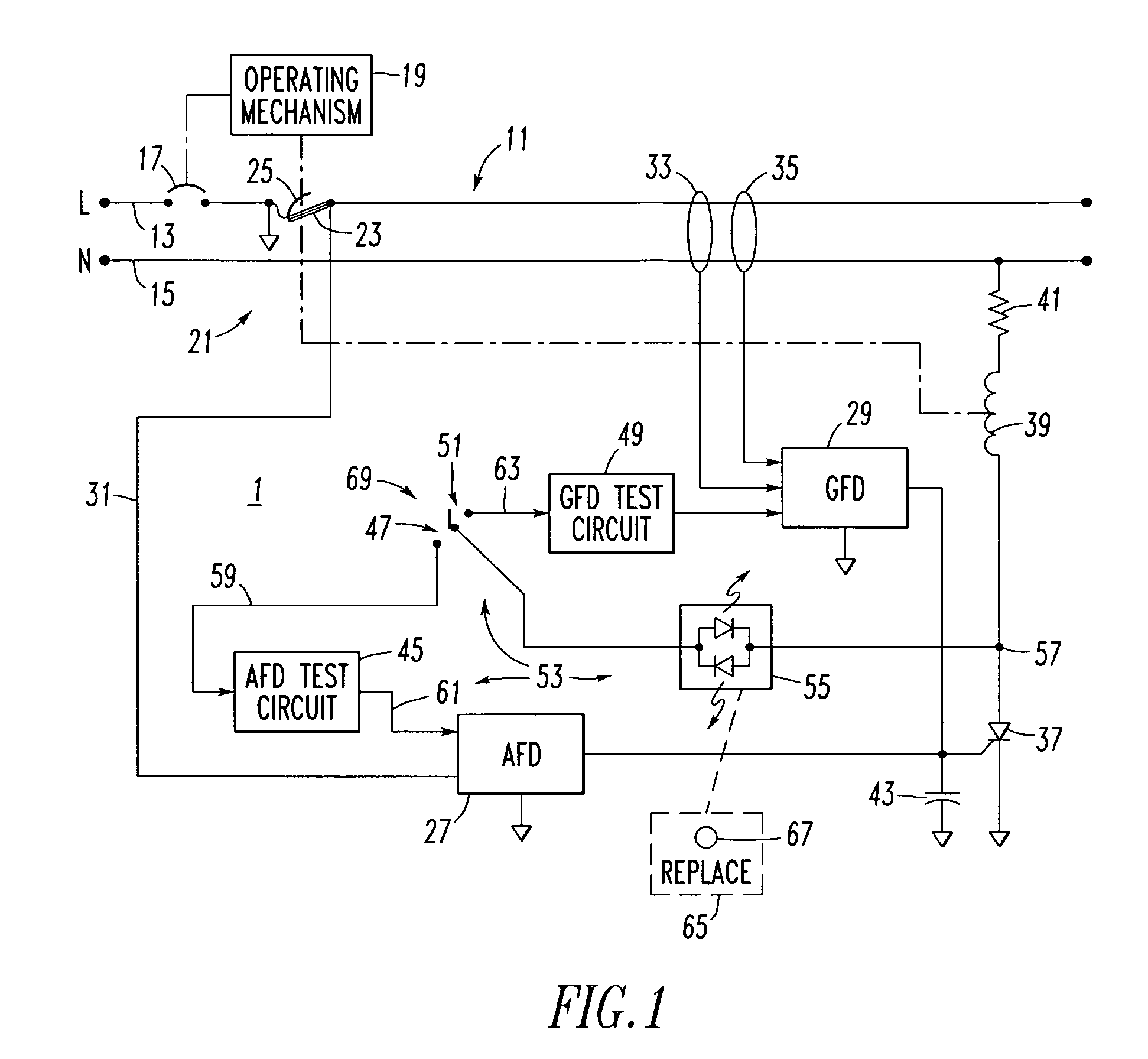

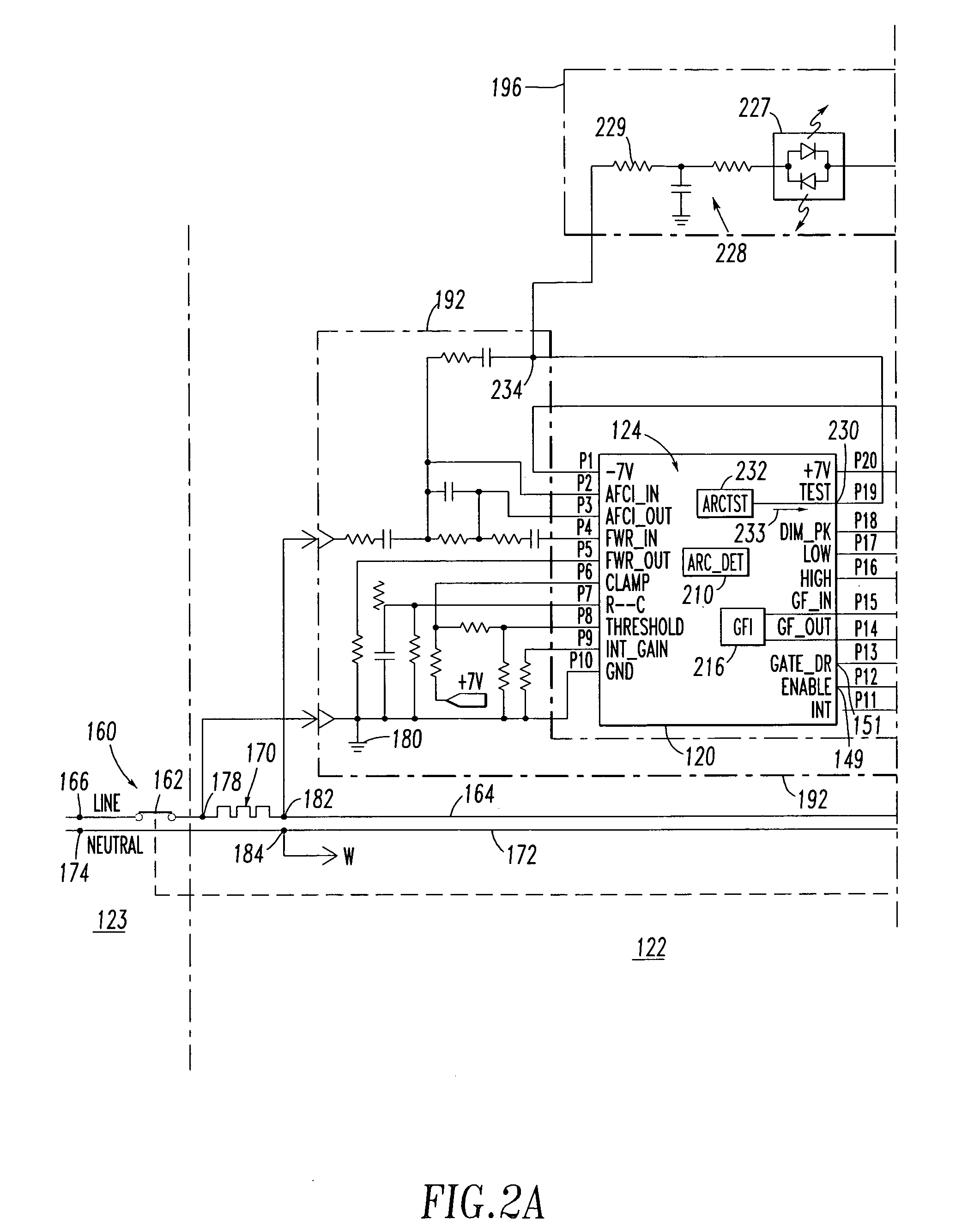

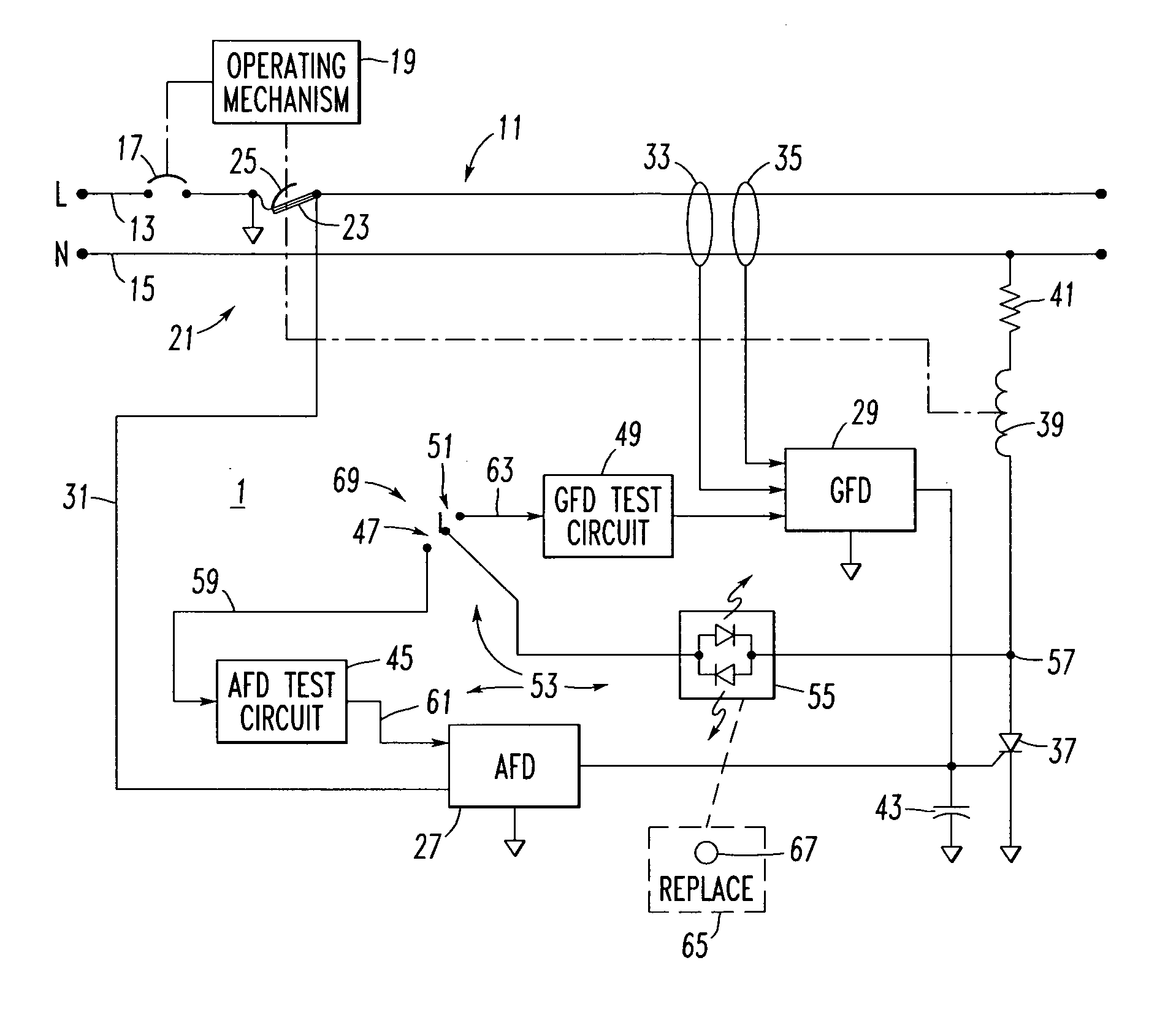

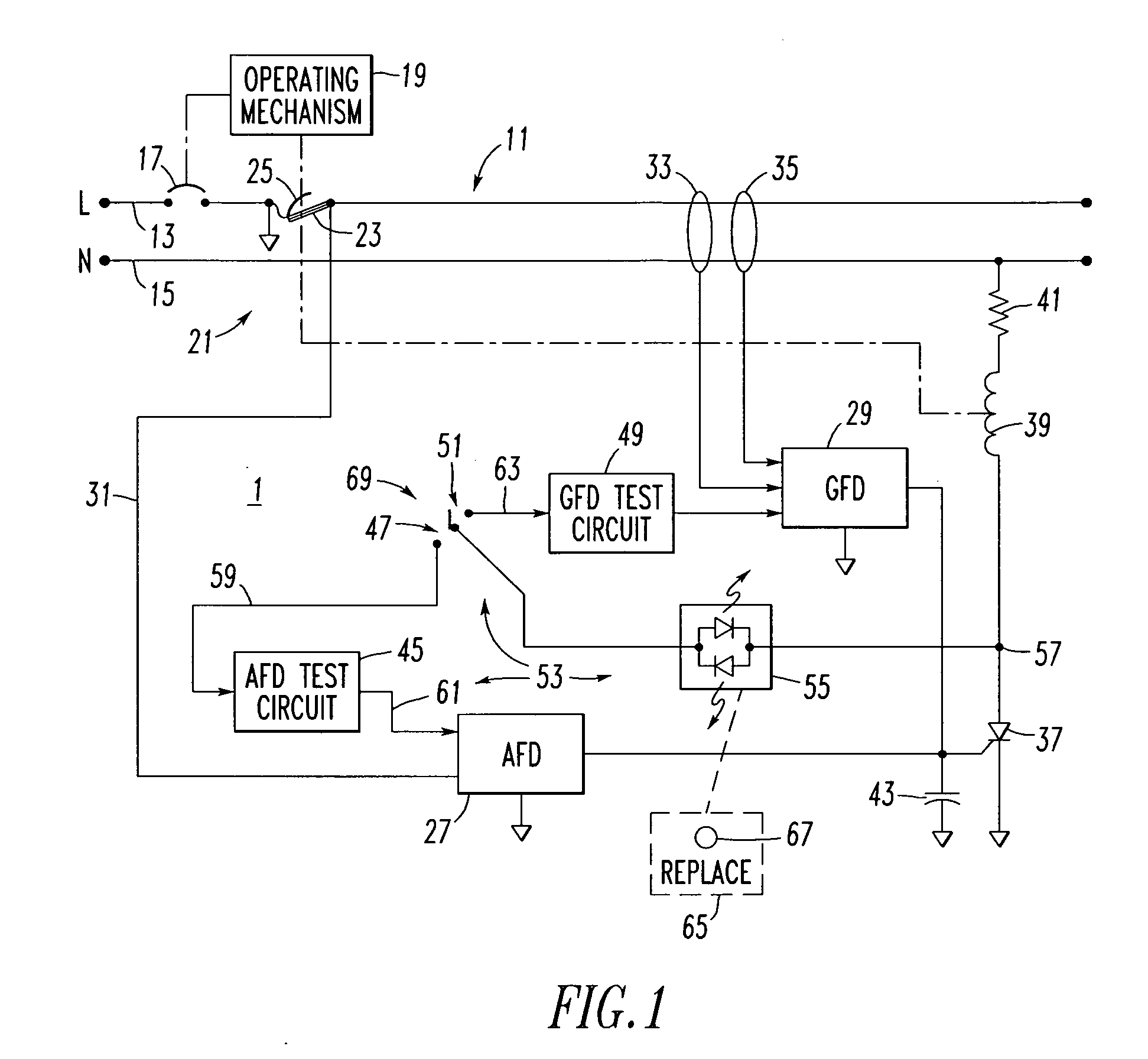

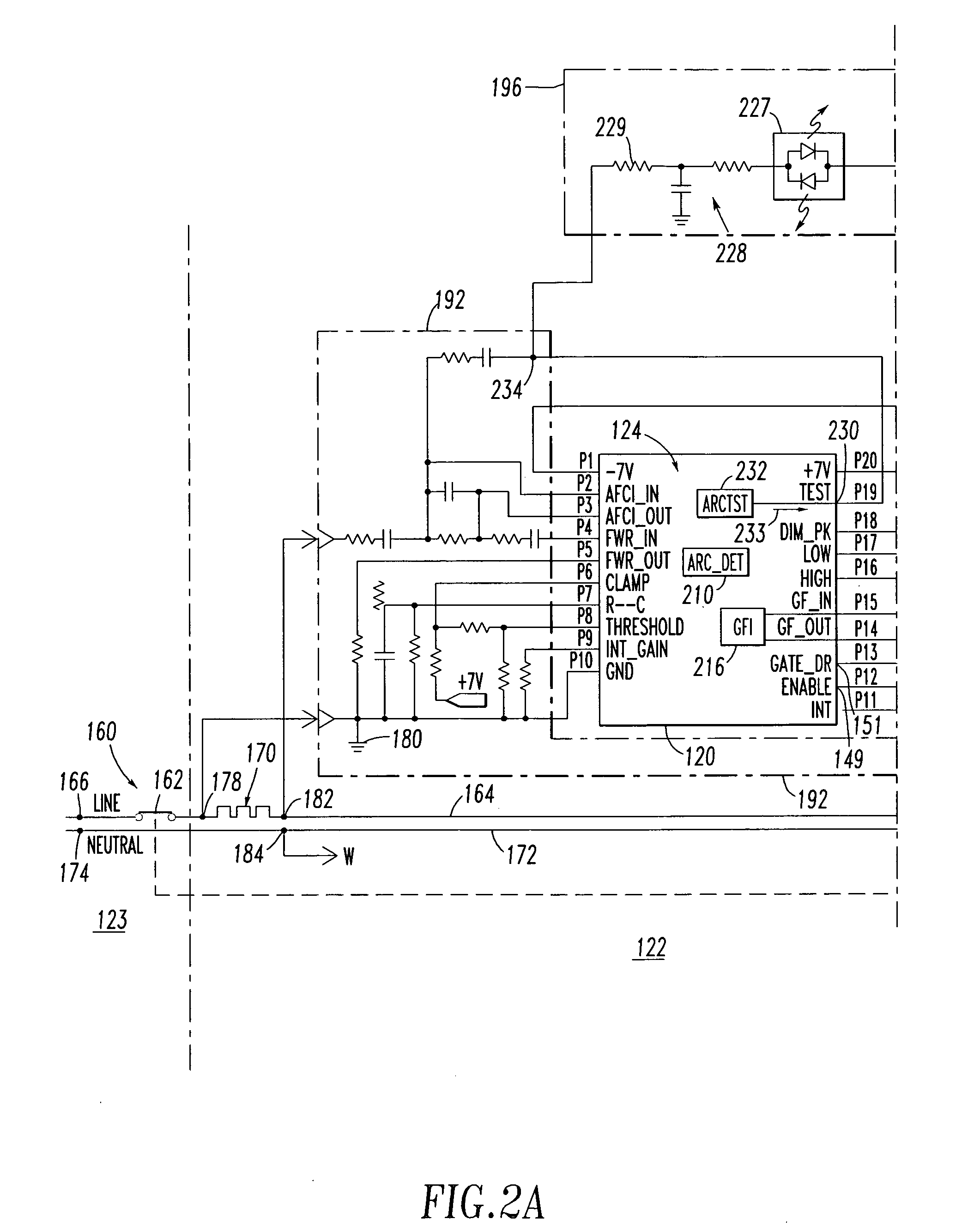

Circuit interrupter including arc fault test and/or ground fault test failure indicator

ActiveUS7215520B2Protective switch detailsEmergency protective arrangement detailsElectricityFault indicator

A circuit breaker includes a test circuit having one or two indicators, an arc fault signal generator, and first and second test switches. A first indicator is electrically connected in series with the first test switch. This series combination provides a first alternating current signal to the arc fault signal generator, which provides an arc fault signal to an arc fault trip circuit, in order to trip open separable contacts in response to closure of the first test switch. The series combination of the second test switch and the second indicator provides a second alternating current signal to a ground fault trip circuit, in order to trip in response to closure of the second test switch. The indicators provide a visual indication of failure of the arc fault or ground fault trip circuits to trip in response to closure of the first or second test switches, respectively.

Owner:EATON INTELLIGENT POWER LTD

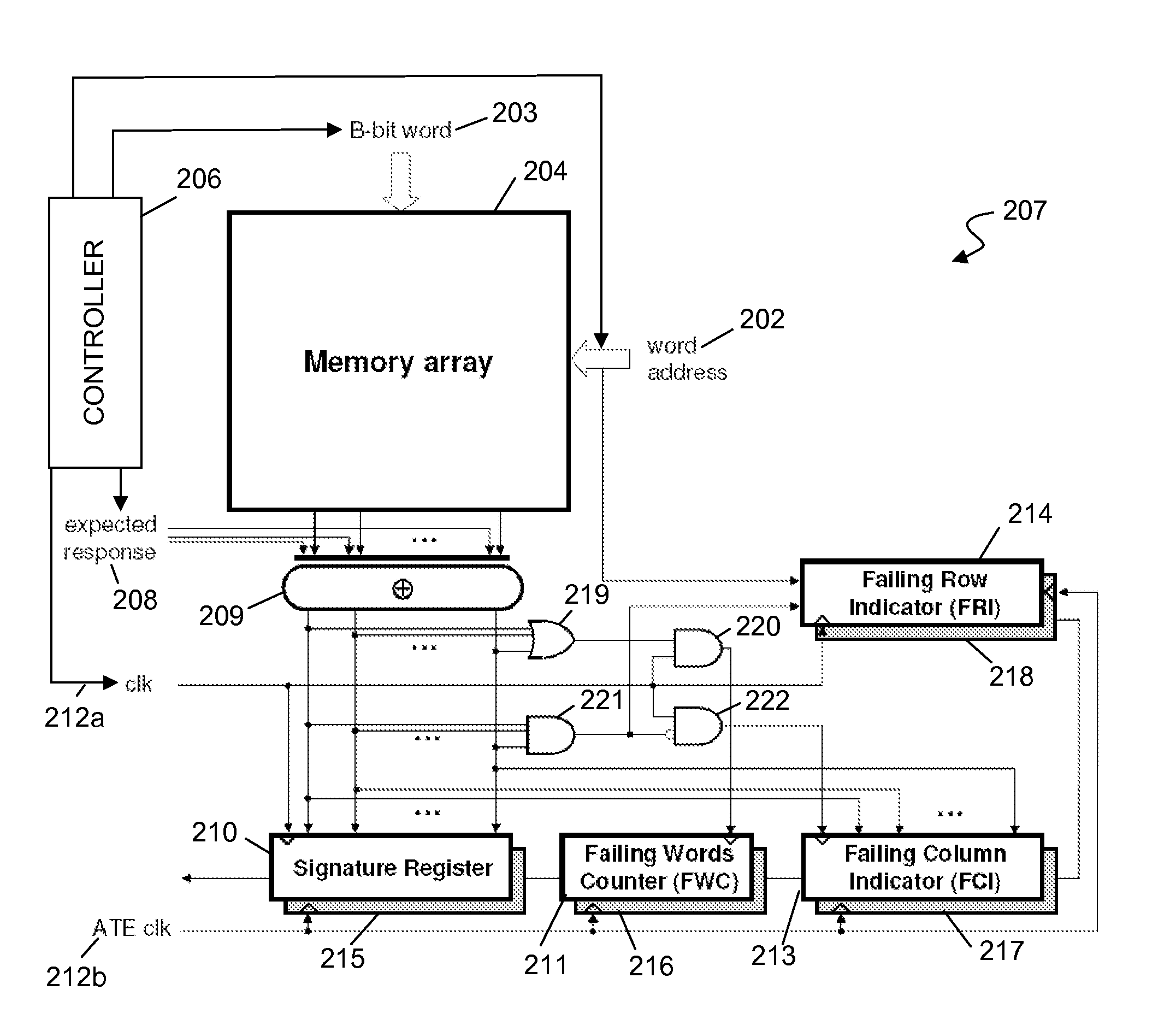

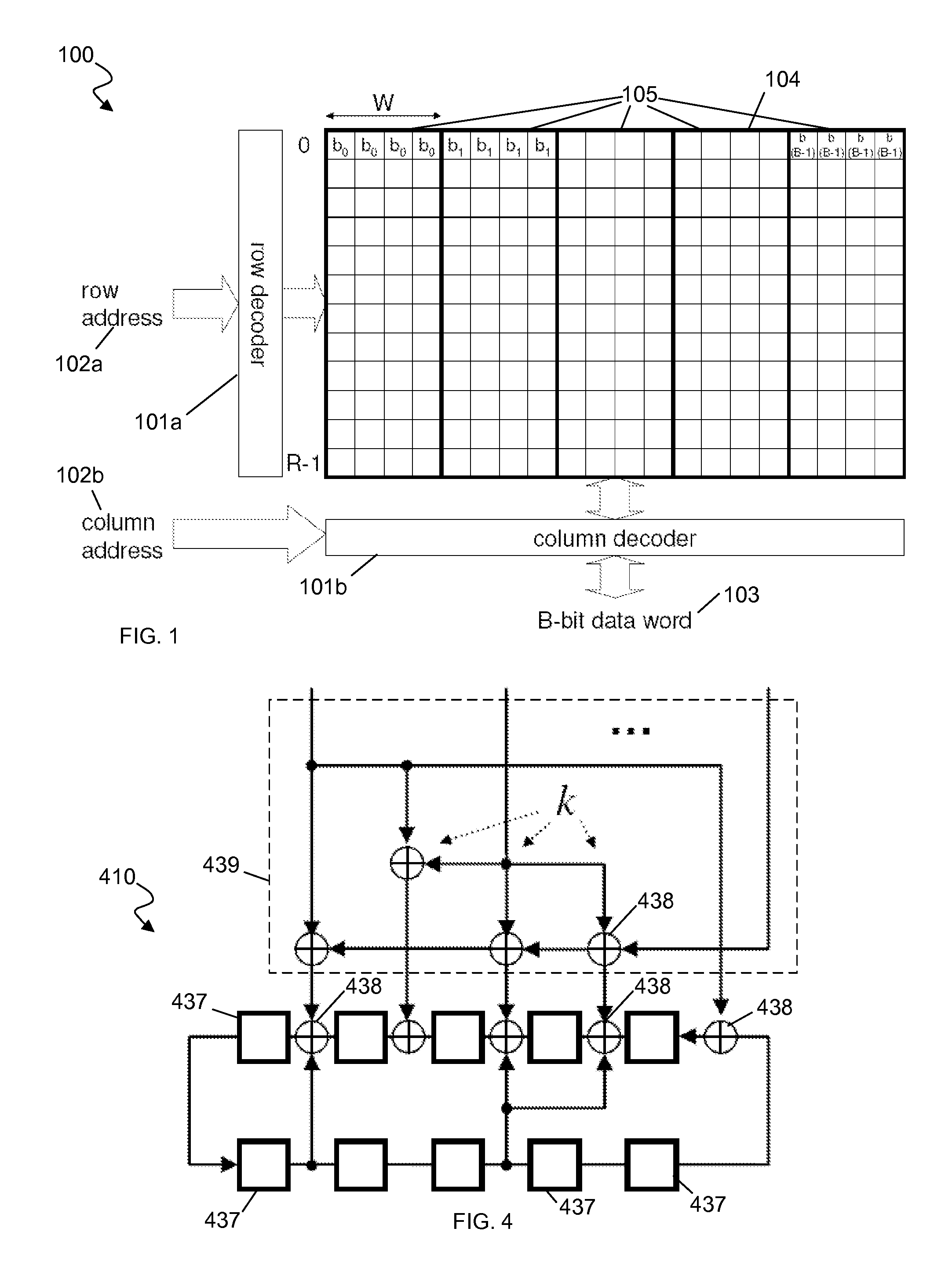

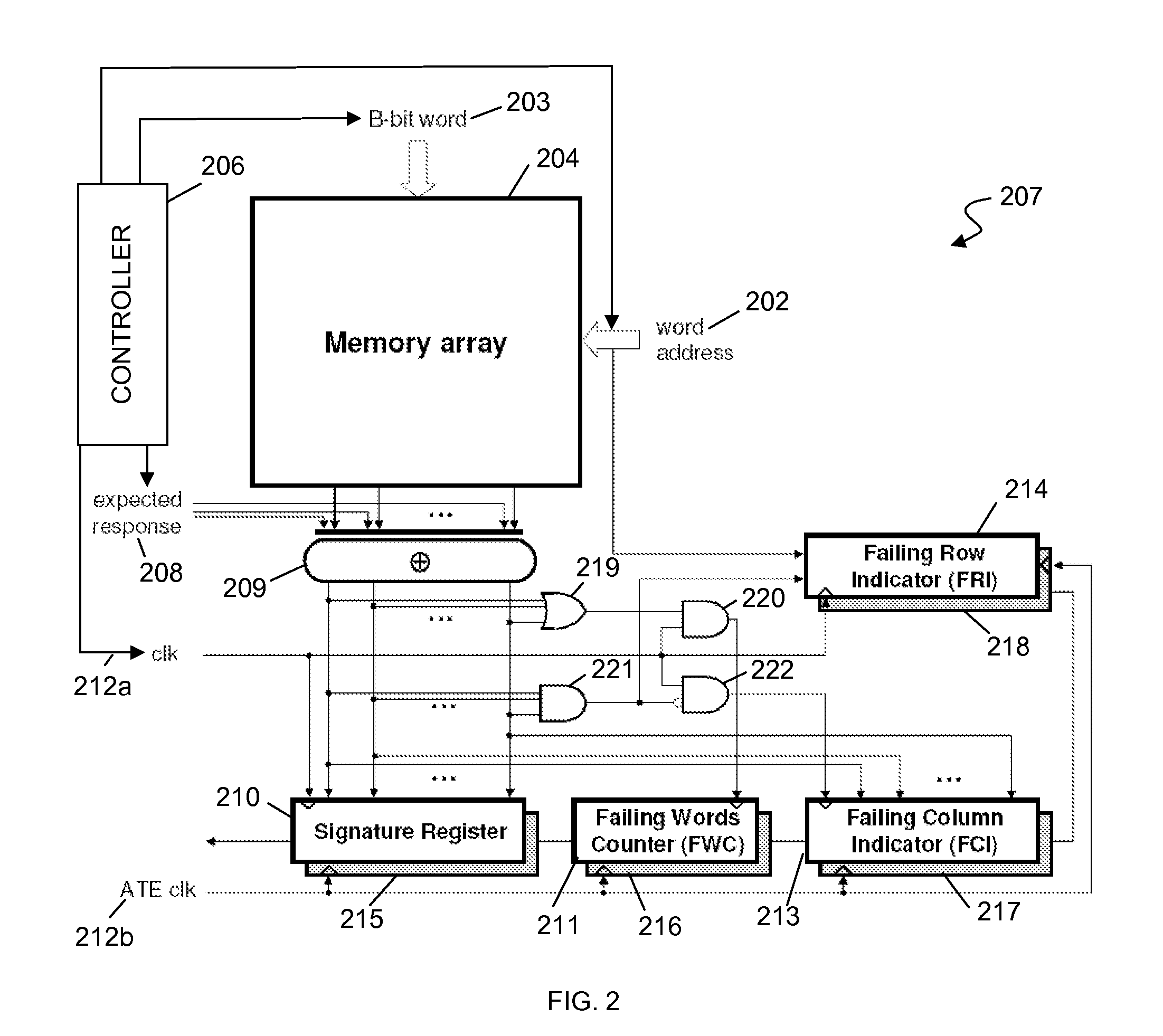

Fault diagnosis in a memory bist environment

InactiveUS20110055646A1Data failureProvide time efficiencyFunctional testingStatic storageBack structureAutomatic test equipment

Disclosed are methods and devices for temporally compacting test response signatures of failed memory tests in a memory built-in self-test environment, to provide the ability to carry on memory built-in self-test operations even with the detection of multiple time related memory test failures. In some implementations of the invention, the compacted test response signatures are provided to an automated test equipment device along with memory location information. According to various implementations of the invention, an integrated circuit with embedded memory (204) and a memory BIST controller (206) also includes a linear feed-back structure (410) for use as a signature register that can temporally compact test response signatures from the embedded memory array during a test step of a memory test. In various implementations the integrated circuit may also include a failing words counter (211), a failing column indicator (213), and / or a failing row indicator (214) to collect memory location information for a failing test response.

Owner:MENTOR GRAPHICS CORP

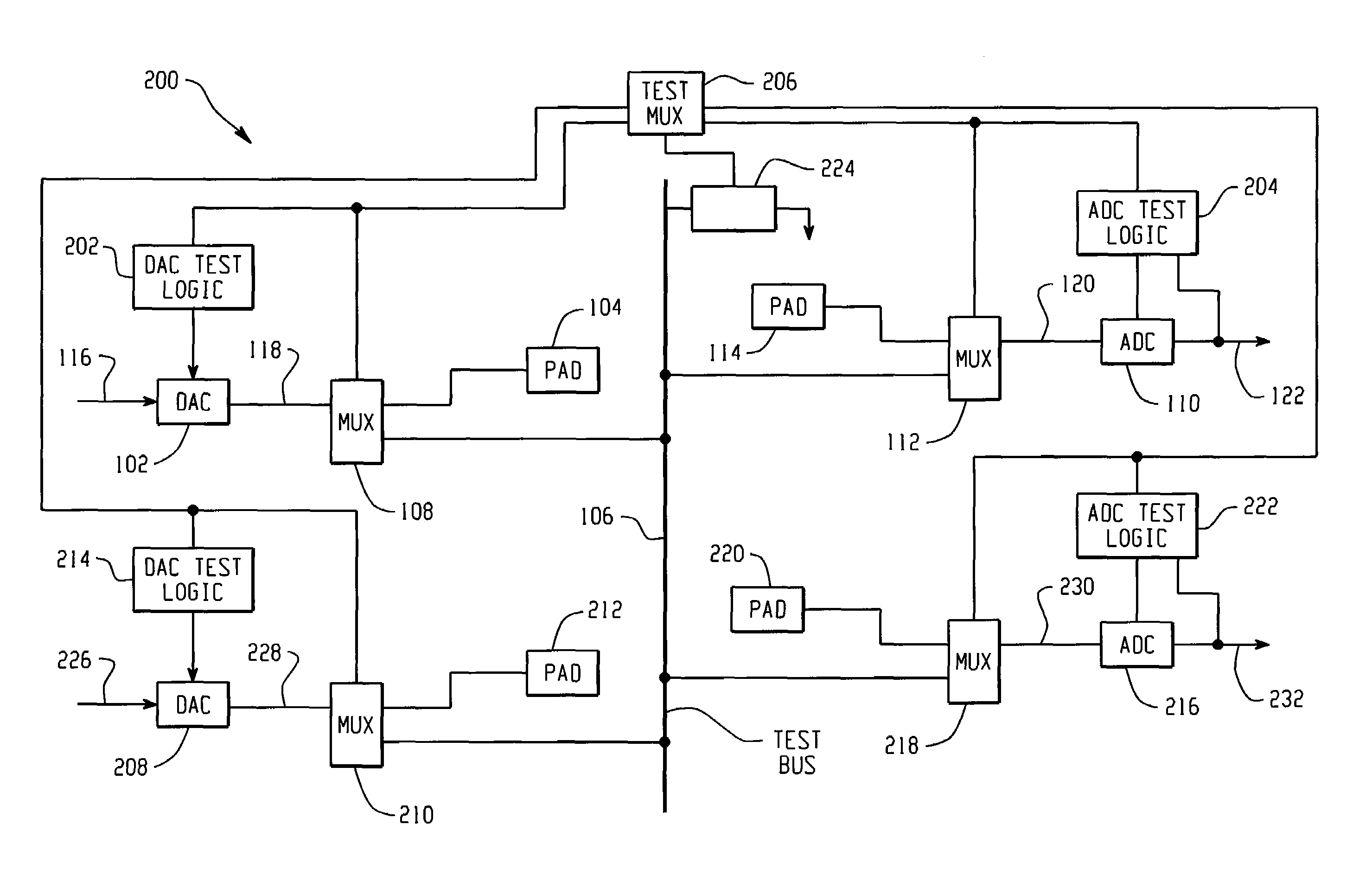

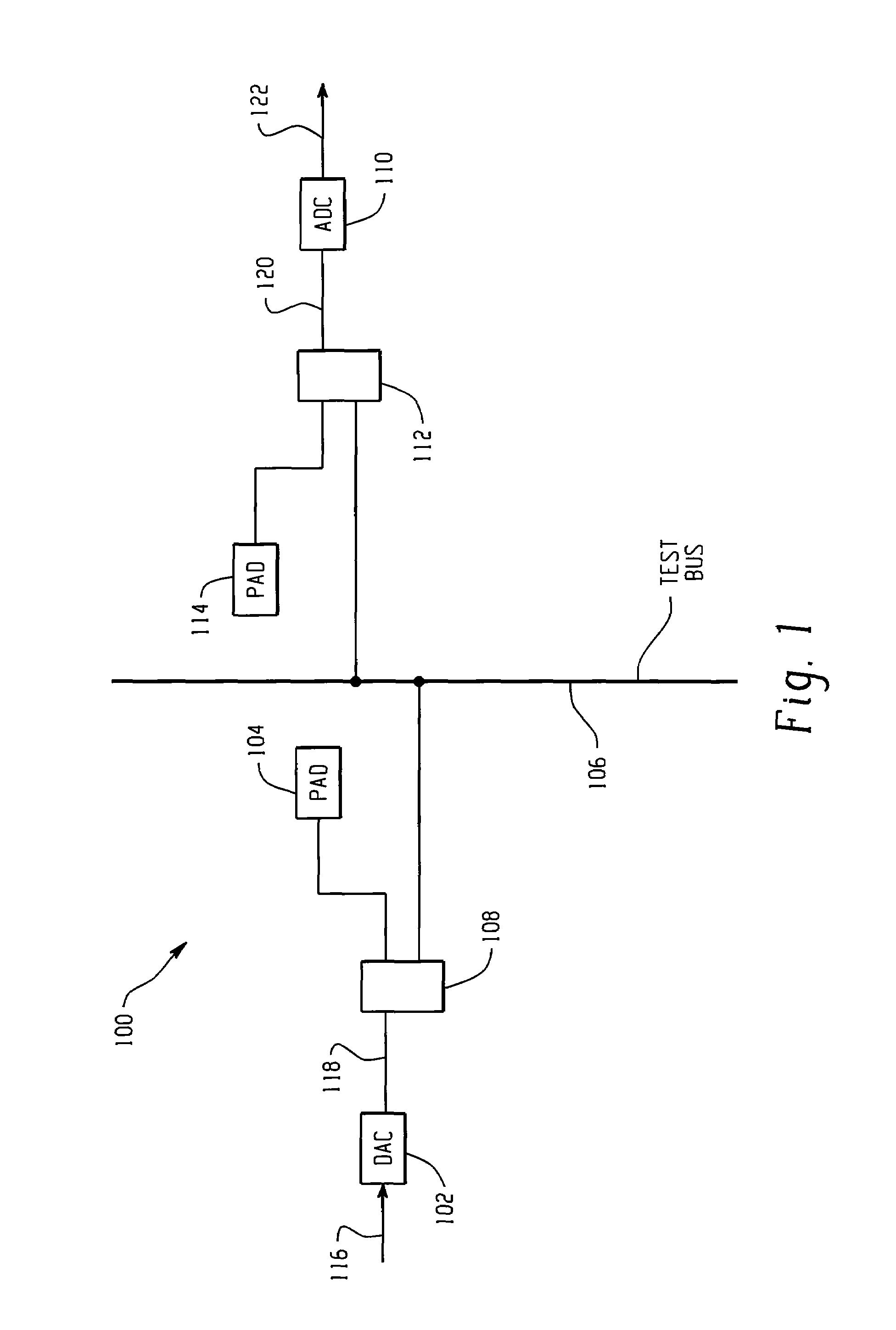

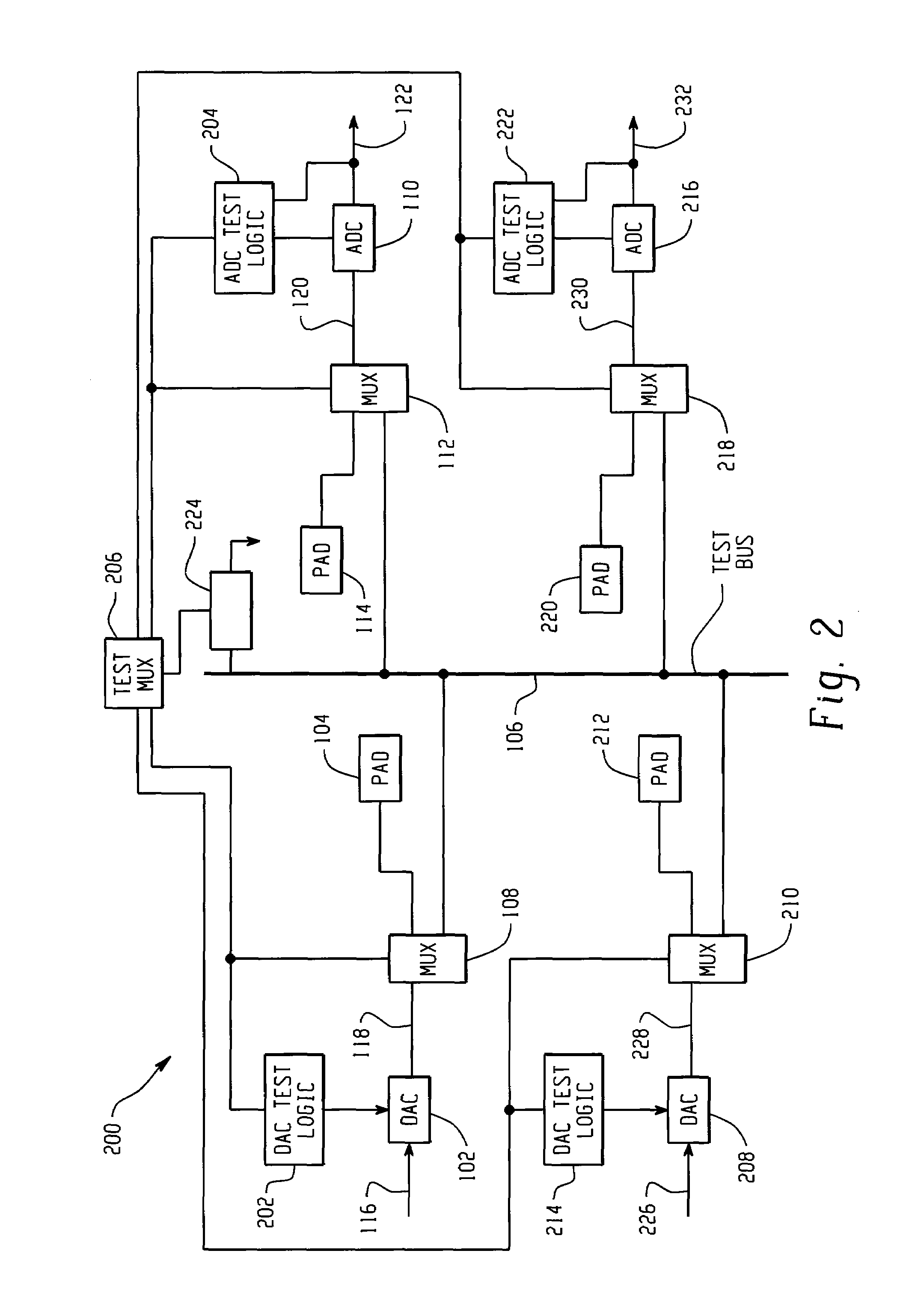

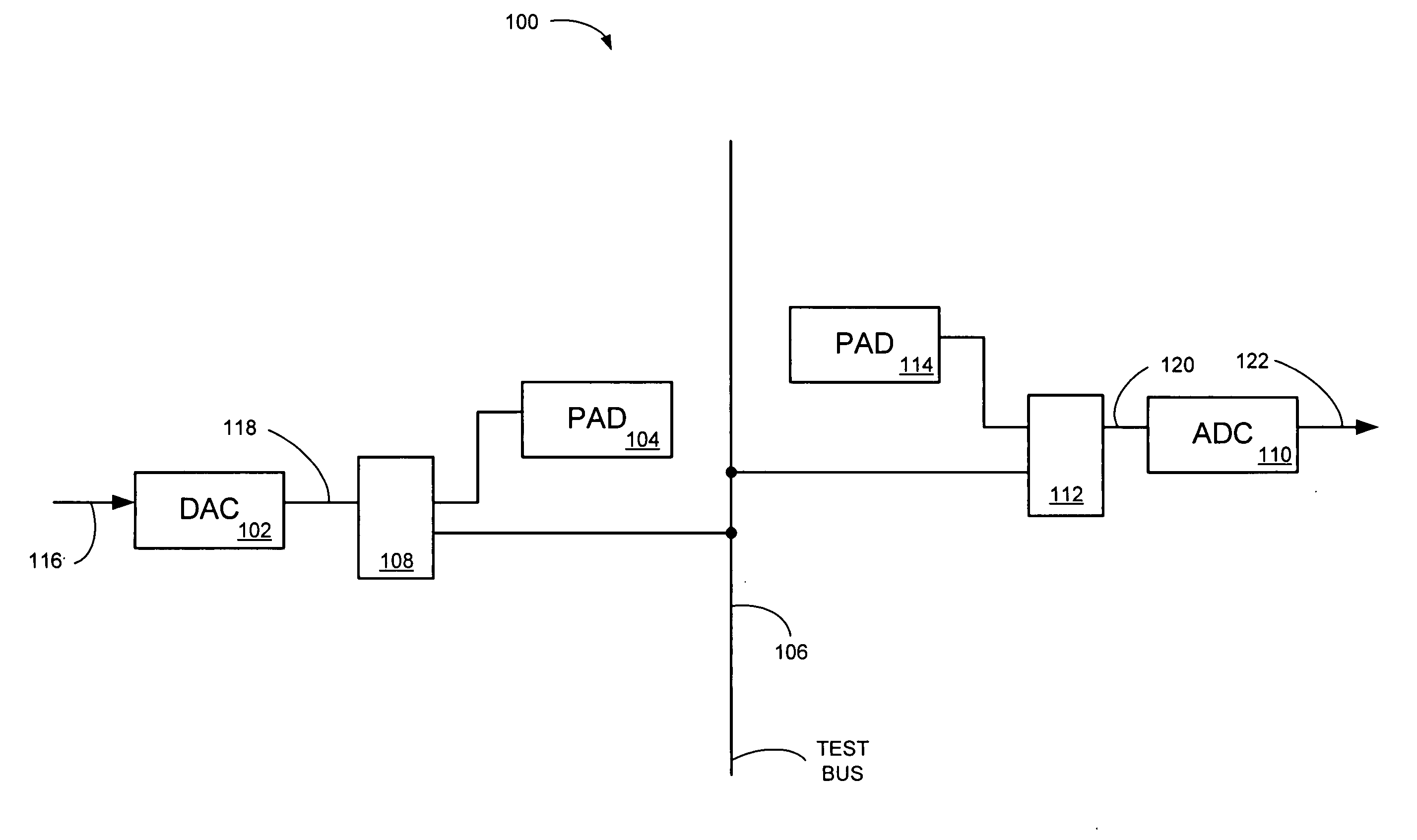

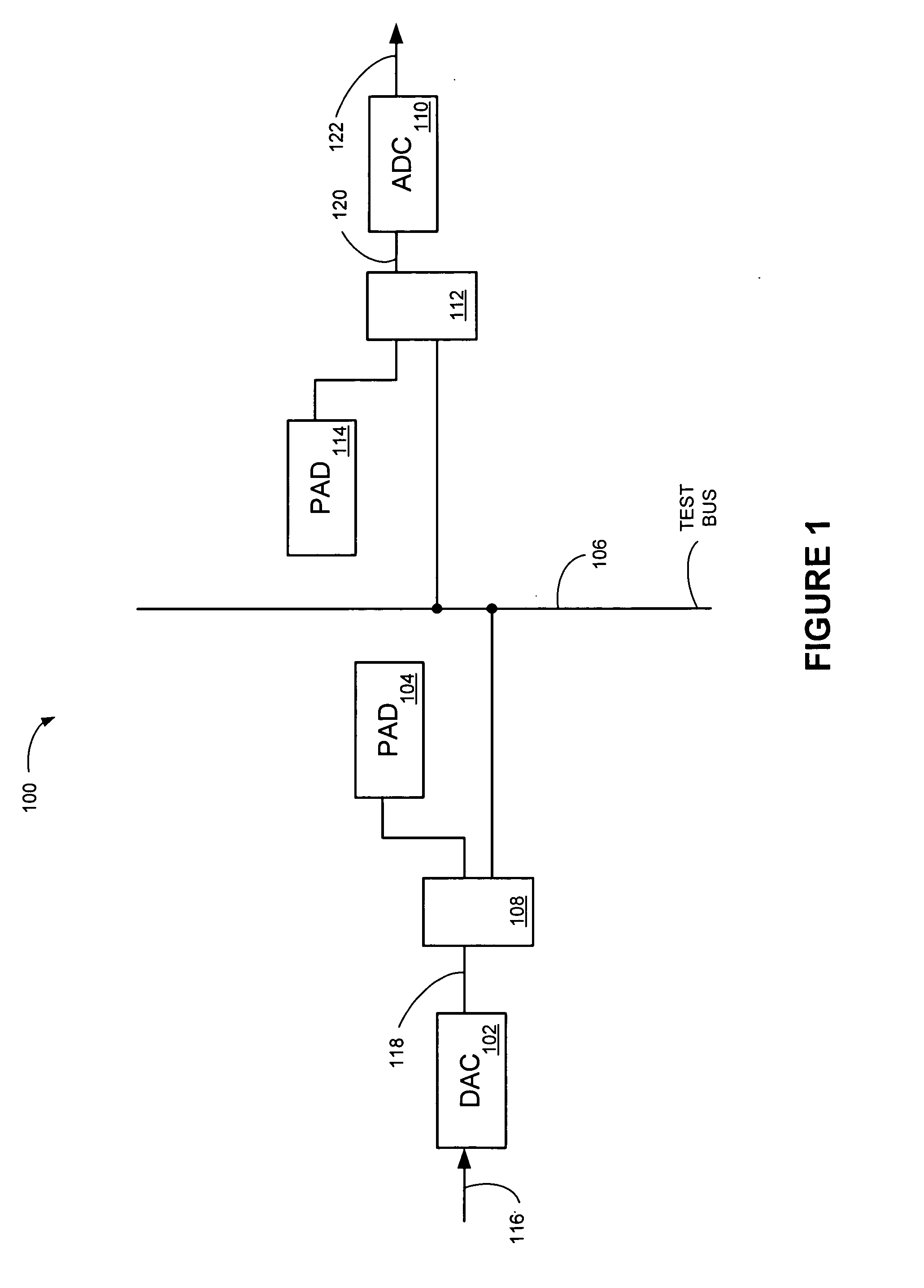

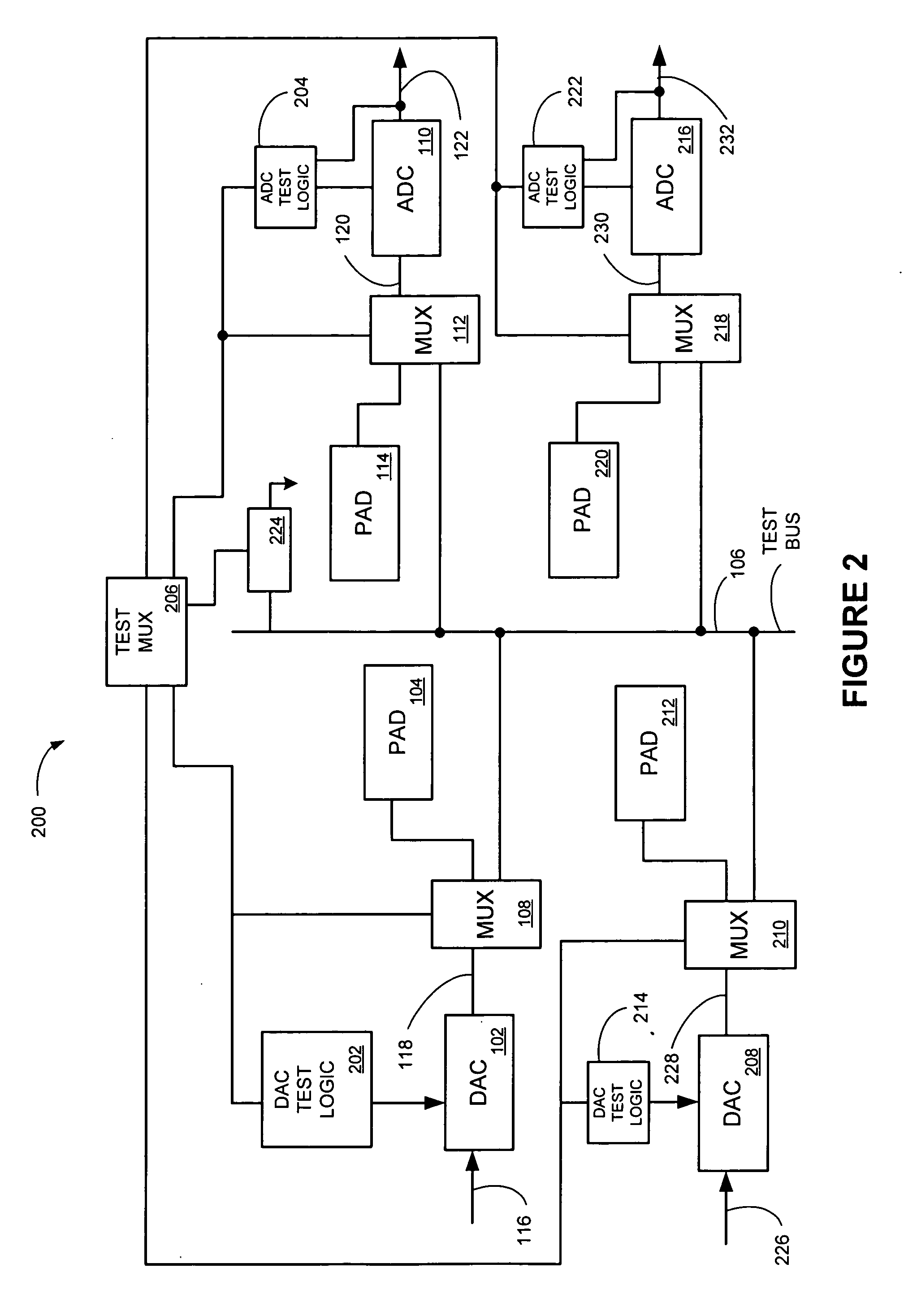

Digital BIST test scheme for ADC/DAC circuits

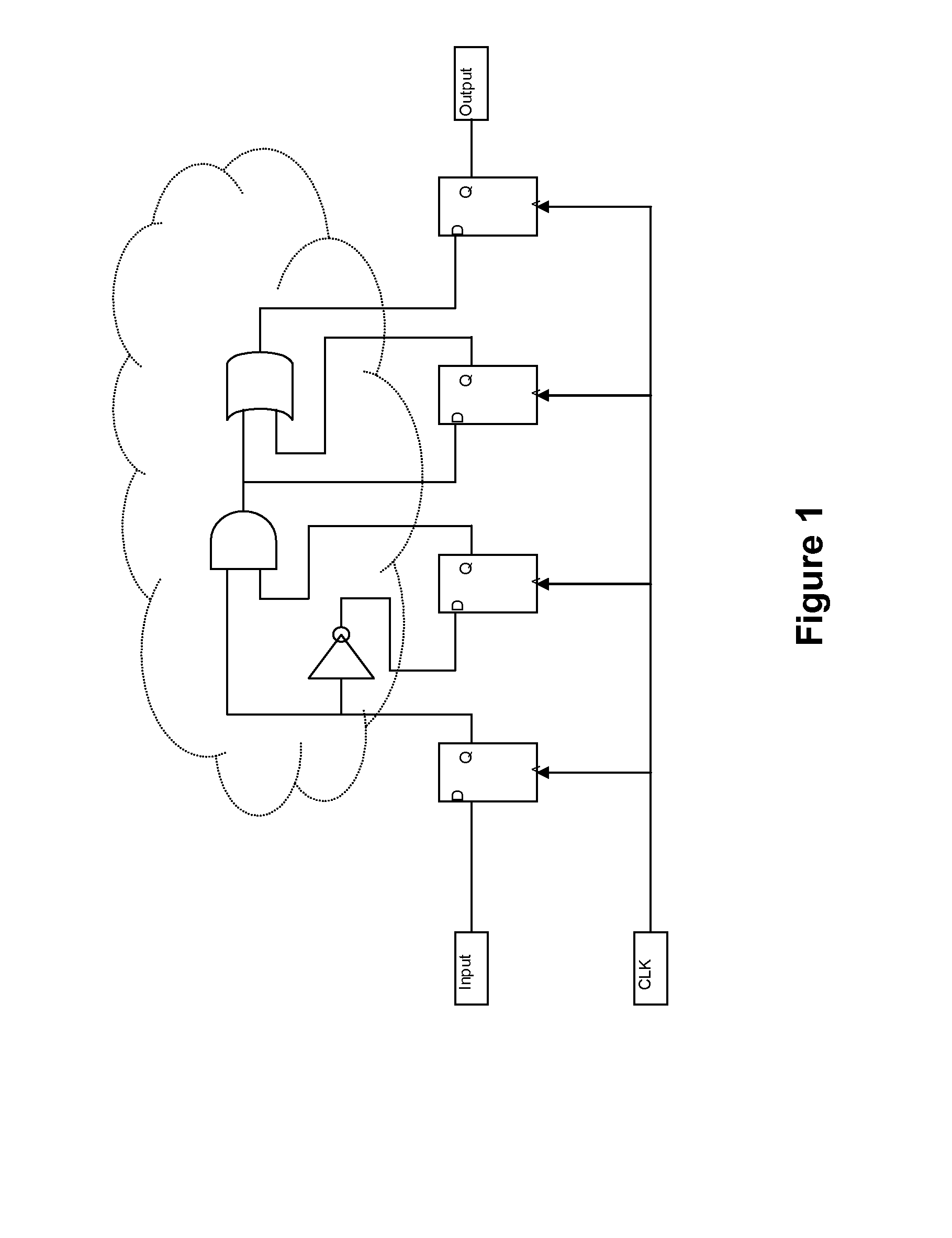

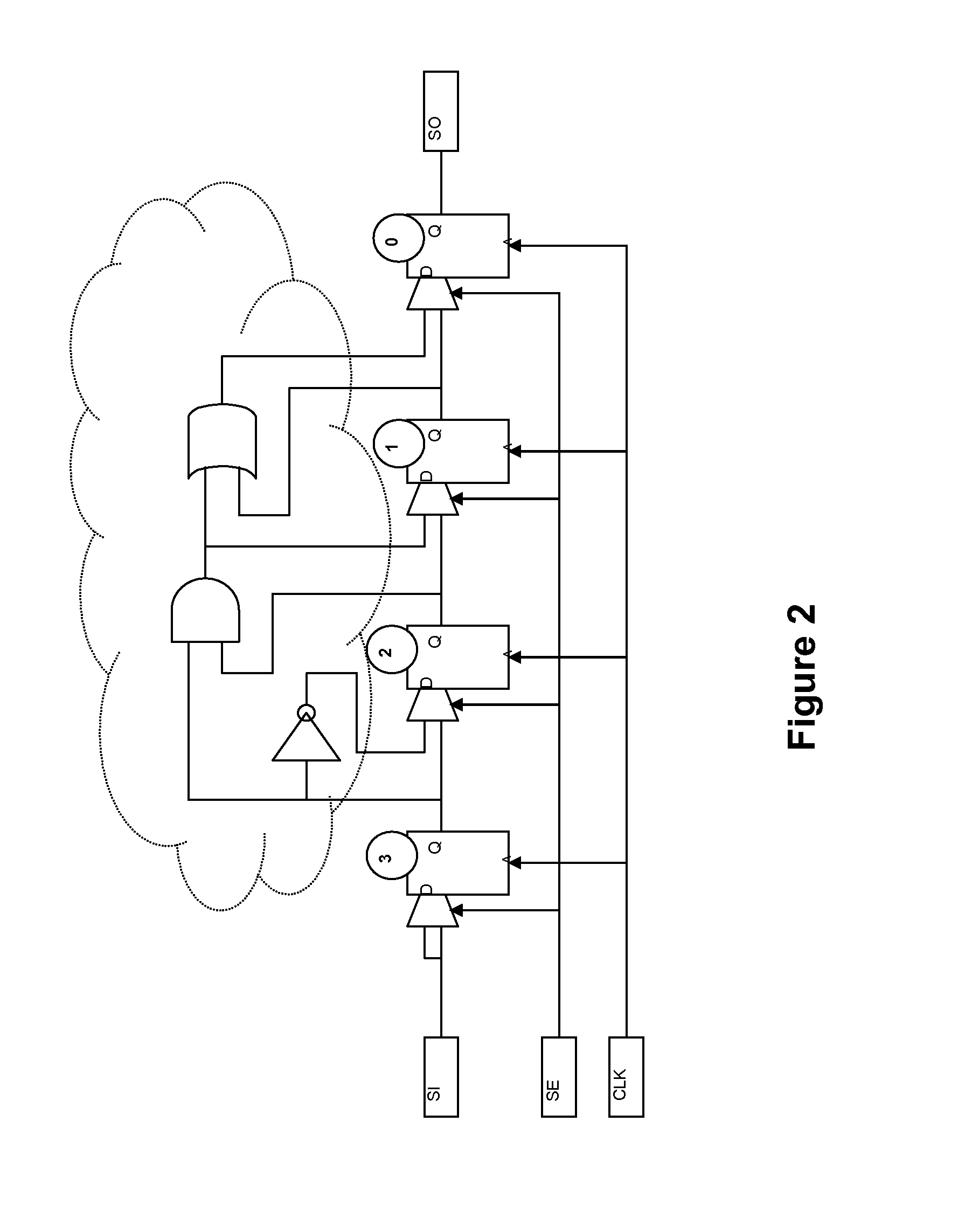

InactiveUS7271751B2Test accurateShorten test timeElectric signal transmission systemsElectrical testingMultiplexerClock rate

A generalized method for testing DACs (Digital to Analog Converters) and ADCs (Analog to Digital Converters), such as Sigma Delta (Successive Approximation), Pipeline or Flash ADCs. The DACs and ADCs are tested in pairs using a Digital Tester and on chip test circuitry. The DACs and ADCs may be tested at the highest clock frequency allowed in the specification, shortening test time. The test circuits required for this test scheme comprise cell logic two multiplexer cells and an internal Analog Test Bus. This scheme is extendable to the testing of many DACs and ADCs on the same IC. The number of DACs and ADCs need not be equal. Furthermore, the DACs may have more (or less) bits (addresses) than the ADCs. An ADC may be tested with more than one DAC or vice versa to determine which cell is at fault if a test fails.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

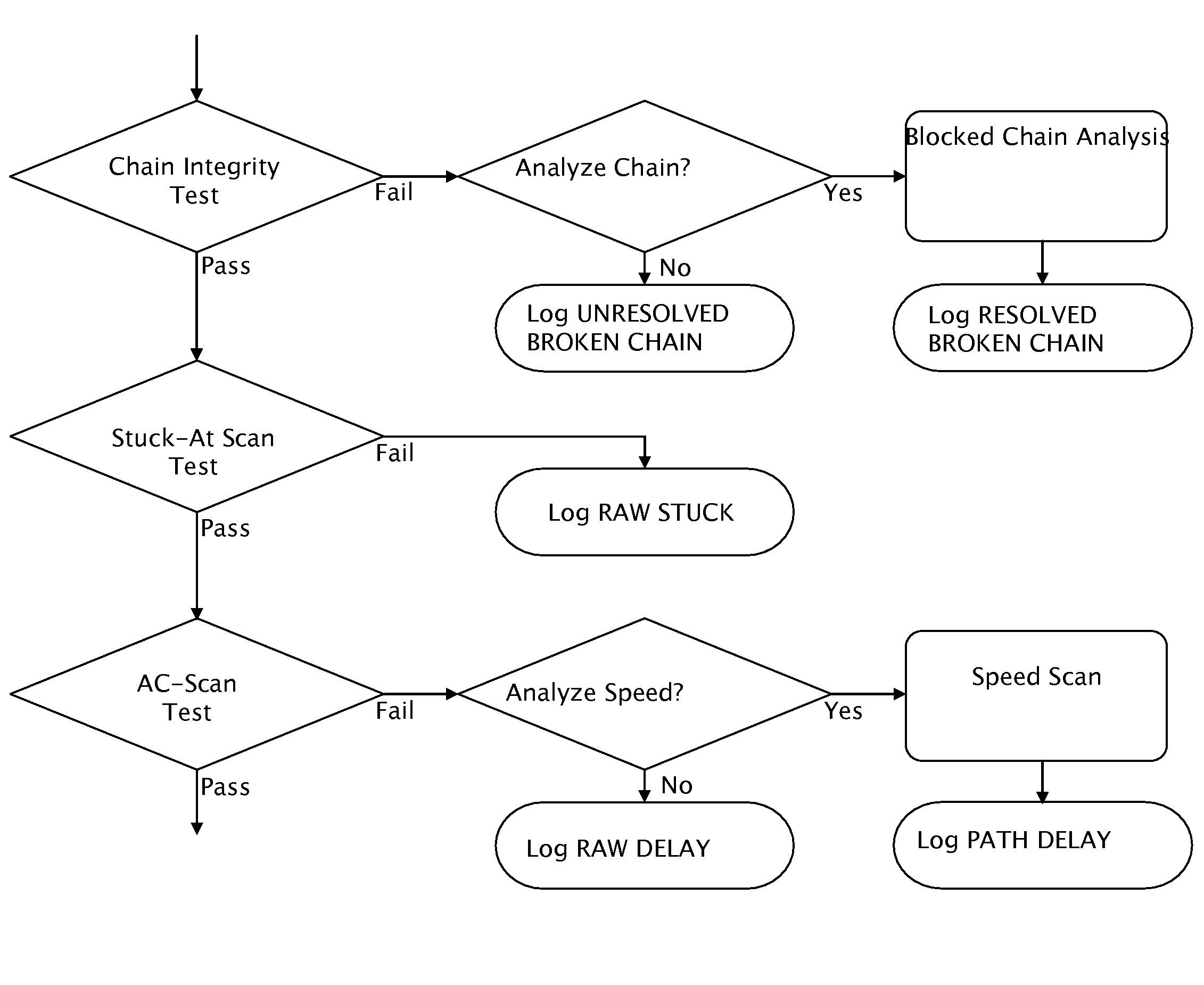

Process for improving design-limited yield by localizing potential faults from production test data

ActiveUS20080091981A1Reduce locationElectronic circuit testingError detection/correctionElectrical FailureAutomatic test equipment

A process for improving design-limited yield by collecting test fail data, converting to electrical faults, and localizing to physical area on semiconductor die. The steps of identifying an area on a wafer containing a fault to enable the analysis of specific defects, accumulating data suitable for yield monitoring analysis based on pattern test failures logged on scan cells in scan chains on automatic test equipment, and translating scan cell and scan chain failure reports to geometric locations of electrical structures on wafers.

Owner:ADVANTEST CORP

Method of Detecting False Test Alarms Using Test Step Failure Analysis

Identifying false test alarms to a developer. A code build is executed in a test system that includes computing functionality and computing infrastructure that is able to execute the build. Executing the code build includes running a plurality of system and integration tests on the code build. As a result of executing the code build, a system and integration test failure is identified. One or more characteristics of the system and integration test failure are identified. The characteristics of the system and integration test failure are compared to characteristics of a set of historical previous known false test alarms. False test alarms are failures caused by a factor other than a factor for which a test is being run. Based on the act of comparing, information is provided to a developer with respect to if the system and integration test failure is potentially a false test alarm.

Owner:MICROSOFT TECH LICENSING LLC

Circuit interrupter including arc fault test and/or ground fault test failure indicator

ActiveUS20060018059A1Protective switch detailsEmergency protective arrangement detailsFault indicatorElectricity

A circuit breaker includes a test circuit having one or two indicators, an arc fault signal generator, and first and second test switches. A first indicator is electrically connected in series with the first test switch. This series combination provides a first alternating current signal to the arc fault signal generator, which provides an arc fault signal to an arc fault trip circuit, in order to trip open separable contacts in response to closure of the first test switch. The series combination of the second test switch and the second indicator provides a second alternating current signal to a ground fault trip circuit, in order to trip in response to closure of the second test switch. The indicators provide a visual indication of failure of the arc fault or ground fault trip circuits to trip in response to closure of the first or second test switches, respectively.

Owner:EATON INTELLIGENT POWER LTD

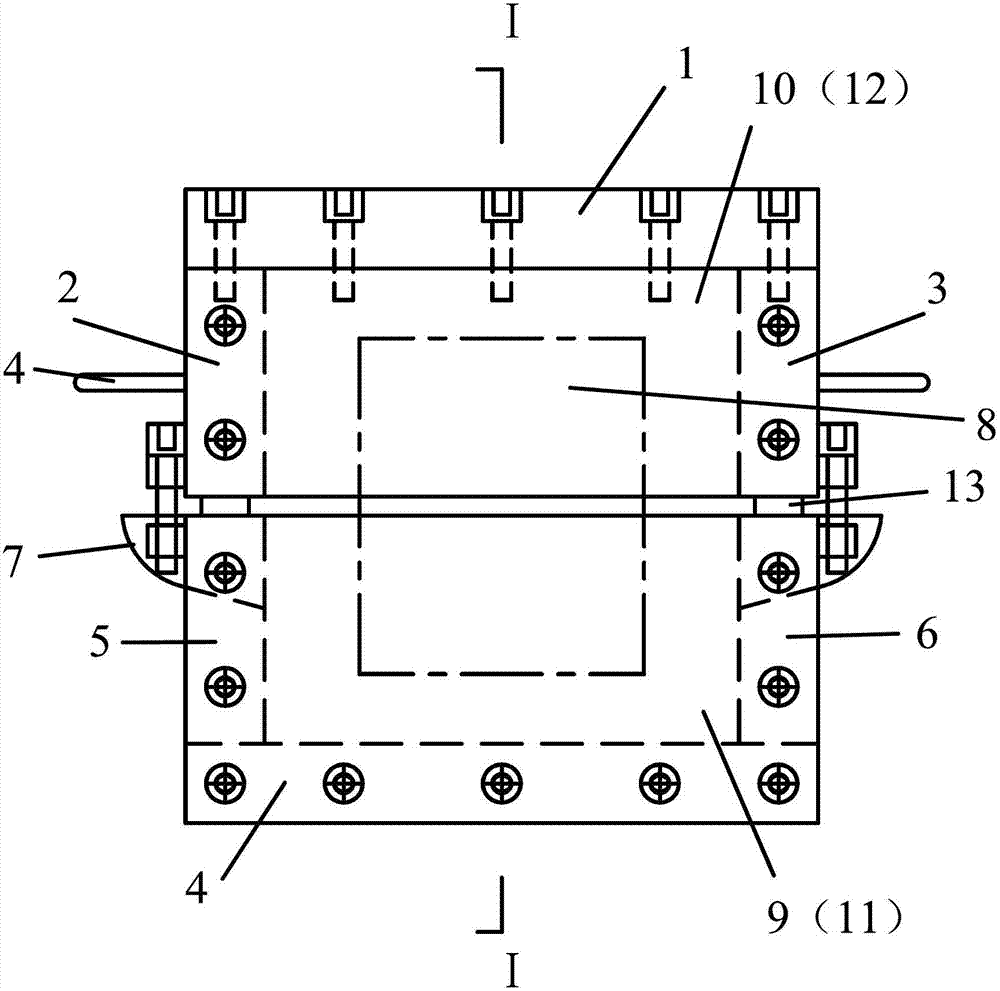

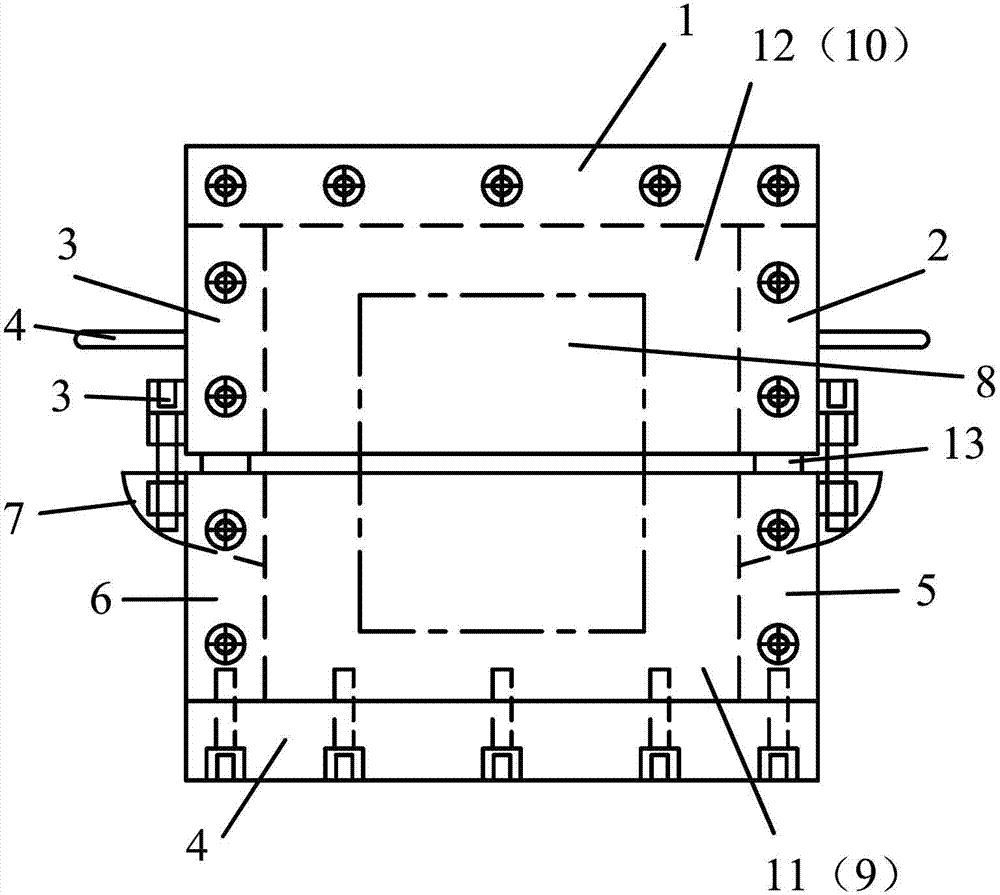

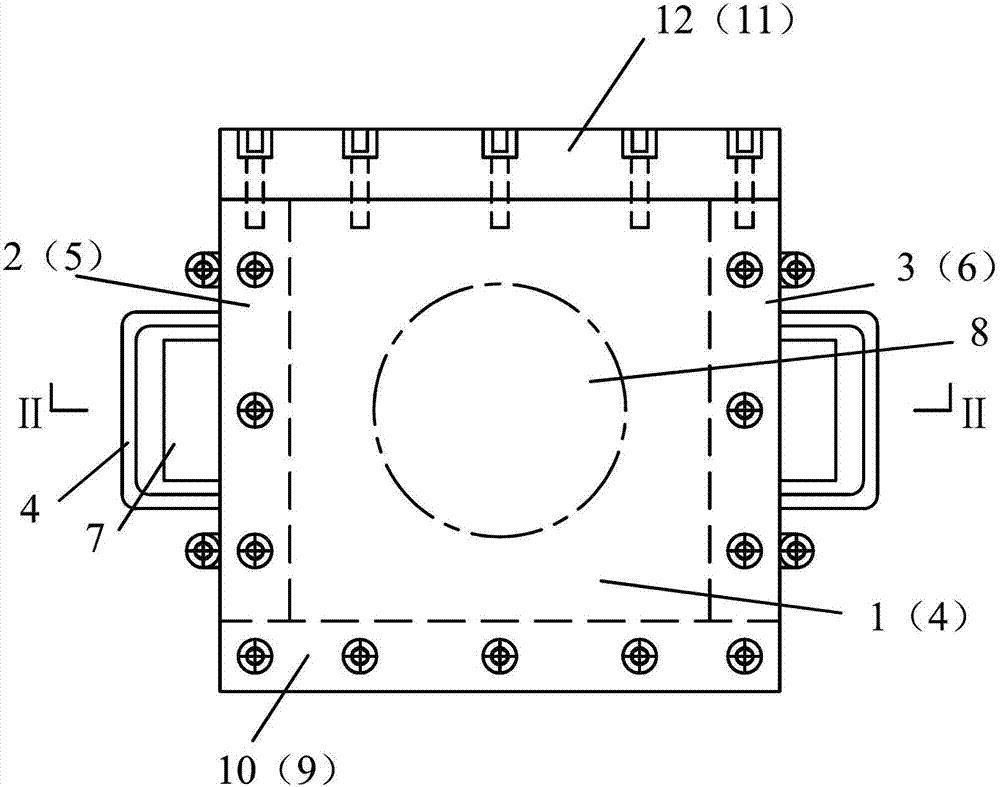

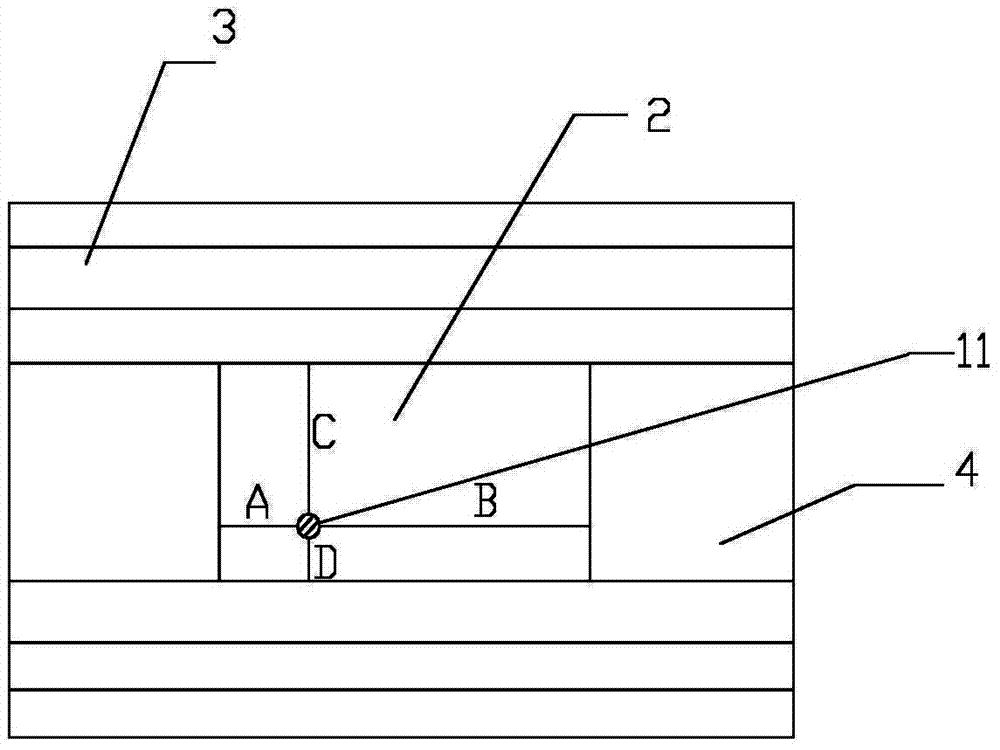

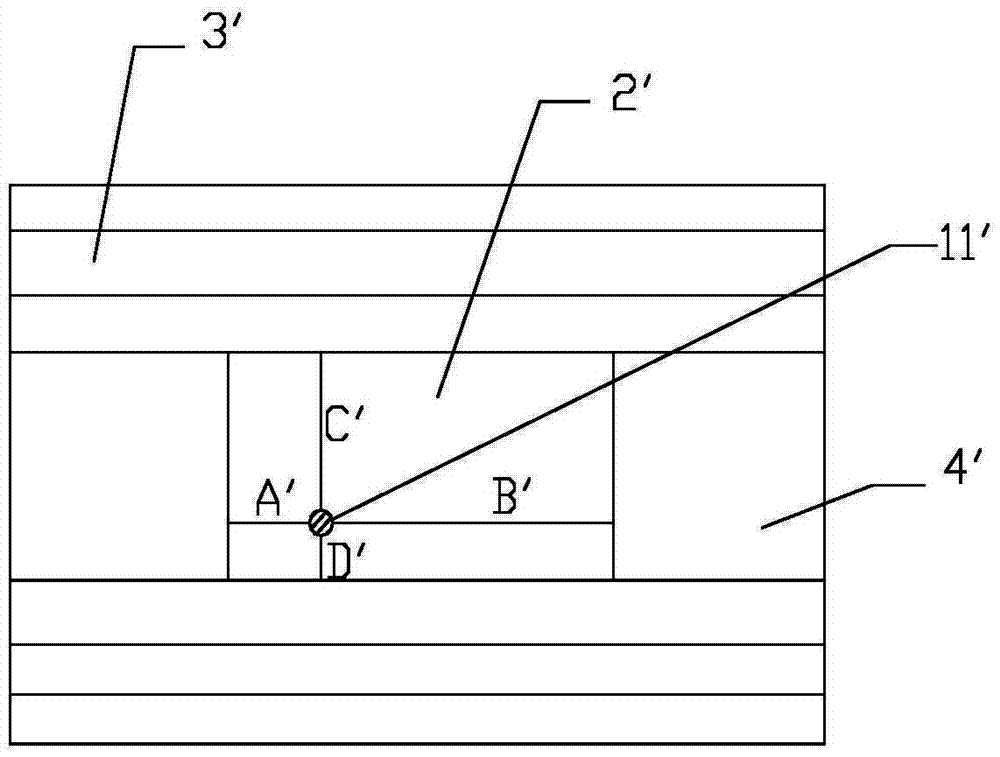

Rock structural surface shear test method and implementation apparatus thereof

ActiveCN102735555ASolve the problem of not being damagedResolve Shear DeformationMaterial strength using steady shearing forcesFilling materialsRock sample

The invention discloses a rock structural surface shear test method and an implementation apparatus thereof. The method mainly comprises the steps that: an upper part and a lower part of a rock sample are respectively fixed in an upper opened shearing box and a lower opened shearing box with opposite opening surfaces through filling, wherein a certain distance is kept between the opening surfaces of the upper and lower shearing boxes, such that the rock sample block shear test structural surface is exposed between the opening surfaces of the upper and lower shearing boxes; a pair of shear loads with opposite directions are implemented on the upper and lower shearing boxes, and the loads act upon the rock sample block through the filling materials in the shearing boxes; the loads further act upon the rock sample block structural surface, such that the shear strength parameter of the rock sample block structural surface is obtained. According to the invention, the rock structural surface is subjected to a shear test, such that structural surface damage of the rock sample block during a moving process is effectively avoided, and test failure caused by damaged structural surface is prevented. The influence of cement upon sample block tests in prior arts is completely eliminated, and the true shear strength parameter of the rock structural surface can be obtained.

Owner:SICHUAN UNIV

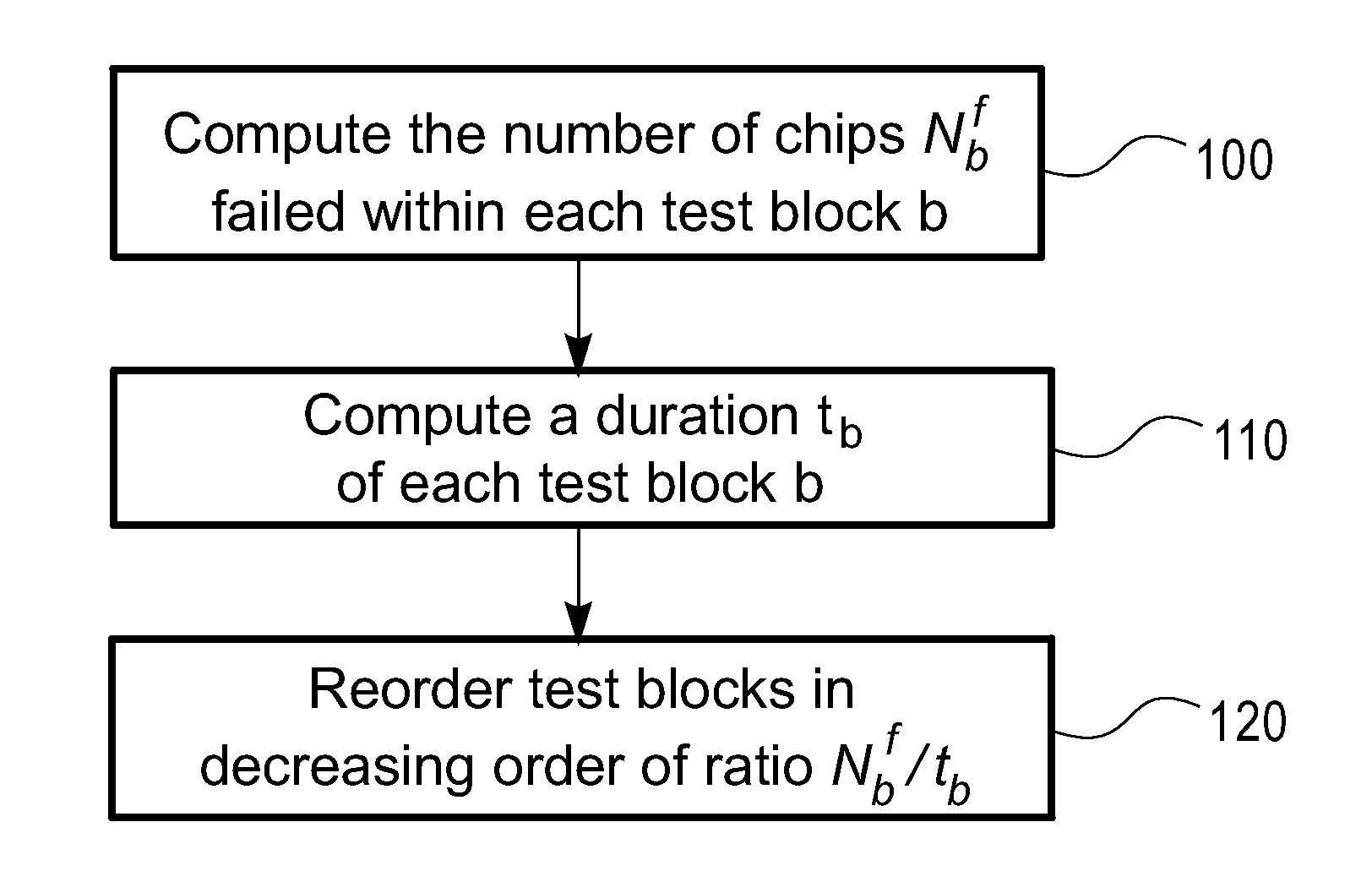

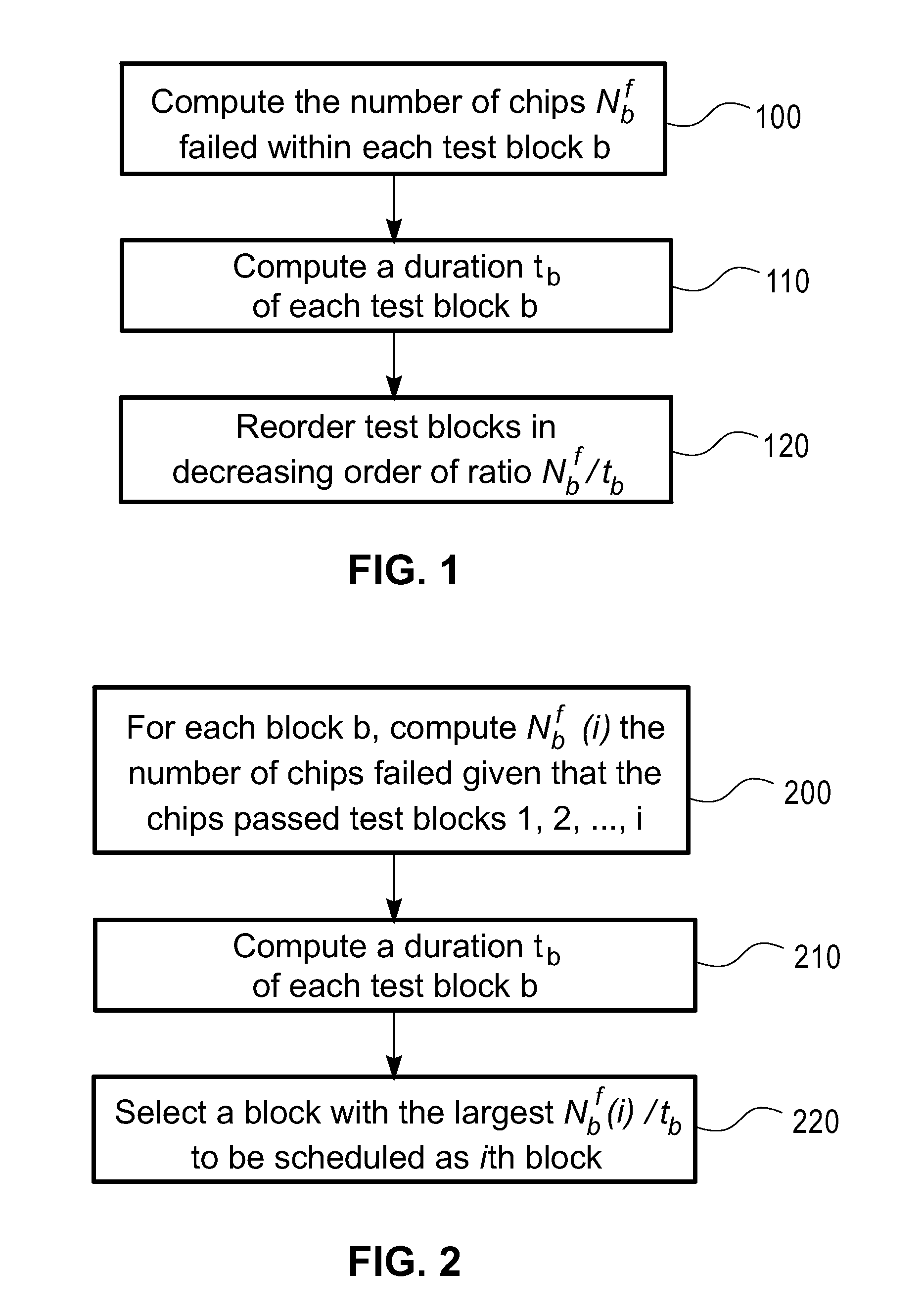

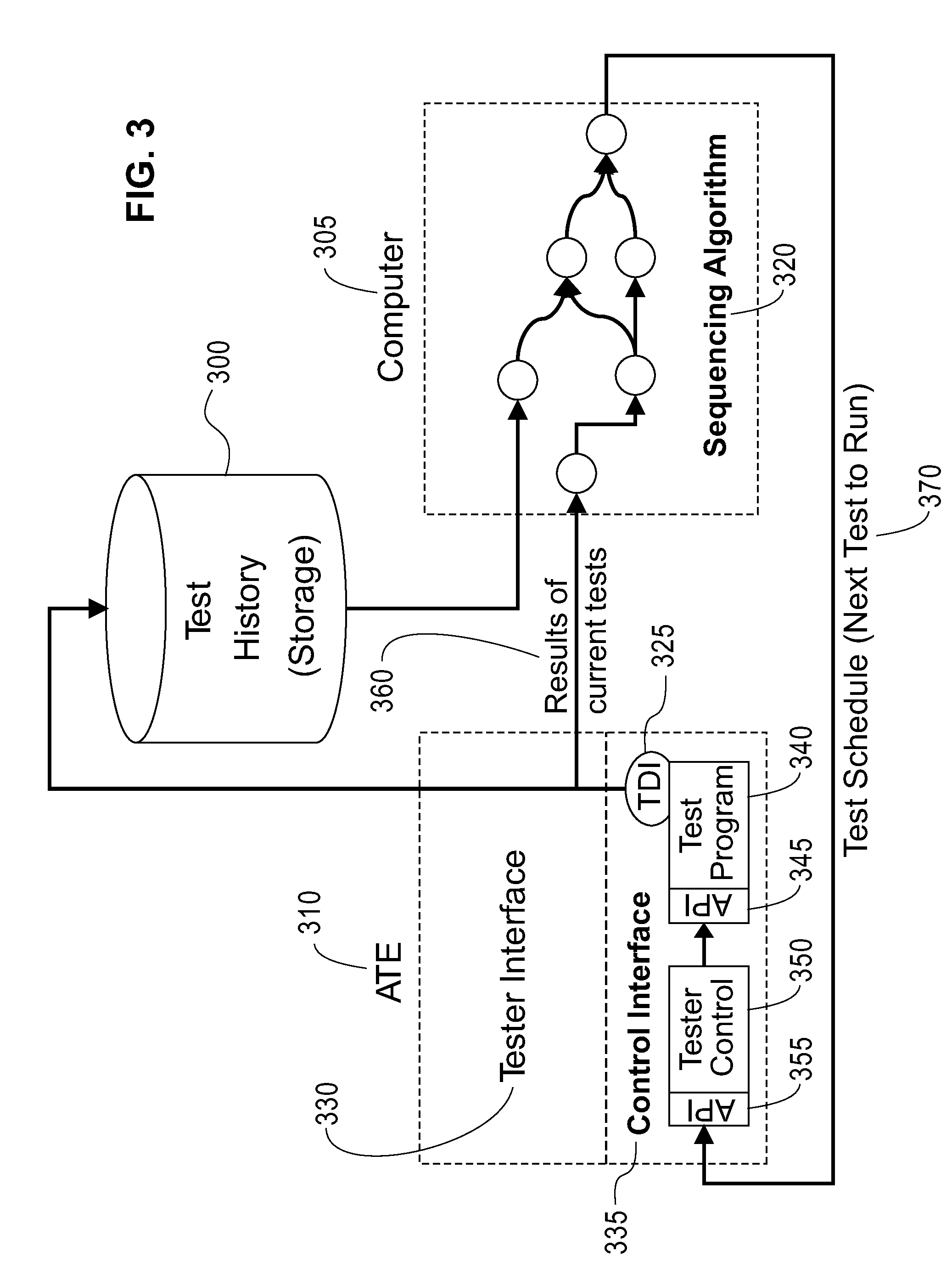

Optimal test flow scheduling within automated test equipment for minimized mean time to detect failure

InactiveUS20110288808A1Minimize timeResistance/reactance/impedenceFunctional testingTest flowOptimal test

The present invention describes a method and system for optimizing a test flow within each ATE (Automated Test Equipment) station. The test flow includes a plurality of test blocks. A test block includes a plurality of individual tests. A computing system schedule the test flow based one or more of: a test failure model, test block duration and a yield model. The failure model determines an order or sequence of the test blocks. There are at least two failure models: independent failure model and dependant failure model. The yield model describes whether a semiconductor chip is defective or not. Upon completing the scheduling, the ATE station conducts tests according to the scheduled test flow. The present invention can also be applied to software testing.

Owner:IBM CORP

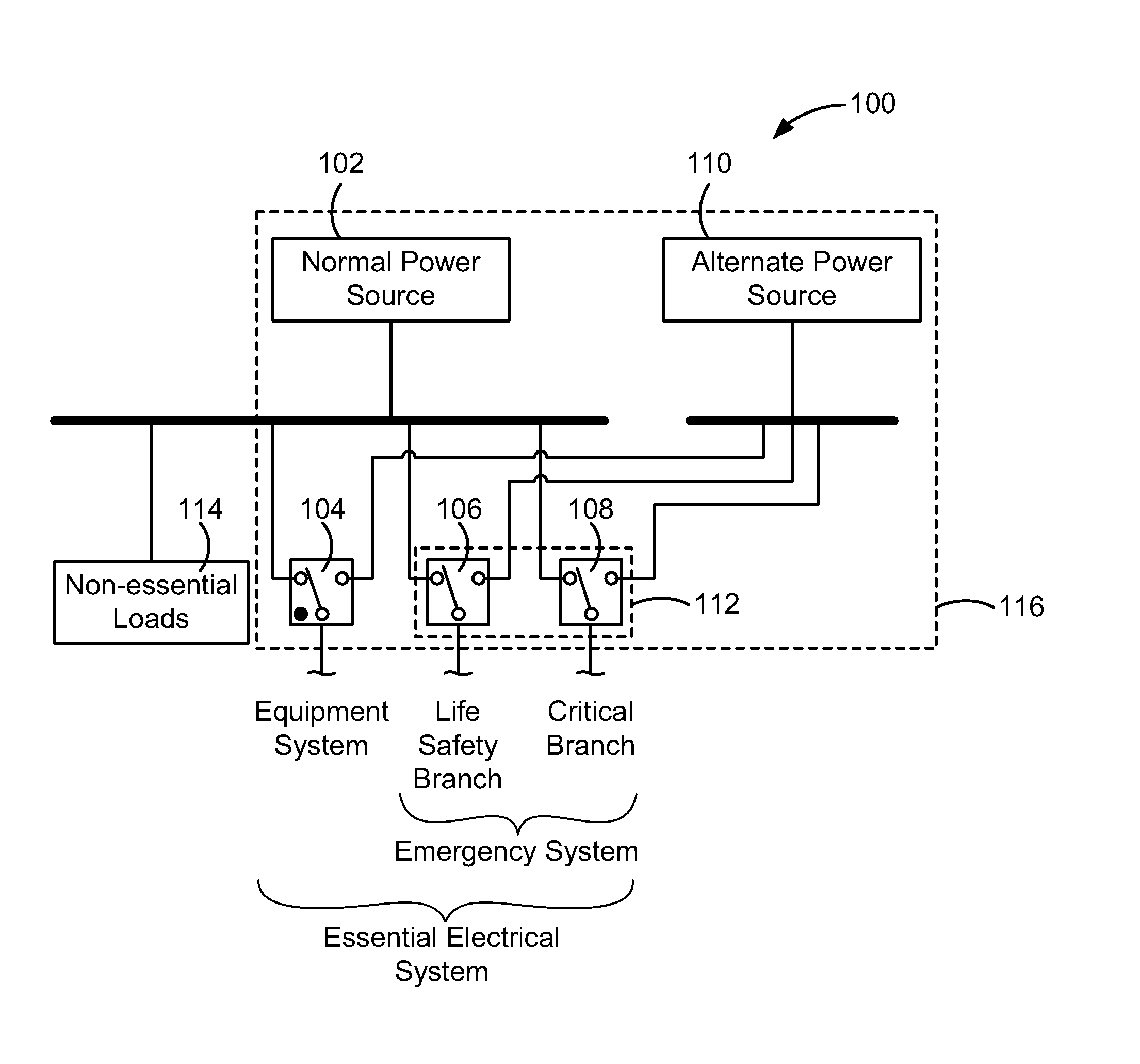

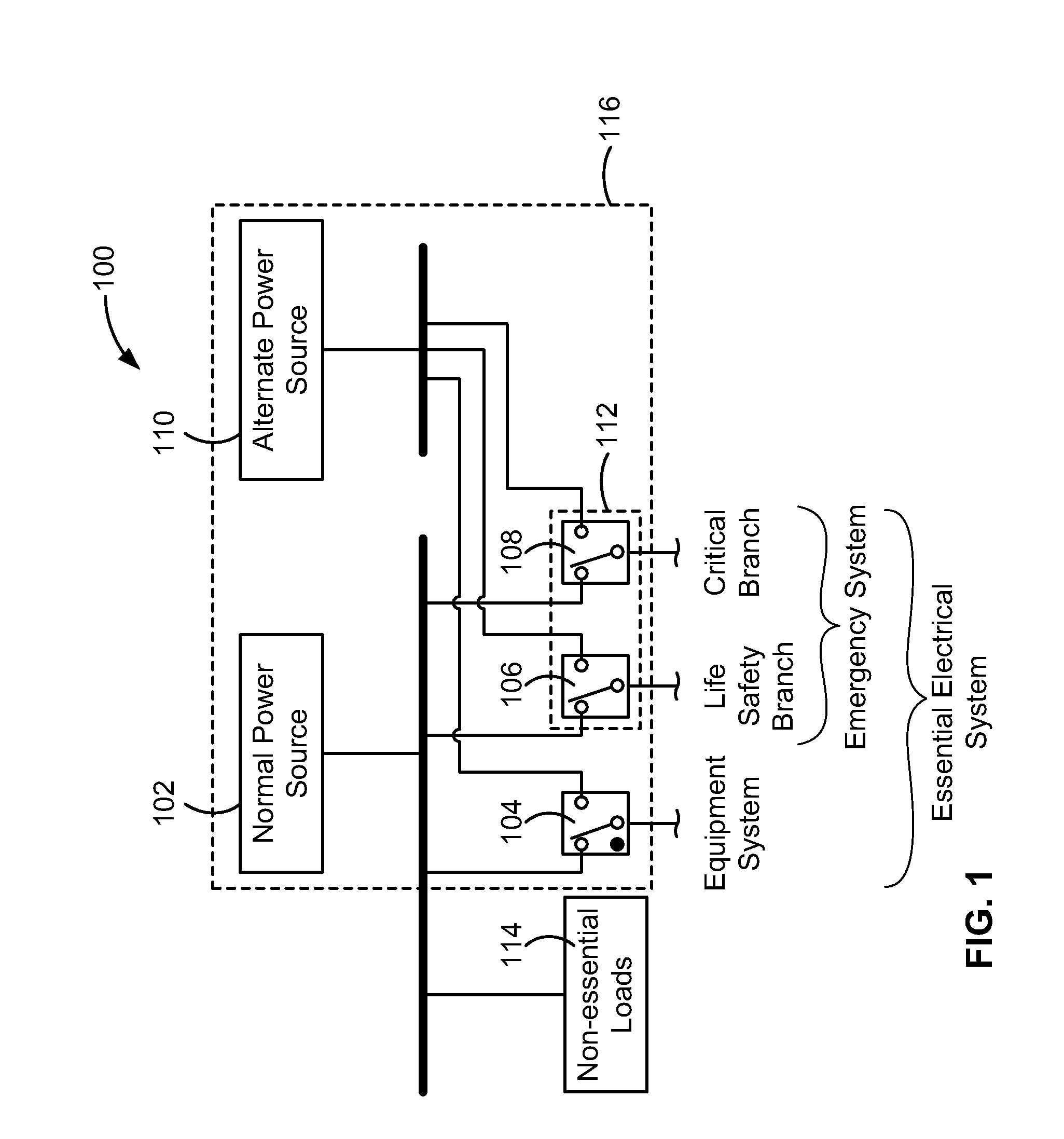

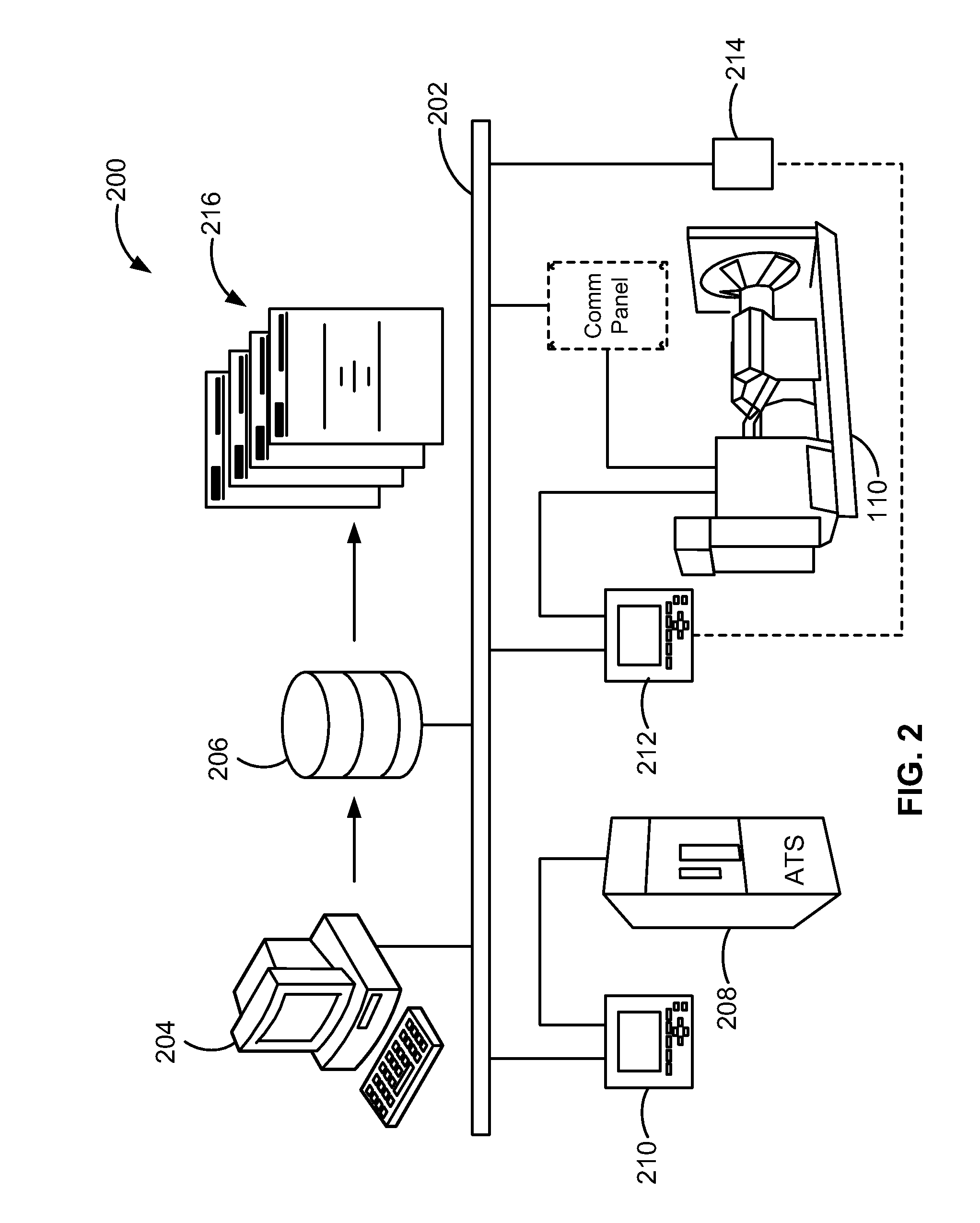

Automated emergency power supply system (EPSS) test reporting criticality of epss test failure

ActiveUS20120105097A1Improve reliabilityReduce the burden on personnelPower supply testingElectricityTransfer switch

Owner:SCHNEIDER ELECTRIC USA INC

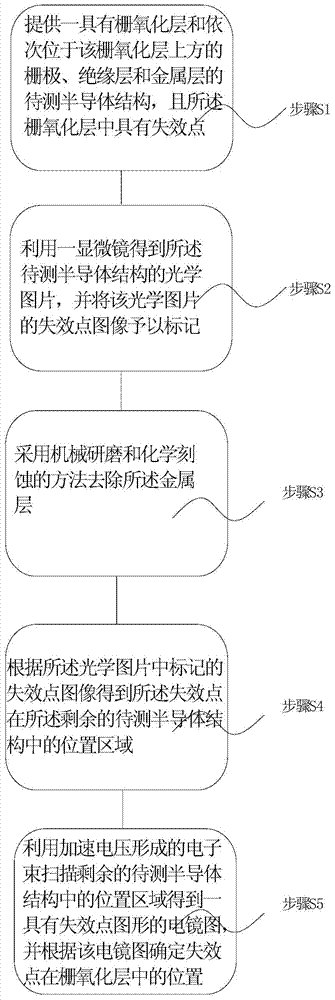

Gate oxide failure point positioning method

ActiveCN103926264AIncrease success rateImproving Efficiency in Breakdown Voltage Test Failure AnalysisSemiconductor/solid-state device testing/measurementMaterial analysis by measuring secondary emissionSemiconductor structureScanning electron microscope

The invention discloses a gate oxide failure point positioning method. after removal of a metal layer, a semiconductor structure to be measured obtained after removal of the metal layer is scanned by the use of an electron beam formed by medium and high accelerating voltage so as to obtain an electron microscope with a failure point pattern; and according to the electron microscope, the position of the failure point in a gate oxide is determined so as to more precisely position a breakdown point of the gate oxide. Furthermore, success rate of gate oxide breakdown voltage test failure analysis is raised effectively; preparation time of a follow-up transmission electron microscope sample is further shortened; efficiency of gate oxide breakdown voltage test failure analysis is raised; and necessary conditions are provided for the preparation of the transmission electron microscope sample which requires precise positioning. In addition, the breakdown point of the gate oxide and failure analysis of the gate oxide can still be positioned precisely when an optical positioning machine cannot be used.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

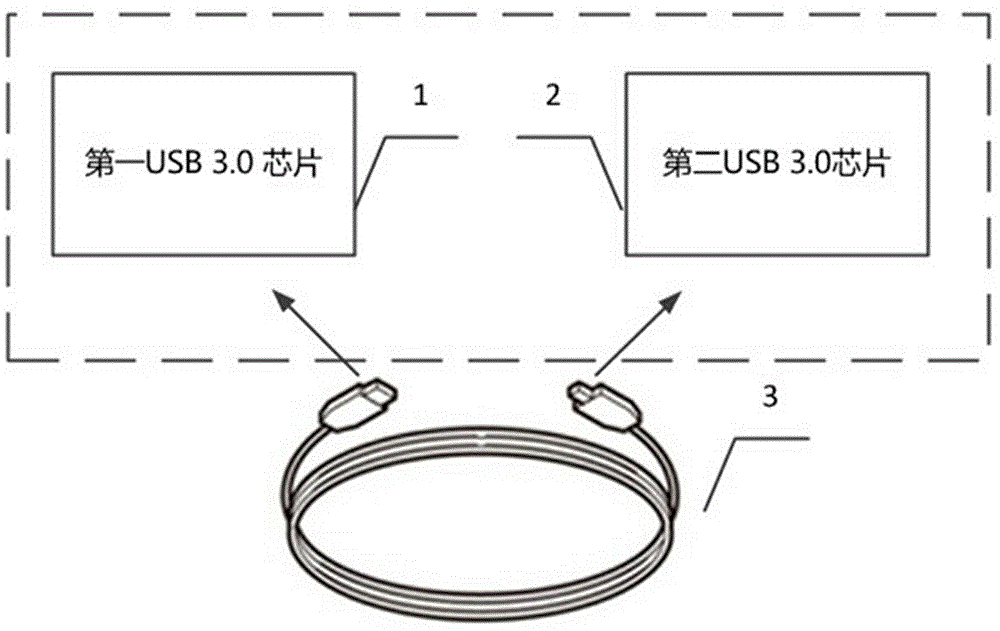

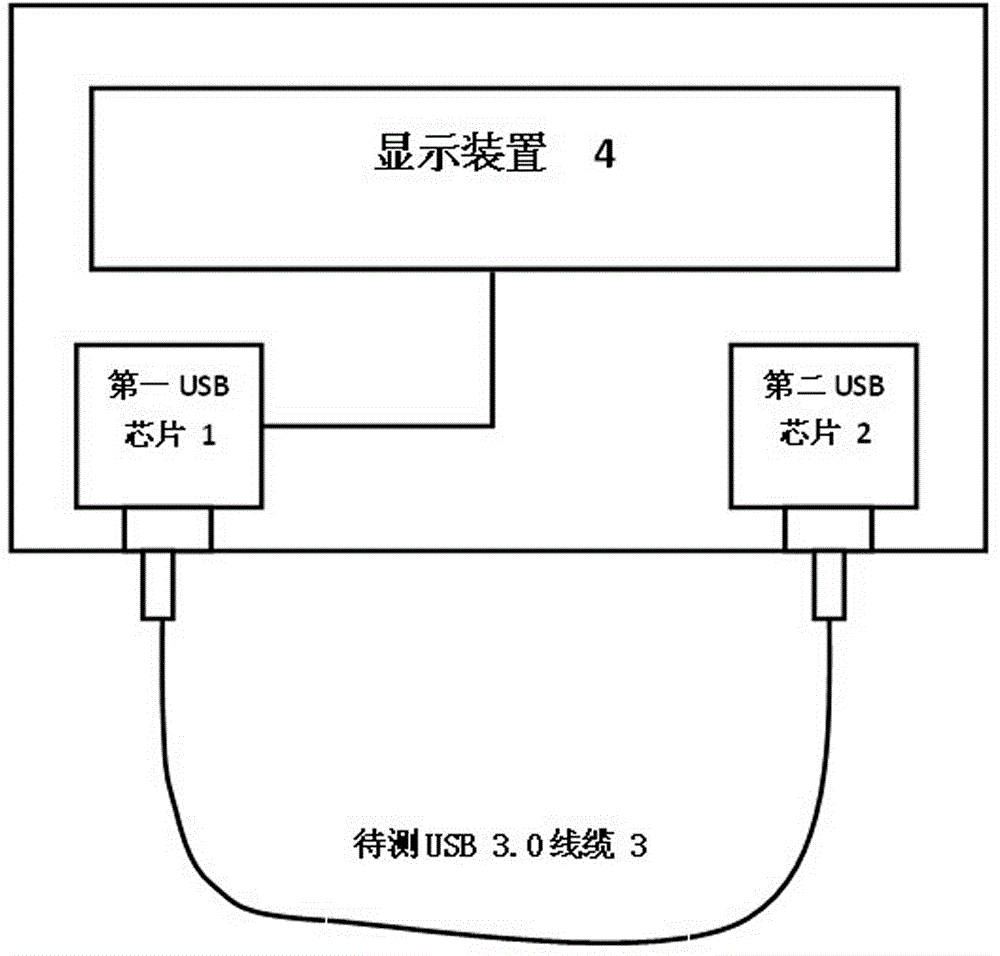

USB 3.0 cable testing method and device

The invention discloses a USB 3.0 cable testing method and device. The device comprises two USB 3.0 chips and a USB 3.0 cable to be tested, wherein the USB 3.0 cable to be tested is connected between the two chips. The two USB 3.0 chips are set to enter a loop mode, the training result of the loop mode of the USB chips is observed, and whether the cable to be tested is normal or not is judged. If the USB chips cannot enter the loop mode, the cable to be tested cannot be practically used. If the USB chip can enter the loop mode, the quality of the cable to be tested is judged according to the error number in the USB chips. When the error number is larger than a threshold value, testing is thought to be unsuccessful. According to the USB 3.0 cable testing method and device, the loop mode is utilized, the operation mode is simple, cost is low, the using process of a final user is simulated in the testing process, the testing result is in good consistency with the performance of the USB 3.0 cable in the final using process, the worker involving frequency is very low in the testing process, and testing efficiency is greatly improved.

Owner:EVERPRO TECH COMPANY

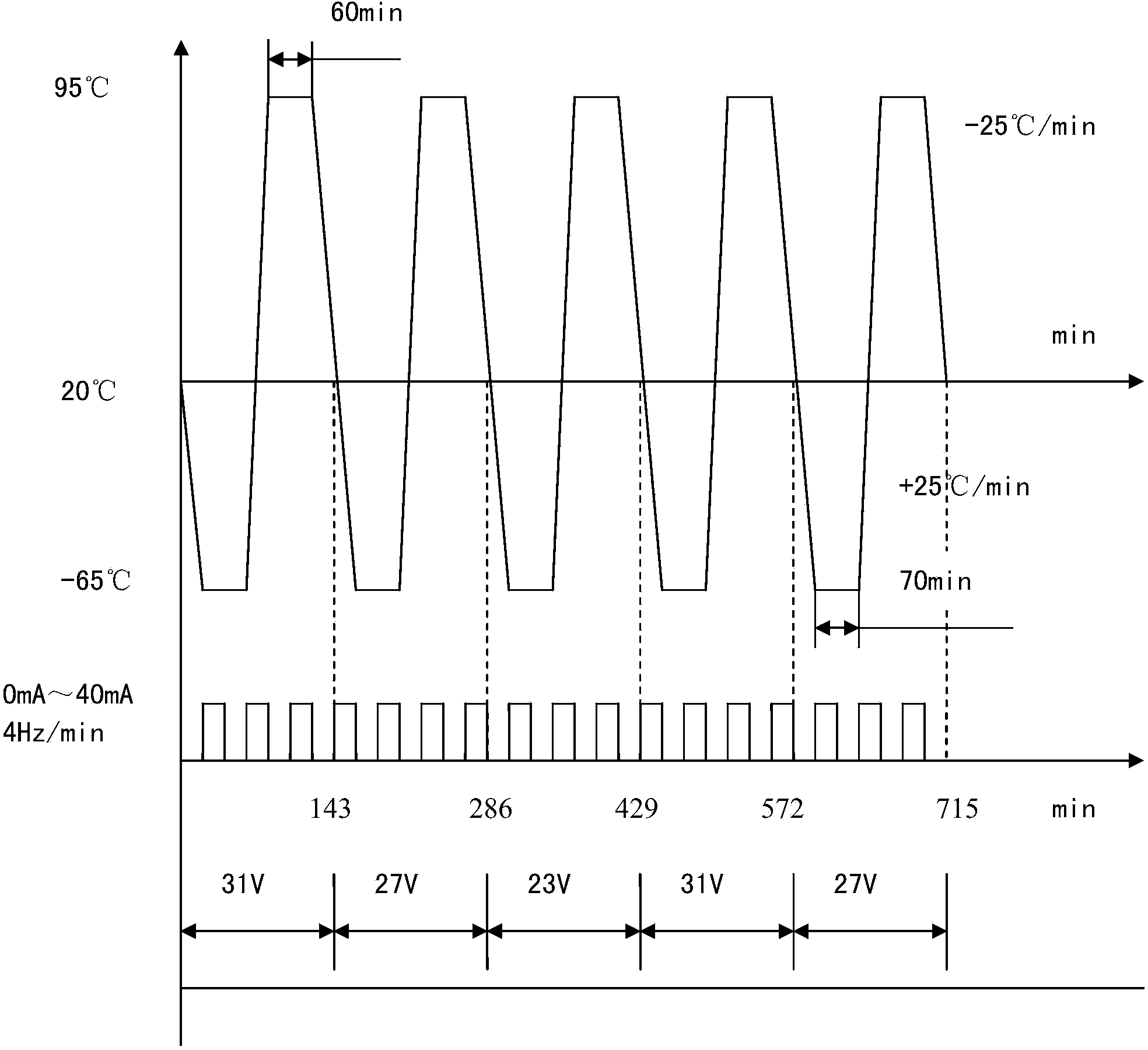

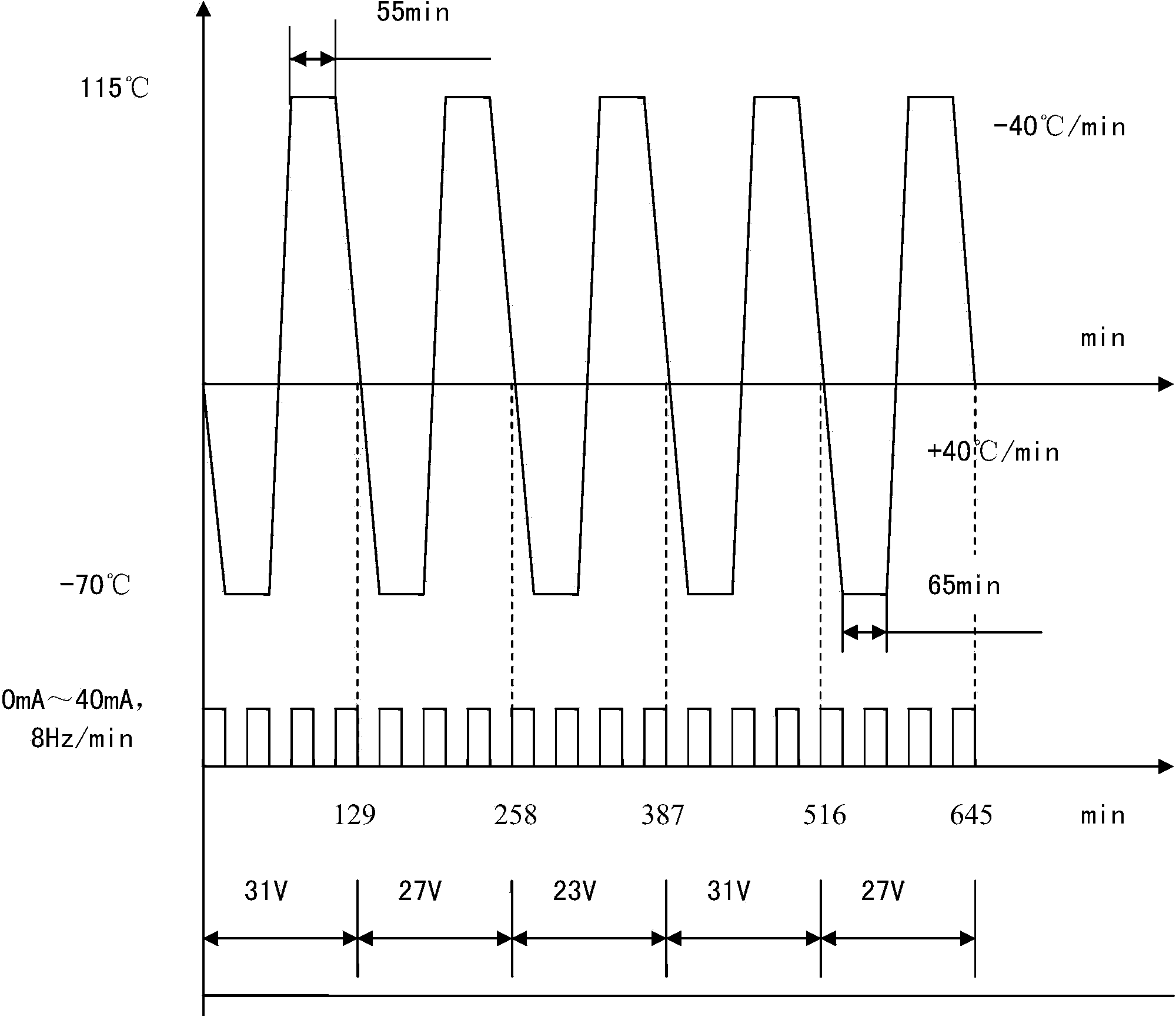

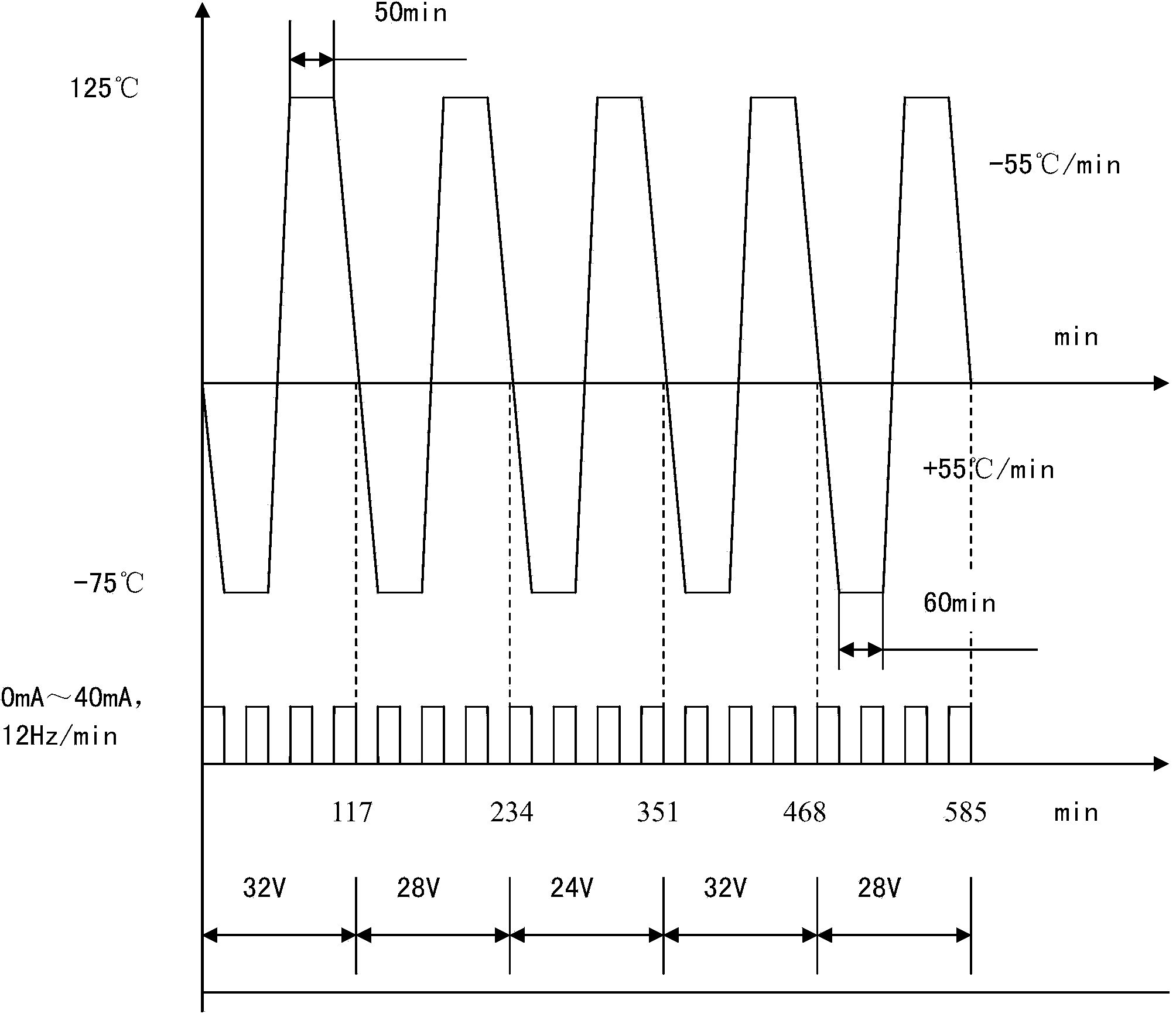

Method for testing failure of airplane antiskid brake control box under condition of temperature cycle

InactiveCN104049630APlay a green effect of energy saving and consumption reductionPotential for failureElectric testing/monitoringJet aeroplaneEngineering

The invention provides a method for testing failure of an airplane antiskid brake control box under the condition of temperature cycle. According to the method, the antiskid brake working current is applied in the temperature cycle test process of the airplane antiskid brake control box. The high temperature value in the temperature cycle process is determined according to the high temperature working limit of the antiskid brake control box, the low temperature value in the temperature cycle process is determined according to the low temperature working limit of the antiskid brake control box, and the determined temperature cycle profile is suitable for testing the manufacturing defect that the antiskid brake control box is sensitive to steady change and can stimulate hidden dangers of the antiskid brake control box in the working state so as to effectively verify whether the development defect of the antiskid brake control box exists or not and provides the improvement suggestions according to the test result.

Owner:XIAN AVIATION BRAKE TECH

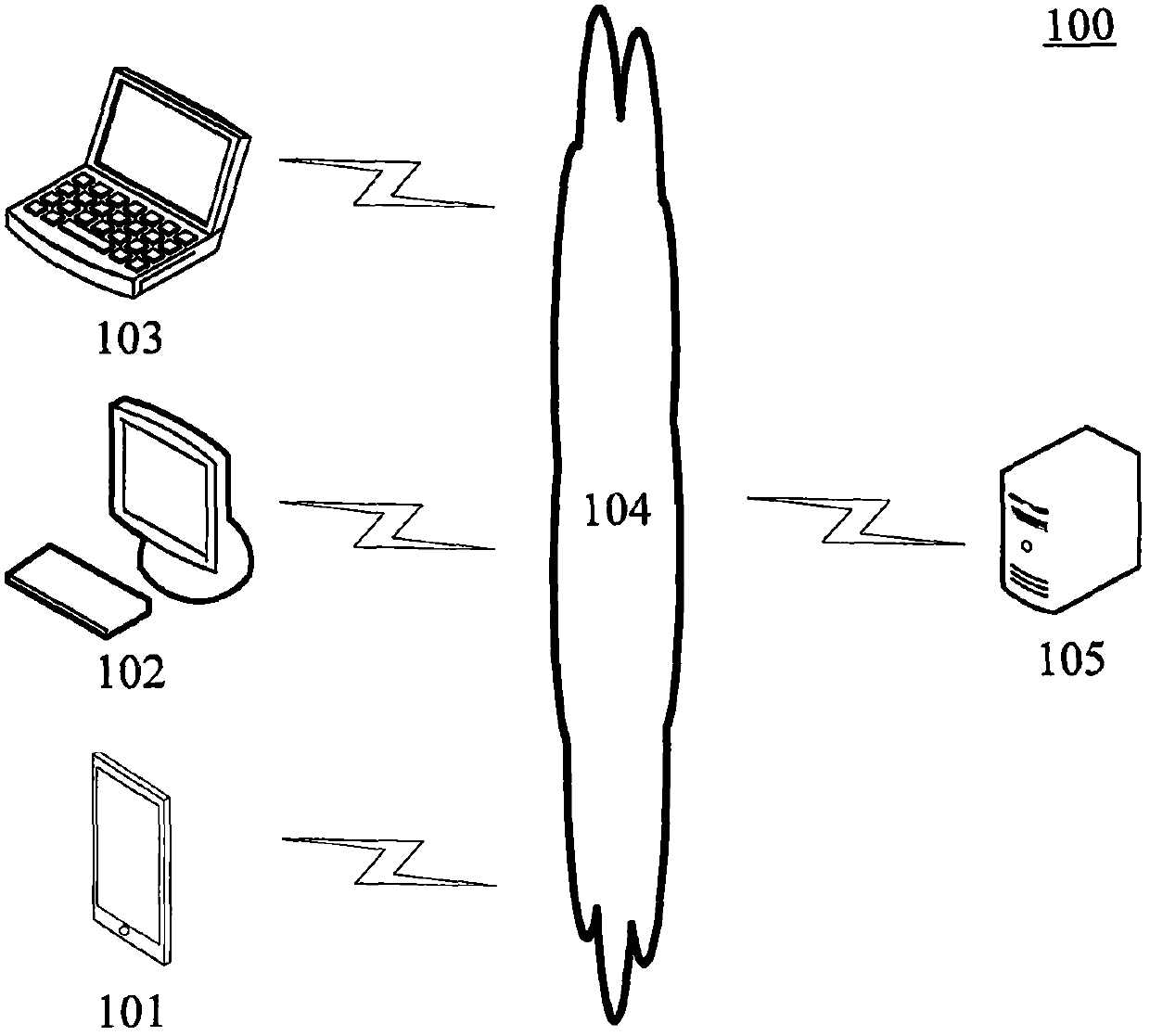

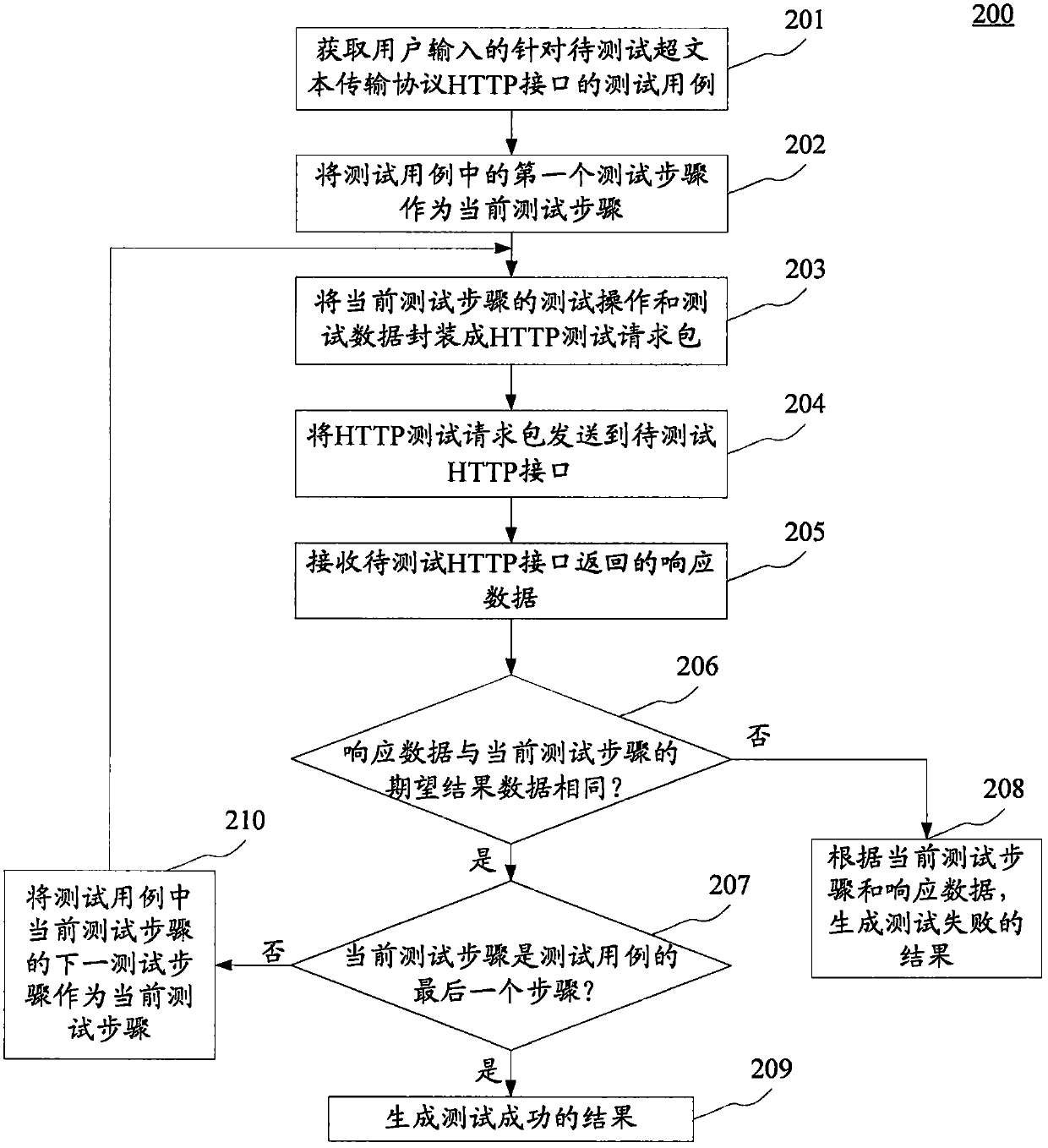

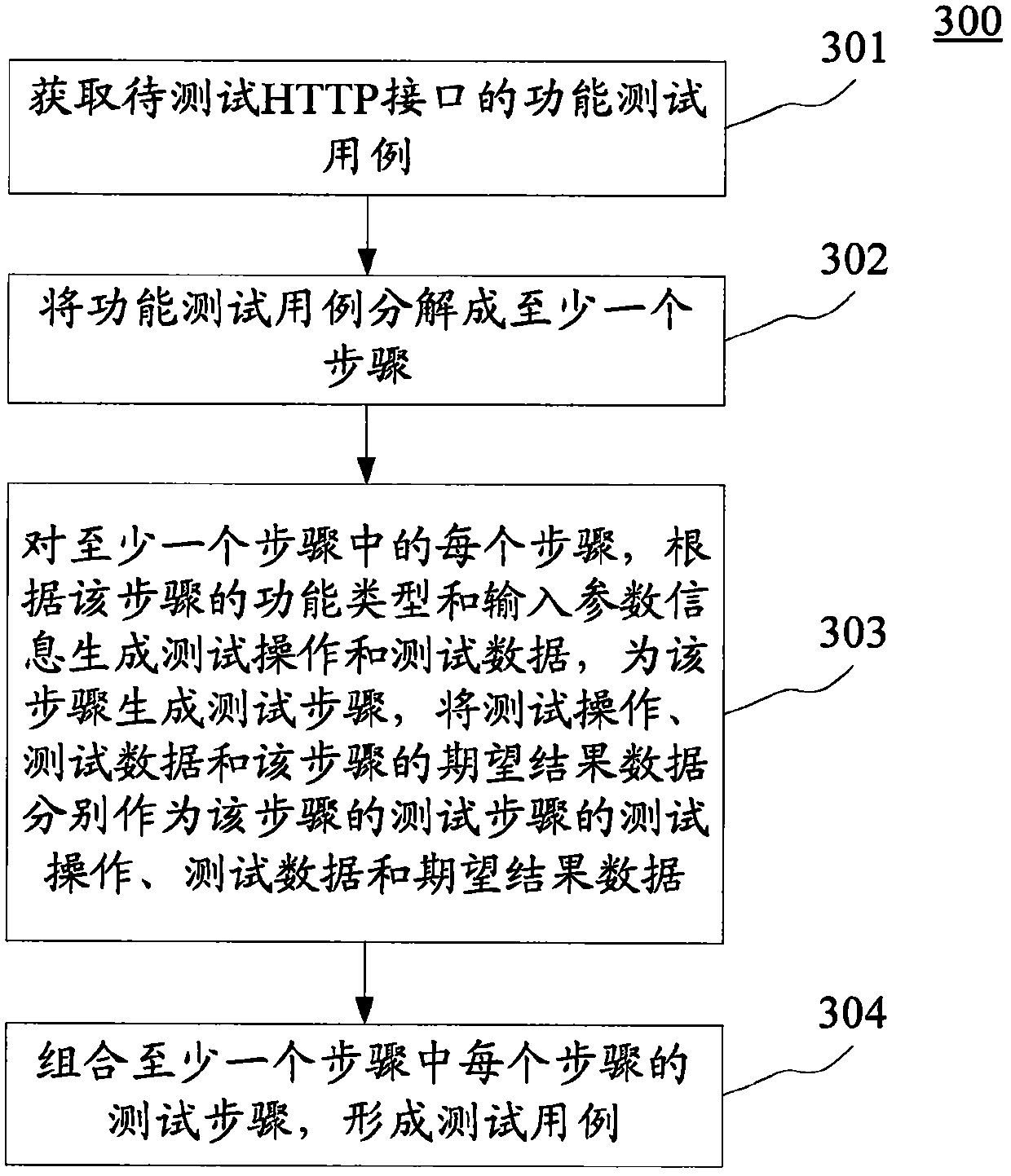

HTTP interface test method and apparatus

PendingCN107797911AAchieve independenceSpeed up developmentSoftware testing/debuggingTest efficiencyComputer hardware

The invention discloses an HTTP interface test method and apparatus. A specific embodiment of the method comprises the steps of obtaining a test case input by a user and aiming at a to-be-tested HTTPinterface; taking a first test step in the test case as a current test step, and executing the following HTTP interface test steps of packaging test operation and test data of the current test step into an HTTP test request package and sending the HTTP test request package to the to-be-tested HTTP interface; judging whether response data returned by the to-be-tested HTTP interface is the same as expected result data of the current test step or not, and if the response data is different from the expected result data, generating a test failure result; if the response data is the same as the expected result data, further judging whether the current test step is a final step of the test case or not, and if yes, generating a test success result; and if not, taking the next test step as the current test step, and continuing to execute the HTTP interface test steps. According to the method and the apparatus, the HTTP interface test efficiency is improved.

Owner:BEIJING JINGDONG SHANGKE INFORMATION TECH CO LTD +1

Digital bist test scheme for ADC/DAC circuits

InactiveUS20070182612A1Test accurateShorten test timeElectric signal transmission systemsElectrical testingGreek letter sigmaAnalog-to-digital converter

A generalized method for testing DACs (Digital to Analog Converters) and ADCs (Analog to Digital Converters), such as Sigma Delta (Successive Approximation), Pipeline or Flash ADCs. The DACs and ADCs are tested in pairs using a Digital Tester and on chip test circuitry. The DACs and ADCs may be tested at the highest clock frequency allowed in the specification, shortening test time. The test circuits required for this test scheme comprise cell logic two multiplexer cells and an internal Analog Test Bus. This scheme is extendable to the testing of many DACs and ADCs on the same IC. The number of DACs and ADCs need not be equal. Furthermore, the DACs may have more (or less) bits (addresses) than the ADCs. An ADC may be tested with more than one DAC or vice versa to determine which cell is at fault if a test fails.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

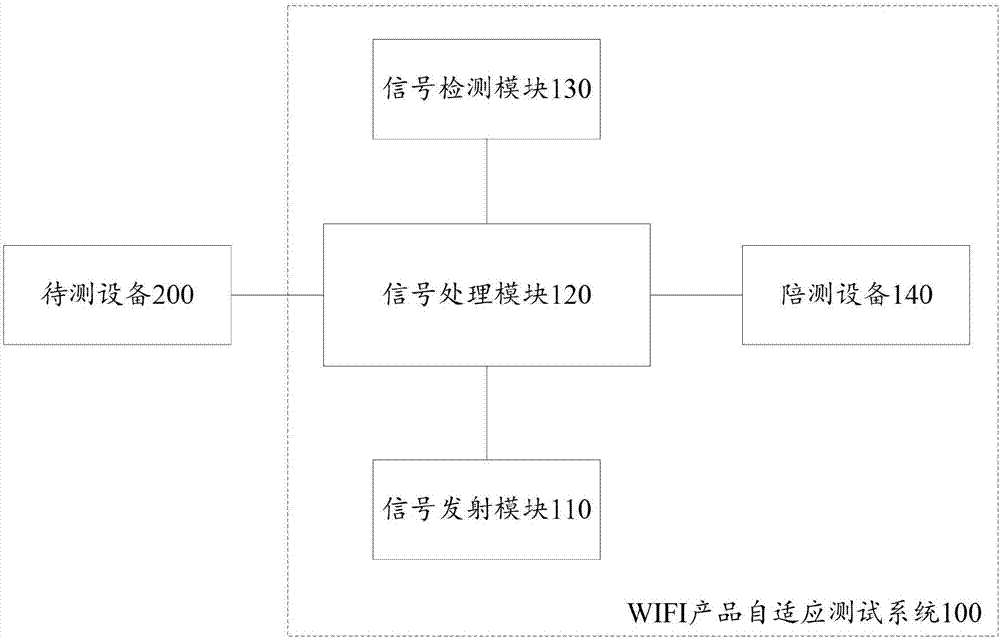

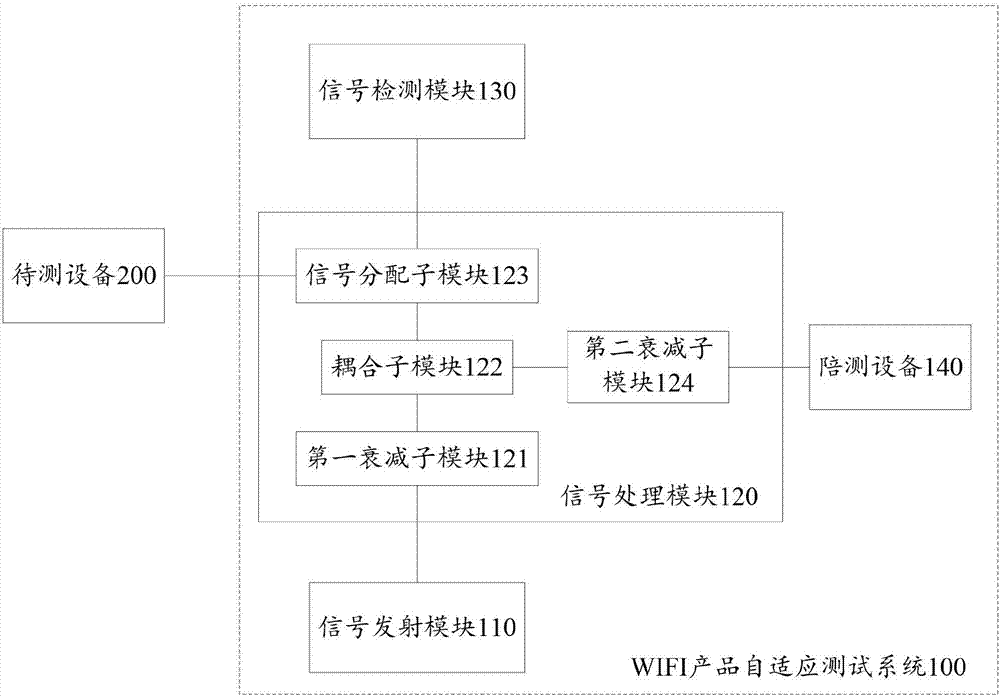

WIFI product adaptivity test system and method

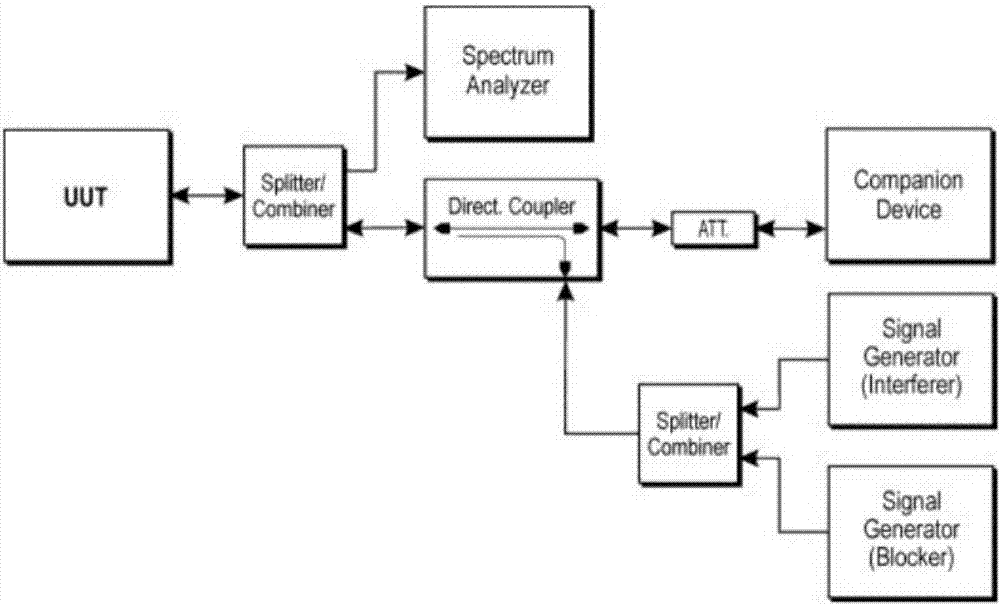

InactiveCN107888300ALower requirementNo conflictTransmitters monitoringReceivers monitoringUltrasound attenuationComputer module

The self-adaptive test system for WIFI products of the present invention includes: a signal transmitting module, a signal processing module, a signal detection module and accompanying testing equipment; wherein: the signal transmitting module is used to send interference signals and blocking signals to the signal according to pre-configured working parameters A processing module; a signal processing module, which is used to attenuate the interference signal and the blocking signal according to the pre-acquired attenuation data, and then couple them to the communication link between the device under test and the device under test; it is also used to transmit the signal sent by the device under test The test signal is sent to the signal detection module and the accompanying test device after signal processing; the signal detection module is used to detect the test signal after signal processing; when the test signal is detected, it is determined that the self-adaptive test of the device under test is unqualified; When no test signal is detected, it is determined that the adaptive test of the device under test is qualified. The invention reduces the test cost, and each module of the test is easy to obtain and easy to operate.

Owner:台州市吉吉知识产权运营有限公司

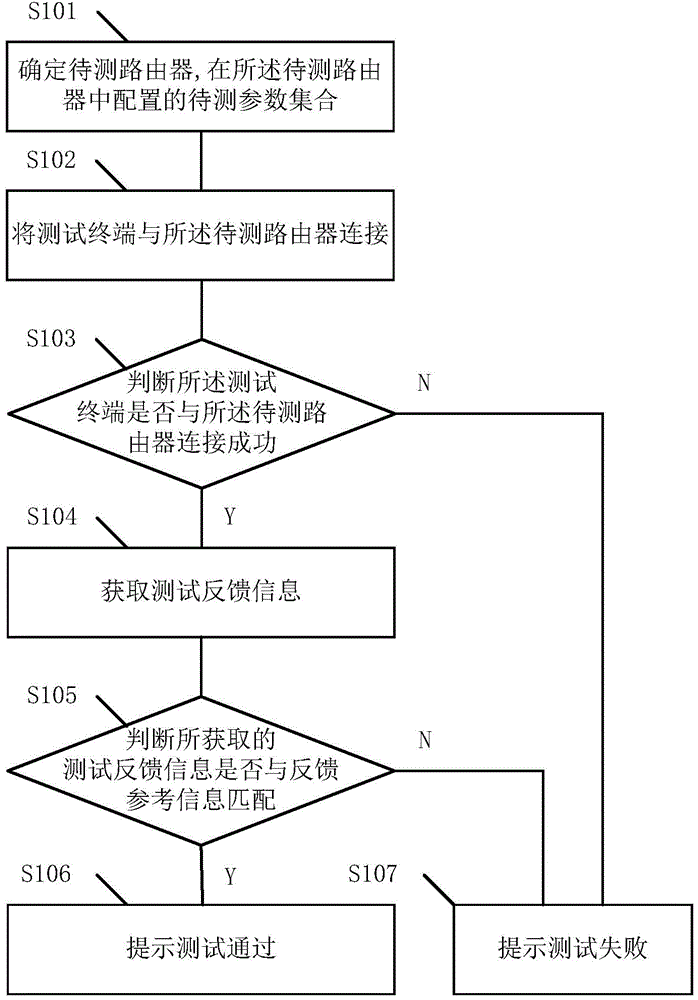

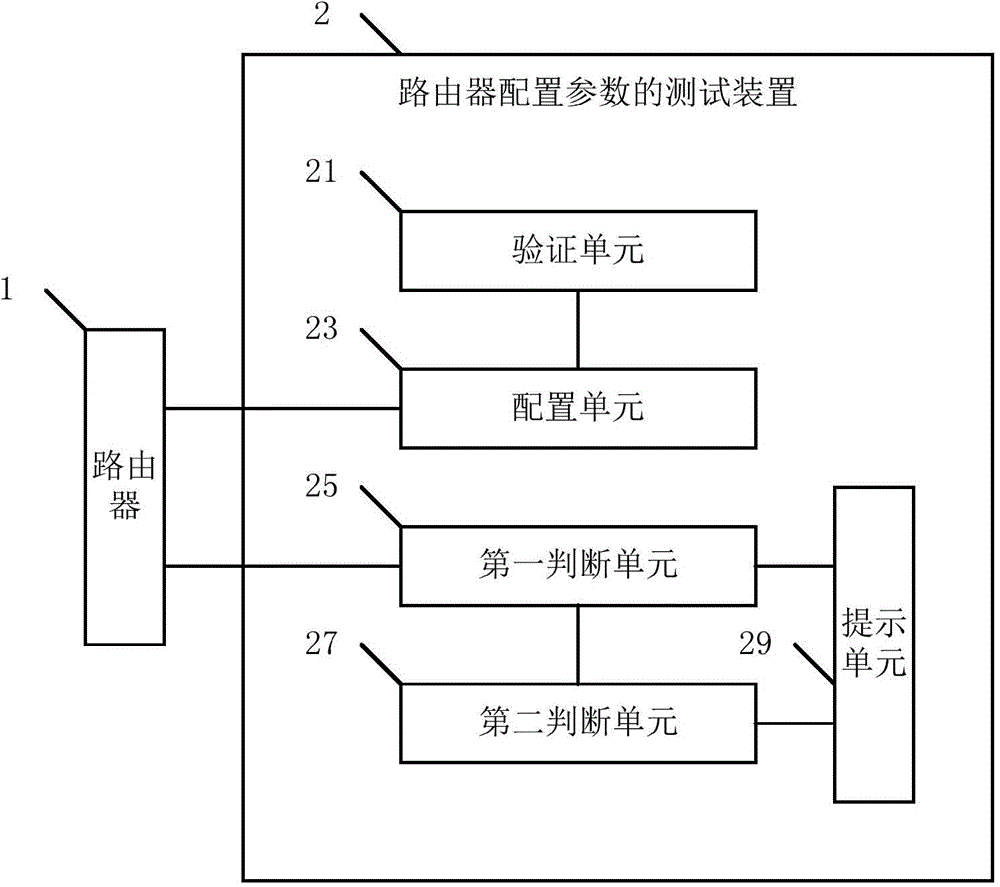

Method and device for testing configuration parameters of router

ActiveCN104486158AReduce labor costsShorten the test cycleData switching networksSoftware engineeringTest failure

The invention provides a method and a device for testing configuration parameters of a router. The method comprises the following steps: determining the router to be tested; configuring a set of the parameters to be tested in the router to be tested; connecting a testing terminal with the router to be tested; determining whether the testing terminal is connected successfully with the testing router or not; if so, acquiring the test feedback information, and determining whether the acquired test feedback information is in matching with the feedback reference information or not; if the matching is successful, reminding of test pass; if the matching fails, reminding of test failure. According to the technical scheme, the method has the advantages that the plurality of parameters of the router are automatically tested, so that the cost of labor in testing can be reduced, the test cycle is reduced, the cost of product development is reduced, and error test rate caused by repetitive operation can be avoided.

Owner:台州市吉吉知识产权运营有限公司

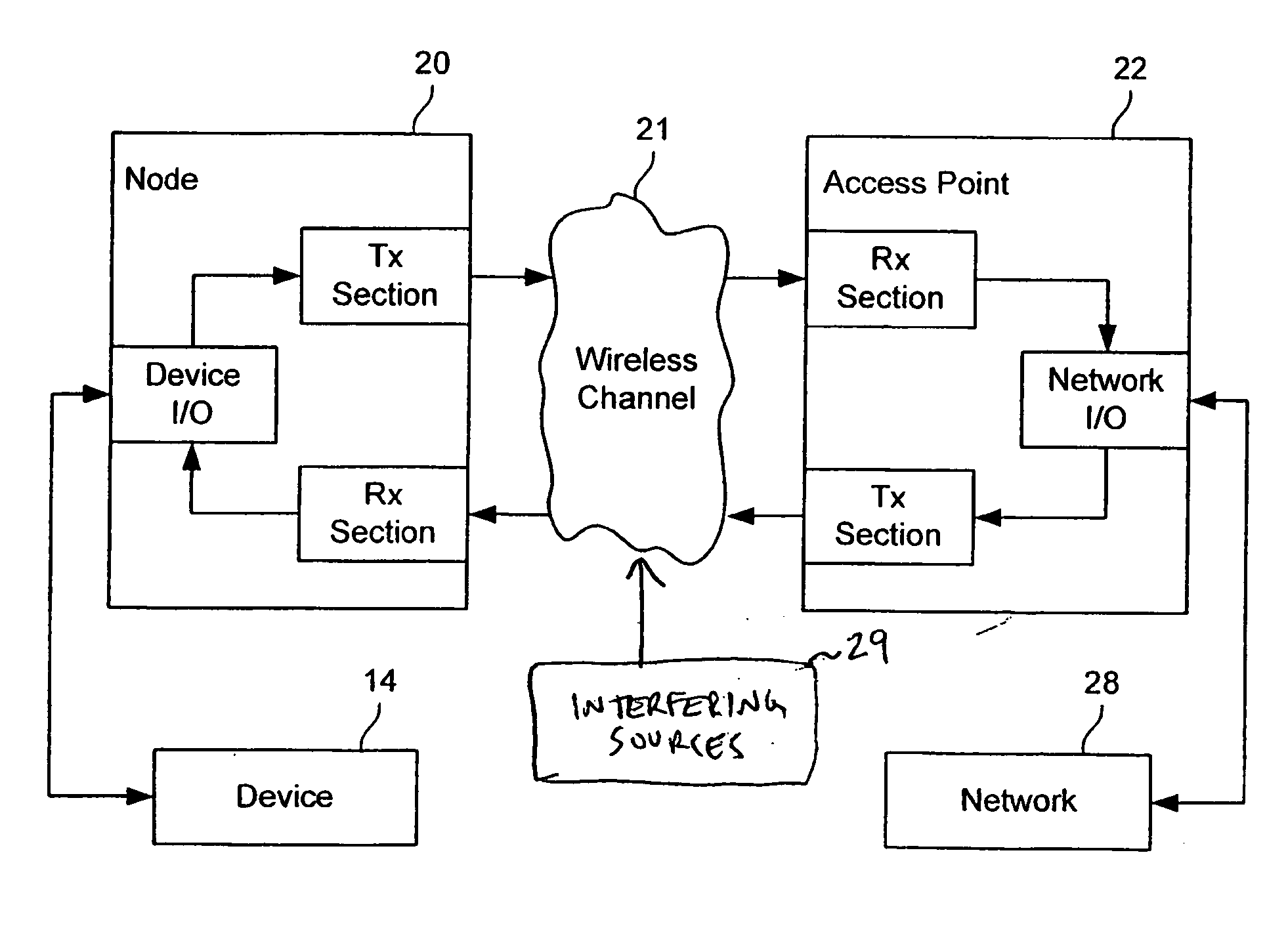

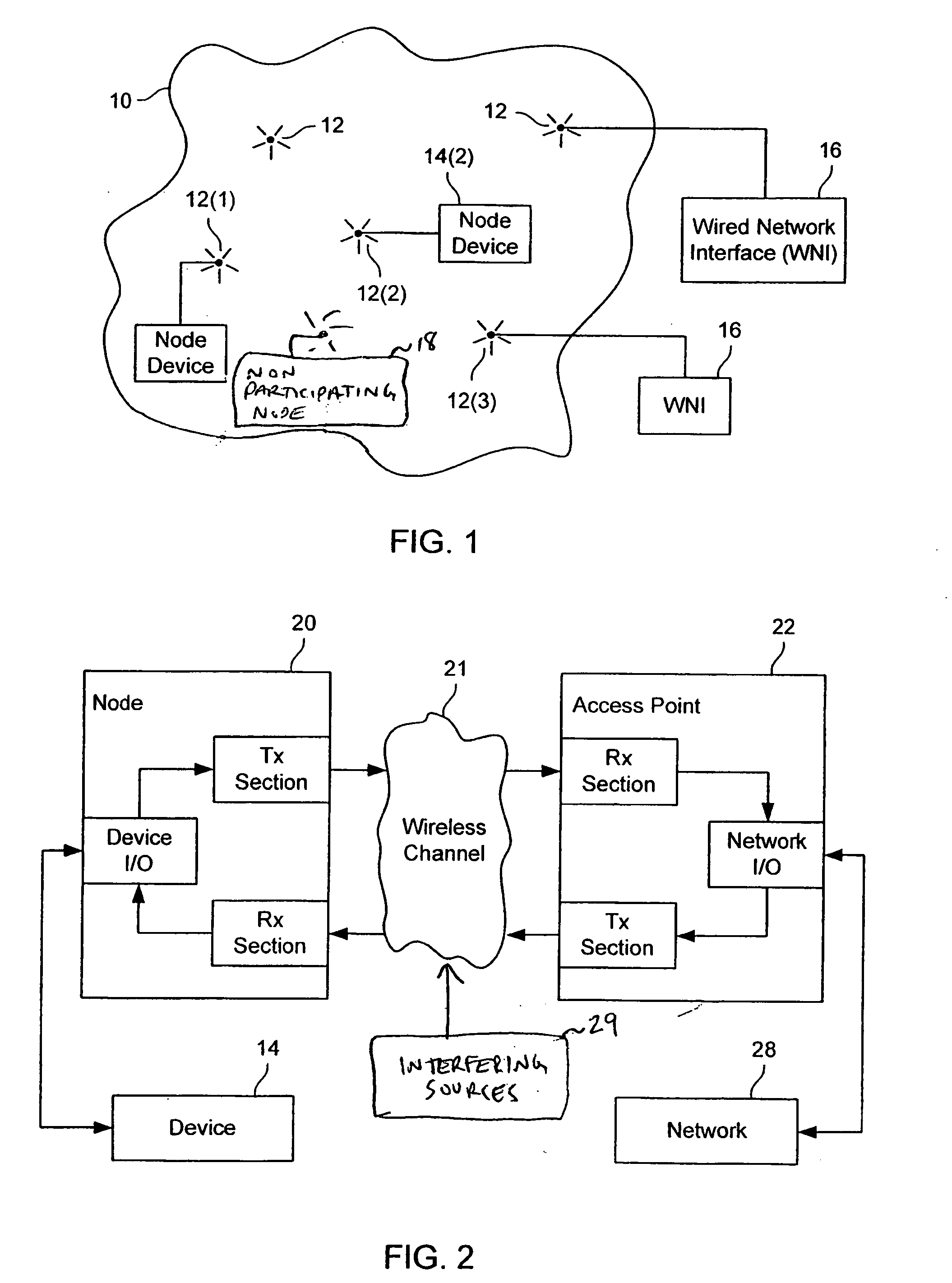

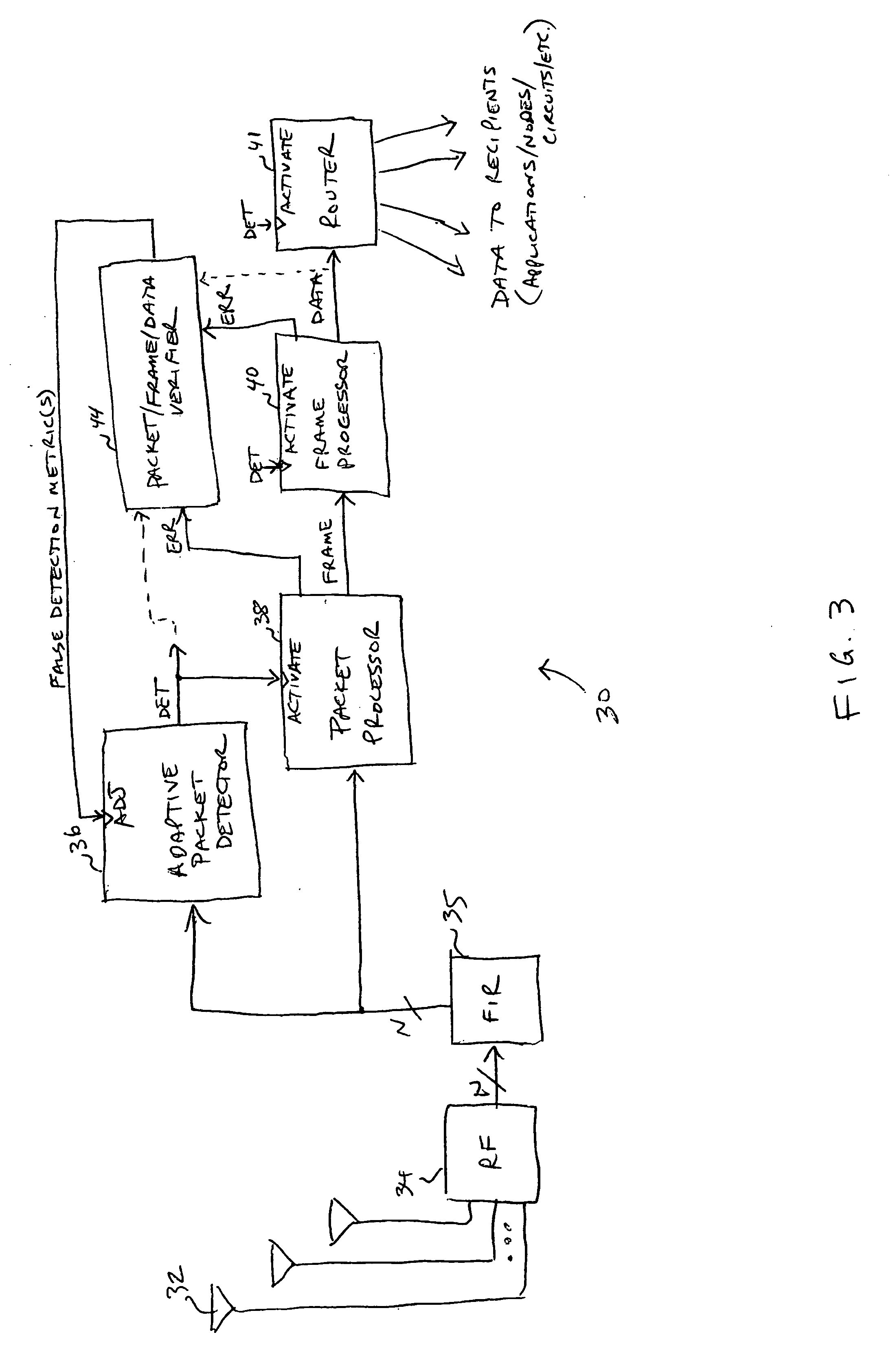

Adaptive packet detection for detecting packets in a wireless medium

ActiveUS20050190786A1Reduce probabilityError preventionNetwork traffic/resource managementData fieldSelf adaptive

In a packet detector, one or more tests are performed for packet detection according to packet detection parameters associated with the one or more tests, a rate of false detection is measured, and the packet detection parameters are adjusted accordingly to reduce the rate of false detection. The rate of false detection might be determined by analyzing post-detection and processing of a signal deemed to be a signal representing a packet for a failure of decoding indicative of a false detection. Such analysis might include testing for a failed SFD search, training symbol anomalies, poor conditioning of metrics used to determine frequency offset and OFDM timing, incorrect data fields, or the like.

Owner:QUALCOMM INC

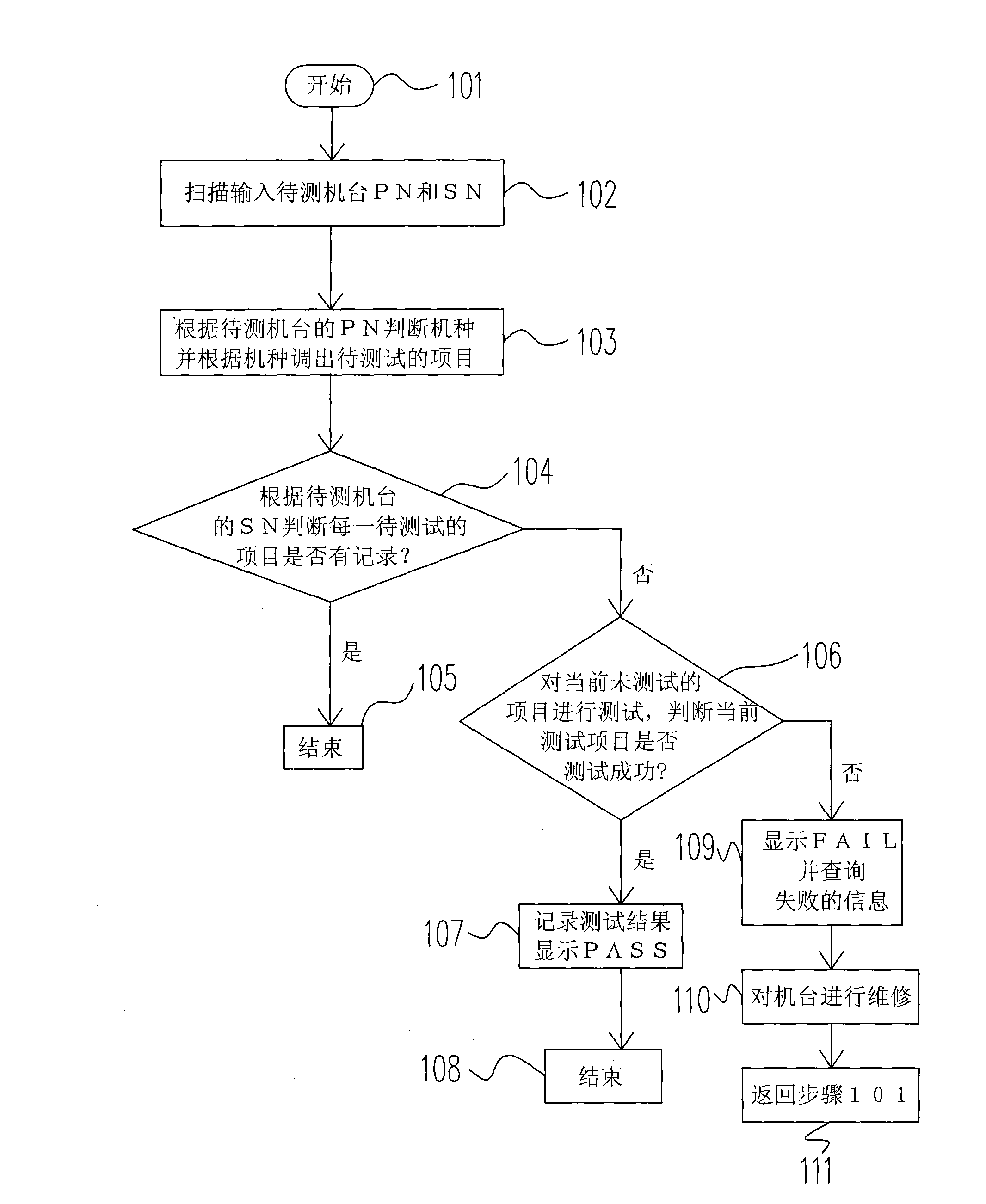

Method for automatically testing machine platform

InactiveCN101526570AEasy and fast testingEasy to knowElectrical testingSoftware engineeringTest failure

The invention provides a method for automatically testing a machine platform, which is used for testing various machine types of a Dot hill system. The method mainly comprises the following steps: a, beginning testing; b, scanning a part number and a serial number input to the machine platform to be tested; c, judging the machine type according to the part number and calling out corresponding items to be tested; d, inquiring whether each item to be tested has record according to the serial number, and judging the tested items and the non-tested items of the machine platform to be tested; e, if each test item has record, ending the test, and preparing the test for a next machine platform to be tested; and f, if the current test item has no record, testing the non-tested items, judging whether the test is successful, and returning to step a till the test of all non-tested items is ended. The method is not only convenient and quick to test, but also is convenient for a tester to acquire the reason causing test failure.

Owner:MITAC COMP (SHUN DE) LTD

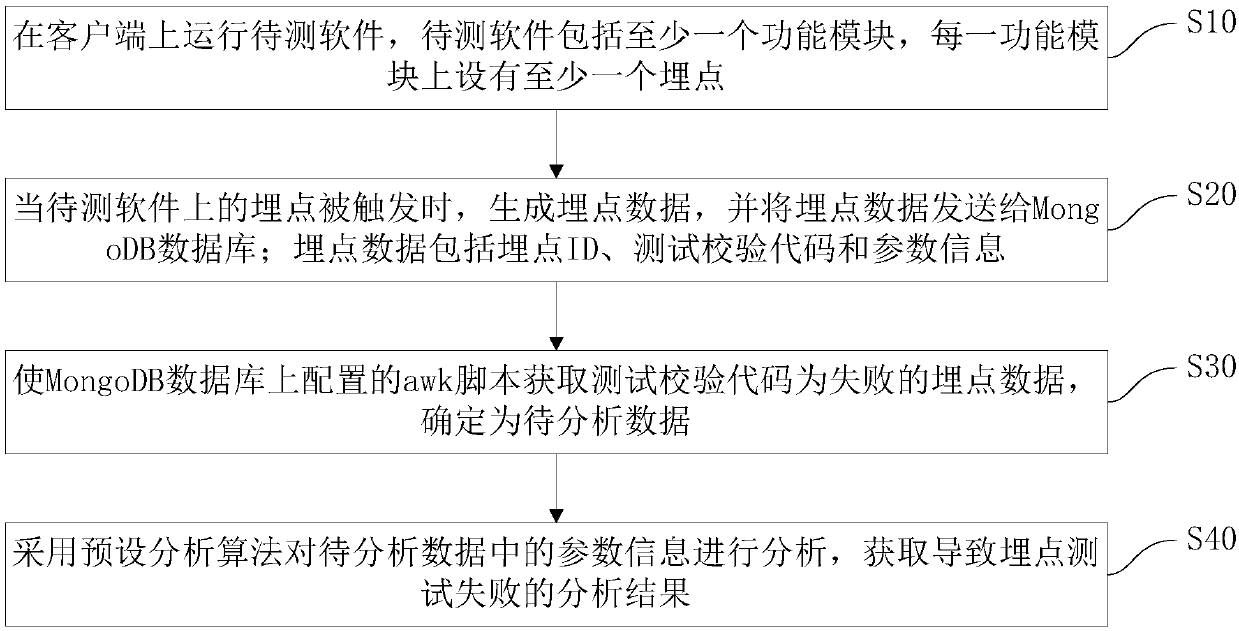

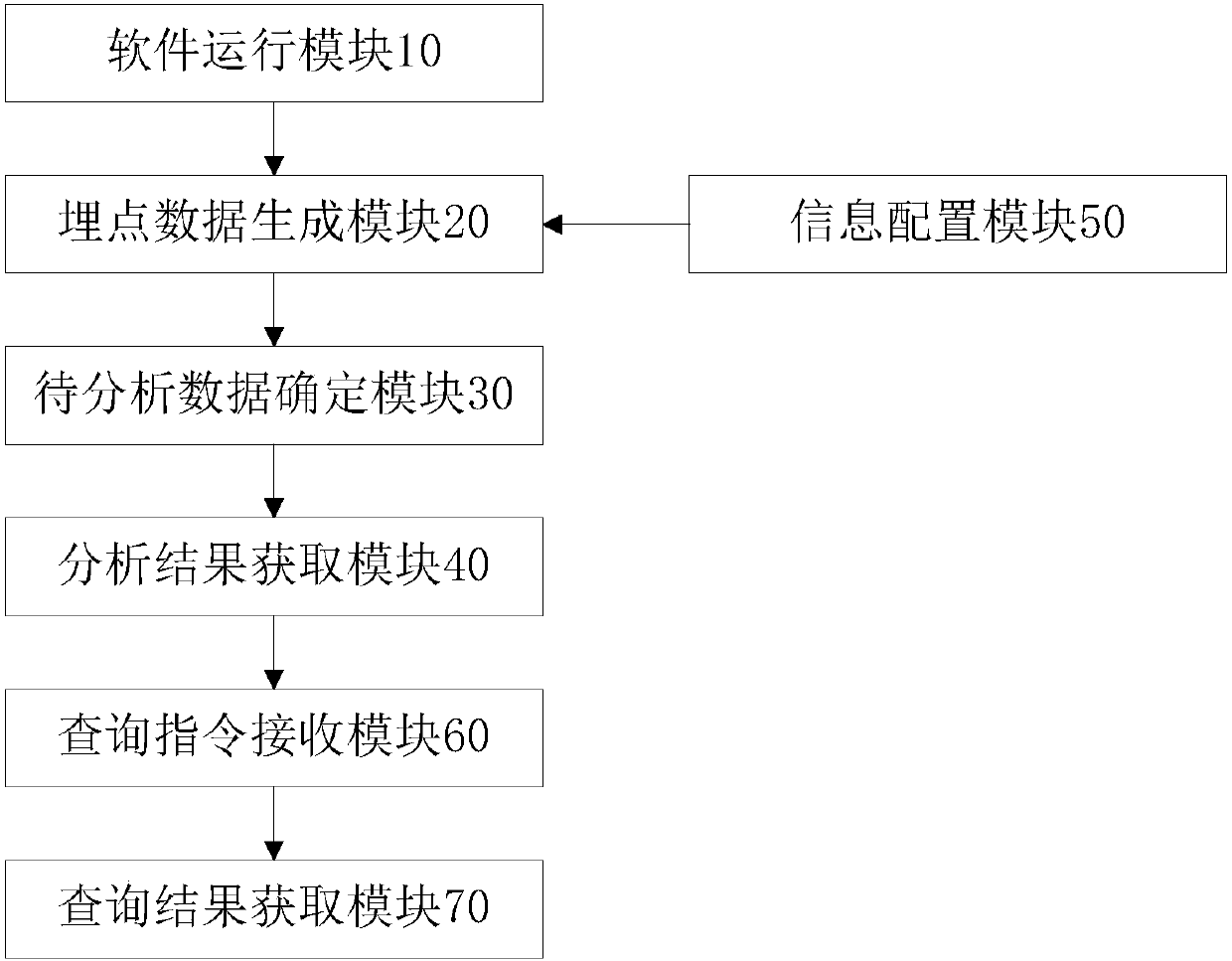

Software testing method and device

ActiveCN107688530AIncrease flexibilityLower the thresholdSoftware testing/debuggingAnalysis dataSoftware engineering

Owner:PING AN TECH (SHENZHEN) CO LTD

Fully-automatic interface pressure measurement method, device, compute device and storage medium

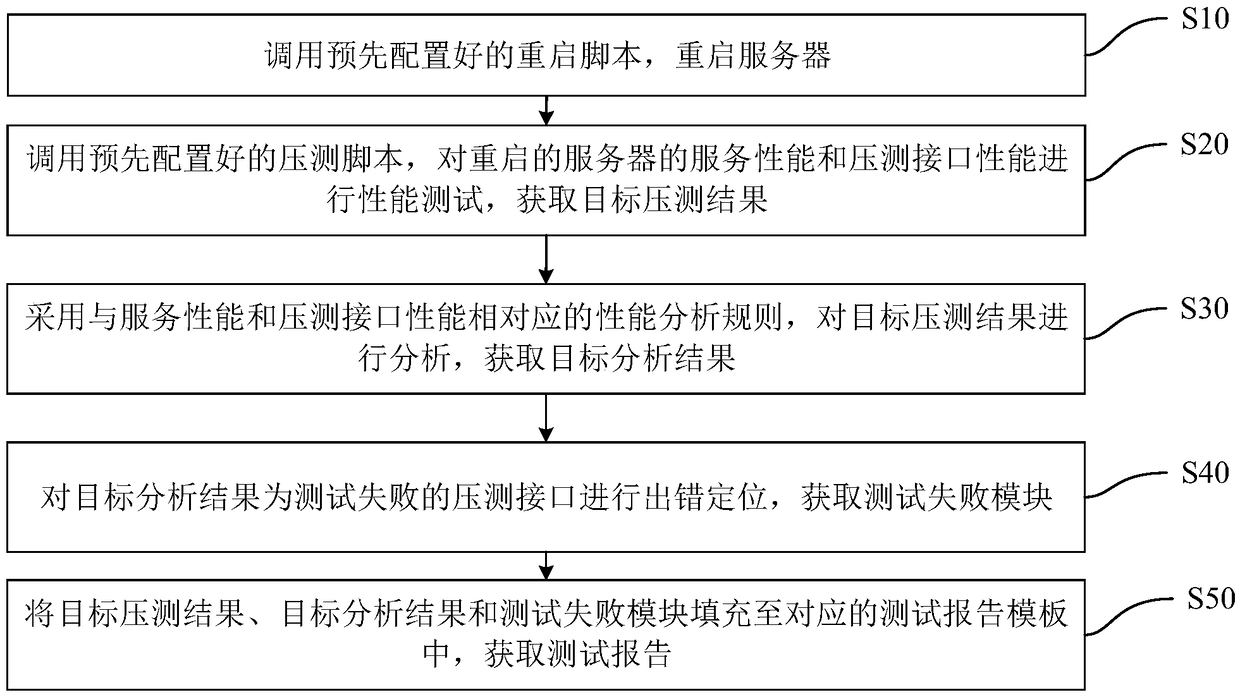

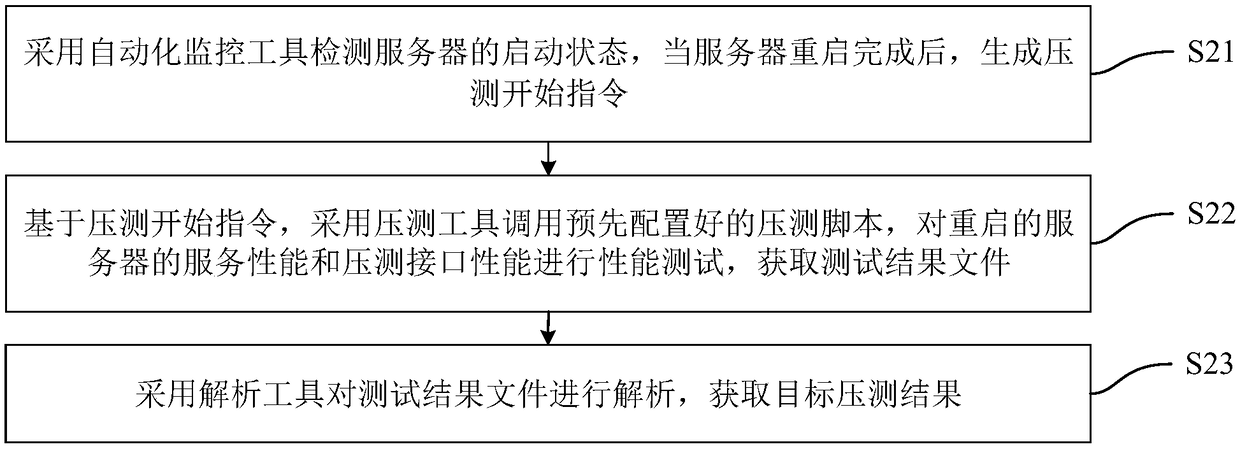

PendingCN109491891AEnsure objectivityImprove acquisition efficiencySoftware testing/debuggingTarget analysisTest script

The invention discloses a fully automatic interface pressure measuring method and device, a computer device and a storage medium. The method comprises the following steps of: calling a pre-configuredrestart script to restart a server; the pre-configured pressure test script is called to test the service performance and pressure test interface performance of the restarted server and obtain the target pressure test result. The performance analysis rules corresponding to the service performance and the pressure measurement interface performance are adopted to analyze the target pressure measurement results and obtain the target analysis results. The pressure test interface whose target analysis result is test failure is positioned for error and the test failure module is obtained. The targetpressure test results, the target analysis results and the test failure module are filled into the corresponding test report template to obtain the test report, so as to solve the problem that the manual analysis of pressure test results takes a long time.

Owner:ONE CONNECT SMART TECH CO LTD SHENZHEN