Built-in self-testing circuit of memory suitable for various periodic testing algorithms

A built-in self-test and memory technology, applied in static memory, instruments, etc., can solve problems such as unfavorable test cost and debugging requirements, inability to use other algorithms, and high development cost, so as to enhance test flexibility, shorten development cycle, and operate convenient effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

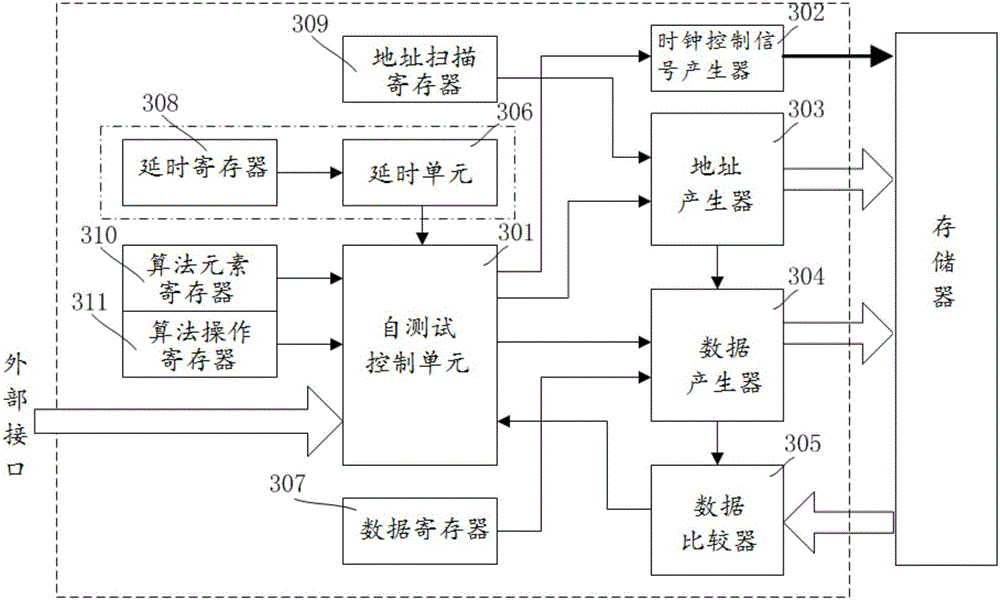

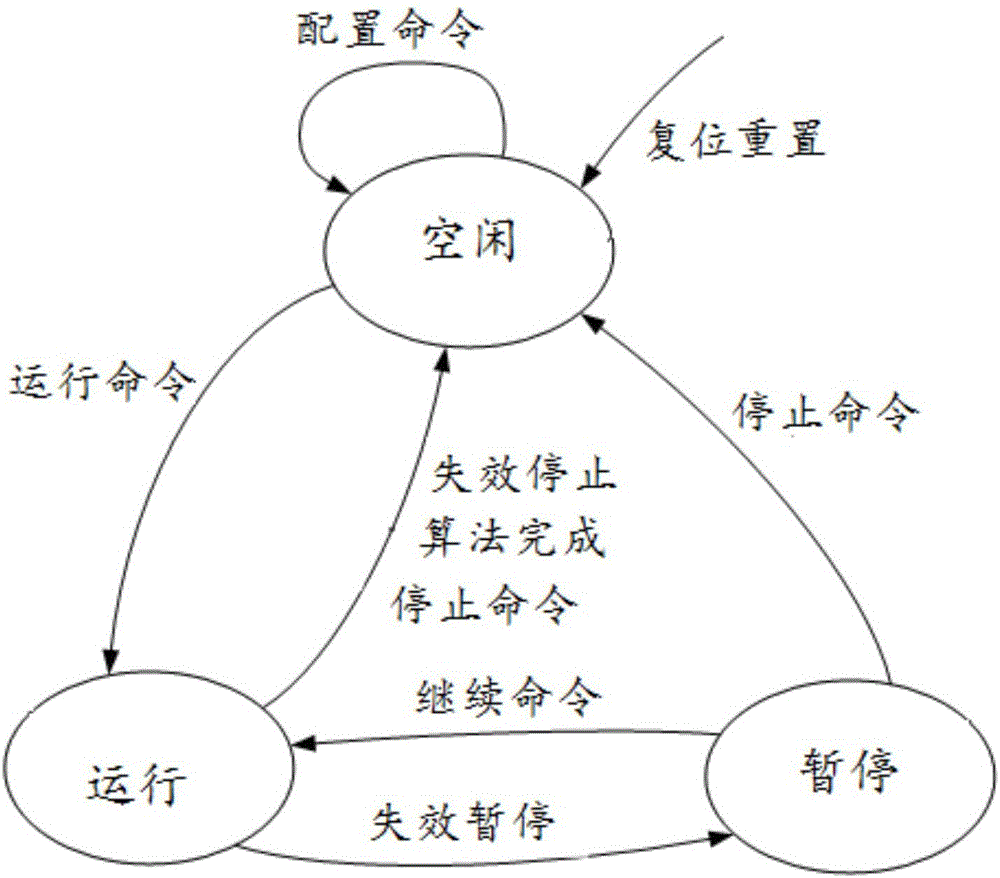

[0025] The invention discloses a general MBIST circuit capable of testing various periodic algorithms for memory. The general algorithm operation core of the circuit, and the configurable characteristics of the specific algorithm can reduce the difficulty of MBIST design, shorten the project development cycle, and strengthen the test and problem analysis capabilities of the memory.

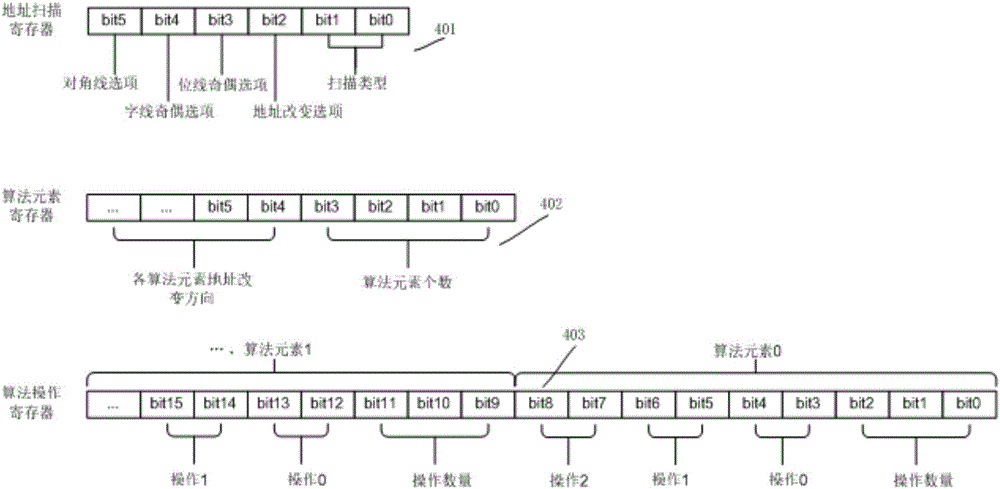

[0026] For the convenience of describing the MBIST circuit of the present invention, here is a brief description of the memory test algorithm. A memory test algorithm is usually notated as: { (Operation 0, Operation 1 ...); ↑ (Operation 0, Operation 1 ...); ↓ (Operation 0, Operation 1 ...); ...}. The test algorithm as a whole is composed of a group of algorithm el...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More