Patents

Literature

163 results about "Memory failure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

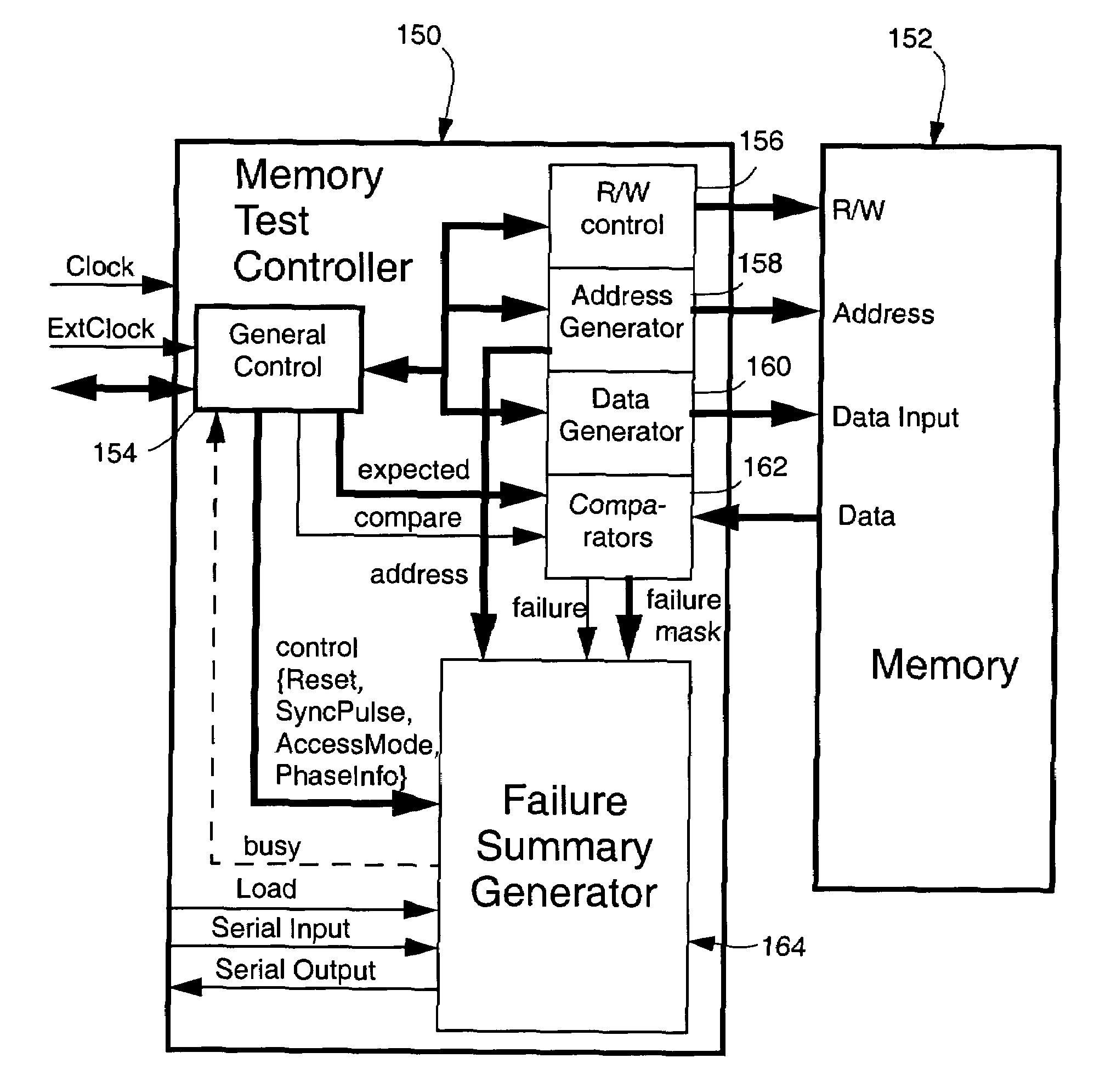

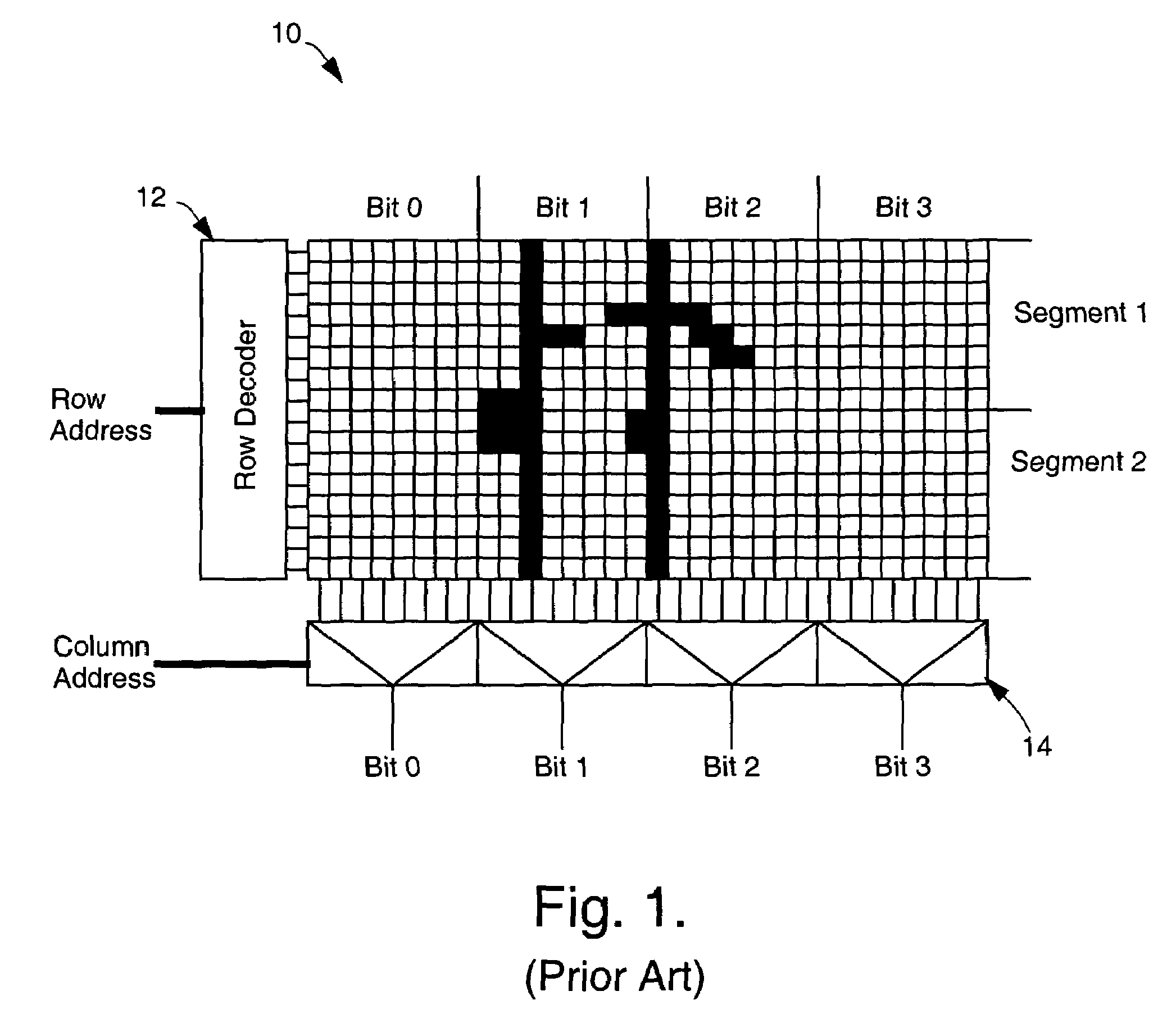

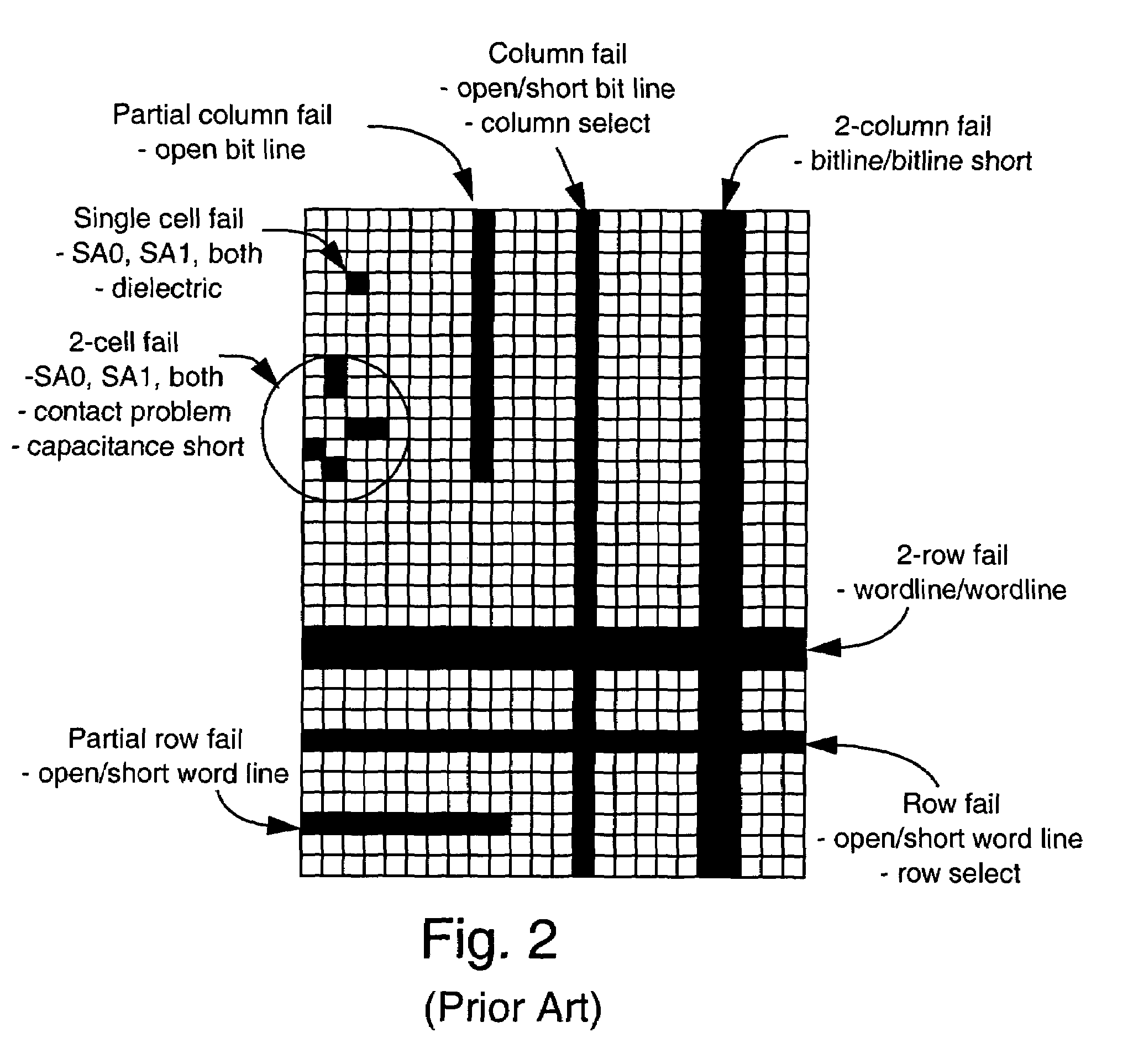

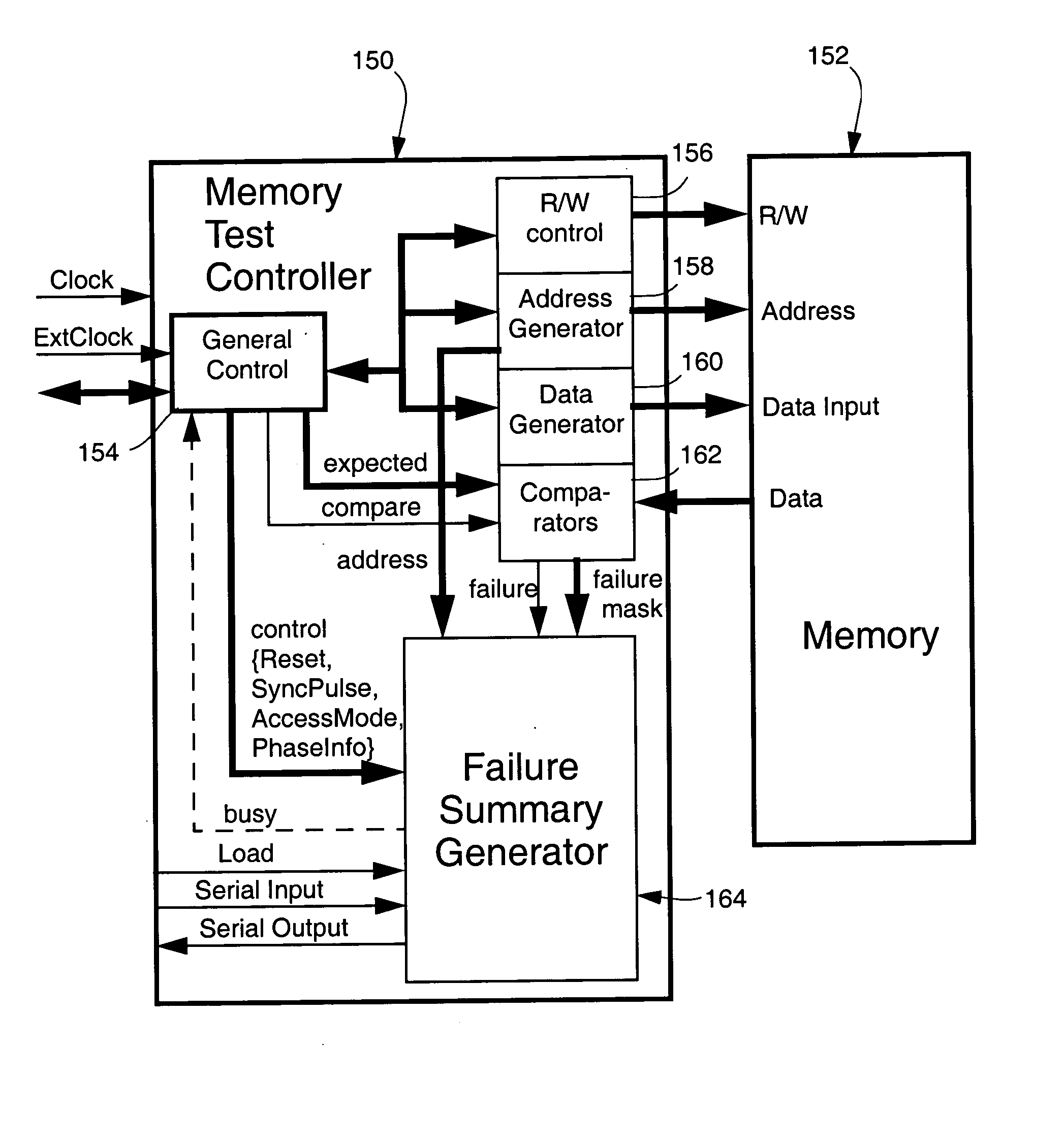

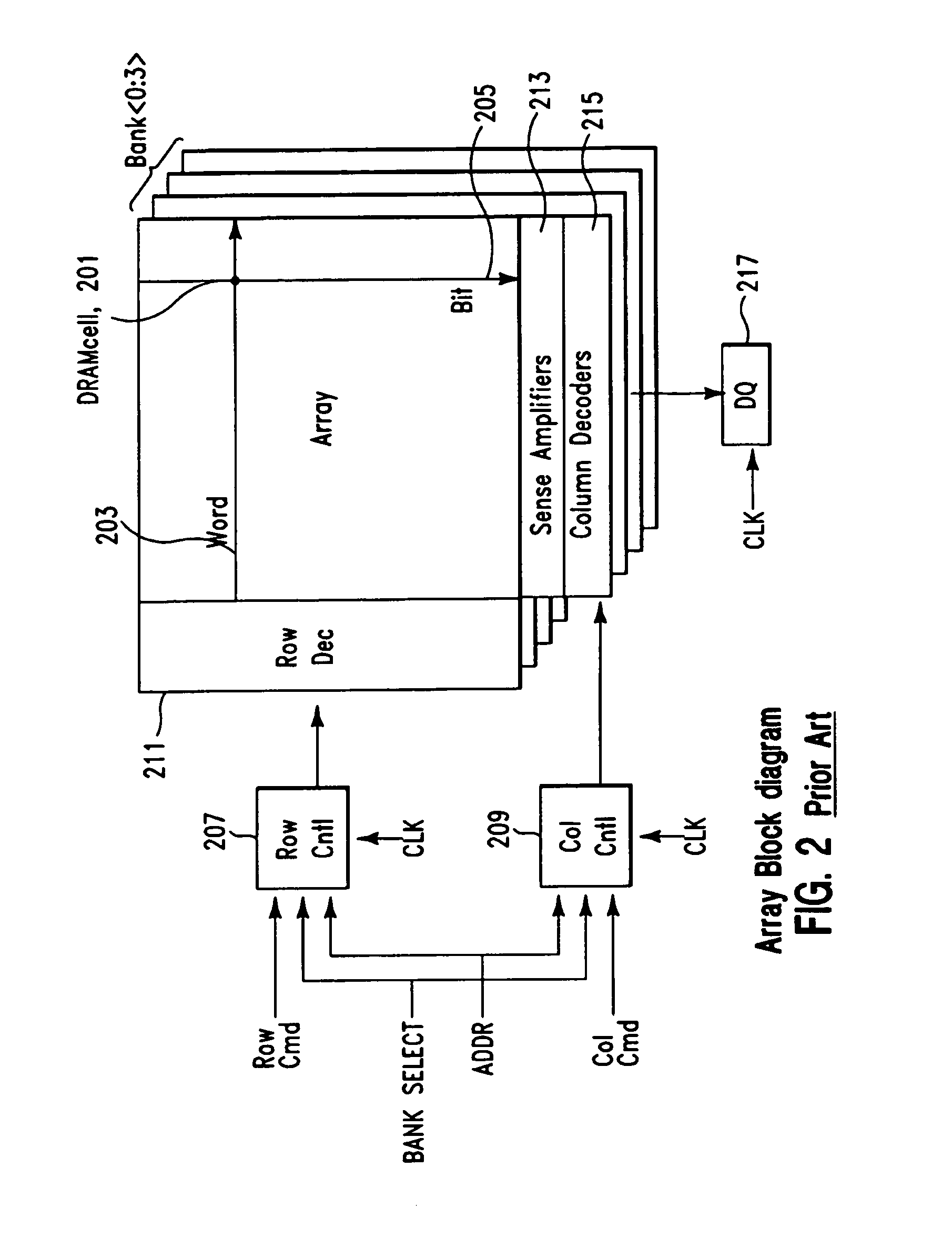

Method and circuit for collecting memory failure information

A method and circuit for collecting memory failure information on-chip and unloading the information in real time while performing a test of memory embedded in a circuit comprises, for each column or row of a memory under test, testing each memory location of the column or row according to a memory test algorithm under control of a first clock, selectively generating a failure summary on-circuit while testing each column or row of the memory; and transferring the failure summary from the circuit under control of a second clock within the time required to test the next column or row, if any, of the memory under test.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

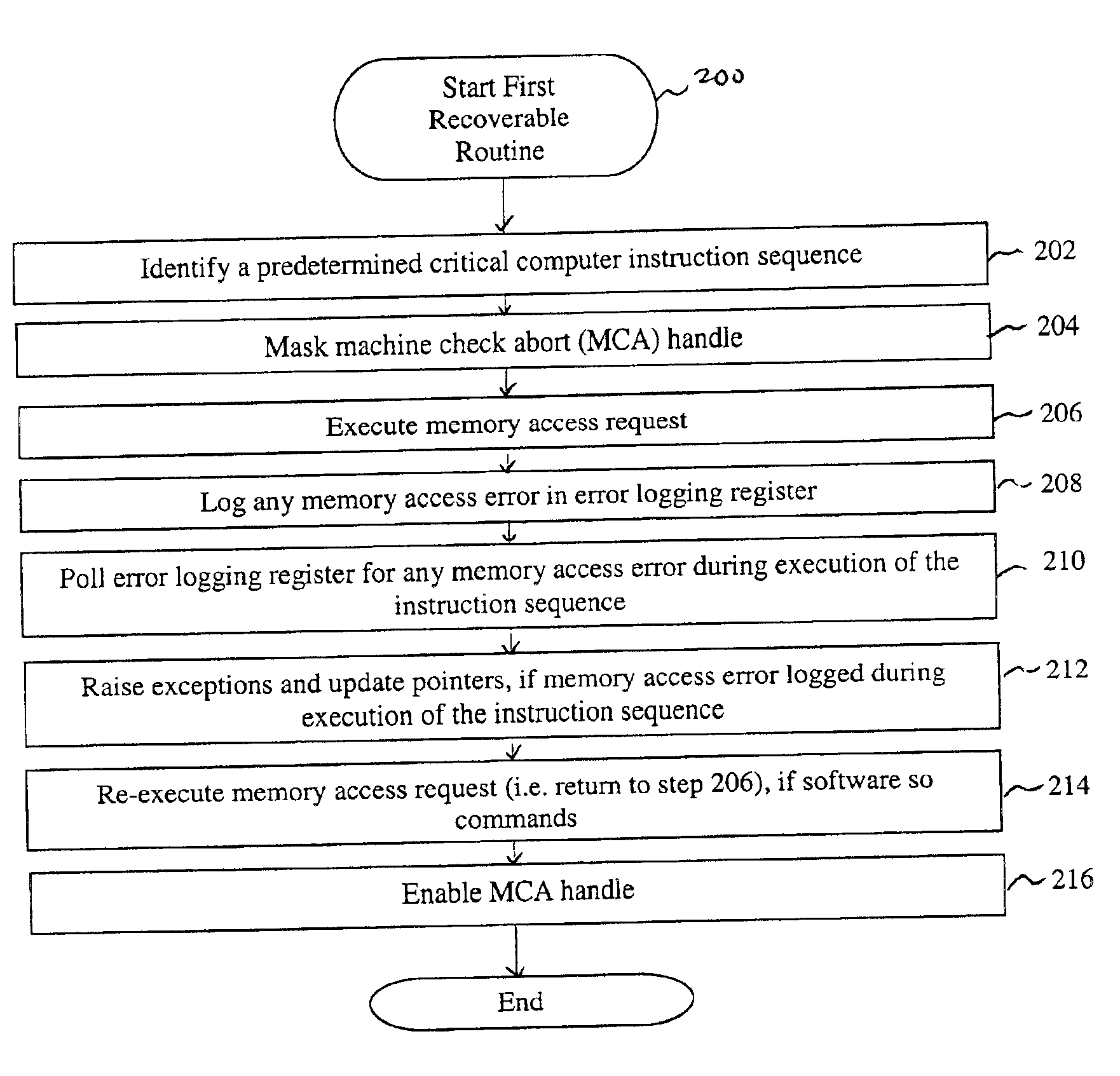

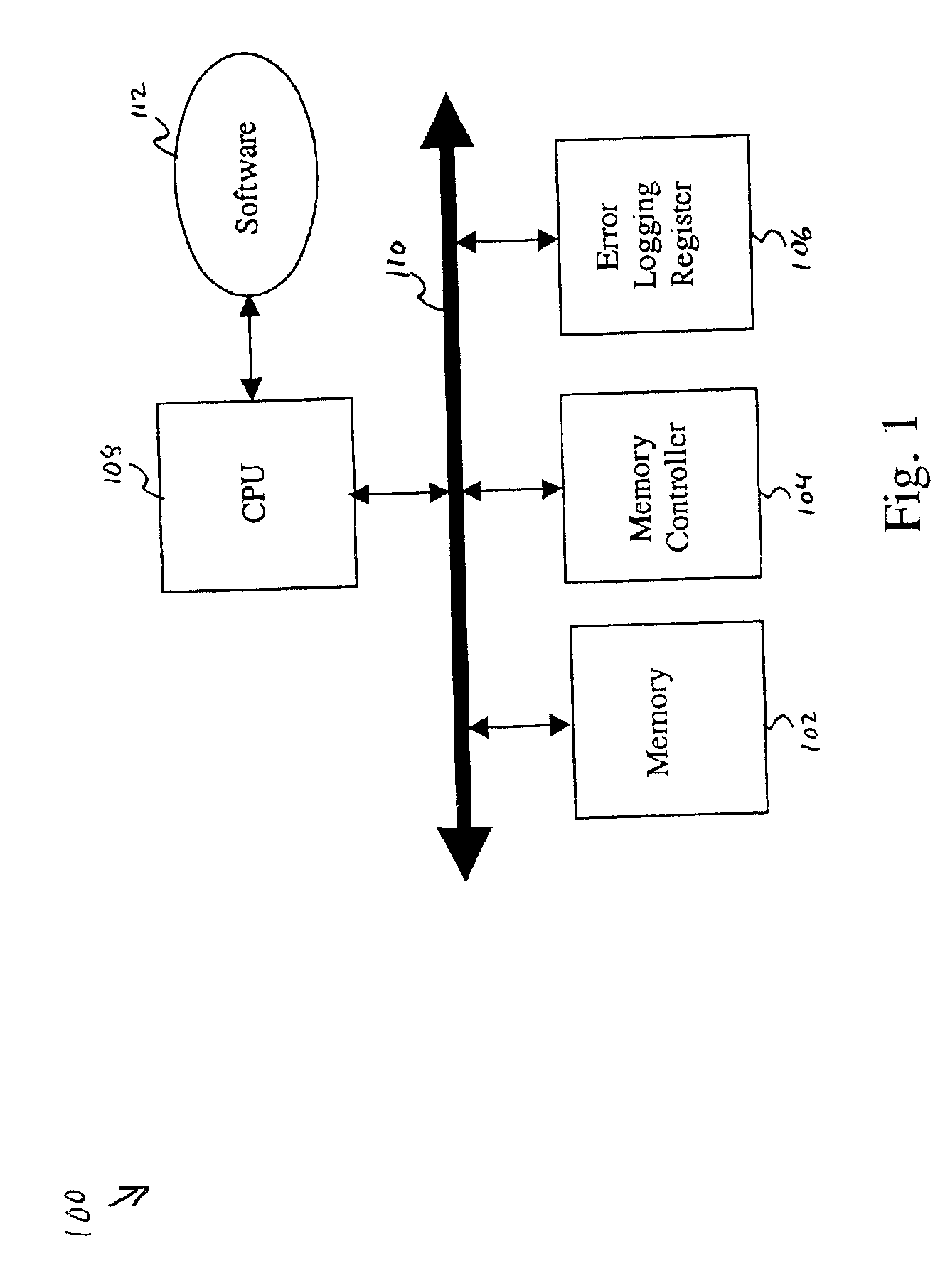

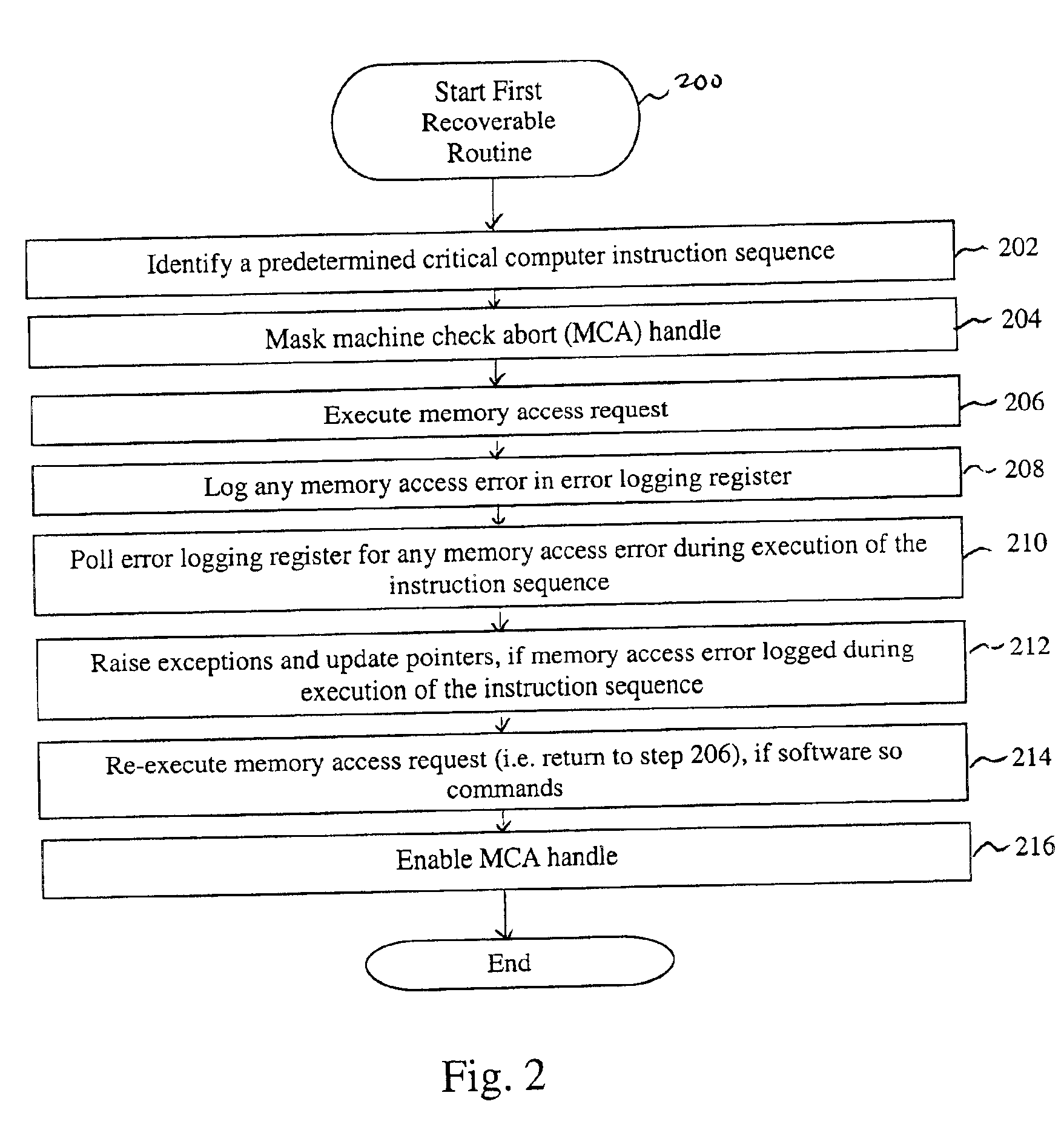

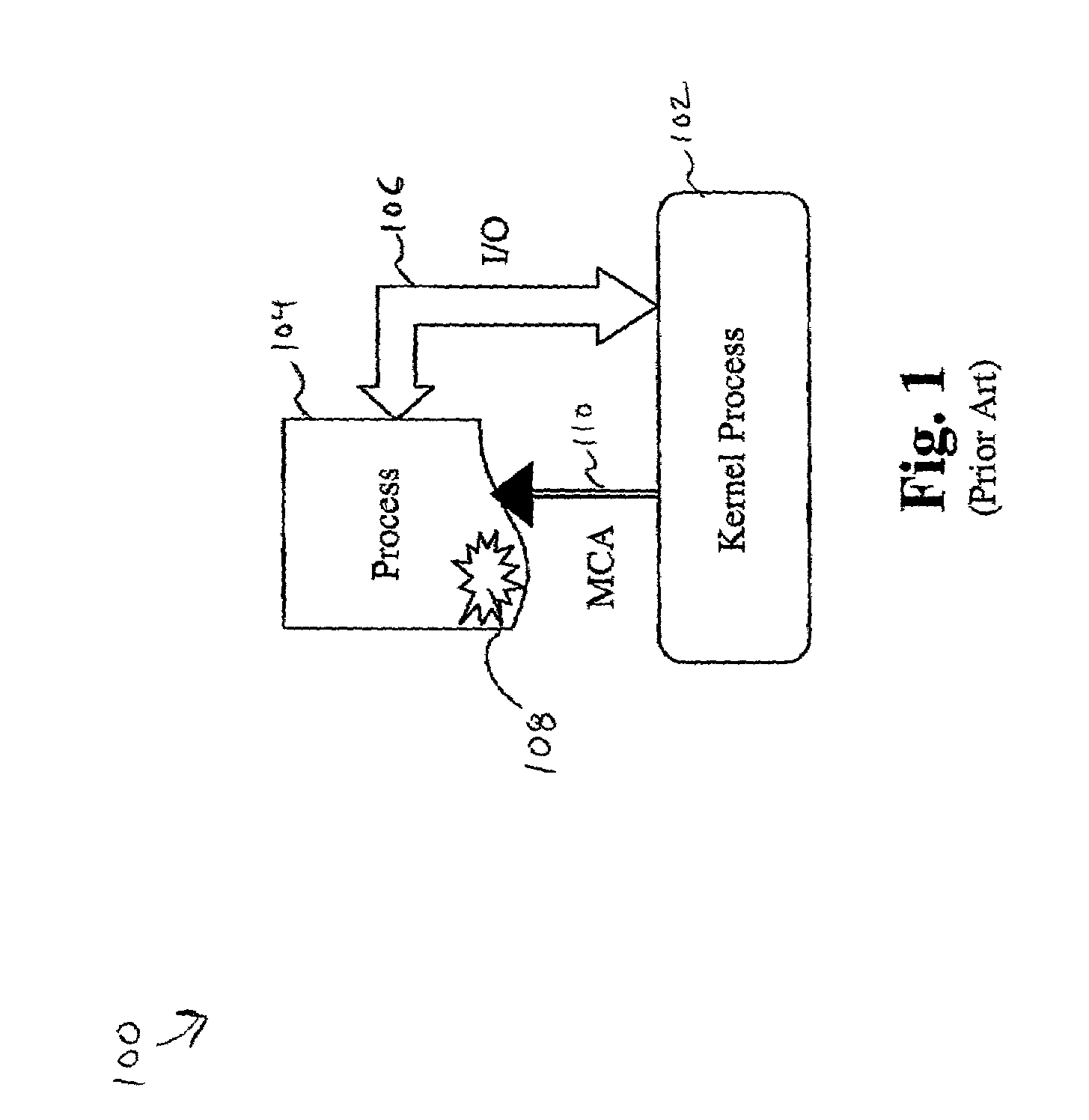

System and method for recovering from memory failures in computer systems

InactiveUS6851074B2Responding to errorRespond effectivelyNon-redundant fault processingRedundant operation error correctionProcessor registerComputerized system

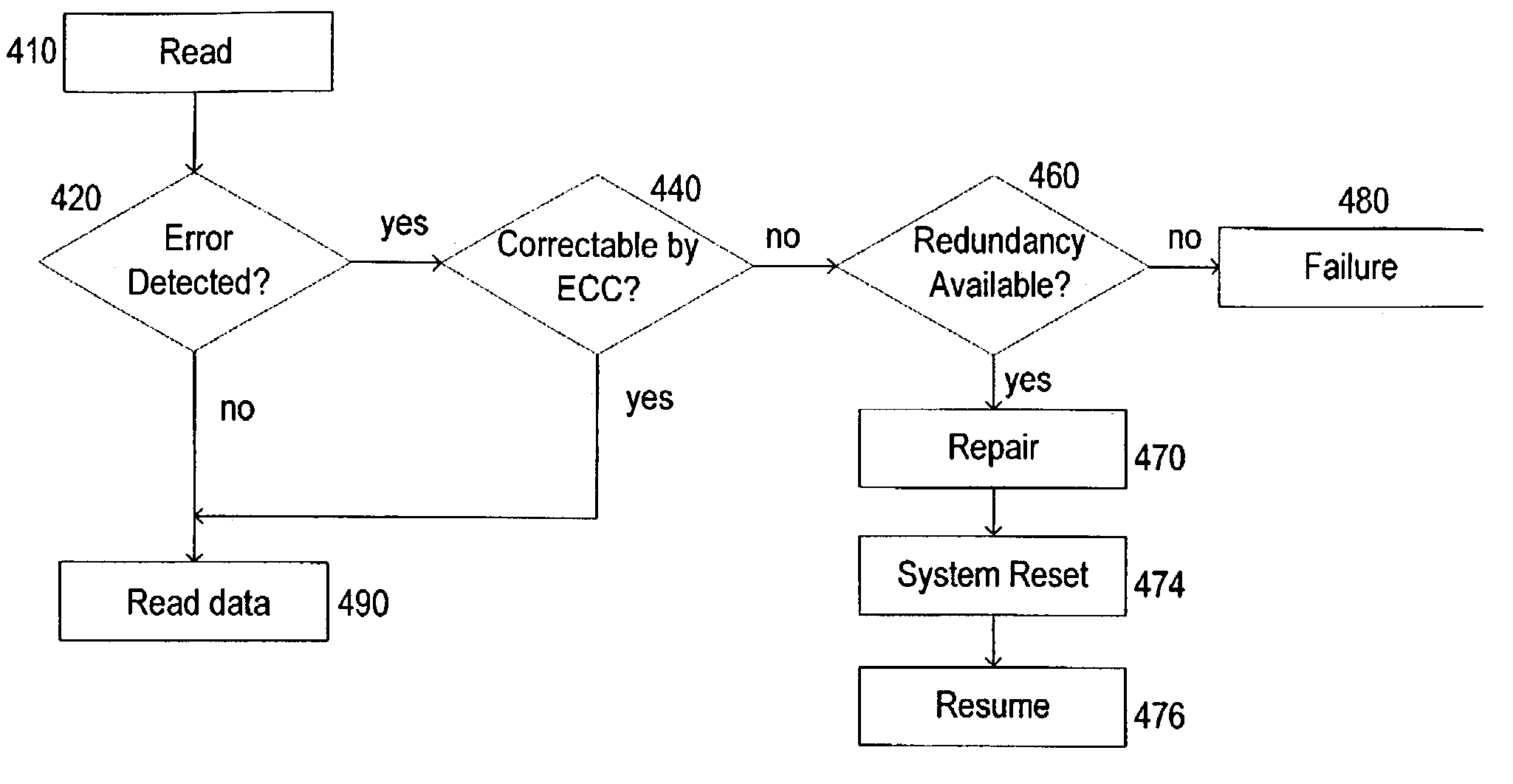

The present invention is a system and method for recovering from memory failures in computer systems. The method of the present invention includes the steps of: identifying a predetermined instruction sequence; monitoring for memory access errors in response to the request; logging a memory access error in an error logging register; polling the register for any logged memory access error during execution of the instruction sequence; and raising exceptions, if the memory access error is logged. Within the system of the present invention, memory access errors are stored in an error logging register, machine check abort handles are masked, and memory controllers are under full control of the software so that memory access errors can be intercepted and responded to without necessitating a system reboot or application restart. The present invention is particularly applicable to O / S code which can not otherwise recover from memory errors except by rebooting.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

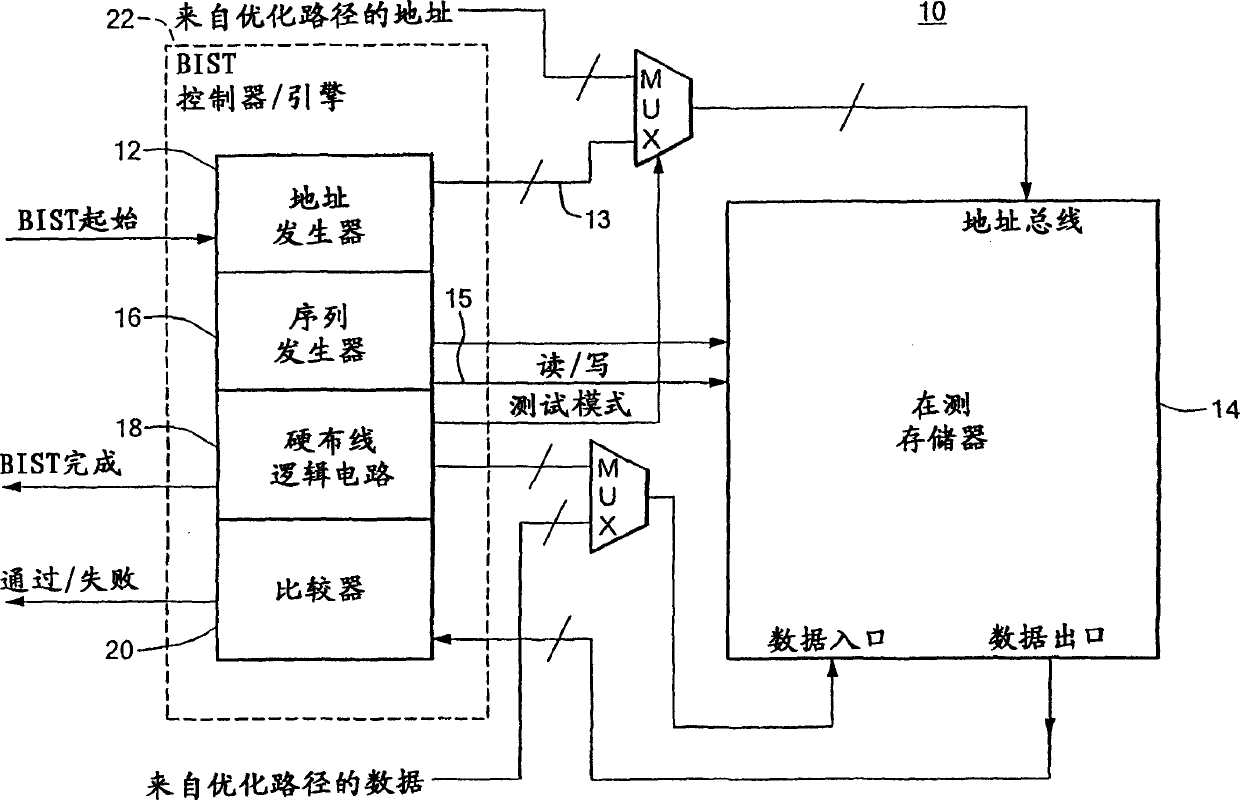

Method and circuit for collecting memory failure information

ActiveUS20050047229A1Quantity minimizationError detection/correctionDigital storageTest algorithmComputer science

A method and circuit for collecting memory failure information on-chip and unloading the information in real time while performing a test of memory embedded in a circuit comprises, for each column or row of a memory under test, testing each memory location of the column or row according to a memory test algorithm under control of a first clock, selectively generating a failure summary on-circuit while testing each column or row of the memory; and transferring the failure summary from the circuit under control of a second clock within the time required to test the next column or row, if any, of the memory under test.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

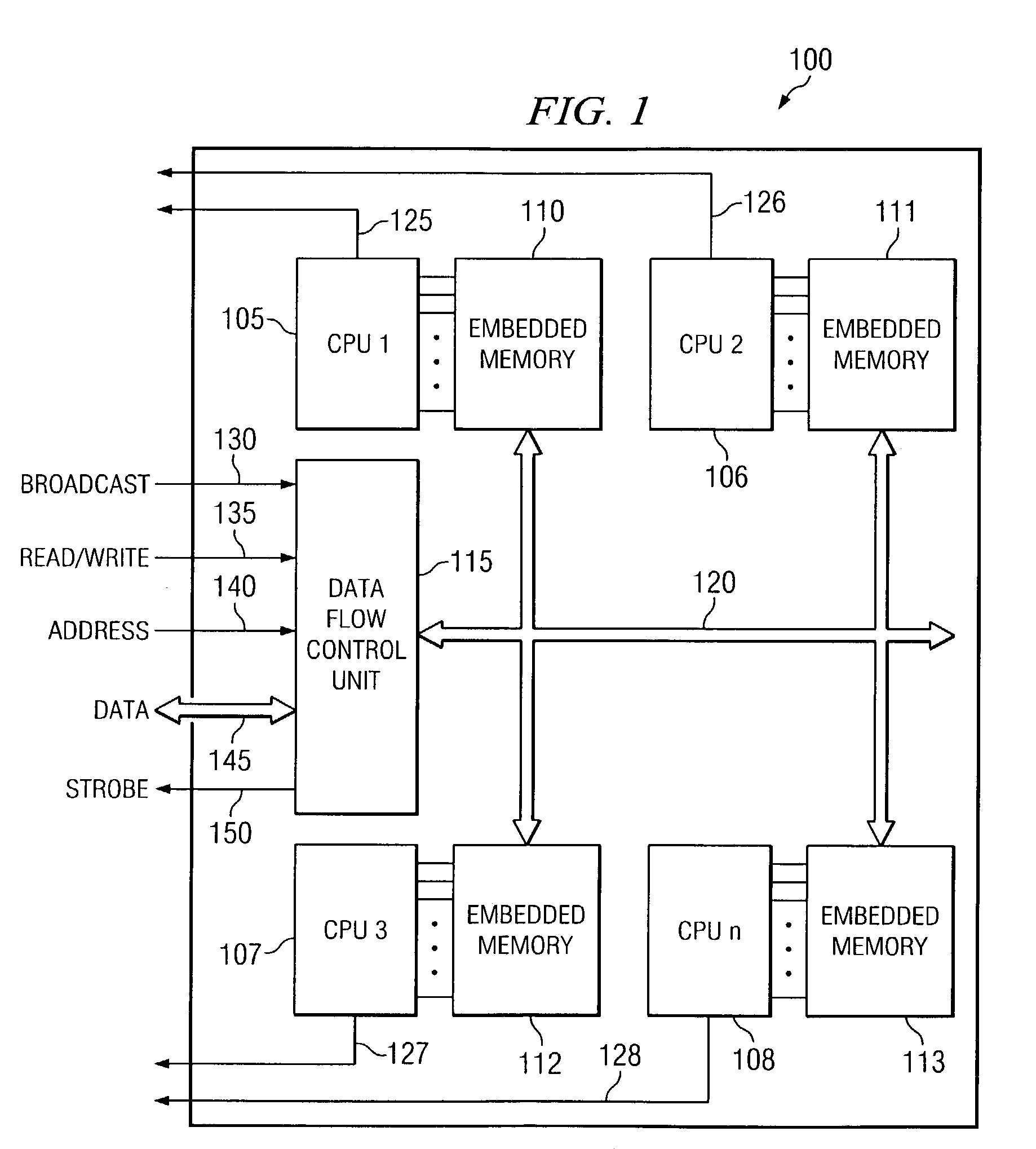

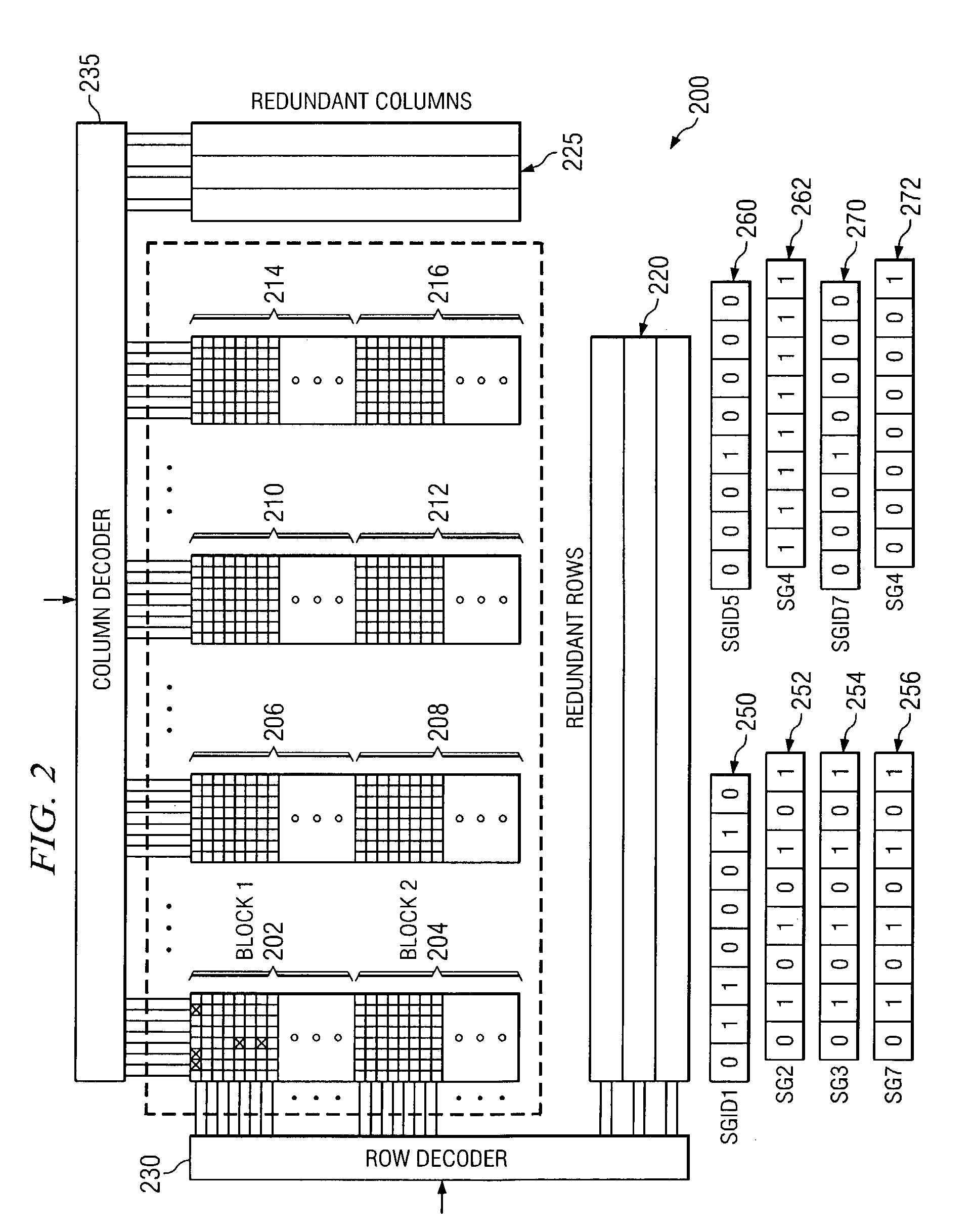

Method and system for memory testing and test data reporting during memory testing

ActiveUS7734966B1Reduced pin countNarrow interfaceElectronic circuit testingError detection/correctionAnalysis dataHigh memory

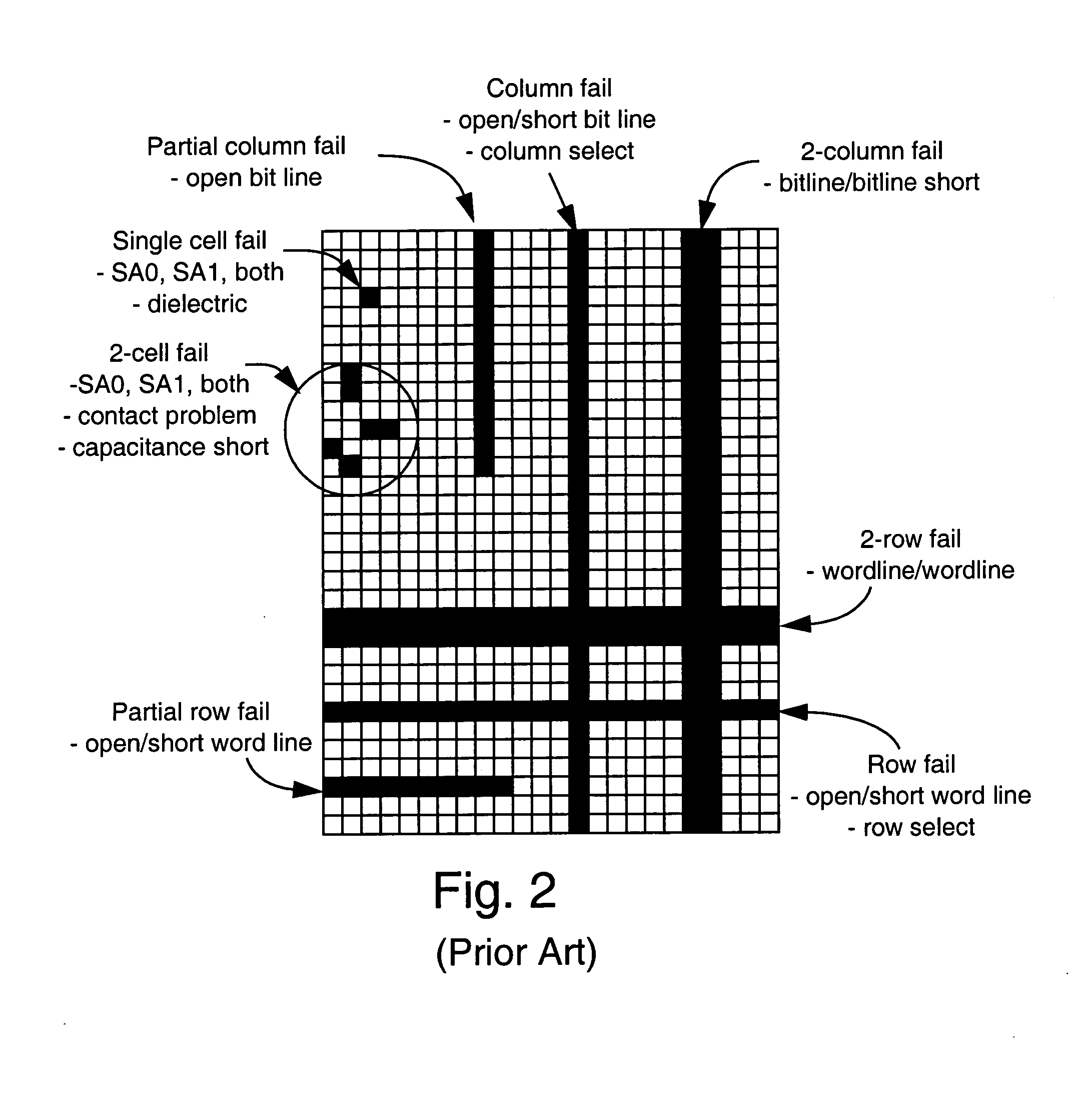

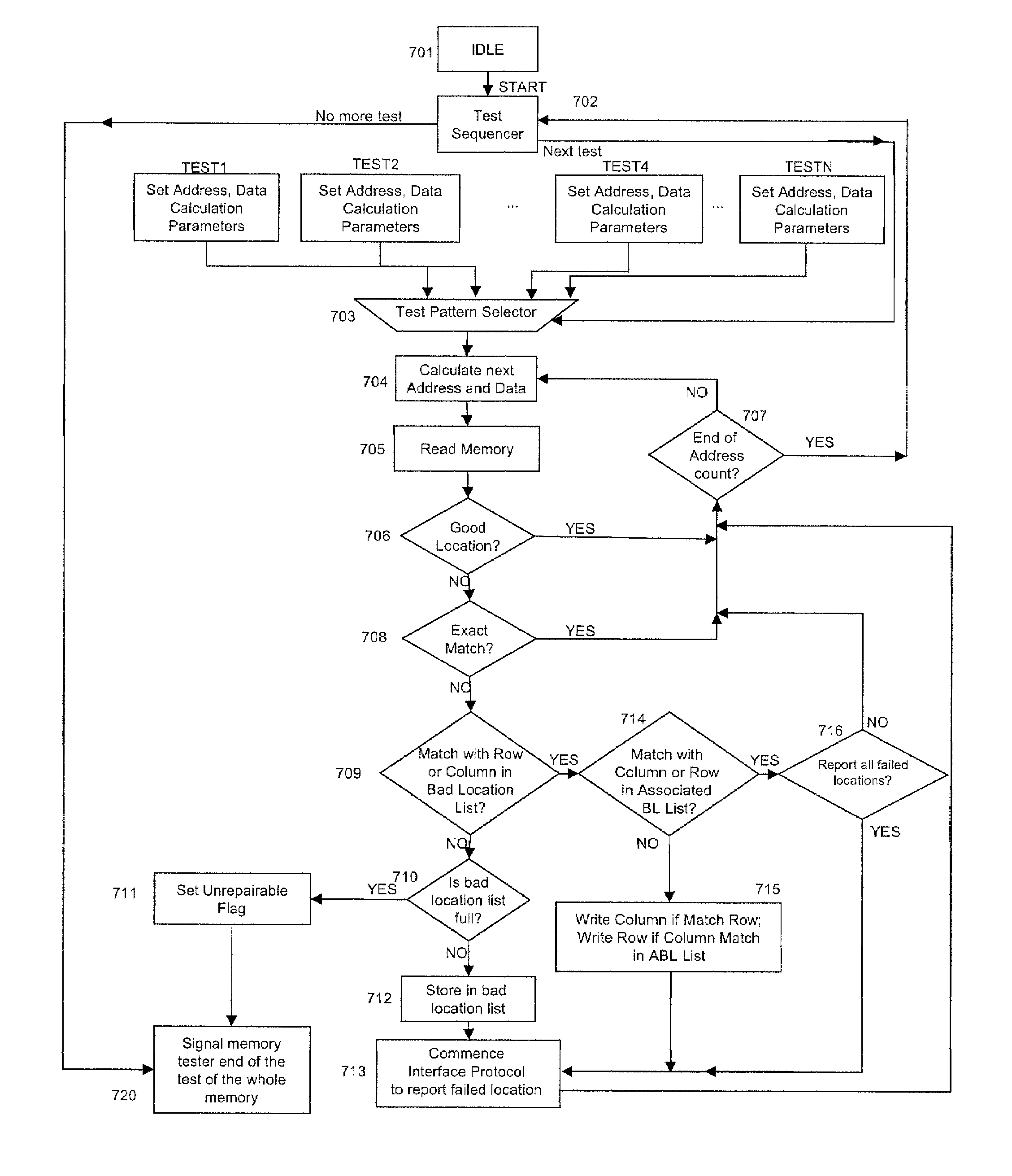

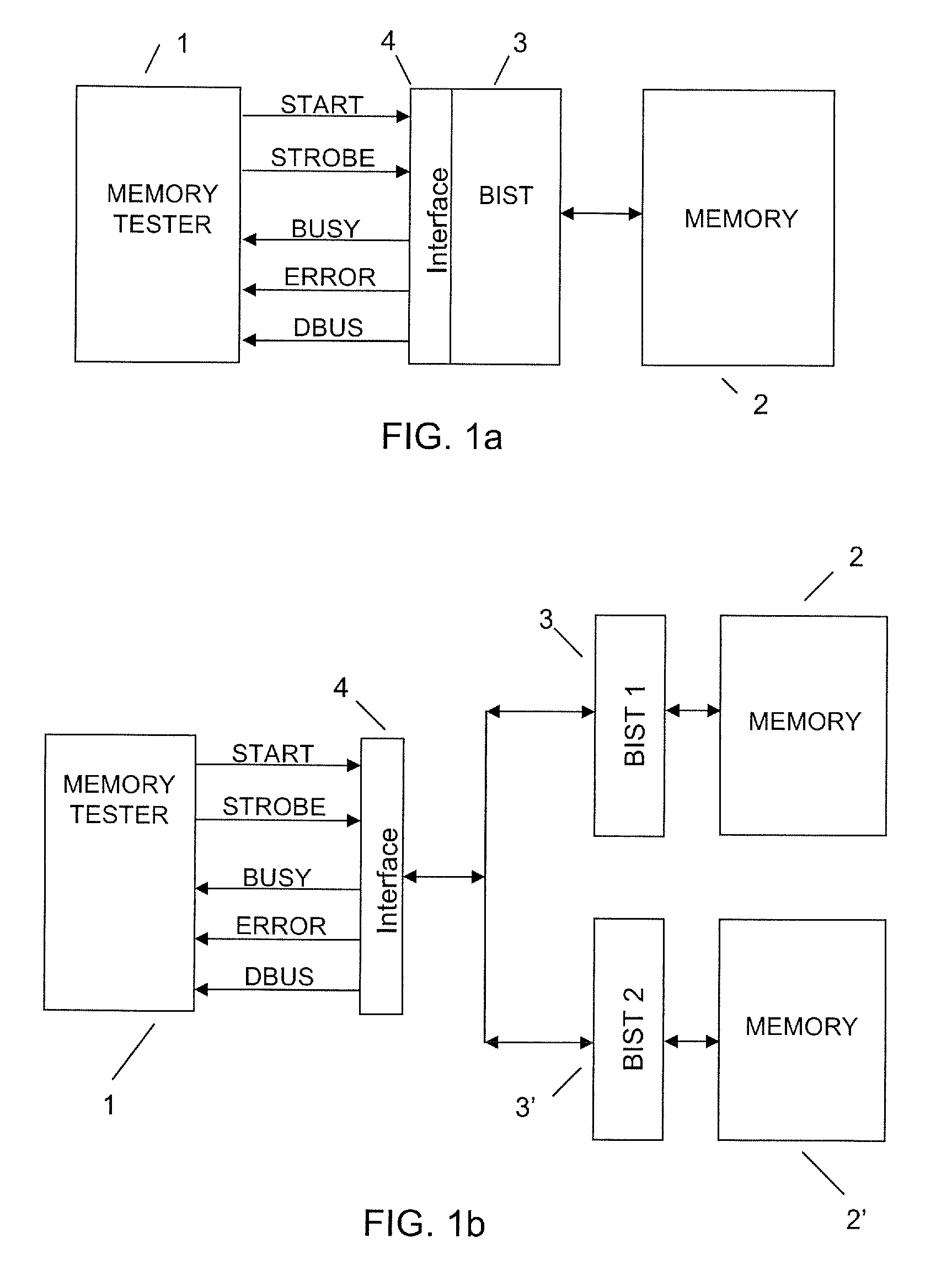

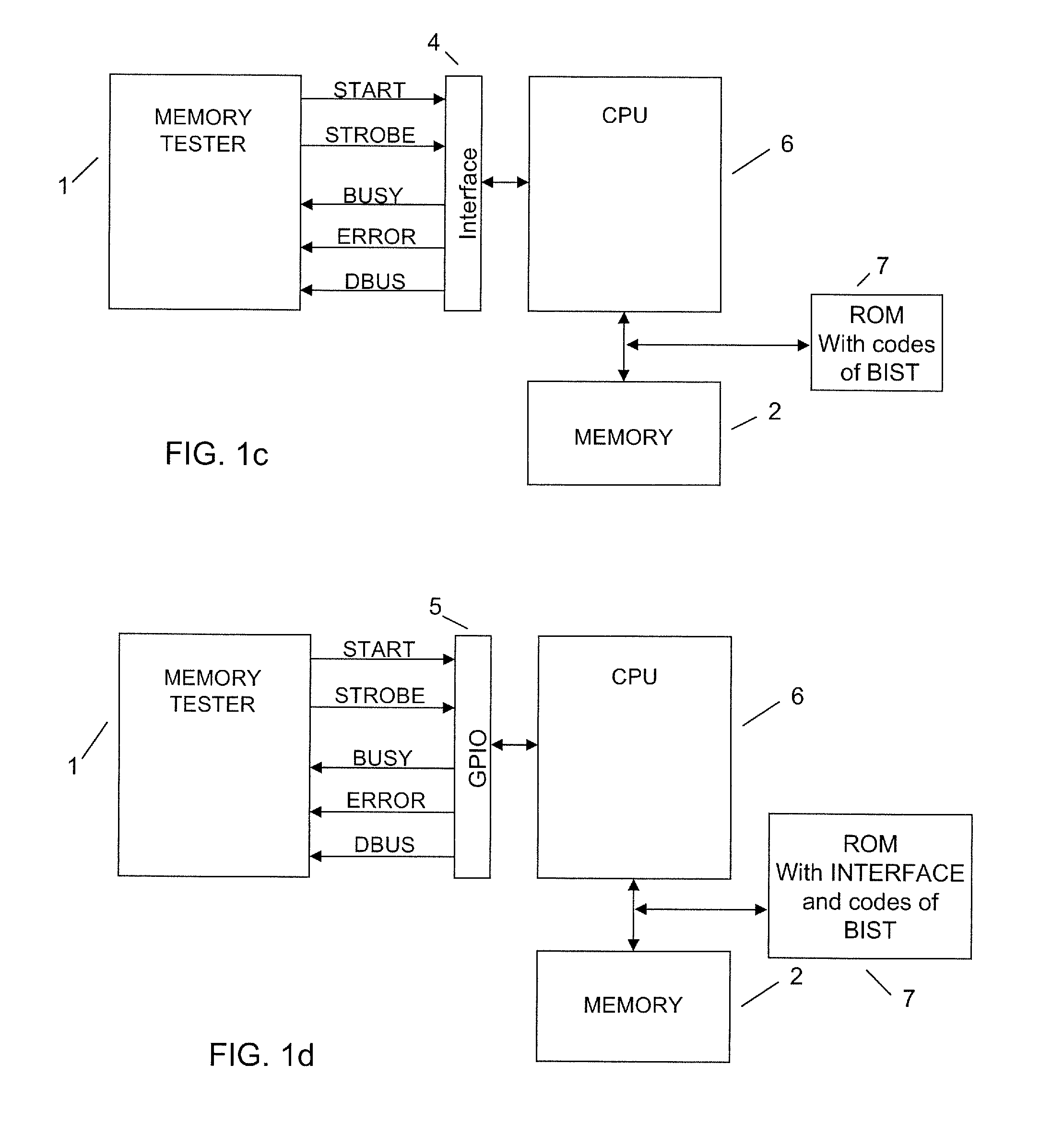

The present invention provides a method and system for improving memory testing efficiency, raising the speed of memory testing, detecting memory failures occurring at the memory operating frequency, and reducing data reported for redundancy repair analysis. The memory testing system includes a first memory tester extracting failed memory location information from the memory at a higher memory operating frequency, an external memory tester receiving failed memory location information at a lower memory tester frequency, and an interface between the first memory tester and the external memory tester. The memory testing method uses data strobes at the memory tester frequency to clock out failed memory location information obtained at the higher memory operating frequency. In addition, the inventive method reports only enough information to the external memory tester for it to determine row, column and single bit failures repairable with the available redundant resources. The present invention further provides a redundant resource allocation system, which uses a bad location list and an associated bad location list to classify failed memory locations according to a predetermined priority sequence, and allocates redundant resources to repair the failed memory locations according to the priority sequence.

Owner:MARVELL ASIA PTE LTD

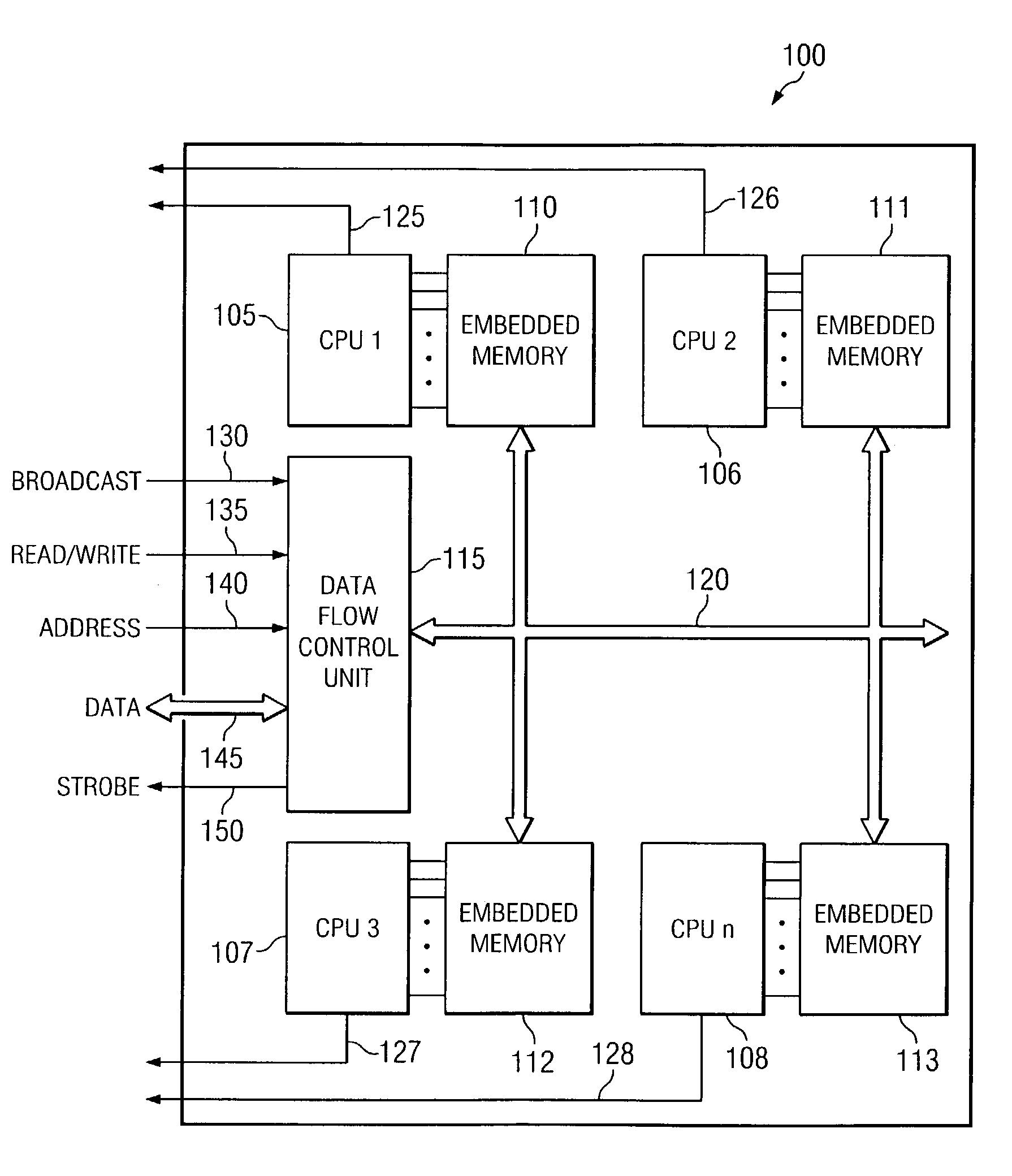

Method and apparatus for testing embedded memory on devices with multiple processor cores

ActiveUS7155637B2Shorten test timeTiming failureElectronic circuit testingMemory loss protectionData streamTested time

The disclosed method and apparatus enables the testing of multiple embedded memory arrays associated with multiple processor cores on a single computer chip. According to one aspect, the disclosed method and apparatus identifies certain rows and columns within each of the embedded memory arrays that need to be disabled and also identifies certain redundant rows and columns in the embedded memory array to be activated. According to another aspect, the disclosed method and apparatus generates a map indicating where each of the memory failures occurs in each embedded memory array. If the testing process determines that the embedded memory array cannot be repaired, then a signal is provided directly to an external testing device indicating that the embedded memory array is non-repairable. Similarly, if the testing process determines that the failures in the embedded memory array can be repaired, then a signal is provided directly to an external testing apparatus indicating that the embedded memory array is repairable. Lastly, if no failures are found in an embedded memory array, then a signal is provided to an external testing apparatus indicating that the embedded memory array contains no failures. Based upon these status signals, the external testing device can determine which set of data (i.e., repair data and / or failure map data) to off-load from each embedded memory array and which sets of data to disregard, thereby reducing the memory test time for a device. Another aspect of the disclosed method and apparatus is a data flow control unit that controls the flow of input and output data to each of the embedded memory arrays. This device broadcasts the test program to each of the embedded memory arrays at the same time thereby enabling the simultaneous testing of multiple embedded memory arrays. Yet another aspect of the disclosed method and apparatus is a shorthand notation for indicating where memory failures occur within an embedded memory array.

Owner:TEXAS INSTR INC

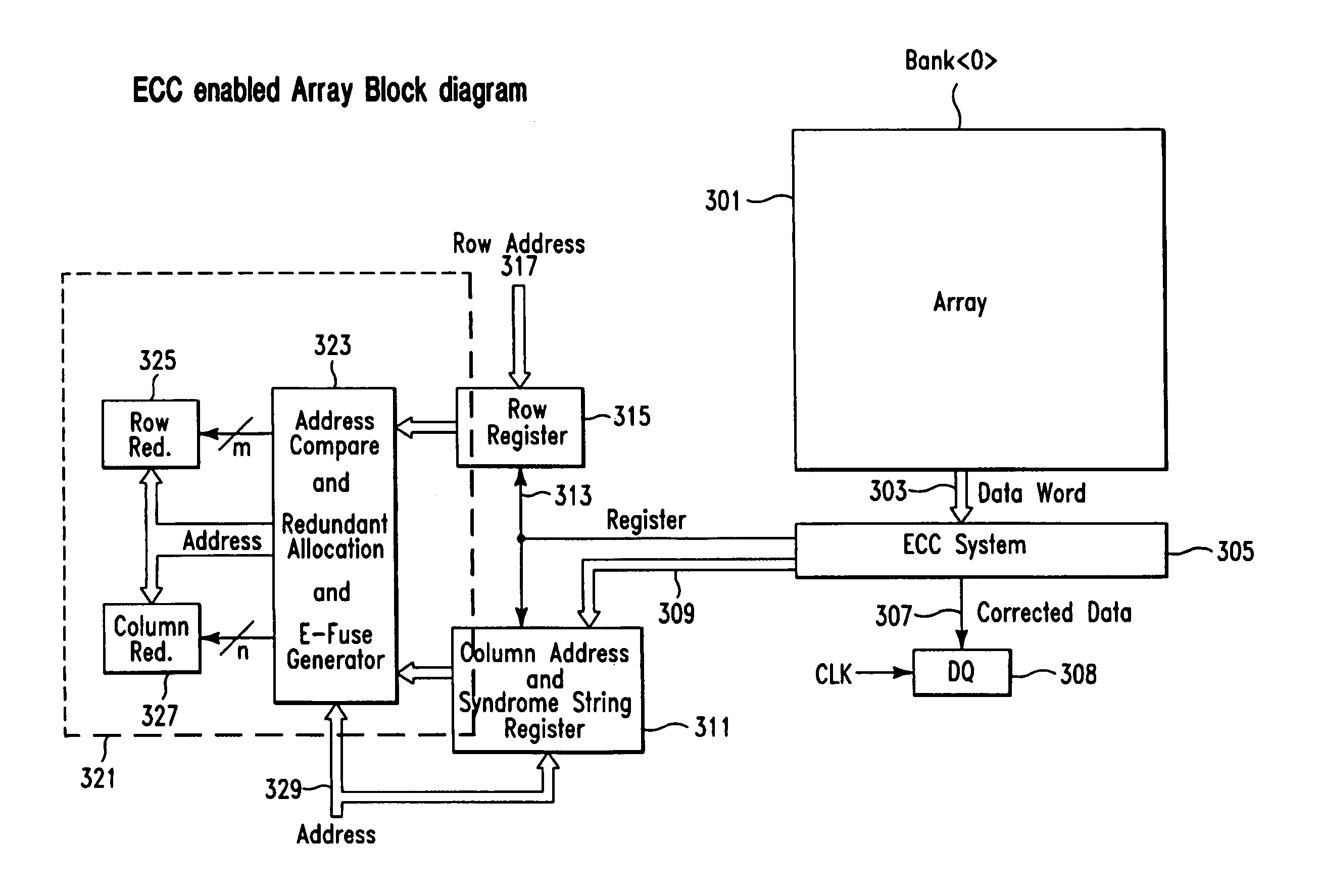

ECC based system and method for repairing failed memory elements

An ECC based system and method within an integrated circuit memory for self-repair of a failed memory element is disclosed. The method includes processing, within the integrated circuit, data and check bits retrieved from addressed memory locations therein. The locations of memory failures are automatically recorded within the integrated circuit. Logic circuits within the integrated circuit automatically identify failure patterns based on the locations. Based on the identified failure patterns, logic circuits within the integrated circuit then permanently replace a failed memory element with an appropriate redundancy element, using devices such as electronic fuse or antifuse. In this manner, the integrated circuit automatically identifies and effects self repair of a failed memory element therein.

Owner:IBM CORP

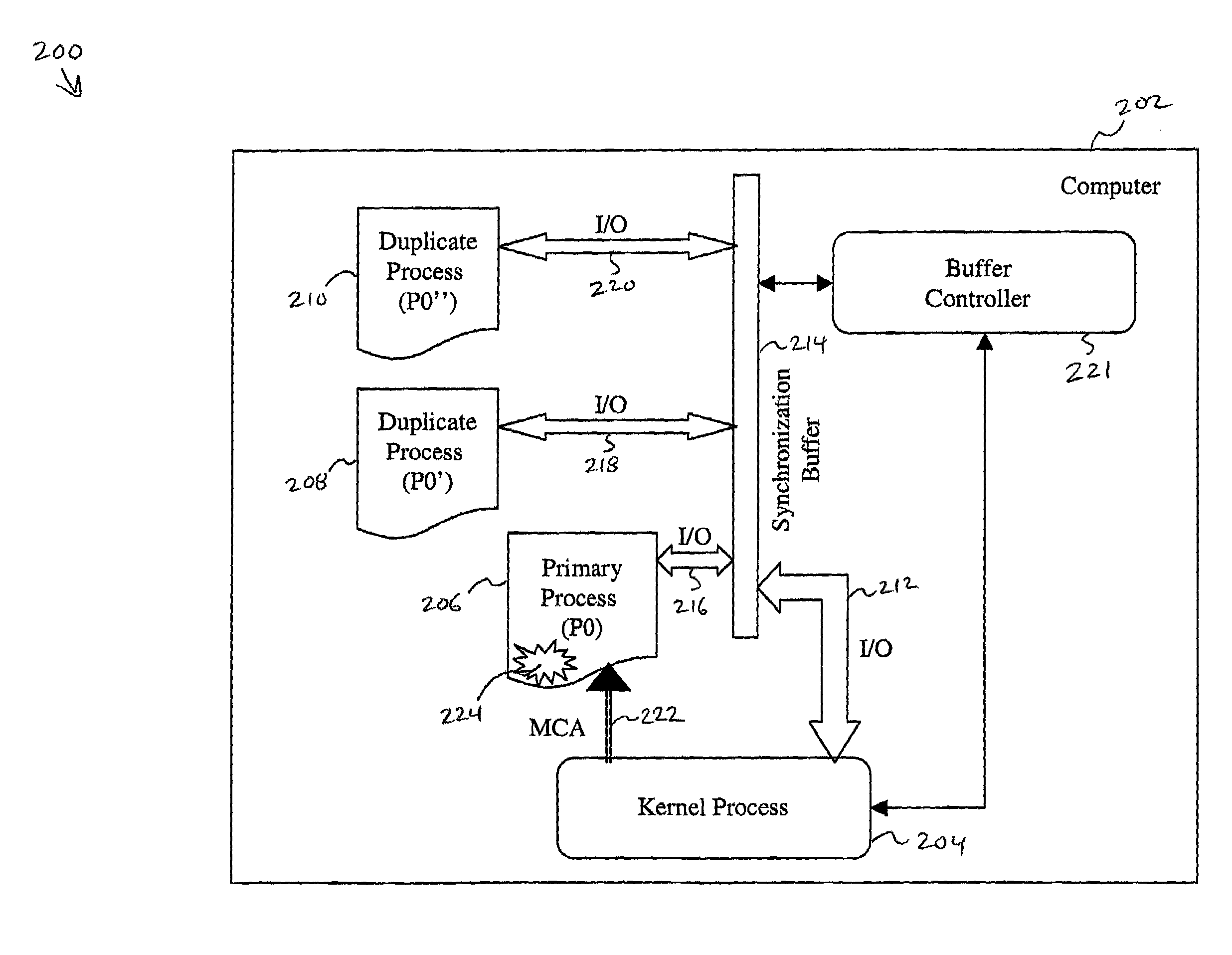

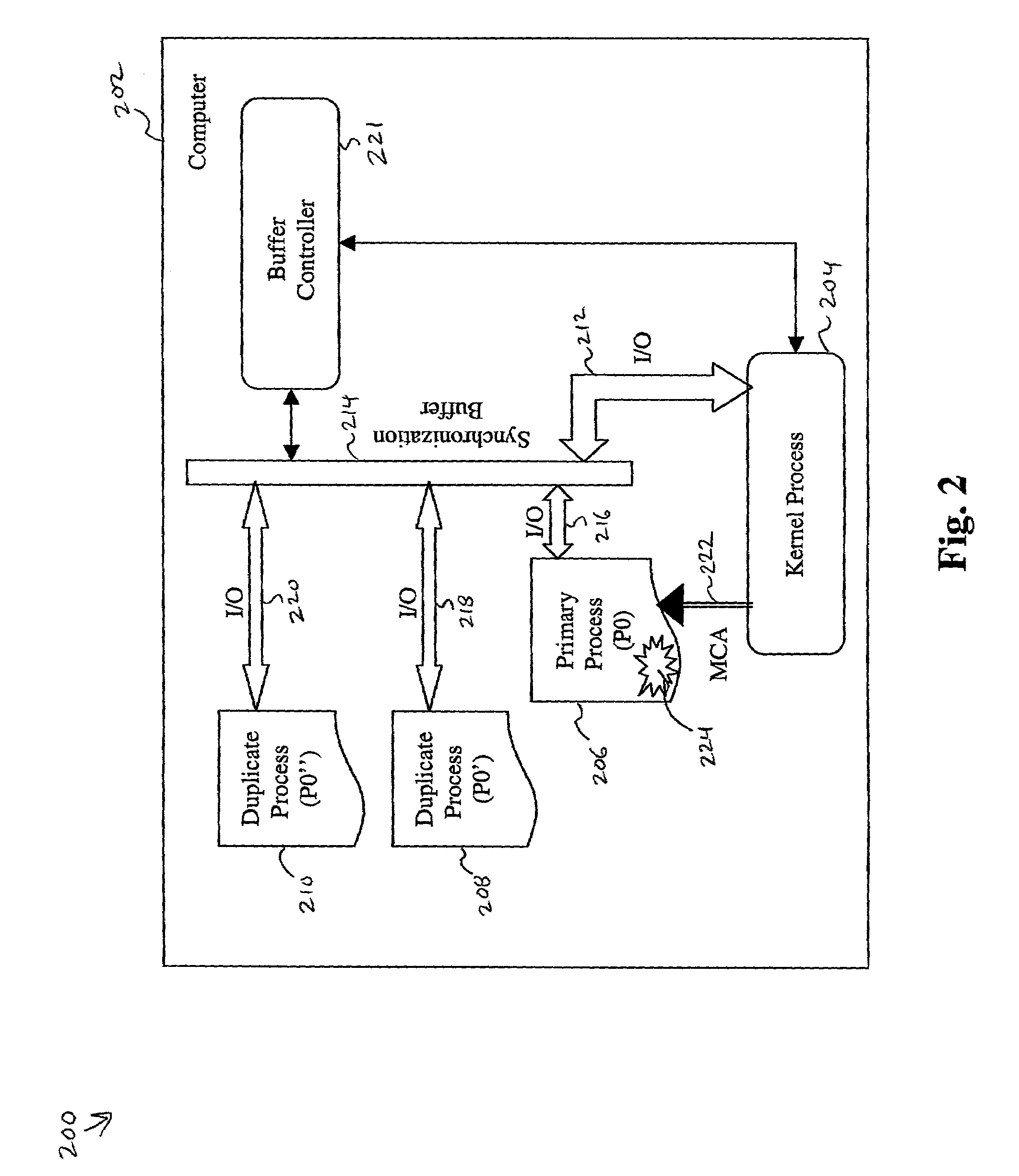

System and method for memory failure recovery using lockstep processes

A system and method for memory failure recovery is disclosed. The method discloses the steps of maintaining a predetermined number of duplicate and primary processes; keeping the processes in synchronization; managing the processes so that a single process image is presented to an external environment; detecting a computer system exception which affects one of the processes; and terminating the affected process. The system discloses, a primary process memory space which hosts a primary process; a duplicate process memory space which hosts a duplicate process corresponding to the primary process; a synchronization buffer which keeps the duplicate process in synchronization with the primary process; a processor which generates an exception signal in response to detection of a memory failure condition which affects the primary process; and an operating system which receives the exception signal, terminates the affected primary process, and maintains a predetermined number of primary and duplicate processes.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

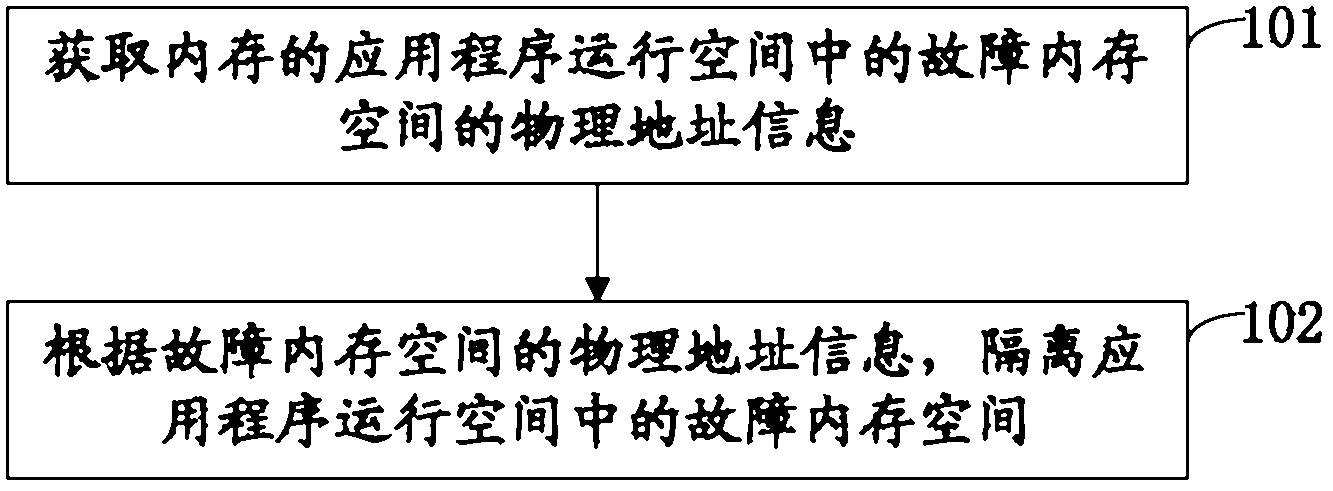

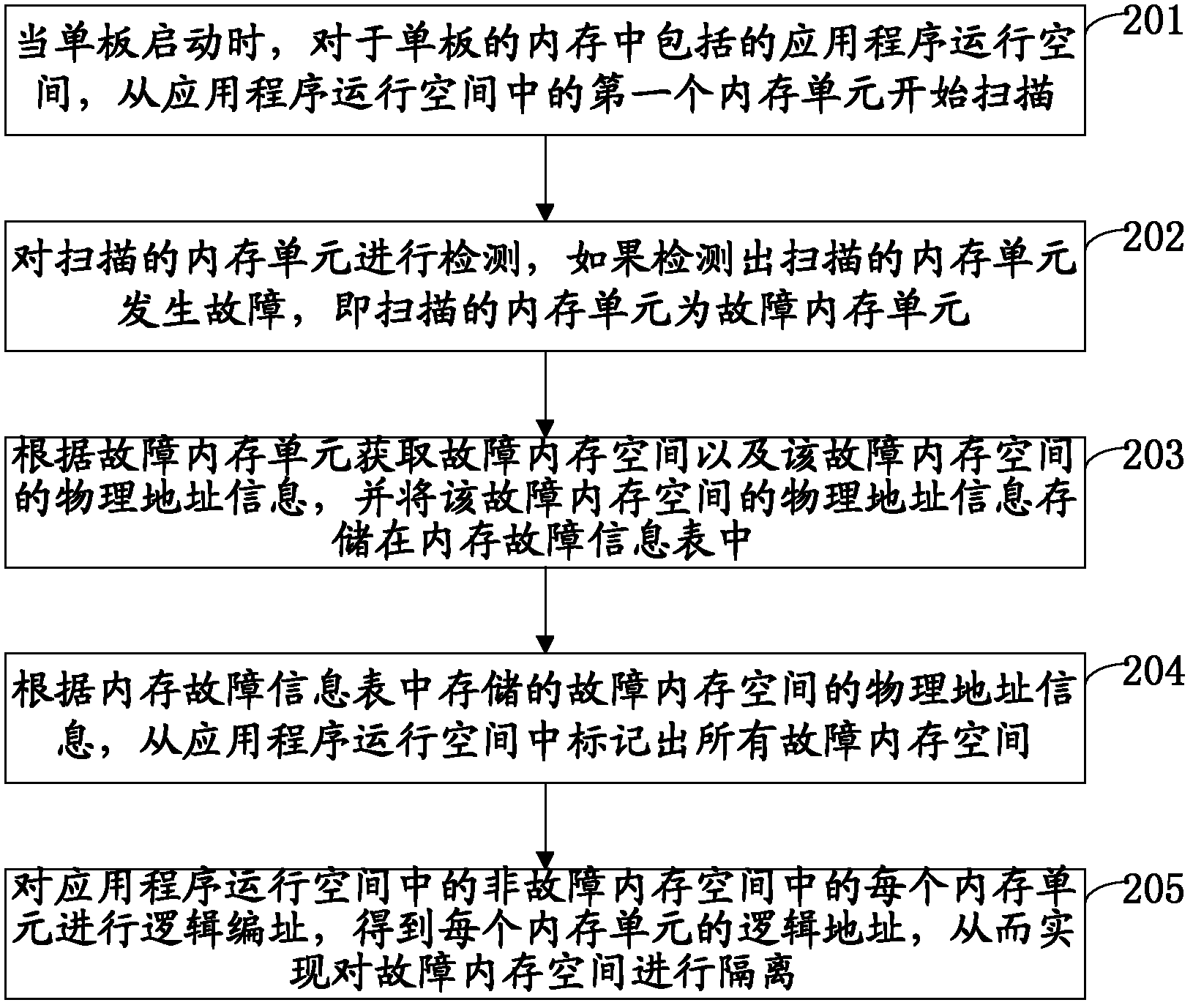

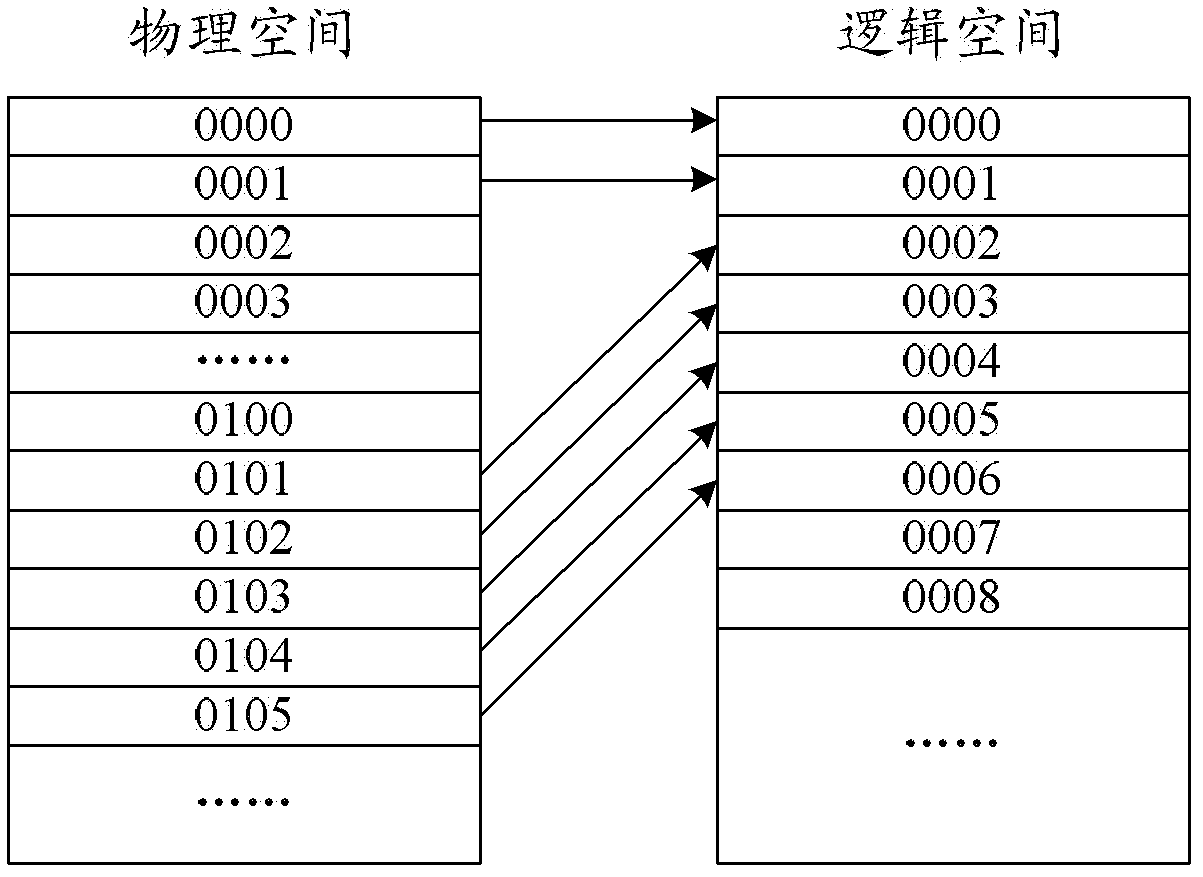

Method and device for eliminating memory failure

The invention discloses a method and a device for eliminating memory failure, belonging to the technical field of computers. The method comprises the following steps of: acquiring the physical address information of a failure memory space in an application program operation space of a memory; and isolating a failure memory space in the application program operation space according to the physical address information of the failure memory space. The device comprises an acquisition module and an isolation module. The method and the device can eliminate the memory failure.

Owner:BEIJING HUAWEI DIGITAL TECH

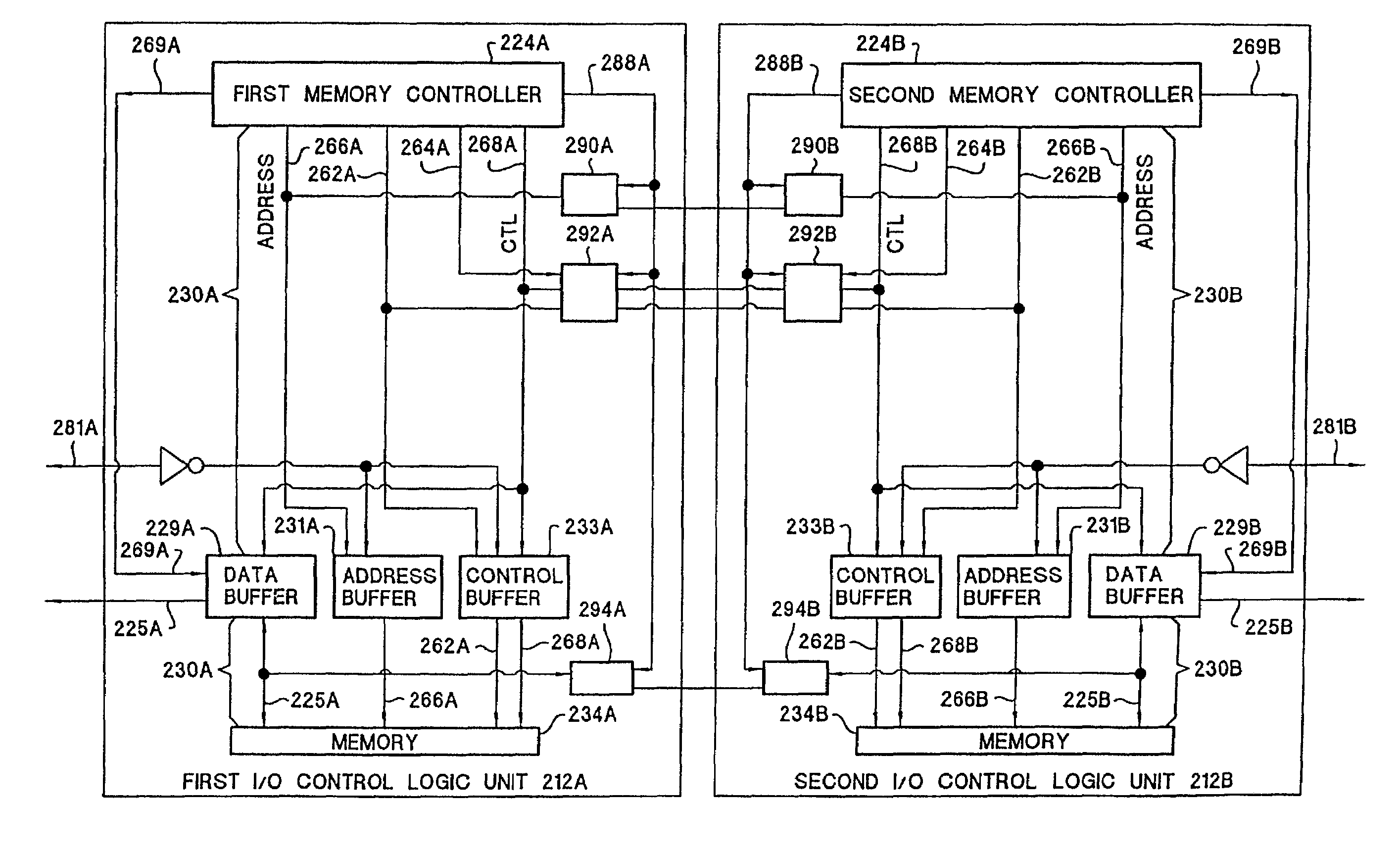

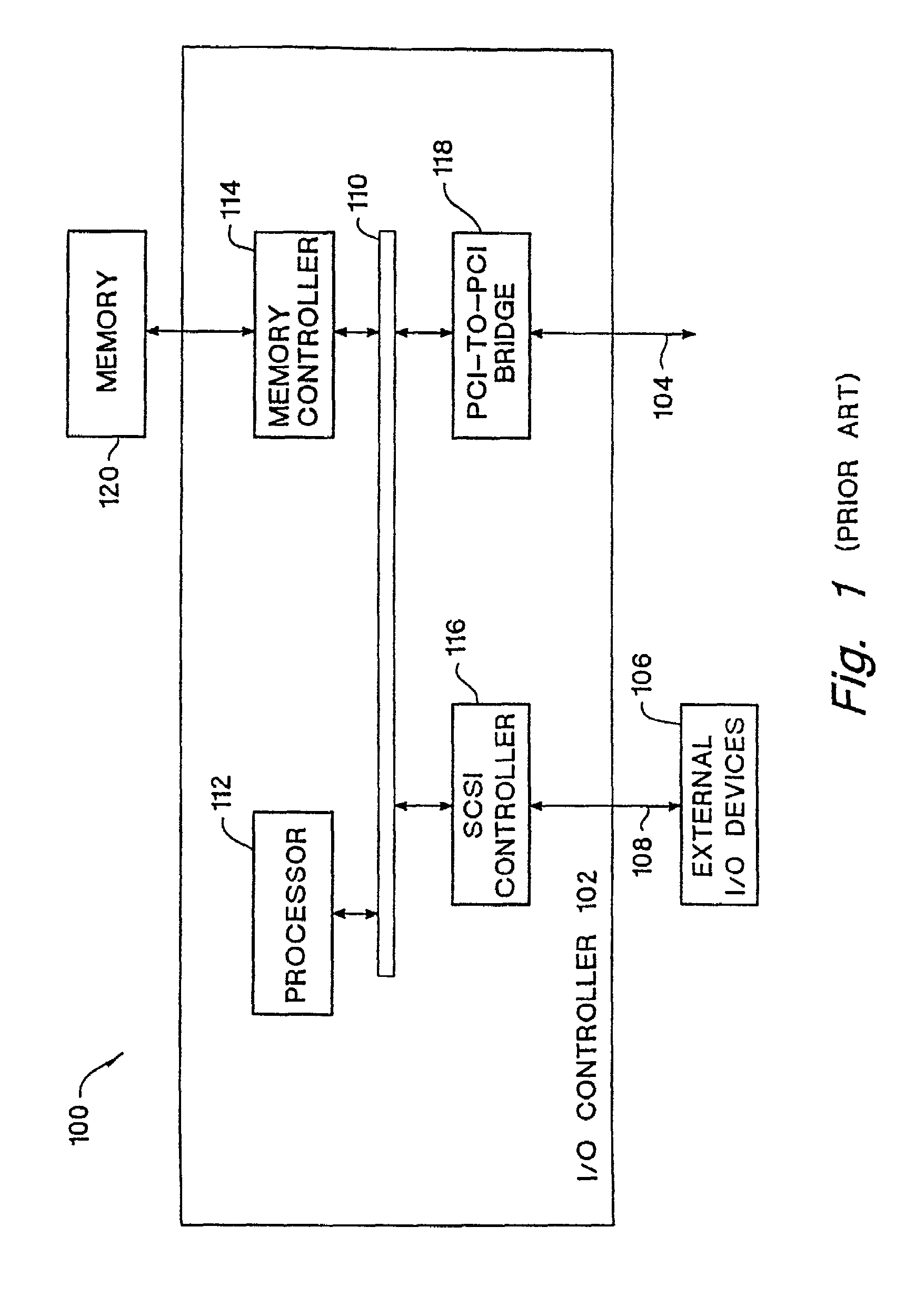

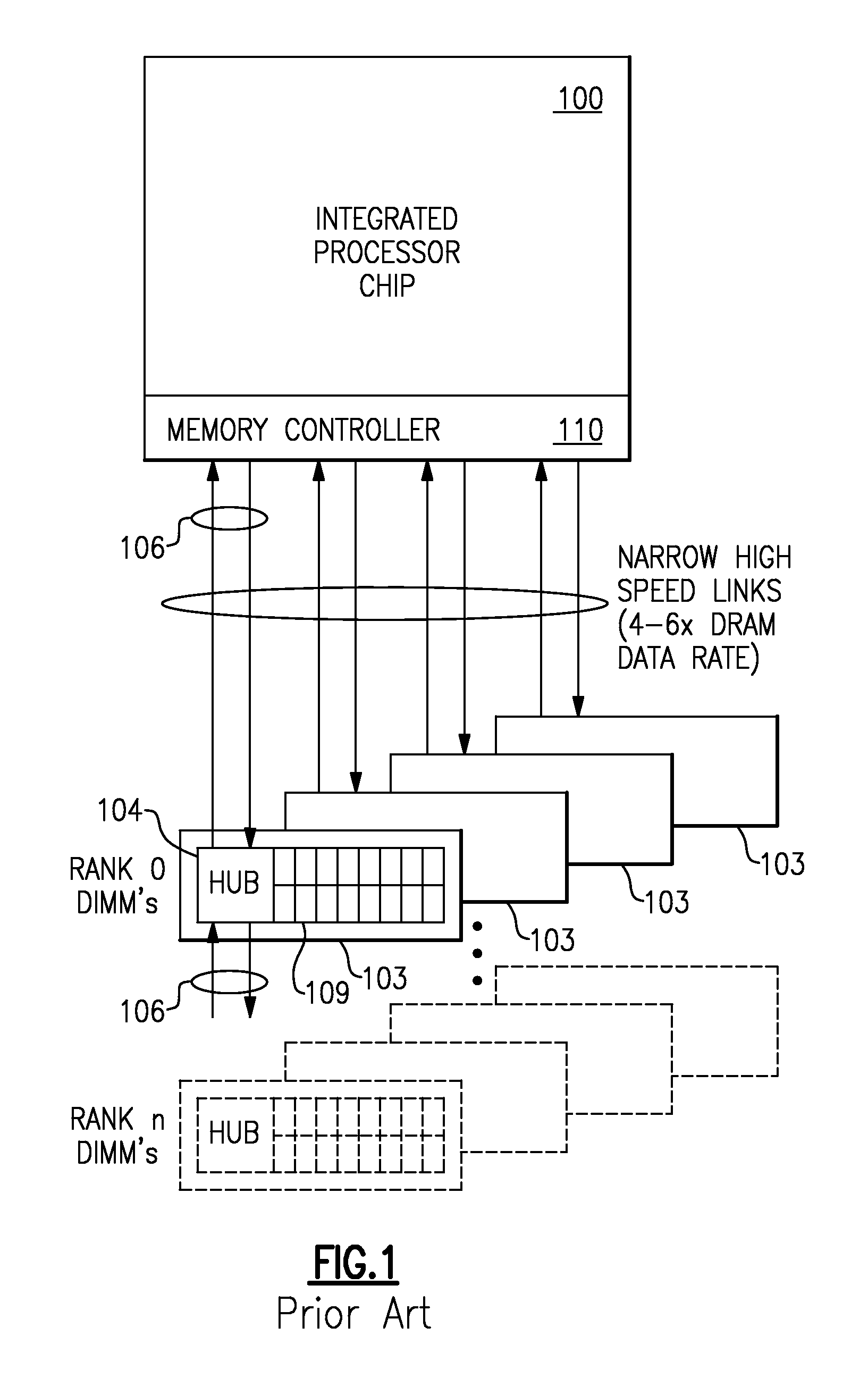

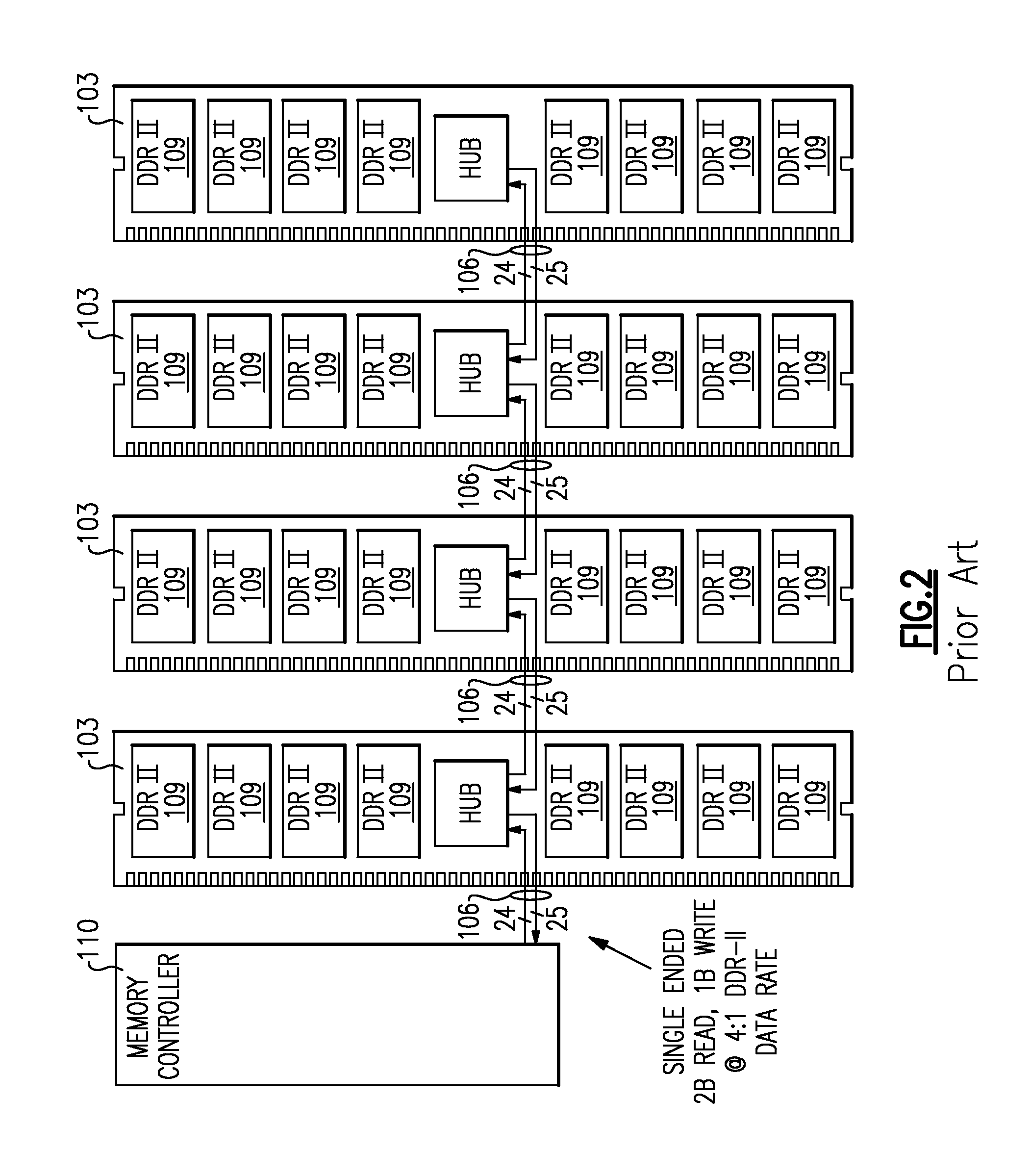

Memory controller supporting redundant synchronous memories

A reliable fault-tolerant I / O controller supporting redundant synchronous memories is described. The I / O controller includes multiple I / O control logic units where each I / O control logic unit is in communication with a host server and external peripheral devices. Each I / O control logic unit includes a processor, a memory, and a memory controller. A master I / O control logic unit services I / O transactions from the host server and the external peripheral devices. A slave I / O control logic unit operates in a quiescent state until the master I / O control logic unit experiences a memory failure. At such time, the slave I / O control logic unit resumes operation of the I / O controller. In order to facilitate the switchover from the master I / O control logic unit to the slave I / O control logic unit, the master memory controller performs concurrent memory write operations in both the master and slave memories. The concurrent memory write operations ensure that the memories in both I / O control logic units are in a consistent state in order for the switchover to occur without loss of data.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

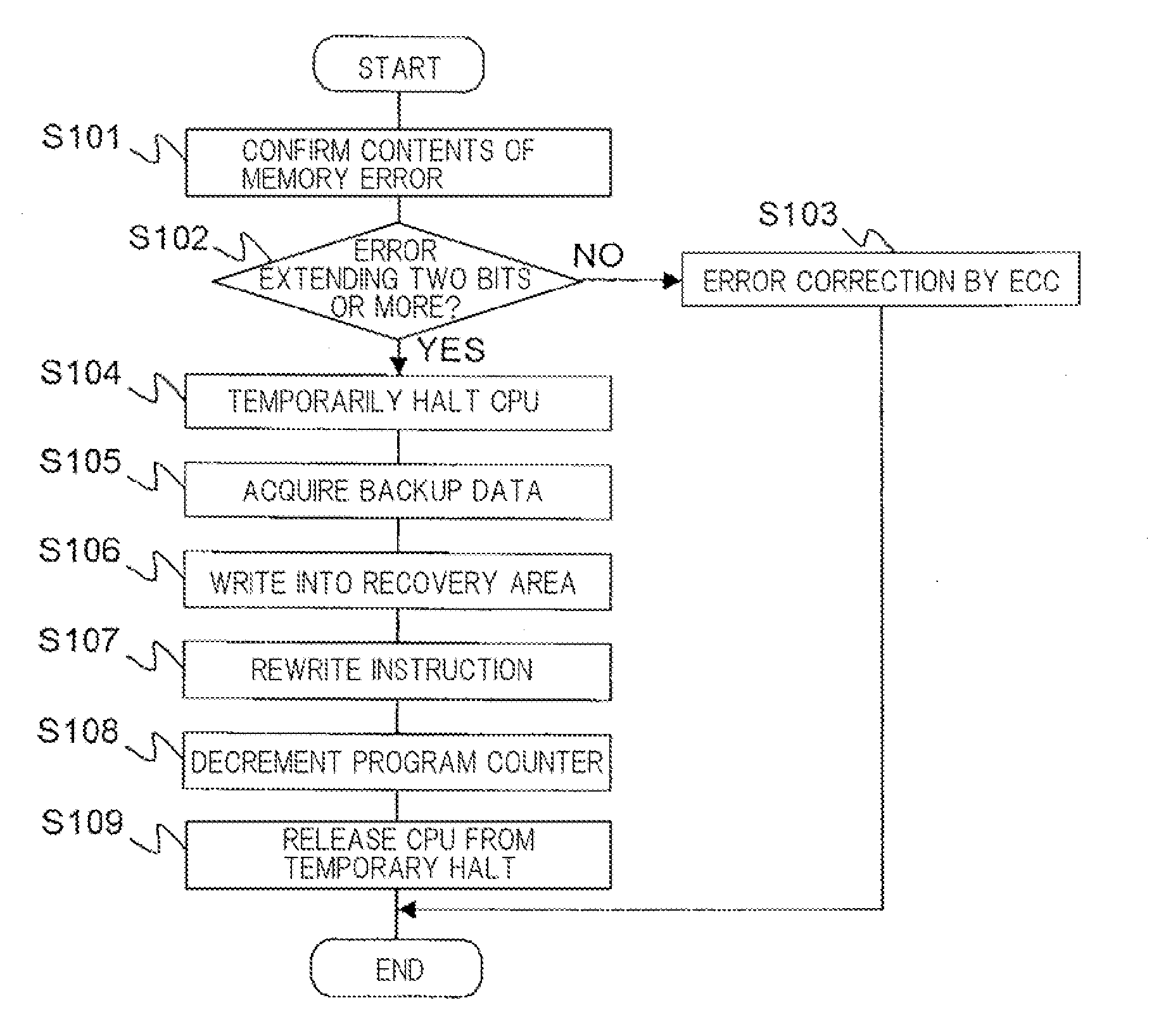

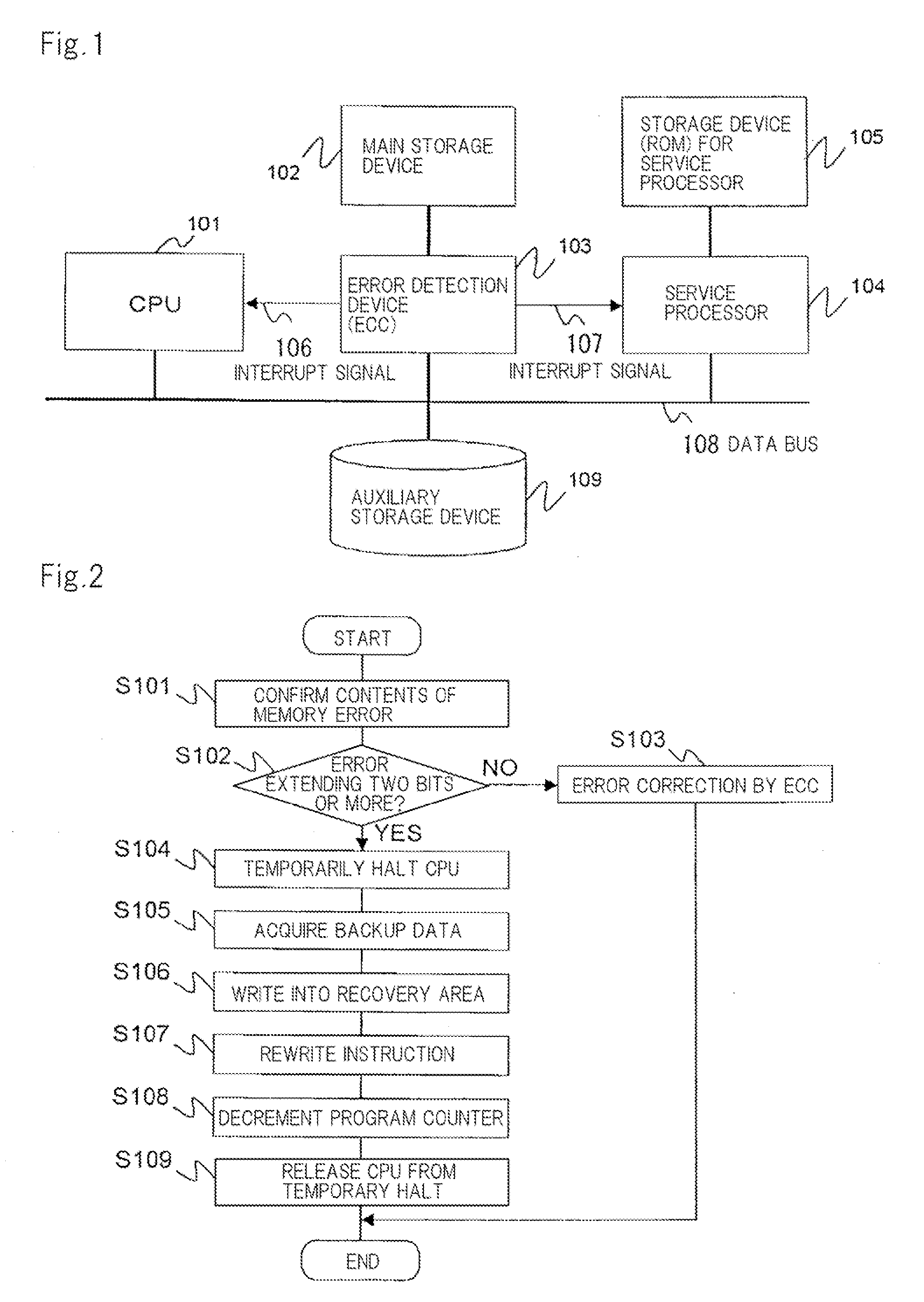

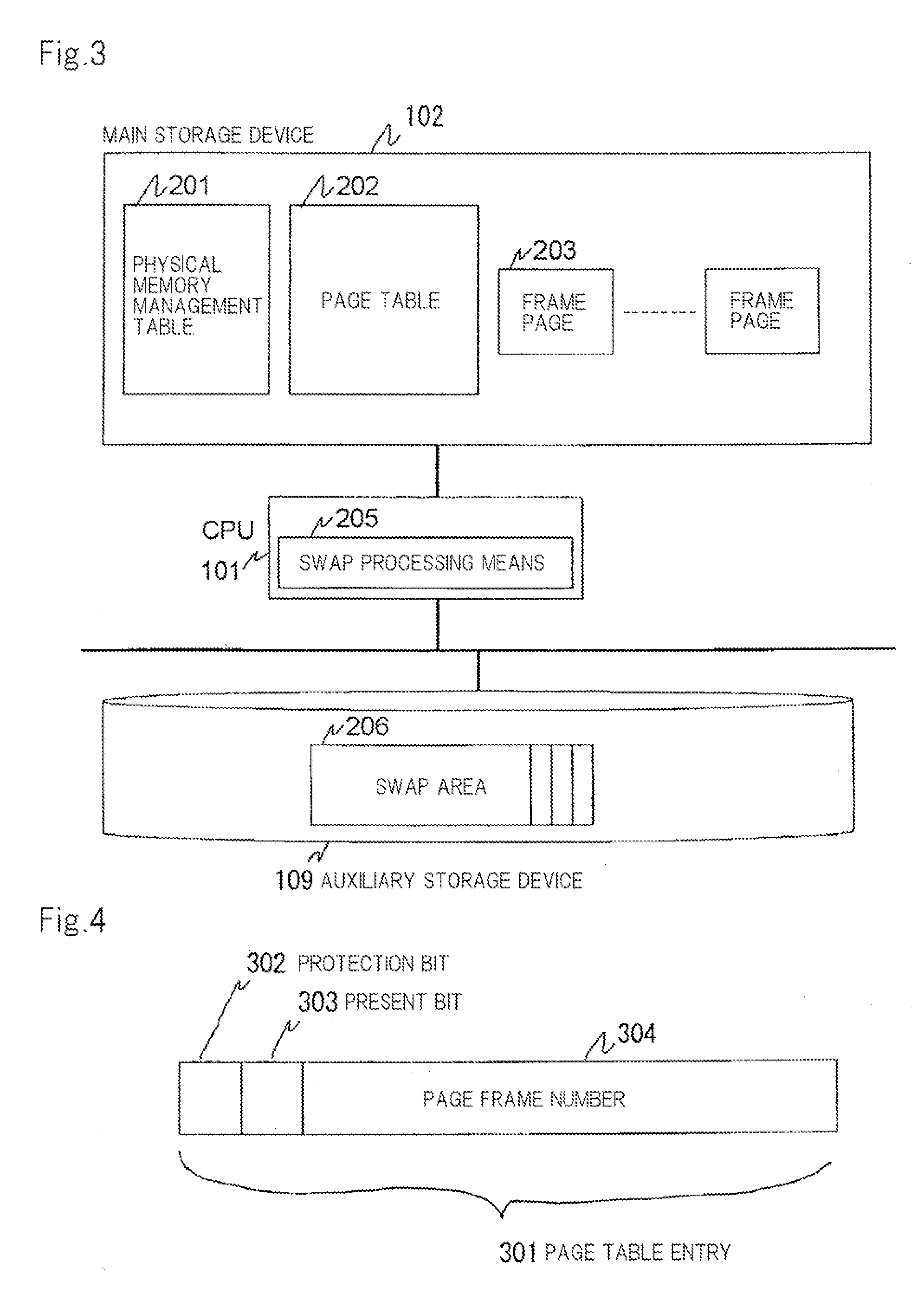

Memory failure recovery method, information processing apparatus, and program

ActiveUS20100318845A1Non-redundant fault processingRedundant operation error correctionRecovery methodInformation processing

Upon occurrence of a memory error which is difficult to correct, CPU interrupts a process under execution in response to interrupt signal output from error detection device, and transfers the control to the OS. The OS references attributes of a page stored in a page frame which has suffered the memory error. When read-only is indicated, physical memory management table is updated to set the page frame, which has suffered the error, into a disabled state. Then, page table is updated such that a virtual page stored in the page frame which has suffered the error is not assigned to any page frame, followed by resumption of the execution of the process. After execution of the process is resumed, a page fault process is invoked to store the virtual page which has encountered the memory error in another normal page frame.

Owner:NEC CORP

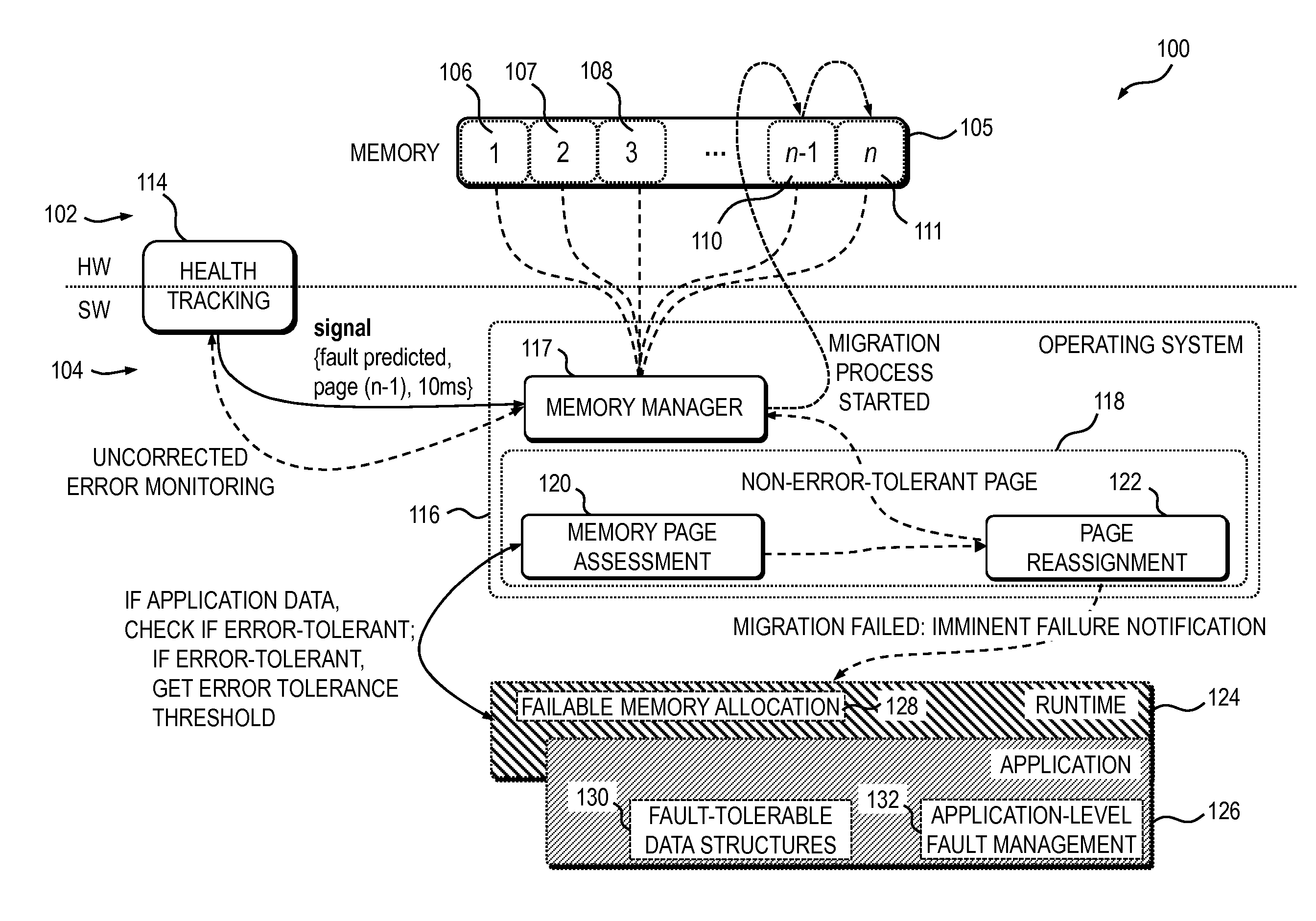

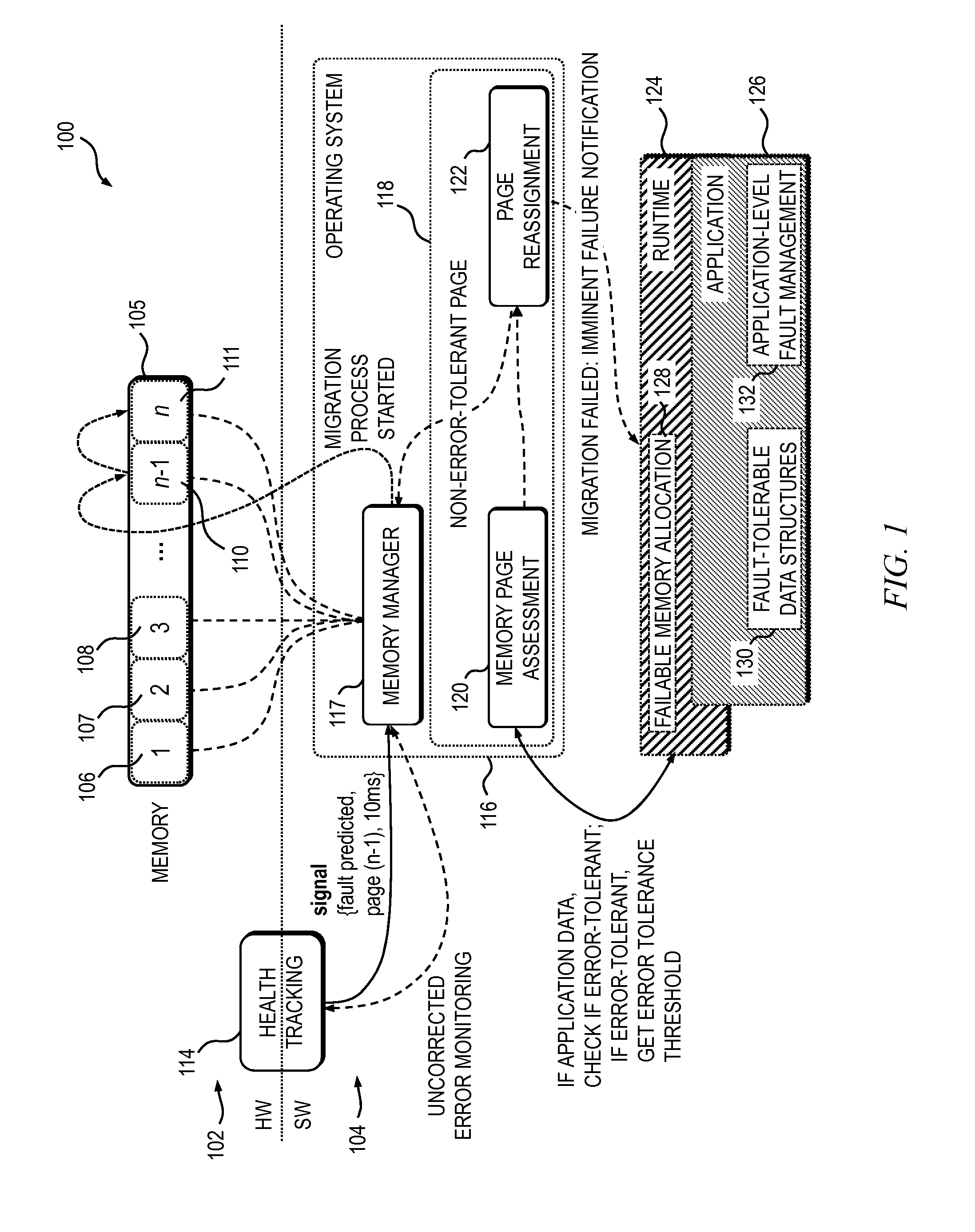

Method and apparatus for faulty memory utilization

InactiveUS20150074367A1Promote migrationAvoid failureInput/output to record carriersReliability/availability analysisOperational systemTerm memory

A method for faulty memory utilization in a memory system includes: obtaining information regarding memory health status of at least one memory page in the memory system; determining an error tolerance of the memory page when the information regarding memory health status indicates that a failure is predicted to occur in an area of the memory system affecting the memory page; initiating a migration of data stored in the memory page when it is determined that the data stored in the memory page is non-error-tolerant; notifying at least one application regarding a predicted operating system failure and / or a predicted application failure when it is determined that data stored in the memory page is non-error-tolerant and cannot be migrated; and notifying at least one application regarding the memory failure predicted to occur when it is determined that data stored in the memory page is error-tolerant.

Owner:IBM CORP

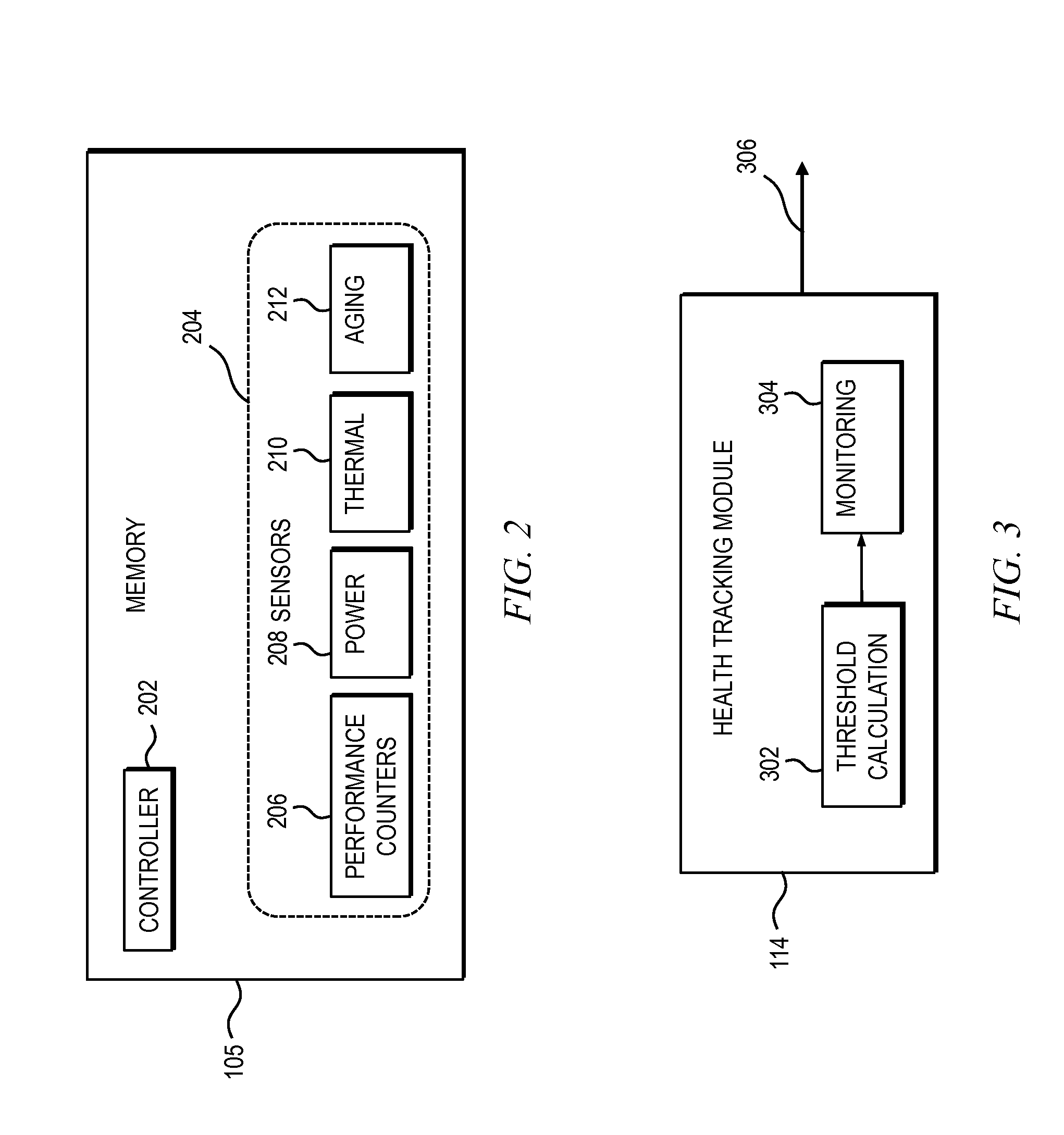

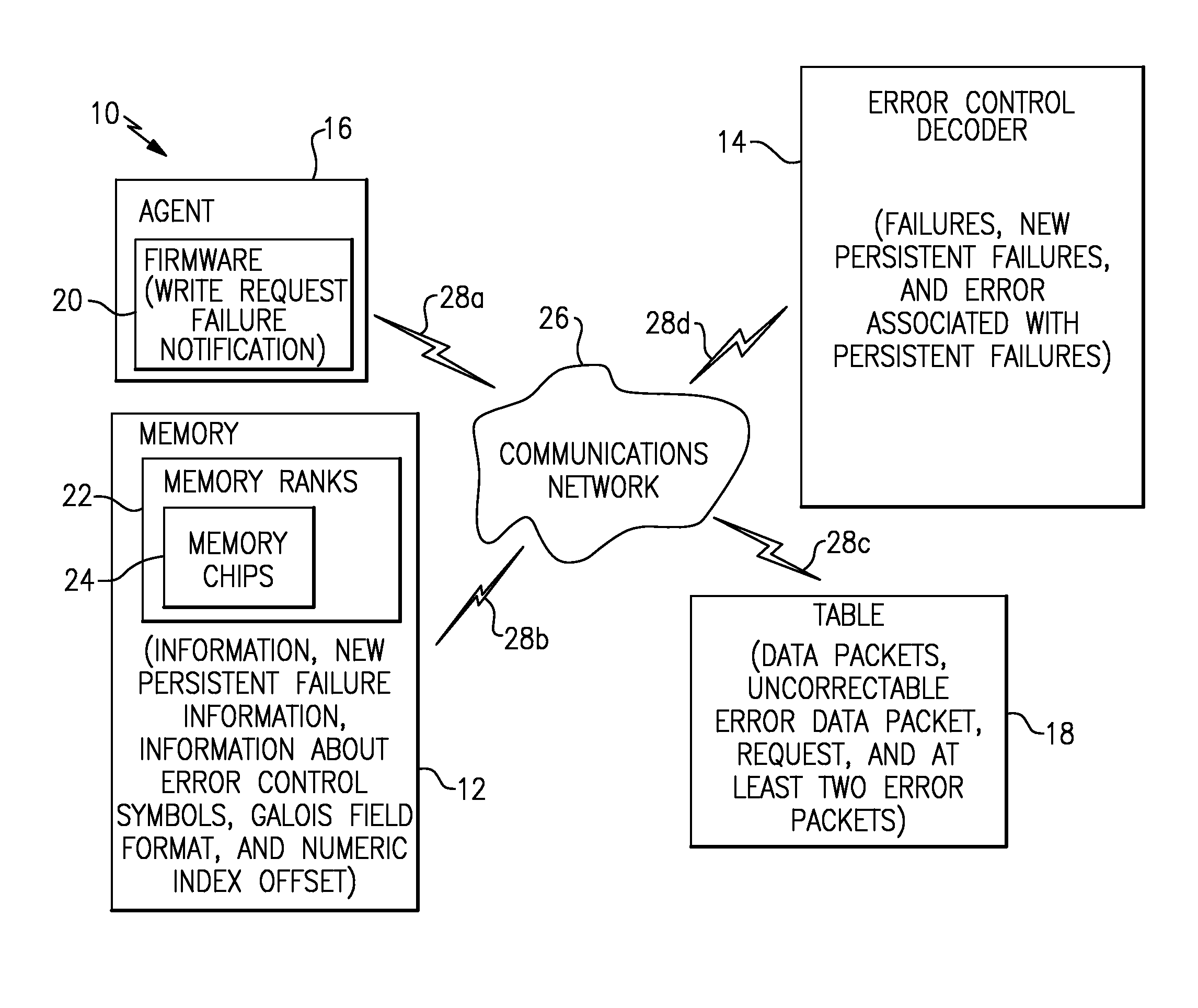

System to Improve Memory Failure Management and Associated Methods

InactiveUS20100293437A1Improves memory failure managementImprove memory failure managementError preventionTransmission systemsFailure managementComputer science

A system to improve memory failure management may include memory, and an error control decoder to determine failures in the memory. The system may also include an agent that may monitor failures in the memory. The system may further include a table where the error control decoder may record the failures, and where the agent can read and write to.

Owner:IBM CORP

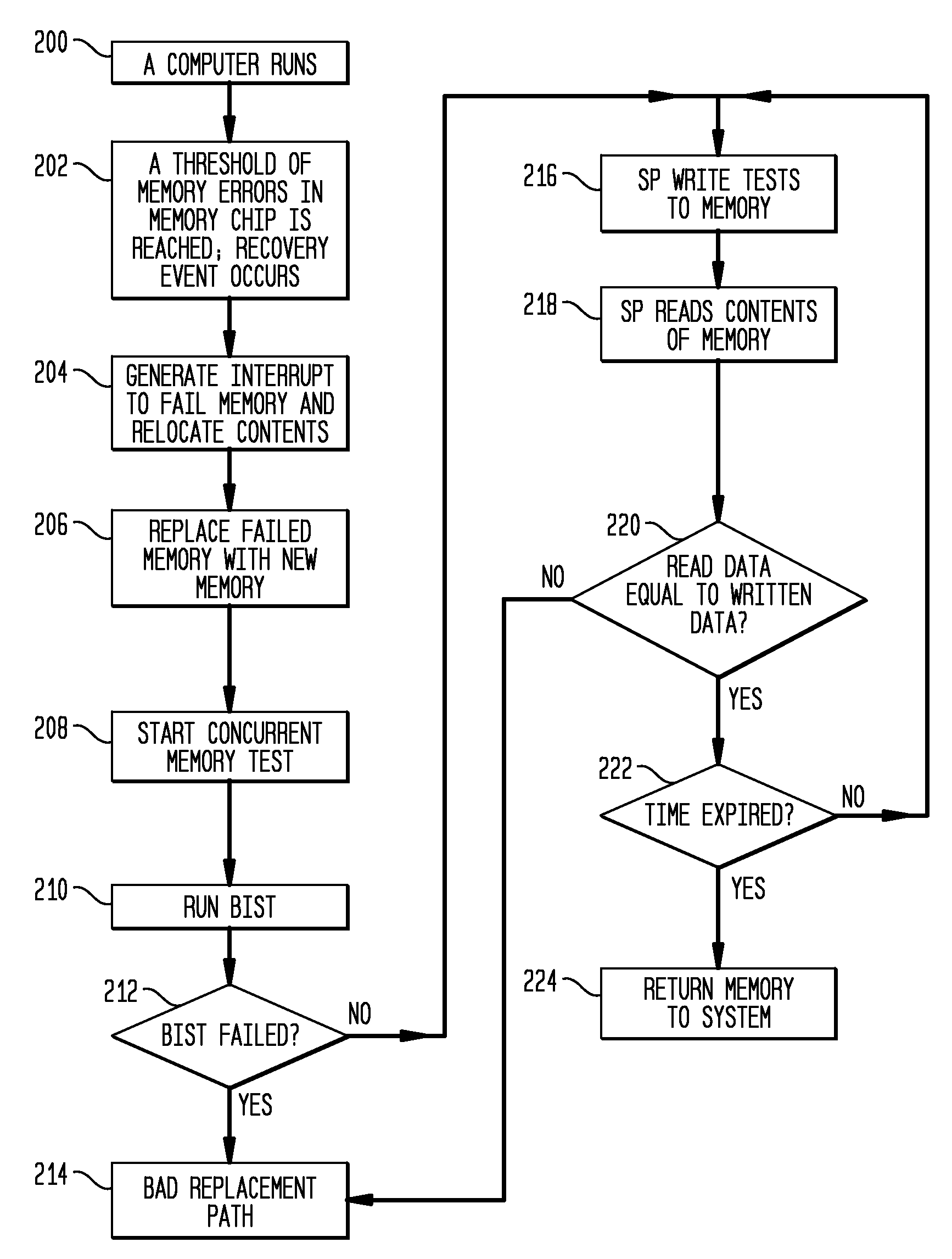

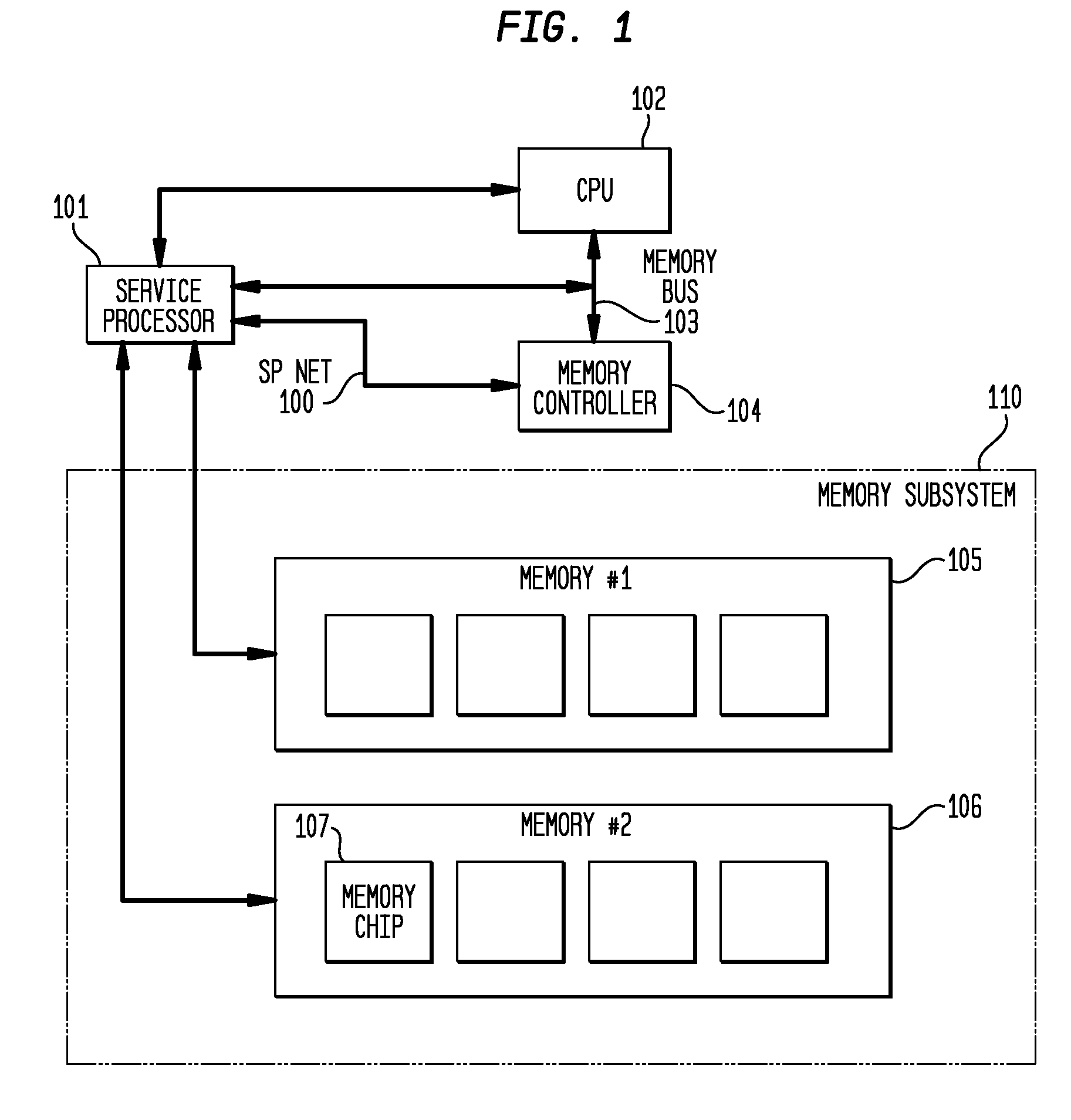

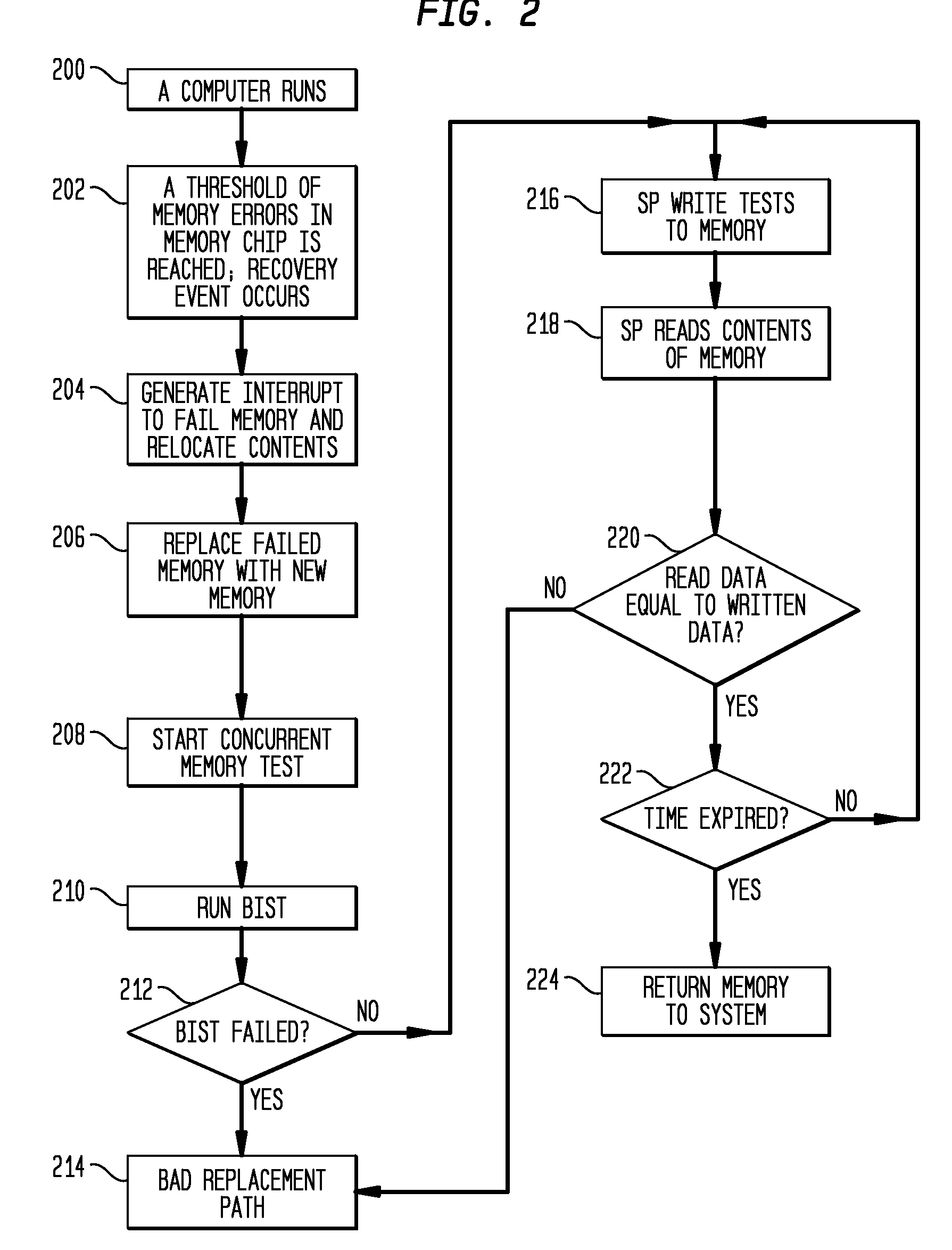

Method, Apparatus and Program Product to Concurrently Detect, Repair, Verify and Isolate Memory Failures

Method and system for repairing memory failure in a computer system in one aspect determines one or more test patterns and time duration for testing the new memory unit that replaced a failed memory unit. The test pattern is written to the new memory unit and read from the new memory unit. The read pattern is compared to the test pattern that was used to write. If the read test pattern and the written test pattern doe not match, a further repair action is taken. If they match, writing and reading of the test pattern repeats until the time duration for testing expires. The new memory unit may be configured as available for use when the write and read test completes successfully for the testing time duration.

Owner:LENOVO GLOBAL TECH INT LTD

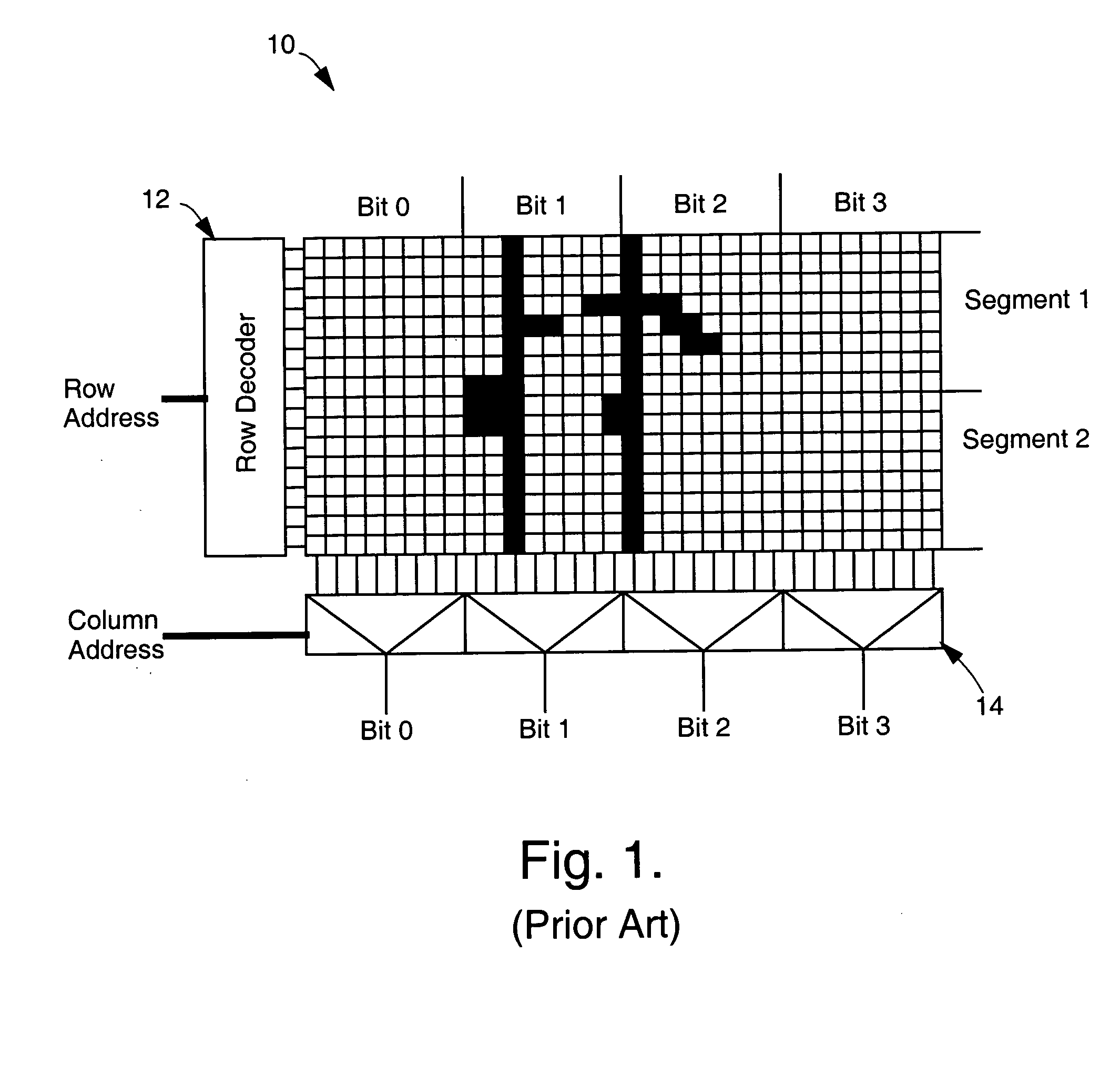

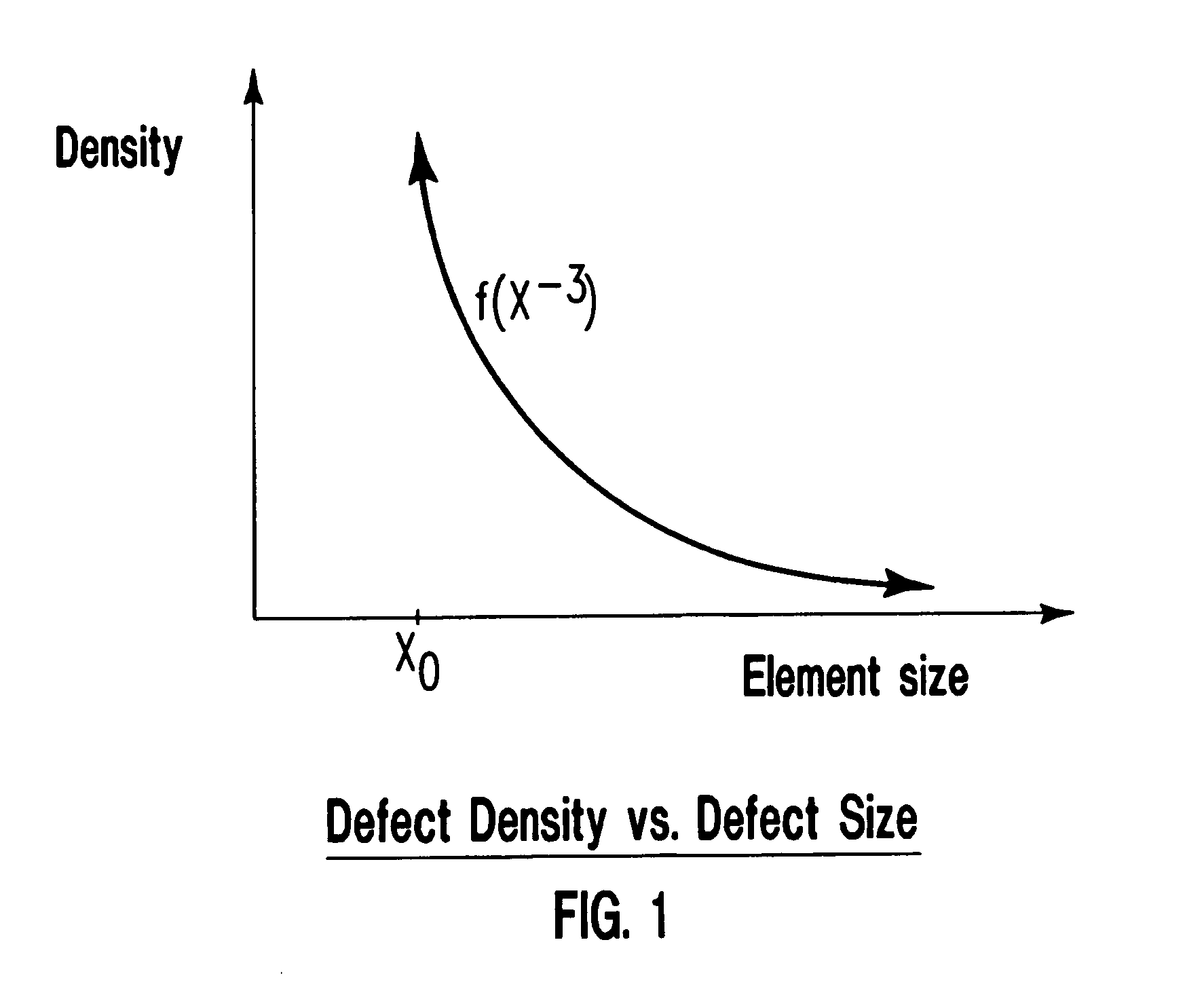

Reducing memory failures in integrated circuits

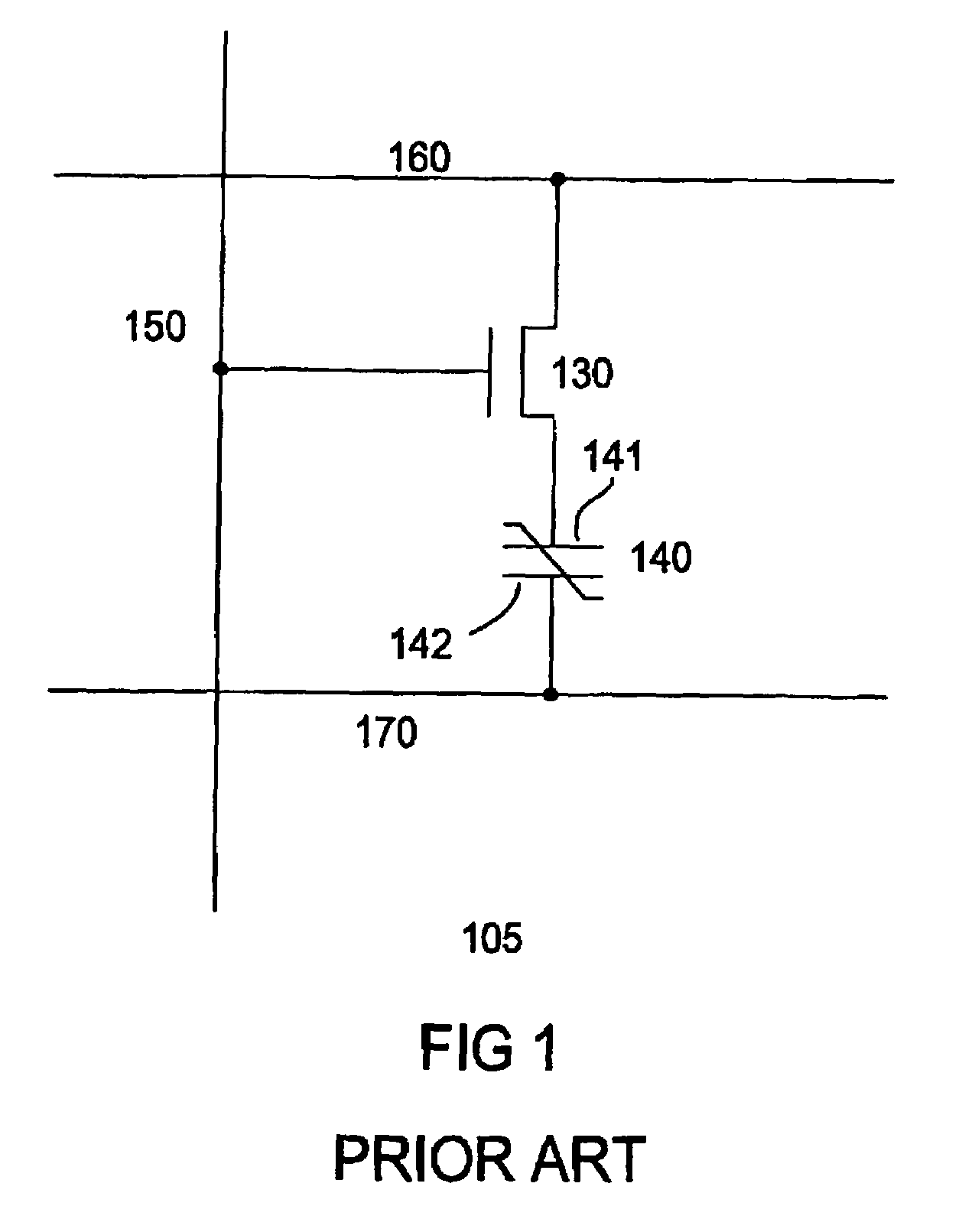

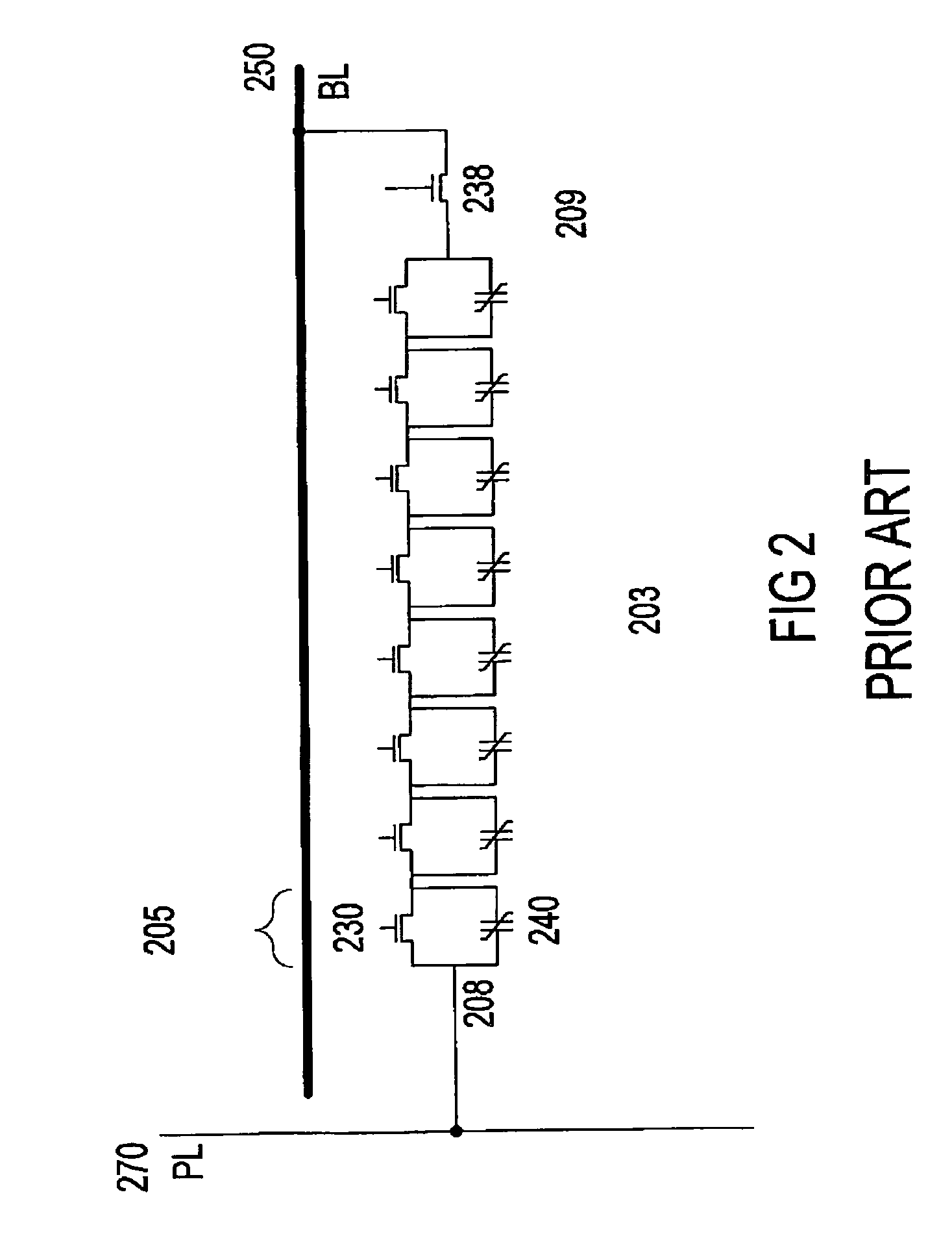

InactiveUS7187602B2Improve reliabilityRead-only memoriesDigital storageIntegrated circuit layoutDependability

Owner:POLARIS INNOVATIONS

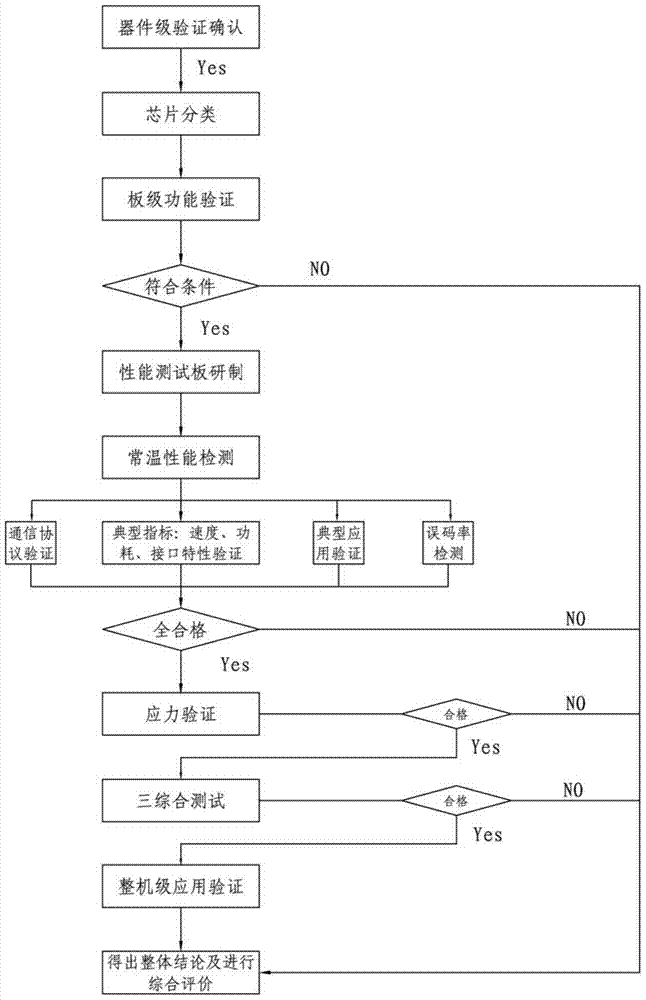

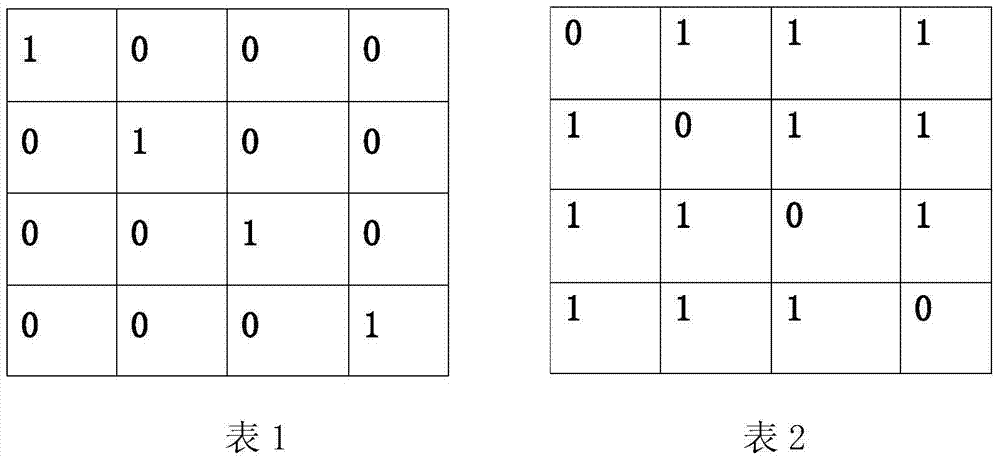

Aviation application-based verification method for domestic storages

ActiveCN103700407AVerify reverse failureValidation failureFunctional testingStatic storageAviationMemory faults

The invention provides an aviation application-based verification method for domestic storages. The aviation application-based verification method sequentially comprises the following steps: 1) storage chip detection; 2) board level functionality test; 3) board level performance test; 4) complete machine level verification; 5) comprehensive analysis and evaluation. According to the aviation application-based verification method disclosed by the invention, basic environment adaptation verification is performed on the applications of the domestic storages on aviation weapon systems, and the single memory unit faults, single memory unit reversal faults, inter-unit coupling faults and memory faults and unit sensitization faults of the various storages, as well as the data retention faults of the changes of unit logical values due to electric leakage after some periods, can be verified, thus providing a beneficial guarantee for domestic development of the aviation weapon systems.

Owner:AVIC NO 631 RES INST

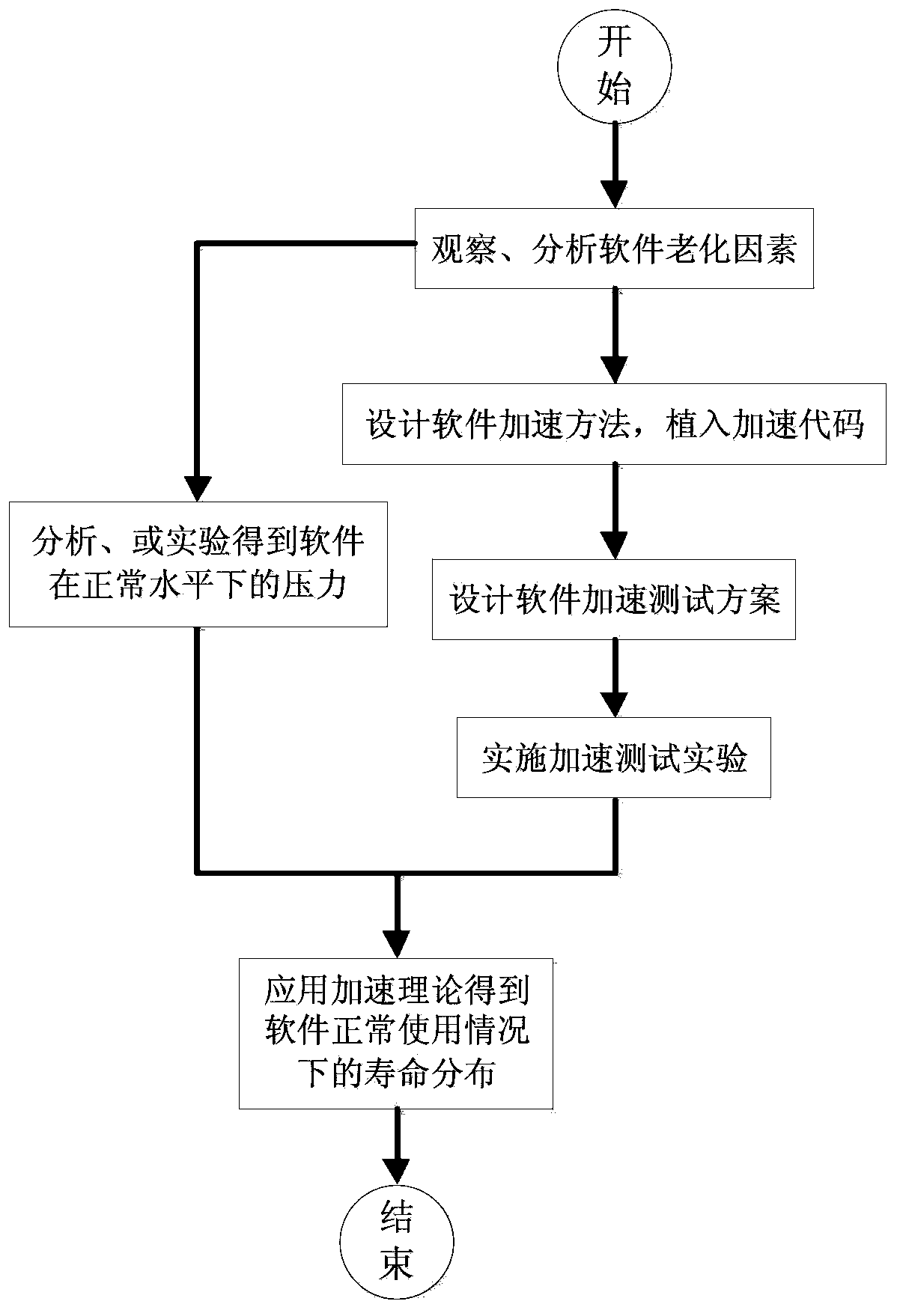

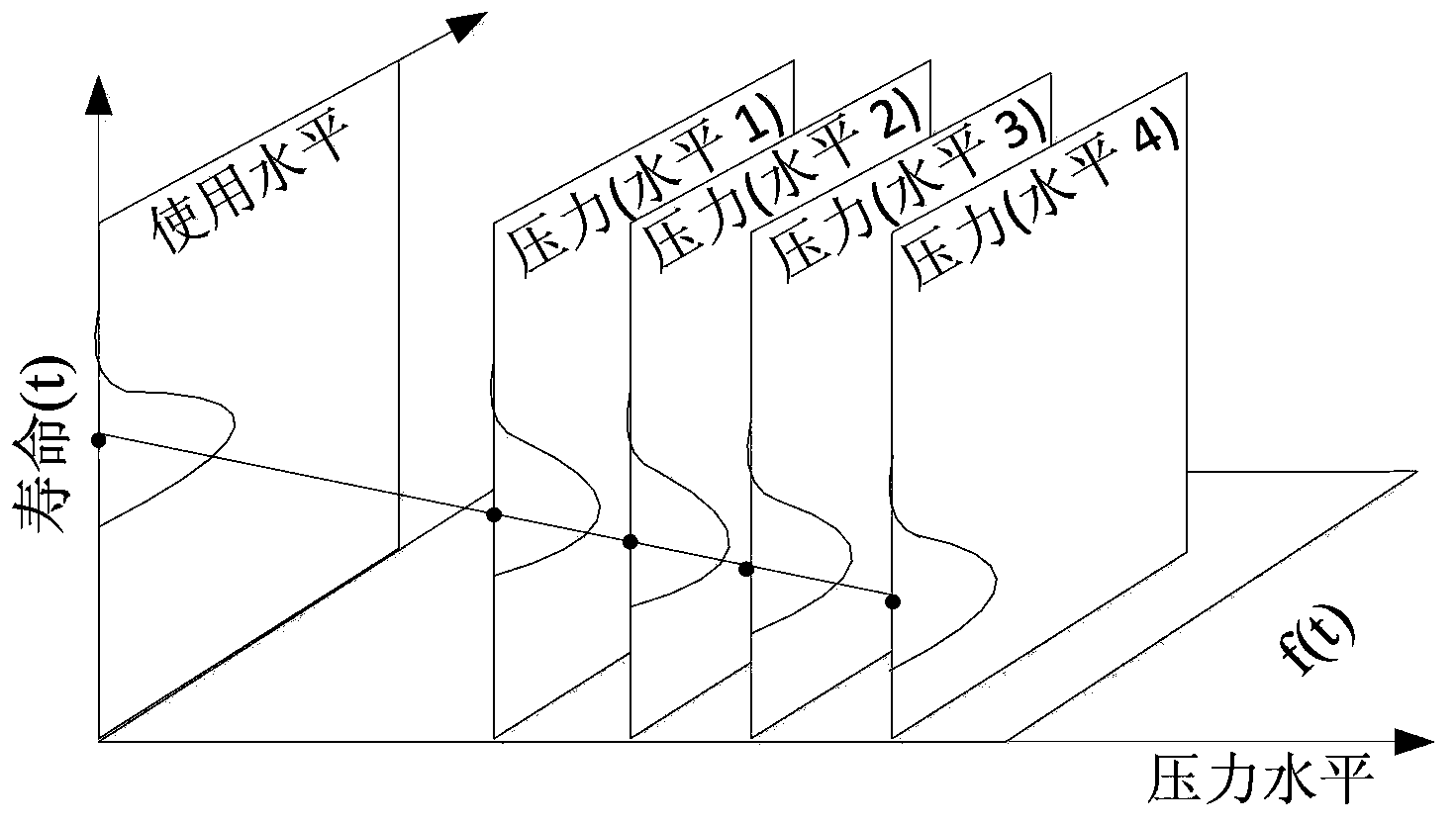

Software accelerating life test method

The invention relates to the field of software performance test, and particularly relates to a software accelerating life test method used for carrying out life test to the software producing aging phenomena by adopting the accelerating life test theory. The software accelerating life test method comprises the following steps: adding codes injected with memory failures; setting accelerating-level pressure value N as 4, 8, 12 and 16, and running a program; recoding failure time TTF, and saving data; estimating sample distribution of software lifetime; establishing a suitable relationship between the lifetime and the pressure, and estimating distribution of average failure time of system being tested under a non-accelerating circumstance. The deployment and implementation of the invention aims to carry out an accelerating life test to the software producing aging phenomena, the lifetime data of software under an accelerating circumstance is obtained through the short time-consuming accelerating life test, the real lifetime of the software under the non-accelerating circumstance is calculated, so that the probability distribution of the software lifetime under a normal use condition is obtained.

Owner:HARBIN ENG UNIV

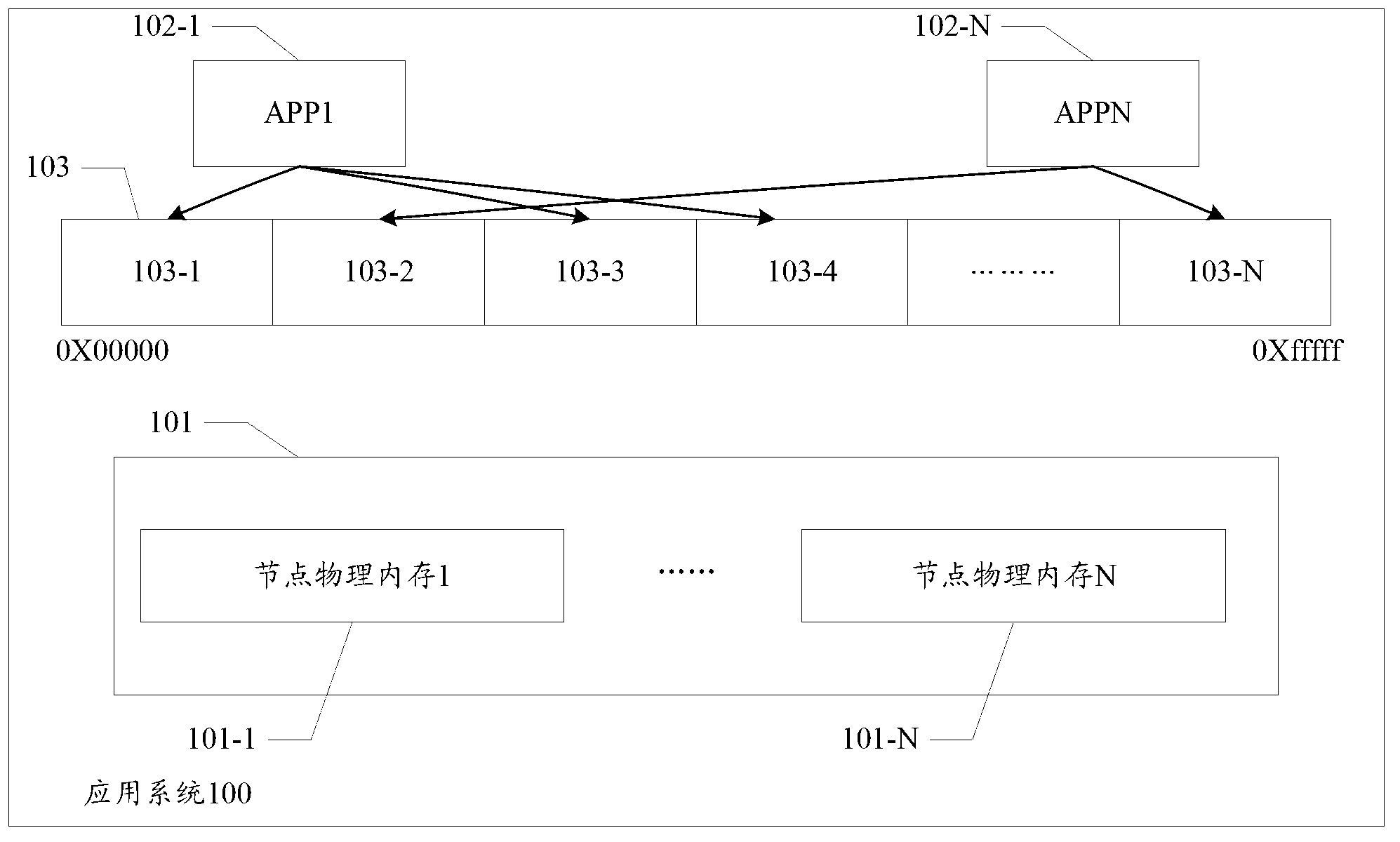

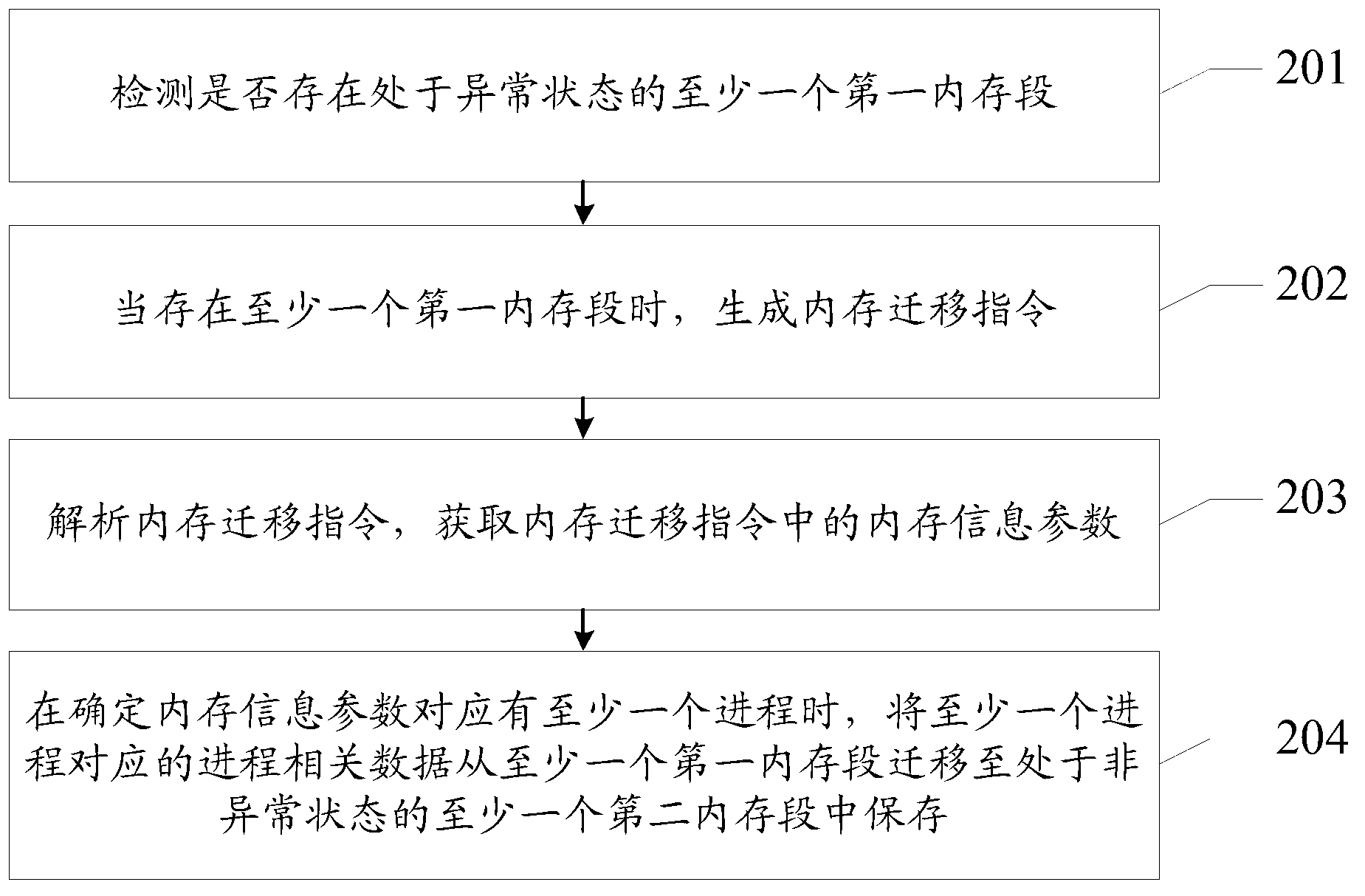

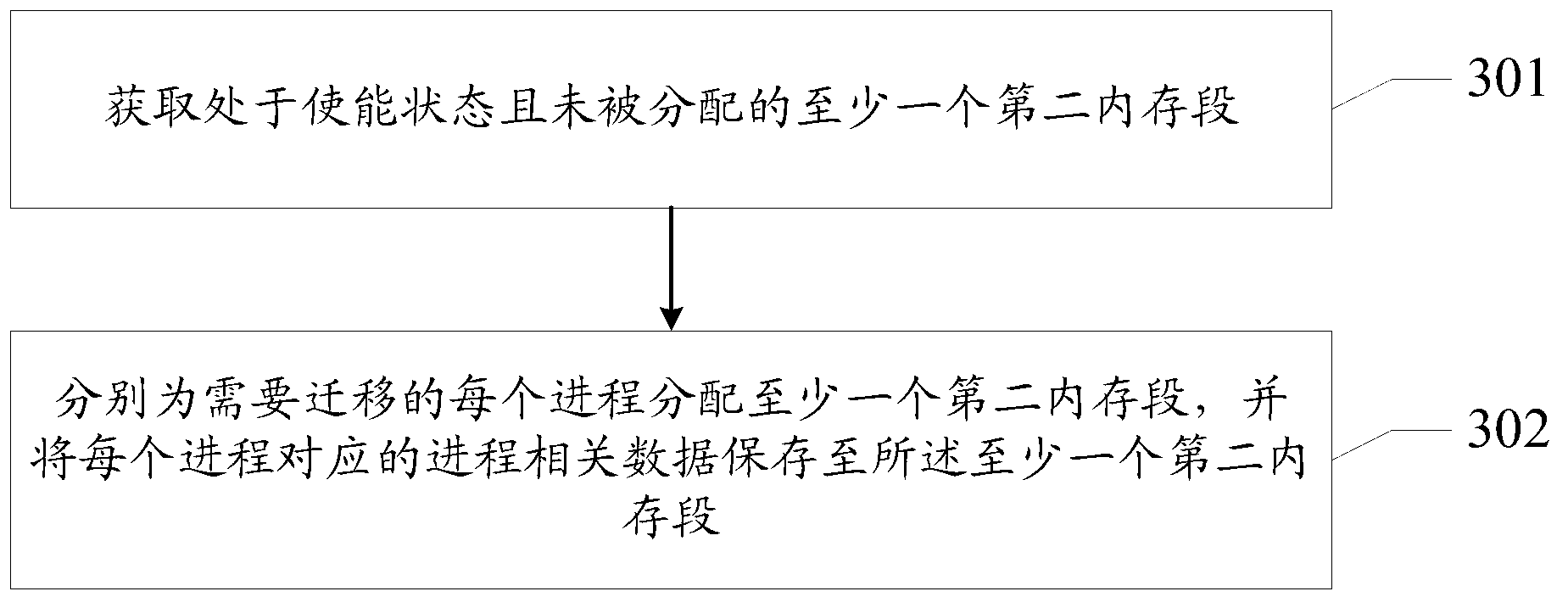

Memory migration method, memory migration device and equipment

InactiveCN103324582AAchieve migrationAvoid the problem of process terminationMemory adressing/allocation/relocationParallel computingNormal state

An embodiment of the invention provides a memory migration method, a memory migration device and equipment. The method includes the steps: detecting whether at least one first memory segment is in an abnormal state or not; generating a memory migration instruction when at least one first memory segment is in the abnormal state; analyzing the memory migration instruction; acquiring memory information parameters for indicating whether at least one first memory segment corresponds to at least one progress or not in the memory migration instruction; and migrating relevant data corresponding to at least one process to at least one second memory segment in the normal state from at least one first memory segment and storing the relevant data when at least one first memory segment corresponds to at least one process. Therefore, the problem of service interruption in a memory caused by memory failure in the prior art can be solved, so that running stability and reliability of service processes in a system are improved.

Owner:HUAWEI TECH CO LTD

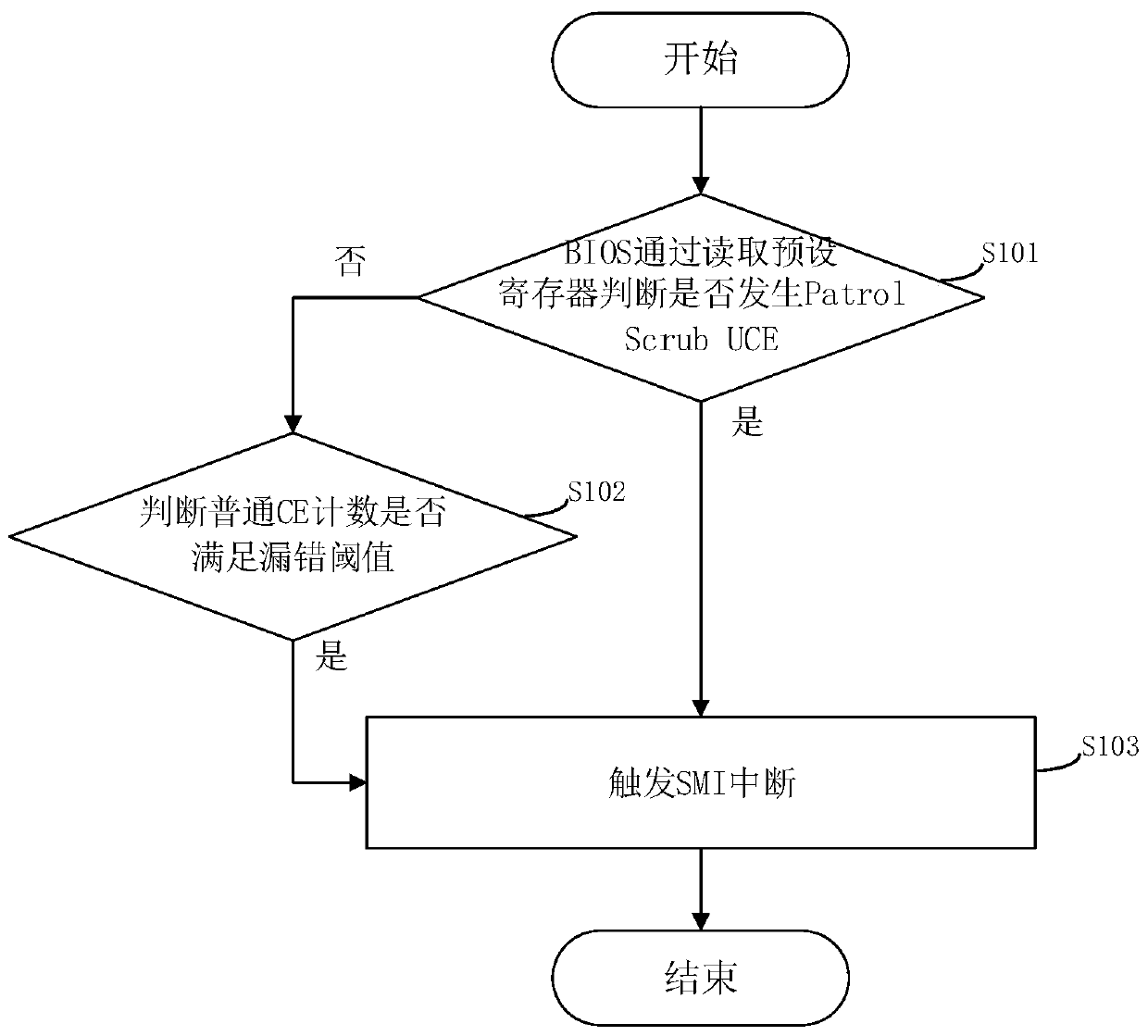

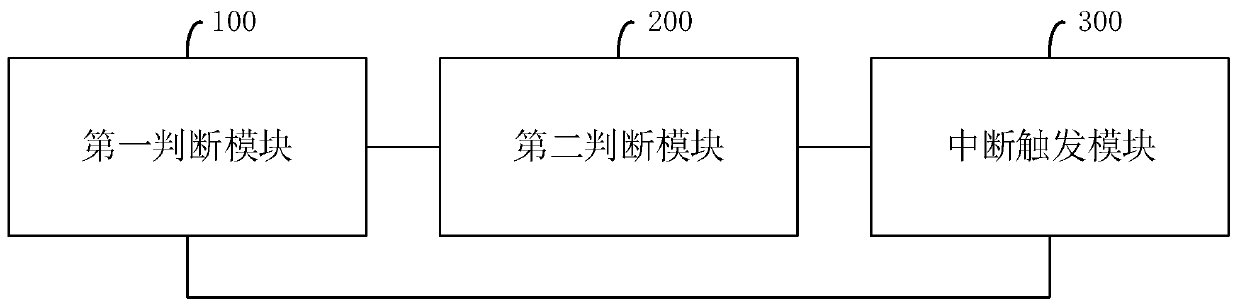

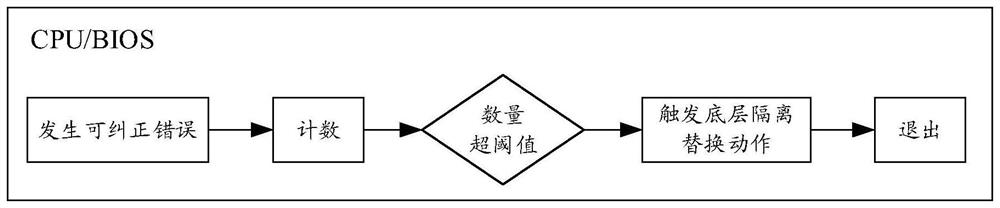

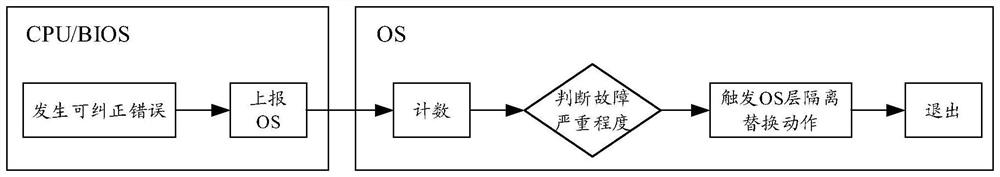

Memory CE fault processing method, system and related device

The invention provides a fault processing method for a memory CE. The fault processing method comprises the steps of enabling a BIOS to judge whether Patrol Scrub UCE occurs or not by reading a presetregister; if not, judging whether the common CE count meets a missed error threshold value or not; and if the Patrol Scrub UC or the common CE count meets the missed error threshold value, triggeringSMI interruption. According to the invention, when the Patrol Scrub UCE occurs, SMI interruption is triggered the BIOS is prevented from counting as a common CE, so that the BIOS can discover the Patrol Scrub UCE in time; server operation and maintenance personnel can obtain memory fault information in time; and monitoring of the memory state of the server is facilitated. The invention further provides a fault processing system for the memory CE, a computer readable storage medium and fault processing equipment for the memory CE, which have the above beneficial effects.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

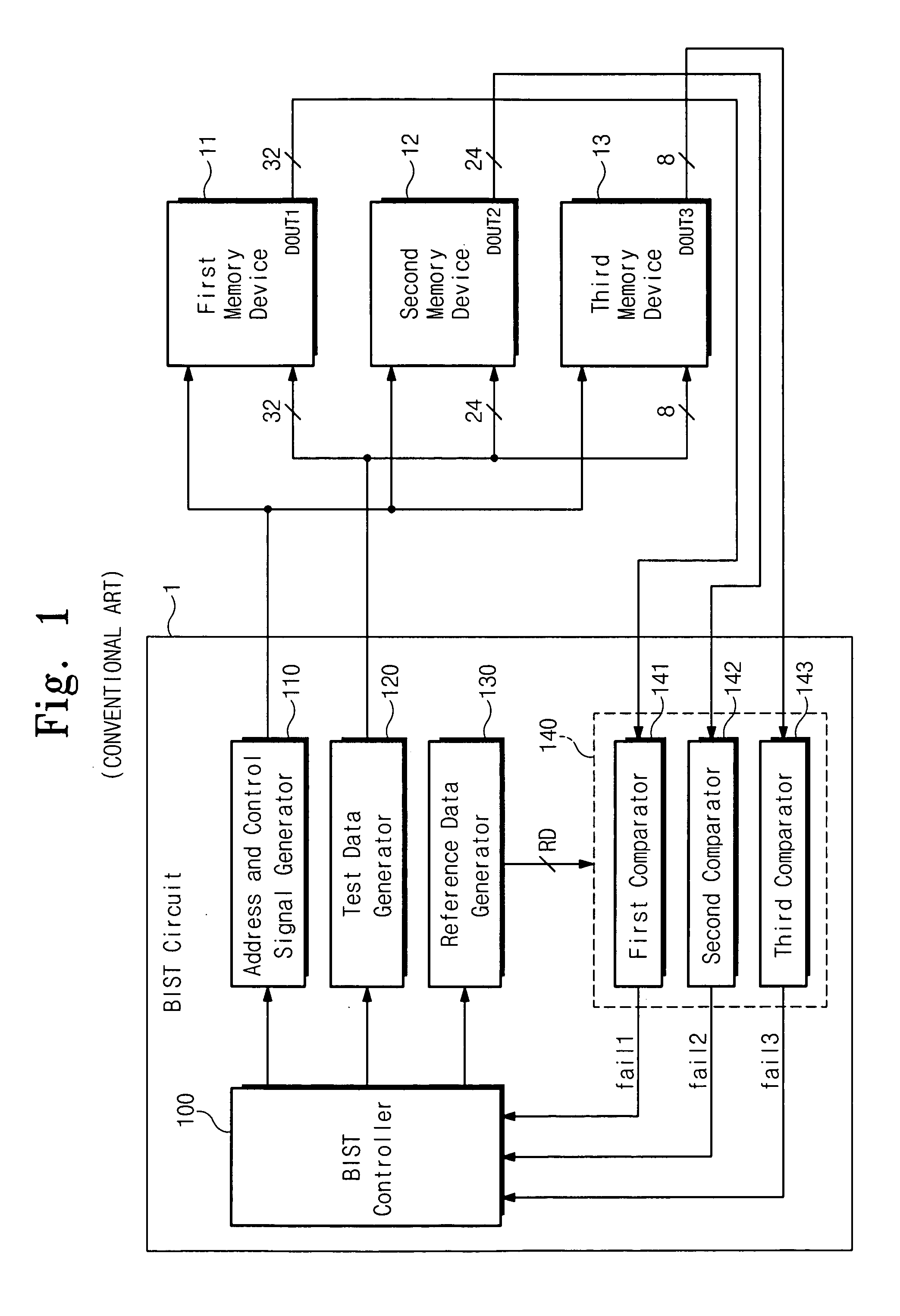

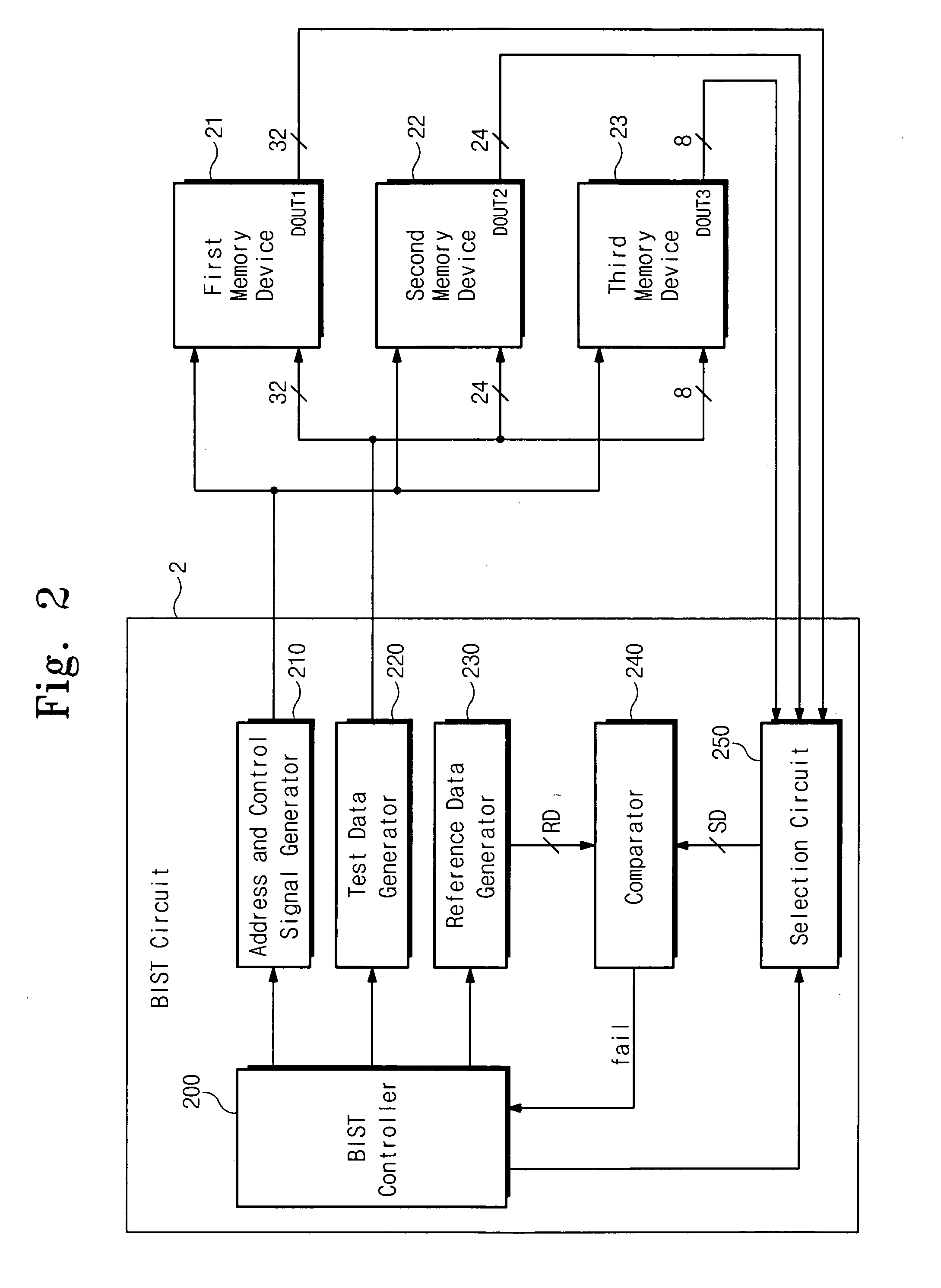

Semiconductor device for detecting memory failure and method thereof

A semiconductor device for testing memory, including a BIST controller for testing a plurality of memory devices, an address and control signal generator for generating address and control signals for reading data from the plurality of memory devices, a test data generator for generating test data, and a fail detector for determining memory failure. Another semiconductor device for testing at least one of a plurality of memory devices, including a BIST controller for testing a plurality of memory devices, an address and control signal generator for generating address and control signals for reading data from the plurality of memory devices, a test data generator for generating test data, a reference data generator for generating reference data, and a fail detector for determining memory failure. A method of determining memory failure, including writing data to a plurality of memory devices, reading the data from the plurality of memory devices, comparing corresponding addresses of the read data simultaneously, outputting a single fail signal when the comparing step determines at least one of the read data from the plurality of memory devices as not being equal. A semiconductor device for testing memory, including a BIST controller for testing a plurality of memory devices, an address and control signal generator for generating address and control signals for reading data from the plurality of memory devices, a test data generator for generating test data, a reference data generator for generating reference data, a selection circuit for selecting the read data from one of the plurality of memory devices, and a comparator for comparing the read data from one of the plurality of memory devices with the reference data. A semiconductor device for testing memory, including a BIST controller for testing a plurality of memory devices, an address and control signal generator for generating address and control signals for reading data from the plurality of memory devices, a test data generator for generating test data, and a single comparison unit for determining memory failure in at least two of the plurality of memory devices. A method of determining memory failure, including writing data to a plurality of memory devices, reading the data from the plurality of memory devices, comparing corresponding addresses of the read data of at least two of the plurality of memory devices in a single comparison unit.

Owner:SAMSUNG ELECTRONICS CO LTD

System to improve memory failure management and associated methods

InactiveUS8352806B2Improves memory failure managementImprove memory failure managementError preventionTransmission systemsFailure managementComputer science

A system to improve memory failure management may include memory, and an error control decoder to determine failures in the memory. The system may also include an agent that may monitor failures in the memory. The system may further include a table where the error control decoder may record the failures, and where the agent can read and write to.

Owner:IBM CORP

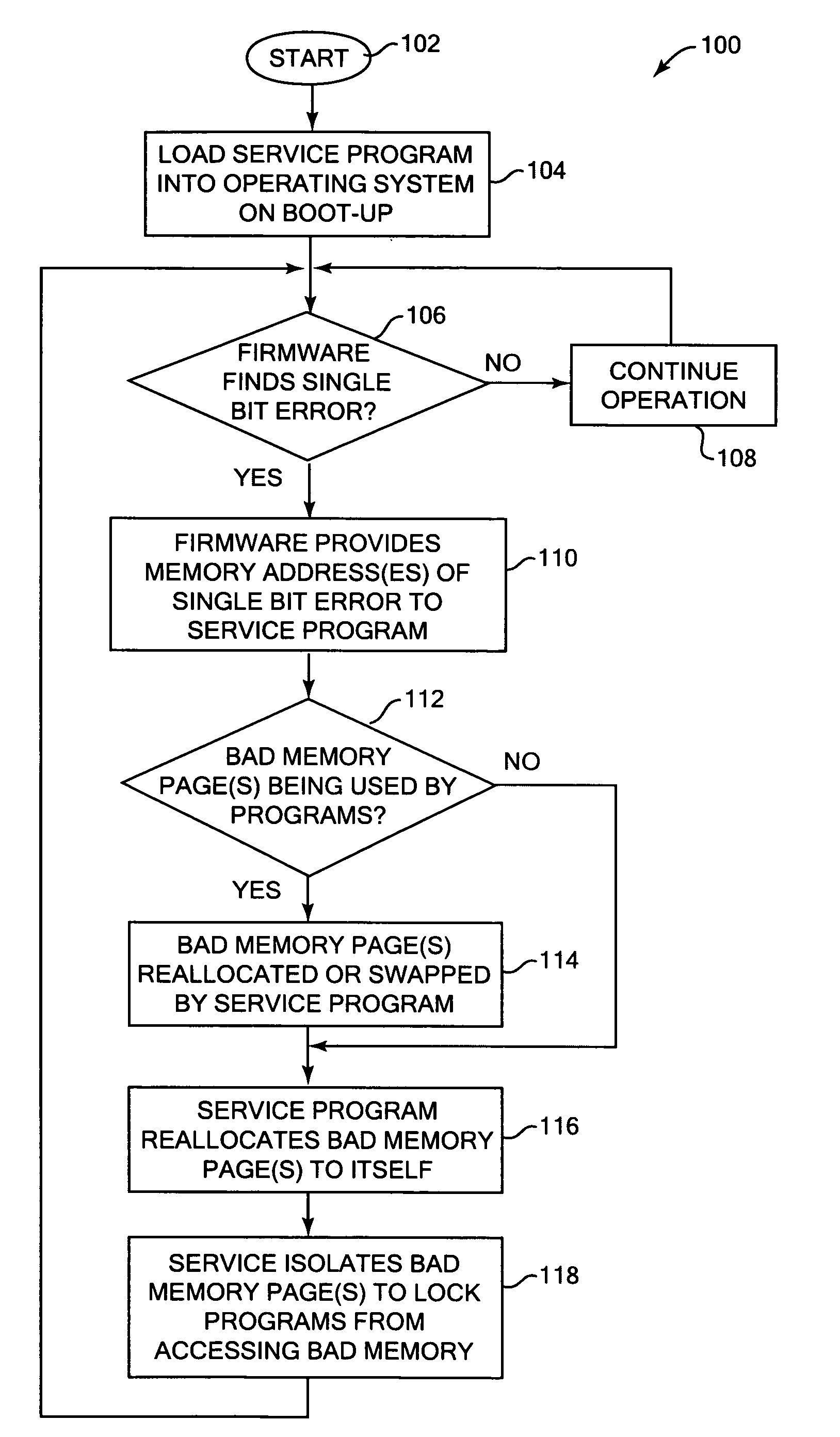

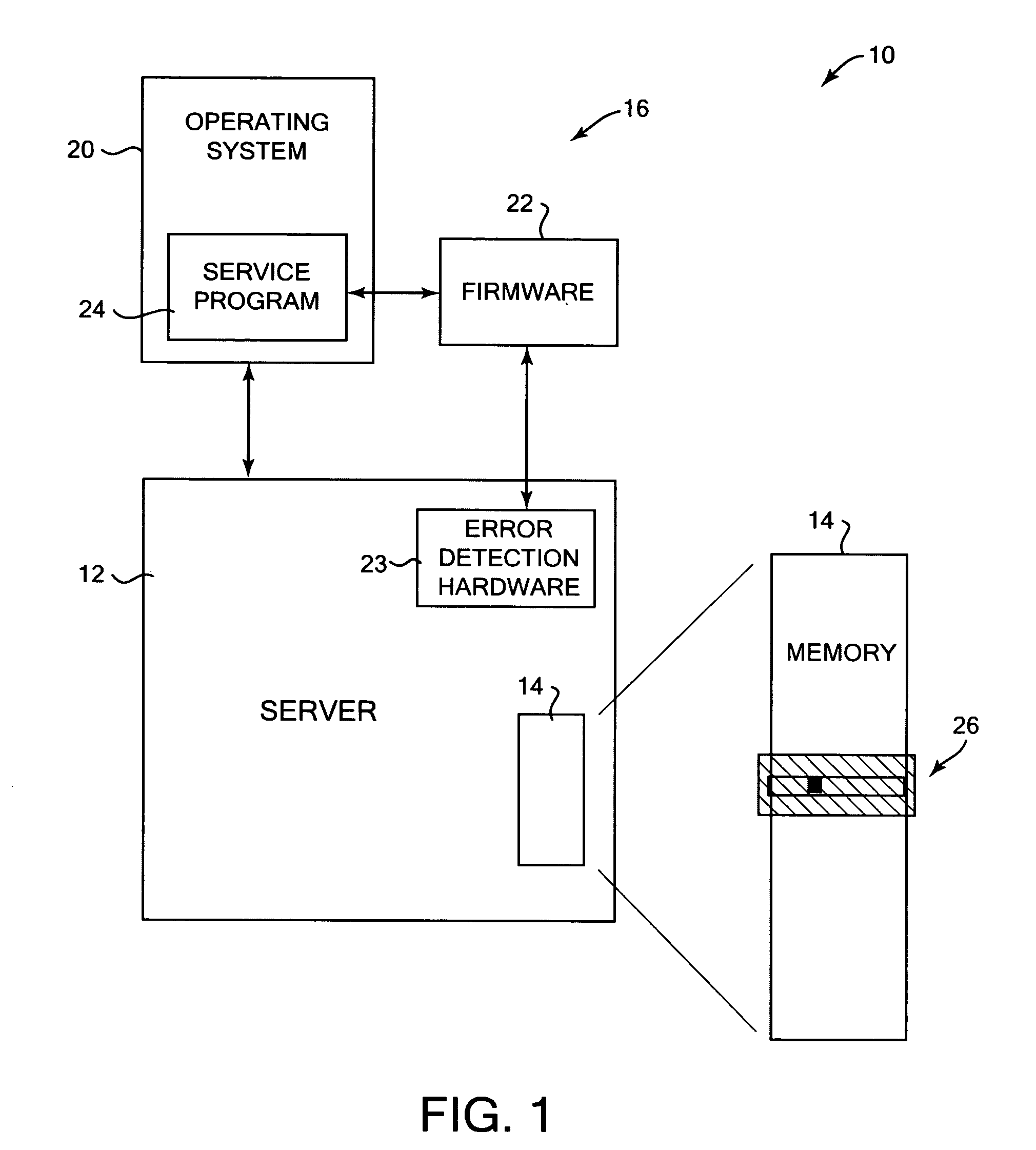

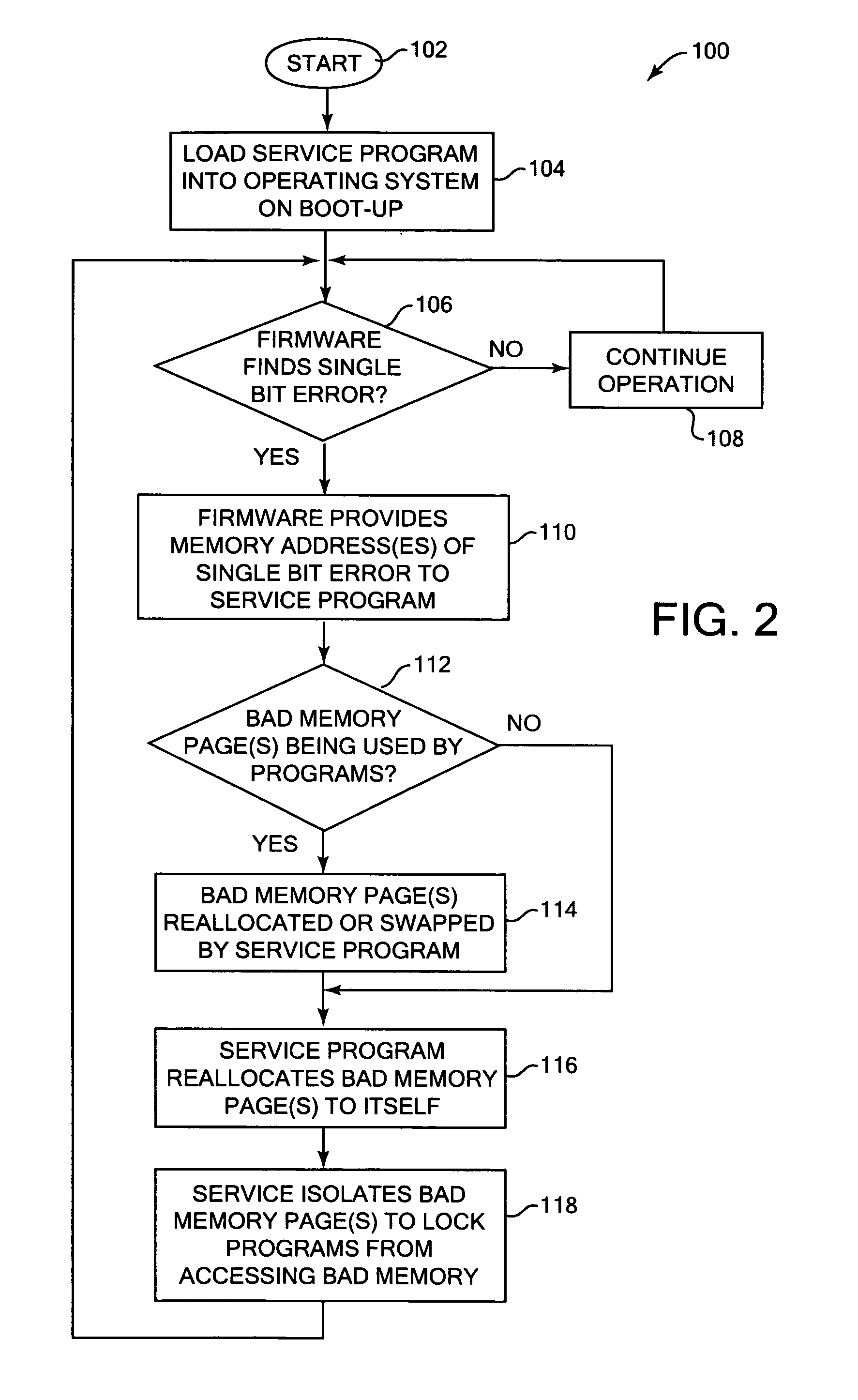

Method and system for reducing memory faults while running an operating system

ActiveUS7308603B2Reduce failureError detection/correctionStatic storageMemory faultsOperational system

Method and system for reducing memory faults for computer systems. In one aspect, a notification is received that indicates that a single bit error has been detected in a portion of memory of the computer system. A service program is used to isolate the portion of the memory that includes the detected single bit error by allocating the portion of memory to itself, such that the portion of memory may no longer be accessed for data reading or writing by programs running on the computer system.

Owner:GOOGLE LLC

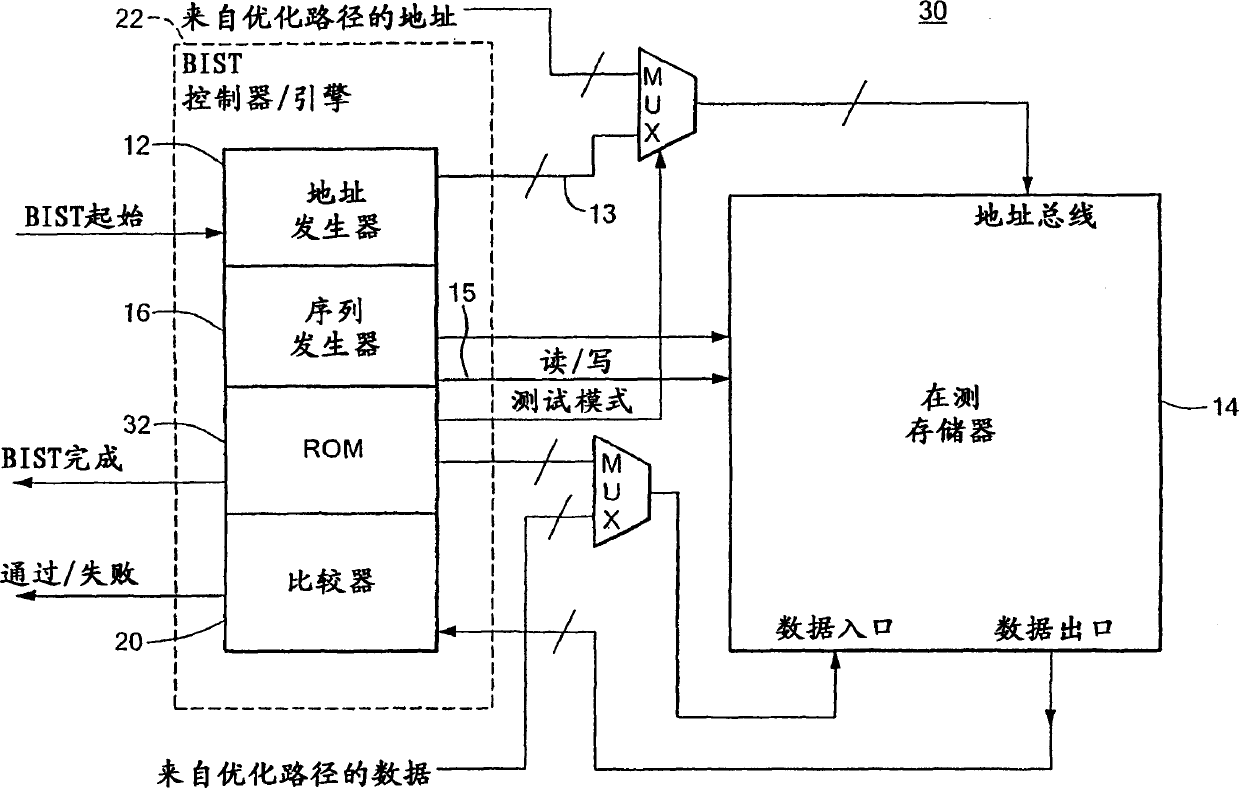

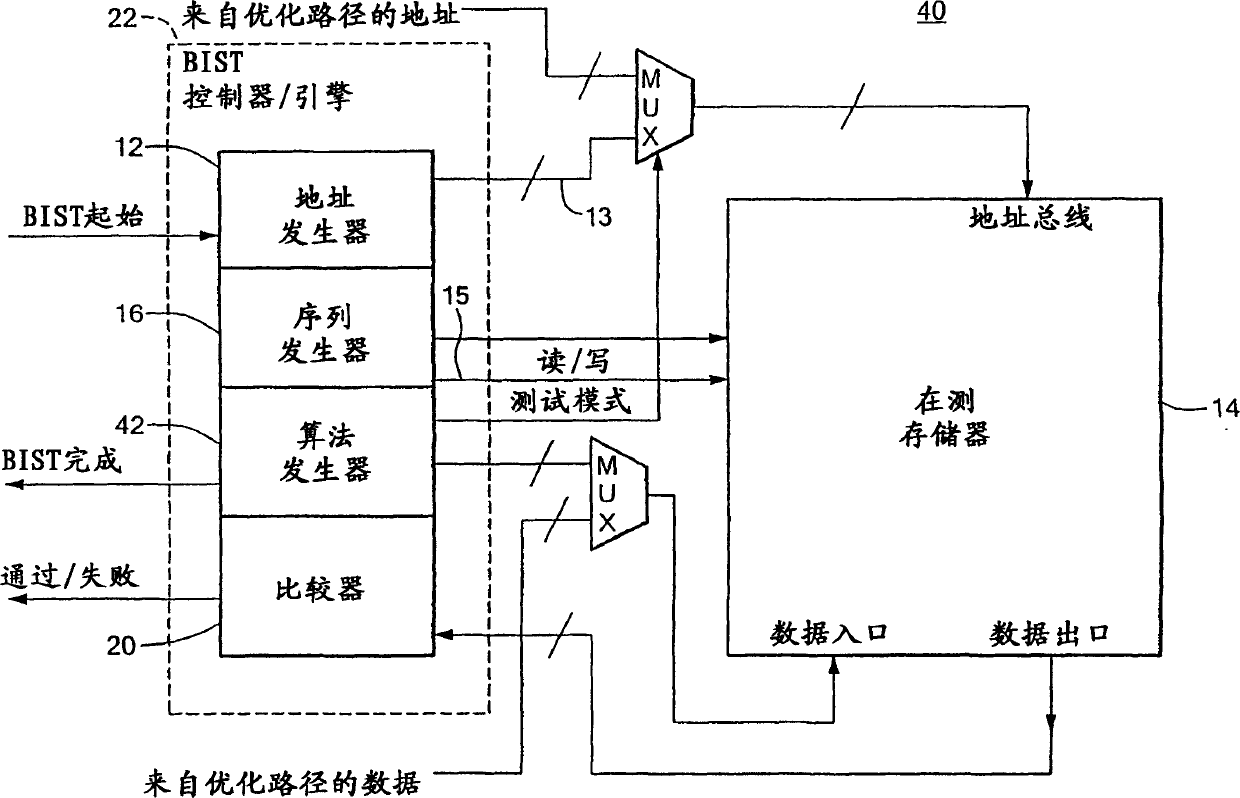

Universally accessible fully programmable memory built-in self-test (mbist) system and method

A universally accessible fully programmable memory built-in self-test (MBIST) system including an MBIST controller having an address generator configured to generate addresses for a memory under test, a sequencer circuit configured to deliver test data to selected addresses of the memory under test and reading out that test data, a comparator circuit configured to compare the test data read out of the memory under test to the test data delivered to the memory under test to identify a memory failure, and an externally accessible user programmable pattern register for providing a pattern of test data to the memory under test. The system includes an external pattern programming device configured to supply the pattern of test data to the user programmable data pattern register.

Owner:ANALOG DEVICES INC

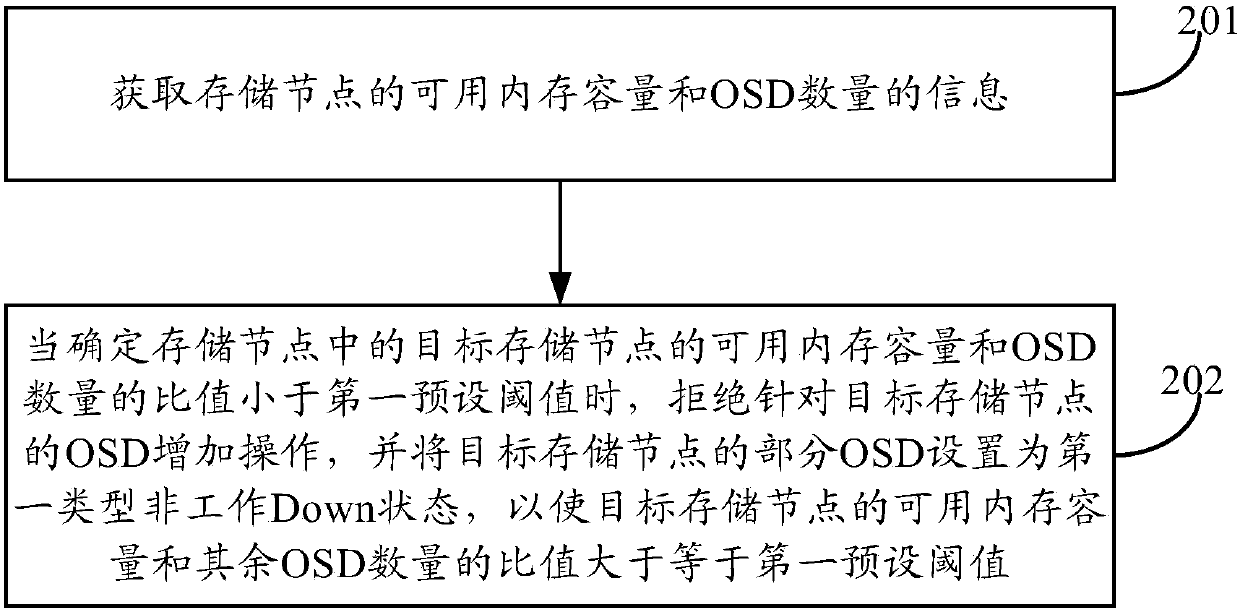

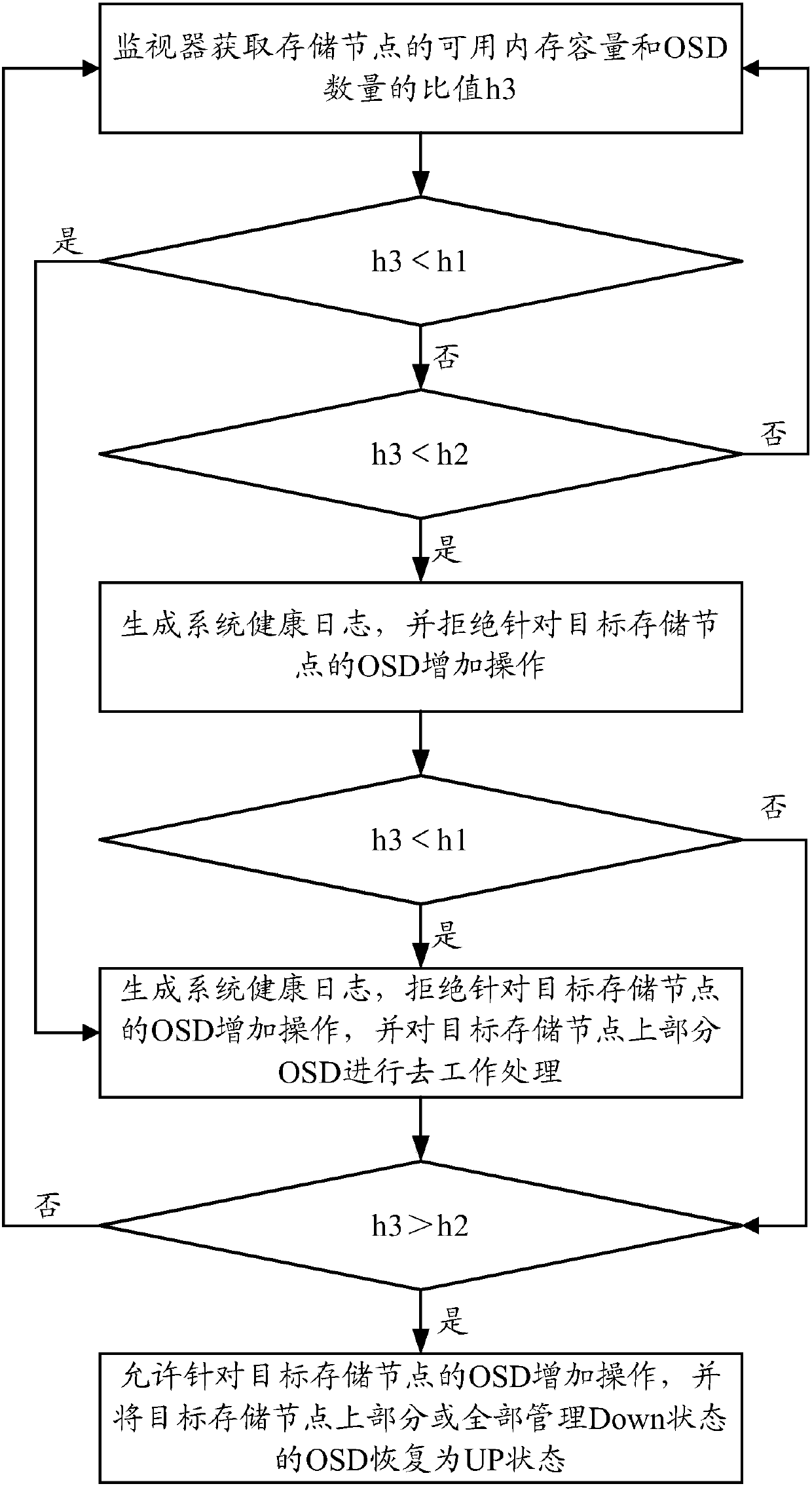

Method and device for handling faults

ActiveCN107729185AAvoid OSD performance bottlenecksReduce riskHardware monitoringRedundant operation error correctionObject storageFault handling

The invention provides a method and a device for handling faults. The method includes acquiring information of available memory capacity of storage nodes and the quantities of object storage devices OSD; rejecting OSD addition operation on target storage nodes when ratios of the available memory capacity of the target storage nodes to the quantities of the OSD are smaller than first preset thresholds and setting partial OSD of the target storage nodes in first types of non-working Down states to allow the ratios of the available memory capacity of the target storage nodes to the quantities ofthe other OSD to be larger than or equal to the first preset thresholds. The other OSD refer to the available OSD, except for the partial OSD set in the first types of Down states, among the OSD of the target storage nodes. The method and the device have the advantage that risks of possible OSD performance bottleneck and data recovery failure after faults of memories on the storage nodes occur canbe prevented by the aid of the method and the device.

Owner:NEW H3C TECH CO LTD

Memory device and fault repairing method thereof

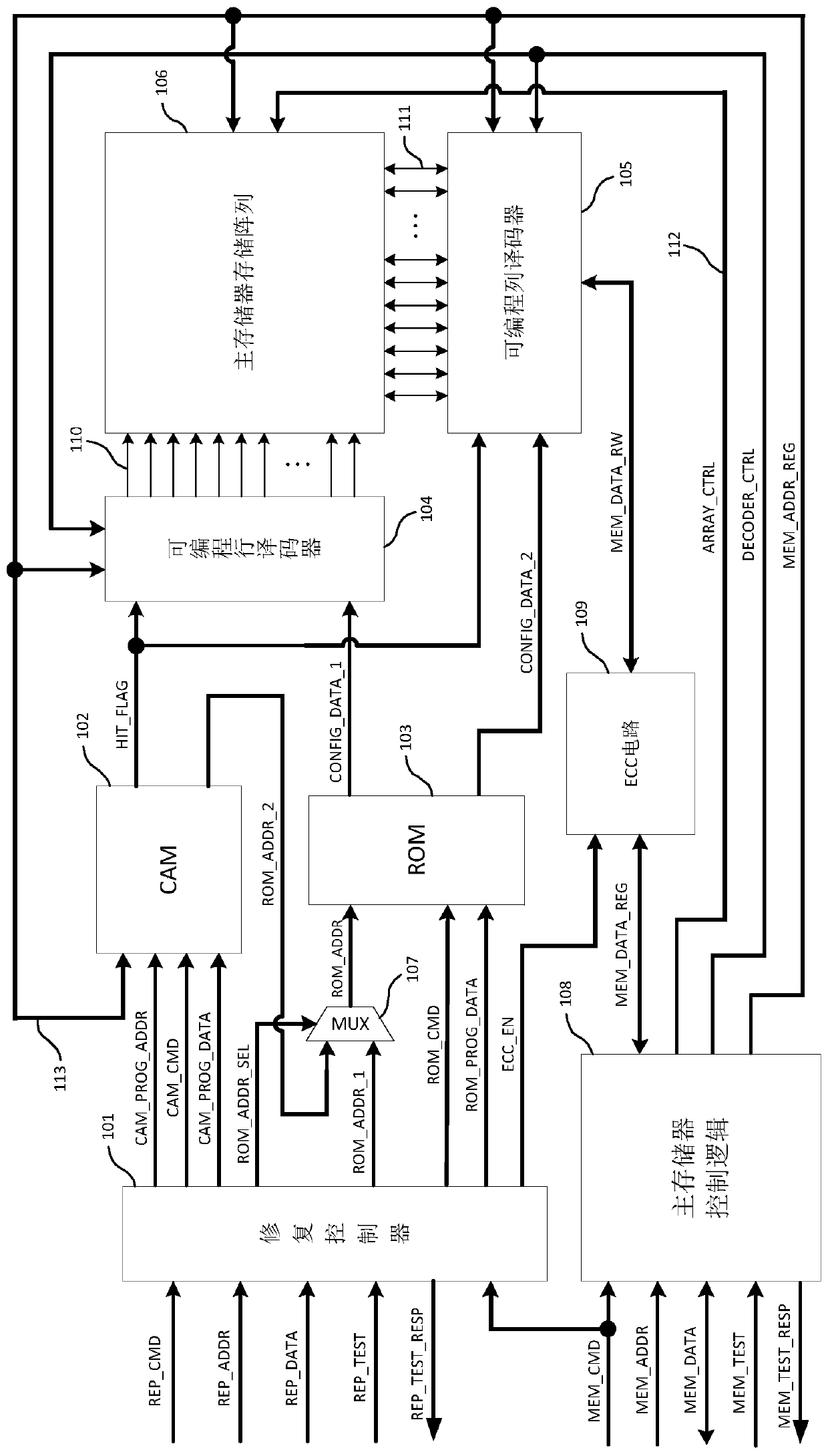

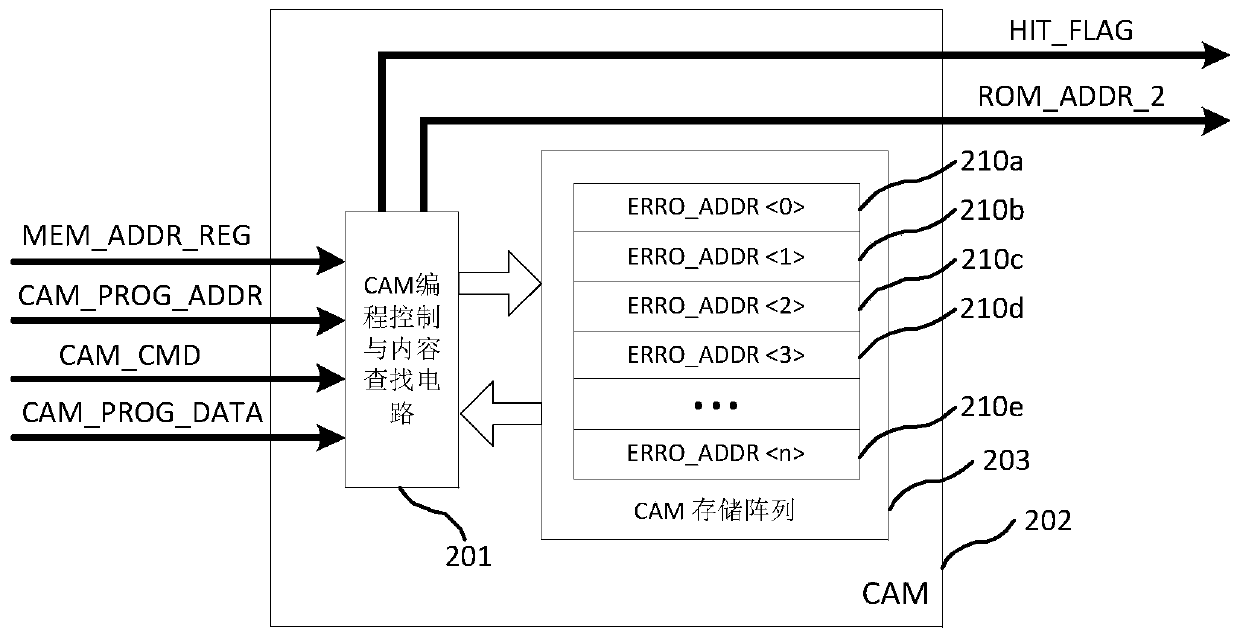

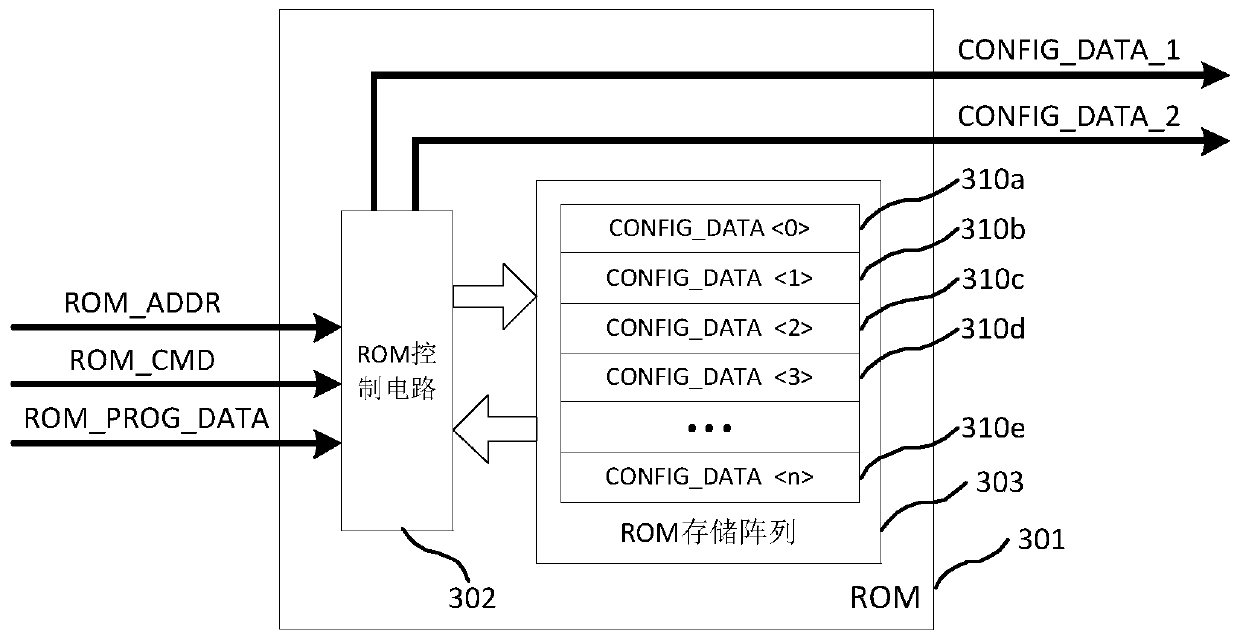

A circuit architecture of a memory device includes: a main memory circuit for implementing storage of user data; and the main memory fault repair circuit is used for realizing repair of storage faultsin the main memory. The main memory circuit comprises a memory array circuit designed in an array partitioning mode. In a main memory failure repair circuit, a CAM is used to store a failure addressof a main memory, and an ROM is used to store configuration data for configuring a programmable address decoder in a main memory circuit. A memory fault repair method includes repair schemes for wordfaults, row faults, and column faults of a memory device. A memory fault test and fault repair process for fault detection, fault analysis, and fault repair prior to memory device packaging includes arepairability determination method of a memory device and an operating method of programming a fault repair circuit of the memory device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

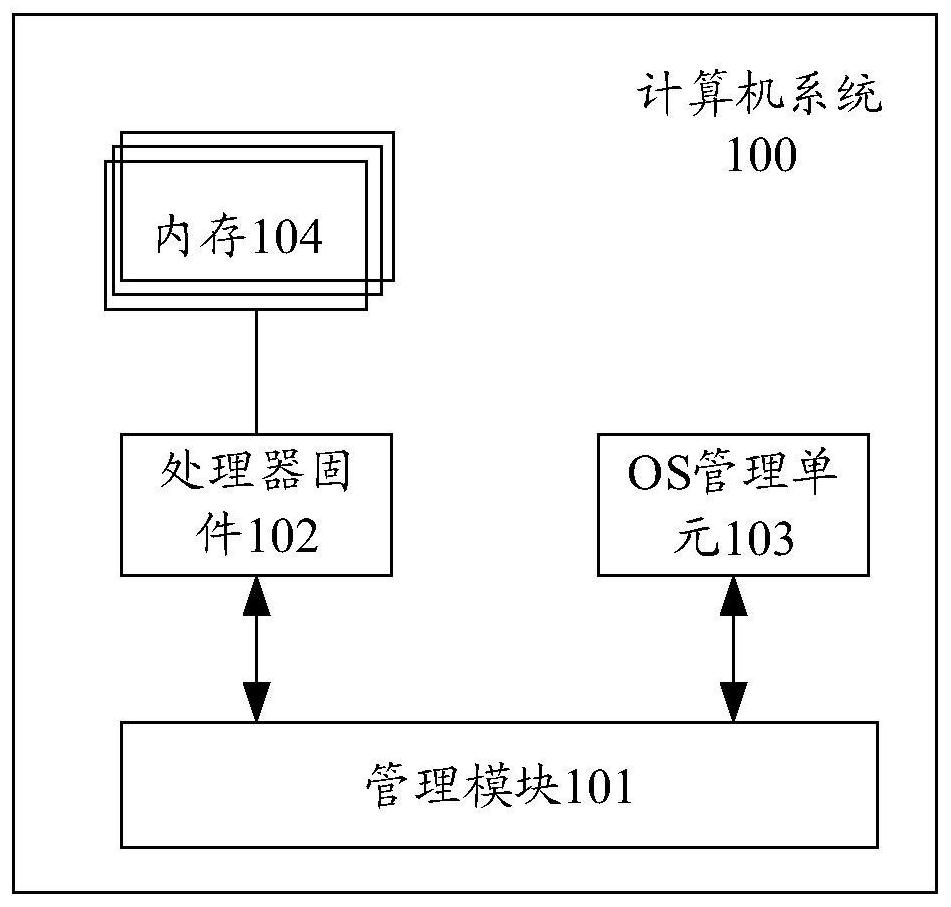

Memory fault processing method and device

The embodiment of the invention discloses a memory fault processing method and device, relates to the technical field of computers, and solves the problem of system downtime caused by memory faults in the prior art. According to the specific scheme, a management module obtains the error information of a memory; the management module adopts a machine learning algorithm to determine a fault characteristic mode of the memory or adopts an isolation repair technology for repairing the memory based on the error information of the memory; and the management module determines to repair the memory by adopting at least one of hardware isolation or software isolation based on the fault feature mode of the memory or the isolation repair technology adopted for repairing the memory.

Owner:HUAWEI TECH CO LTD

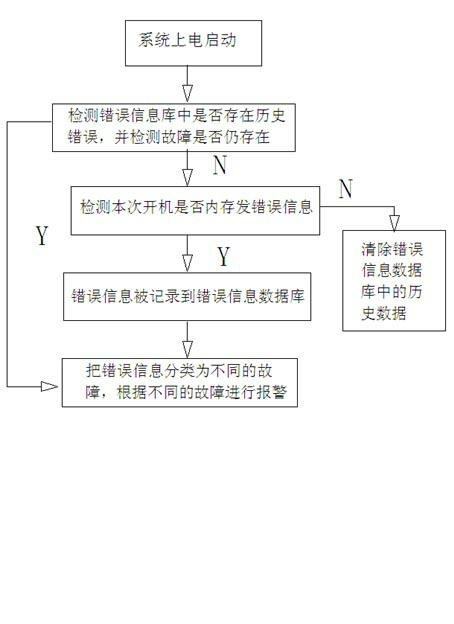

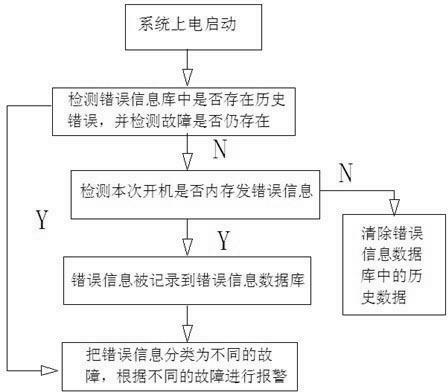

Server memory failure alarm method

InactiveCN102609350AEnhanced reliability featuresEasy maintenanceHardware monitoringDependabilityBad memory

The invention provides a server memory failure alarm method. A software program is used for recognizing memory error messages at a startup stage of a server system, the messages are transmitted to a management chip embedded into a main board and are judged in a classified manner, and alarm is given according to levels. The system comprises a failure information recognition unit, an error message database and an alarm unit, wherein the failure information recognition unit is used for acquiring the error messages sent out by a memory component in the system to provide evidence for judging memory failure, the error message database is used for collecting and transmitting the memory error messages, and the alarm unit is used for selecting different failure alarm modes according to different error messages. By implementing the memory failure alarm method in the server system, reliability of the system can be enhanced to a large extent, maintenance is facilitated, and the total image of the system is improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

Wafer test method for memory chip with redundant cell

The present invention discloses a wafer test method for a memory chip with a redundant cell. The method comprises the steps of: step one. according to an array structure of a main zone and a structure of a redundant cell of a memory chip on a wafer, setting length of a line address and a column address of a memory of a memory failure address in a memory test machine; step two. testing a chip unit, and after performing an OR operation on a testing result of each line, storing the testing result into a memory of the memory failure address with a same line address; step three. reading content of each line in the memory of the memory failure address to obtain a quantity of failed line and line addresses; and step four. determining whether each failed line of the main zone of the memory chip can be restored, and if yes, allocating a redundant cell to replace the failed line of the main zone of the memory chip. The method provided by the present invention can effectively reduce testing time and reduce testing costs.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

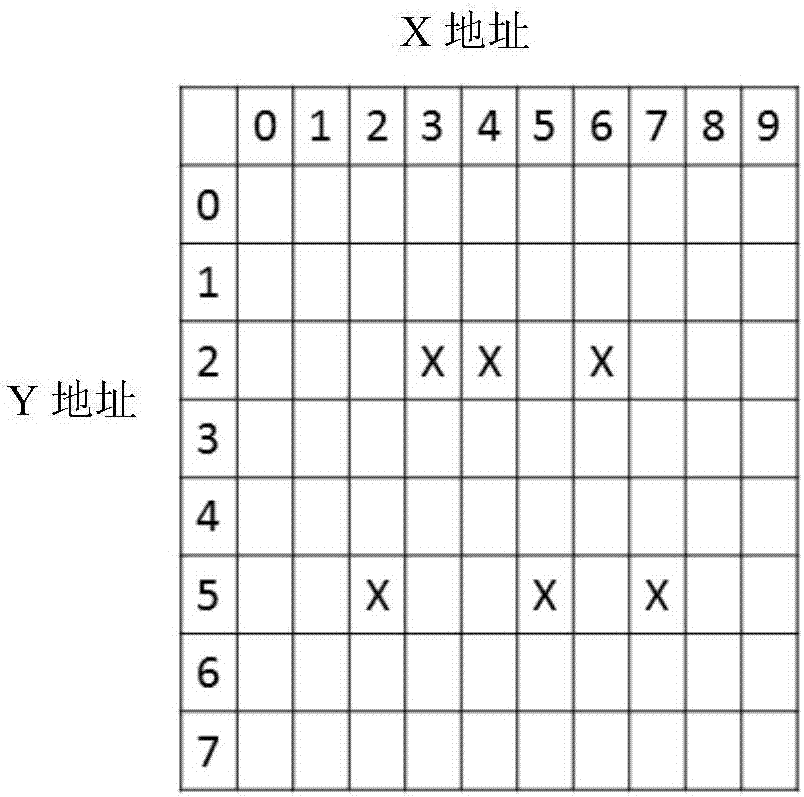

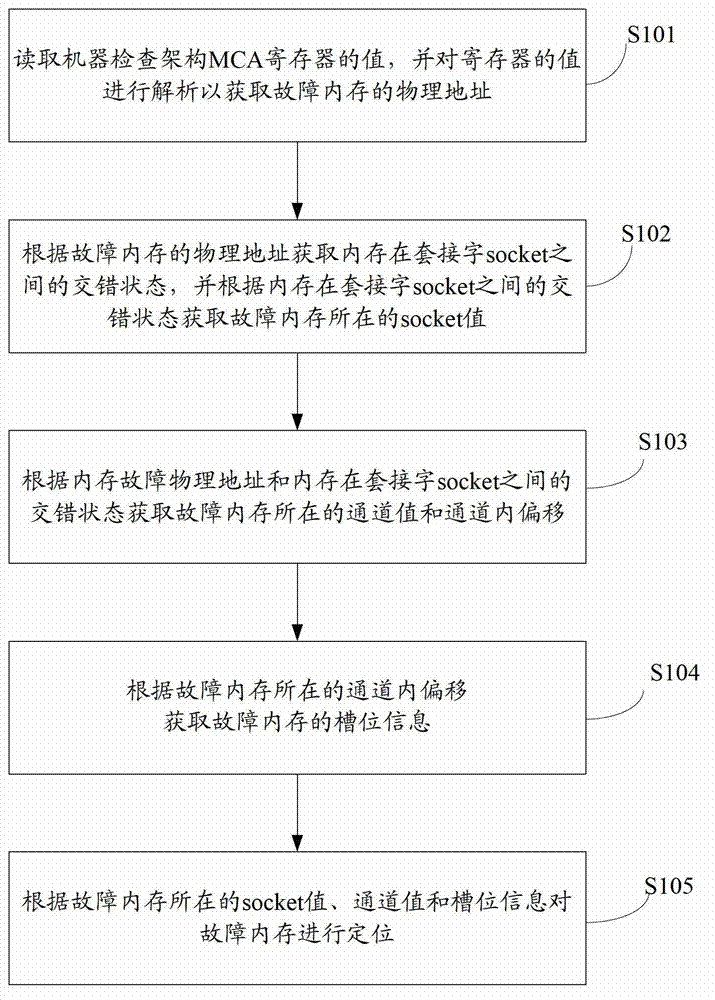

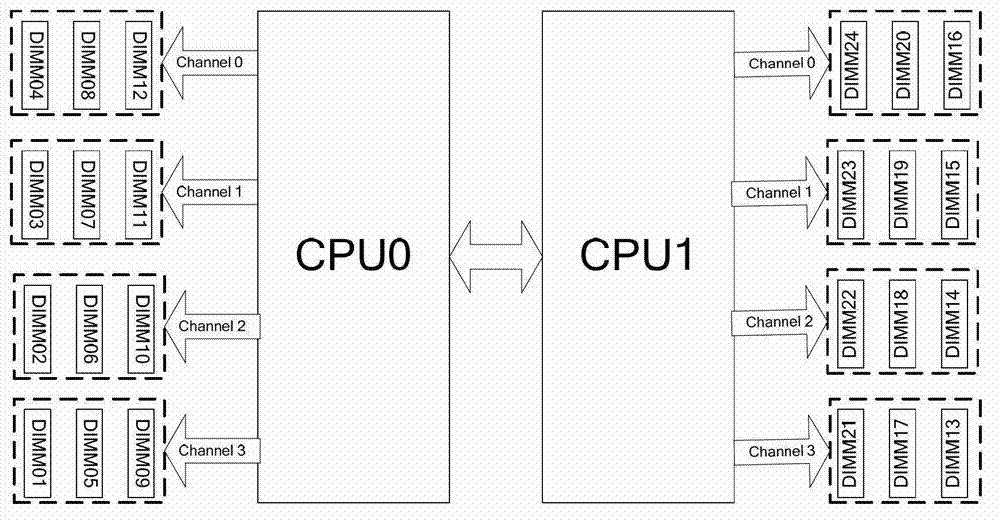

Method and device for automatically positioning internal memory fault

ActiveCN103197999APrecise positioningReduce operation and maintenance costsDetecting faulty computer hardwareInternal memoryData center

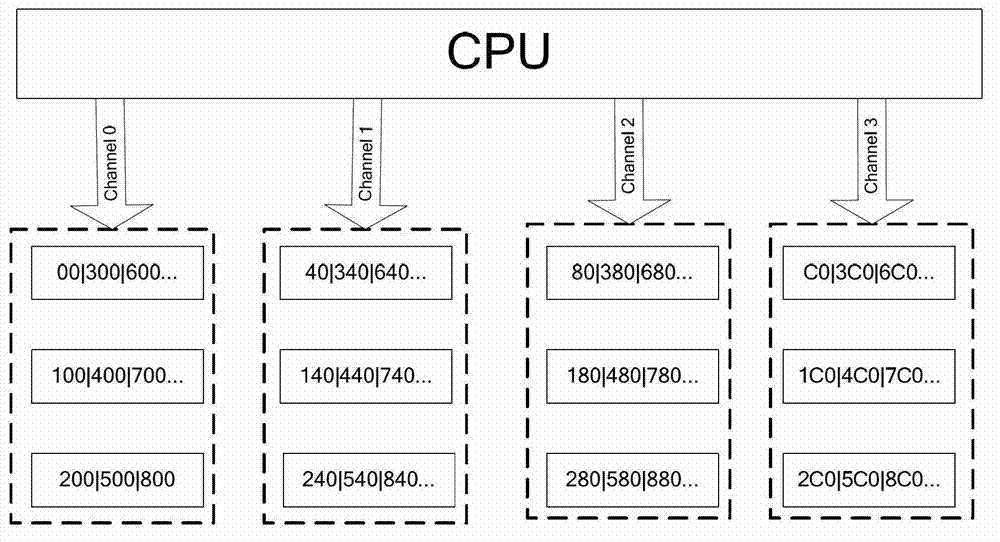

The invention provides a method for automatically positioning an internal memory fault. The method includes the following steps: reading a value of a machine check architecture (MCA) register, analyzing the value to obtain physical address of a fault internal memory, obtaining staggering state of the internal memory between a socket, obtaining the socket value of the fault internal memory according to the staggering state, acquiring channel value and excursion in the channel according to the staggering state of the internal memory physical address and the internal memory between the socket, acquiring groove position information of the fault internal memory according to the excursion in the channel and positioning the fault internal memory according to the socket value, the channel value and the groove position information of the fault internal memory. The method can accurately position groove position of the fault internal memory, maintains the internal memory matched with other methods, improves internal memory fault monitoring rate and reduces data center operation and maintenance cost. A device for automatically positioning the internal memory fault is further provided.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

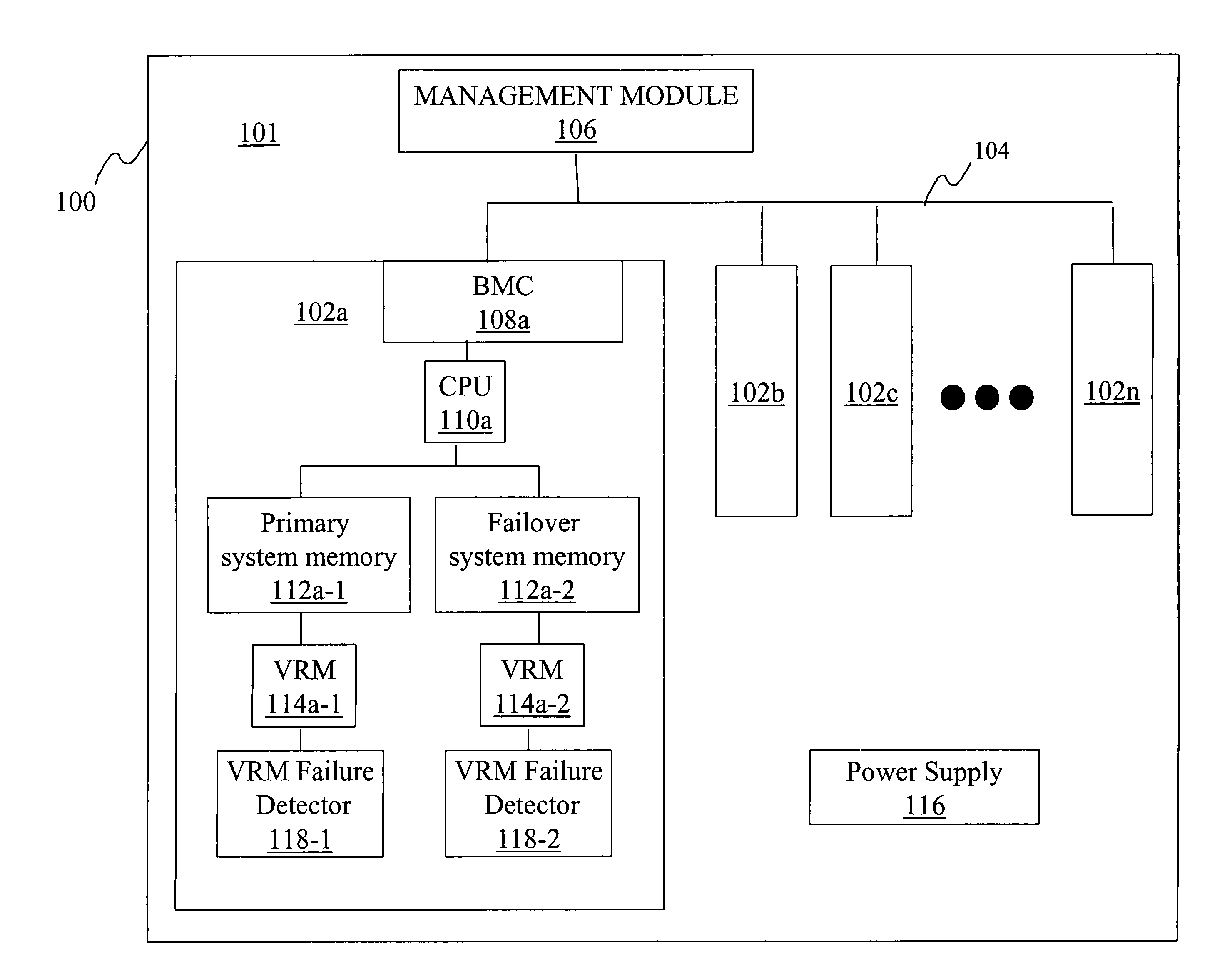

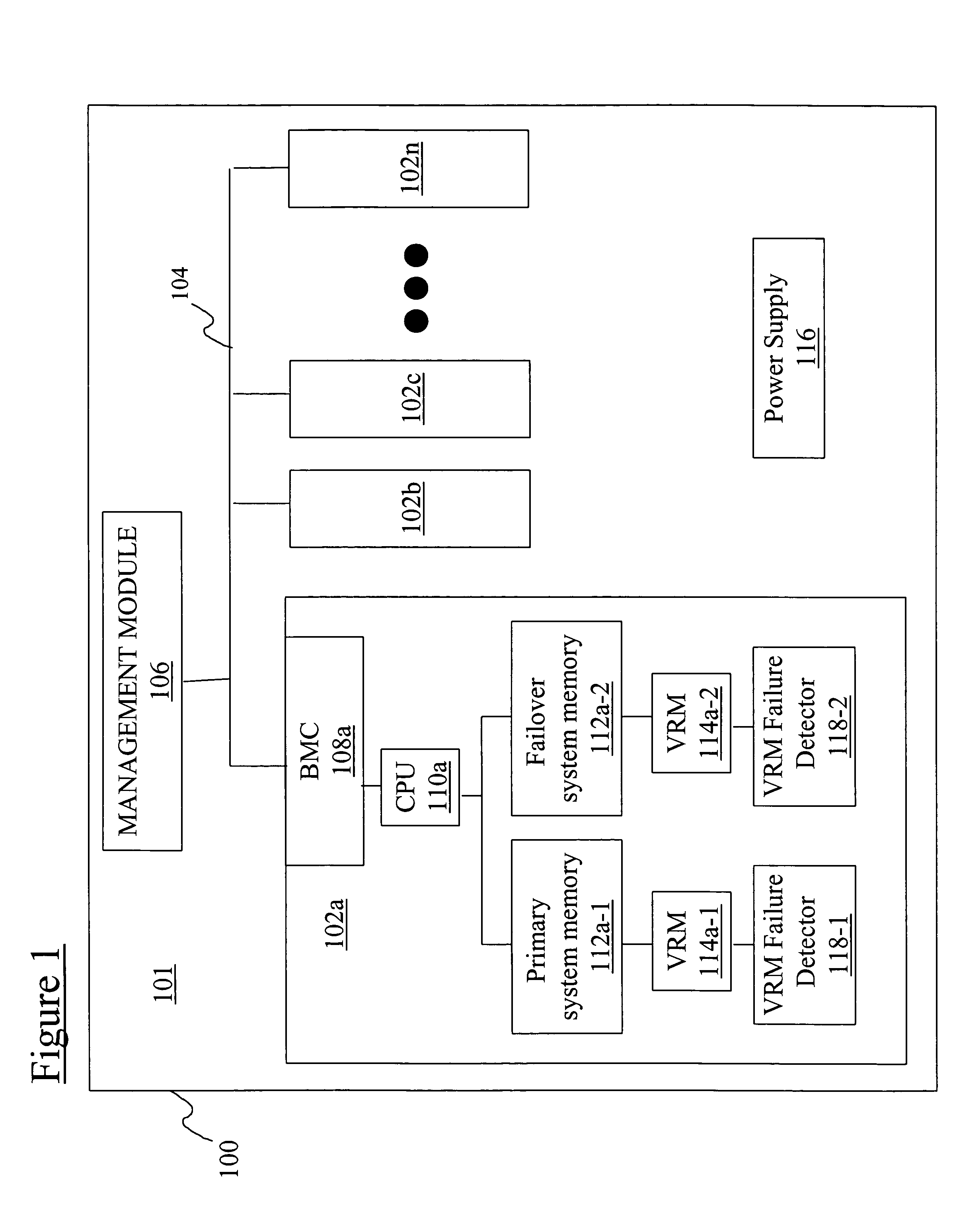

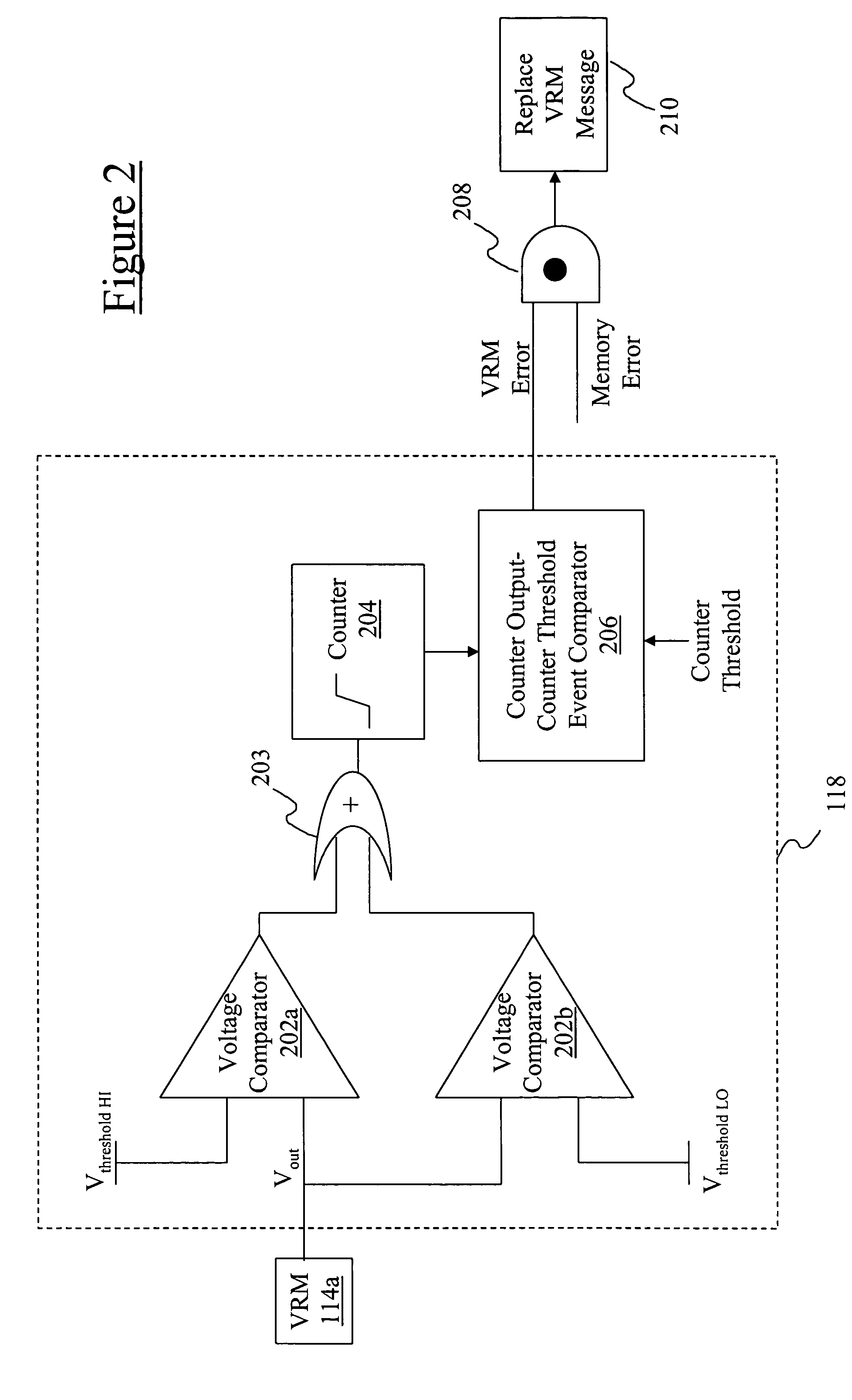

Monitoring VRM-induced memory errors

A method and system for improving Field Replacement Unit (FRU) isolation in memory sub-systems by monitoring Voltage Regulator Module (VRM) induced memory errors. A comparator compares the output voltage coming from the VRM to memory. If the comparator detects a VRM output voltage transient that is outside a rated threshold, then a counter is increased by one. If the counter exceeds a count threshold, a VRM error is posted. If a memory failure occurs within a predetermined period of time, then the VRM error pinpoints the VRM output voltage transient as being the likely cause of the memory failure.

Owner:INT BUSINESS MASCH CORP

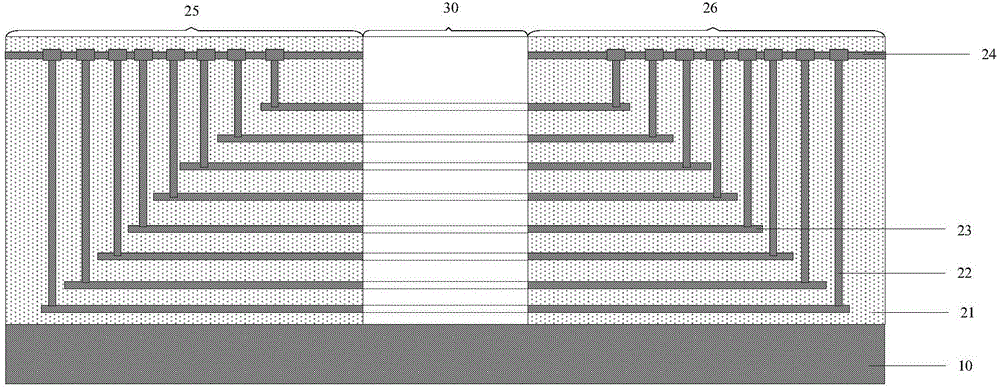

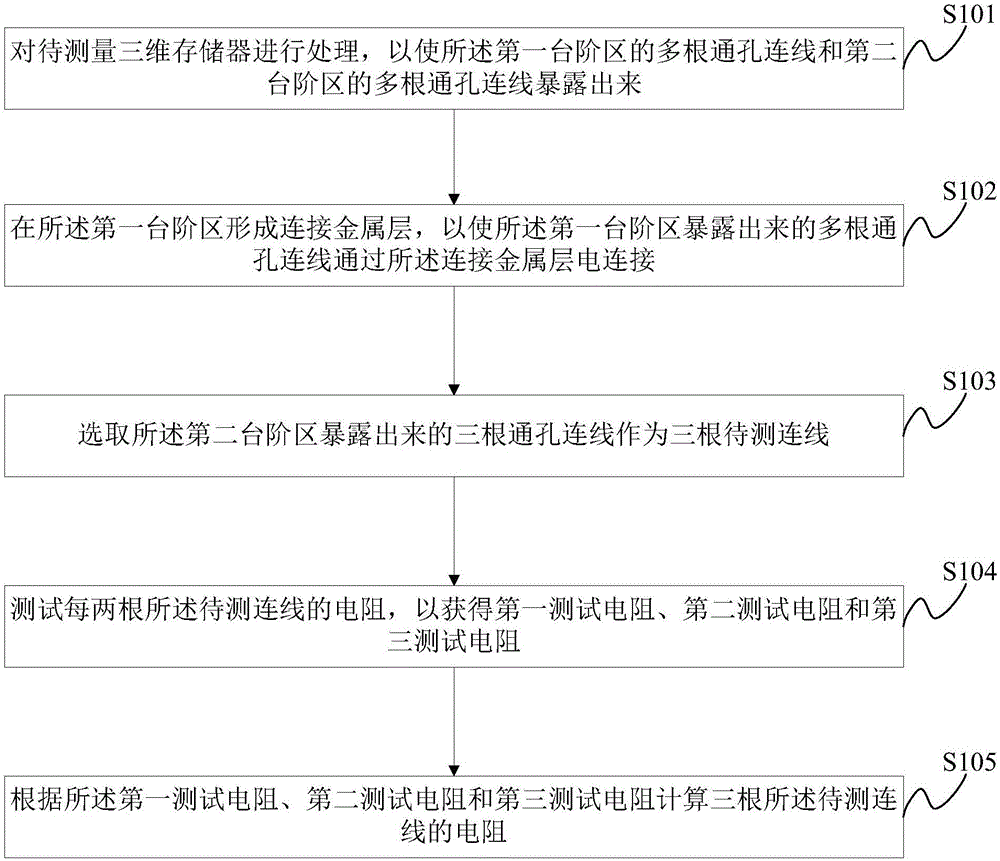

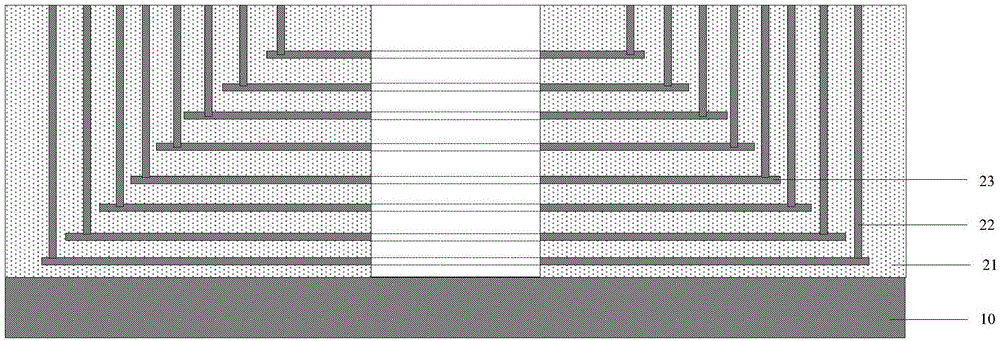

Word line resistance test method and three-dimensional memory failure analysis method

ActiveCN107527661ARealize measurementResistance/reactance/impedenceStatic storageLine resistanceFailure analysis

The invention discloses a word line resistance test method and a three-dimensional memory failure analysis method. According to the word line resistance test method, first, multiple through hole connecting lines in a first step region and a second step region of a three-dimensional memory are exposed; second, by forming a connection metal layer in the first step region, multiple word lines are connected with the connection metal layer through the through hole connecting lines; and last, resistance of every two to-be-tested connecting lines is tested in the second step region, the resistance of the three to-be-tested connecting lines is calculated according to first test resistance, second test resistance and third test resistance obtained through testing, that is, word line resistance corresponding to the three to-be-tested connecting lines is obtained, therefore, measurement of the word line resistance in the three-dimensional memory is realized, and a foundation is laid for performing failure analysis on the three-dimensional memory.

Owner:YANGTZE MEMORY TECH CO LTD