Pure metal oxide semiconductor (MOS) structure voltage reference source with high power supply rejection ratio

A high power supply rejection ratio, MOS structure technology, applied in the direction of adjusting electrical variables, control/regulation systems, instruments, etc., can solve the problems of increasing quiescent current, high process cost, reducing start-up circuits, etc., to improve voltage suppression performance, reduce The difficulty of circuit design and the effect of high power supply rejection ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

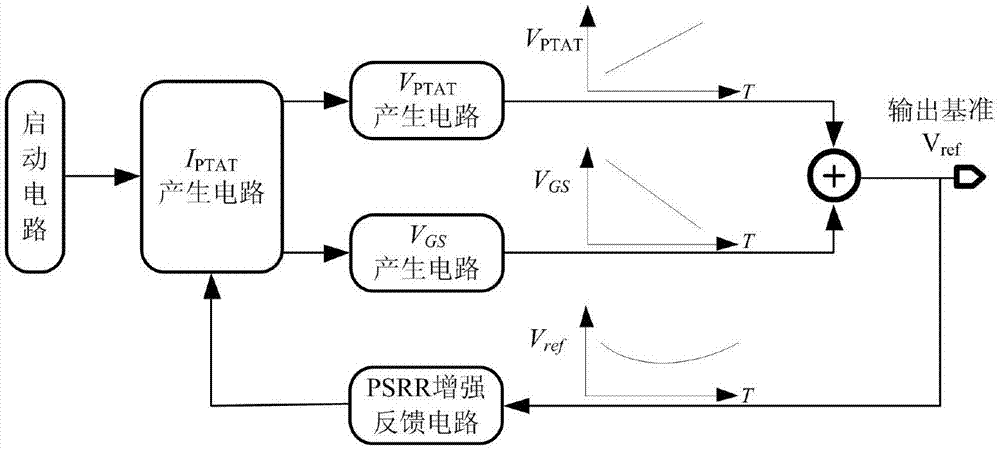

[0021] The principles and features of the present invention will be described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

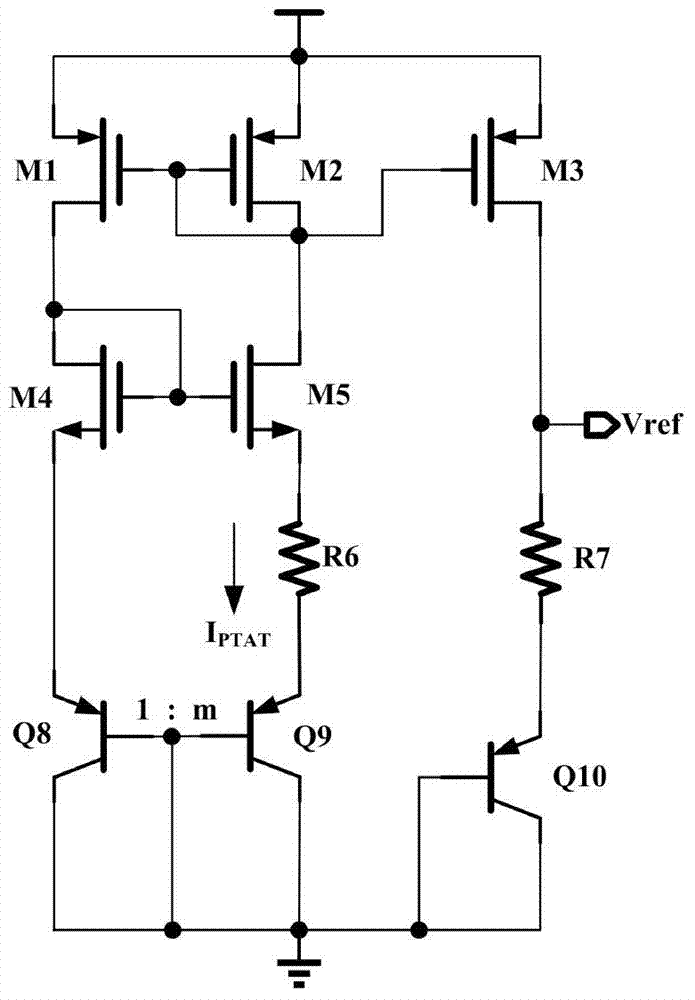

[0022] Such as figure 1, is a traditional bandgap reference circuit using transistors and resistors as the core. It is a transistor base-emitter voltage VBE with a negative temperature coefficient and a thermal voltage VT with a positive temperature coefficient. The voltage is weighted and added to obtain an output voltage with zero temperature coefficient, but in the CMOS process, the triode has problems such as too large area and high power consumption, and the model of the parasitic triode is not accurate enough.

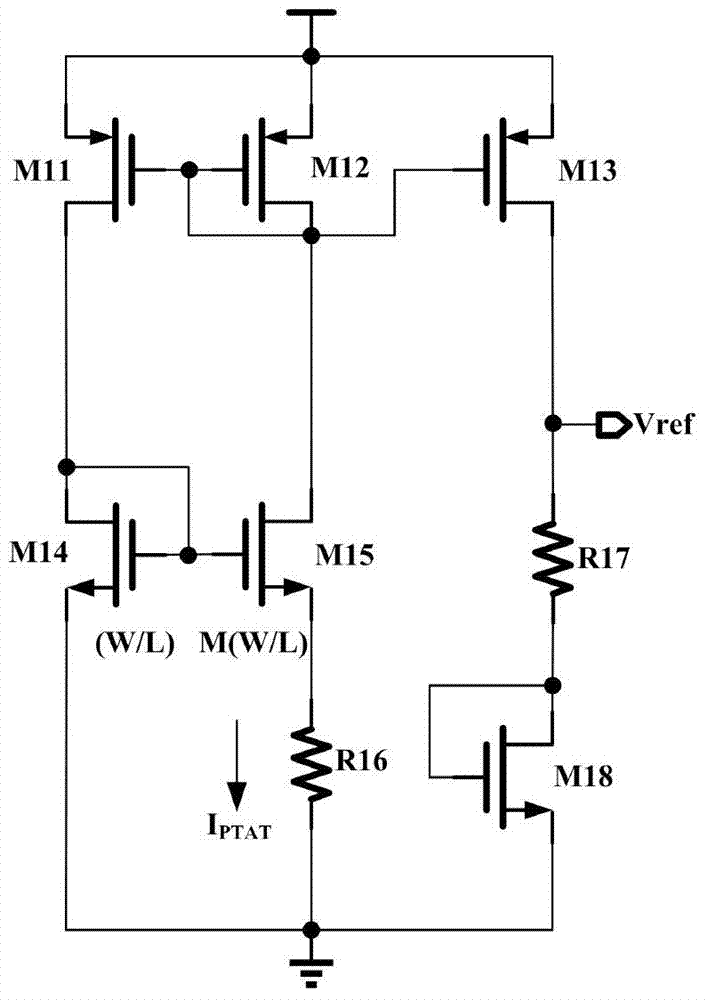

[0023] Such as figure 2 , is a voltage reference circuit using MOS tubes and resistors as the core, wherein MOS tubes M14 and M15 work in the sub-threshold region. This circuit uses the negative...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More