Patents

Literature

118 results about "Logic testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Nuclear power DCS platform test device based on simulation system and test method thereof

ActiveCN106257367AMeet functional requirementsRealize functionElectric testing/monitoringAutomatic controlNuclear power

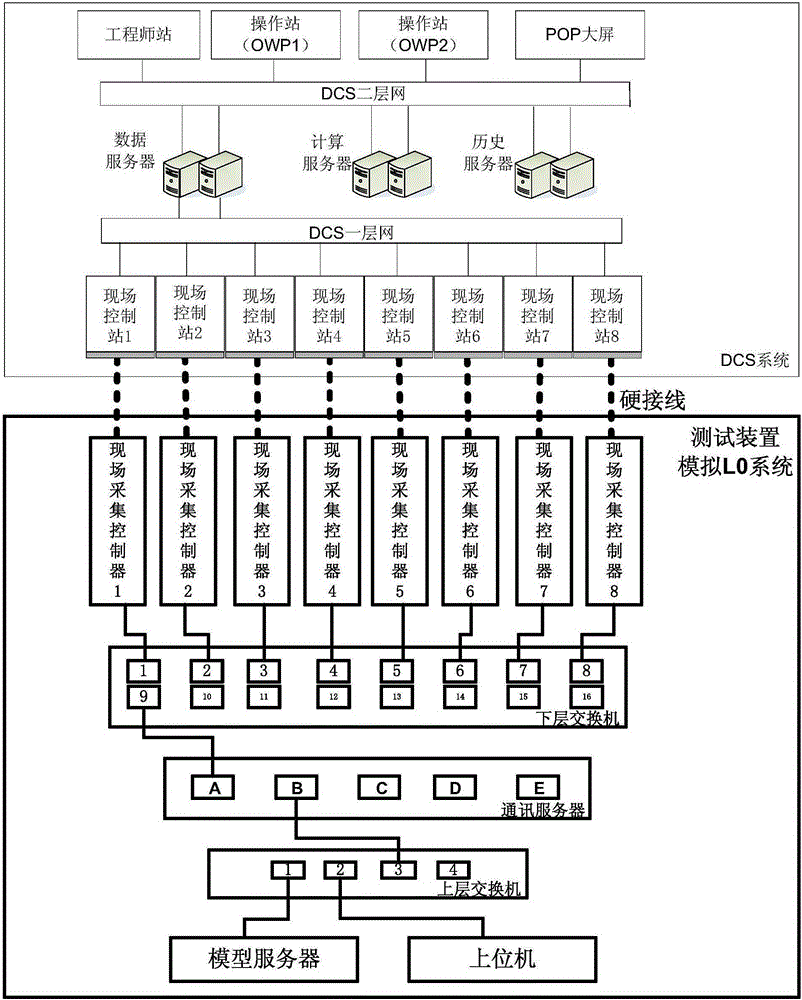

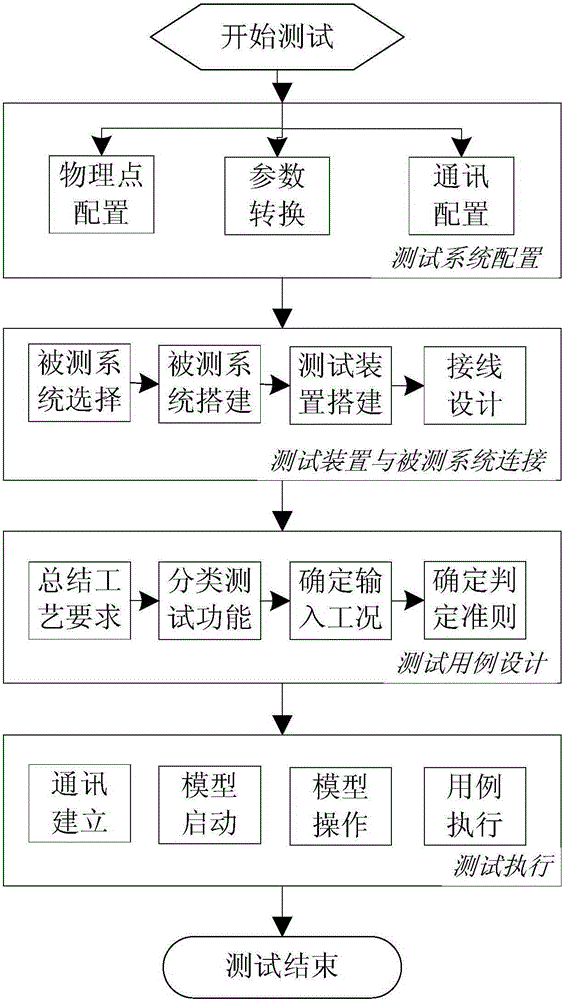

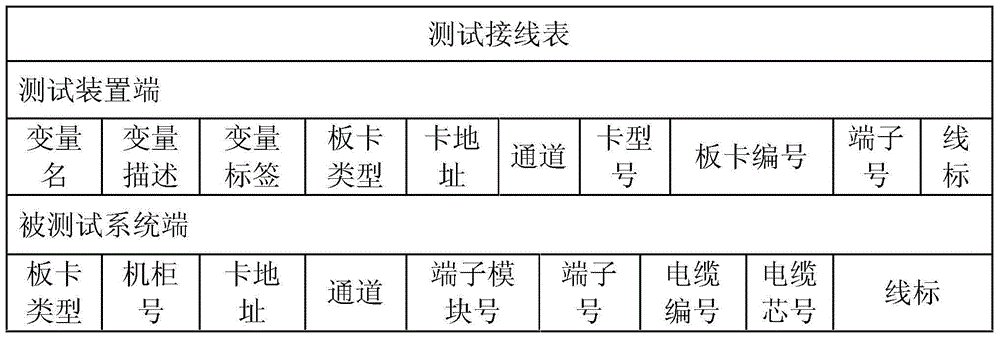

The invention belongs to the technical field of automatic control of instruments and meters, and particularly relates to a nuclear power DCS platform test device based on a simulation system and a test method thereof. The device comprises a model server which operates all the system simulation models including chemical and volume control systems; an upper computer of which the function is communication configuration and operates monitoring control frames; and a communication server which realizes data communication between field acquisition controllers and the model server, wherein the port A of the communication server is connected with a lower switch and the port B is connected with an upper switch. The model server is connected with the first port of the upper server, the upper computer is connected with the second port of the model server, and the communication server is connected with the third port of the upper switch. The field acquisition controllers 1-8 are connected with the first to eight ports of the lower switch. The problems that the conventional hardware simulation technology does not perform modeling and cannot realize simulation of the actual physical and technical process control of a power plant can be solved, and the problems that logic testing cannot realize testing according to the technical control requirements can also be solved.

Owner:CHINA NUCLEAR CONTROL SYST ENG

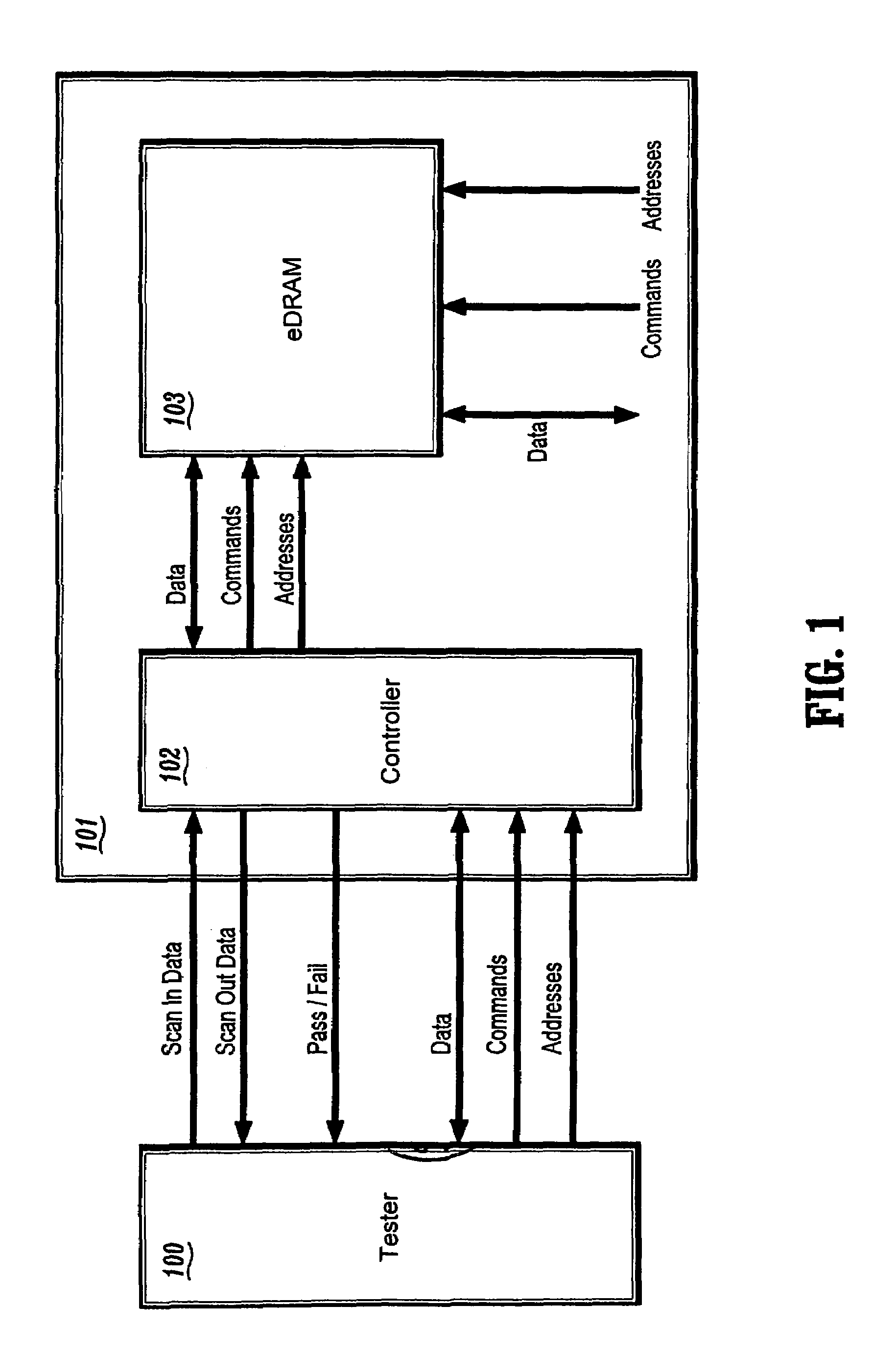

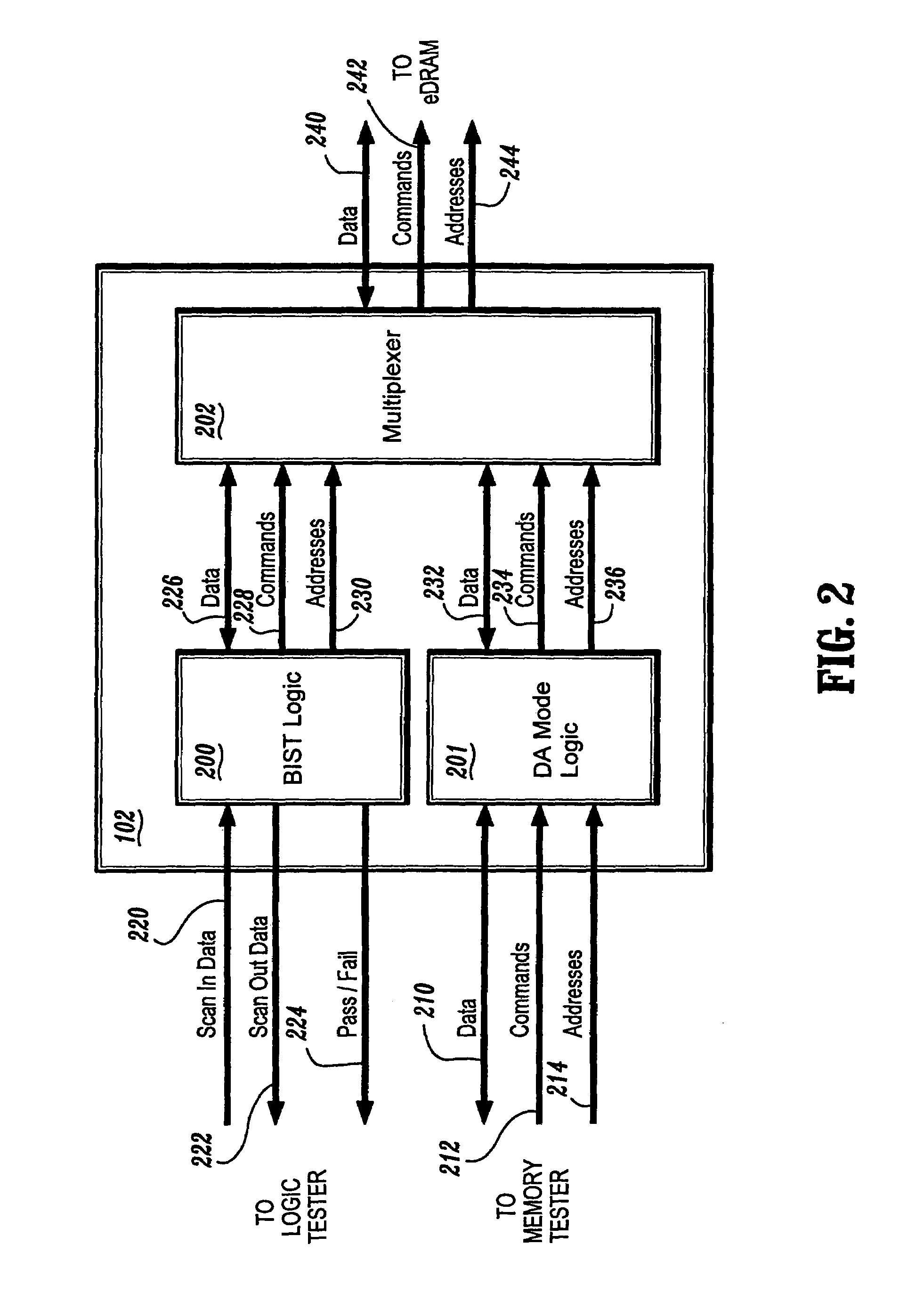

Circuit and method for testing embedded DRAM circuits through direct access mode

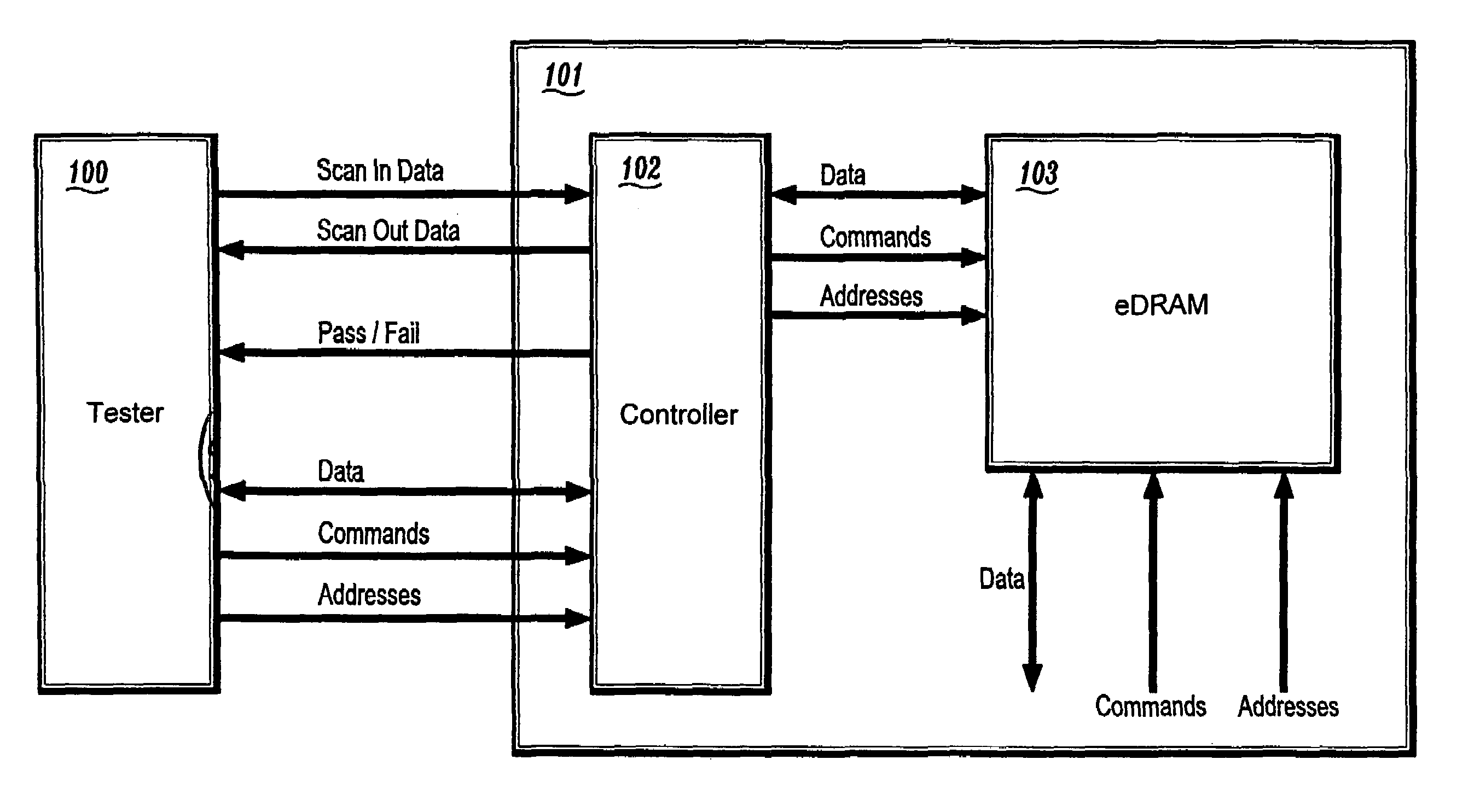

A circuit and method for testing an eDRAM through a test controller with direct access (DA) mode logic is provided. The circuit and method of the present invention allows the testing of eDRAMs with a conventional memory tester. The present invention provides a semiconductor device including an embedded dynamic random access memory (eDRAM) for storing data, the eDram including a plurality of memory cells, and a test controller for testing the plurality of memory cells to determine if the cells are defective, the test controller including built-in self-test (BIST) logic circuitry for performing tests and for interfacing to a logic tester, and direct access mode logic circuitry for interfacing the eDRAM with an external memory tester. The test controller further comprises a multiplexer for multiplexing data, commands, and addresses from the BIST logic circuitry and the direct access mode logic circuitry to the eDRAM.

Owner:POLARIS INNOVATIONS LTD

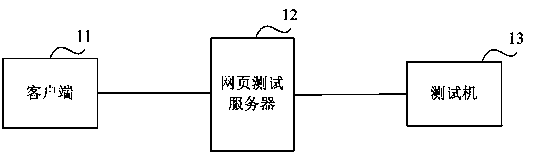

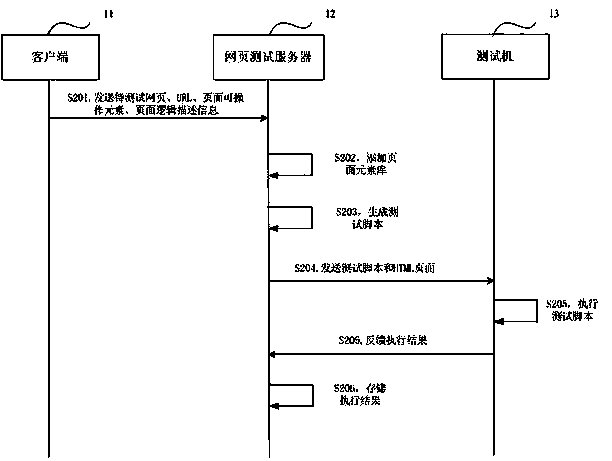

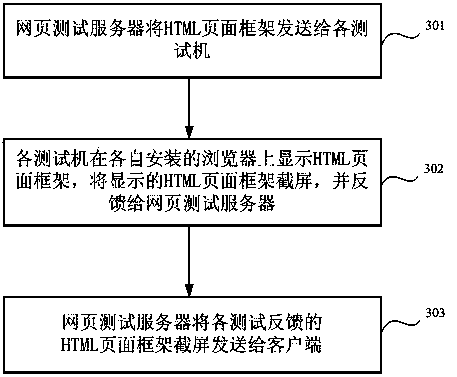

Method, device and system for testing web page

ActiveCN103729285AImplement automated testingLower the thresholdSoftware testing/debuggingSpecial data processing applicationsGraphical user interfaceTest script

The invention discloses a method, device and system for testing a web page. The method comprises the steps that the web page to be tested, the URL of the web page to be tested, page controllable elements extracted from the web page to be tested and the page logical description information of the web page to be tested are sent by a client side and received by a web page test server, and the URL and the page controllable elements of the web page to be tested are added to a page element base; the web page test server generates a graphic user interface according to the page logical description information of the web page to be tested and the page element base; an instruction for selecting the page controllable elements in the web page URL is received, the corresponding page controllable elements in the web page URL are selected from the page element base according to the instruction through the graphic user interface, and a test script is generated according to the page logical description information; the web page test server sends the generated test script and the web page to be tested to a tester for web page testing, web page logic is tested through the graphical test scheme, and the threshold of the web page logic testing is lowered.

Owner:TENCENT TECH (SHENZHEN) CO LTD

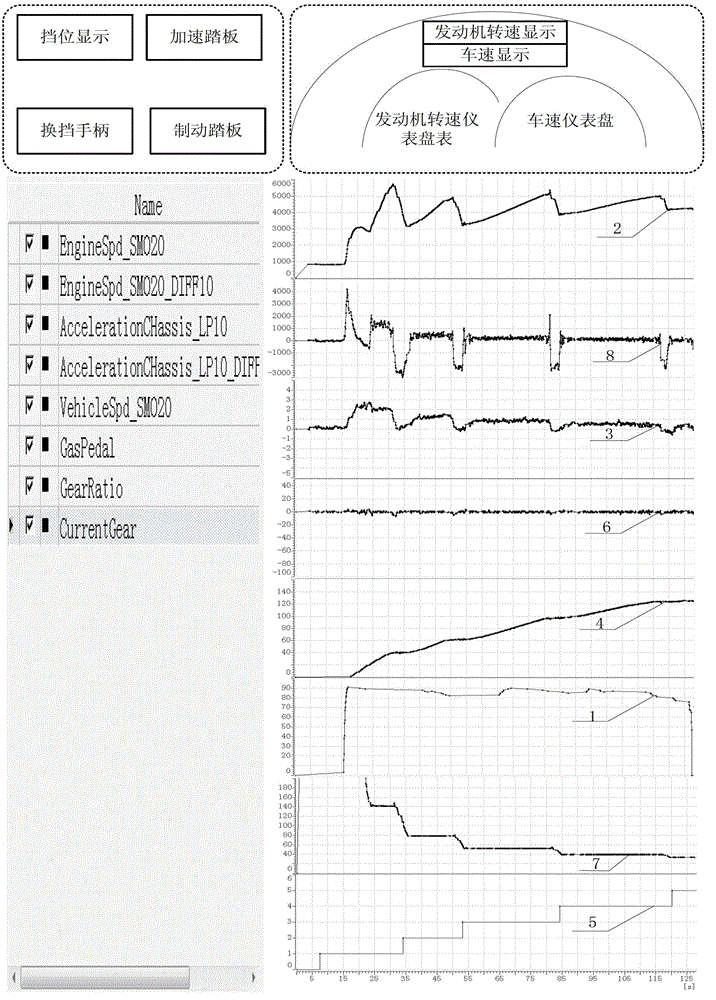

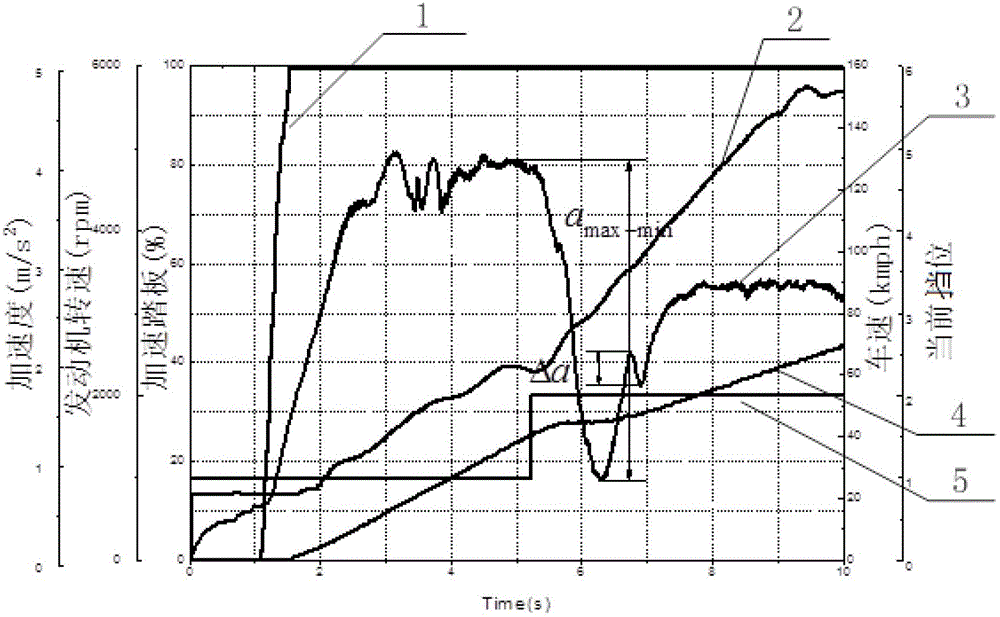

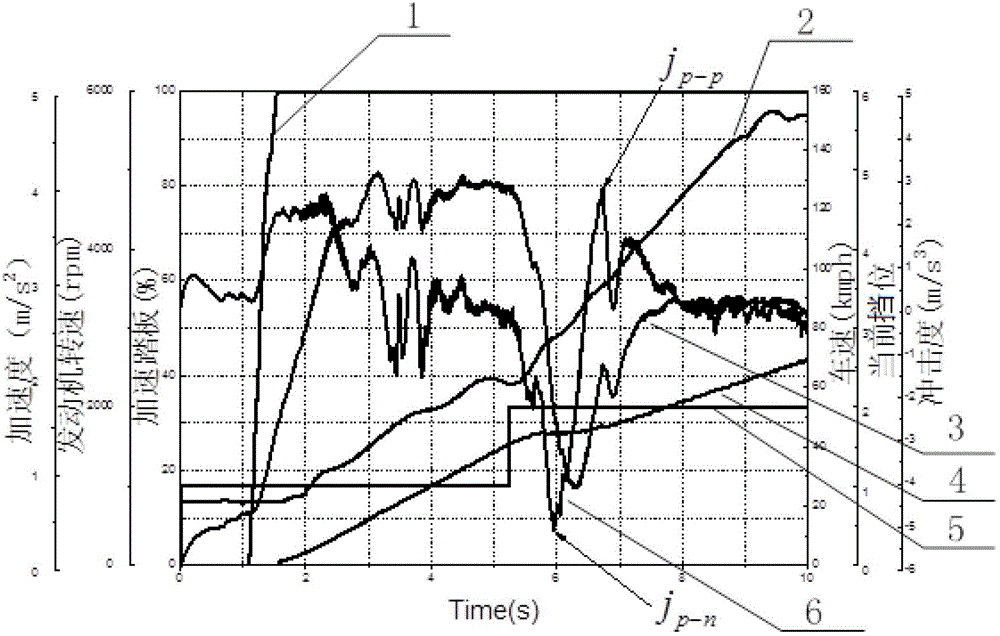

Vehicle gear-shifting quality evaluation testing method and system

The invention discloses a vehicle gear-shifting quality evaluation testing method, which comprises the steps of: 1) at a vehicle gear-shifting quality evaluation testing preparation stage: establishing a vehicle database by adopting an SQL (structured query language) server; establishing a vehicle gear-shifting quality evaluation module by adopting MATLAB / Simulink and determining the core algorithm of the vehicle gear-shifting quality evaluation module; and selecting the type of a vehicle to be tested and a testing system to be used; 2) at a vehicle gear-shifting quality testing stage: conducting gear-shifting rule testing, Tip in testing, Tip out testing, Fast Off testing, brake control logic testing, operability testing, start testing, acceleration testing and driving during a traffic jam; and 3) at a vehicle gear-shifting quality evaluation stage: calling data of the vehicle database as data input of the vehicle gear-shifting quality evaluation model and obtaining an evaluation result through data processing and the like; and outputting the evaluation result a graphical user and result display interface. The invention additionally provides a vehicle gear-shifting quality evaluation testing system.

Owner:JILIN UNIV

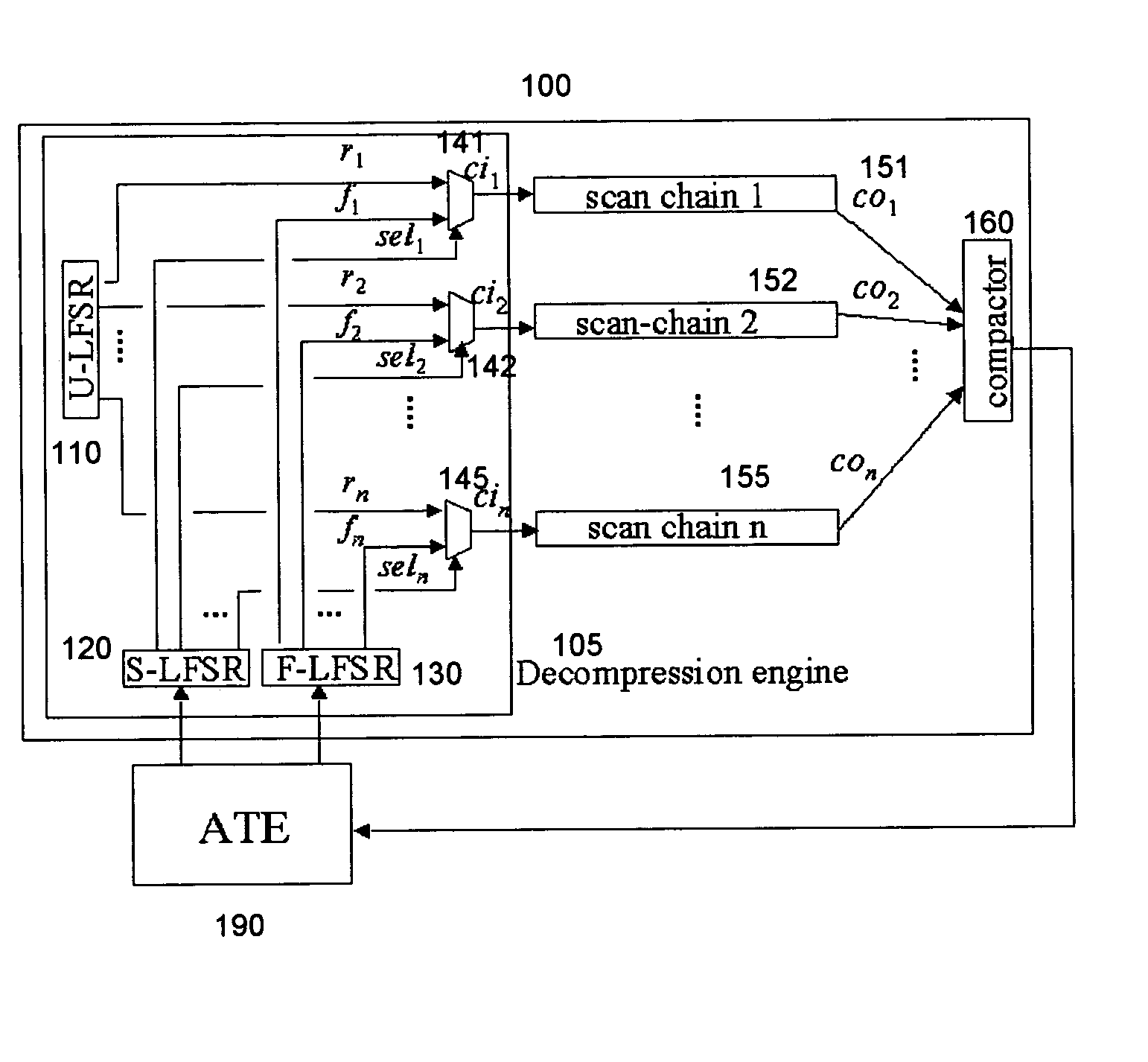

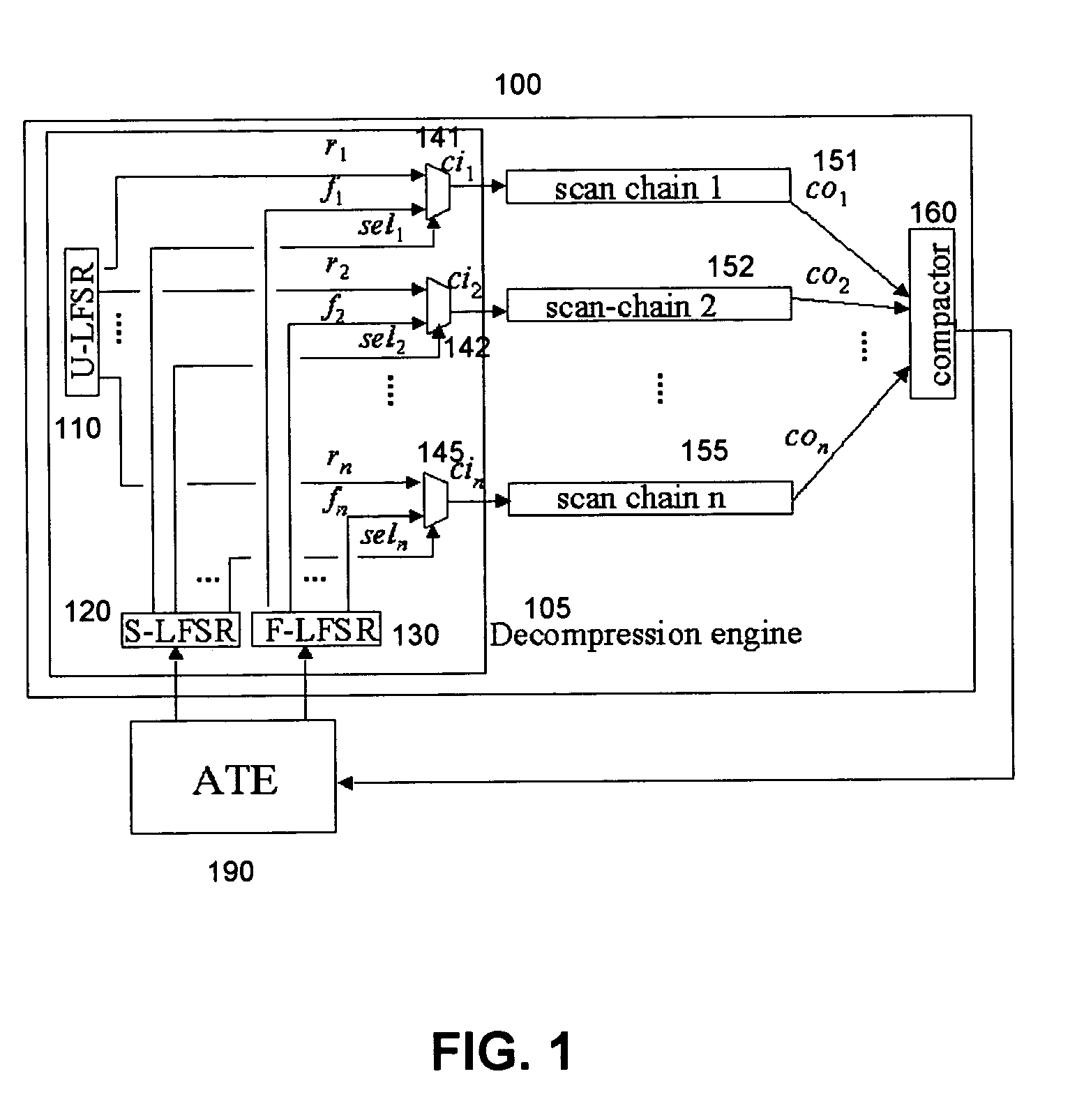

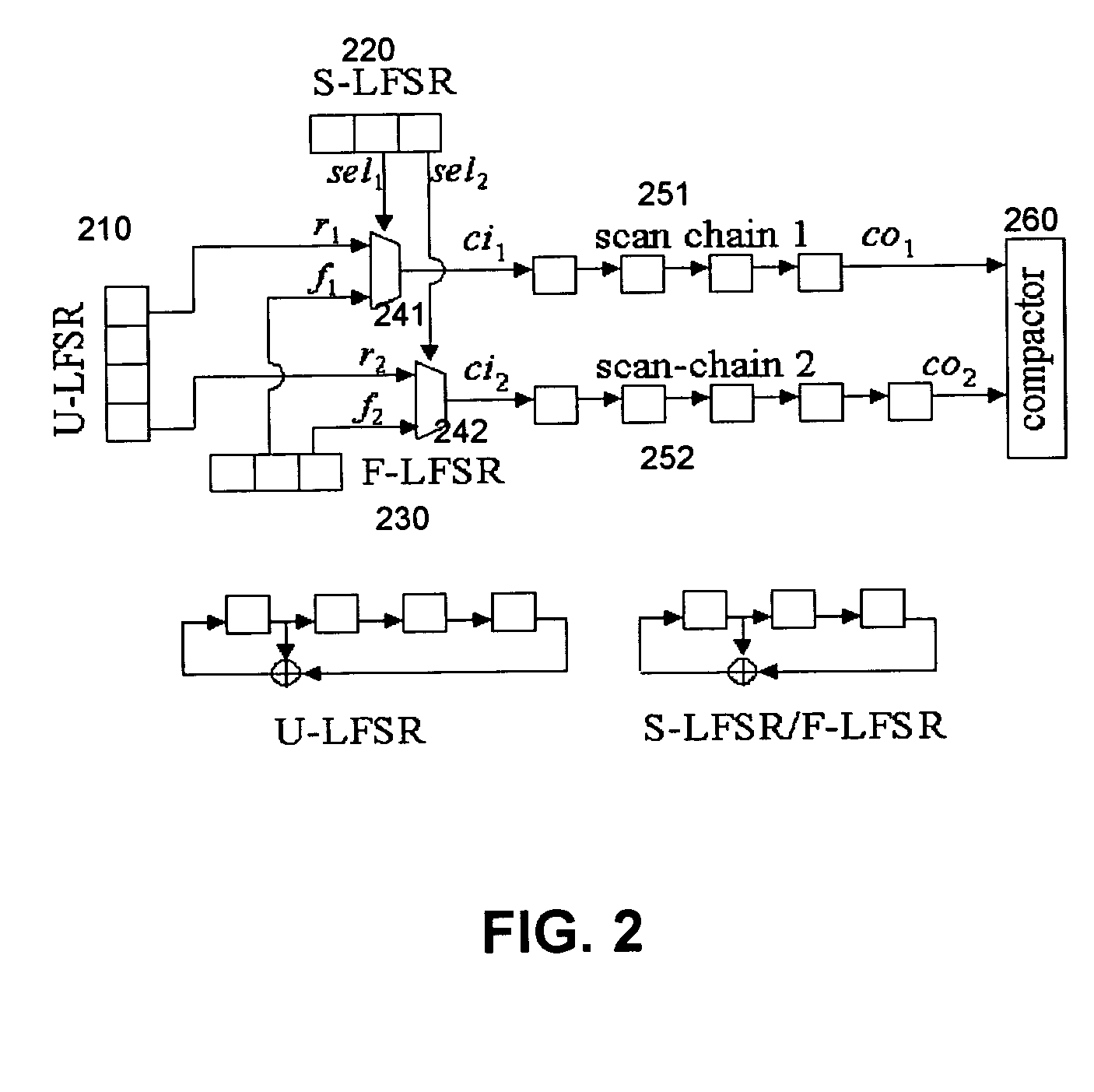

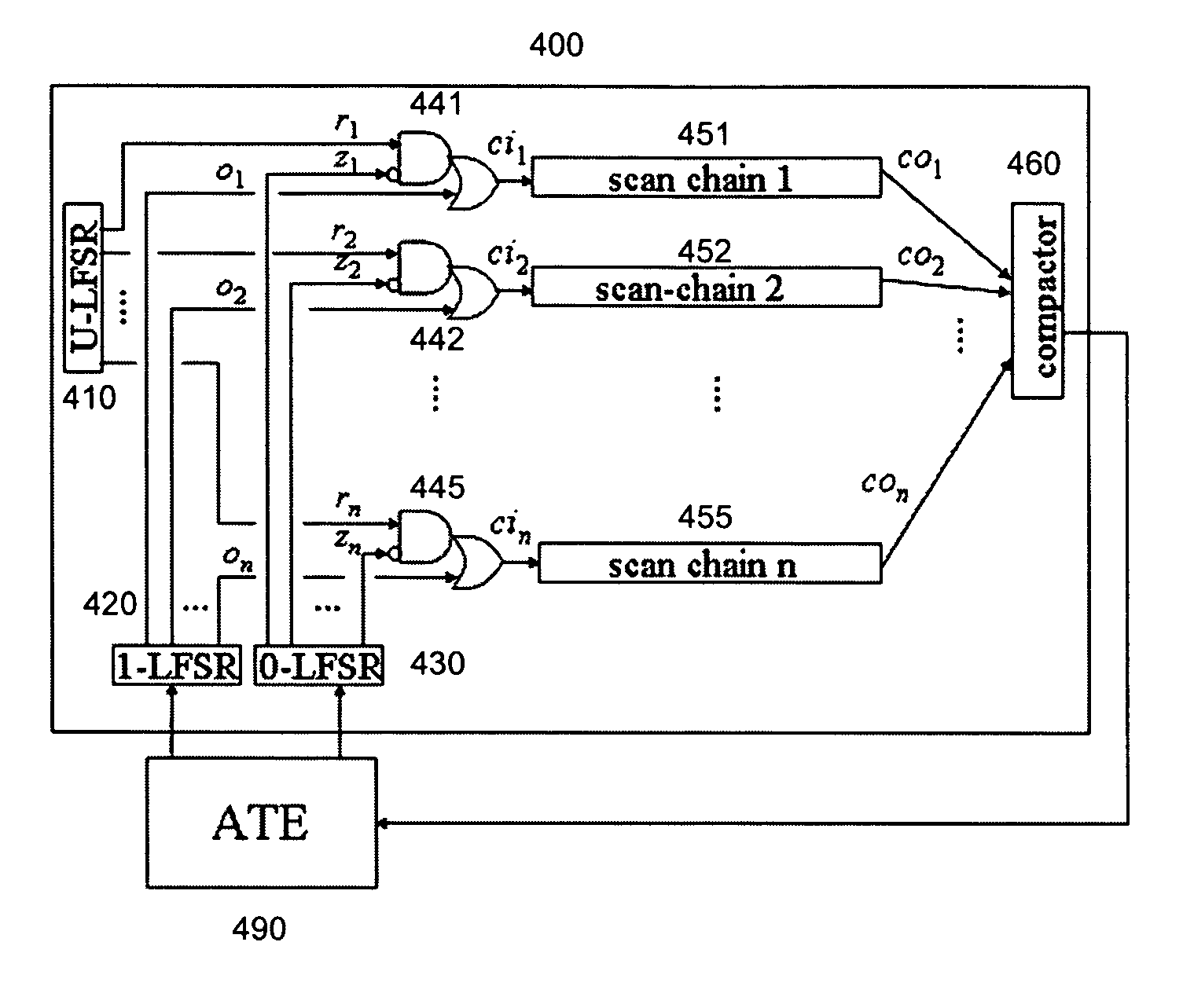

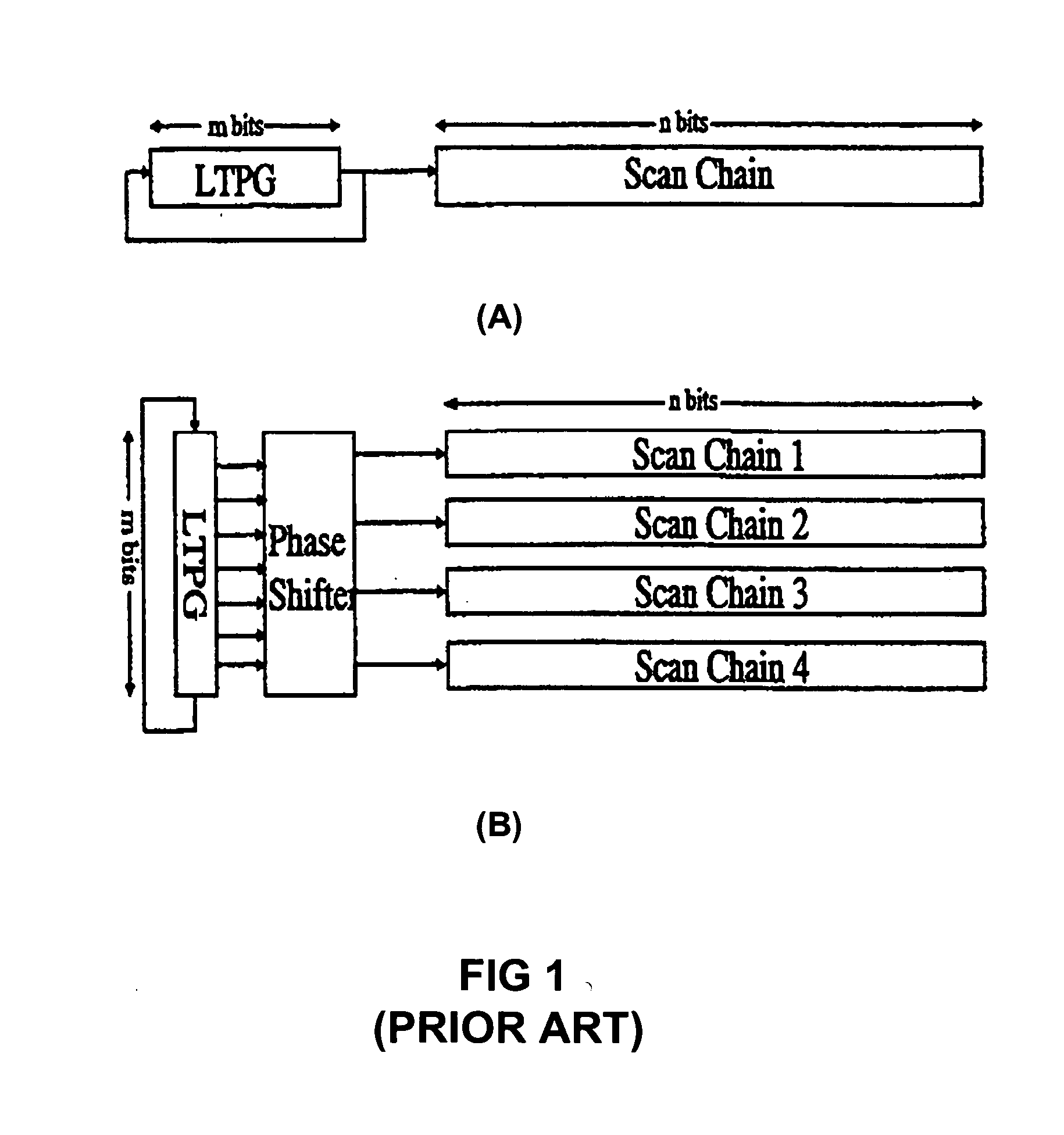

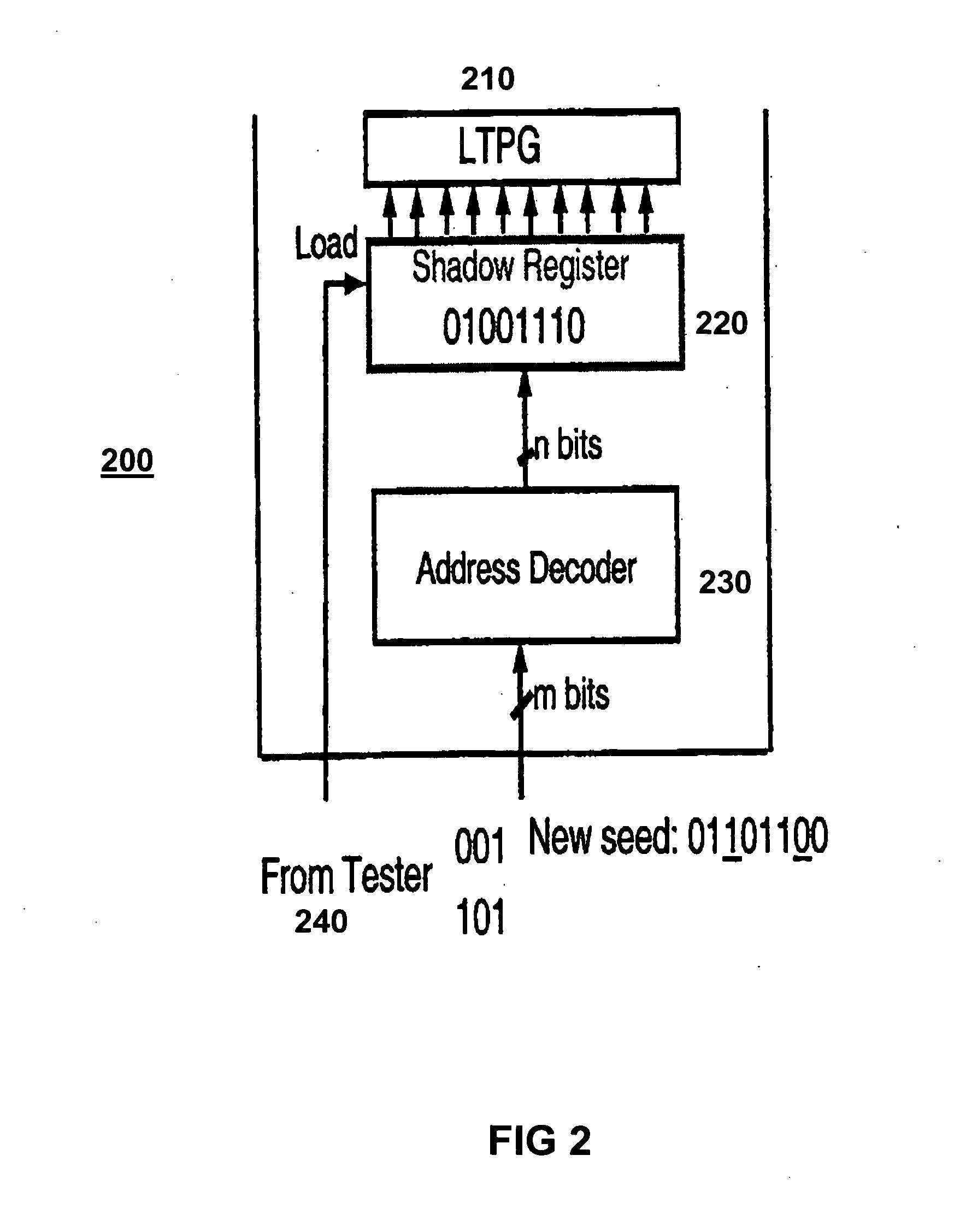

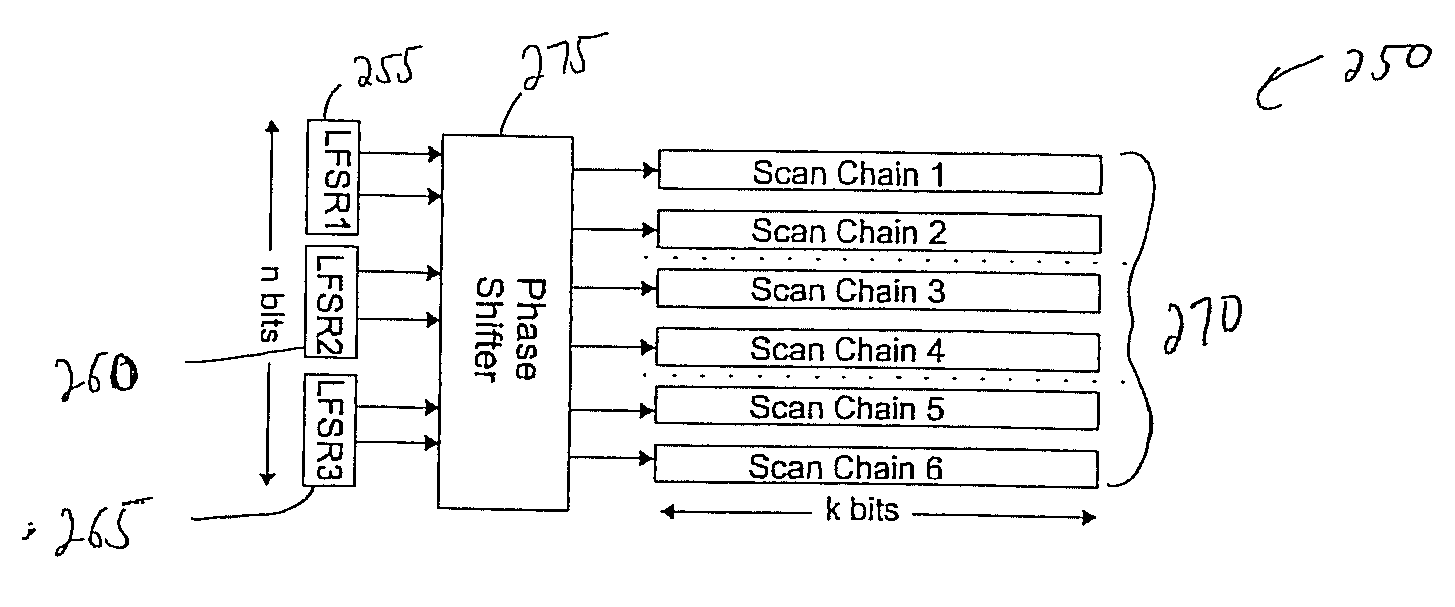

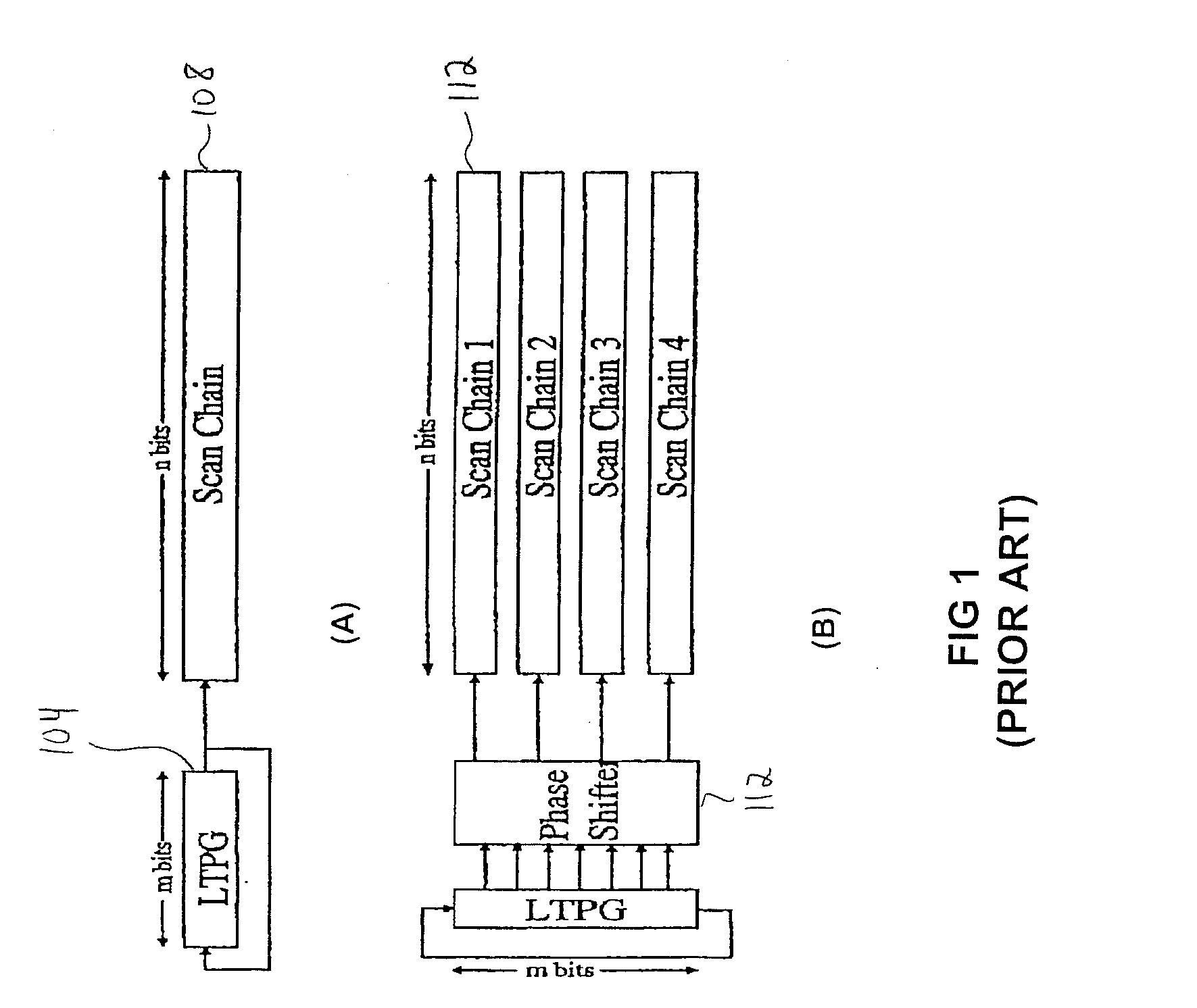

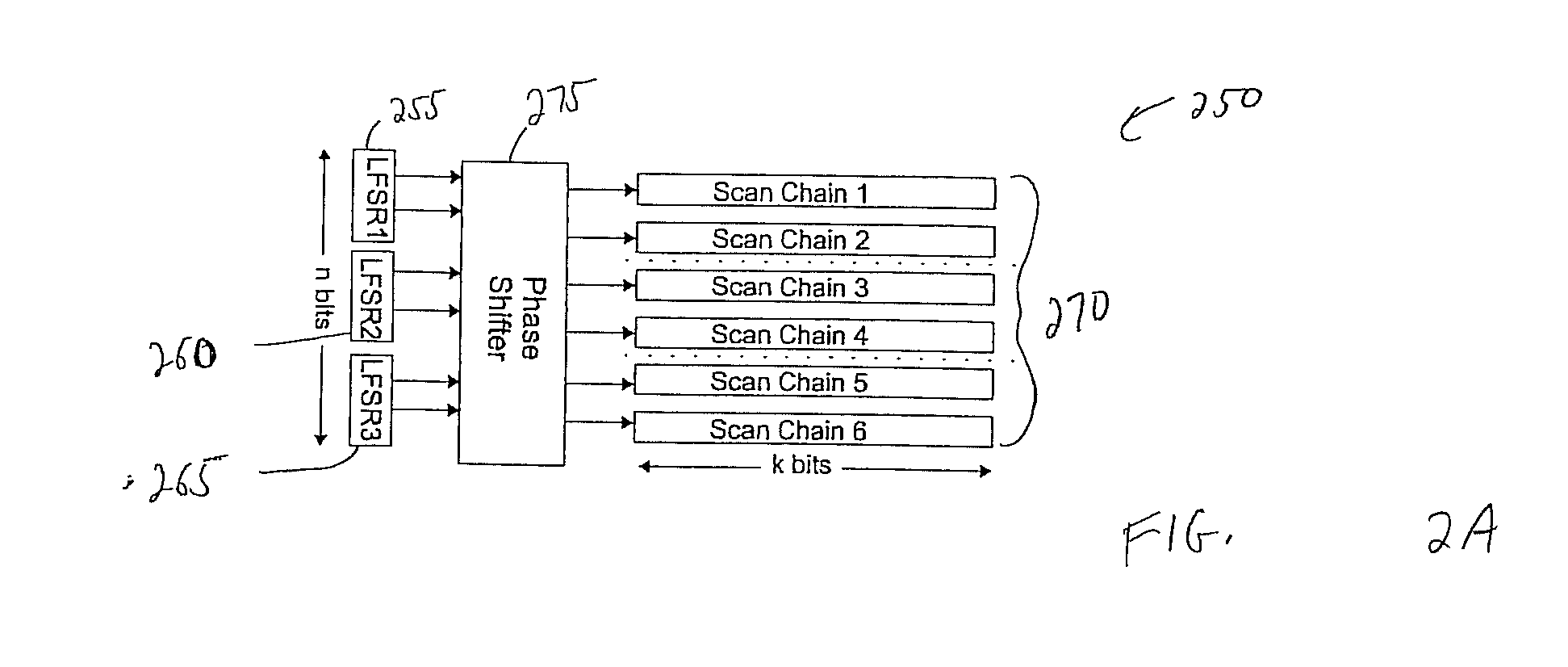

Externally-loaded weighted random test pattern compression

InactiveUS20060015787A1Easy to implementElectronic circuit testingError detection/correctionComputer hardwareLogic testing

The present invention is directed to a logic testing architecture with an improved decompression engine and a method of decompressing scan chains for testing logic circuits.

Owner:NEC CORP

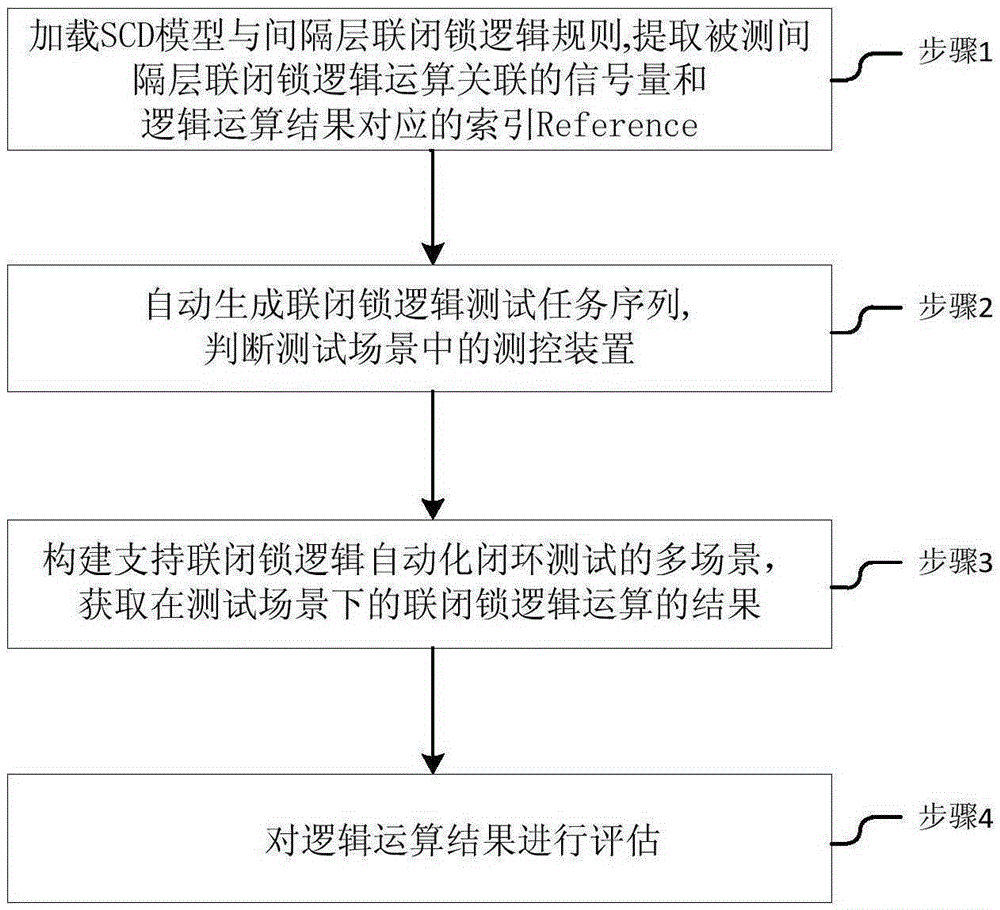

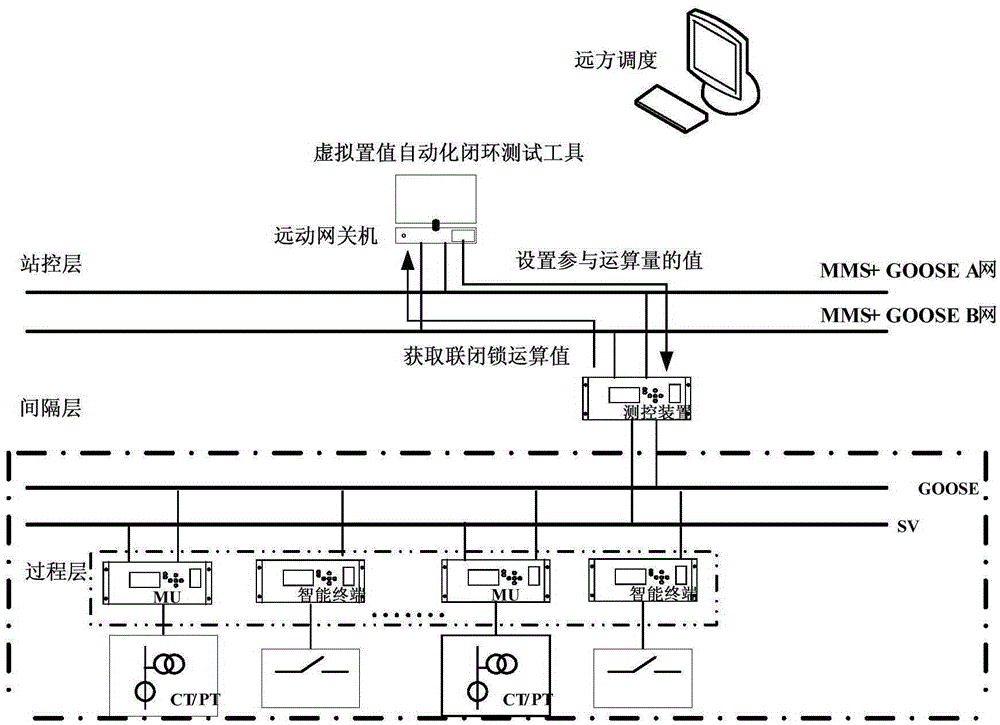

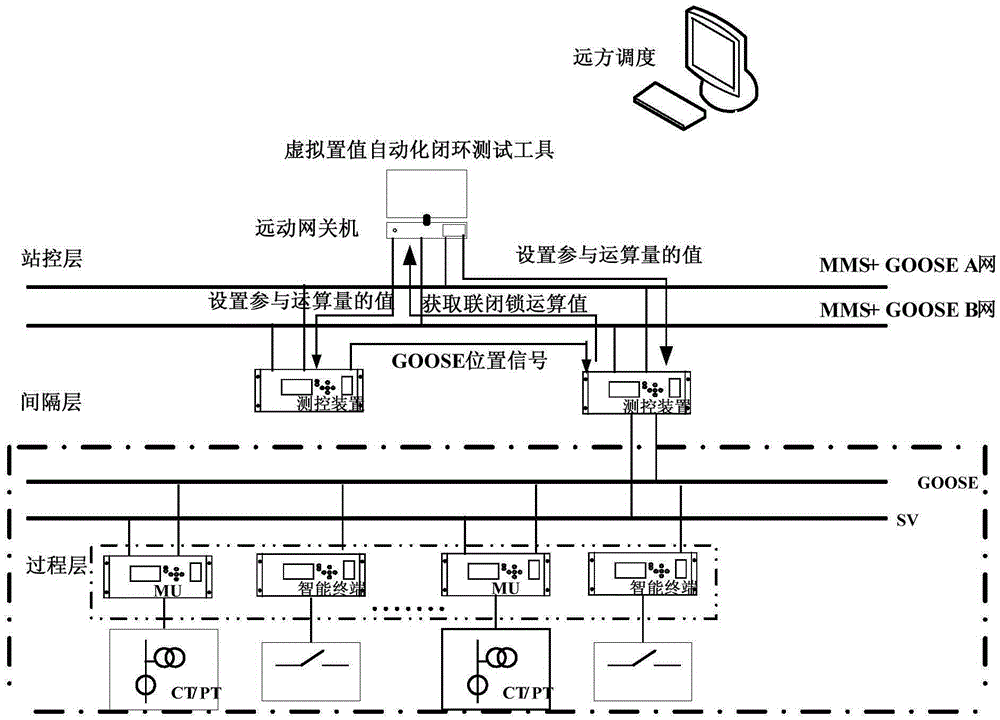

Automatic closed-loop testing method for connecting-and-locking logic of substation bay level

ActiveCN105388370AImplement testAvoid testable drawbacksElectrical testingTest efficiencyLogical operations

The invention provides an automatic closed-loop testing method for a connecting-and-locking logic of a substation bay level. The automatic closed-loop testing method comprises the steps of loading a substation configuration description (SCD) model and a bay level connecting-and-locking logic role, extracting a semaphore which is related with a tested bay level connecting-and-locking logic operation and a reference that corresponds with a logical operation result; automatically generating a connecting-and-locking logic testing task sequence, and determining a testing-and-control device in a testing scene; wherein each testing task comprises a name and a description of primary equipment of the connecting-and-locking logic test, a related semaphore, a corresponding number, an index and a connecting-and-locking logic prediction result; constructing multiple scenes which supports automatic closed-loop testing of the connecting-and-locking logic, and acquiring the connecting-and-locking logical operation result in the testing scene; and evaluating the logical operation result. The automatic closed-loop testing method is suitable for in-substation local automatic closed-loop testing and remote scheduling automatic closed-loop testing, and furthermore has functions of preventing reconstruction and expansion of device which requires power-off operation, improving testing efficiency, saving time-wasting and labor-wasting working cost in manual testing and ensuring high correctness of an error locking preventing logic.

Owner:CHINA ELECTRIC POWER RES INST +2

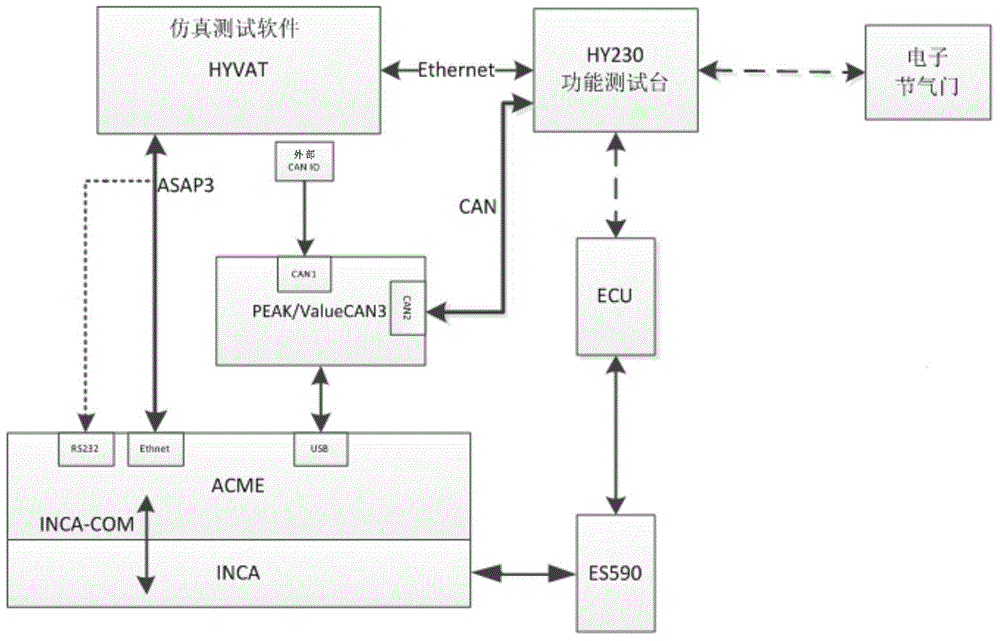

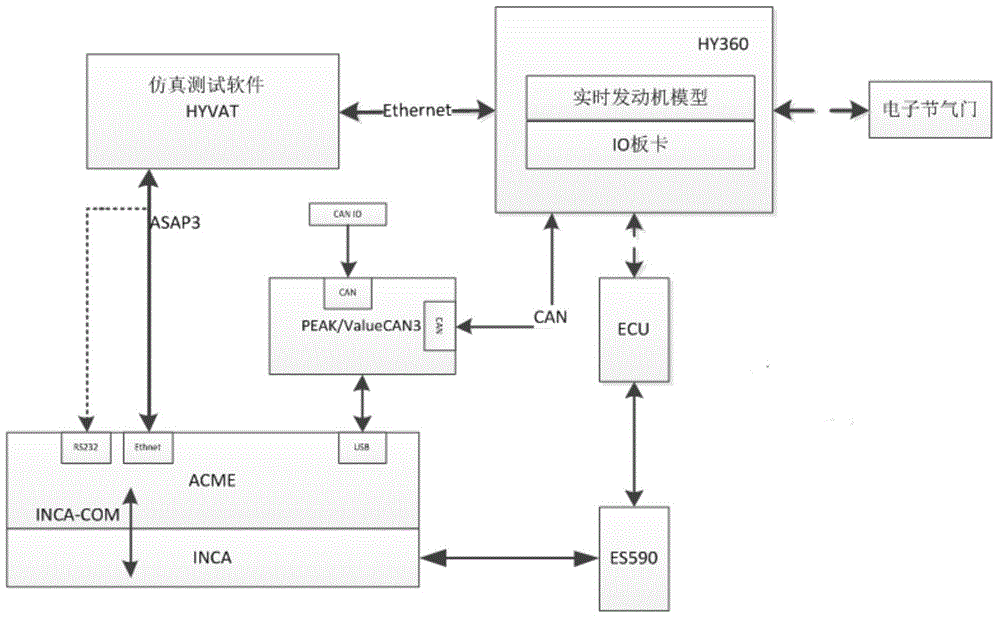

Automatic calibration simulation testing system for ECU stand

ActiveCN104898647AReduce calibration costsReduce calibration timeElectric testing/monitoringReal-time simulationElectronic throttle

The invention discloses an automatic calibration simulation testing system for an ECU stand. The system comprises an engine controller unit (ECU), calibration equipment ES590, a calibration PC (Personal Computer) machine for operating calibration software INCA and automatic calibration software ACME, a simulation testing system PC machine for operating simulation testing software HYVAT, PeakCAN / ValueCAN3USBCAN communication equipment, a simulation hardware platform and an electronic throttle valve, wherein the simulation hardware platform comprises one of an HY230 function test bed and a real-time simulation system HY360 capable of simulating various sensor signals required by the ECU and providing a simulation load for the ECU. Test cases are developed on the simulation testing system, so that logic test of automatic calibrated cases on the stand is realized, the automatic calibrated cases are sufficiently verified without occupying precious stand resources, and the calibration cost is reduced; and the automatic calibration simulation testing system can also be used for pre-calibration of the ECU stand, so as to shorten the real stand calibration time.

Owner:GUANGZHOU JINHONGYUAN ELECTRONICS TECH

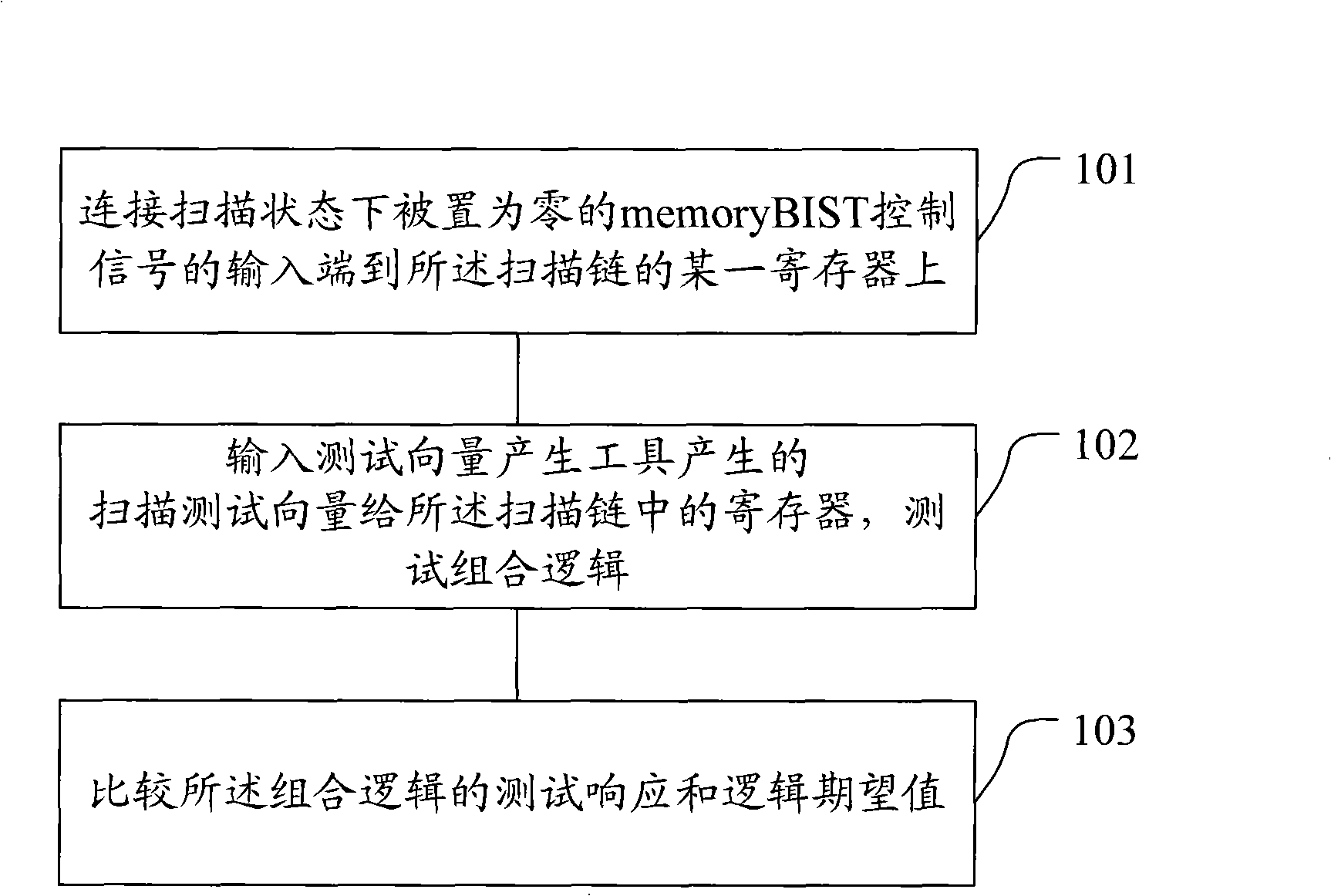

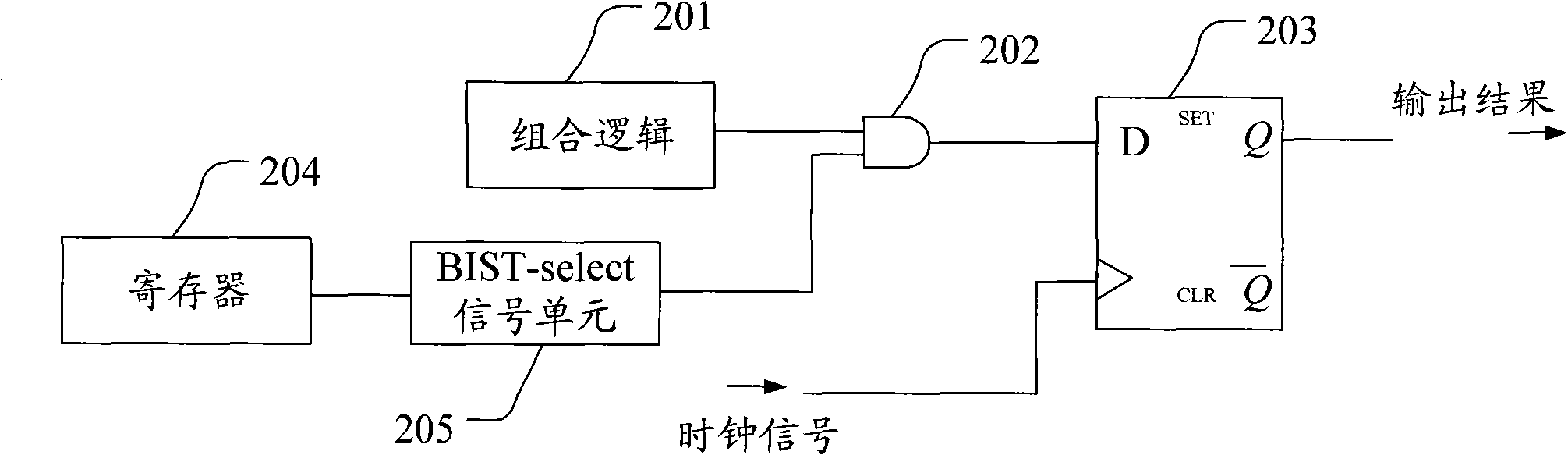

Method for increasing test coverage of scan chain and device thereof

ActiveCN101515479AImprove test coverageImprove testabilityStatic storageControl signalProcessor register

The invention provides a method for increasing the test coverage of a scan chain and a device thereof; wherein, the method for increasing the test coverage of the scan chain comprises: an input end of built-in self testing control signals of a memory being set to be zero in a scanning mode is connected into one register in the scan chain; scan test vector generated by a test vector generation tool is input into the scan chain comprising the register to test combinational logic; the test response and logic expected value of the combinational logic are compared. The method for increasing the test coverage of the scan chain provided by the invention causes that the built-in self testing control signals of the memory can be controlled when the scan chain tests, and realizes the testability of the built-in self testing logic of the memory in the scan mode, thus increasing the logic test coverage of the scan chain test and further increasing the whole test coverage of a chip.

Owner:BEIJING VIMICRO ARTIFICIAL INTELLIGENCE CHIP TECH CO LTD

Voltage time type logic tester and test method

PendingCN107064790ARealize logic checkRealize telemetry and telematics auxiliary function testCircuit interrupters testingLoop controlControl engineering

The invention discloses a voltage time type logic tester and a test method. The tester comprises a distribution terminal logic test module, a section switch opening time test module, a closing peak current test module, and a tele-signaling and telemetry aided test module. The distribution terminal logic test module comprises a control circuit, a contactor in the control circuit is connected with a contactor main output circuit, and the contactor main output circuit is connected with a power output end. The section switch opening time test module comprises an hour meter which automatically records the opening time of a switch. The closing peak current test module comprises a current transformer connected in series to the output port of a distribution terminal, and tests the closing peak current through a current meter. The tele-signaling and telemetry aided test module comprises an adjustable voltage and current output module and an analog switch, and the adjustable voltage and current output module outputs adjustable voltage and current and works together with the analog switch to complete tele-signaling and telemetry function test. Voltage time type distribution terminal logic verification, section switch closing peak current test, section switch opening time test, and tele-signaling and telemetry aided function test can be implemented.

Owner:STATE GRID SHANDONG ELECTRIC POWER +1

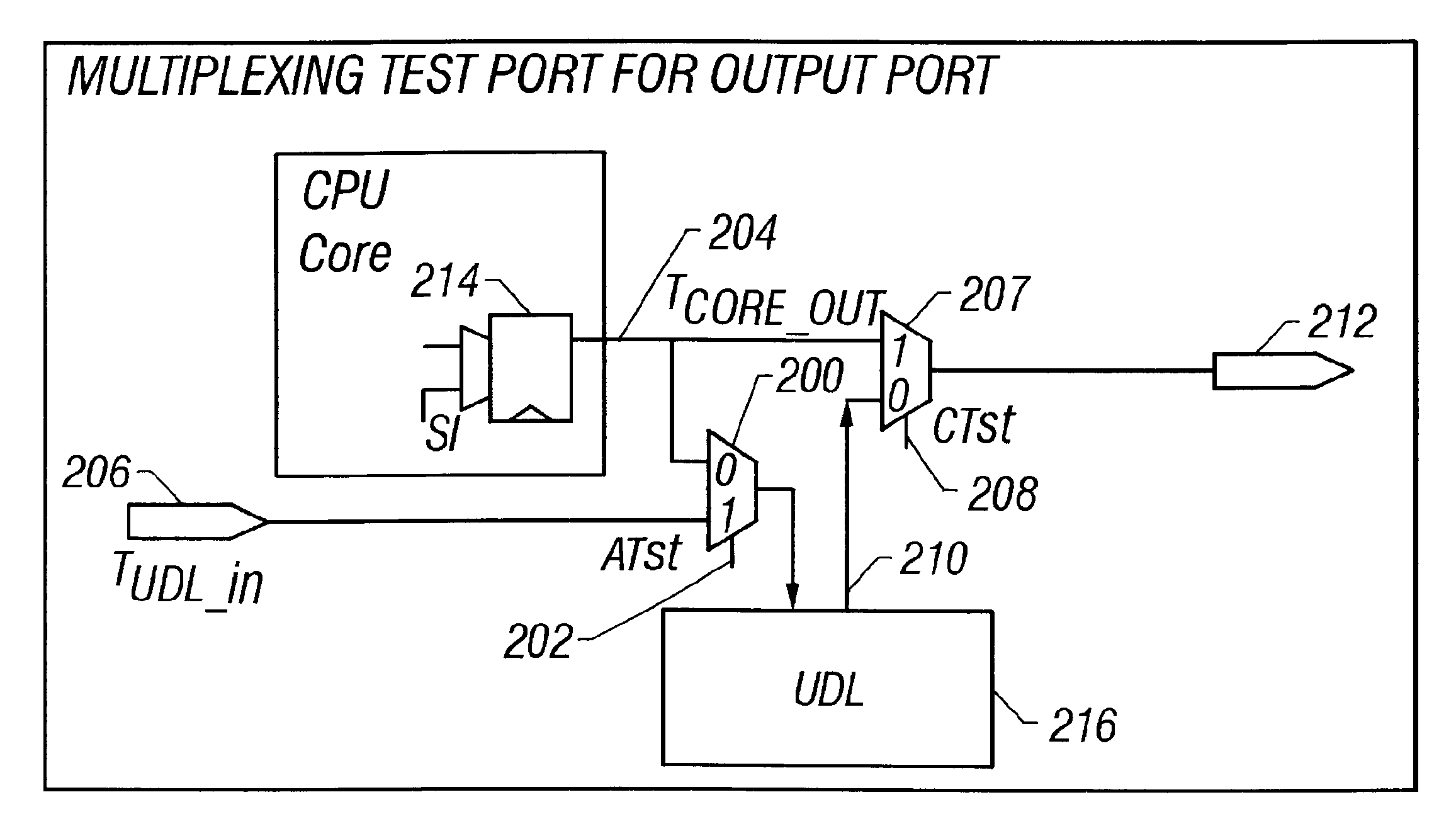

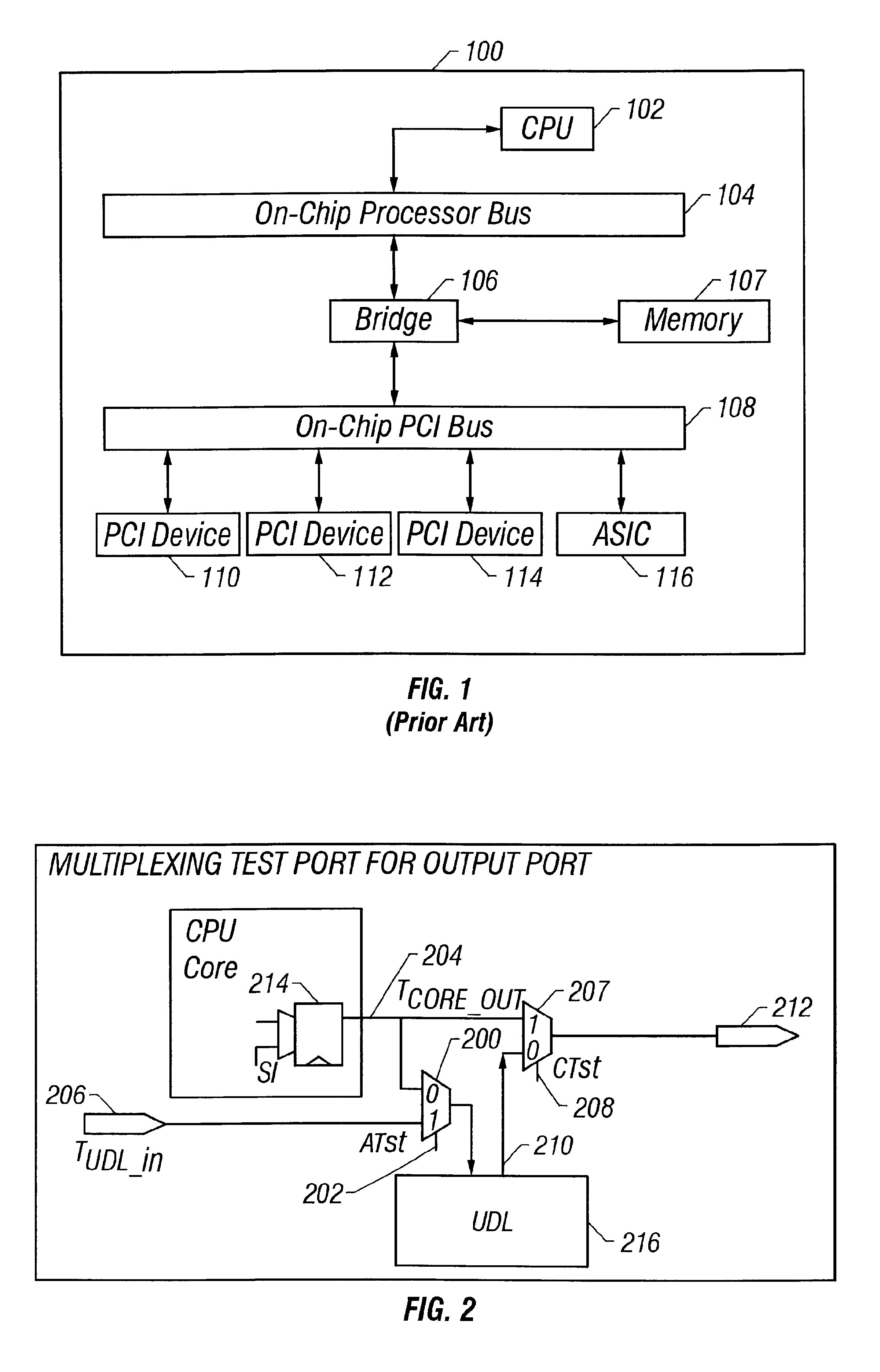

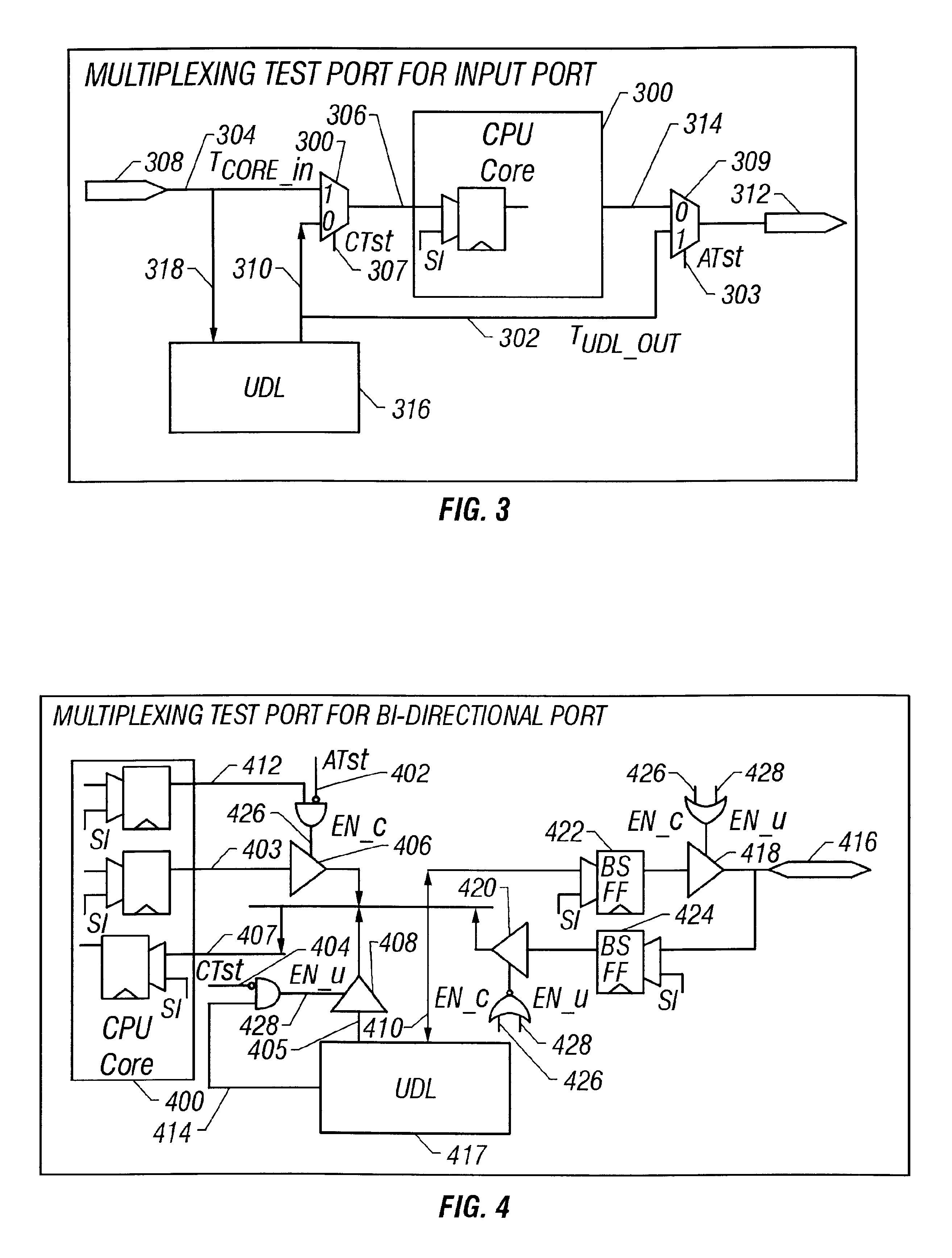

Direct access logic testing in integrated circuits

A method and circuit for allowing direct access logic testing in integrated circuits. In one embodiment, an interface between integrated circuit core logic and integrated circuit user-defined logic is exposed, and the integrated circuit core logic and the integrated circuit user-defined logic is tested via the exposed interface. In another embodiment, an integrated circuit has logic selection circuitry connected with core logic and user-defined logic. The logic selection circuitry is used to selectively test the core logic and user-defined logic.

Owner:RENESAS ELECTRONICS AMERICA

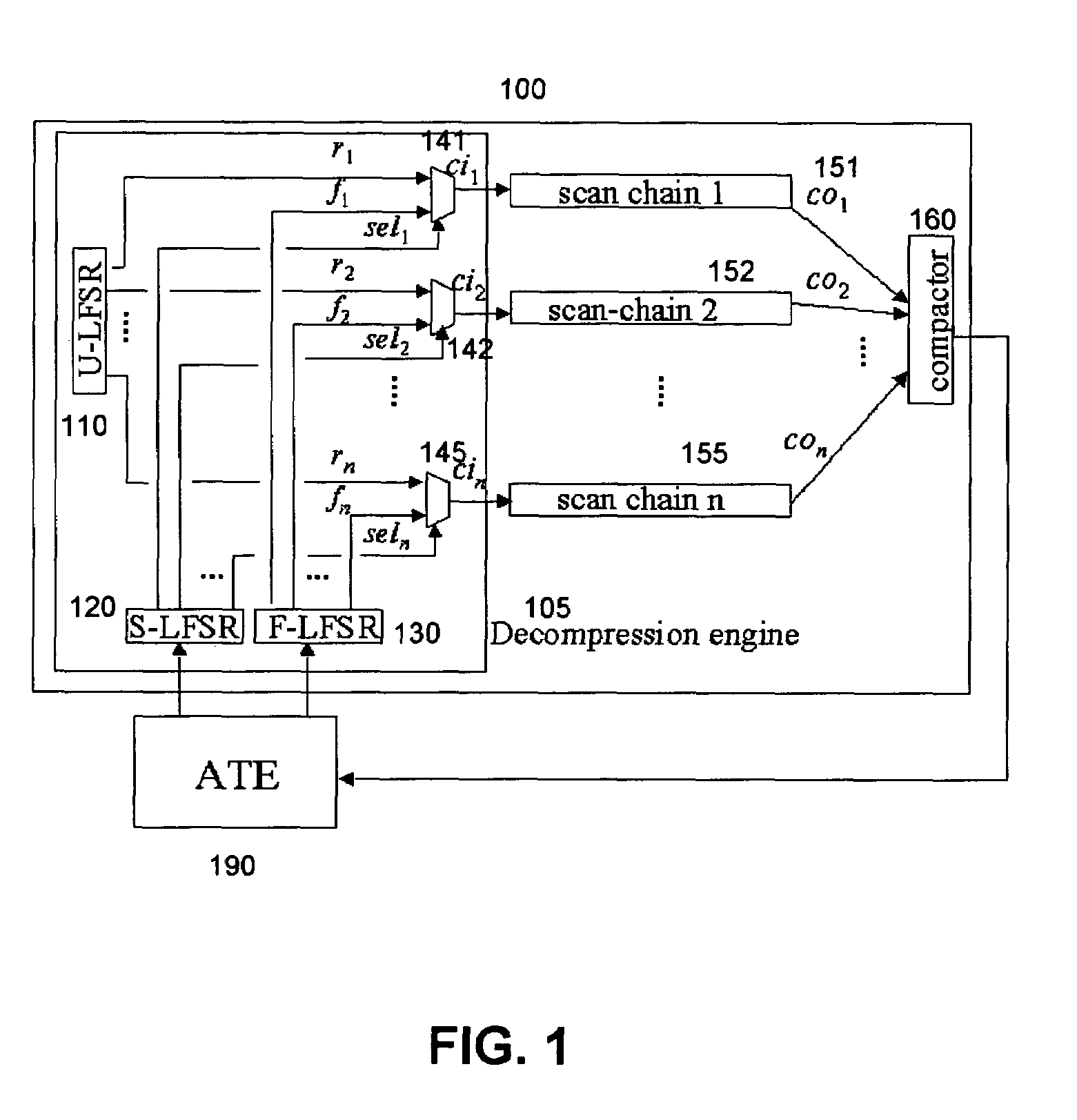

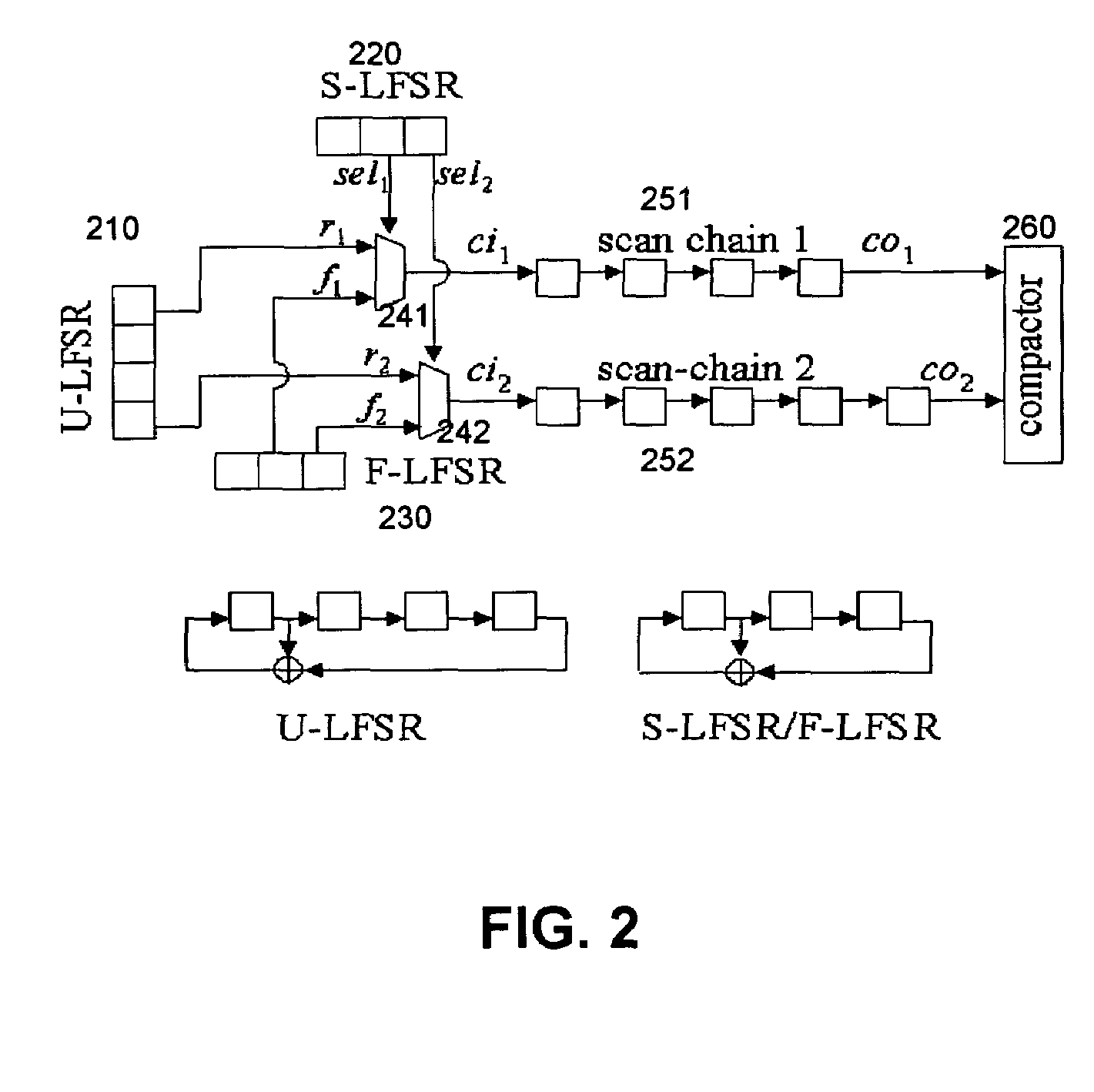

Externally-loaded weighted random test pattern compression

InactiveUS7284176B2Easy to implementElectronic circuit testingError detection/correctionComputer hardwareLogic testing

The present invention is directed to a logic testing architecture with an improved decompression engine and a method of decompressing scan chains for testing logic circuits.

Owner:NEC CORP

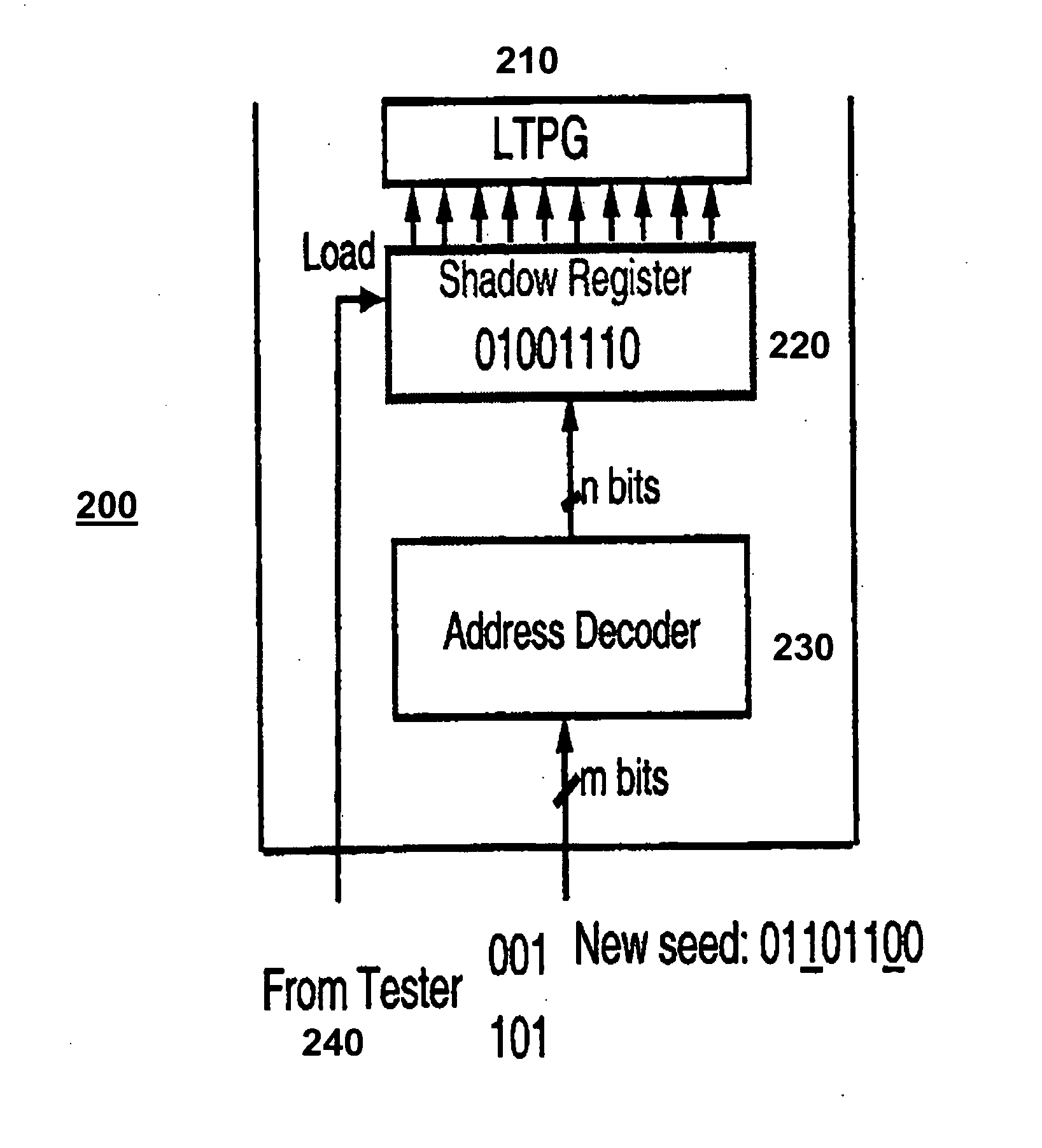

Test pattern compression with pattern-independent design-independent seed compression

InactiveUS20060112320A1Improve performanceShorten the timeElectronic circuit testingError detection/correctionEngineeringLogic testing

The present invention is directed to a logic testing architecture with an improved decompression engine that compresses the seeds of a linear test pattern generator in a manner that is independent of the test pattern set.

Owner:NEC CORP

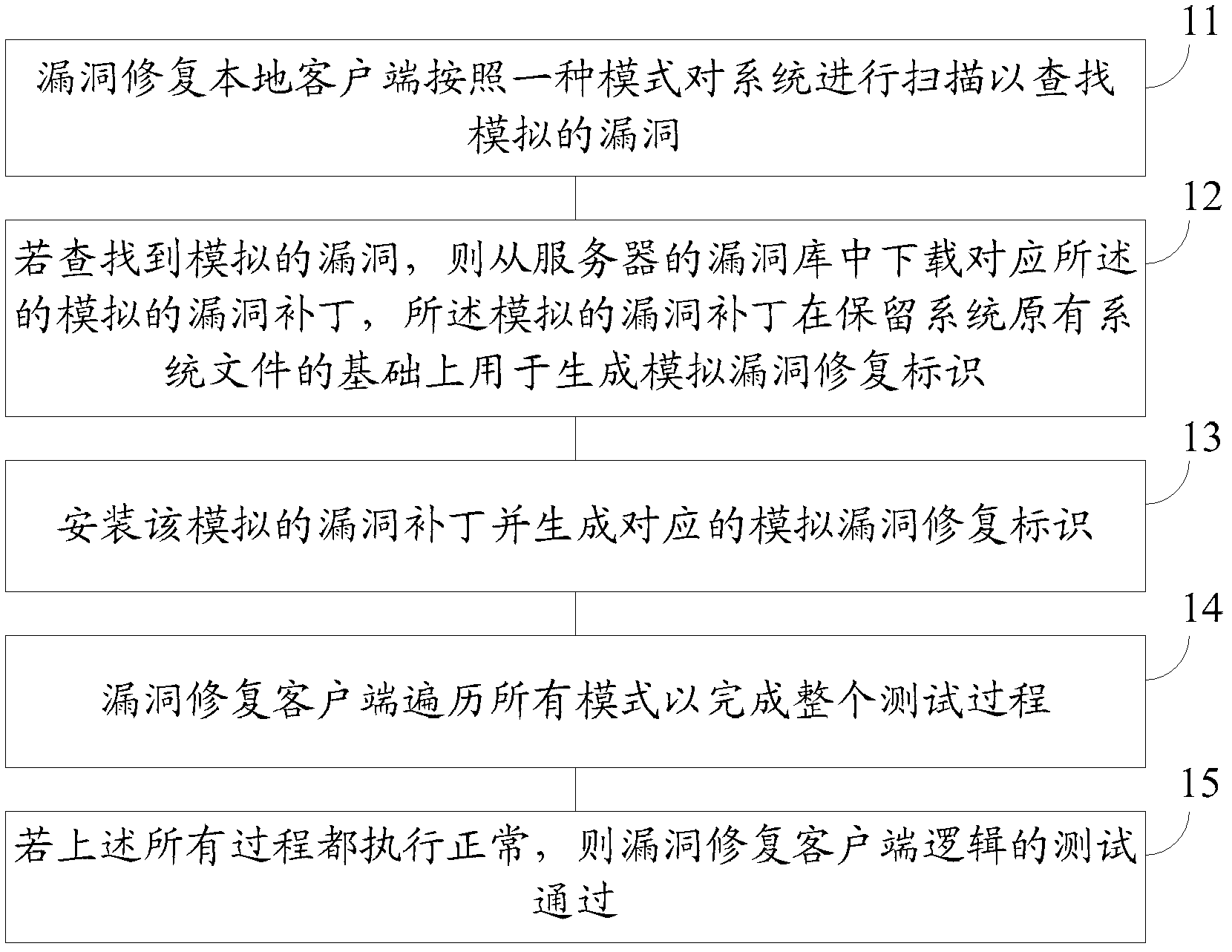

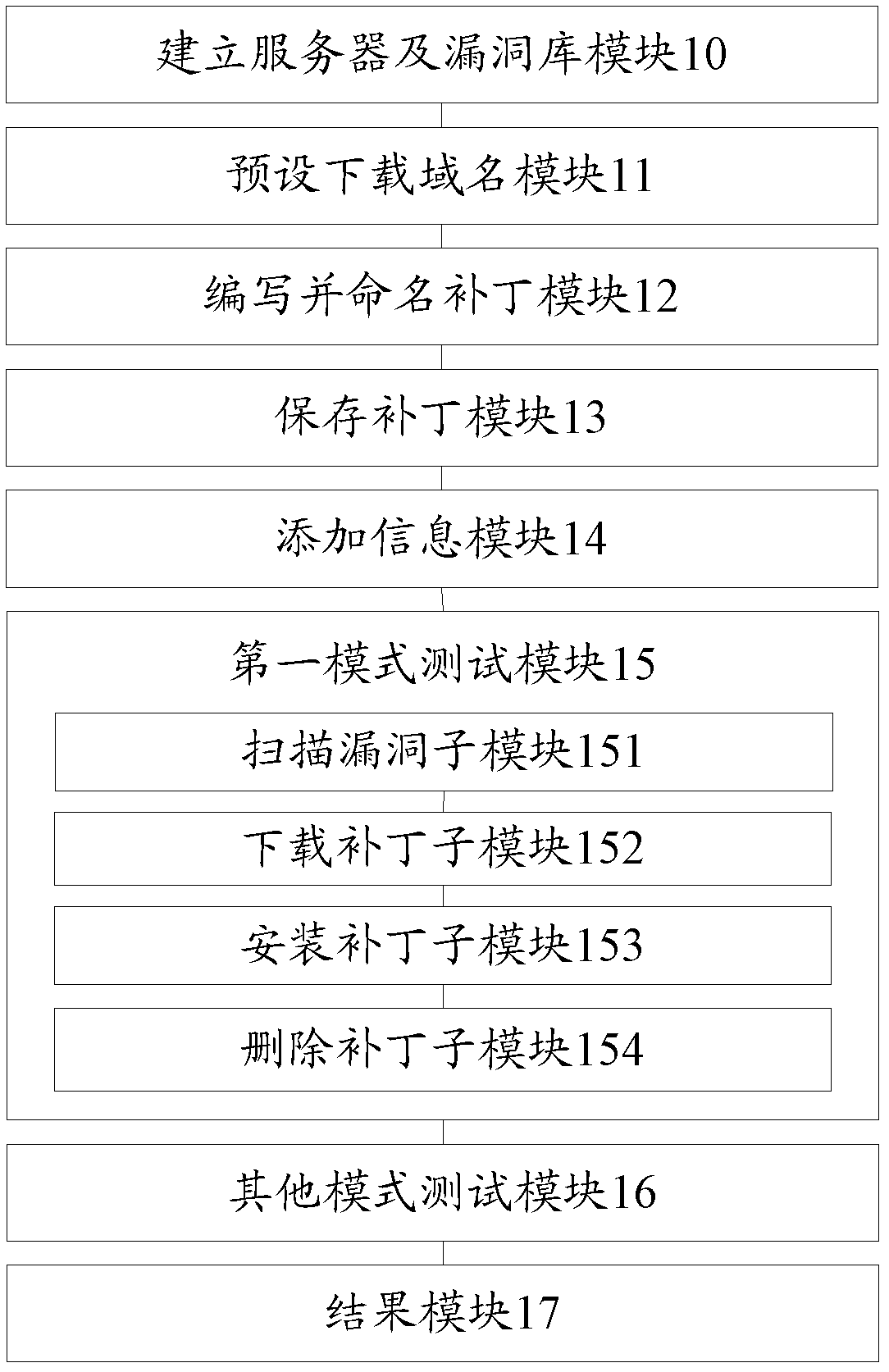

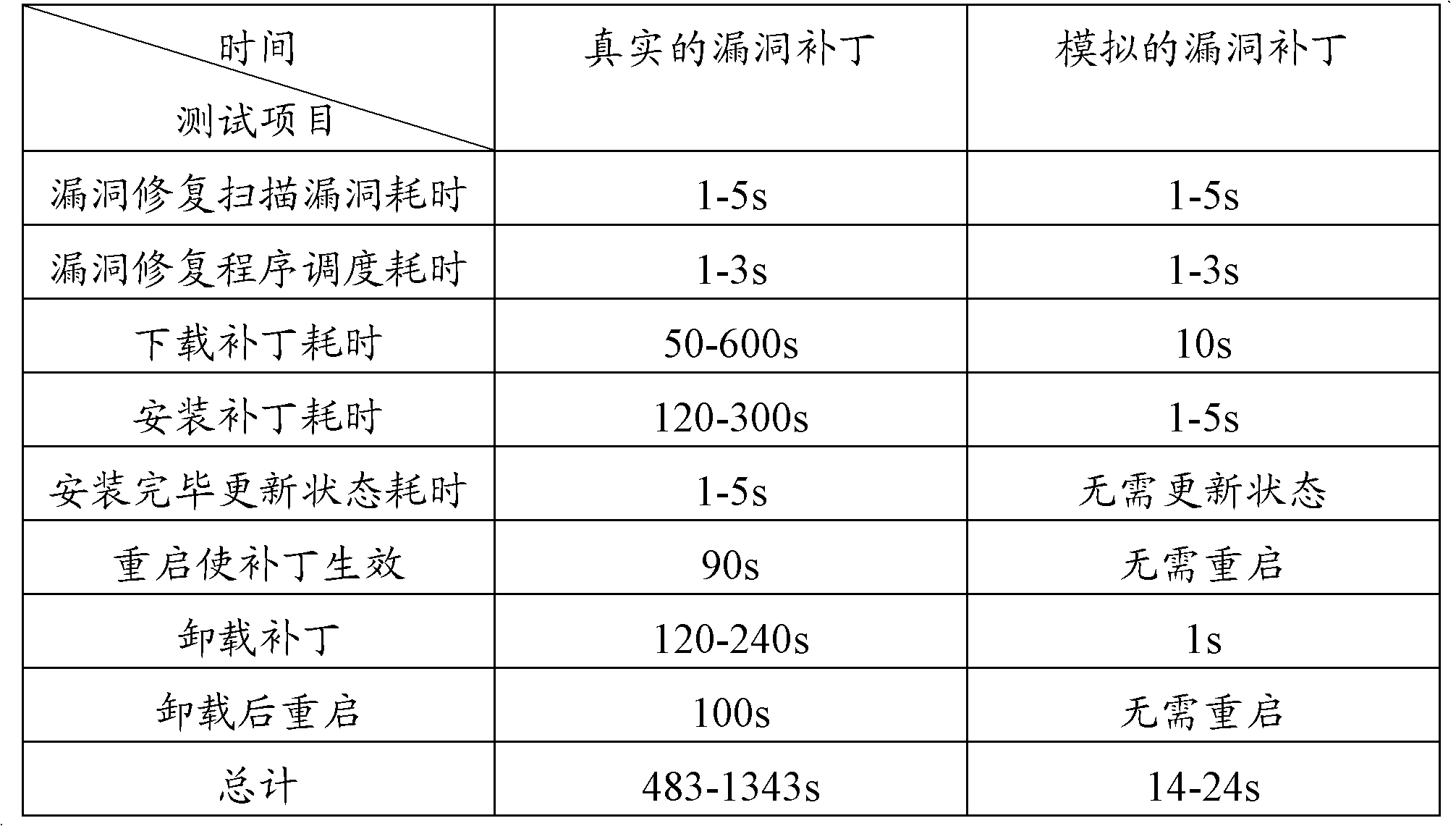

Bug-fixing client logic testing method and bug-fixing client logic testing system

ActiveCN102592084AImprove download speedFast installationComputer security arrangementsSoftware testing/debuggingLogic testingAnalog hole

The invention provides a bug-fixing client logic testing method and a bug-fixing client logic testing system, which are used for solving the problem that efficiency is affected due to time wasted for bug-fixing client logic. The bug-fixing client logic testing method includes: scanning the system to find out simulated bugs by a bug-fixing client according to a certain mode; downloading corresponding simulated bug patches from a bug base of a server if the simulated bugs are found, and generating simulated bug fixing identification marks on the basis that original system files of the system are reserved by the simulated bug patches; installing the simulated bug patches and generating corresponding the simulated bug fixing identification marks; traversing all modes to complete the whole testing process by the bug fixing client; determining that the bug-fixing client logic testing passes when the above processes are normally executed. The patches can be downloaded and installed quickly, time of the bug-fixing client logic testing is shortened, and testing efficiency is improved.

Owner:BEIJING QIHOO TECH CO LTD

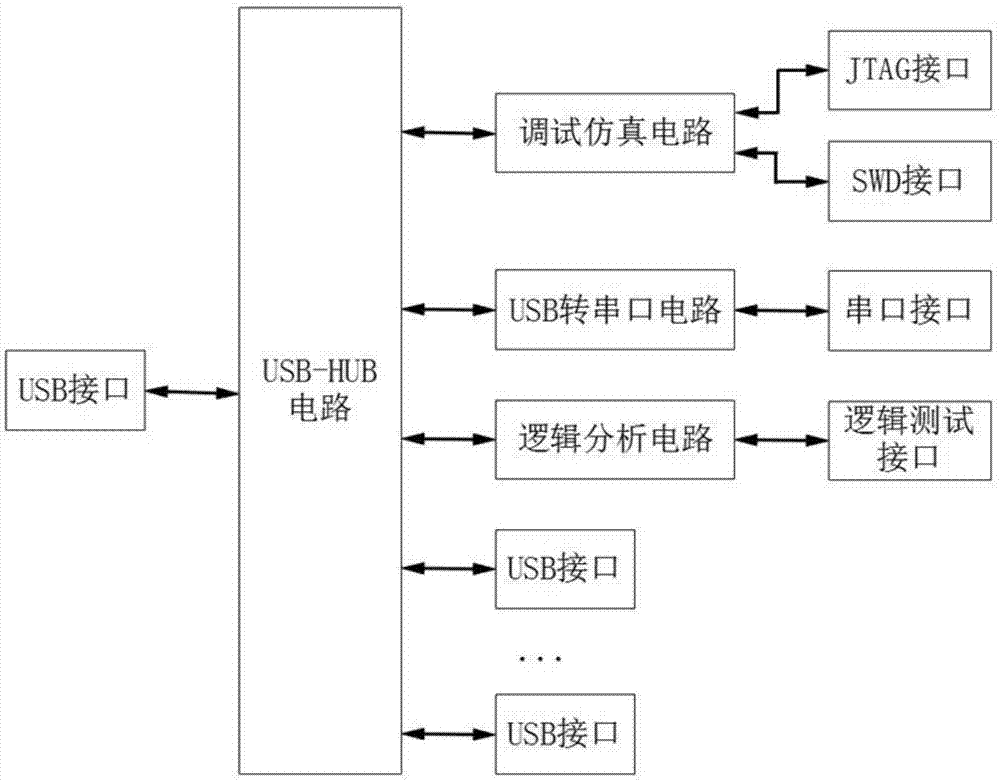

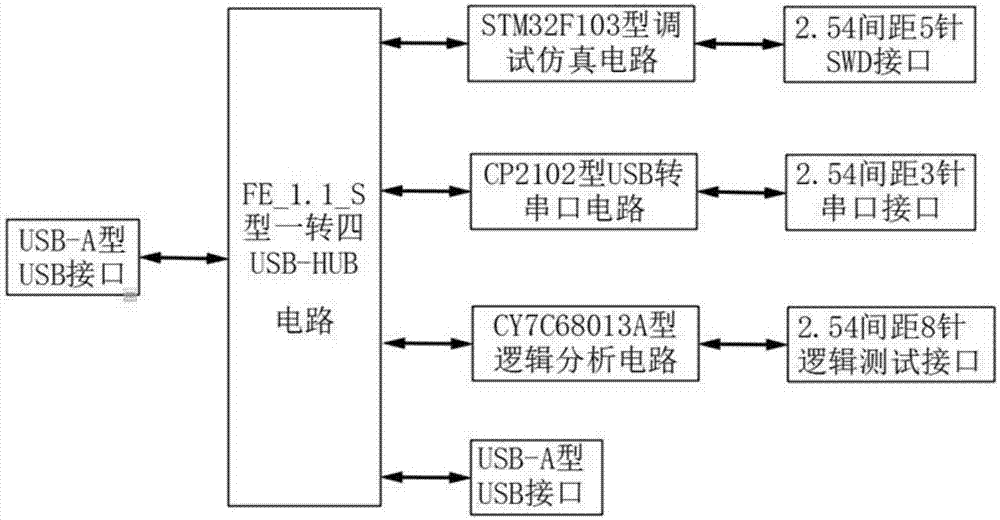

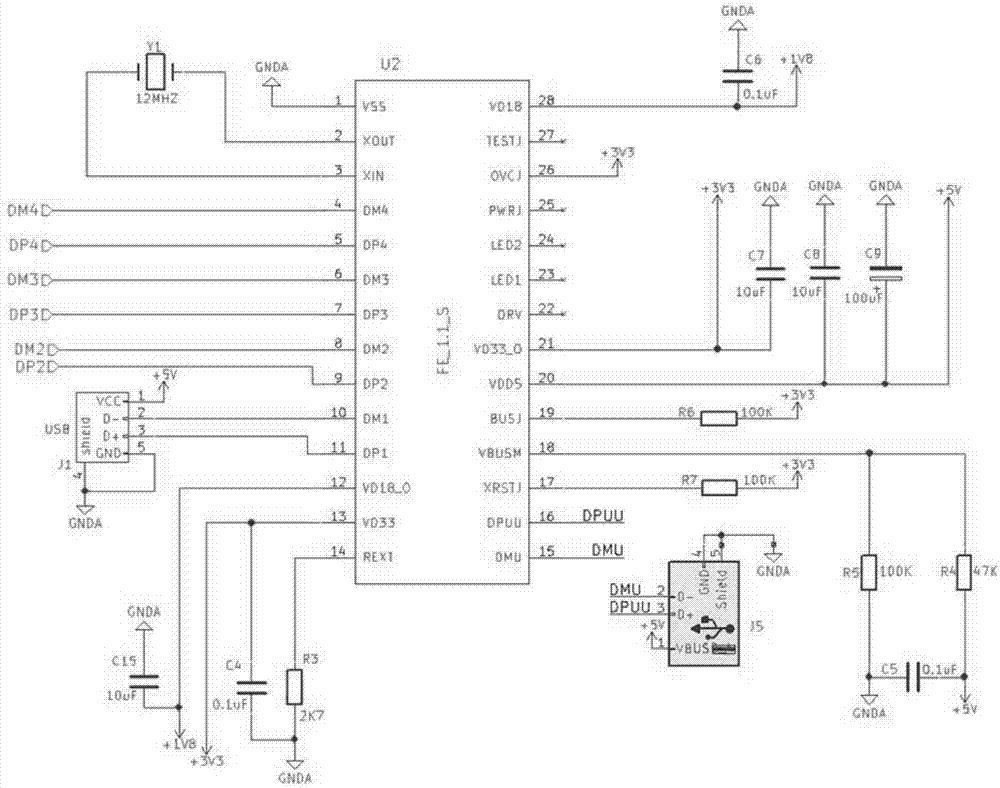

Multifunctional embedded development tool with USB interface

PendingCN107341111AImplement extensionsReduce work intensitySoftware testing/debuggingUSB hubJoint Test Action Group

The invention discloses a multifunctional embedded development tool with a USB interface and belongs to the technical field of embedded development. The multifunctional embedded development tool consists of a circuit board, the USB interface, a USB-HUB circuit, a USB to serial port circuit, a debugging and simulation circuit, a logical analysis circuit, JTAG interface, an SWD interface, a serial port interface and a logical test interface. The multifunctional embedded development tool only needs the USB interface to be connected with a computer to achieve the functions of debugging and simulation, serial port test, logical analytic test, code downloading and the like together with software of the computer, so that functional demands for debugging and simulation, testing, maintenance and the like of development of embedded software in various stages, cross use of multiple tools is not needed, accordingly, the working intensity of embedded software development testing and maintenance is reduced, and the working efficiency is improved.

Owner:BEIJING AOPTEK SCI +1

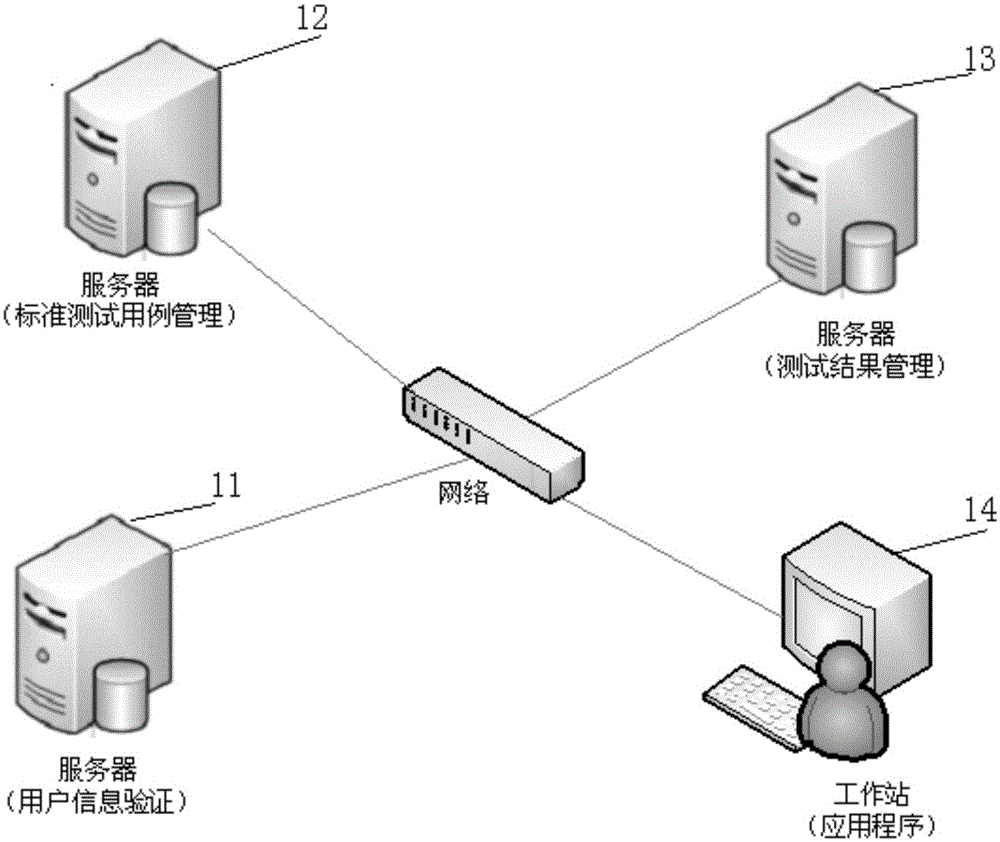

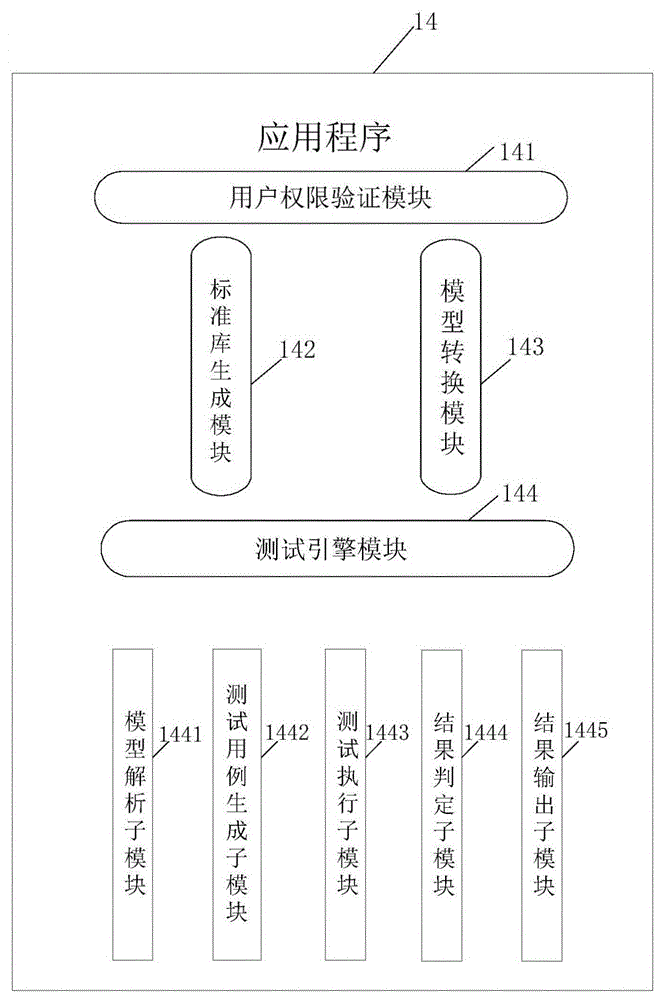

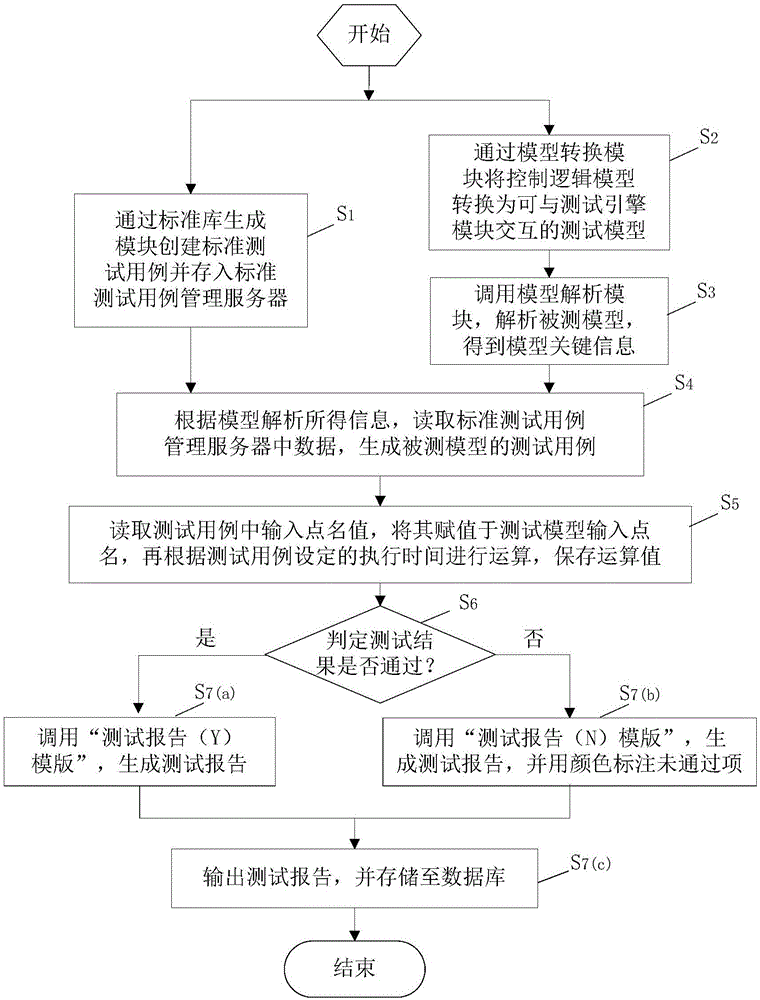

Test system and test method for control logic

InactiveCN105005295AReduce manual operationsReduce human errorElectric testing/monitoringLogic testingLab test method

The invention provides a test system and a test method for a control logic. The test system comprises a user information verification server, a standard test case management server, a test result management server and an application workstation. The application workstation comprises a user authority verification module, a standard base generating module, a model conversion module and a test engine module. The application workstation connects the user information verification server, the standard test case management server and the test result management server through a network. The test system and the test method for the control logic according to the invention can automatically generate test causes and perform a testing verification operation in a batch manner, thereby greatly reducing manual operation, making a user finish the control logic testing verification operation conveniently and quickly, reducing the number of man errors and improving testing quality and testing efficiency.

Owner:SHANGHAI NUCLEAR ENG RES & DESIGN INST CO LTD

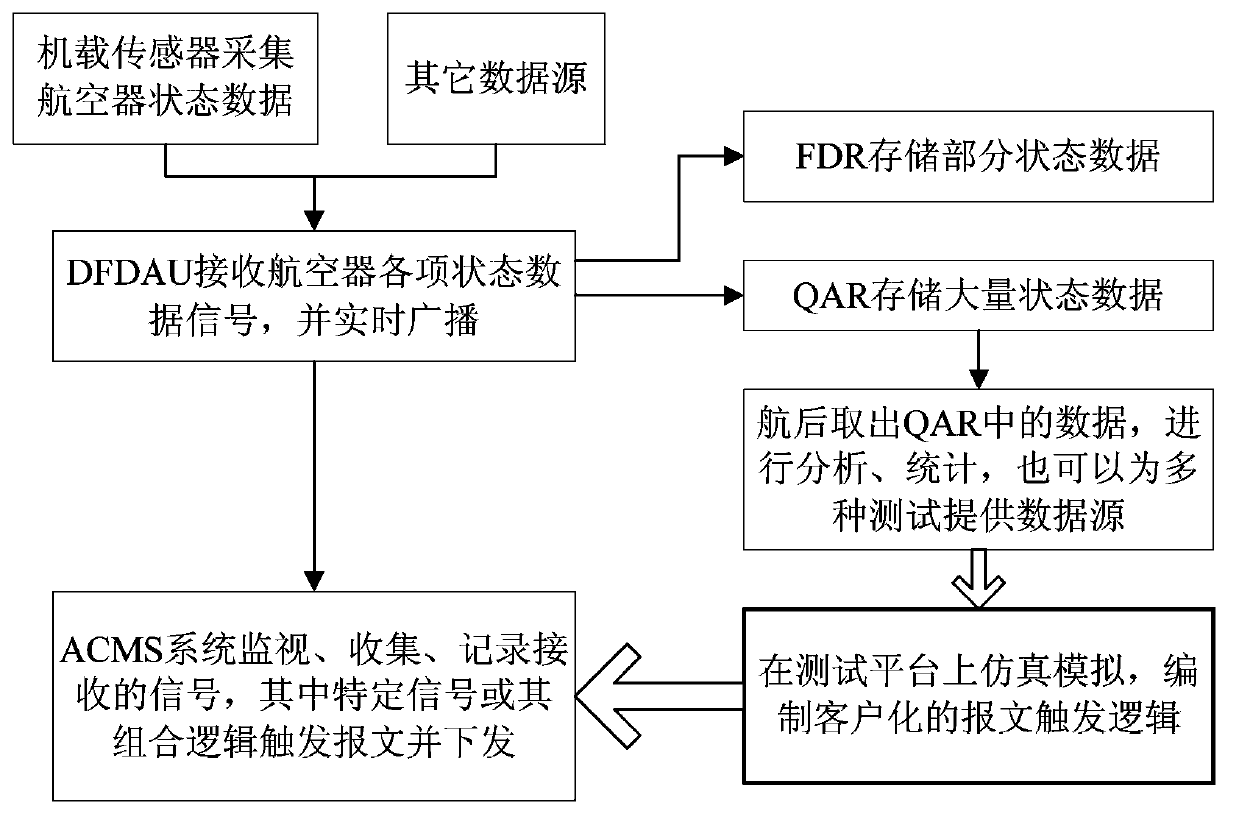

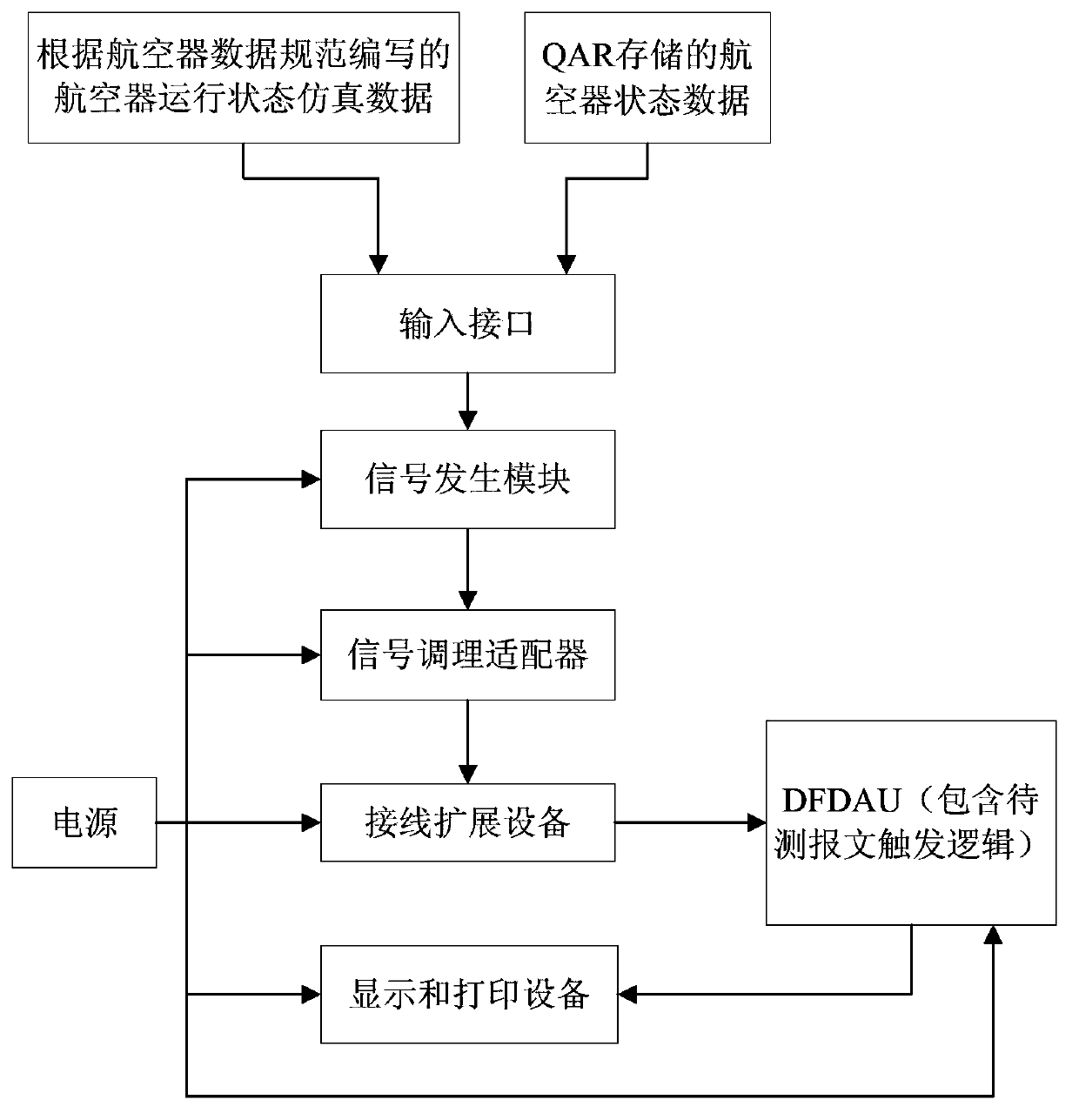

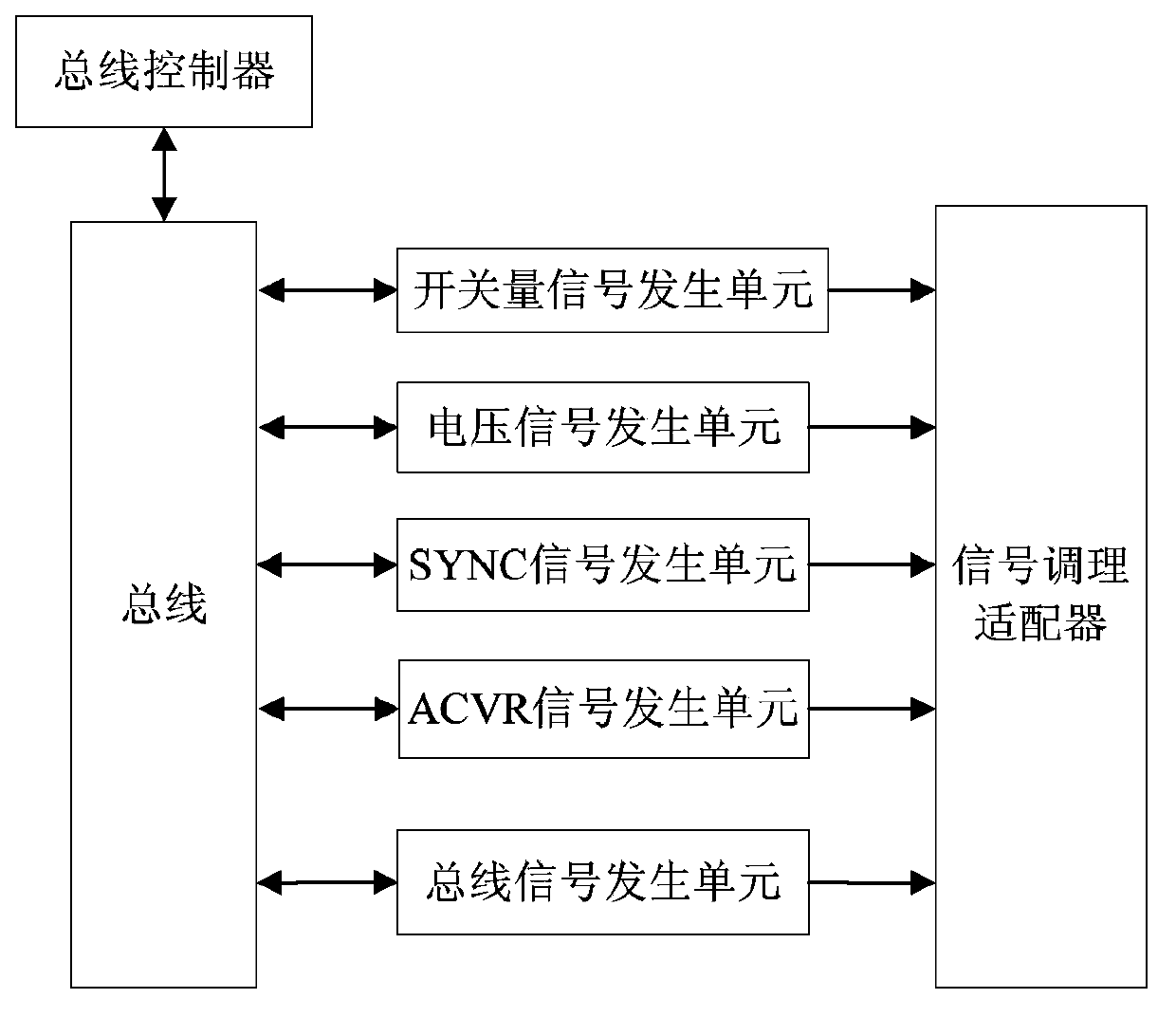

Test platform and test method for aircraft message trigger logic

ActiveCN104184758AControl safety arrangementsRegistering/indicating working of vehiclesDisplay deviceLogic testing

The present invention relates to a platform and method for testing aircraft message trigger logics. Apparatus for testing message trigger logics of aircraft comprises: DFDAU (Digital Flight Data Acquisition Unit), which is adapted to receive message trigger logics to be tested; an input interface, which is adapted to receive data of aircraft condition; and a simulation signal generator, which is adapted to generate simulation signals according to the data of aircraft condition; wherein, the DFDAU is adapted to receive the simulation signals, and generate messages according to the message trigger logics to be tested.

Owner:AIR CHINA LTD

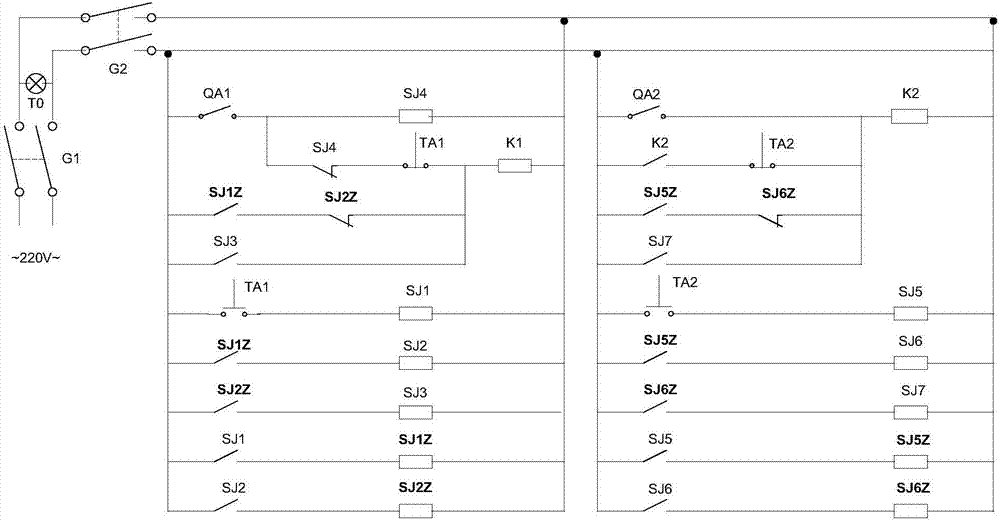

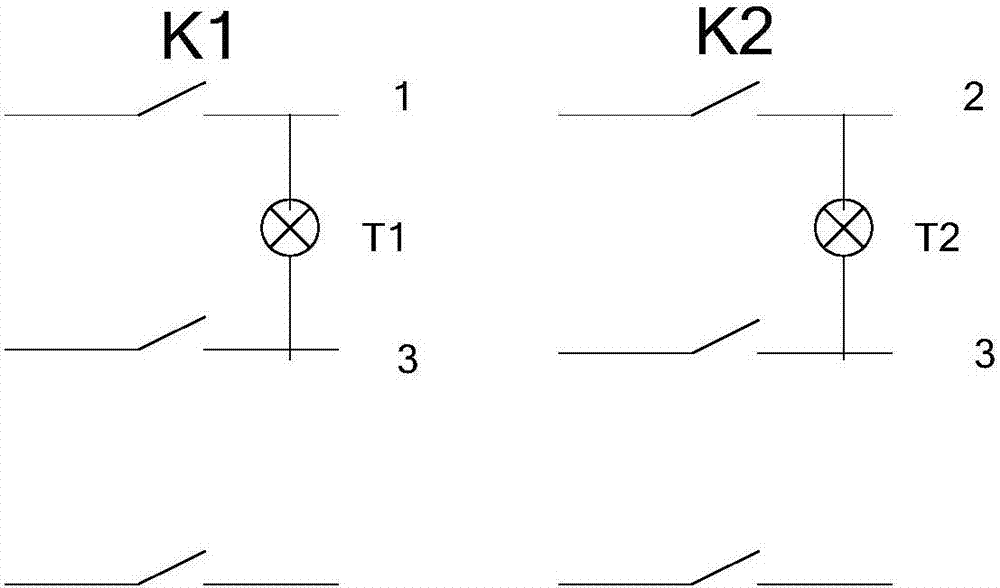

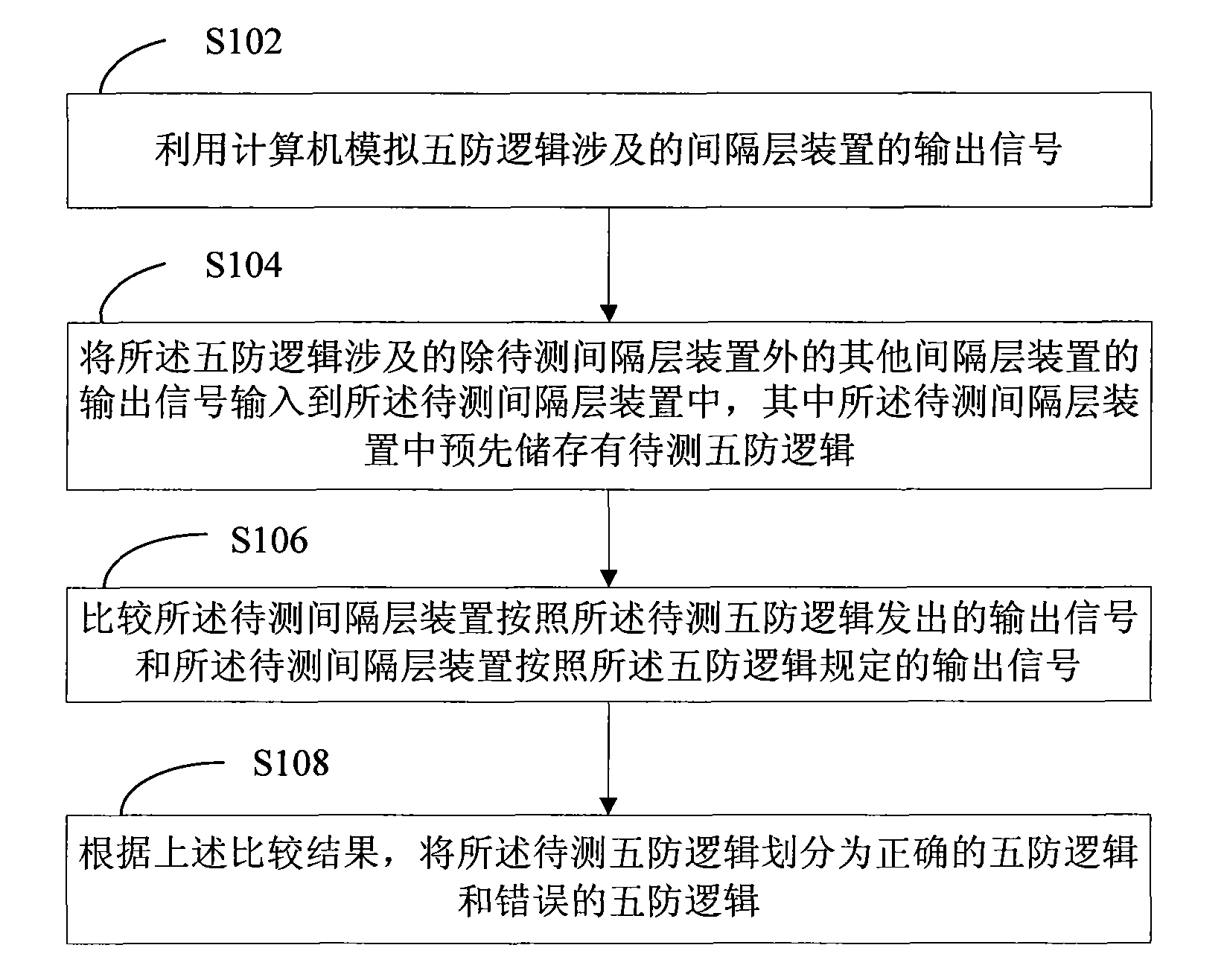

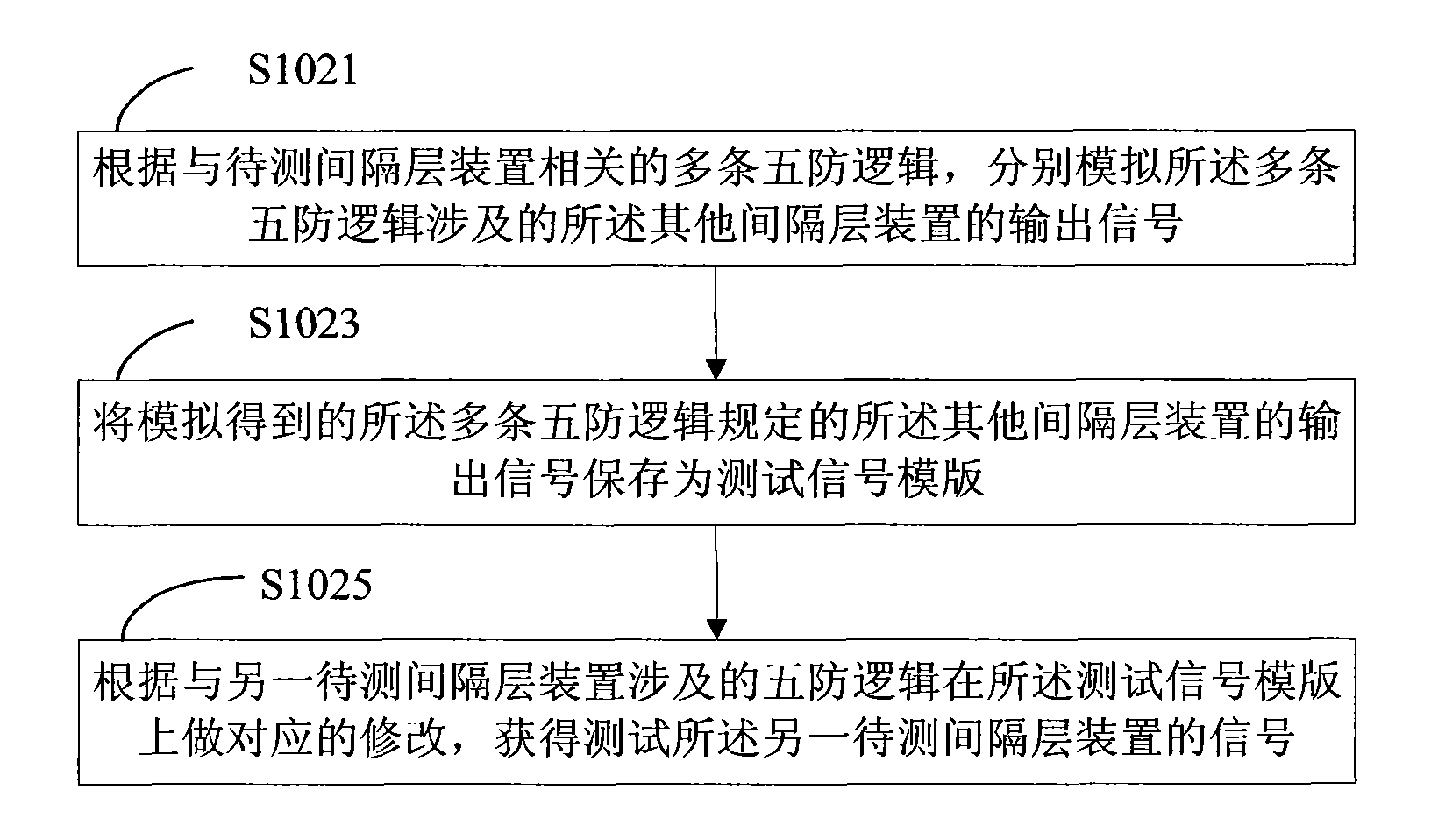

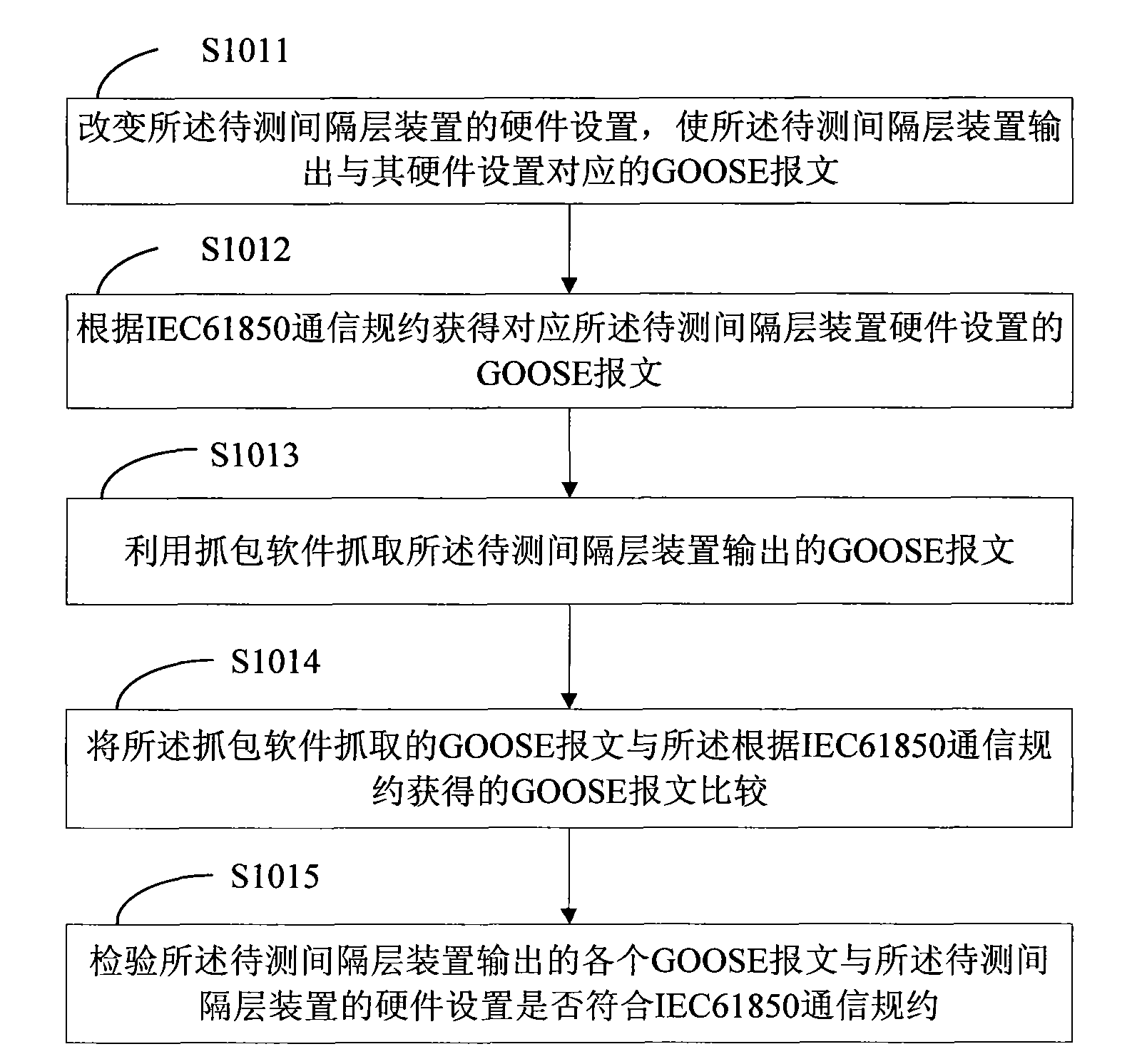

Five-prevention logic testing method and system of transformer substation

ActiveCN101776913ARealize detectionReduce stepsTesting/monitoring control systemsTransformerEngineering

The invention relates to five-prevention logic testing method and system of a transformer substation. The method comprises the following steps of: imitating output signals of a spacer layer device relevant to five-prevention logic by a computer; inputting output signals of other spacer layer devices other than the spacer layer device to be tested relevant to the five-prevention logic to the spacer layer device to be tested, wherein five-prevention logic to be tested is prestored in the spacer layer device to be tested; comparing output signals issued by the spacer layer device to be tested according to the five-prevention logic to be tested with output signals specified by the spacer layer device to be tested according to the five-prevention logic; and dividing the five-prevention logic to be tested into accurate five-prevention logic and false five-prevention logic. The five-prevention logic testing method and system of the transformer substation can conveniently and rapidly detect the five-prevention logic of the transformer substation.

Owner:ELECTRIC POWER RES INST OF GUANGDONG POWER GRID

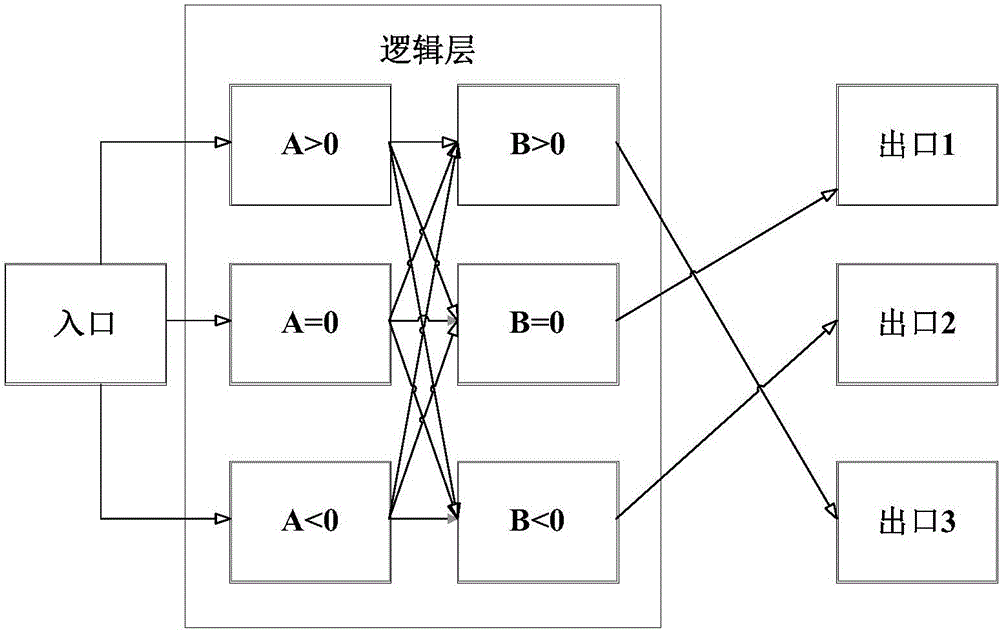

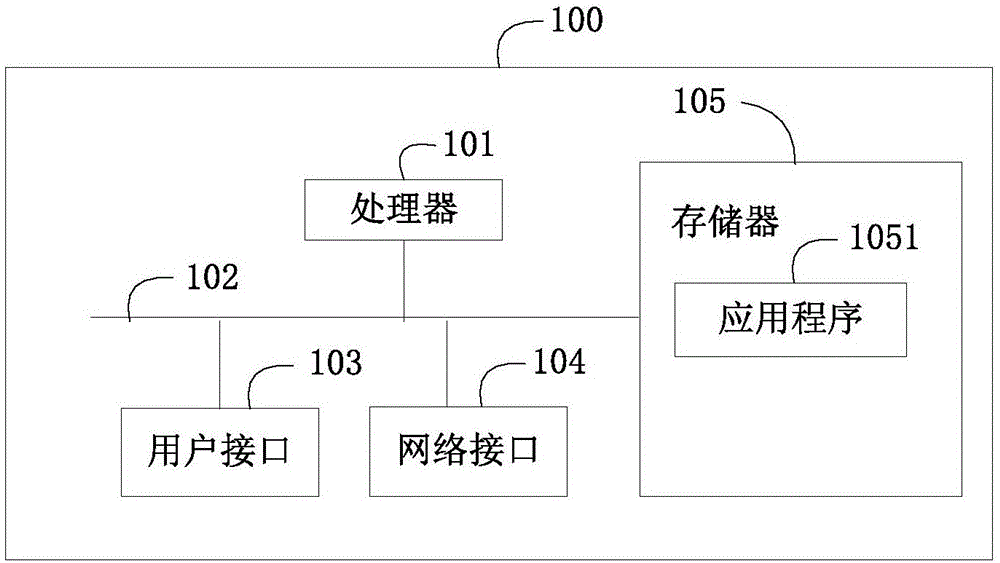

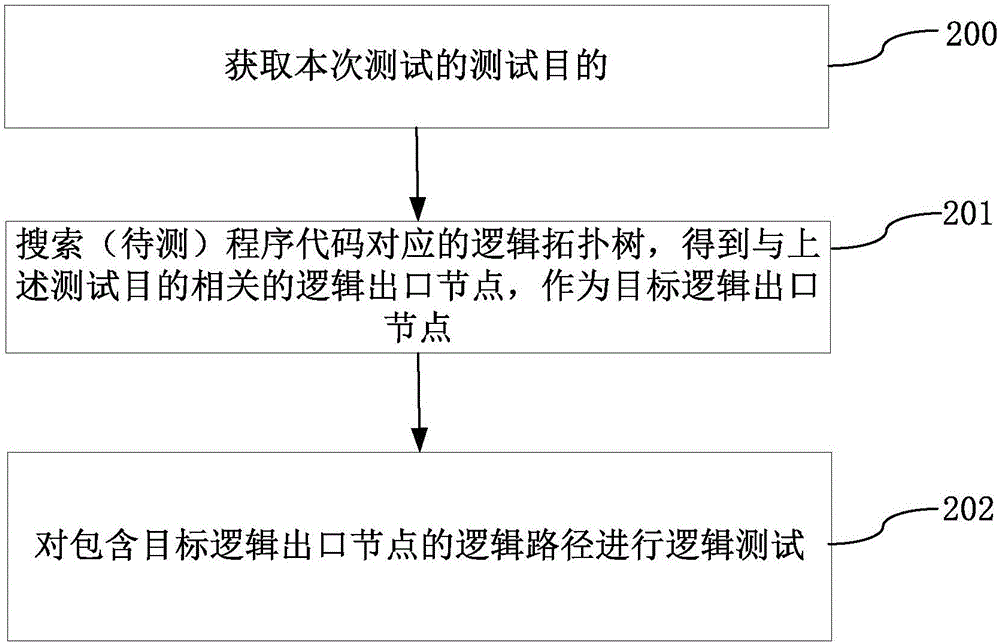

Program code testing method and device

The embodiment of the invention discloses a program code testing method and device and aims at reducing massive detection brought by traditional route coverage and solving the problem that the detection has not pertinence. The program code testing method comprises the steps that the testing purpose of a test is obtained; a logic topological tree corresponding to a procedure code is searched to obtain a logic outlet node relevant to the testing purpose and serving as a target logic outlet node; the target logic outlet node is used as a starting point, and logic testing is conducted on a logic path containing the target logic outlet node in the logic topological tree. It is thus clear that in the embodiment, logic testing is conducted on a logic path containing the target logic outlet node relevant to the testing purpose, rather than logic testing conducted on all logic paths. Due to the fact that the test is the logic test based on the testing purpose, the program code testing scheme provided by the embodiment has more pertinence compared with traditional white box testing.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Method and Apparatus for Testing Logic Circuit Designs

InactiveUS20070113129A1Electronic circuit testingError detection/correctionLogic circuit designTester device

Disclosed is a logic testing system that includes a decompressor and a tester in communication with the decompressor. The tester is configured to store a seed and locations of scan inputs and is further configured to transmit the seed and the locations of scan inputs to the decompressor. The decompressor is configured to generate a test pattern from the seed and the locations of scan inputs. The decompressor includes a first test pattern generator, a second test pattern generator, and a selector configured to select the test pattern generated by the first test pattern generator or the test pattern generated by the second test pattern generator using the locations of scan inputs.

Owner:NEC CORP

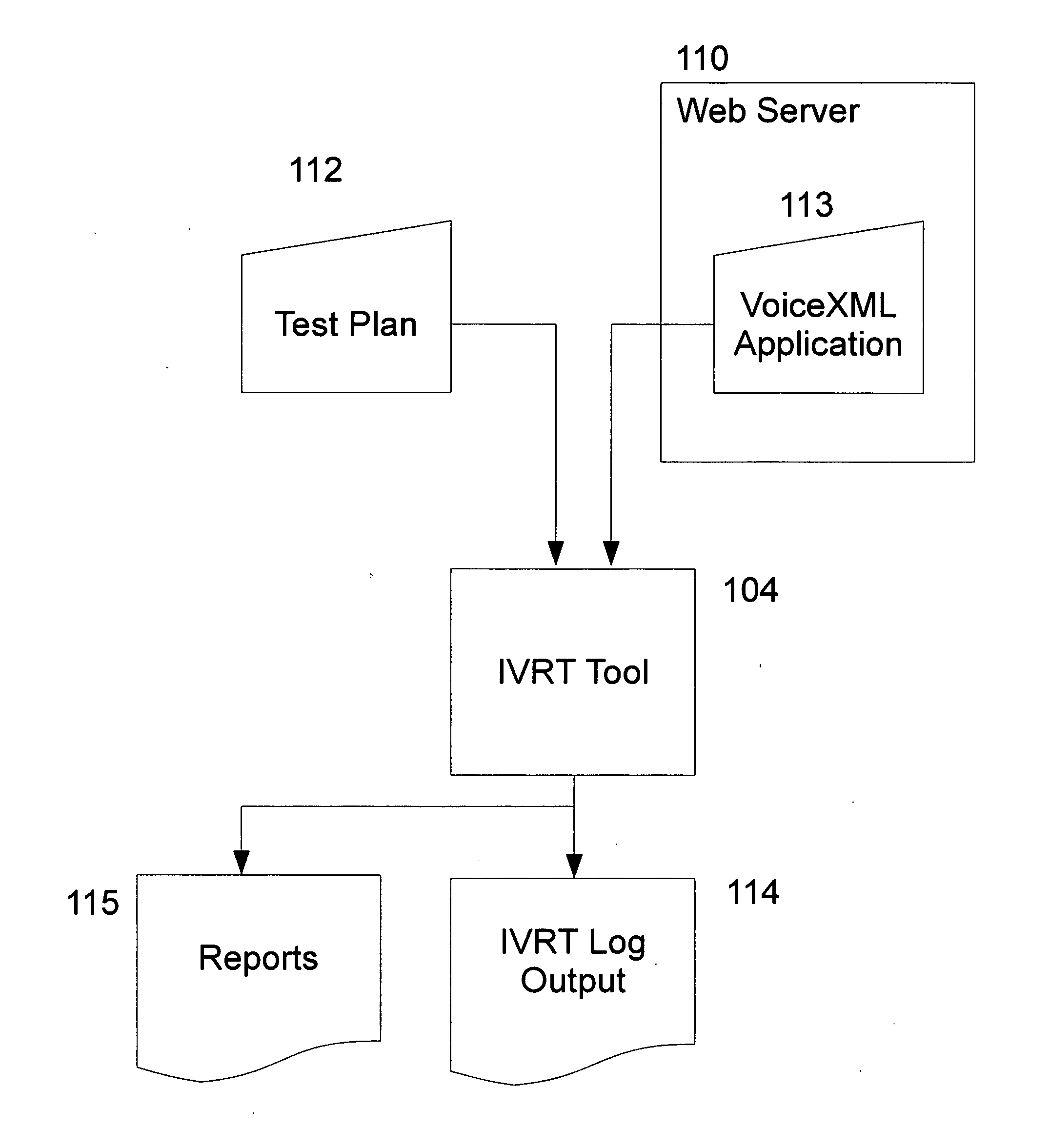

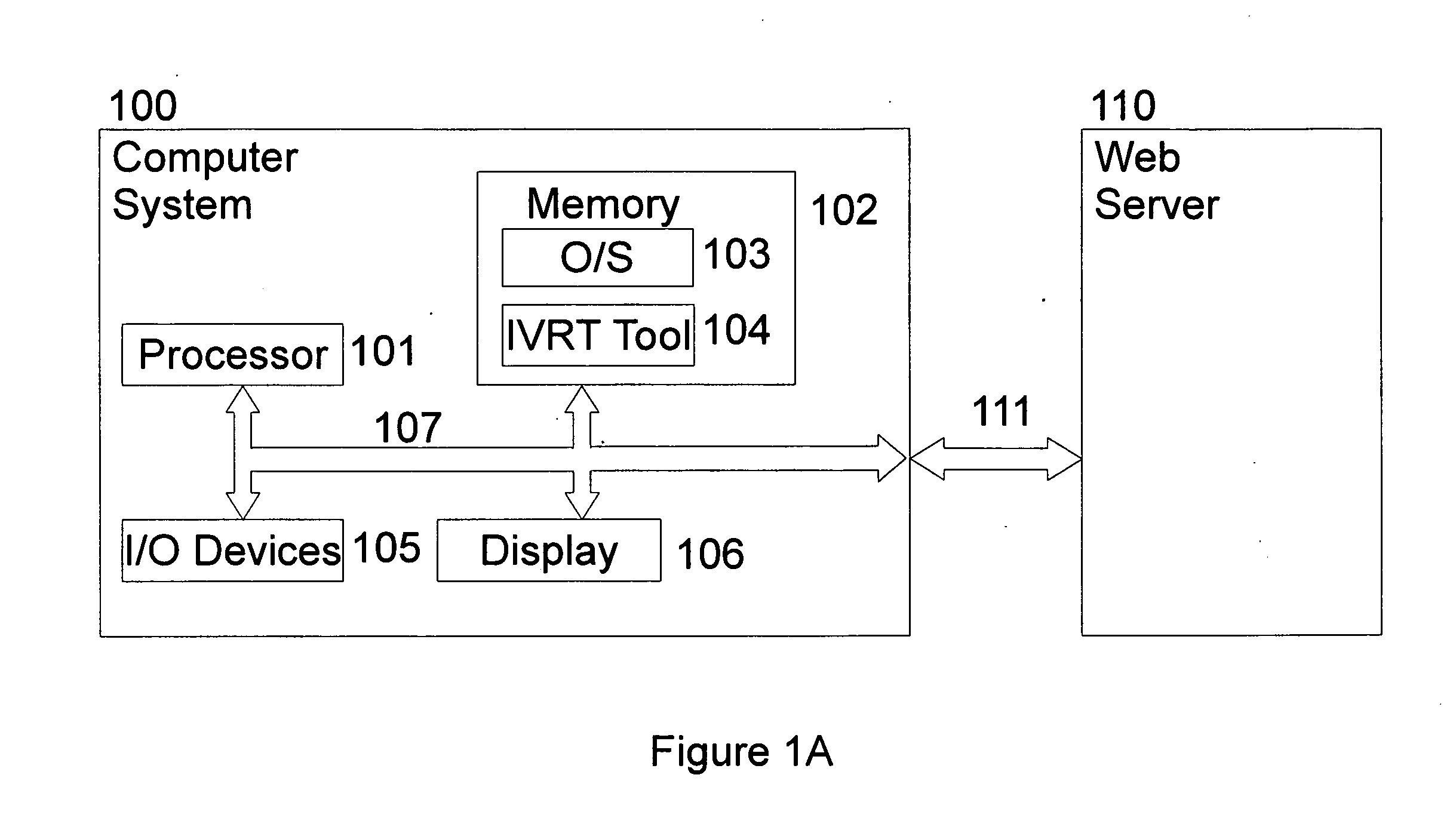

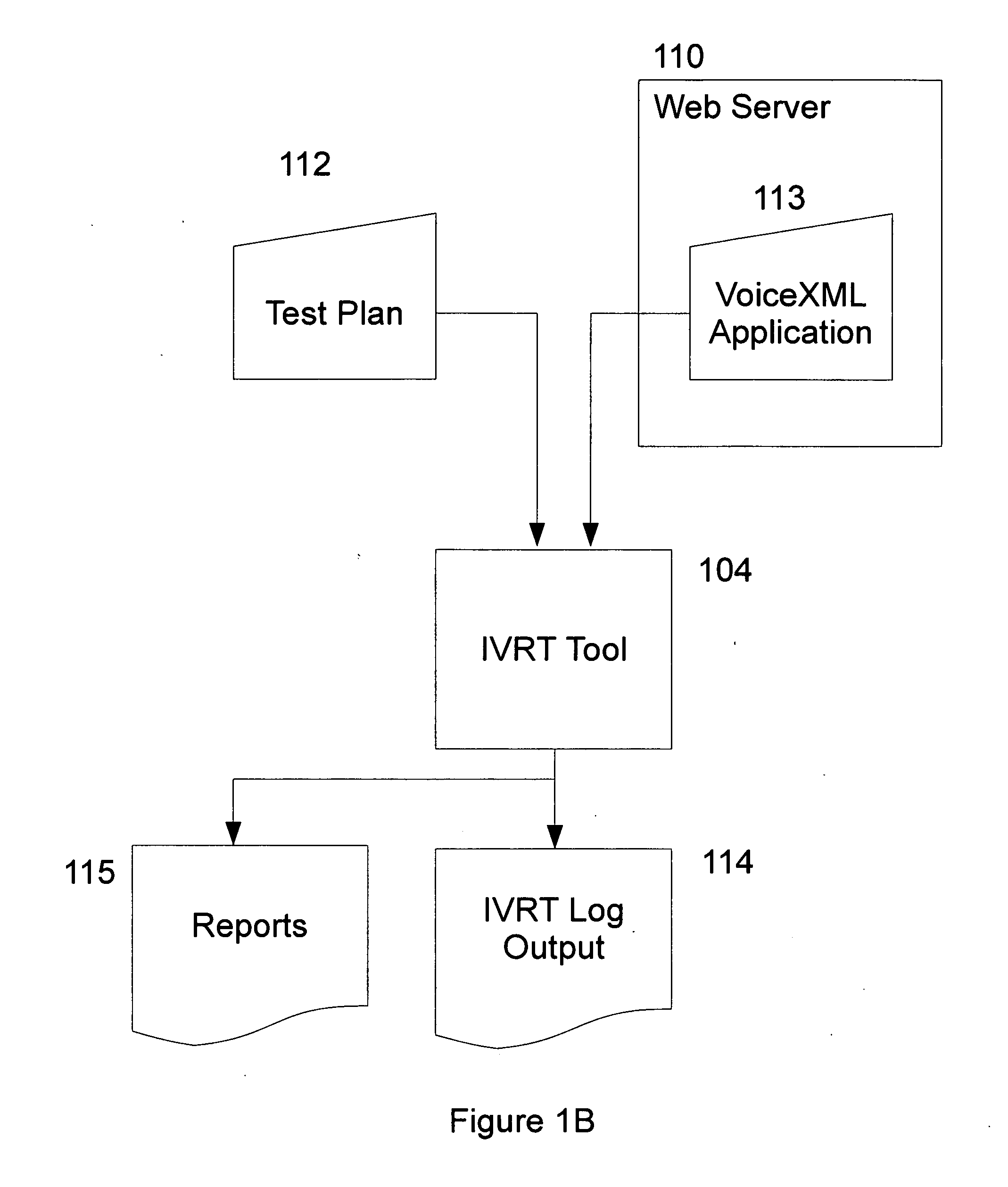

Method and system for VoiceXML quality assurance.

InactiveUS20110145641A1Sufficient flexibilityTesting is superfluousSoftware testing/debuggingRegression testingQuality assurance

A software quality assurance tool (“IVRT”) for VoiceXML applications is described. IVRT makes speech and telephony irrelevant to the testing of VoiceXML logic. IVRT follows a machine-readable “Test Plan” to execute the logic of an application. The Plan provides the results of telephony interactions. Testing is done without live callers, and runs at computer speed. A Plan contains any number of calls, to guide the application execution through all logic paths. The tool executes the application in a live environment with respect to all non-telephony functions, particularly web interactions, to test the application's web logic. IVRT executes multiple threads, acting as simultaneous callers, to provide controlled load web logic testing. The tool summarizes Plan “coverage”. For regression testing, IVRT tests an updated application with its original Test Plan and compares the log to previous logged output. Differences indicate potential regression failures.

Owner:EVANS DANIEL D

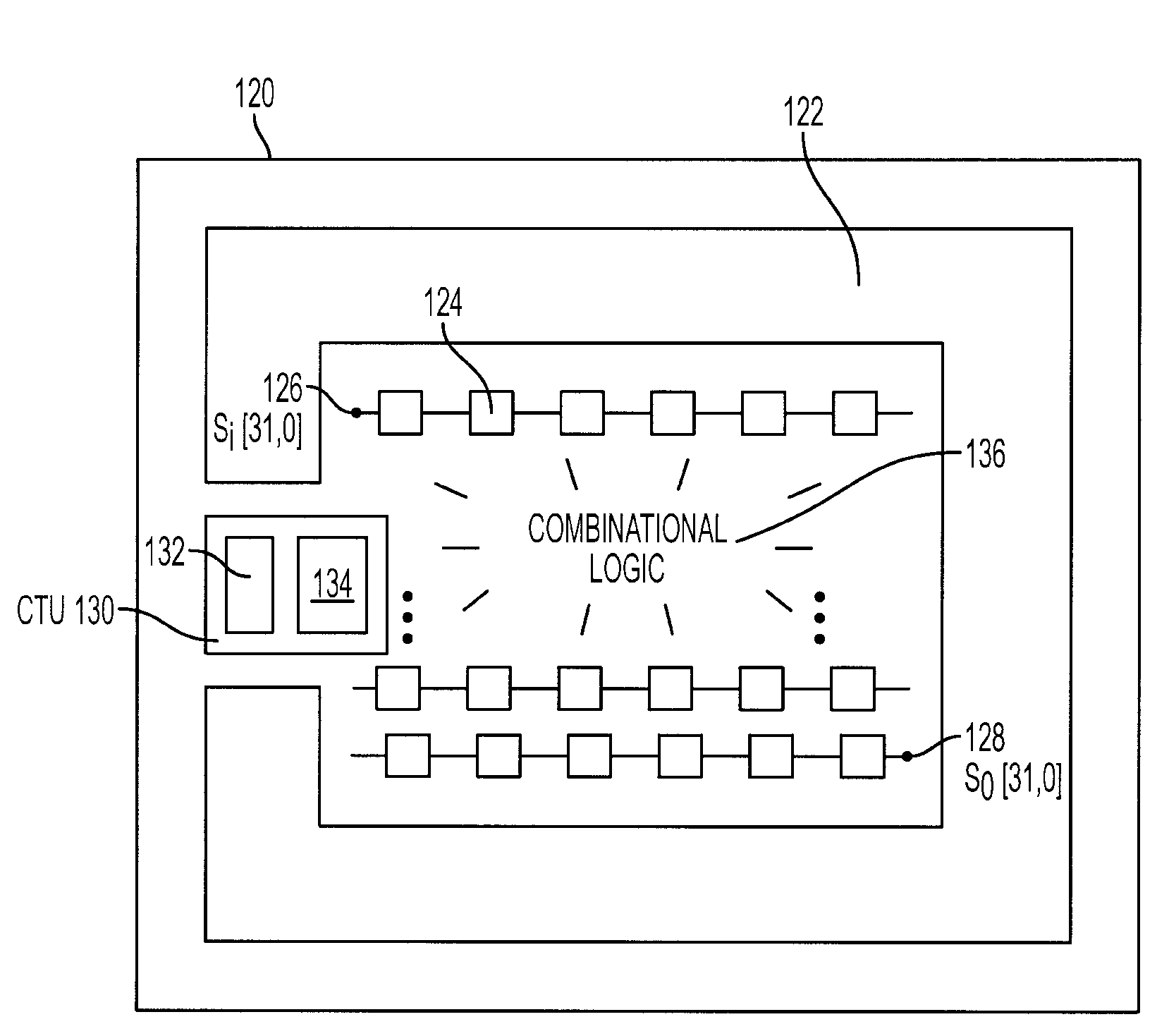

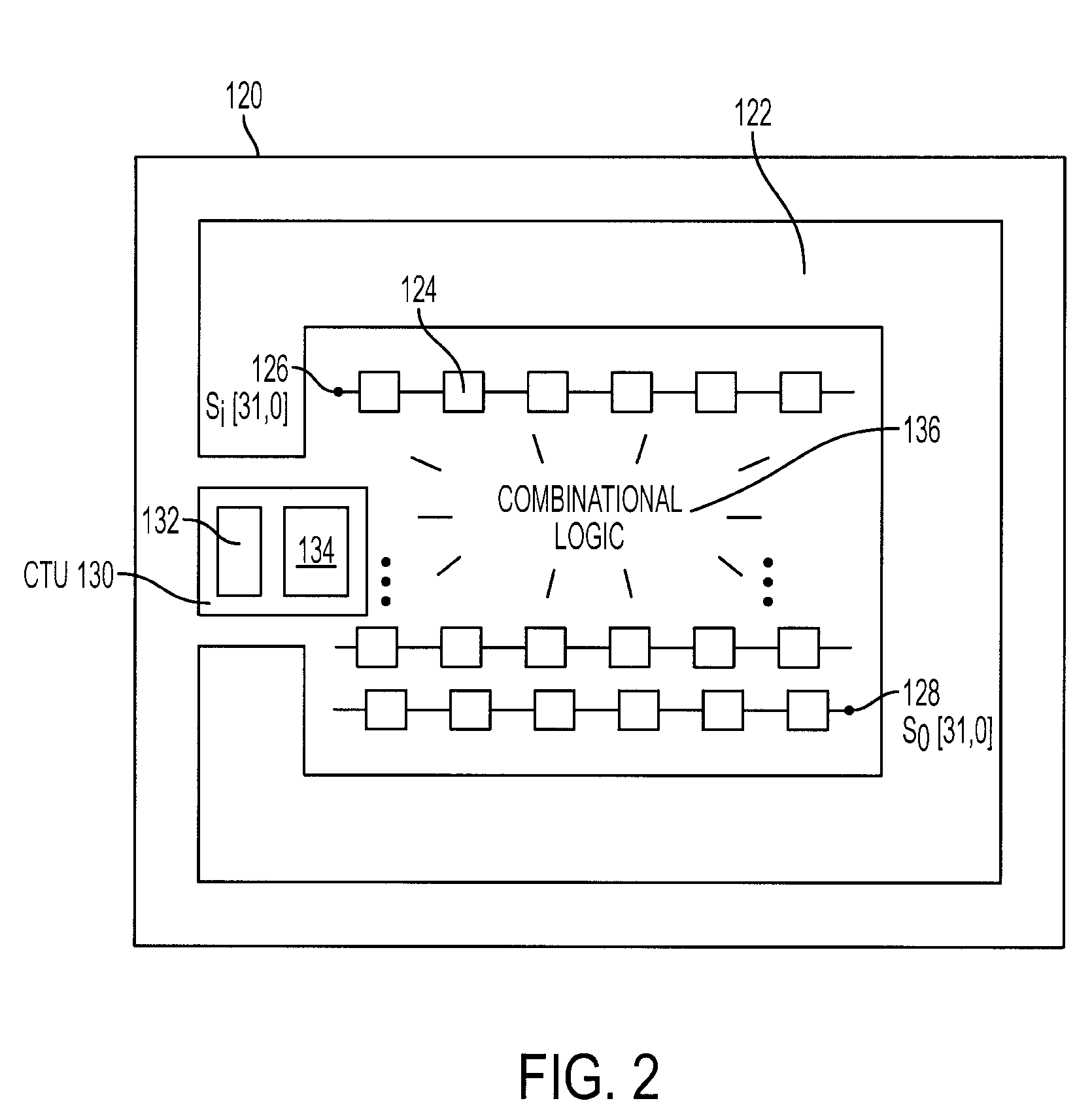

Decoder for pin-based scan test

ActiveUS7313745B1Lower performance requirementsElectronic circuit testingEngineeringSequential logic

An integrated circuit design block includes combinational and sequential logic defining core logic of the integrated circuit design block, and boundary logic defined at an outer region of the integrated circuit design block. The integrated circuit design block also includes a control test unit that has a scan chain decoder and a boundary scan decoder. The scan chain decoder includes scan chain select circuitry for enabling the scan chain decoder during scan testing of the core logic. The scan chain select circuitry further includes a pin for disabling the scan chain decoder during testing of the boundary logic. The scan chain decoder is limited to share pins defined by the boundary scan decoder, and is both 4-pin and 5-pin IEEE 1149.1 compliant.

Owner:ORACLE INT CORP

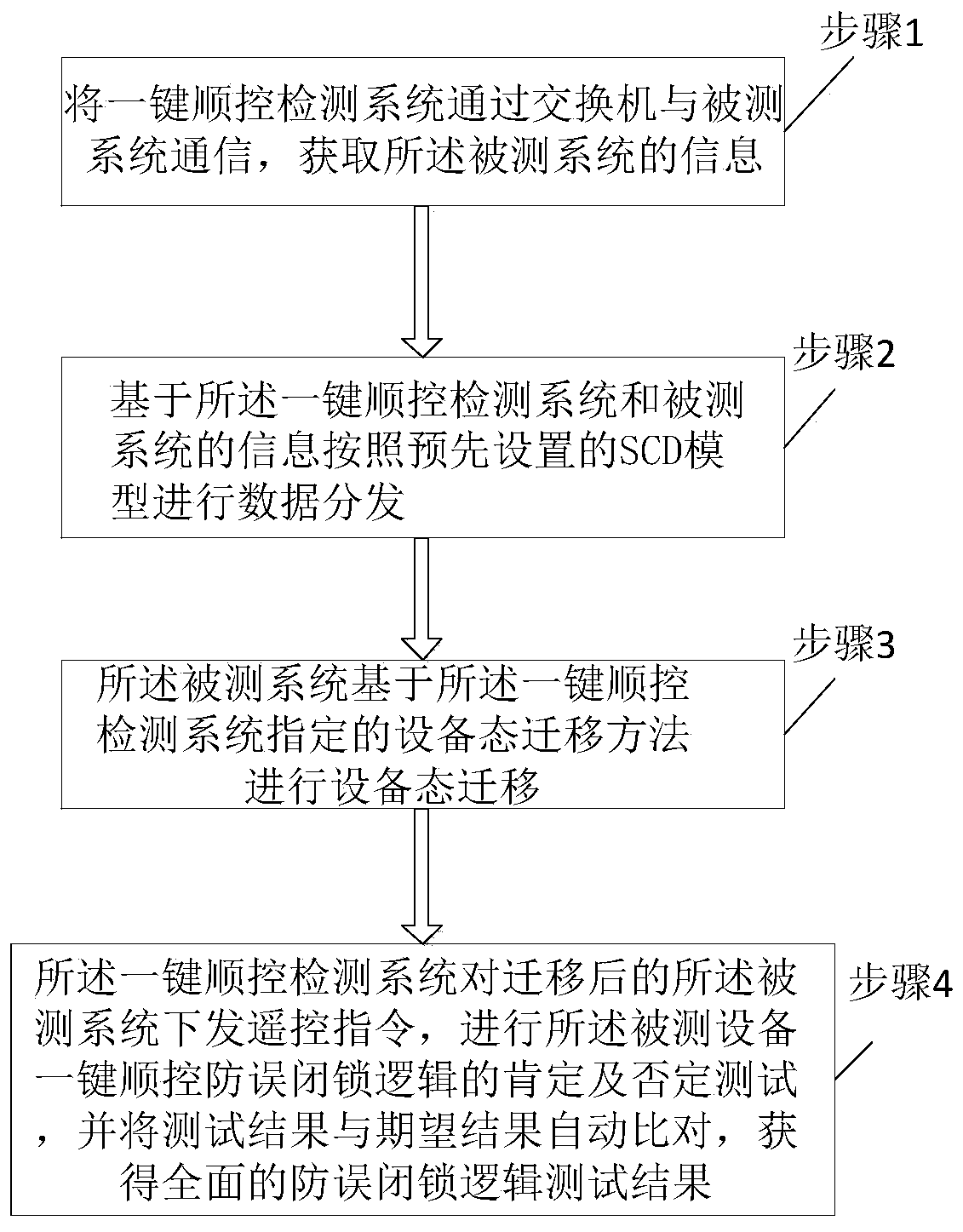

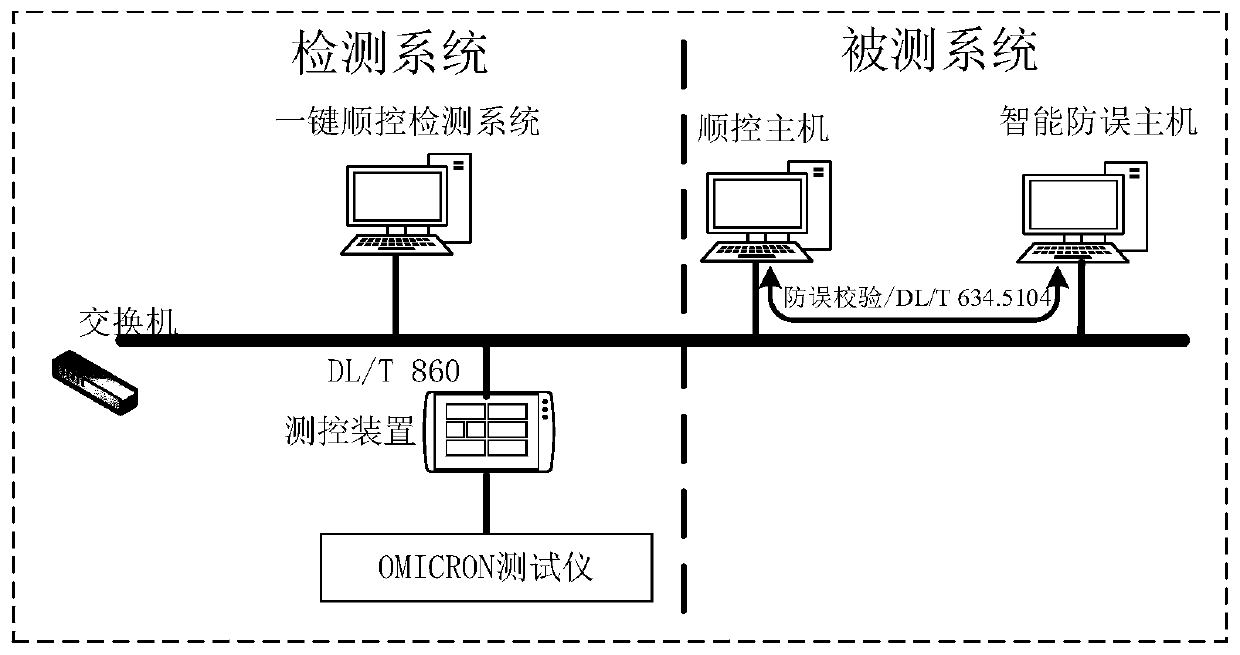

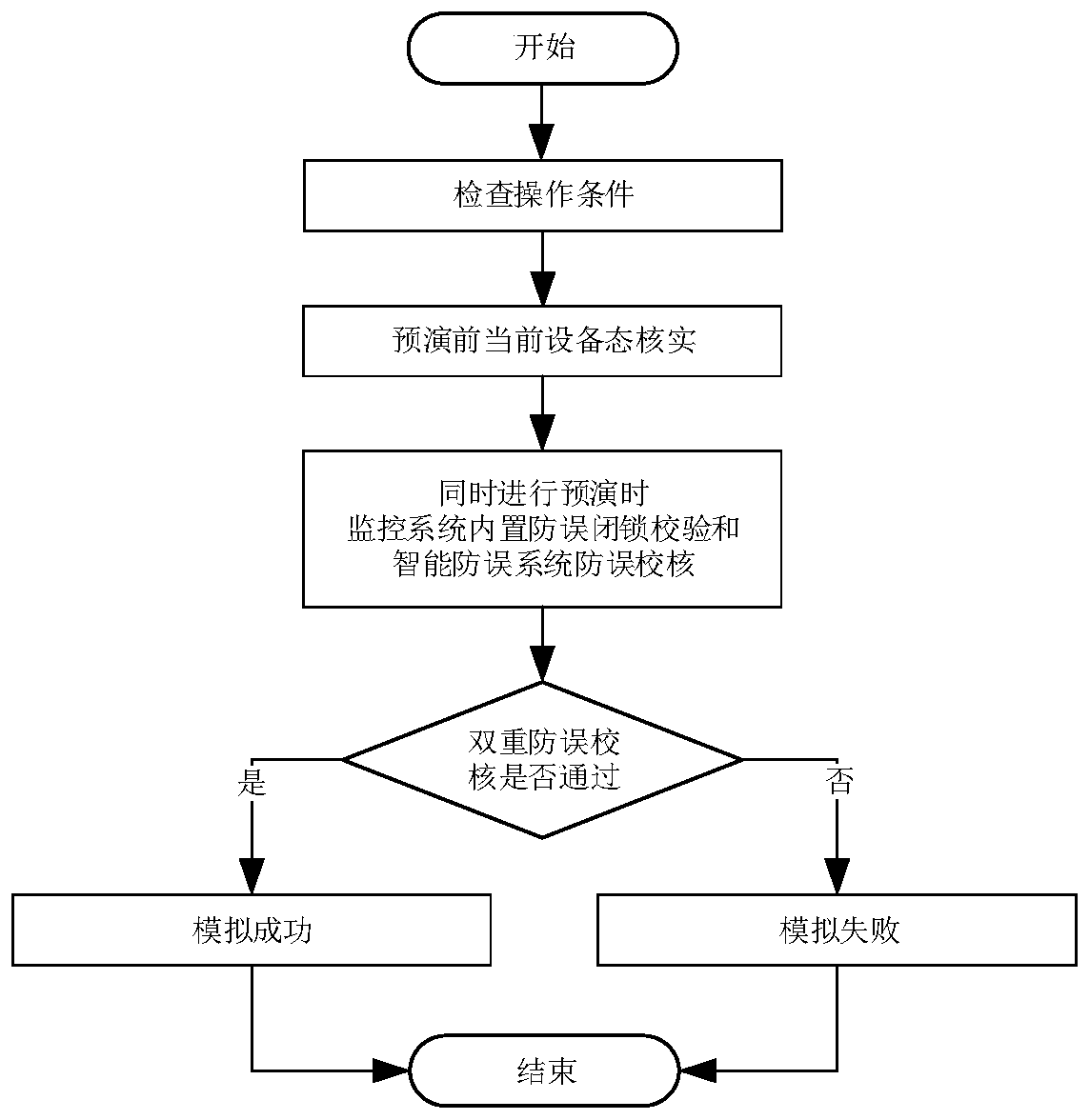

Detection method and system for one-key sequential control system of intelligent substation

PendingCN110989547ARealize logic decouplingUnified test dataProgramme controlElectric testing/monitoringWiring diagramSystem under test

The invention discloses a detection method and system for a one-key sequential control system of an intelligent substation, and the method comprises the steps: a one-key sequential control detection system communicating with a detected system through a switcher, and obtaining the information of the detected system; performing data distribution according to a preset SCD model based on the information of the one-key sequential control detection system and the detected system; the detected system performing equipment state migration based on an equipment state migration method specified by the one-key sequential control detection system; the one-key sequential control detection system issuing a remote control instruction to the migrated detected system, performing positive and negative testson the one-key sequential control anti-misoperation locking logic of the tested equipment, and automatically comparing a test result with an expected result to obtain a comprehensive anti-misoperationlocking logic test result; wherein the SCD model is designed on the basis of a main wiring diagram containing various wiring modes of a one-key sequential control detection system. According to the technical scheme provided by the invention, logic decoupling of the equipment state and the current test equipment is realized through equipment state migration, the test configuration is simplified, and the correctness and the coverage rate of an anti-error logic test are improved.

Owner:CHINA ELECTRIC POWER RES INST

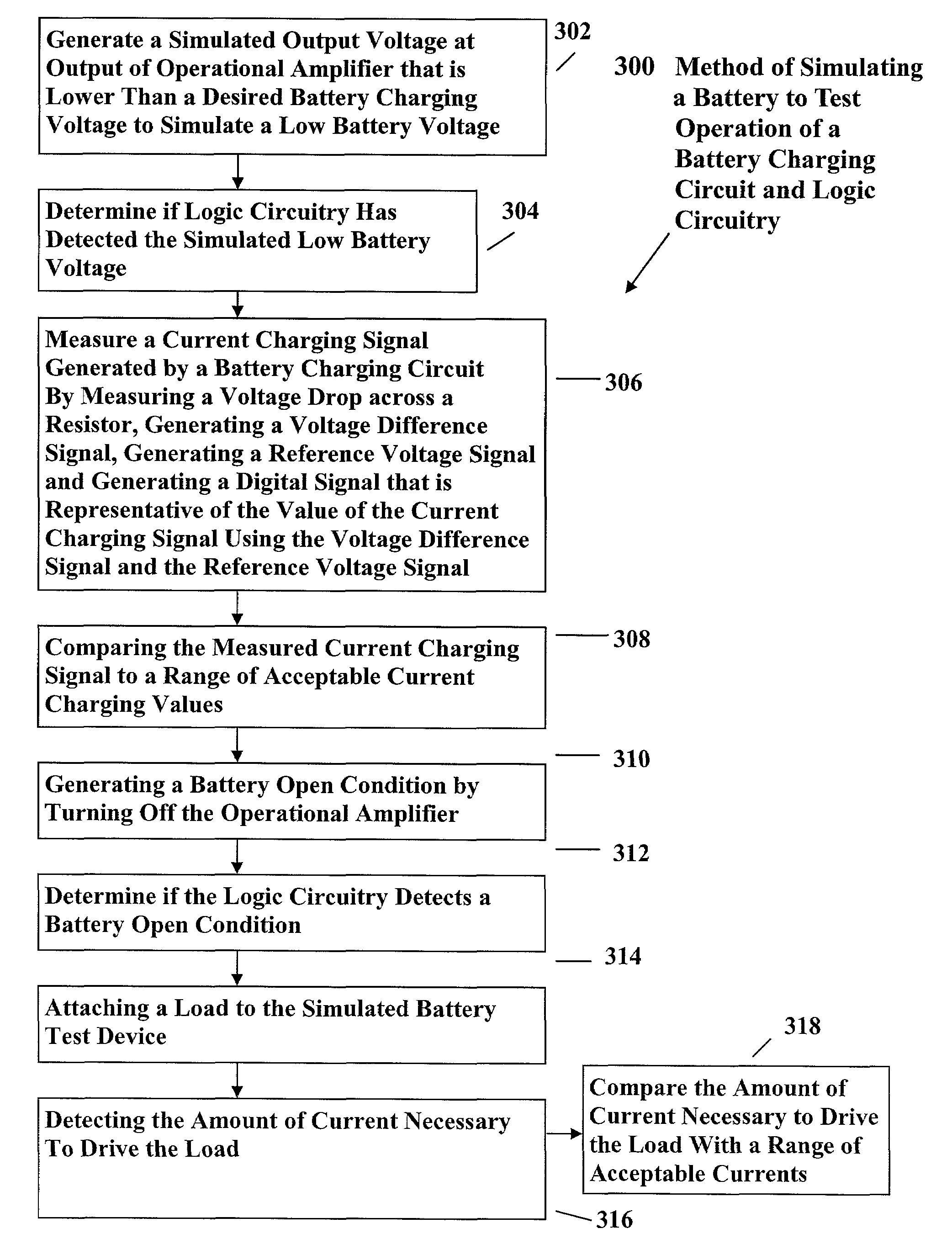

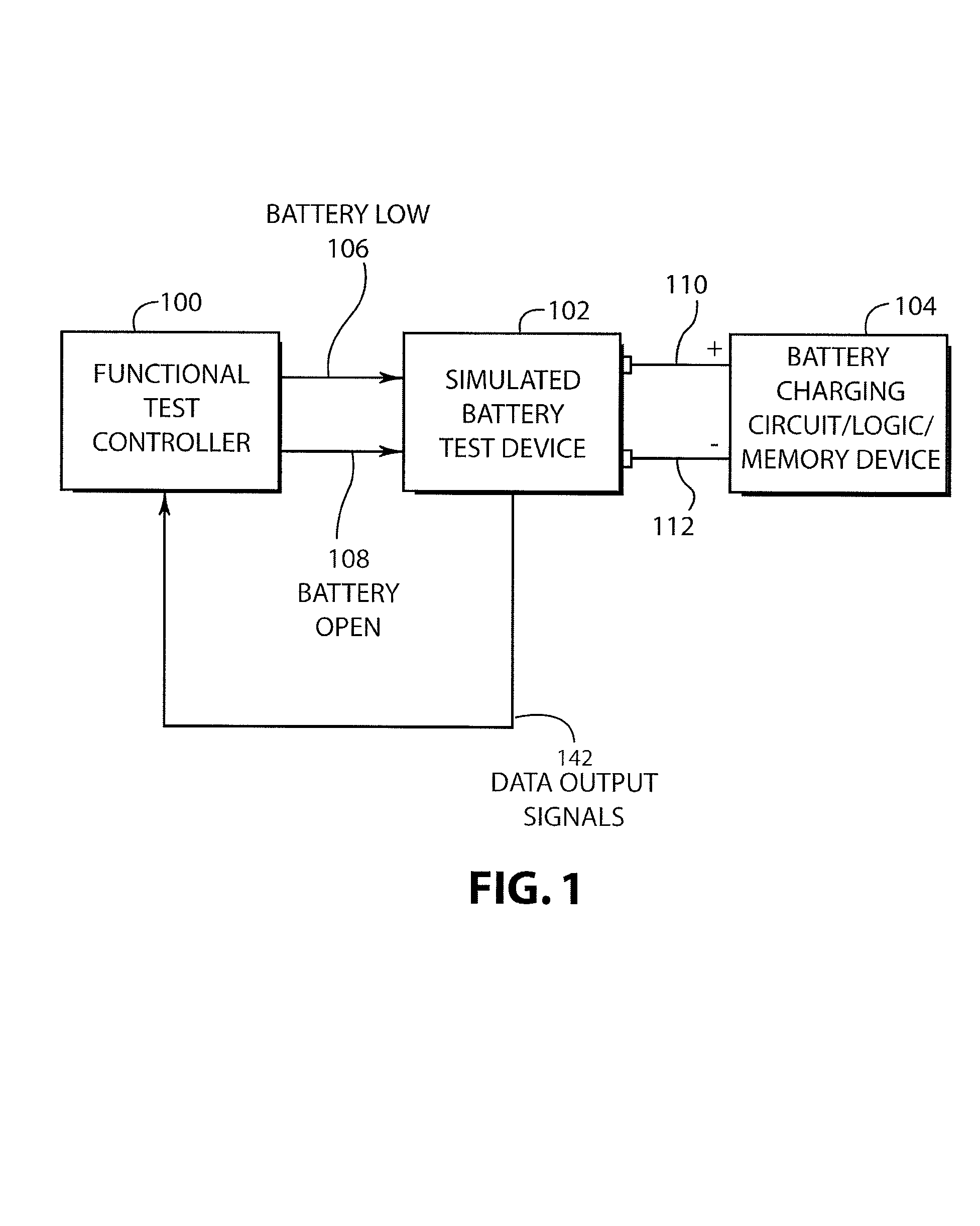

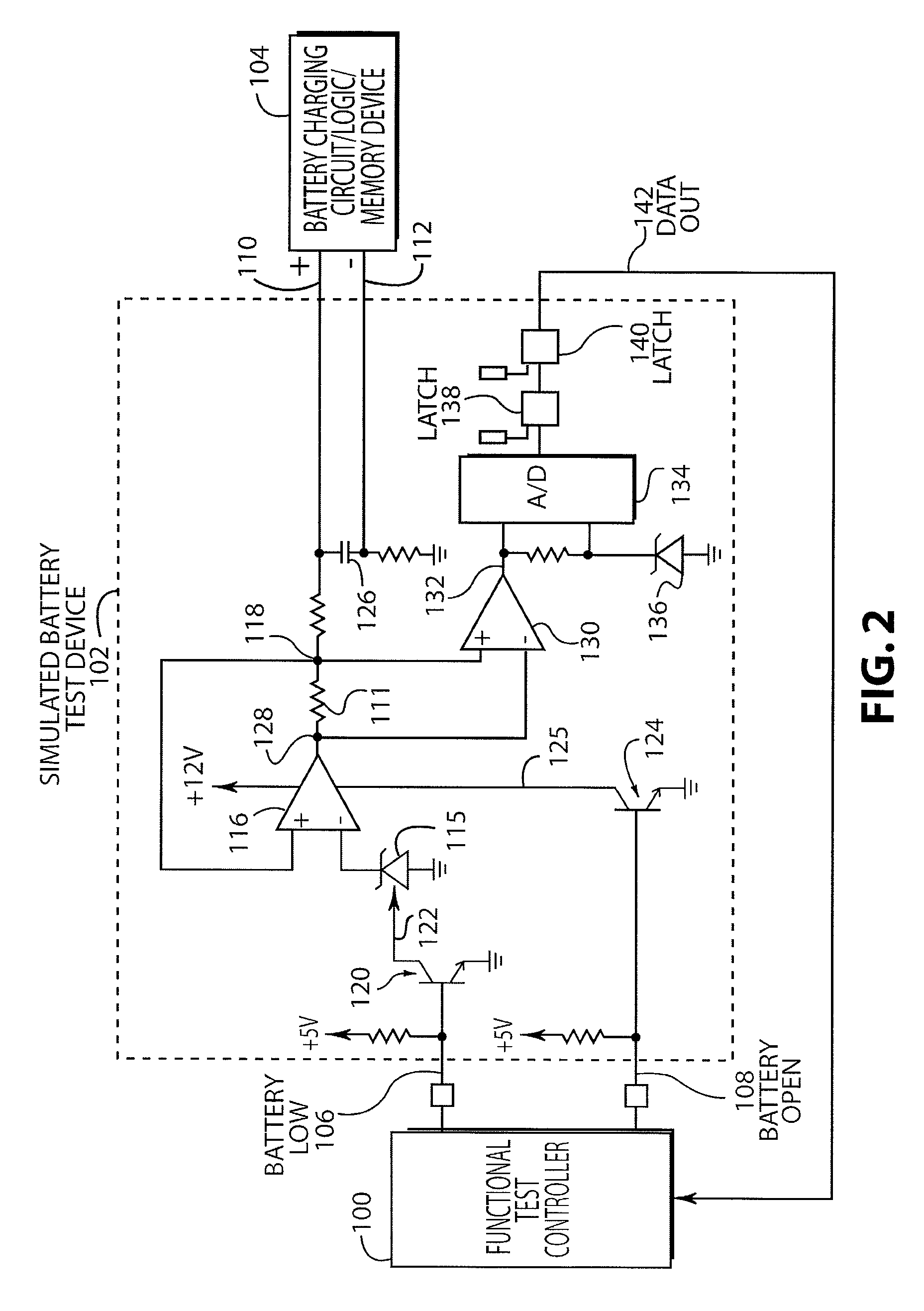

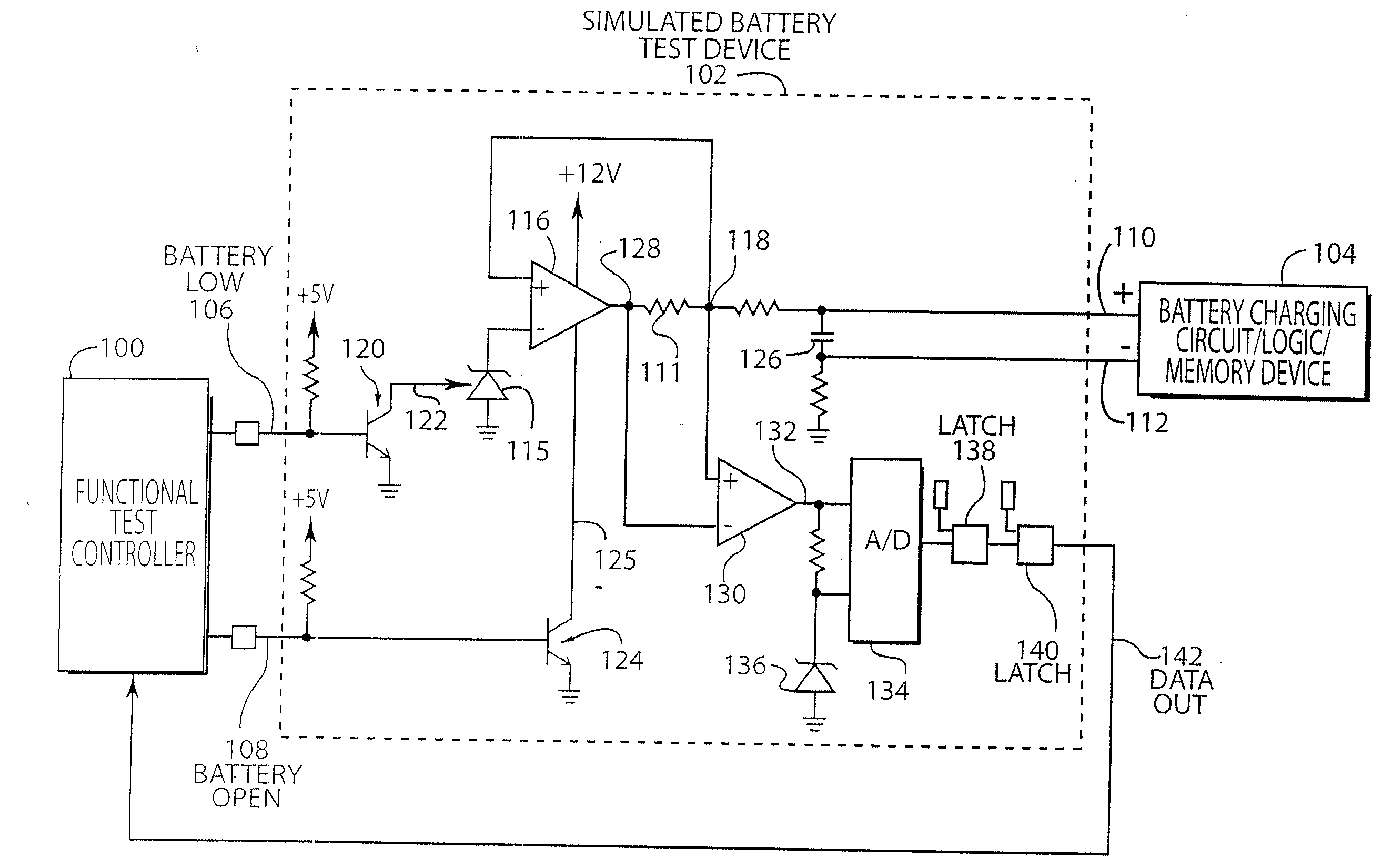

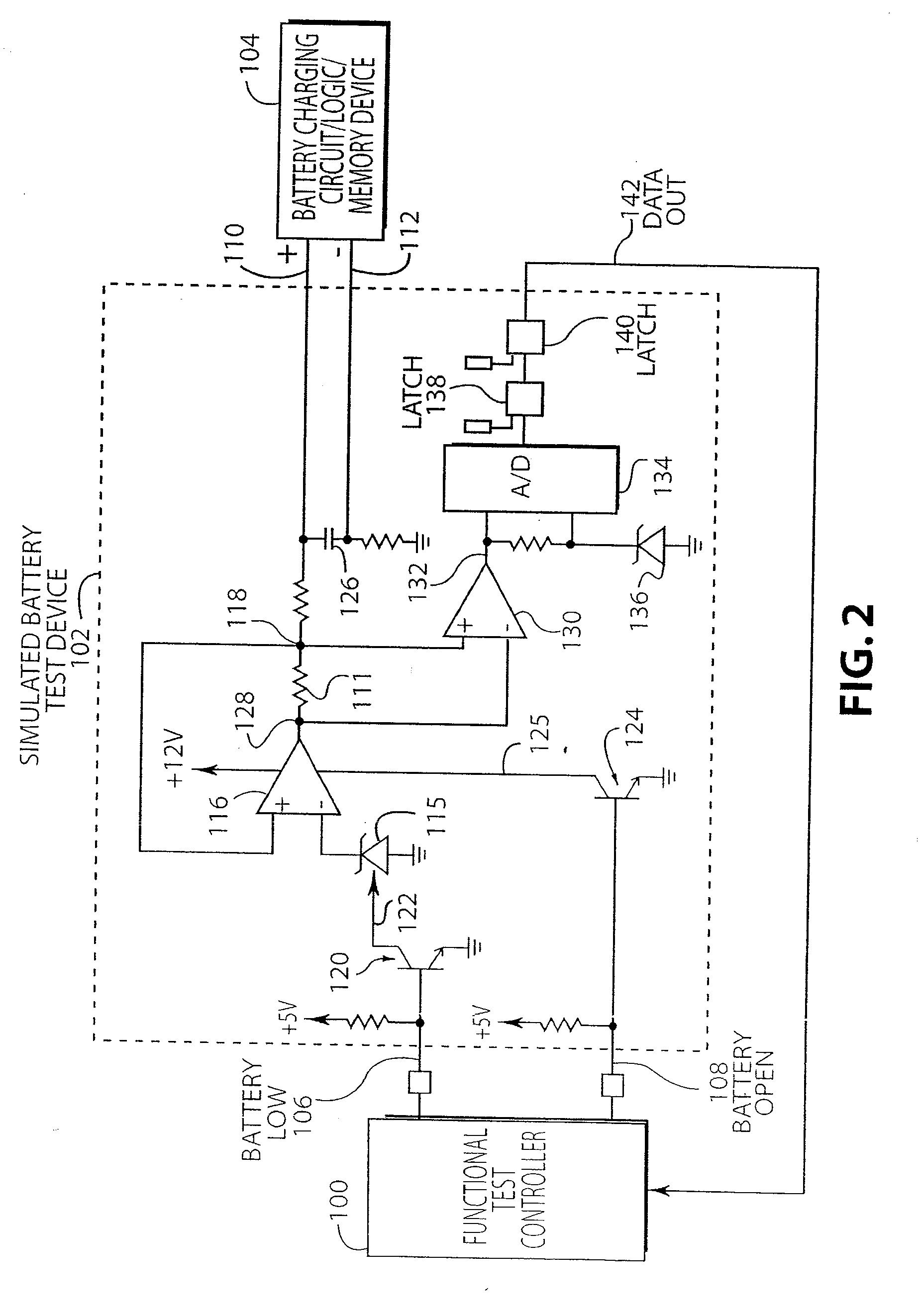

Simulated battery logic testing device

A simulated battery test device and method that is capable of testing a battery charging circuit and logic circuit to determine proper operation. An operational amplifier is used that can both source and sink current to simulate the operation of the battery. A battery low signal can be generated using the simulated battery test device to test a battery charging circuit and logic circuit in a battery low condition. In addition, a battery open signal can be generated to test the battery charging and logic circuit in a battery open condition. Charging currents are detected to determine if currents fall within an acceptable range.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

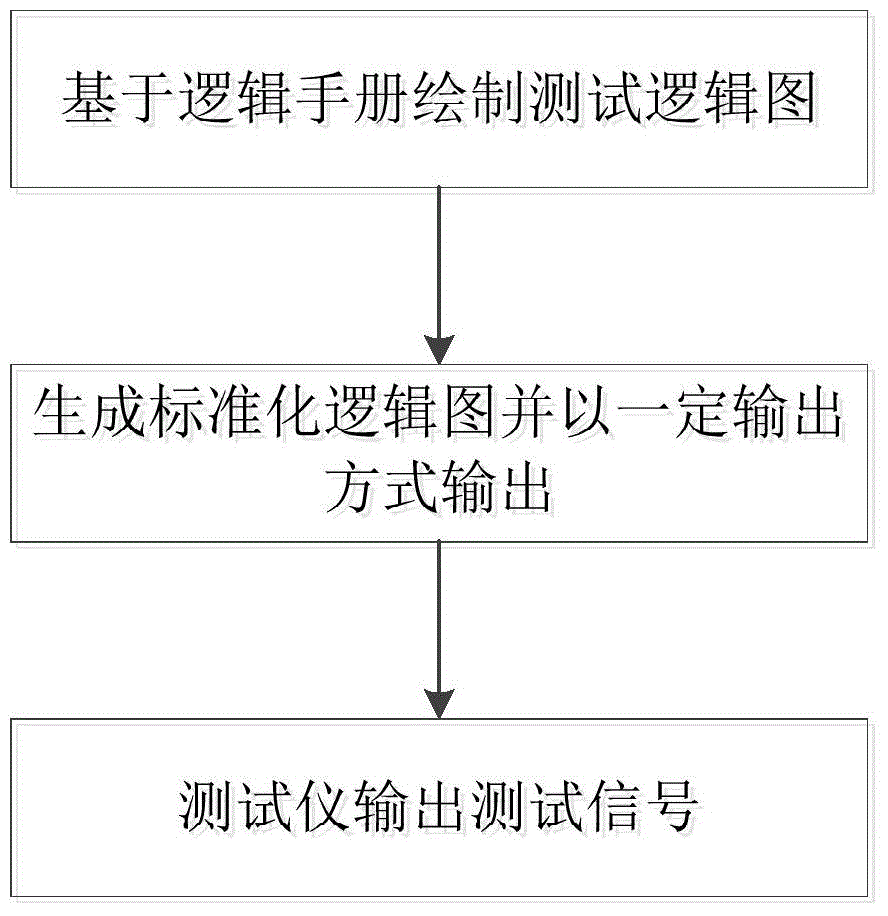

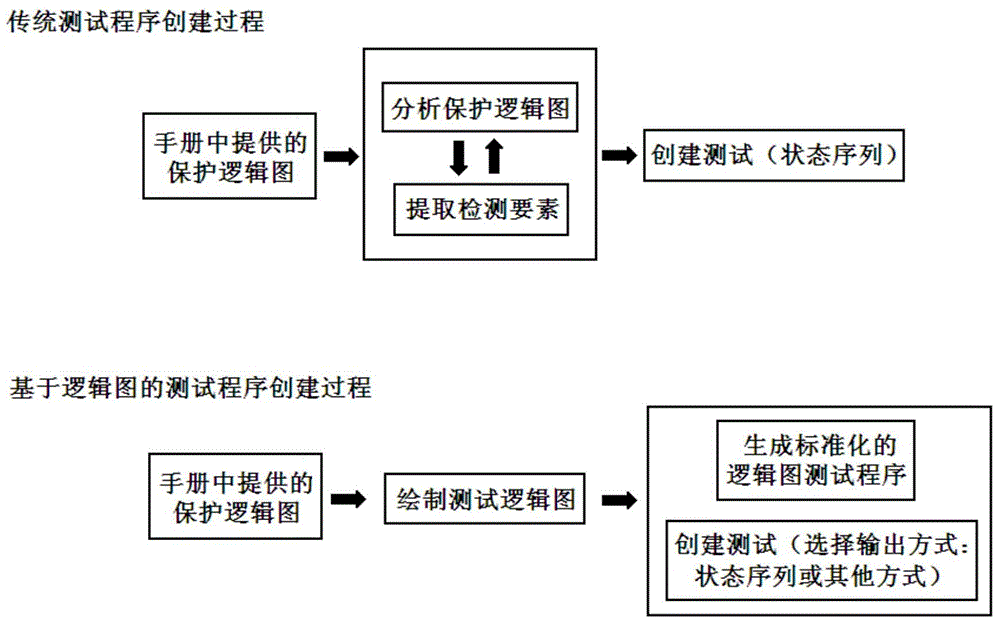

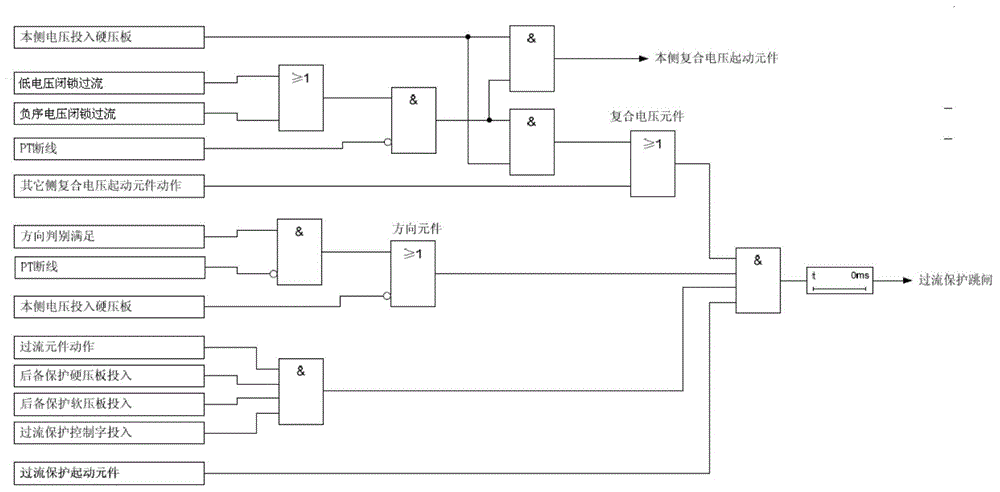

Relay protection testing system and method

InactiveCN105823940AAccurate assessmentReduce human analysis errorsElectrical testingSoftware engineeringTest status

The present invention provides a relay protection test system and method, the relay protection test system includes a test module and a tester, the test module sends test parameters and control instructions to the tester; the tester outputs test signal and receive the action feedback signal of the device under test, compare the test signal output by the tester, the expected action result with the action feedback signal, and realize the relay protection test; the test module is used to The meta library constructs a test logic diagram, and generates a standardized logic test state sequence according to the logic diagram. The system provided by the invention enables users to establish a test logic model simply, intuitively and accurately so as to conduct professional tests of complex functions and logical relationships, which is the development direction of the specialization and standardization of relay protection testing.

Owner:STATE GRID CORP OF CHINA +1

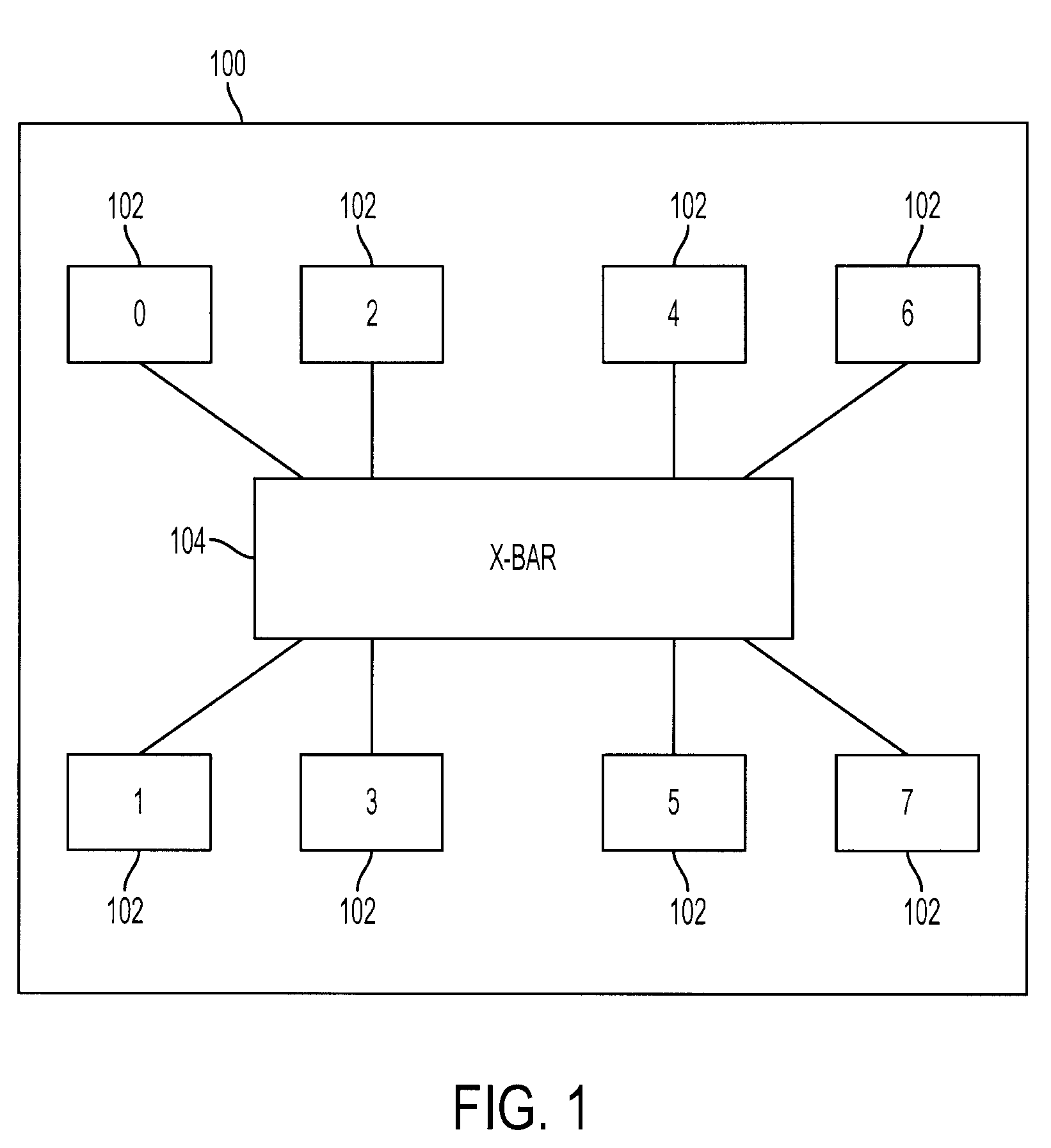

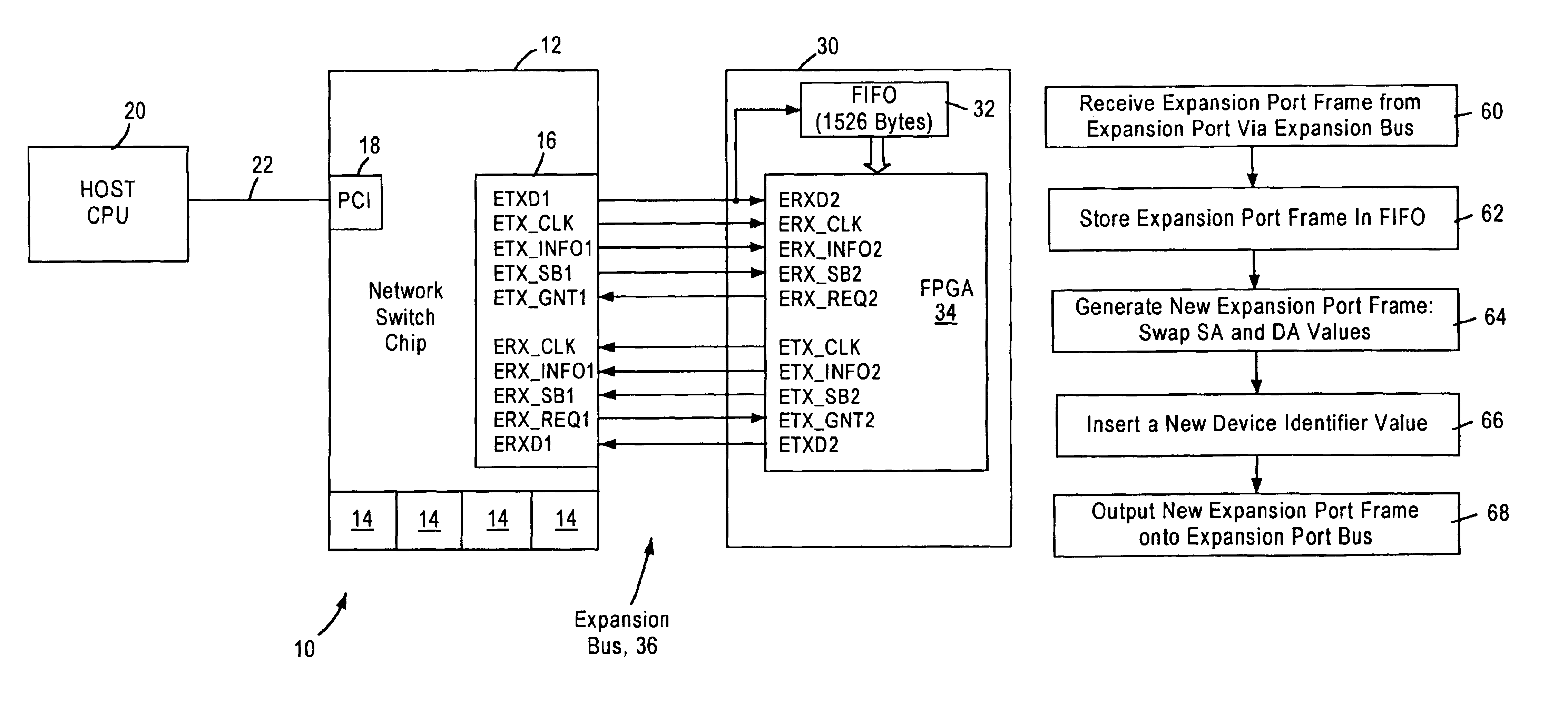

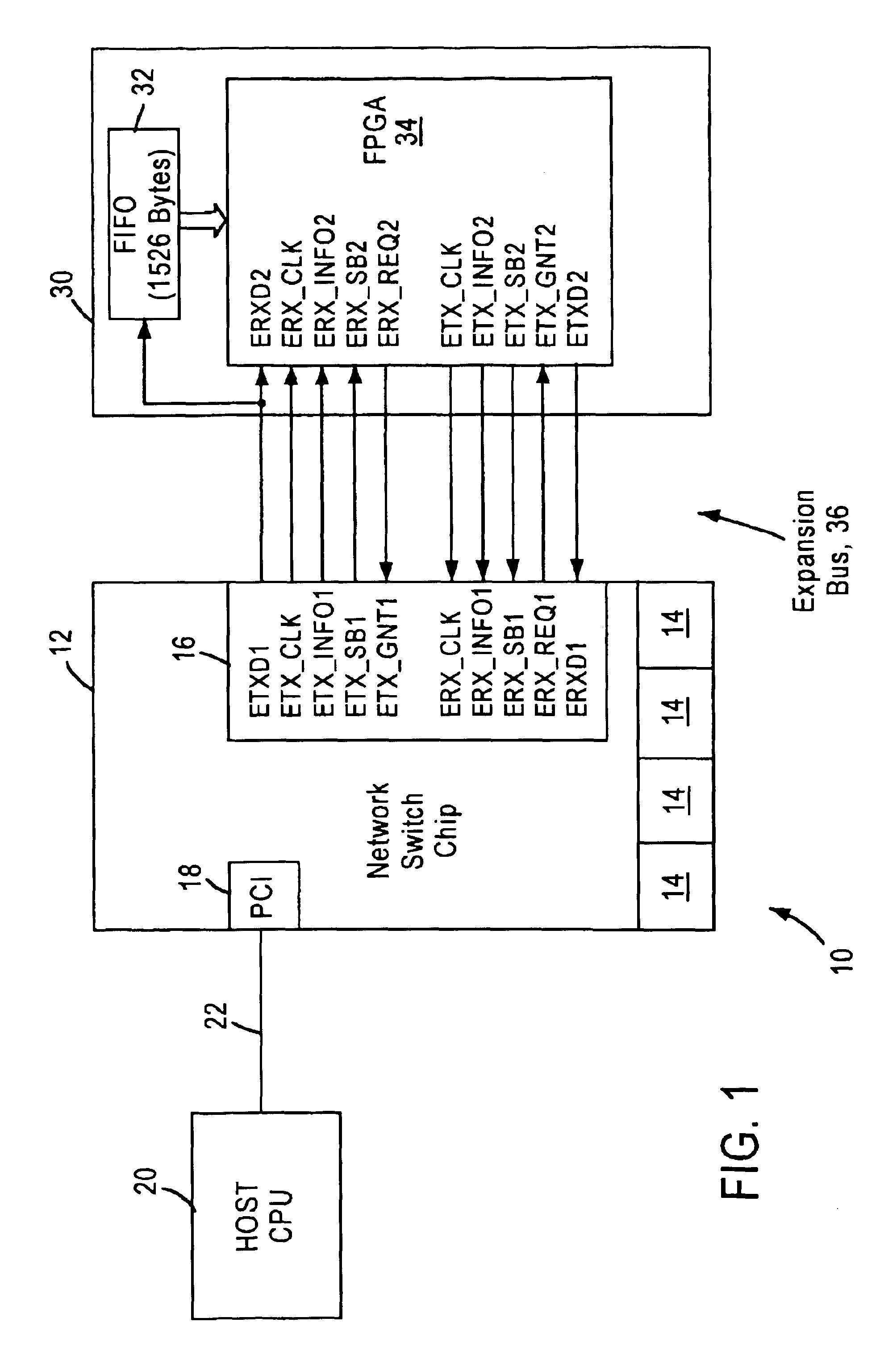

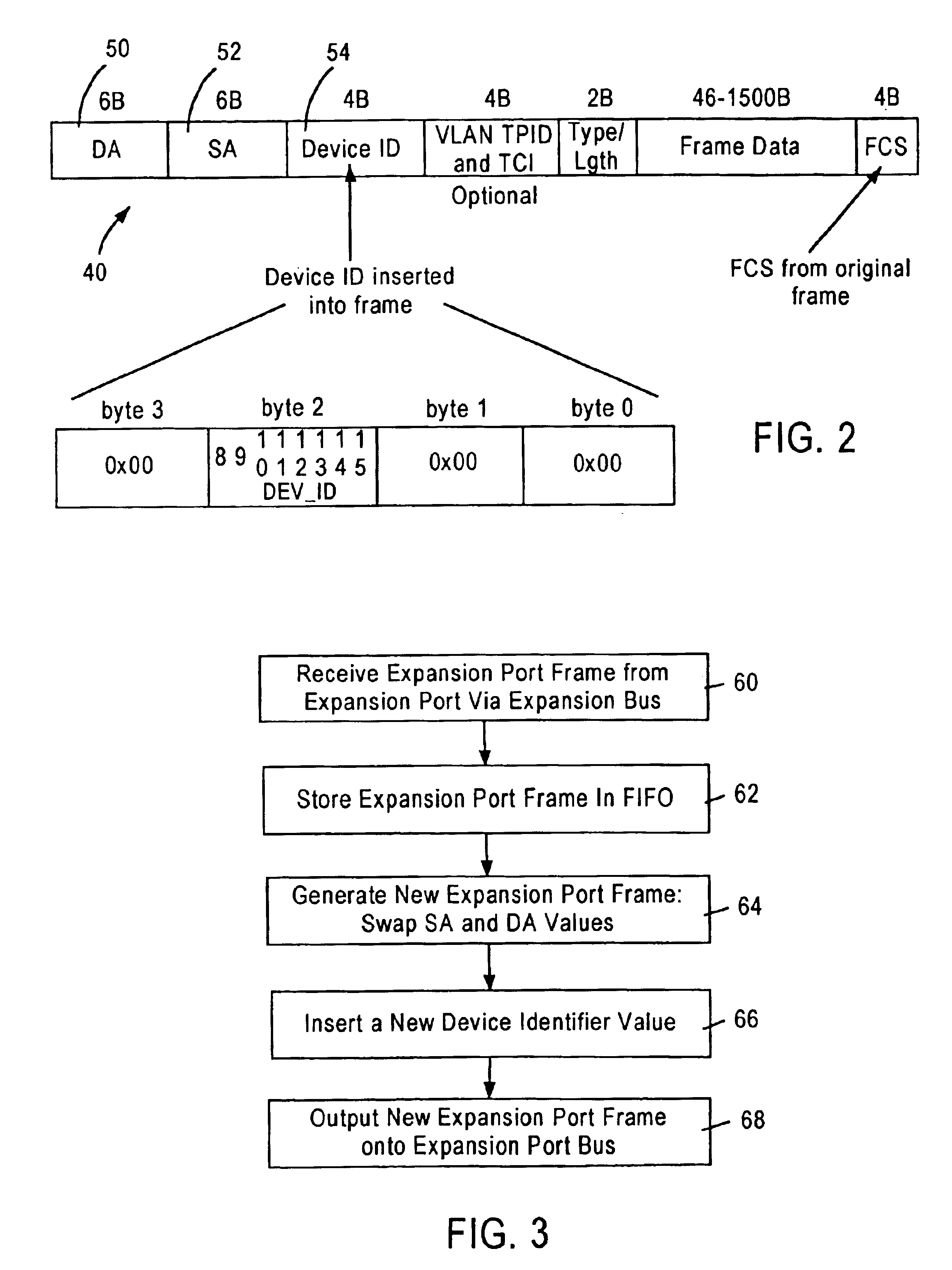

Arrangement for testing network switch expansion port using external logic to emulate connected expansion port

InactiveUS6912202B1Error prevention/detection by using return channelCorrect operation testingTest engineerLogic cell

A network switch chip having an expansion port configured for transferring data according to a prescribed bus protocol is tested using an external logic unit (e.g., a field programmable gate array) configured to emulate a connected expansion port. The external logic unit is configured for receiving an expansion port frame from the expansion port via an expansion bus, generating a new expansion port frame, and outputting the new expansion port frame to the expansion port via the expansion bus. Hence, a test engineer can validate the expansion port of the network switch chip by detecting the reception of the new expansion port frame by the expansion port. Hence, the expansion port of the network switch chip can be tested without the necessity of a second network switch chip.

Owner:ADVANCED MICRO DEVICES INC

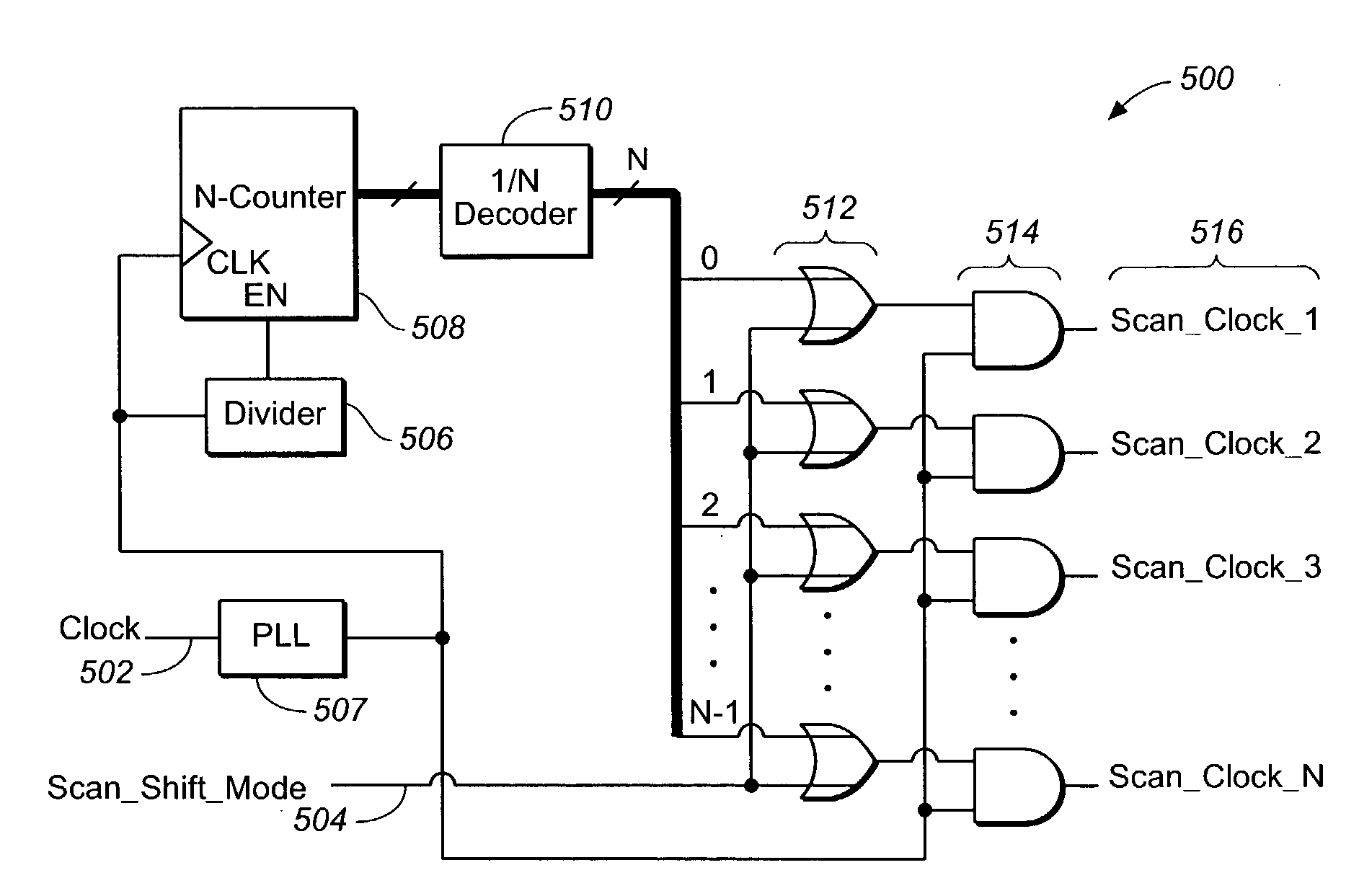

On-chip scan clock generator for ASIC testing

A scan clock generator includes a clock signal input for receiving a clock signal, a scan shift mode signal input for receiving a scan shift mode signal, and a sequence controller coupled to the clock signal input for gating a selected number of clock signal pulses at a time to generate a sequence of nonconcurrent scan clock signals at separate outputs respectively in response to a first state of the scan shift mode signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

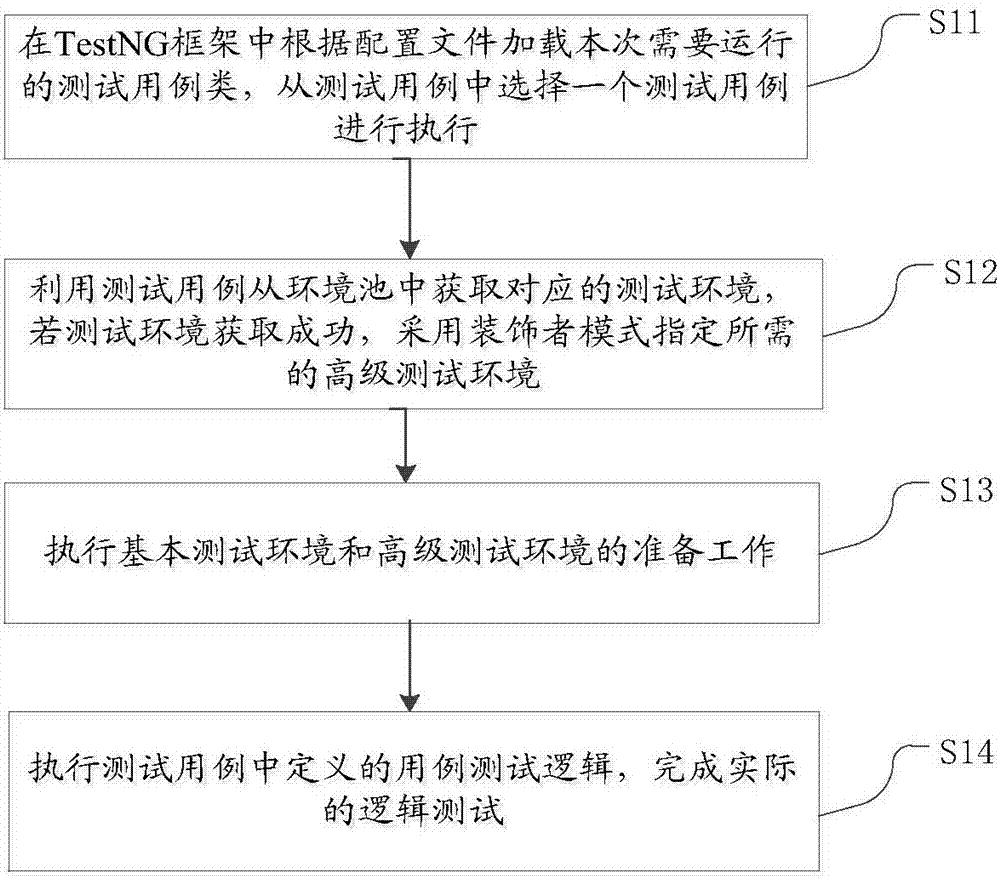

Automated testing running method

InactiveCN107315686AAchieve decouplingSolving unsolvable use case decoupling problemsSoftware testing/debuggingLogic testingAutomatic testing

The invention discloses an automated testing running method. The method comprises the steps of loading a test case class needed to run currently according to a configuration file in a TestNG framework, and selecting a test case to be executed from test cases; obtaining a corresponding test environment from an environment pool by utilizing the test case, and if the test environment is obtained successfully, specifying a required advanced test environment by adopting a decorator mode; executing preparation work of a basic test environment and the advanced test environment; and executing case test logic defined in the test case to finish actual logic testing. According to the method, the test environment is effectively utilized and the test time is shortened.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

Simulated battery logic testing device

A simulated battery test device and method that is capable of testing a battery charging circuit and logic circuit to determine proper operation. An operational amplifier is used that can both source and sink current to simulate the operation of the battery. A battery low signal can be generated using the simulated battery test device to test a battery charging circuit and logic circuit in a battery low condition. In addition, a battery open signal can be generated to test the battery charging and logic circuit in a battery open condition. Charging currents are detected to determine if currents fall within an acceptable range.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

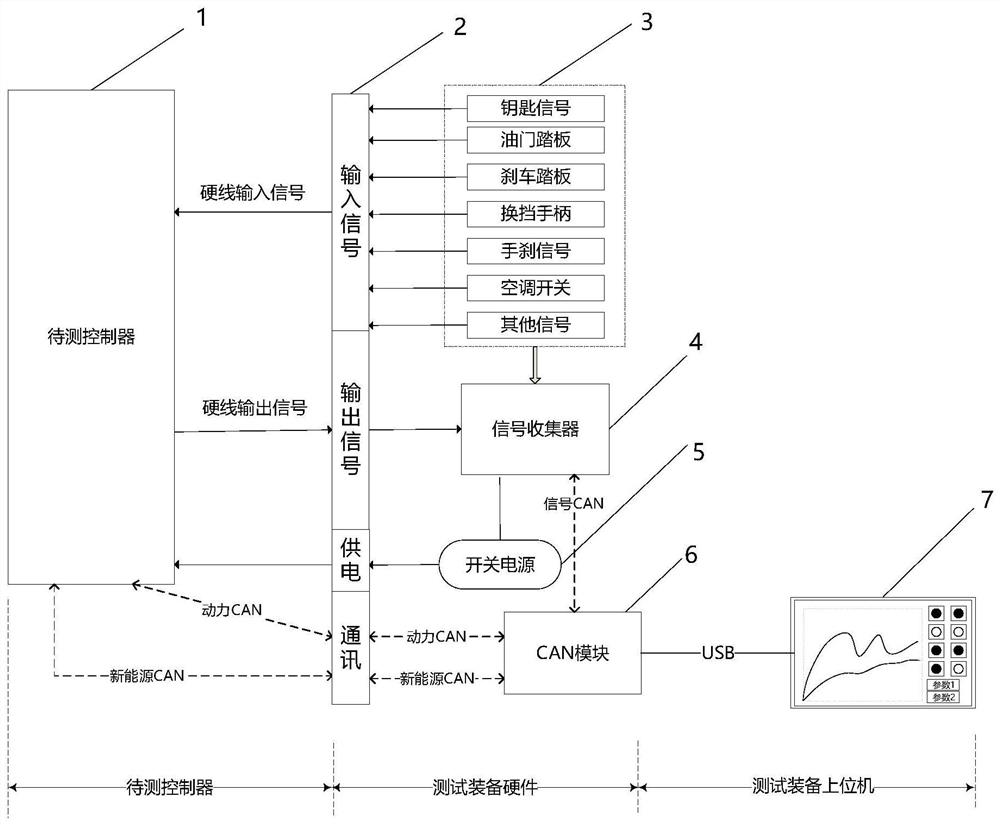

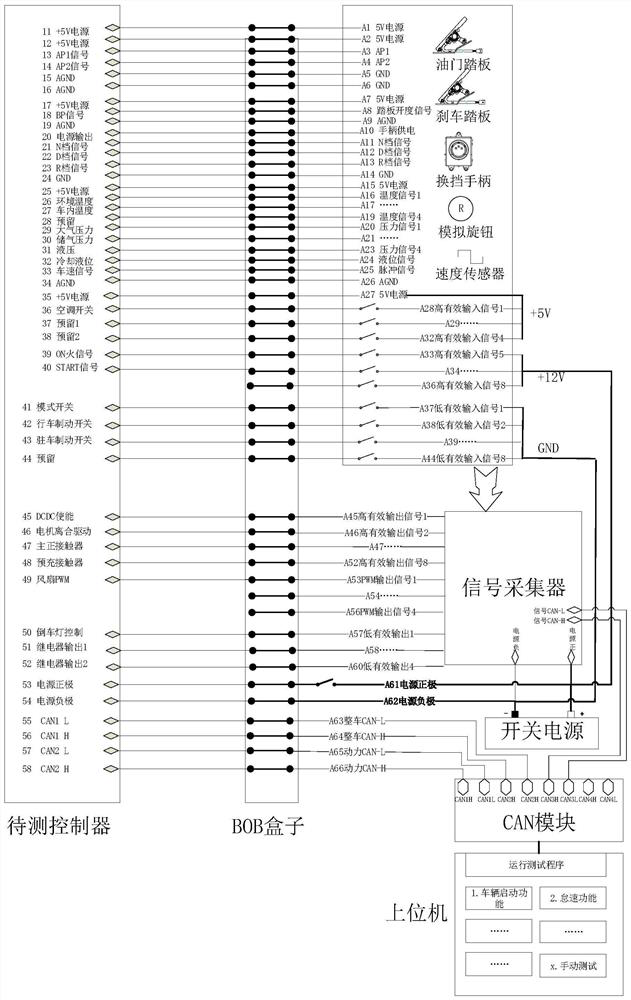

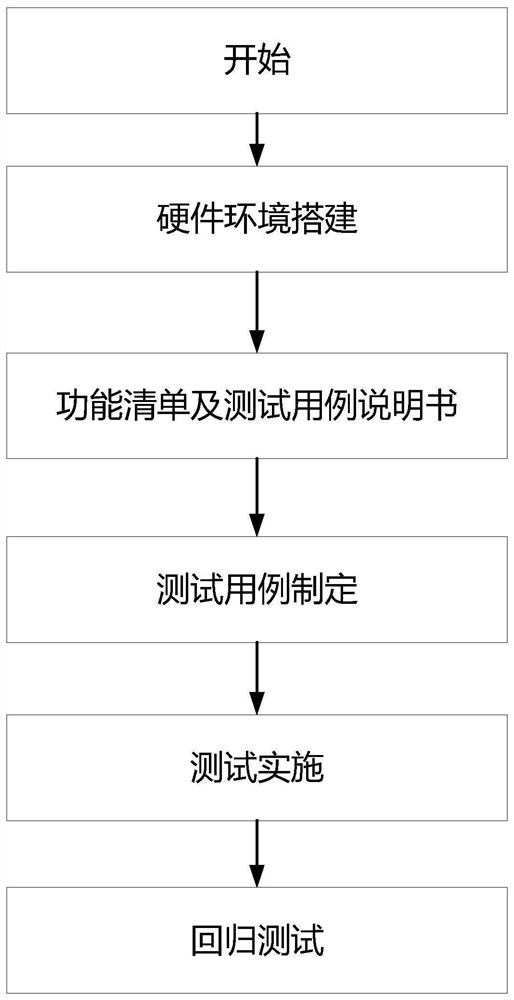

Offline vehicle logic test system and test method

PendingCN112362362AApplicable development needsHighly integratedVehicle testingElectric testing/monitoringControl engineeringLogic testing

The invention relates to an offline vehicle logic test system and test method. The system comprises a controller to be tested, a quick plug box, an external accessory, a signal collector, a switchingpower supply, a CAN module and an upper computer. The offline vehicle logic test system is practical in controller function adaptability change verification or verification of only newly added function logic, is high in integration level, high in applicability and convenient to use, and is more suitable for development requirements of various conventional controllers of medium and small companies.

Owner:DONGFENG OFF ROAD VEHICLE CO LTD

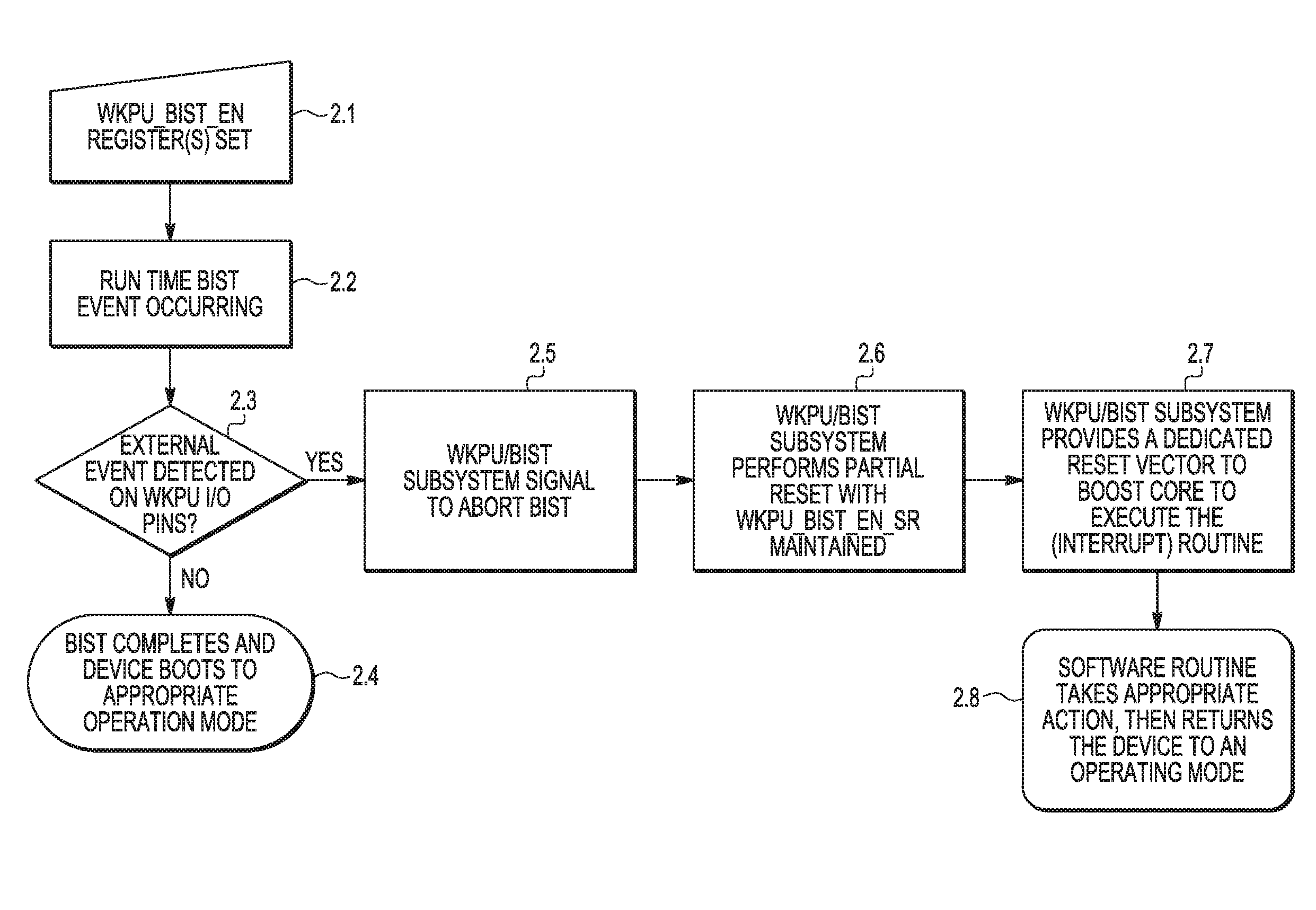

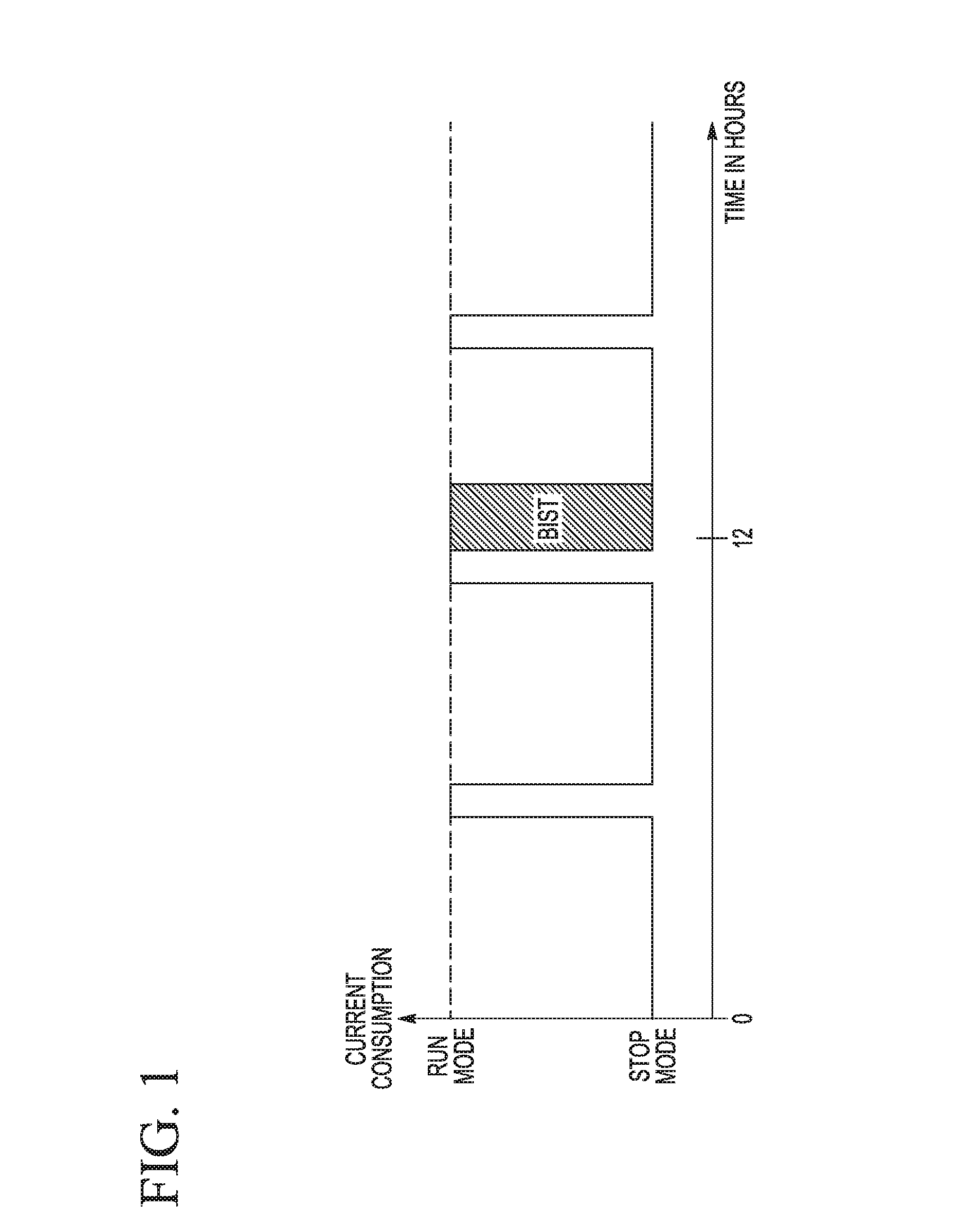

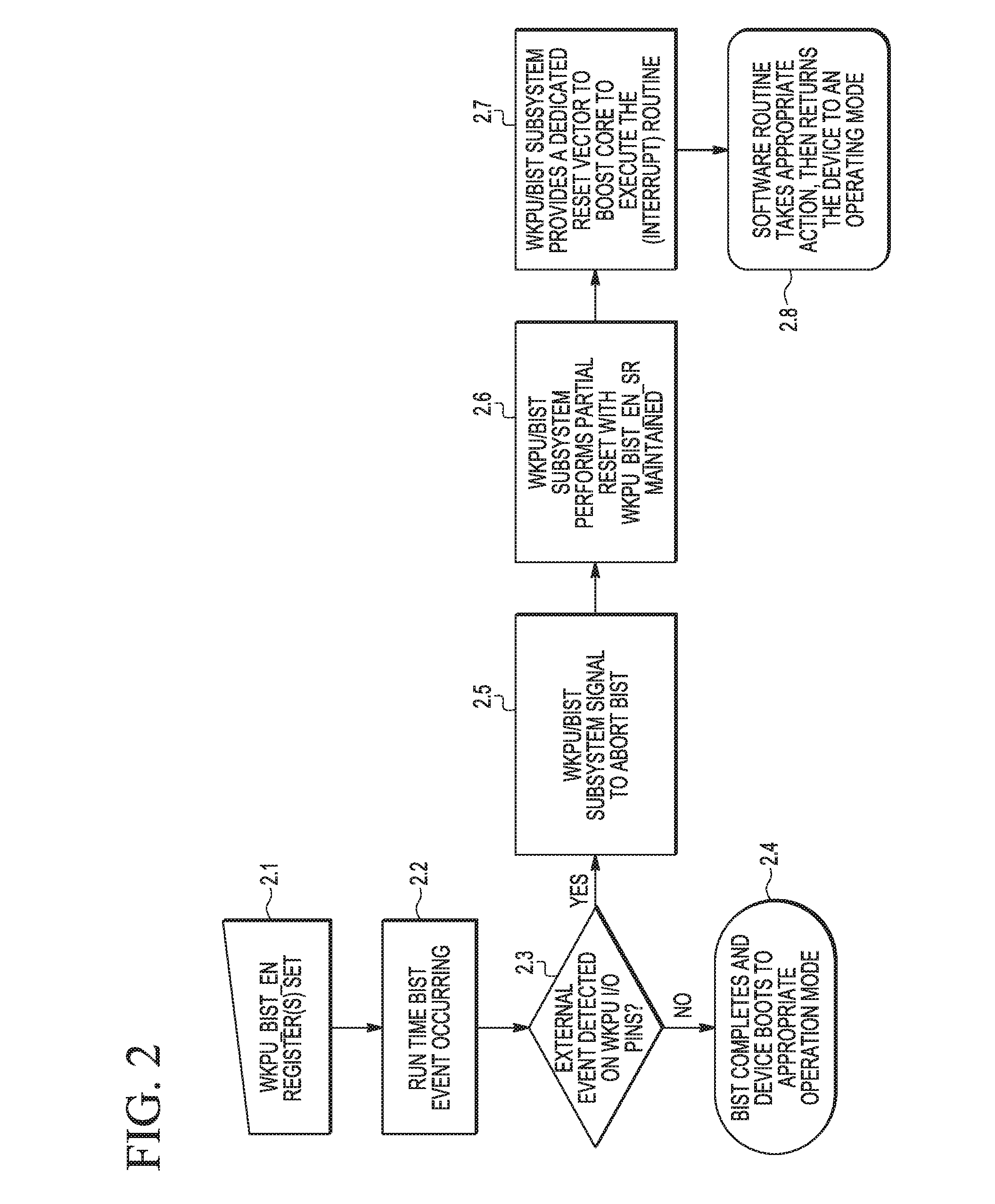

Data processing device and method of conducting a logic test in a data processing device

InactiveUS20160275008A1Detecting faulty hardware by power-on testSoftware testing/debuggingLogic testingProcessing element

A data processing device, comprising a processing unit and a test control unit connected to the processing unit, is described. The processing unit and the test control unit are arranged to: start a logic test of the processing unit; detect a test abort event; and, in response to the test abort event, perform an event response action which comprises aborting the logic test and booting the processing unit, said booting including executing an event handling routine. The event response action may comprise setting a reset vector to an address of the event handling routine. System availability may thus be improved. In particular, the delay between capturing an asynchronous signal and responding to it may be reduced. The test abort event may, for example, be an asynchronous event having certain pre-defined characteristics.A method of operating a data processing device is also described.

Owner:NXP USA INC