Circuit and method for generating test vectors required by built-in self-test of integrated circuit

A built-in self-test and test vector technology, applied in the field of test vector generation technology, deterministic test vector compression and decompression, can solve the problems of data sequence occupying test time, deterministic test vector occupying storage unit, etc., to save hardware Overhead, test time reduction, effect of memory cell reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

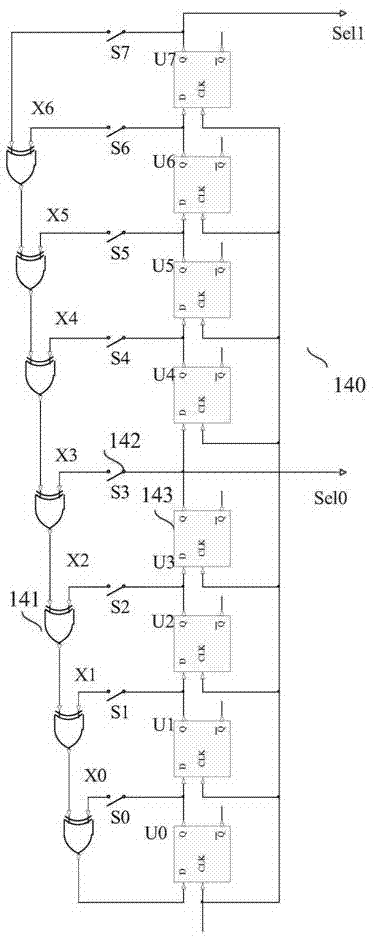

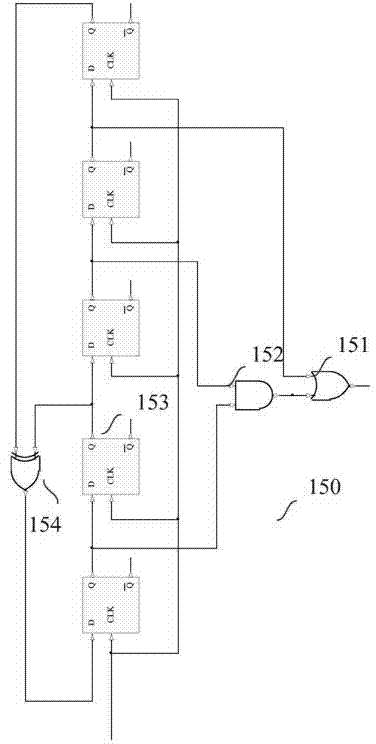

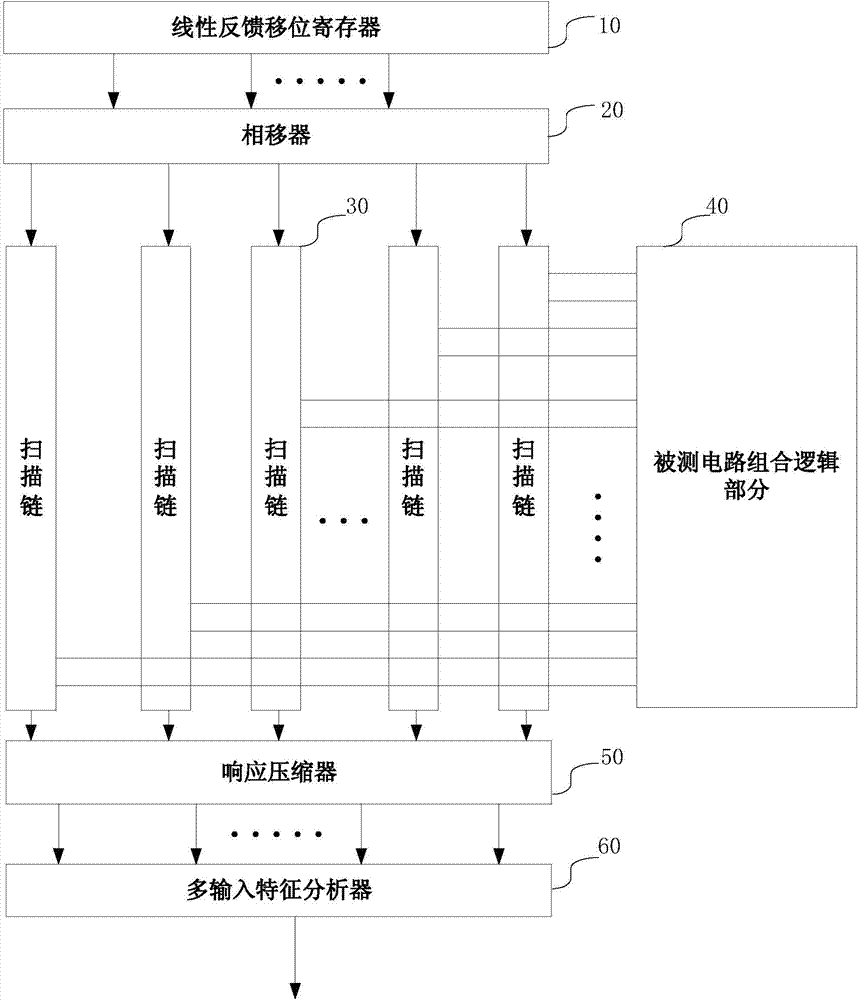

[0047] Such as figure 2 It shows a structural block diagram of the first integrated circuit built-in self-test required test vector generation circuit 100 of the present invention, refer to figure 2 The embodiment showing the device of the present invention is a block diagram of a built-in self-test test vector generation circuit 100 using a mixed mode, the mixed mode is both random test generation and deterministic test generation, that is, 2 of the present invention a testing phase. refer to figure 2 The built-in self-test test vector generation circuit 100 includes an address counter 110, a sequence counter 120, a seed and polynomial coefficient storage unit 130, a sequence generator 140, a weight generation logic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More