Compression method for test data of irrational number storage test vector

A technology of test vector and test data, applied in the field of test data compression of irrational number storage test vector, can solve the problems of large amount of test data, reduced algorithm flexibility, long running time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

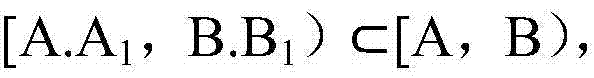

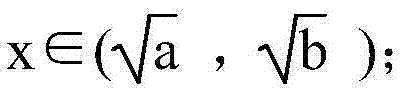

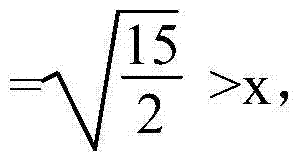

Image

Examples

Embodiment Construction

[0027] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0028] The invention combines automatic test vector generation with irrational number coding, reduces the number of test vectors corresponding to coded and easy-to-test fault points, and achieves the purpose of reducing test data. The test data compression method of the irrational number storage test vector guided by the fault coverage rate of the present invention will be described in detail below in combination with specific examples.

[0029] a. Generate a fault list containing several faults according to the circuit structure of the integrated circuit to be tested.

[0030] b. Select any fault, run the automatic test v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More