Patents

Literature

76 results about "Test data compression" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Accelerated scan circuitry and method for reducing scan test data volume and execution time

InactiveUS7197681B2Shorten the timeReduce volumeElectronic circuit testingError detection/correctionCouplingControl signal

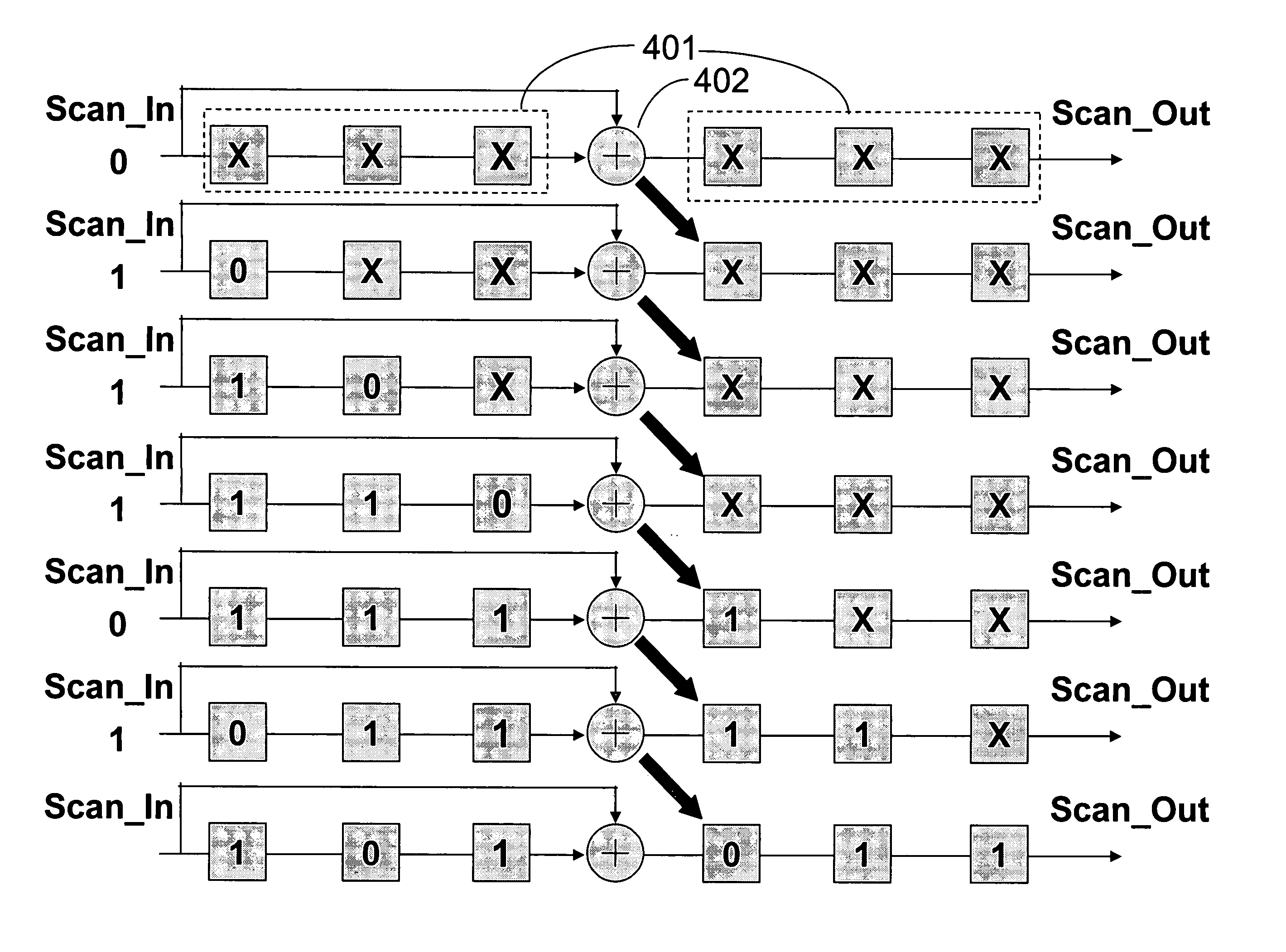

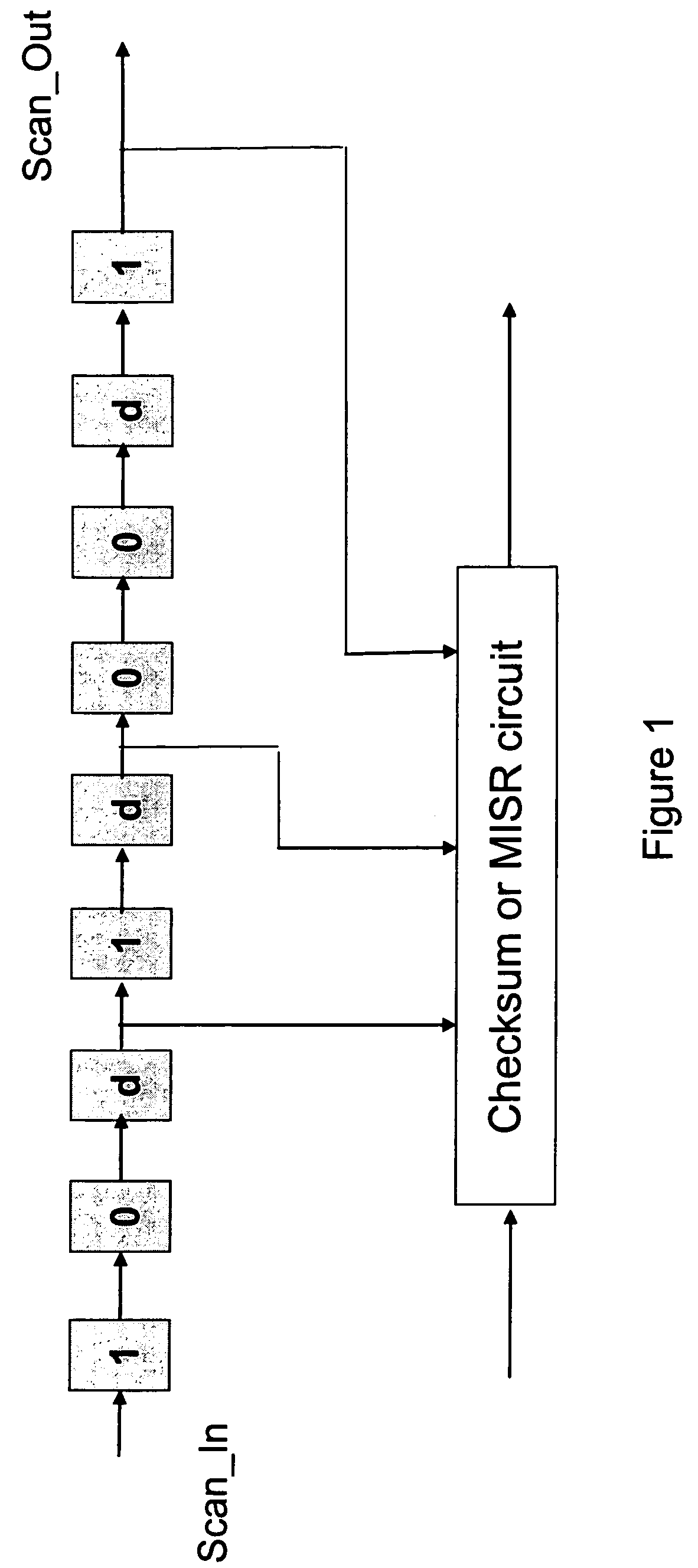

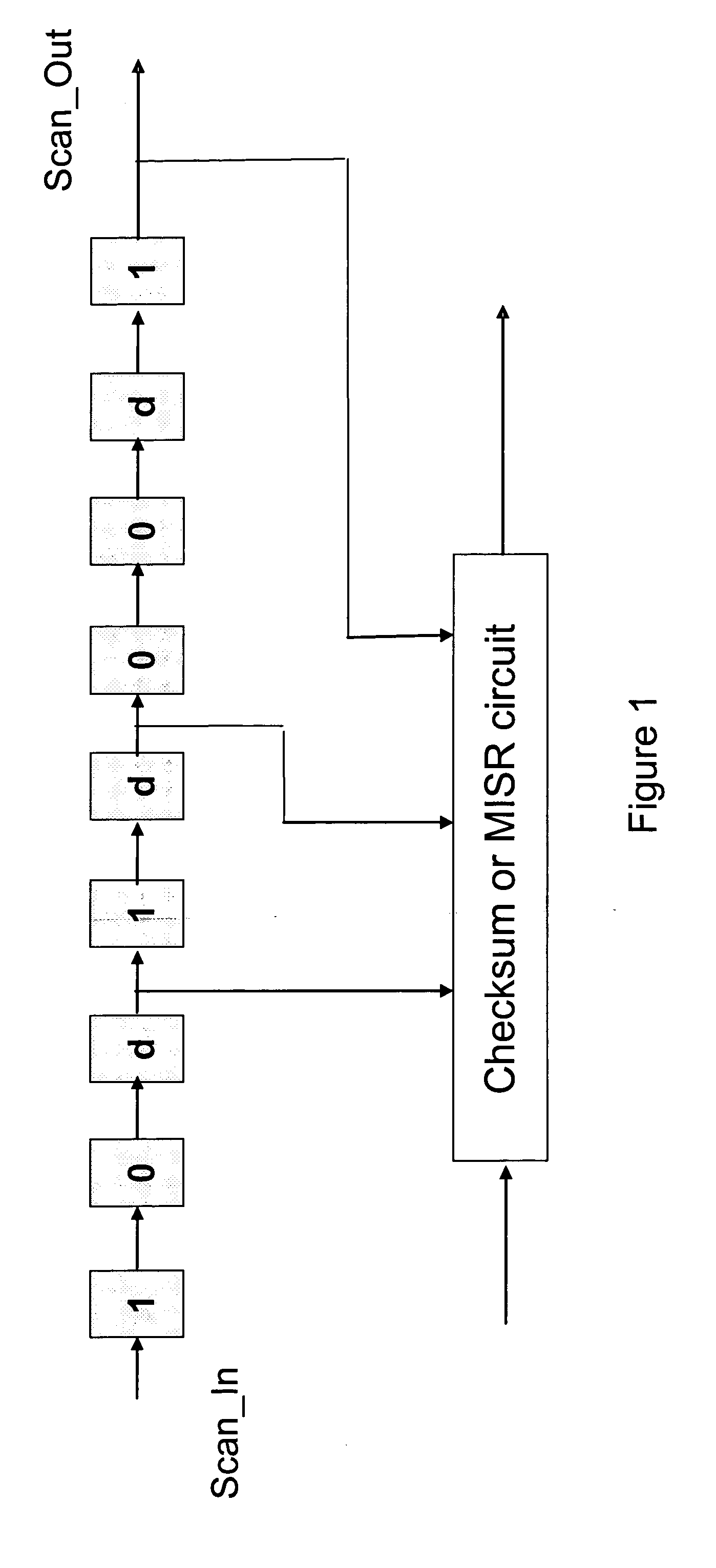

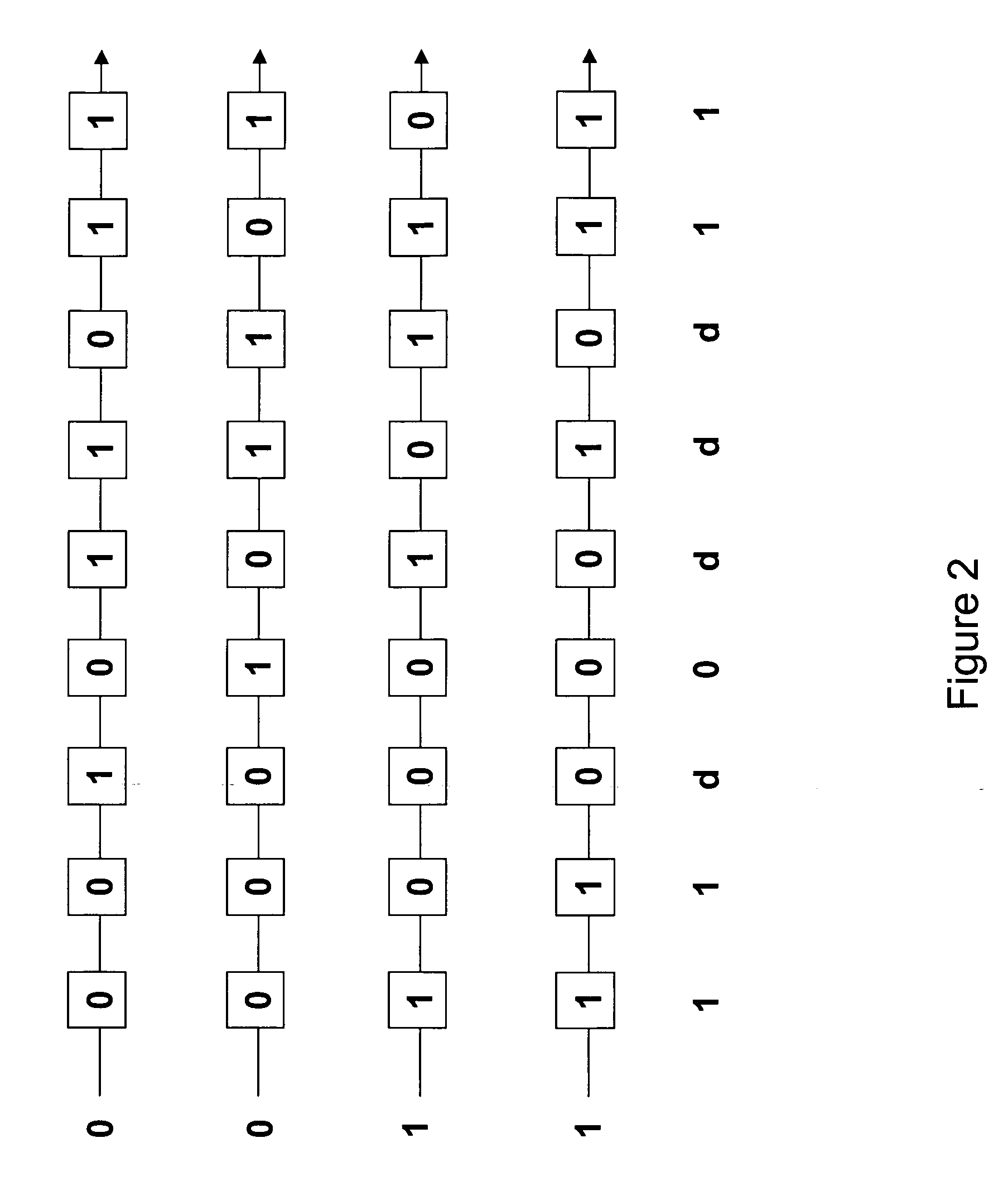

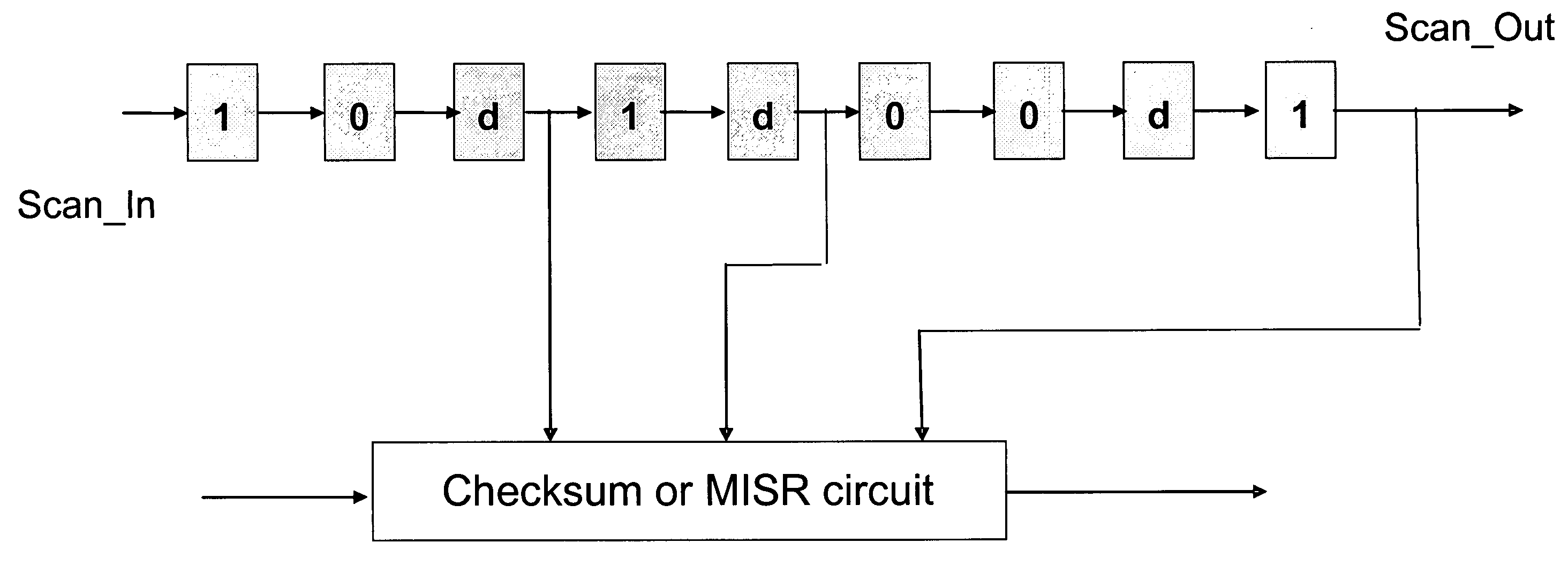

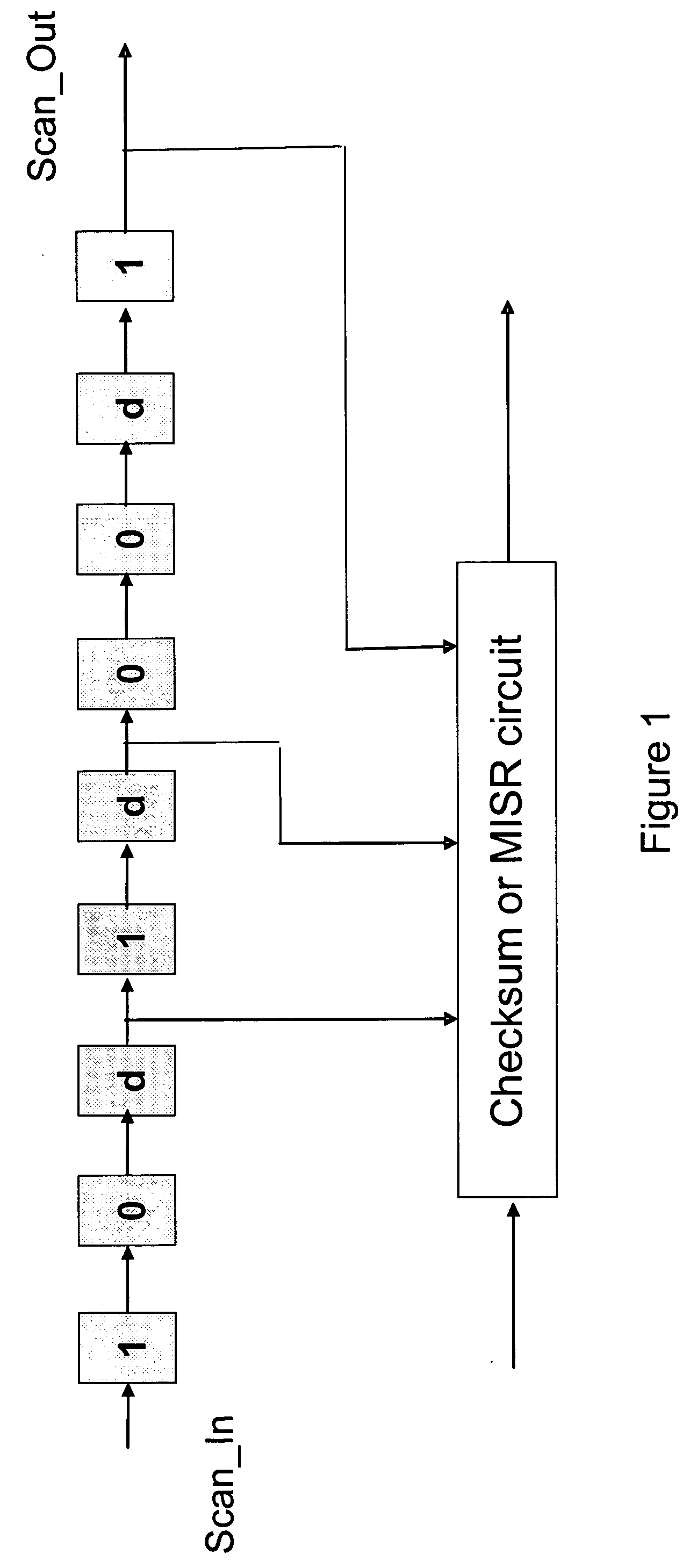

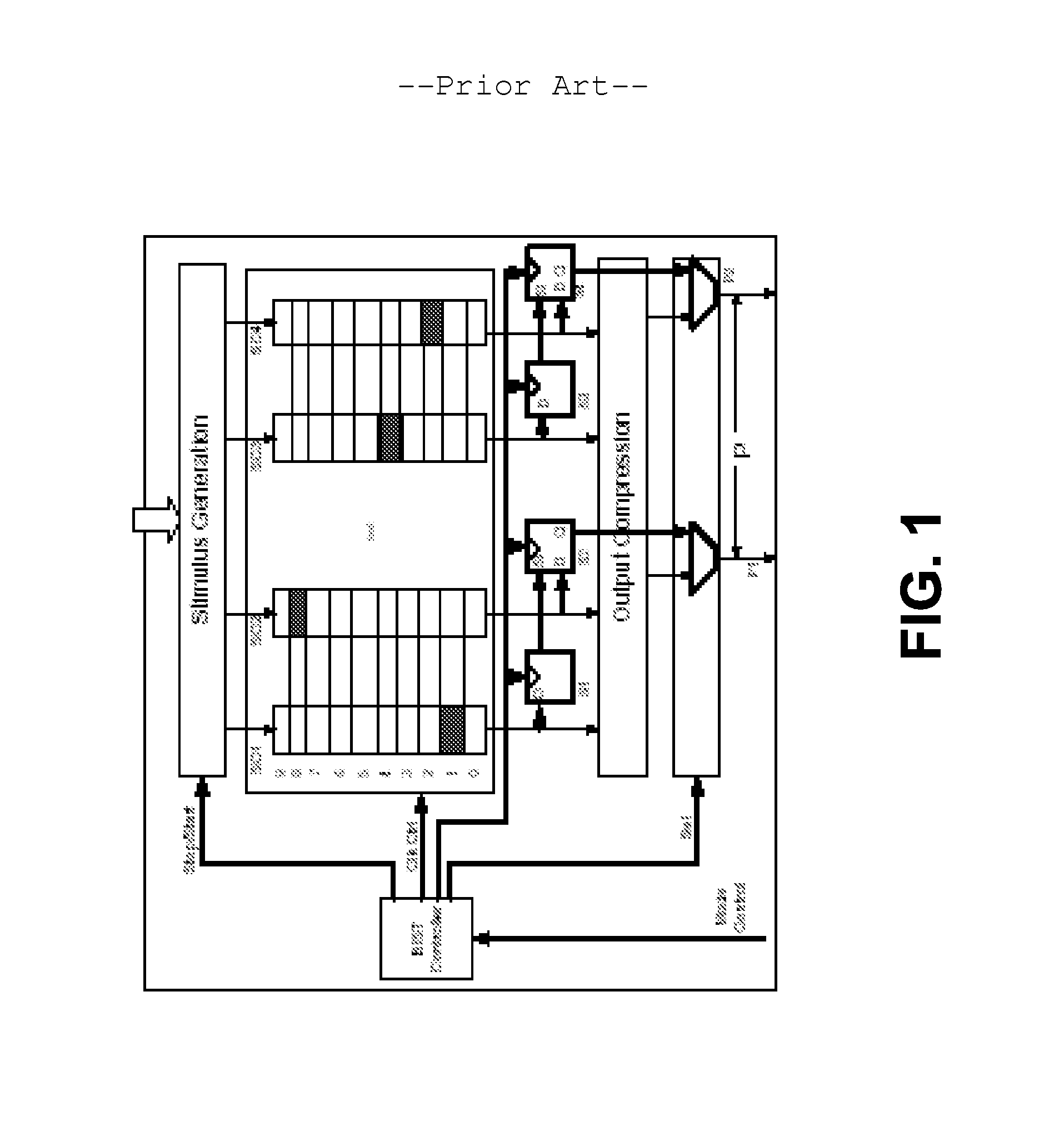

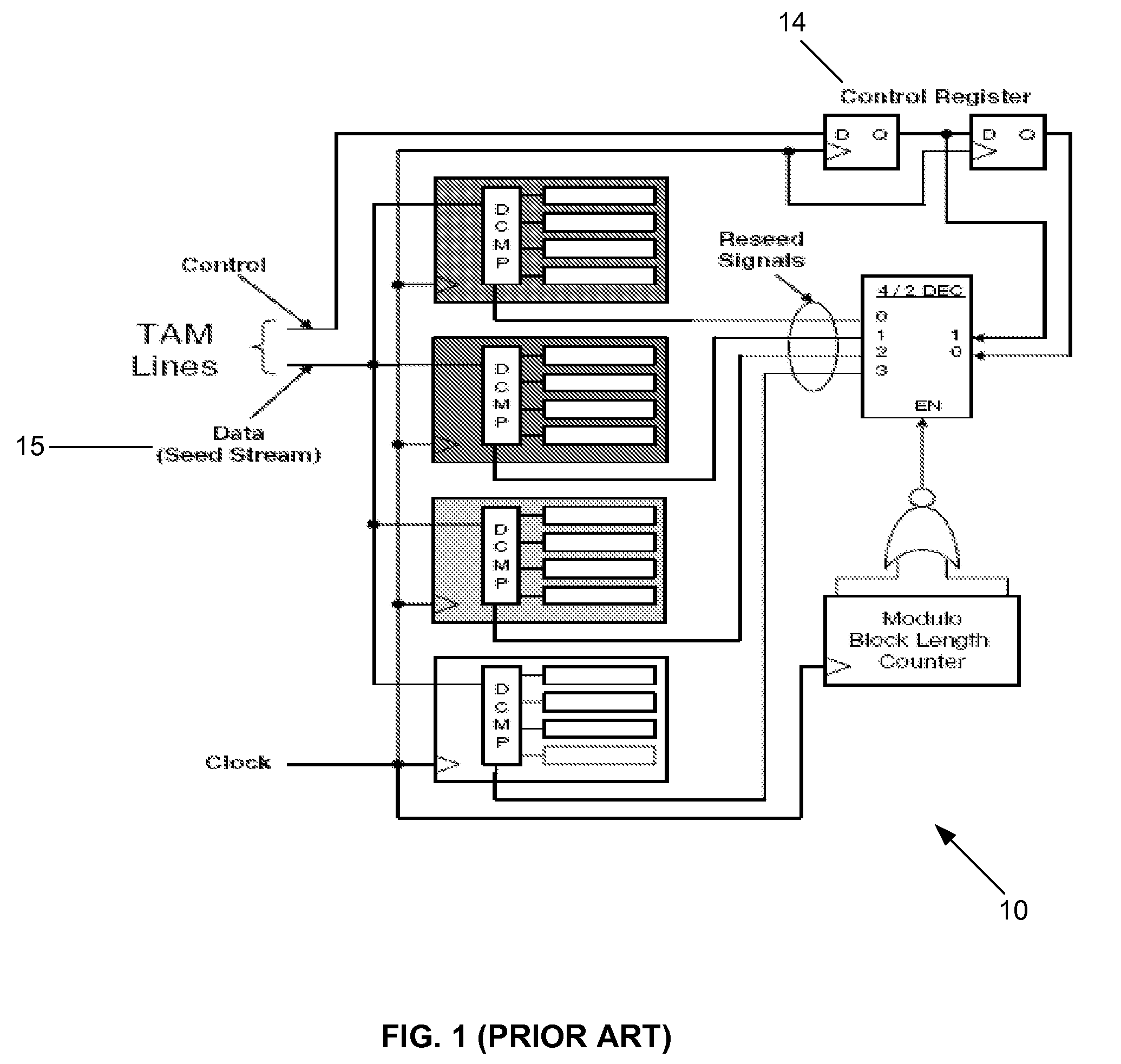

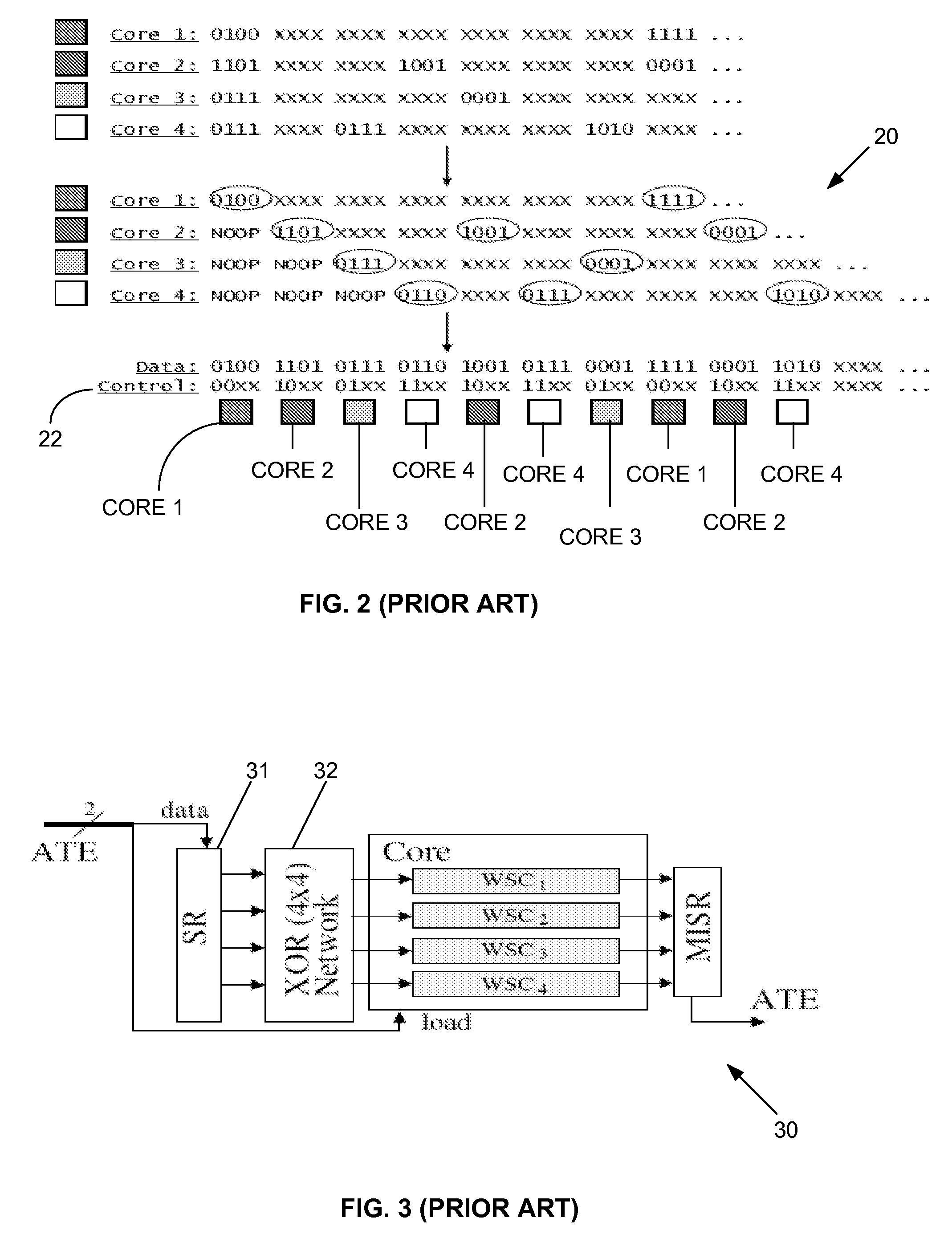

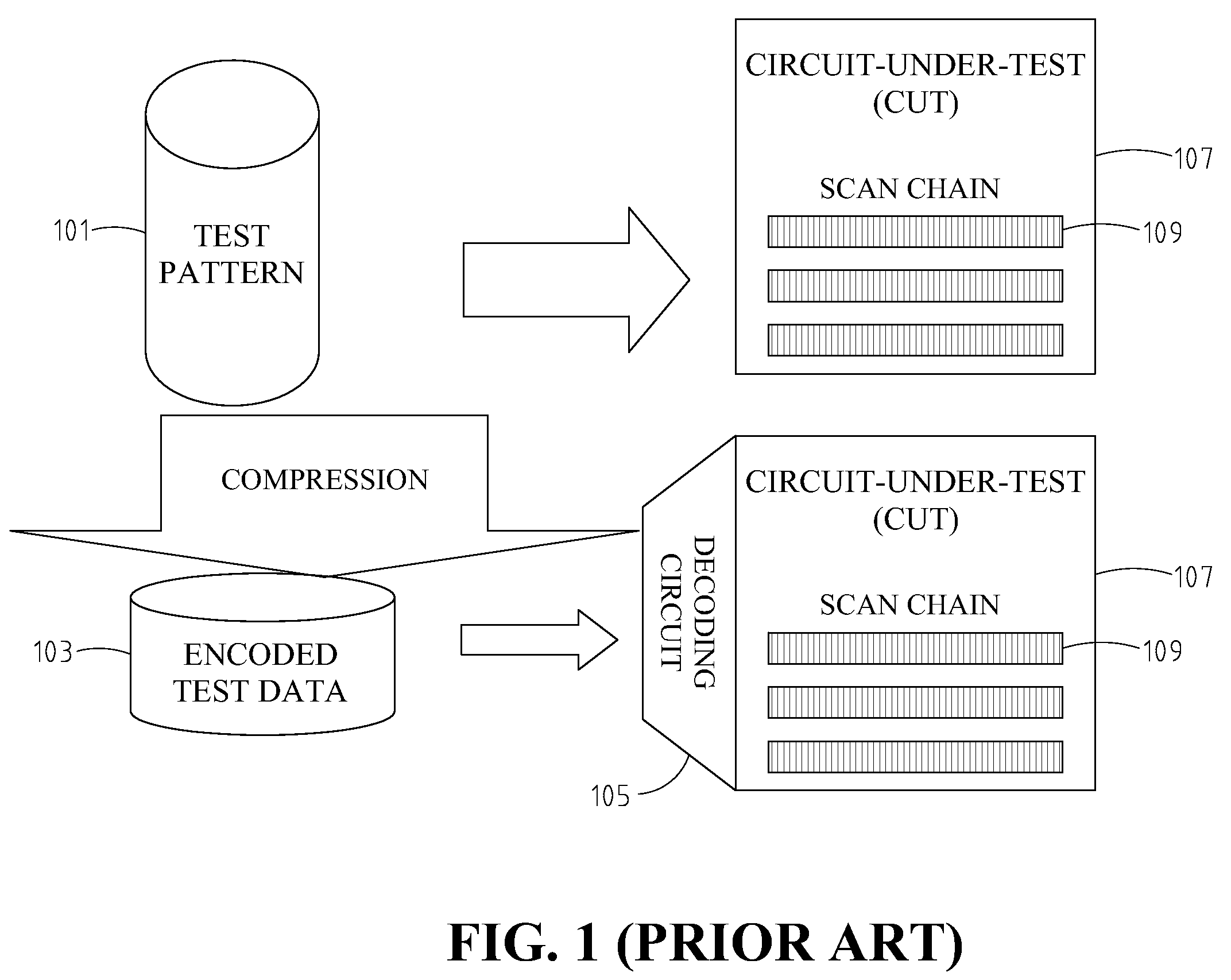

An architecture and methodology for test data compression using combinational functions to provide serial coupling between consecutive segments of a scan-chain are described. Compressed serial-scan sequences are derived starting from scan state identifying desired Care_In values and using symbolic computations iteratively in order to determine the necessary previous scan-chain state until computed previous scan-chain state matches given known starting scan-chain state. A novel design for a new flip-flop is also presented that allows implementing scan-chains that can be easily started and stopped without requiring an additional control signal. Extensions of the architecture and methodology are discussed to handle unknown (X) values in scan-chains, proper clocking of compressed data into multiple scan-chains, the use of a data-spreading network and the use of a pseudo-random signal generator to feed the segmented scan-chains in order to implement Built In Self Test (BIST).

Owner:AMERICAN PATENTS LLC +1

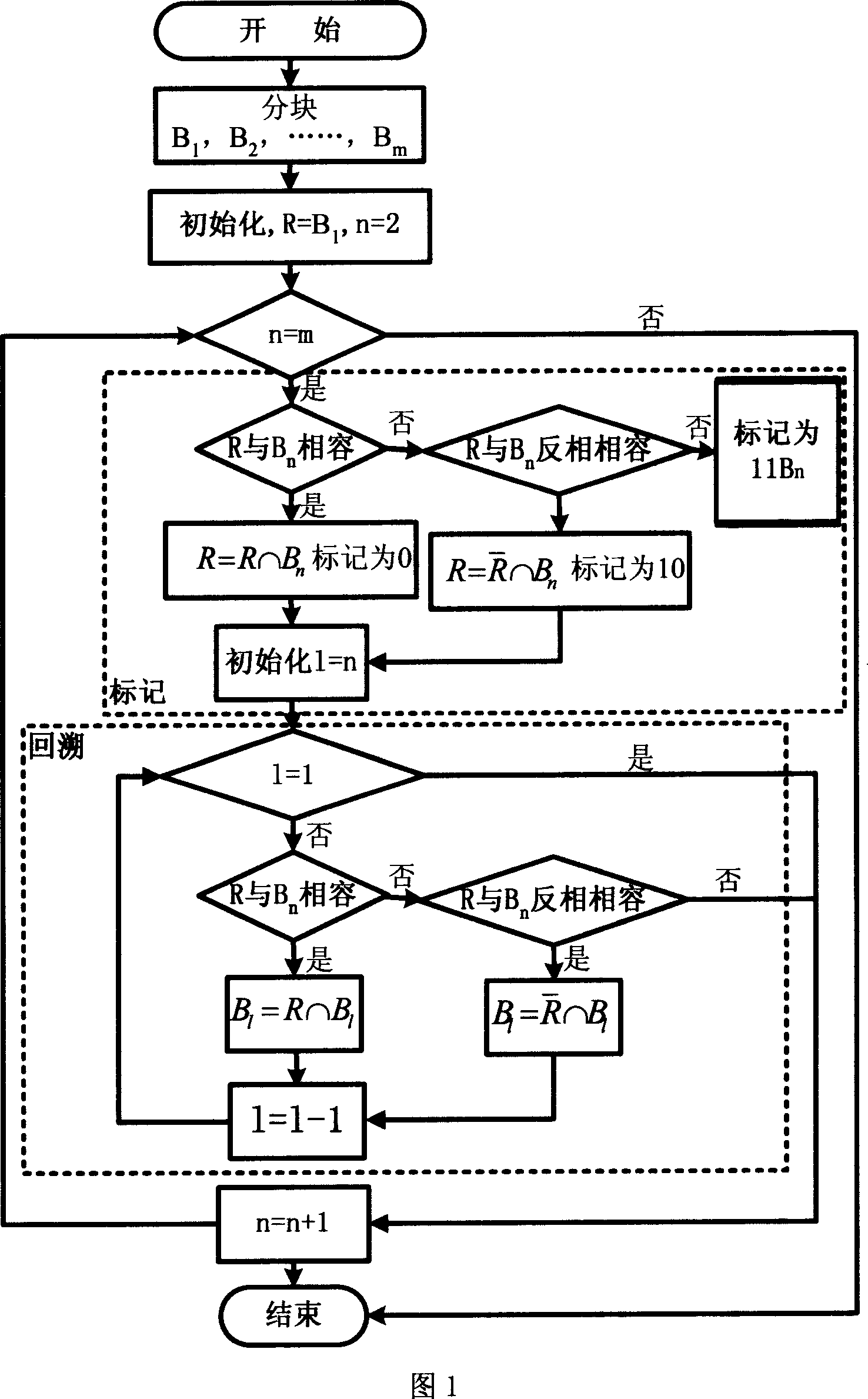

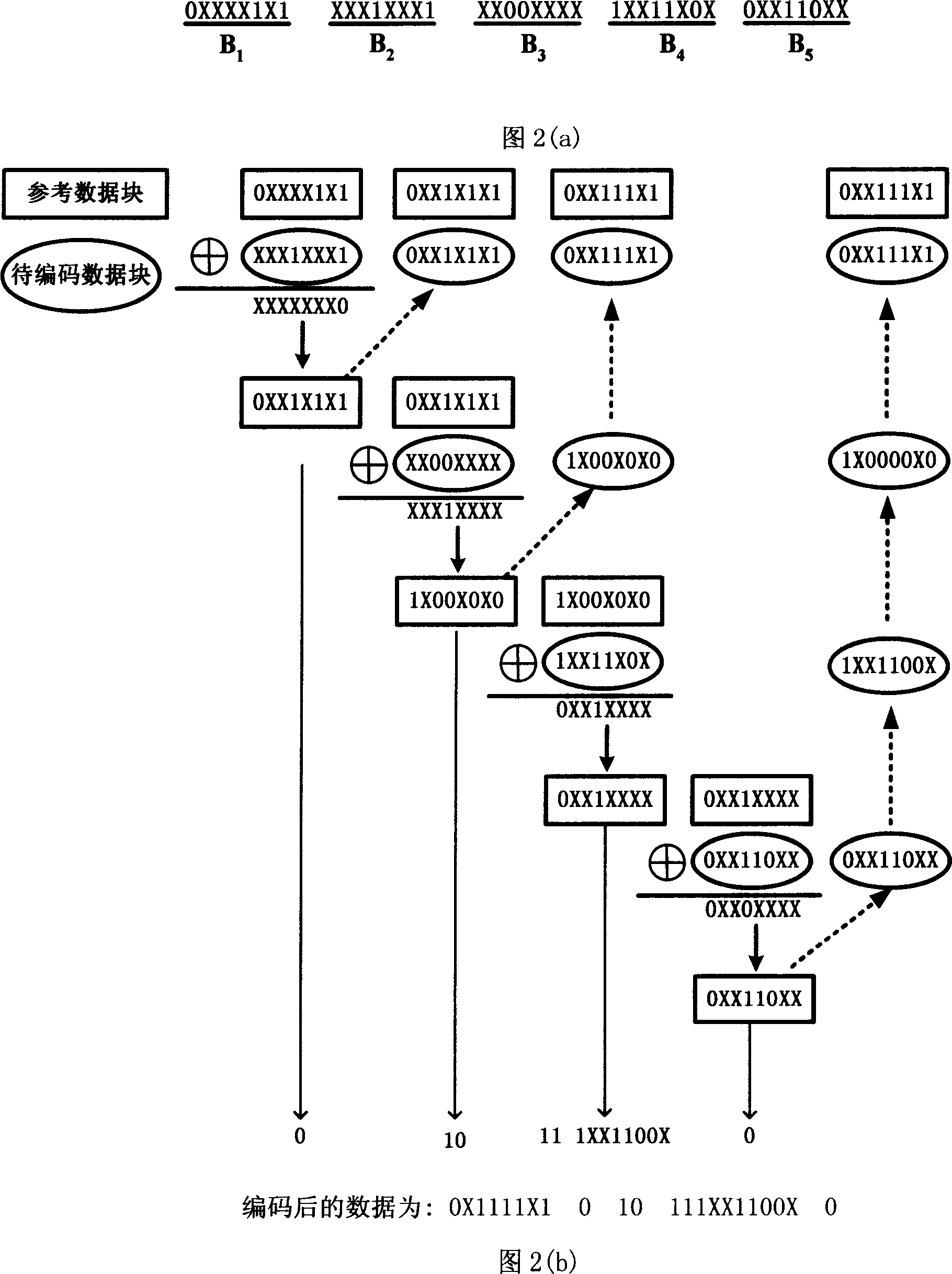

System chip test data compression method of block mark

InactiveCN101000367AGood compatibilityAchieve compressionDigital circuit testingSpecial data processing applicationsComputer hardwareTest data

A method for compressing test data of block-labeled system chip utilizes both complete block of data block to be coded and with zero label in compatible to reference data block as well as complete block of data block to coded and with ten label in anti-phase compatible to reference data block simultaneously to dynamically update reference data block in order to increase compatible probability or anti-phase compatible probability of reference data block and data block to be coded.

Owner:HEFEI UNIV OF TECH

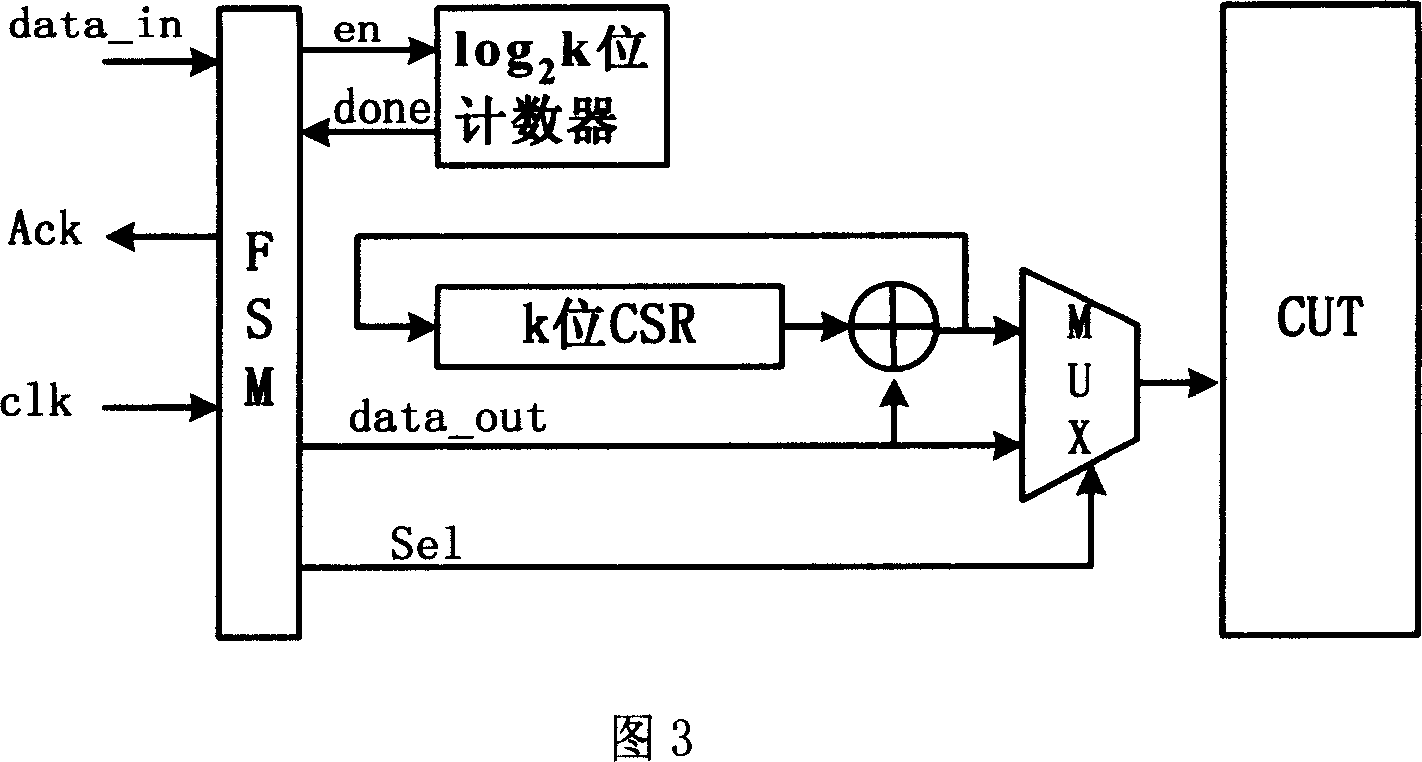

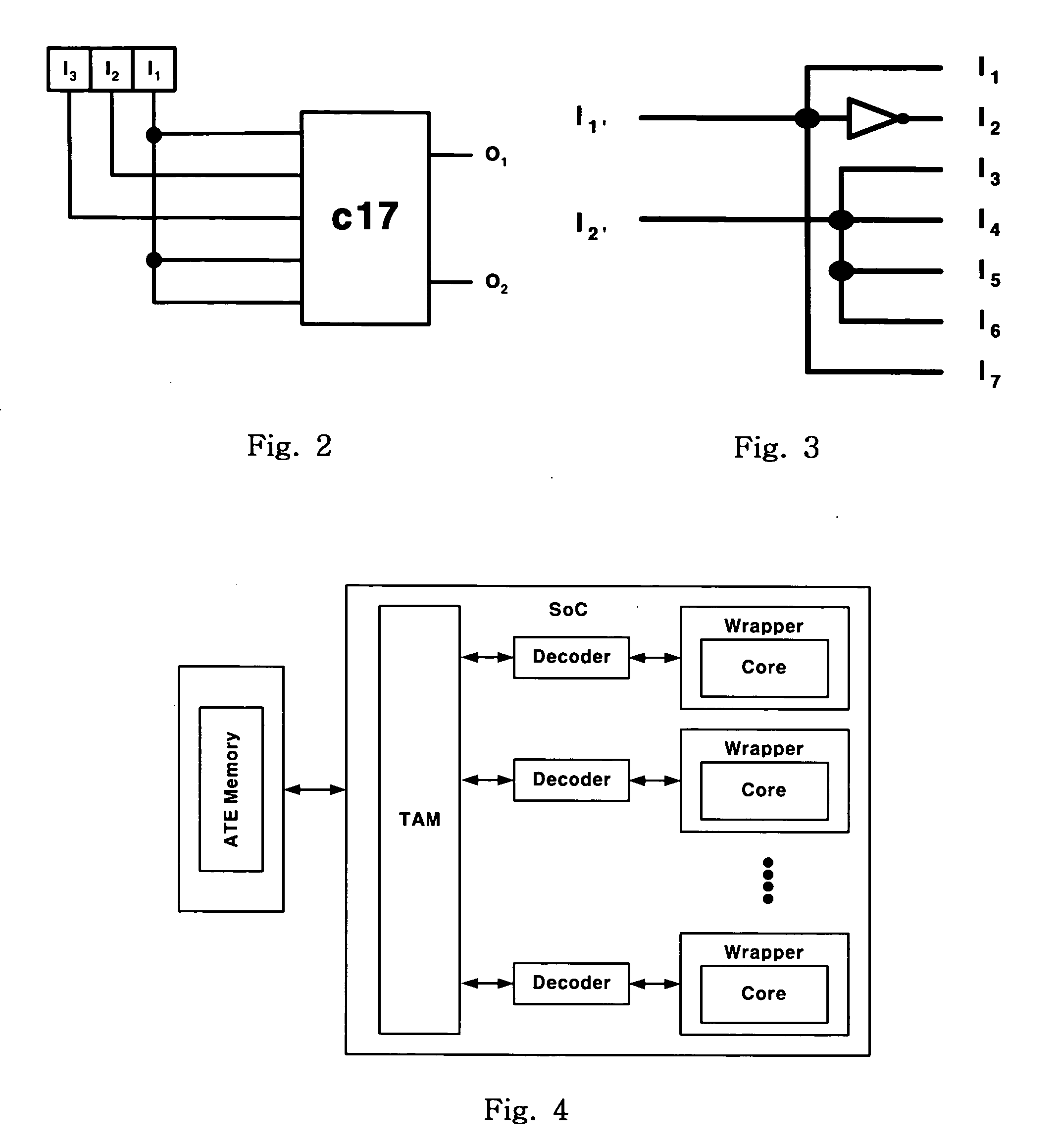

Compressing method for SOC testing data suitable for suitable for multi-scanning chain designing core

InactiveCN101042714AImprove compression efficiencyImprove fault coverageSpecial data processing applicationsFault coverageComputer architecture

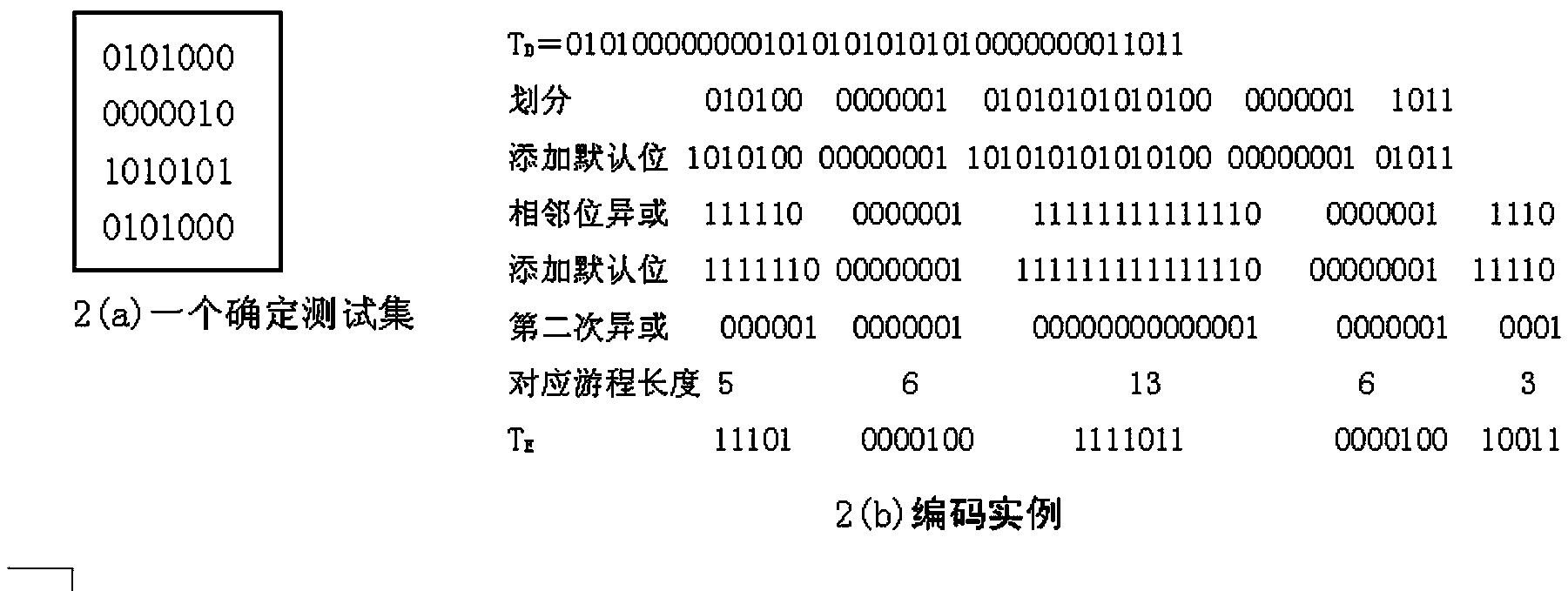

This invention relates to one SOC test data compression method for multi-scanning linkage design in SOC test technique, which solves the problems of current method for large volume of data and non-module fault coverage rate with high cost and comprises the following steps: a, ranking the test set TD according to multiple links; b, using similar group to divide formula set; c, ranking each set of decreasing order; d, setting dictionary items number; e, zero plus index code, one plus test section to express each test section to get compressed test set TE.

Owner:HARBIN INST OF TECH

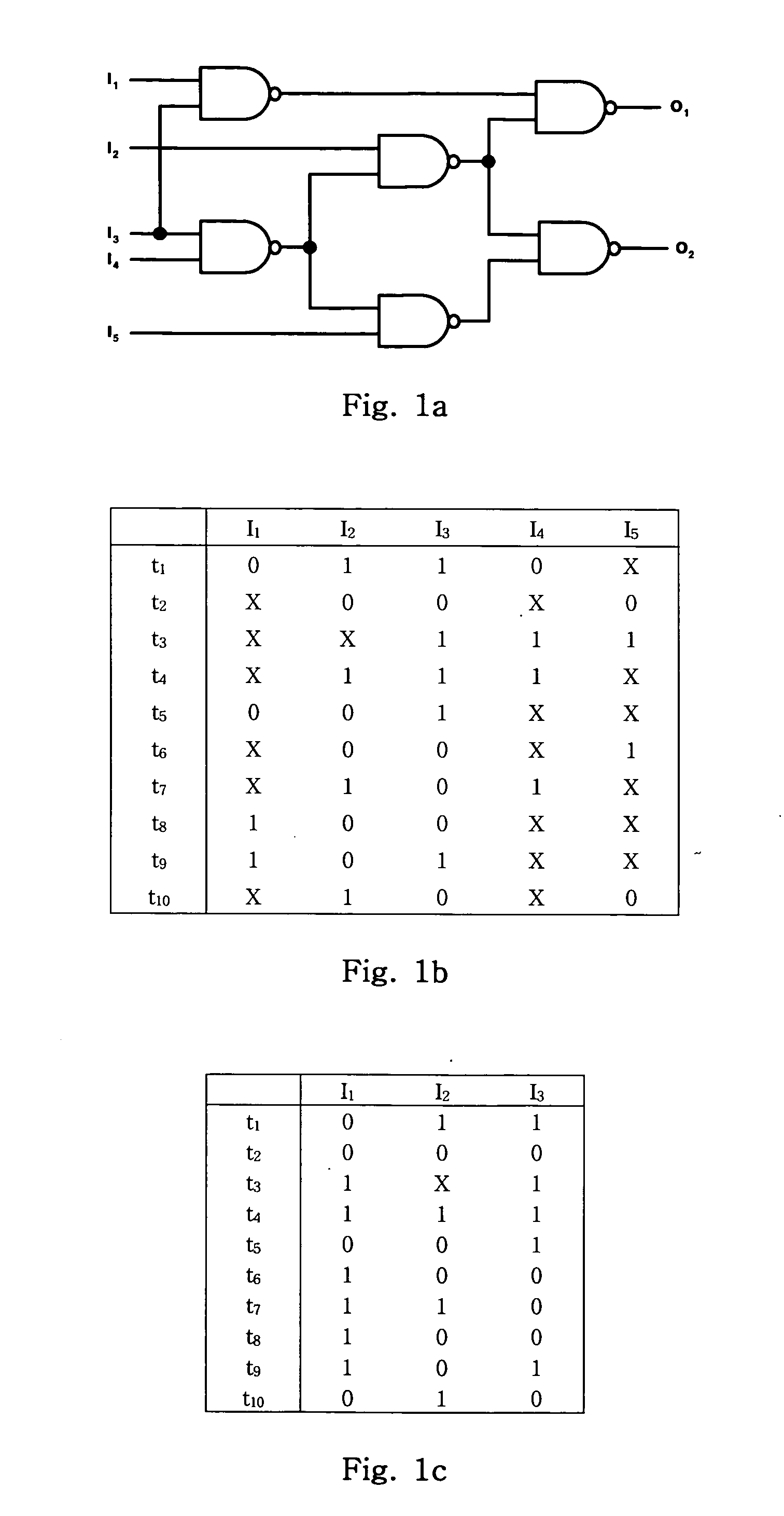

Test data compression method of integrated circuit test

InactiveCN101968528ASolve storage problemsElectronic circuit testingTest set encodingIntegrated circuit layout

The invention provides a test data compression method of an integrated circuit test, which adopts an original test data storing law and then reduces the original test data storing law to obtain needed original test data when the test is applied, that is to say, the storage of the integral original test data is changed into the storage of one or a plurality of corresponding irrational numbers. The test data compression method of the integrated circuit test particularly comprises the following steps of: generating a determined complete test set recorded as a test vector set by adopting an automatic test mode generation tool; cascading all test vectors; filling independent bits; counting a run-length; transforming into decimal numbers; and transforming into the irrational numbers. The invention has the advantages of theoretically unlimitedly compressing the test data by changing the storage of codes of the integral test set into the storage of an encoding law and fundamentally solving the problem of storage of the test data.

Owner:ANQING NORMAL UNIV

Device and method for determinacy self-testing test data compression

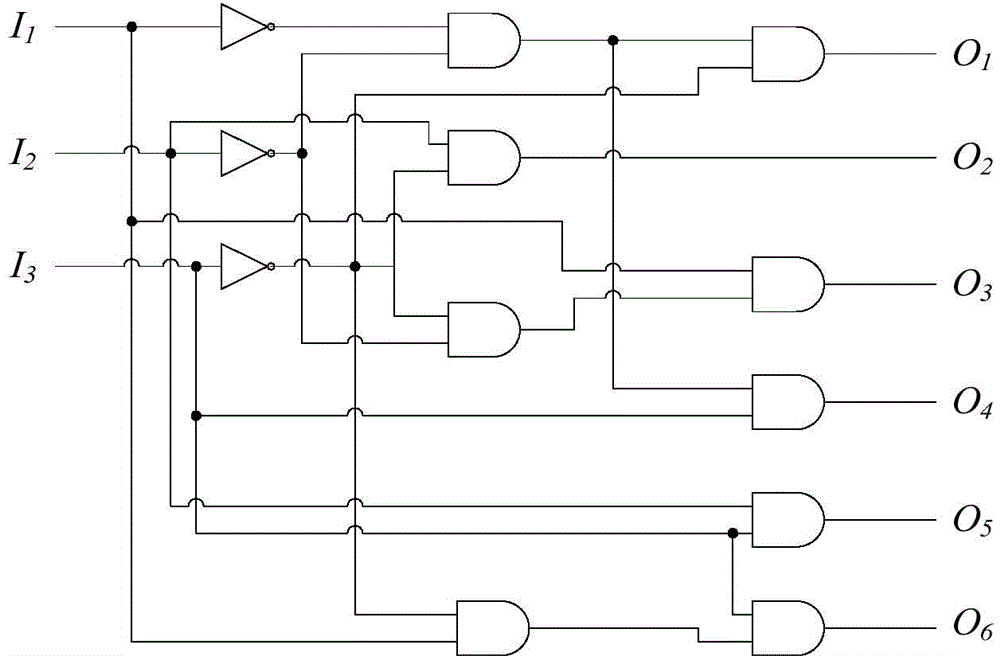

ActiveCN101226228ASave storage spaceCoverage with a high probability of failureElectrical testingLogic circuits using elementary logic circuit componentsFault coverageData memory

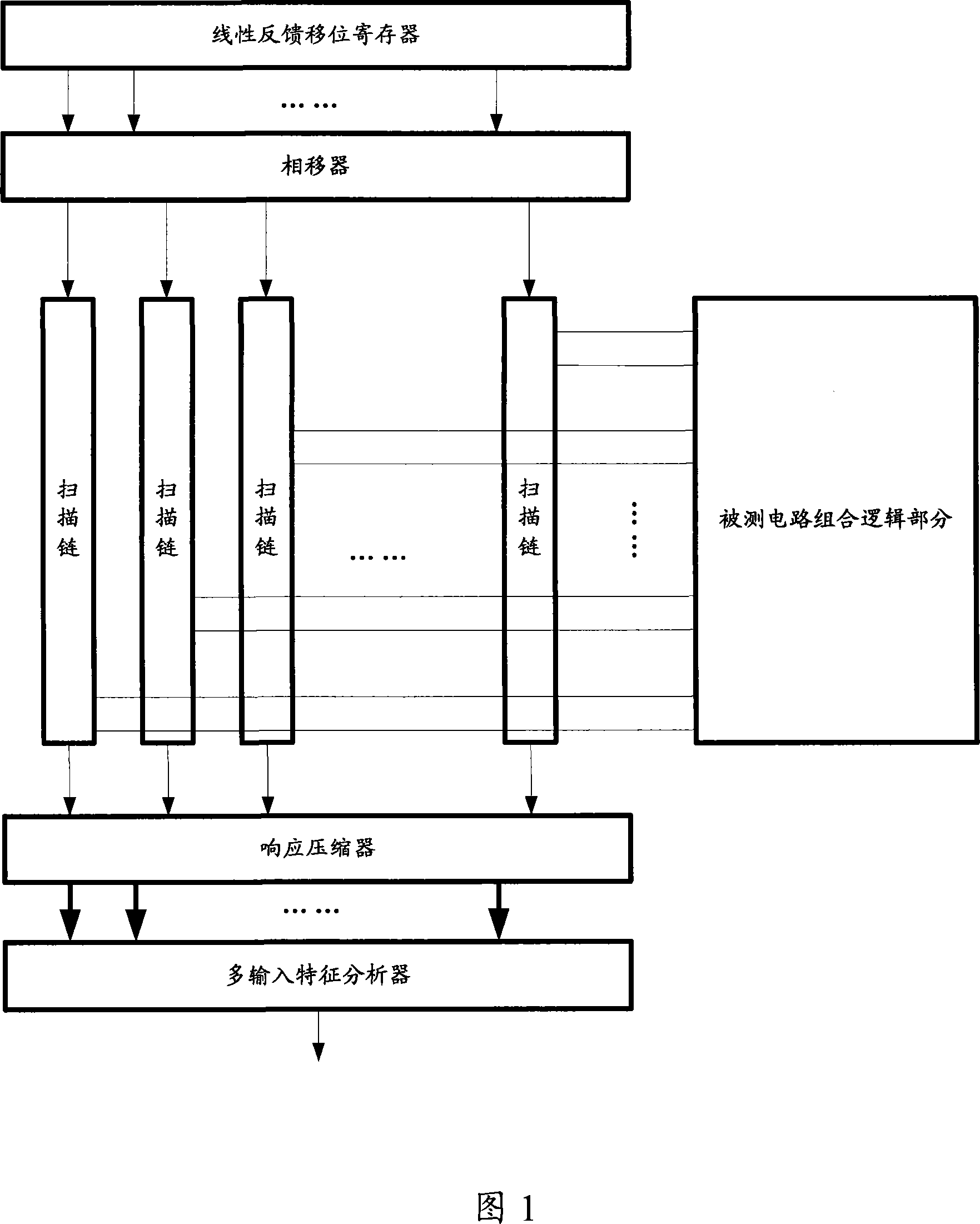

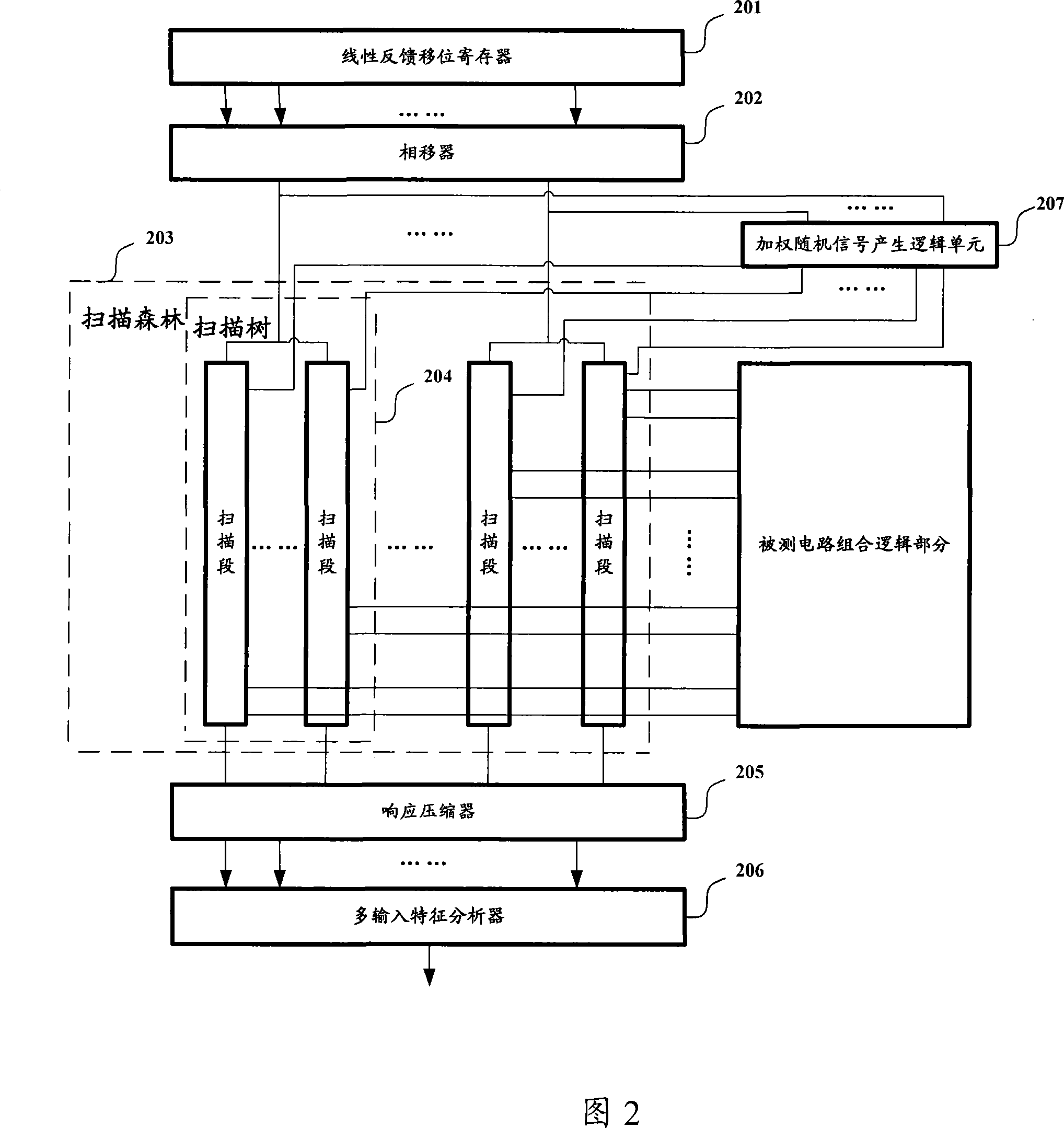

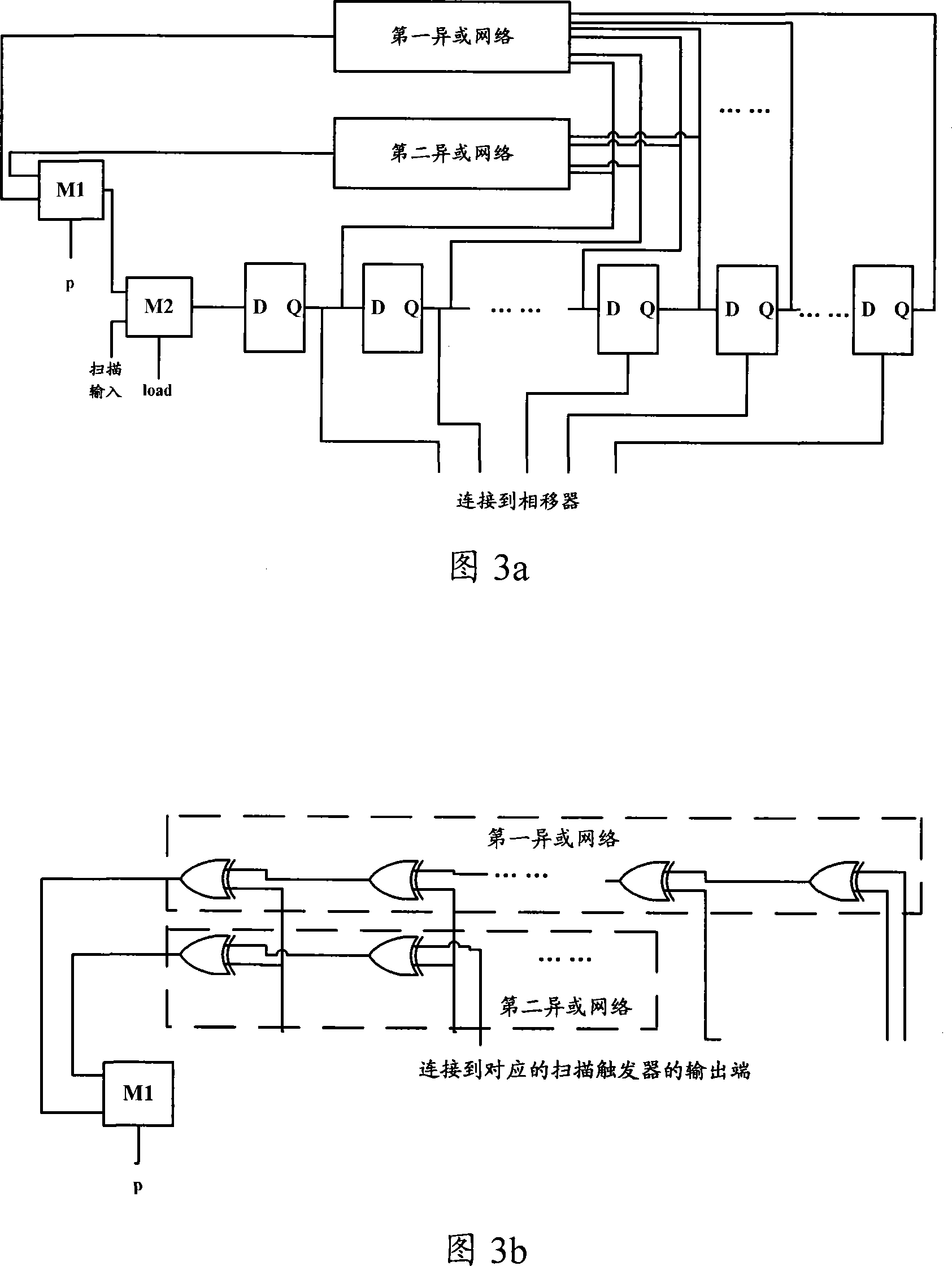

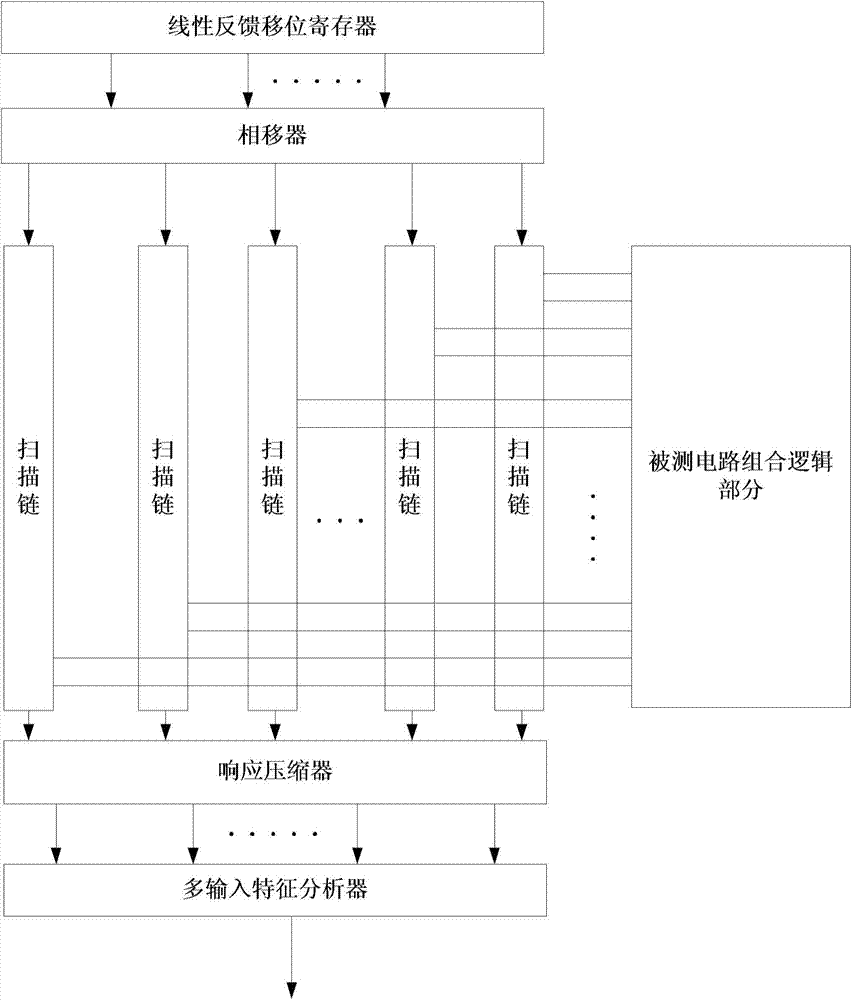

The invention relates to a method for compressing the test data of integrated circuit, belonging to integrated circuit technical field, in particular to a deterministic self-test test data compressor. The invention comprises a phase shifter, a response compressor, a linear feedback shift register with a first and a second xor network while the shift register is connected with the phase shift, a scanning tree and a weigh random signal generating logic unit while the scan forest is connected with the phase shift, the gating signal end of the scan forest is connected with the weight random signal generating logic unit, and the output of the scan forest is connected with the response compressor. The invention further provides a deterministic self-test test data compression method. The invention uses the weight random signal generating logic unit to control the frequency of special signal of the input signal of the scan forest, to improve the fault coverage rate into the false random self-test process, to reduce the test data memory space generated by deterministic test vector.

Owner:TSINGHUA UNIV

Test data compression method, data uncompress device and data uncompress method

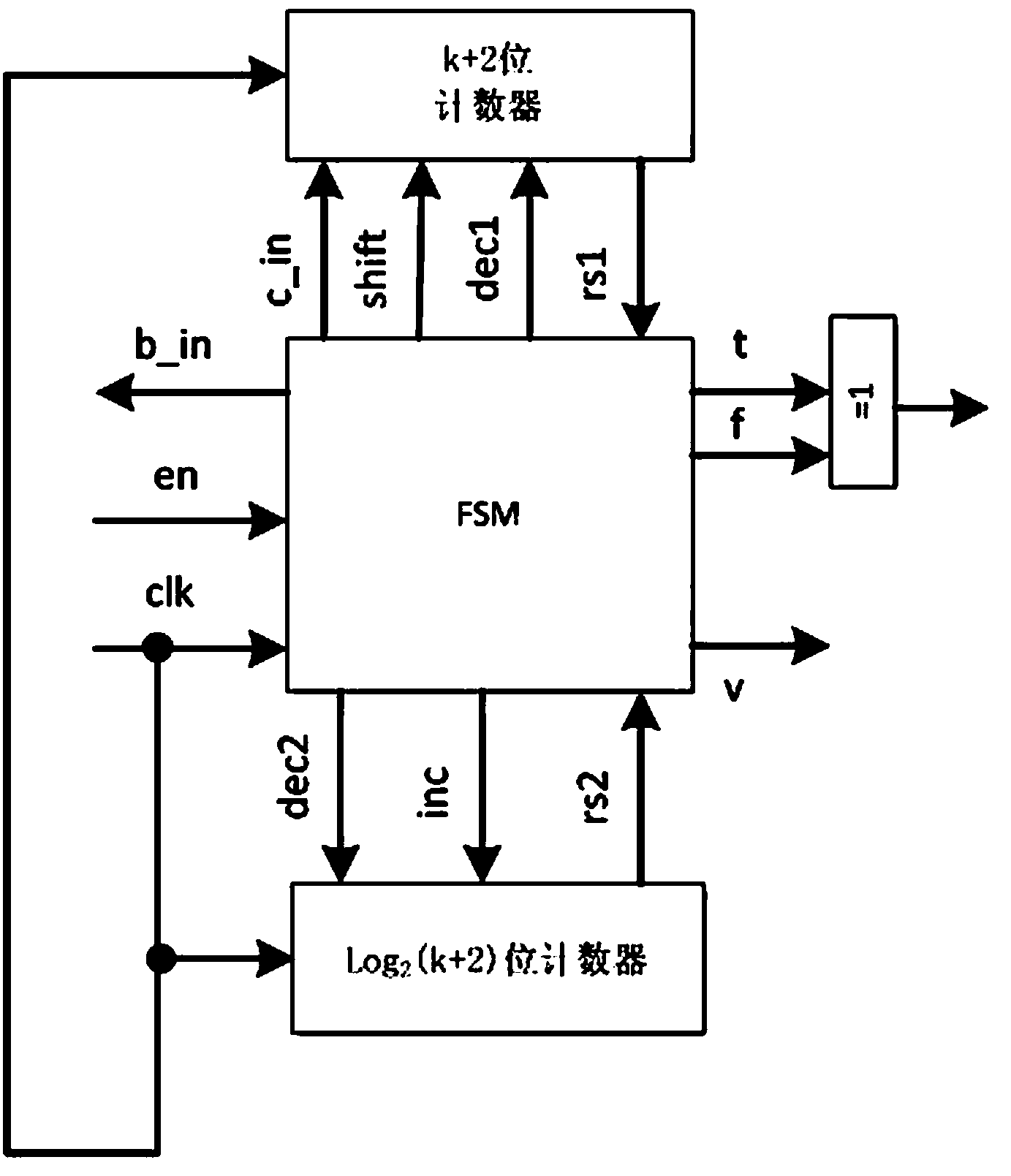

ActiveCN103499787AReduce the number of bitsSave storage spaceElectrical testingShift registerExclusive or

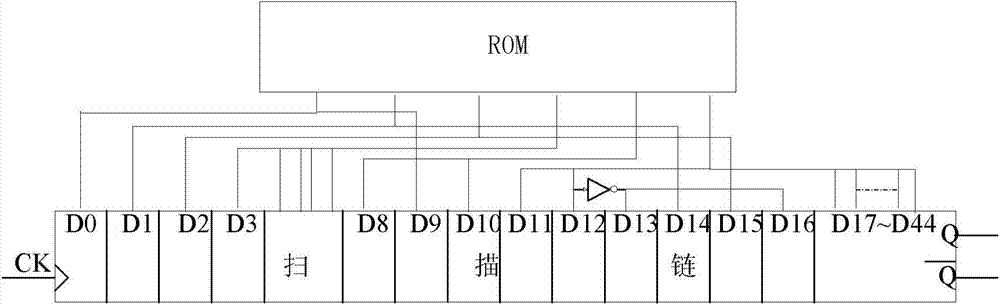

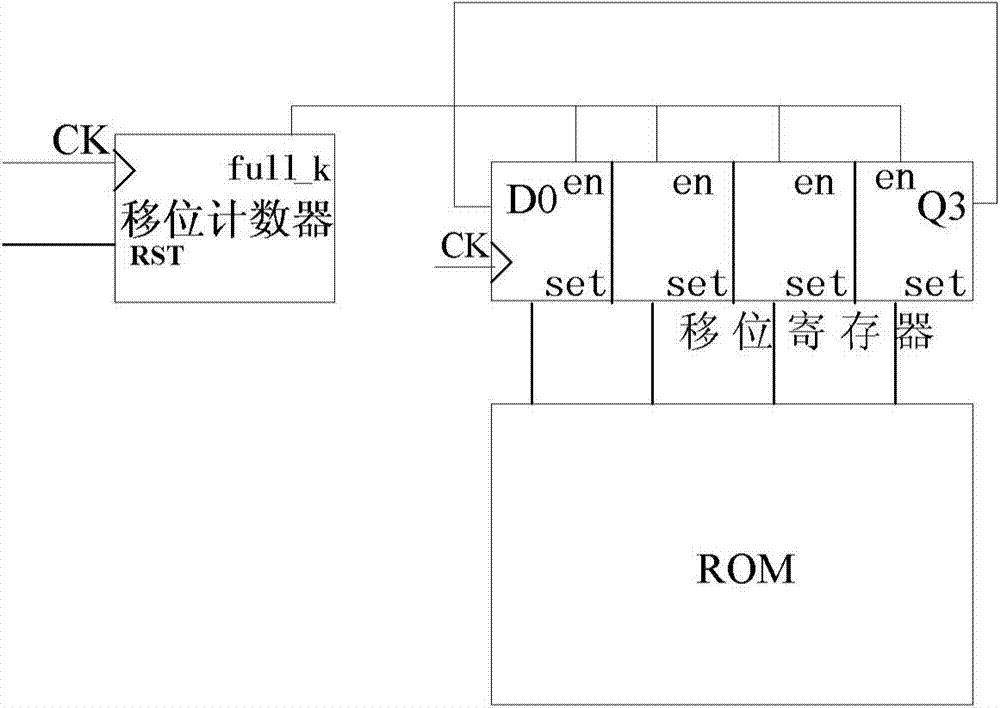

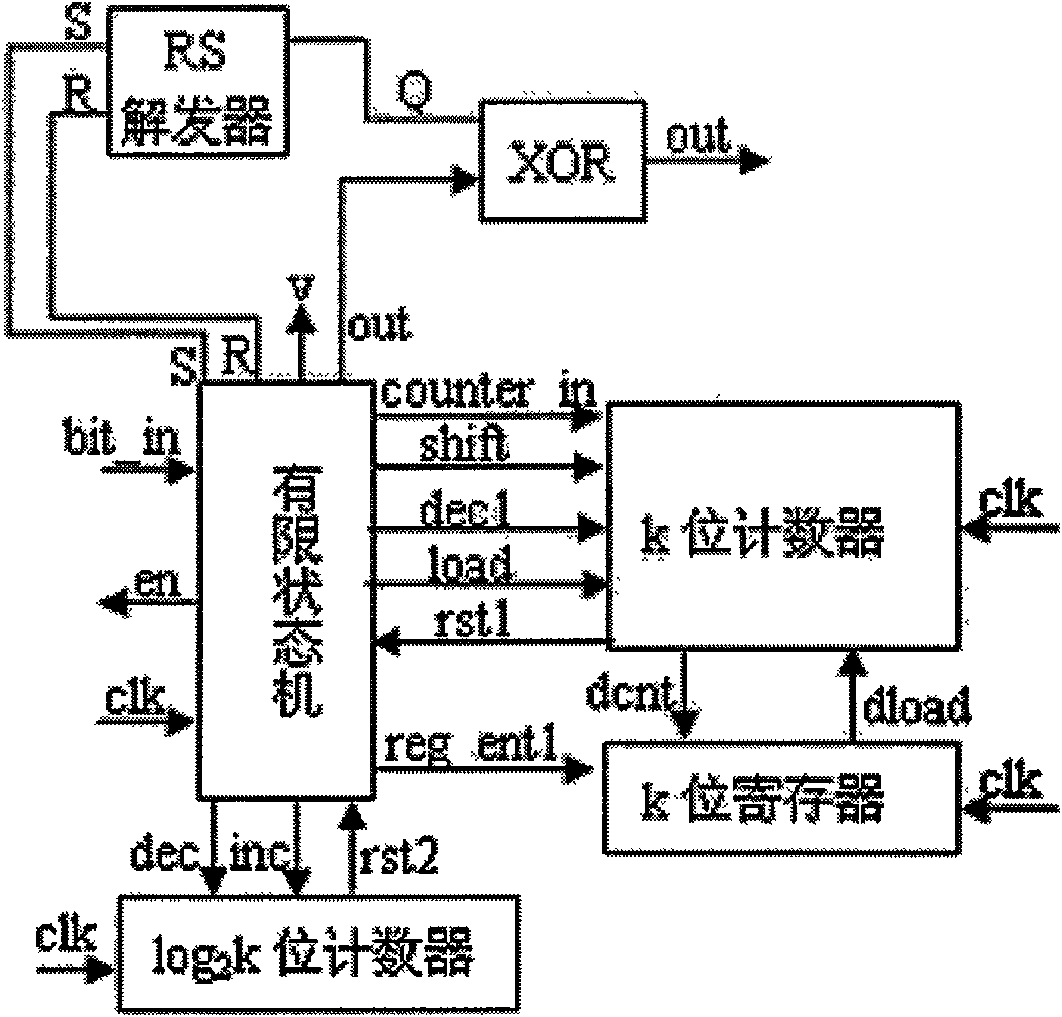

The invention discloses a deterministic self-testing test data compression method, a data uncompress device and a data uncompress method. The compression method comprises cluster compression, and the combination of the cluster compression, input simplification compression and shifting compression. The data uncompress device comprises a bit counter, a vector quantity counter, a shift counter, a cluster shifting register, an address counter, a comparator, a exclusive-OR gate, an input compression register and a phase inverter. According to the scheme, due to the fact the cluster shifting input simplification compression method is adopted, input compression is firstly conducted on test data with faults difficult to test, cluster compression is conducted on the test data processed by input compression, and shifting compression is conducted on the test data processed by cluster compression, so that the number of memory cells which need to be stored in a built-in self-testing circuit ROM is reduced, and hardware overhead of the built-in self-testing circuit is saved.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

Method for test data compression coding and decoding with same run length and special decoding unit

InactiveCN101604974AAchieve compressionElectronic circuit testingCode conversionVariable-length codeData compression

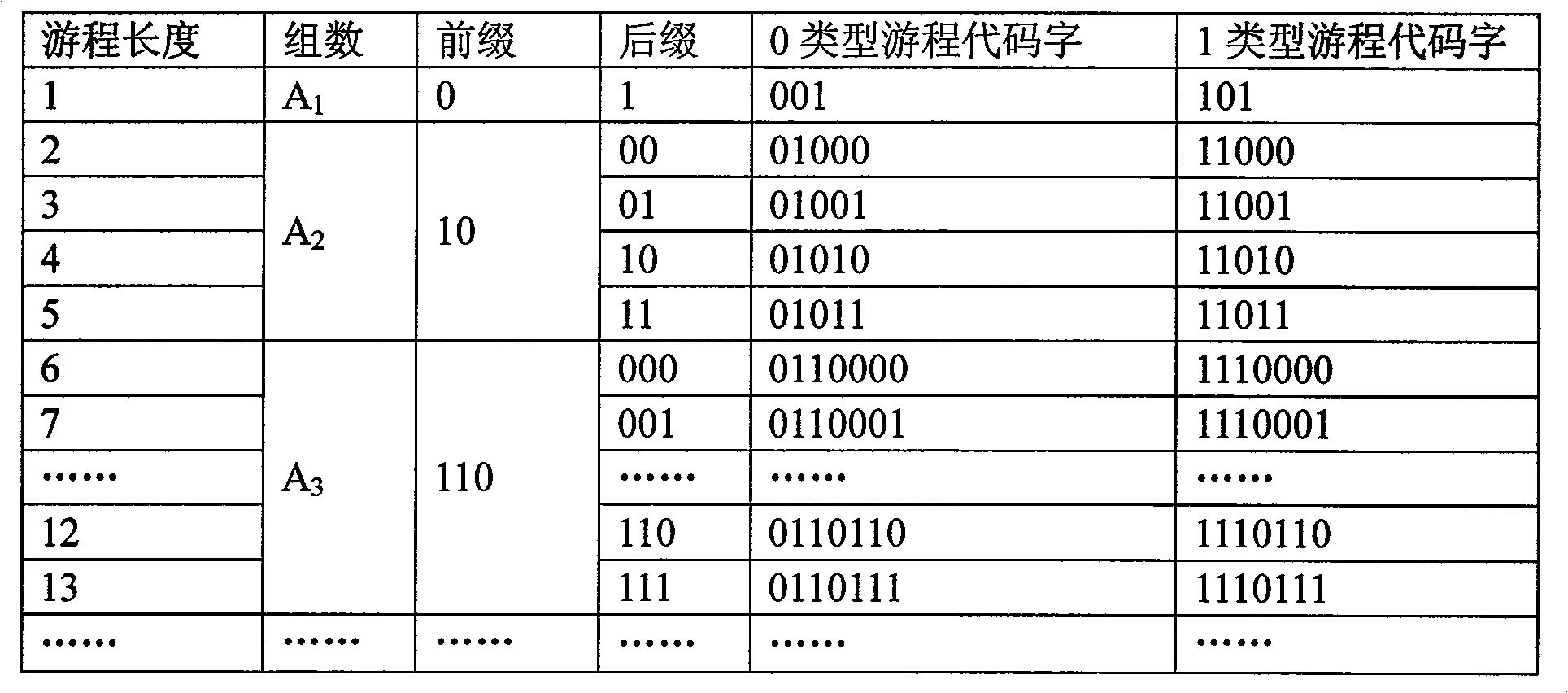

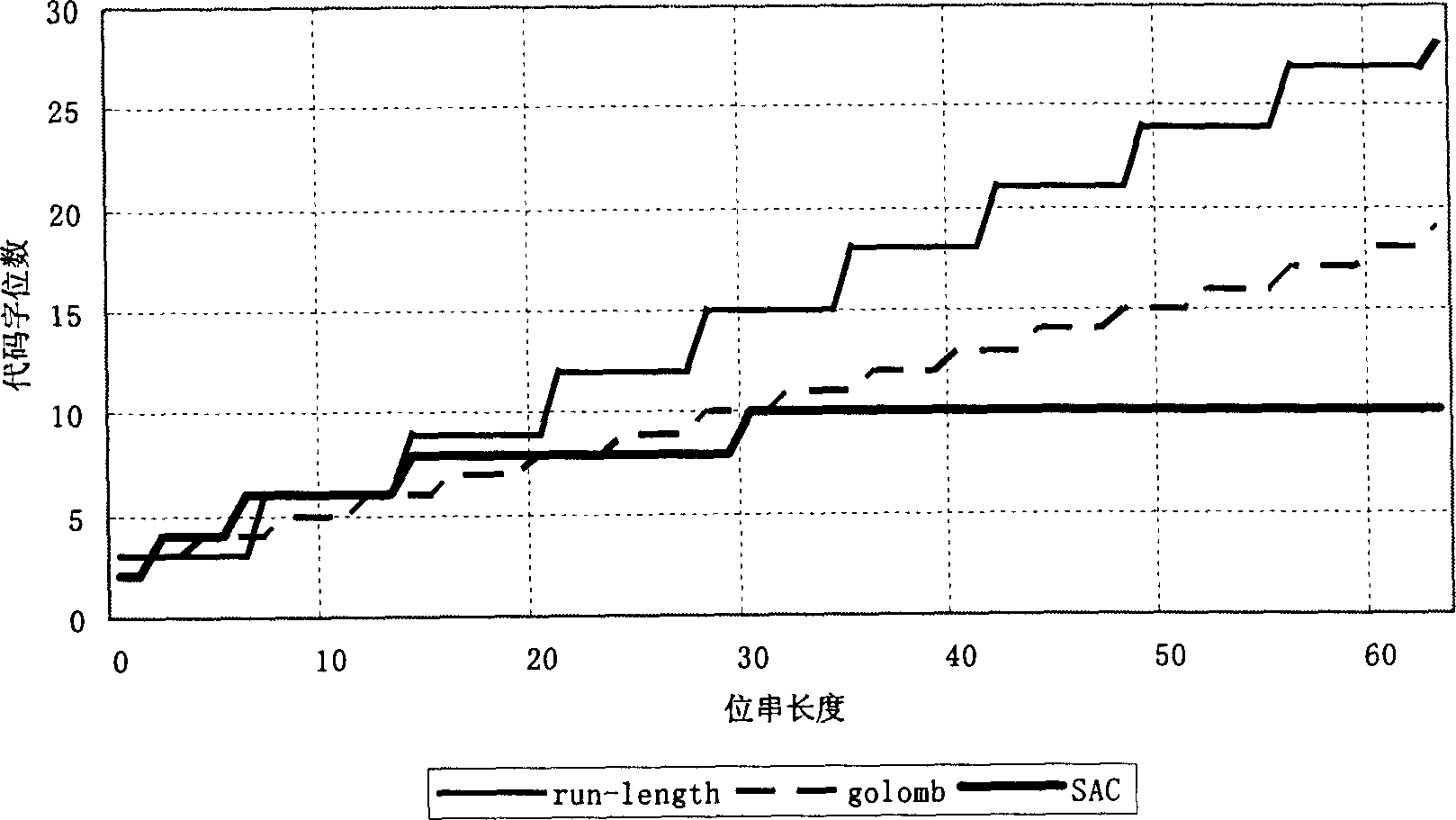

The invention relates to a method for test data compression coding and decoding with same run length and a special decoding unit of a large scale integrated circuit, which belong to the technical field of integrated circuit test. In order to reduce the memory capacity of the test data and shorten the testing application time, the invention discloses a method for test data compression coding of the large scale integrated circuit, which comprises the following steps executed by a computer for storing programs: firstly, using a bit string as a basic unit to perform numerical statement on the runs of type 0 and type 1, partitioning the test data, and counting the length of the bit string; secondly, coding the length of the bit string by using two different types of coding modes so that the coding modes not only consider that variable length codes use short code words to replace long original bit strings but also consider the relativity between the runs, and the subsequent runs of continuous runs with the same run length can be further expressed by the short code words so as to achieve the data compression. The decoding method performs decompression by using the decoding unit aiming at the compression method.

Owner:陈向前

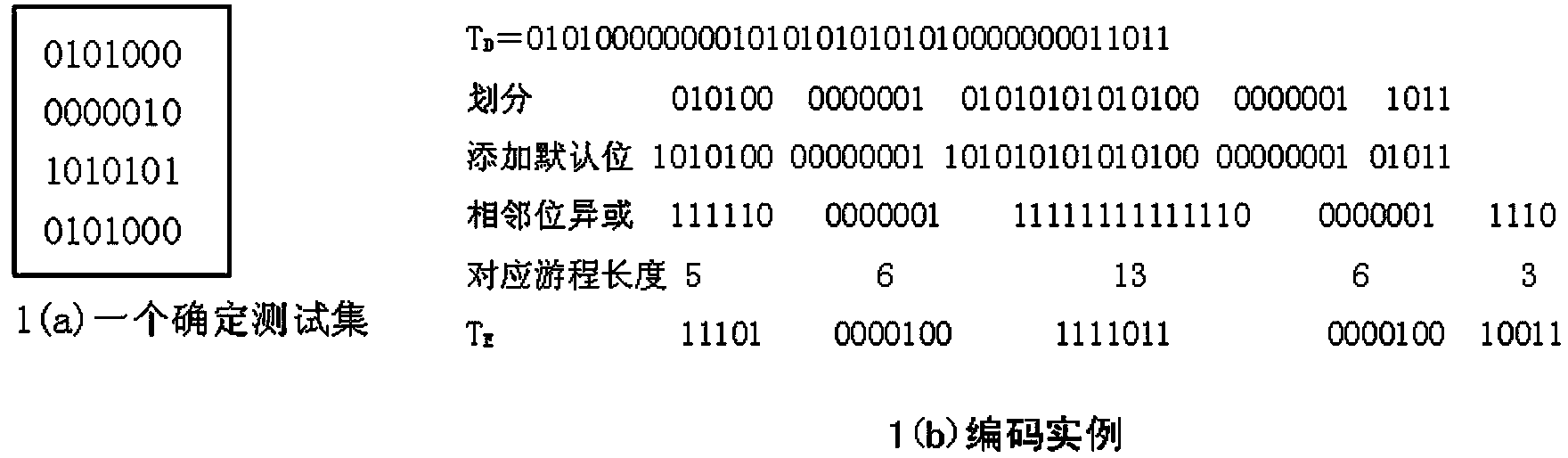

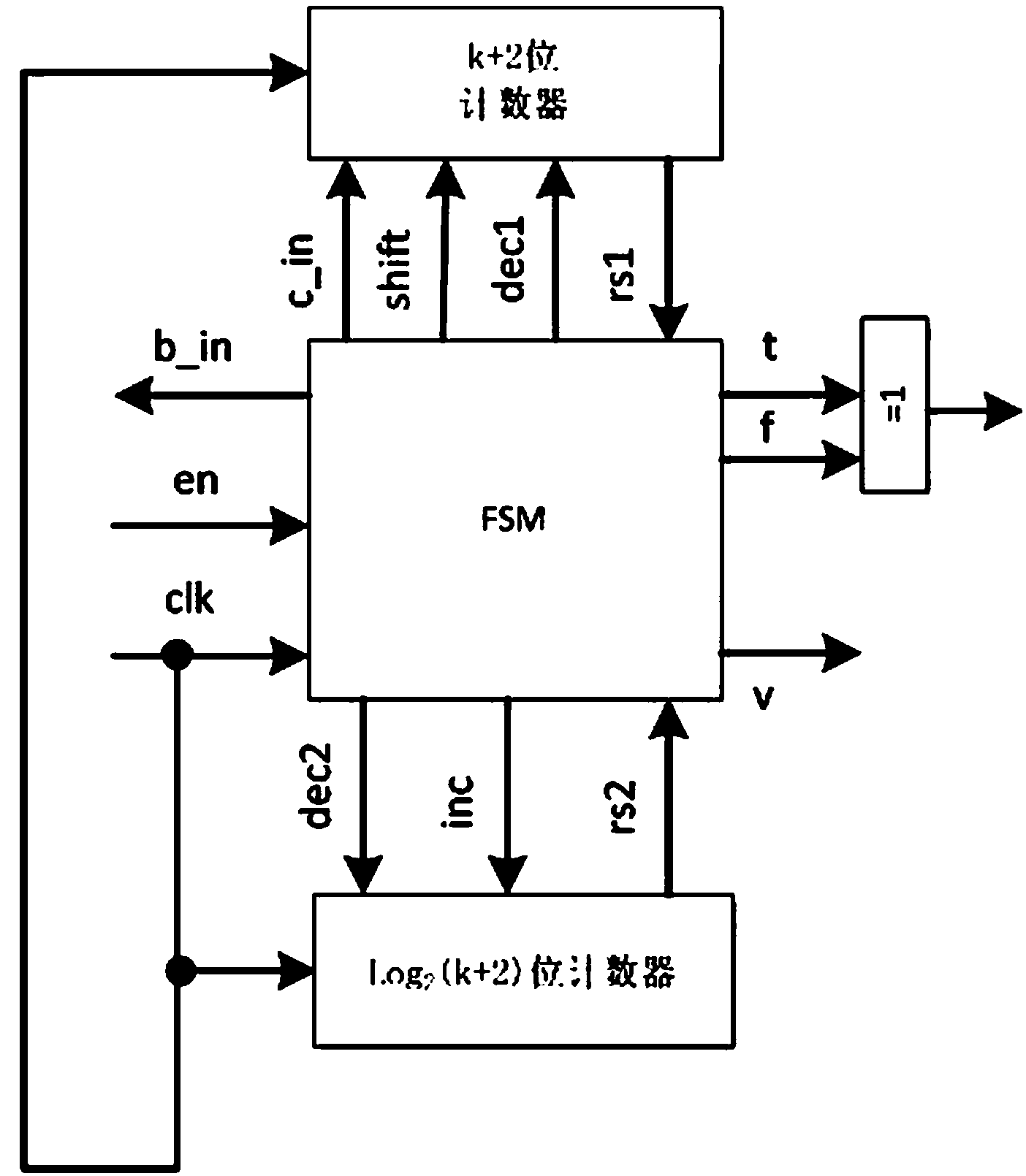

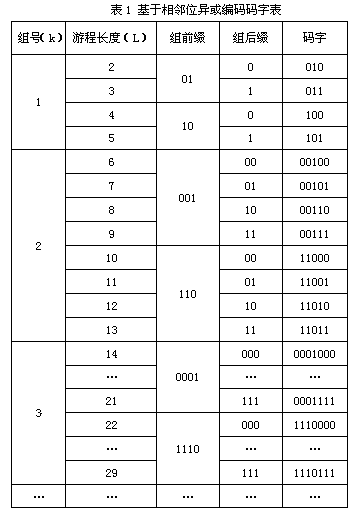

Testing data compression and decompression method based on secondary exclusive-or operation

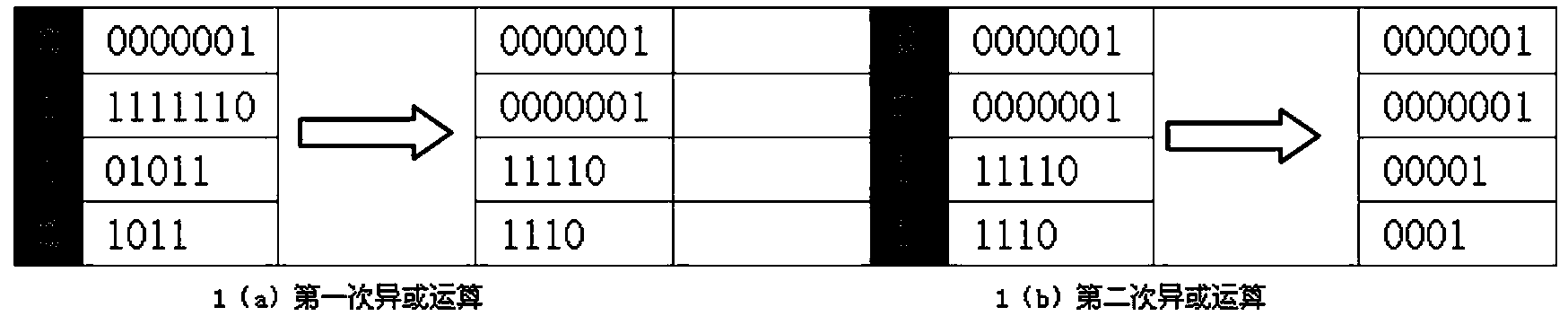

The invention provides a testing data compression and decompression method based on secondary exclusive-or operation, and the testing data compression and decompression method can reduce the partition number and increase the shortest run length so as to further improve the compression rate. The method provided by the invention can reduce the partition number and increase the shortest run length so as to further improve the compression rate by combining consecutive 01 or 10 sequences into a codeword by ortho-position exclusive-or. Through the decoding analysis, additional hardware overhead of a decoding structure of the method is less, and the method is independent of a circuit being tested, so that the method has excellent ratio of compression rate to hardware overhead.

Owner:ANQING NORMAL UNIV

Test data encoding compression method

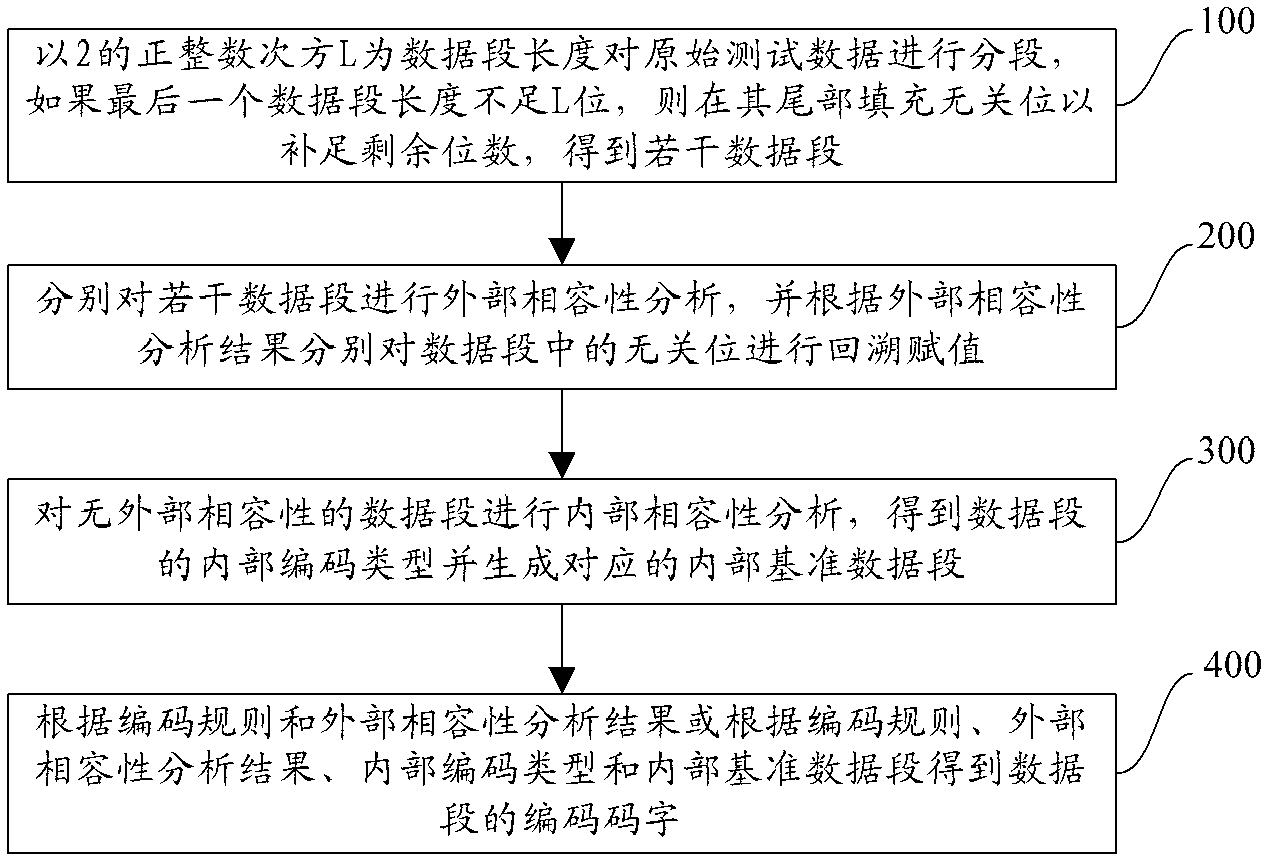

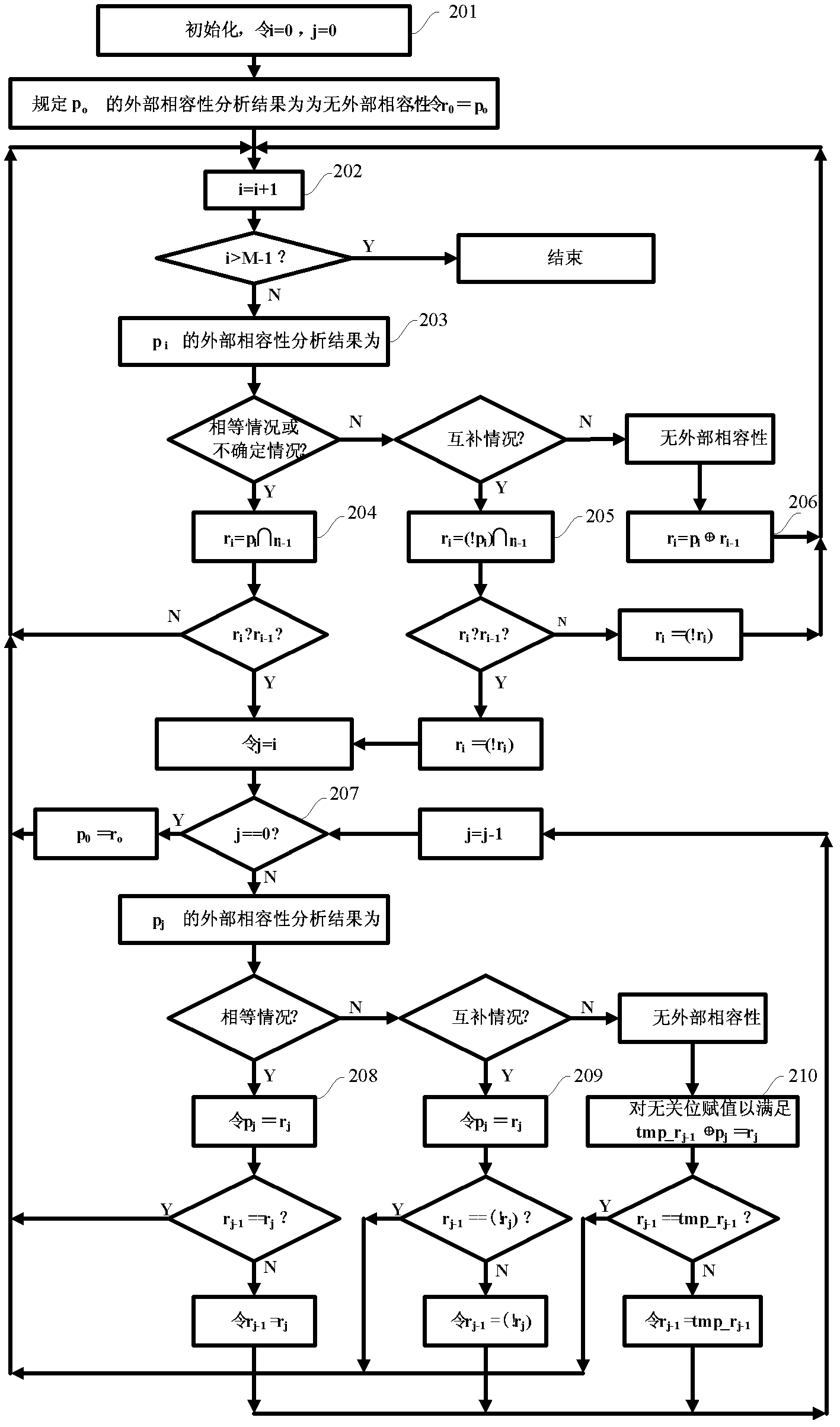

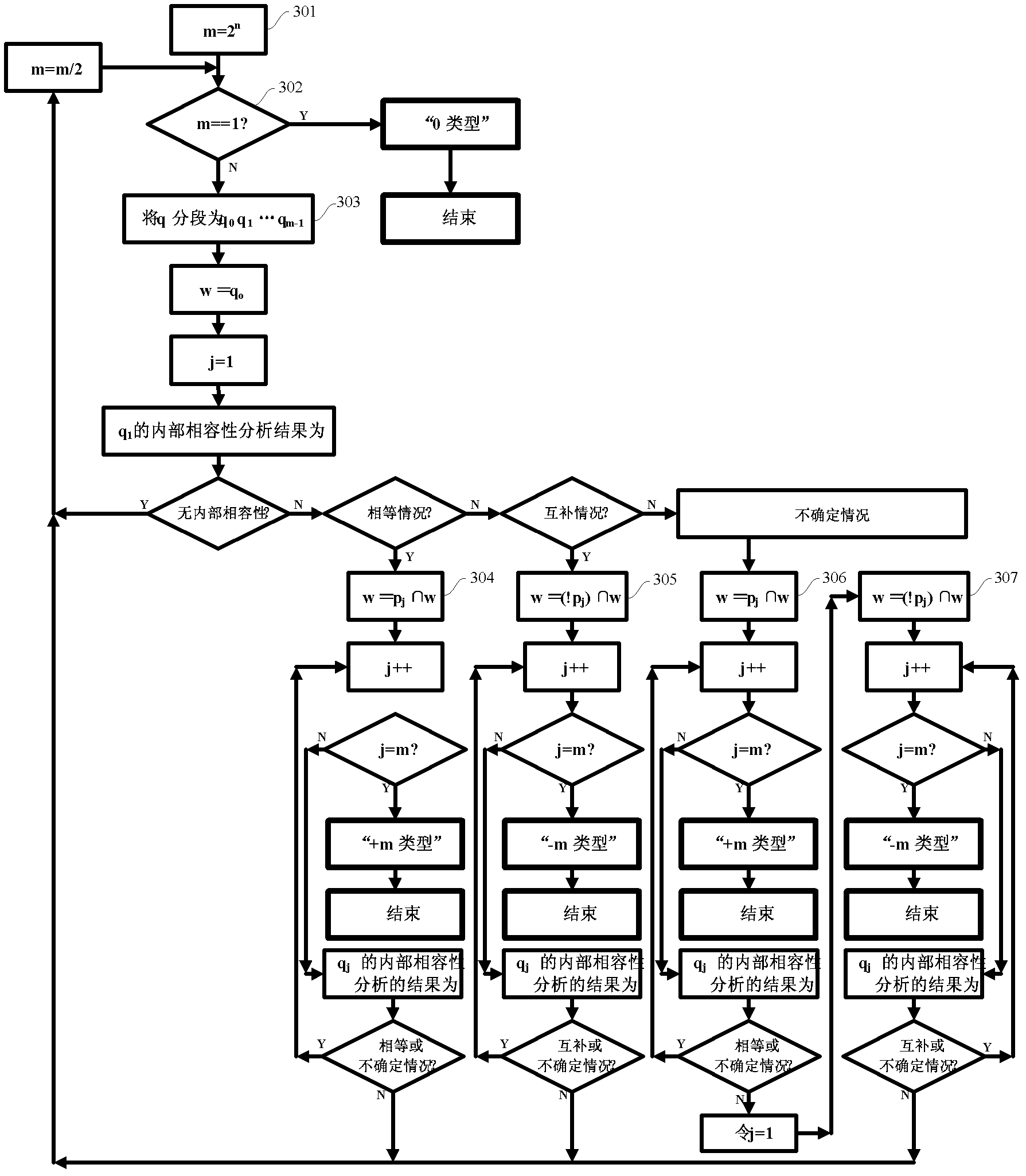

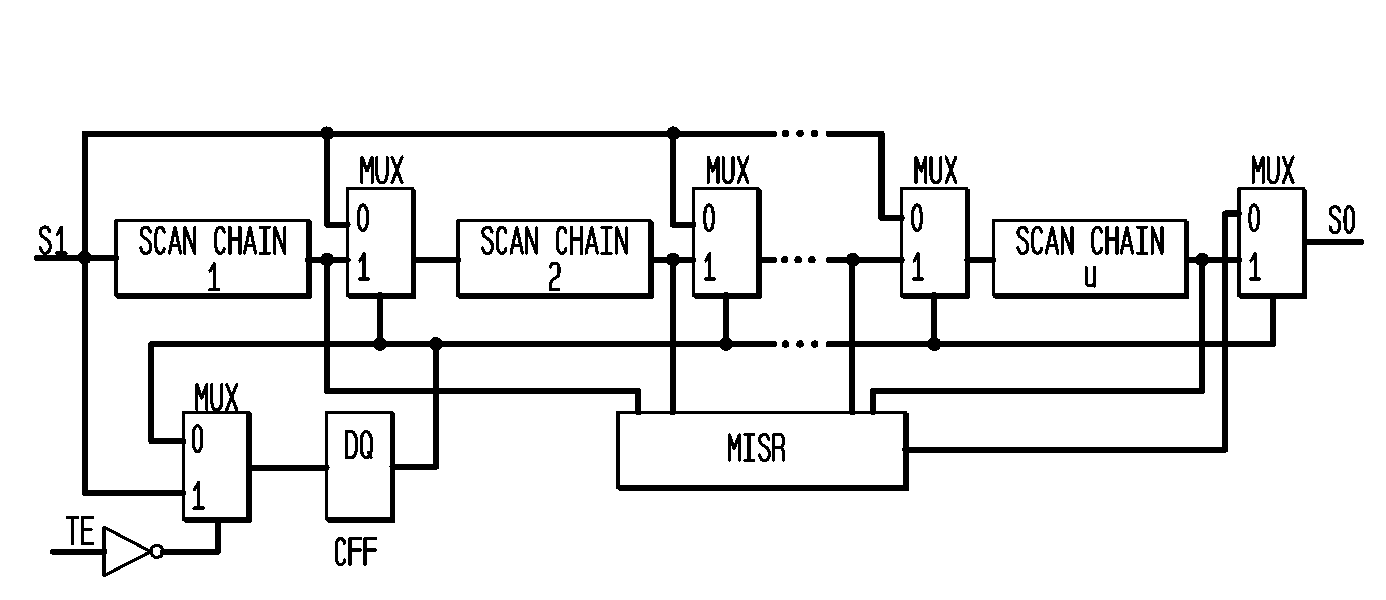

InactiveCN102592682ADouble compressionIncrease the compression ratioStatic storageComputer hardwareBaseline data

The invention relates to a test data encoding compression method. The test data encoding compression method comprises the following steps of: segmenting original test data by using L as a data section length, wherein L is a positive integer power of 2; if the length of the last data section is less than L bits, then filling X-bits at the tail part of the last data section to complement the residual bits, and obtaining a plurality of data sections; respectively carrying out external compatibility analysis on the plurality of data sections, carrying out backtracking and value assignment on the X-bits in the data sections according to an external compatibility analysis result; carrying out internal compatibility analysis on the data sections without external compatibility to obtain internal encoding types of the data sections and generate corresponding internal reference data sections; and obtaining encoding code words of the data sections according to an encoding rule and the external compatibility analysis result or according to the encoding rule, the external compatibility analysis result, the internal encoding types and the internal reference data sections. The invention has the characteristics of realizing double compression of the test data and improving test data compression ratio.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

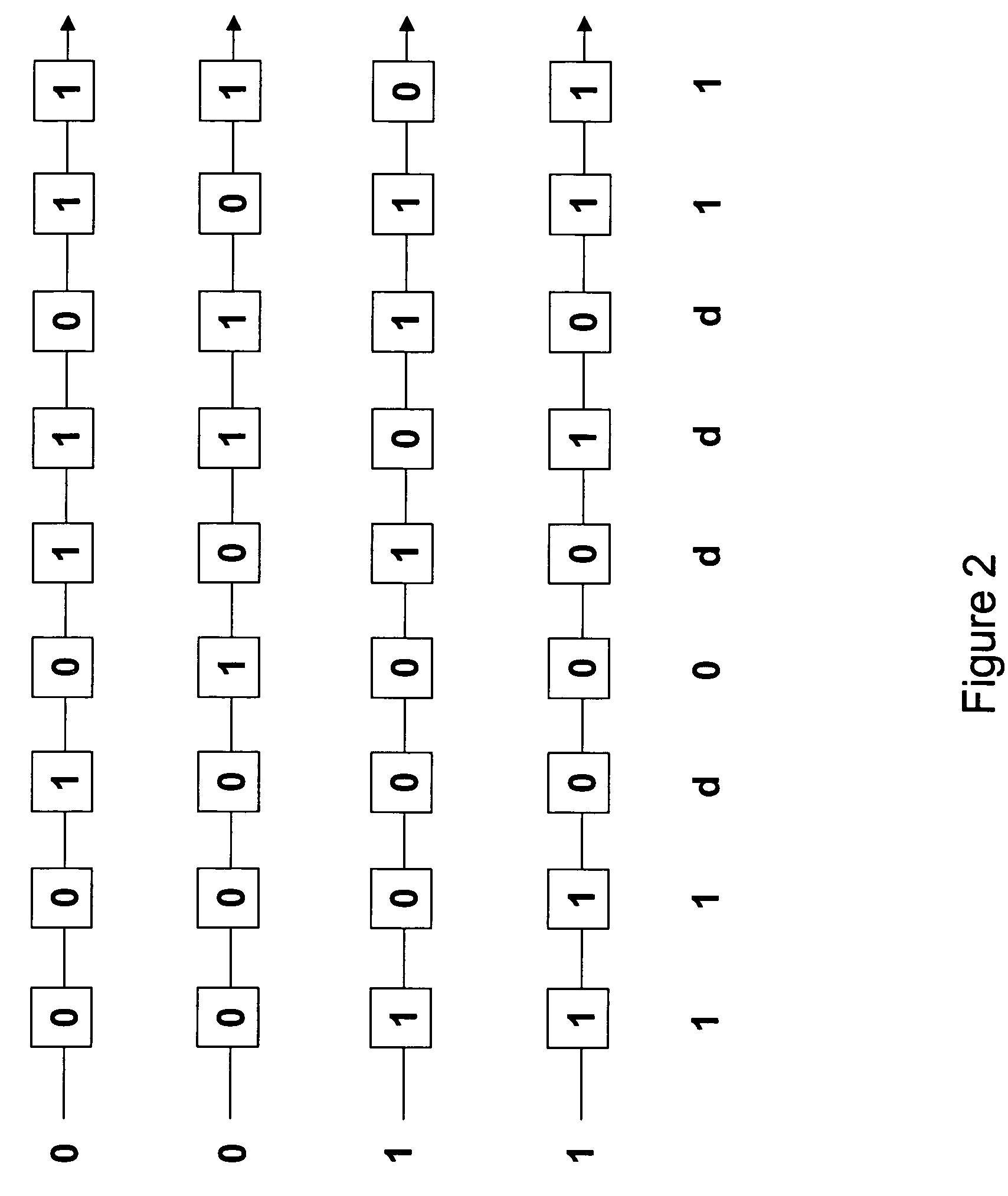

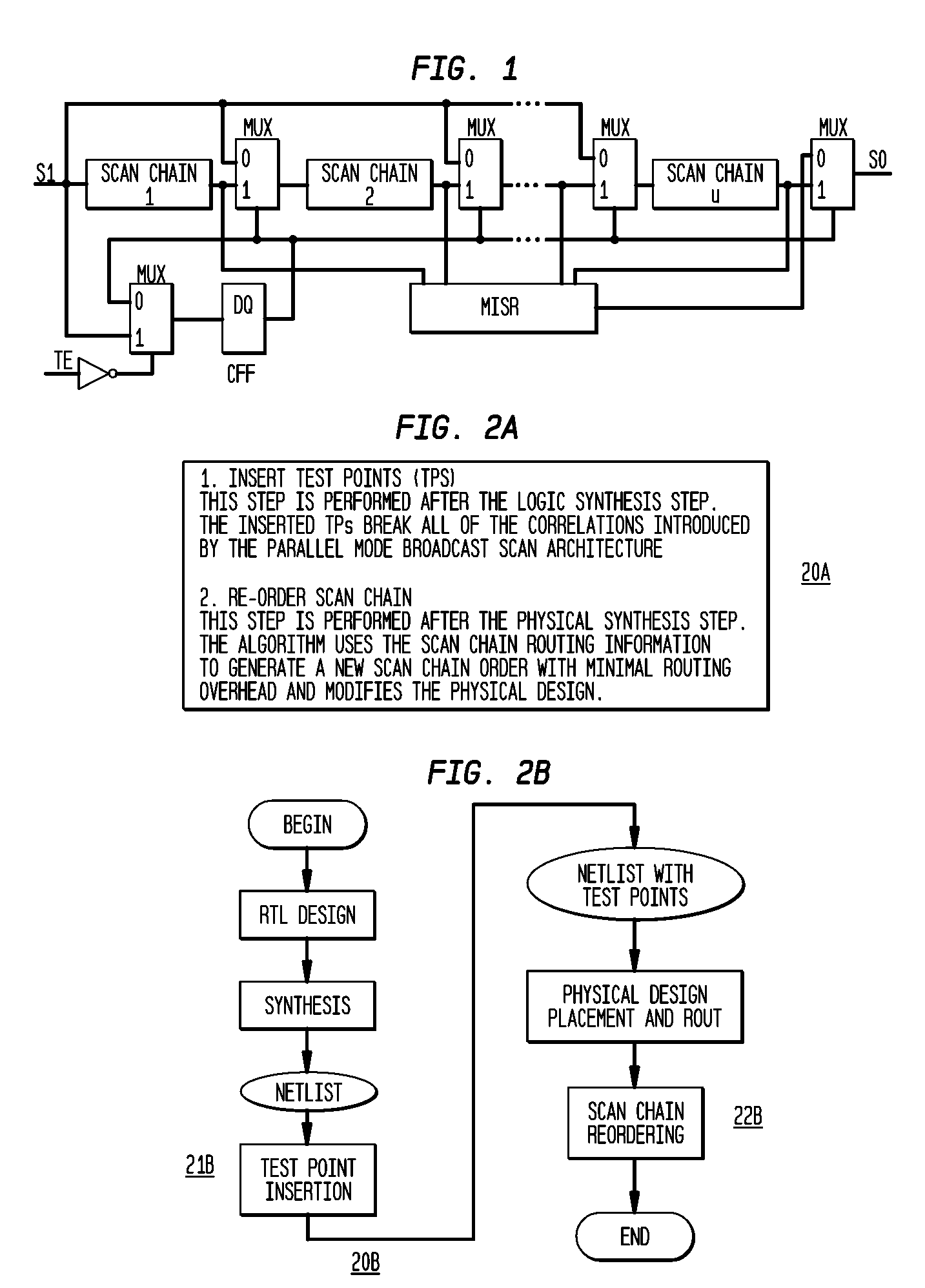

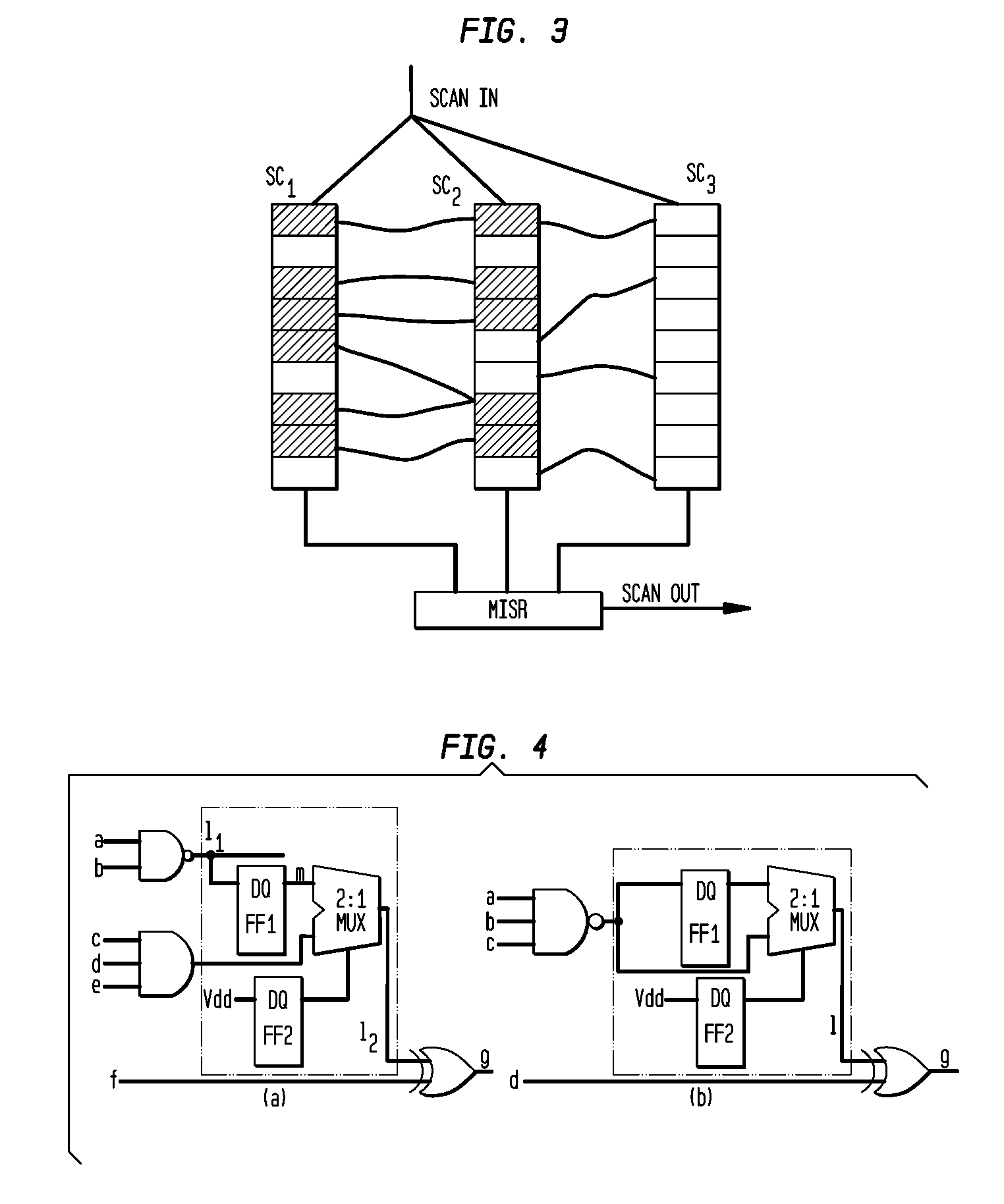

Test Point Insertion and Scan Chain Reordering for Broadcast-Scan Based Compression

InactiveUS20080195904A1Easy to compressImprove fault coverageElectronic circuit testingFunctional testingFault coverageCompression test

A method for increasing fault coverage and compression with a broadcast scan-based test data compression circuit includes inserting test points for breaking correlations existing between scan inputs that belong to same scan slices making some faults un-testable with a broadcast scan-based test data compression circuit; and reordering scan inputs for further reducing correlations between scan inputs that belong to the same scan slices.

Owner:NEC LAB AMERICA

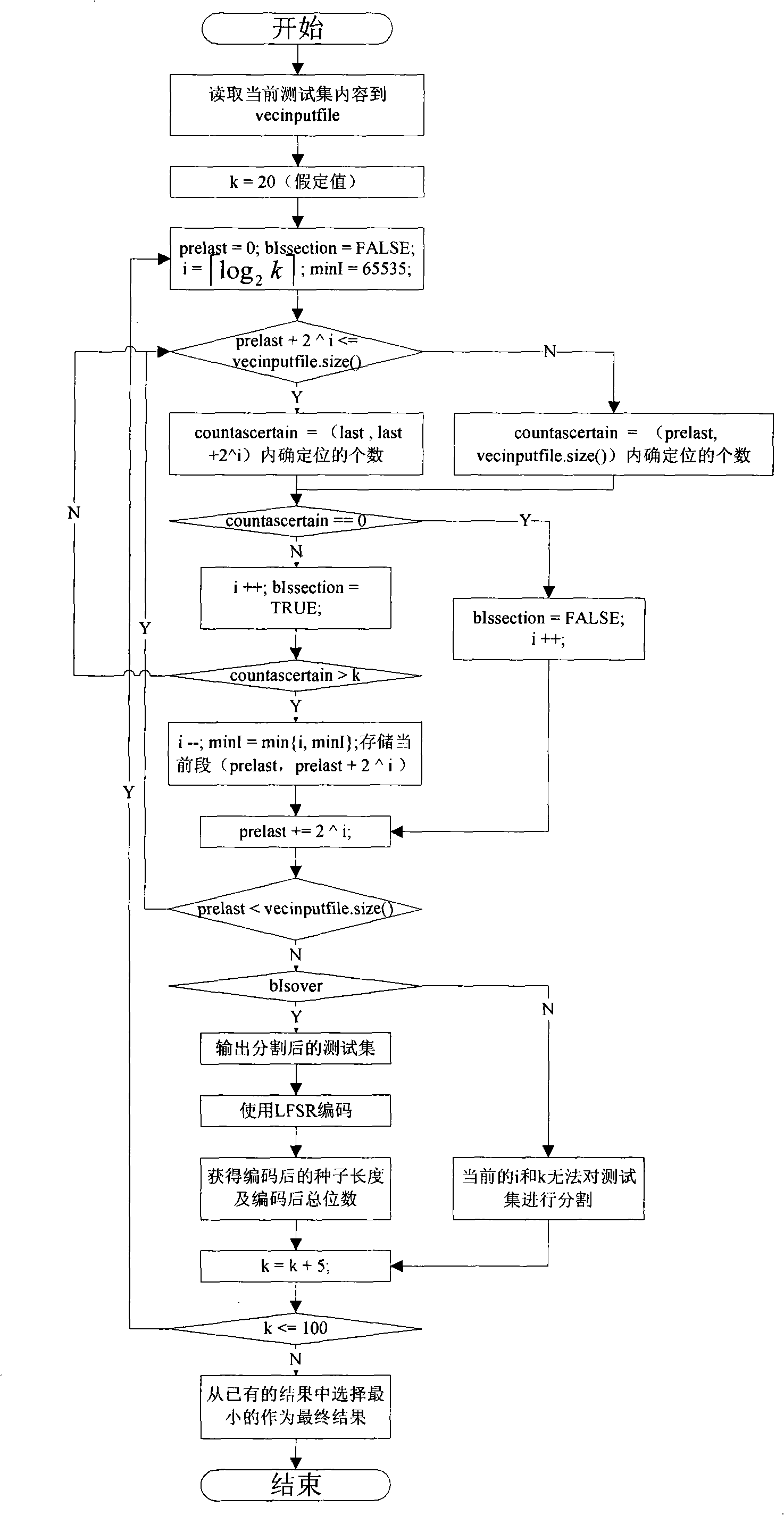

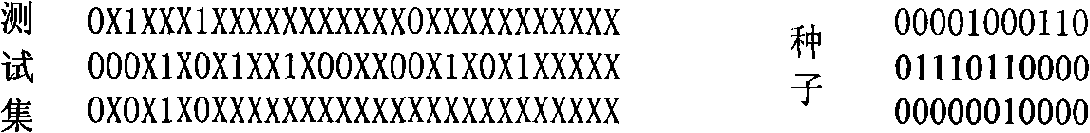

Exponent cut LFSR replanting VLSI test data compression method

InactiveCN101493499AImprove coding efficiencyShorten data lengthElectrical testingData compressionApplication time

The invention provides a method for compressing power-number-slit LFSR reseeding VLSI testing data, which is characterized in that: after the testing vector is cascaded, the segmentation is carried out according to the positioning number so that the length of each segment is just the power number of two; furthermore, the positioning number contained by each segment is equal to or less than and mostly approaching to a determinate constant k; subsequently, the compressing is carried out by a linear feedback shift register LFSR. The method is a non-invading data compressing testing method and requires no change of the structure of the circuit to be tested, in particular to the structure of the scanning chain in the circuit; furthermore, memory capacity required for data testing is reduced and the testing application time is shortened.

Owner:HEFEI UNIV OF TECH

Testing data compression code, decoding method and special decoding element of slice system

The method is as the follows. To make statistic for the ratio of 0 and 1 in original test data, all extranous bits are assigned to be 0 and to code as per 0 string if 0 data bits are less then, data bits in the original test data, otherwise to code as per 1 string. Using bit sting as basic unit to divide the said test data for counting length of the bit string code table of adaptive variable length compression method is utilized to convert bit string length into code word to achieve data compression. The decoding method uses decoding unit organized with adaptive variable length compression method to carry on decoding.

Owner:TSINGHUA UNIV

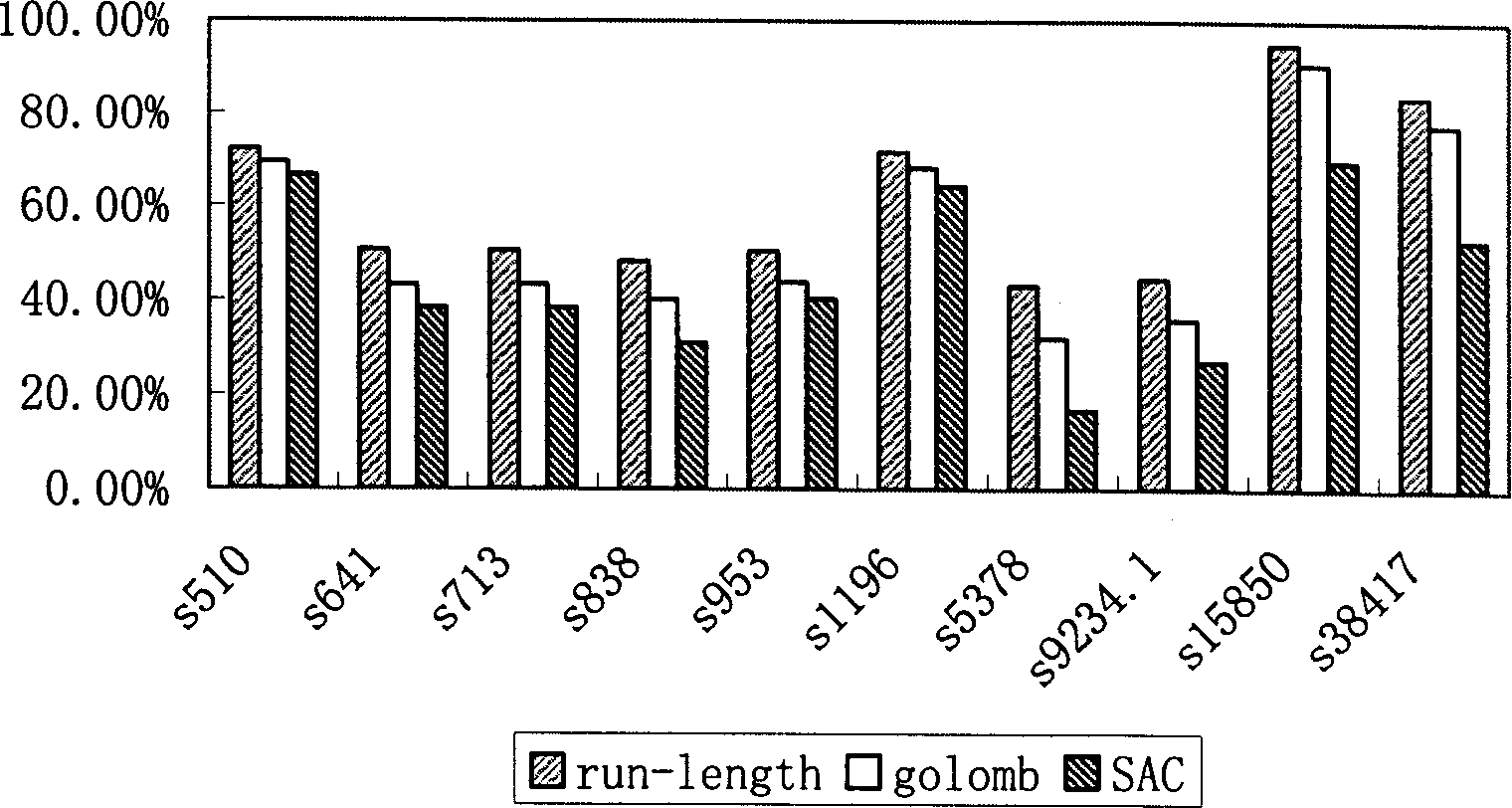

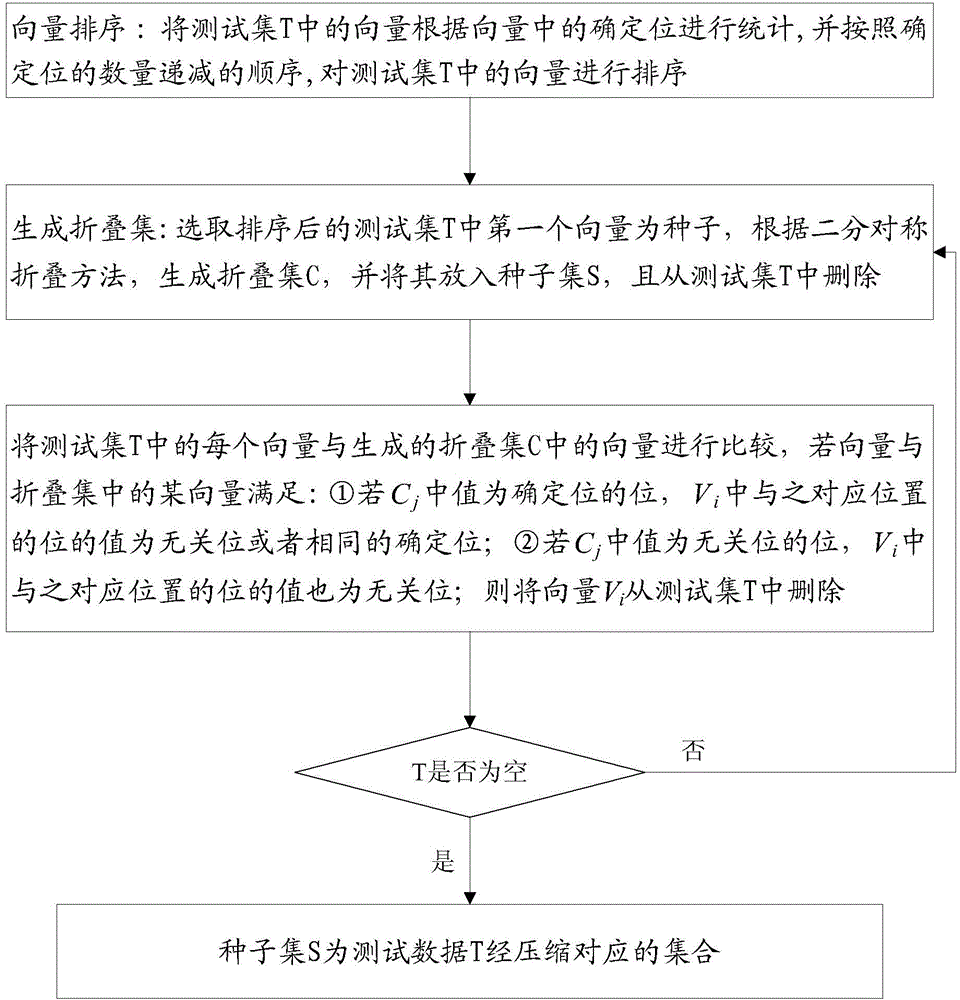

Method of efficiently compressing and decompressing test data using input reduction

A new test data compression method and decompression apparatus is invented for SoC (System-on-a-Chip) architecture. The method is based on analyzing the factors that influence test parameters: compression ratio and hardware overhead. To improve compression ratio, the proposed method is based on Modified Statistical Coding (MSC) and input reduction (IR) scheme, as well as a novel mapping and re-ordering algorithm proposed in a preprocessing step. Unlike previous approaches using the CSR architecture, the inventive method is to compress original test data, but not Tdiff, and decompress the compressed test data without the CSR architecture. Therefore, the proposed method leads to better compression ratio with lower hardware overhead than previous works. An experimental comparison on ISCAS '89 benchmark circuits validates the proposed method.

Owner:KANG SUNG HO +3

Testing data compression and decompression method based on ortho-position exclusive or operation

InactiveCN104038233AReduce overheadReduce the number of runsCode conversionData compressionOrtho position

The invention aims to deal with overlarge testing data number to provide a testing data compression and decompression method based on ortho-position exclusive-or operation, and the testing data compression and decompression method can reduce the partition number and increase the shortest run length by using a ortho-position exclusive-or method to combine consecutive 01 or 10 sequences into a codeword, wherein the consecutive 01 or 10 sequences are respectively sued as one codeword of one run; and experimental results show that the compression ratio is further improved. Through the decoding analysis, additional hardware overhead of a decoding structure of the method is less, and the method is independent of a circuit being tested, so that the method has excellent ratio of compression rate to hardware overhead.

Owner:ANQING NORMAL UNIV

Compression method for test data of irrational number storage test vector

ActiveCN104753541AReduce the number of codesReduce the number of test vectorsElectronic circuit testingCode conversionFault coverageCompression method

The invention discloses a compression method for test data of an irrational number storage test vector and relates to a fault coverage guided compression method for the test data of the irrational number storage test vector. The compression method comprises the following steps of firstly, generating a fault list according to a circuit structure of an integrated circuit to be tested; secondly, running an automatic test vector generation tool for faults to generate test vectors of corresponding faults; thirdly, counting the lengths of runs; fourthly, performing preliminary estimation on corresponding ranges of irrational numbers; fifthly, dichotomising the ranges of the irrational numbers, and successively approximating; sixthly, filling independent bits; seventhly, performing random test; eighthly, judging whether the fault list in the seventh step is empty or not, if the fault list is empty, turning to the ninth step, and otherwise, turning to the second step; ninthly, ending, and returning all records such as integers m and l corresponding to all the irrational numbers. According to the compression method disclosed by the invention, the coding of the irrational numbers and the generation of the automatic test vectors are combined, so that on one hand, coding numbers, corresponding to the test vectors, of easily-detected fault points are reduced, and on the other hand, the fault coverage is improved.

Owner:池州华宇电子科技股份有限公司

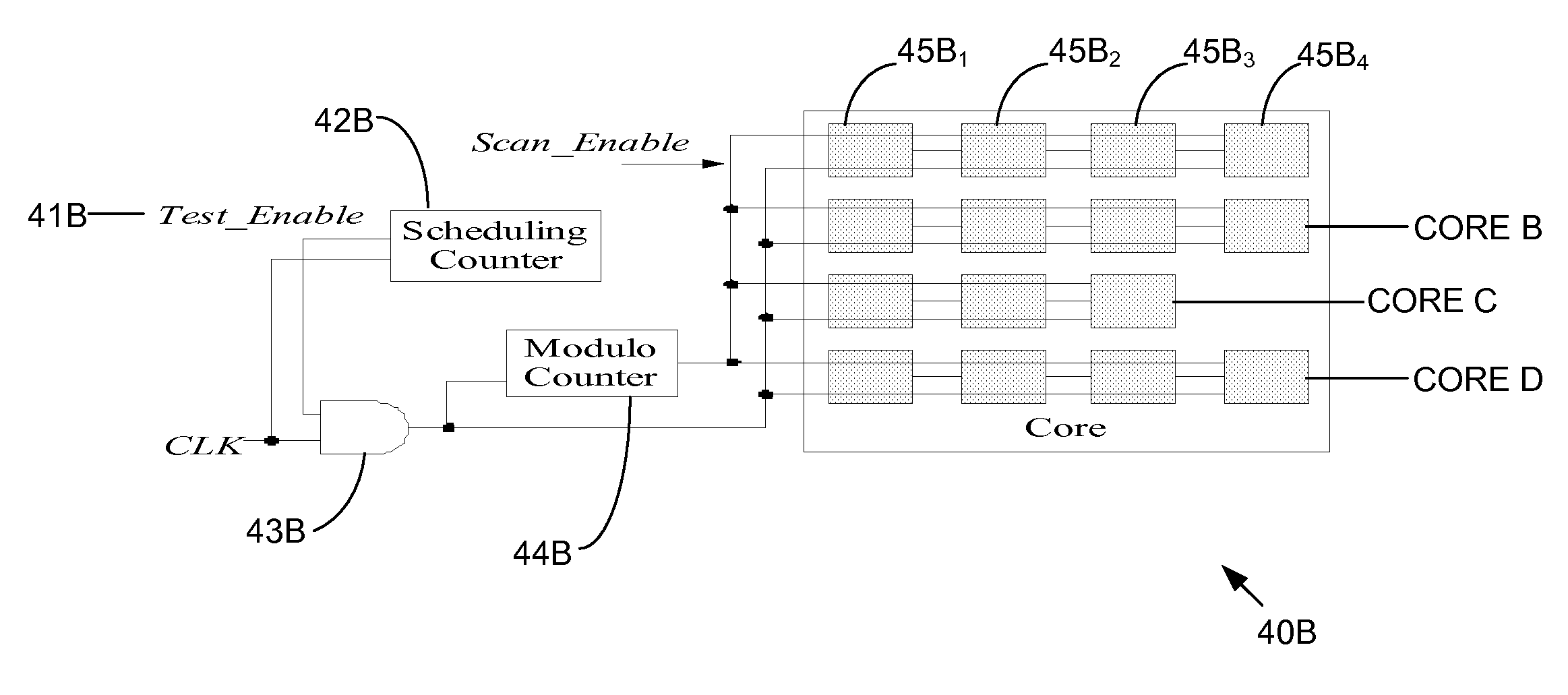

Accelerated scan circuitry and method for reducing scan test data volume and execution time

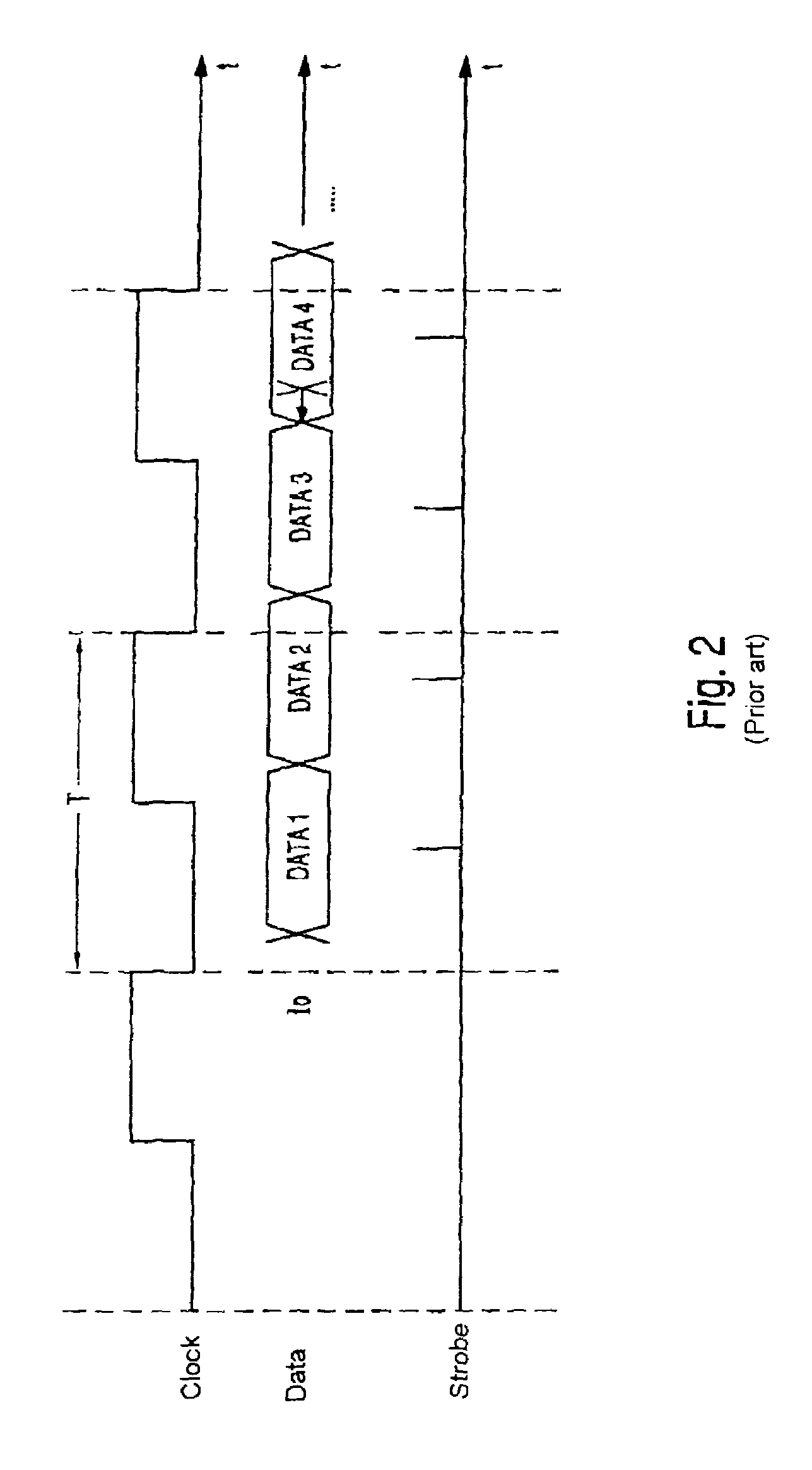

InactiveUS20050154948A1Shorten the timeReduce volumeElectronic circuit testingError detection/correctionCouplingControl signal

An architecture and methodology for test data compression using combinational functions to provide serial coupling between consecutive segments of a scan-chain are described. Compressed serial-scan sequences are derived starting from scan state identifying desired Care_In values and using symbolic computations iteratively in order to determine the necessary previous scan-chain state until computed previous scan-chain state matches given known starting scan-chain state. A novel design for a new flip-flop is also presented that allows implementing scan-chains that can be easily started and stopped without requiring an additional control signal. Extensions of the architecture and methodology are discussed to handle unknown (X) values in scan-chains, proper clocking of compressed data into multiple scan-chains, the use of a data-spreading network and the use of a pseudo-random signal generator to feed the segmented scan-chains in order to implement Built In Self Test (BIST).

Owner:AMERICAN PATENTS LLC

Accelerated scan circuitry and method for reducing scan test data volume and execution time

InactiveUS20050028060A1Avoid excessive data volumeReduce the numberElectronic circuit testingError detection/correctionCouplingControl signal

An architecture and methodology for test data compression using combinational functions to provide serial coupling between consecutive segments of a scan-chain are described. Compressed serial-scan sequences are derived starting from scan state identifying desired Care_In values and using symbolic computations iteratively in order to determine the necessary previous scan-chain state until computed previous scan-chain state matches given known starting scan-chain state. A novel design for a new flip-flop is also presented that allows implementing scan-chains that can be easily started and stopped without requiring an additional control signal. Extensions of the architecture and methodology are discussed to handle unknown (X) values in scan-chains, proper clocking of compressed data into multiple scan-chains, the use of a data-spreading network and the use of a pseudo-random signal generator to feed the segmented scan-chains in order to implement Built In Self Test (BIST).

Owner:INTELLECTUAL VENTURES I LLC +1

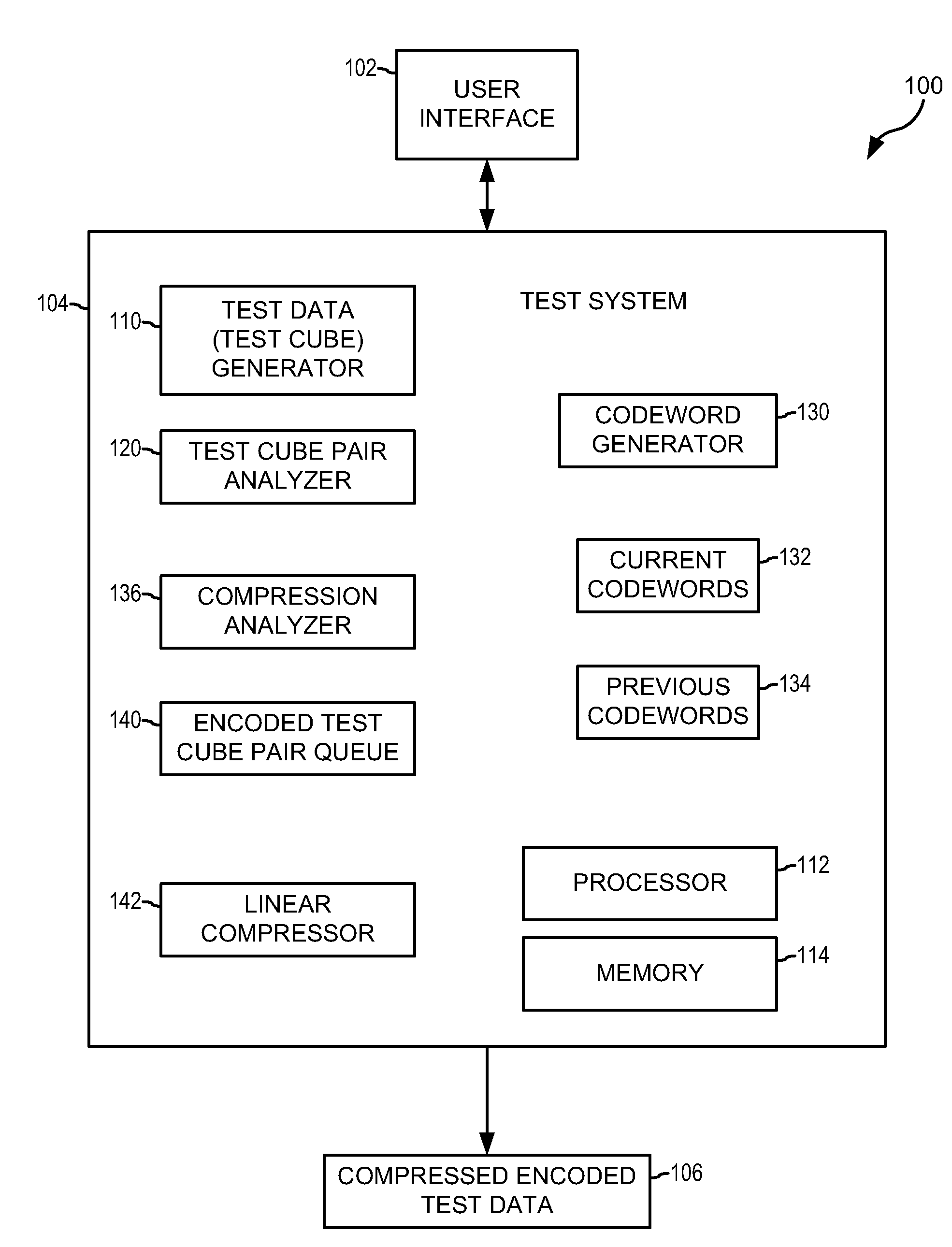

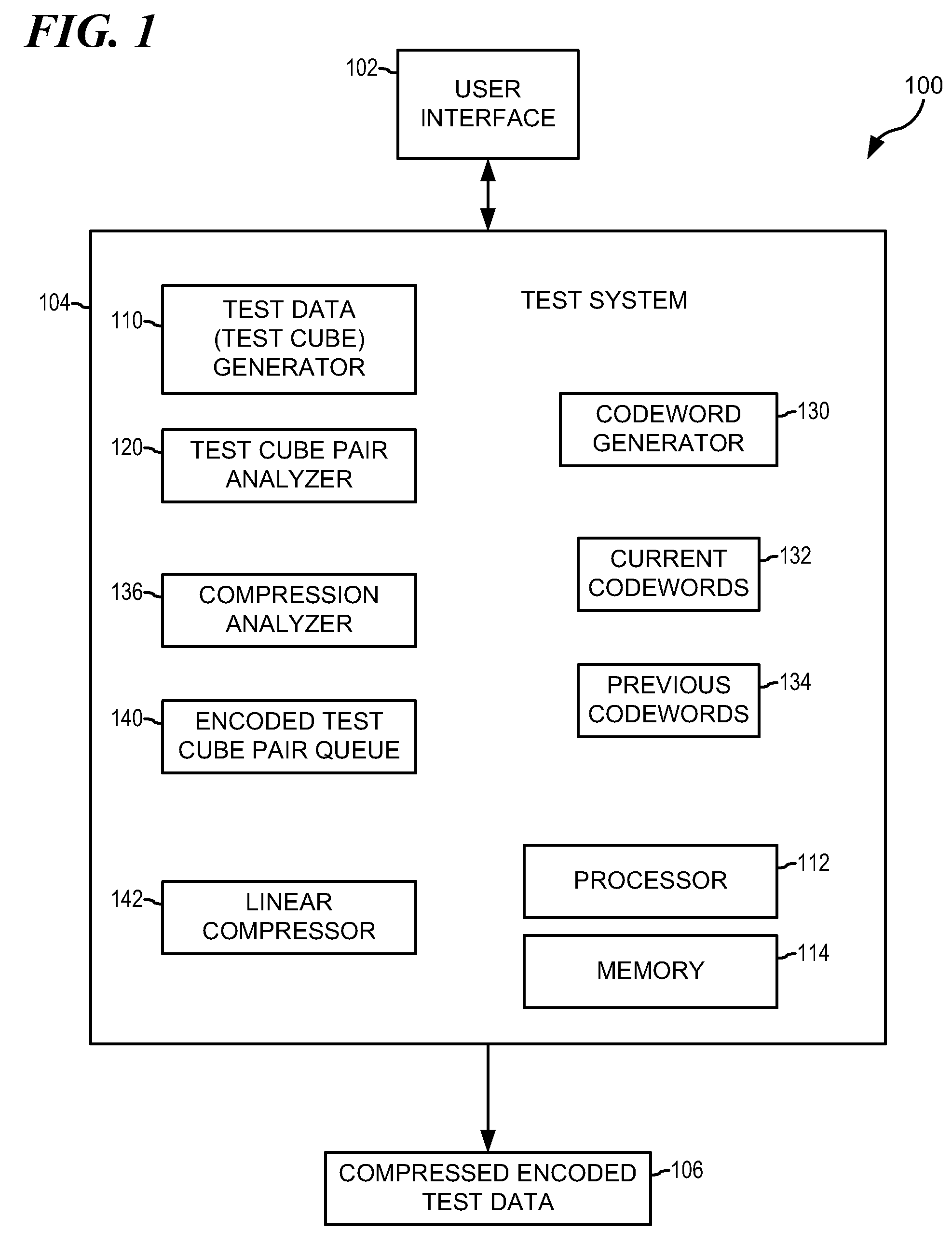

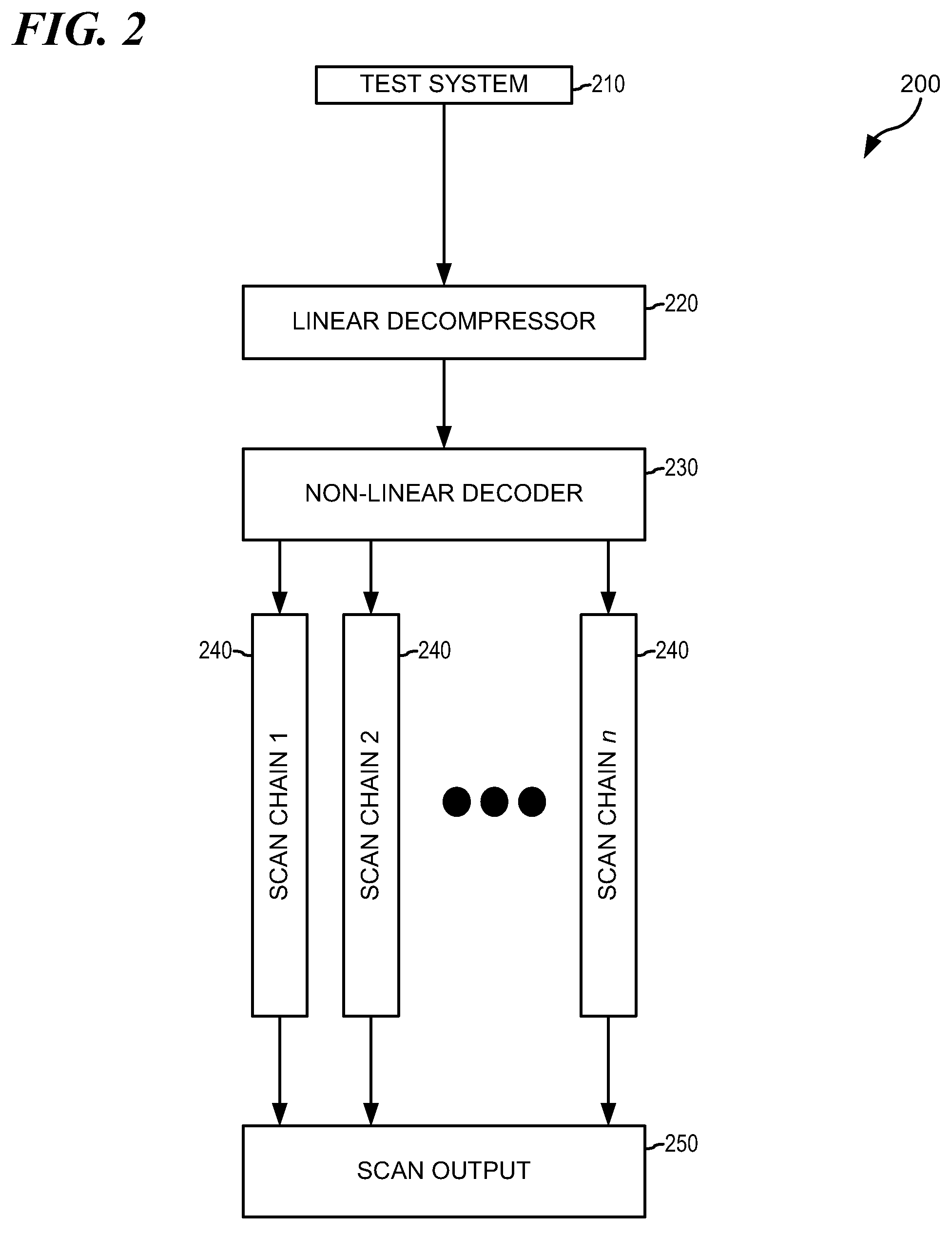

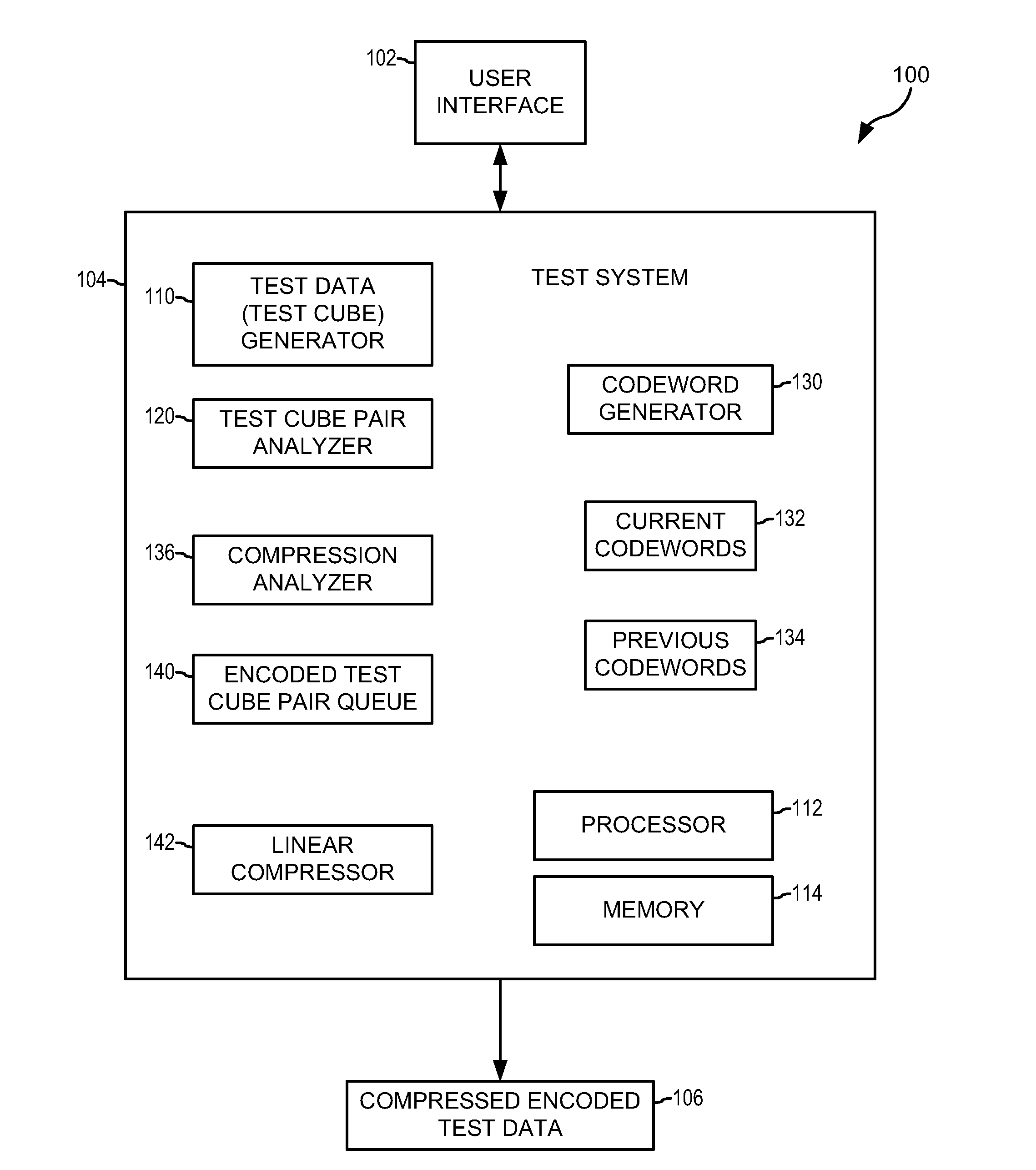

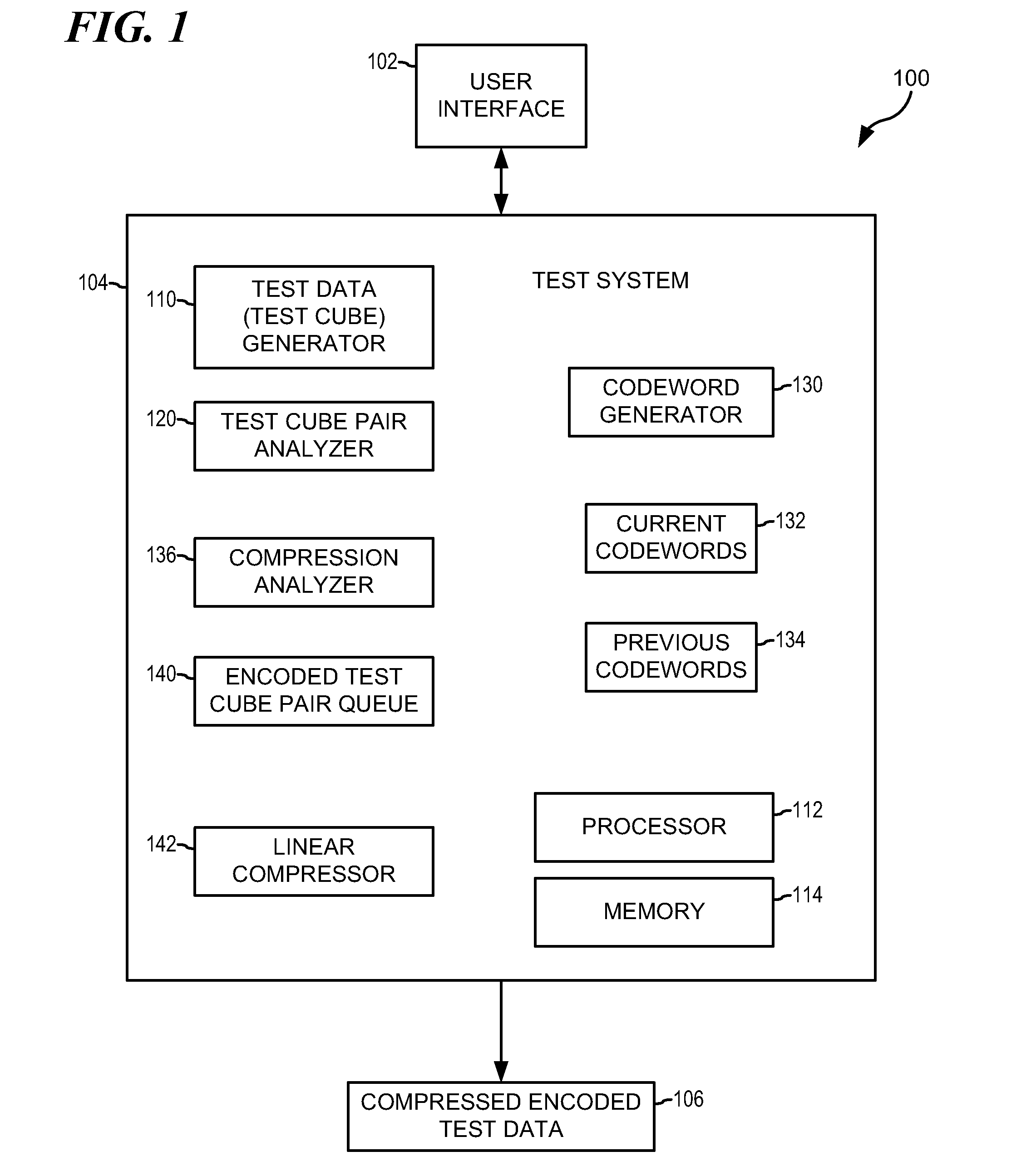

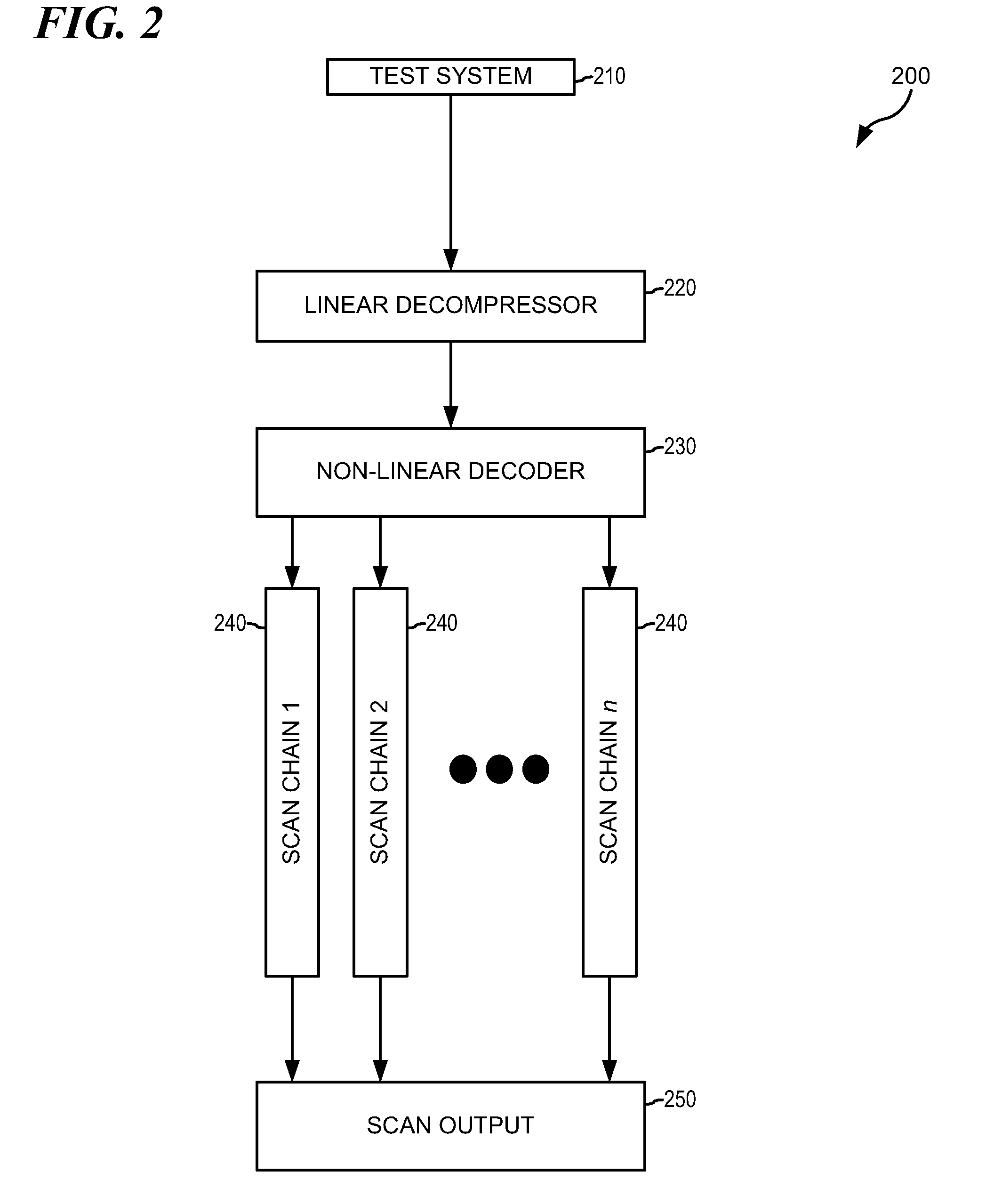

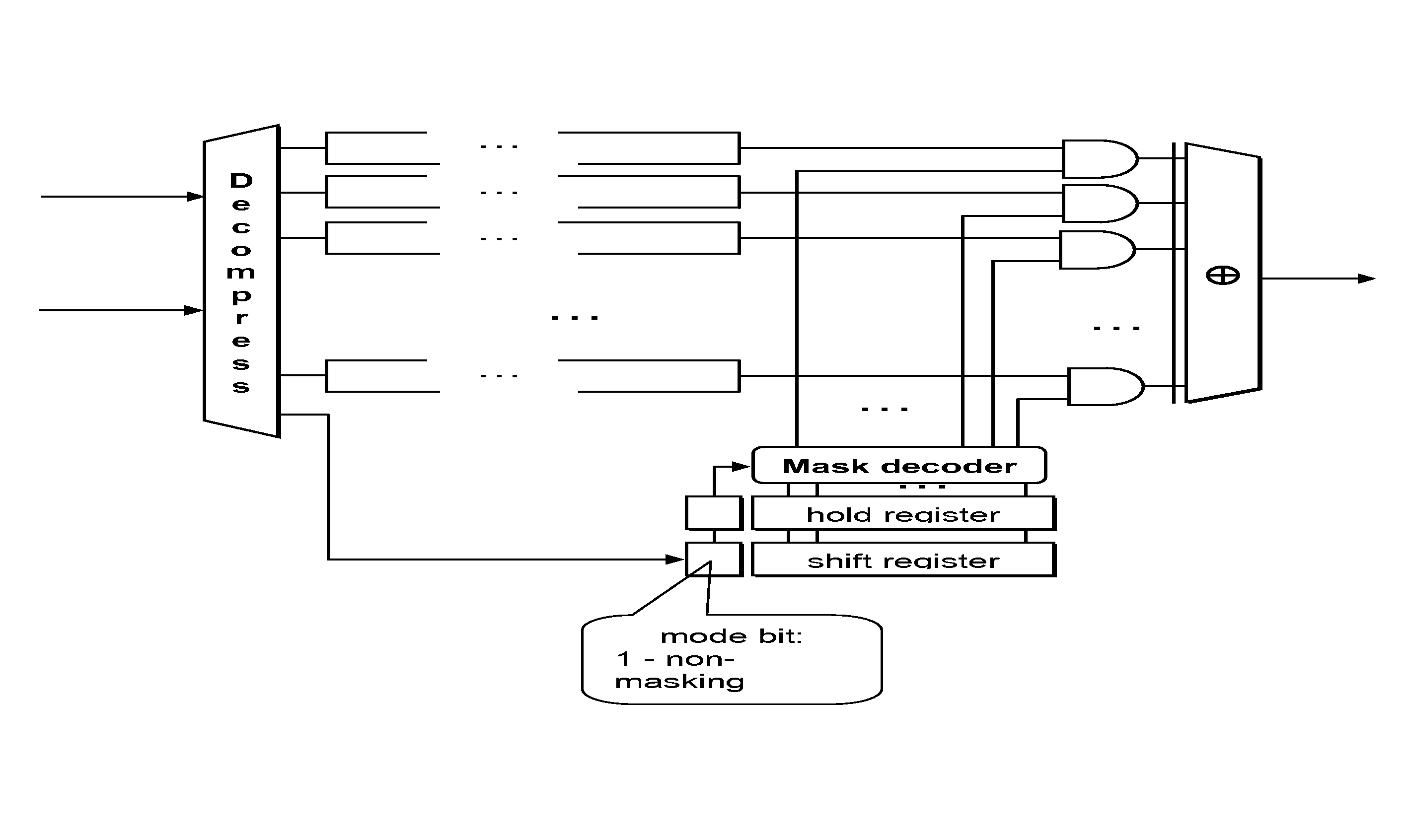

System and Method for Adaptive Nonlinear Test Vector Compression

InactiveUS20080263418A1Electronic circuit testingError detection/correctionData compressionParallel computing

A system comprises a decompressor configured to receive an input test vector and to generate an output vector in response to the input test vector. A decoder couples to the decompressor and comprises a reset pattern detector, a lookup table, and control logic. The reset pattern detector (RPD) is configured to scan the output vector to identify a predetermined reset pattern. The control logic couples to the RPD and the lookup table and is configured to direct operation of the lookup table in a first mode or a second mode based on whether the output vector comprises the predetermined reset pattern, as identified by the RPD. The lookup table is configured to receive the output vector, to operate in the first mode, comprising storing one of a plurality of codeword sets, each codeword set comprising a plurality of pairs of codewords and associated data; and to operate in the second mode, comprising generating test data blocks in response to identified codewords in the output vector.A method for adaptive test data compression includes receiving an input vector. The input vector is decompressed to generate an output vector. A determination is made whether the output vector comprises a reset pattern. In the event the output vector comprises a reset pattern, one of a plurality of codeword sets is loaded into a lookup table; each codeword set comprising a plurality of pairs of codewords and associated data. In the event the output vector does not comprise a reset pattern, codewords in the output vector are identified and test data blocks are generated in response to identified codewords.

Owner:IBM CORP

System and Method for Nonlinear Statistical Encoding in Test Data Compression

InactiveUS20080263423A1Easy to understandElectronic circuit testingError detection/correctionComputer hardwareComparative test

A method for test data compression includes generating a plurality of test cubes, each test cube comprising test cube data. Each test cube is compared with at least one other test cube, as test cube pairs, to generate a compatibility rating for each compared test cube pair. The compared test cube pair with the highest compatibility rating is determined. The compared test cube pair with the highest compatibility rating is grouped into a test cube set. The remaining test cubes are grouped into test cube sets, as test cube pairs, based on the compatibility ratings of the compared test cube pairs.For at least one test cube set, a new codeword set is generated. Test cube data is grouped into blocks based on the new codeword set. Compression for the grouped test cube data is computed. A determination is made whether compression is improved as compared to a previous codeword set. If compression is not improved, the test cube set is encoded with the new codeword set to generate an encoded test cube set. If compression is improved, the previous codeword set is set as the new codeword set, and the steps are repeated beginning with generating a new codeword set. The encoded test cube sets are concatenated to form a decompressed encoded test stream. The decompressed encoded test stream is compressed to form a compressed test stream.

Owner:IBM CORP

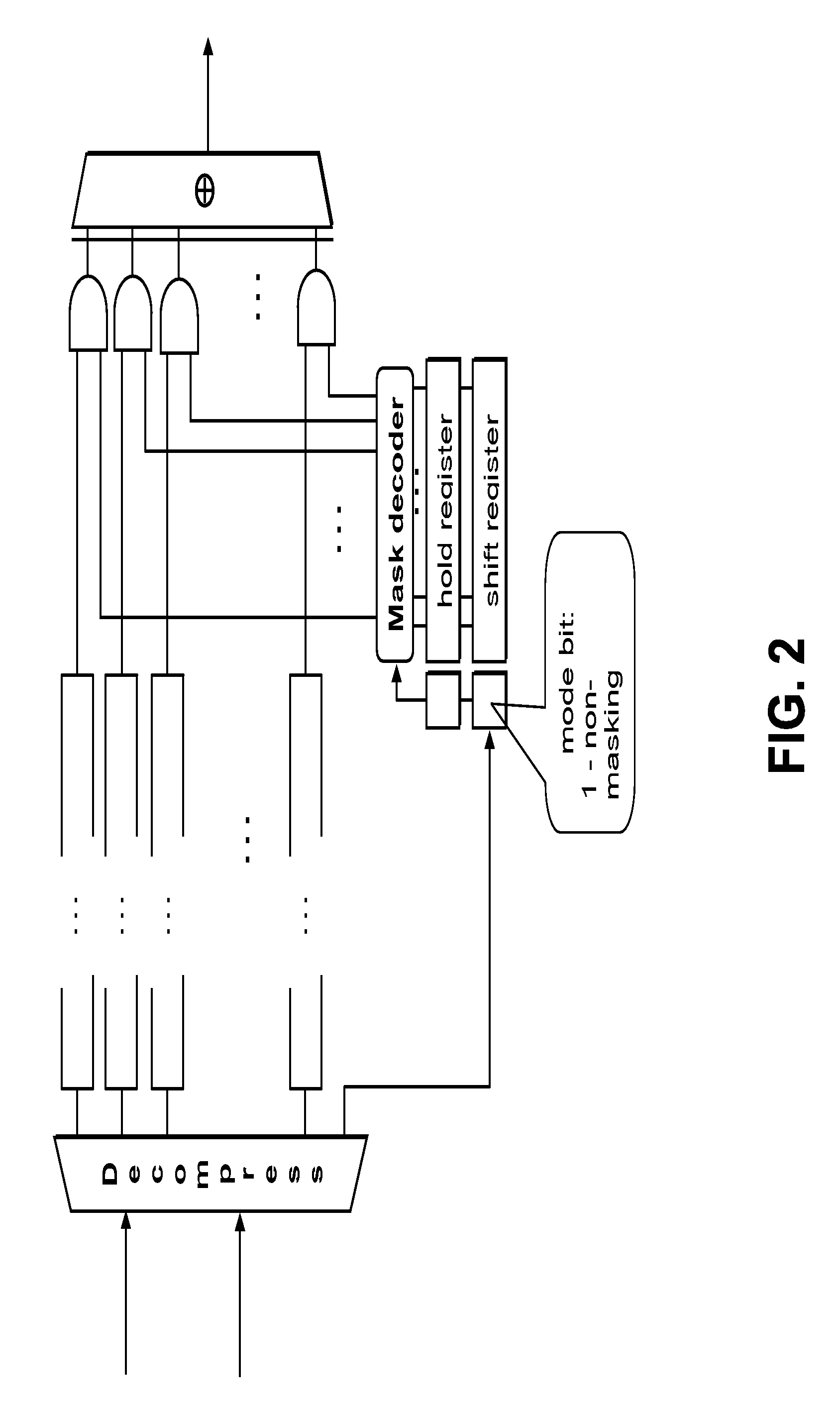

Accurately identifying failing scan bits in compression environments

X-masking registers are added in front of a compactor in test data compression environment to remove unknown values. The X-masking registers block out some chains due to unknown values and select other chains to feed the compactor. This X-masking capability is used to select one scan cell to observe at a time after a failure is observed at the compactor output.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

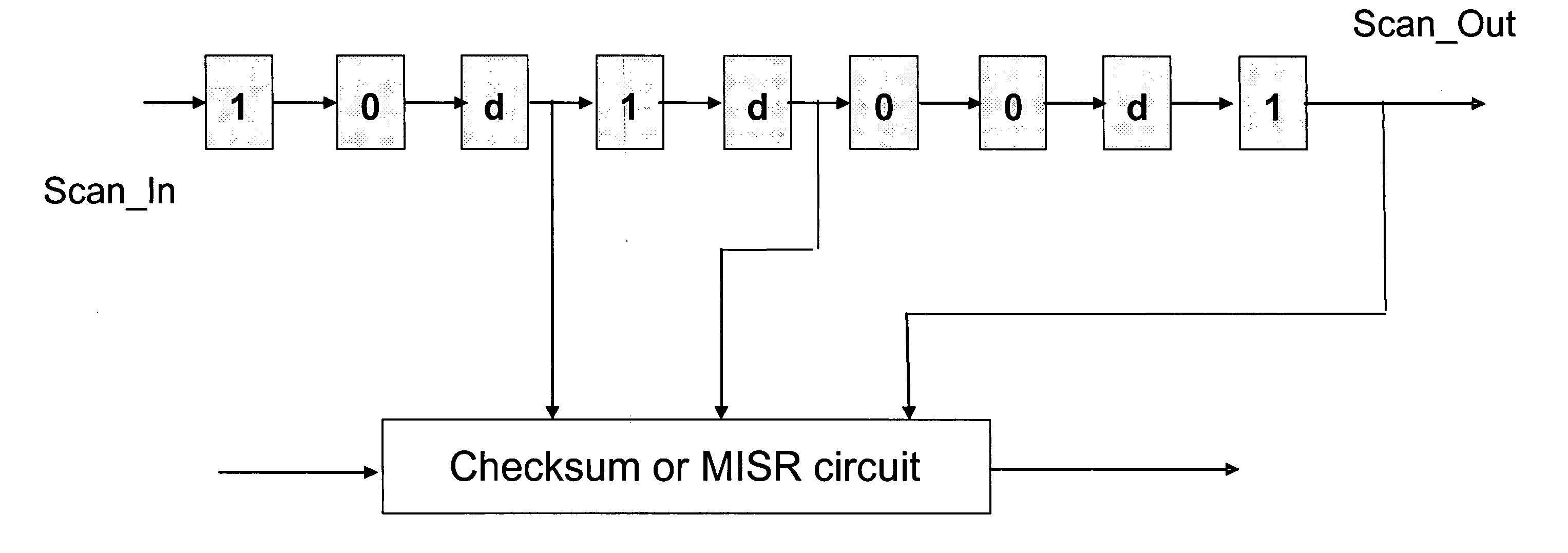

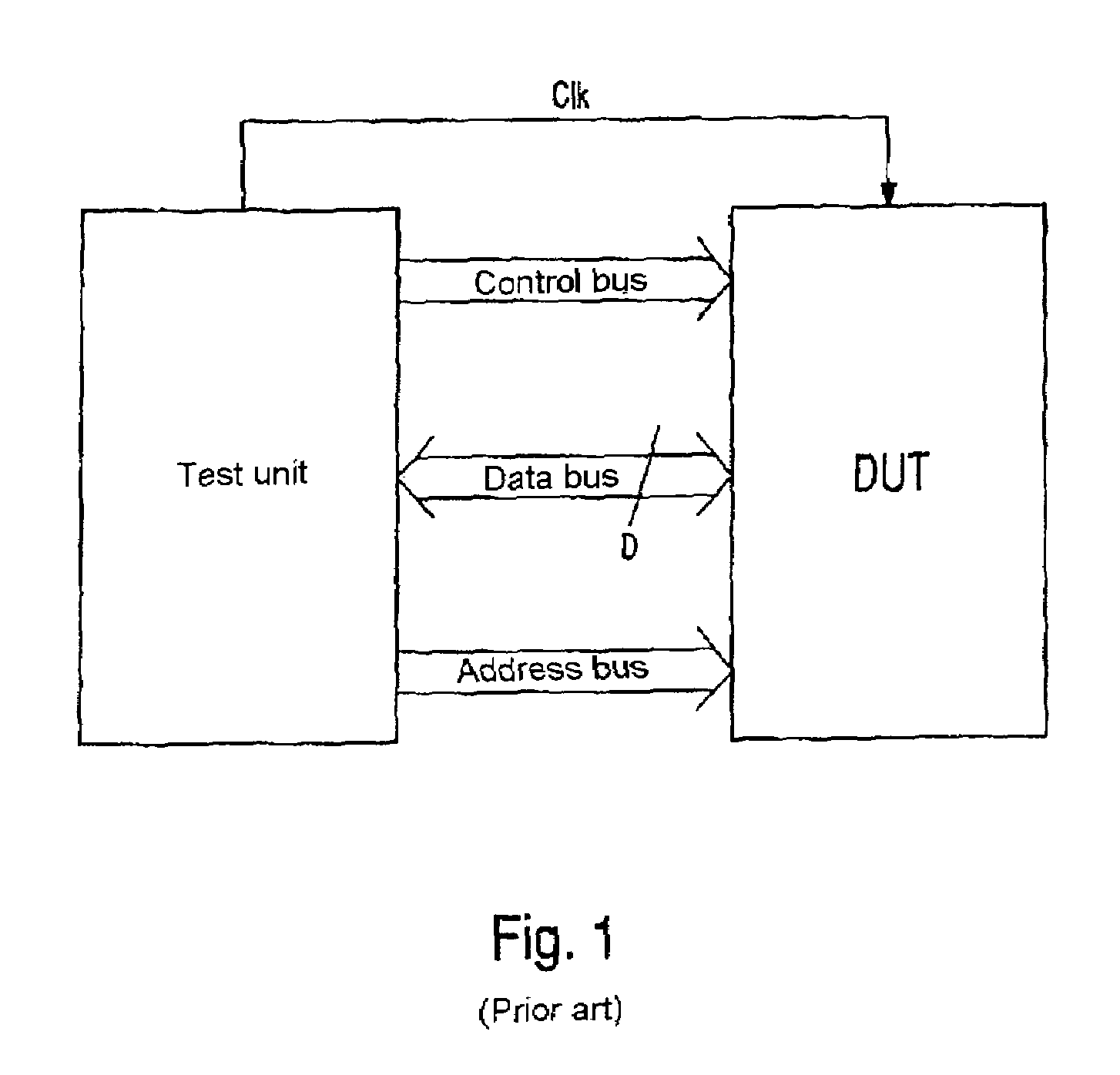

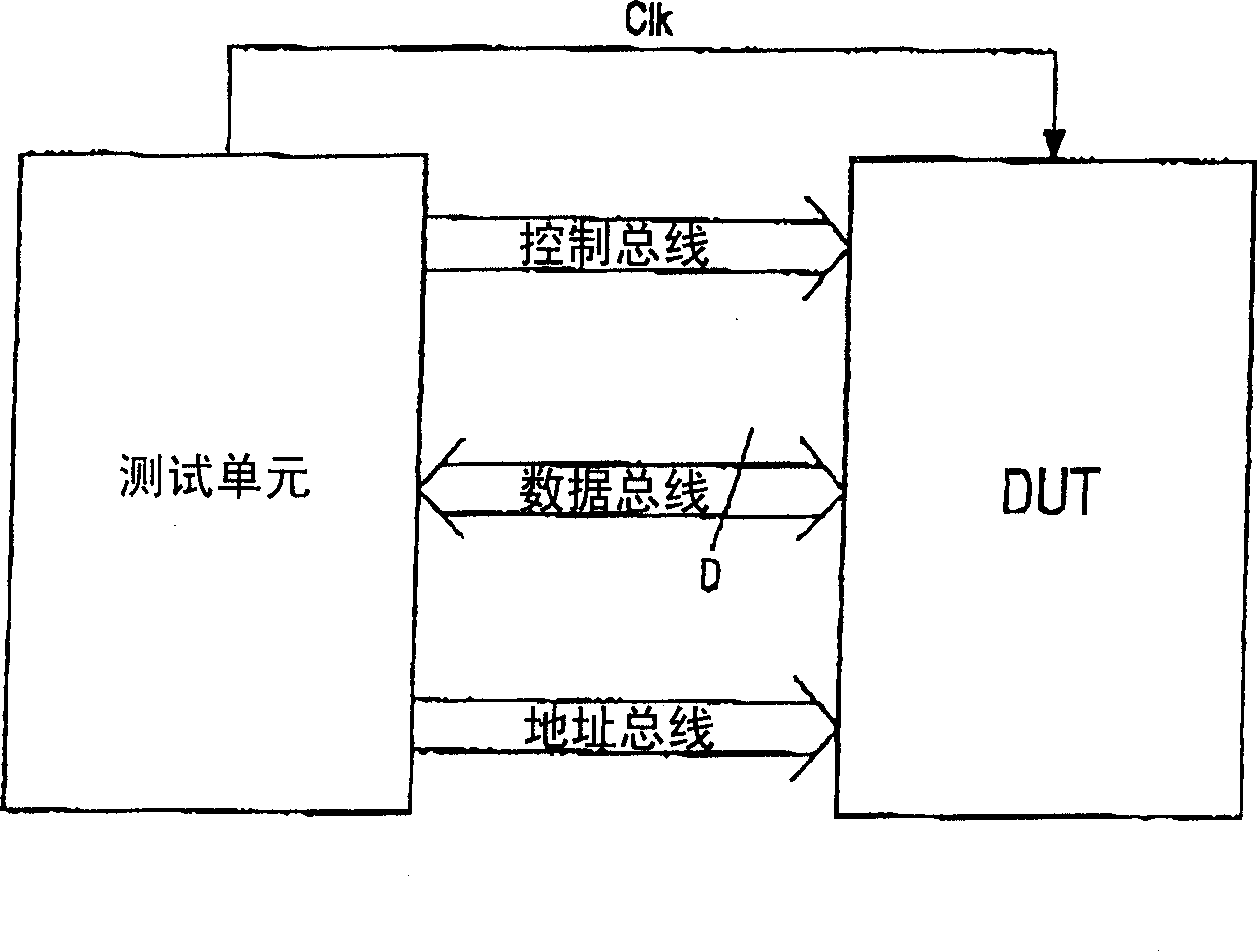

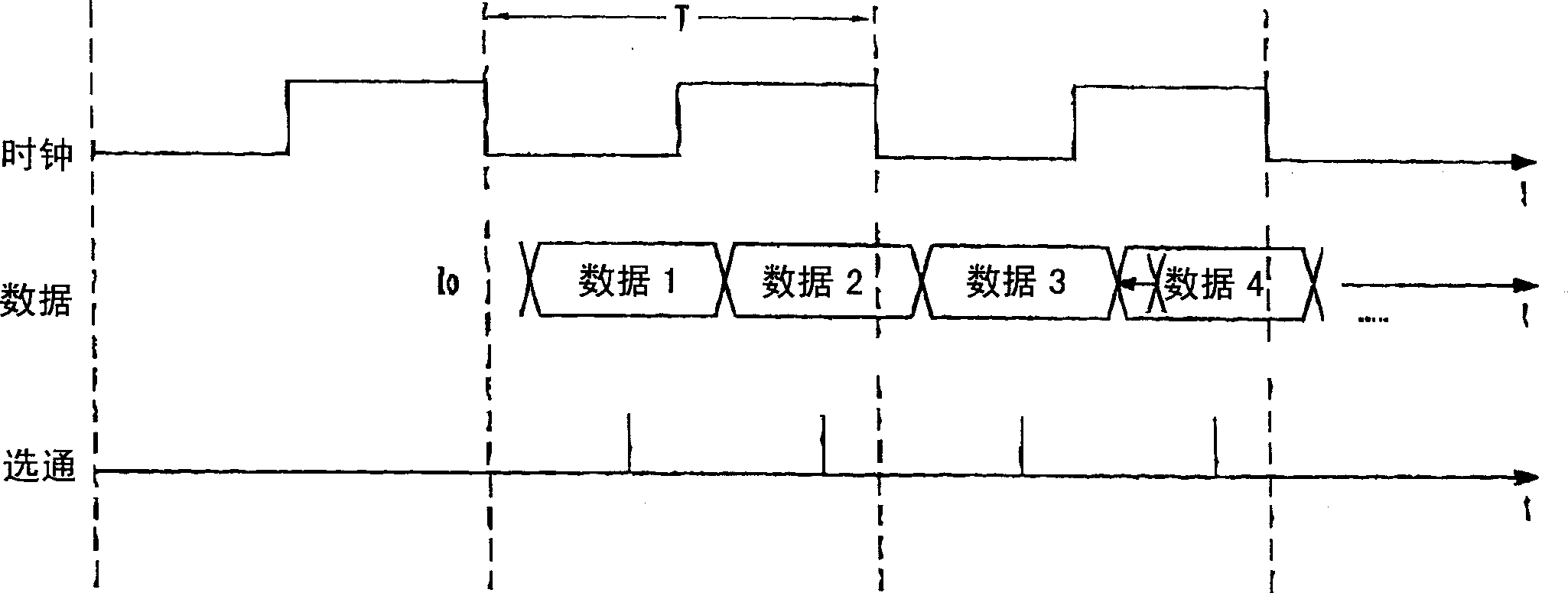

Testing a data store using an external test unit for generating test sequence and receiving compressed test results

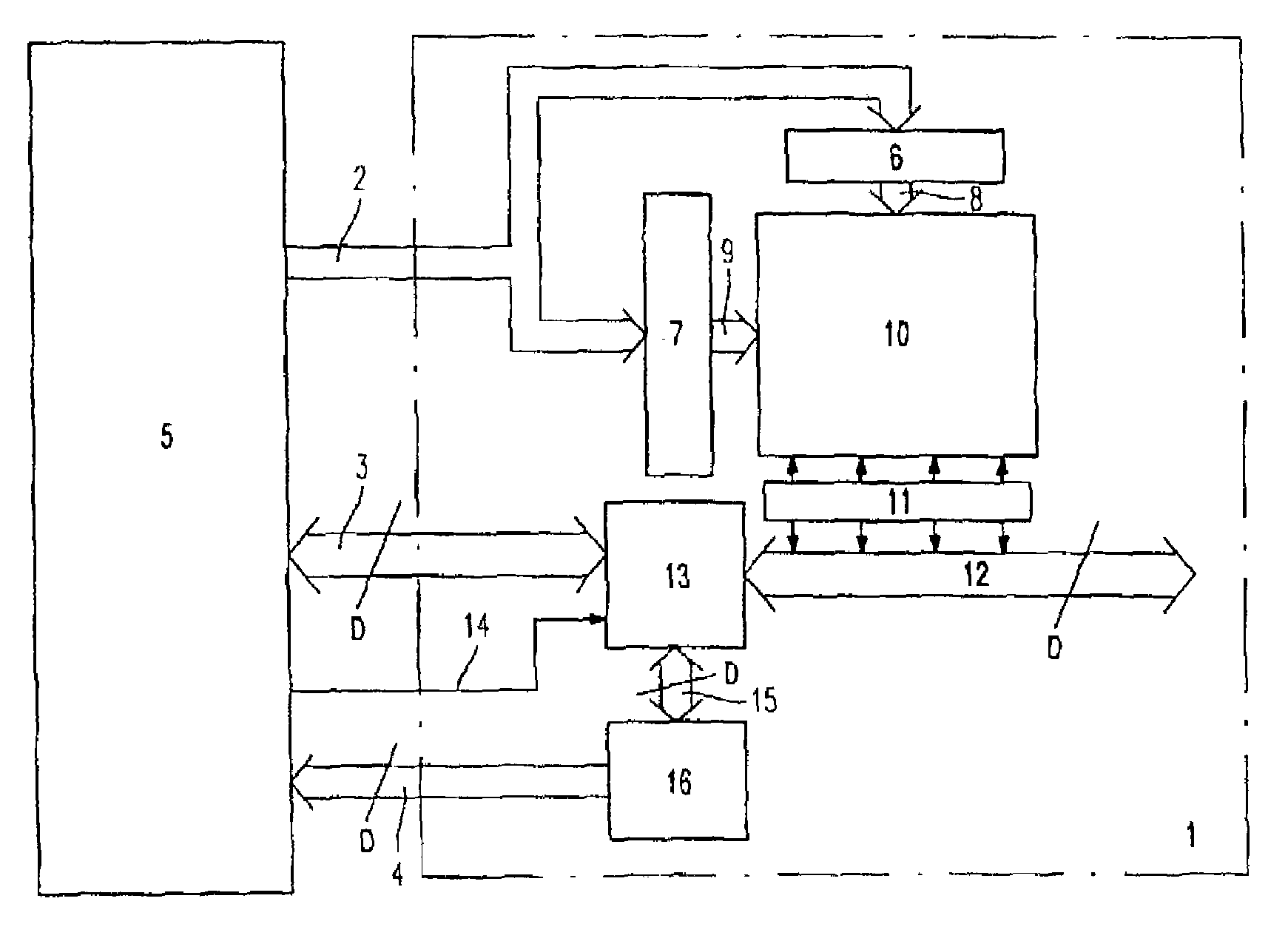

InactiveUS7428662B2High operating requirementsReduce clock frequencyElectronic circuit testingError detection/correctionAudio power amplifierReference test

Disclosed is a test method for testing a data store having an integrated test data compression circuit where the data store has a memory cell array with a multiplicity of addressable memory cells, read / write amplifiers for reading and writing data to the memory cell via an internal data bus in the data store and a test data compression circuit which compresses test data sequences, which are each read serially from the memory cell array, with stored reference test data sequences in order to produce a respective indicator data item which indicates whether at least one data error has occurred in the test data sequence which has been read.

Owner:POLARIS INNOVATIONS

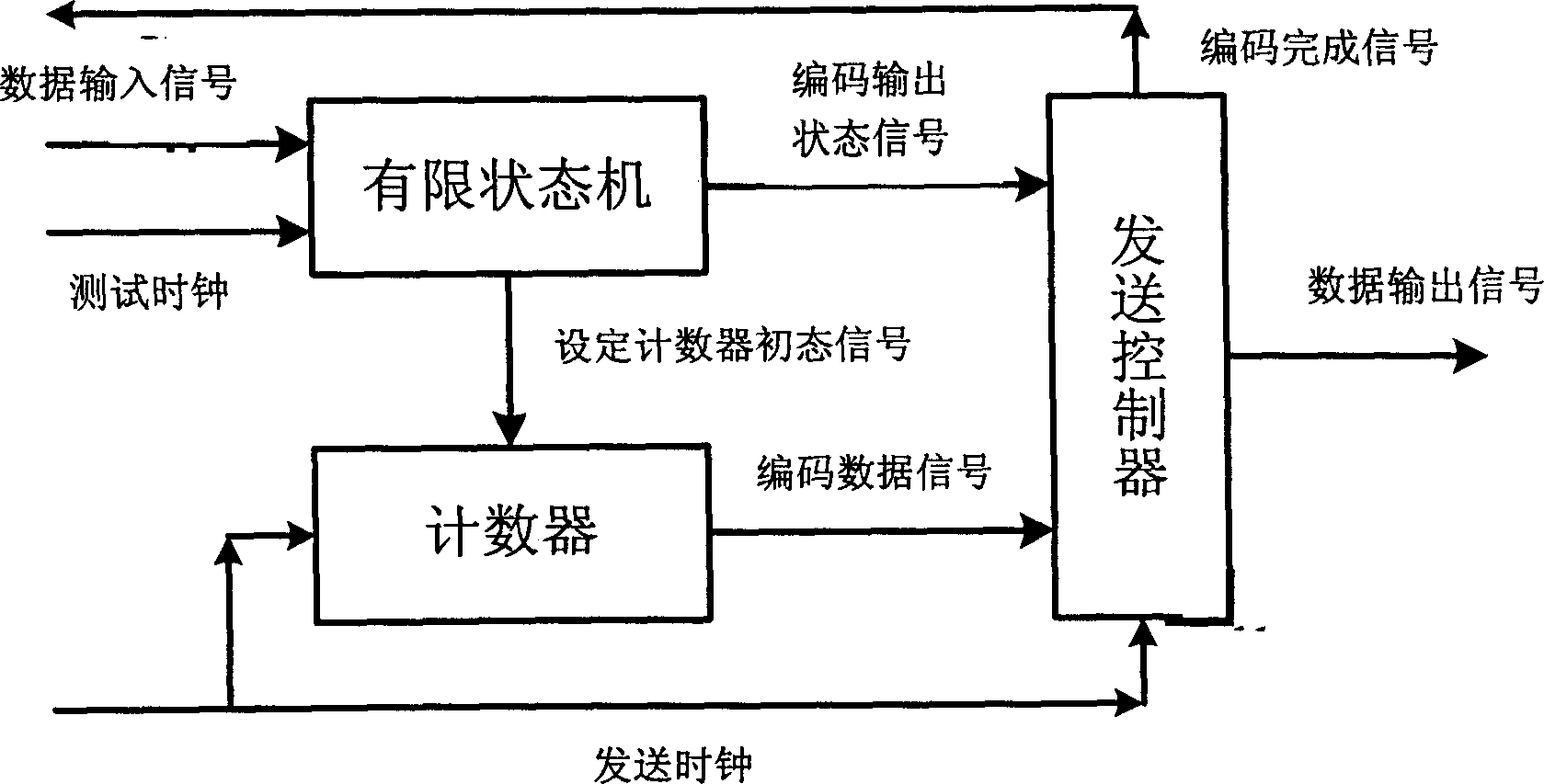

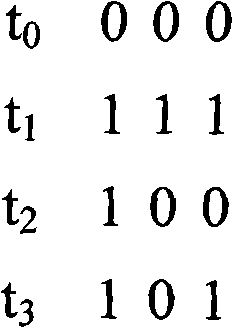

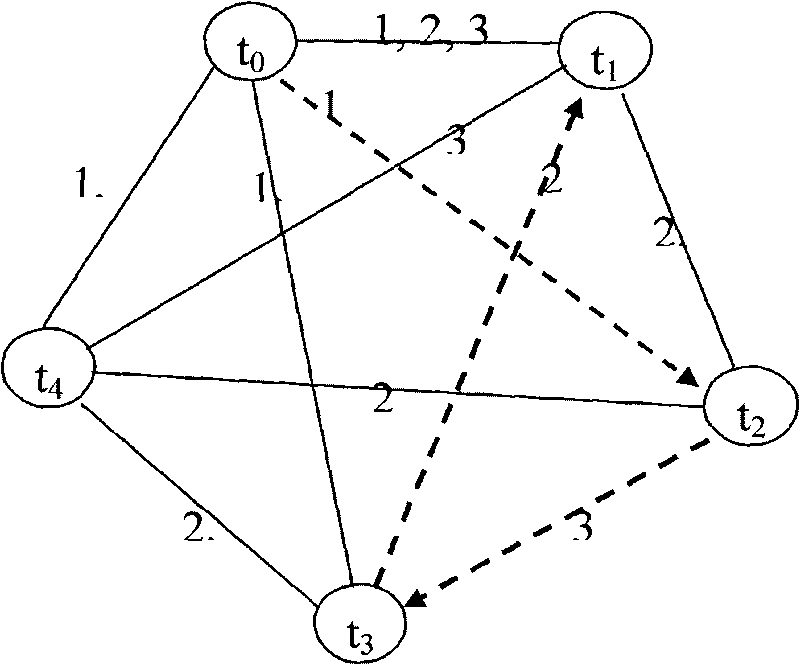

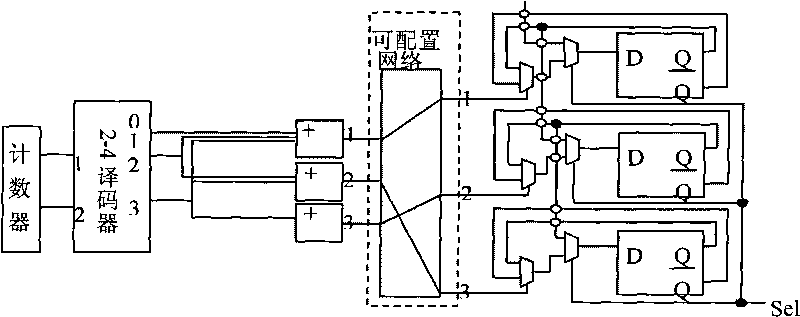

Method for compressing built-off self-test data of system-on-a-chip and special decoding unit thereof

InactiveCN101762782ATo achieve the purpose of compressing dataIncrease flexibilityElectrical testingComputer scienceSystem on a chip

The invention relates to an integrated circuit testing technology, in particular to a method for compressing test data in built-off self-test (BOST) method for a system-on-a-chip and a special decoding unit thereof. By embedding an entire test set into different inversion sequences, the purpose of compressing the data can be achieved only by storing the seeds of the inversion sequences; the inversion rule for the inversion sequences can be different, so as to improve the compression flexibility. The invention also provides a special decoding unit for realizing the method for compressing the built-off self-test data of the system-on-a-chip. The special decoding unit comprises a counter, a decoder or a gate for spreading the number of the inversion sequences, a configurable network for controlling the inversion position from the seeds to generation of the test vector, and a D trigger with output feedback.

Owner:ANQING NORMAL UNIV

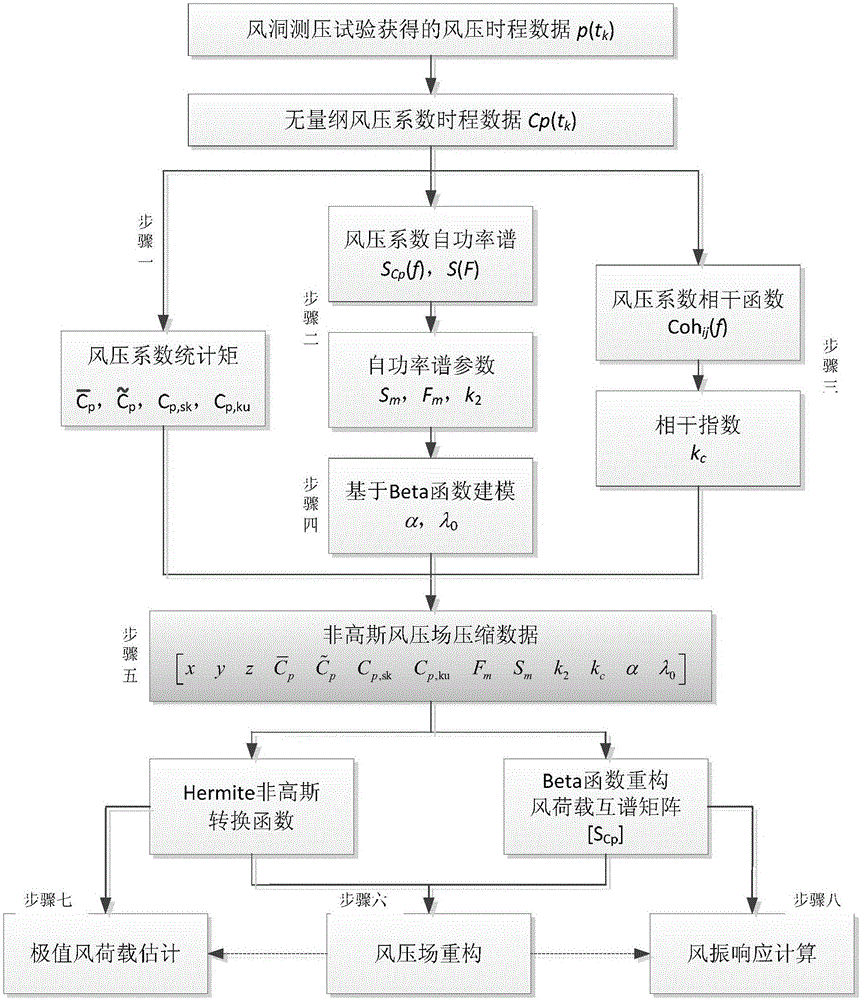

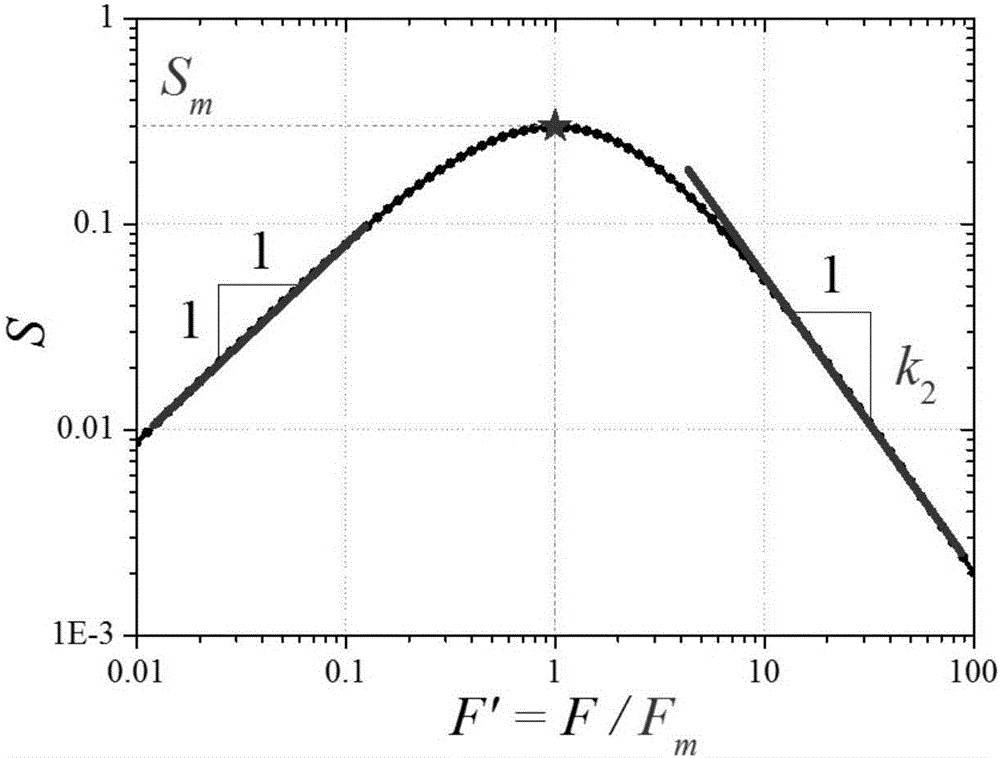

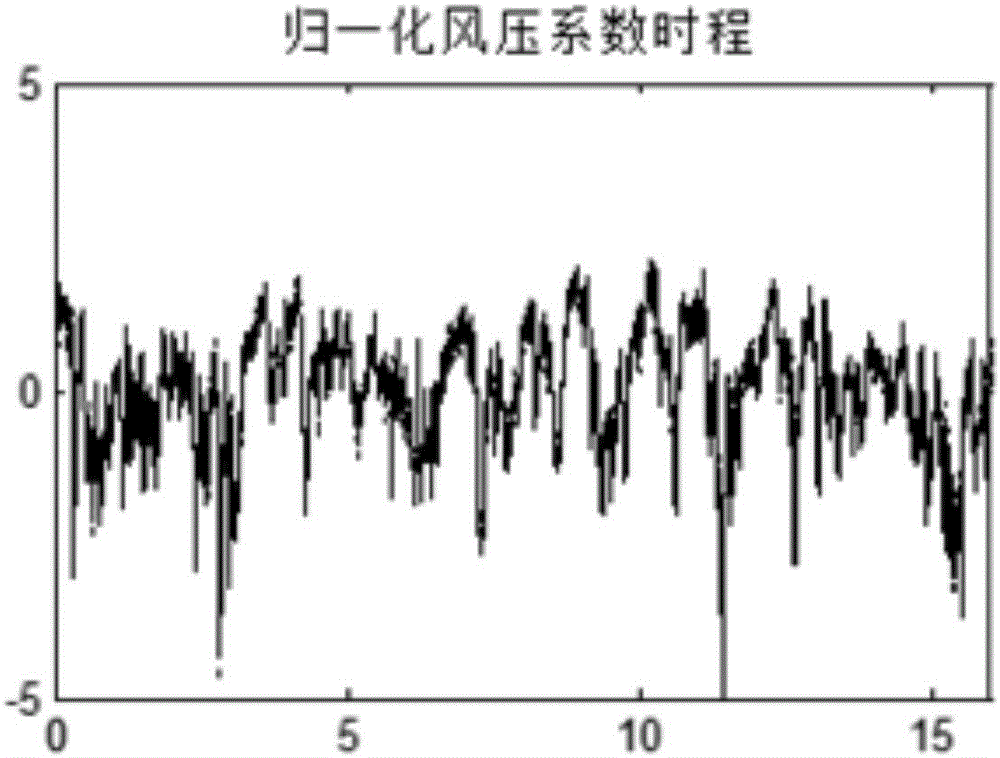

Building wind tunnel pressure measurement test data compression method

ActiveCN106330197AAchieve the purpose of compressionEfficient storageCode conversionData compressionFrequency spectrum

The invention relates to a building wind tunnel pressure measurement test data compression method. The invention aims at solving the problem that the little attention is paid to frequency domain characteristics of wind load and correlation in the prior art, resulting in a data compression error and an actual application error. The statistical information of the data is reconstructed by the Hermite polynomial, and the spectrum information is reconstructed by the Beta function theory, and a compressed wind pressure filed can be reconstructed at last in combination with random simulation technology. By adoption of the building wind tunnel pressure measurement test data compression method provided by the invention, the building wind tunnel pressure measurement data of GB and TB levels can be compressed to the KB and MB levels, and a novel information extracting and modeling method is provided for the high-dimension time-course large data of the wind load changing with time and space so as to achieve the data compression purpose at last. The building wind tunnel pressure measurement test data compression method is applied to the field of building wind tunnel pressure measurement tests.

Owner:黑龙江省工研院资产经营管理有限公司

Test Data Compression Method for System-On-Chip Using Linear-Feedback Shift Register Reseeding

InactiveUS20080065940A1Improve coding efficiencyConvenient timeElectronic circuit testingLogical operation testingSystem testingLinear feedback shift register

A method includes obtaining an equivalent core of multiple cores in a System-on-Chip circuit, and applying linear-feedback shift register LFSR reseeding for compressing test data of the equivalent core.

Owner:NEC CORP

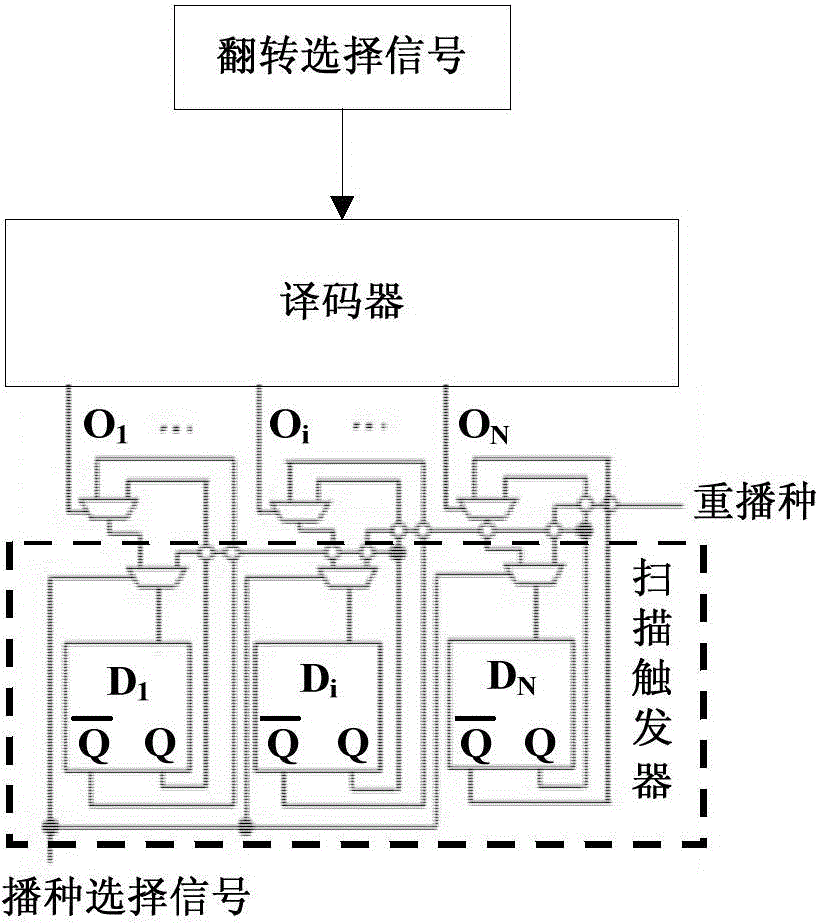

Test data compression method based on dichotomy symmetric folding technology

The invention discloses a test data compression method based on a dichotomy symmetric folding technology. Vectors in a test set are arranged according to the degressive sequence of the number of determined bits. The first vector in the sequenced test set is selected as a seed, and a folding set is generated. The vectors in the test set are compared with vectors in the folding set, if Cj is the bit of the determined bit, the value of the bit, corresponding to Cj in position, in Vi is the unrelated bit or the same determined bit, or if the value in Cj is the bit of the unrelated bit, the value of the bit, corresponding to Cj in position, in Vi is the unrelated bit; the vector VI is deleted from the test set. The process is repeatedly carried out till the test set is null, and the obtained seed set S is the corresponding result of the test data T through compression. Compared with the prior art, the test data compression method has the following advantages that the non-invasive type test data compression method is adopted, a tested circuit structure is not changed, the structure of a scan chain in the circuit is not changed, the seed set is used for covering the whole test set, the compression rate is increased, the testing power consumption is reduced, and the test application time is shortened.

Owner:SHANGHAI TAIYU INFORMATION TECH

Test data compression method capable of rapidly searching irrational number

InactiveCN102932000AIncrease optionalityImprove search rateCode conversionRunning timeComputer science

The invention discloses a test data compression method capable of rapidly searching an irrational number. The test data compression method comprises the following steps of: generating a determined complete test set T and marking the number of test vectors of the complete test set to be N; marking cascading of all test vectors to be S and the length of cascading to be w; calculating the length of runs and ending till reaching an irrelevant position and converting the length information of runs into a decimal x for representing; searching the irrational number and expanding the irrational number to a decimal, wherein the front p items of the decimal are just equal to x, and only integers, namely m, n, l, k and p are stored in the compression process. The test data compression method disclosed by the invention has the advantages that methods of first searching the irrational number and then carrying out bit-by-bit comparison are adopted in the irrelevant bit filling process, and thus the selectivity of the irrational number and the probability of searching the irrational number are increased; and according to the test data compression method, an interval bisection method is adopted in the irrational number searching process, and therefore the operating time can be prolonged according to a logarithm rule.

Owner:詹文法

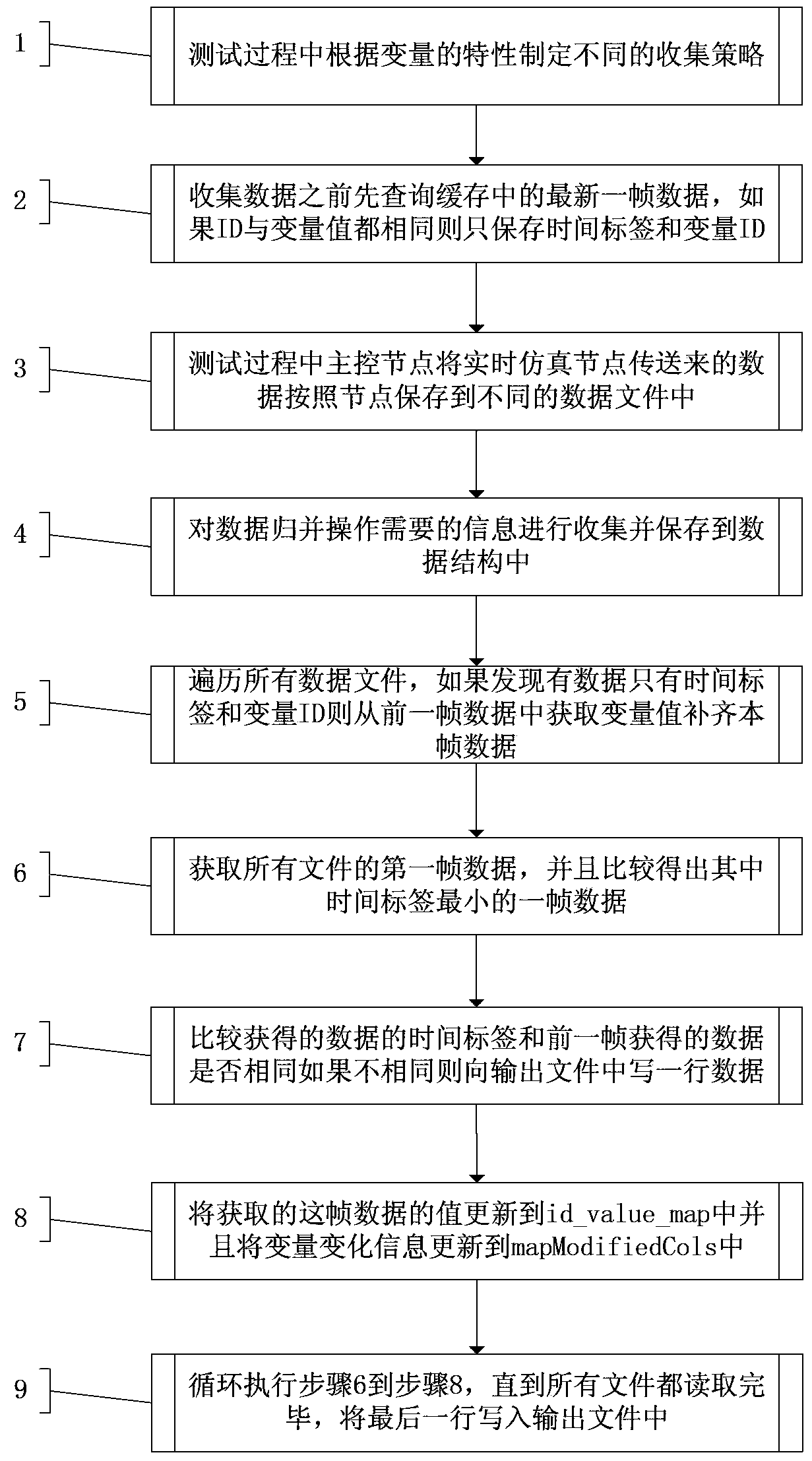

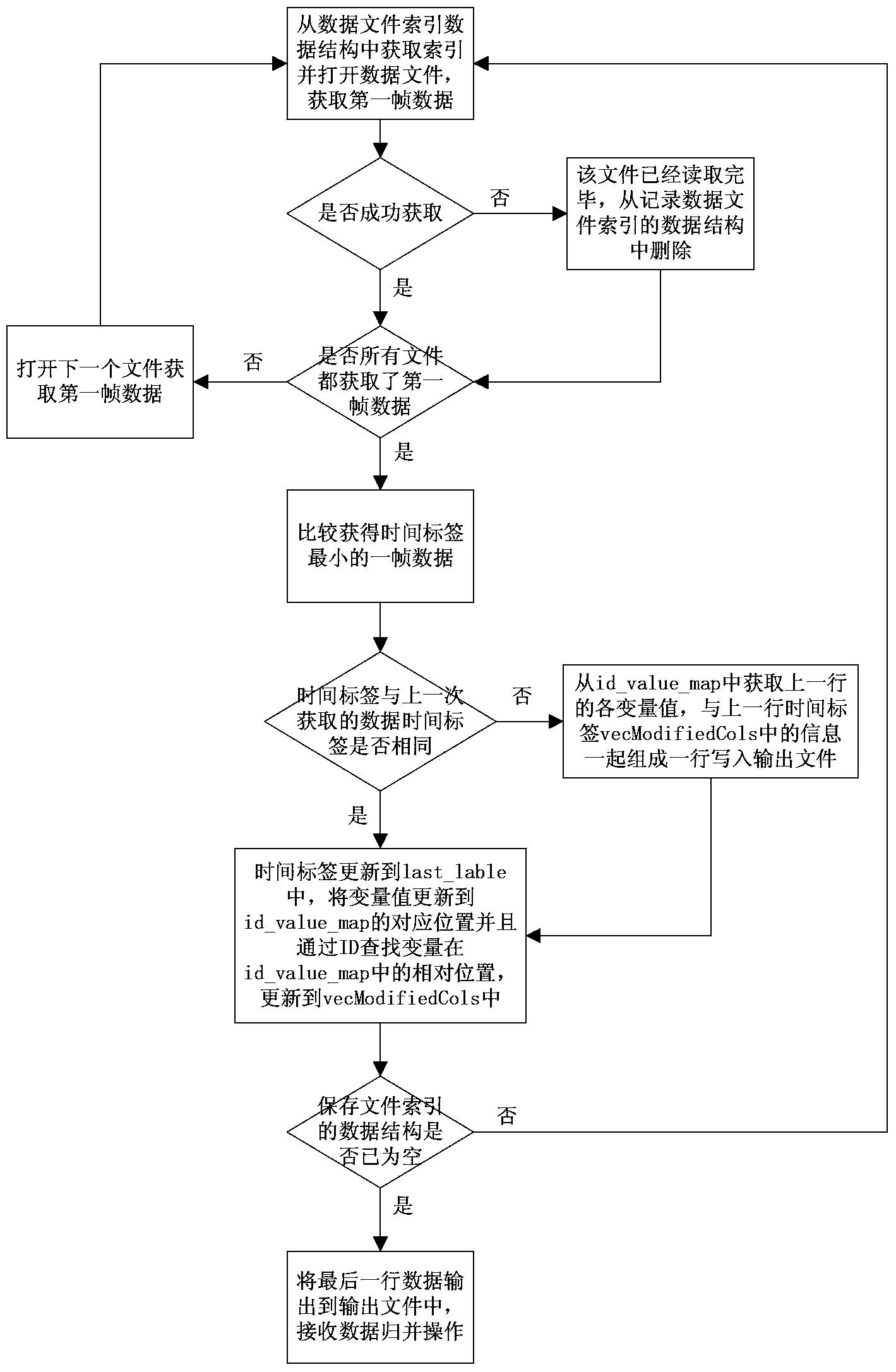

Multichannel test data compressing and merging method for distributed real-time test system

ActiveCN103488564ANo lossSoftware testing/debuggingSpecial data processing applicationsReal-time simulationData file

A multichannel test data compressing and merging method for a distributed real-time test system comprises nine steps of (1) formulating a collecting strategy according to variate features; (2) inquiring newest frame data in a cache, and storing a time label and variate ID (identification) if the ID is the same with a variate value; (3) storing data transmitted from real-time simulated nodes in files by using a master control node; (4) merging and processing information and storing the information in a data structure; (5) traversing data files, and acquiring the variate value from a former frame data to supplement local frame data if only the time label and the variate ID exist; (6) acquiring first frame data of all files, and comparing the first frame data to obtain the frame data with the smallest time label; (7) judging whether the obtained time label is the same with that of the former frame data or not, and writing a line of data to an output file if the obtained time label is different from that of the former frame data; (8) updating the acquired frame data to an id_value_map, and updating changed information so as to bring convenience to next comparison; and (9) repeatedly carrying out the step (6), the step (7) and the step (8) until all files are read, and writing the last line in the output file.

Owner:BEIHANG UNIV

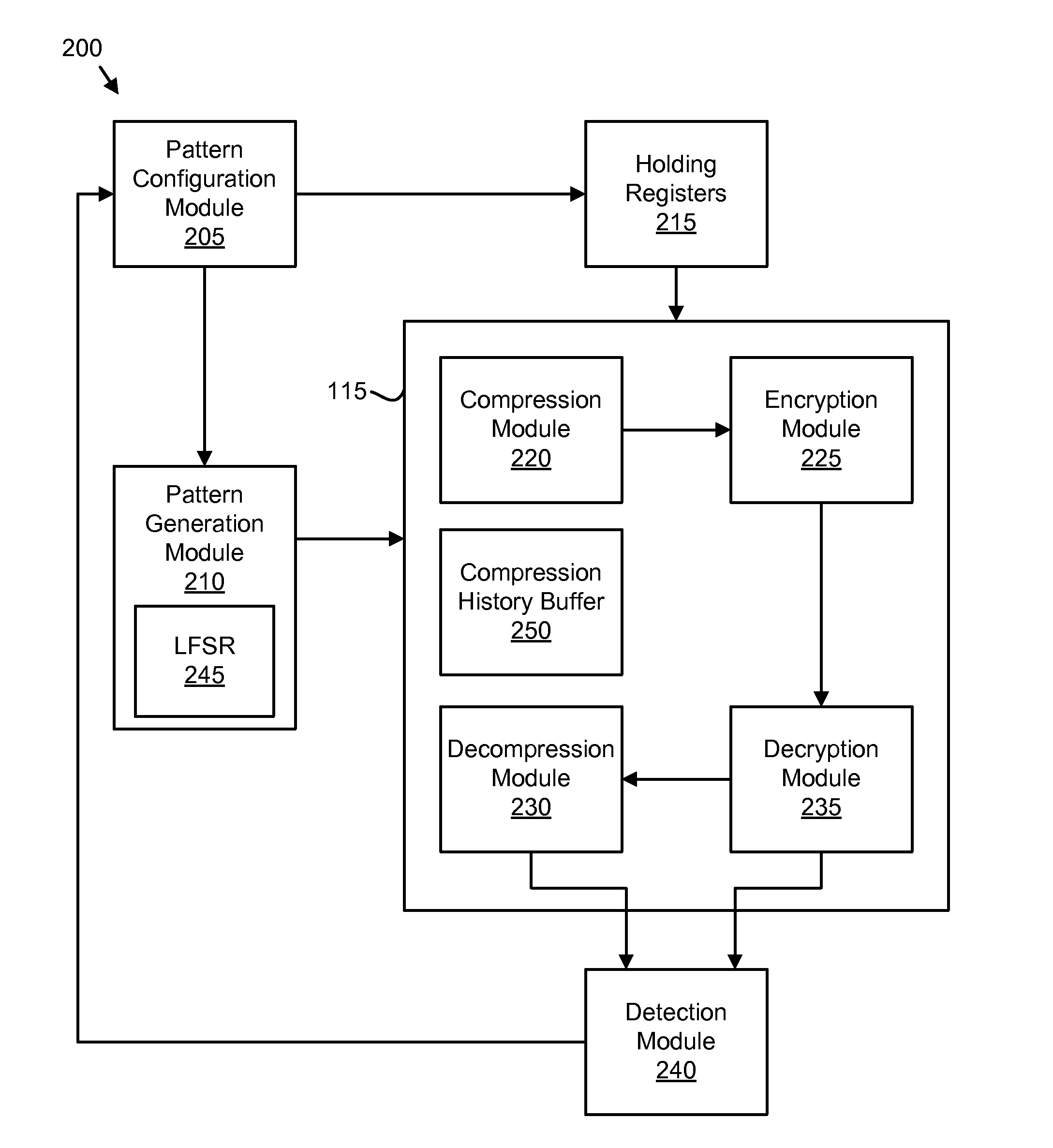

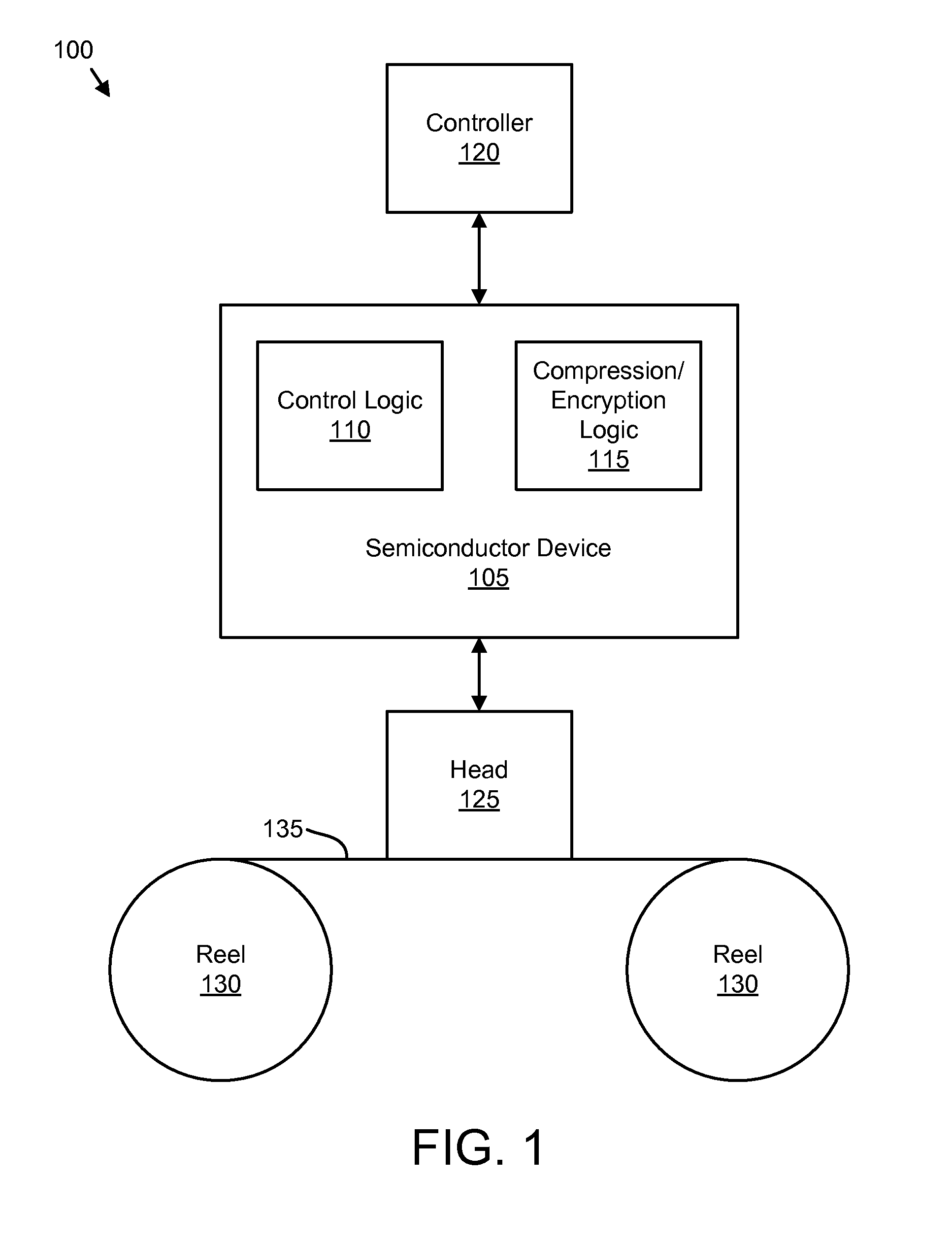

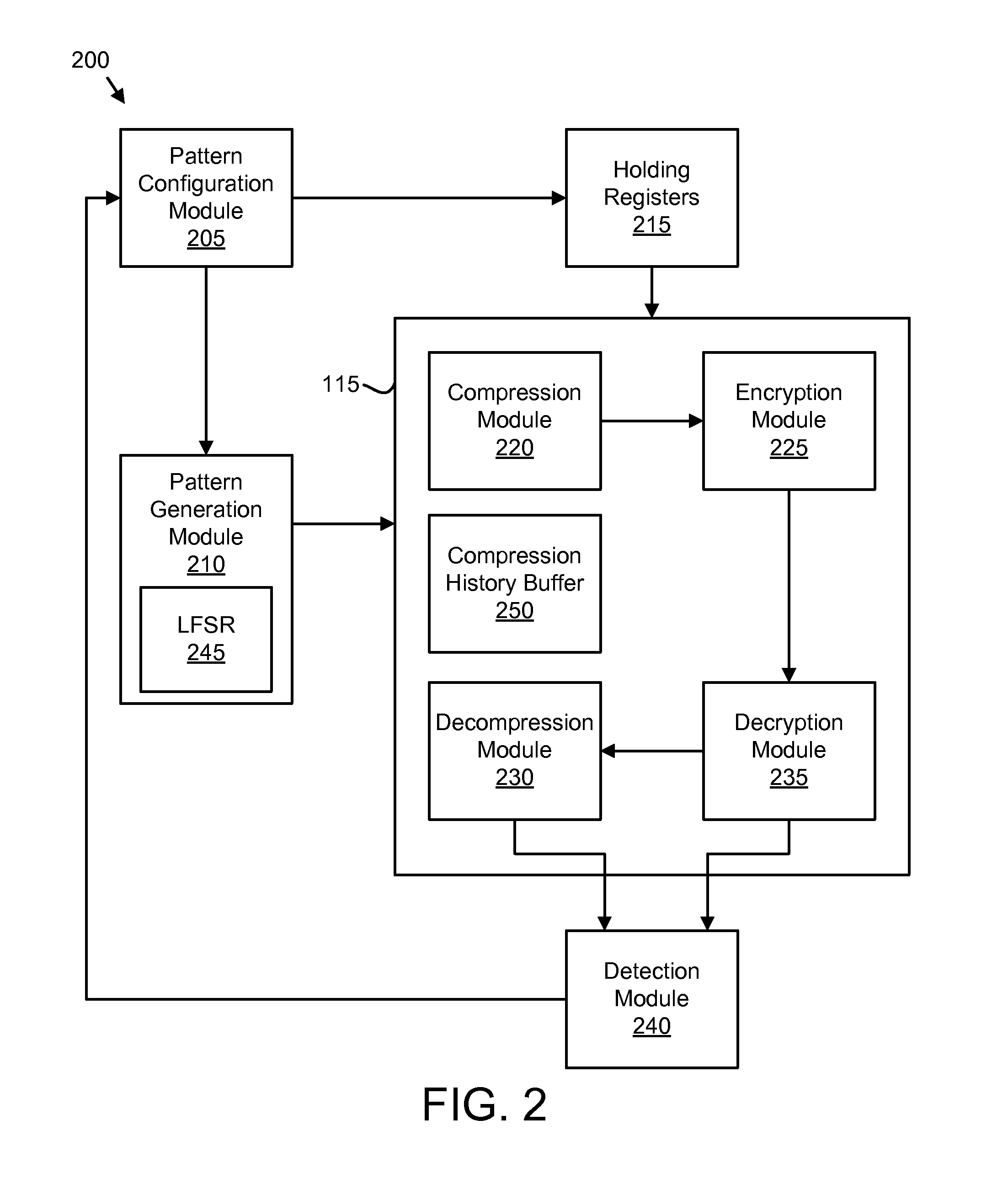

Apparatus, system, and method for testing data compression and data encryption circuitry

InactiveUS20080240419A1Efficient testingError detection/correctionSecret communicationData compressionProcessor register

An apparatus, system, and method are disclosed for testing data compression and data encryption circuitry. A pattern configuration module generates initial pattern parameters. Holding registers store the initial pattern parameters. A pattern generation module generates patterns for compression / encryption logic. A detection module detects a failure of the compression / encryption logic. The failure of the compression / encryption logic may be a cyclic redundancy check failure of a decompression module and / or a message authentication code failure of a decryption module.

Owner:IBM CORP

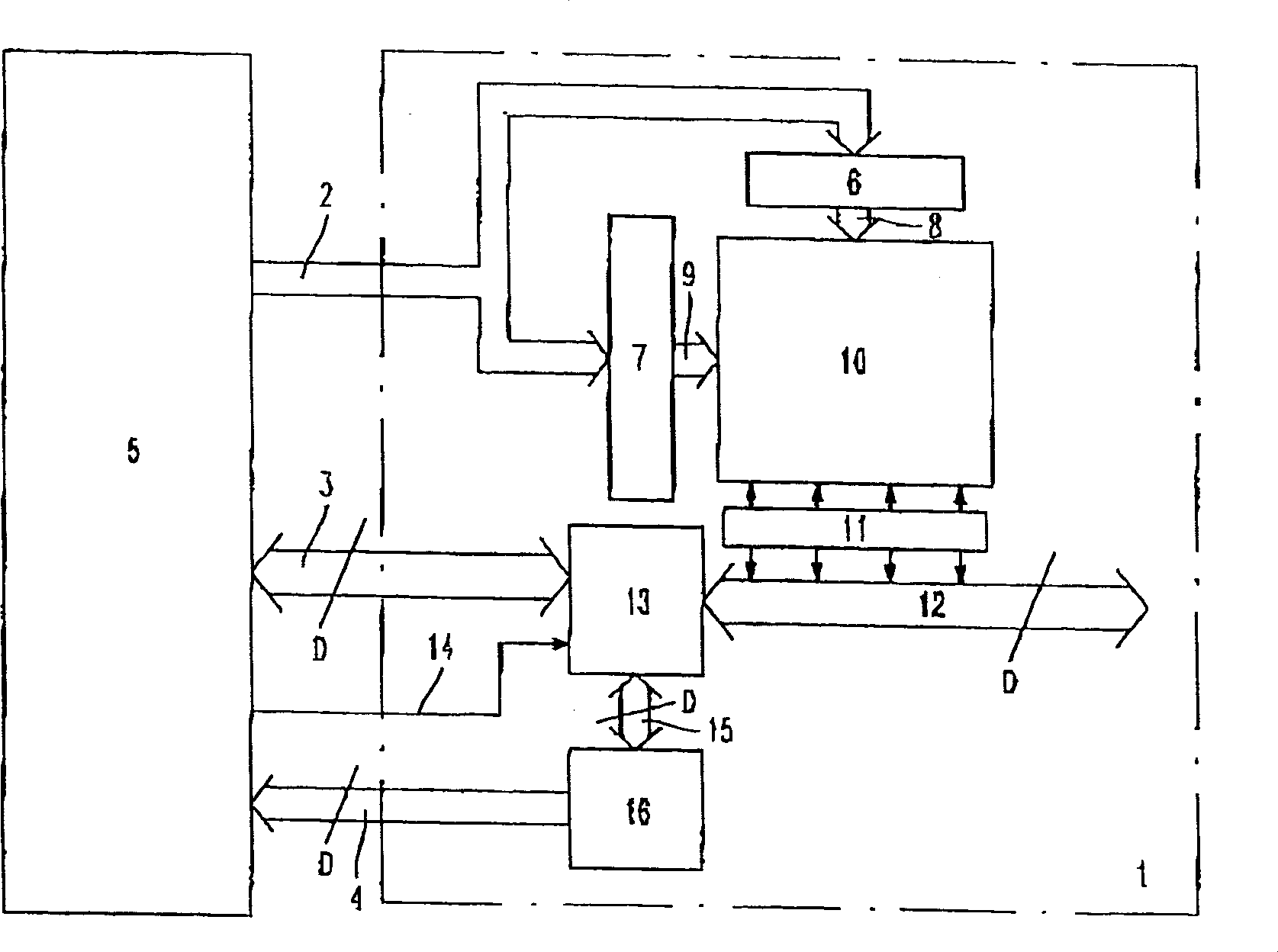

Test method for testing data memory

Test method for testing a data store having an integrated test data compression circuit (16), where the data store (1) has a memory cell array (10) with a multiplicity of addressable memory cells, read / write amplifiers (12) for reading and writing data to the memory cell via an internal data bus (12) in the data store (1), and a test data compression circuit (16) which compresses test data sequences, which are each read serially from the memory cell array (10), with stored reference test data sequences in order to produce a respective indicator data item which indicates whether at least one data error has occurred in the test data sequence which has been read.

Owner:INFINEON TECH AG

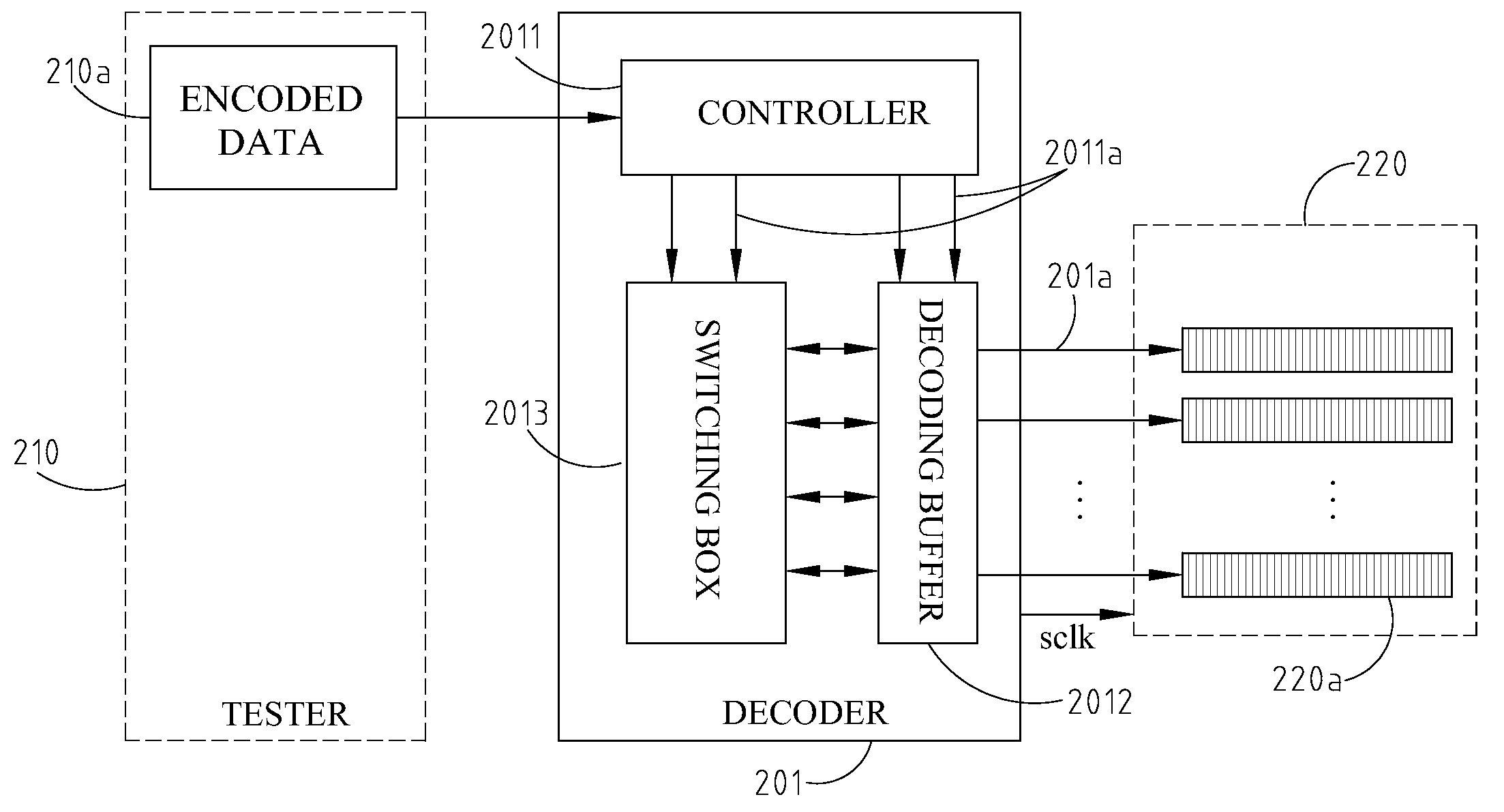

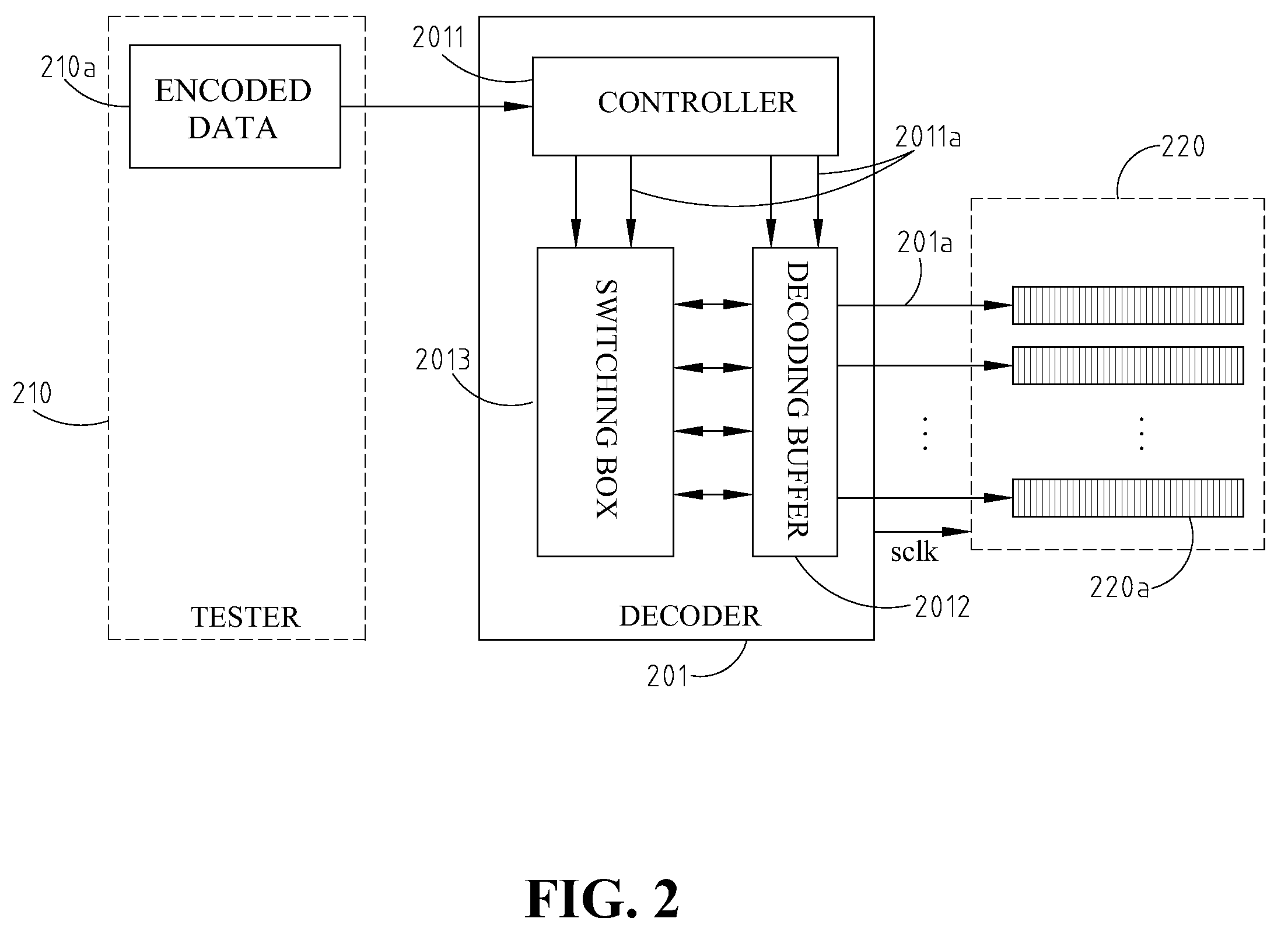

Scan Test Data Compression Method And Decoding Apparatus For Multiple-Scan-Chain Designs

InactiveUS20080133990A1Effectively overcome problemReduce data transfer timeElectronic circuit testingComputer hardwareFault coverage

Disclosed is a scan test data compression method and decoding apparatus for multiple-scan-chain designs. The apparatus comprises a on-chip decoder connected to a tester. The decoder includes a decoding buffer configured as a multilayer architecture, a controller, and a switching box for receiving a shift signal or a copy signal. The decoding buffer is used to store decoded test data. While the decoder decodes the encoded data, it transmits control signals to both the decoding buffer and the switching box from the controller, and sends the decoded data to scan chains of a CUT for testing through the decoding buffer. This invention has the advantages of simple encoding method, high compression rate, low power consumption in testing, and without the fault coverage loss.

Owner:IND TECH RES INST