Exponent cut LFSR replanting VLSI test data compression method

A technology of test data and compression method, applied in the direction of measuring electricity, measuring device, measuring electrical variables, etc., can solve the problems of few chip test points, large amount of test data, incompatibility, etc., to reduce data length and improve coding efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

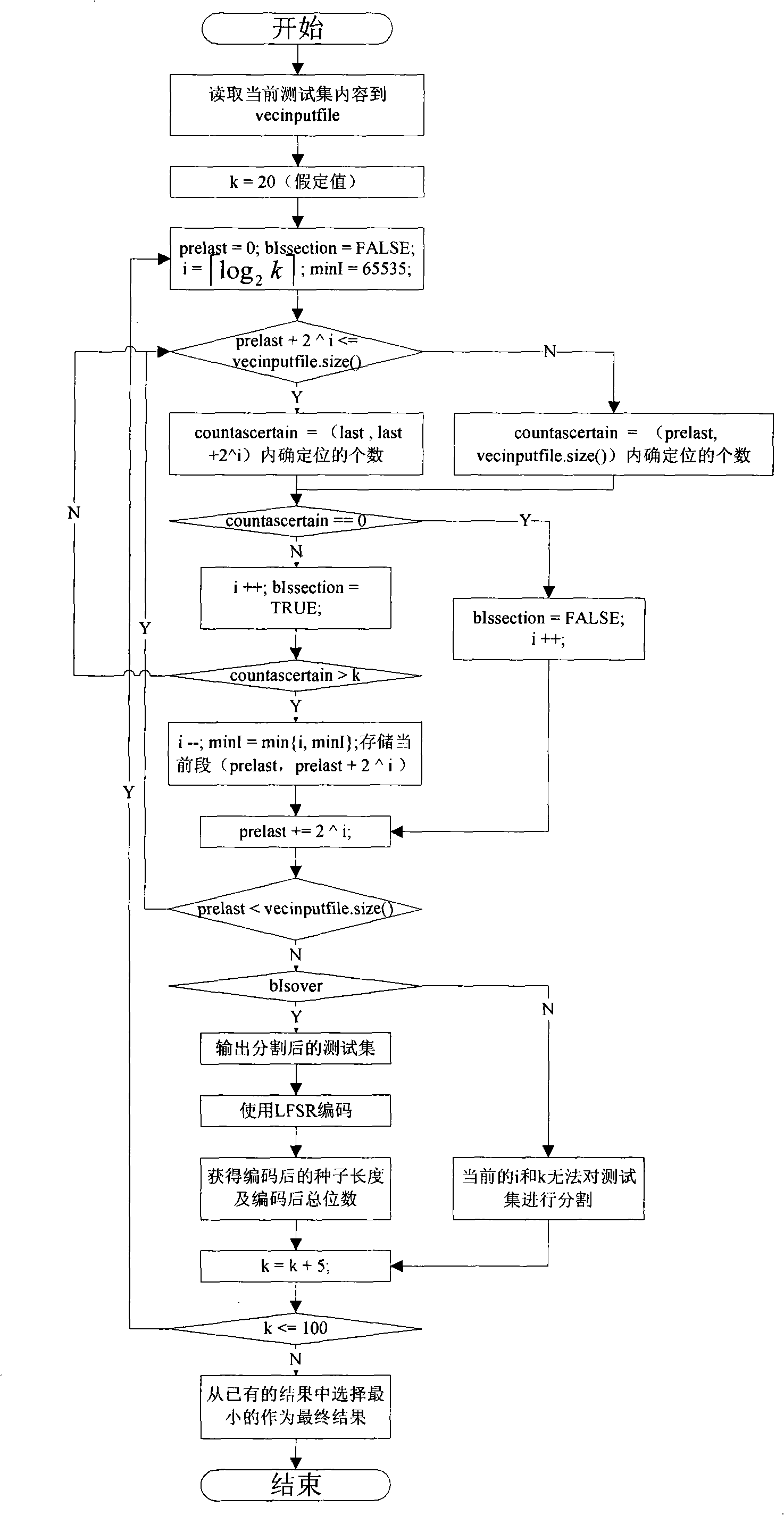

[0030] Implement the present invention and carry out as follows:

[0031] a. Carry out pseudo-random test to the circuit under test, and use the fault simulation tool to determine the untested faults, and then use the automatic test pattern generation tool (ATPG) to generate a certain test set T for the untested faults;

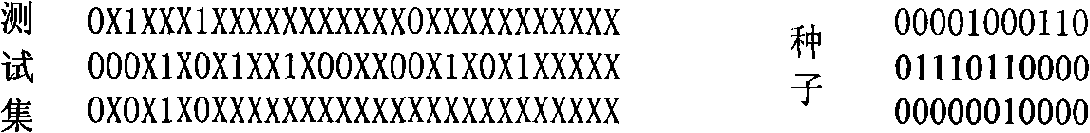

[0032] b. Carrying out test vector concatenation on the test set T, the concatenation is to connect the tail of the previous test vector to the head of the next test vector, and form a test sequence T after concatenating all the test vectors 2 ;

[0033] c. The test sequence T to be formed 2 According to the constant k segmentation, the segmentation strategy is to make the number of certain bits contained in each segment equal to or less than and closest to a certain constant k after segmentation. The specific method is to start from the test sequence T 2 Take a subsequence of length m at the beginning of sequentially calculated from T 2 The length of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More