Device and method for determinacy self-testing test data compression

A test data and compression device technology, which is applied in the direction of measuring devices, measuring electricity, and measuring electrical variables, etc., can solve the problems of large test data storage space and low probability of difficult-to-measure failures, and achieve the reduction of storage space and reduction of storage space Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

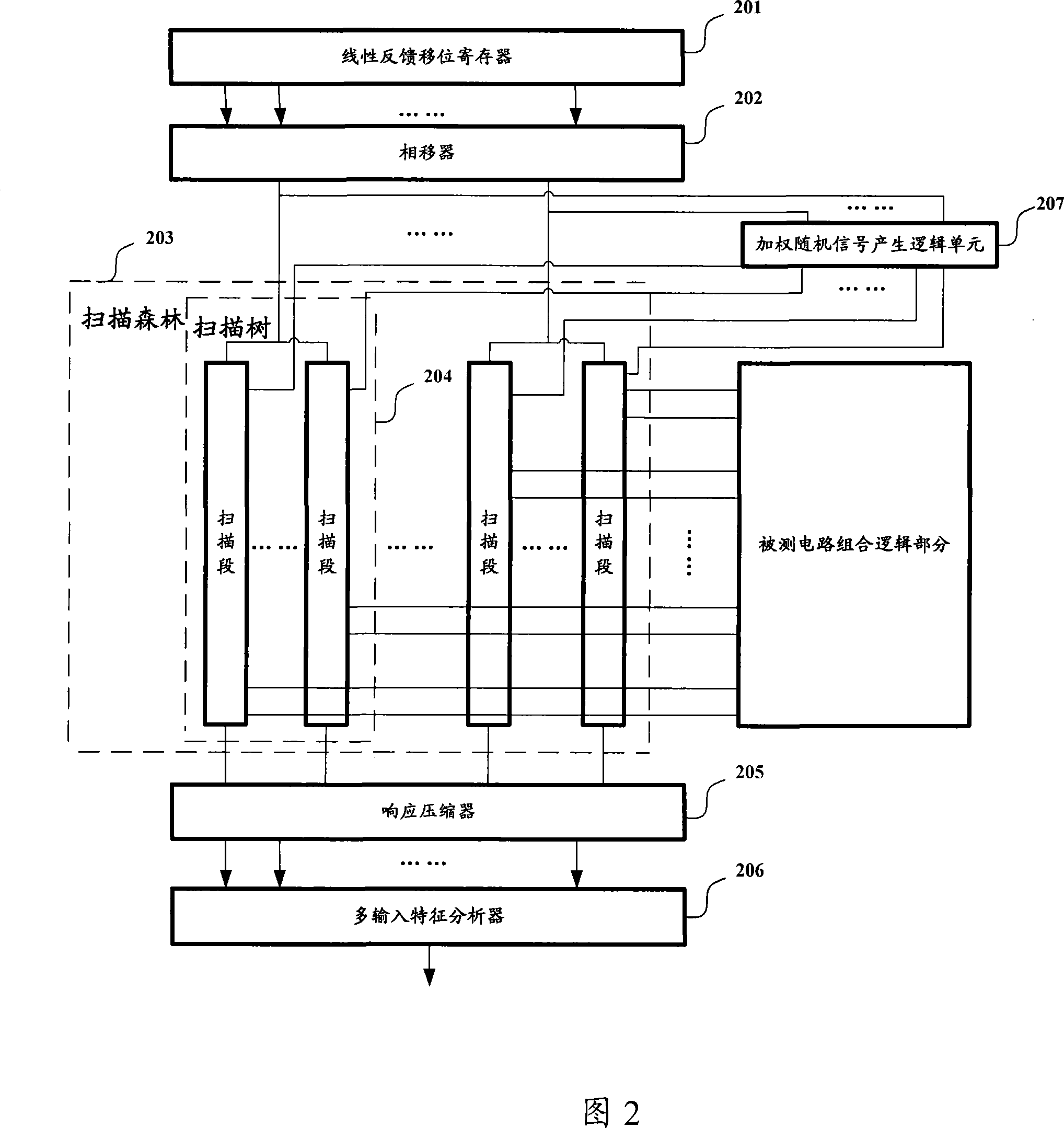

[0060] The embodiment of the present invention adopts a structured scan forest, so that the deterministic test vectors are reduced in the process of deterministic self-test, and weighted control is performed on the probability of a specific signal value of the input scan forest signal, thereby increasing the false Fault coverage during random self-testing, thereby reducing the amount of test data storage for deterministic test vectors.

[0061] The embodiment of the present invention provides a deterministic self-test test data compression device, as shown in FIG. Compressor 205, multi-input feature analyzer 206.

[0062] A linear feedback shift register 201, the output end of which is connected to the input end of the phase shifter 202;

[0063] The scan forest 203 includes at least one scan flip-flop group, and the scan flip-flop group is composed of scan flip-flops having a common subsequent unit in the combinatorial logic part of the circuit under test;

[0064] The weig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More