System chip test data compression method of block mark

A technology for testing data and system chips, applied in digital circuit testing, electronic circuit testing, electrical digital data processing, etc., can solve problems such as few chip test points, complex decoding, and inability to perform full-speed testing, so as to reduce test time and reduce The effect of storage capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

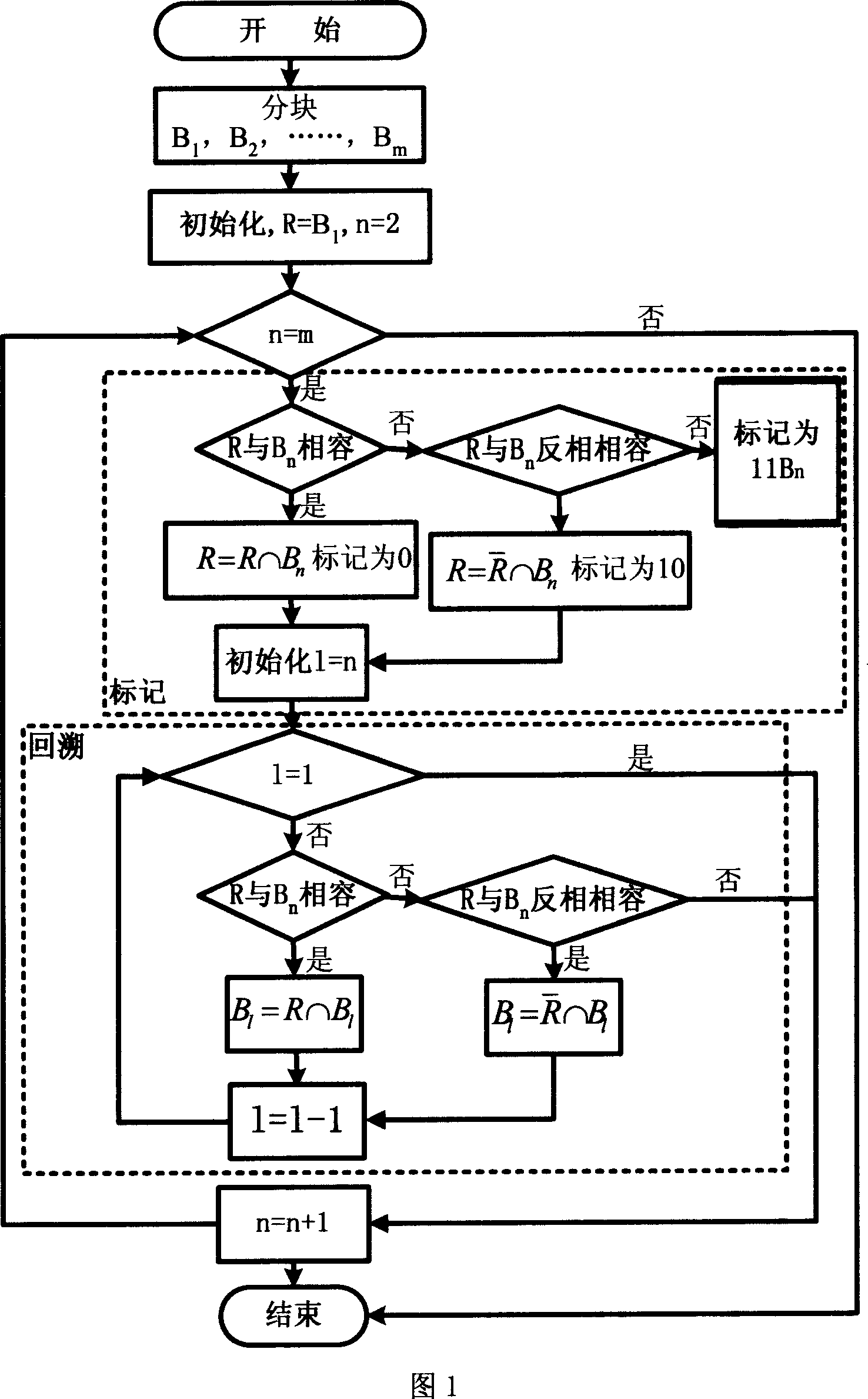

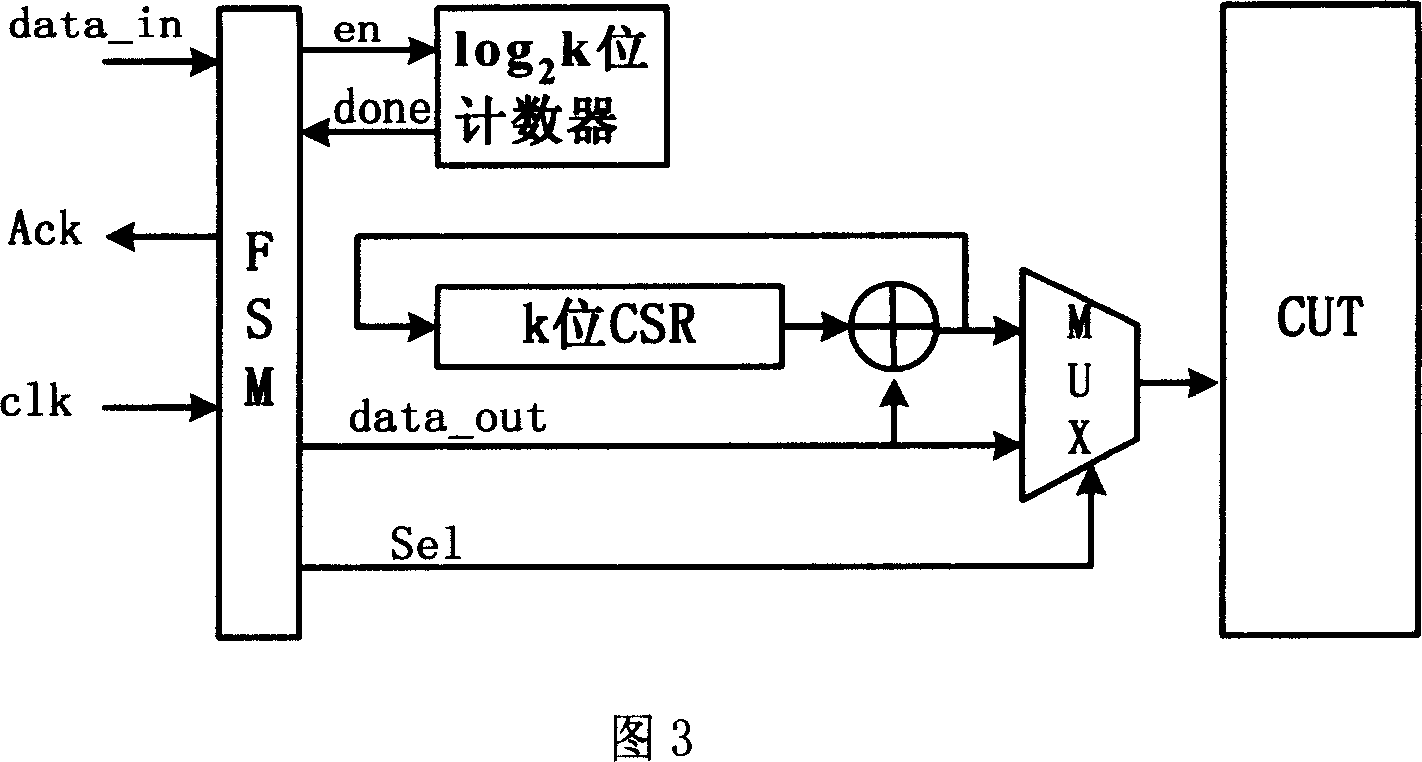

[0030] Implement the present invention and carry out as follows:

[0031] 1. Use the automatic test pattern generation (ATPG) tool to generate a definite complete test set T;

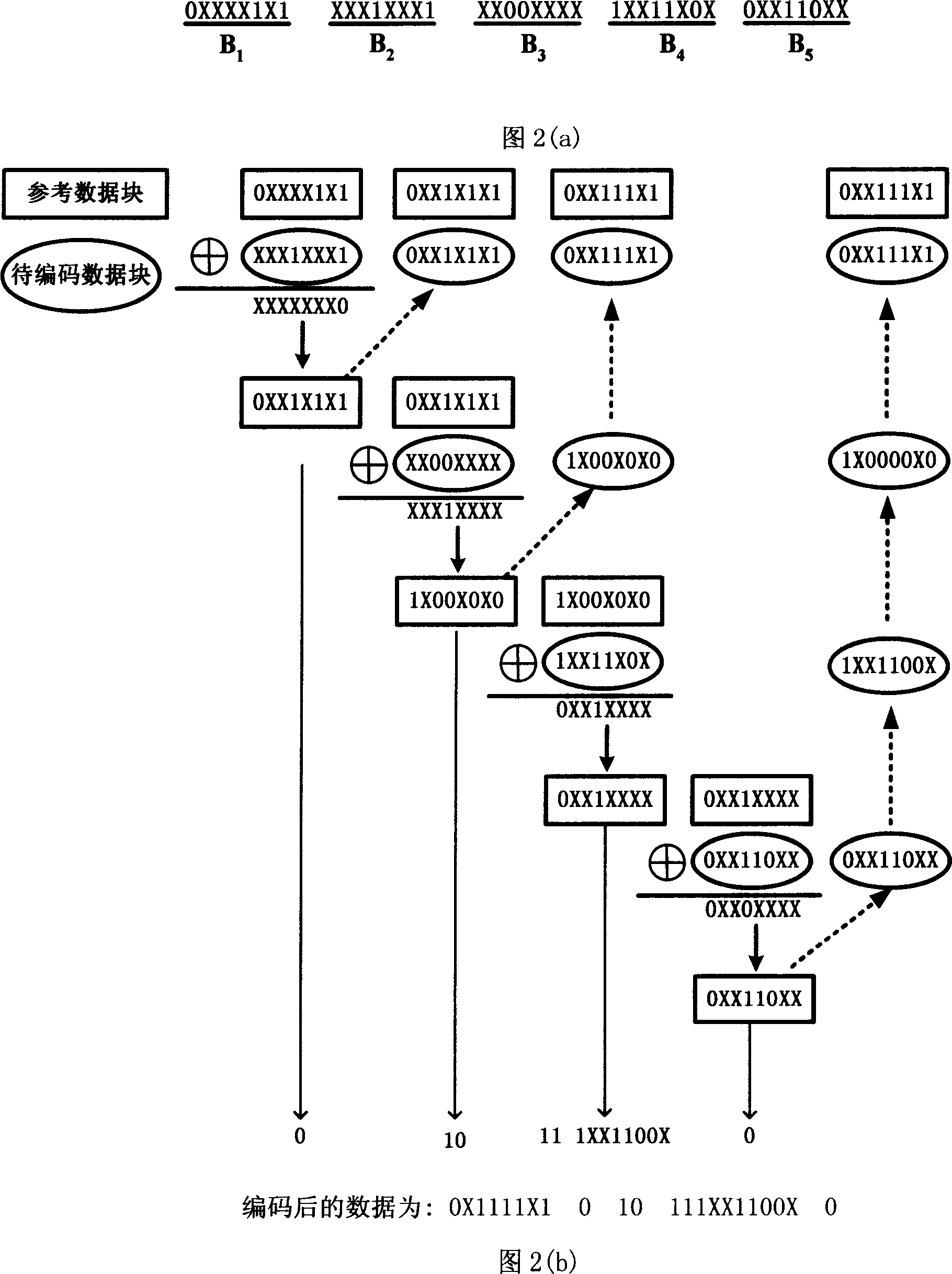

[0032] 2. Mark the complete test set T into blocks. First, each test vector in the complete test set T is divided into k-bit blocks by k bits, and if the last block of the test vector is less than k bits, it is filled to k bits with irrelevant bits to ensure the final block The number of digits is k, and each block is recorded as B in sequence 1 , B 2 , B 3 , B 4 , B 5 ,...B m , initialize the reference data block R and the data block B to be encoded n (n is an integer, 2≤n≤m), that is, R=B 1 , B n =B 2 ;

[0033]3. Encoding process, judging the reference data block R and the data block B to be encoded n Whether it is compatible or anti-phase compatible, if R and B n compatible, then B n Encoded as 0, while bitwise combining R and B n Intersect (R∩B n ) to dynamically update the referenc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More