Method for compressing built-off self-test data of system-on-a-chip and special decoding unit thereof

A system chip and data compression technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of increasing the test process, expensive automatic test equipment, limited test points for direct control or observation, etc., to achieve increased flexibility sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

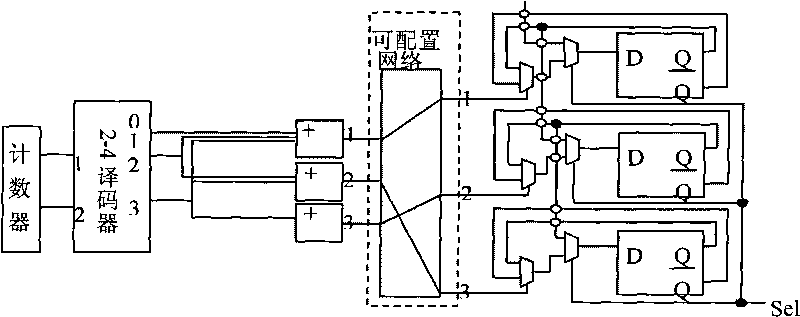

[0022] The method for generating the fully determined test set in step a of the compression method is as follows:

[0023] The ATPG tool is used to generate a definite complete test set T, and the test vectors contained in the test set T can test all faults. The choice of ATPG tool is to make the generated test vector contain extraneous bits. The next step is to compress the generated complete test set T. Build a sequence diagram:

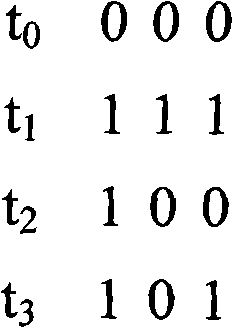

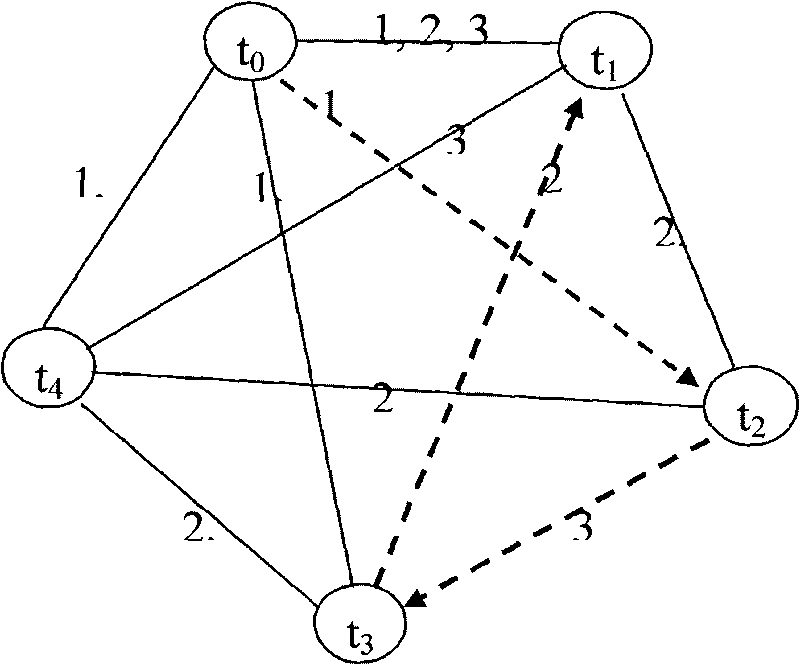

[0024] See figure 1 , figure 2 , The sequence diagram in step b of the compression method is obtained by combining figure 1 In t 0 , T 1 , T 2 , T 3 , T 4 As a vertex, the edge represents the flip relationship between the test vectors corresponding to the two vertices, and the position that needs to be flipped between them is recorded on the edge, such as t 0 To t 2 Need to flip the first place. Find the largest embeddable flip sequence:

[0025] Select vertex t 0 As the starting point, to the vertex t 1 , T 2 , T 3 , T 4 The number of values corresp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More