Generation and verification method of test vector

A technology of test vectors and verification methods, which is applied in the field of generation and verification of functional test vectors, can solve problems such as low work efficiency, large workload, and different numbers of signal names, and achieve the effect of improving production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

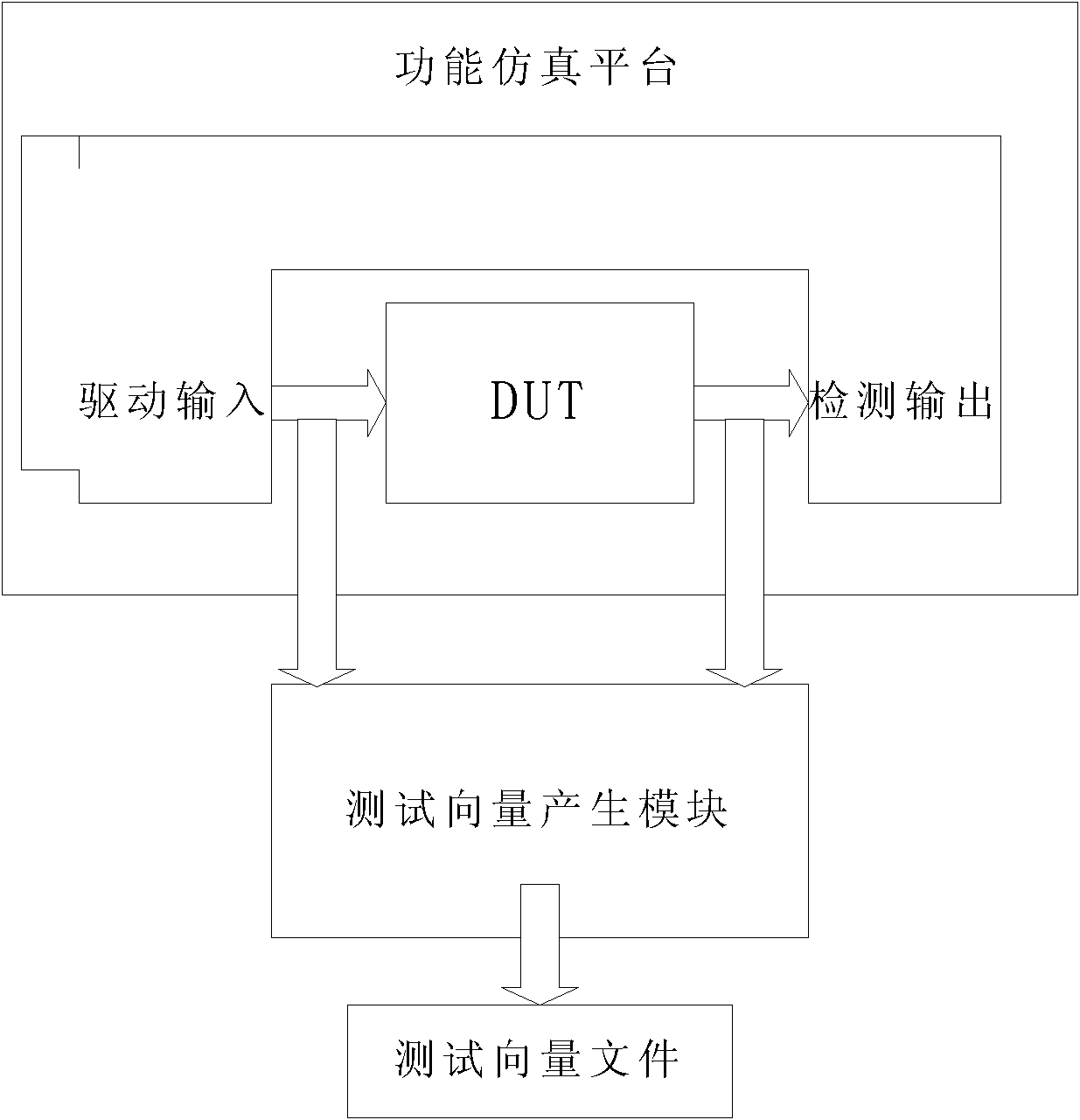

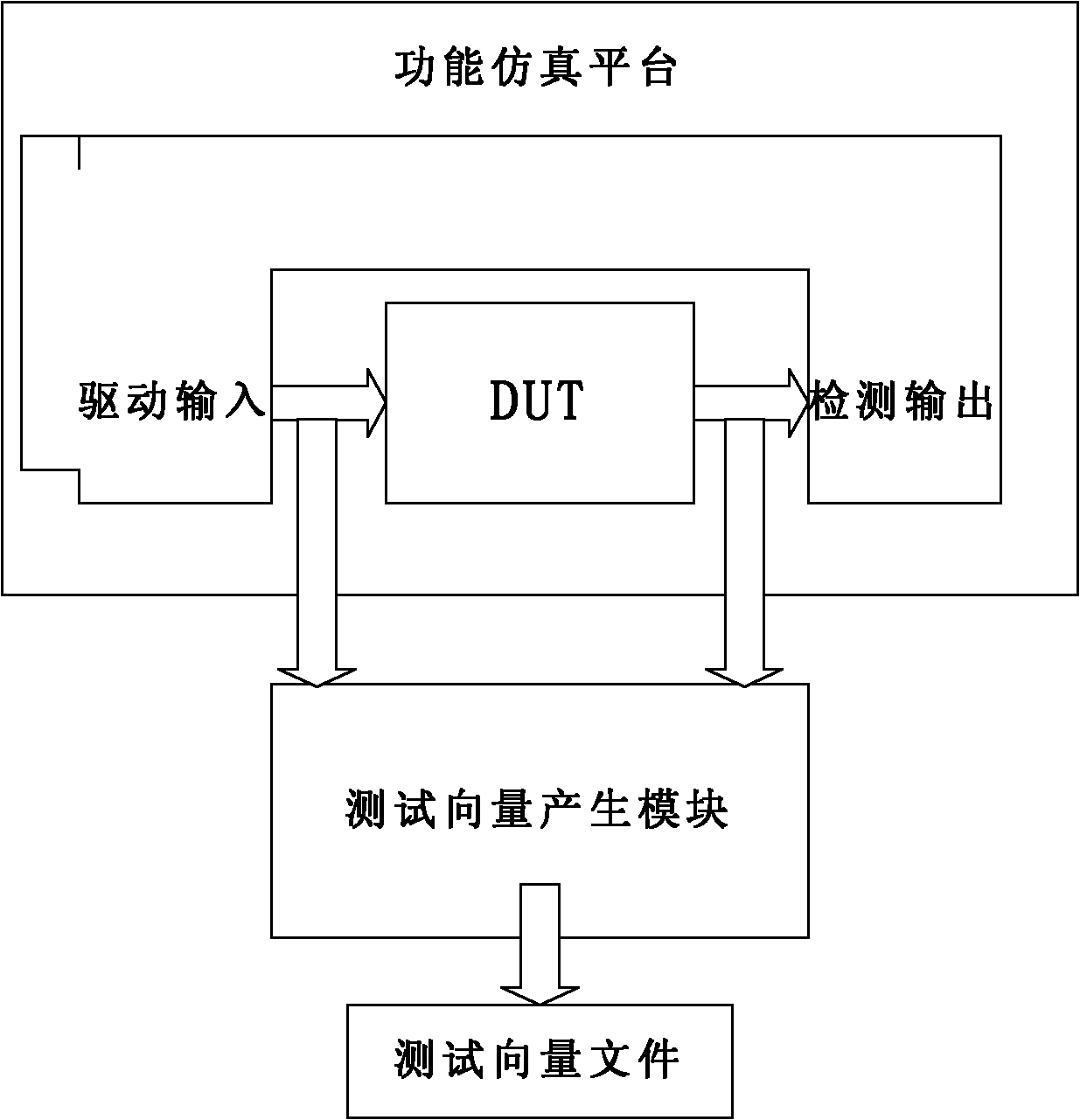

[0029] see figure 1 , the method for generating test vectors of the present invention, its preferred embodiment is realized by the following steps:

[0030] Step 1: Create a hardware description language HDL file and define a file variable for recording test vectors; the hardware description language HDL file contains a test vector generation module with or without input and output signals; the name of the module can be named "vector_gen_tb " can also be any other identifier that meets the grammatical requirements;

[0031] Step 2: Define a corresponding signal for each input and output signal of the entity to be tested in the module of step 1), which is used to monitor the input and output values of the entity to be tested; when necessary, an initial value can also be given;

[0032] Step 3: When the input and output signals of the DUT to be tested are reversed, assign the corresponding signals in step 2) to The legal vector representation value of the corresponding test ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More