Debug system having assembler correcting register allocation errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

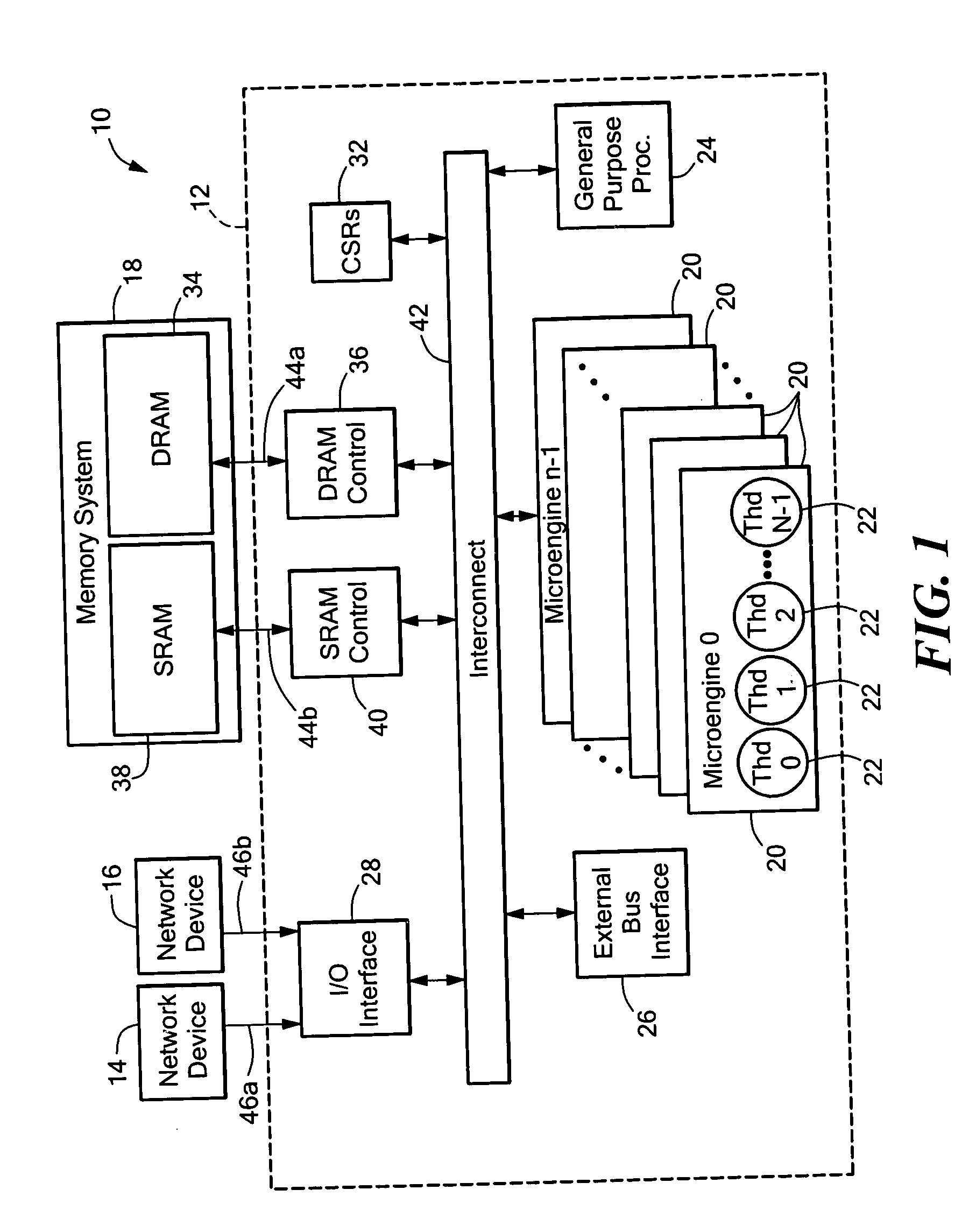

[0027] Referring to FIG. 1, a system 10 includes a processor 12 coupled to one or more I / O devices, for example, network devices 14 and 16, as well as a memory system 18. The processor 12 includes multiple processors (“microengines” or “MEs”) 20, each with multiple hardware controlled execution threads 22. In the example shown, there are “n” microengines 20, and each of the microengines 20 is capable of processing multiple threads 22, as will be described more fully below. In the described embodiment, the maximum number “N” of threads supported by the hardware is eight. Each of the microengines 20 is connected to and can communicate with adjacent microengines.

[0028] In one embodiment, the processor 12 also includes a processor 24 that assists in loading microcode control for the microengines 20 and other resources of the processor 12, and performs other general-purpose computer type functions such as handling protocols and exceptions. In network processing applications, the process...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More