Patents

Literature

174 results about "Register assignment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for register allocation in presence of hardware constraints

ActiveUS20060225061A1Reduce the amount requiredMinimize the numberSoftware engineeringProgram controlRegister allocationParallel computing

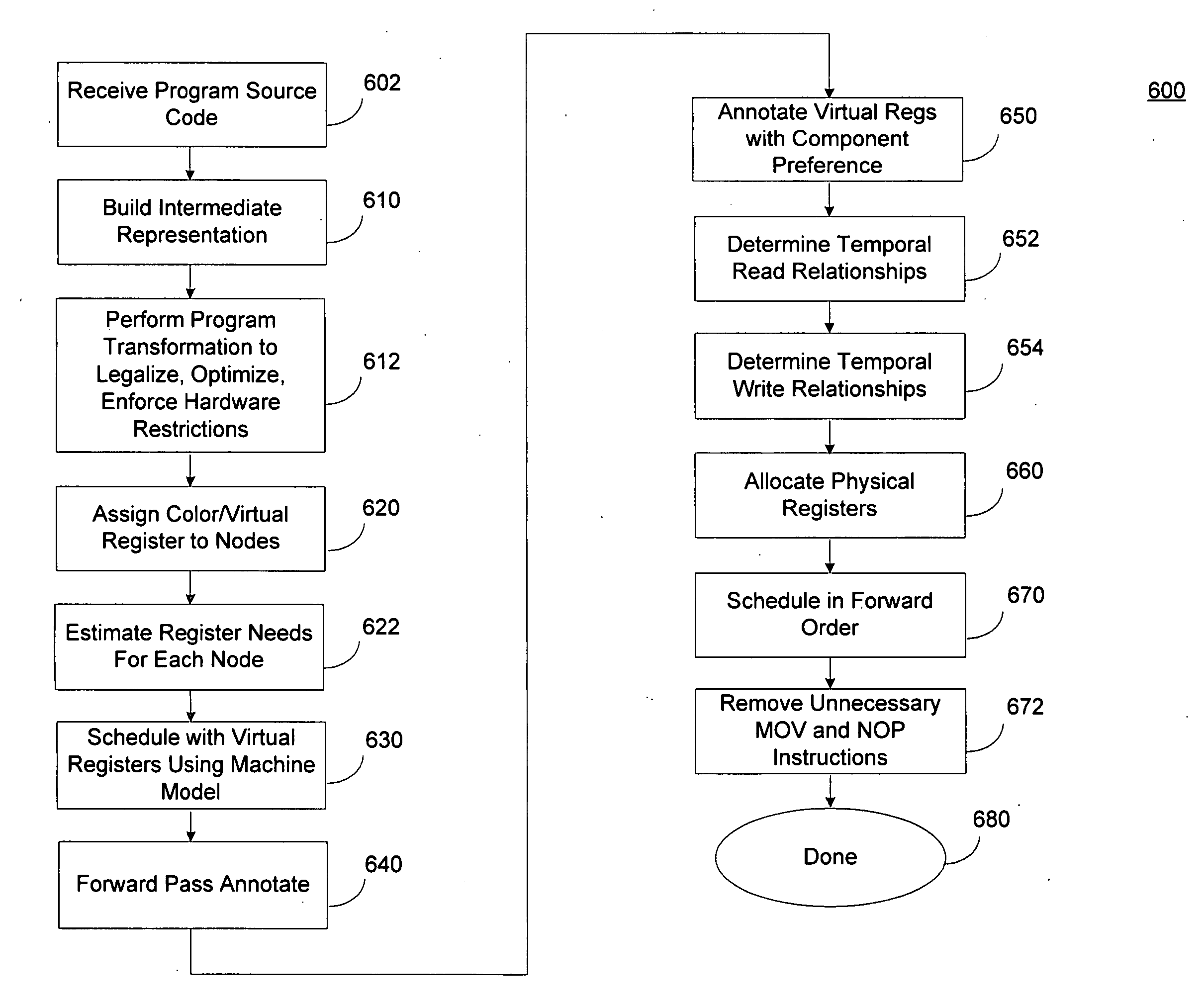

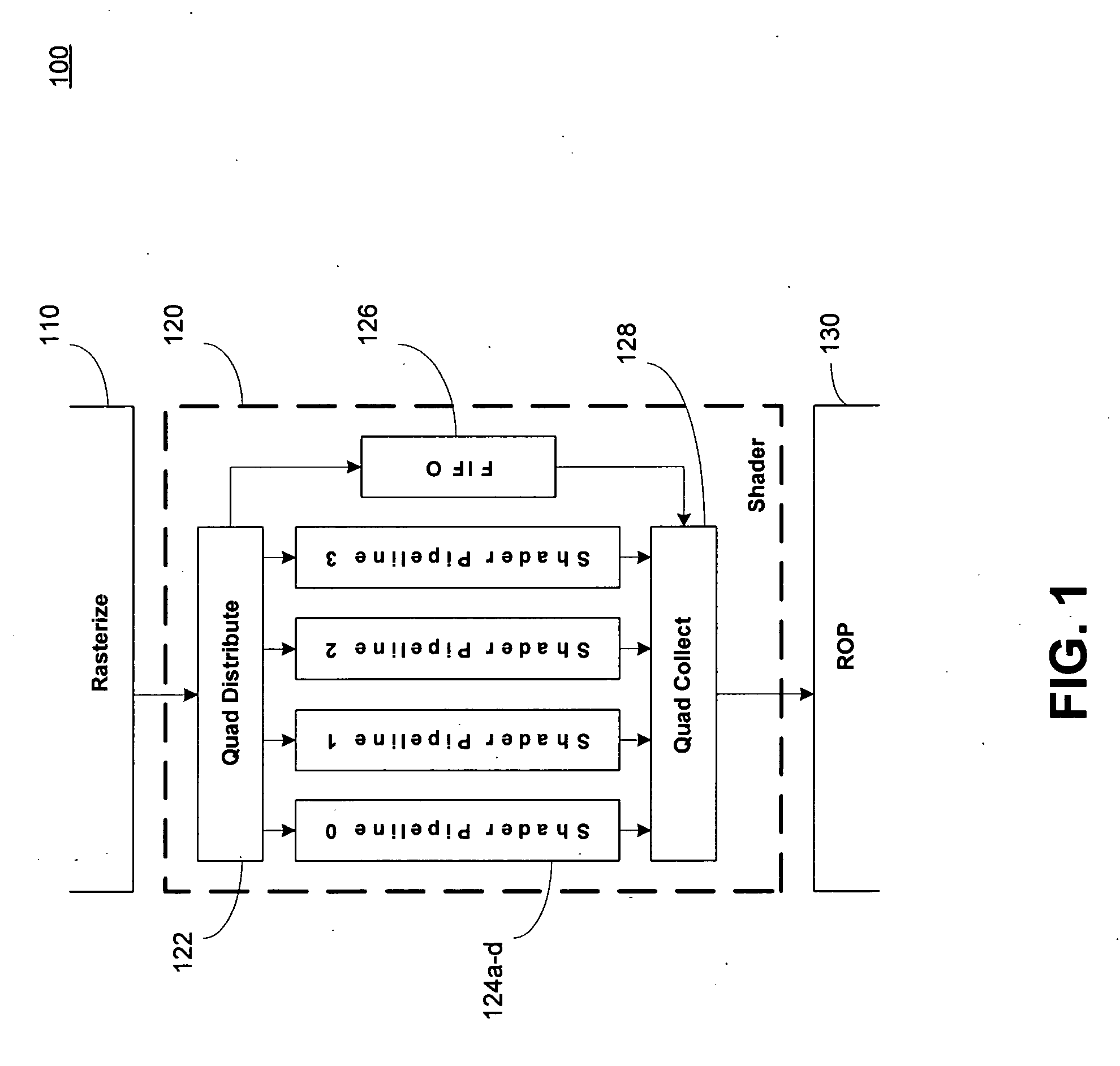

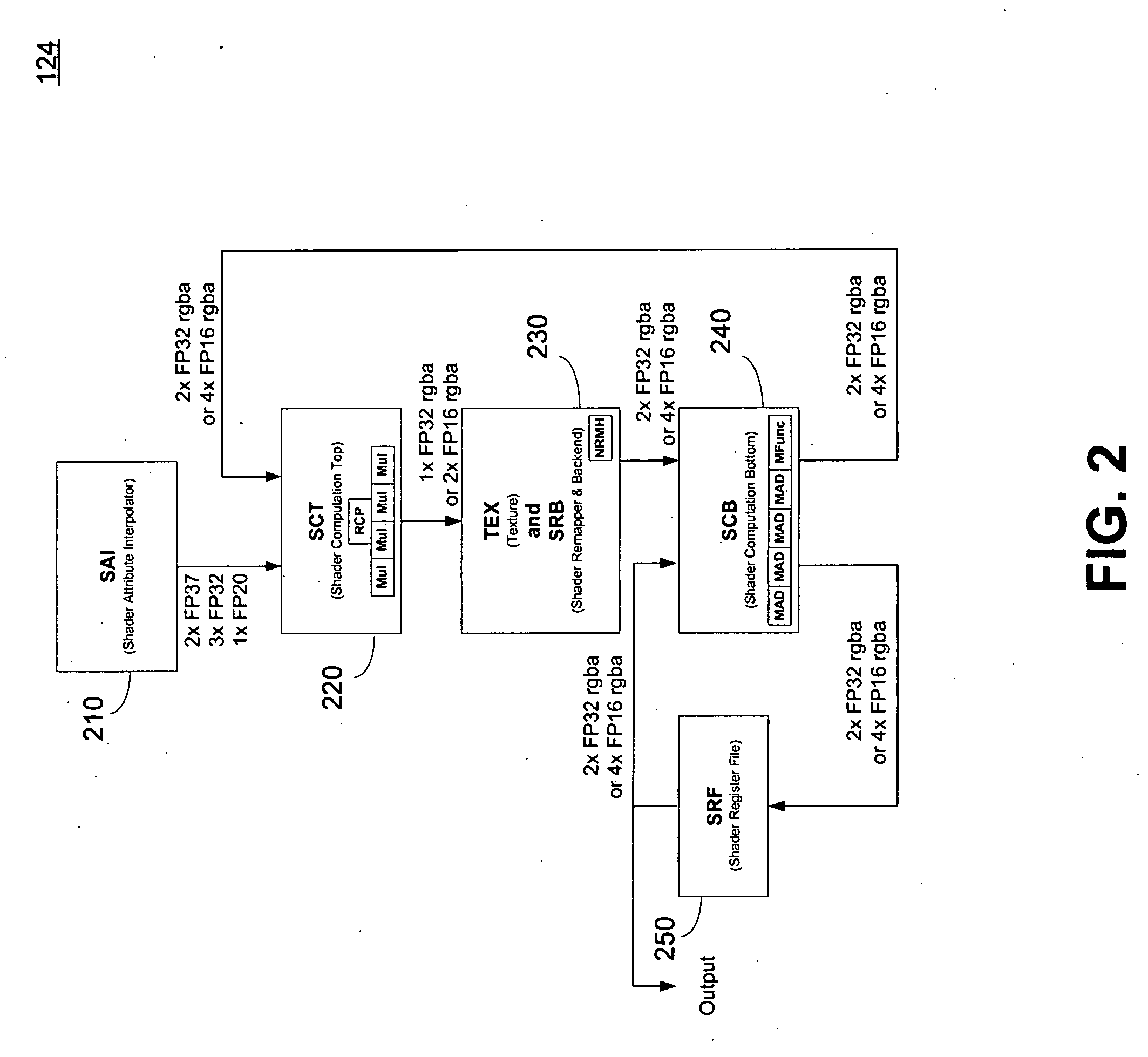

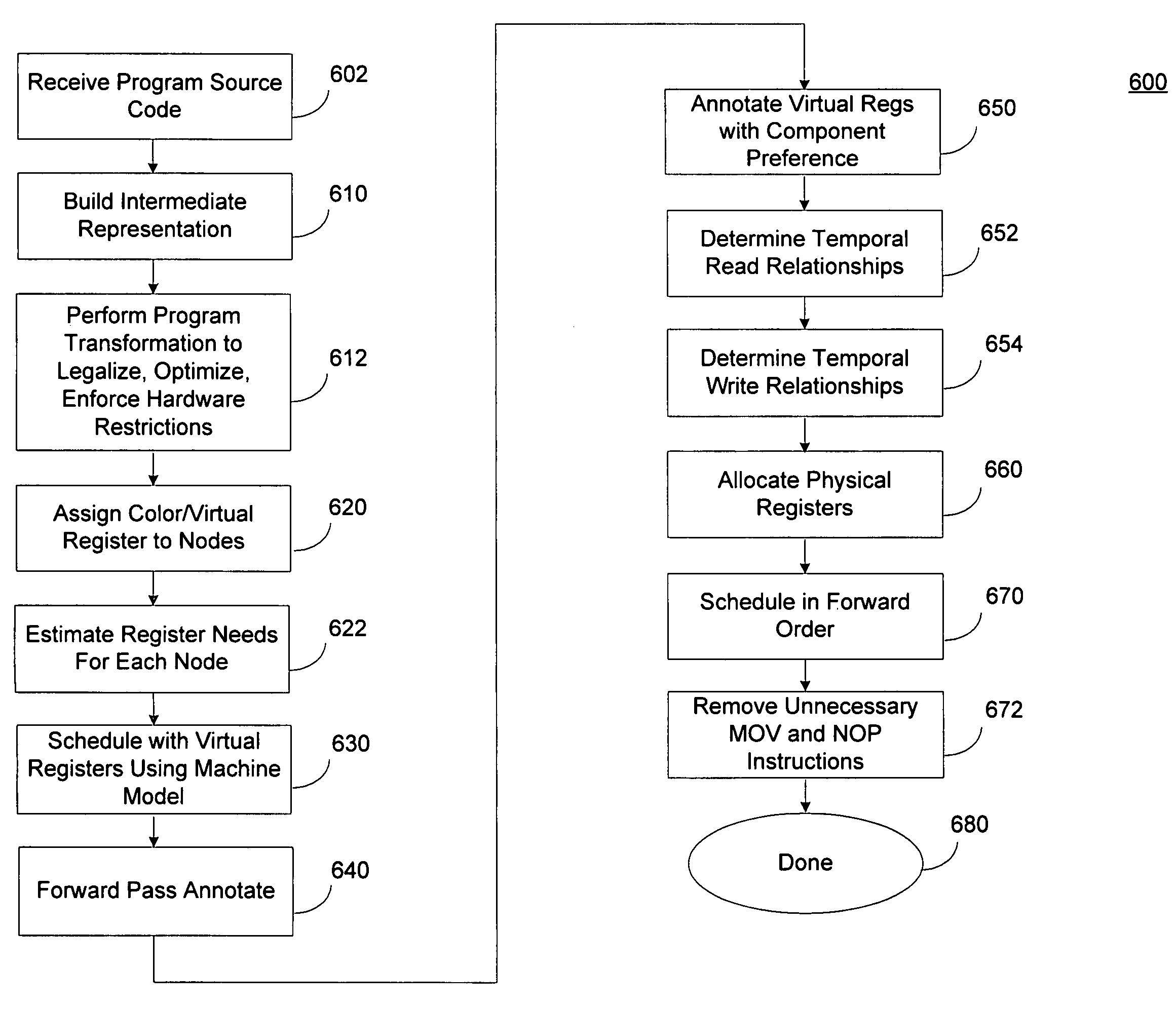

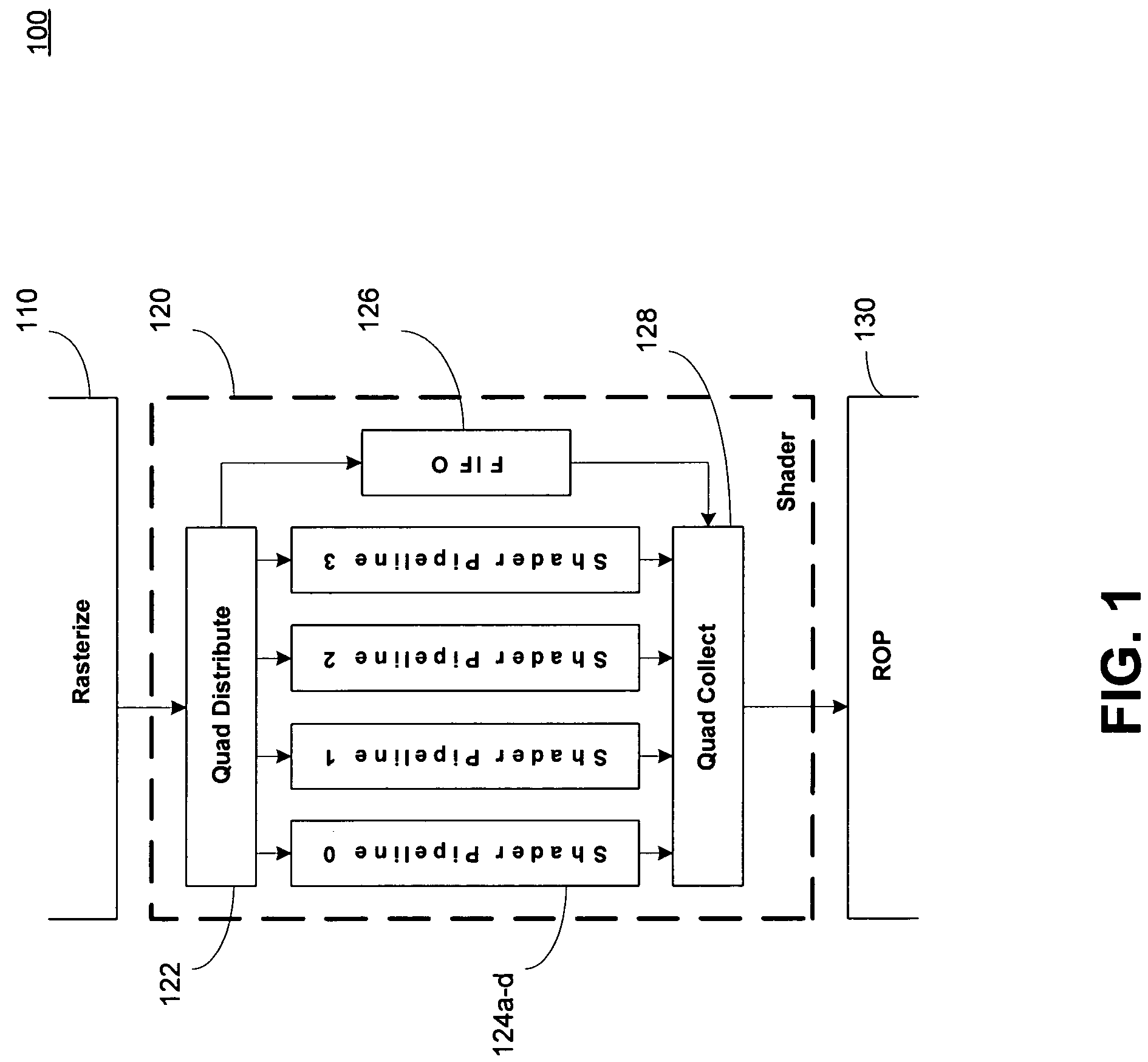

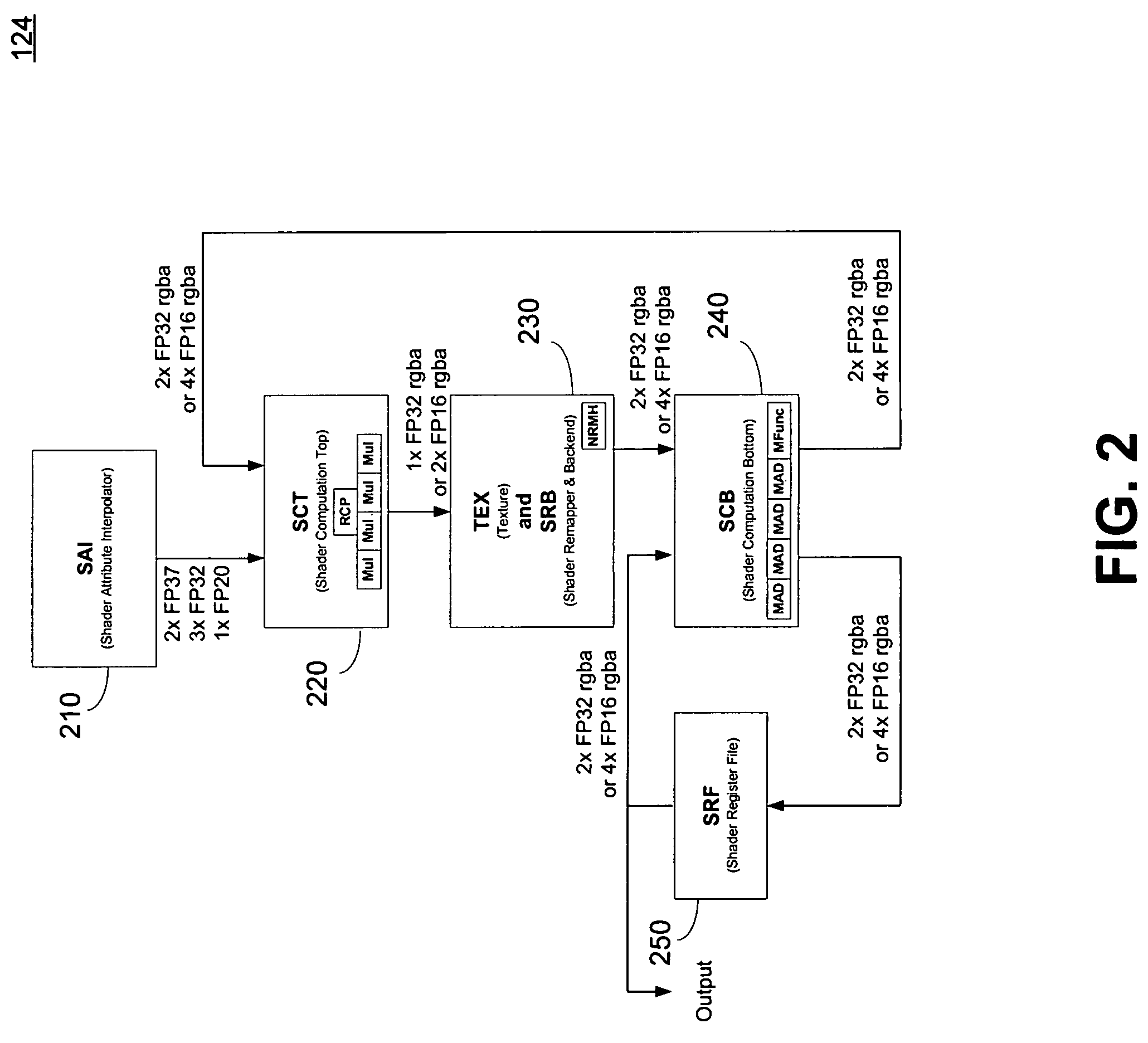

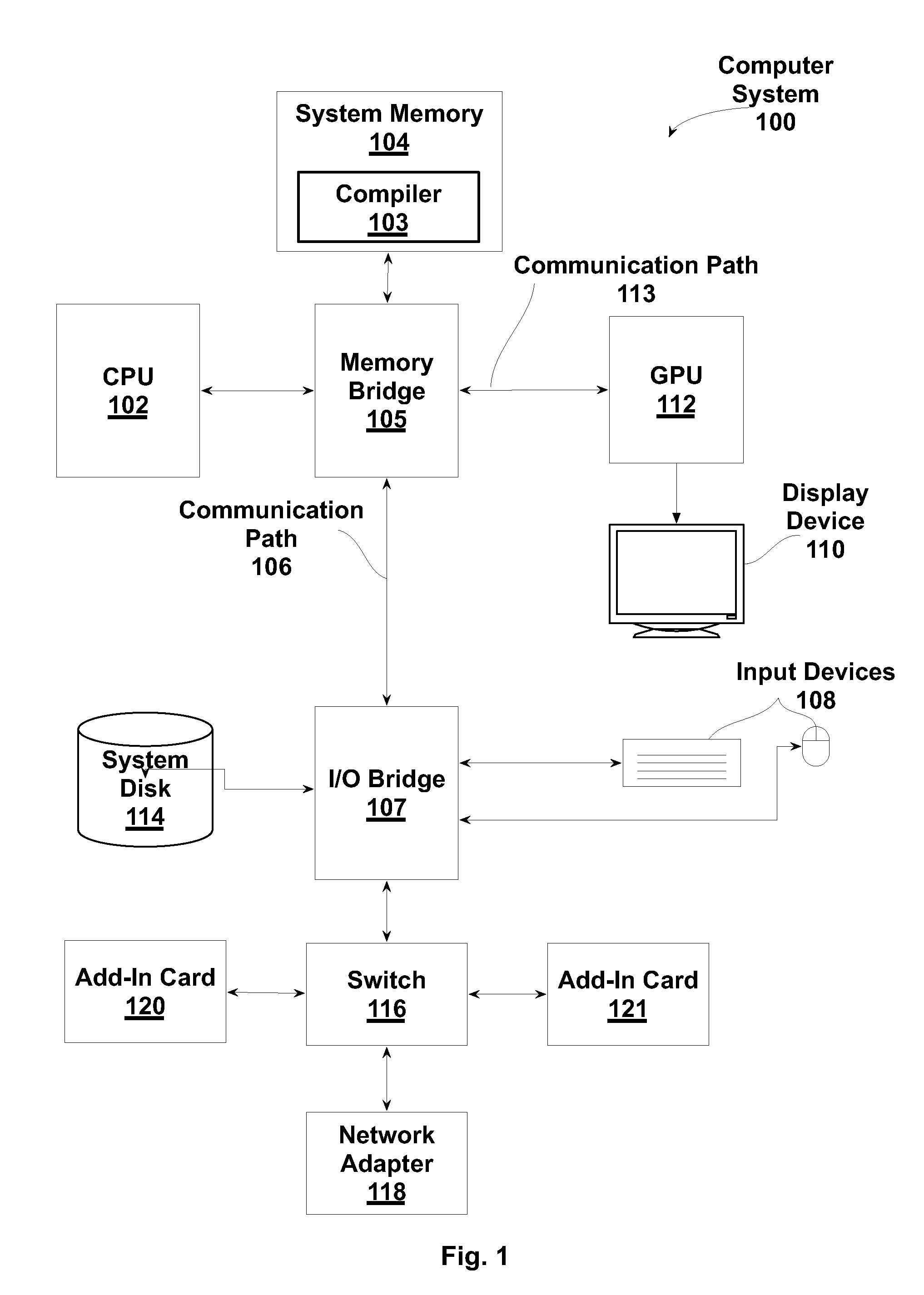

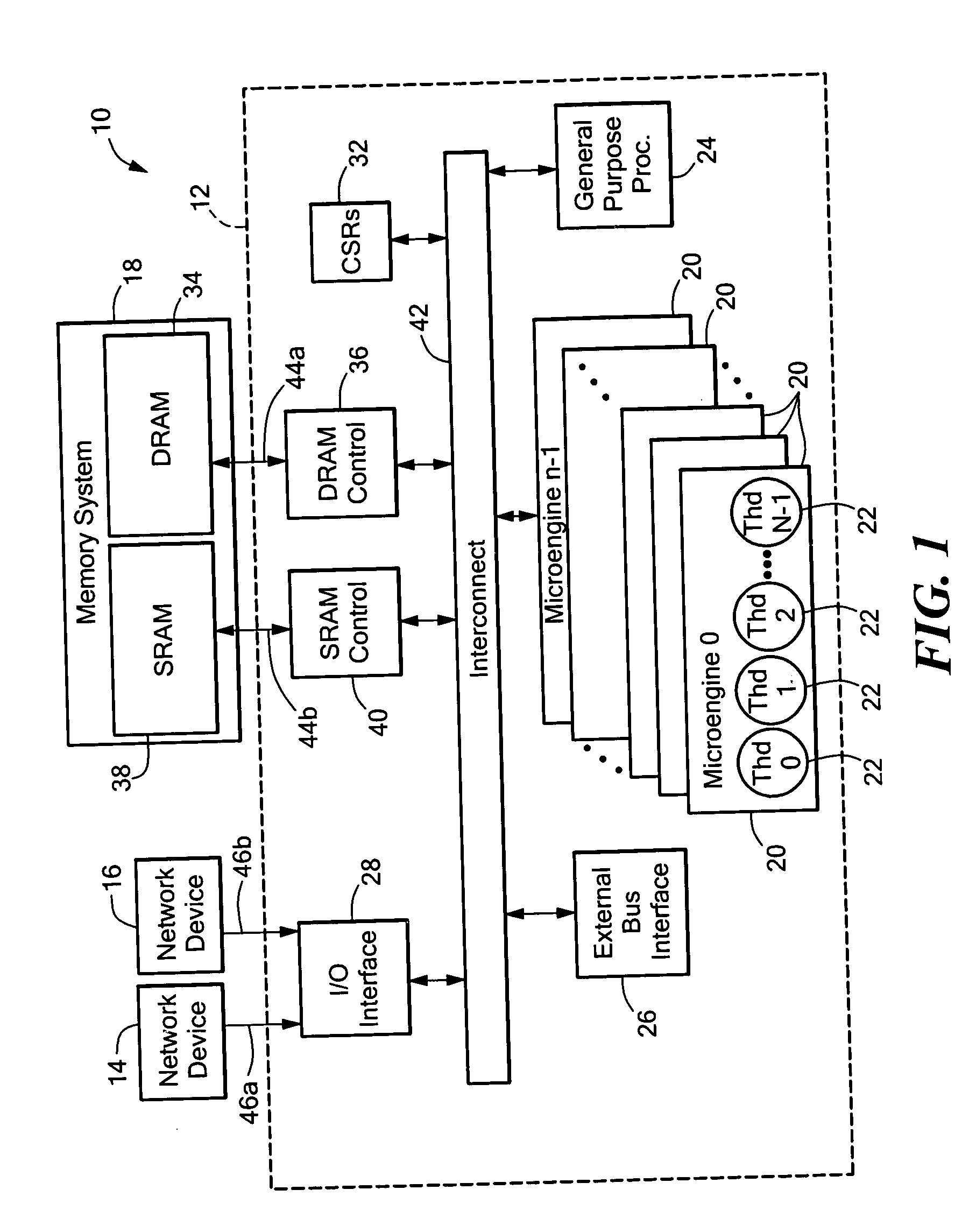

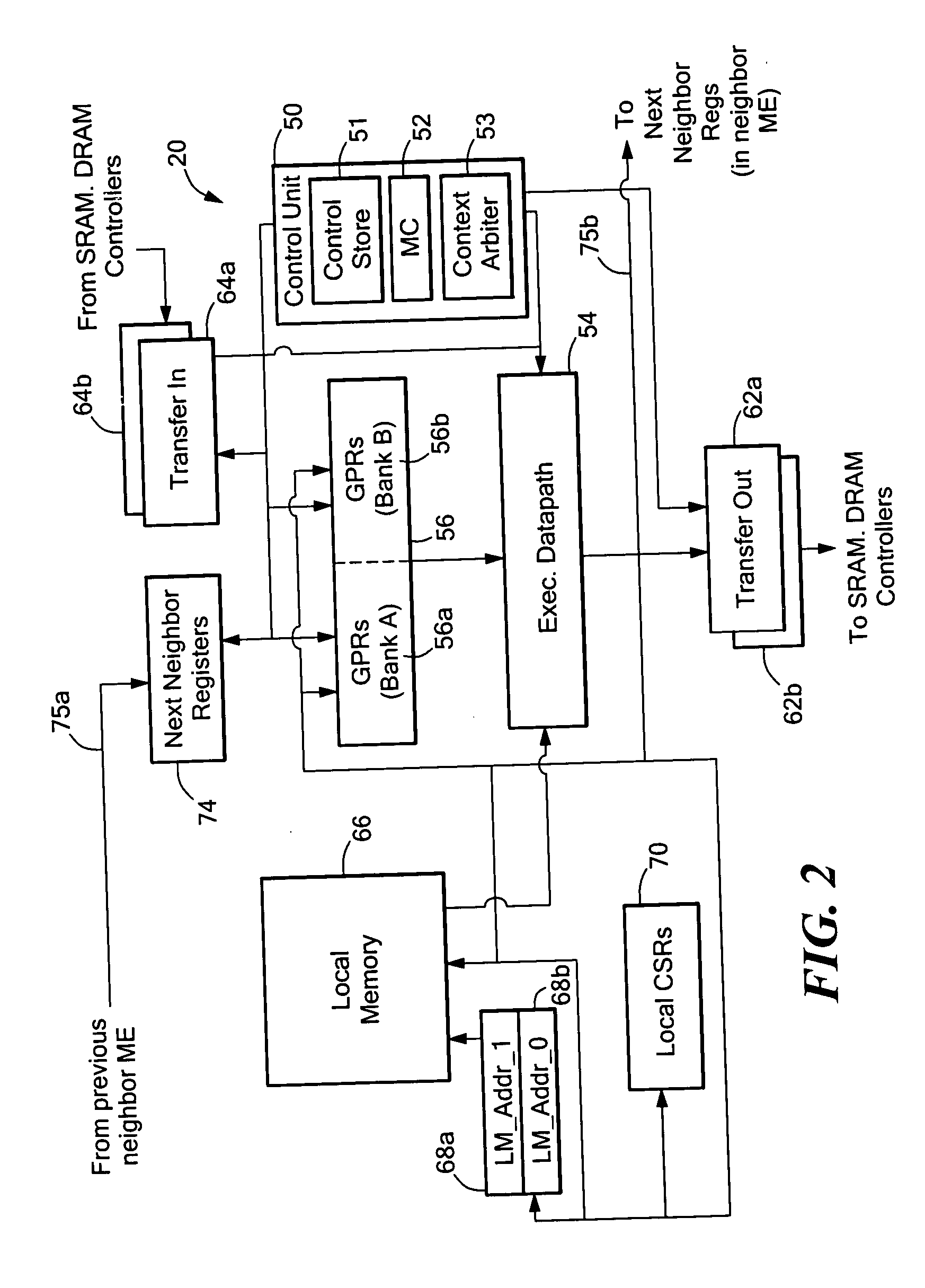

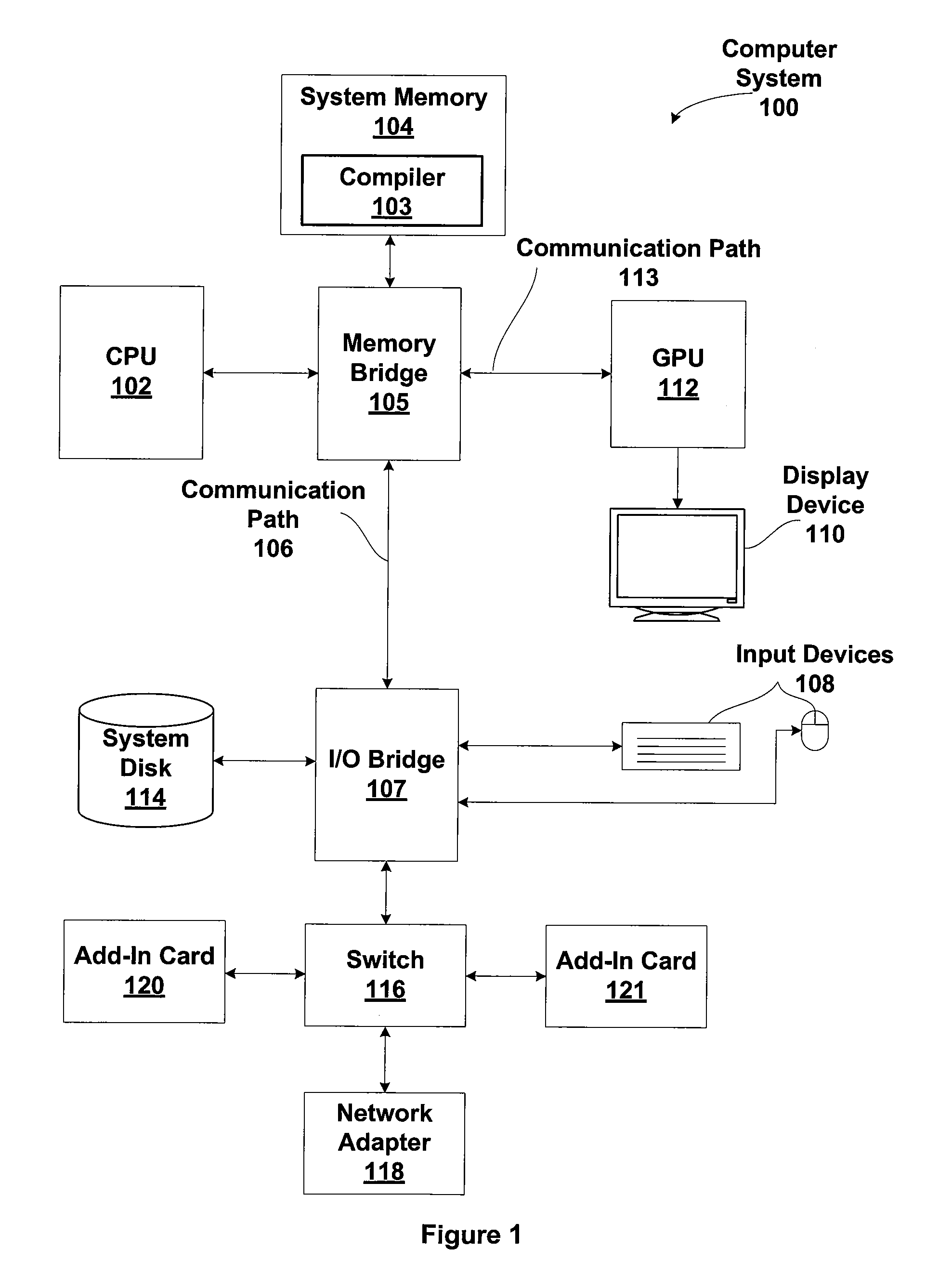

A method and apparatus for optimizing register allocation during scheduling and execution of program code in a hardware environment. The program code can be compiled to optimize execution given predetermined hardware constraints. The hardware constraints can include the number of register read and write operations that can be performed in a given processor pass. The optimizer can initially schedule the program using virtual registers and a goal of minimizing the amount of active registers at any time. The optimizer reschedules the program to assign the virtual registers to actual physical registers in a manner that minimizes the number of processor passes used to execute the program.

Owner:NVIDIA CORP

Post-register allocation profile directed instruction scheduling

ActiveUS7770161B2Software engineeringSpecial data processing applicationsRegister allocationProcessor register

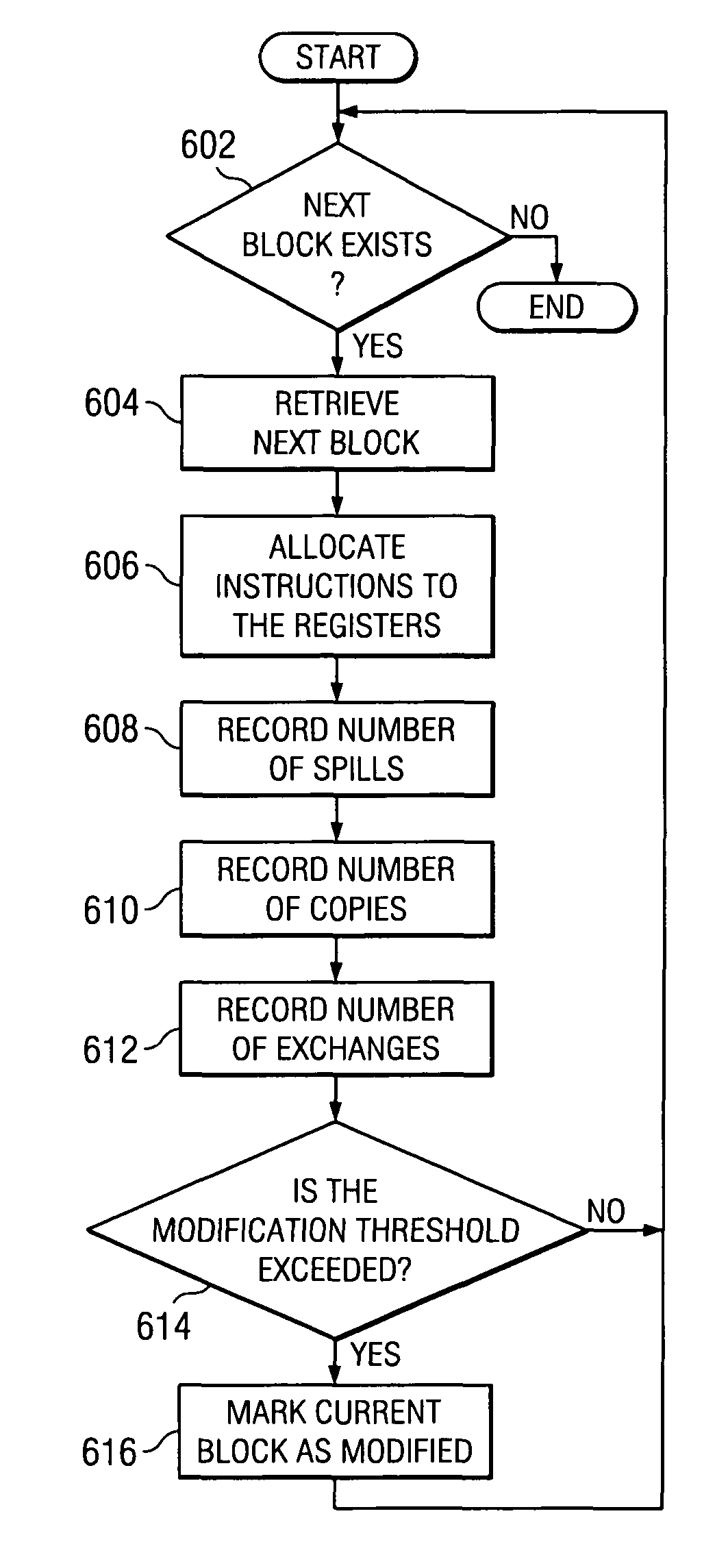

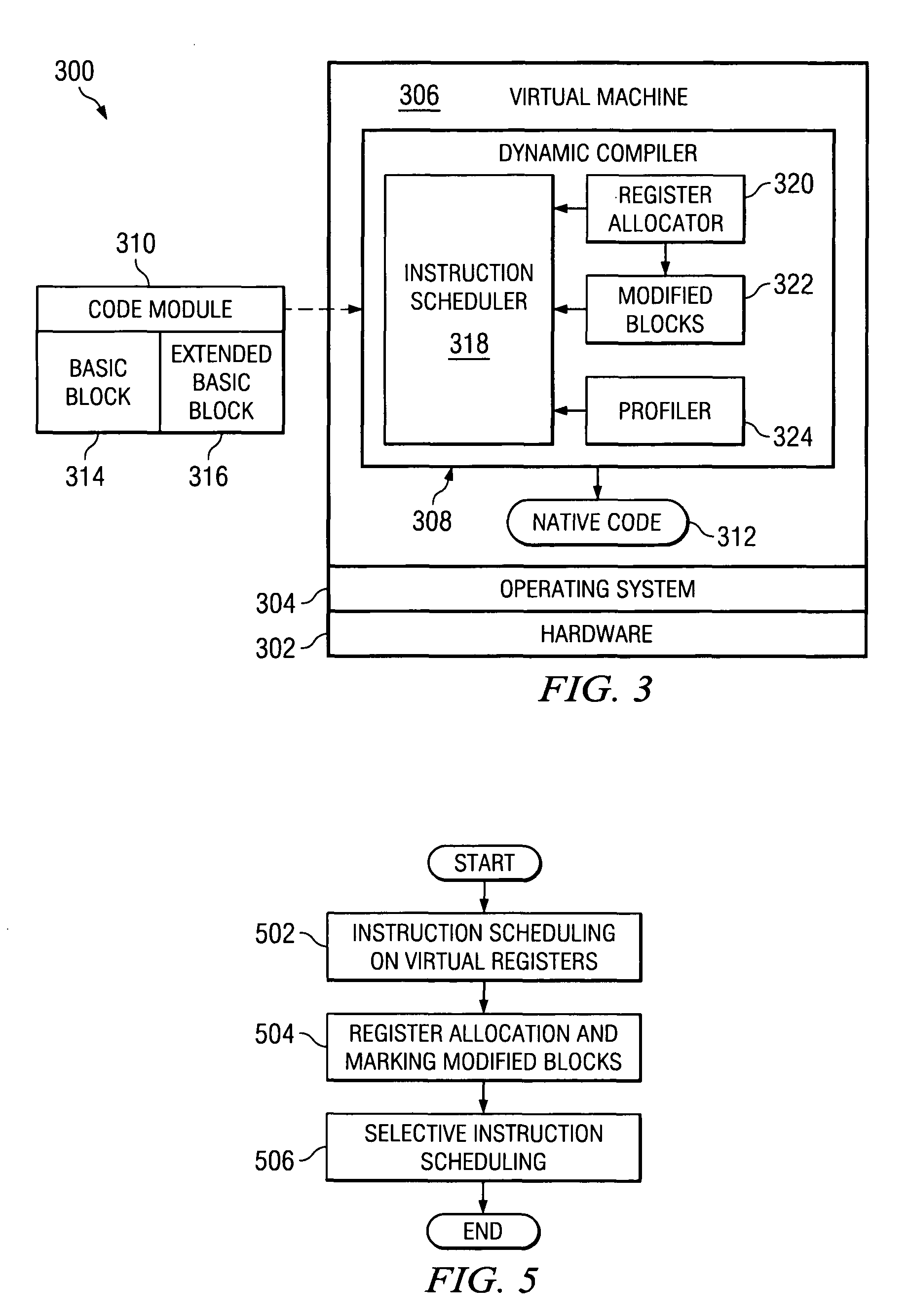

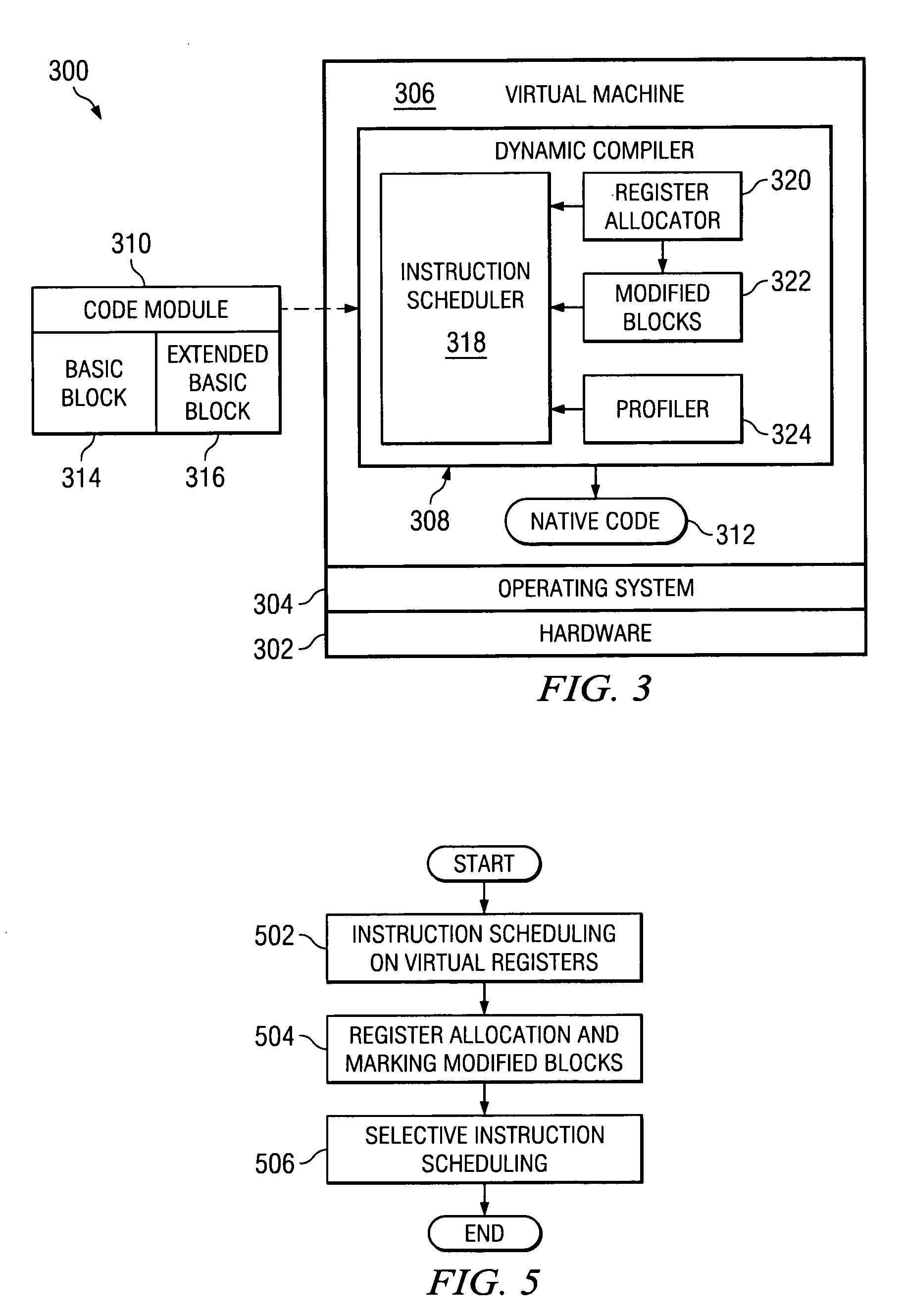

A computer implemented method, system, and computer usable program code for selective instruction scheduling. A determination is made whether a region of code exceeds a modification threshold after performing register allocation on the region of code. The region of code is marked as a modified region of code in response to the determination that the region of code exceeds the modification threshold. A determination is made whether the region of code exceeds an execution threshold in response to the determination that the region of code is marked as a modified region of code. Post-register allocation instruction scheduling is performed on the region of code in response to the determination that the region of code is marked as a modified region of code and the determination that the region of code exceeds the execution threshold.

Owner:TWITTER INC

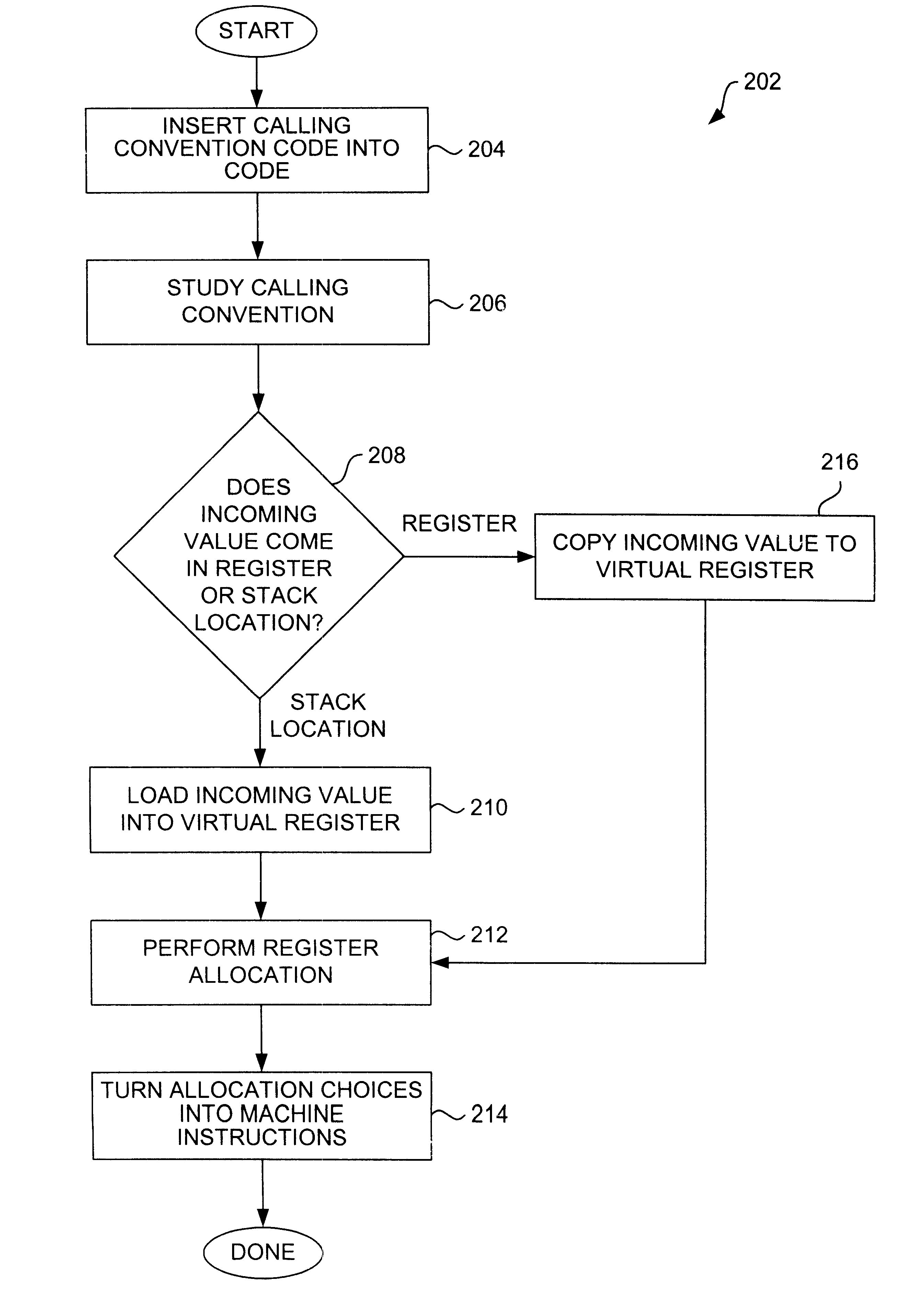

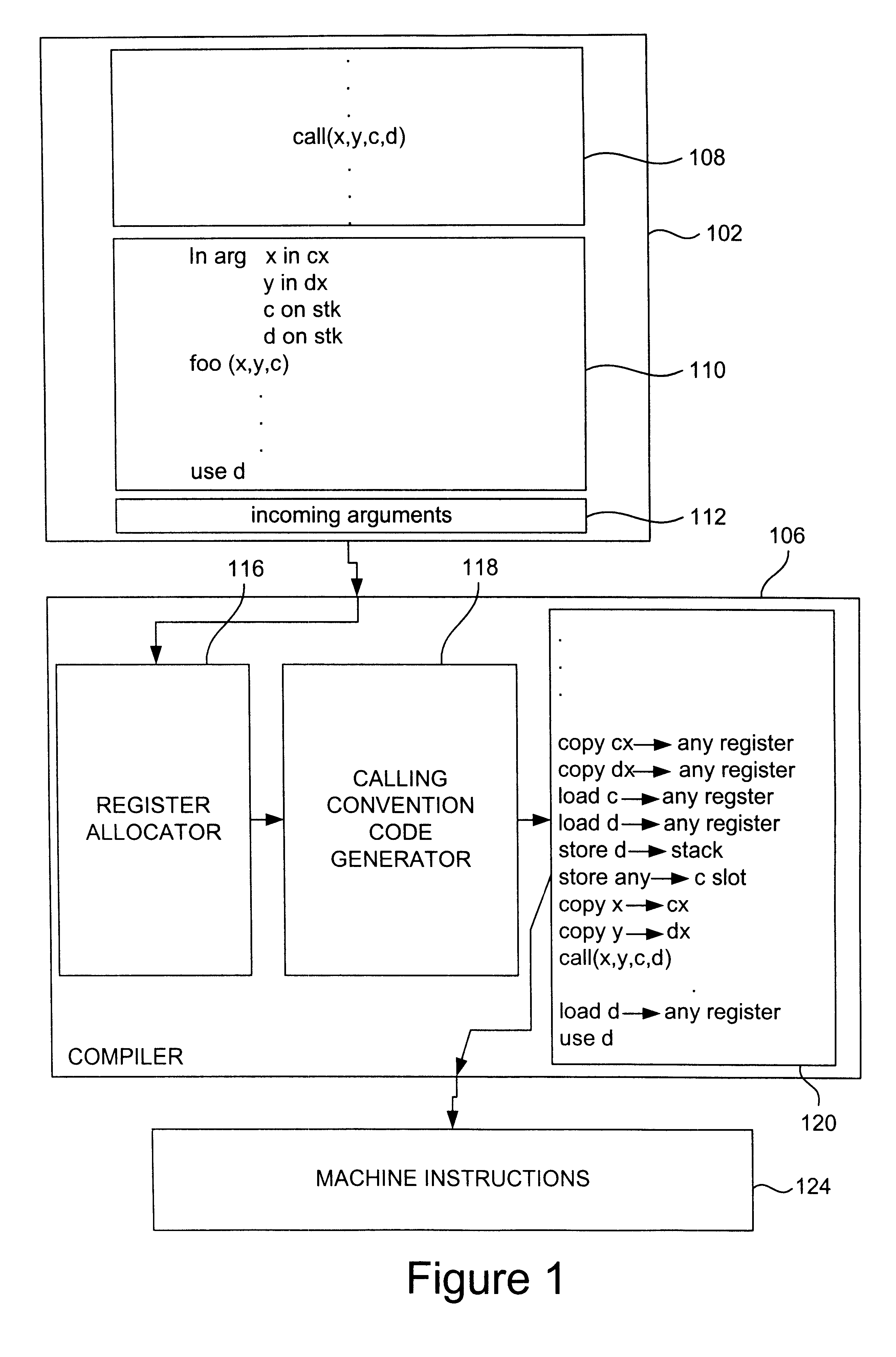

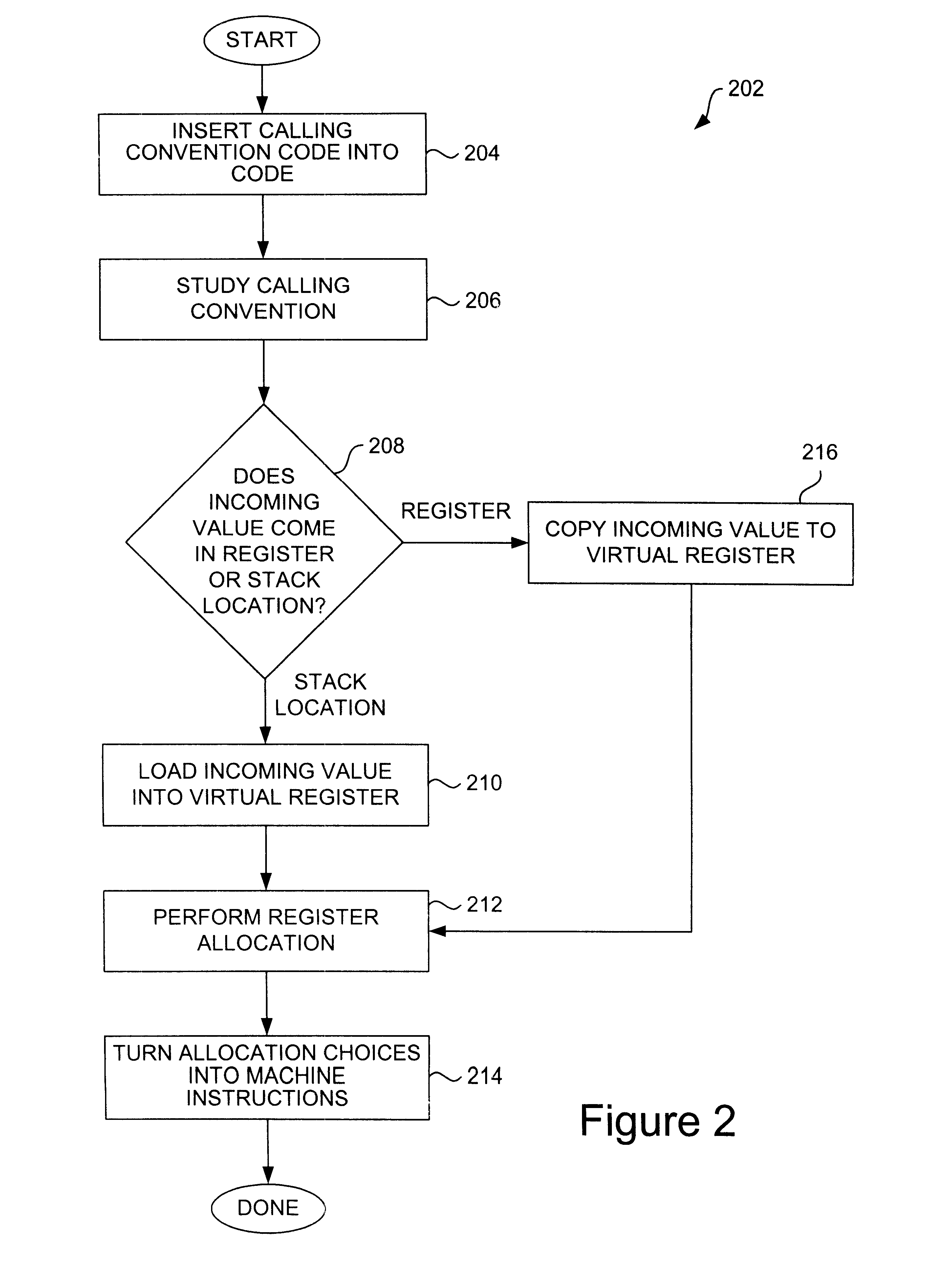

Method and apparatus for building calling convention prolog and epilog code using a register allocator

InactiveUS6408433B1Generate efficientlyEasy to transplantSoftware engineeringProgram controlRegister allocationProcessor register

Methods and apparatus for enabling a register allocator to build a calling convention are disclosed. According to one aspect of the present invention, a computer-implemented method for generating code associated with a calling convention includes obtaining compilable source code, and identifying at least one argument associated with the calling convention. The location of the argument with respect to memory space is described by a register mask. The method also includes performing a register allocation using a register allocator that is arranged to allocate registers. During the register allocation, code associated with the calling convention is produced automatically by the spill-code mechanism in the allocator without requiring the use of a specialized prolog or epilog code generator.

Owner:ORACLE INT CORP

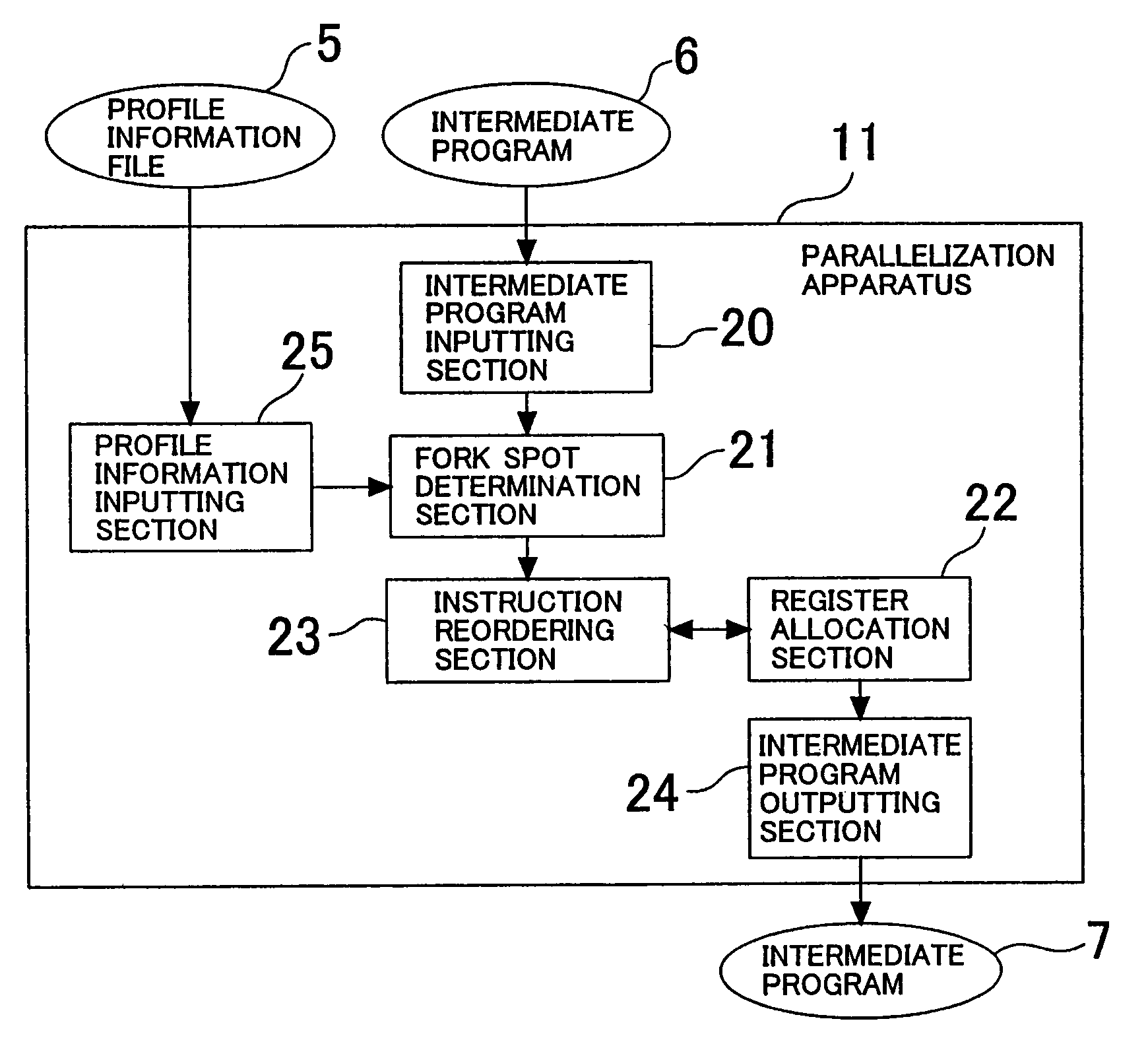

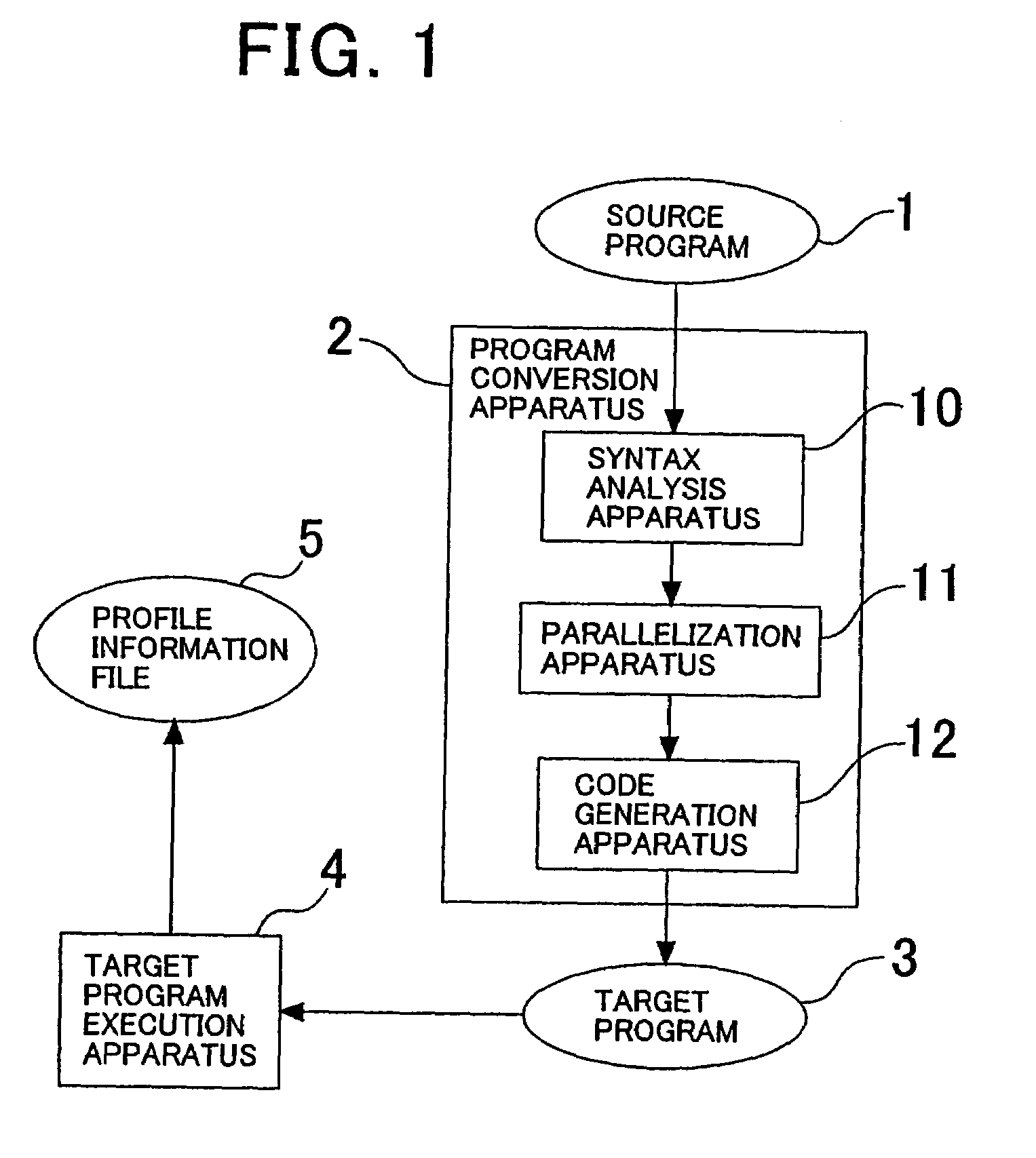

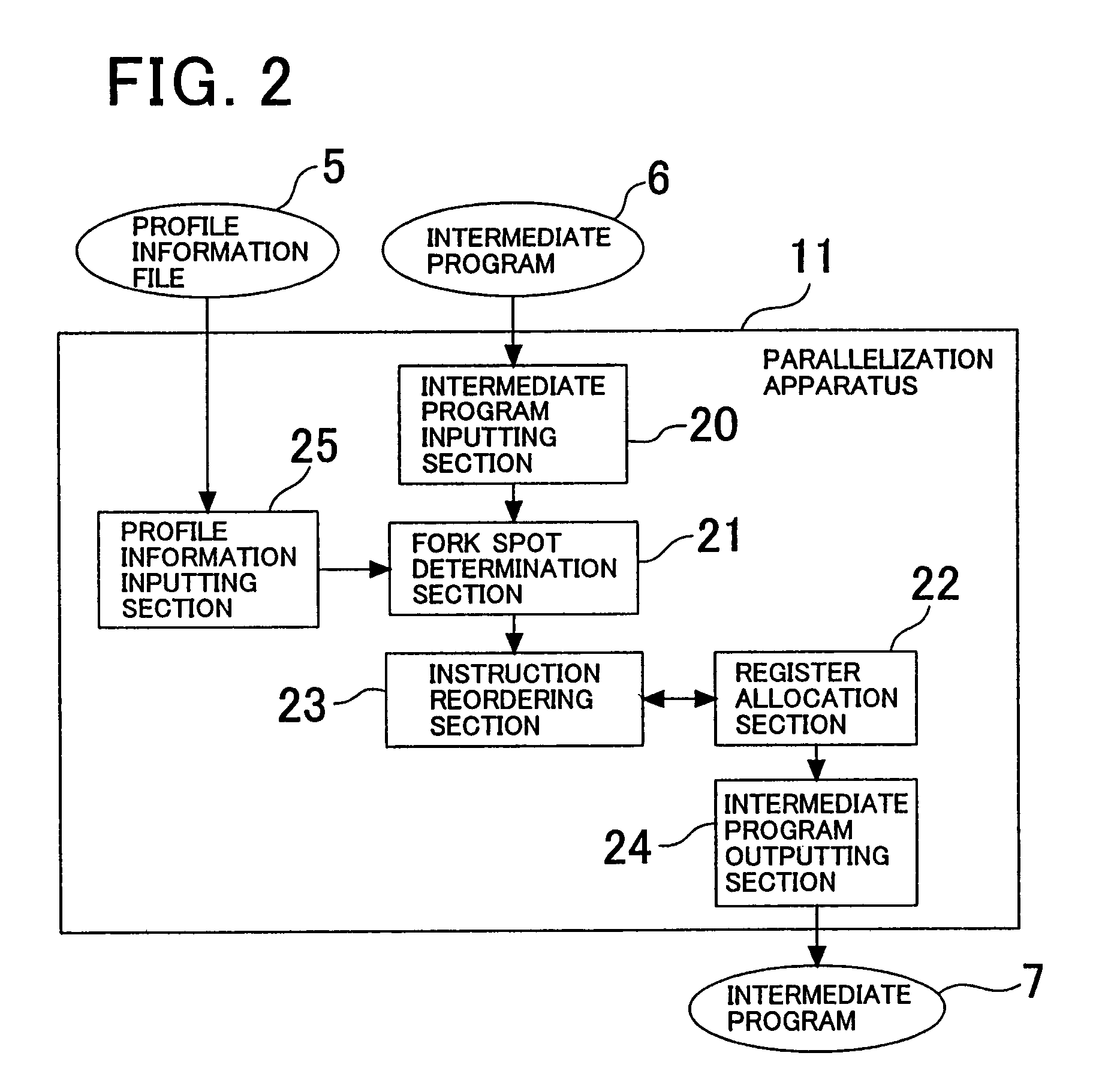

Branch instruction conversion to multi-threaded parallel instructions

InactiveUS7010787B2Process is performedImprove performanceProgram initiation/switchingProgram synchronisationRegister allocationProcessor register

The invention provides a program conversion apparatus which performs parallelization for a multi-thread microprocessor on an intermediate program level. A parallelization apparatus of the program conversion apparatus includes a fork spot determination section, a register allocation section and an instruction reordering section. The fork spot determination section determines a fork spot and a fork system based on a result of a register allocation trial performed by the register allocation section, the number of spots at which memory data dependence is present, and branching probabilities and a data dependence occurrence frequency obtained from a profile information file. The instruction reordering section reorders instructions preceding to and succeeding the FORK instruction in accordance with the determination.

Owner:NEC CORP

Method and apparatus for register allocation in presence of hardware constraints

ActiveUS7681187B2Reduce the amount requiredMinimize the numberSoftware engineeringProgram controlRegister allocationProcessor register

A method and apparatus for optimizing register allocation during scheduling and execution of program code in a hardware environment. The program code can be compiled to optimize execution given predetermined hardware constraints. The hardware constraints can include the number of register read and write operations that can be performed in a given processor pass. The optimizer can initially schedule the program using virtual registers and a goal of minimizing the amount of active registers at any time. The optimizer reschedules the program to assign the virtual registers to actual physical registers in a manner that minimizes the number of processor passes used to execute the program.

Owner:NVIDIA CORP

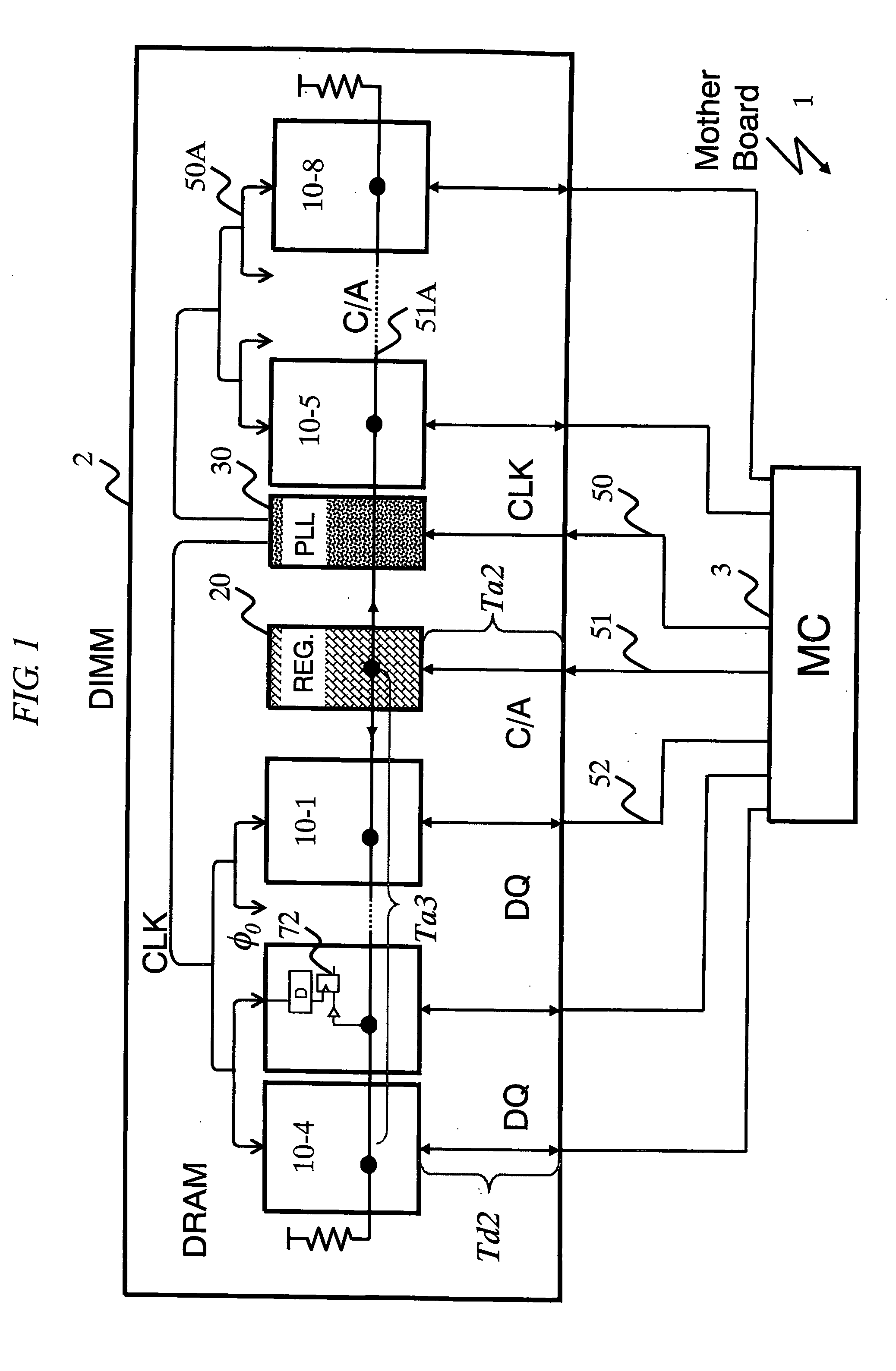

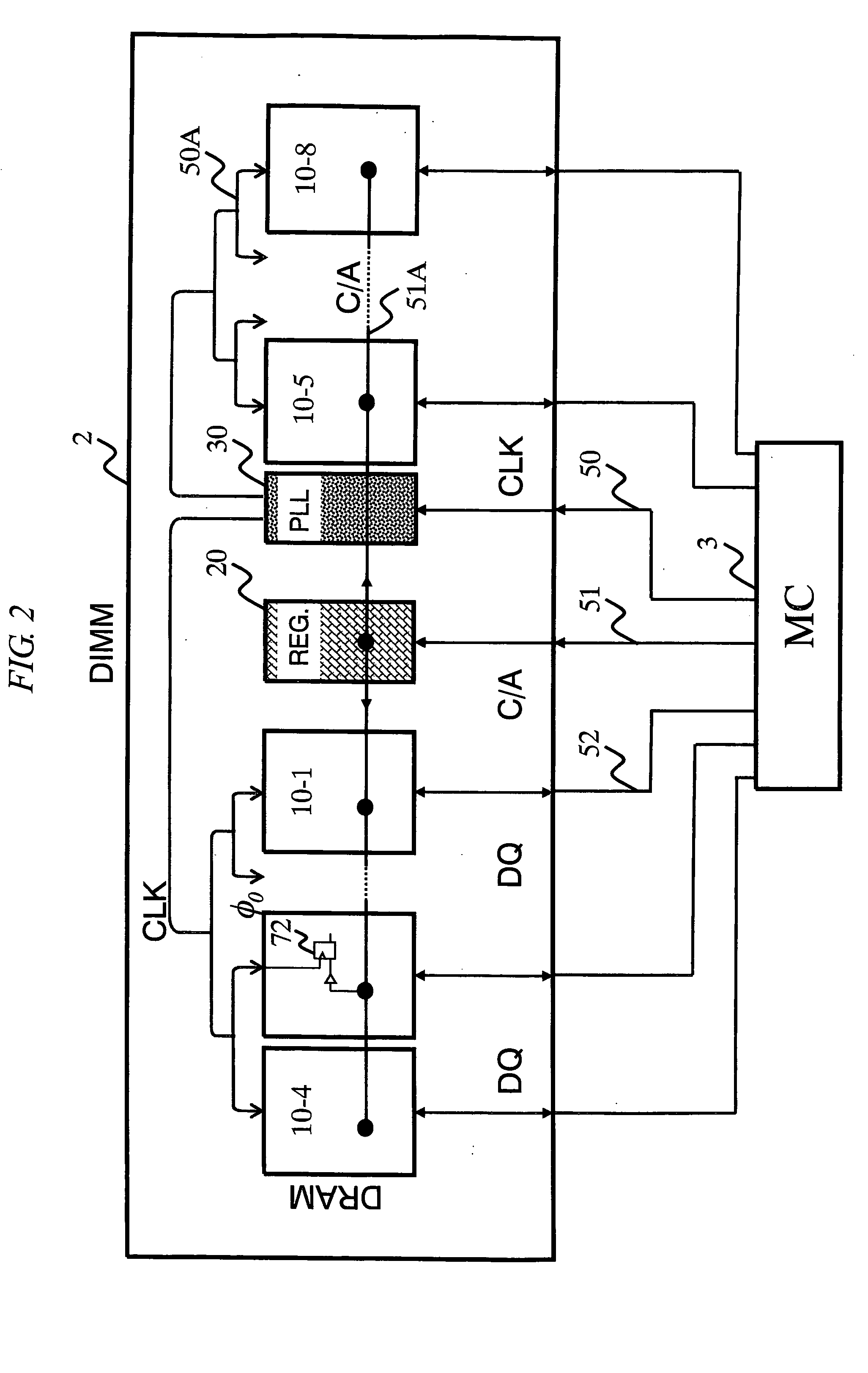

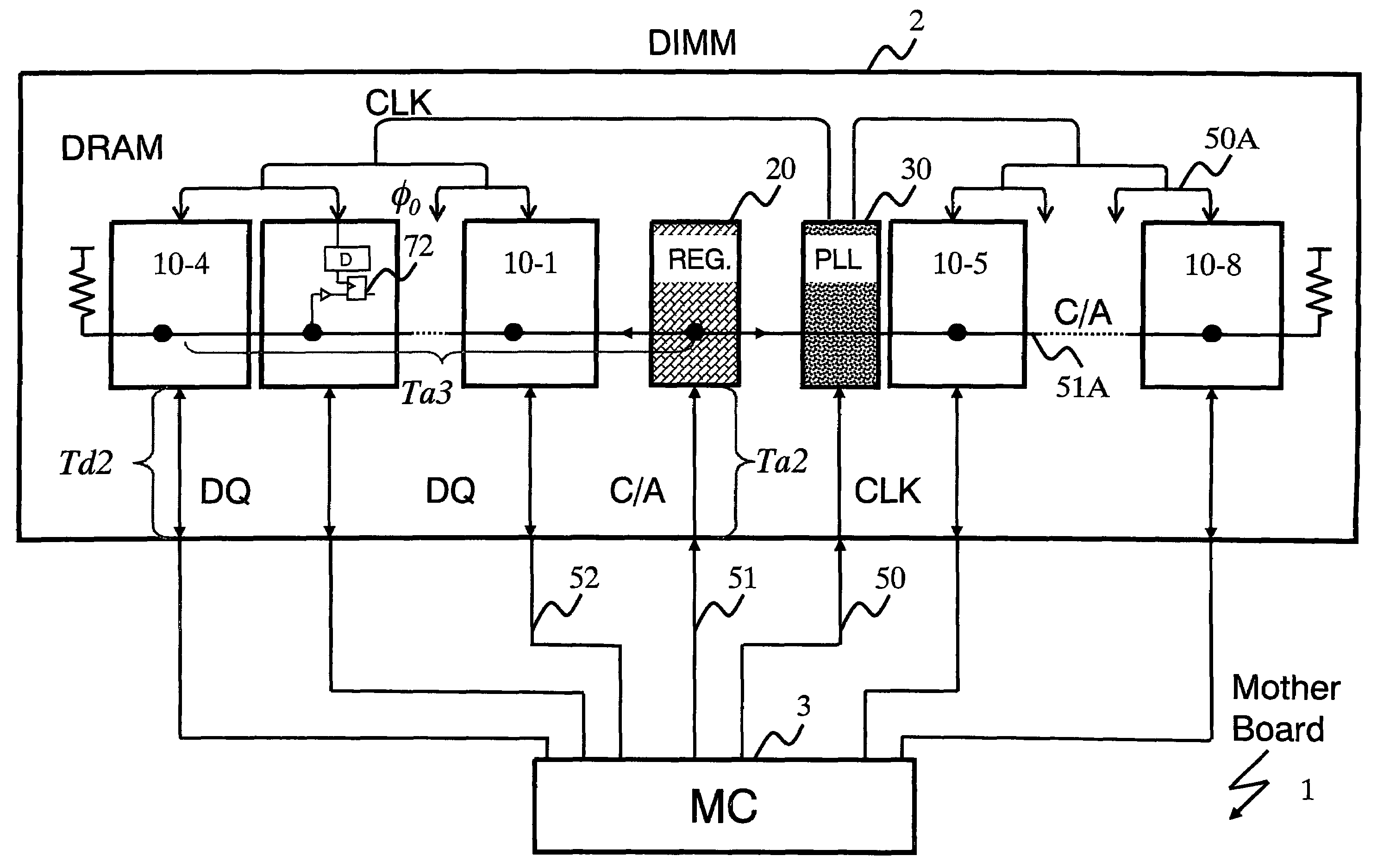

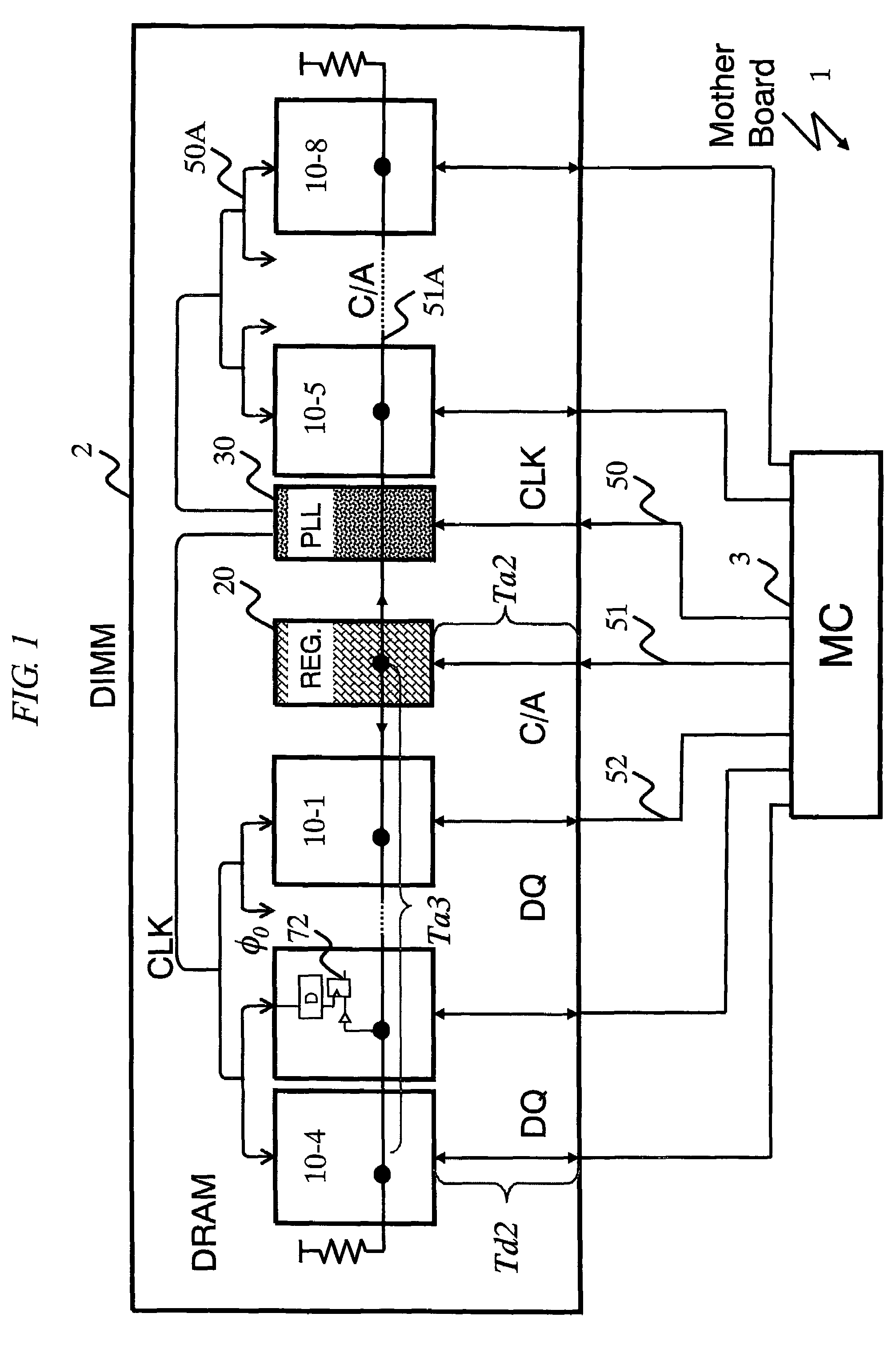

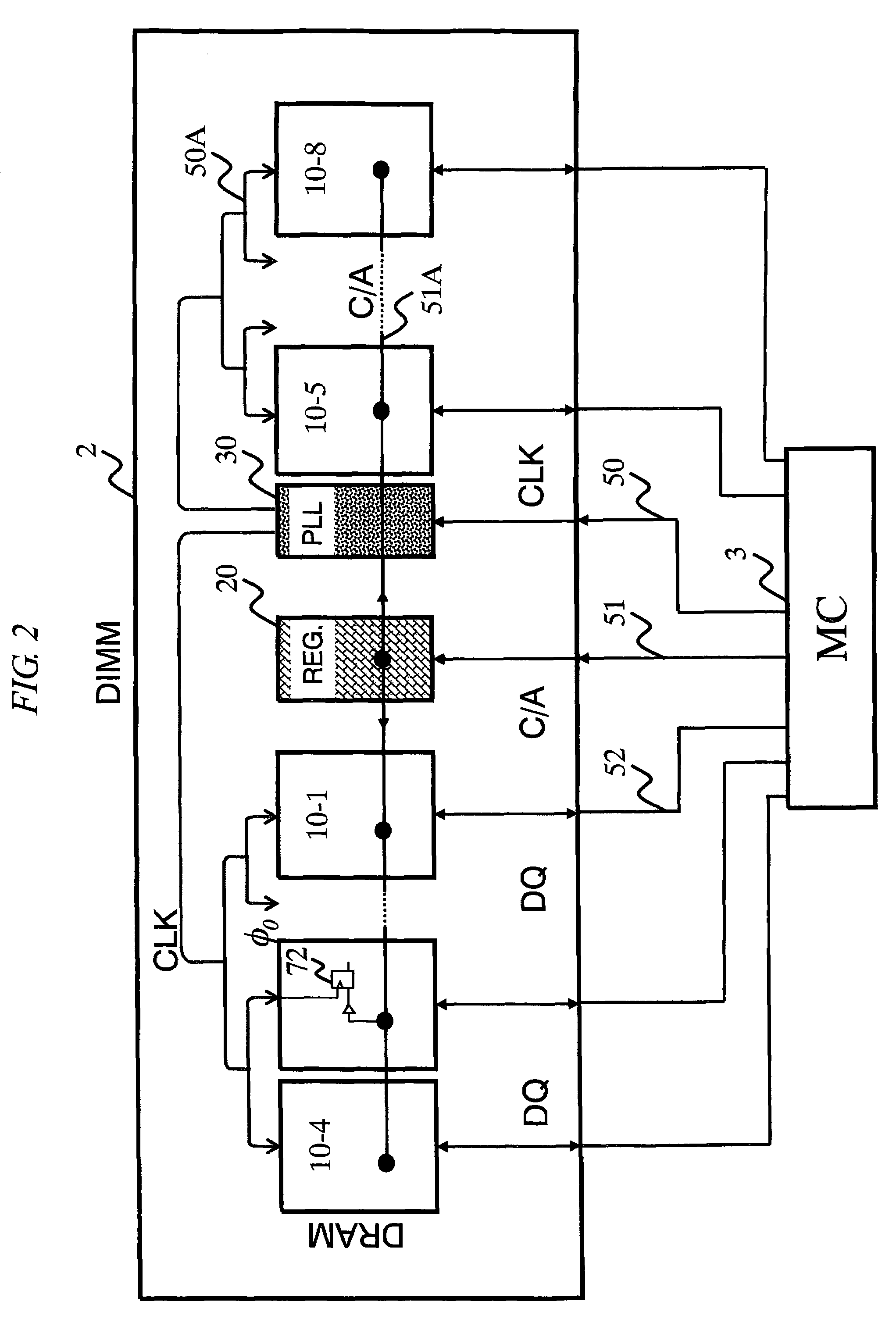

Semiconductor memory module, memory system, circuit, semiconductor device, and DIMM

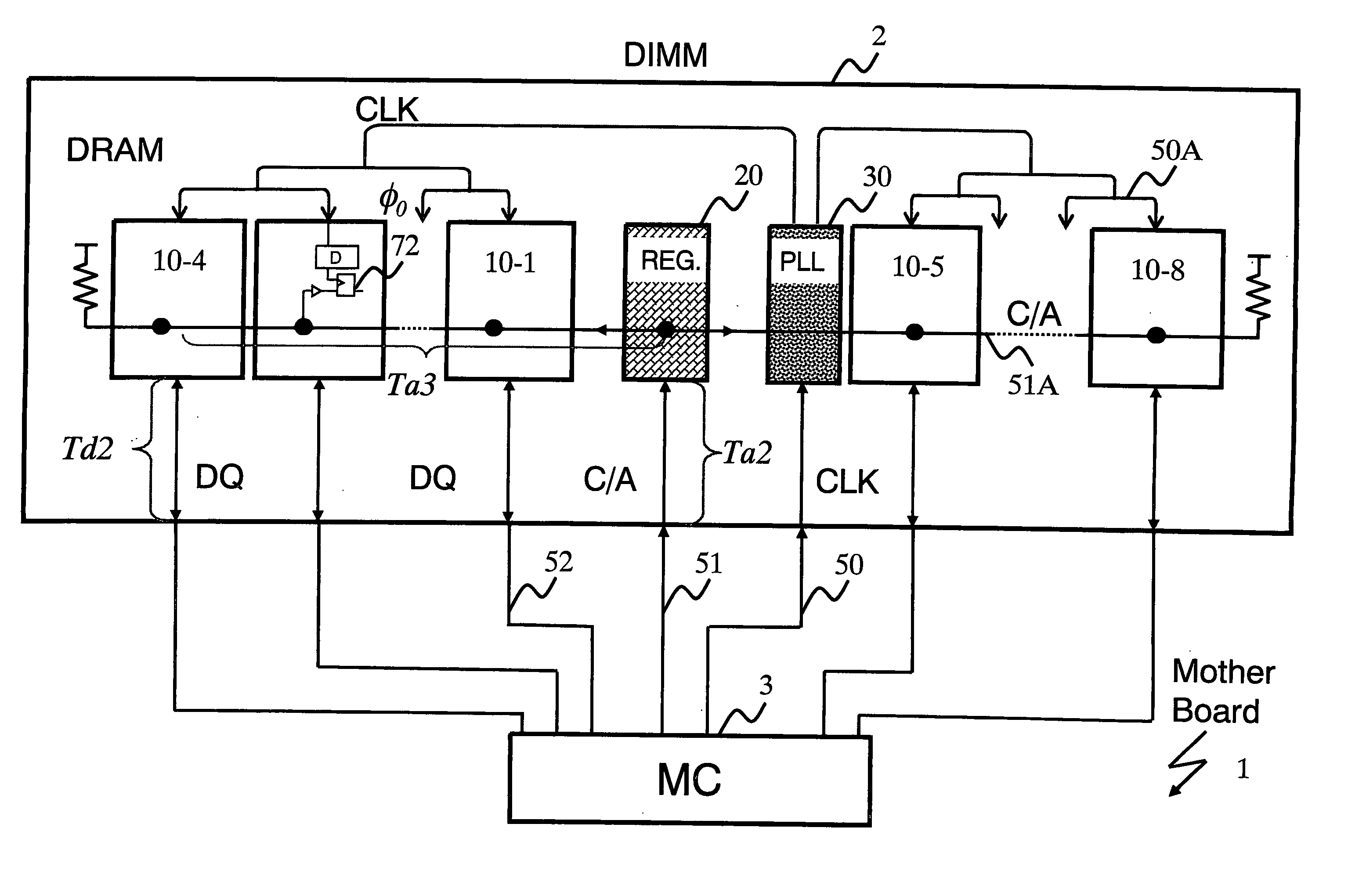

InactiveUS20050174878A1Adjust in timeEliminate time differenceDigital storageGenerating/distributing signalsDIMMDevice material

There is the problem that since C / A signals in a DIMM are distributed to respective DRAMs through a register in the DIMM and DQ signals are wired directly from terminals in the DIMM, their timing is difficult to synchronize. The register for speeding up the C / A signals of the DIMM that operates with high speed is provided, and a wiring from the register is set to a daisy-chain wiring. Then, by a timing adjustment circuit provided in the DRAM, a wiring delay time difference between the C / A signals and the clock signals, which are different depending on positions of the DRAMs, is such that the sum of a delay time from the register to each DRAM and a delay amount due to the timing adjustment circuit is made equal to a delay time of the farthest DRAM.

Owner:LONGITUDE SEMICON S A R L

Semiconductor memory module, memory system, circuit, semiconductor device, and DIMM

InactiveUS7095661B2Without increasing wiring density and number of substrate layerLow costDigital storageGenerating/distributing signalsDIMMProcessor register

There is the problem that since C / A signals in a DIMM are distributed to respective DRAMs through a register in the DIMM and DQ signals are wired directly from terminals in the DIMM, their timing is difficult to synchronize. The register for speeding up the C / A signals of the DIMM that operates with high speed is provided, and a wiring from the register is set to a daisy-chain wiring. Then, by a timing adjustment circuit provided in the DRAM, a wiring delay time difference between the C / A signals and the clock signals, which are different depending on positions of the DRAMs, is such that the sum of a delay time from the register to each DRAM and a delay amount due to the timing adjustment circuit is made equal to a delay time of the farthest DRAM.

Owner:LONGITUDE SEMICON S A R L

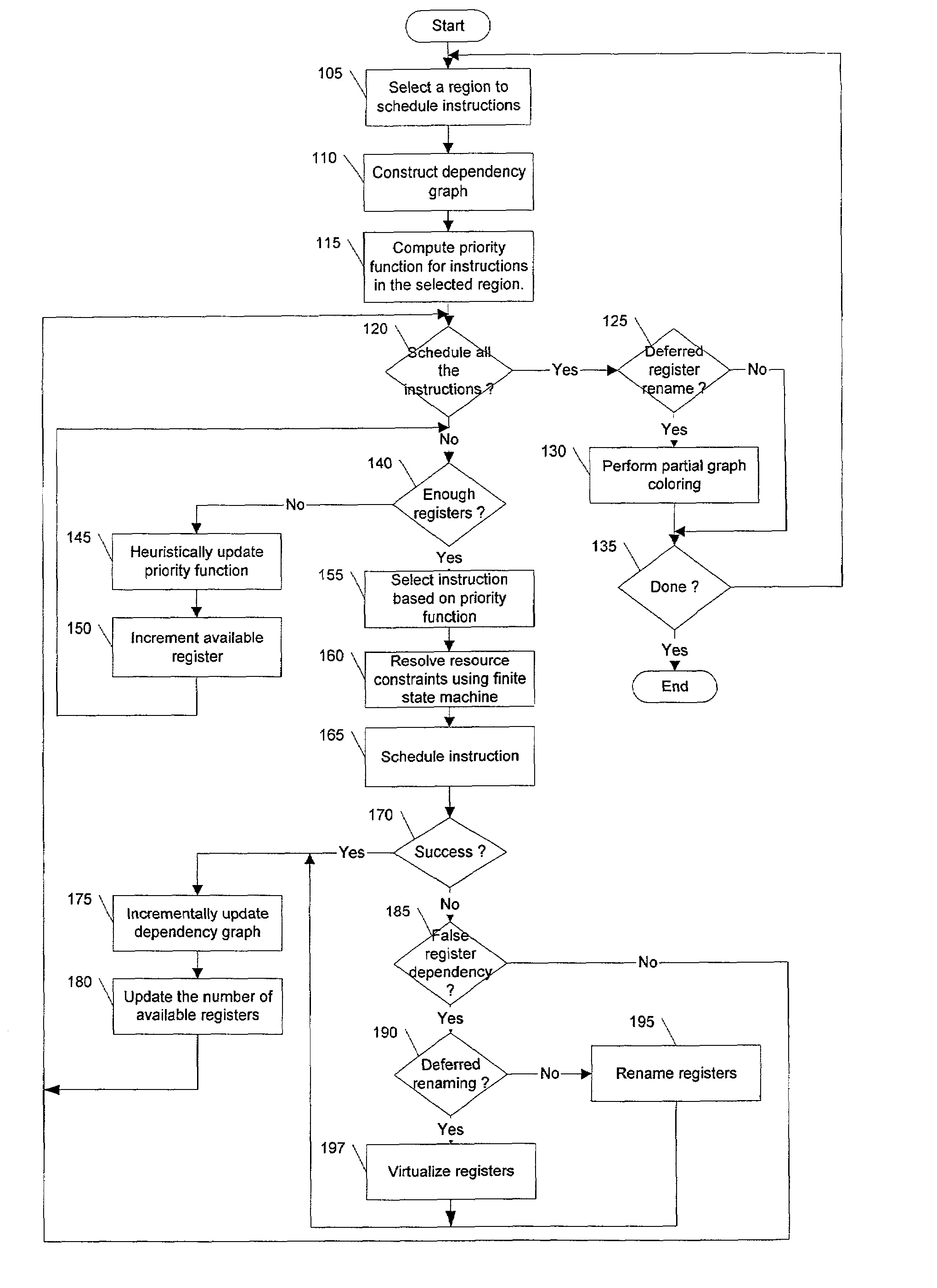

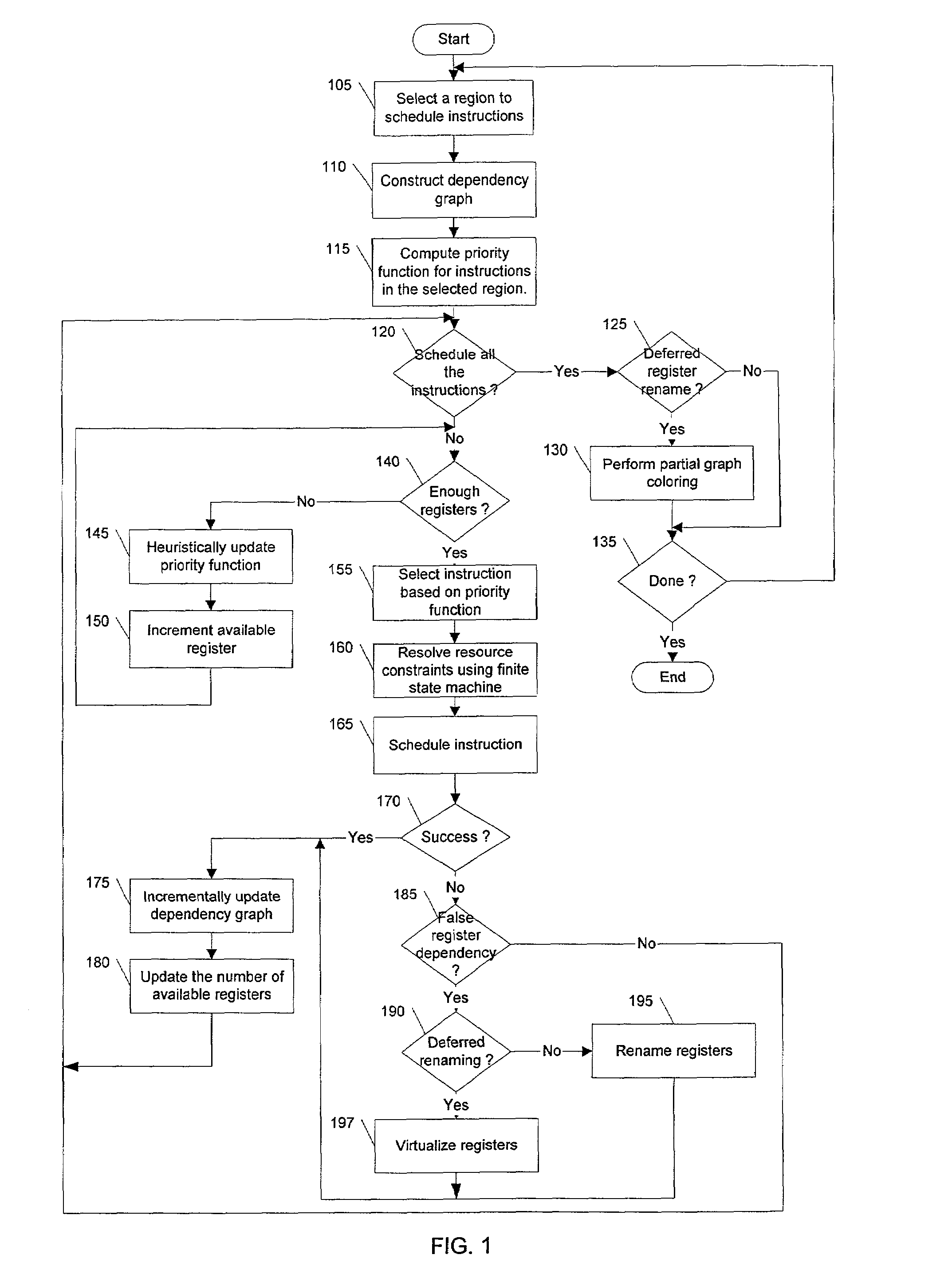

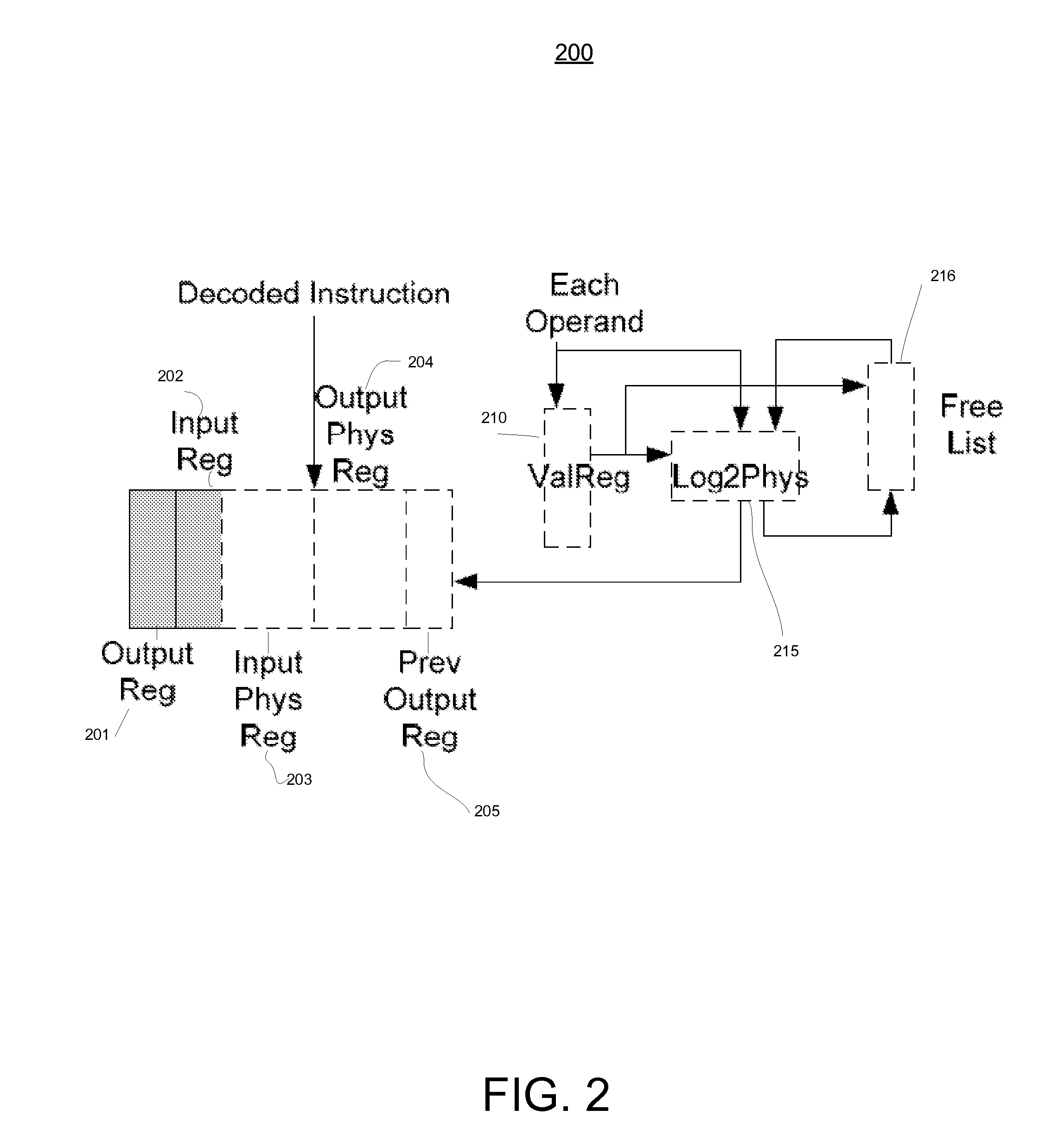

Method and apparatus for integrated instruction scheduling and register allocation in a postoptimizer

The present invention describes a method of efficiently optimizing instruction scheduling and register allocation in a post optimizer. The method removes false register dependencies between pipelined instructions by building an incremental (partial) interference graph of register allocation for scheduled instructions. False dependency graph indicates the amount of parallelism in the data flow graph. The incremental interference graph uses a mix of virtual and physical registers. The interference graph is built incrementally as an instruction schedular schedules each instruction. The optimization is done incrementally on localized code. The physical register mapping is maximized and virtual registers are created on demand basis.

Owner:ORACLE INT CORP

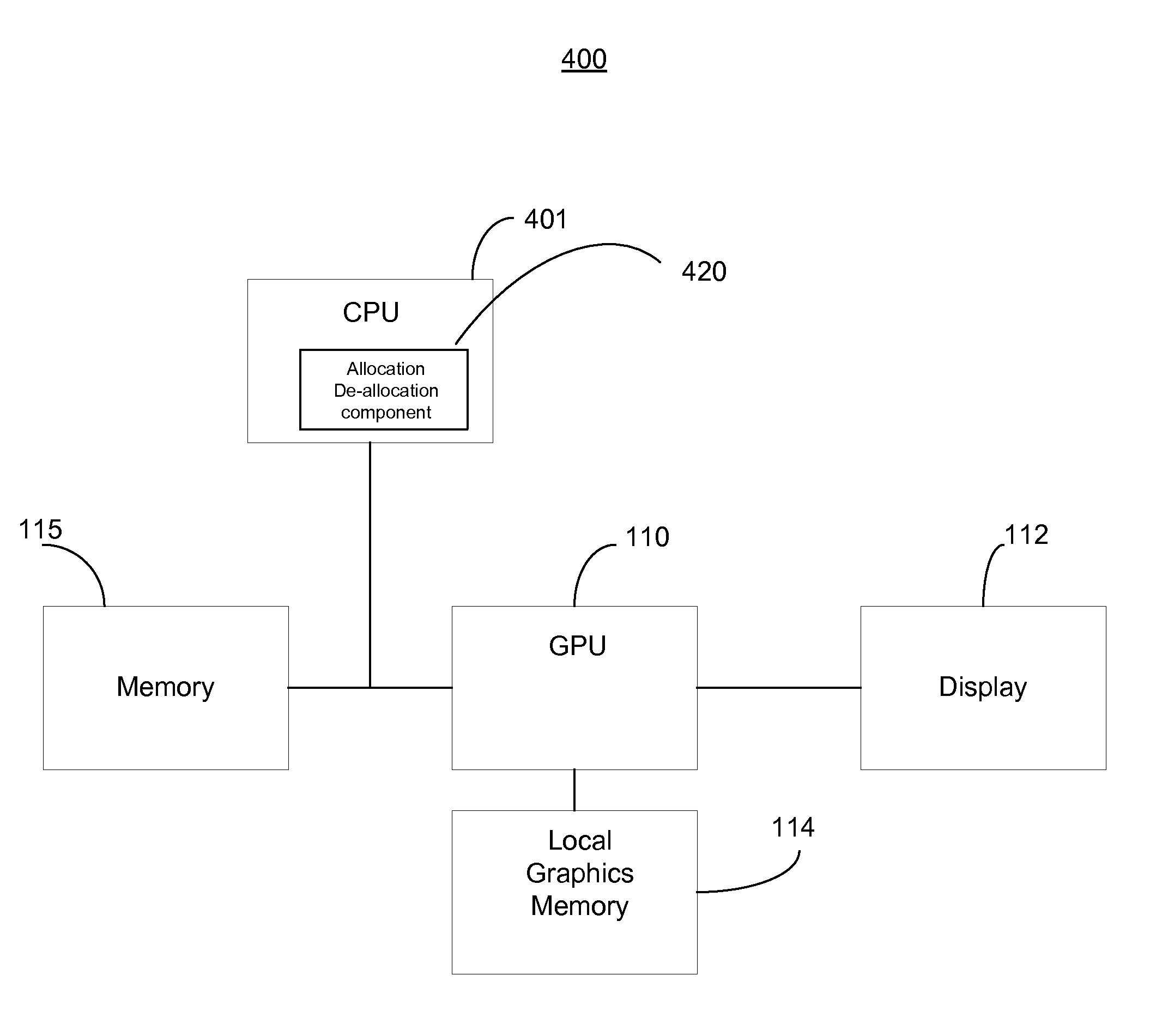

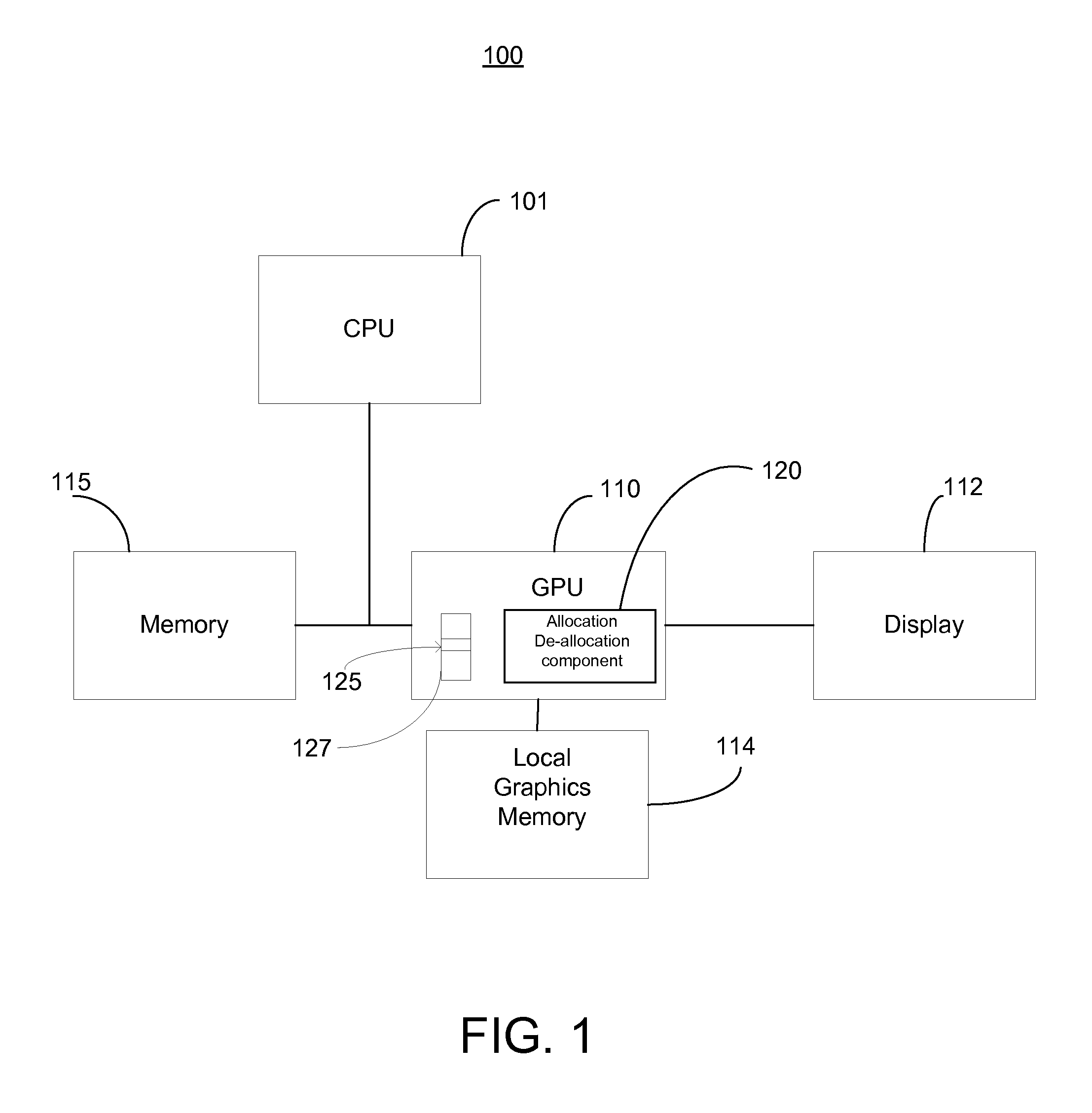

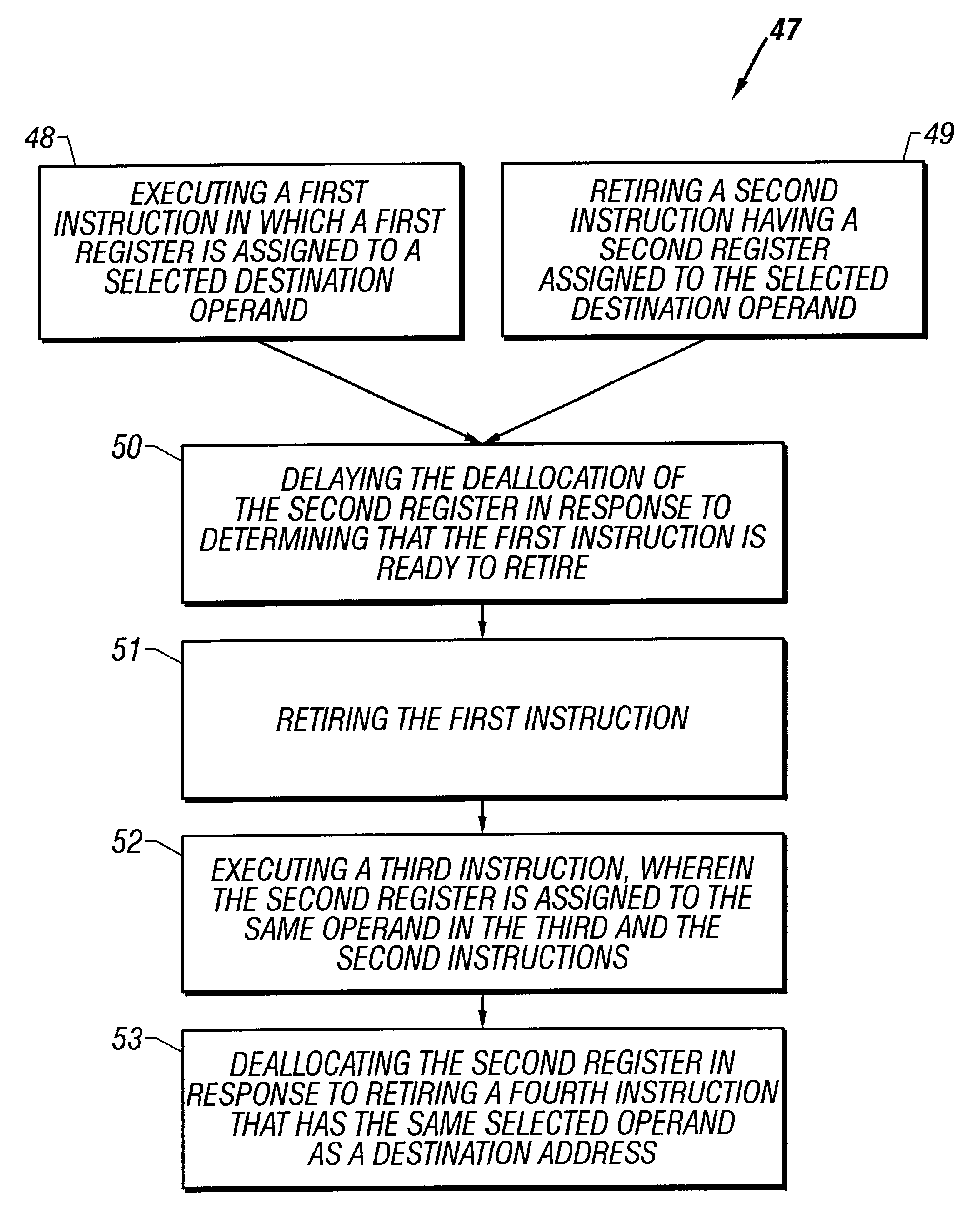

On demand register allocation and deallocation for a multithreaded processor

InactiveUS20110161616A1Increase profitHigh performance lowMemory adressing/allocation/relocationMicro-instruction address formationRegister allocationRegister assignment

A system for allocating and de-allocating registers of a processor. The system includes a register file having plurality of physical registers and a first table coupled to the register file for mapping virtual register IDs to physical register IDs. A second table is coupled to the register file for determining whether a virtual register ID has a physical register mapped to it in a cycle. The first table and the second table enable physical registers of the register file to be allocated and de-allocated on a cycle-by-cycle basis to support execution of instructions by the processor.

Owner:NVIDIA CORP

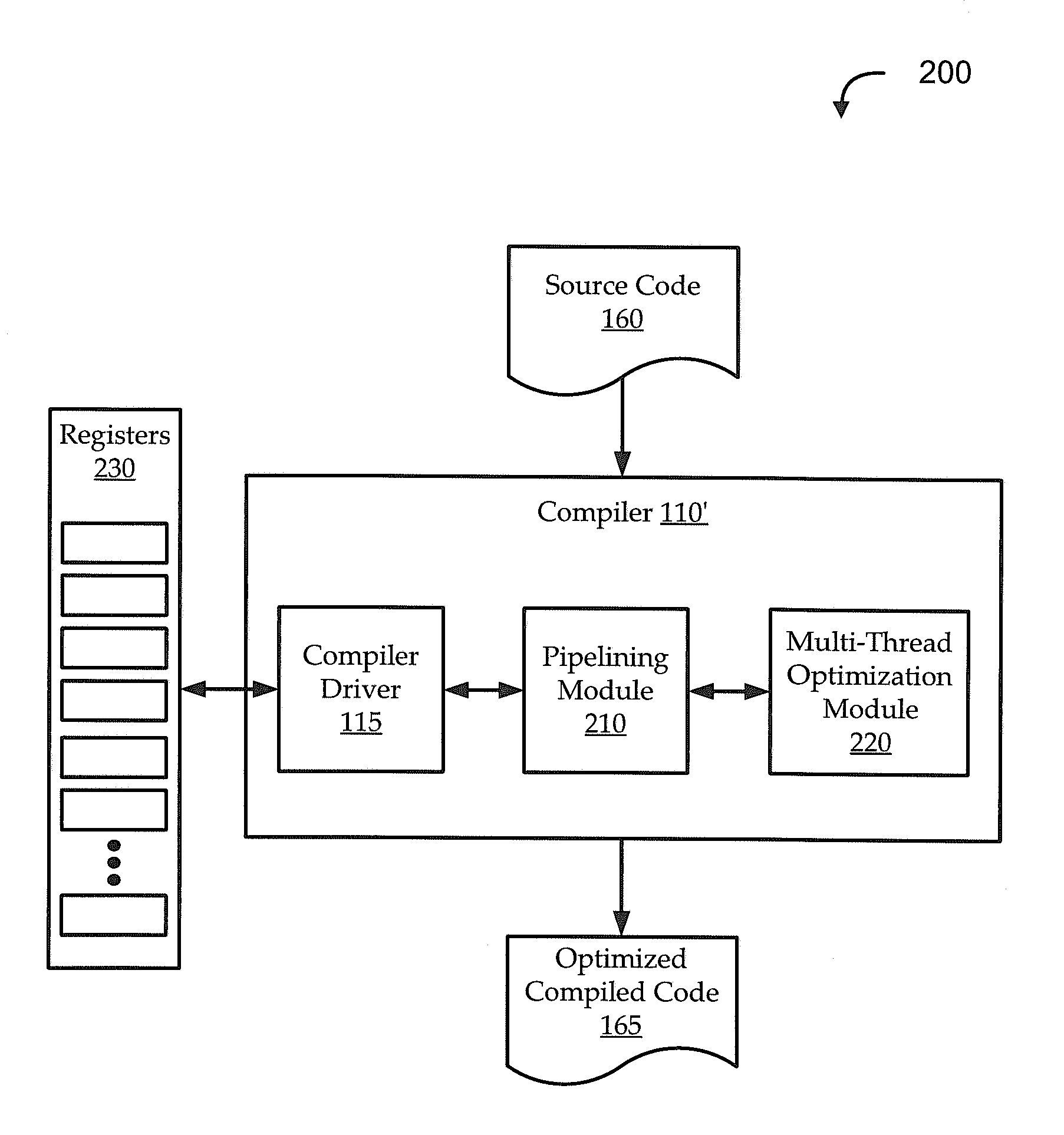

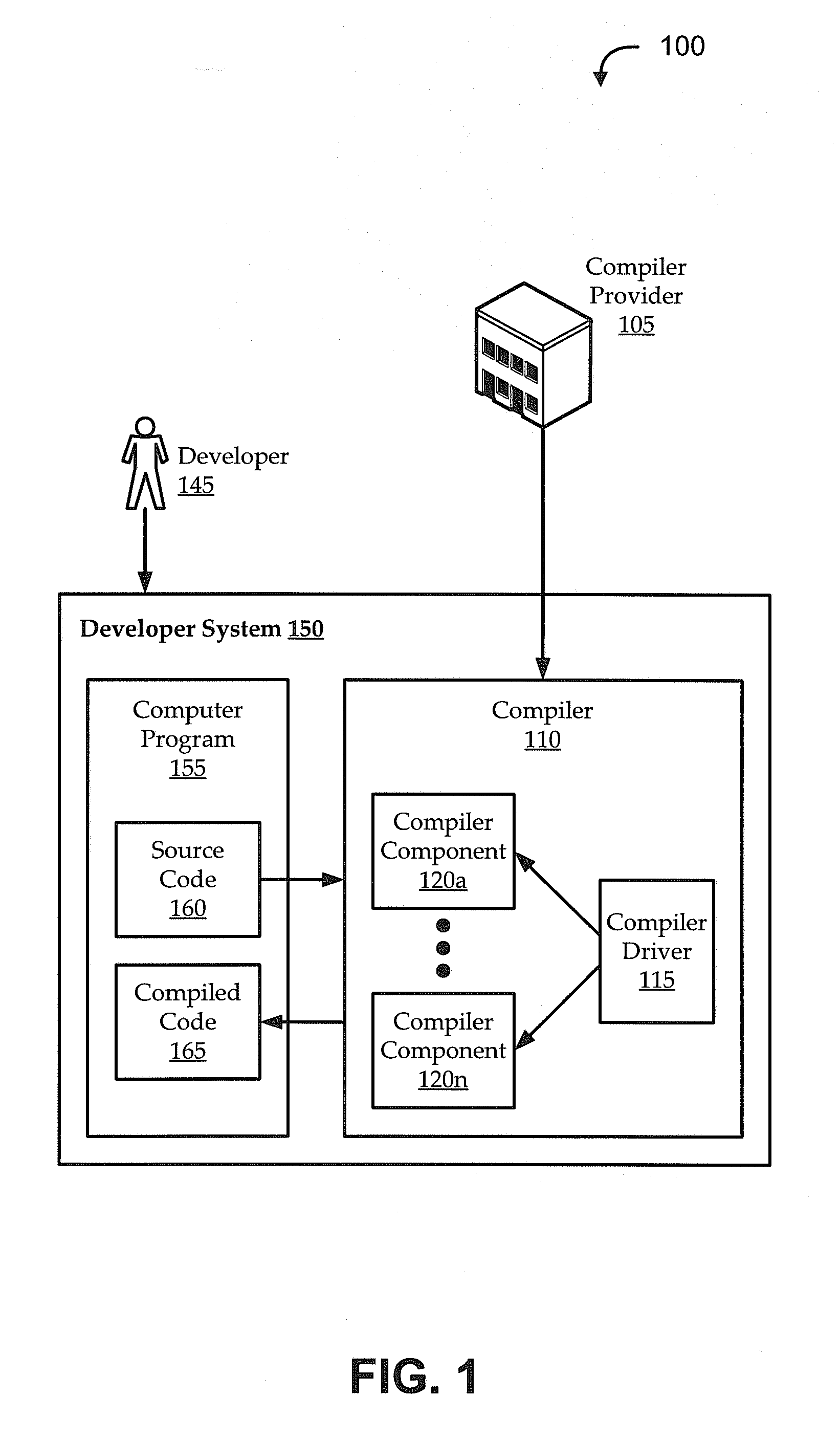

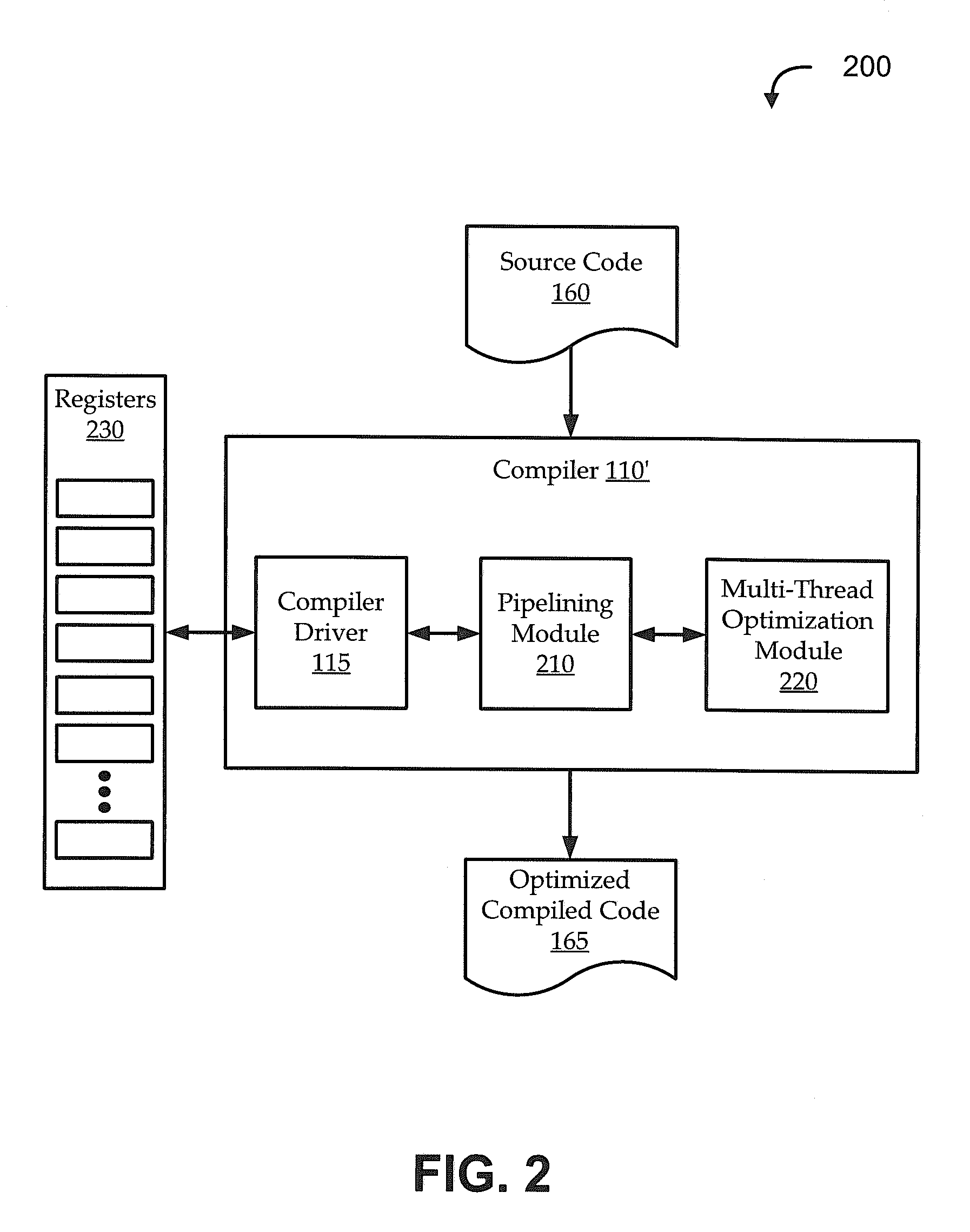

Throughput-aware software pipelining for highly multi-threaded systems

ActiveUS20130111453A1Reducing scalarityReducing latency settingSoftware engineeringProgram controlResource utilizationProcessor register

Embodiments of the invention provide systems and methods for throughput-aware software pipelining in compilers to produce optimal code for single-thread and multi-thread execution on multi-threaded systems. A loop is identified within source code as a candidate for software pipelining. An attempt is made to generate pipelined code (e.g., generate an instruction schedule and a set of register assignments) for the loop in satisfaction of throughput-aware pipelining criteria, like maximum register count, minimum trip count, target core pipeline resource utilization, maximum code size, etc. If the attempt fails to generate code in satisfaction of the criteria, embodiments adjust one or more settings (e.g., by reducing scalarity or latency settings being used to generate the instruction schedule). Additional attempts are made to generate pipelined code in satisfaction of the criteria by iteratively adjusting the settings, regenerating the code using the adjusted settings, and recalculating whether the code satisfies the criteria.

Owner:ORACLE INT CORP

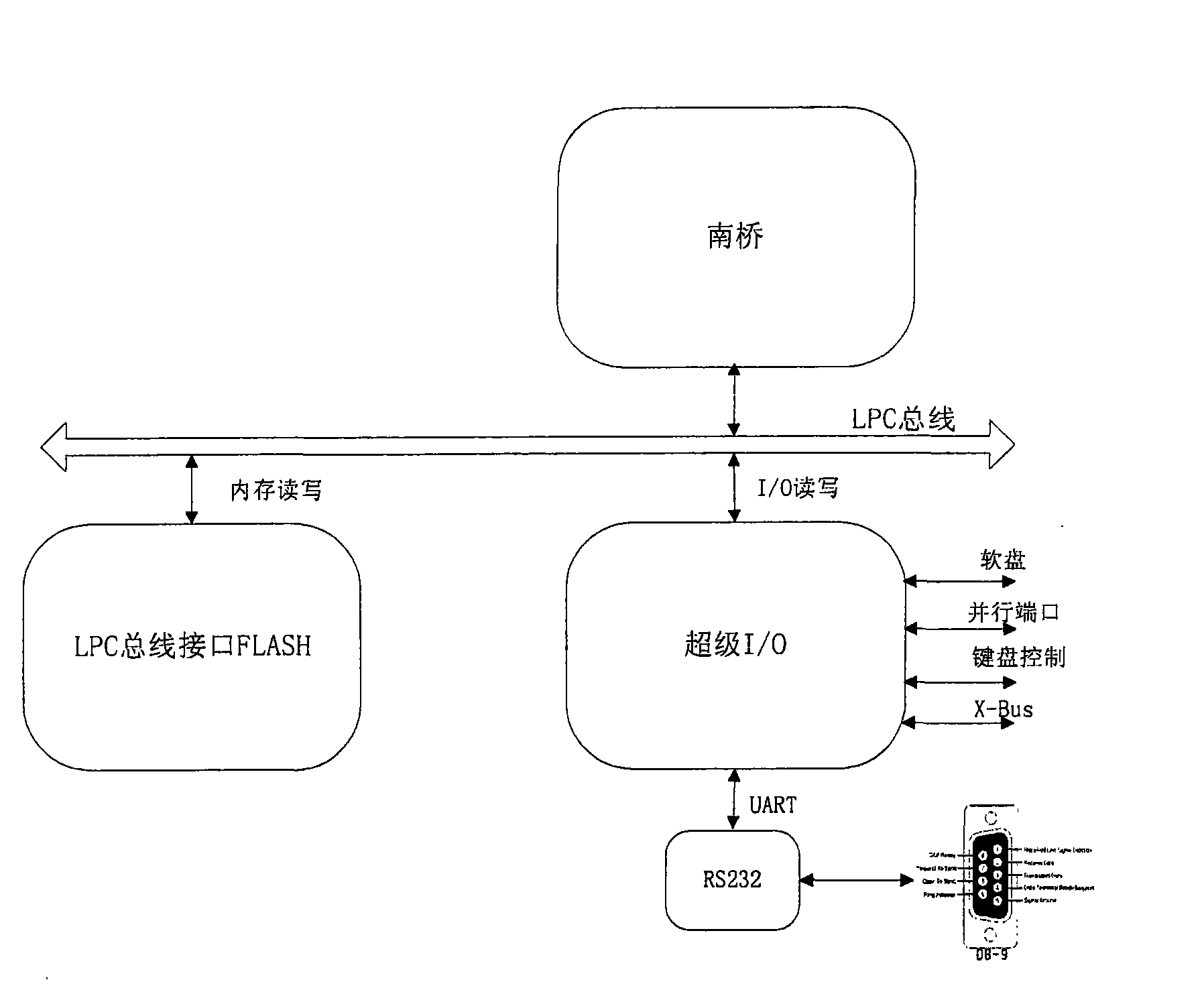

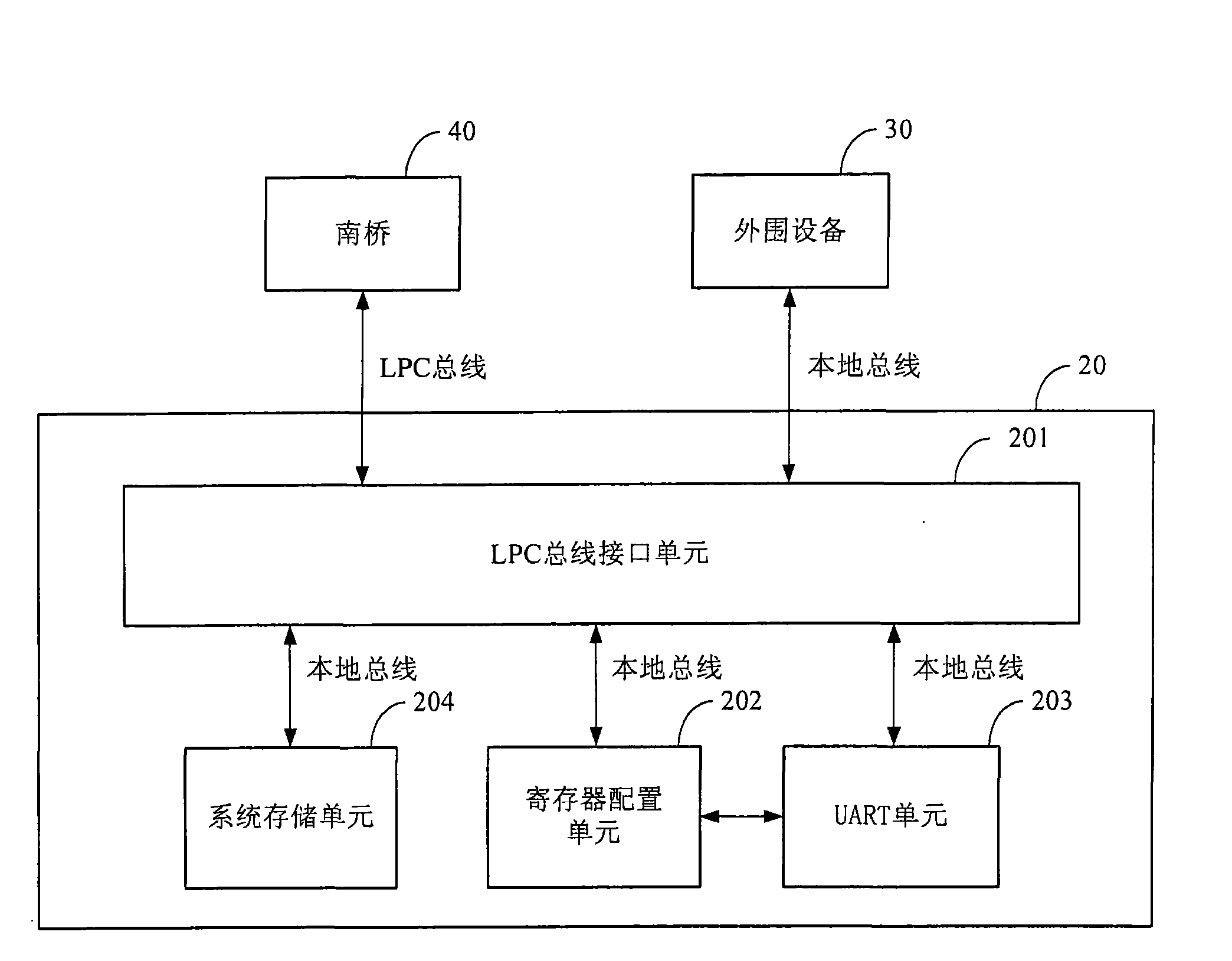

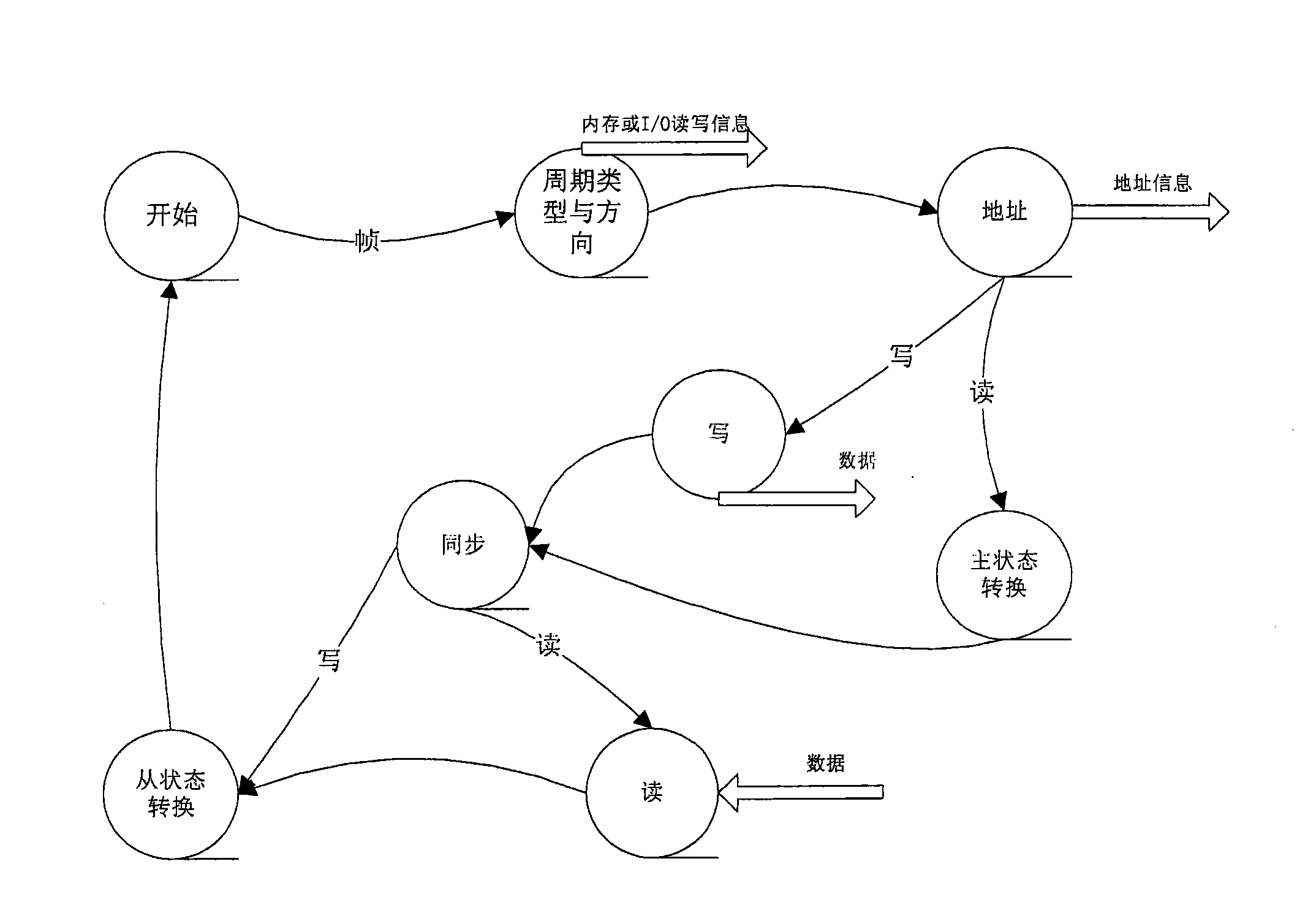

Signal conversion device and method as well as communication equipment

ActiveCN101989244AReduce complexityReduce usageElectric digital data processingRegister allocationMemory address

The embodiment of the invention provides a signal conversion device and method as well as communication equipment. The signal conversion device comprises an LPC (Low Pin Count) bus interface unit, a register configuration unit and a UART (Universal Asynchronous Receiver Transmitter) unit, wherein the LPC bus interface unit is used for performing protocol analysis on signals from an LPC bus and outputting local signals through a local bus, and the local signals comprise a control signal, an address signal and a data signal; the register configuration unit is used for configuring registers of the UART unit according to the local signals; the registers of the UART unit are allocated in a memory address space and an I / O address space; and the UART unit is used for converting data from the LPCbus into serial data according to the local signals and the values of configured registers of the UART unit and then outputting the serial data through a UART interface or outputting the serial data received by the UART interface to the LPC bus through the local signals. The embodiment of the invention can simplify the configuration process of the registers of the USRT unit.

Owner:HUAWEI TECH CO LTD

Technique for allocating register to variable for compiling

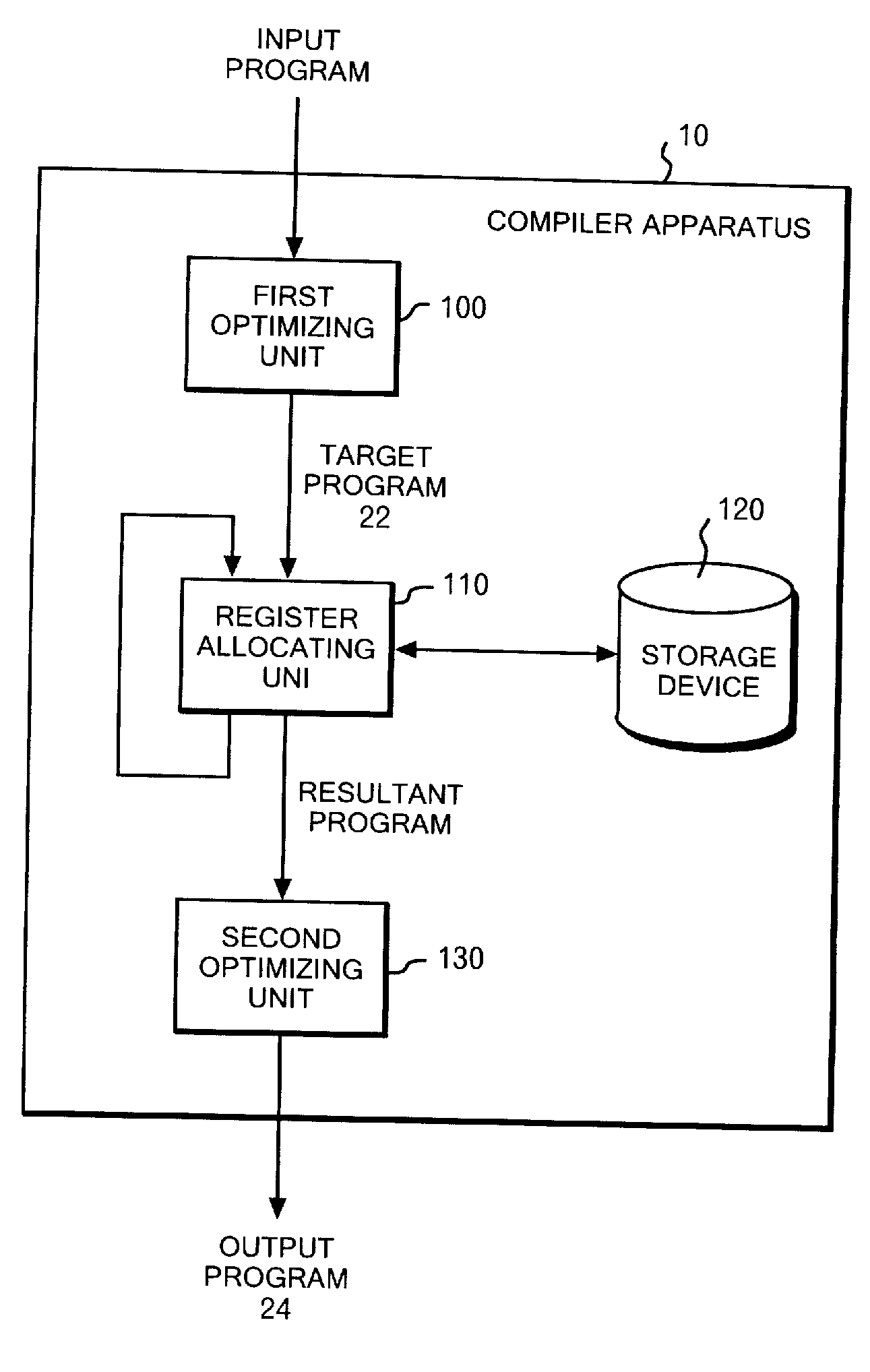

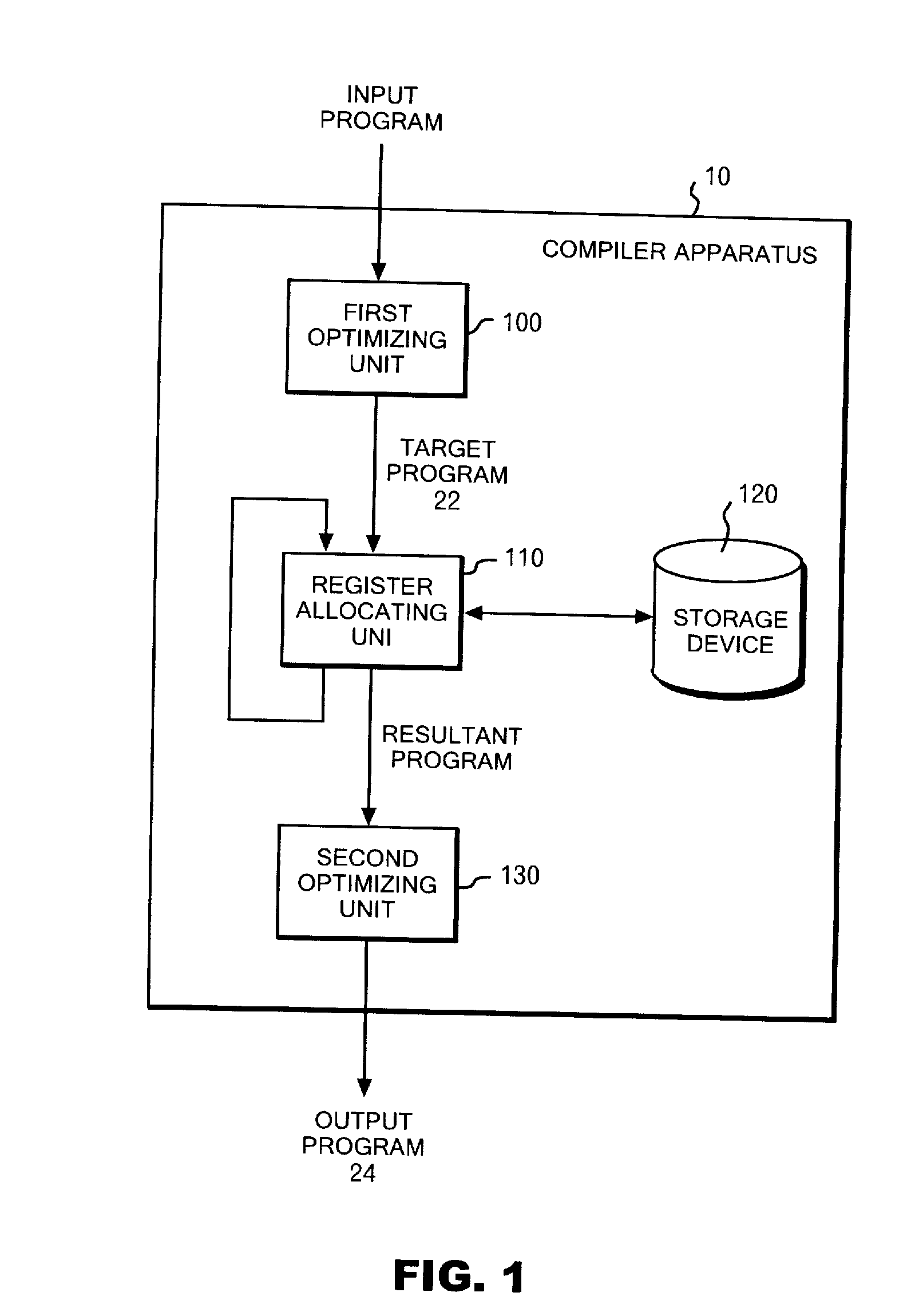

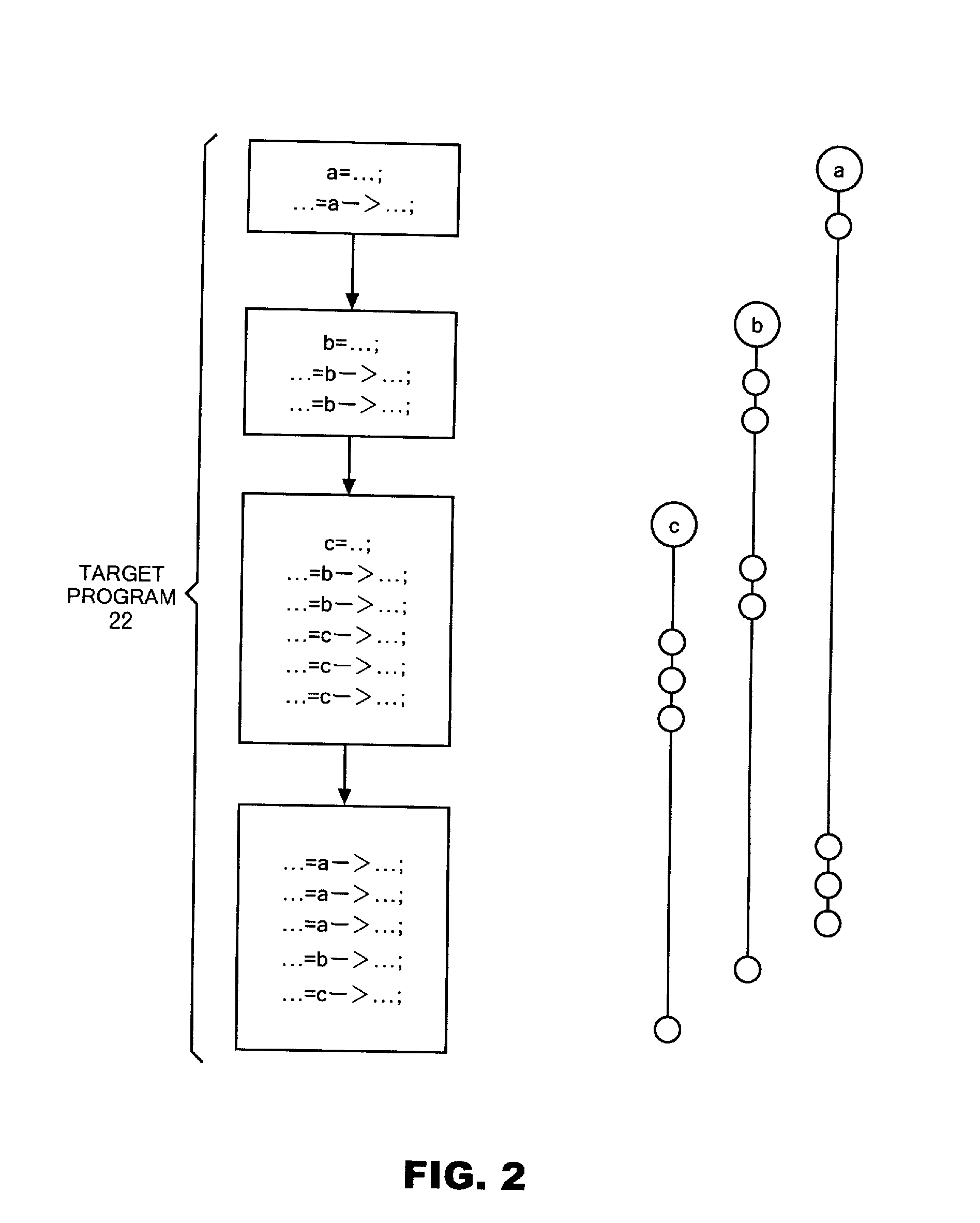

InactiveUS20090064112A1Reliable changeSoftware engineeringProgram controlRegister assignmentProcessor register

The present invention relates to allocating registers to variables in order to compile a program. In an embodiment of the present invention a compiler apparatus stores interference information indicating an interference relationship between variables, selects a register and allocates the register to each variables in accordance with a predetermined procedure, without allocating the same register to a set of variables having interference relationships. The compiler further replaces multiple variables having the same register allocated thereto with a new variable and generates an interference relationship by merging the interference relationships each concerning one of multiple variables. The compiler further updates interference information according to the generated interference relationship and allocates to each variable in the program using the new variable a register, selected in accordance with the predetermined procedure without allocating the same register to a set of variables having the interference relationships, based on the updated interference information.

Owner:IBM CORP

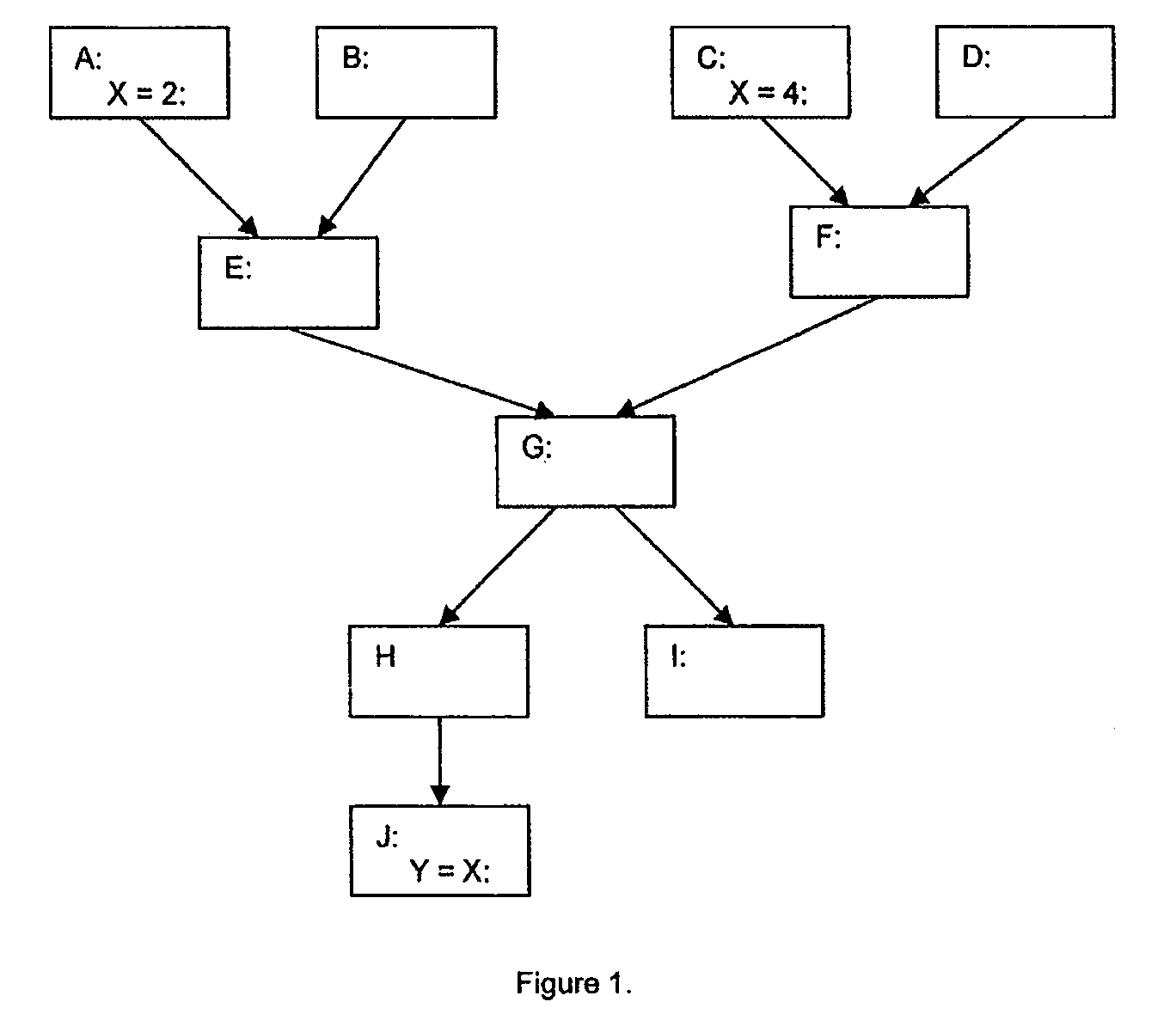

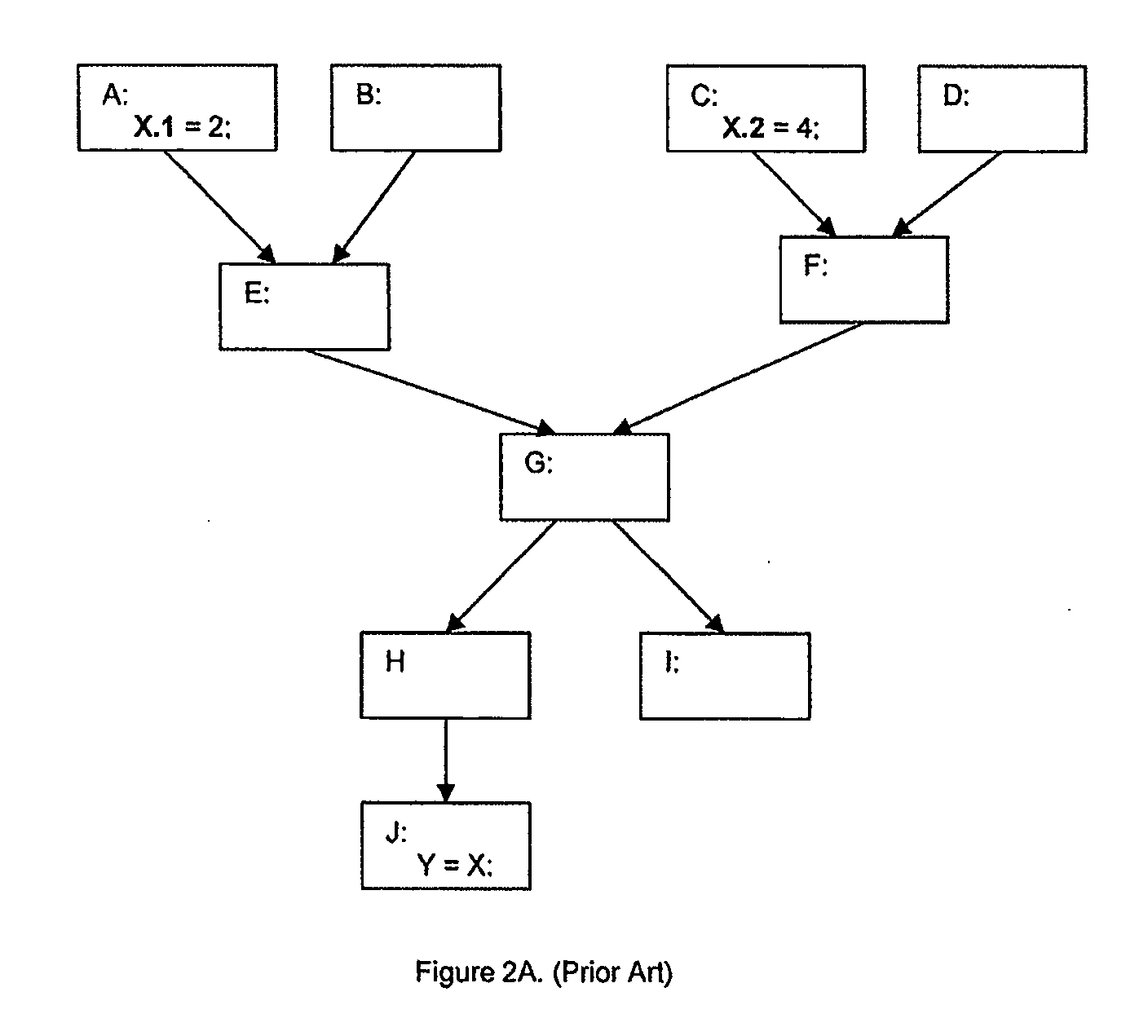

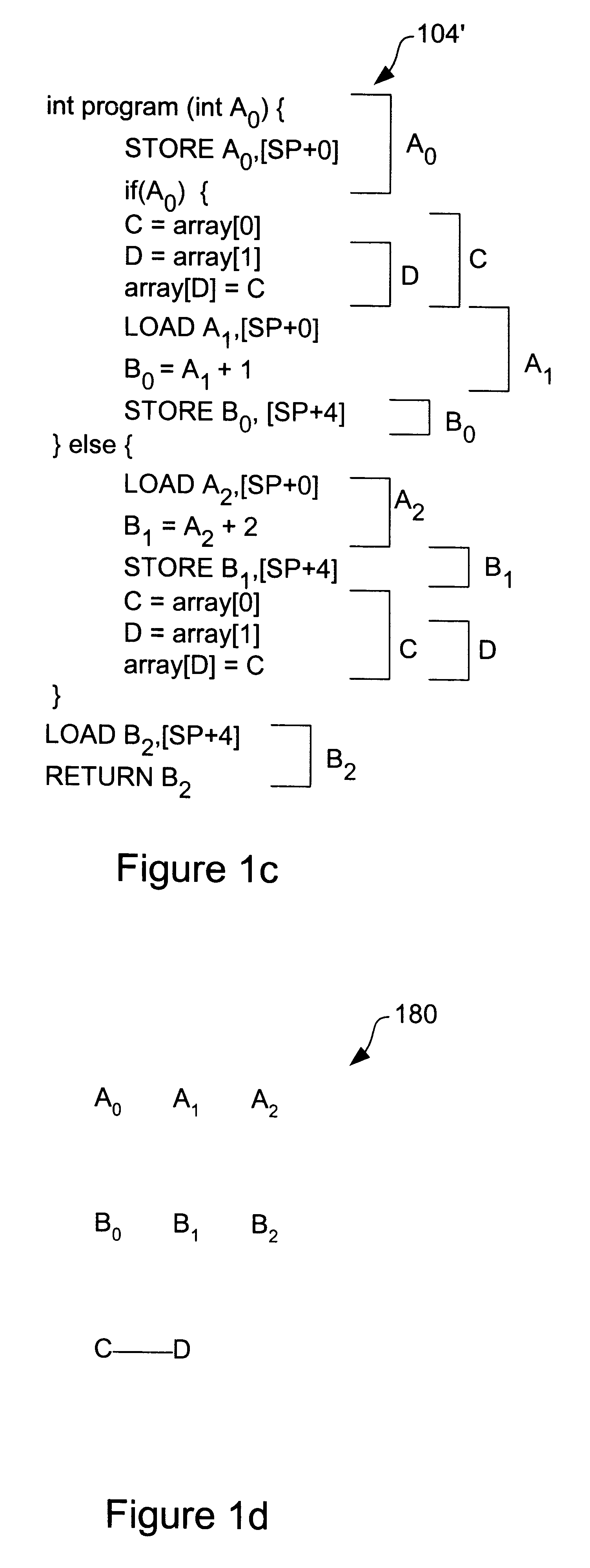

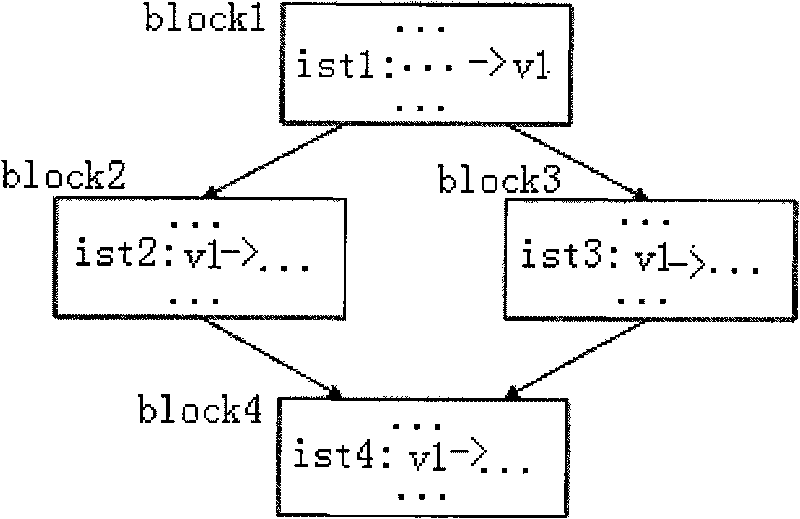

Highly scalable parallel static single assignment for dynamic optimization on many core architectures

A method, system, and computer readable medium for converting a series of computer executable instructions in control flow graph form into an intermediate representation, of a type similar to Static Single Assignment (SSA), used in the compiler arts. The indeterminate representation may facilitate compilation optimizations such as constant propagation, sparse conditional constant propagation, dead code elimination, global value numbering, partial redundancy elimination, strength reduction, and register allocation. The method, system, and computer readable medium are capable of operating on the control flow graph to construct an SSA representation in parallel, thus exploiting recent advances in multi-core processing and massively parallel computing systems. Other embodiments may be employed, and other embodiments are described and claimed.

Owner:INTEL CORP

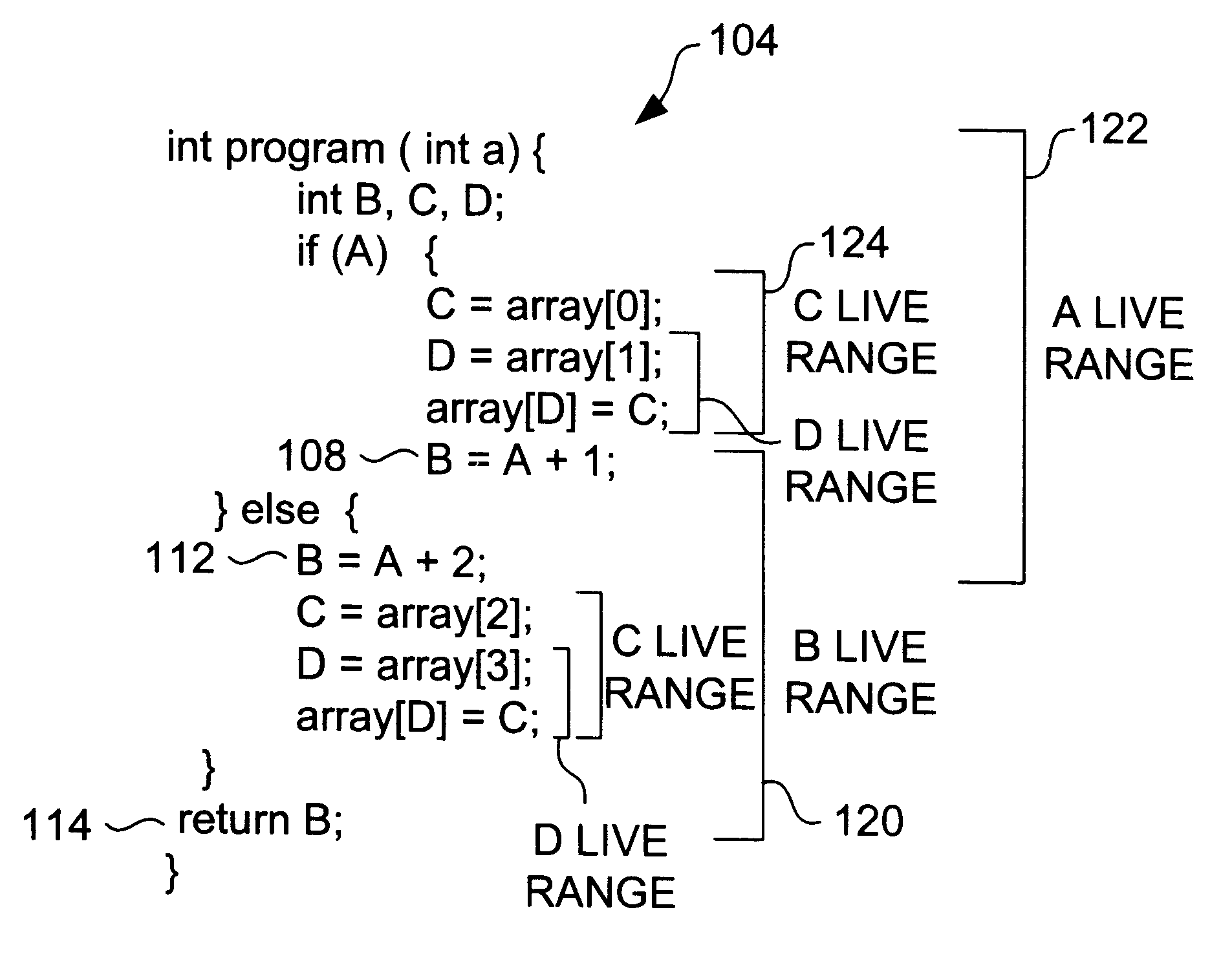

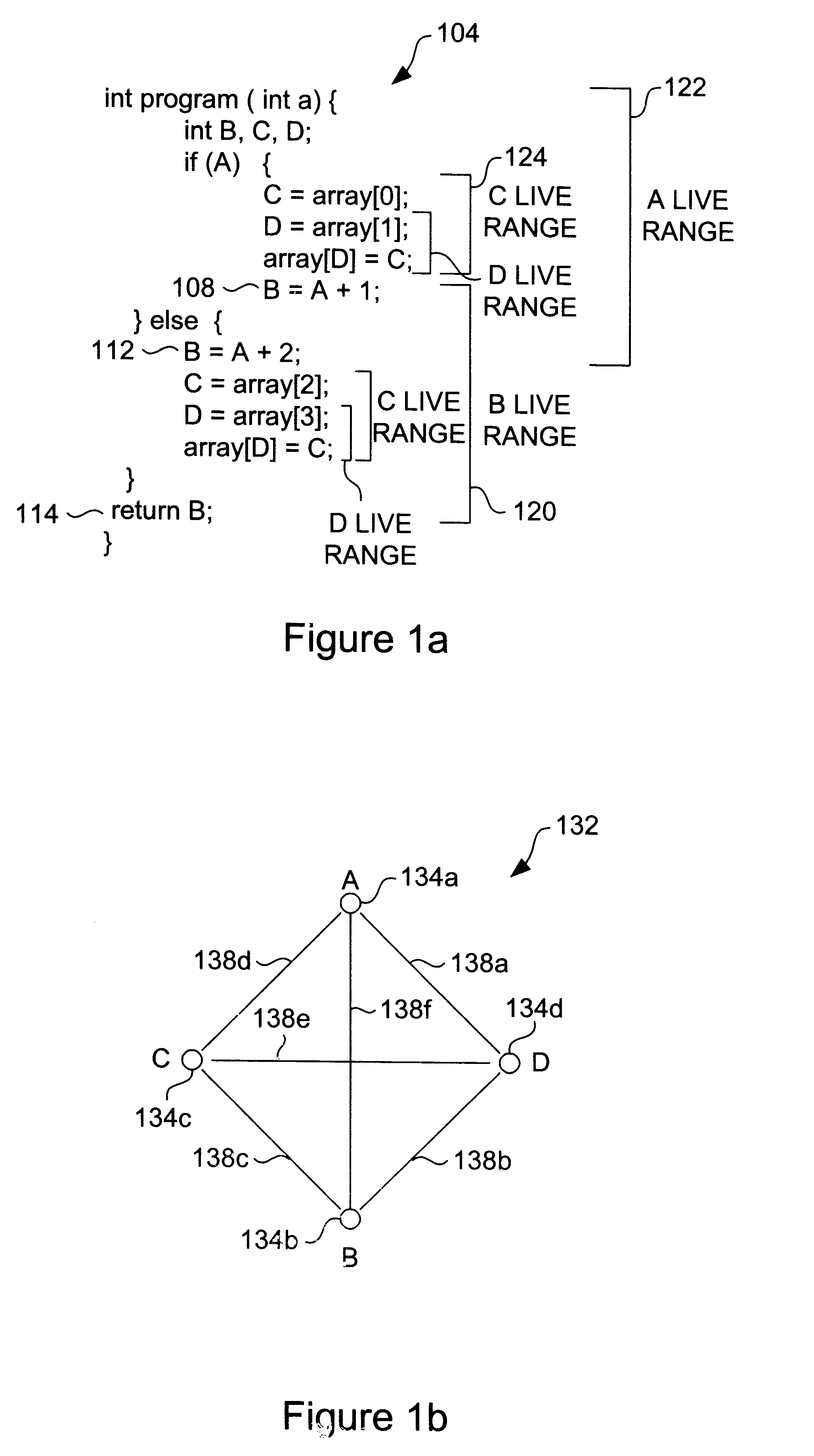

Method and apparatus for allocating stack slots

Methods and apparatus for allocating and using stack space are disclosed. According to one aspect of the present invention, a computer-implemented method for allocating stack space in an object-based system includes obtaining source code that is suitable for compilation and includes a definition associated with a variable. During register allocation, stack slots and machine registers are treated substantially similarly. This includes the steps of building an interference graph, copy coalescing, attempting to color the interference graph, and determining if the attempt to color the interference graph is successful. If the coloring attempt is not successful, then in lieu of normal spill code being inserted, register-to-register copies, e.g., "reg-reg" copies, are inserted in the source code. The "reg-reg" copies include copies associated with both stack slots and machine registers.

Owner:ORACLE INT CORP

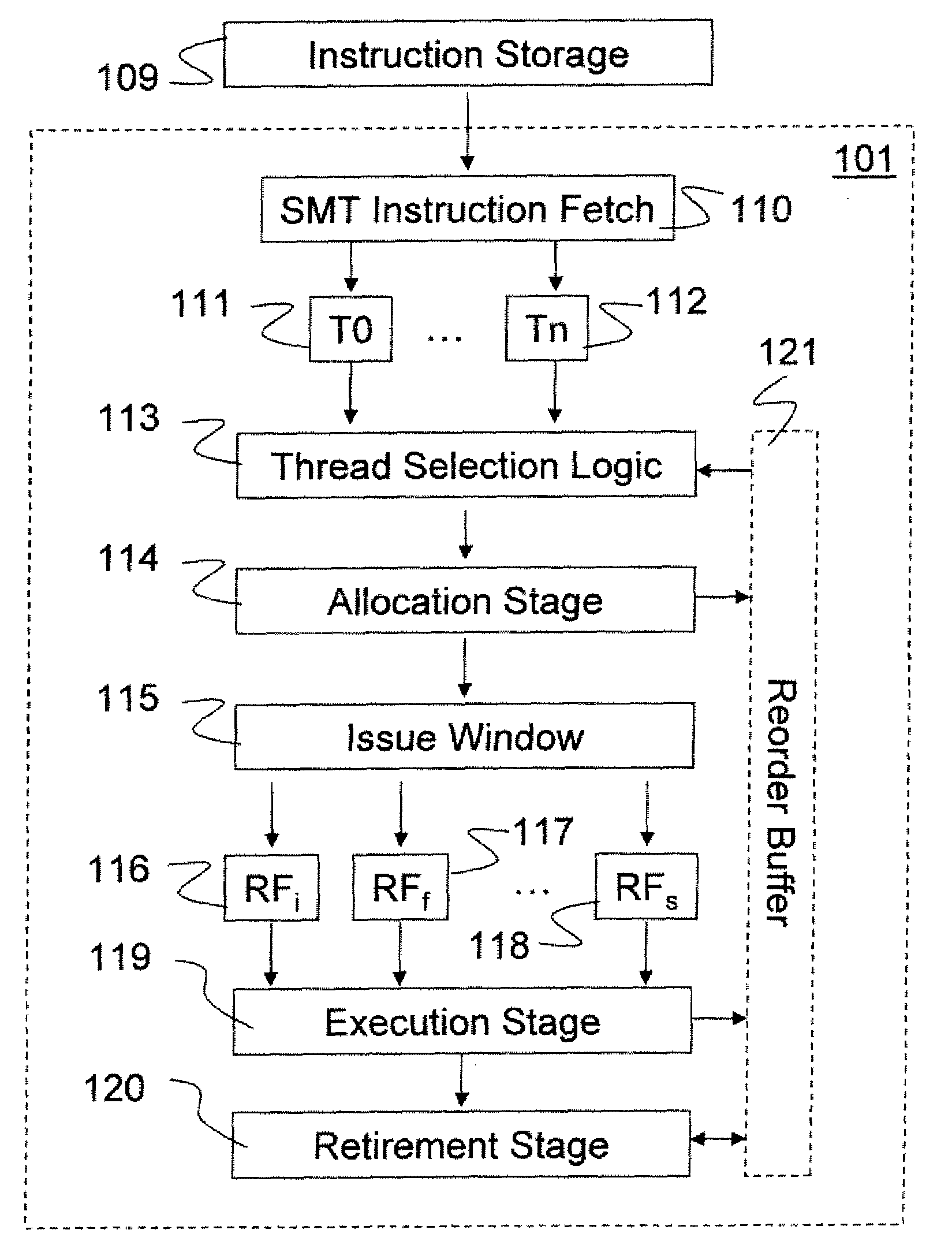

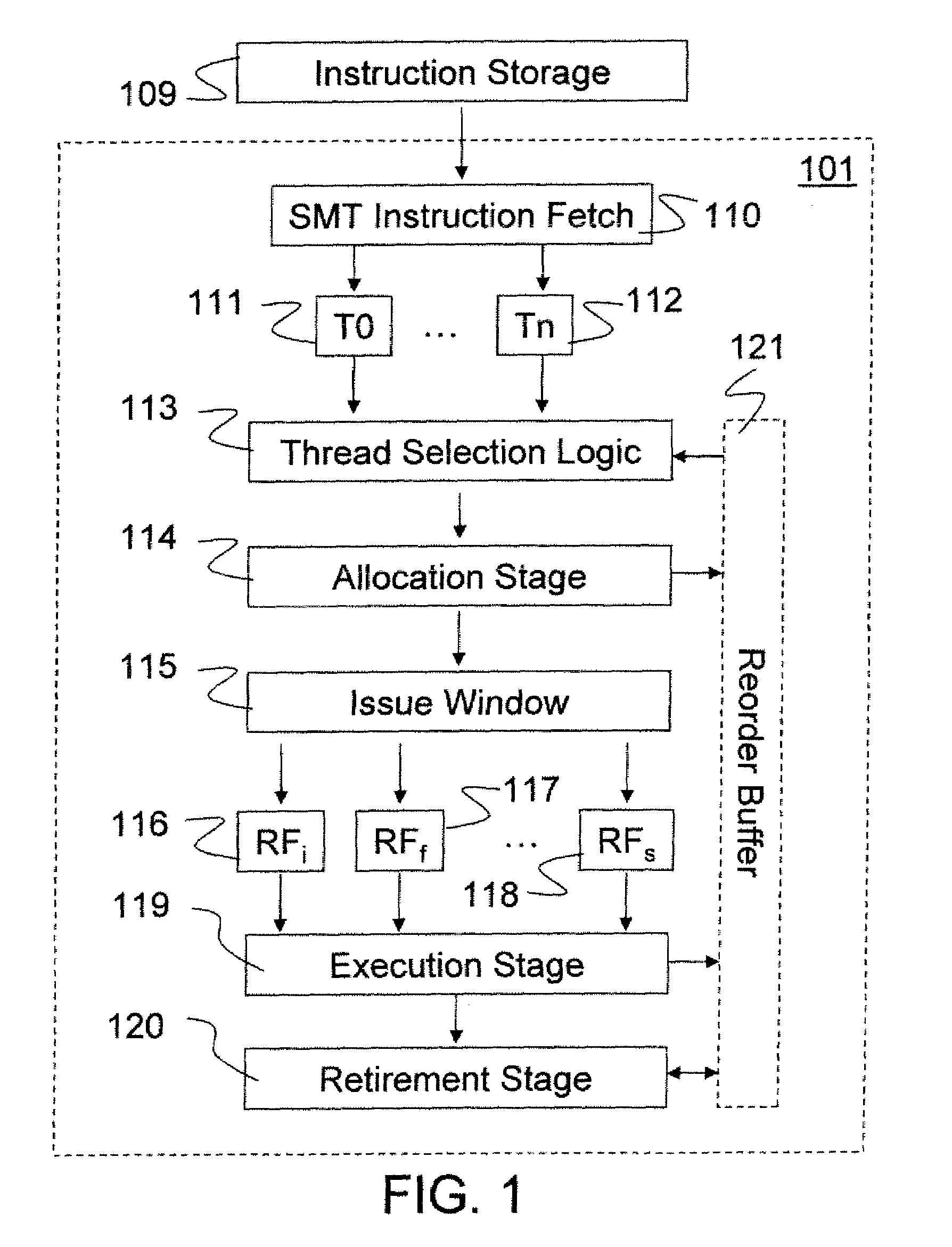

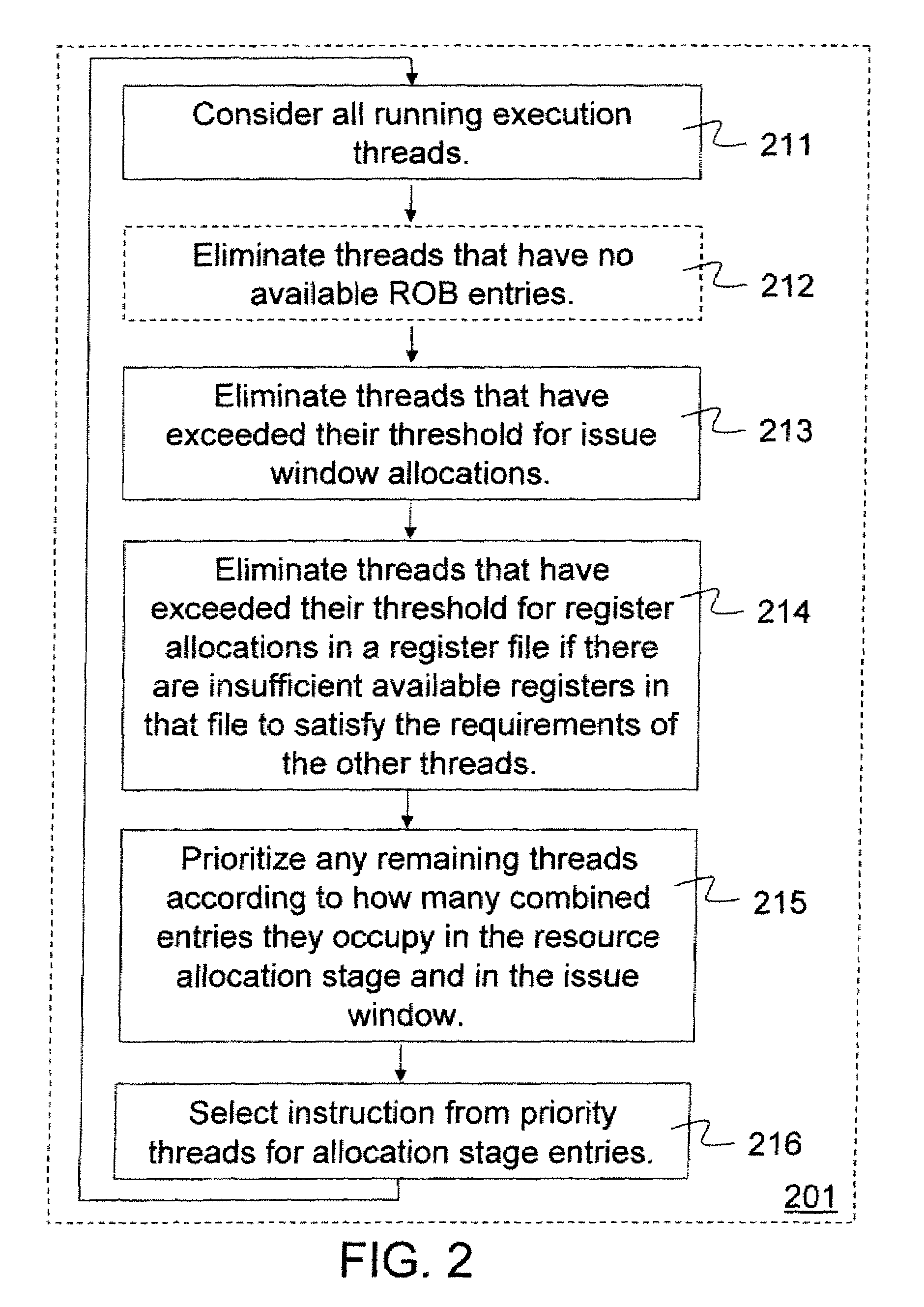

Method and apparatus for selection among multiple execution threads

Methods and apparatus for selecting and prioritizing execution threads for consideration of resource allocation include eliminating threads for consideration from all the running execution threads: if they have no available entries in their associated reorder buffers, or if they have exceeded their threshold for entry allocations in the issue window, or if they have exceeded their threshold for register allocations in some register file and if that register file also has an insufficient number of available registers to satisfy the requirements of the other running execution threads. Issue window thresholds may be dynamically computed by dividing the current number of entries by the number of threads under consideration. Register thresholds may also be dynamically computed and associated with a thread and a register file. Execution threads remaining under consideration can be prioritized according to how many combined entries the thread occupies in the resource allocation stage and the issue window.

Owner:INTEL CORP

Inter-procedure global register allocation method

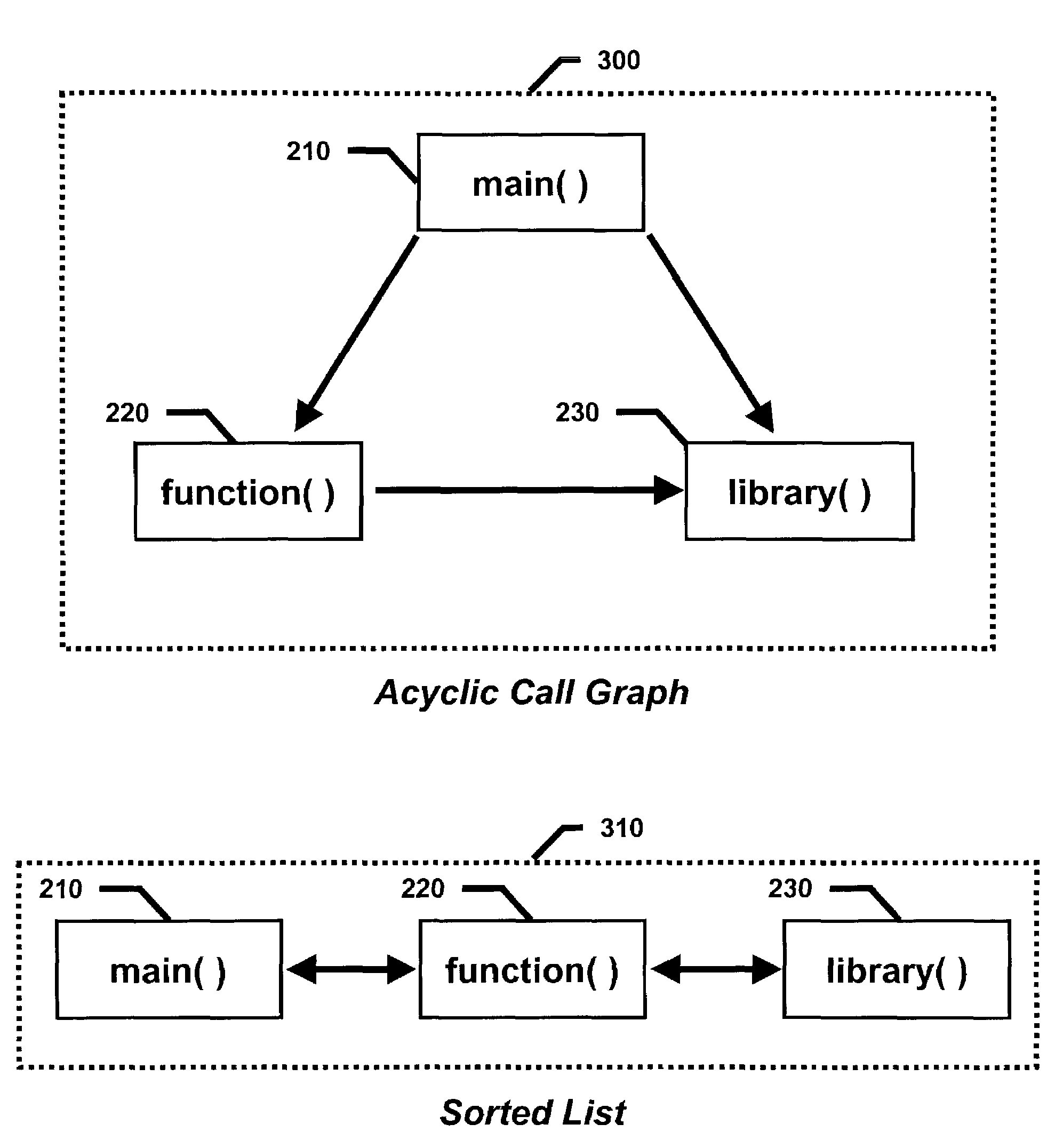

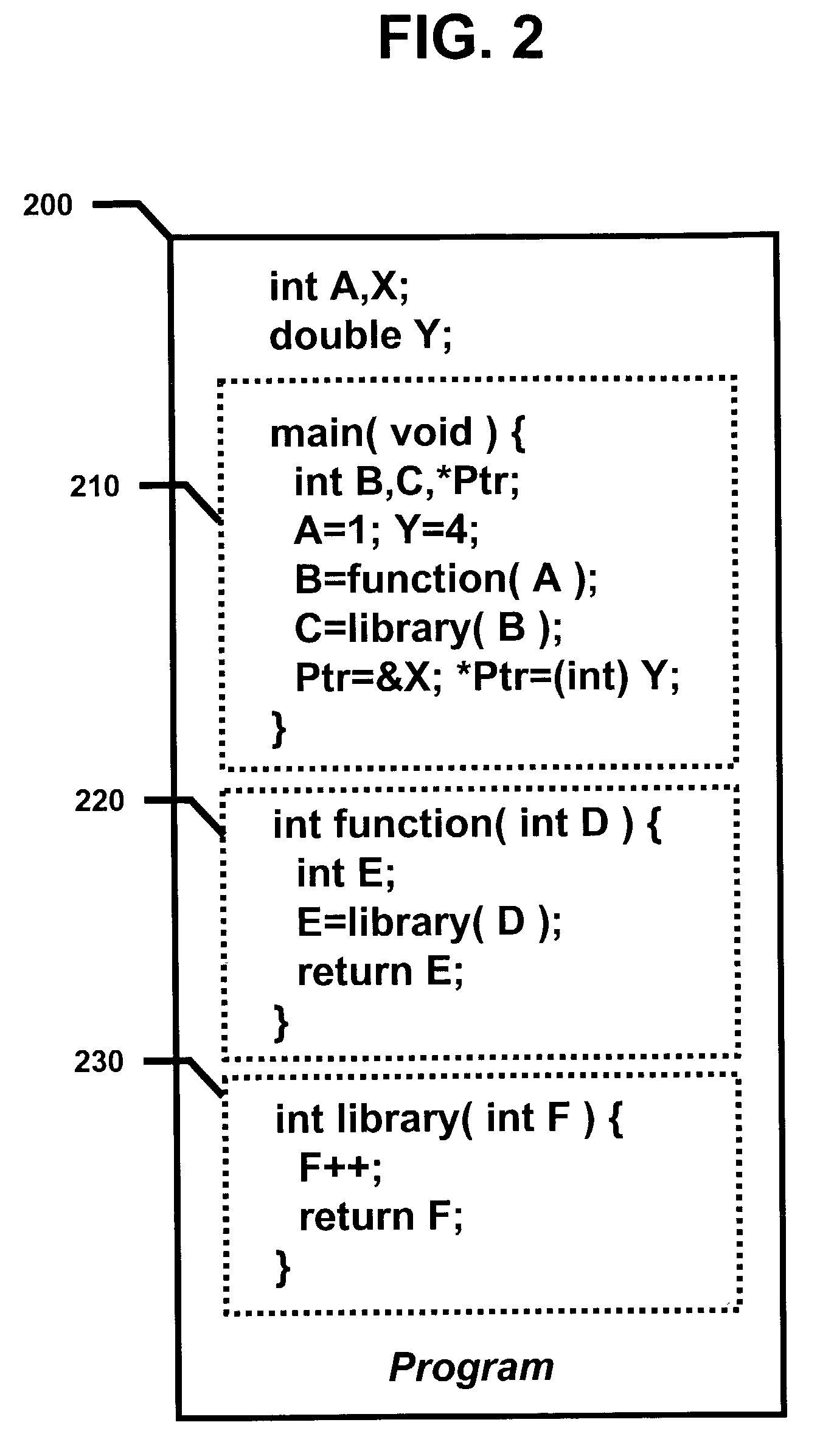

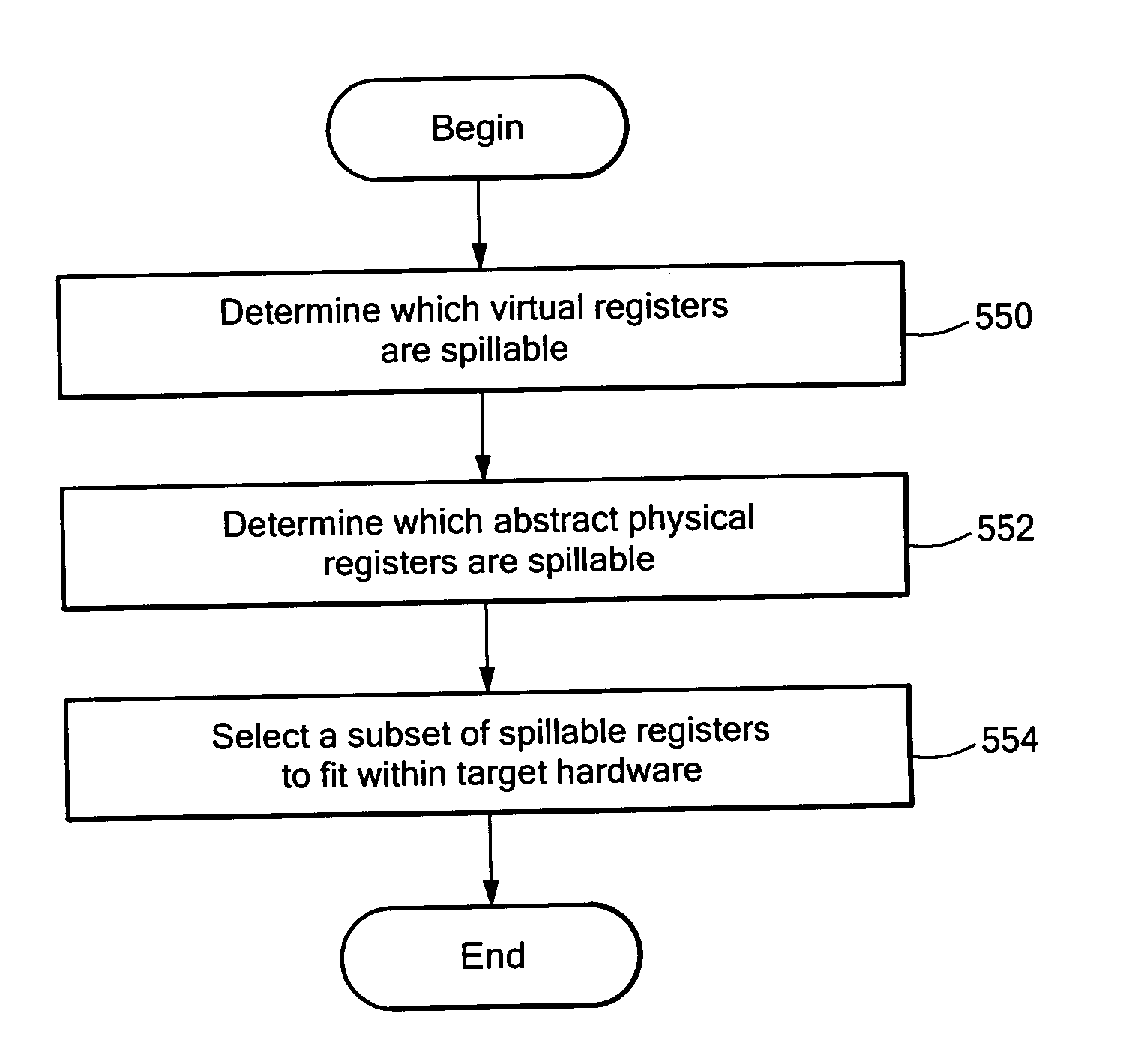

Embodiments of the present invention provide a method and system for optimizing processor register allocation. Variables from an acyclic call graph having a plurality of functions may be identified and a plurality of virtual registers may be created by assigning each of the identified variables to at least one virtual register. An interference graph may be constructed based on the plurality of virtual registers and may be colored with a plurality of physical registers. If the interference graph is not colorable, then at least one virtual register may be spilled from the interference graph.

Owner:INTEL CORP

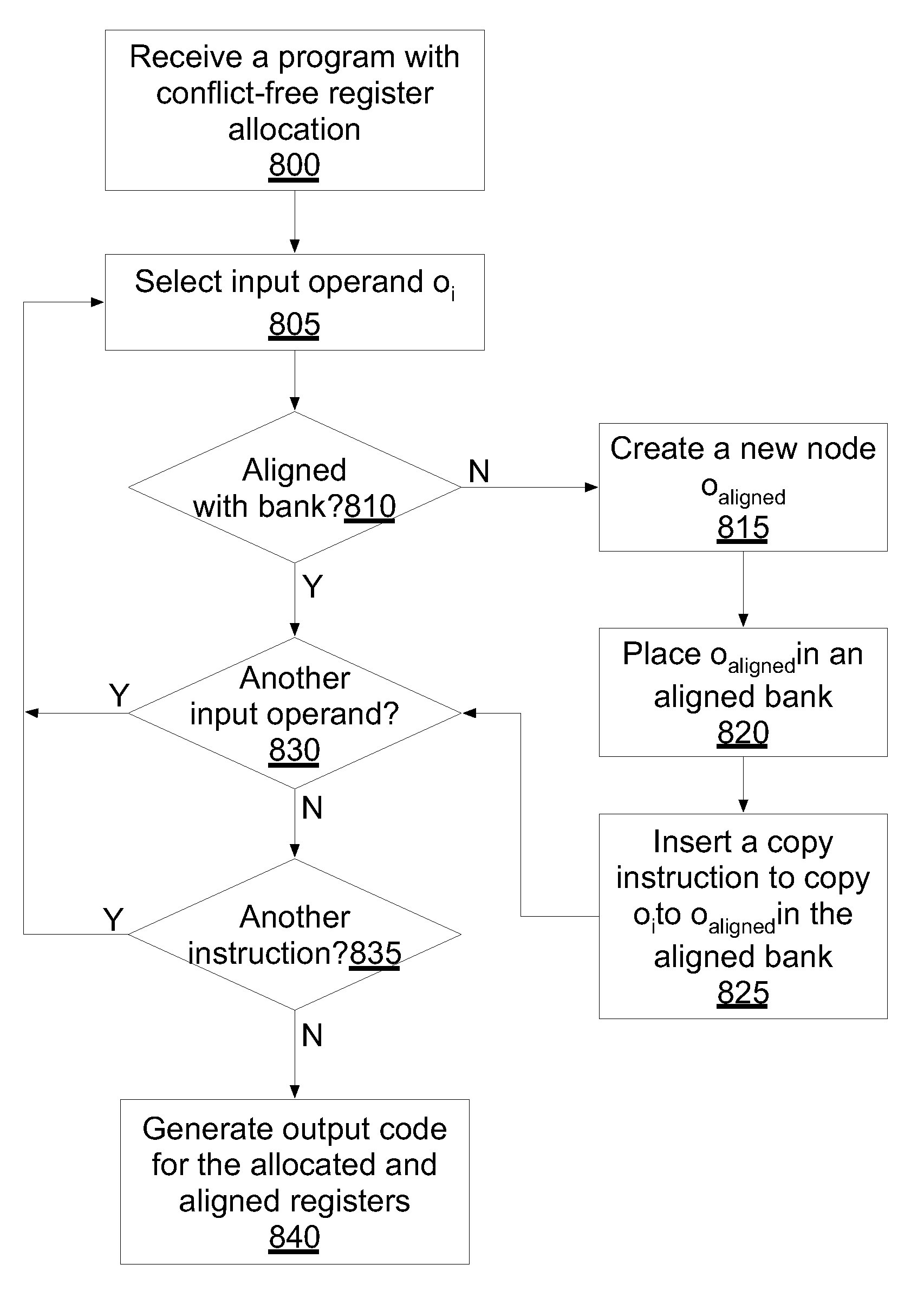

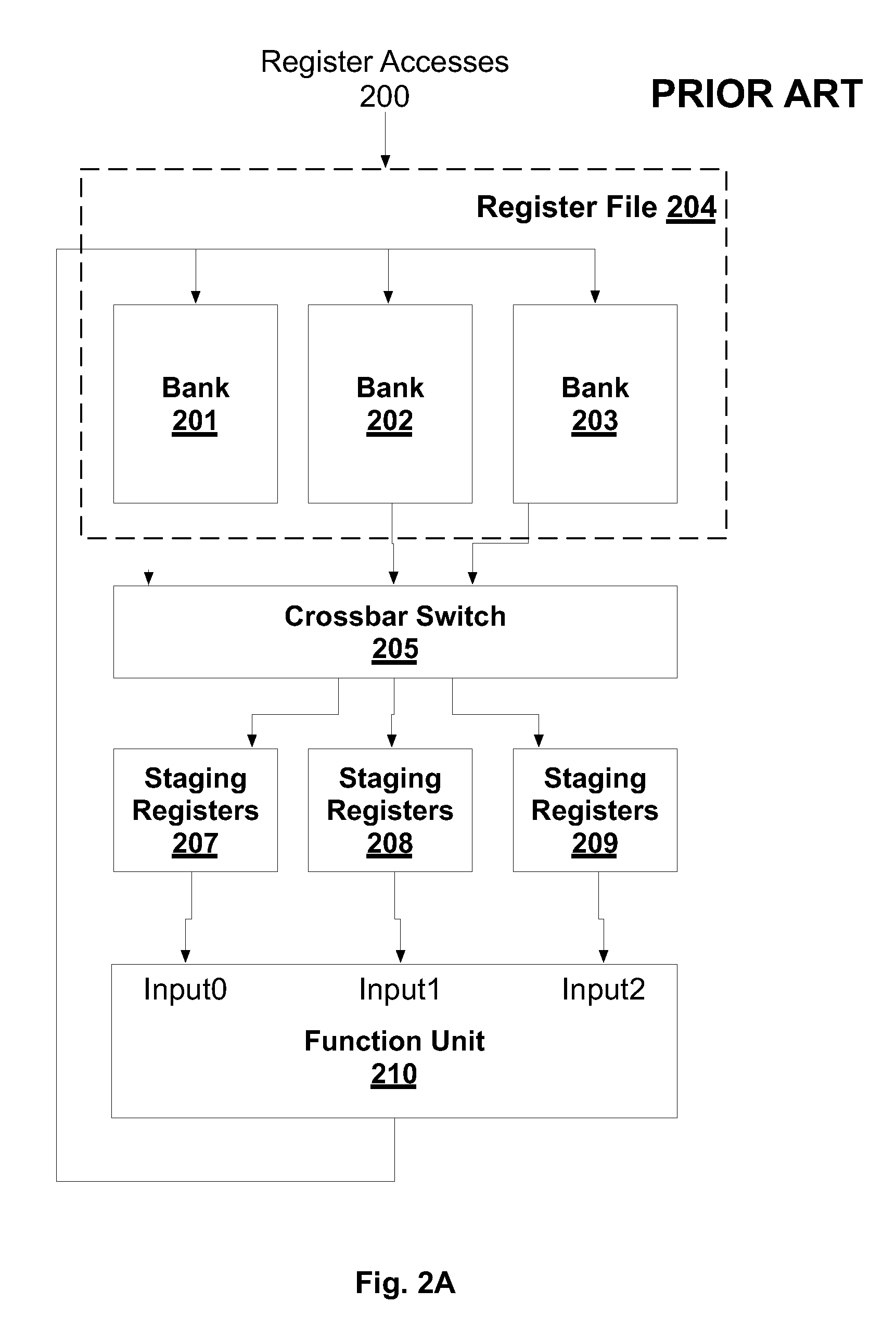

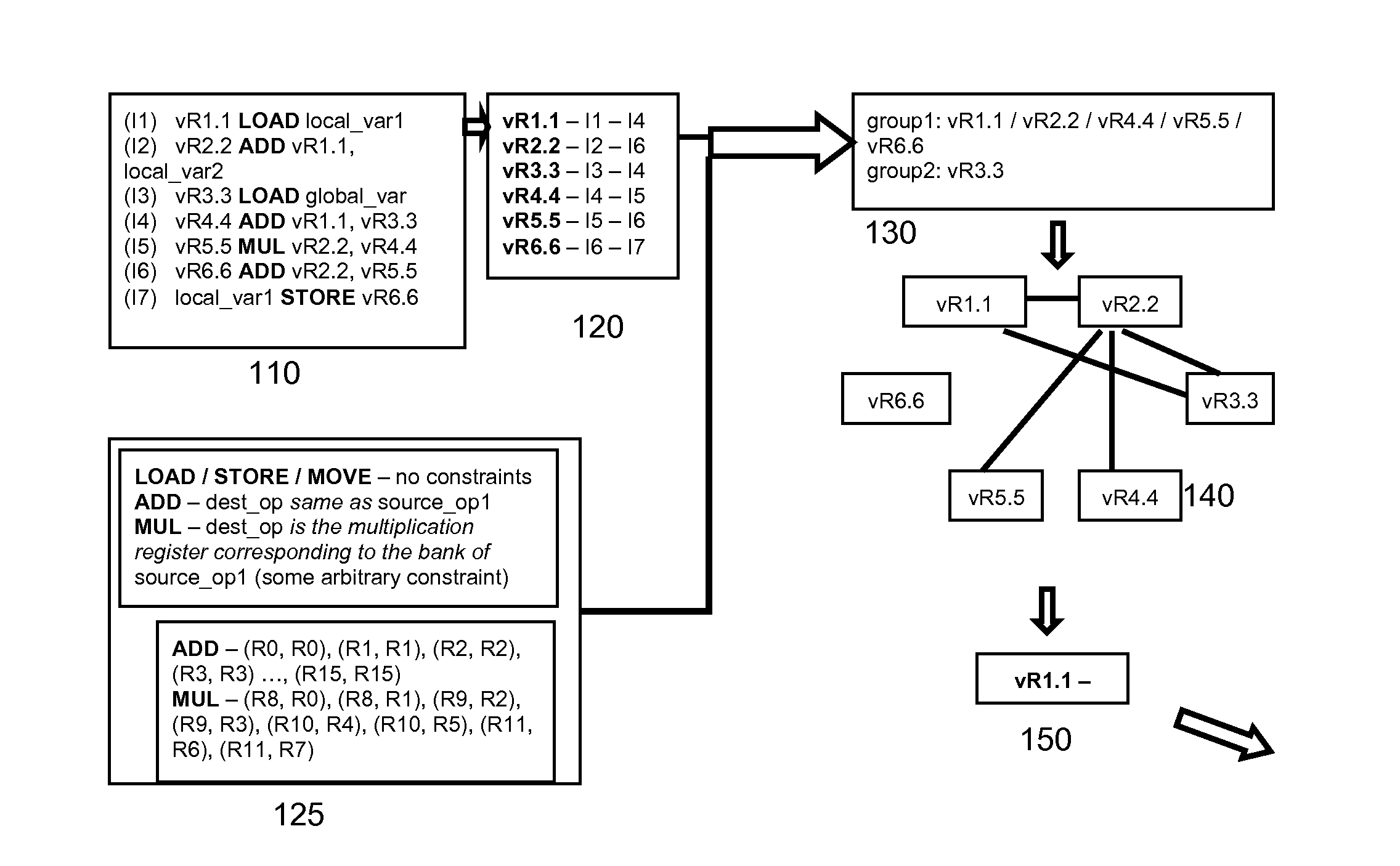

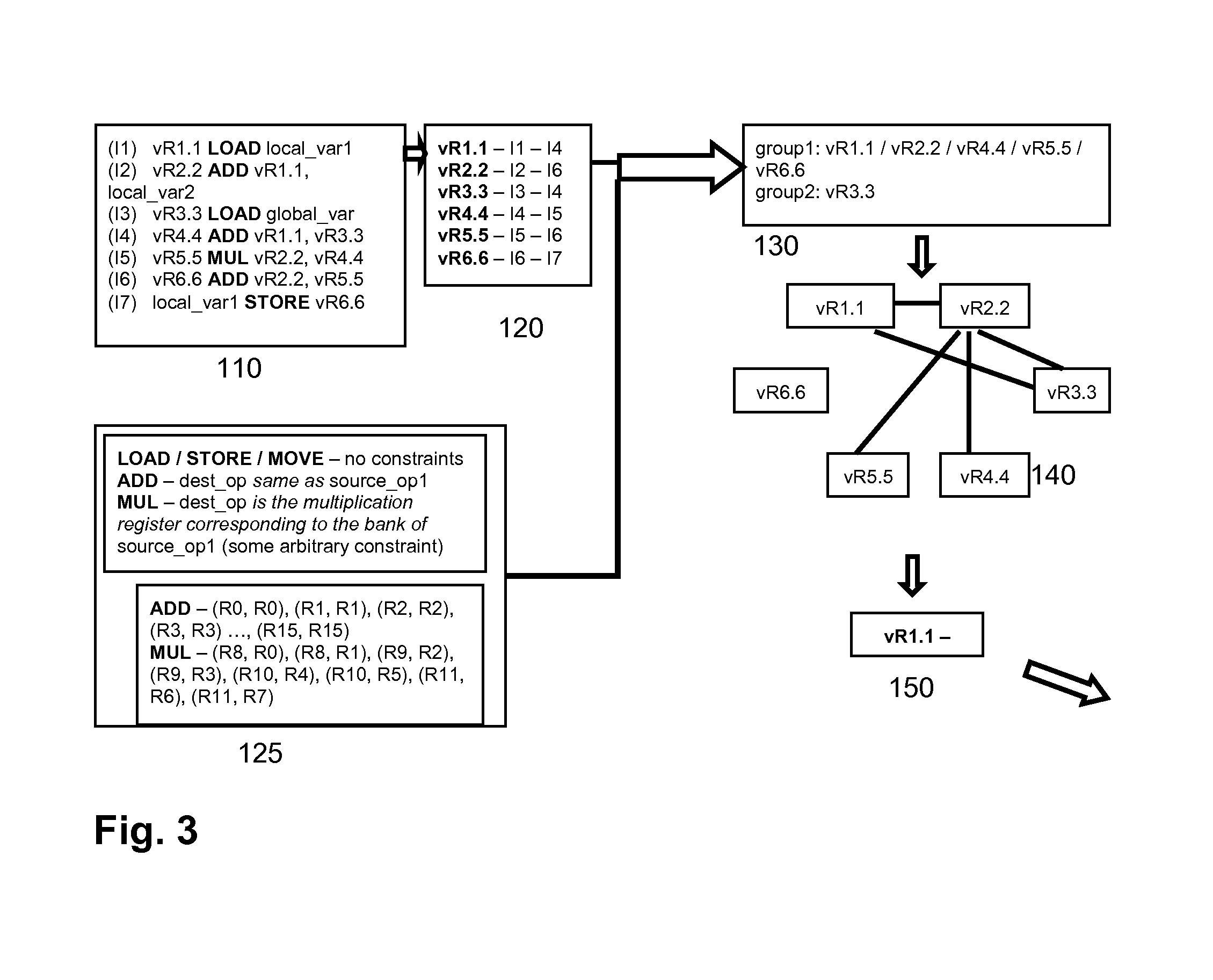

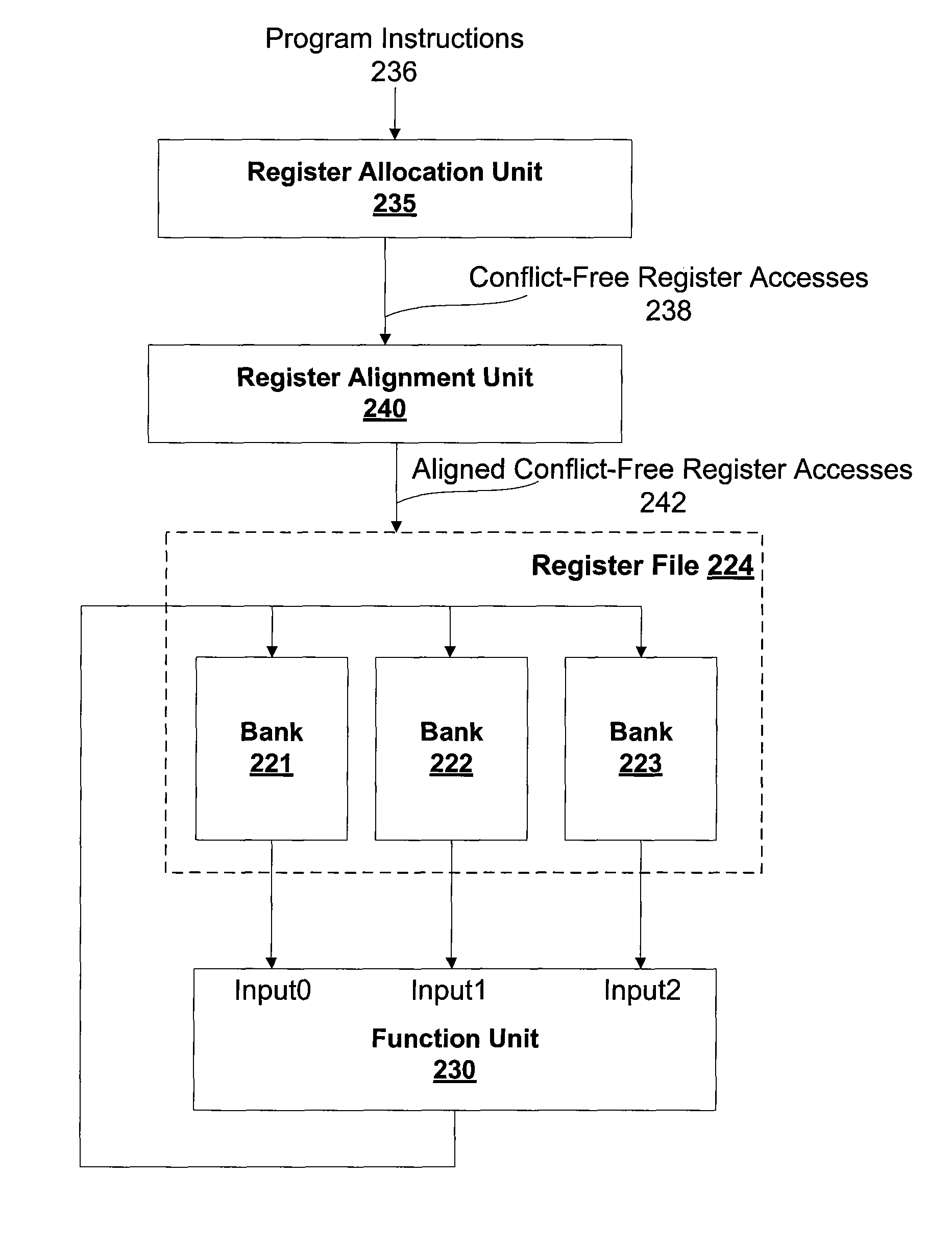

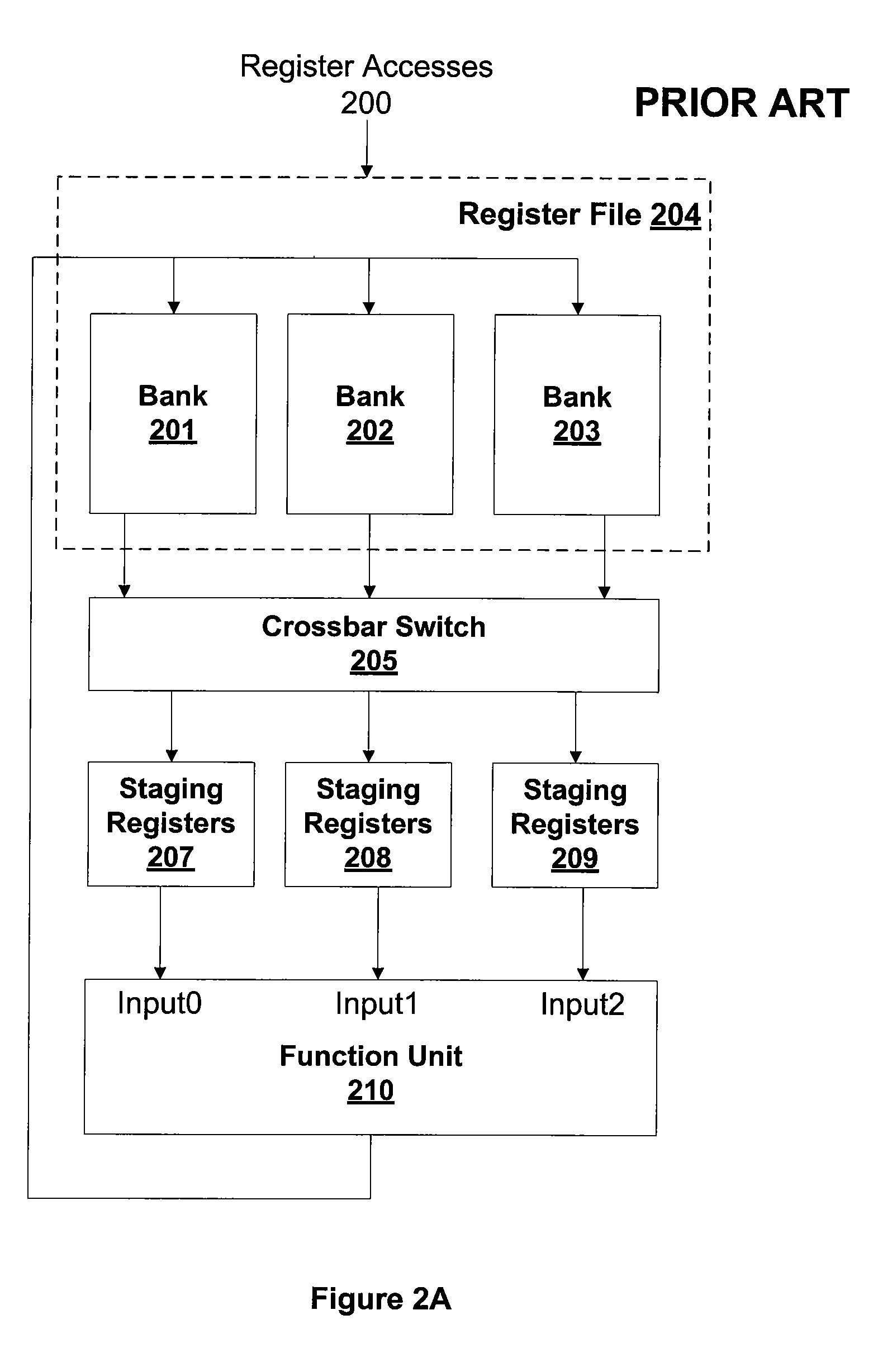

Conflict-free register allocation using a multi-bank register file with input operand alignment

ActiveUS8555035B1Small sizeLower latencySoftware engineeringDigital computer detailsRegister allocationProcessor register

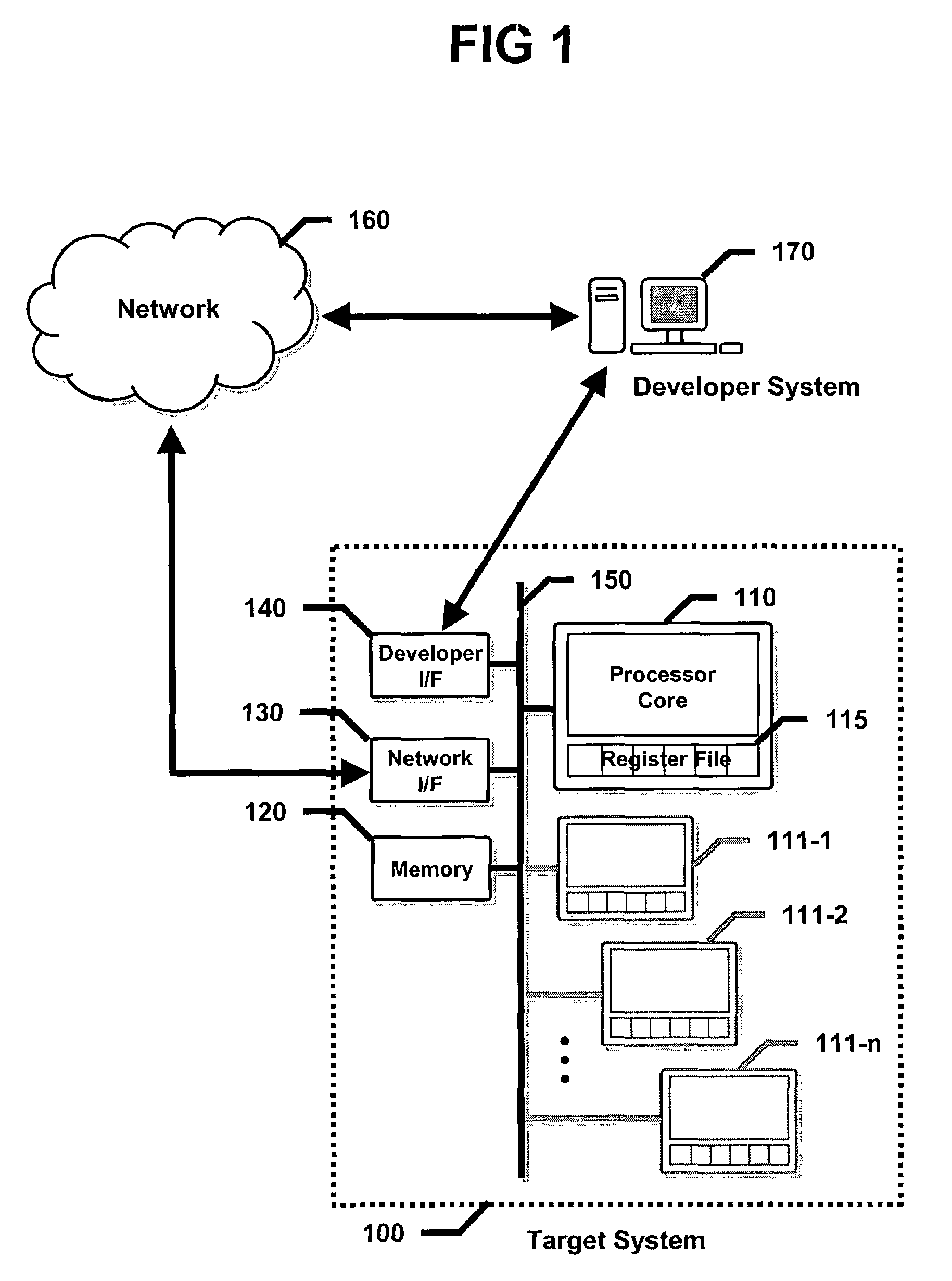

One embodiment of the present invention sets forth a technique for using a multi-bank register file that reduces the size of or eliminates a switch and / or staging registers that are used to gather input operands for instructions. Each function unit input may be directly connected to one bank of the multi-bank register file with neither a switch nor a staging register. A compiler or register allocation unit ensures that the register file accesses for each instruction are conflict-free (no instruction can access the same bank more than once in the same cycle). The compiler or register allocation unit may also ensure that the register file accesses for each instruction are also aligned (each input of a function unit can only come from the bank connected to that input).

Owner:NVIDIA CORP

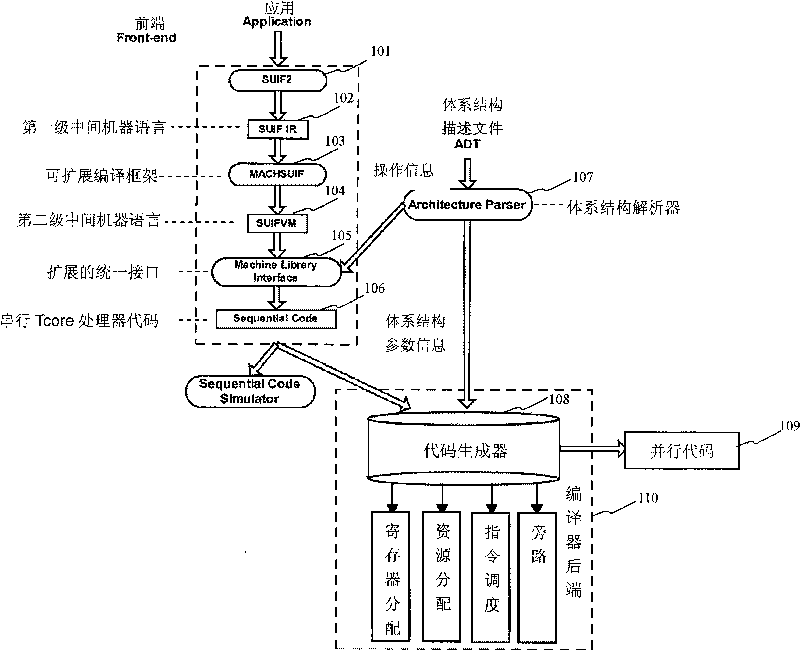

Compiler system based on TCore configurable processor

InactiveCN101694627AStable supportSolving inefficienciesGenetic modelsProgram controlFormateProcessor register

The invention discloses a compiler system based on a configurable processor, adopting an intermediate language format to carry out the organization of a compiler and finishing the distribution and instruction scheduling of a register by a linear trace and a genetic algorithm, wherein the compiler comprises an SUIF2, a first-level intermediate machine language SUIF IR, an extensible compiling framework MACHSUIF, a second-level intermediate machine language SUIFVM, a consolidated extension interface Machine Library Interface, a serial configurable processor code Sequential Code, an architecture parser, a code generator, a configurable architecture description file ADT and a parallel configurable processor code. The invention enables the compiler to efficiently finish the generation of codes and solves the long-term problem that the compiler based on a TTA architecture processor has low efficiency through the combination of the front end of the compiler based on an intermediate formate and the rear end of the compiler based on two heuristic algorithms of the linear trace and the genetic algorithm.

Owner:TIANJIN UNIV

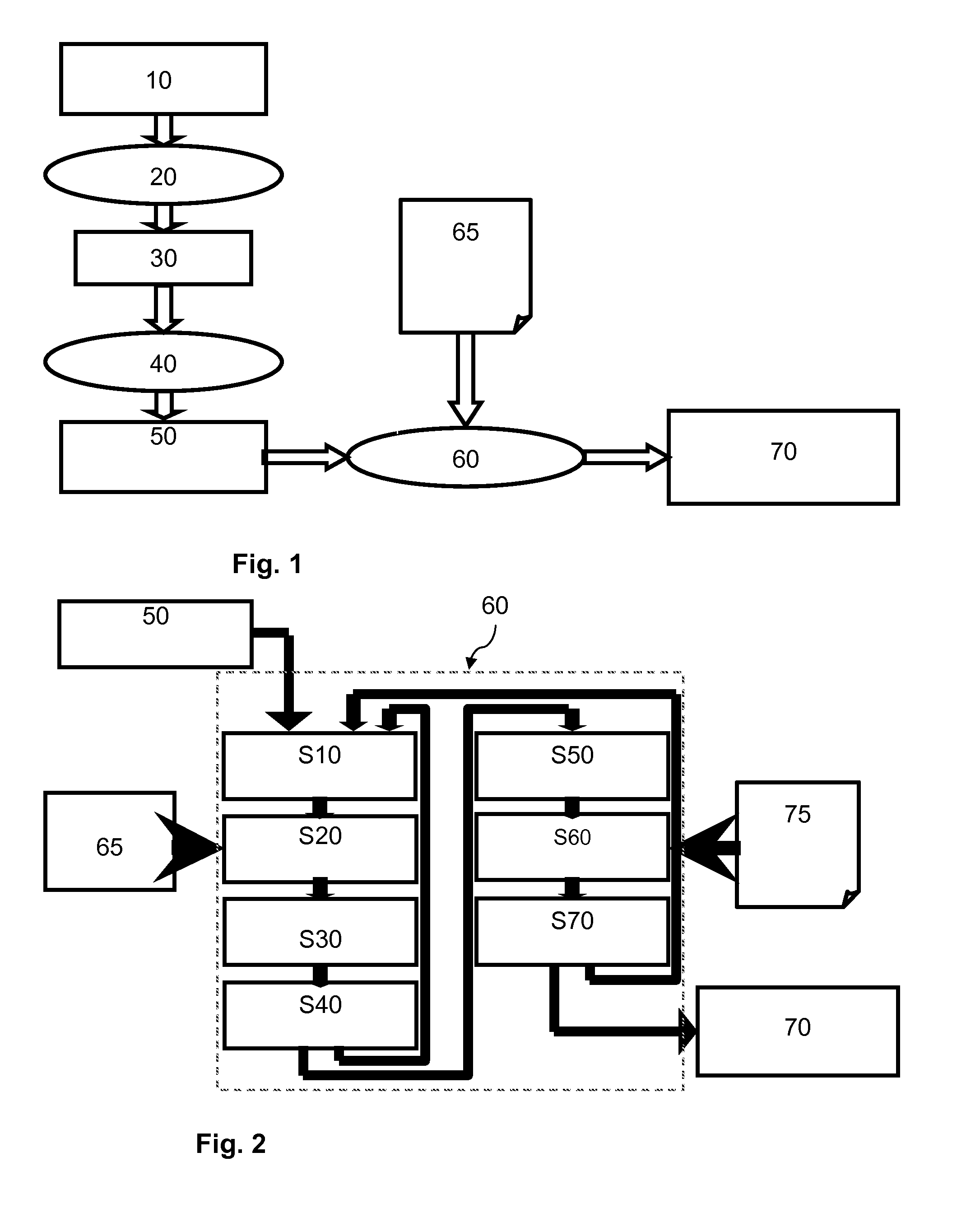

Optimization method for compiler, optimizer for a compiler and storage medium storing optimizing code

The invention pertains to an optimization method for a compiler, comprising providing a model of inter-operand constraints of physical registers of a target-platform of a compilation; and a) providing an intermediate representation of a source code using virtual registers; b) grouping the virtual registers of the intermediate representation based on the model of inter-operand constraints into two or more groups, each group comprising at least one virtual register; c) if for at least one group at least one interference of virtual registers within the group occurs, amending the intermediate representation to resolve at least one interference and jumping to step b); otherwise d) providing a representation of a group interference graph of interferences between the groups; and e) allocating virtual registers to physical registers using a coloring scheme on the representation of the group interference graph. The invention also refers to a corresponding optimizer for a compiler and a computer-readable storage medium storing optimizing code.

Owner:NXP USA INC

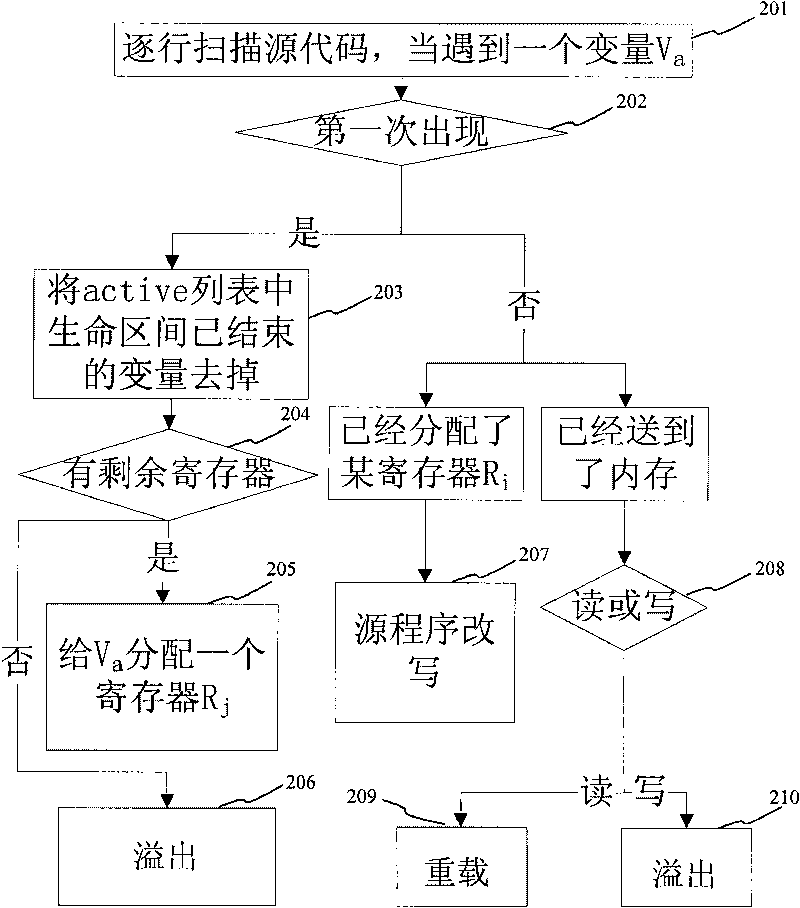

Register allocation method for optimizing stack space

InactiveCN101710291AReduce overflowReduce occupancyProgram controlMemory systemsRegister allocationProcessor register

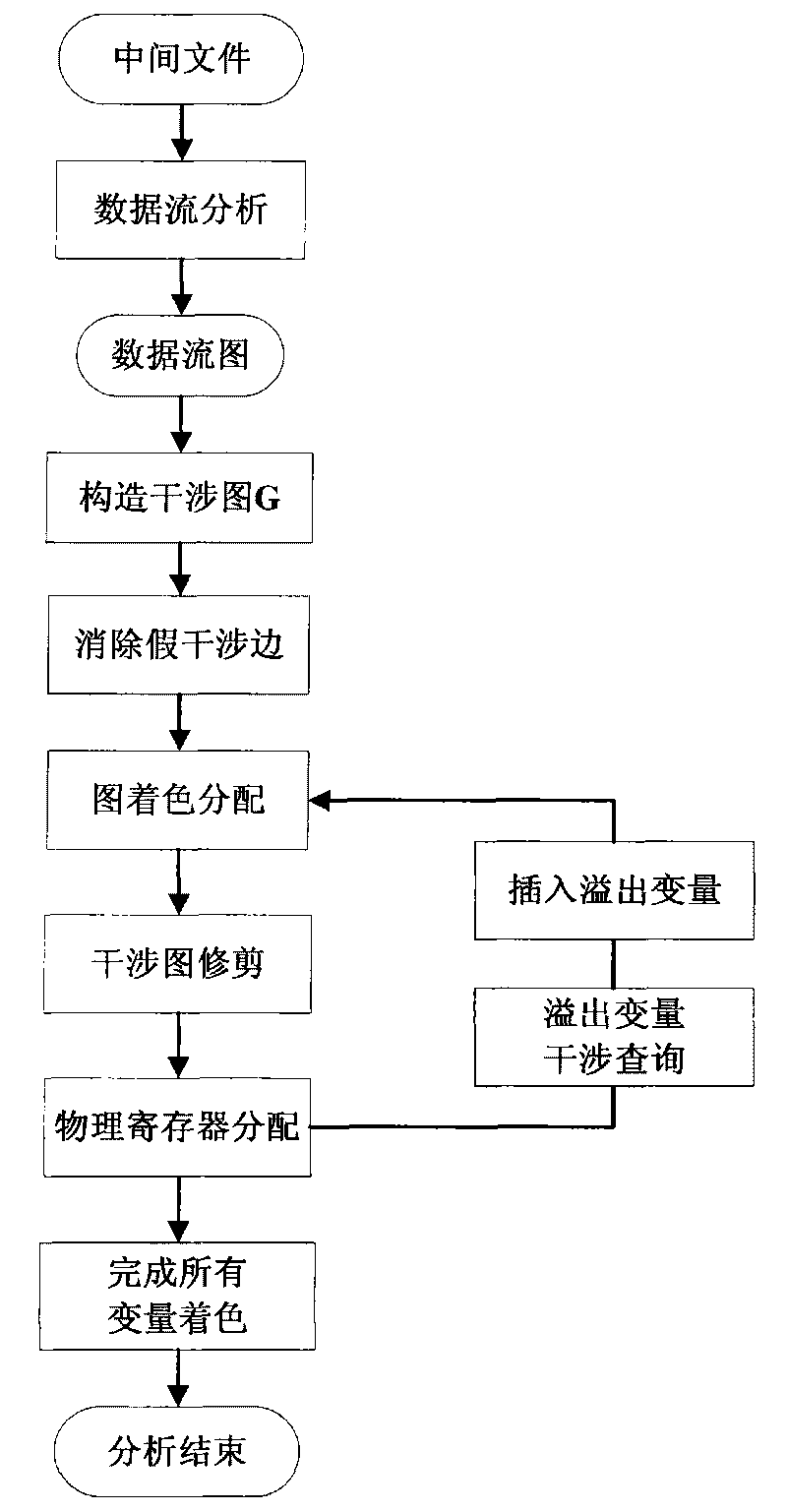

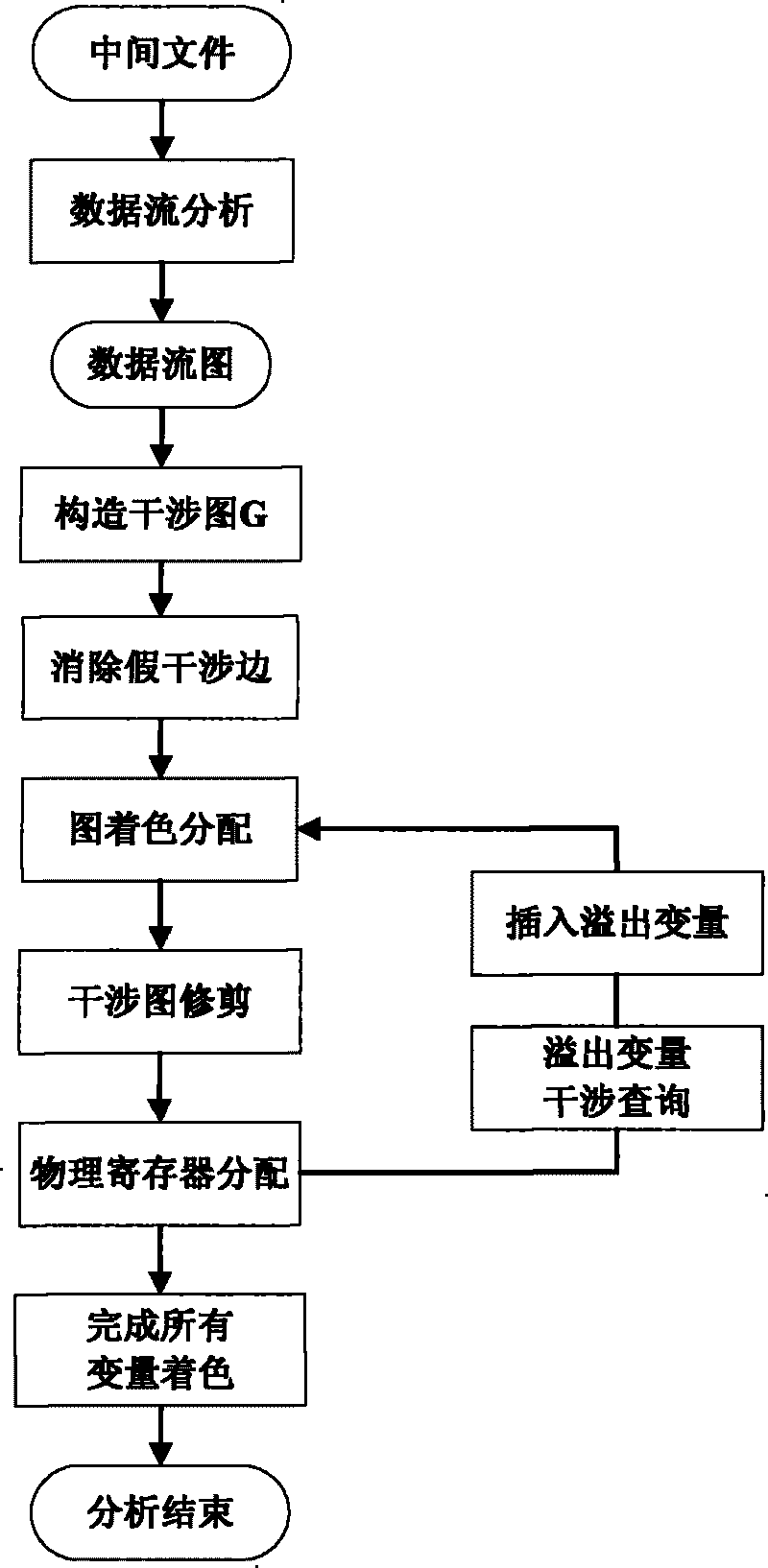

The invention provides a register allocation method for optimizing stack space, which comprises the following steps: 1, analyzing a program intermediate file by a register allotter to obtain a data flow diagram; 2, constructing interference patterns of program variables according to the data flow diagram; 3, optimizing the interference patterns to eliminate false interference edges; 4, trying to color the interference patterns, if the step is successful, indicating no variable overflow and stopping allocating the registers, and otherwise performing the next step; 5, abridging the interferencepatterns, and overflowing the low-priority variables to a stack; 6, allocating the number of actual physical registers for the highest-priority virtual registers; and 7, aiming at the overflow nodes of the step 5), inserting the corresponding codes, and querying the accurate interference patterns of the step 3) to allocate the same stack offset for noninterference overflow variables. The method for eliminating the false interference edges comprises the steps: for two interference variables, further analyzing interference variables which are not intersected with an inference register to deletea connection line of the two variables and eliminate the false interference edges.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

Debug system having assembler correcting register allocation errors

InactiveUS20050210457A1Error detection/correctionProgram controlRegister allocationParallel computing

An assembler, which can be provided as part of a debugger and / or development system, avoids register allocation errors, such as register bank conflicts and / or insufficient physical registers, automatically.

Owner:INTEL CORP

Register allocation and code spilling using interference graph coloring

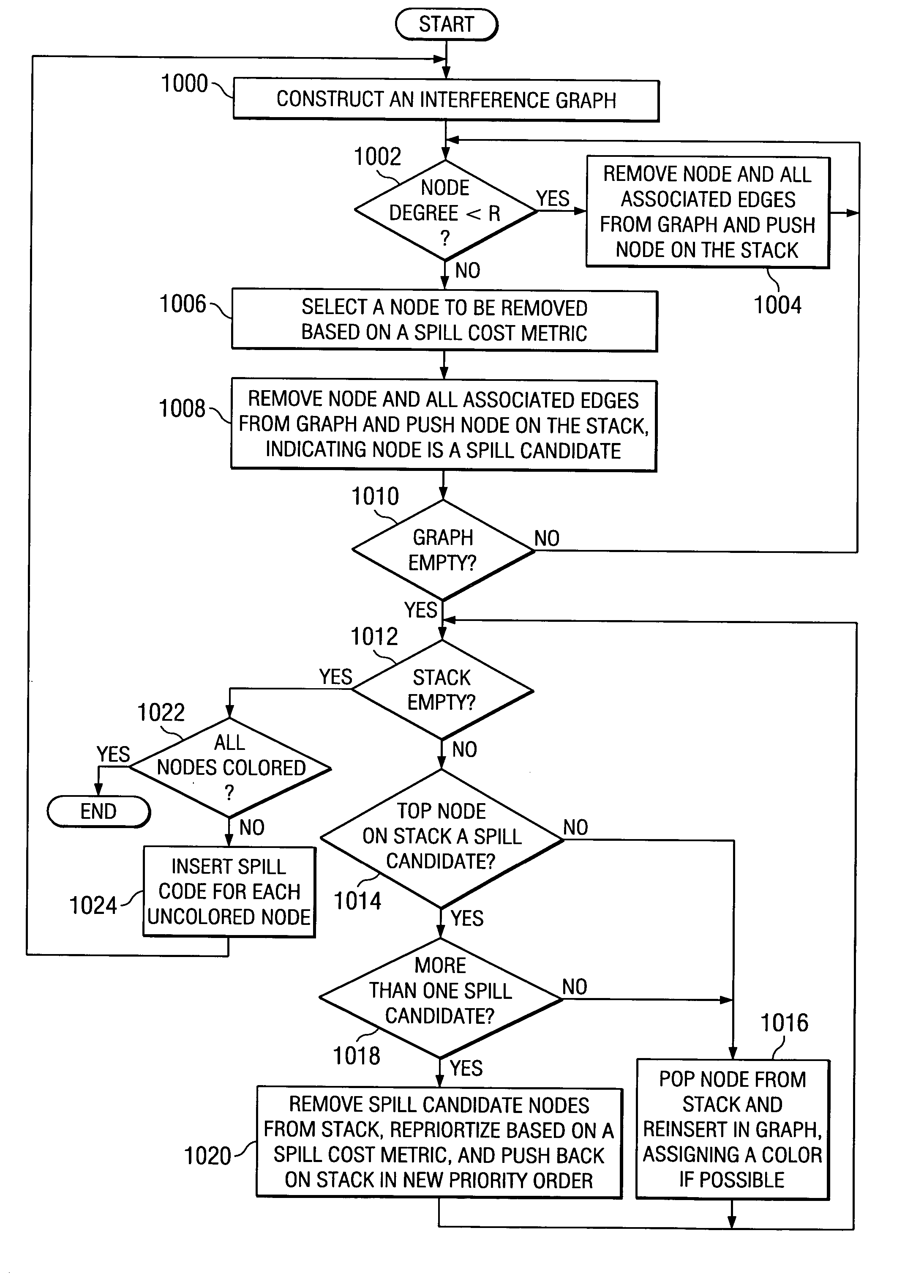

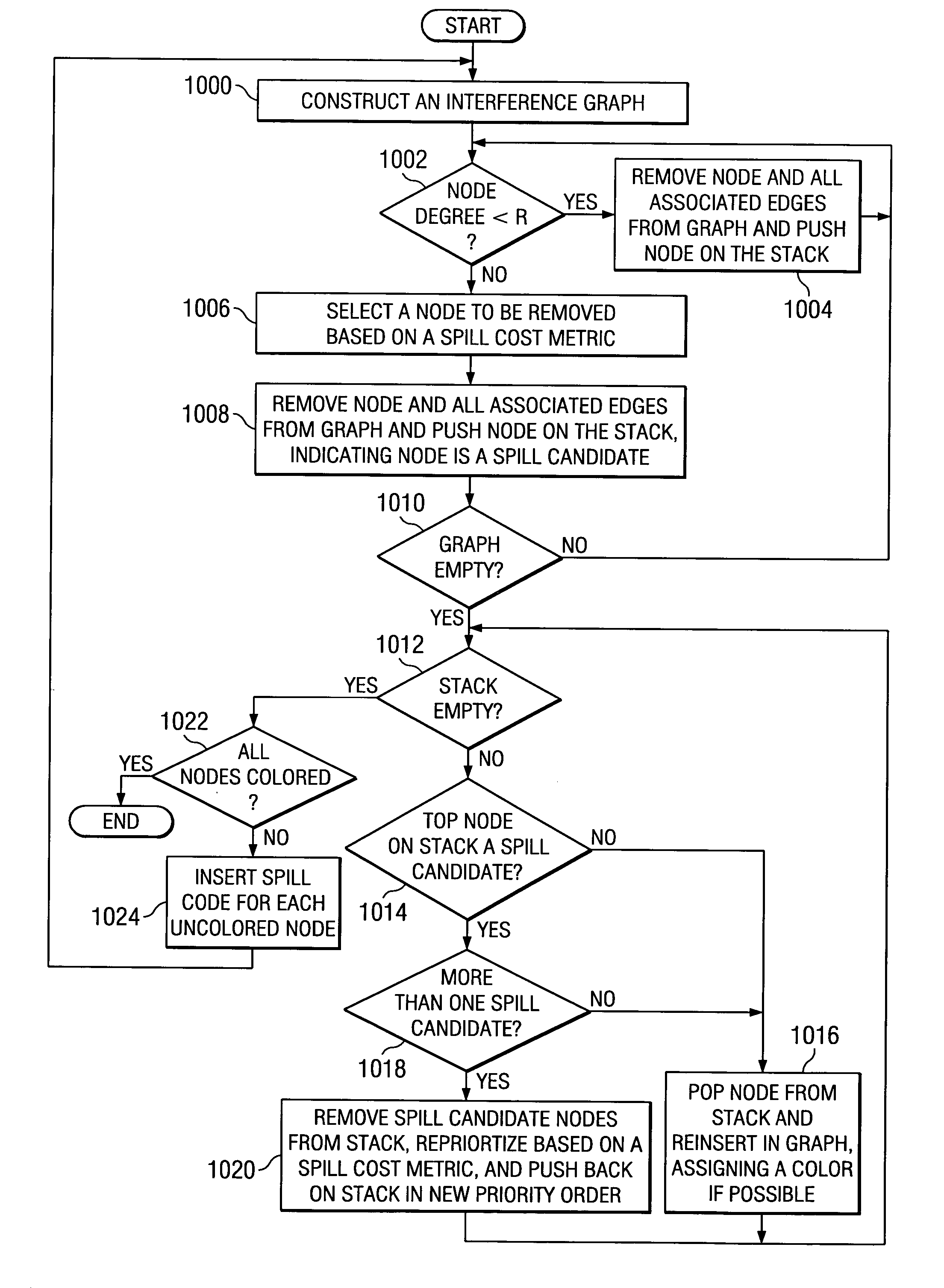

ActiveUS20050039175A1Achieve colorColor interferenceSoftware engineeringSpecific program execution arrangementsRegister allocationCost metric

An improved method is provided for performing register allocation in a compiler. This method determines the allocation of a plurality R of registers of a processor for use during the execution of a software program. The register allocation process is treated as a graph-coloring problem, such that an interference graph is constructed for the software program, the graph is simplified, and an R-coloring the interference graph to the extent possible is attempted. Then, spill code is inserted in the software program each for each uncolored node of the graph, a new interference graph is constructed, and the process is repeated. During the simplification process, nodes with degree greater than or equal to R are removed from the graph in an order dictated by a spill cost metric. During the coloring process, these same nodes are reinserted in the graph in an order dictated by reapplying the spill cost metric.

Owner:TEXAS INSTR INC

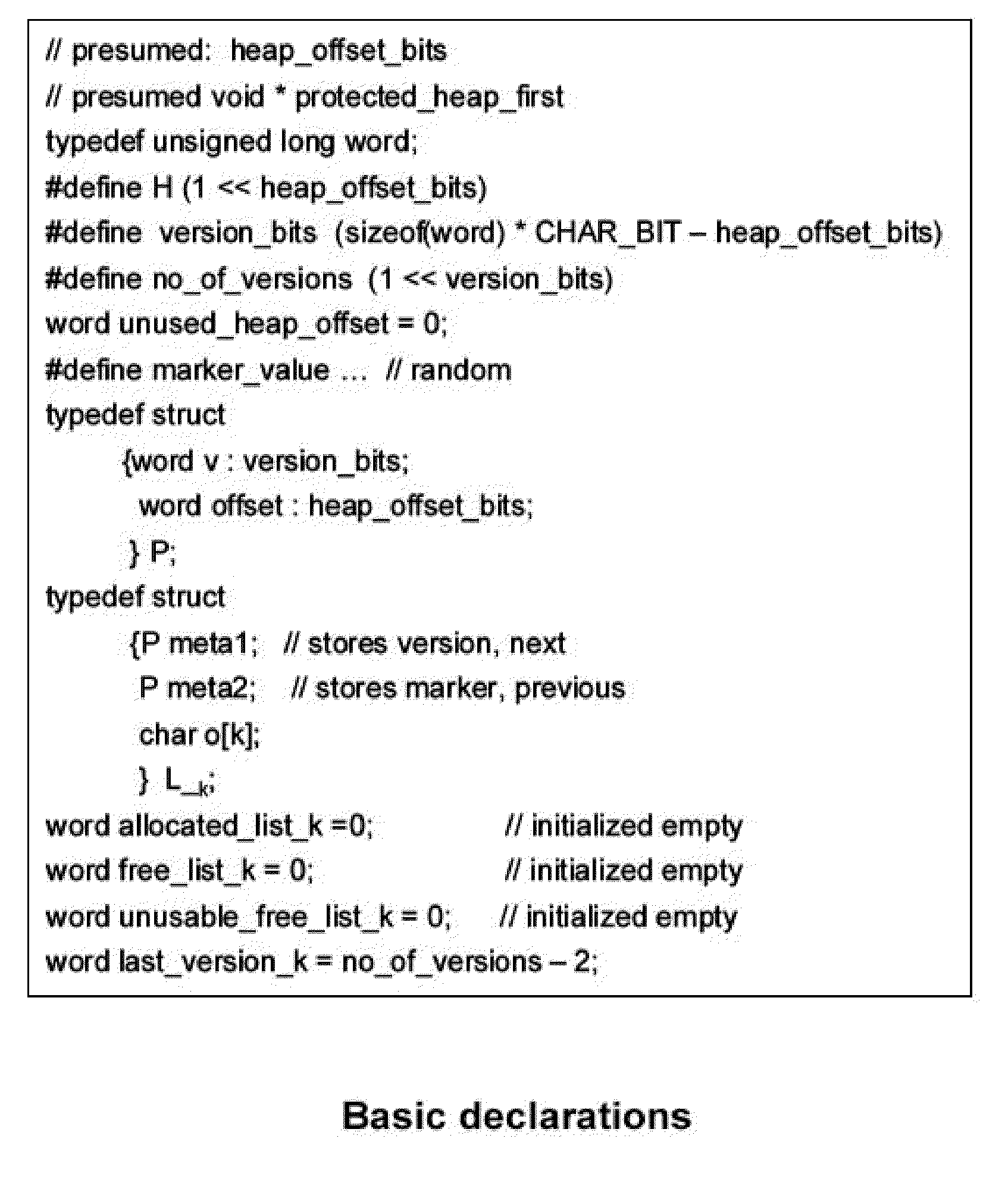

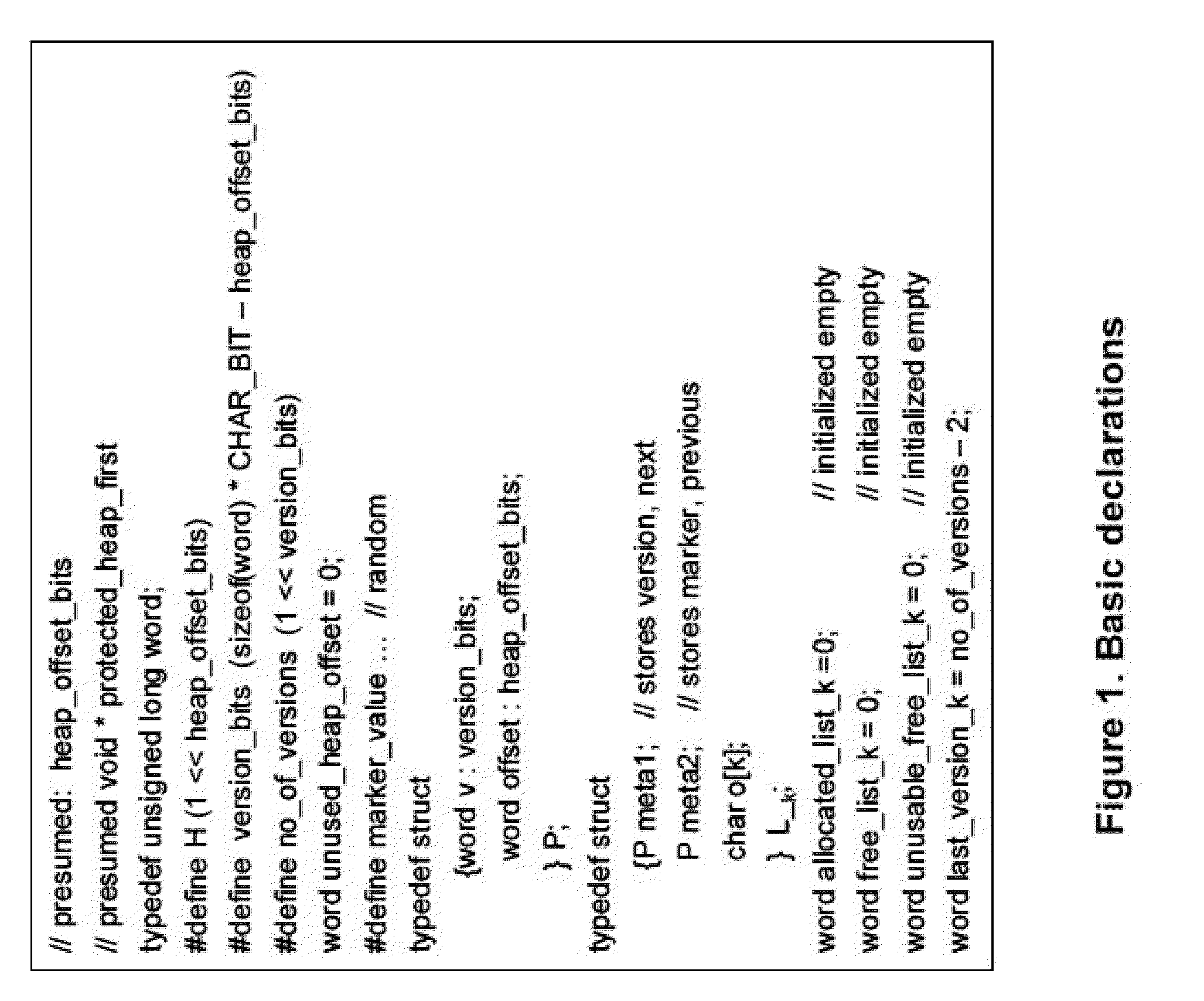

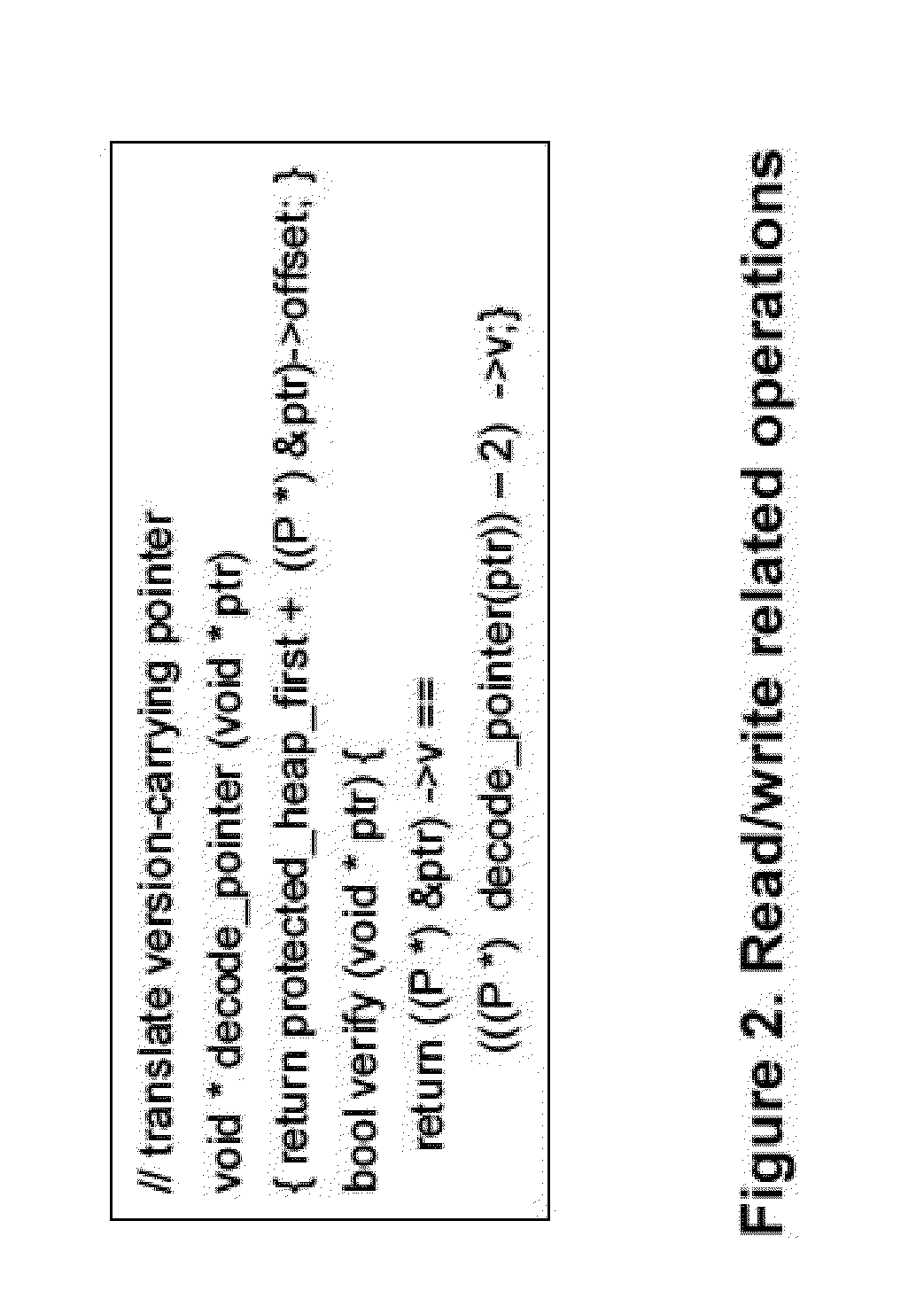

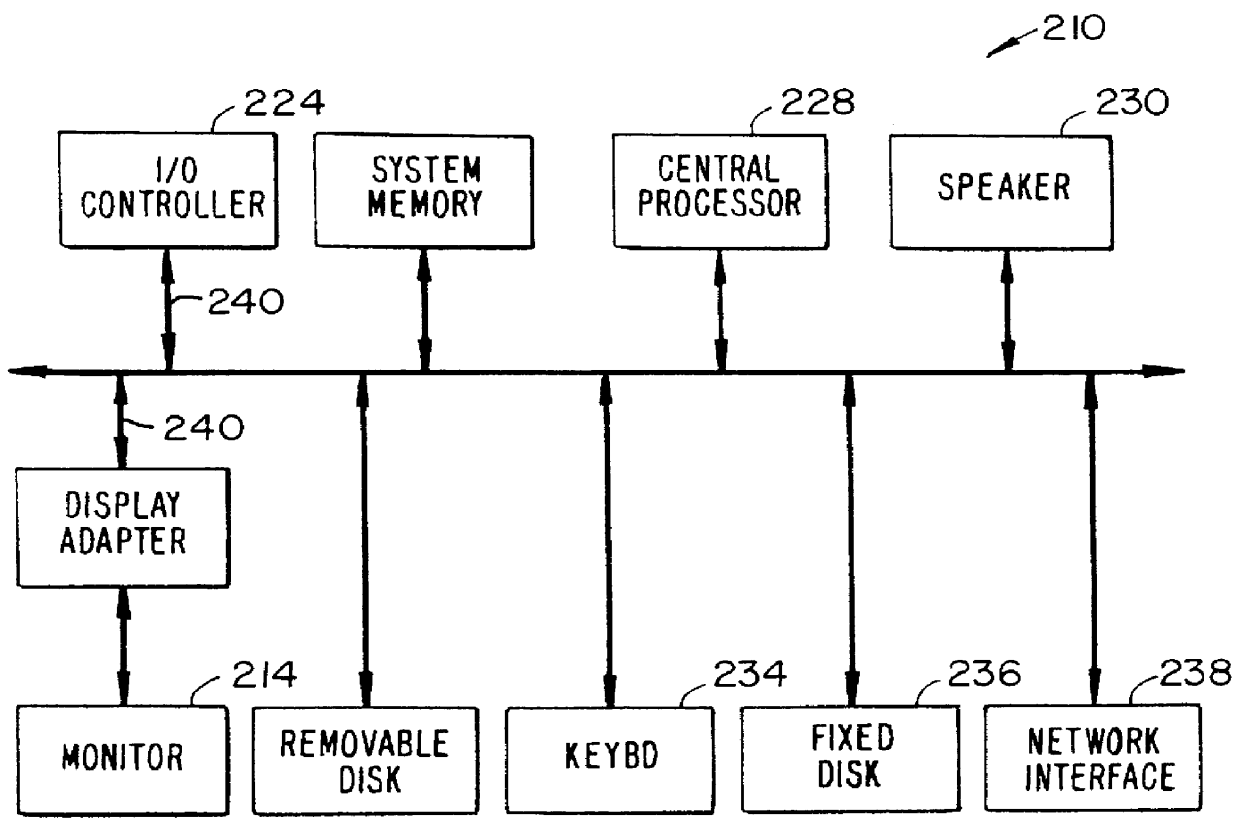

Systems and methods for backward-compatible constant-time exception-protection memory

Embodiments of the invention provide a table-free technique for detecting all temporal and spatial memory access errors in programs supporting general pointers. Embodiments of the invention provide such error checking using constant-time operations. Embodiments of the invention rely on fat pointers, whose size is contained within standard scalar sizes (up to two words) so that atomic hardware support for operations upon the pointers is obtained along with meaningful casts in-between pointers and other scalars. Optimized compilation of code becomes possible since the scalarized-for-free encoded pointers get register allocated and manipulated. Backward compatibility is enabled by the scalar pointer sizes, with automatic support provided for encoding and decoding of fat pointers in place for interaction with unprotected code.

Owner:IBM CORP

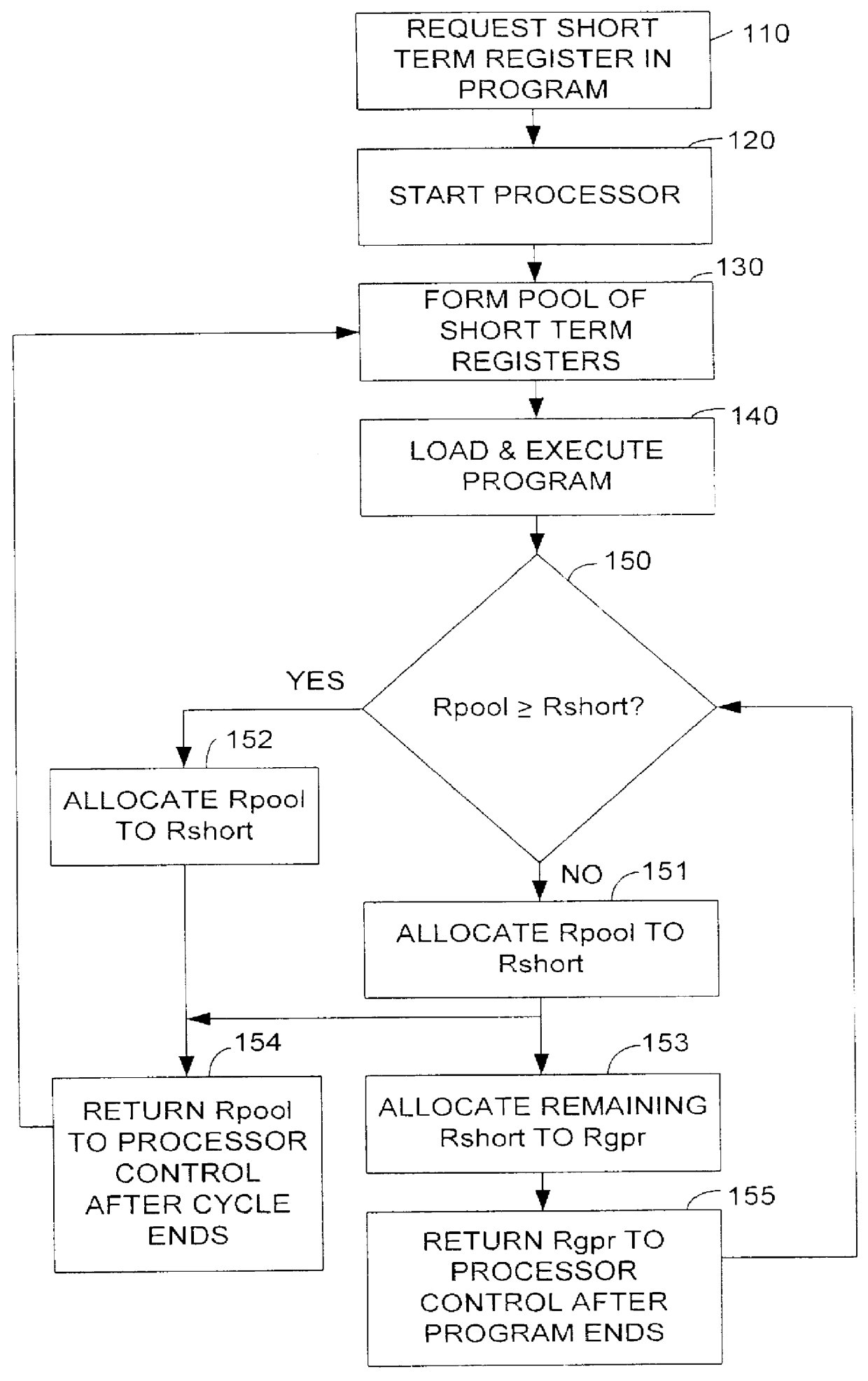

Method for conserving memory storage using a pool of short term memory registers

InactiveUS6151670AMore memory resourceConserving memory storageResource allocationRegister arrangementsLong term dataShort-term memory

A method for conserving processor registers during the execution of a program in which short term data having a short processing period and long term data having a long processing period are processed. The method includes the acts of: providing a program having a first address space for addressing the short term data and a second address space for addressing the long term data, defining within the processor a first plurality of pooled registers for storing the short term data, executing said program, allocating, responsive to the program, at least one of the pooled registers to the first address space, controlling, via said program, the allocated pool register for the duration of said short processing period, and terminating program control of the allocated pool register upon the expiration of said short processing period.

Owner:CREATIVE TECH CORP

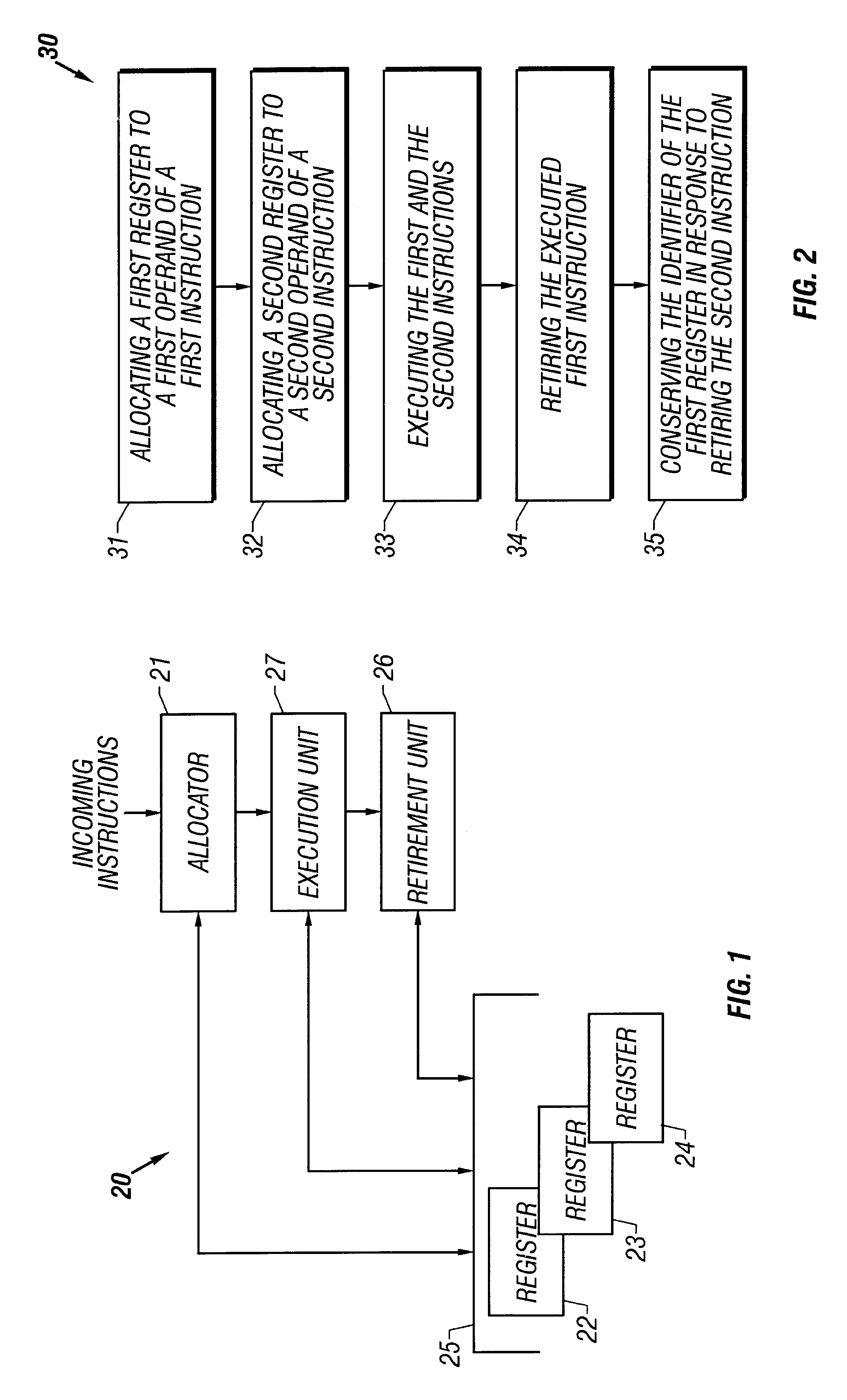

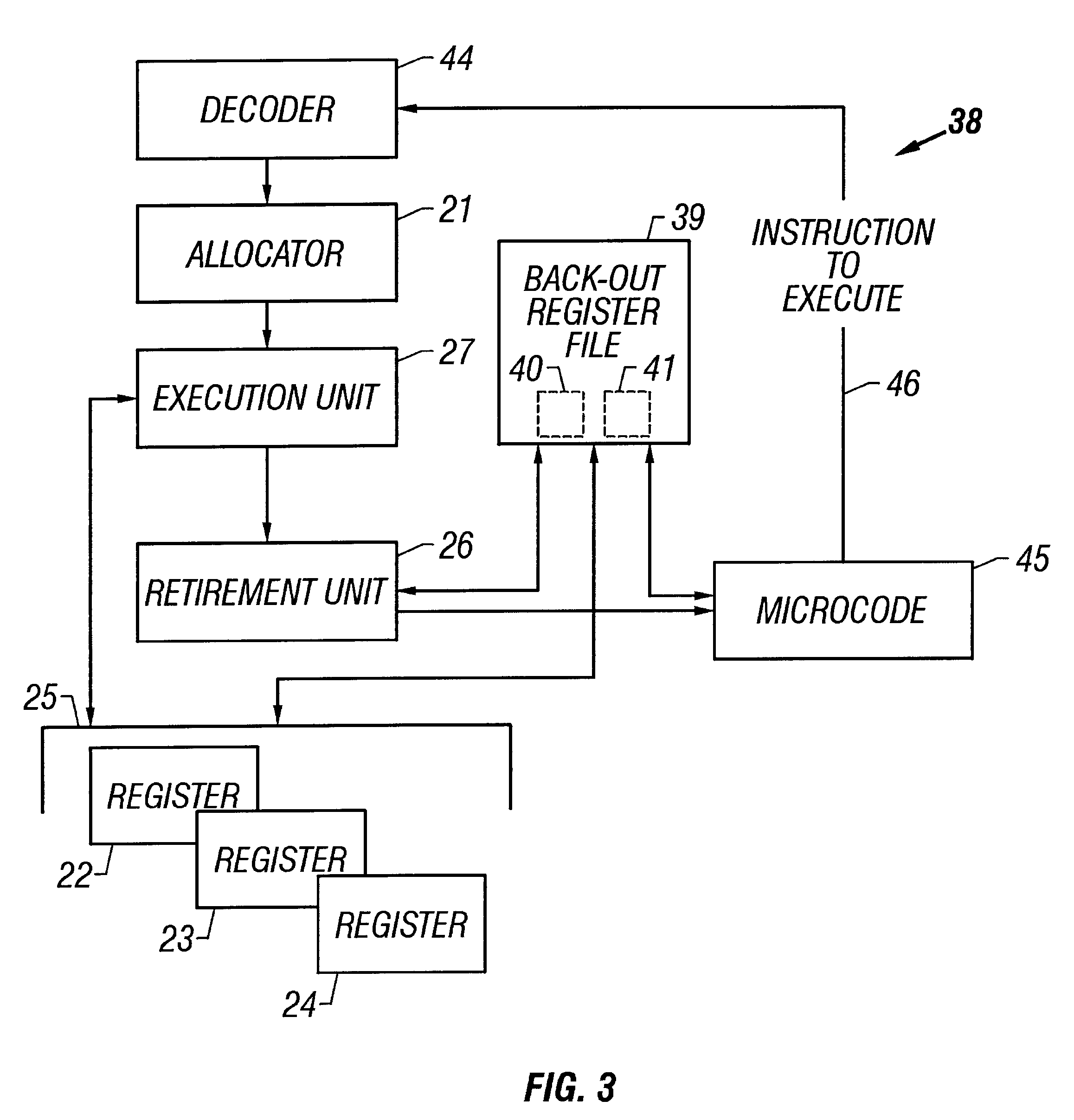

Backing out of a processor architectural state

InactiveUS6412067B1Digital computer detailsConcurrent instruction executionComputer architectureProcessor register

Owner:INTEL CORP

Post-register allocation profile directed instruction scheduling

ActiveUS20070150880A1Software engineeringSpecial data processing applicationsRegister allocationScheduling instructions

A computer implemented method, system, and computer usable program code for selective instruction scheduling. A determination is made whether a region of code exceeds a modification threshold after performing register allocation on the region of code. The region of code is marked as a modified region of code in response to the determination that the region of code exceeds the modification threshold. A determination is made whether the region of code exceeds an execution threshold in response to the determination that the region of code is marked as a modified region of code. Post-register allocation instruction scheduling is performed on the region of code in response to the determination that the region of code is marked as a modified region of code and the determination that the region of code exceeds the execution threshold.

Owner:TWITTER INC

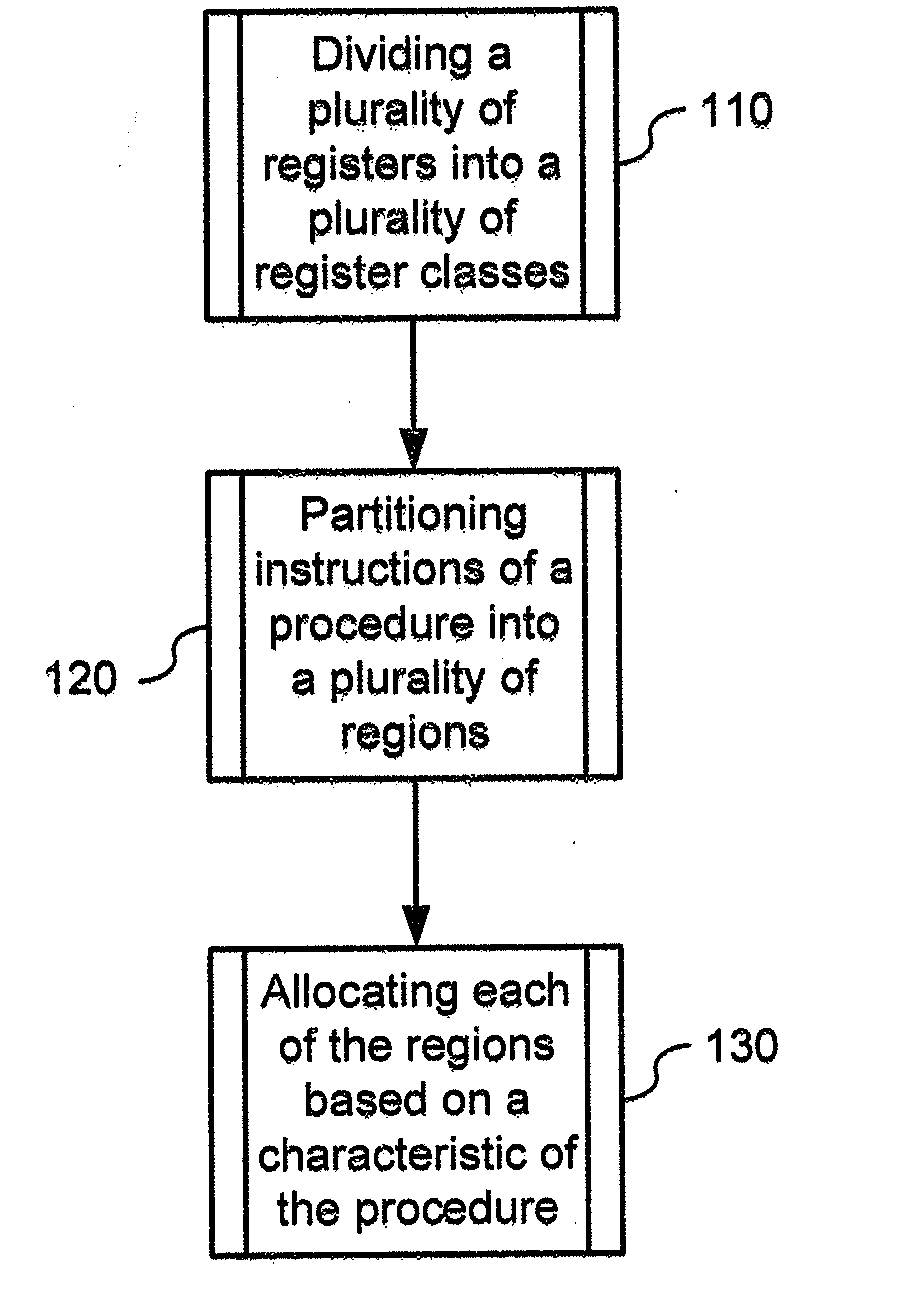

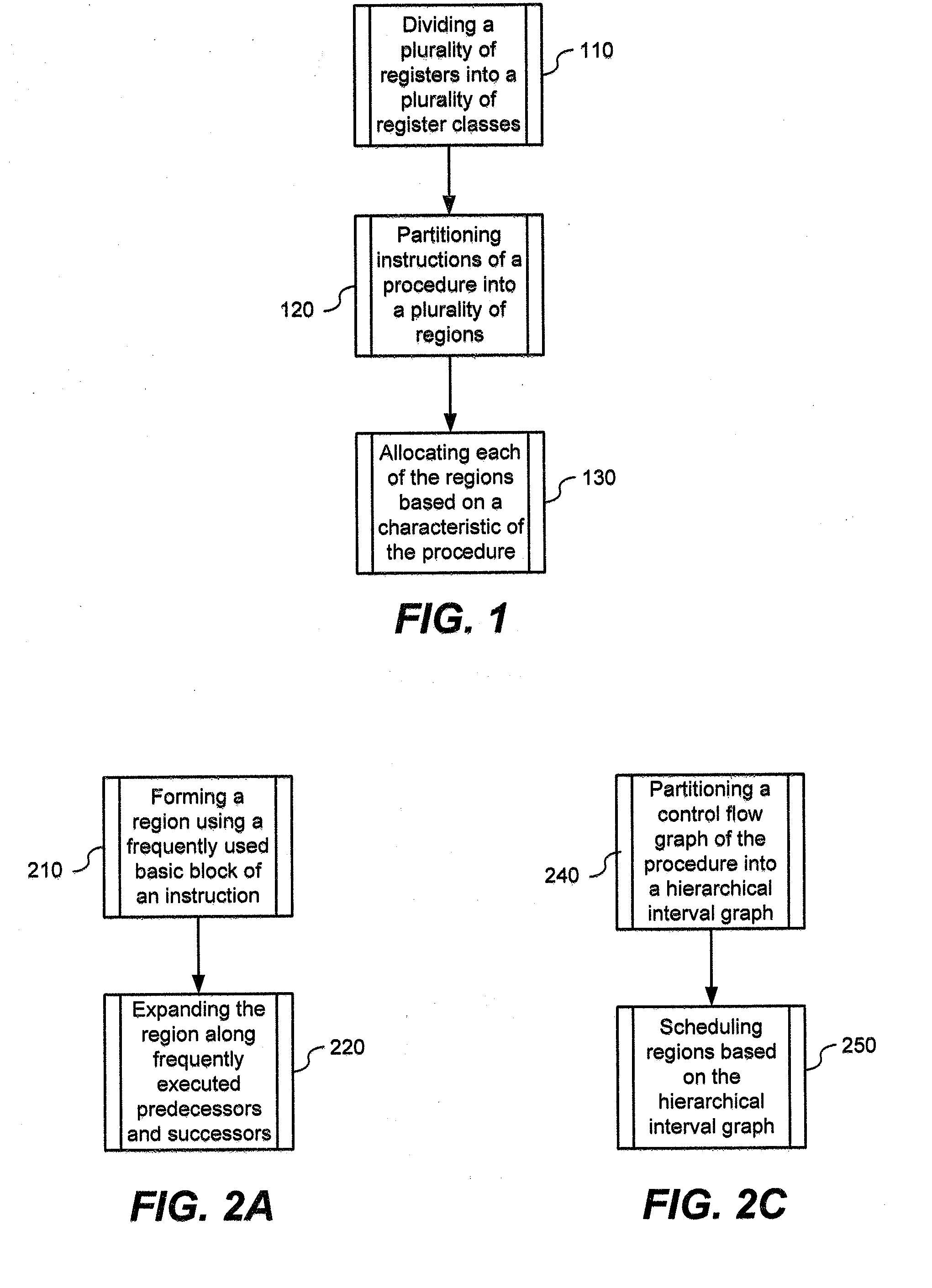

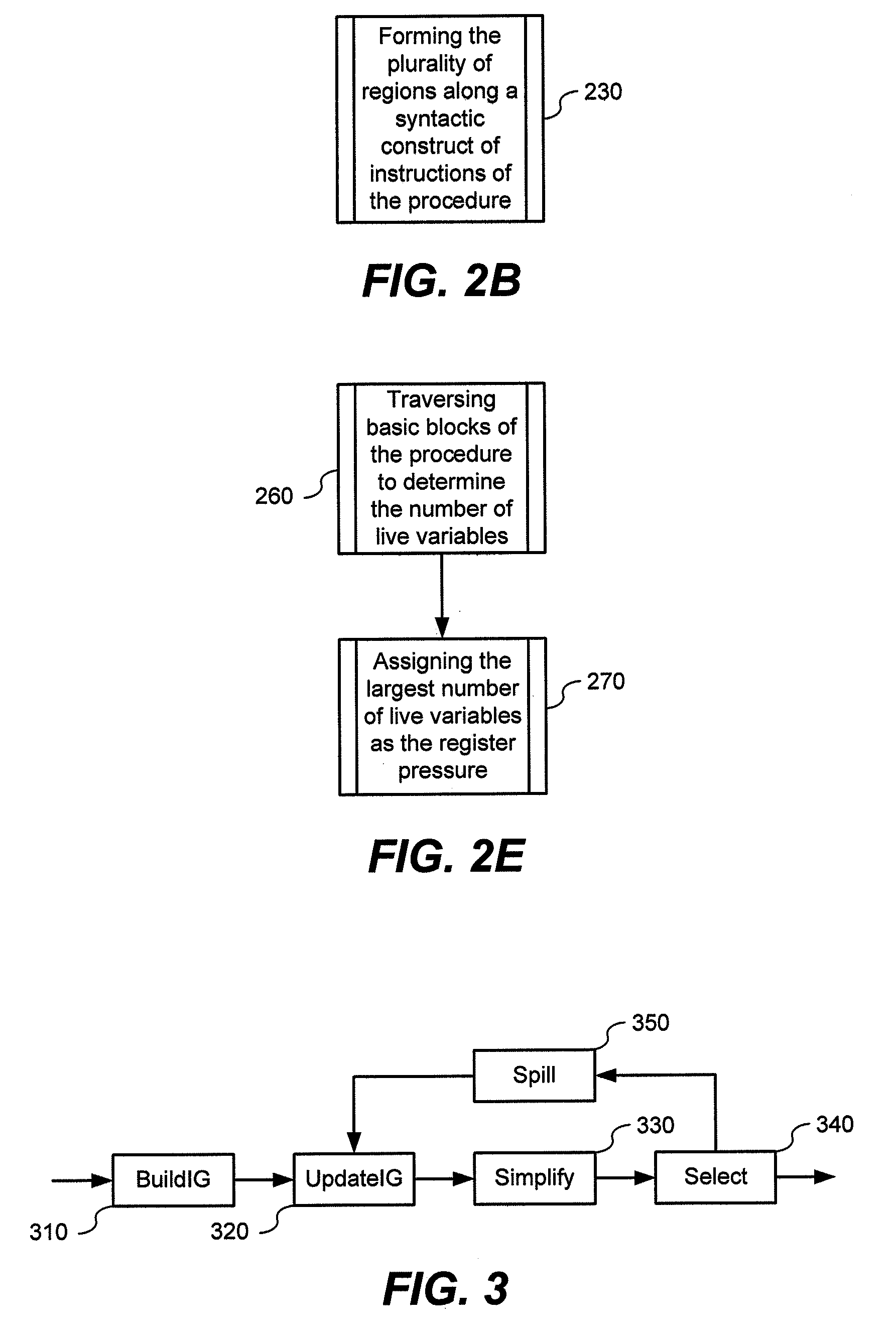

System, method, and computer-program product for scalable region-based register allocation in compilers

A region-based register allocation system, method, and computer-program product not only provides a scalable framework across multiple applications, but also improves application runtime. They include a register pressure based model, to determine when using multiple regions may be profitable, the use of different regions for each register class, and a new region formation algorithm.

Owner:HEWLETT PACKARD DEV CO LP

Conflict-free register allocation

ActiveUS8832671B1Small sizeLower latencyResource allocationRegister arrangementsRegister allocationProcessor register

One embodiment of the present invention sets forth a technique for using a multi-bank register file that reduces the size of or eliminates a switch and / or staging registers that are used to gather input operands for instructions. Each function unit input may be directly connected to one bank of the multi-bank register file with neither a switch nor a staging register. A compiler or register allocation unit ensures that the register file accesses for each instruction are conflict-free (no instruction can access the same bank more than once in the same cycle). The compiler or register allocation unit may also ensure that the register file accesses for each instruction are also aligned (each input of a function unit can only come from the bank connected to that input).

Owner:NVIDIA CORP

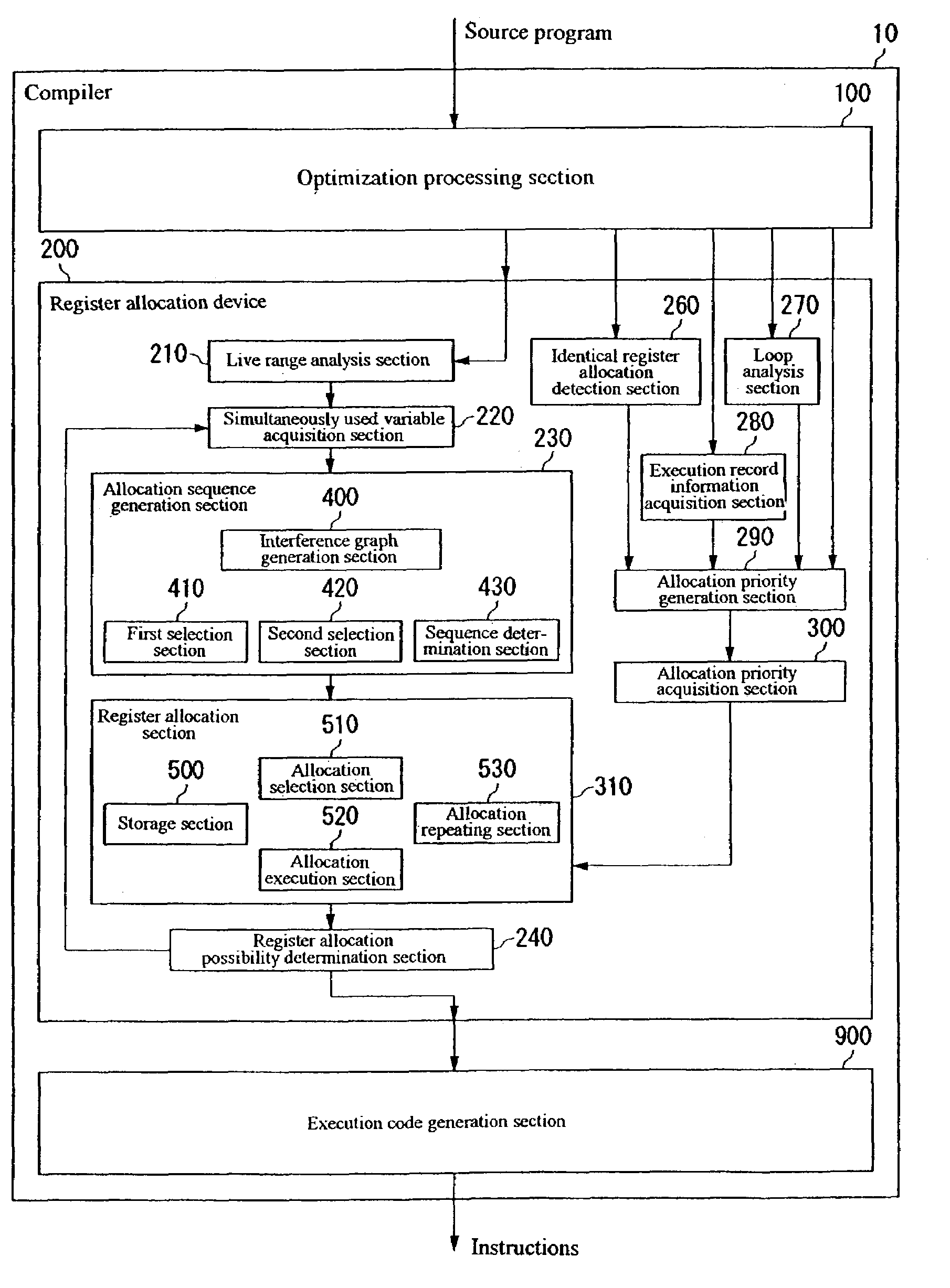

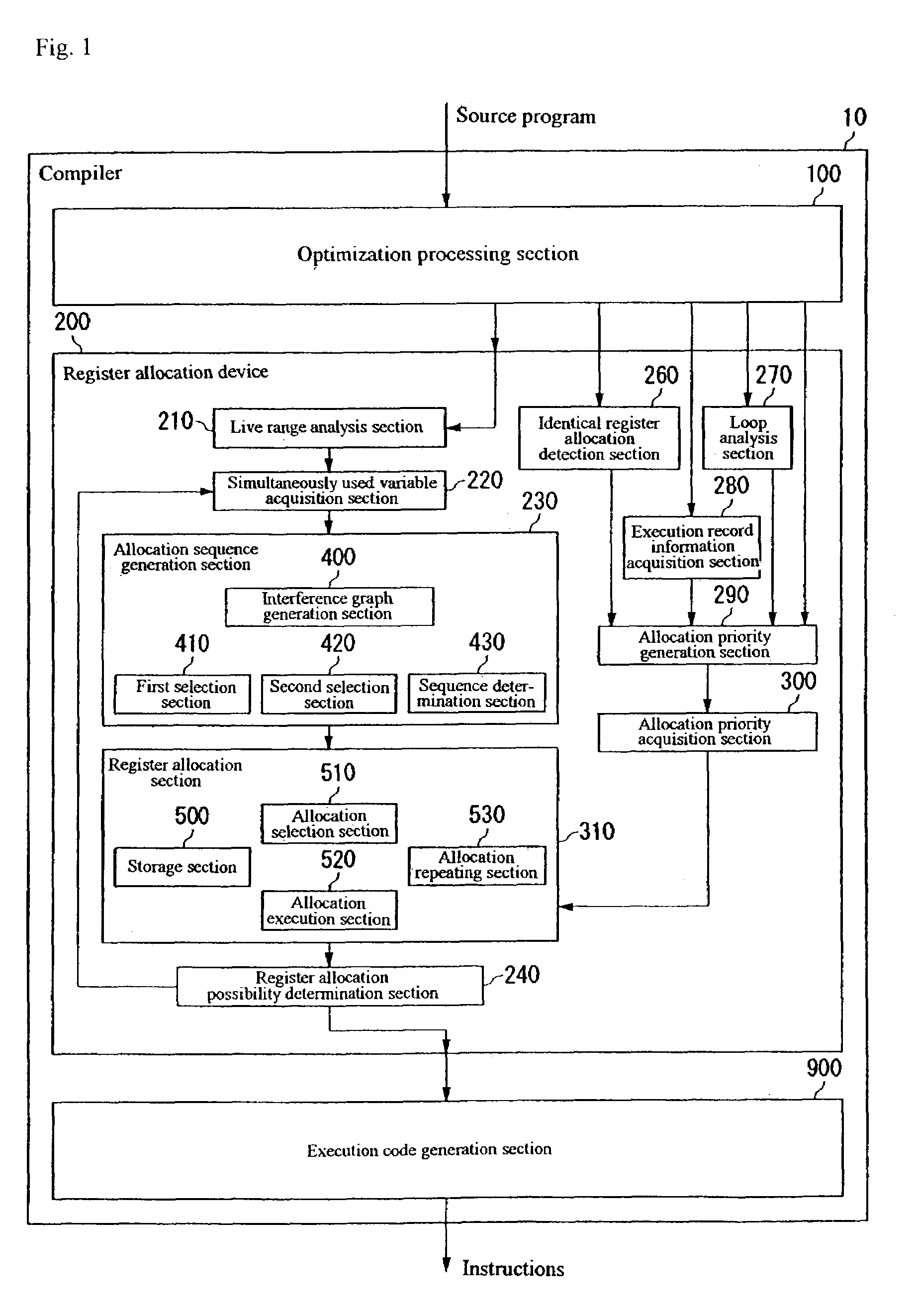

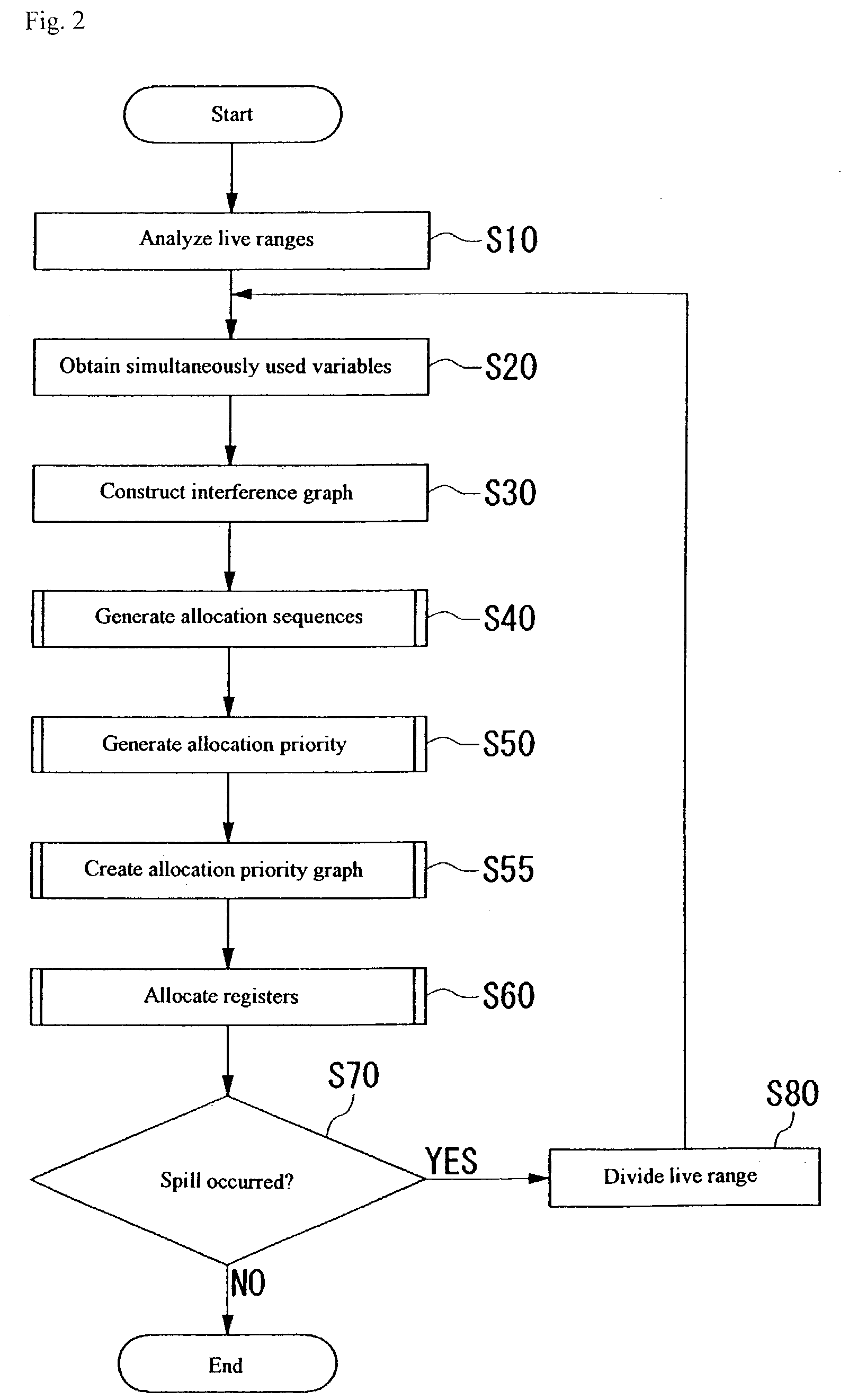

Compiler register allocation and compilation

Assigns suitable registers to a plurality of variables. A compiler converts a source program into instructions for a processor having: a simultaneously used variable acquisition section which obtains, with respect to each of a plurality of variables used in the source program, some of the other variables used simultaneously with the variable; an allocation sequence generation section which generates a plurality of allocation sequences between the plurality of variables to allocate each variable to one of the plurality of registers different from those to which some of the other variables used simultaneously with the variable are allocated; an allocation priority acquisition section which obtains allocation priorities indicating to which one of the plurality of registers each variable is allocated with priority; and a register allocation section which allocates the variables to registers in accordance with an allocation sequence selected on the basis of the allocation priorities.

Owner:IBM CORP

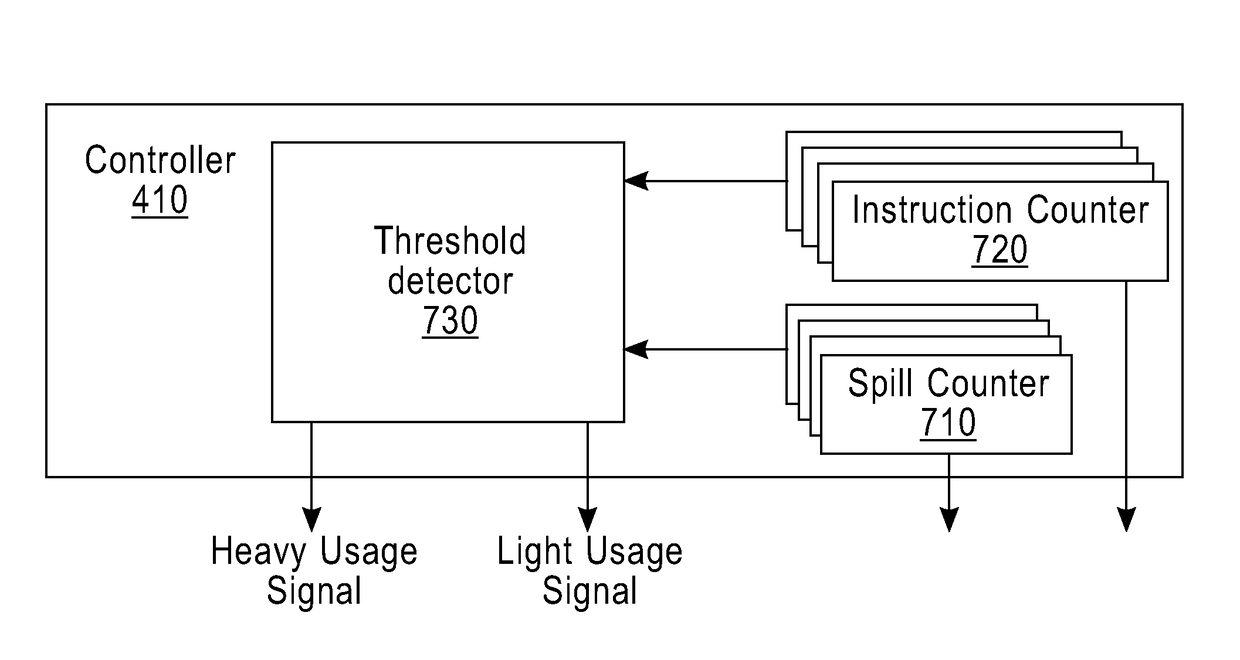

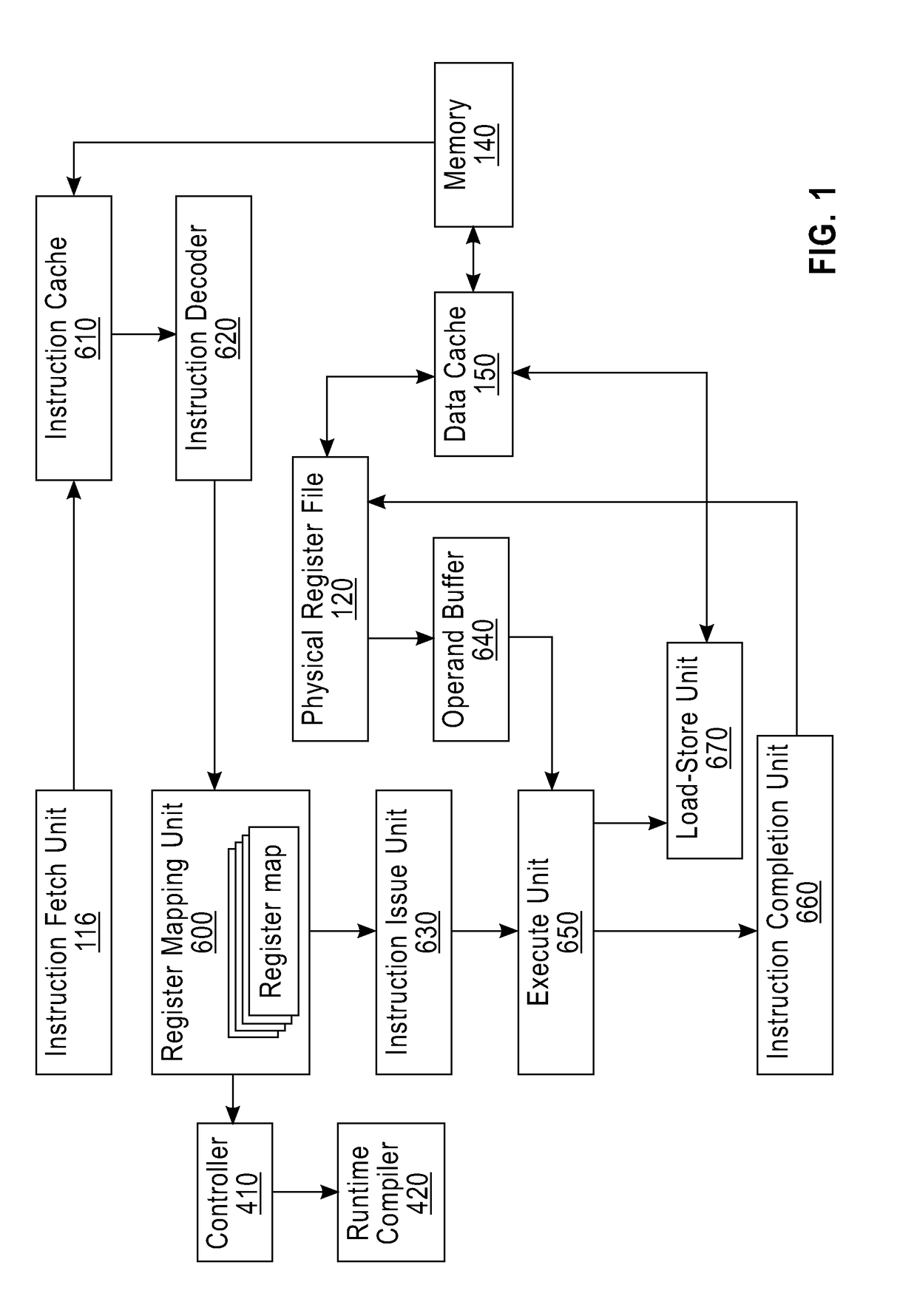

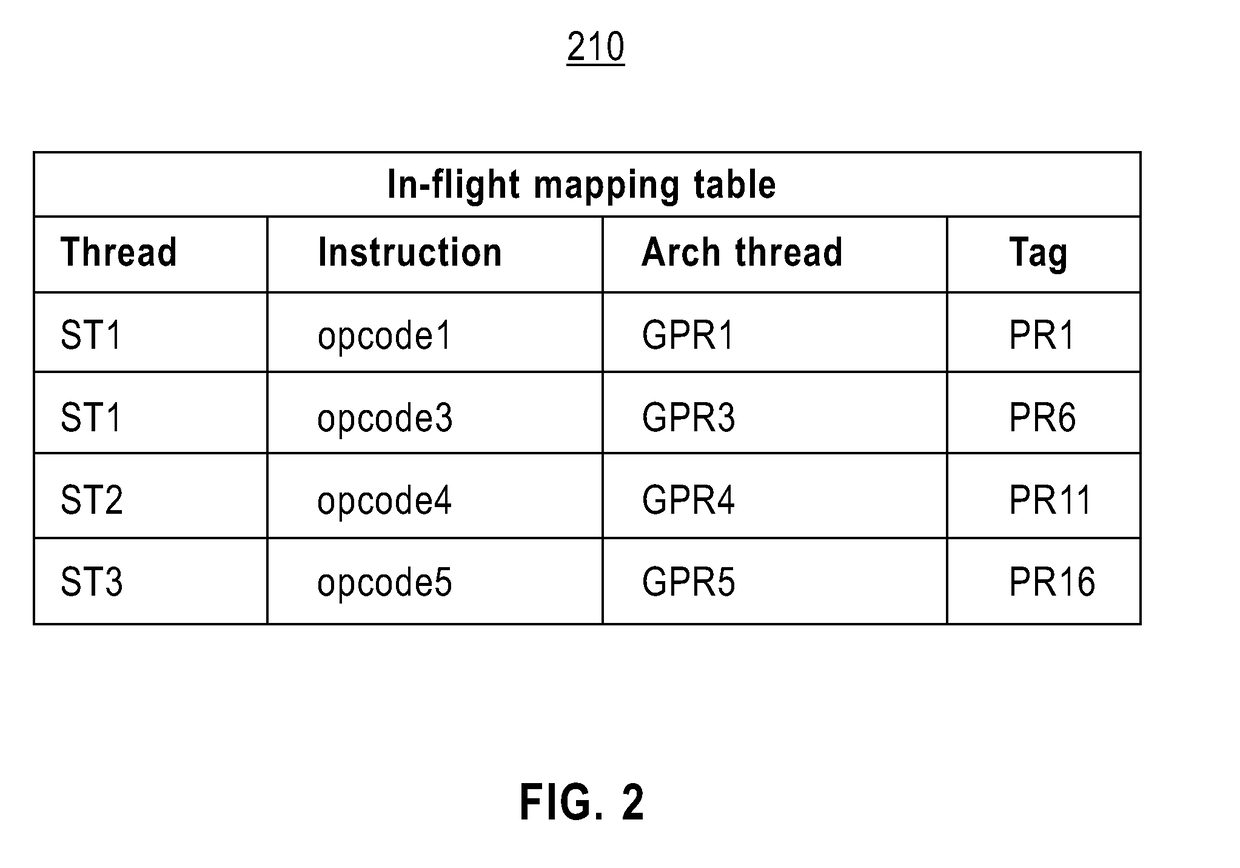

Dynamic physical register allocation across multiple threads

ActiveUS20180239604A1Improve system performanceResource allocationRegister arrangementsRegister allocationHardware thread

A computer system includes a processor, main memory, and controller. The processor includes a plurality of hardware threads configured to execute a plurality of software threads. The main memory includes a first register table configured to contain a current set of architected registers for the currently running software threads. The controller is configured to change a first number of the architected registers assigned to a given one of the software threads to a second number of architected registers when a result of monitoring current usage of the registers by the software threads indicates that the change will improve performance of the computer system. The processor includes a second register table configured to contain a subset of the architected registers and a mapping table for each software thread indicating whether the architected registers referenced by the corresponding software thread are located in the first register table or the second register table.

Owner:IBM CORP