Dynamic physical register allocation across multiple threads

a register allocation and physical register technology, applied in the field of processor threads, can solve the problems of declining efficiency of processing cores, and achieve the effect of improving the overall system performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016]The inventive concept will be described in more detail with reference to the accompanying drawings, where exemplary embodiments of the present disclosure have been illustrated. Throughout the drawings, same or like reference numerals are used to represent the same or like components. However, the present inventive concept can be implemented in various manners, and thus should not be construed to be limited to the embodiments disclosed herein. On the contrary, those embodiments are provided for the thorough and complete understanding of the present disclosure to convey the scope of the present disclosure to those skilled in the art.

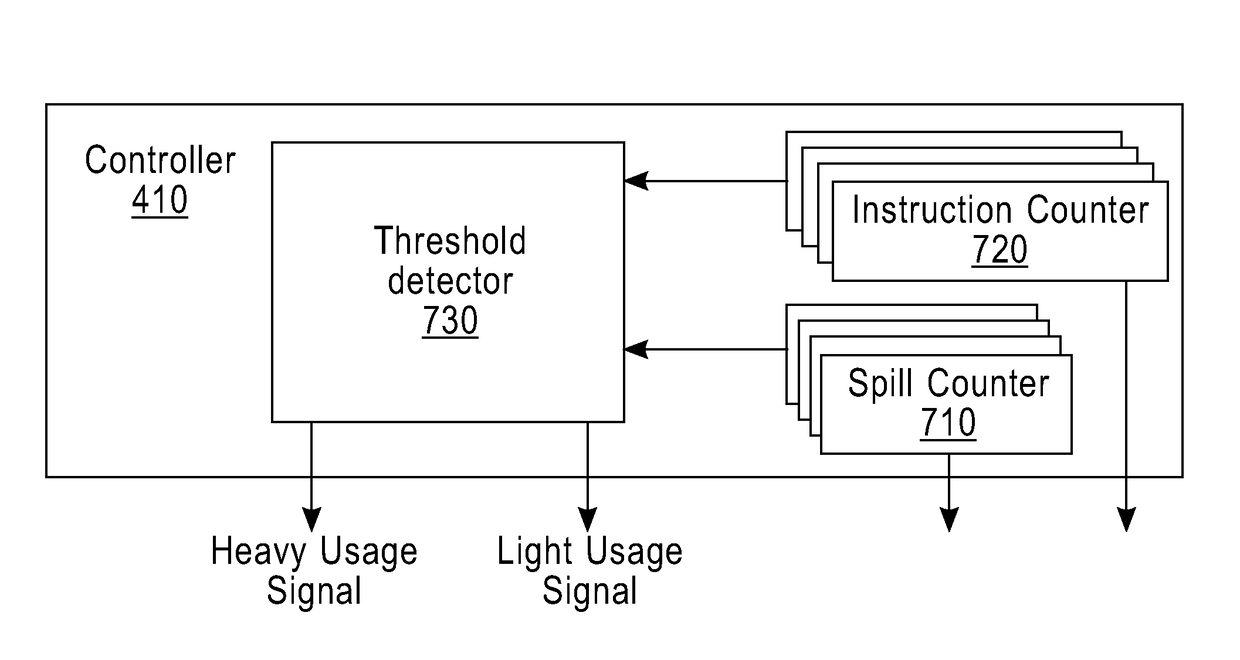

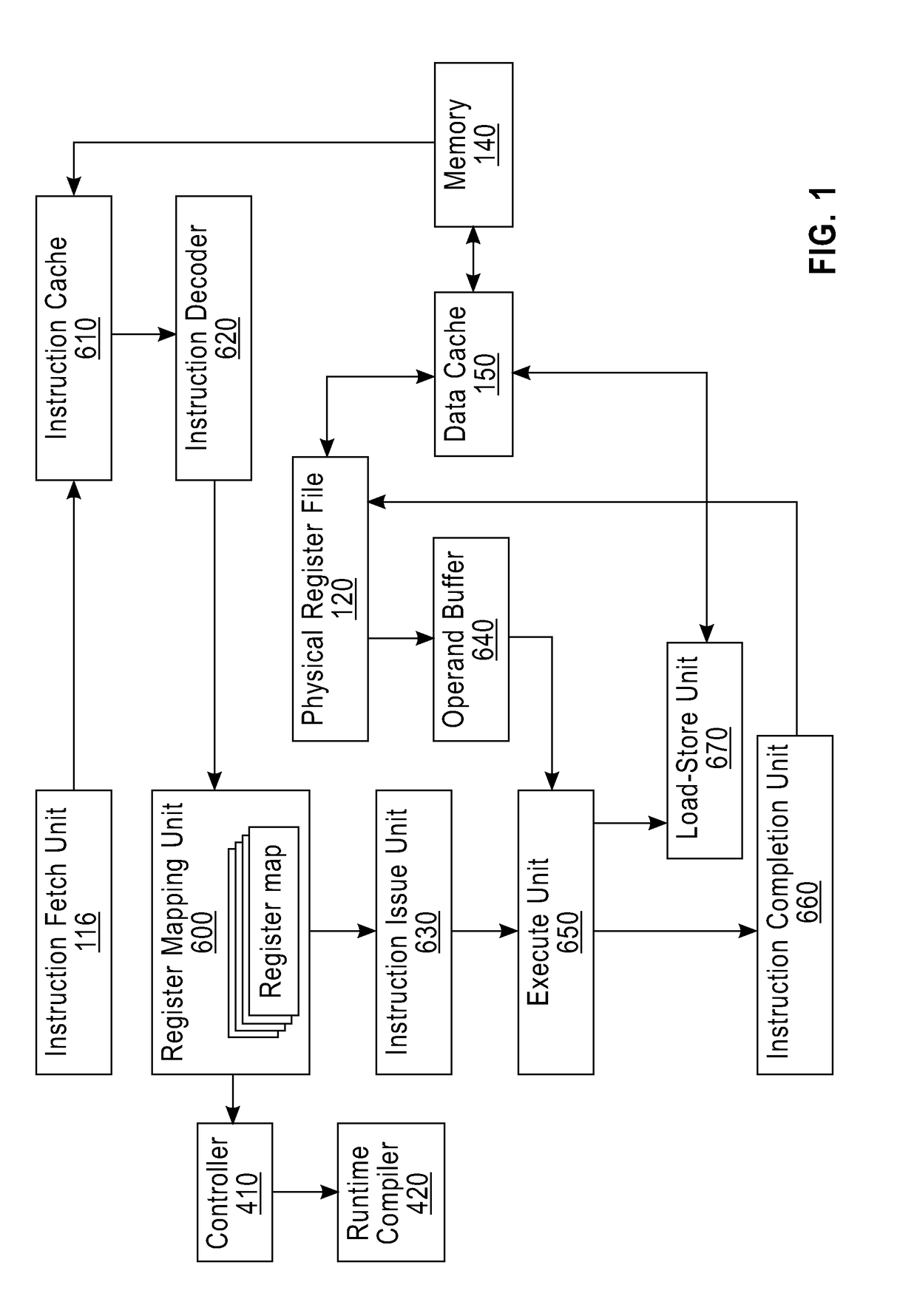

[0017]FIG. 1 illustrates an example system for managing threads. The instruction fetch unit 116 fetches instructions from memory 140 through the instruction cache 610. Fetched instructions are decoded using the instruction decoder 620. In the process of decoding, the architected registers needed by the instruction either as source operands or as dest...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More