Patents

Literature

57 results about "Test register" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A test register, in the Intel 80386 and Intel 80486 processor, was a register used by the processor, usually to do a self-test. Most of these registers were undocumented, and used by specialized software. The test registers were named TR3 to TR7. Regular programs don't usually require these registers to work. With the Pentium, the test registers were replaced by a variety of model-specific registers (MSRs).

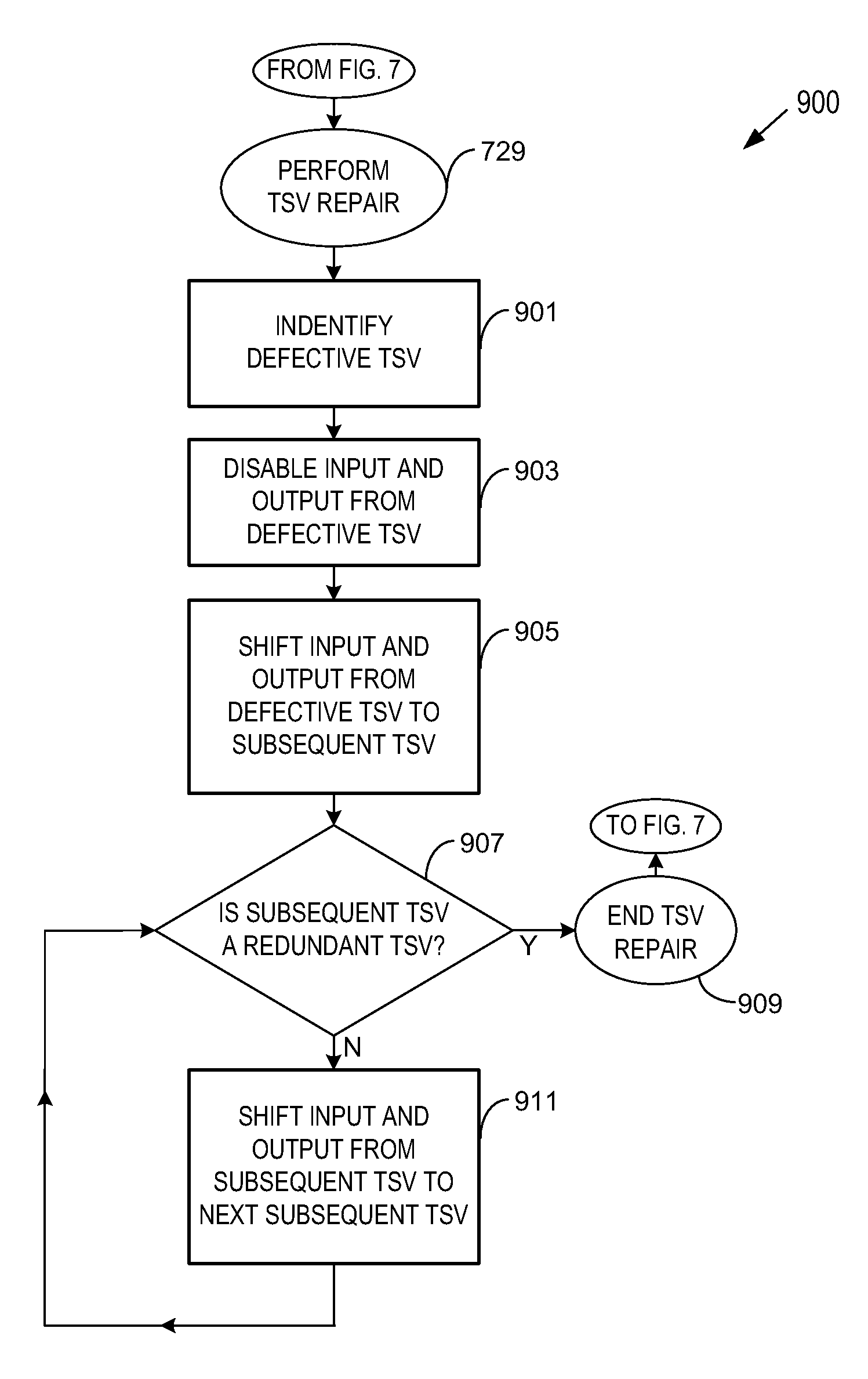

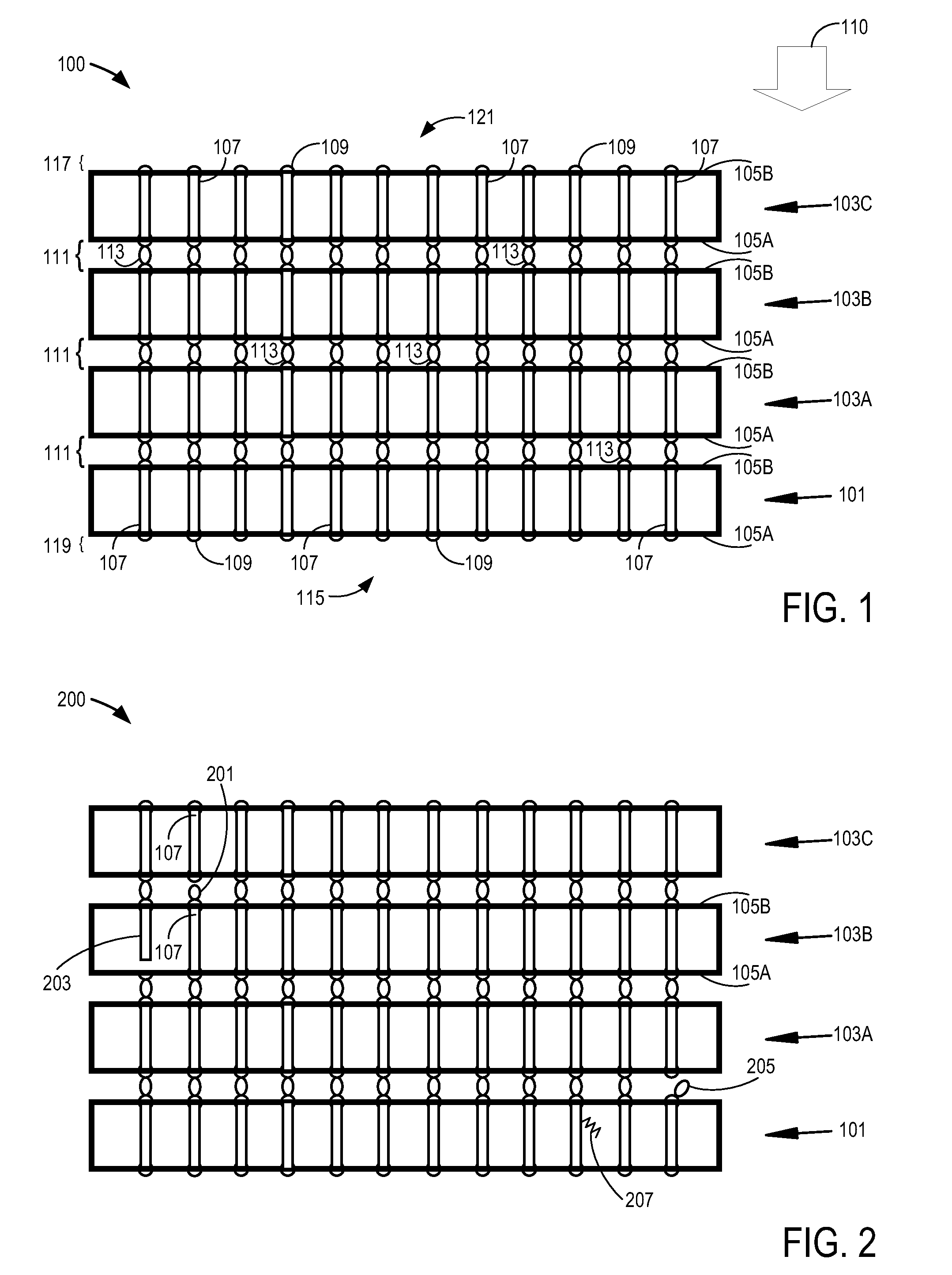

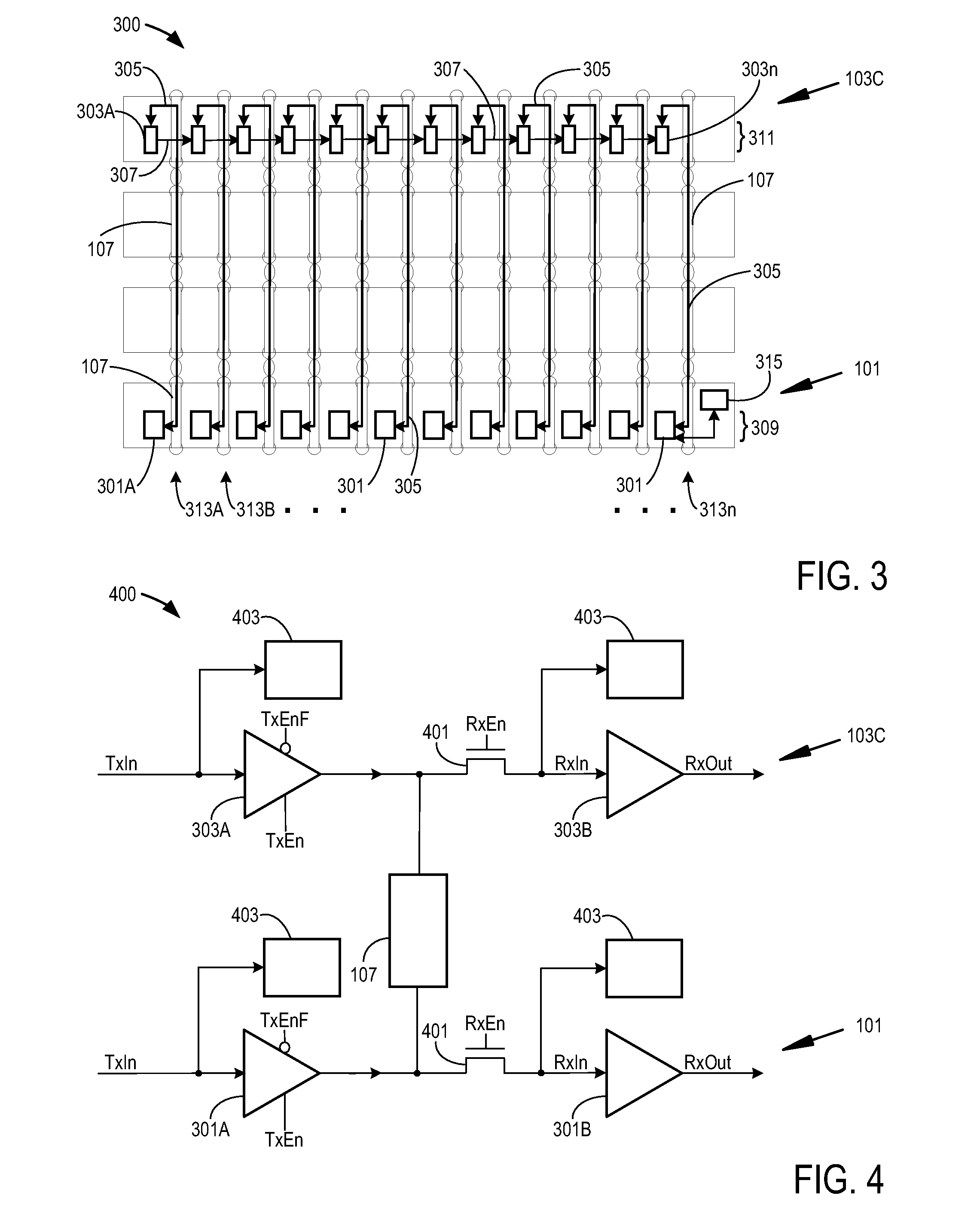

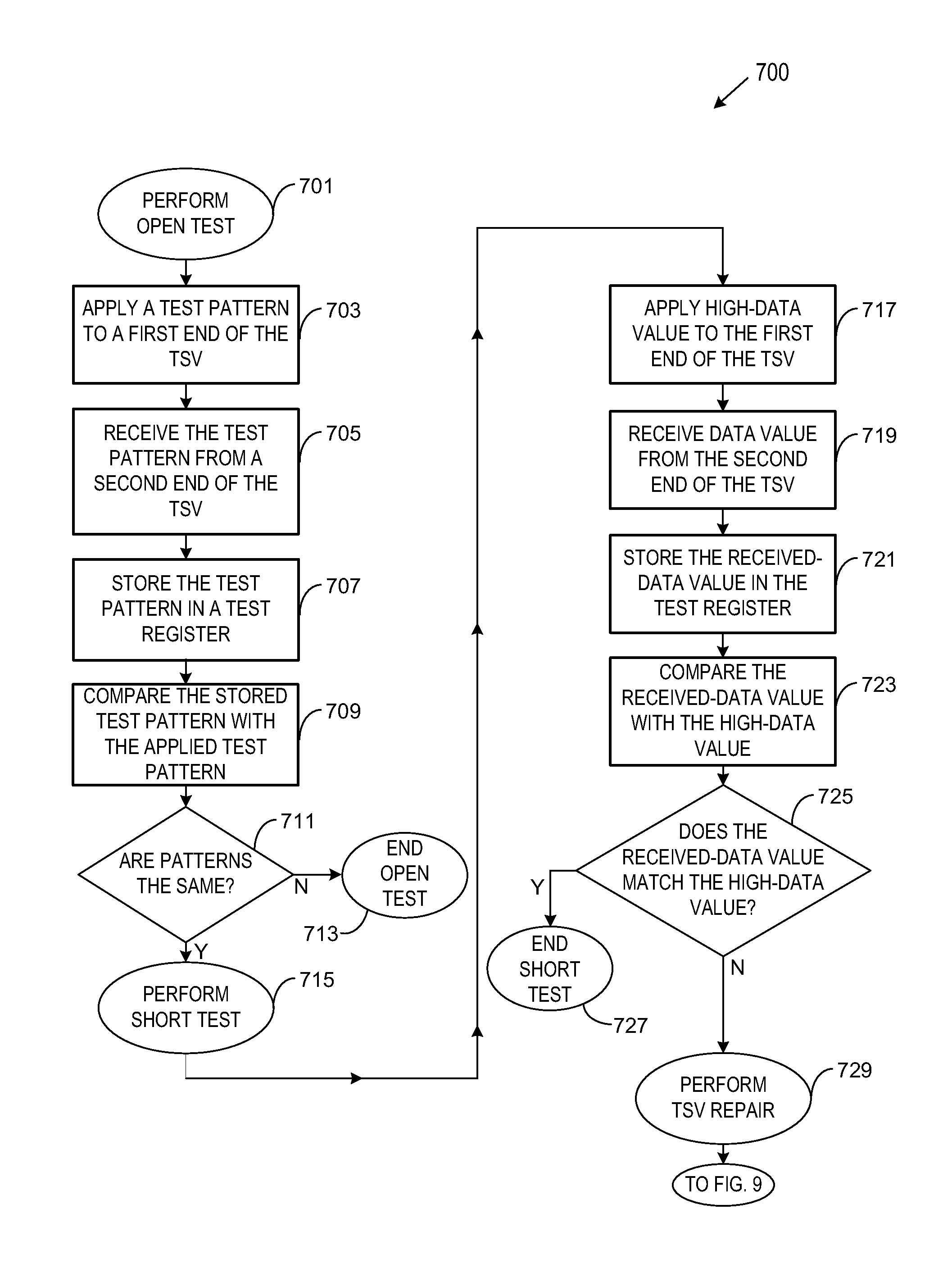

Through-substrate via (TSV) testing

ActiveUS20130230932A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsData valueComparator

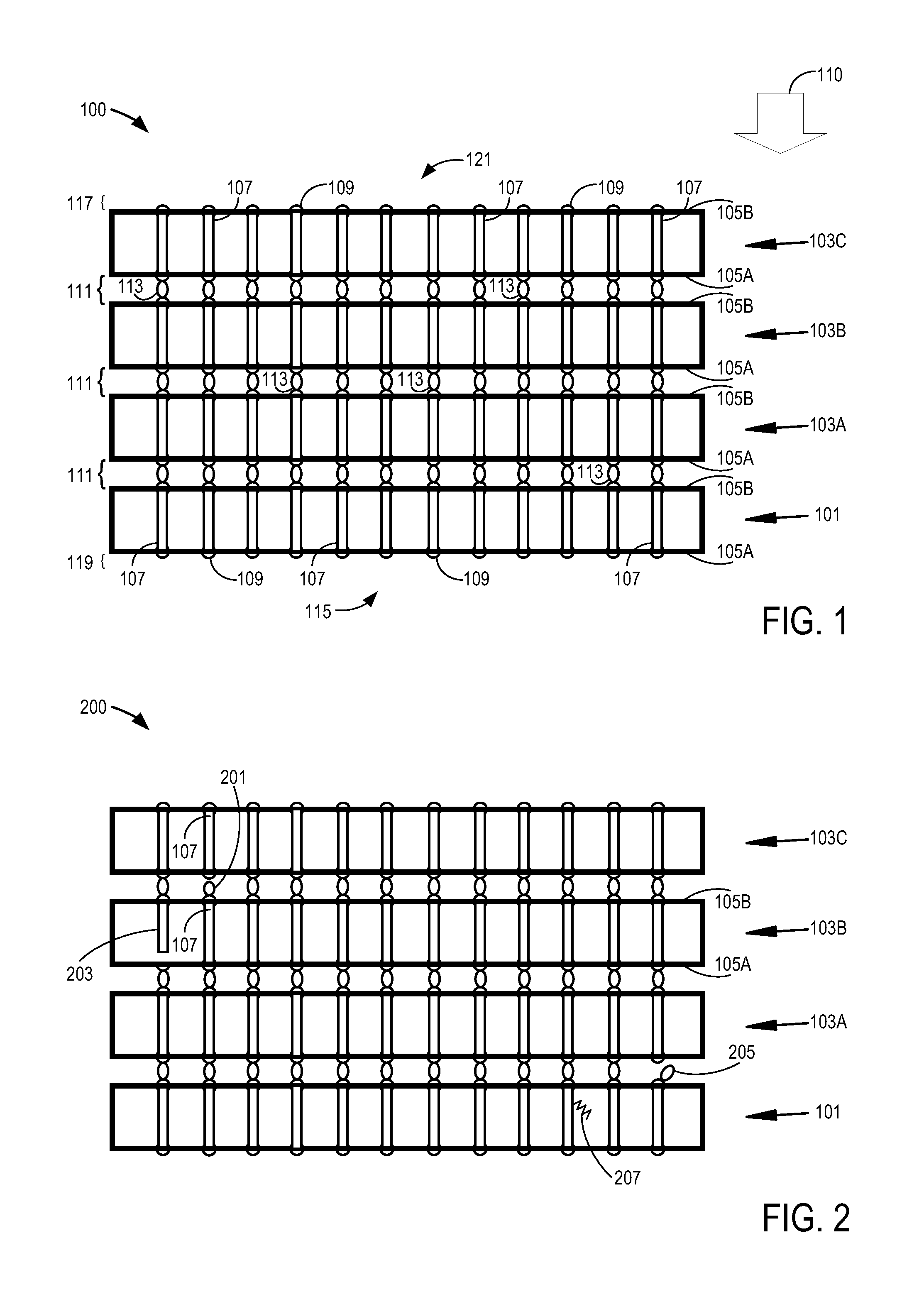

Various embodiments comprise apparatuses and methods for testing and repairing through-substrate vias in a stack of interconnected dice. In various embodiments, an apparatus is provided that includes a number of through-substrate vias to couple to one or more devices, at least one redundant through-substrate via to allow a repair of the apparatus, and a pair of pull-up devices coupled to the through-substrate vias and the redundant through-substrate via to provide a high-data value to the first end of the respective through-substrate vias. A test register is coupled the second end of each of the through-substrate vias and the redundant through-substrate via to store a received version of the high-data value. A comparator compares the high-data value with the received version of the high-data value to test the through-substrate vias for short-circuit connections.

Owner:MICRON TECH INC

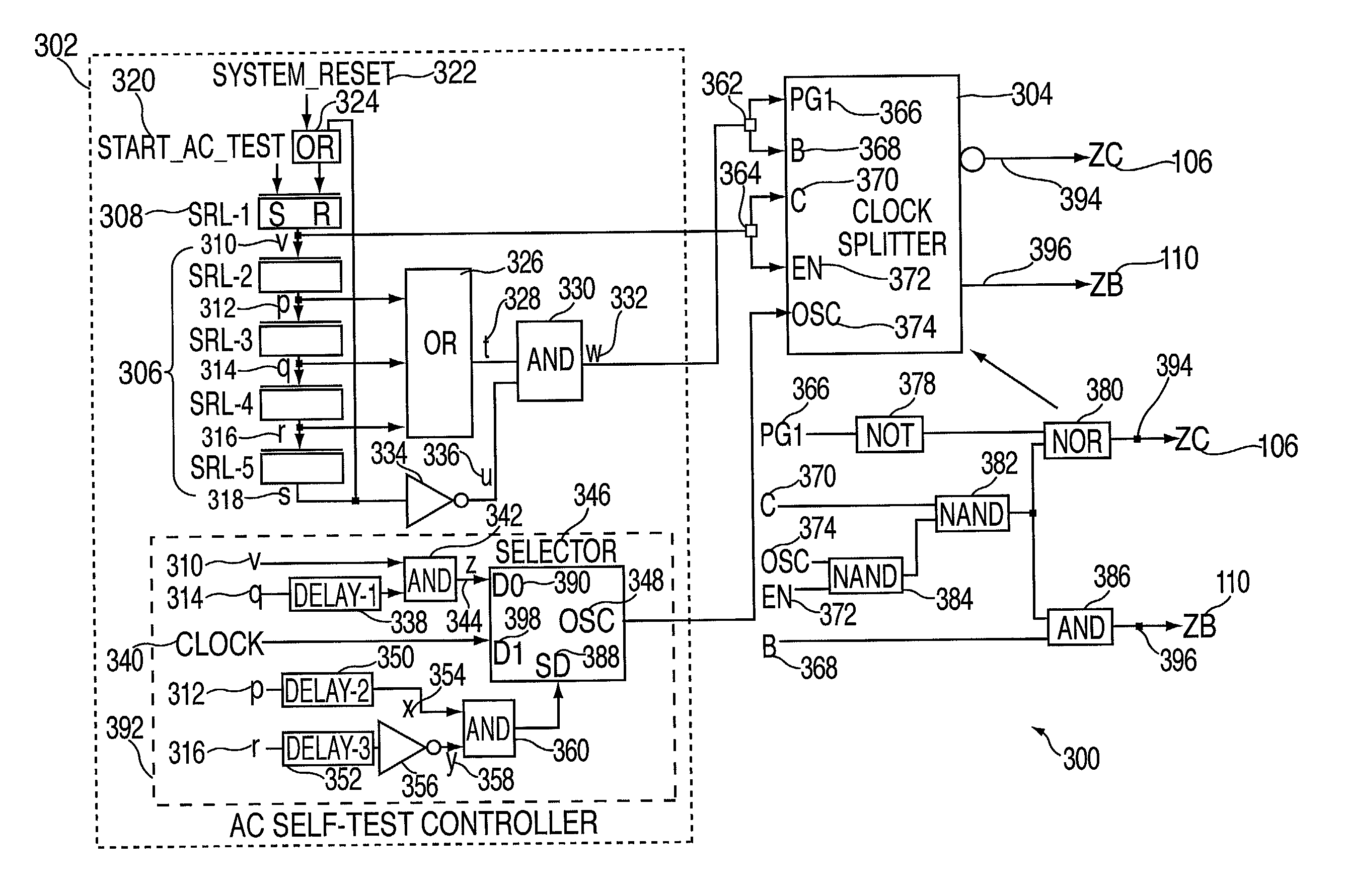

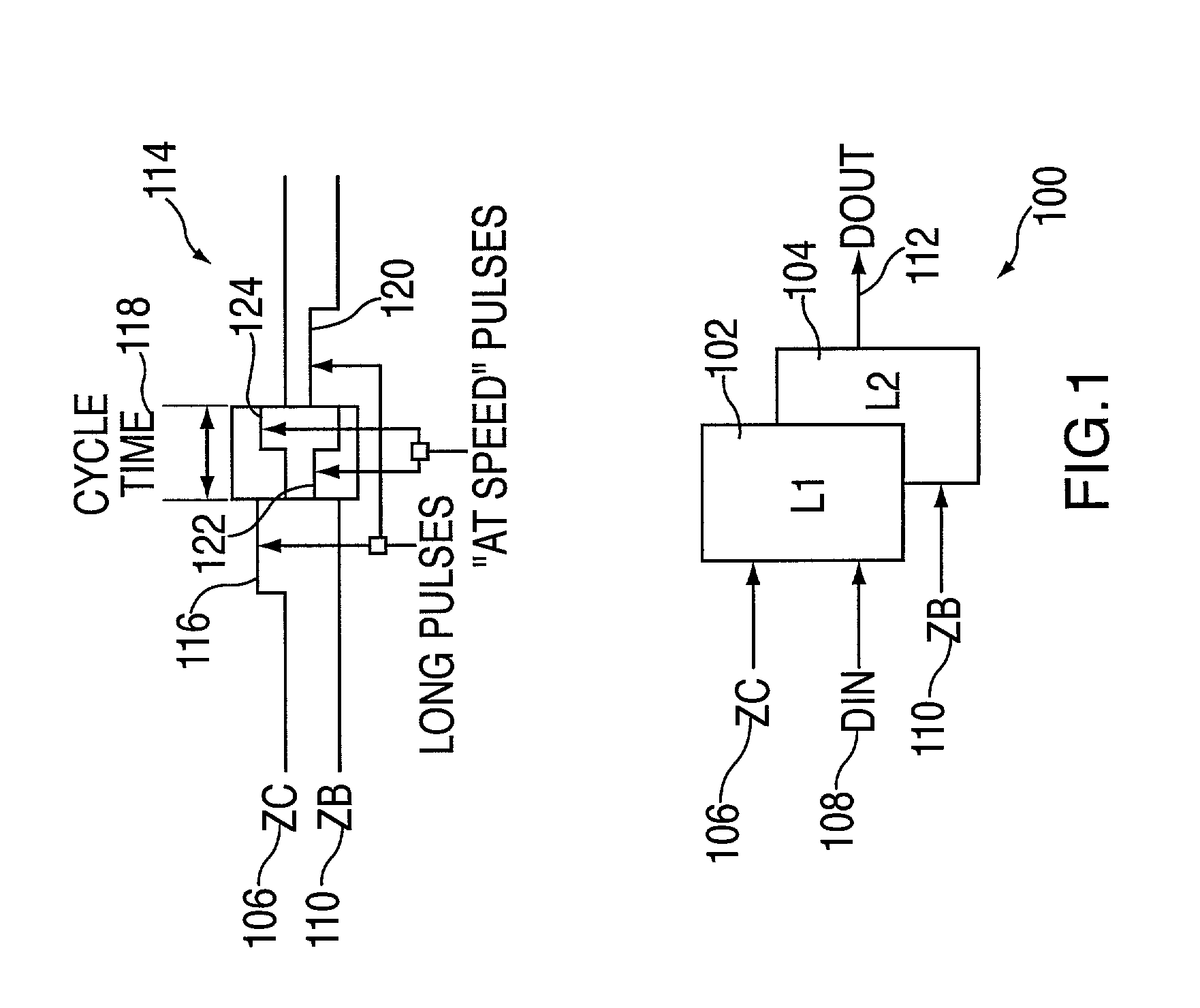

Method and system for an on-chip AC self-test controller

A method for performing AC self-test on an integrated circuit, including a system clock for use during normal operation. The method includes applying a long data capture pulse to a first test register in response to the system clock, and further applying at an speed data launch pulse to the first test register in response to the system clock. Inputting the data from the first register to a logic path in response to applying the at speed data launch pulse to the first test register. Applying at speed data capture pulse to a second test register in response to the system clock. Inputting the output from the logic path to the second test register in response to applying the at speed data capture pulse to the second register. Applying a long data launch pulse to the second test register in response to the system clock.

Owner:GLOBALFOUNDRIES INC

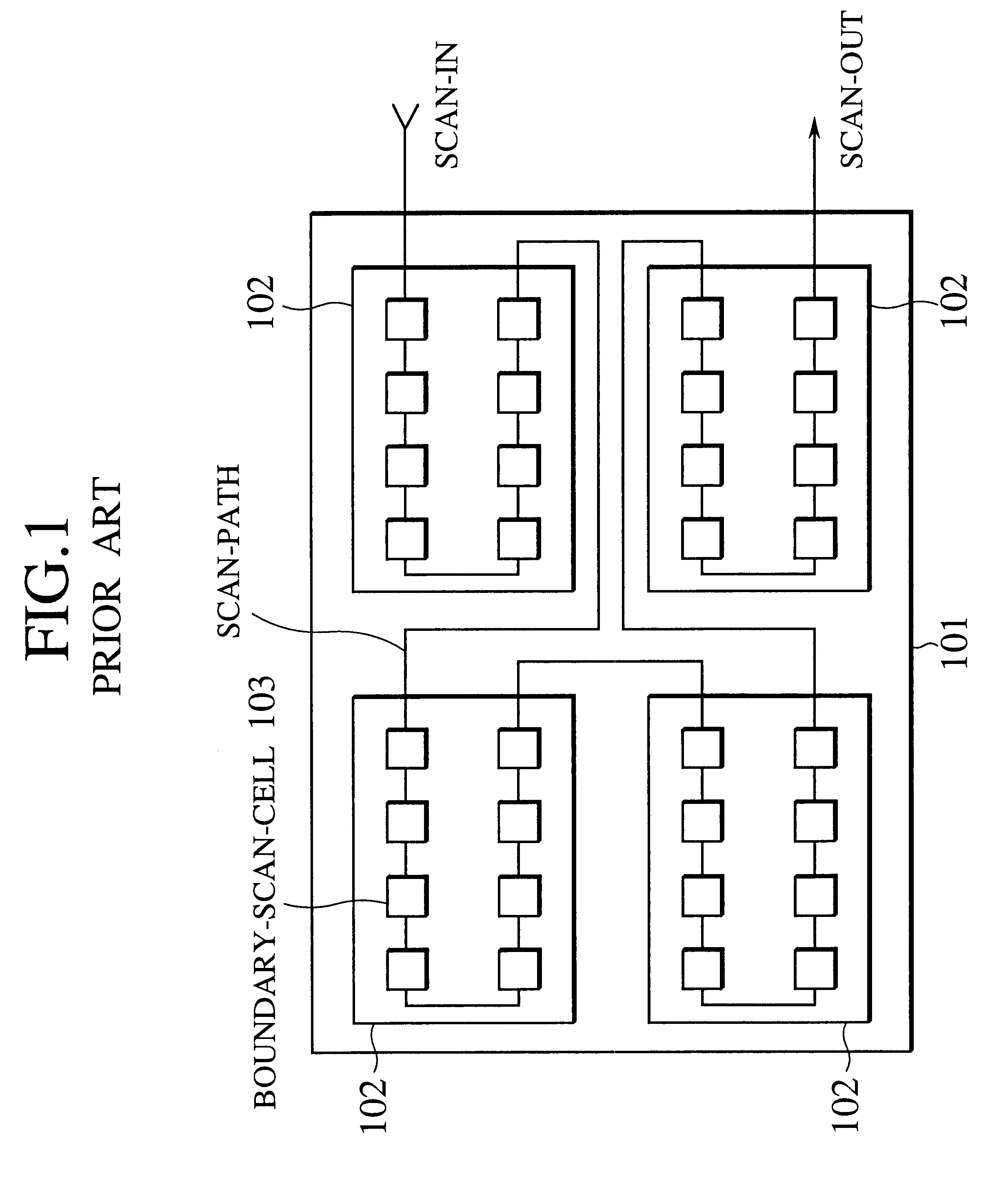

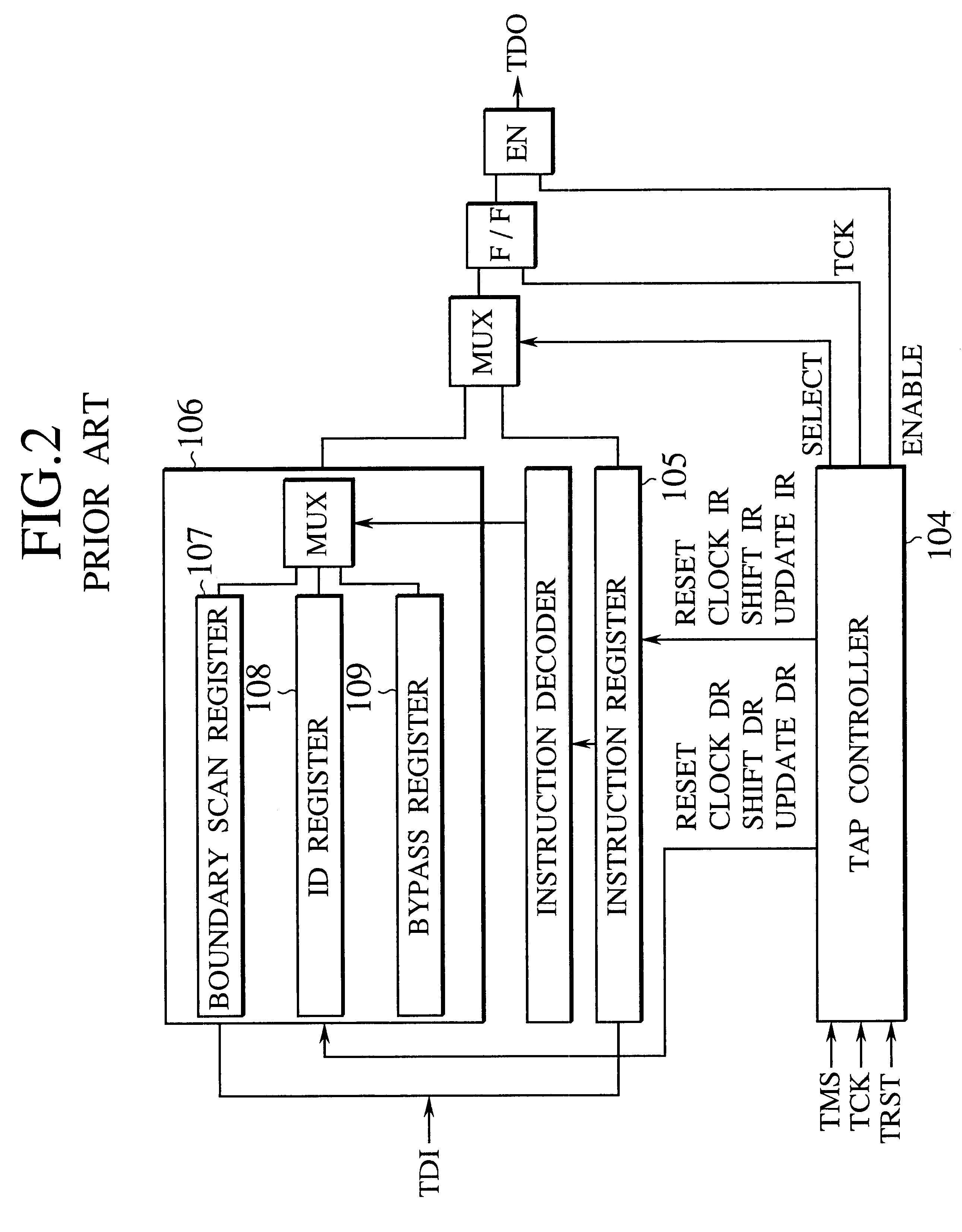

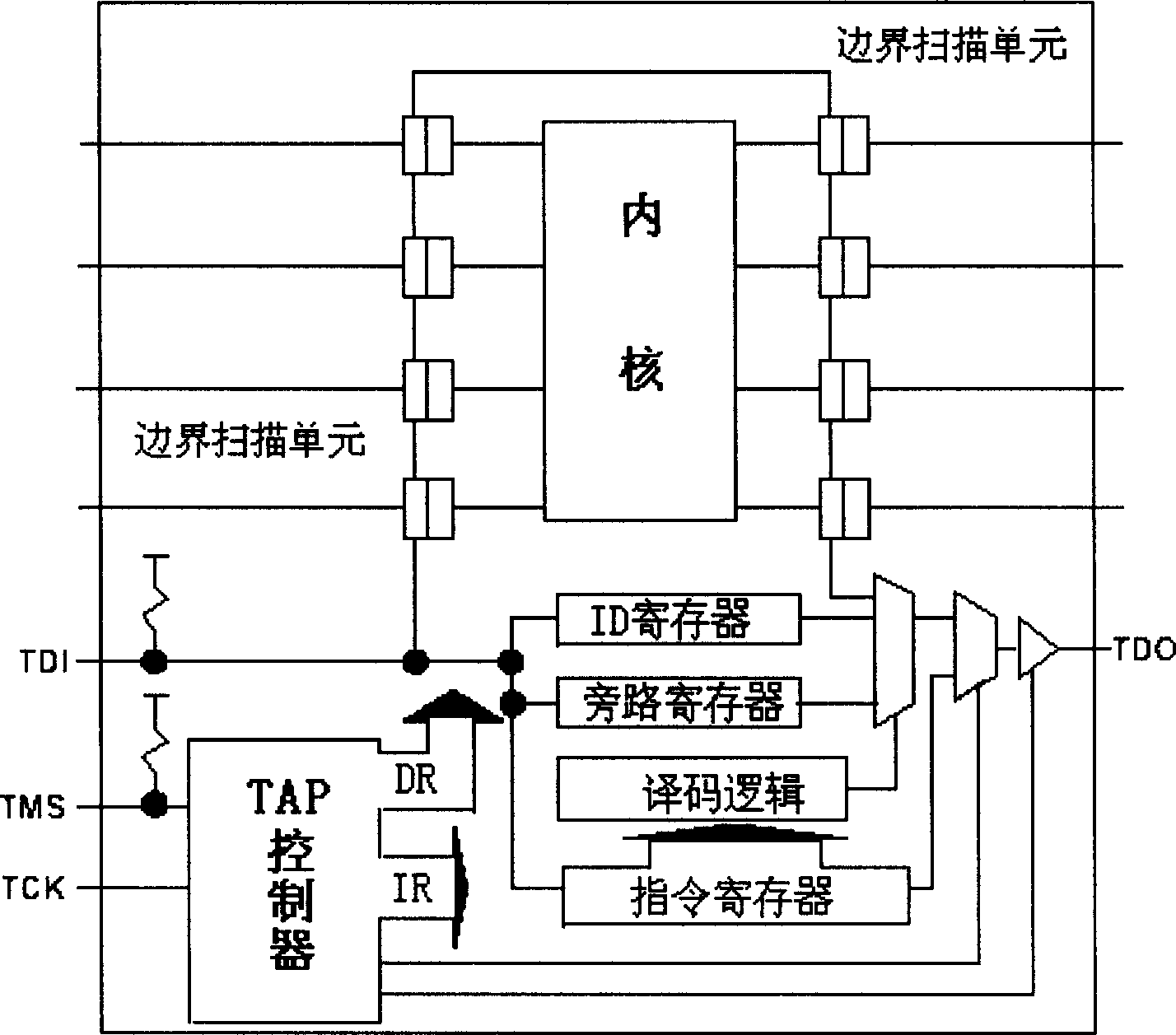

Semiconductor device provided with a boundary-scan test circuit

A semiconductor device provided with a compact Boundary-Scan test circuit is shown. The Boundary-Scan test circuit comprises a Boundary-Scan test register which is composed of bit elements serially connected to each other in the form of a scan path and each of which is connected respectively to one of pads of the semiconductor device, wherein part of the bit elements of said Boundary-Scan test register functions also as an ID-Code register while an initial bit element of said Boundary-Scan test register functions also as a bypass register for bypassing the subsequent bit elements of said Boundary-Scan test register.

Owner:KK TOSHIBA

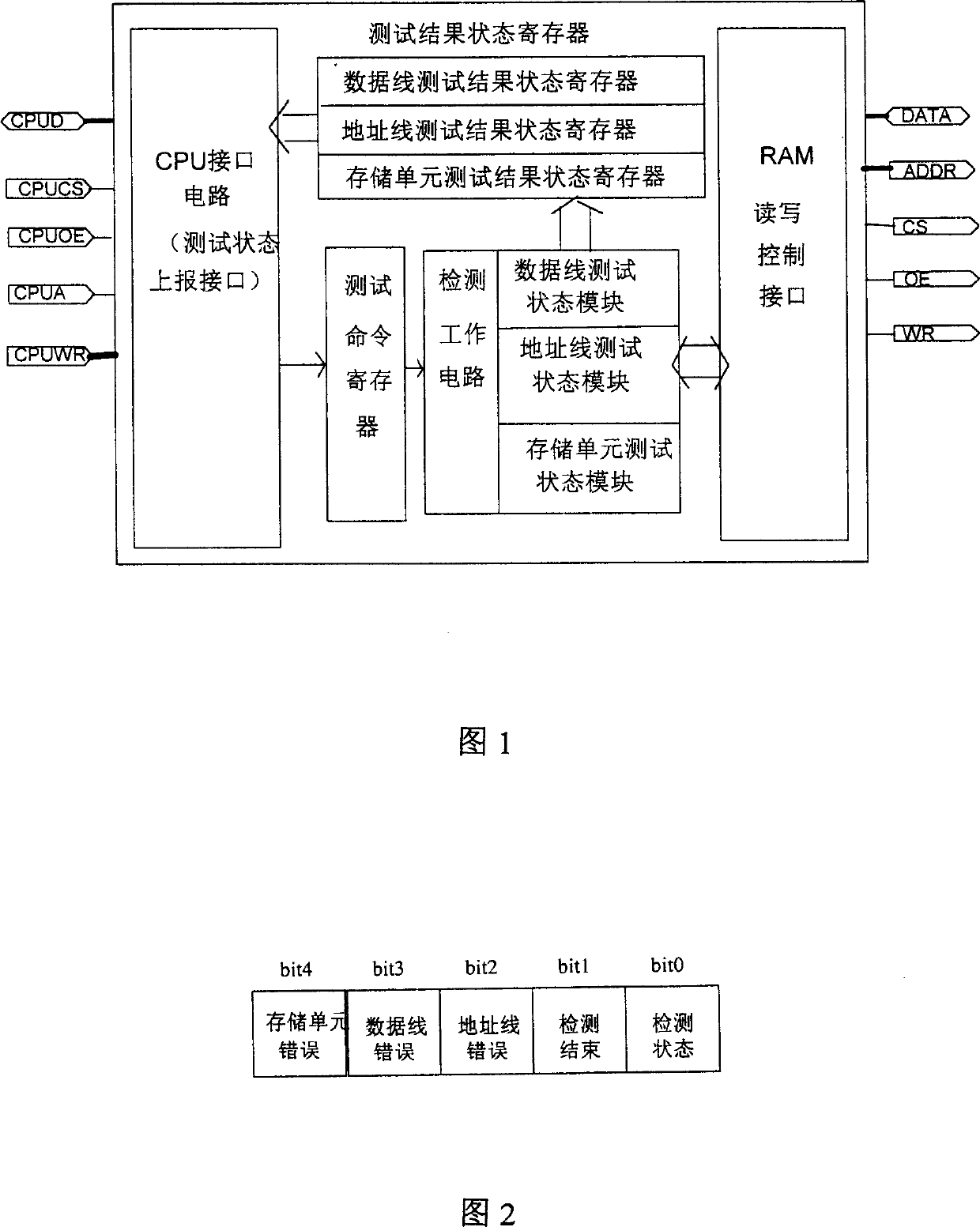

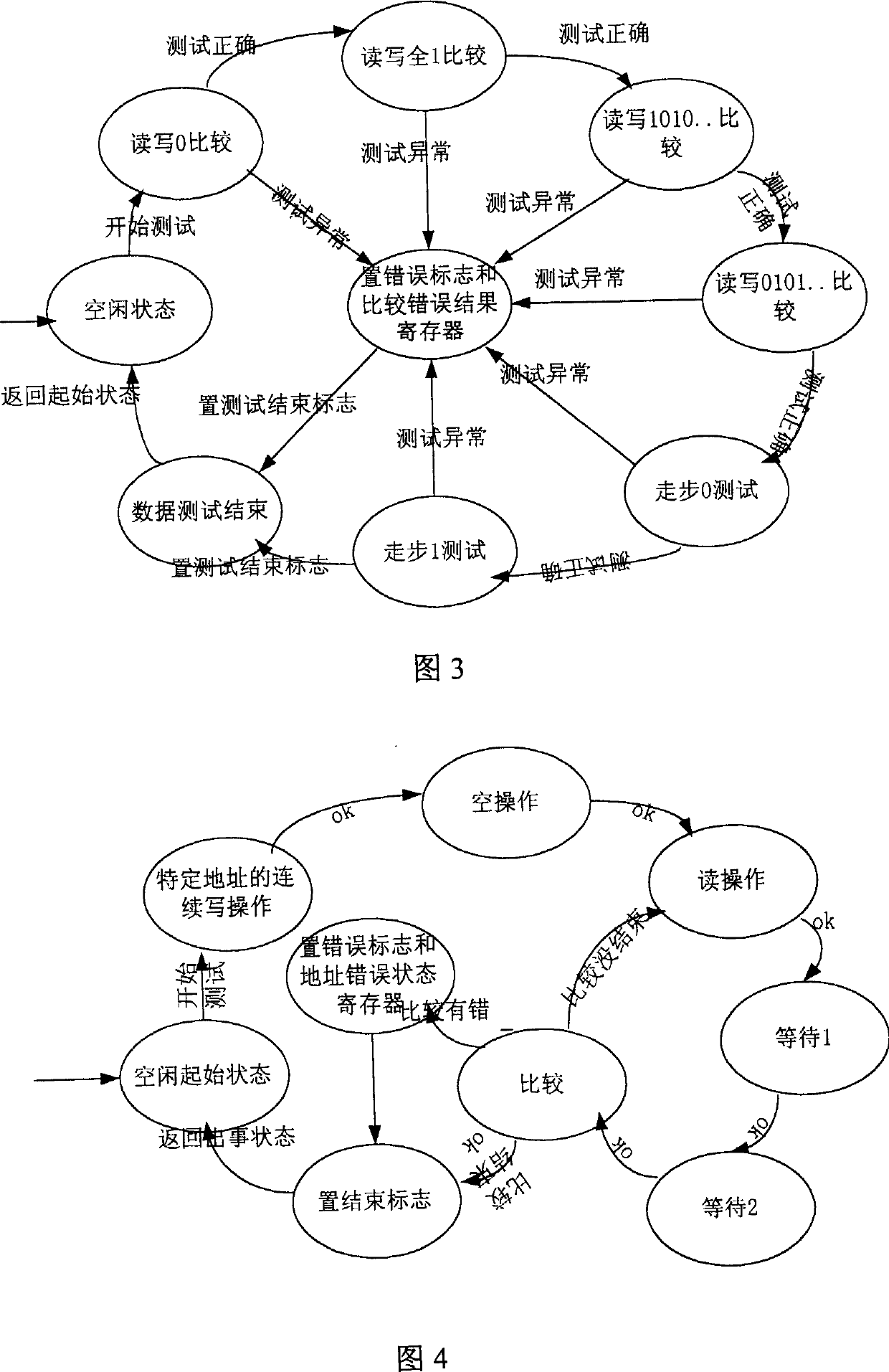

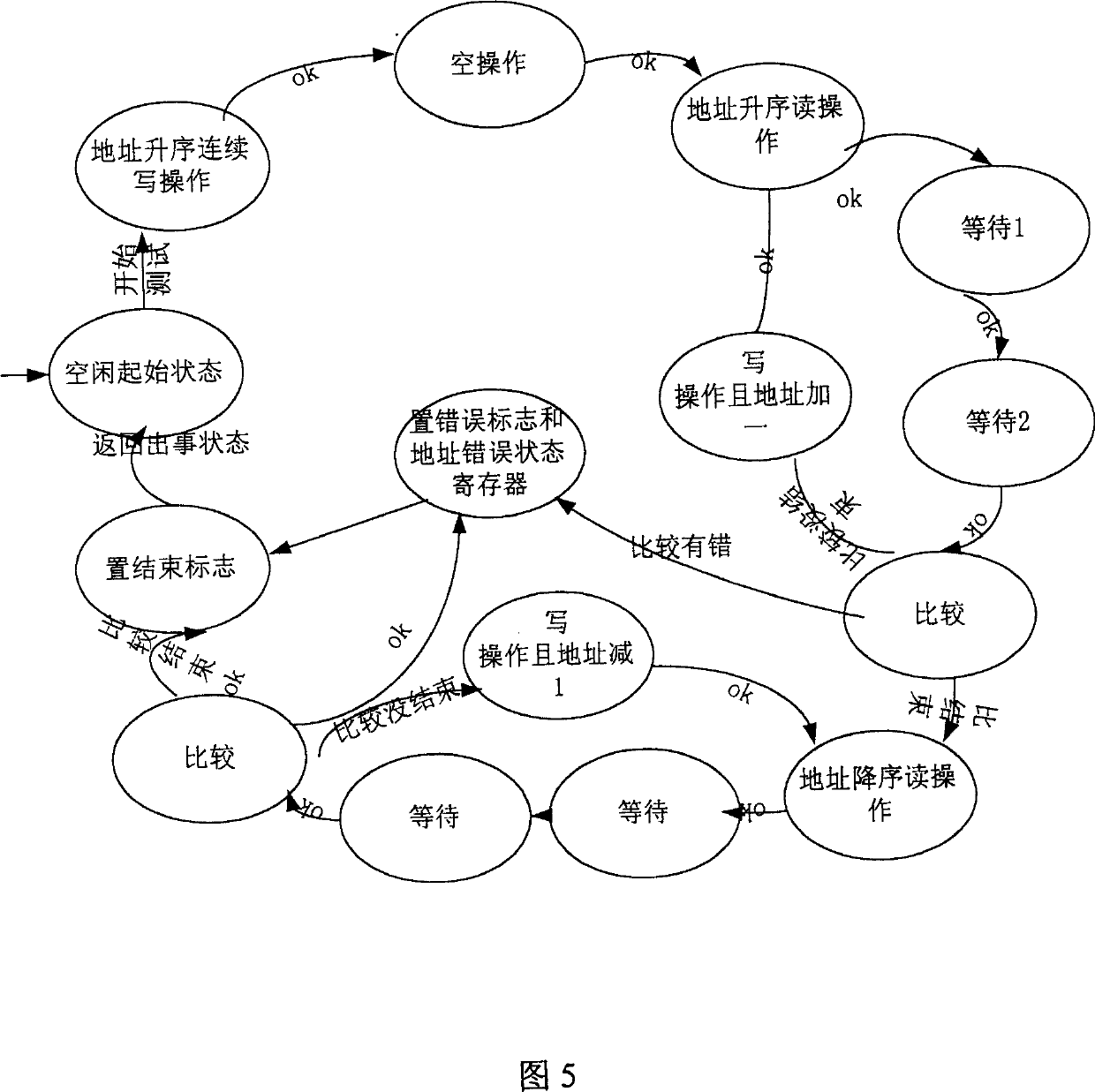

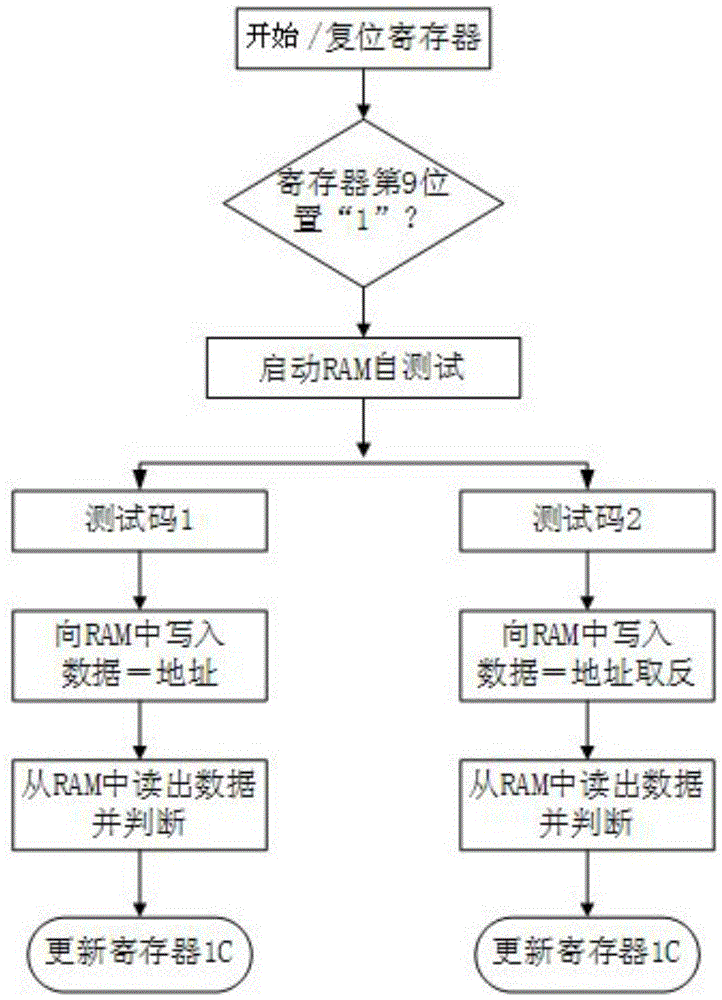

RAM high speed test control circuit and its testing method

InactiveCN1427420AEfficient detectionComprehensive testSemiconductor/solid-state device testing/measurementElectronic circuit testingTest typesStep test

A control circuit for high-speed test of RAM is disclosed, which is based on hardware logic for correct location of failure and high test efficiency. Its test method includes such steps as setting up the state of test command register, choosing test type, strobing test register, testing data lines by comparison, testing address lines by comparison, step test of memory units, and analyzing error type by reading state registers.

Owner:HUAWEI TECH CO LTD

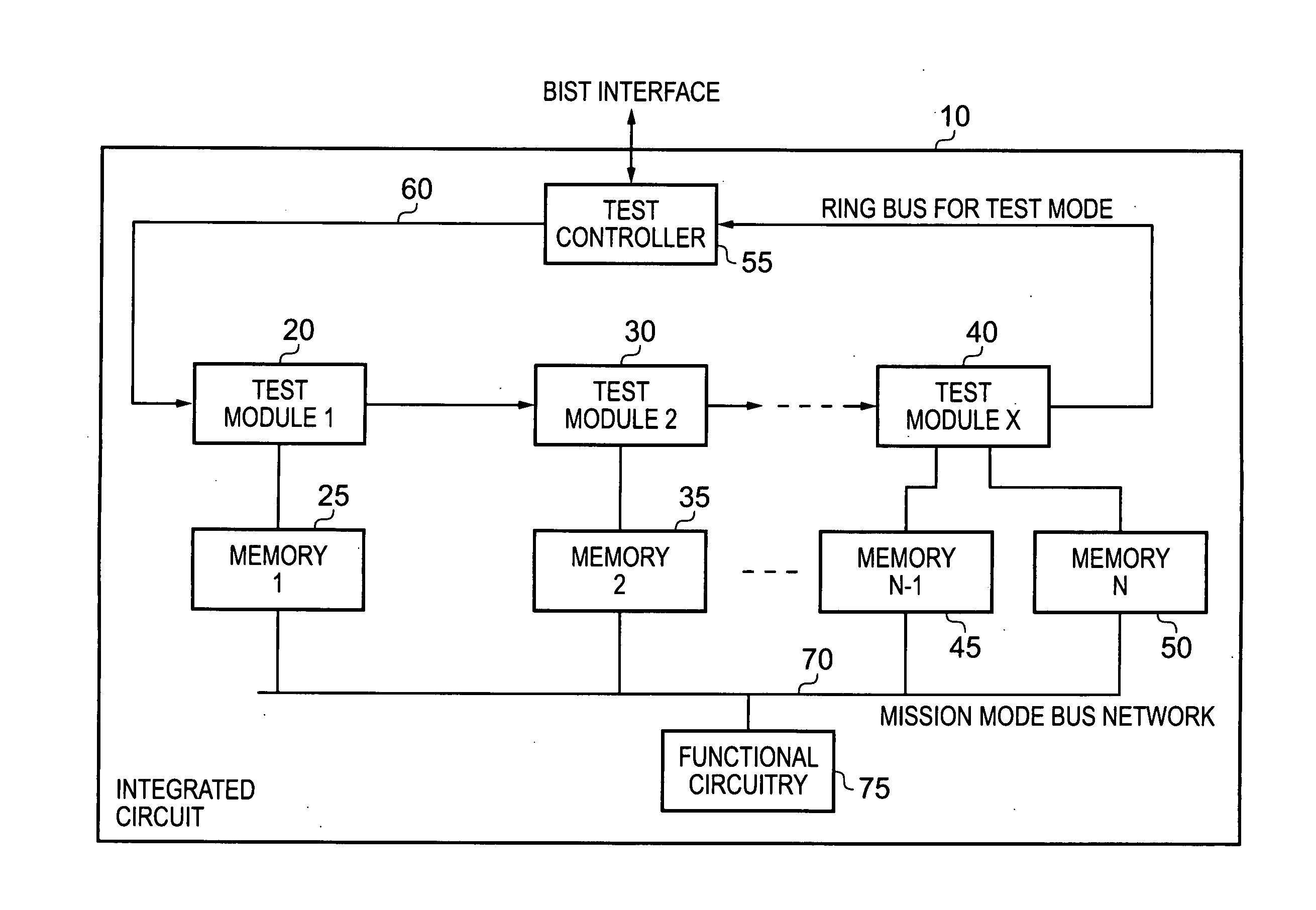

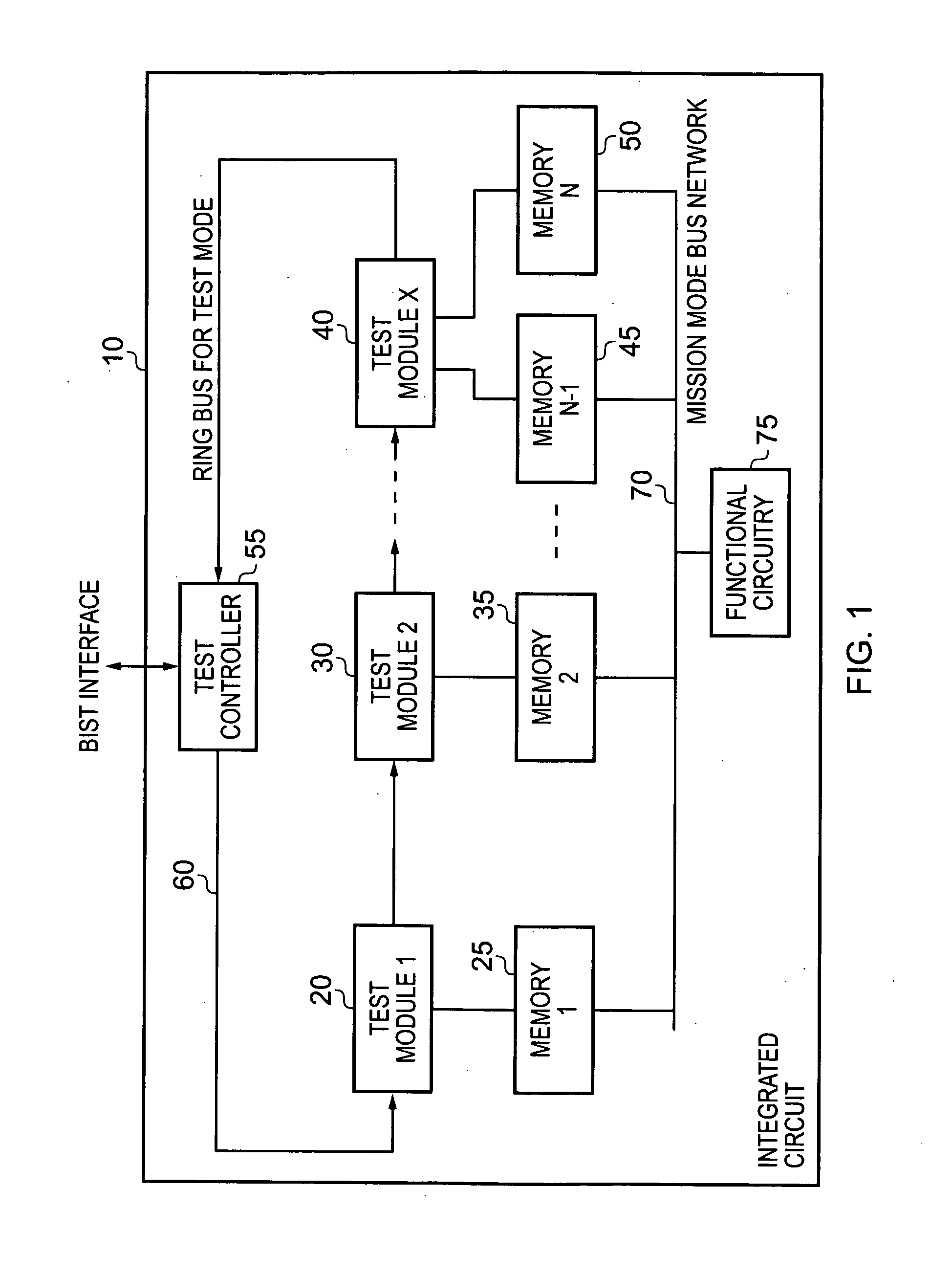

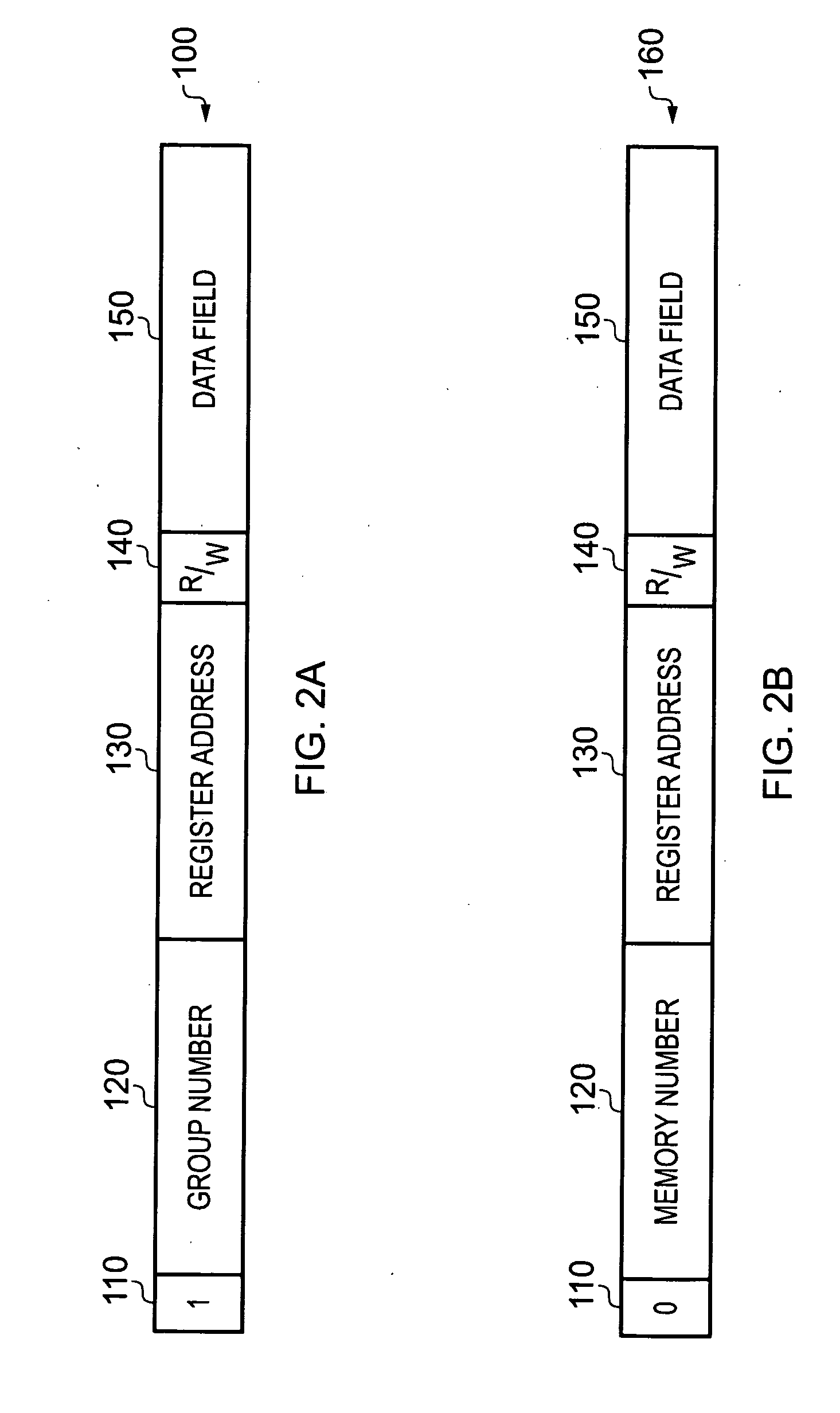

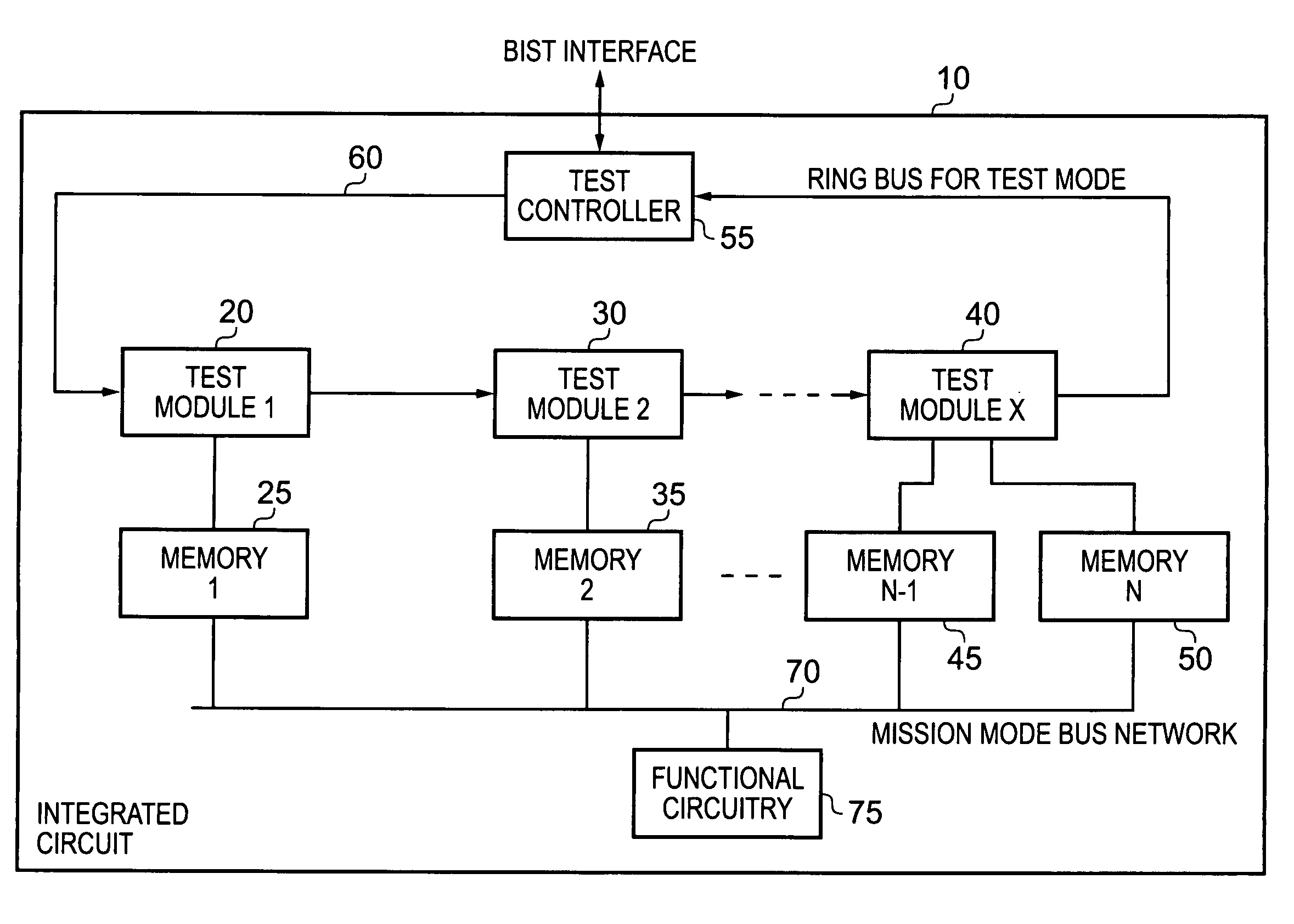

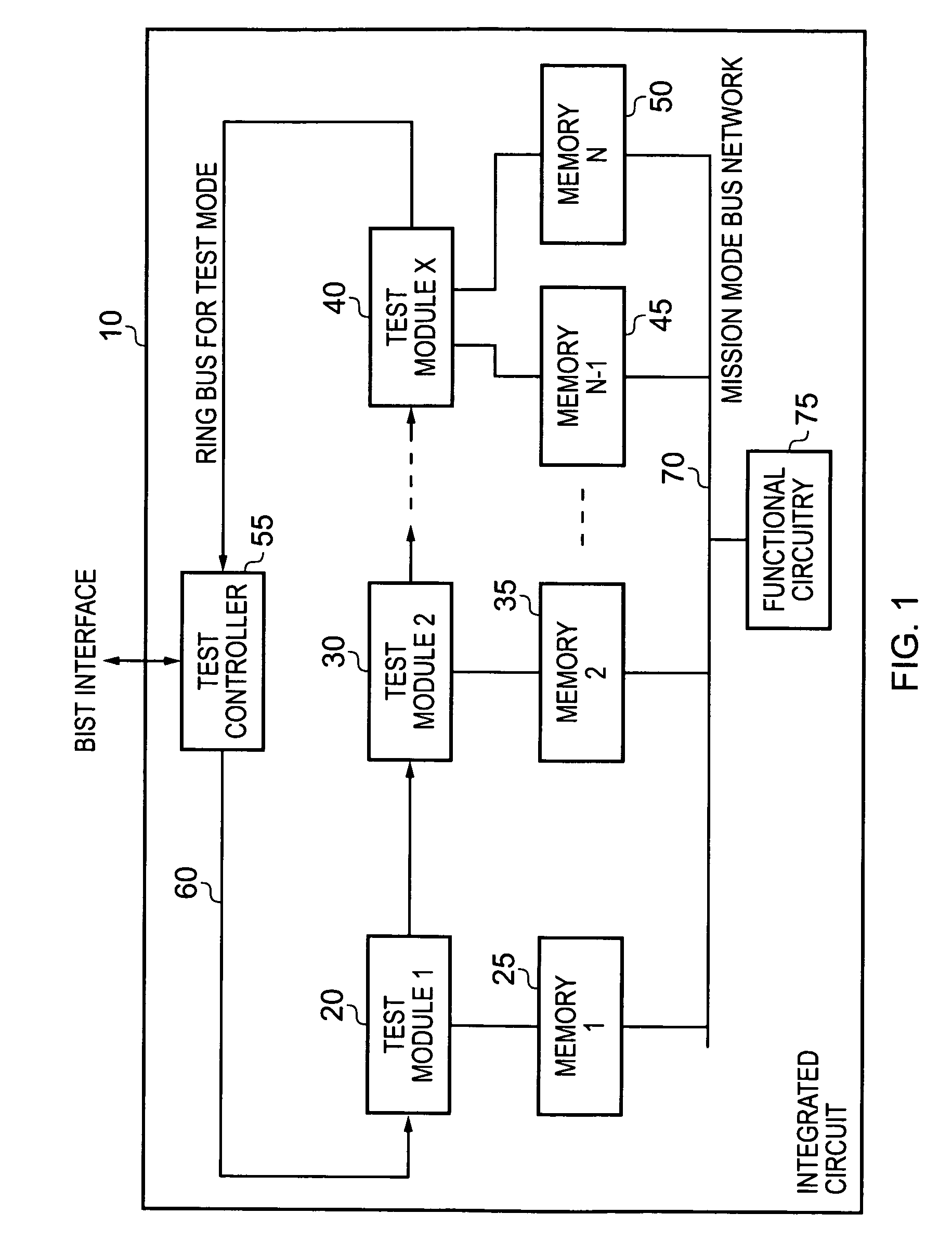

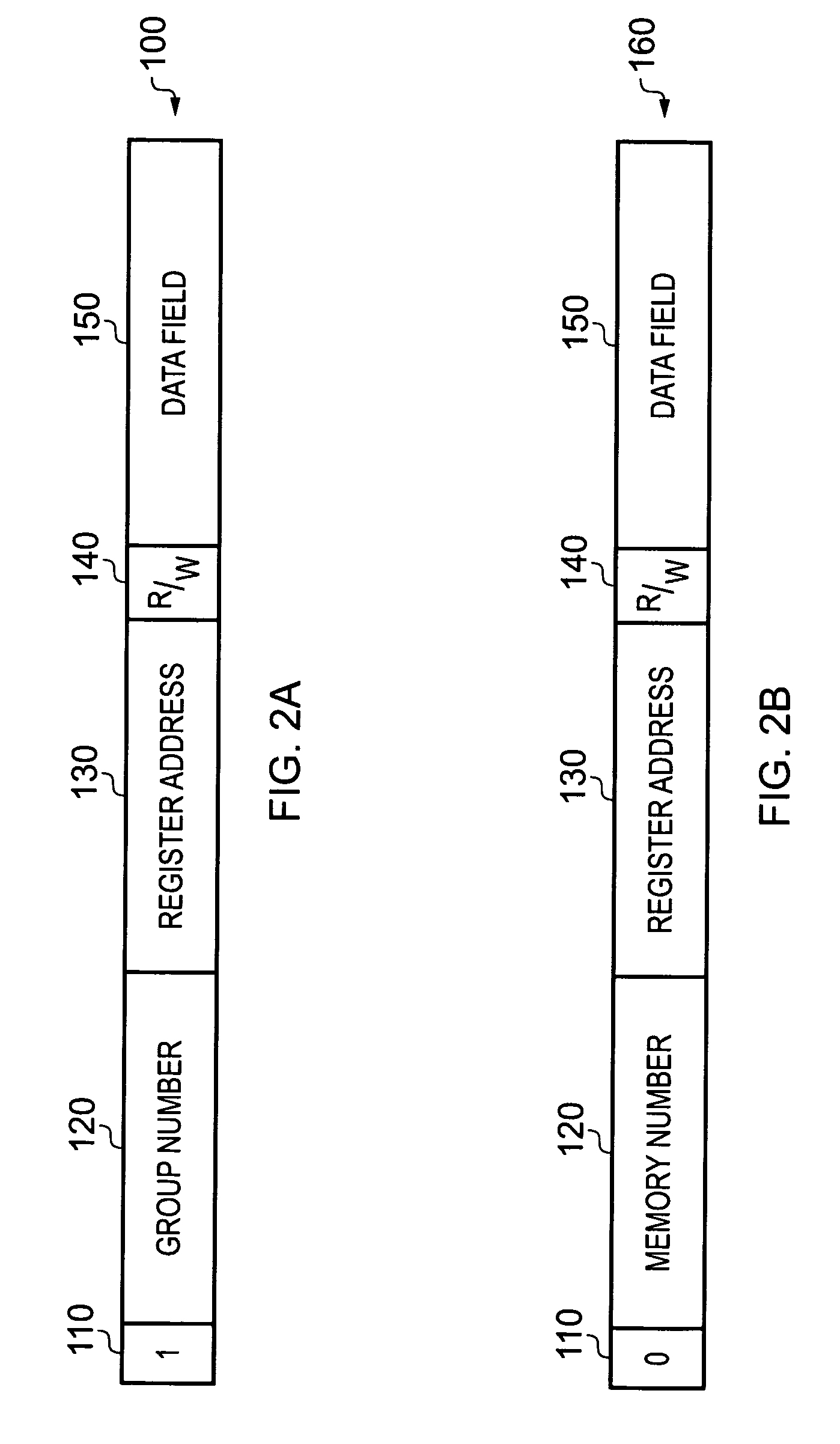

Integrated circuit and method for testing memory on the integrated circuit

ActiveUS20120204069A1Simplify the viewing processAvoid problemsError detection/correctionStatic storageProcessor registerComputer module

An integrated circuit comprises a plurality of memory units and at least one memory test module, each memory test module having at least one associated memory unit from the plurality of memory units. Each memory test module comprises a set of test registers for each associated memory unit, and a test engine configured, for each associated memory unit, to perform a test operation on that associated memory unit dependent on the status of the set of registers provided for that associated memory unit. A transaction interface of the memory test module receives a transaction specifying a register access operation, the transaction providing a first address portion having encodings allowing individual memory units to be identified and groups of memory units to be identified, and a second address portion identifying one of the test registers within the set to be an accessed register for the register access operation. Decode circuitry within each memory test module is then responsive to the transaction to selectively perform the register access operation if it is determined that the memory test module includes a set of test registers associated with a memory unit identified either individually or as part of a group by the transaction. Such an approach provides a simple programmer's view of the memory test system allowing any transaction to be targeted at an individual memory unit or at arbitrary combinations of memory units as defined by the memory groups.

Owner:ARM LTD

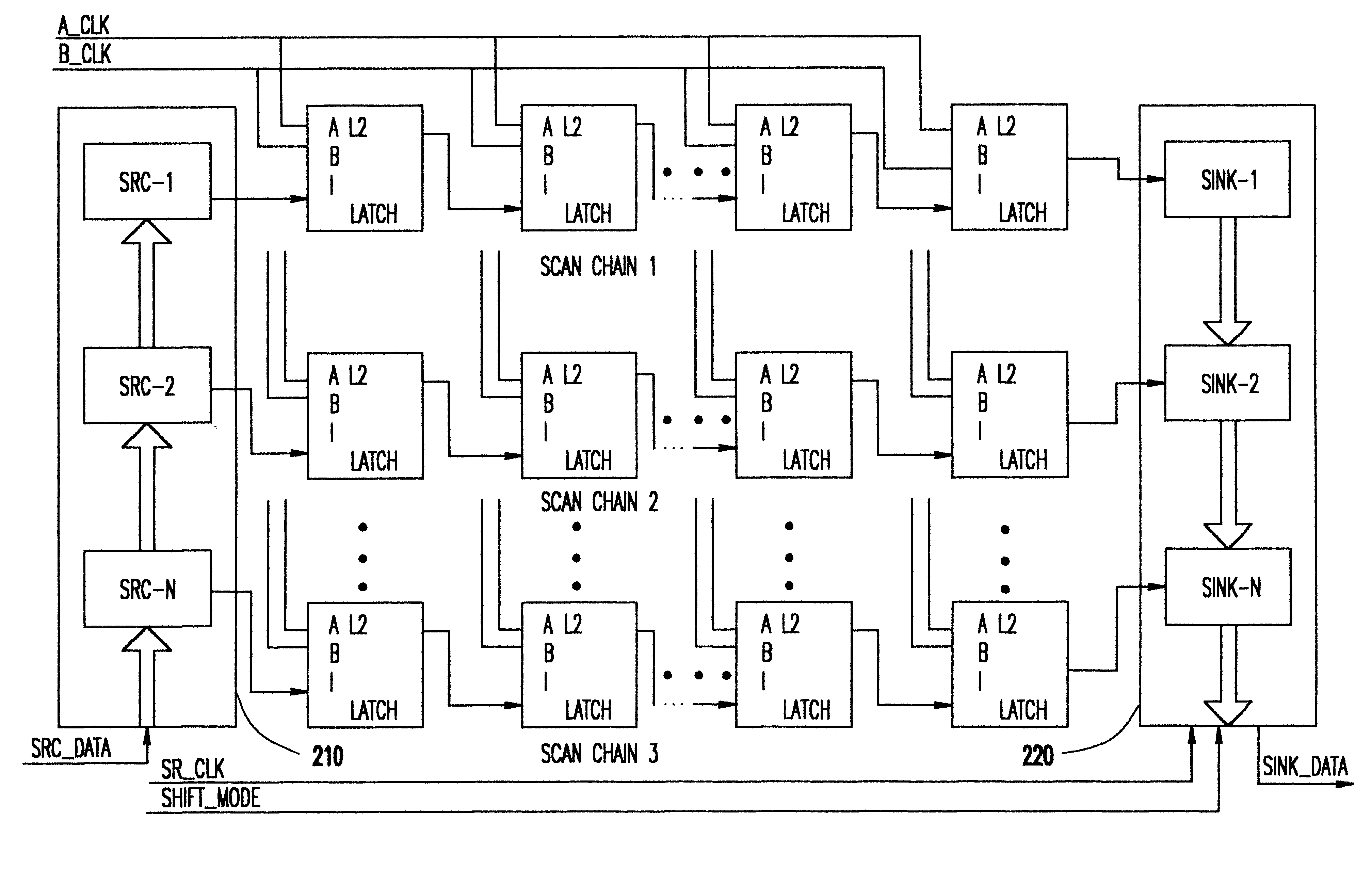

High speed sink/source register to reduce level sensitive scan design test time

InactiveUS6591388B1Reducing time and tester apparatus overheadShorten test timeElectronic circuit testingLogic circuitsRegister allocationShift register

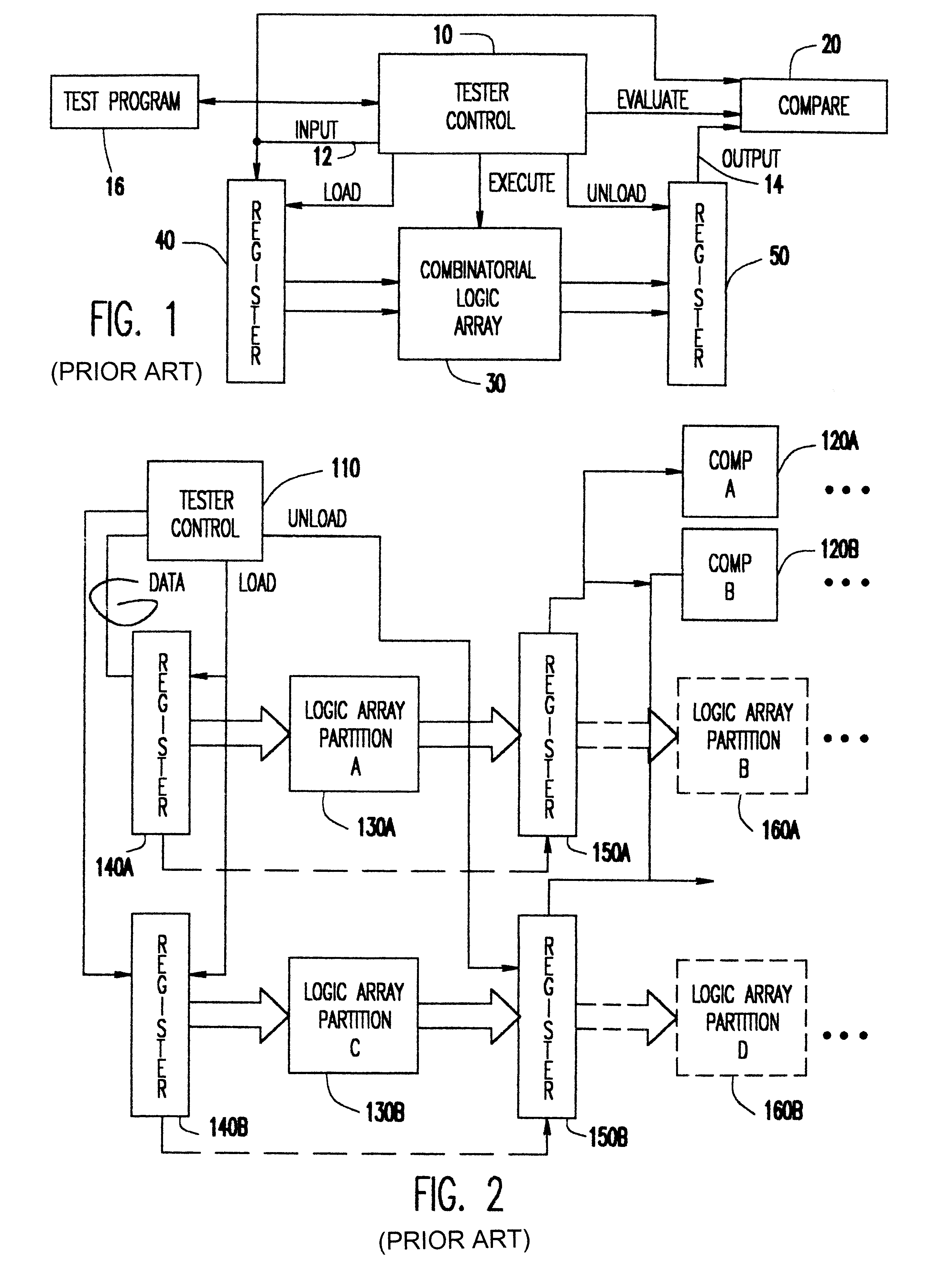

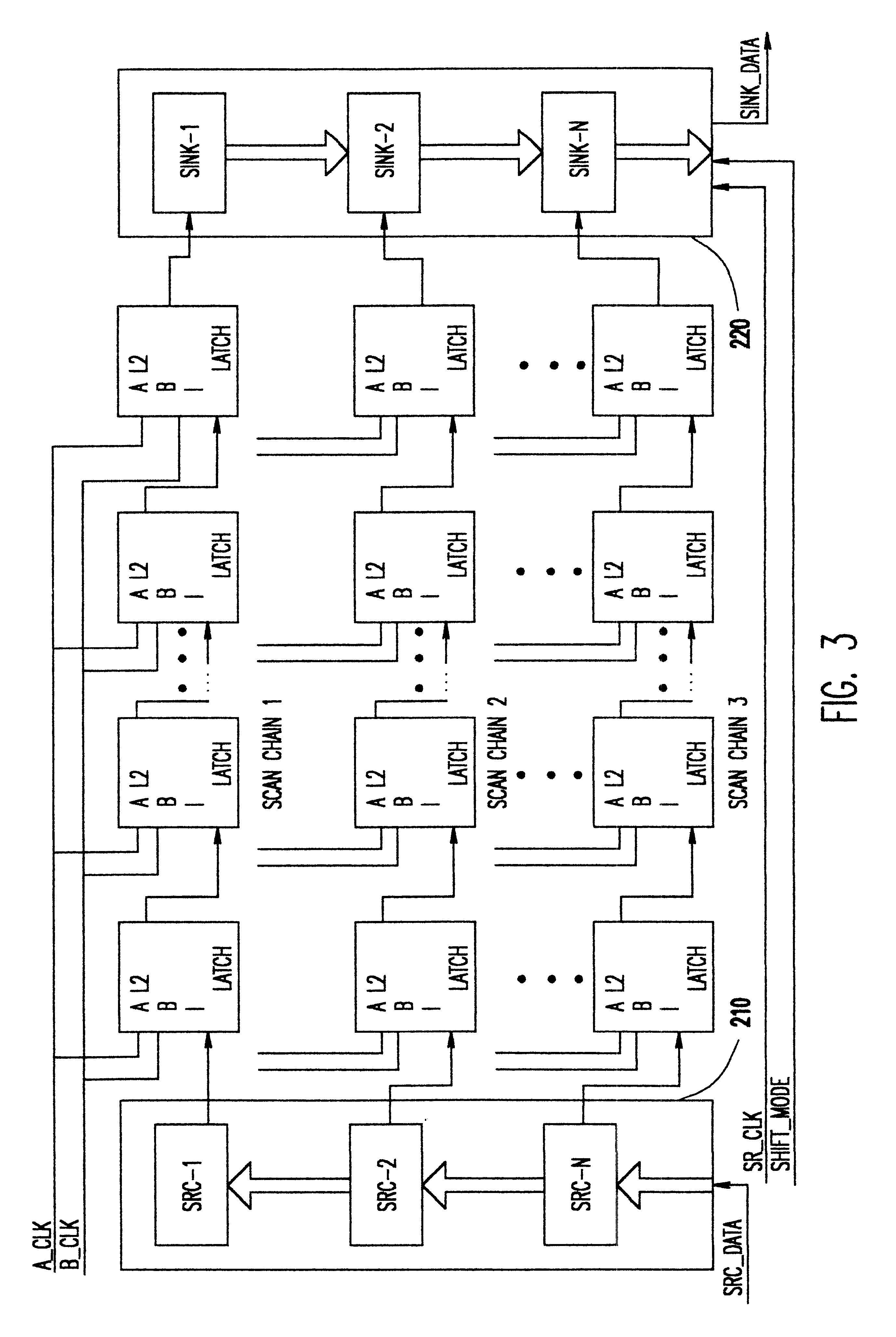

Test data is provided through shift registers, operated at a high clock rate comparable to or exceeding a normal high speed clock rate of a chip being tested, to each of a plurality of scan chains configured from registers present on the chip; respective latches of which are connected to inputs and outputs of logic array partitions to be tested. Reduced test clock rate of input and output circuits of the scan chains is accommodated by high speed source and sink shift registers. The source and sink registers are fully loaded and unloaded between consecutive test clock signals and test signals are preferably applied to and collected from the chip in a single serial string through a single pair of tester input / output pins. Testing time is thus reduced without requiring design time and chip space for a clock tree optimized for high speed operation while use of testers of reduced cost and having an arbitrarily small number of input / output pin pairs and independent of test register configuaration on the chip can be used.

Owner:IBM CORP

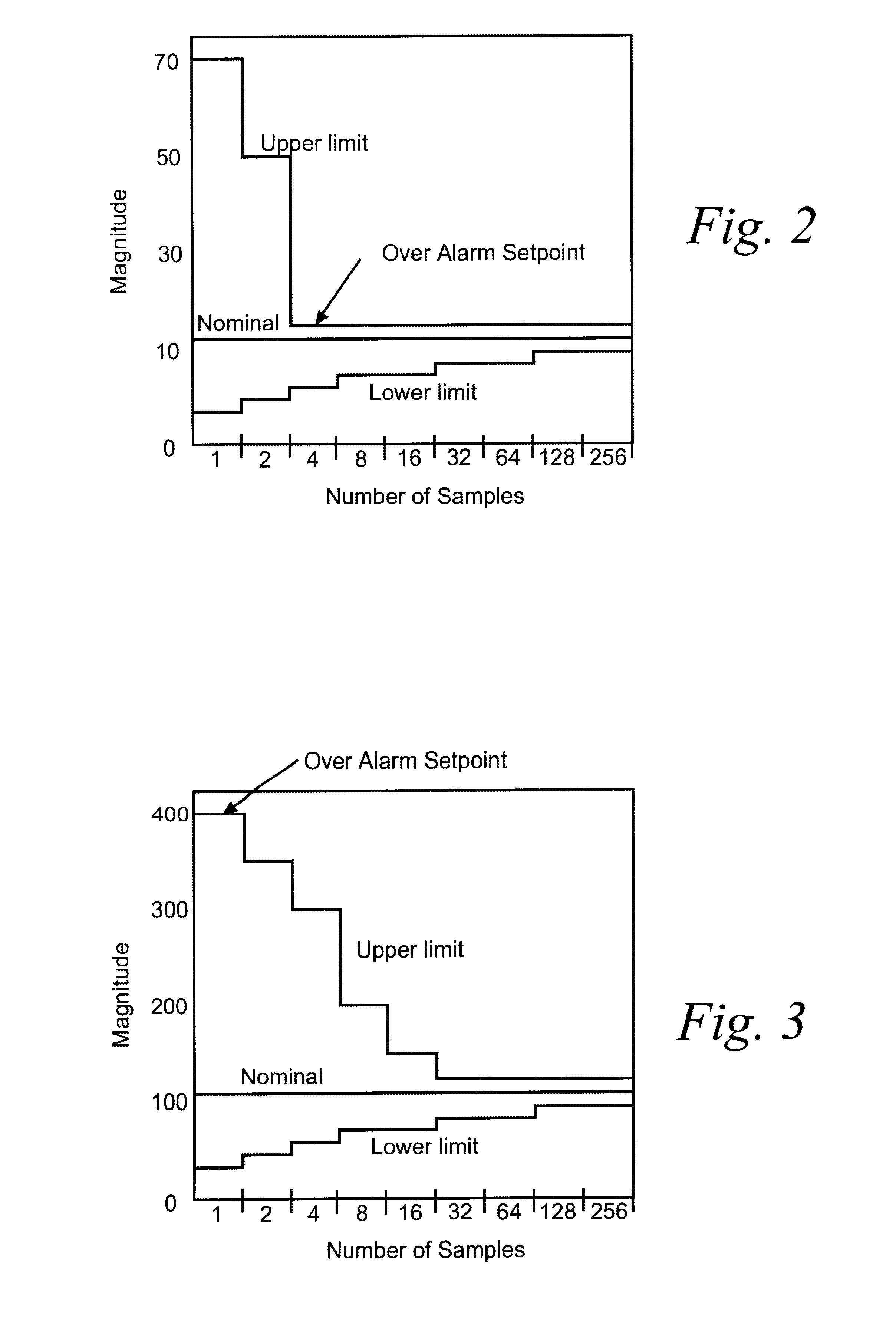

Automated alarm setpoint learning in an electrical meter

InactiveUS6639518B1Minimal productionCurrent/voltage measurementSpecial tariff metersProcessor registerEngineering

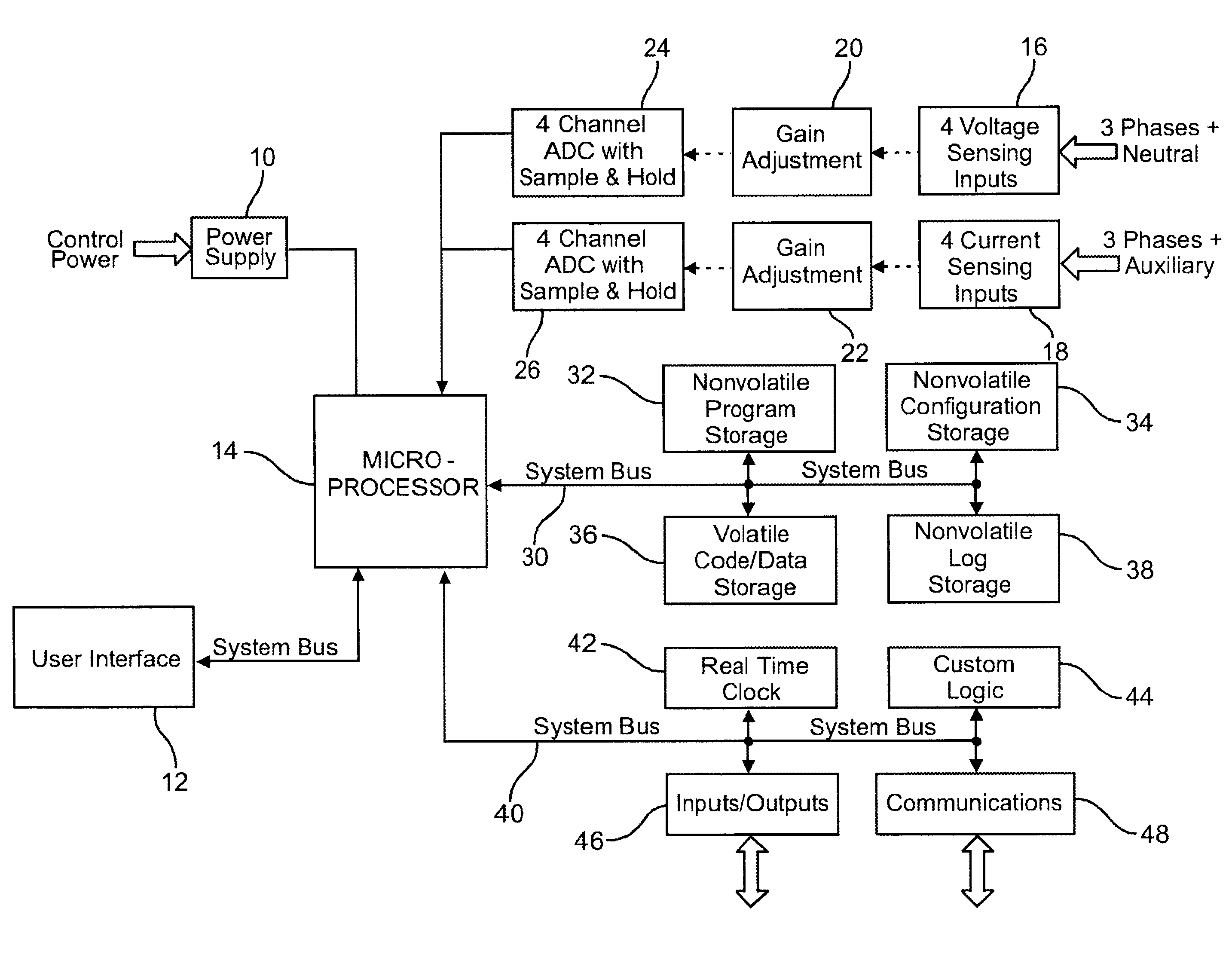

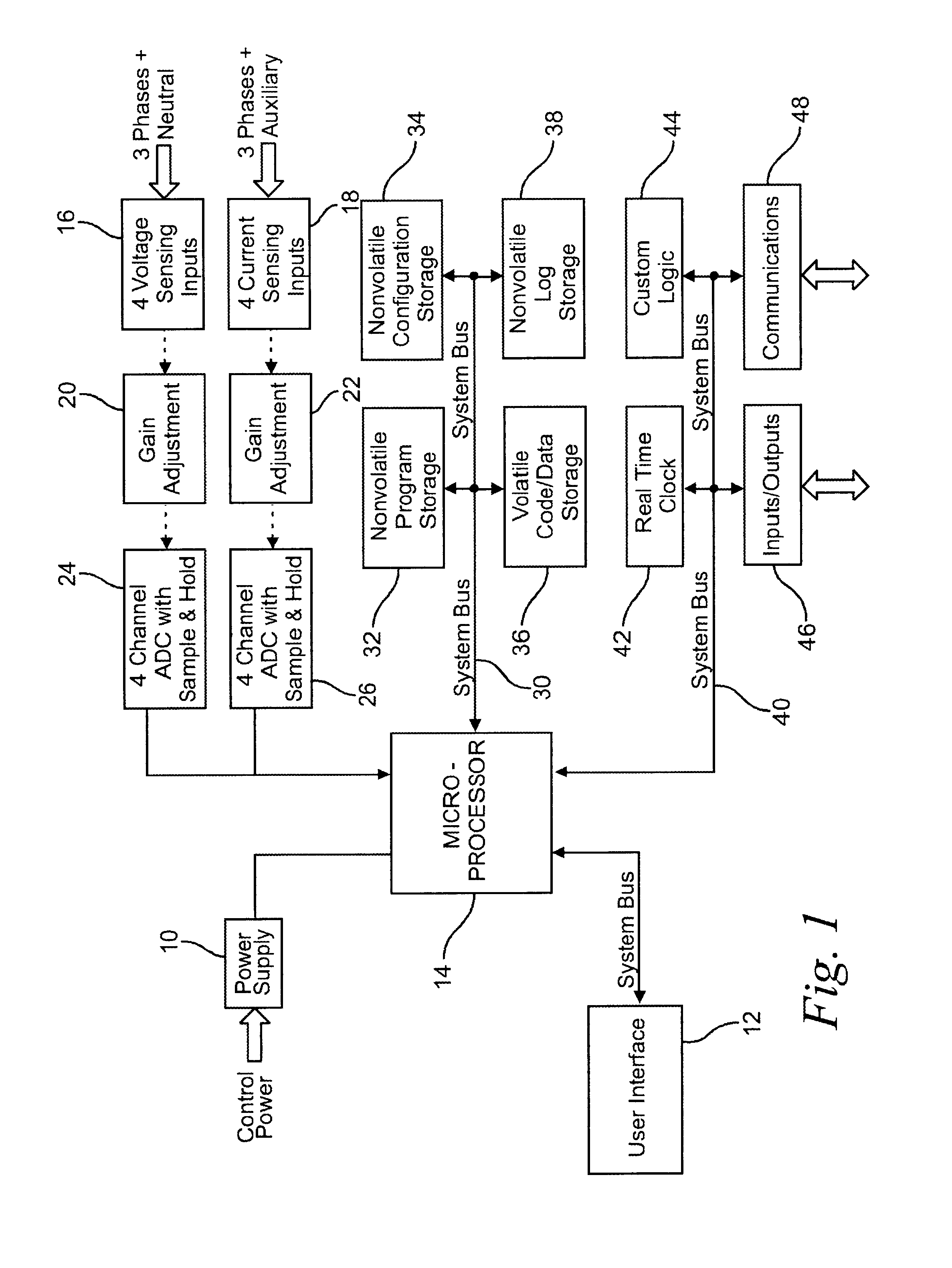

A circuit monitor monitors one or more metered values in an electrical circuit, and includes a system for selecting alarm setpoints based upon learned characteristics of normal operation of metered values. The circuit monitor includes a controller and a memory. The memory includes a test register of alarms selected to be part of a learning process. The controller includes summaries and characterizes the one or more metered values as histogram formatted data corresponding to metered values identified by a test register of alarms selected to be part of a learning process. The controller stores the histogram formatted data in the memory and organizes the stored data into a plurality of memory locations, each covering a fixed range of time duration. The controller selects setpoints which produce a minimum product of metered value multiplied by time duration for Over Alarms or a maximum product of metered value multiplied by time duration for Under Alarms.

Owner:SQUARE D CO

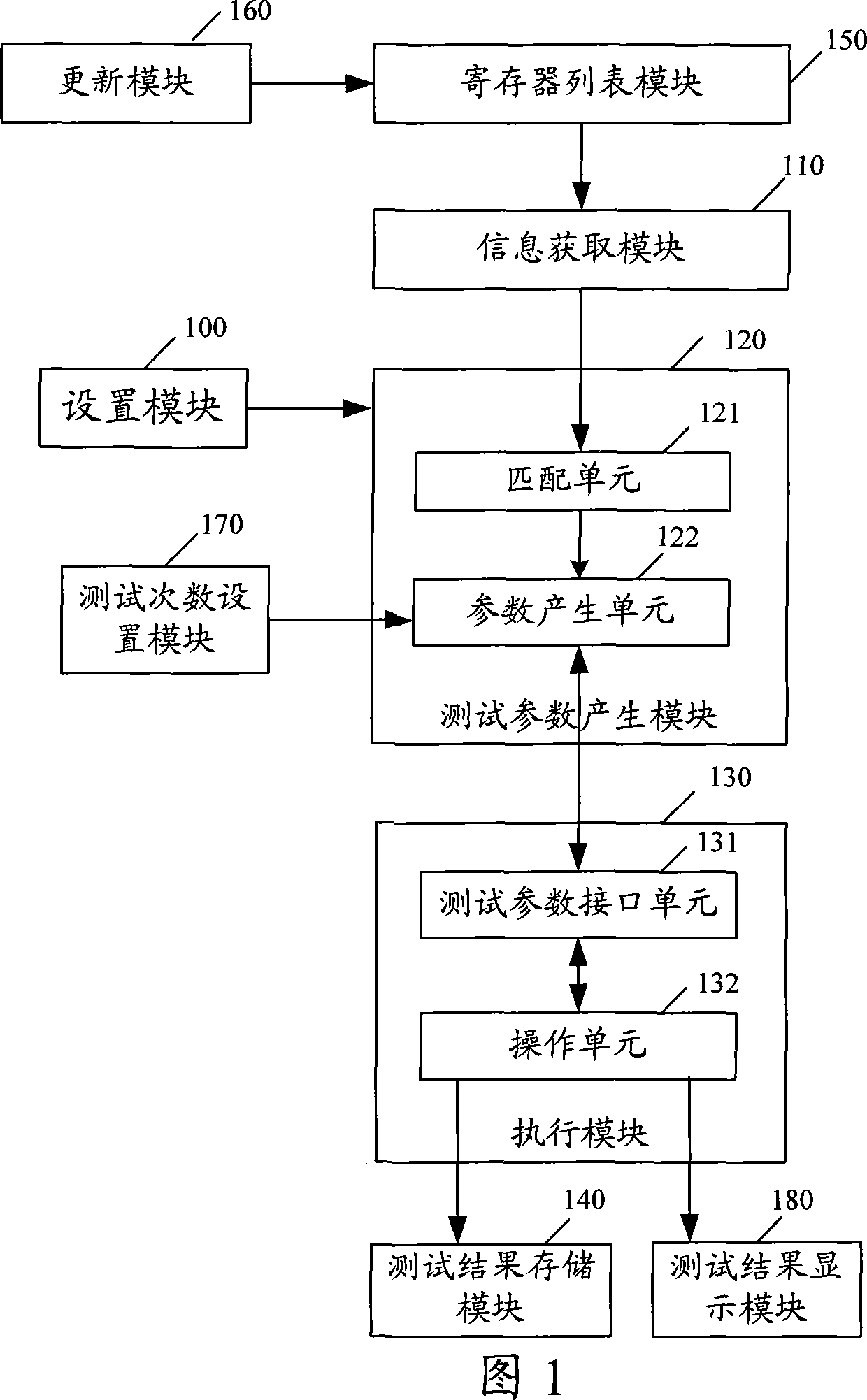

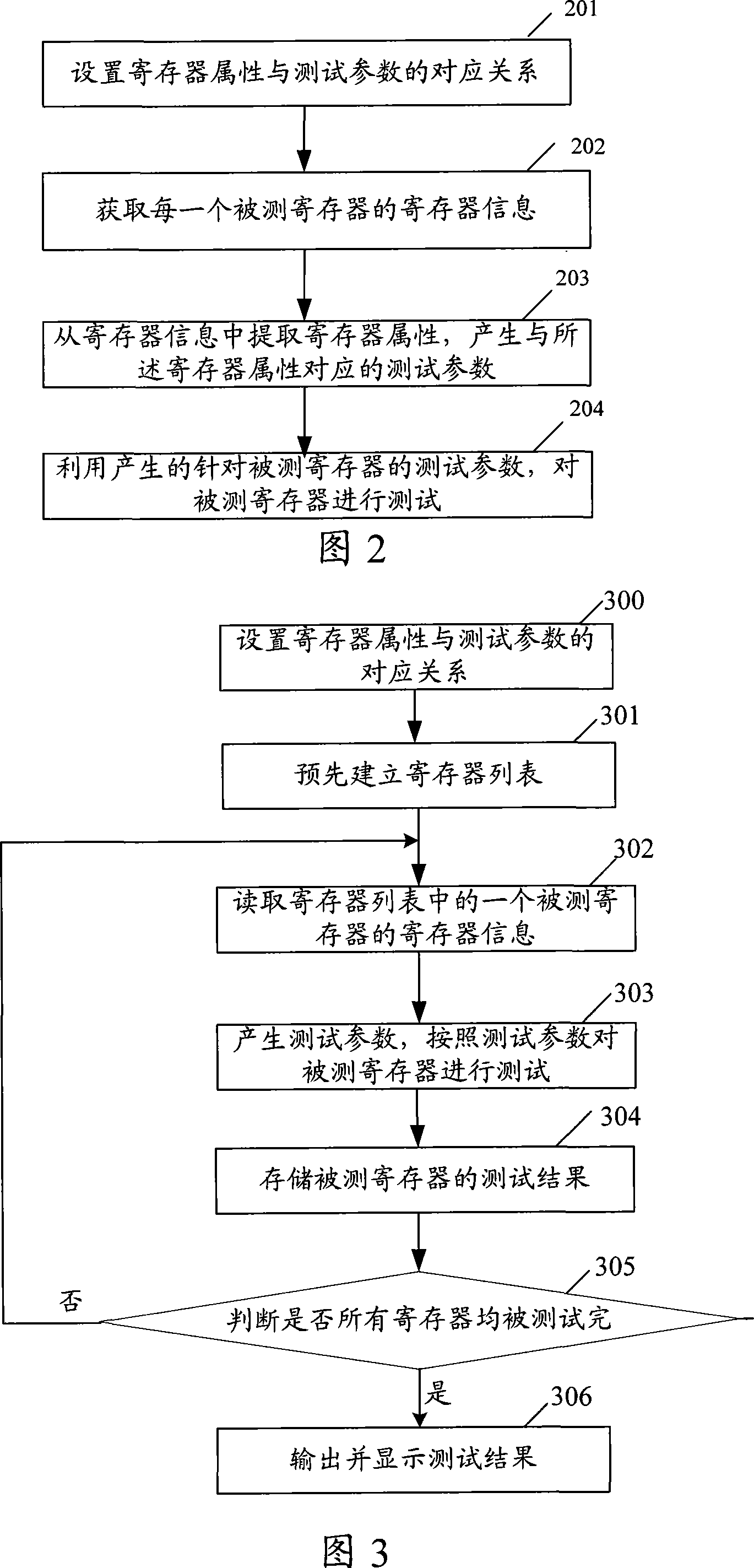

Register testing method and system

InactiveCN101131875AReduce workloadAvoid missing testStatic storageProcessor registerInformation gain

This invention discloses a kind of system which can realize the test of the register, the system includes: the setting module, sets the corresponding relation between the property of the register and the test parameter; information gain module, gains each register information in the tested register, the said register information includes the register property; test parameter produce module, gains the register property from the register information which is gained by the information gain module, produces the corresponding test parameter of the said register property; execute module, uses the said test parameter produced by the said register property produce module to test the said tested register, gets the test result of the tested register. This invention also discloses the register test method, using this invention can reduce the workload of the register test.

Owner:VIMICRO CORP

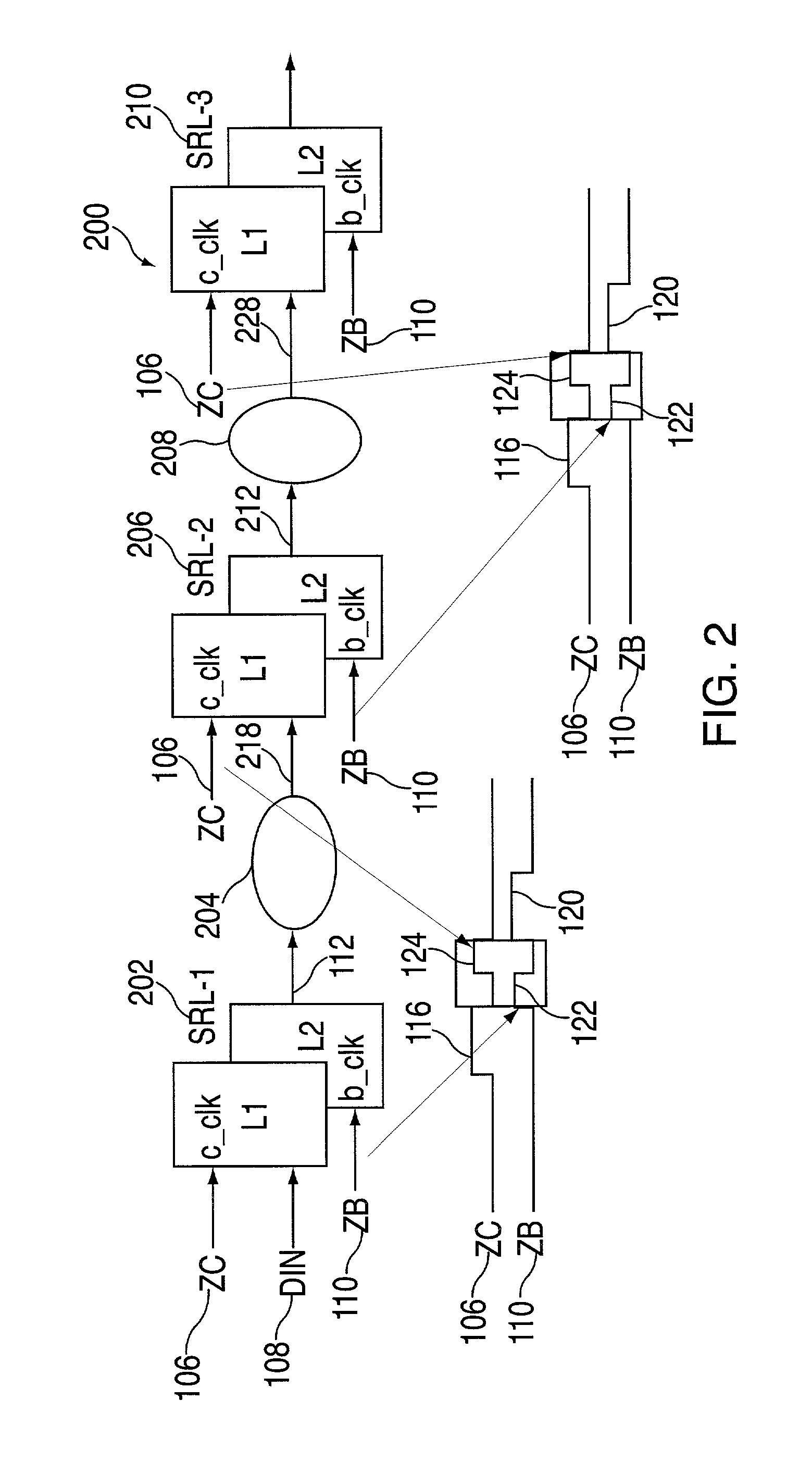

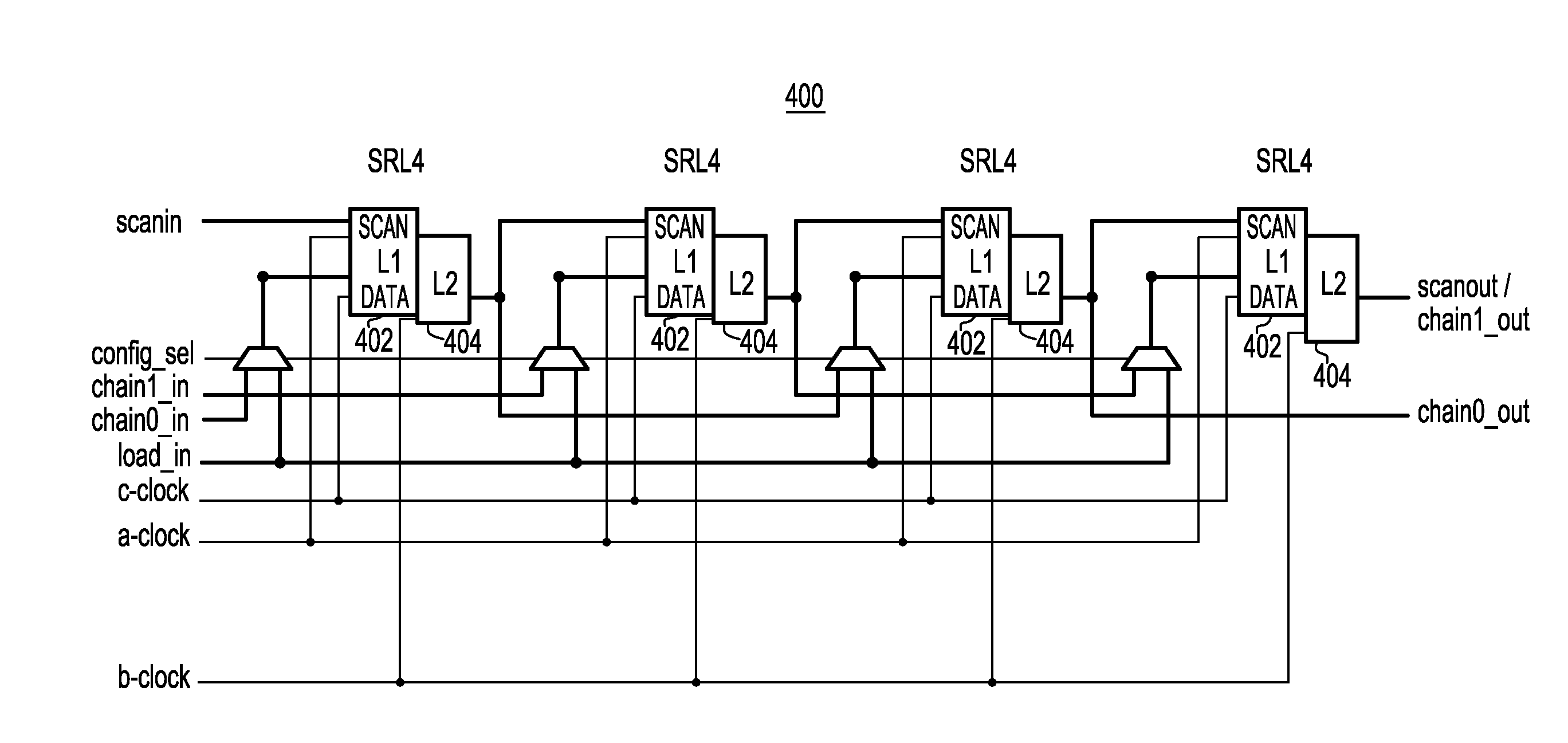

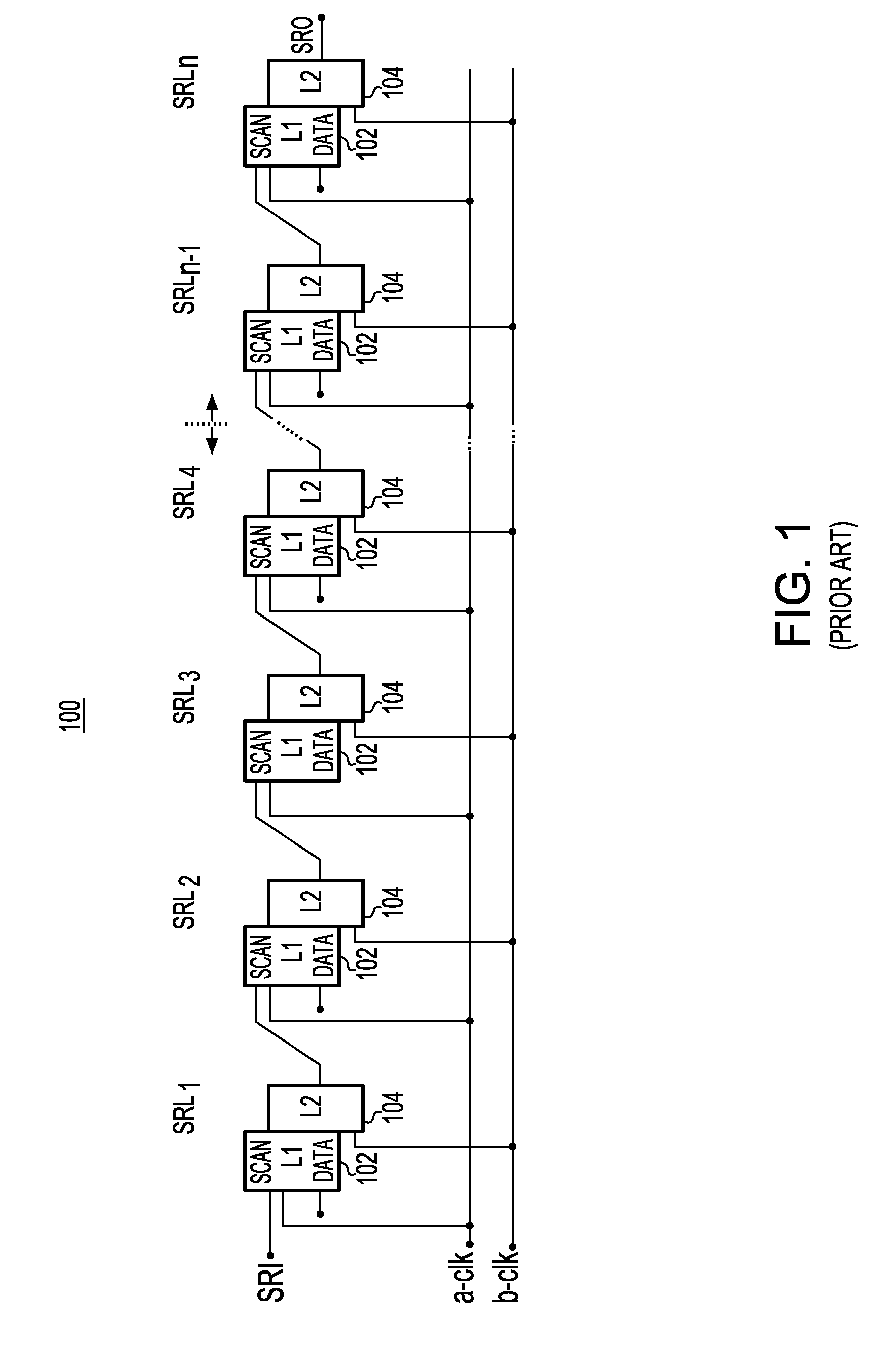

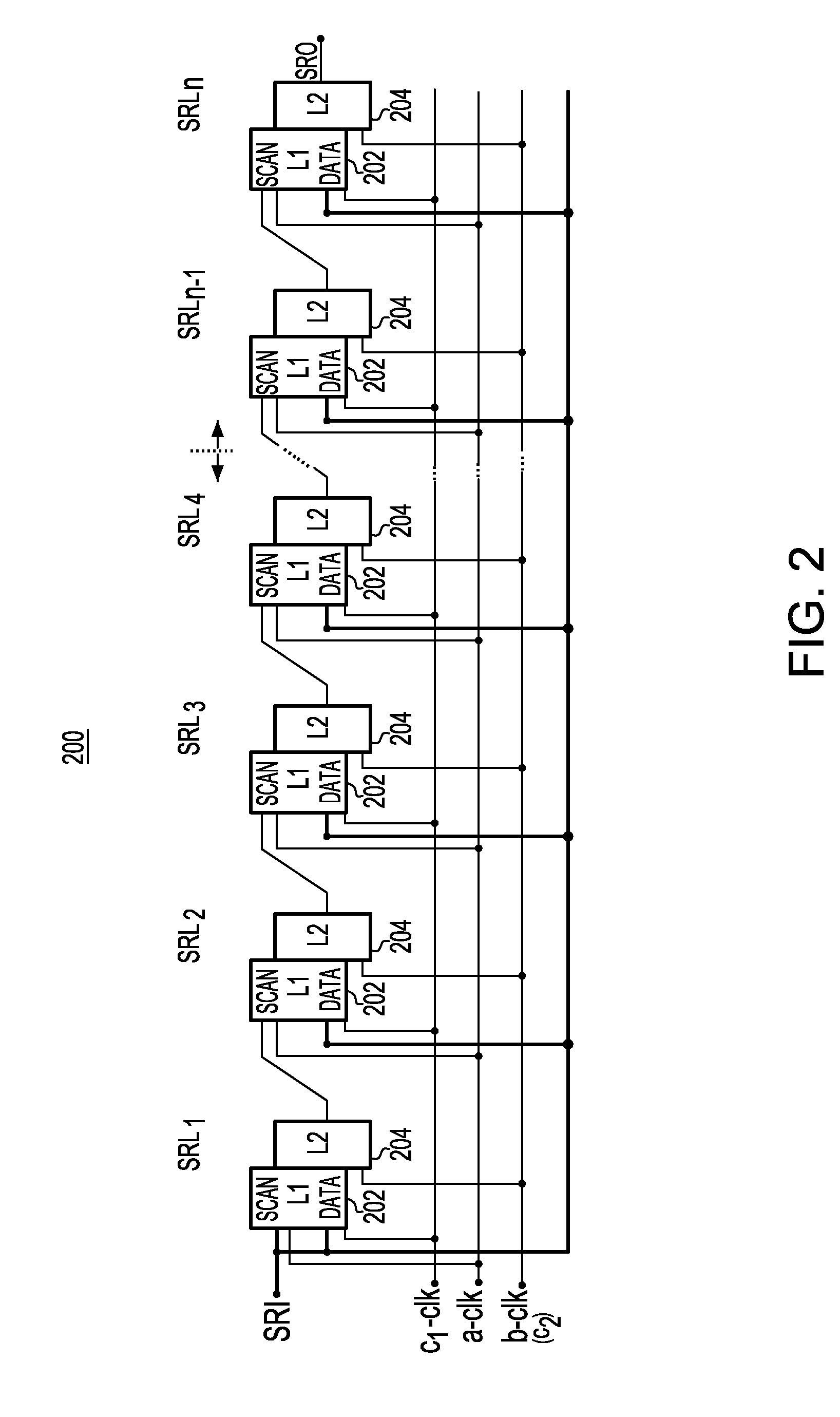

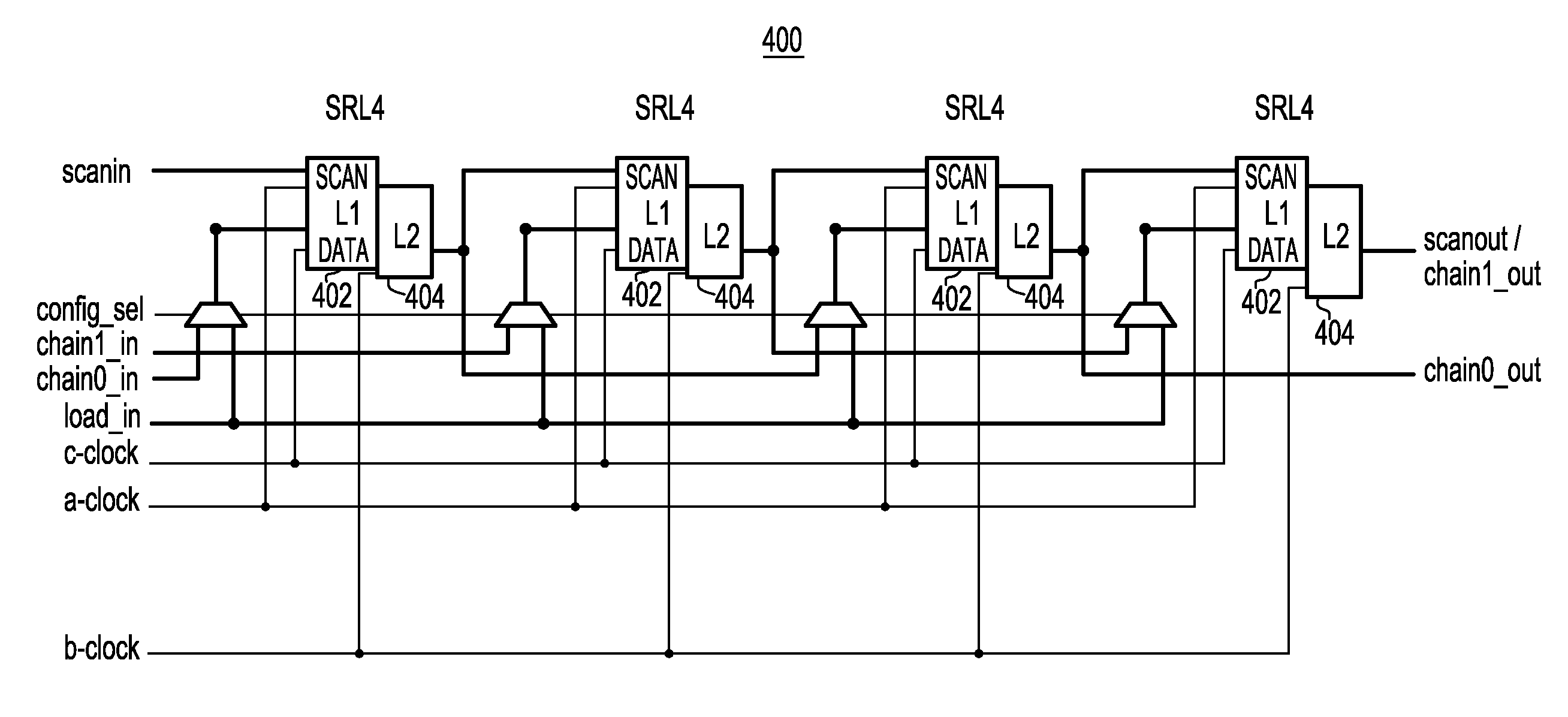

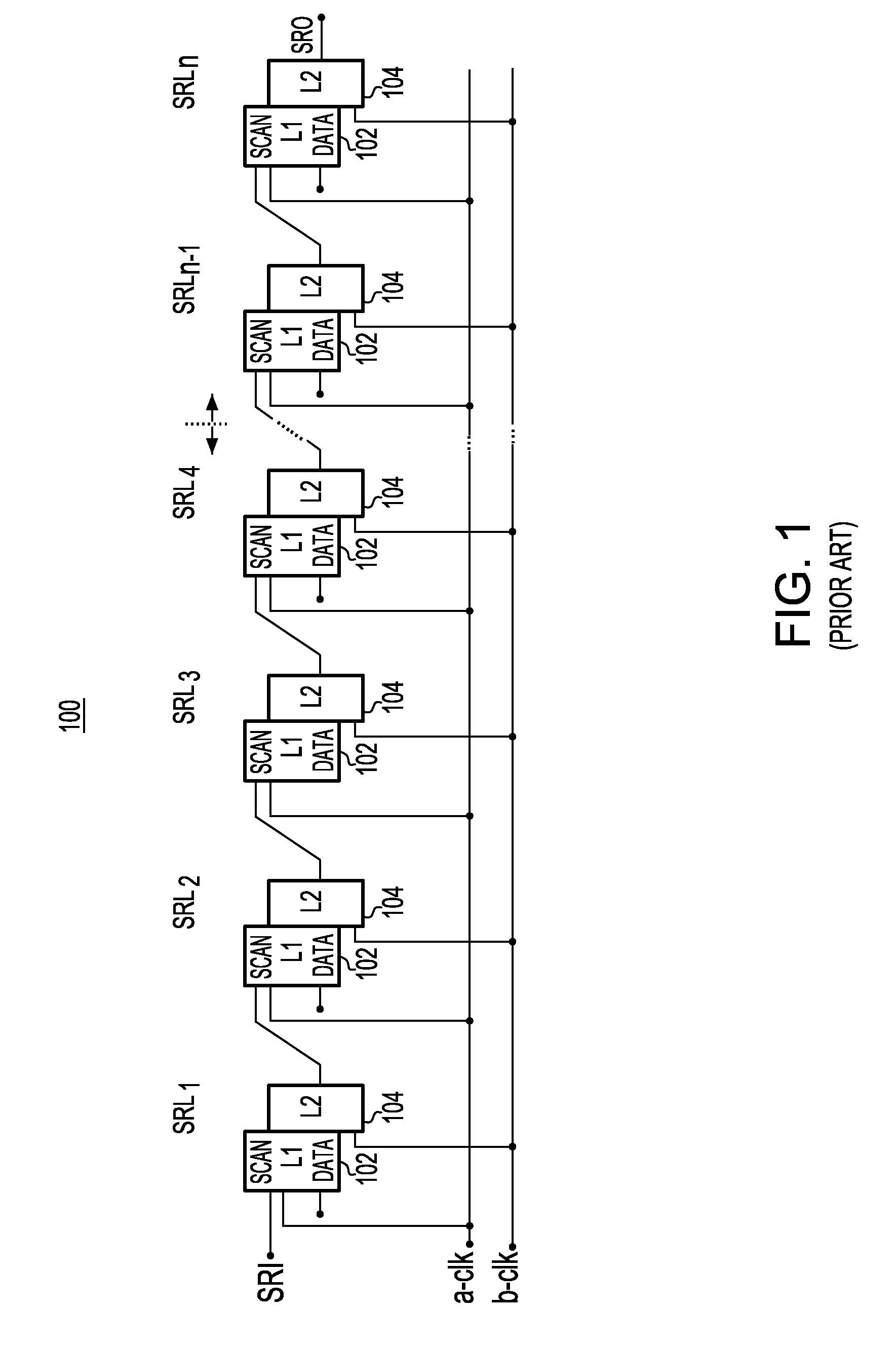

Diagnosable general purpose test registers scan chain design

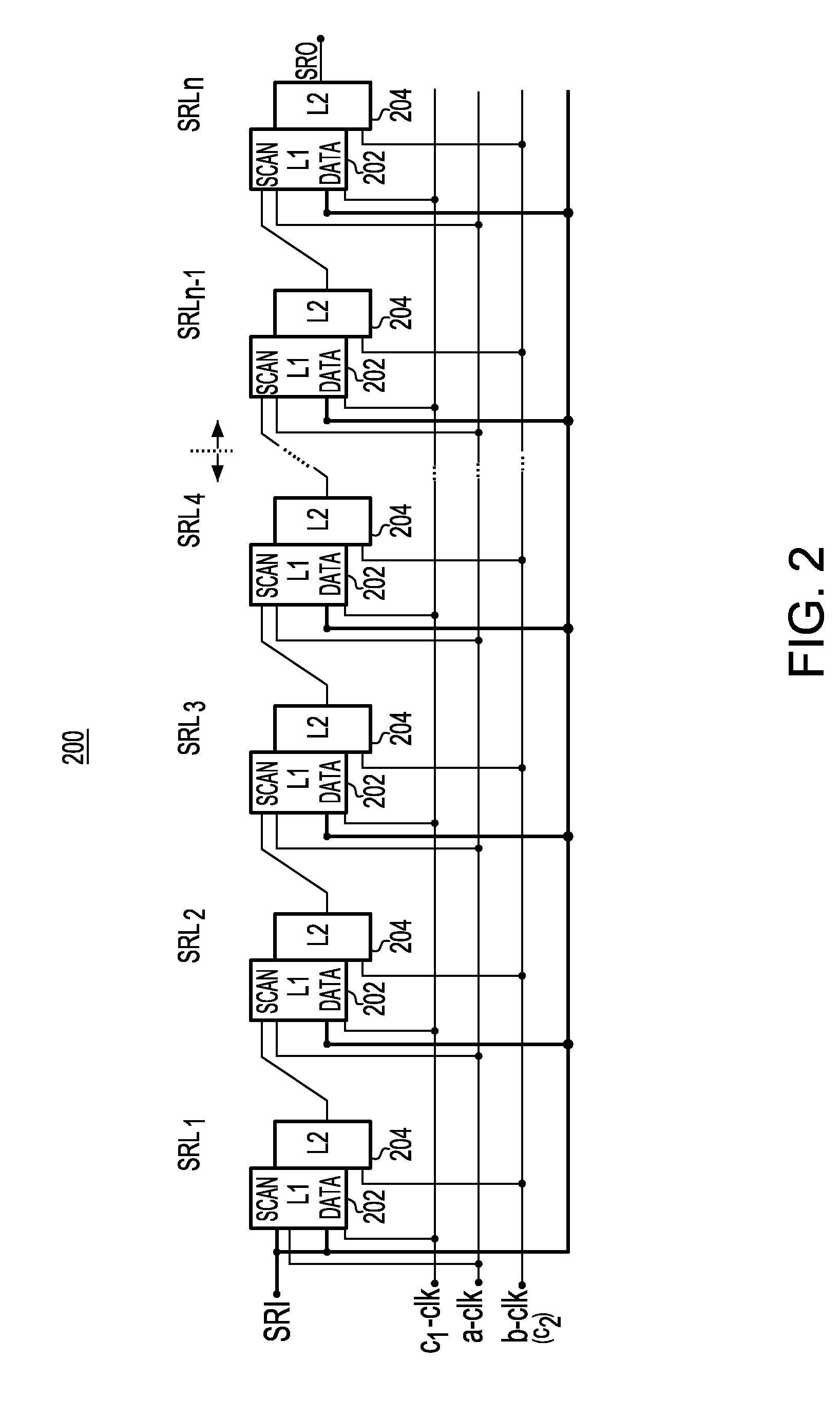

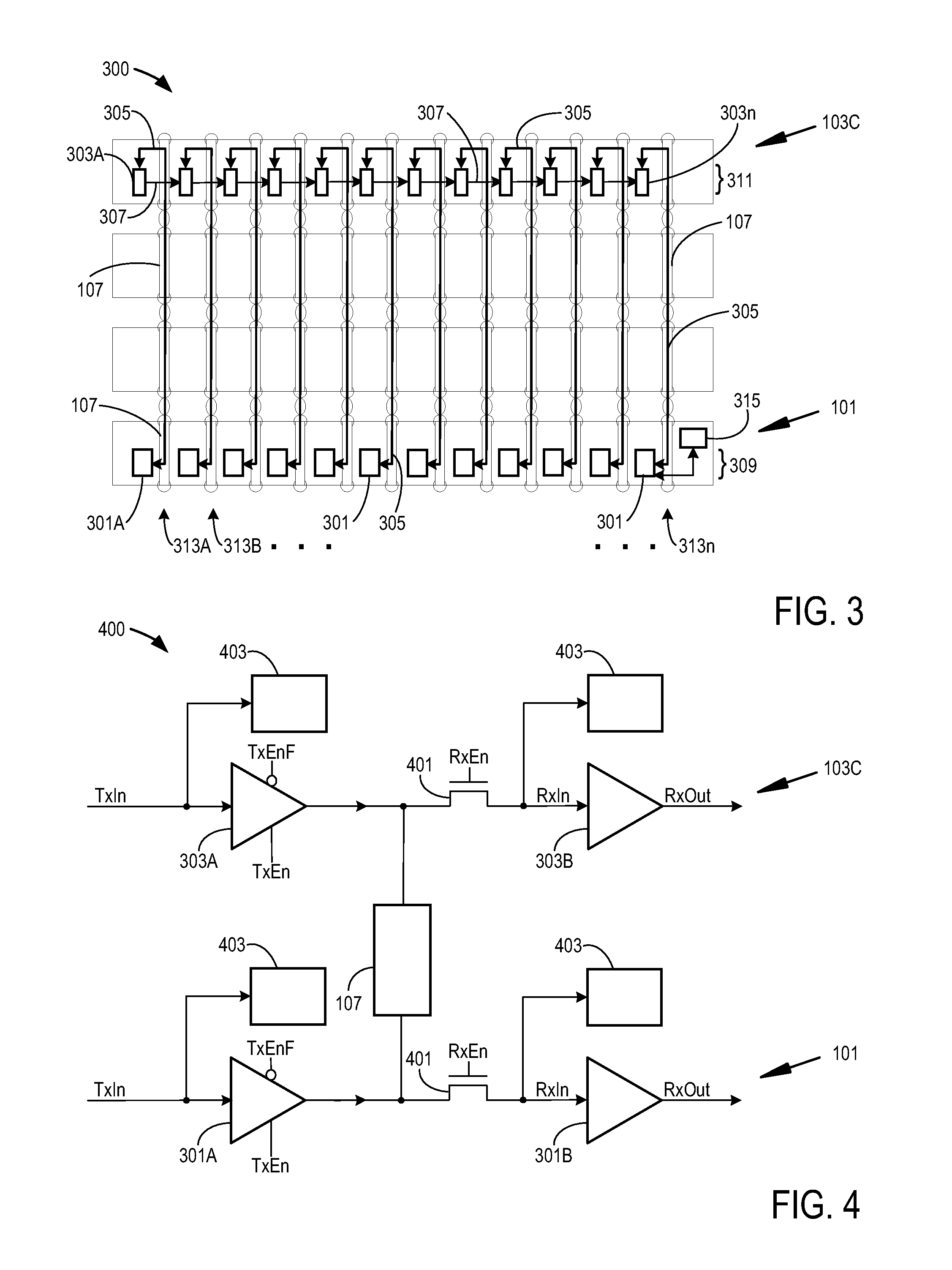

ActiveUS20090217116A1Rapid localizationRapidly localizing defectElectronic circuit testingError detection/correctionShift registerGeneral purpose

A structural design-for-test for diagnosing broken scan chain defects of long non-scannable register chains (GPTR) The GPTR and the system for testing and diagnosing the broken LSSD scan-only chains rapidly localize defects to the failing Shift Register Latch (SRL) pair. The GPTR modifies the latches used in the GPTR scan chain to standard LSSD L1 / L2 master-slave SRL type latch pairs; connects all the system ports of the L1 latches to the Shift Register Input (SRI) and clocked by the system C1-clk while the L1 scan port is clocked by the A-clk and L2 scan port is clocked only by the B-clk. The L1 latches are connected to at least one multiplexer having a first output connected to an input of each odd SRL, and a second output connected to an input port of each even SRL. In another embodiment, the GPTR includes a plurality of multiplexers respectively coupled to the master-slave latch pairs, wherein a first set of multiplexers have their respective output attached to an input of the odd L1 latches, and a second set of the multiplexers have their respective output attached to an input port of the even L1 latches.

Owner:MARVELL ASIA PTE LTD

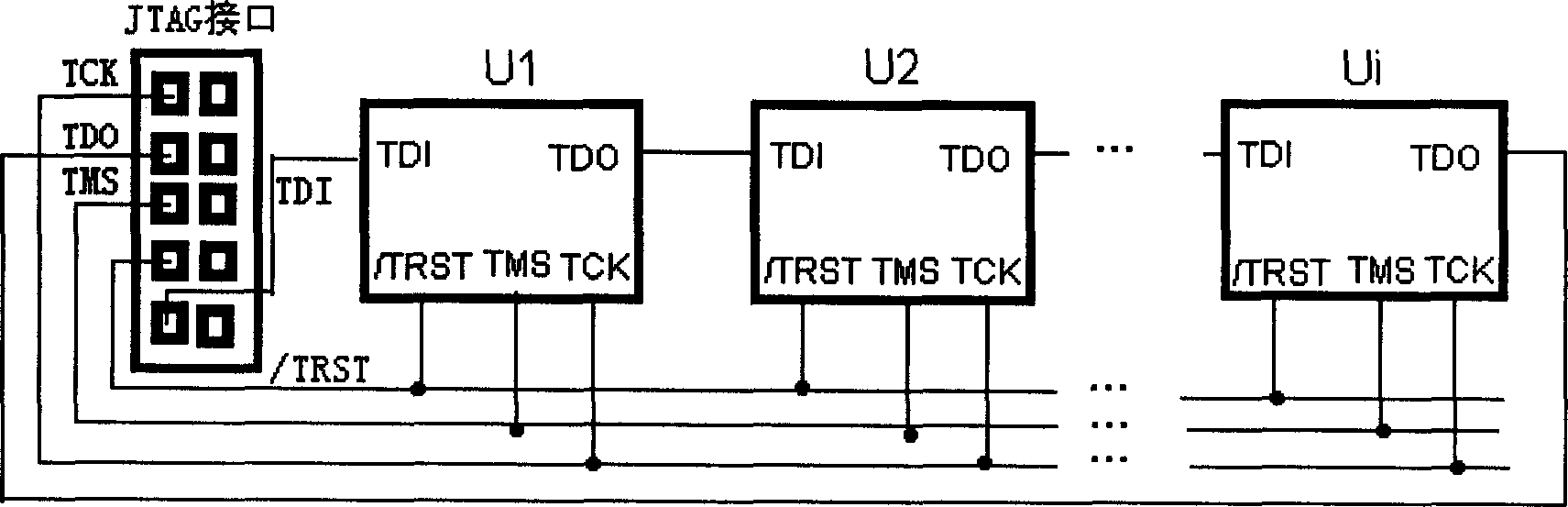

Boundary Scanning chain self-testing method

InactiveCN1580799AThe test content is completeElectronic circuit testingDetecting faulty computer hardwareProcessor registerTest sequence

Owner:HUAWEI TECH CO LTD

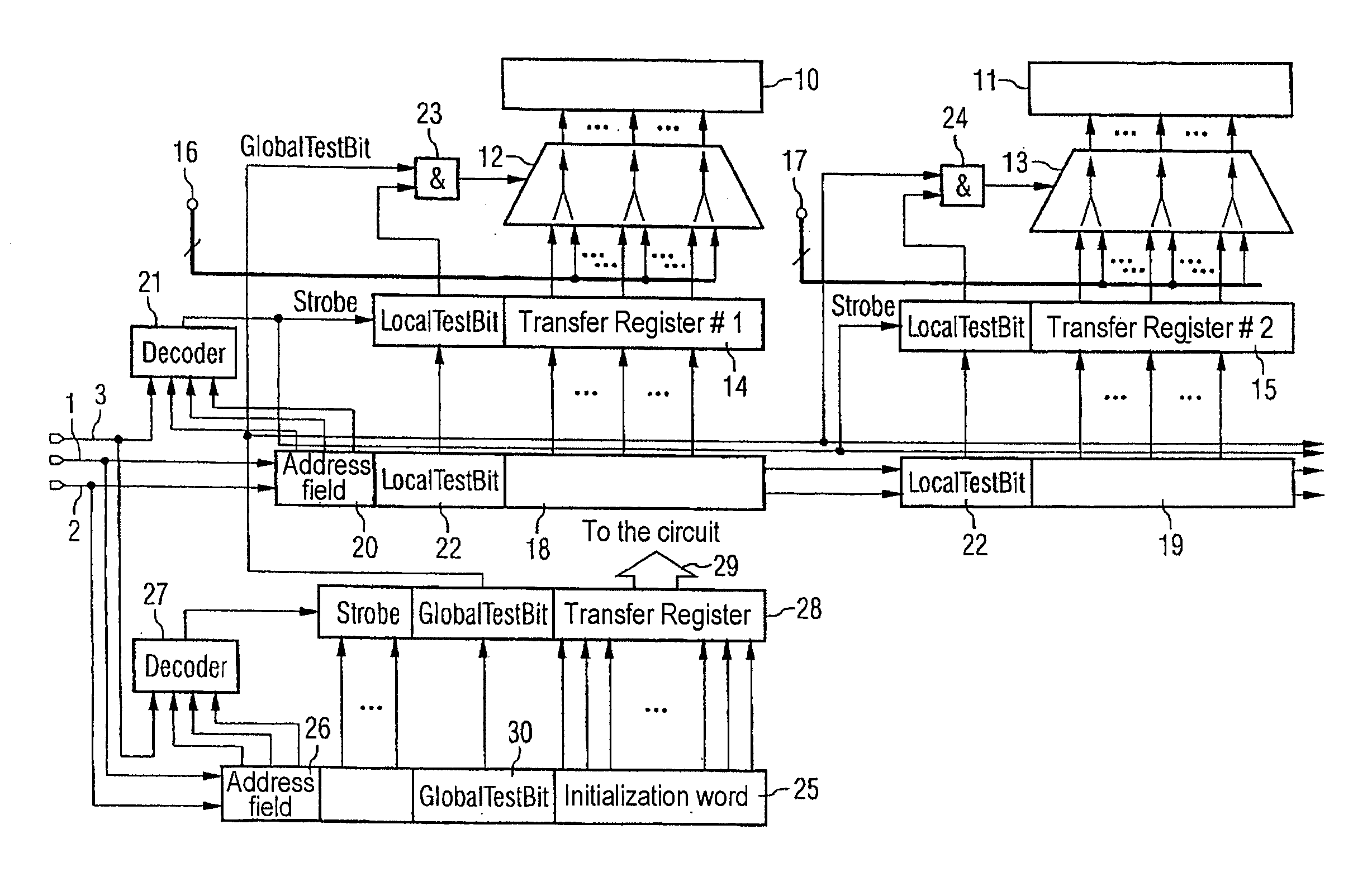

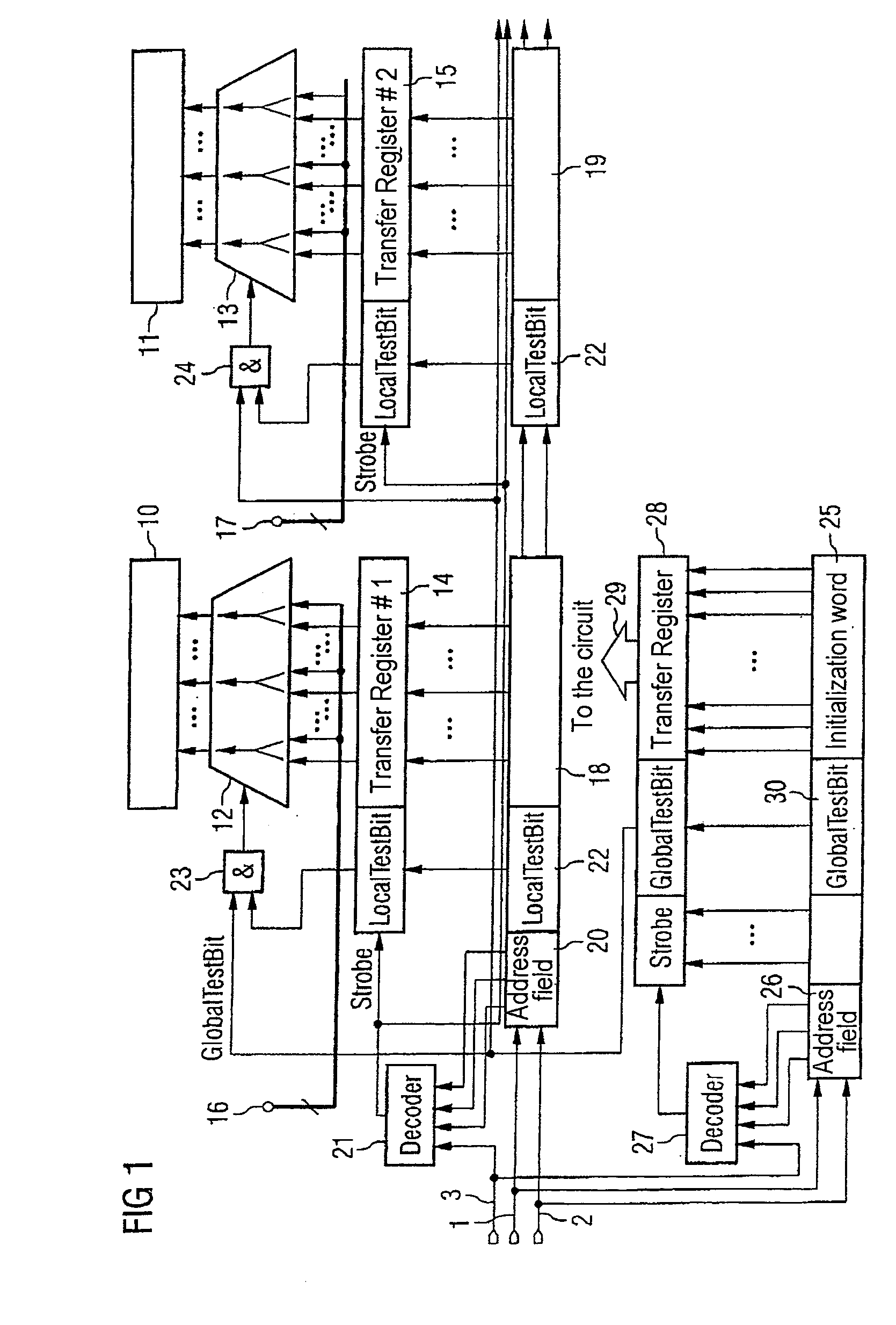

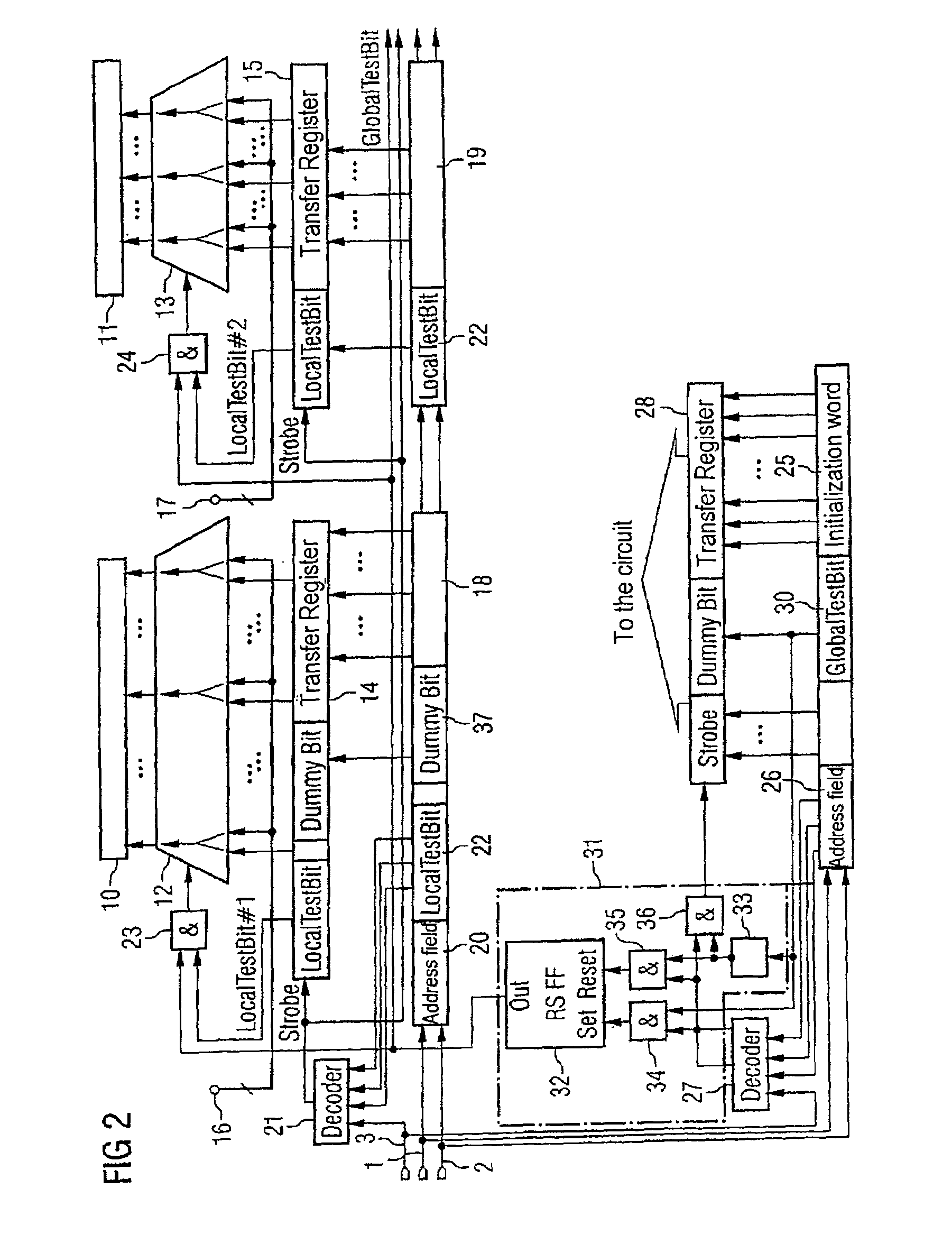

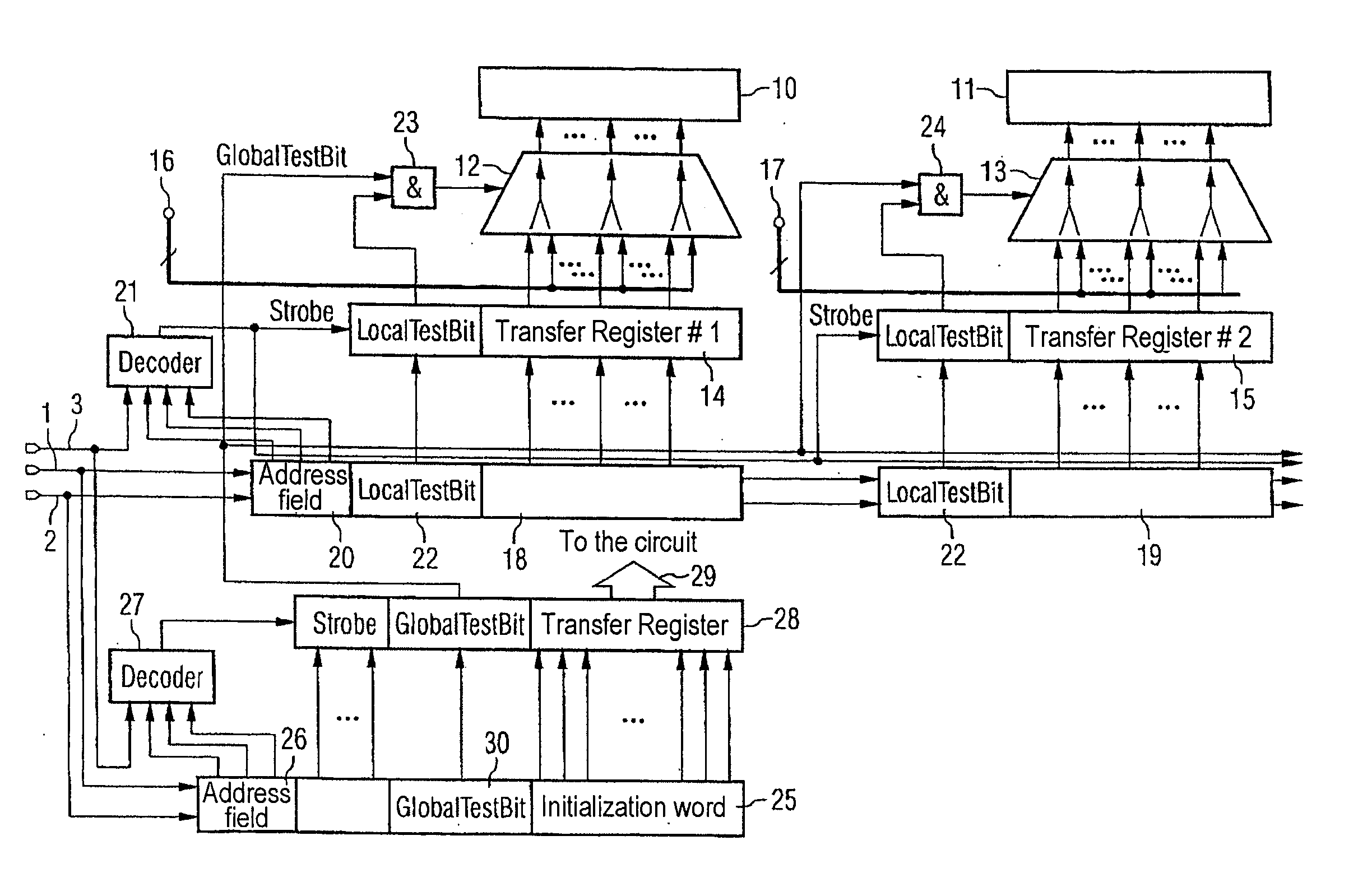

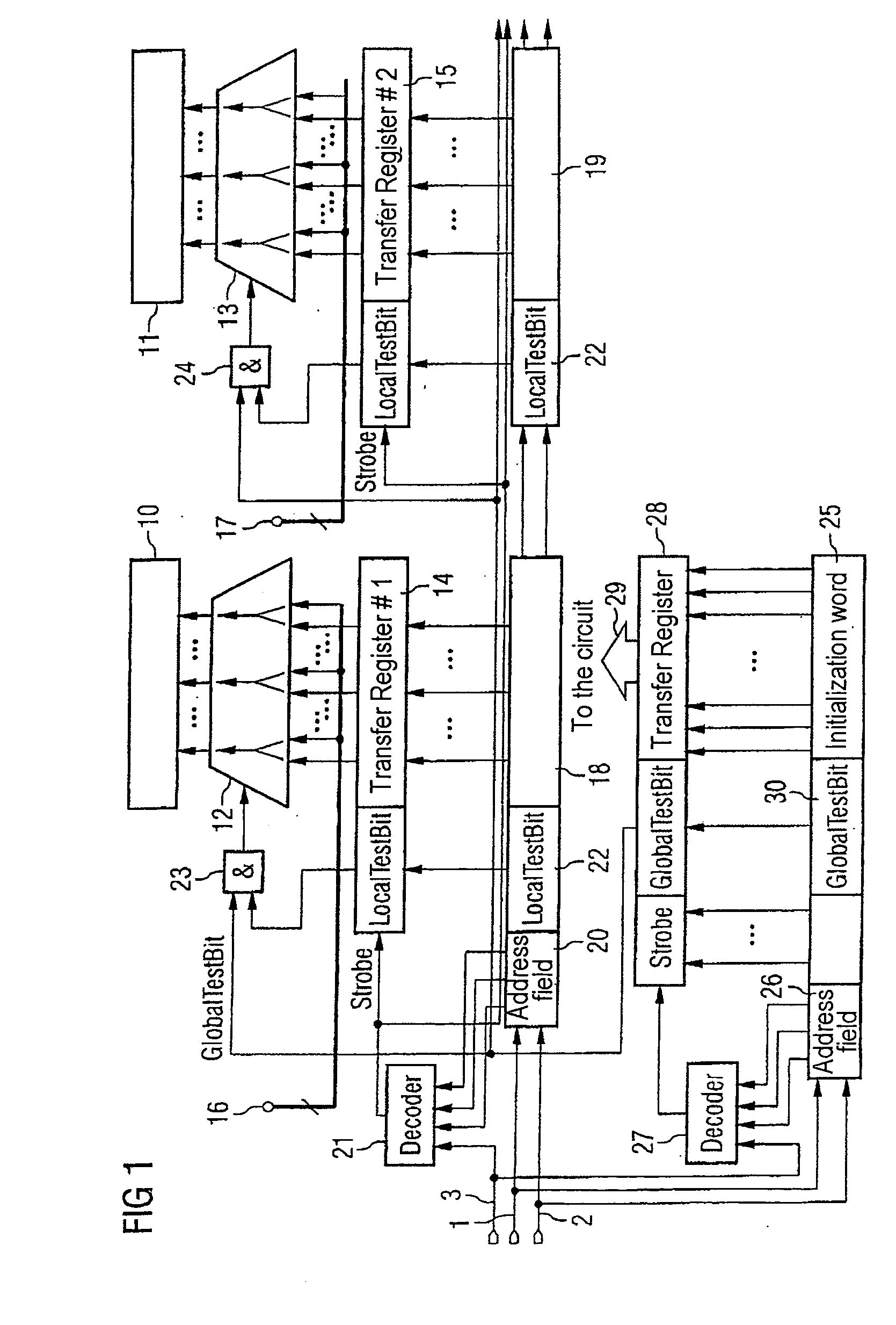

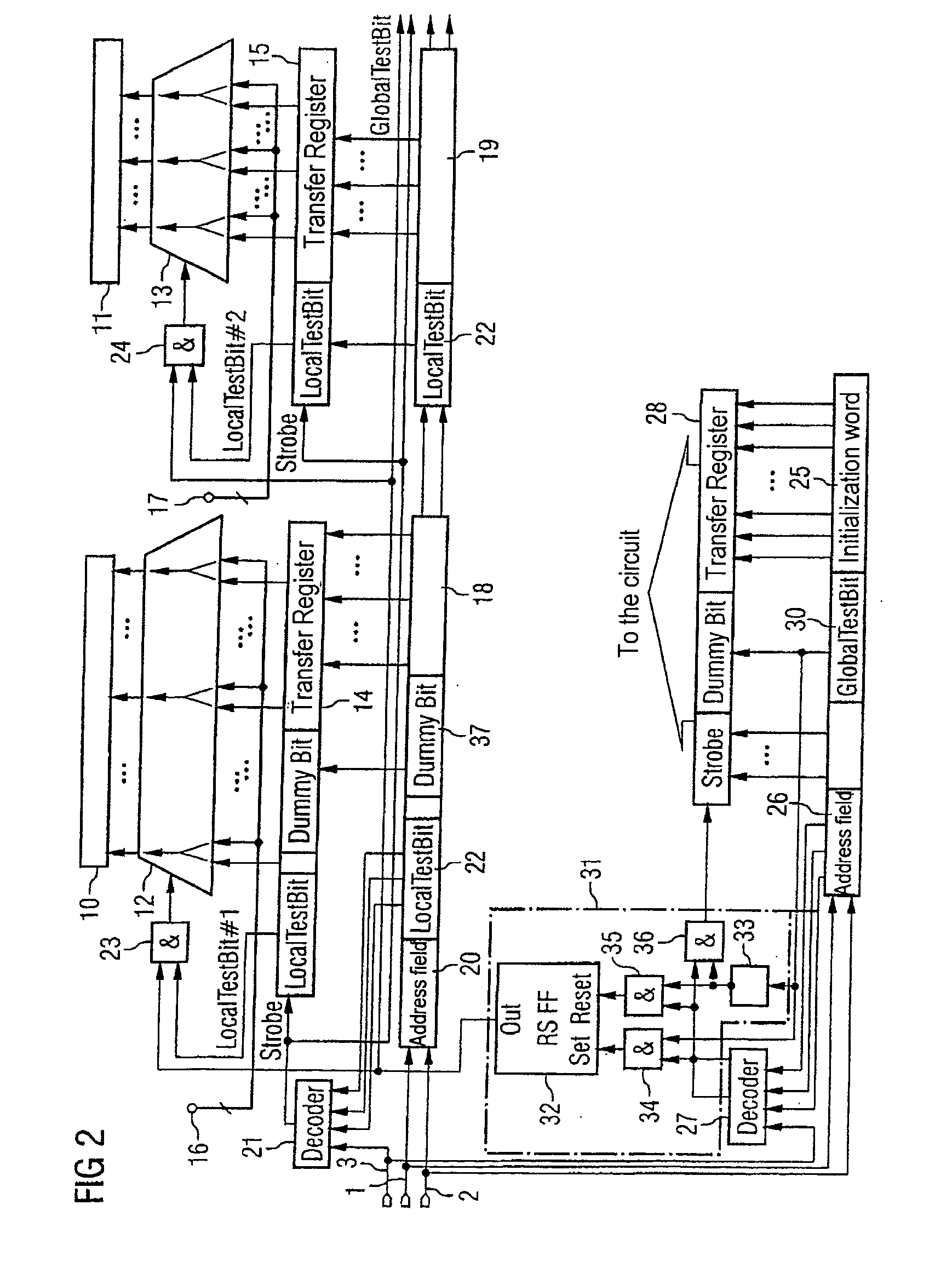

Integrated circuit

InactiveUS7213183B2Little involvementScarce address spaceDigital circuit testingArchitecture with single central processing unitProcessor registerMultiplexer

The invention is directed to an integrated circuit that includes a plurality of functional circuit blocks. Respective associated multiplexers are used to change over between a normal mode and a test mode. The input side of the multiplexers each have a test register connected thereto which is coupled to a serial bus. A control unit controls the transfer of test data to a selected function block on the basis of the state of a mode-of-operation memory cell in the respective test register. This means that there is little involvement required to put individual function blocks of a chip deliberately into a test mode and to program them as appropriate, while other function blocks are operating in normal mode. The principle described allows a high degree of flexibility with regard to the testing of integrated circuits with a multiplicity of functional assemblies.

Owner:INTEL CORP

Integrated circuit and method for testing memory on the integrated circuit

ActiveUS8839057B2Simplify the viewing processAvoid problemsElectronic circuit testingStatic storageProcessor registerComputer module

Owner:ARM LTD

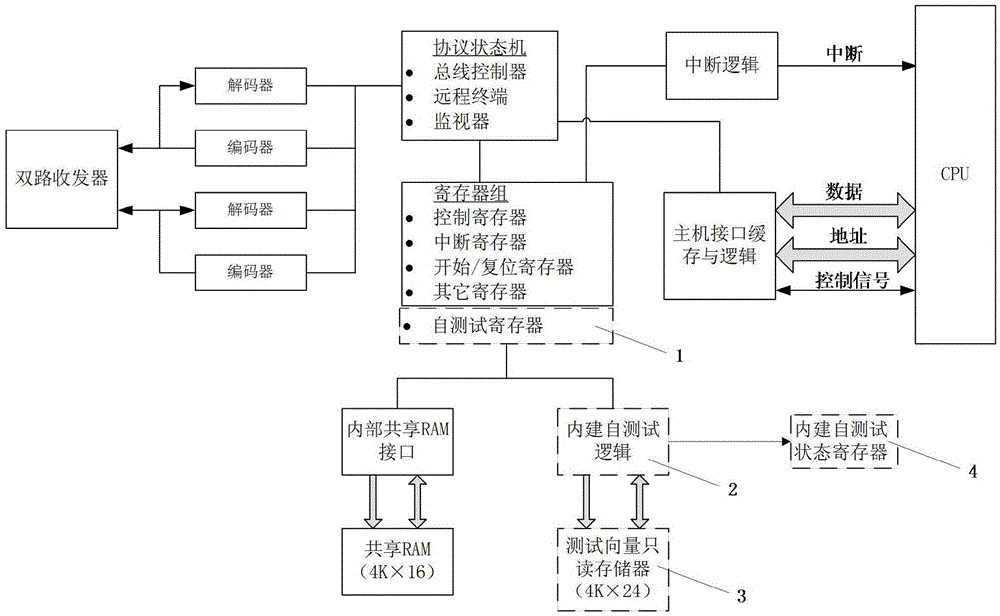

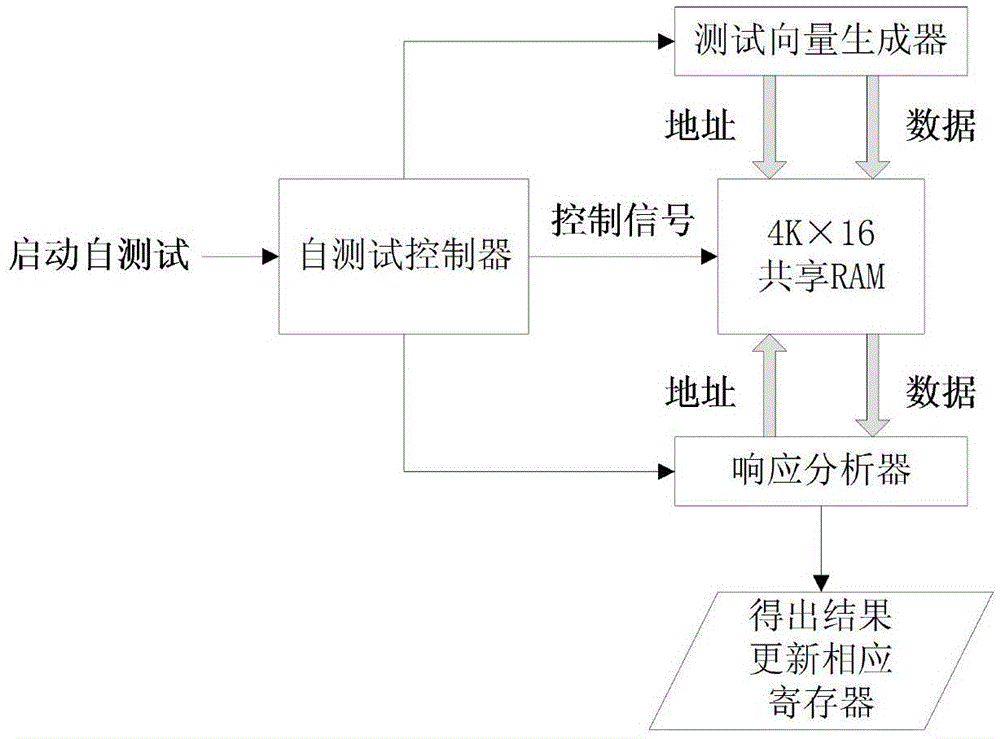

Built-in self-test circuit suitable for 1553 bus protocol

ActiveCN105572565AGuaranteed CompatibilityLow costElectronic circuit testingTest efficiencyCoverage ratio

The invention relates to a built-in self-test (BIST) circuit suitable for a 1553 bus protocol, comprising a self-test register, a BIST logic member, a read only memory for storing test vectors, and a BIST state register. The circuit is provided with a BIST function; partial reserved bits in the start / reset register of an original protocol processor are used for controlling the start and reset of the BIST function; in self-test, the test vector states of current operation are recorded in a corresponding self-test register; self-test results are recorded in the data bit corresponding to the BIST state register. The BIST circuit does not change the structure of an original protocol processor, is only provided with the BIST logic member and the read only memory for storing vectors, and can guarantee a high test coverage ratio, greatly mitigate the circuit test program development difficulty, and improve test efficiency.

Owner:58TH RES INST OF CETC

Diagnosable general purpose test registers scan chain design

ActiveUS7908534B2Rapid localizationRapidly localizing defectElectronic circuit testingStatic storageShift registerMultiplexing

A structural design-for-test for diagnosing broken scan chain defects of long non-scannable register chains (GPTR) The GPTR and the system for testing and diagnosing the broken LSSD scan-only chains rapidly localize defects to the failing Shift Register Latch (SRL) pair. The GPTR modifies the latches used in the GPTR scan chain to standard LSSD L1 / L2 master-slave SRL type latch pairs; connects all the system ports of the L1 latches to the Shift Register Input (SRI) and clocked by the system C1-clk while the L1 scan port is clocked by the A-clk and L2 scan port is clocked only by the B-clk. The L1 latches are connected to at least one multiplexer having a first output connected to an input of each odd SRL, and a second output connected to an input port of each even SRL. In another embodiment, the GPTR includes a plurality of multiplexers respectively coupled to the master-slave latch pairs, wherein a first set of multiplexers have their respective output attached to an input of the odd L1 latches, and a second set of the multiplexers have their respective output attached to an input port of the even L1 latches.

Owner:MARVELL ASIA PTE LTD

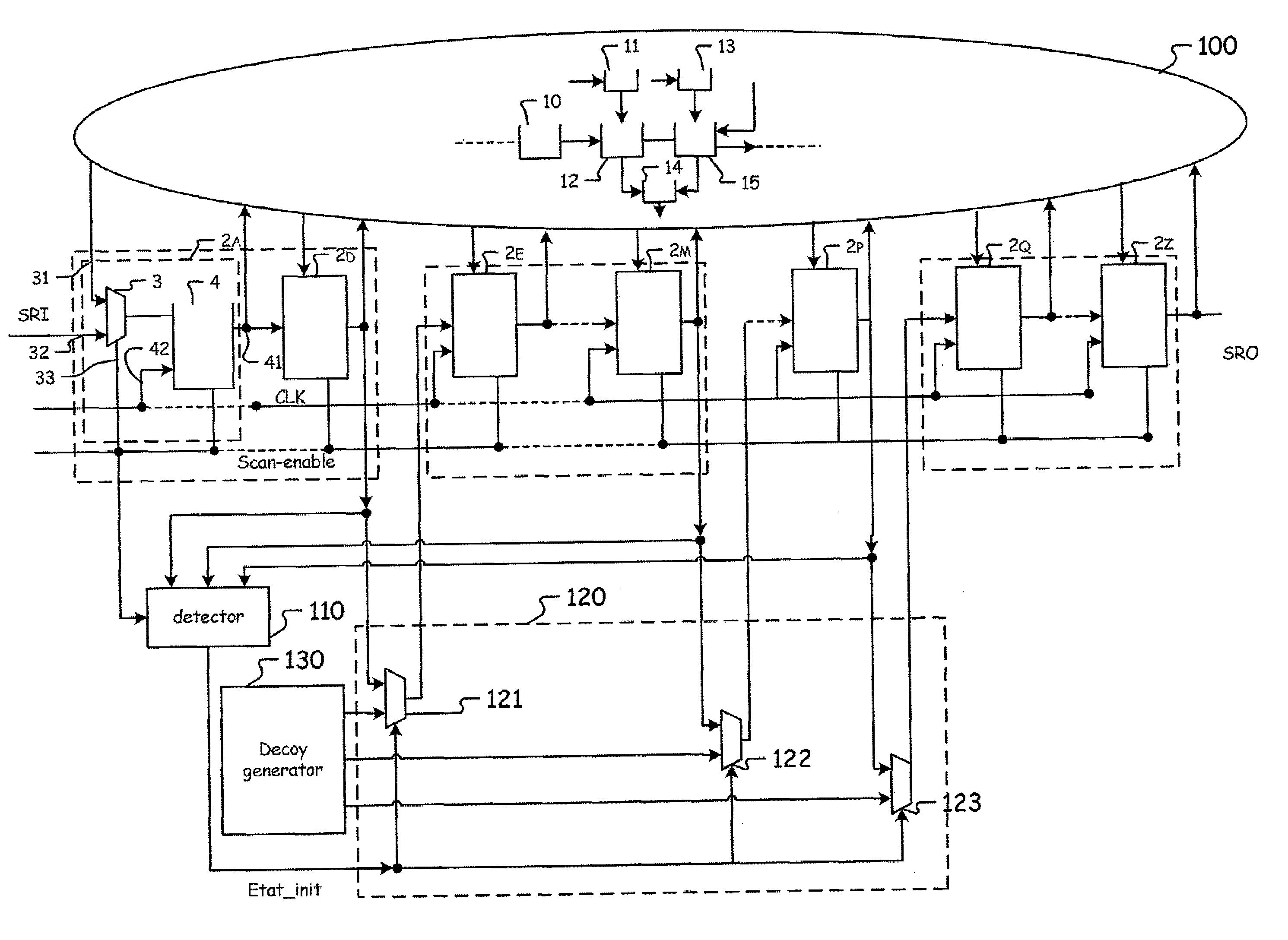

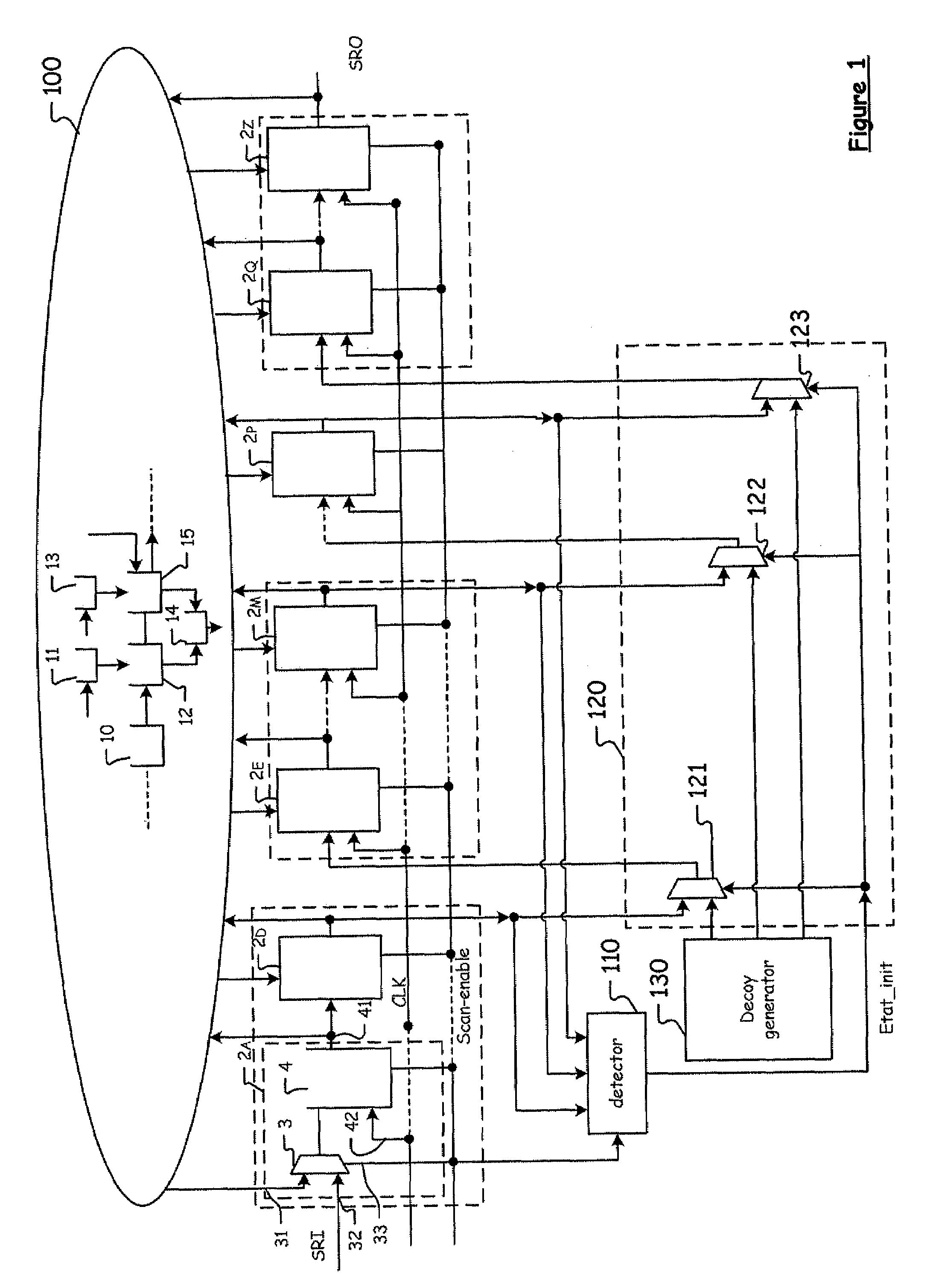

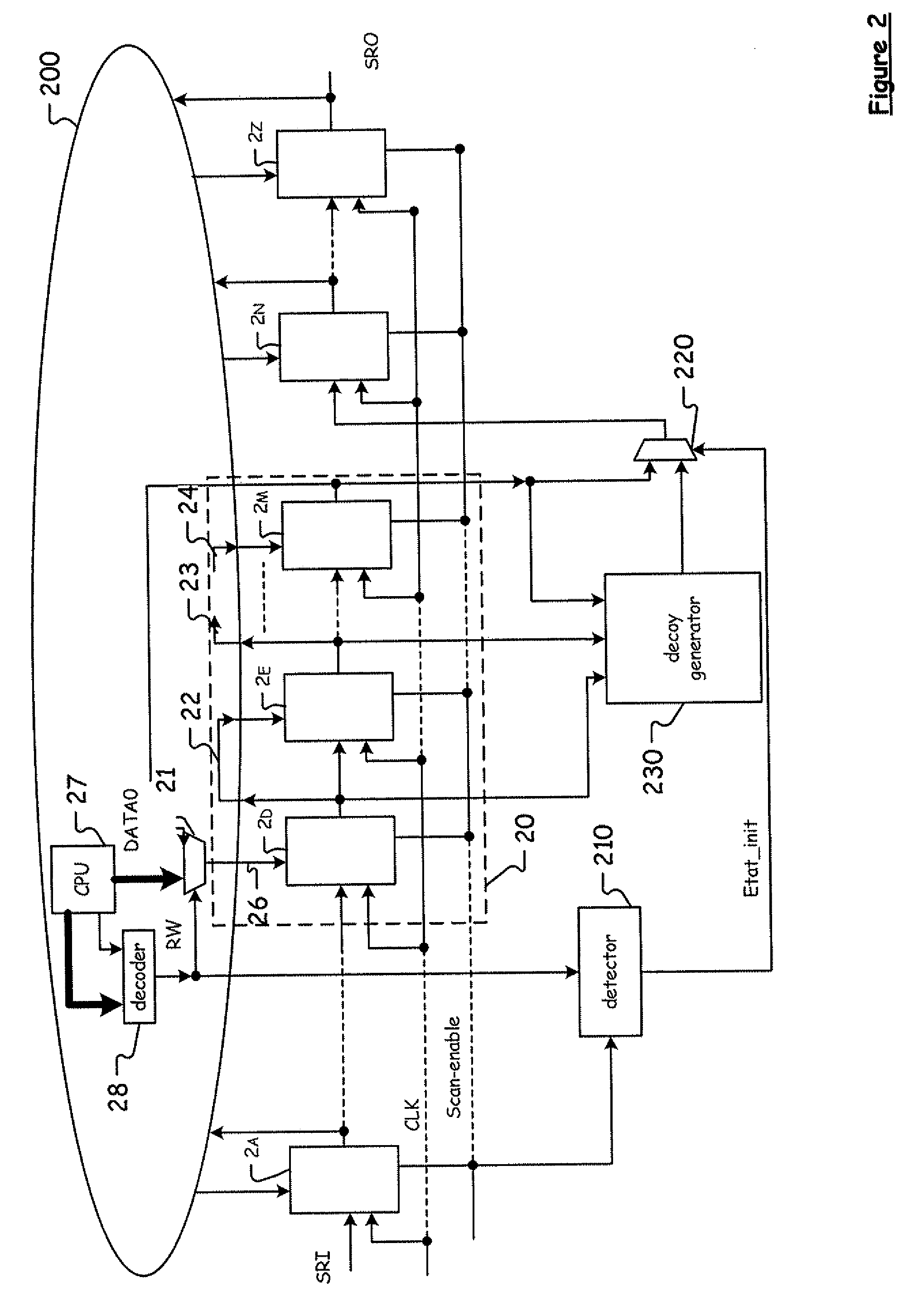

Electronic circuit comprising a test mode secured by insertion of decoy data in the test chain, associated method

An electronic circuit includes configurable cells each having a test input and an output. The configurable cells are connected to one another in a chain in a predefined order via their test input and their output to form a test register based on receiving a chaining command signal. The electronic circuit also includes a detection circuit activated by the chaining command signal to produce a state signal representing a state of initialization of a first set of configurable cells A multiplexing circuit selectively connects the test input of each configurable cell to a second set of the configurable cells either to the output of a preceding configurable cell or to an output of a decoy data generator based on the state signal.

Owner:STMICROELECTRONICS SRL

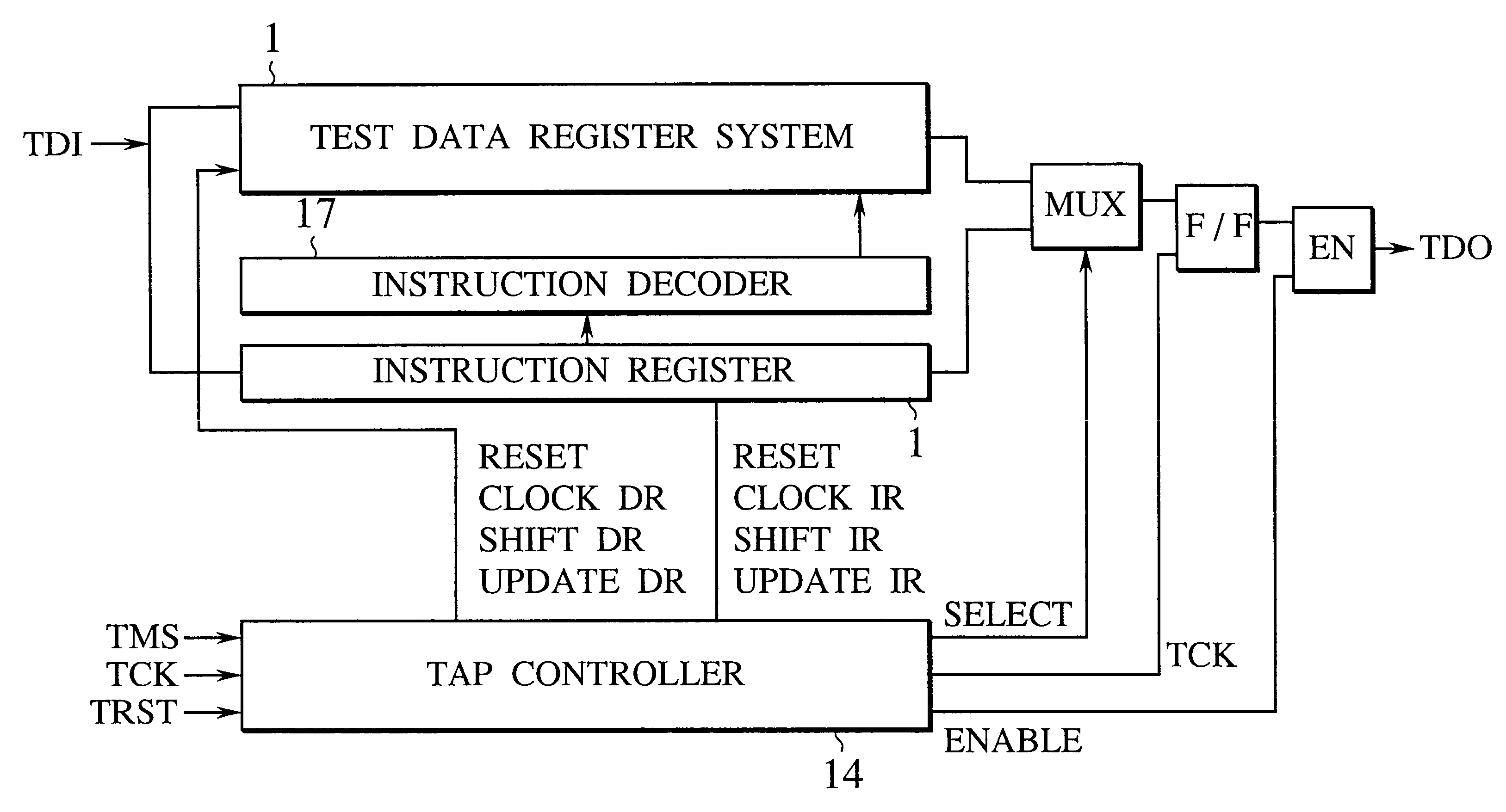

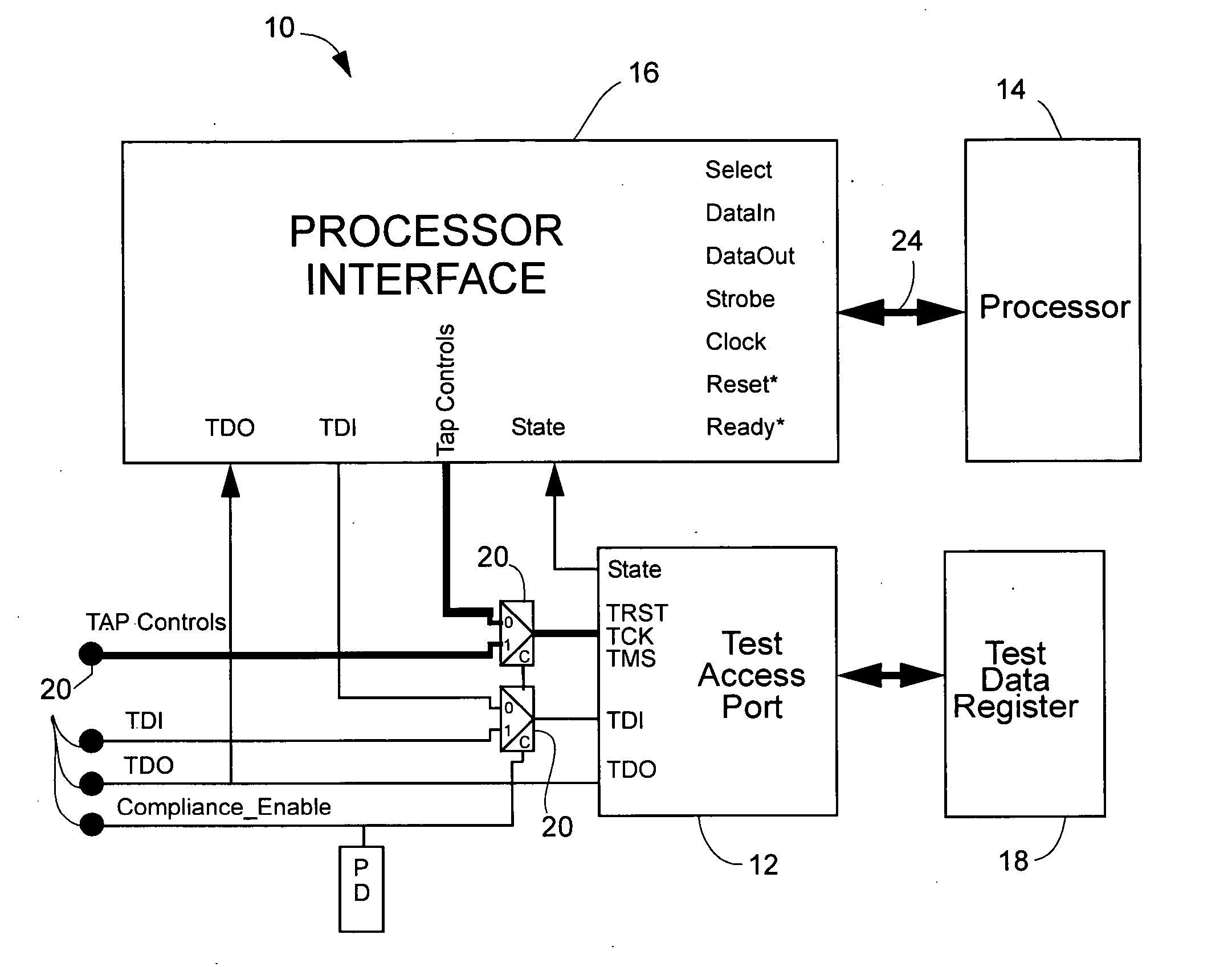

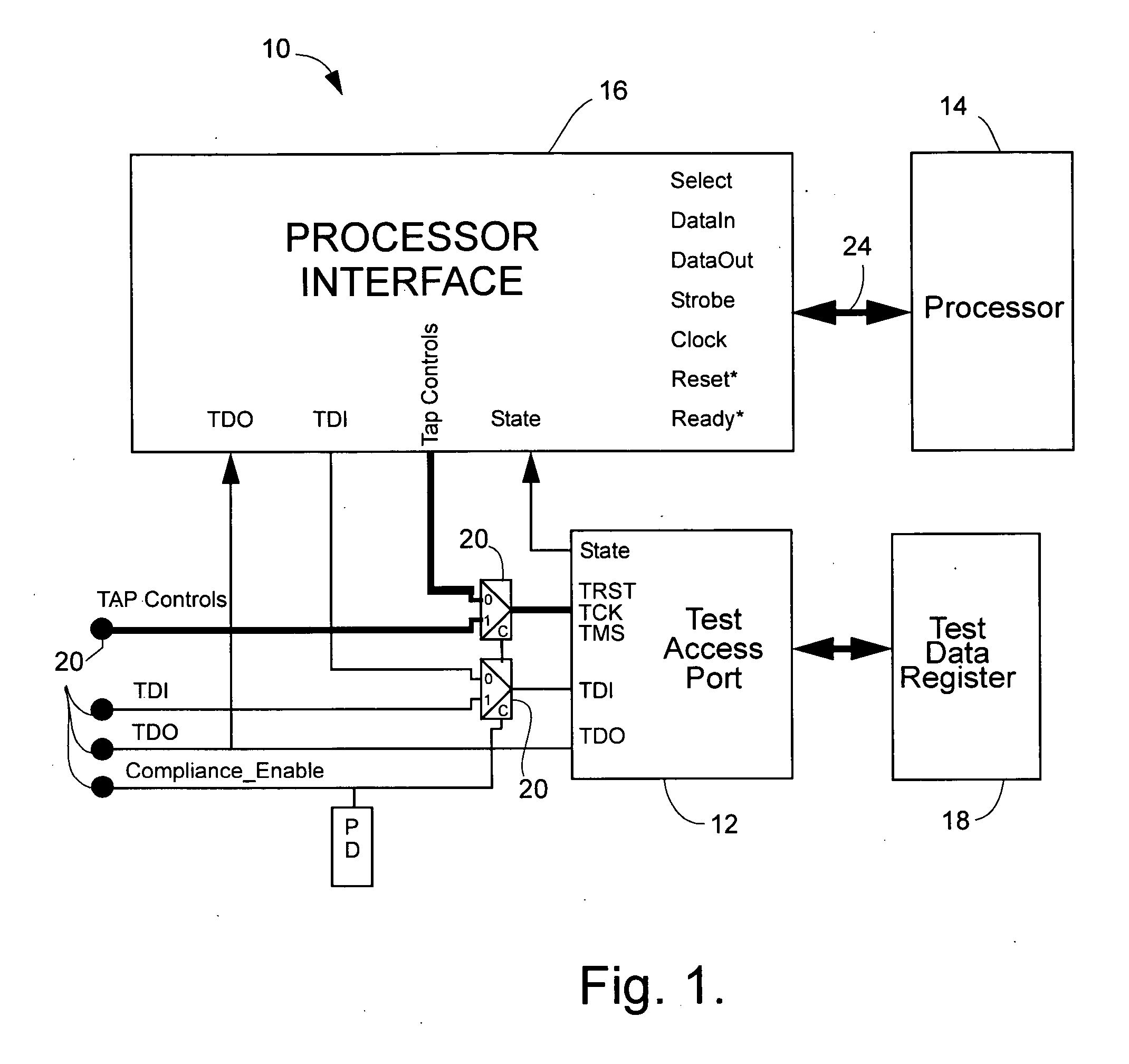

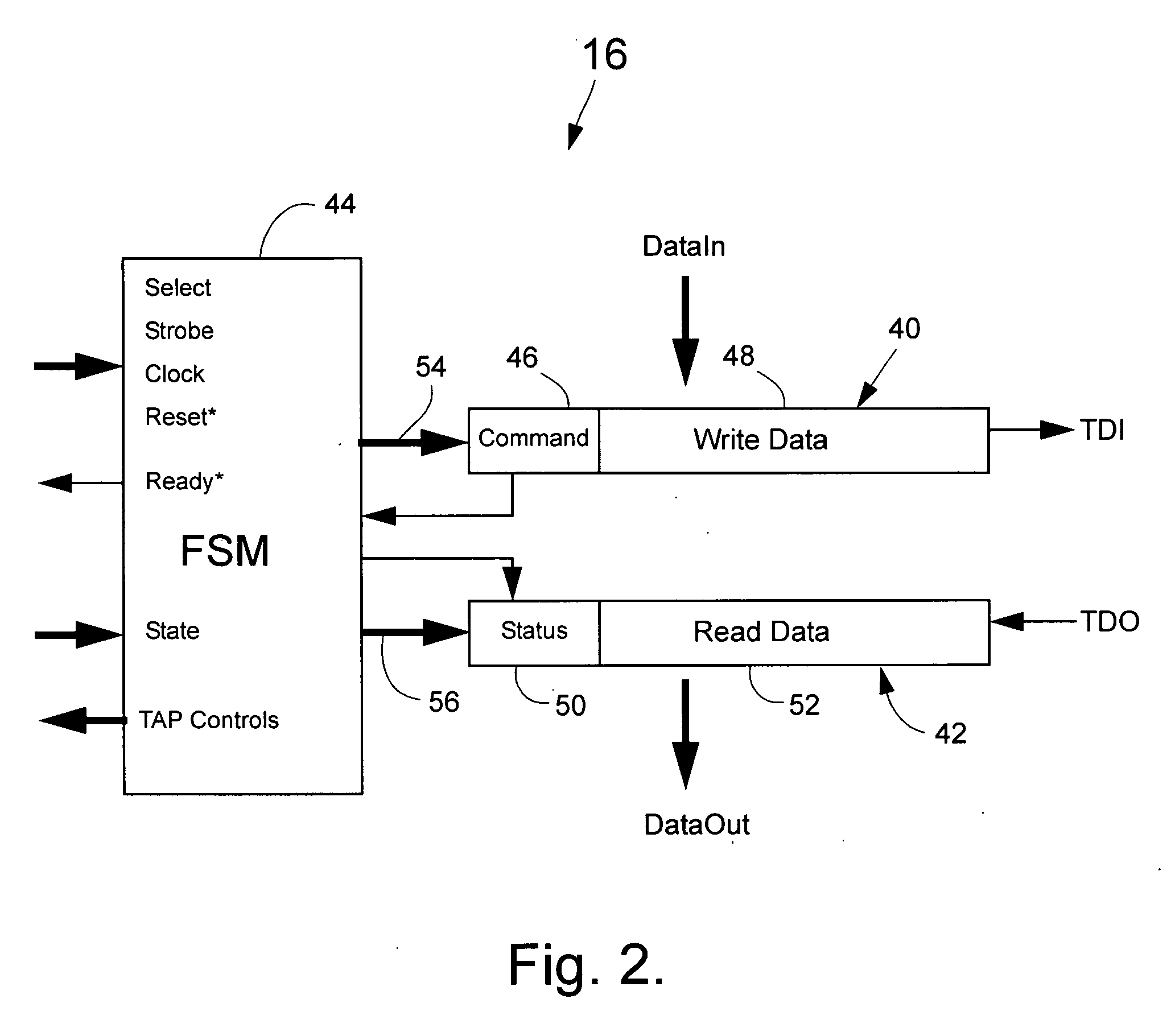

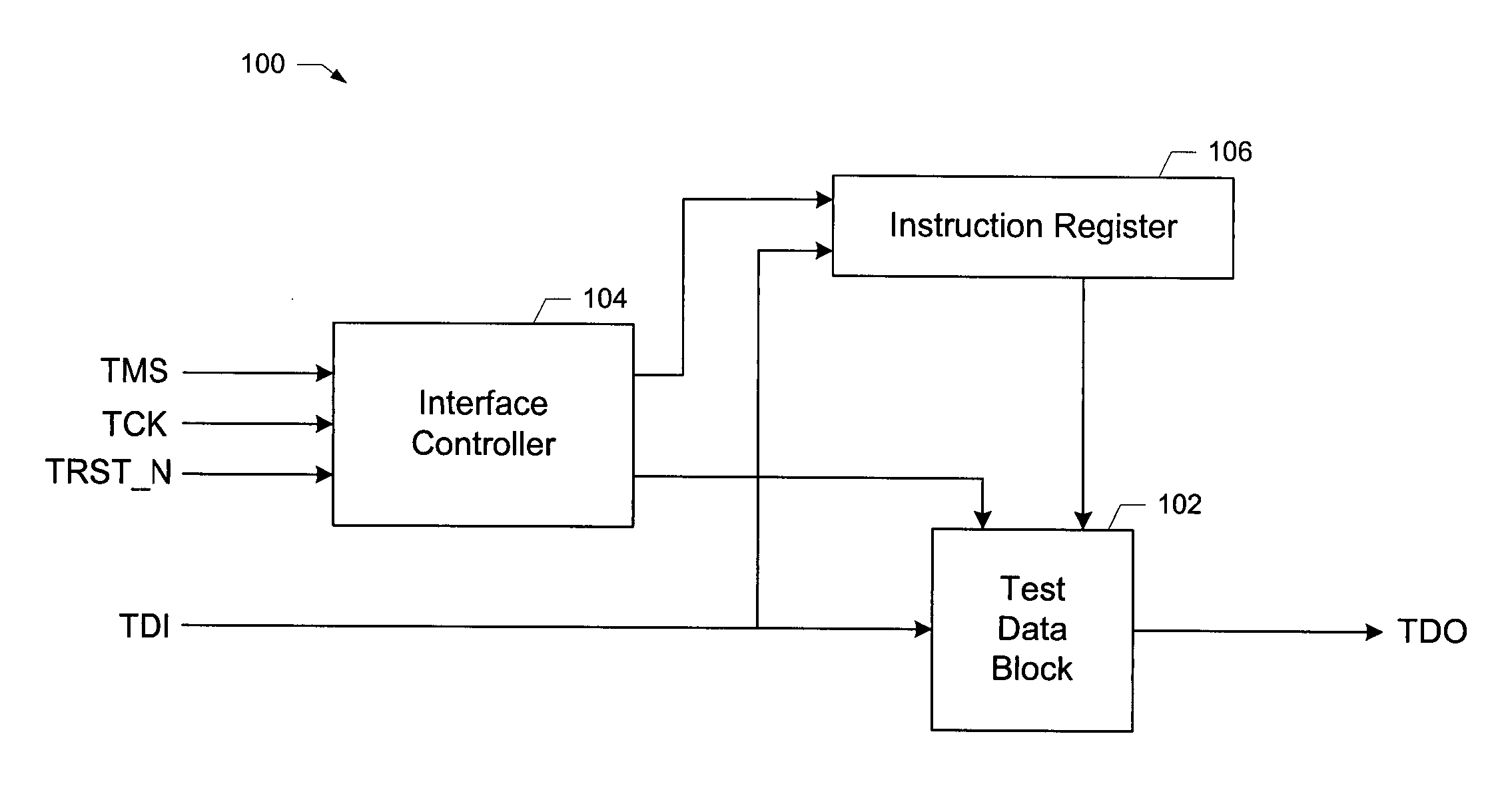

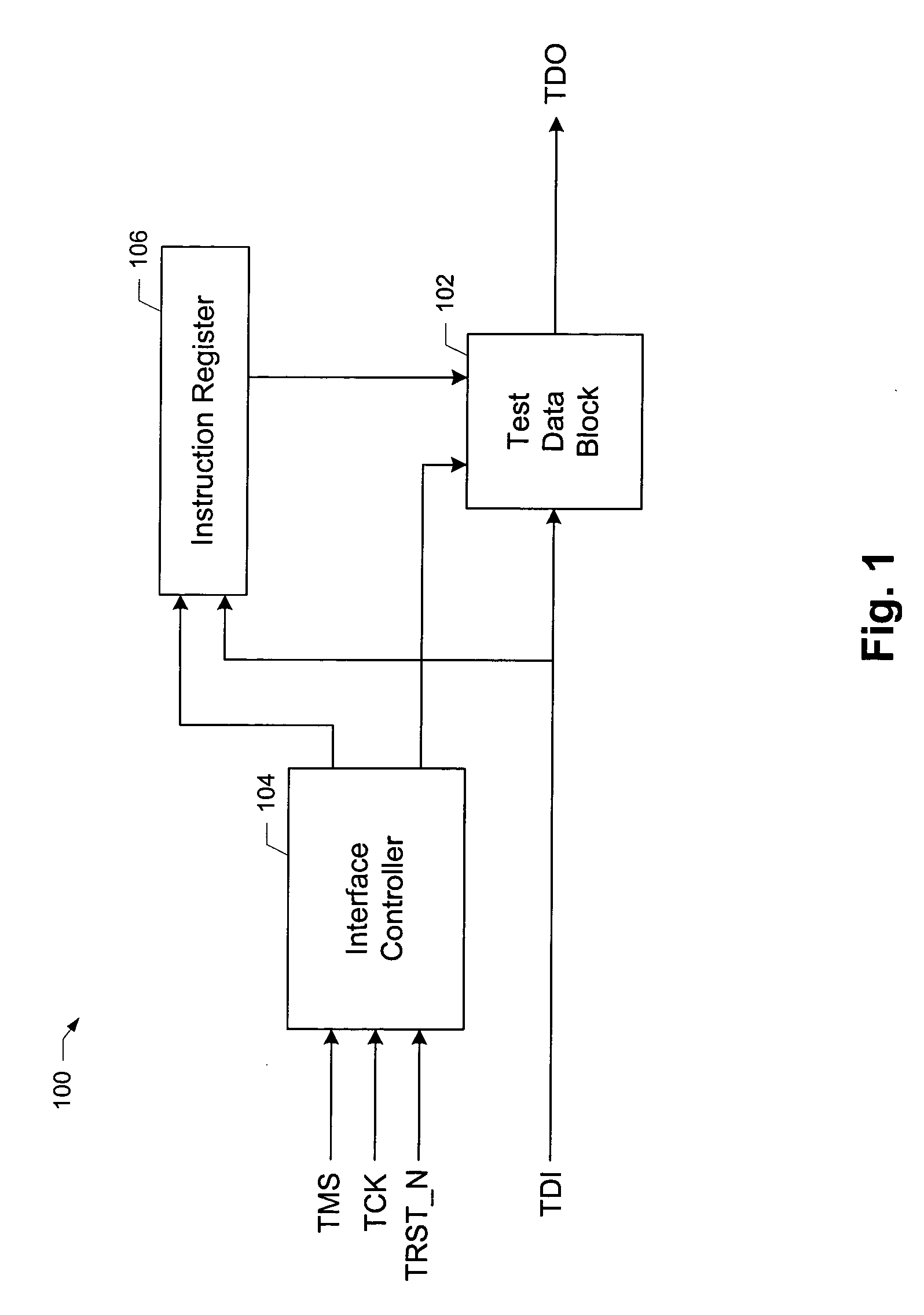

Processor interface for test access port

A processor interface for test access port comprises a write buffer for storing data output by a processor and having a command field, a data field, and a serial output connected to a serial input of the test access port, a read buffer for storing data output by the test access port for access by the processor and having a data field, and a serial input connected to a serial output of the test access port; and a control circuit responsive to a command stored in the command field for generating test access port control signals for transferring test data from the write buffer to the test register and from the test register to the read buffer via test access port serial input and serial output.

Owner:LOGICVISION

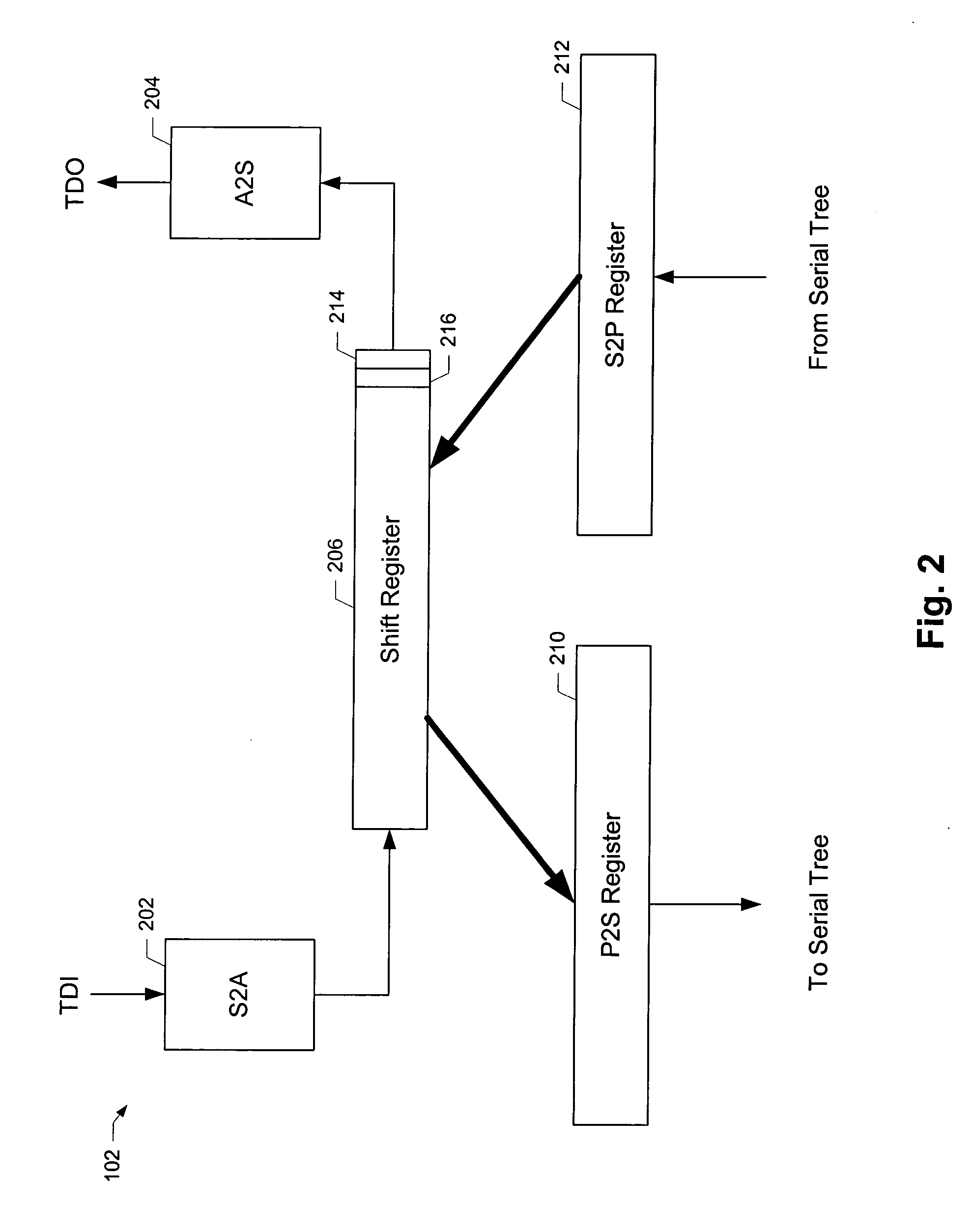

Methods and apparatus for providing test access to asynchronous circuits and systems

InactiveUS20050013356A1Easy to testPromote conversionPulse automatic controlElectronic circuit testingAsynchronous circuitData translation

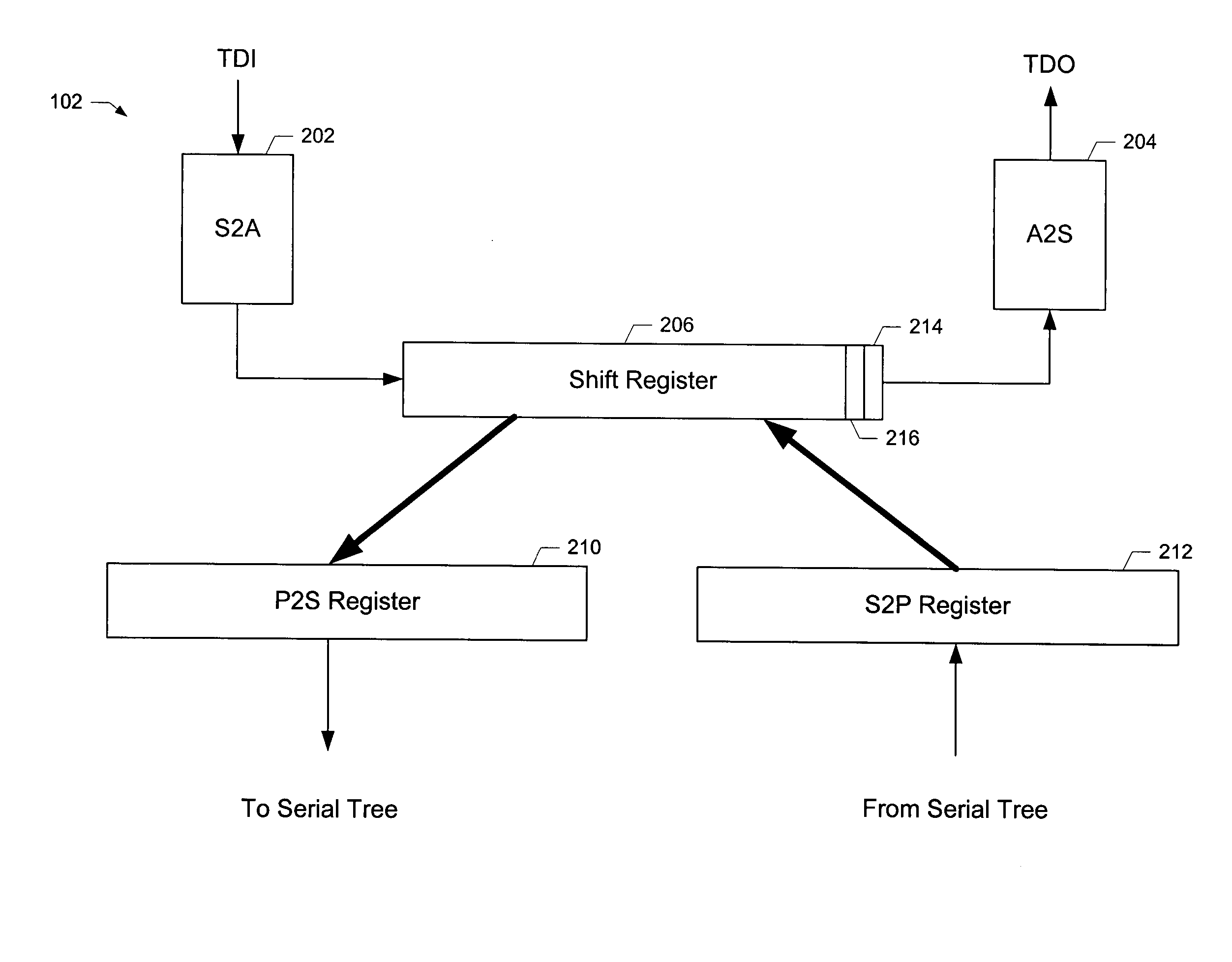

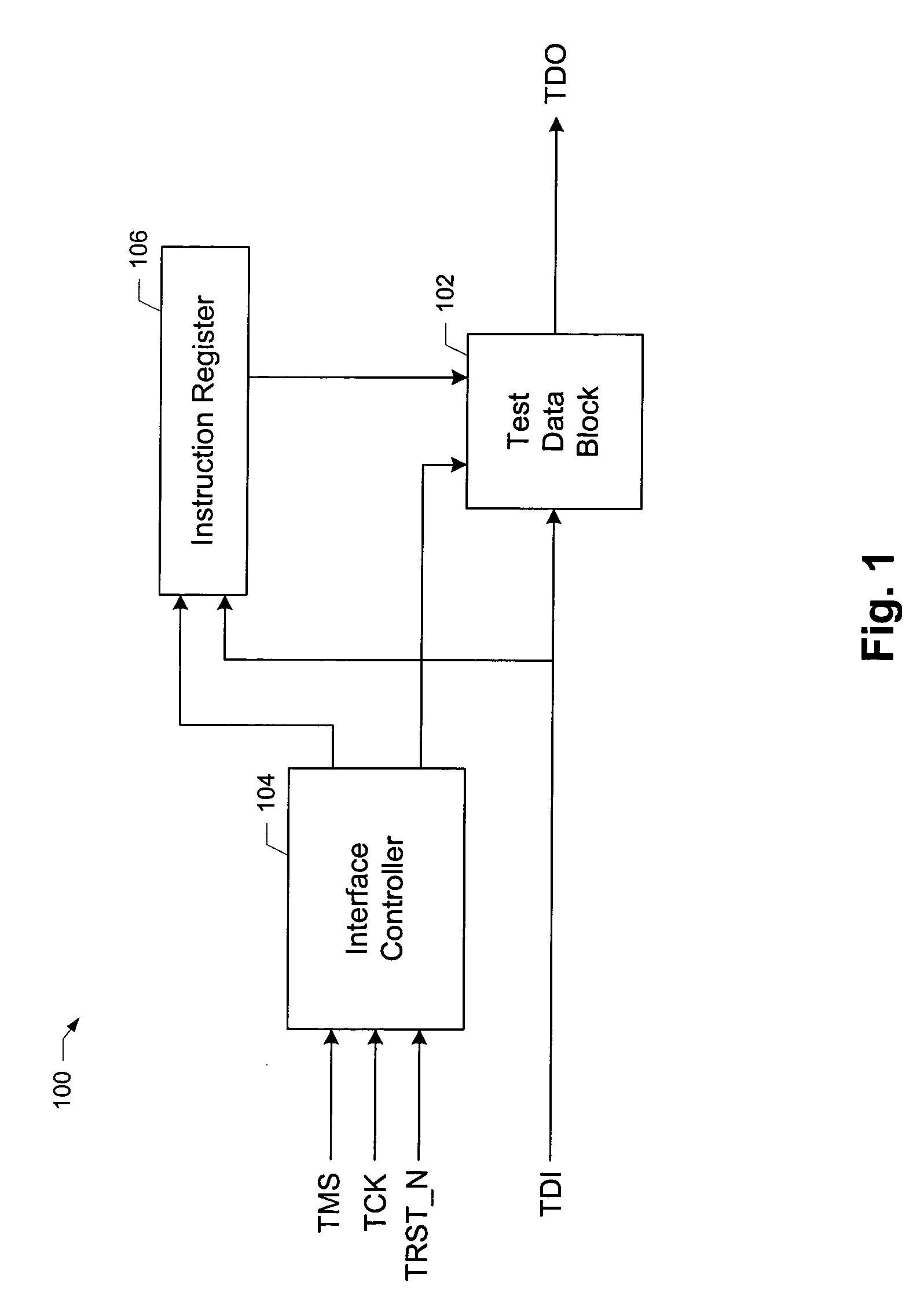

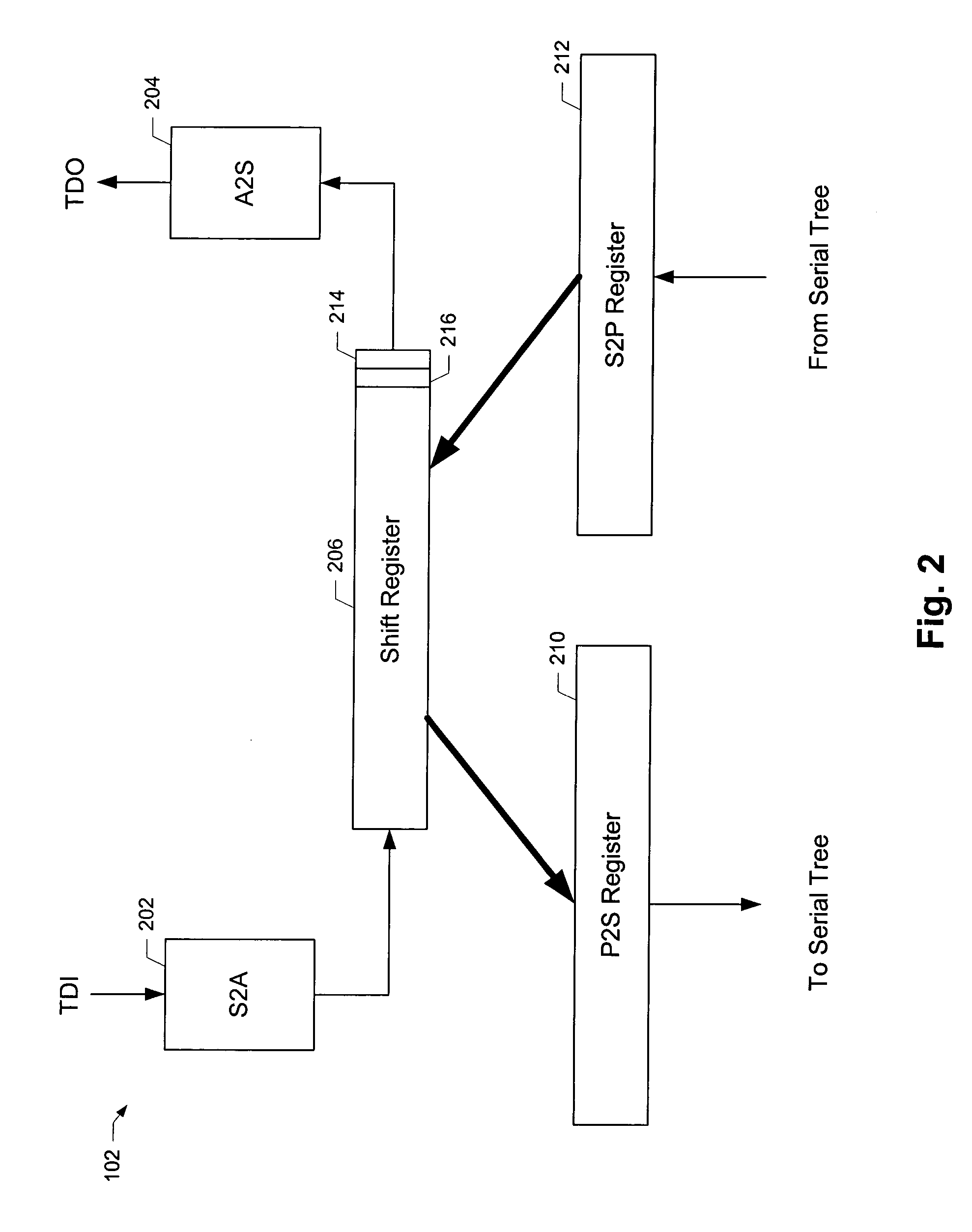

Methods and apparatus are described for providing test access by synchronous test equipment to an asynchronous circuit. Synchronous-to-asynchronous (S2A) conversion circuitry is operable to receive synchronous input data serially from the synchronous test equipment and convert the synchronous input data to asynchronous input data. Asynchronous logic is operable to transmit the asynchronous input data to a first test register in the asynchronous circuit, and to transmit asynchronous output data received from a second test register in the asynchronous circuit. The asynchronous output data results from application of the asynchronous input data to the asynchronous circuit. Operation of the asynchronous logic is synchronized at least in part with a clock signal associated with the synchronous test equipment. Asynchronous-to-synchronous (A2S) conversion circuitry is operable to receive the asynchronous output data from the asynchronous logic, convert the asynchronous output data to synchronous output data, and serially transmit the synchronous output data to the synchronous test equipment.

Owner:INTEL CORP

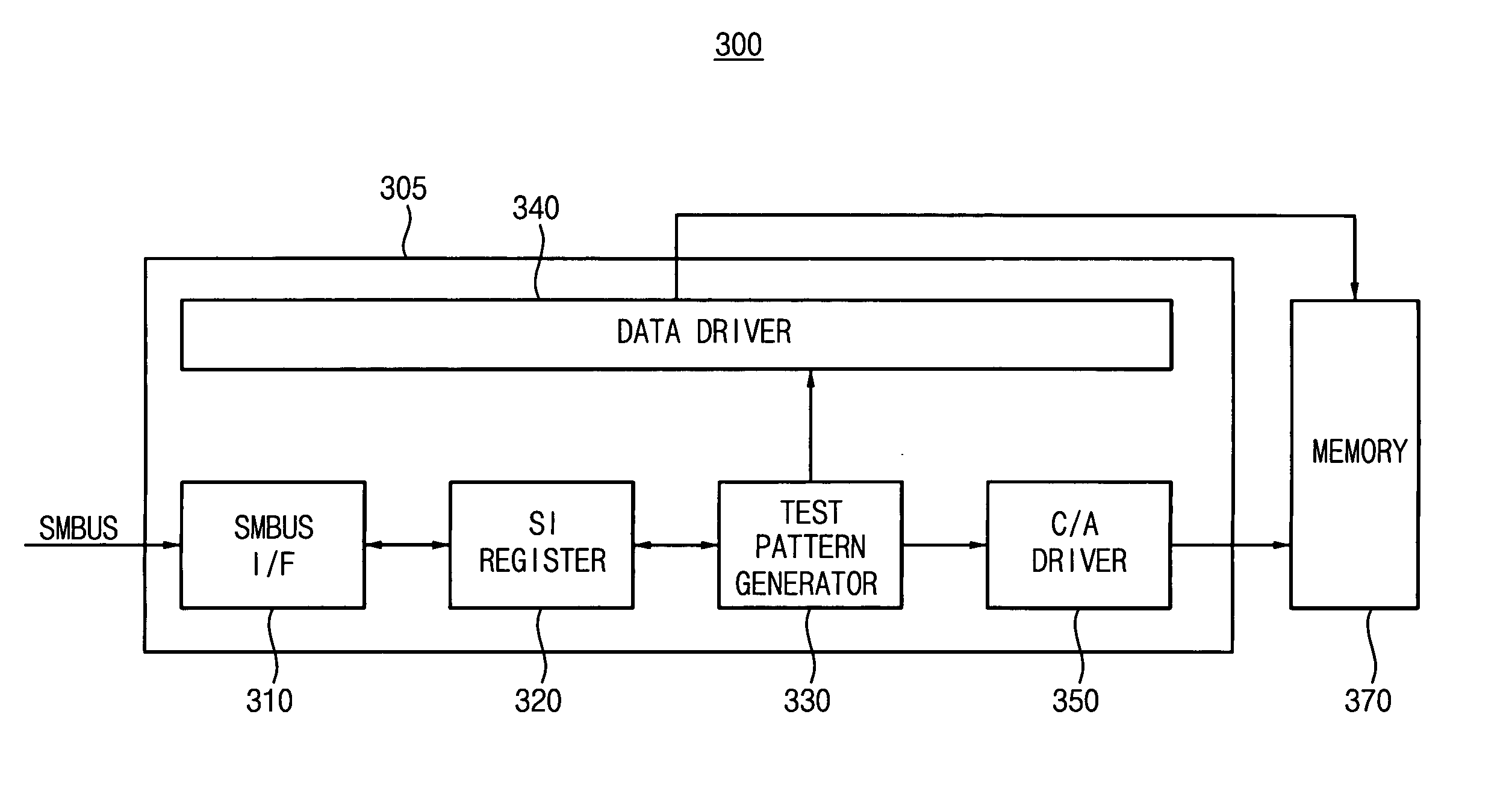

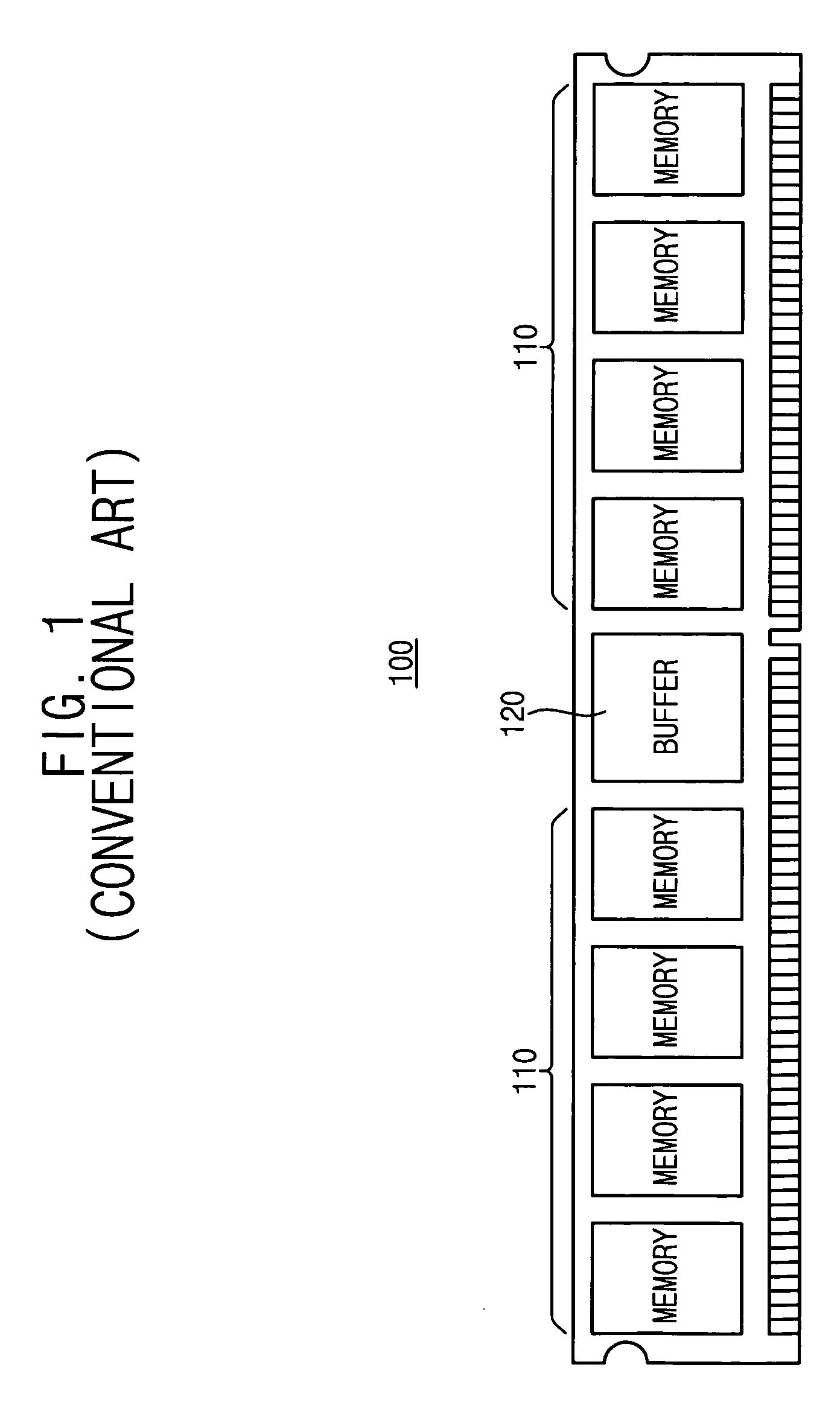

Buffer for testing a memory module and method thereof

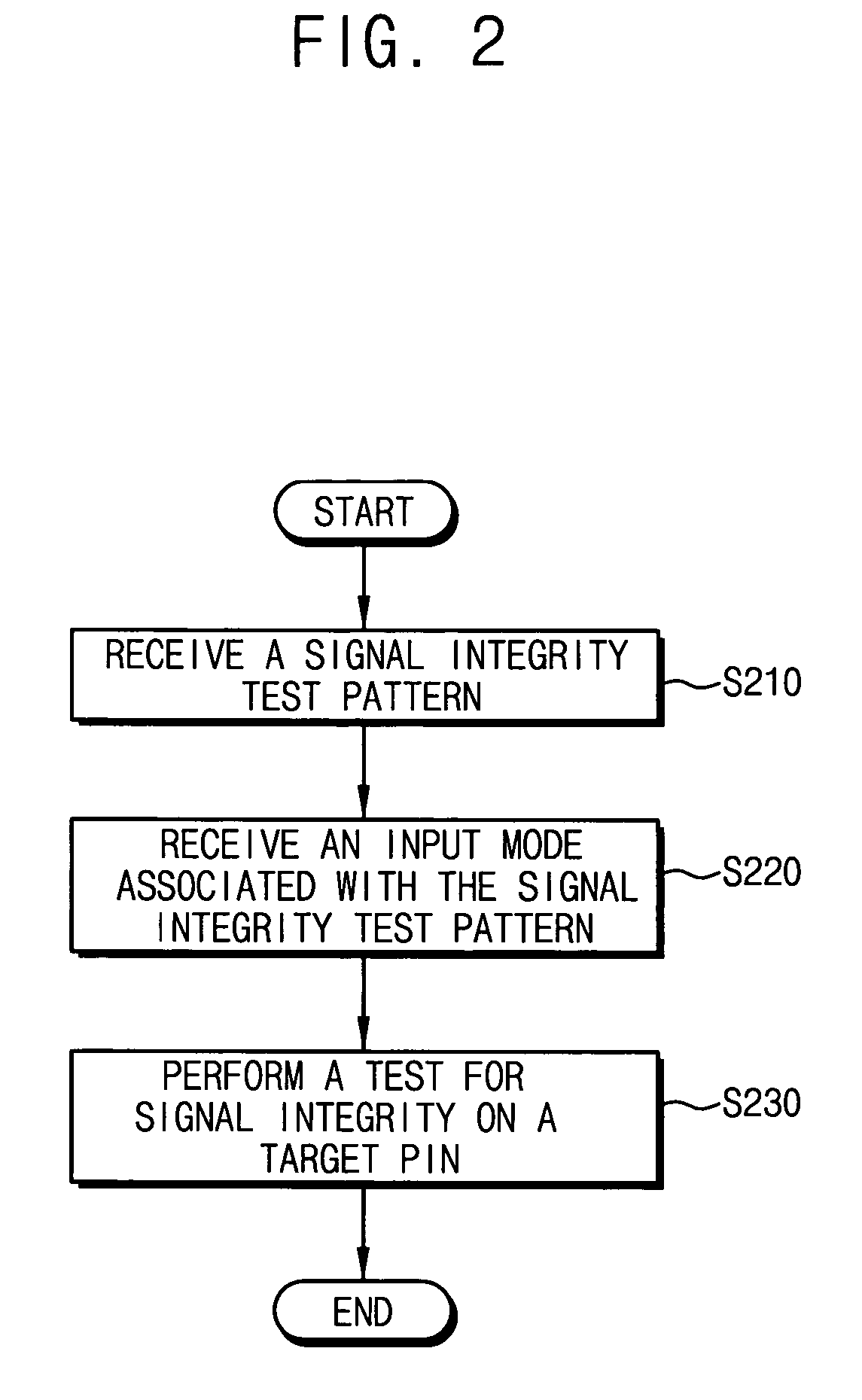

In a method, a test pattern and an associated input mode may be received where the input mode may indicate a manner of applying the test pattern. An output test pattern is applied to at least one of a plurality of memory interface pins in accordance with the input mode. In a buffer, a test register may be configured to receive and store a test pattern and an associated input mode where the input mode may indicate a manner of applying the test pattern. The buffer may further include a test pattern generator configured to repeatedly generate an output test pattern based on the associated input mode.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods and apparatus for providing test access to asynchronous circuits and systems

InactiveUS7260753B2Easy to testPromote conversionPulse automatic controlElectronic circuit testingAsynchronous circuitData translation

Methods and apparatus are described for providing test access by synchronous test equipment to an asynchronous circuit. Synchronous-to-asynchronous (S2A) conversion circuitry is operable to receive synchronous input data serially from the synchronous test equipment and convert the synchronous input data to asynchronous input data. Asynchronous logic is operable to transmit the asynchronous input data to a first test register in the asynchronous circuit, and to transmit asynchronous output data received from a second test register in the asynchronous circuit. The asynchronous output data results from application of the asynchronous input data to the asynchronous circuit. Operation of the asynchronous logic is synchronized at least in part with a clock signal associated with the synchronous test equipment. Asynchronous-to-synchronous (A2S) conversion circuitry is operable to receive the asynchronous output data from the asynchronous logic, convert the asynchronous output data to synchronous output data, and serially transmit the synchronous output data to the synchronous test equipment.

Owner:INTEL CORP

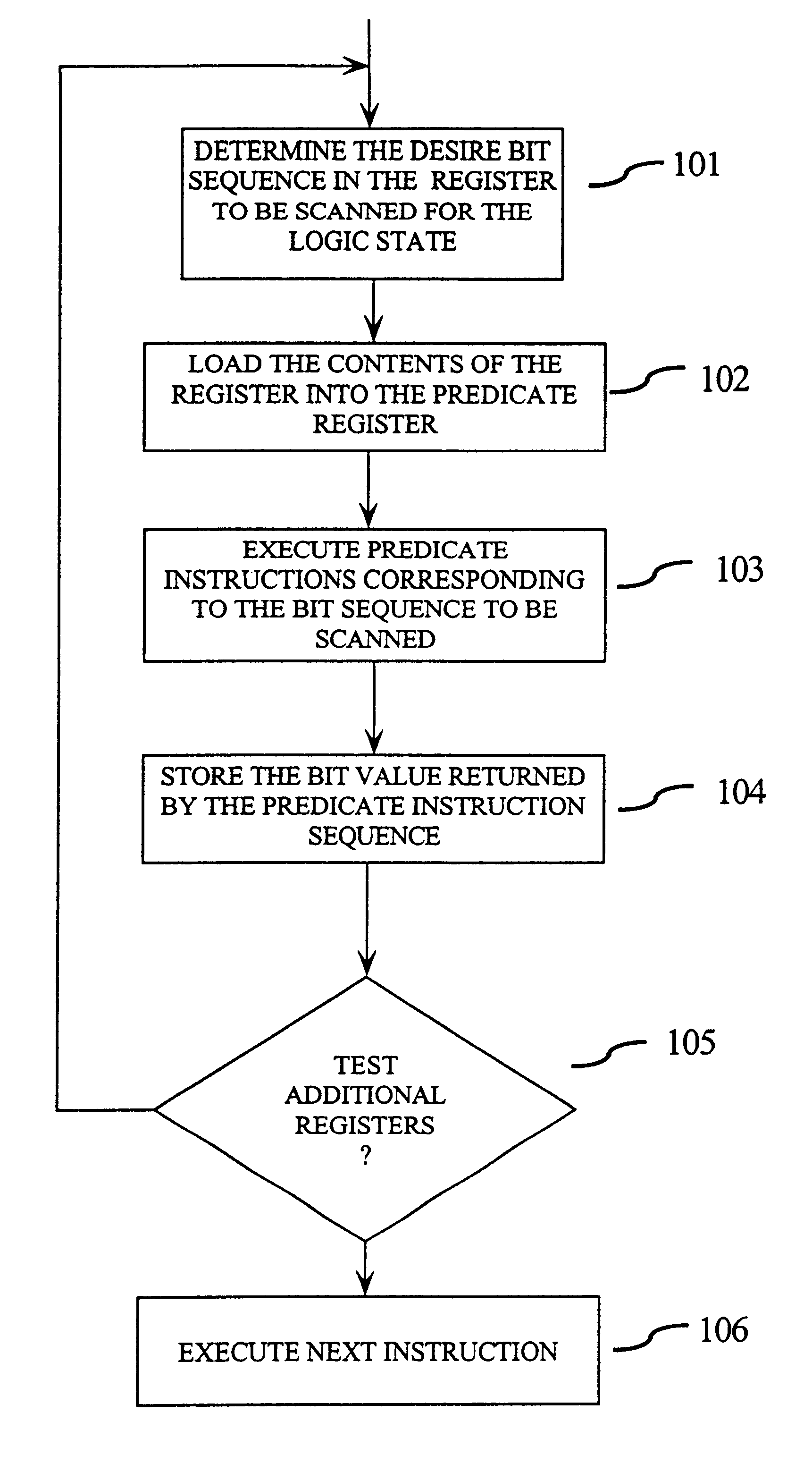

Register bit scanning

InactiveUS6654878B1Digital computer detailsConcurrent instruction executionPowerPCProcessor register

Testing register bits and in particular bitmask registers is a method employed in many computer architectures (e.g., IBM PowerPC, IA32, VAX, etc.) to manage instruction flow within a processor. Since the testing or scanning of bitmask registers for the first occurrence of a logic state (e.g., logic one) is done quite often, register scanning is implemented in hardware in these processors. Other computer architectures (e.g., Intel IA64) manage instruction flow with alternate methods and therefore do register scanning as a software construct. When software written for the first computer architecture (e.g., IBM PowerPC) is ported to a system with IA64 architecture, the program would execute with reduced speed. The IA64 architecture uses the EPIC instruction protocol and as such executes predicate instructions that employ a predicate register where each bit of the predicate register can be associated as the true or false result of a comparison. To scan a register in the IA64 architecture the register contents are loaded into the predicate register and a sequence of predicate instructions are executed in the order that the bits are to be scanned for the desired condition. The sequence of predicate instruction sequence returns the register bit that passes the predicate condition. In this manner the speed of register scanning necessary for the ported software can be increased over the software scanning of the IA64 architecture.

Owner:GOOGLE LLC

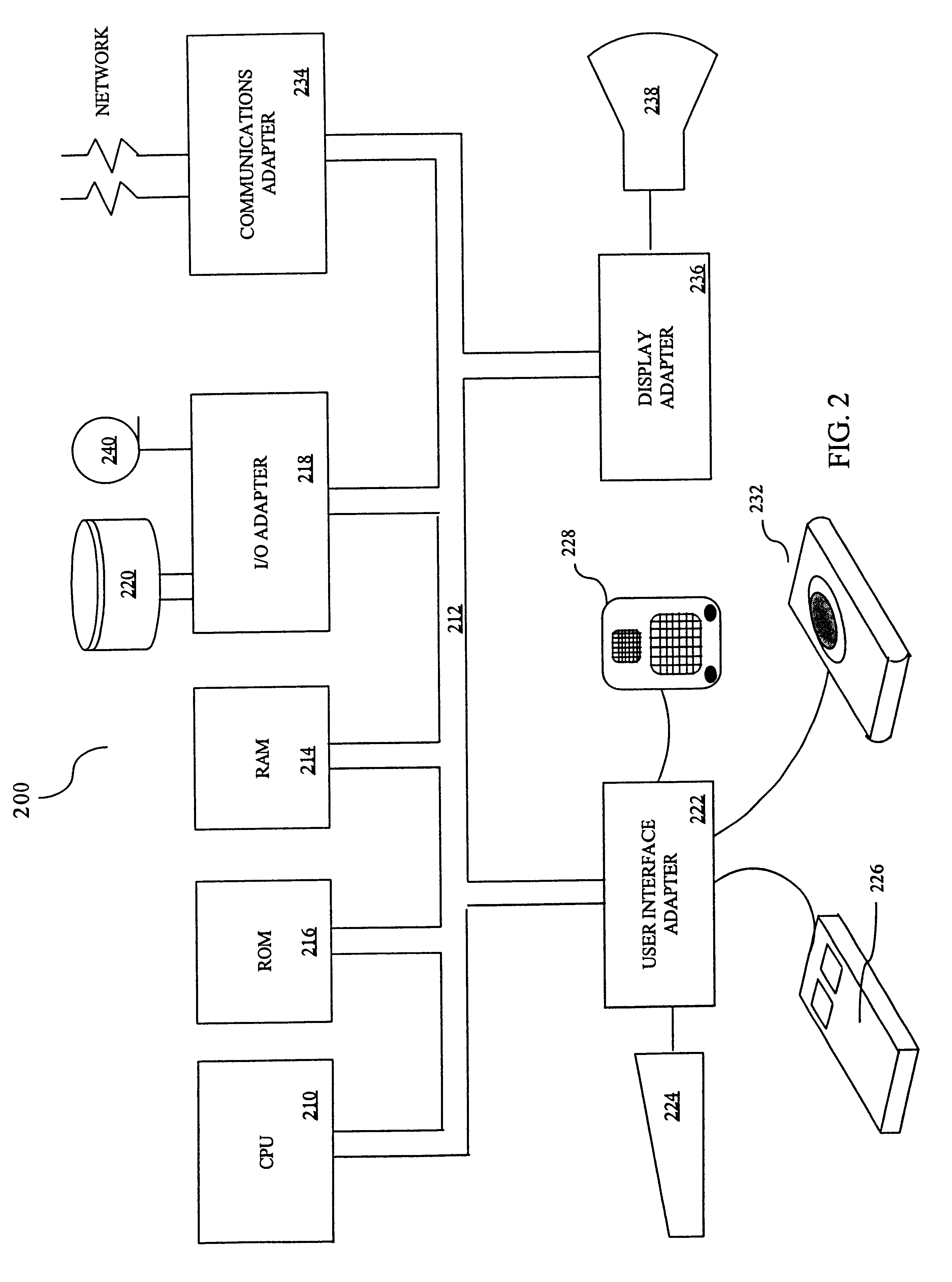

Automatic testing for programmable networks of control signals

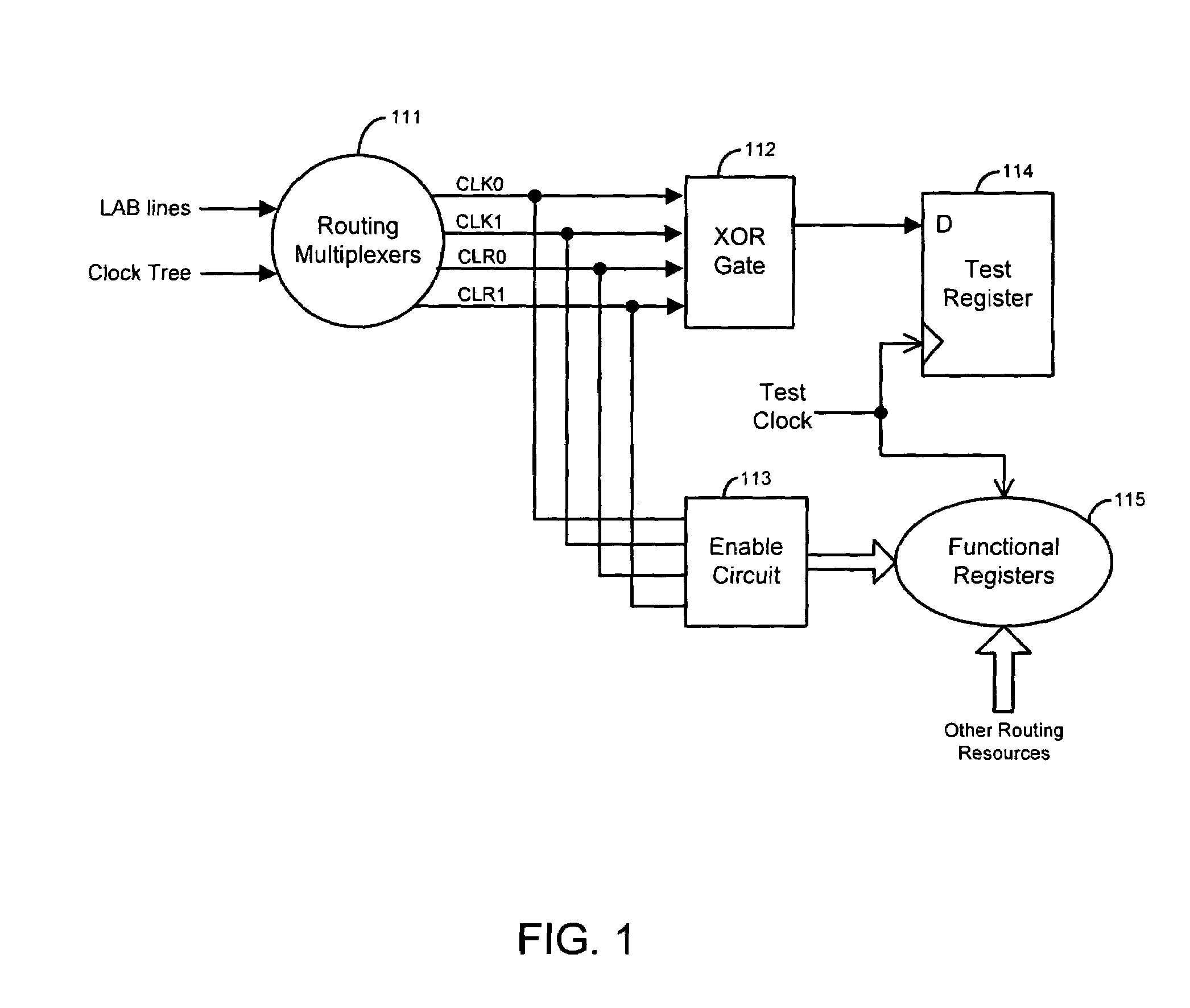

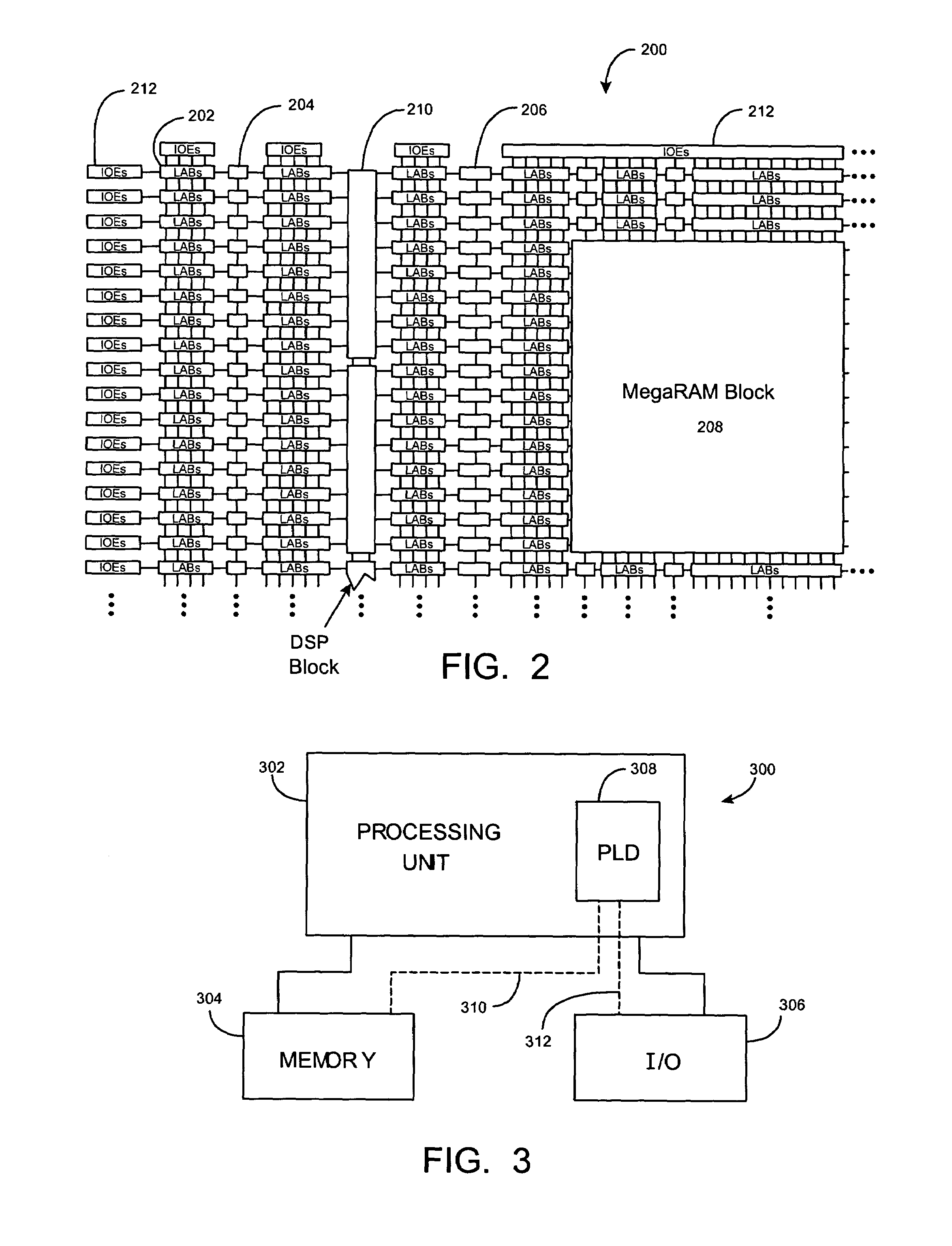

Techniques are provided for testing routing resources that route control signals on programmable integrated circuits (ICs). Control signals (such as clock signals) are routed through a logic gate to a test register. Values of the control signals are stored in the test register, transmitted outside the IC, and then compared to expected values to identify defects in the programmable interconnections. An enable circuit couples the control signals to functional registers on the programmable IC during user mode. The enable circuit decouples the control signals from the functional registers so that the control signals do not interfere with tests of the functional registers during test mode. During the test procedures, the control signals are treated as data signals and are not used to control other registers on the IC.

Owner:ALTERA CORP

Method and apparatus for testing circuit modules

InactiveUS6920582B2Without limitationElectronic circuit testingError detection/correctionSample ModeProcessor register

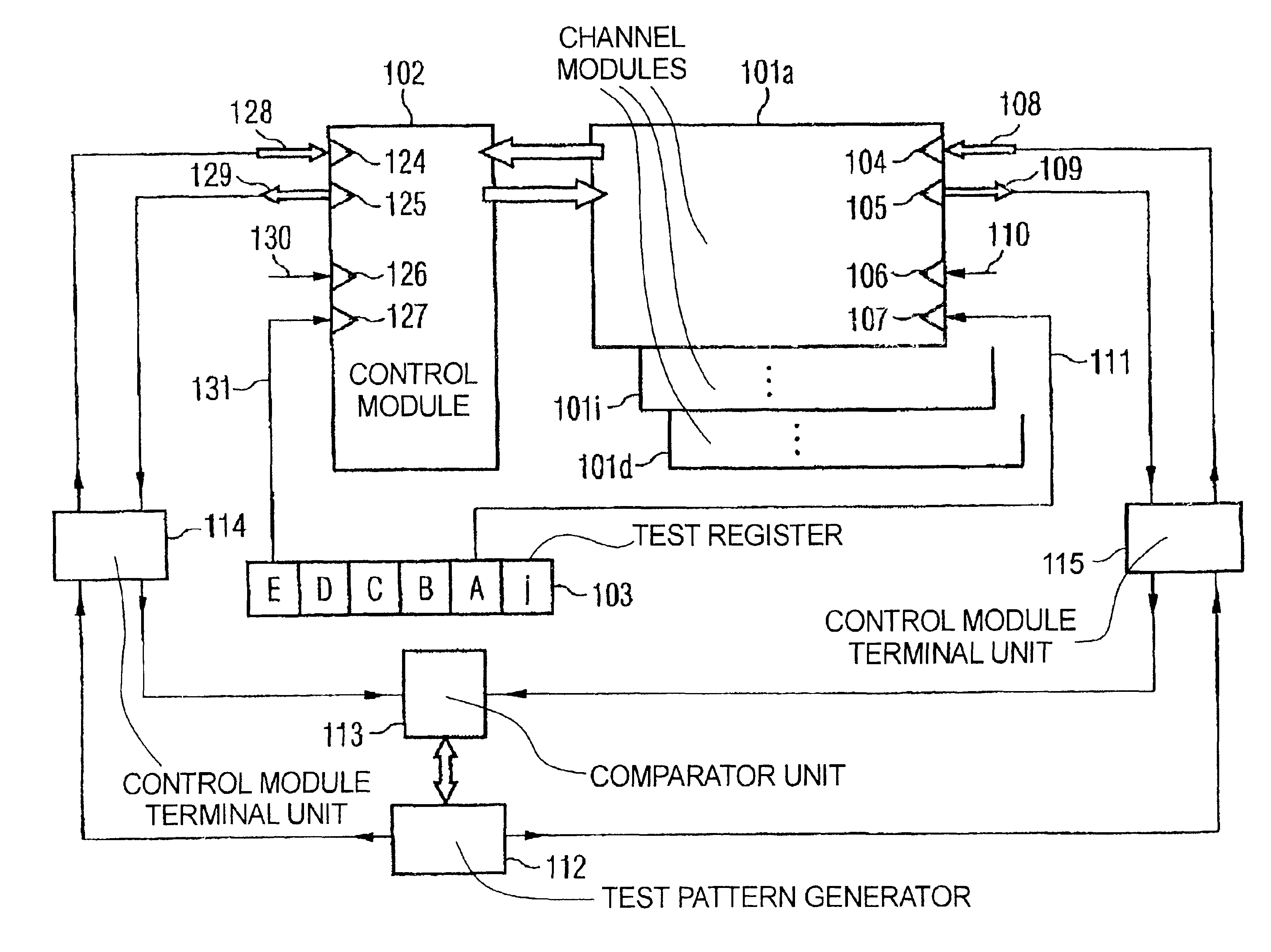

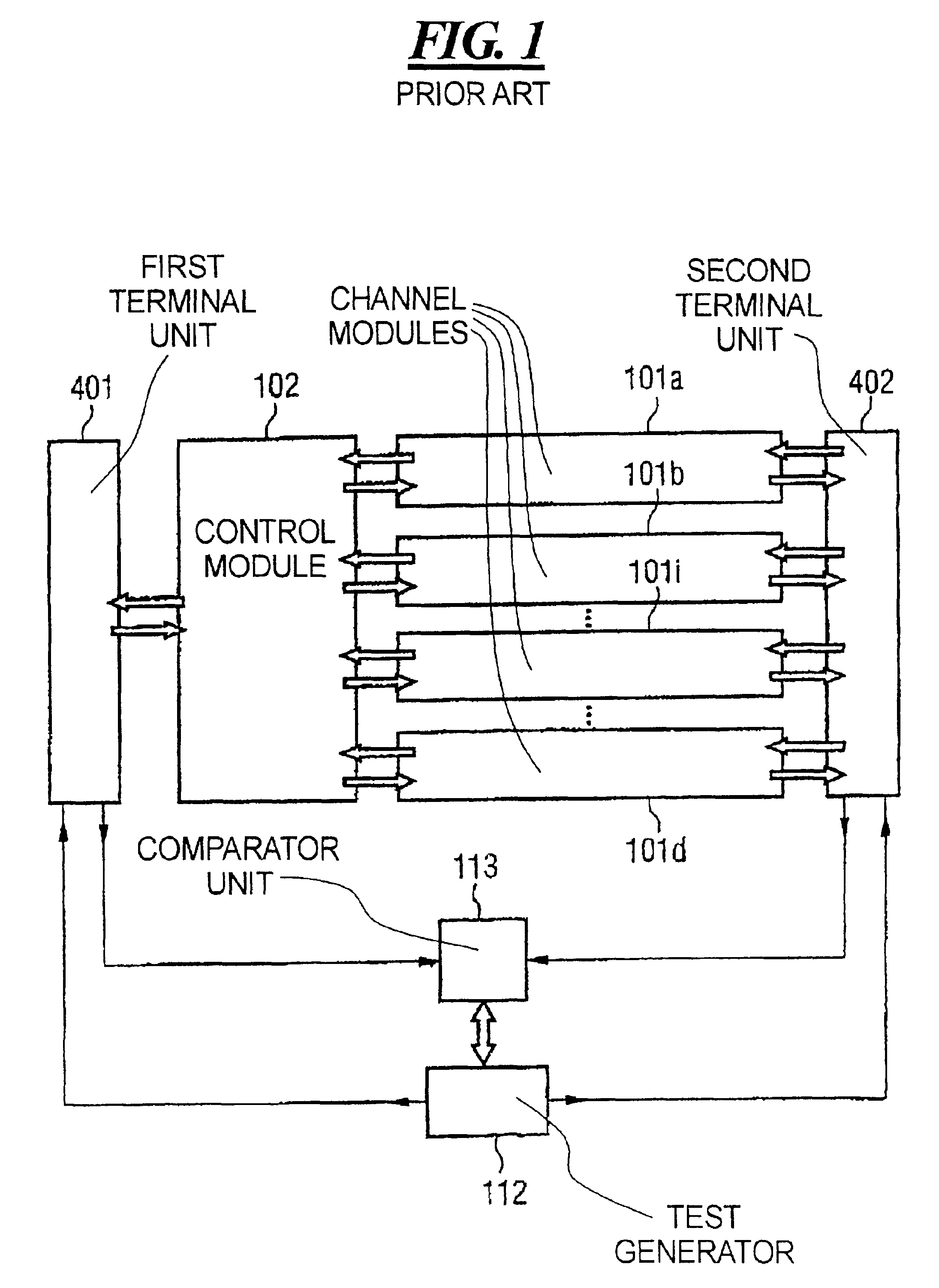

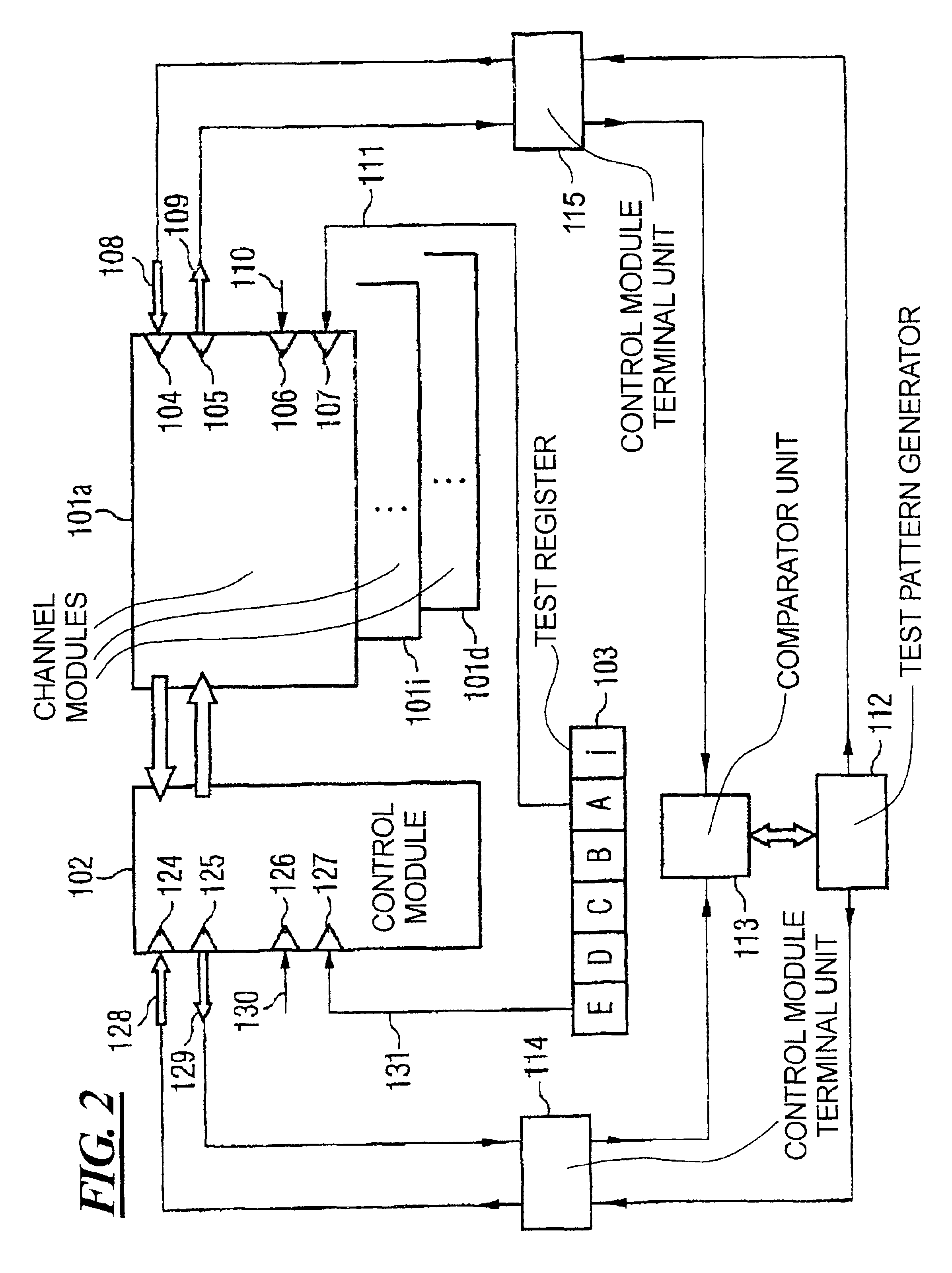

A method and apparatus for testing by sampling vectors circuit modules designated as channel models or as control modules and containing scan chains. Use is made of a test register which provides at least one control sampling mode signal for control modules and furthermore provides at least one channel sampling mode signal for channel modules. Channel modules and control modules can occur as circuit modules multiply with identical scan chains, enabling efficient testing in a manner that saves memory space. A logic is designed for the read-out of sampling output signals after testing of the scan chains via a read-out terminal unit of a test device, thus providing a comparison with desired sampling output signals for channel modules or for control modules in a comparator unit.

Owner:INFINEON TECH AG

Semiconductor device and method for testing the same

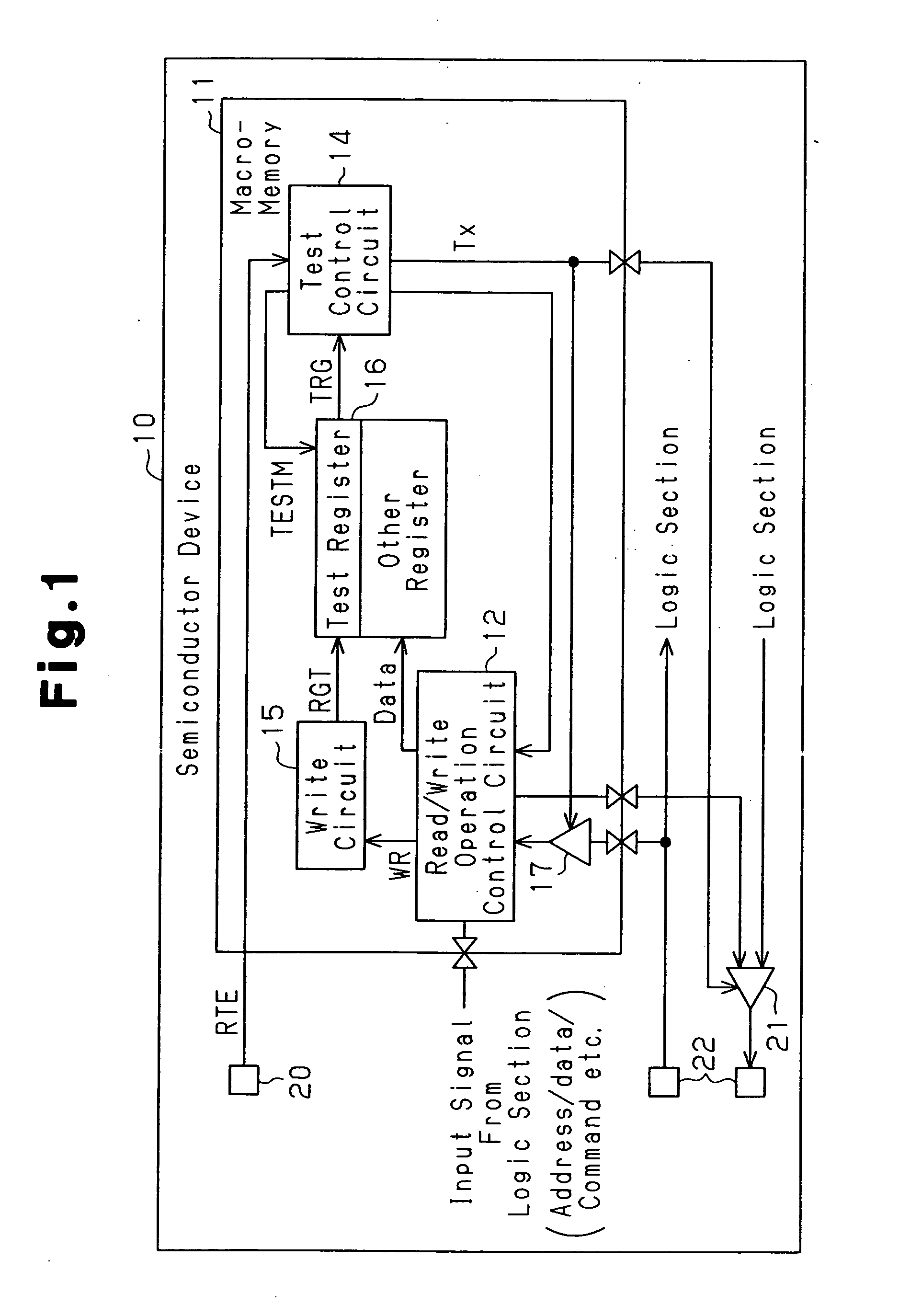

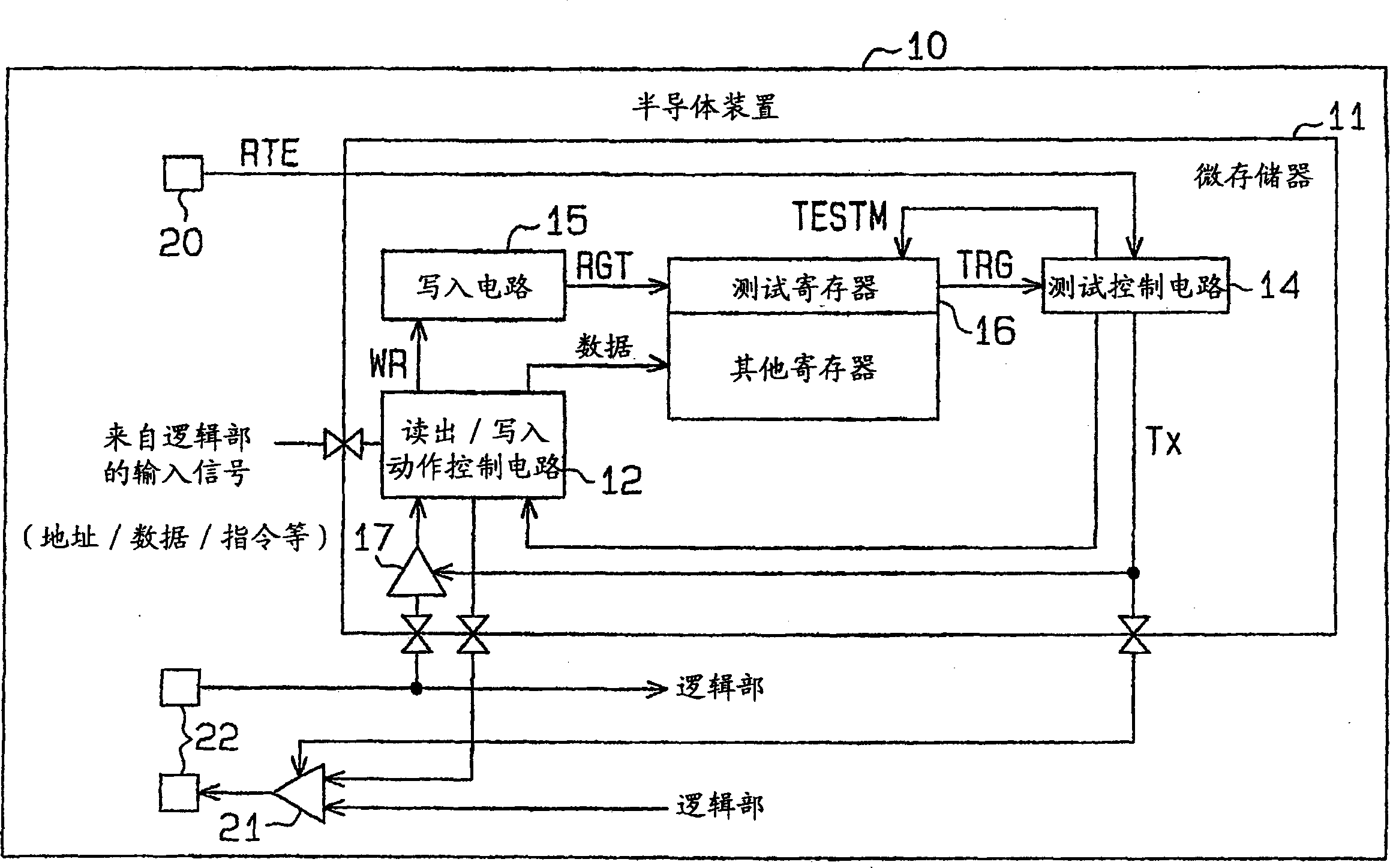

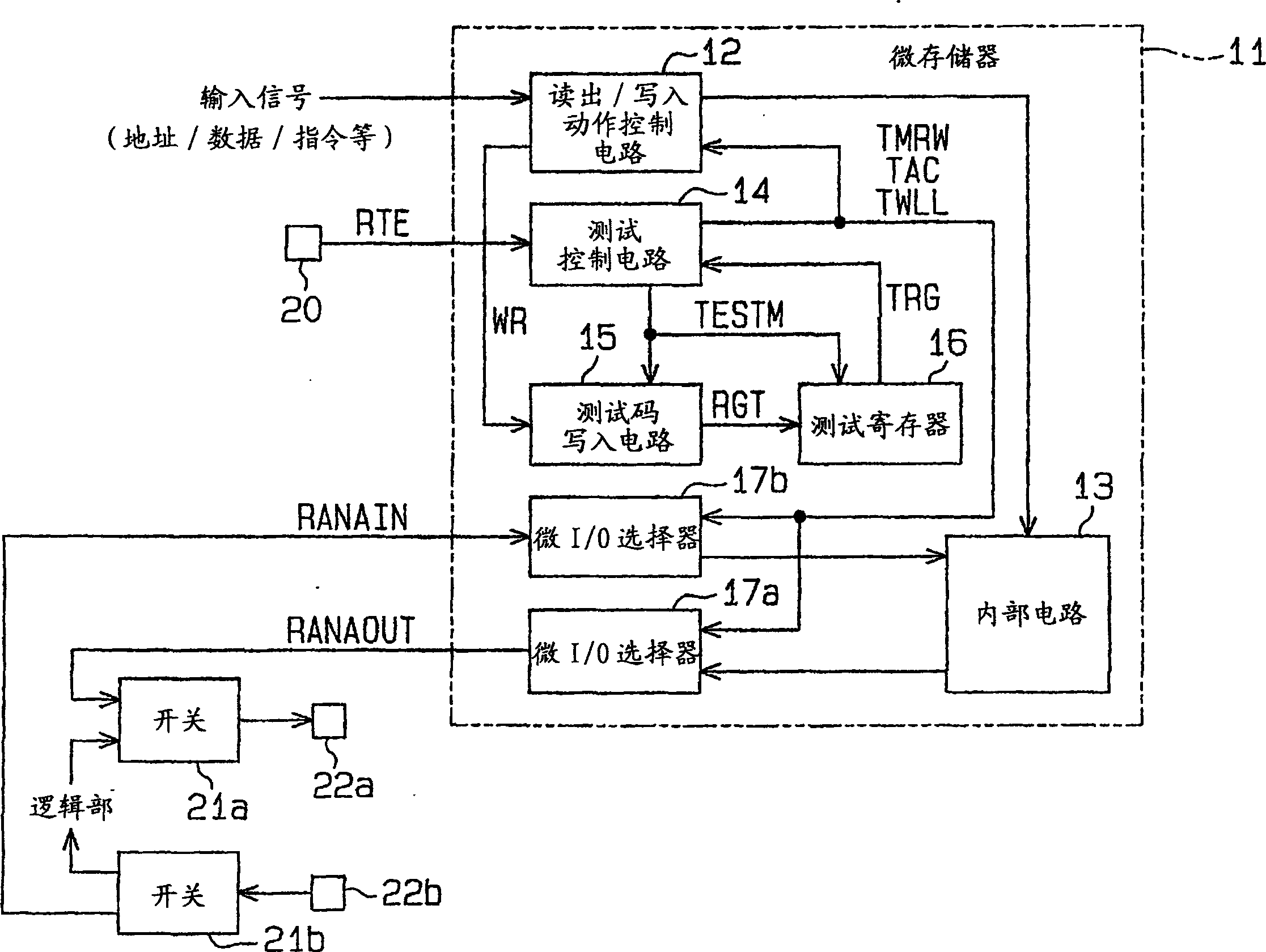

InactiveUS20050149792A1Increase heightIncreased die sizeDigital circuit testingStatic storageControl signalDevice material

A semiconductor device capable that shortens test time with a simple circuit configuration and prevents enlargement of the circuit area for testing. The semiconductor device has a macro memory and a logic section mounted thereon. The macro memory includes an operation control circuit for executing a read / write operation of data in accordance with an input signal containing an address, data, and a command. A test register for storing data to select a test mode is arranged in a storage area of the macro memory that is selected by an address. A write circuit generates a control signal enabling the writing of data to the test register in response to a write command provided from the operation control circuit.

Owner:FUJITSU LTD

Integrated circuit

InactiveUS20050210347A1Reduce probabilityLittle involvementDigital circuit testingArchitecture with single central processing unitMultiplexerNormal mode

The invention is directed to an integrated circuit that includes a plurality of functional circuit blocks. Respective associated multiplexers are used to change over between a normal mode and a test mode. The input side of the multiplexers each have a test register connected thereto which is coupled to a serial bus. A control unit controls the transfer of test data to a selected function block on the basis of the state of a mode-of-operation memory cell in the respective test register. This means that there is little involvement required to put individual function blocks of a chip deliberately into a test mode and to program them as appropriate, while other function blocks are operating in normal mode. The principle described allows a high degree of flexibility with regard to the testing of integrated circuits with a multiplicity of functional assemblies.

Owner:INTEL CORP

Through-substrate via (TSV) testing

ActiveUS9157960B2Digital circuit testingSemiconductor/solid-state device testing/measurementData valueComparator

Various embodiments comprise apparatuses and methods for testing and repairing through-substrate vias in a stack of interconnected dice. In various embodiments, an apparatus is provided that includes a number of through-substrate vias to couple to one or more devices, at least one redundant through-substrate via to allow a repair of the apparatus, and a pair of pull-up devices coupled to the through-substrate vias and the redundant through-substrate via to provide a high-data value to the first end of the respective through-substrate vias. A test register is coupled the second end of each of the through-substrate vias and the redundant through-substrate via to store a received version of the high-data value. A comparator compares the high-data value with the received version of the high-data value to test the through-substrate vias for short-circuit connections.

Owner:MICRON TECH INC

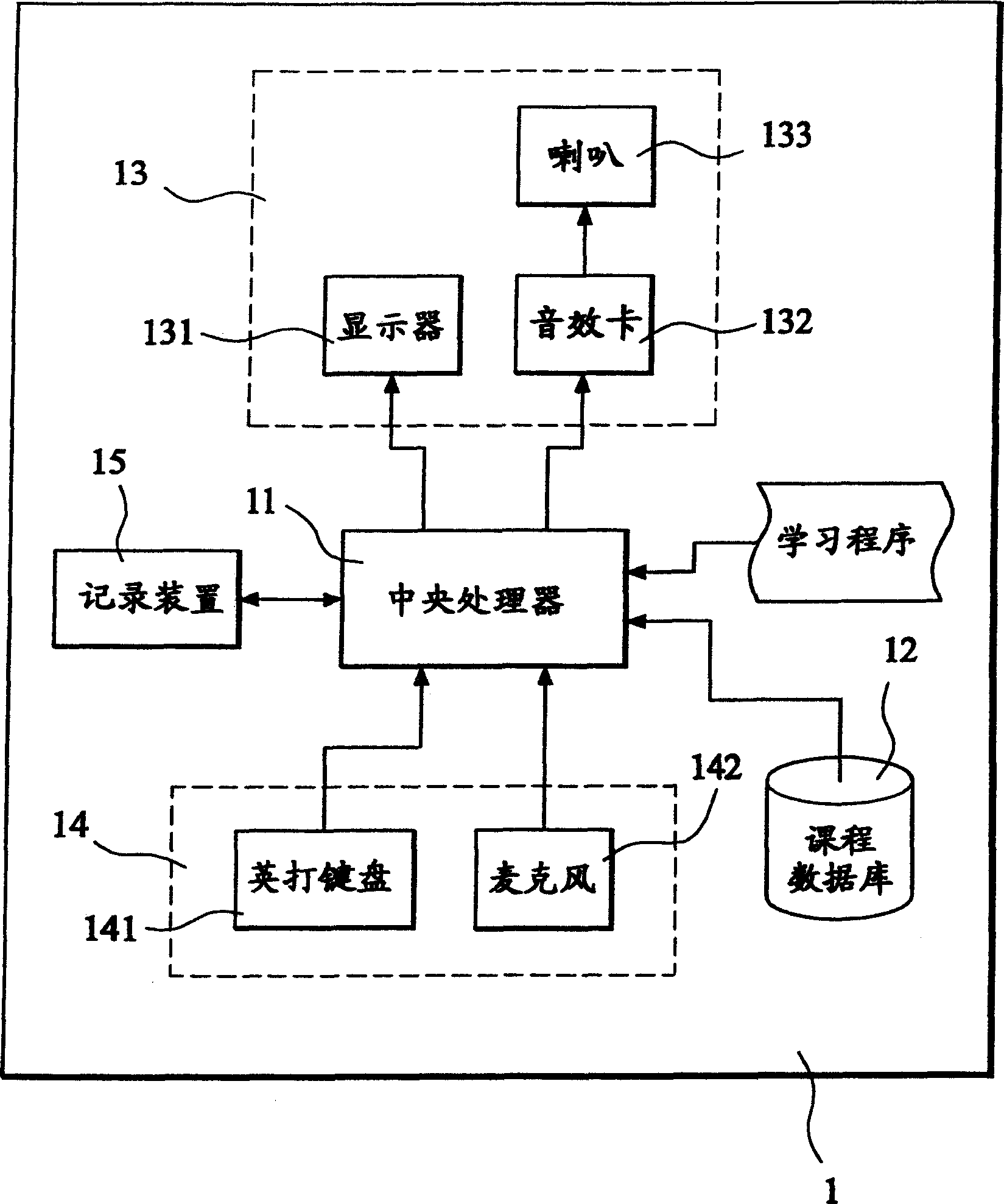

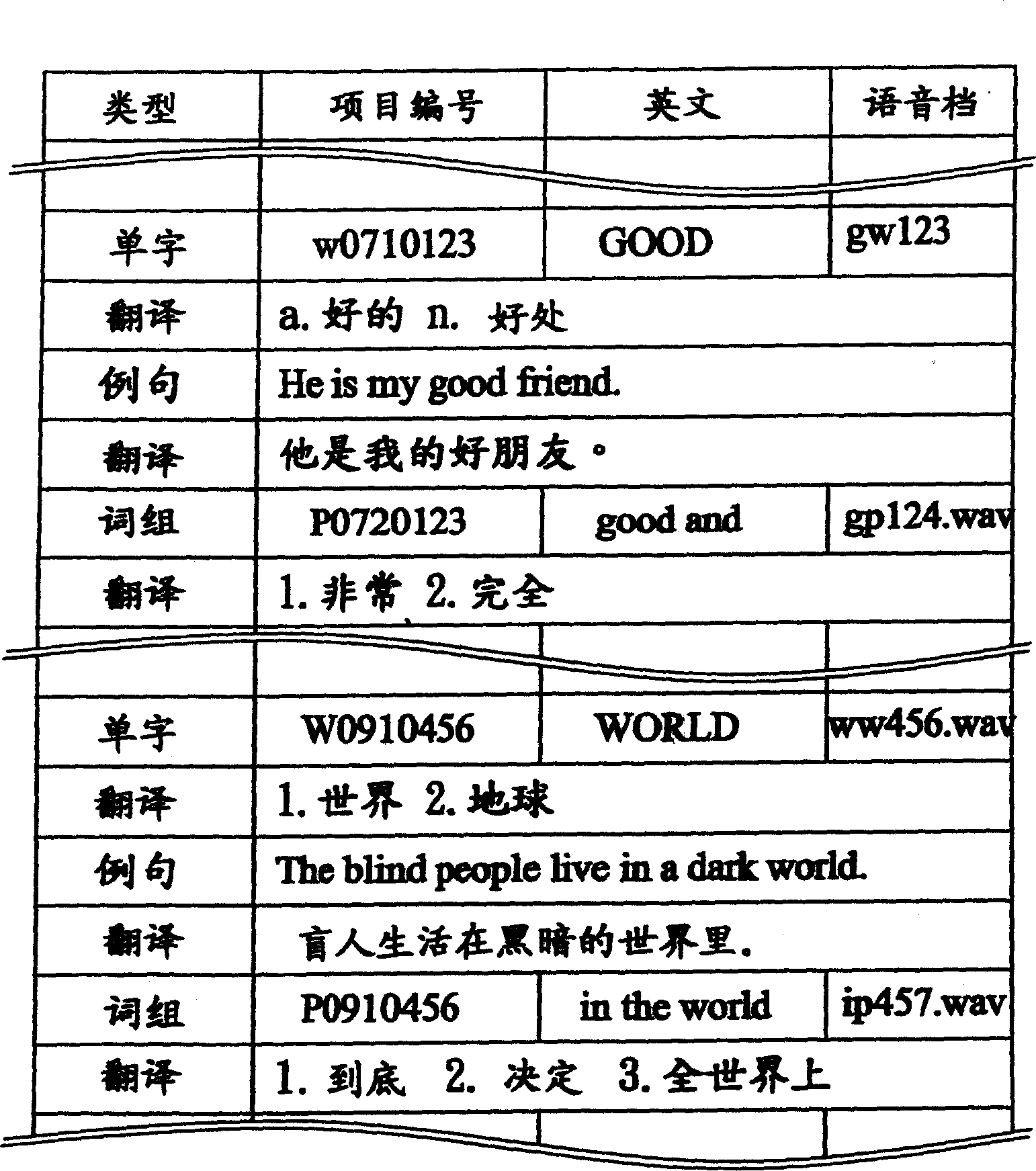

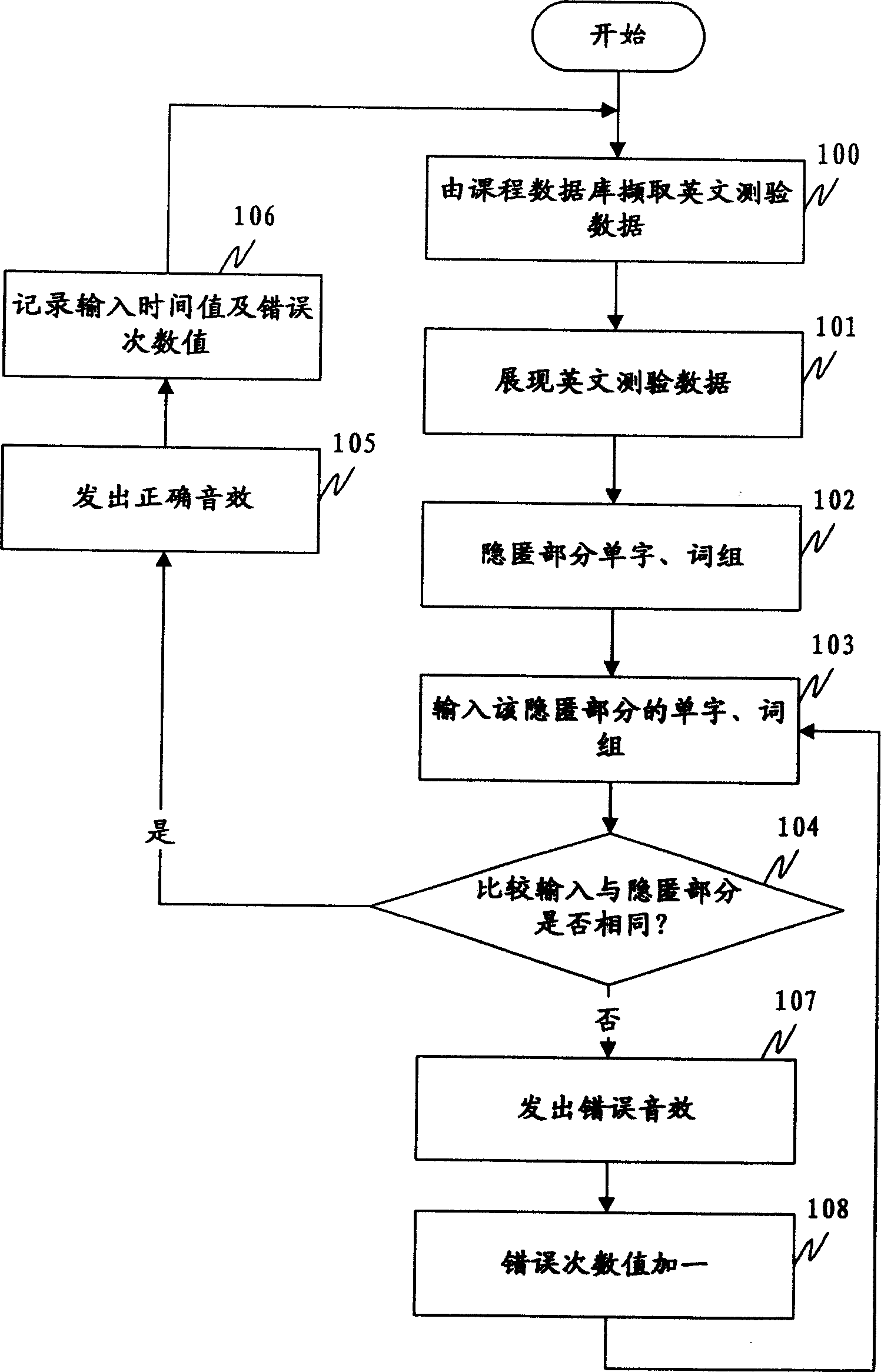

English learning and testing system

InactiveCN1607519AFast learningSpecial data processing applicationsSpecific program execution arrangementsWord groupComputer science

An English study and test system includes a course database, a guiding device, an input device, a register device and a central processor. A study and test program can be carried according to the course or random number to generate said English test data to be resolved to single words, phrases, examples and coherent grammars, translations and phones, part of the data is hidden to be output to the guiding device to guide students to input exercises of said hidden part from said input device to compare if the input exercises are the same with said hidden part to compute said input time value and error times and store them in a test register list then to generate new English test data to continue the exercise.

Owner:陈青章 +1

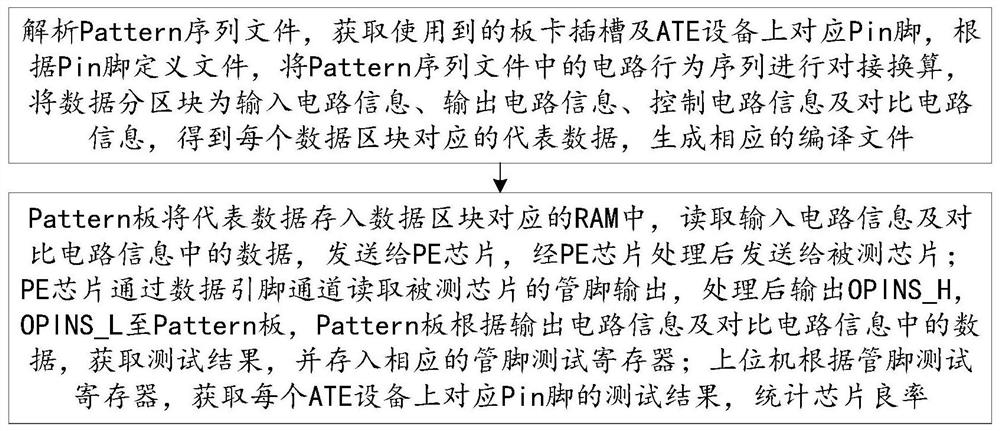

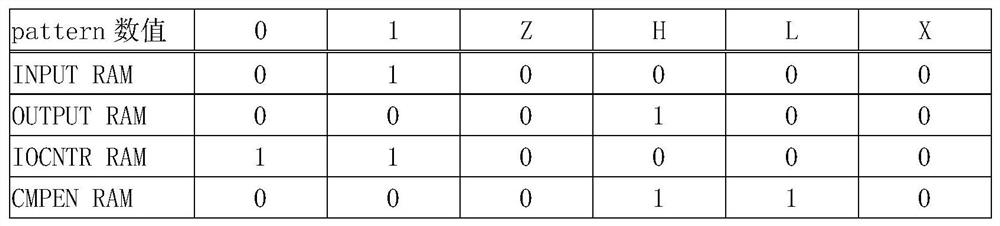

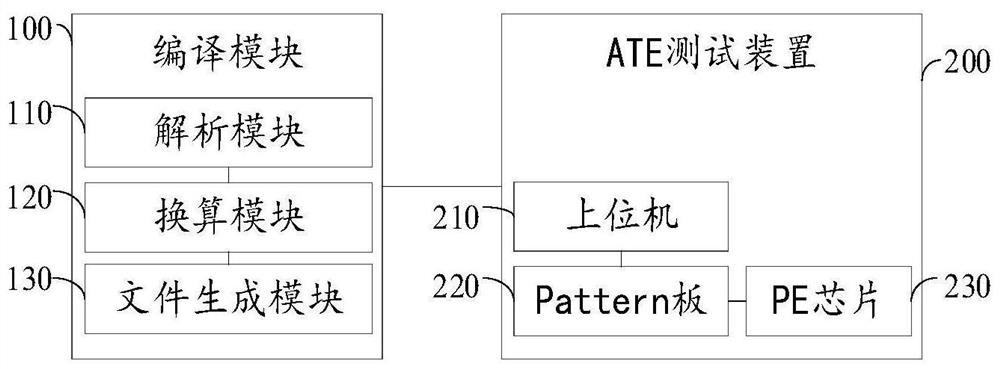

Pattern compiling and downloading test method and system for ATE equipment

ActiveCN112630622ANo waste of resourcesImprove Parallel Testing EfficiencyTotal factory controlAutomated test systemsPattern sequenceTest efficiency

The invention discloses a pattern compiling and downloading test method and system for ATE equipment, and the method comprises a compiling step: analyzing a pattern sequence file, obtaining a used board card slot and a corresponding Pin pin on the ATE equipment, carrying out the butt-joint conversion of a circuit behavior sequence according to a Pin pin definition file, partitioning the data into input circuit information, output circuit information, control circuit information and comparison circuit information, and generating corresponding compiled files; a test step: reading data in the input circuit information and the comparison circuit information by the Pattern board according to the compiled file, processing the data by the PE chip, and sending the processed data to the tested chip; enabling the PE chip to read the pin output of the tested chip through the data pin channel, processing the pin output and outputting the processed pin output to the Pattern board, and enabling the Pattern board to acquire a test result according to the output circuit information and the data in the comparison circuit information and storing the test result into the pin test register; and enabling the upper computer to perform statistical operation on the chip yield. According to the invention, no Pin range limitation exists, and the utilization rate of board card test channel resources and the parallel test efficiency are improved.

Owner:珠海芯业测控有限公司

Data processing with configurable registers

ActiveUS7823033B2Register arrangementsElectronic circuit testingData processing systemGeneral purpose

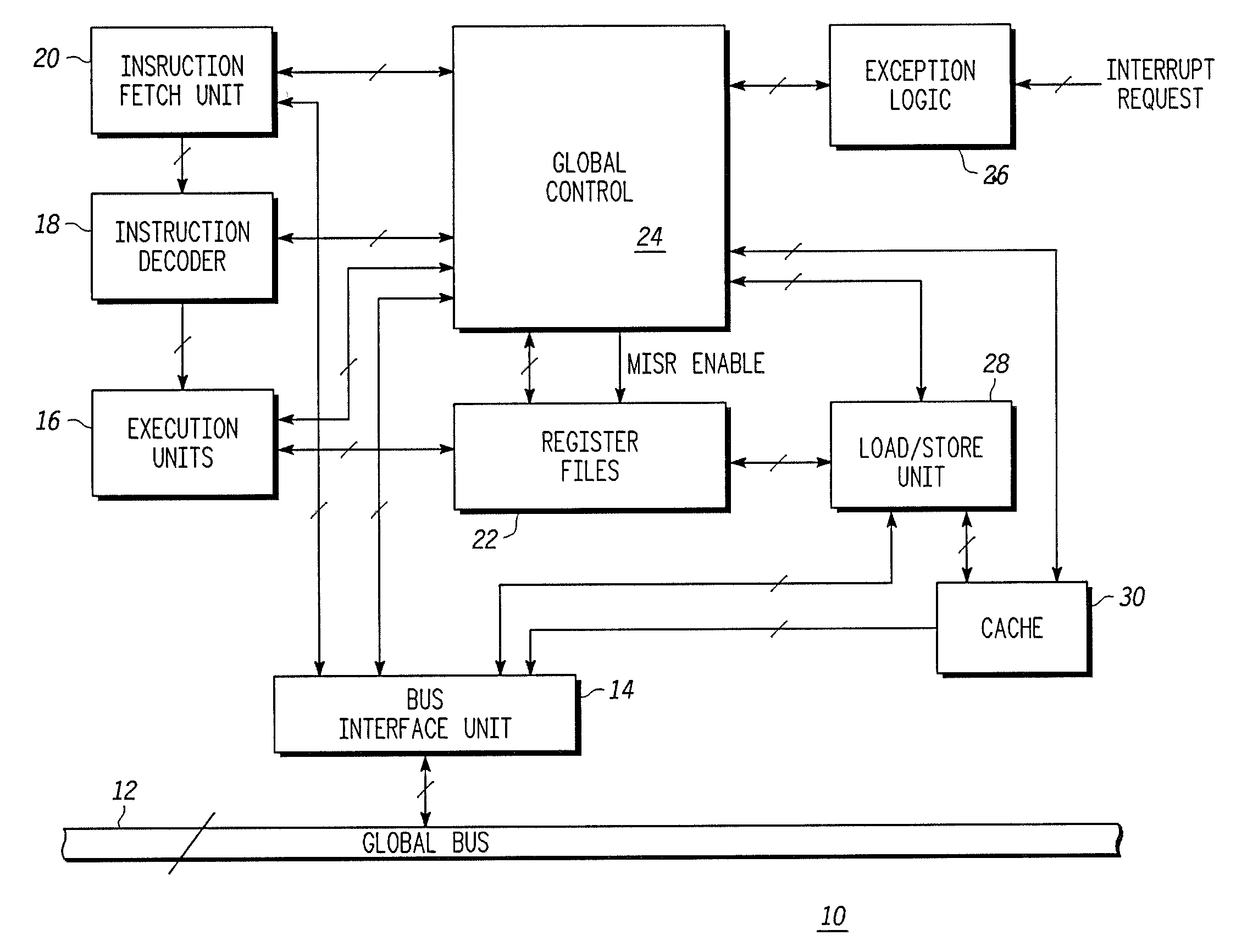

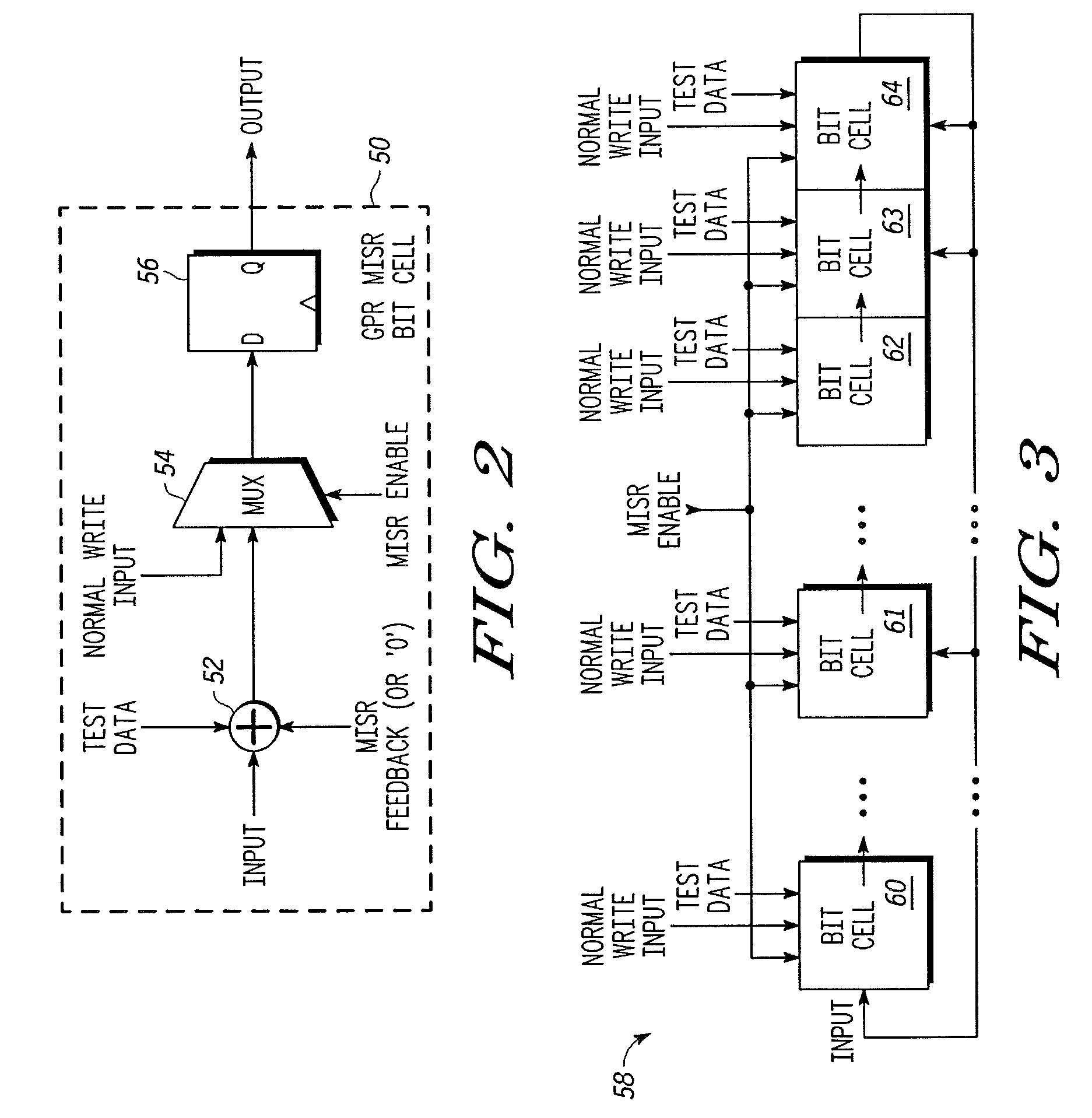

A data processing system includes functional circuitry which performs at least one data processing function, a register file coupled to the functional circuitry and having a plurality of general purpose registers (GPRs) which are included as part of a user's programming model for the data processing system, where a portion of the plurality of GPRs are reconfigurable as test registers during a test mode, and control circuitry which provides a test enable indicator to the register file. The portion of the plurality of GPRs, in response to the test enable indicator indicating the test mode is enabled, operates to accumulate test data from predetermined circuit nodes within the functional circuitry. In one aspect, the portion of the plurality of GPRs are reconfigured as multiple input shift registers (MISRs) during the test mode and generate signatures based on the test data.

Owner:NXP USA INC

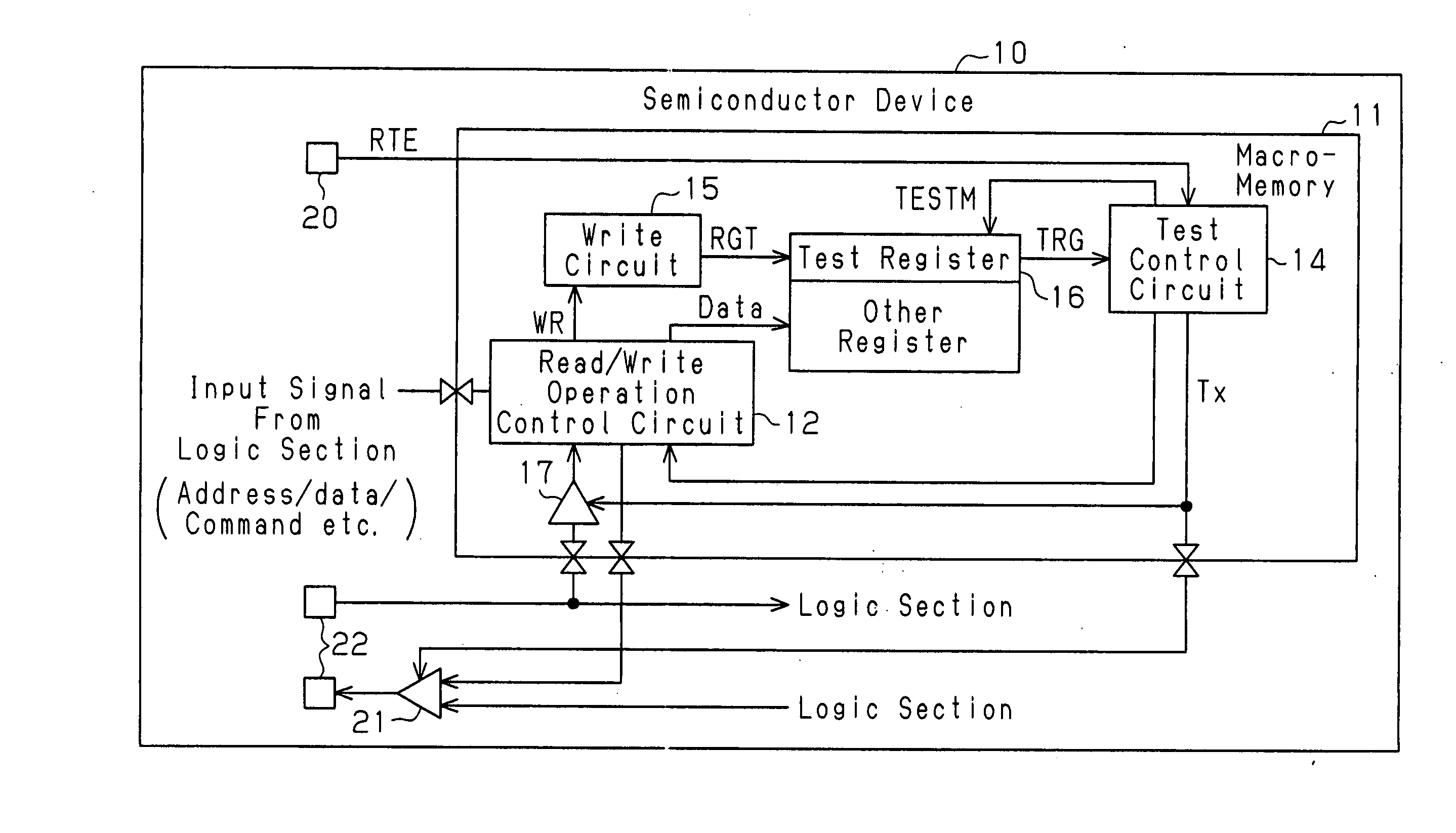

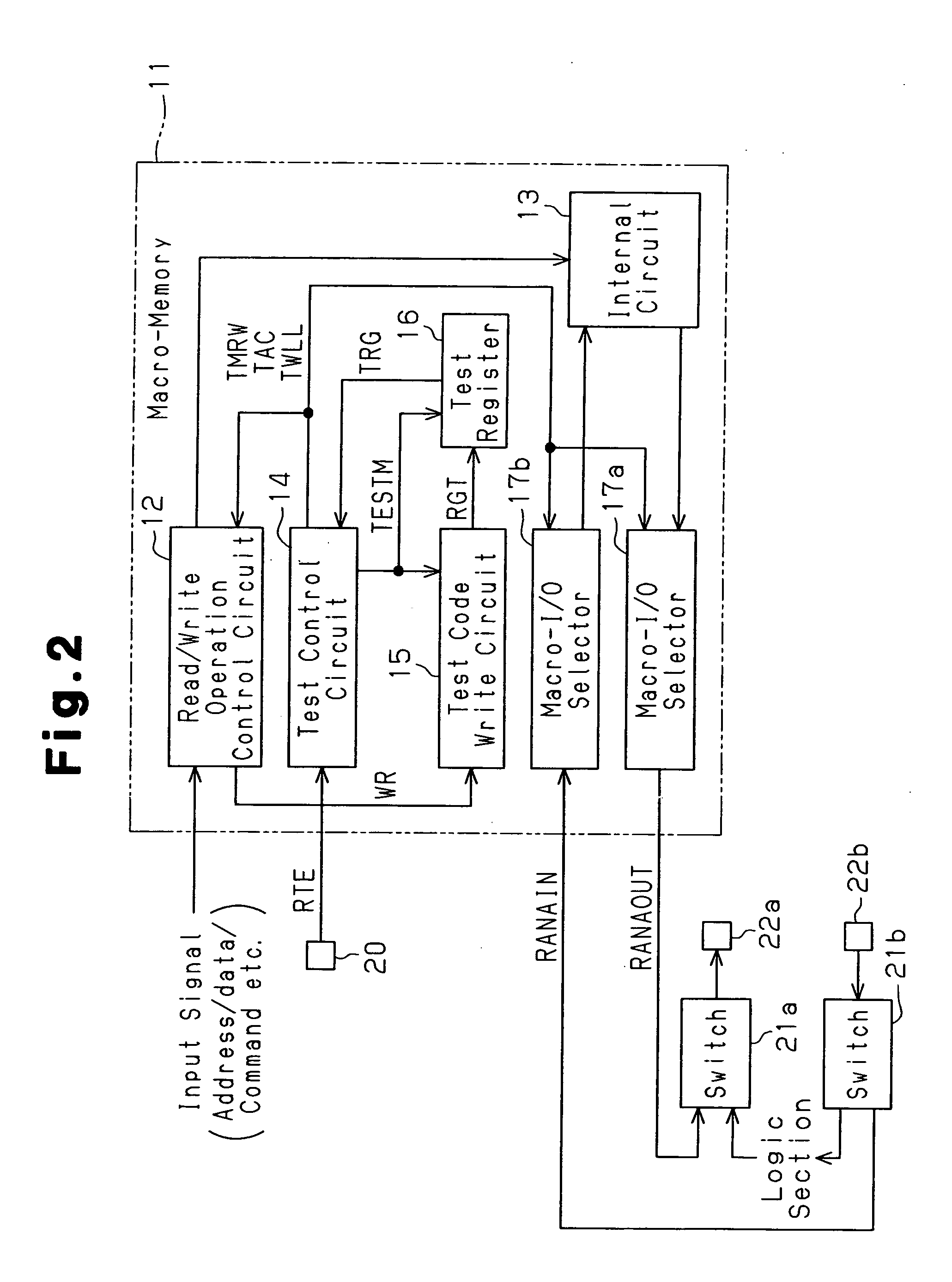

Semiconductor device and method for testing the same

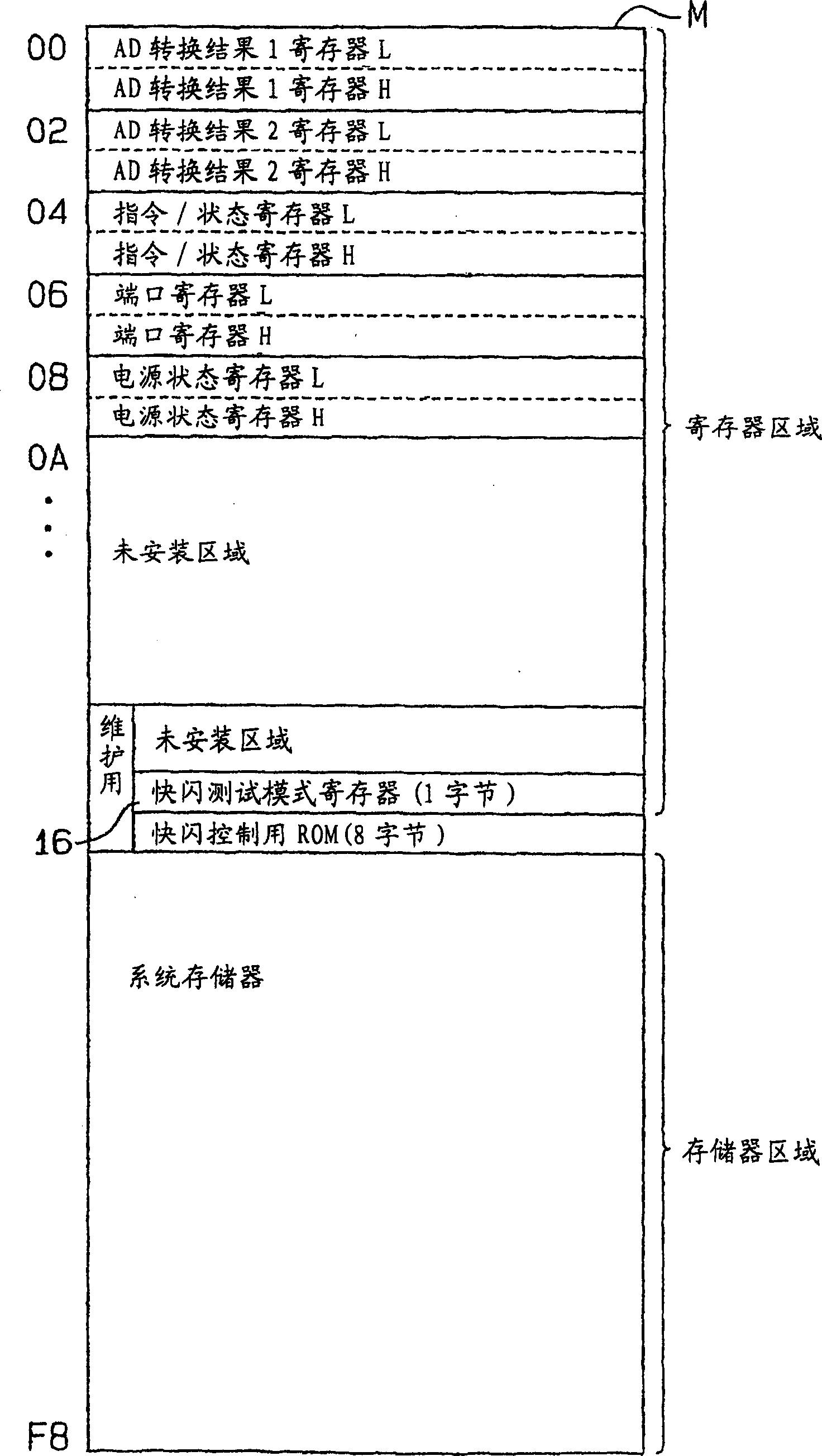

A semiconductor device wherein a simple circuit arrangement is used to shorten the test time and suppress increase of circuit area required for the test. The semiconductor device (10) has a micro-memory (11) consolidated with a logic part. The micro-memory (11) includes an operation control circuit (12) for executing data read / write operations in accordance with input signals including addresses, data and commands. A storage area of the micro-memory (11) that is selected by an address includes a test register (16) for storing data used for selecting a test mode. A write circuit (15) produces, in response to a write command supplied from the operation control circuit (12), a control signal (RGT) for permitting an operation of writing data into the test register (16).

Owner:FUJITSU LTD

A testable multiprocessor system and a method for testing a processor system

InactiveCN101124547AValid choiceWill not be disturbedError detection/correctionElectrical testingTest inputProcessor register

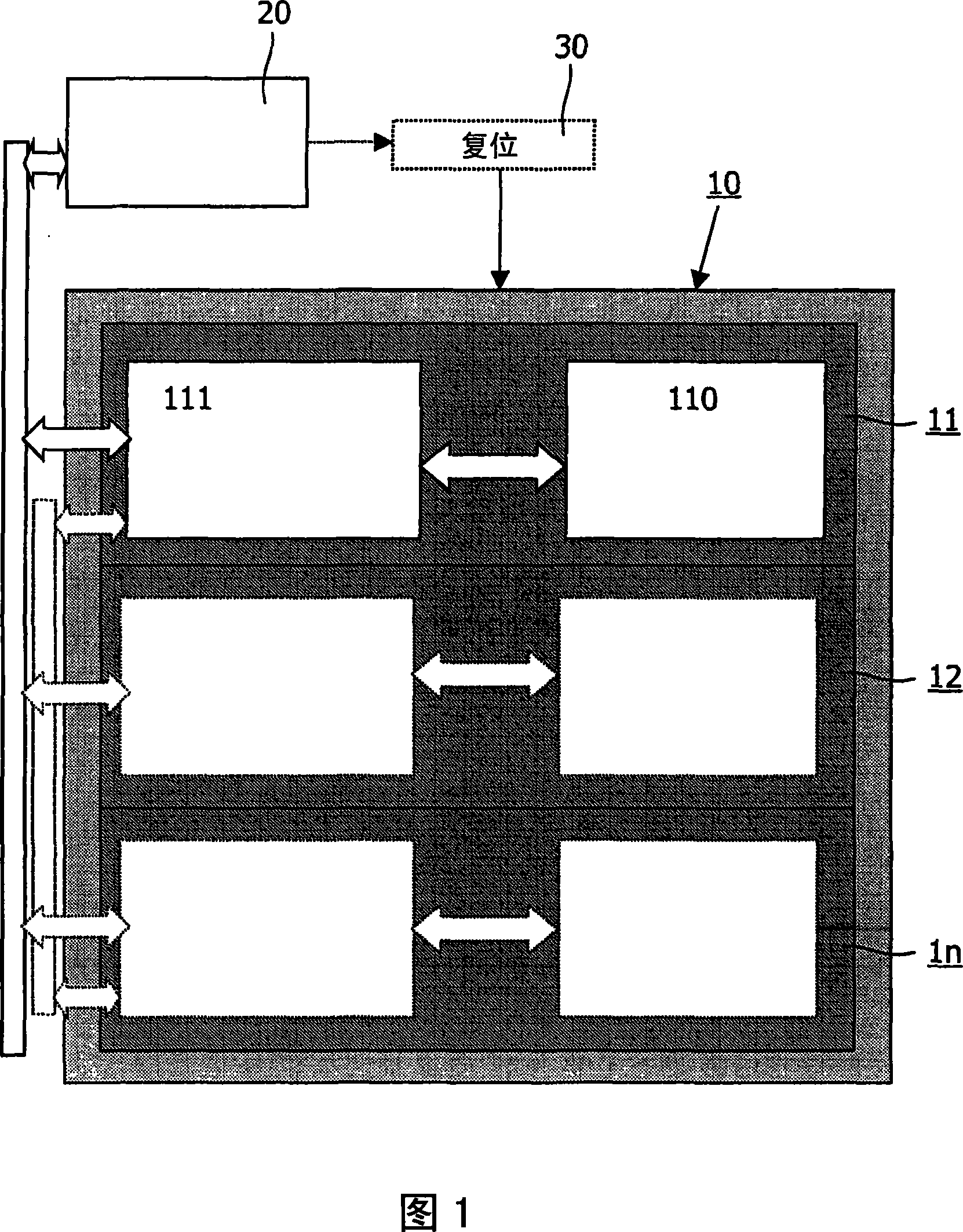

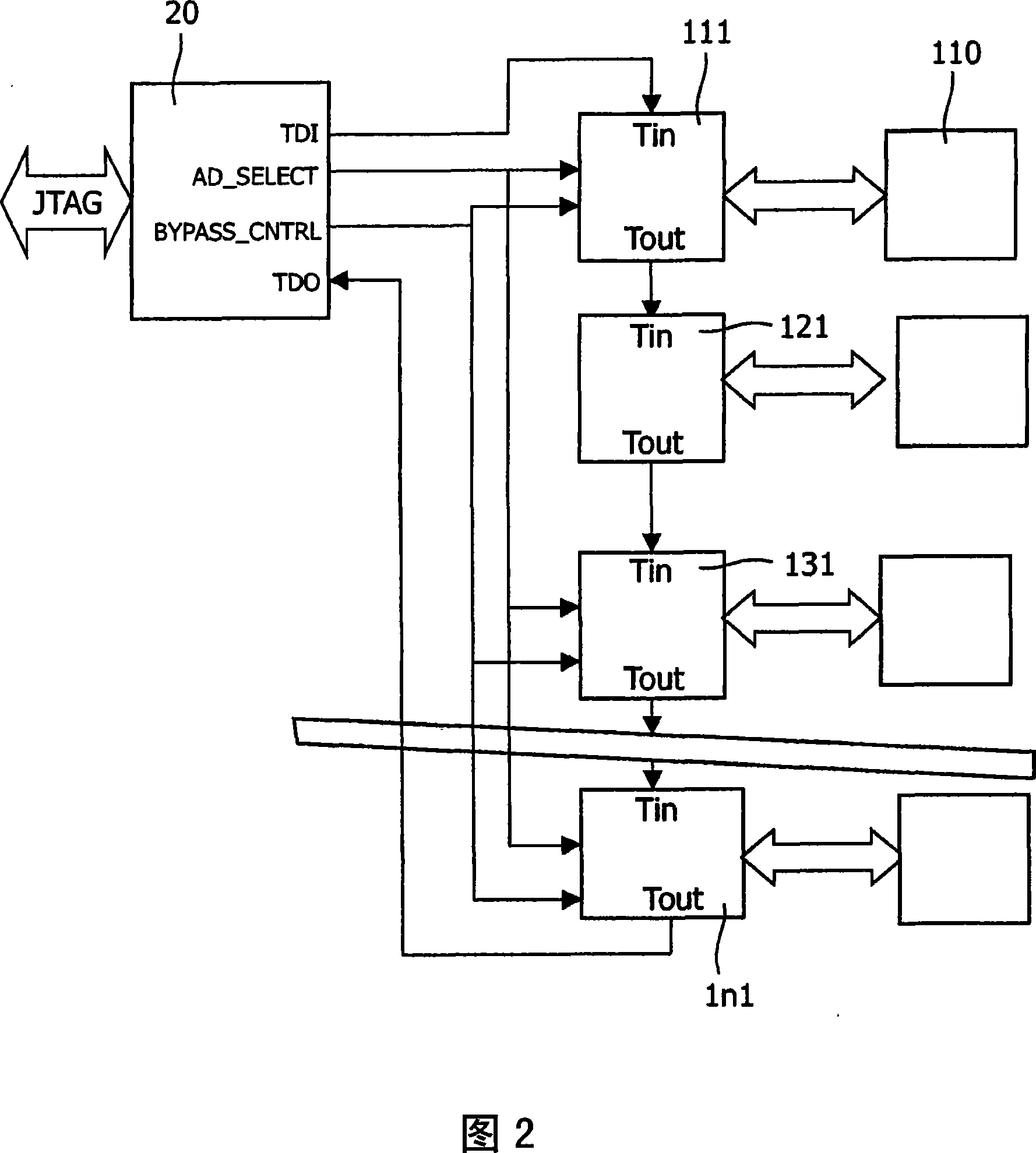

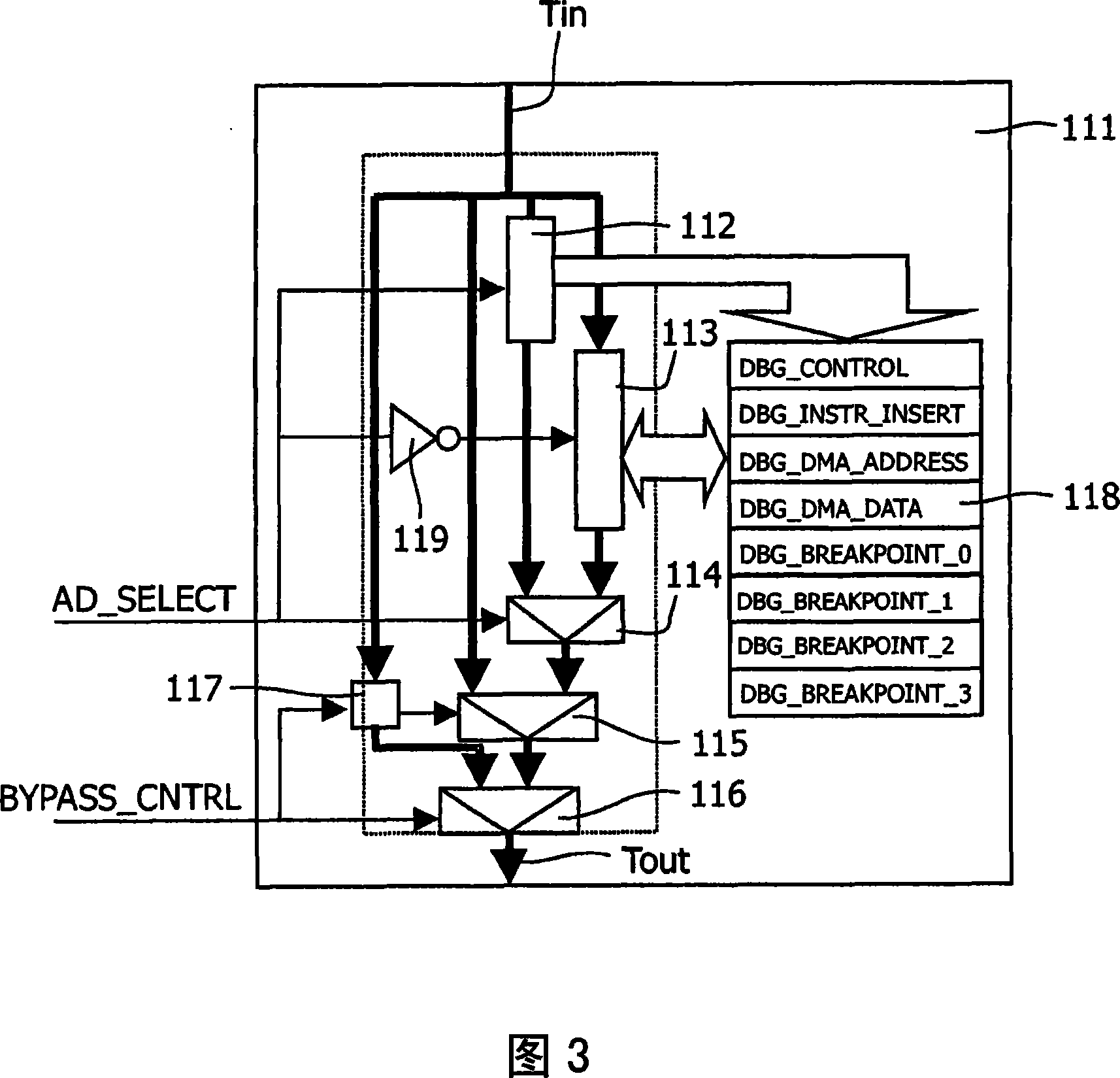

A testable processor system (10,20) comprises a plurality of modules (11,12,...In). Each module (11) comprises a processor unit (110) and a debug controller (111). The debug controllers are coupled to a common test access point controller (TAP- controller 20), and have a test data input (Tin), a test data output (Tout) and at least one test register (112, 113). The test data inputs and outputs of the debug controllers (111, 121, 131, ...,InI) are arranged in a scan chain having an input for receiving test input data (TDI) from the TAP-controller and an output for providing test output data (TDO) to the TAP-controller. At least one debug controller (111) has a selection facility (115) to select whether data in the scanchain is either shifted through the at least one test register (112) of that debug controller (111) or is immediately forwarded from the test data input (Tin) to the test data output (Tout) of that debug controller. The at least one debug controller has a bypass register (117) which controls the selection facility. The TAP-controller (20) provides a control signal (BYPASS CNTRL) which, when active, selects the bypass register as part of the scan chain.

Owner:NXP BV