A testable multiprocessor system and a method for testing a processor system

A processor system, processor unit technology, applied in the direction of electrical digital data processing, instrumentation, measuring electrical, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

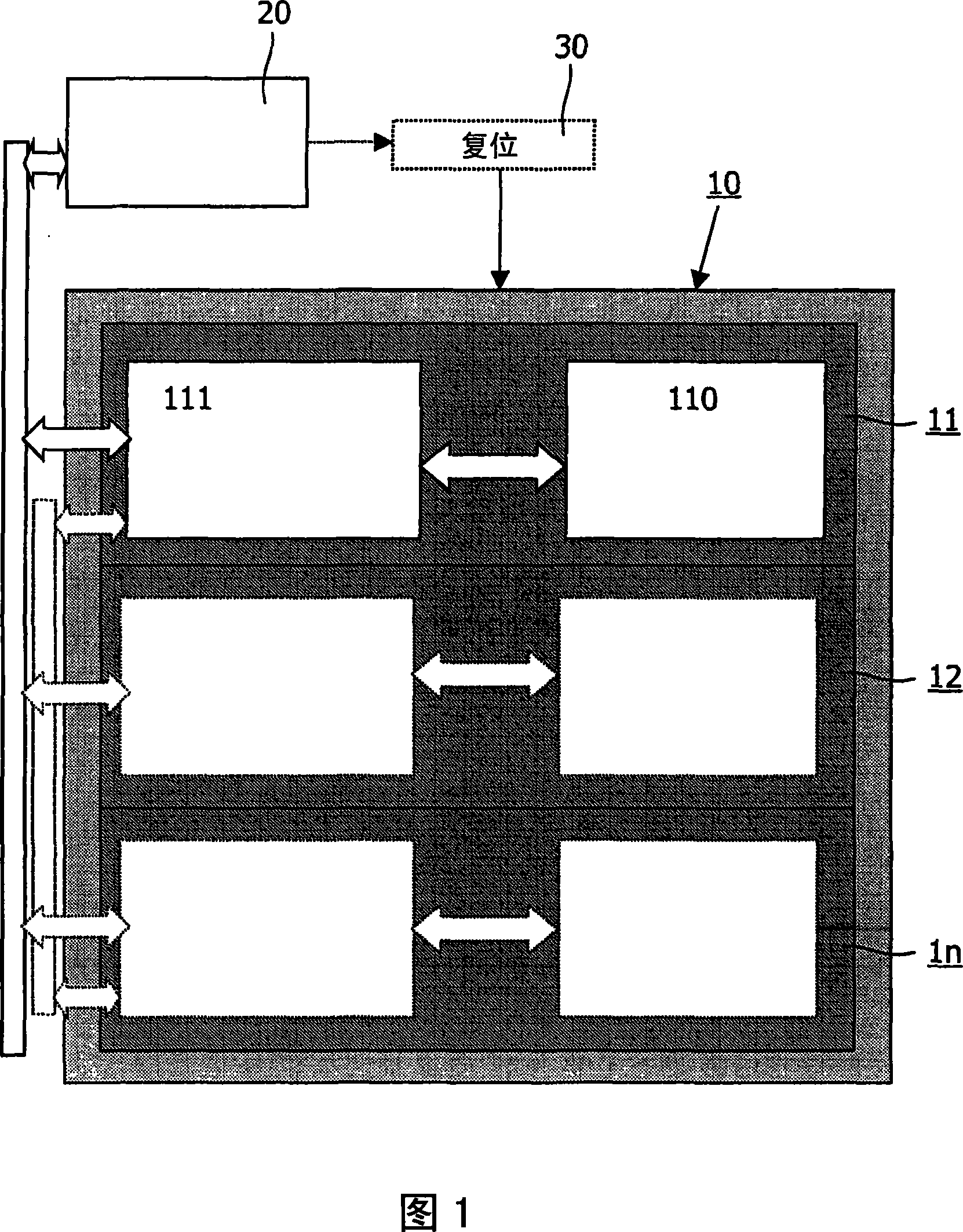

[0020] Fig. 1 schematically shows a testable processor system 10, 20 comprising a plurality of modules 11, 12, . . . , 1n. Each module includes a processor unit 110 and a debug controller 111 . The debug controller 111 is connected to a common TAP controller, such as the JTAG TAP controller 20 .

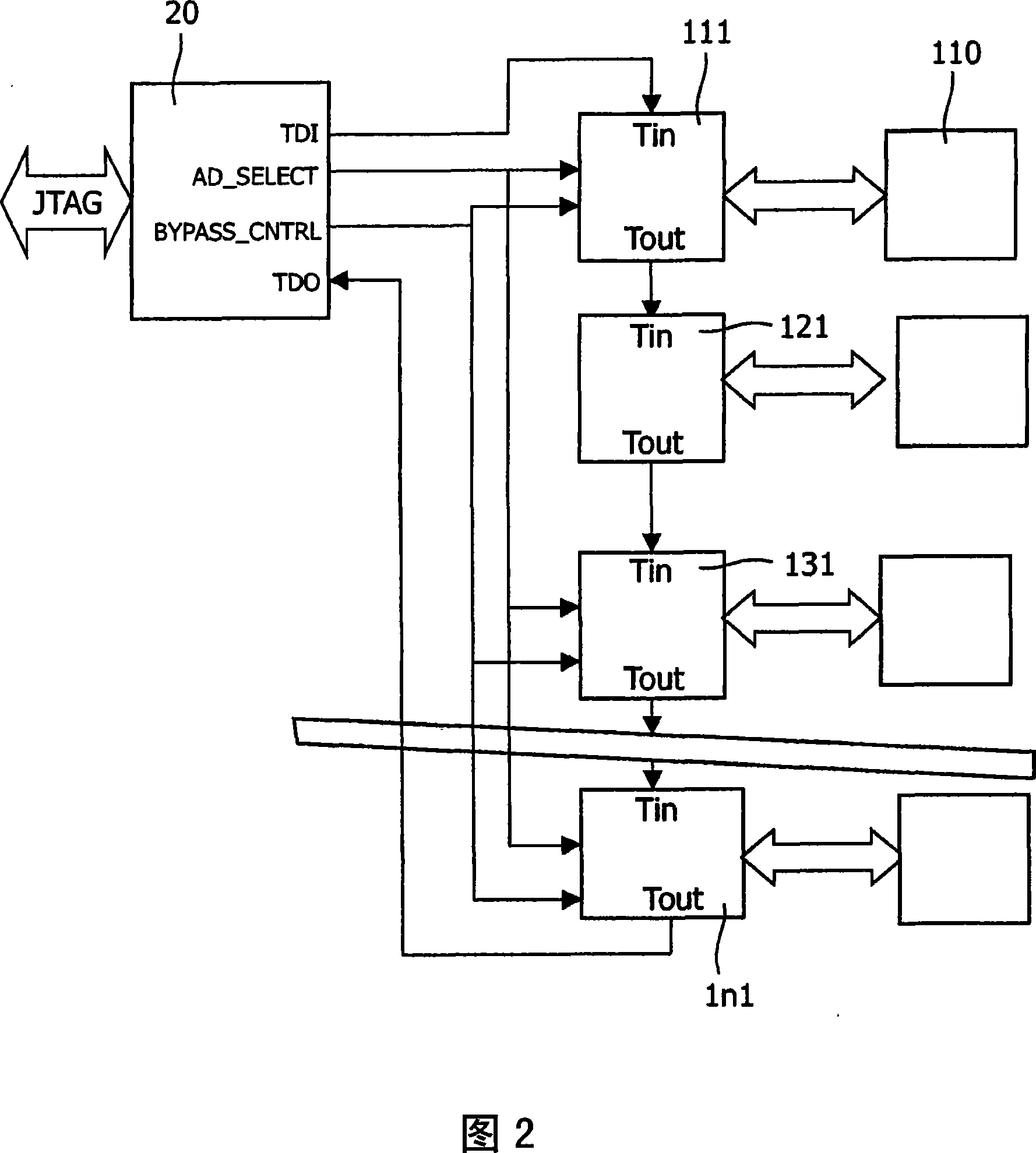

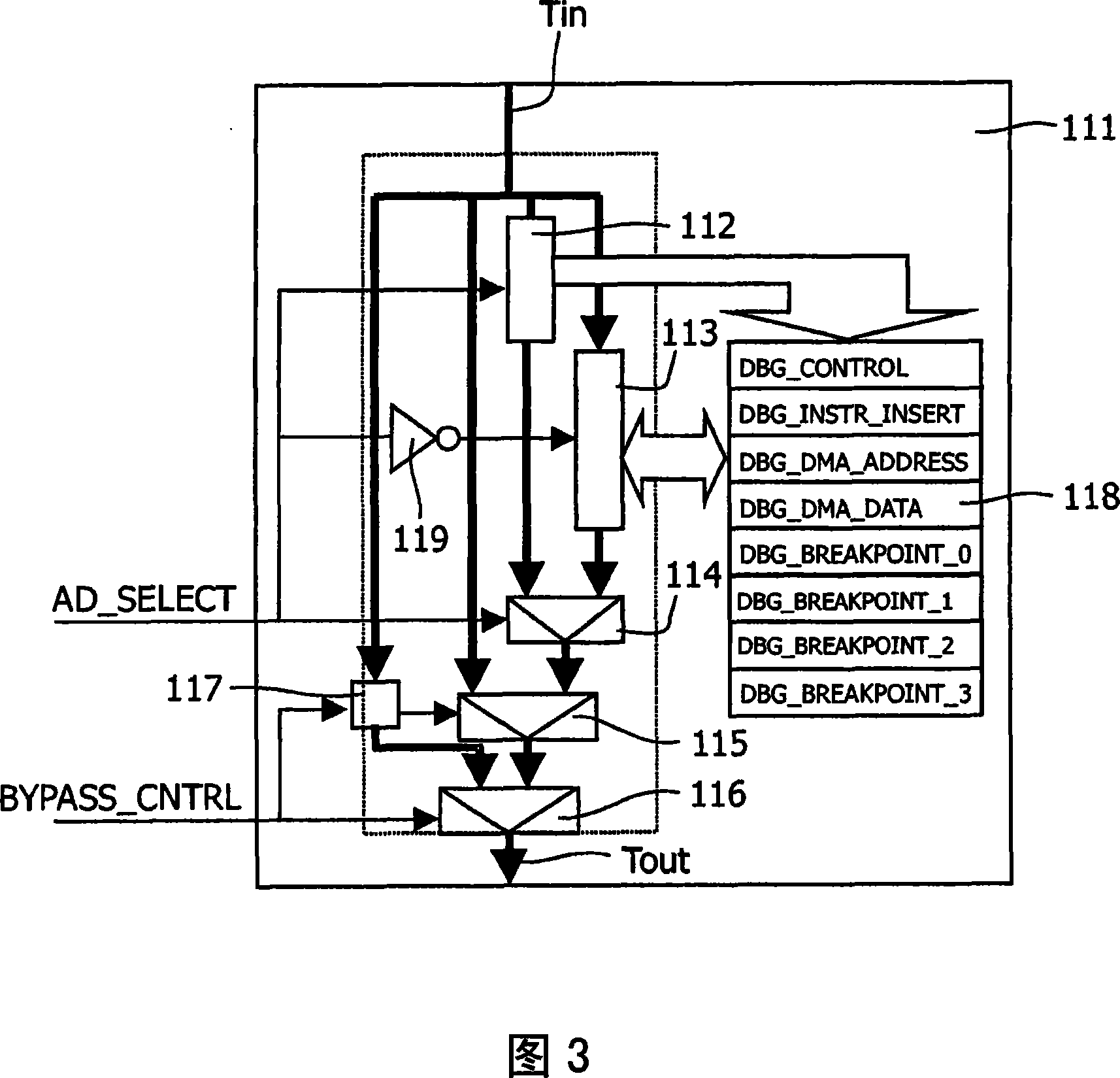

[0021] Figures 2 and 3 show a part of the system in more detail. The debug controllers 111, 121, 131, . . . , 1n1 have test data input terminals Tin and test data output terminals Tout and at least one test register (FIG. 3: 112, 113). In the illustrated embodiment, the debug controller has a test address register 112 and a test data register 113 . The test data input and output of the debug controller are arranged in a scan chain having an input for receiving test data data from the TAP controller, and an input for providing test data data TDO to the TAP controller. output. At least one debug controller 111 has a selection tool 115 that enables data in the scan chain to be moved...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More