Patents

Literature

75 results about "Bit Test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The BT x86 assembly language instruction stands for Bit Test and was added to the x86 instruction set with the 80386 processor. BT copies a bit from a given register to the carry flag.

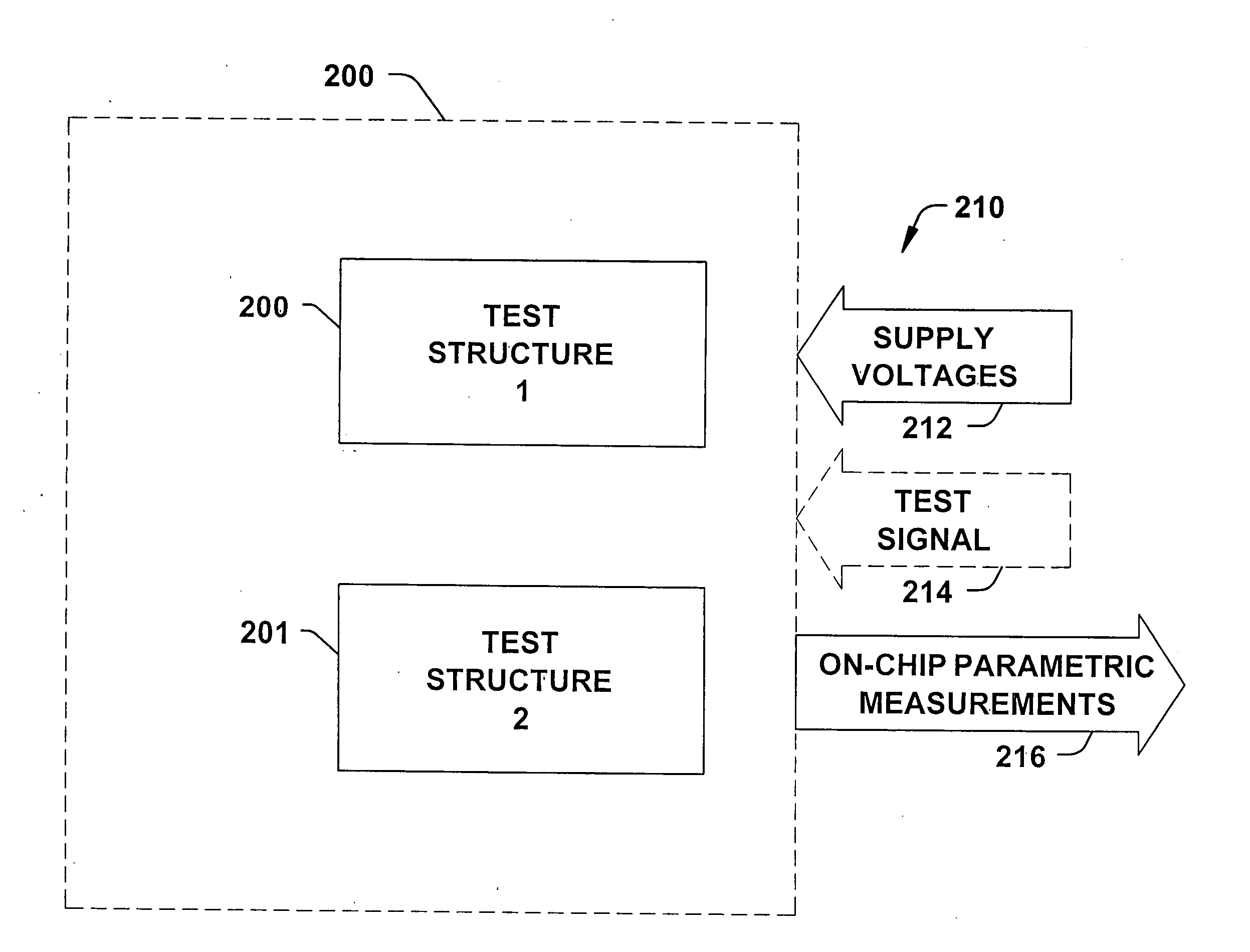

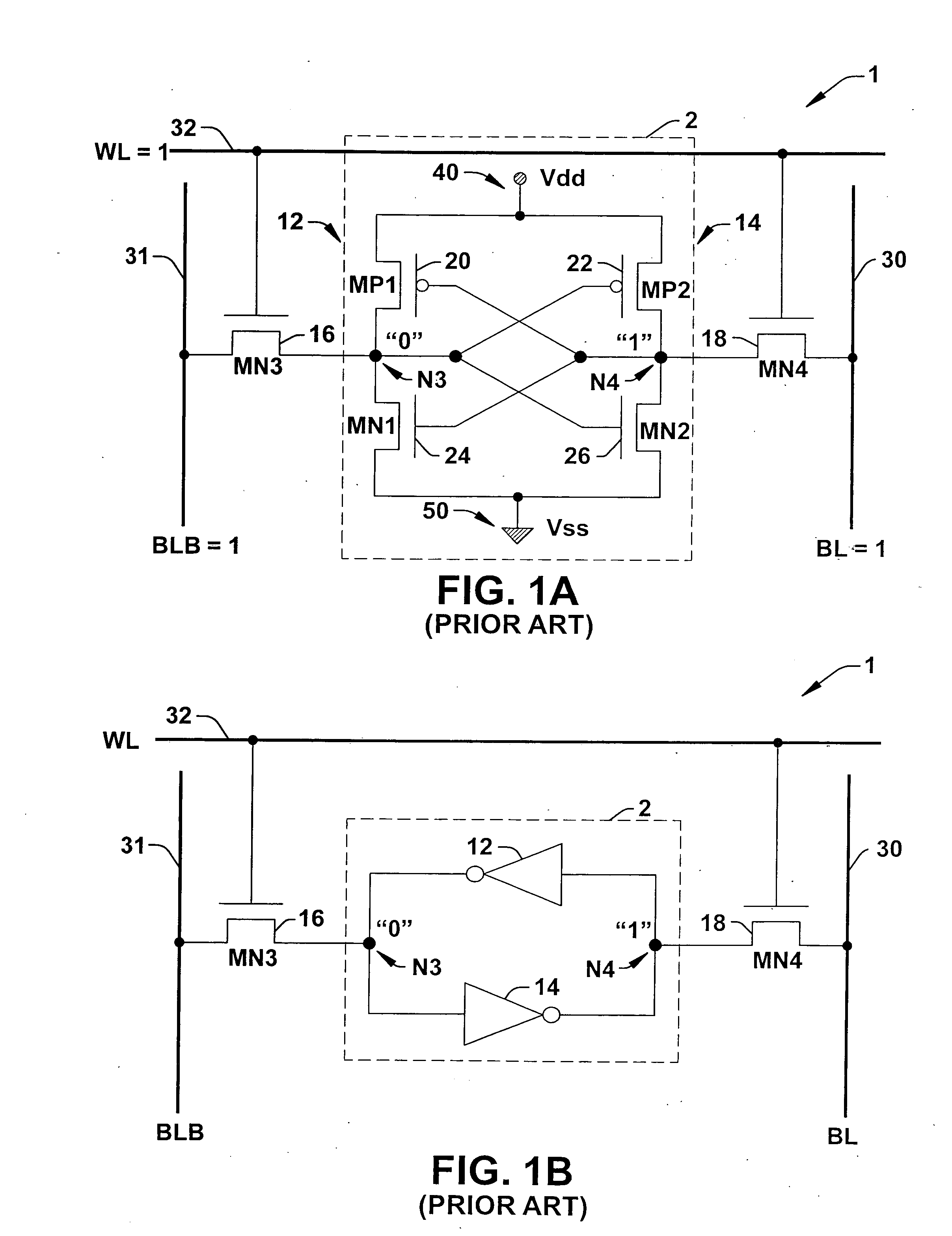

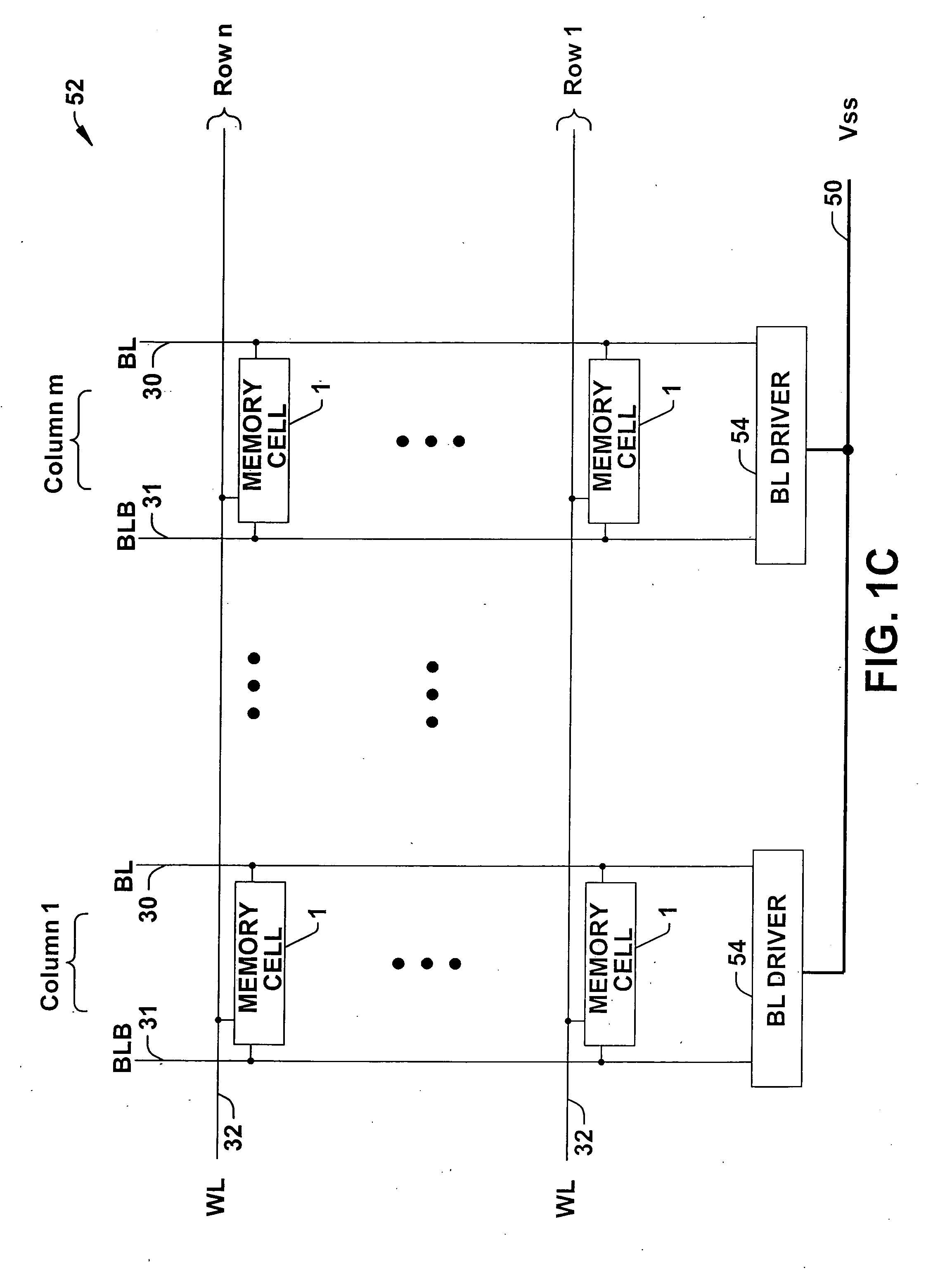

SRAM static noise margin test structure suitable for on chip parametric measurements

Owner:TEXAS INSTR INC

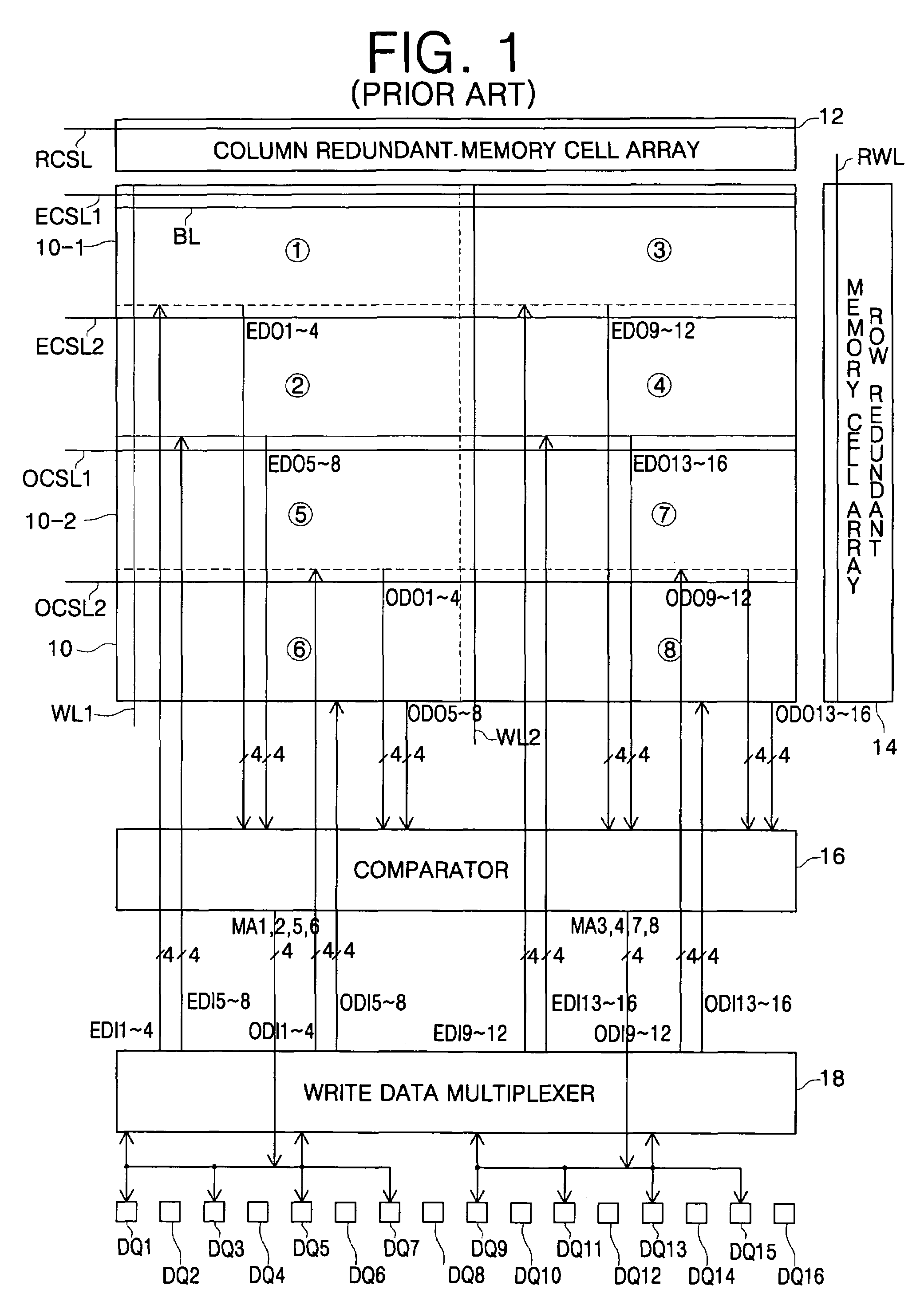

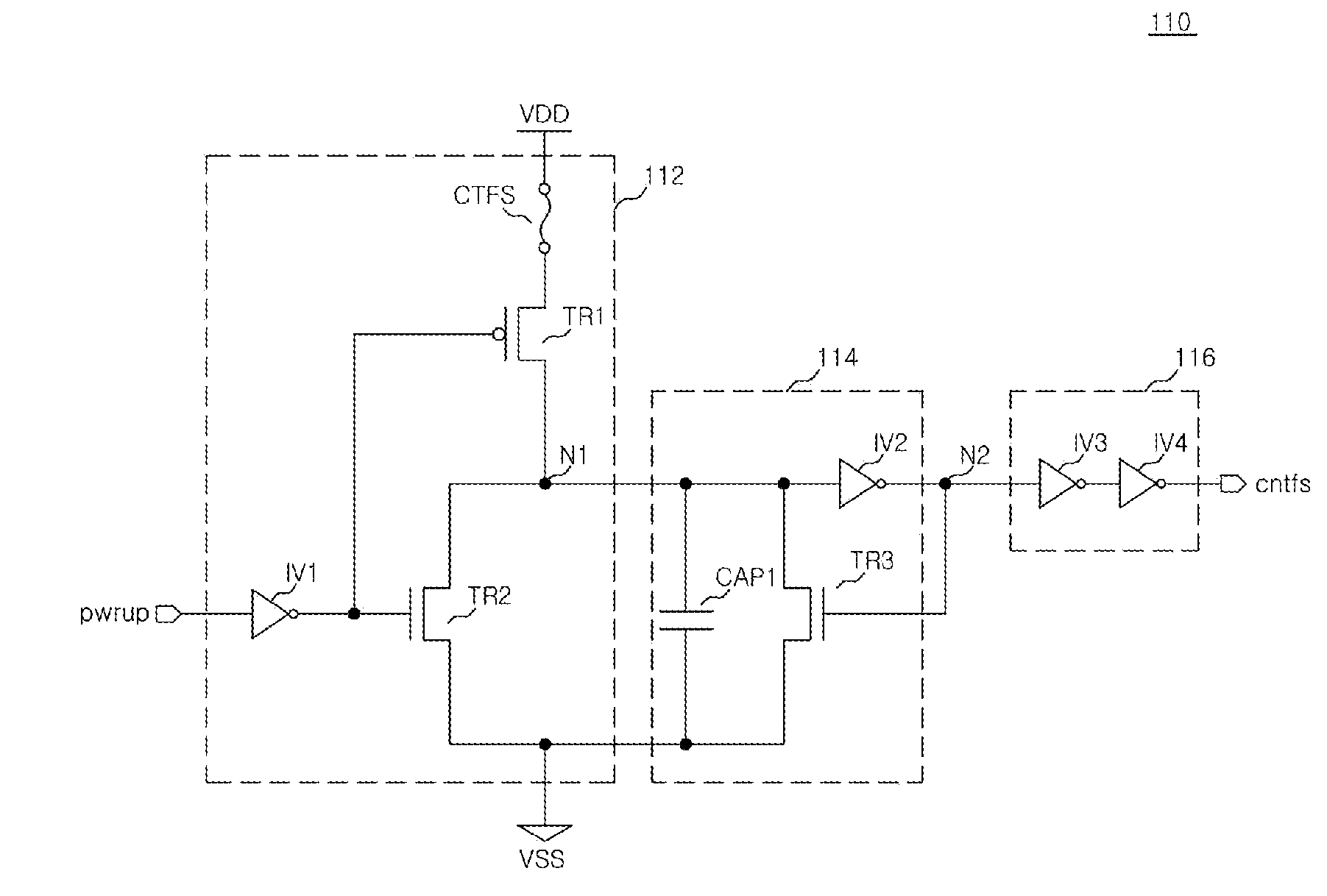

Systems and methods for simultaneously testing semiconductor memory devices

Owner:SAMSUNG ELECTRONICS CO LTD

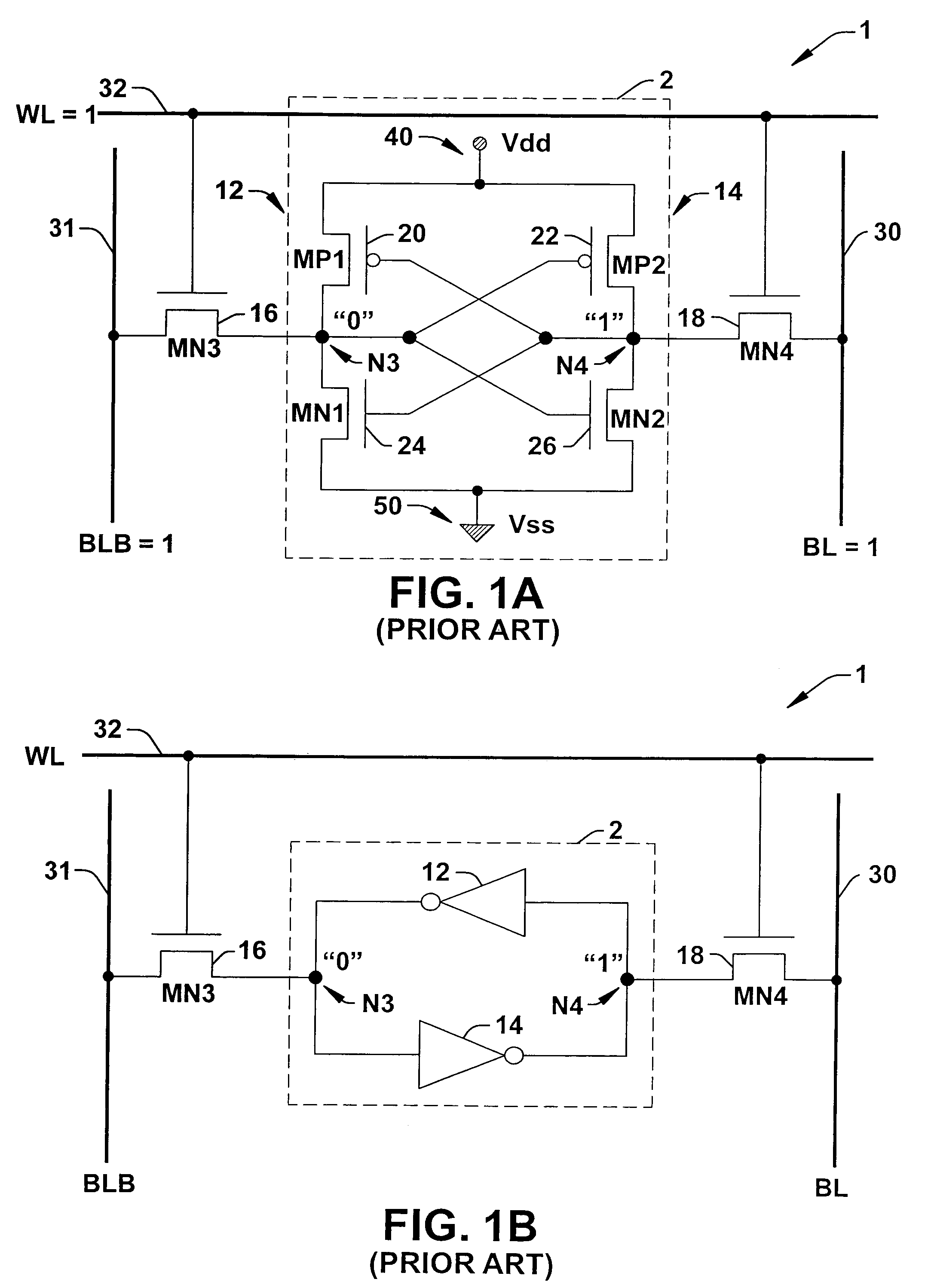

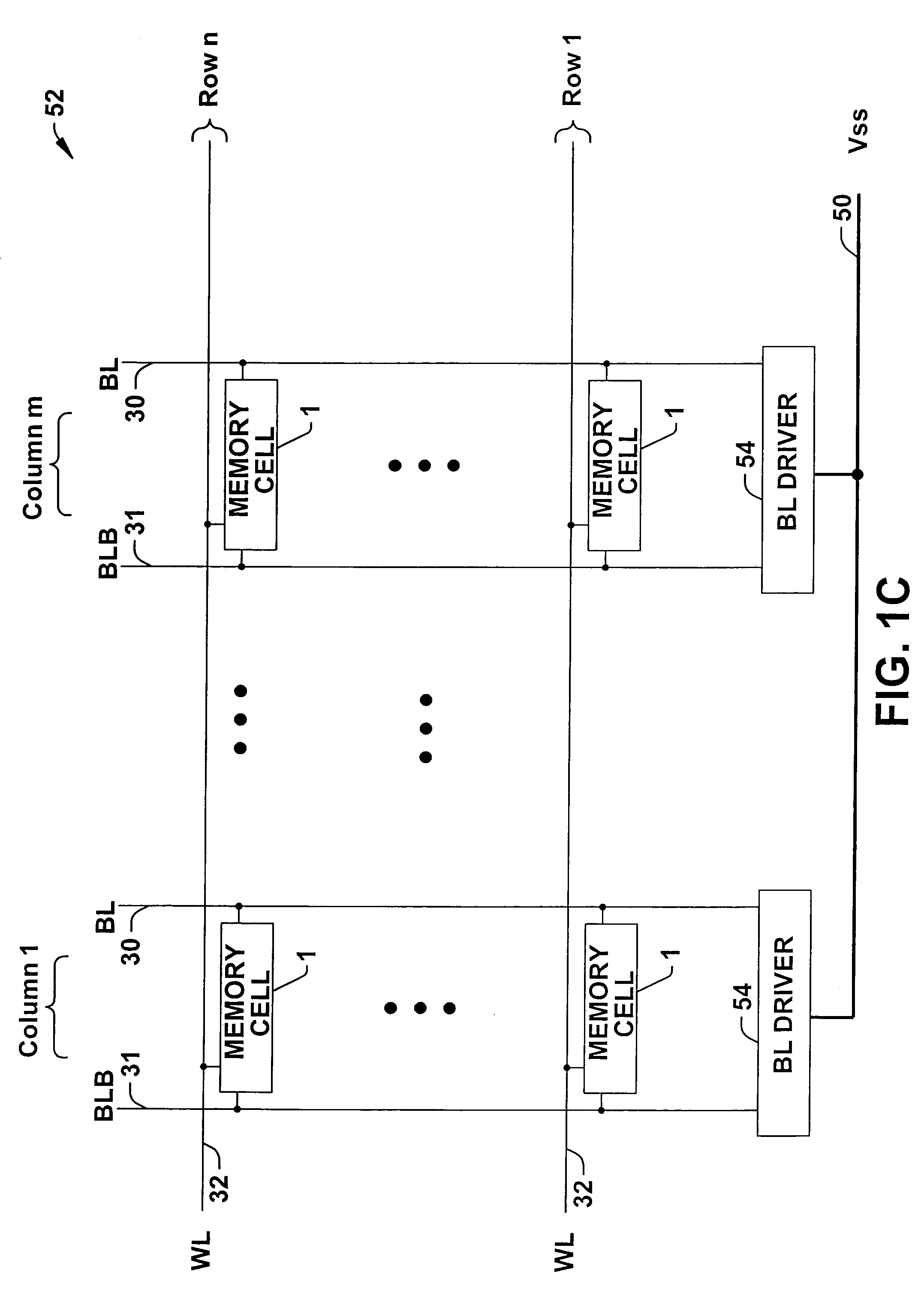

SRAM static noise margin test structure suitable for on chip parametric measurements

A set of memory cell test structures and a method are disclosed for assessment of the static noise margin (SNM) of a memory cell or an array of such cells, for example, of SRAM cells of an integrated circuit device, using discrete point measurement structures provided either on-chip or within the scribe lines. In one embodiment, the set of memory structures comprises first and second test structures, individually comprising a memory cell, having one or more left and right half-bit test structures having hard-wired connections between select nodes of each memory cell half-bit and one or more voltage supplies. The half-bits of the first test structure are configured for measuring respective left and right standby SNM values, and the half-bits of the second test structure are configured for measuring respective left and right cell ratio values at respective output nodes of the structures, using applied supply voltages for on-chip assessment of the static noise margin of the memory cells. The method applies the supply voltages to select nodes of the test structures, measures left and right standby SNM values at a first test structure, measures left and right cell ratio values at a second test structure, determines a first difference between the left half-bit standby SNM value and the right half-bit cell ratio value, determines a second difference between the right half-bit standby SNM value and the left half-bit cell ratio value, and determines a smaller one of the first and second difference values proportional to an SNM value of the cell.

Owner:TEXAS INSTR INC

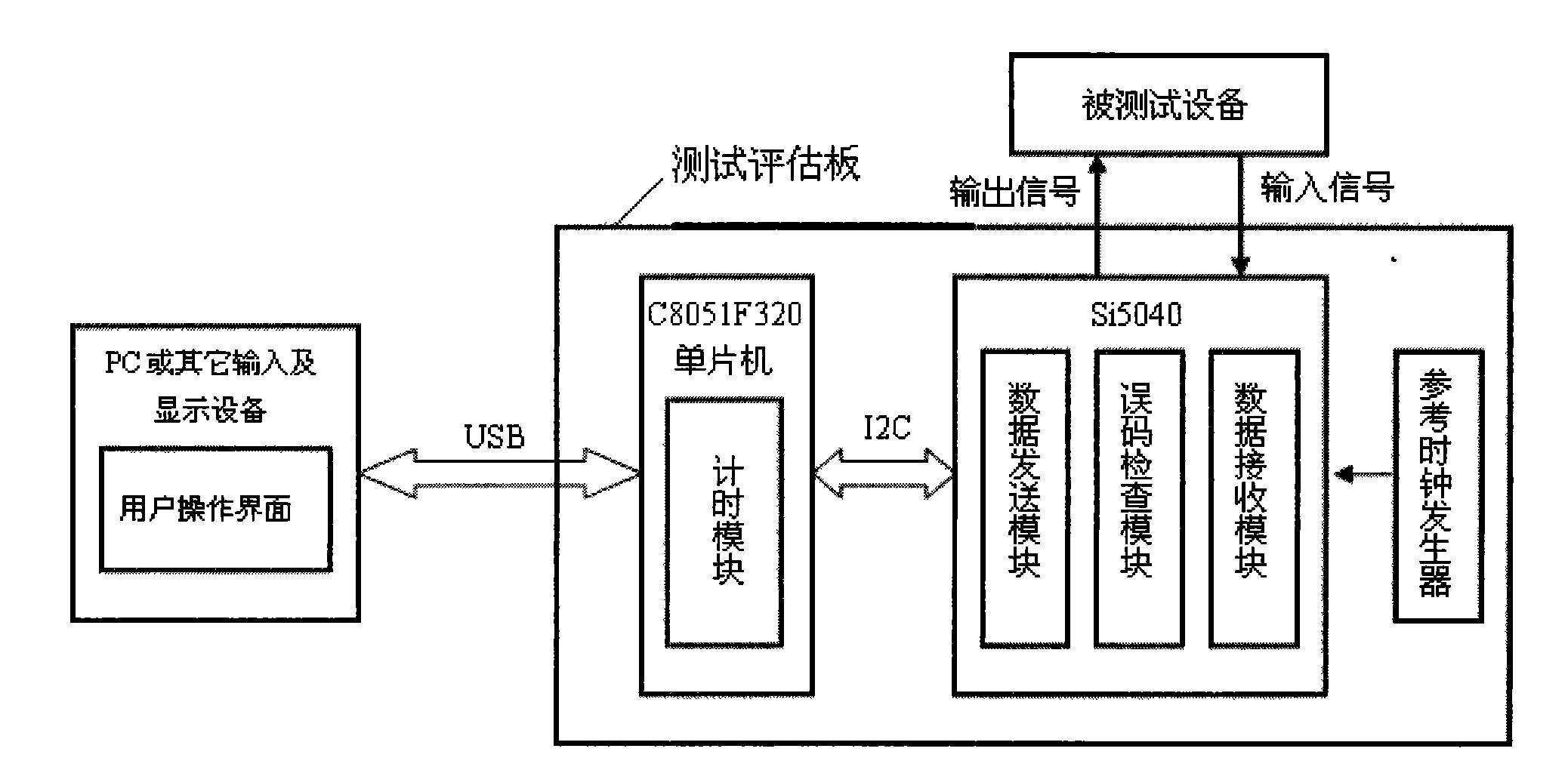

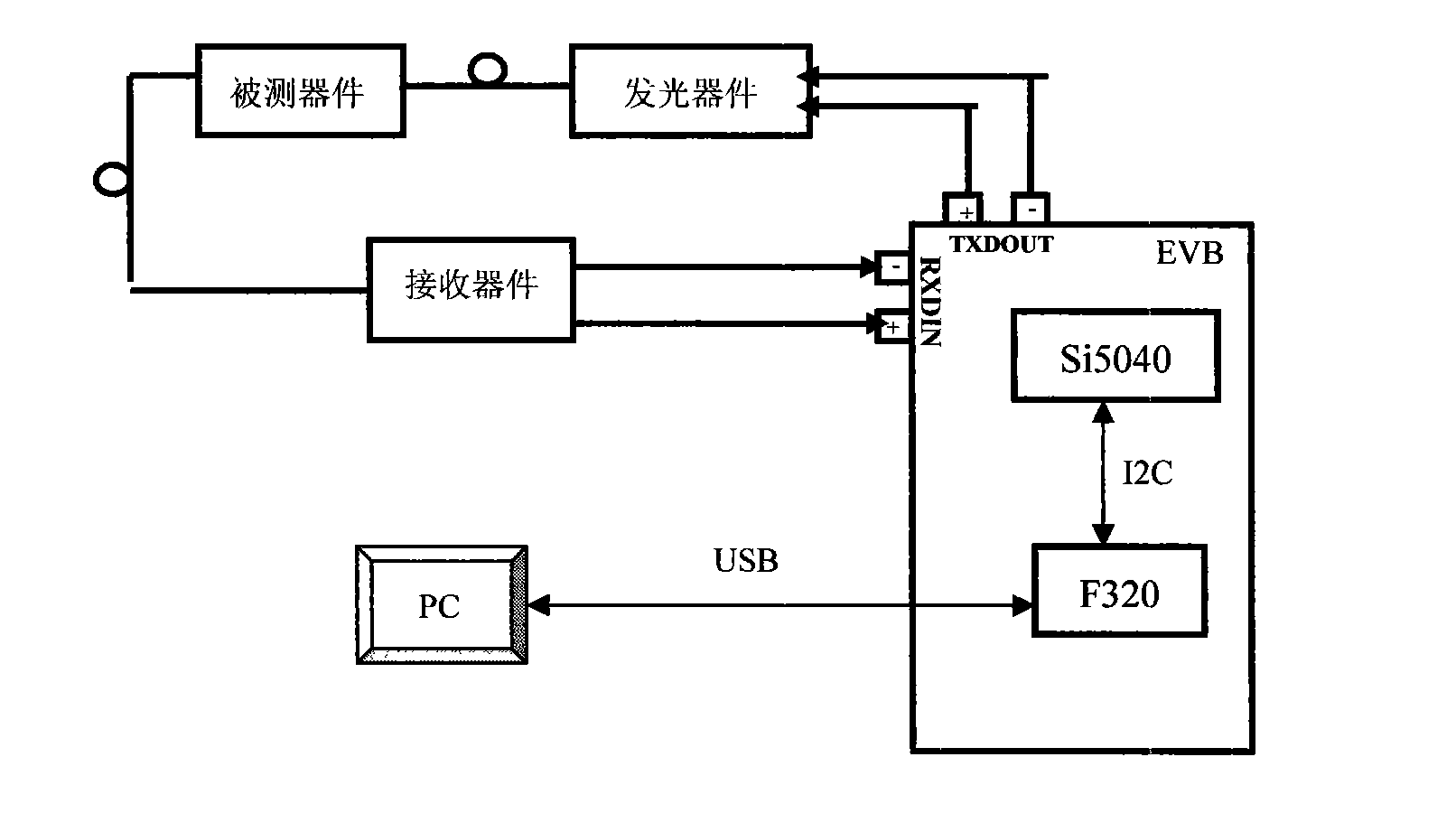

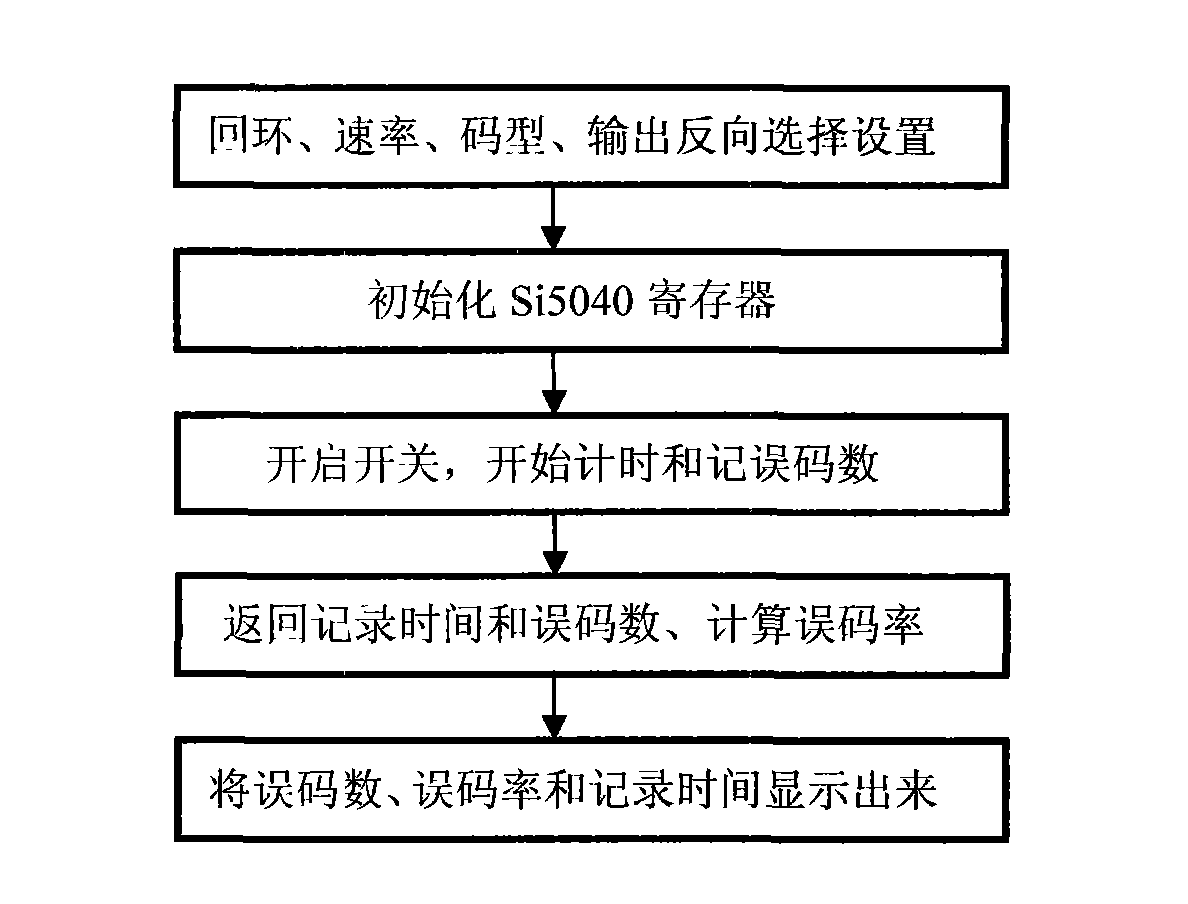

10 Gbps bit error analyzing instrument

InactiveCN101640566AHighly integratedReduce volumeError detection/prevention using signal quality detectorElectromagnetic transmissionMicrocontrollerMicrocomputer

The invention discloses a 10 Gbps bit error analyzing instrument and aims to provide a bit error analyzing instrument which has low cost, simple and convenient operation and convenient carrying and issuitable for engineering field test. The 10 Gbps bit error analyzing instrument comprises an evaluation board and a single chip microcomputer of C8051 series, wherein the evaluation board can carry out communication with a PC, and a bit error test chip which is connected with equipment to be tested is arranged on the evaluation board; and the single chip microcomputer is used for carrying out communication with an upper PC and a lower test chip, and is provided with a USB interface which carries out communication with the PC and an I2C double line type serial bus which is connected with the bit error test chip to carry out communication and control. The bit error test chip provides sent bit flow and total amount of bit error to the PC through the single chip microcomputer, and the sent bit flow is obtained by test time recorded by the single chip microcomputer and appointed frequency output by the test chip. The invention has the advantages of convenience, rapidness and accurate bit error analysis test and is suitable for performance test of a 10 Gbps communication system.

Owner:SUPERXON (CHENGDU) TECH LTD

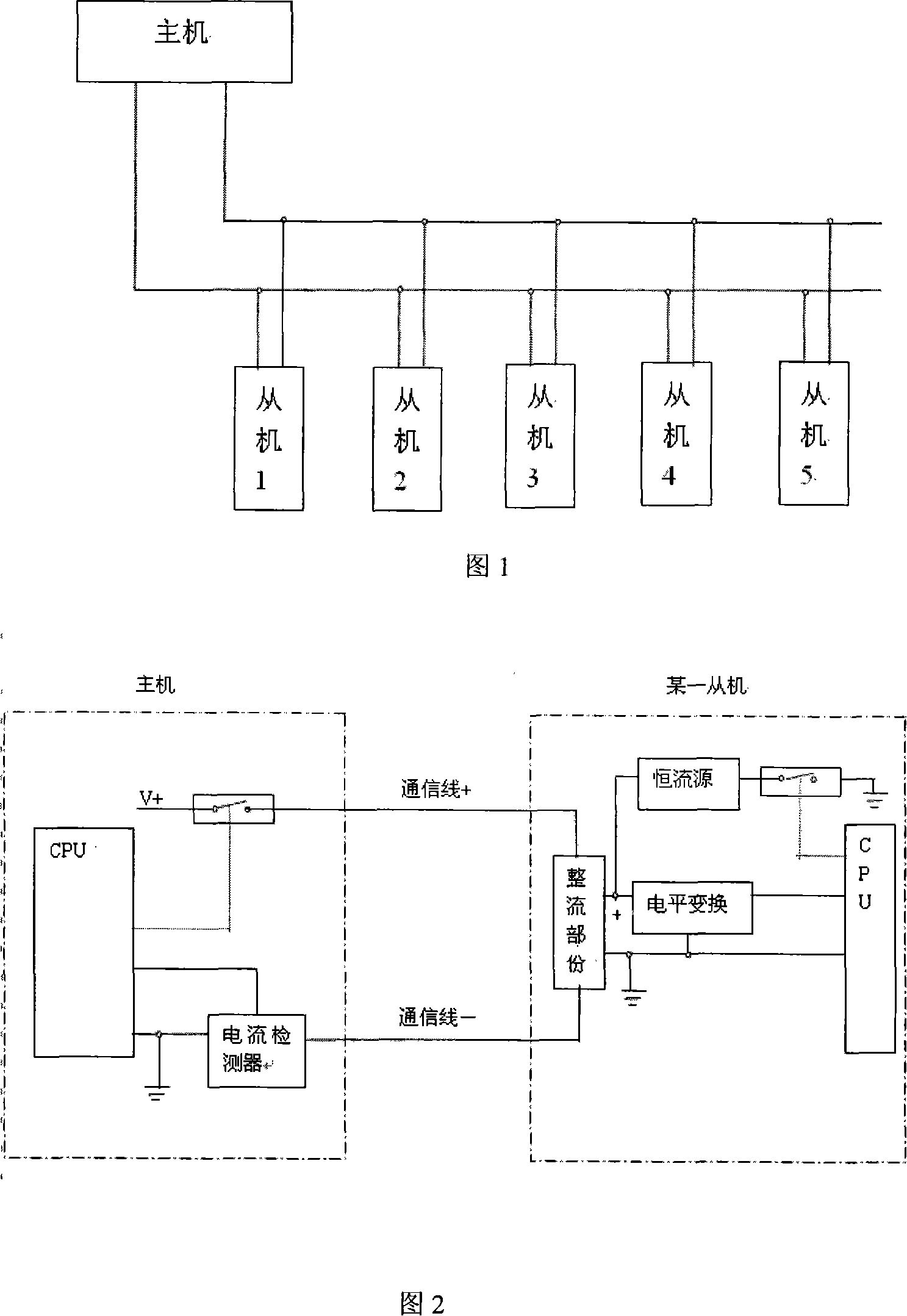

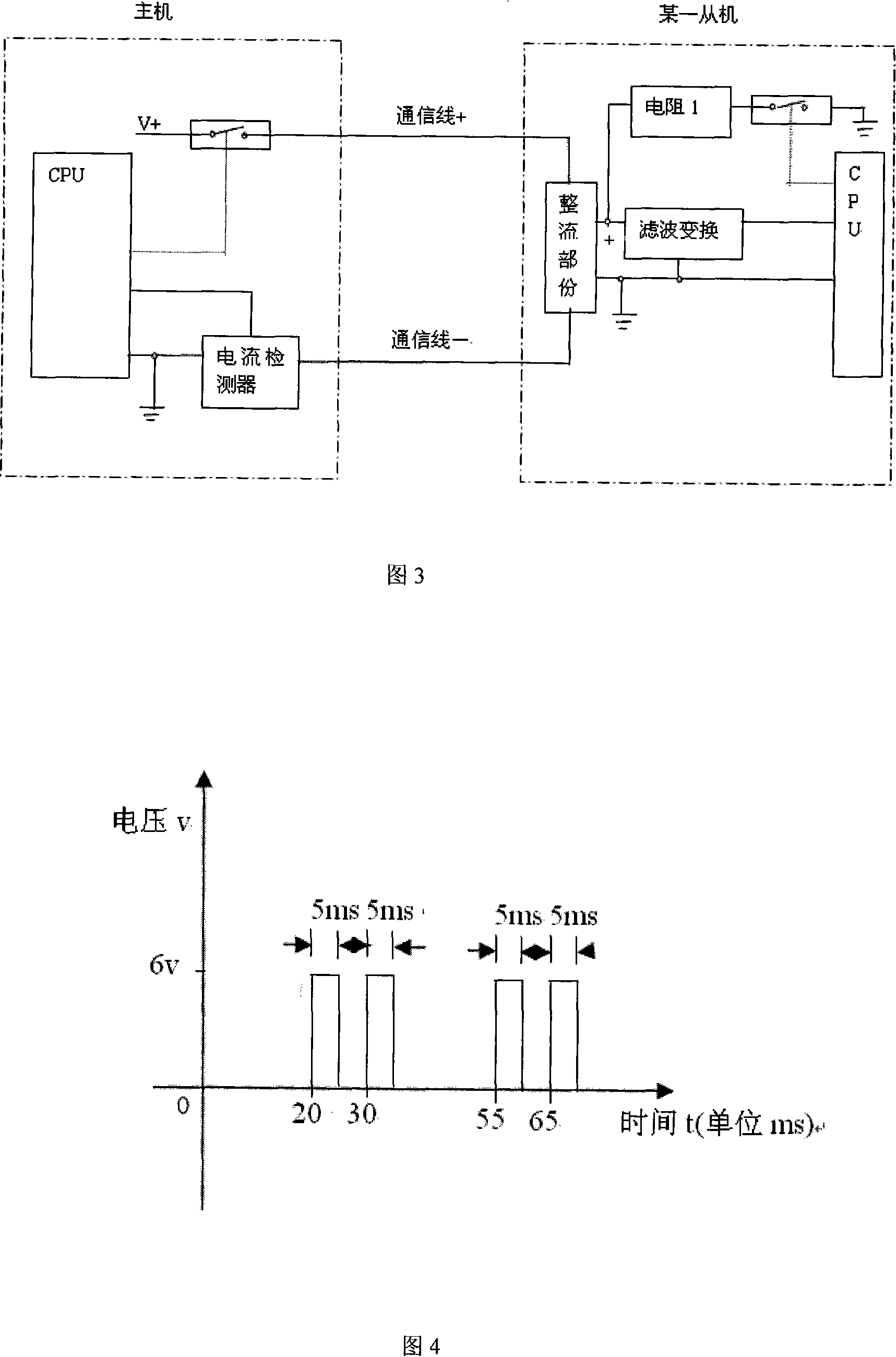

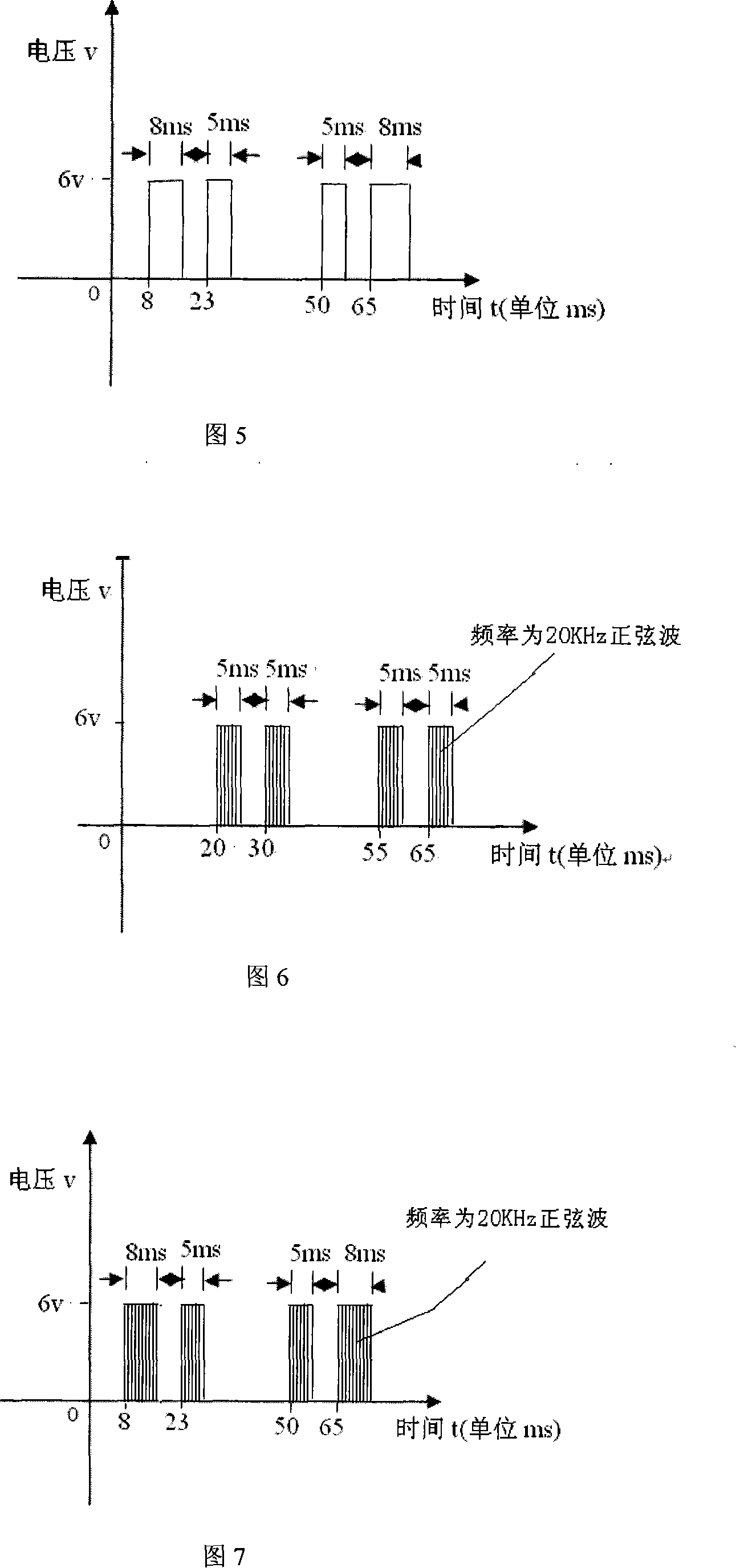

Slave computer address detection method in master-slave mode serial communication

ActiveCN101140553AImprove reliabilityEasy to detectElectric digital data processingNetwork connectionCommunication link

The invention relates to a slave machine address test method for a master-slave type serial communication in the technical field of electronic communication. The method is as follows: In accordance with a pre-defined coding rule between a host computer and slave machines, the host computer sends the first scanning command to zero registers in the slave machines; the host computer sends address bit test signal according to the binary bit length of the slave machine address; the slave machines follow the address binary bit value to perform current feedback for the signal, and determine whether perform continuous feed according to the variation; the host computer can identify the address of the first slave machine; then, the second scanning command is launched, and the rest slave machines zero registers respectively before repeating the actions in the previous execution step; the host computer can identify the address of the second slave machine, and identically, test address of the rest slave machines, until the detected addresses of the slave machines are all 1. The invention can simplify communication links and interface circuits, increase communication convenience and efficiency of host computers and slave machines, and increase test possibility of network interconnection. Therefore, the invention can lower comprehensive cost of relevant products, and have rather high value in actual application.

Owner:BEIJING QAML OF SCI & TECH CO LTD

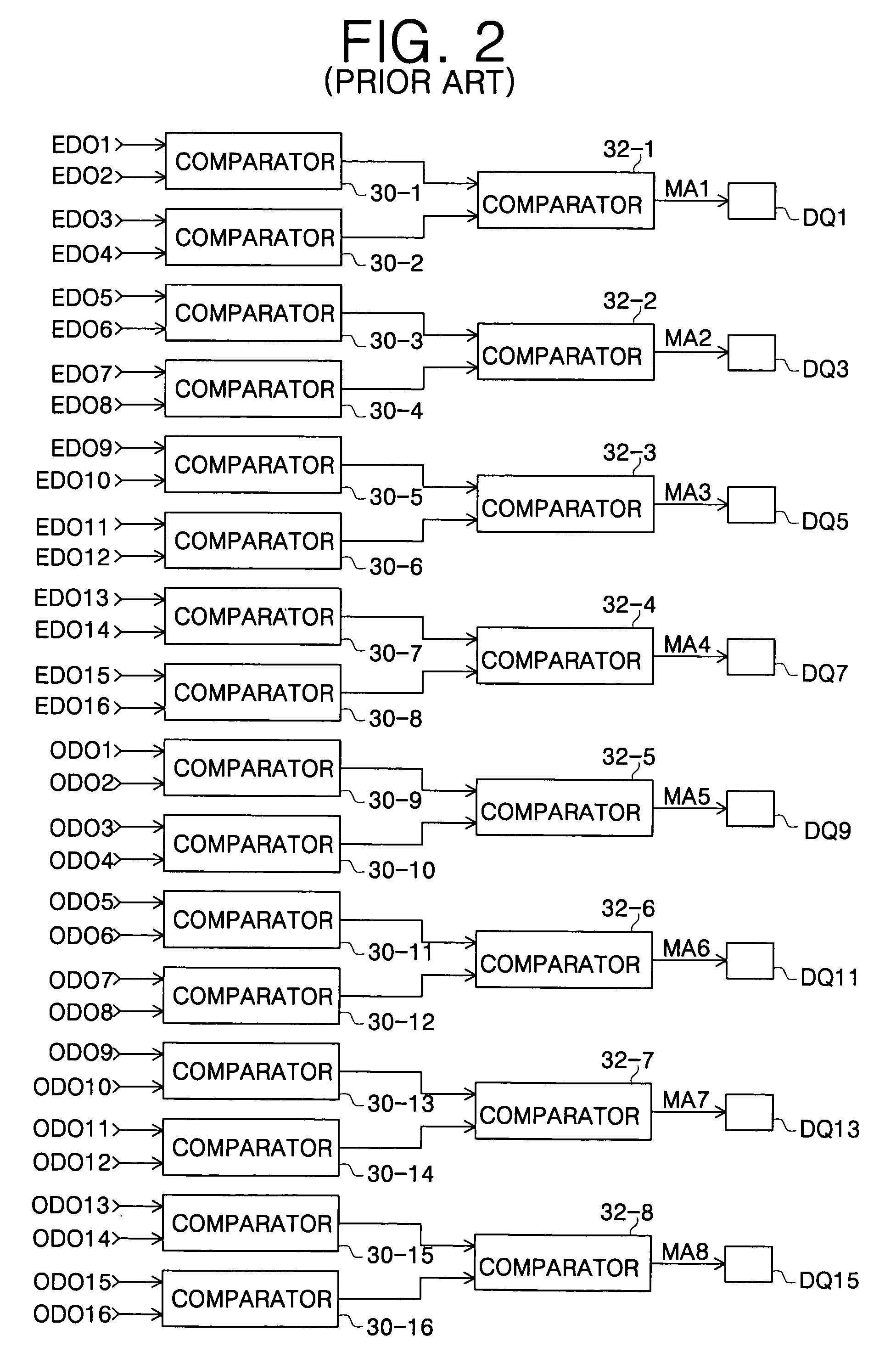

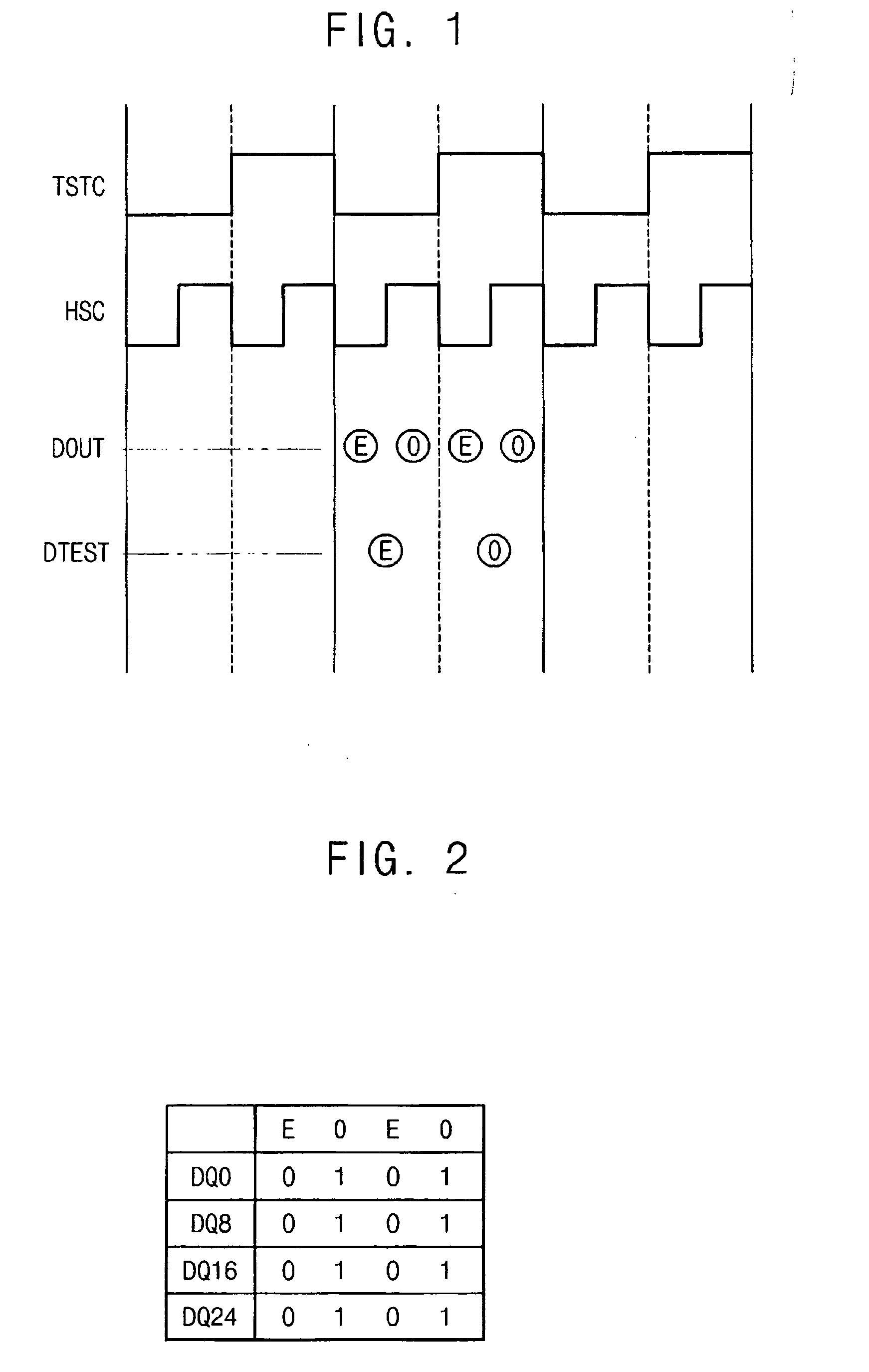

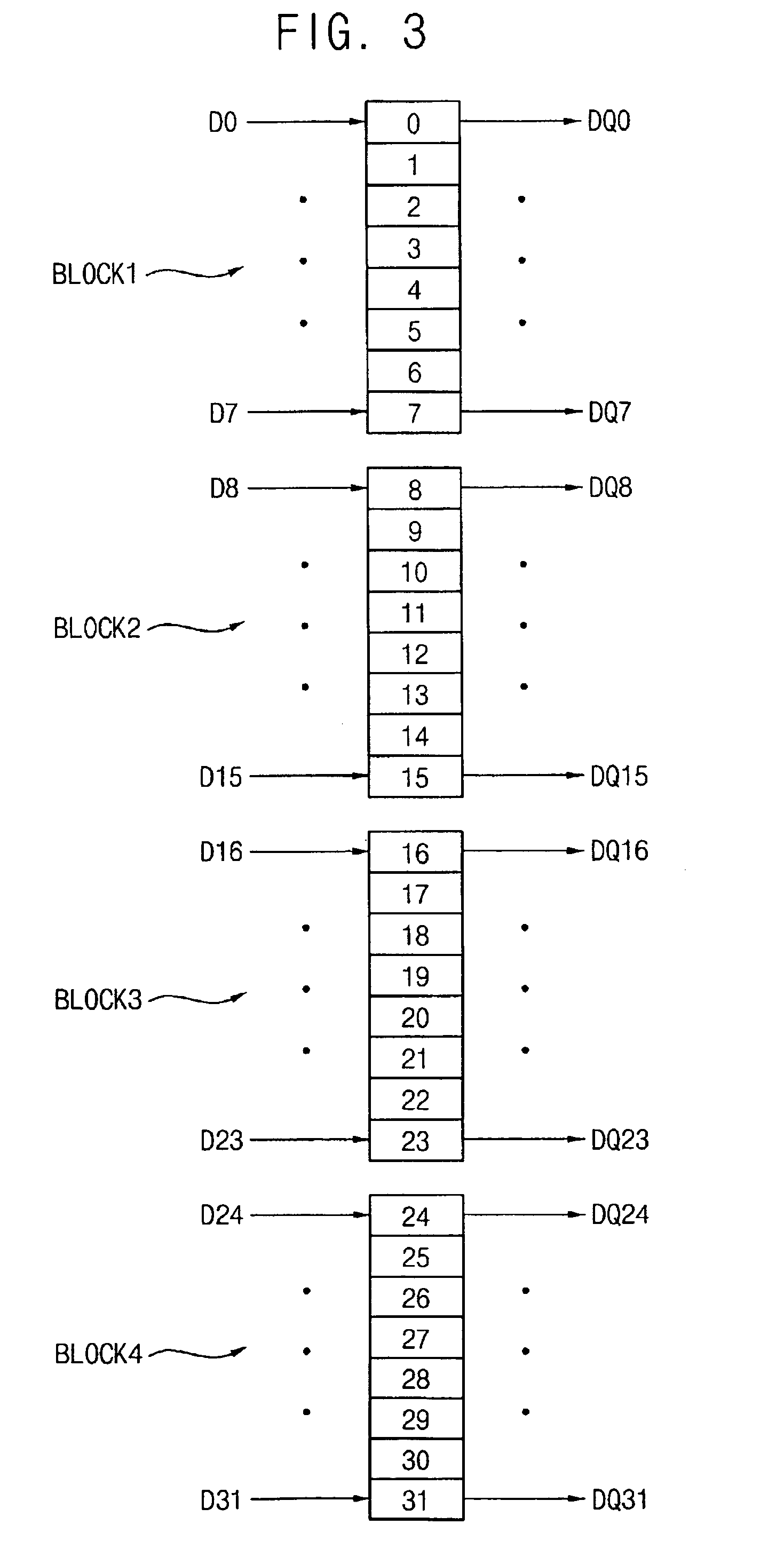

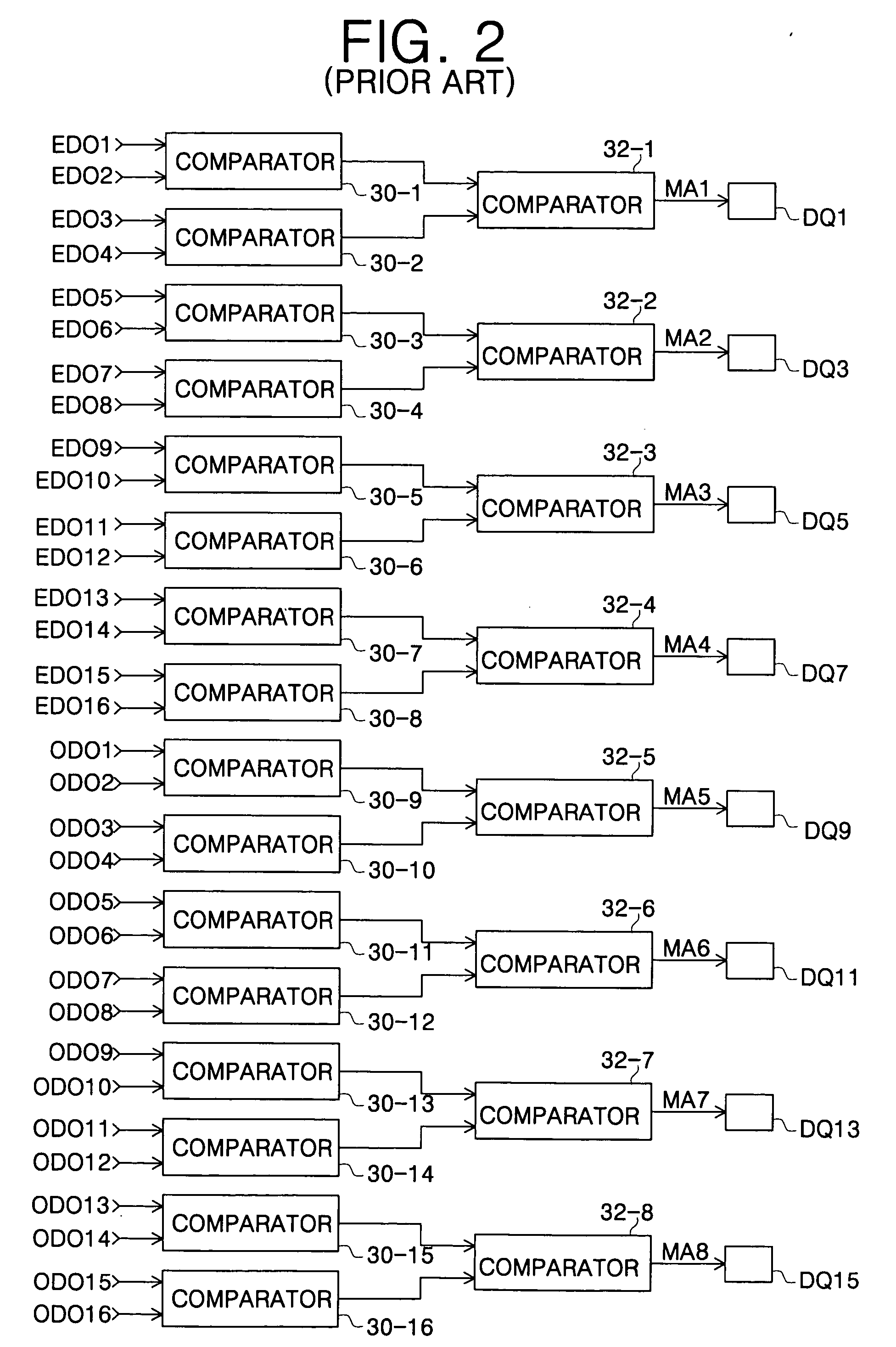

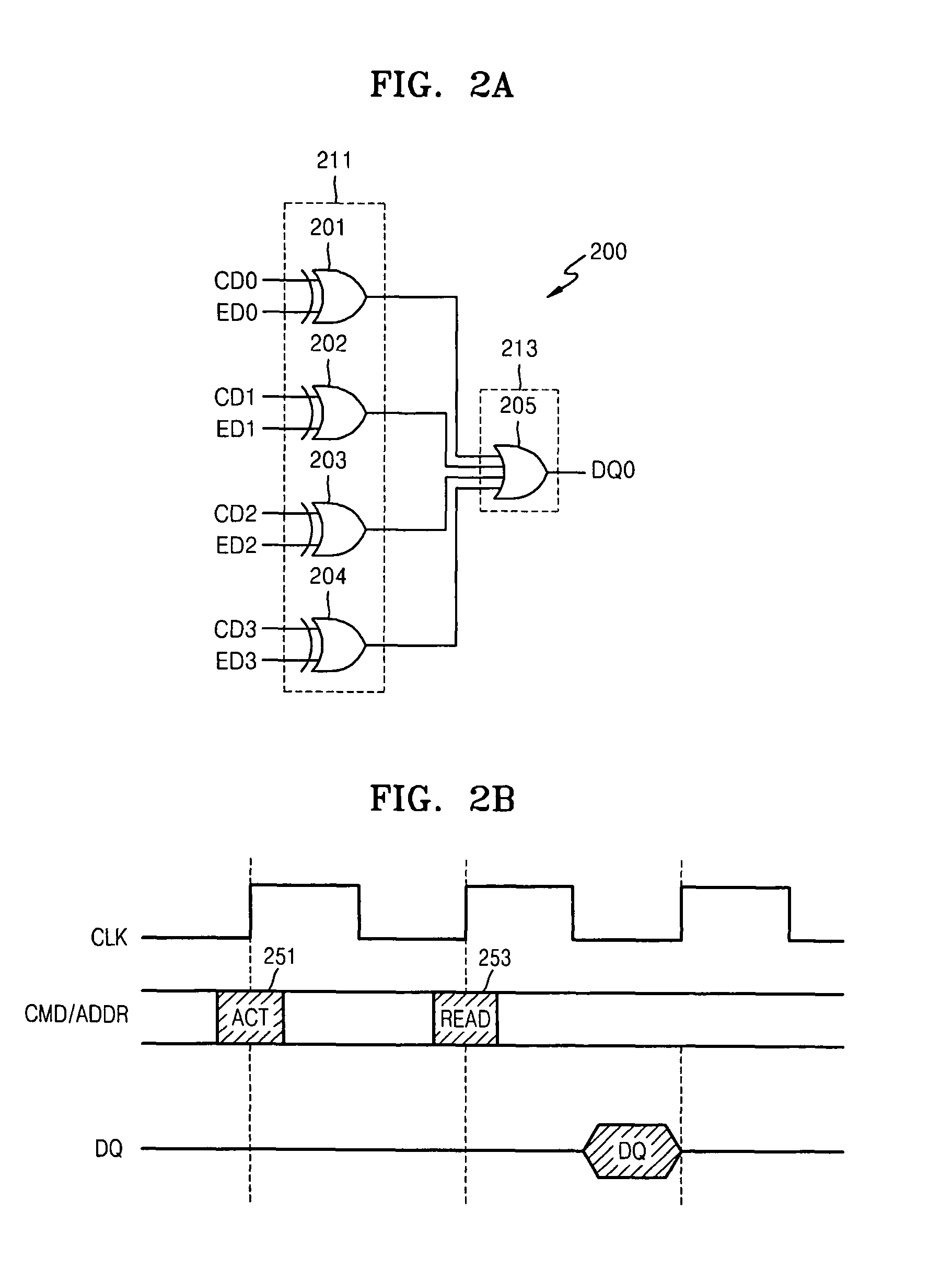

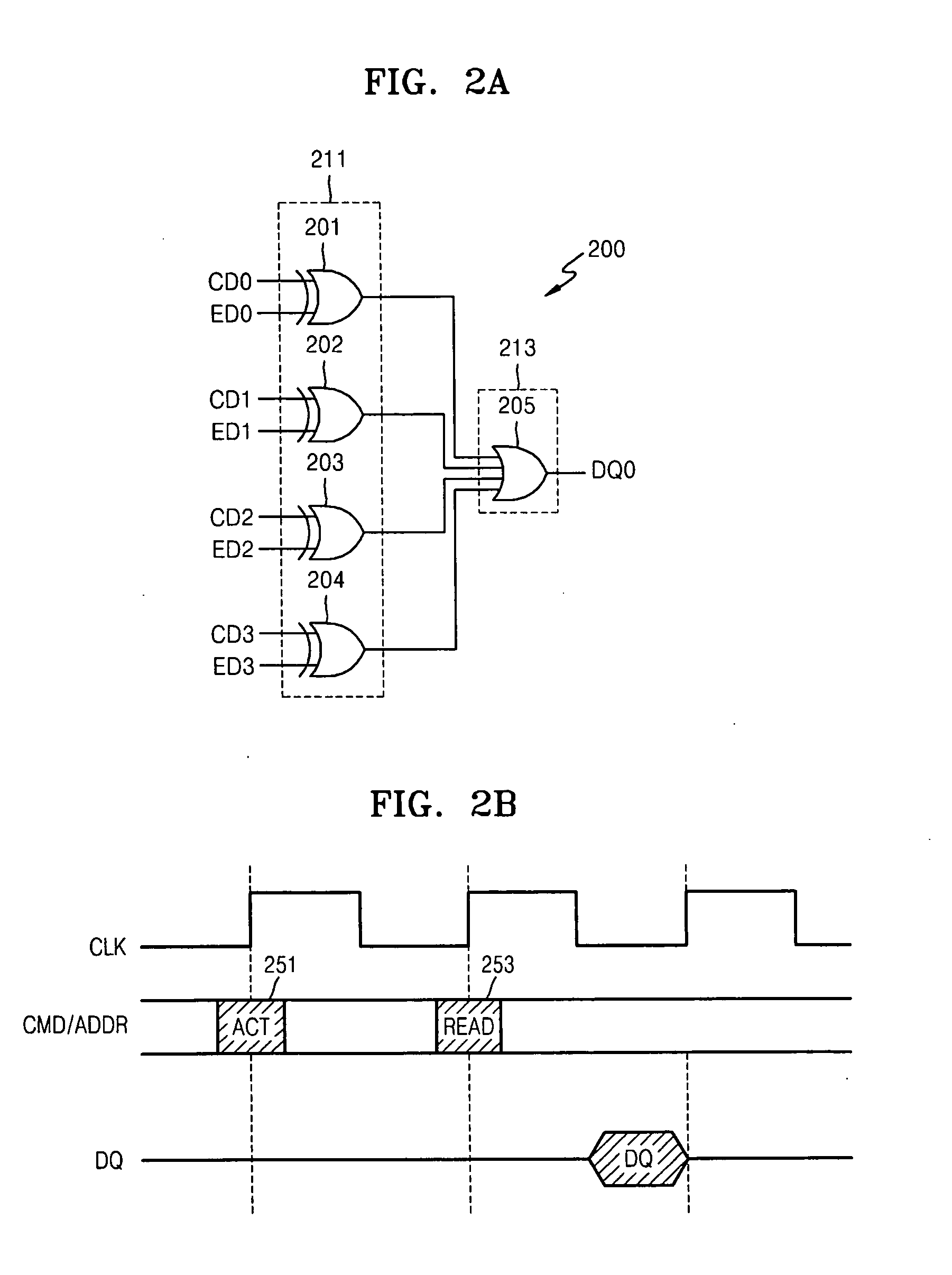

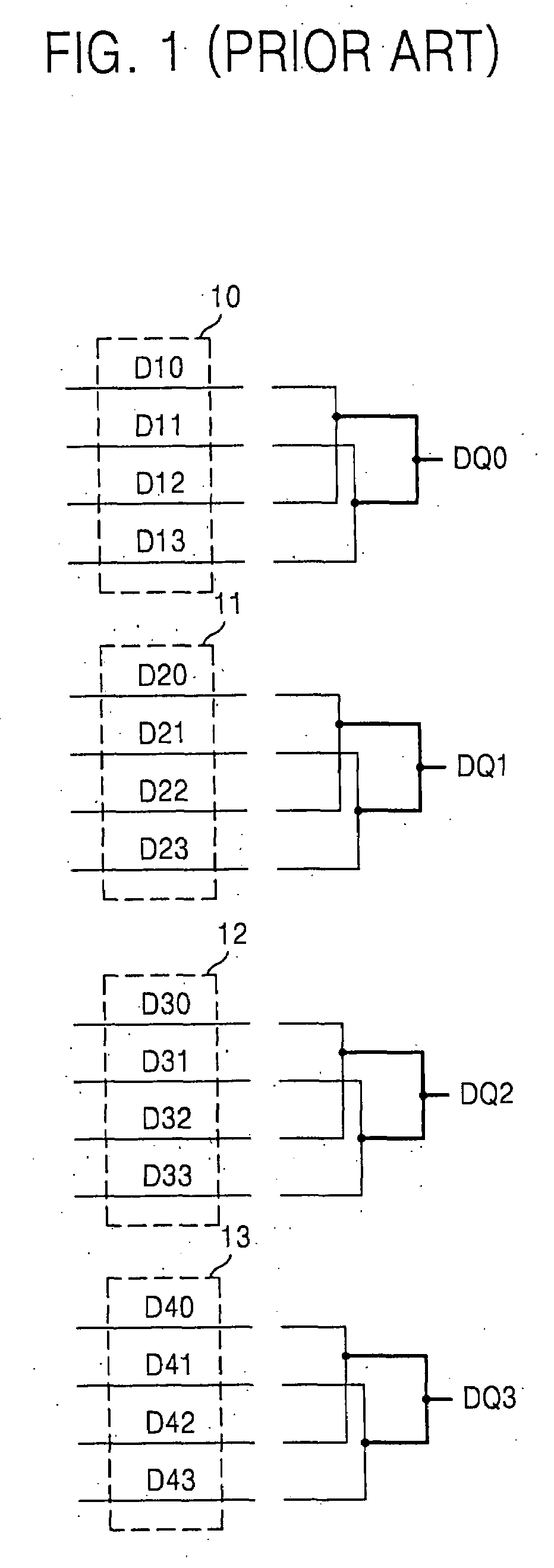

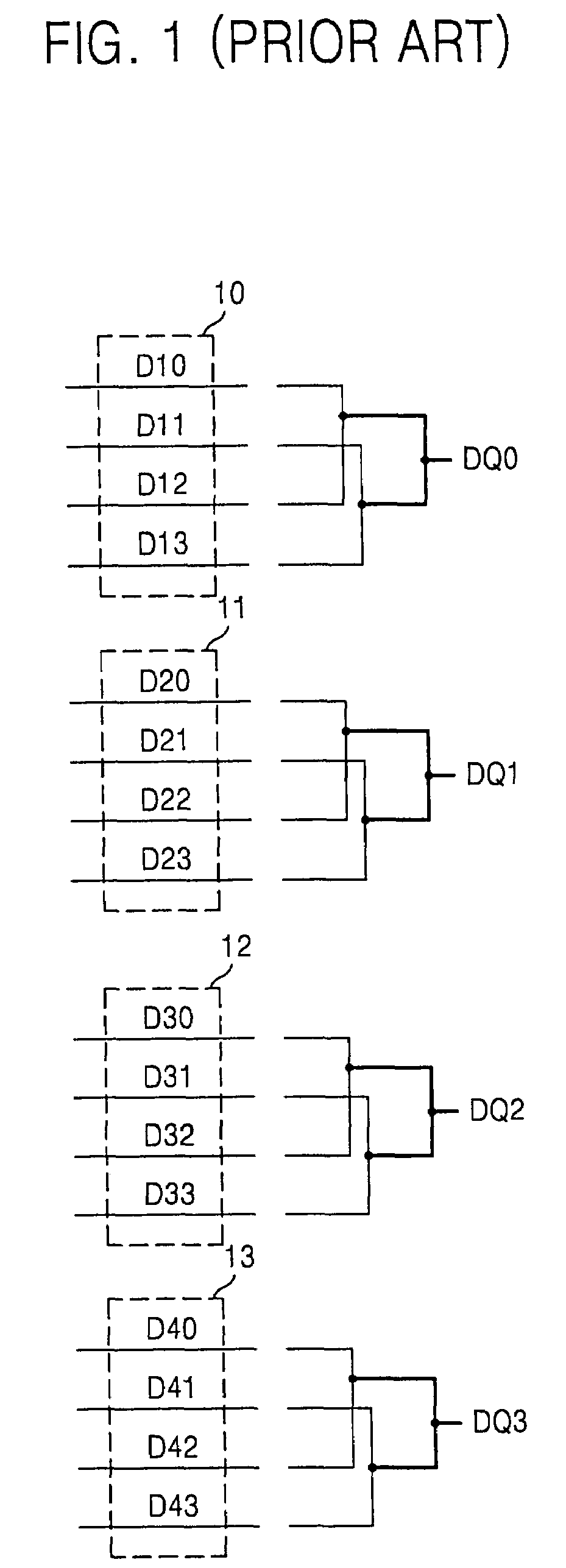

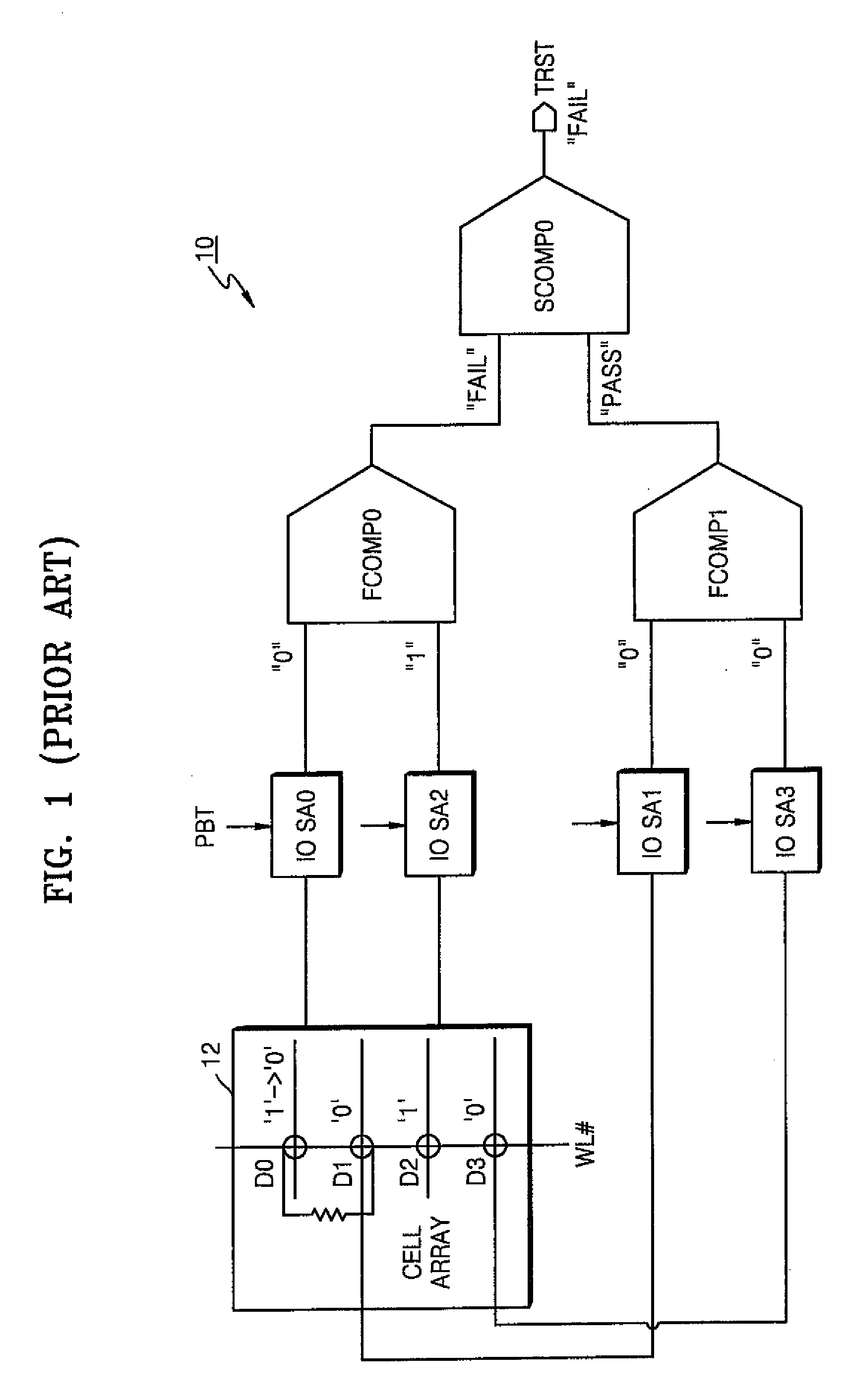

Circuit and method of testing semiconductor memory devices

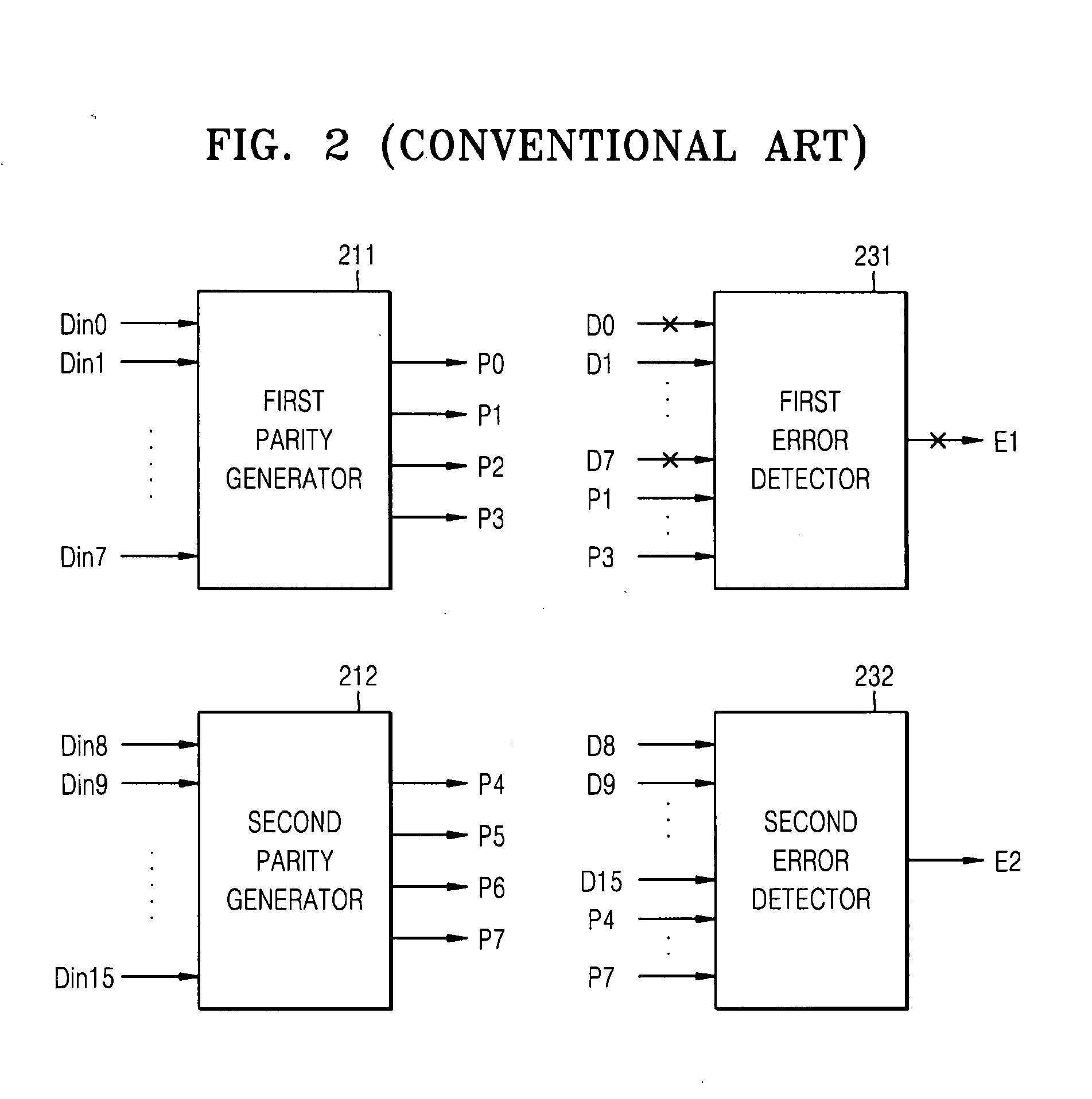

InactiveUS20070101225A1The test result is accurateElectronic circuit testingError detection/correctionBit TestComparator

A circuit for testing a semiconductor memory device includes a data comparator and a signal aligner. The data comparator compares a first output data and a second output data provided from an output buffer circuit. The data comparator determines whether logical states of the first output data and the second output data are identical to generate a comparison signal. The signal aligner aligns the first output data and the comparison signal, and generates a plurality of test signals in response to a clock signal. The test signals includes an even bit test data, an odd bit test data, an even bit comparison test data and an odd bit comparison test data. The even bit data and the odd bit data are simultaneously tested by using one pattern, and a correct test result is yielded even when test data are all inverted.

Owner:SAMSUNG ELECTRONICS CO LTD

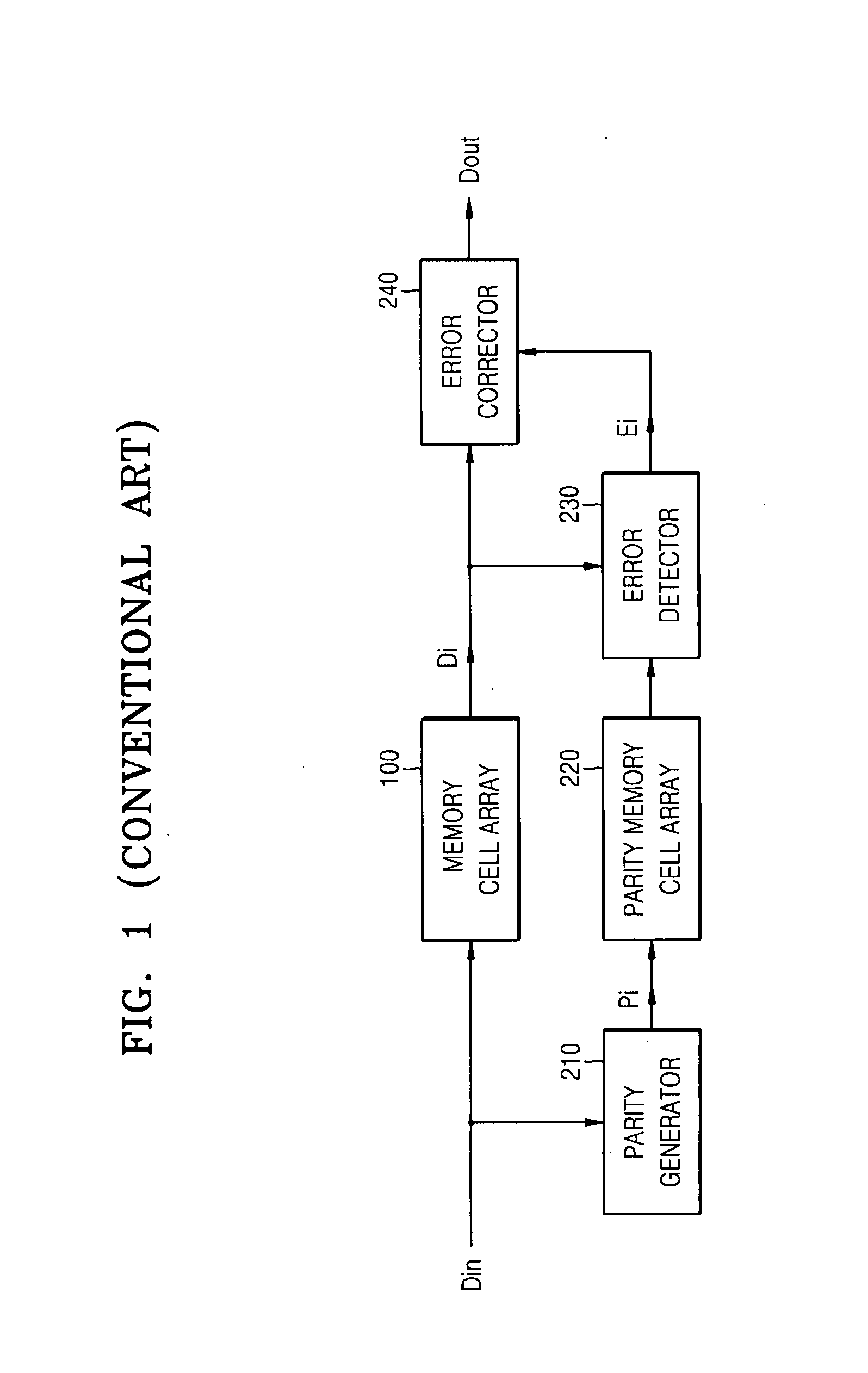

Parallel bit test device and method using error correcting code

Example embodiments are directed to a parallel bit test device and method using error correcting code. The parallel bit test device may include an error detecting and correcting unit configured to count the number of fail bits in an m-bit data signal, for example, by comparing bits of the m-bit data signal with corresponding bits of expected data, where m is a positive integer, and to output correction signals. The error detecting and correcting unit may be further configured to perform at least one logic operation on a correction control signal and comparison signals. The correction control signal may be generated in response to a test mode register set (TMRS) signal set and input by a user such that the logic level of the correction control signal may vary according to the counted number of fail bits. Each comparison signal may include information about a fail bit and the address of the fail bit.

Owner:SAMSUNG ELECTRONICS CO LTD

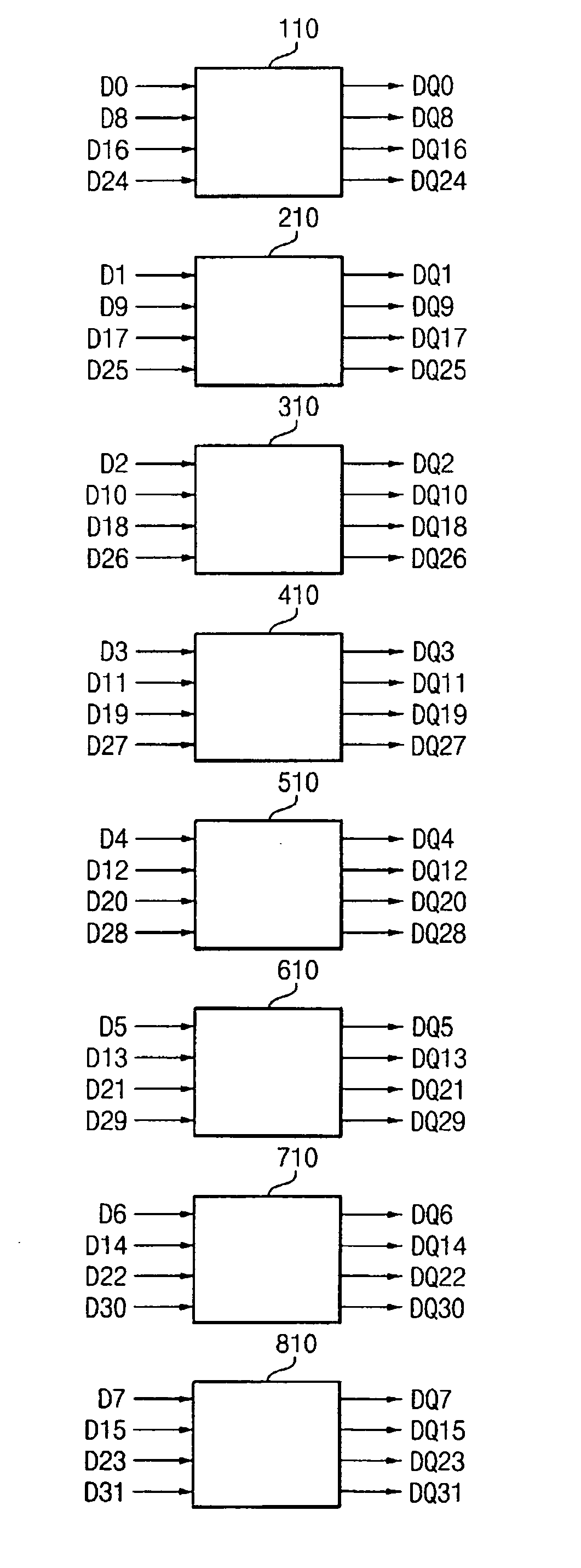

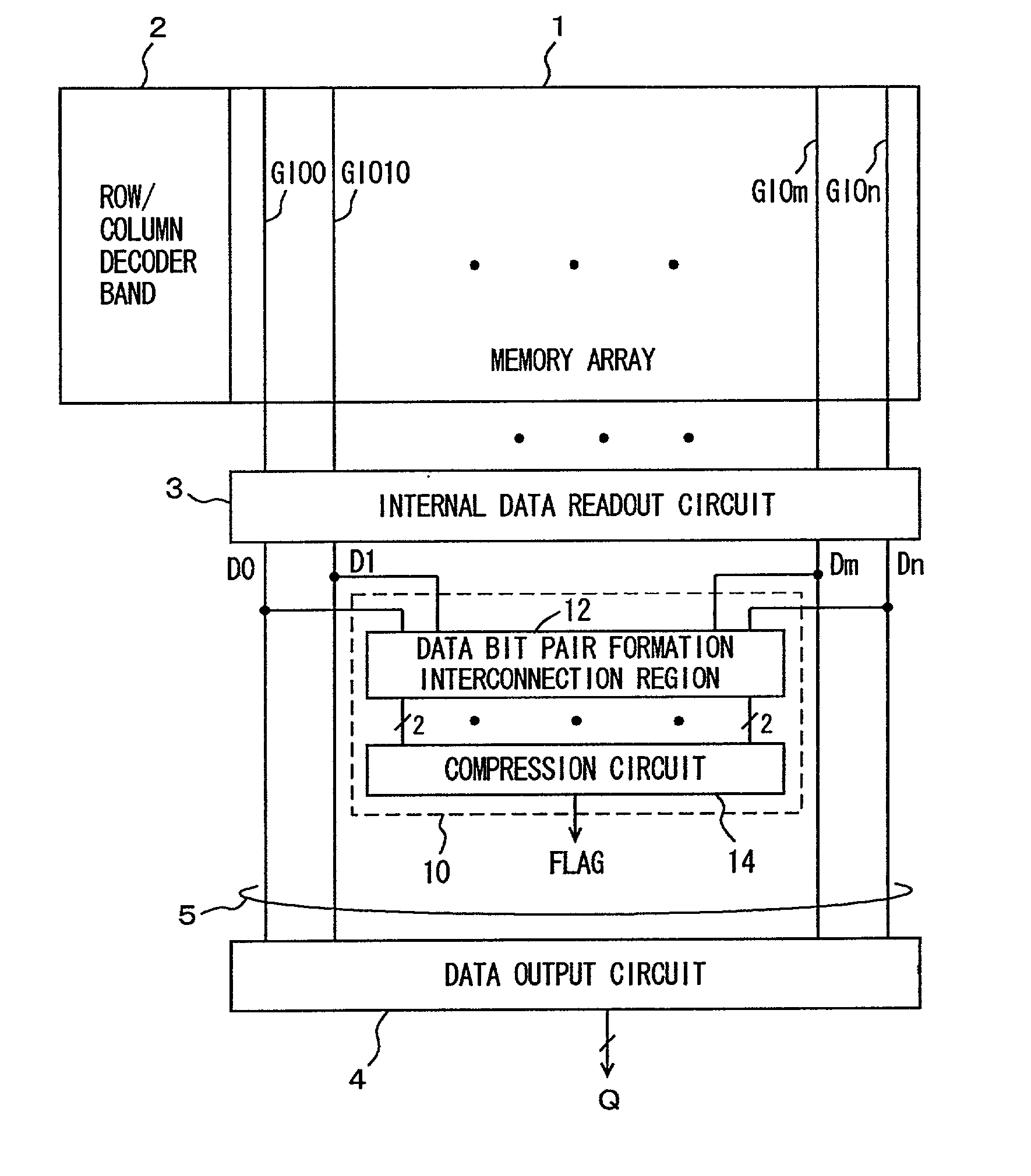

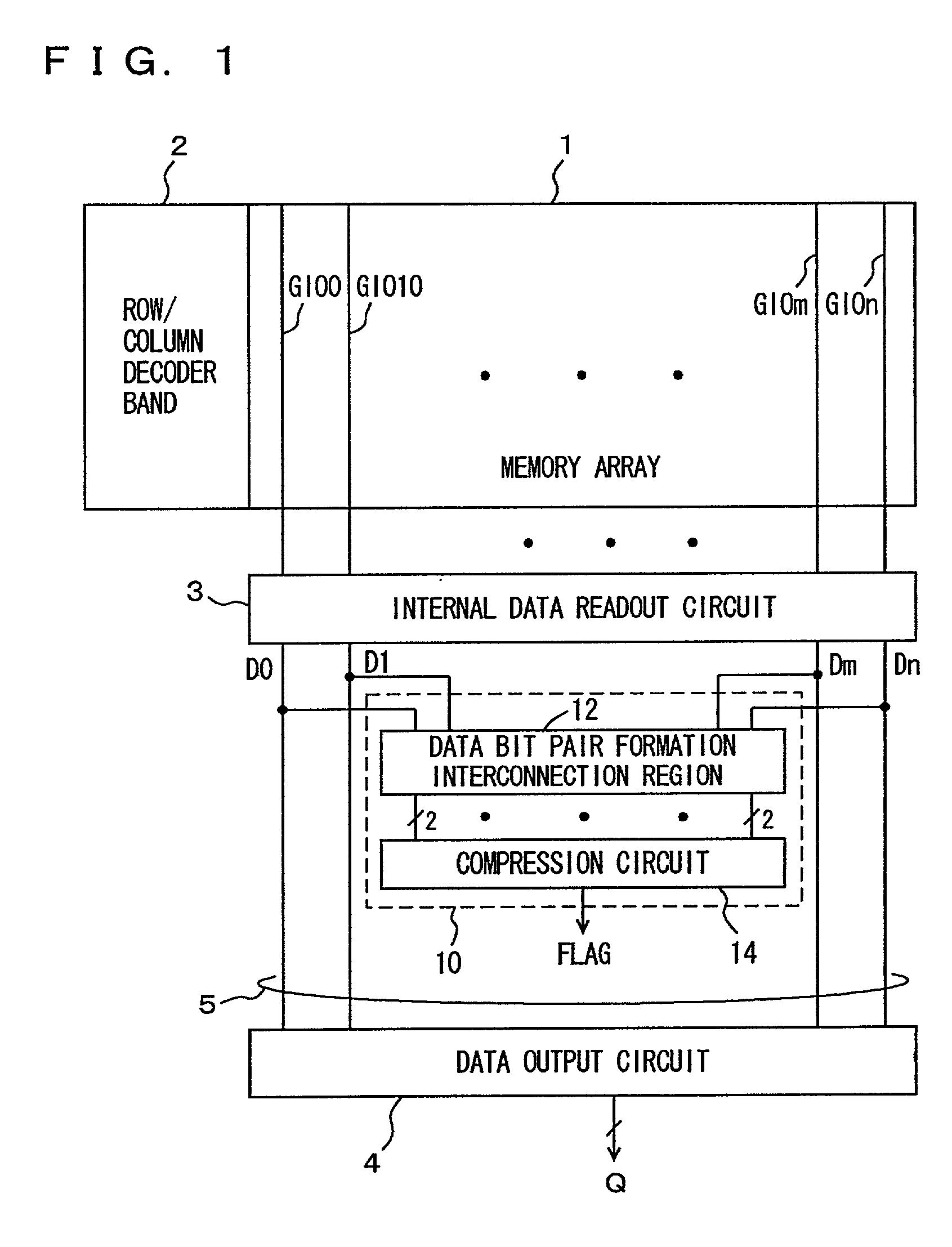

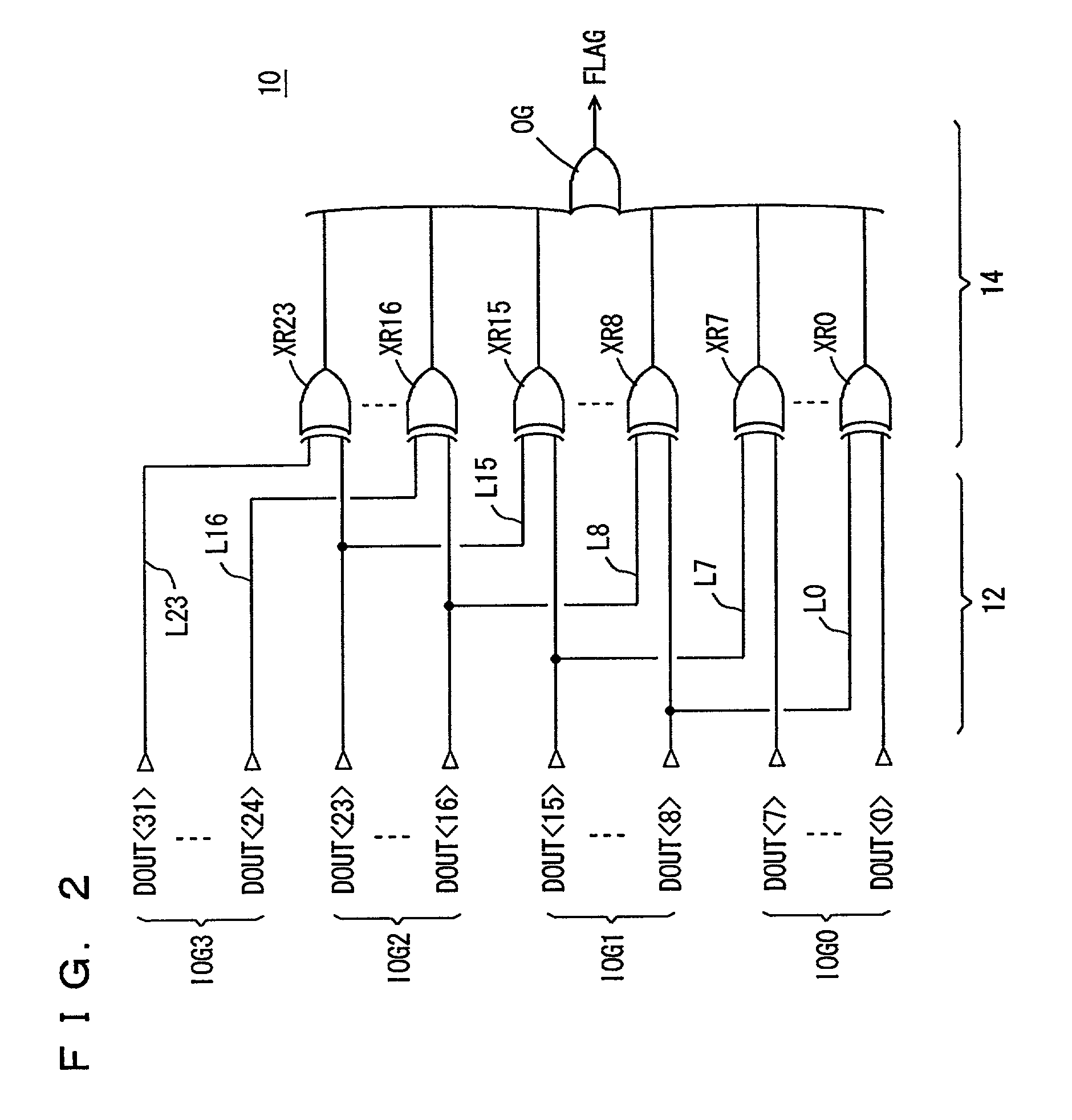

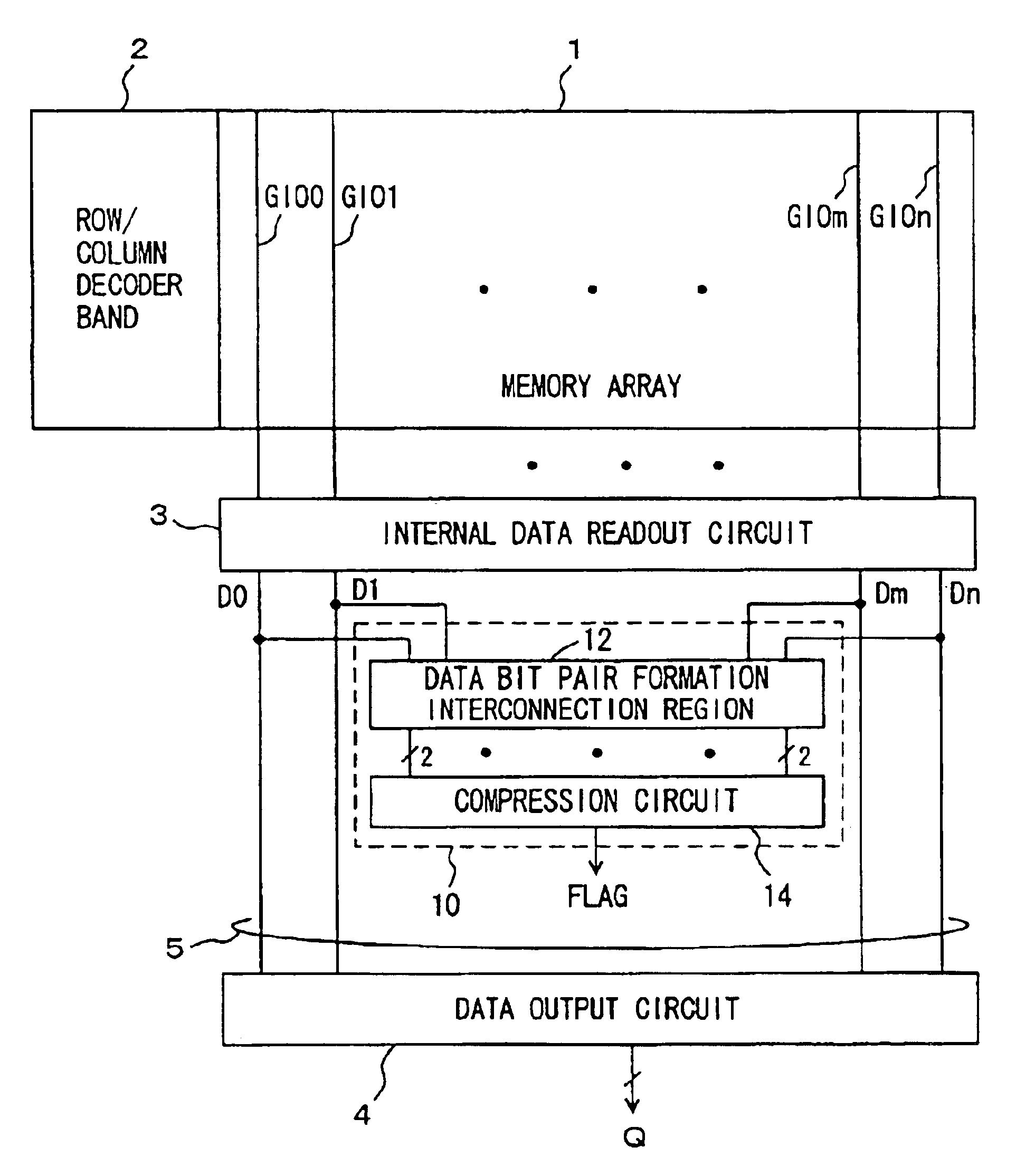

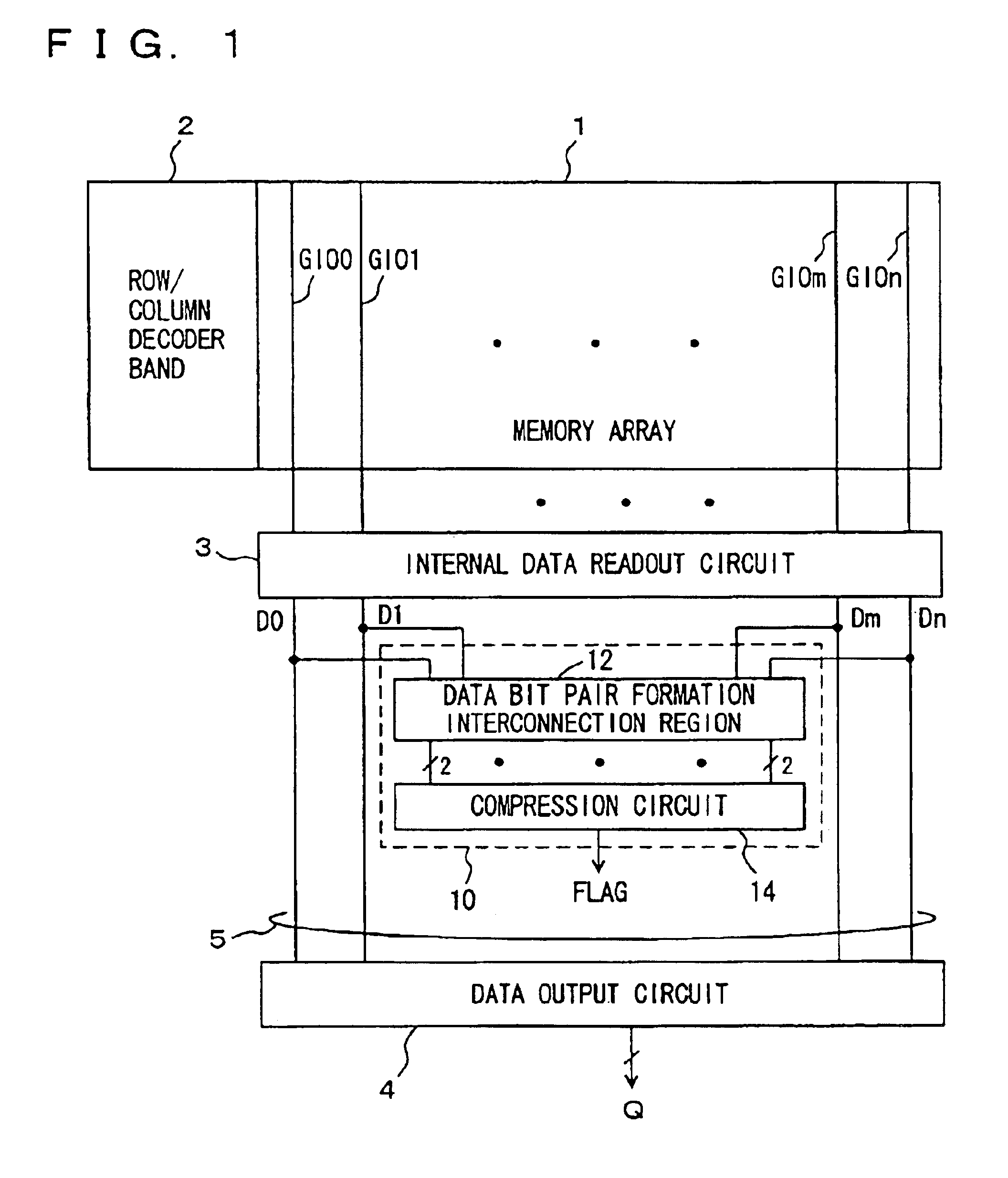

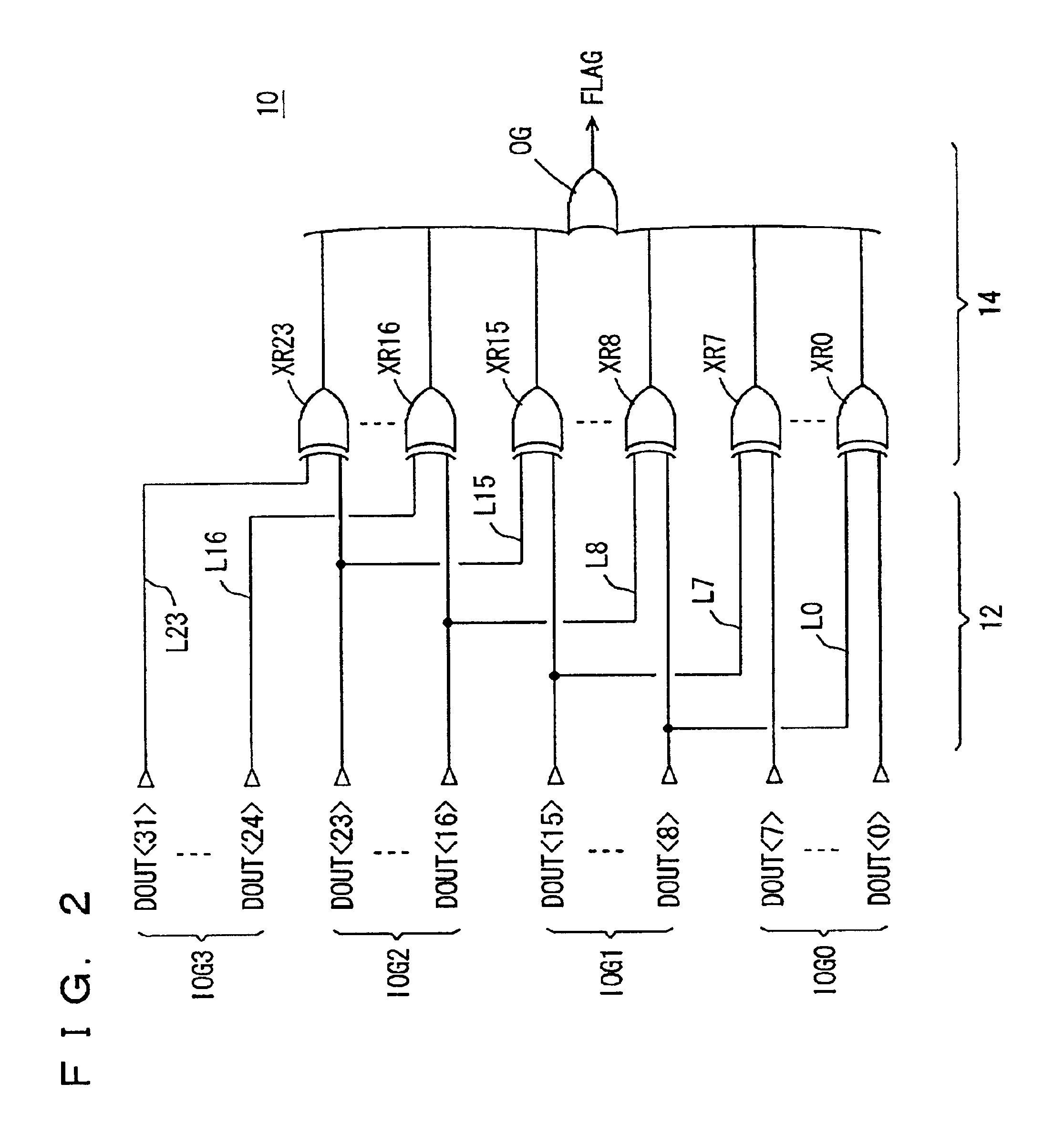

Multi-bit test circuit

InactiveUS20020129308A1Fast timeShorten interconnect lengthElectronic circuit testingDigital storageBit TestMatch/mismatch

Internal read out data bits are divided into a plurality of data groups, and data bits in corresponding positions in different data groups are paired off. A determination gate is provided to each pair of data bits, and determining operation is performed in each pair to compress the result of determination to finally generate a 1-bit flag indicating a match / mismatch in logic level among the internal read out data. Consequently, a multi-bit test circuit that has a reduced layout area and can perform high-speed multi-bit determination is provided.

Owner:RENESAS ELECTRONICS CORP

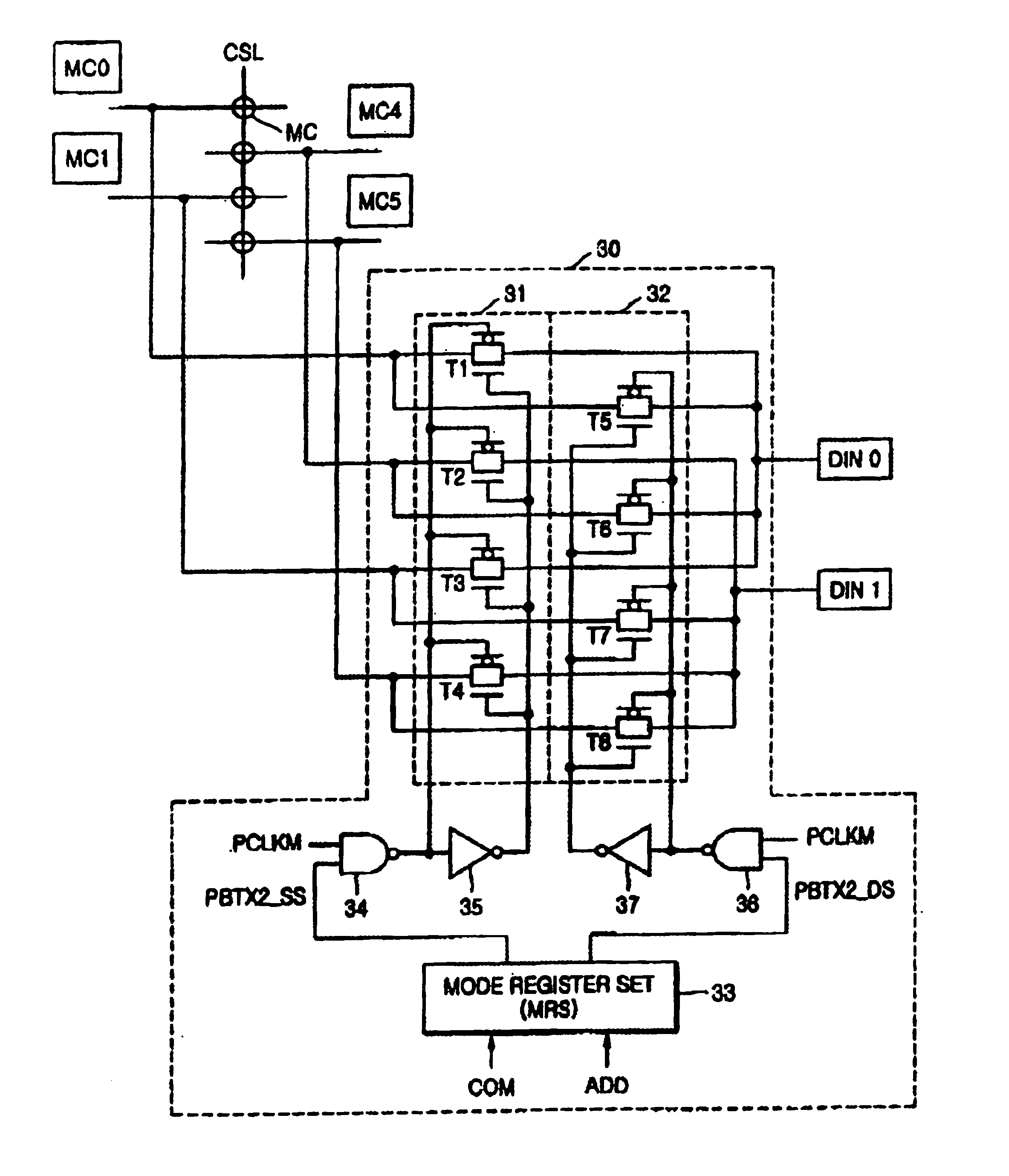

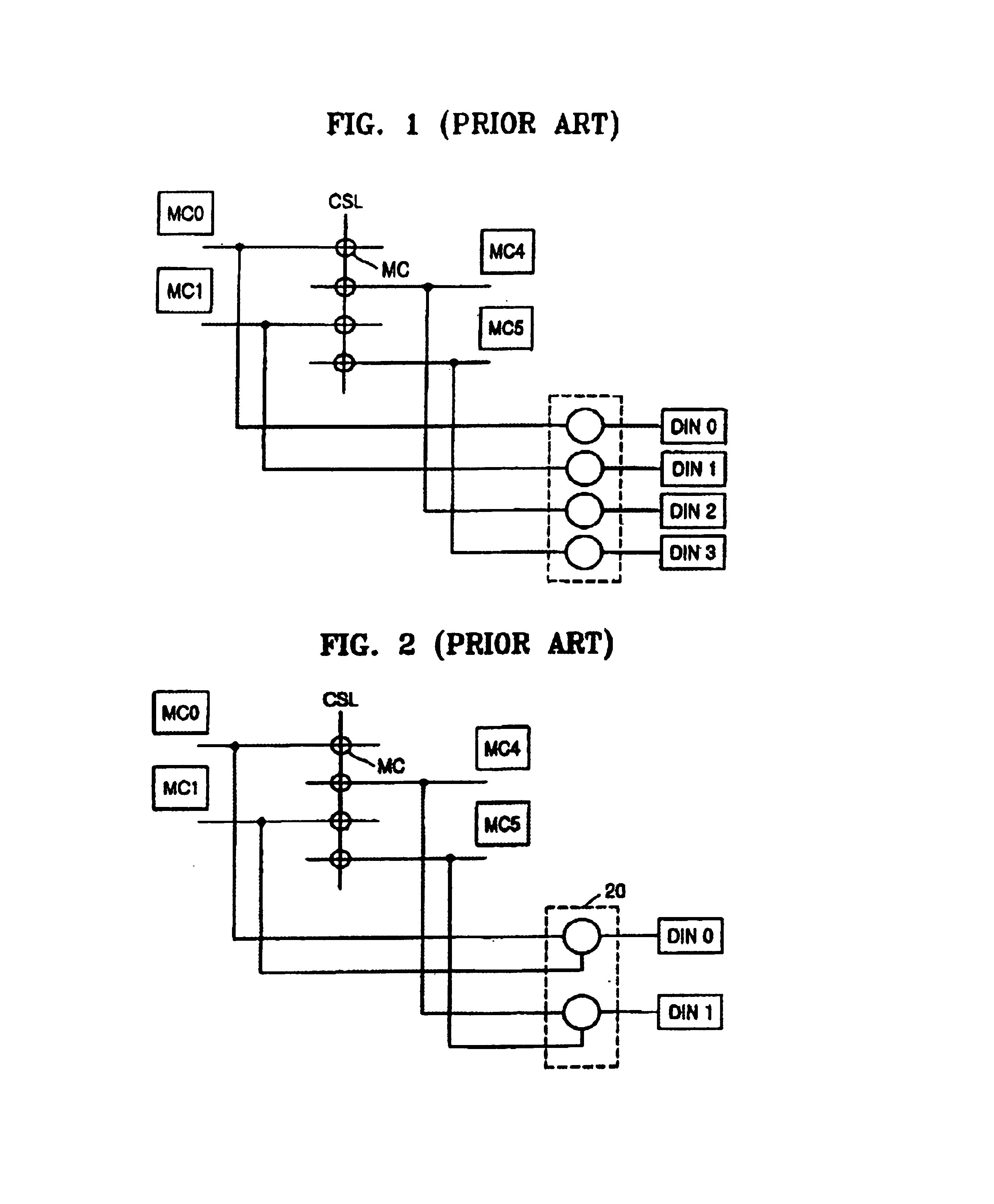

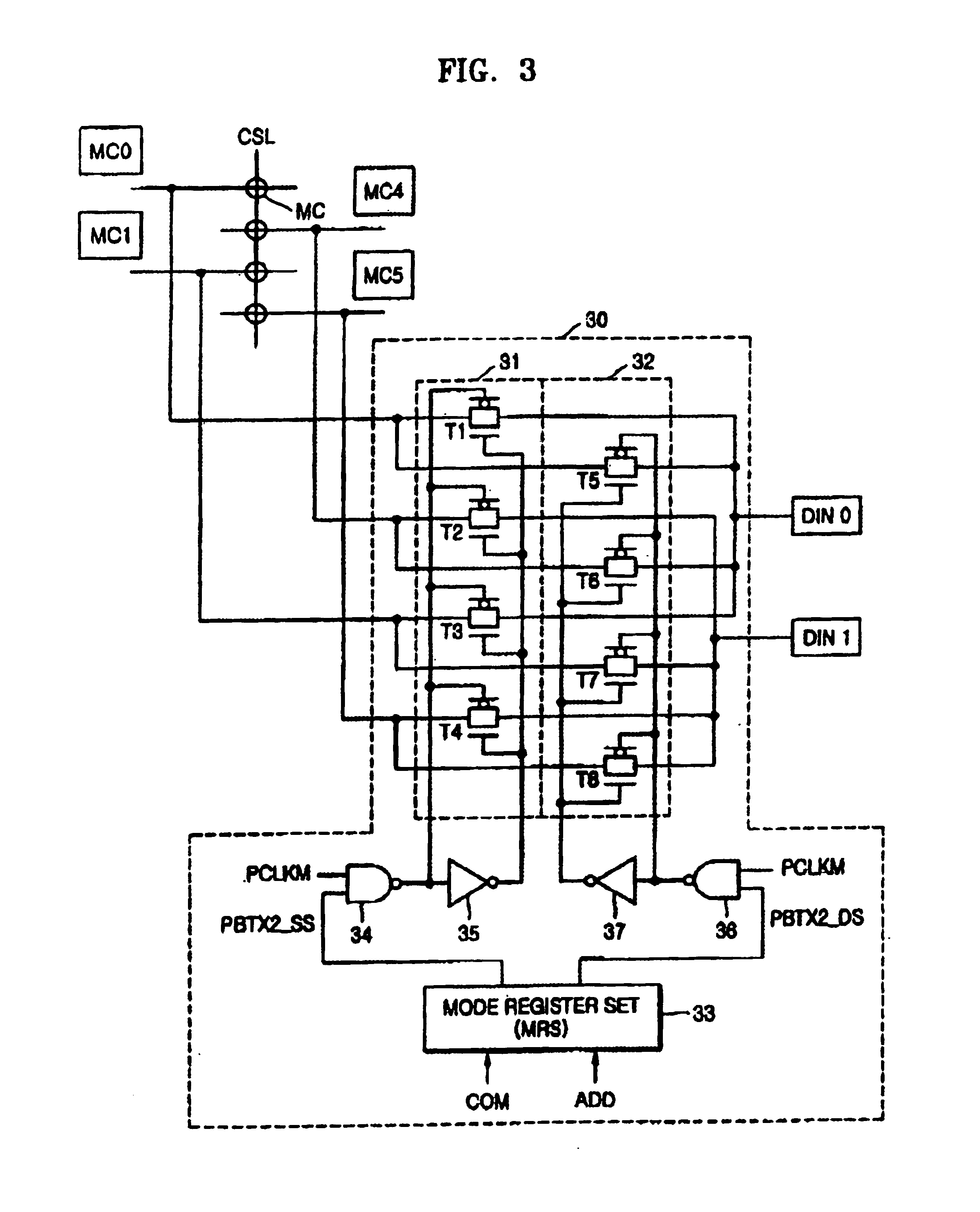

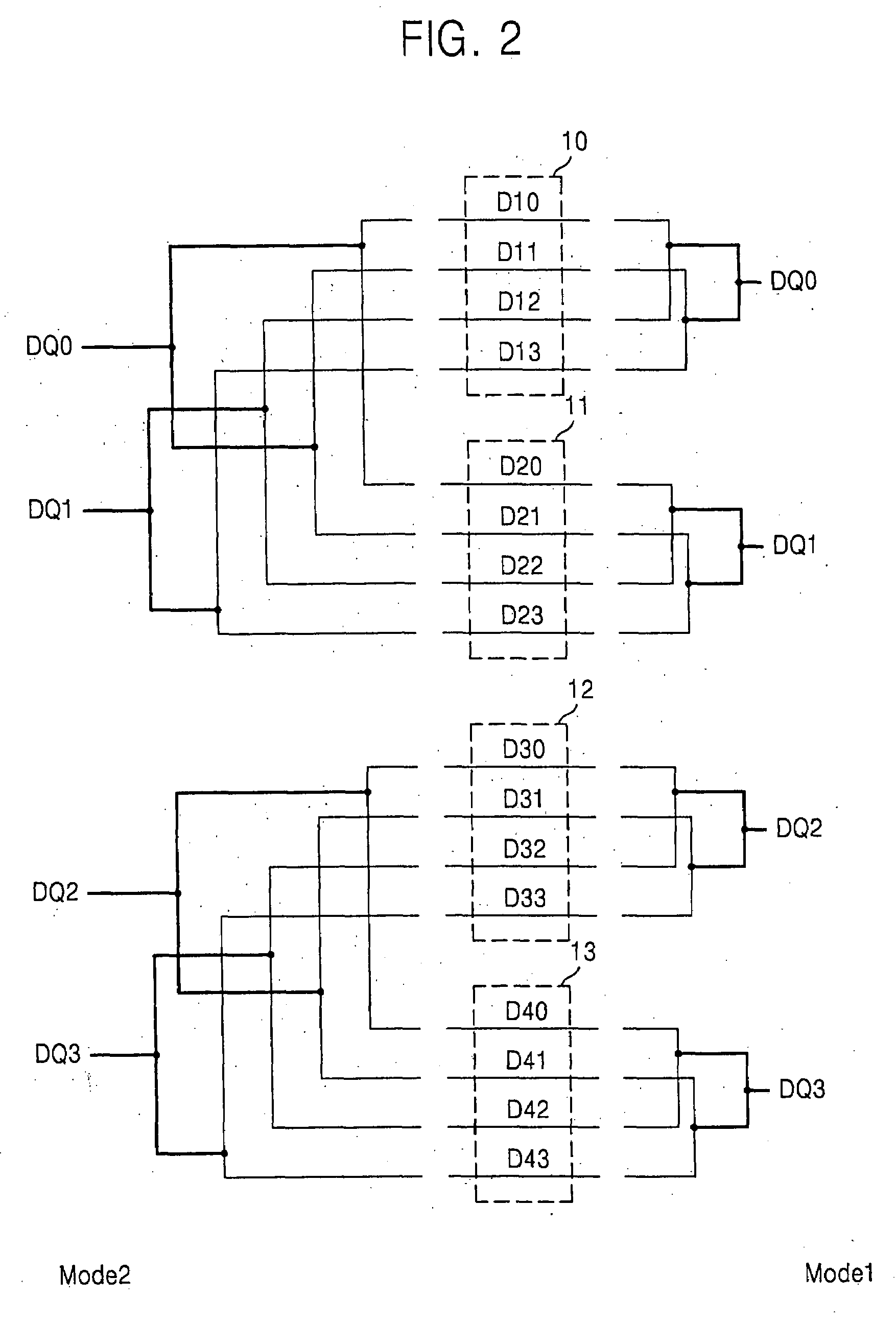

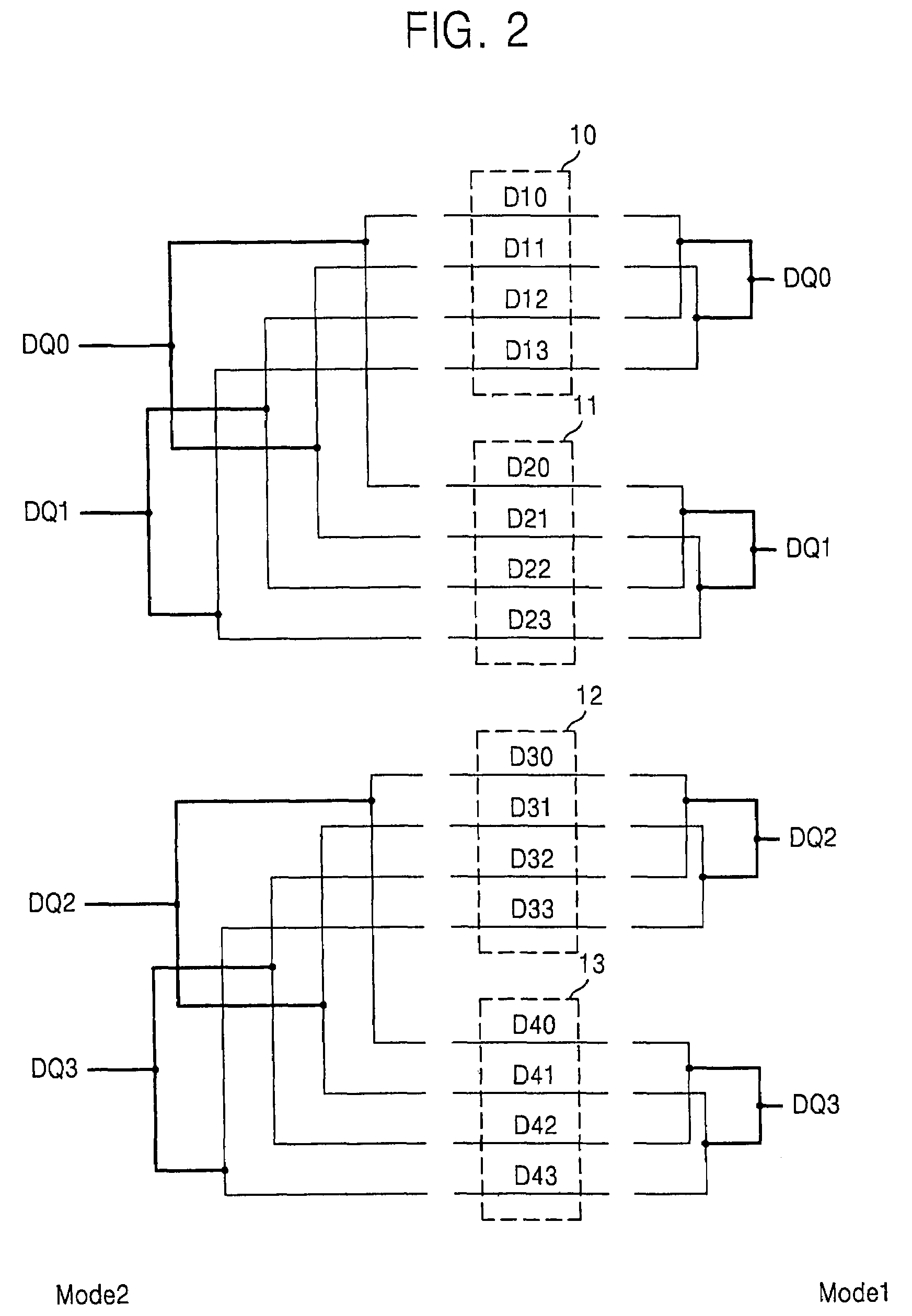

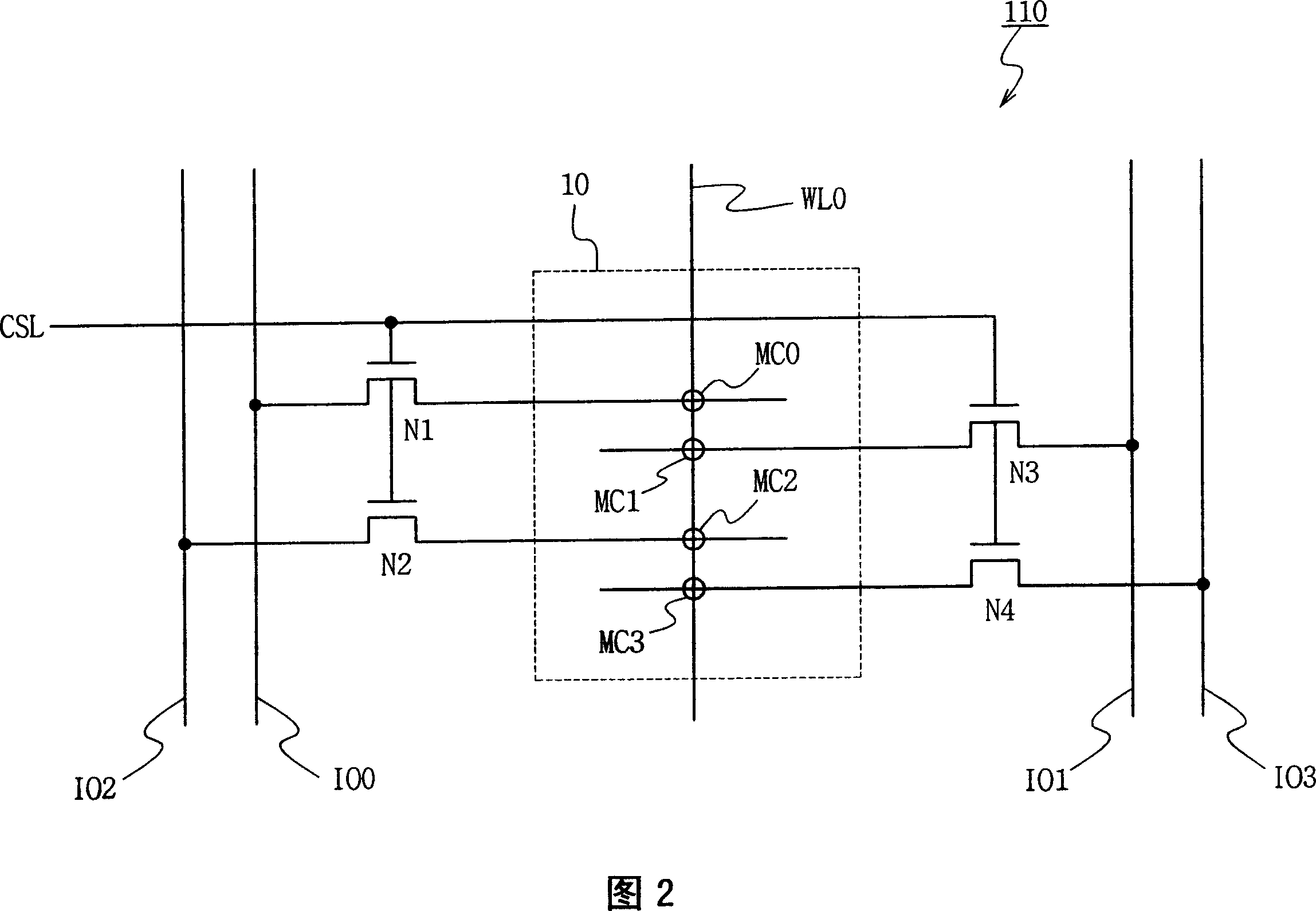

Circuit and method for transforming data input/output format in parallel bit test

Provided are a circuit and a method for transforming a data input / output format of a semiconductor memory device which is capable of generating various types of data patterns when the number of memory cells connected to one column selection line is greater than the number of data input pins. The circuit for transforming a data input / output format of a semiconductor memory device includes a first transmission circuit, a second transmission circuit, and a mode register set (MRS). The first transmission circuit is activated when a first test mode signal is enabled, receives n data inputs from n data input ends, and transmits the n data inputs to m memory cells. Here, n and m are natural numbers and m is greater than n. The second transmission circuit is activated when a second test mode signal is enabled, receives n data inputs from the n data input ends, and transmits the n data inputs to the m memory cells. The mode register set (MRS) receives a command and an address from outside the semiconductor device and outputs the first test mode signal and the second test mode signal according to combinations of the command and the address. In particular, data that is transmitted to adjacent memory cells of the m memory cells is inputted to different input ends of the n data input ends.

Owner:SAMSUNG ELECTRONICS CO LTD

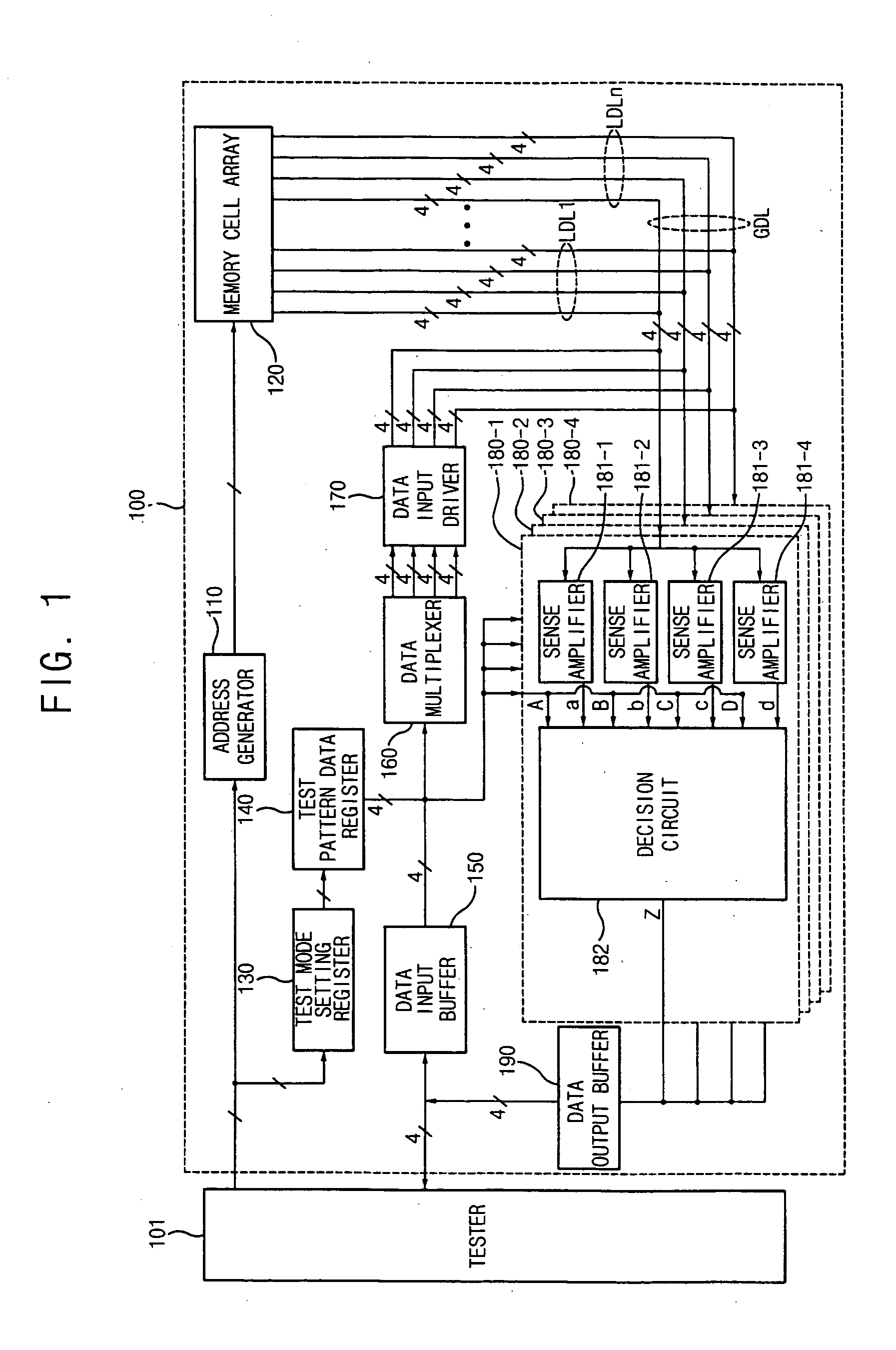

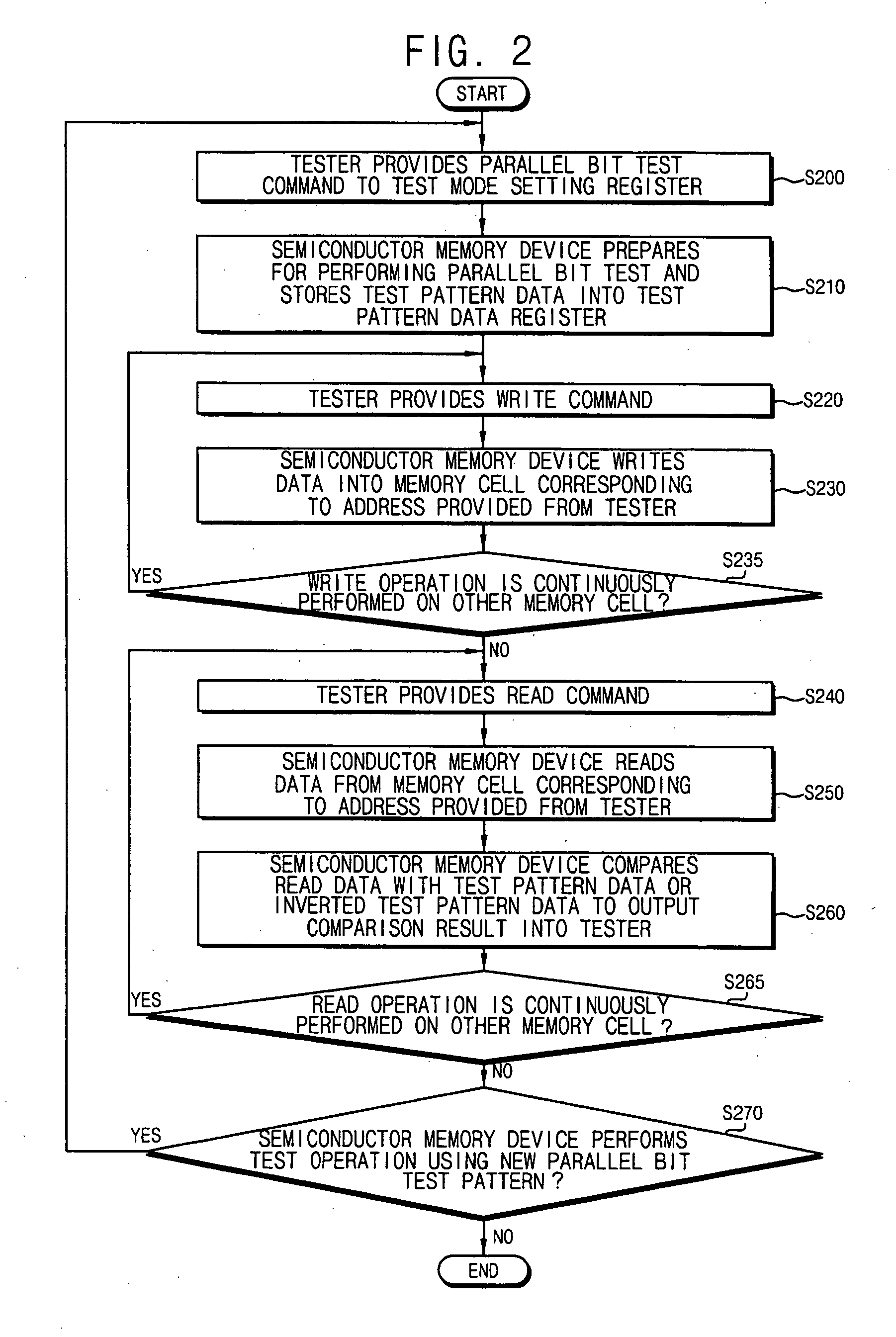

Parallel bit testing device and method

InactiveUS20050257107A1Electronic circuit testingKitchenware cleanersComputer hardwareDecision circuit

A memory device includes a memory cell array to store data, a register to store test data, and a decision circuit to invert the test data and to determine a failure of at least one memory cell within the memory cell array responsive to the data, the test data, and the inverted test data.

Owner:SAMSUNG ELECTRONICS CO LTD

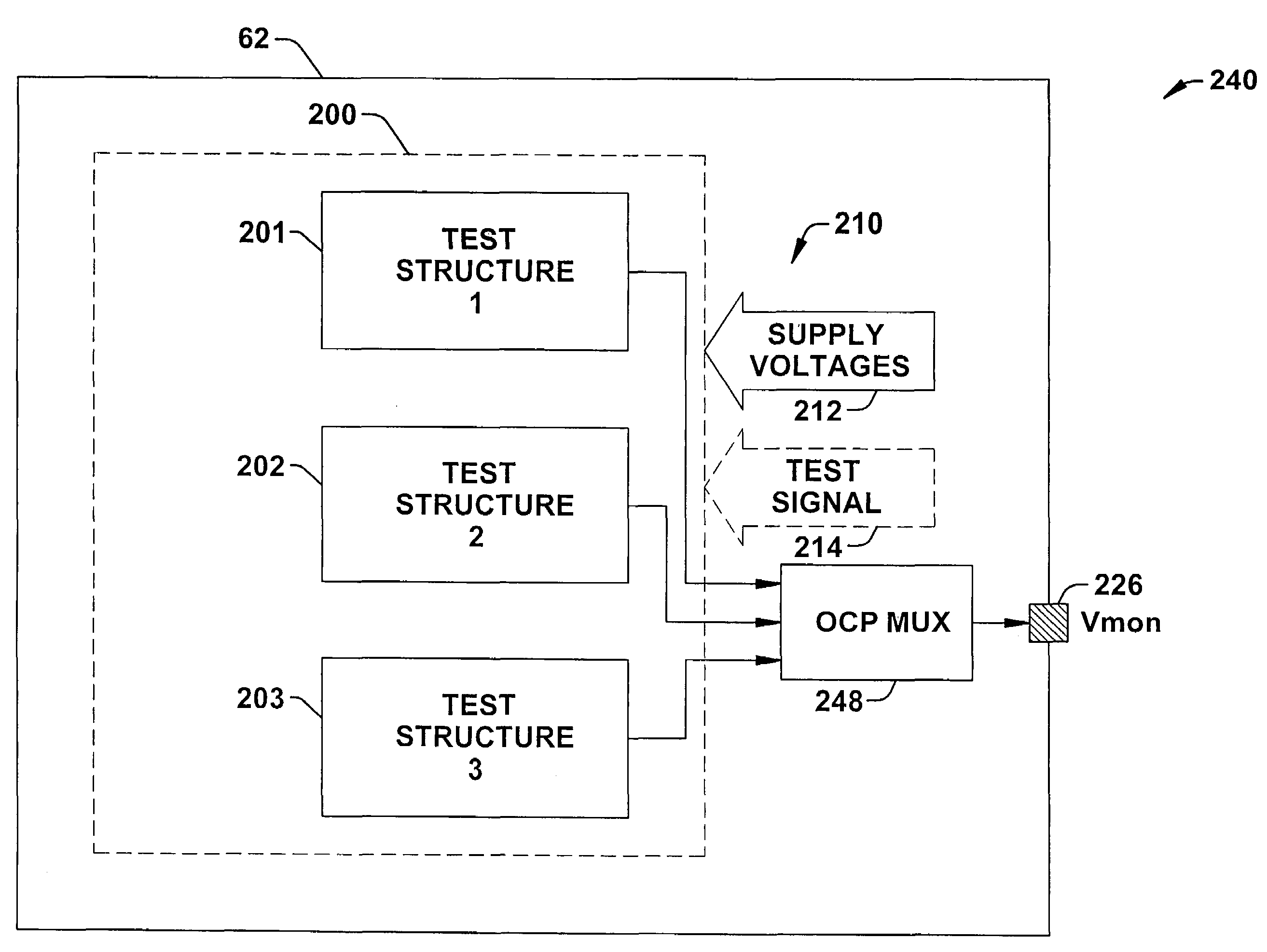

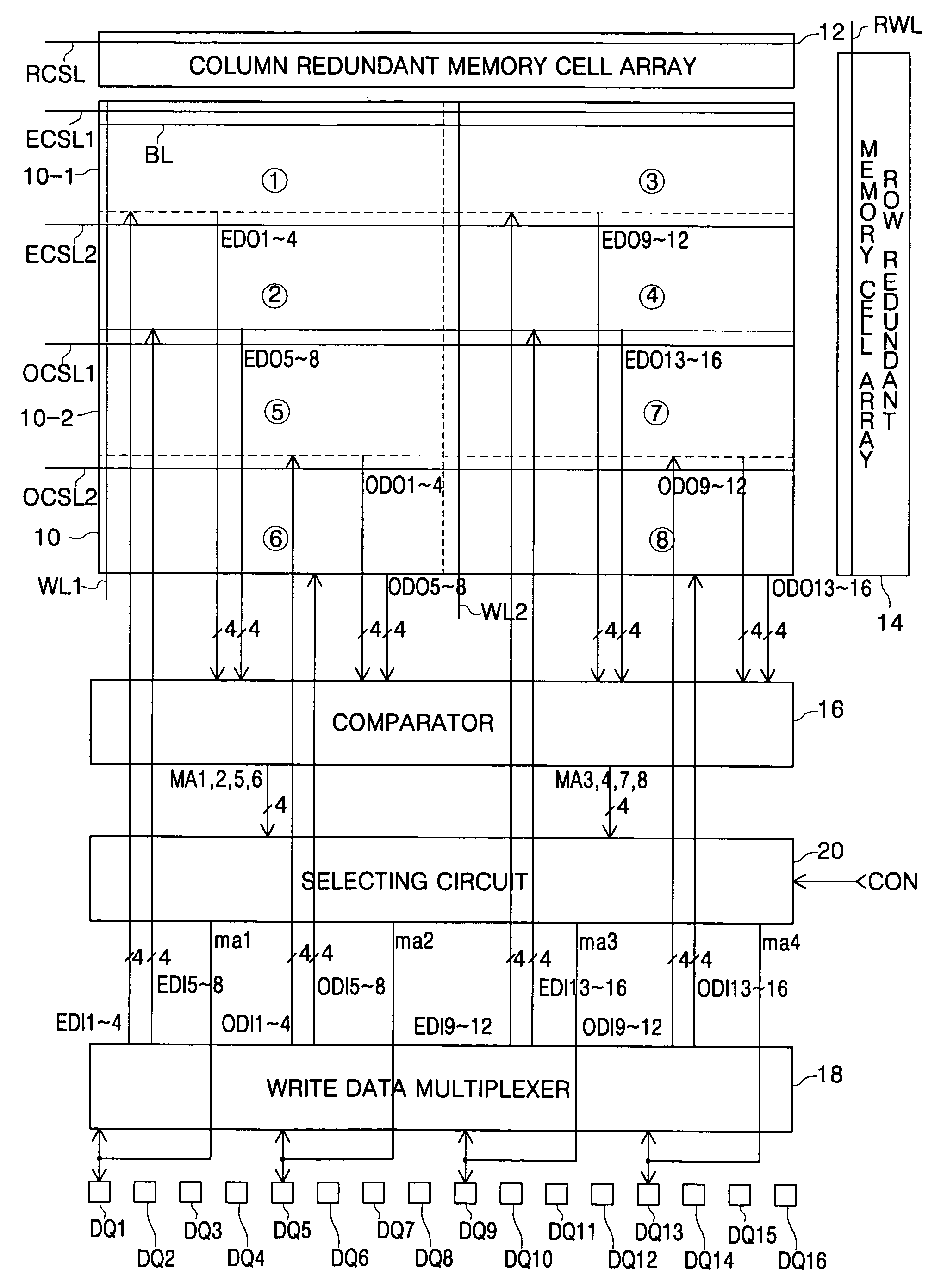

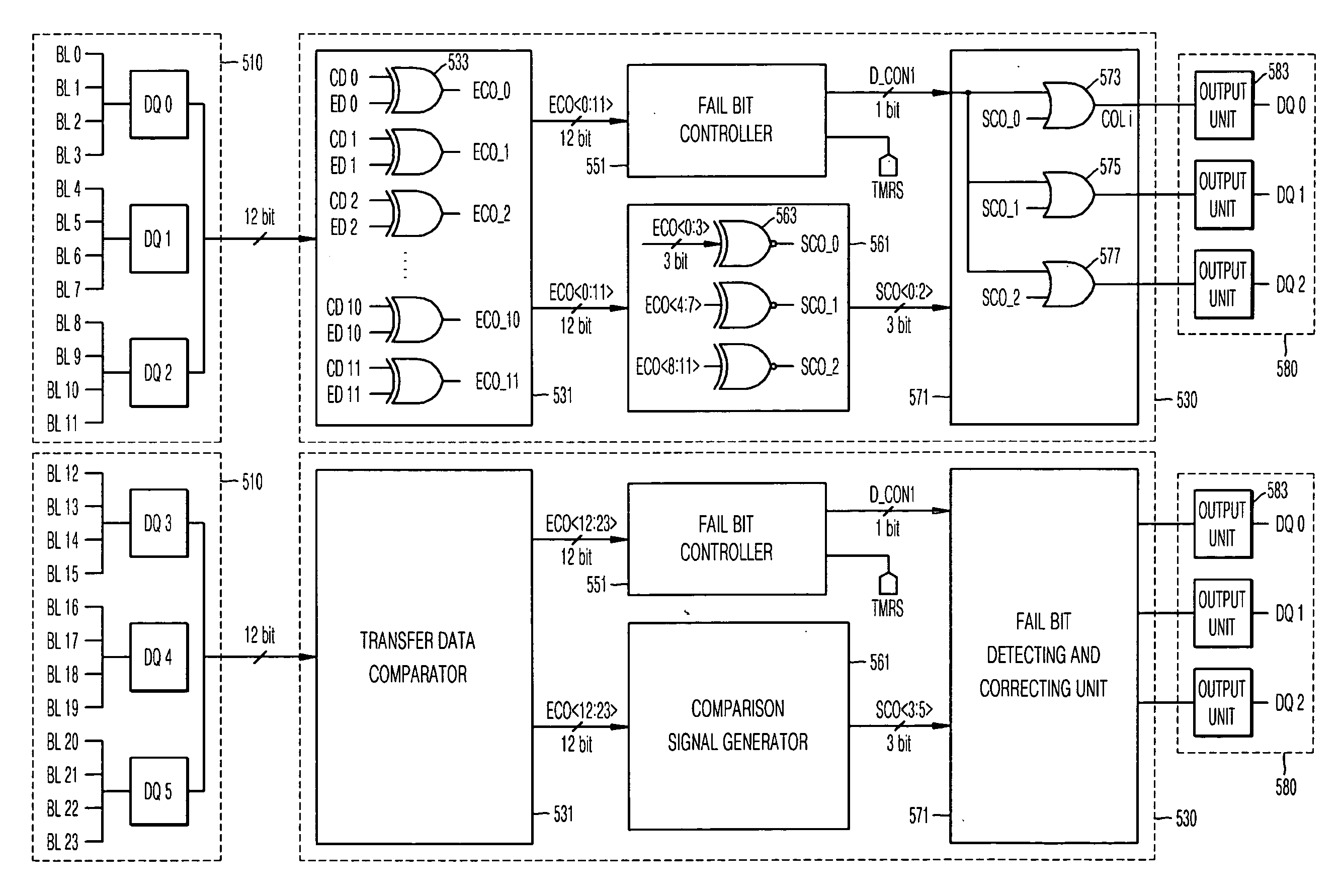

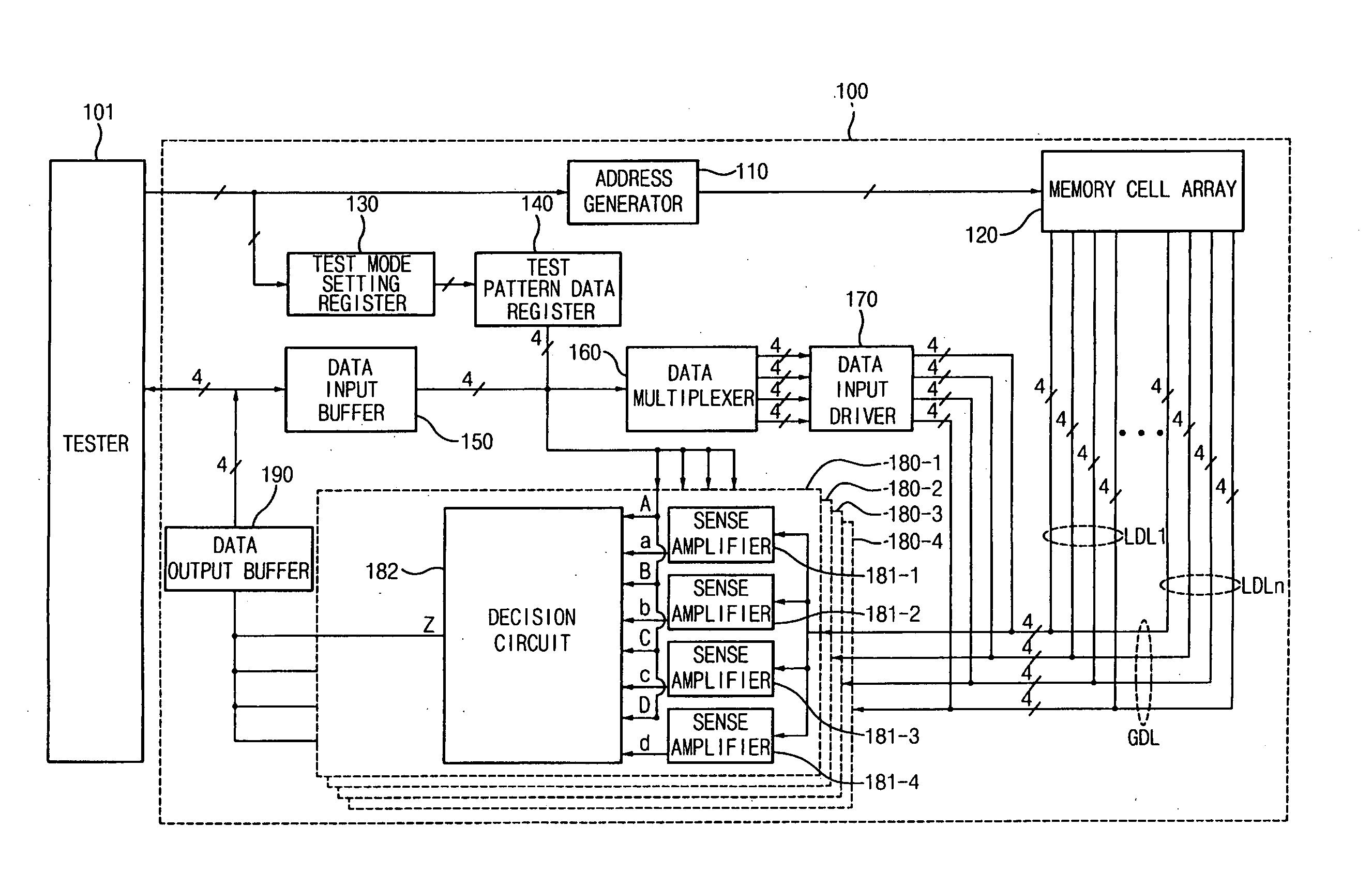

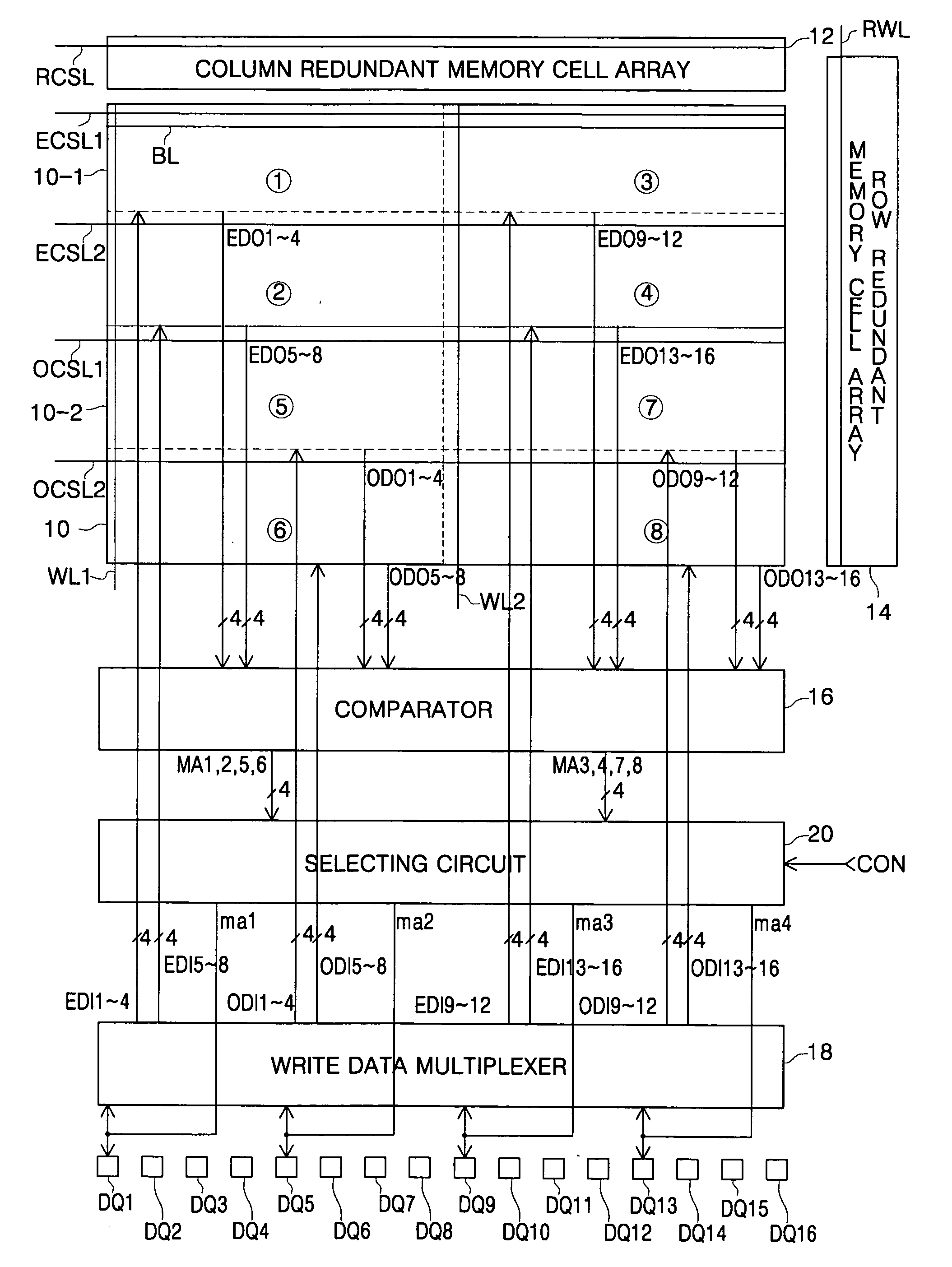

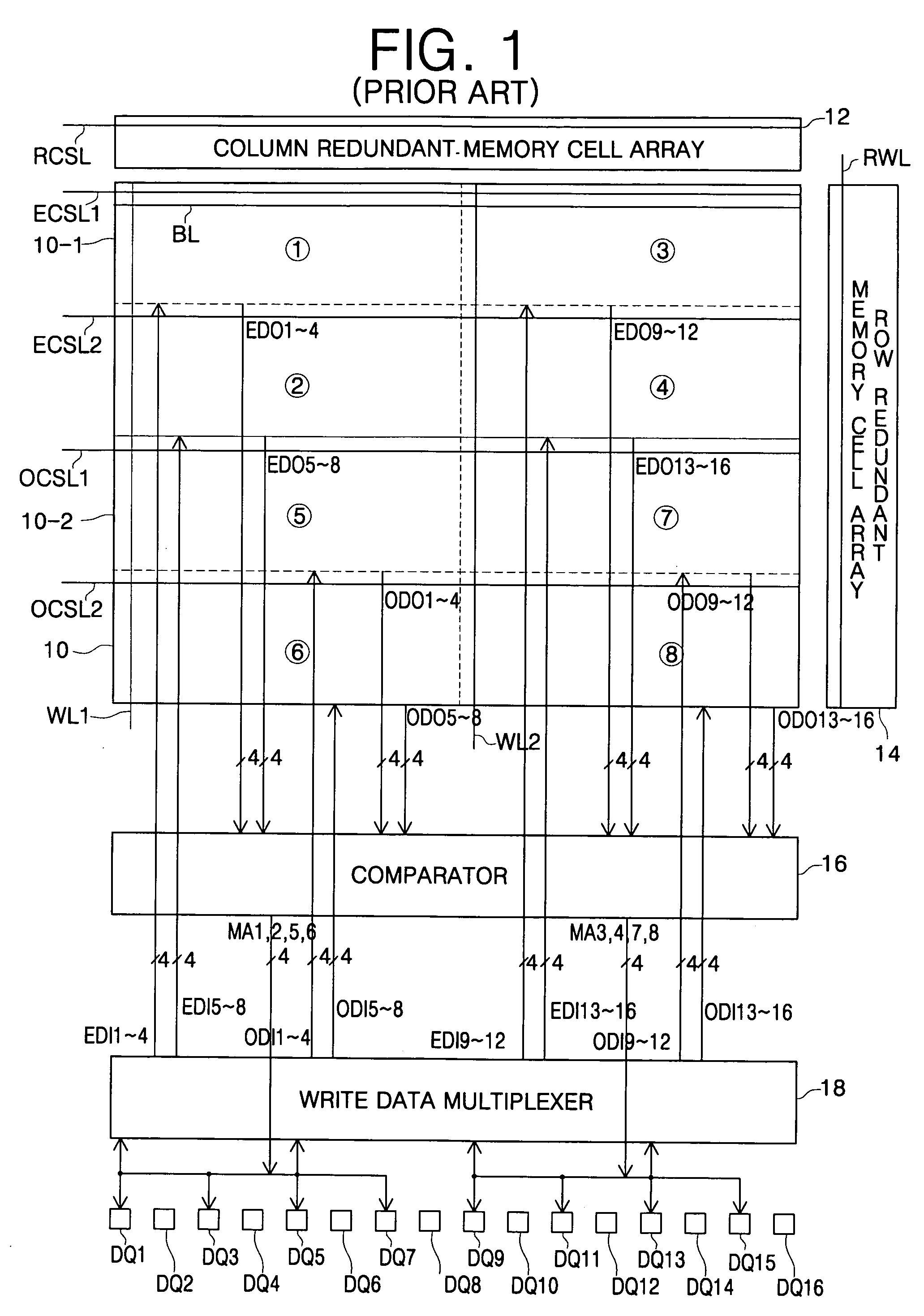

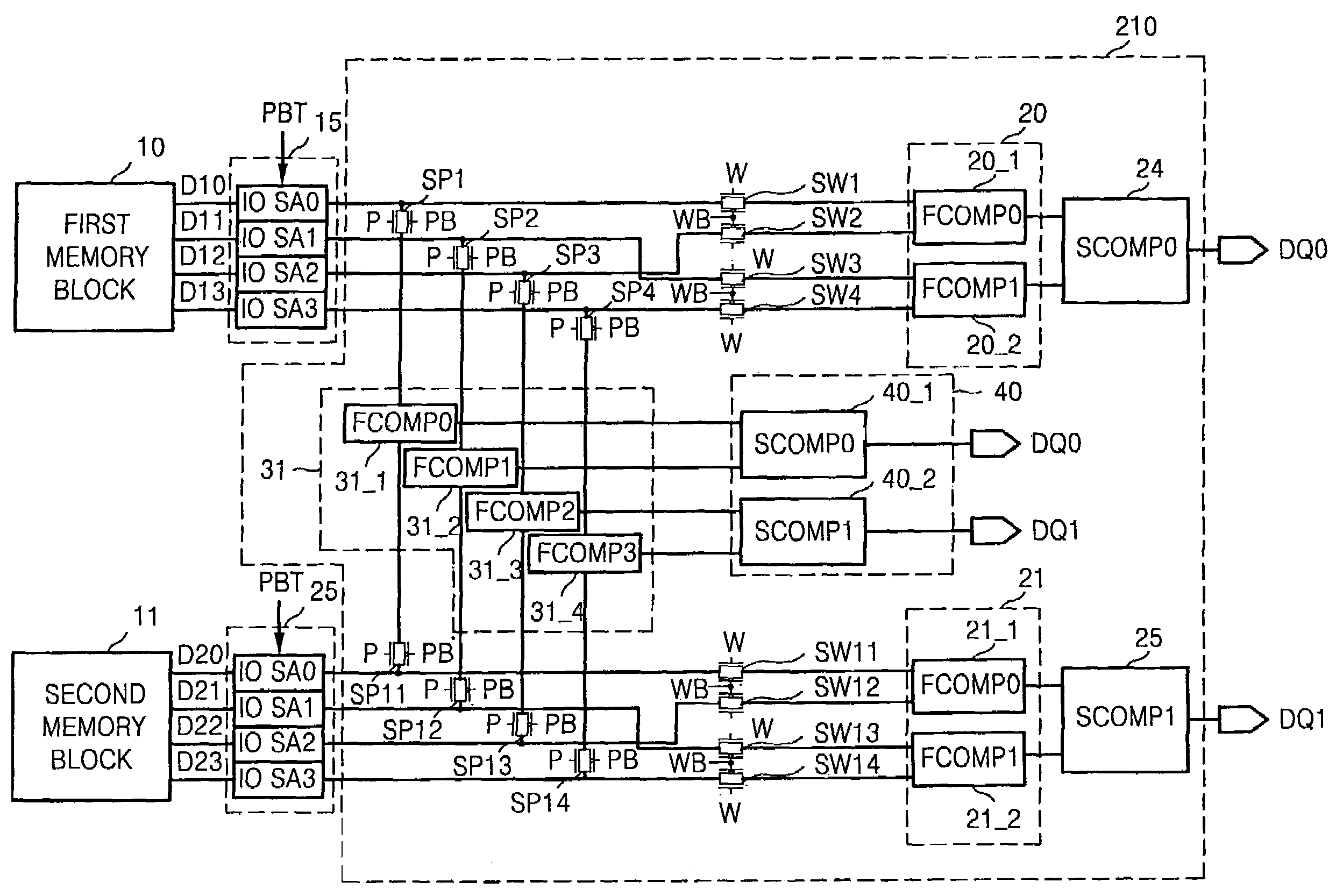

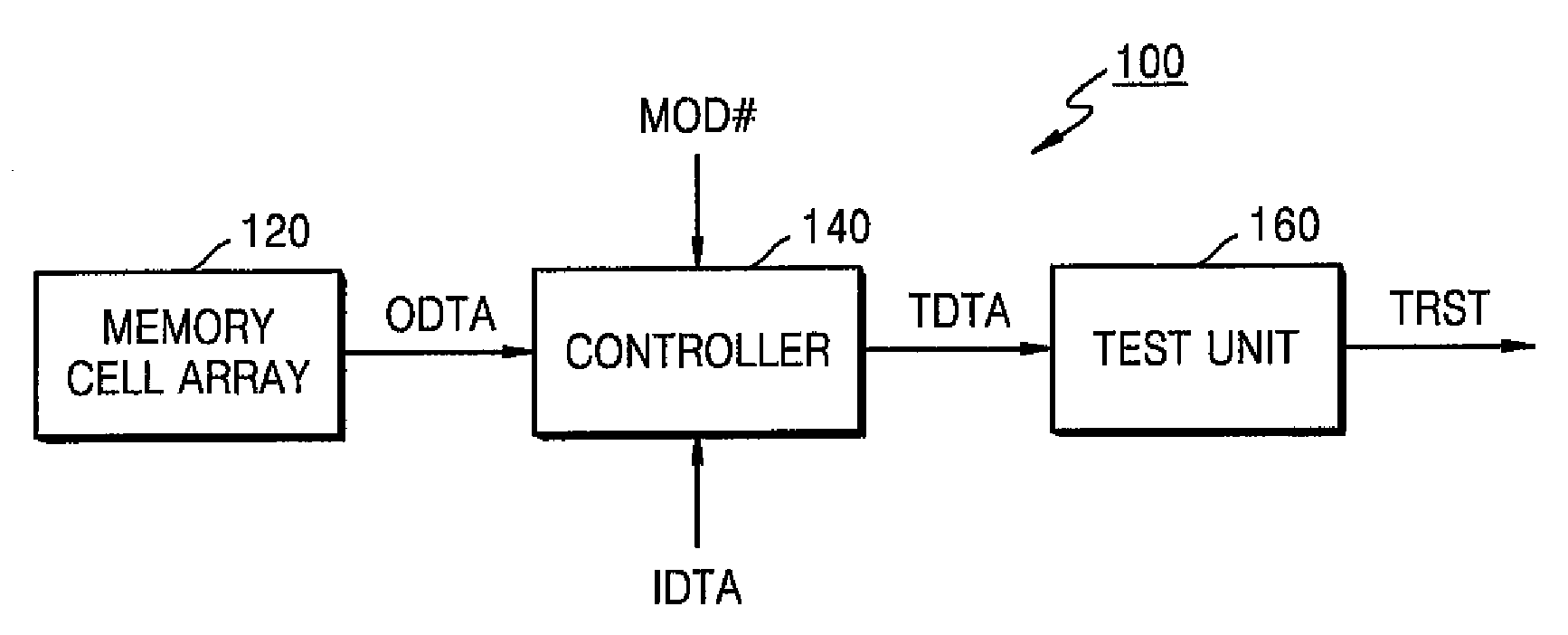

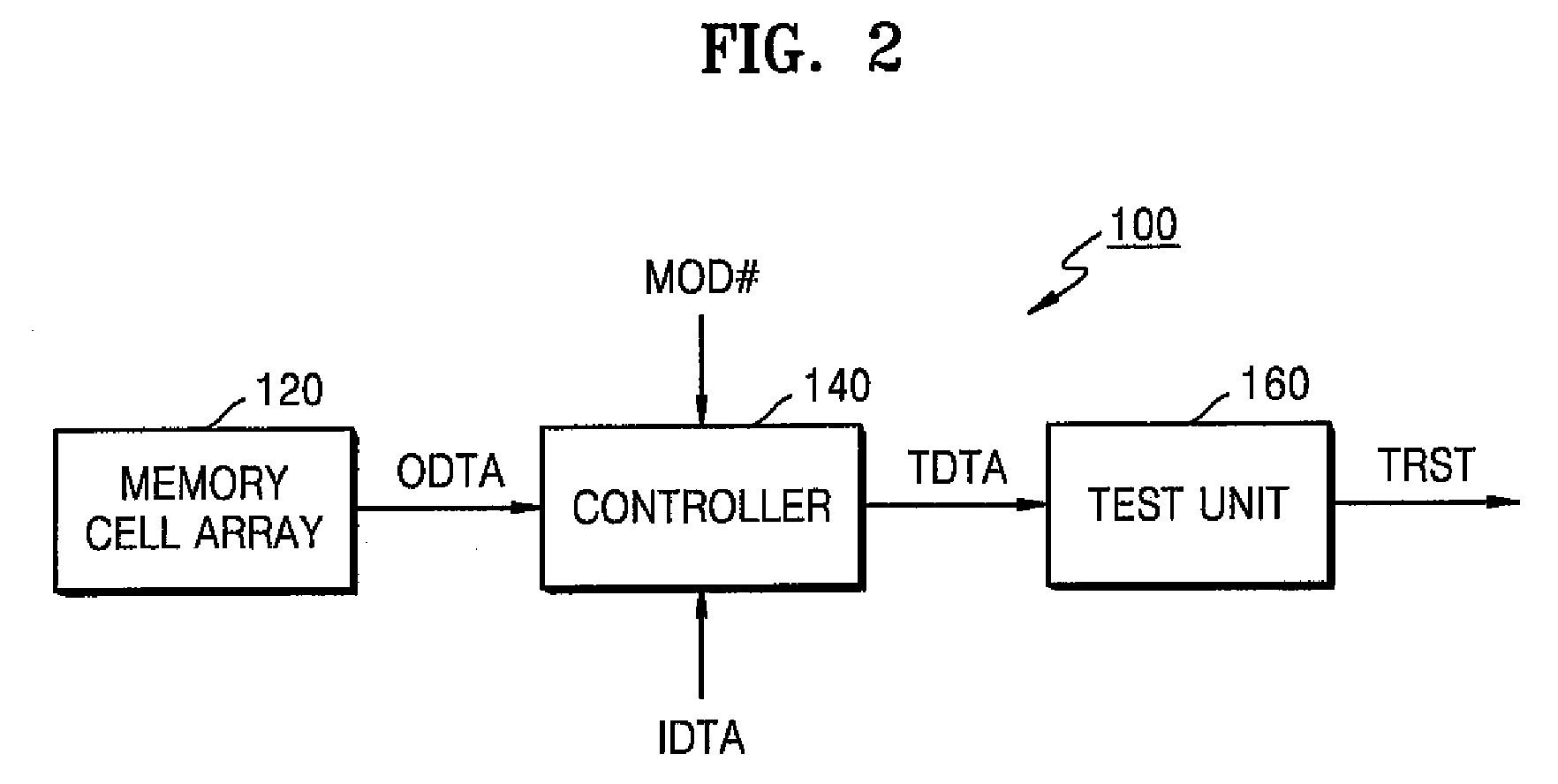

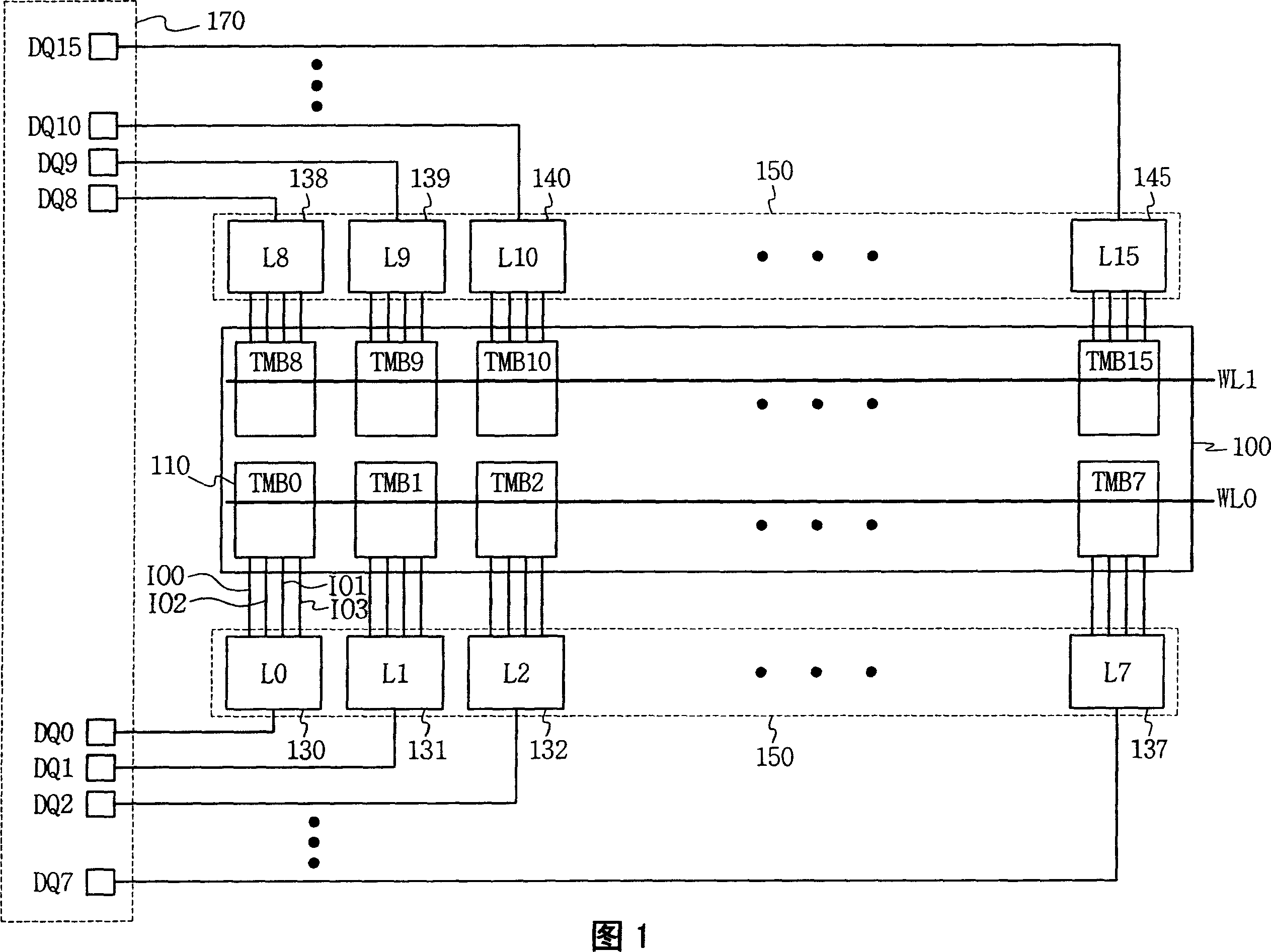

Systems and methods for simultaneously testing semiconductor memory devices

A method for testing a memory cell array of a semiconductor memory device in a parallel bit test mode includes selecting first data from one of a plurality of memory regions in the memory array for output from the memory device via an input / output pad, and then selecting second data from another of the plurality of memory regions for output via the input / output pad. The first and second data can be selected from memory regions sharing a row select or a column select control line. Alternatively, one of the first and second data can be selected from memory regions sharing a row select control line, and the other can be selected from memory regions sharing a column select control line. Therefore, a parallel bit test can be performed using fewer input / output pads, and a larger number of semiconductor memory devices can simultaneously be tested. Related circuits are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

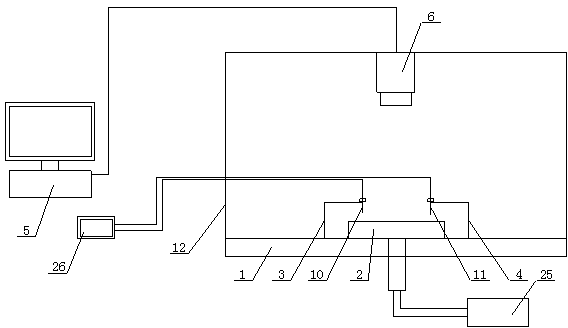

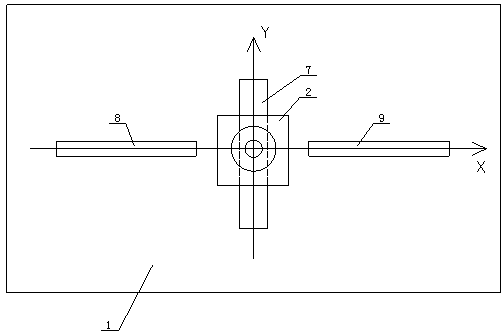

Automatic double-probe test platform based on bitmap tracking method

InactiveCN103592548AImplement automated testingRealize the processing functionElectrical testingMeasurement instrument housingEngineeringBit Test

An automatic double-probe test platform based on a bitmap tracking method mainly comprises a base, a carrying table, a first probe support, a second probe support, a main control computer, a first driving mechanism and a camera, wherein the first driving mechanism drives the carrying table to rotate in the horizontal plane and to be lifted up, the camera is arranged above the carrying table, the shooting direction of the camera faces downwards, the carrying table can rotate, be lifted up and move in the Y-axis direction, and the first probe support and the second probe support can carry out horizontal movements and horizontal mirror symmetry movements in the same direction. According to the automatic double-probe test platform based on the bitmap tracking method, the automatic locating of double probes is achieved through a bitmap control technology, the automated locating tests of two testing points of a sample is achieved accordingly, the labor intensity of testing personnel is reduced greatly, and the testing accuracy is improved. The automatic double-probe test platform based on the bitmap tracking method is novel in locating mode, the rotating movable type carrying table and the movable symmetrical open type double probe supports are utilized ingeniously, the probes can be located at any two testing points of the sample to be tested, and the automatic double-probe test platform can meet testing demands.

Owner:NANTONG UNIVERSITY

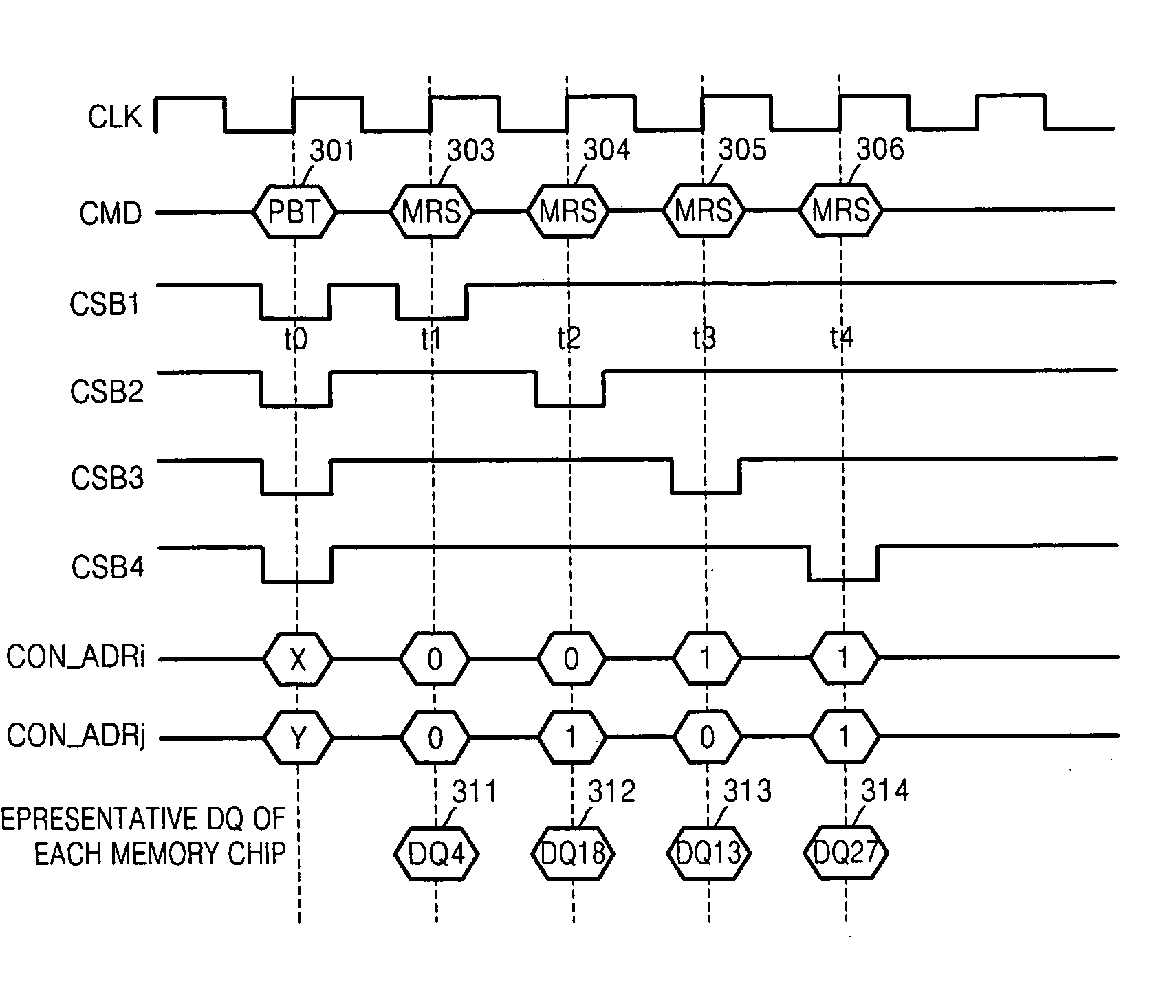

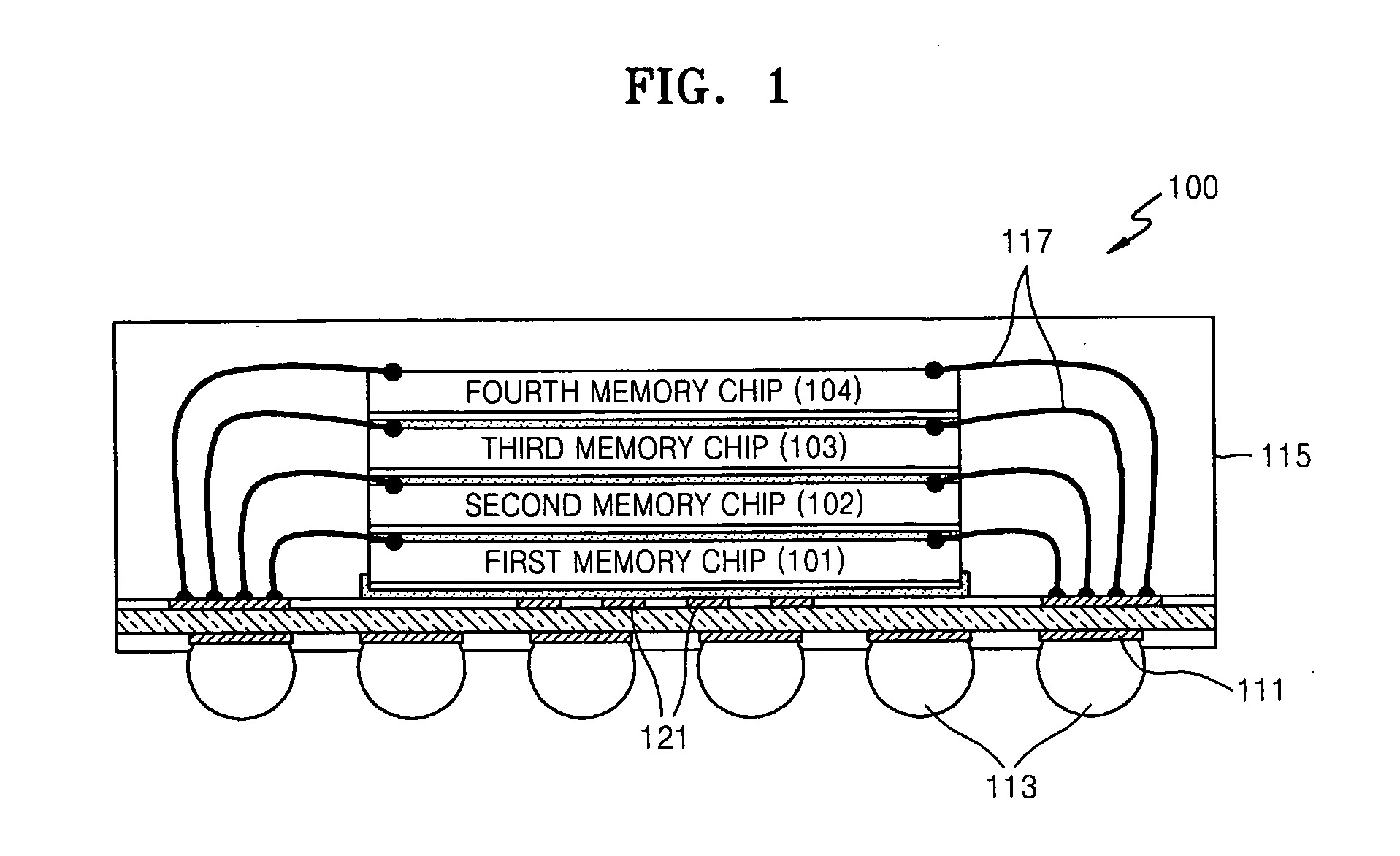

Parallel bit test apparatus and parallel bit test method capable of reducing test time

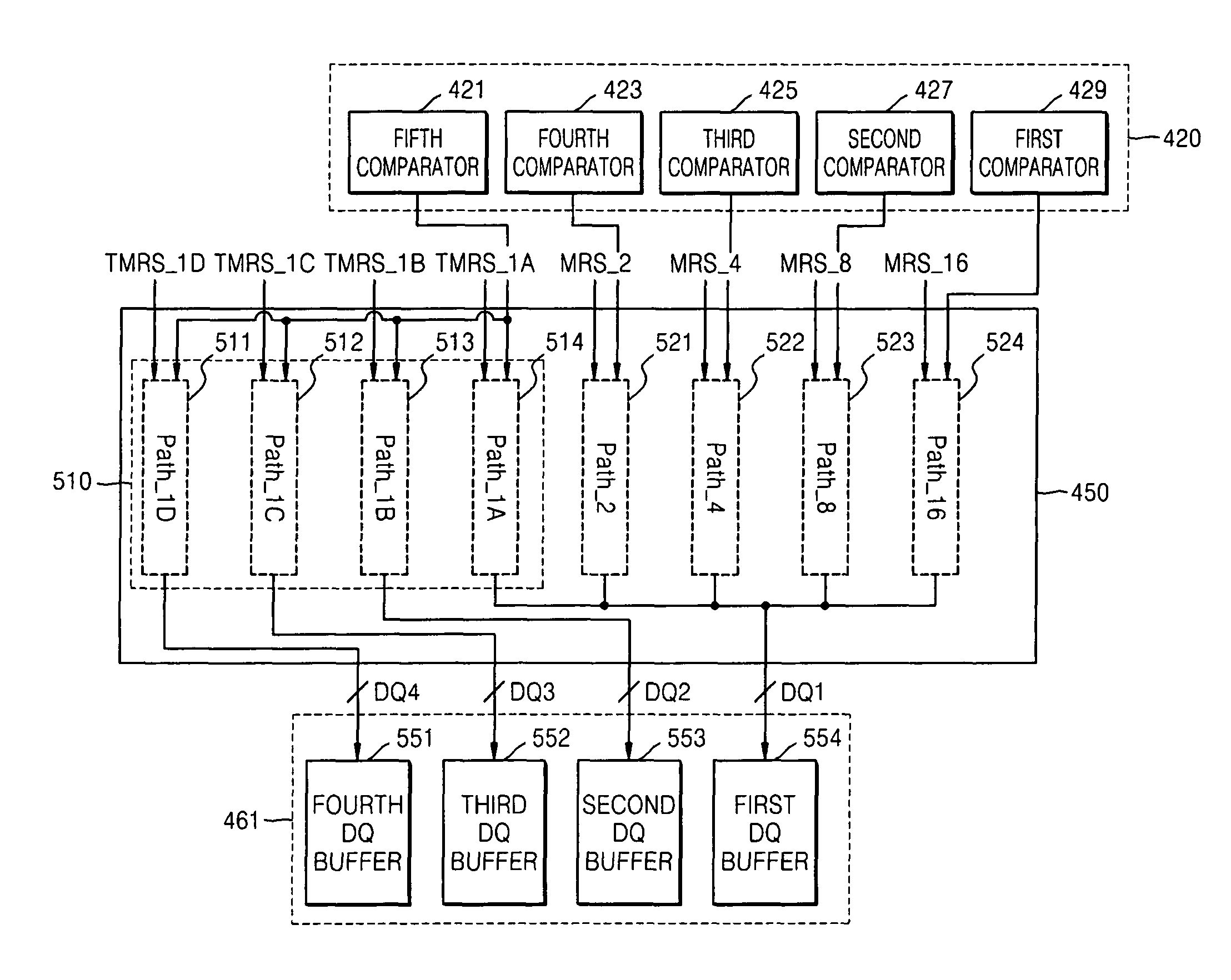

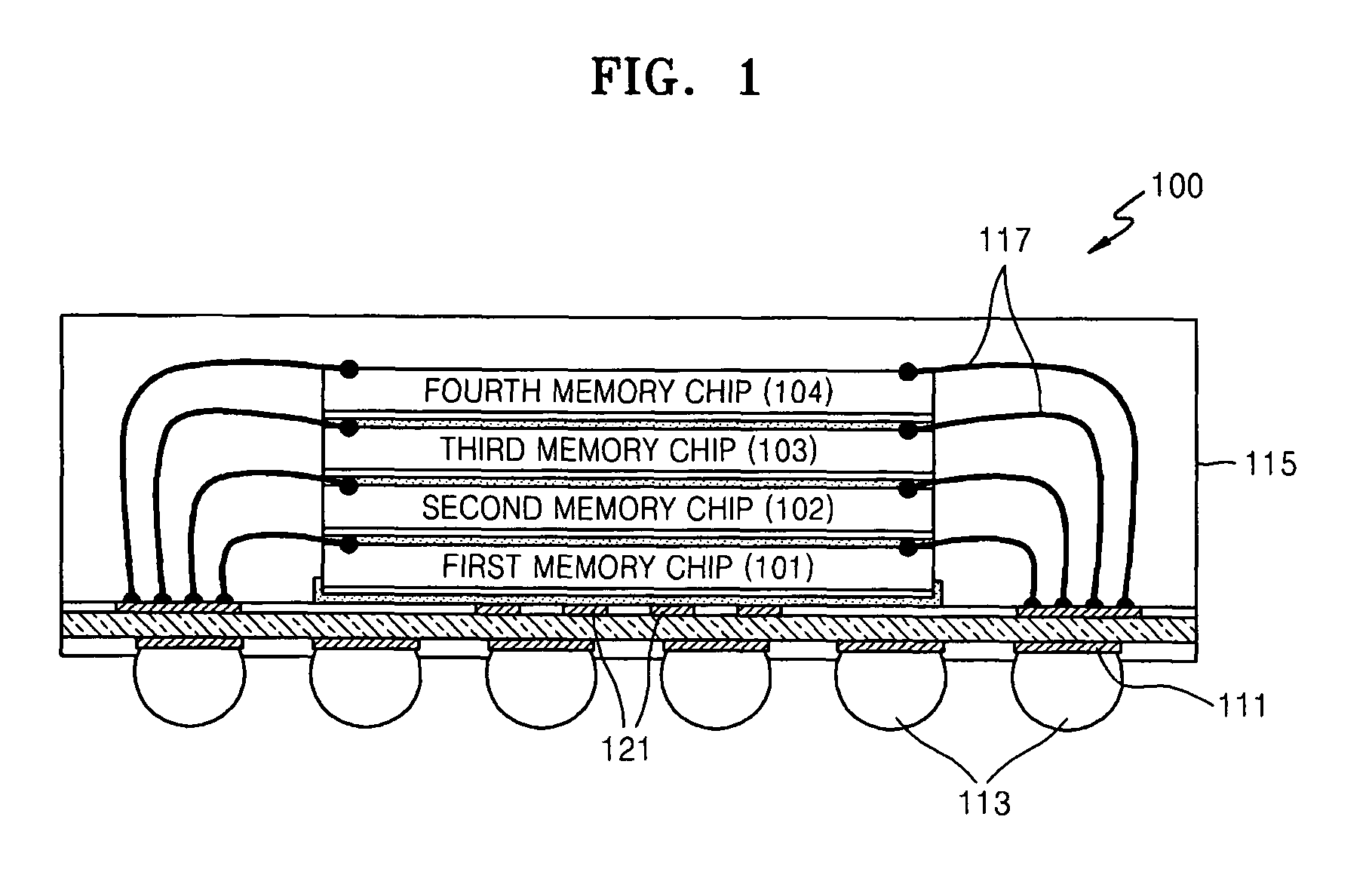

A parallel bit test (PBT) apparatus, included in memory chips that are stacked in a multi-chip package (MCP) and that share a set of data signal lines, may include: a comparing unit to output a data signal representative of a comparison between test data signals provided to a given one of the memory chips and corresponding data signals output therefrom, respectively; and a coding unit to output the representative data signal using a first subset of the shared set of data signal lines, the first subset not overlapping other subsets used by coding units corresponding to the other ones of the memory chips, respectively, the coding unit selecting one or more of the data signal lines amongst the shared set of data signal lines for inclusion in the first subset according to a first test mode register set (MRS) signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Multi-bit test circuit

InactiveUS6854078B2Fast timeShorten interconnect lengthElectronic circuit testingDigital storageBit TestMatch/mismatch

Internal read out data bits are divided into a plurality of data groups, and data bits in corresponding positions in different data groups are paired off. A determination gate is provided to each pair of data bits, and determining operation is performed in each pair to compress the result of determination to finally generate a 1-bit flag indicating a match / mismatch in logic level among the internal read out data. Consequently, a multi-bit test circuit that has a reduced layout area and can perform high-speed multi-bit determination is provided.

Owner:RENESAS ELECTRONICS CORP

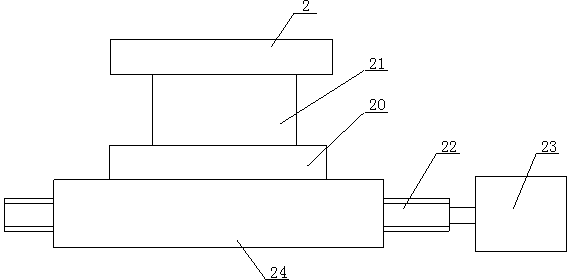

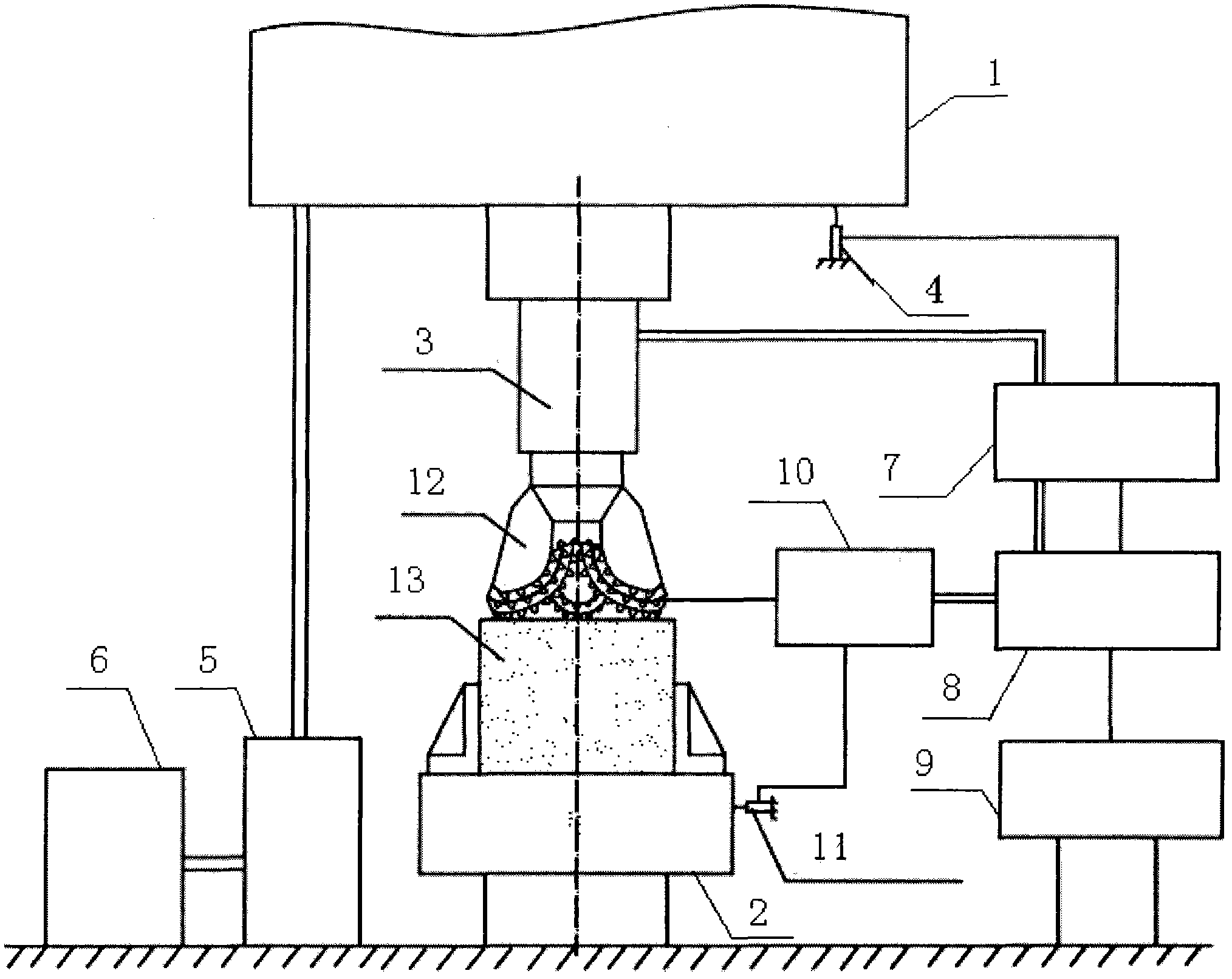

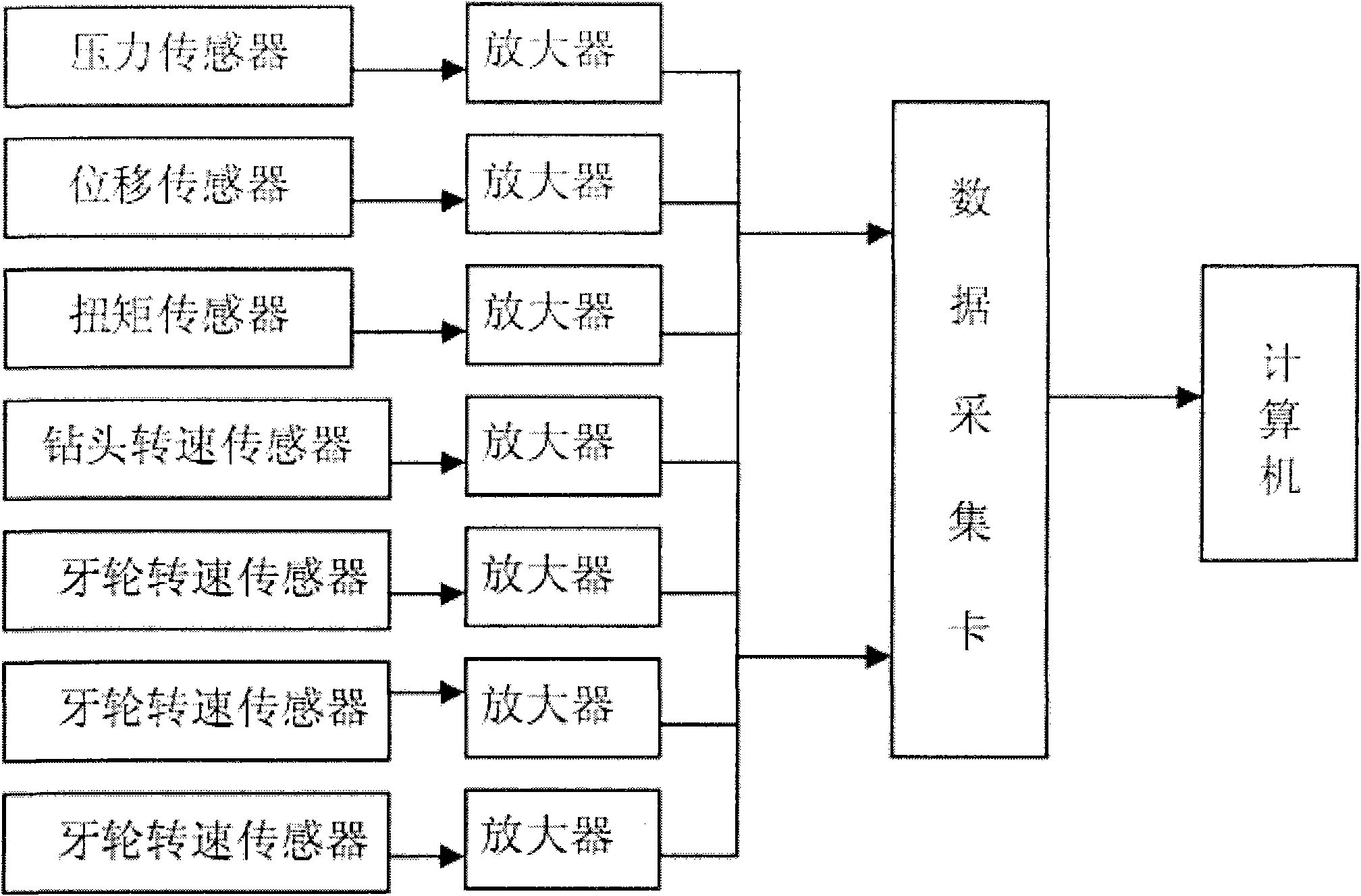

Test system of full gauge drilling bit rock breaking

InactiveCN103105289ATruly reflect the characteristics of rock breakingMachine part testingWell drillingRate of penetration

The invention discloses a test system of full gauge drilling bit rock breaking. The test system of the full gauge drilling bit rock breaking is mainly formed by a drilling bit test rack (1), a lower turnplate (2), a measuring connector (3) and a displacement sensor (4), wherein the lower turnplate (2) is arranged below the drilling bit test rack (1), the measuring connector (3) is installed on the drilling bit test rack (1), the drilling bit test rack (1) is connected with a driving device, and the measuring connector (3) and the displacement sensor (4) are both connected with an identical measuring and control device. The rate of penetration and the broken shaft bottom of different rock breaking of the drilling bit under a certain parameter condition are mainly detected, and characteristics of the rock breaking with the drilling bit can be reflected simply and really.

Owner:陈洪伟

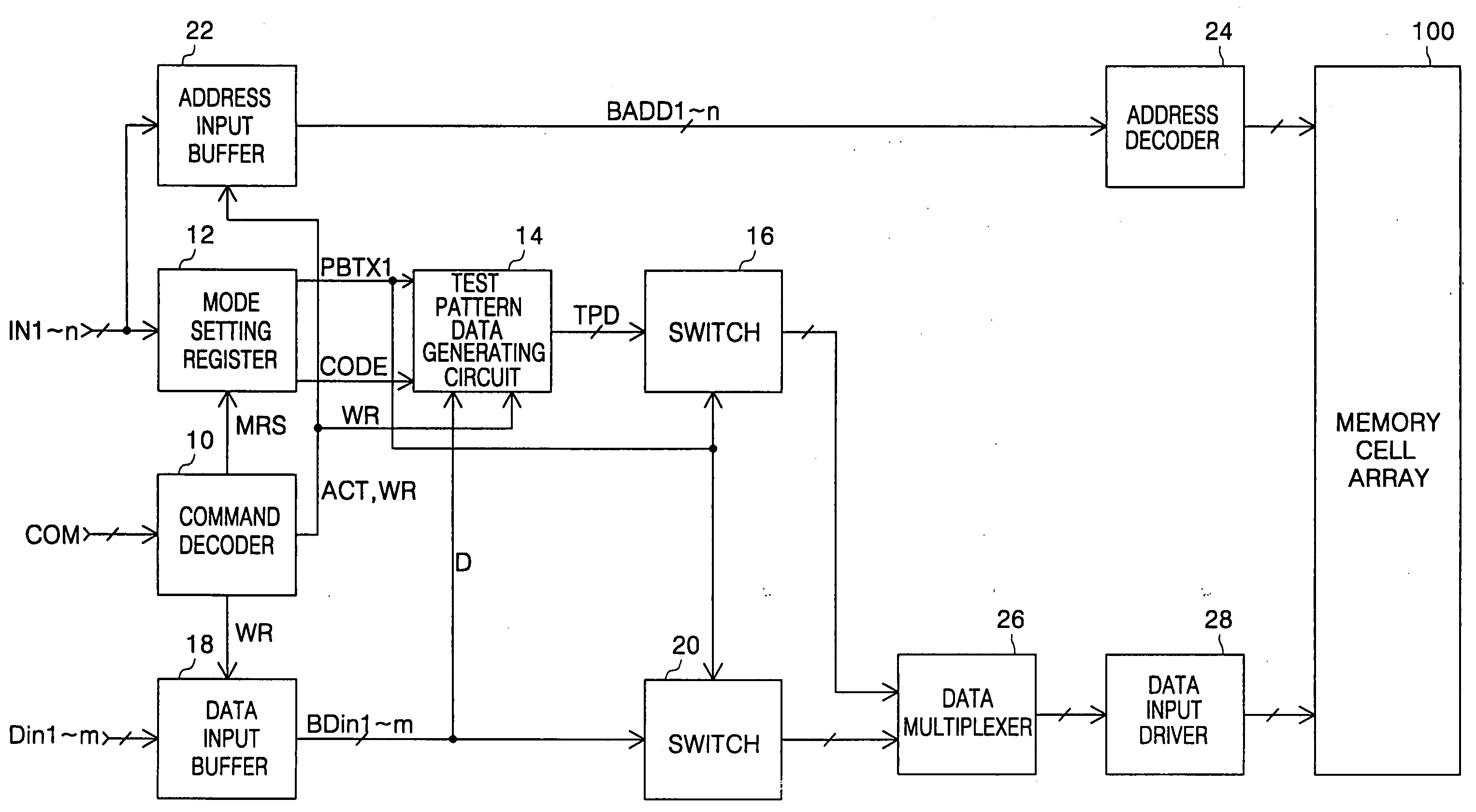

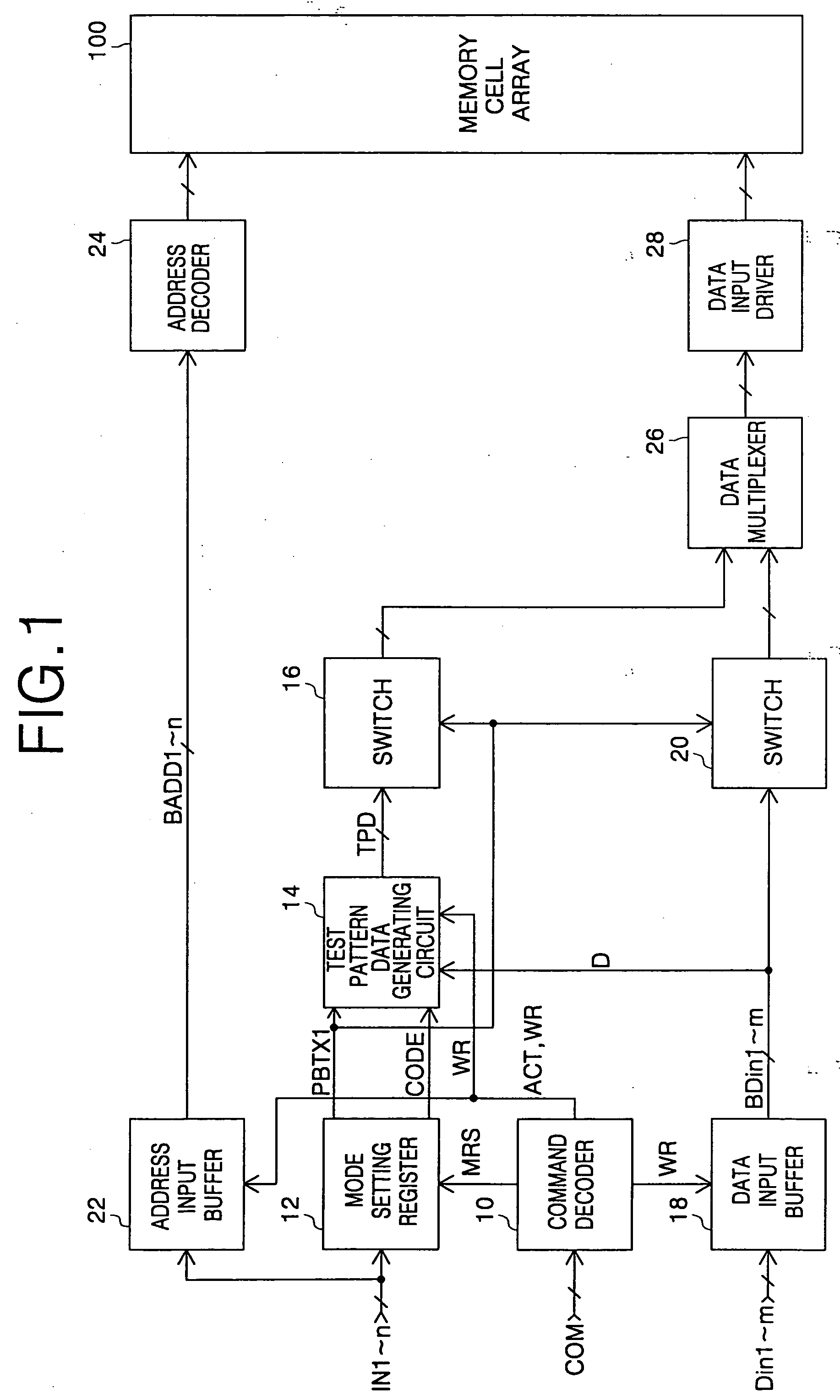

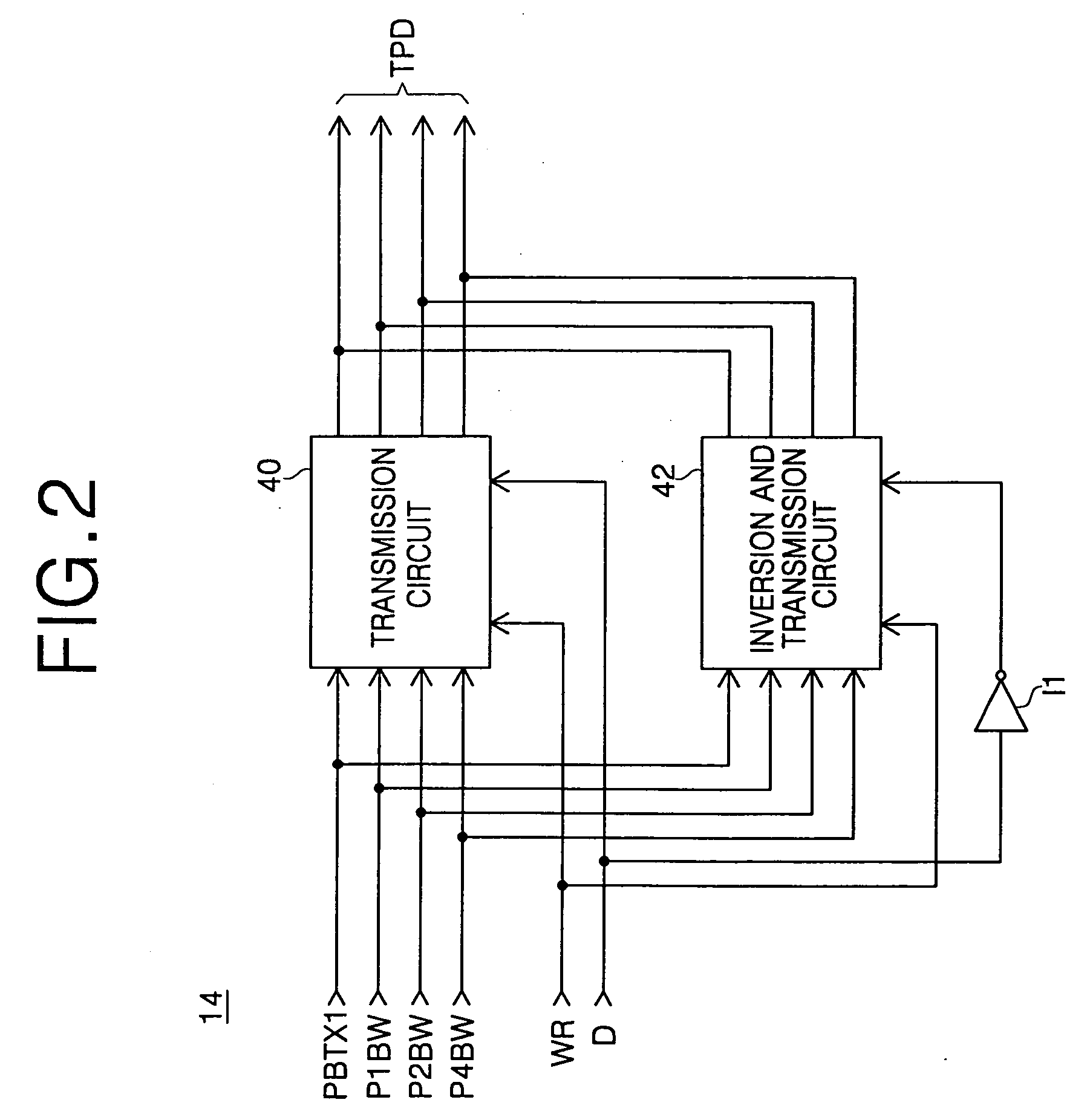

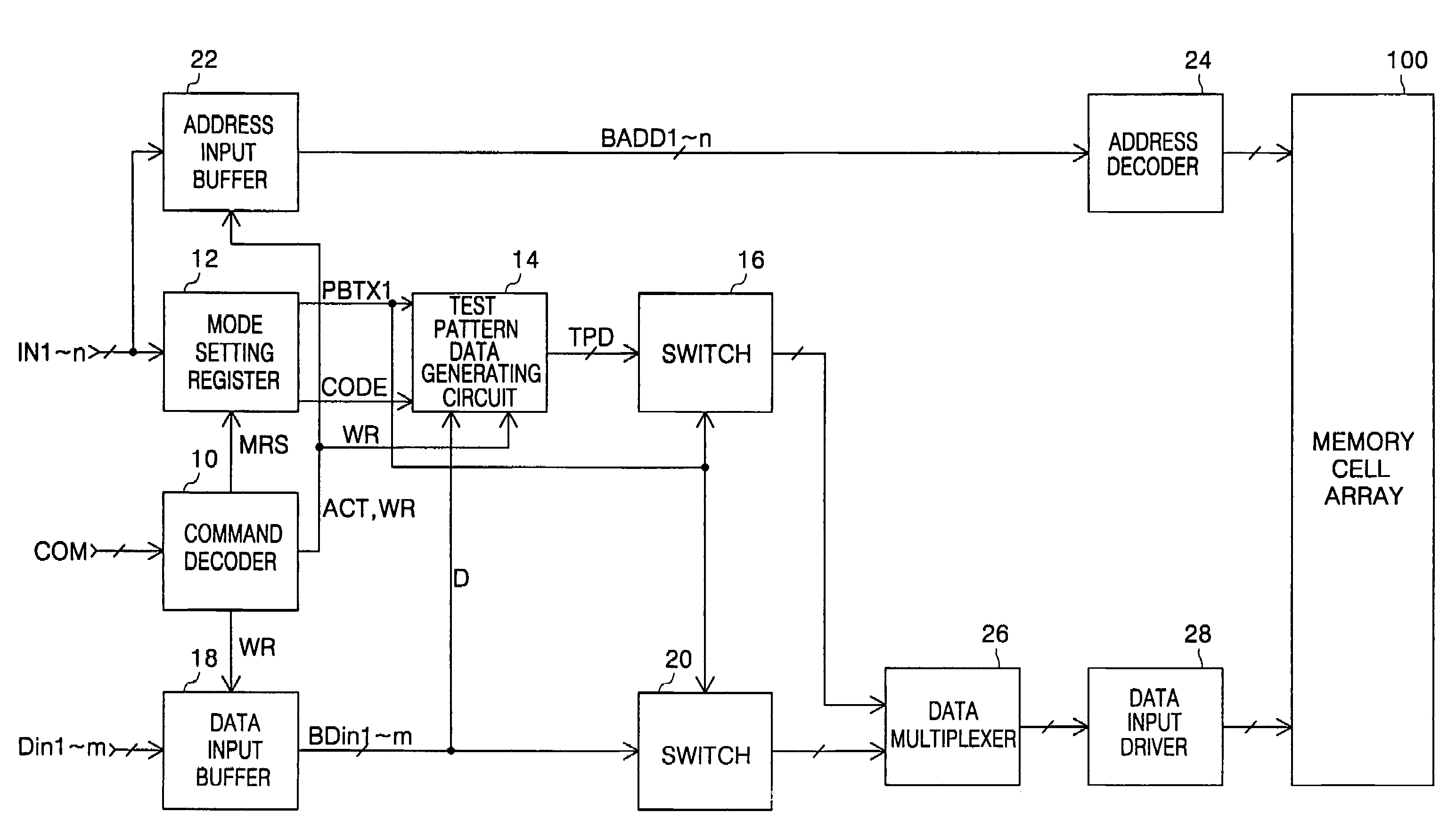

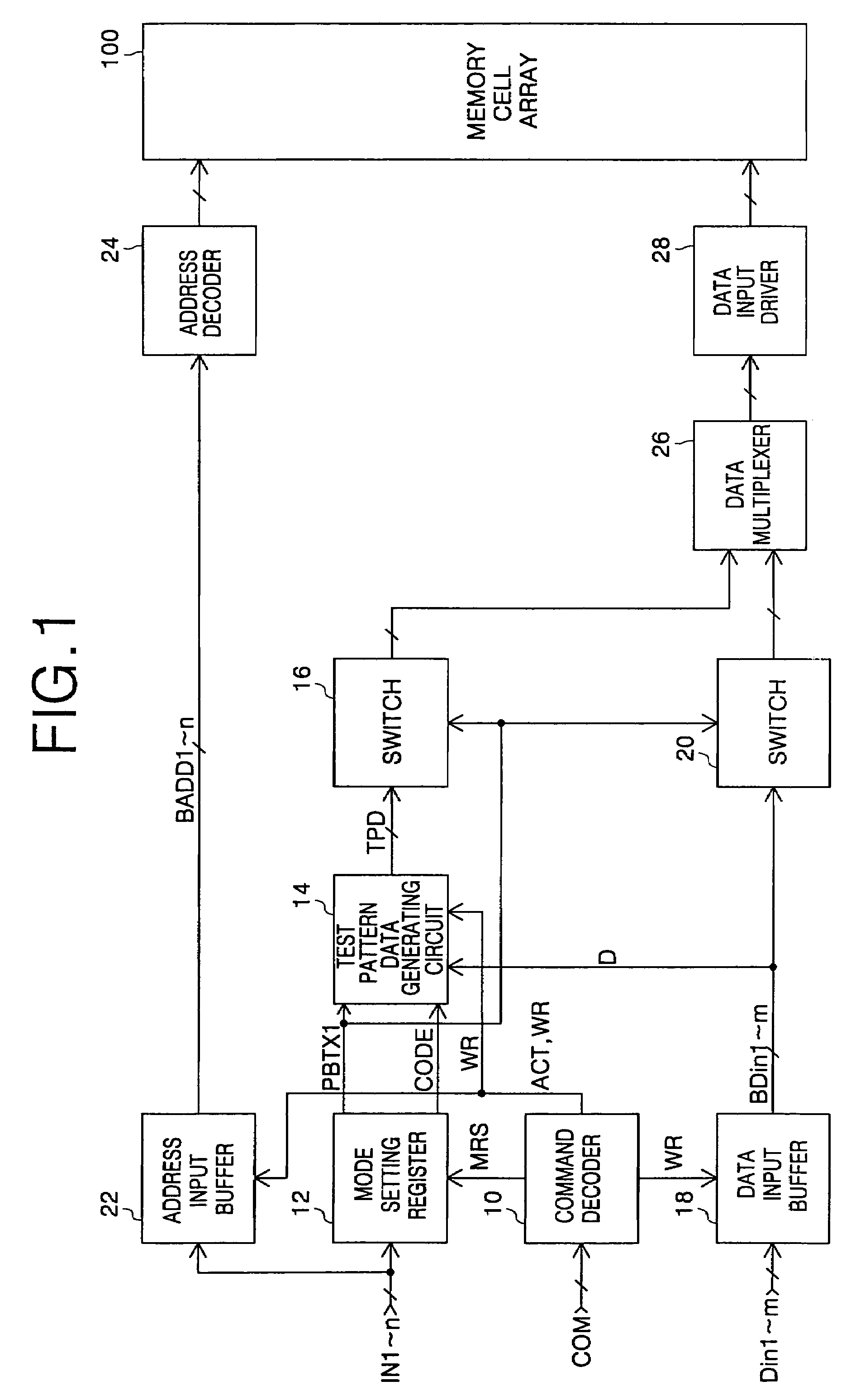

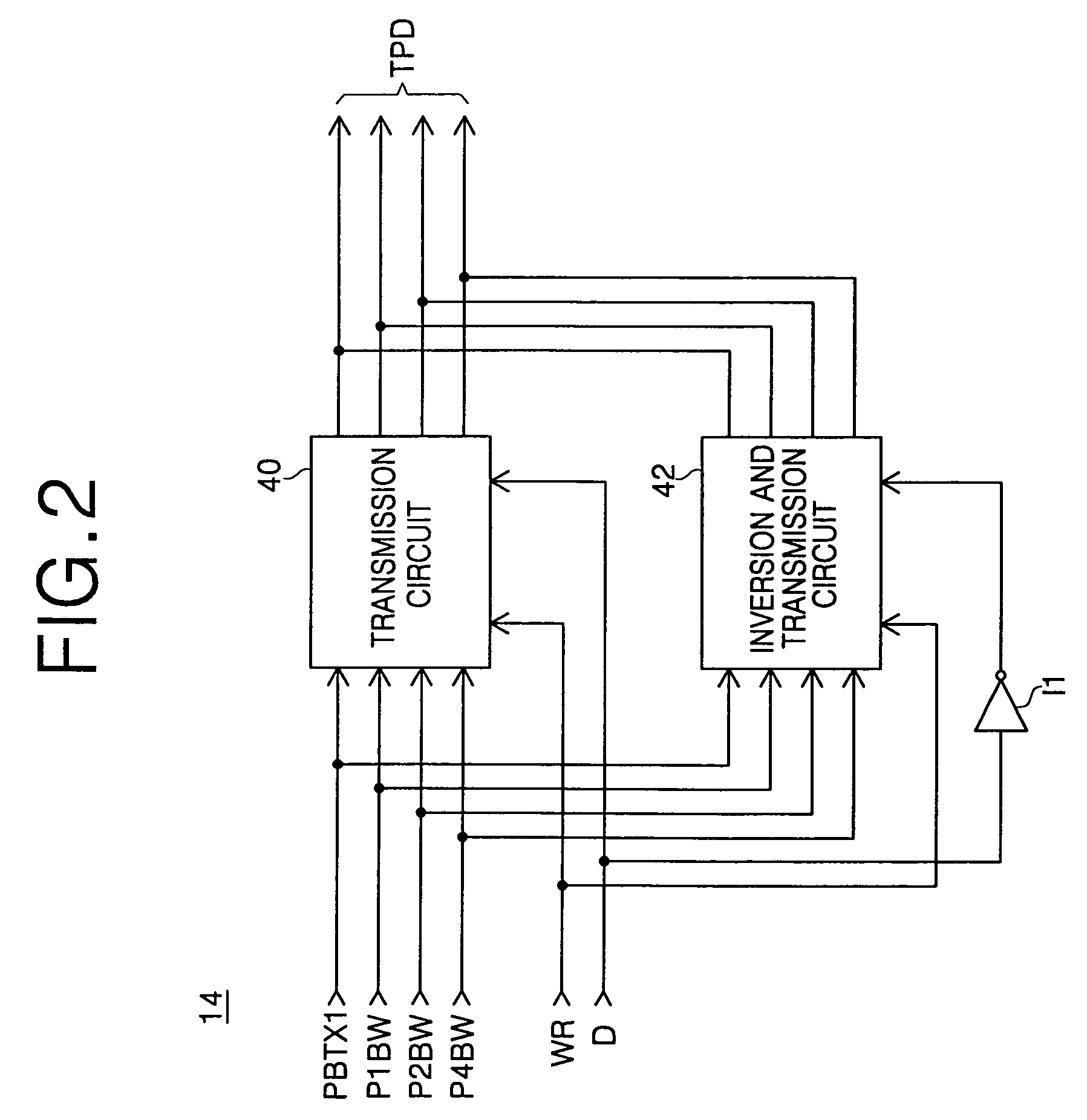

Semiconductor memory device and test pattern data generating method using the same

ActiveUS20050108607A1Reduce in quantityElectronic circuit testingError detection/correctionBit TestSemiconductor

A semiconductor memory device includes a mode setting register for generating a parallel bit test signal and a code according to an externally applied mode setting register code in response to a mode setting command; a data input circuit for receiving and outputting at least one bit of externally applied data in response to a write command; and a test pattern data generating circuit for receiving the parallel bit test signal and a predetermined bit from the code to generate a test pattern data in response to the at least one bit of externally applied data received from the data input circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

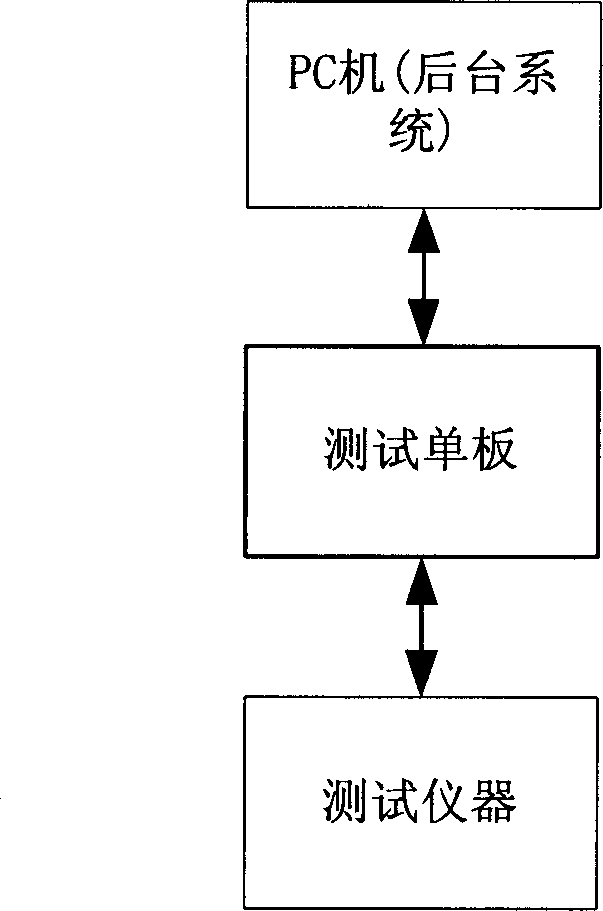

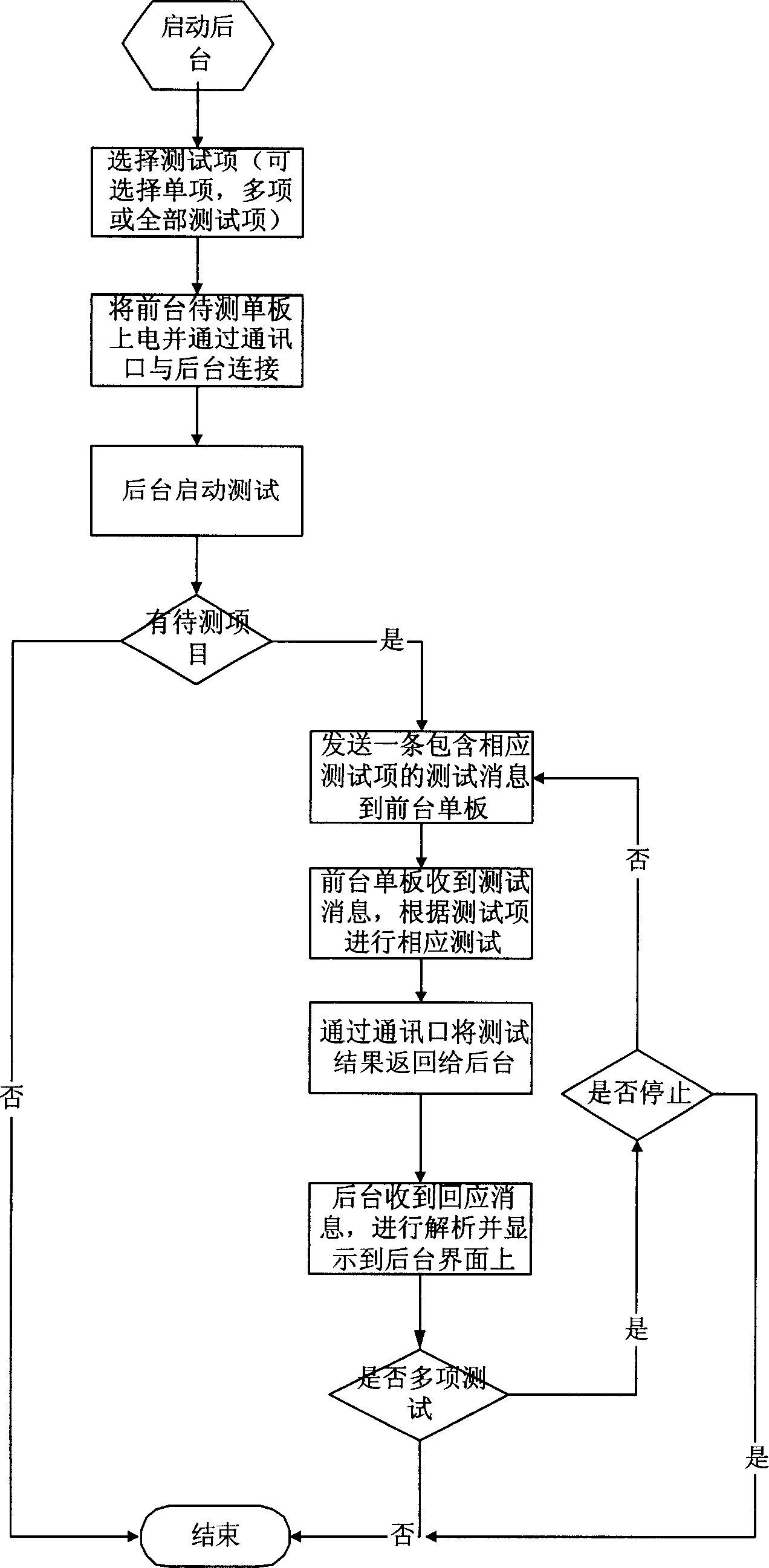

Method of realizing single board station testing and its system

The invention is a method and system for realizing mono-chip working position testing, and the method includes the steps: starting up a testing background system and selecting the required testing items; communicating a foreground mono-chip with the background system, where the foreground mono-chip is normally power-on and enters in a testing mode; the background system starts up testing and sends the information corresponding to the testing items to the foreground mono-chip in turn; the foreground mono-chip receives the information to resolve it and makes a testing processing flow on it and after primary testing is completed, returns tested result in a fixed information returning form to the background system; the background system receives the tested result and then makes the corresponding resolution according to different testing items and displays the tested result in the interface of the background system. The invention raises the speed of a MCU processing other functions.

Owner:ZTE CORP

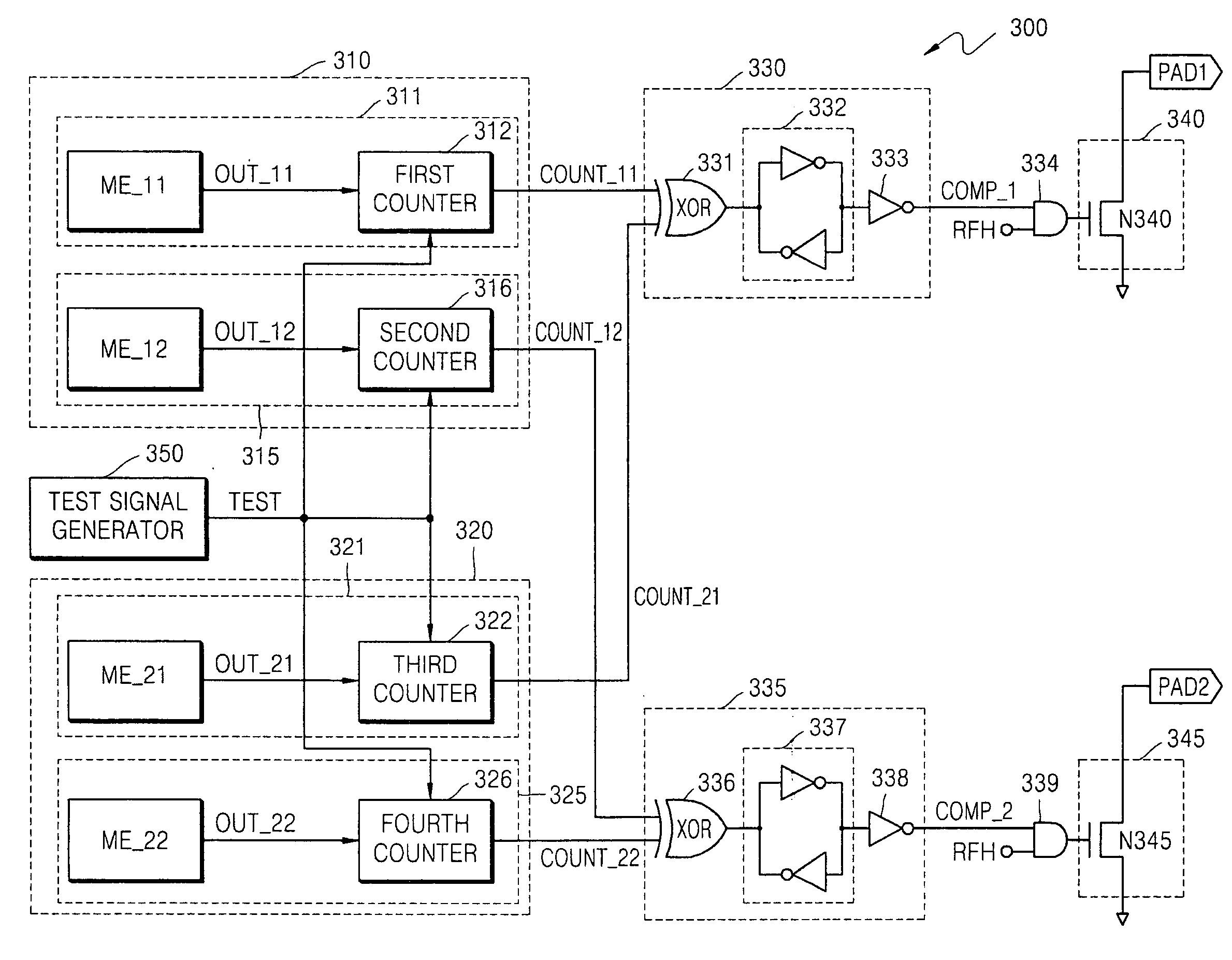

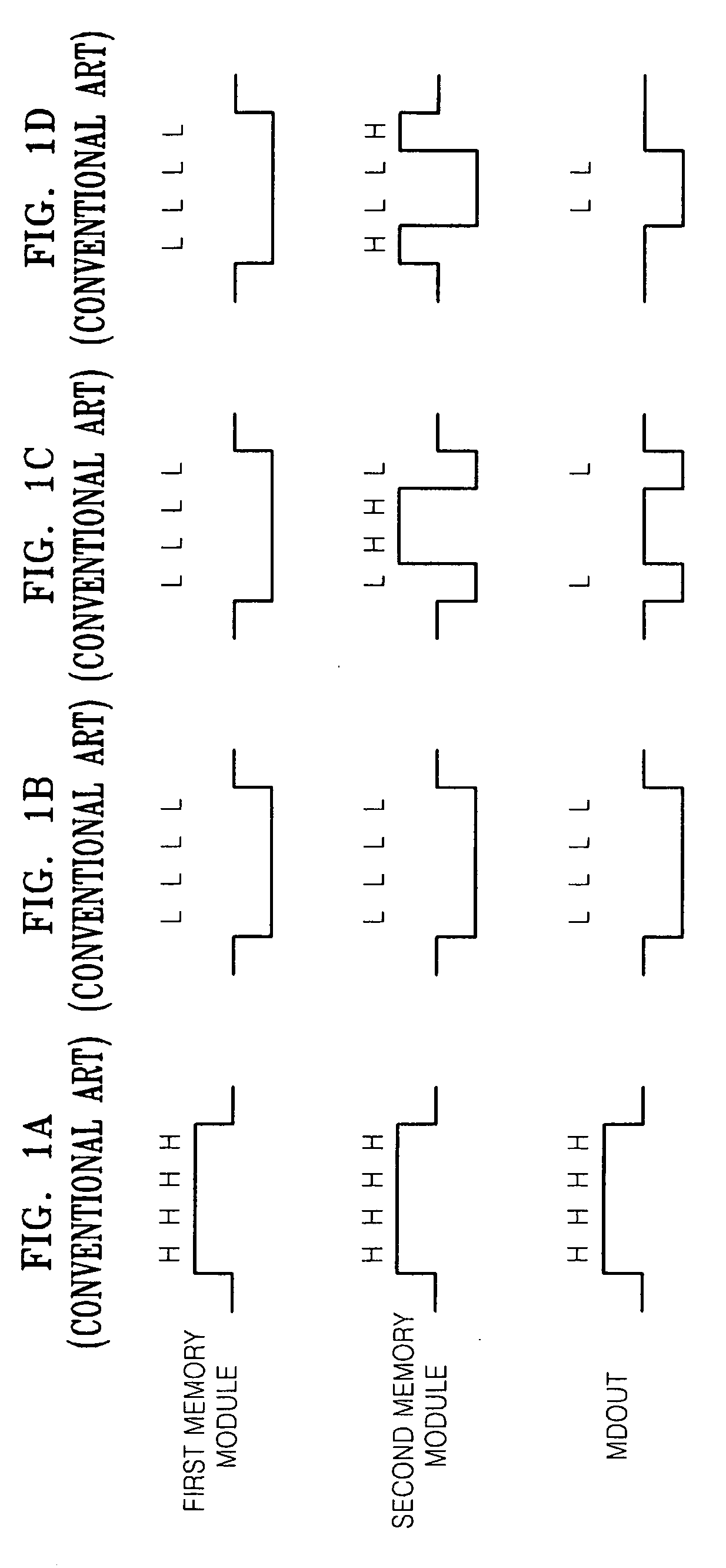

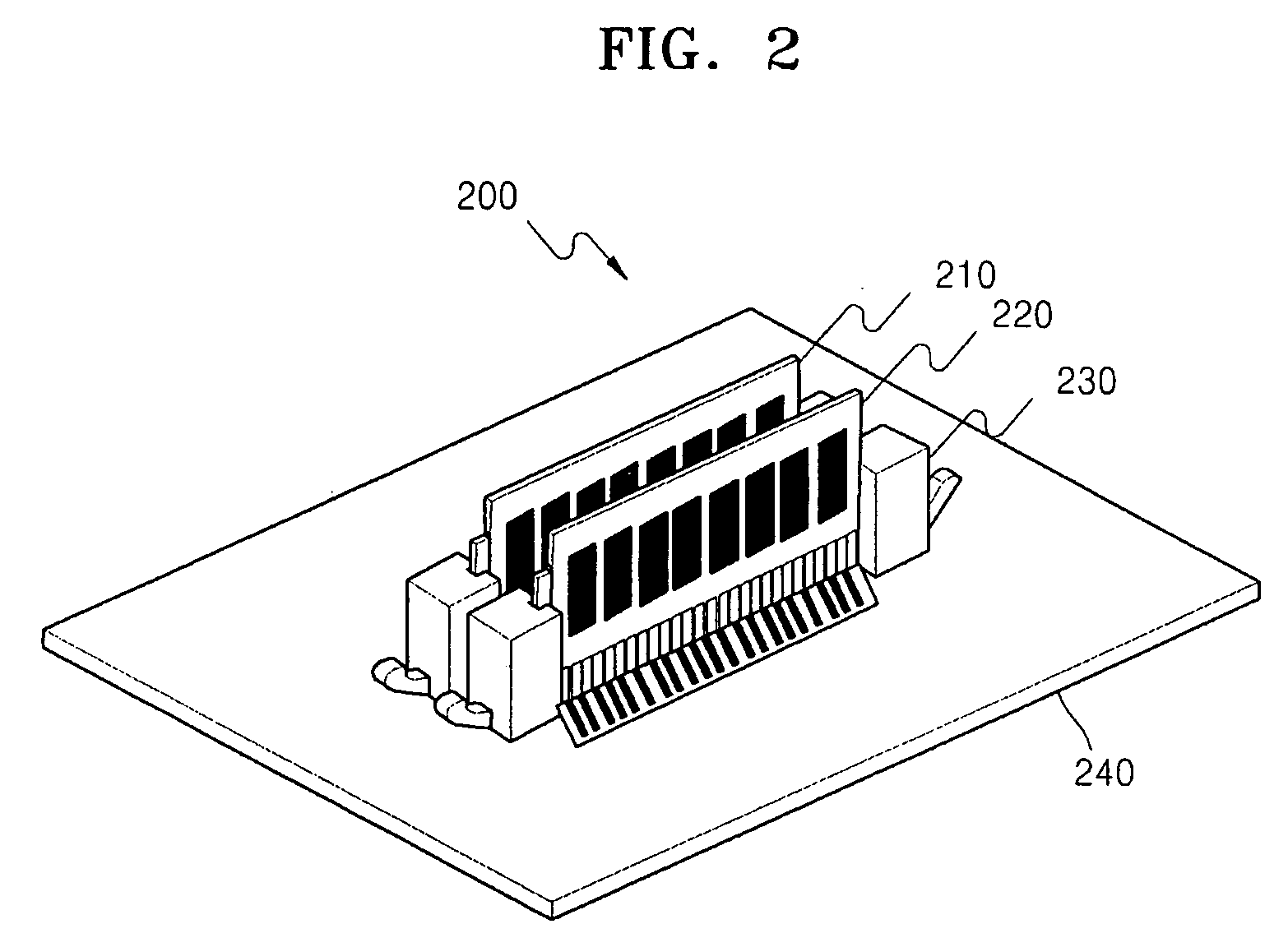

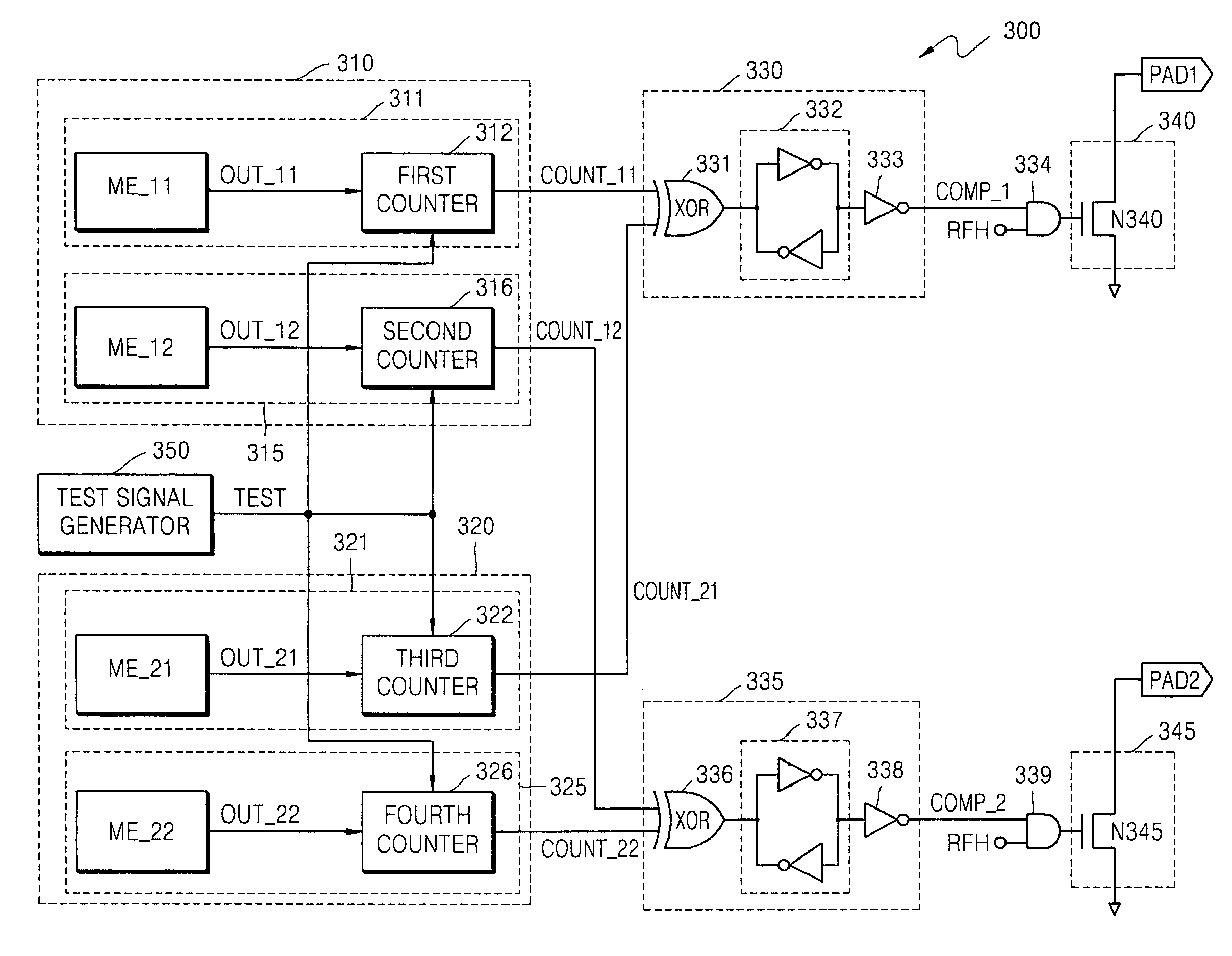

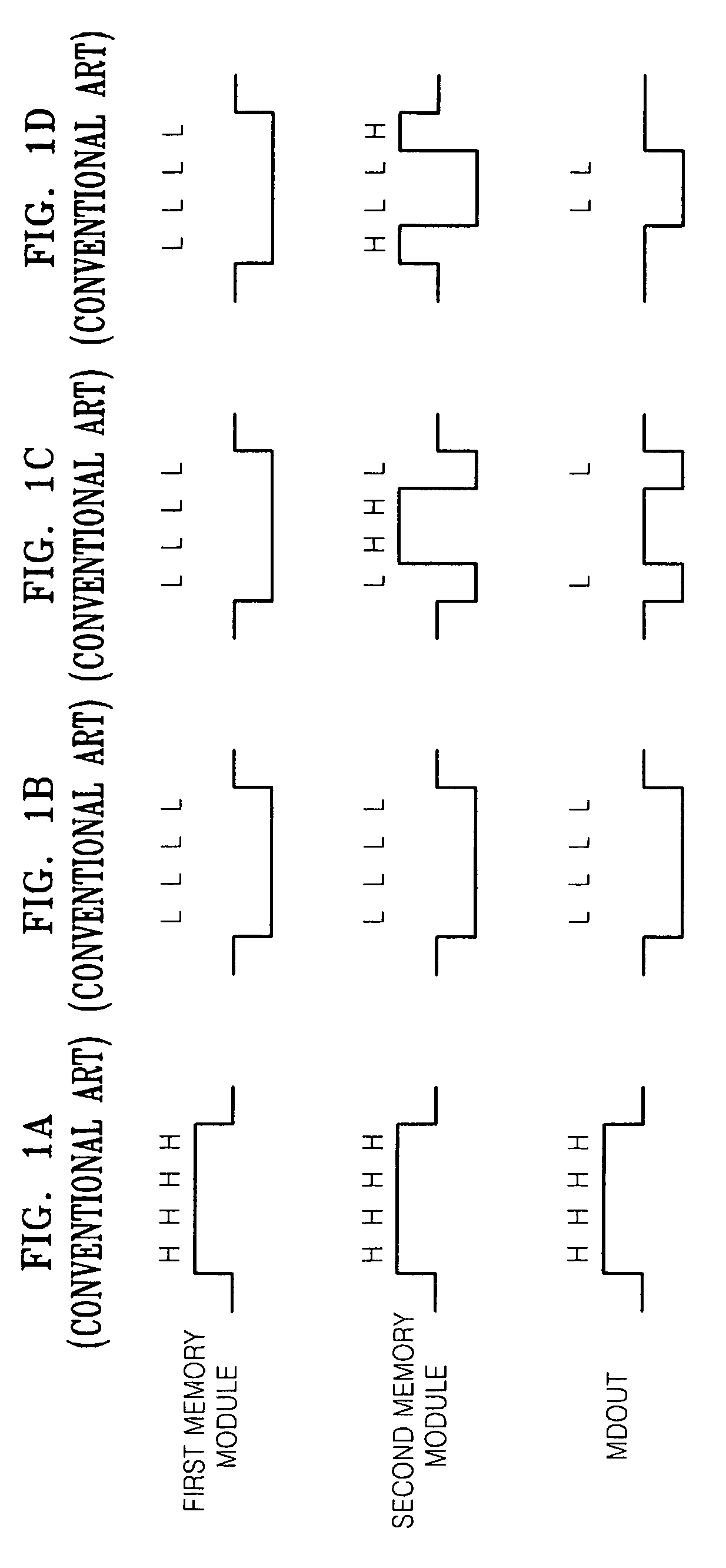

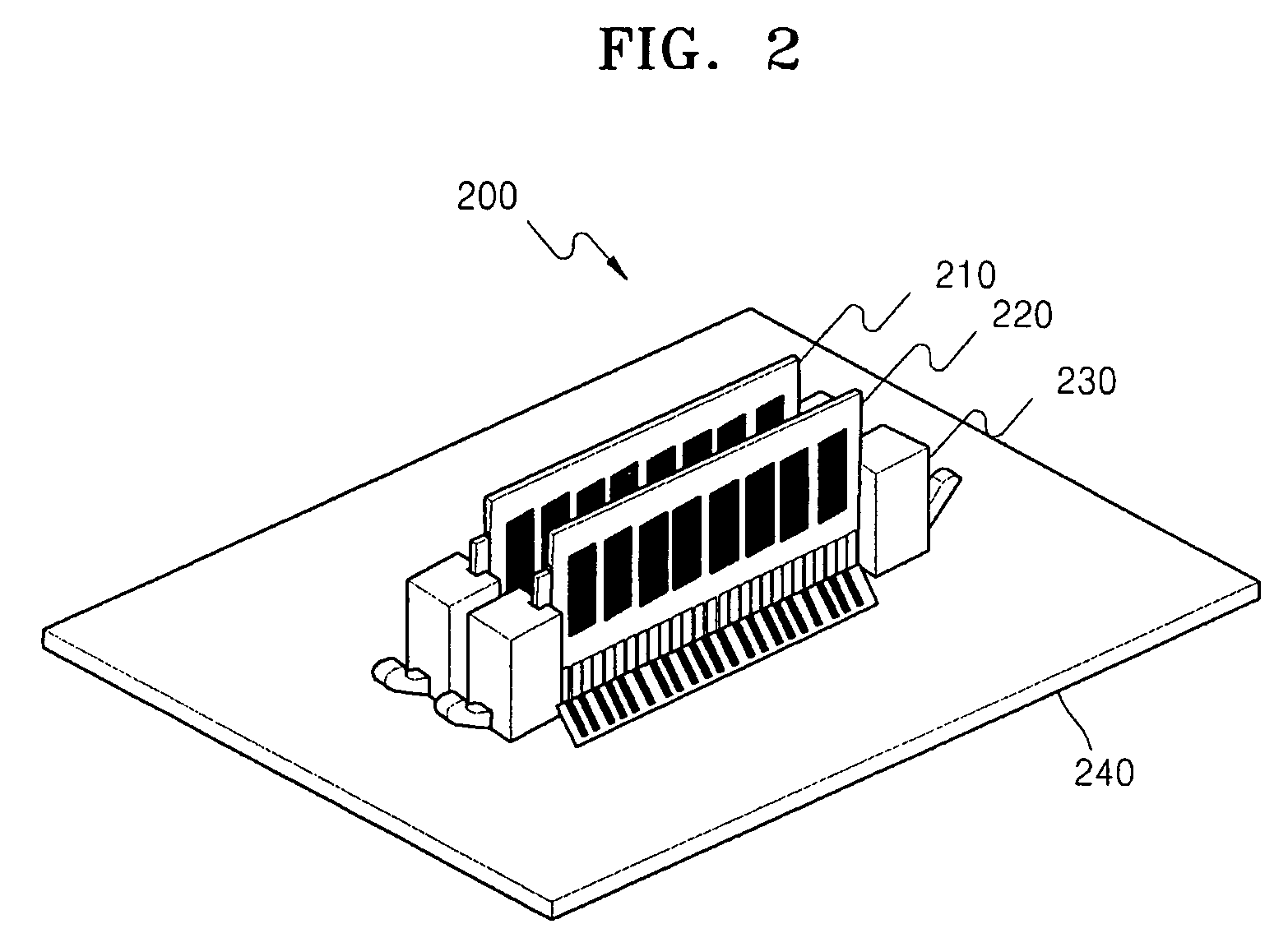

Test system for conducting Parallel bit test

InactiveUS20090228747A1Reduce the possibility of errorFault responseStatic storageParallel computingBit Test

Provided is a test system conducting a parallel bit test. The test system, conducting a parallel bit test on a plurality of memory modules mounted on a socket, comprises a plurality of counters and a comparator. Each of the counters counts the number of data output signals in the same logic state, among the data output signals outputted from each memory of the memory modules, and outputs a count signal. The comparator compares the count signal outputted from each of the counters and outputs a comparison signal corresponding to a defect of the memory modules. According to the test system, defects in a memory module can be accurately detected and a possibility of an error in the detection can be reduced when a plurality of memory modules are tested, as compared to conventional test systems.

Owner:SAMSUNG ELECTRONICS CO LTD

Parallel bit test apparatus and parallel bit test method capable of reducing test time

InactiveUS20080168316A1Reduce testing costsReduce the amount requiredError detection/correctionCode conversionMemory chipData signal

A parallel bit test (PBT) apparatus, included in memory chips that are stacked in a multi-chip package (MCP) and that share a set of data signal lines, may include: a comparing unit to output a data signal representative of a comparison between test data signals provided to a given one of the memory chips and corresponding data signals output therefrom, respectively; and a coding unit to output the representative data signal using a first subset of the shared set of data signal lines, the first subset not overlapping other subsets used by coding units corresponding to the other ones of the memory chips, respectively, the coding unit selecting one or more of the data signal lines amongst the shared set of data signal lines for inclusion in the first subset according to a first test mode register set (MRS) signal.

Owner:SAMSUNG ELECTRONICS CO LTD

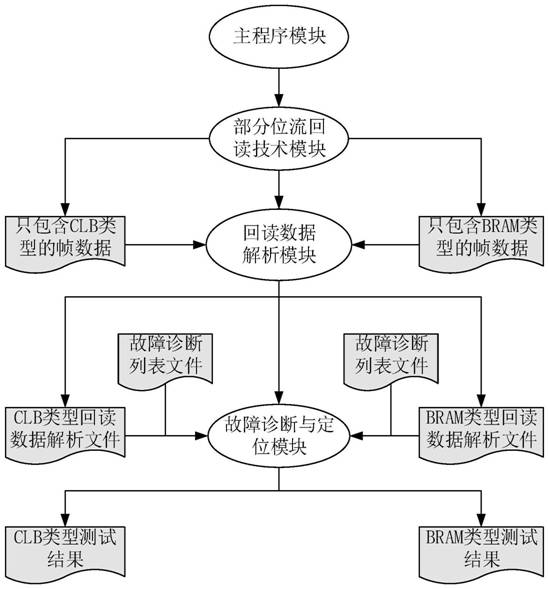

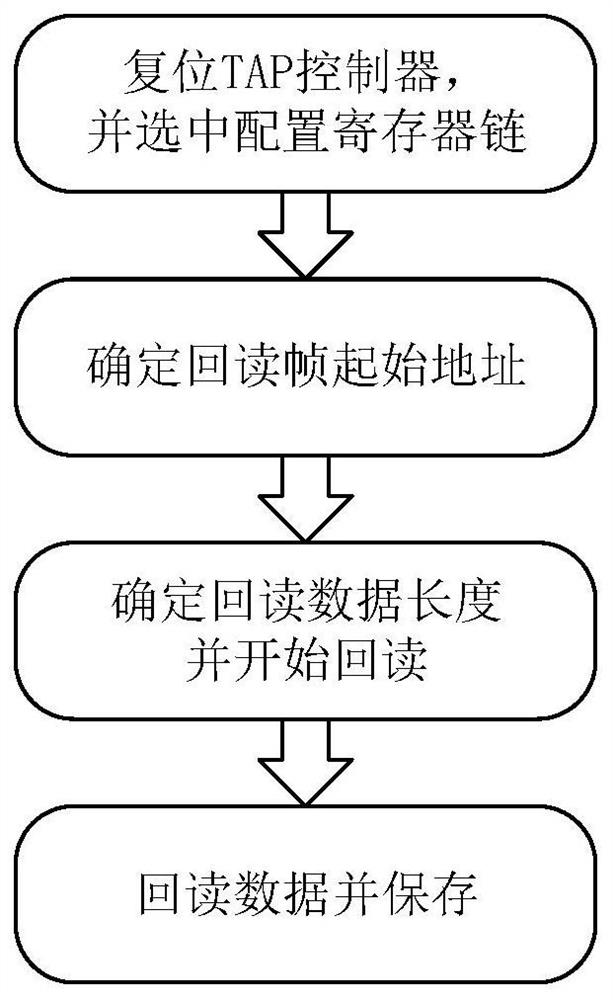

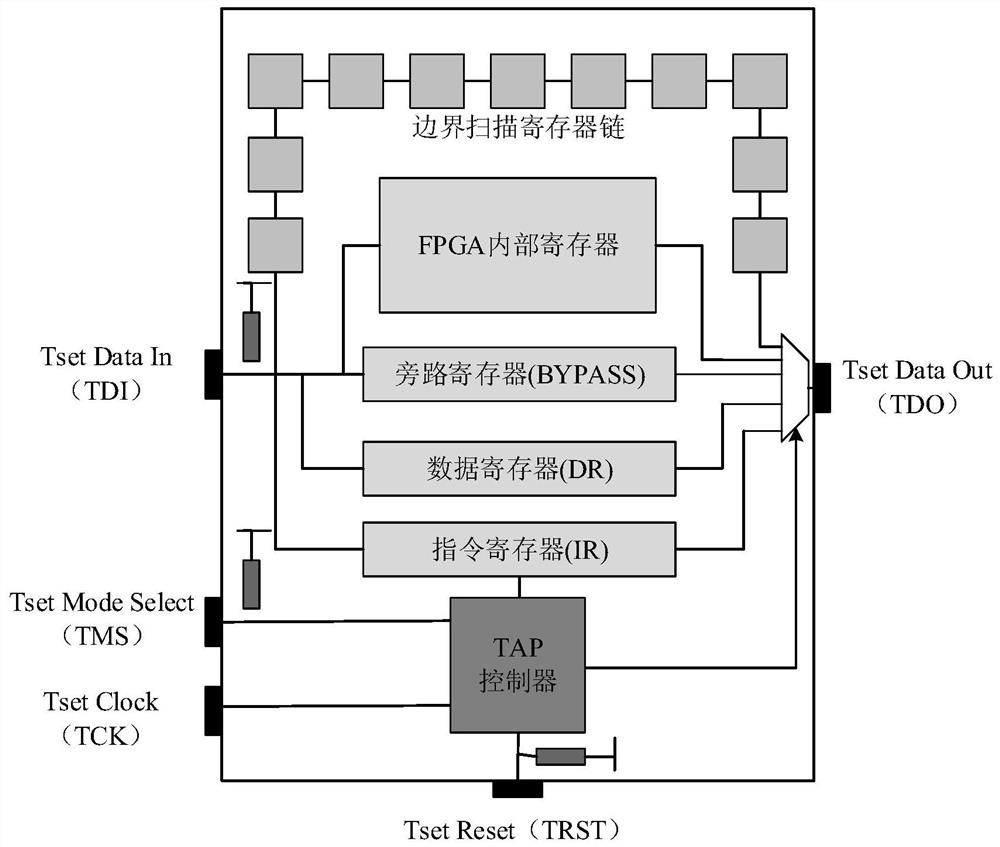

Partial bit stream read-back technology for testing internal resources of an FPGA

PendingCN112698994AVersatilityPortableFaulty hardware testing methodsComputer architectureEngineering

The invention belongs to the field of FPGAs (Field Programmable Gate Array), and particularly relates to a partial bit stream read-back technology for testing internal resources of an FPGA (Field Programmable Gate Array), which can improve the defects of an existing FPGA internal resource testing method. The method comprises the following steps: firstly, resetting a test access interface controller, setting a read-back starting frame address, and starting bit stream read-back operation from the address; and then setting the length of the read-back data to be used for stipulating the total number of frames read from the start frame address to the completion of the read-back, and then setting the FPGA to be in a read-back state; after the setting is completed, enabling the last step to start reading data from the FPGA configuration register chain and store the data, so that the data can be used by an FPGA test platform based on a partial bit stream read-back technology. A partial bit stream read-back technology is adopted, so that the high efficiency of FPGA internal resource testing is ensured, the universality is higher, and the method can be transplanted to different series of FPGAs to be used for testing the FPGA internal resources.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Semiconductor memory device and test pattern data generating method using the same

ActiveUS7257754B2Reduce in quantityElectronic circuit testingError detection/correctionBit TestSemiconductor

Owner:SAMSUNG ELECTRONICS CO LTD

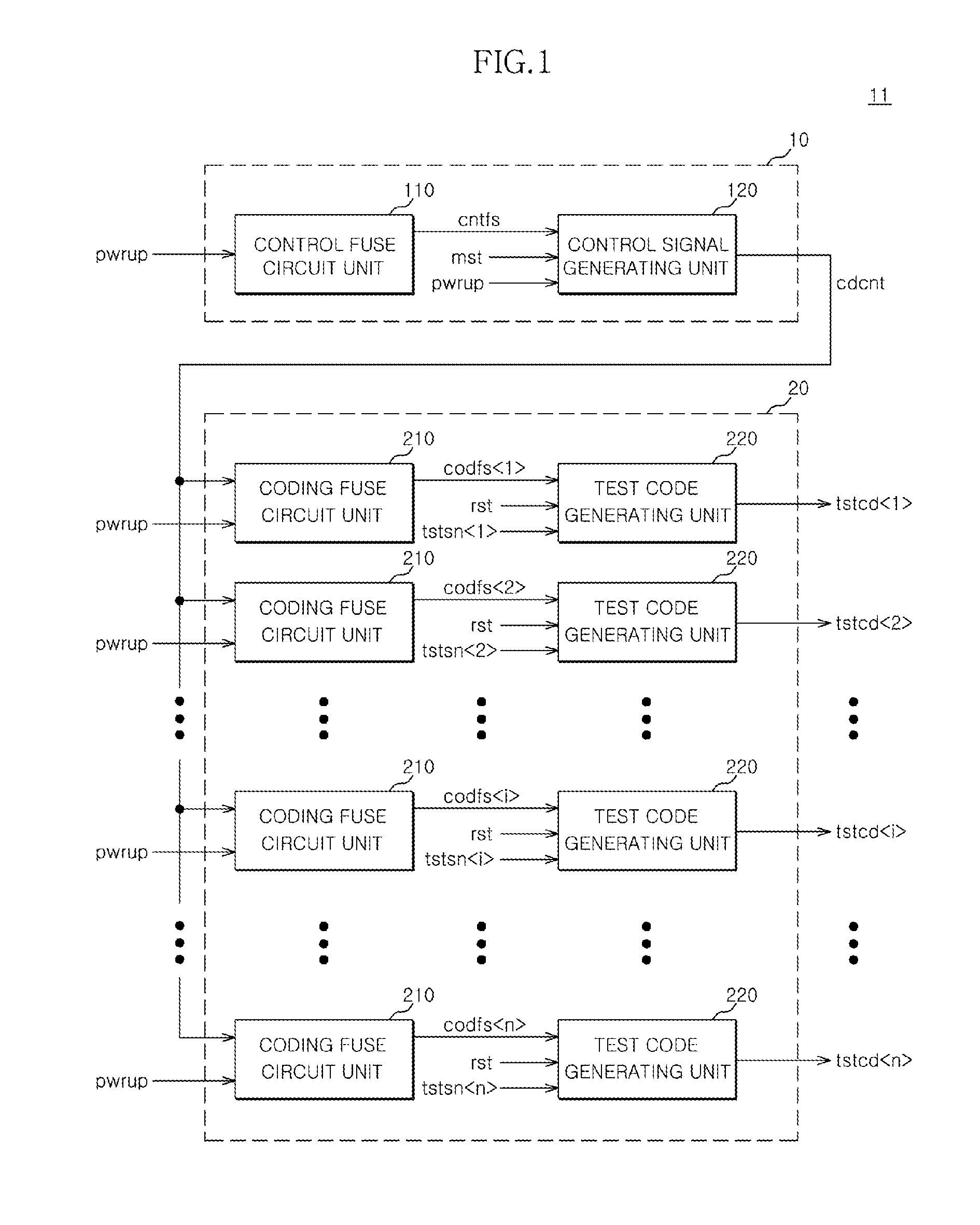

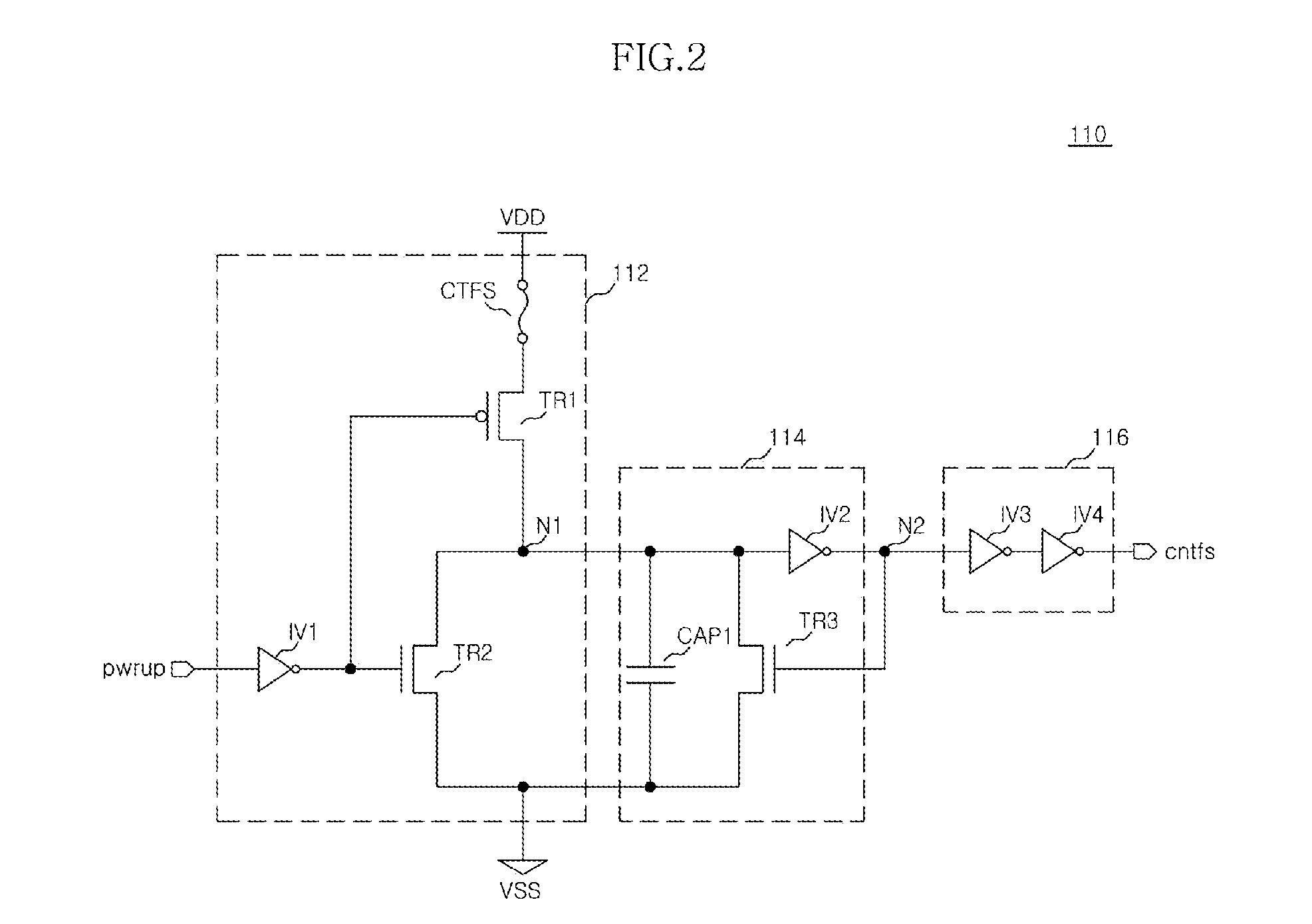

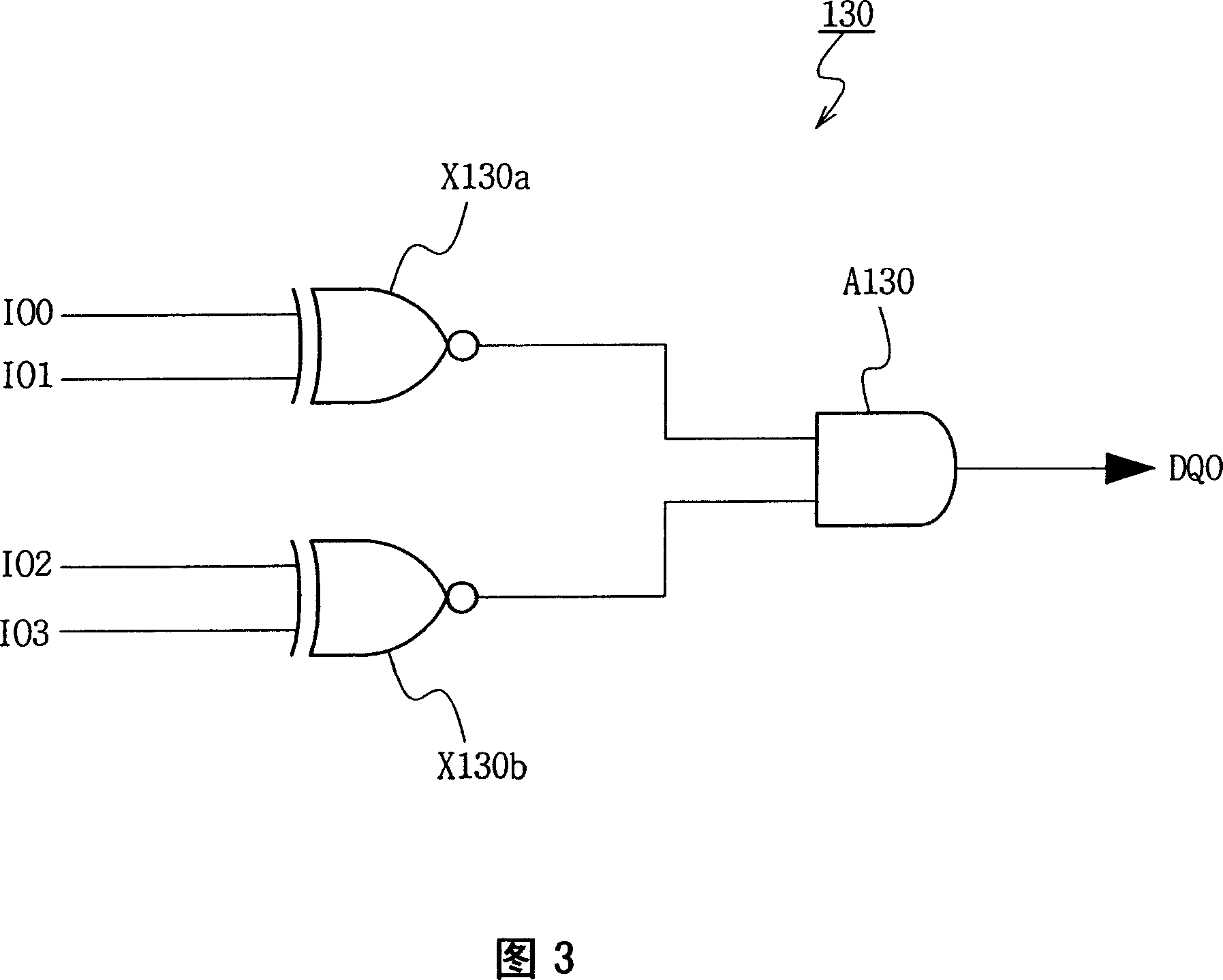

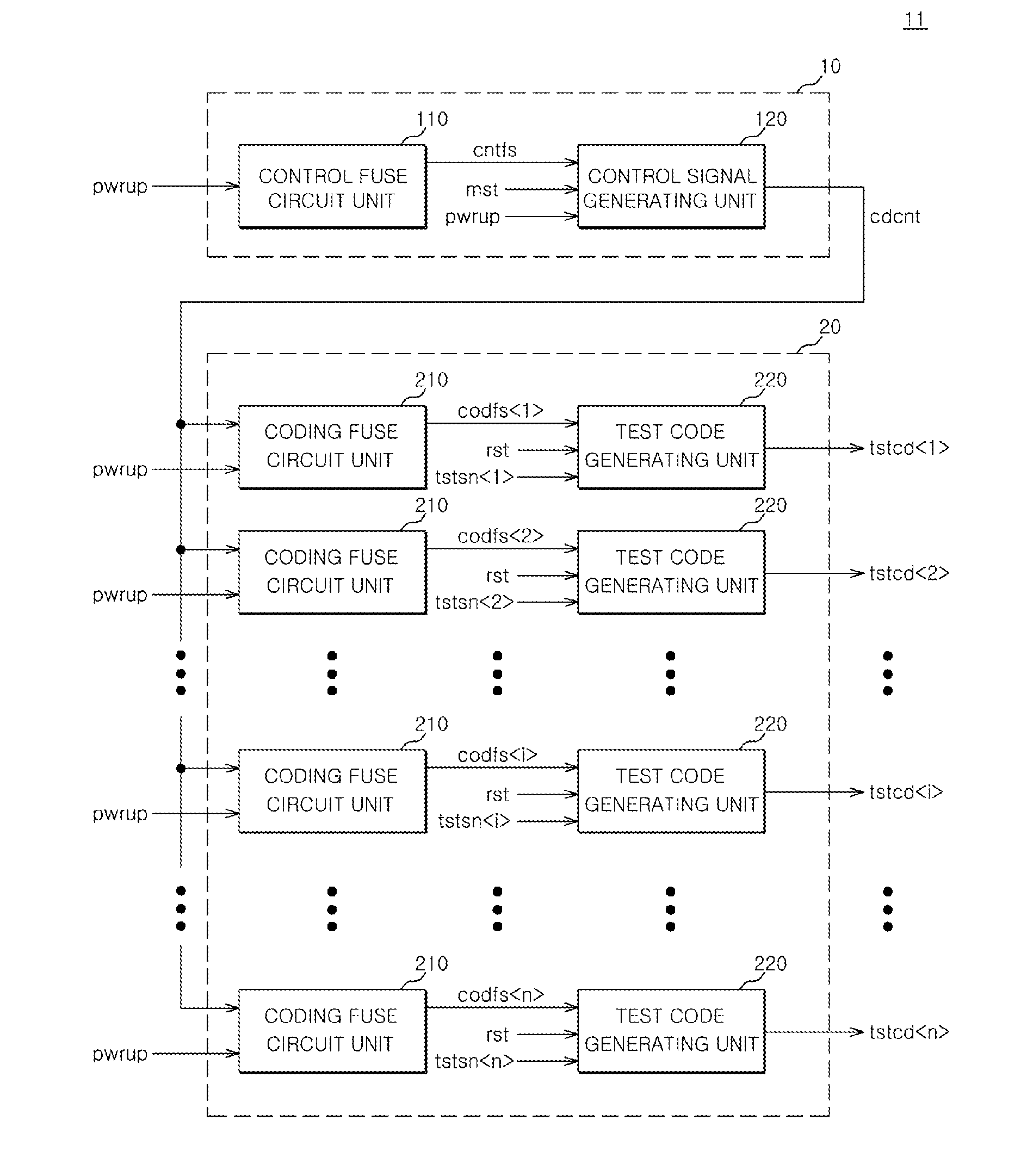

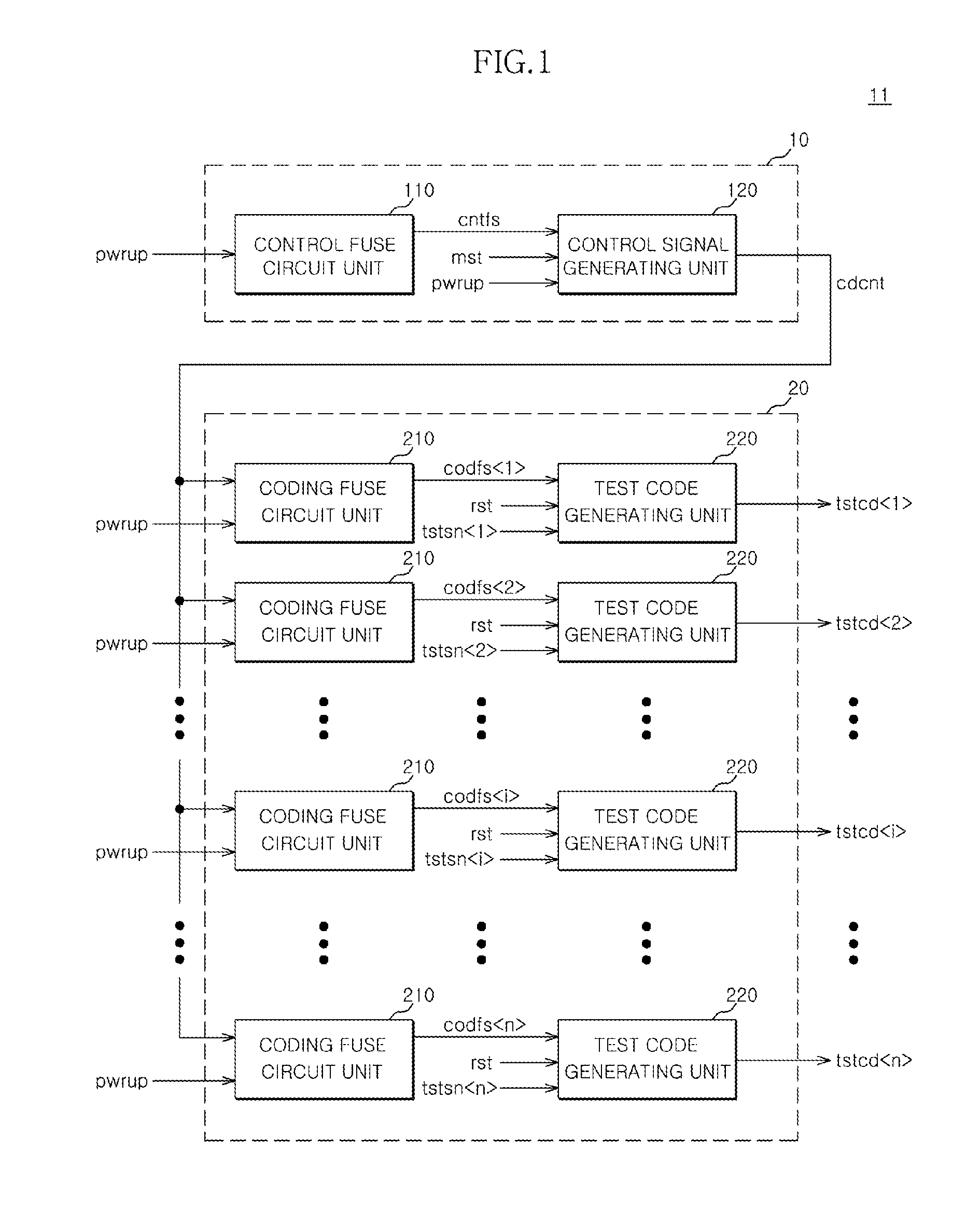

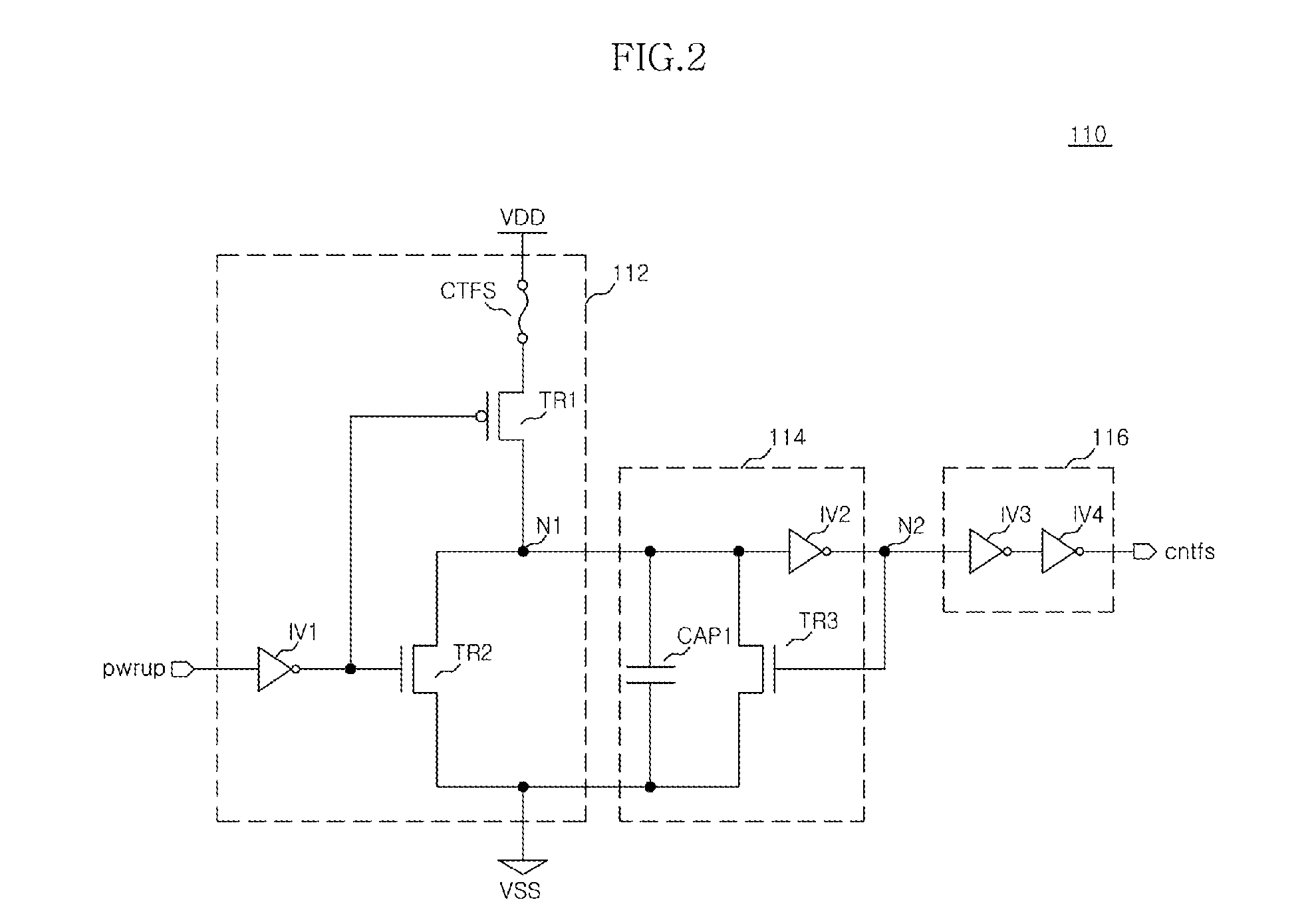

Apparatus and method of setting test mode in semiconductor integrated circuit

ActiveUS20090003101A1Improve adaptabilityLow costBatteries circuit arrangementsSemiconductor/solid-state device testing/measurementCoding blockControl signal

An apparatus for setting a test mode in a semiconductor integrated circuit includes a test mode control block that generates a coding control signal according to whether or not a control fuse is cut, and a test mode coding block that sets default values of a multi-bit test code in response to the coding control signal.

Owner:SK HYNIX INC

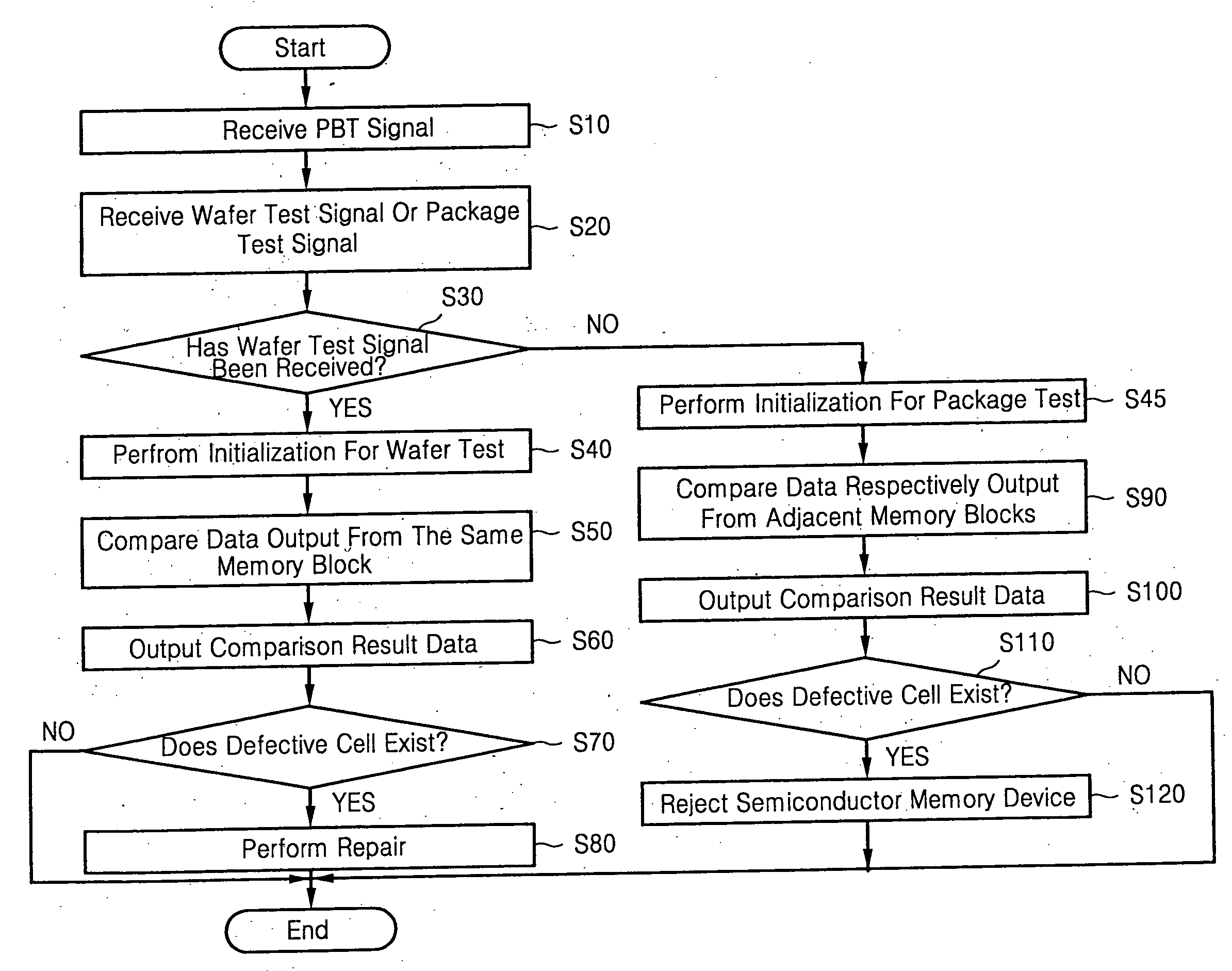

Parallel bit test circuit and method for semiconductor memory device

ActiveUS20070288812A1Remove restrictionsElectronic circuit testingError detection/correctionHemt circuitsBit Test

A semiconductor memory device performs a parallel bit test on a plurality of memory blocks by writing test pattern data into the plurality of memory blocks, outputting two bits from each memory block in parallel and comparing the two bits output from each memory block with each other in a first test mode, and outputting two bits from respectively different memory blocks and comparing the two bits output from the respectively different memory blocks with each other in a second test mode.

Owner:SAMSUNG ELECTRONICS CO LTD

Parallel bit test circuit and method for semiconductor memory device

ActiveUS7624317B2Remove restrictionsElectronic circuit testingError detection/correctionHemt circuitsBit Test

A semiconductor memory device performs a parallel bit test on a plurality of memory blocks by writing test pattern data into the plurality of memory blocks, outputting two bits from each memory block in parallel and comparing the two bits output from each memory block with each other in a first test mode, and outputting two bits from respectively different memory blocks and comparing the two bits output from the respectively different memory blocks with each other in a second test mode.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device capable of arbitrarily setting the number of memory cells to be tested and related test method

A semiconductor memory device and related test method are disclosed. Test data is defined from a group of M test bits selected from either input data or corresponding output data. A parallel bit test is then conducted on the test data. The M test bits include N test bits, where N is less than M, selected on a bit by bit basis from the output data, and L test bits, where N+L=M, selected from the input data. The selection of input data may be made in accordance with a don't care case for selected test data.

Owner:SAMSUNG ELECTRONICS CO LTD

Test hardware system for full-scale bit test

InactiveCN102466498AEasy to operateHigh degree of automationMeasurement devicesAudio power amplifierData acquisition

The invention discloses a test hardware system for a full-scale bit test, which is mainly composed of a pressure sensor, a displacement sensor, a torque sensor, a bit rotation speed sensor, and three tooth wheel rotation speed sensors which are all independently connected with amplifiers. All the amplifiers are connected with the same data acquisition card. The data acquisition card is connected with a computer. According to the test hardware system for the full-scale bit test disclosed by the invention, the control and test of the whole full-scale bit test process can be finished in a manner that the computer is operated by a person; the traditional way of finishing the test and data acquisition by manual operation of test control table buttons and the computer is displaced; the test operation process is simplified; and the automation degree of the test process is increased.

Owner:常萍

Parallel bit test circuits for testing semiconductor memory devices and related methods

An integrated circuit device includes a test circuit and at least one flag generator circuit. The test circuit is configured to generate first and second sets of test results in parallel in response to a memory test operation. The first and second sets of test results respectively correspond to first and second memory banks. The test circuit is further configured to merge respective ones of the first set of test results with respective ones of the second set of test results to provide a set of merged test results to respective ones of a set of output terminals of the integrated circuit device. The at least one flag generator circuit is configured to generate a first flag signal that indicates a presence of at least one memory test error in the first set of test results, and a second flag signal that indicates a presence of at least one memory test error in the second set of test results. Based on the set of merged test results and the first and second flag signals, the test circuit may determine which of the memory blocks of the first and second memory banks includes a defective memory cell therein.

Owner:SAMSUNG ELECTRONICS CO LTD

Apparatus and method of setting test mode in semiconductor integrated circuit

ActiveUS7761757B2Improve adaptabilityLow costBatteries circuit arrangementsSemiconductor/solid-state device testing/measurementCoding blockControl signal

An apparatus for setting a test mode in a semiconductor integrated circuit includes a test mode control block that generates a coding control signal according to whether or not a control fuse is cut, and a test mode coding block that sets default values of a multi-bit test code in response to the coding control signal.

Owner:SK HYNIX INC

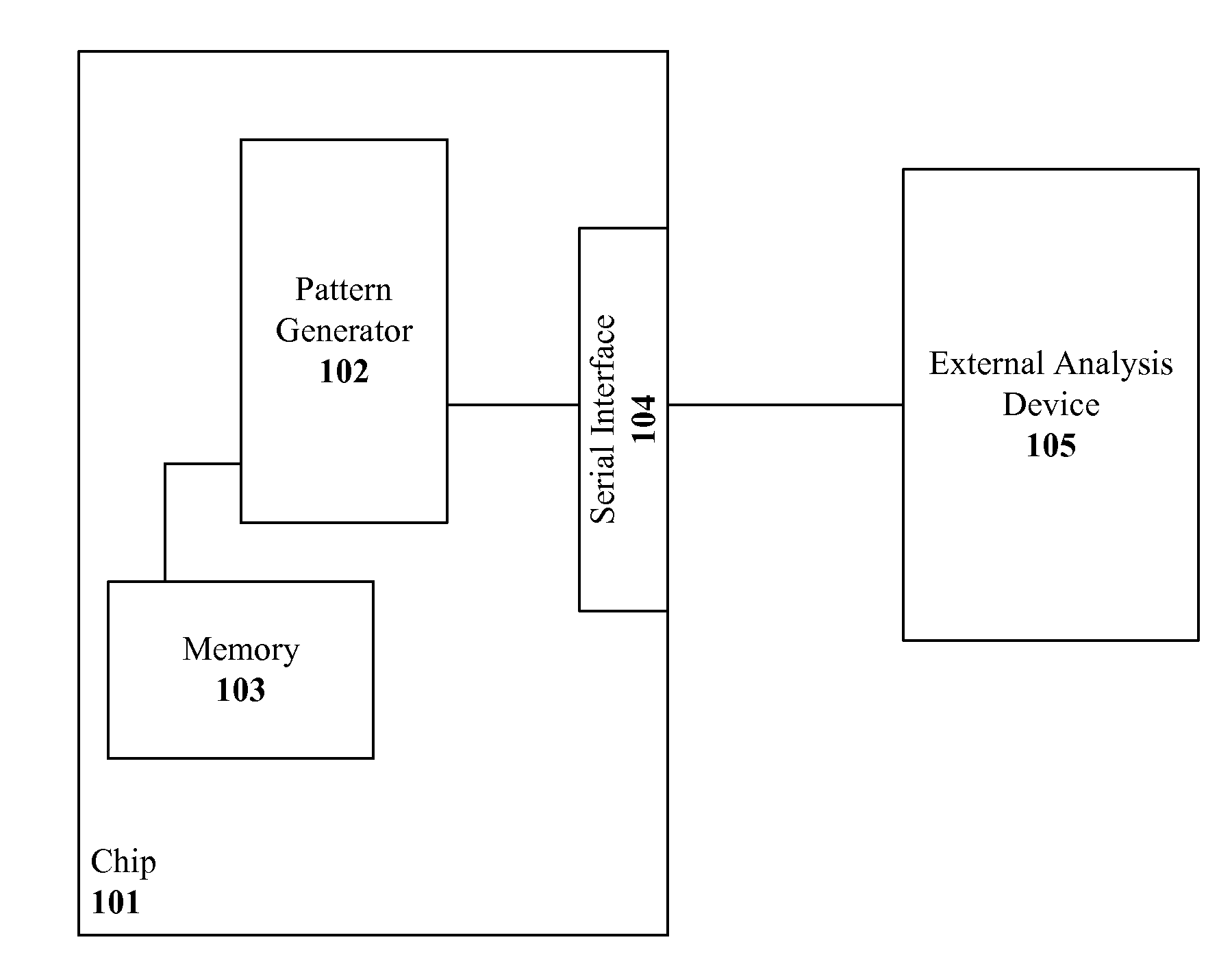

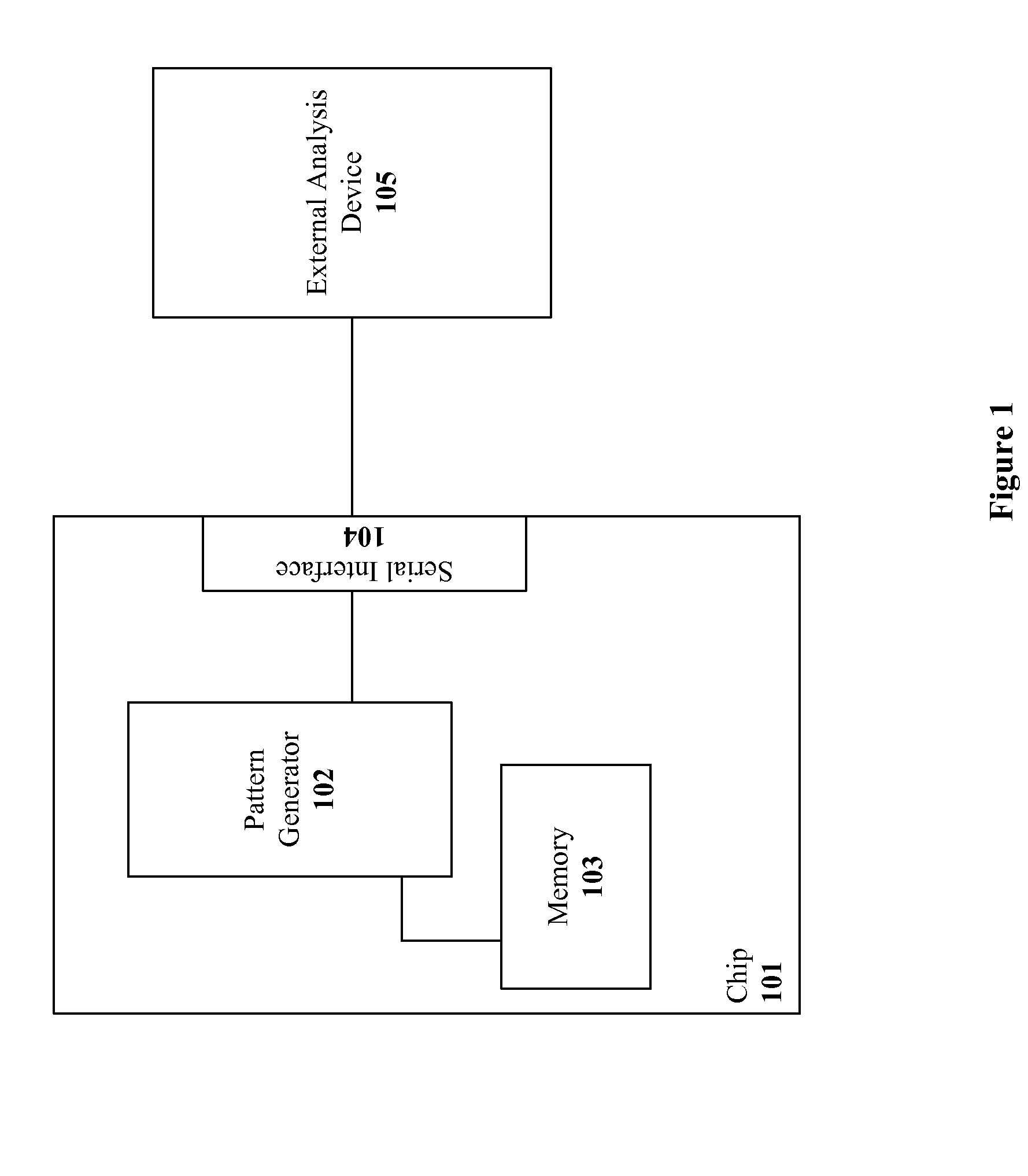

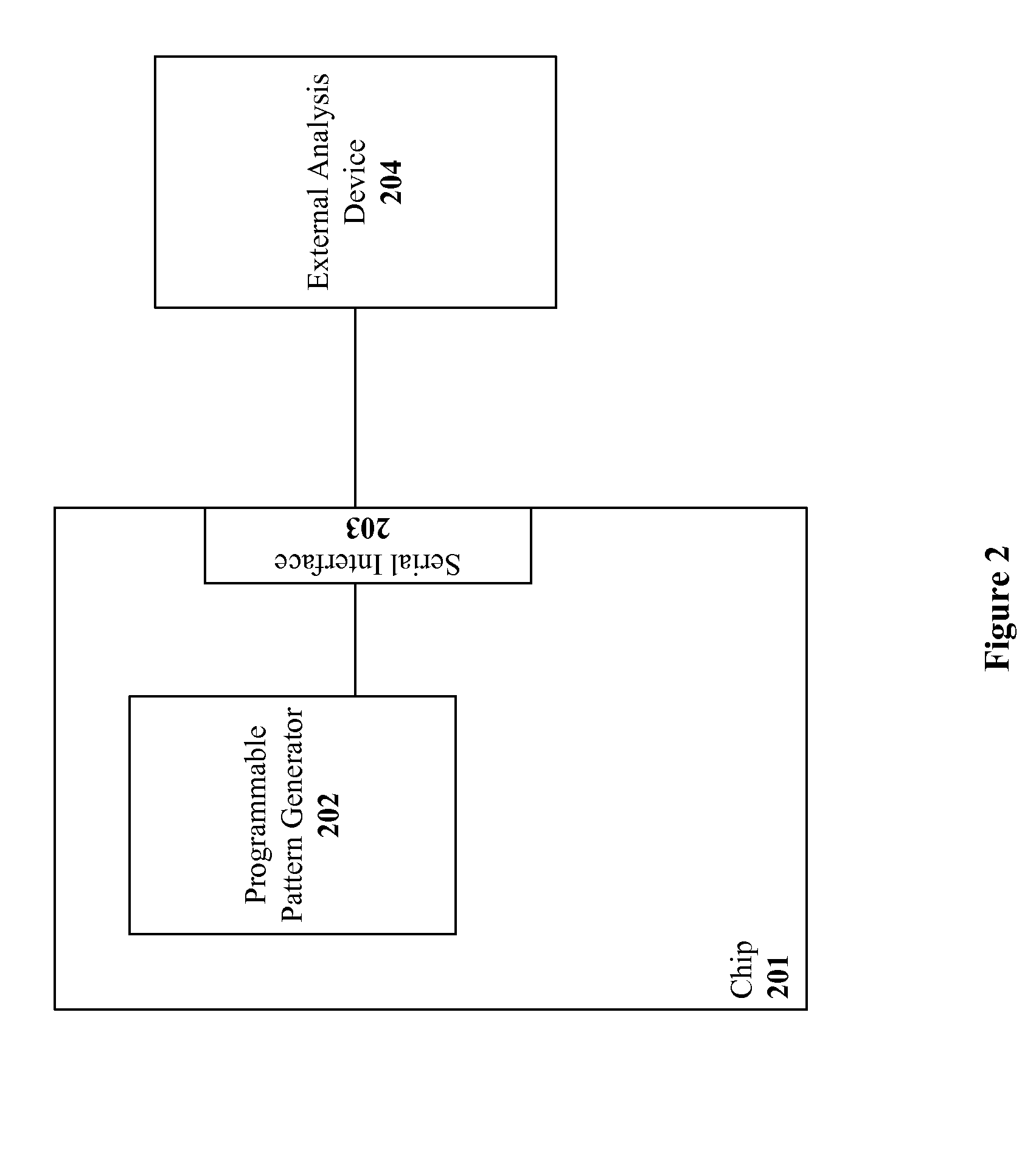

Complex Pattern Generator for Analysis of High Speed Serial Streams

InactiveUS20080307283A1Facilitate signal testingConvenient verificationResistance/reactance/impedenceElectronic circuit testingTest engineerTheoretical computer science

The present invention provides systems, devices and methods for generating user-defined test patterns within serial controller to facilitate signal testing and verification. These user-defined test patterns may be generated to more accurately reflect the actual traffic of a device-under-test or system, as well as allow a test engineer to more accurately test the boundaries of the device or system. In various embodiments of the invention, a programmable patterns generator is provided for generating user-defined test patterns that may be used during a testing procedure. This programmable pattern generator allows a user to define a particular test pattern by providing bit-by-bit test values, by defining a combination of canned sequences, or by supplementing one or more canned sequences with additional test bits.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Test system for conducting parallel bit test

InactiveUS7979760B2Reduce the possibility of errorError detection/correctionStatic storageParallel computingBit Test

Provided is a test system conducting a parallel bit test. The test system, conducting a parallel bit test on a plurality of memory modules mounted on a socket, comprises a plurality of counters and a comparator. Each of the counters counts the number of data output signals in the same logic state, among the data output signals outputted from each memory of the memory modules, and outputs a count signal. The comparator compares the count signal outputted from each of the counters and outputs a comparison signal corresponding to a defect of the memory modules. According to the test system, defects in a memory module can be accurately detected and a possibility of an error in the detection can be reduced when a plurality of memory modules are tested, as compared to conventional test systems.

Owner:SAMSUNG ELECTRONICS CO LTD