RAM high speed test control circuit and its testing method

A test method and test control technology, applied in the direction of semiconductor/solid-state device test/measurement, electronic circuit test, instrument, etc., can solve the problem of inconvenient maintenance, fault location, RAM fault type information statistical analysis, test speed can not meet the speed requirements, RAM The fault location is not detailed, and the maintenance and fault type statistics are convenient, the cost of test equipment is low, and the test is flexible.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

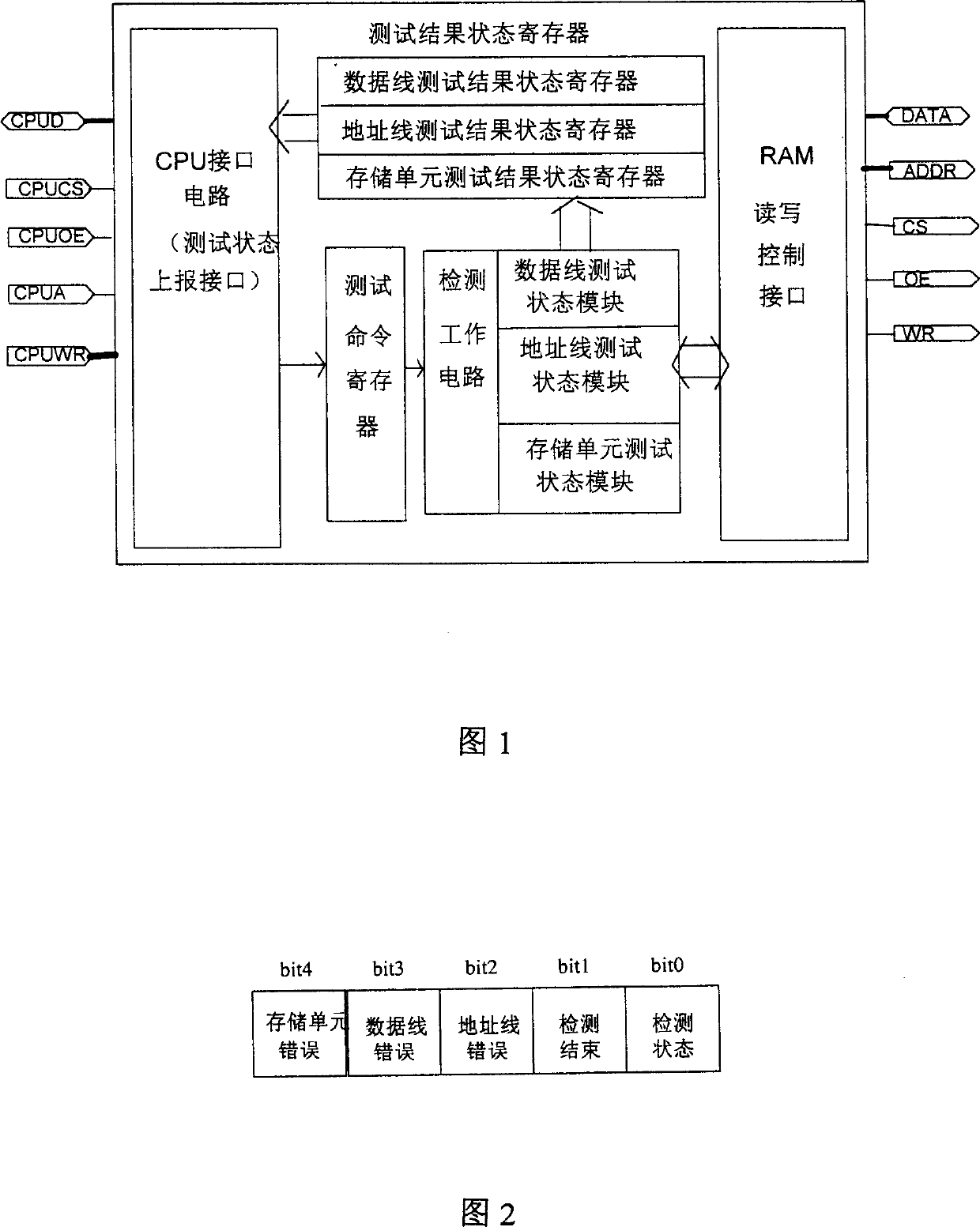

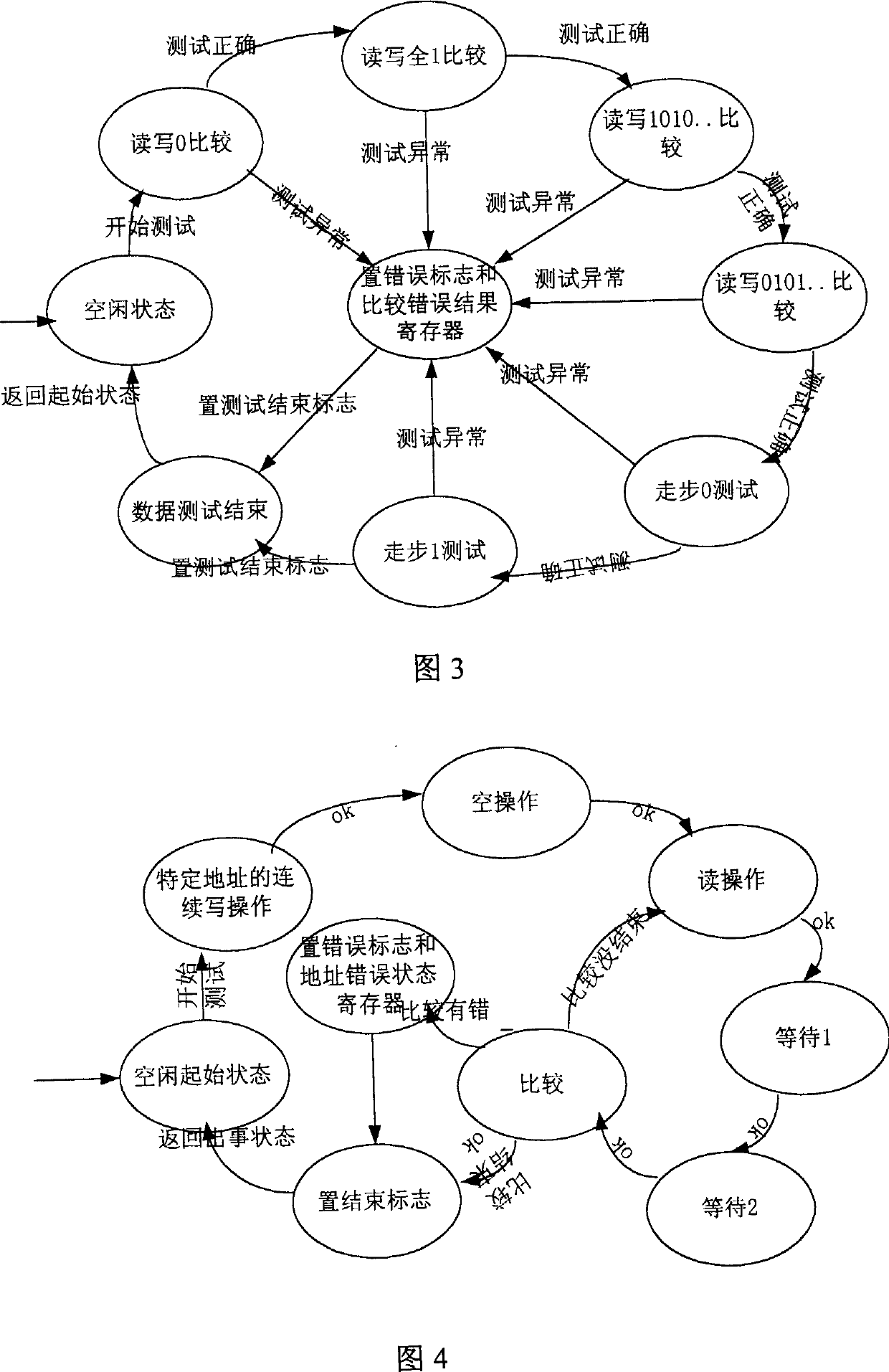

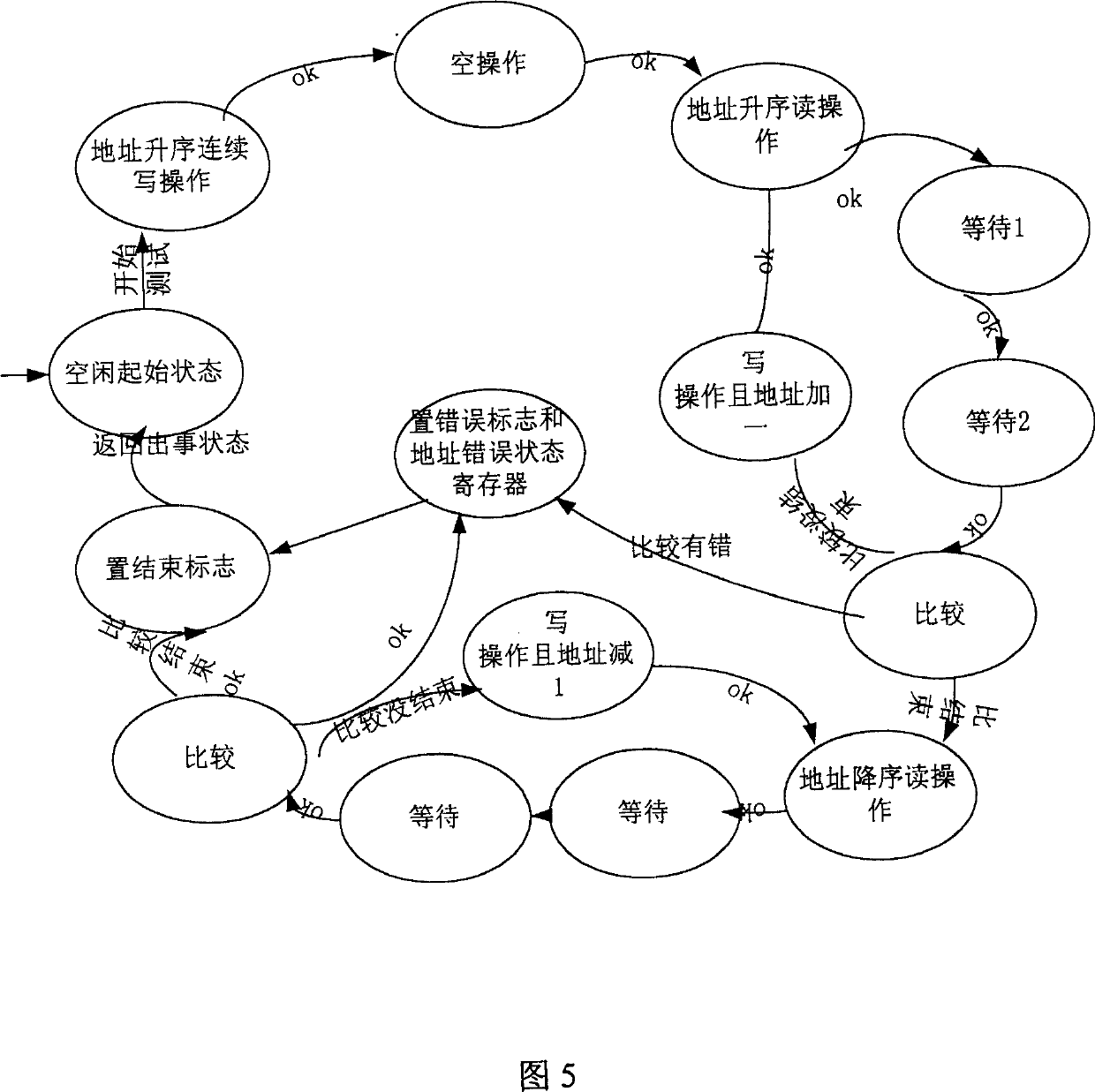

[0029] The diagnostic process of the data memory RAM is to check the effectiveness of each memory cell to perform read / write operations. The test of the memory includes three basic aspects: one is the test of the data line, the other is the test of the address line and the decoding, and the third is the test of the storage unit; the detection of the RAM is to pass a certain test pattern to test the memory unit and address decoding circuit functions for quick and efficient checks. The test of the storage unit can cover the errors of the data line test and the address line test. The purpose of adding a separate data line and address line test is to locate the fault of the detailed data line address line test.

[0030] The RAM detection control circuit of the present invention is shown in FIG. 1 . The circuit includes: a CPU interface circuit, a RAM read-write control interface, a test command register, a test result status register and a test working circuit. Each part is furt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More