Semiconductor device and method for testing the same

An inspection method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, measuring devices, etc., can solve problems such as increased circuit area and LSI mold size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

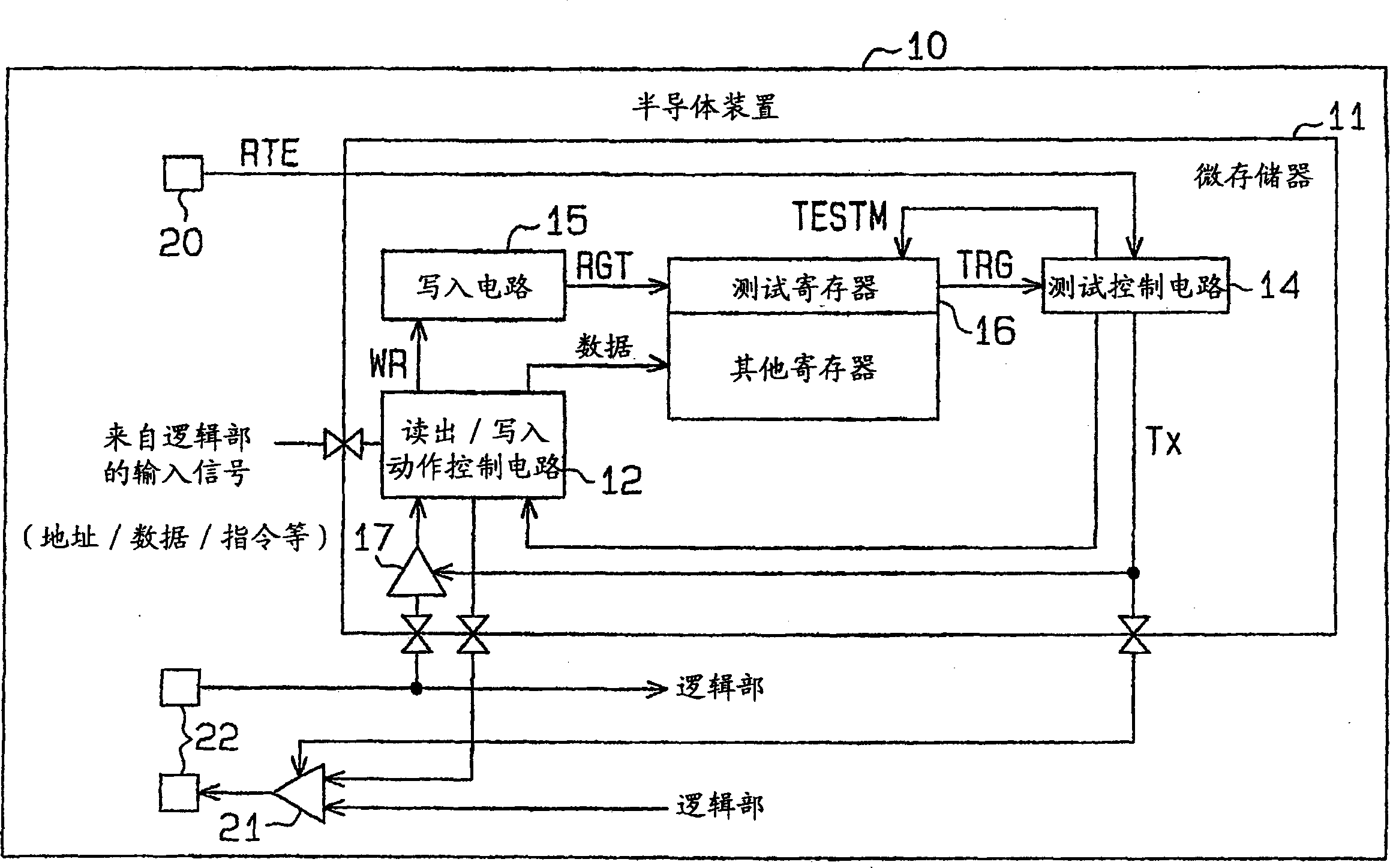

[0030] figure 1 It is a schematic block diagram of a semiconductor device 10 according to an embodiment of the present invention. The semiconductor device 10 has a storage unit (micro memory) 11 mixed with a logic unit. An operation control circuit 12 is provided in the micro memory 11, and the operation control circuit 12 executes data read / write operations based on input signals including addresses, data, and commands. In a storage area (address space) selected by an address contained in an input signal, a test storage circuit 16 is provided, and the test storage circuit 16 stores data for selecting a test mode. The write circuit 15 supplies a control signal RGT allowing data to be written into the test memory circuit 16 in response to a write command WR supplied from the operation control circuit 12 . In the test memory circuit 16, the data Data included in the input signal is written in accordance with the control signal RGT.

[0031] The operation control circuit 12 is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More