Patents

Literature

1460 results about "Tests times" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Medical characterization system

ActiveUS10332630B2Determining effectElectrocardiographyHealth-index calculationData sourceContinuous parameter

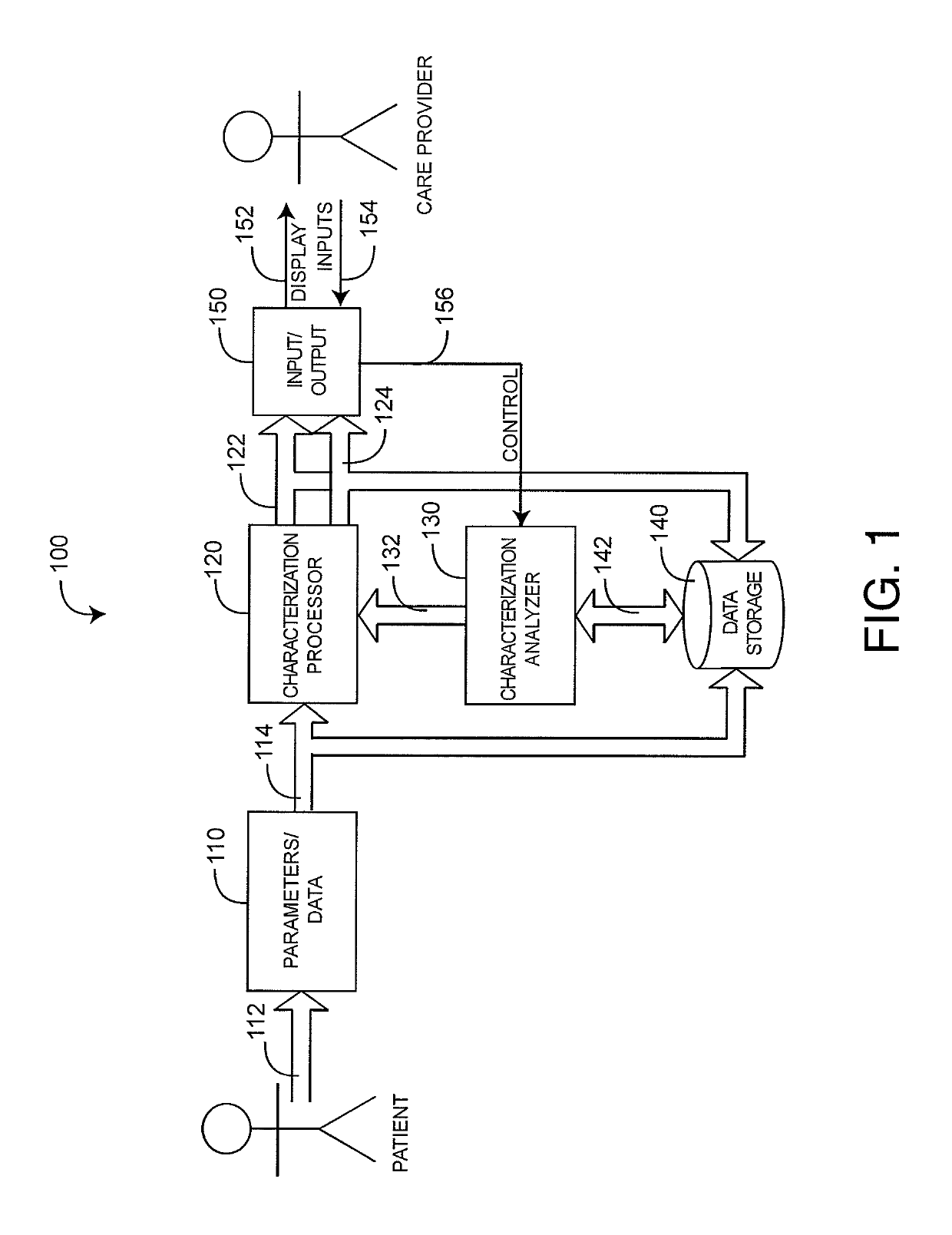

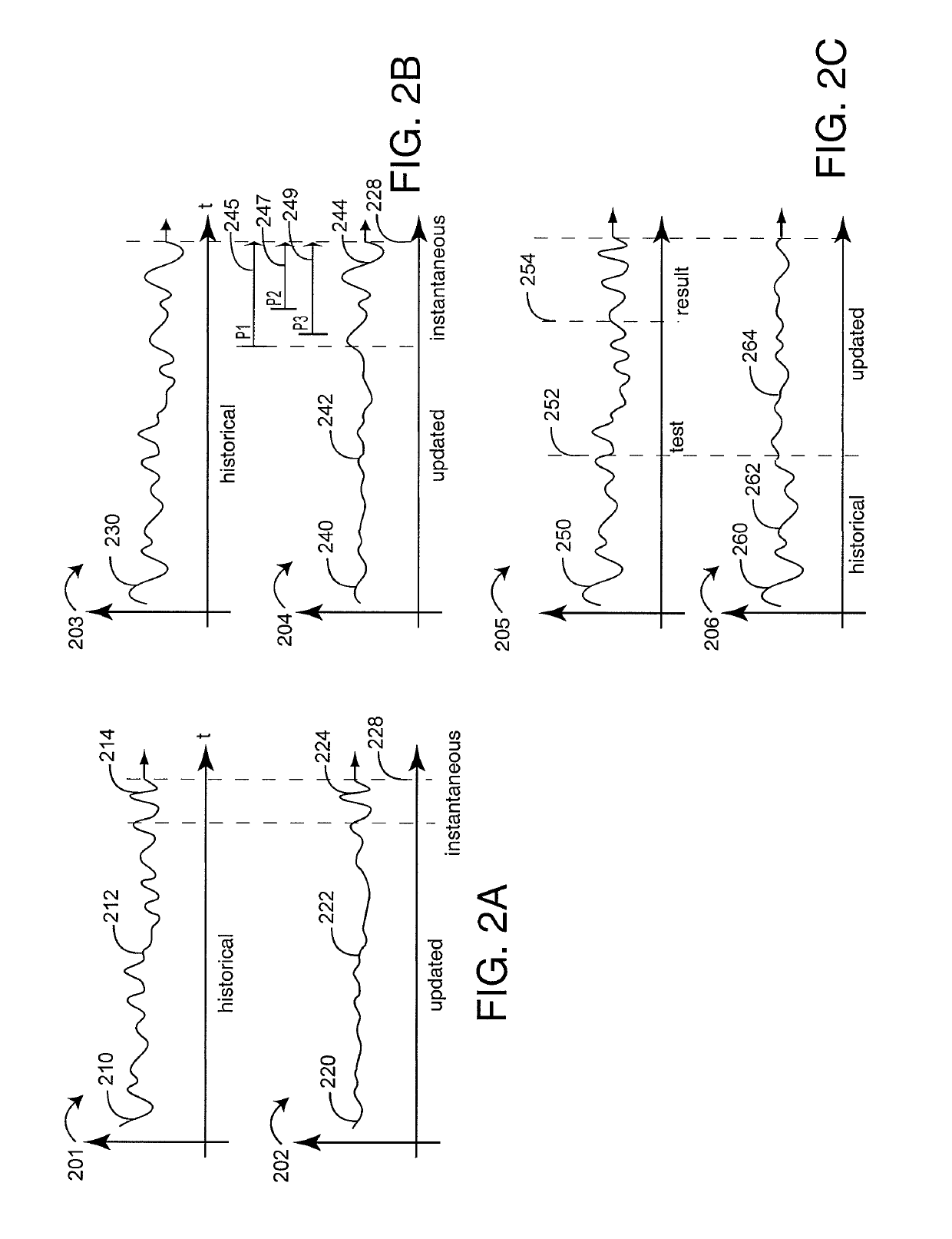

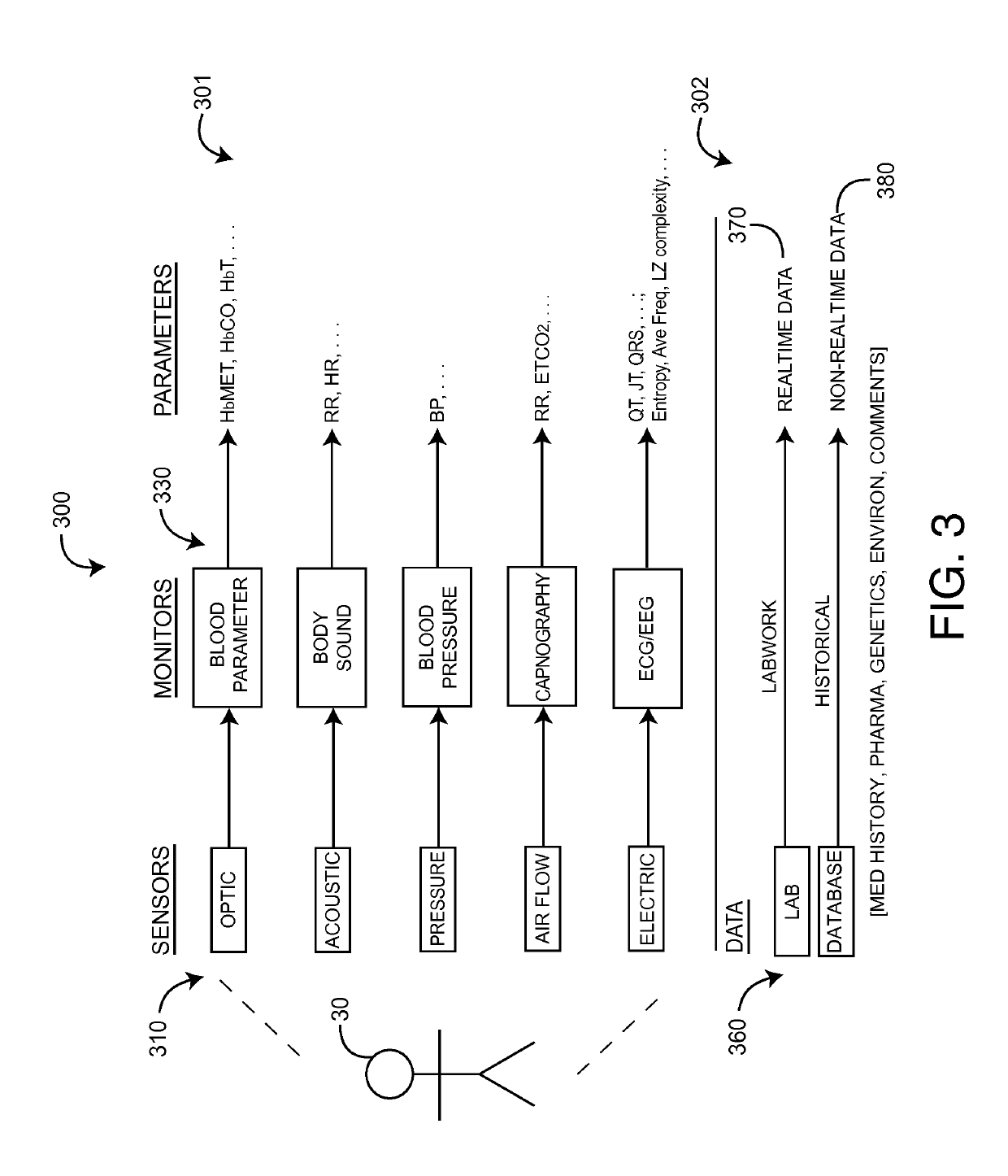

A medical characterization system is configured to input medical-related continuous parameters and discrete data so as to calculate a characterization timeline indicative of a physiological condition of a living being. A data source is in sensor communications with a patient so as to generate a continuous parameter. The data source also provides test data responsive to the patient at a test time. The test data is available to a characterization processor at a result time. The characterization processor is also responsive to the continuous parameter so as to generate a medical characterization as a function of time. A characterization analyzer enables the characterization processor to update the medical characterization in view of the test data as of the test time.

Owner:JPMORGAN CHASE BANK NA

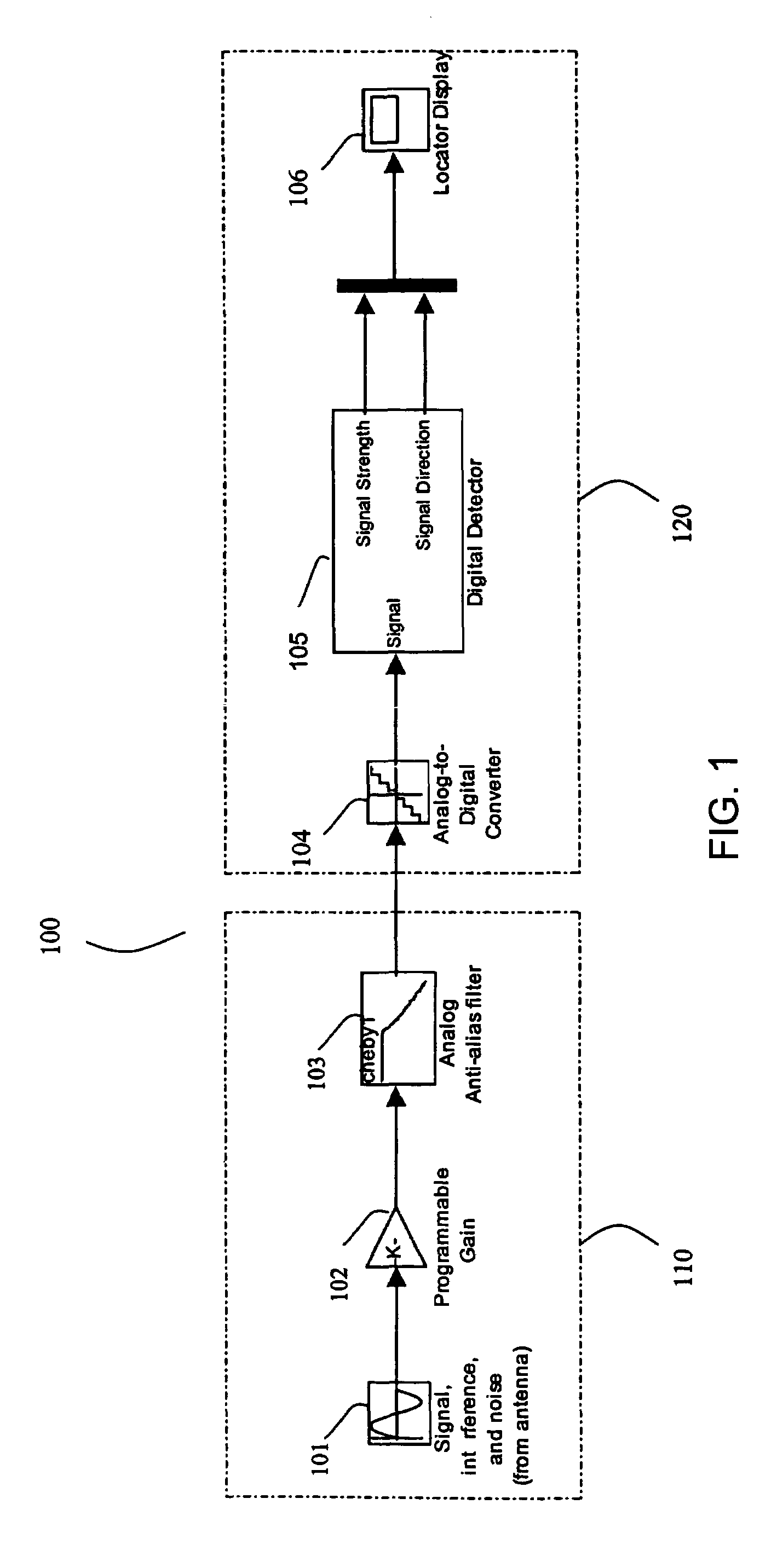

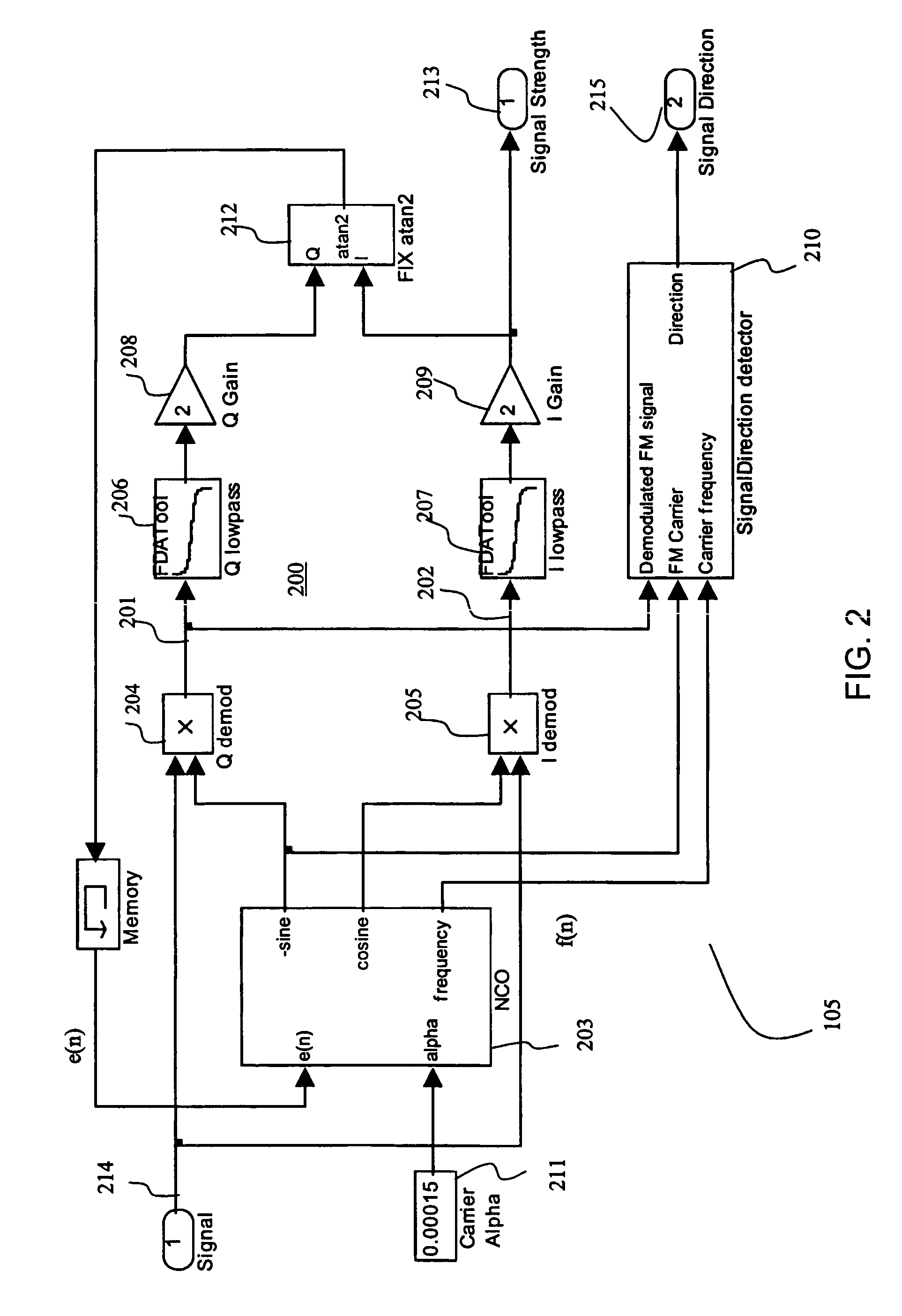

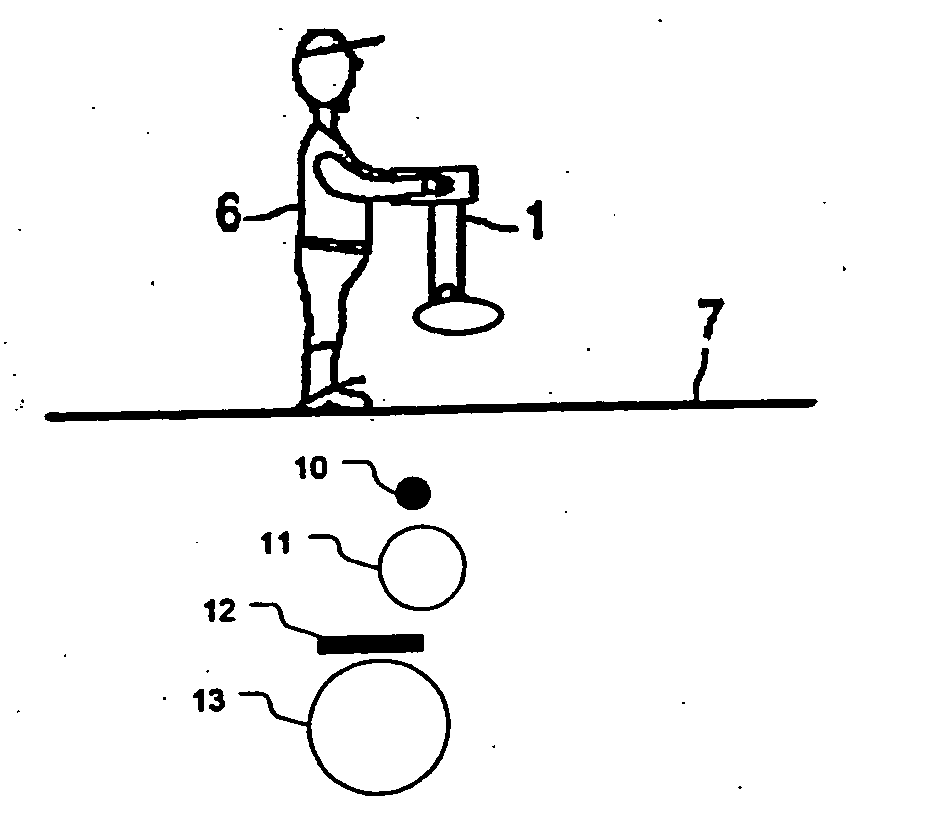

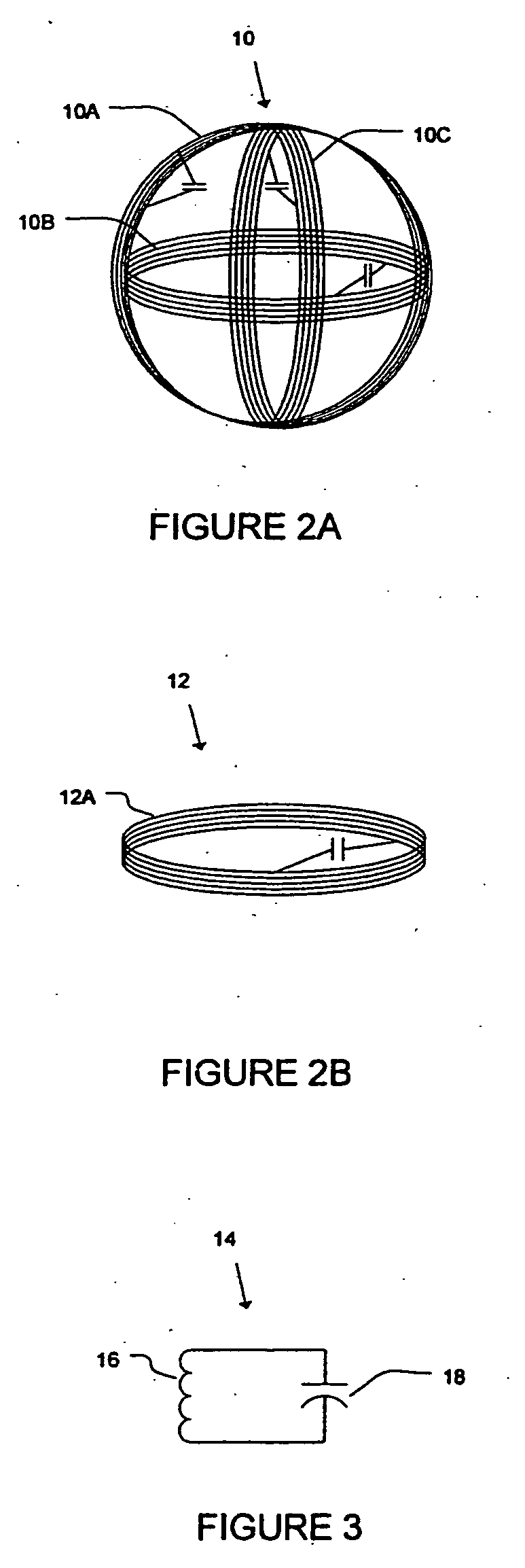

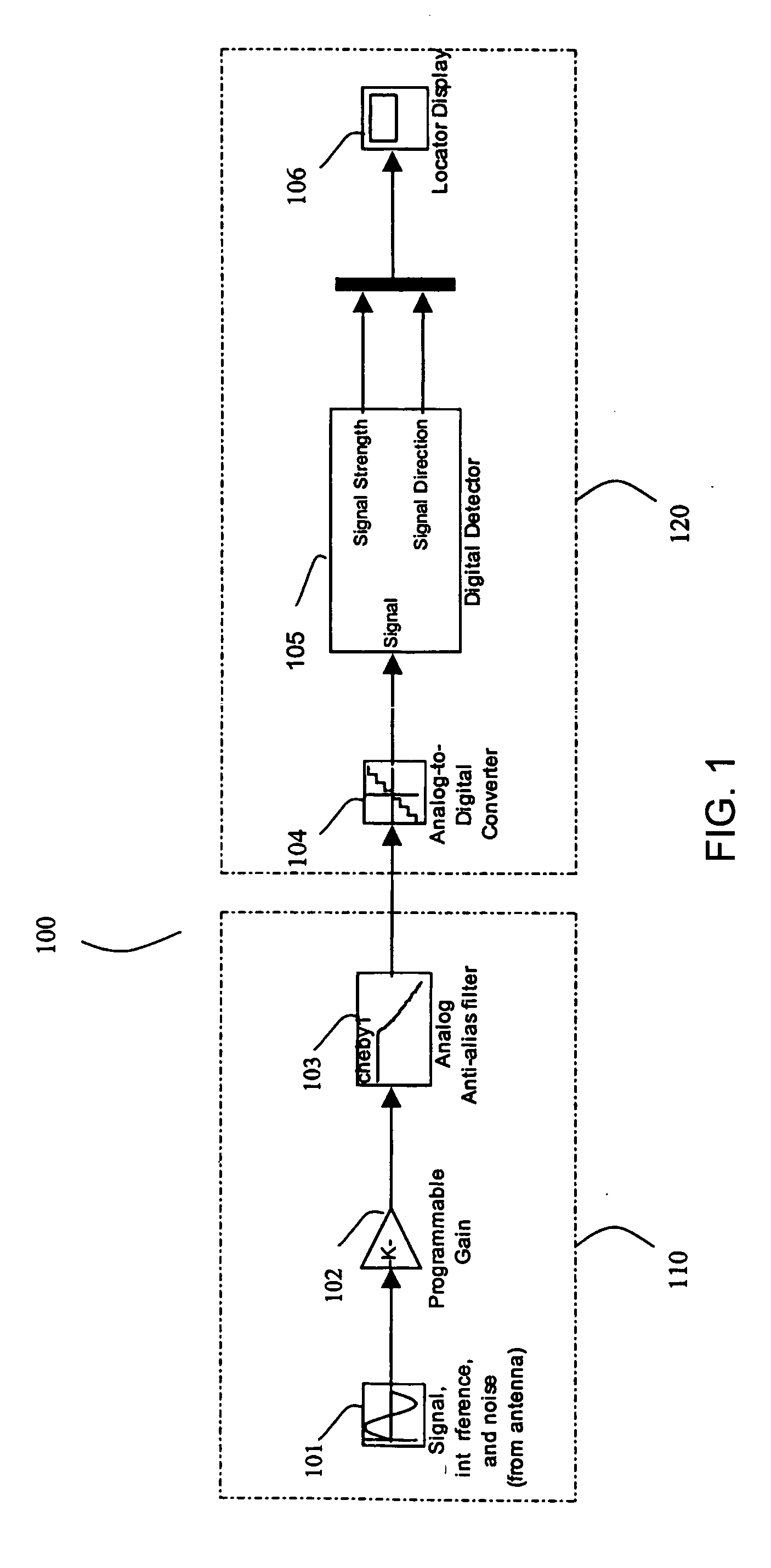

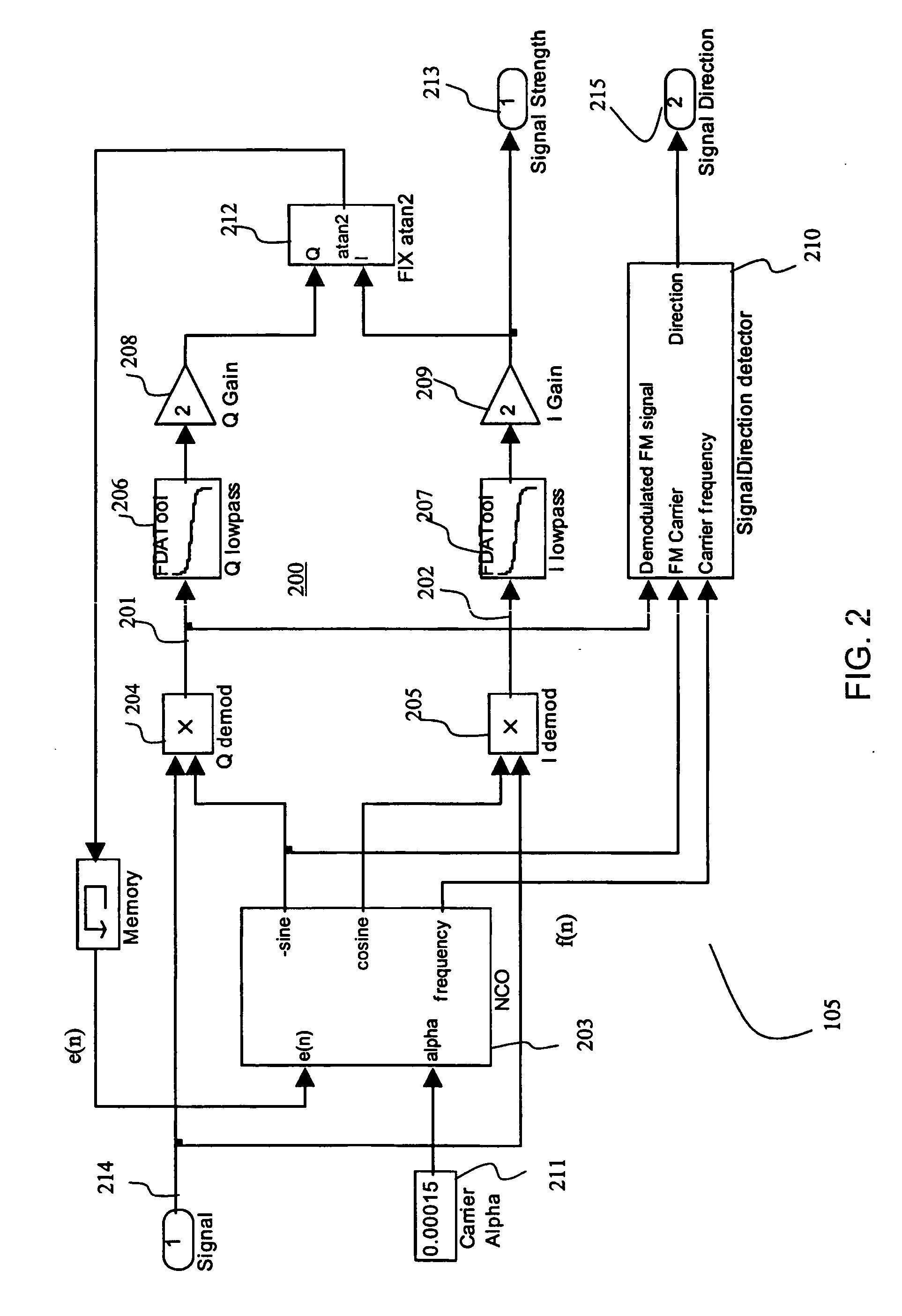

Method and apparatus for digital detection of electromagnetic signal strength and signal direction in metallic pipes and cables

InactiveUS7062414B2Low hardware requirementsWide resistance to component tolerancesAmplifier modifications to reduce noise influenceDigital computer detailsDigital signal processingCarrier signal

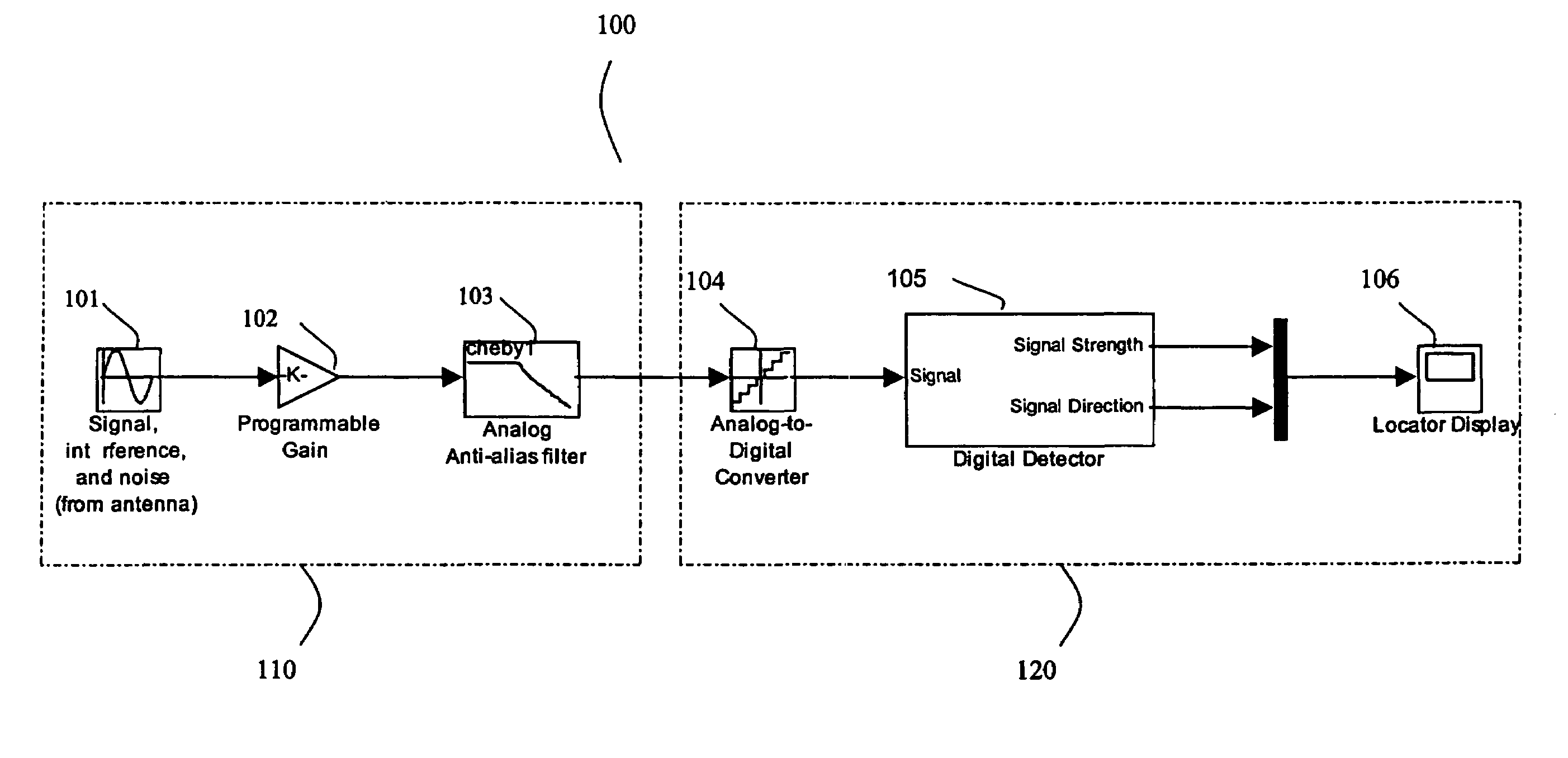

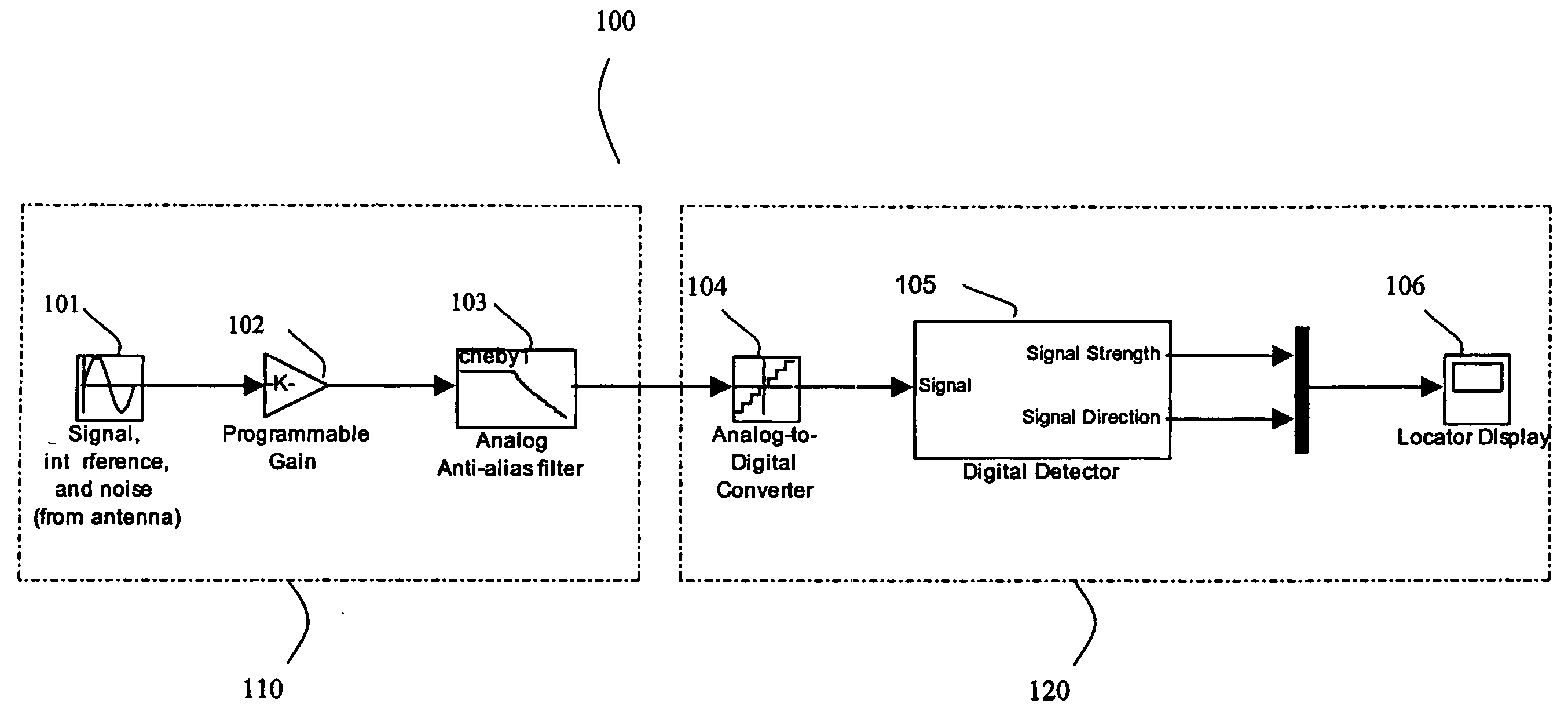

A new digital architecture for metallic pipe and cable locators, providing accurate estimation of the fundamental locate parameters, electromagnetic signal strength and signal direction, and utilizing a nested Digital Phase-Locked Loop (DPLL) structure is disclosed. The obstacles to signal direction measurement in low SINR environments using the signal select method are overcome and a more precise phase comparison between the carrier and the FM modulation signals is obtained. The architecture further significantly reduces analog front-end hardware requirements, offers wider resistance to component tolerances, lower calibration and test time, and provides flexible frequency selectivity. Locators according to the present invention provide accurate estimation of the fundamental physical parameters of line location (electromagnetic signal strength and signal direction) in extremely noisy environments, using Digital Signal Processing (DSP) methods.

Owner:BUSAN TRANSPORTATION CORPORATION

Method and apparatus for digital detection of electronic markers using frequency adaptation

ActiveUS20070040558A1High-precision identificationReliable discriminationPipe laying and repairElectric/magnetic detectionTested timeAnalog front-end

Owner:BUSAN TRANSPORTATION CORPORATION

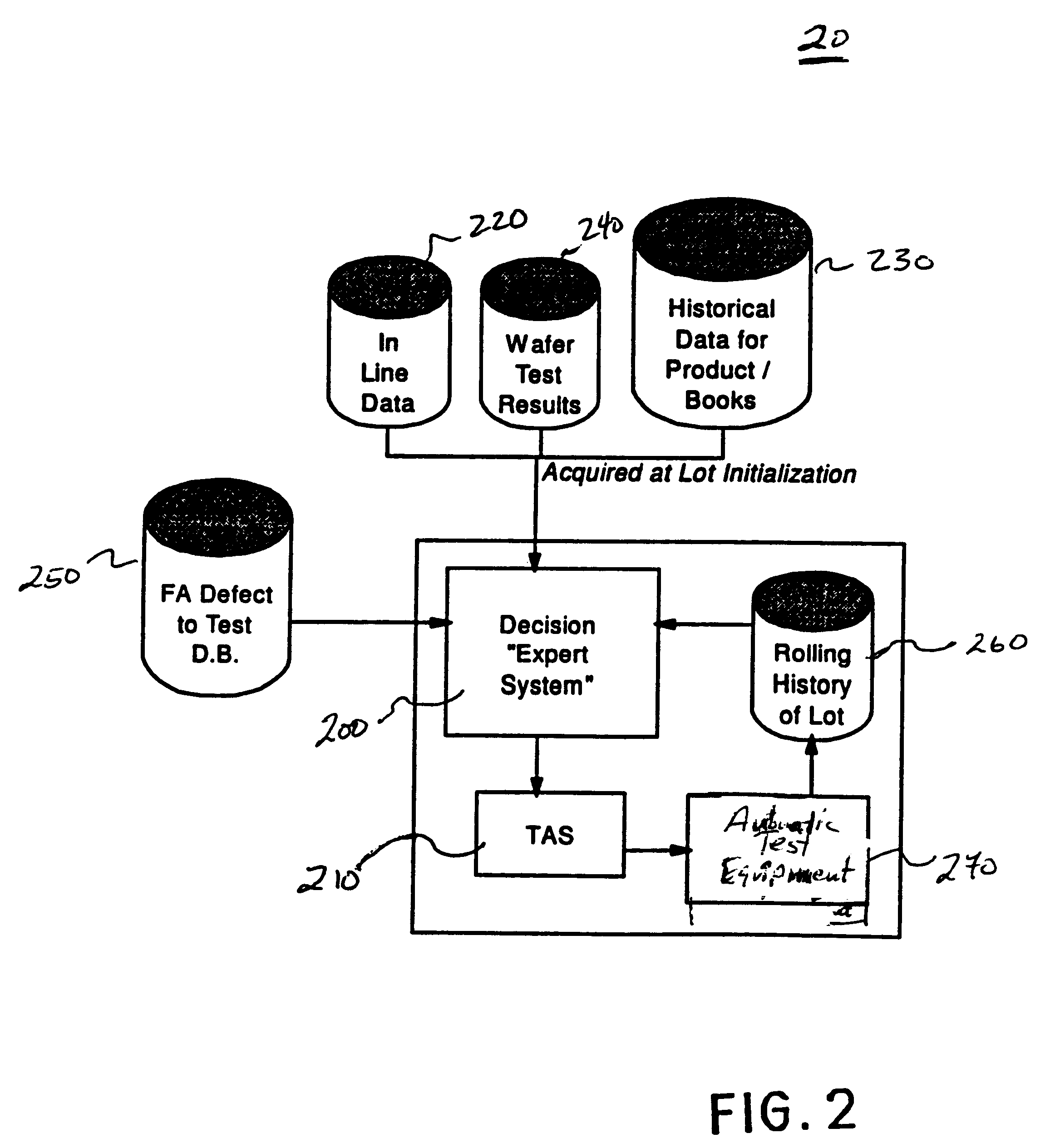

Method for test optimization using historical and actual fabrication test data

InactiveUS6618682B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingQuality levelWafer fabrication

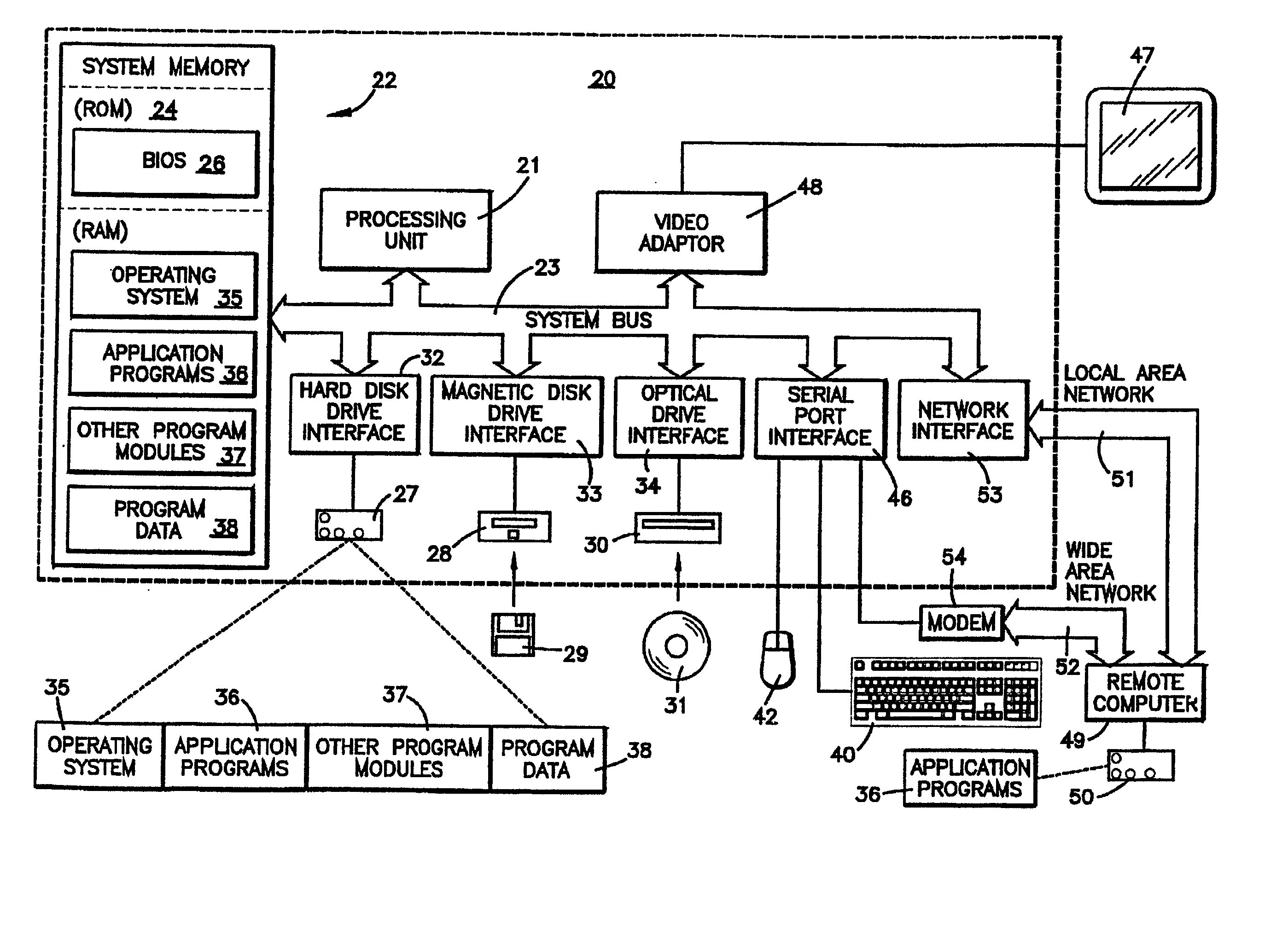

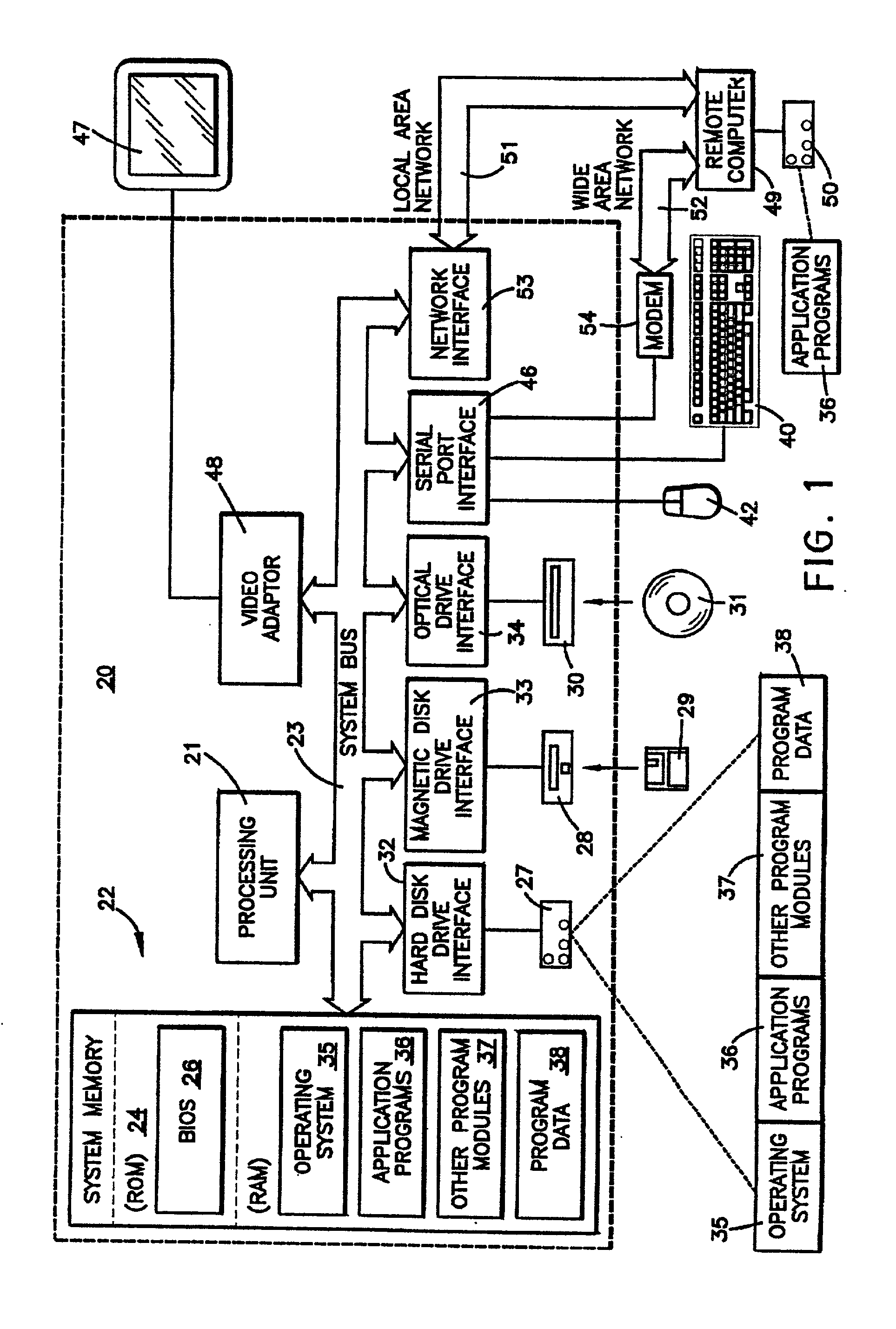

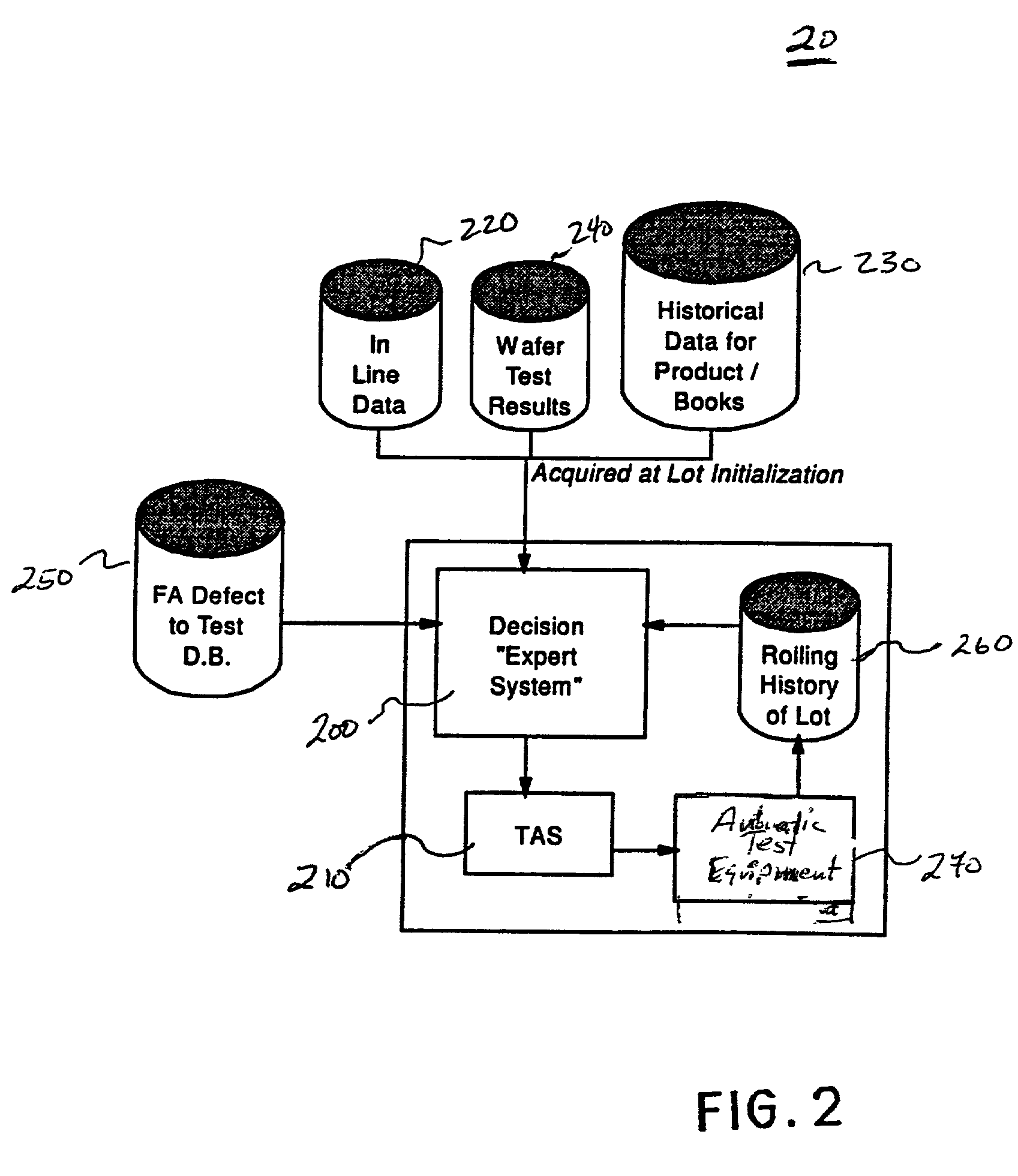

A method and system are provided that minimize wafer or package level test time without adversely impacting yields in downstream manufacturing processes or degrading outgoing quality levels. The method provides optimization by determining, a priority, the most effective set of tests for a given lot or wafer. The invention implements a method using a processor-based system involving the integration of multiple sources of data that include: historical and realtime, product specific and lot specific, from wafer fabrication data (i.e., process measurements, defect inspections, and parametric testing), product qualification test results, physical failure analysis results and manufacturing functional test results. These various forms of data are used to determine an optimal set of tests to run using a test application sequence, on a given product to optimize test time with minimum risk to yield or product quality.

Owner:CADENCE DESIGN SYST INC

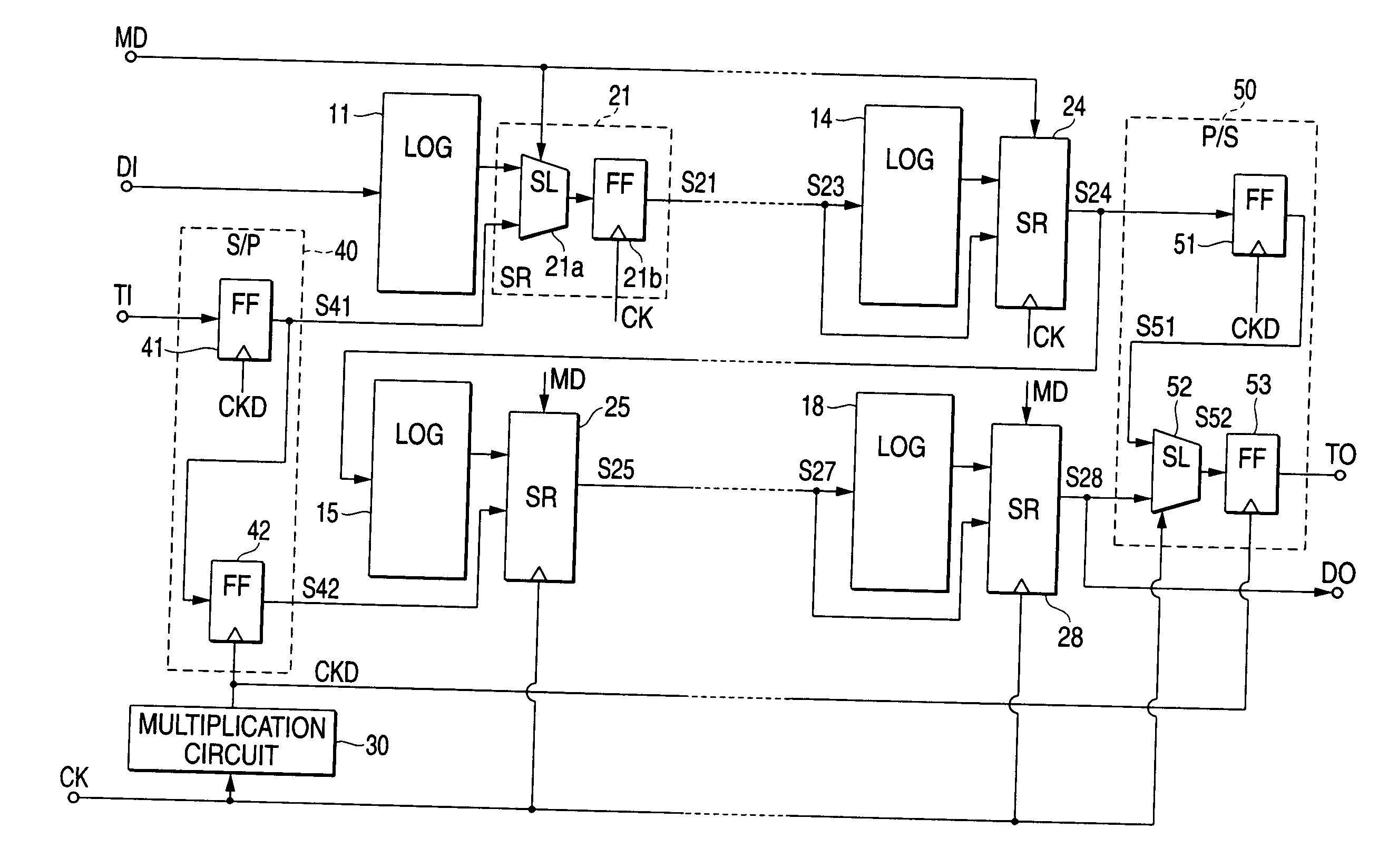

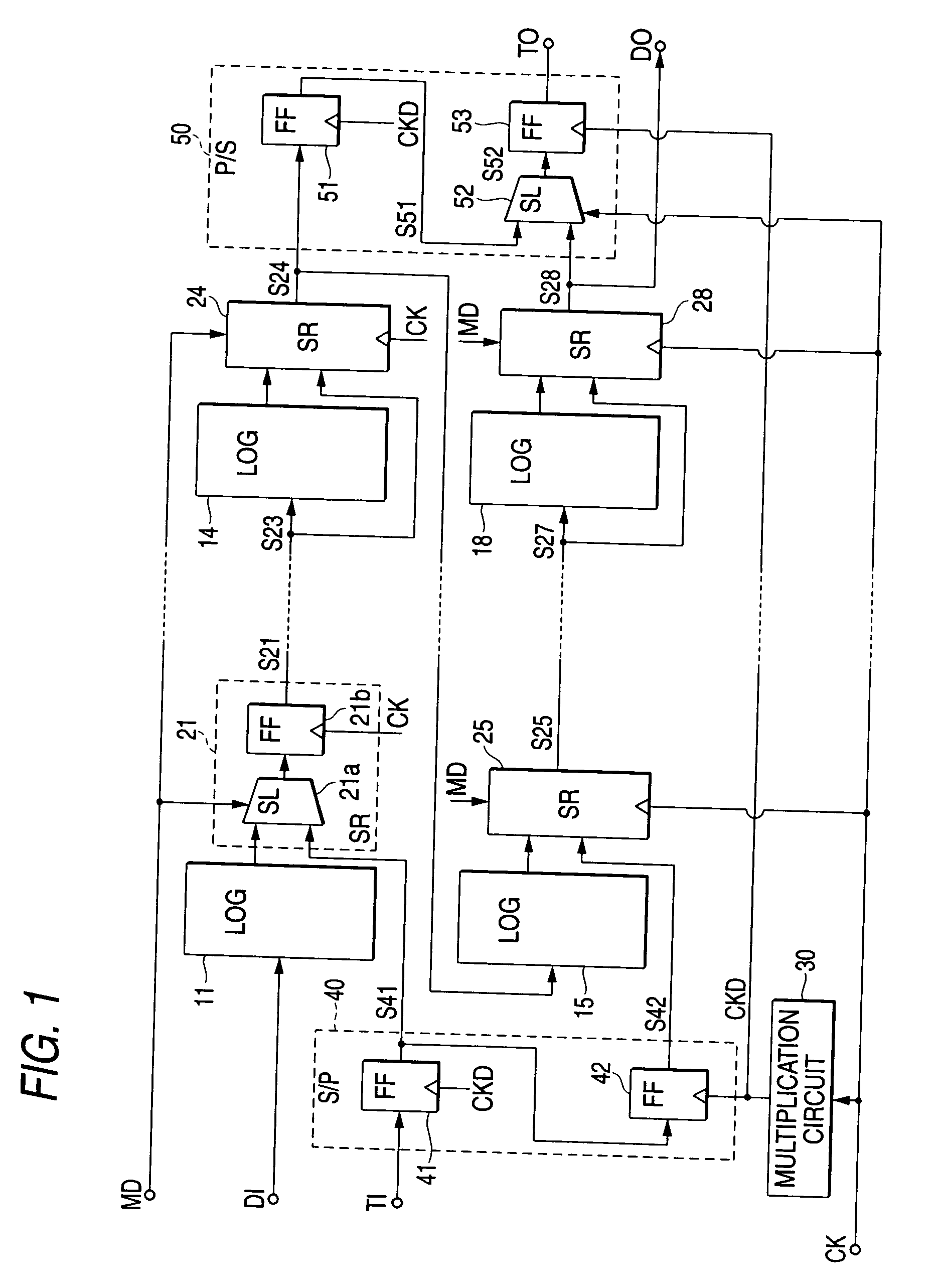

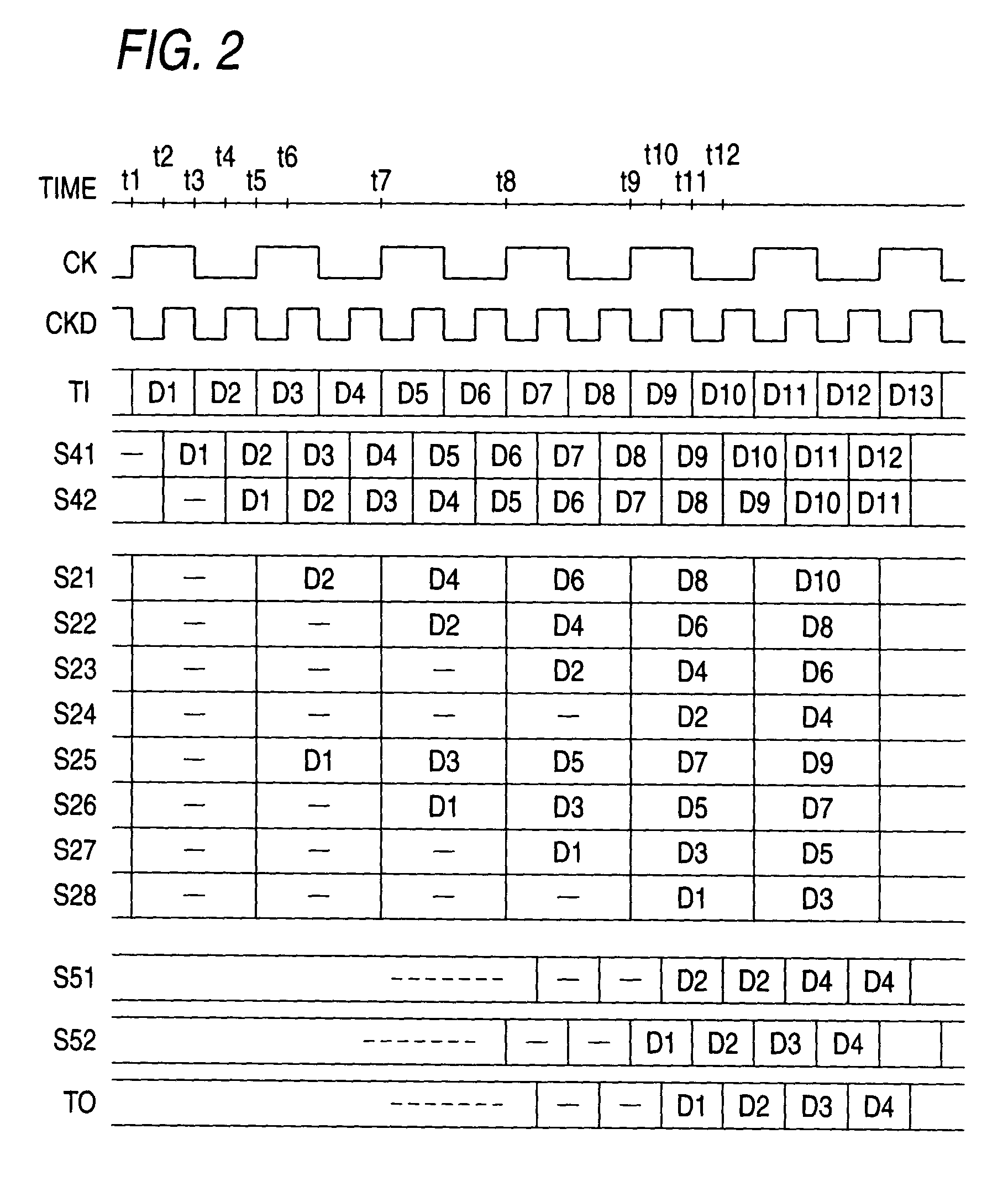

Semiconductor integrated circuit with a test circuit

A shift scan chain includes logic circuit blocks 11-18 and scan registers 21-28 connected at stages succeeding them. The shift chain is divided into divisional chains including the scan registers 21-24 and the scan registers 25-28. In the test operation mode of a semiconductor integrated circuit, test input data TI are supplied in synchronism with a multiplied clock signal CKD at a frequency twice of that of a clock signal CK. The test input data TI are converted by a serial / parallel conversion circuit 40 into parallel data S41 and S42, which are respectively supplied to the head scan registers 21 and 25 of the corresponding divisional chains. The length of each divisional chains becomes ½, and a test time period can be shortened.

Owner:LAPIS SEMICON CO LTD

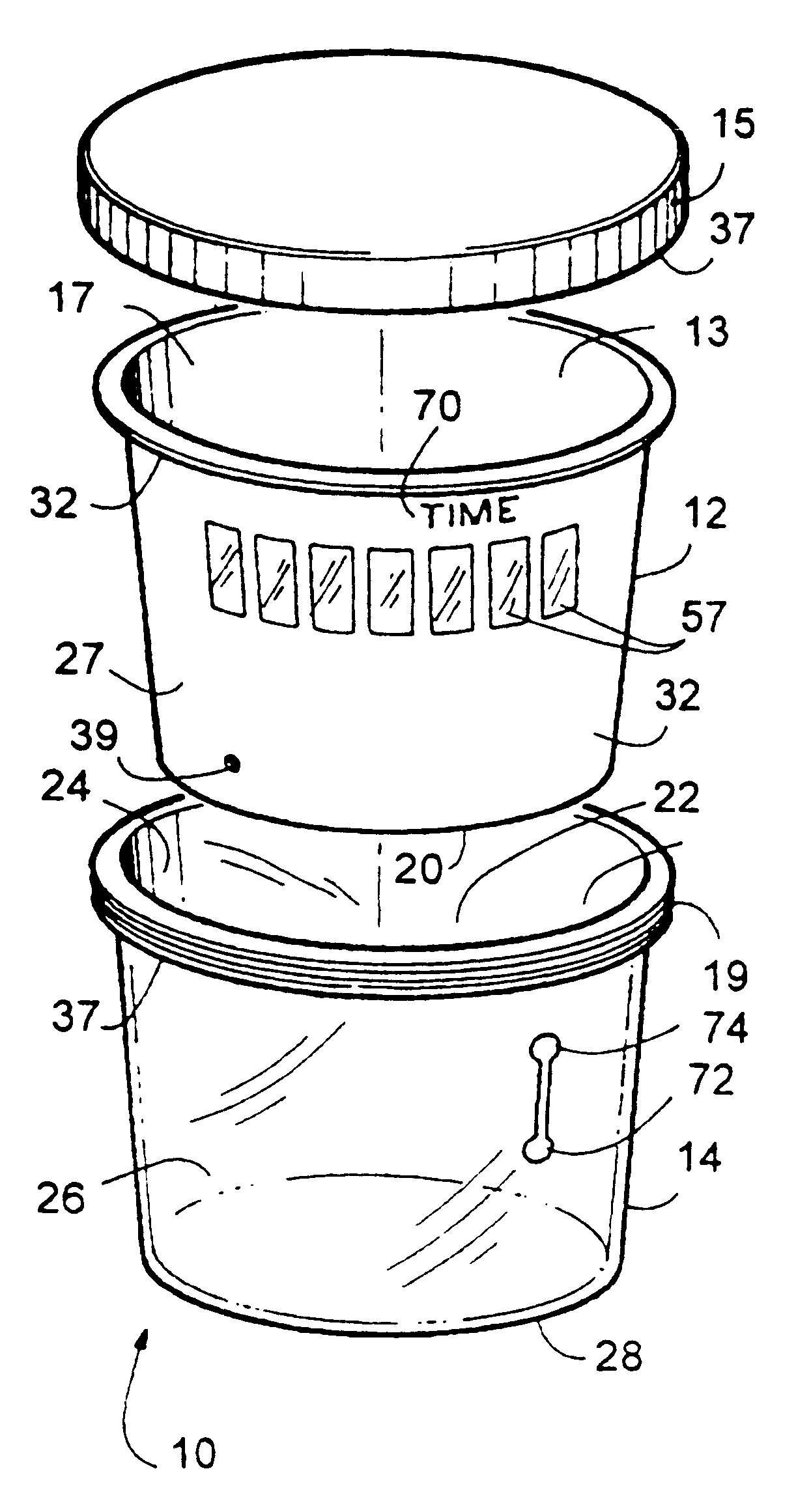

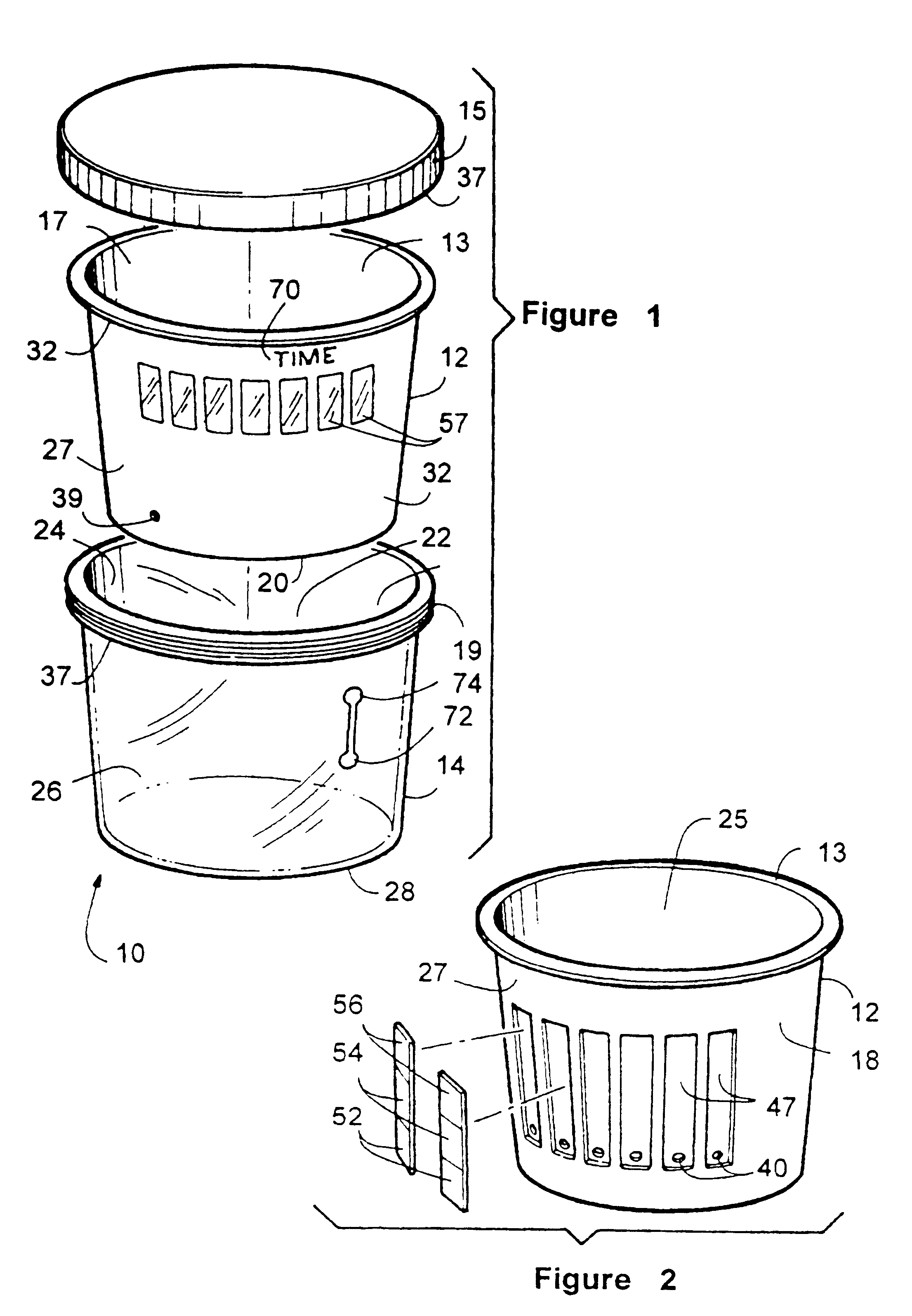

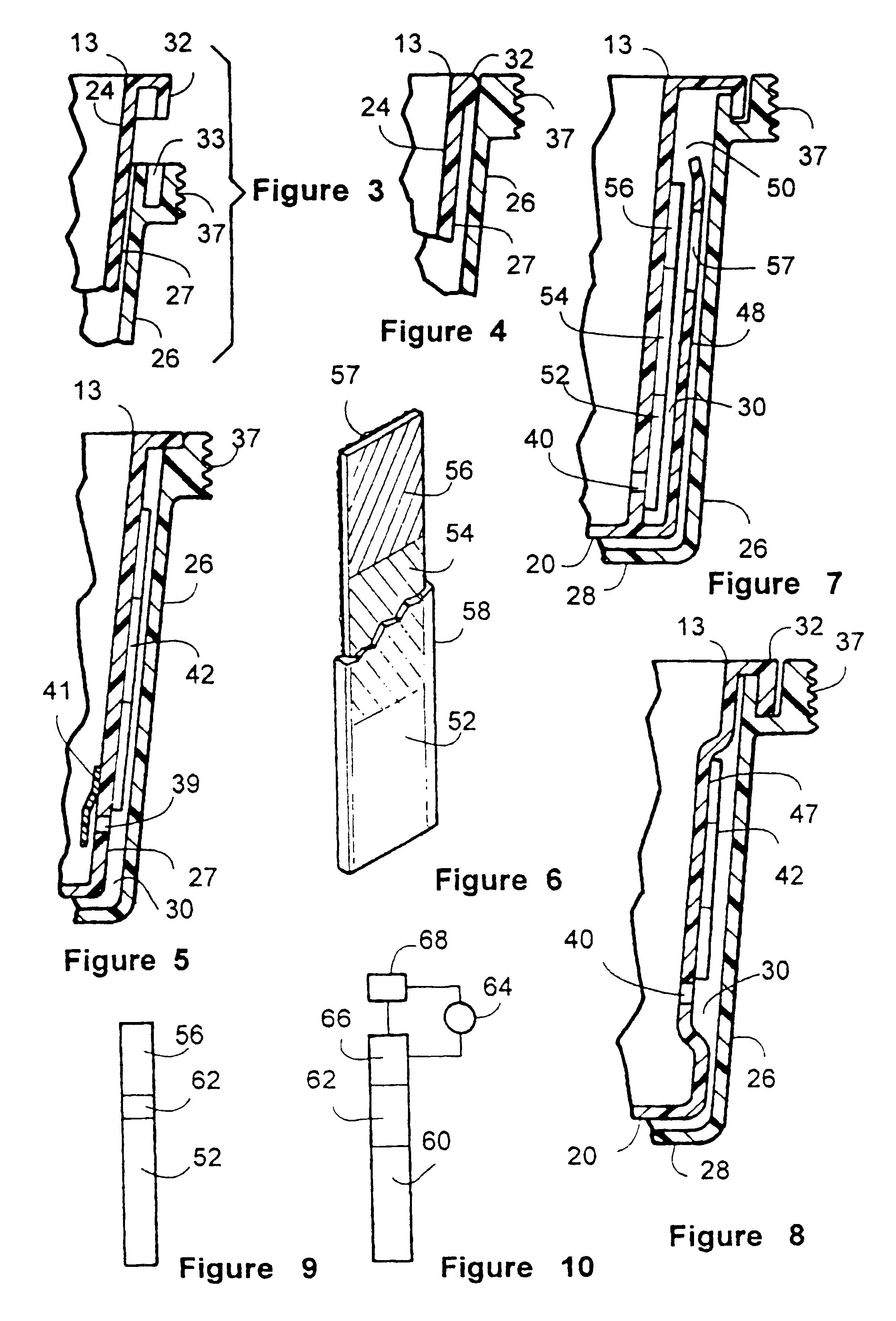

Diagnostic testing kit for collection and testing of fluid samples with user configurable test strips and timer

InactiveUS6616893B1Analysis using chemical indicatorsMaterial analysis by observing effect on chemical indicatorEngineeringReactive agent

A diagnostic testing kit for collection of fluid samples comprising a reservoir cup insertable into a container vessel. Fluid placed in the cup is communicated to reactive test strips located in a separation cavity between the cup and the container vessel when assembled. The test strips have a reactive agent impregnated in them that reacts to specific substances in the fluid and provide a visual result through the sidewall of the container vessel to the user. An optional alarm is provided to show minimum and maximum test times.

Owner:PHAM TUAN

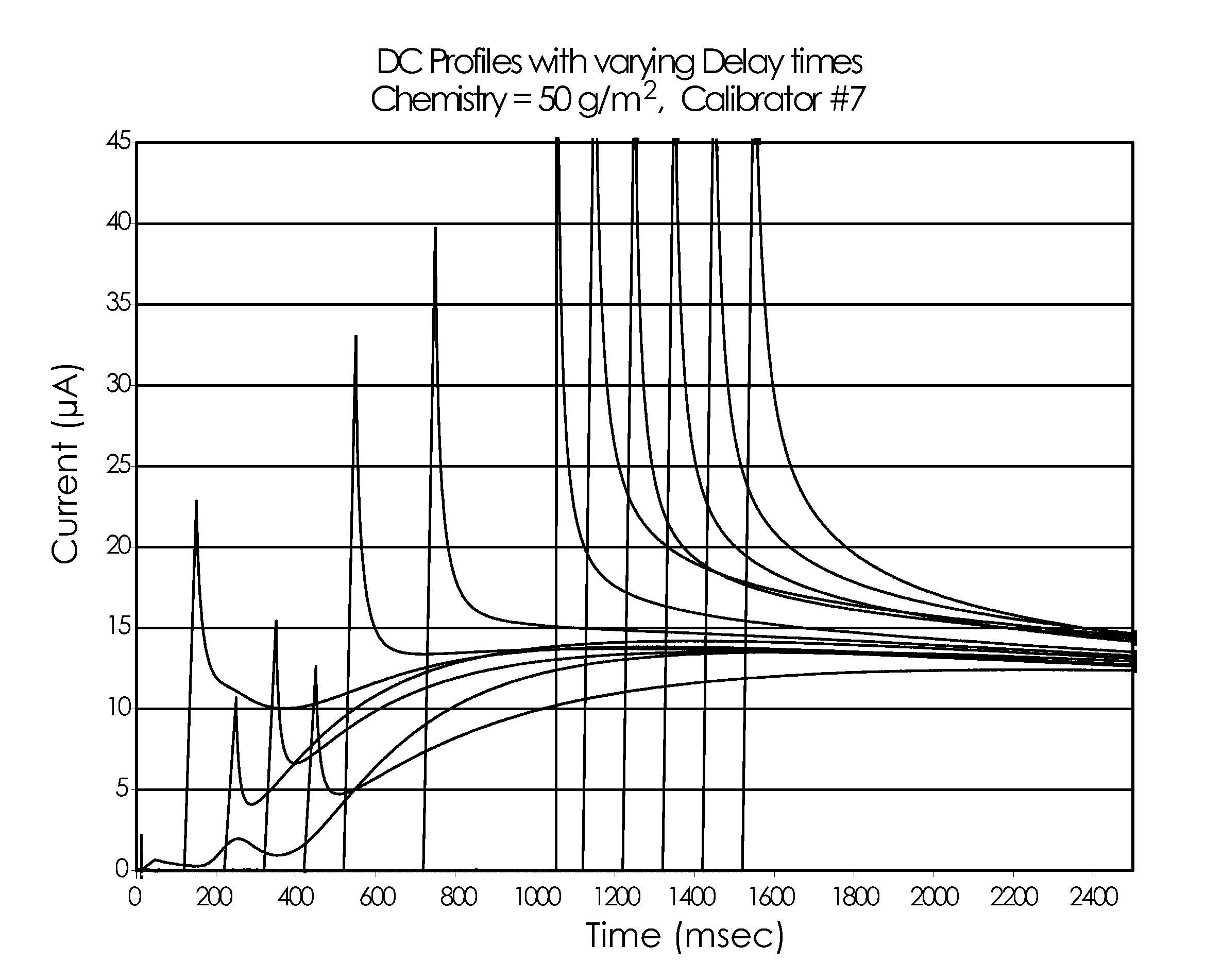

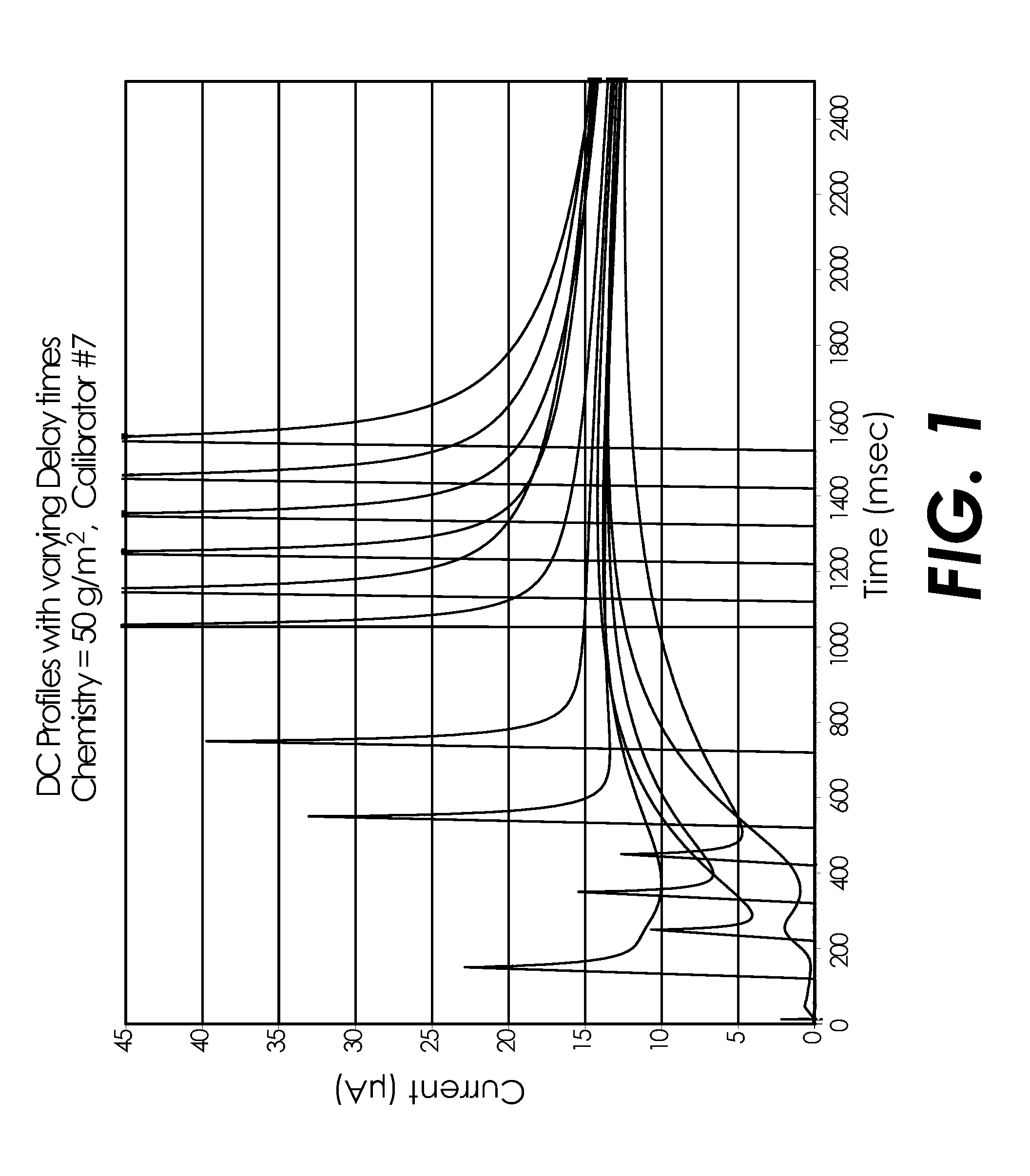

System and method for determining the concentration of an analyte in a sample fluid

InactiveUS20100170807A1Minimize timeMaterial thermal conductivityWeather/light/corrosion resistanceAnalyteSystem error

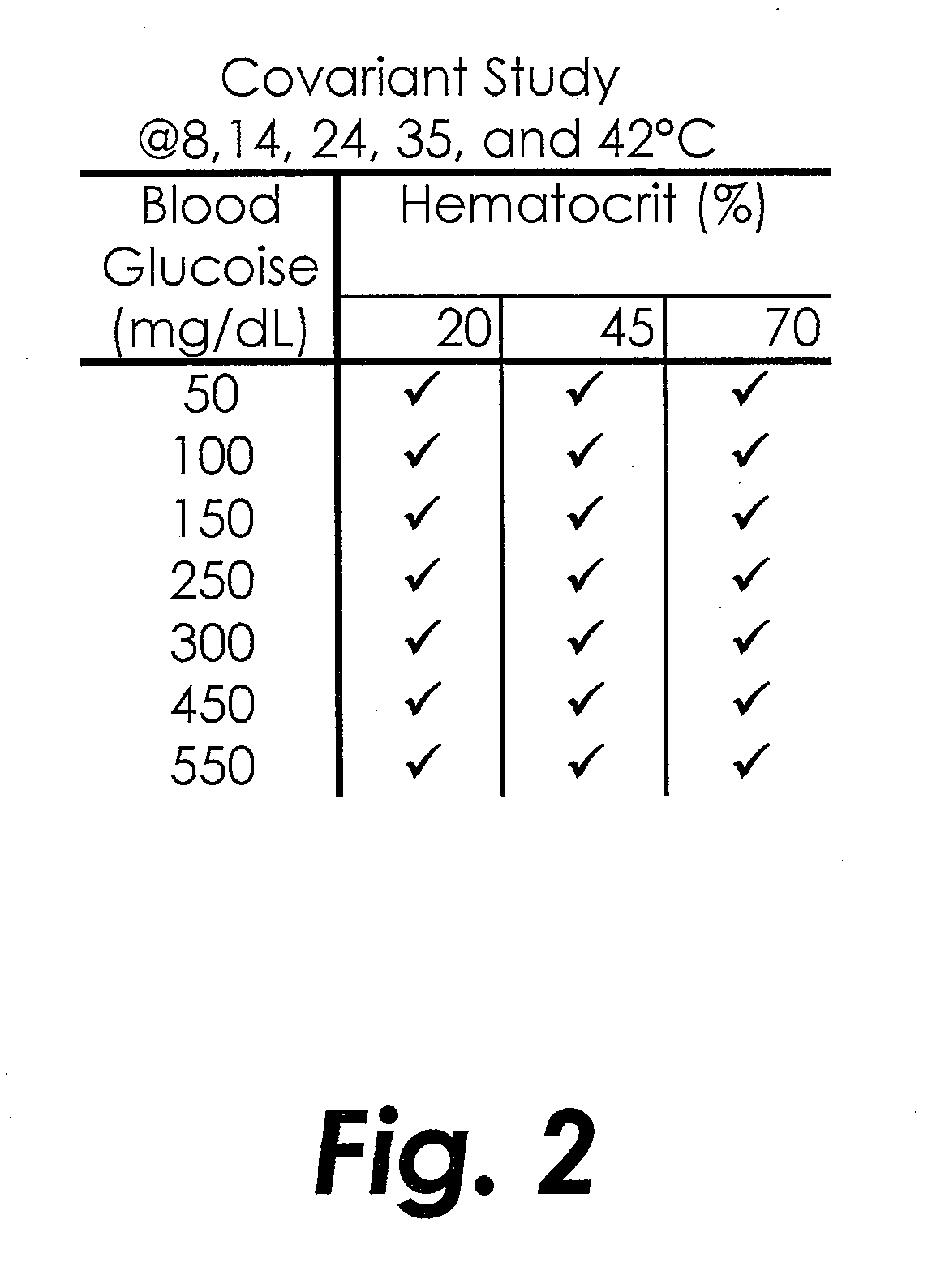

The present disclosure relates to various methods for measuring the amount of an analyte present in a biological fluid using an electrochemical testing process. Various embodiments are disclosed, including the use of AC test signals and the performance of tests having a Total Test Time within about 2.0 seconds or less, and / or having a clinically low Total System Error.

Owner:ROCHE DIABETES CARE INC

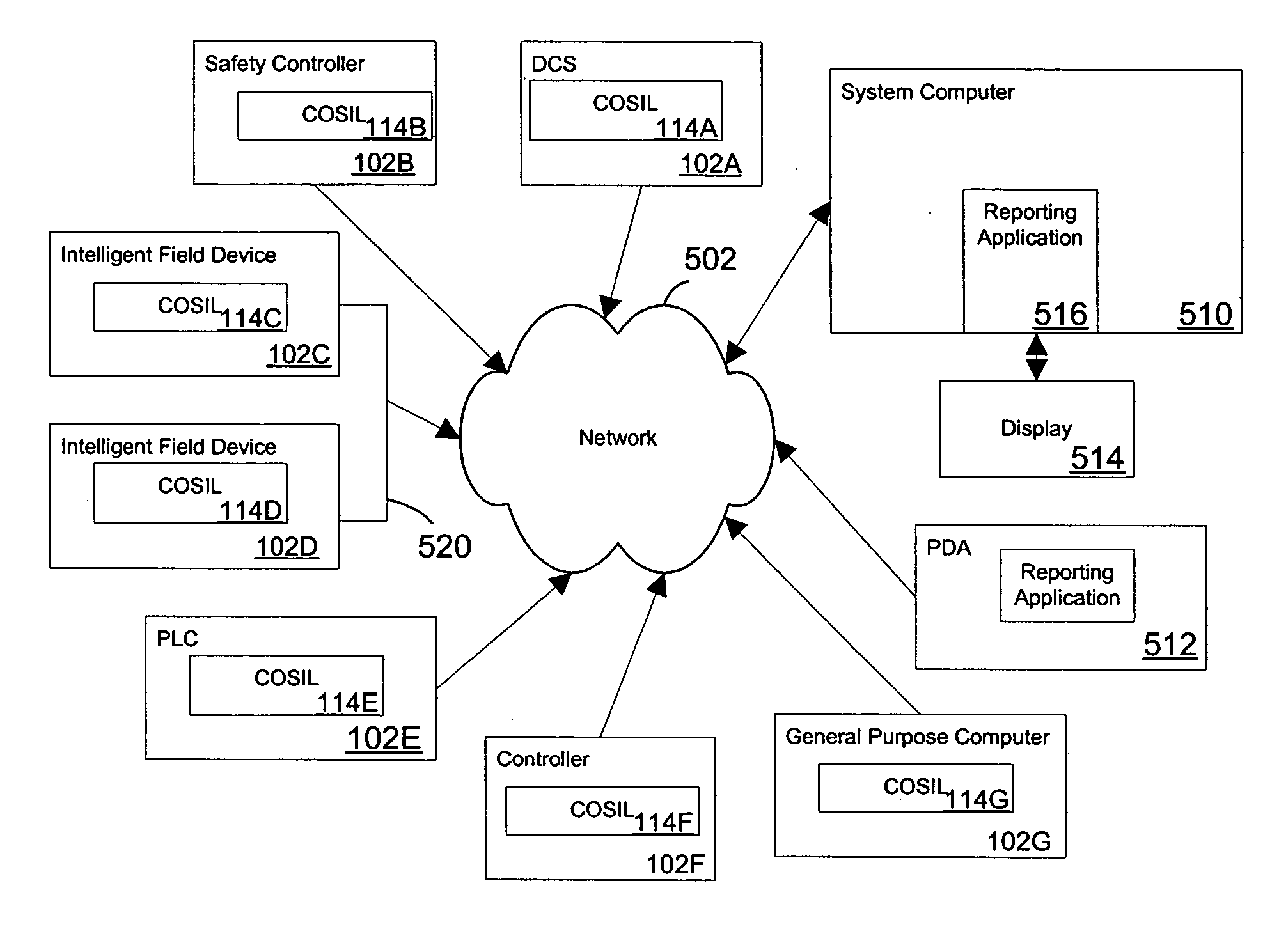

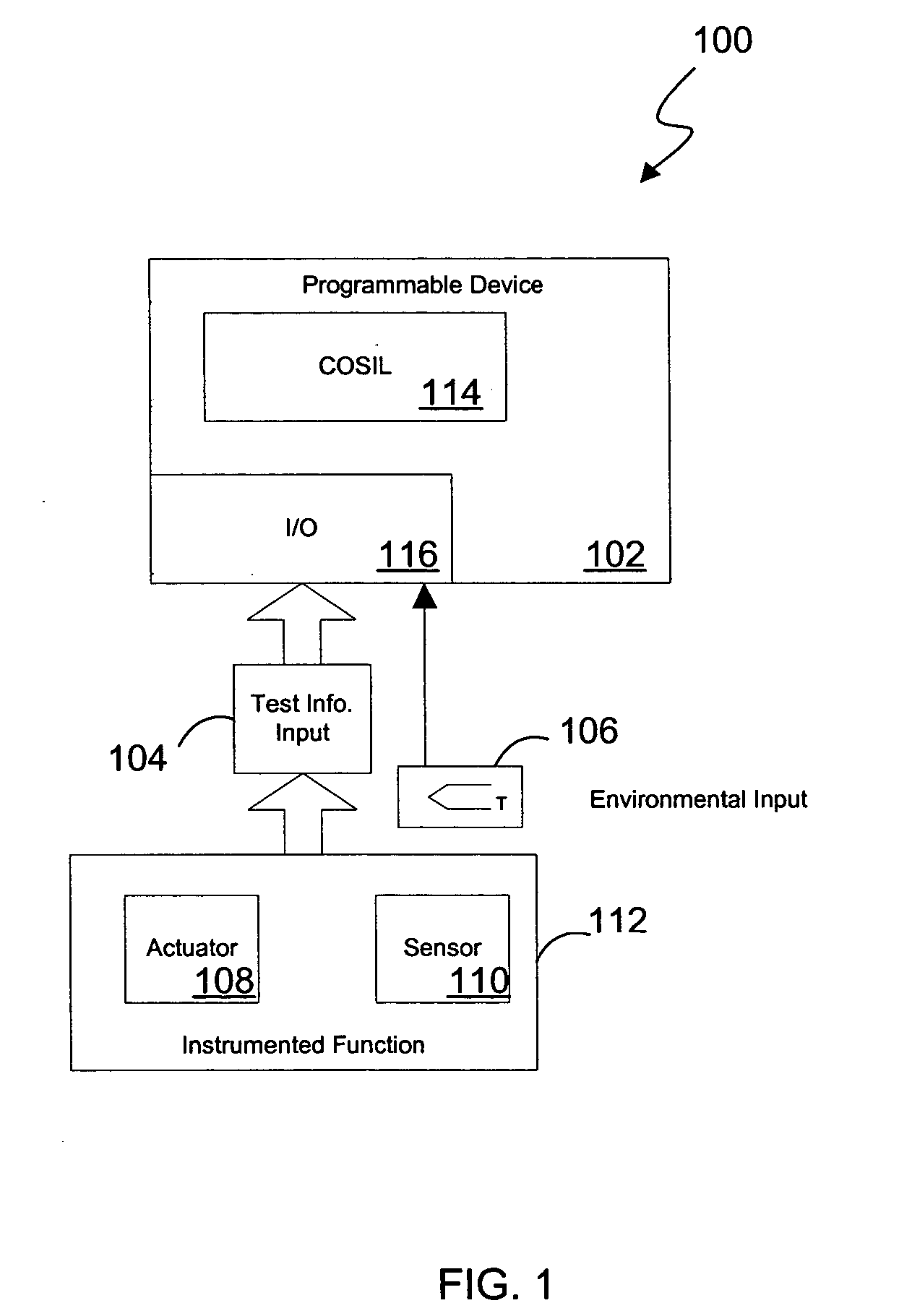

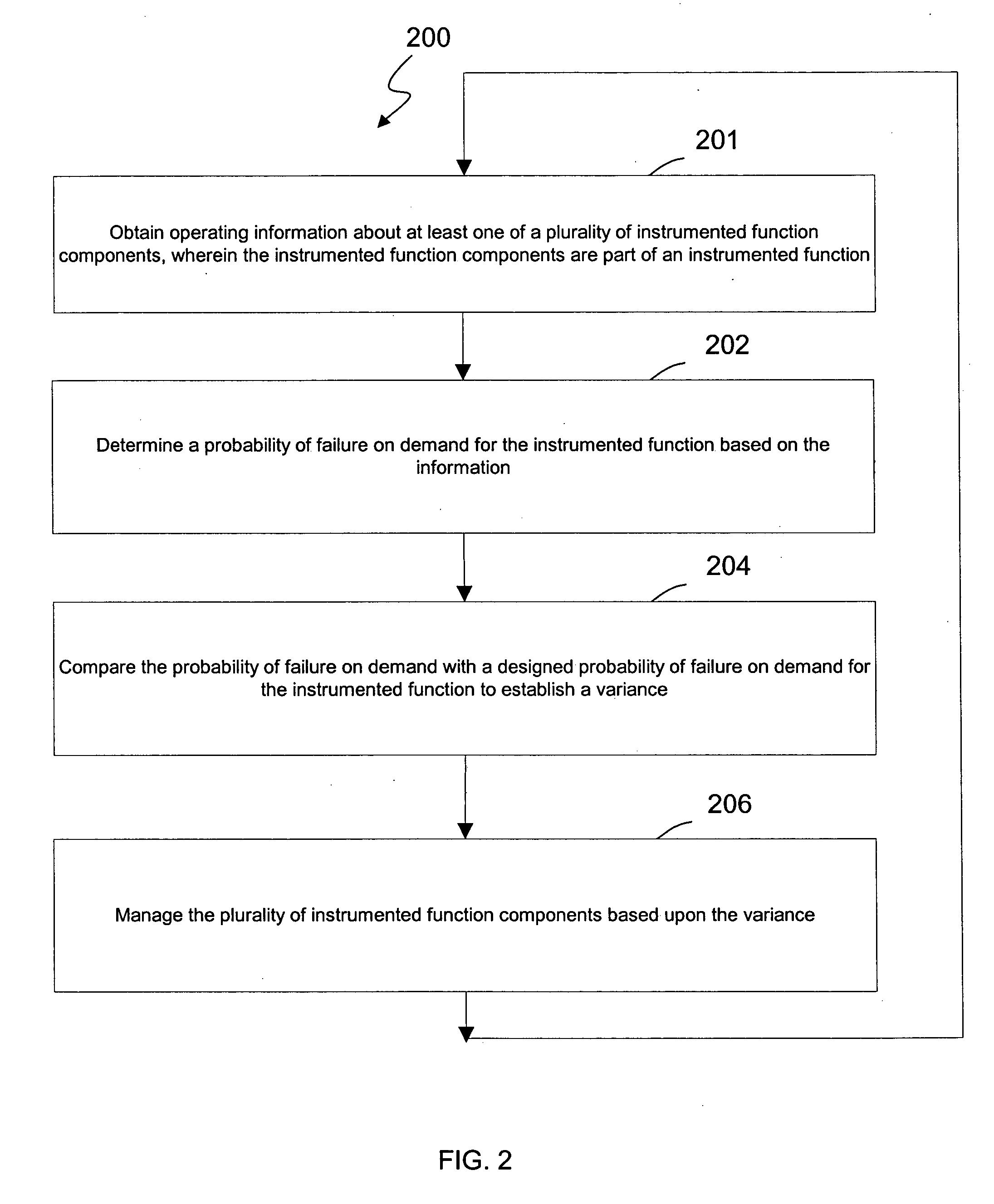

System and method for continuous online safety and reliability monitoring

ActiveUS20050027379A1Safety arrangmentsElectric testing/monitoringInstrument functionSafety Integrity Level

A system and method for continuous online safety and reliability monitoring is disclosed. The method includes the steps of obtaining operating information about at least one of a plurality of instrumented function components, which are part of an instrumented function, and determining a probability of failure on demand for the instrumented function based on the operating information. In variations, operating information includes status information, which may be received from and / or provided to an asset management application. In some variations, instantaneous probability of failure on demand, online mean time to failure (MTTF), and online safety integrity level (SIL) are also calculated for an instrumented function. In yet further variations, the system allows a user to predict probability of failure on demand values into the future based on hypothetical and / or future planned test times.

Owner:SCHNEIDER ELECTRIC SYST USA INC

Method for test optimization using historical and actual fabrication test data

InactiveUS20020155628A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingQuality levelWafer fabrication

A method and system are provided that minimize wafer or package level test time without adversely impacting yields in downstream manufacturing processes or degrading outgoing quality levels. The method provides optimization by determining, a priority, the most effective set of tests for a given lot or wafer. The invention implements a method using a processor-based system involving the integration of multiple sources of data that include: historical and realtime, product specific and lot specific, from wafer fabrication data (i.e., process measurements, defect inspections, and parametric testing), product qualification test results, physical failure analysis results and manufacturing functional test results. These various forms of data are used to determine an optimal set of tests to run using a test application sequence, on a given product to optimize test time with minimum risk to yield or product quality.

Owner:CADENCE DESIGN SYST INC

Method and apparatus for digital detection of electromagnetic signal strength and signal direction in metallic pipes and cables

ActiveUS20050096879A1Reduced analog front-end hardware requirementWide resistance to componentAmplifier modifications to reduce noise influenceDigital computer detailsDigital signal processingCarrier signal

A new digital architecture for metallic pipe and cable locators, providing accurate estimation of the fundamental locate parameters, electromagnetic signal strength and signal direction, and utilizing a nested Digital Phase-Locked Loop (DPLL) structure is disclosed. The obstacles to signal direction measurement in low SINR environments using the signal select method are overcome and a more precise phase comparison between the carrier and the FM modulation signals is obtained. The architecture further significantly reduces analog front-end hardware requirements, offers wider resistance to component tolerances, lower calibration and test time, and provides flexible frequency selectivity. Locators according to the present invention provide accurate estimation of the fundamental physical parameters of line location (electromagnetic signal strength and signal direction) in extremely noisy environments, using Digital Signal Processing (DSP) methods.

Owner:BUSAN TRANSPORTATION CORPORATION

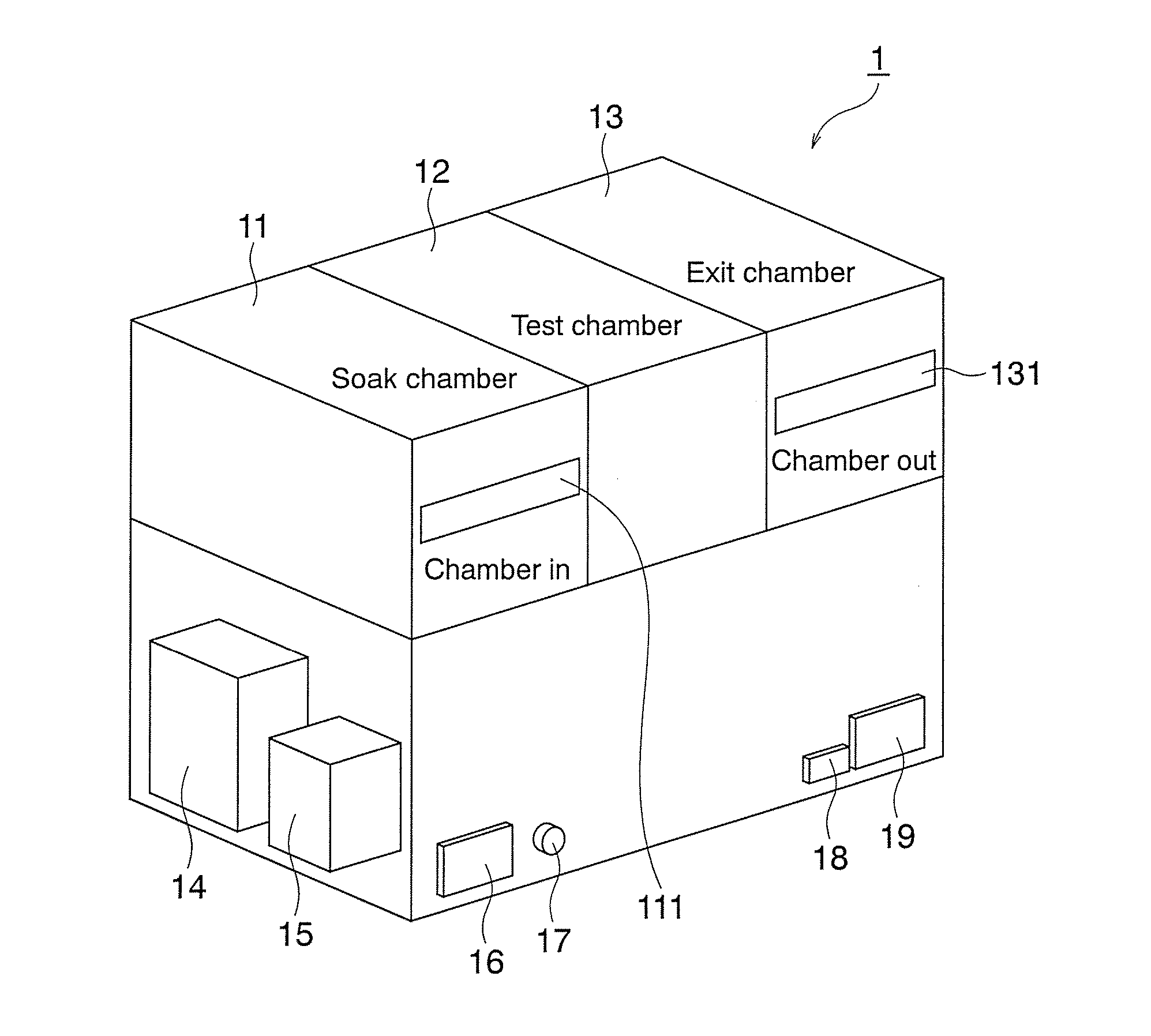

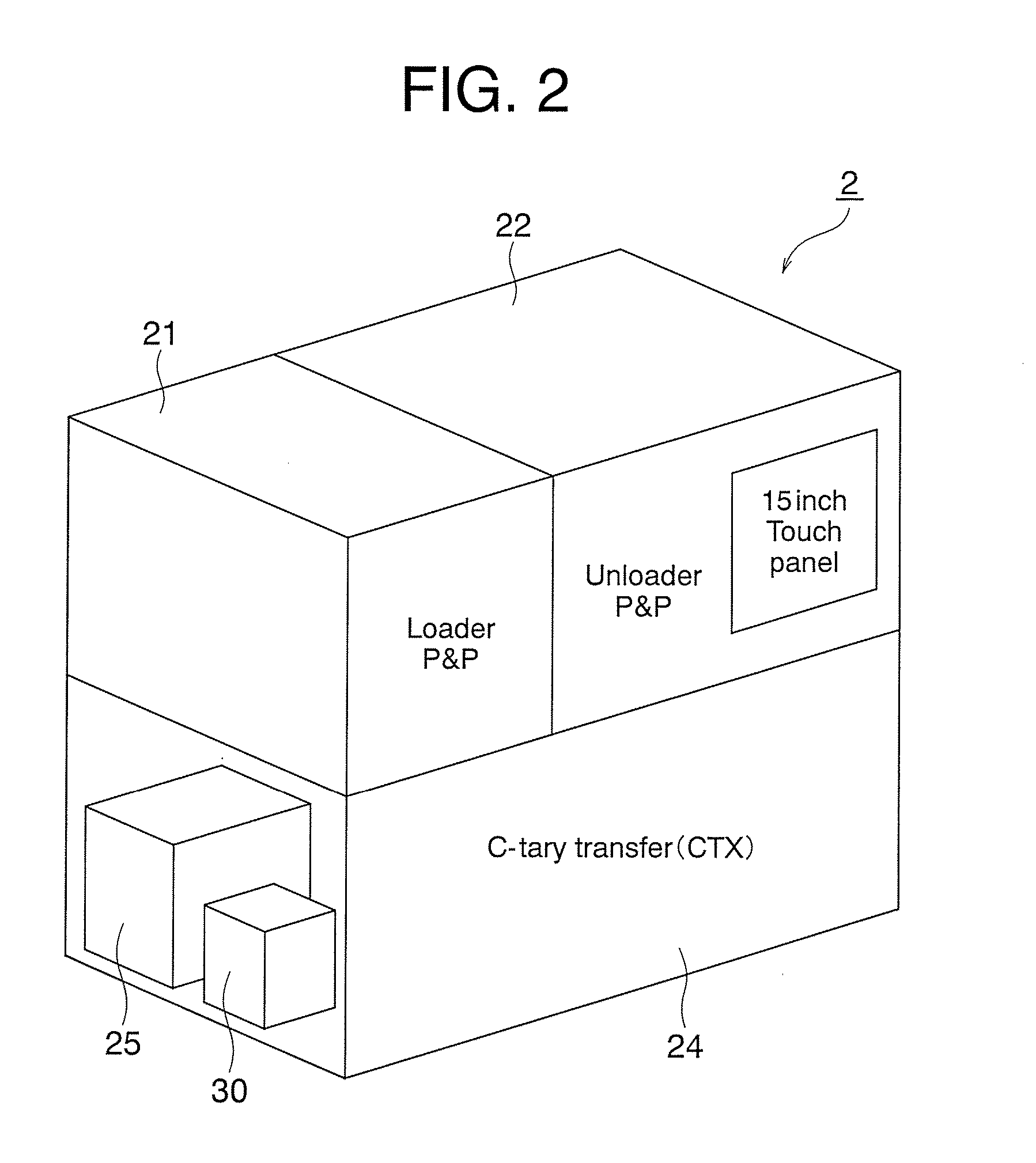

Electronic Device Test Apparatus and Method of Configuring Electronic Device Test Apparatus

InactiveUS20080042667A1Efficiency of test does not fallOptimize system configurationSemiconductor/solid-state device testing/measurementElectronic circuit testingTester deviceEngineering

A handler is configured by, separably and connectably, a plurality of types of handling modules of different throughputs and a plurality of types of test modules of different numbers of simultaneous measurements and / or test temperatures. Based on the maximum number of measurable pins of the tester outputting a test pattern and examining a response pattern, the number of terminals of the DUTs, and the test time, the throughput of the handling module and the number of simultaneous measurements and / or test temperature of the test module are selected and combined.

Owner:ADVANTEST CORP

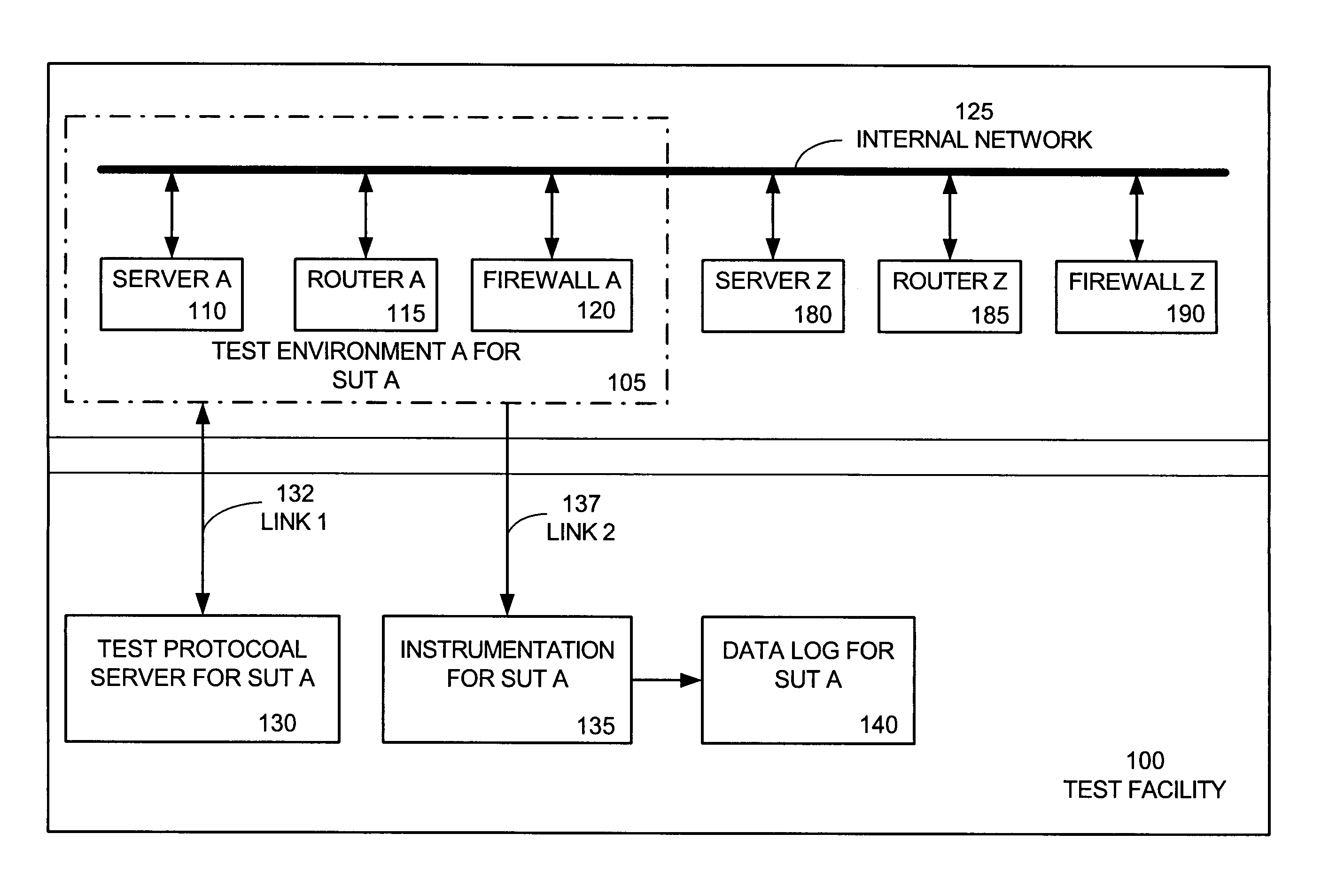

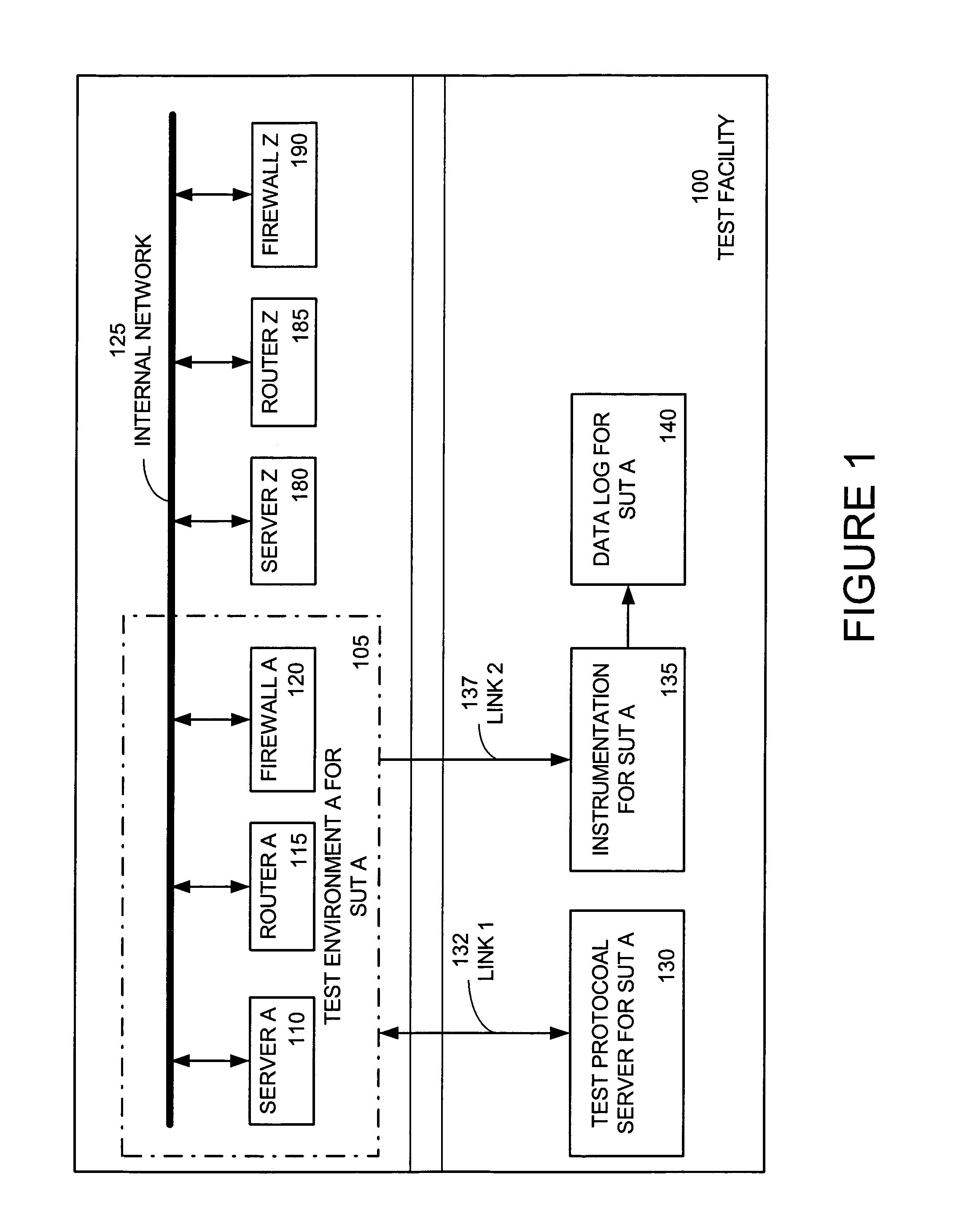

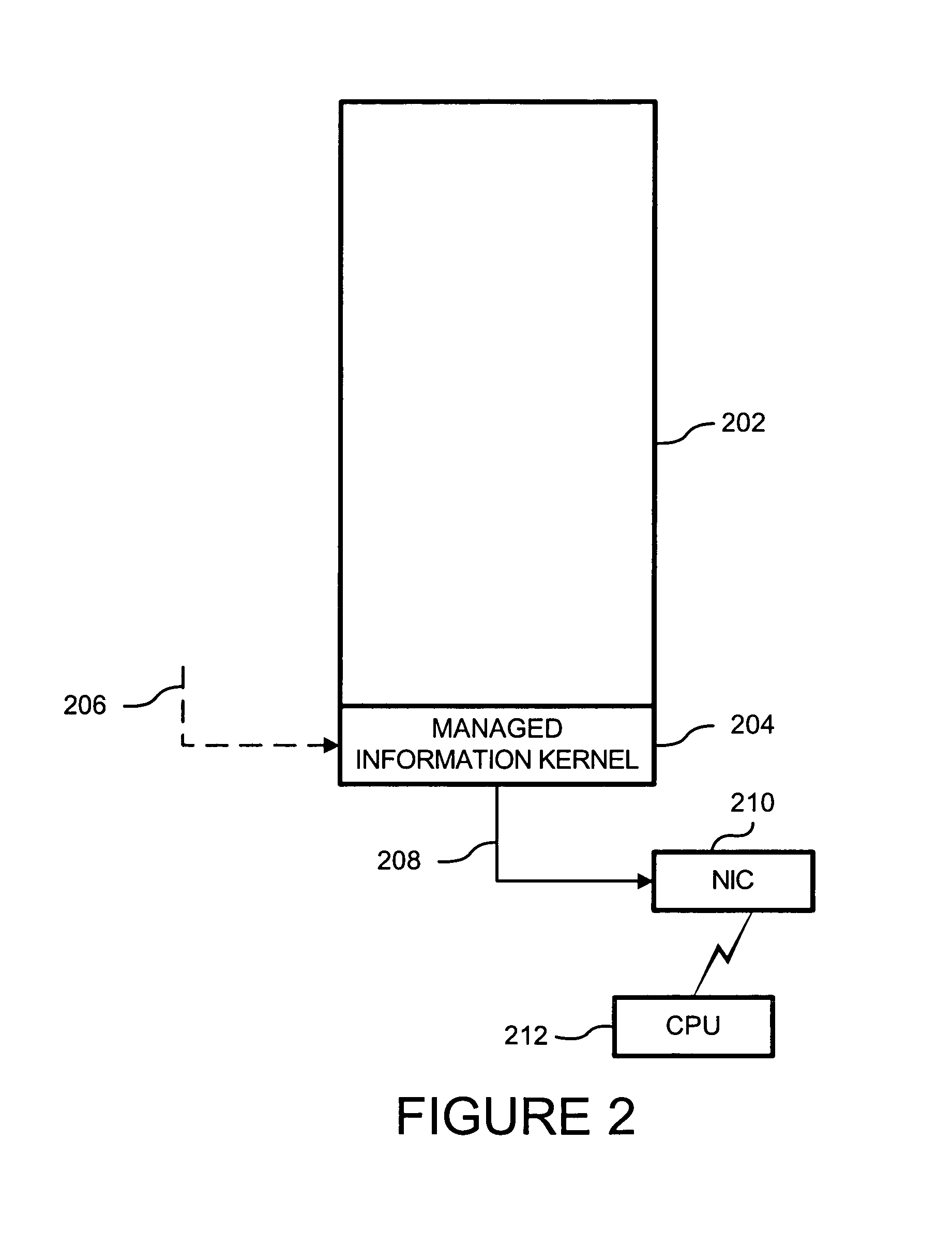

System and method of testing software and hardware in a reconfigurable instrumented network

A method of testing a computer system in a testing environment formed of a network of routers, servers, and firewalls. Performance of the computer system is monitored. A log is made of the monitored performance of the computer system. The computer system is subjected to hostile conditions until it no longer functions. The state of the computer system at failure point is recorded. The performance monitoring is done with substantially no interference with the testing environment. The performance monitoring includes monitoring, over a sampling period, of packet flow, hardware resource utilization, memory utilization, data access time, or thread count. A business method entails providing a testing environment formed of a network of network devices including routers, servers, and firewalls, while selling test time to a customer on one or more of the network devices during purchased tests that test the security of the customer's computer system. The purchased tests are conducted simultaneously with other tests for other customers within the testing environment. Customer security performance data based on the purchased tests is provided without loss of privacy by taking security measures to ensure that none of the other customers can access the security performance data. The tests may also be directed to scalability or reliability of the customer's computer system. Data about a device under test is gathered using a managed information kernel that is loaded into the devices operating memory before its operating system. The gathered data is prepared as managed information items.

Owner:AVANZA TECH

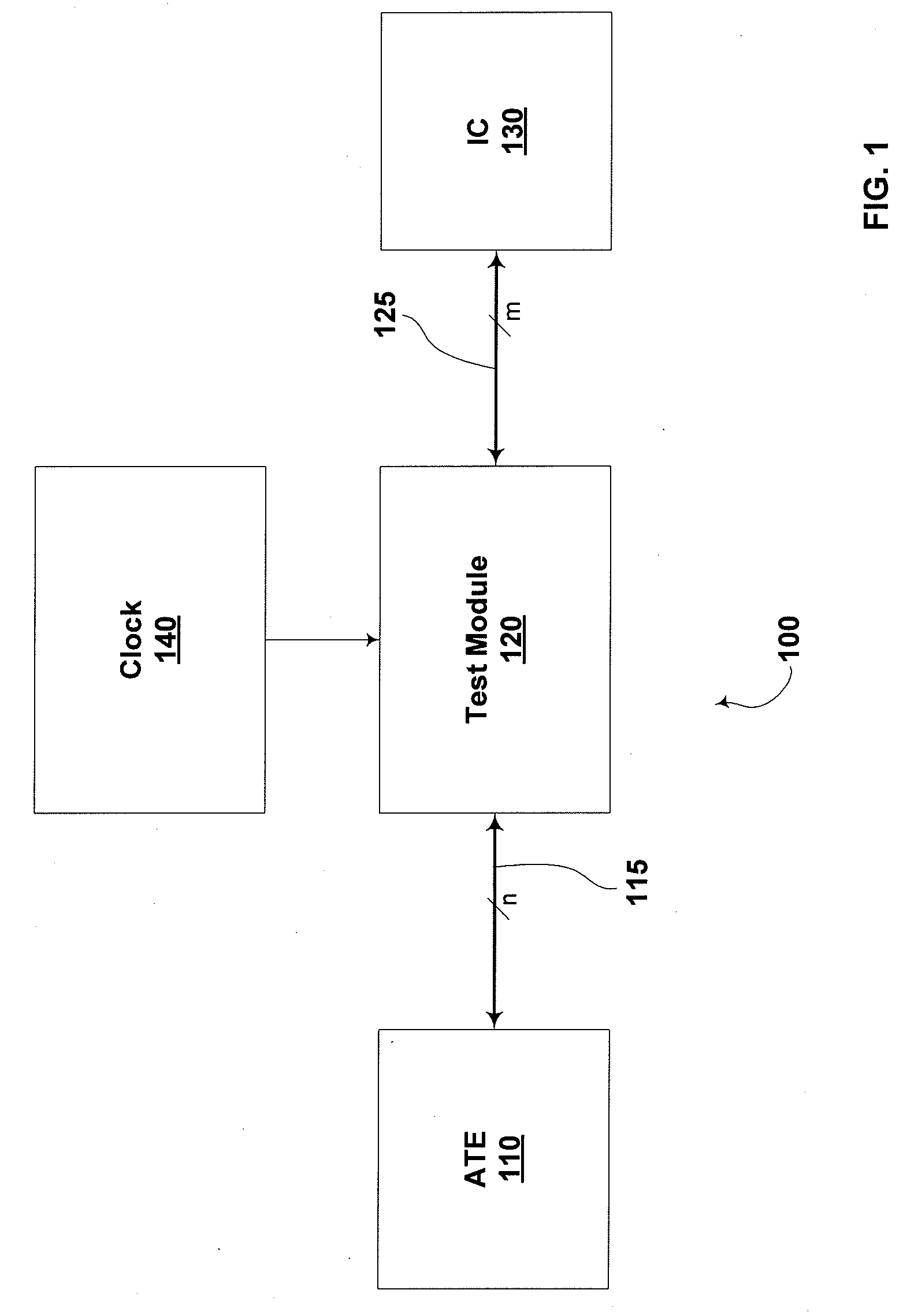

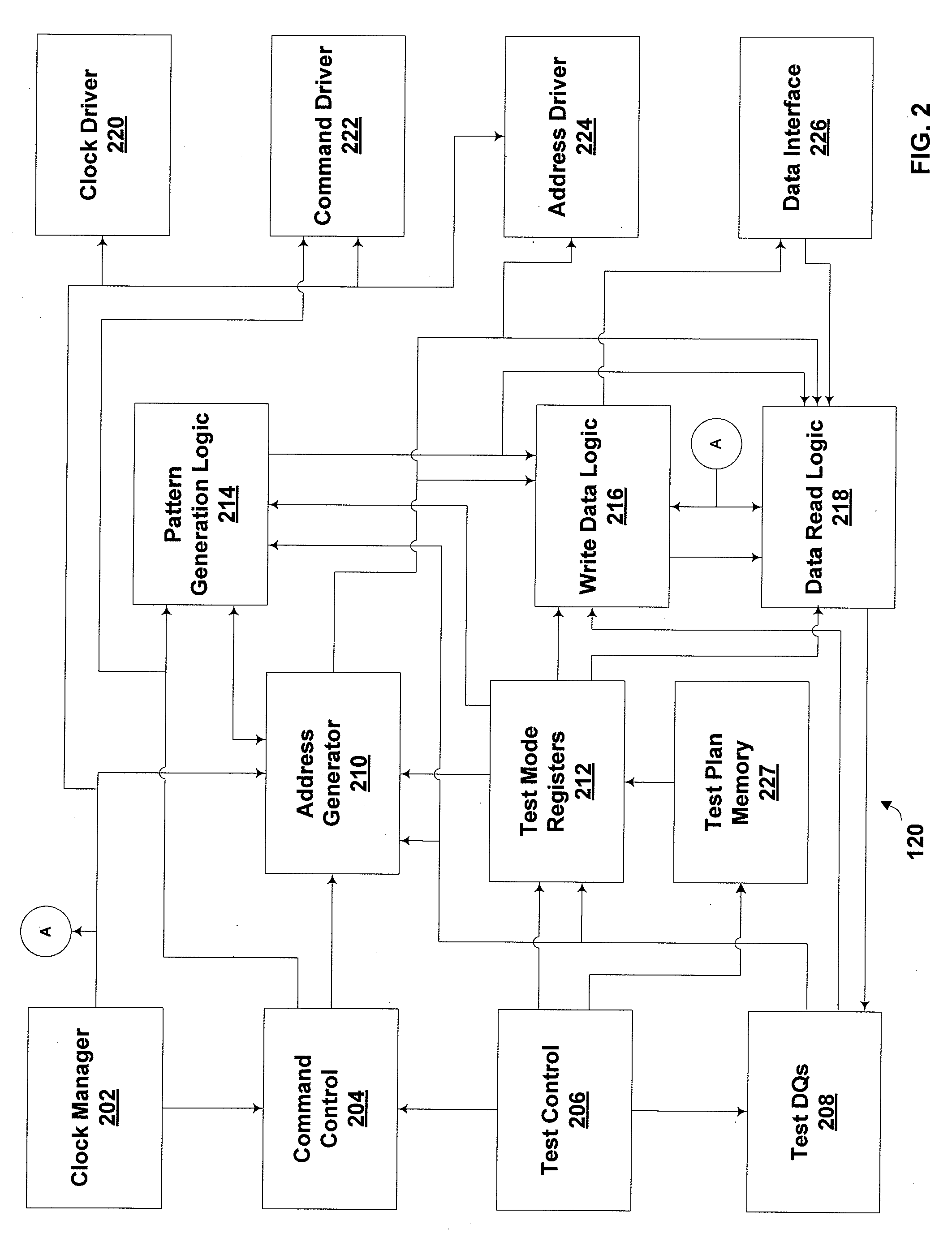

Integrated Circuit Testing Module Configured for Set-up and Hold Time Testing

InactiveUS20070067687A1Electronic circuit testingError detection/correctionTest setIntegrated circuit

Systems and methods of testing integrated circuits are disclosed. The systems include a test module configured to operate between automated testing equipment and an integrated circuit to be tested. The testing interface is configured to test time sensitive parameters of the integrated circuit. The testing interface includes components for generating addresses, commands, and test data to be conveyed to the integrated circuit as well as a clock adjustment component. By adjusting the clock synchronization controlling the test signals to be conveyed to the integrated circuit, set-up time and hold time can be tested. The systems are configured to test set-up time and hold time of individual data channels, for example, an individual address line of the integrated circuit.

Owner:RAMBUS INC

Gas analyzer calibration checking device

InactiveUS20050273016A1Improve accuracyHigh selectivityWithdrawing sample devicesSynthetic resin layered productsEngineeringMoisture

Owner:EXALENZ BIOSCIENCE LTD

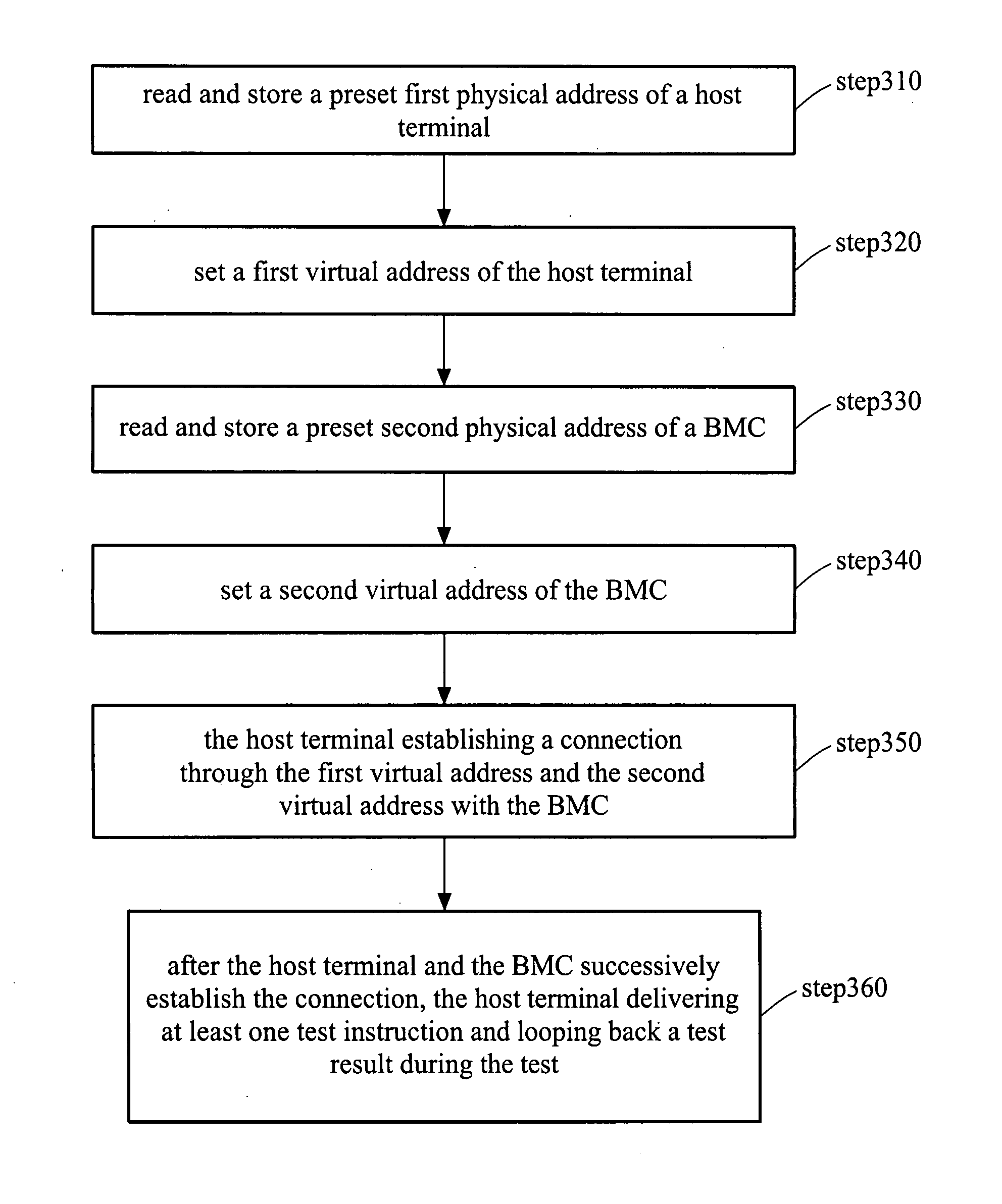

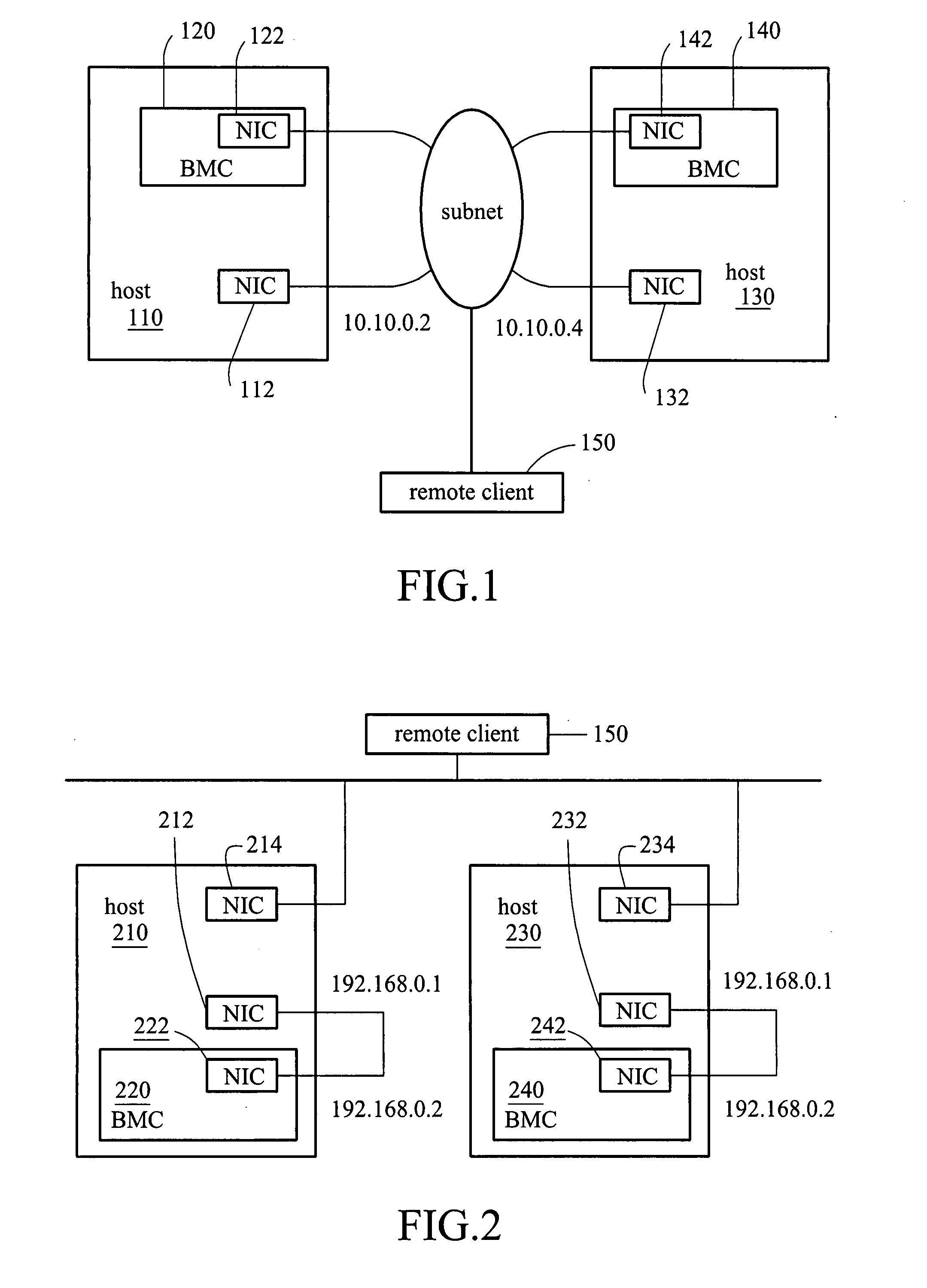

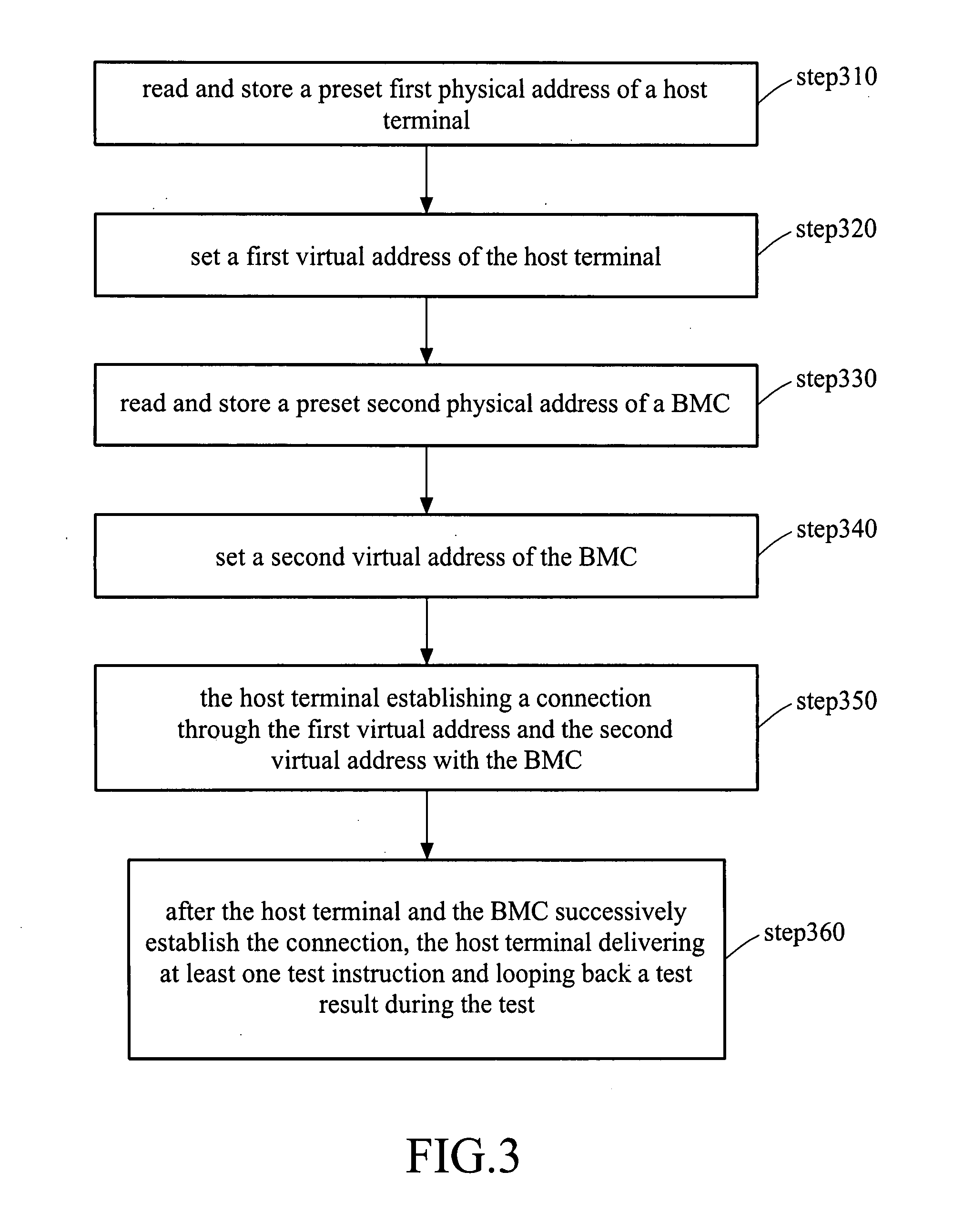

Test system using local loop to establish connection to baseboard management control and method therefor

InactiveUS20080205286A1Shorten the timeError prevention/detection by using return channelFrequency-division multiplex detailsCyclic testInner loop

A test system using a local loop to establish connection to baseboard management control is provided. The test system includes more than one host terminals having at least one network interface card (NIC) and at least one baseboard management controller (BMC) having one NIC. After establishing a connection for test between the host terminals and a remote subscriber, a connection for loop test is established with the BMC through a virtual address, so as to deliver a test instruction to the BMC for testing and to loop back a test result. The test system establishes the connection for loop test through the virtual address so as to perform a remote platform test similar to an inner loop test. Therefore, the test result will not be influenced by a network environment setting, and thus a batch test can be adopted to save the test time.

Owner:INVENTEC CORP

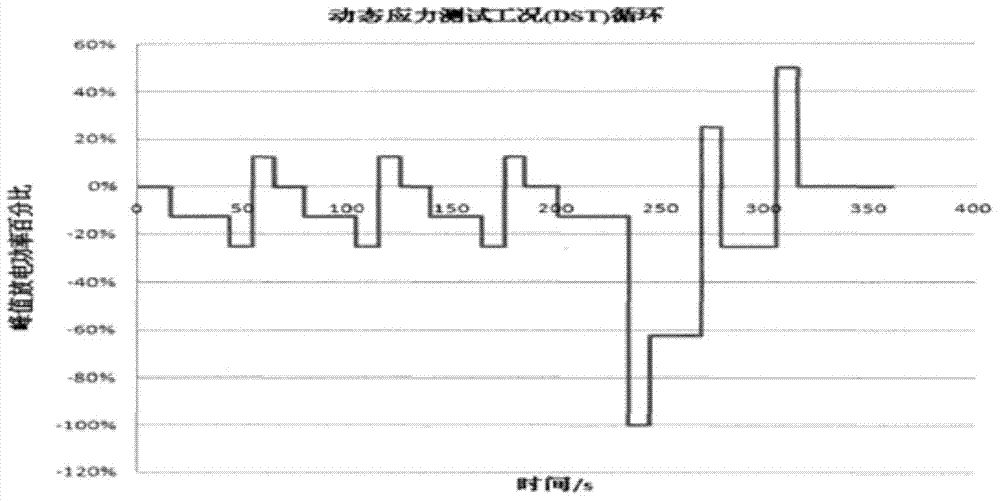

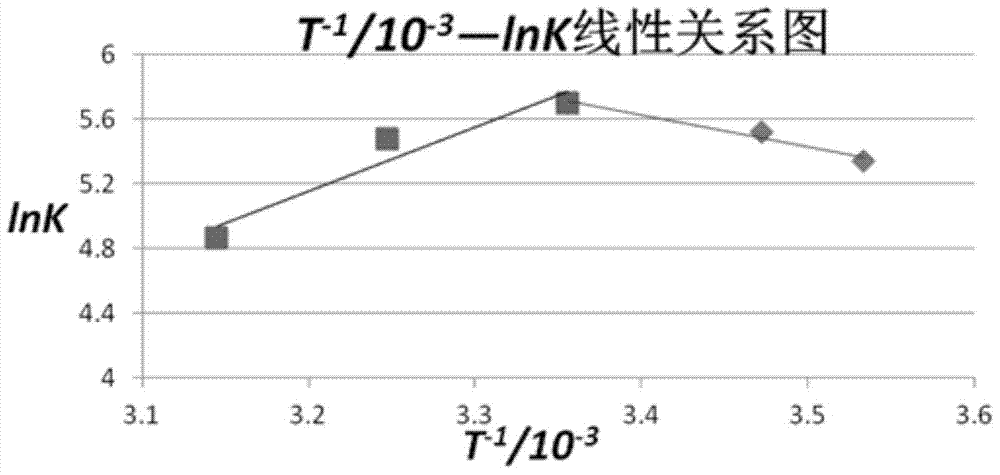

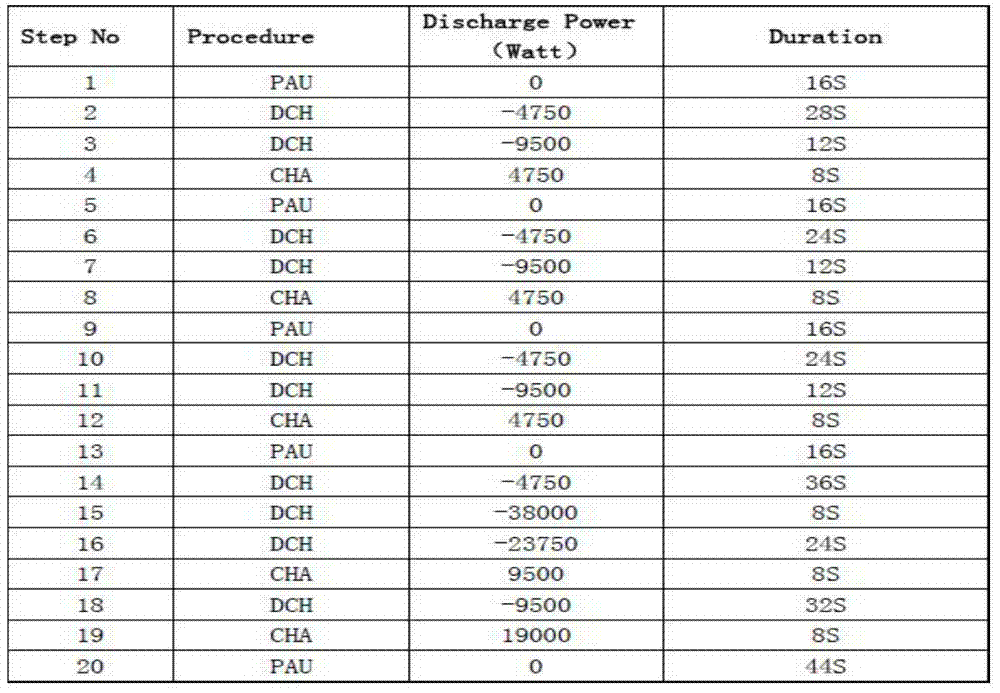

Method for predicting cycle life of battery pack for electric car

InactiveCN104714189AAccelerated agingEvaluate Cycle Life PerformanceElectrical testingCyclic testPredictive methods

The invention relates to a method for predicting the cycle life of a battery pack for an electric car. The method comprises the following steps: step I, carrying out standard capacity test on the battery pack at normal temperature, and recording a real standard capacity of the battery pack; step II, carrying out dynamic stress working condition circulating test on the battery pack, returning to the step I after multiple times of working condition circulating test is ended, recording the test times of the standard capacity, ending the circulating test at the temperature if the real capacity of the standard capacity test for continuous 4 to 6 times is less than 80 percent of the rated capacity, wherein the test times of the standard capacity indicate the cycle life of the battery pack; step III, repeating the step I and the step II, and testing the cycle life of the battery pack under multiple temperature points. According to the method, the battery pack cycle life data at the grouped time is collected, a fitted equation is obtained by virtue of data processing, and the cycle life of a lithium ion battery at present can be predicted.

Owner:CHERY AUTOMOBILE CO LTD

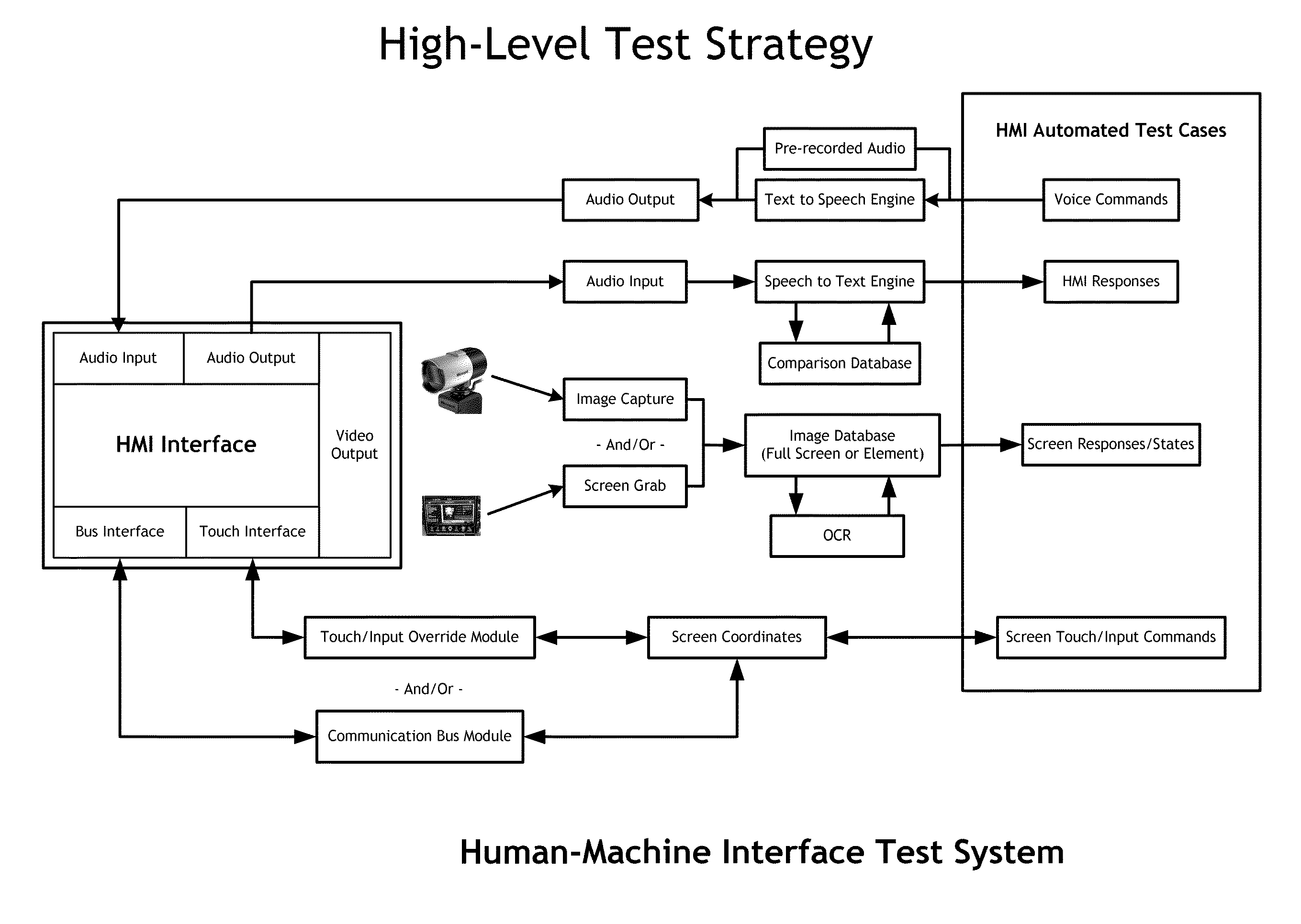

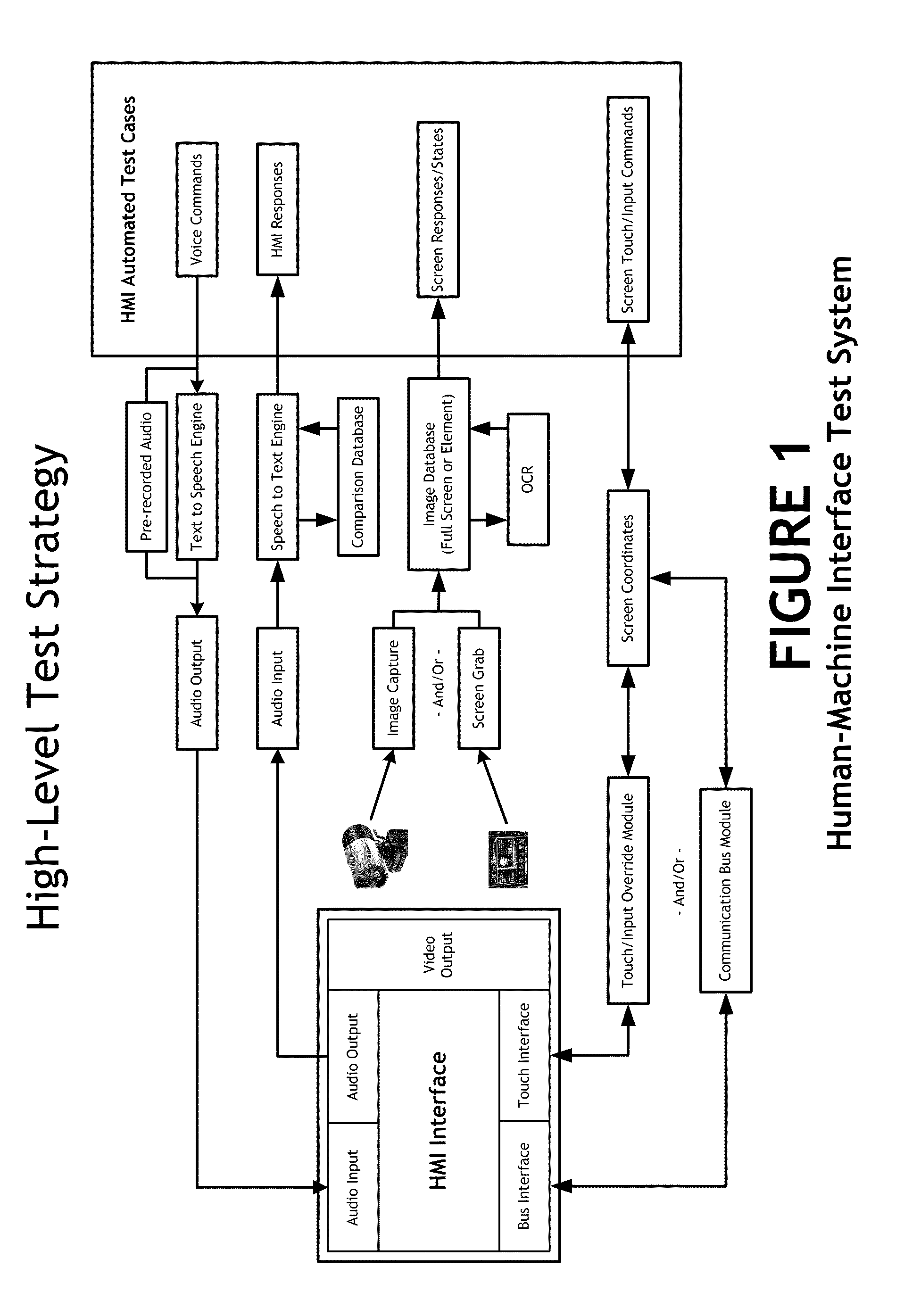

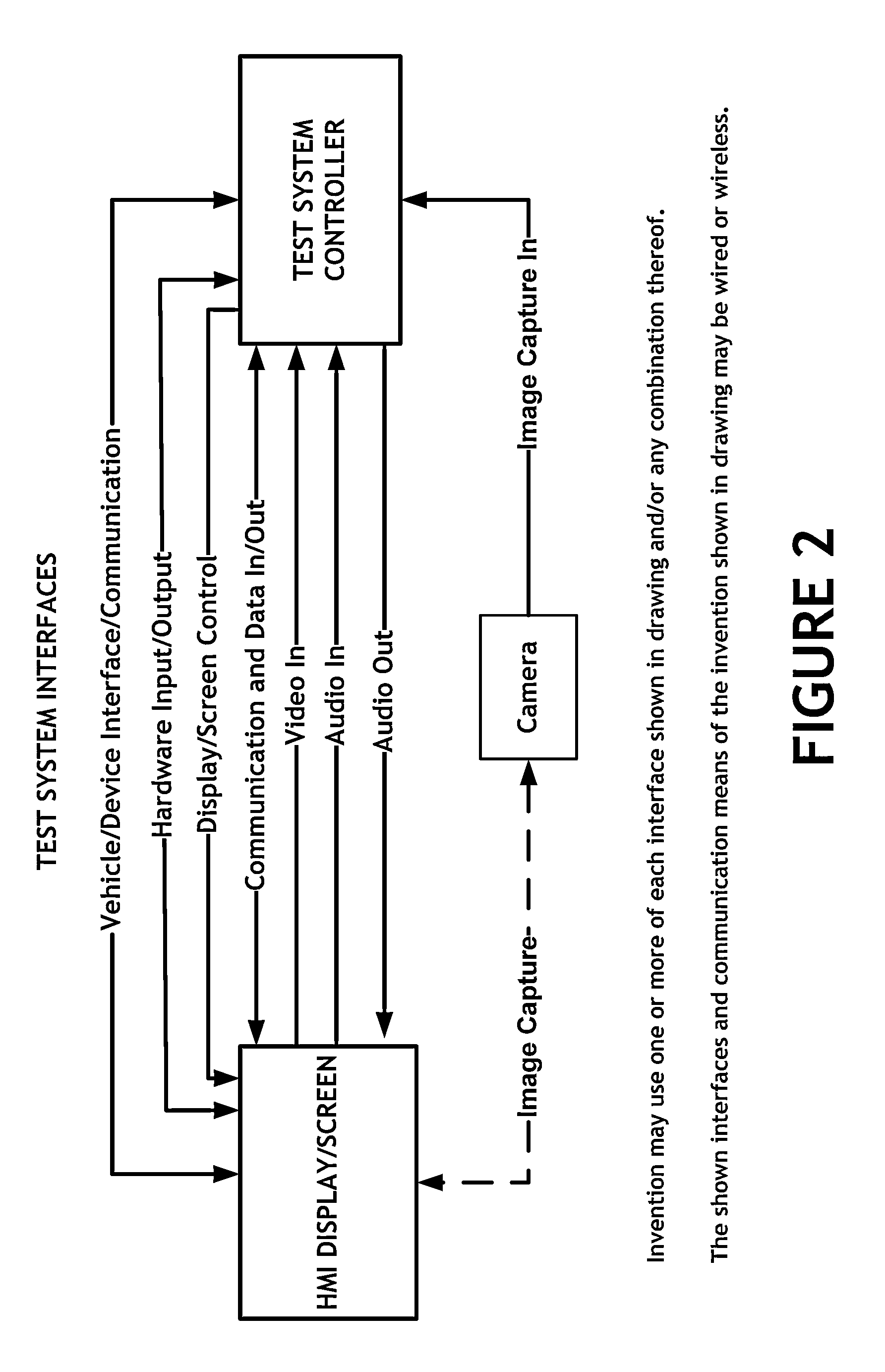

Human-Machine Interface Test System

ActiveUS20140303756A1Complete testFully testedComputer controlError detection/correctionHuman interactionComputer hardware

The human-machine interface test system enables the automated testing of vehicle interface systems and consumer electronics devices, replacing testing and validation that previously had required human interaction. The human-machine interface device (HMI test object or device under test) does not need to be altered (via hardware or software modifications or additions) to be able to be tested using the human-machine interface test system. The HMIts involves the automated audio input generation and output analysis, visual verification of a display screen with graphics and texts display, including touch and gesture interface control and feedback, external device interface, as well as data logging for communication between the HMI device and the rest of the system, that will replace the testing and validation that previously required human interaction. The HMIts provides more accurate and reliable results from the conducted tests, increasing repeatability and consistency in a controlled environment, while significantly decreasing test time.

Owner:FEV NORTH AMERICA INC

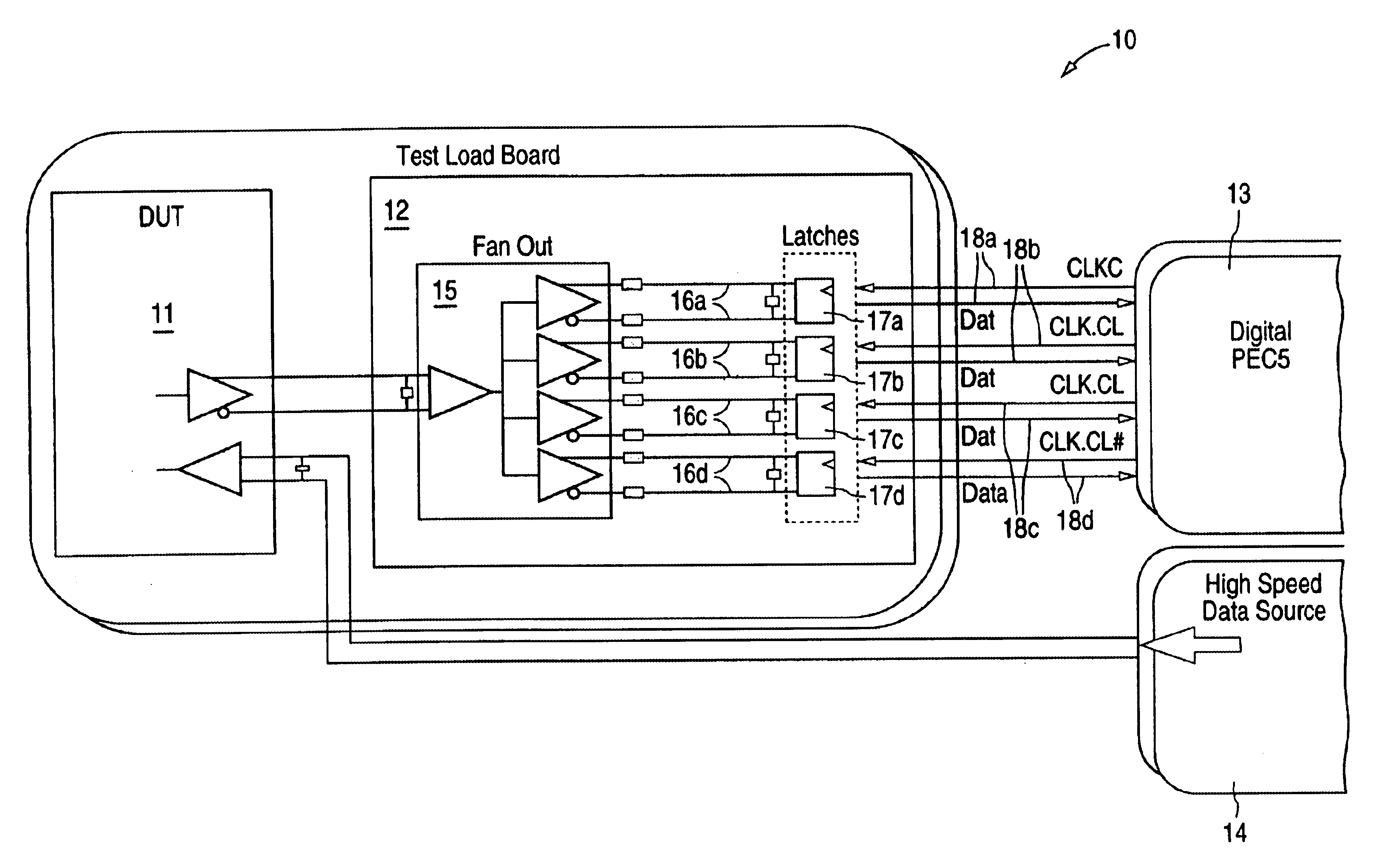

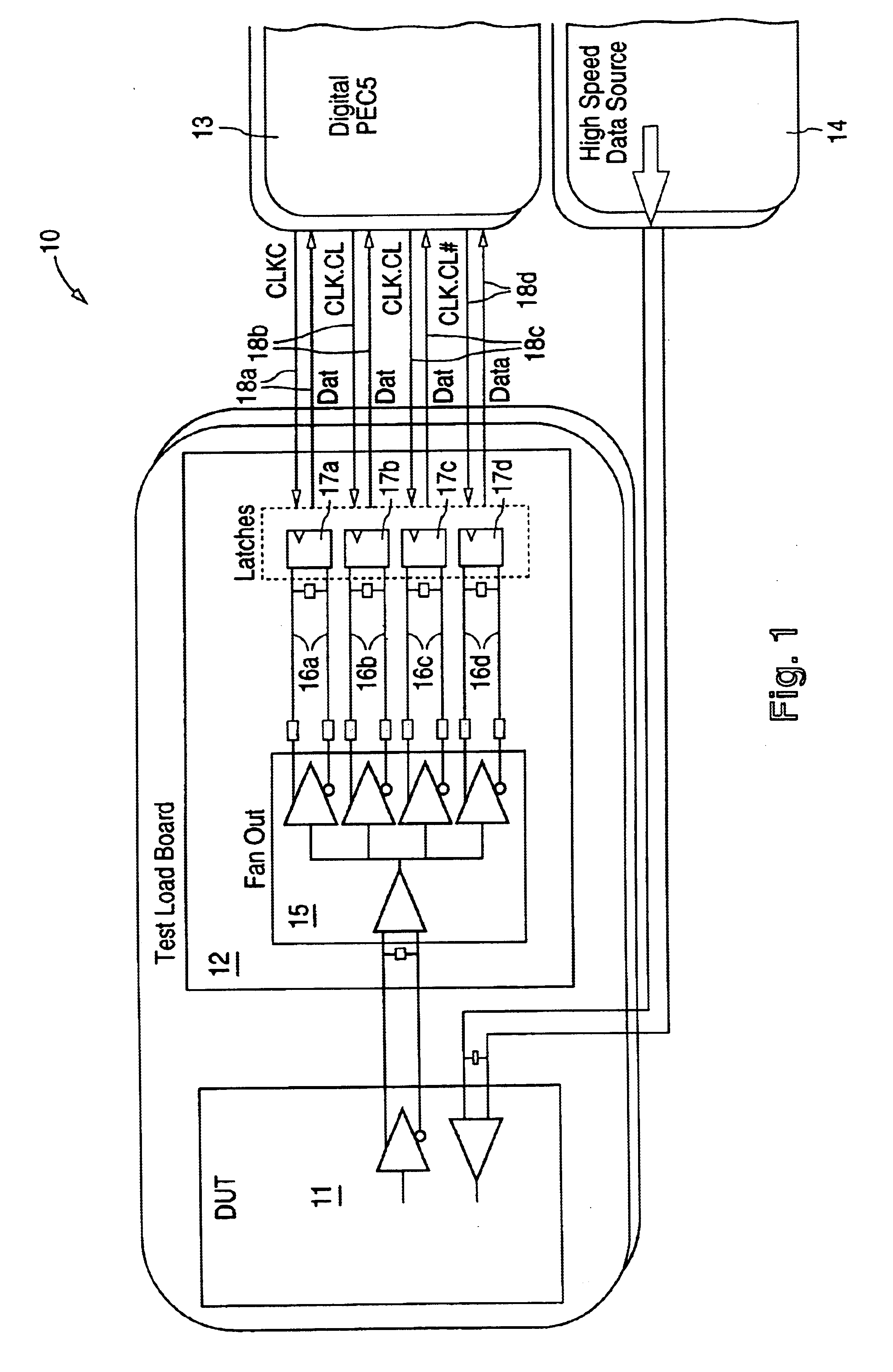

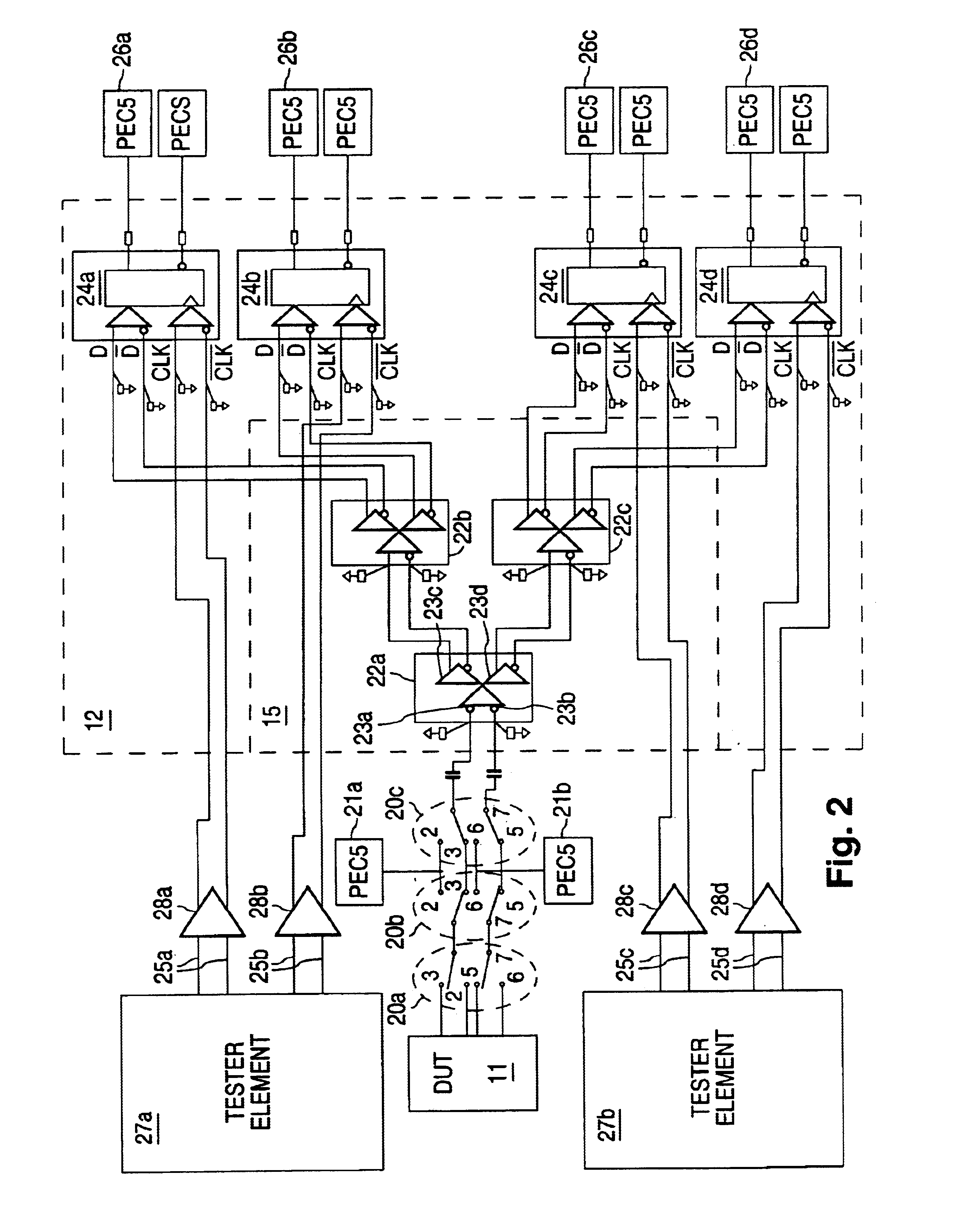

Method and apparatus for high speed IC test interface

InactiveUS6859902B1Save the total testing timeEffective real-time captureDigital circuit testingError detection/correctionData streamCommunication device

A testing method and circuit used to test high-speed communication devices on Automatic Test Equipment—ATE. The method and circuit provide a solution to testing very high speed (2.5 Gbps and above) integrated circuits. The circuit fans out the data streams from the output of the Device Under Test (DUT) to multiple tester channels which under-sample the streams. The testing method and circuit also allow for the injection of jitter into to the DUT at the output of the DUT. The skipping of data bits inherent in multi-pass testing is avoided by duplicating the tester resources to achieve effective real-time capture (saving test time and improving Bit Error Rate). Moreover the circuit synchronizes different DUTs with the timing of ATE hardware independent of DUT output data. Also, a calibration method is used compensate for differing trace lengths and propagation delay characteristics of test circuit components.

Owner:CREDENCE SYSTEMS

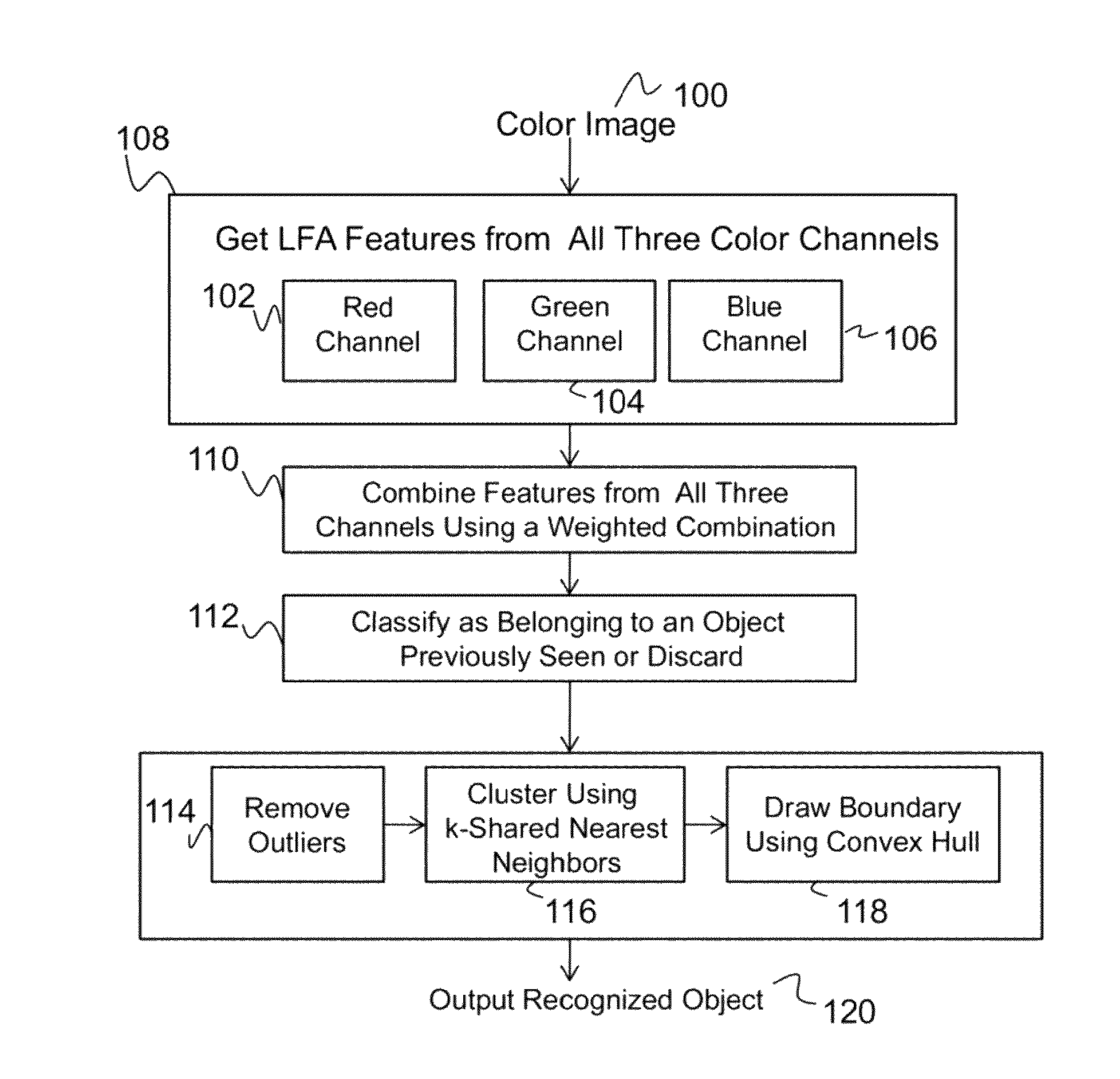

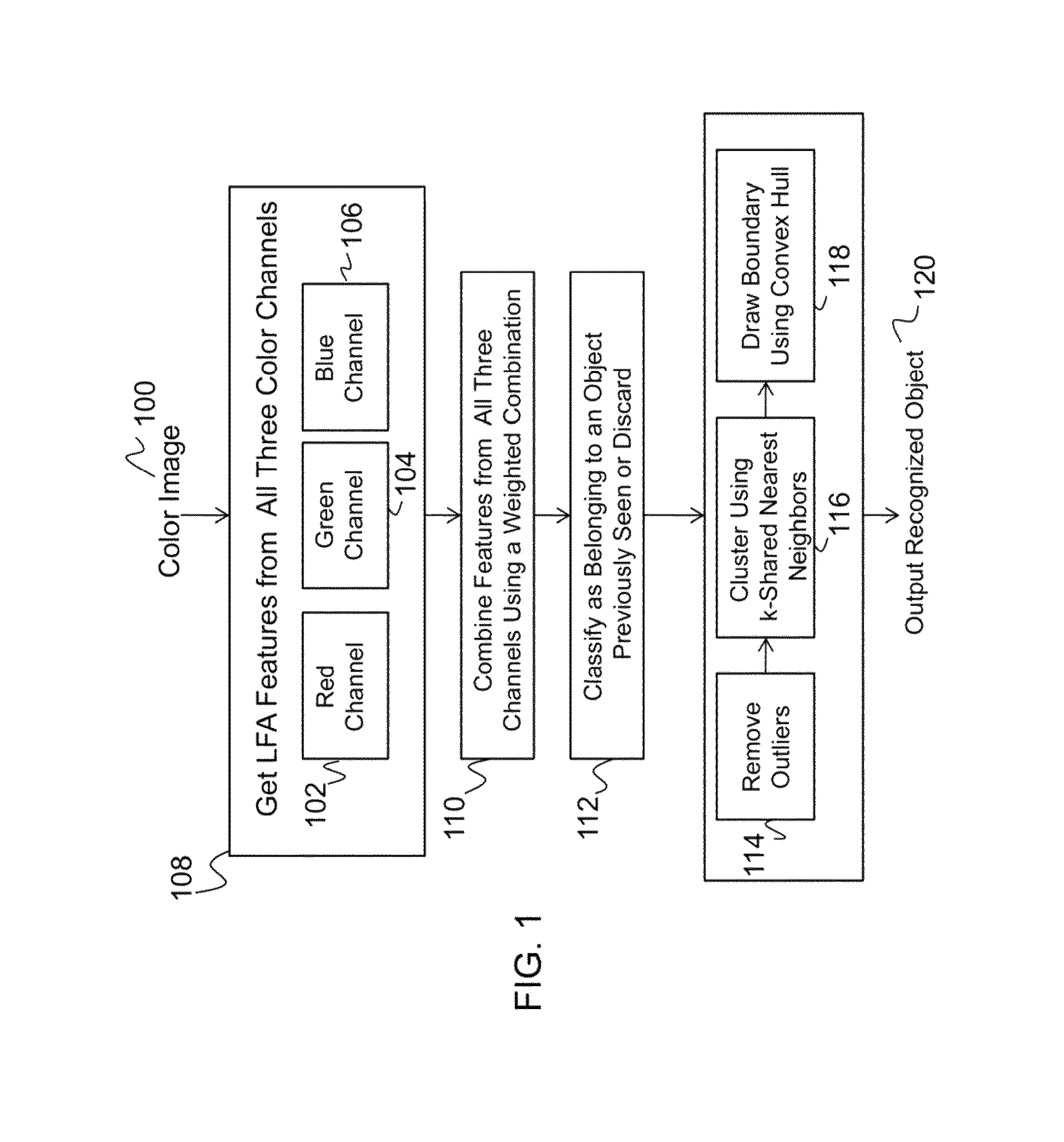

System for three-dimensional object recognition and foreground extraction

The present invention describes a system for recognizing objects from color images by detecting features of interest, classifying them according to previous objects' features that the system has been trained on, and finally drawing a boundary around them to separate each object from others in the image. Furthermore, local feature detection algorithms are applied to color images, outliers are removed, and resulting feature descriptors are clustered to achieve effective object recognition. Additionally, the present invention describes a system for extracting foreground objects and the correct rejection of the background from an image of a scene. Importantly, the present invention allows for changes to the camera viewpoint or lighting between training and test time. The system uses a supervised-learning algorithm and produces blobs of foreground objects that a recognition algorithm can then use for object detection / recognition.

Owner:HRL LAB

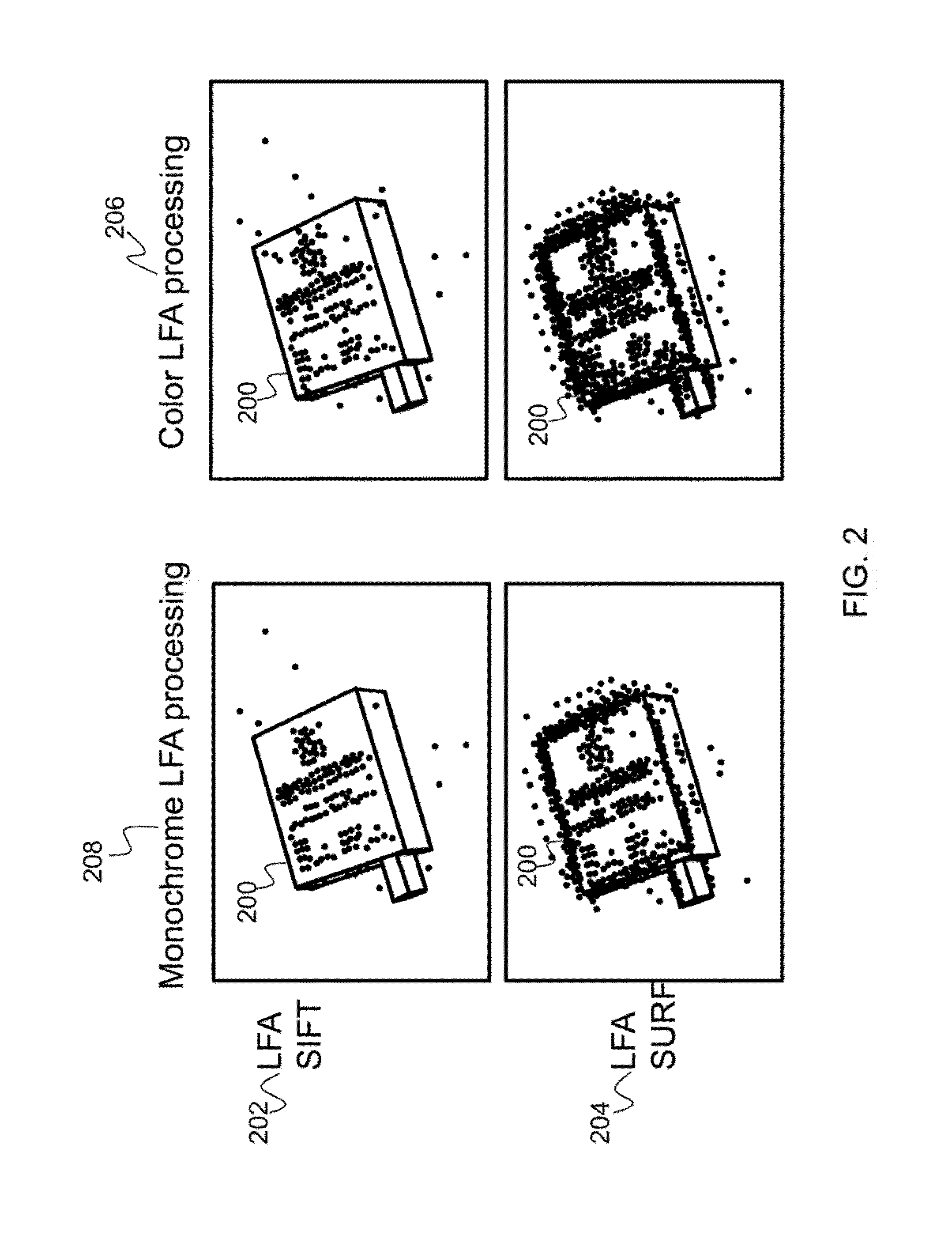

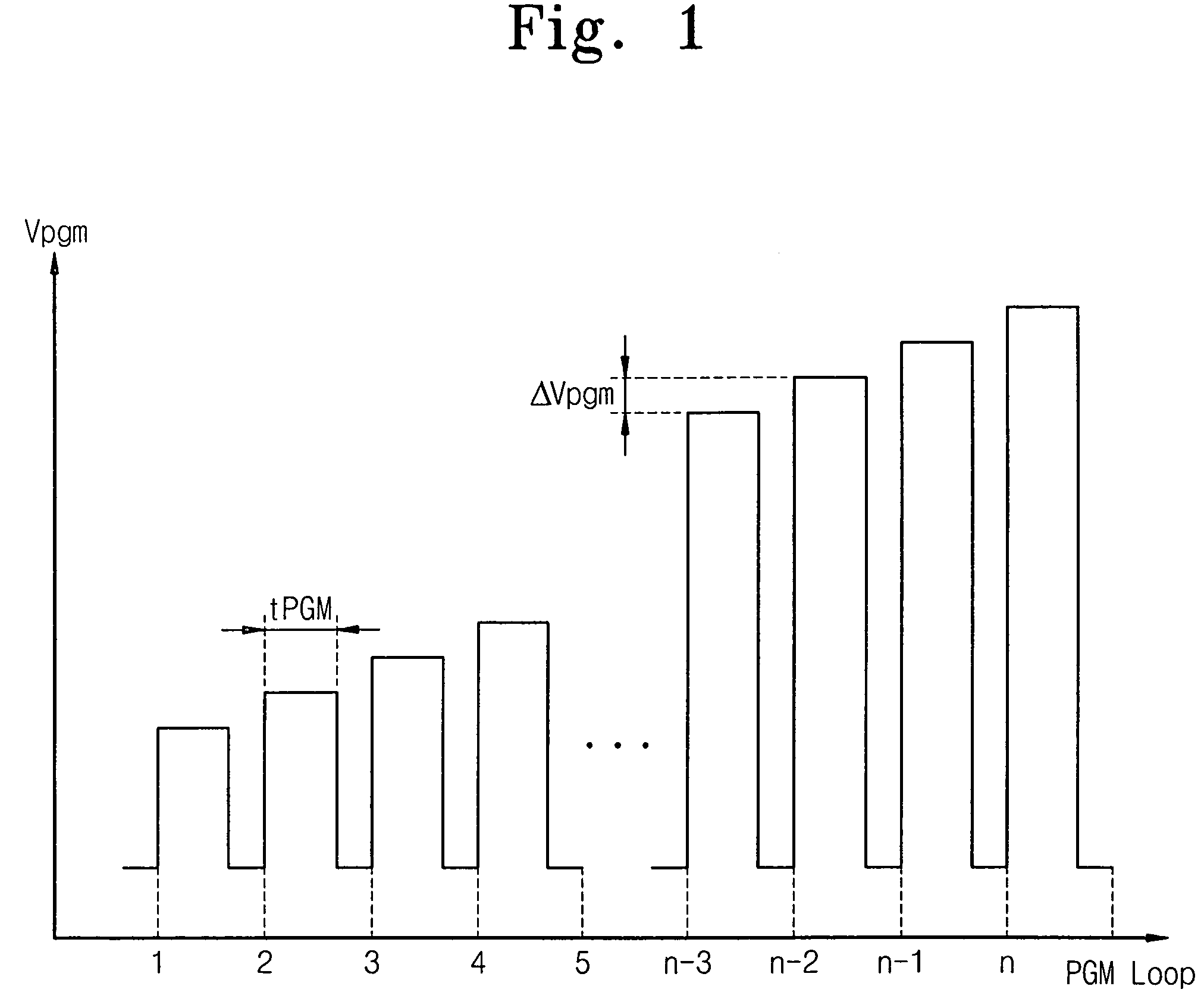

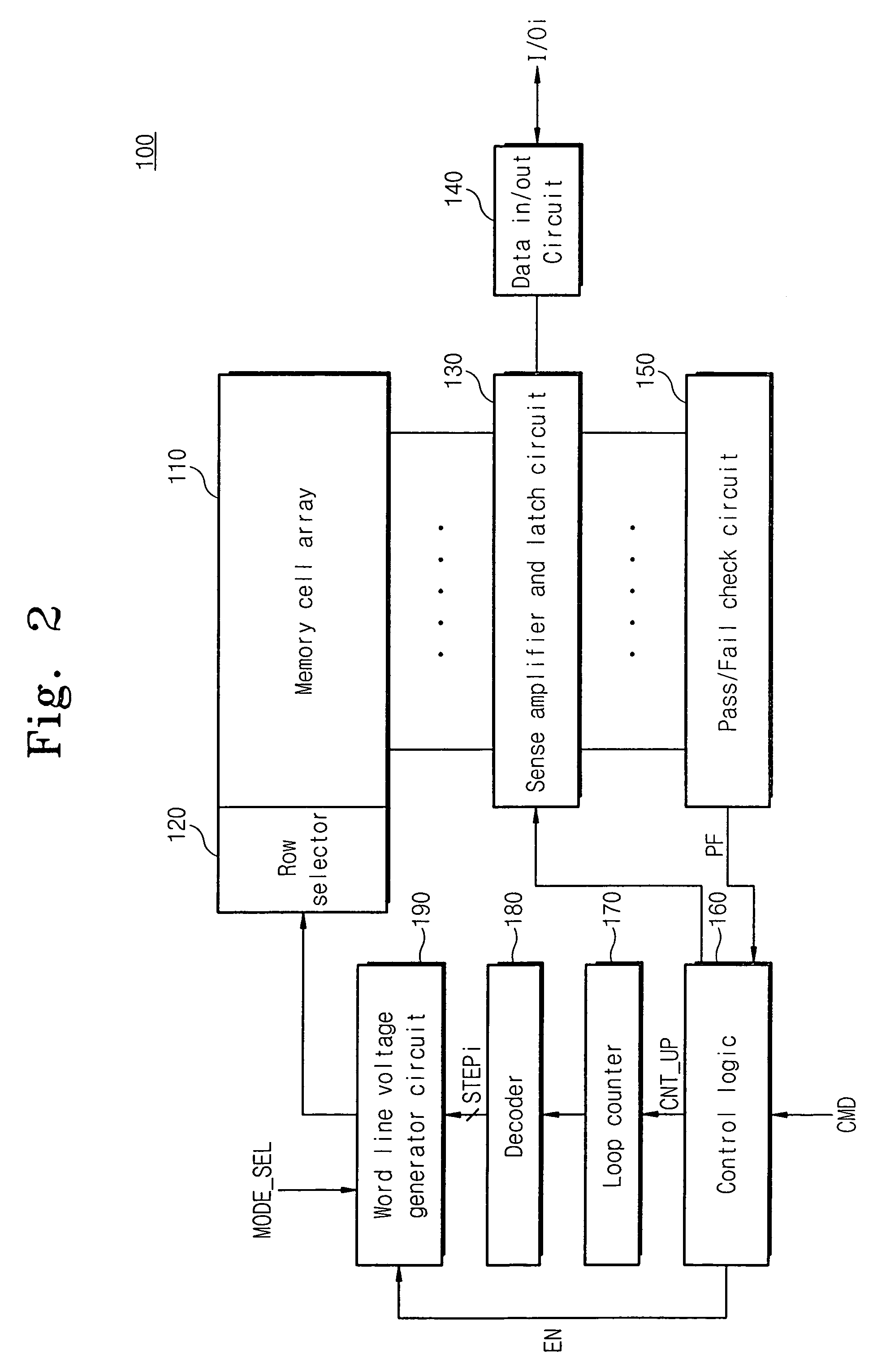

Non-volatile memory device capable of changing increment of program voltage according to mode of operation

A non-volatile memory device includes a word line voltage generator circuit for generating a word line voltage to be supplied to a selected row in response to step control signals and a program controller for sequentially activating the step control signals during a program cycle. During the program cycle, the word line voltage generator circuit controls the increment of the word line voltage differently according to the mode of operation, namely, a test mode or a normal mode. Thus test time can be shortened.

Owner:SAMSUNG ELECTRONICS CO LTD

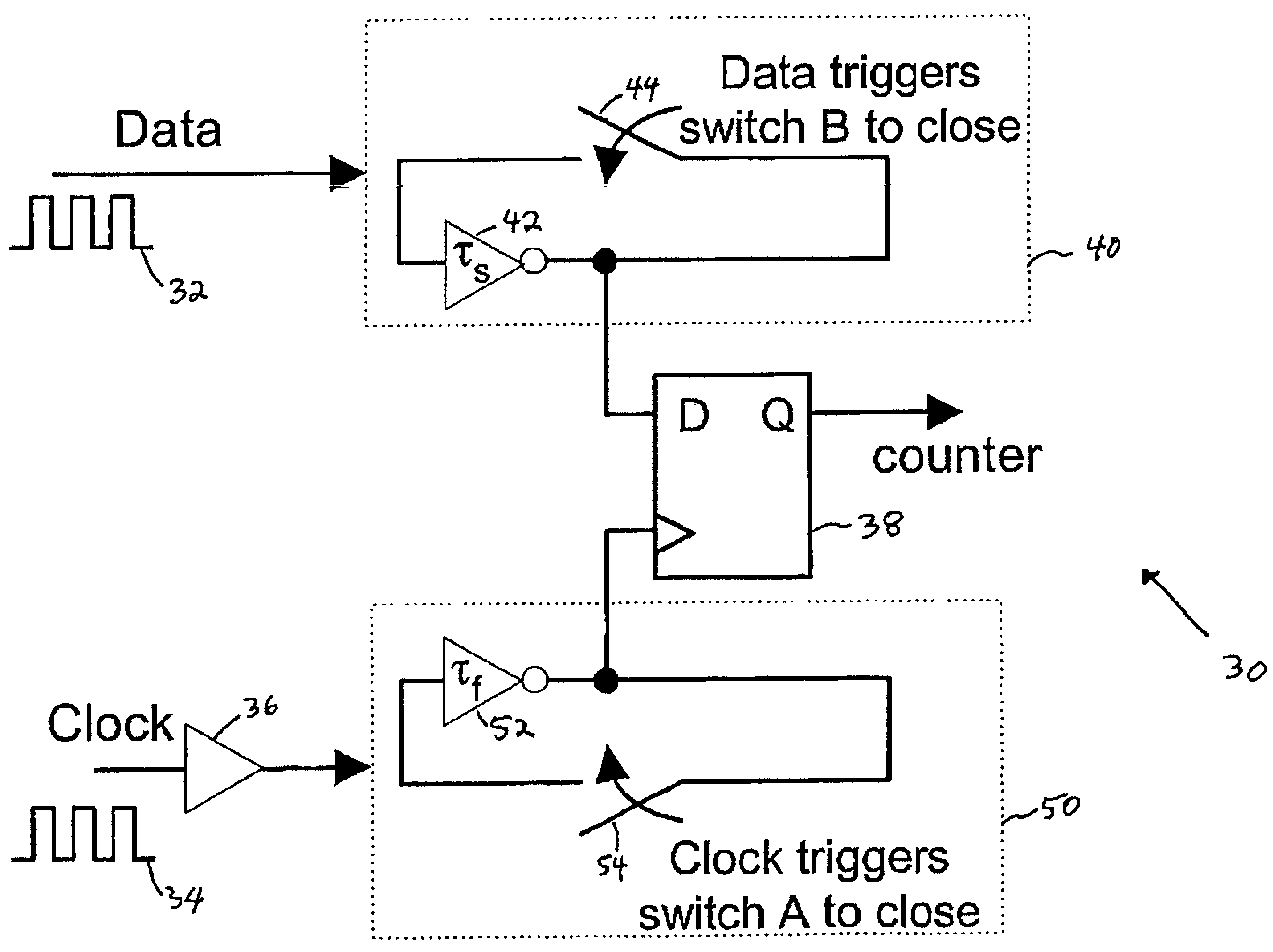

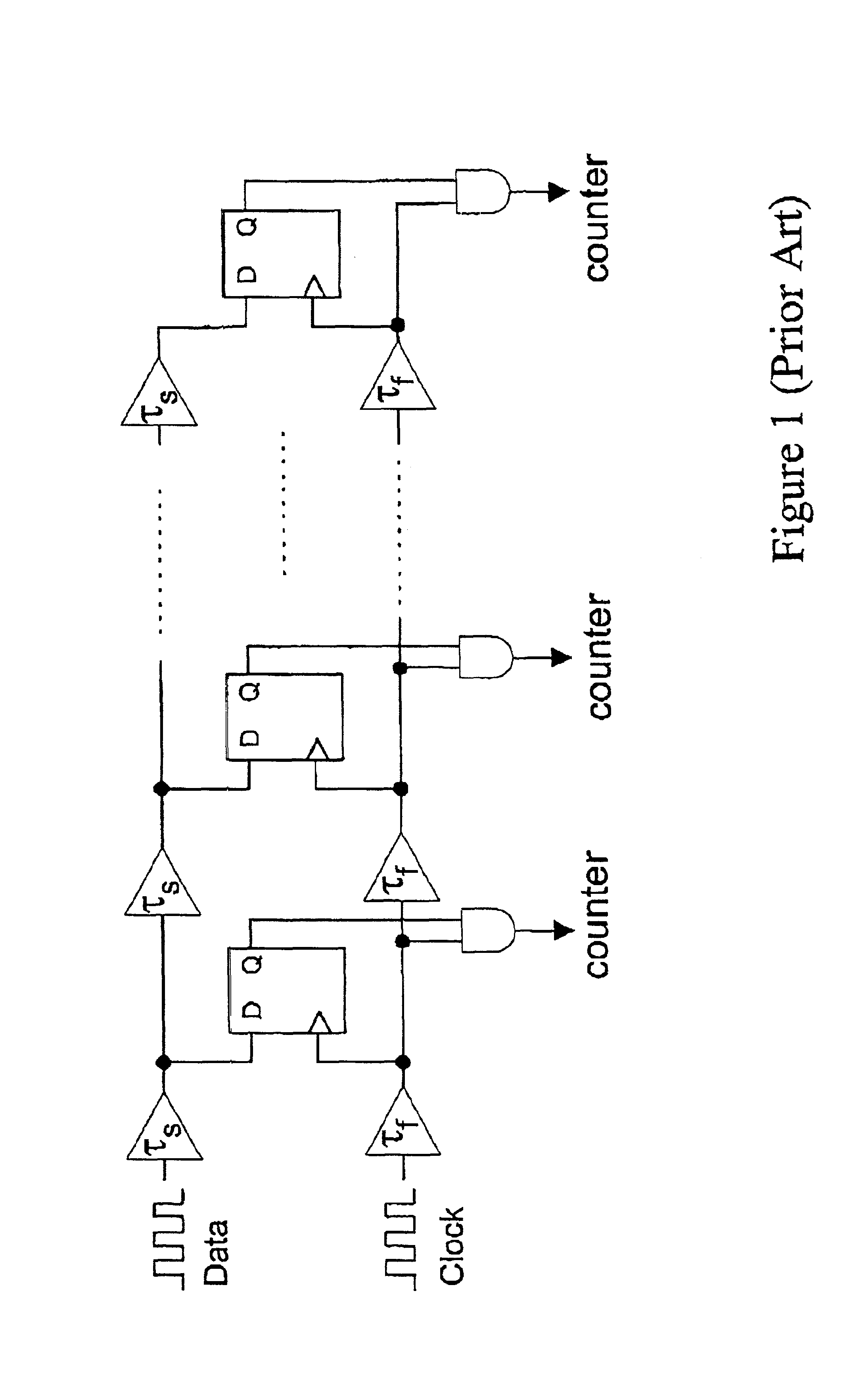

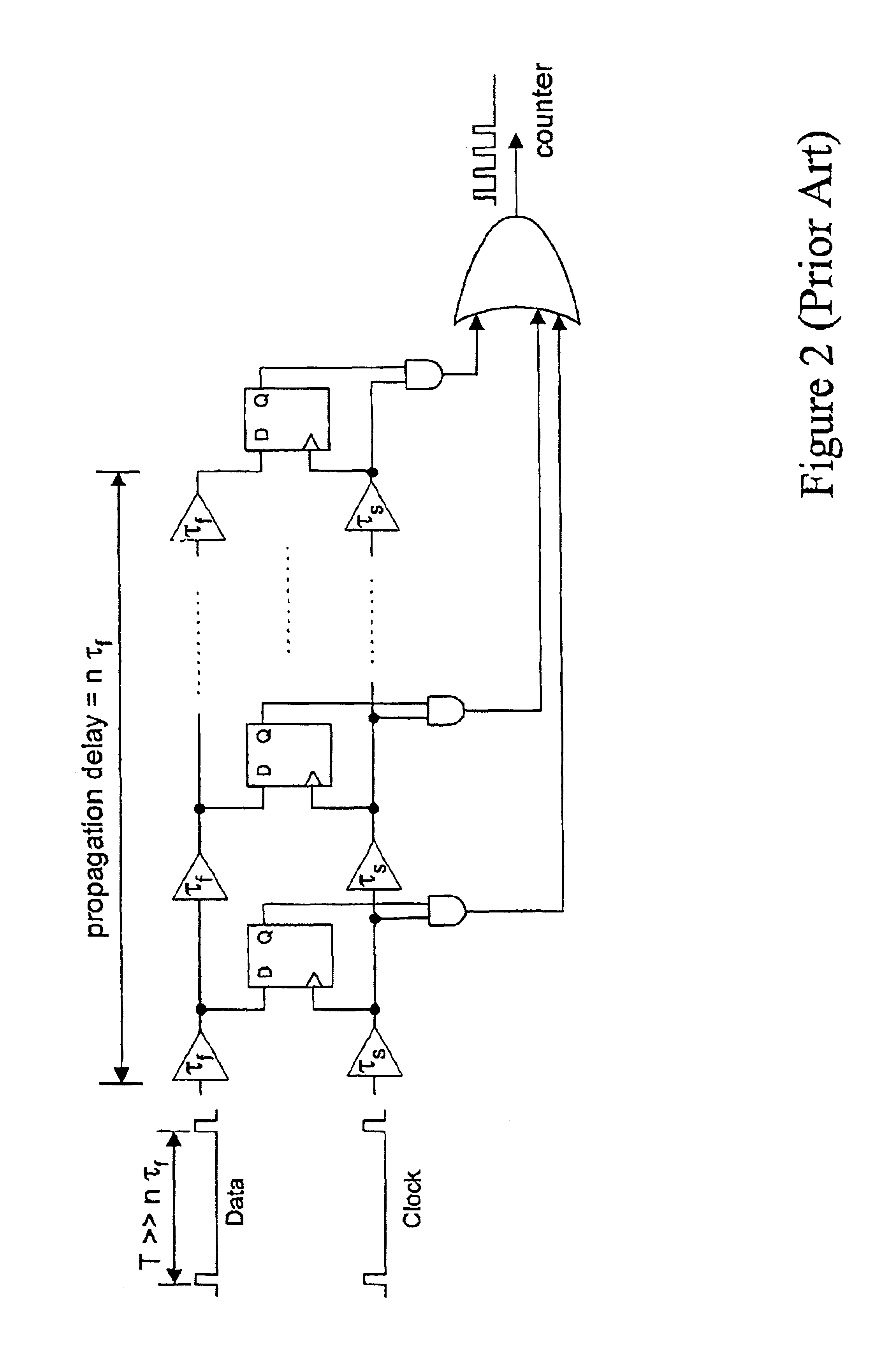

Timing measurement device using a component-invariant vernier delay line

InactiveUS6850051B2Reduced measurement timeAvoid matching problemsPulse characteristics measurementsFrequency to phase shift conversionSingle stageMeasurement device

In recent years, much effort has been placed on improving the performance of timing and jitter measurement devices using Delay Locked Loop (DLL) and Vernier Delay Line (VDL) techniques. However, these approaches require highly matched elements in order to reduce differential non-linearity timing errors. In an attempt to reduce the requirement on element matching, a component-invariant VDL technique is disclosed that enables the measurement device to be synthesized from an RTL description. The present invention is based on a single-stage VDL structure, which is used to mimic the behavior of a complete VDL. Furthermore, as test time is an important consideration during a production test, a method and system is provided that reduces test time at the expense of additional hardware.

Owner:MCGILL UNIV

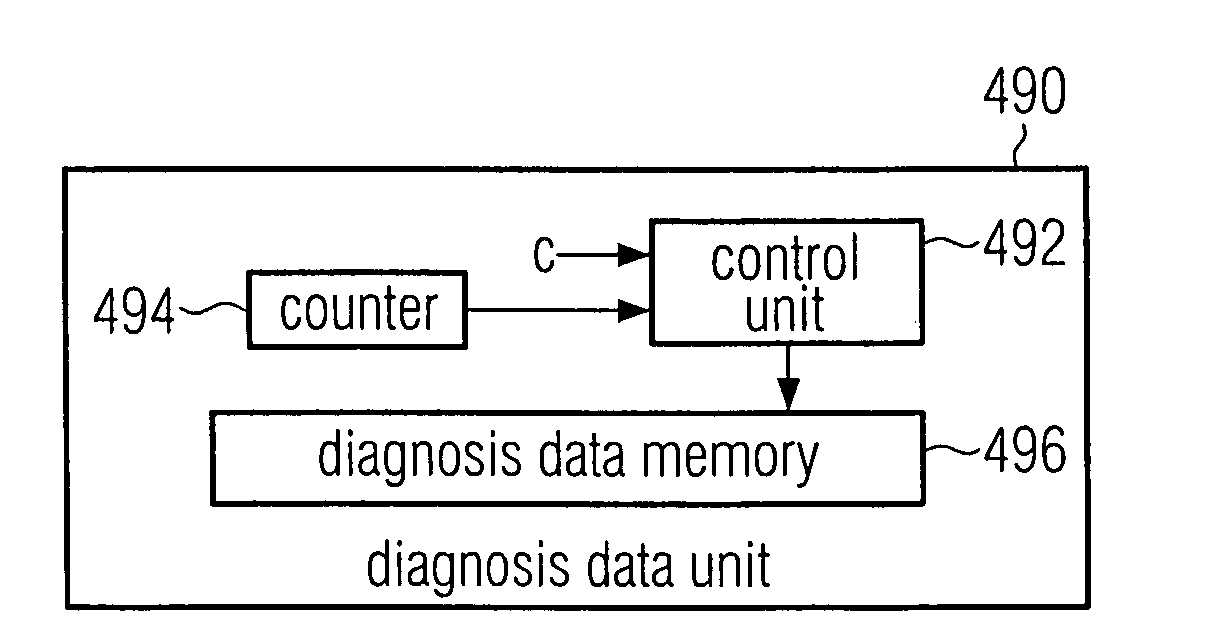

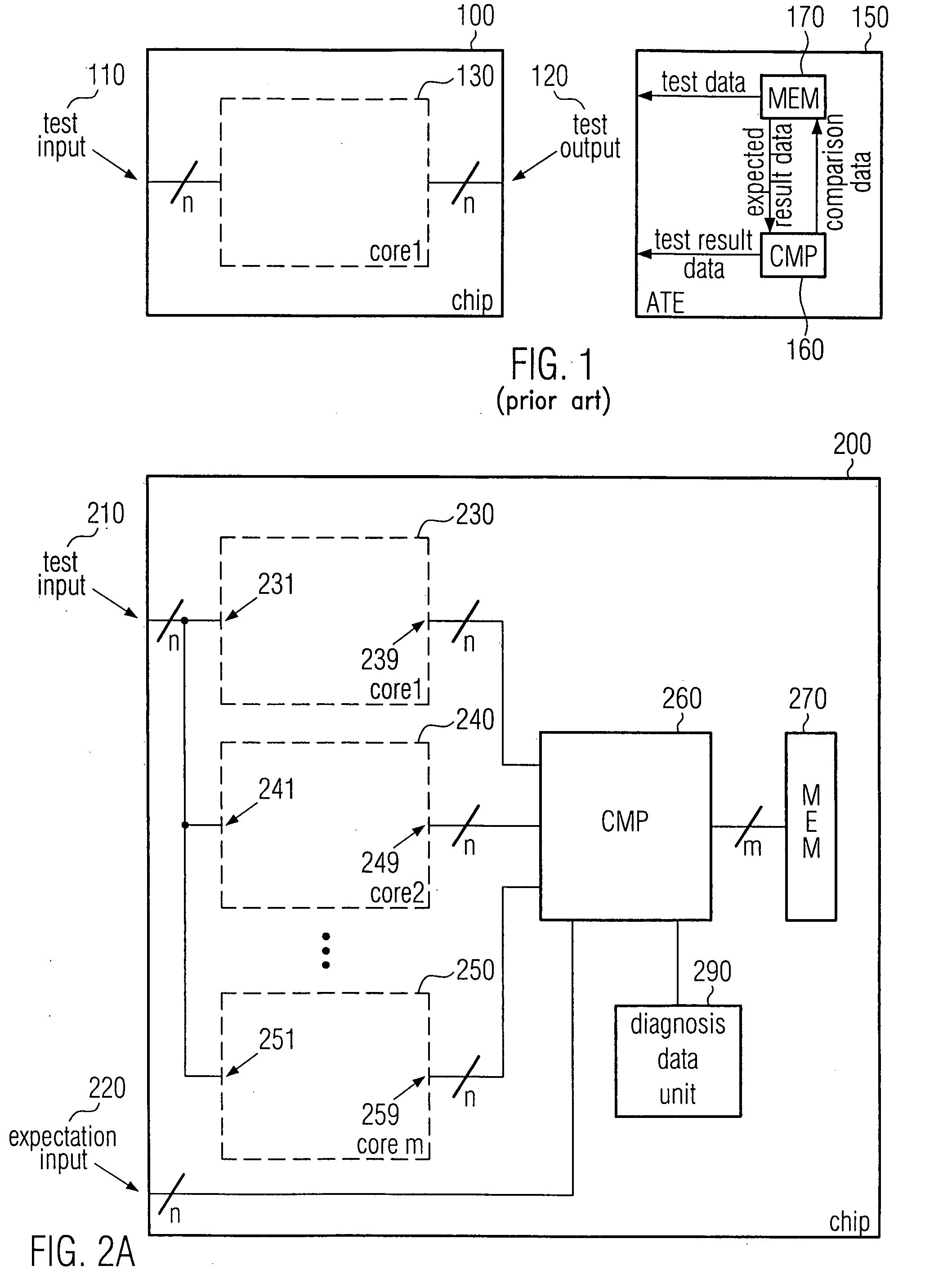

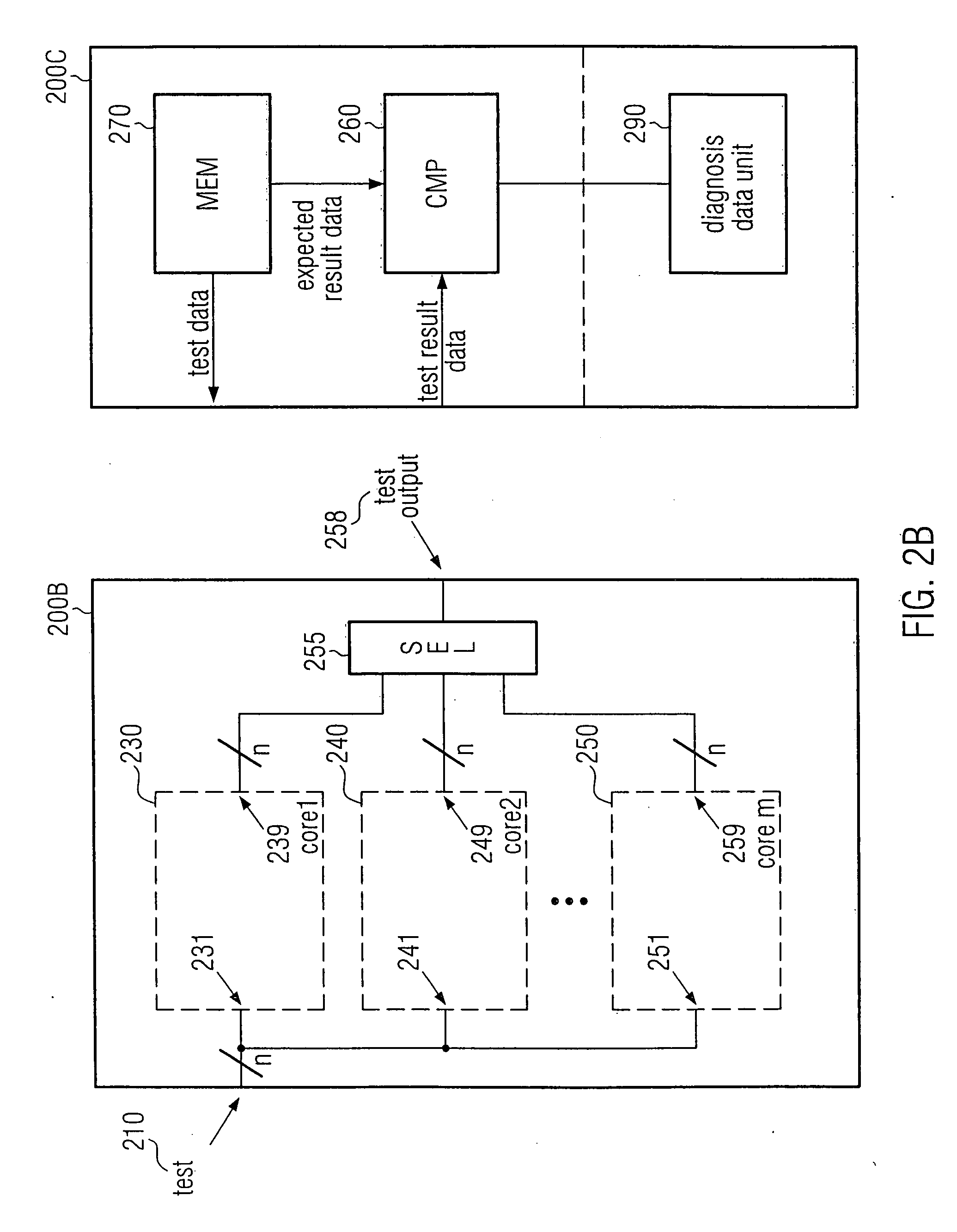

Storing multicore chip test data

ActiveUS20080148120A1Improve efficiencyElectronic circuit testingLogical operation testingDiagnostic dataTest analysis

An integrated chip architecture is provided which allows for efficiently testing multiple cores included in the integrated chip architecture and storing corresponding diagnosis data which include an indication of the failure-causing test data and the corresponding test analysis data. Embodiments are provided which enable that the test time and the number of required Input / Output test pins is nearly independent from the number of cores included in the multicore chip. The presented embodiments provide a multicore chip architecture which allows for providing input data to the multiple cores in parallel for simultaneously testing the multiple cores, and analyzing the resulting multiple test outputs on chip. As a result of this analysis embodiments may store on chip an indication for those cores that have not successfully passed the test, together with respective diagnosis data.

Owner:ADVANCED MICRO DEVICES INC

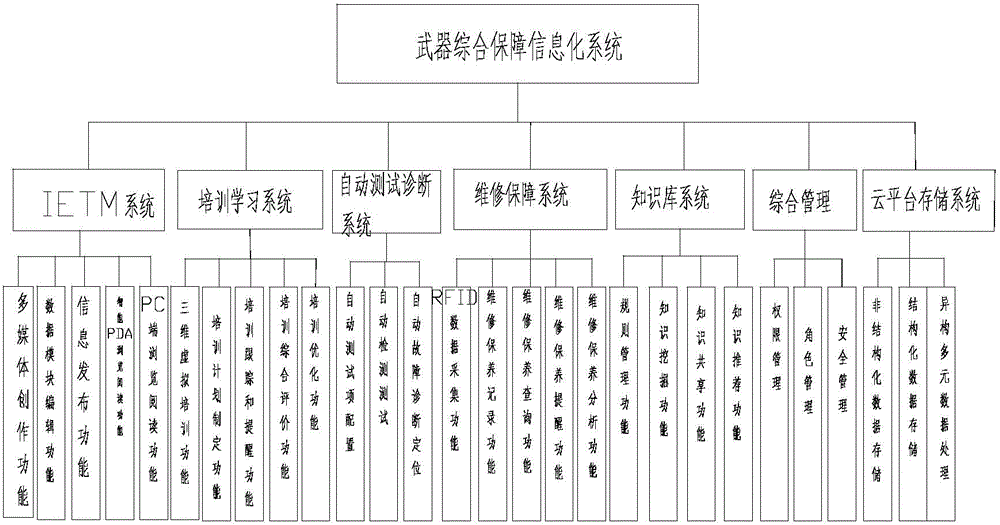

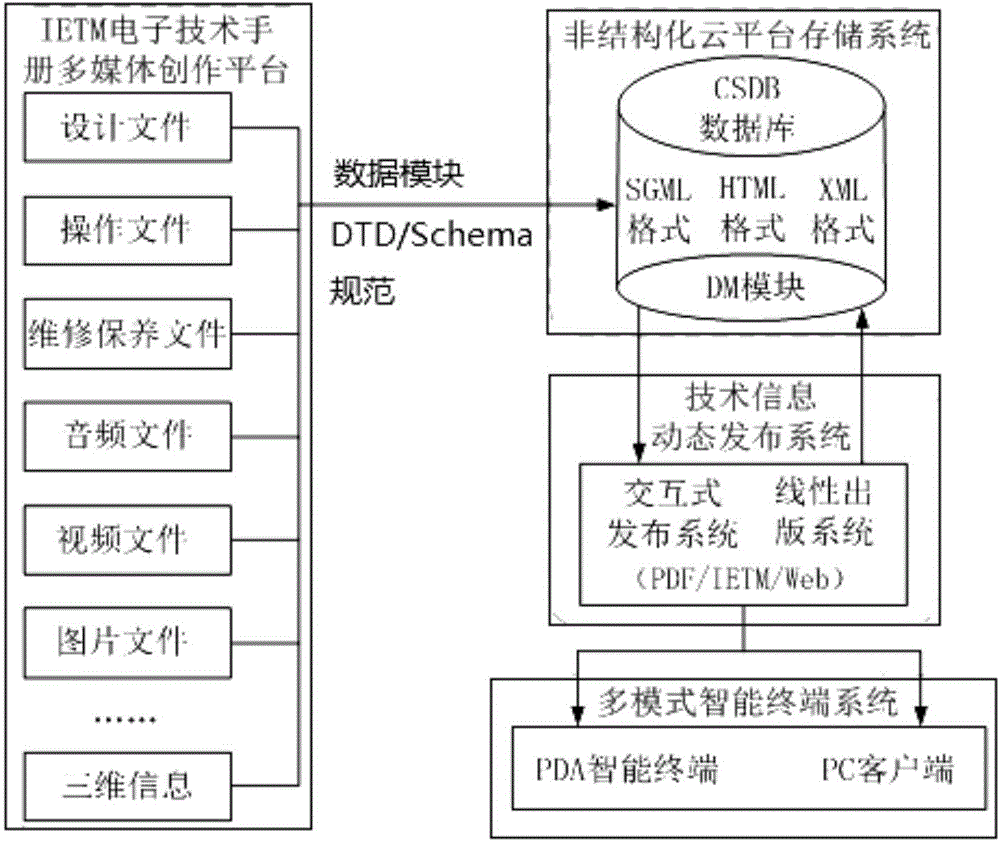

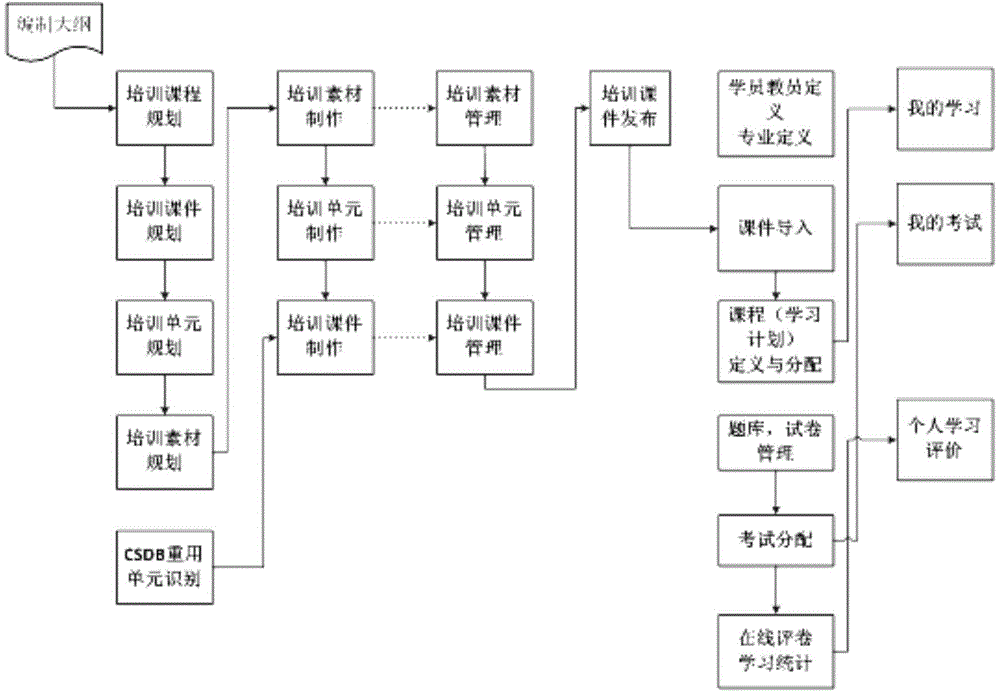

Compressive guarantee system for equipment based on IETM

InactiveCN104657903AIntuitive imageImprove security efficiencyCosmonautic condition simulationsData processing applicationsInformatizationDecomposition

The invention discloses a compressive guarantee system for equipment based on an IETM. The compressive guarantee system comprises a business system and a platform support system, wherein the business system comprises an IETM system, a training learning system, an automatic test and diagnosis system, a maintenance support informatization system and a knowledge base system, wherein the platform support system comprises a cloud platform storage system and a compressive management system. The compressive guarantee system disclosed by the invention is combined in image-text, linked in audio and video, visual and intuitional, and friendly to interface, and is capable of carrying out three-dimensional demonstration, operation and decomposition, automatic navigation, depth search, phenomenon and fault association, automatic test and smart fault analysis; the compressive guarantee efficiency is improved; the operating error rate is reduced; the use and maintenance complexity of the system is lowered; the fault treatment time is shortened; the test time is shortened; the compressive guarantee system is a scientific and reasonable training system; the training learning cycle is shortened; a knowledge base system is accumulated and shared; and the dependence on personal experience is reduced.

Owner:SICHUAN AEROSPACE SYST ENG INST

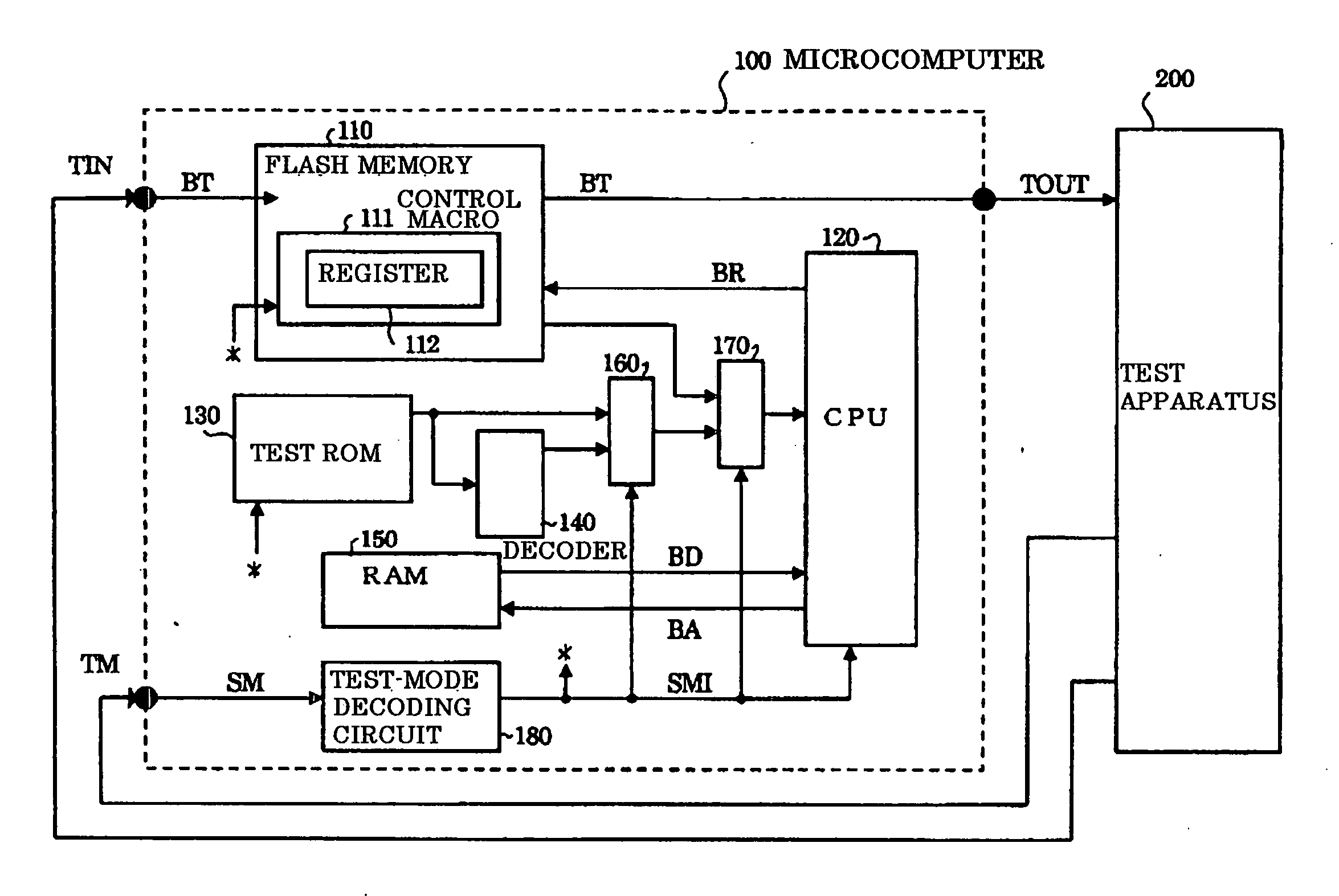

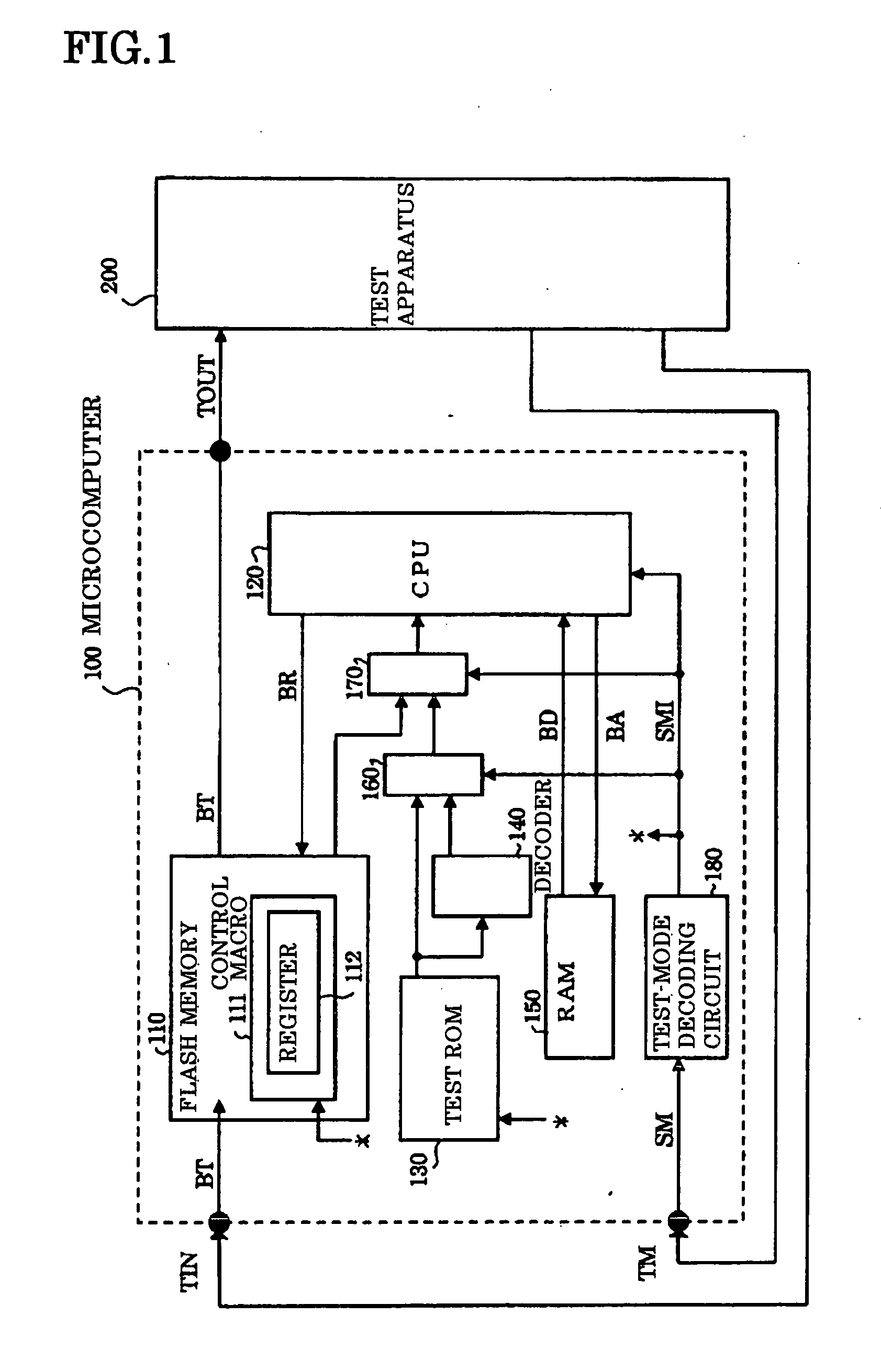

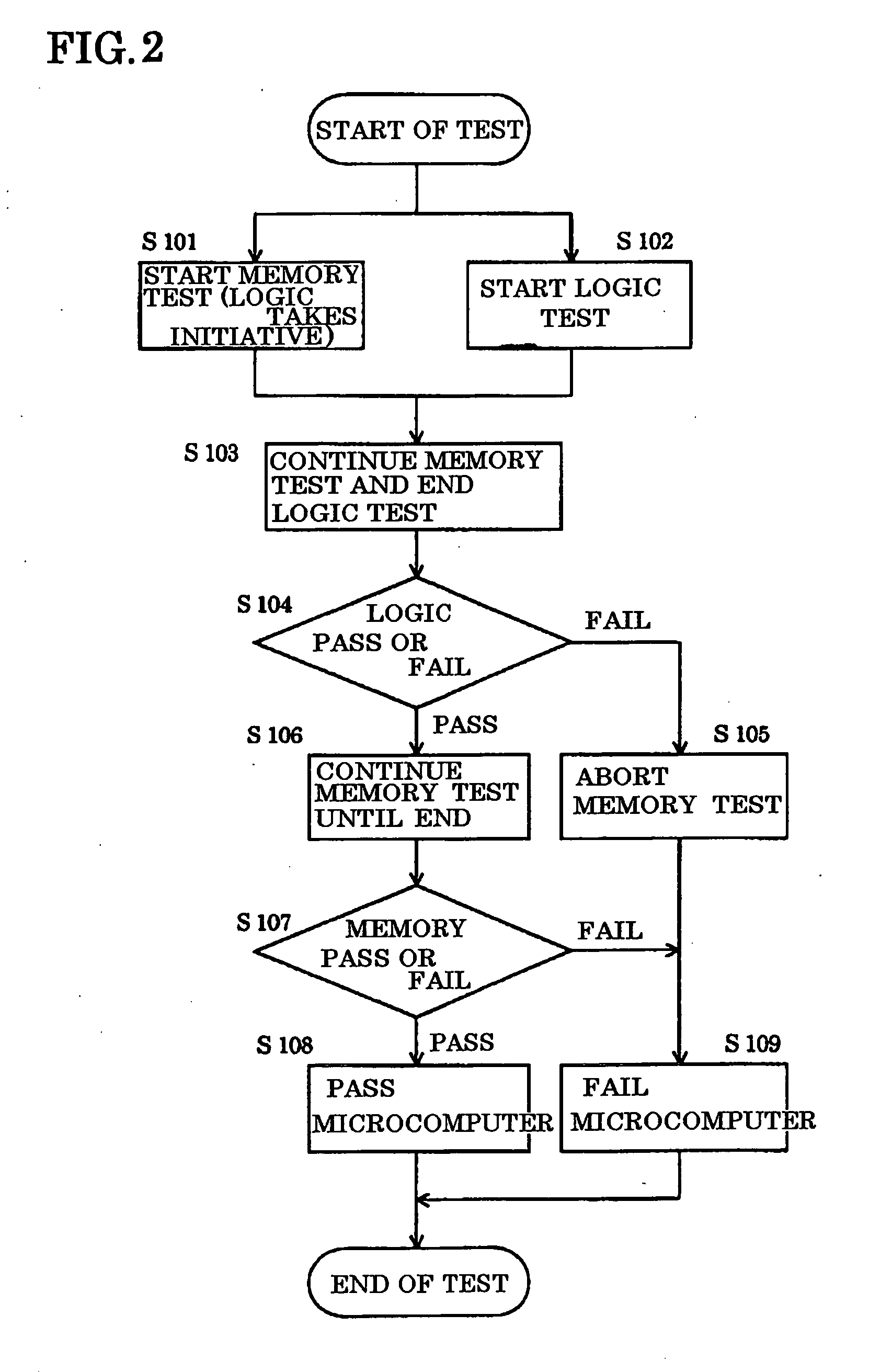

Microcomputer and method of testing same

InactiveUS20050210348A1Shorten test timeSmall sizeMemory loss protectionElectronic circuit testingMicrocomputerTested time

A microcomputer includes a memory such as a flash memory; a logical circuit such as a CPU; a test ROM storing a test program for testing at least the logical circuit; and recording means capable of storing, as a flag, the result of testing at least one of the memory and logical circuit. The memory and the logical circuit are tested simultaneously to shorten test time. The test-result flag is checked upon being stored. When the flag indicates failure of the logical circuit, testing of the memory is aborted, and vice versa.

Owner:NEC ELECTRONICS CORP

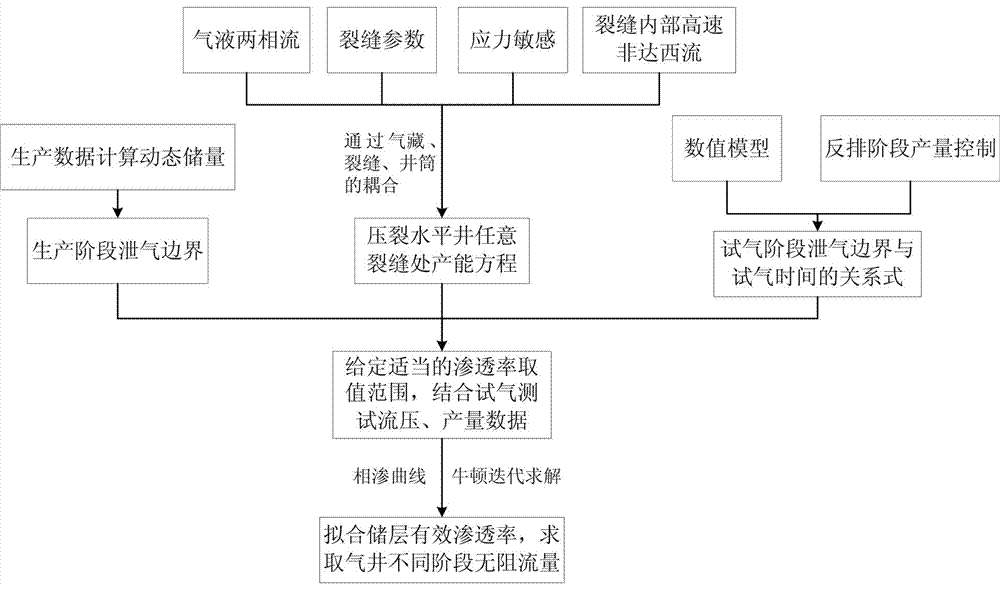

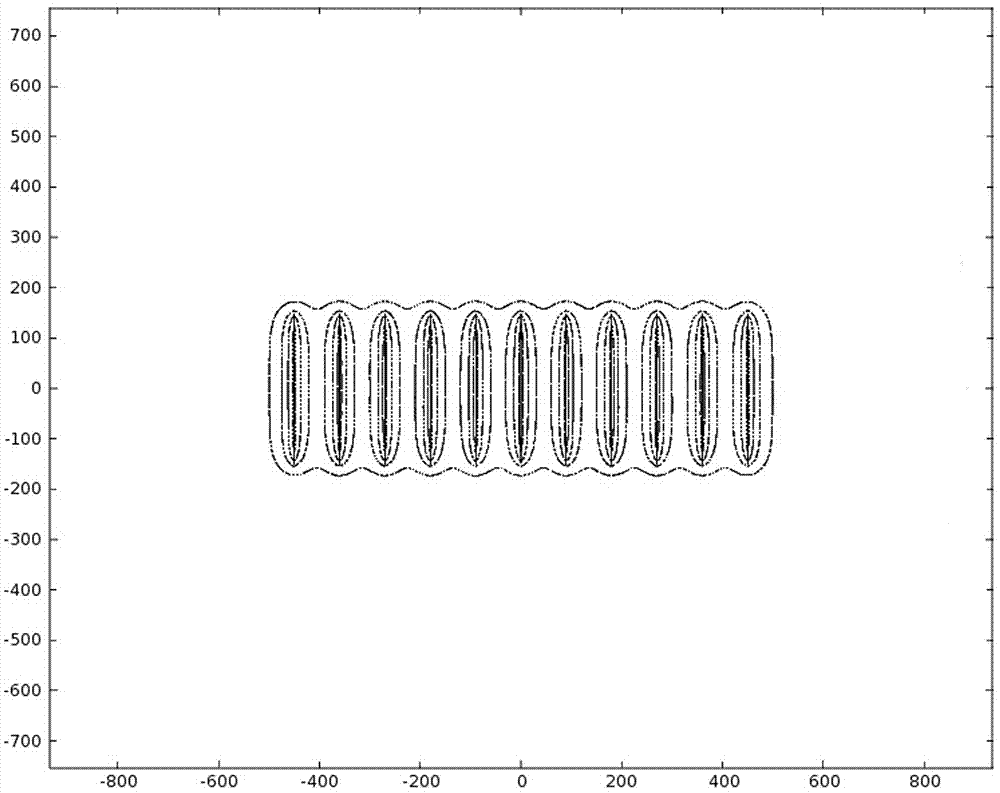

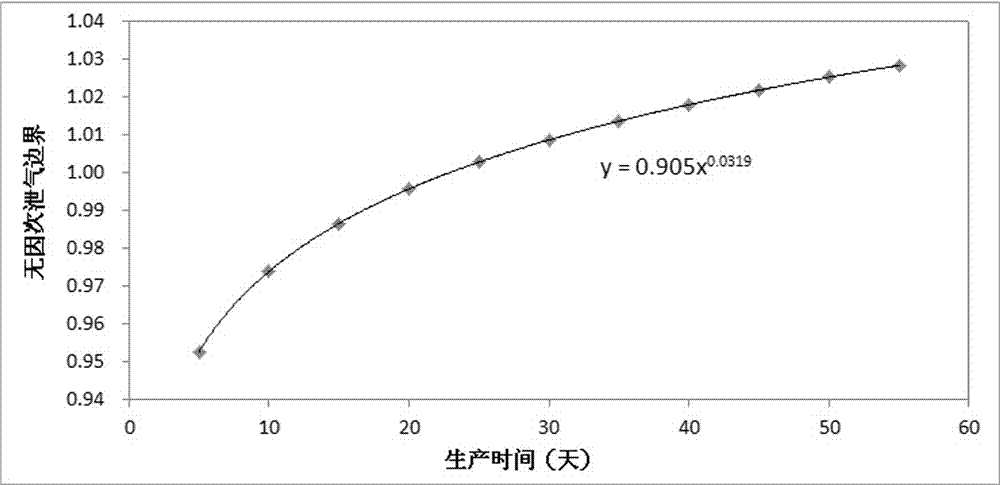

Method for predicting dynamic open-flow capacity of fractured horizontal wells for tight sandstone gas reservoirs

InactiveCN107301306AImprove reliabilityPracticalData processing applicationsDesign optimisation/simulationRock corePredictive methods

The invention relates to the field of gas field development research, in particular to a method for predicting dynamic open-flow capacity of fractured horizontal wells for tight sandstone gas reservoirs. The method includes coupling gas reservoirs, fracture and wellbores to obtain gas and liquid two-phase flow productivity equations for optional fracture locations of the fractured horizontal wells; building corresponding fractured horizontal well numerical models on the basis of reservoir stratum parameters and fracture parameters to obtain relation curves and fitting relational expressions of non-dimensional gas release boundaries and gas test time; computing gas release boundaries of the fractured horizontal wells at production phases by the aid of dynamic reserves inverse processes; solving the gas and liquid two-phase flow productivity equations on the basis of phase permeability curves obtained by rock core tests so as to obtain the dynamic open-flow capacity of the fractured horizontal wells at the different production phases. The method has the advantages that influence of difference of physical parameters of reservoir strata, change of the fracture parameters, difference of gas well open-flow test time, external fracturing fluid and movable water of formations on open-flow capacity is taken into consideration, accordingly, the open-flow capacity of the fractured horizontal wells at the different production phases can be predicted by the aid of the method, and the prediction practicality and reliability can be improved.

Owner:SINOPEC NORTH CHINA OIL & GAS CO

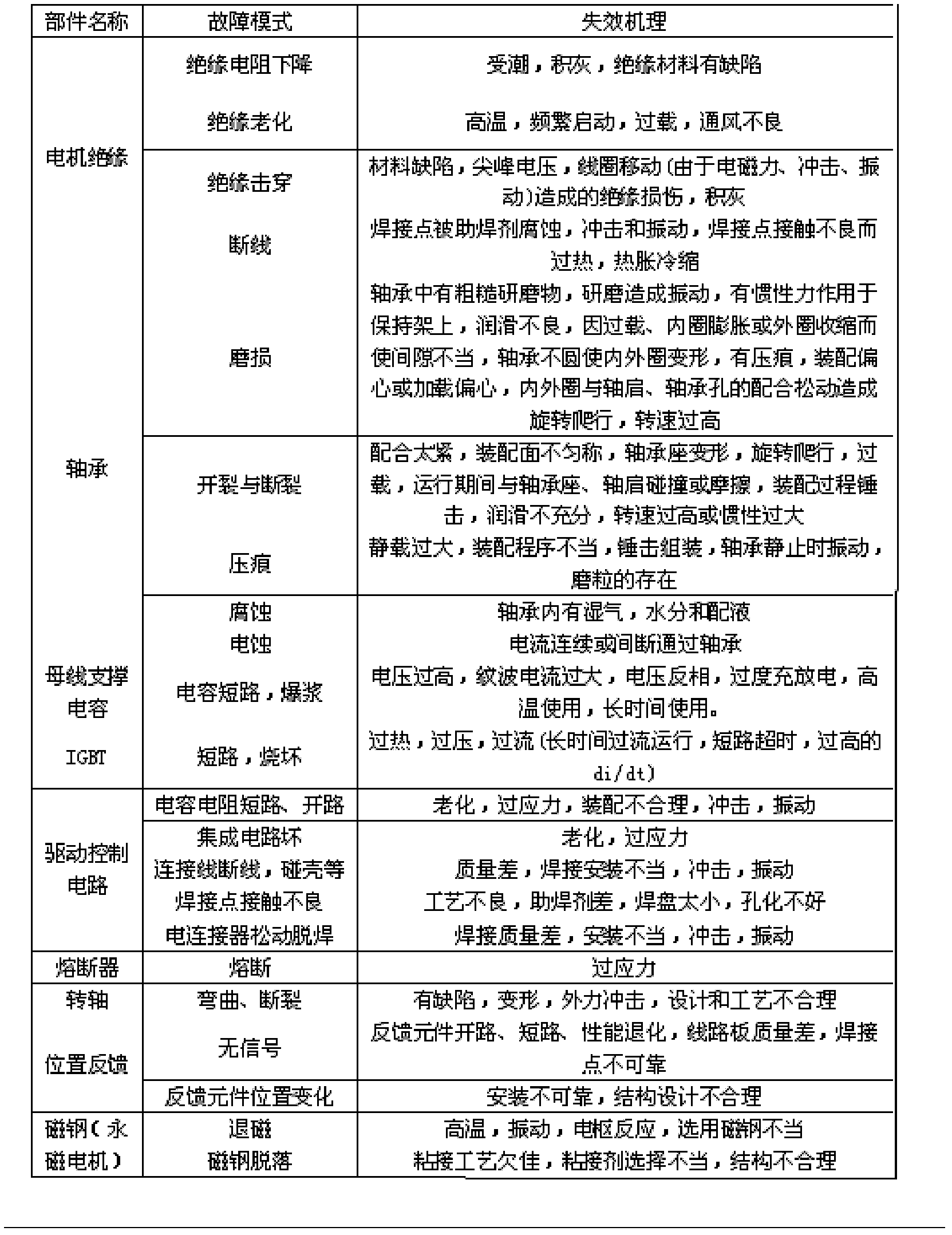

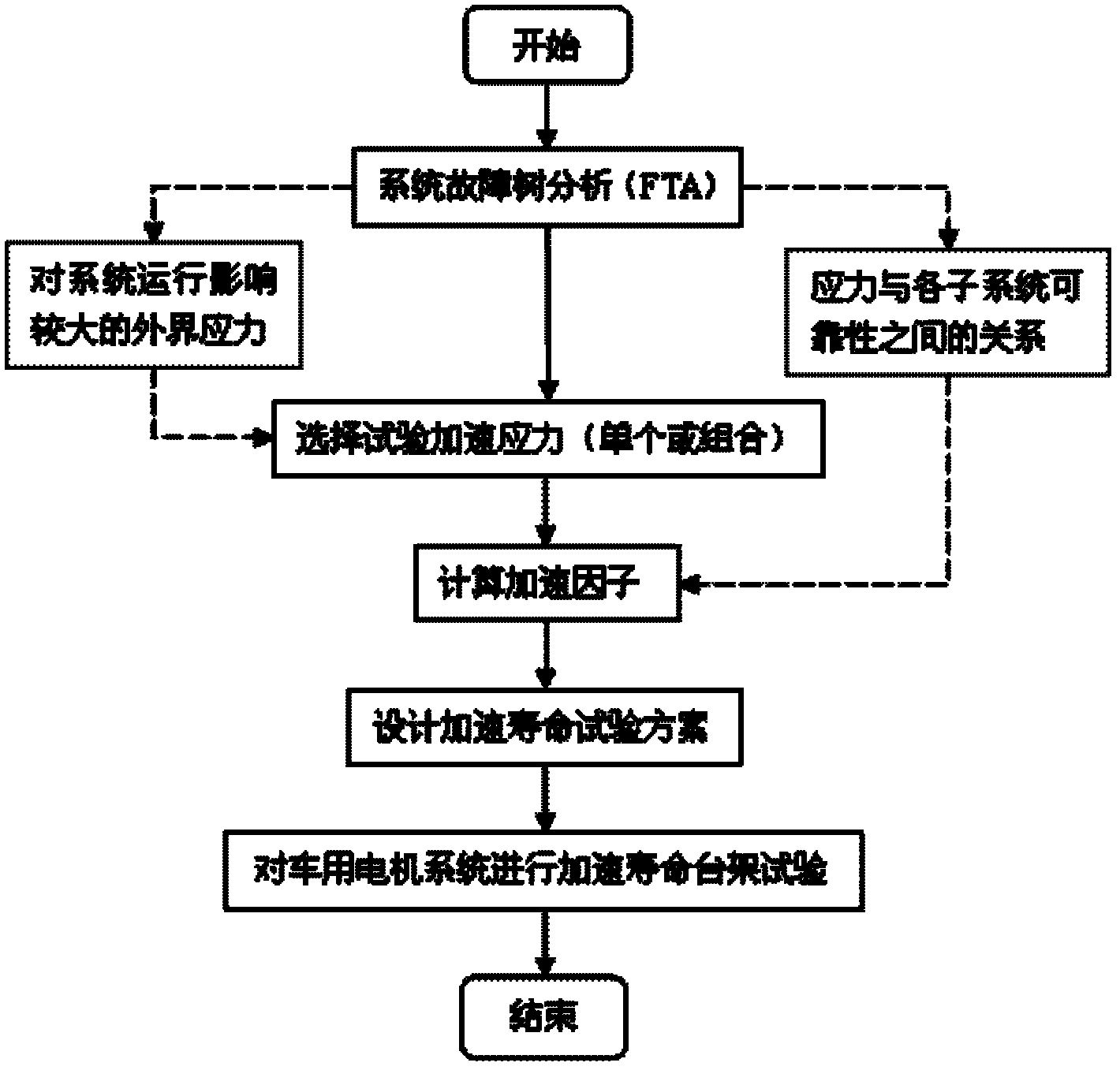

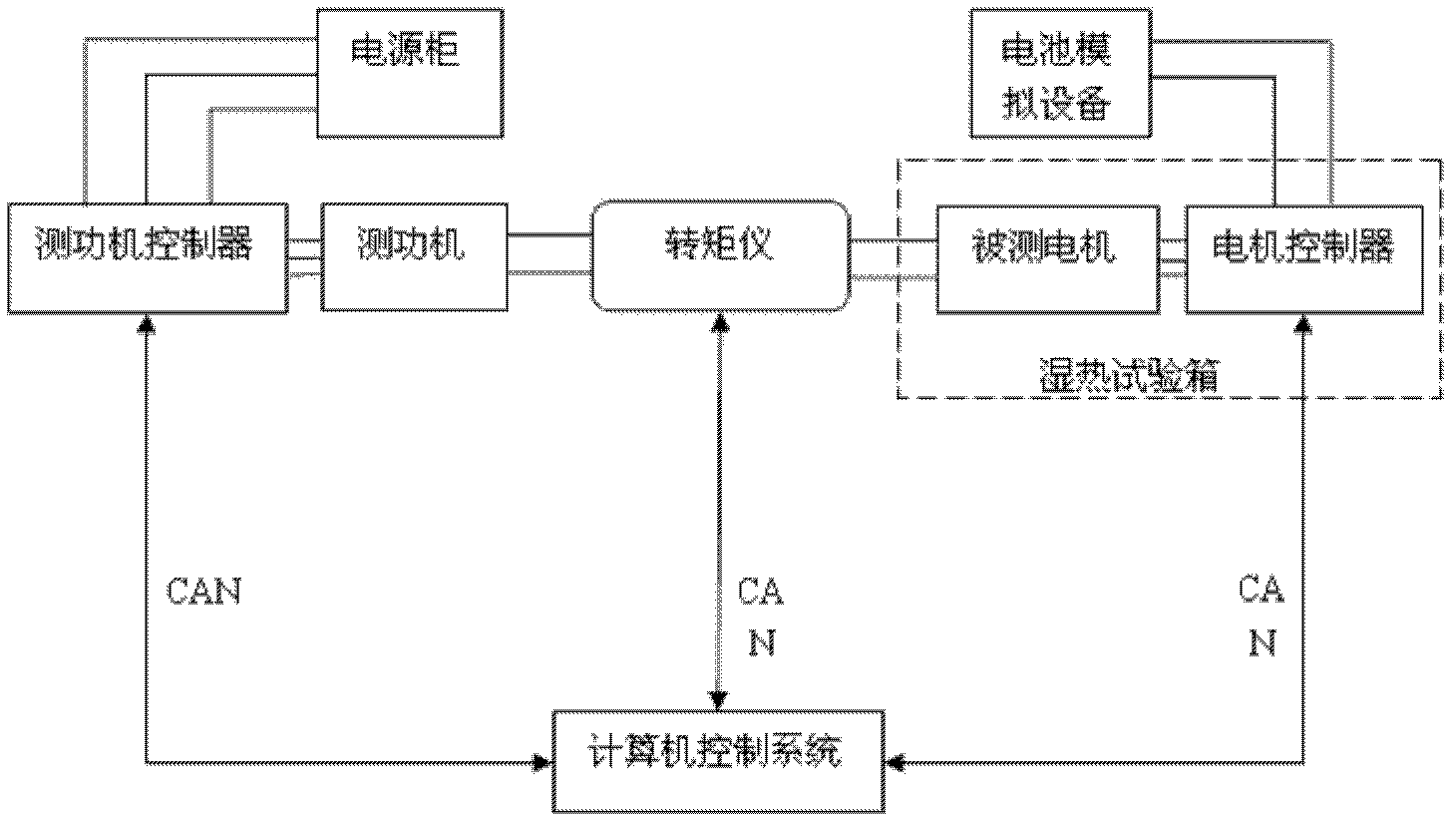

Method for estimating endurance life of vehicle motor driving system

The invention relates to a rack test method for accelerating service life and estimating the reliability of a vehicle motor driving system. By considering actual operation environments and work conditions of a vehicle motor system, a service life factor and a corresponding average service life can be calculated through specifically analyzing different failure mechanisms and influence factors of all key parts, so as to establish a service accelerating curve of al the key parts; and invalid data of all the key parts under a normal stress condition are obtained through extrapolating the curve. And then, a service life predicated value of the vehicle motor driving system is obtained according to the data, and determined replacing or maintaining time of the vehicle motor driving system is displayed to a user. By utilizing the rack test method to carry out rack service life examining test, the test time can be effectively reduced, the cost is reduced and the researching period is shortened; and the rack test method disclosed by the invention can help workers of electric vehicle manufacturers or vehicle 4S stores to conveniently know about the service life of the vehicle and the replacing or maintaining time of the vehicle.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

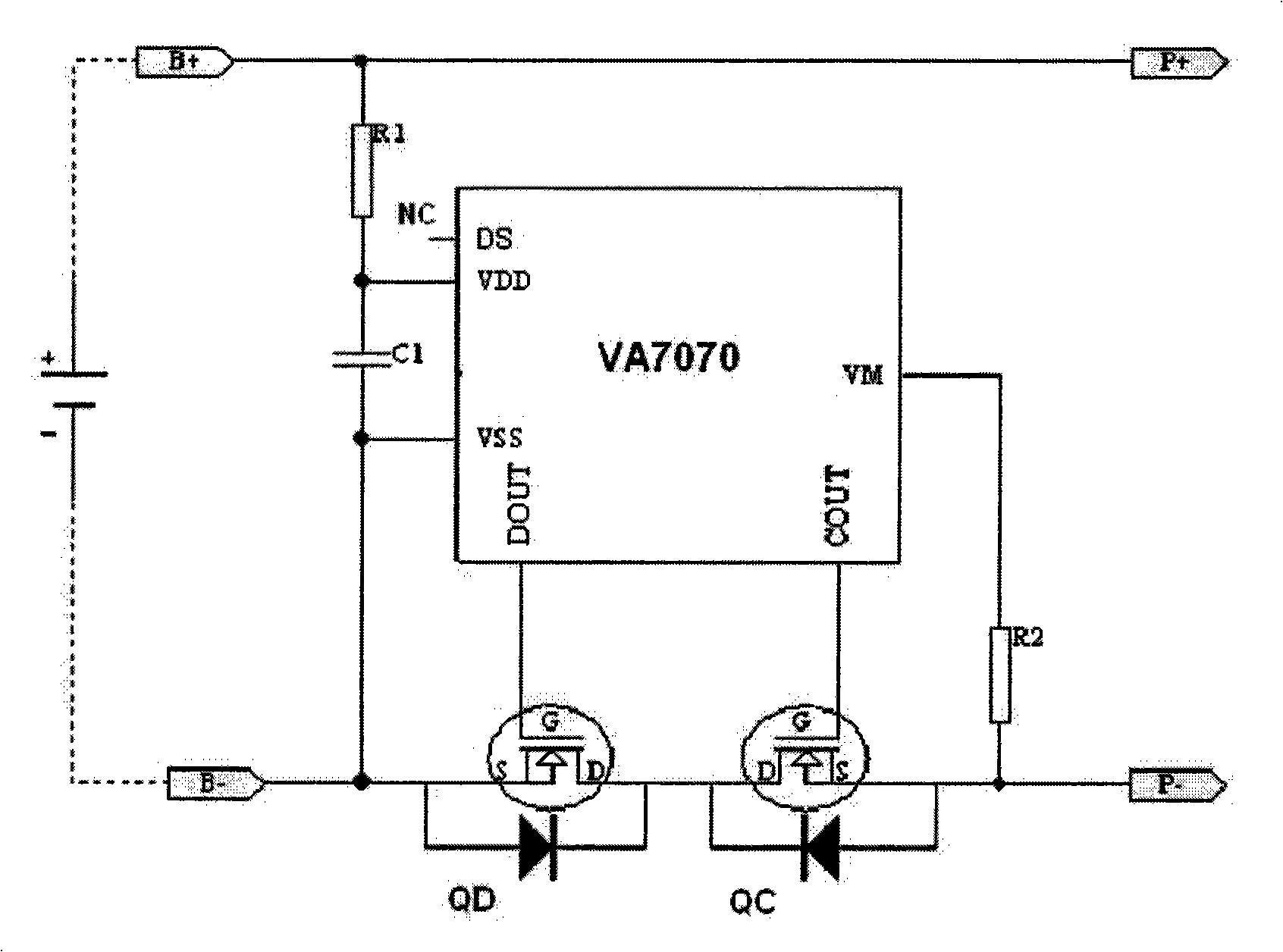

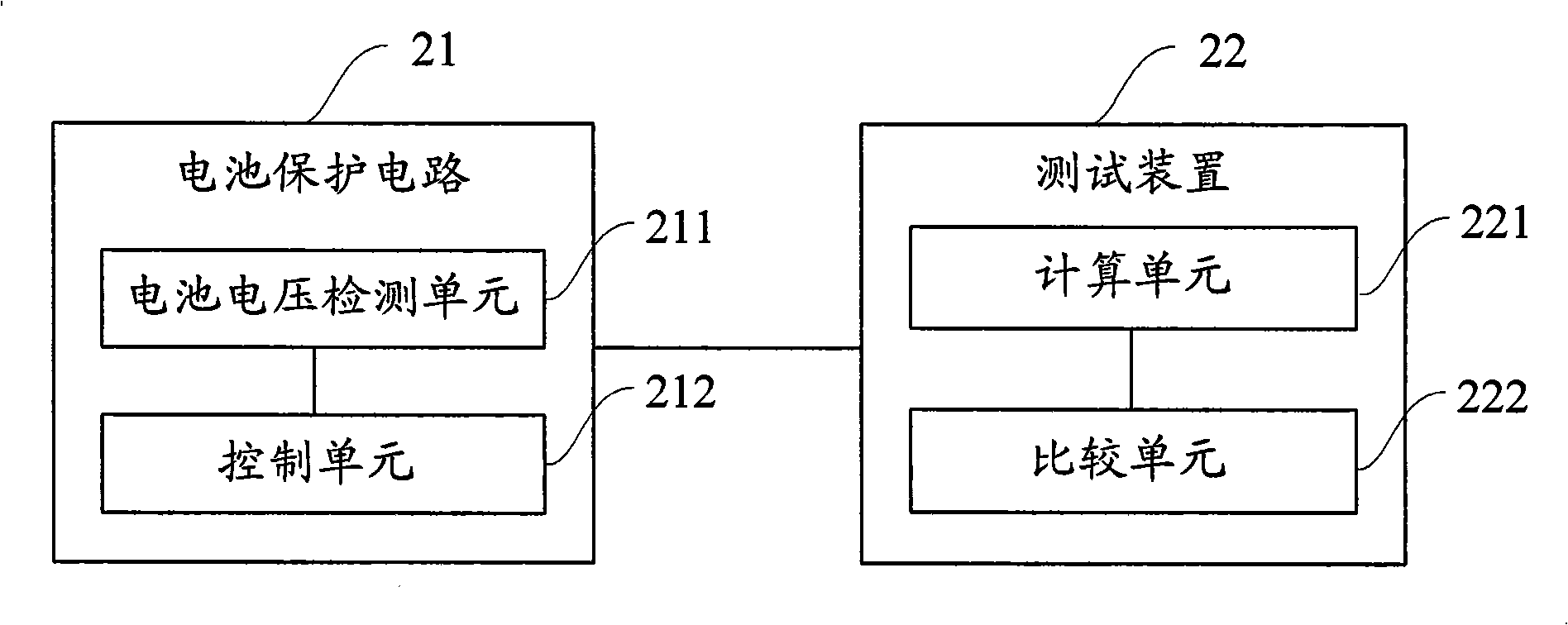

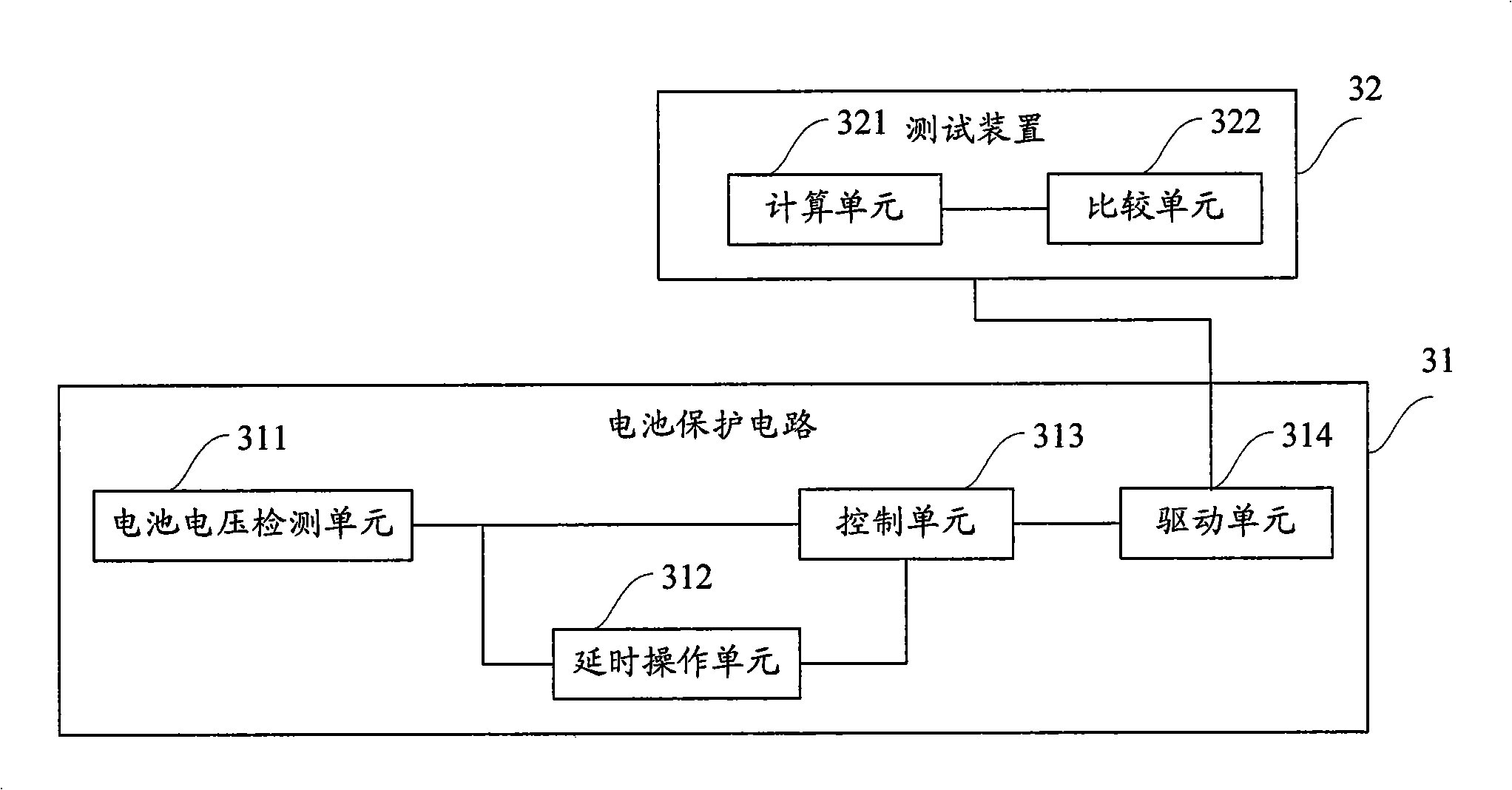

Battery protection circuit, testing device and method for battery protection circuit

ActiveCN101527448AWill not affect the resultDoes not affect test feedbackCurrent/voltage measurementEmergency protective circuit arrangementsElectrical batteryEngineering

The invention provides a testing device of a battery protection circuit, the battery protection circuit comprises a battery voltage detection unit for sending a protection trigger signal when detecting that the Vcc voltage of a power port reaches a preset protection threshold; and a control unit for generating an impedance regulation signal according to the protection trigger signal, and the impedance regulation signal is used for regulating the impedance between the power port in a drive unit and a charge protection execution end Cout or a discharge protection execution end Dout. The testing device comprises a calculation unit for calculating the voltage difference between the power port and the charge protection execution end Cout or the discharge protection execution end Dout; and a comparison unit for comparing the voltage difference calculated at this time with the voltage difference calculated at the last time, if the comparison result exceeds the preset difference value, then test feedback information is output. The invention can simplify the test operation and reduce the test time on the basis of not affecting the normal use of the circuit.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

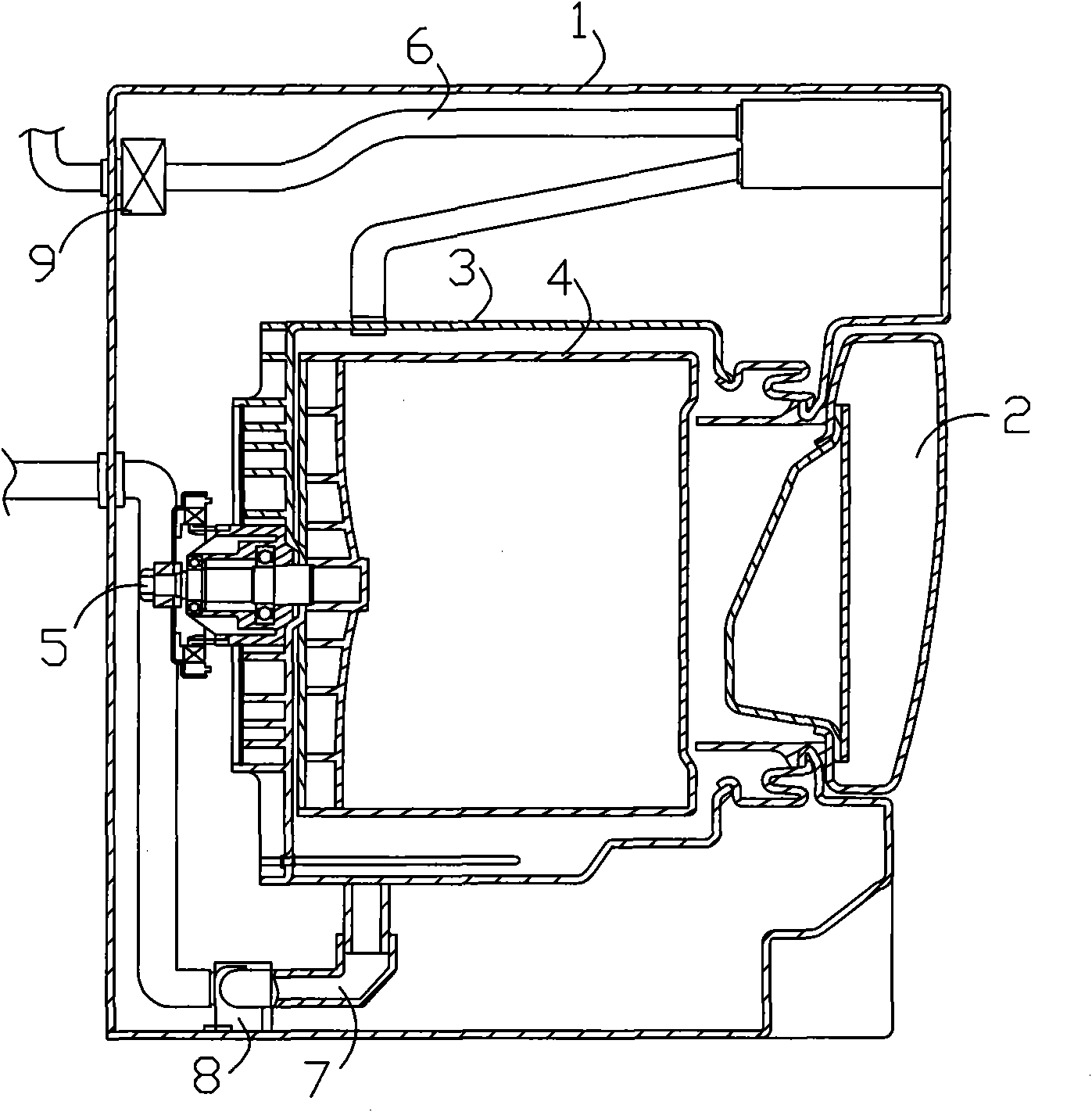

Self-weighing method for drum-type washing machine

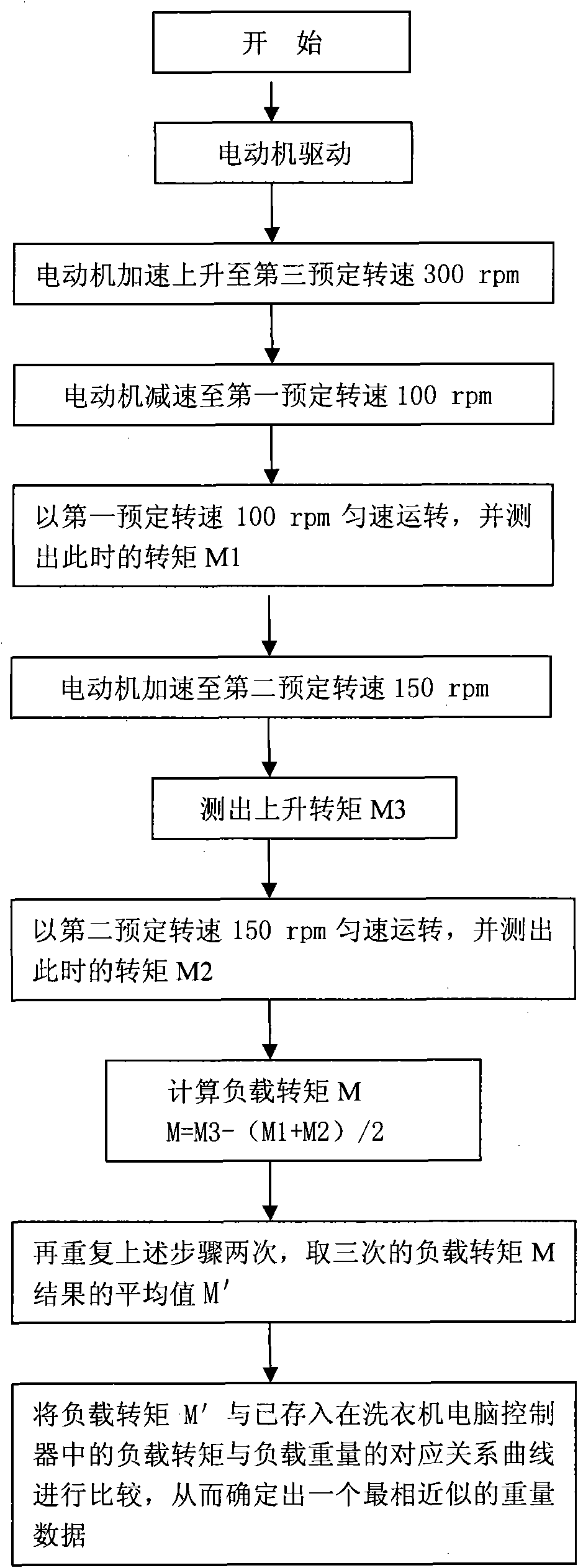

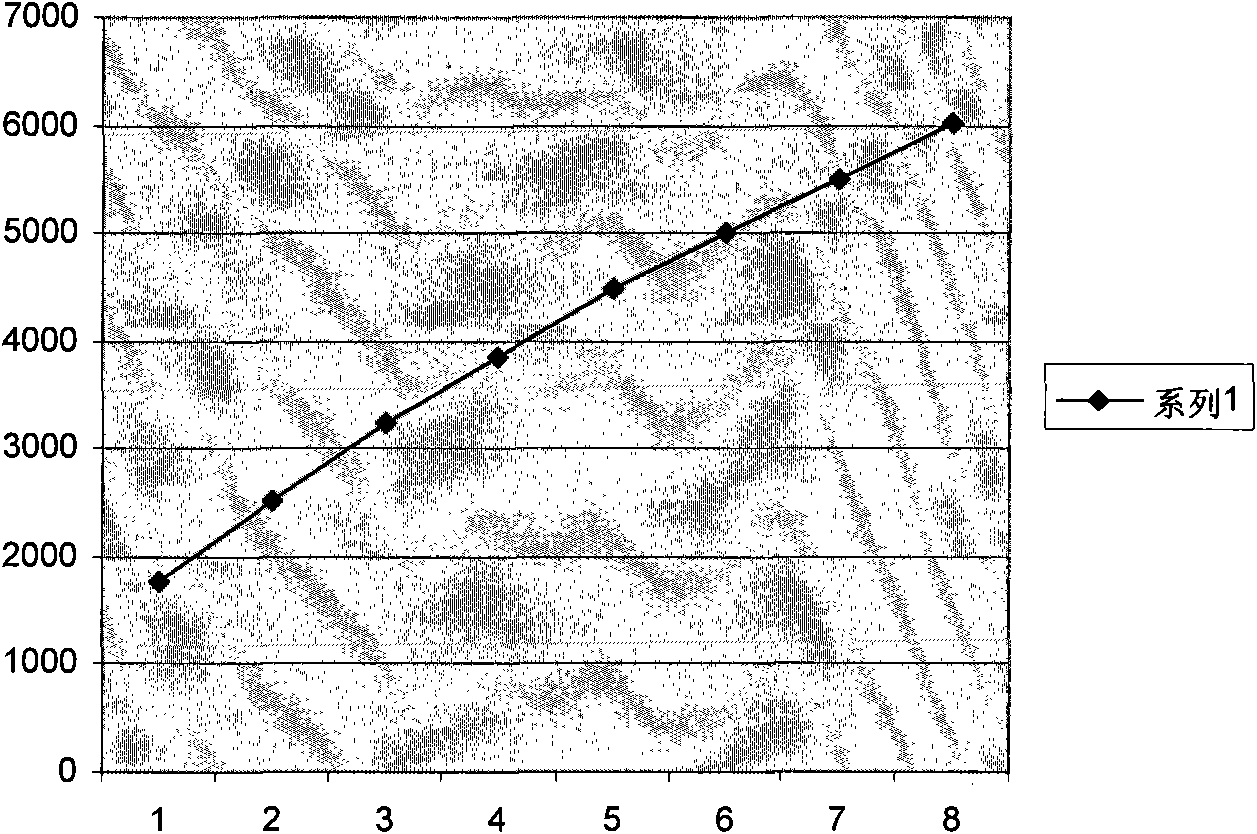

ActiveCN101526388AAccurate measurementAutomatic weighing is accurateOther washing machinesControl devices for washing apparatusLoad torqueControl theory

The invention relates to a self-weighing method for a drum-type washing machine. Firstly, controlling a motor to reach a first preset speed and to rotate at the first preset speed constantly, and measuring the torque of the motor rotating constantly at the first preset speed; secondly, controlling the motor to accelerate from the first preset speed to a second preset speed, and measuring the accelerating torque of the motor accelerating from the first preset speed to the second preset speed; thirdly, controlling the motor to rotate constantly at the second preset speed, and measuring the torque of the motor rotating constantly at the second preset speed; and finally, working out a corresponding load torque by subtracting an average value of the torque of the motor rotating constantly at the first preset speed and the torque of the motor rotating constantly at the second preset speed from the accelerating torque of the motor accelerating from the first preset speed to the second preset speed according to the test results, and after a correction step, comparing the obtained load torque with a curve, pre-stored in a computer controller of the washing machine, of the corresponding relation of a load torque and a load weight to obtain a most similar weight data. The method has the advantages of high test accuracy and short test time.

Owner:QINGDAO HAIER WASHING MASCH CO LTD

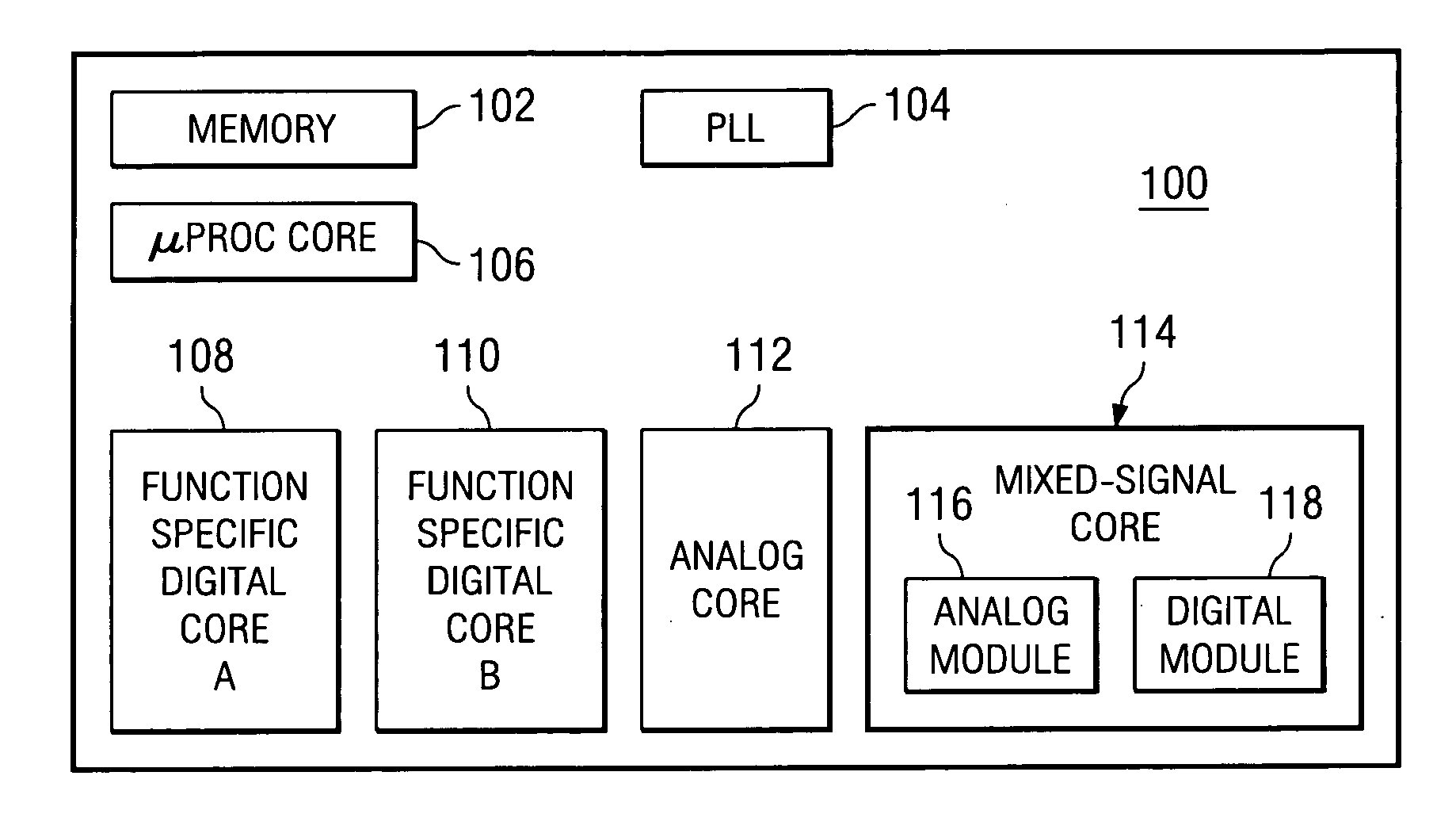

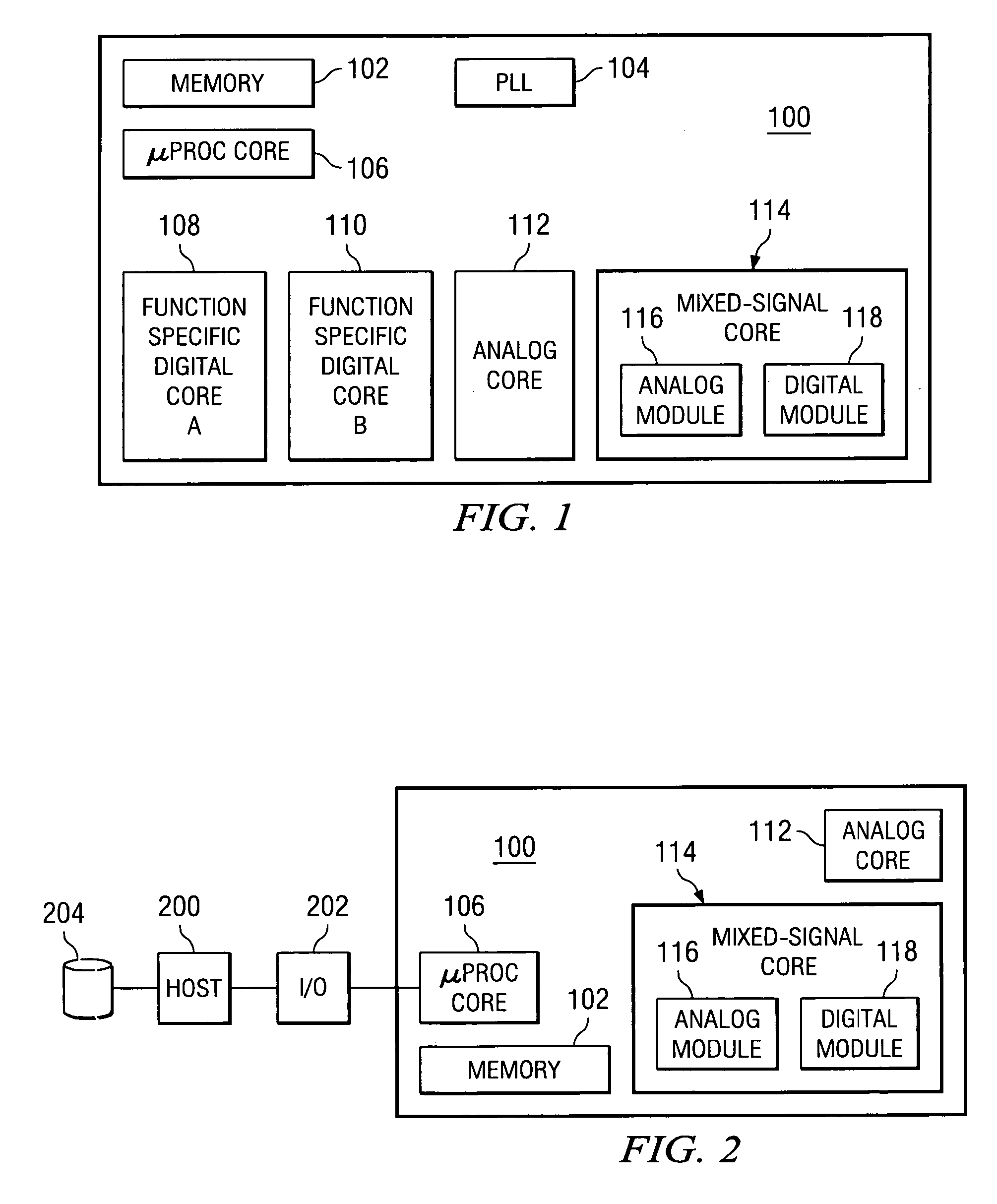

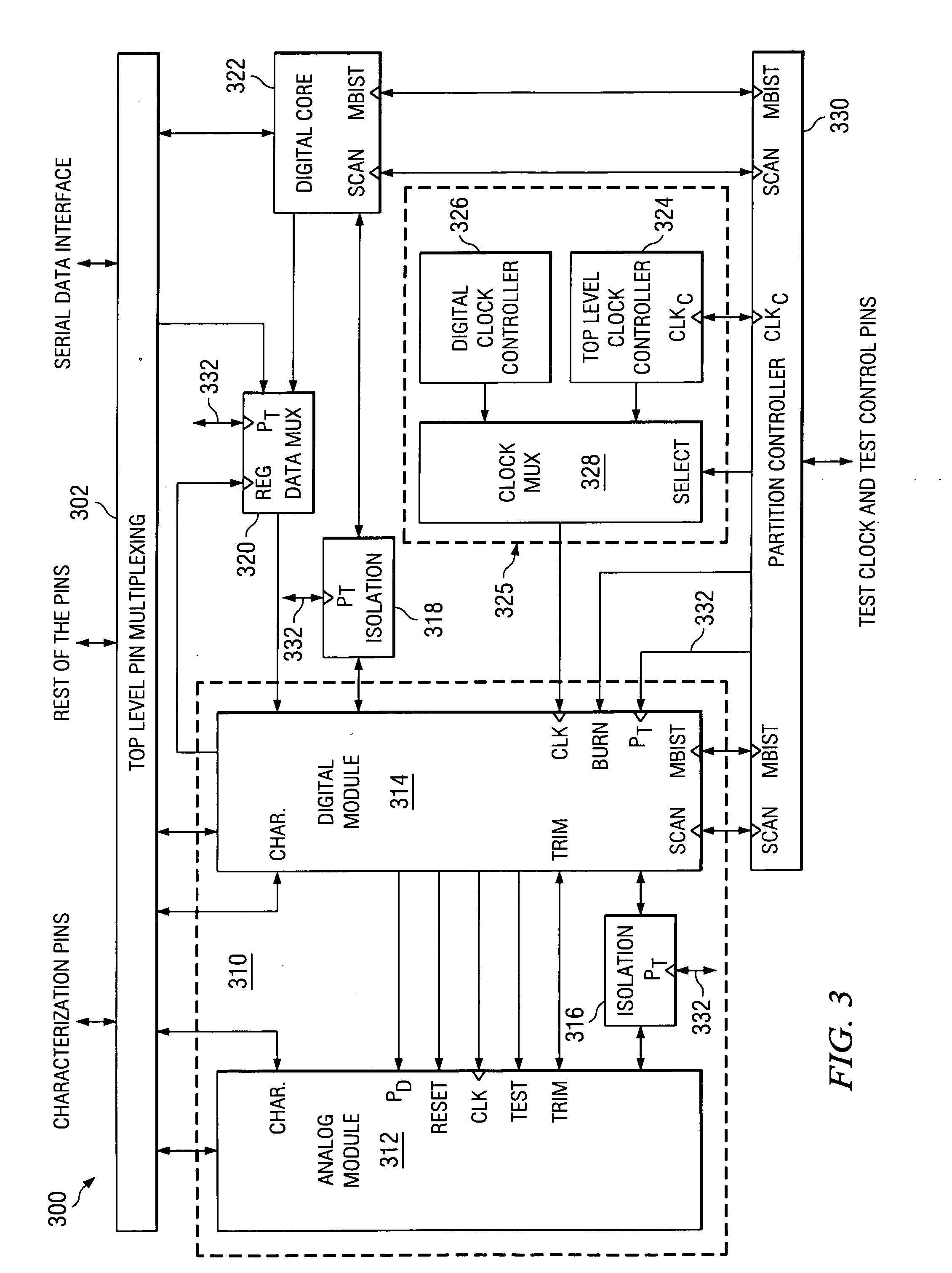

Mixed-signal core design for concurrent testing of mixed-signal, analog, and digital components

ActiveUS20050065747A1Shorten test timeReducing test development timeDigital circuit testingResistance/reactance/impedenceDigital interfaceTested time

A mixed-signal core disclosed herein is designed for efficient concurrent testing analog, mixed-signal, and digital components. One tester may test all components and, thereby, reduce test time without losing full test coverage. An analog module includes all the analog and mixed-signal components of the mixed-signal core, while a first digital module includes digital components required for functional / parametric verification of the mixed-signal components within the analog module. A first virtual boundary connects the analog and the first digital modules to gate the signal transfer during testing. A second digital module includes the remaining digital components of the mixed-signal core, whereby a second virtual boundary separates it from the first digital module. This type of partitioning enables the mixed-signal core to have three modes of operation, wherein the first mode of operation provides digital interface characterization testing of the first and second digital module and analog characterization / trimming testing of the analog module. In the second mode of operation, concurrent testing of the analog module and the first and second digital module is conducted; wherein analog characterization / trimming testing is performed on the analog module and digital interface characterization testing is performed on the first digital module, while SCAN / BIST testing is performed on the second digital module. In the third mode of operation, non-concurrent testing of the analog module, the first digital module, and the second digital module is enabled; wherein SCAN / BIST testing of the first digital module and the second digital module is enabled, while the analog module is powered down.

Owner:TEXAS INSTR INC

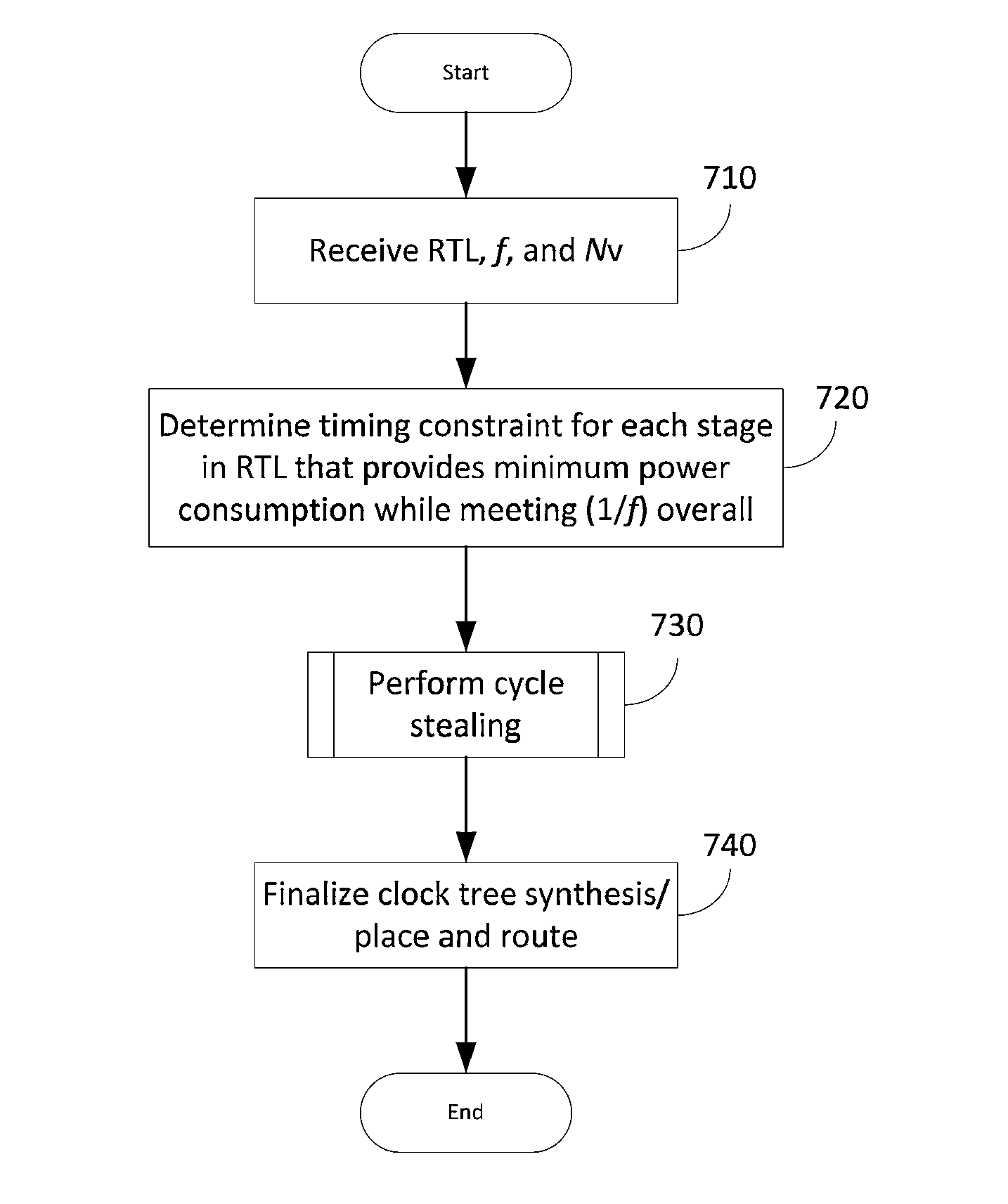

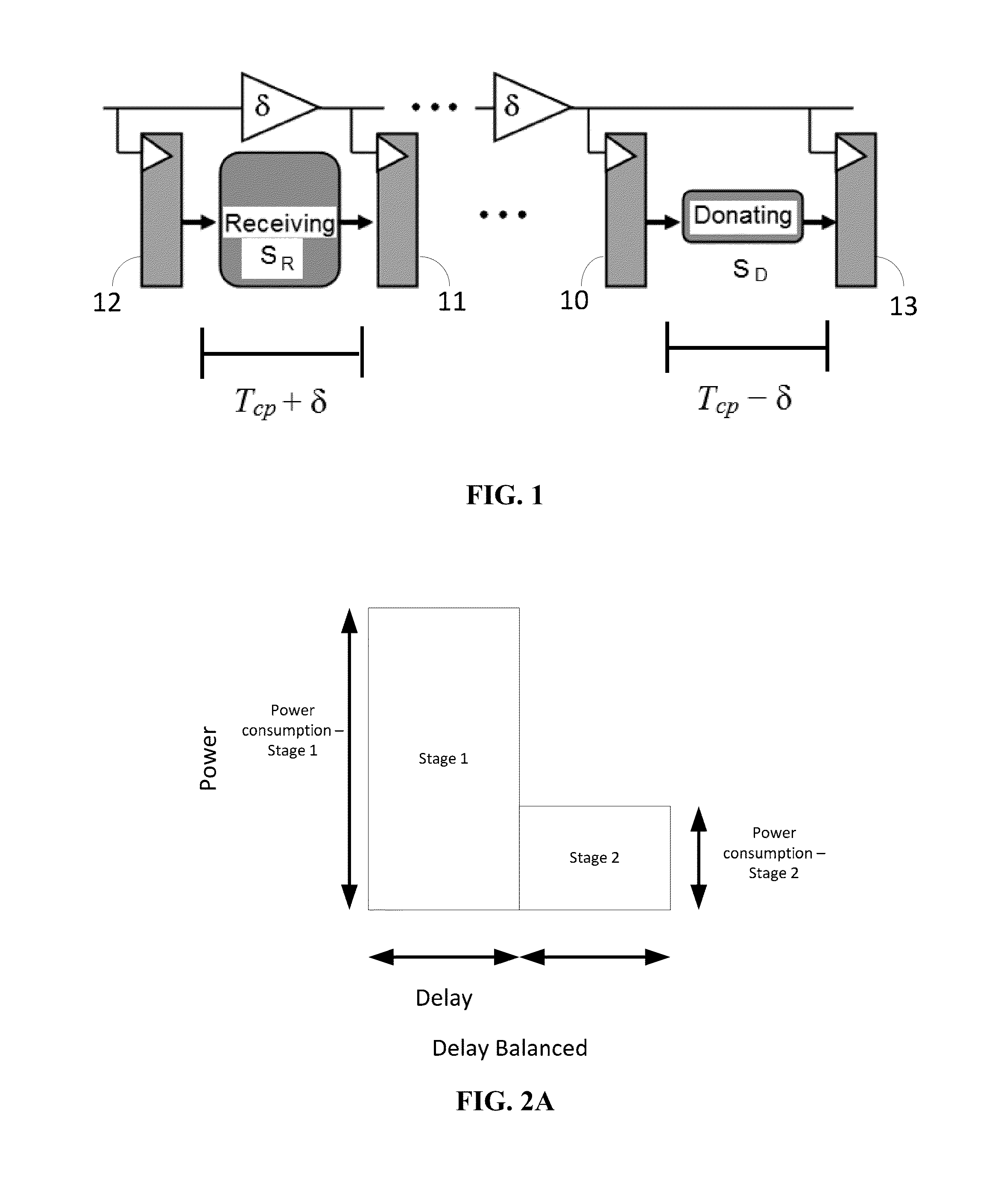

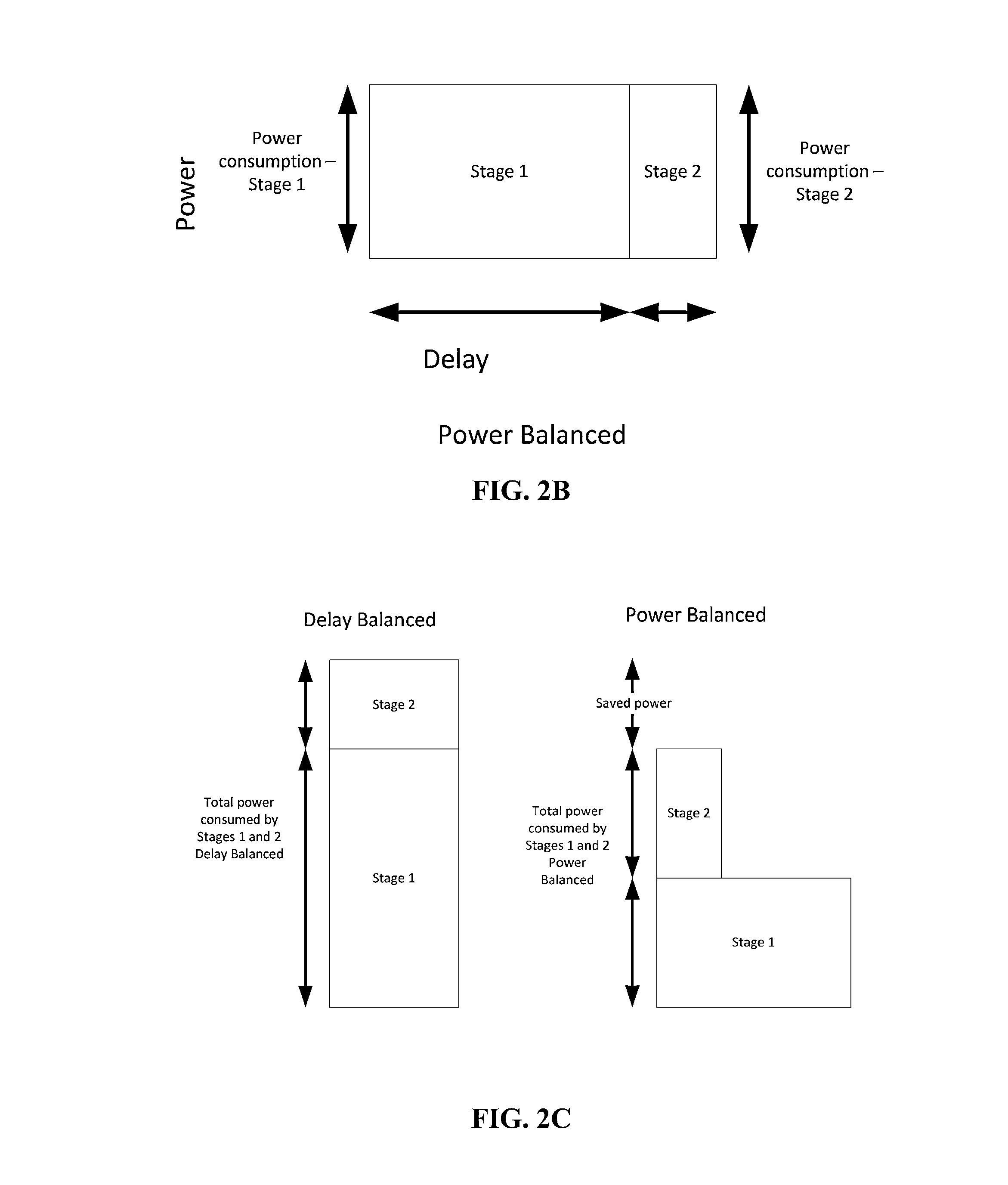

Power balanced pipelines

InactiveUS20130111425A1Reduce power disparitySmall and less leakyCAD circuit designSoftware simulation/interpretation/emulationOperational systemPower balancing

Power balancing techniques are provided for improving power efficiency of pipelined processors. A design-level implementation can be incorporated during synthesis of pipeline clocks in which a register transfer level (RTL) code, operating frequency, and available voltage domains are used to perform cycle time stealing with, and optimize for, power efficiency. A test-level implementation can be incorporated during testing of a chip in which delay and power measurements are used to perform calculations based on cycle time stealing and optimization of power efficiency. The calculations are then used to perform voltage scaling and / or adjust tunable delay buffers. Process variations may also be corrected during test time. A run-time approach can be incorporated for dynamic power balancing in which the operating system keeps track of one or more performance indicators such as a count of floating point instructions and uses a look-up table to provide the appropriate delays.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS