Patents

Literature

129 results about "Analog circuit design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Trustworthy structural synthesis and expert knowledge extraction with application to analog circuit design

ActiveUS20090307638A1Detecting faulty computer hardwareCAD circuit designAnalog circuit designAnalytic model

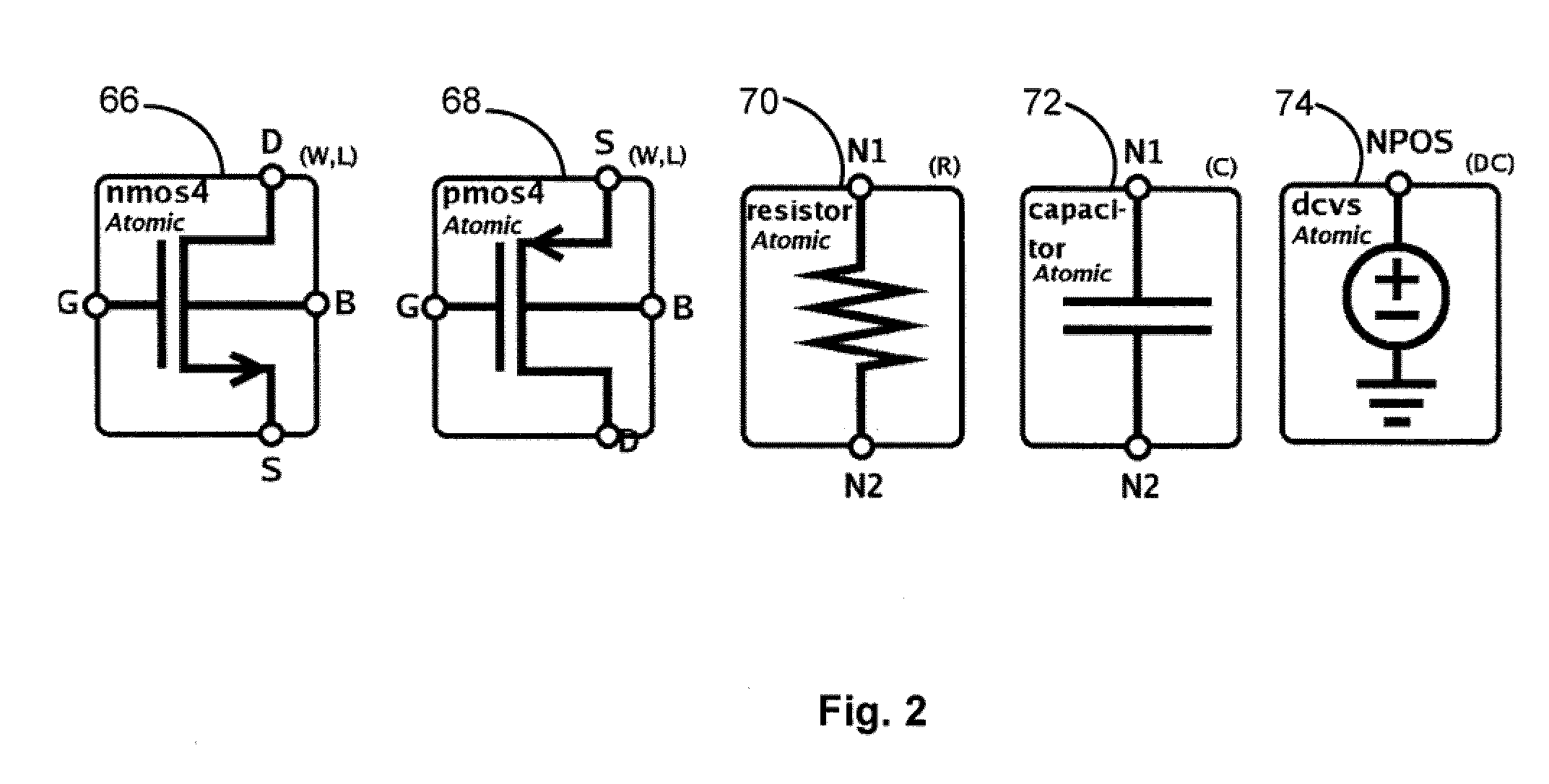

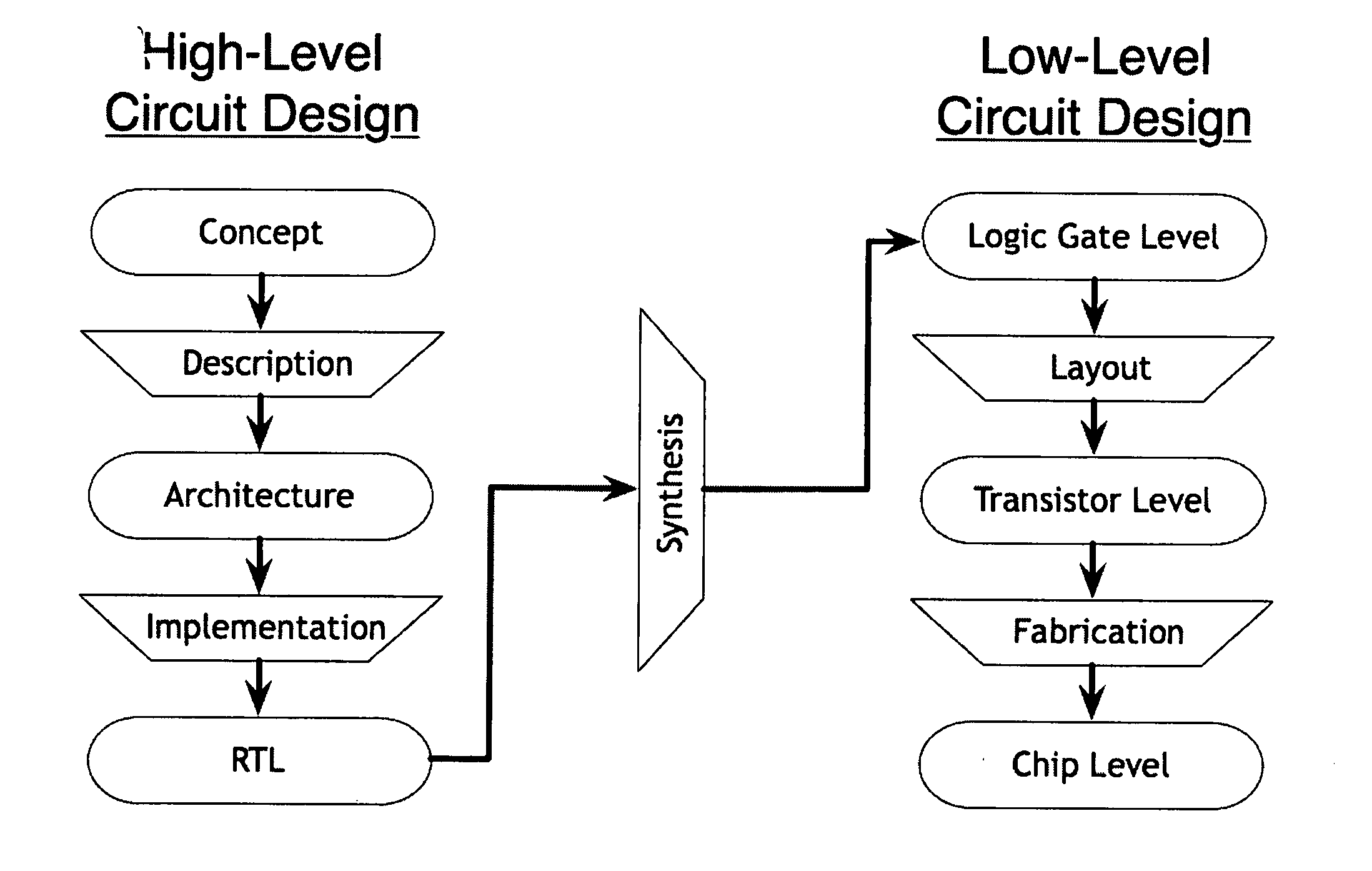

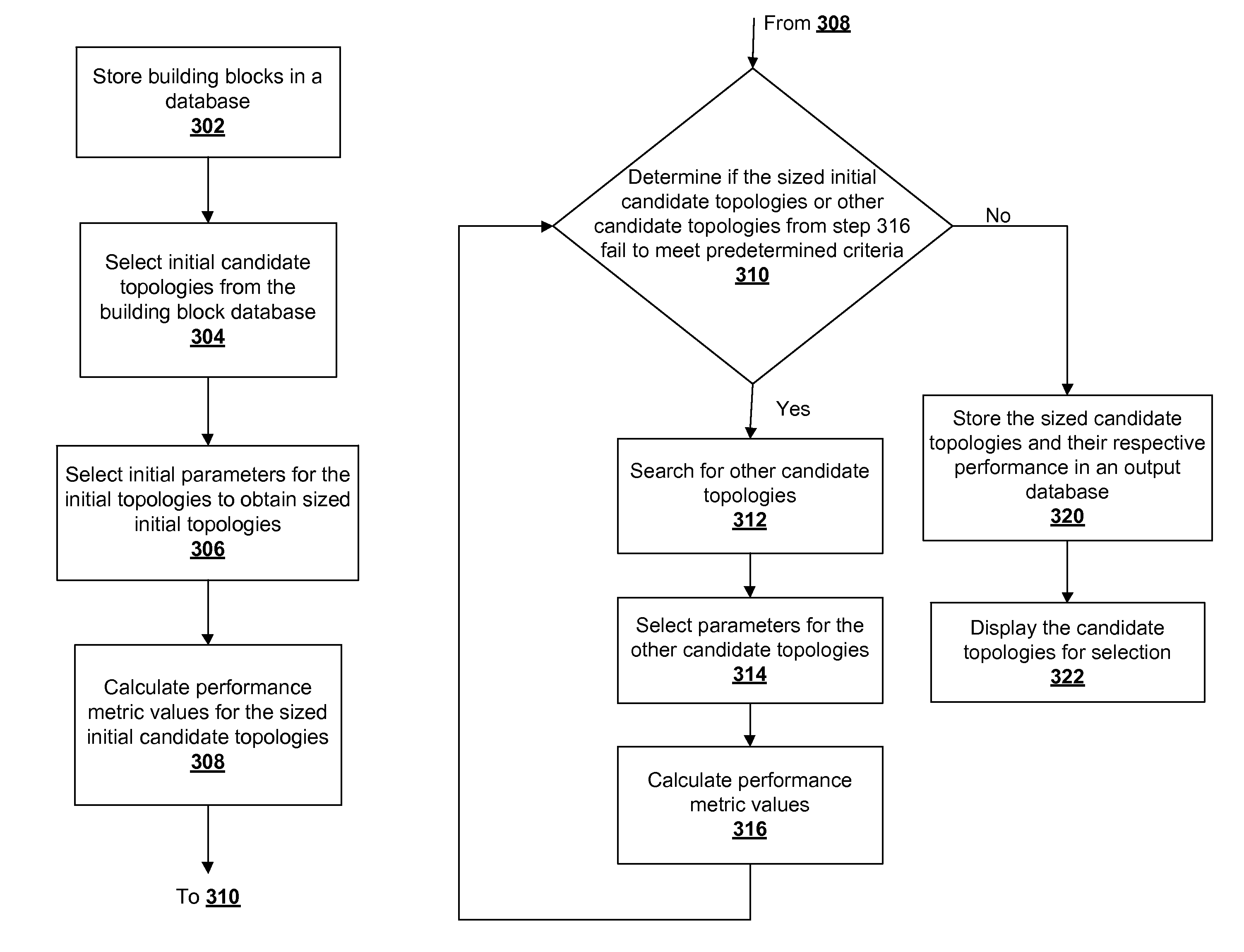

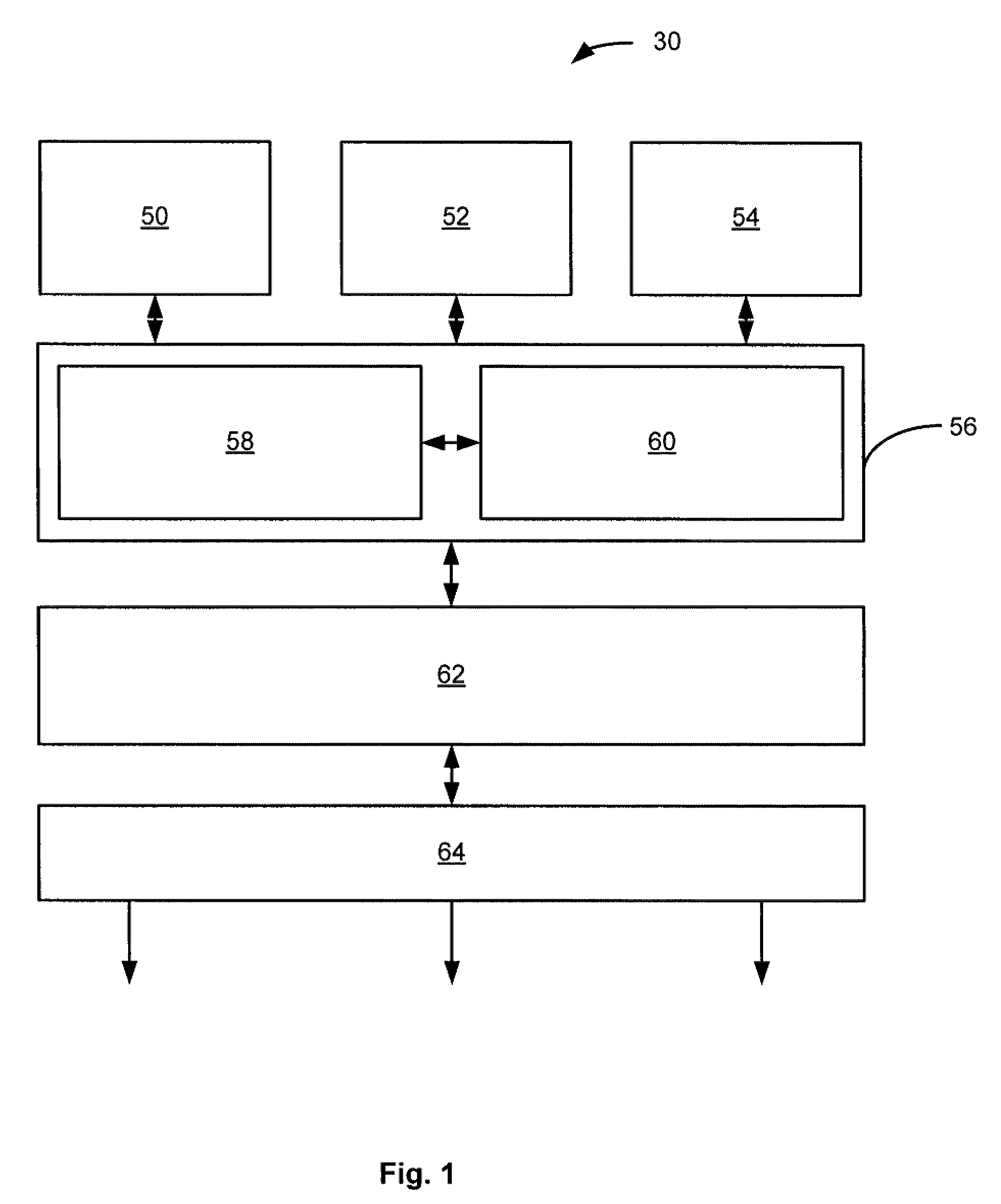

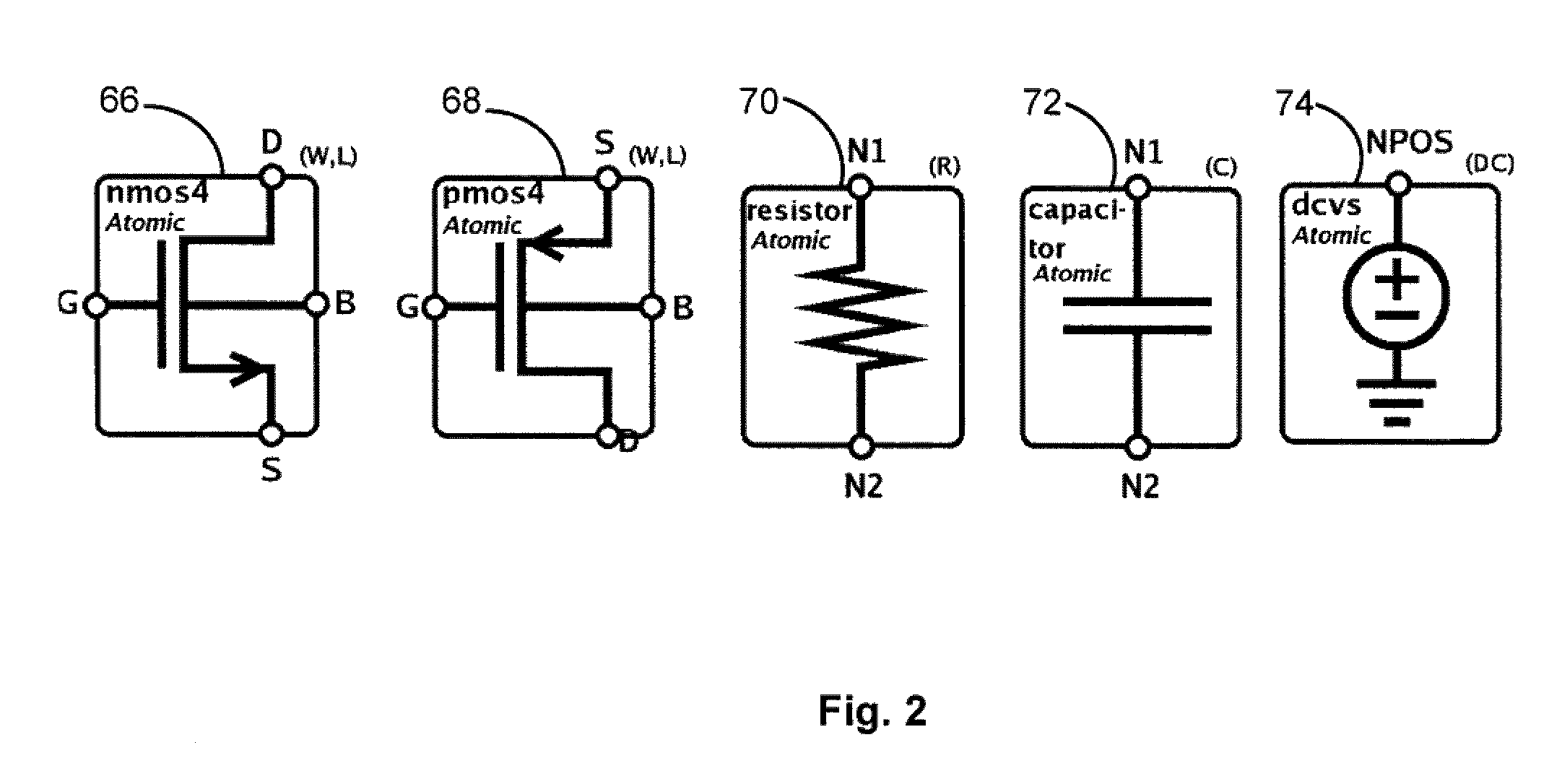

A system and method that does trustworthy multi-objective structural synthesis of analog circuits, and extracts expert analog circuit knowledge from the resulting tradeoffs. The system defines a space of thousands of possible topologies via a hierarchically organized combination of designer-trusted analog building blocks, the resulting topologies are guaranteed trustworthy. The system can perform a search based on a multi-objective evolutionary algorithm that uses an age-layered population structure to balance exploration vs. exploitation, with operators that make the search space a hybrid between vector-based and tree-based representations. A scheme employing average ranking on Pareto fronts is used to handle a high number of objectives. Good initial topology sizings are quickly generated via multi-gate constraint satisfaction. To explicitly capture expert analog design knowledge, data mining is employed on the sized circuits to: automatically generate a decision tree for navigating from performance specifications to topology choice, to do global nonlinear sensitivity analysis, and to generate analytical models of performance tradeoffs.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Automatically generating an input sequence for a circuit design using mutant-based verification

InactiveUS20070294655A1Facilitates appending additional constraintFacilitates user verificationDetecting faulty computer hardwareDigital storageAnalog circuit designControl signal

One embodiment of the present invention provides a system that automatically generates an input sequence for a circuit design using mutant-based verification. During operation, the system receives a description of the circuit design. Next, the system determines a target value for a control signal in the description and a mutant value for the control signal. The system then determines if an input sequence exists for the circuit design that stimulates the control signal to the target value and causes the effects of the target value and the effects of the mutant value to reach an observation point in the circuit such that the effects of the target value and the effects of the mutant value differ at the observation point. If such an input sequence exists, the system then simulates operation of the circuit design using the input sequence. During simulation, the system generates two sets of signal outputs for the circuit design. The first set of signal outputs is affected by the target value for the control signal, while the second set of signal outputs is affected by the mutant value for the control signal.

Owner:RGT UNIV OF CALIFORNIA

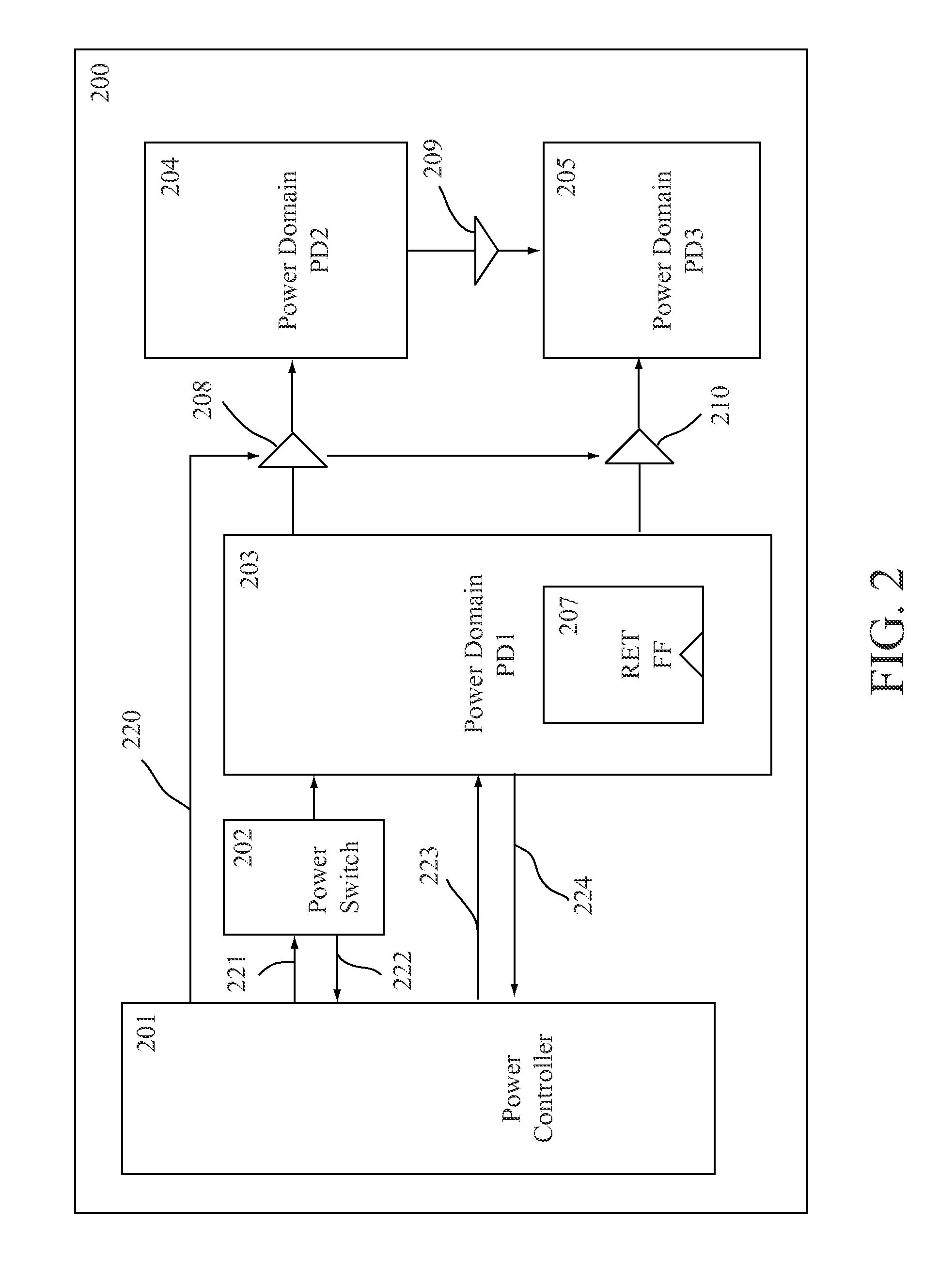

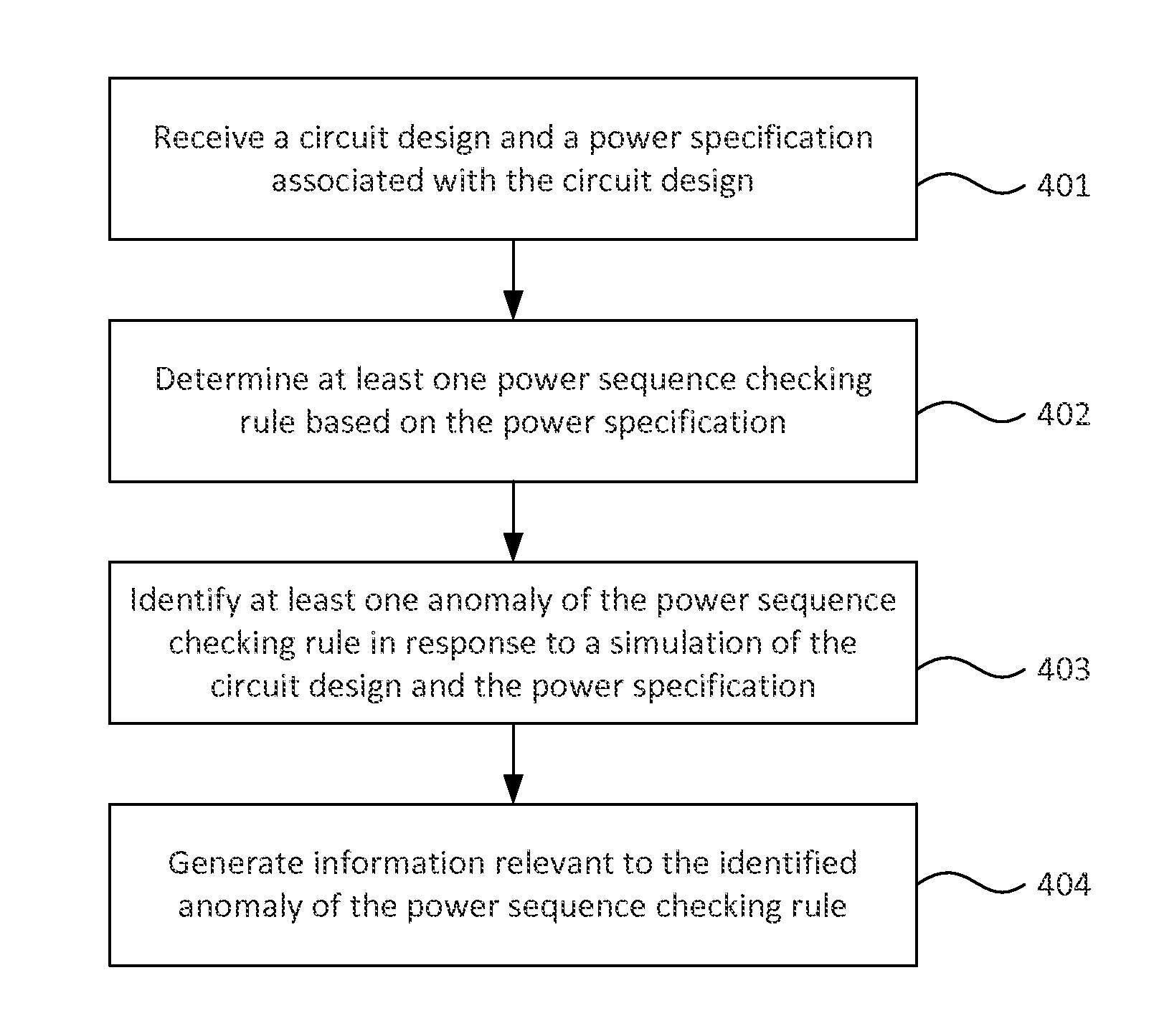

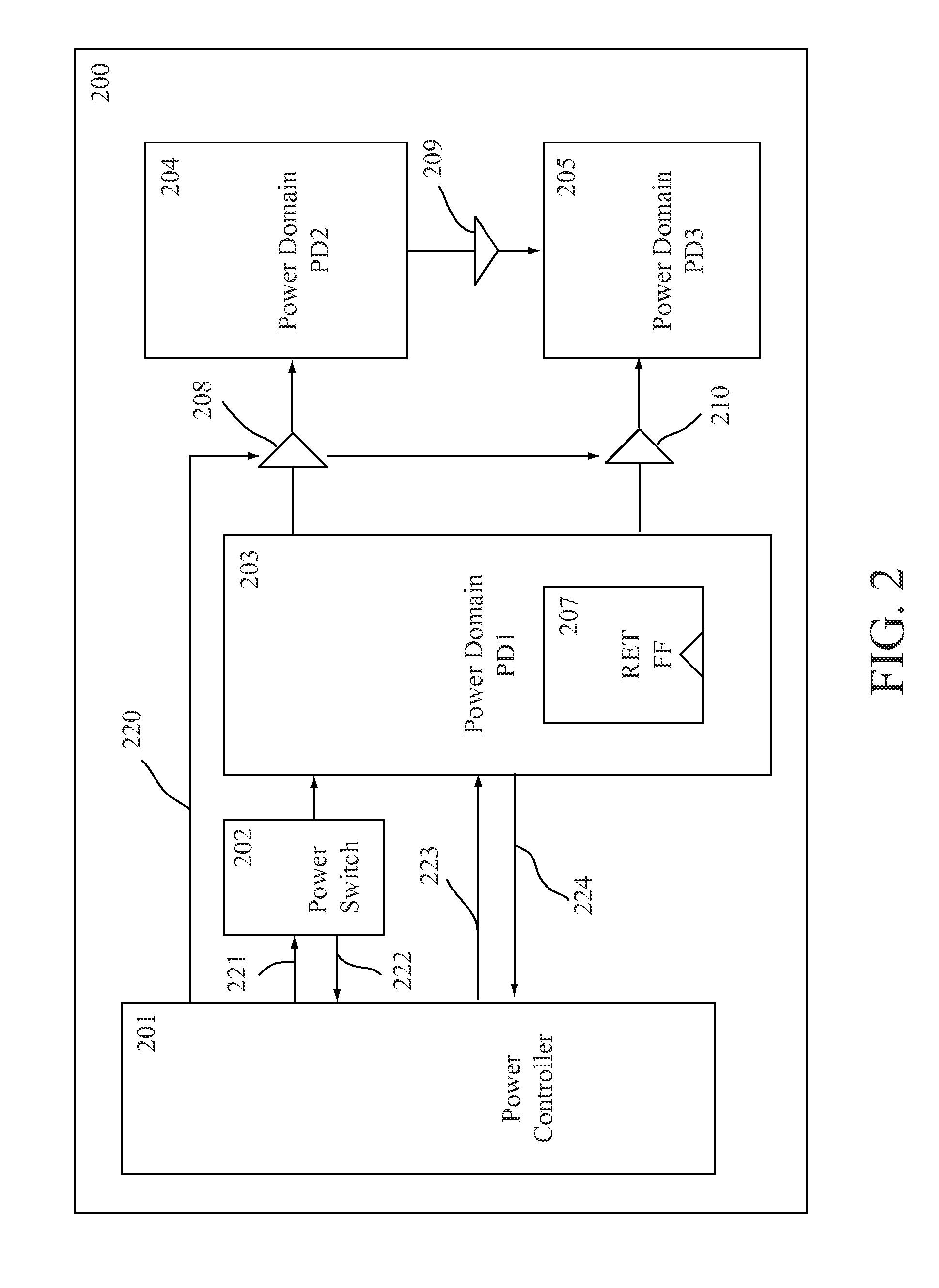

Method for detecting and debugging design errors in low power IC design

ActiveUS20130305207A1Detecting faulty computer hardwareDesign optimisation/simulationAnalog circuit designCircuit design

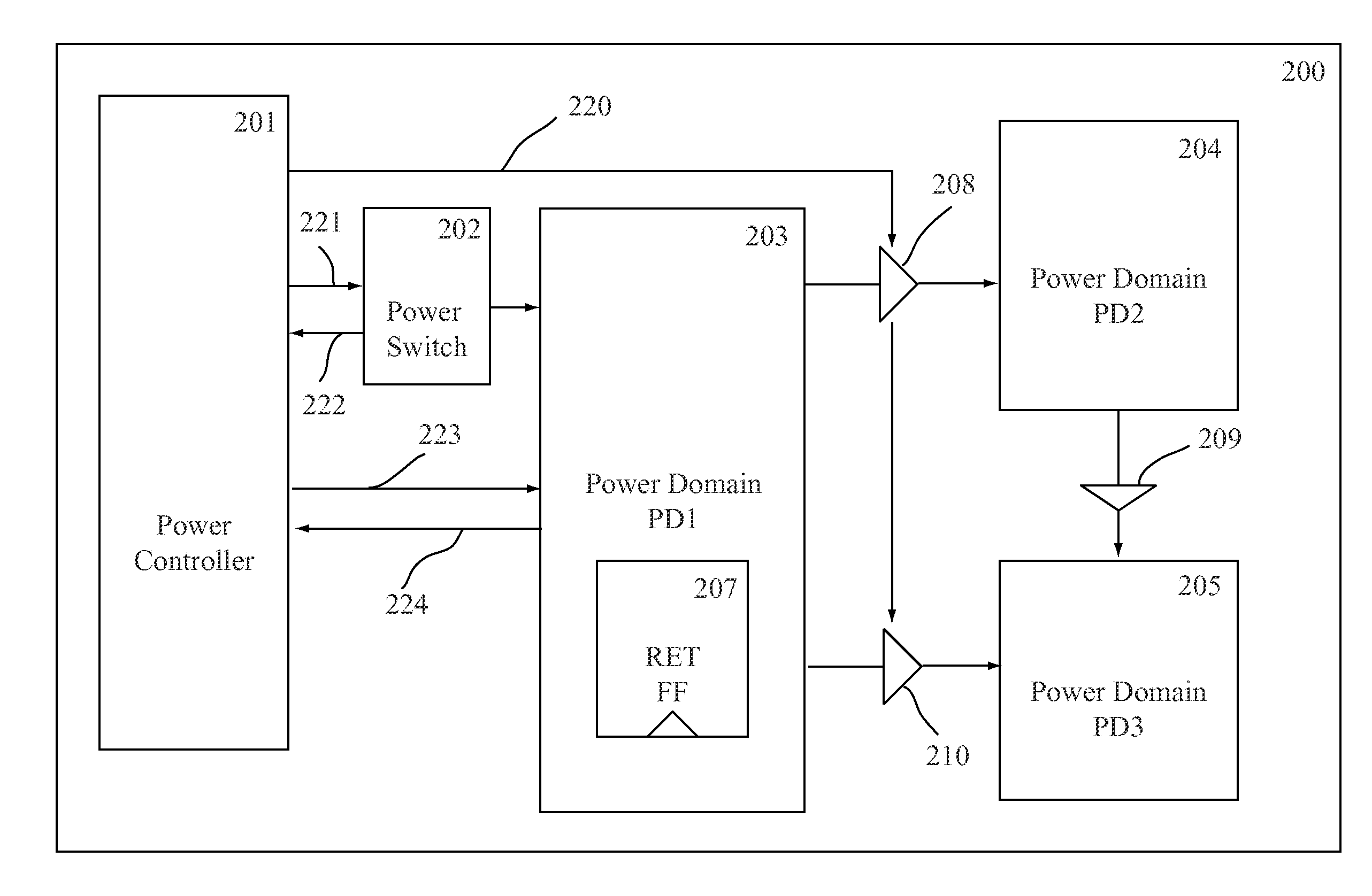

A method for detecting anomalies in signal behaviors in a simulation of a low power IC includes receiving a circuit design and a power specification of the IC, determining at least one power sequence checking rule from the power specification, simulating the circuit design and the power specification to obtain a dump file, identifying at least one anomaly of the at least one power sequence checking rule based on the dump file, and generating information relevant to the identified anomaly of the at least one power sequence checking rule. The method further includes setting up a context in a debugger for debugging the anomaly by displaying a waveform of misbehaved signals associated with the anomaly in a waveform window, and a portion of the circuit design and / or a portion of the power specification associated with the anomaly in a text window.

Owner:SYNOPSYS INC

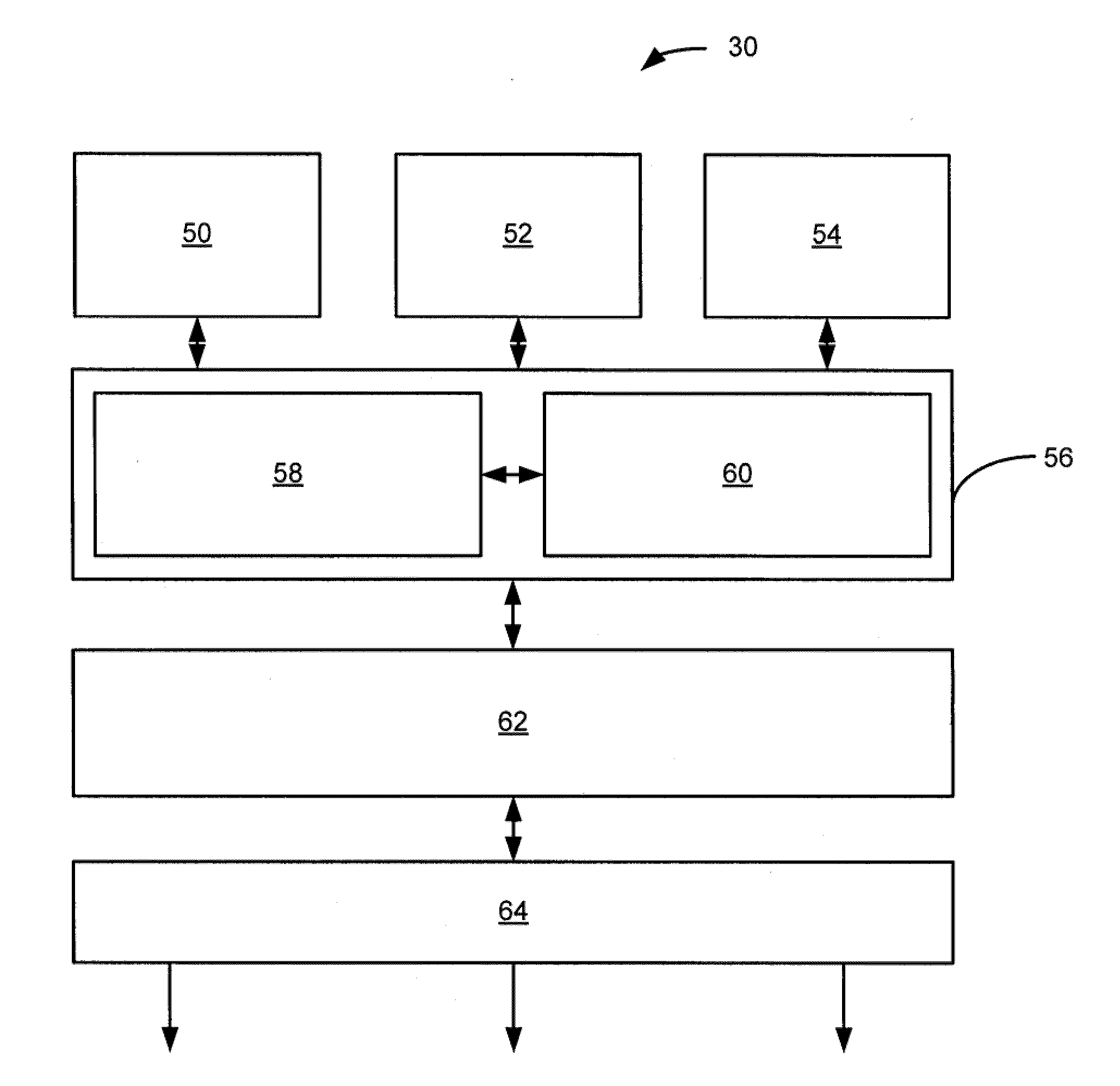

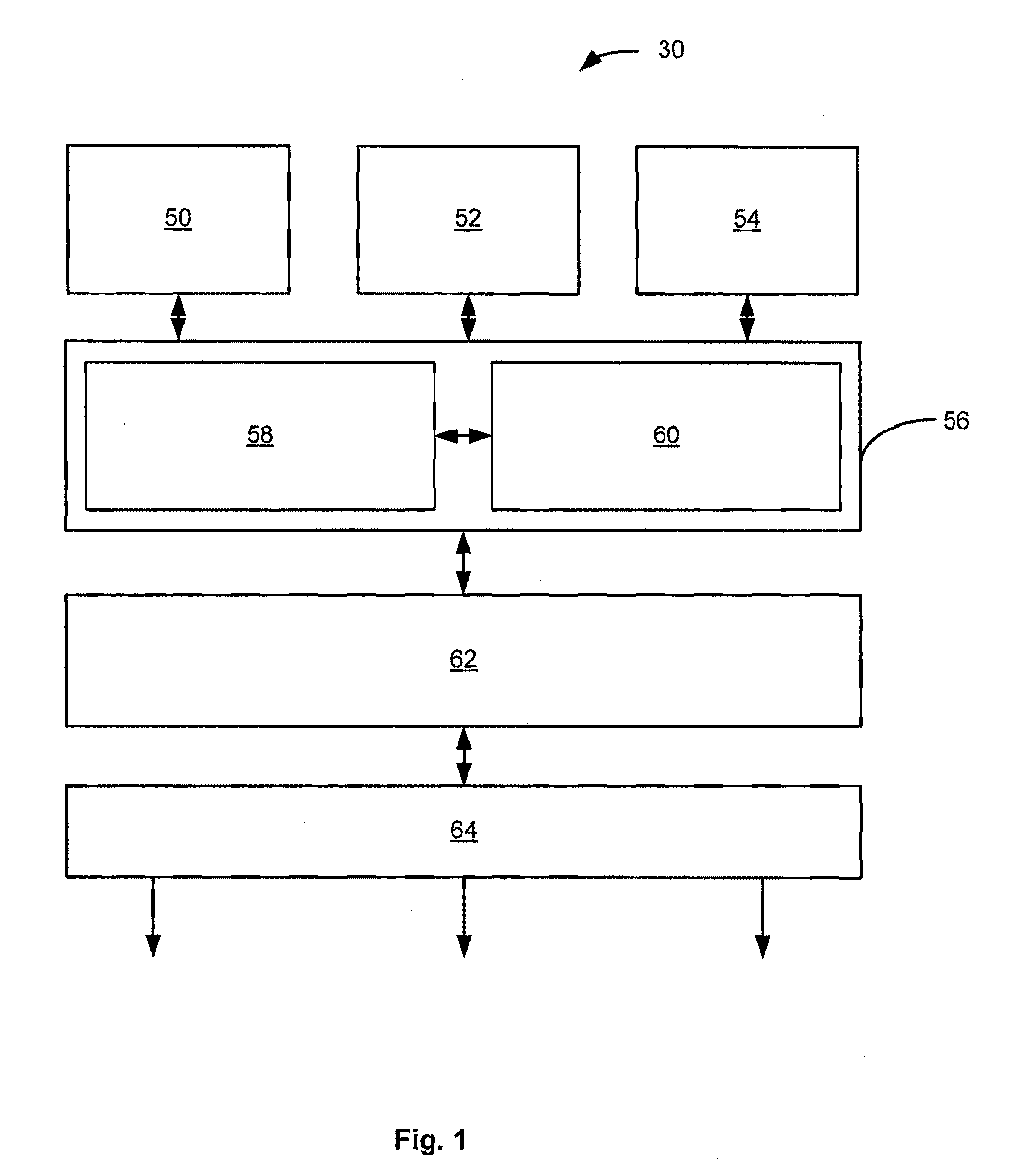

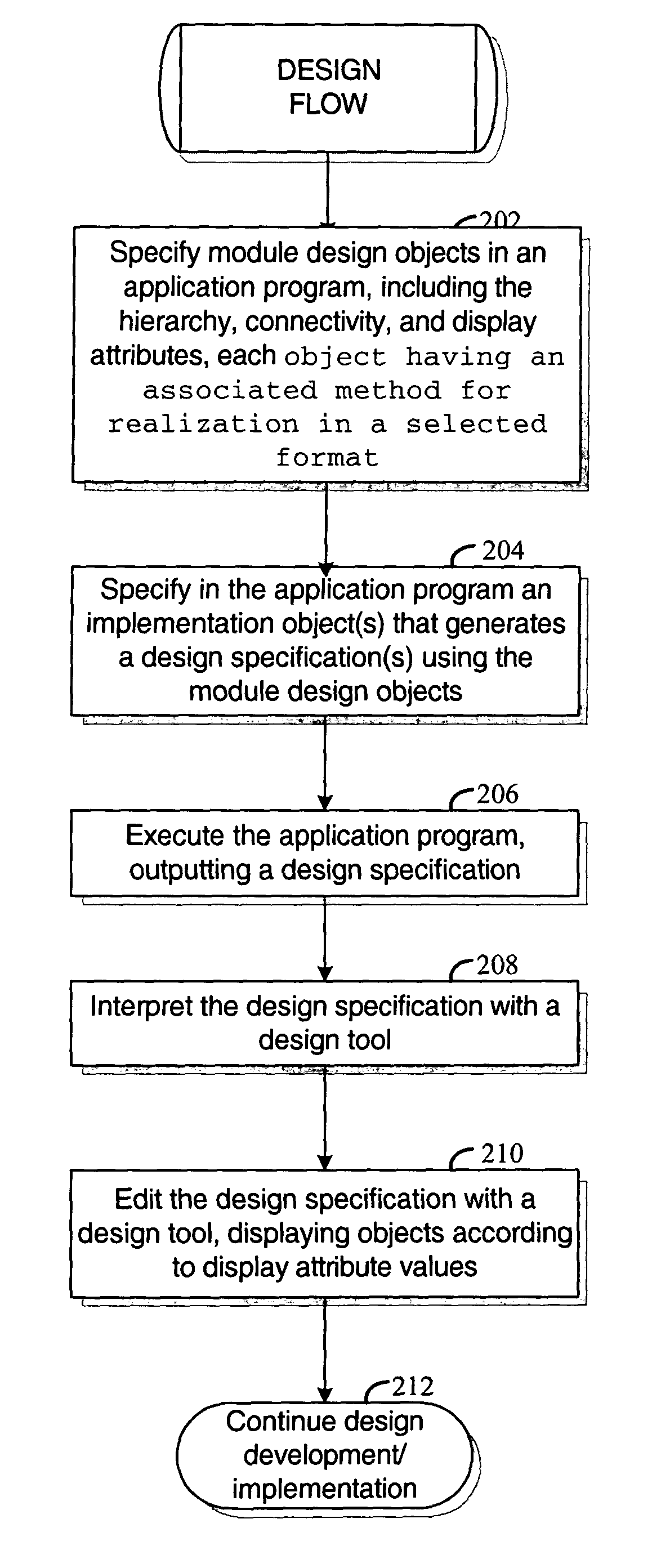

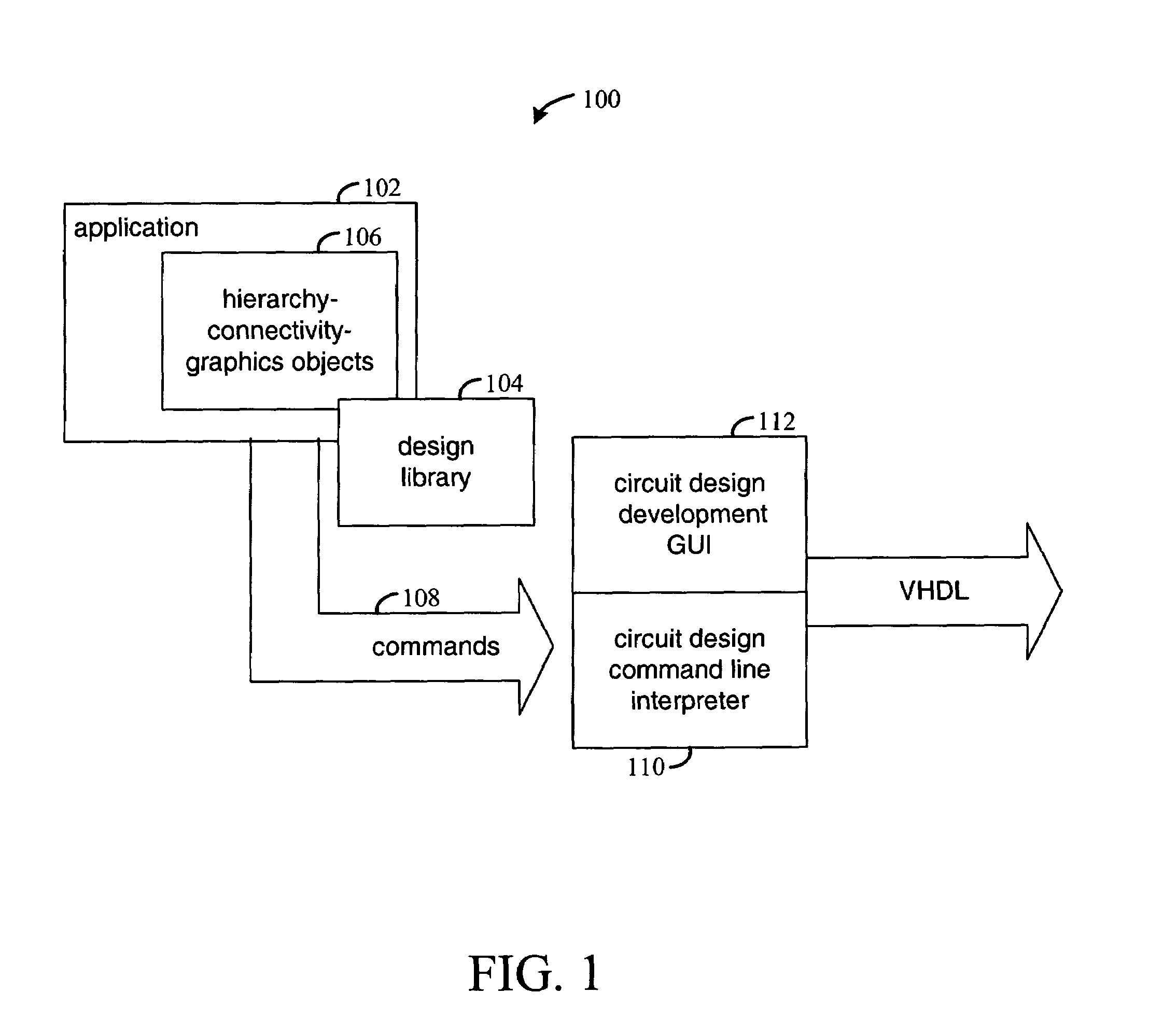

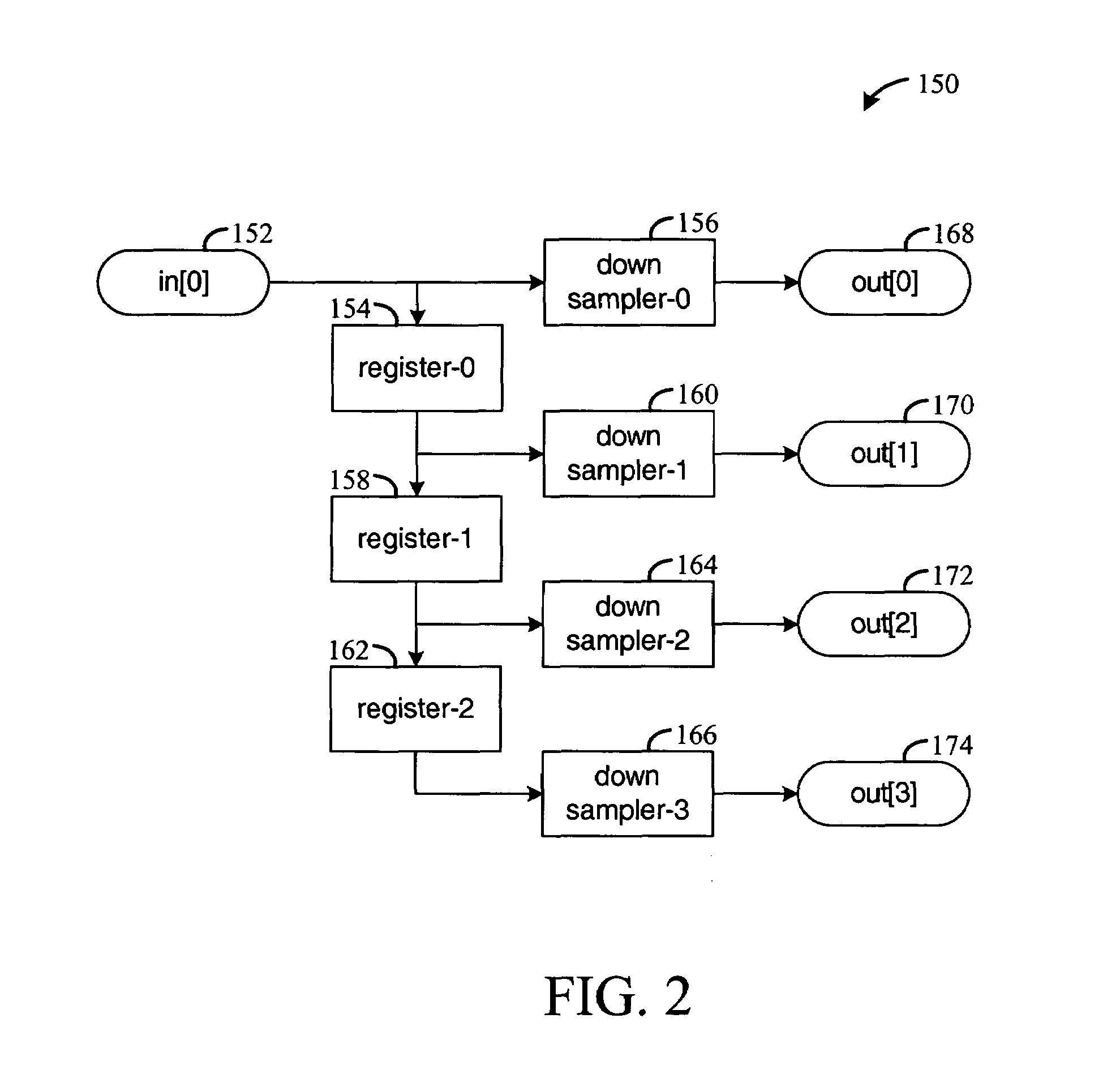

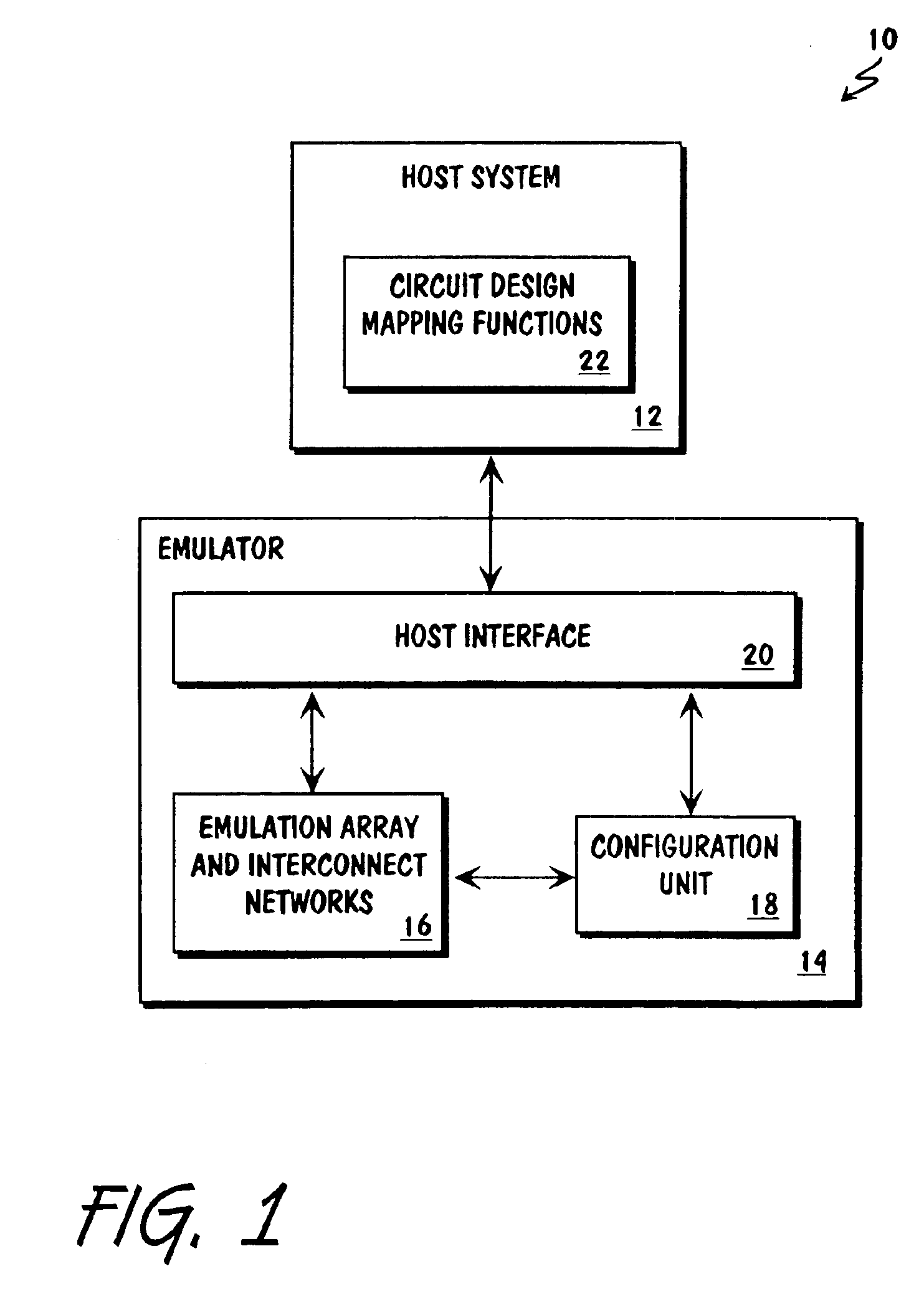

Specification of the hierarchy, connectivity, and graphical representation of a circuit design

Method and apparatus for creating a circuit design. An object-oriented program instantiates a plurality of objects that model a circuit design. The objects have hierarchy attributes, connectivity attributes, and display attributes that describe a plurality of modules. The hierarchy attributes define parent-child relationships between modules, the connectivity attributes define input-output connections between modules, and the display attributes define a layout of the modules for viewing. Each of the objects has an associated method for generating a design specification in a selected format. When the program is executed, the design specification is generated from the set of objects. Depending on the capabilities of the available tools, the modules and logic elements are displayed in accordance with the display attributes either from the object-oriented program or from the design specification.

Owner:XILINX INC

Trustworthy structural synthesis and expert knowledge extraction with application to analog circuit design

A system and method that does trustworthy multi-objective structural synthesis of analog circuits, and extracts expert analog circuit knowledge from the resulting tradeoffs. The system defines a space of thousands of possible topologies via a hierarchically organized combination of designer-trusted analog building blocks, the resulting topologies are guaranteed trustworthy. The system can perform a search based on a multi-objective evolutionary algorithm that uses an age-layered population structure to balance exploration vs. exploitation, with operators that make the search space a hybrid between vector-based and tree-based representations. A scheme employing average ranking on Pareto fronts is used to handle a high number of objectives. Good initial topology sizings are quickly generated via multi-gate constraint satisfaction. To explicitly capture expert analog design knowledge, data mining is employed on the sized circuits to: automatically generate a decision tree for navigating from performance specifications to topology choice, to do global nonlinear sensitivity analysis, and to generate analytical models of performance tradeoffs.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

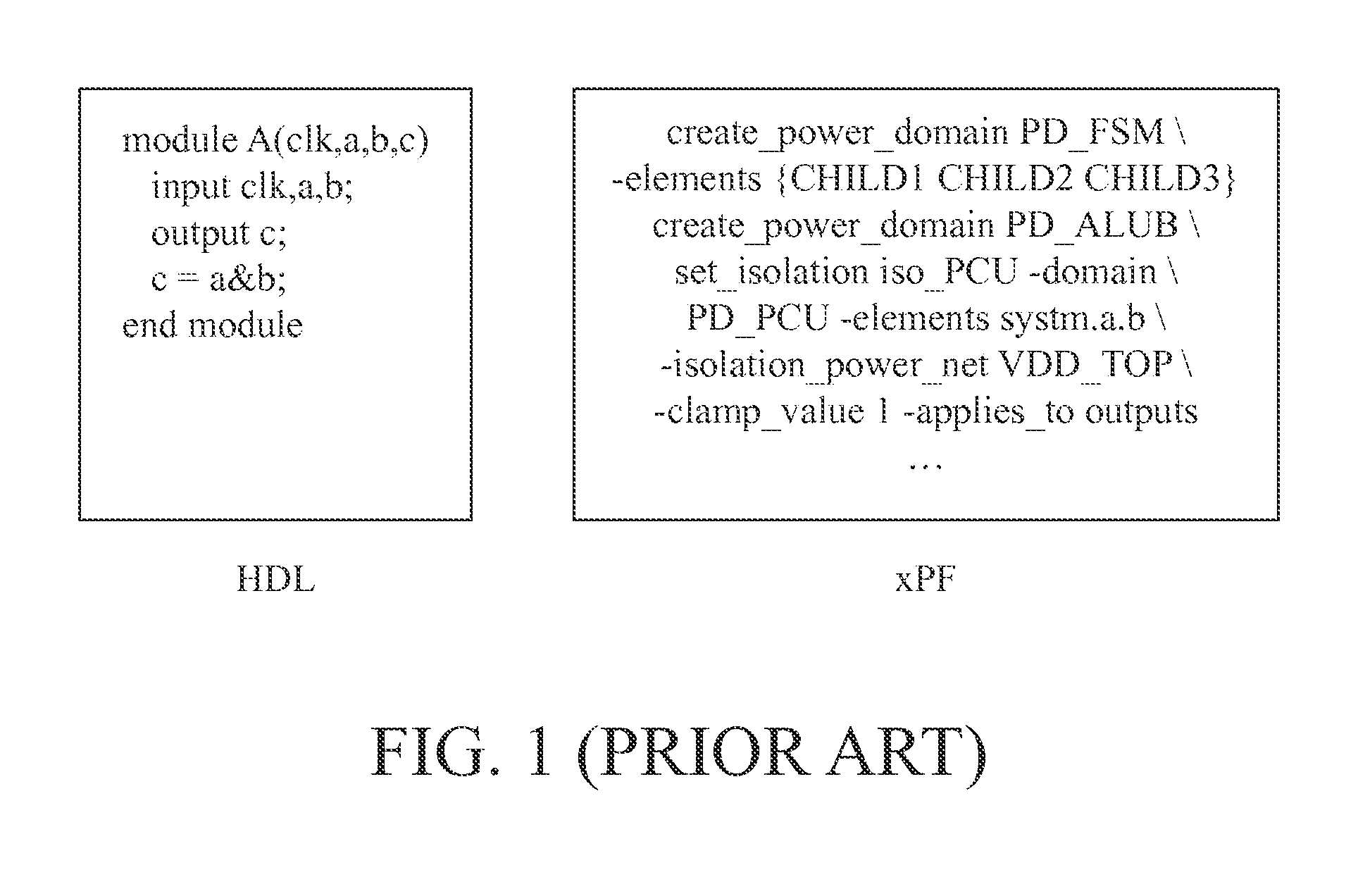

Simulation of a programming language specification of a circuit design

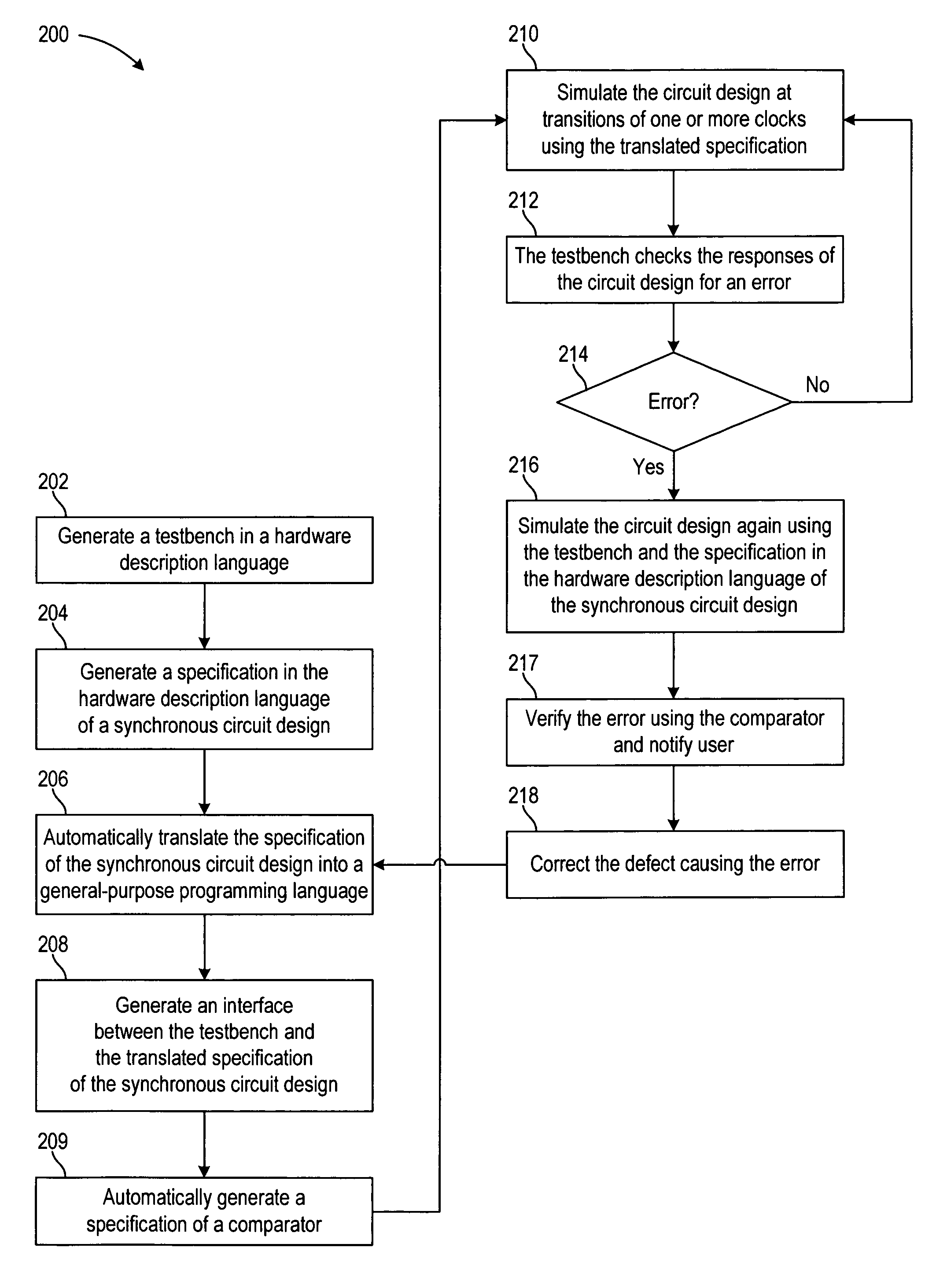

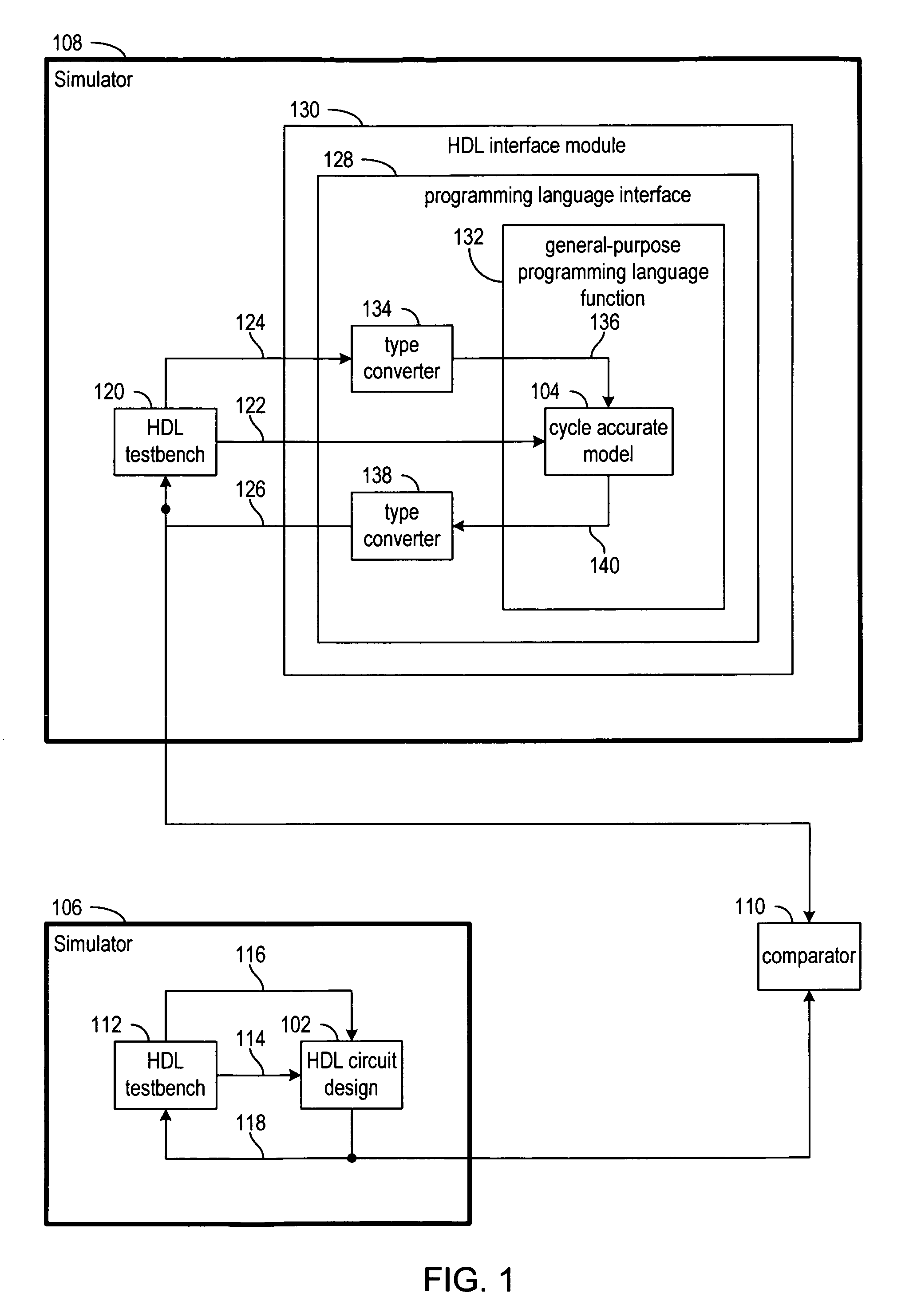

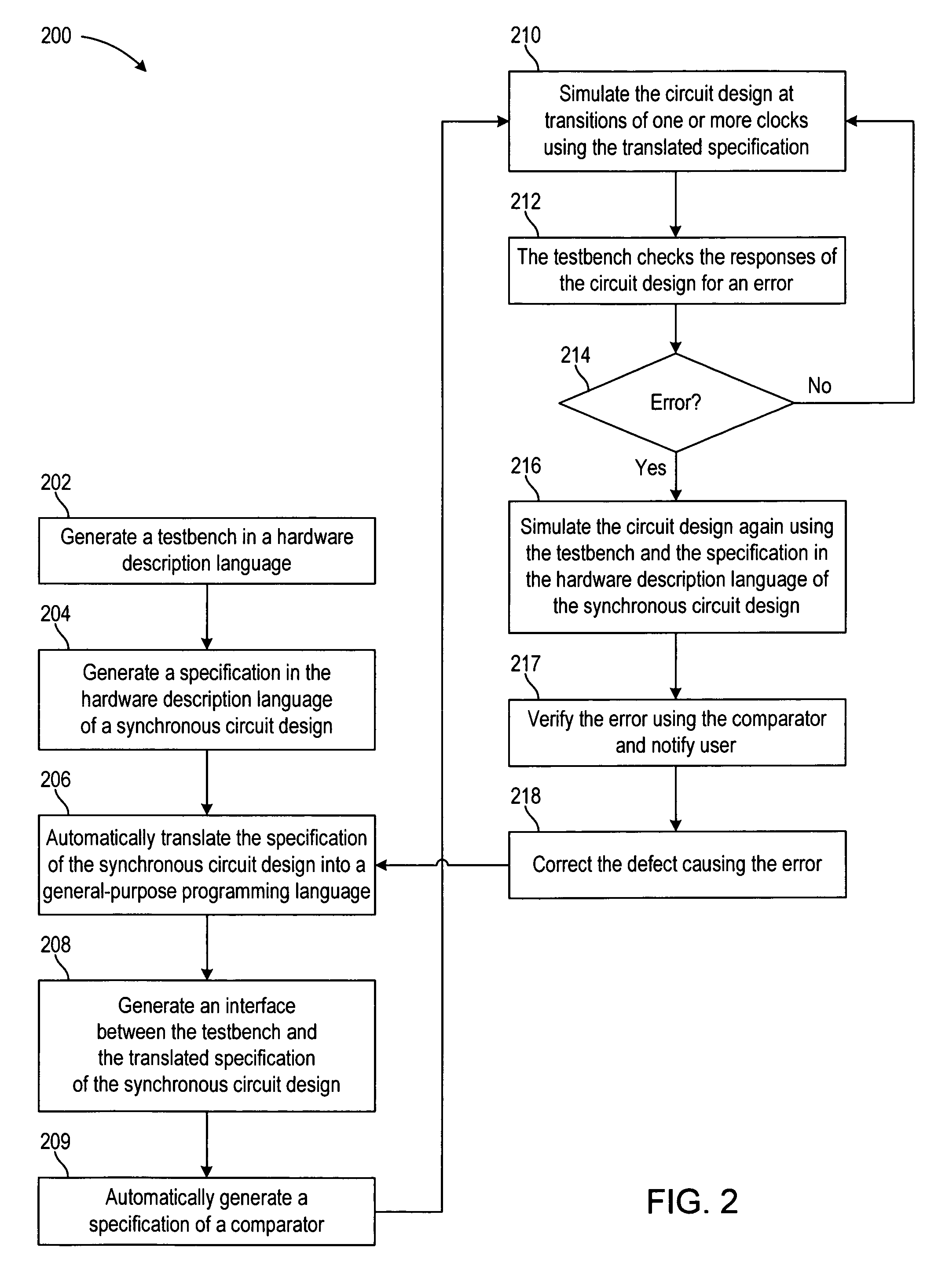

ActiveUS7437701B1CAD circuit designSpecial data processing applicationsAnalog circuit designTheoretical computer science

Various approaches for simulating a circuit design are disclosed. In one approach, a first specification of a testbench and a second specification of the circuit design are generated in a hardware description language. The circuit design is synchronous to at least one clock signal. The second specification of the circuit design is automatically translated into a third specification in a general-purpose programming language, and the third specification specifies the behavior of the circuit design at transitions of the at least one clock signal. A fourth specification of an interface between the first specification of the testbench and the third specification of the circuit design is automatically generated. A first behavior of the circuit design is simulated using the first and third specifications linked by the fourth specification and the stimuli from the test bench.

Owner:XILINX INC

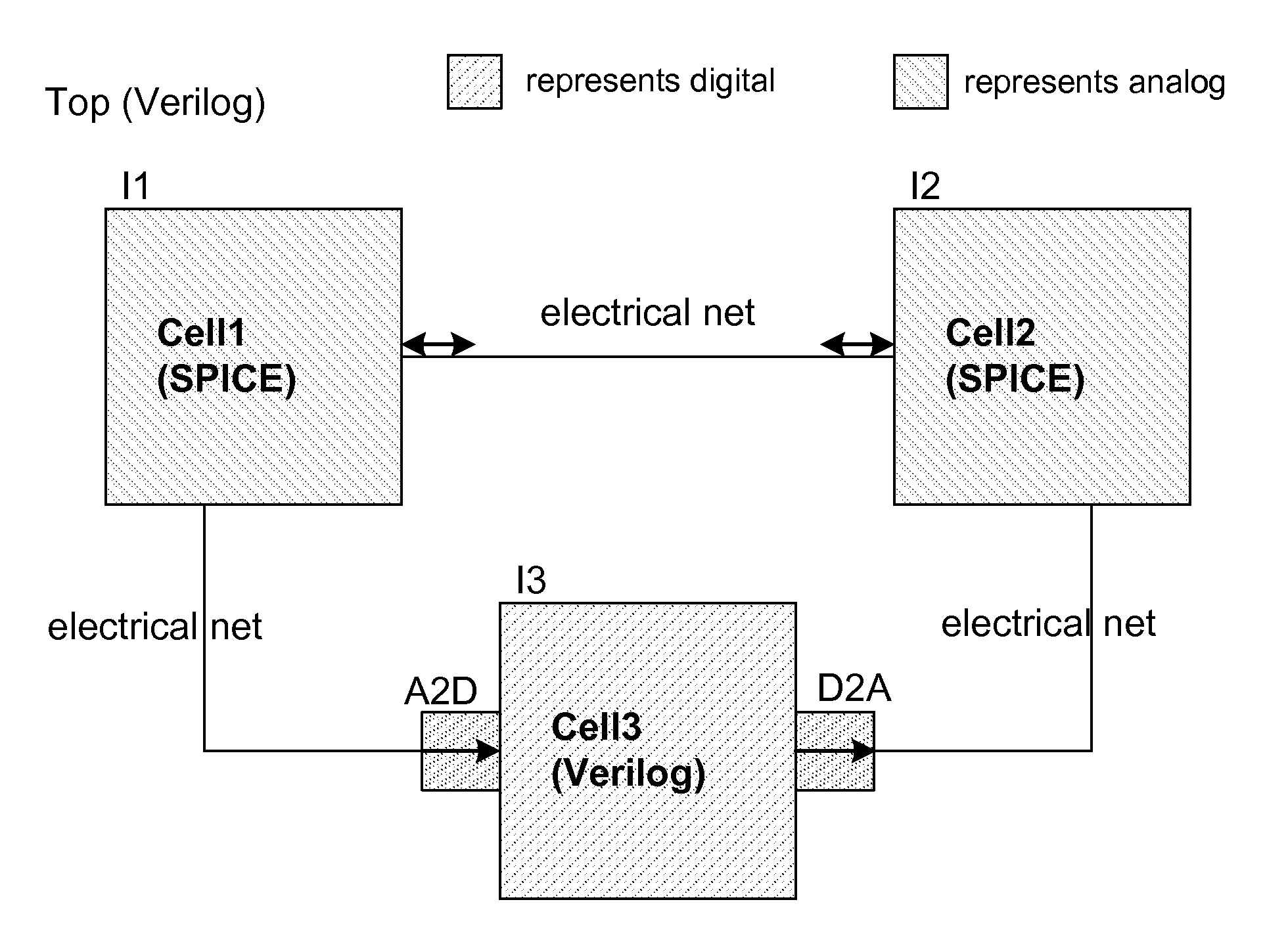

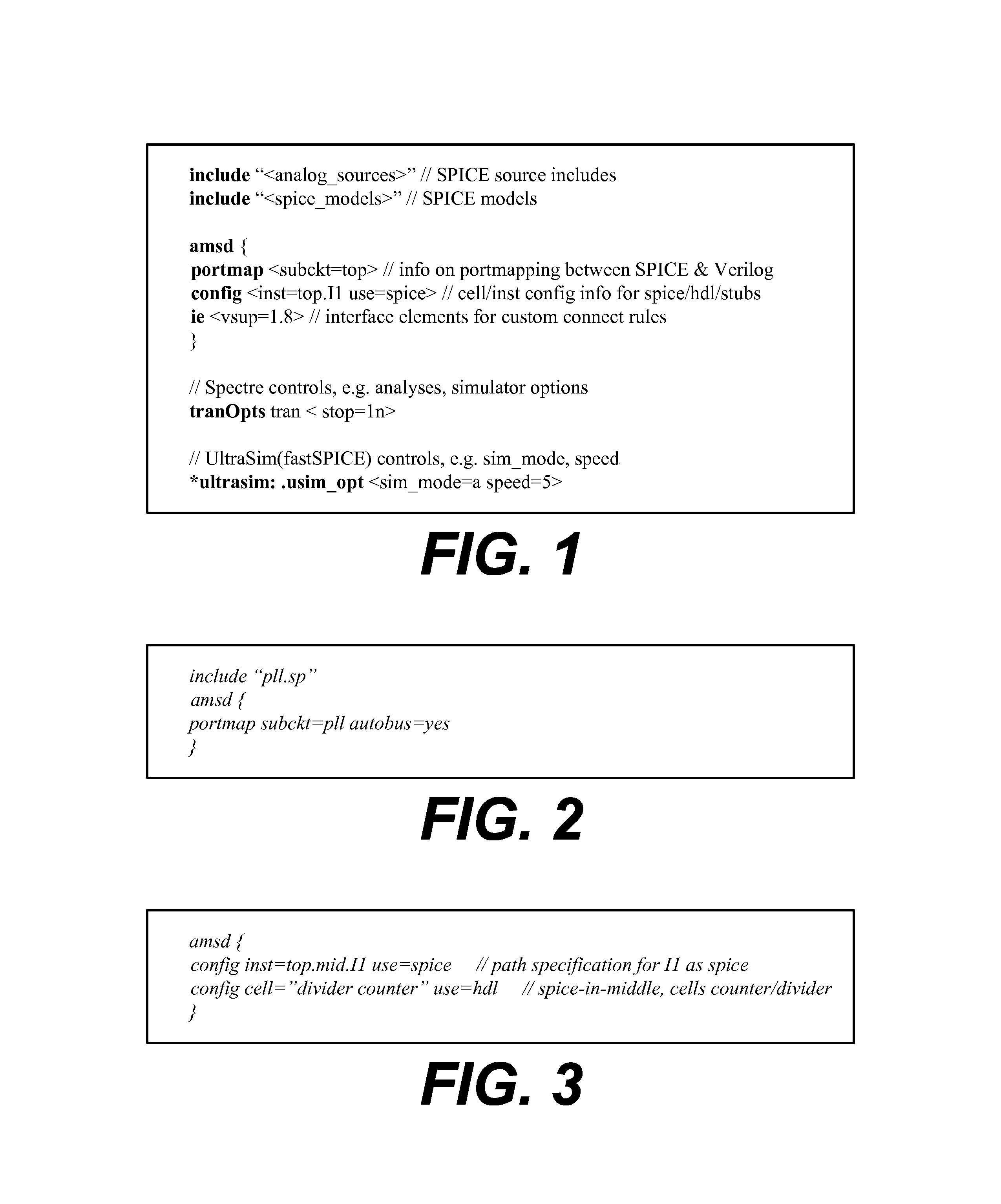

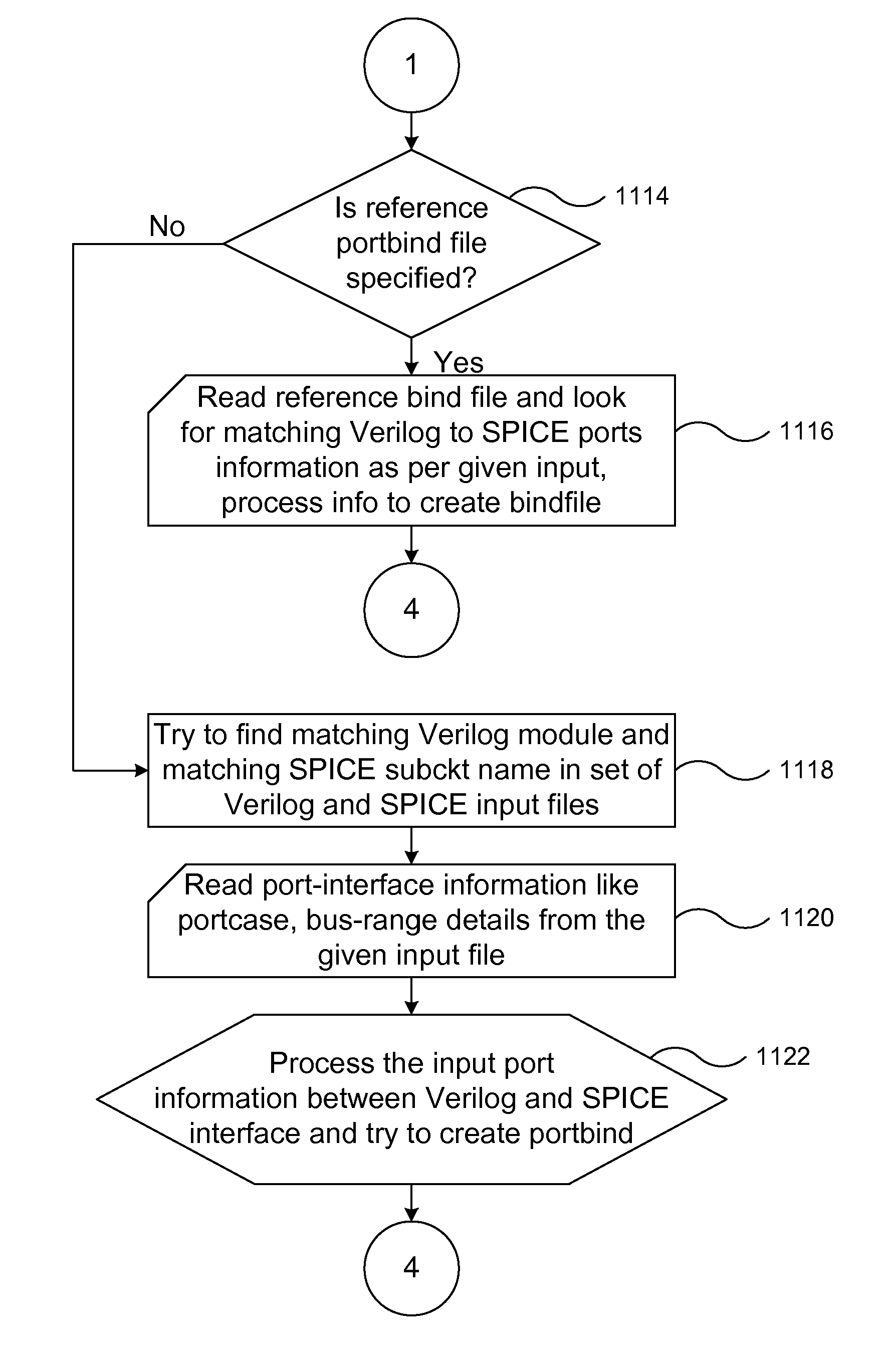

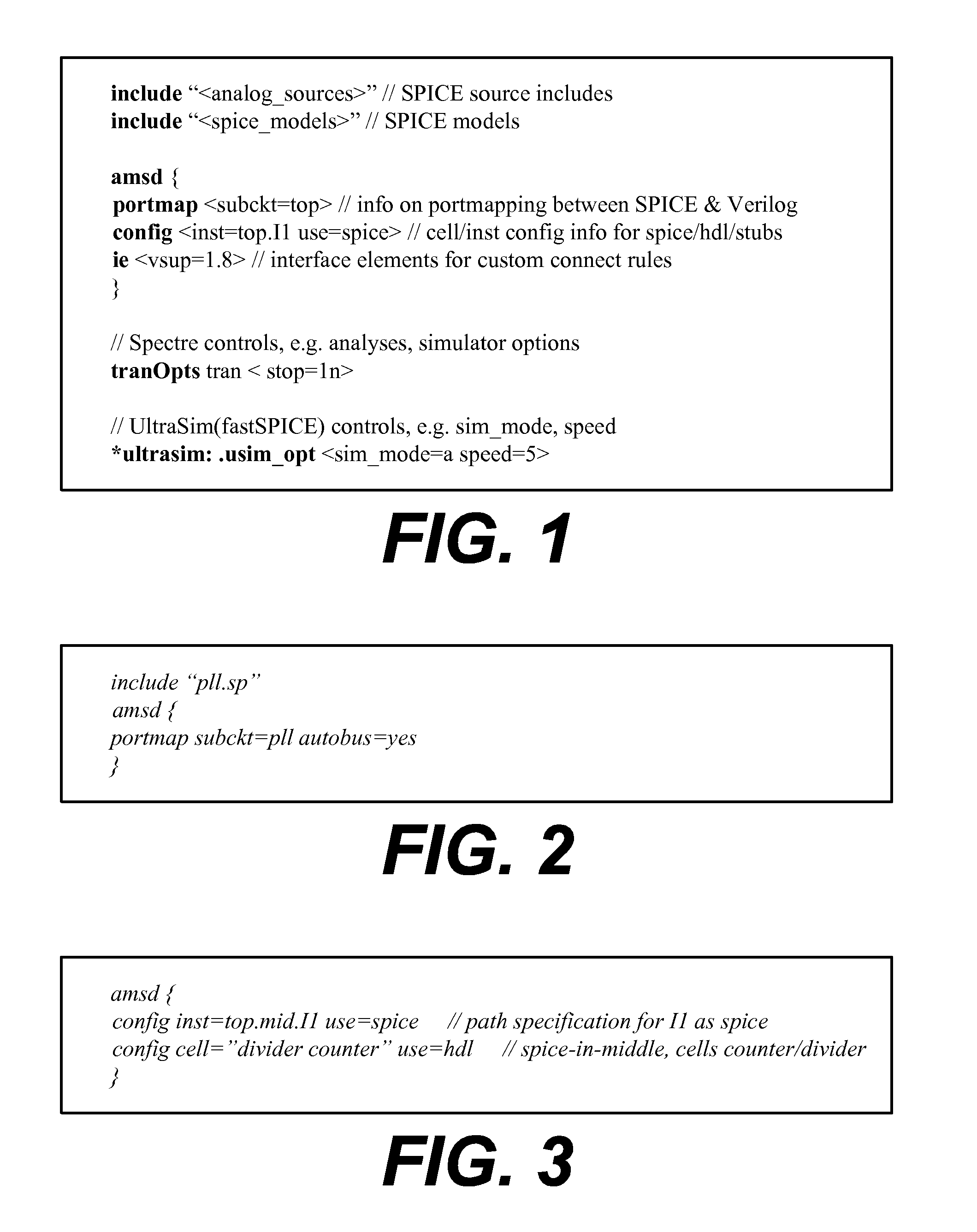

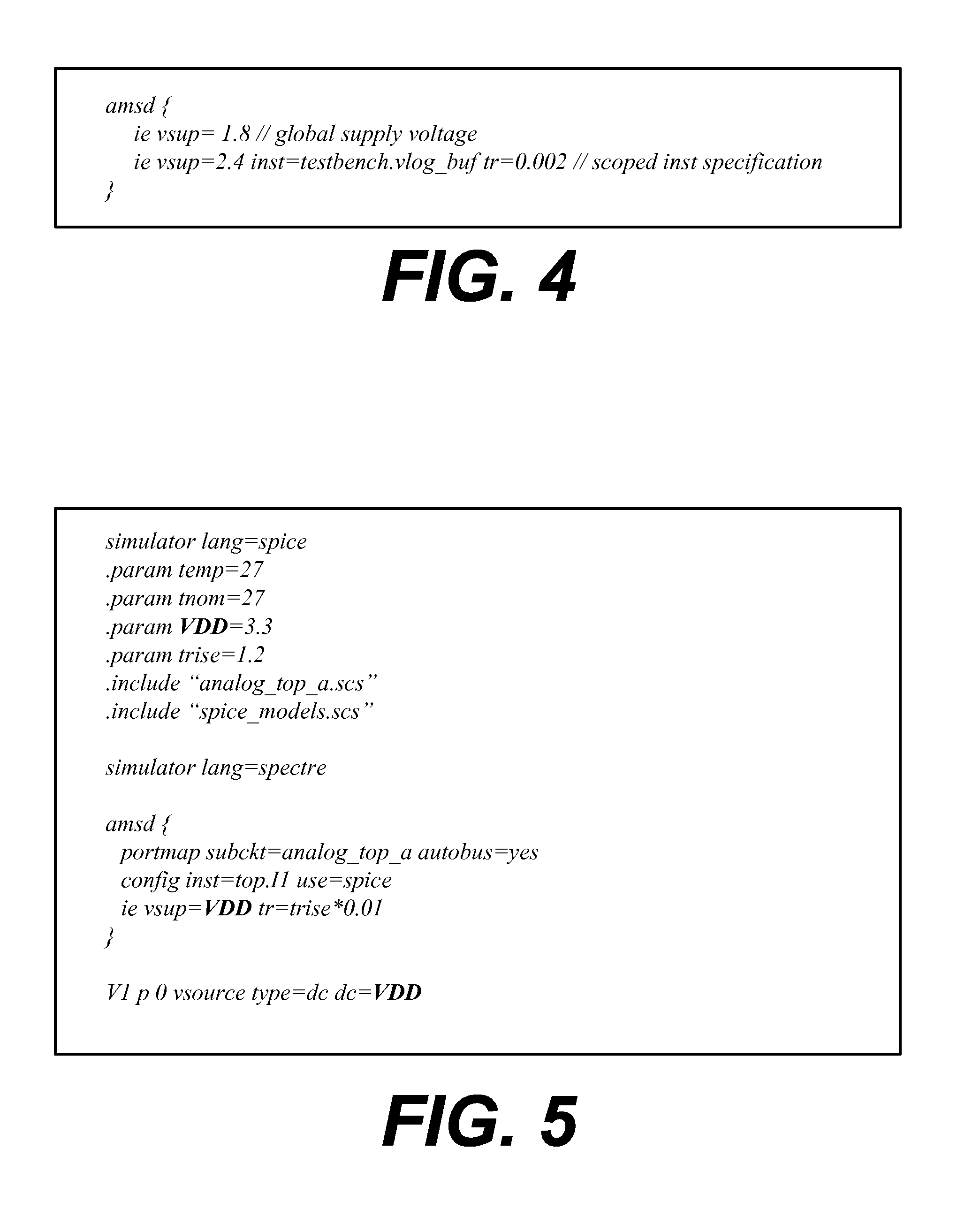

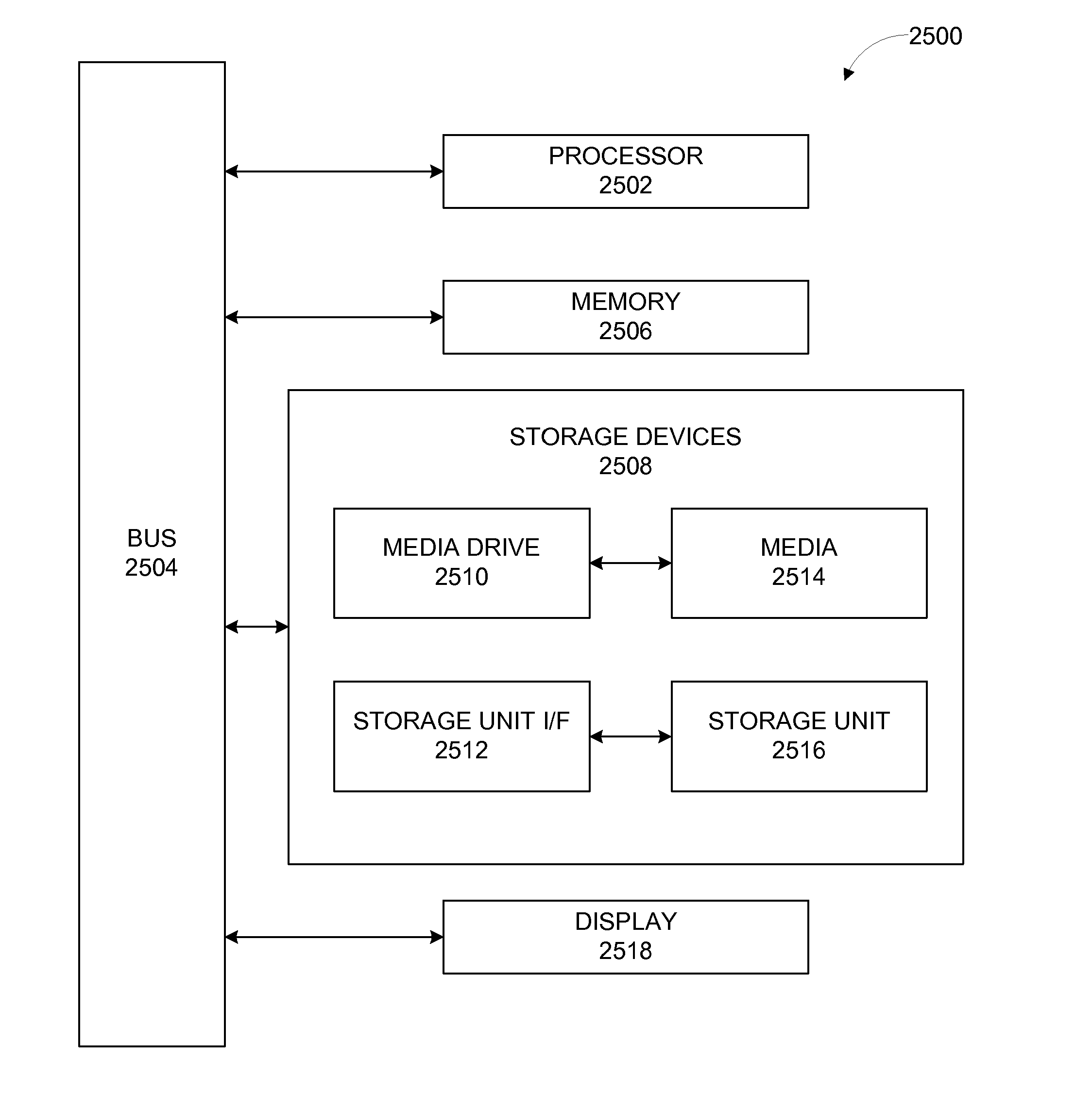

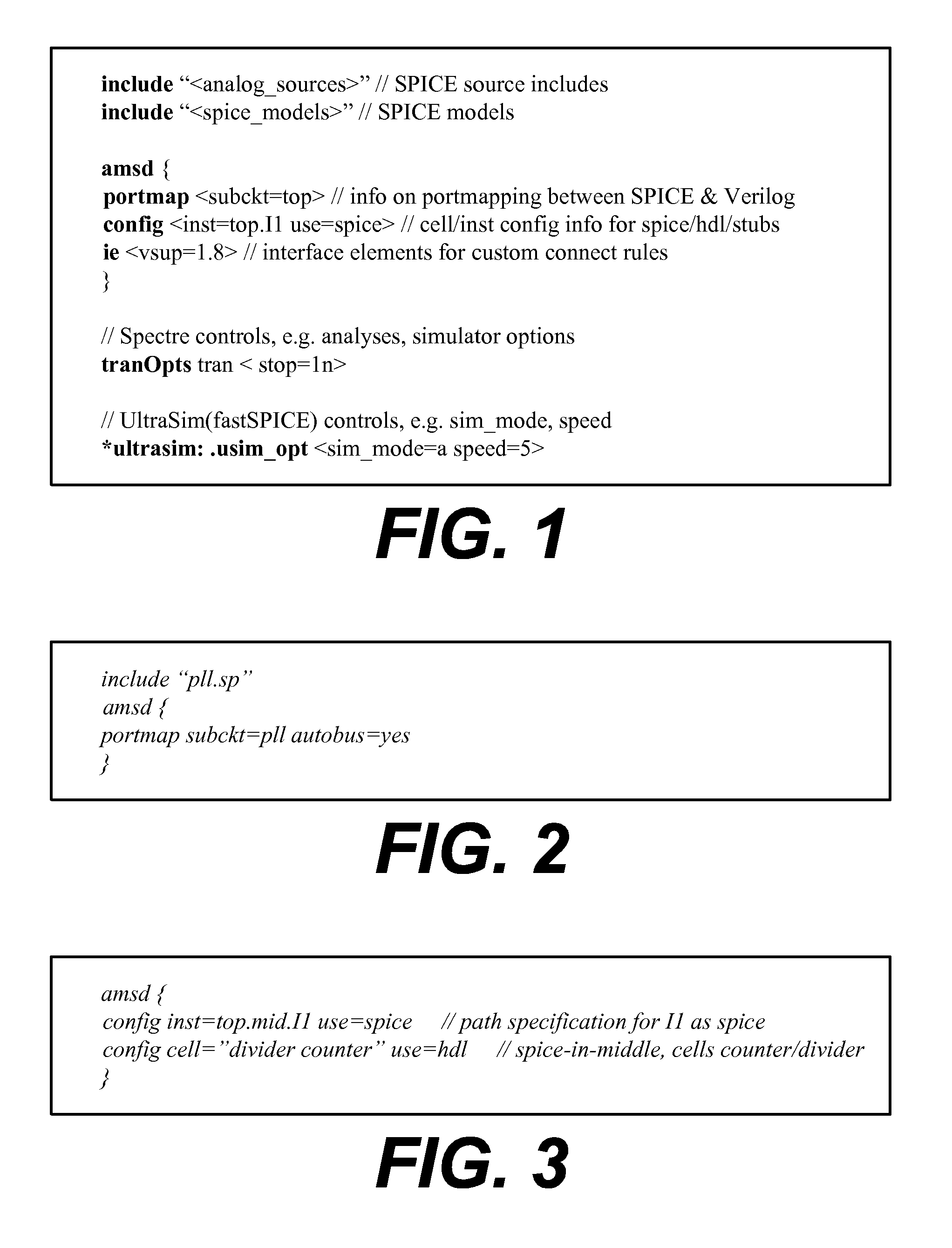

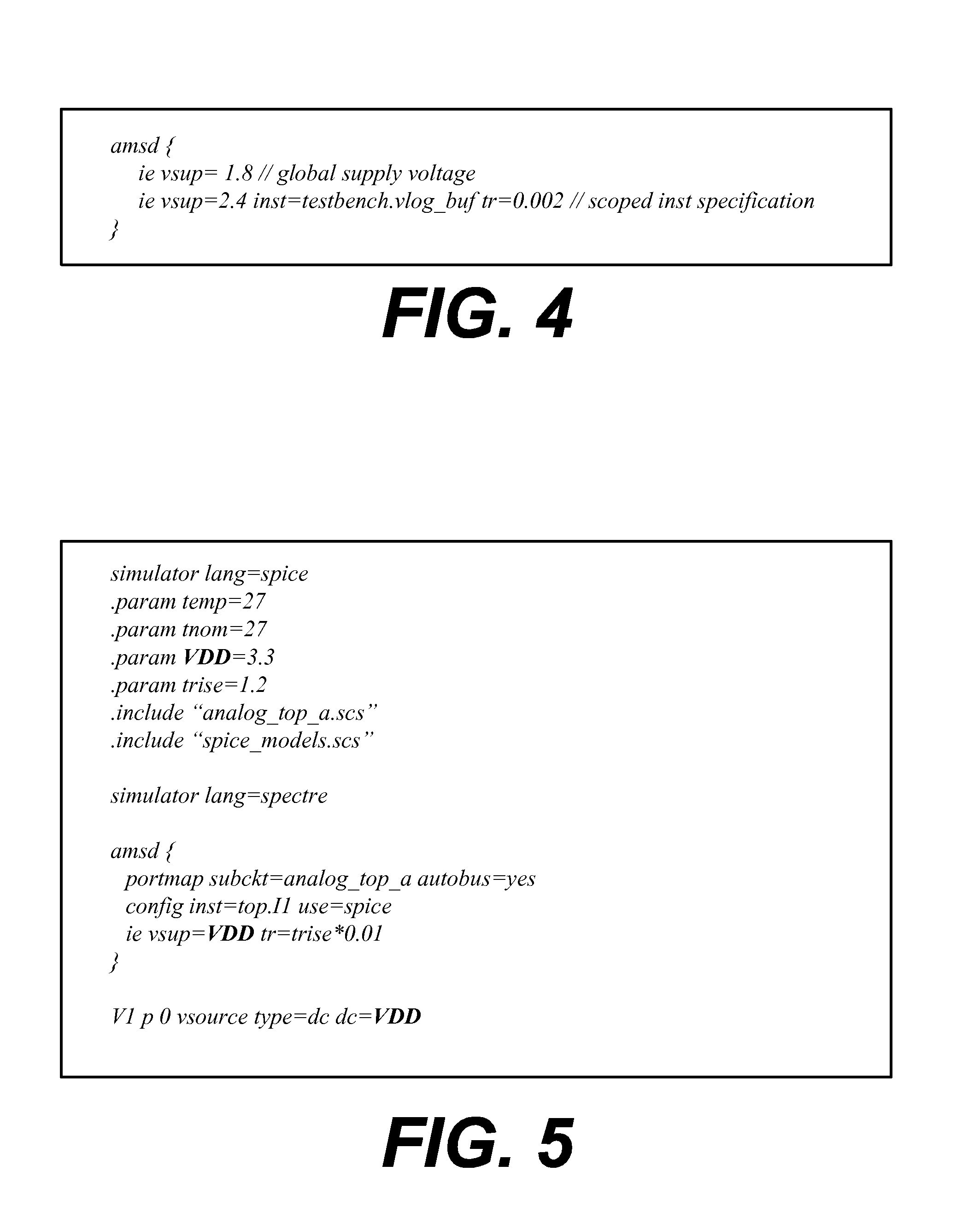

Method and apparatus for AMS simulation of integrated circuit design

ActiveUS8201137B1Ease and abilityEasy to createDetecting faulty computer hardwareAnalogue computers for electric apparatusAnalog circuit designUser input

A method to create an integrated circuit that includes digital and analog components comprising: displaying on a computer system display, user input to the computer system that specifies parameter information to determine a binding between an analog circuit design component and a digital circuit design component; saving the user specified parameter information within a file that also specifies at least a portion of the analog circuit design; associating the analog circuit design component a first design block of an integrated circuit that also includes a second digital design block coupled to the first design block; using parameter information to determine a binding between the first analog circuit design component and the first digital circuit design component; saving the determined binding in computer readable storage media.

Owner:CADENCE DESIGN SYST INC

Reloadable just-in-time compilation simulation engine for high level modeling systems

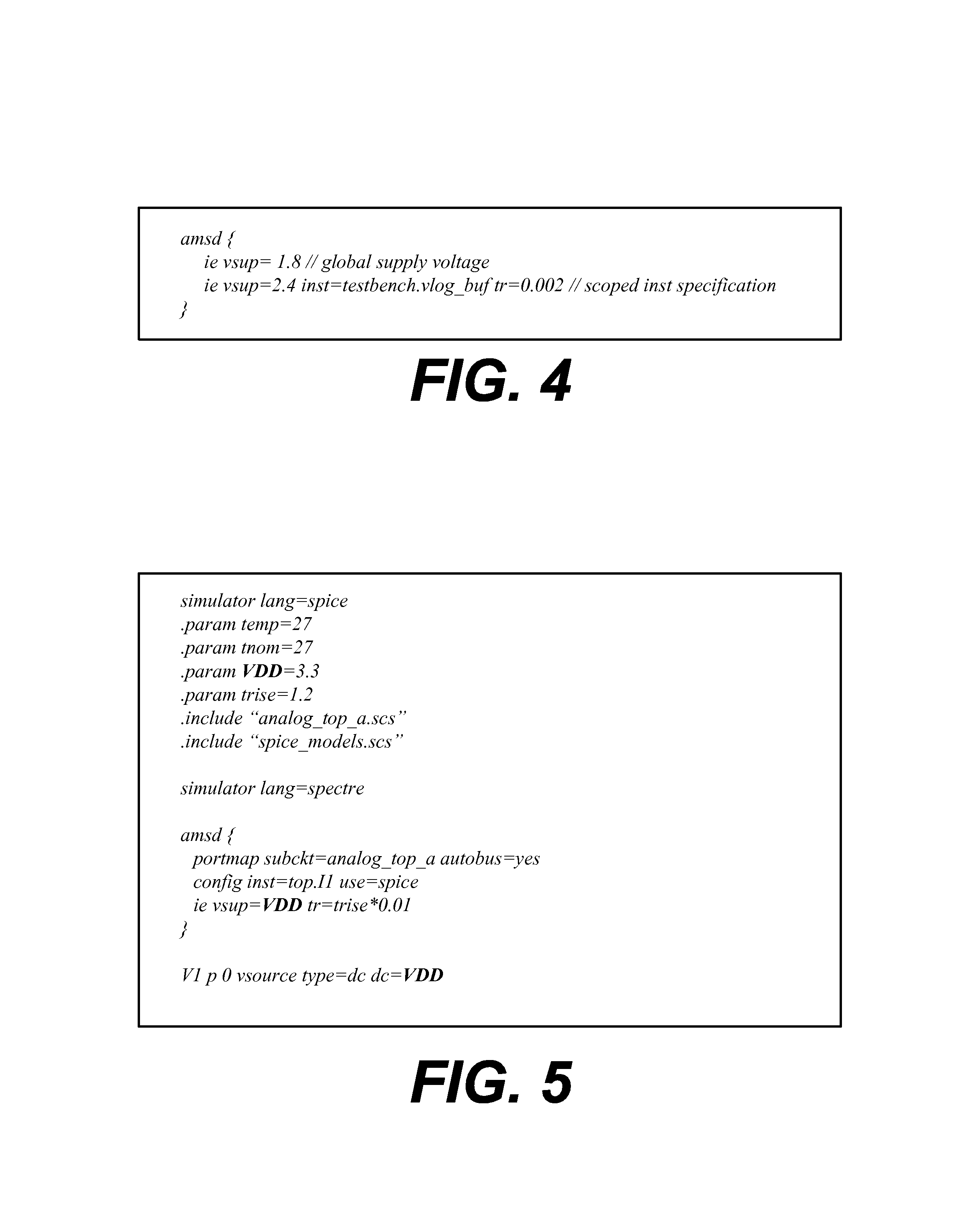

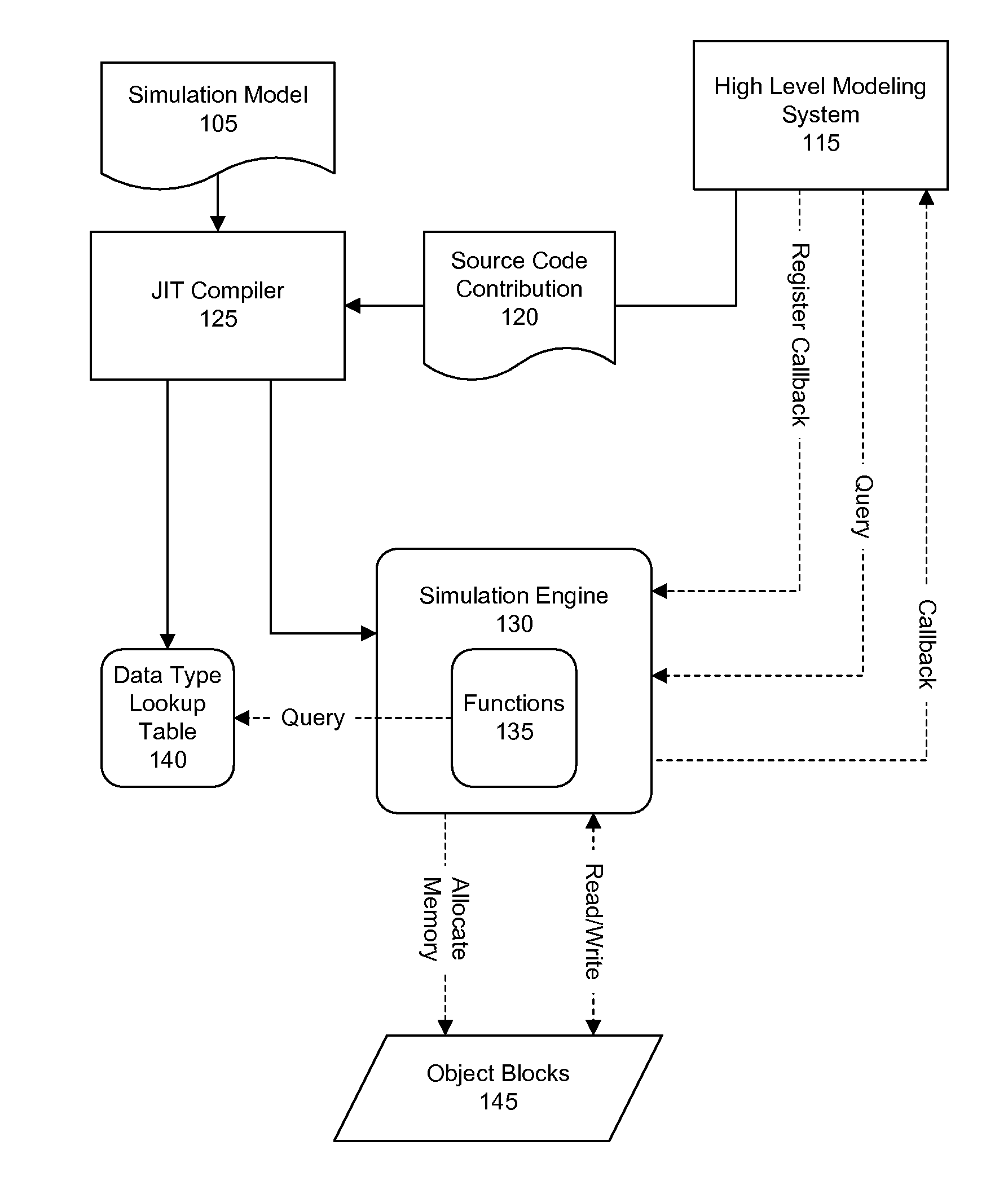

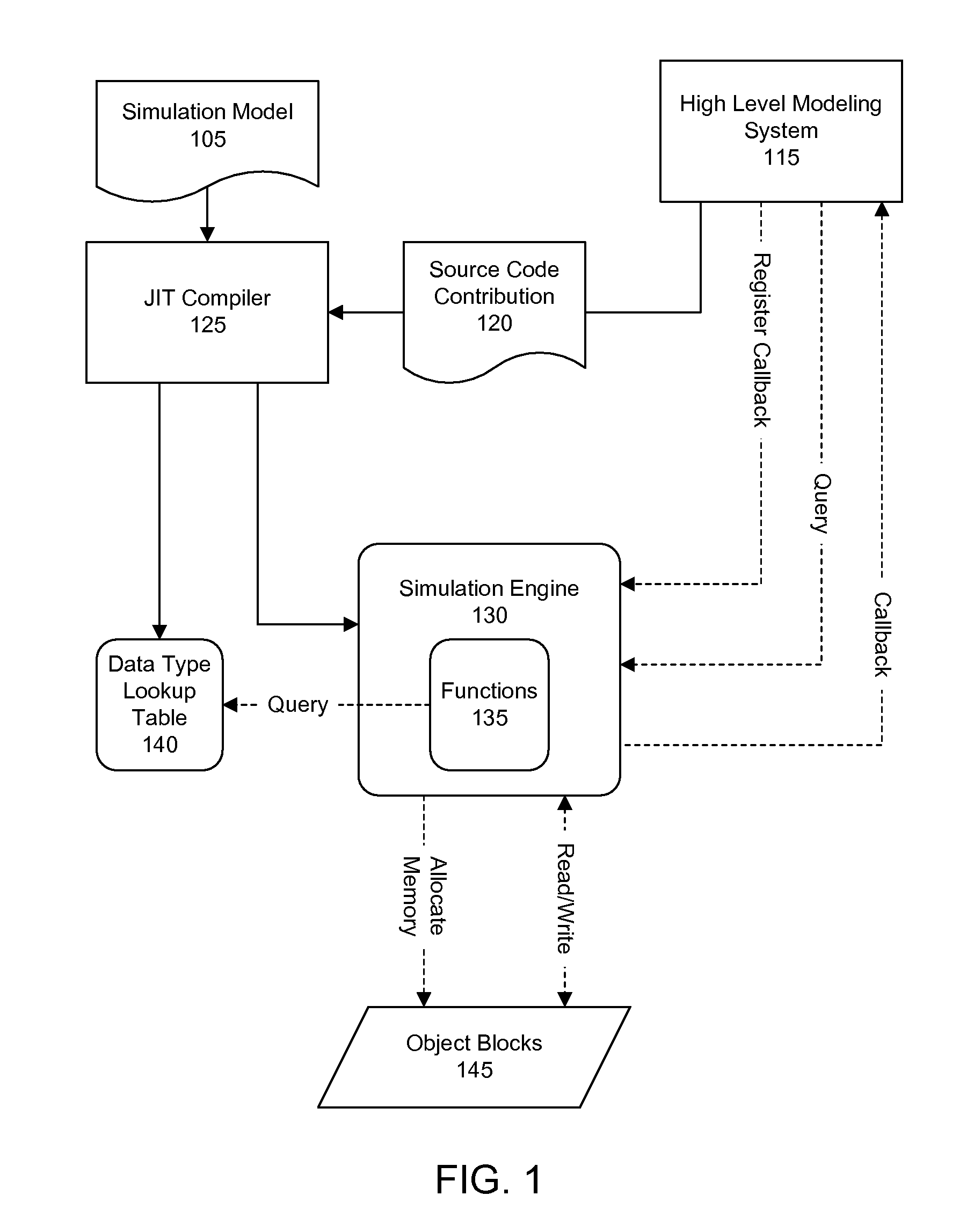

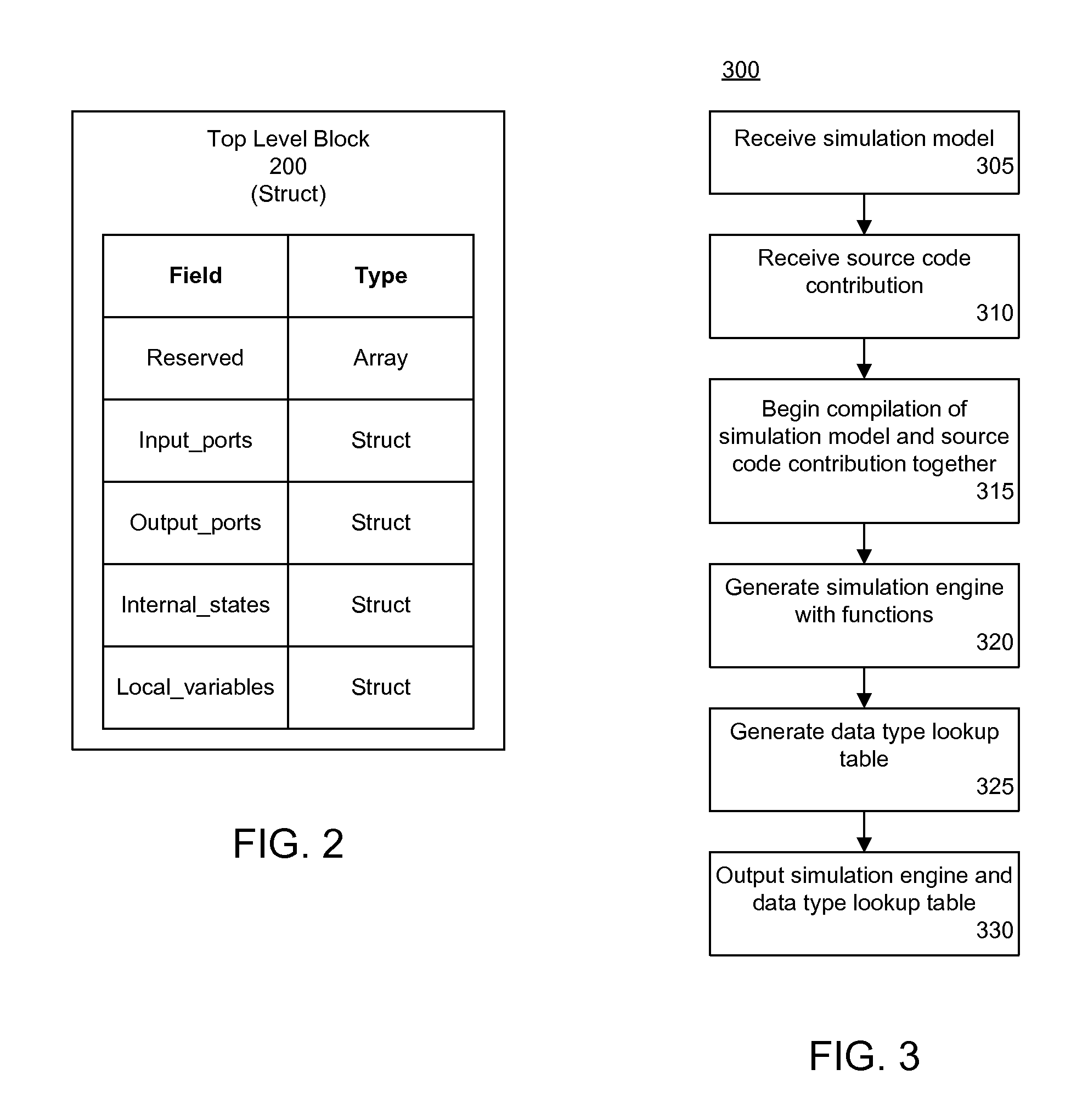

ActiveUS8352229B1Analogue computers for electric apparatusProgram controlAnalog circuit designJust-in-time compilation

A computer-implemented method of creating a simulation engine for simulating a circuit design can include receiving a source code contribution from a high level modeling system and receiving a simulation model specified in an interpretive language that specifies the circuit design. The source code contribution can be compiled together with the simulation model using a Just-In-Time compiler. A simulation engine, specified in native machine code, can be output as a single, integrated software component formed from the source code contribution and the simulation model.

Owner:XILINX INC

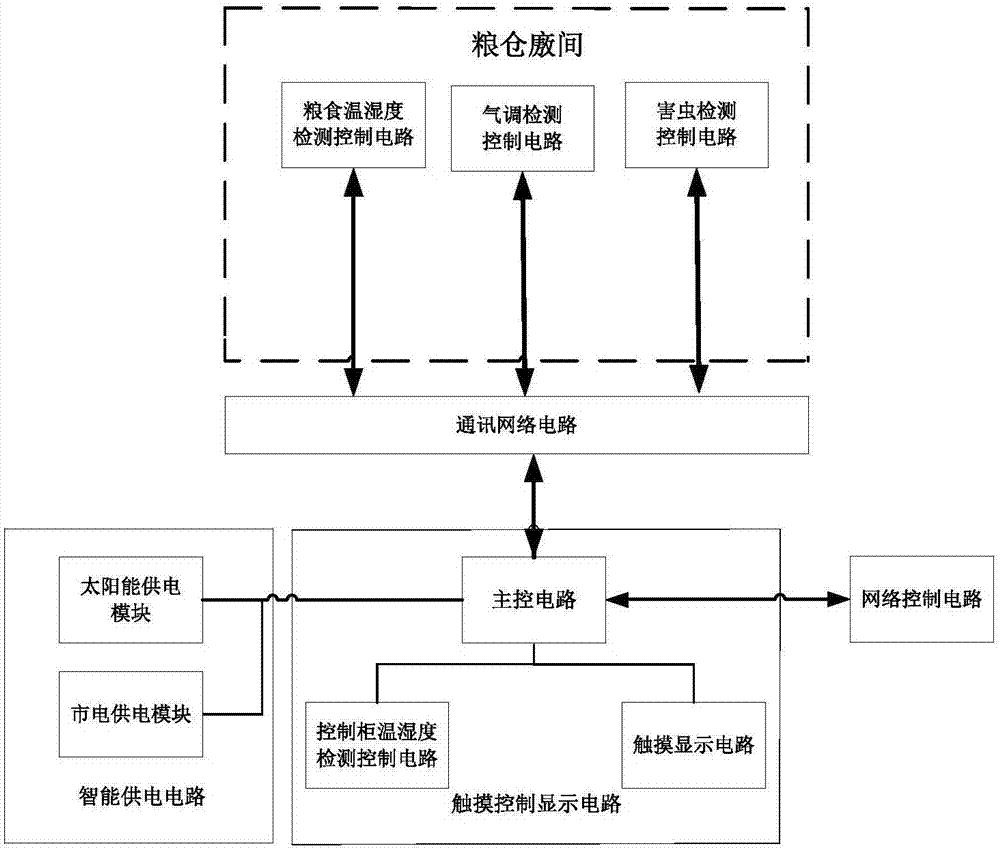

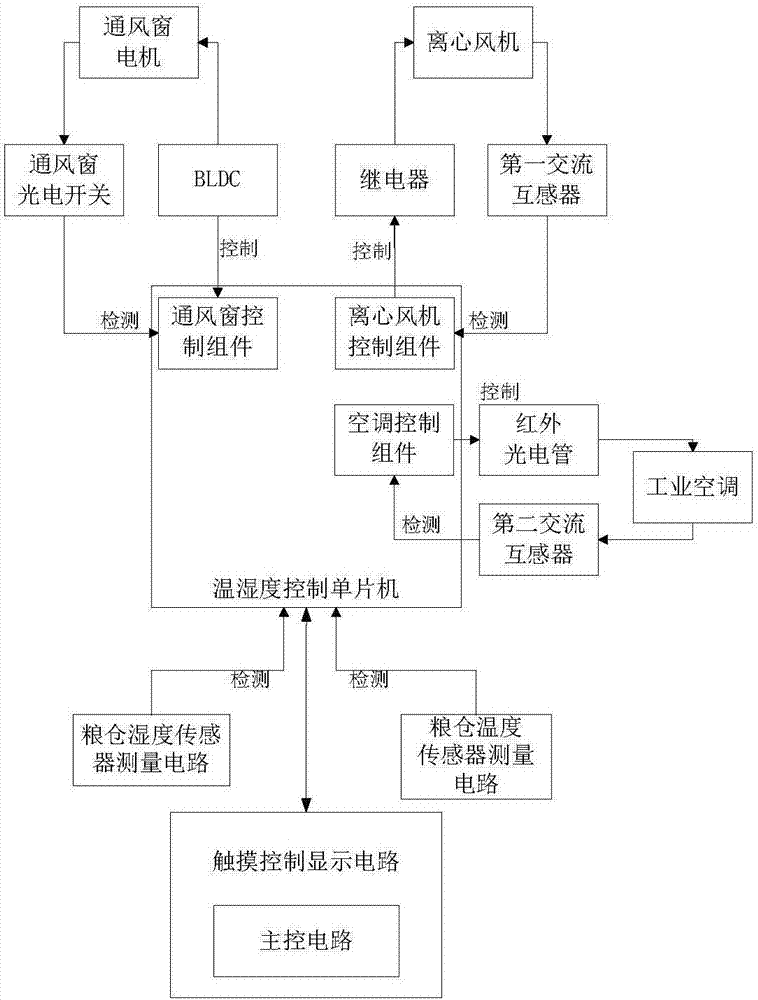

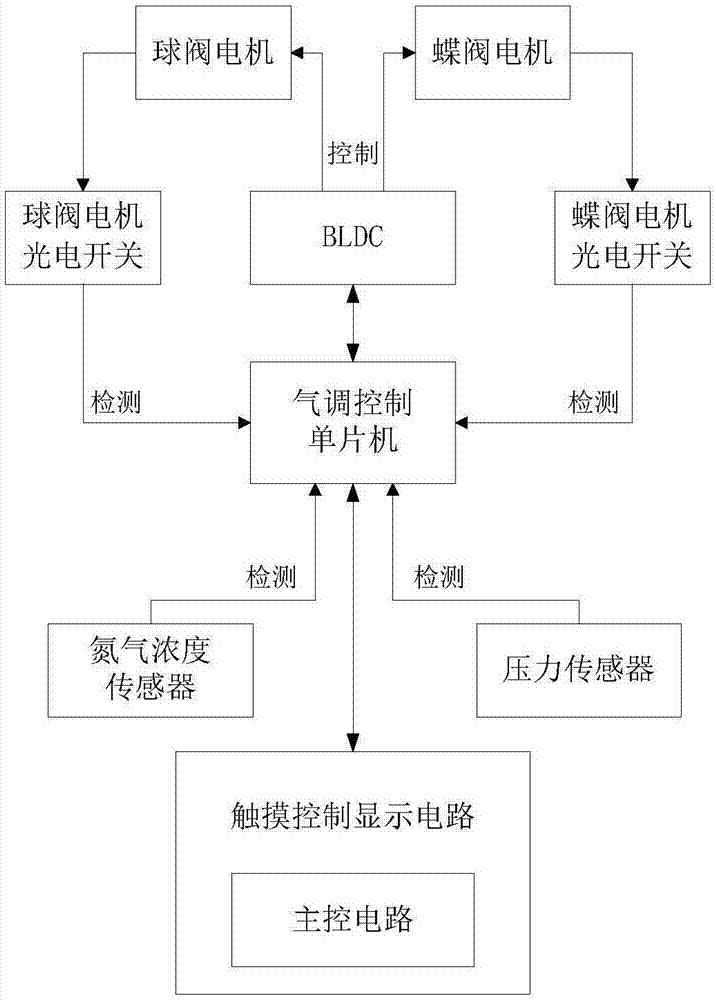

Control circuit of intelligent and integrated display control system of granary

ActiveCN107168273AImprove detection accuracyHigh degree of detection automationTotal factory controlSimultaneous control of multiple variablesAnalog circuit designControl system

The invention discloses a control circuit of an intelligent and integrated display control system of a granary. The control circuit comprises a grain temperature and humidity detection control circuit, a gas conditioning detection control circuit, a pest detection control circuit, an intelligent power supply circuit, a communication network circuit, a touch control display circuit and a network control circuit, wherein the intelligent power supply circuit is connected with the touch control display circuit, the touch control display circuit is connected with the grain temperature and humidity detection control circuit, the gas conditioning detection control circuit and the pest detection control circuit by means of the communication network circuit, and the touch control display circuit comprises a main control circuit, a touch display circuit connected with the main control circuit and a control cabinet temperature and humidity detection control circuit, thus the corresponding control system can be adjusted in one or more ways of a local intelligent mode, a local manual mode, a network intelligent mode and a network manual mode. The control circuit adopts a modular and analog circuit design, and creates an ideal grain storage environment.

Owner:ANHUI BOWEI CHANGAN ELECTRONICS

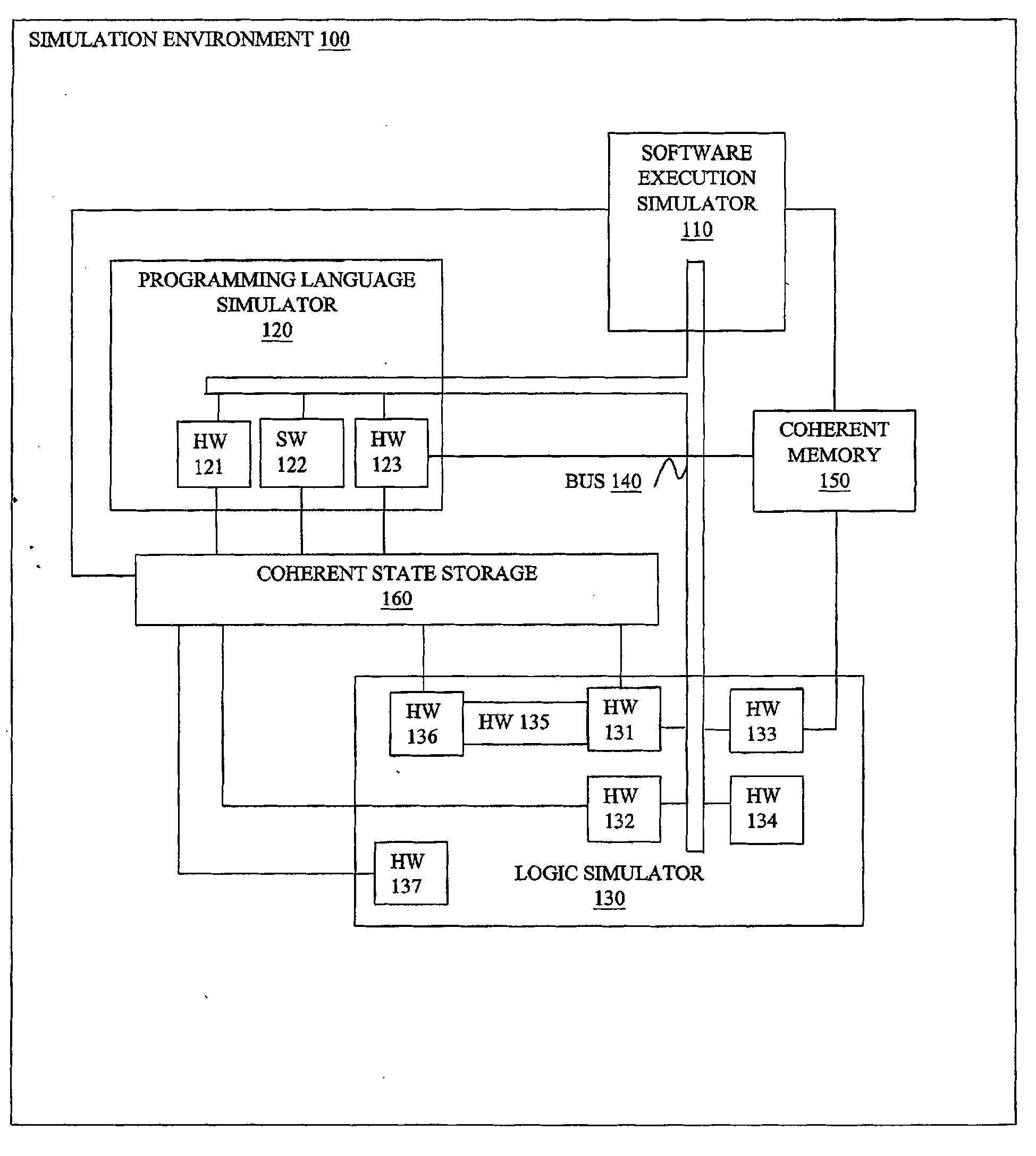

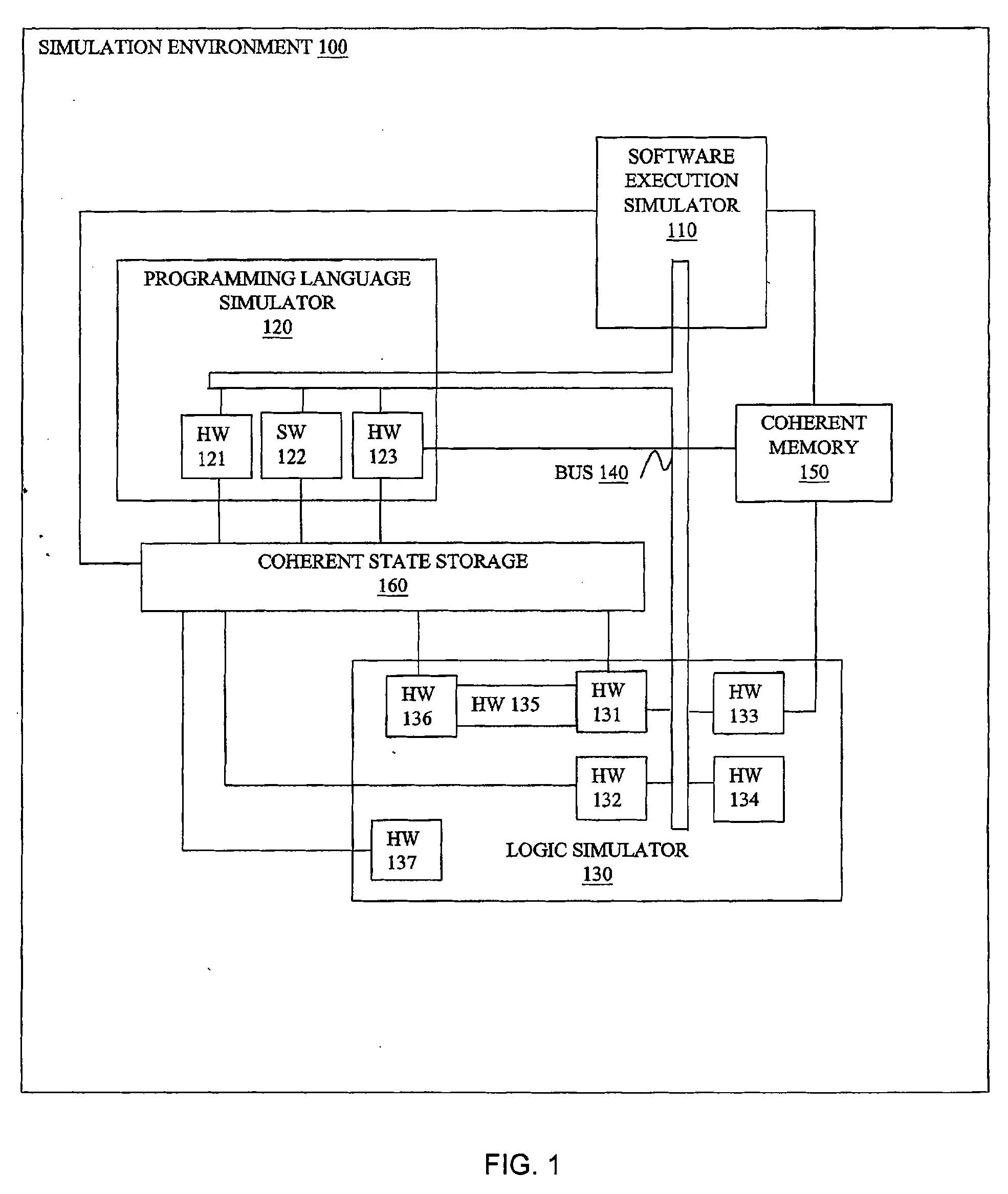

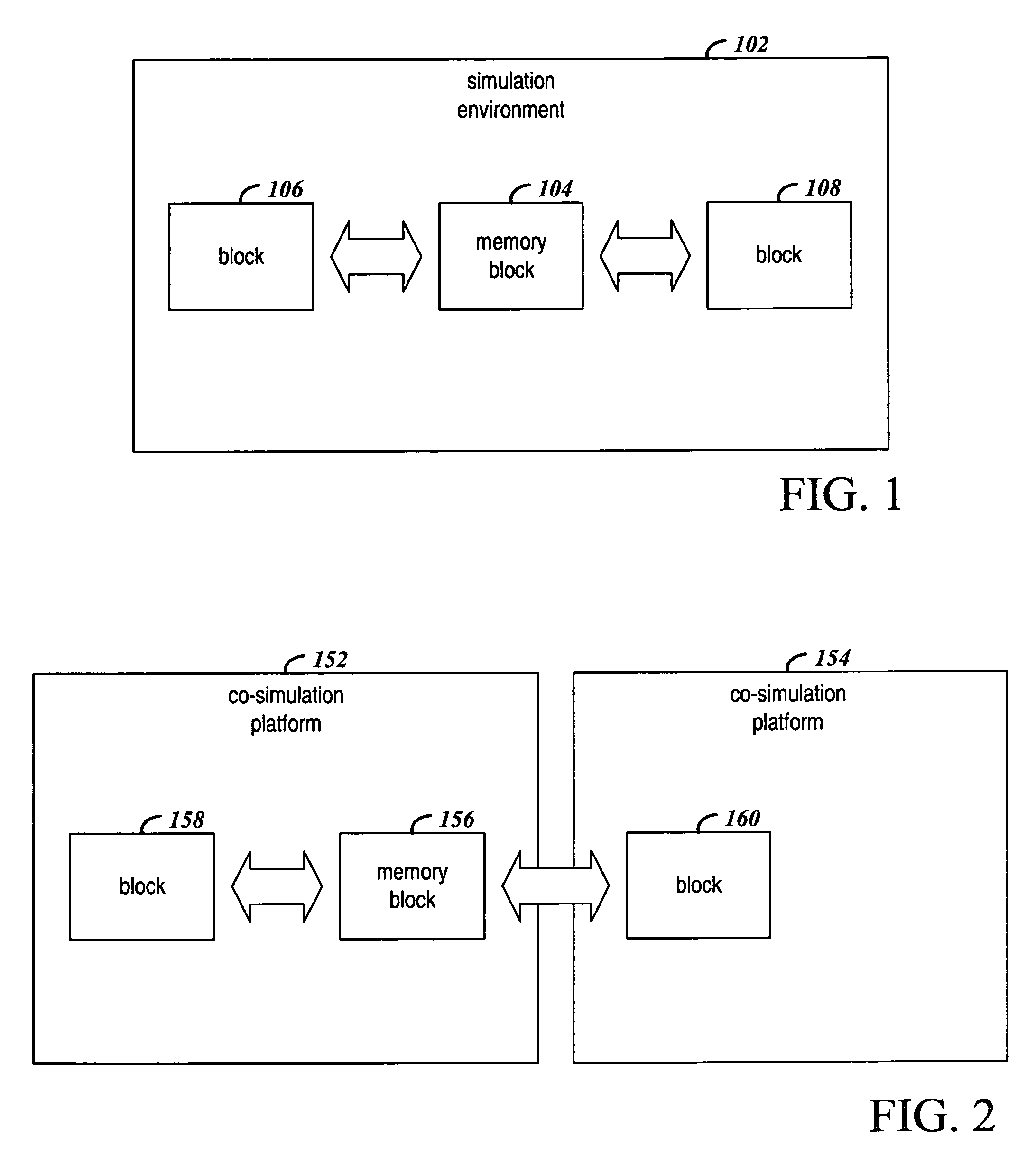

Coherent state among multiple simulation models in an eda simulation environment

InactiveUS20080215304A1Analogue computers for electric apparatusCAD circuit designAnalog circuit designCoherent states

A circuit design is simulated in a simulation environment. When a simulation model in the simulation environment transfers state information to a second simulation model, the simulation environment receives the state information and makes it available to the second simulation model without simulating the transfer through the simulated circuit design.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

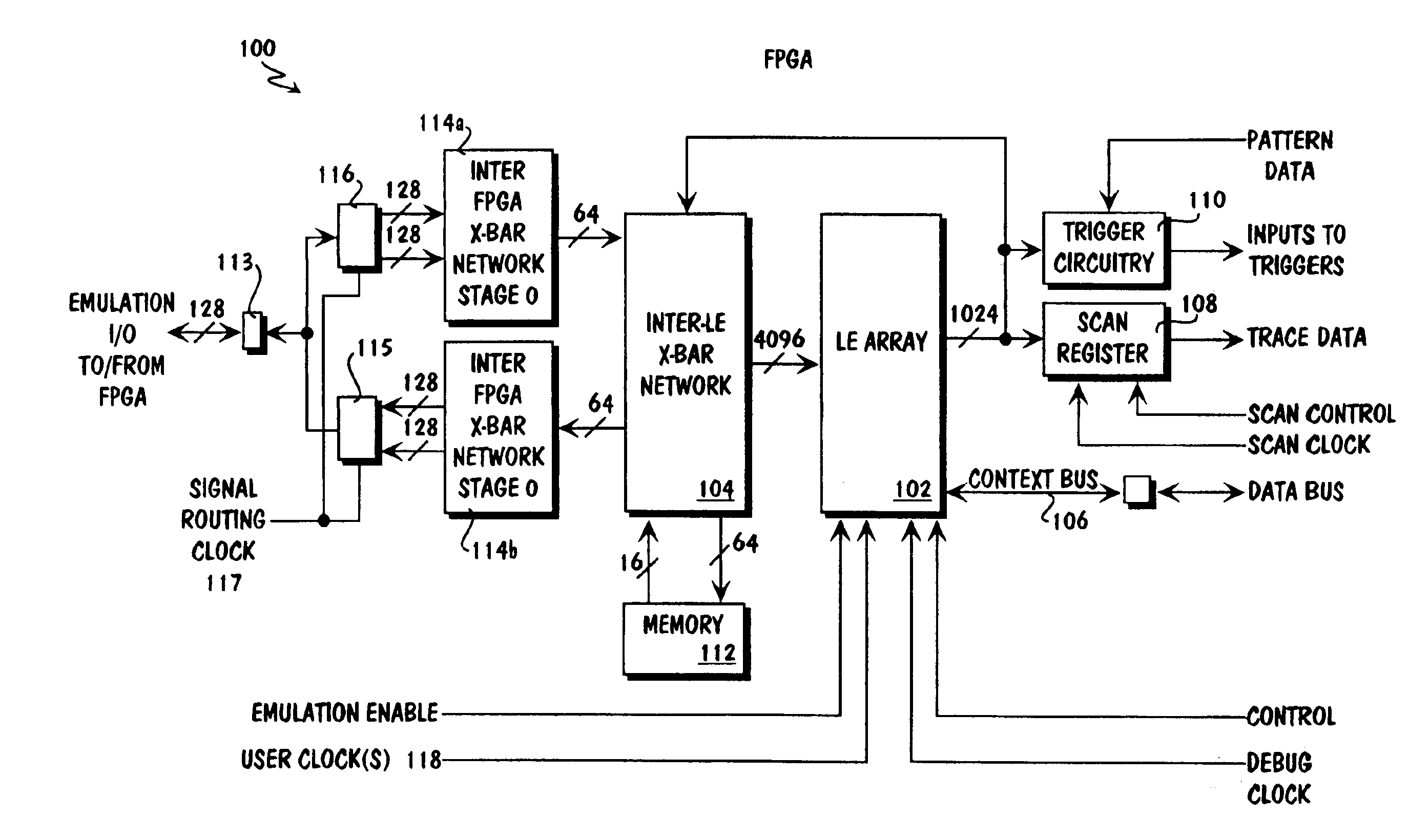

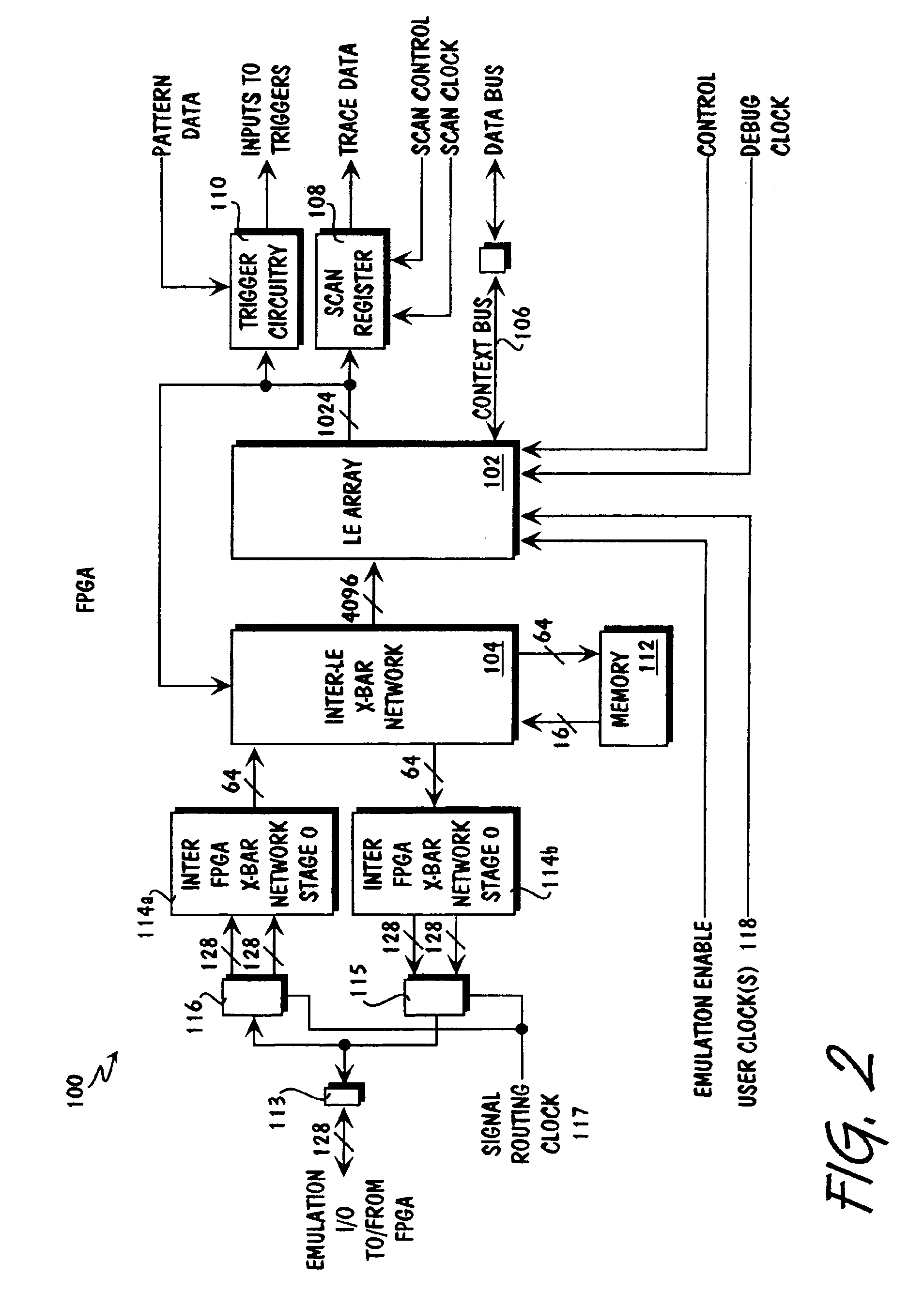

Regionally time multiplexed emulation system

InactiveUS6947882B1Detecting faulty computer hardwareSemiconductor/solid-state device manufacturingAnalog circuit designSignal routing

A regionally time multiplexed emulation system includes an emulator for emulating a circuit design. The emulator includes a plurality of reconfigurable logic devices with buffered I / O pins and reconfigurable logic elements. The reconfigurable logic devices are reconfigurable to emulate a circuit design using at least one user clock to clock the logic elements and at least one signal routing clock to time multiplex the routing of emulation signals between the reconfigurable logic devices, with the at least one signal routing clock being independent of the at least one user clock.

Owner:MENTOR GRAPHICS HLDG +1

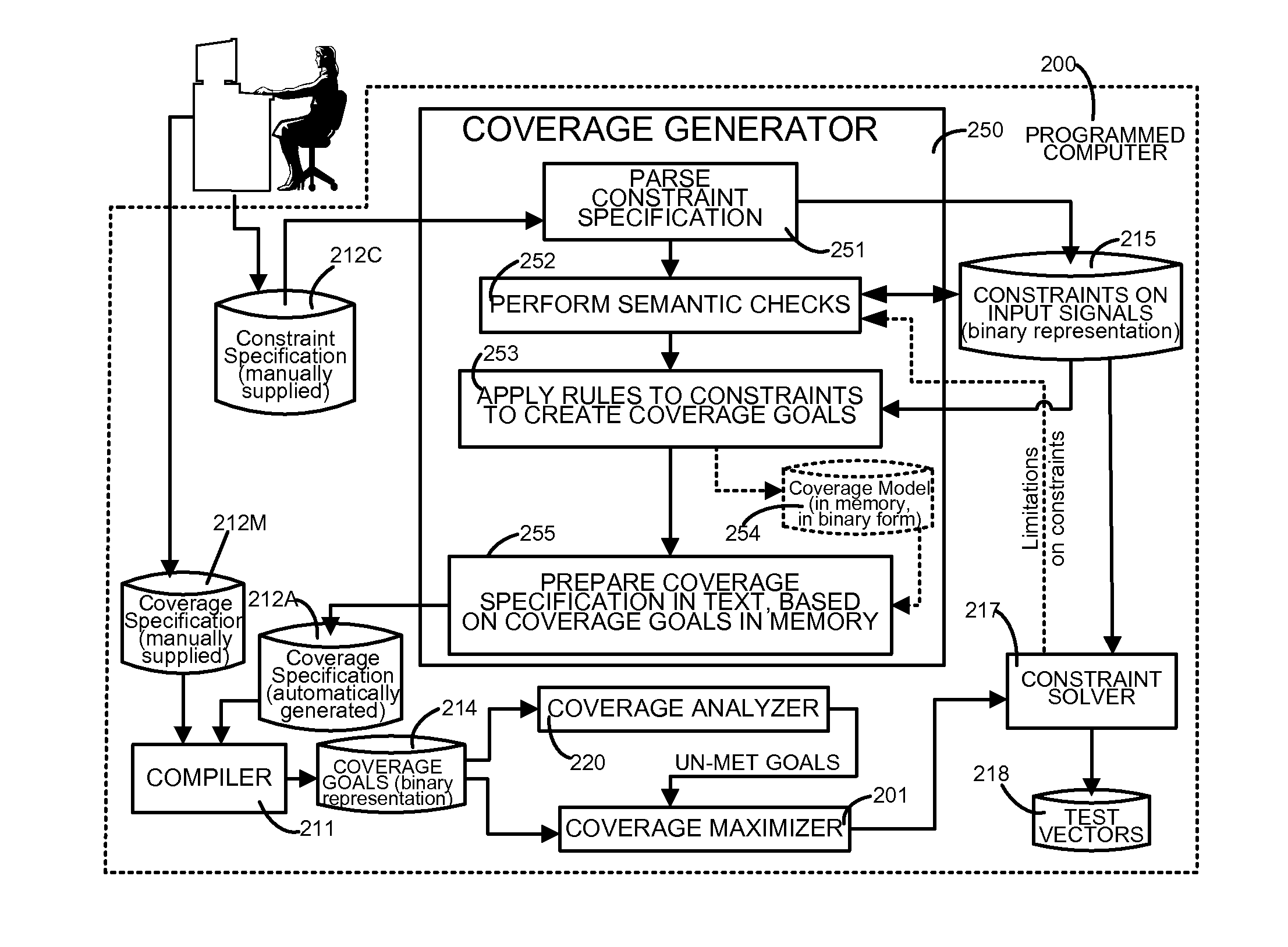

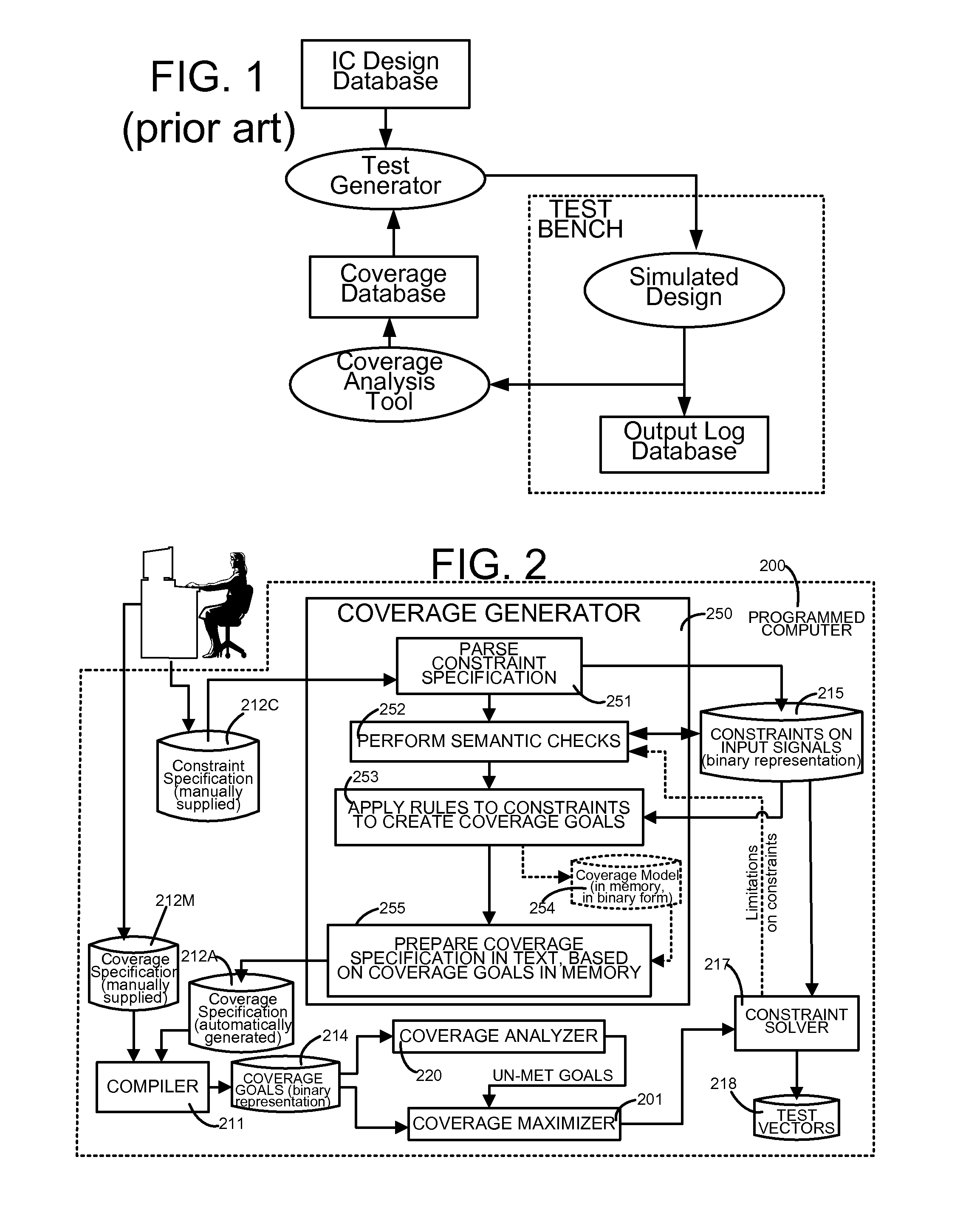

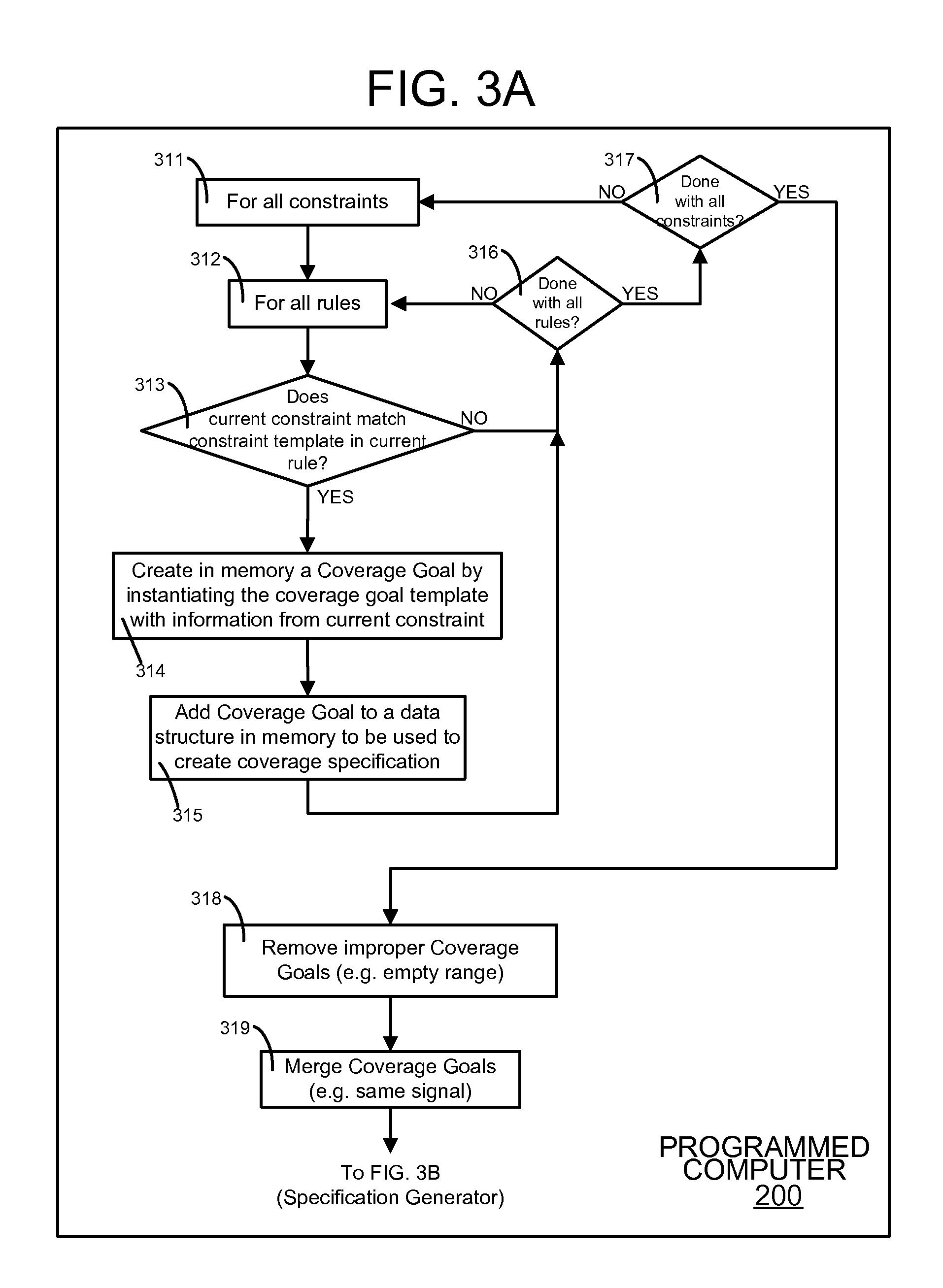

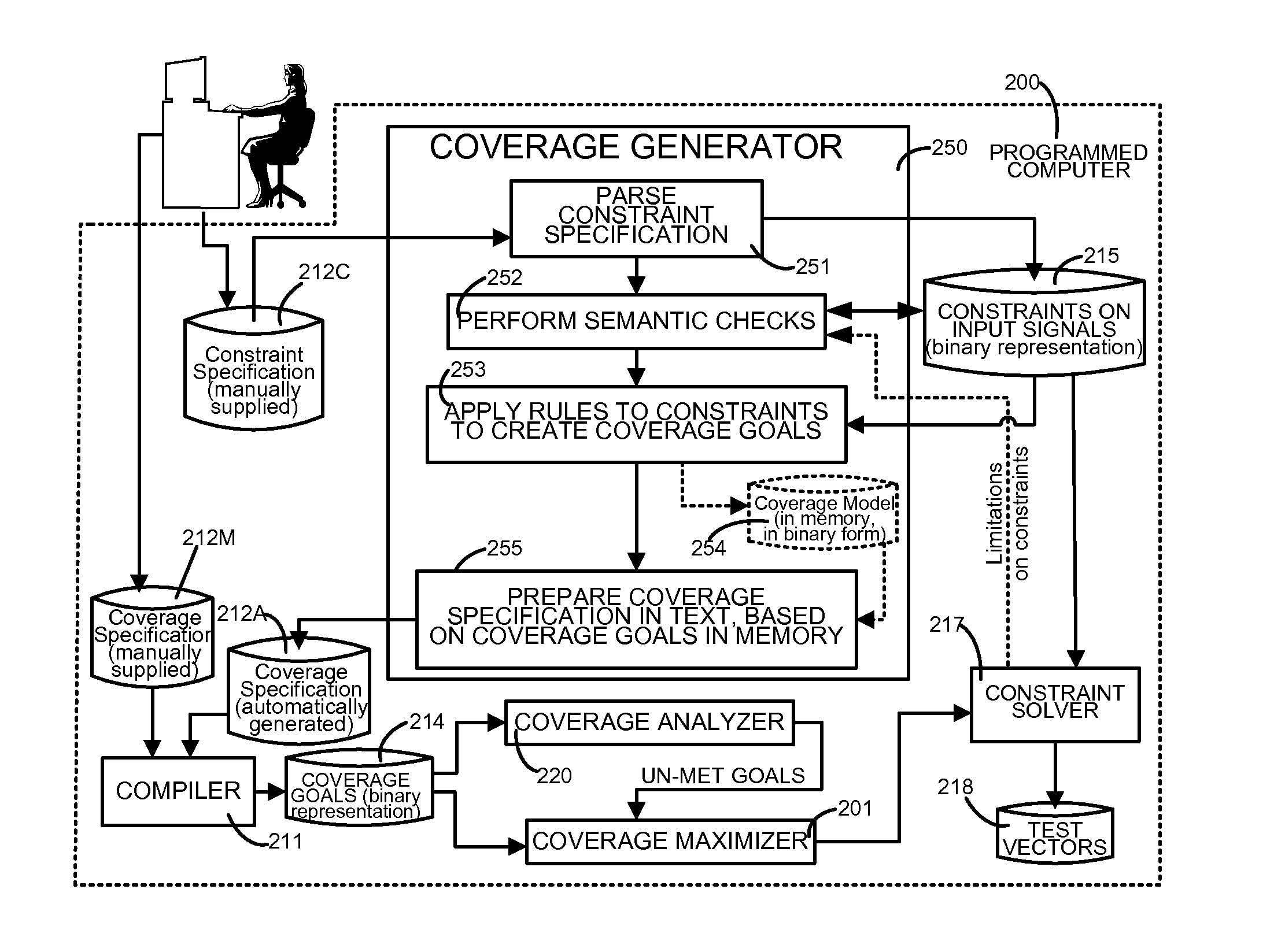

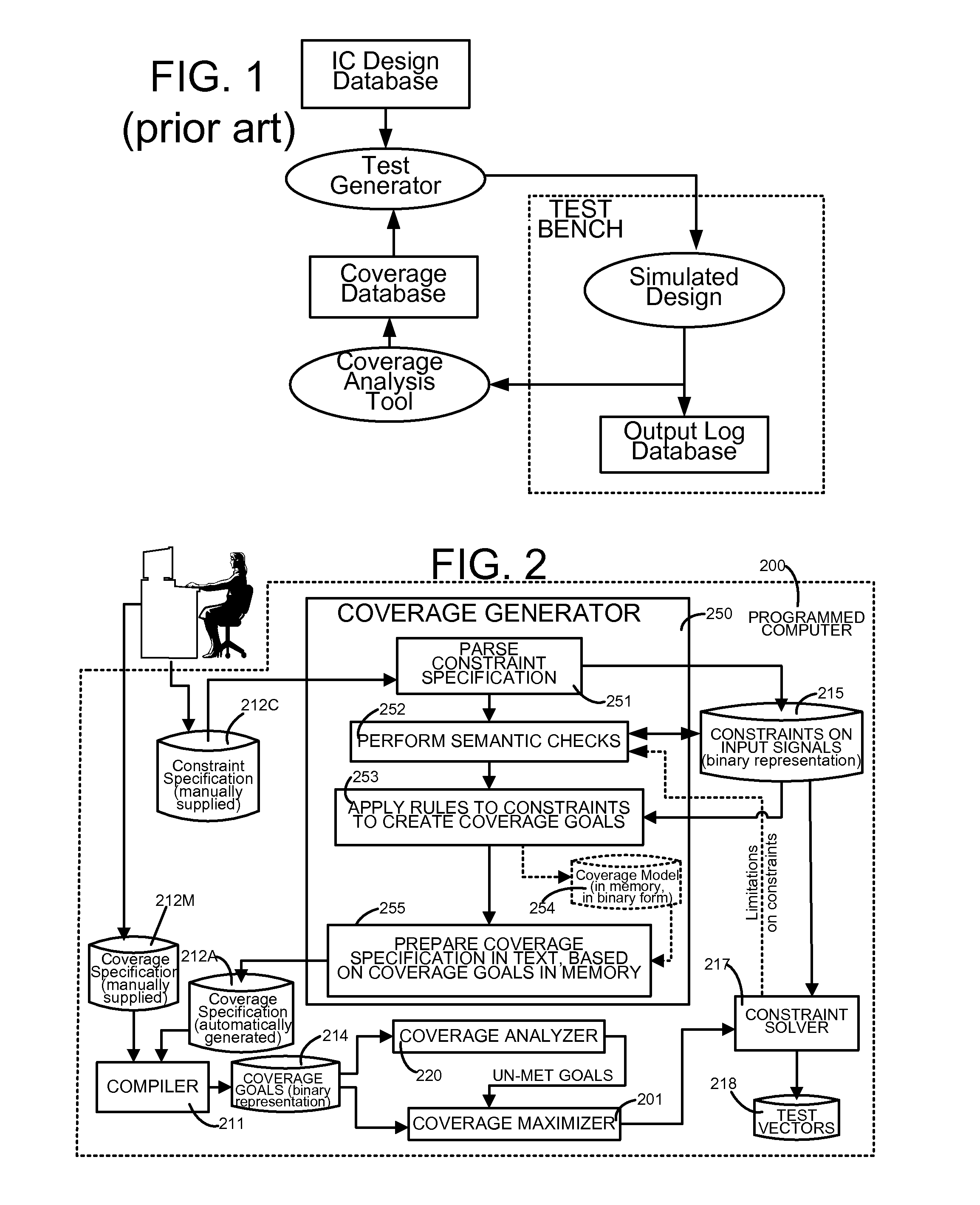

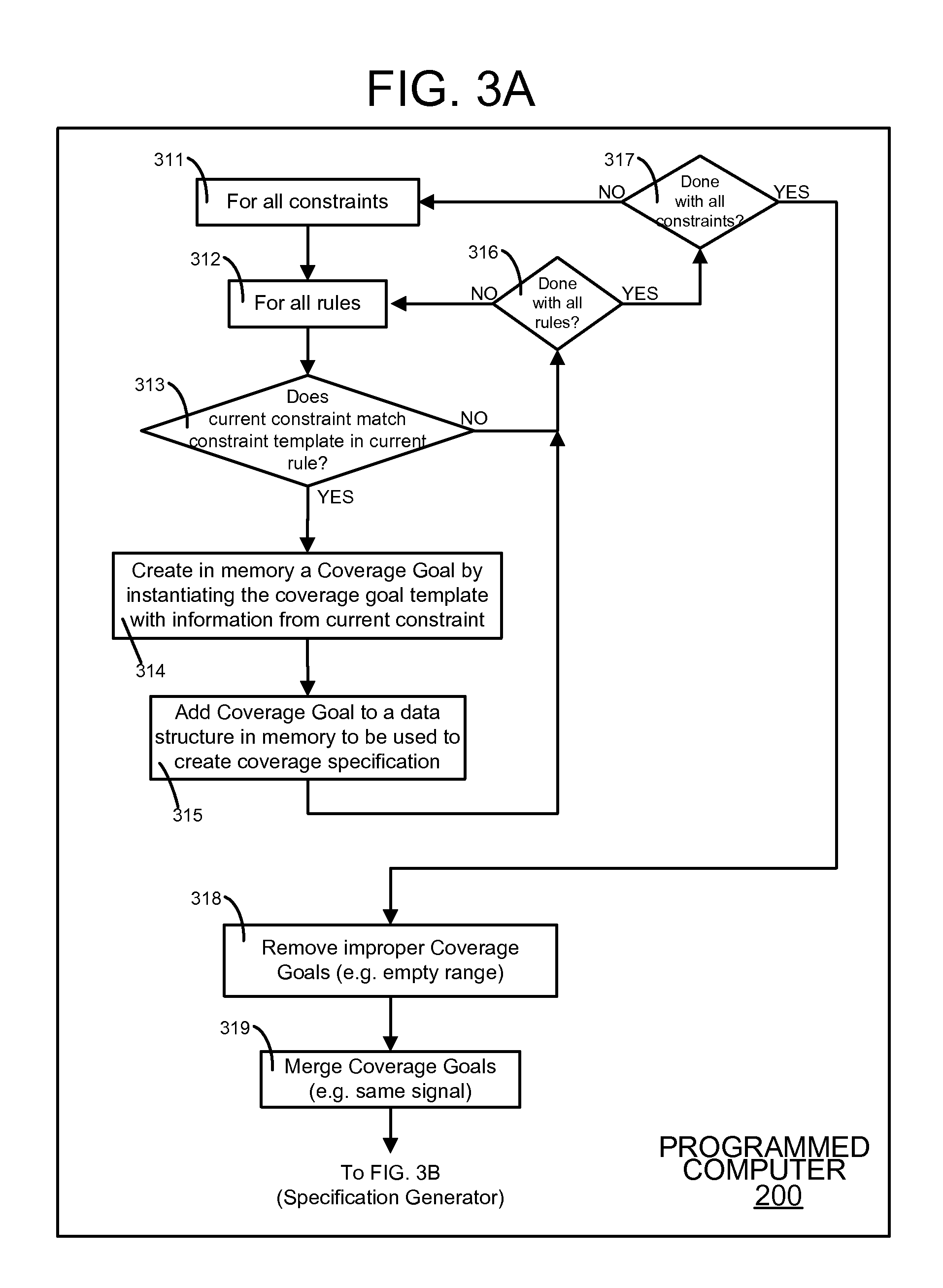

Method for automatically extracting a functional coverage model from a constraint specification

ActiveUS7904846B2Electronic circuit testingDetecting faulty computer hardwareAnalog circuit designAlgorithm

Owner:SYNOPSYS INC

Method for automatically extracting a functional coverage model from a constraint specification

ActiveUS20090037859A1Electronic circuit testingDetecting faulty computer hardwareAnalog circuit designAlgorithm

A computer is programmed to automatically generate in memory, goals for functional verification of a design of a circuit by use of constraints that are specified in the normal manner. Specifically, a predetermined set of rules are automatically applied to the constraints, on random values for signals to be input to the circuit during simulation of the design. Application of the rules identifies one or more templates of goal(s) to be met. The computer is programmed to automatically use constraint(s) and template(s) to instantiate goal(s) in memory. Each goal identifies a signal to be input to the circuit, and defines a counter for a value of the signal. The goals are used in the normal manner, i.e. used to measure coverage of functional verification during simulation of the design of the circuit.

Owner:SYNOPSYS INC

Method and apparatus for ams simulation of integrated circuit design

ActiveUS20120198405A1Ease and abilityEasy to readComputer aided designSoftware simulation/interpretation/emulationAnalog circuit designUser input

Owner:CADENCE DESIGN SYST INC

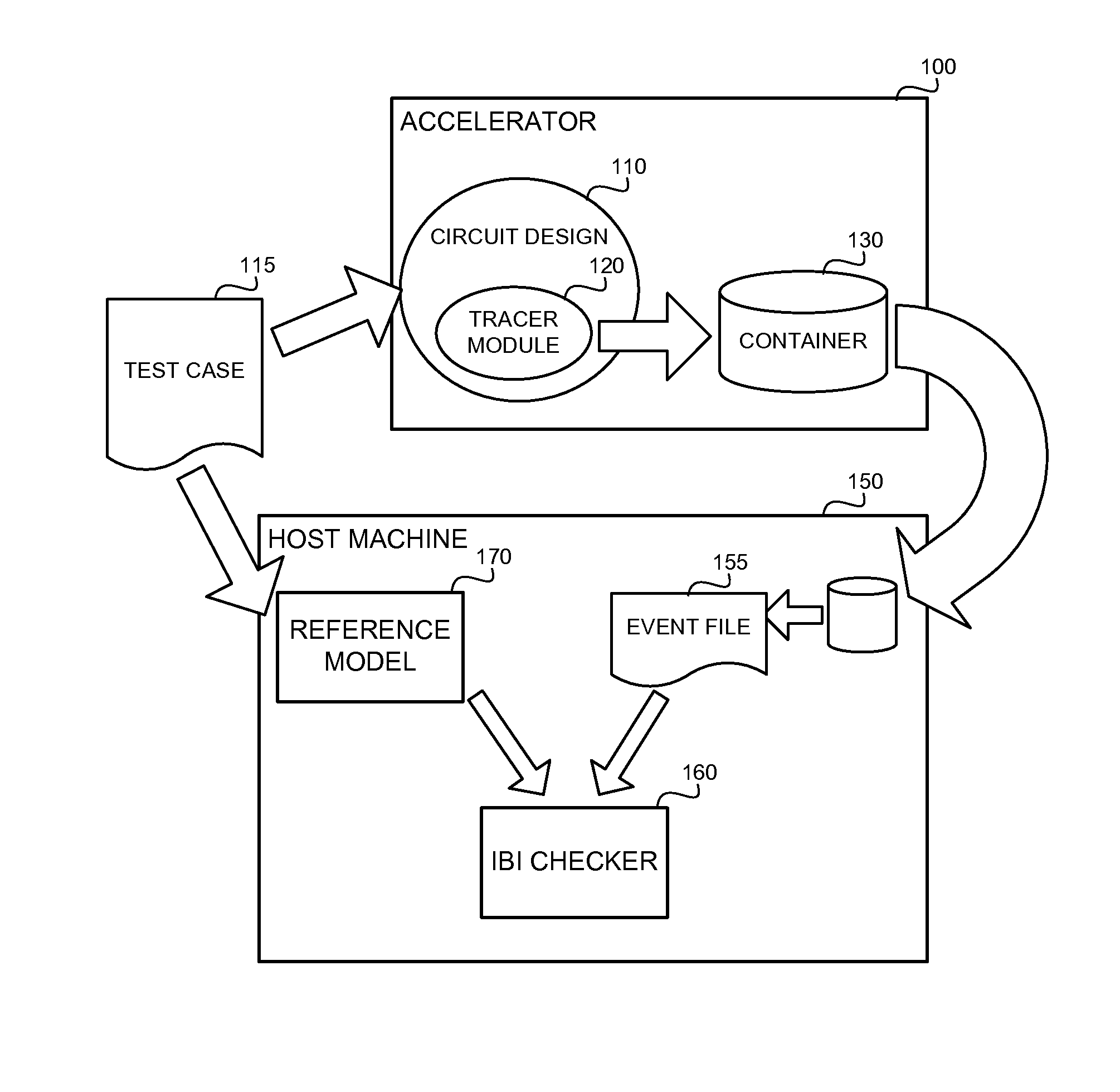

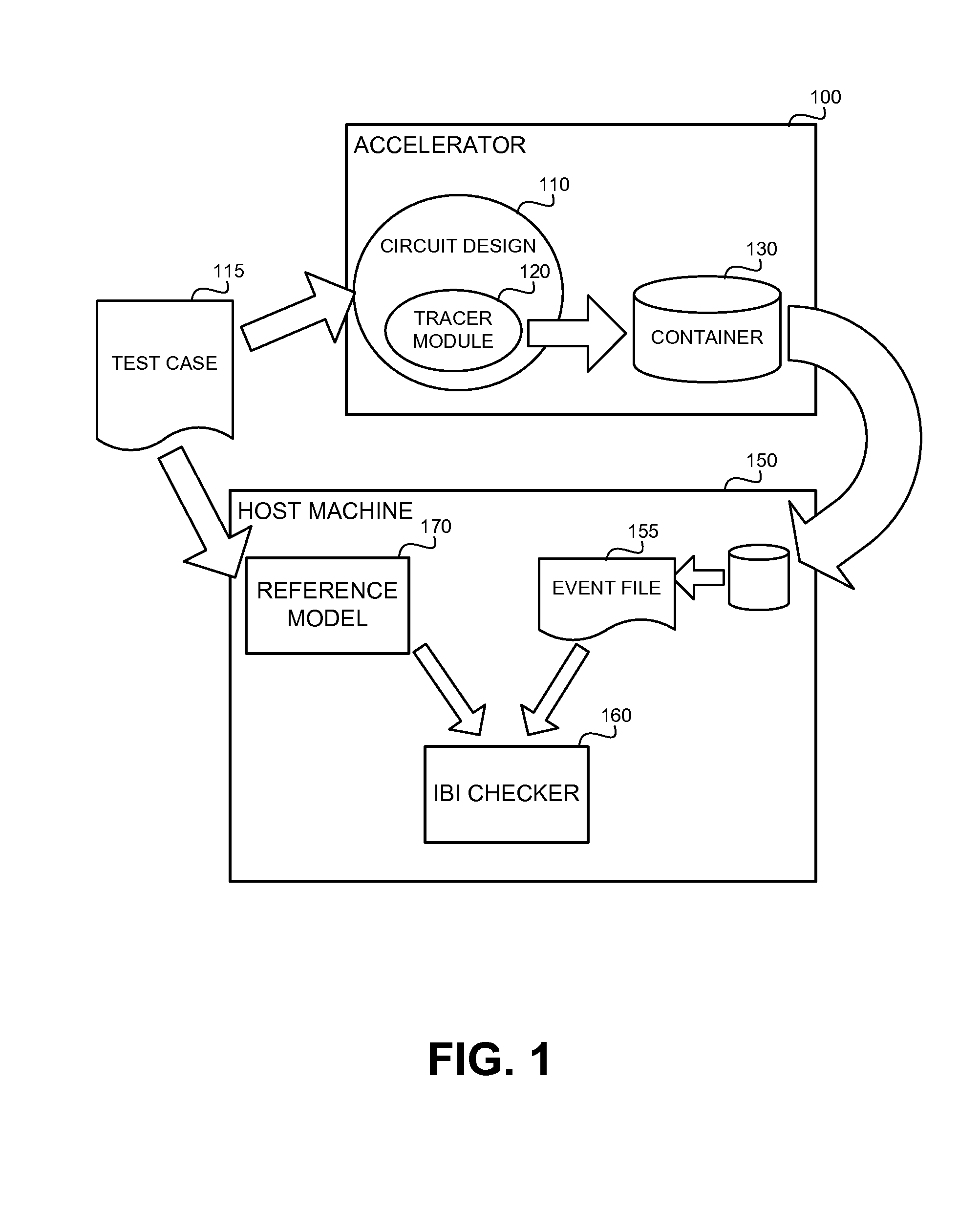

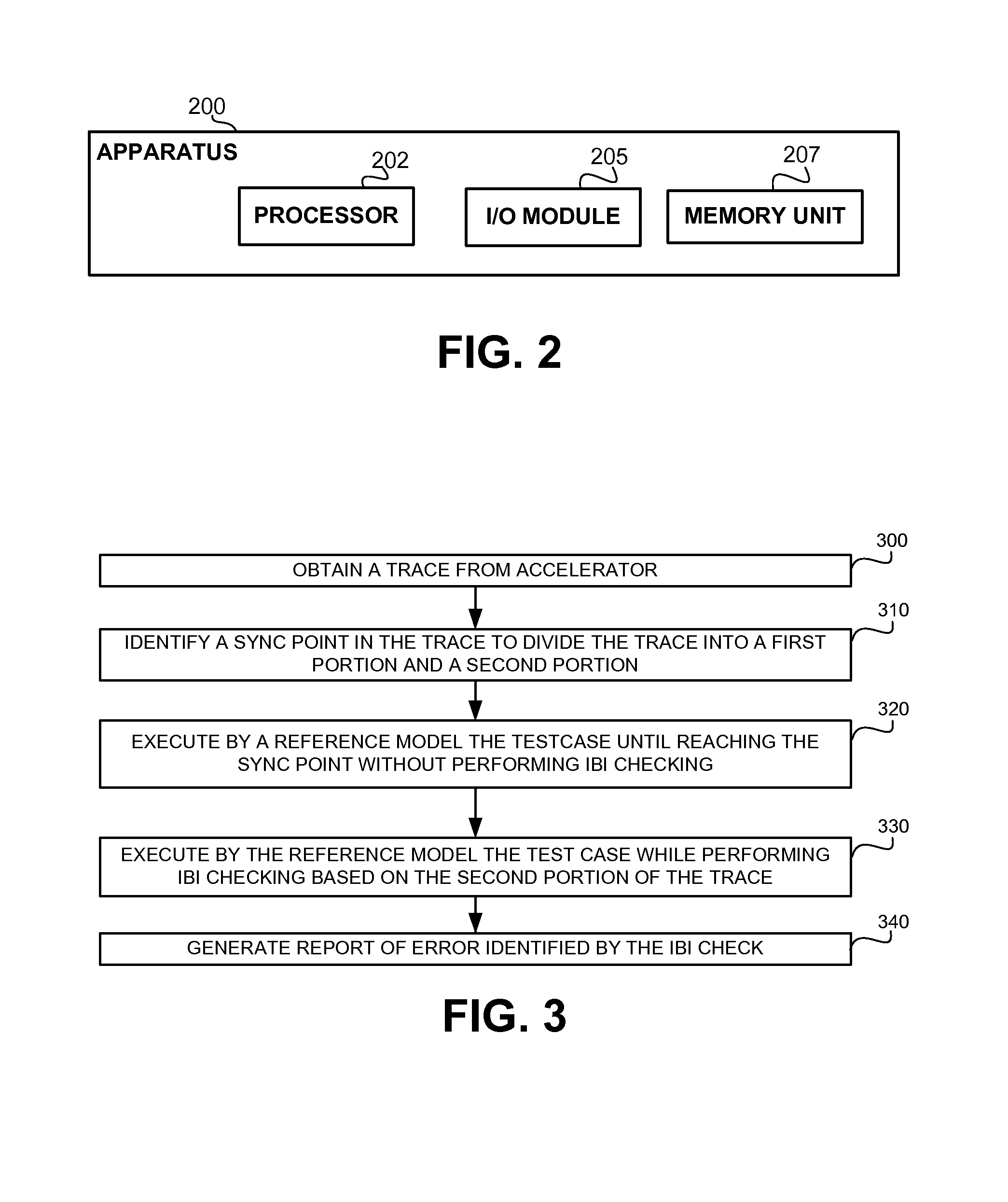

Partial Instruction-by-instruction checking on acceleration platforms

InactiveUS20140019929A1Computer aided designSoftware simulation/interpretation/emulationReference modelAnalog circuit design

A method, apparatus, and product for partial instruction-by-instruction checking on acceleration platforms. The method comprising: obtaining a trace from an hardware accelerator, wherein the trace is generated by the hardware accelerator during simulation of an execution of a test case on a circuit design; identifying a synchronization point in the trace; simulating execution of the test case by a reference model until reaching the synchronization point; and performing instruction-by-instruction checking in order to identify an error in the circuit design based on the simulated execution by the hardware accelerator, wherein the instruction-by-instruction checking is performed with respect to a portion of the trace that relates to operation after executing the synchronization point, wherein the instruction-by-instruction checking utilizes the reference model to determine an expected outcome of each event recorded in the portion of the trace.

Owner:GLOBALFOUNDRIES INC

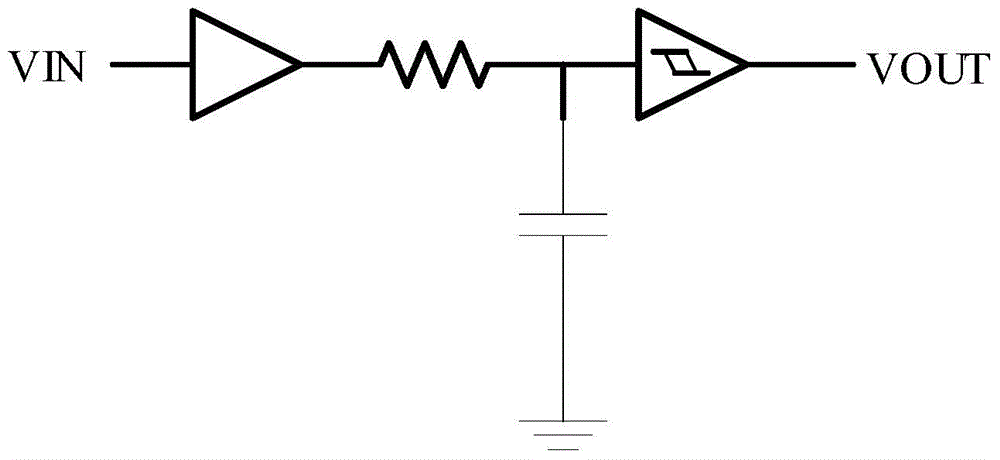

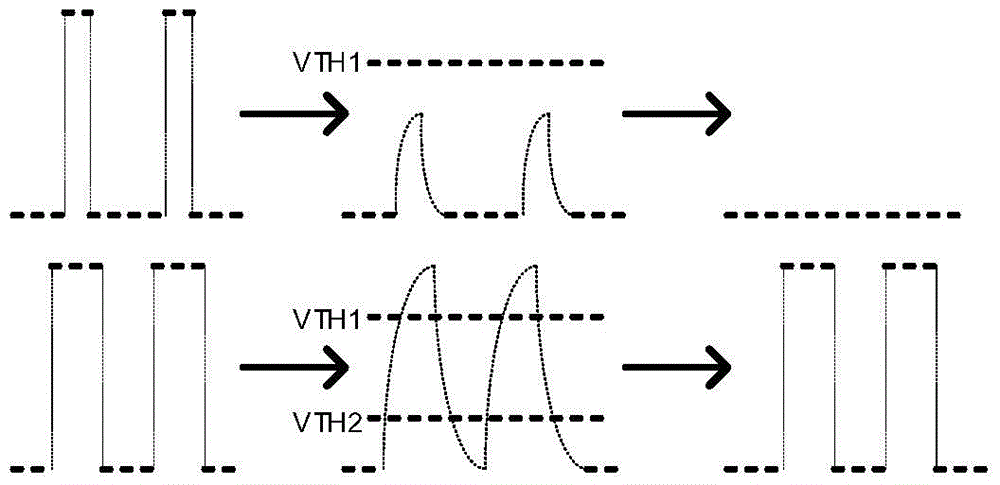

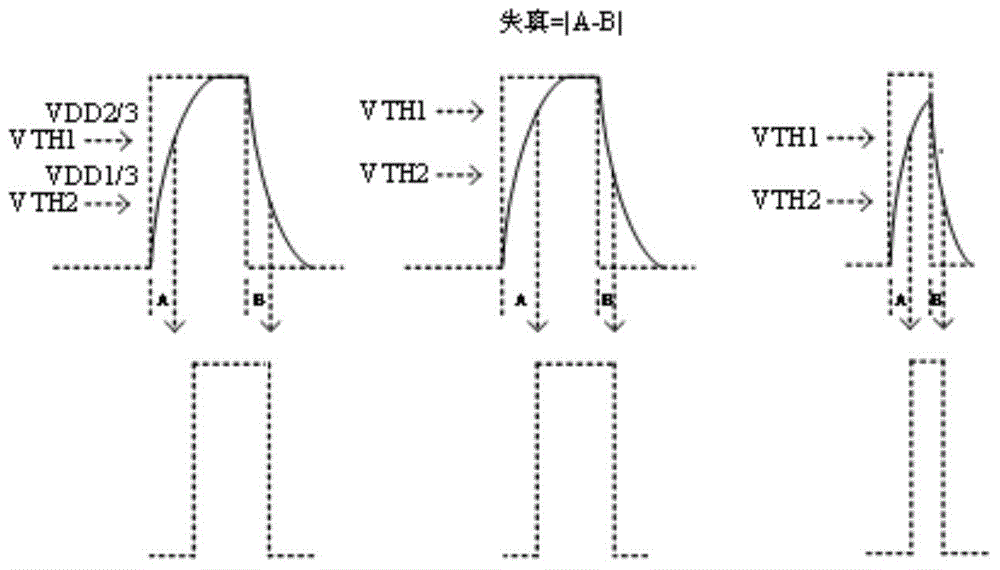

Pulse filtering circuit and method thereof

ActiveCN105187036AAvoiding problems with narrow pulse distortionAvoid strict requirements for thresholdsSingle output arrangementsAnalog circuit designEngineering

The present invention relates to a pulse filtering circuit and a method thereof, wherein the pulse filtering circuit comprises: a receiving circuit (001) for receiving a pulse signal; a filtering circuit (002) for detecting the width of the pulse signal; and an output and feedback circuit (003) for outputting a feedback control signal to the filtering circuit (002) according to the width of the pulse signal, and adjusting the outputted pulse signal into a same-phase pulse signal, and outputting; and the filtering circuit (002) sets the width of the pulse signal according to the feedback control signal. The present invention can transport the pulse signal having the width that is greater than the set width without distortion, and avoid the distortion of the narrow pulse in a traditional circuit, so the present invention has important application value in the field of analog circuit design.

Owner:SICHUAN YICHONG TECH CO LTD

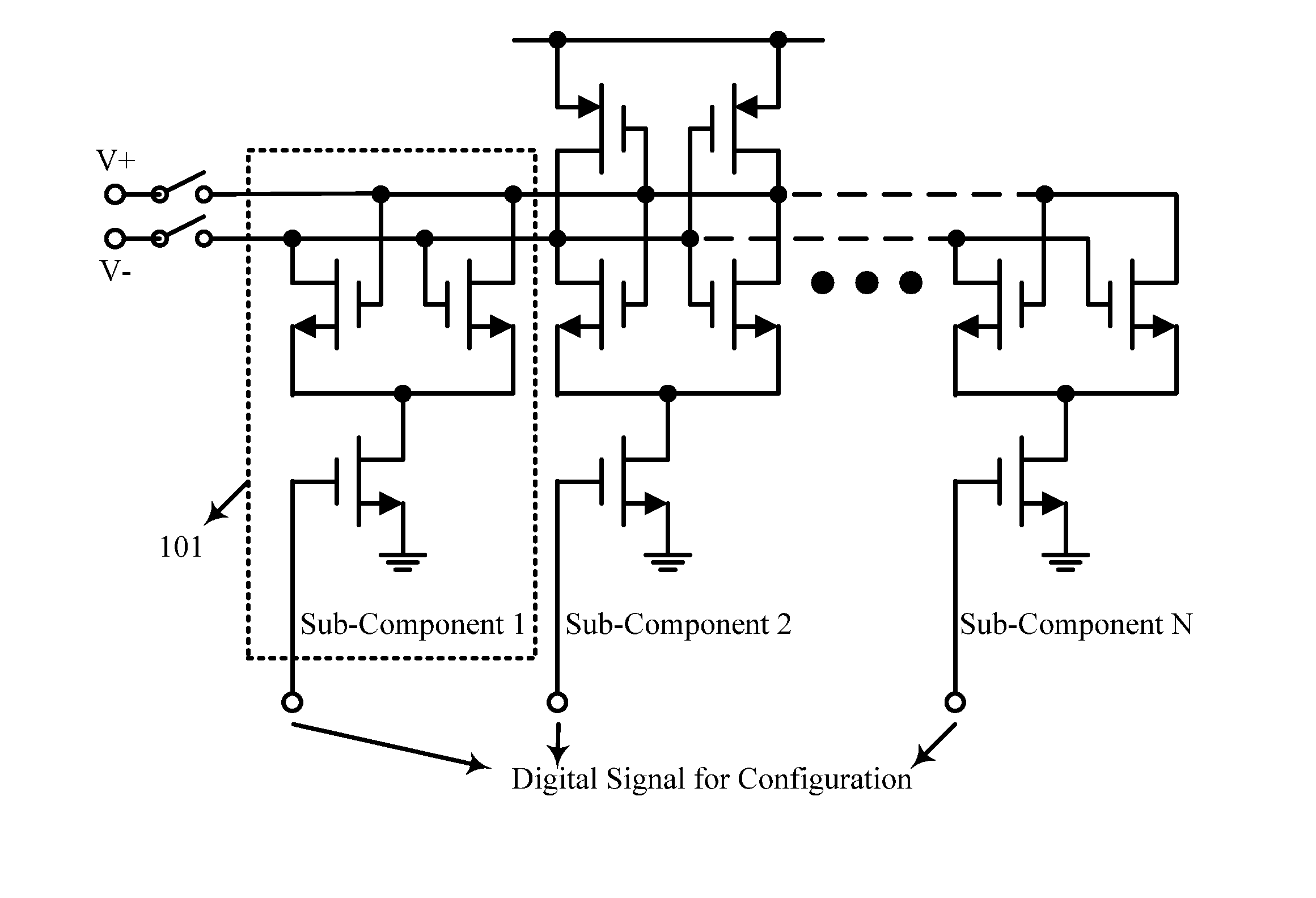

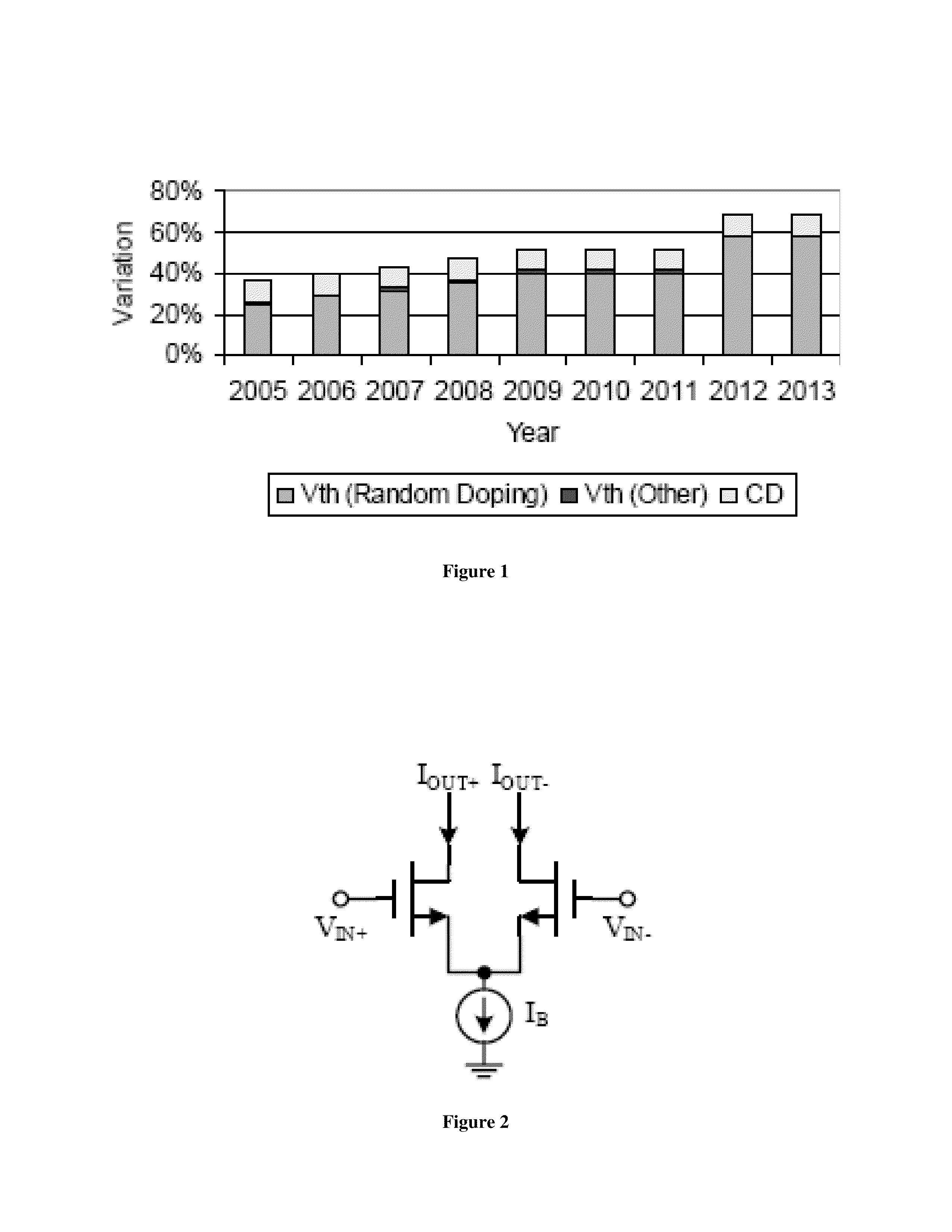

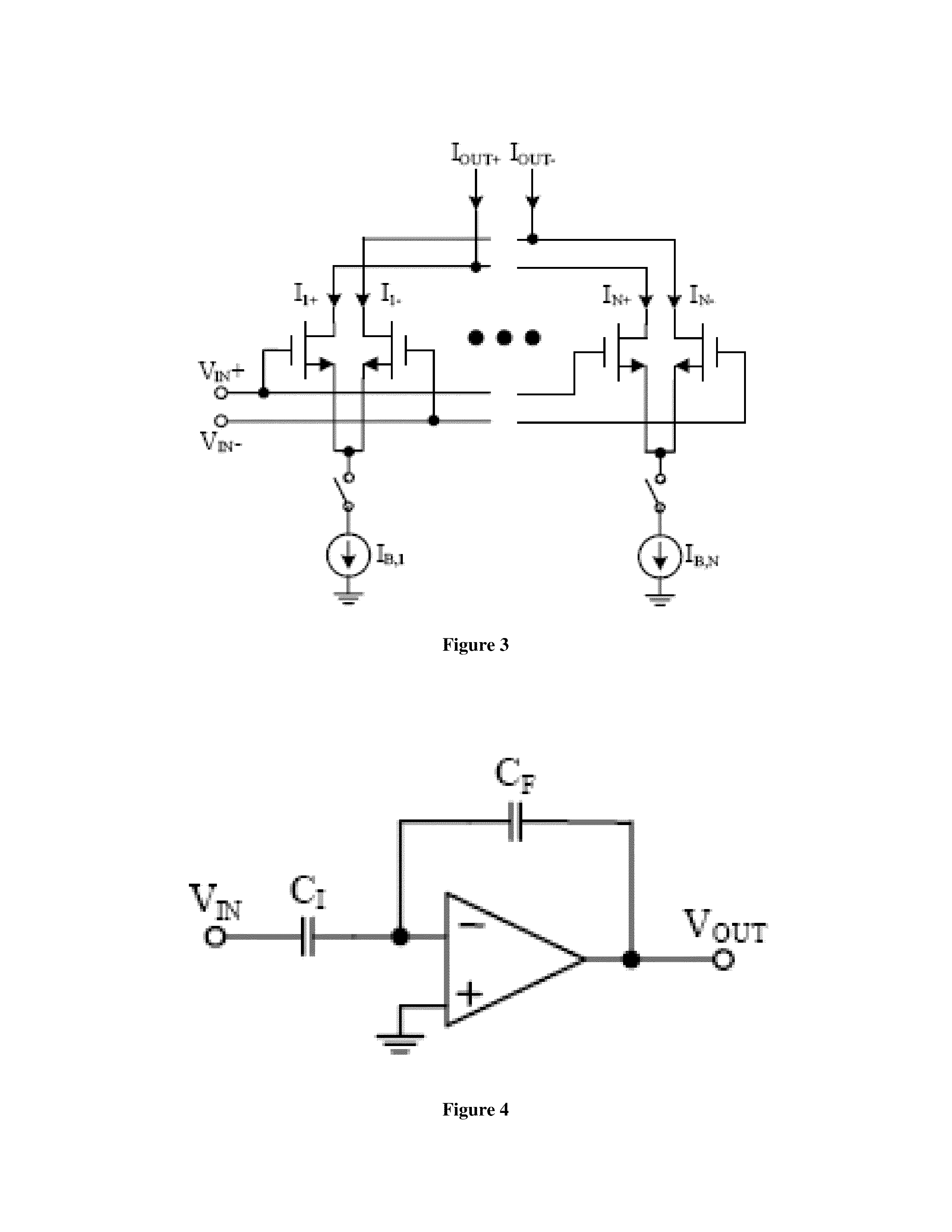

Tunable integrated circuit design for nano-scale technologies

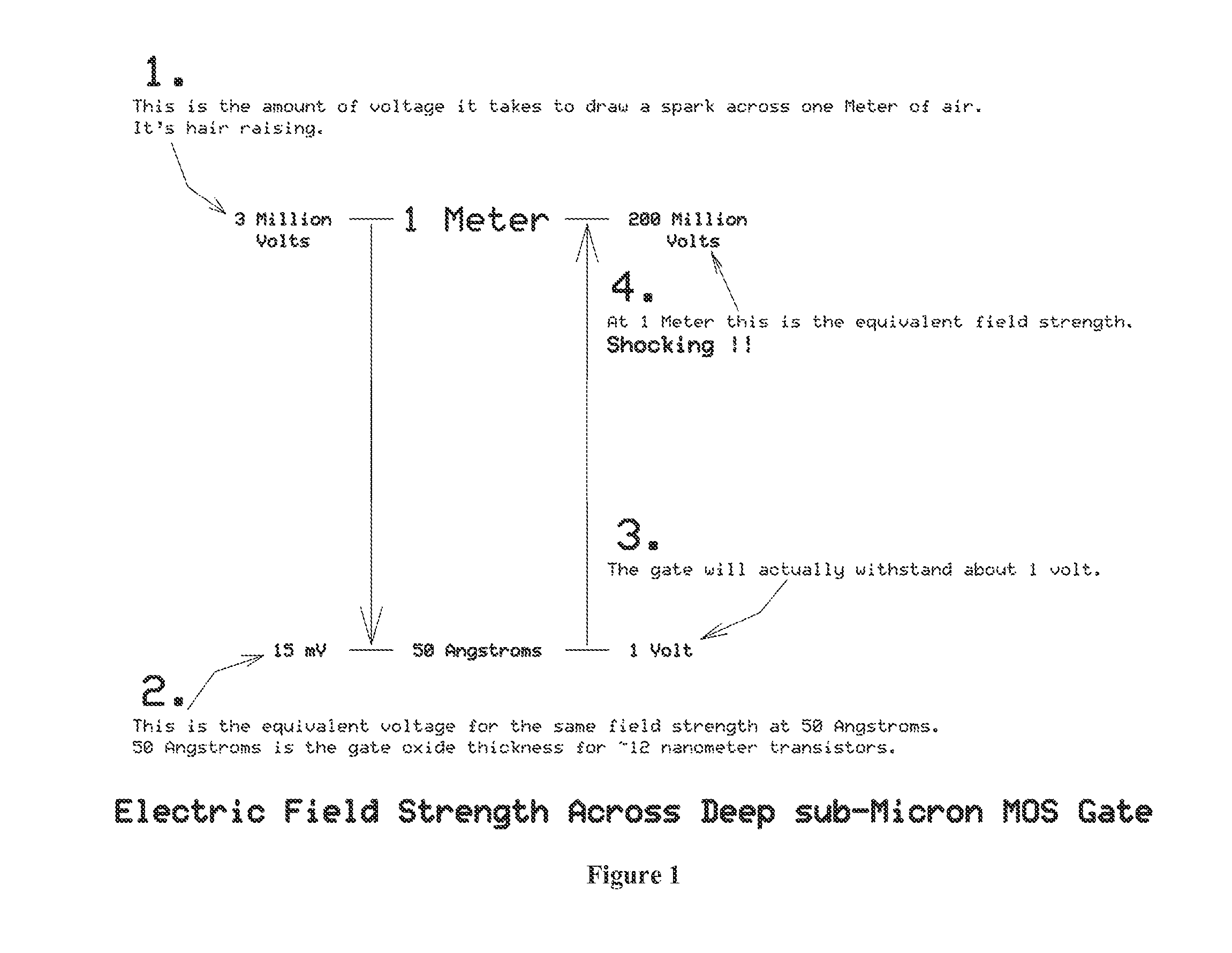

InactiveUS7945868B2Reduce random mismatchPromote robustnessReliability increasing modificationsMultiple-port active networksAnalog circuit designDynamic programming

The invention discloses a method for tuning nano-scale analog-circuit designs in order to reduce random-device mismatches and optimize said design, where nano-scale devices potentially have large-scale process variations. The method includes providing a tunable circuit topology, wherein each nano-scale device comprises a single component or comprises multiple parallel components. Each component is decomposed into multiple discrete sub-components, wherein each said sub-component either operates in parallel with other like components to effectively operate like one bigger component. The sub-components are subjected to a dynamic-programming process to adaptively select the sub-components to be kept operational, while configuring the nonselected sub-components to be nonoperational, based on the measurement of at least one operational parameter.

Owner:CARNEGIE MELLON UNIV

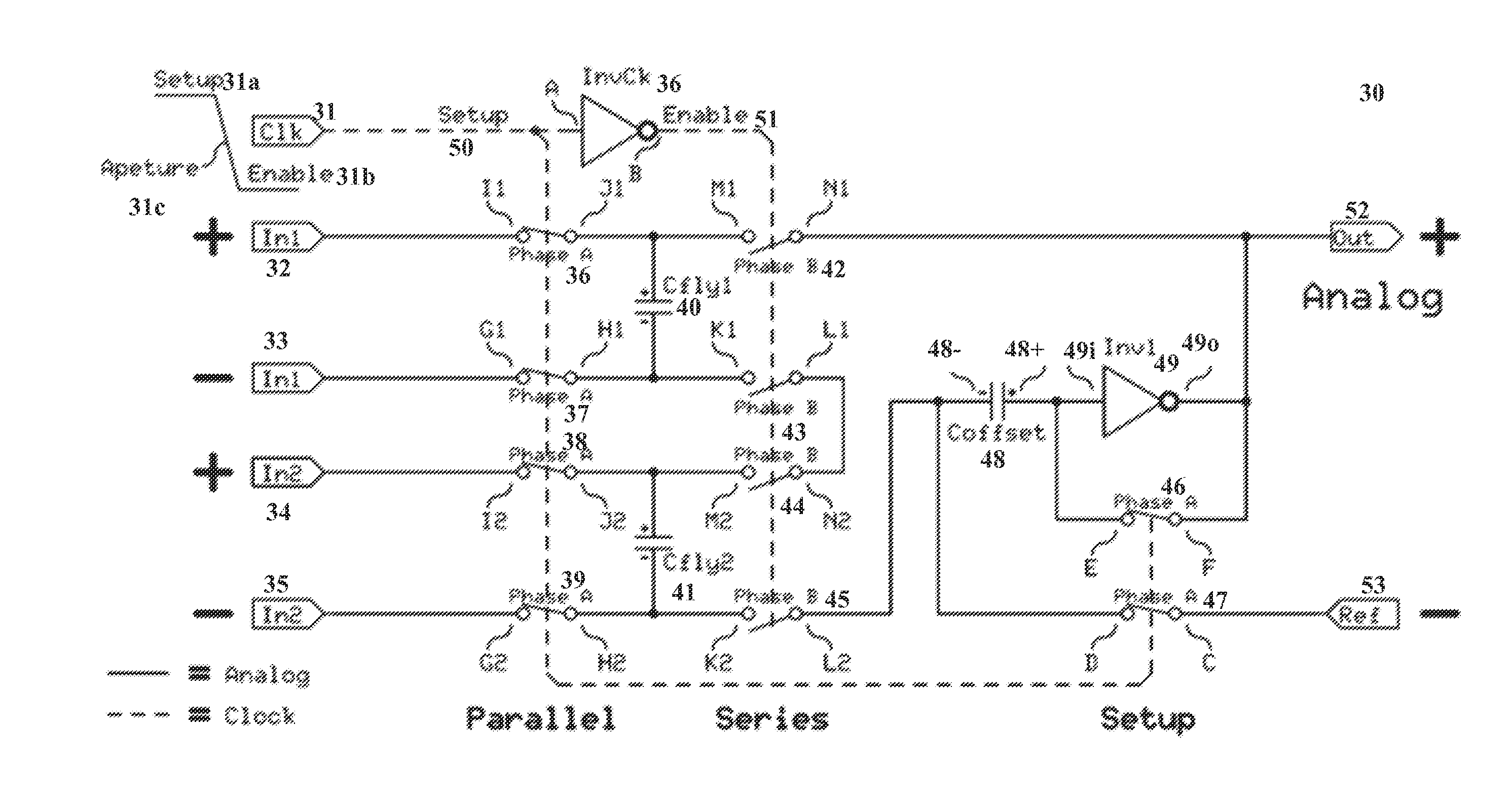

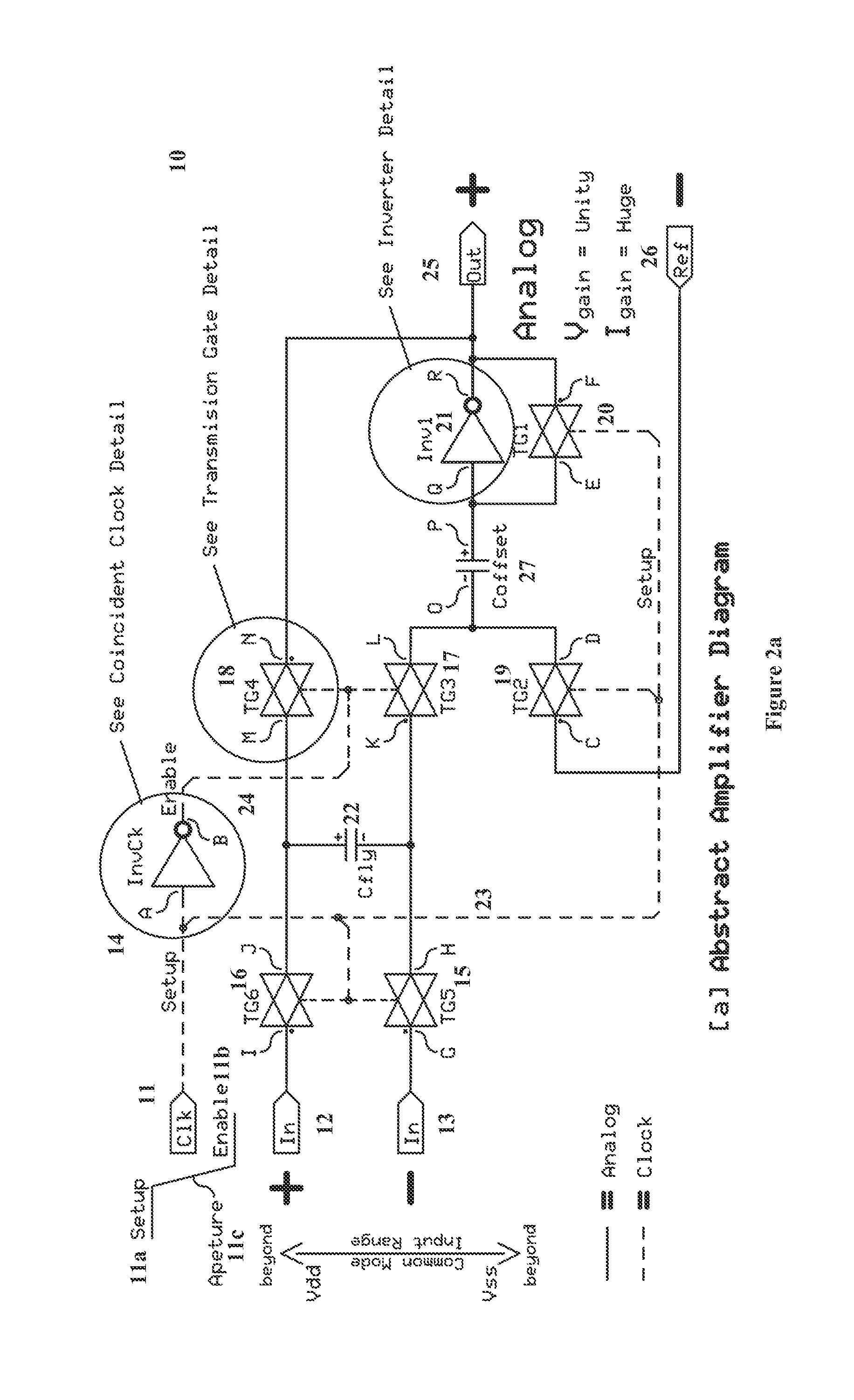

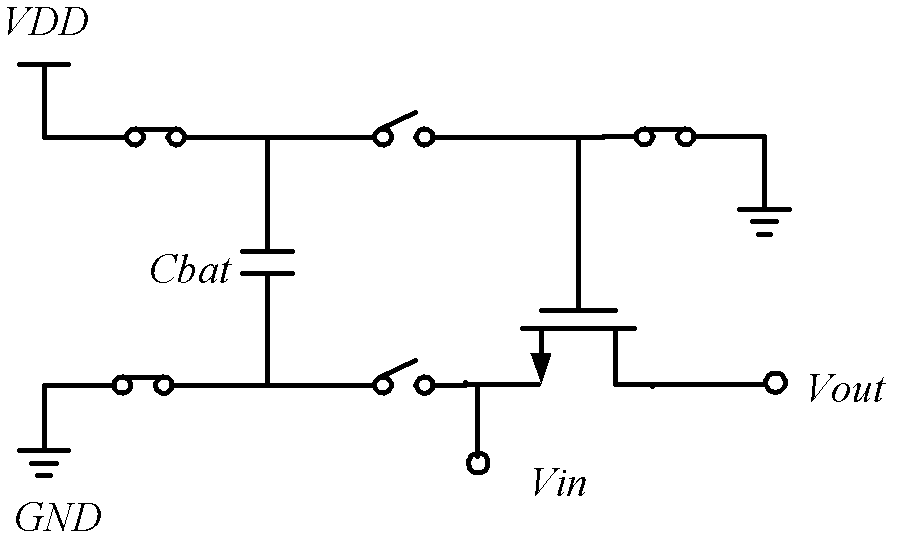

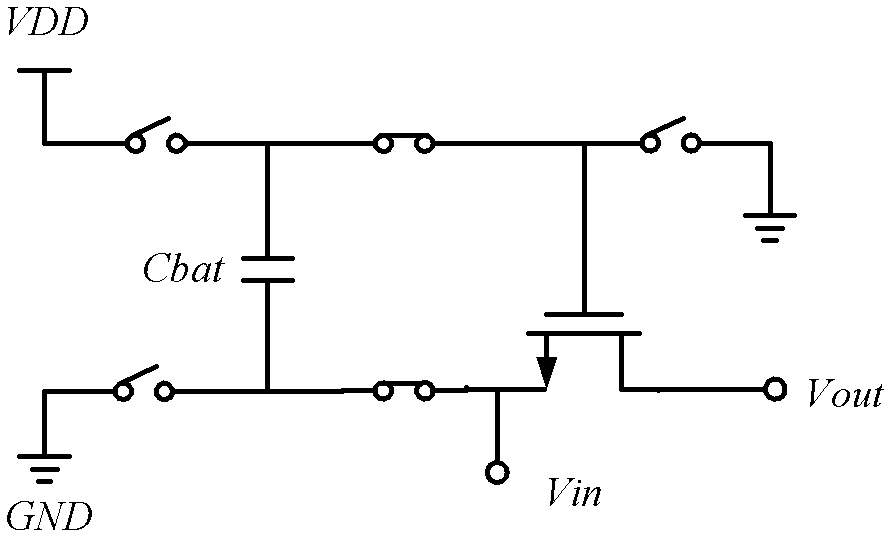

Analog amplifiers and comparators

ActiveUS20150070091A1Reduce noiseRaise the ratioDifferential amplifiersAmplification control detailsCapacitanceAnalog circuit design

An innovative analog circuit design using digital components is disclosed. Embodiments of the present invention includes, but not limited to analog amplifiers and comparators. An amplifier of an embodiment of the present invention includes an inverter, a plurality of switches, offset capacitor and flying capacitor. The one terminal of the offset capacitor is connected to the input of the inverter. During setup phase of clock signals, the switches are configured to connect input and output of the inverter and to connect the flying capacitor to input terminals of the amplifier, respectively, for storing a differential input voltage. Then, during the enable phase of the clock signals, the switches are configured to connect the first terminal of the second capacitor and the first terminal of the first capacitor, and to connect the second terminal of the second capacitor to the output of the inverter.

Owner:SCHOBER ROBERT C +1

Method for detecting and debugging design errors in low power IC design

ActiveUS8832615B2Detecting faulty computer hardwareDesign optimisation/simulationAnalog circuit designCircuit design

A method for detecting anomalies in signal behaviors in a simulation of a low power IC includes receiving a circuit design and a power specification of the IC, determining at least one power sequence checking rule from the power specification, simulating the circuit design and the power specification to obtain a dump file, identifying at least one anomaly of the at least one power sequence checking rule based on the dump file, and generating information relevant to the identified anomaly of the at least one power sequence checking rule. The method further includes setting up a context in a debugger for debugging the anomaly by displaying a waveform of misbehaved signals associated with the anomaly in a waveform window, and a portion of the circuit design and / or a portion of the power specification associated with the anomaly in a text window.

Owner:SYNOPSYS INC

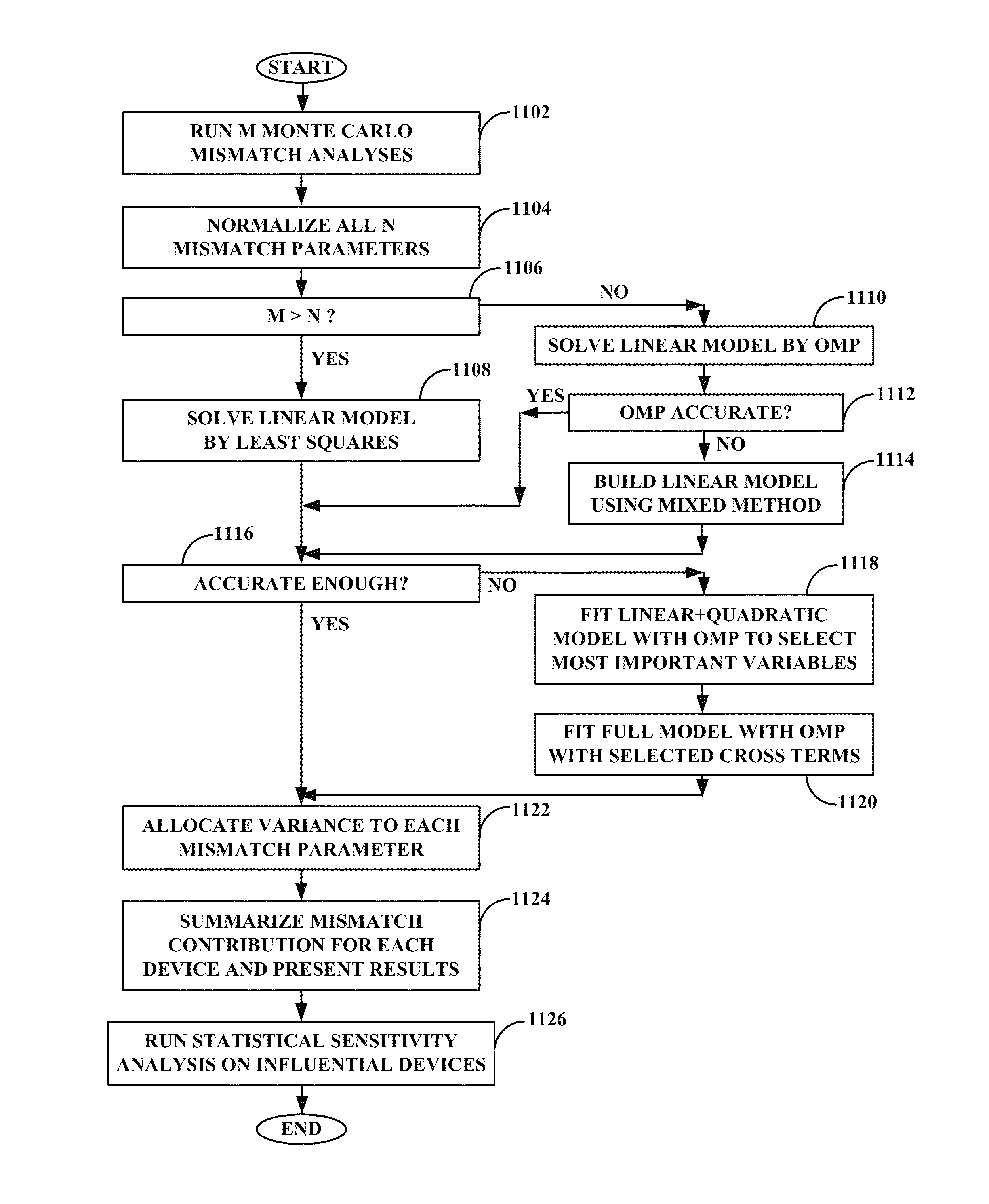

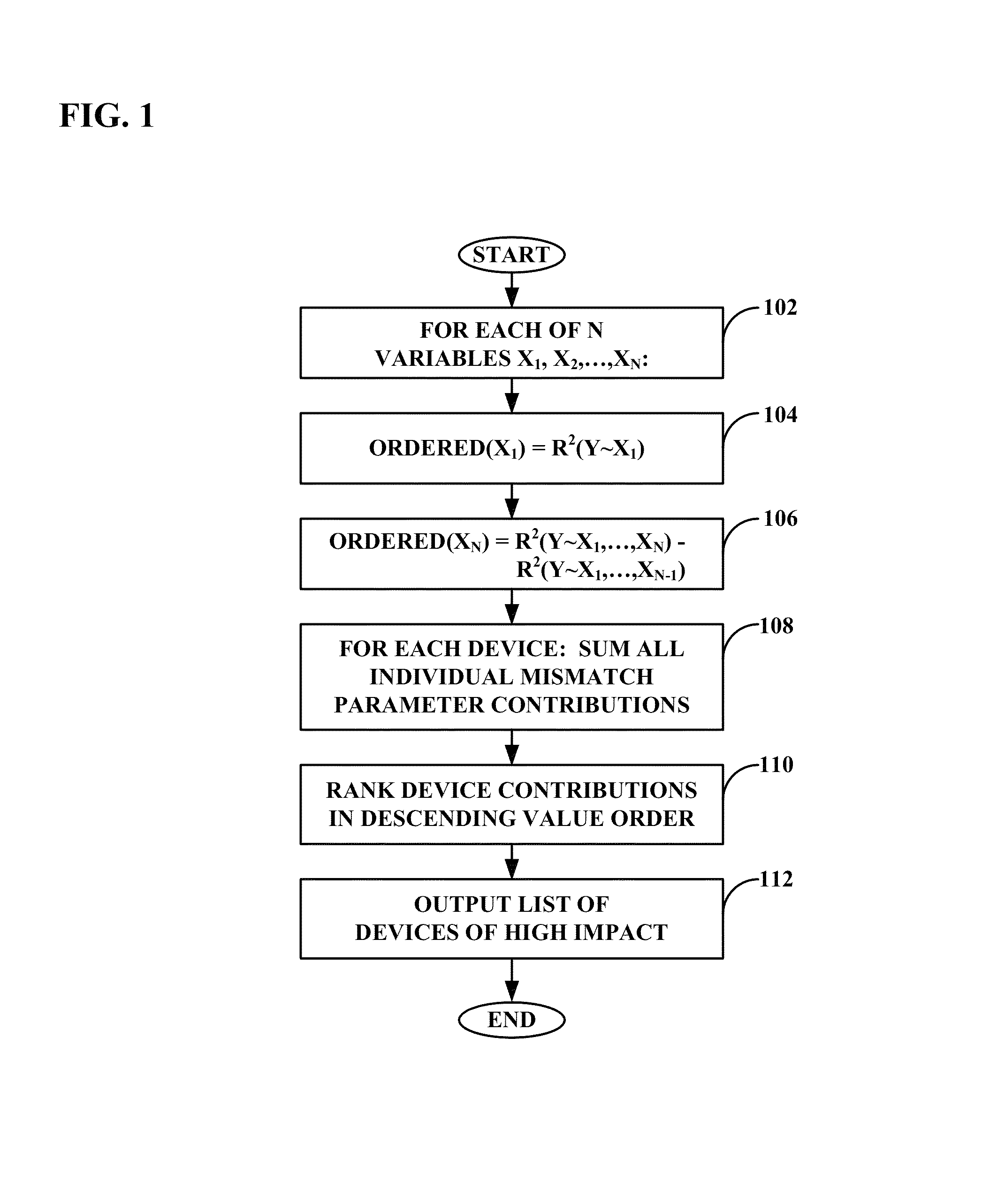

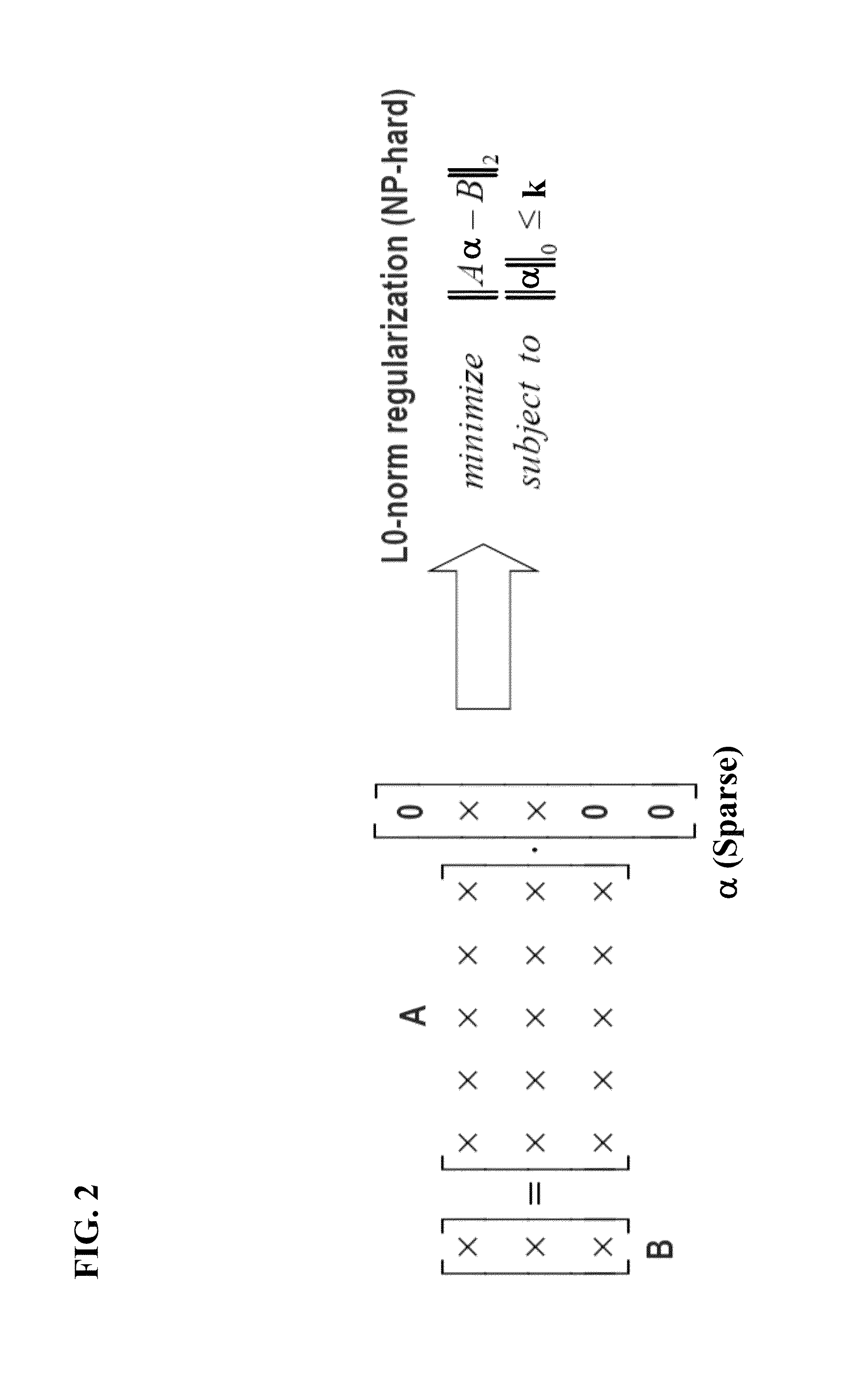

Device mismatch contribution computation with nonlinear effects

ActiveUS8954910B1Design optimisation/simulationCAD circuit designAnalog circuit designQuadratic model

A system, method, and computer program product for computing device mismatch variation contributions to circuit performance variation. Embodiments estimate which individual devices in a simulated circuit design have the largest impact on circuit performance, while requiring far fewer simulations than traditional multivariate linear regressions. When the samples exceed the mismatch parameters, a linear model is solved by least squares. Otherwise, a linear model is solved by orthogonal matching pursuit (OMP), and if that solution is too inaccurate then a new mixed method builds a better linear model. If the linear solution is too inaccurate, a full linear and quadratic model is made using OMP to select the most important variables, and the full model is fitted using OMP with selected cross terms. The embodiments summarize the output variance in each device, and rank the mismatch contributions based on the summarized contributions.

Owner:CADENCE DESIGN SYST INC

Method and apparatus for ams simulation of integrated circuit design

ActiveUS20120198411A1Ease and abilityEasy to readDetecting faulty computer hardwareComputer programmed simultaneously with data introductionAnalog circuit designUser input

A method to create an integrated circuit that includes digital and analog components comprising: displaying on a computer system display, user input to the computer system that specifies parameter information to determine a binding between an analog circuit design component and a digital circuit design component; saving the user specified parameter information within a file that also specifies at least a portion of the analog circuit design; associating the analog circuit design component a first design block of an integrated circuit that also includes a second digital design block coupled to the first design block; using parameter information to determine a binding between the first analog circuit design component and the first digital circuit design component; saving the determined binding in computer readable storage media.

Owner:CADENCE DESIGN SYST INC

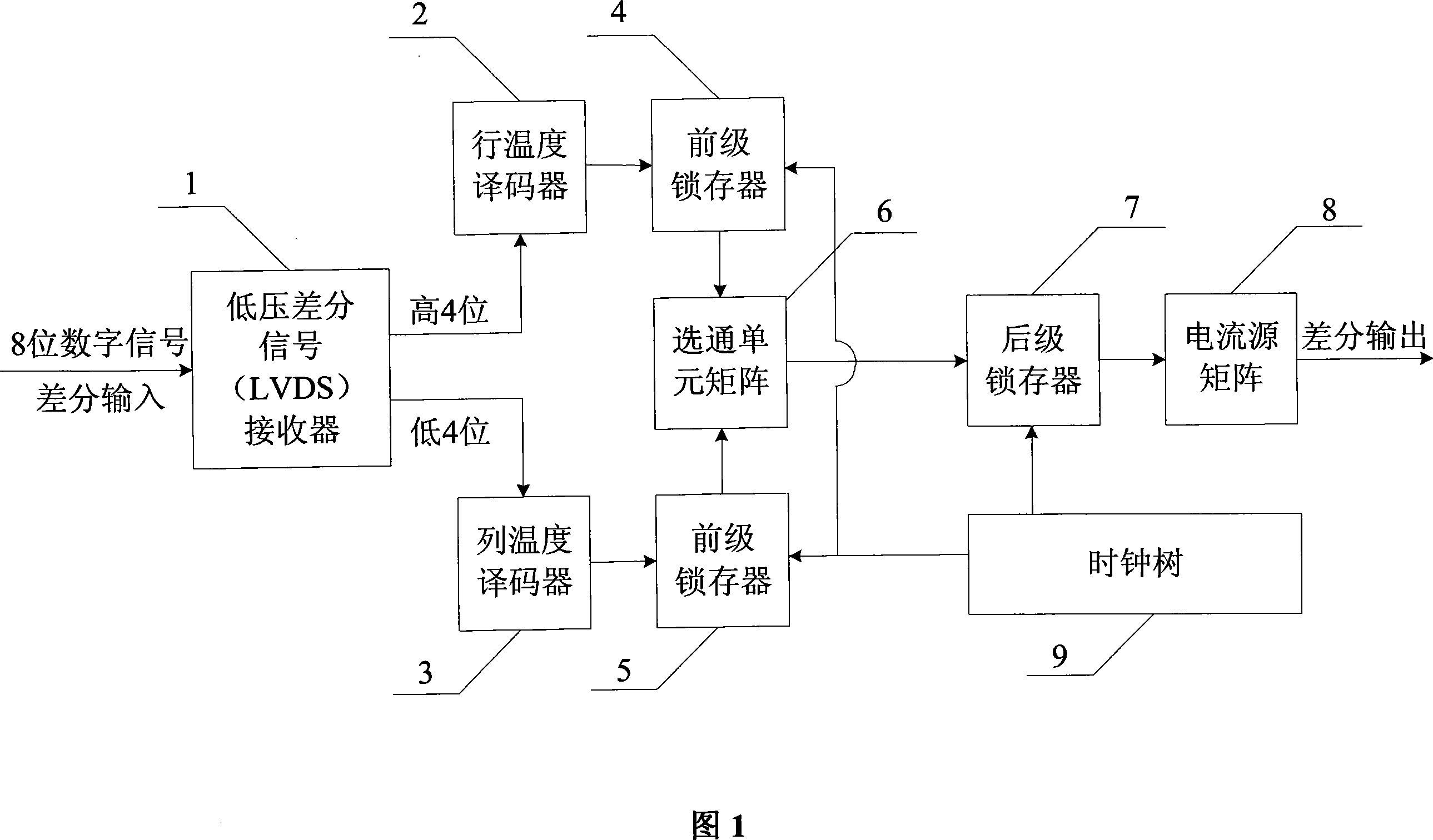

Digital-to-analog converter

InactiveCN101159434AIncrease conversion rateAvoid skewElectric signal transmission systemsDigital-analogue convertorsAnalog circuit designEngineering

The invention adopts full modeling circuit design and, based on a new circuit realizing structure, provides a super high-speed digital to analog converter with 8-digit precision and 2Ghz rate, all realized by the adoption of CMOS process design. The main body of the digital to analog converter is comprised of the following components: low-pressure difference signal receiver, line temperature encoder, field temperature encoder, forestage locking device, gating unit matrix, backdrop locking device, current source matrix and time tree. The invention adapts to the volume of digital signal inputted at super-high speed; solves the issue of skew signals; meanwhile increases the carrying capacity; directly outputs votage signal; meanwhile enhances I-V converting rate; strengths the symmetry of design; increase the precision of outputted signals; and adds fake switch in the current source matrix so as to enhance the precision of I-V conversion. The invention can be widely applied to military and civil use, such as: deep-space detection, electronic countermeasure, radio navigation, precise guidance, mobile communication as well as high resolution digital TV.

Owner:BEIHANG UNIV

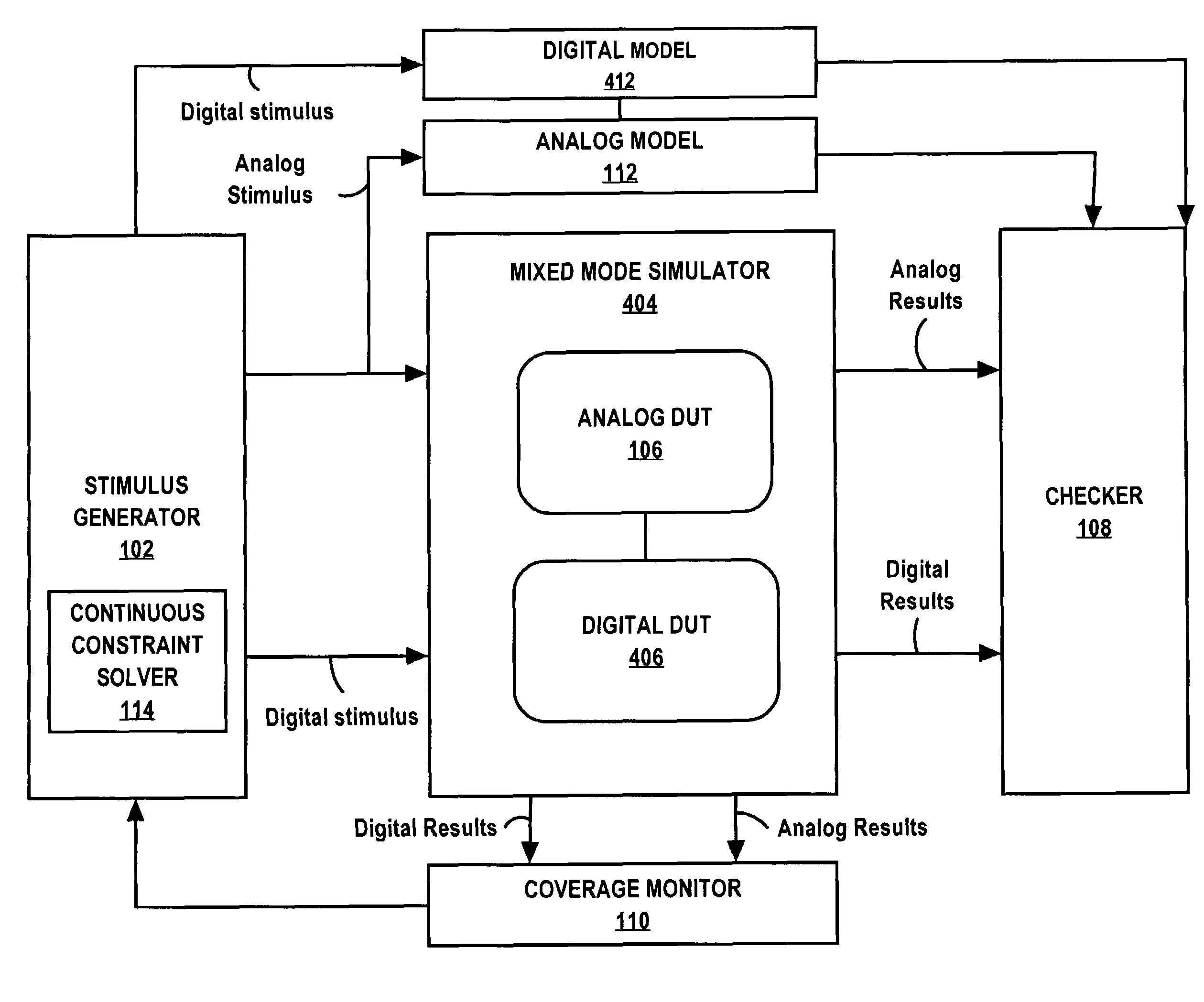

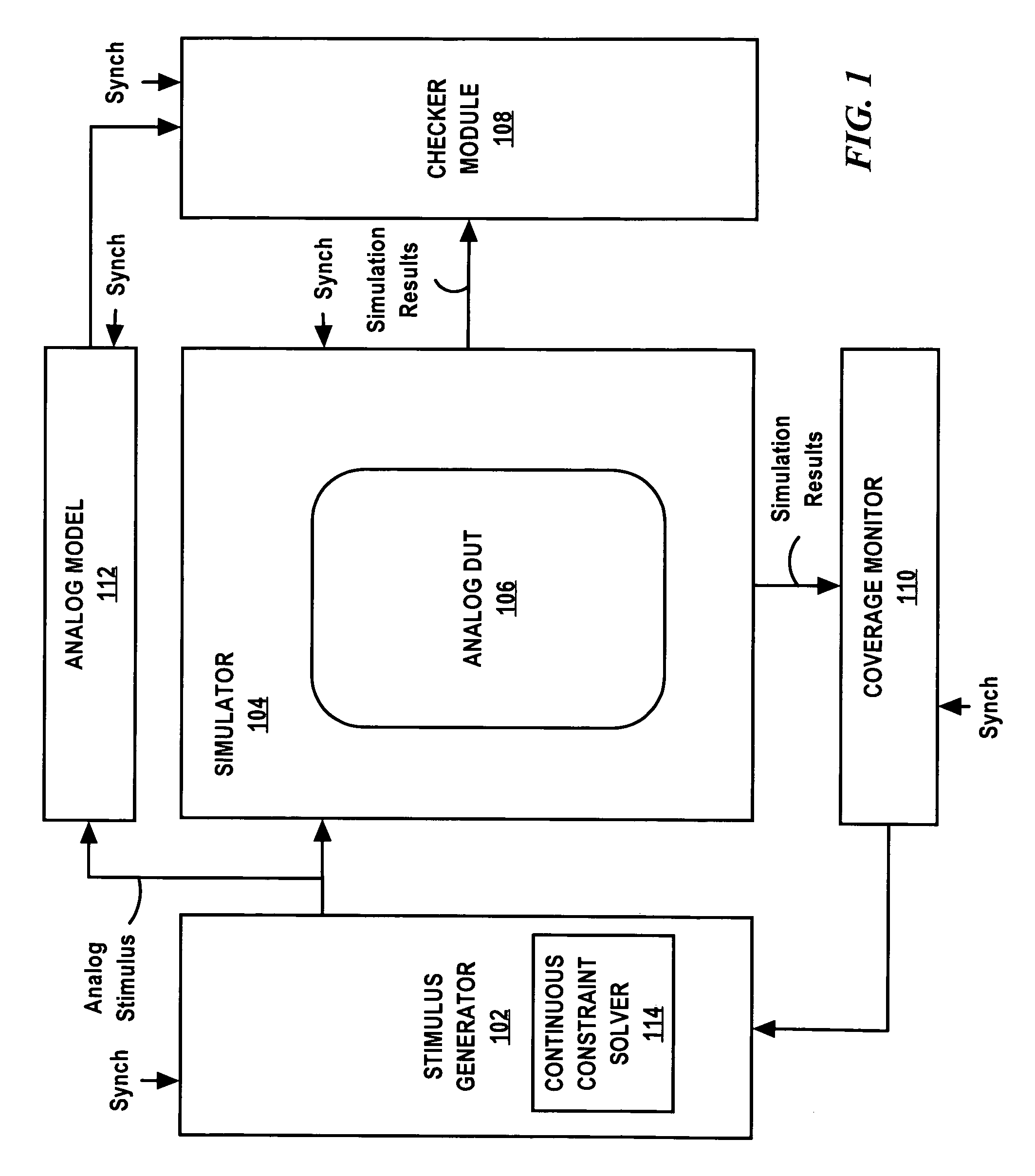

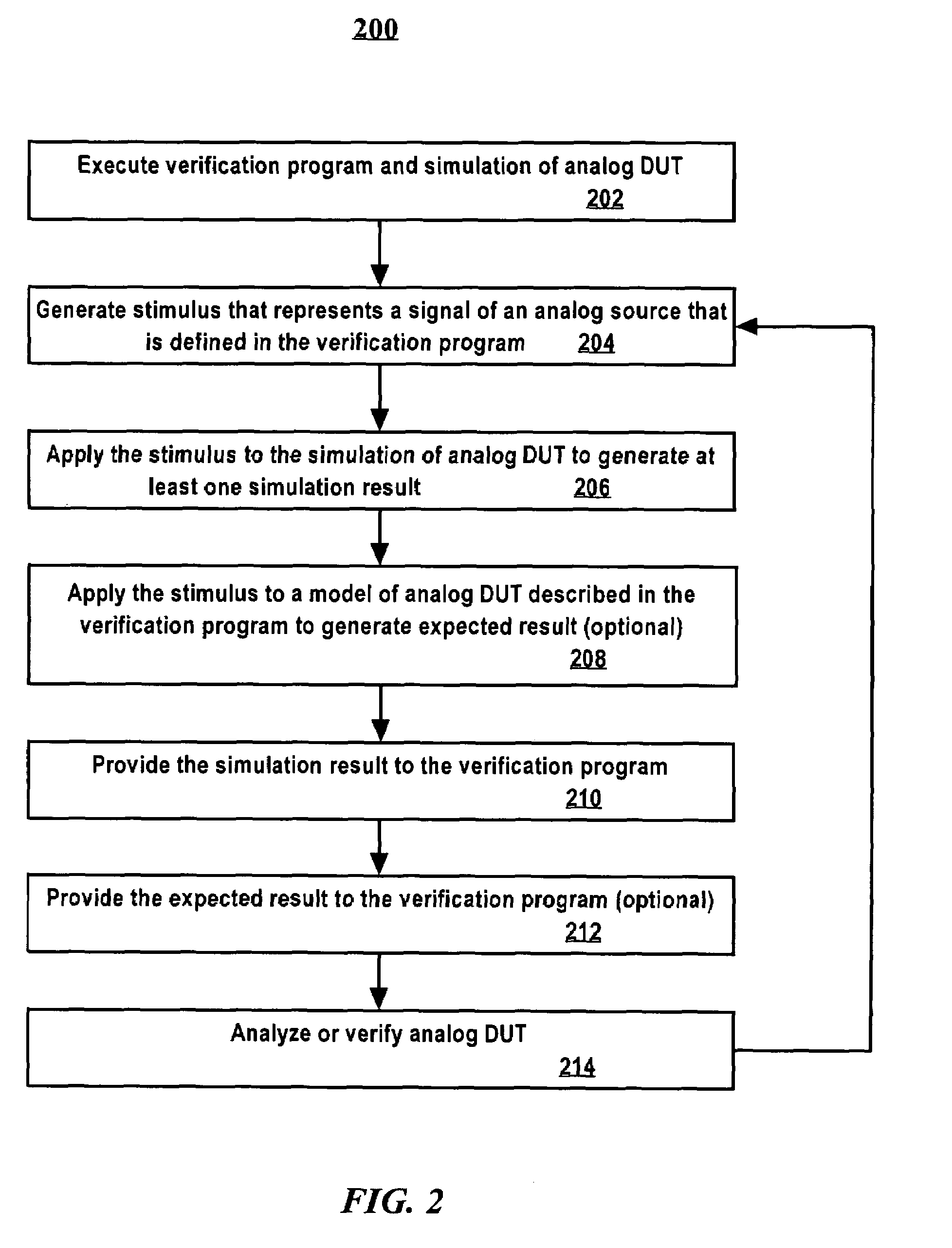

Method to analyze an analog circuit design with a verification program

InactiveUS7643979B2Electronic circuit testingTesting/calibration of speed/acceleration/shock measurement devicesAnalog circuit designElectricity

Data structures and algorithms are provided to automatically generate an analog stimulus to apply to a simulation of the analog DUT. A constraint solver is provided to determine suitable values to use in the stimulus generation. The suitable values are random values within a range of allowed values. For example, a number of different stimuli are generated for successive application to the analog DUT, each with a different magnitude within a range of allowed magnitudes. Data structures and algorithms are provided to monitor analog electrical properties at nodes of the analog DUT. Data structures and algorithms are provided to define constraints on the analog electrical properties and determine whether the constraints were violated. Data structures and algorithms are provided to define simulation coverage conditions in the analog domain and determine whether the defined analog domain coverage conditions have been satisfied.

Owner:RAMBUS INC

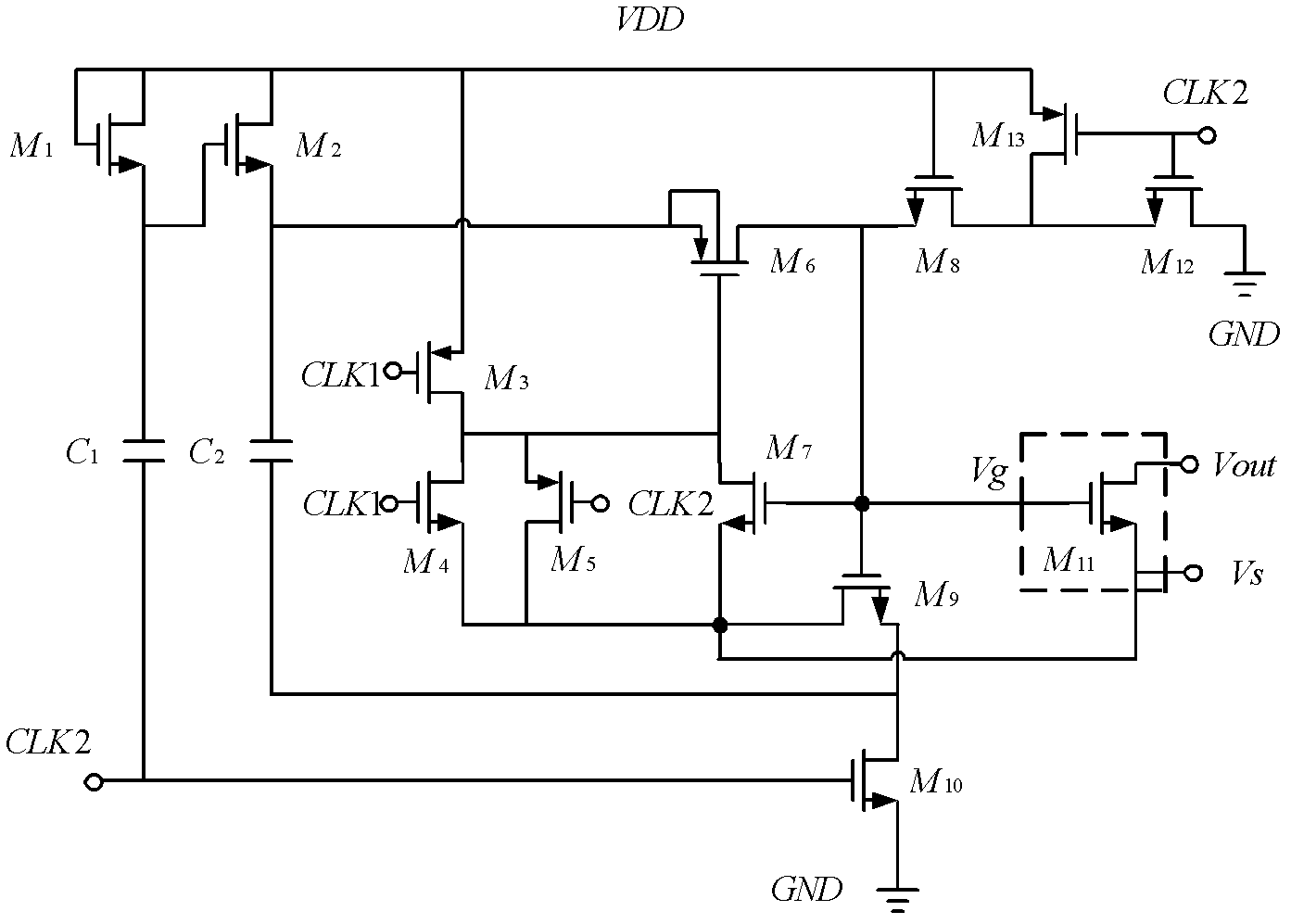

Analog-to-digital converter and electronic equipment

ActiveCN102571091AInhibition effectHigh precisionAnalogue-digital convertersAnalog circuit designCharge injection

The invention provides an analog-to-digital converter and electronic equipment and belongs to the field of analog circuit design. According to a gate-voltage bootstrapped switch circuit in the analog-to-digital converter, two transistors are connected with each other through a transmission gate (TG) and connected with an input signal Vin. By connecting the two transistors through the TG, influence of charge injection and clock feed-through on the input signal Vin can be effectively eliminated, and sampling accuracy is improved.

Owner:昆山启达微电子有限公司

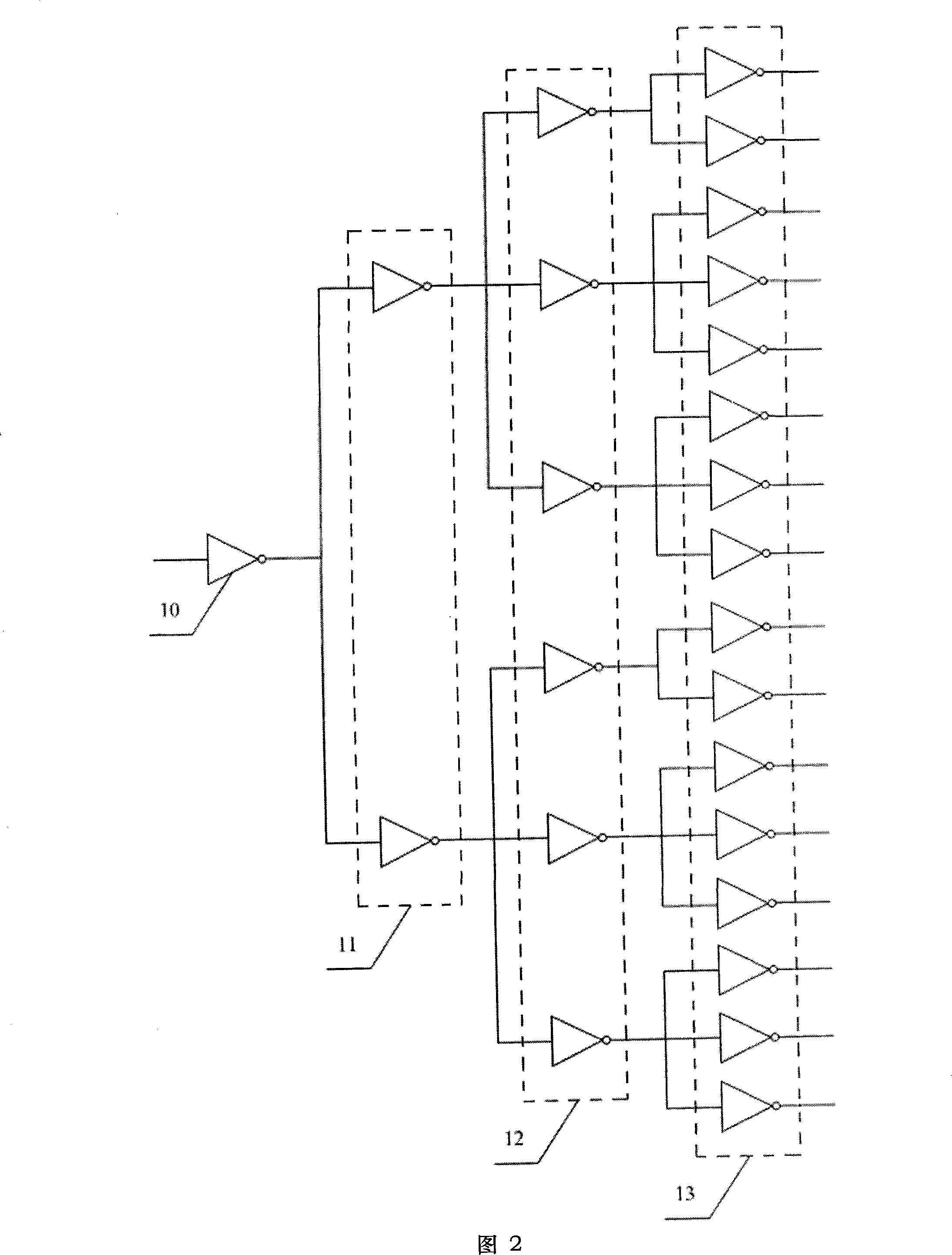

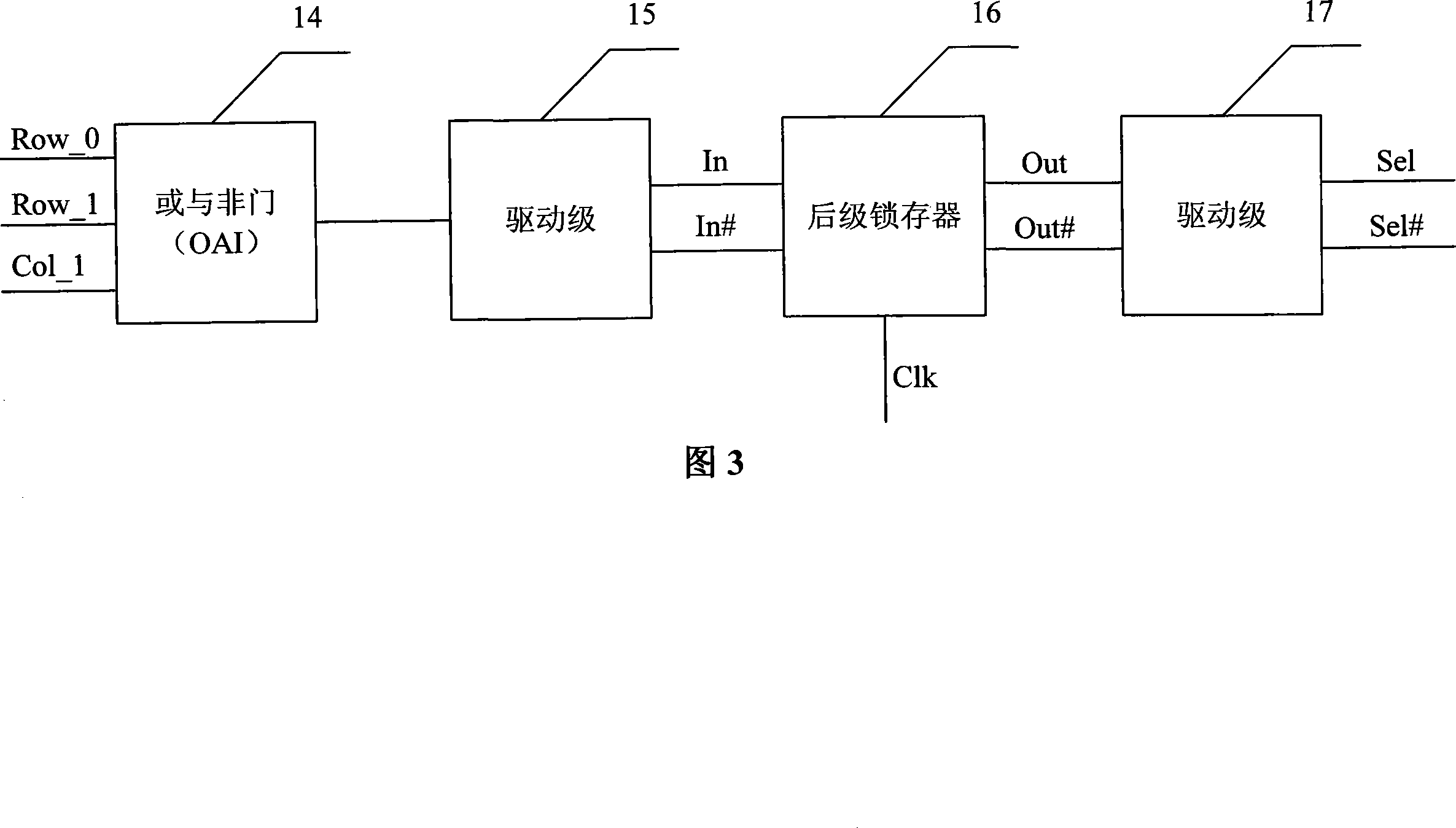

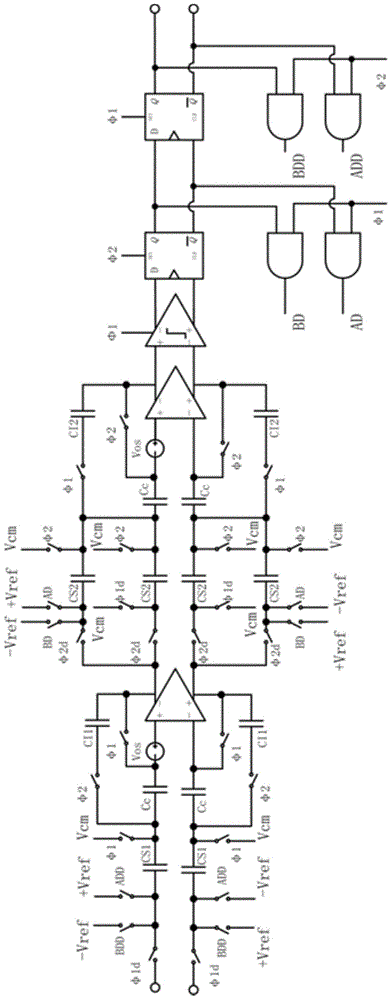

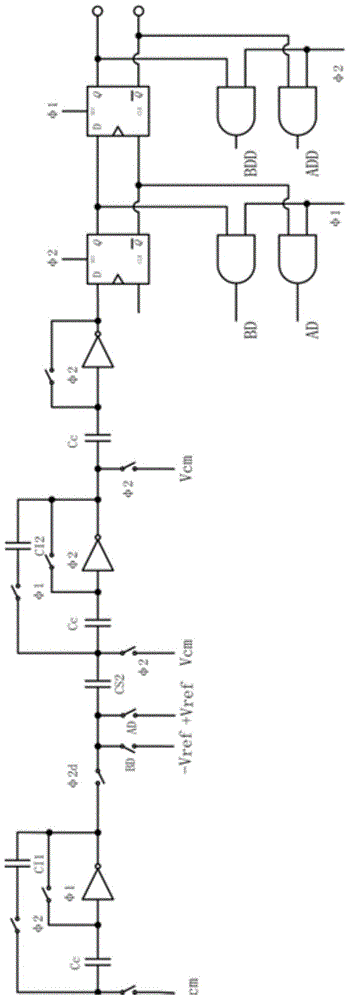

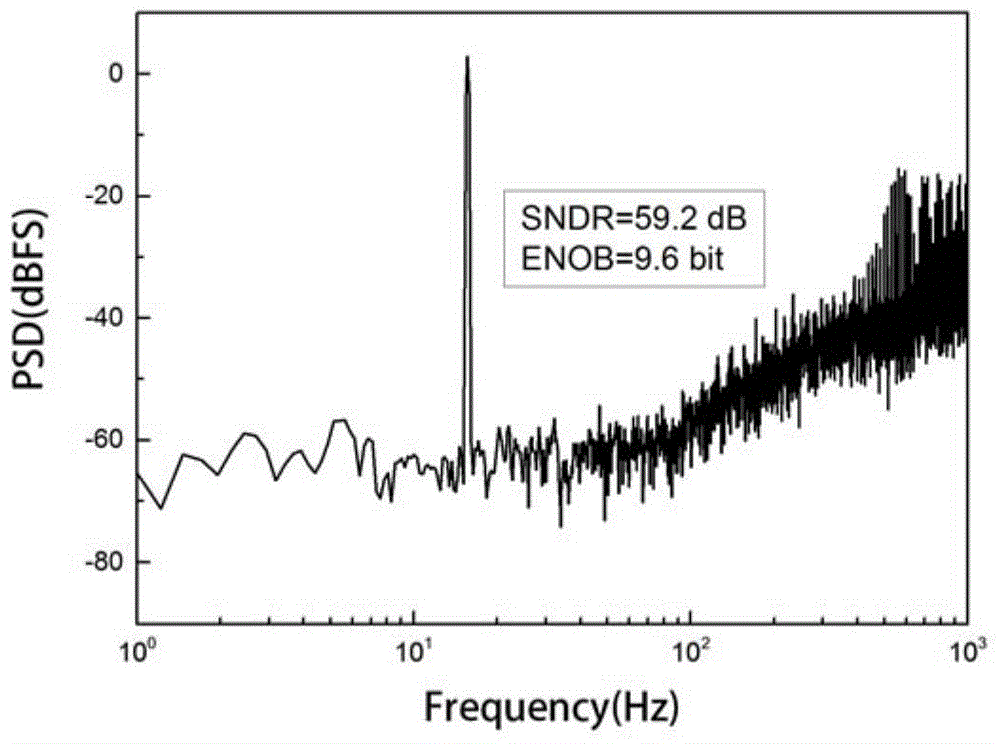

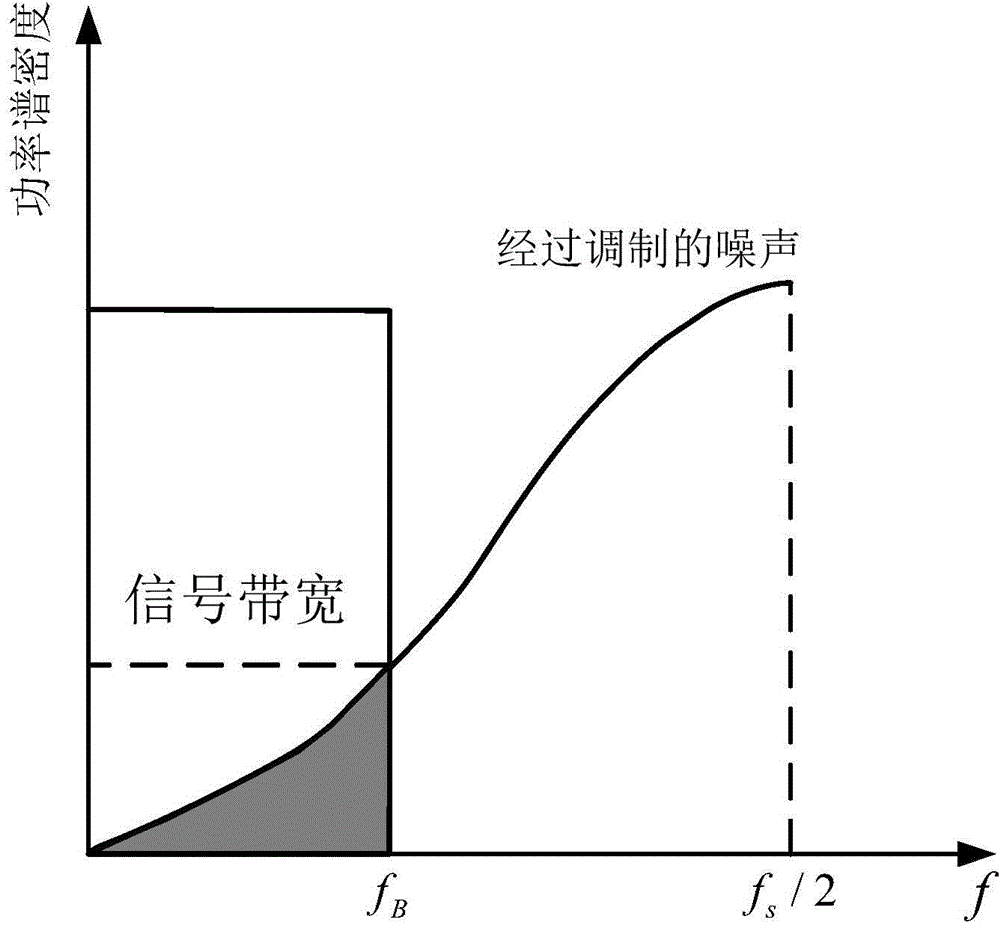

Fully digital Sigma-Delta modulator based on phase inverter

ActiveCN104901700AIn line with the design trend of full digitalizationReduce power consumptionAnalogue conversionAnalog circuit designDigital down converter

The present invention discloses a fully digital Sigma-Delta modulator based on a phase inverter. The fully digital Sigma-Delta modulator comprises two integrators based on digital phase inverters which stabilize a working point under the effect of the auto-zero technology to realize feedback function in the integral process, a comparator based on a phase inverter which stabilizes a working point under the effect of the auto-zero technology to realize a high precision low power consumption voltage comparison function, and a feedback control logic formed by D latches and a gate circuit. The fully digital Sigma-Delta modulator can work normally under extremely low power supply voltage, the current utilization efficiency is high, and the power consumption is extremely low. A traditional amplifier is not used, however a digital module is used to carry out analog circuit design, the problems of small dynamic range, insufficient intrinsic gain, noise degradation and the like in the voltage design can be avoided, and the fully digital Sigma-Delta modulator is in accordance with the fully digital design trend of an analog-digital converter.

Owner:TSINGHUA UNIV

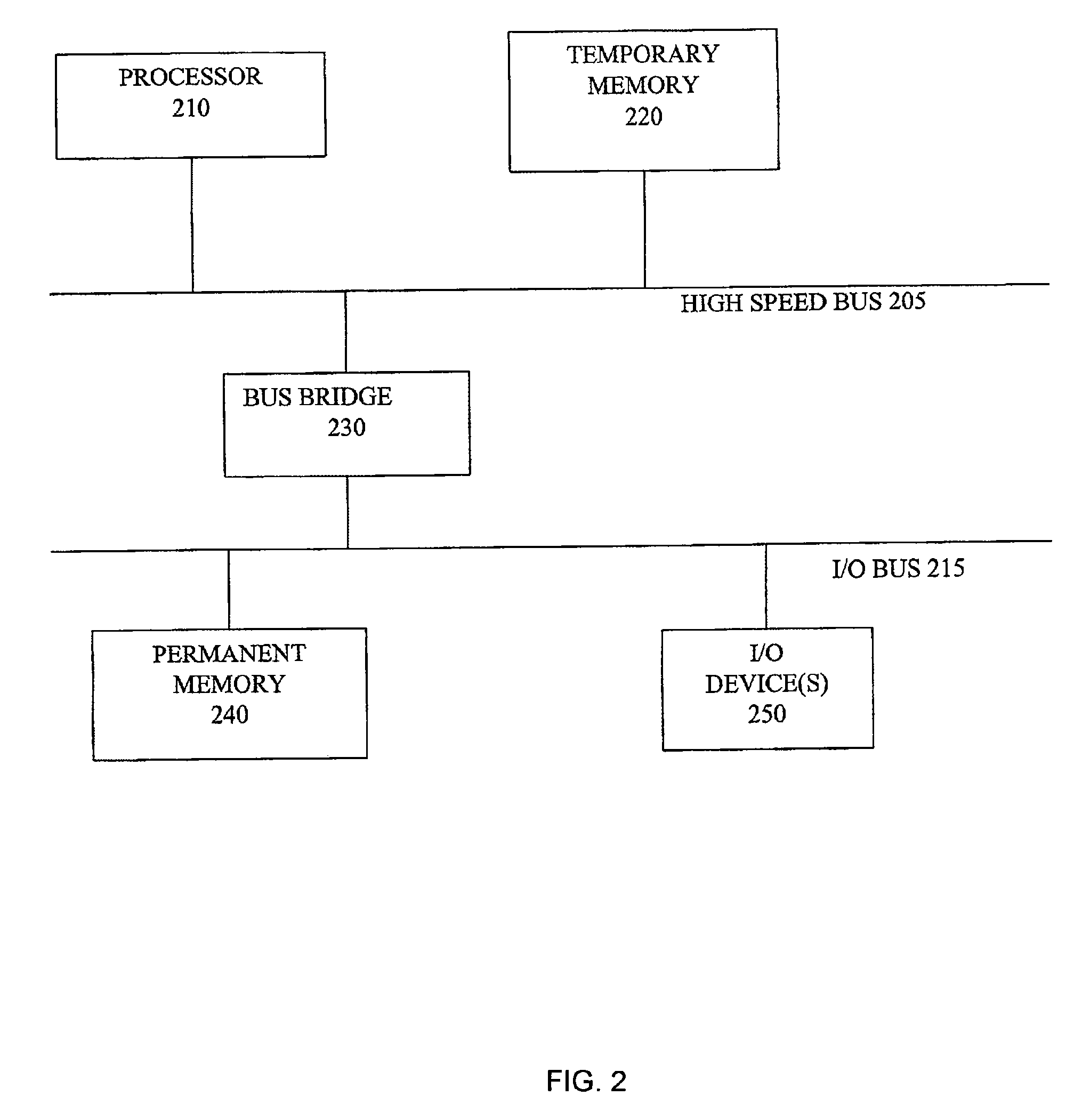

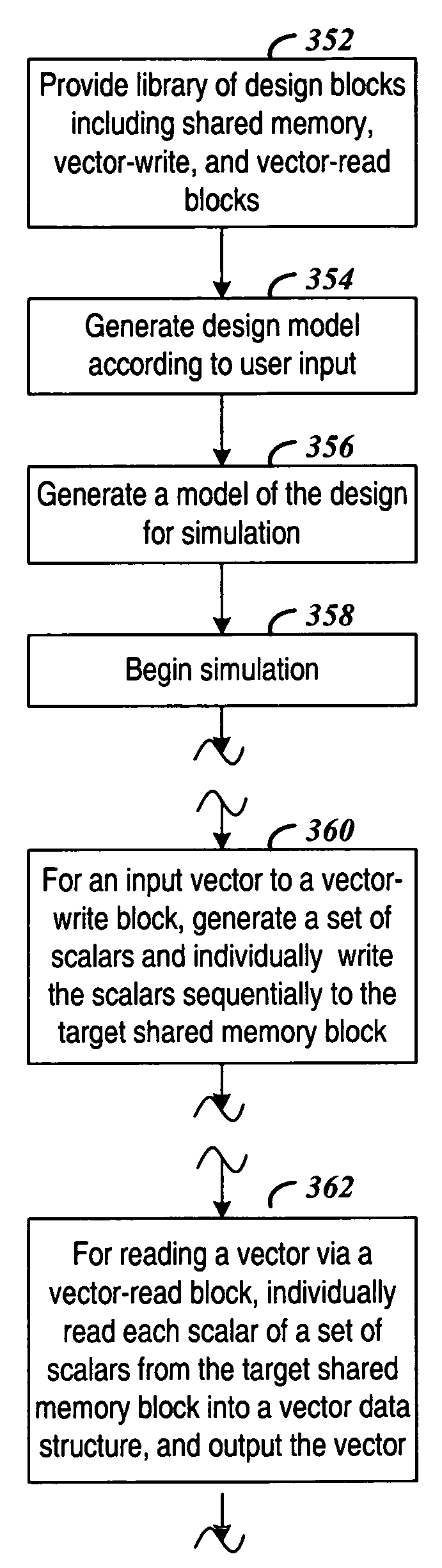

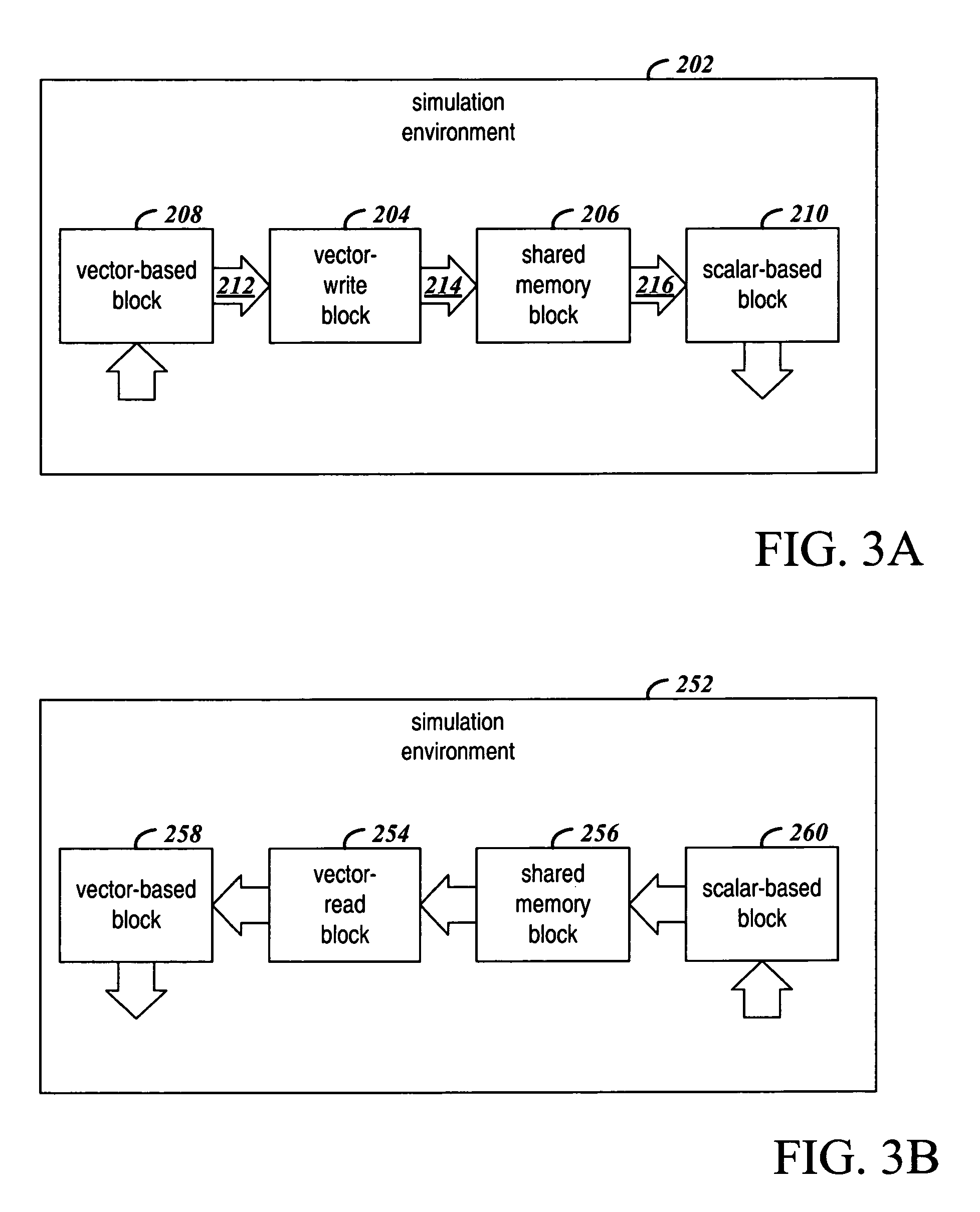

Vector interface to shared memory in simulating a circuit design

ActiveUS7343572B1CAD circuit designSoftware simulation/interpretation/emulationAnalog circuit designScalar Value

A first block, a second block, a shared memory, and a third block are generated in a circuit design in response to user input control. The first block is coupled to the second block, the second block is coupled to the shared memory, and the shared memory is coupled to the third block in response to user input control. During one cycle of a simulation, the second block, in response to the first block, accesses a set of scalar values in the shared memory using scalar accesses. During one cycle of the simulation, the set of scalar values is transferred between the second block and the first block. During the simulation, the shared memory is accessed by the third block using scalar accesses.

Owner:XILINX INC

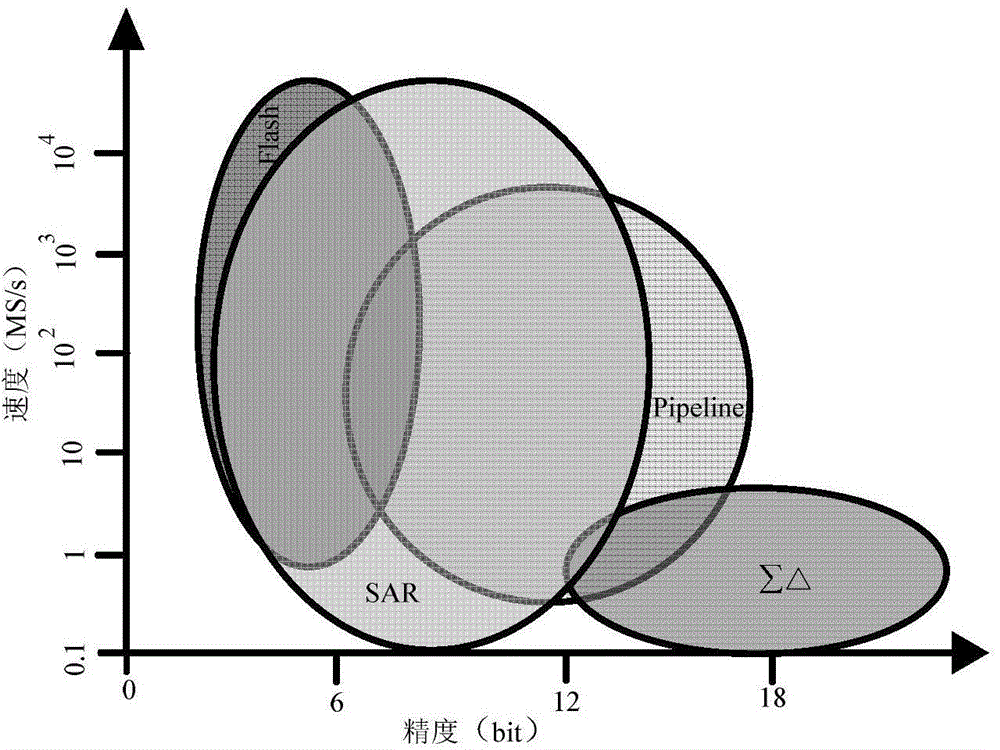

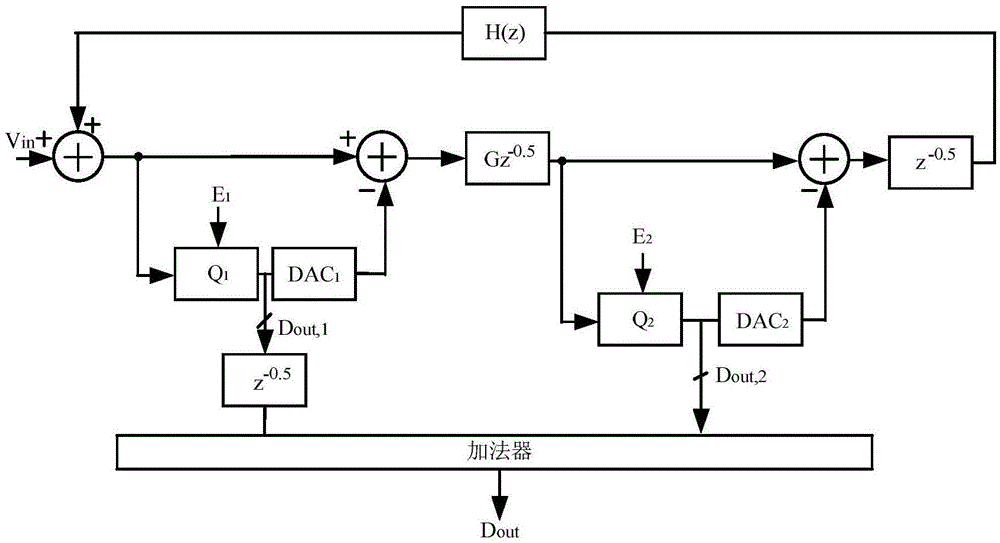

Noise-shaping flash successive approximation register analog-to-digital converter (Noise-Shaping Flash-SAR ADC)

InactiveCN104682958AReduce complexityAvoid functional relationshipsAnalogue/digital conversionElectric signal transmission systemsAnalog circuit designNoise shaping

The invention discloses a noise-shaping flash successive approximation register analog-to-digital converter (Noise-Shaping Flash-SAR ADC), belonging to the field of microelectronics and solid-state electronics. The ADC comprises a front-stage Flash ADC and a rear-stage SAR ADC; the input voltage of the front-stage Flash ADC is obtained by summation of input voltage Vin and a difference value between input of the rear-stage SAR ADC and analog output of the rear-stage SAR ADC; digital output of the front-stage Flash ADC is Dout, 1; the input voltage of the rear-stage SAR ADC is voltage of a difference value between the input of the front-stage Flash ADC and the analog output of the front-stage Flash ADC after passing through a unit delay module; digital output of the rear-stage SAR ADC is Dout, 2; finally a conversion result is obtained by dislocation summation of the Dout, 1 and the Dout, 2. Complexity in design of analog circuits is reduced while establishment of function relationship between G and H (z) is avoided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

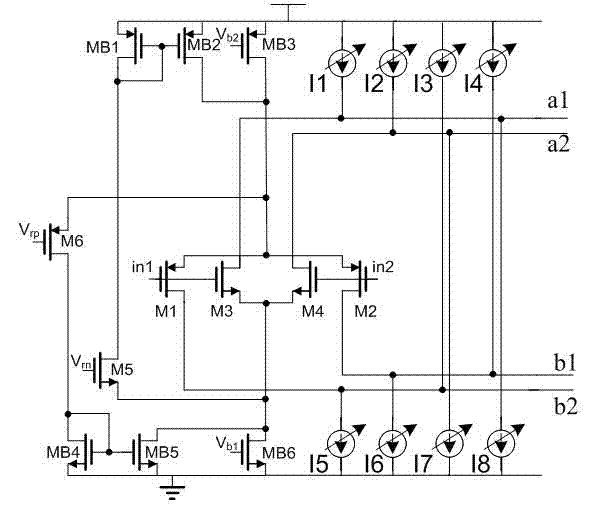

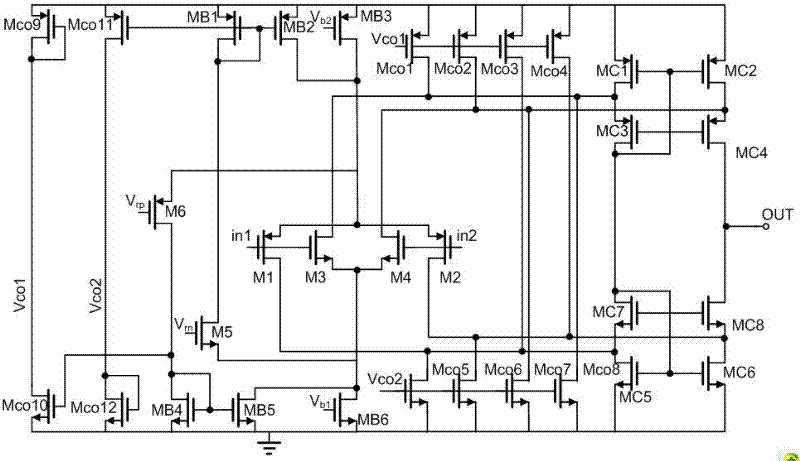

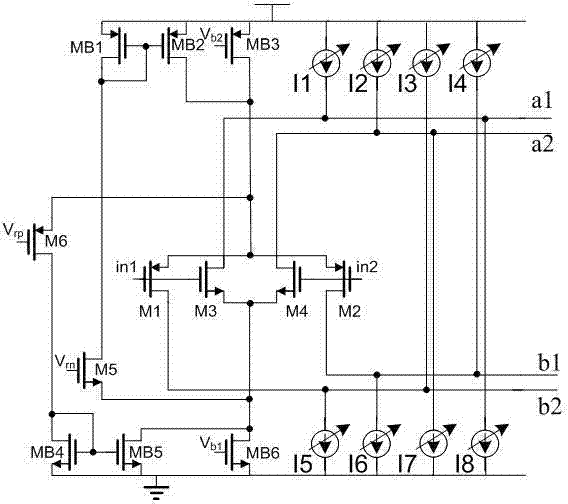

Rail-to-rail input stage with current compensation function

InactiveCN102355212AReduced output driftDifferential amplifiersDc-amplifiers with dc-coupled stagesAnalog circuit designEngineering

The invention belongs to the technical field of analogue circuit designing, and particularly discloses a rail-to-rail input stage with a current compensation function. The rail-to-rail input stage is formed by connecting four input differential tubes, eight triple current mirrors and eight compensation variable current sources by a circuit. The rail-to-rail input stage realizes current compensation under different input common mode levels by utilizing the variable current sources to make direct current extracted from a post stage unrelated with the input common mode levels, thereby reducing the output imbalance of the post stage.

Owner:FUDAN UNIV

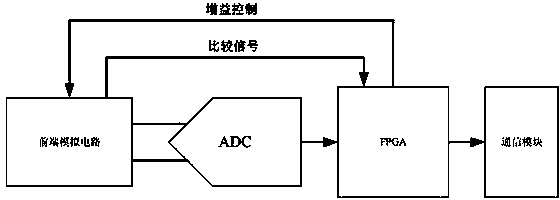

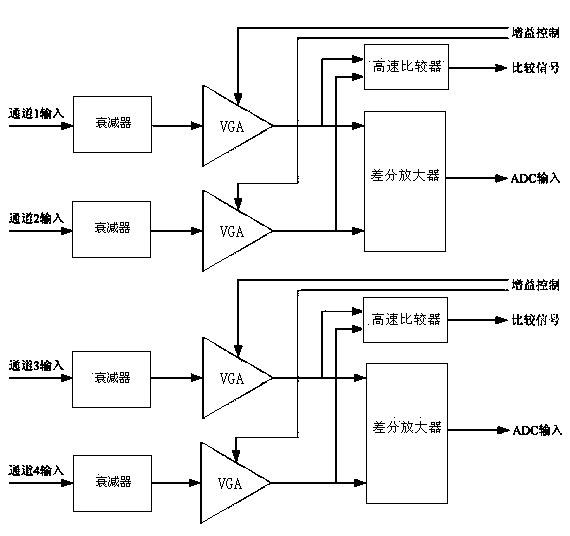

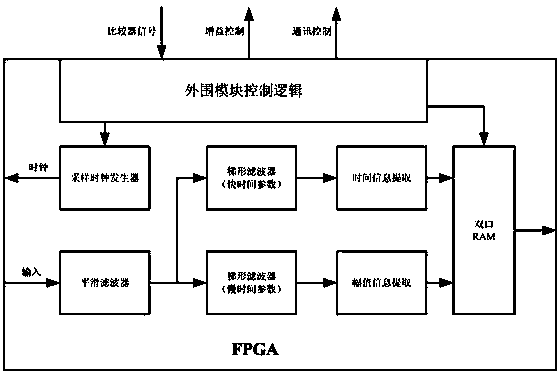

Multichannel digital spectrometer with function of spectrum stabilization

ActiveCN104035124AProcessing speedWith spectrum stabilization functionX-ray spectral distribution measurementPhysicsAnalog circuit design

The invention relates to the technical field of nuclear radiation detection and provides a multichannel digital spectrometer with a function of spectrum stabilization. The multichannel digital spectrometer comprises a front end analog circuit, a high speed and high precision analog to digital converter (ADC) circuit, a high-speed field programmable gate array (FPGA) circuit and a communication module, wherein the front end analog circuit, the high speed and high precision ADC circuit, the FPGA circuit and the communication module are serially connected with one another, a nuclear pulse signal enters the spectrometer from the front end analog circuit and enters the ADC circuit after signal conditioning, the ADC circuit completes digital conversion of an analog signal, subsequently, the signal enters the FPGA circuit to be subjected to digital signal processing, and a processing result is transmitted to a computer through the communication module. The FPGA circuit provides a gain control signal to the front end analog circuit according to the calculation result and receives a comparative result of a high-speed comparator in the front end analog circuit. According to the multichannel digital spectrometer with the function of spectrum stabilization, a brand new front end analog circuit design and a high speed and high precision ADC are used, the processing speed of the digital spectrometer is greatly increased, the multichannel digital spectrometer can be simultaneously connected with at most four energy spectrum type detectors, and the application range is more wide.

Owner:武汉海王核能装备工程有限公司

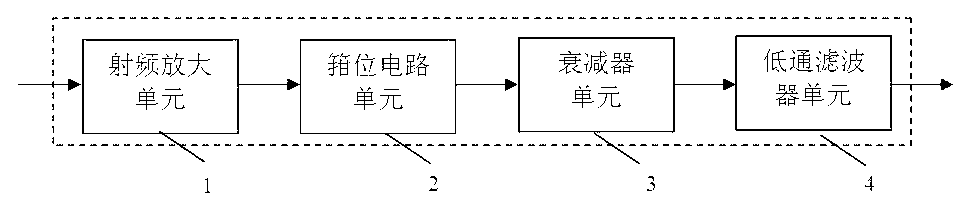

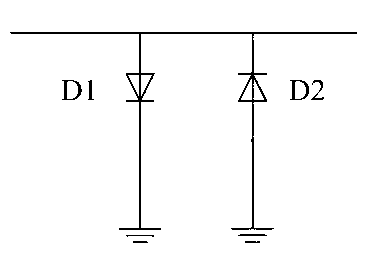

Navigation receiver anti-saturation device based on direct radio frequency sampling

ActiveCN103323860AAddress dynamic requirementsReduce complexitySatellite radio beaconingAnalog circuit designLow-pass filter

The invention provides a navigation receiver anti-saturation device based on direct radio frequency sampling. The device aims to solve the difficulties that an existing multimode navigation receiver receives multiple carrier frequencies at the same time, and accordingly an existing analog circuit is very complicated in design and high in manufacturing cost. The device is composed of a radio frequency amplifying unit, a clamp circuit unit, an attenuator unit and a low-pass filter unit. A signal receiving end of the radio frequency amplifying unit is connected with a radio frequency band-pass filter outside the device. A signal output end of the radio frequency amplifying unit is sequentially in serial connection with the clamp circuit unit, the attenuator unit and the low-pass filter unit. The navigation receiver anti-saturation device has the advantages of solving the difficulties that according to the multimode navigation receiver based on direct radio frequency sampling, strong interference of signals causes ADC sampling saturation, effectively reducing design complexity of the multimode navigation receiver, and meeting dynamic requirements of a radio frequency receiver.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST