Preparation method of silicon nano-wire field-effect transistor

A field-effect transistor, silicon nanowire technology, applied in nanotechnology, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as collapse, fracture of small silicon pillars, and difficulty in achieving uniform silicon pillars, and achieve optimal morphology, Process compatibility, the effect of shortening the molding time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] The present invention is described in further detail below in conjunction with accompanying drawing:

[0058] In order to make the object, technical solution and advantages of the present invention clearer, the method for fabricating an n-type vertical silicon nanowire-enclosed gate field effect transistor will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings. The manufacturing method of the p-type vertical silicon nanowire-enclosed gate field effect transistor only needs to exchange the corresponding n-type and p-type regions in the process.

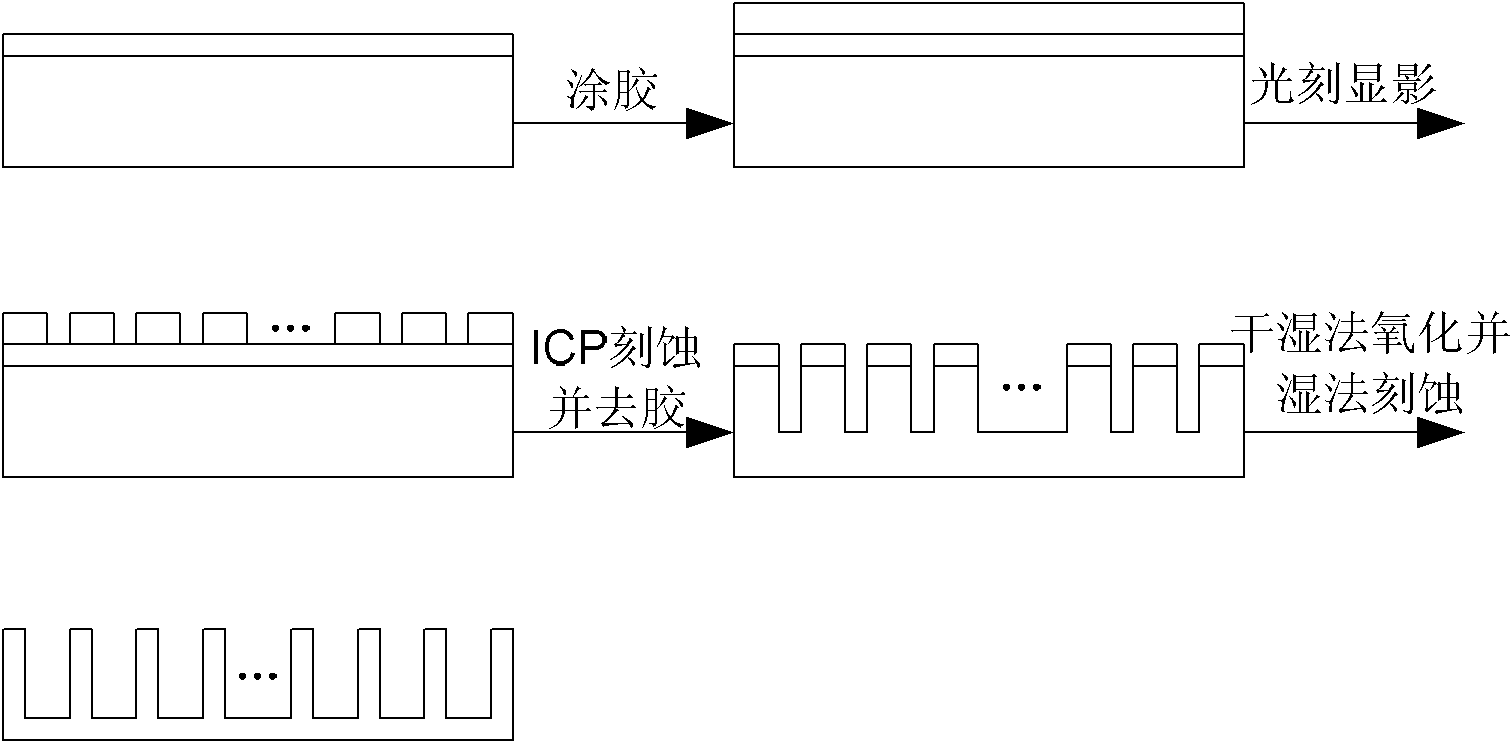

[0059] Step 1: Follow the figure 1 Shown is the flow chart of the process for fabricating vertical silicon nanowires.

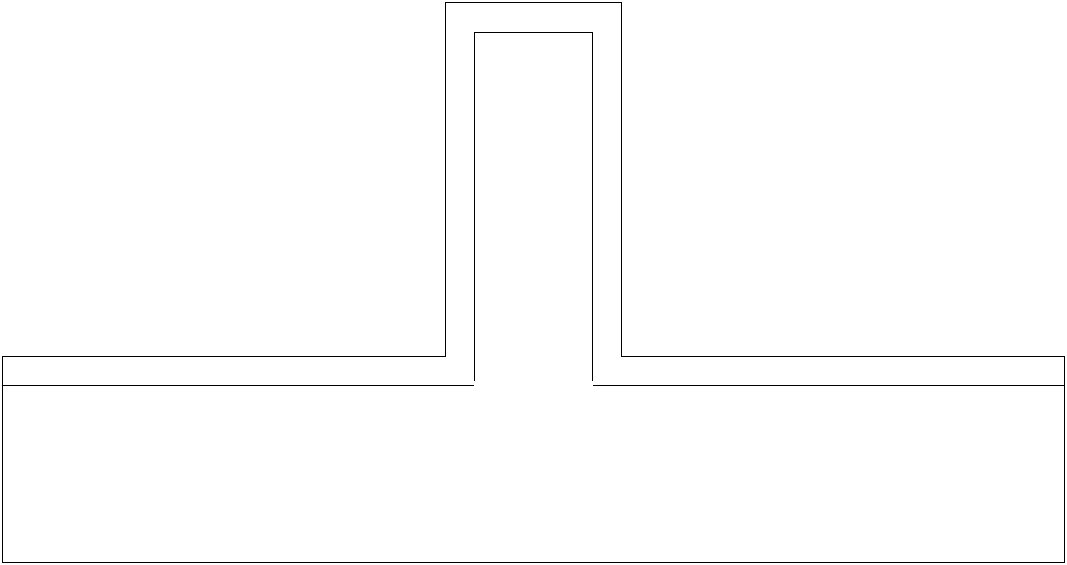

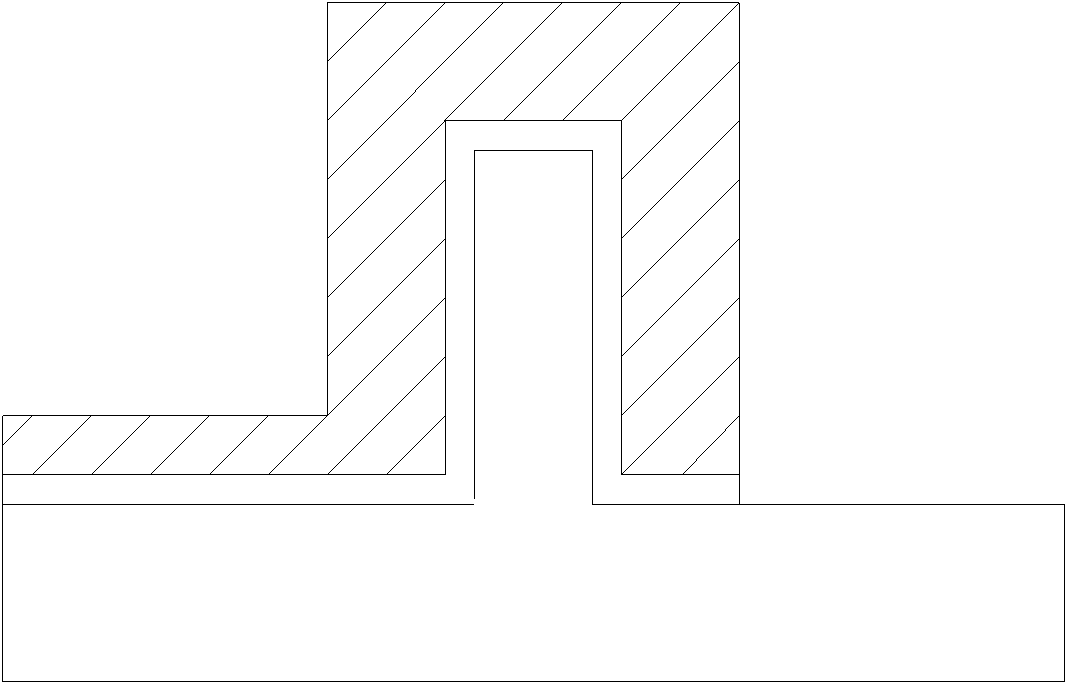

[0060] First: SiO growth on cleaned substrate 2 Dielectric layer, gluing, pre-baking, exposure, development, film hardening.

[0061] The substrate is a P-type (100) silicon substrate, and the silicon chip is passed through acetone, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More