Optimized l-type tunneling field effect transistor and its preparation method

A tunneling field effect and transistor technology, which is applied in semiconductor/solid-state device manufacturing, diodes, semiconductor devices, etc., can solve the problems of small driving current, application limitations, and serious bipolar effect, and achieve the reduction of tunneling probability and production The process is simple and easy, and the effect of suppressing the bipolar effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

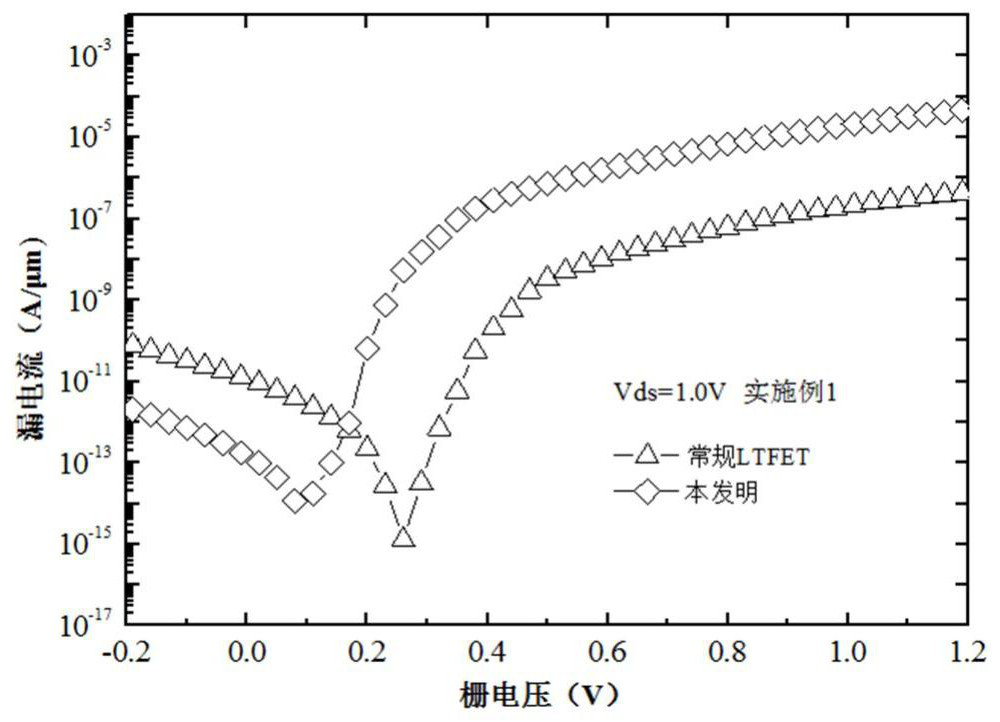

Embodiment 1

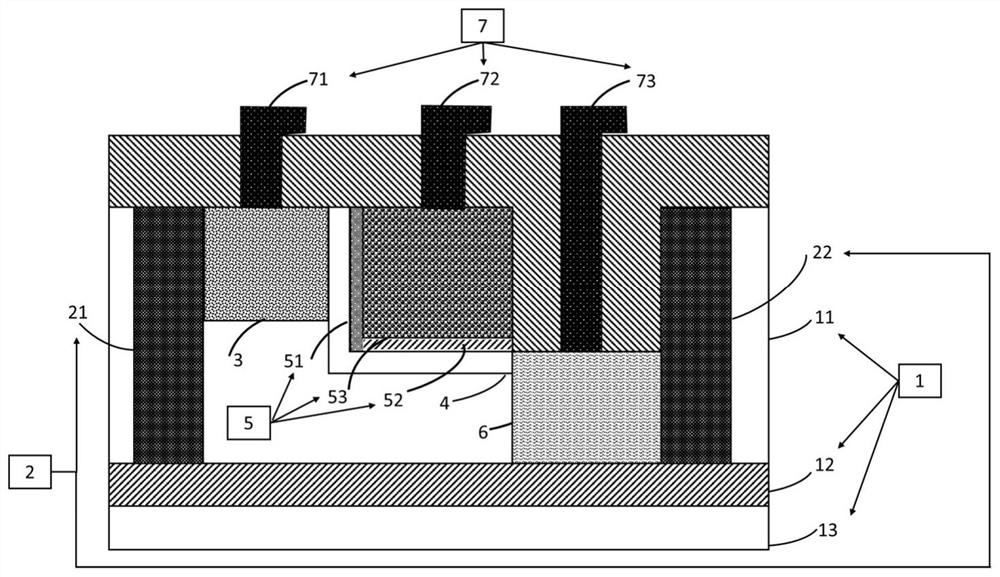

[0030] Embodiment 1, manufacturing a tunneling field effect transistor in which the distance between the drain region and the right border of the gate region is a quarter of the gate length.

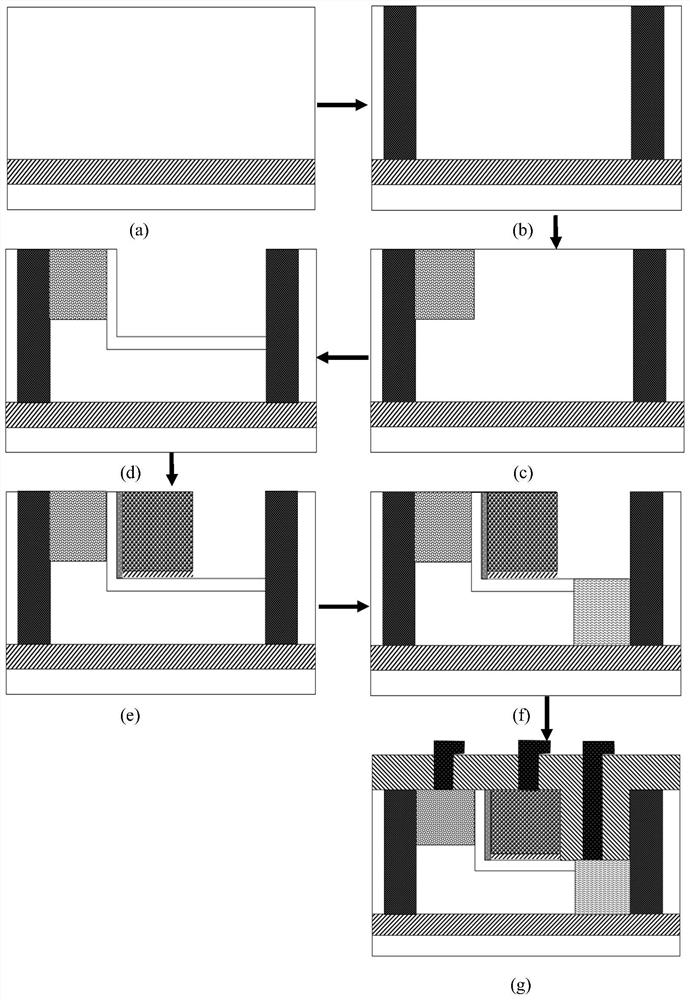

[0031] Step 1, make SOI substrate, such as figure 2 (a).

[0032] 1a) dry oxygen oxidation on the underlying initial silicon wafer to form a buried oxide layer;

[0033] 1b) A top silicon epitaxial layer is grown on the buried oxide layer by an epitaxial growth process to form an SOI substrate.

[0034] Step 2, etching on both sides of the top layer of silicon to form isolation grooves, such as figure 2 (b).

[0035] 2a) Growth of SiO on the top silicon surface of the SOI substrate 2 , forming the first SiO 2 layer, and then grow the first Si on the surface of the layer 3 N 4 layer, forming the first protective layer;

[0036] 2b) using a photolithography machine to form a shallow trench isolation pattern on the first protection layer by a photolithography process;

[0037] 2c...

Embodiment 2

[0067] Embodiment 2, manufacturing a tunneling field effect transistor in which the distance between the drain region and the right border of the gate region is half the gate length.

[0068] Step 1, making SOI substrate, such as figure 2 (a).

[0069] The specific implementation of this step is the same as Step 1 of Example 1.

[0070] Step 2, etching on both sides of the top layer of silicon to form isolation grooves, such as figure 2 (b).

[0071] The specific implementation of this step is the same as step 2 of embodiment 1.

[0072] Step 3, forming a doping concentration of 10 on the top silicon surface 19 cm -3 source area, such as figure 2 (c).

[0073] 3.1) Growth of SiO on top silicon surface 2 , forming a second SiO 2 layer, and then grow a second Si on the surface of the layer 3 N 4 layer, forming a second protective layer;

[0074] 3.2) using a photolithography machine to form a source region pattern at a set position on the second protective layer b...

Embodiment 3

[0089] Embodiment 3, manufacturing a tunneling field effect transistor in which the distance between the drain region and the right border of the gate region is three quarters of the gate length.

[0090] The first step is to make the SOI substrate, such as figure 2 (a).

[0091] The specific implementation of this step is the same as Step 1 of Example 1.

[0092] The second step is to etch and form isolation grooves on both sides of the top silicon, such as figure 2 (b).

[0093] The specific implementation of this step is the same as step 2 of embodiment 1.

[0094] The third step is to form a doping concentration of 10 on the top silicon surface 20 cm -3 source area, such as figure 2 (c).

[0095] First, grow SiO on the top silicon surface 2 , forming a second SiO 2 layer, and then grow a second Si on the surface of the layer 3 N 4 layer, forming a second protective layer;

[0096] Next, using a photolithography machine, a source region pattern is formed at a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More