Low-doped tunneling field-effect transistor based on germanium-silicon heterojunction and double-gate technology and manufacturing method

A technology of tunneling field effect and manufacturing method, which is applied in the field of less-doped tunneling field effect transistors, can solve the problems of increasing the on-state current, etc., achieve the reduction of the tunneling distance, increase the on-state current, and improve the electron tunneling efficiency effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

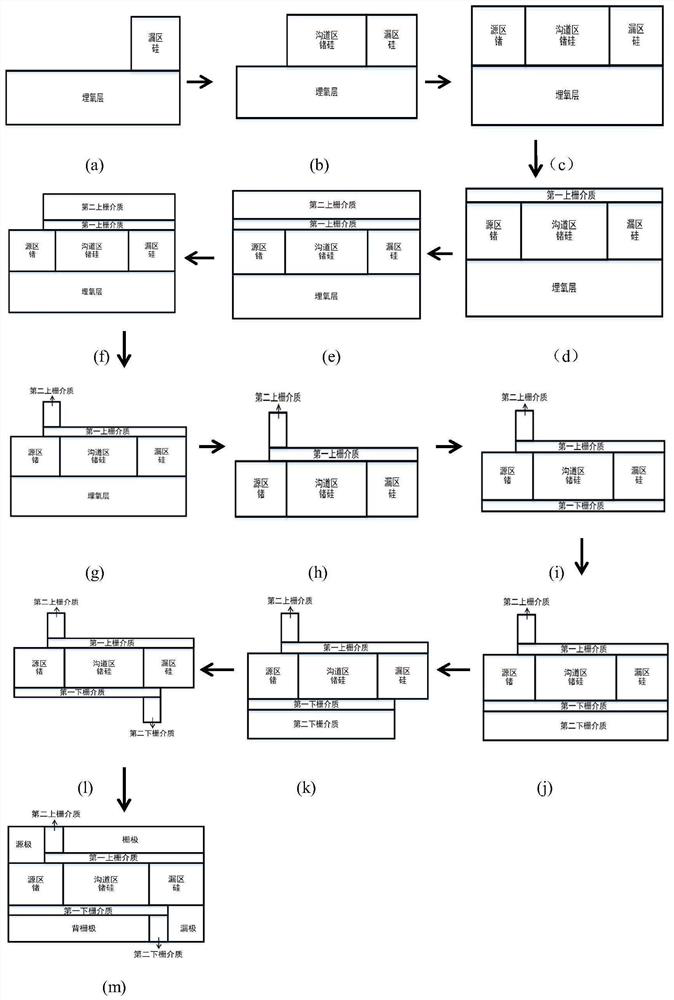

[0033] In order to make the objects and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

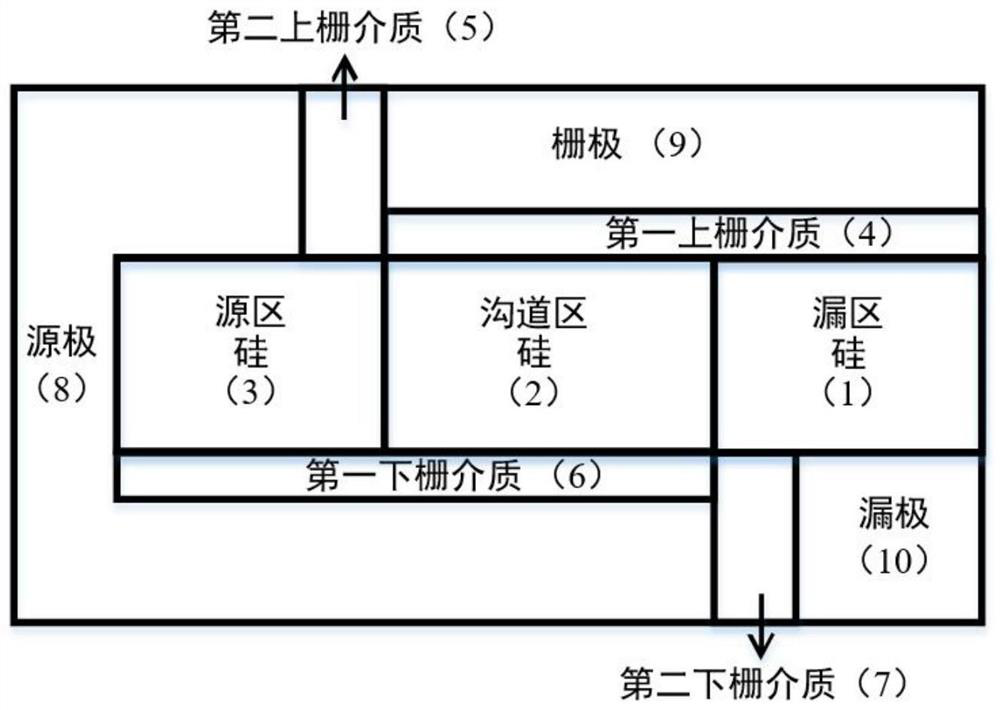

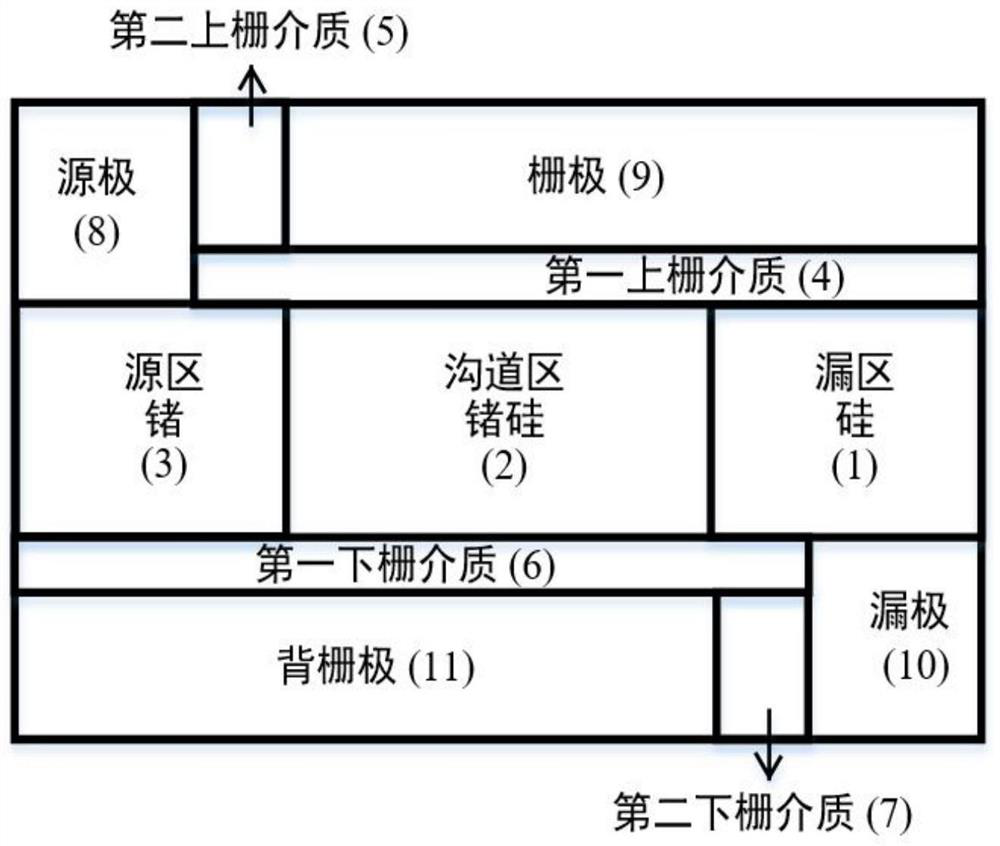

[0034] refer to figure 2 The device of the present invention includes a drain region 1, a channel region 2, a source region 3, a first upper gate dielectric 4, a second upper gate dielectric 5, a first lower gate dielectric 6, a second lower gate dielectric 7, and a source 8 , gate 9 and drain 10. in:

[0035] The channel region 2 has a height of 5±0.5nm, a length of 20±1nm, and a doping concentration of 1×10 18 / cm 3 , using germanium silicon material, which is located on the left side of the drain region 1, and is used to provide high channel carrier mobility;

[0036] The source region 3 has a height of 5±0.5nm, a length of 25±1nm, and a doping concentration of 1×10 18 / cm 3 , using a germanium material, which is located on the left side of the channel regi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More