Manufacturing method of low-temperature ohmic contact of III group nitride electronic device

A technology for ohmic contact and electronic devices, which is applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc. It can solve problems such as surface degradation of Group III nitrides, affect device dynamic characteristics and power output capabilities, and increase ohmic contact. area, reduce the contact barrier, and increase the effect of electron tunneling probability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

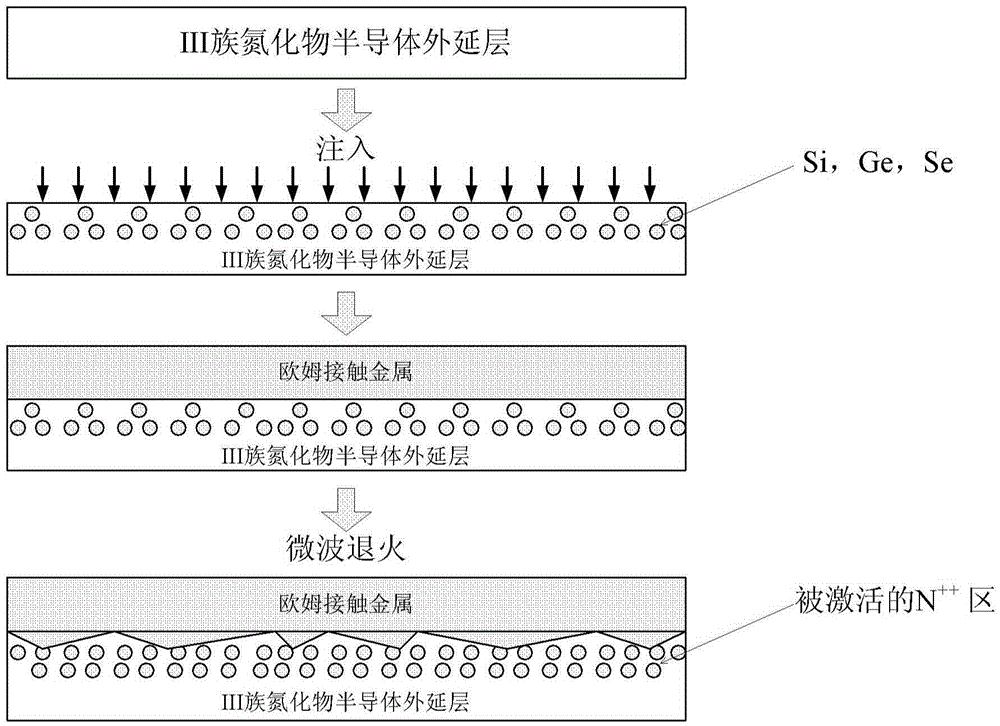

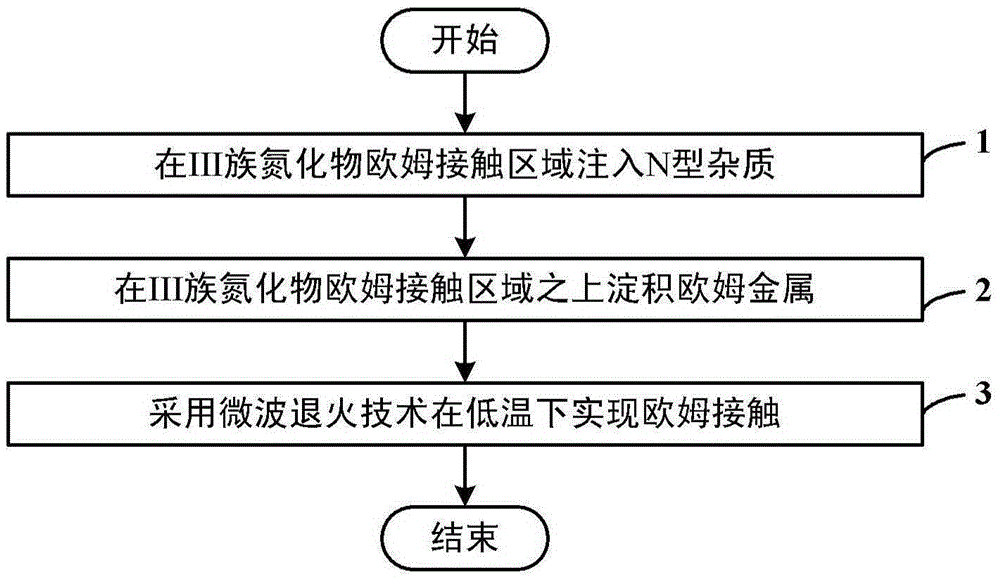

[0024] Such as figure 1 and figure 2 as shown, figure 1 It is a flow chart of the manufacturing process of the low-temperature ohmic contact of the III-nitride electronic device according to the first embodiment of the present invention, figure 2 It is a flow chart of a method for manufacturing a low-temperature ohmic contact of a III-nitride electronic device according to a first embodiment of the present invention, and the method includes the following steps:

[0025] Step 1: Implanting N-type impurities in the III-nitride ohmic contact region; in this step, the N-type impurities can be Si elements, Ge elements, Se elements or co-doped implants of the above elements and N elements.

[0026] Step 2: Deposit ohmic metal on the III-nitride ohmic contact area implanted with N-type impurities; in this step, the ohmic metal can be gold-containing multilayer metal or gold-free multilayer metal, wherein gold The multilayer metal is any structure in Ti / Al / Ni / Au structure, Ti / Al / ...

Embodiment 2

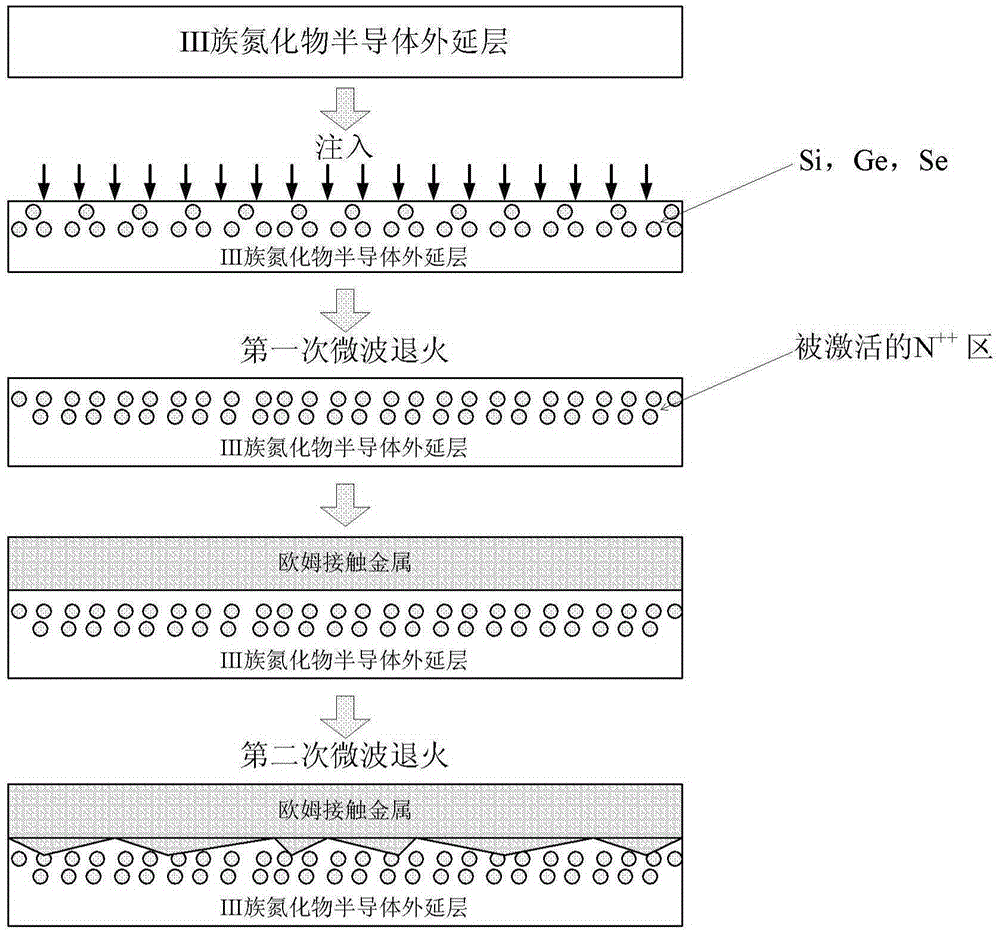

[0029] Such as image 3 and Figure 4 as shown, image 3 It is a flow chart of the manufacturing process of the low-temperature ohmic contact of the III-nitride electronic device according to the second embodiment of the present invention, Figure 4 It is a flowchart of a method for manufacturing a low-temperature ohmic contact of a III-nitride electronic device according to a second embodiment of the present invention, and the method includes the following steps:

[0030] Step a: Implanting N-type impurities in the III-nitride ohmic contact region; in this step, the N-type impurities may be Si elements, Ge elements, Se elements or co-doped implants of the above elements and N elements.

[0031] Step b: Use microwave annealing technology to activate the implanted N-type impurities; in this step, use microwave annealing technology to activate the N-type impurities at a low temperature below 800°C to form N ++ doping.

[0032]Step c: Deposit ohmic metal on the III-nitride oh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com