Tunneling field-effect transistor capable of restraining nolinear opening of output and preparation method thereof

A tunneling field effect, transistor technology, applied in diodes, semiconductor devices, semiconductor/solid-state device manufacturing, etc., can solve problems such as large output resistance, achieve steep sub-threshold slopes, reduce production costs, and improve device output characteristics. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

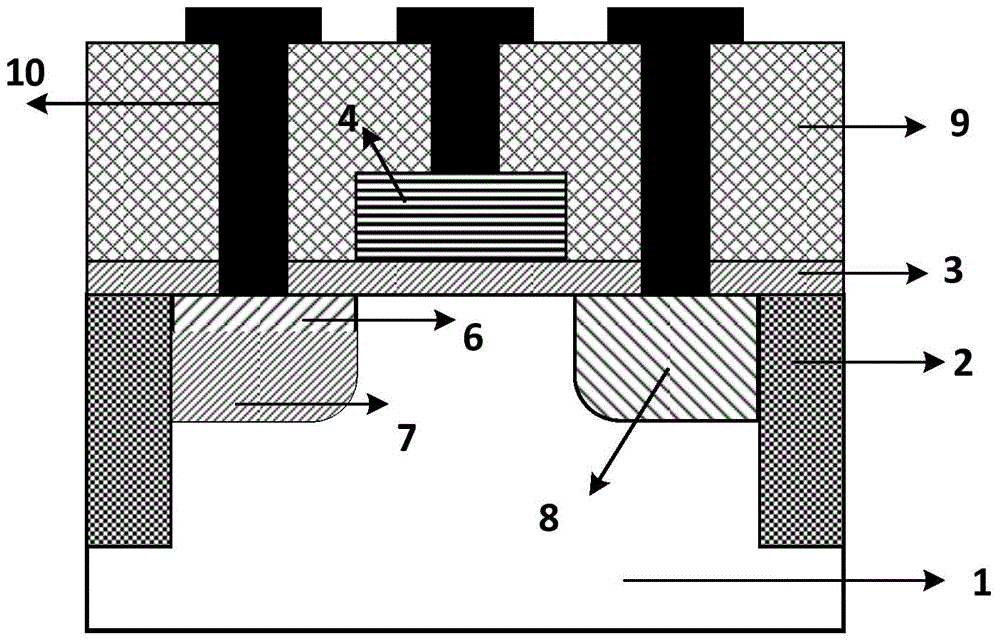

[0043] The implementation method of the tunneling field effect transistor for suppressing output nonlinear turn-on according to the present invention will be further described through specific embodiments below in conjunction with the accompanying drawings.

[0044] The specific implementation steps are as Figure 2-Figure 7 Shown: (This example takes N-type devices as an example, and P-type devices can be deduced by analogy)

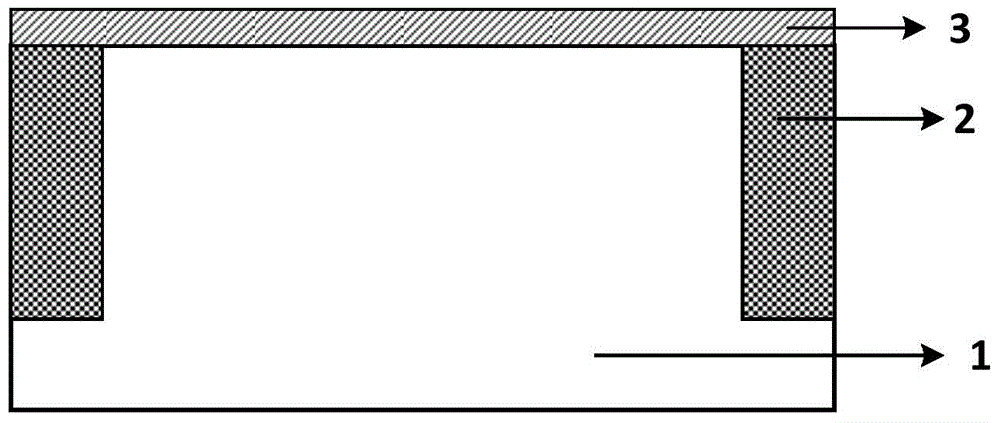

[0045] 1. The substrate doping concentration is lightly doped (about 1E13cm -3 -1E15cm -3 ), a layer of silicon dioxide is initially thermally oxidized on the InGaAs substrate 1 with a crystal orientation of , with a thickness of about 10 nm, and a layer of silicon nitride (Si 3 N 4 ), with a thickness of about 100nm, and then use shallow trench isolation technology to make STI isolation 2 in the active area, and then perform CMP, such as figure 2 shown.

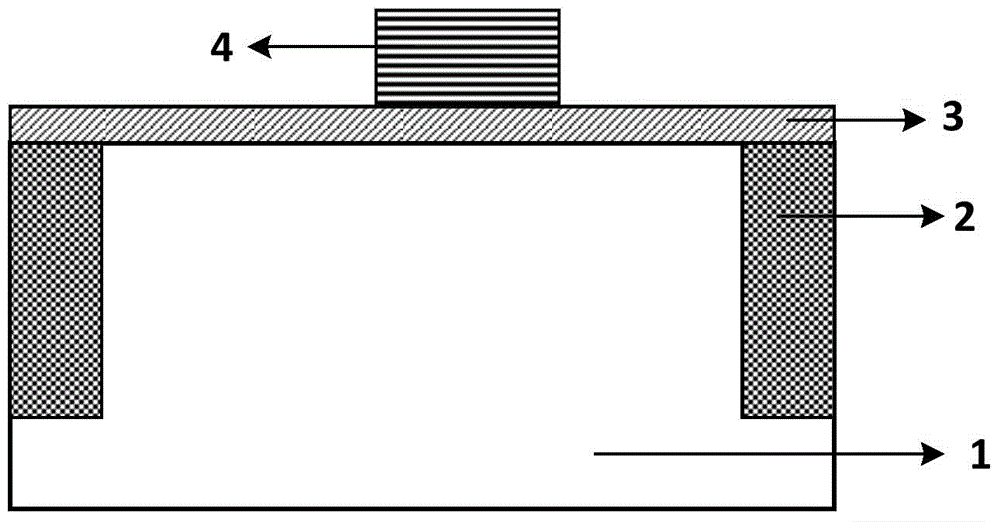

[0046] 2. Float away the silicon dioxide initially grown on the surface, and then thermally ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com